Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41 results about "Memory-mapped I/O" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory-mapped I/O (MMIO) and port-mapped I/O (PMIO) (which is also called isolated I/O) are two complementary methods of performing input/output (I/O) between the central processing unit (CPU) and peripheral devices in a computer. An alternative approach is using dedicated I/O processors, commonly known as channels on mainframe computers, which execute their own instructions.

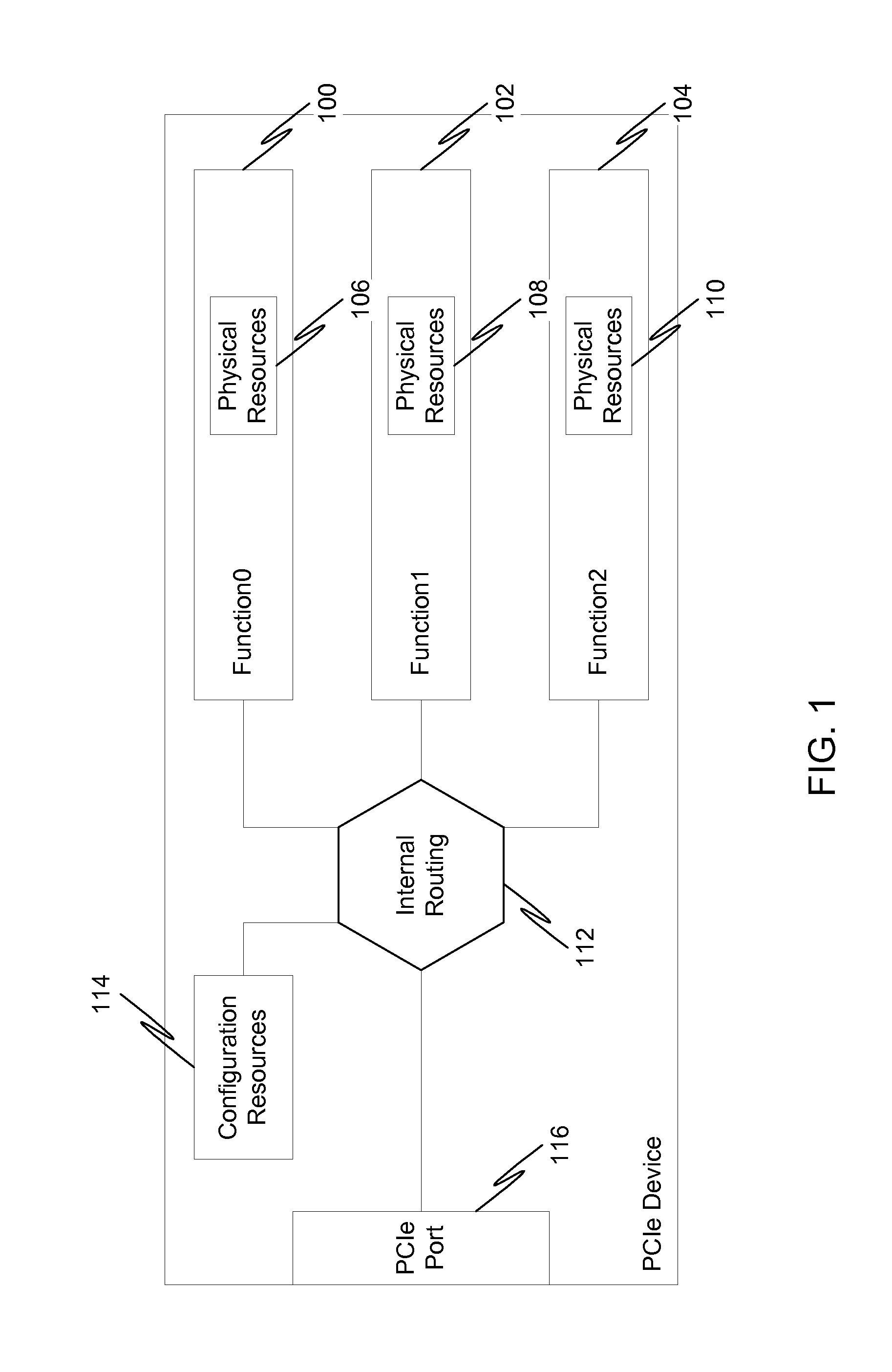

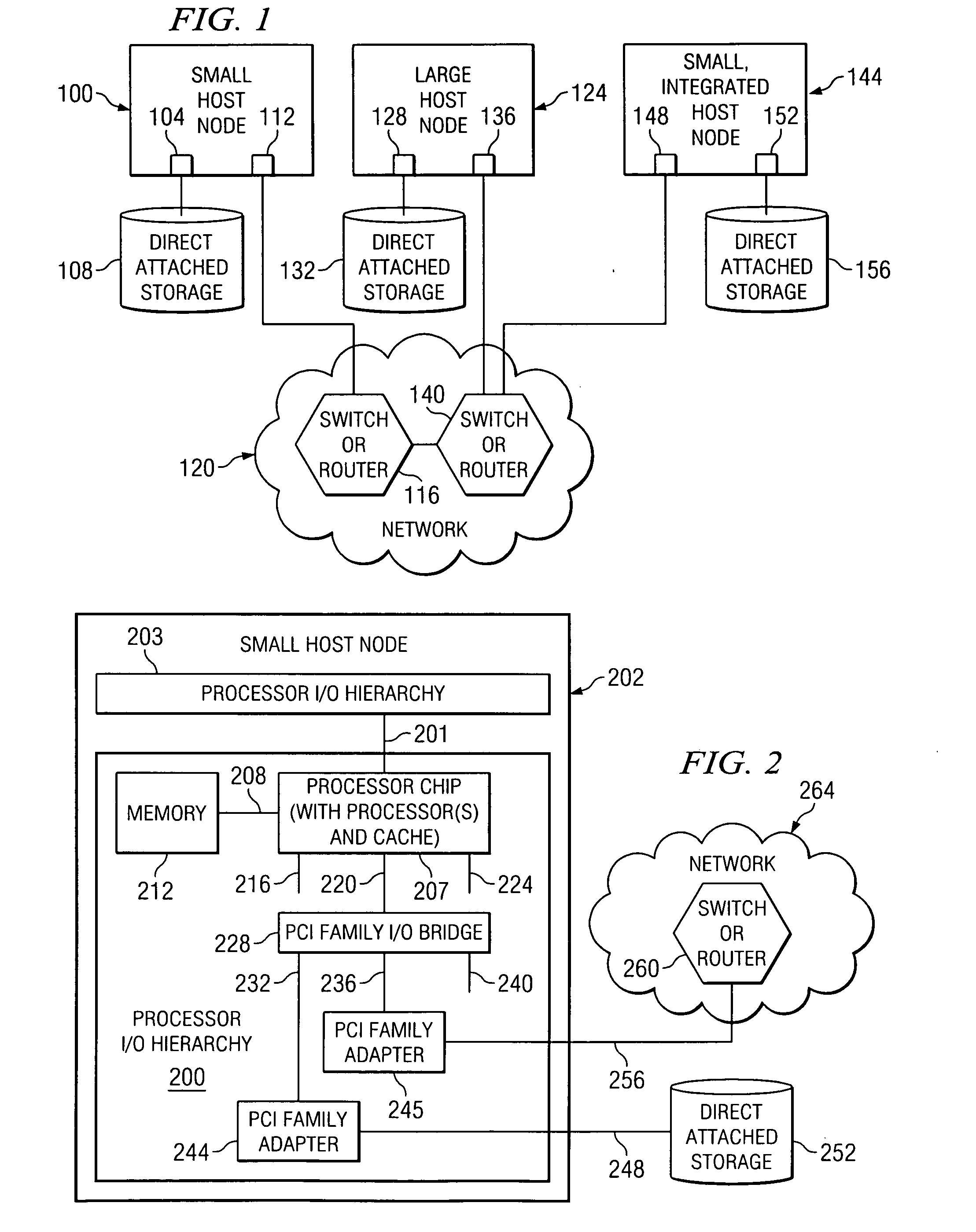

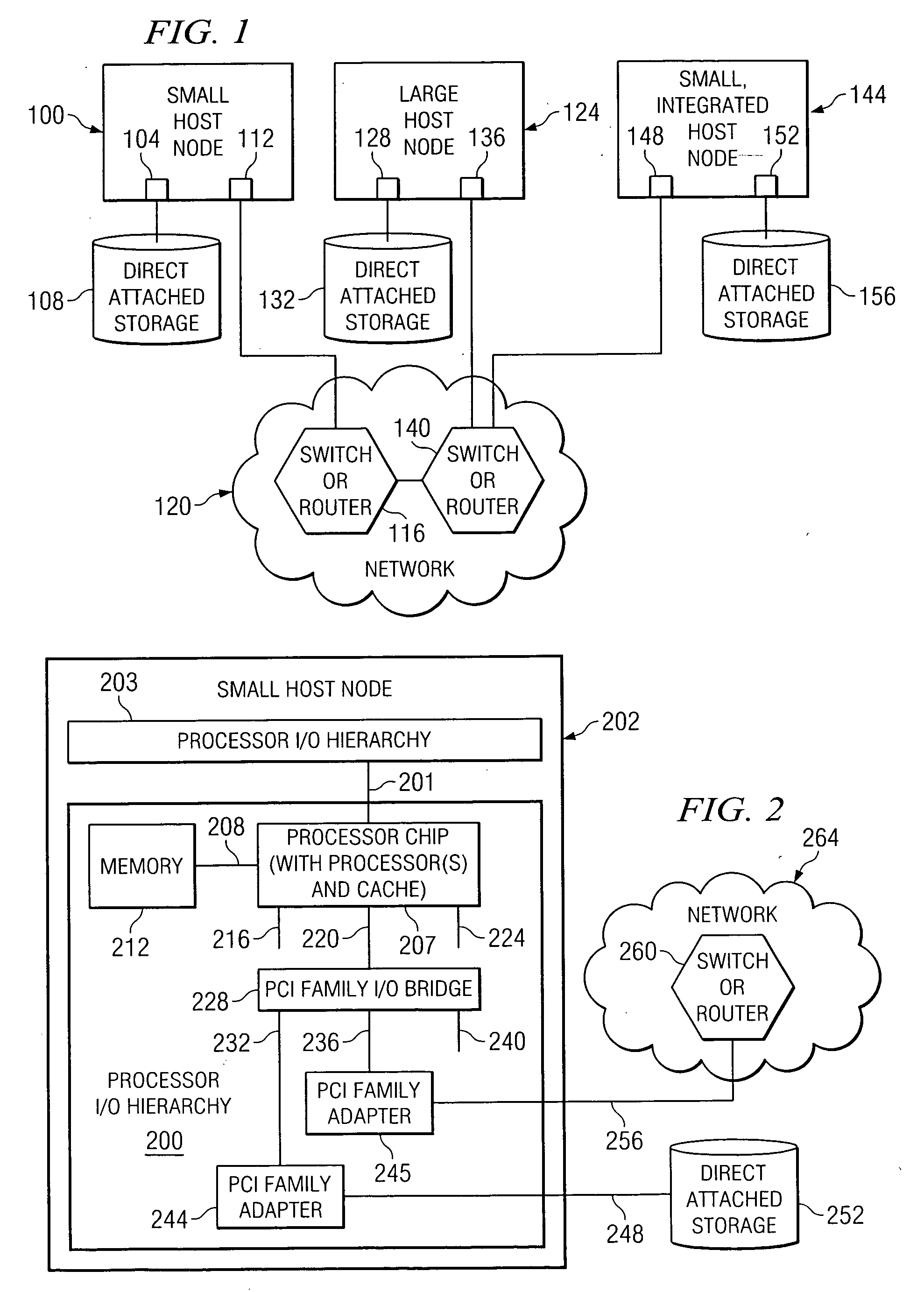

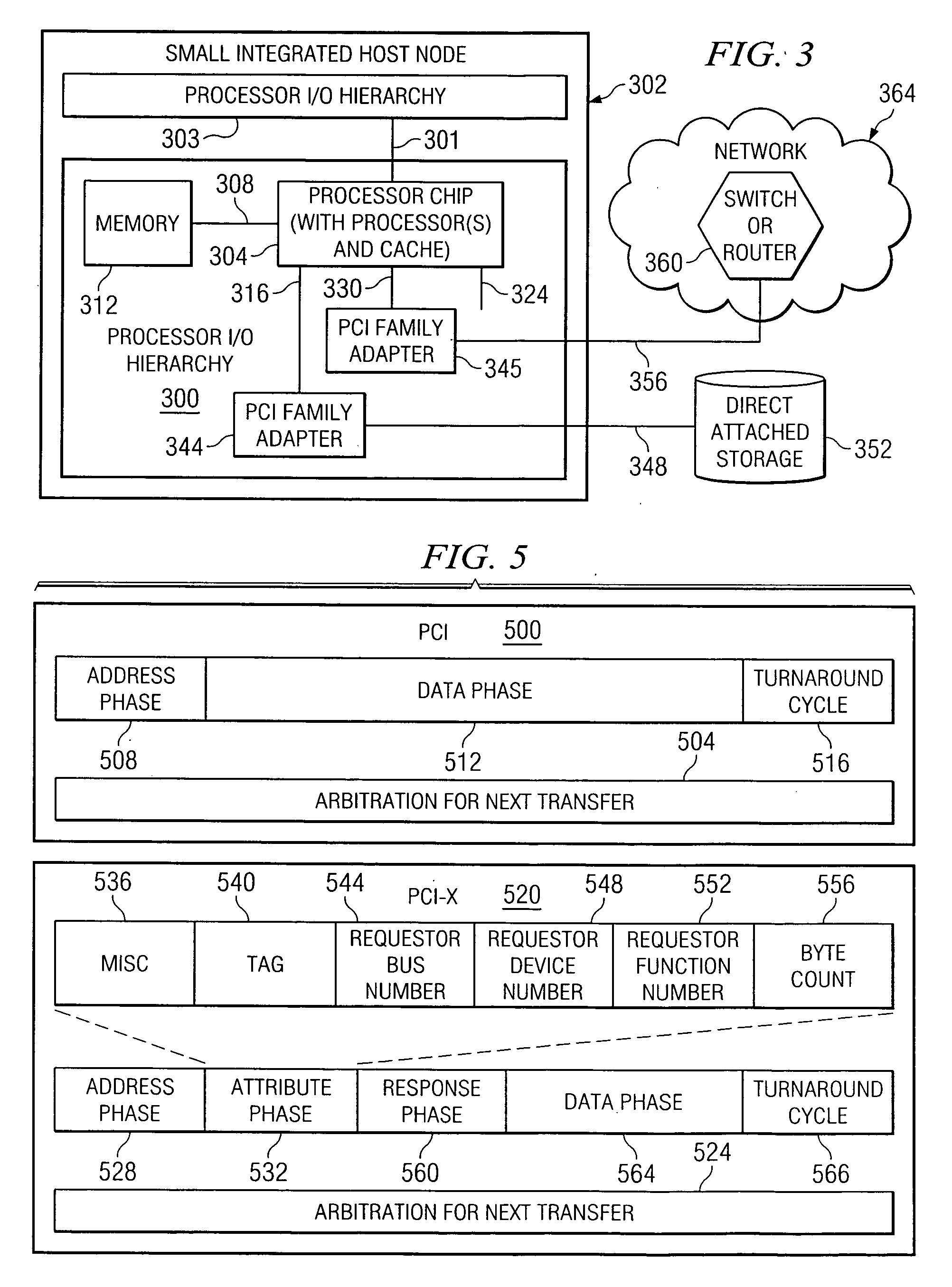

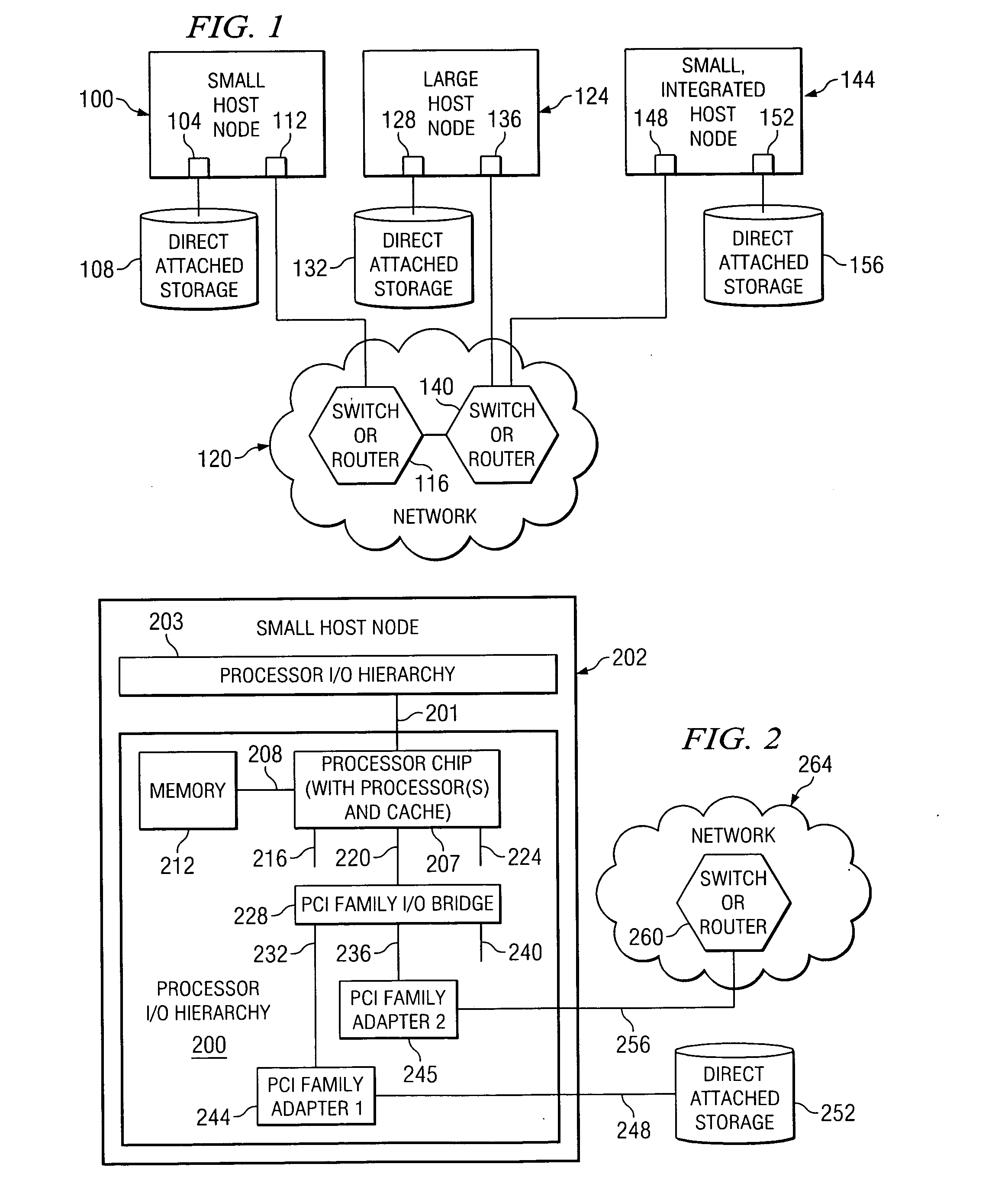

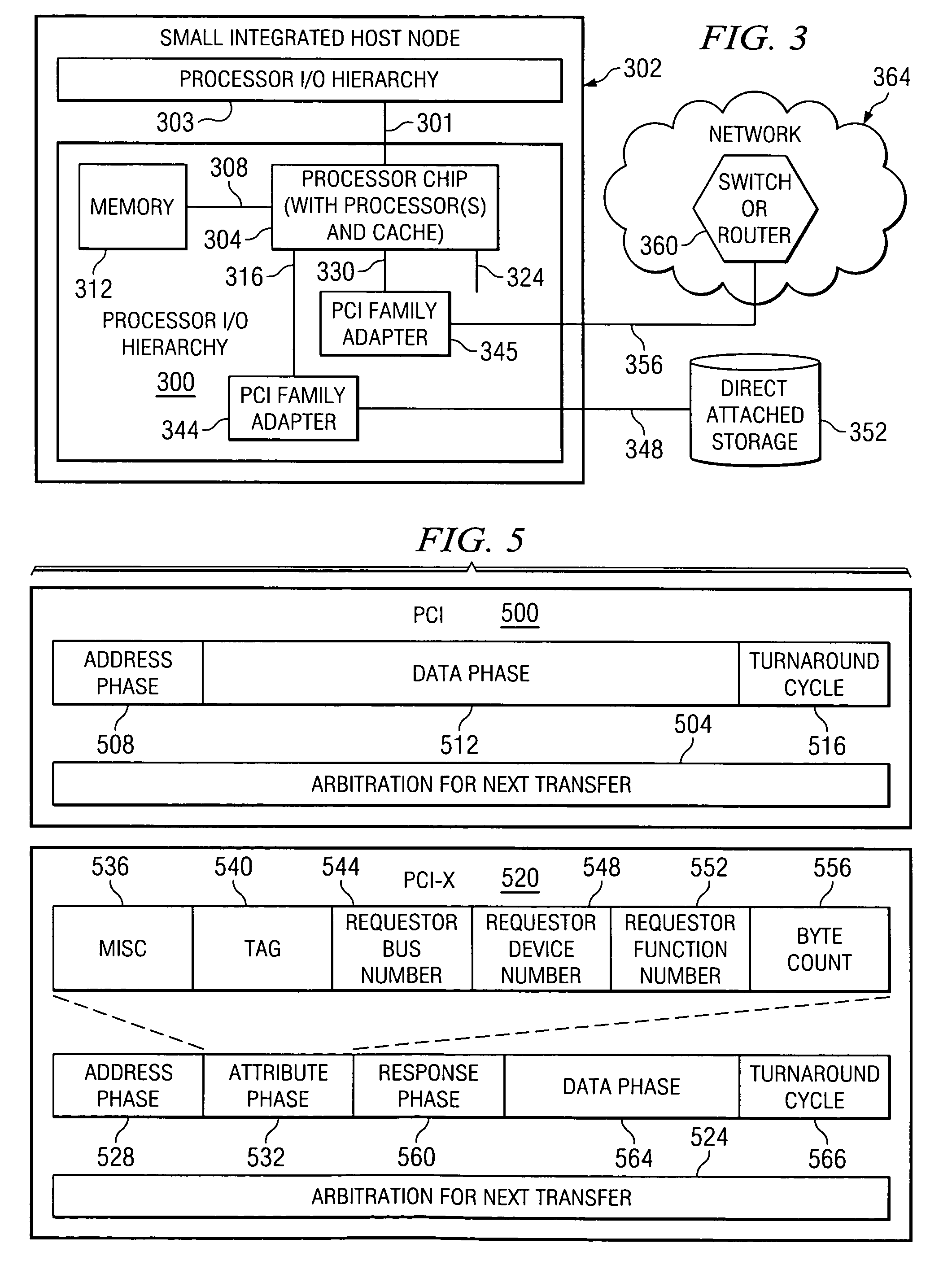

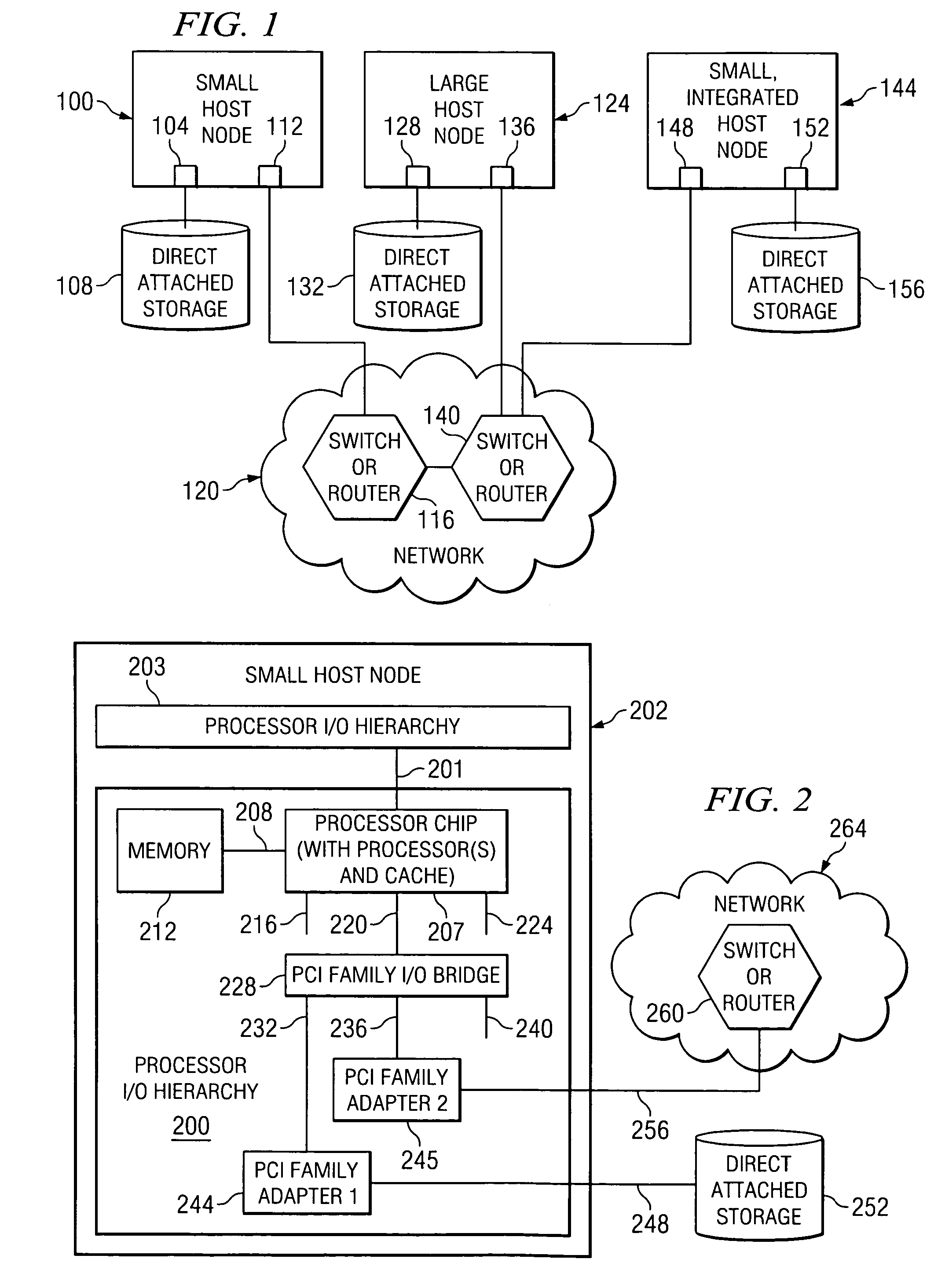

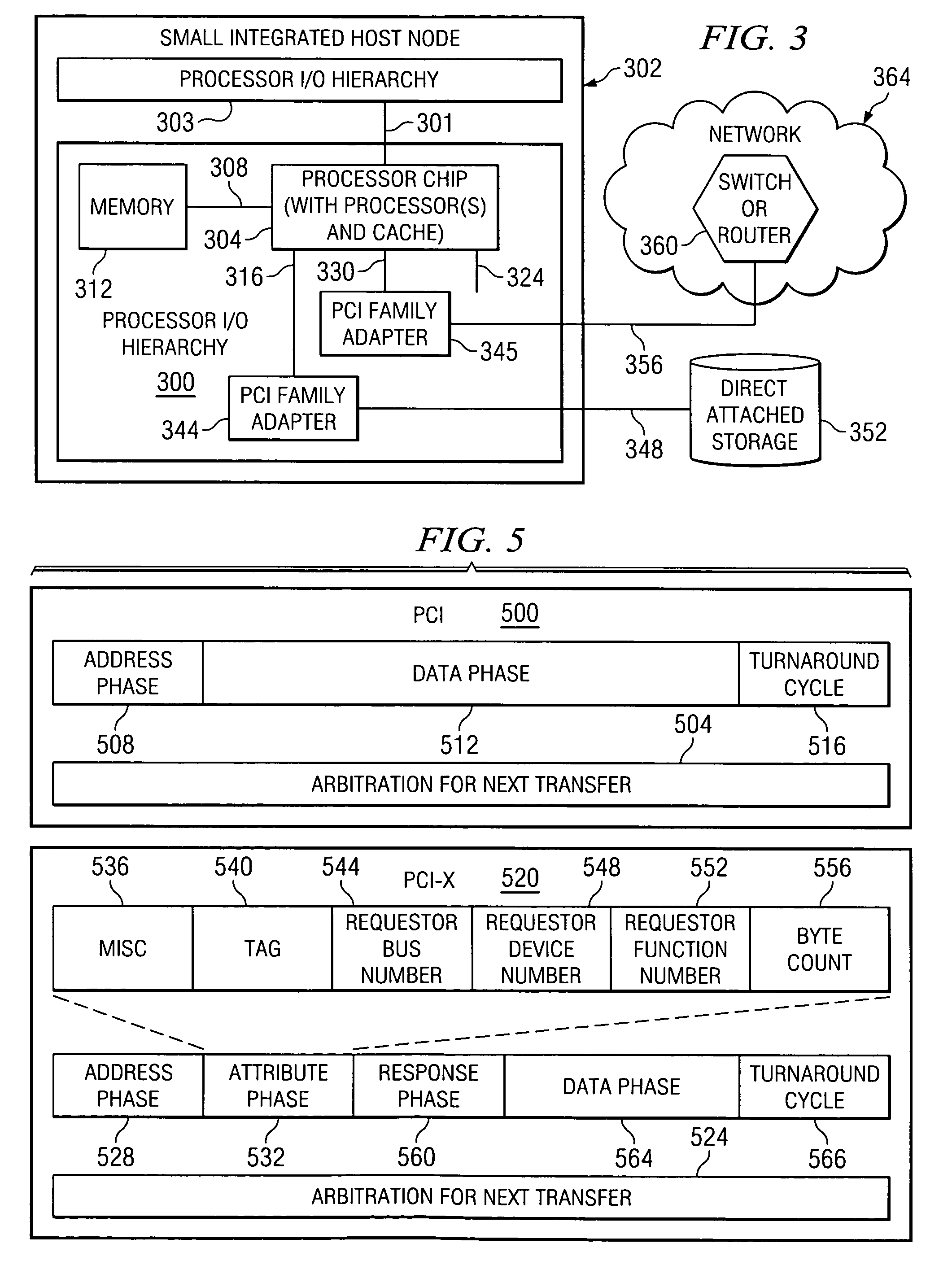

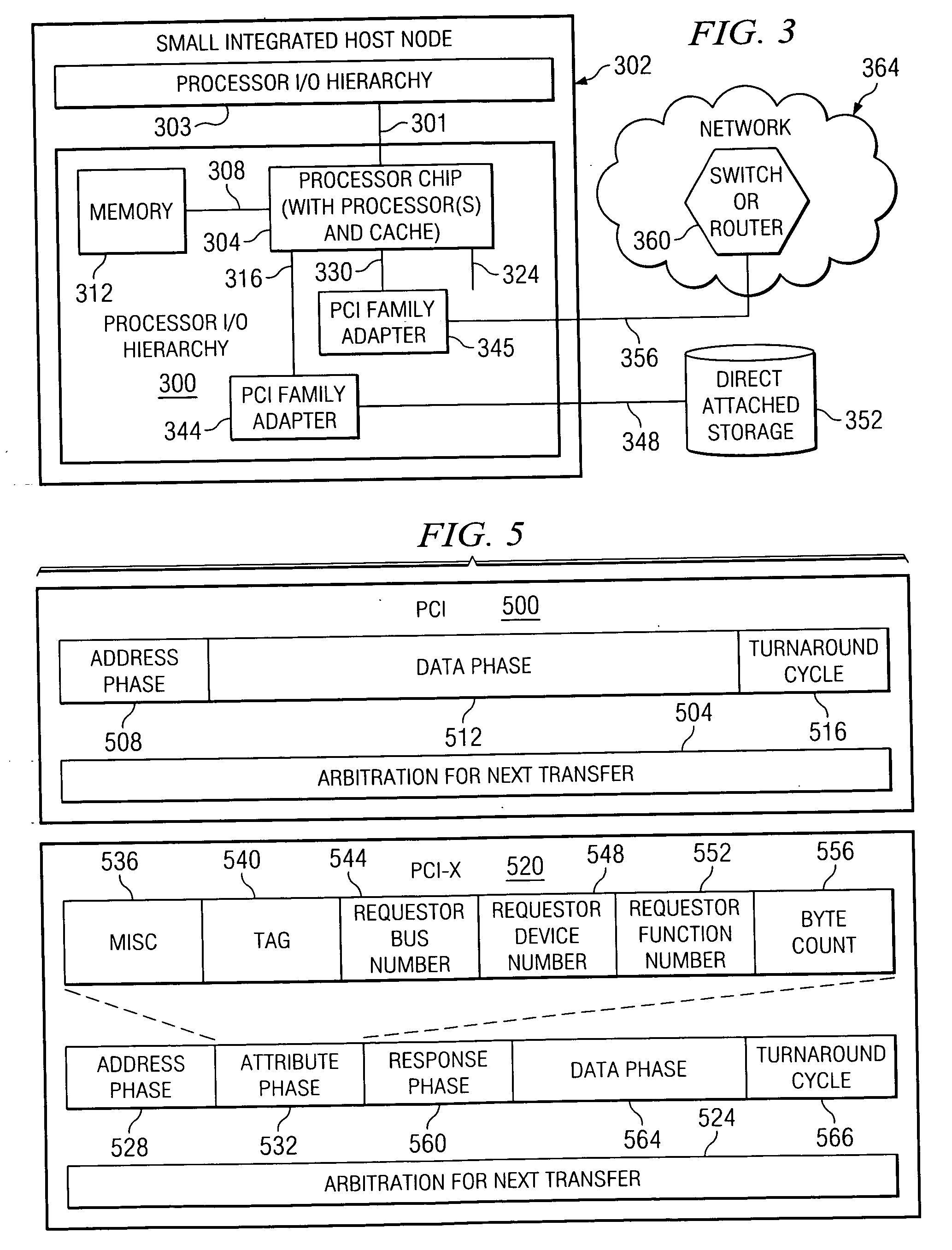

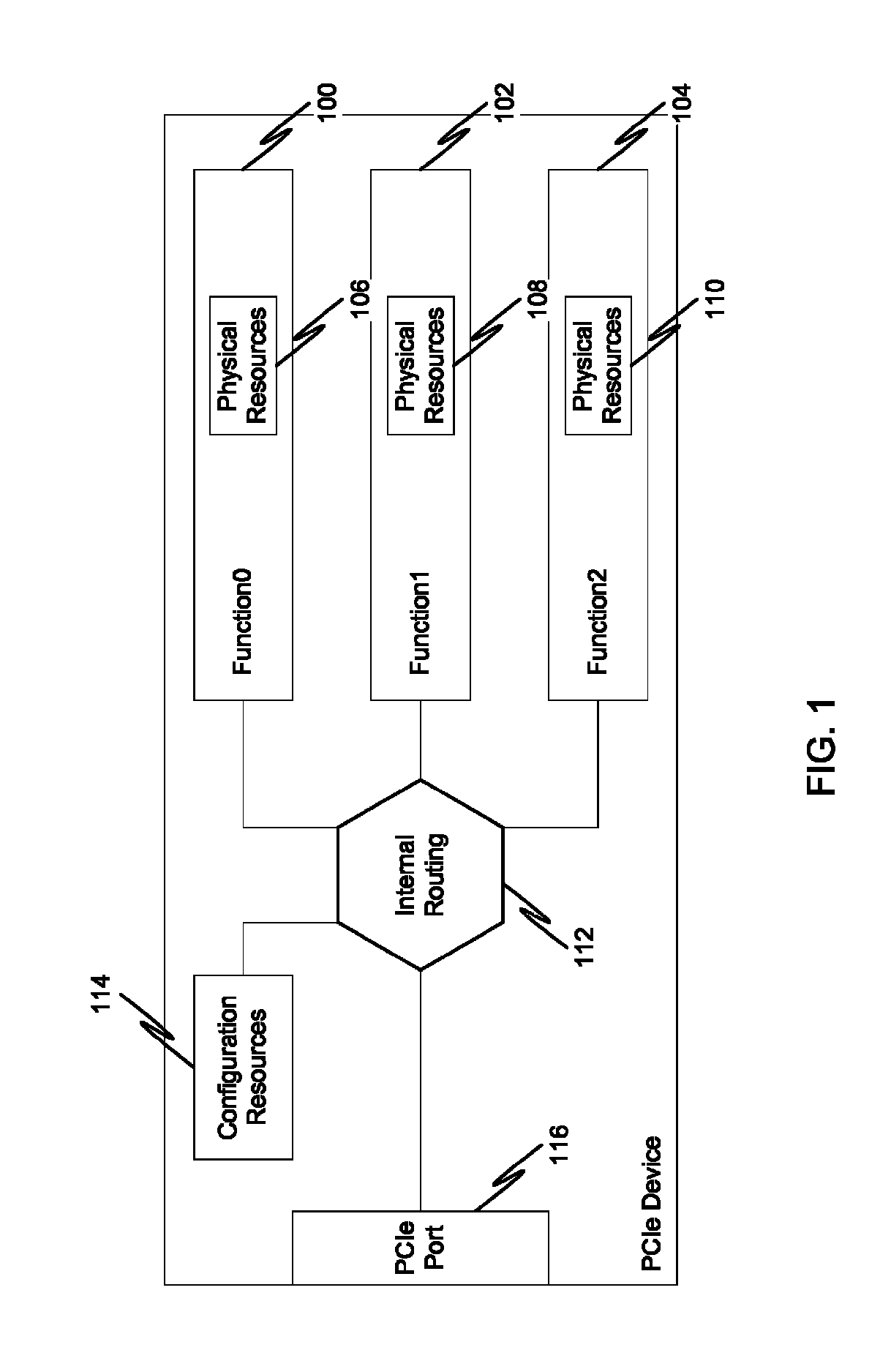

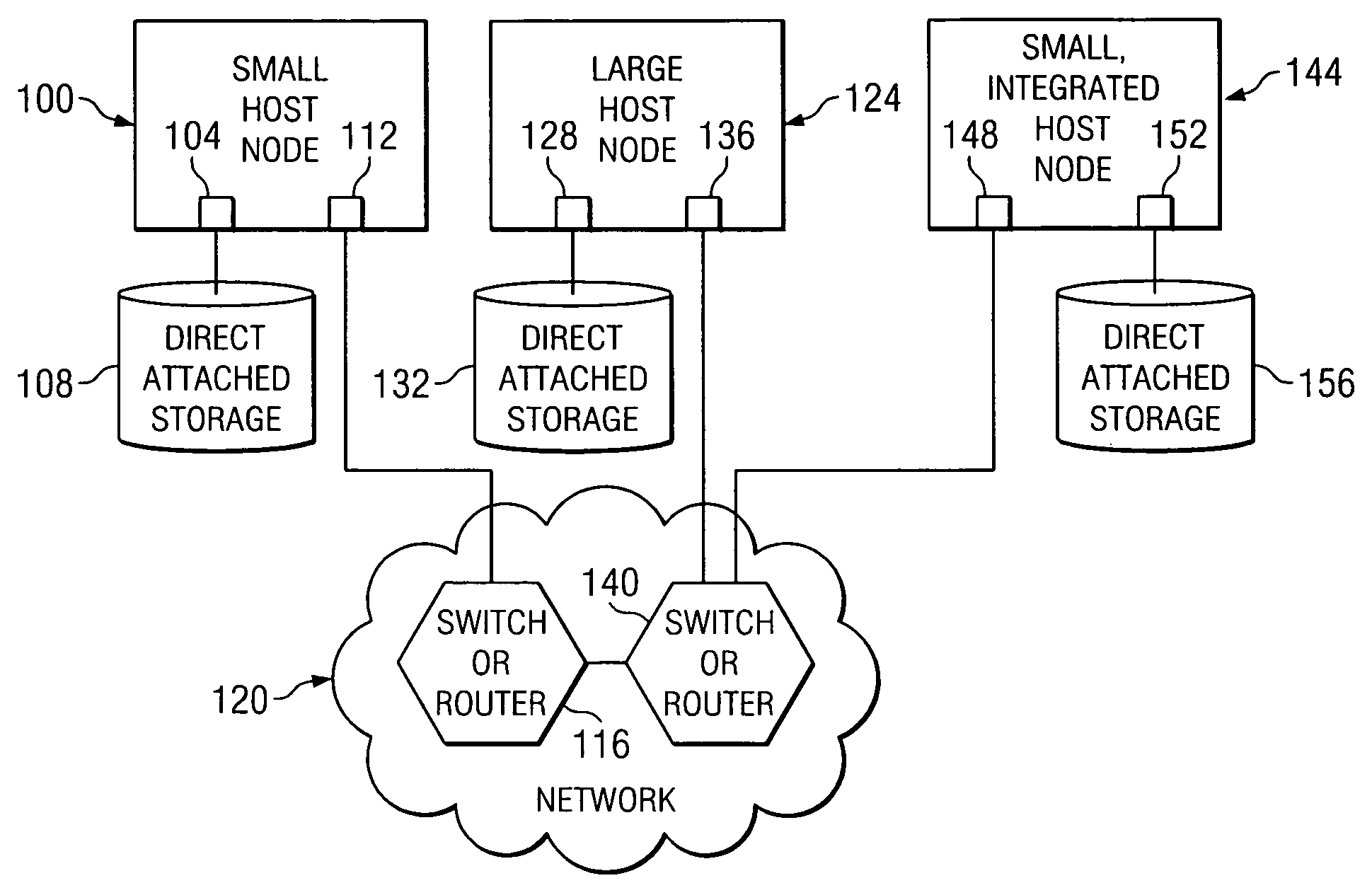

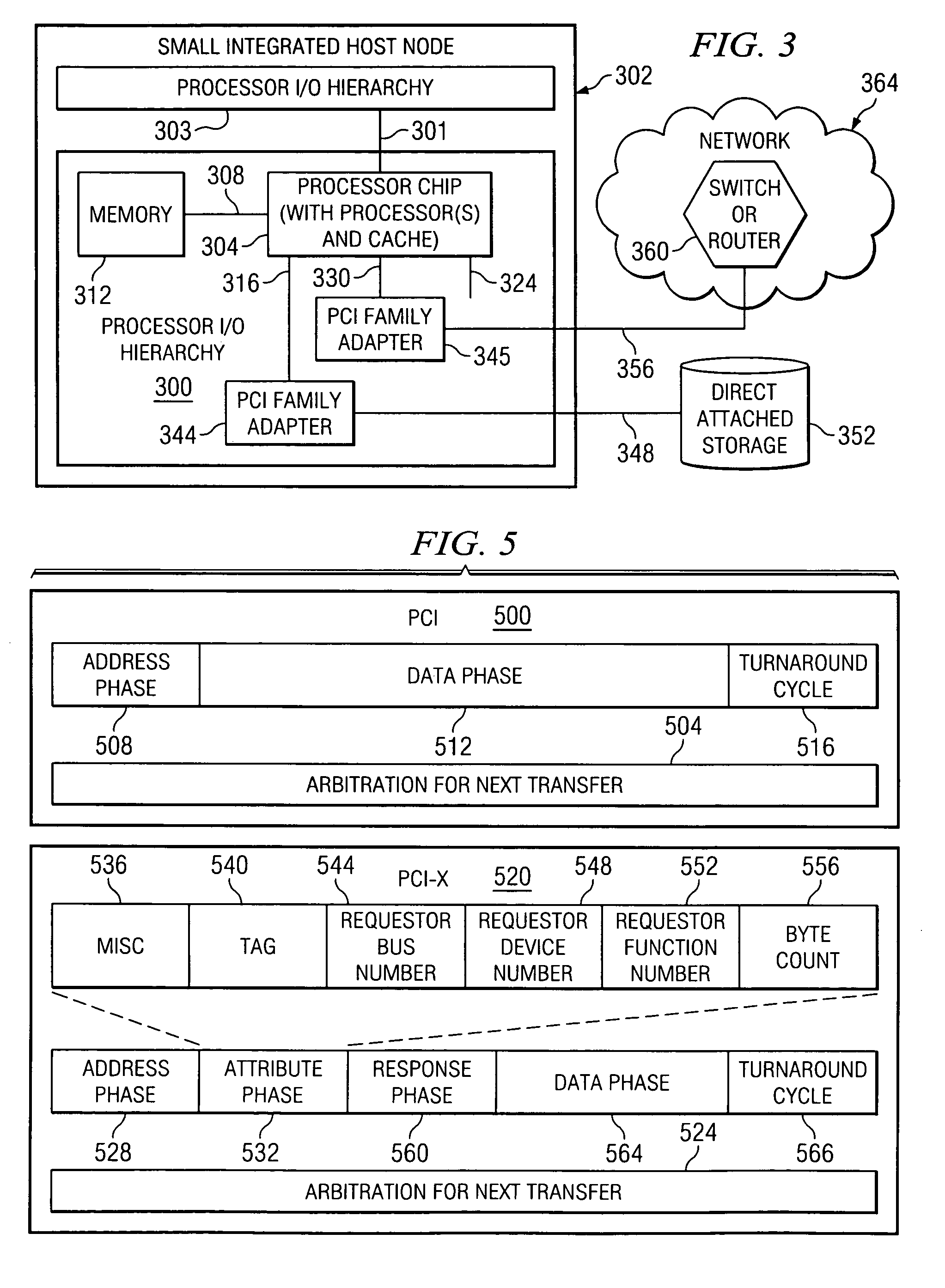

Method and system for native virtualization on a partially trusted adapter using adapter bus, device and function number for identification

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to use a PCI adapter identifier to associate its resources to a system image and isolate them from other system images thereby providing I / O virtualization is provided. Specifically, the present invention is directed to a mechanism for sharing among multiple system images a conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to use a PCI adapter identifier to associate its resources to a system image and isolate them from other system images, thereby providing I / O virtualization.

Owner:IBM CORP

Multi-root sharing of single-root input/output virtualization

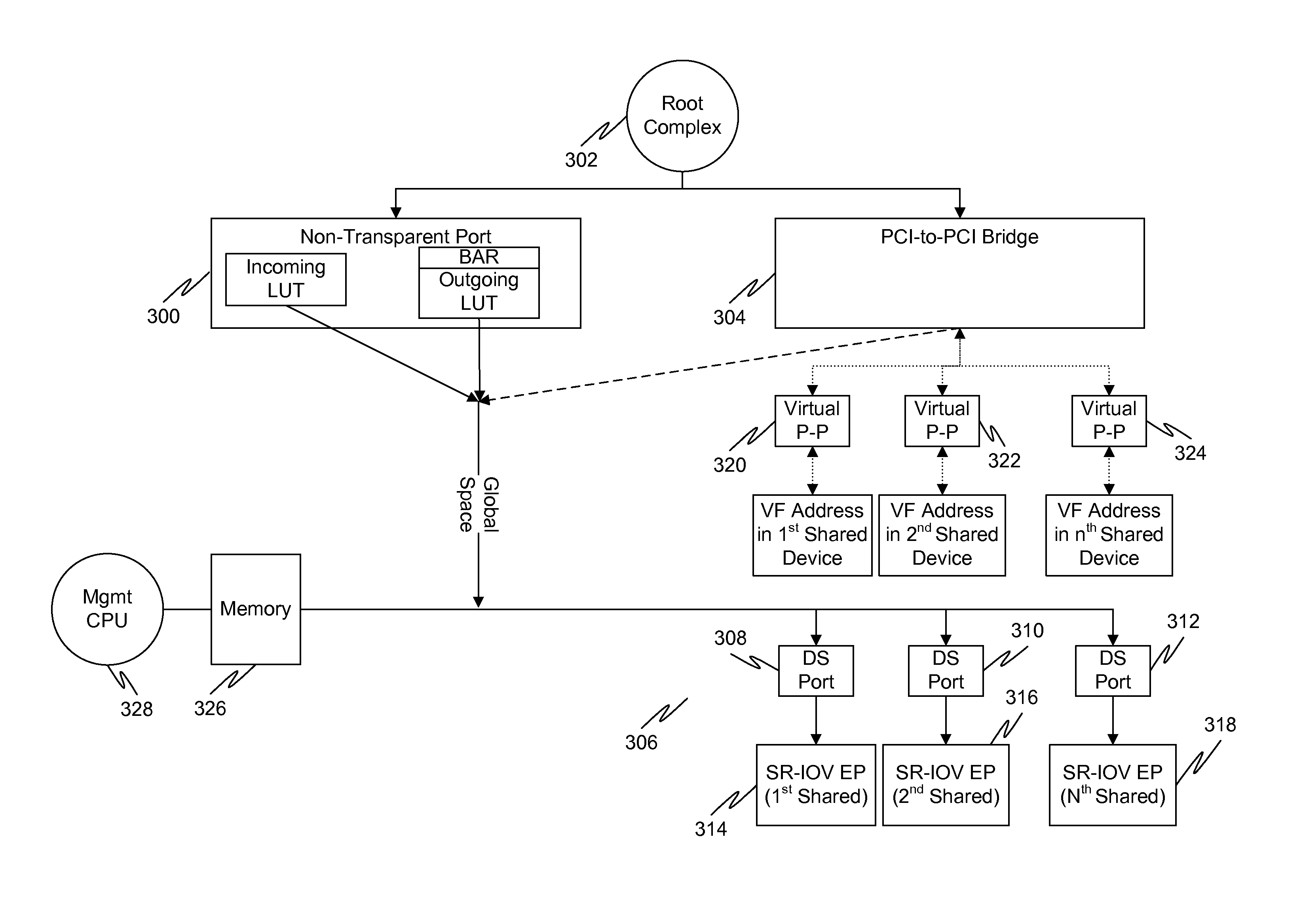

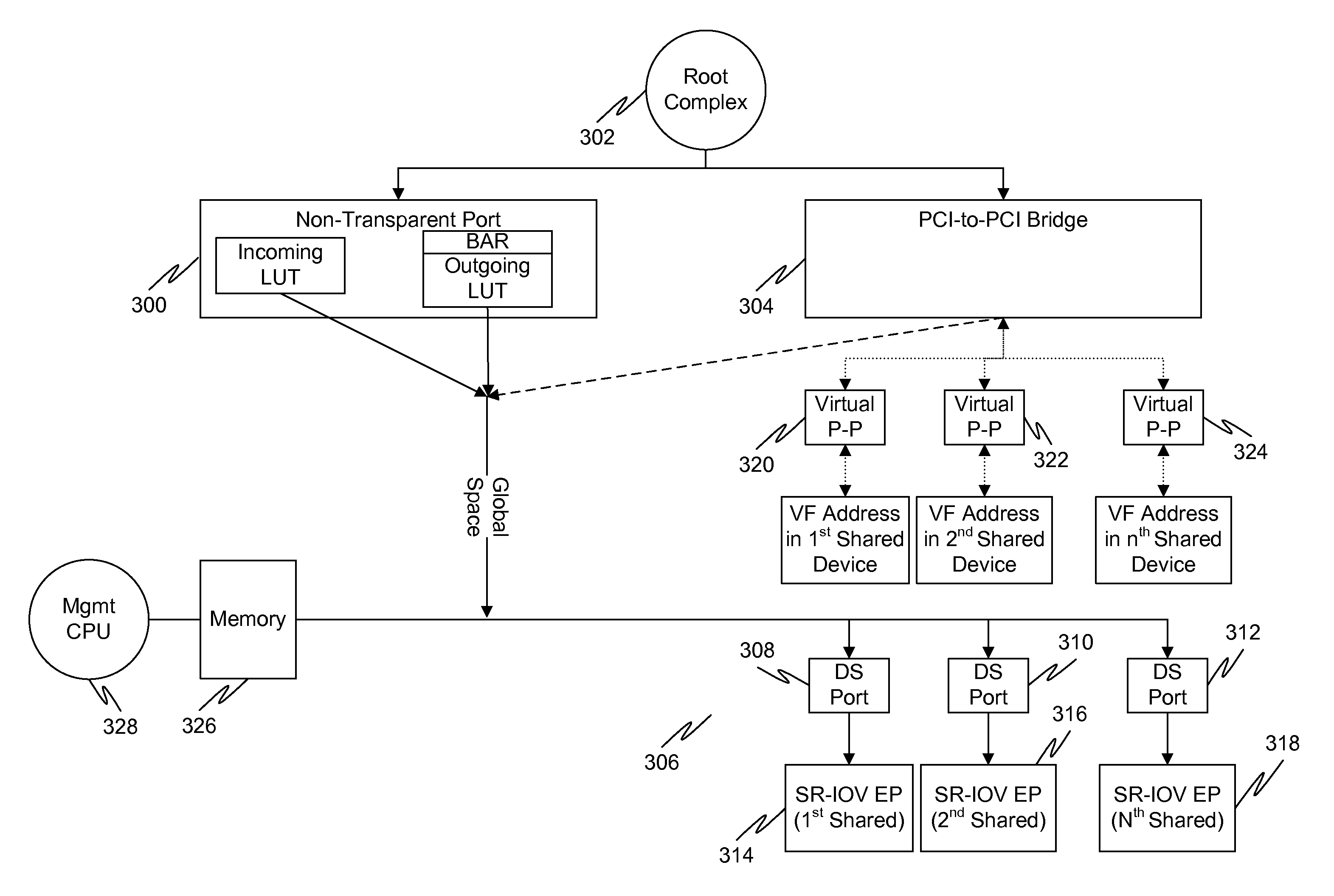

In a first embodiment of the present invention, a method for multi-root sharing of a plurality of single root input / output virtualization (SR-IOV) endpoints is provided, the method comprising: CSR redirection to a management processor which either acts as a proxy to execute the CSR request on behalf of the host or filters it and performs an alternate action, downstream routing of memory mapped I / O request packets through the switch in the host's address space and address translation with VF BAR granularity, upstream routing of requests originated by I / O devices by table lookup indexed by Requester ID, and requester ID translation using a fixed local-global RID offset.

Owner:AVAGO TECH INT SALES PTE LTD

System, method, and computer program product for a fully trusted adapter validation of incoming memory mapped I/O operations on a physical adapter that supports virtual adapters or virtual resources

InactiveUS20060212608A1Memory adressing/allocation/relocationInput/output processes for data processingData processing systemTerm memory

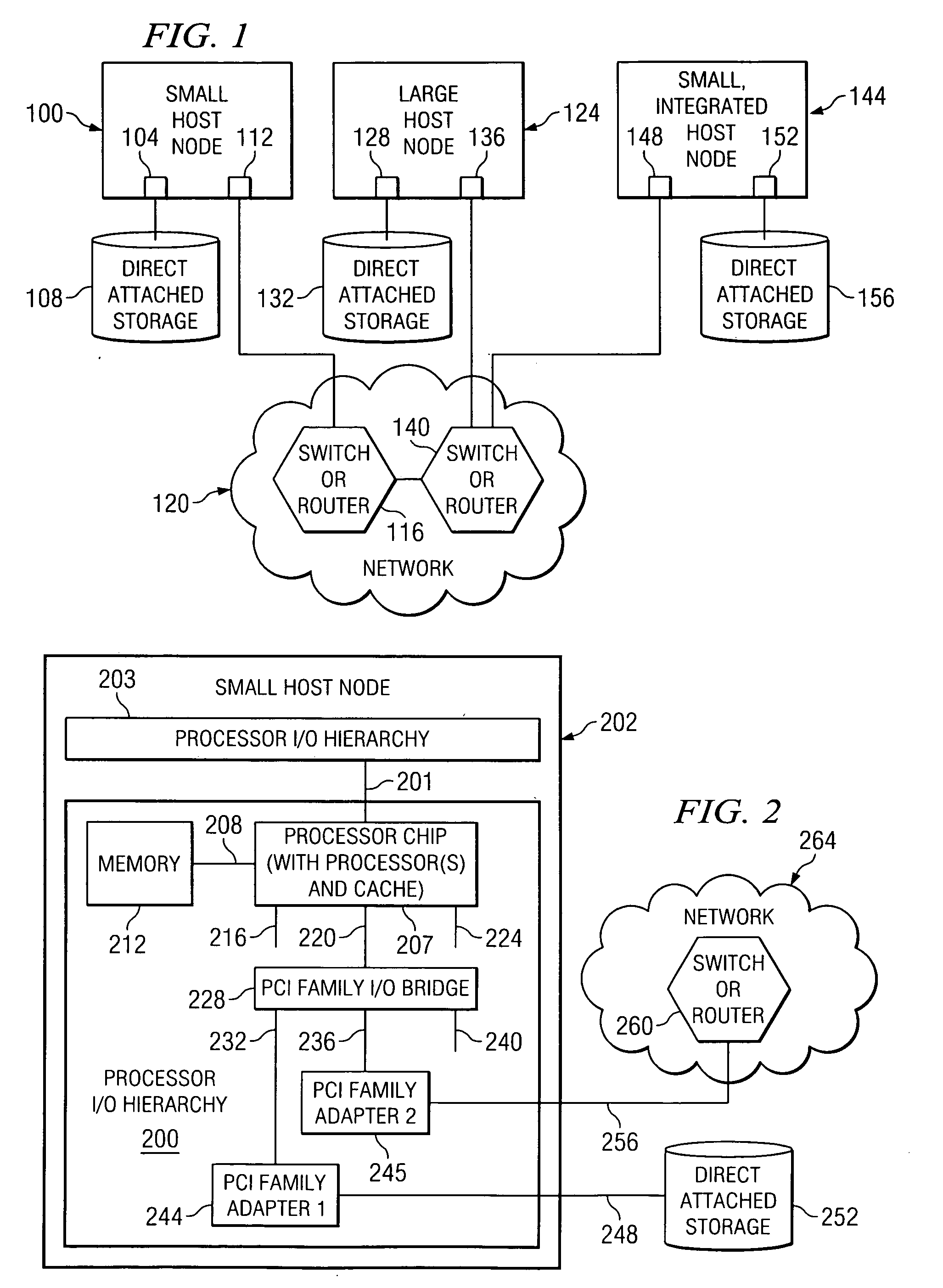

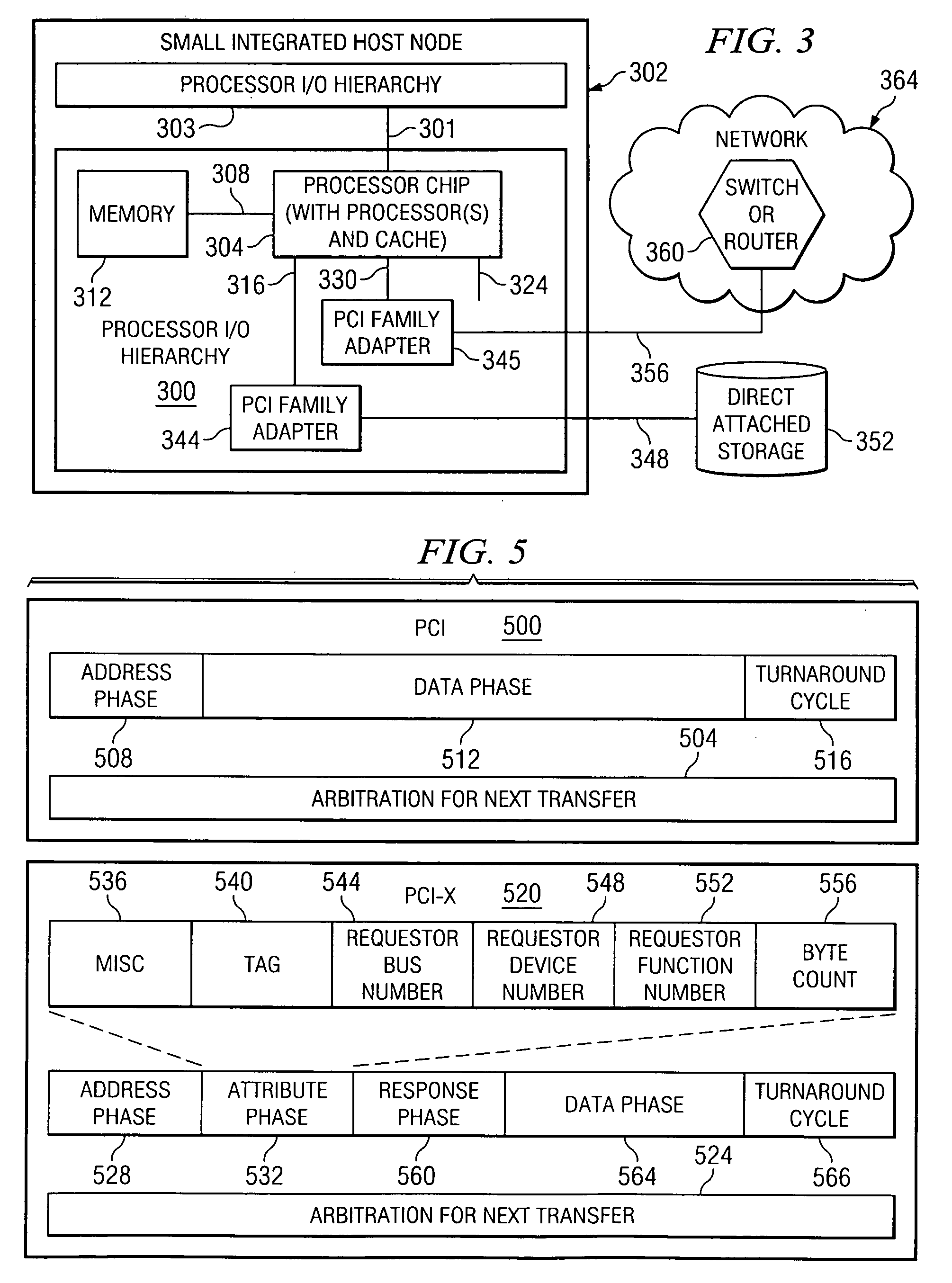

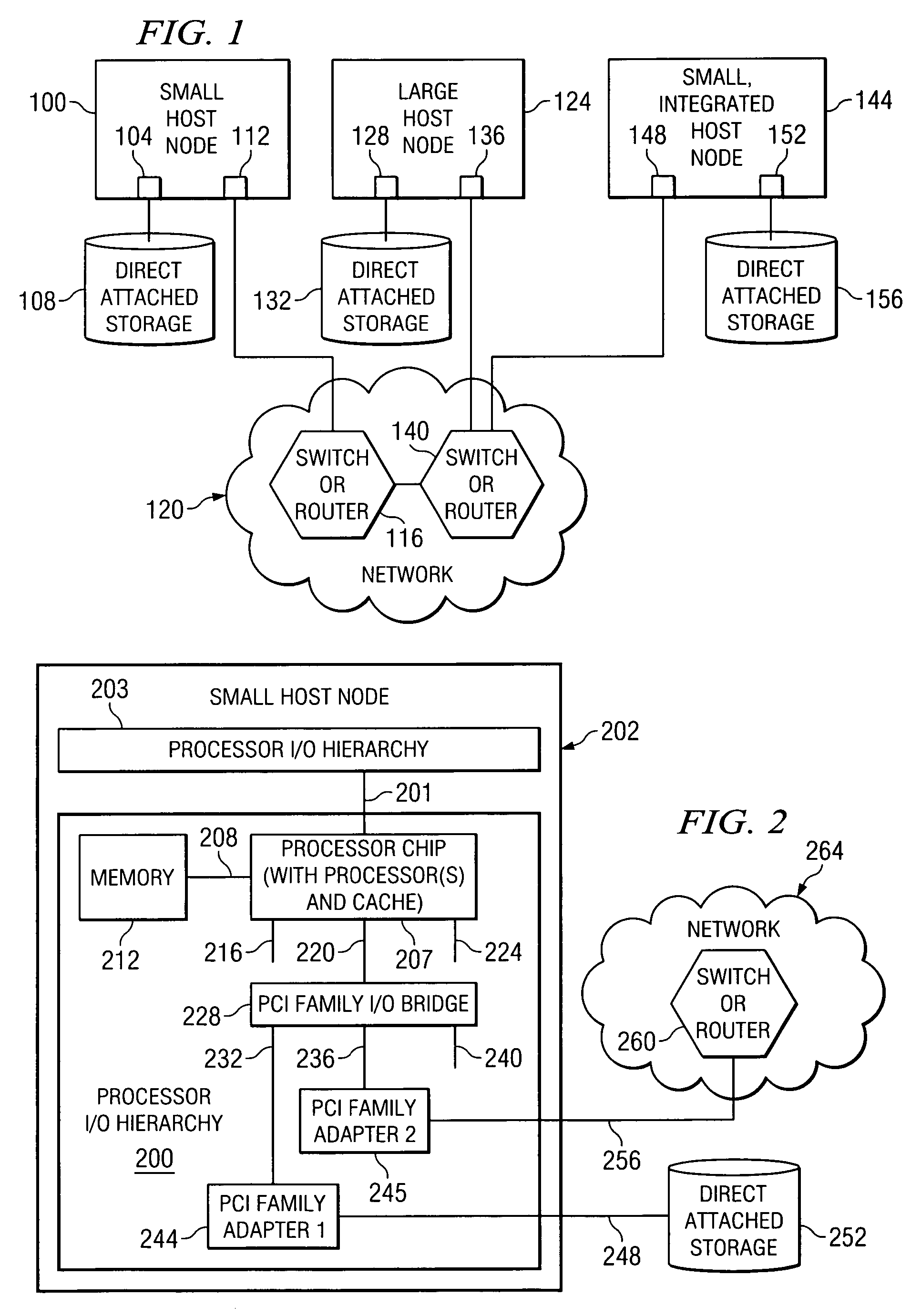

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter to validate that a memory mapped I / O address referenced by an incoming I / O operation is associated with a virtual host that initiated the incoming memory mapped I / O operation is provided. Specifically, the present invention is directed to a mechanism for sharing a PCI family I / O adapter and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided that allows a single physical I / O adapter to validate that a memory mapped I / O address referenced by an incoming memory mapped I / O operation used to initiate an I / O transaction is associated with a virtual host that initiated the incoming memory mapped I / O operation.

Owner:IBM CORP

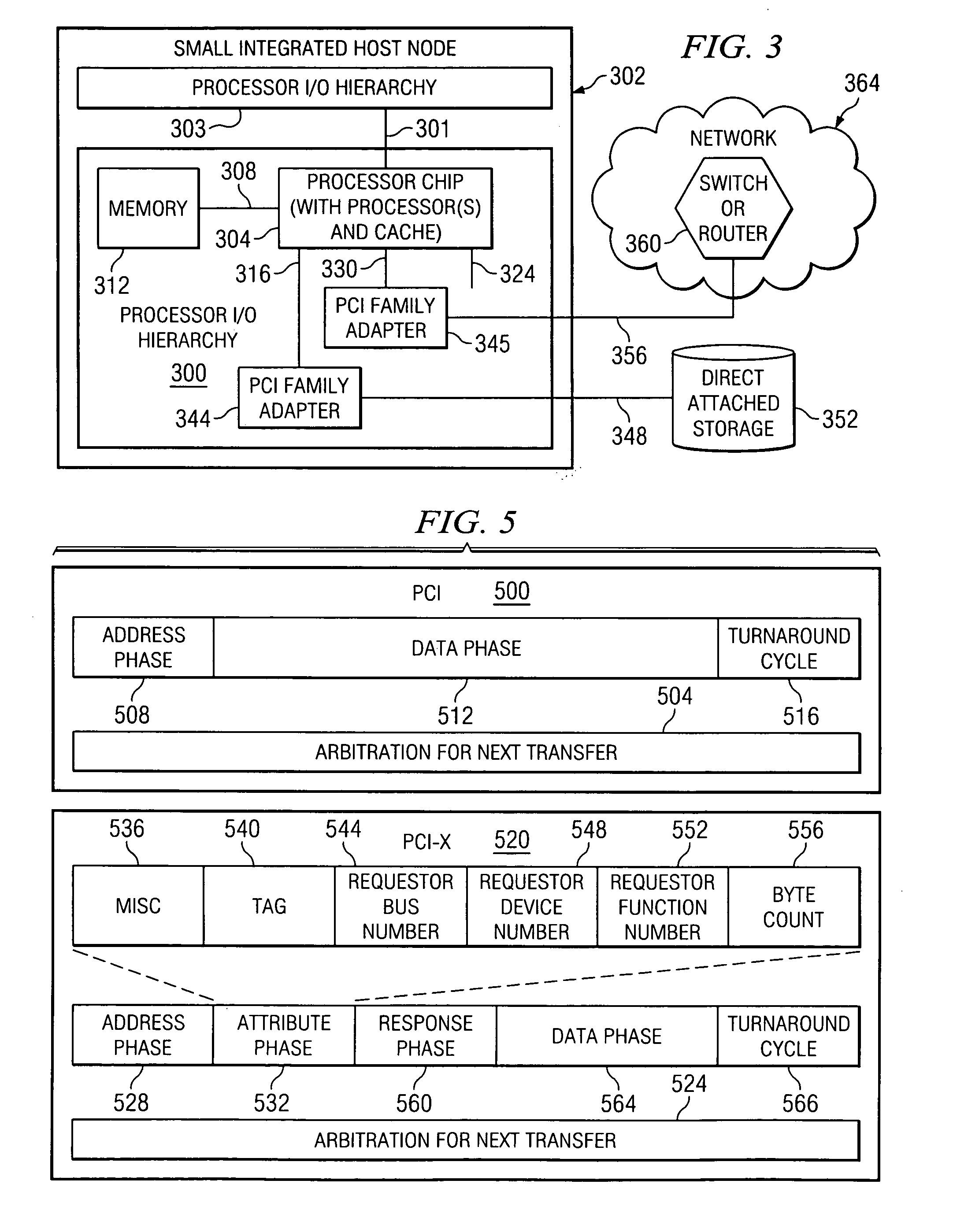

System and method of virtual resource modification on a physical adapter that supports virtual resources

A method, computer program product, and distributed data processing system for modifying one or more virtual resources that reside within a physical adapter, such as a peripheral component interconnect (PCI), PCI-X, or PCI-E adapter, and that are associated with a virtual host is provided. Specifically, the present invention is directed to a mechanism for sharing conventional PCI I / O adapters, PCI-X I / O Adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for host to adapter communications. A mechanism is provided for directly modifying one or more virtual resources that reside within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter, and that are associated with a virtual host.

Owner:IBM CORP

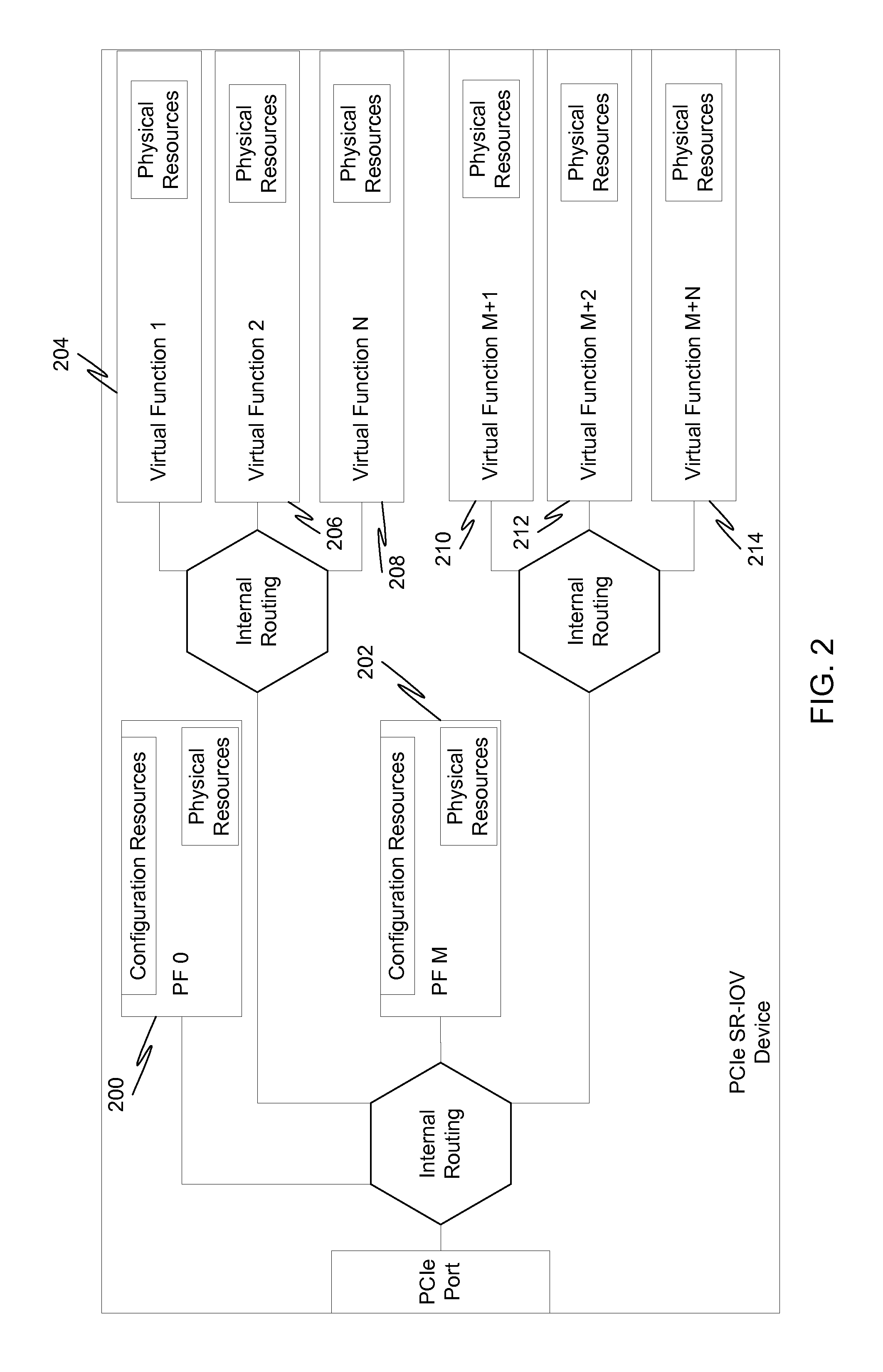

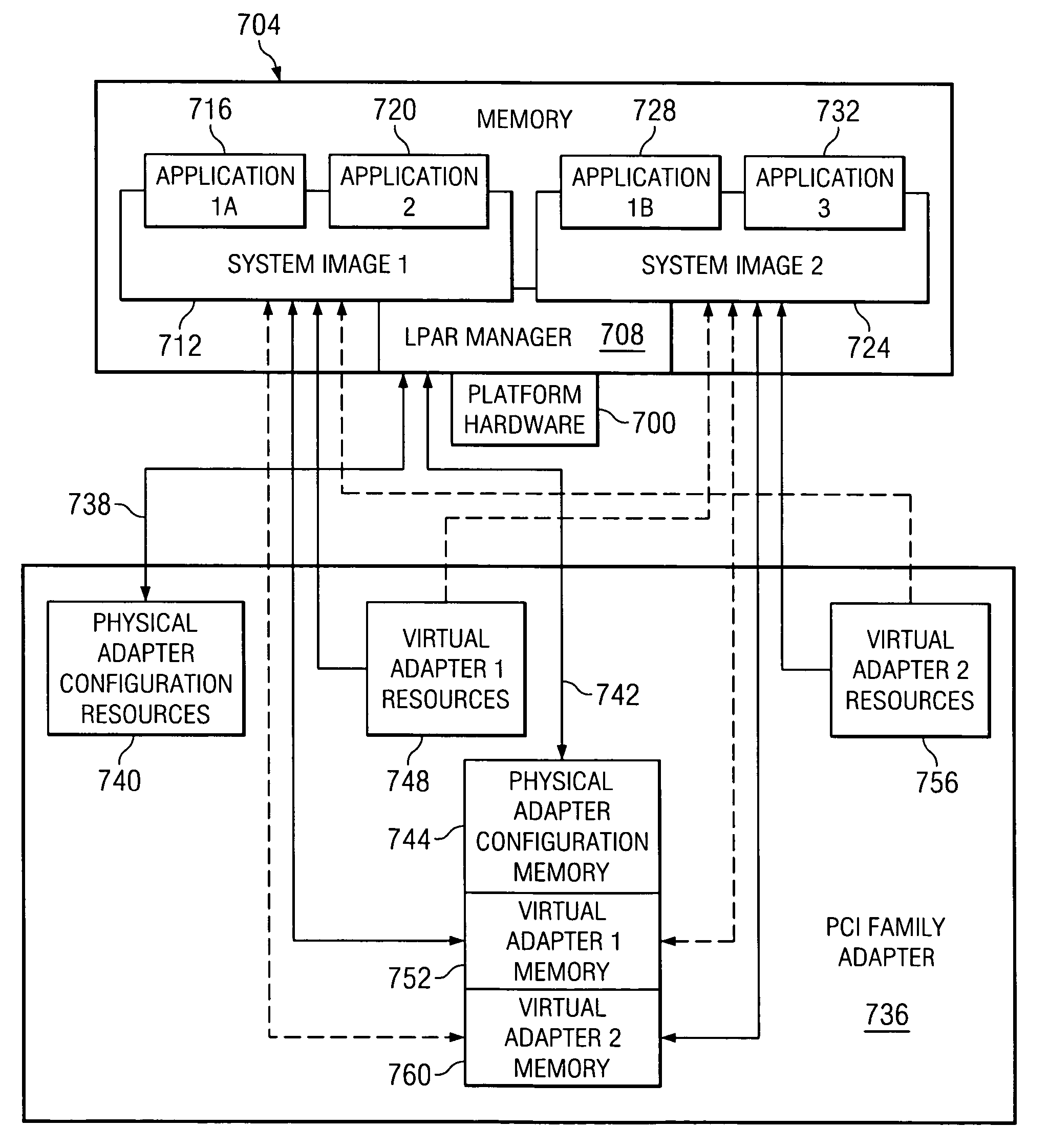

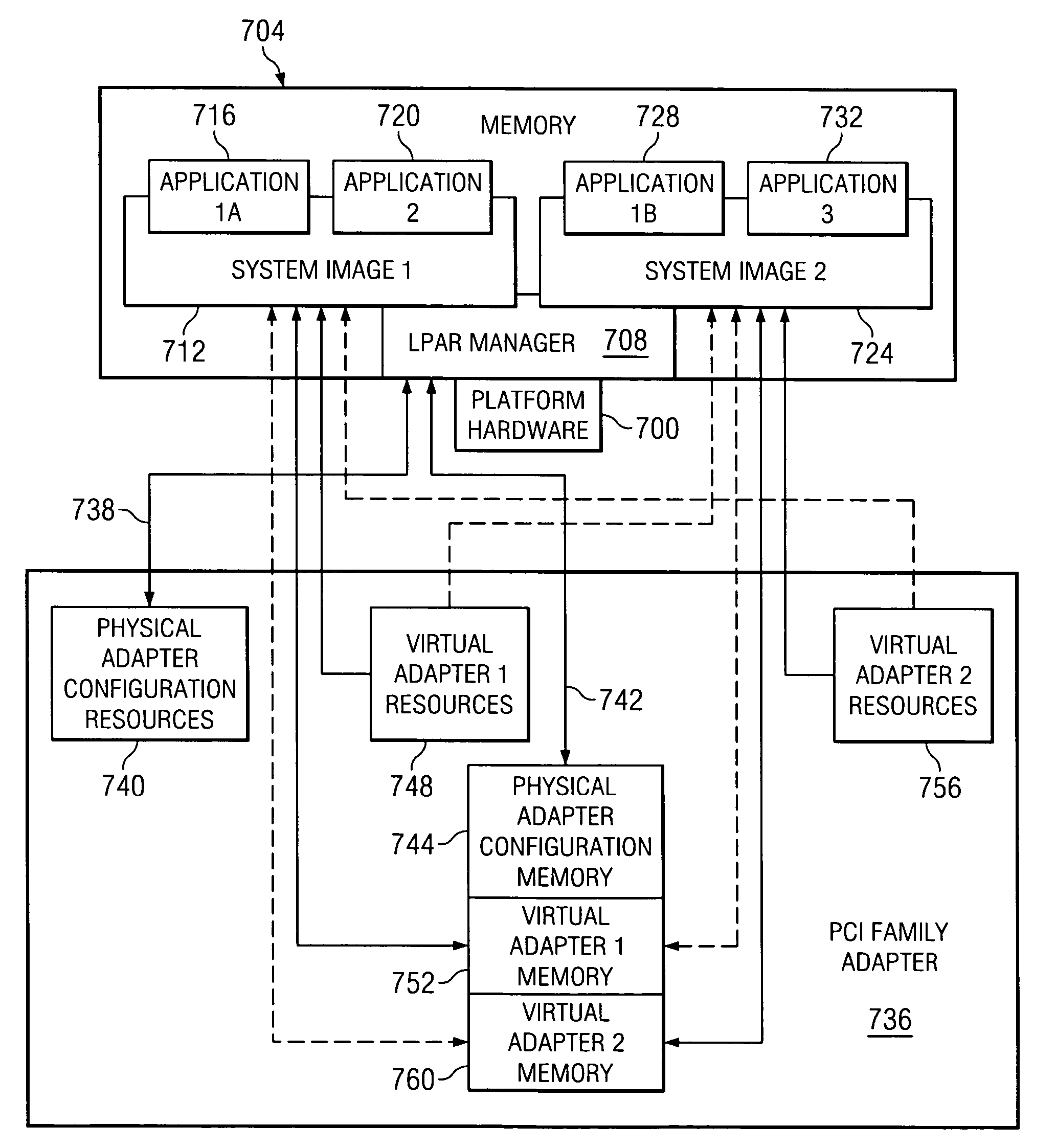

Data processing system, method, and computer program product for creation and initialization of a virtual adapter on a physical adapter that supports virtual adapter level virtualization

InactiveUS20060195618A1Program controlInput/output processes for data processingMemory addressData processing system

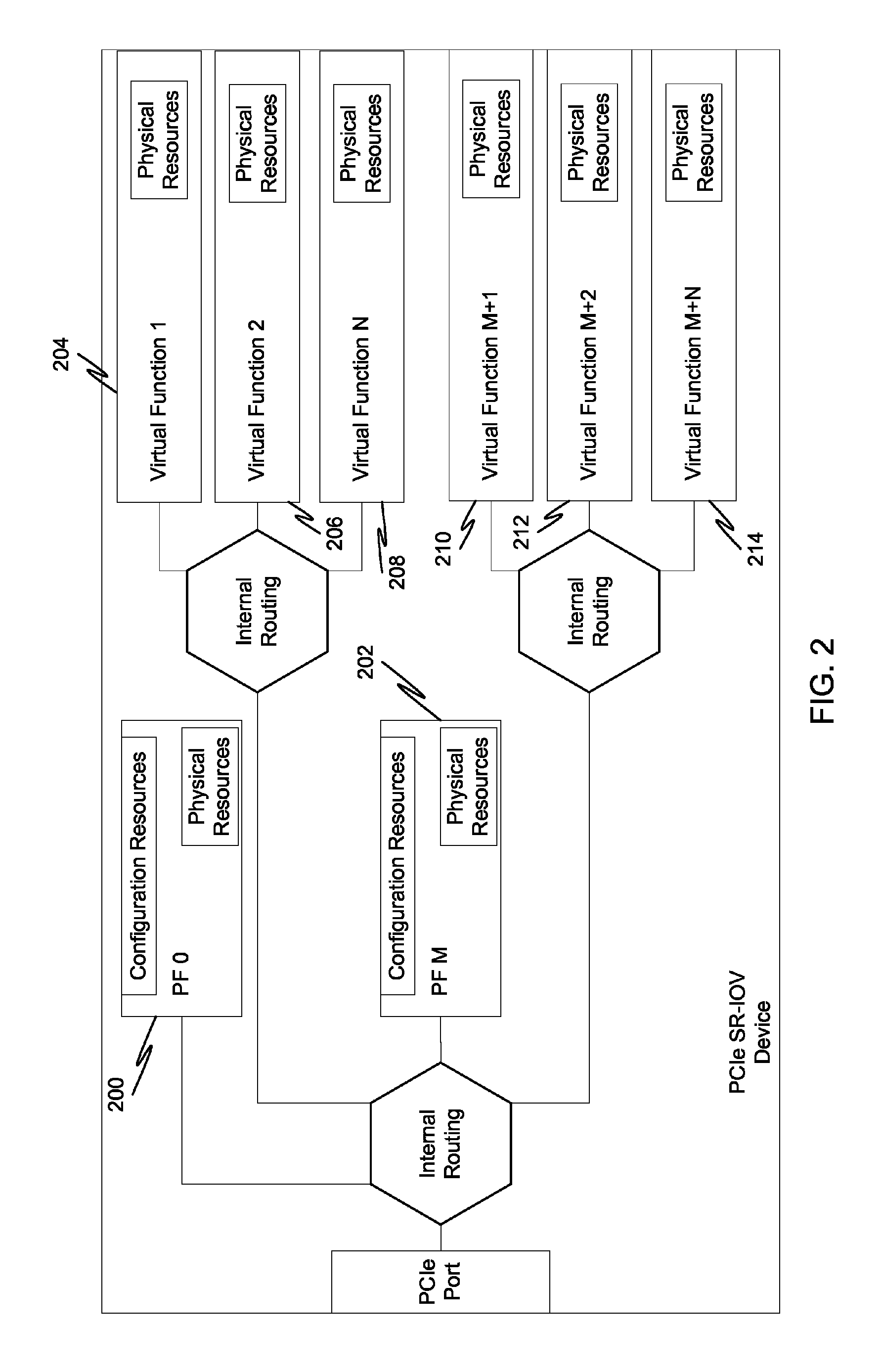

A method, computer program product, and distributed data processing system for directly sharing an I / O adapter that directly supports adapter virtualization and does not require an LPAR manager or other intermediary to be invoked on every I / O transaction is provided. The present invention also provides a method, computer program product, and distributed data processing system for directly creating and initializing a virtual adapter and associated resources on a physical adapter, such as a PCI, PCI-X, or PCI-E adapter. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided for directly creating and initializing a virtual adapter and associated resources within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter. Additionally, each virtual adapter has an associated set of host side resources, such as memory addresses and interrupt levels, and adapter side resources, such as adapter memory addresses and processing queues, and each virtual adapter is isolated from accessing the host side resources and adapter resources that belong to another virtual or physical adapter.

Owner:IBM CORP

Association of host translations that are associated to an access control level on a PCI bridge that supports virtualization

InactiveUS20060195675A1Memory adressing/allocation/relocationInput/output processes for data processingTrusted componentsPCI Express

A method, computer program product, and distributed data processing system that allows a system image within a multiple system image virtual server to directly expose a portion, or all, of its associated system memory to a shared PCI adapter without having to go through a trusted component, such as a Hypervisor. Specifically, the present invention is directed to a mechanism for sharing conventional PCI I / O adapters, PCI-X I / O Adapters, PCI-Express I / O Adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications.

Owner:IBM CORP

Association of host translations that are associated to an access control level on a PCI bridge that supports virtualization

InactiveUS7398337B2Memory adressing/allocation/relocationInput/output processes for data processingTrusted componentsPCI Express

A method, computer program product, and distributed data processing system that allows a system image within a multiple system image virtual server to directly expose a portion, or all, of its associated system memory to a shared PCI adapter without having to go through a trusted component, such as a Hypervisor. Specifically, the present invention is directed to a mechanism for sharing conventional PCI I / O adapters, PCI-X I / O Adapters, PCI-Express I / O Adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications.

Owner:INT BUSINESS MASCH CORP

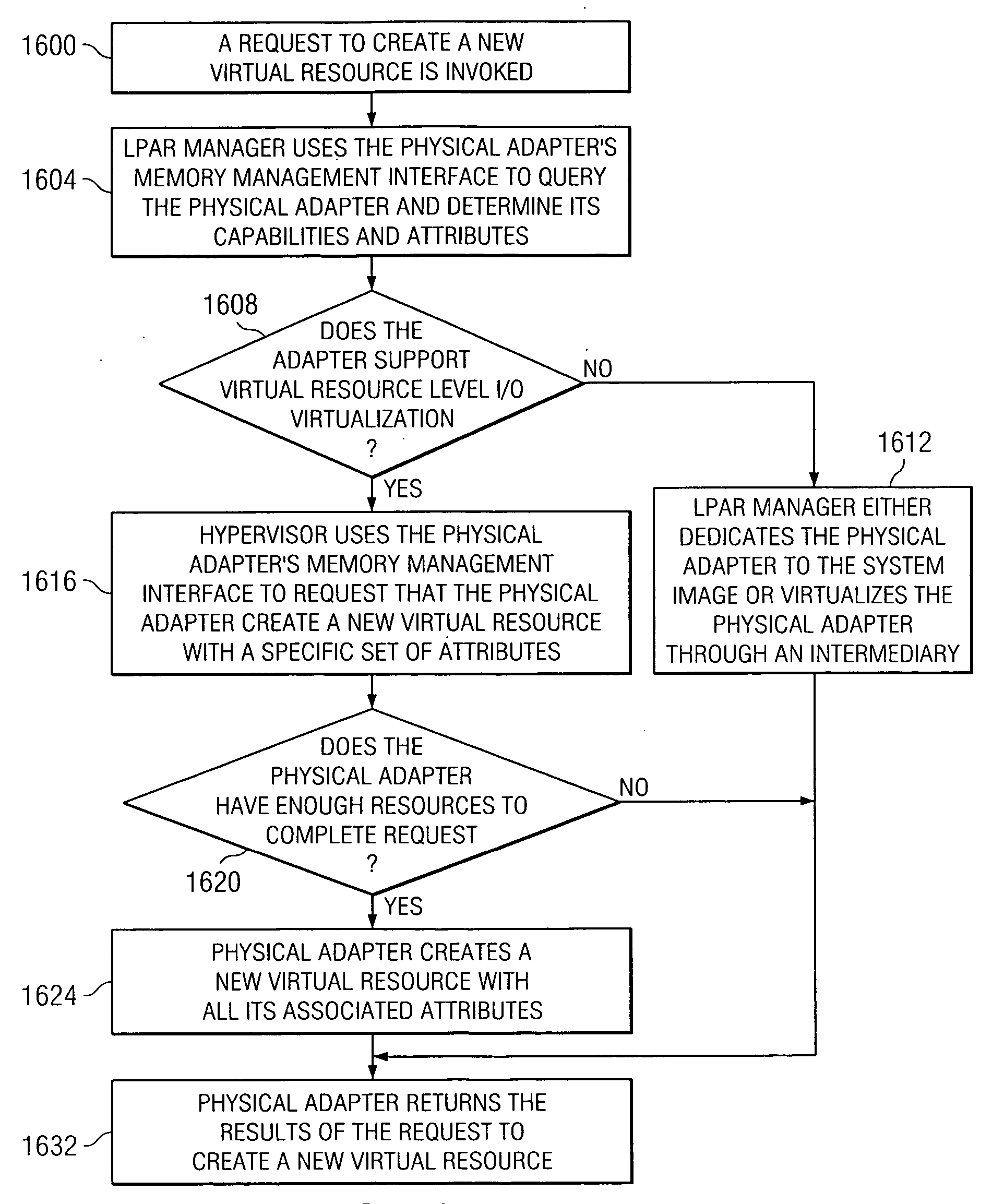

System and method for virtual resource initialization on a physical adapter that supports virtual resources

ActiveUS20060195620A1Memory adressing/allocation/relocationComputer security arrangementsResource virtualizationTerm memory

A method, computer program product, and distributed data processing system for directly sharing a network stack offload I / O adapter that directly supports resource virtualization and does not require a LPAR manager or other intermediary to be invoked on every I / O transaction is provided. The present invention also provides a method, computer program product, and distributed data processing system for directly creating and initializing one or more virtual resources that reside within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter, and that are associated with a virtual host. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for host to adapter communications. A mechanism is provided for directly creating and initializing one or more virtual resources that reside within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter, and that are associated with a virtual host.

Owner:IBM CORP

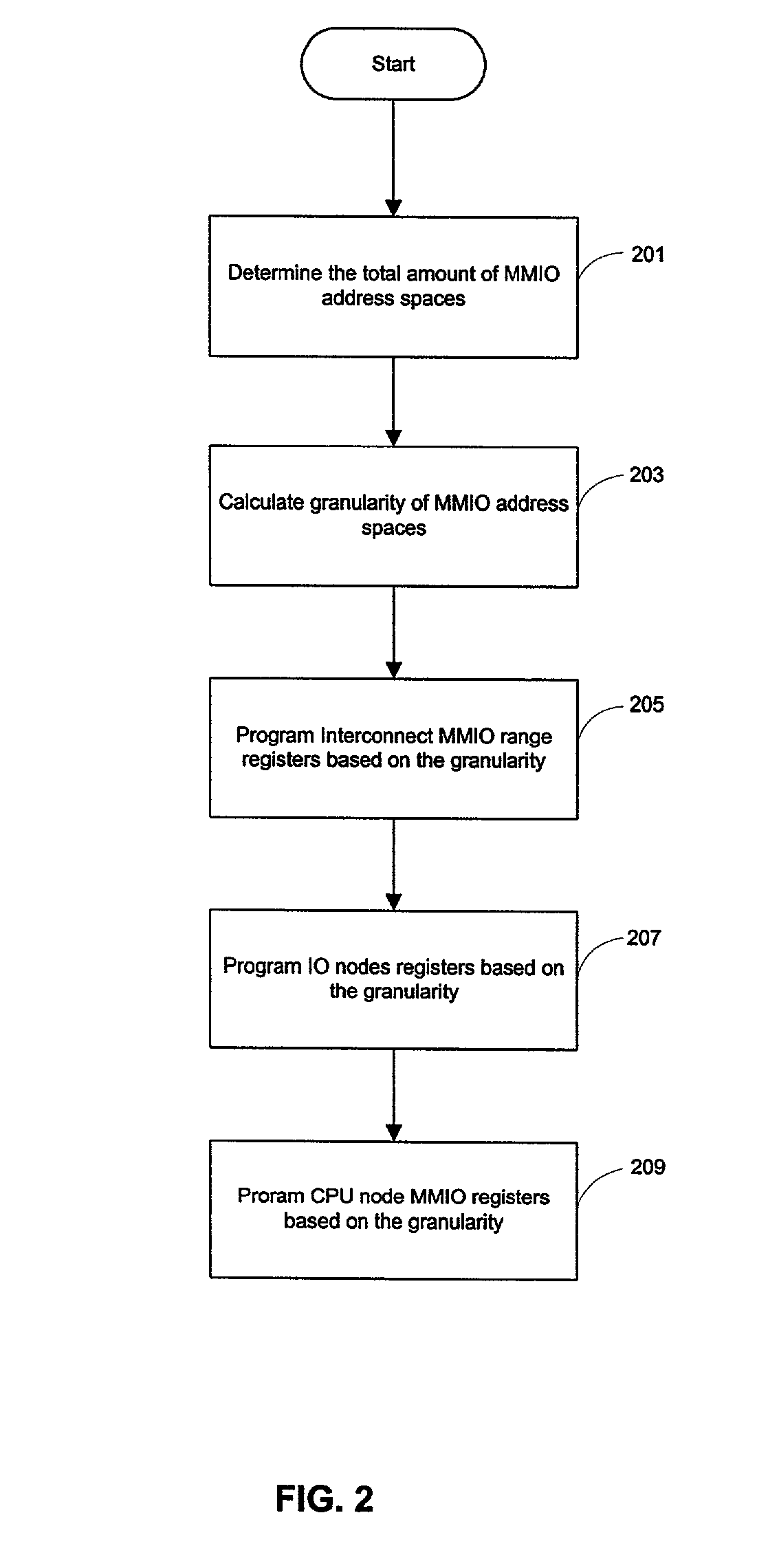

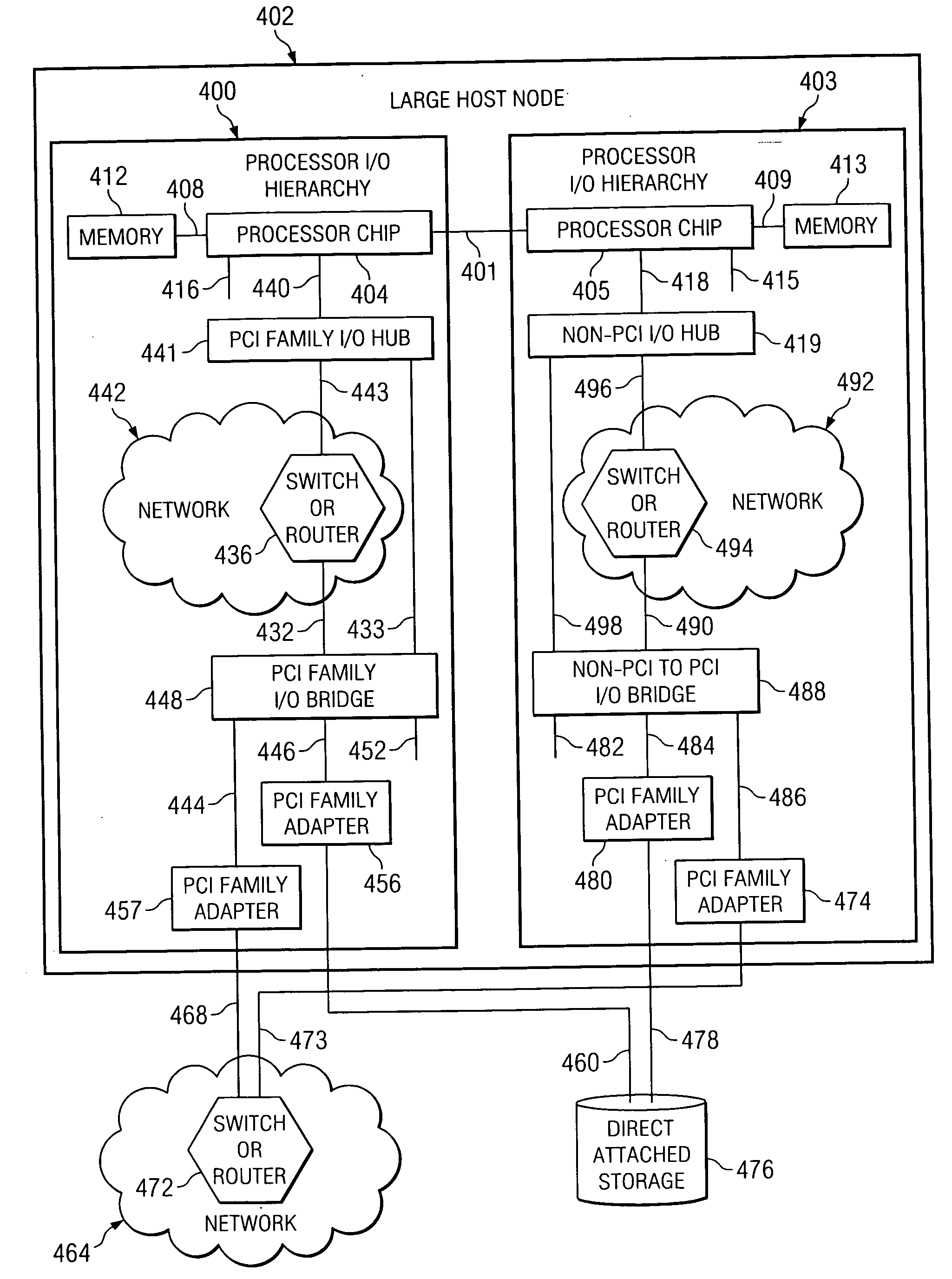

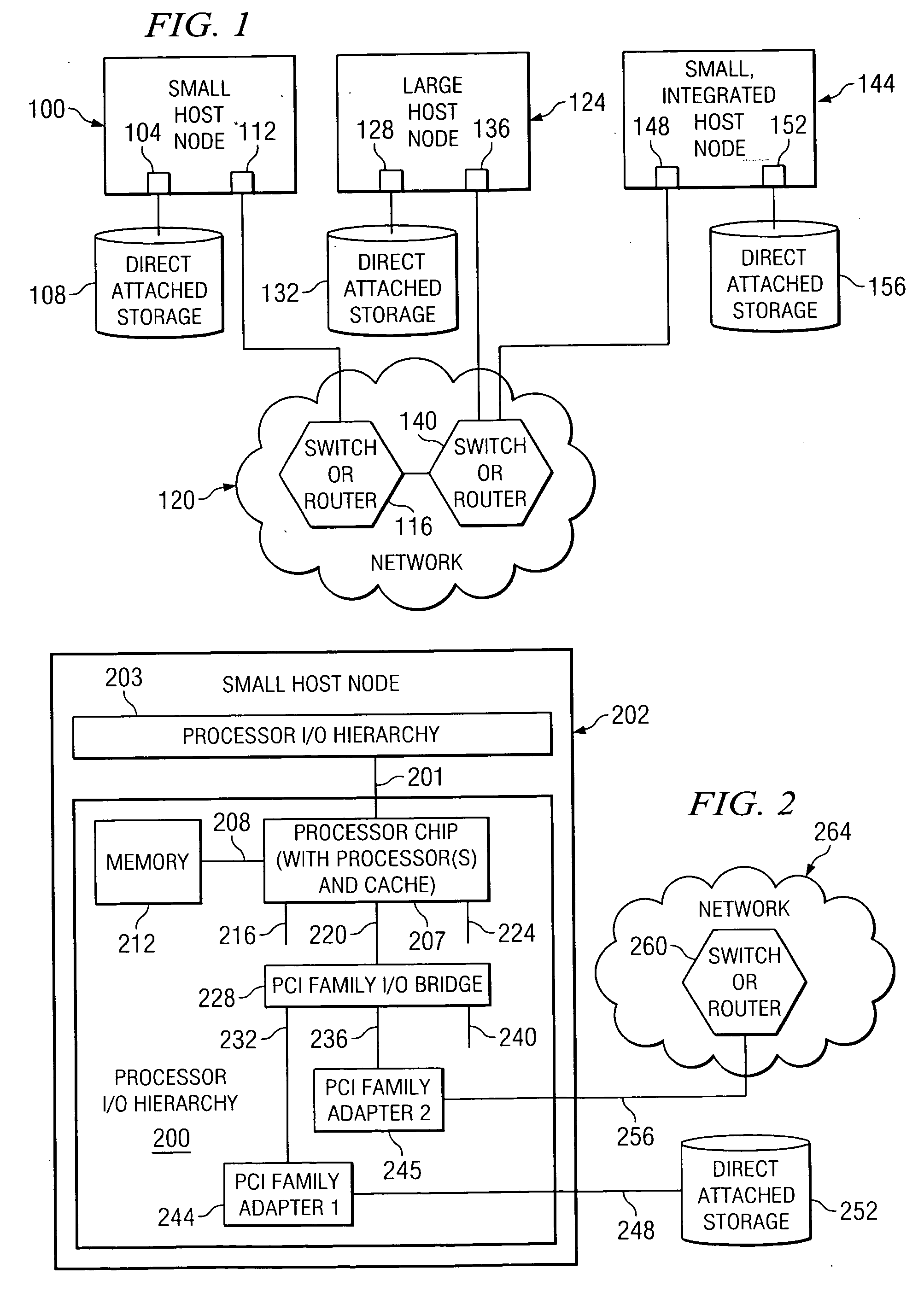

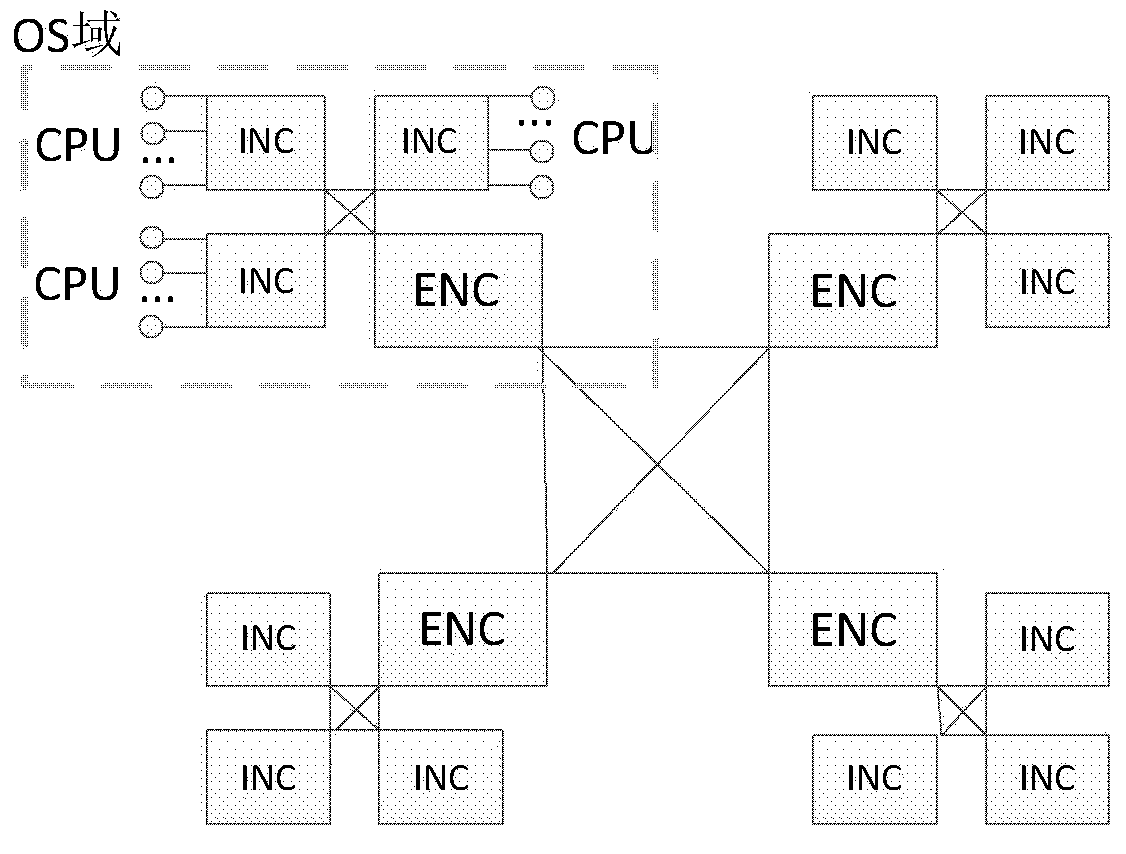

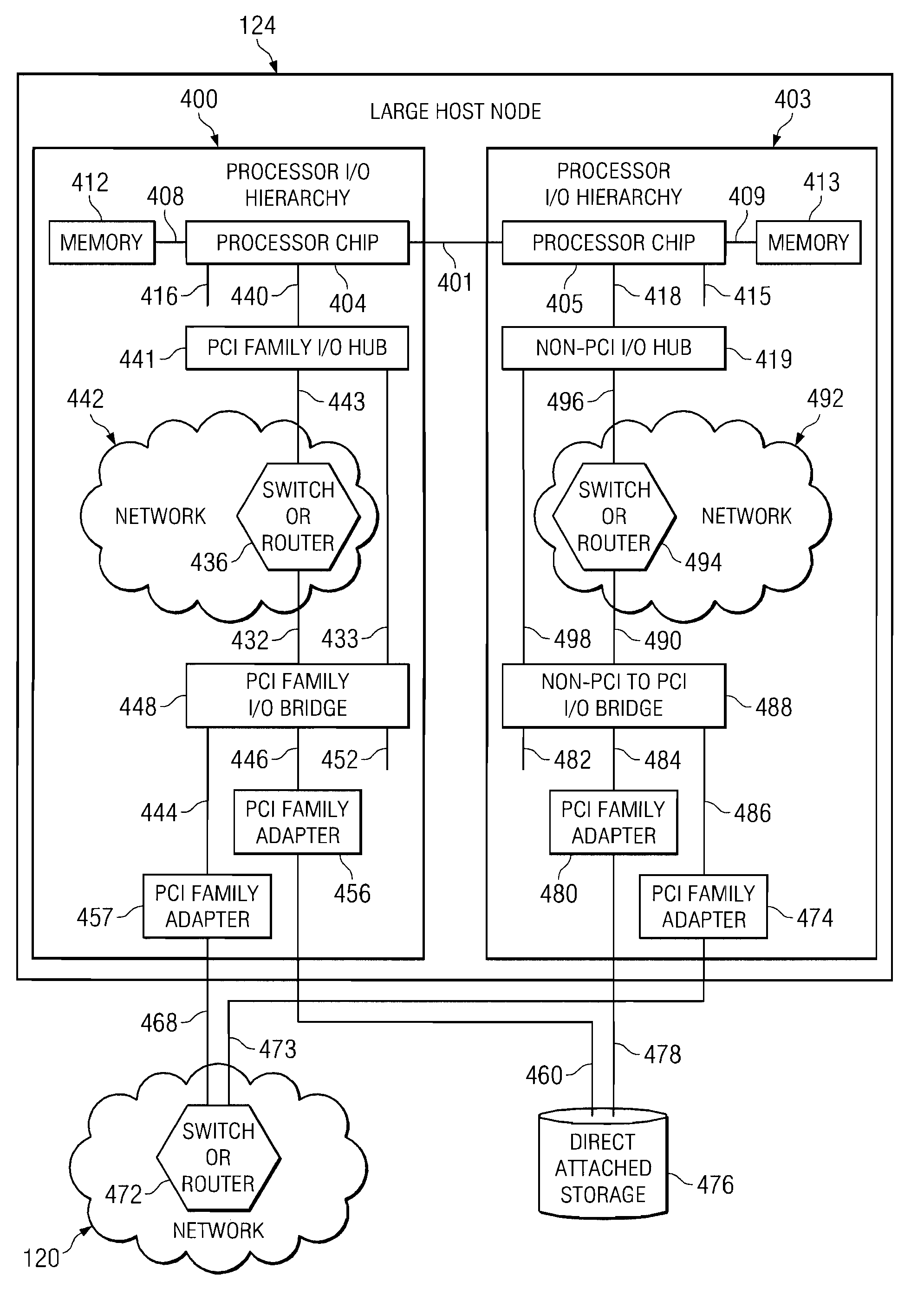

Dynamic determination of memory mapped input output range granularity for multi-node computer system

InactiveUS7213081B2Efficiently usMemory adressing/allocation/relocationDigital computer detailsGranularityProcessor register

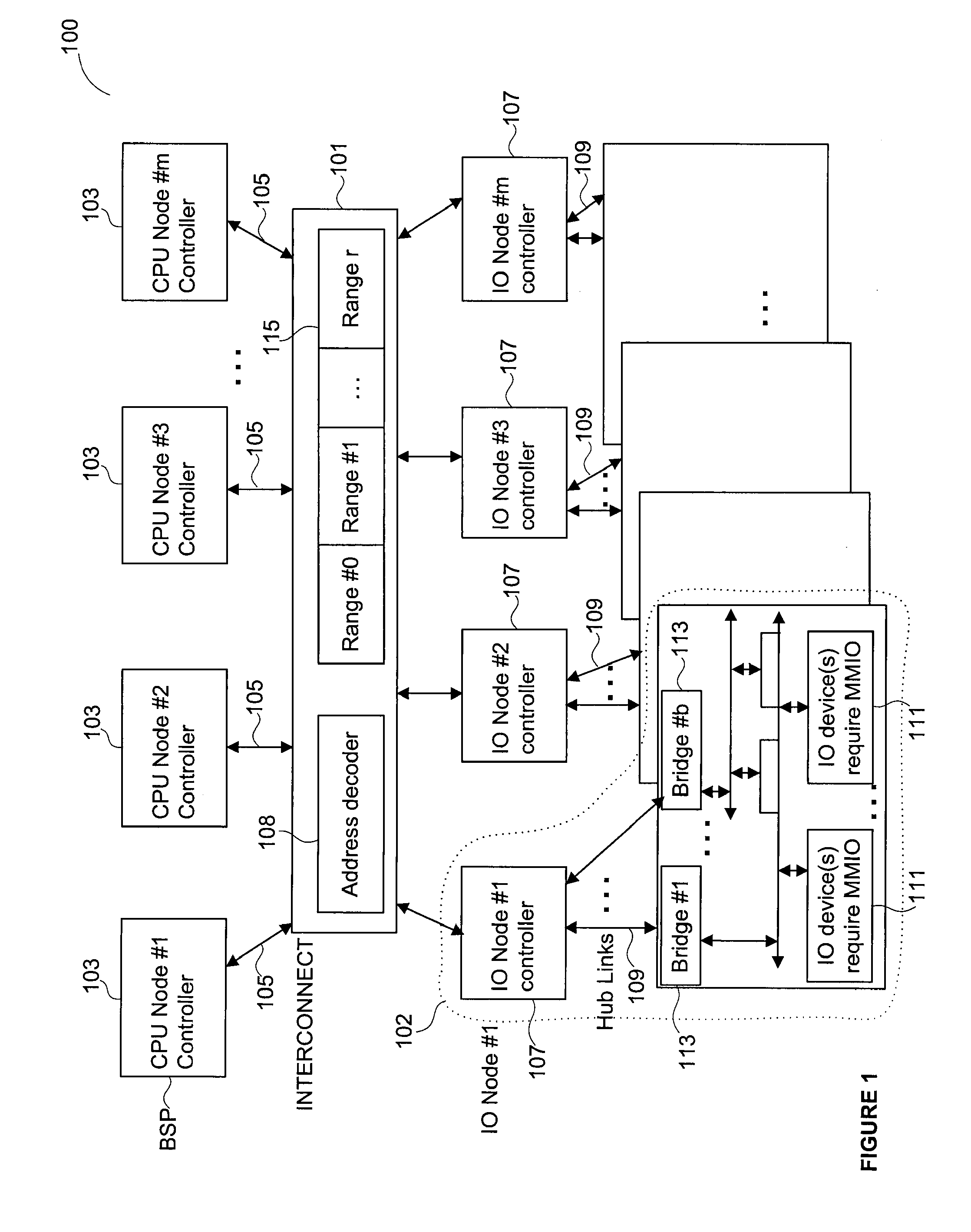

A method and system enables dynamic support of memory mapping devices in a multi-node computer system. One of central process unit (CPU) nodes determines a total amount of MMIO address spaces that are needed for all MMIO devices and generates an optimized granularity to support the total amount of MMIO address spaces. Based on the granularity, a CPU node controller configures MMIO range registers of the interconnect and other MMIO registers in IO nodes and CPU node controllers to support dynamic changes of MMIO address space requirements of the system.

Owner:FUJITSU LTD

System and method for destroying virtual resources in a logically partitioned data processing system

InactiveUS20060195619A1Memory adressing/allocation/relocationMultiprogramming arrangementsTerm memoryPCI Express

A method, computer program product, and distributed data processing system for directly destroying one or more virtual resources that reside within a physical adapter and that are associated with a virtual host. Specifically, the present invention is directed to a mechanism for sharing conventional Peripheral Component Interconnect (PCI) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for host to adapter communications.

Owner:IBM CORP

Multi-root sharing of single-root input/output virtualization

In a first embodiment of the present invention, a method for multi-root sharing of a plurality of single root input / output virtualization (SR-IOV) endpoints is provided, the method comprising: CSR redirection to a management processor which either acts as a proxy to execute the CSR request on behalf of the host or filters it and performs an alternate action, downstream routing of memory mapped I / O request packets through the switch in the host's address space and address translation with VF BAR granularity, upstream routing of requests originated by I / O devices by table lookup indexed by Requester ID, and requester ID translation using a fixed local-global RID offset.

Owner:AVAGO TECH INT SALES PTE LTD

Native virtualization on a partially trusted adapter using PCI host memory mapped input/output memory address for identification

InactiveUS20060195623A1Internal/peripheral component protectionProgram controlMemory addressTerm memory

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to associate its resources to a system image and isolate them from other system images, thereby providing I / O virtualization is provided. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to associate its resources to a system image and isolate them from other system images thereby providing I / O virtualization.

Owner:IBM CORP

Method for virtual resource initialization on a physical adapter that supports virtual resources

ActiveUS7546386B2Memory adressing/allocation/relocationComputer security arrangementsData processing systemResource virtualization

A method for directly sharing a network stack offload I / O adapter that directly supports resource virtualization and does not require a LPAR manager or other intermediary to be invoked on every I / O transaction is provided. The present invention also provides a method, computer program product, and distributed data processing system for directly creating and initializing one or more virtual resources that reside within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter, and that are associated with a virtual host. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for host to adapter communications. A mechanism is provided for directly creating and initializing one or more virtual resources that reside within a physical adapter, such as a PCI, PCI-X, or PCI-E adapter, and that are associated with a virtual host.

Owner:IBM CORP

Method and system for fully trusted adapter validation of addresses referenced in a virtual host transfer request

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to validate that a direct memory access address referenced by an incoming I / O transaction that was initiated through a memory mapped I / O operation are associated with a virtual adapter or virtual resource that is referenced by the incoming memory mapped I / O operation is provided. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O Adapters, PCI-Express I / O Adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A single physical I / O adapter validates that one or more direct memory access addresses referenced by an incoming I / O transaction initiated through a memory mapped I / O operation are associated with a virtual adapter or virtual resource that is referenced by the incoming memory mapped I / O operation.

Owner:IBM CORP

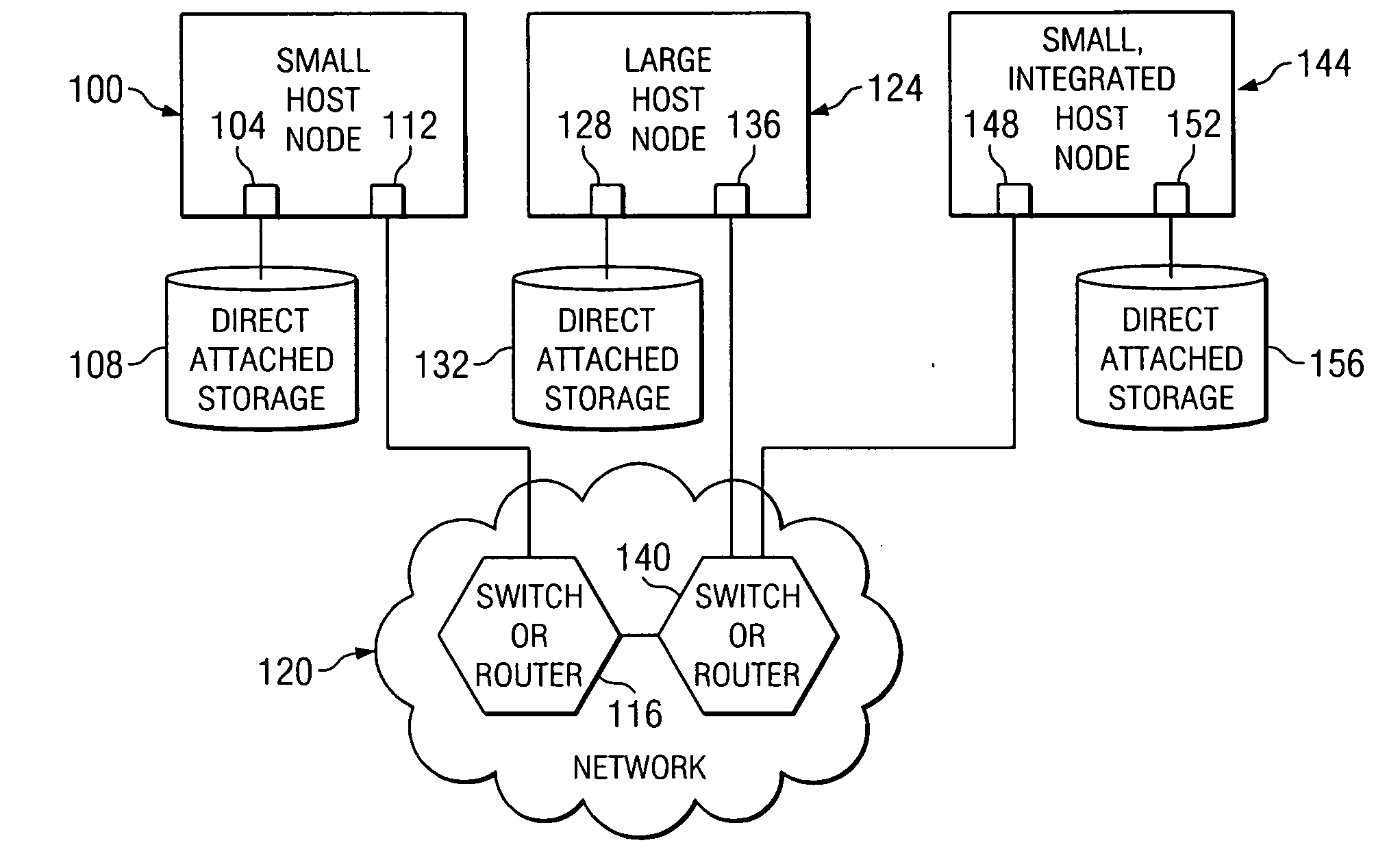

Memory space management and mapping for memory area network

A mechanism for simultaneous multiple host access to shared centralized memory space via a virtualization protocol utilizing a network transport. The invention combines local memory interfacing with the handling of multiple hosts implementing virtualized memory-mapped I / O systems, such that the memory becomes a global resource. The end result is a widely distributed memory-mapped computer cluster, sharing a 2̂64 byte memory space.

Owner:NUON

RDMA (Remote Direct Memory Access) communication method between non-tightly-coupled systems of sharing system address space

ActiveCN104202391AFast data transferData transmission is stableTransmissionDirect memory accessRemote direct memory access

The invention provides an RDMA (Remote Direct Memory Access) communication method between non-tightly-coupled systems of a sharing system address space. A destination node is remotely accessed by a source node through a direct memory access instruction and a remote direct memory access RDMA connection is established between the source node and the destination node; data transmission is executed between the source node and the destination node after the RDMA connection is established; the RDMA connection is released after the data transmission is achieved, wherein shared memory resources and I / O resources of the remote destination node are mapped into a local MMIO (Memory-Mapped I / O) address space of the source node. According to the RDMA communication method between the non-tightly-coupled systems of the sharing system address space, the rapid stable data transmission between non-tightly-coupled nodes can be implemented.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

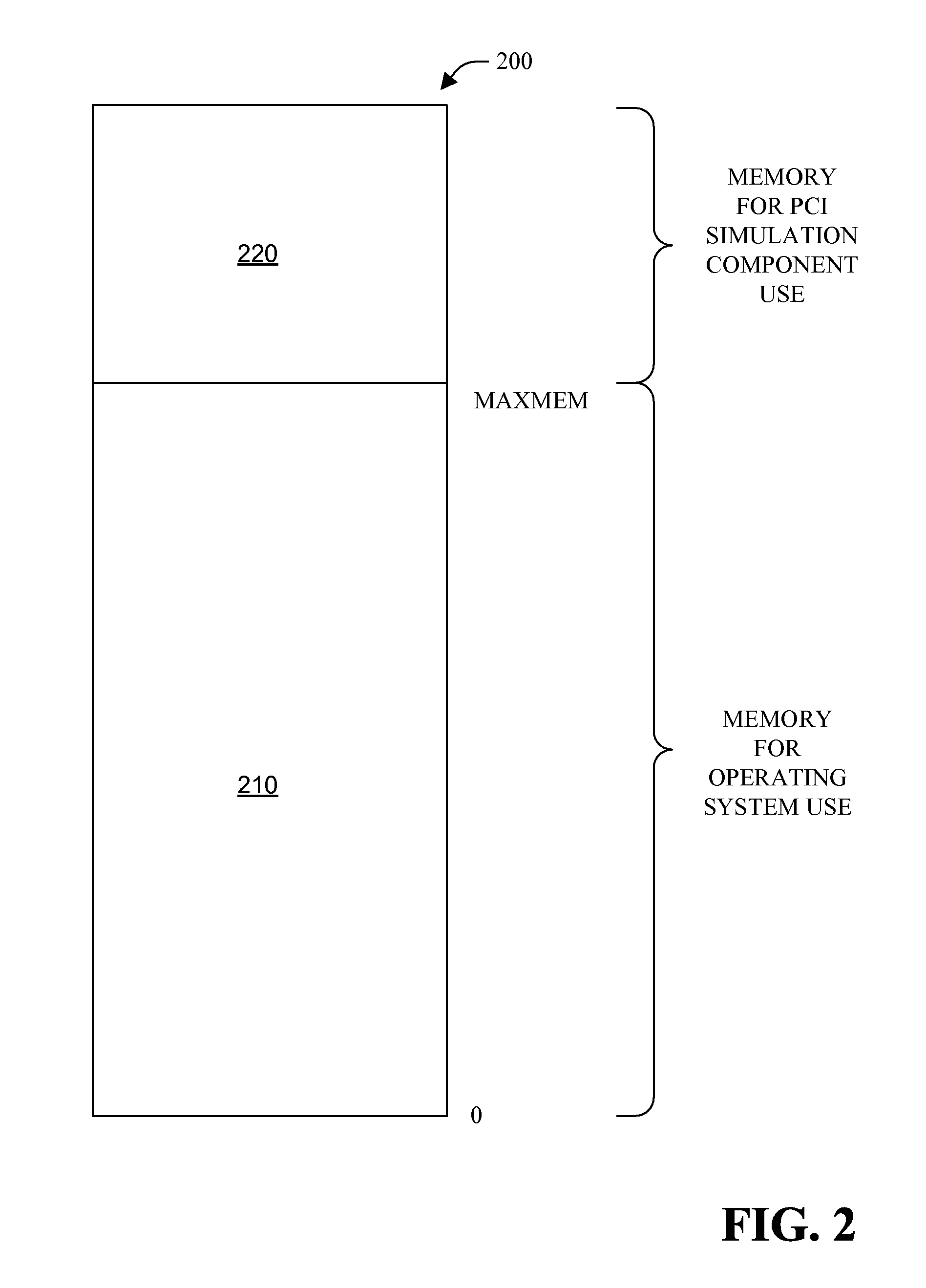

Simulation of a PCI device's memory-mapped I/O registers

InactiveUS20060241930A1High simulationReduce difficultyMemory architecture accessing/allocationMemory adressing/allocation/relocationOperational systemParallel computing

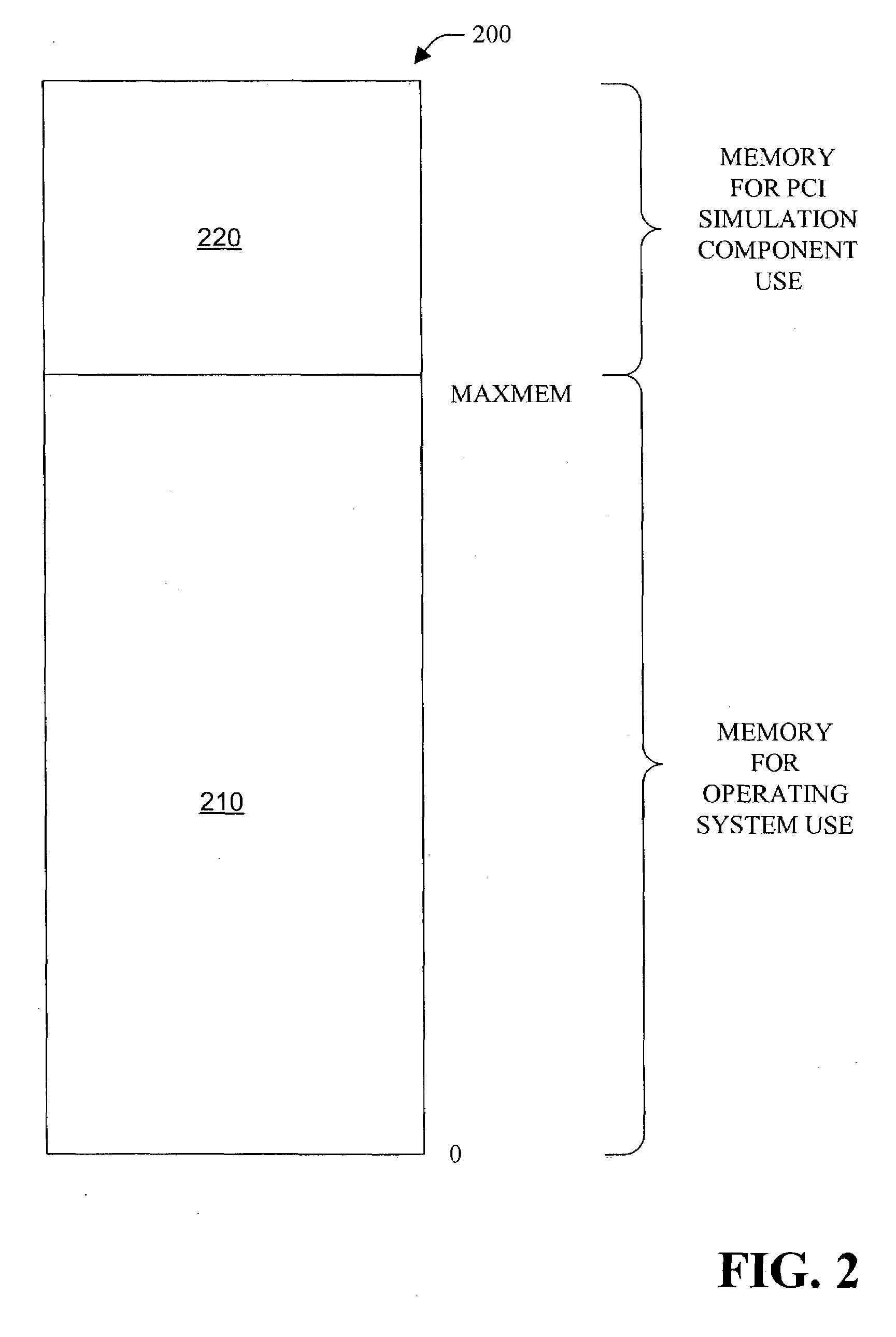

A component, system and method for simulation of a PCI device's memory-mapped I / O register(s) are provided. The PCI simulation component has an initialization component, a configuration space simulator and a memory-mapped I / O space simulator. The initialization component can claim an amount of memory by modifying the amount of memory that an operating system has available to it. The initialization component further identifies to the operating system that at least some of the claimed memory resides on a PCI bus. The configuration space simulator causes the operating system to accept that the simulated PCI device is present in the system. The memory-mapped I / O space simulator simulates behavior of a simulated PCI device and can comprise can comprise a thread that monitors the simulated memory-mapped I / O registers for a change in order to simulate behavior of the simulated PCI device. Additionally and / or alternatively, the memory-mapped I / O space simulator can comprise a thread that changes at least one of the simulated memory mapped I / O registers in order to simulate behavior of the simulated PCI device.

Owner:MICROSOFT TECH LICENSING LLC

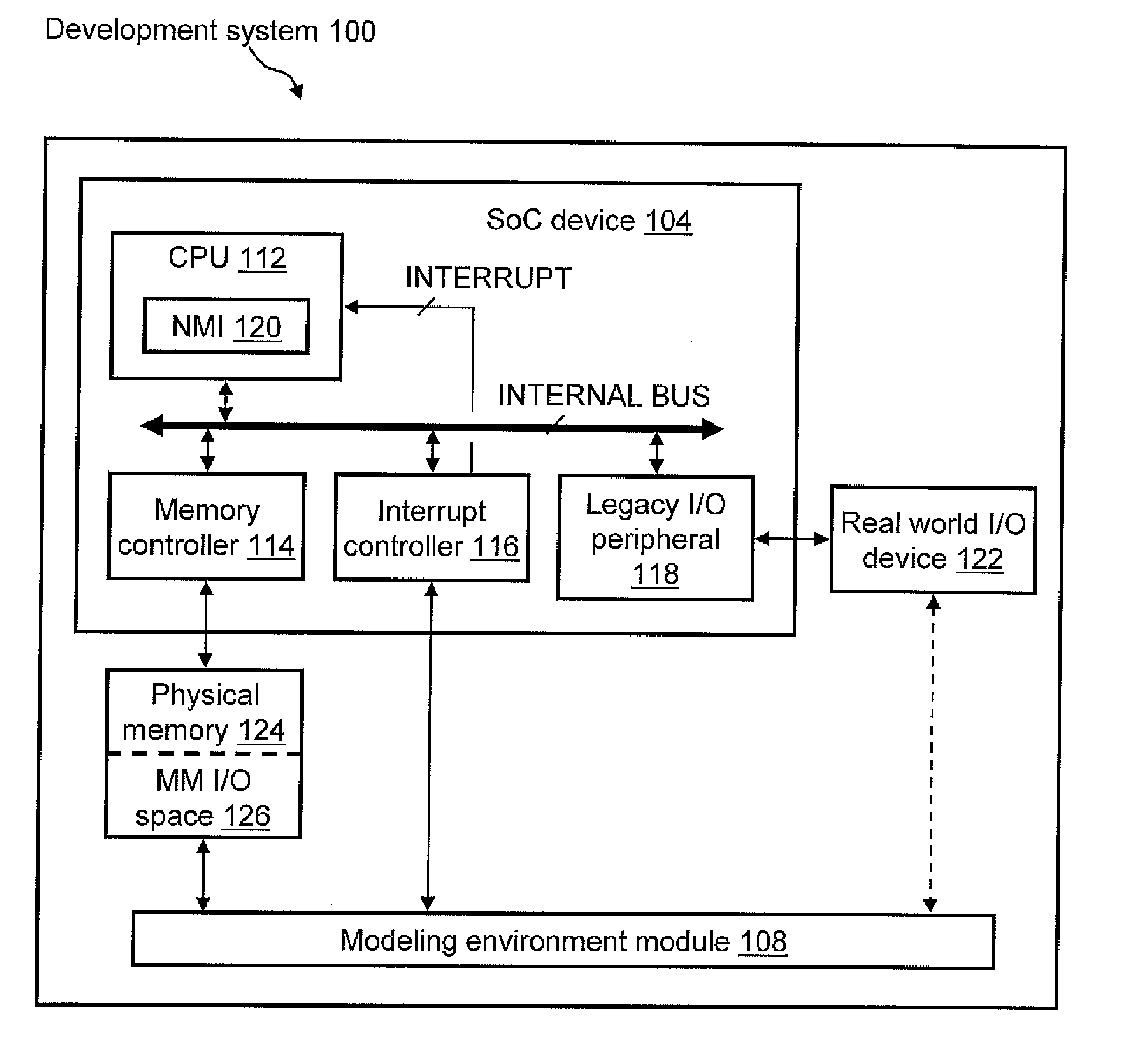

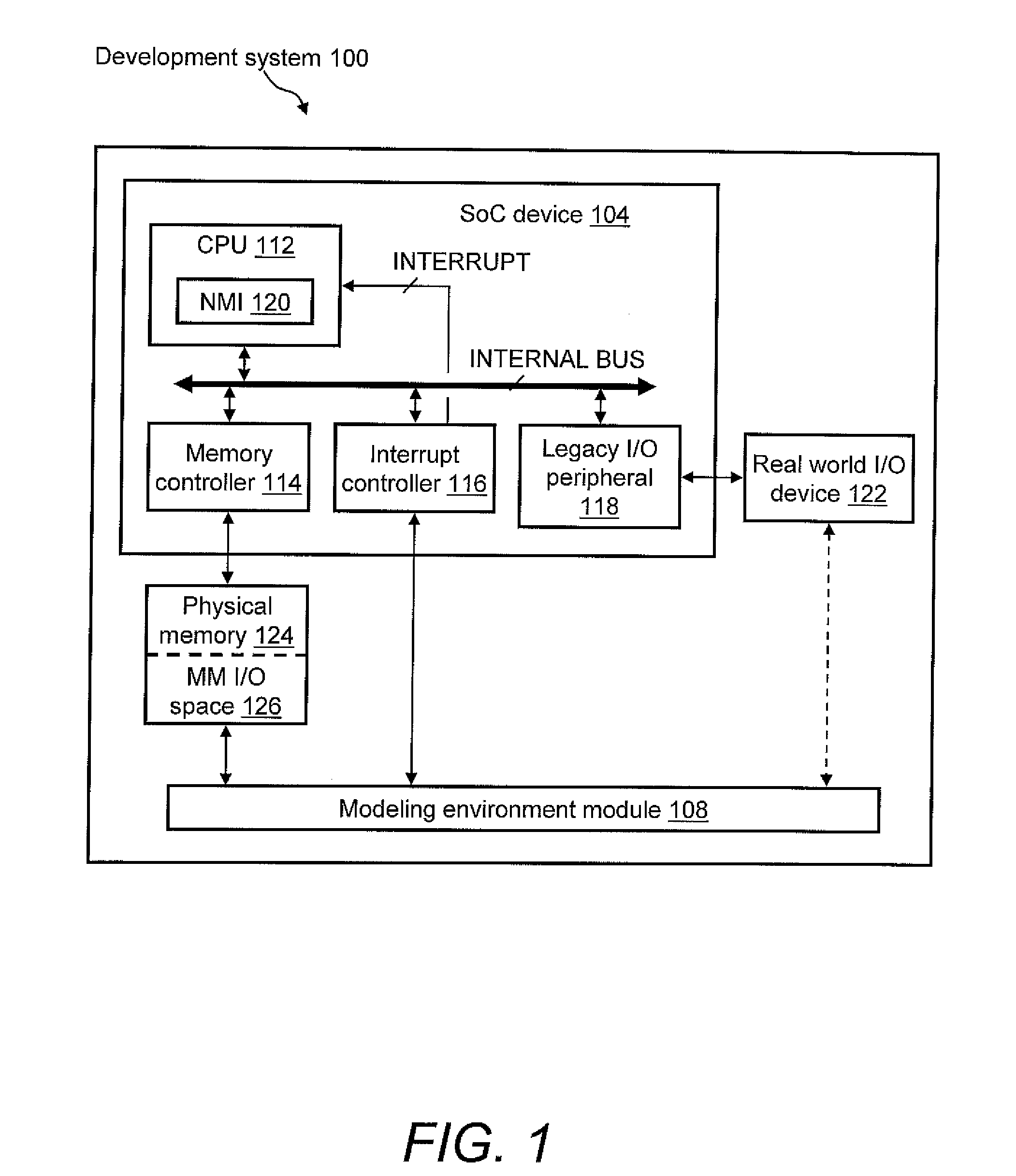

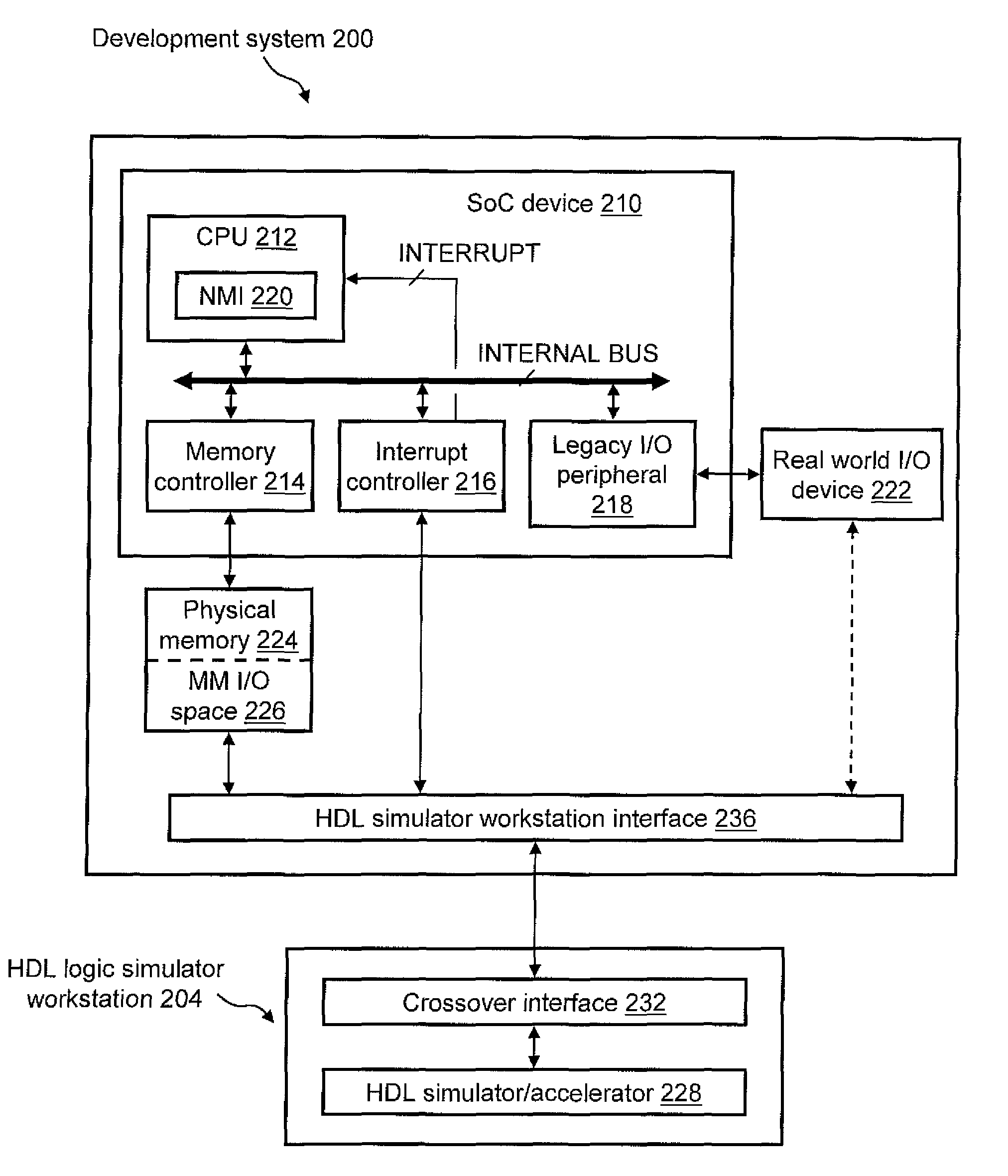

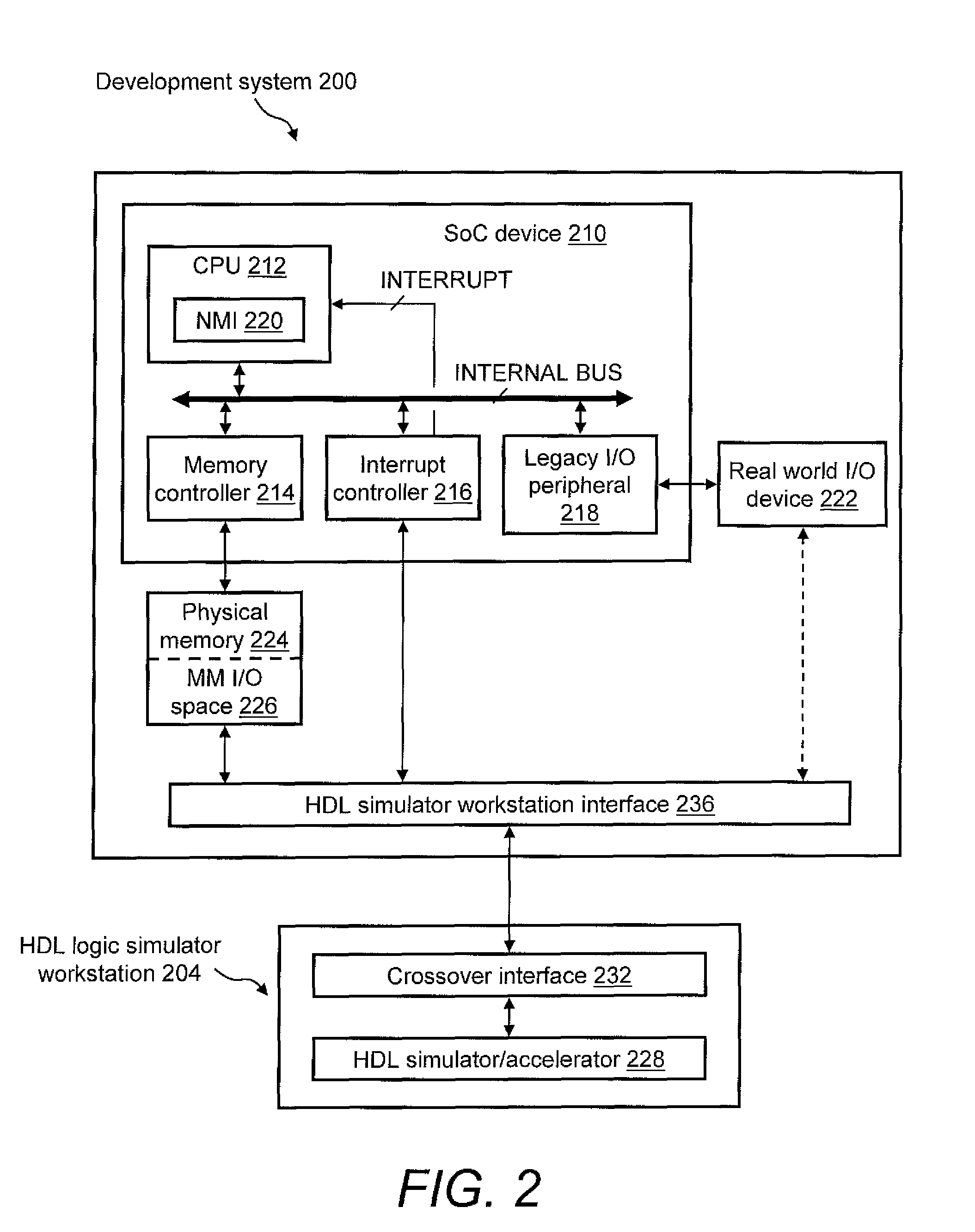

System and method for developing embedded software in-situ

ActiveUS20080184193A1Analogue computers for electric apparatusComputer aided designEmbedded softwareModel Number

A development system for developing new peripheral software code for new peripheral hardware that will be used in a new integrated system. The development system includes a legacy, or preexisting, integrated system substantially the same as the new integrated system. A model of the new peripheral hardware is made. Each I / O register of the model is mapped into memory-mapped I / O space. Development code corresponding to the new peripheral software code is executed on the preexisting hardware so as to interact with the model via the memory-mapped I / O space. In one embodiment, the model is executed as an embedded model on the preexisting integrated system. In another embodiment, the model is executed as a non-embedded model on a hardware descriptive language simulator.

Owner:GLOBALFOUNDRIES US INC

Apparatus and method for combining writes to I/O

InactiveUS7206865B2Input/output processes for data processingData conversionSpatial correlationData store

An apparatus and method for outbound I / O write-combining are described. In one embodiment the method includes the detection of a write transaction request directed to an I / O device. Once detected, it is determined whether an address associated with the detected write transaction falls within a predetermined write-combinable range of the memory mapped I / O space assigned to the I / O device. When the transaction address falls within a write-combinable range, data associated with the detected write transaction is stored within a buffer corresponding to the transaction address. Accordingly, one embodiment of the present invention provides write-combining for data written to an I / O port associated with a memory mapped I / O address space.

Owner:MICRON TECH INC

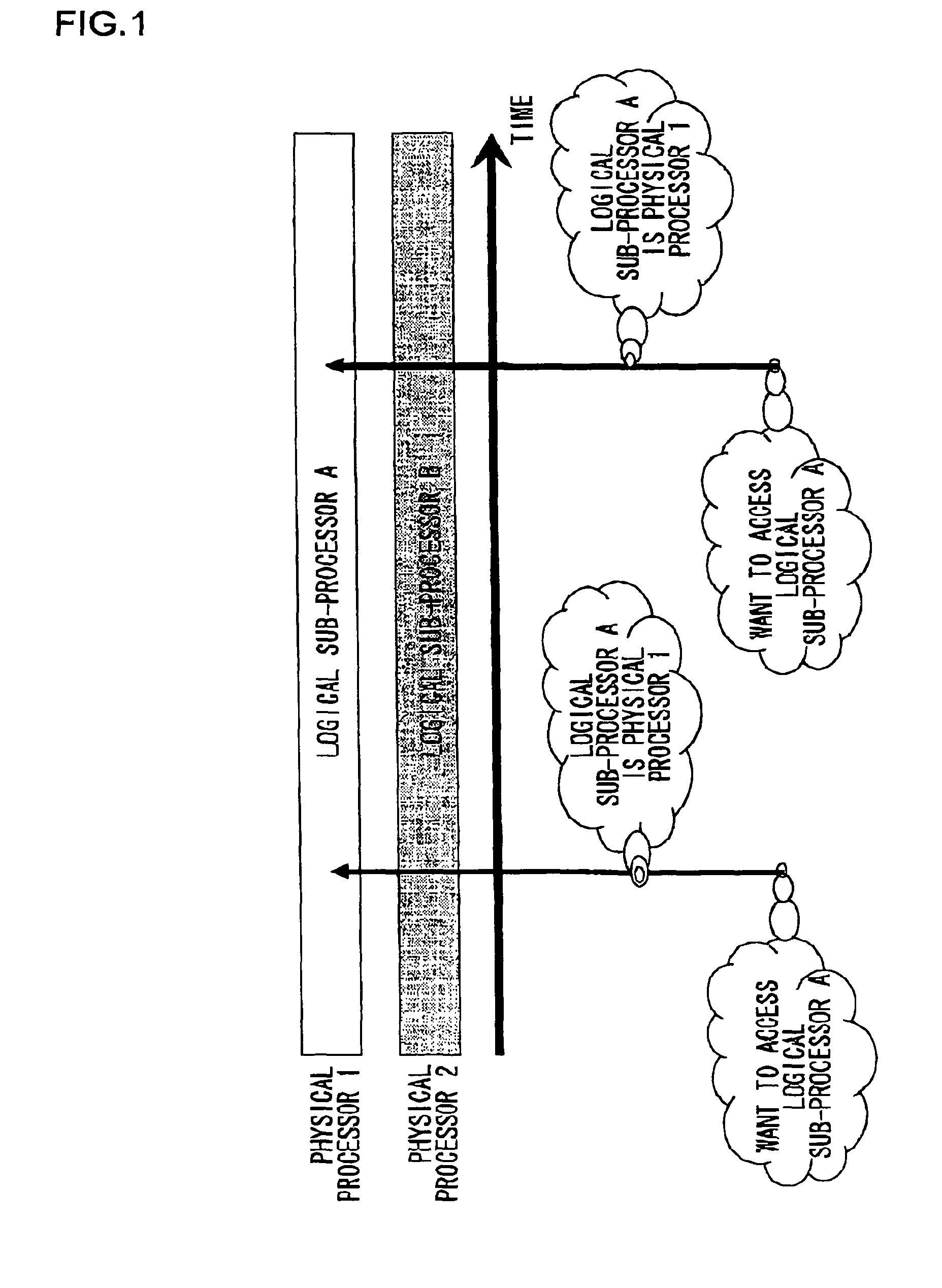

Accessing copy information of MMIO register by guest OS in both active and inactive state of a designated logical processor corresponding to the guest OS

ActiveUS8151275B2Improve accessibilityEfficient data processingSpecific access rightsMemory systemsComputer hardwarePhysics processing unit

A method and an apparatus for storing a copy of memory-mapped I / O (MMIO) register are provided for enhancing data processing efficiency. In a structure in which data processing is executed by associating a plurality of logical processors with a physical processor by timing sharing, a host OS stores copy information, namely, shadow, of the MMIO register corresponding to a logical processor in memory both in an active state where a physical processor is allocated to a logical processor corresponding to a guest OS and in an inactive state where no physical processor is allocated to a logical processor. This structure enables a guest OS to gain faster access to the MMIO register through the shadow by memory access, instead of a direct access to the MMIO register, so as to achieve efficient data processing.

Owner:SONY COMPUTER ENTERTAINMENT INC

Method and system for fully trusted adapter validation of addresses referenced in a virtual host transfer request

ActiveUS7475166B2Error preventionFrequency-division multiplex detailsData processing systemDirect memory access

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to validate that a direct memory access address referenced by an incoming I / O transaction that was initiated through a memory mapped I / O operation are associated with a virtual adapter or virtual resource that is referenced by the incoming memory mapped I / O operation is provided. Specifically, the present invention is directed to a mechanism for sharing conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O Adapters, PCI-Express I / O Adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A single physical I / O adapter validates that one or more direct memory access addresses referenced by an incoming I / O transaction initiated through a memory mapped I / O operation are associated with a virtual adapter or virtual resource that is referenced by the incoming memory mapped I / O operation.

Owner:IBM CORP

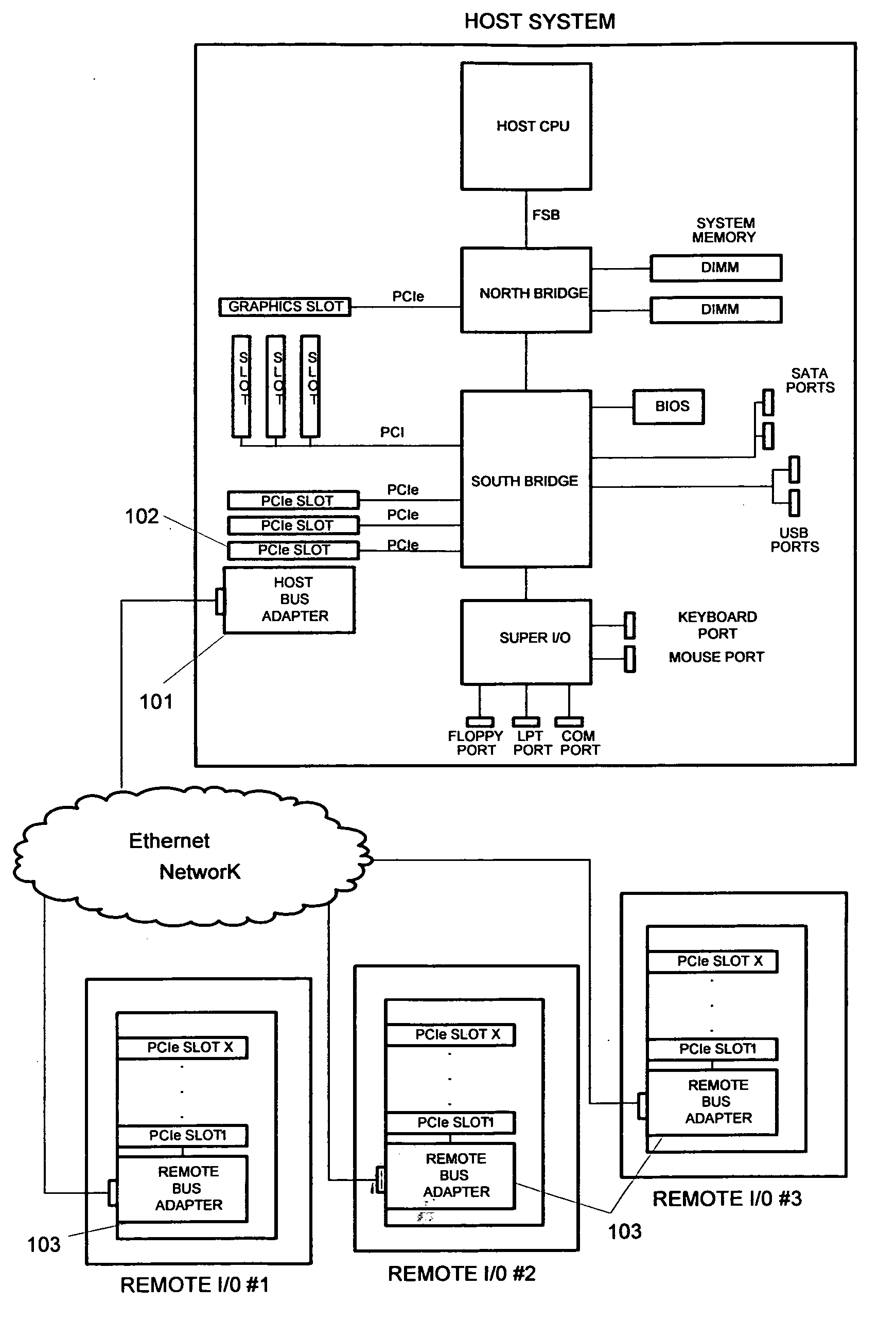

Host bus adapter with network protocol auto-detection and selection capability

InactiveUS20100161838A1Good choiceIntuitive experienceTransmissionInput/output processes for data processingNetworking protocolResource virtualization

A mechanism for detecting, associating, establishing, and executing an optimal virtualization protocol between a host and a given virtualized device. An Intelligent Host Bus Adapter (IHBA) is claimed that combines storage virtualization with I / O system resource virtualization and incorporates both Dynamic Storage Configuration Protocol (DSCP) and Dynamic I / O Configuration Protocol (DICP) on a common CPU offload platform. The invention enables a comprehensive virtualization solution that includes automatic detection and selection of optimal storage virtualization as well as memory-mapped I / O virtualization protocols on a per resource basis.

Owner:DANIEL DAVID A

Simulation of a PCI device's memory-mapped I/O registers

InactiveUS7155379B2High simulationReduce difficultyMemory architecture accessing/allocationMemory adressing/allocation/relocationOperational systemParallel computing

A component, system and method for simulation of a PCI device's memory-mapped I / O register(s) are provided. The PCI simulation component has an initialization component, a configuration space simulator and a memory-mapped I / O space simulator. The initialization component can claim an amount of memory by modifying the amount of memory that an operating system has available to it. The initialization component further identifies to the operating system that at least some of the claimed memory resides on a PCI bus. The configuration space simulator causes the operating system to accept that the simulated PCI device is present in the system. The memory-mapped I / O space simulator simulates device and can comprise can comprise a thread that monitors the simulated memory-mapped I / O registers for a change in order to simulate behavior of the simulated PCI device. Additionally and / or alternatively, the memory-mapped I / O space simulator can comprise a thread that changes at least one of the simulated memory mapped I / O registers in order to simulate behavior of the simulated PCI device.

Owner:MICROSOFT TECH LICENSING LLC

System, method, and computer program product for a fully trusted adapter validation of incoming memory mapped I/O operations on a physical adapter that supports virtual adapters or virtual resources

InactiveUS7386637B2Memory adressing/allocation/relocationInput/output processes for data processingData processing systemVirtual hosting

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter to validate that a memory mapped I / O address referenced by an incoming I / O operation is associated with a virtual host that initiated the incoming memory mapped I / O operation is provided. Specifically, the present invention is directed to a mechanism for sharing a PCI family I / O adapter and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided that allows a single physical I / O adapter to validate that a memory mapped I / O address referenced by an incoming memory mapped I / O operation used to initiate an I / O transaction is associated with a virtual host that initiated the incoming memory mapped I / O operation.

Owner:IBM CORP

Method and device for starting basic input/output system (BIOS)

ActiveCN105867945ADoes not affect free spaceMemory architecture accessing/allocationDigital computer detailsBIOSMemory-mapped I/O

The embodiment of the invention provides a method and device for starting a basic input / output system (BIOS) and relates to the field of computers. On the premise of large-scale number extension of central processing units (CPUs) contained by a cache coherent non-uniform memory access (CC-NUMA) system, the BIOS starting does not affect occupation capacity of a memory-mapped I / O (MMIO) space and an available memory space below a first address of a global access address of the system. According to the concrete scheme, by distribution of local MMCFGs in a space of a node below a first address of a local access address of the node in a first access mode, memory initialization is performed; when memory unified addressing of the system is performed, the positions of addresses of MMCFG spaces of the node in the global access address of the system are moved, and are moved from the space below the first address to a space which is above the first address and can be accessed in a second access mode. The method and the device are used for BIOS starting.

Owner:HUAWEI TECH CO LTD

Method for destroying virtual resources in a logically partitioned data processing system

InactiveUS7543084B2Memory adressing/allocation/relocationMultiprogramming arrangementsData processing systemPCI Express

A method for directly destroying one or more virtual resources that reside within a physical adapter and that are associated with a virtual host. Specifically, the present invention is directed to a mechanism for sharing conventional Peripheral Component Interconnect (PCI) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for host to adapter communications.

Owner:INT BUSINESS MASCH CORP

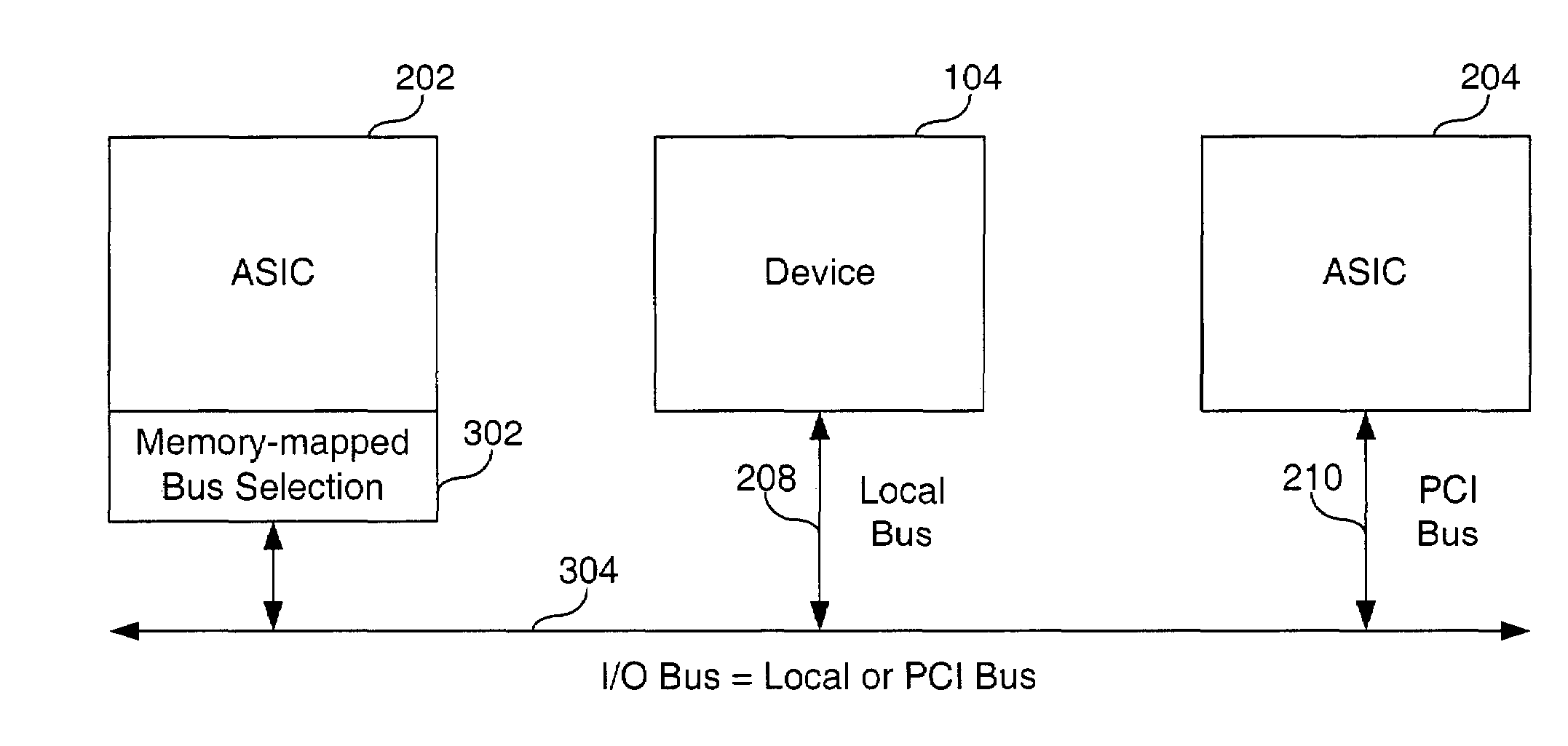

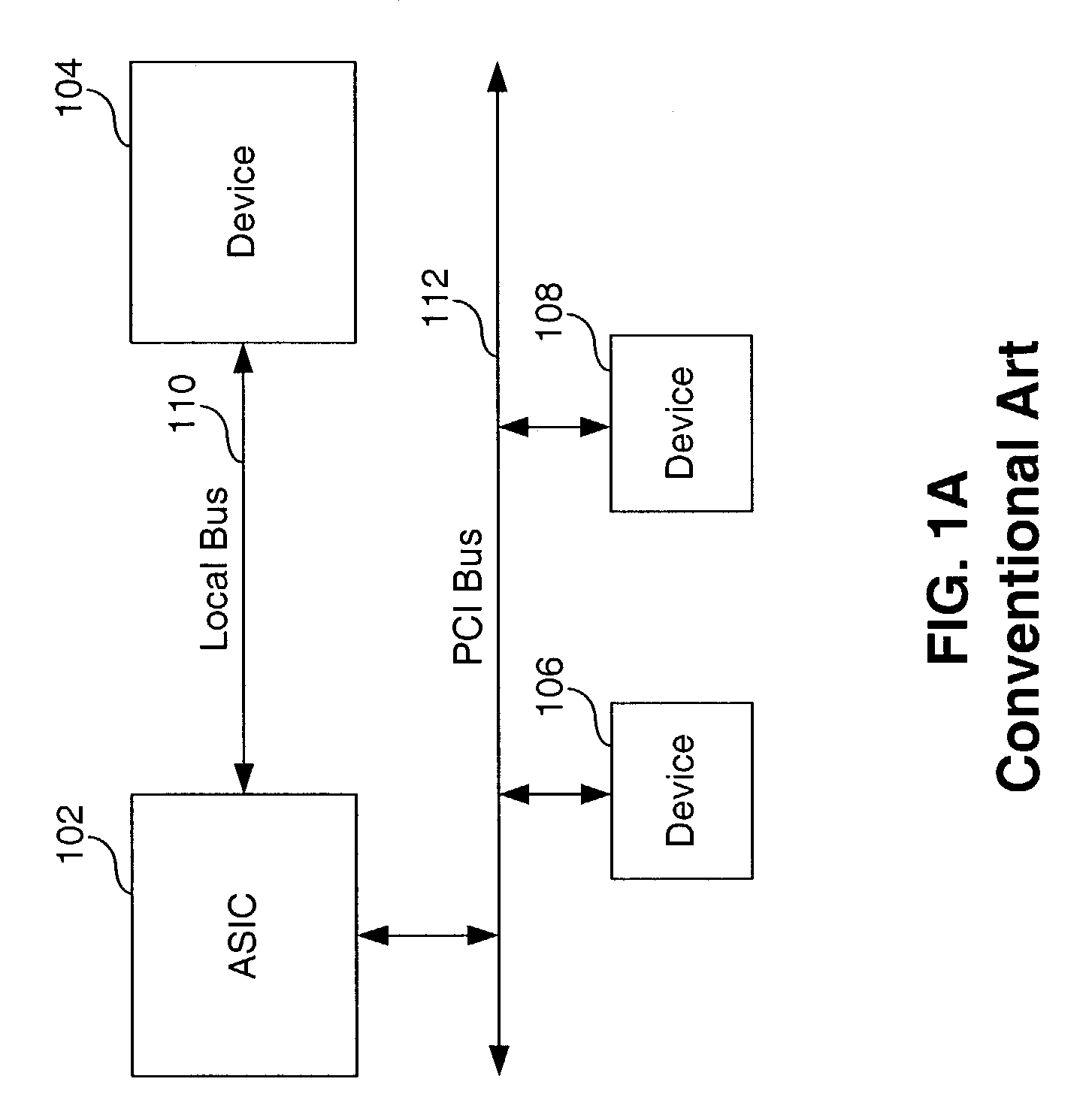

Memory mapped I/O bus selection

InactiveUS7039748B2Electric digital data processingClient-sideApplication-specific integrated circuit

A mechanism and method for redefining an application specific integrated circuit's I / O bus structure in real-time. The mechanism includes an address map block, a state machine block, and a bus arbitration block. At initialization, the address map is configured to divide the address space into regions and type of bus structure. When an I / O access is requested by a client (e.g., CPU, DMA controller, etc.), the request is mapped into a region and type of bus structure by the address map block. The region and type of bus structure is used by the state machine. The state machine determines the syntax and protocol for the region and type of bus. The state machine signals the bus arbitration block to grant I / O bus ownership when it is available. Once ownership is granted, I / O bus pins are defined and access is granted.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System and method for developing embedded software in-situ

ActiveUS8234624B2Analogue computers for electric apparatusComputer aided designEmbedded softwareModel Number

Owner:GLOBALFOUNDRIES U S INC

Method and apparatus for resolving additional load misses in a single pipeline processor under stalls of instructions not accessing memory-mapped I/O regions

InactiveUS7133968B2Reduces aggregate memory access timeShorten the timeMemory adressing/allocation/relocationConcurrent instruction executionMemory addressMissing data

An in-order single-issue microprocessor detects data cache misses generated by instructions behind a stalled instruction in the microprocessor pipeline and issues memory requests on the processor bus for the missing data so as to overlap with resolution of the stalled instruction, which may also be a cache miss. The data cache has pipeline stages that parallel portions of the main microprocessor pipeline. Replay buffers are employed to save the state, i.e., instructions and associated data addresses, of the parallel data cache stages so that instructions above the stalled instruction can continue to proceed down through the data cache and access the cache memory to generate cache misses. The data cache pipeline stages are restored upon detection that the stall will terminate. The bus requests for the missing data are issued only if the stalled instruction does not access a memory-mapped I / O region of the memory address space.

Owner:IP FIRST

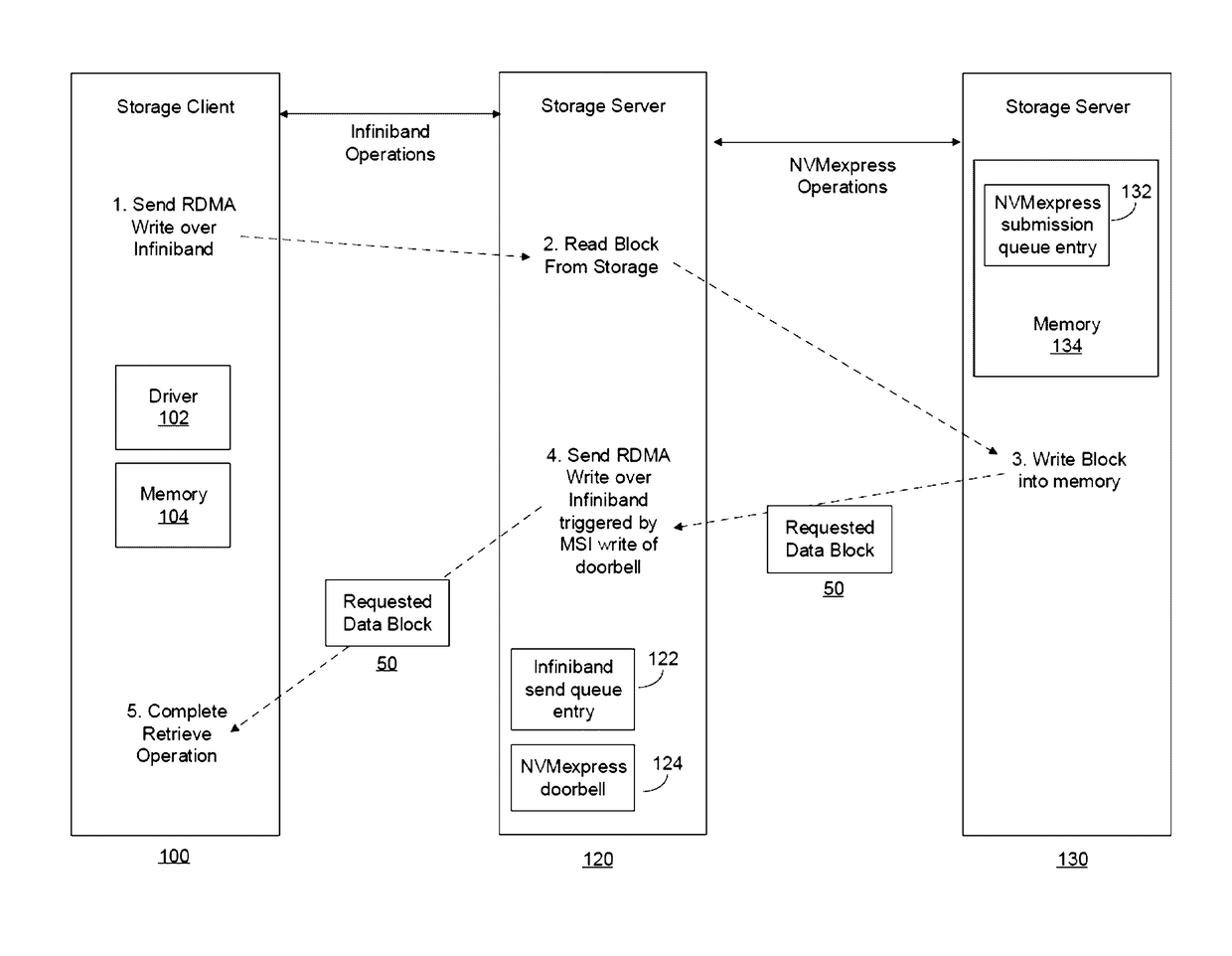

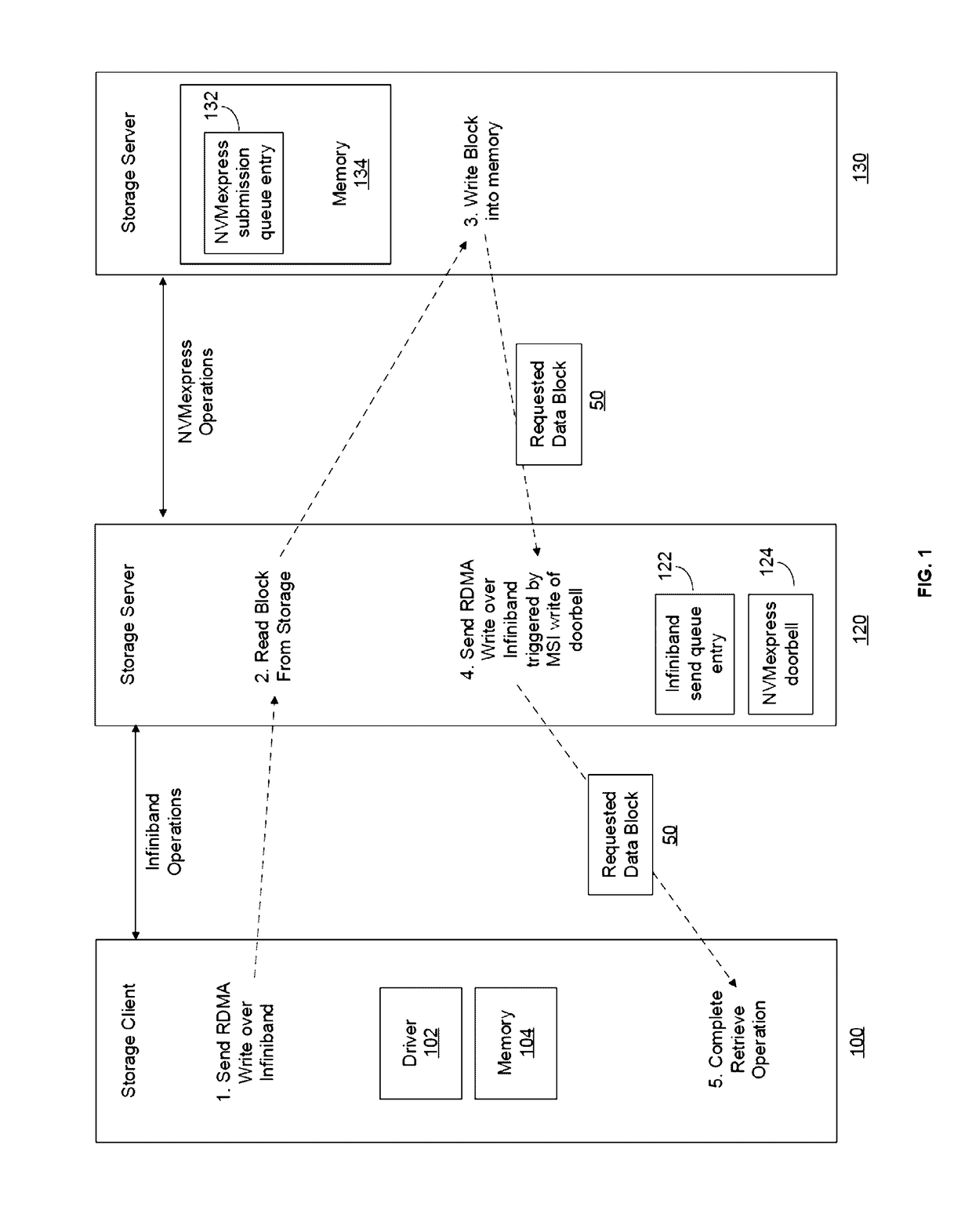

Scalable data using RDMA and MMIO

ActiveUS9658782B2Input/output to record carriersDigital computer detailsRemote direct memory accessMemory map

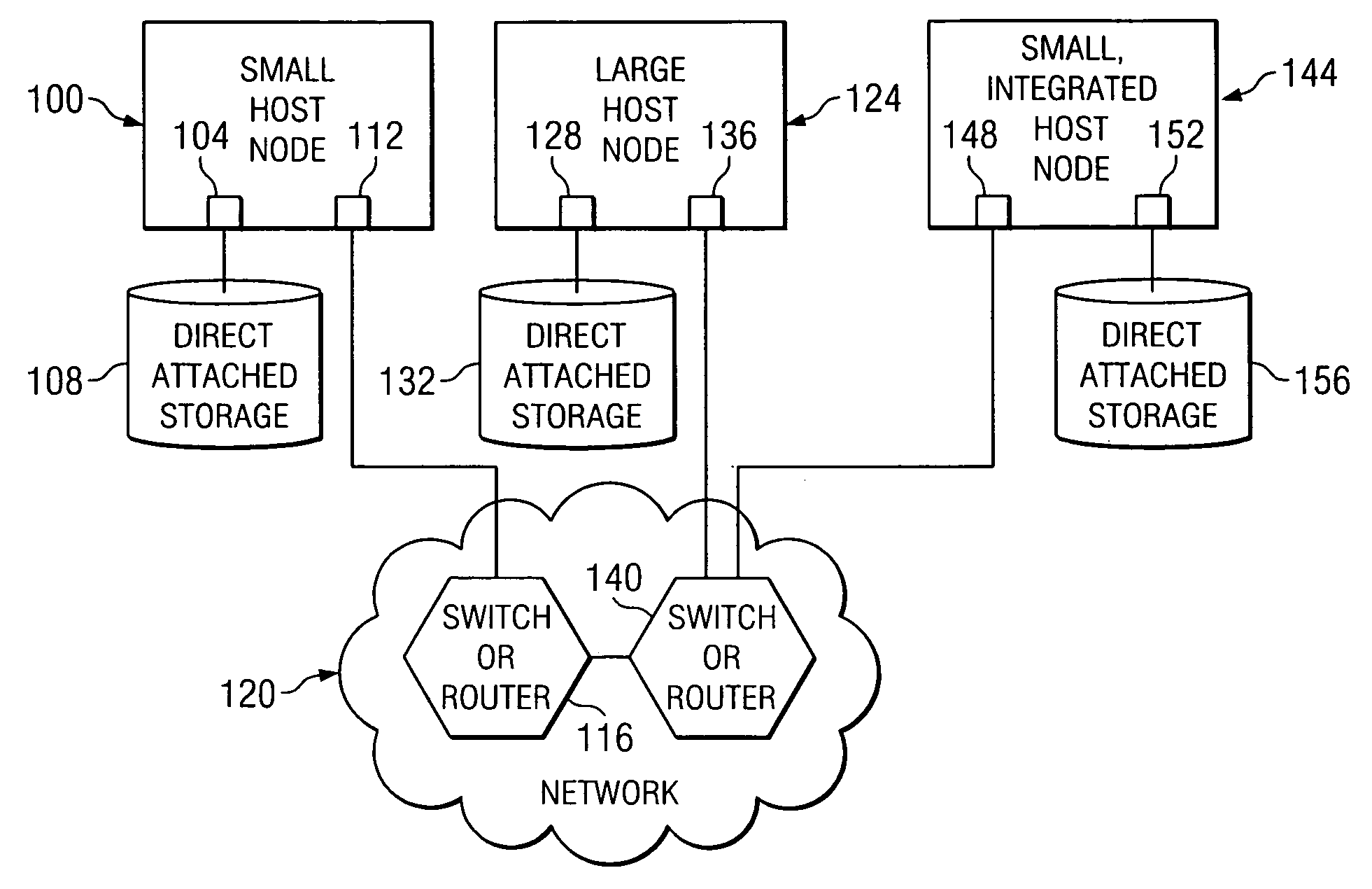

To improve upon some of the characteristics of current storage systems in general and block data storage systems in particular, exemplary embodiments combine state-of-the art networking techniques with state-of-the-art data storage elements in a novel way. To accomplish this combination in a highly effective way, it is proposed to combine networking remote direct memory access (RDMA) technique and storage-oriented memory mapped input output (MMIO) technique in a system to provide direct access from a remote storage client to a remote storage system with little to no central processing unit (CPU) intervention of the remote storage server. In some embodiments, this technique may reduce the required CPU intervention on the client side. These reductions of CPU intervention potentially reduce latency while providing performance improvements, and / or providing more data transfer bandwidth and / or throughput and / or more operations per second compared to other systems with equivalent hardware.

Owner:NVIDIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com