Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55 results about "Delayed Memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definitions - Delayed Memory. Delayed Memory (n.) 1.(MeSH)The active mental process of keeping out and ejecting, banishing from consciousness, ideas or impulses that are unacceptable to it.

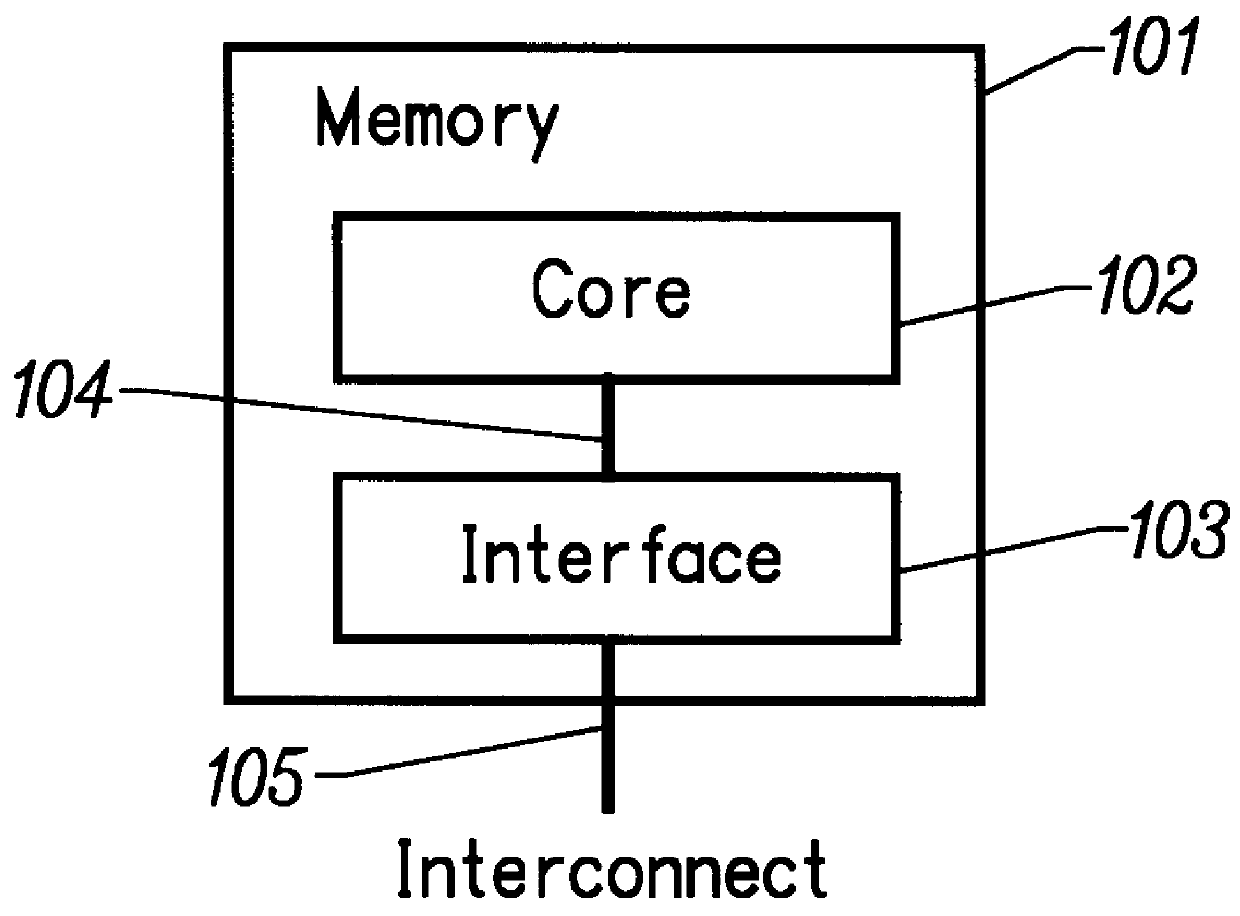

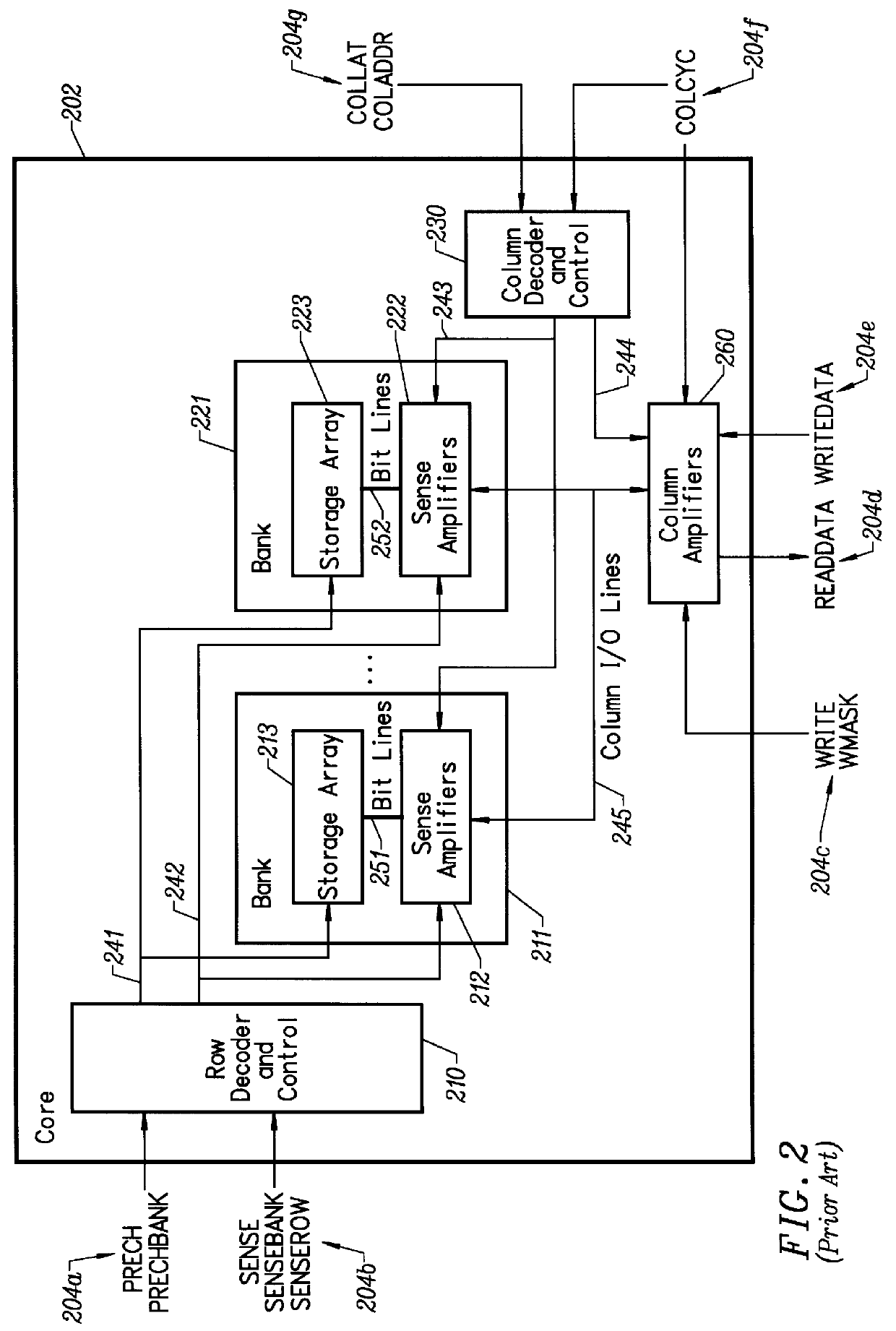

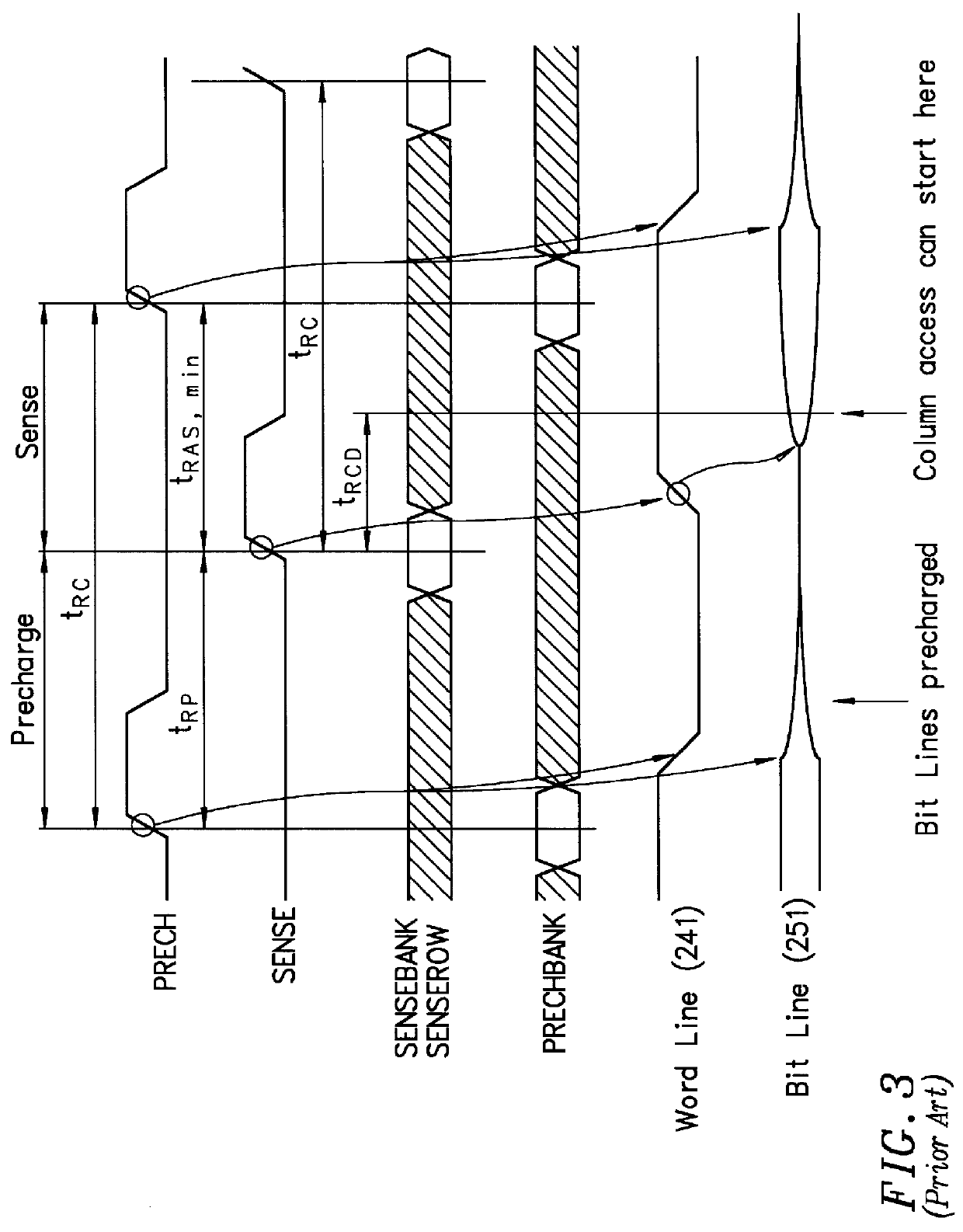

High performance cost optimized memory with delayed memory writes

A memory device includes an interconnect with control pins and bidirectional data pins. A memory core stores data. A memory interface circuit is connected to the interconnect and the memory core. The memory interface circuit includes a delay circuit to establish a write delay during a memory core write transaction such that the memory core write transaction has a processing time that is substantially equivalent to a memory core read transaction. The delay circuit delays the memory core write transaction for a time corresponding to the time required for signals to travel on the interconnect.

Owner:RAMBUS INC +1

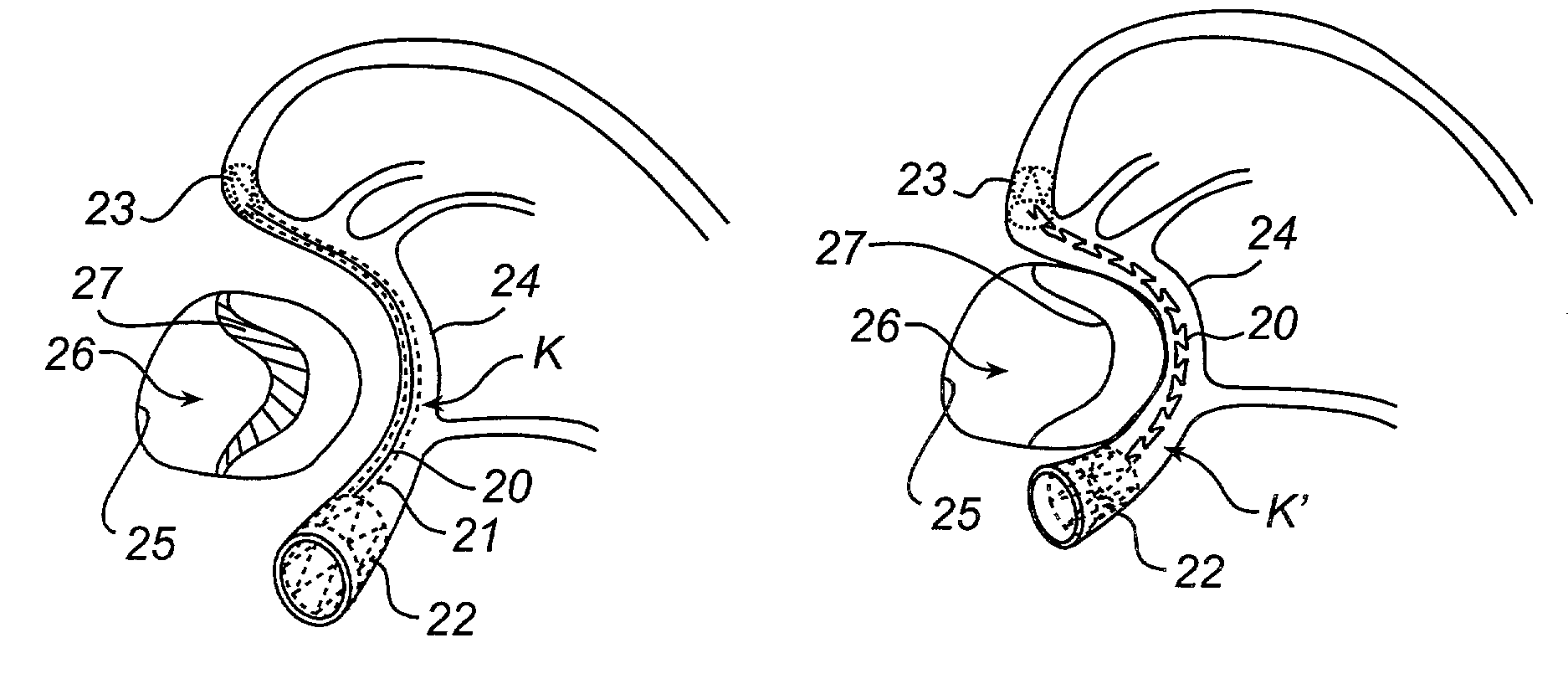

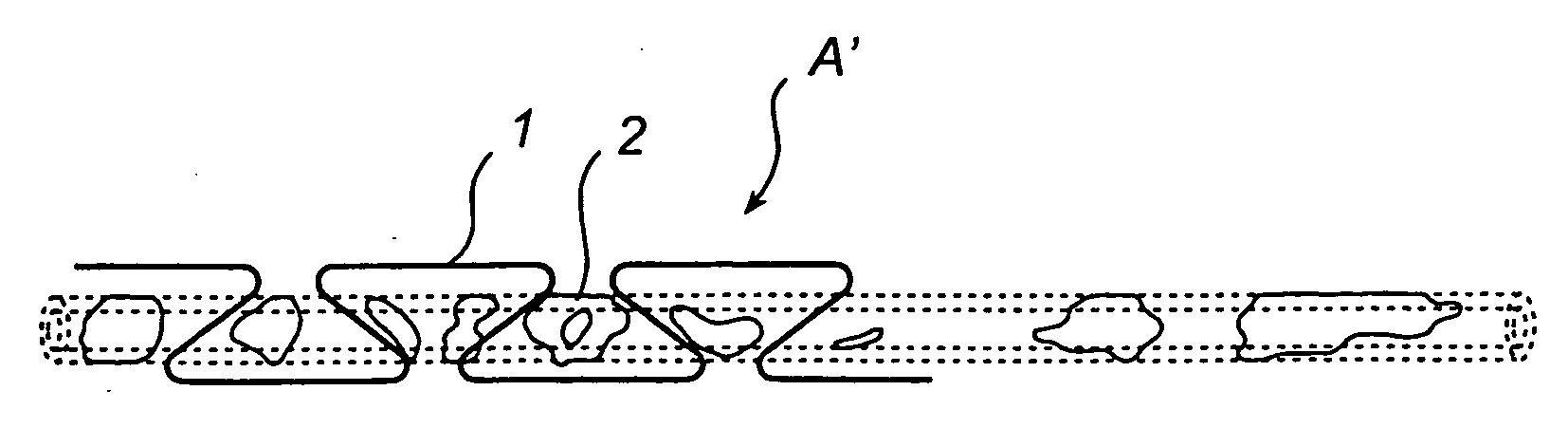

Delayed memory device

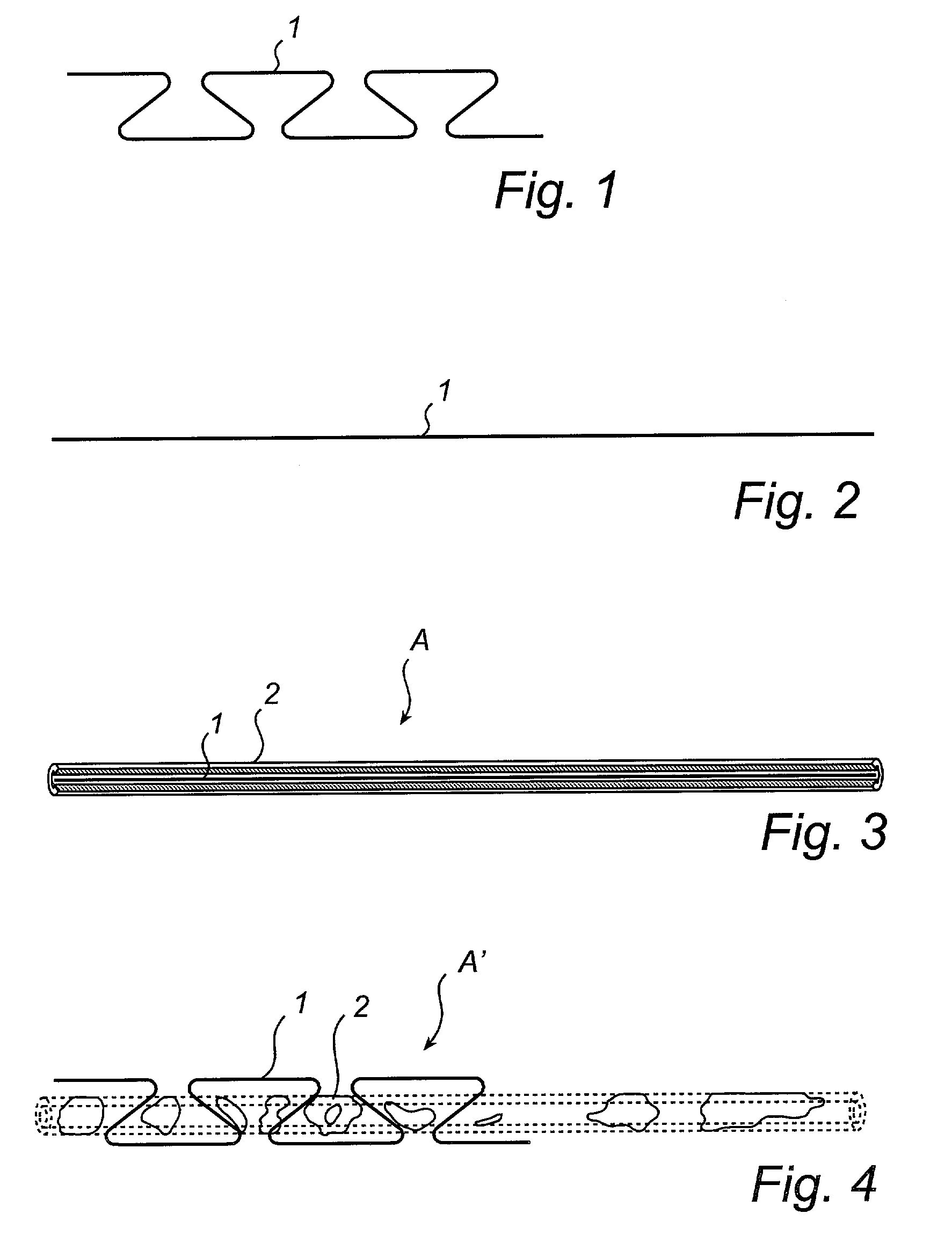

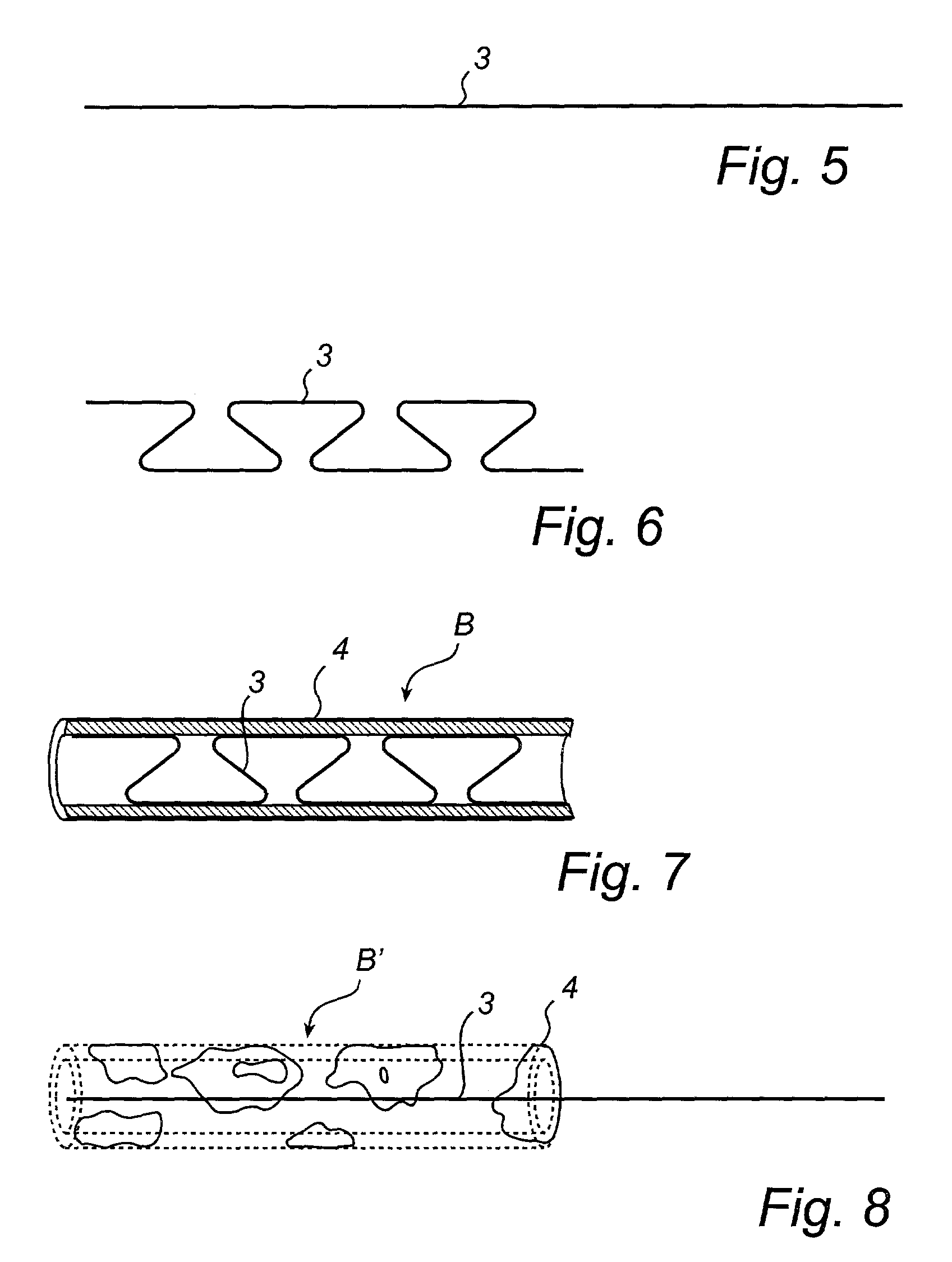

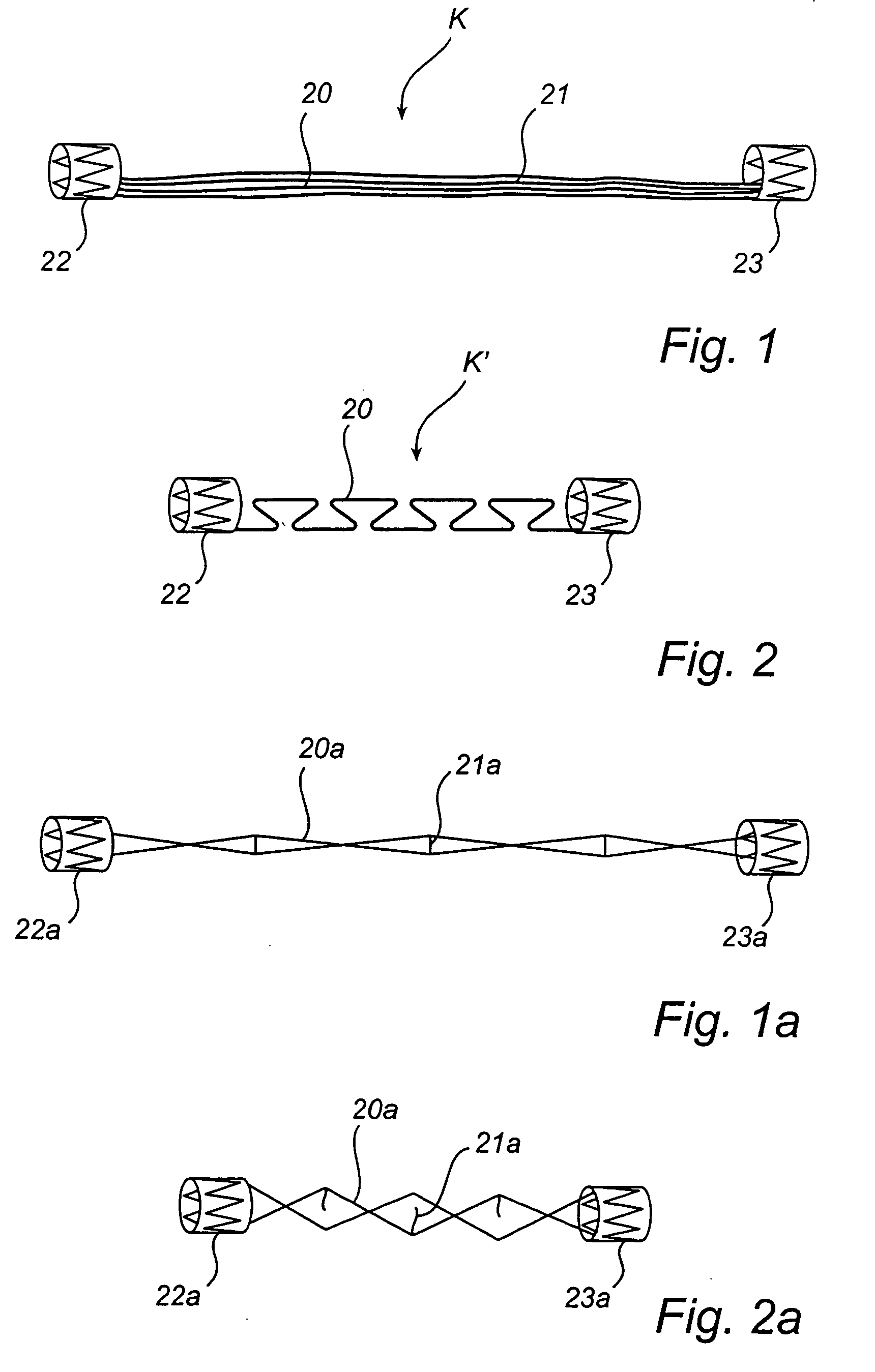

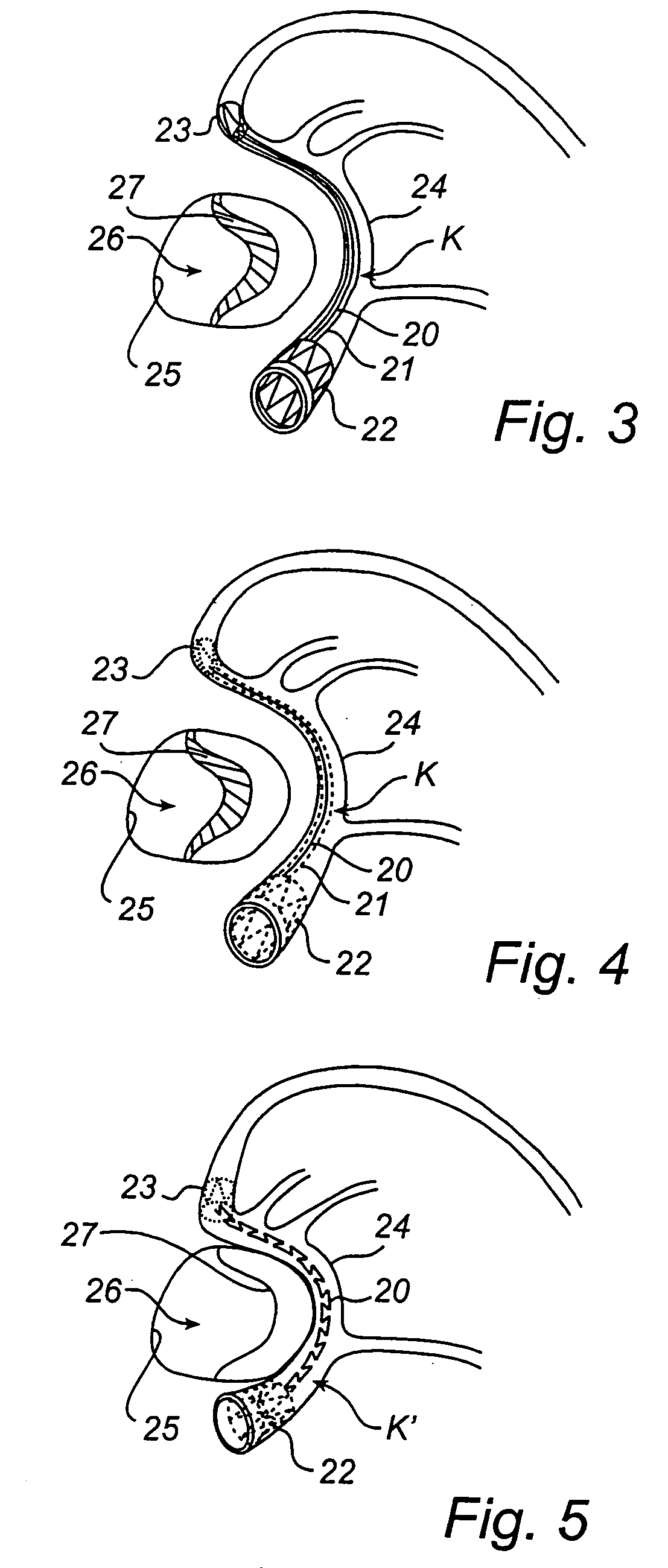

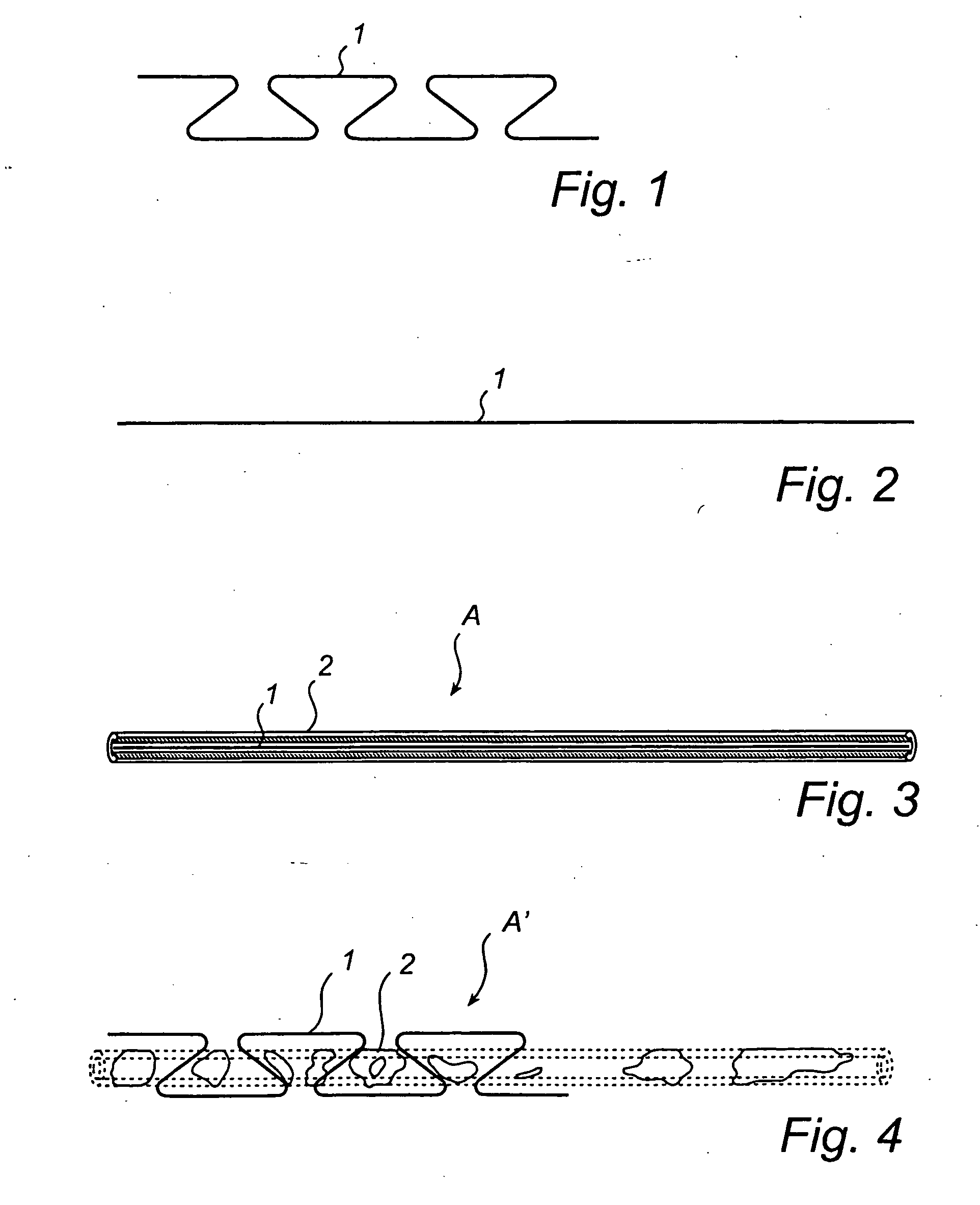

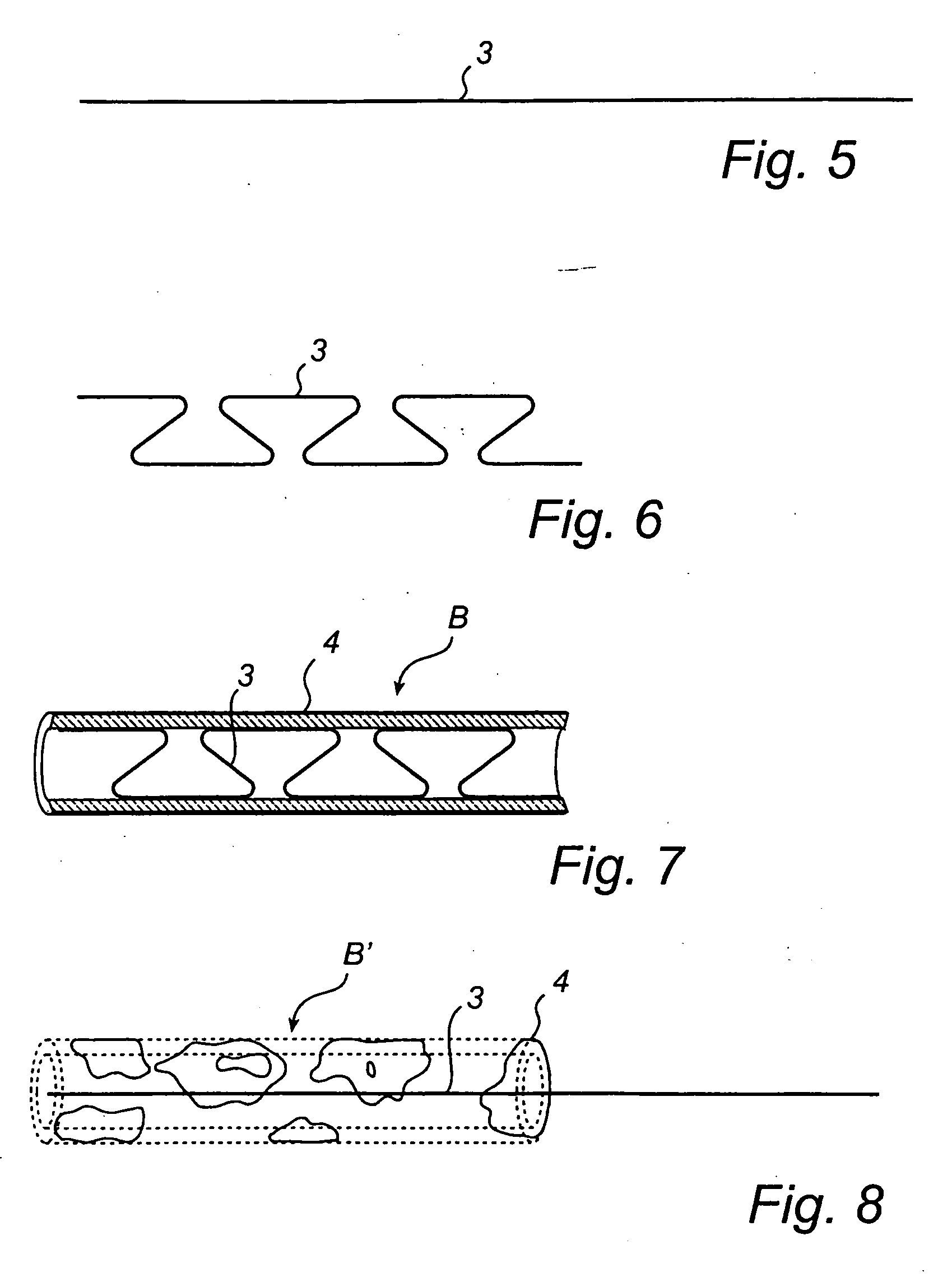

A medical device and a method for providing a change of shape in a part of the body of an organism. The device is insertable into the body of the organism and comprises a member having a preferred state of shape and having a tendency to transfer its shape towards said preferred state of shape when being in a non-preferred state of shape. The device further comprises a resorbable means which is arranged to hold the member in the non-preferred state of shape and to delay the transfer when the device is inserted into the body of the organism by counteracting said transfer during resorption of the resorbable means by the surrounding body of the organism.

Owner:EDWARDS LIFESCIENCES AG

Delayed memory device

ActiveUS20050080483A1Easy to manufactureConvenient ArrangementStentsBronchiShape changeDelayed Memory

A device for reshaping a cardiac valve (26), which is elongate and has such dimensions as to be insertable into a cardiac vessel (24). The device has two states, in a first state (K) of which the device has a shape that is adaptable to the shape of the vessel (24), and to the second state (k′) of which the device is transferable from said first state (K). Further, the device comprises a fixing means (22,23;22a,23a) for fixing the ends of the device within the vessel (24), when the device is first positioned therein, a shape-changing member (20;20a) for transferring the device to the second state (K′) by reshaping it, and a delay means (21;21a) for delaying said reshaping until the fixing of the ends of the device has been reinforced by keeping said device in said first state (K) until the delay means (21;21a) is resorbed.

Owner:EDWARDS LIFESCIENCES AG

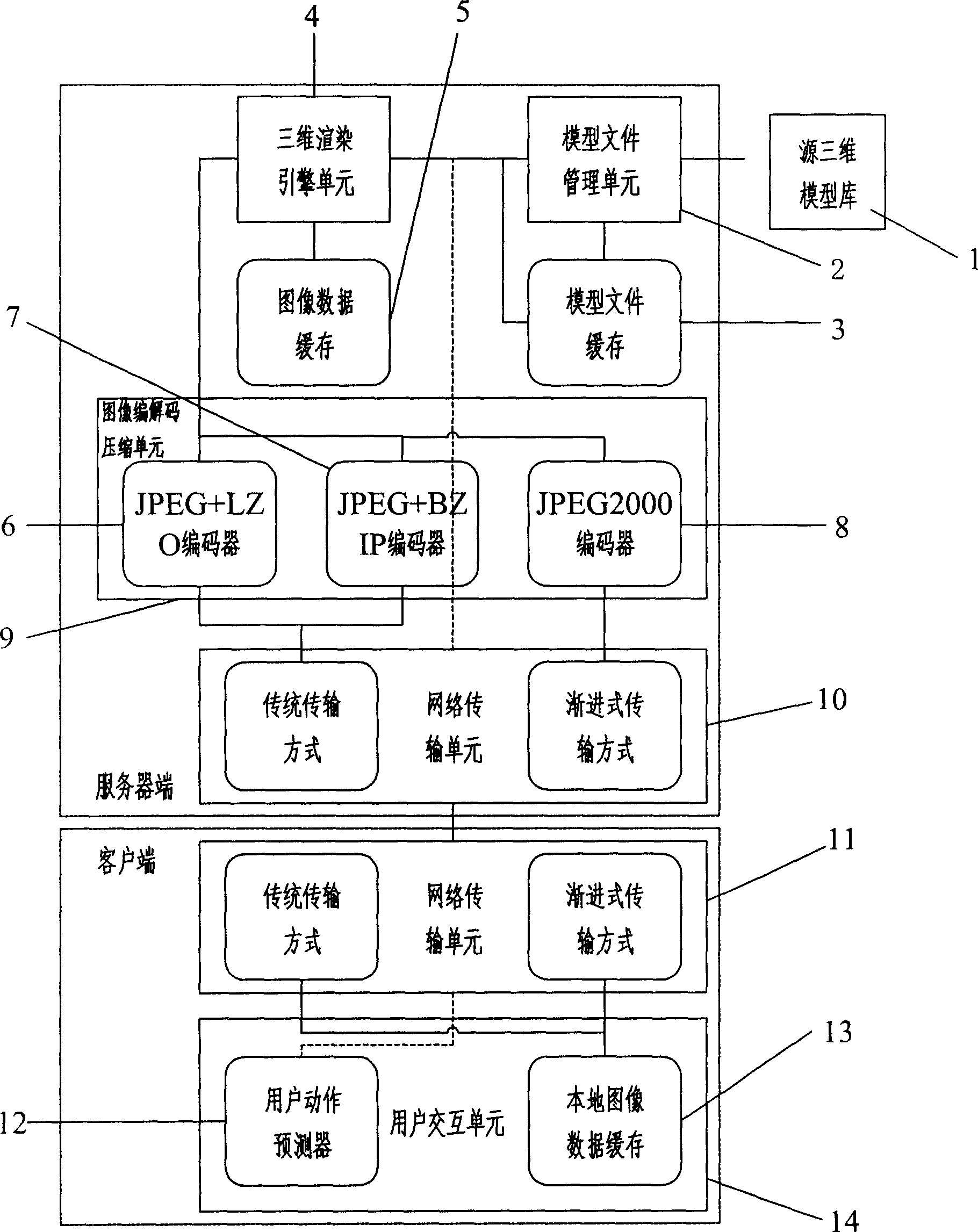

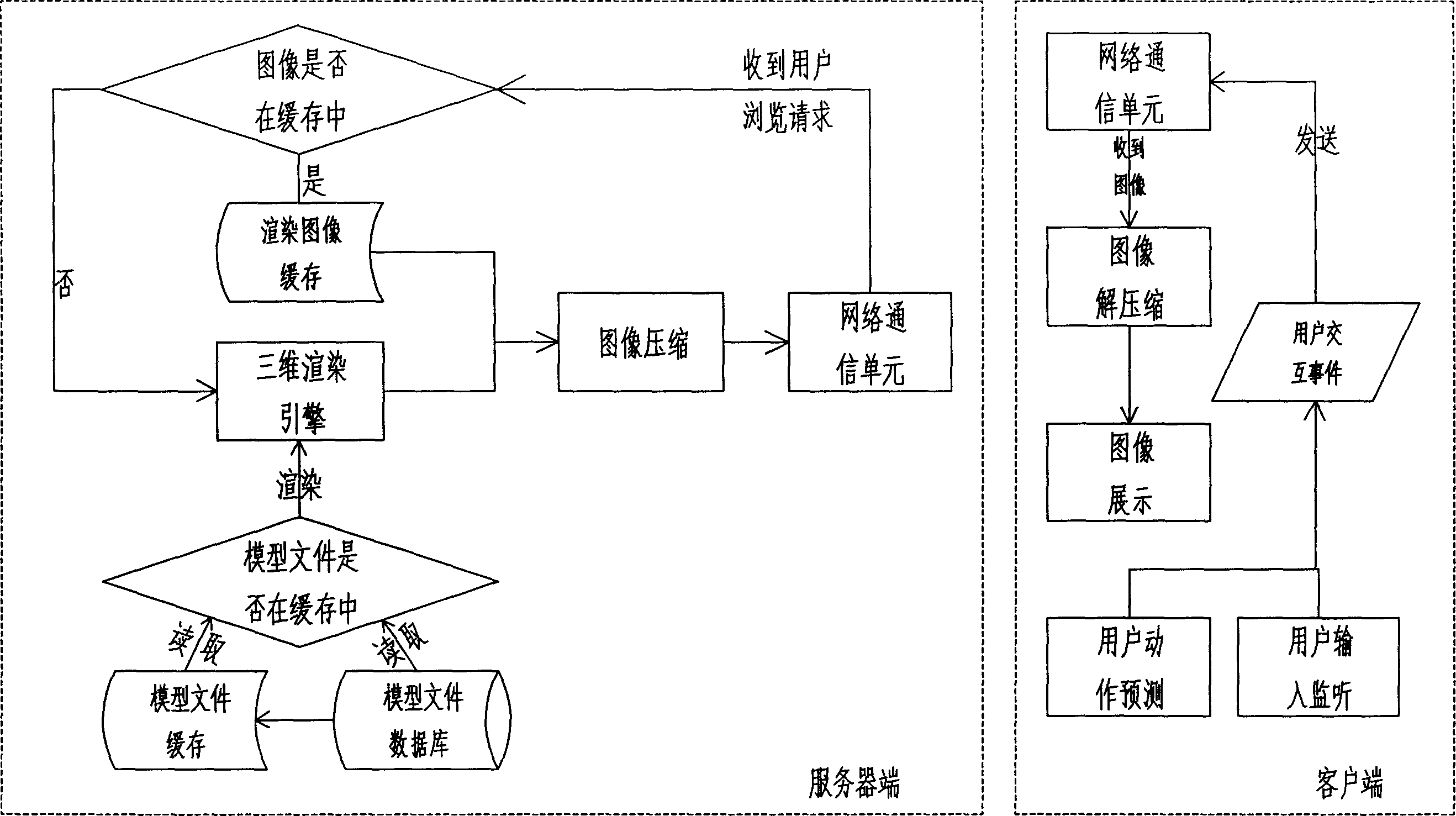

Three-dimensional remote rendering system and method based on image transmission

InactiveCN1845177AEasy to viewImprove real-time performanceTransmission3D-image renderingDelayed MemoryClient-side

The invention discloses a three-dimension remote romance system, based on graph transmission, which comprises interactive server terminal and user terminal. Wherein, the server terminal has mode file manage unit, three-dimension romance engine unit, graph code decode compress unit, and network transmission unit; the user terminal has network transmission unit and user interactive unit; when the server terminal receives the browse request of user terminal via the network transmission unit, the mode file manage unit reads the mode file that requesting browse; using three-dimension romance engine unit to romance generate graph data, via the graph code decode compress unit to be compressed, and via network transmission unit, to be sent to the user terminal; user terminal decodes the data of compressed graph, to display it via user interface. The invention uses progressive transmission, multistage delay memory, and the prediction based on user interaction to realize the balance between high real-time property and high accurate browse, to support quick beautiful romance effect to general user.

Owner:ZHEJIANG UNIV

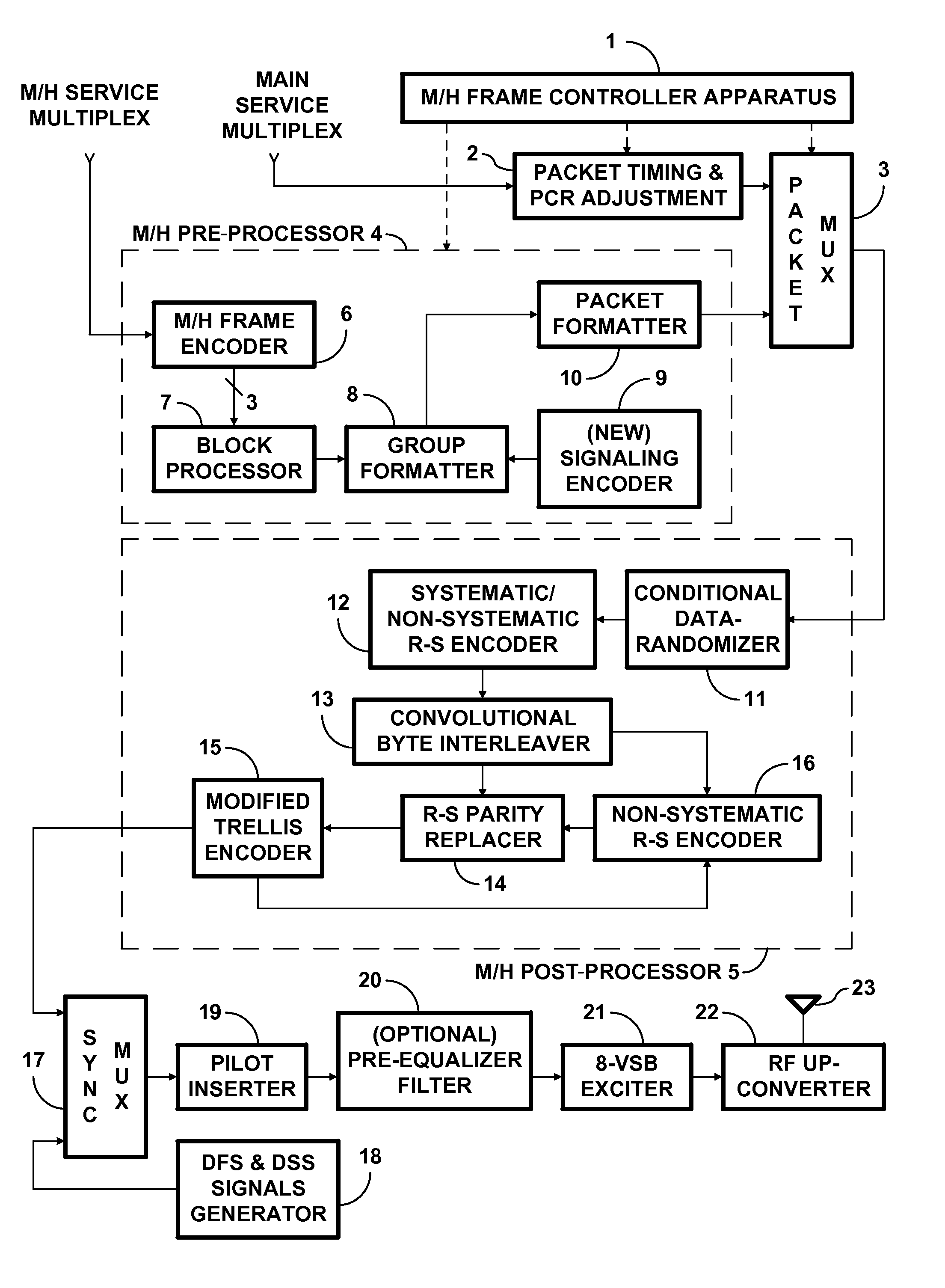

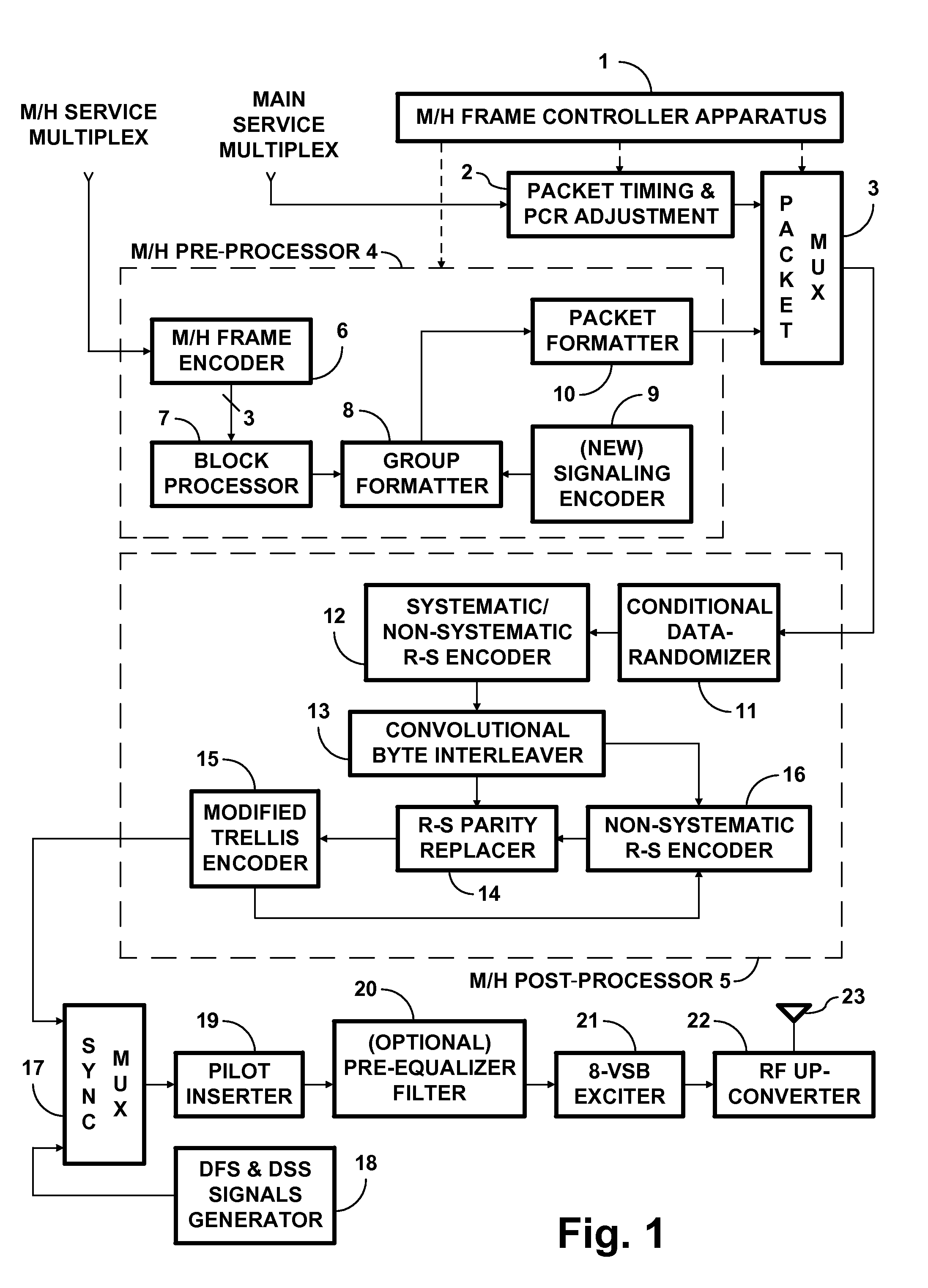

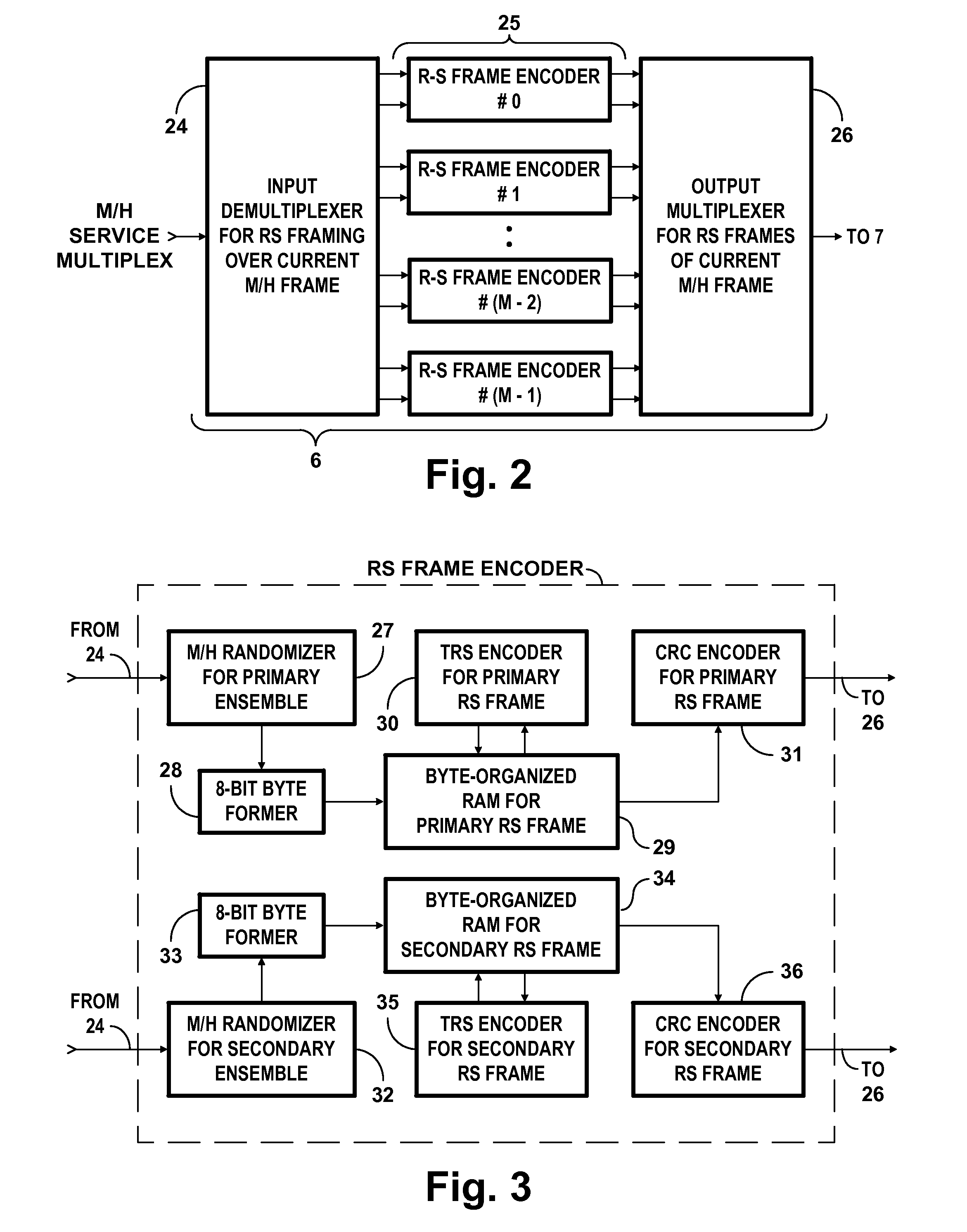

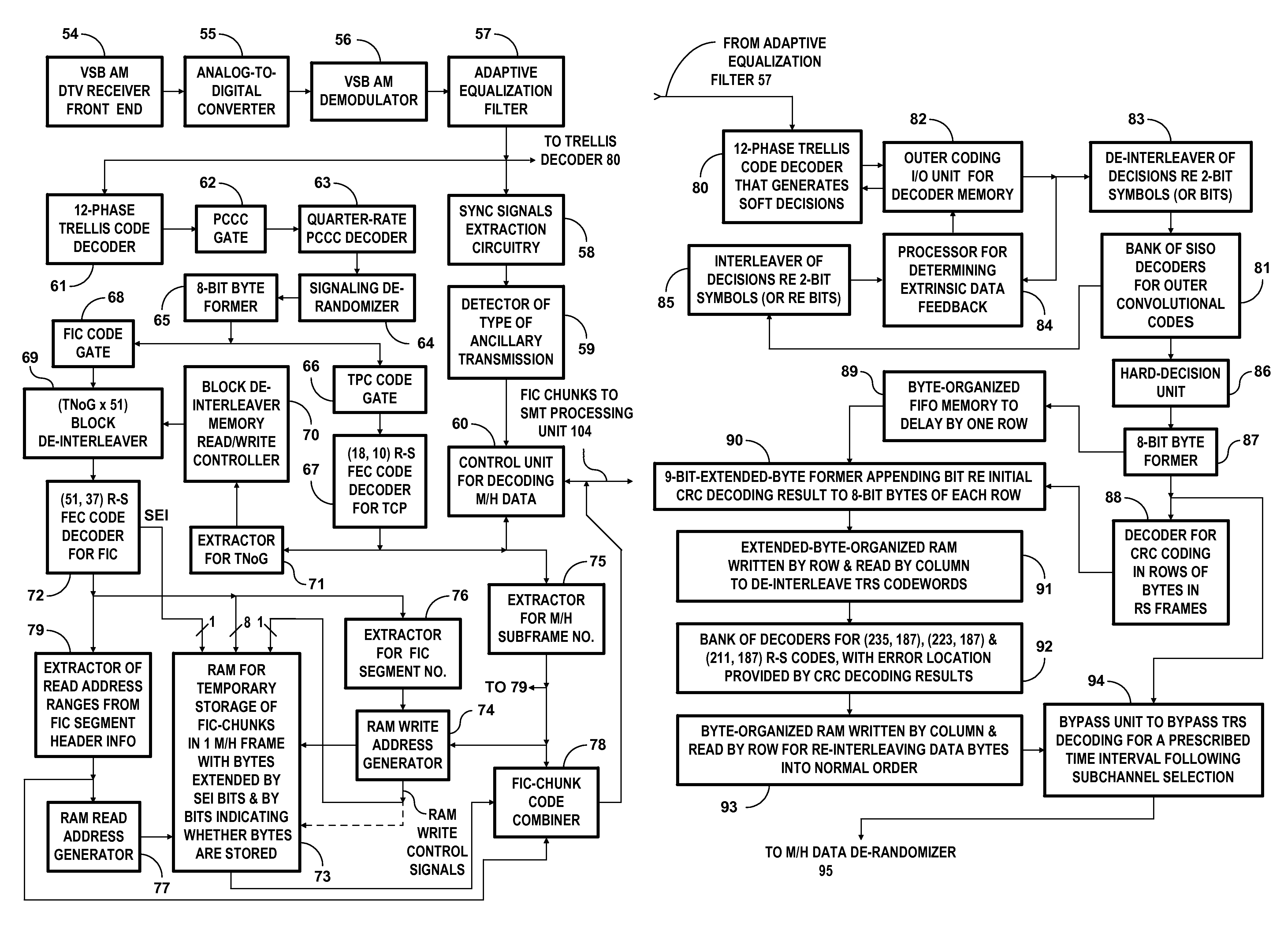

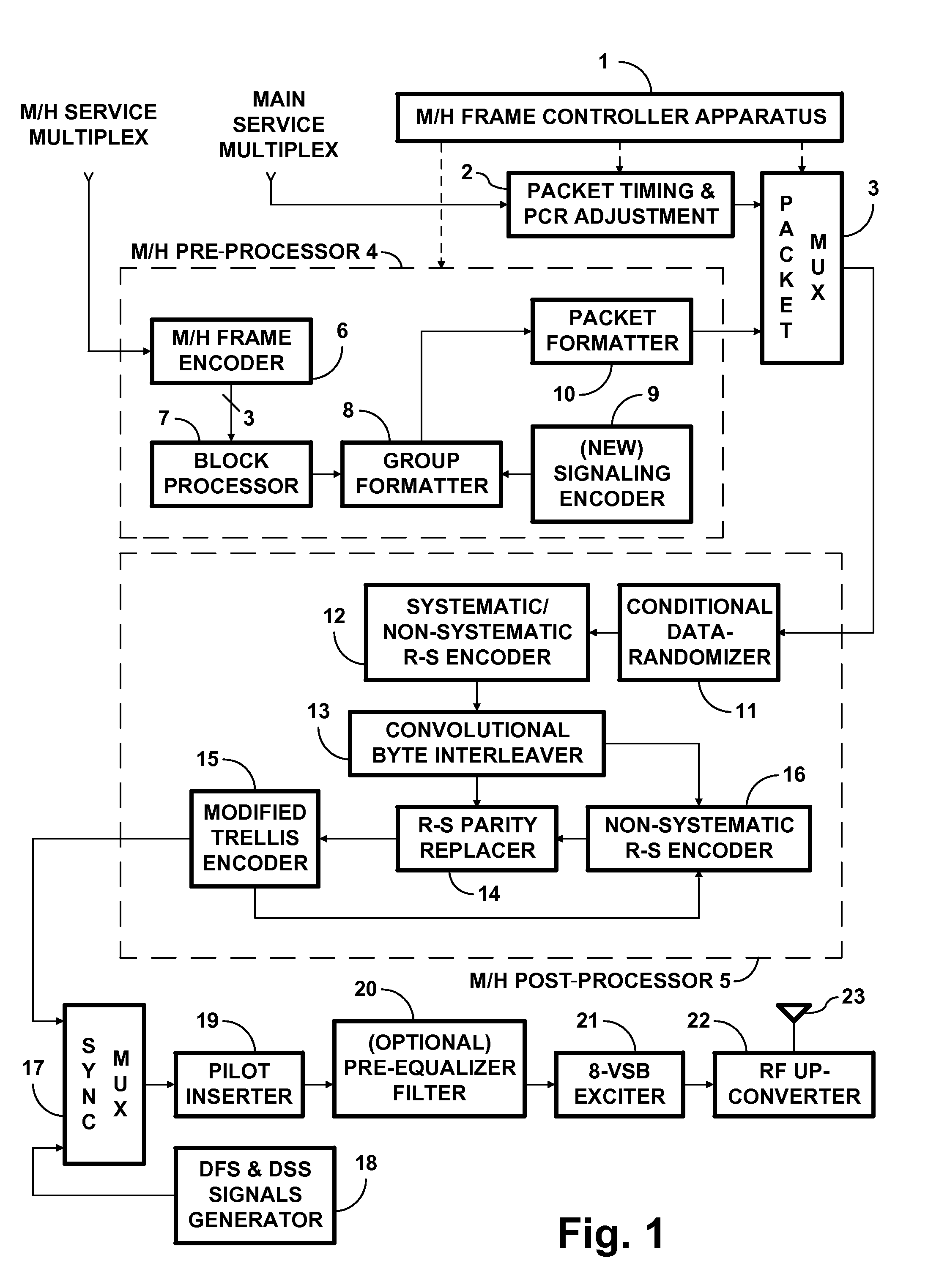

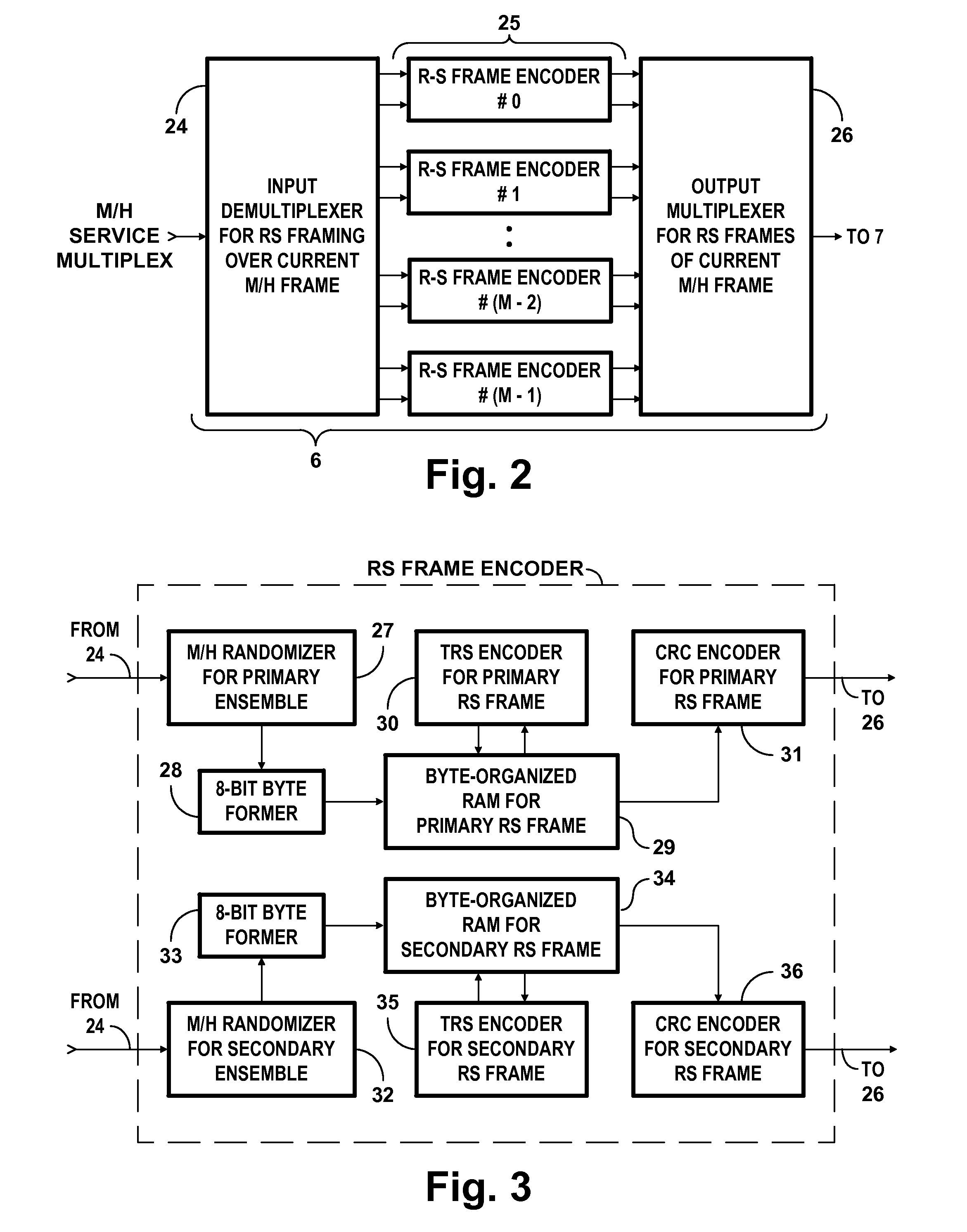

Apparatus for adapting reception modes of a mobile DTV receiver in response to signaling

ActiveUS20100149427A1Avoid delayTelevision system detailsAmplitude demodulation by homodyne/synchrodyne circuitsDTV receiverDelayed Memory

Implementation of Fast Information Channel (FIC) signaling when Chunks of FIC information span more than one sub-Frame of an M / H Frame is described. FIC signaling is advanced further at the digital television (DTV) transmitters than originally proposed, thereby eliminating need for substantial amounts of delay memory for coded M / H data in receivers for such data. Each FIC-Chunk includes a bit indicating when it is not applicable only to M / H Frames yet to be received but is also applicable to an M / H Frame being currently received. This facilitates reception being more quickly established after a change in DTV channel selection. Transmission Parameter Channel (TPC) signaling pertaining to the M / H Frame being currently received continues to the conclusion of the M / H Frame, so the total number of M / H Groups in each M / H sub-Frame is signaled to facilitate de-interleaving of the FIC signaling. Code combining of FIC Chunks is described.

Owner:SAMSUNG ELECTRONICS CO LTD

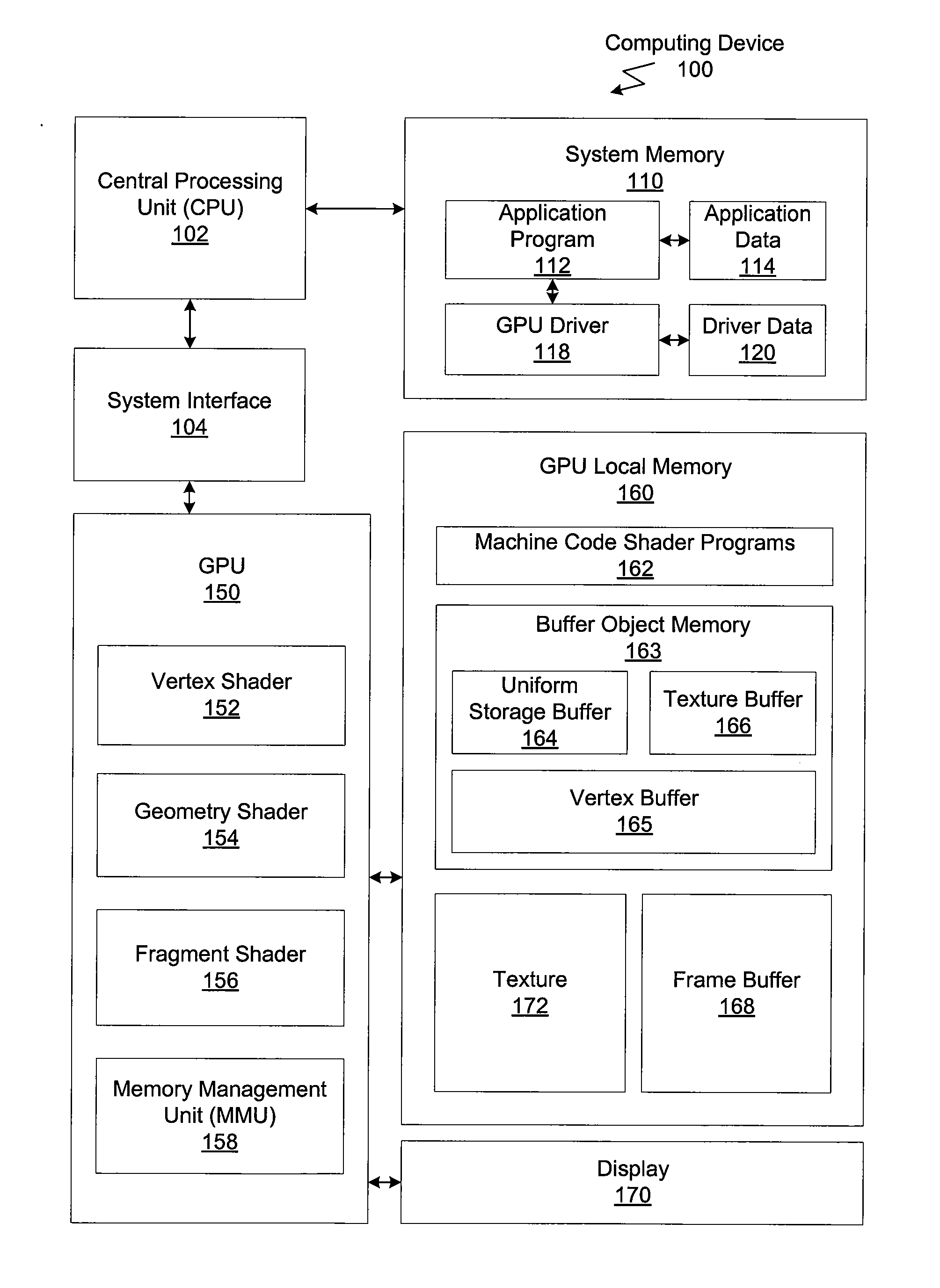

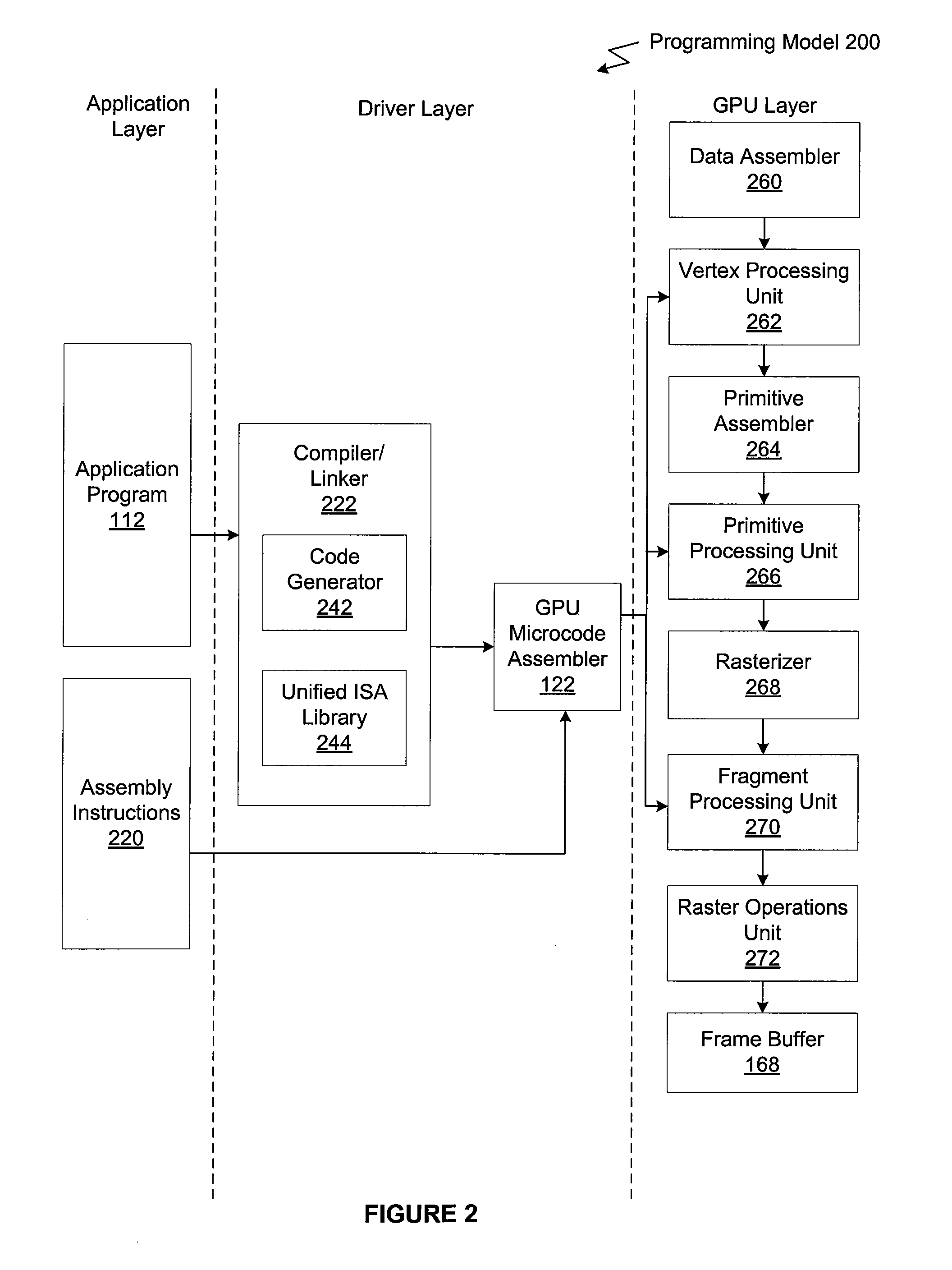

Memory coherency in graphics command streams and shaders

ActiveUS20110063313A1Simple technologyCathode-ray tube indicatorsProcessor architectures/configurationDelayed MemoryParallel computing

One embodiment of the present invention sets forth a technique for performing a computer-implemented method that controls memory access operations. A stream of graphics commands includes at least one memory barrier command. Each memory barrier command in the stream of graphics command delays memory access operations scheduled for any command specified after the memory barrier command until all memory access operations scheduled for commands specified prior to the memory barrier command have completely executed.

Owner:NVIDIA CORP

Delayed memory device

A delivery system for delivering a prosthetic heart valve to a native valve site within the human vasculature. The prosthetic valve is disposed on a balloon at the end of a balloon catheter. The balloon catheter passes through a delivery sleeve assembly and handle. A pull wire travels from the handle to a distal end of the delivery sleeve assembly. Actuation of the handle pulls on the pull wire, which causes openings in a slotted tube of the delivery sleeve assembly to close, thus causing the delivery sleeve assembly to bend. A stretchable cover is placed over the slotted tube for biasing the steerable catheter toward a straight position. Once advanced to the native valve site, the prosthetic valve is deployed by inflating the balloon.

Owner:EDWARDS LIFESCIENCES AG

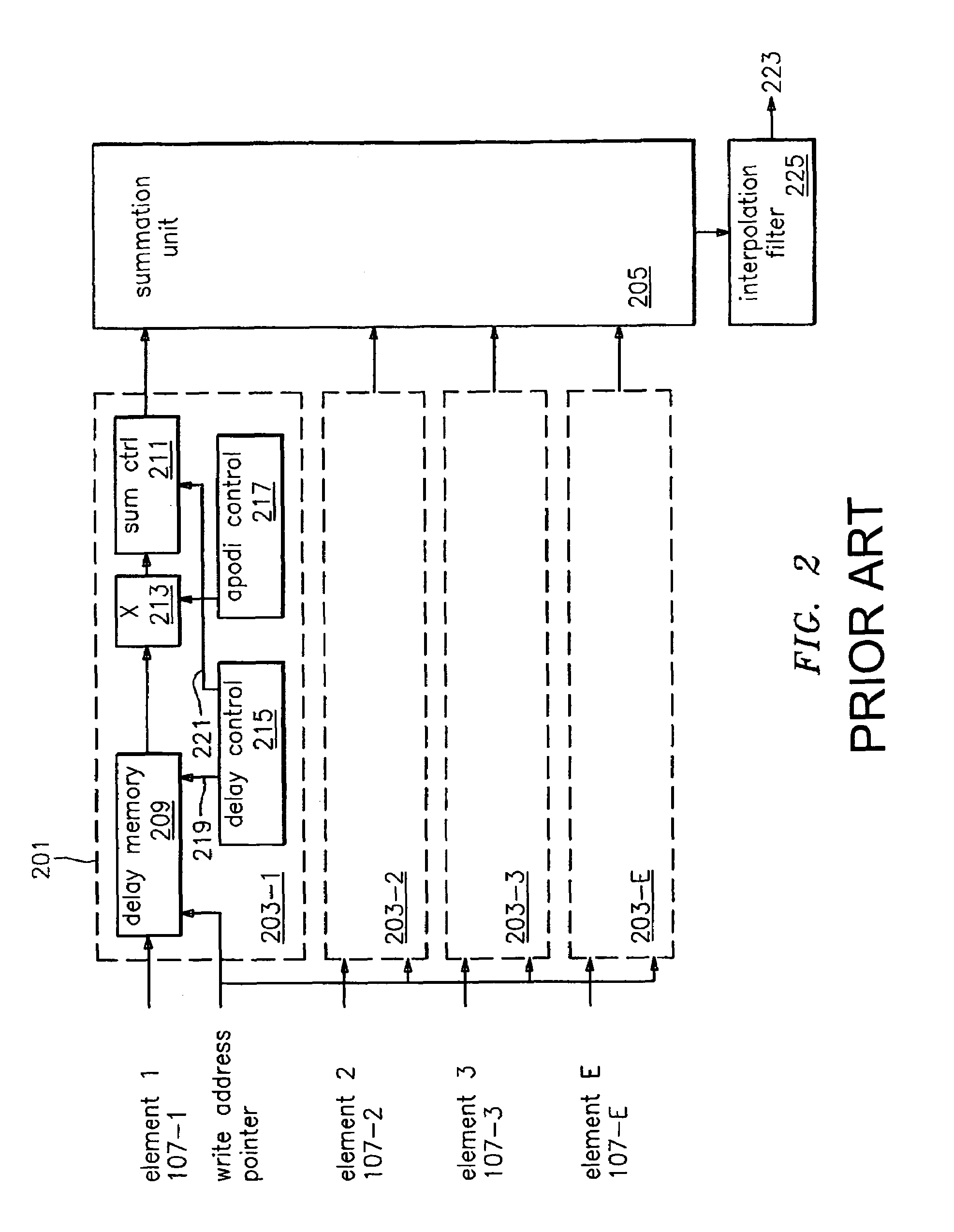

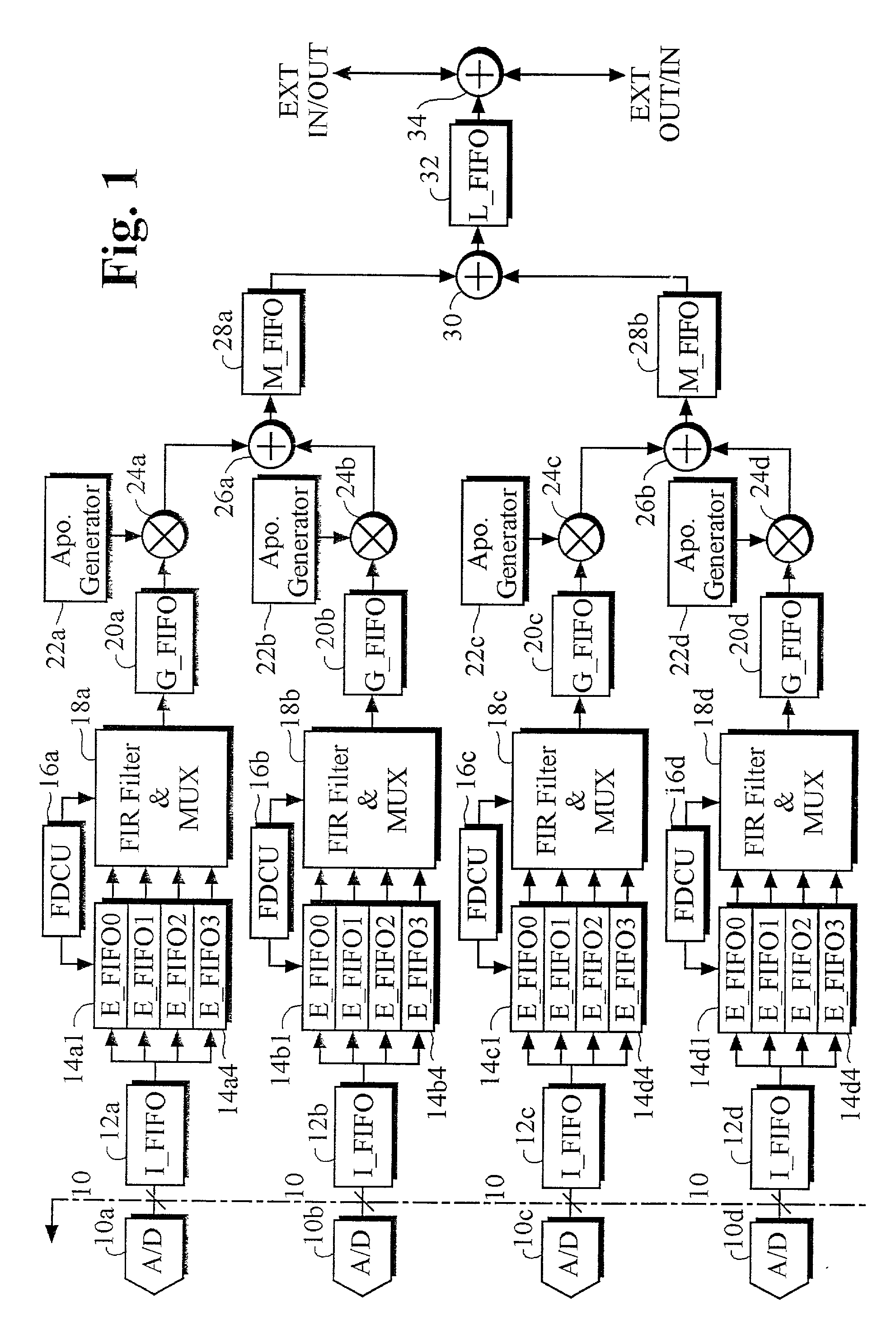

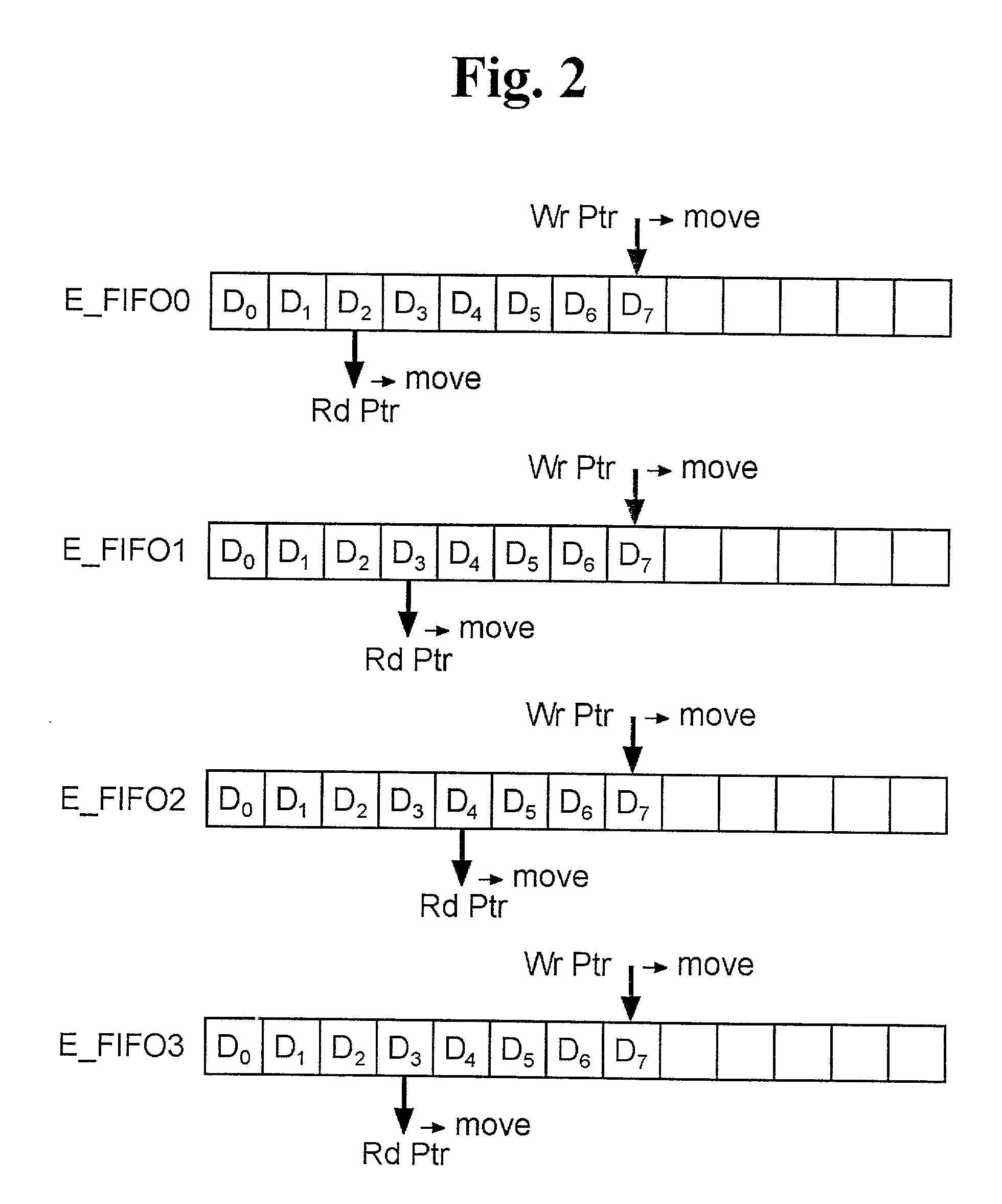

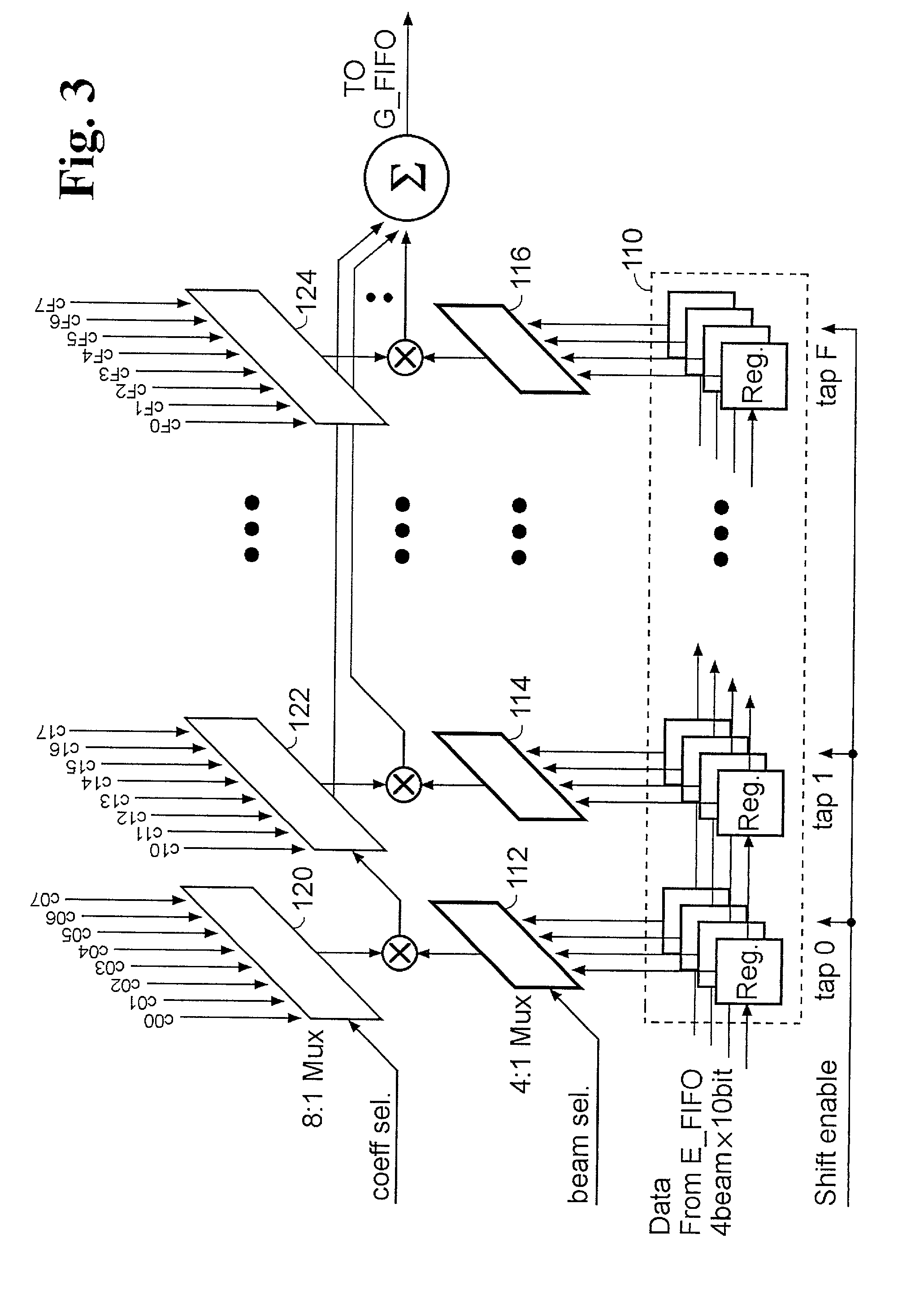

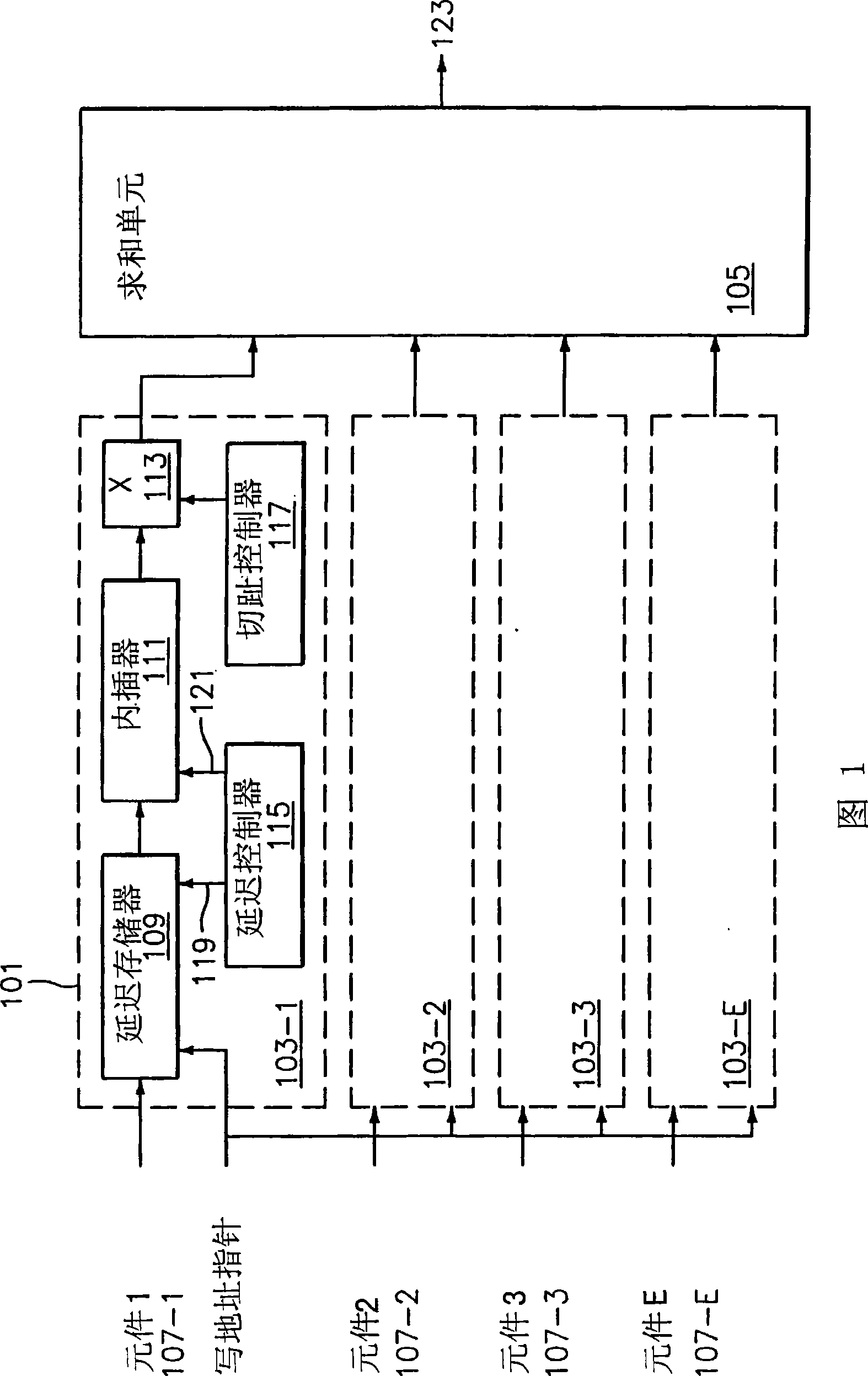

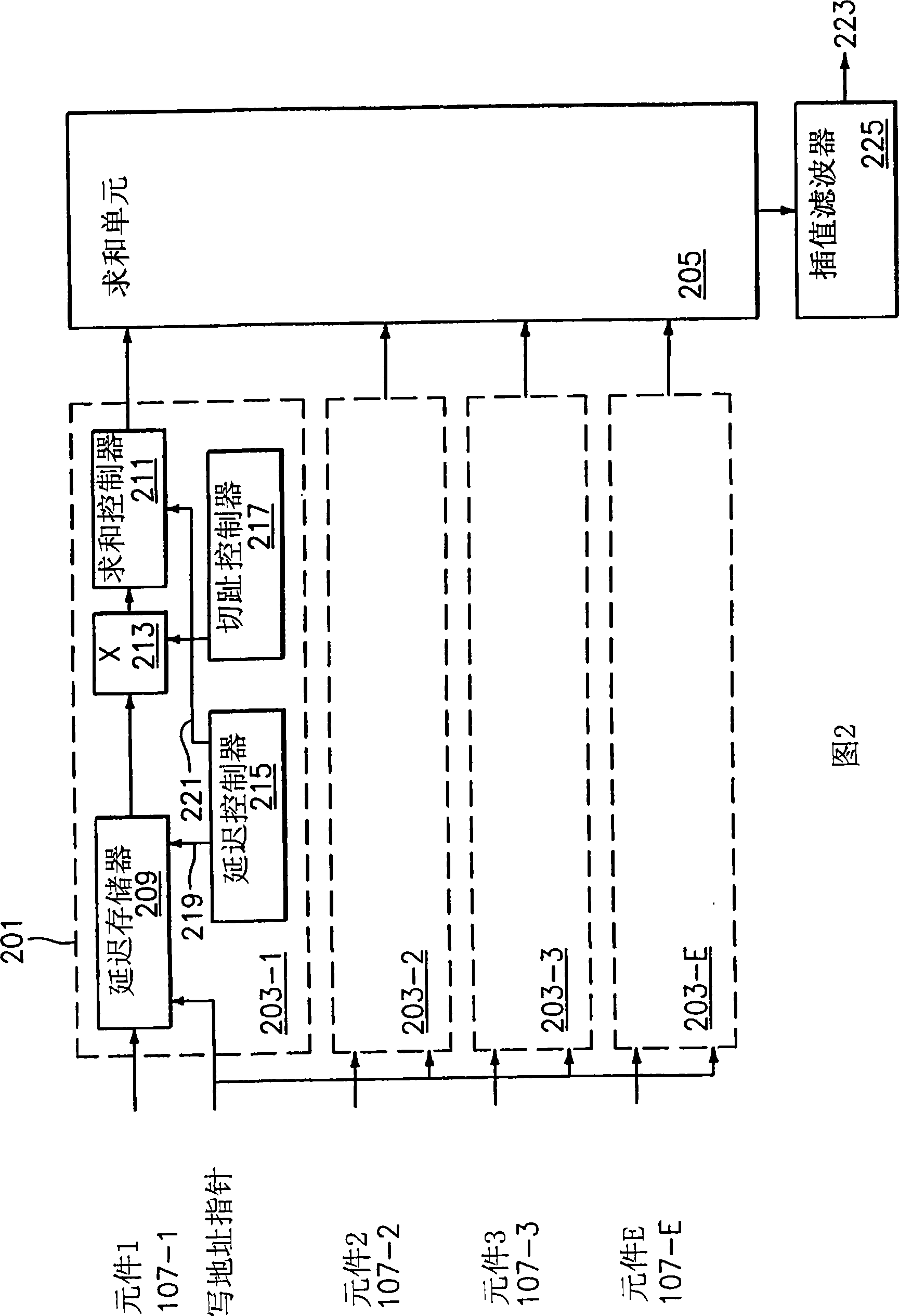

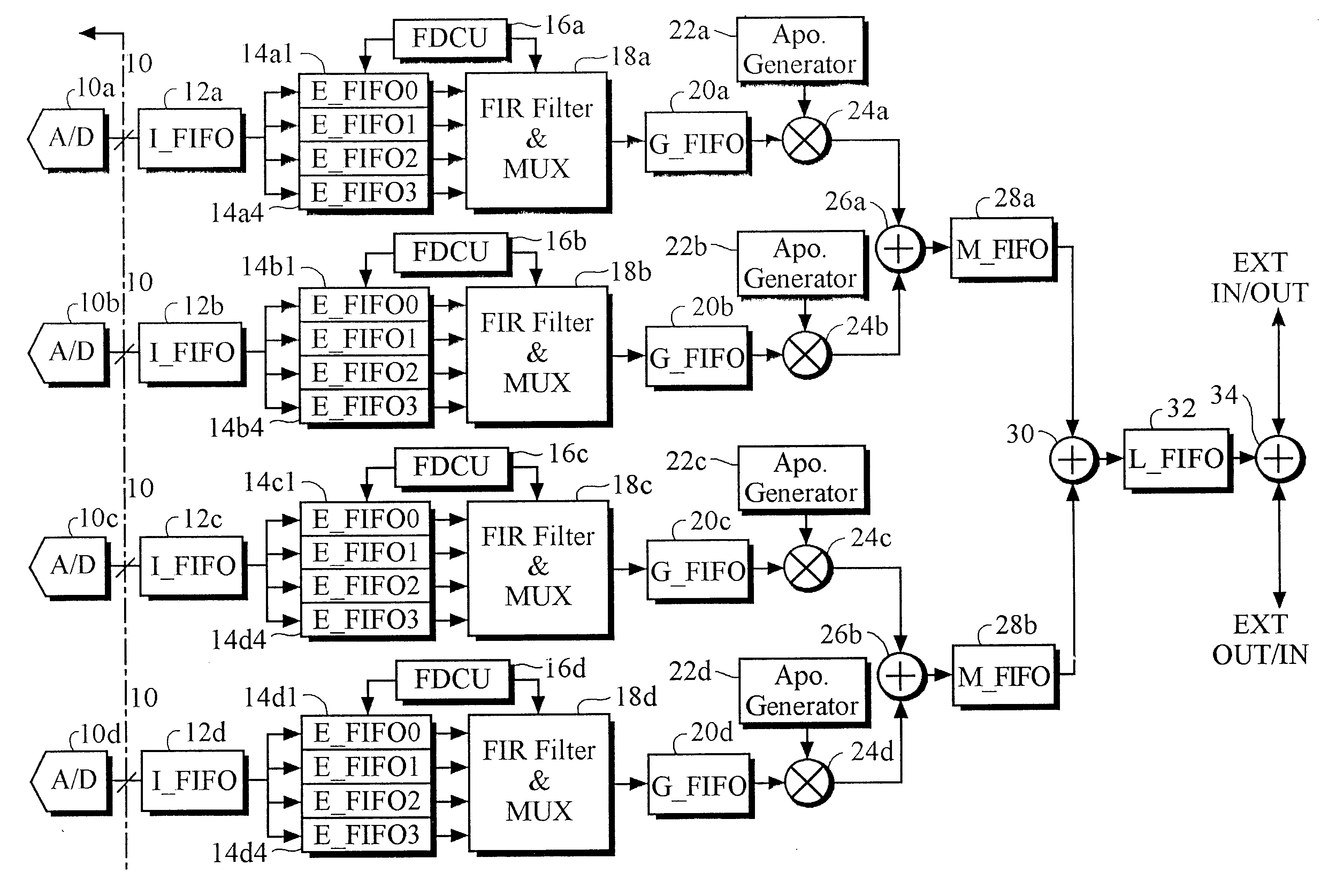

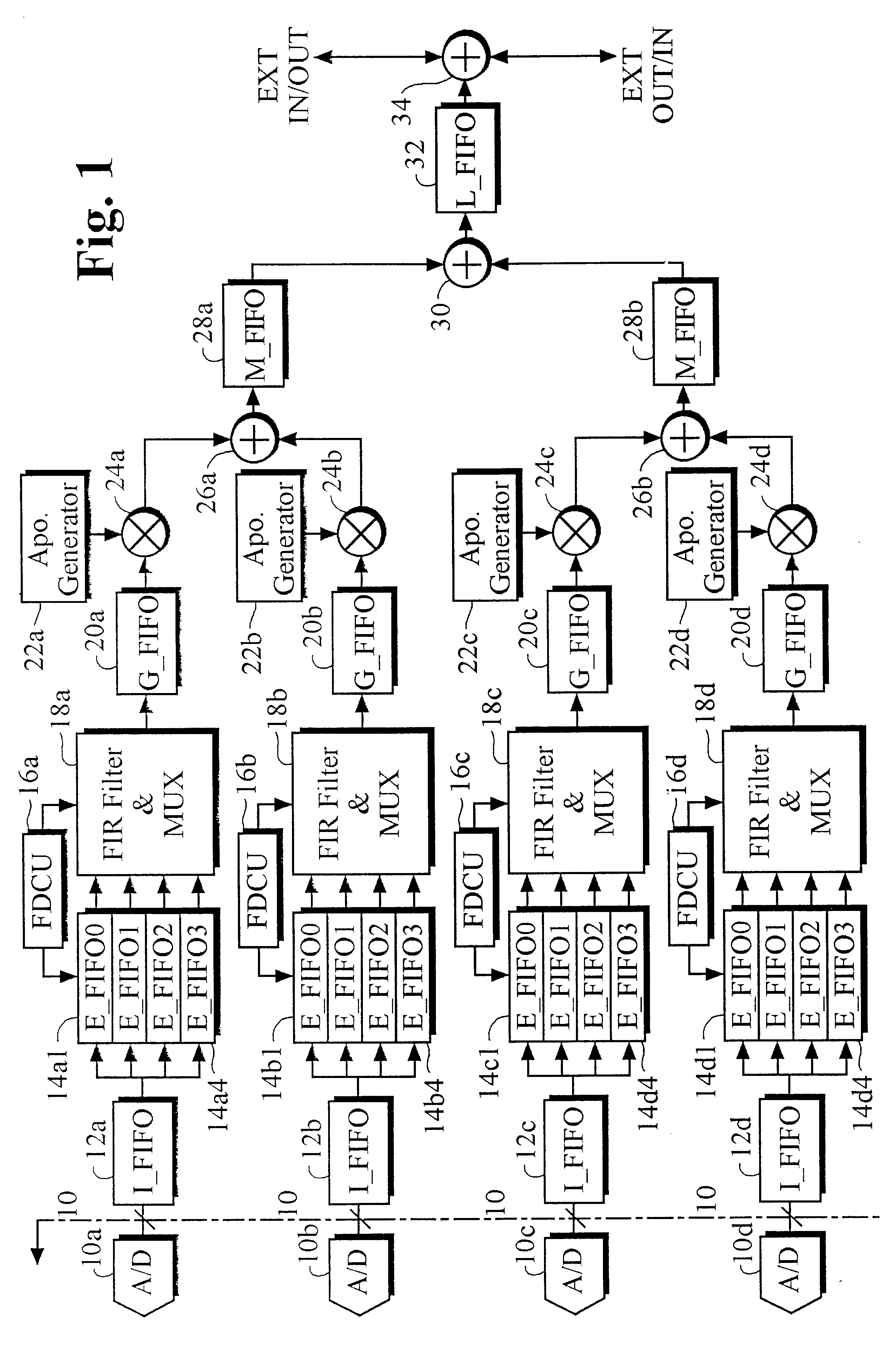

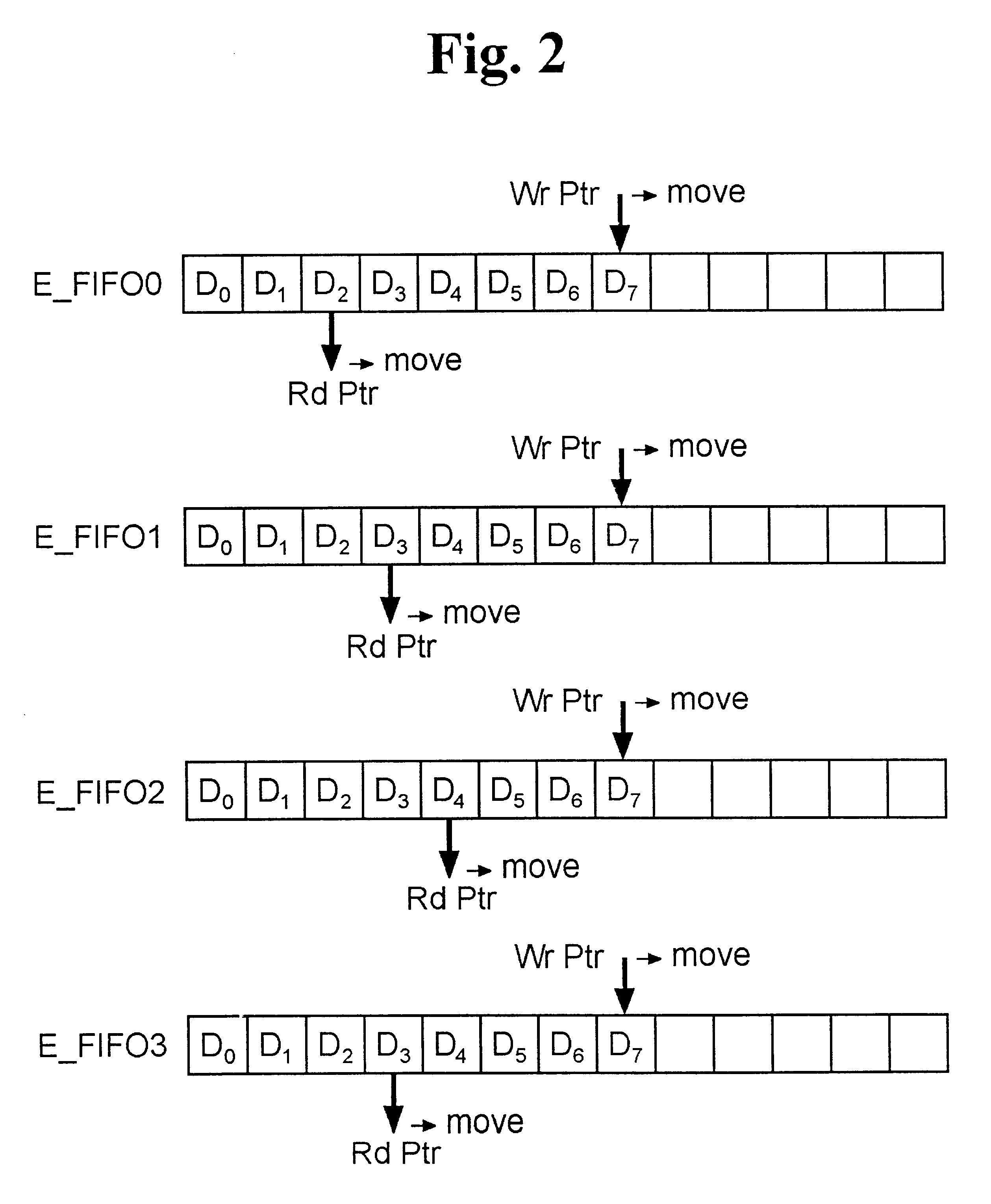

Ultrasound receive beamformer

InactiveUS7508737B1Reduce hardware complexitySound producing devicesPhotographyMultiplexingDelayed Memory

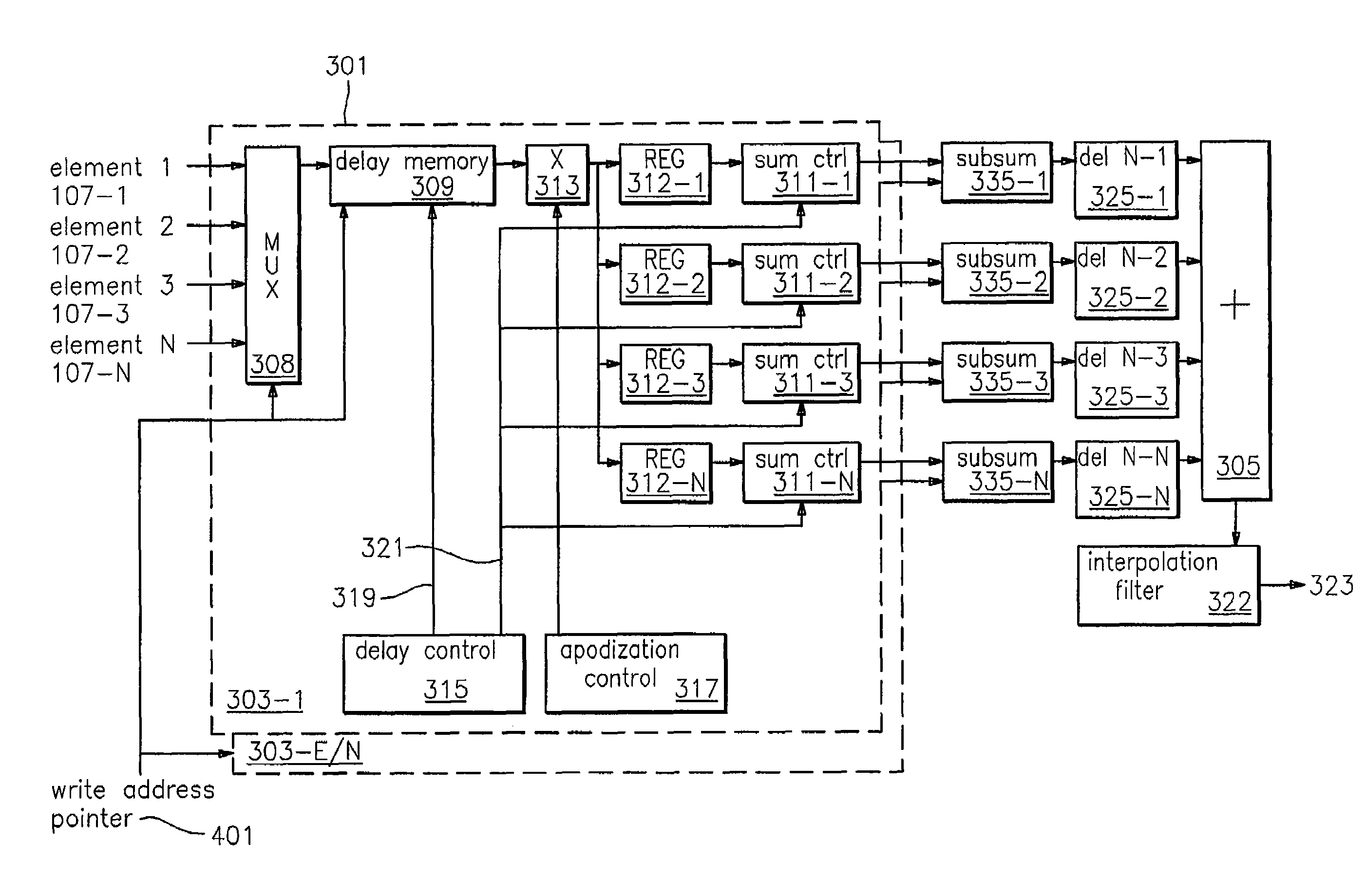

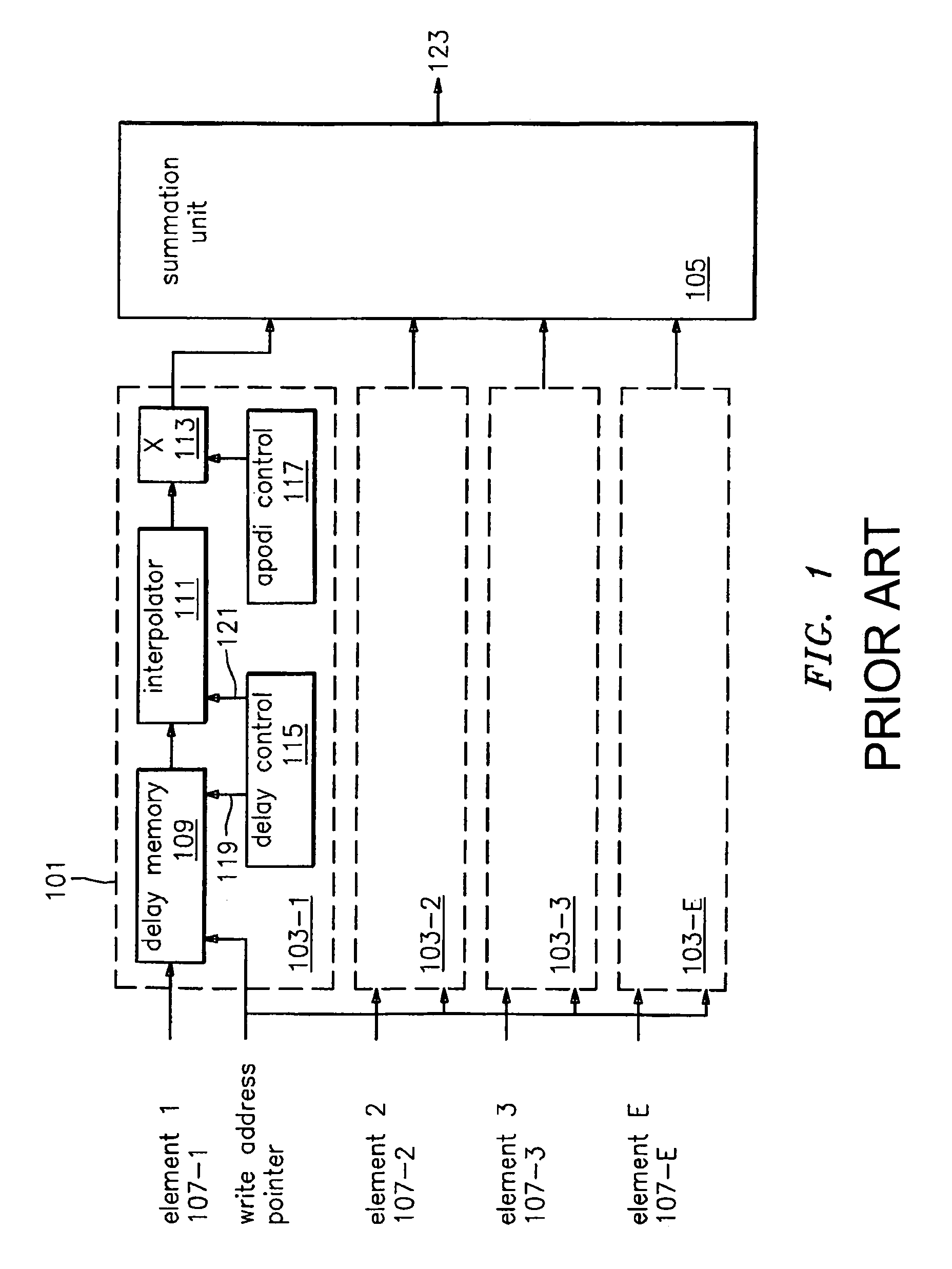

In an ultrasound receive beamformer signals from two or more aperture elements are multiplexed at the input of each beamformer channel, stored in different portions of a delay memory, delayed and apodized in a time-multiplexed fashion, demultiplexed at the output of the channel, and summed in different summation units running at an upsampled rate. The partial sums are then time-aligned, summed to produce the total upsampled beam sum, filtered and decimated in an interpolation filter to produce the beamformed signal.

Owner:HITACHI LTD

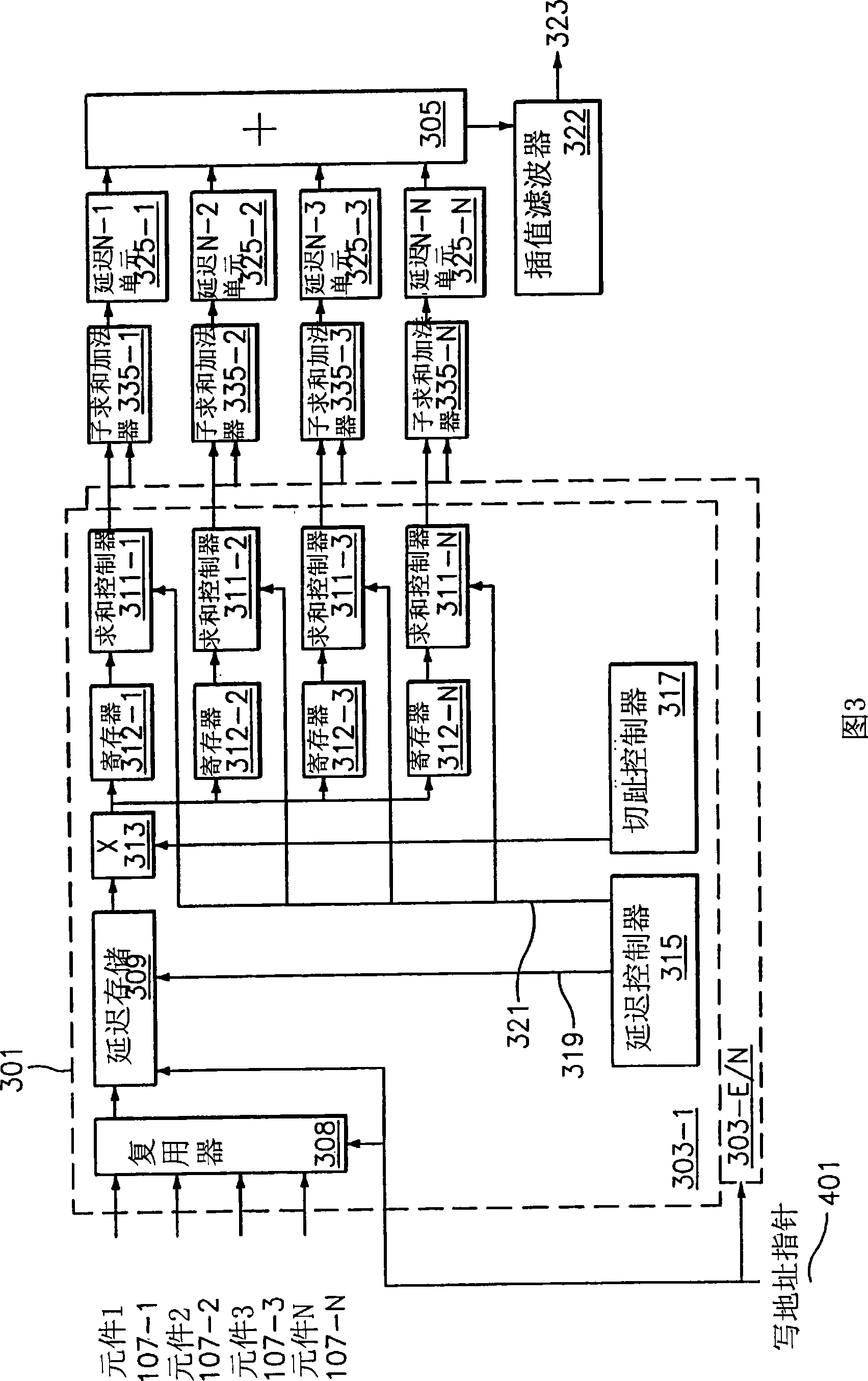

Ultrasound receive beamforming apparatus using multi stage delay devices

InactiveUS20010051772A1Wave based measurement systemsHeart/pulse rate measurement devicesTransducerDelayed Memory

By using a novel structure of a beamformer which produce data for multiple receive scanlines in a time multiplexed manner, the size of the delay memory is reduced. An ultrasound receive beamforming apparatus for processing signals received from an array of transducers, comprises: a plurality of beamforming devices for applying delays to data samples of M channels. Each of said beamforming devices includes: a predetermined number of per-channel delay elements which provide first delays to the data samples of M channels, to provide delayed data per each channel and per each receive beam, first adders for adding the delayed data of not less than 2 channels provided from the per-channel delay elements, and multi-channel delay elements which provide second delays to the outputs of the first adders.

Owner:MEDISON CO LTD

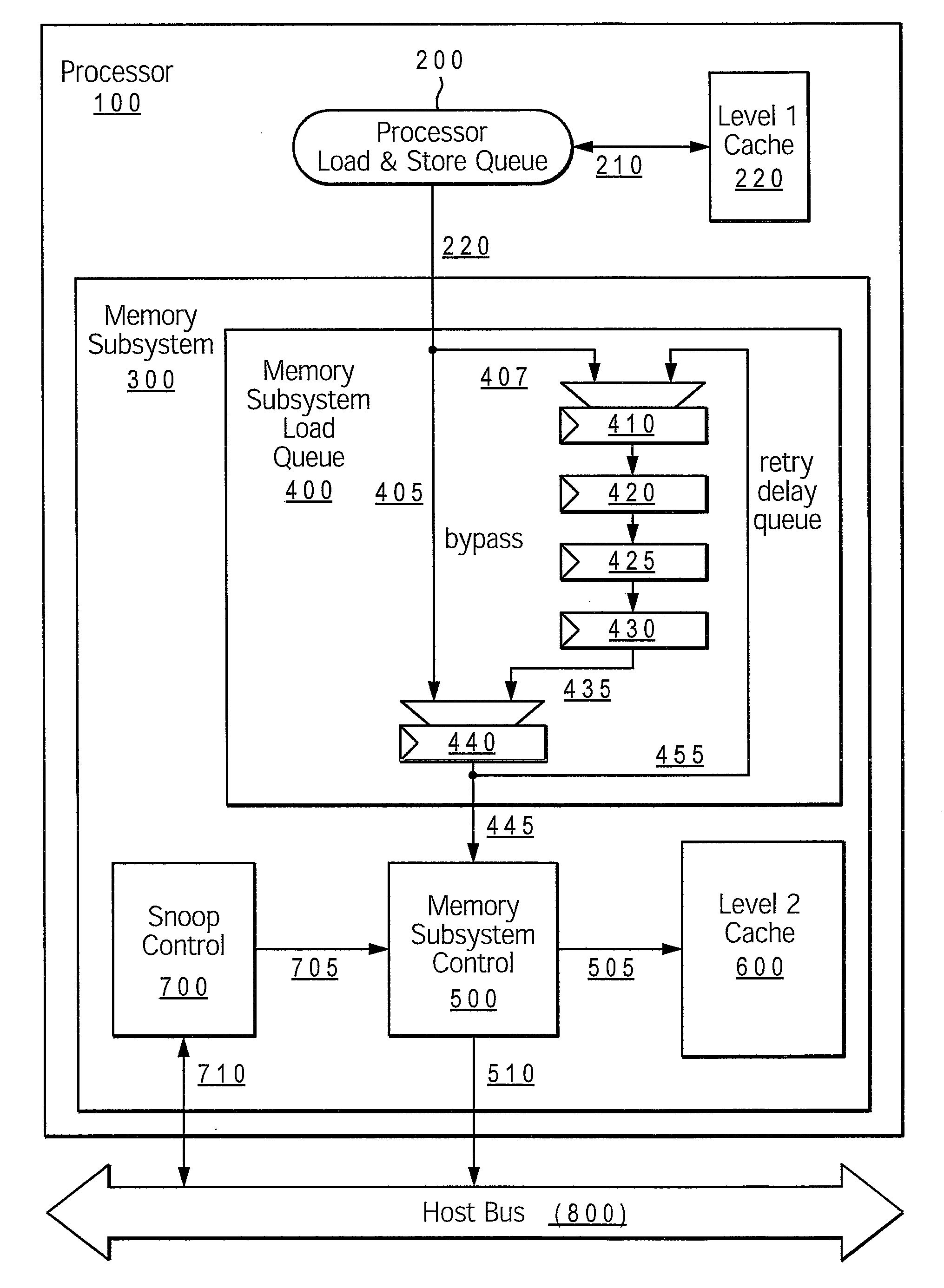

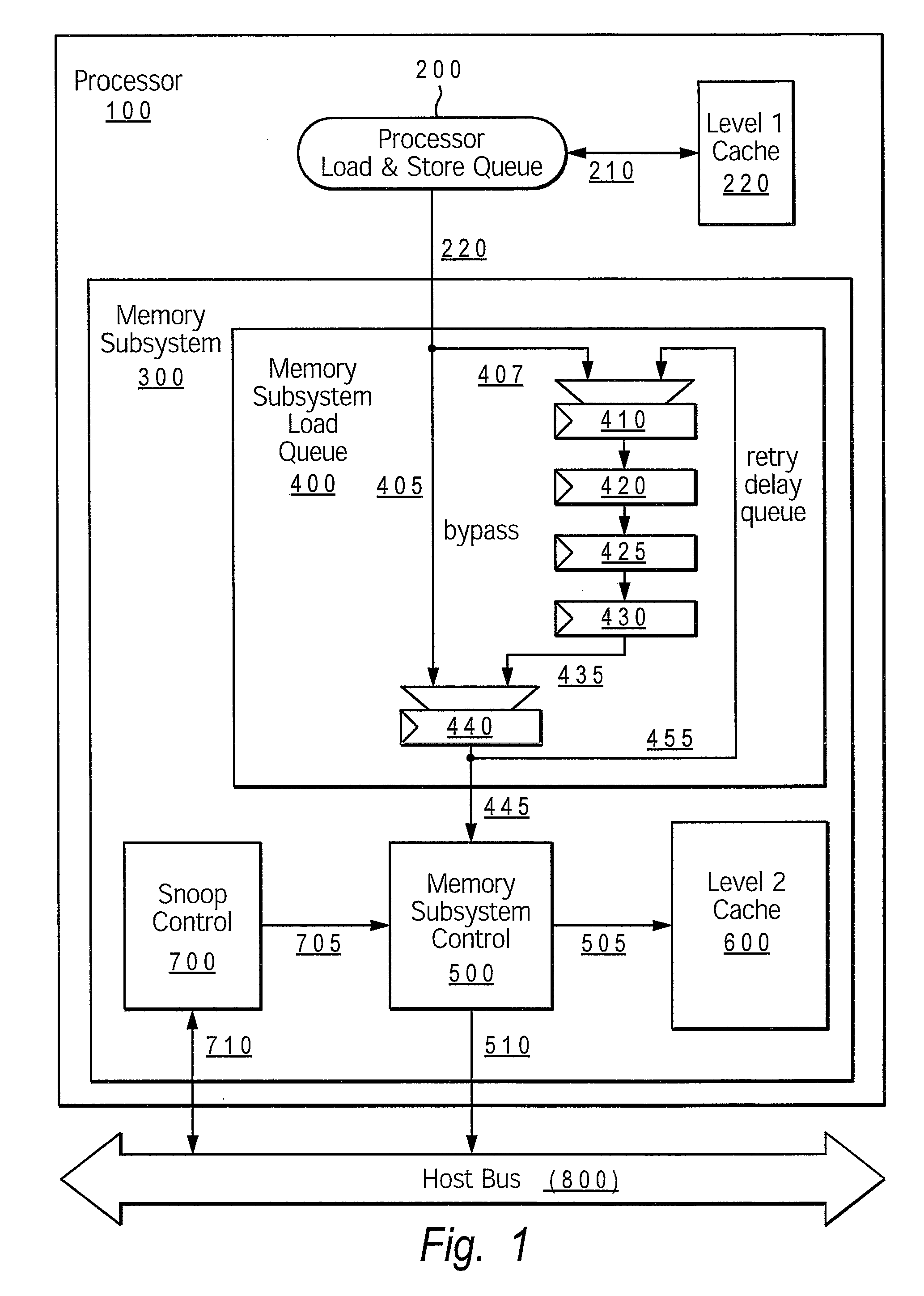

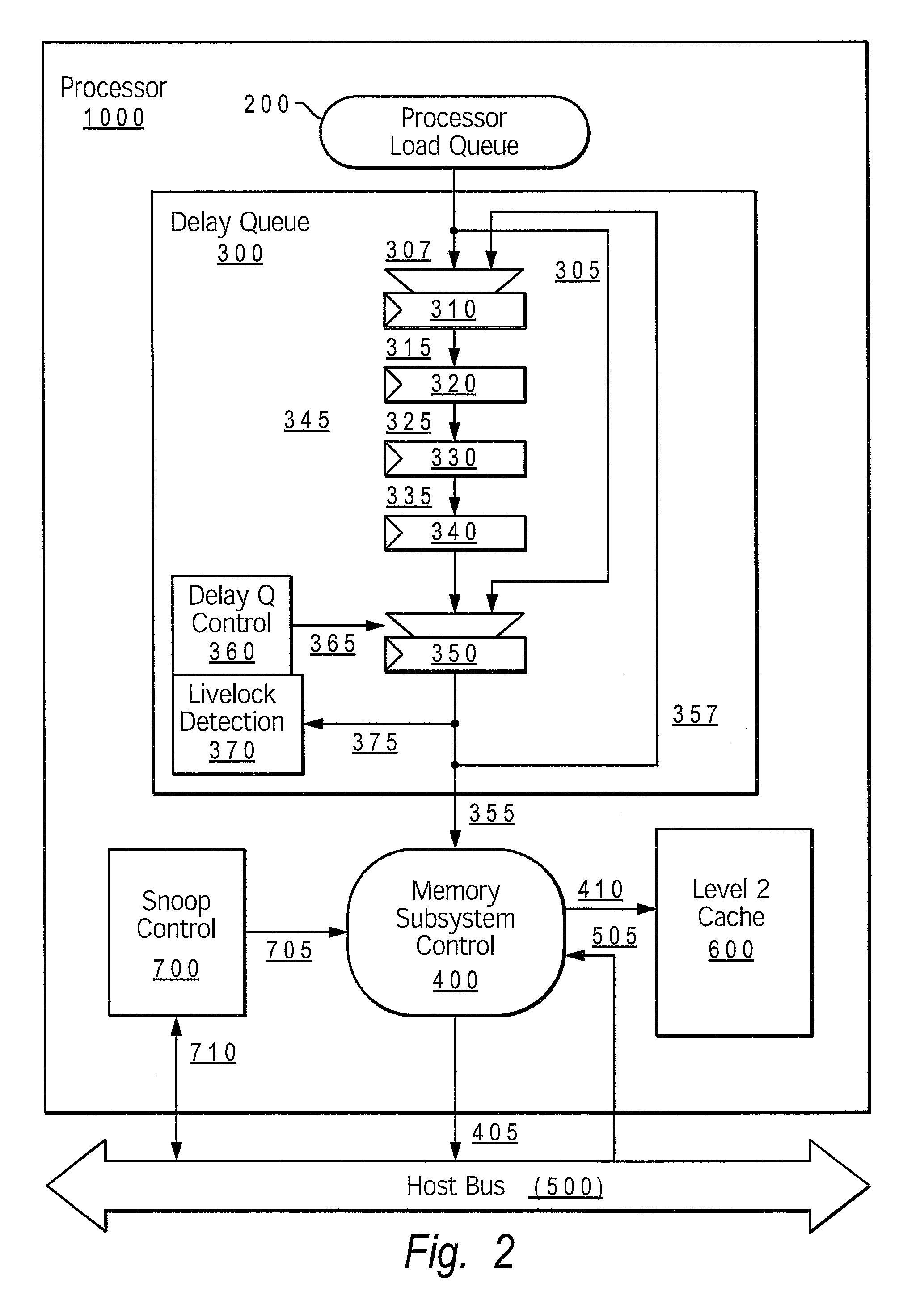

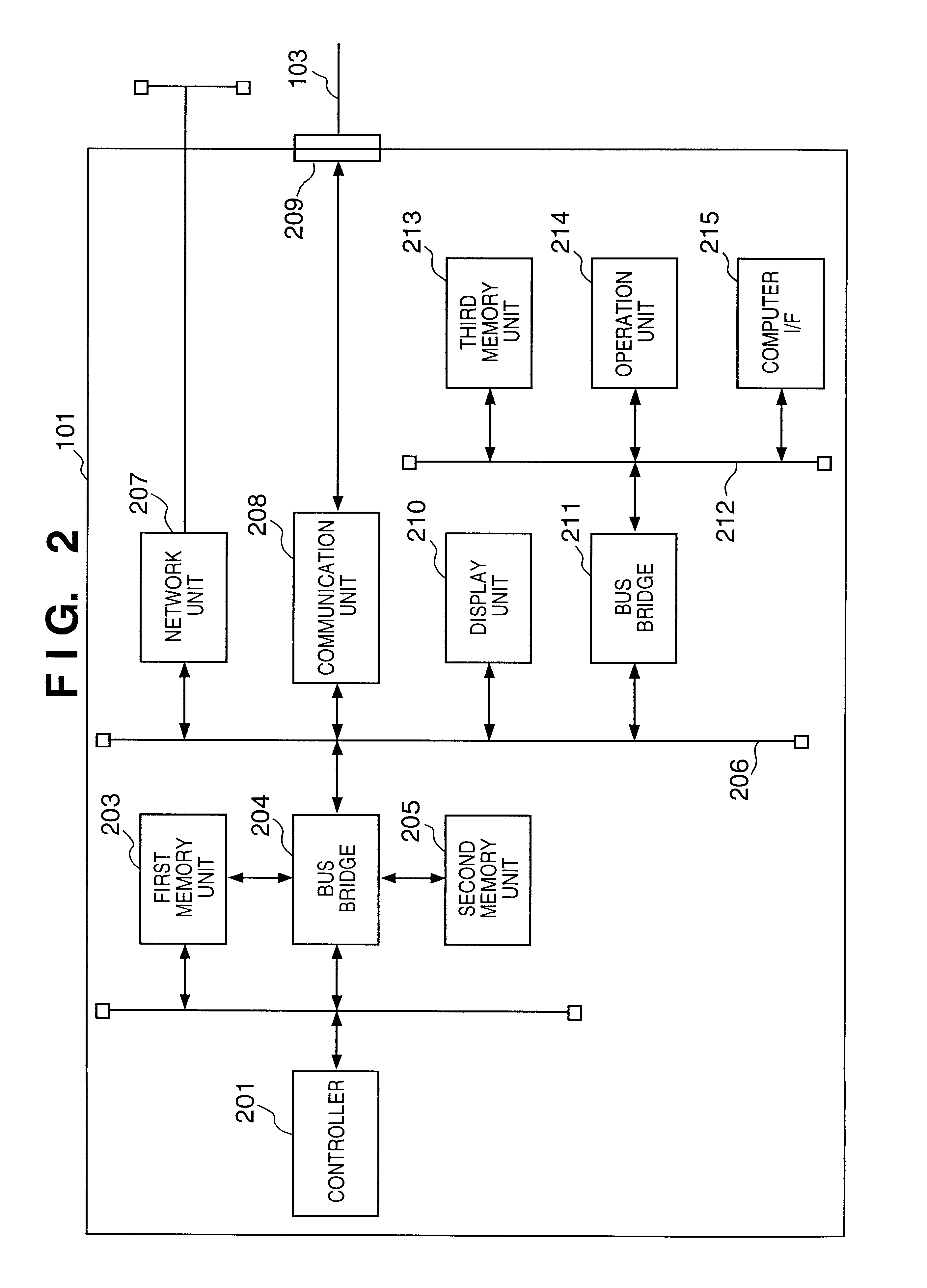

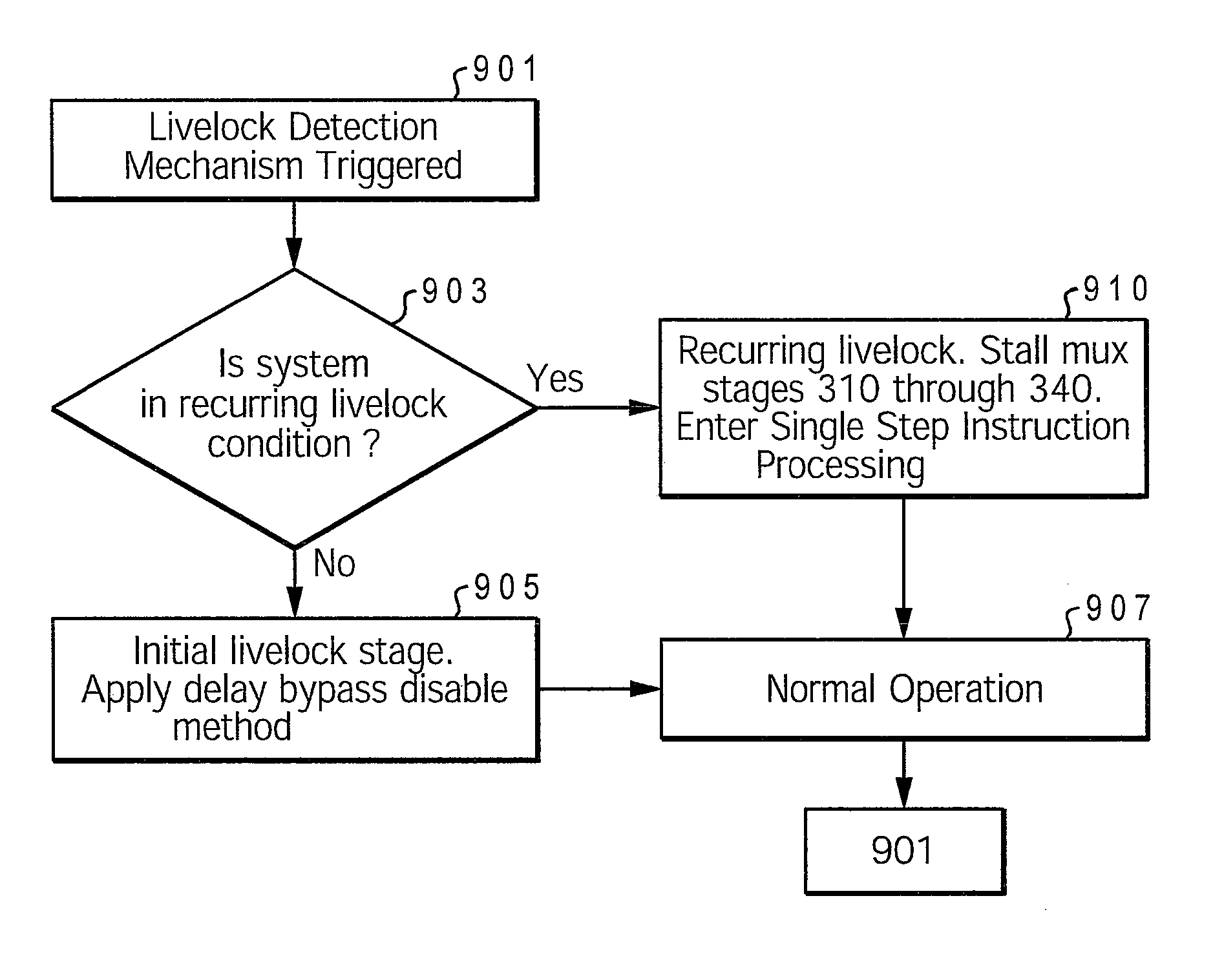

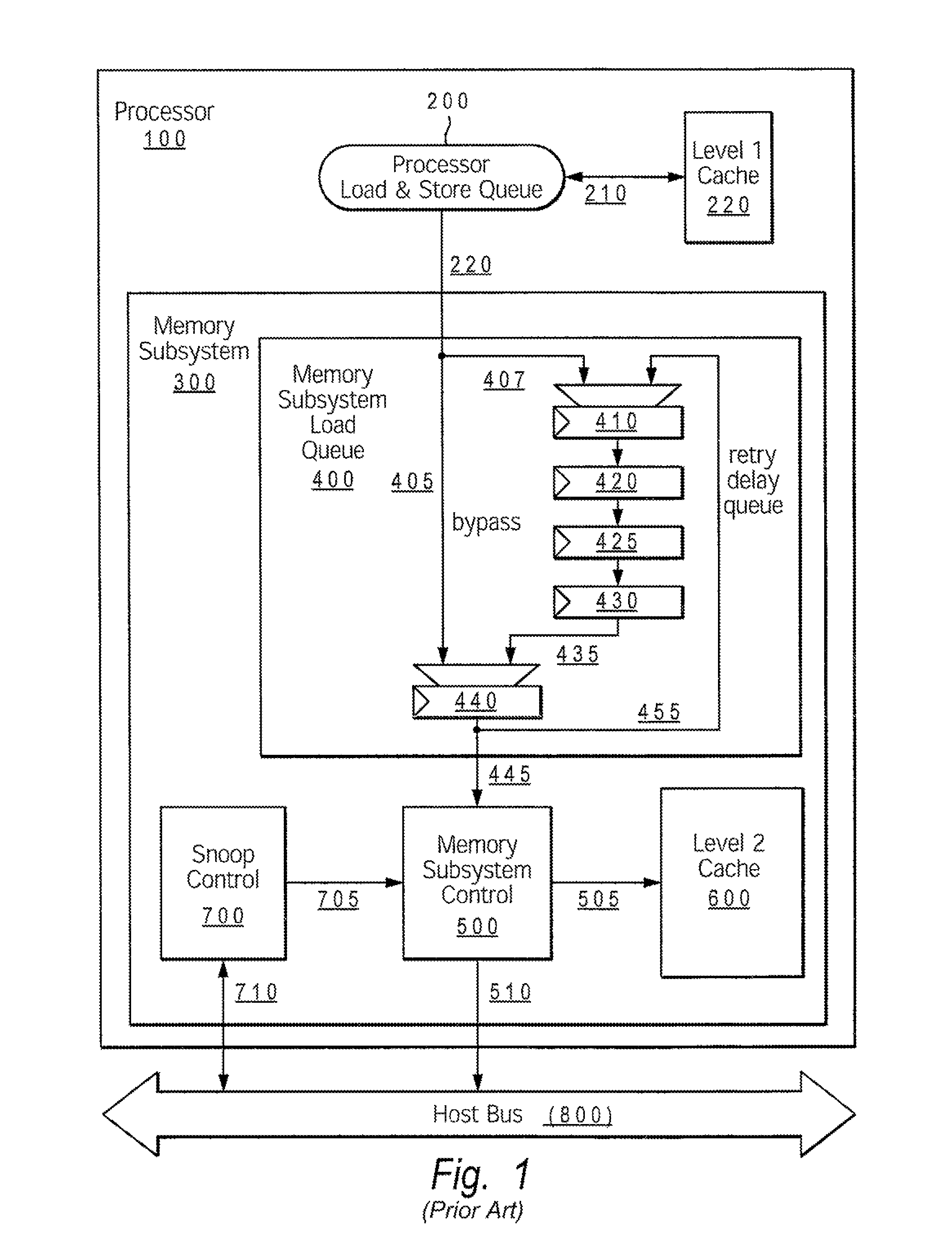

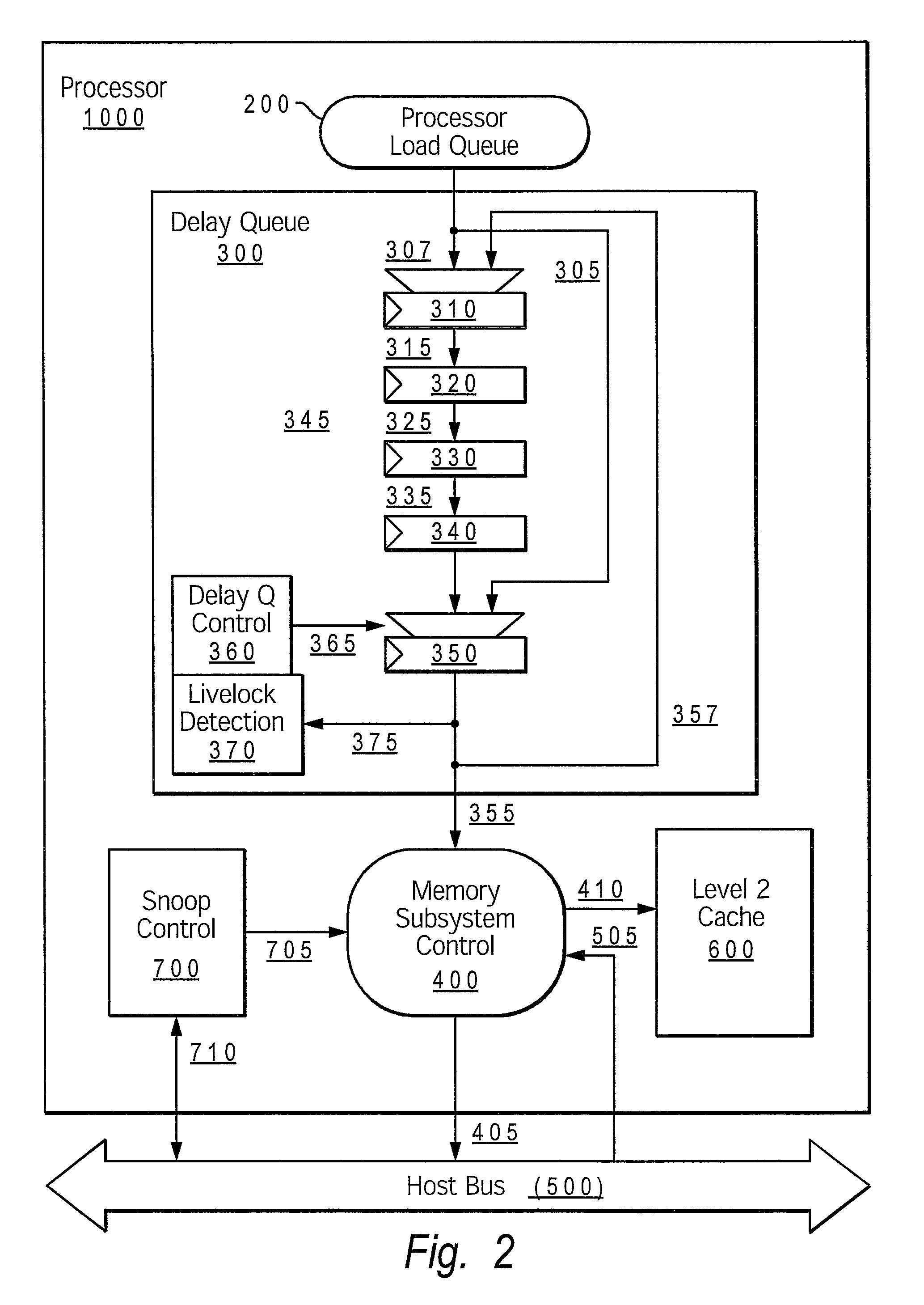

Structure for dynamic livelock resolution with variable delay memory access queue

InactiveUS20080301374A1Memory adressing/allocation/relocationDigital computer detailsImage resolutionParallel computing

A design structure for resolving the occurrence of livelock at the interface between the processor core and memory subsystem controller. Livelock is resolved by introducing a livelock detection mechanism (which includes livelock detection utility or logic) within the processor to detect a livelock condition and dynamically change the duration of the delay stage(s) in order to alter the “harmonic” fixed-cycle loop behavior. The livelock detection logic (LDL) counts the number of flushes a particular instruction takes or the number of times an instruction re-issues without completing. The LDL then compares that number to a preset threshold number. Based on the result of the comparison, the LDL triggers the implementation of one of two different livelock resolution processes. These processes include dynamically configuring the delay queue within the processor into one of two different configurations and changing the sequence and timing of handling memory access instructions, based on the specific configuration of the delay queue.

Owner:IBM CORP

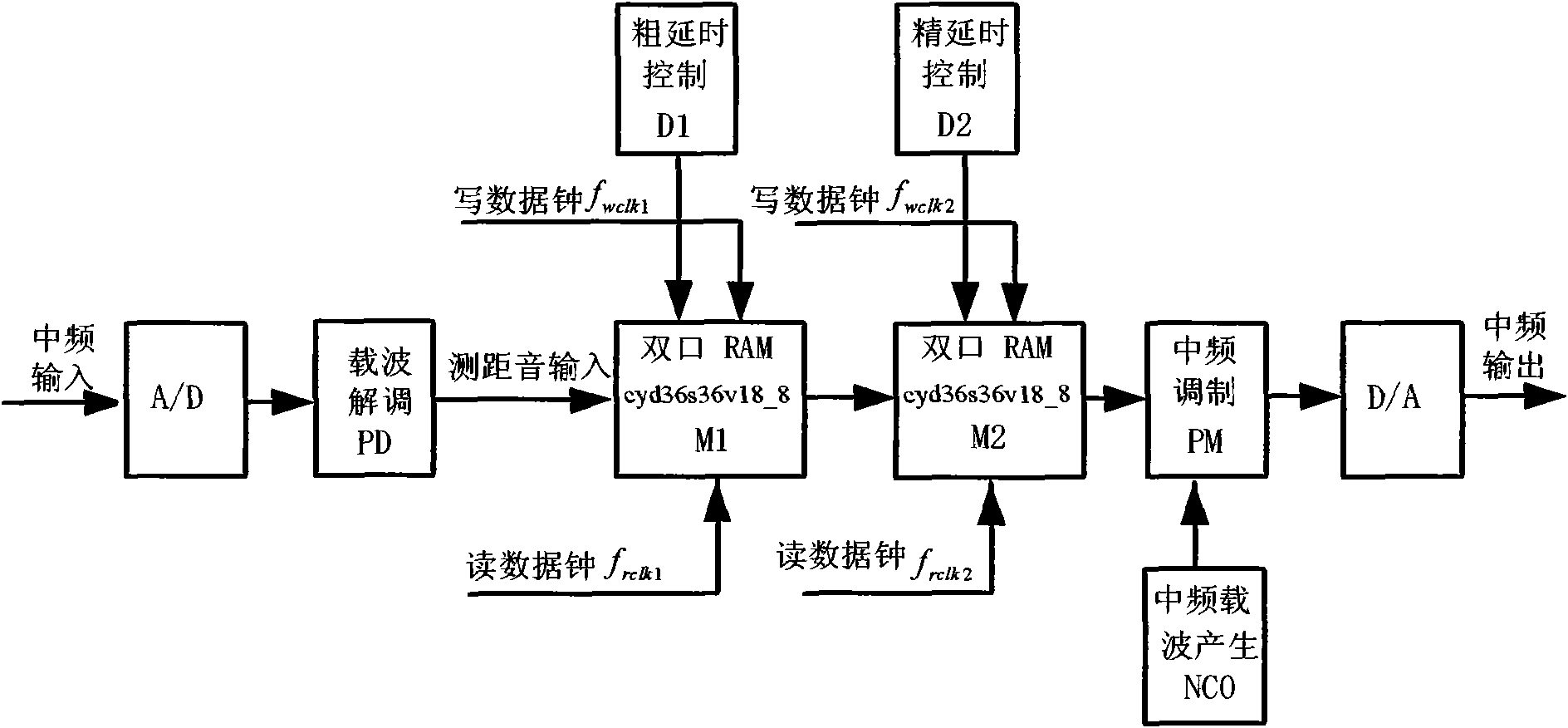

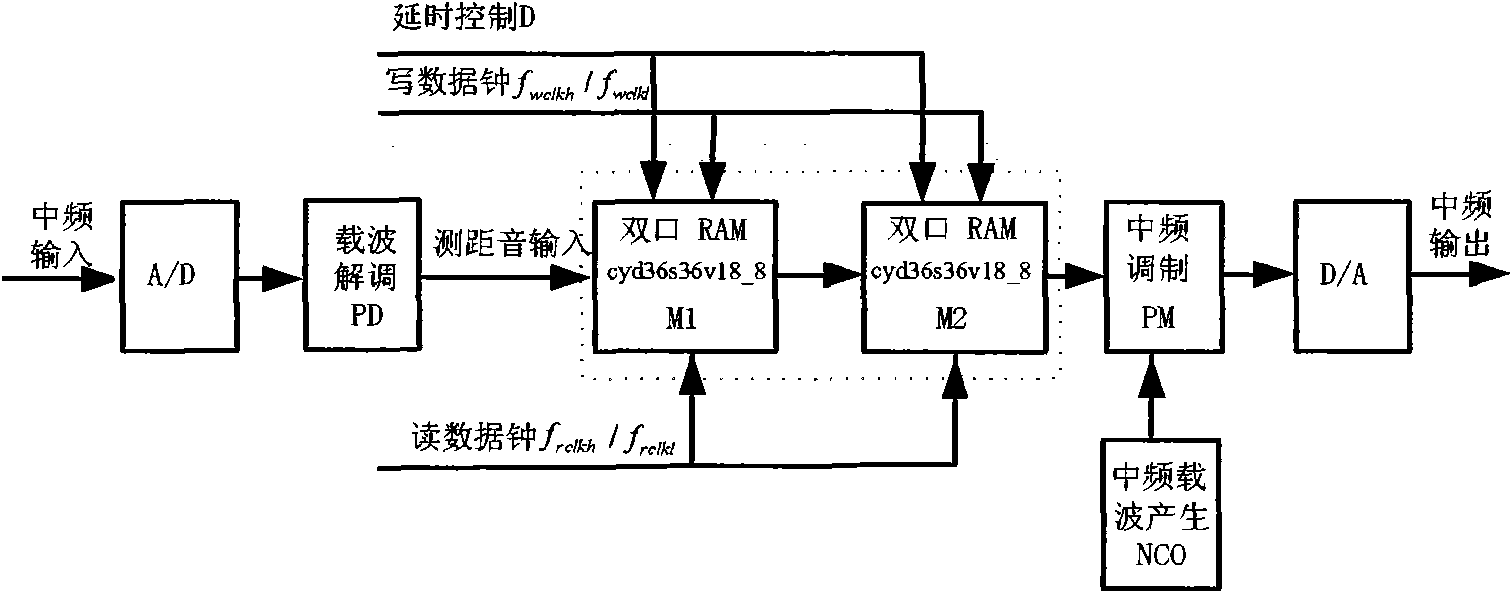

Method for simulating dynamic target signals with high accuracy

ActiveCN101825699ARealize dynamic simulationGuaranteed accuracyWave based measurement systemsIntermediate frequencyTarget signal

The invention provides a method for simulating dynamic target signals with high accuracy, aiming to provide a treatment method which has little hardware resource consumption and can carry out remote and high-accuracy dynamic simulation. In the method, distance measurement sounds are obtained by carrying carrier demodulation on received intermediate frequency signals and are stored in a memory group used as distance delay, a Doppler frequency corresponding to speed in track parameters is added on a data reading clock to carry out asynchronous data reading and writing, a double-port RAM (RandomAccess Memory) is utilized as a distance delay memory, an extremely remote distance is divided into thick and thin distances by a limited storage space to carry out combination simulation or carry out step simulation based on the requirements of distance and the accuracy; and a sum path direction, a difference path direction and a difference path pitching attenuator are utilized to calculate sum and difference signal amplitude based on angle data and an antenna direction diagram in the rack parameters, calculate the attenuation quantity of the attenuator and respectively control sum path output signal amplitude and difference path output signal amplitude to carry out angle simulation, thereby realizing dynamic simulation with different distances and different accuracy.

Owner:10TH RES INST OF CETC

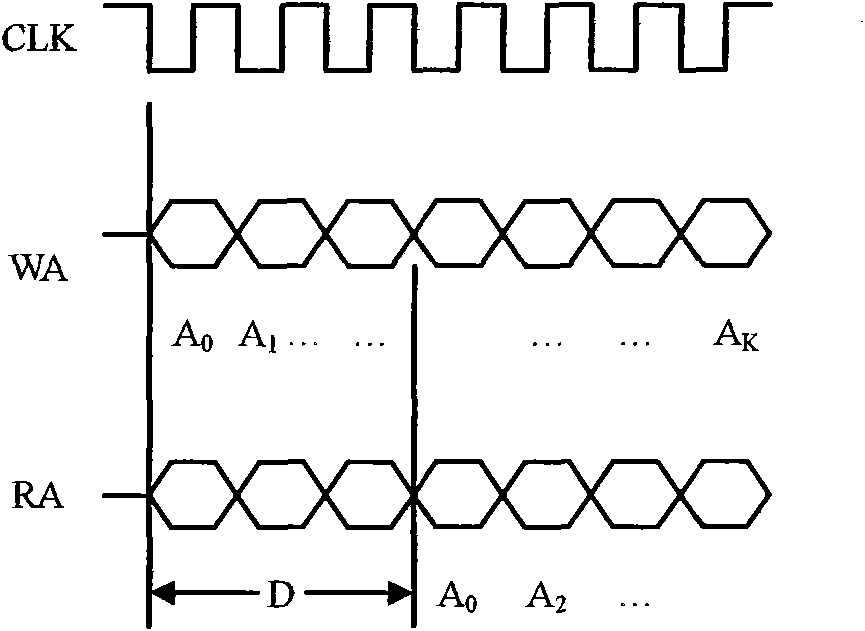

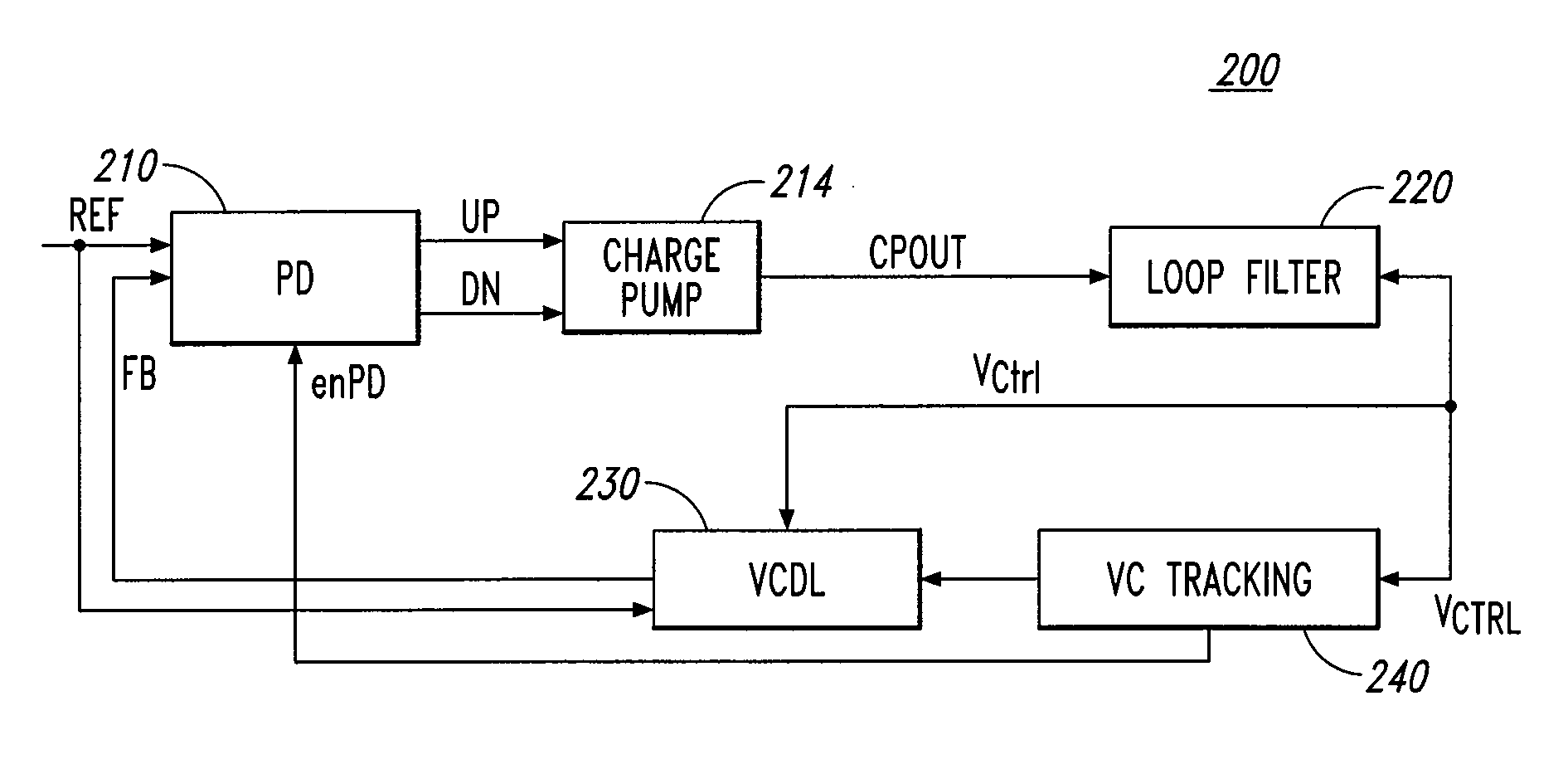

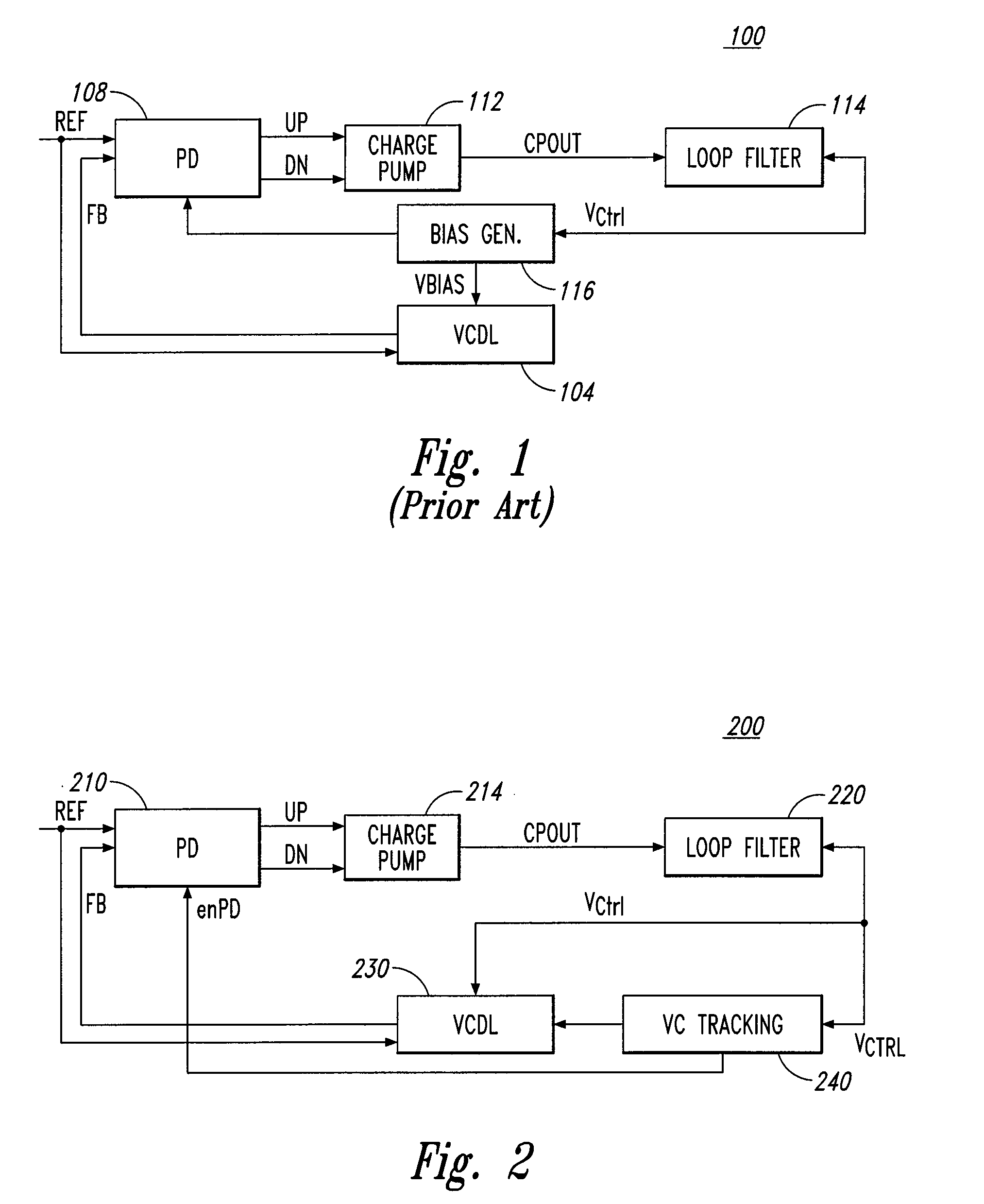

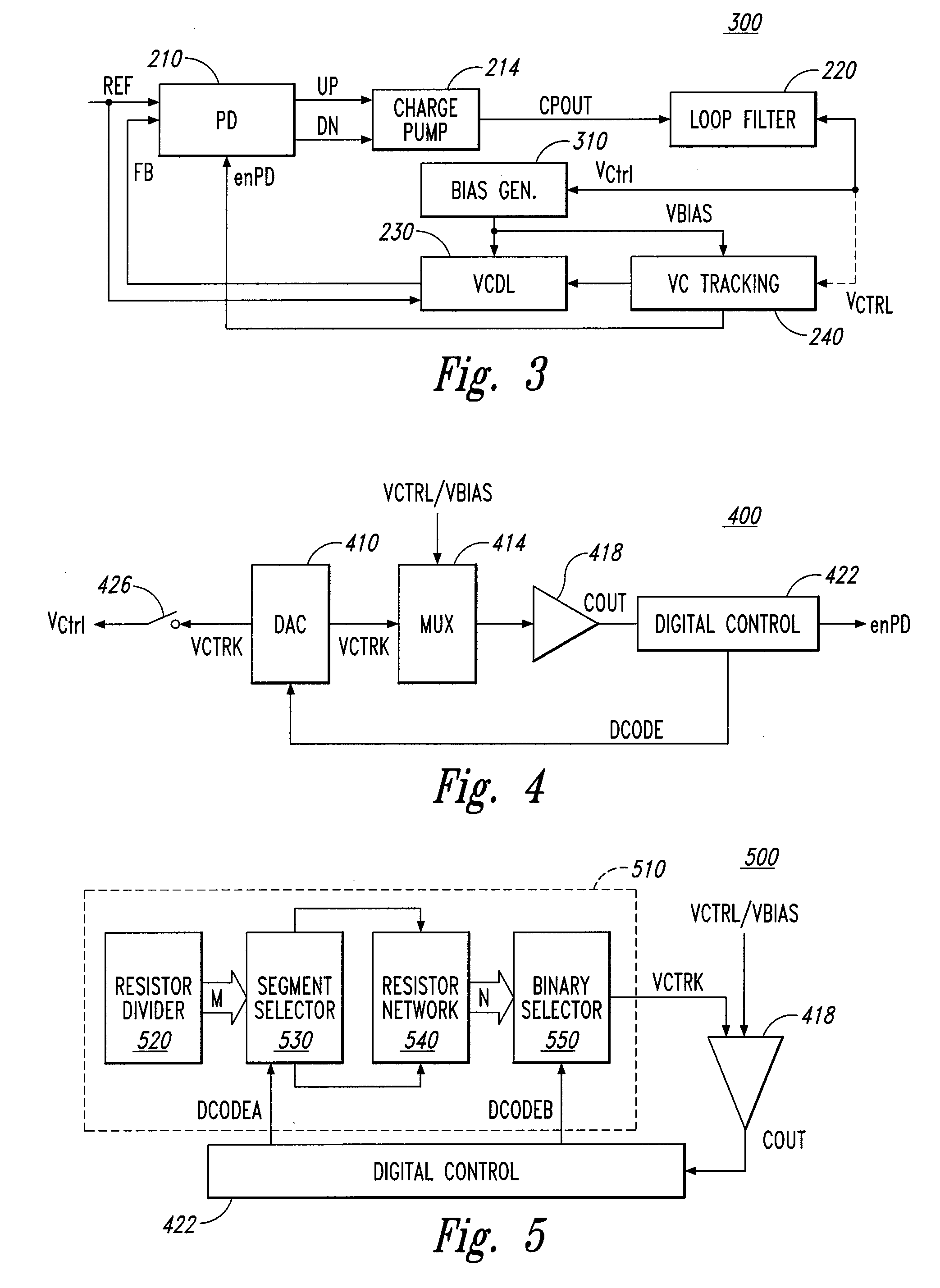

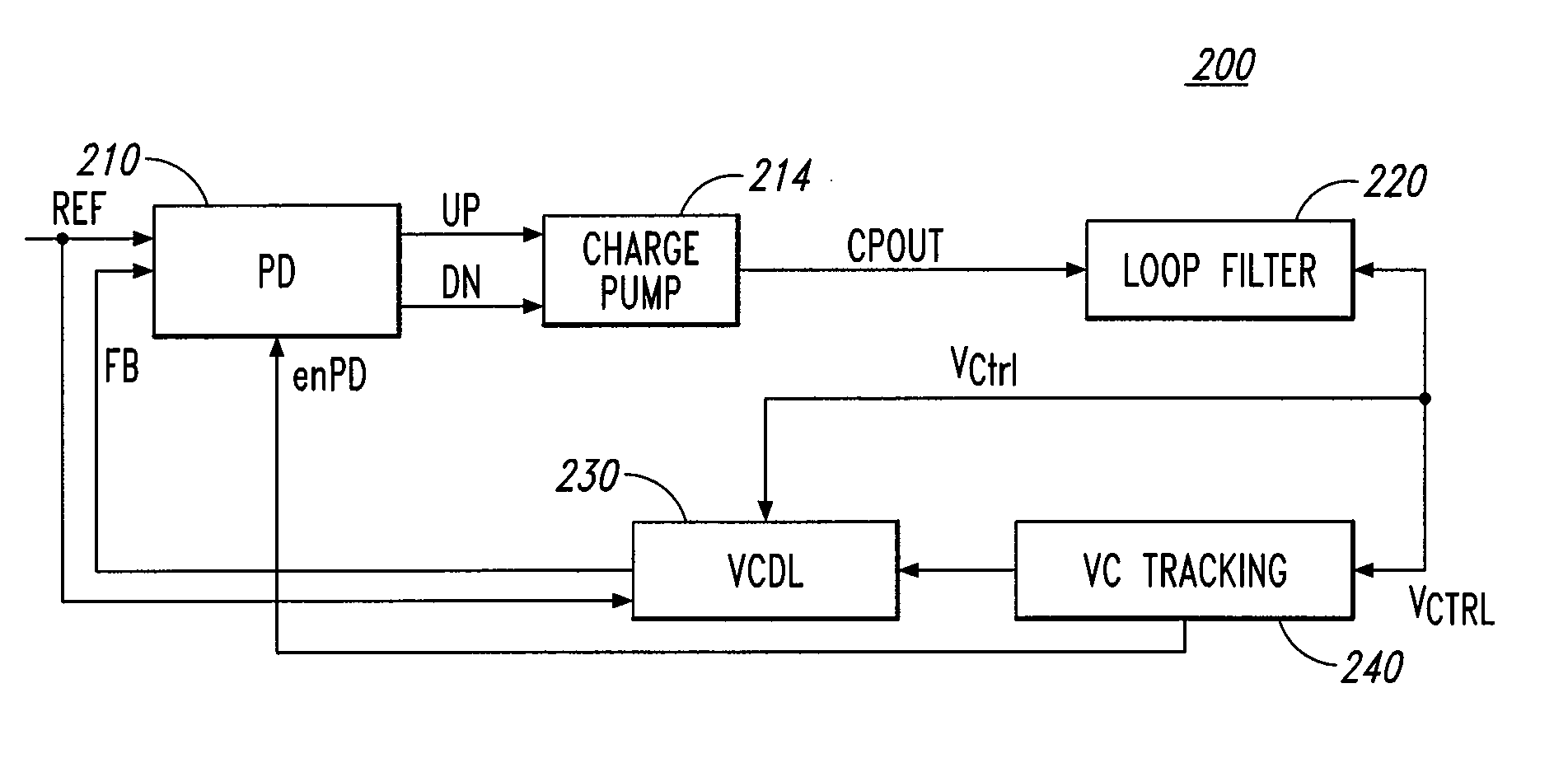

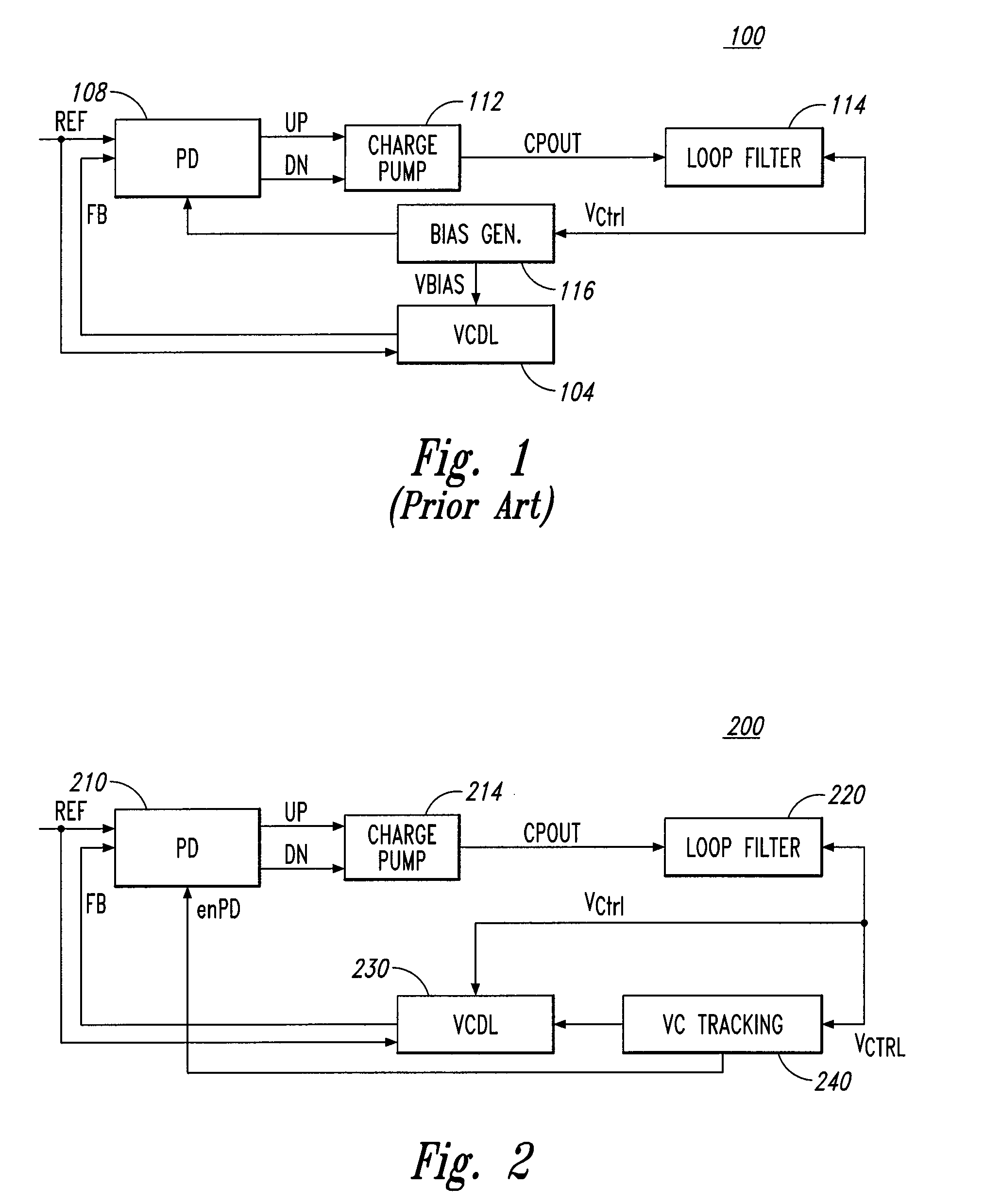

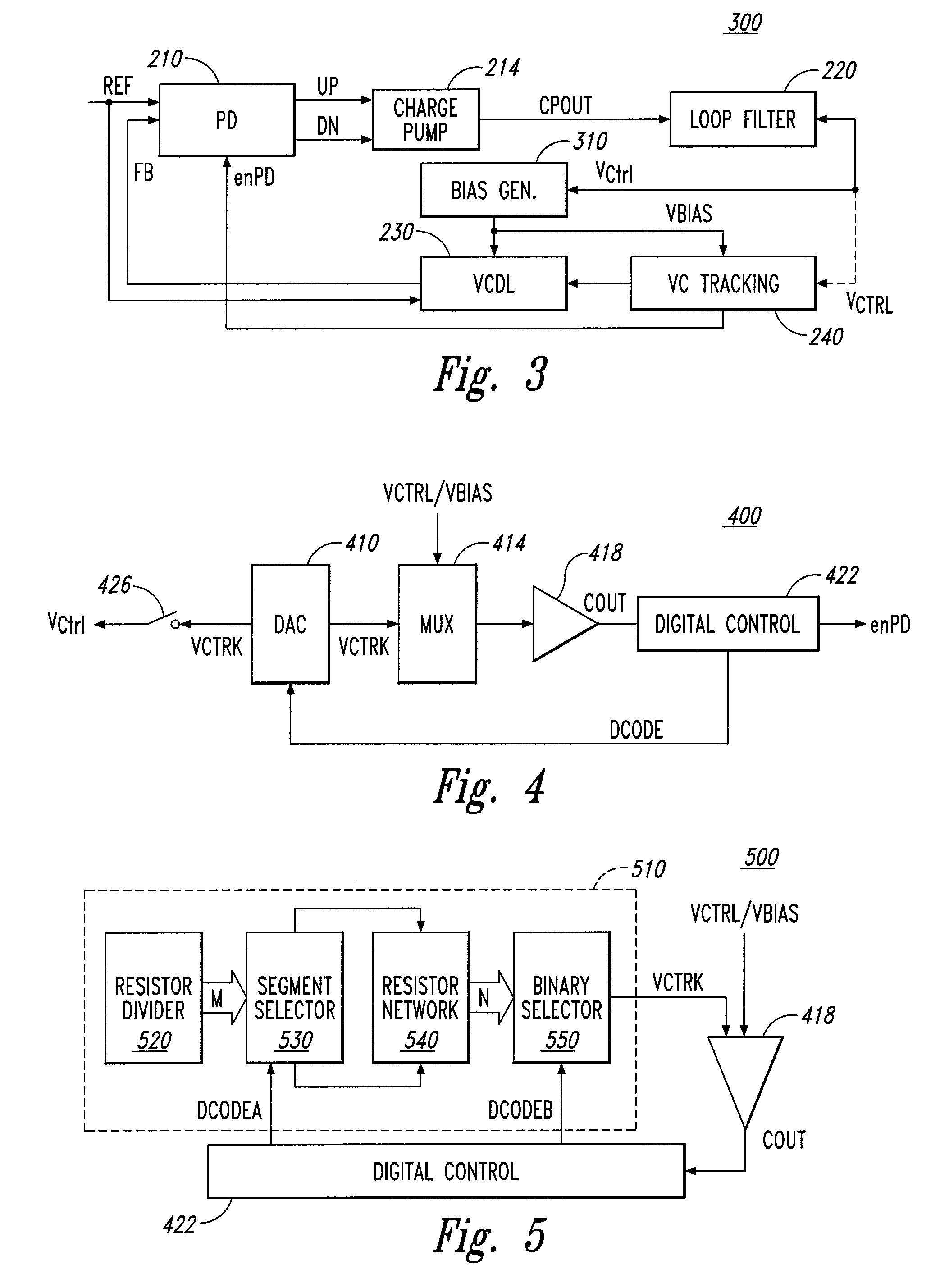

Control voltage tracking circuits, methods for recording a control voltage for a clock synchronization circuit and methods for setting a voltage controlled delay

Memories, clock synchronization circuits, clock synchronization controller circuits, and methods for setting a voltage controlled delay of a clock synchronization circuit and tracking and recording the control voltage are disclosed. For example, a clock synchronization controller provides an initial control voltage to the voltage controlled delay during initialization of the synchronization circuit until a phase dependent control voltage stabilizes. The stable phase dependent control voltage is substituted for the initial control voltage. Following stabilization of the phase dependent control voltage, a phase detector of the clock synchronization circuit is activated. A recovery control voltage is provided by the clock synchronization controller to the voltage controlled delay during recovery of the clock synchronization from a power-saving mode until the phase dependent control voltage stabilizes.

Owner:MICRON TECH INC

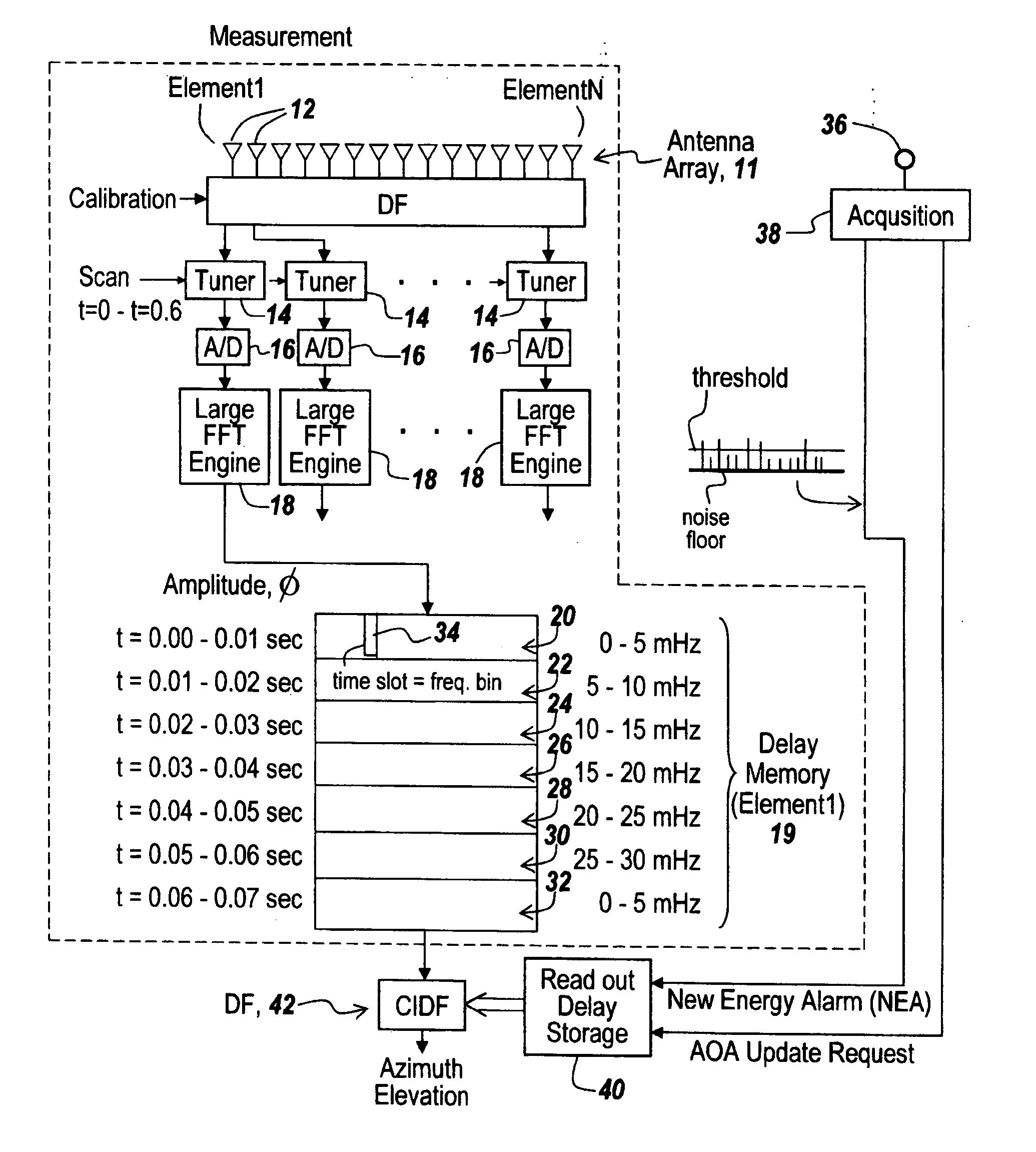

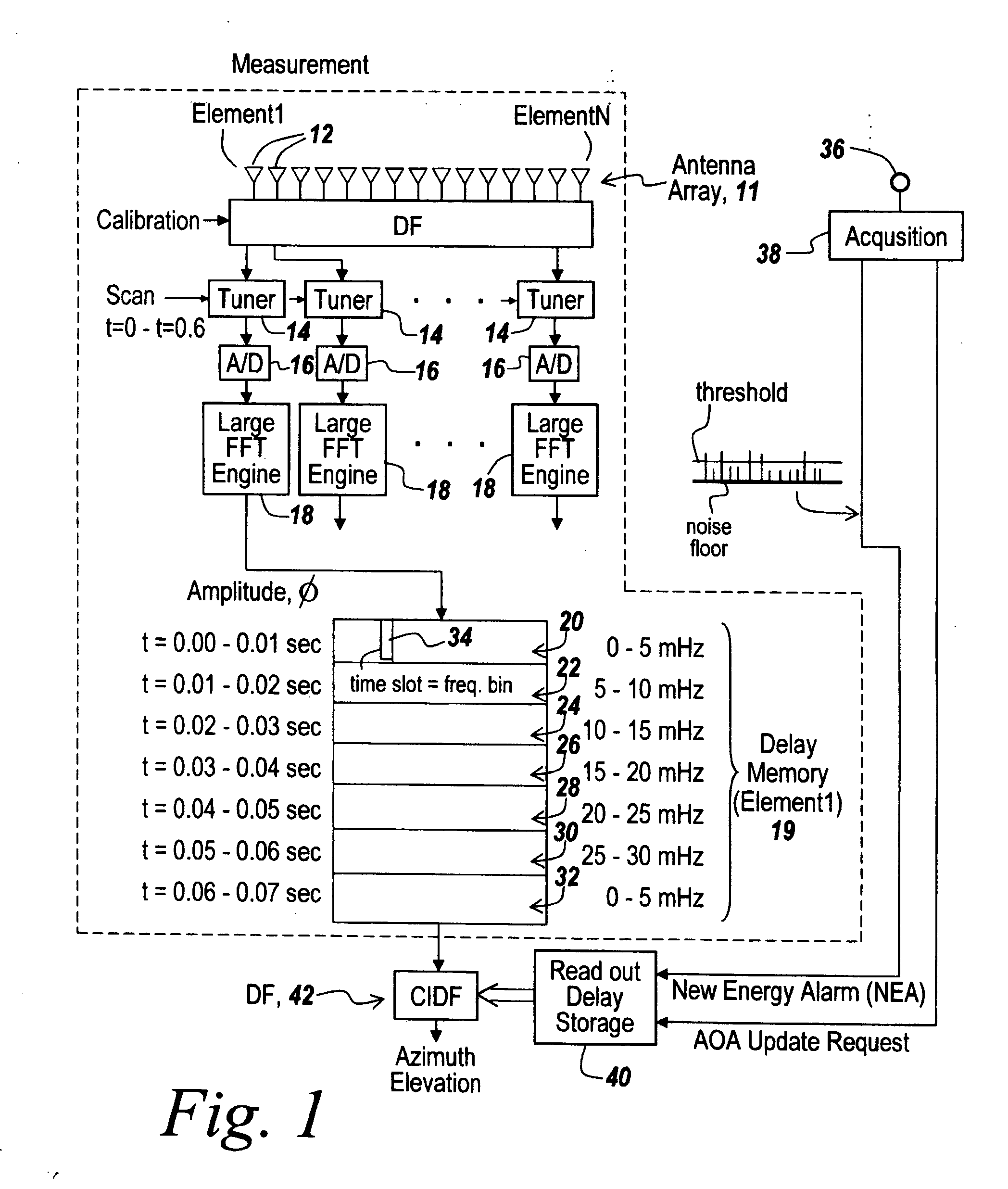

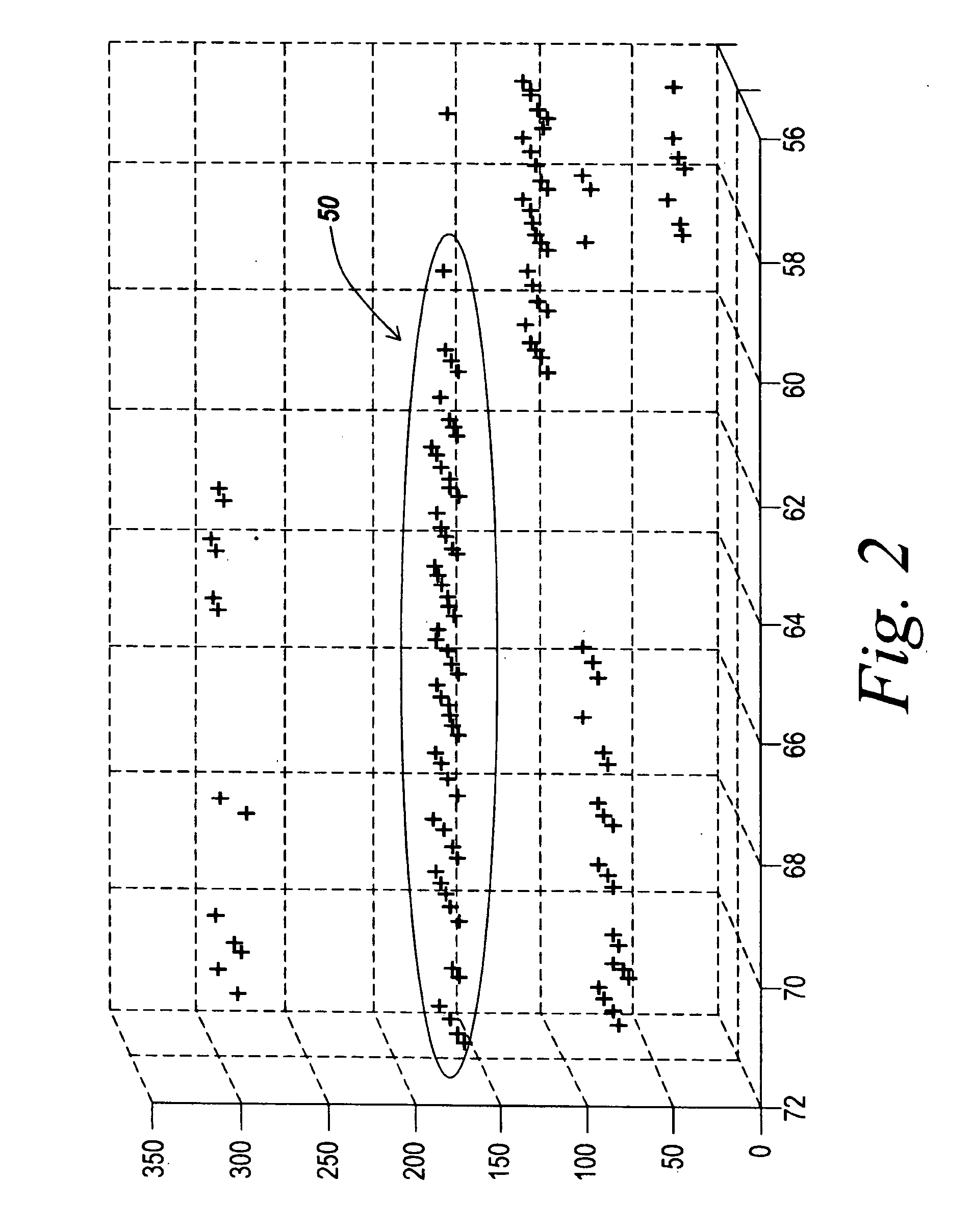

Method and apparatus for direction finding

ActiveUS20060227050A1Refine line of bearing accuracyKeep for a long timeMulti-channel direction-finding systems using radio wavesPosition fixationDelayed MemorySignal of interest

A direction finding system is used in which a number of adjacent bands are sequentially measured in fast rotation, with the results from each of the bands being FFT processed to provide amplitude and phase information on all of the signals existing within the band. Upon ascertaining that one wishes to do a direction finding process, one merely accesses the information in the delay memory so that direction finding resources are only allocated to signals of interest and such that one does not have to re-do an FFT upon finding a signal of interest.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

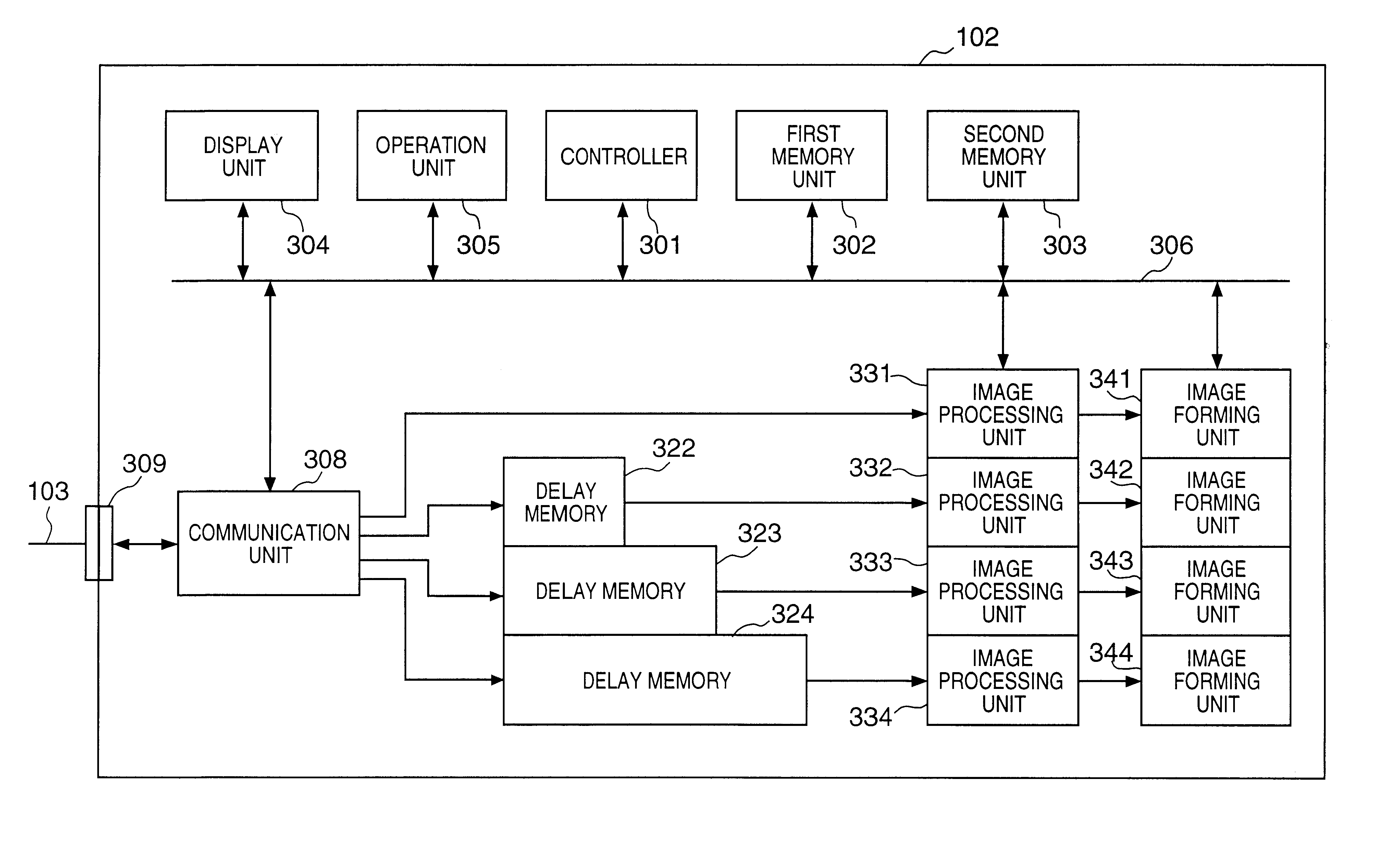

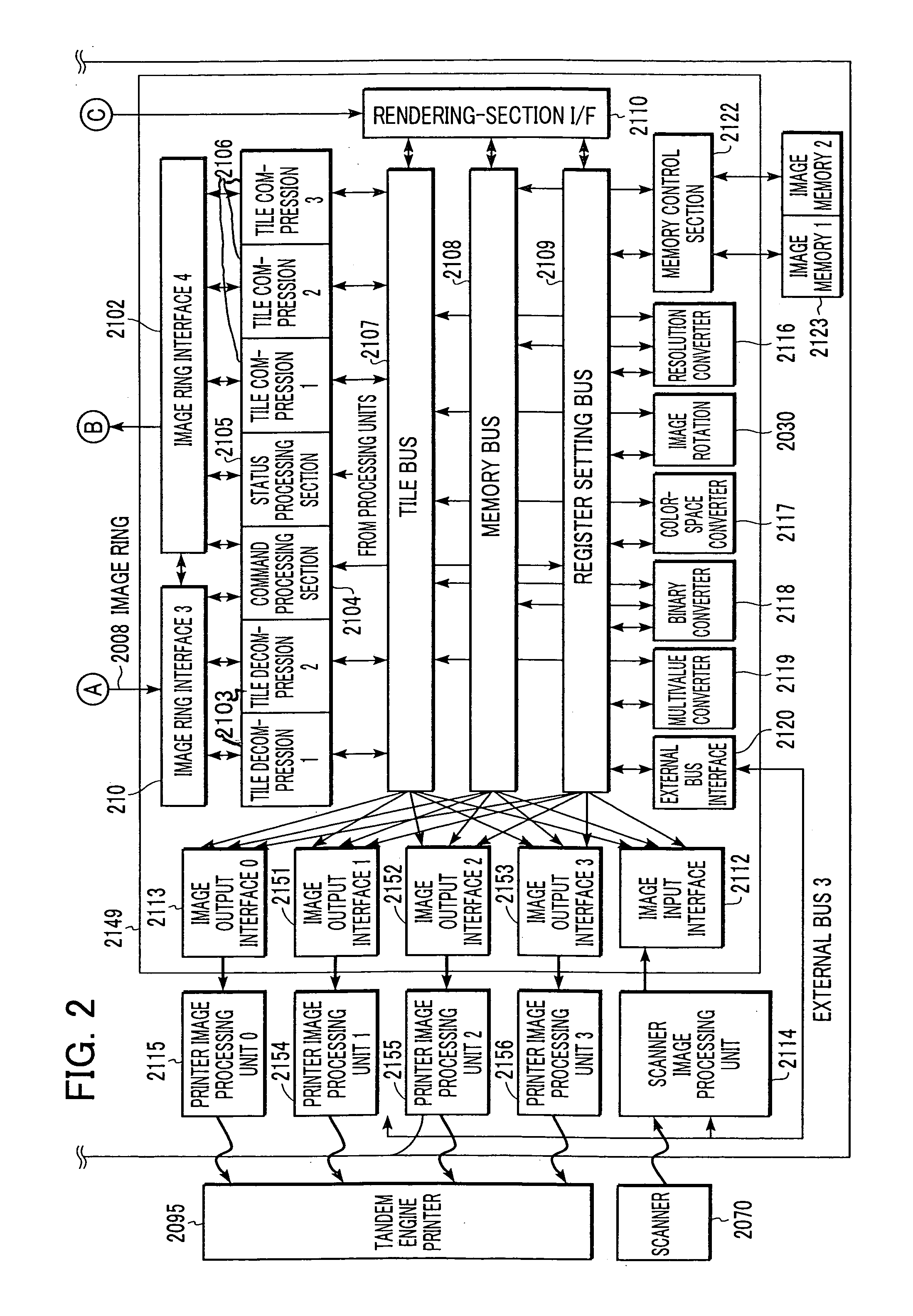

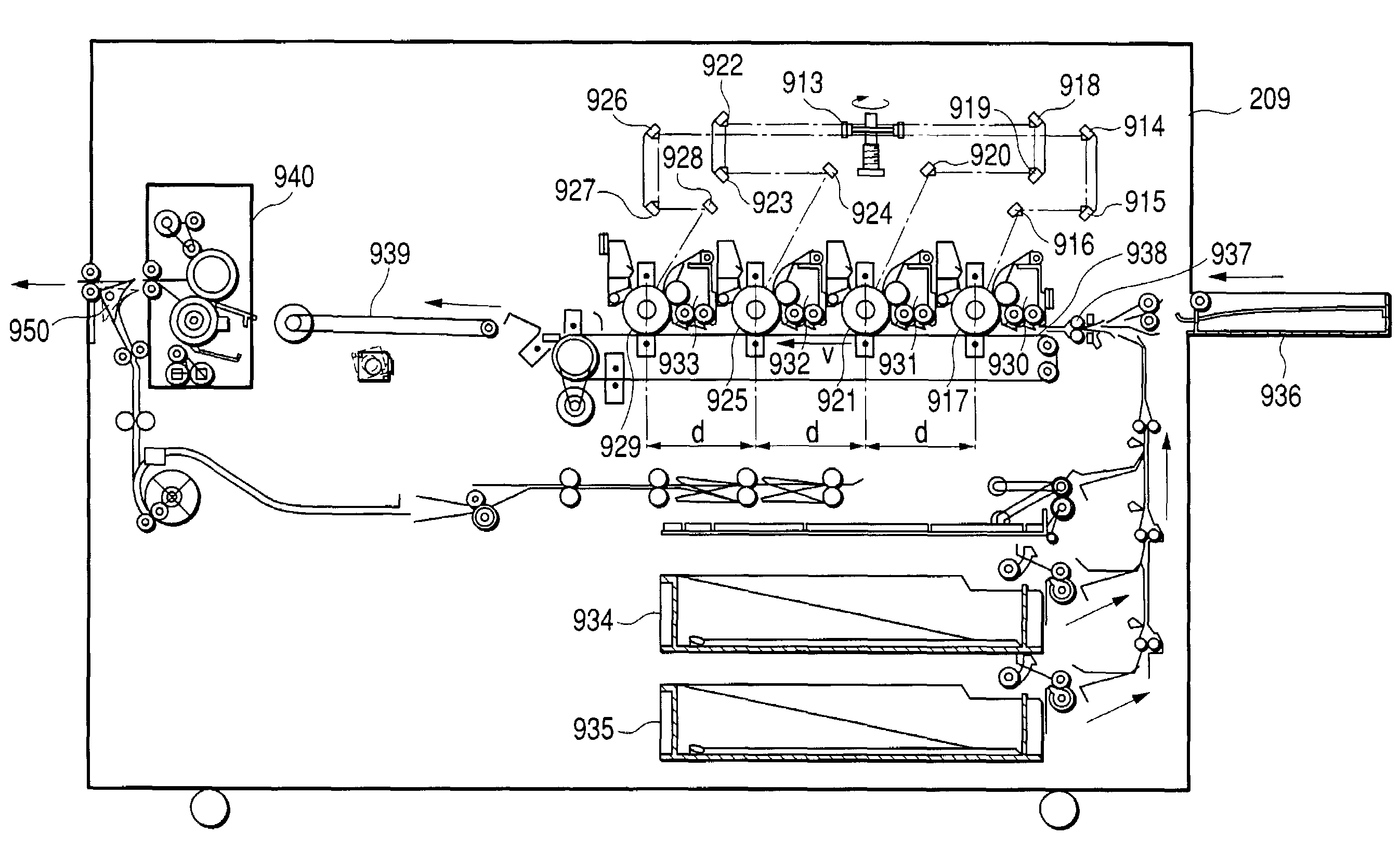

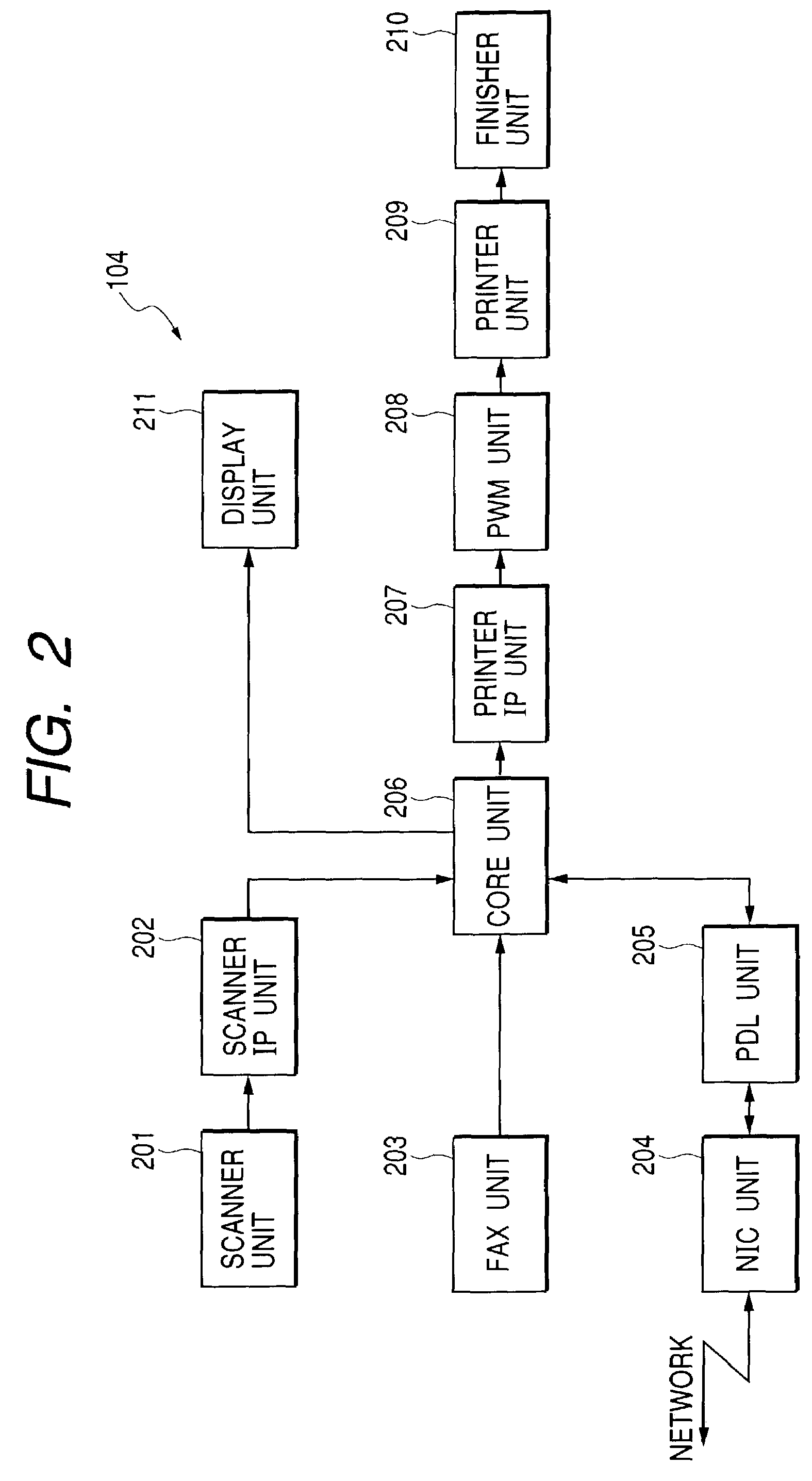

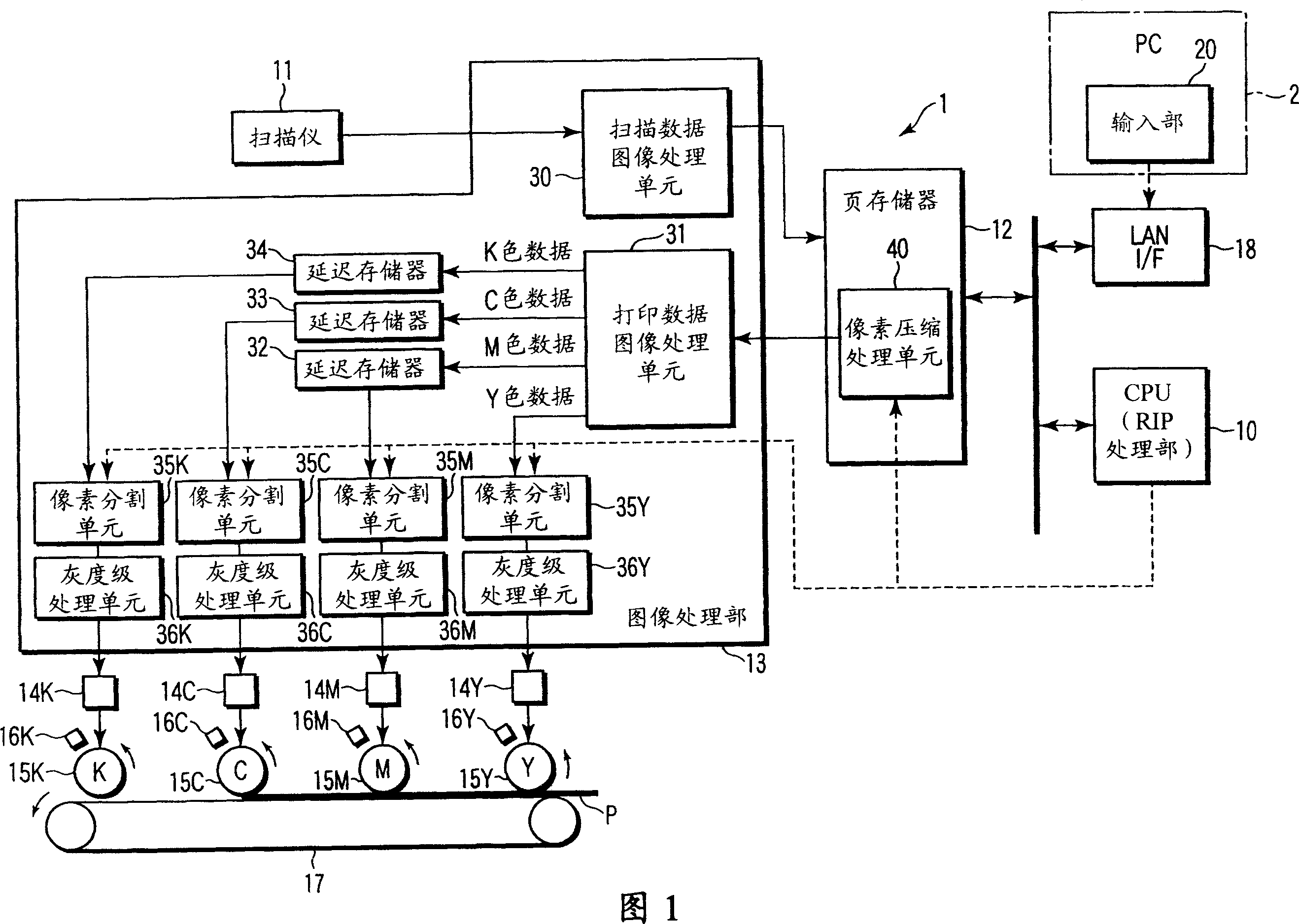

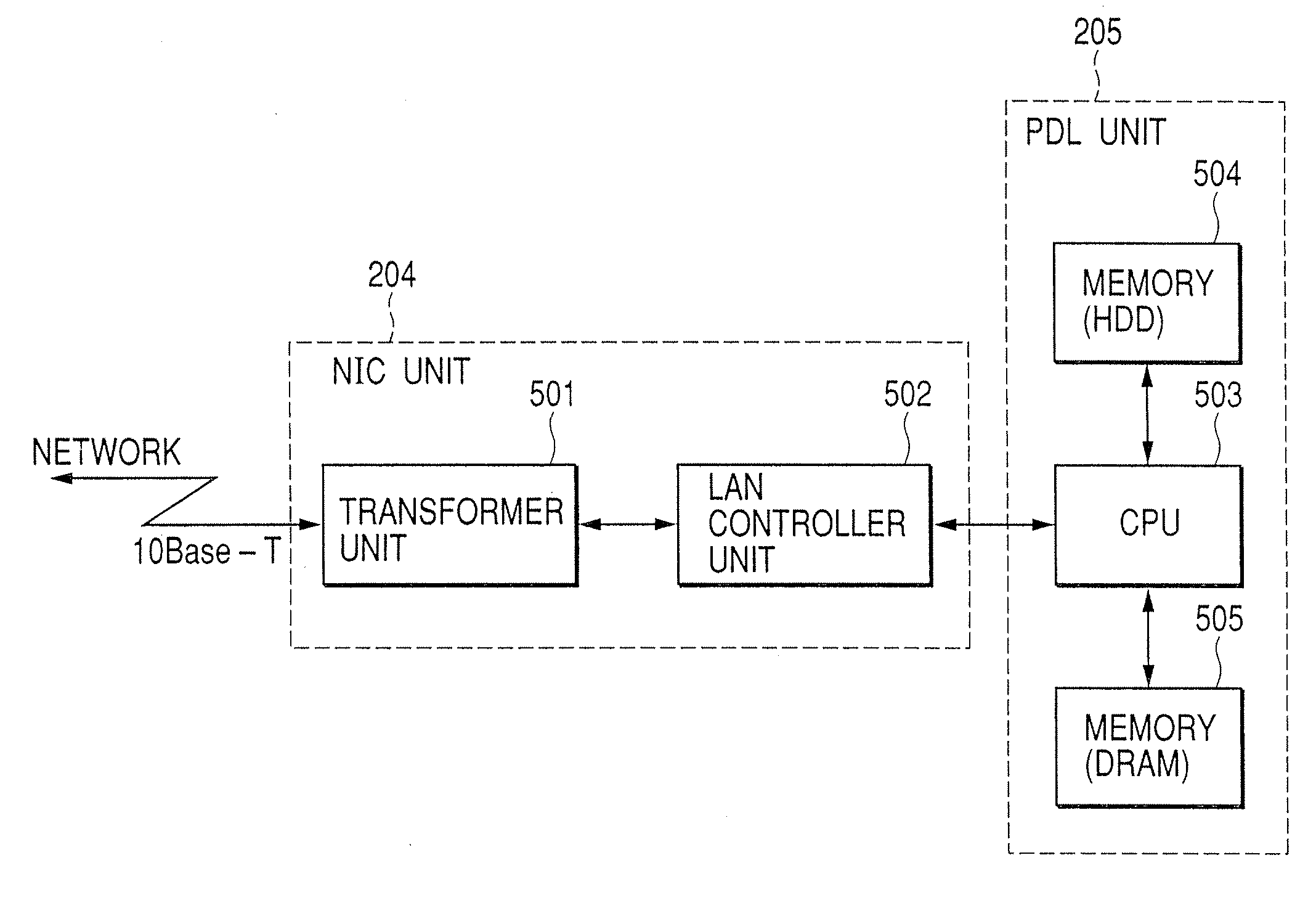

Image processing system, apparatus, method, and software

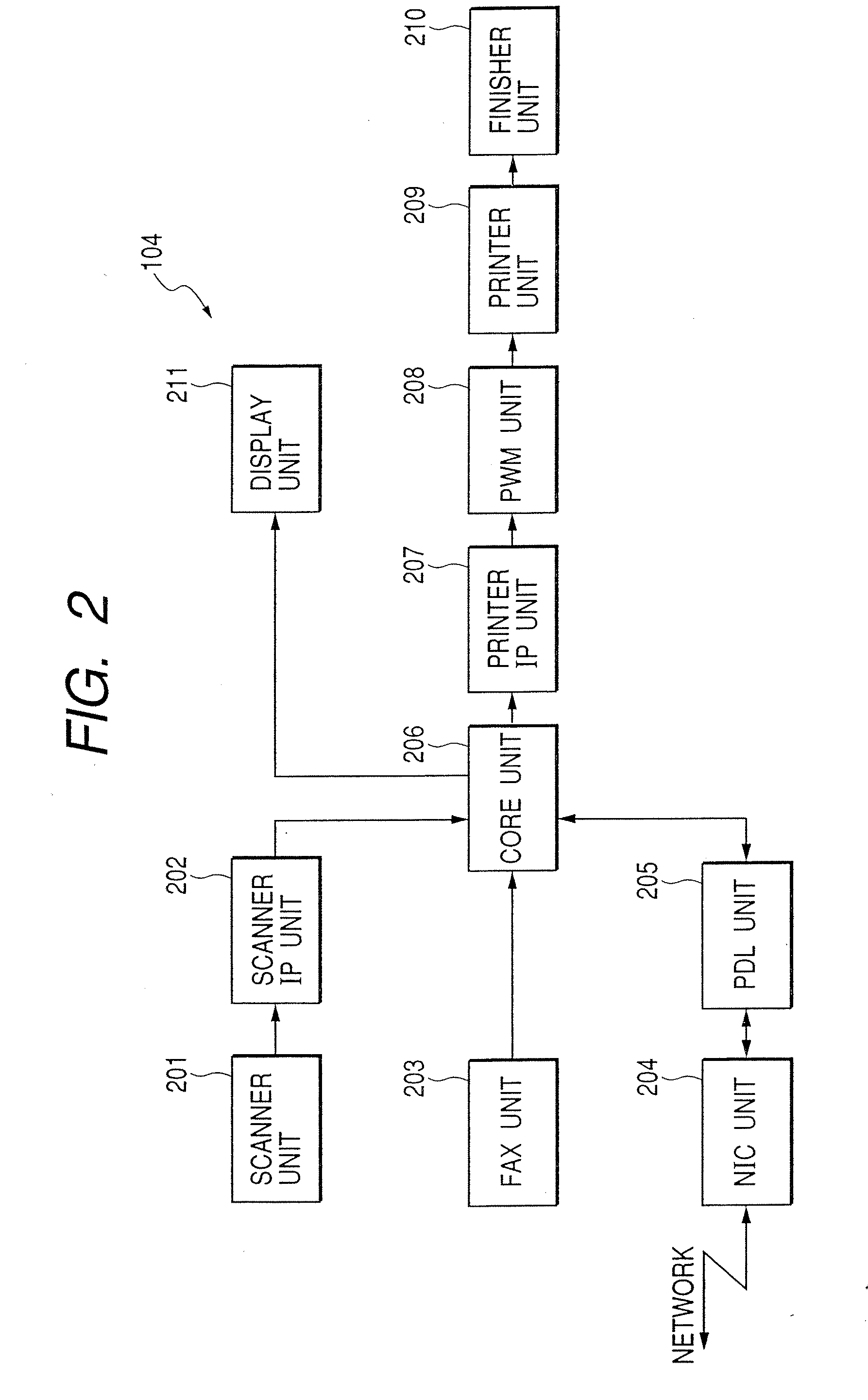

InactiveUS7196713B1Increase speedReduce construction costsRecording apparatusVisual representatino by photographic printingColor imageImaging data

To correct the distance between respective drums and supply image data, an image processing system using a 4-drum type color image forming apparatus requires a large-capacity image memory for temporarily storing transferred image data, and is inevitably expensive. In this invention, image data of four colors isochronously transferred via a high-speed serial interface such as an IEEE 1394 interface are respectively supplied to image processing units and image forming units via delay memories. Therefore, the time difference required for the print sheet to reach each drum can be corrected in each image forming unit to appropriately form an image at a high speed and low cost.

Owner:CANON KK

Structure for dynamic livelock resolution with variable delay memory access queue

A design structure for resolving the occurrence of livelock at the interface between the processor core and memory subsystem controller. Livelock is resolved by introducing a livelock detection mechanism (which includes livelock detection utility or logic) within the processor to detect a livelock condition and dynamically change the duration of the delay stage(s) in order to alter the “harmonic” fixed-cycle loop behavior. The livelock detection logic (LDL) counts the number of flushes a particular instruction takes or the number of times an instruction re-issues without completing. The LDL then compares that number to a preset threshold number. Based on the result of the comparison, the LDL triggers the implementation of one of two different livelock resolution processes. These processes include dynamically configuring the delay queue within the processor into one of two different configurations and changing the sequence and timing of handling memory access instructions, based on the specific configuration of the delay queue.

Owner:IBM CORP

Control voltage tracking circuits, methods for recording a control voltage for a clock synchronization circuit and methods for setting a voltage controlled delay

Memories, clock synchronization circuits, clock synchronization controller circuits, and methods for setting a voltage controlled delay of a clock synchronization circuit and tracking and recording the control voltage are disclosed. For example, a clock synchronization controller provides an initial control voltage to the voltage controlled delay during initialization of the synchronization circuit until a phase dependent control voltage stabilizes. The stable phase dependent control voltage is substituted for the initial control voltage. Following stabilization of the phase dependent control voltage, a phase detector of the clock synchronization circuit is activated. A recovery control voltage is provided by the clock synchronization controller to the voltage controlled delay during recovery of the clock synchronization from a power-saving mode until the phase dependent control voltage stabilizes.

Owner:MICRON TECH INC

Ultrasound receive beamformer

InactiveCN101427928AUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsDelayed MemoryEngineering

Owner:ALOKA CO LTD

Ultrasound receive beamforming apparatus using multi stage delay devices

InactiveUS6494842B2Ultrasonic/sonic/infrasonic diagnosticsWave based measurement systemsDelayed MemoryTransducer

By using a novel structure of a beamformer which produce data for multiple receive scanlines in a time multiplexed manner, the size of the delay memory is reduced. An ultrasound receive beamforming apparatus for processing signals received from an array of transducers, comprises: a plurality of beamforming devices for applying delays to data samples of M channels. Each of said beamforming devices includes: a predetermined number of per-channel delay elements which provide first delays to the data samples of M channels, to provide delayed data per each channel and per each receive beam, first adders for adding the delayed data of not less than 2 channels provided from the per-channel delay elements, and multi-channel delay elements which provide second delays to the outputs of the first adders.

Owner:MEDISON CO LTD

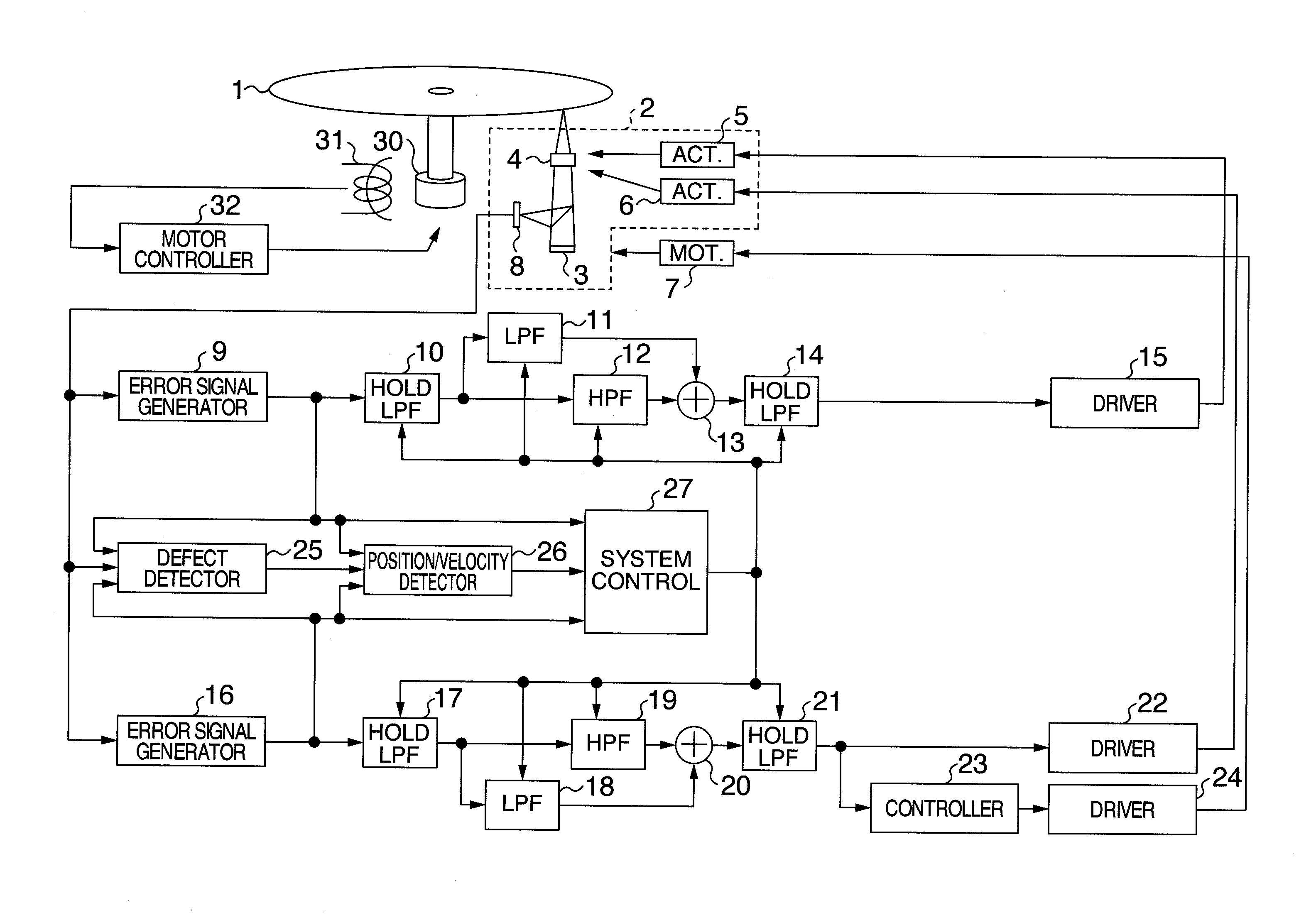

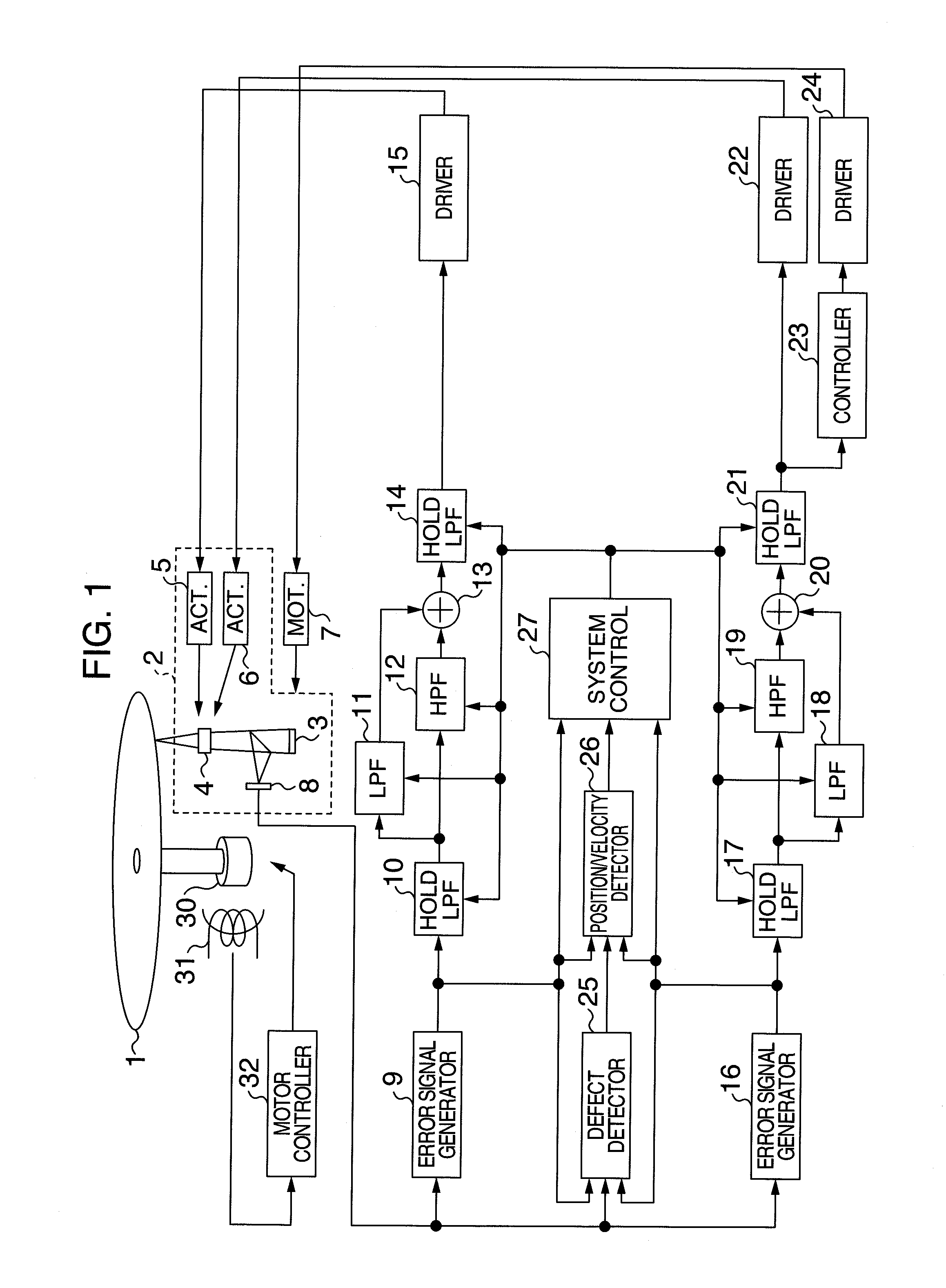

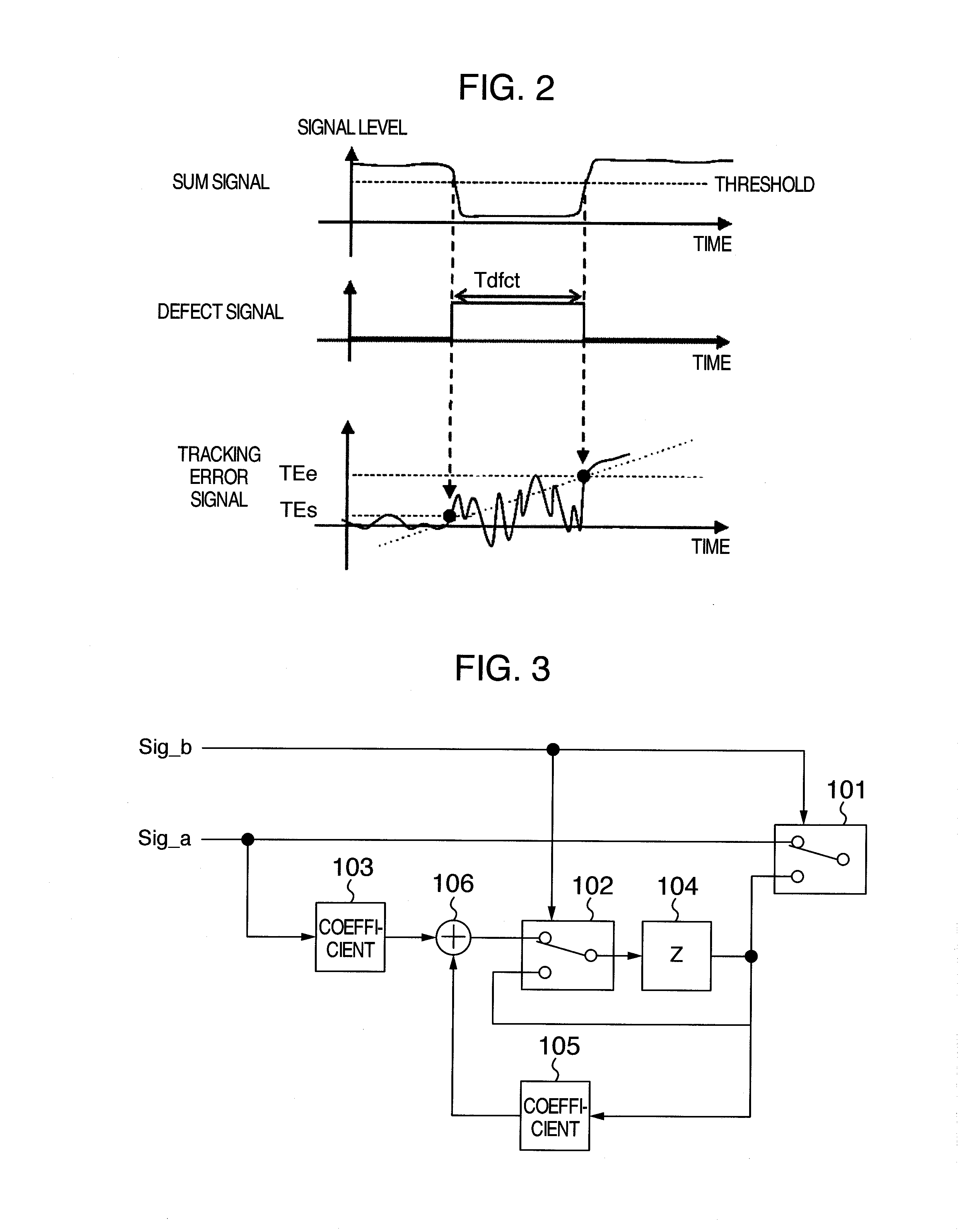

Optical disc apparatus

InactiveUS20130064058A1Reduce the impactReliable controlCombination recordingRecord information storageDelayed MemoryDigital filter

An optical disc apparatus includes a focus controller including a first digital filter, tracking controller including a second filter, focus actuator driver, tracking actuator driver, defect detector for detecting a defect on an optical disc, and a system controller for controlling the focus controller, the tracking controller and the defect detector. The system controller holds an input and output of at least one of either the focus controller or the tracking controller on the basis of the output of the defect detector, and sets an initial value in a delay memory of the digital filter of the controller held upon awake of the hold state.

Owner:HITACHI CONSUMER ELECTRONICS CORP

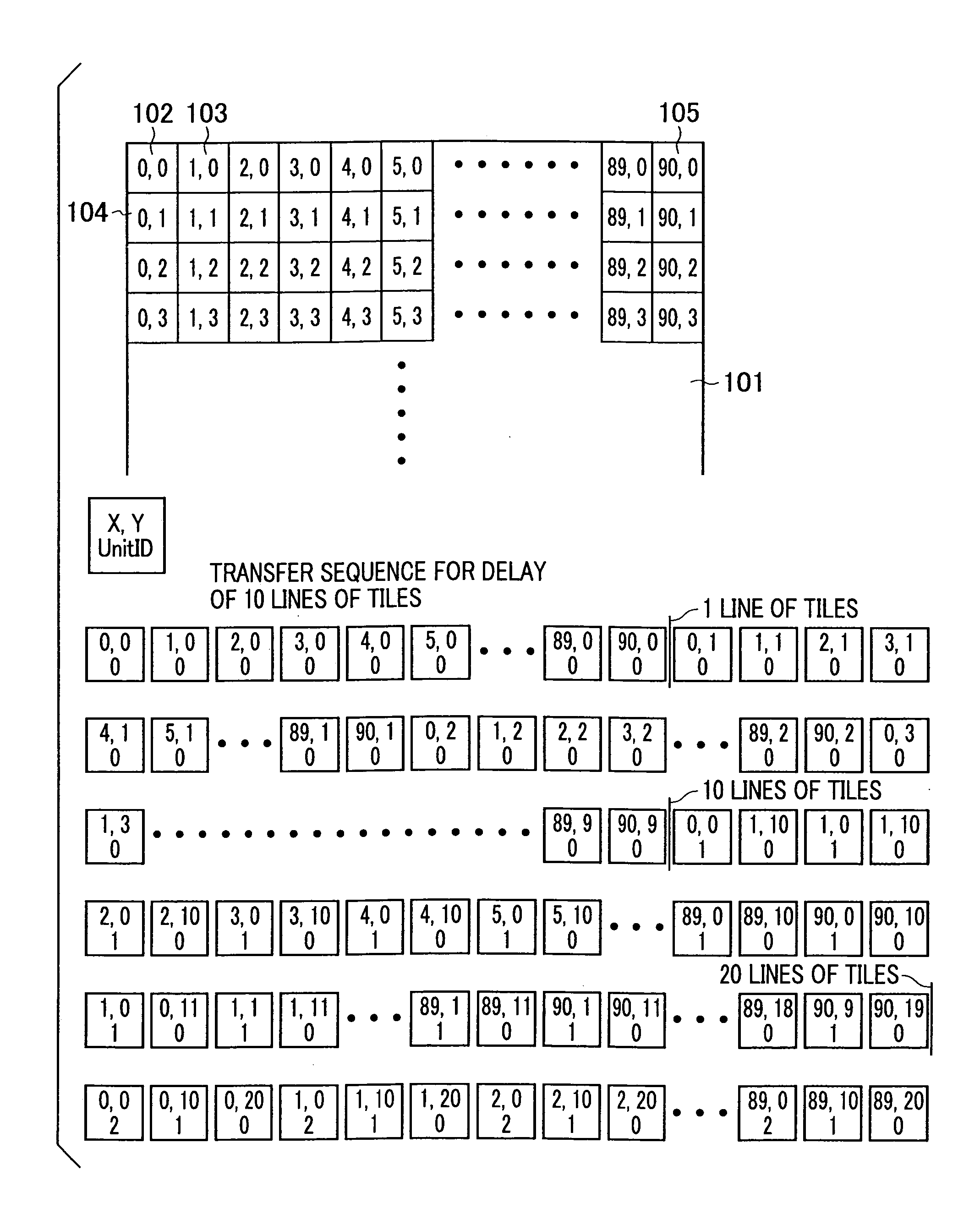

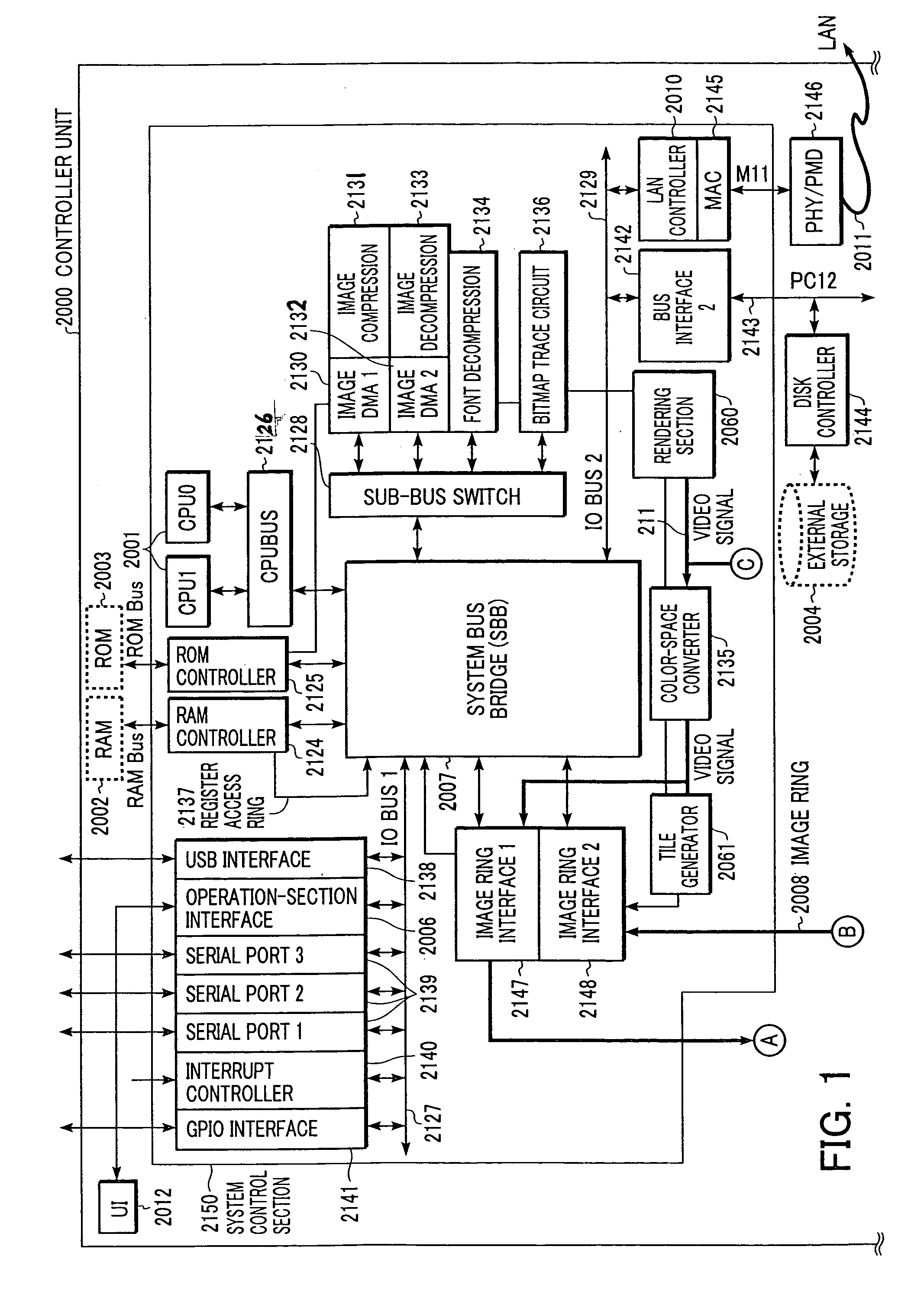

Image-forming controller, method therefor, program, and storage medium

InactiveUS7362471B2Low costEliminate needDigitally marking record carriersDigital computer detailsComputer graphics (images)Rgb image

A controller for a four-drum printer eliminates a need for an expensive inter-drum delay memory, which has been conventionally used, to print an RGB image and allows a multifunction machine, printer, and the like to be provided at low cost. An image ring interface reads an image data containing the same tile, which is stored in a tile pattern in a RAM, four times with a delay corresponding to a delay (10 lines of tiles) of image formation between image forming sections, and sequentially transfers the image data to four image output interfaces.

Owner:CANON KK

Apparatus for adapting reception modes of a mobile DTV receiver in response to signaling

ActiveUS8116400B2Television system detailsAmplitude demodulation by homodyne/synchrodyne circuitsDTV receiverDelayed Memory

Owner:SAMSUNG ELECTRONICS CO LTD

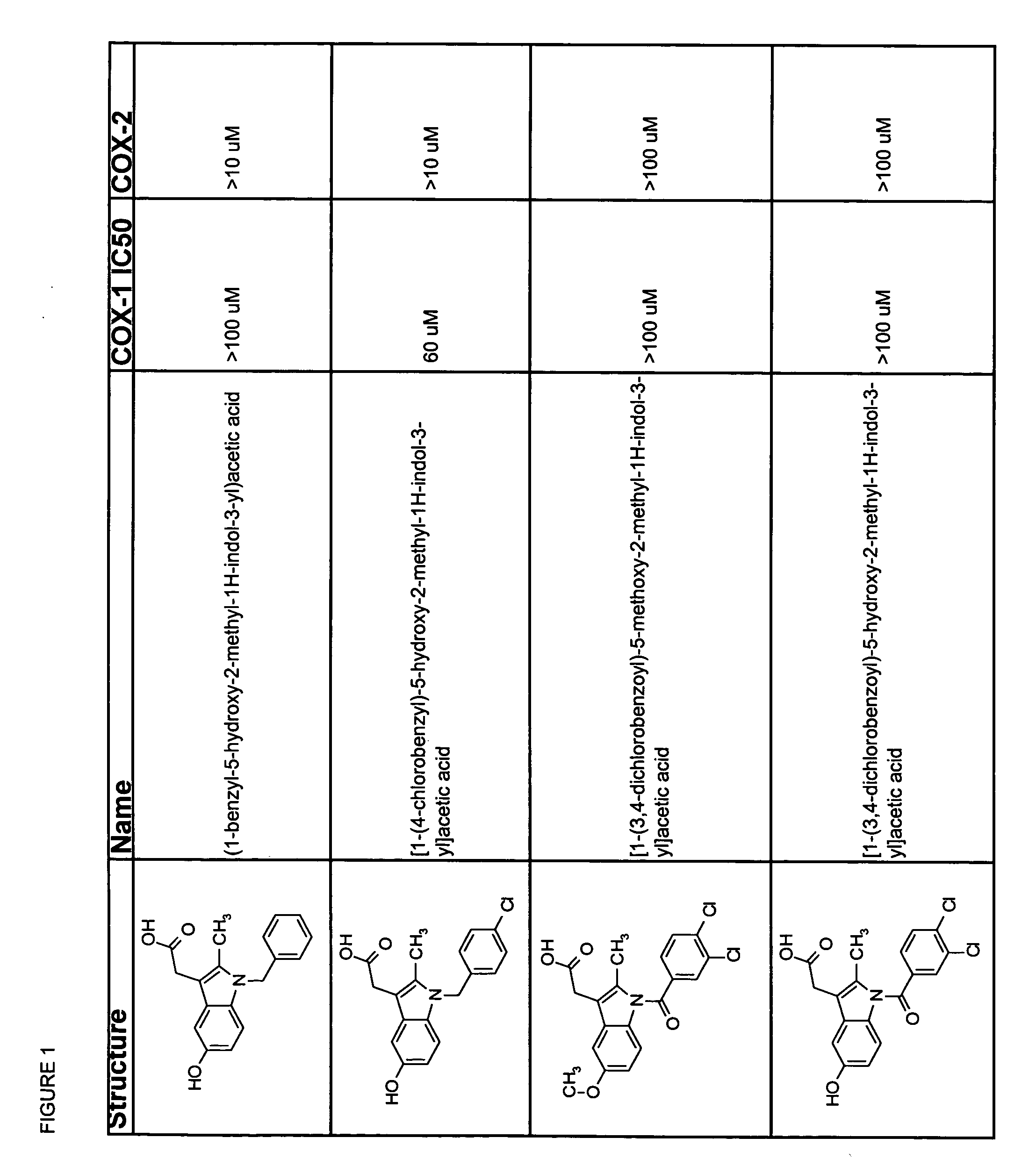

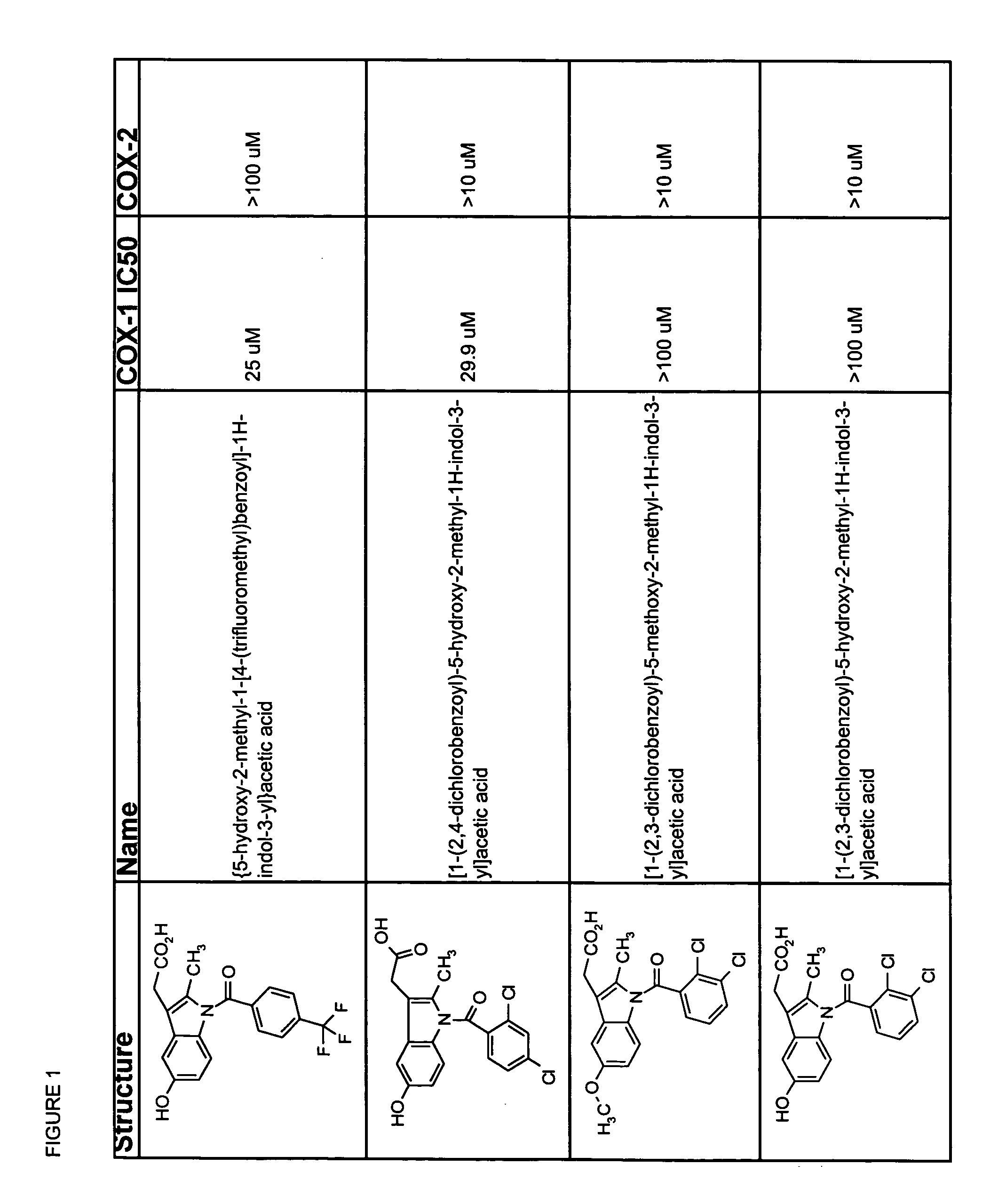

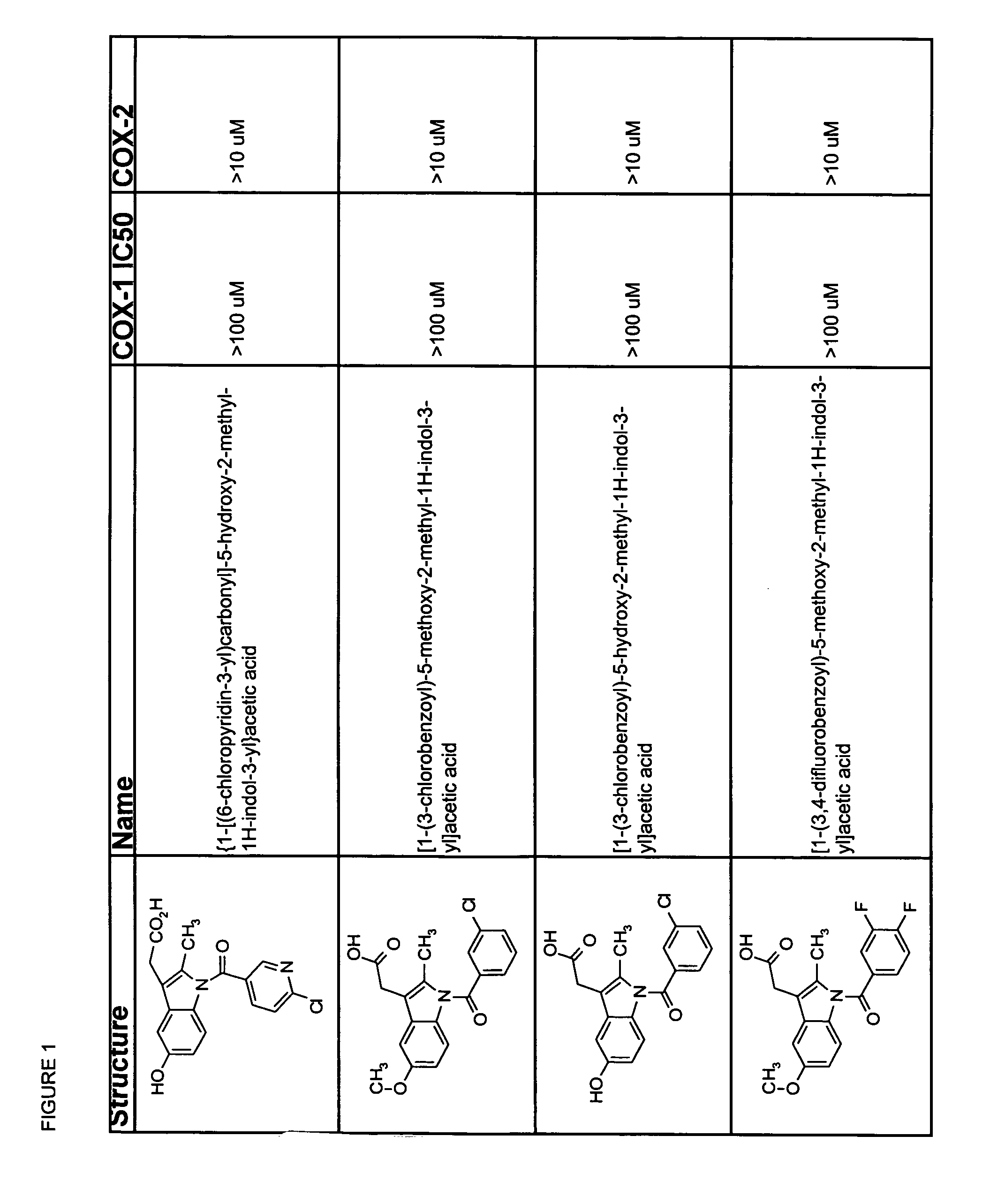

Methods for the protection of memory and cognition

InactiveUS20050004104A1Function increaseSlowing or reducing cognitive impairment or memory lossBiocideNervous disorderMemory retentionAmnesia

The invention features certain compounds useful in the treatment of memory disorders, i.e., they reduce or delay memory loss or they enhance memory retention. Because certain of the compounds do not substantially inhibit either COX-1 or COX-2 at therapeutically relevant doses, these compounds are far less likely to cause gastrointestinal ulceration than is indomethacin, which is known to inhibit both COX-1 and COX-2. Certain of the compounds inhibit the activity of DAO at therapeutically relevant doses. Among the memory disorders that can be treated are AD, mild cognitive impairment (MCI; a common precursor to AD), and memory loss or cognitive impairment associated with vascular dementias, amnesia, dementia, AIDS dementia, Huntington's Disease, hydrocephalus, depression, Pick's Disease, Creutzfeldt-Jakob Syndrome, electroconvulsive therapy, or Parkinson's Disease.

Owner:IRONWOOD PHARMA

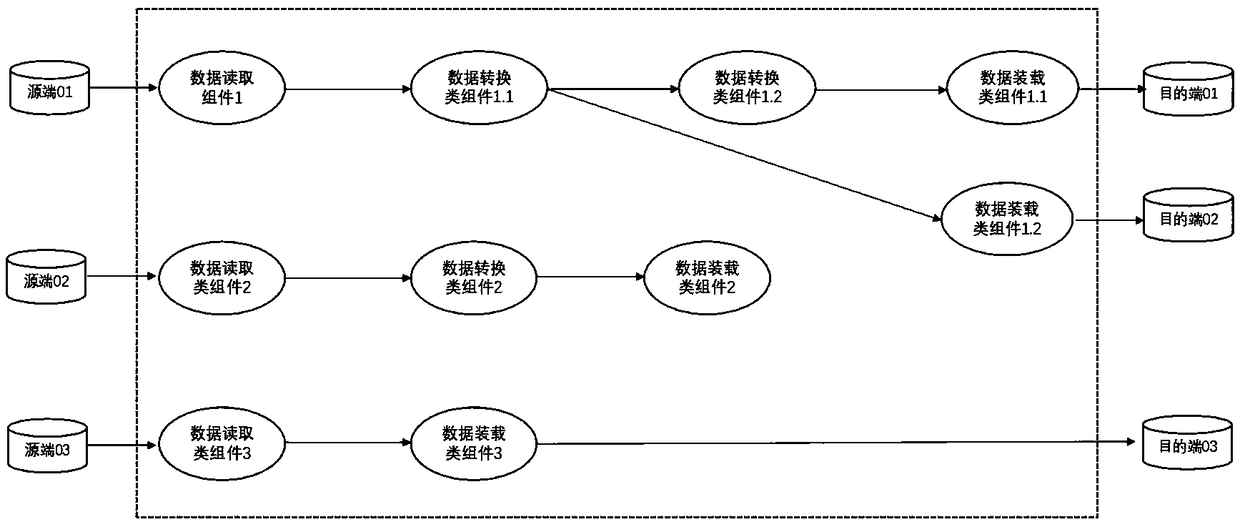

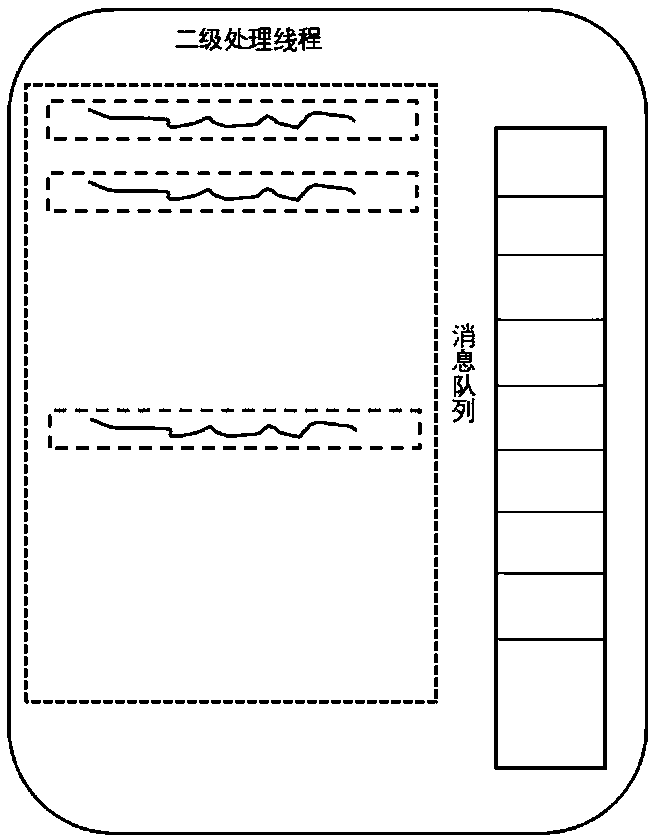

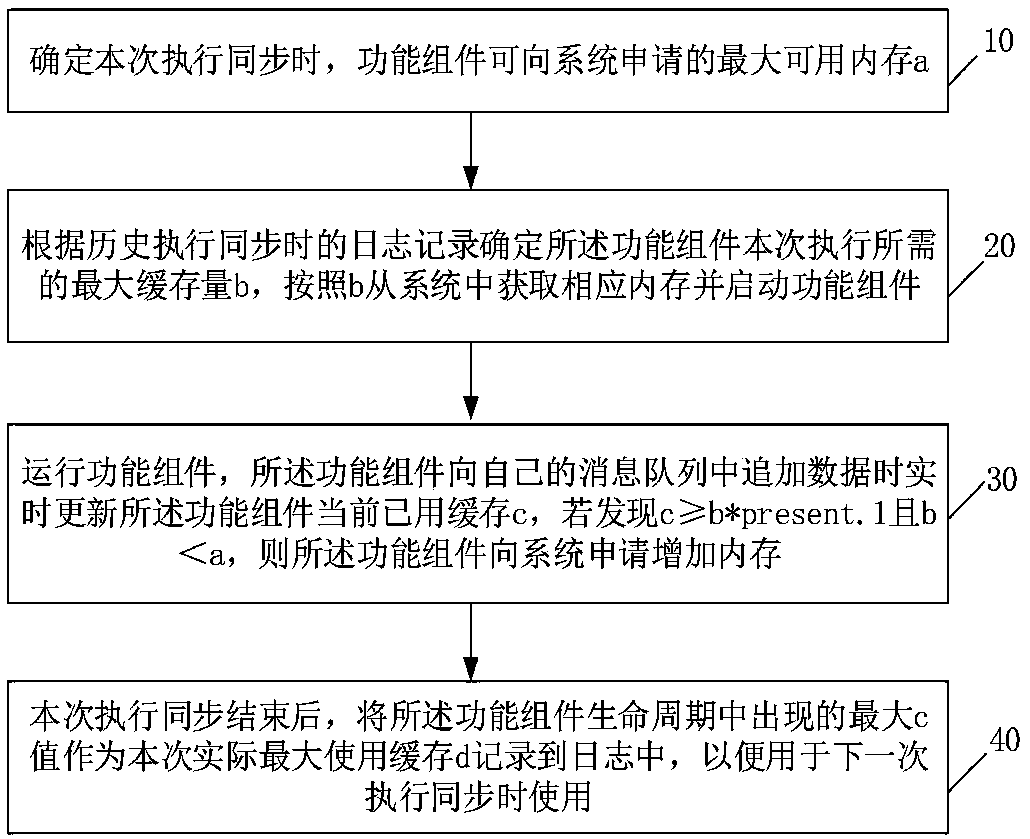

Self-adaptive dynamic adjustment method and device of data synchronization system

ActiveCN109492018AFull distribution and utilizationEffective distribution and utilizationDatabase management systemsDatabase distribution/replicationMessage queueData synchronization

The invention relates to the technical field of data synchronization, in particular to a self-adaptive dynamic adjustment method and a device for a data synchronization system. The method comprises the following steps: determining a maximum available memory a that a functional component can apply to the system when synchronization is executed this time; according to the history log record, determining the maximum amount of delay memory b required for this execution, obtaining the corresponding memory from the system and starting the functional components; when the functional component appendsdata to its own message queue, updating the currently used cache c in real time. If c >= b*present.1 and b < a, it applies to the system for increasing memory. At that end of this execution, the maximum c value is log as the actual maximum usage cache for the next use. By increasing the maximum amount of slow memory for historical execution in the log, the functional component can determine the amount of cache usage required for this execution according to the log record, and adjust the memory adaptively at run time; at the same time, it can dynamically increase the first-level thread and thesecond-level thread according to the actual operation, and improve the performance of data synchronization.

Owner:WUHAN DAMENG DATABASE +1

Process for preparing preserved apple

InactiveCN101167519AImprove developmentSimple preparation processConfectionerySweetmeatsDelayed MemorySugar

Disclosed is a process for preparing apple preserved fruit, which is characterized in that the process for preparing comprises <1> cleaning, separately cutting and pre-cooking apples; <2> cooking apples in sugar liquor charged with additives for 60-120 minutes according to weight proportion of 10:0.4-0.8 under temperature of 100 DEG C; <3> charging sugar liquor every 20-30 minutes according to weight proportion of 10:0.3-1.2 during the process of cooking; <4> fishing out apples to be dried and shaped; and <5> completing production after the cooling, ultraviolet disinfecting and packing. The process for preparing apple preserved fruit has the advantages that <1> the preparing art is simple and clean, <2> the product belongs to the pure-natural nourishing food, <3> the product is convenient for eating, with delicious taste, <4> the product keeps a plurality of nutriment contained in apples, which facilitates the product to be rich in nutrition, thereby promoting cerebra development, delaying memory declining and resisting caducity after long time eating, and <5> the transportation is convenient, and the product can be stored for a long time.

Owner:TIANJIN CHINESE & BRITISH NANOMETER TECH DEV

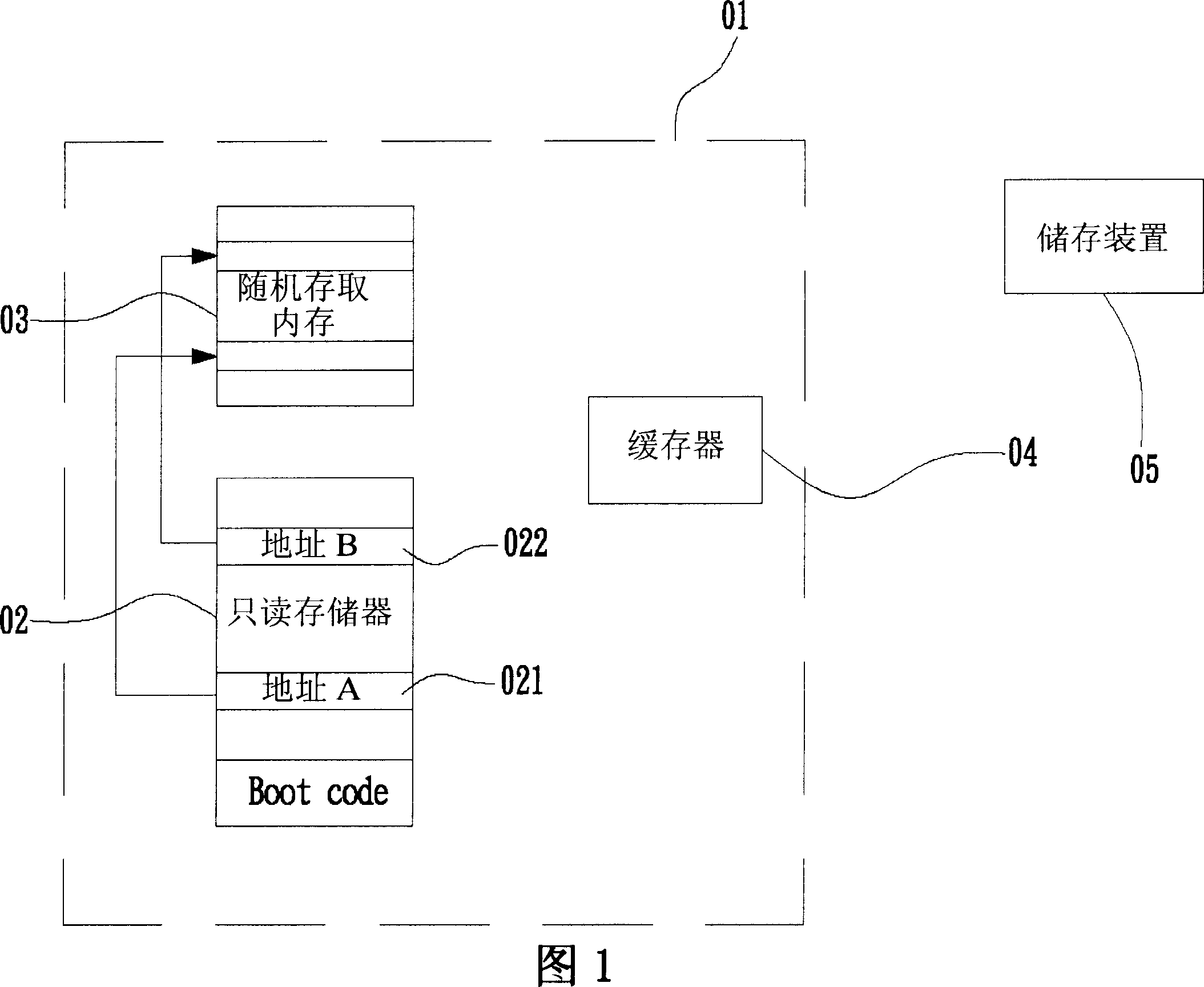

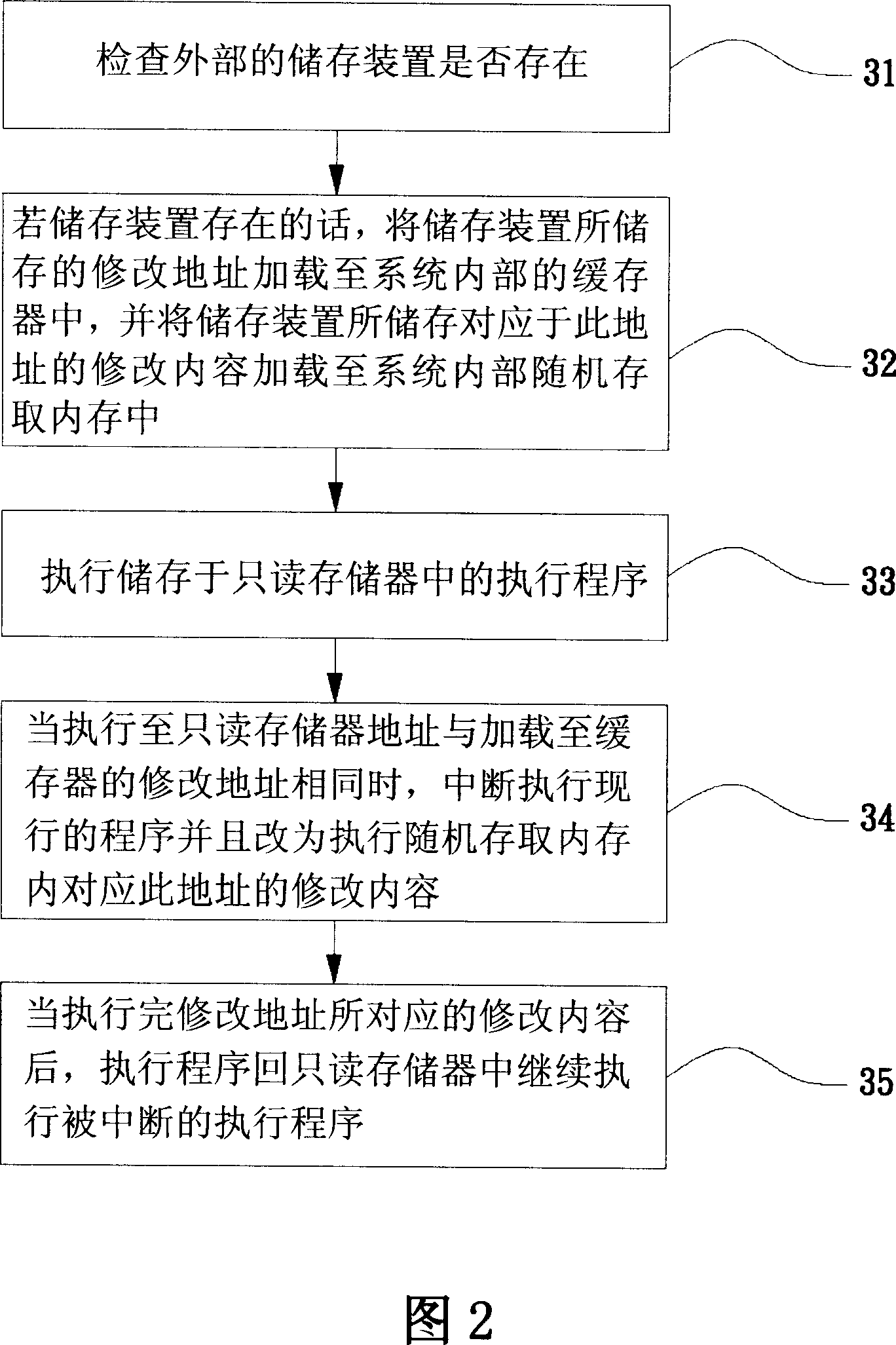

Amending method for content of built-in program code of ROM

The invention relates to a updating method of the ROM internal procedure code, the modification address and contents which are stored in a external memory are separately loaded to a delayed memory and a random access RAM, when the code program of the ROM is executed to modification address, it turns to the random access RAM to execute modification contents, the other program will be executed continuously after the modification contents are executed. With the method in the invention, part of the program can be updated without replacing the ROM.

Owner:MEDIATEK INC

Image forming apparatus having plural image supporting bodies

InactiveUS7224481B2Eliminate inconvenienceShorten sheet intervalElectrographic process apparatusVisual presentationComputer graphics (images)Delayed Memory

In a color printer having plural photosensitive drums for respective recording color components, when images are continuously formed on recording sheets, lengths of image data of one page in its main scan direction and its sub scan direction are held for plural pages. Then, image data writing and reading addresses to and from a delay memory for delaying the image data according to an inter-drum distance are controlled for each page on the basis of the held lengths of the image data in its main scan direction and its sub scan direction, whereby an interval between the successively transported recording sheets is shortened.

Owner:CANON KK

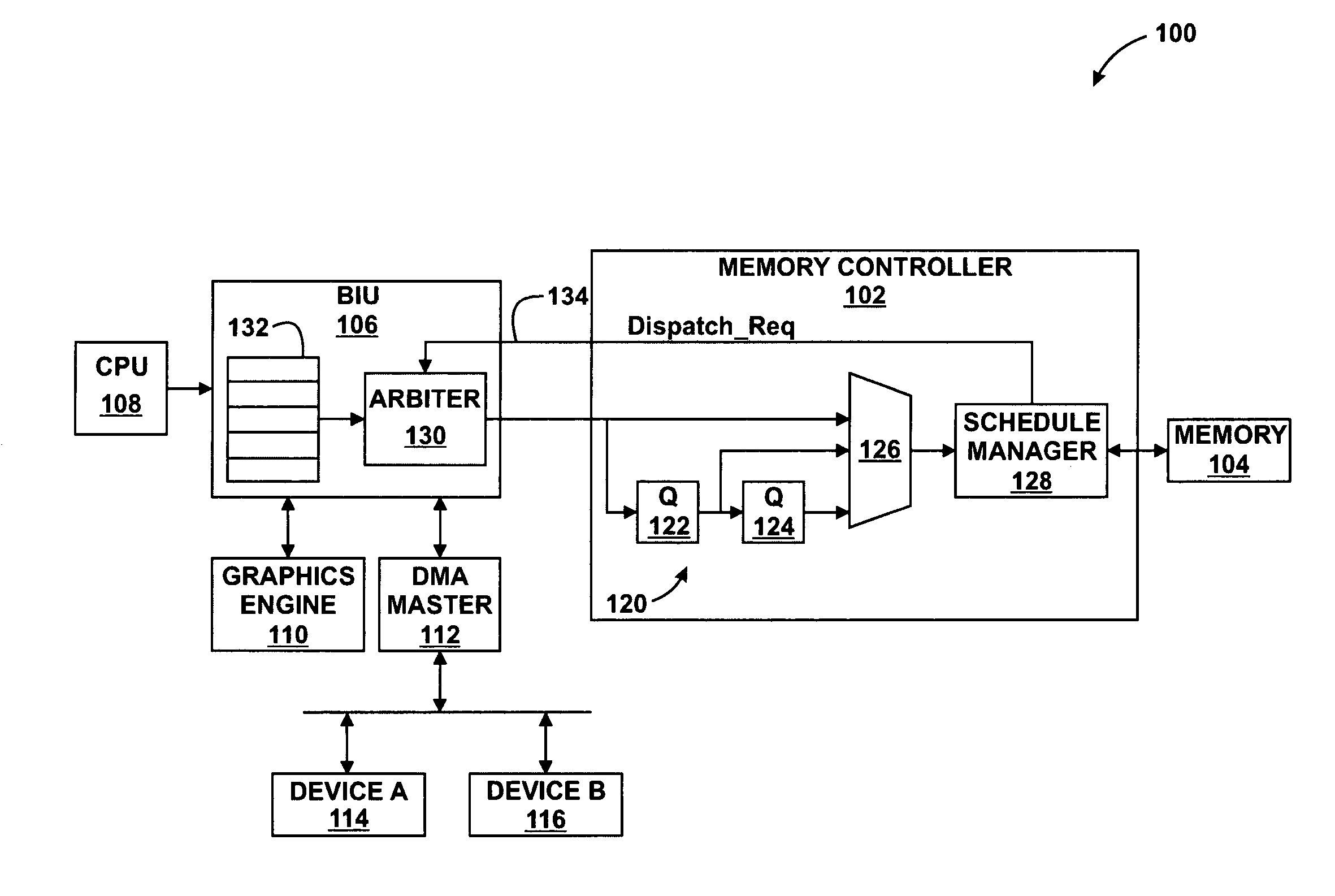

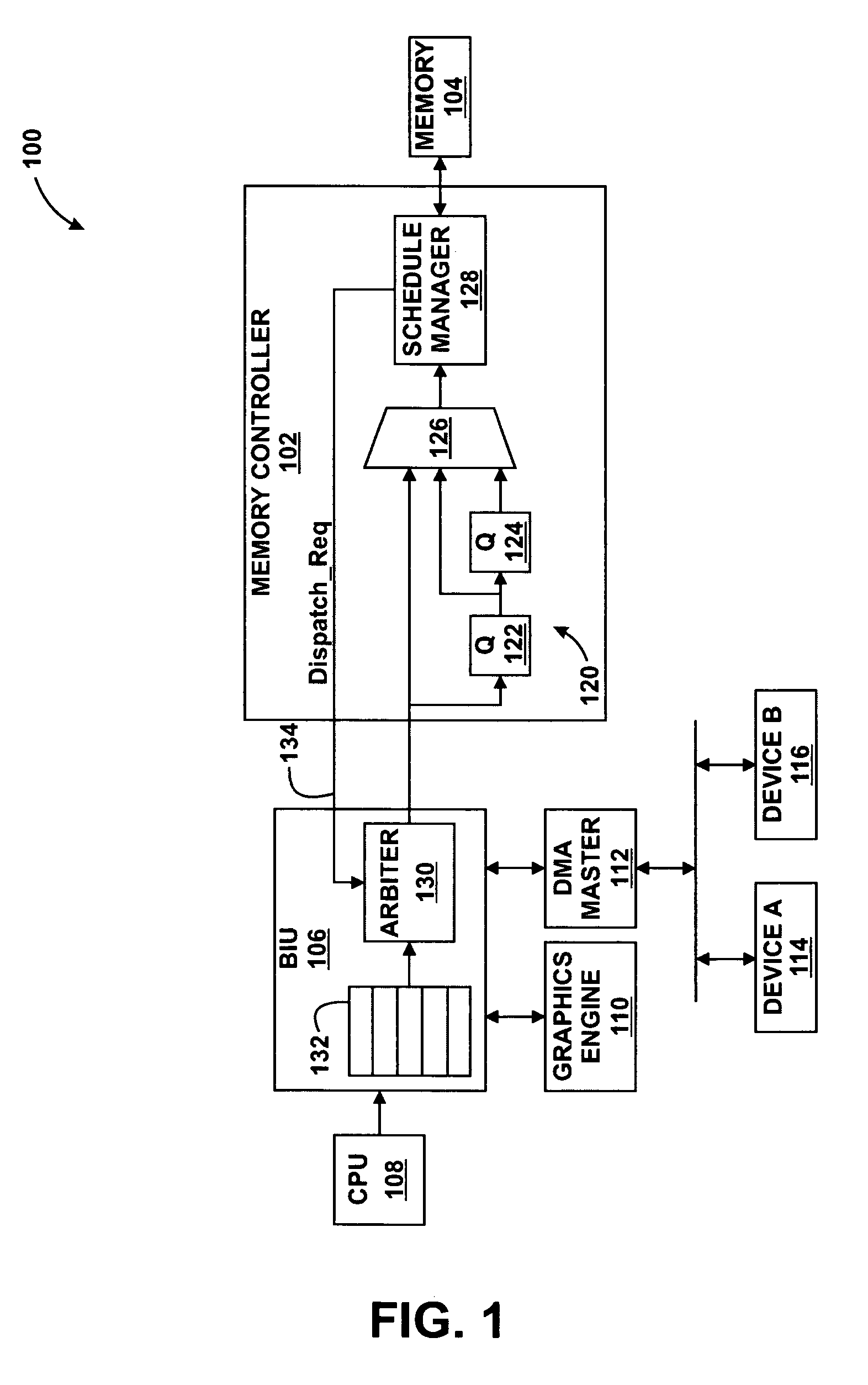

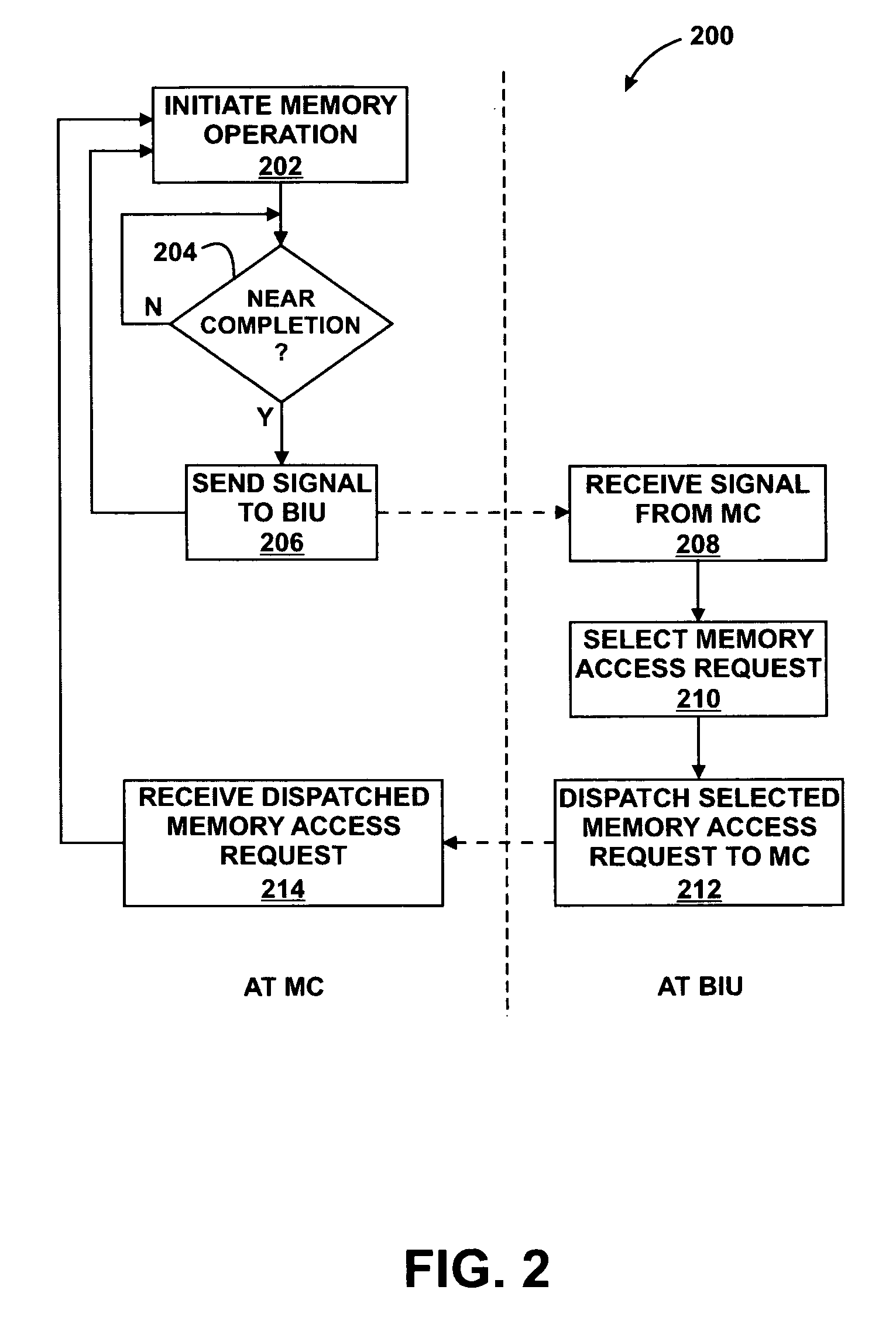

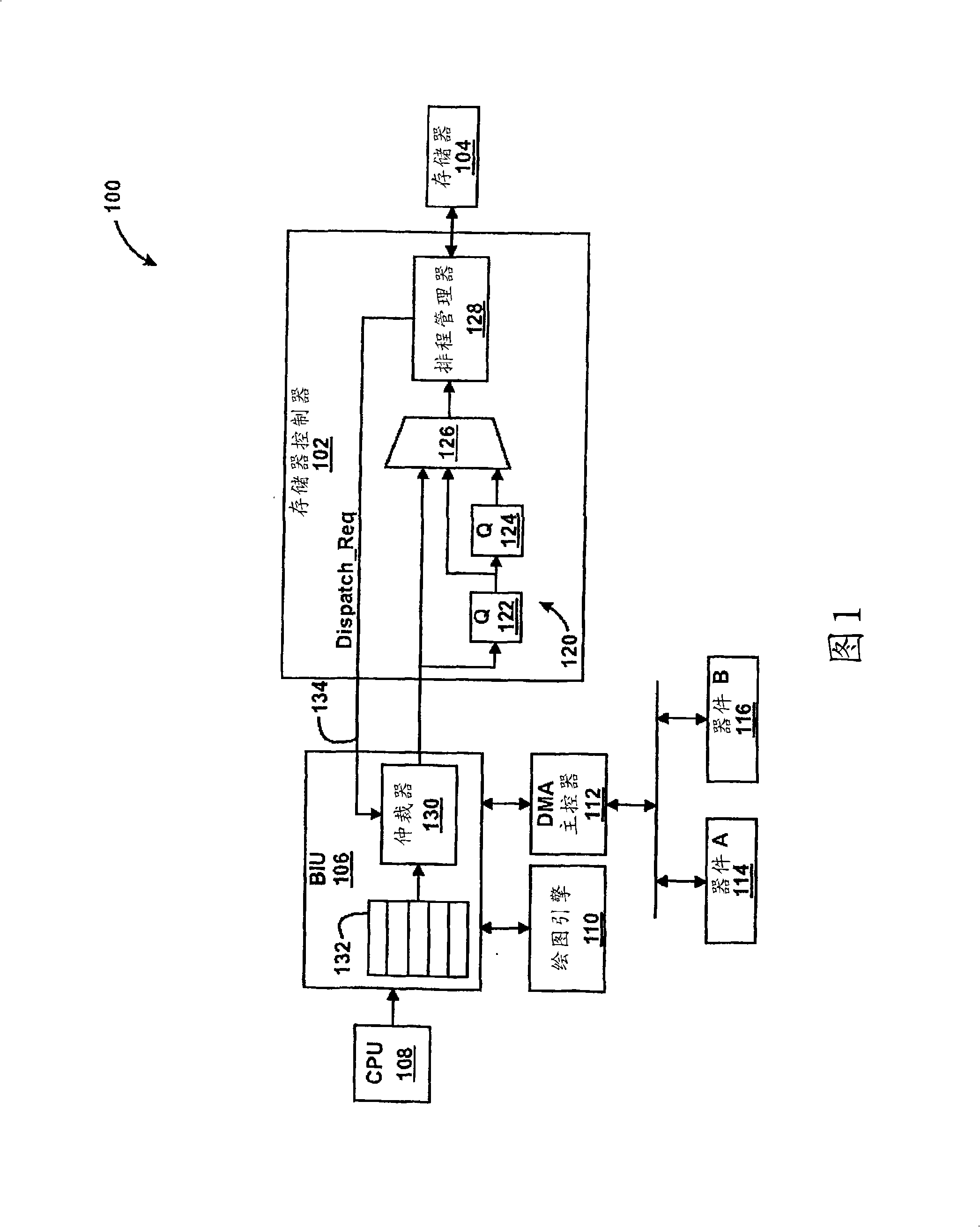

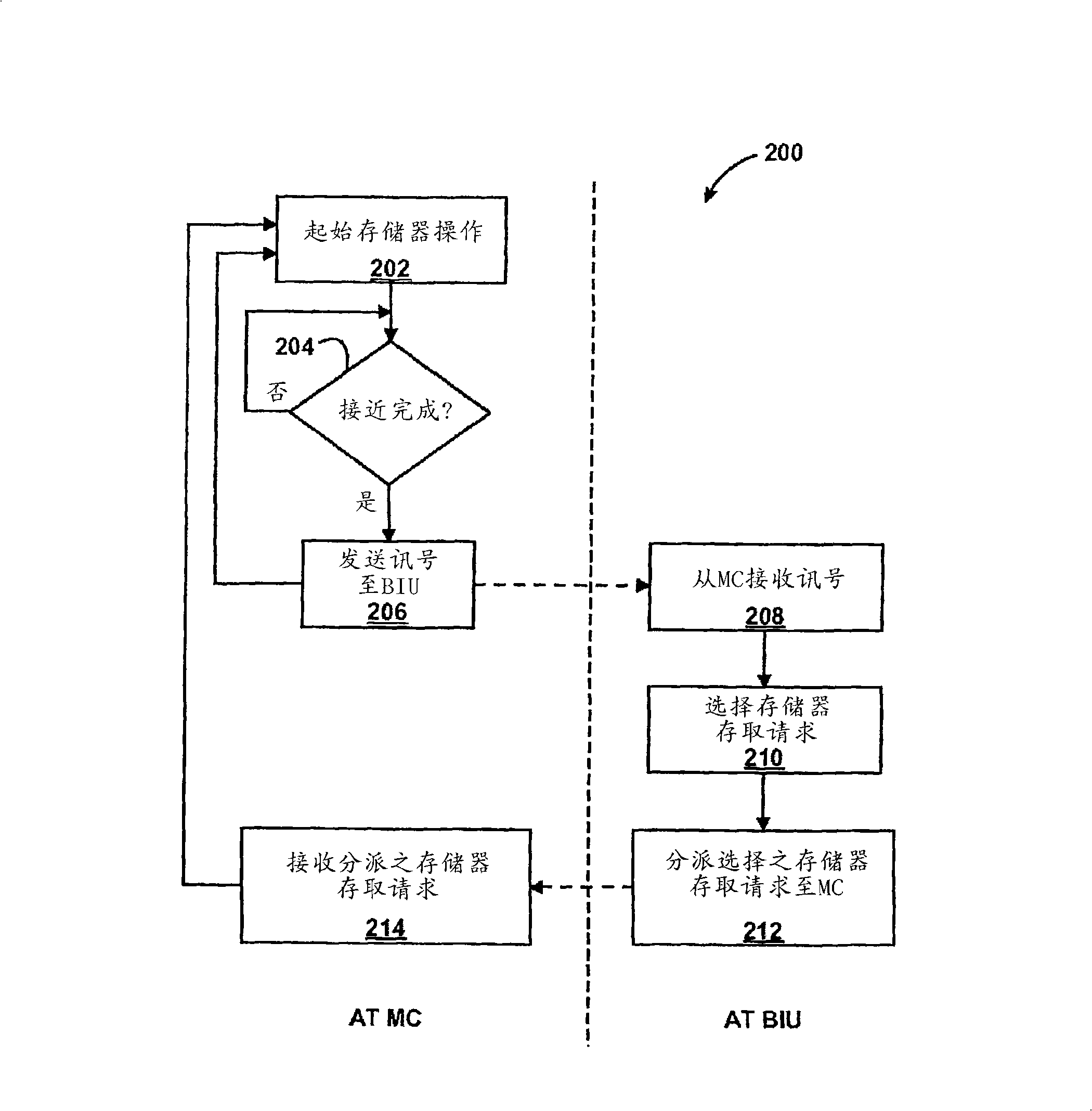

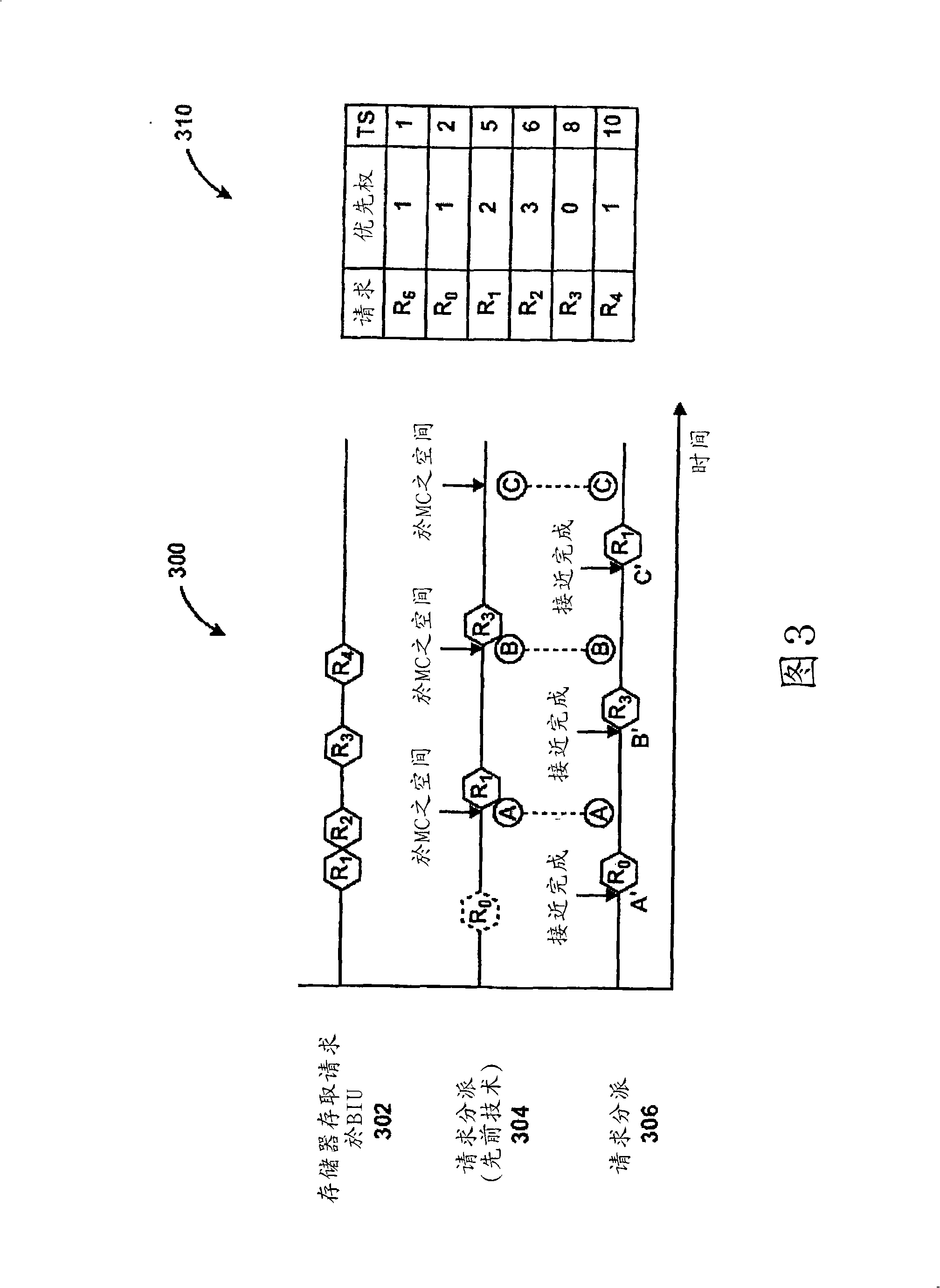

Delayed memory access request arbitration

A method for delayed memory access request arbitration includes dispatching a first memory access request to a memory controller and dispatching a second memory access request to the memory controller in response to an anticipated completion of a memory access operation represented by the first memory access request. Another method includes receiving a first memory access request at a bus interface unit at a first time, dispatching a second memory access request to a memory controller at a second time subsequent to the first time, receiving a third memory access request at the bus interface unit at a third time subsequent to the second time, dispatching the third memory access request to the memory controller at a fourth time subsequent to the third time and dispatching the first memory access request to the memory controller at a fifth time subsequent to the fourth time.

Owner:ADVANCED MICRO DEVICES INC

Delayed memory access request arbitration

A method for delayed memory access request arbitration includes dispatching a first memory access request to a memory controller (102) and dispatching a second memory access request to the memory controller (102) in response to an anticipated completion of a memory access operation represented by the first memory access request. Another method includes receiving a first memory access request at a bus interface unit (106) at a first time, dispatching a second memory access request to a memory controller (102) at a second time subsequent to the first time, receiving a third memory access request at the bus interface unit (106) at a third time subsequent to the second time, dispatching the third memory access request to the memory controller (102) at a fourth time subsequent to the third time and dispatching the first memory access request to the memory controller (102) at a fifth time subsequent to the fourth time.

Owner:ADVANCED MICRO DEVICES INC

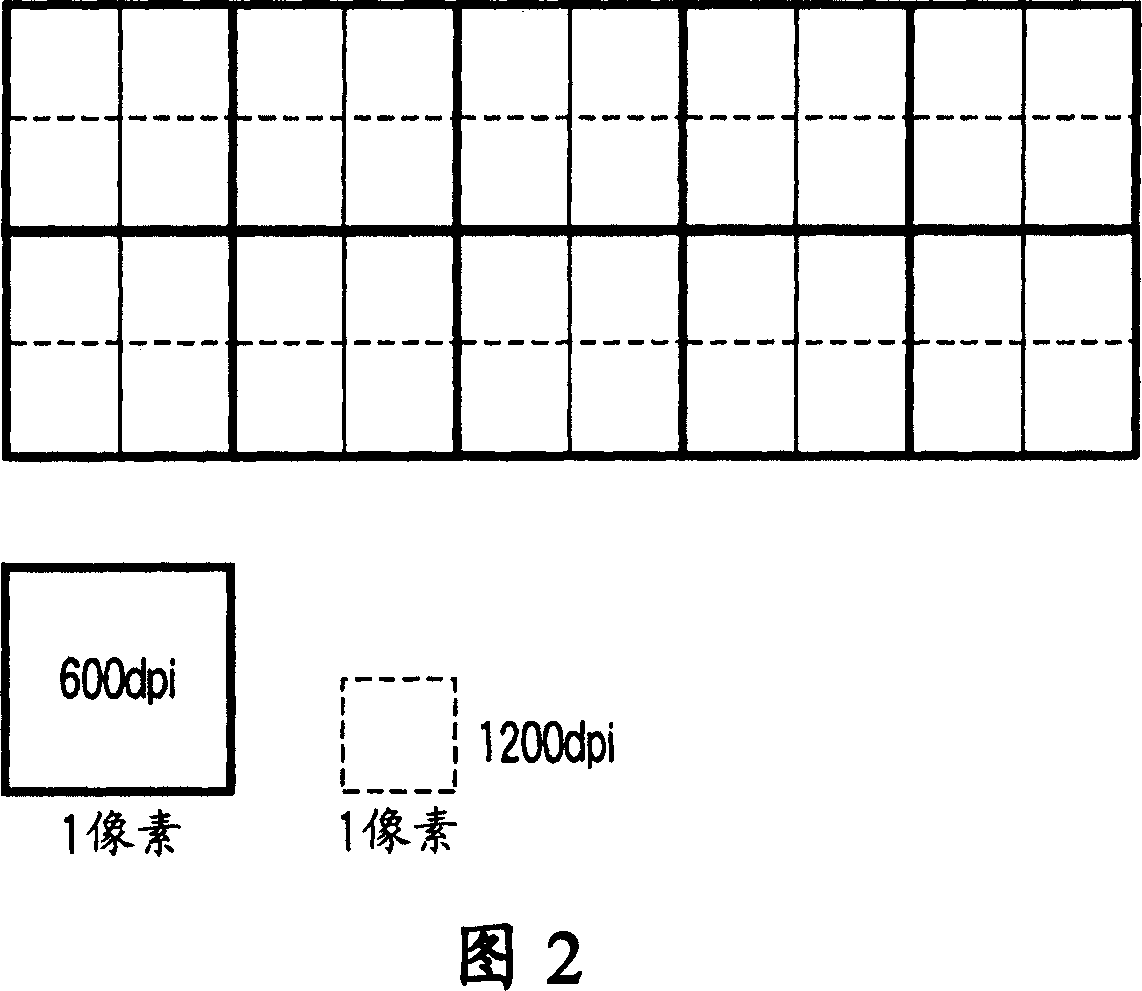

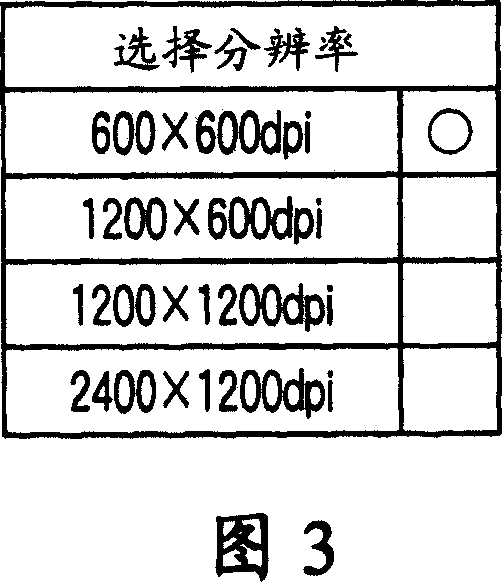

Color image forming apparatus and image forming method

InactiveCN1932666AHigh-resolutionReduce data volumeVisual presentationElectrographic process apparatusColor imageComputer graphics (images)

If a CPU is informed that ''1200x1200 dpi'' is selected from an input unit, the CPU switches a normal 8-bit RIP process with 600x600 dpi to a 1-bit RIP process with 1200x1200 dpi. Image data, which has become 1-bit data with 1200 dpi, is stored in a page memory. A pixel packing process unit executes (2x2) packing when the image data stored in the page memory is to be output from the page memory. The packed Y color image data is restored, without delay, to a normal pixel unit in a pixel division unit. The packed M color image data is restored, with a delay in a delay memory, to a normal pixel unit in the pixel division unit. The packed C color image data is restored, with a delay in the delay memory, to a normal pixel unit in the pixel division unit. The packed K color image data is restored, with a delay in the delay memory, to a normal pixel unit in the pixel division unit.

Owner:KK TOSHIBA +1

Image forming apparatus having plural image supporting bodies

InactiveUS20070126850A1Eliminate inconvenienceShorten sheet intervalDigitally marking record carriersDigital computer detailsComputer graphics (images)Delayed Memory

In a color printer having plural photosensitive drums for respective recording color components, when images are continuously formed on recording sheets, lengths of image data of one page in its main scan direction and its sub scan direction are held for plural pages. Then, image data writing and reading addresses to and from a delay memory for delaying the image data according to an inter-drum distance are controlled for each page on the basis of the held lengths of the image data in its main scan direction and its sub scan direction, whereby an interval between the successively transported recording sheets is shortened.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com