Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31results about How to "Save query time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

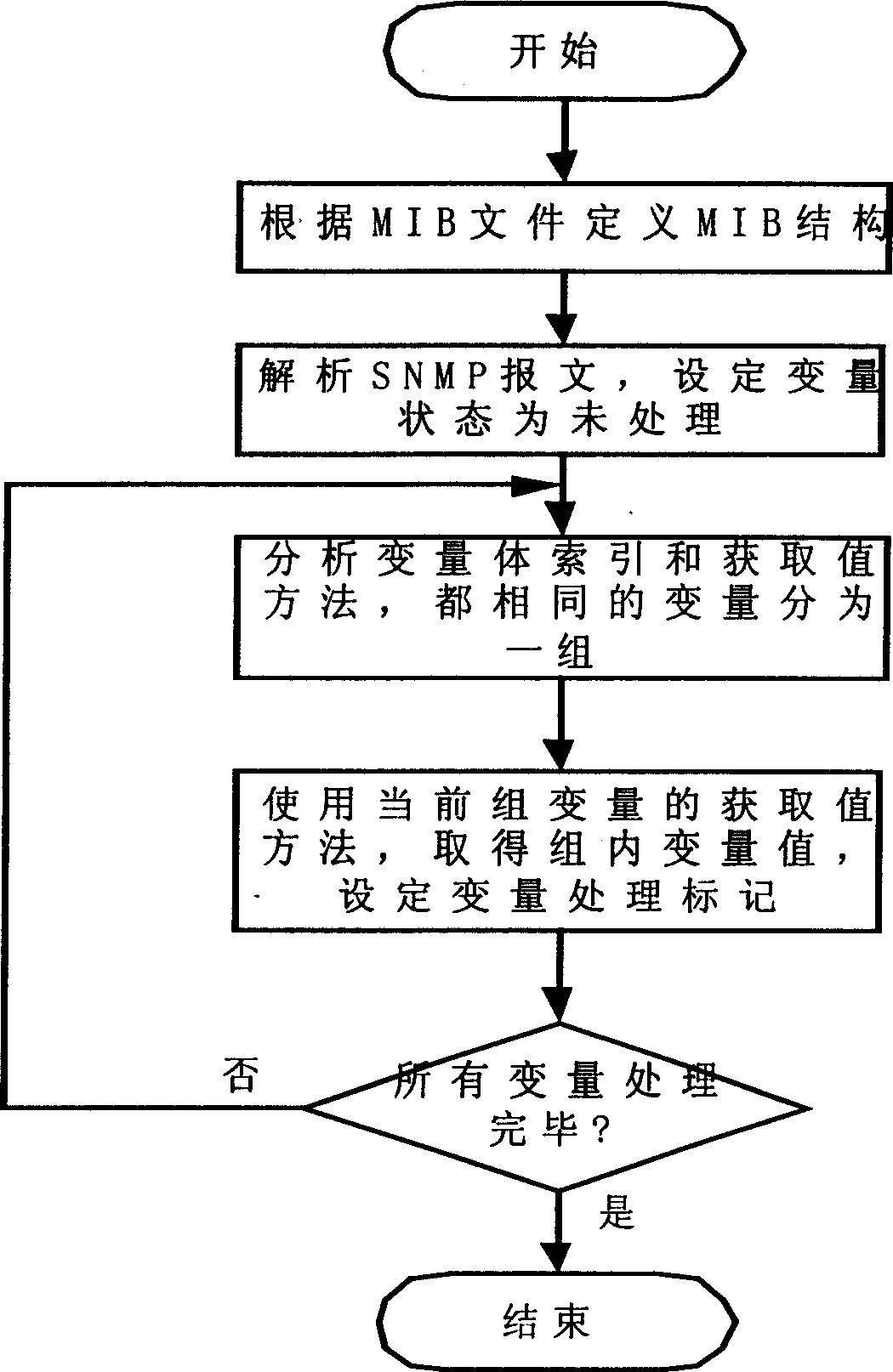

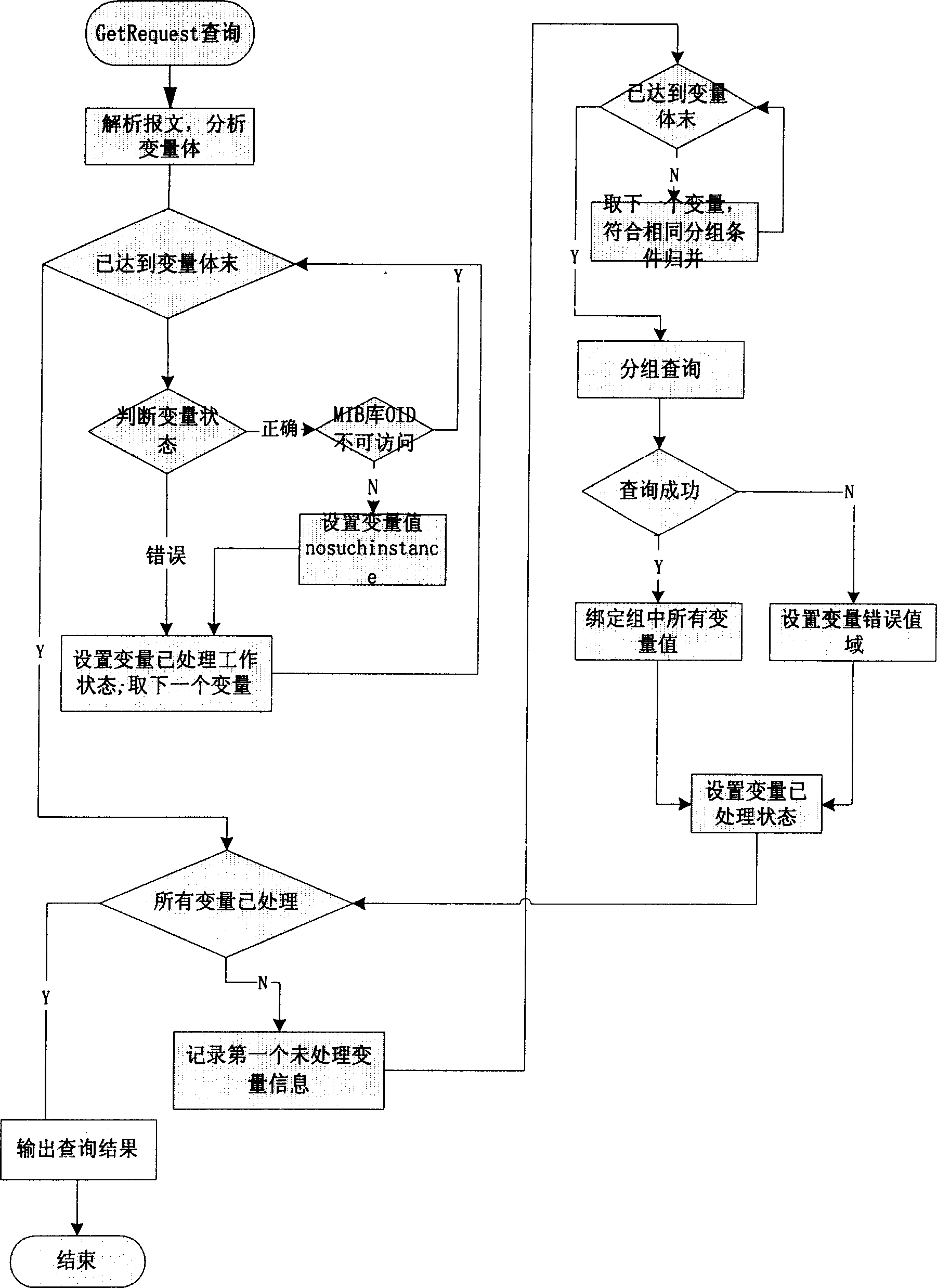

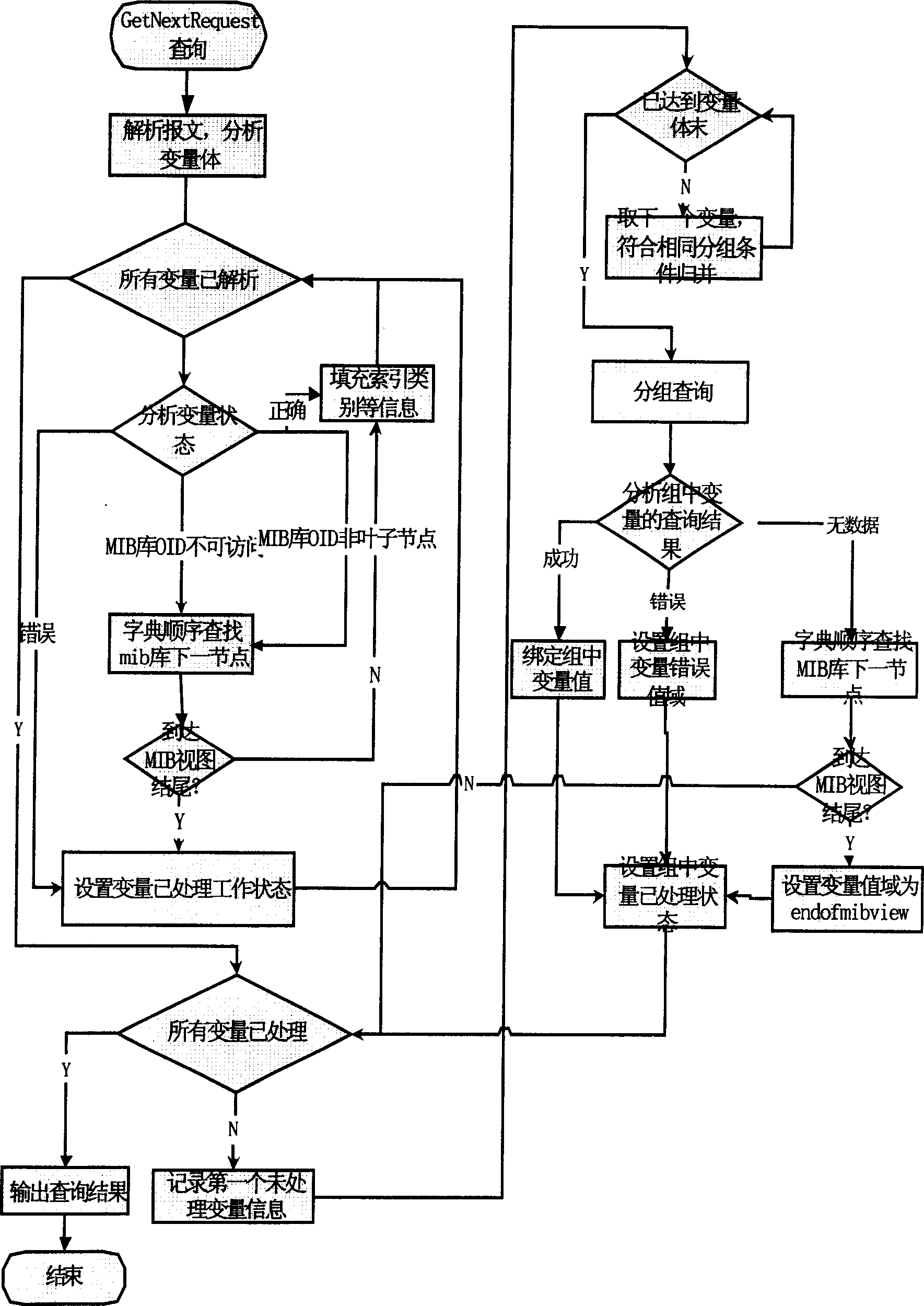

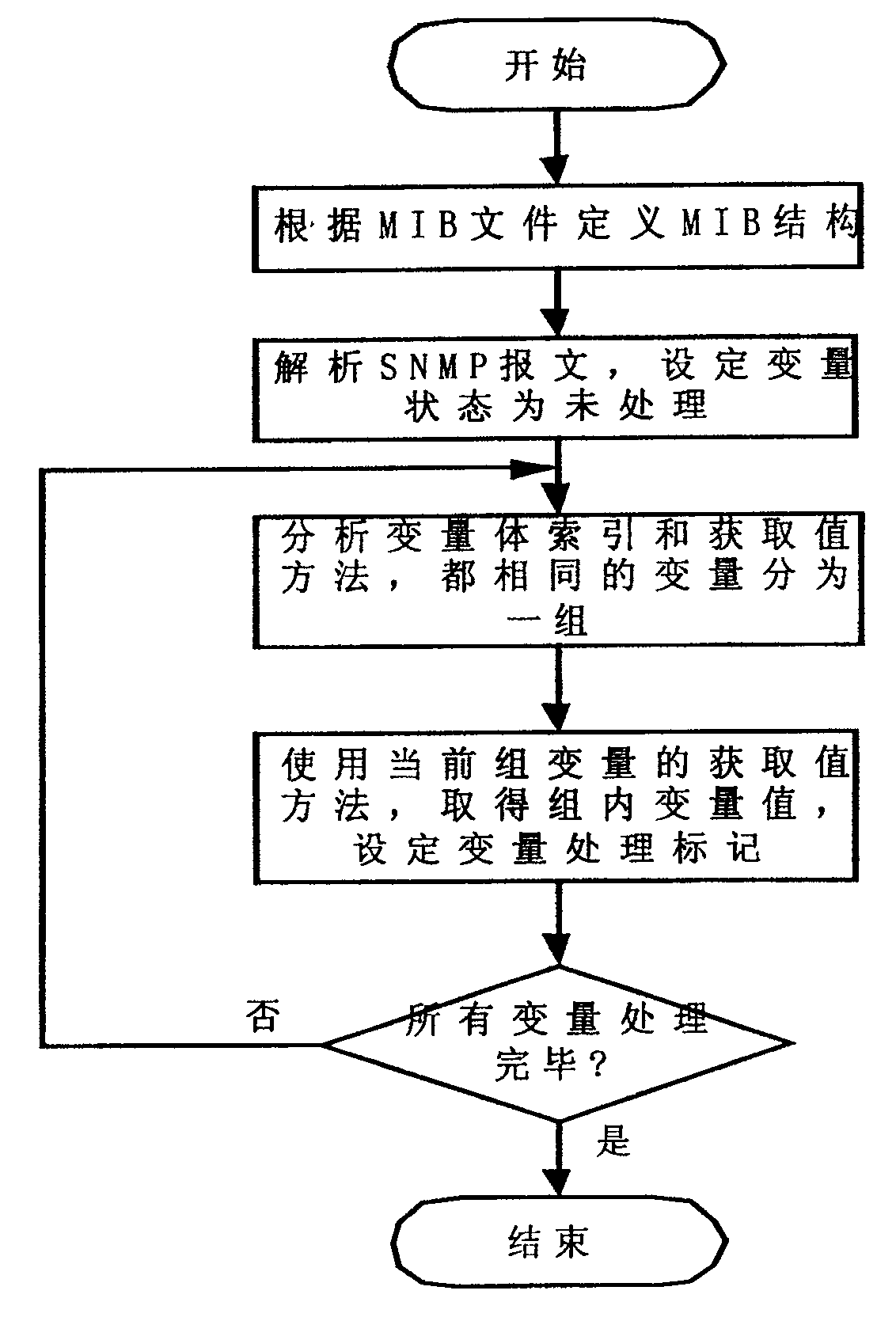

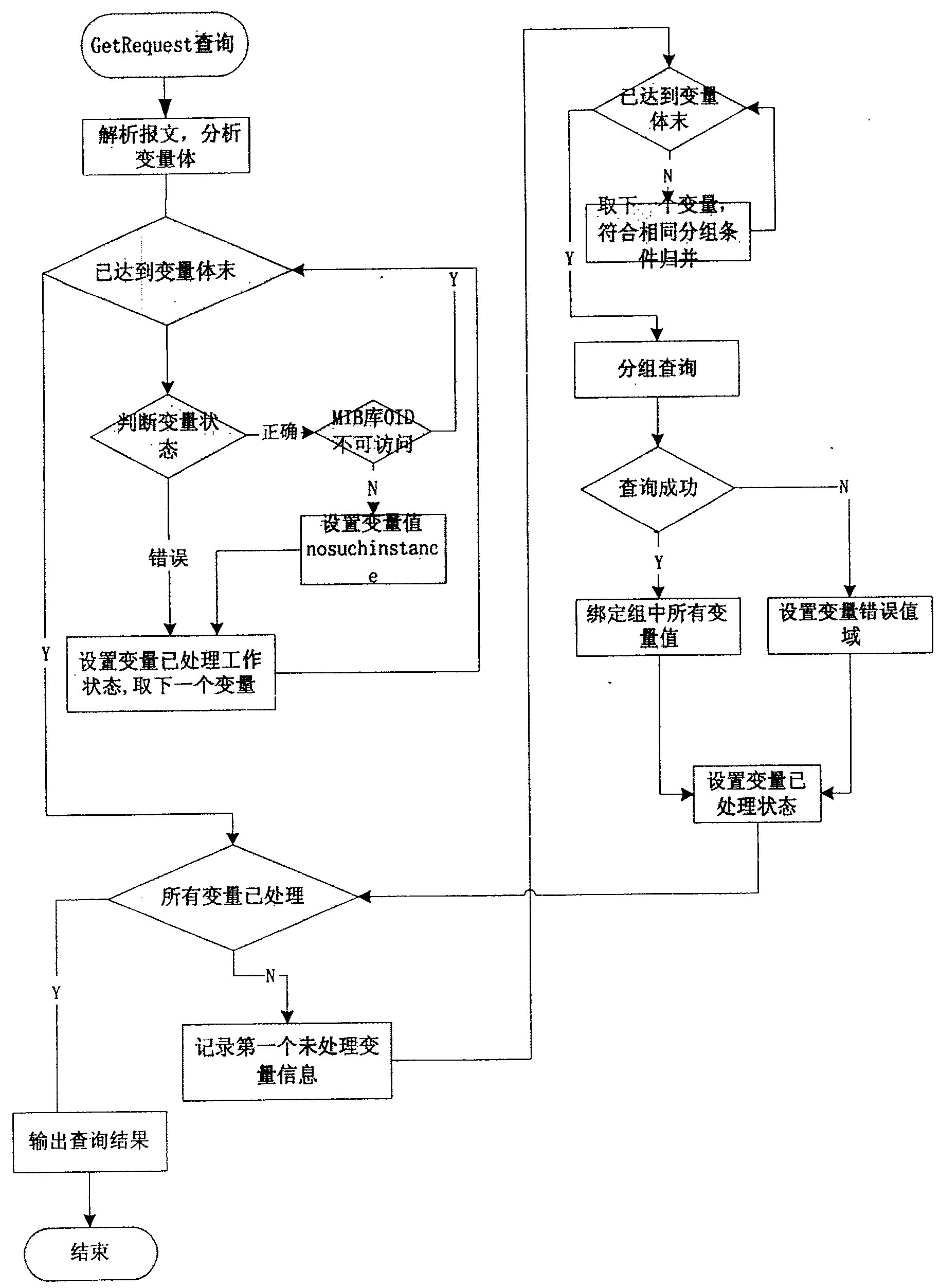

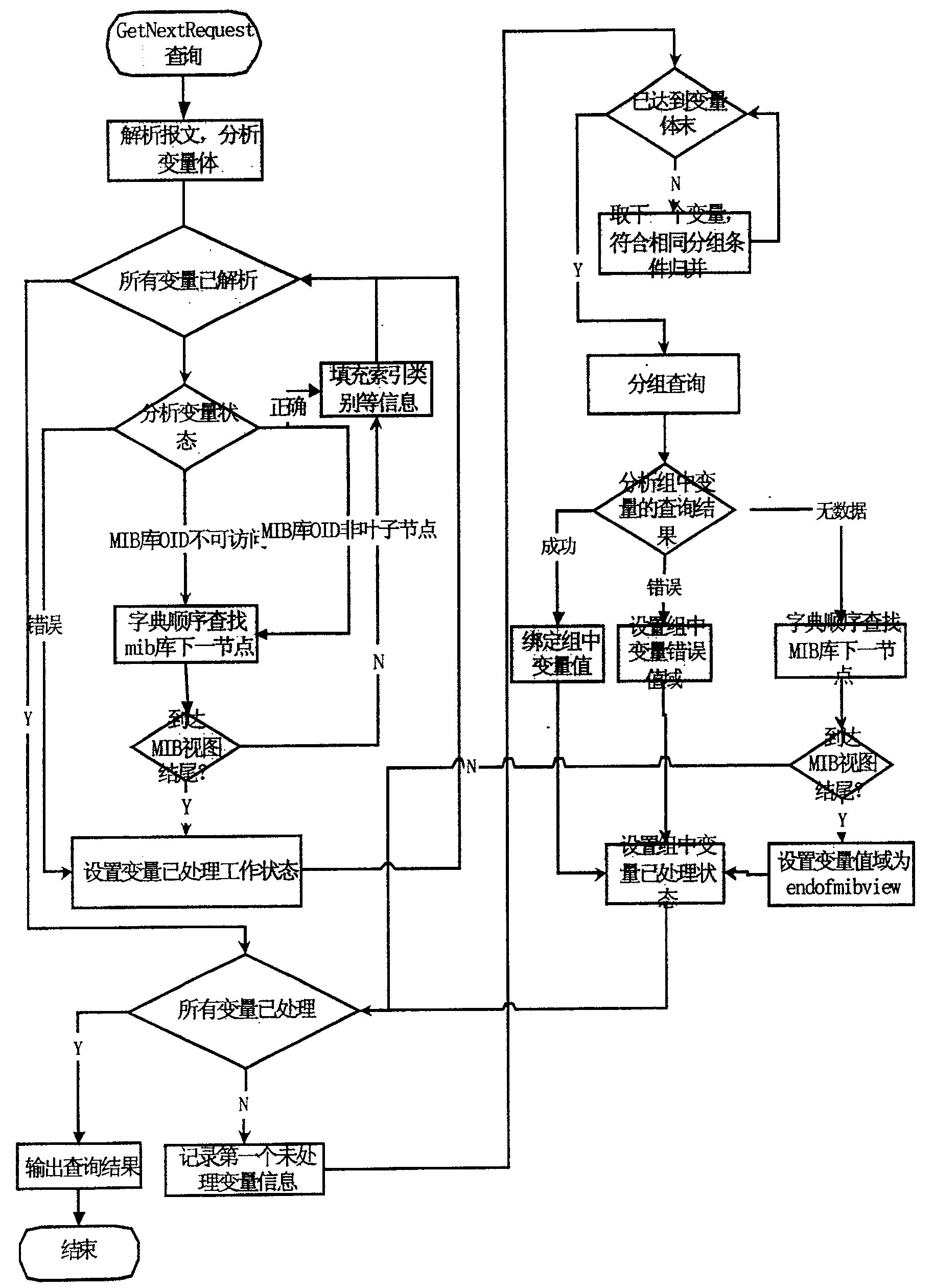

Method of using simple network management protocol to act multirariant block inquiry

InactiveCN1753402AOvercome speedOvercome resourcesTransmissionInformation repositoryManagement information base

This invention relates to a packet inquiry method for SNMP proxy multiple variables, which defines the data structure of a SNMP proxy management information library based on the files, analyses SNMP messages, variables and processes them to design their state and the air working state and packet the un-processed variable based on the message operation kinds of the SNMP messages, dispatches the obtaining values of the objects in the packets, inquires data based on the information of the objects and the variable index values in the management information library to bind values of the variables if the enquiry is successful and mark the variables a processed state and processes them to design the variable state and working state if it is not successful and repeates the above steps till all of their working states are processed.

Owner:南通国邦科技发展有限公司

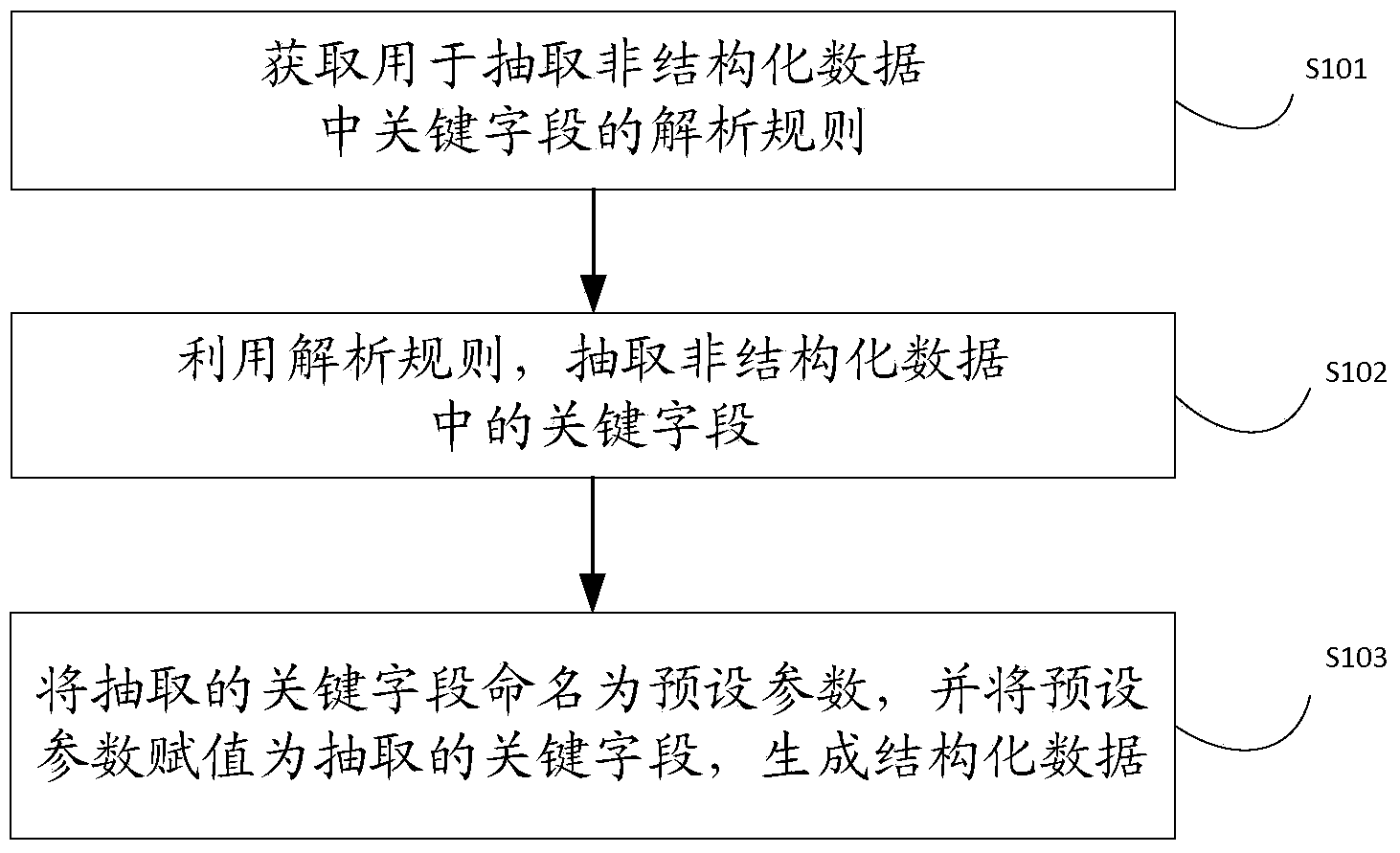

Unstructured data processing method and device

InactiveCN104239506AEasy to query statisticsSave spaceSpecial data processing applicationsUnstructured dataData science

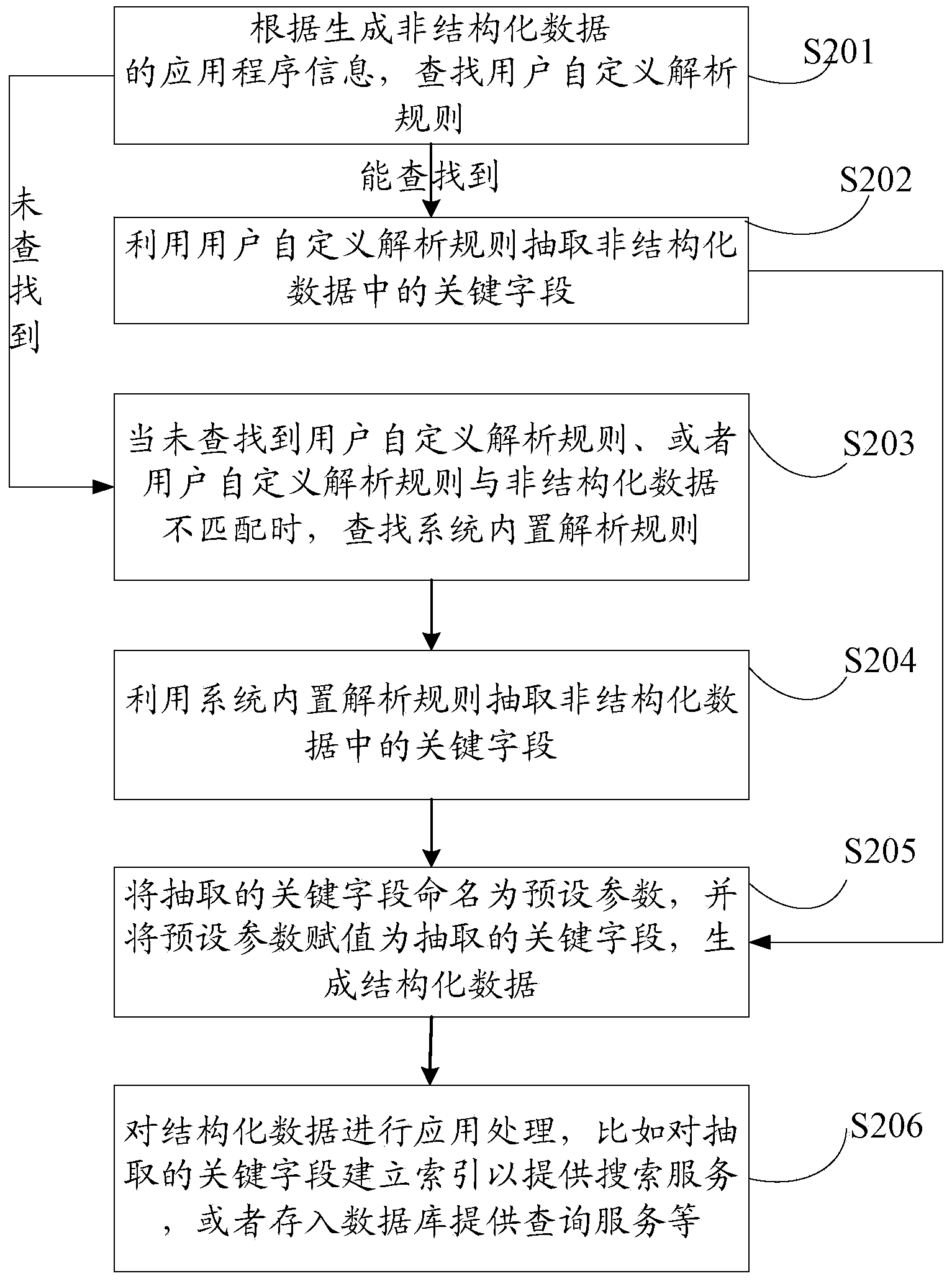

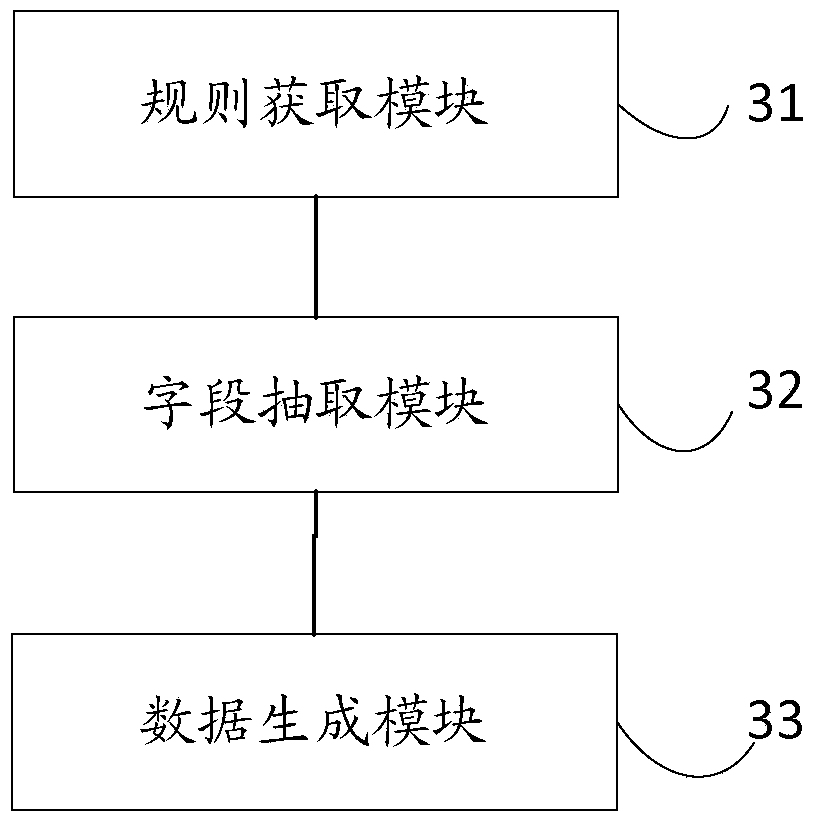

The invention provides an unstructured data processing method and device, which are used for converting unstructured data into structured data. The method comprises the following steps: acquiring a resolving rule for extracting a key field in unstructured data; extracting the key field in the unstructured data by using the analyzing rule; naming the extracted key field as a preset parameter, and assigning the preset parameter as the extracted key field to generate structured data. According to the technical scheme, the unstructured data can be converted into the structured data, so that convenience is brought to inquiry and statistics, and the calculation space and inquiry time are saved.

Owner:BEIJING YOUTEJIE INFORMATION TECH

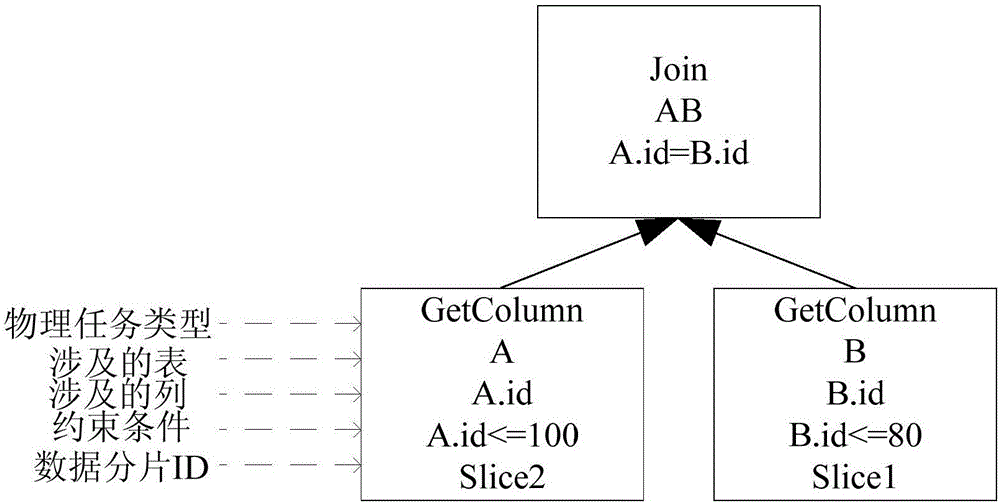

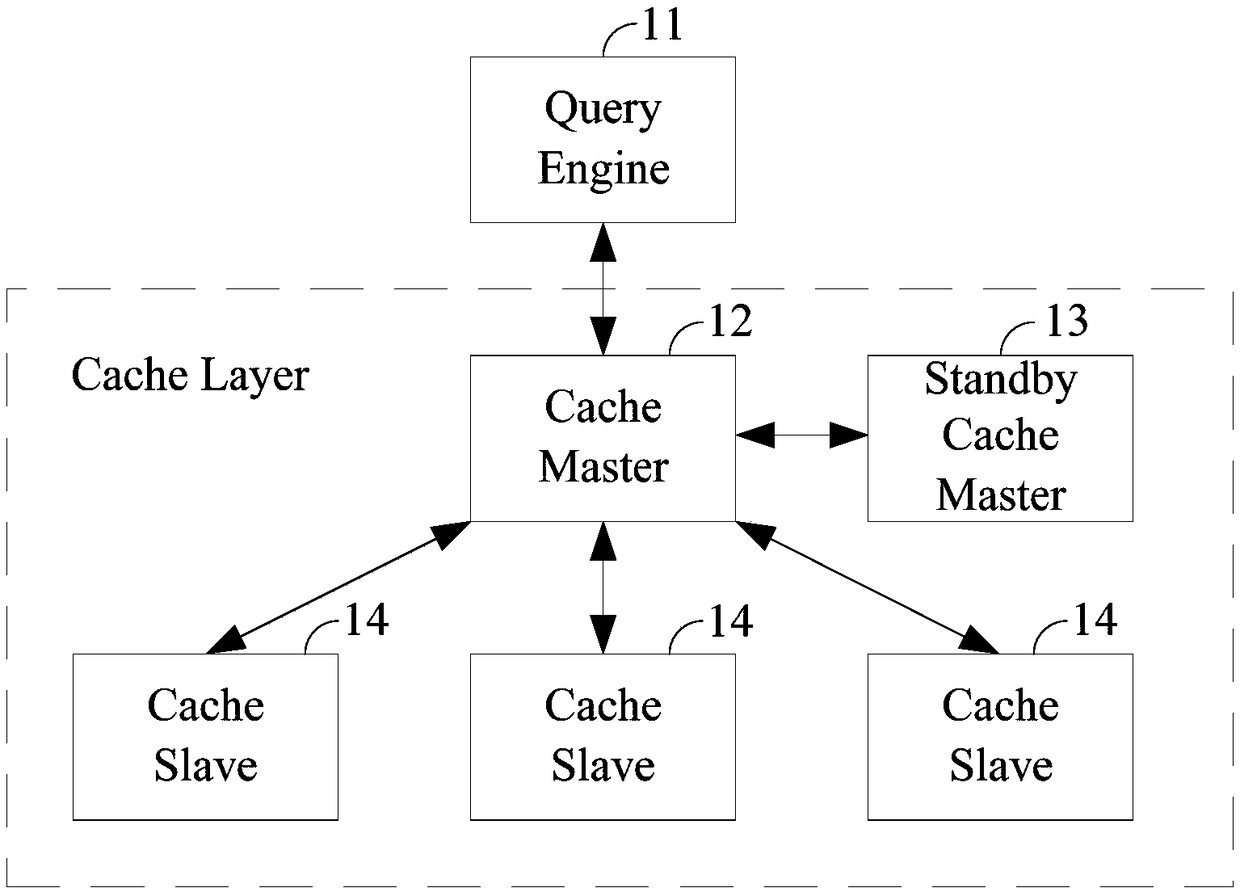

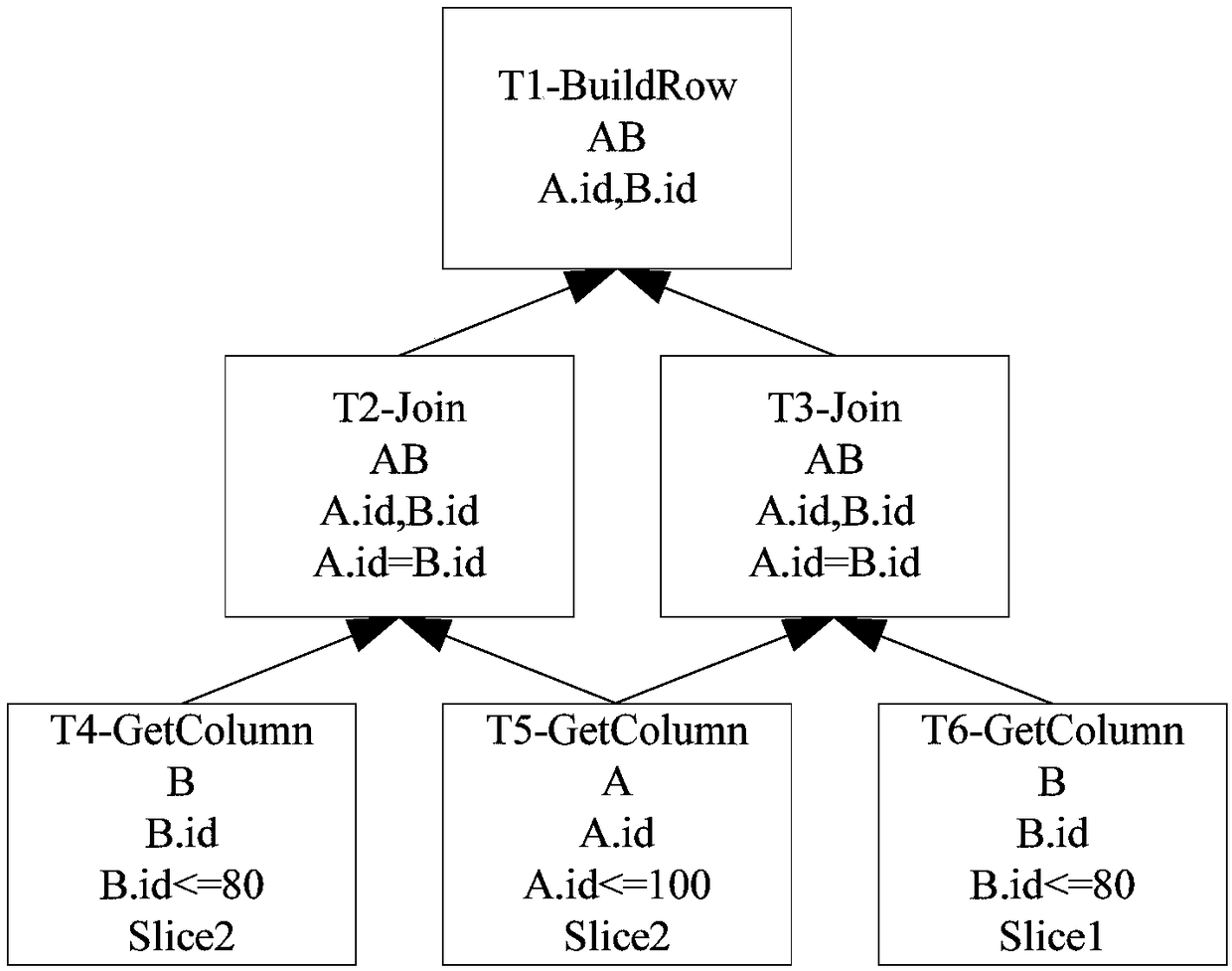

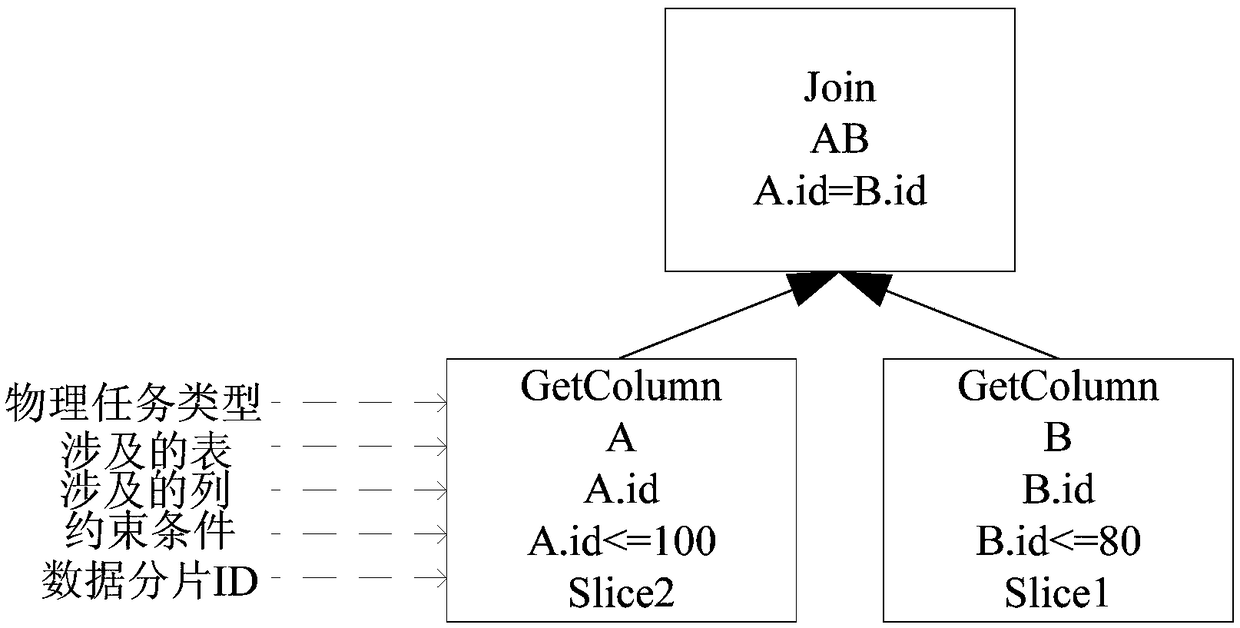

Cache management method of distributed internal memory column database

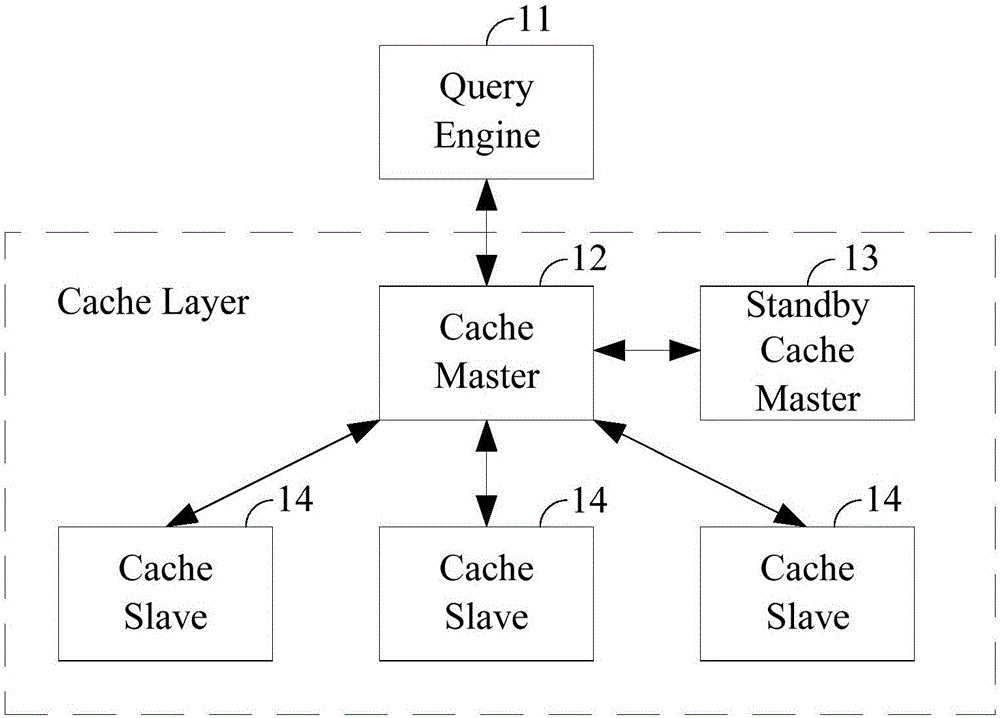

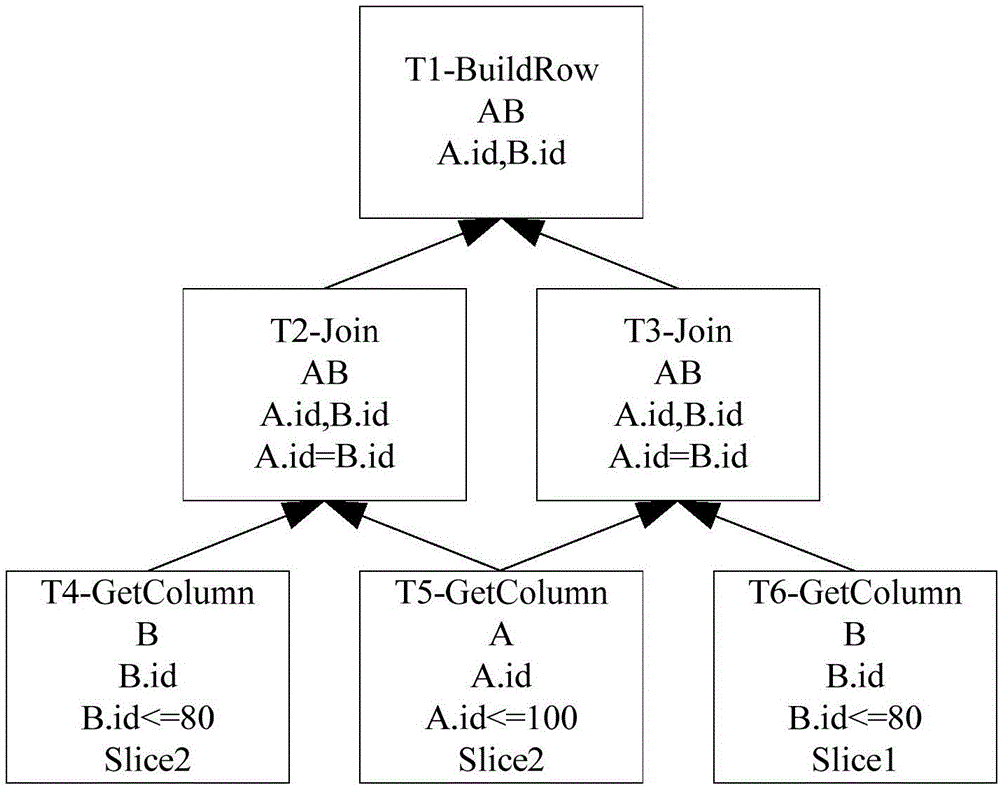

ActiveCN106294772AReduce calculations for repetitive tasksReduce query timeSpecial data processing applicationsExecution planDistributed memory

The invention discloses a cache management method of a distributed internal memory column database. The cache management method comprises the steps that cache queues are established on cache master control nodes; each physical task is used as a root node to cut the physical execution plan the node is located so as to obtain the cache calculation track corresponding to each physical task; cache feature trees are established on the cache master control nodes according to the cache calculation track corresponding to each physical task; when query requests arrive, an execution engine is queries to parse SOL statements into the physical execution plans; layer-level transversal is conducted on each node in the physical execution plans starting from the root nodes of the physical execution plan to execute, and whether the cache calculation track corresponding to each physical task is matched with the corresponding cache feature tree or not is judged; if yes, actual cache data of the physical tasks is directly read from the cache nodes, if not, the physical tasks are calculated. According to the cache management method of a distributed internal memory column database, weather a cache hits the target or not is rapidly detected through an efficient cache matching algorithm, and the query efficiency is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

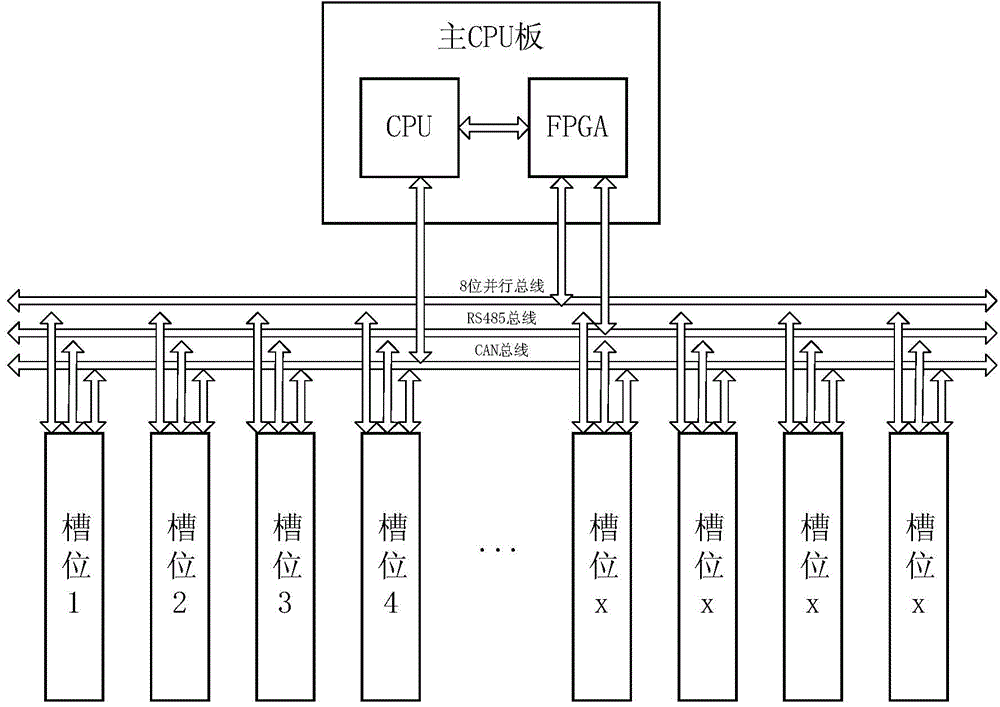

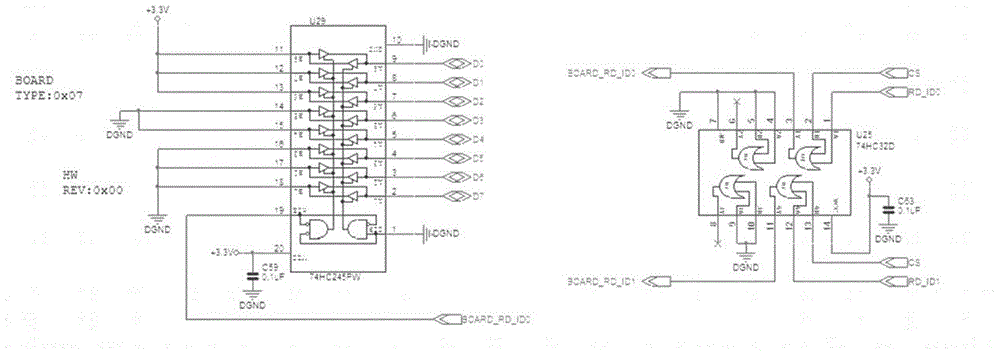

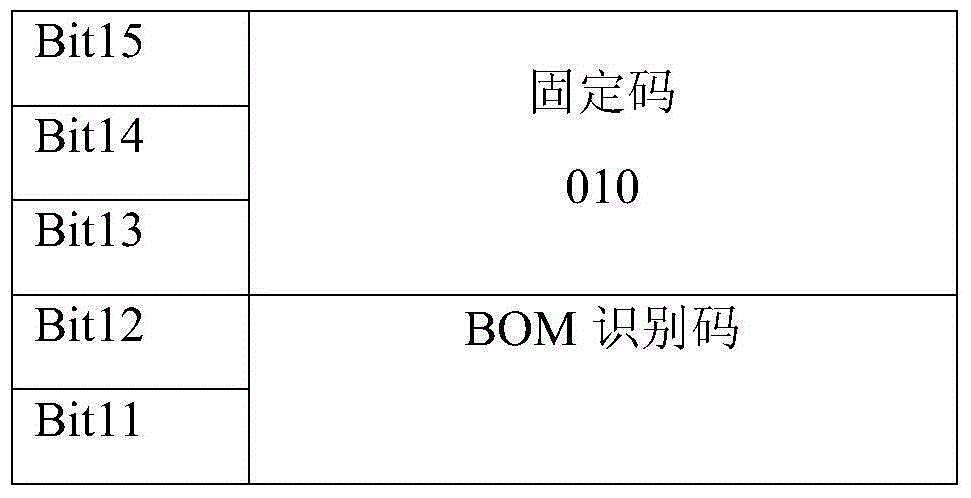

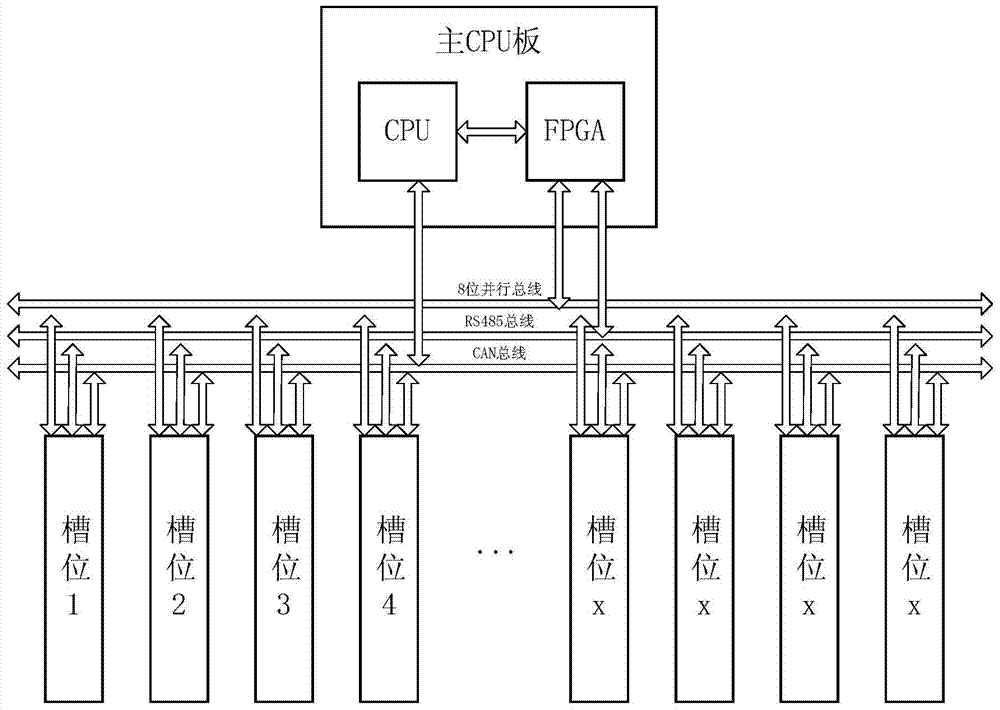

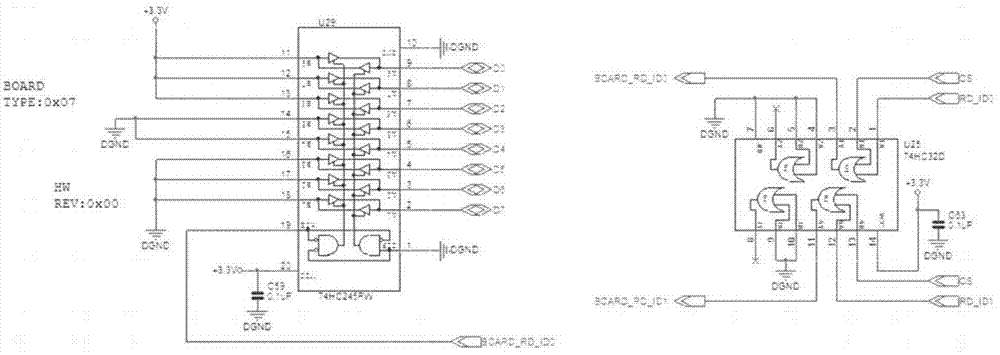

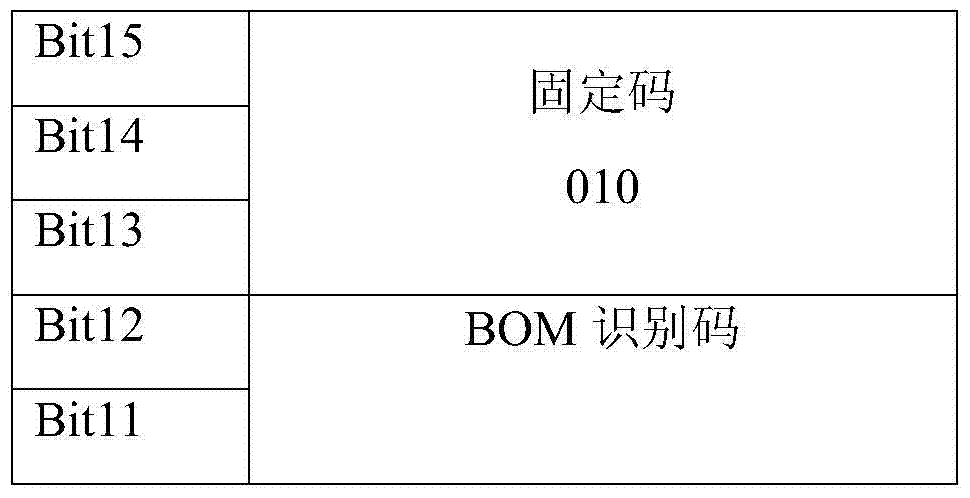

FPGA-based (Field Programmable Gate Array-based) IO (Input/Output) bus device with automatic recognition function

ActiveCN104484301AImprove versatilityEasy to handleElectric digital data processingInformation functionExternal data

The invention relates to an FPGA-based (Field Programmable Gate Array-based) IO (Input / Output) bus device with an automatic recognition function, and belongs to the technical field of buses. The IO bus device comprises a CPU (Central Processing Unit), an FPGA, slot position plates, a parallel bus, a serial bus and a field bus, wherein the CPU and the FPGA are used for carrying out data interaction through an external bus, and the FPGA and the slot position plates are interacted through the parallel bus or the serial bus; the CPU and the slot position plates are directly interacted through the field bus; the FPGA is used for providing a plate address for the CPU and helping the CPU to send and receive data, a state machine is arranged in the FPGA, and the state machine can be used for selecting plate interfaces in a circulation mode to read plate information and data signals. The FPGA-based IO bus device has a self-recognition plate information function, so that the reliability of data interaction is enhanced. The communication among plates is more flexible, and upgrading of a device platform is facilitated. The FPGA serves as a bridge of the CPU and external data, and the interaction of plate data is carried out through the serial bus and the parallel bus.

Owner:NANJING INTELLIGENT APP

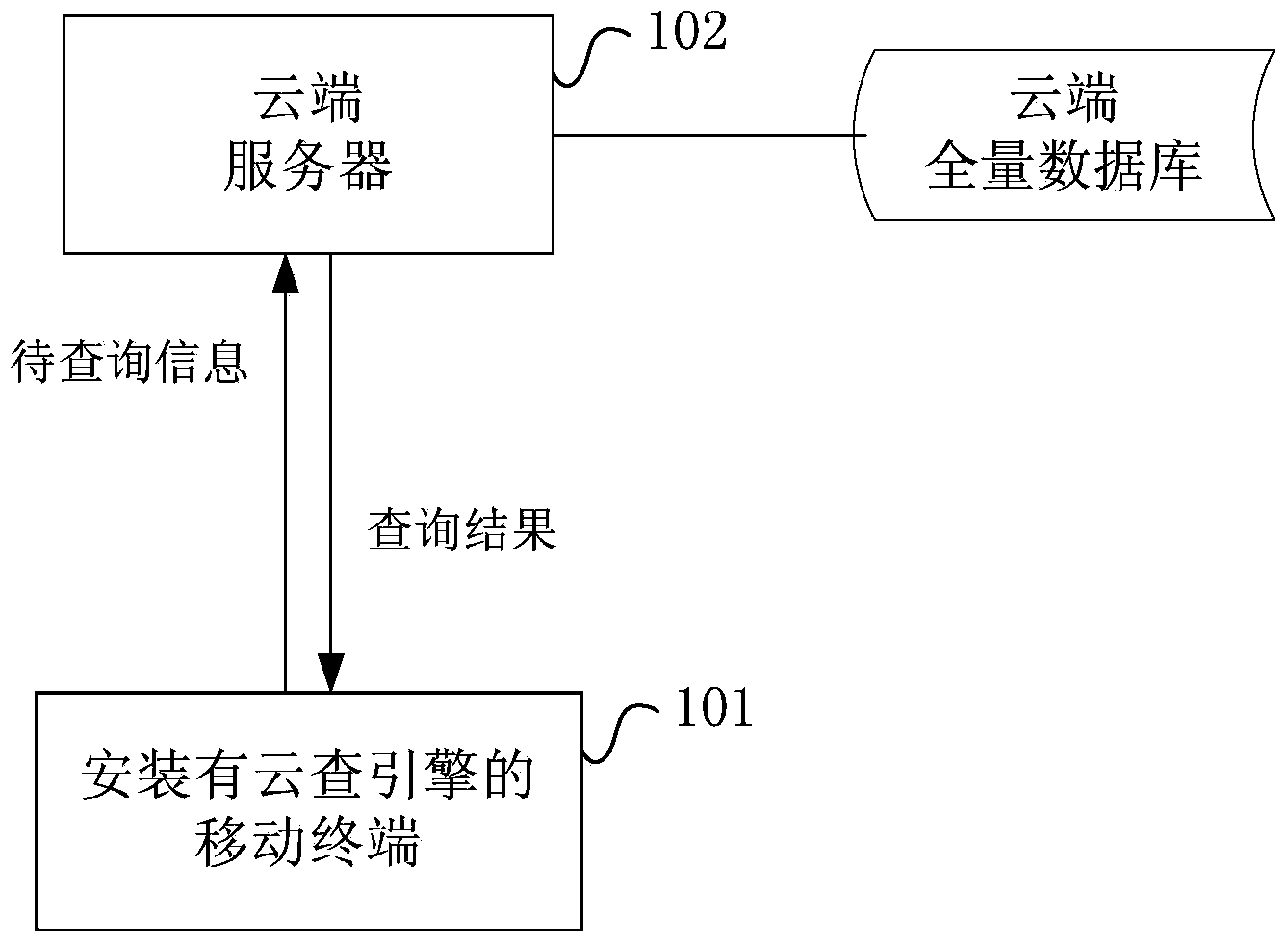

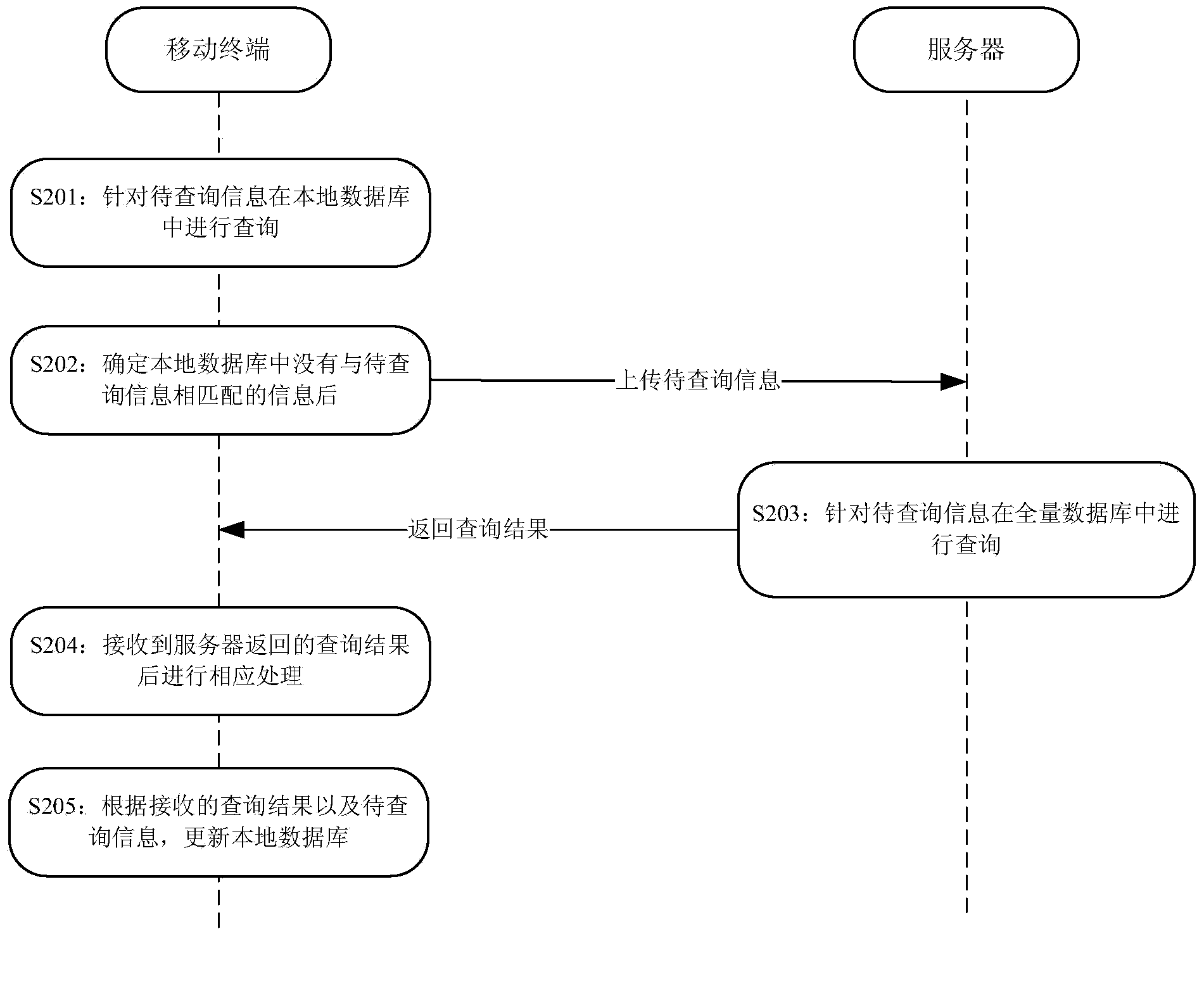

Query and memory space cleaning method and system based on cloud server

InactiveCN104317956AQuery is validEasy to cleanSpecial data processing applicationsComputer scienceOperating system

The invention discloses a query and memory space cleaning method based on a cloud server and a query and memory space cleaning system thereof, wherein the memory space cleaning method based on the cloud server comprises the following steps of: scanning the memory space by a mobile terminal and taking a path of a currently scanned catalogue as to-be-queried information and inquiring it in a local database; confirming that information matched with the to-be-queried information is absent from the local database in the mobile terminal, and uploading the to-be-queried information to the server; collecting garbage from corresponding catalogues by the mobile terminal according to the cleaning strategies of the content returned by the server. Through application of the method and the system, the query efficiency can be improved so as to save the memory space and further improve the cleaning efficiency.

Owner:BEIJING QIHOO TECH CO LTD +1

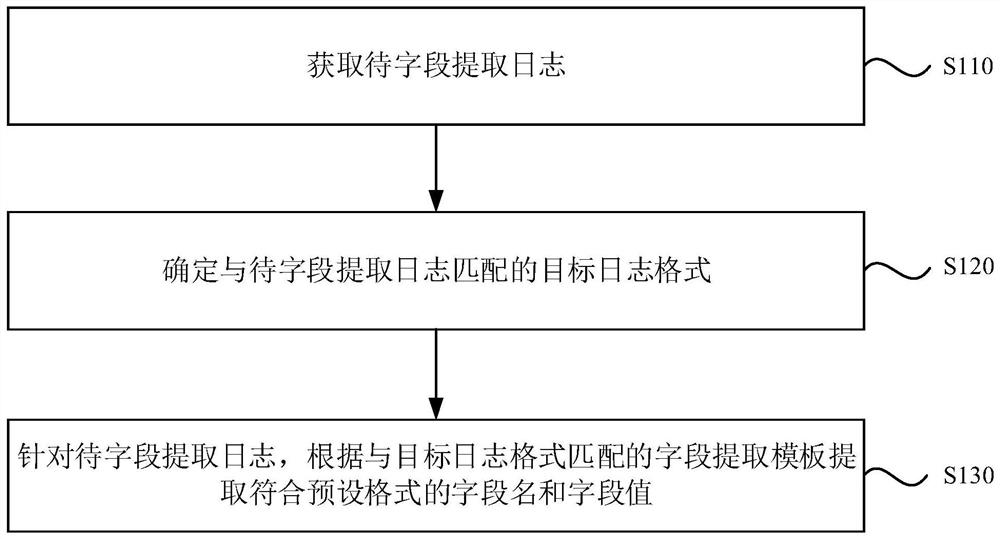

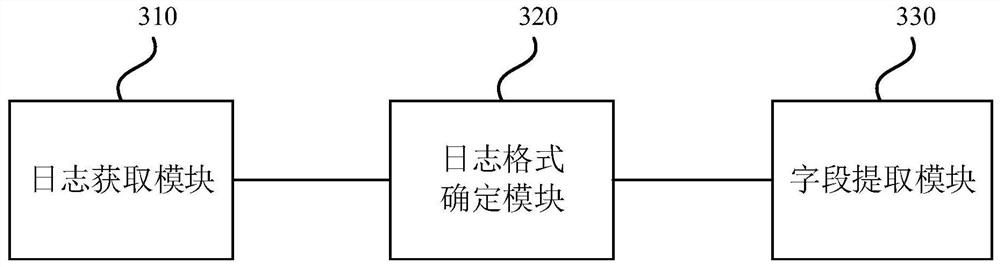

Information extraction method, device and equipment and storage medium

InactiveCN111708860AEasy to query statisticsSave computing space and query timeText database indexingSpecial data processing applicationsInformation extractionEngineering

The embodiment of the invention discloses an information extraction method and device, equipment and a storage medium. The method comprises the steps of obtaining a log to be subjected to field extraction; determining a target log format matched with the log to be subjected to field extraction; for the log to be subjected to field extraction, extracting a field name and a field value which accordwith a preset format according to a field extraction template matched with the target log format, wherein the field extraction template is determined through log clustering training. Through the technical scheme, the fields in the logs are extracted and converted into the unified preset format, the unstructured data can be converted into the structured data, query statistics is facilitated, the calculation space and query time are saved, analysis rule writing does not need to be manually conducted on the logs of each specific format, and the labor cost is reduced.

Owner:BEIJING YOUTEJIE INFORMATION TECH

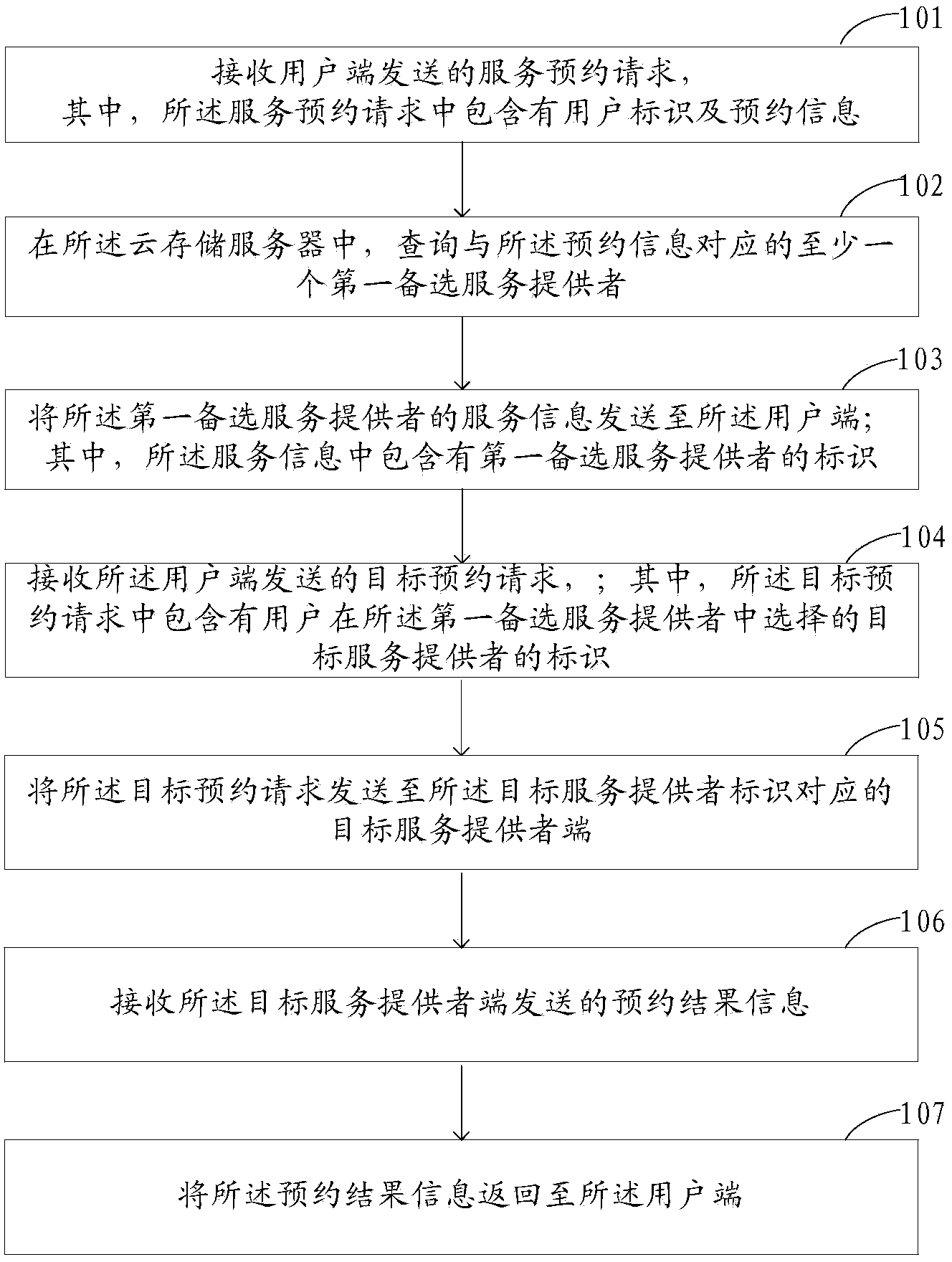

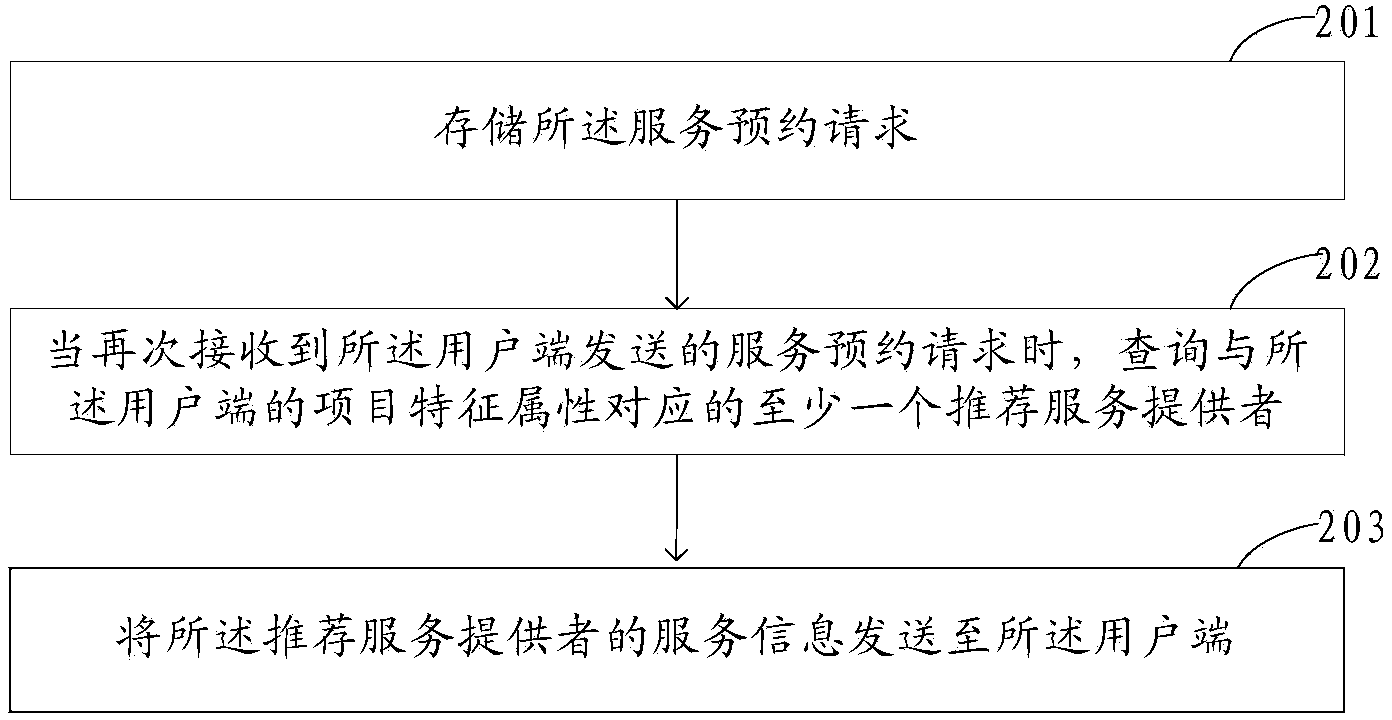

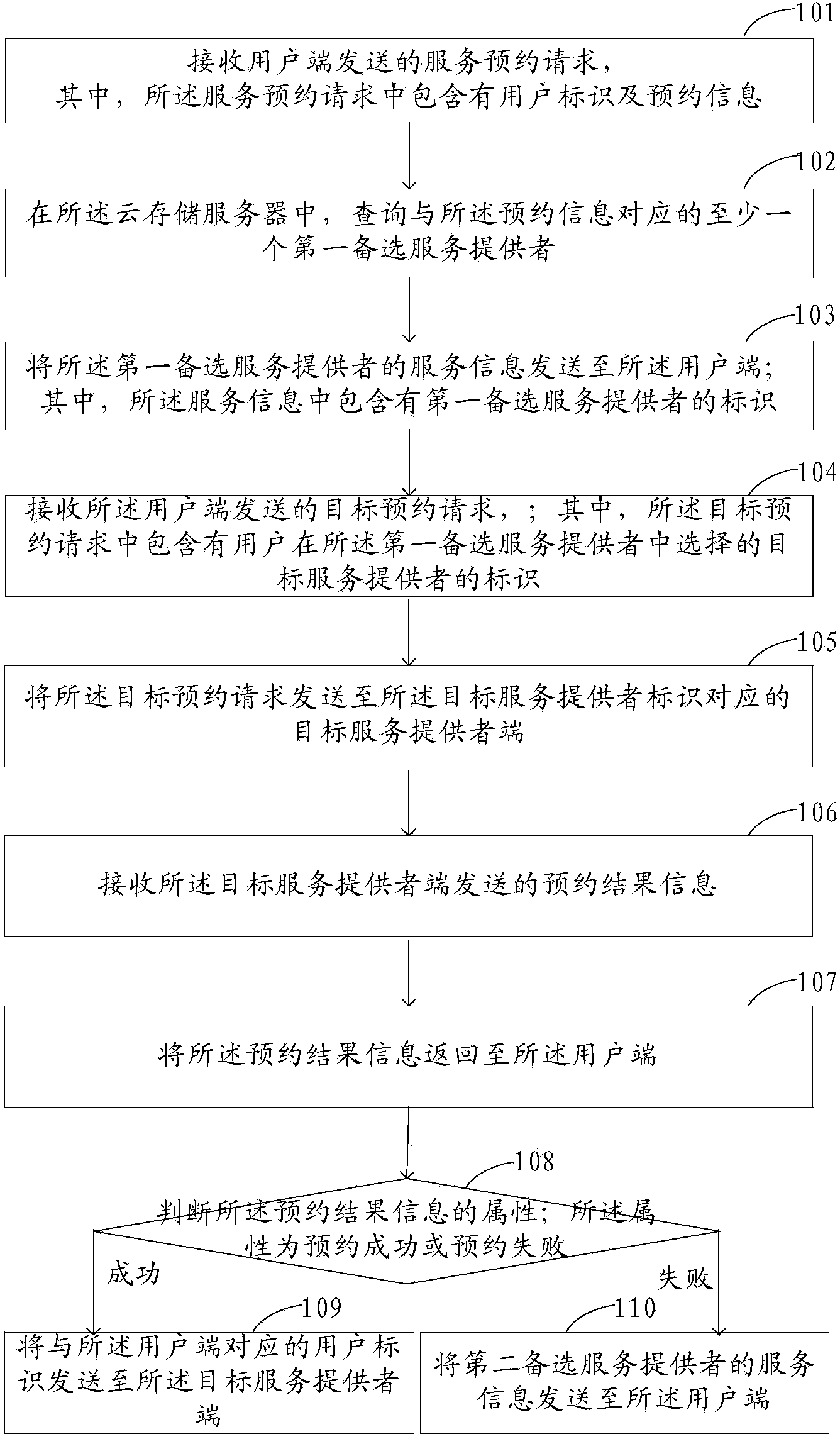

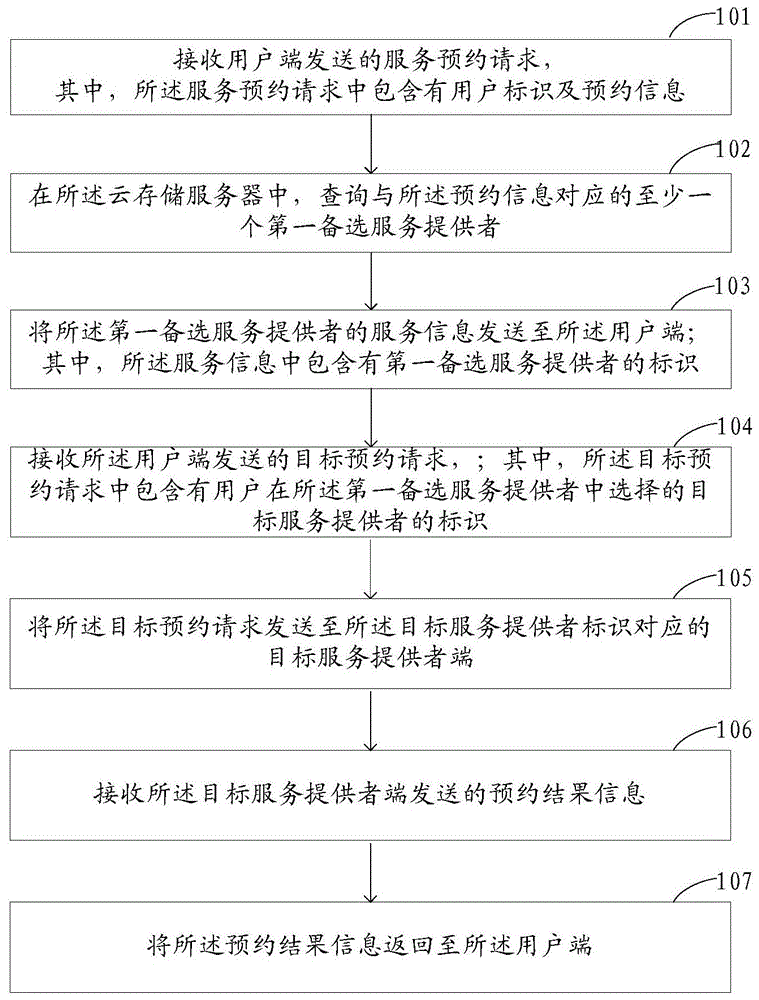

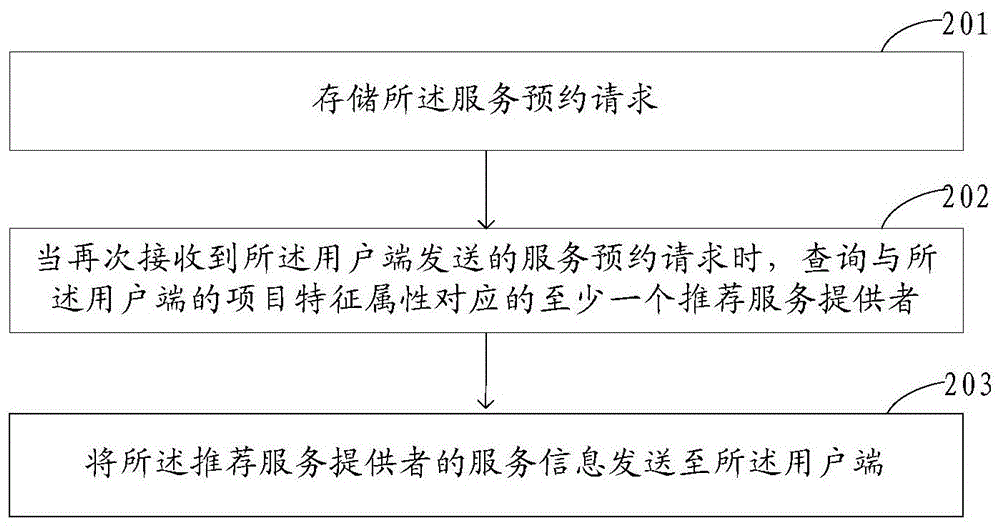

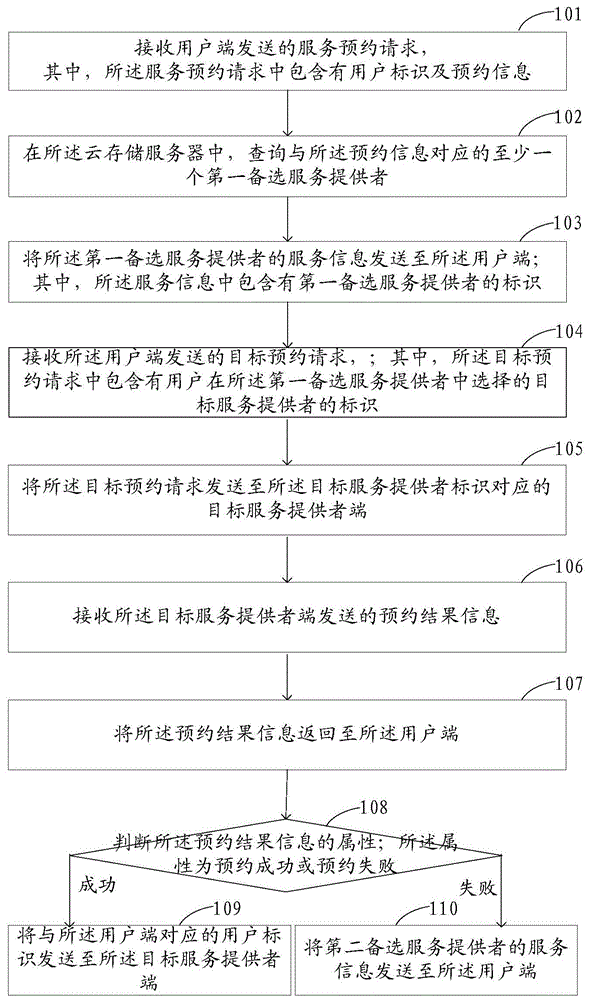

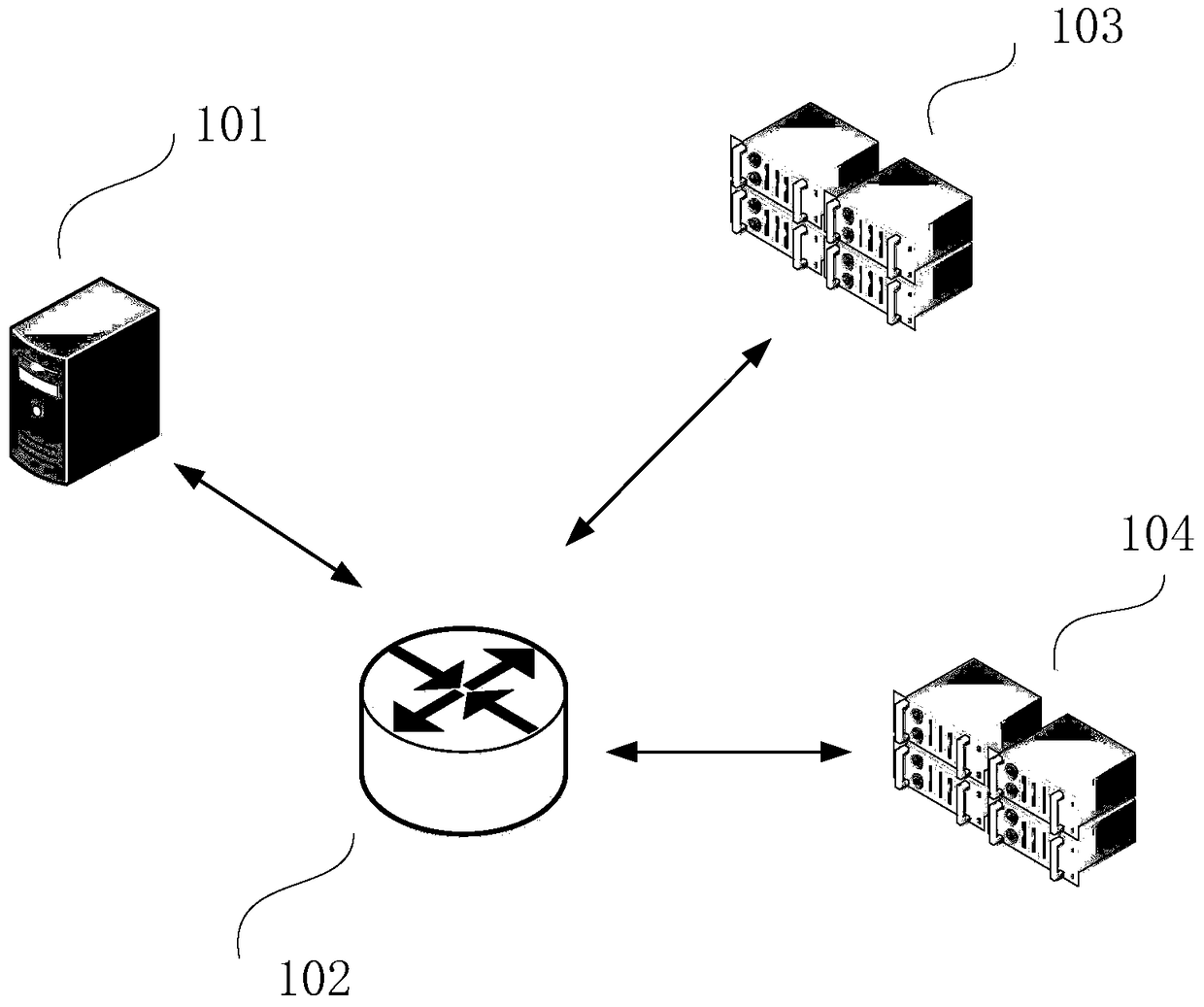

Cloud computing-based service providing method and device

ActiveCN103825940ASave query timeImprove service appointment efficiencyTransmissionComputer networkCloud storage

The invention discloses a cloud computing-based service providing method and device. The method includes the following steps that: a service reservation request containing reservation information, which is transmitted by a user end, is received; at least one first candidate service provider corresponding to the reservation information is inquired in a cloud storage server according to the service reservation request; the first candidate service provider is transmitted to the user end; a target reservation request containing a target service provider identifier, which is transmitted by the user end, is received; the target reservation request is transmitted to a target service provider end corresponding to the target service provider identifier; and reservation result information transmitted by the target service provider end is received and transmitted to the user end. Compared with the prior art in which manual query of the information of service providers is required, and with the method and device of the invention adopted, the manual query of the information of the service providers is not required, and therefore, query procedures and query time can be saved, and service reservation efficiency can be improved.

Owner:昆山中创软件工程有限责任公司

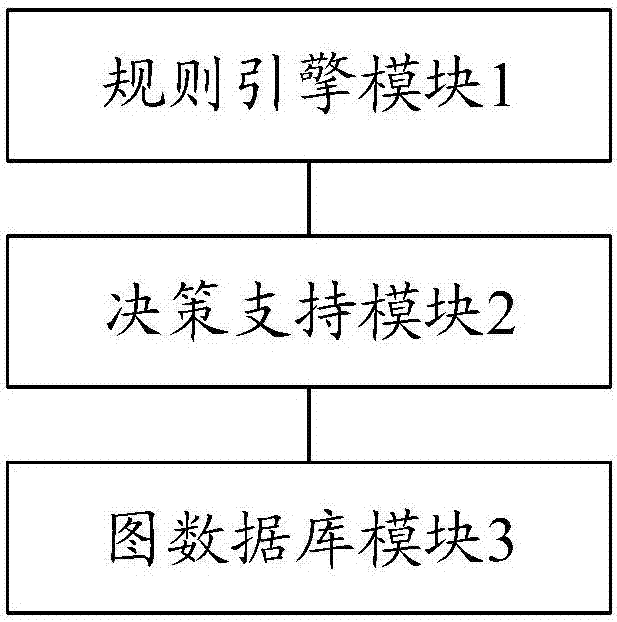

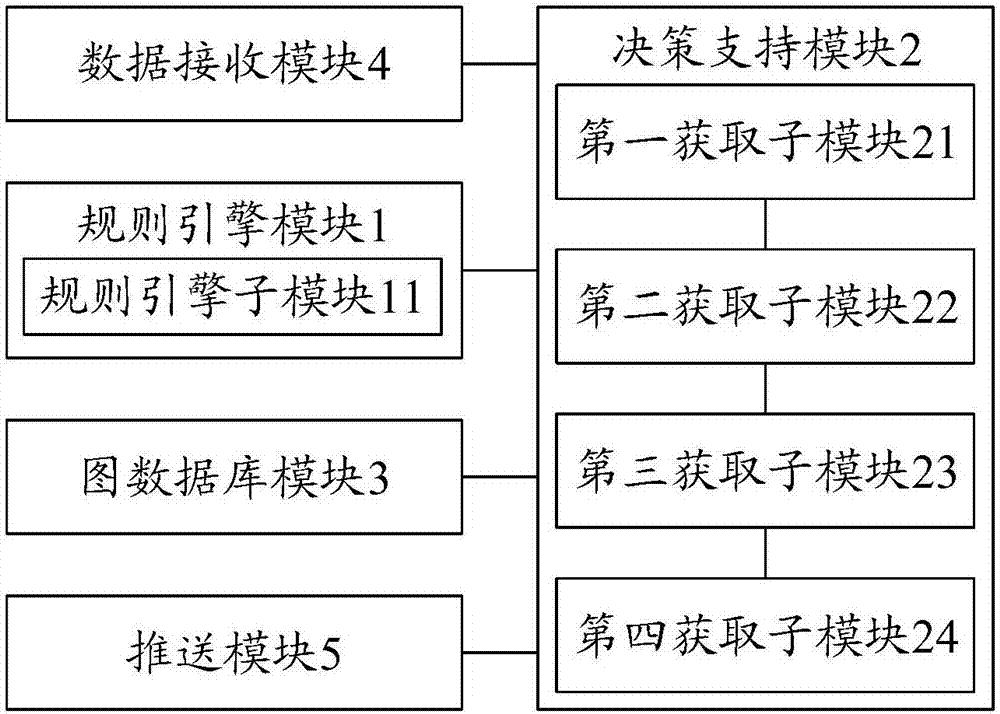

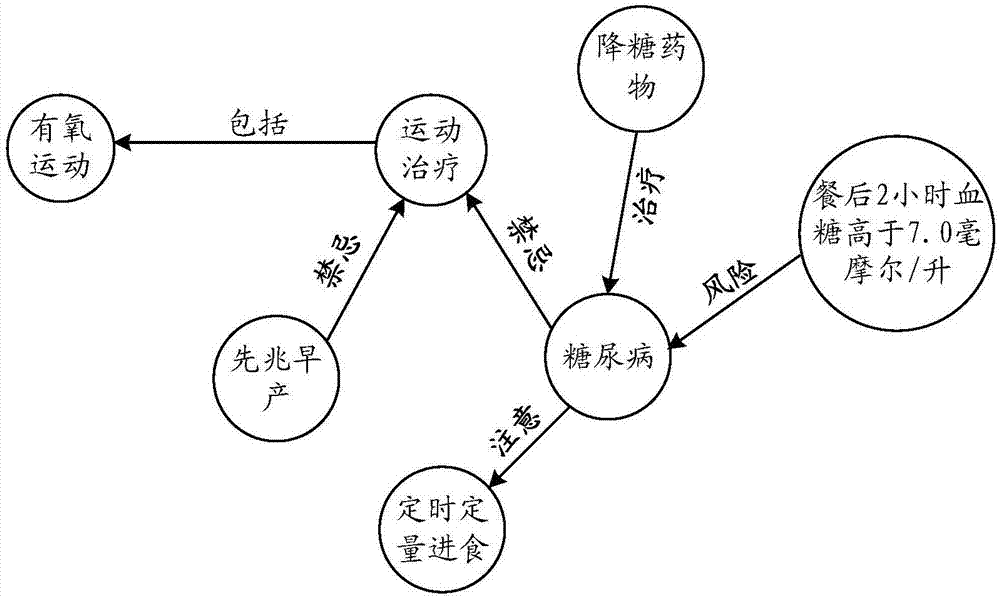

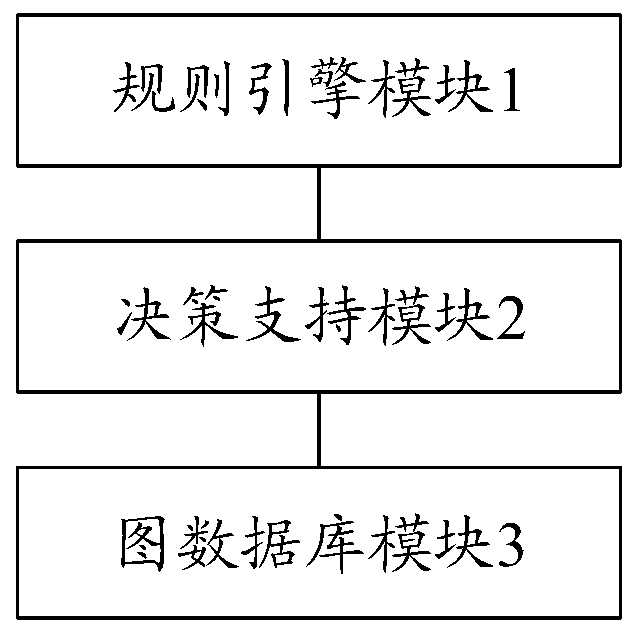

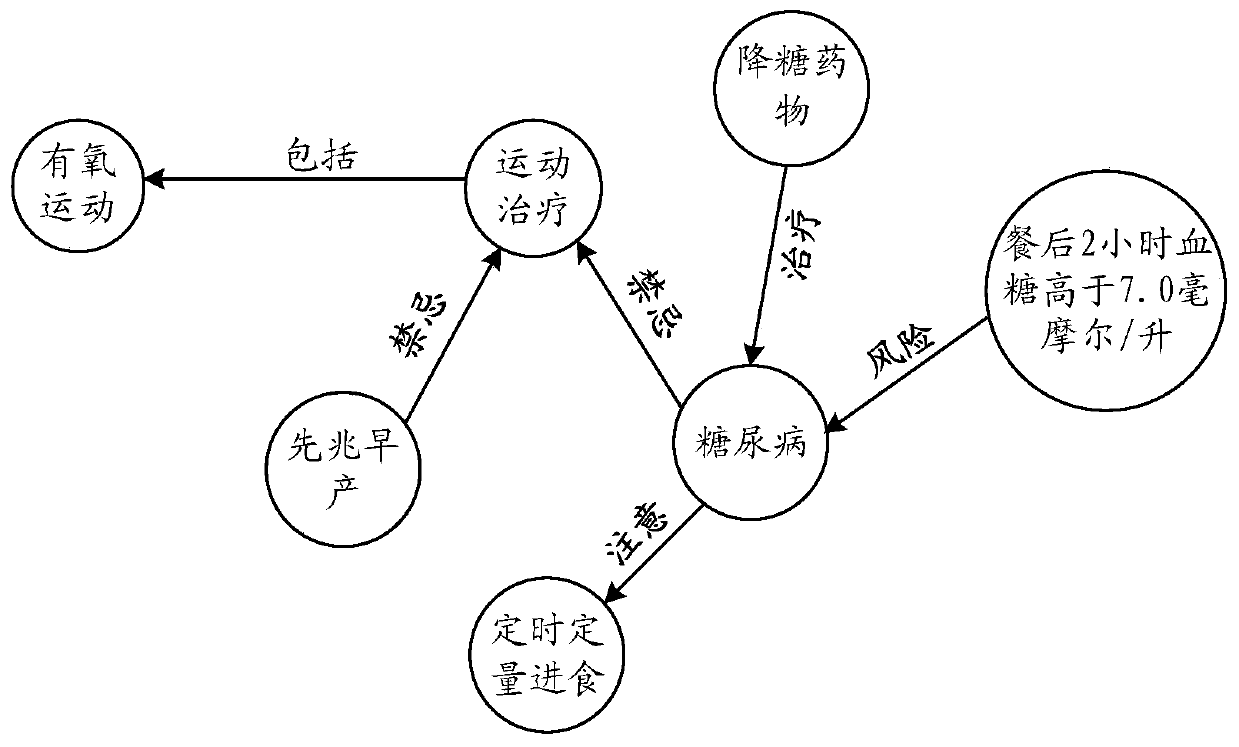

Medical information querying system and method

ActiveCN107239665AReduce loadRespond quickly to mission needsPhysical therapies and activitiesMedical simulationComputer moduleDecision taking

The embodiment of the invention provides a medical information querying system and method. The system comprises a rule engine module, a decision supporting module and a graph database module. The rule engine module is used for receiving clinical data and obtaining querying rules matched with the clinical data; the decision supporting module is used for searching a graph database stored by the graph database module for medical information corresponding to the querying rules obtained by the rule engine module. According to the medical information querying system and method, loads of the rule engine module can be relieved, the task requirement of the decision supporting module can be rapidly responded to, and the efficiency is high; meanwhile, the rule engine module and the graph database module are not coupled, the system development and maintenance complexity is simplified, the storage space is saved, and the querying time is shortened; in addition, the graph database is adopted for storing medical information, so that querying is performed more conveniently and rapidly.

Owner:BOE TECH GRP CO LTD

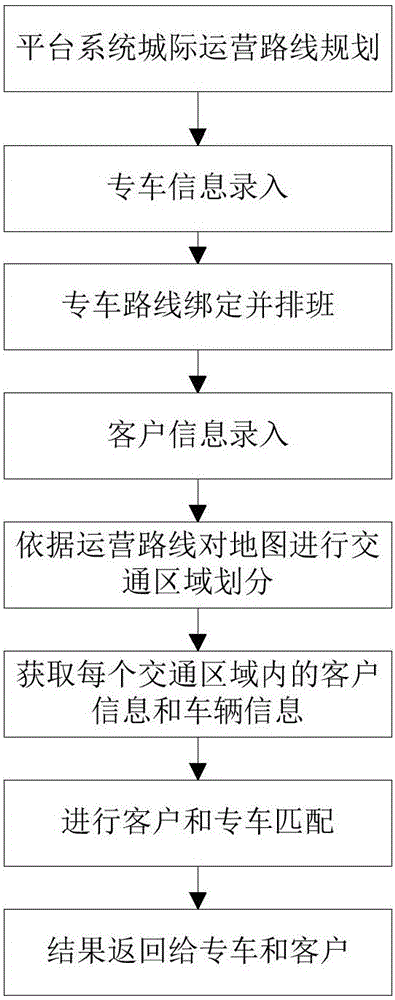

Intercity network reservation special car operation mode

InactiveCN106295856AImprove scheduling efficiencySave query timeReservationsForecastingSimulationOperation mode

The invention relates to a passenger transport special car operation mode, and particularly relates to an intercity network reservation special car operation mode. The intercity network reservation special car operation mode comprises the steps that S1, a platform system sets intercity operation lines, and carries out traffic area division according to the operation lines; S2, special cars input special car information into the platform system through an intelligent terminal; S3, the platform system carries out automatic cycle rolling schedule arrangement on each operation line according to the special car information; S4, customer information is inputted through a mobile phone client; S5, traffic area division is carried out on a map according to the operation lines; S6, customer information and special car information in each traffic area are acquired; S7, the customer information and the special car information in each traffic area are matched according to a matching rule of the platform system, and special car dispatching information is generated; and S8, a matching result is returned back to a corresponding customer and a special car, and special car dispatching operation is carried out. The intercity network reservation special car operation mode can effectively improve the special car operation efficiency, reduce the operation commission and reduce the customer waiting time.

Owner:乐山易通天下网络科技有限公司

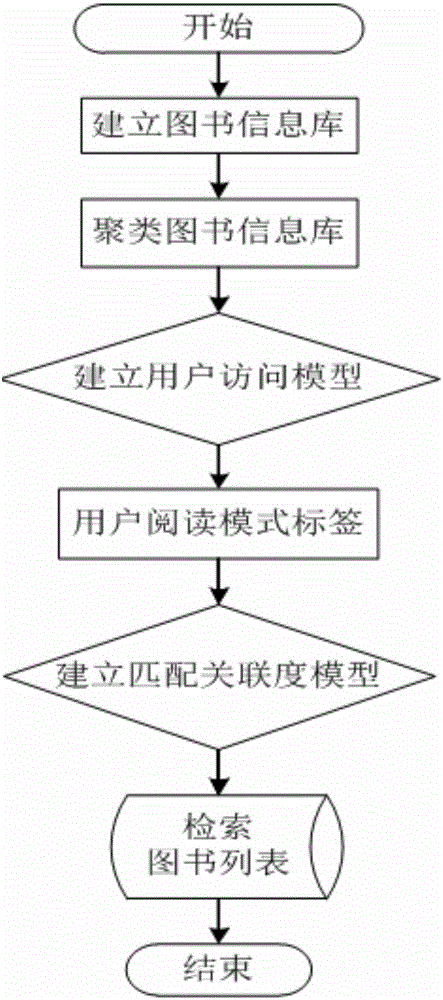

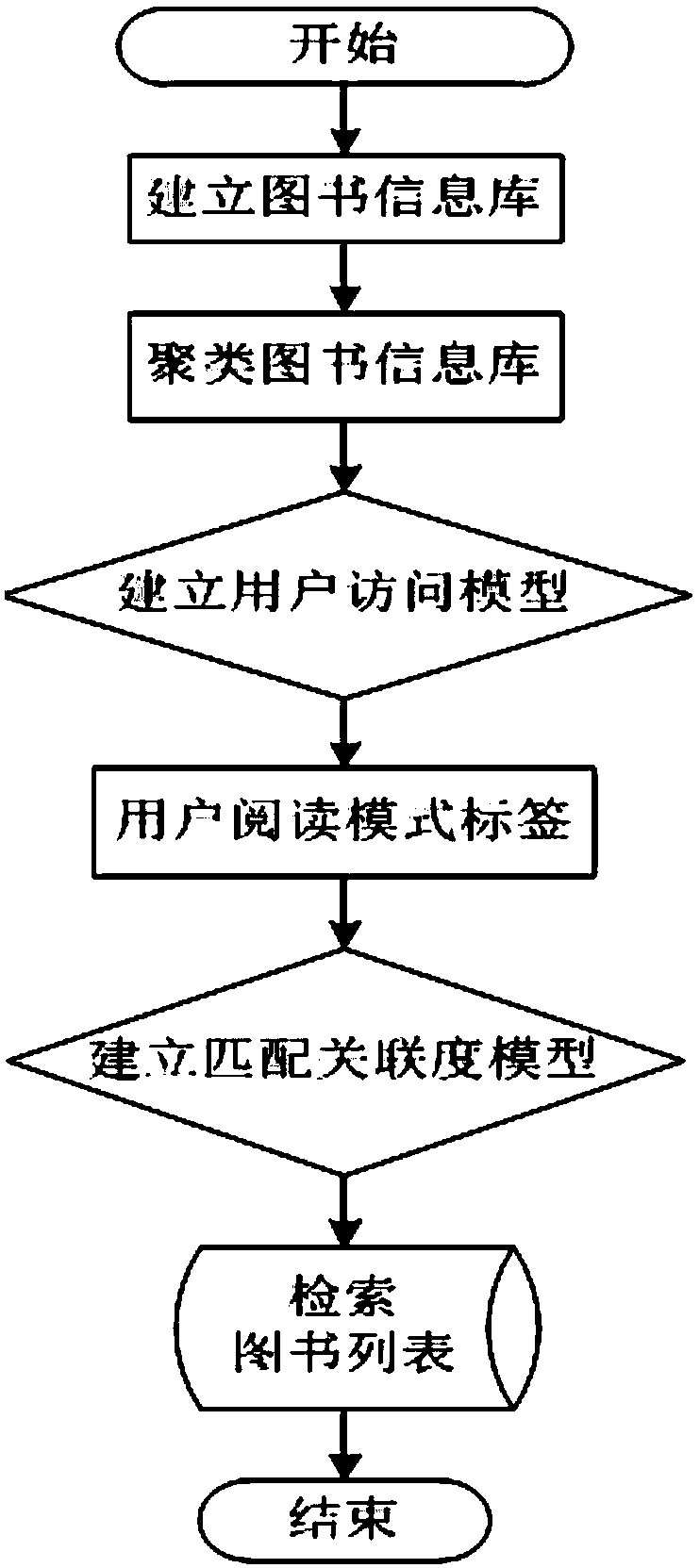

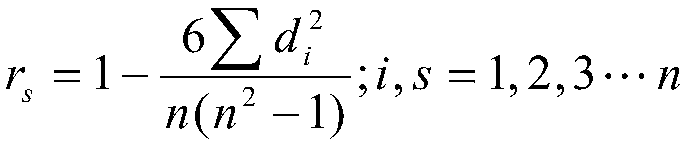

Book retrieval method based on feature extraction

ActiveCN106126626AExact matchExact searchCharacter and pattern recognitionSpecial data processing applicationsInformation repositoryFeature extraction

The invention relates to a book retrieval method based on feature extraction, pertaining to the technical field of network communication. The method comprises following steps: firstly, collecting book information of a book library, extracting label information of books, coding and establishing a book information library to store book information; secondly, gathering books according to elements of book label information, coding books gathered as an original library source for book retrieval and combining with book original labels for book feature reconstruction, and extracting new feature words of a wide range of books as a collection book information library; then, extracting frequency of types of books visited by users in collection book information library, establishing a users' visit model to form users' reading mode labels as users' feature label values; and finally, creating a matching relevancy model for providing retrieval book lists for users who successfully match. The book retrieval method based on feature extraction is capable of retrieving visit features of users in a real-time manner so that user's visit demands can be precisely satisfied.

Owner:KUNMING UNIV OF SCI & TECH

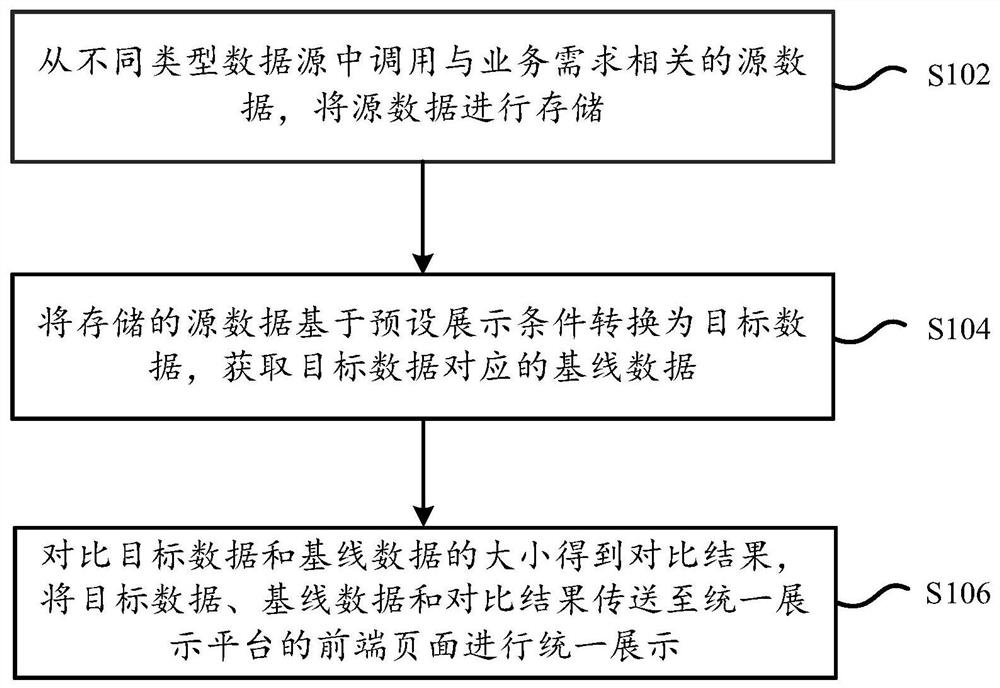

Operation and maintenance monitoring data display method and device, storage medium and computing equipment

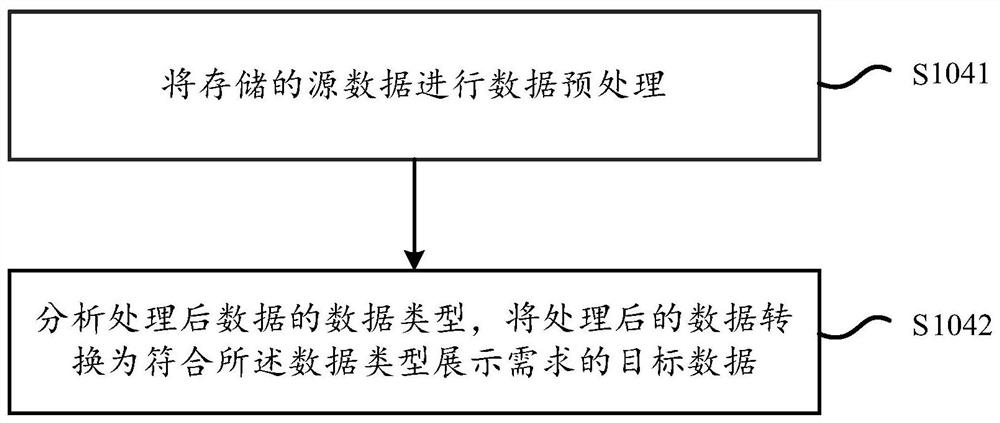

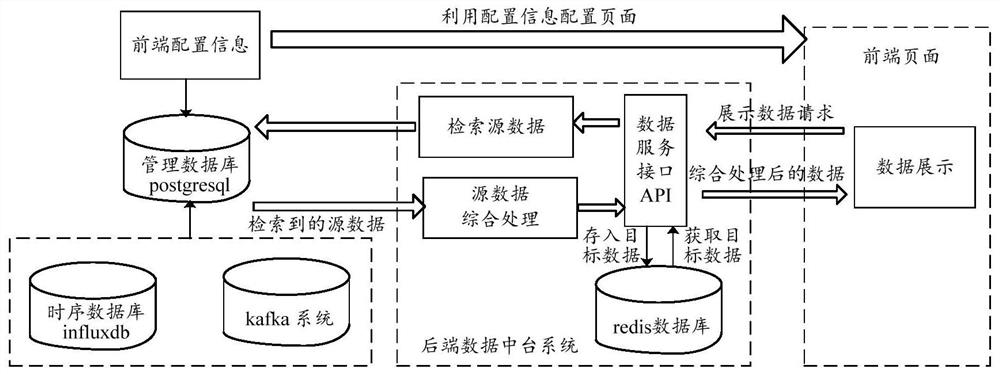

PendingCN112286774ASave query timeRich visual display methodsDatabase management systemsVisual data miningData displayBaseline data

The invention provides an operation and maintenance monitoring data display method and device, a storage medium and computing equipment, and the method comprises the steps: calling source data relatedto a business demand from different types of data sources, and storing the source data; converting the stored source data into target data based on a preset display condition, and obtaining baselinedata corresponding to the target data; and comparing the sizes of the target data and the baseline data to obtain a comparison result, and transmitting the target data, the baseline data and the comparison result to a front-end page of a unified display platform for unified display. According to the embodiment of the invention, the display process of the operation and maintenance monitoring data is not influenced by data source types, different service requirements can be met, the service data concerned by the operation and maintenance personnel can be displayed on the unified platform in a diversified manner, the operation and maintenance personnel do not need to query the monitoring data on multiple platforms, the query time and operation and maintenance manpower can be saved, and visualdisplay modes can be enriched.

Owner:PINGAN PUHUI ENTERPRISE MANAGEMENT CO LTD

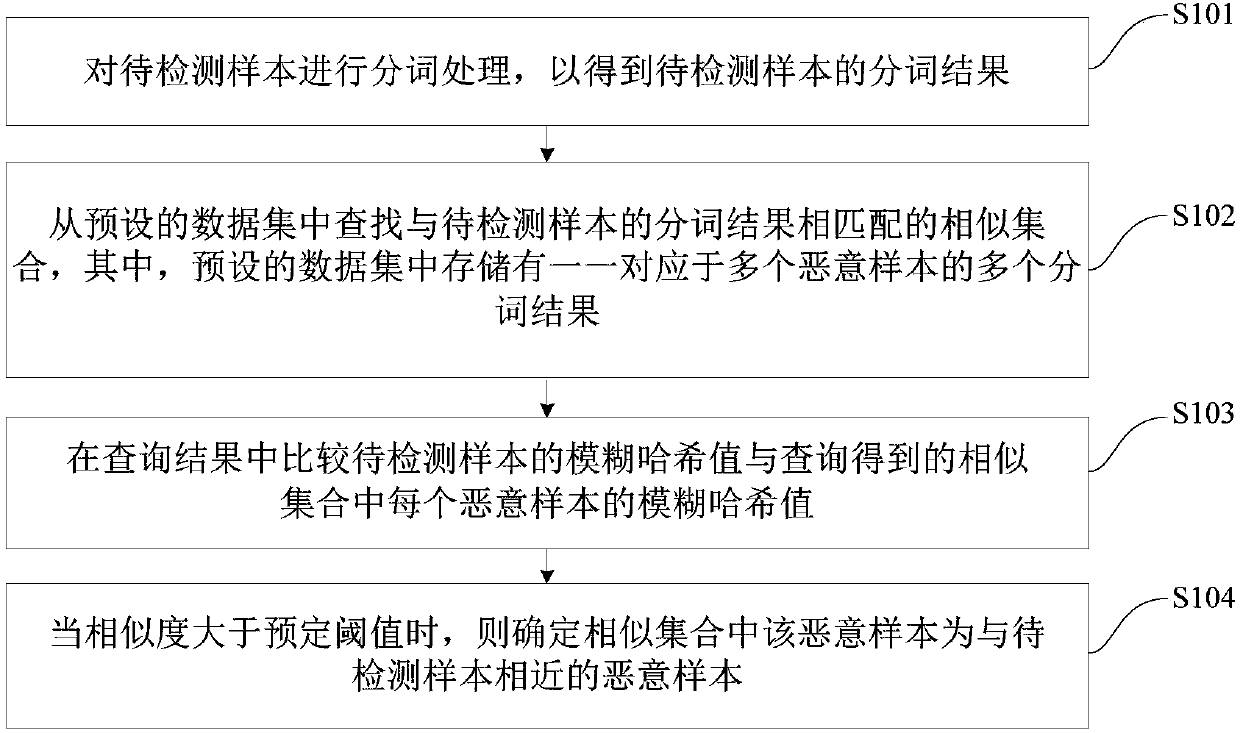

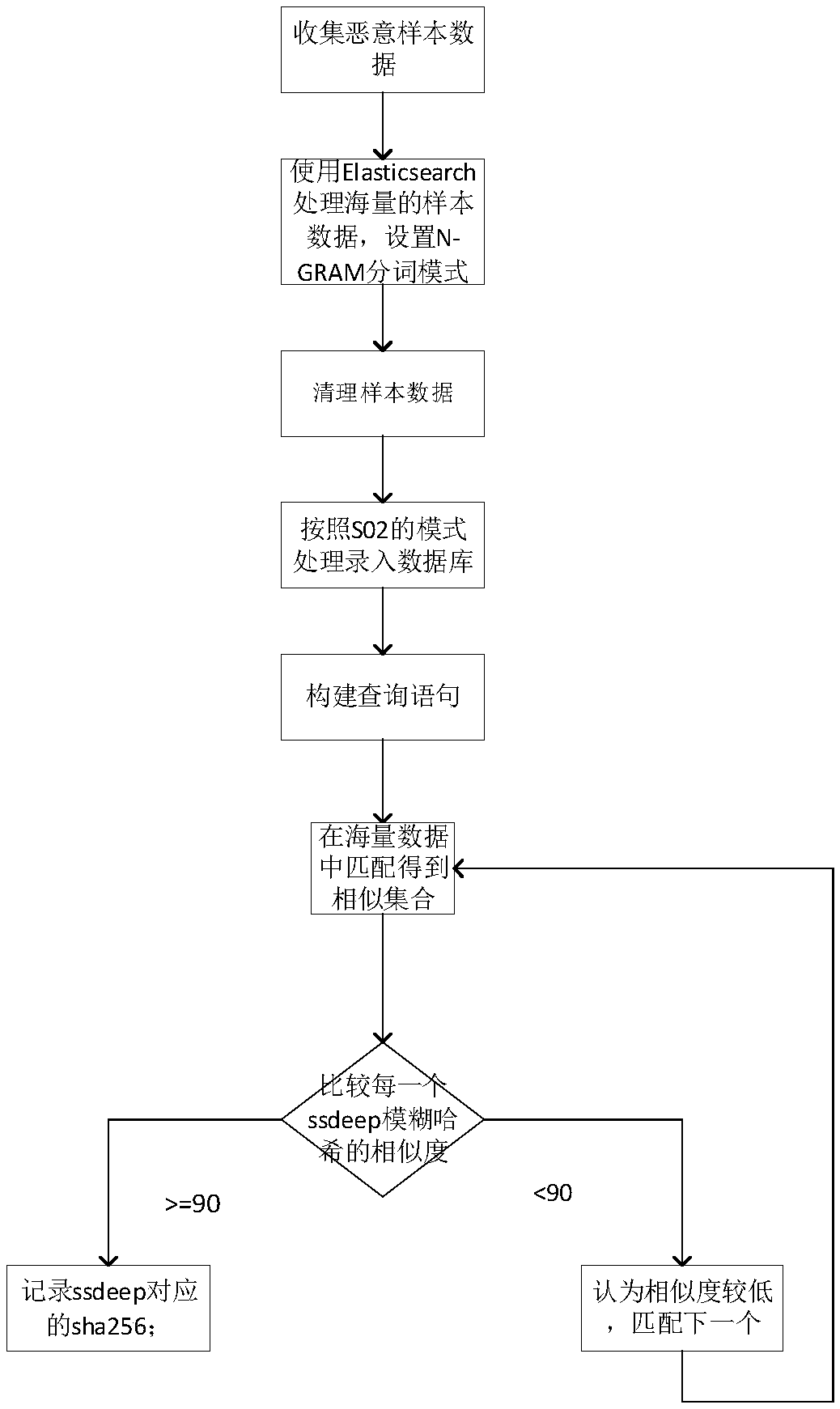

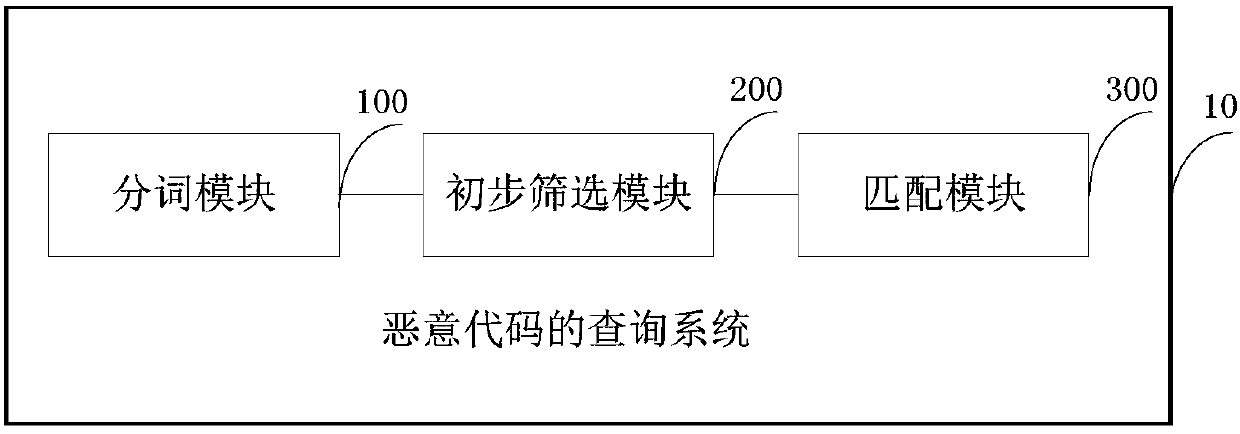

Malicious code query method and system

ActiveCN109977668ASave query timeSimple calculationNatural language data processingPlatform integrity maintainanceAlgorithmData set

The invention discloses a malicious code query method and system, and the method comprises the following steps: carrying out the word segmentation of a to-be-detected sample, so as to obtain a word segmentation result of the to-be-detected sample; searching a preset data set for a similar set matched with the word segmentation results of the sample to be detected, the preset data set storing a plurality of word segmentation results in one-to-one correspondence with the plurality of malicious samples; comparing the fuzzy hash value of the sample to be detected with the fuzzy hash value of eachmalicious sample in the queried similar set; and when the similarity is greater than a preset threshold value, determining that the malicious sample in the similarity set is a malicious sample similarto the to-be-detected sample. According to the method, the word segmentation result of the sample to be detected is matched to obtain the similar set, so that the query time is effectively shortened,the calculation is simplified, and the query efficiency and applicability of malicious codes are effectively improved.

Owner:HARBIN ANTIY TECH

Building property query system

InactiveCN106326366AQuick searchSave query timeBuying/selling/leasing transactionsGeographical information databasesGraphicsRelevant information

The invention relates to the technical field of information services, in particular to a building property query system. The building property query system comprises a city map module, a building registration module and a display module, wherein the building registration module is used for separating buildings into to-be-sold buildings and sold buildings; the building registration module is used for sending the geological location information of the buildings to the city map module, displaying the city location of each building through the city map module, and marking in a city map; when one building is selected in the city map, the building registration module is used for displaying the information of the corresponding building, and the information comprises the number of to-be-sold buildings and the number of sold buildings; the display module is used for displaying the states of building sources; when the information of the buildings is displayed, the display module is used for displaying the data information of the buildings in a graph type. The building property query system has the advantages that by arranging the city map module, the building registration module and the display module, the location and related information of the building property can be quickly queried, the time is saved, and the labor intensity is decreased.

Owner:东莞市房讯资讯股份有限公司

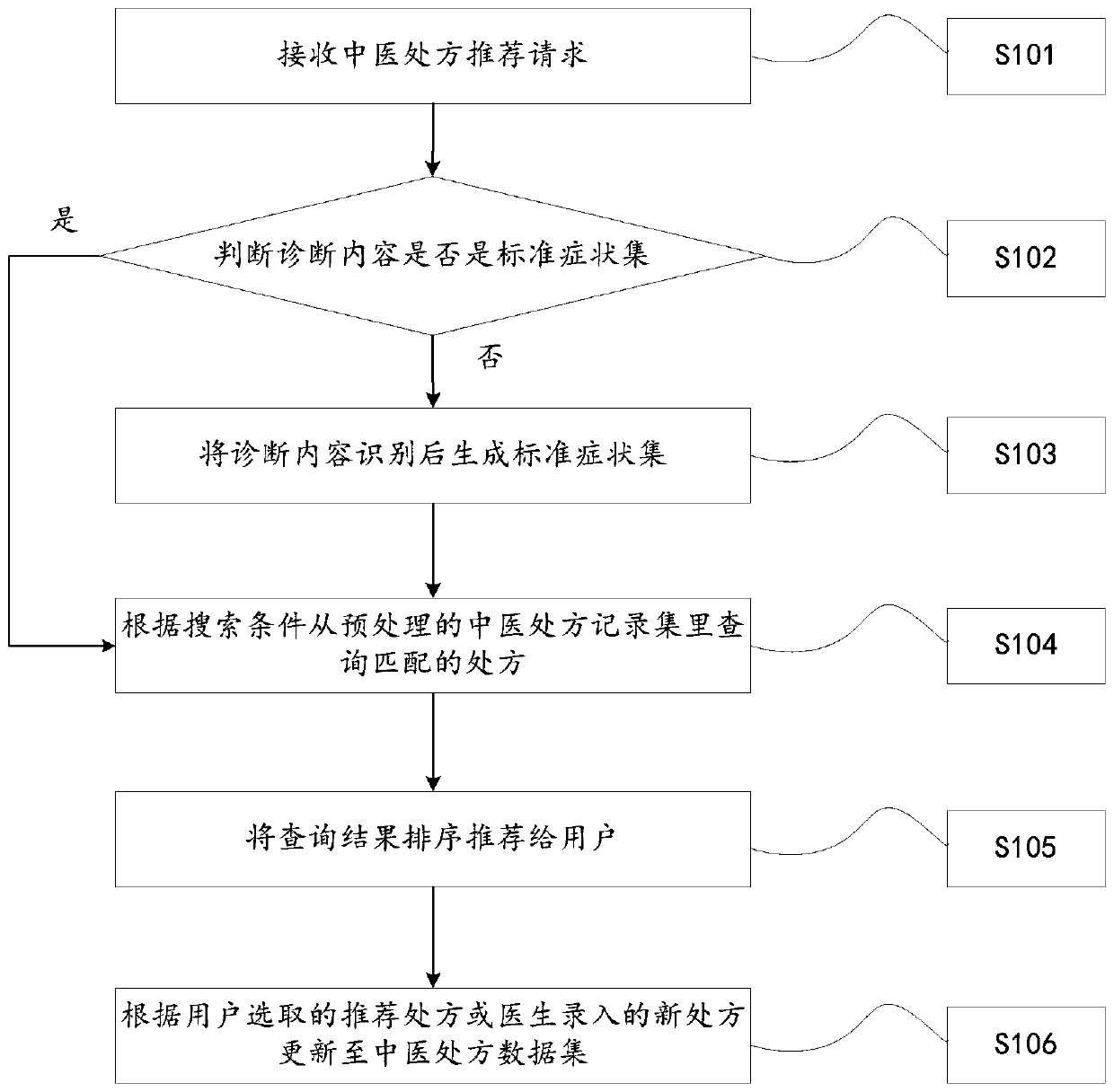

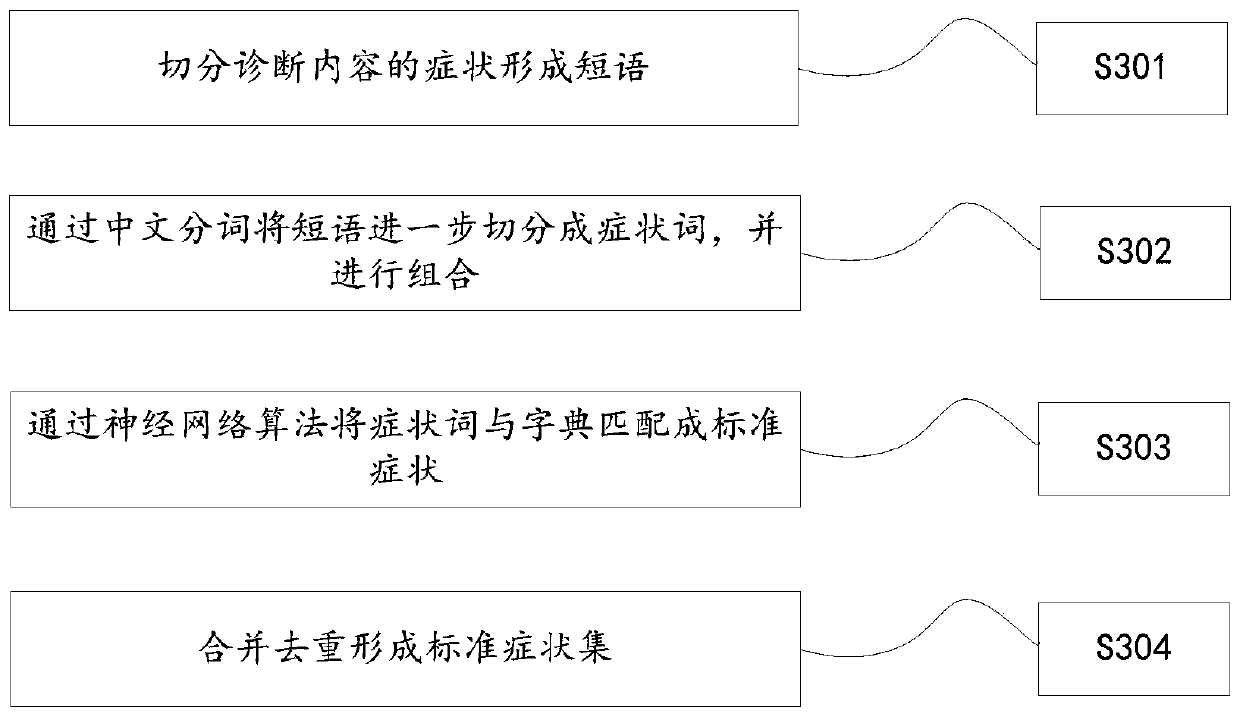

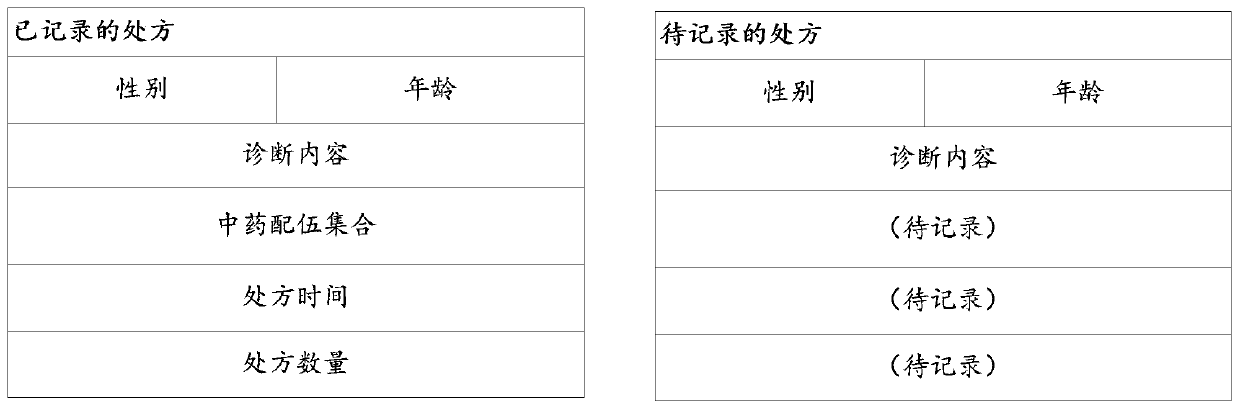

Traditional Chinese medicine prescription recommendation sorting method based on data matching

The invention discloses a traditional Chinese medicine prescription recommendation sorting method based on data matching. The method comprises the steps of receiving a traditional Chinese medicine prescription recommendation request; judging whether the diagnosis content in the traditional Chinese medicine prescription is a standard symptom set or not; and if the diagnosis content is not the standard symptom set, identifying the diagnosis content to generate a standard symptom set, querying matched prescriptions from a preprocessed traditional Chinese medicine prescription record set accordingto search conditions, recommending query results to a user in sequence, and updating recommended prescriptions selected by the user or new prescriptions input by doctors in the traditional Chinese medicine prescription data set. According to the invention, the traditional Chinese medicine prescription record set is maintained in advance, and for symptoms with the same or similar diagnosis content, prescriptions with high use frequency (the number of prescriptions is large) are recommended preferentially, so that doctors can directly and quickly select a traditional Chinese medicine compatibility set for the same symptoms.

Owner:CHENGDU RUIMING MEDICAL INFORMATION TECH

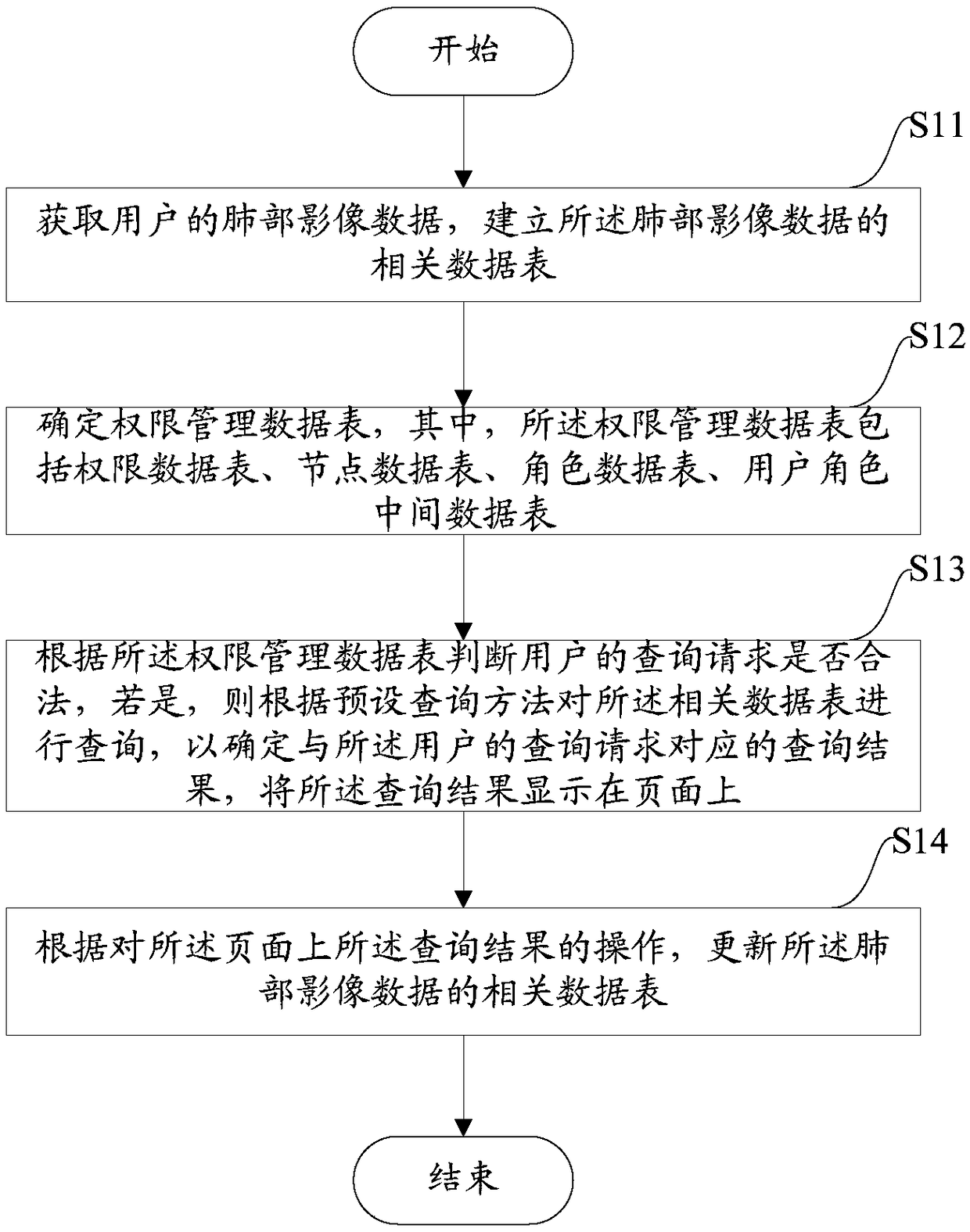

Method and device for establishing lung image database

InactiveCN109087707AOmit to checkImprove efficiencyMedical data miningHealth-index calculationRights managementWorkload

The purpose of the present application is to provide a method and device for establishing a lung image database. The method includes: acquiring lung image data of a user, and establishing a related data table of the lung image data; determining a right management data table, wherein the right management data table includes a right data table, a node data table, a role data table, and a user role intermediate data table; determining whether the user's query request is legal according to the right management data table, querying the related data table according a preset query method so as to determine a query result corresponding to the user's query request if so, and displaying the query result on a page; and updating the related data table of the lung image data according to an operation on the query result on the page. Therefore, the data in different relational tables can be obtained at the same time by inputting the query condition once, the comparison is enhanced, the query workload is reduced, and the query and analysis time is saved.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

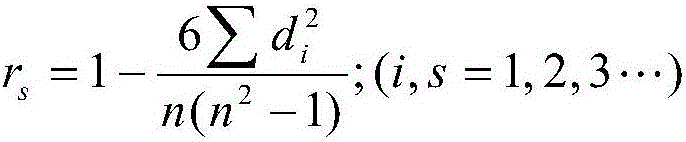

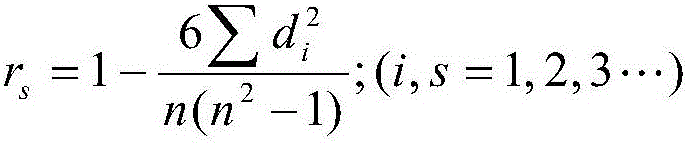

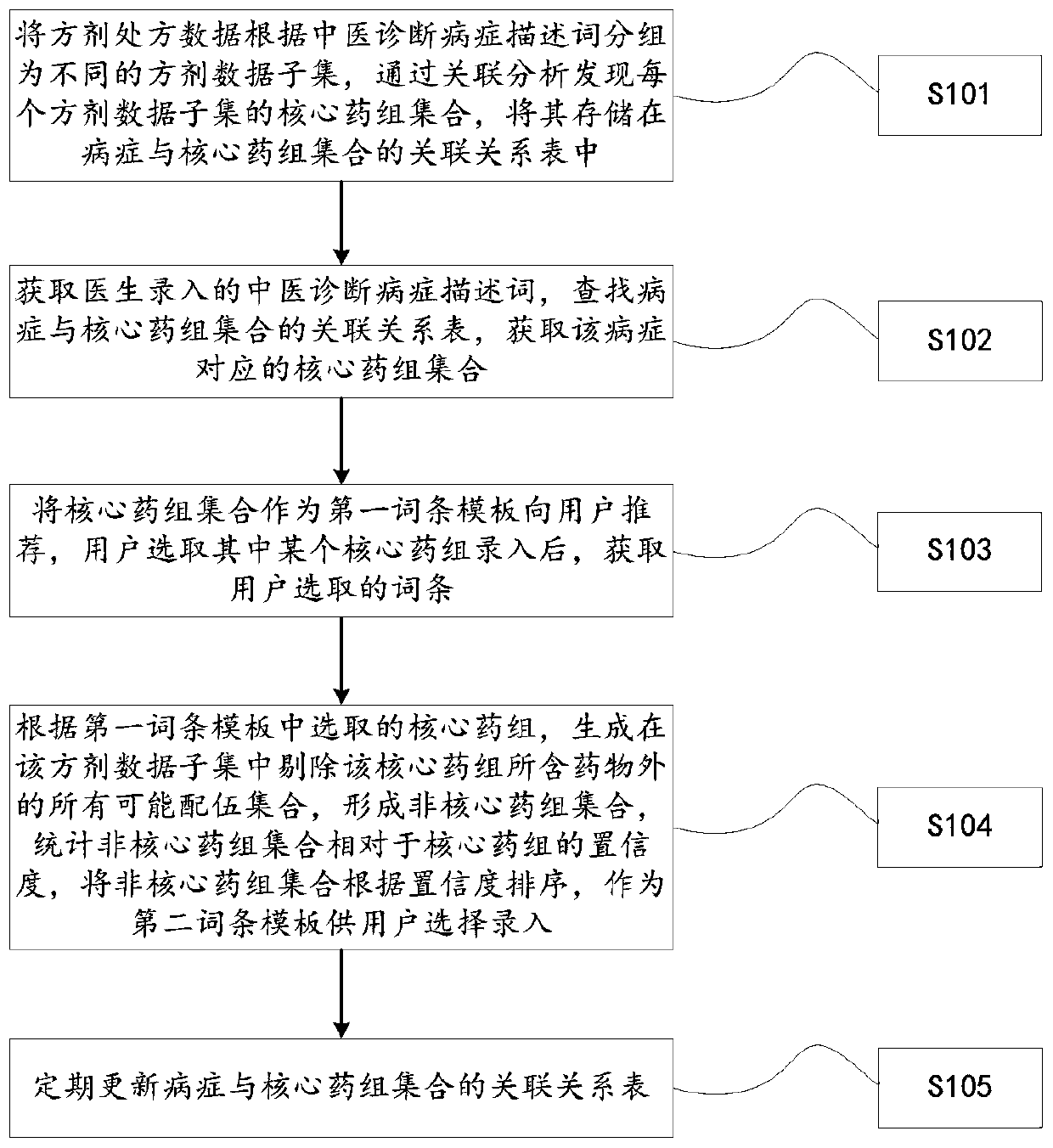

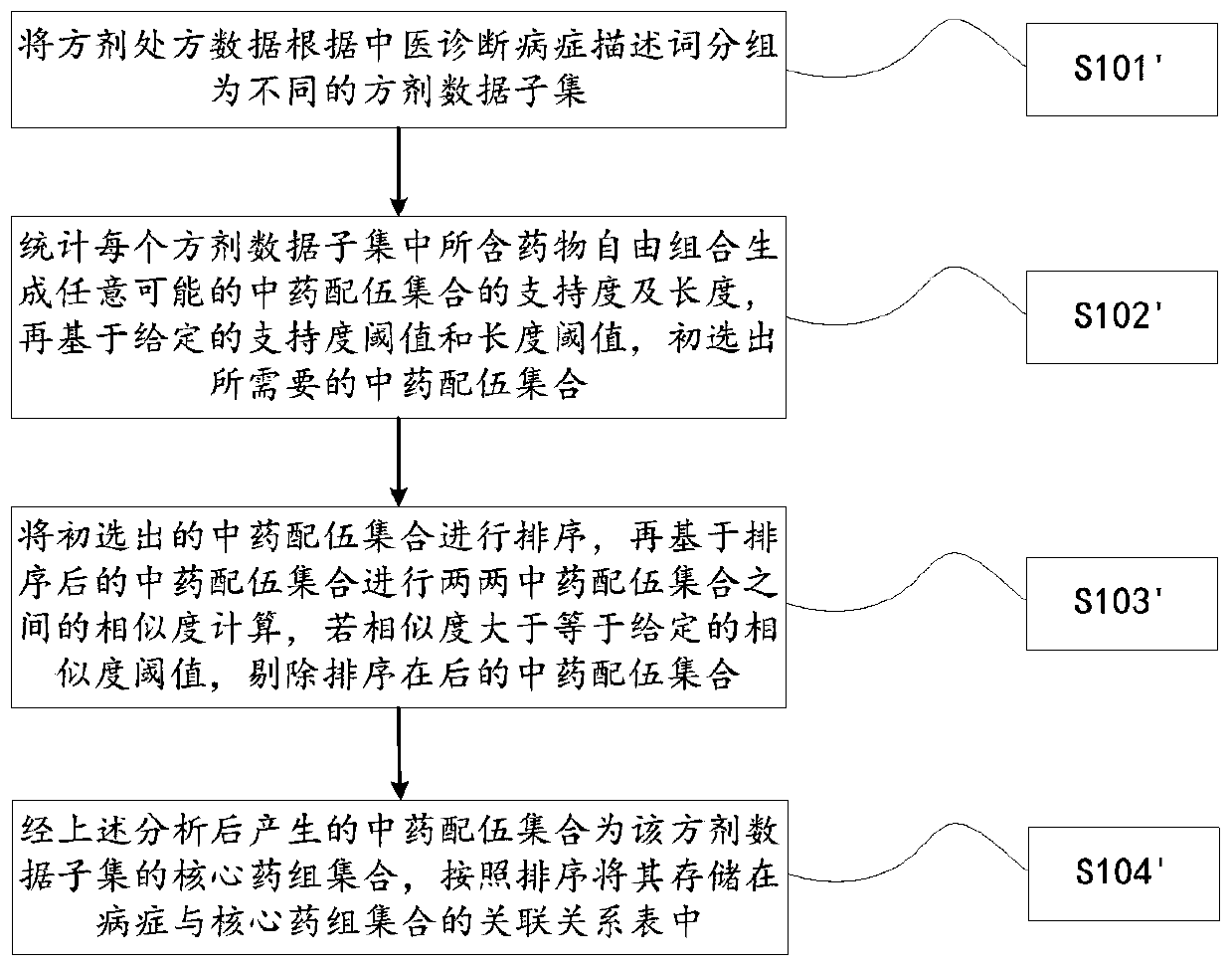

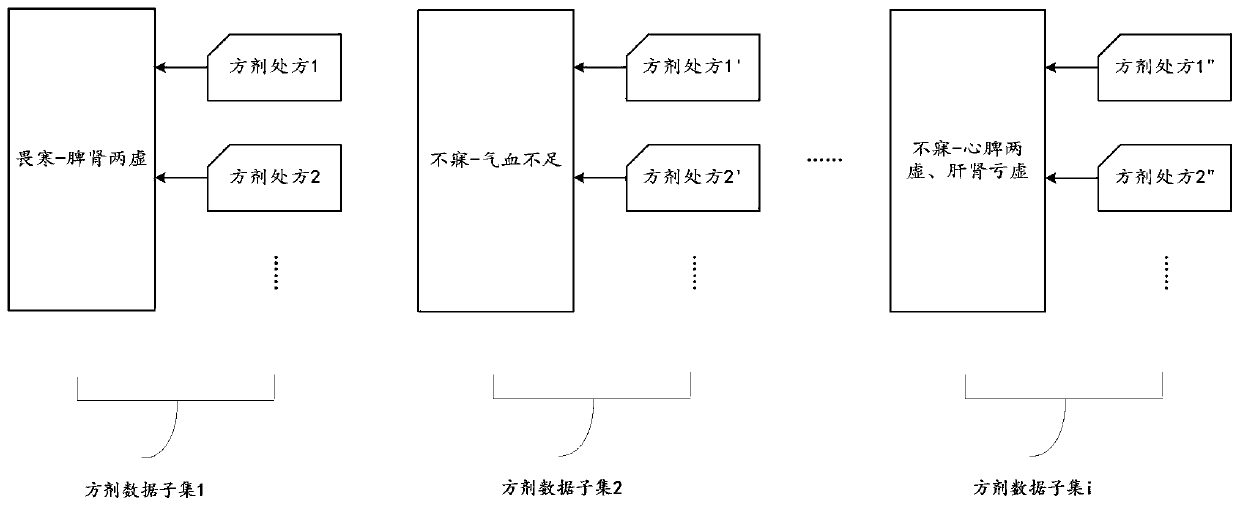

Traditional Chinese medicine compatibility auxiliary decision-making method based on correlation analysis

PendingCN111599487AReduce computationReduce query timeDrug referencesICT adaptationDrug groupPrescription data

The invention discloses a traditional Chinese medicine compatibility auxiliary decision-making method based on correlation analysis. The method comprises the following steps: grouping prescription data into different prescription data subsets according to traditional Chinese medicine diagnosis disease description words, discovering a core medicine group set of each prescription data subset throughcorrelation analysis, and forming an association table of diseases and the core medicine group sets; obtaining a core medicine group set corresponding to the disease from the association table according to a traditional Chinese medicine diagnosis disease description word input by a doctor; recommending the core medicine group set as a first entry template to the user; selecting a core medicine group from the first entry template; generating all possible compatibility sets except medicines contained in the core drug group in the prescription data subset to form a non-core drug group set, counting confidence coefficients of the non-core drug group set relative to the core drug group, sorting the non-core drug group set according to the confidence coefficients, and taking the sorted non-coredrug group set as a second entry template for the user to select and input; and regularly updating the association table of the disease and the core drug group set.

Owner:CHENGDU RUIMING MEDICAL INFORMATION TECH

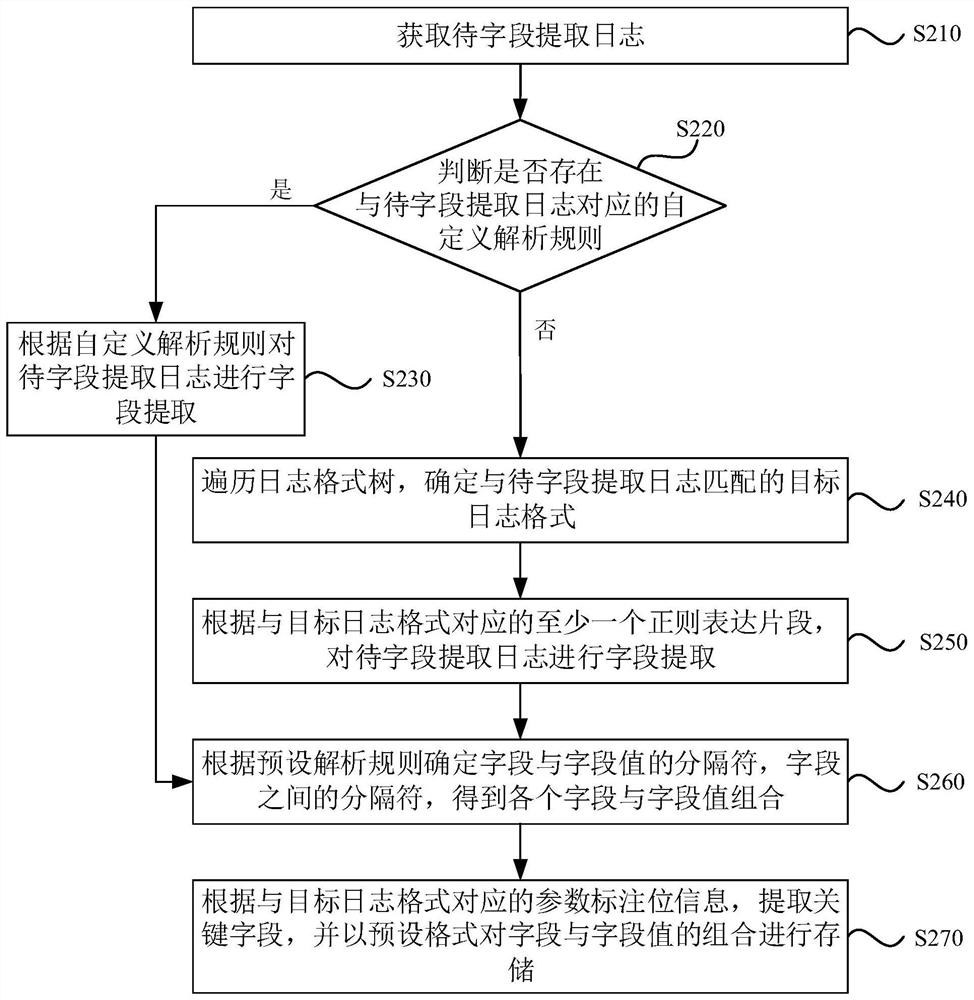

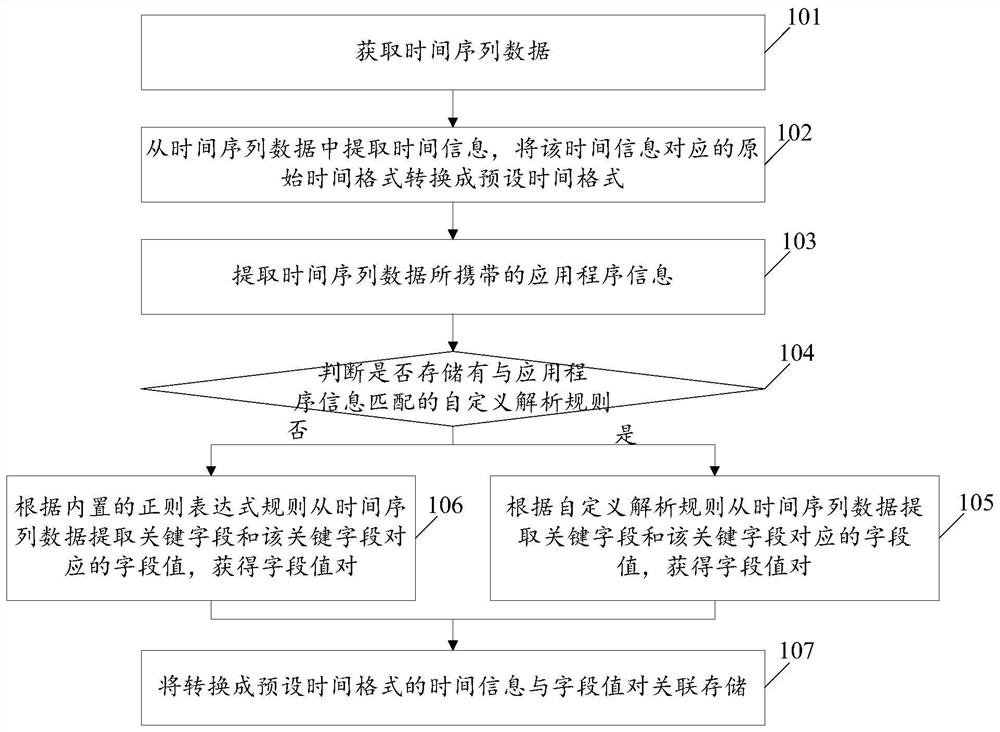

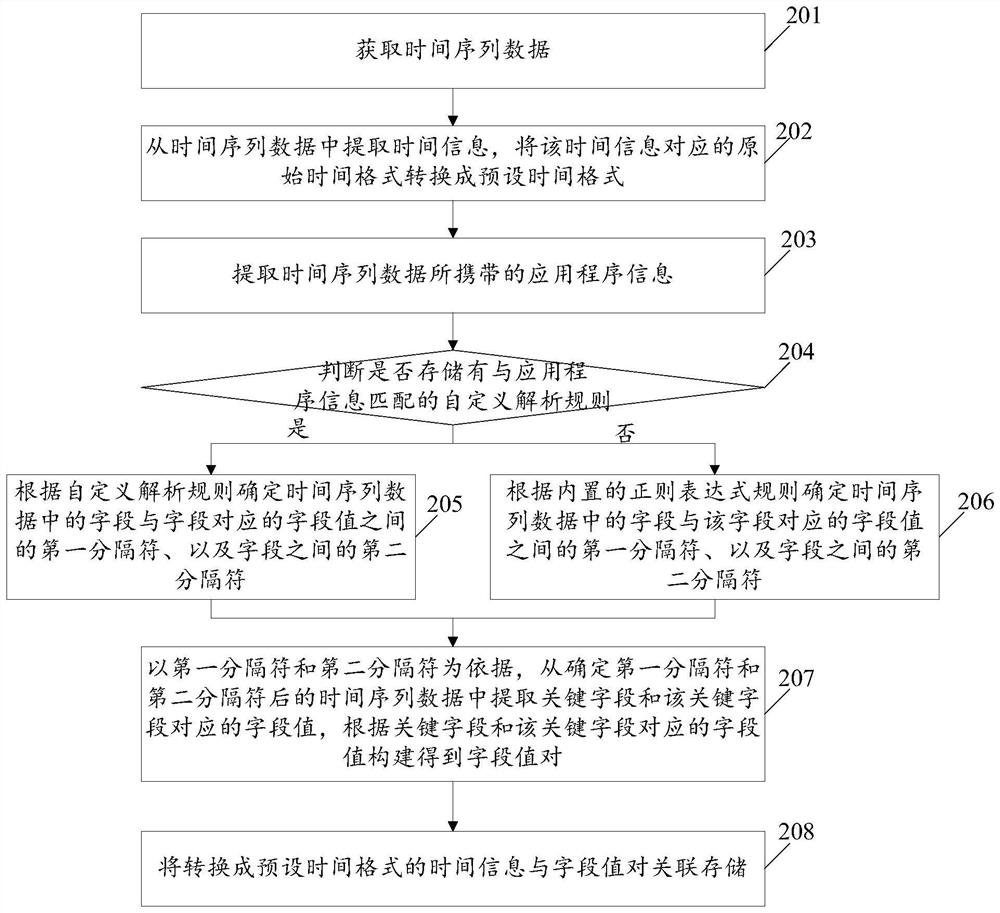

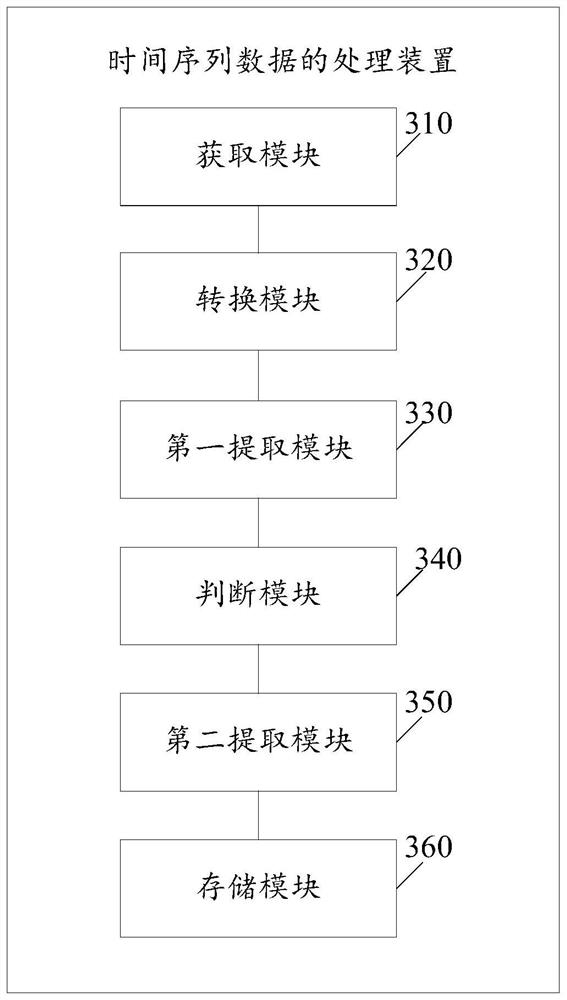

Time series data processing method and device

InactiveCN112527862AEasy to query statisticsSave spaceSpecial data processing applicationsDatabase indexingTime informationApplication procedure

The embodiment of the invention discloses a time series data processing method and device. The method comprises the steps of obtaining time series data; extracting time information from the time sequence data, and converting an original time format corresponding to the time information into a preset time format; extracting application program information carried by the time sequence data; judgingwhether a user-defined analysis rule matched with the program information is stored or not; if so, extracting a key field and a field value corresponding to the key field from the time series data according to a self-defined analysis rule to obtain a field value pair; if not, extracting a key field and a field value corresponding to the key field from the time series data according to a built-in regular expression rule to obtain a field value pair; and associatively storing the time information converted into the preset time format and the field value pair. The fields in the unstructured dataare extracted and converted into the unified format, subsequent query statistics is facilitated, and the purpose of saving calculation space and query time is achieved.

Owner:国网河北省电力有限公司雄安新区供电公司

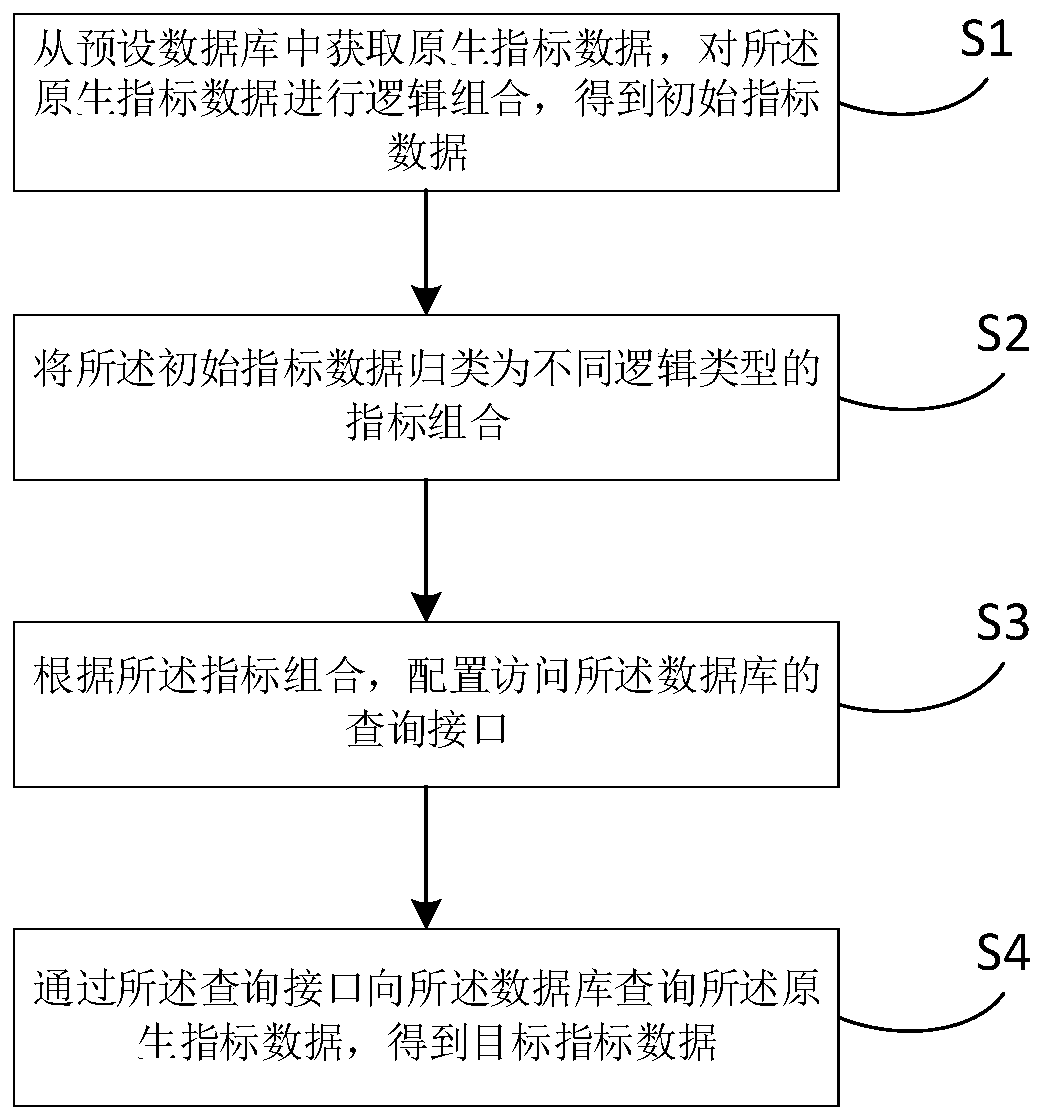

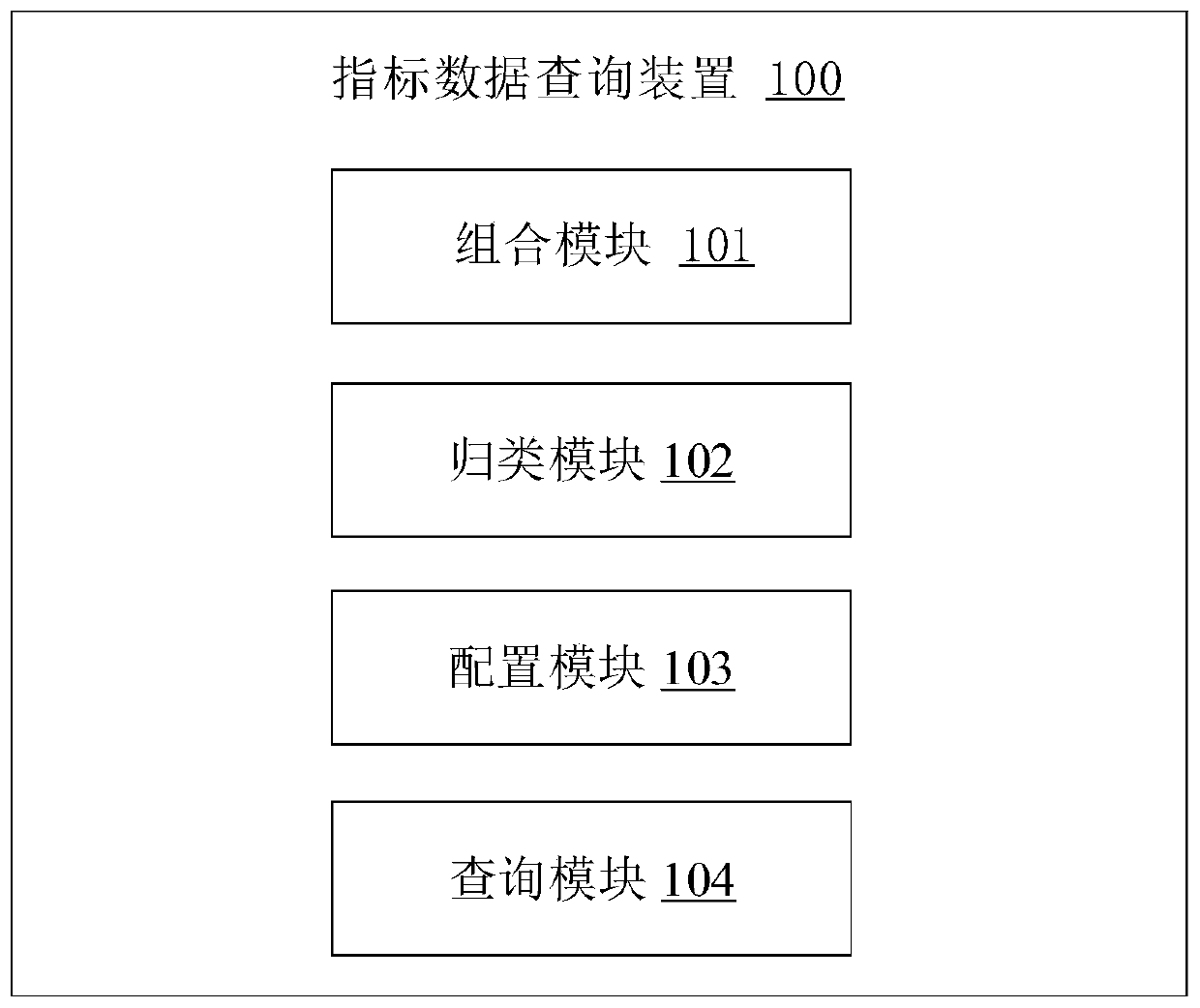

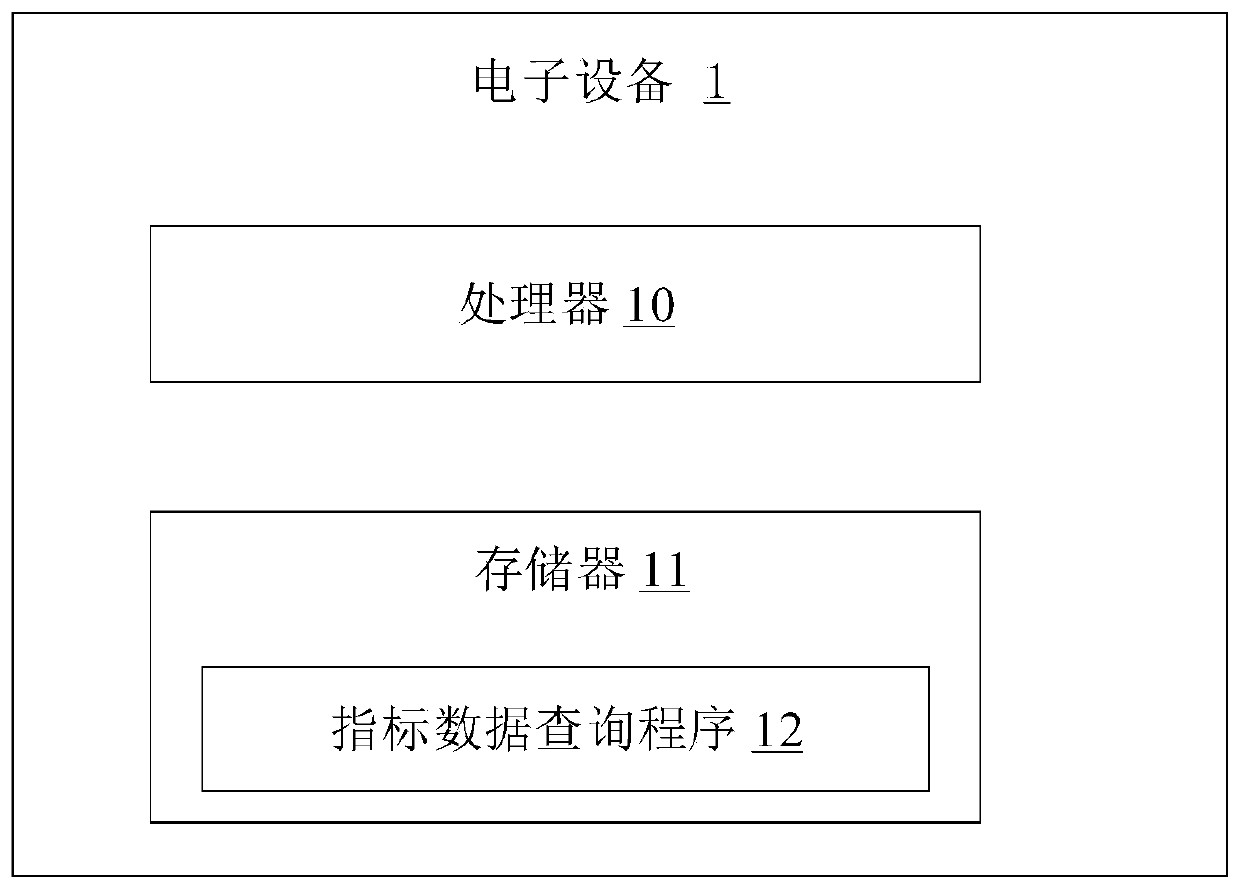

Index data query method and device, electronic equipment and storage medium

PendingCN111352955ASave query timeGuaranteed accuracyDatabase management systemsSpecial data processing applicationsData queryEngineering

The invention relates to the technical field of data processing, and discloses an index data query method, which comprises the steps of obtaining native index data from a preset database, and performing logic combination on the native index data to obtain initial index data; classifying the initial index data into index combinations of different logic types; configuring a query interface for accessing the database according to the index combination; and querying the native index data from the database through the query interface to obtain target index data. The invention further provides an index data query device, electronic equipment and a computer readable storage medium. According to the invention, efficient query of index data can be realized.

Owner:CHINA PING AN PROPERTY INSURANCE CO LTD

A cloud computing-based service provision method and device

ActiveCN103825940BSave query timeImprove service appointment efficiencyTransmissionComputer networkCloud base

The invention discloses a cloud computing-based service providing method and device. The method includes the following steps that: a service reservation request containing reservation information, which is transmitted by a user end, is received; at least one first candidate service provider corresponding to the reservation information is inquired in a cloud storage server according to the service reservation request; the first candidate service provider is transmitted to the user end; a target reservation request containing a target service provider identifier, which is transmitted by the user end, is received; the target reservation request is transmitted to a target service provider end corresponding to the target service provider identifier; and reservation result information transmitted by the target service provider end is received and transmitted to the user end. Compared with the prior art in which manual query of the information of service providers is required, and with the method and device of the invention adopted, the manual query of the information of the service providers is not required, and therefore, query procedures and query time can be saved, and service reservation efficiency can be improved.

Owner:昆山中创软件工程有限责任公司

Method of using simple network management protocol to act multirariant block inquiry

InactiveCN100550896CReduce Duplicate Query OperationsReduce the number of queriesTransmissionInformation repositoryManagement information base

The invention relates to a simple network management protocol SNMP agent multivariate group query method, which defines the data structure of the simple network management protocol agent management information database according to the management information database file, analyzes the simple network management protocol message, analyzes the variable body, and according to the simple network management protocol message The operation type processes each variable, sets the variable state and the working state of the variable, groups unprocessed variables in the variable body, calls the method of obtaining the value of the object in the group, and queries data according to the object information and variable index value information in the management information base , query the value of each variable in the successfully bound group, and mark the variable in the group as processed; if unsuccessful, process each variable in the group according to the simple network management protocol message operation type, set the variable state and working state, and repeat the preceding steps Until all variable working statuses are processed. The method of the invention realizes high-speed completion of multi-variable query and can greatly improve query efficiency.

Owner:南通国邦科技发展有限公司

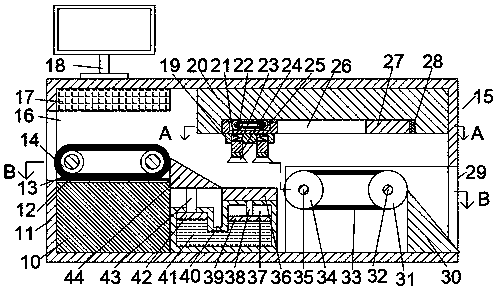

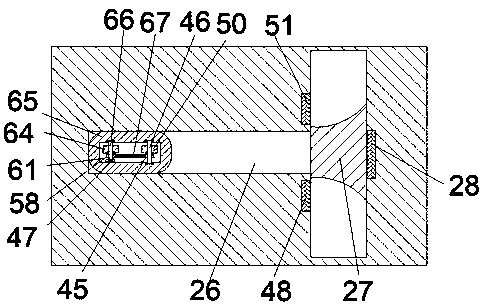

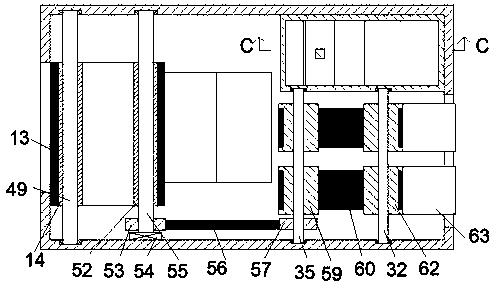

Express processing device based on data terminal

InactiveCN111299163ASave manpower and query timeAvoid mistakesSortingEmbedded systemElectric machinery

The invention discloses an express processing device based on a data terminal. The express processing device comprises a mounting cavity arranged in a first fixing block, a terminal processor is fixedly mounted on the upper end surface of the mounting box, a scanner connected with the terminal processor is fixedly mounted on the upper end wall of the mounting cavity, a driving motor is fixedly mounted on the front end wall of the mounting cavity, the driving motor is in power connection with a first shaft, and a first belt pulley is fixedly mounted on the first shaft. Express items can be processed and conveyed on an express delivery site, and manpower and query time are saved; the express items are placed on a conveyor belt for scanning, and the terminal server prompts and display objectreceiving information, so that errors are avoided, and the express items are classified and processed by the information generated by scanning.

Owner:WUYI PUBA MASCH EQUIP CO LTD

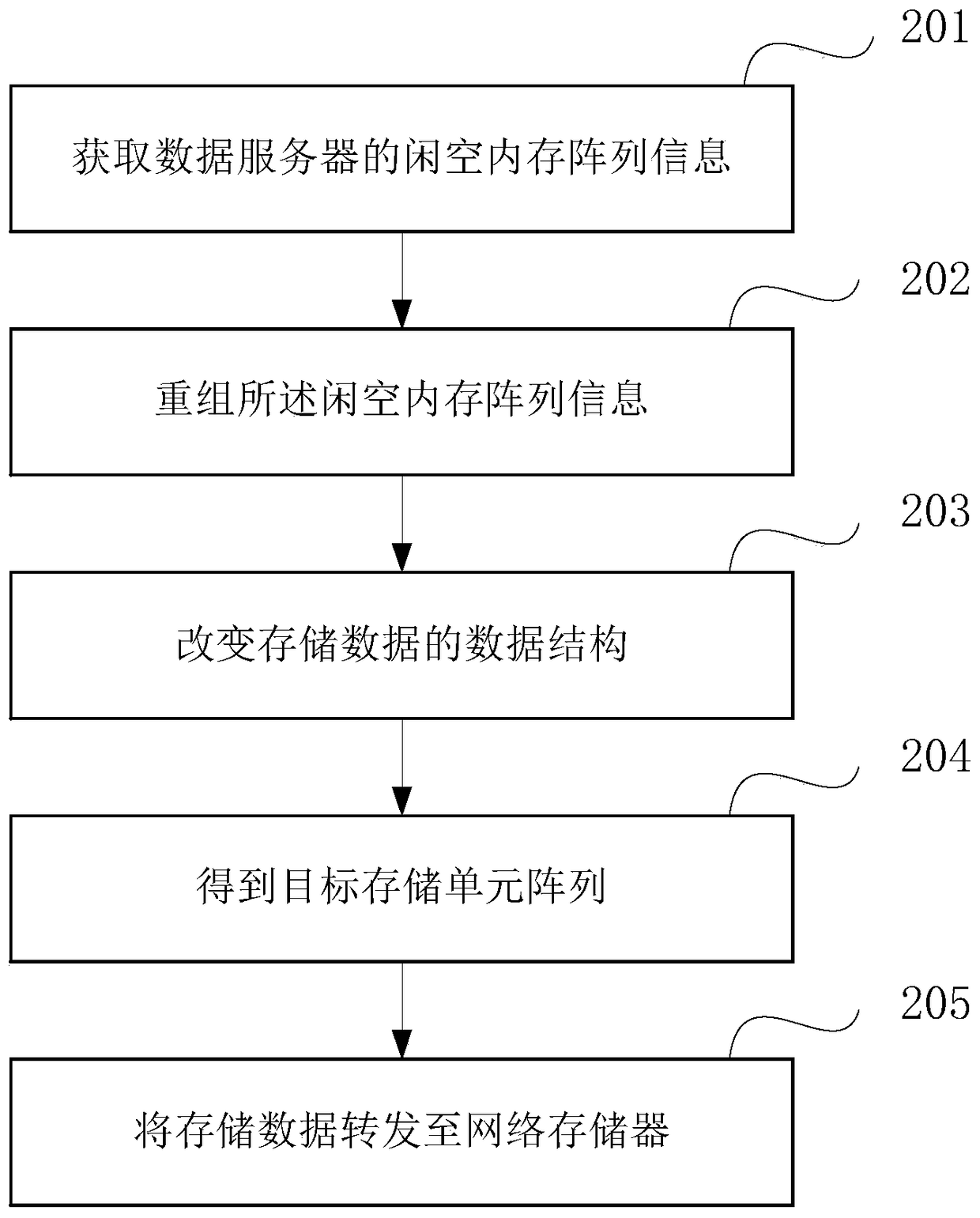

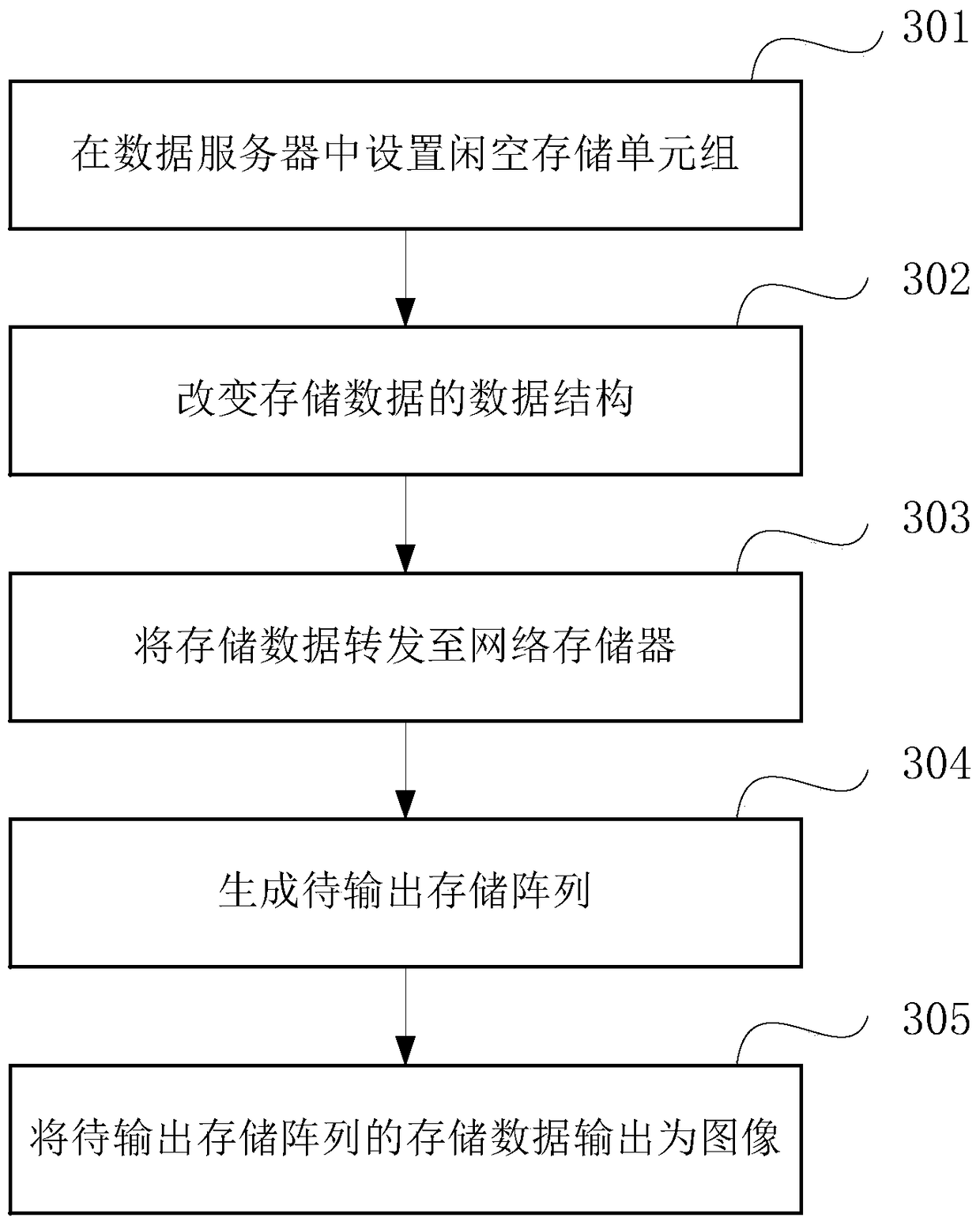

A method for high-speed storage of high-fidelity consecutive frame query numbers and its image output method

ActiveCN105005622BOptimizing Architecture PerformanceSave storage timeOther databases queryingSpecial data processing applicationsEngineeringTerm memory

The invention discloses a method for high-speed storage of high-fidelity continuous-frame queries and an image output method thereof. The method comprises the following steps of: acquiring free memory array information of a data server; recombining the free memory array information, and writing the free memory array information in a free storage unit group of the data server; changing a data structure of storage data by using the free storage unit, and writing the storage data of which the data structure is changed in a target storage unit group; recombining the target storage unit group to obtain a target storage unit array; and forwarding the storage data in the target storage unit array to a network memory. The method has the advantages that: (1) the performance of a storage system can be improved, and various kinds of data are massively stored; (2) the storage speed of the data server and the efficiency are improved; and (3) the data can be inquired and read at a high speed, and the effectiveness requirement of data burst is satisfied.

Owner:肖华

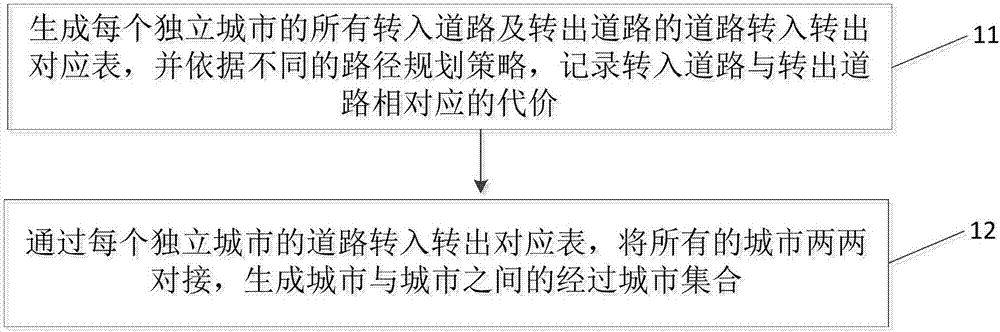

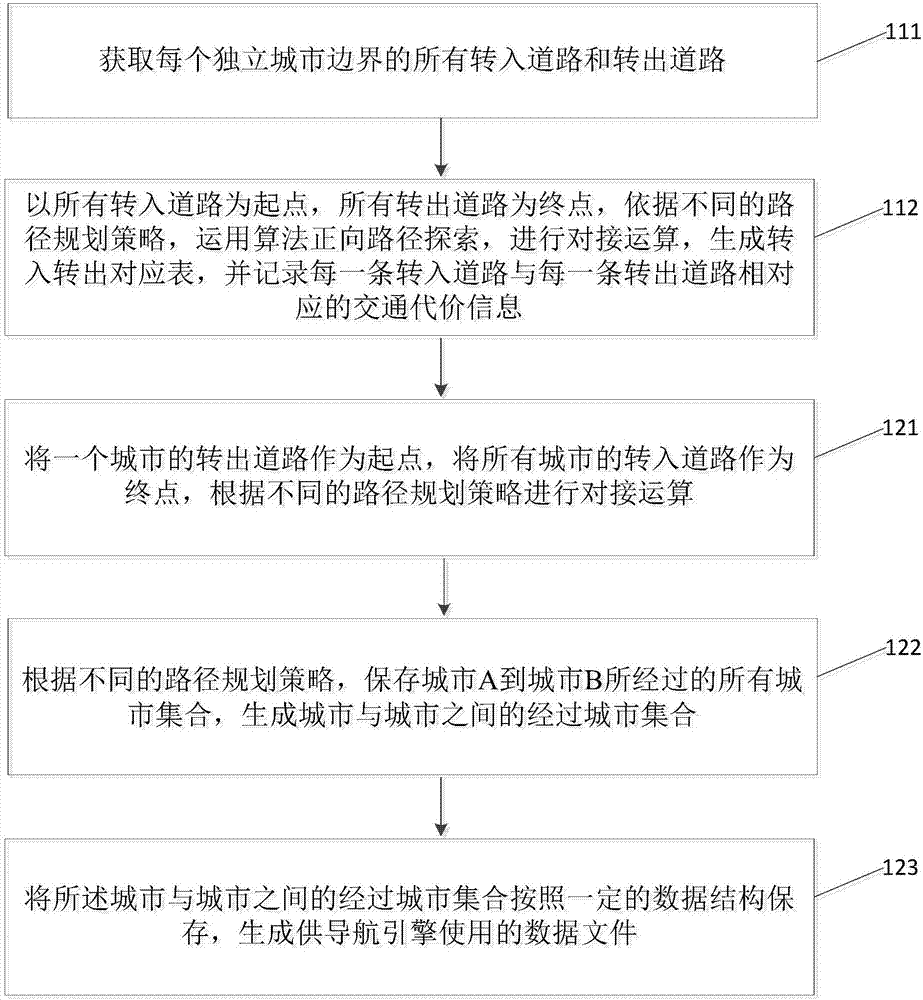

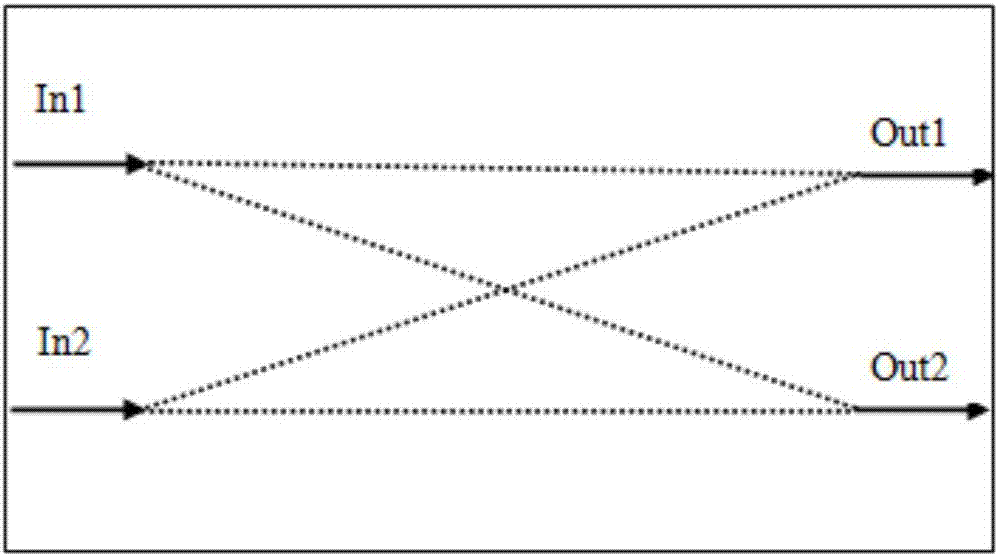

Method and device for generating passing city set between cities

InactiveCN106959115ASkip the path discovery processSave query timeInstruments for road network navigationRoute planningComputer science

The invention provides a method and a device for generating a passing city set between cities. The method comprises the following steps: generating a road turn-in / out corresponding table of all the turn-in roads and turn-out roads of each independent city; recording the cost corresponding to the turn-in roads and turn-out roads according to different route planning strategies, wherein the roads turning into the boundary of the city serve as turn-in roads and the roads turning out of the boundary of the city serve as turn-out roads; and butt-jointing all the cities in pairs according to the road turn-in / out corresponding table of each independent city, thereby generating the passing city set between the cities. According to the invention, the time of generating a passing city set document between the cities is greatly shortened and the memory consumption is greatly reduced.

Owner:上海趣驾信息科技有限公司

An io bus device with self-identification function based on fpga

ActiveCN104484301BImprove versatilityEasy to handleElectric digital data processingInformation functionExternal data

The invention relates to an FPGA-based (Field Programmable Gate Array-based) IO (Input / Output) bus device with an automatic recognition function, and belongs to the technical field of buses. The IO bus device comprises a CPU (Central Processing Unit), an FPGA, slot position plates, a parallel bus, a serial bus and a field bus, wherein the CPU and the FPGA are used for carrying out data interaction through an external bus, and the FPGA and the slot position plates are interacted through the parallel bus or the serial bus; the CPU and the slot position plates are directly interacted through the field bus; the FPGA is used for providing a plate address for the CPU and helping the CPU to send and receive data, a state machine is arranged in the FPGA, and the state machine can be used for selecting plate interfaces in a circulation mode to read plate information and data signals. The FPGA-based IO bus device has a self-recognition plate information function, so that the reliability of data interaction is enhanced. The communication among plates is more flexible, and upgrading of a device platform is facilitated. The FPGA serves as a bridge of the CPU and external data, and the interaction of plate data is carried out through the serial bus and the parallel bus.

Owner:NANJING INTELLIGENT APP

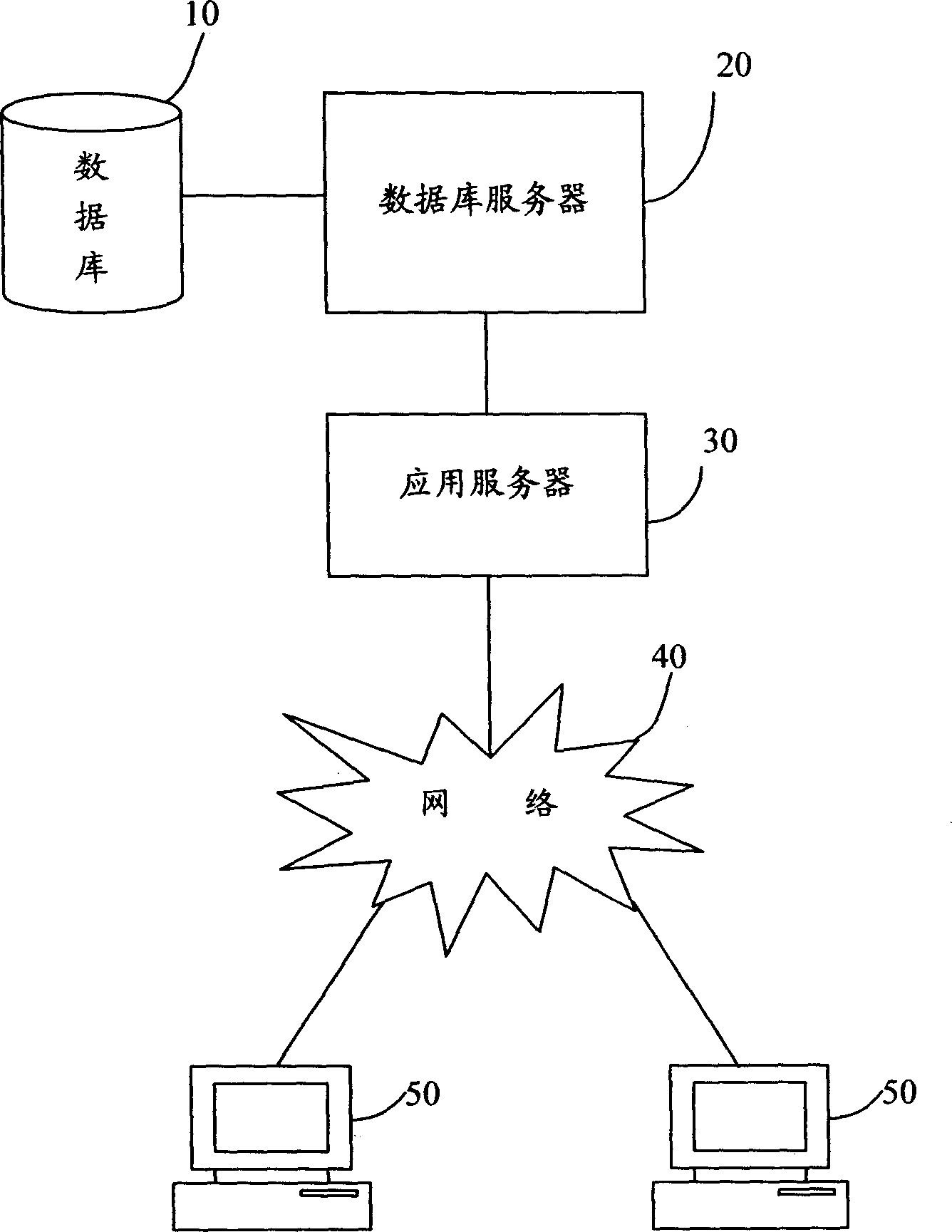

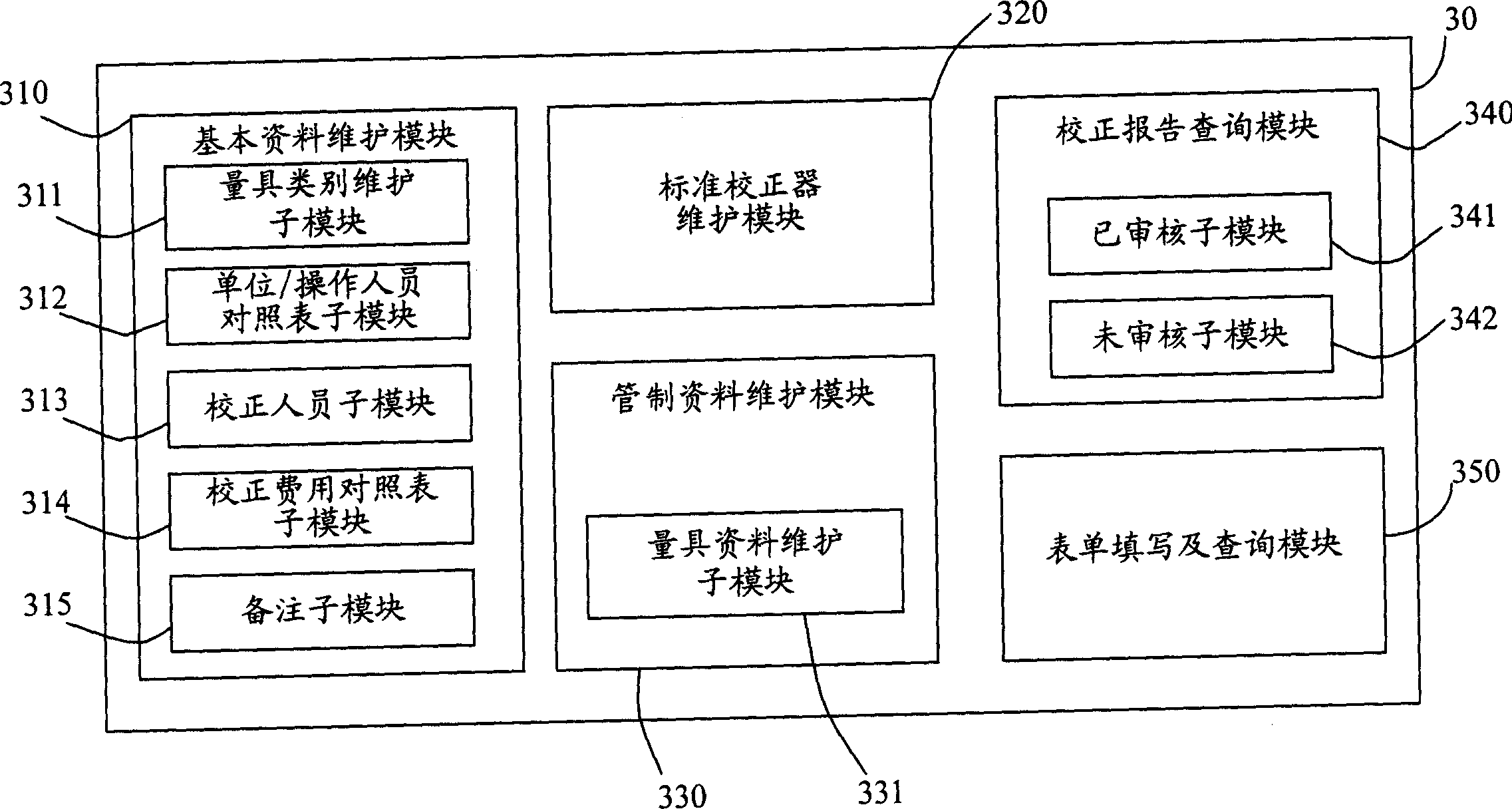

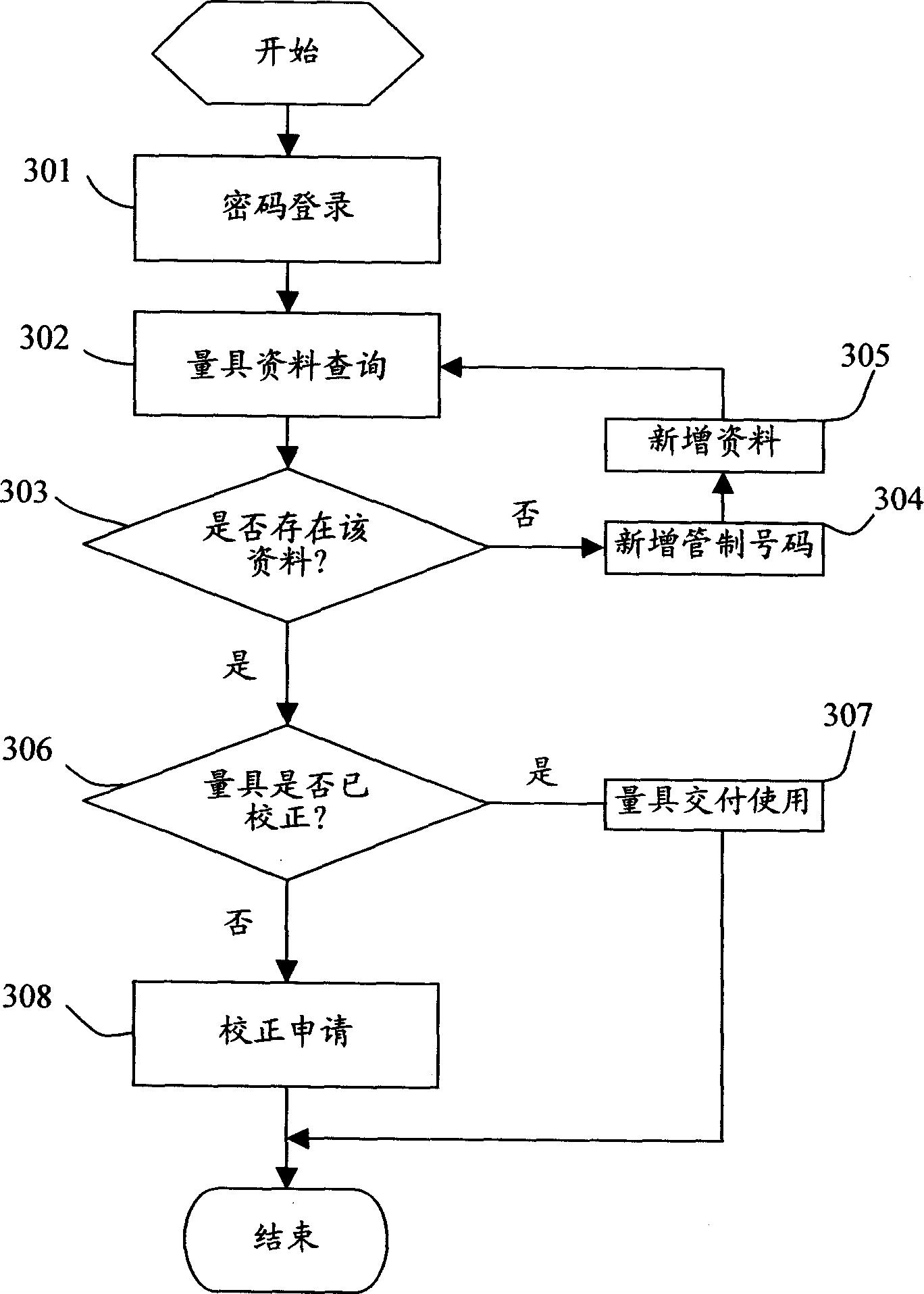

Measuring implement managing system and method

InactiveCN1474293AConvenient querySave query timeMultiple digital computer combinationsSpecial data processing applicationsComputerized systemComputer science

The present invention relates to measuring implement managing system and method. Computer system is used in management and correction job, and the measuring implement manager may perform the increment, amendment, inquiry and other jobs of measuring implement according to preset authority and sends various reports via email to relevant personals to check if necessary. The said management system makes it possible to save great amount of inquiry time and manage the measuring implement effectively.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Cache Management Method for Distributed Memory Columnar Database

ActiveCN106294772BGuaranteed availabilityGuaranteed stabilityDigital data information retrievalSpecial data processing applicationsExecution planInternal memory

The invention discloses a cache management method of a distributed memory columnar database, comprising: establishing a cache queue in a cache master control node; taking each physical task as a root node to cut its physical execution plan to obtain each physical task Corresponding cache calculation track; according to the cache calculation track corresponding to each physical task, a cache feature tree is built in the cache master node; when a query request arrives, the query execution engine parses the SQL statement into a physical execution plan; from the physical execution plan The root node starts to traverse each node in the physical execution plan hierarchically, and judges whether the cache calculation trajectory corresponding to each physical task matches the cache feature tree; if it matches, directly reads the cached actual data of the physical task from the cache slave node, otherwise Compute the physics task. The cache management method of the distributed memory column database provided by the present invention quickly detects whether the cache is hit through an efficient cache matching algorithm, thereby improving query efficiency.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

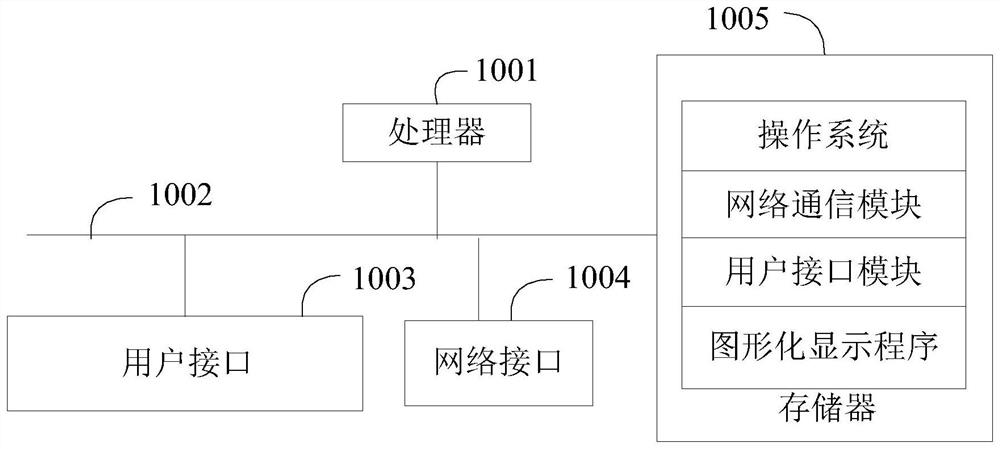

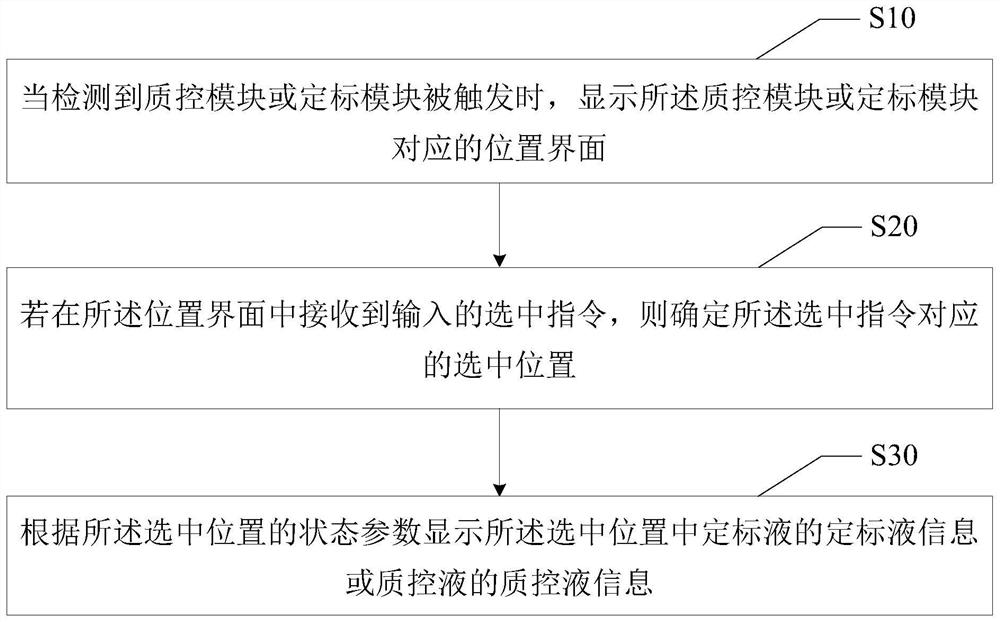

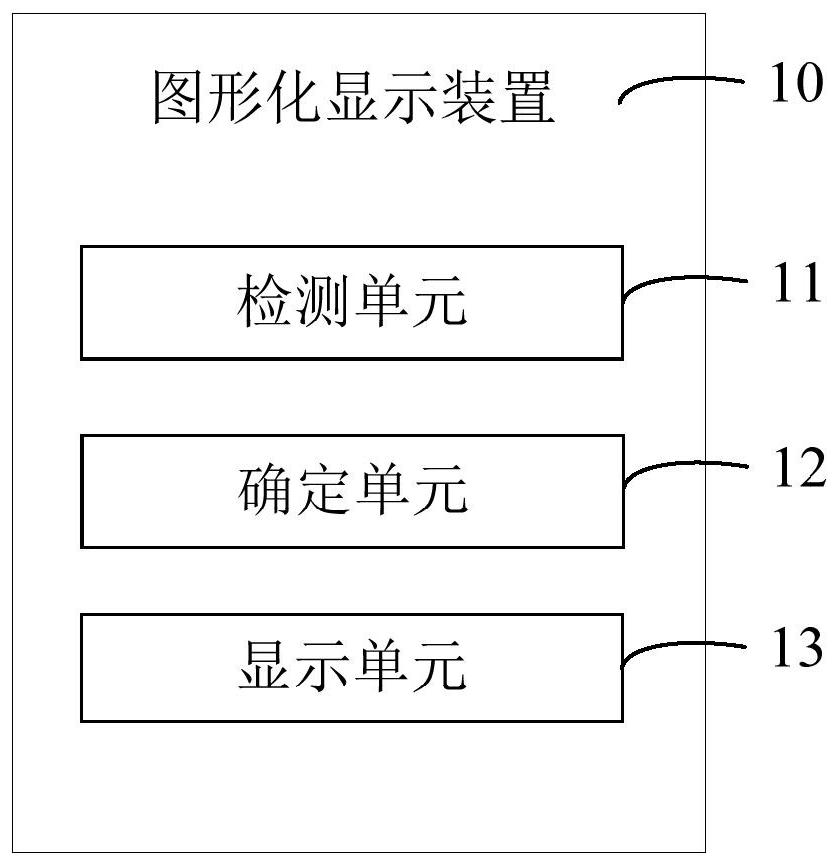

Graphical display device, method and equipment and computer readable storage medium

PendingCN114579018ASave query timeImprove accuracyOther databases browsing/visualisationTotal factory controlGraphical displayQuality control

The invention discloses a graphical display device, method and equipment and a computer readable storage medium, and the graphical display device comprises a detection unit which is used for displaying a position interface corresponding to a quality control module or a calibration module when it is detected that the quality control module or the calibration module is triggered; the determining unit is used for determining a selected position corresponding to an input selected instruction if the input selected instruction is received in the position interface; and the display unit is used for displaying the calibration liquid information of the calibration liquid or the quality control liquid information of the quality control liquid in the selected position according to the state parameters of the selected position. According to the invention, a user can inquire the state information of the sample loaded on each shelf at any time, and the accuracy of inquiring the sample shelf is improved.

Owner:ZYBIO INC

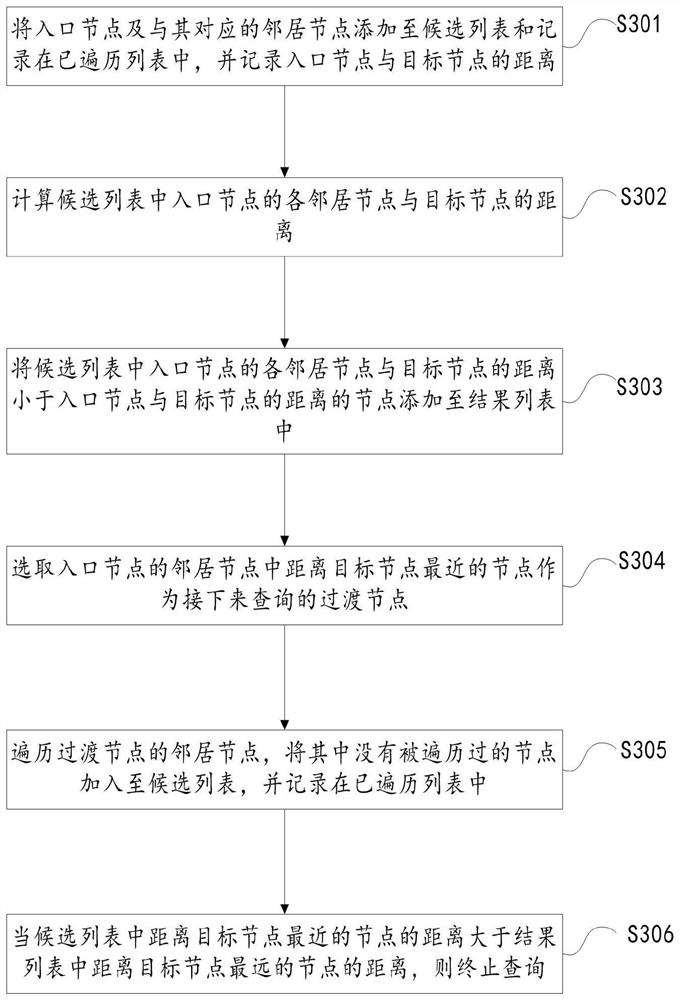

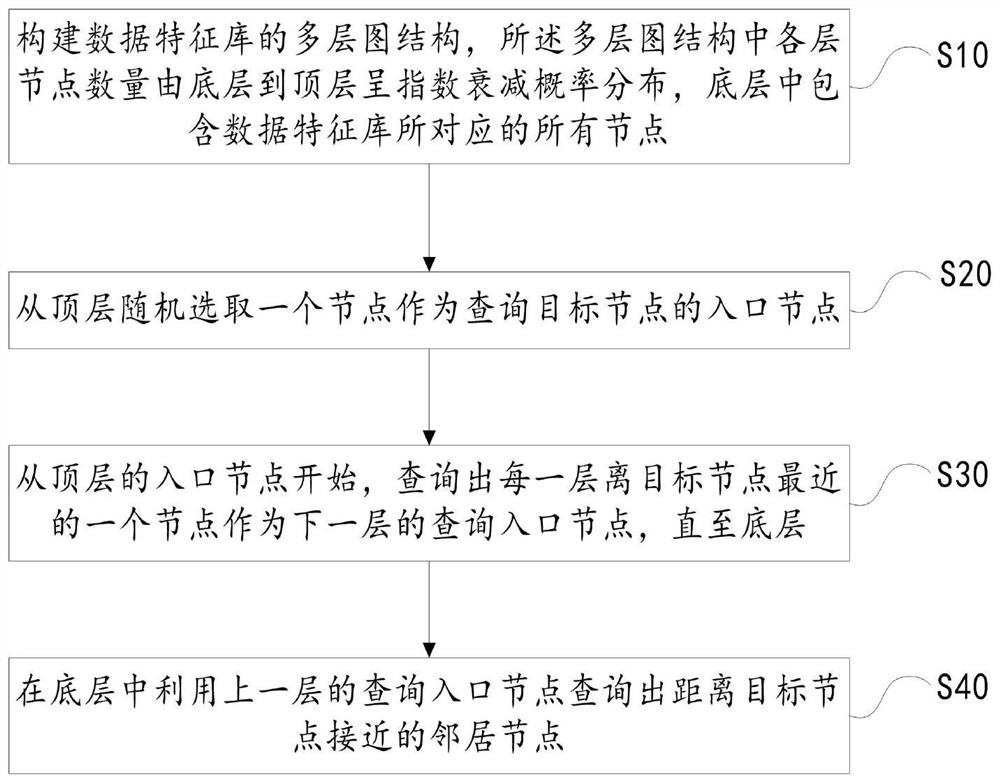

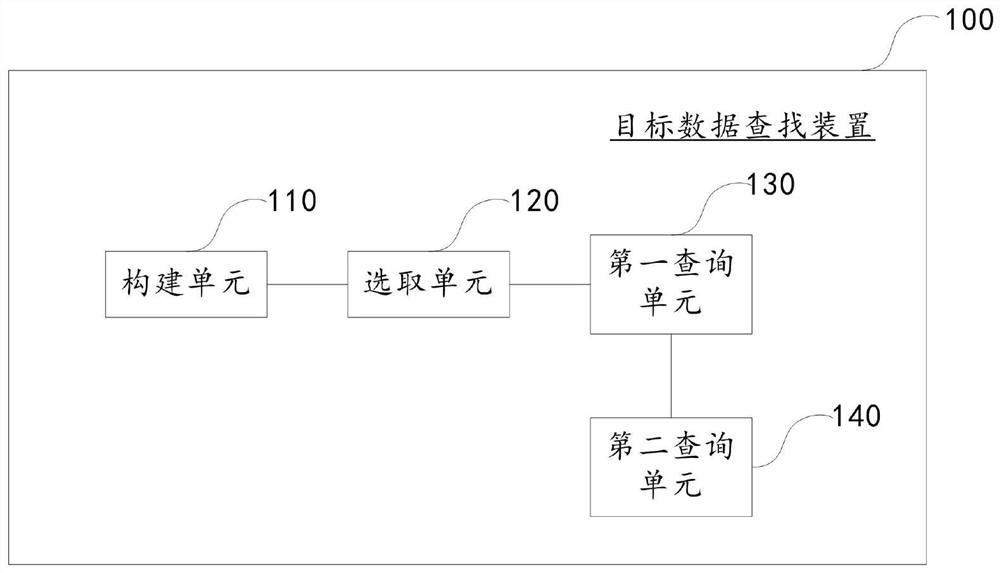

Target data searching method and device, computer equipment and storage medium

PendingCN114385875ASave query timeSave computing timeOther databases indexingSpecial data processing applicationsNode countGoal node

The embodiment of the invention discloses a target data searching method and device, computer equipment and a storage medium, and the method comprises the steps: constructing a multi-layer graph structure of a data feature library, the number of nodes in each layer in the multi-layer graph structure is in exponential decay probability distribution from a bottom layer to a top layer, and the bottom layer comprises all nodes corresponding to the data feature library; randomly selecting a node from a top layer as an entry node of a query target node; from the entry node of the top layer, querying a node, closest to the target node, of each layer as a query entry node of the next layer until the bottom layer; and querying a neighbor node close to the target node by using the query entry node of the upper layer in the bottom layer. According to the method, the node which is queried in the upper layer and is closest to the target node is used as the iteration starting point of the lower layer until the bottom layer, so that a large part of nodes which are far away from the target node can be filtered out in each layer during query, the query and operation time is saved, and the query efficiency is improved.

Owner:深圳市同为数码科技股份有限公司

Medical information inquiry system and method

ActiveCN107239665BReduce loadRespond quickly to mission needsMedical simulationPhysical therapies and activitiesData matchingEngineering

Embodiments of the present invention provide a medical information query system and method. The system includes: a rule engine module, a decision support module and a graph database module; the rule engine module is used to receive clinical data and obtain query rules matching the clinical data; the decision support module is used to Query the medical information corresponding to the query rule acquired by the rule engine module in the graph database stored by the graph database module. The embodiment of the present invention can reduce the load of the rule engine module, so that it can quickly respond to the task requirements of the decision support module, and the efficiency is high; at the same time, the rule engine module is not coupled with the graph database module, which simplifies the development and maintenance of the system complexity, saving storage space and query time; in addition, using graph database to store medical information also makes query more convenient.

Owner:BOE TECH GRP CO LTD

A Book Retrieval Method Based on Feature Extraction

ActiveCN106126626BExact matchExact searchDigital data information retrievalCharacter and pattern recognitionInformation repositoryFeature extraction

The invention relates to a book retrieval method based on feature extraction, which belongs to the technical field of network communication. The present invention first collects data on the book information of the library, extracts the book label information, performs code identification, establishes a book information database, and stores the book information; secondly, performs book clustering according to the book label information elements, and performs category coding on the clustered books As the original library source for retrieving books, combined with the original book tags to reorganize the book features, extract new feature phrases of each category of books as the clustered book information base; According to the frequency of categories, a user access model is established to form a user reading pattern label as a user feature label value; finally, a matching correlation model is established to provide a list of retrieved books for successful matching users. The invention can perform real-time retrieval aiming at user access characteristics, and can accurately meet user access requirements.

Owner:KUNMING UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com