Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Reduce latency variance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

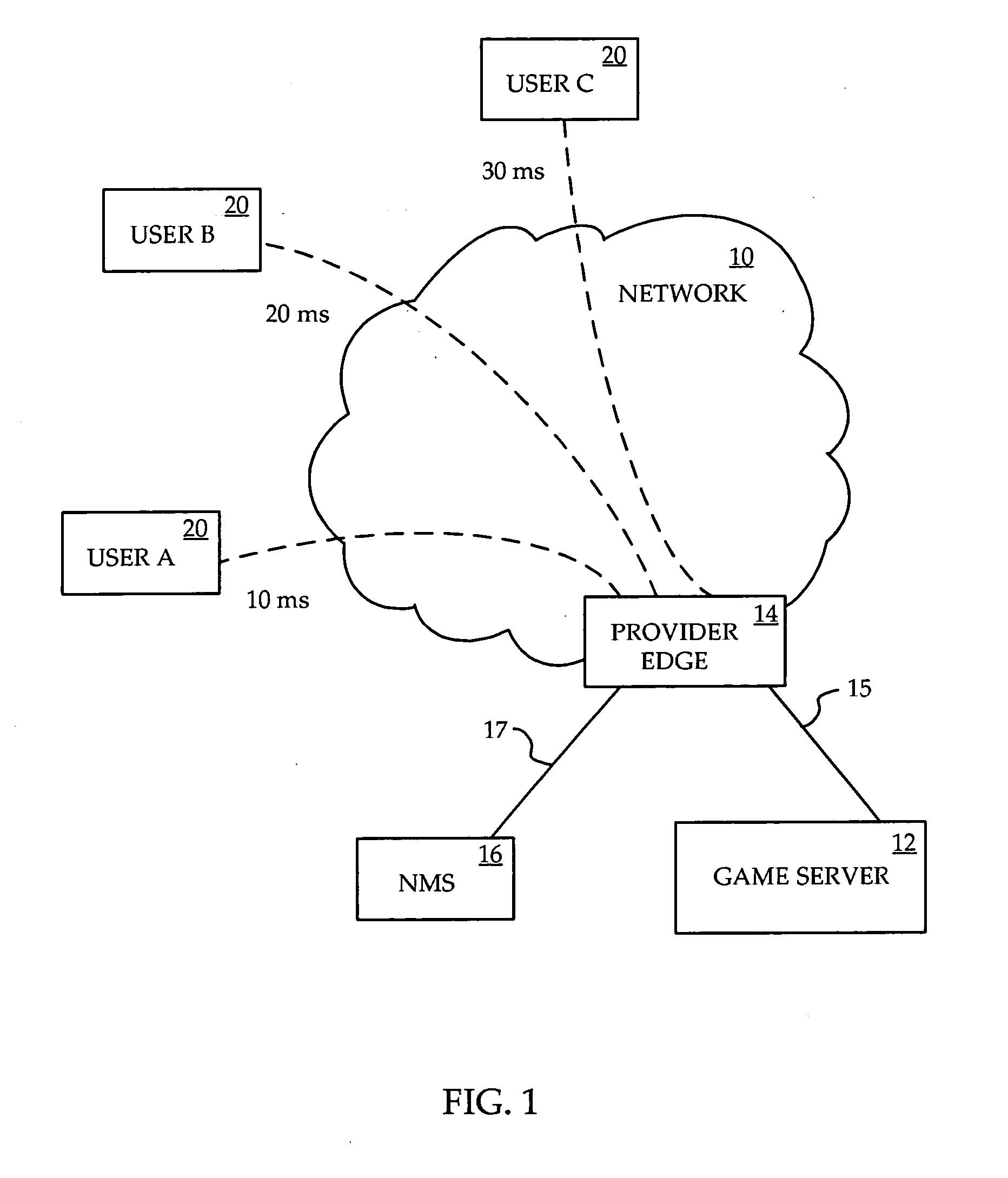

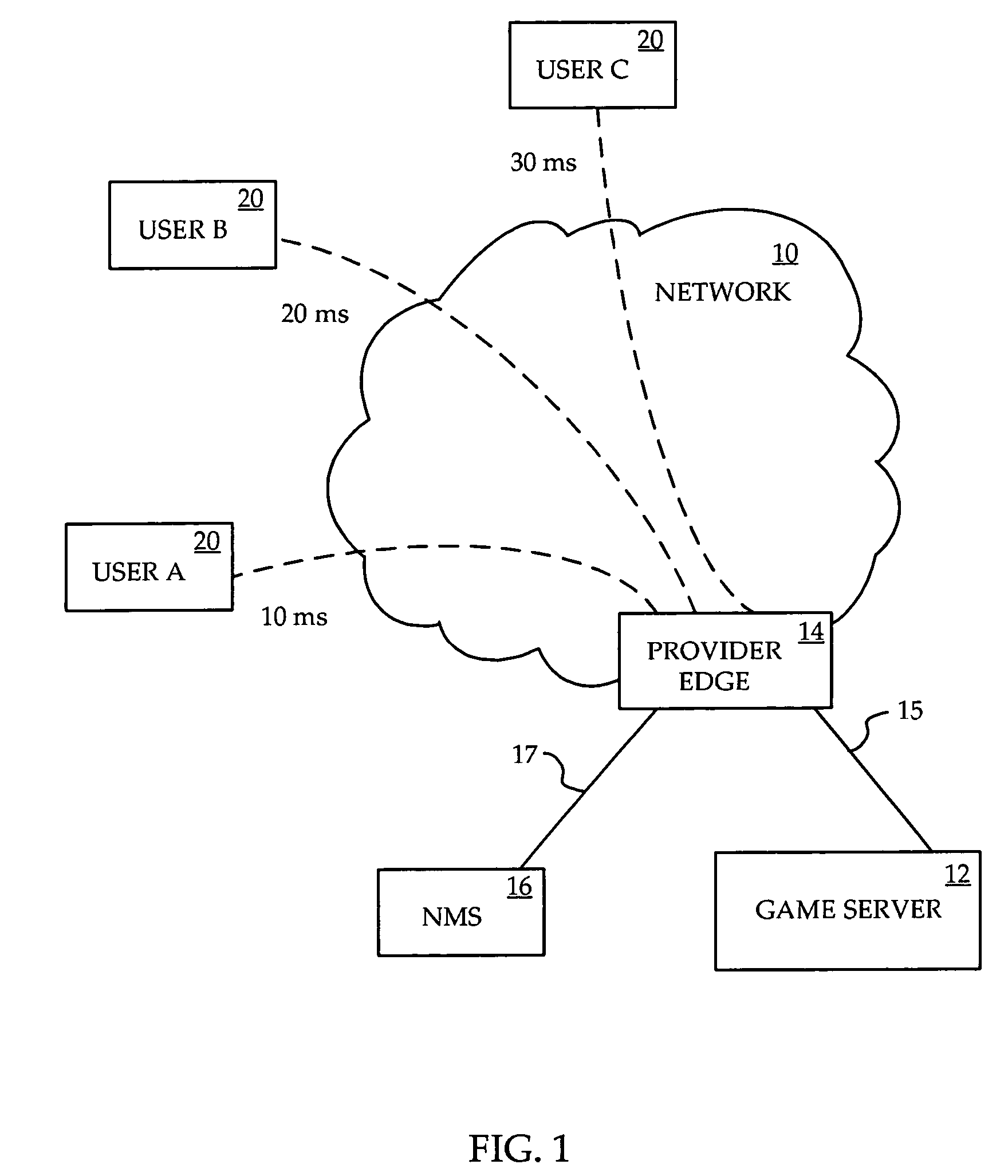

Equalized network latency for multi-player gaming

InactiveUS20070070914A1Reduce latency varianceLatency connectionError preventionFrequency-division multiplex detailsTraffic capacityApplication server

A method is provided for equalizing latency among a group of connections that are being used by the same latency-sensitive application, such as for multi-player network gaming. Delay is added to the packet flow in each connection as necessary at the provider edge router connecting the application server to the network. An NMS connected to the provider edge router continuously monitors the round-trip delay of each connection, determines the additional delay of each connection required to equalize the delays, and informs the provider edge router. The provider edge router buffers traffic on each connection for the respective duration as indicated by the NMS. The NMS may also reroute some of the connections over higher latency resources to reduce the amount of buffering required, which provides the additional advantage of using what might otherwise be less used or economically less valued resources.

Owner:RPX CORP

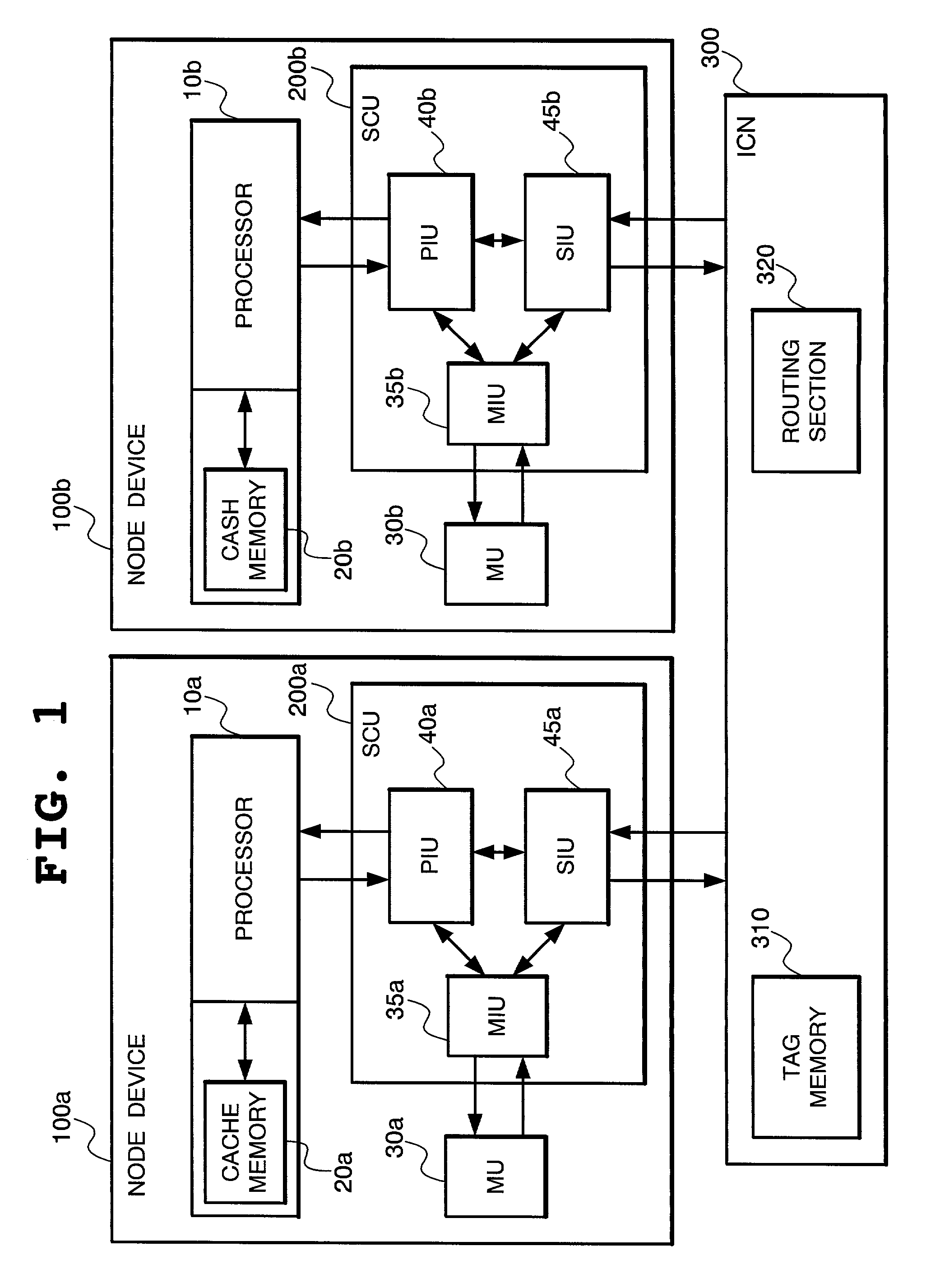

Data access method in the network system and the network system

InactiveUS7093078B2Lower latencyReduce latency varianceMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareAccess method

According to this data access method to be used in a network system, while the tag information is read out from the tag memory, the data is speculatively read out from the memory unit in the self node device. When the read out tag information shows that the speculatively read out data is not found in any of the cache memories, such speculatively read out data is sent to the processor in the self node device. When the read out tag information shows that the speculatively read out data is found in one of the cache memories, the data existing in such cache memory is acquired and sent to the processor in the self node device and the speculatively readout data is abolished.

Owner:NEC CORP

Equalized network latency for multi-player gaming

InactiveUS7889669B2Reduce latency varianceLatency connectionError preventionFrequency-division multiplex detailsTraffic capacityApplication server

A method is provided for equalizing latency among a group of connections that are being used by the same latency-sensitive application, such as for multi-player network gaming. Delay is added to the packet flow in each connection as necessary at the provider edge router connecting the application server to the network. An NMS connected to the provider edge router continuously monitors the round-trip delay of each connection, determines the additional delay of each connection required to equalize the delays, and informs the provider edge router. The provider edge router buffers traffic on each connection for the respective duration as indicated by the NMS. The NMS may also reroute some of the connections over higher latency resources to reduce the amount of buffering required, which provides the additional advantage of using what might otherwise be less used or economically less valued resources.

Owner:RPX CORP

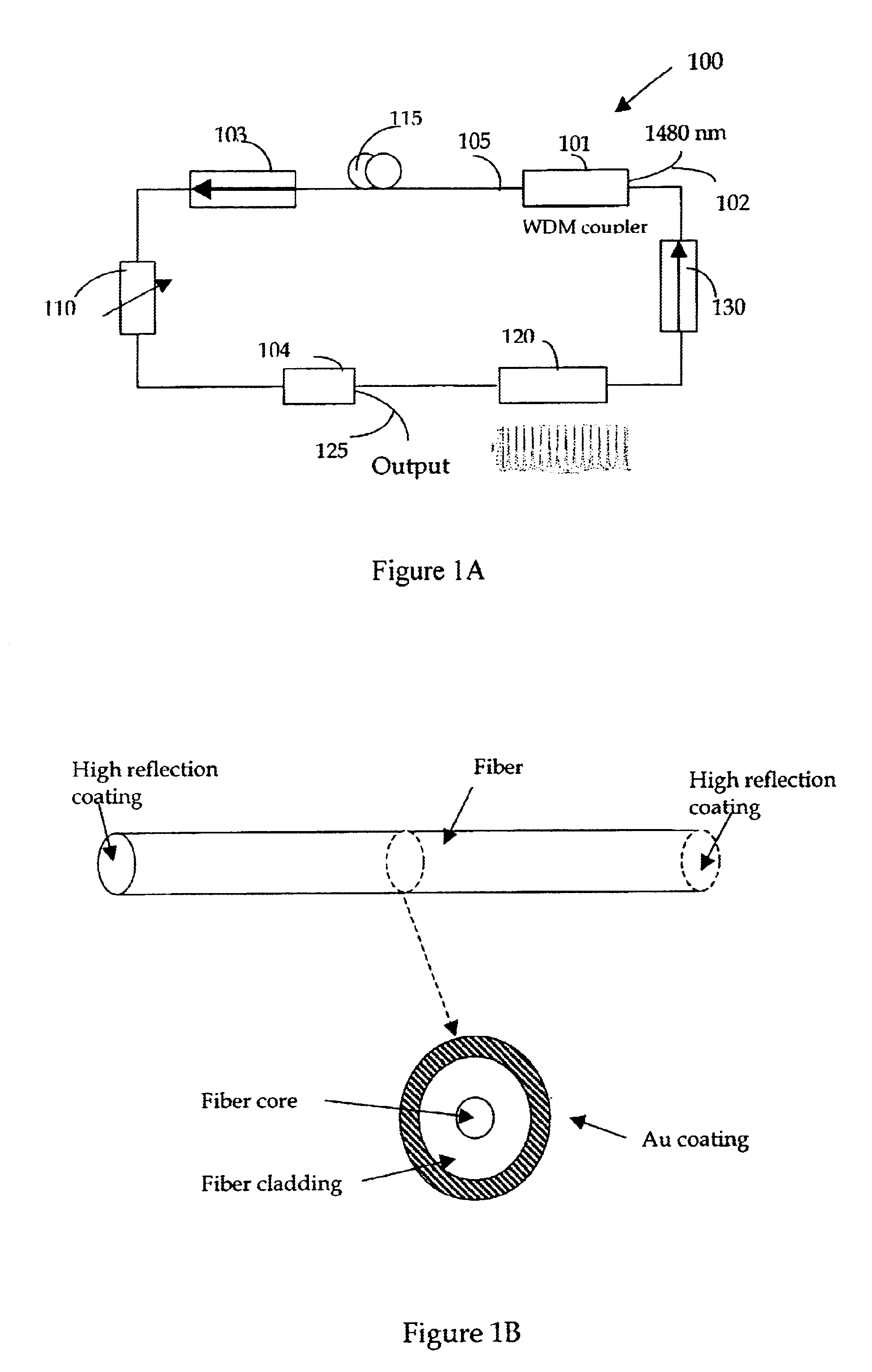

Stable and high speed full range laser wavelength tuning with reduced group delay and temperature variation compensation

InactiveUS6937627B2High speedReduce group delayLaser using scattering effectsActive medium shape and constructionTunable laserAngular difference

A fiber-based ring cavity tunable laser is disclosed in this invention that has full range high speed tuning achieved by combining a optical tunable filter with a period comb-shaped filter with central wavelengths anchored on International Telecommunication Union (ITU) grids. By using segments of dispersion managed fibers with predefined segment lengths the group delay differences are also reduced. The temperature sensitivity of optical transmission is also reduced by arranging the longitudinal axis of different segments of the optical fibers to orient with a relative angular difference, e.g., with an angular difference of ninety degrees.

Owner:LIN JIAN

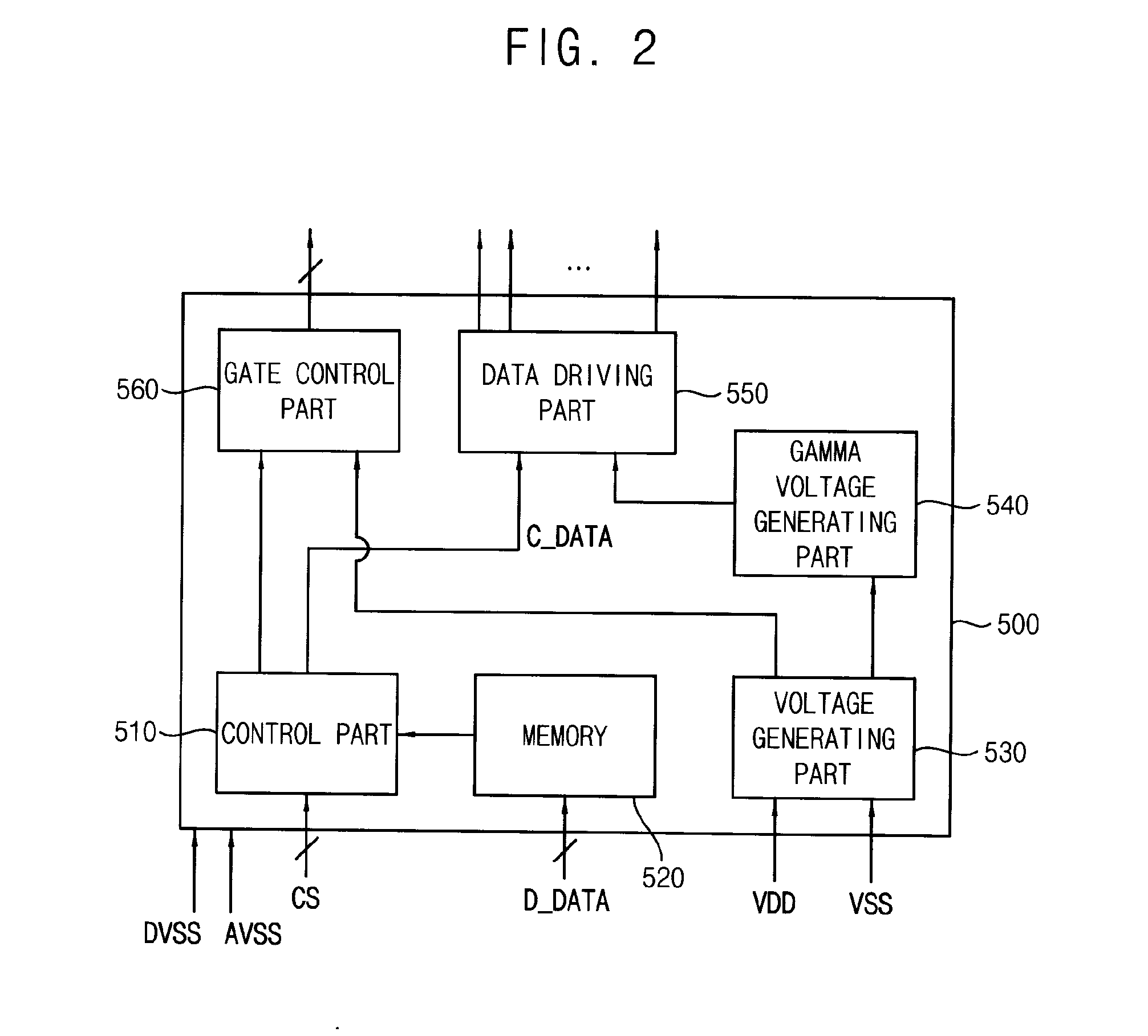

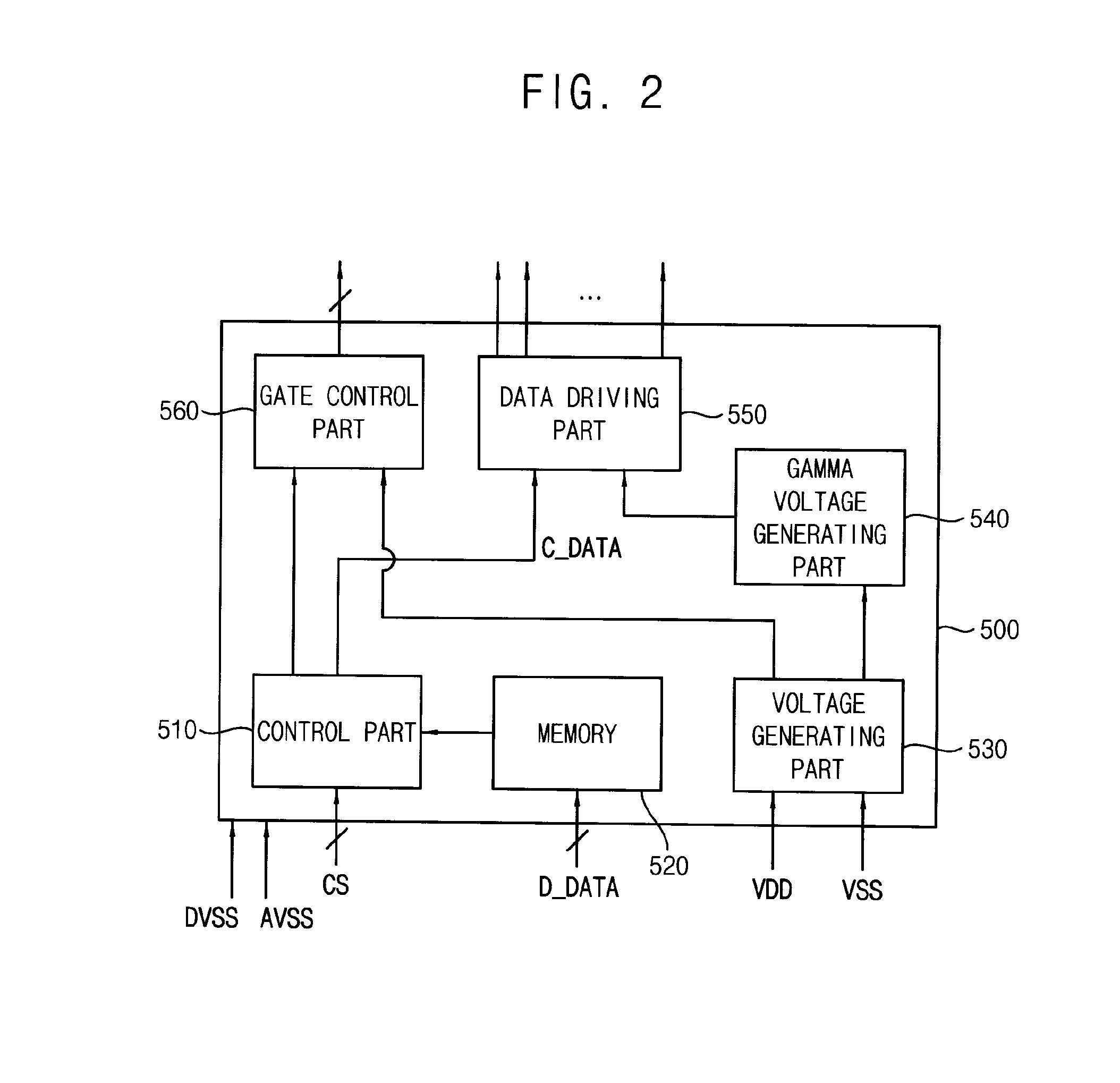

Clock signal generating circuit, display panel module, imaging device, and electronic equipment

InactiveUS20090146711A1Reduce latency varianceAccurate detectionPulse automatic controlCathode-ray tube indicatorsPhase differenceDelayed time

A delay synchronization loop type clock signal generating circuit includes: a delay line for delaying a first clock signal by a set delay amount and outputting; a delay time length setting unit for setting a delay time length of the delay line, based on phase difference between a second clock signal output from an output terminal and the first clock signal; a phase relation determining unit for determining whether or not the phase relation of the first clock signal and the second clock signal are in a particular phase relation; and a phase inversion / non-inversion unit for performing phase inversion of the first clock signal on a transmission path including the delay line, at the time of detecting the particular phase relation.

Owner:JAPAN DISPLAY WEST

Semiconductor device

ActiveUS20080252356A1Reduce areaIncrease motivationElectronic switchingSingle output arrangementsEngineeringSemiconductor

A semiconductor device is provided which has a driving circuit operable to drive a circuit that has a delay, the semiconductor device including: an auxiliary driving circuit operable to accelerate drive of the driving circuit, which receives a drive signal of the driving circuit as an input signal.

Owner:SONY SEMICON SOLUTIONS CORP

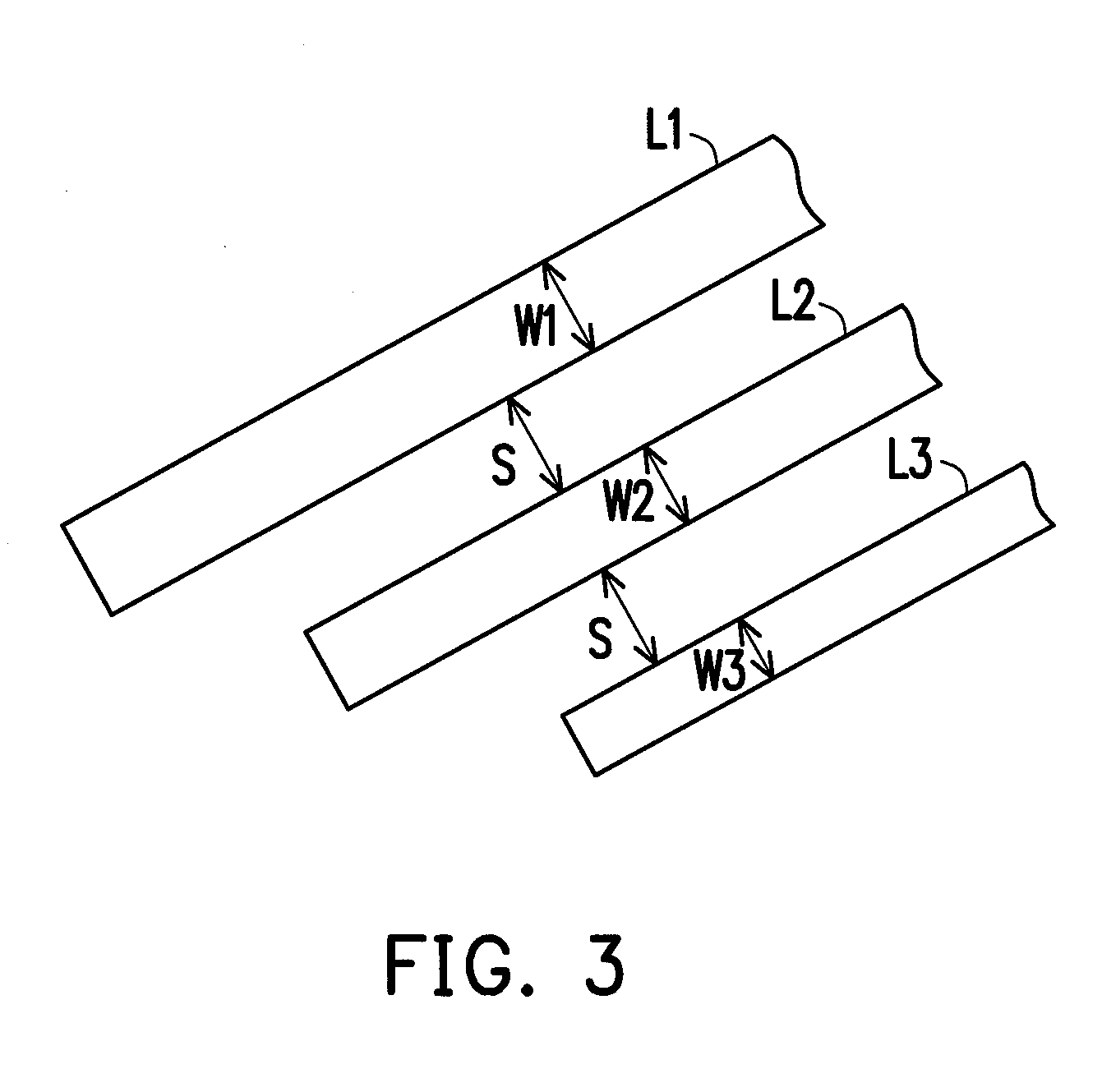

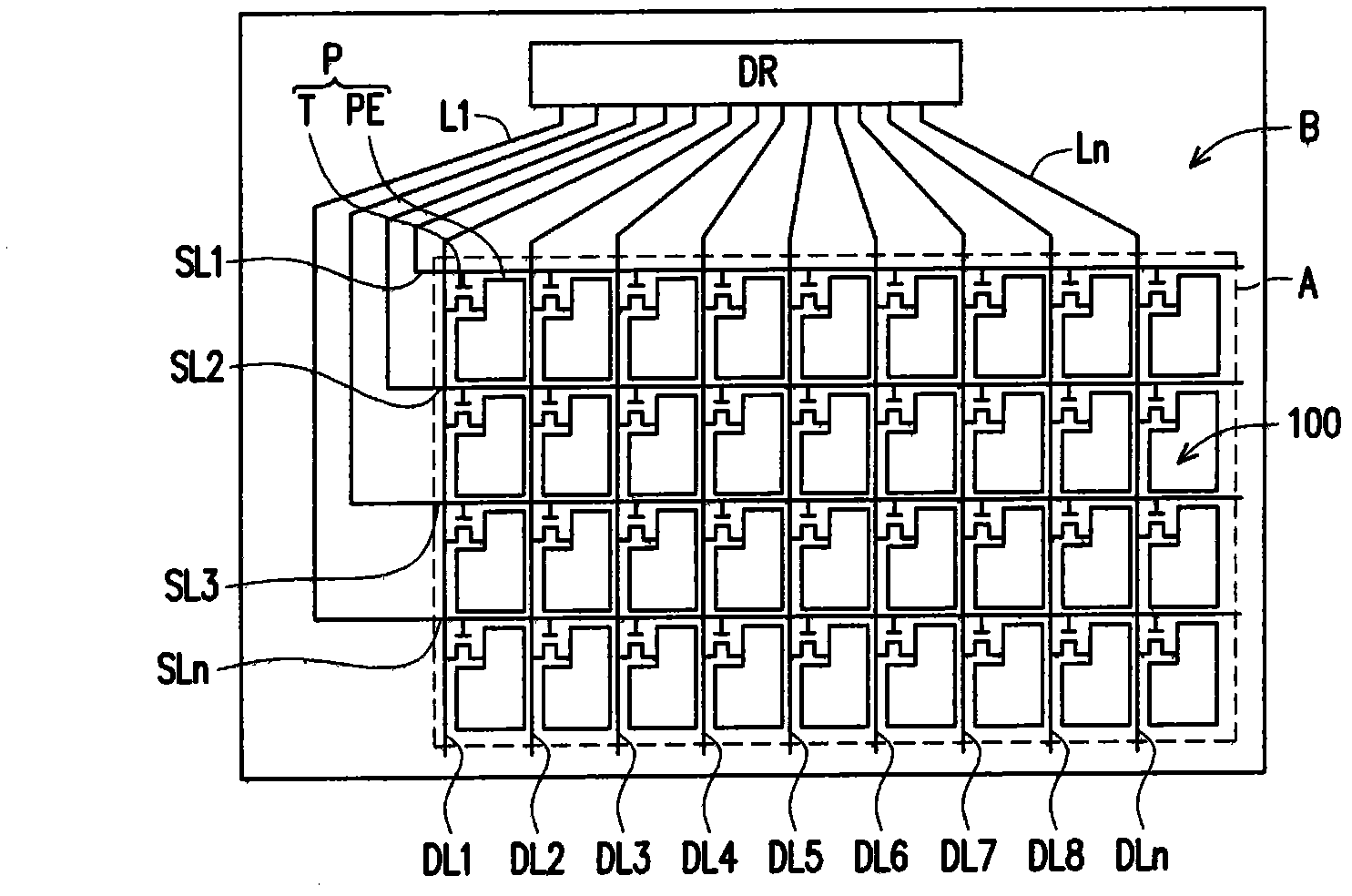

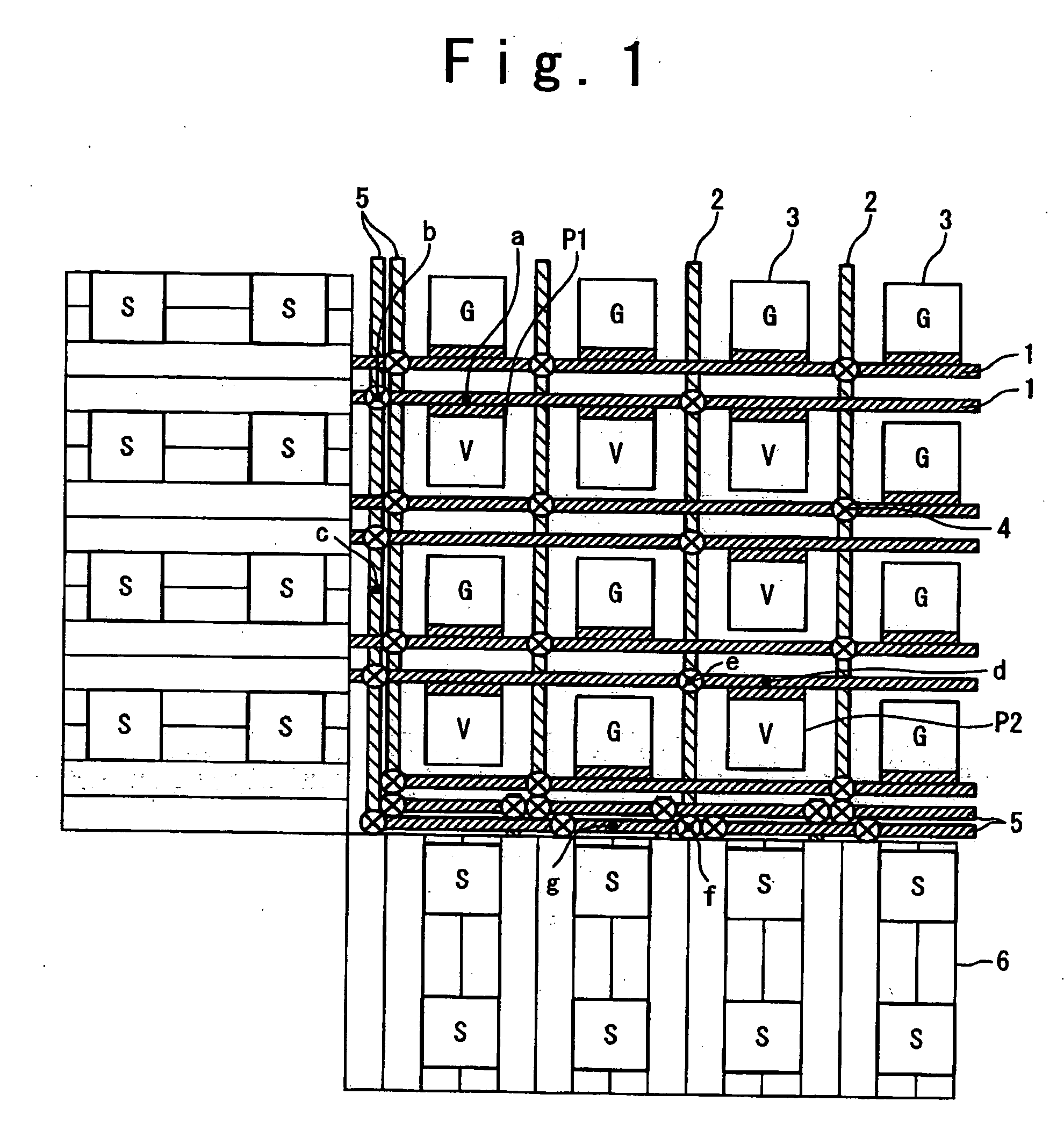

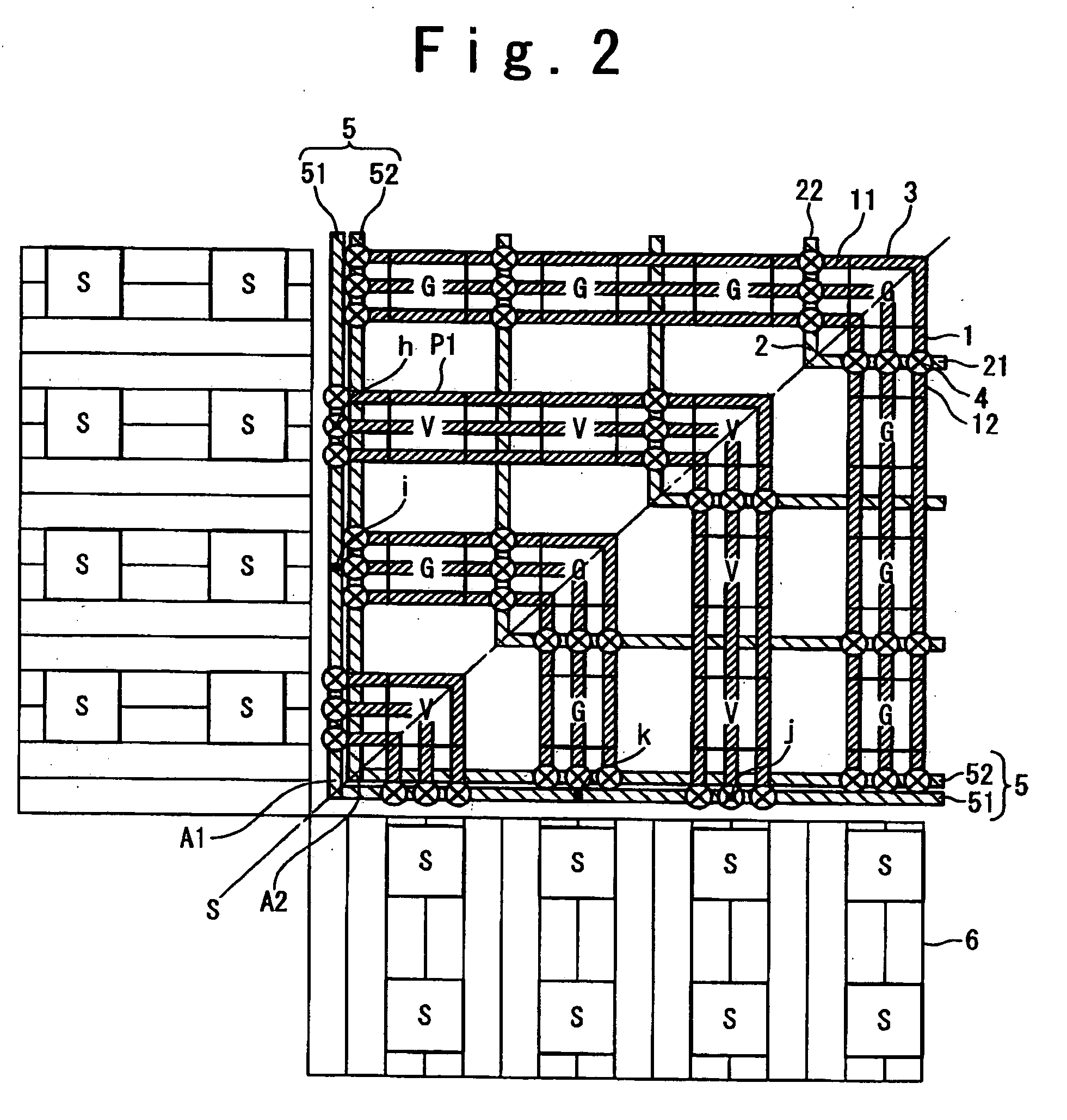

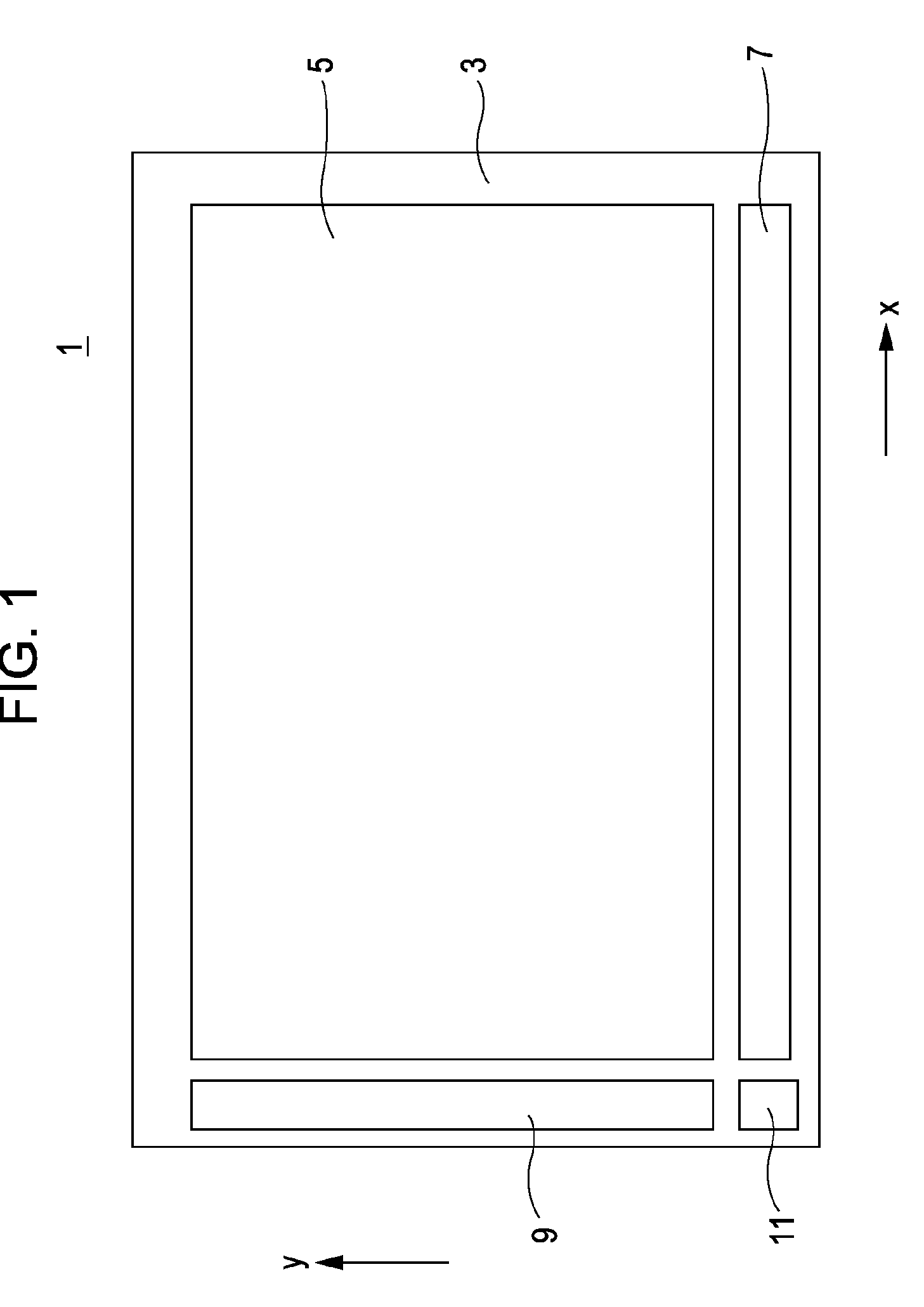

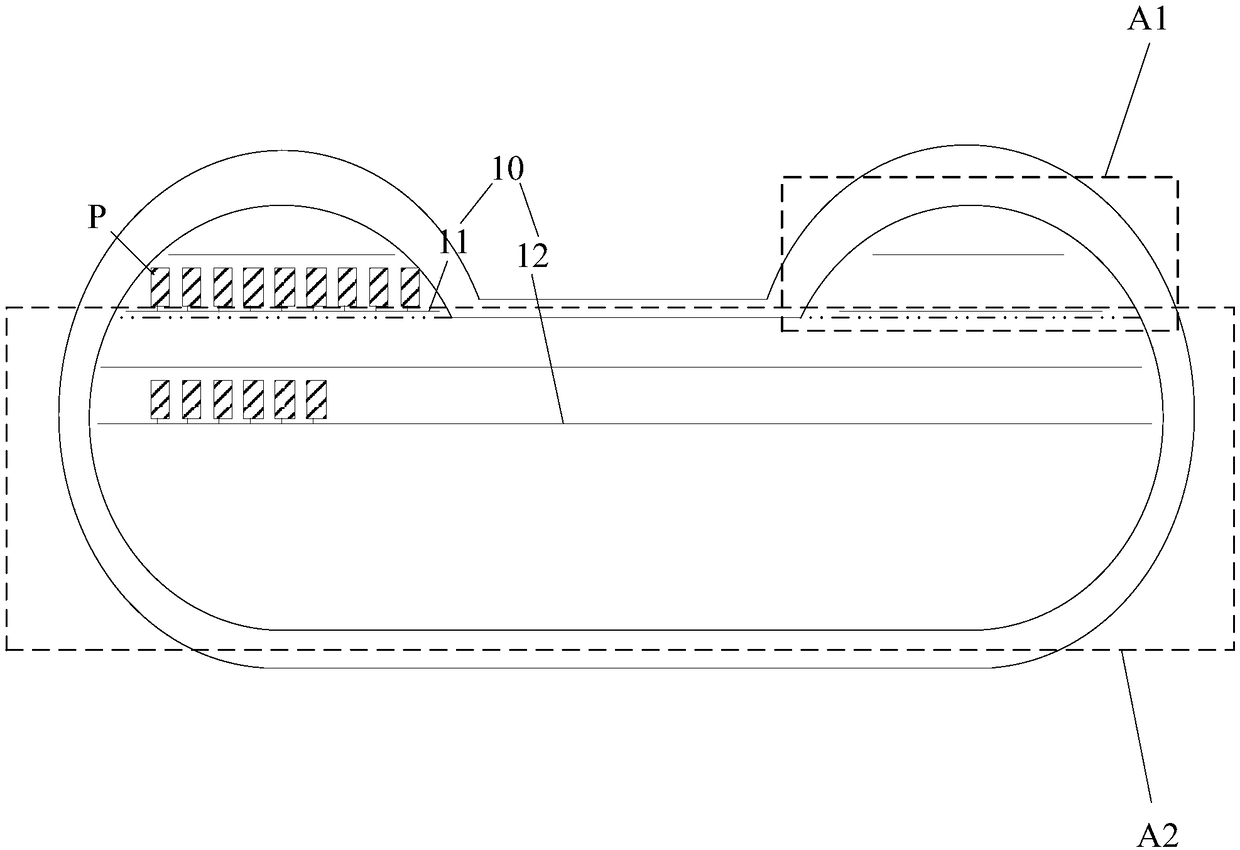

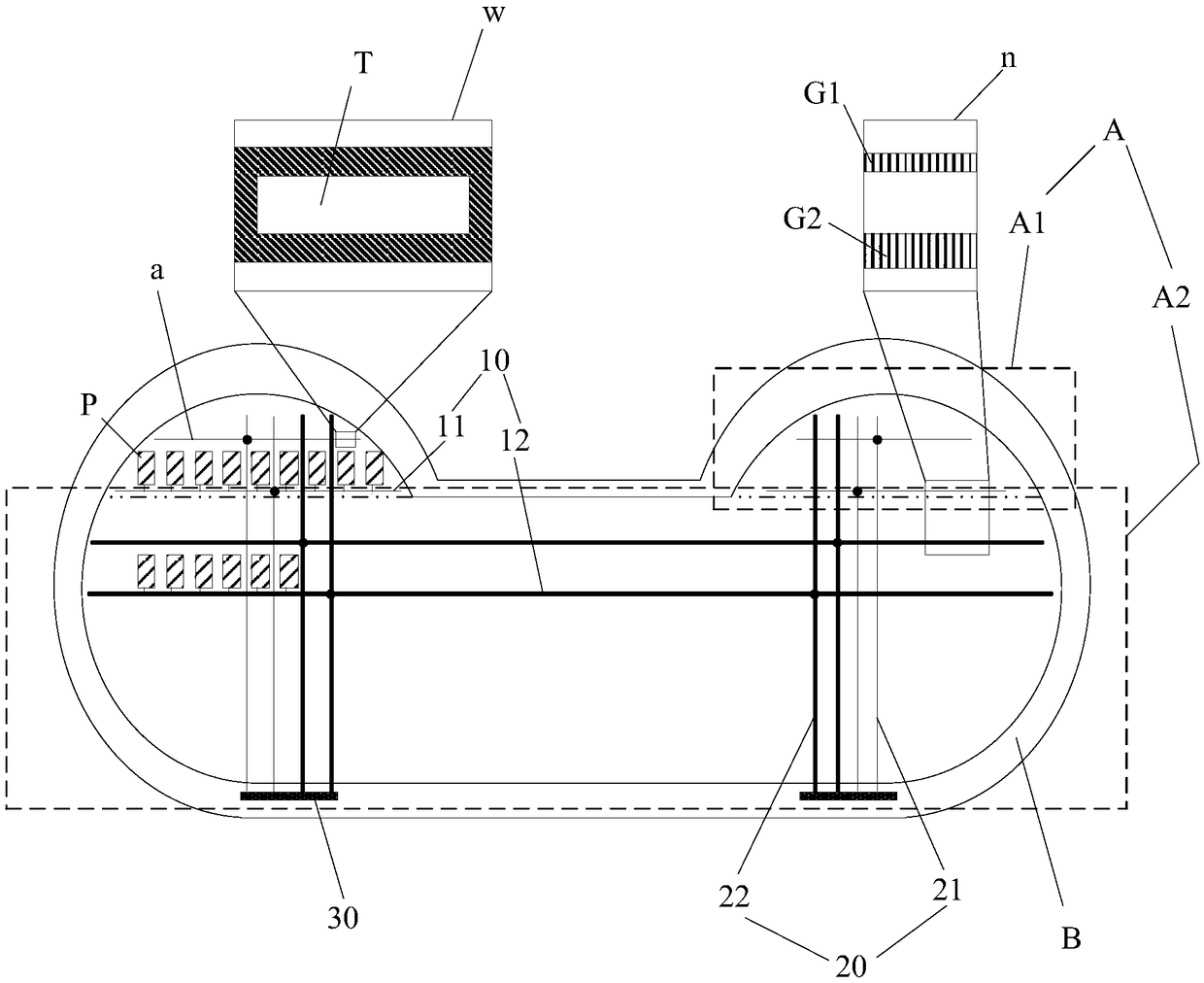

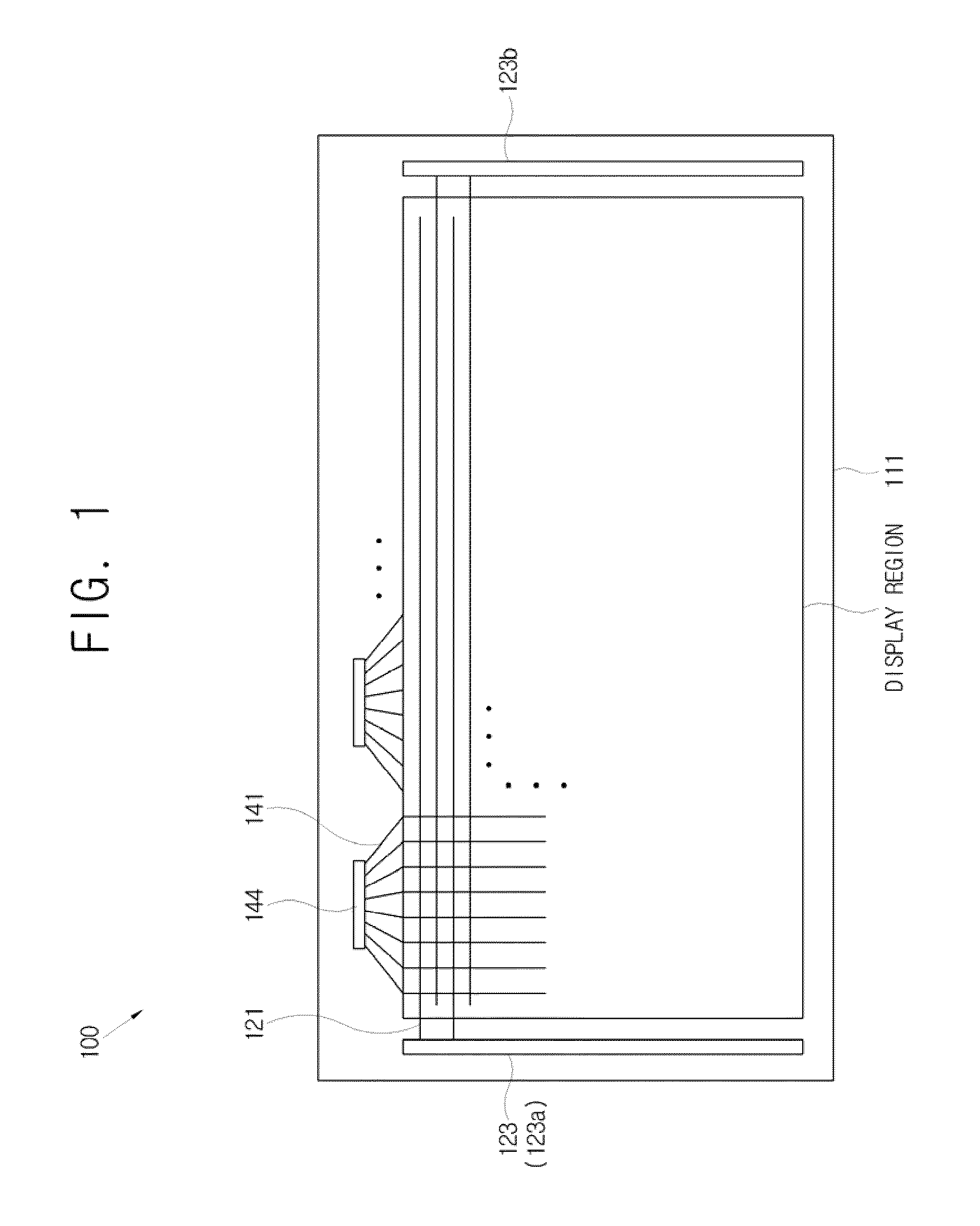

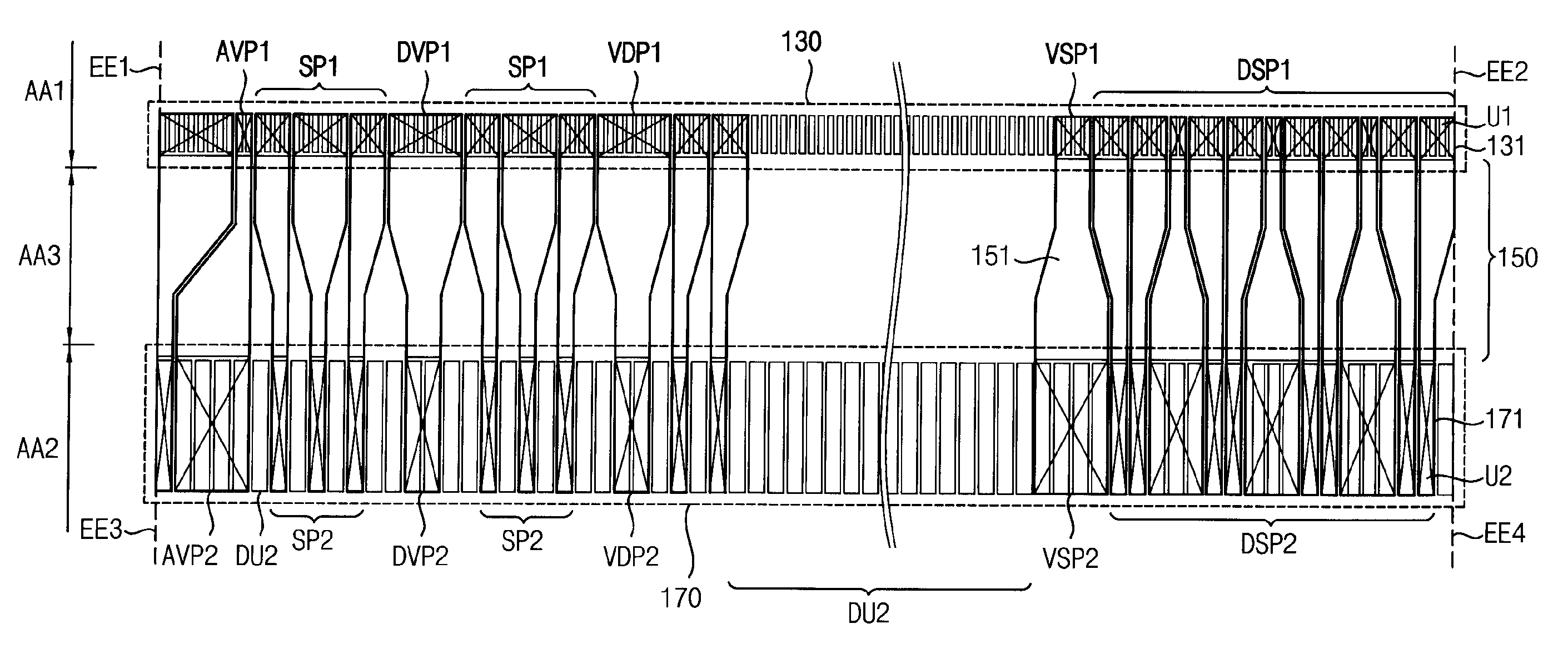

Lead line structure and display panel having the same

InactiveUS20120319623A1Reducing signal delay differenceLength can be narrowedElectric light circuit arrangementPrinted circuitsLine widthEngineering

A display panel having a display region and a non-display region is described. The display panel includes a pixel array, at least one driving device and a plurality of lead lines. The pixel array is disposed in the display region. The driving device is disposed in the non-display region. The lead lines are disposed in the non-display region and are electrically connected to the pixel array and the driving device. The lead lines are arranged into at least one fan-out structure between the pixel array and the driving device. In particular, the (n-1)th lead line has a pitch Pn-1=Wn-1+S, n is an integer larger than 1, Wn-1 represents a line width of the (n-1)th lead line, S represents a space between the adjacent lead lines, and the pitches P1˜Pn-1 of the plurality of lead lines are not completely the same.

Owner:AU OPTRONICS CORP

Lead wire structure and displaying panel possessing the lead wire structure

InactiveCN102323681AShorten the lengthConducive to the development of narrow bordersSolid-state devicesNon-linear opticsWire widthElectrical connection

The invention discloses a lead wire structure and a displaying panel possessing the lead wire structure, comprising a displaying zone and a non-displaying zone. The displaying panel comprises a pixel array, at least one driving device and a plurality of lead wires. The pixel array is located in the displaying zone, and the driving device and the lead wires are located in the non-displaying zone; the lead wires are in electrical connections with the pixel array and the driving device, and are arranged as a fan-shaped structure between the pixel array and the driving device. Especially, the wire distance P<n-1> between the No.(n-1) lead wire and the No. n lead wire is equal to (W<n-1>+S), wherein, the n is a positive integer greater than 1, the W<n-1> represents the wire width of the No.(n-1) lead wire, and the S represents the clearance of adjacent lead wires; wherein, the wire distances P<1> to P<n-1> of the lead wires in the fan-shaped structure are not completely equal.

Owner:AU OPTRONICS CORP

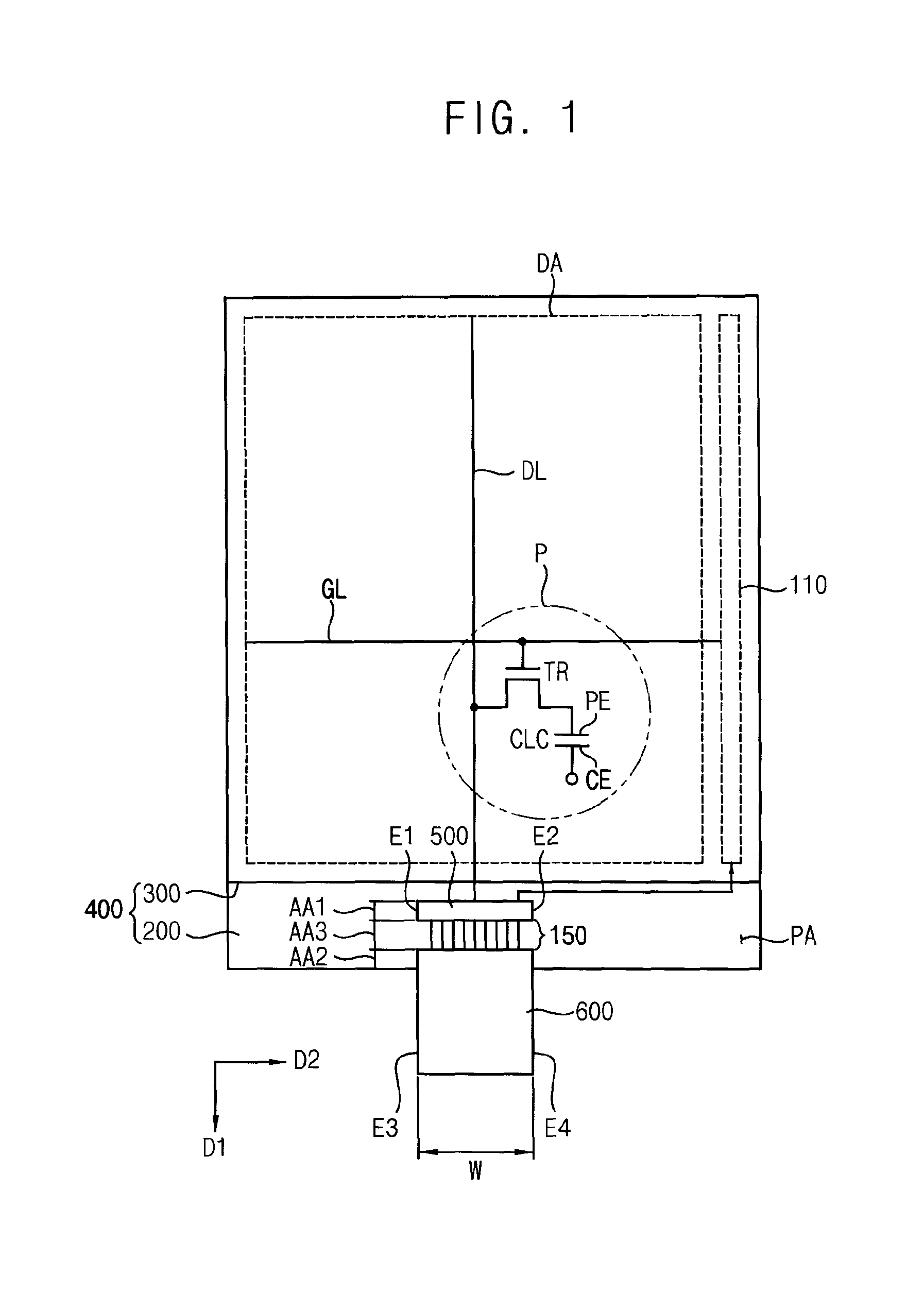

Display substrate and display apparatus having the display substrate

ActiveUS20150145847A1Lower resistanceShorten the line lengthTransistorSolid-state devicesDriver circuitFlexible circuits

A display substrate includes a pixel electrode disposed in a display area, a first pad part disposed in a first area of a peripheral area which is disposed adjacent to the display area, where the first pad part is electrically connected to a driver circuit, a second pad part disposed in a second area of the peripheral area facing the first pad part, where the second pad part is electrically connected to a flexible circuit film which transfers a transmission signal to the driver circuit, and a connection line part disposed in an area between the first and second pad parts as a vertical line type, where the connection line part connects the first and second pad parts to each other.

Owner:SAMSUNG DISPLAY CO LTD

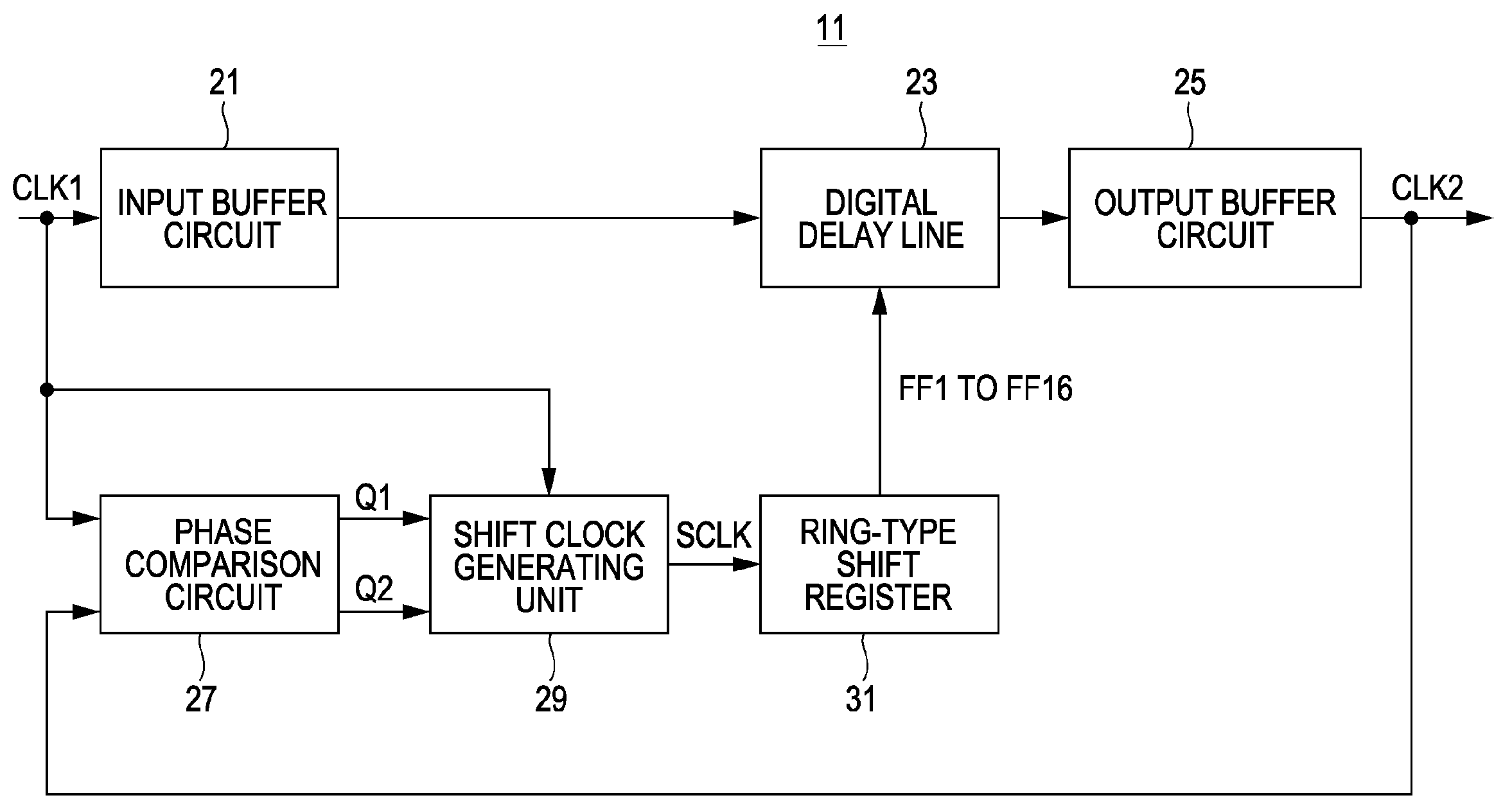

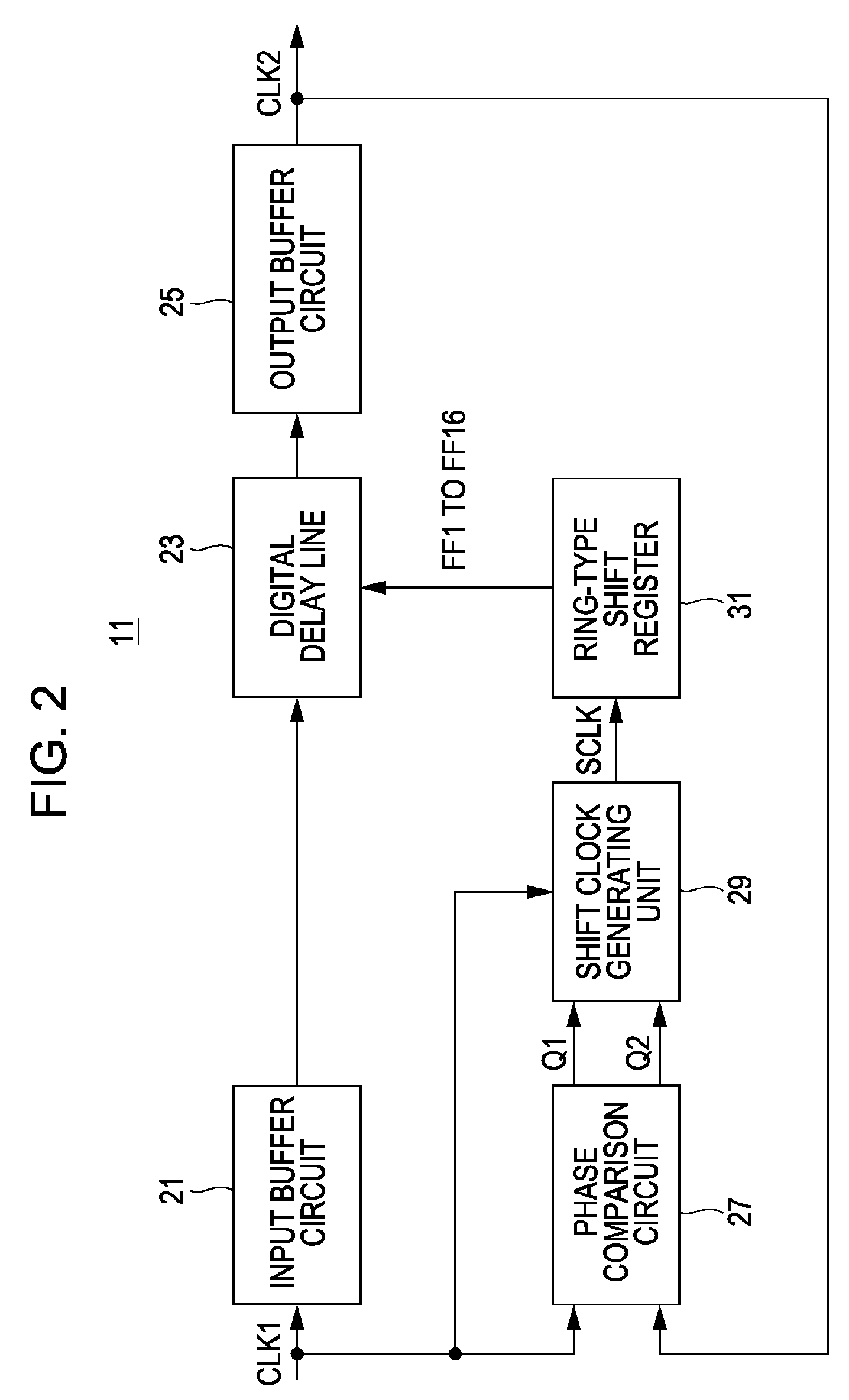

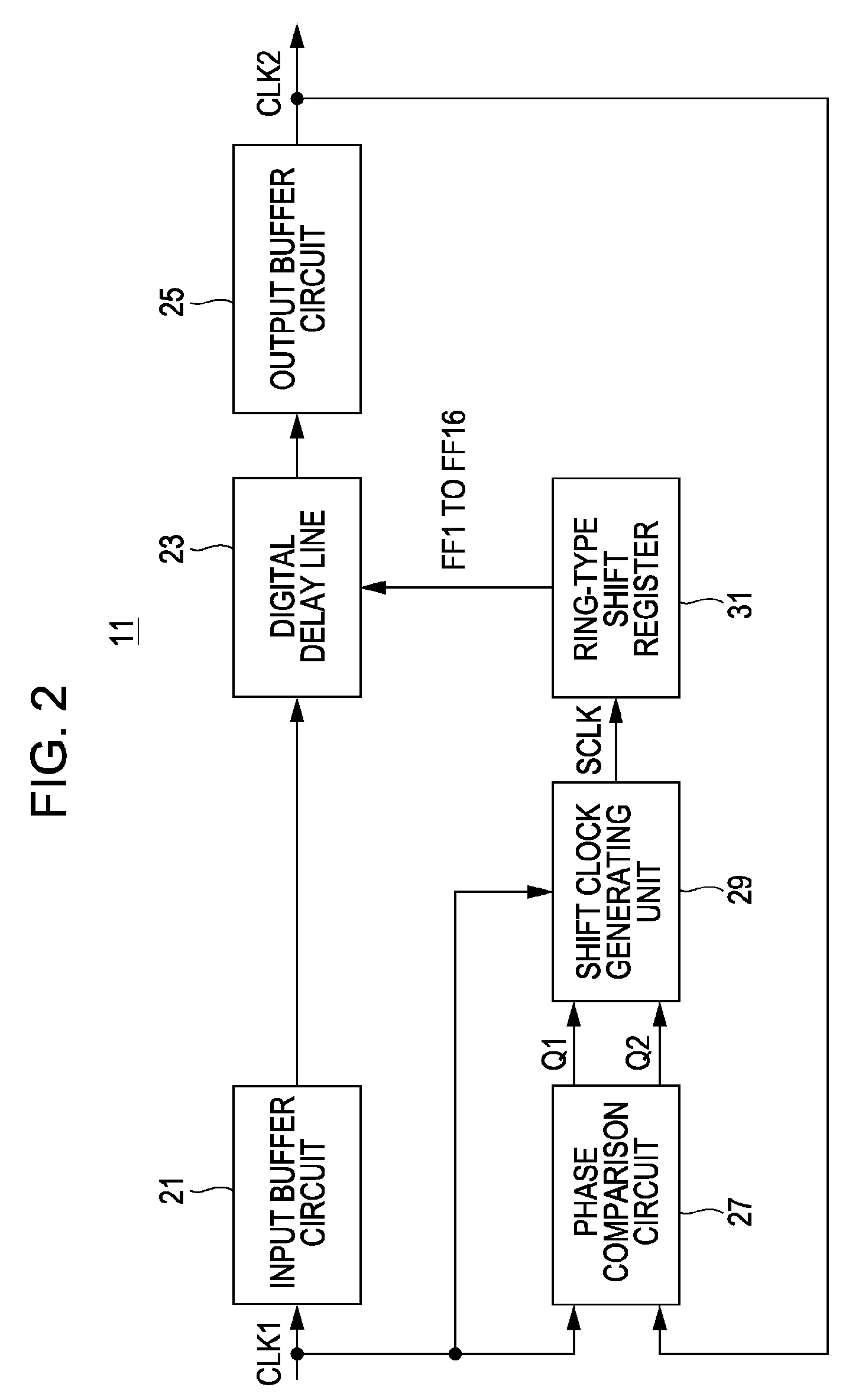

Clock signal generating circuit, display panel module, imaging device, and electronic equipment

ActiveUS20090146713A1Reduce latency varianceShort timeTelevision system detailsPulse automatic controlShift registerProcessor register

A delay synchronization loop type clock signal generating circuit includes: a digital delay line for delaying a first clock signal and generating a second clock signal; a ring-type shift register for setting the delay time length of the digital delay line by flip-flop output of each stage thereof; and a delay amount control unit for controlling supply of shift clocks to the ring-type shift register, based on phase relation between the first clock signal and the second clock signal.

Owner:JAPAN DISPLAY WEST

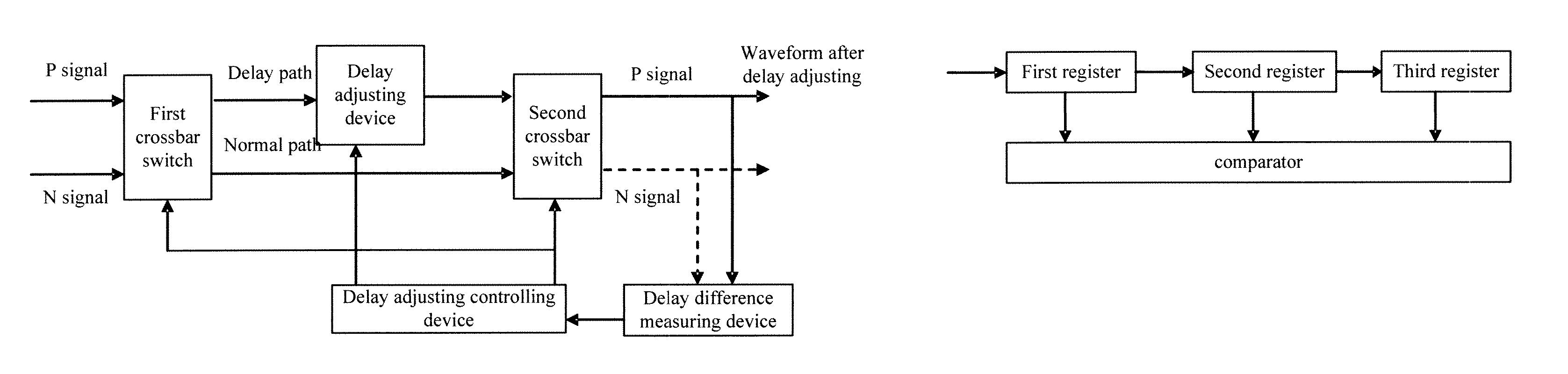

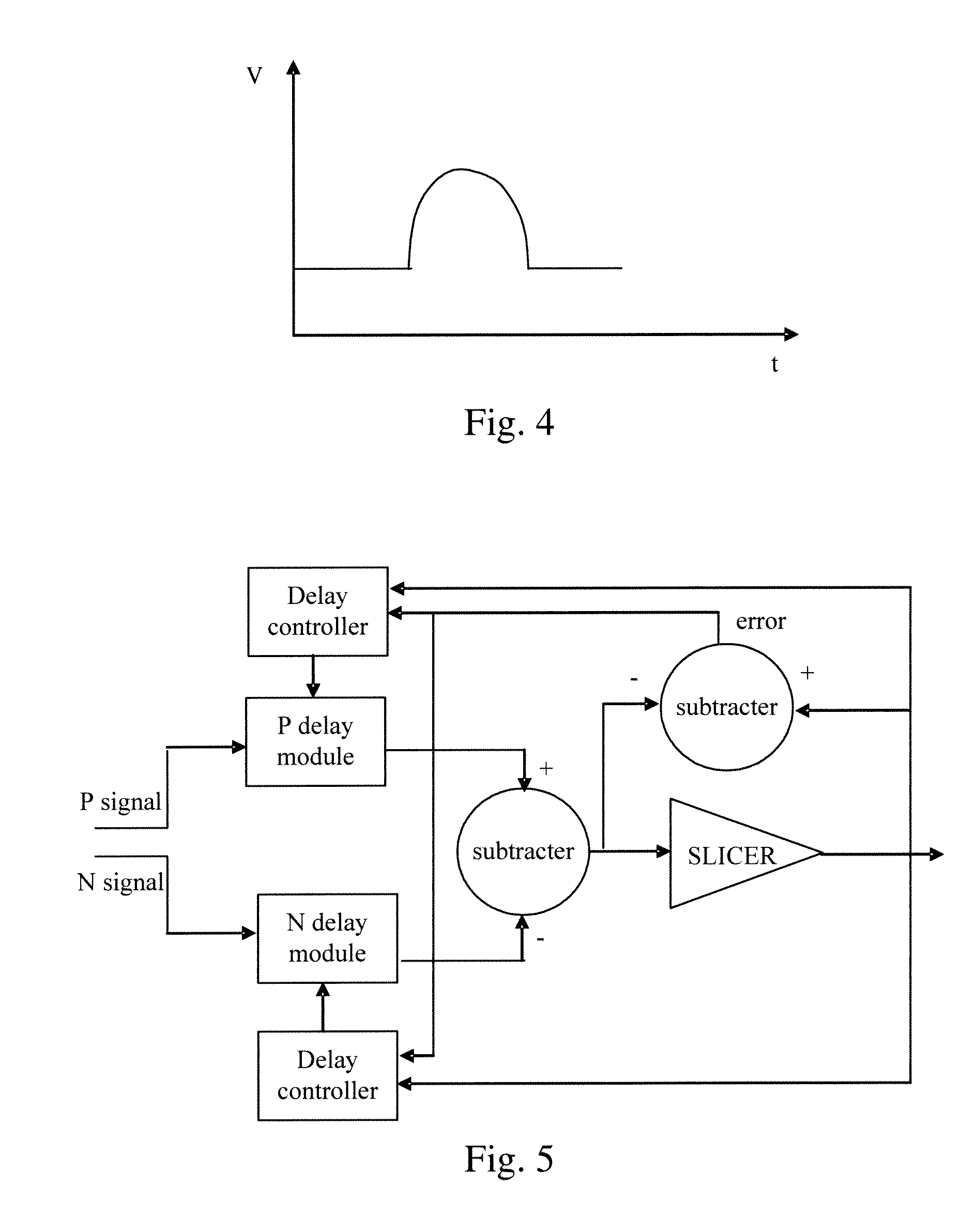

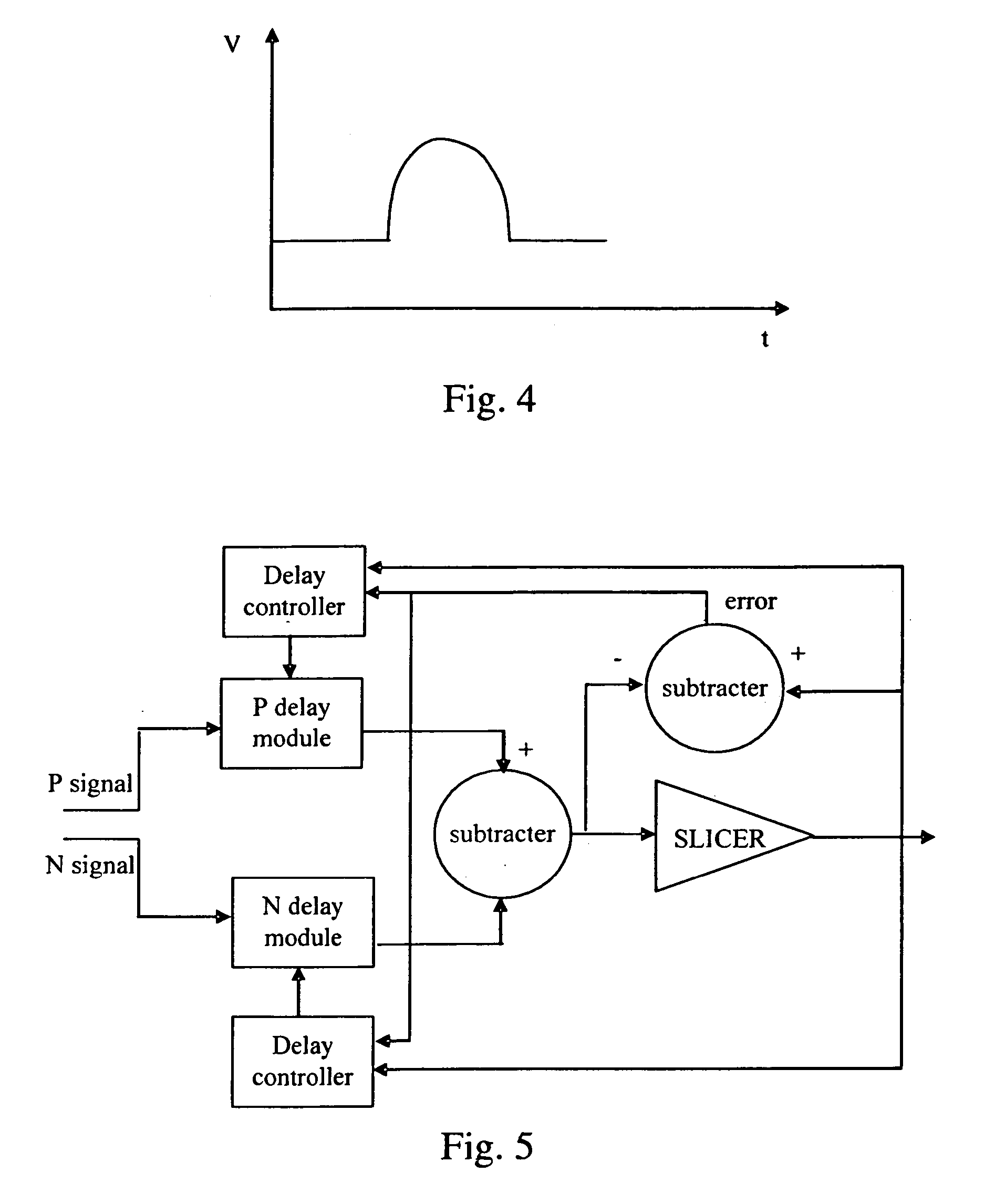

Method for reducing delay difference of differential transmission and system thereof

InactiveUS7538594B2Reduce latency varianceDelay differenceVoltage-current phase angleSingle output arrangementsDifferential signalingDifferential transmission

The present invention discloses a system and method for reducing delay difference of differential transmission, a certain delay difference between waveforms of the P signal and N signal is generated through controlling delay adjustment to P signal or N signal of the differential signals and controlling delay adjustment value simultaneously, to compensate for the delay difference of differential transmission due to the channels. Therefore, the present invention can reduce the delay difference of differential transmission due to property discrepancy of board materials and delay inconsistency among pins of the connectors, and at same time simplify the scheme design.

Owner:HUAWEI TECH CO LTD

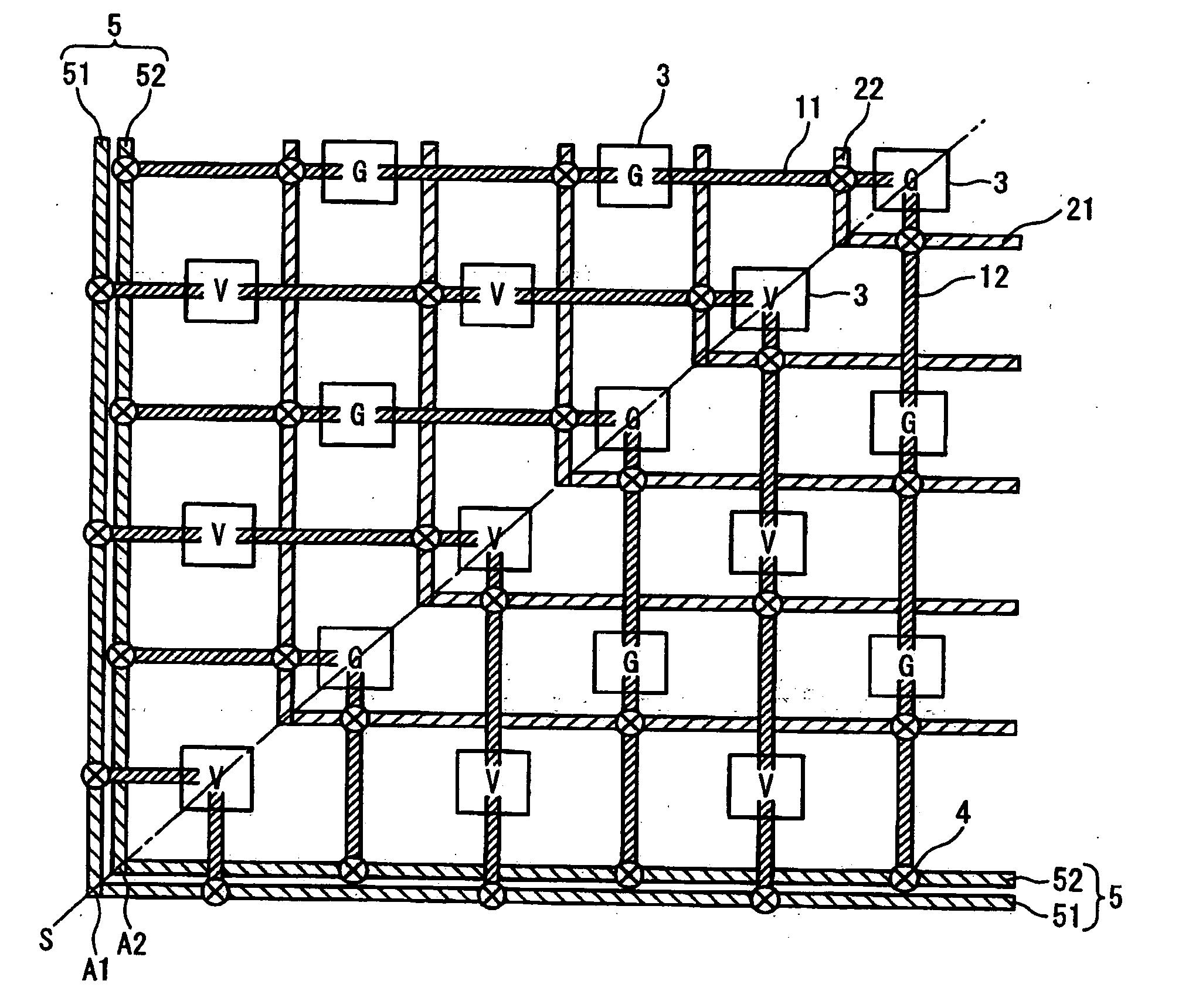

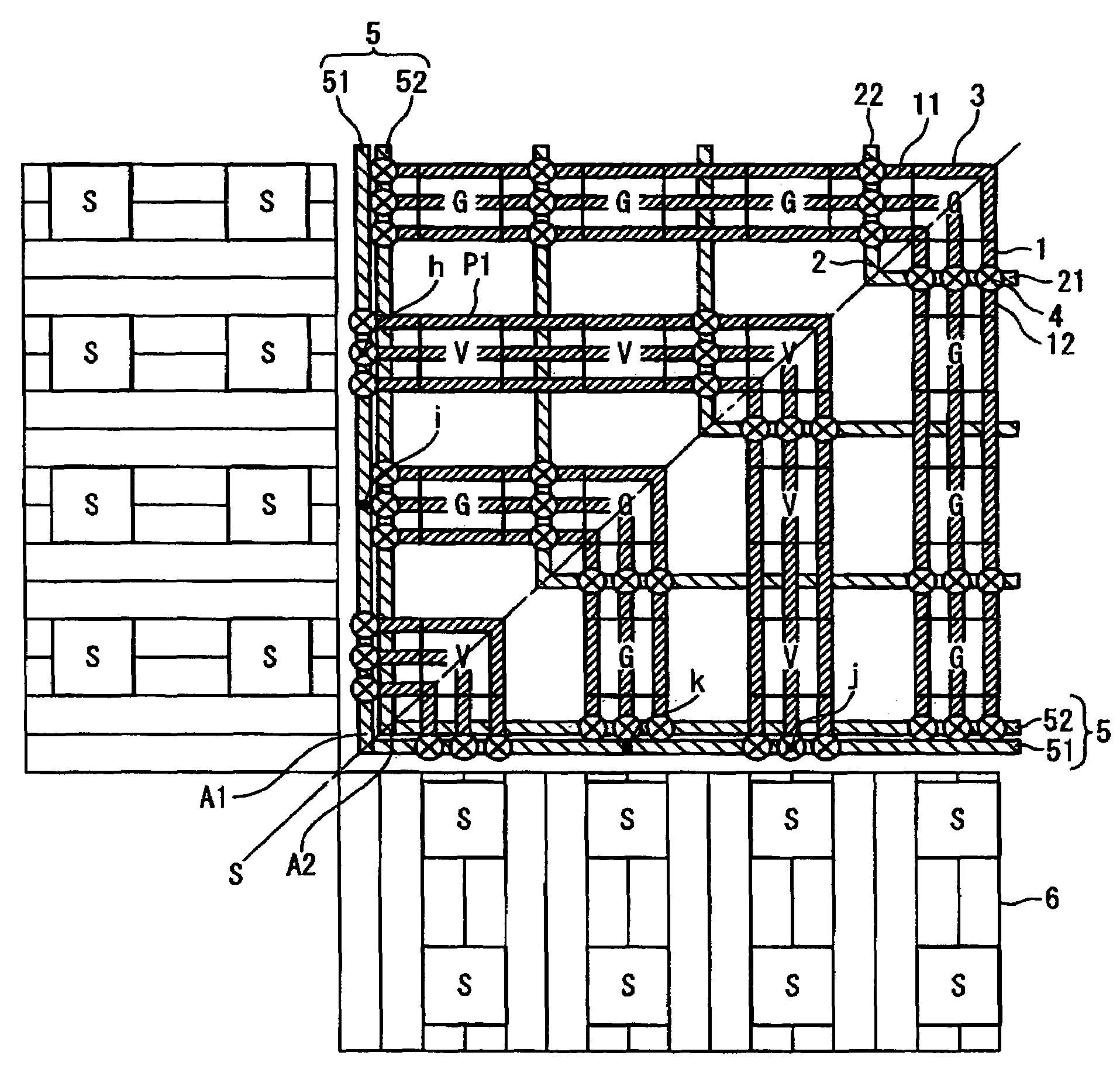

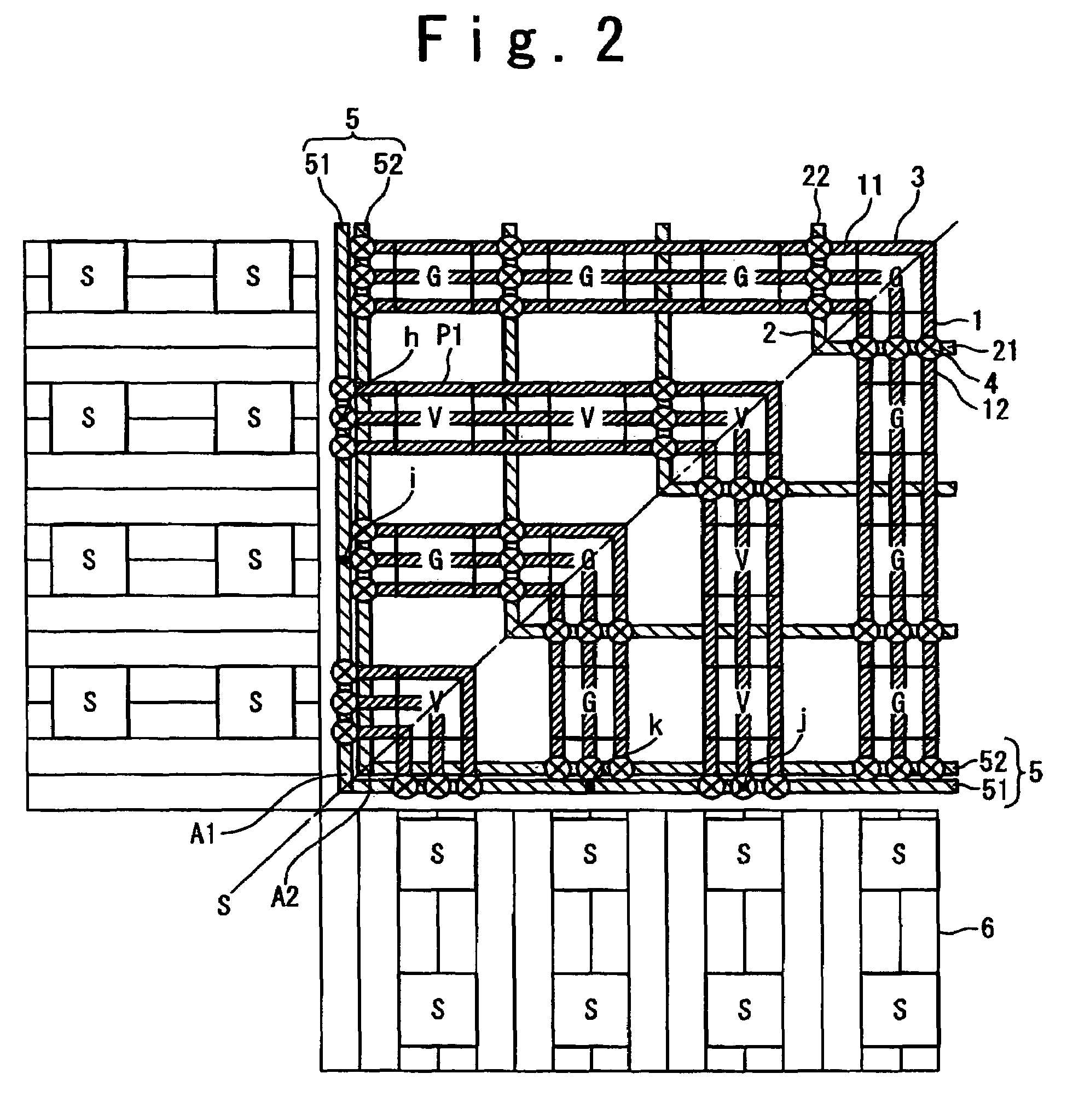

Flip-chip semiconductor device with improved power pad arrangement

InactiveUS20060157868A1Reduces circuit delay differenceSymmetrical distributionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSymmetry line

A semiconductor device is composed of a power supply interconnection extending from a certain starting point in a first direction and also extending from the starting point in a second direction orthogonal to the first direction, a plurality of power pads, and connecting interconnections providing electrical connection between the power supply interconnection and the power pads. The power supply interconnection, the power pads, and the connecting interconnections are arranged in a symmetrical manner with respect to a symmetry line crossing the starting point and extending in a direction at an angle of 45 degree to the first and second directions.

Owner:RENESAS ELECTRONICS CORP

Method for reducing delay difference of differential transmission and system thereof

InactiveUS20070121734A1Reduce delay differenceDelay differenceVoltage-current phase angleSingle output arrangementsEngineeringElectrical and Electronics engineering

The present invention discloses a system and method for reducing delay difference of differential transmission, a certain delay difference between waveforms of the P signal and N signal is generated through controlling delay adjustment to P signal or N signal of the differential signals and controlling delay adjustment value simultaneously, to compensate for the delay difference of differential transmission due to the channels. Therefore, the present invention can reduce the delay difference of differential transmission due to property discrepancy of board materials and delay inconsistency among pins of the connectors, and at same time simplify the scheme design.

Owner:HUAWEI TECH CO LTD

Flip-chip semiconductor device with improved power pad arrangement

InactiveUS7602058B2Reduce latency varianceSymmetrical distributionSemiconductor/solid-state device detailsSolid-state devicesSymmetry lineElectrical connection

A semiconductor device is composed of a power supply interconnection extending from a certain starting point in a first direction and also extending from the starting point in a second direction orthogonal to the first direction, a plurality of power pads, and connecting interconnections providing electrical connection between the power supply interconnection and the power pads. The power supply interconnection, the power pads, and the connecting interconnections are arranged in a symmetrical manner with respect to a symmetry line crossing the starting point and extending in a direction at an angle of 45 degree to the first and second directions.

Owner:RENESAS ELECTRONICS CORP

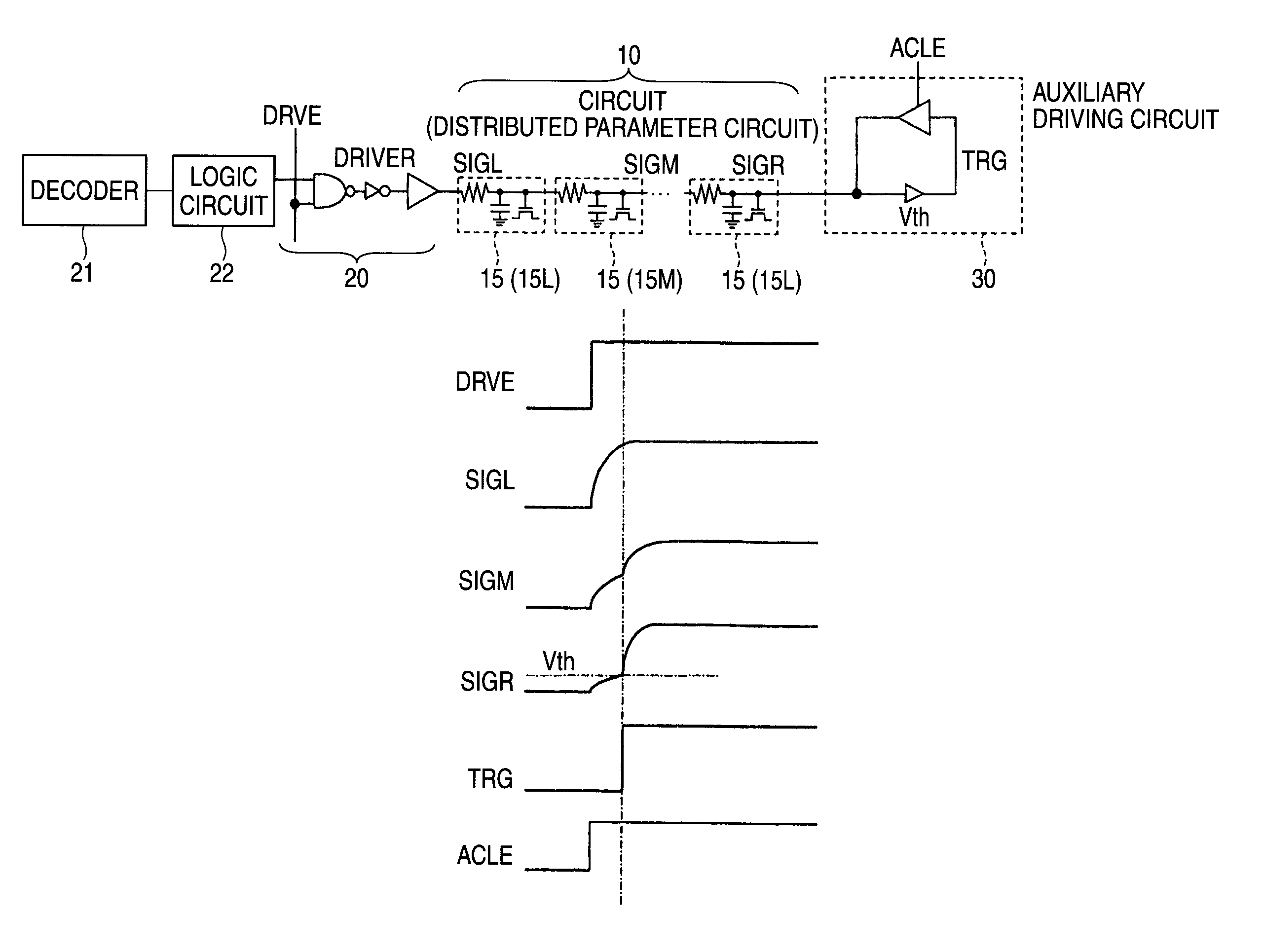

Semiconductor device with auxiliary driving circuit

ActiveUS8659324B2Reduce latency varianceReduce circuit sizeTelevision system detailsSingle output arrangementsDriver circuitAuxiliary circuit

A semiconductor device is provided which has a driving circuit operable to drive a circuit that has a delay, the semiconductor device including: an auxiliary driving circuit operable to accelerate drive of the driving circuit, which receives a drive signal of the driving circuit as an input signal.

Owner:SONY SEMICON SOLUTIONS CORP

Clock signal generating circuit, display panel module, imaging device, and electronic equipment

ActiveUS7880519B2Reduce latency varianceShort timeTelevision system detailsPulse automatic controlShift registerDigital delay line

Owner:JAPAN DISPLAY WEST

Mobile terminal with camera

InactiveUS7522665B2Enhance qualityMinimize processing delayPulse modulation television signal transmissionPicture reproducers using cathode ray tubesReal-time computingMuxponder

A video encoding / decoding apparatus includes an encoding unit which processes video data to be transmitted in unit of slice, a multiplexer / demultiplexer which multiplexes the video data from the encoding unit and de-multiplexes video data received through a communication channel, a decoding unit which processes video data from the multiplexer / demultiplexer in unit of slice. The video information delay is reduced less than or equal to the audio information delay such that there is no need for additional memory to delay the audio information so as to synchronize with the video information.

Owner:LG ELECTRONICS INC

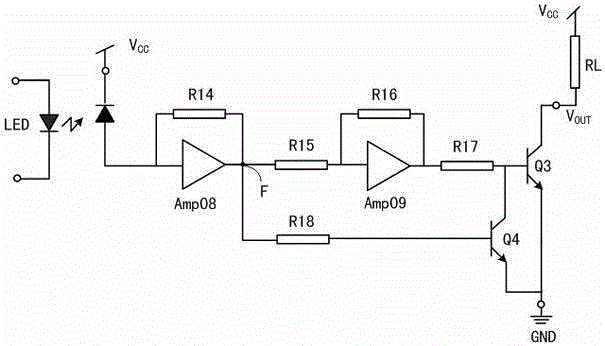

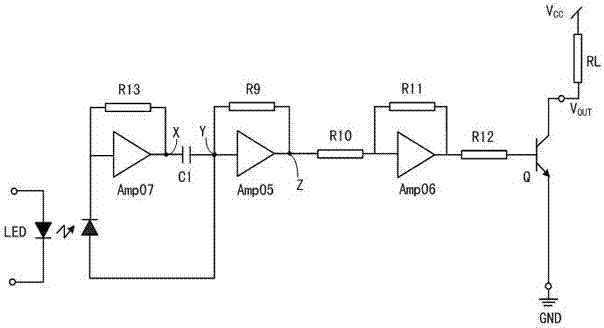

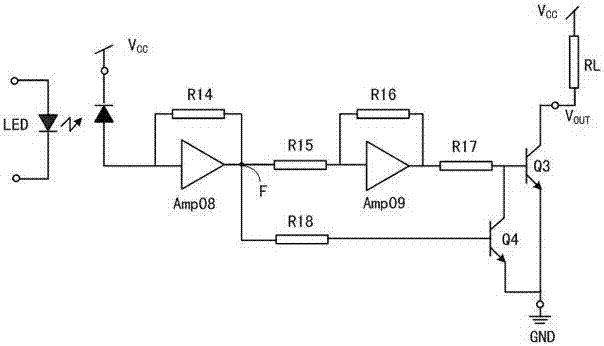

Light receiving circuit

ActiveCN105262548AAccelerated shutdownReduce transmission delayElectromagnetic receiversTime delaysPhotodiode

Provided is a light receiving circuit, comprising four operational amplifiers, eight coupling resistors, an output triode, an auxiliary triode and a photodiode which are connected according to the scheme to respectively form a main line and an auxiliary line, wherein the main line is used for controlling the turn-on / turn-off of triodes; the auxiliary line is used for rapidly discharging the charge stored on the base electrode of the output triode. The invention provides a new light receiving circuit which has the performance of low transmission time delay; meanwhile, the light receiving circuit can reduce the delay difference between two voltage control signals through a second anti-phase amplifier, thereby optimizing output waveforms of the light receiving circuit.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

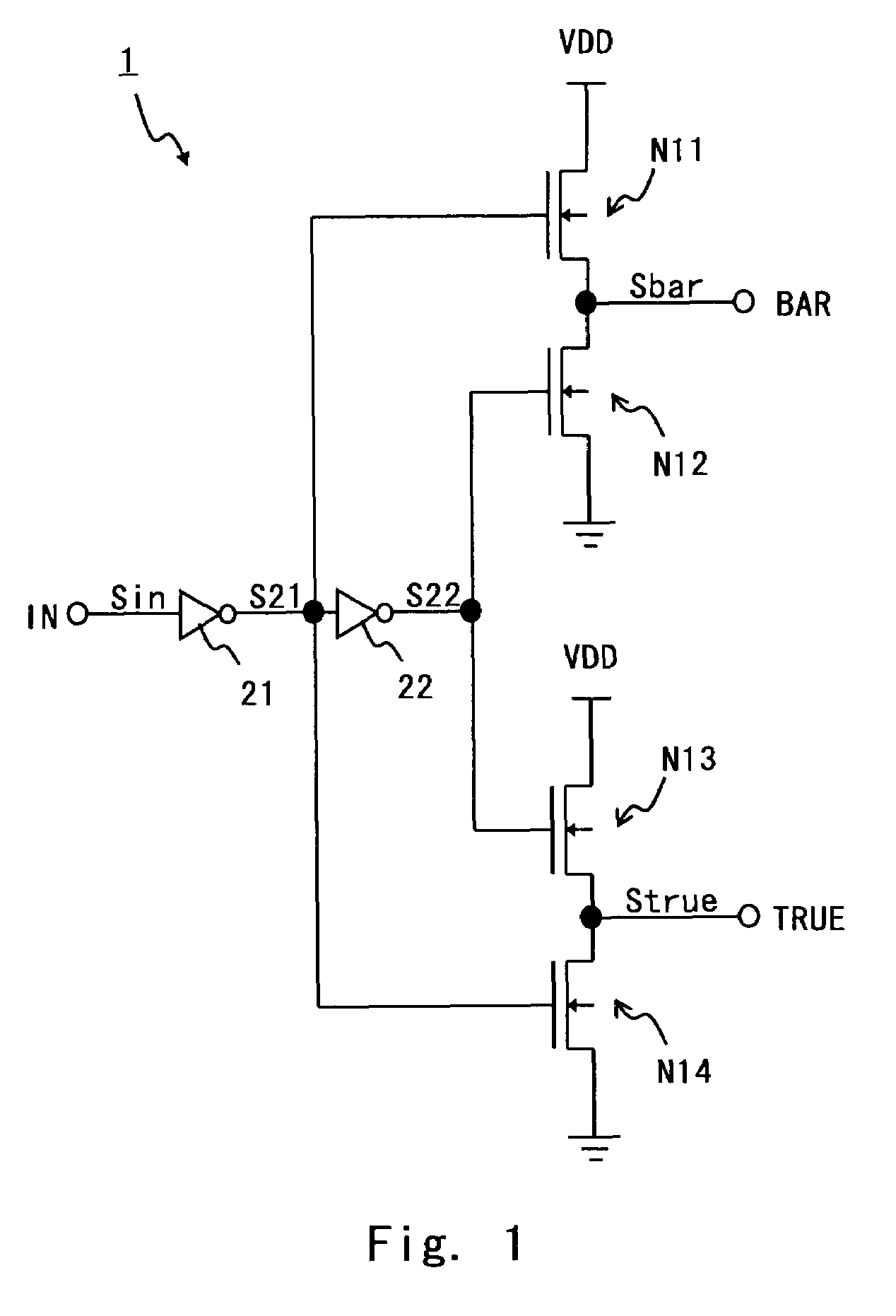

Complementary signal generating circuit

InactiveUS7652506B2Minimize difference in delayInhibition effectLogic circuits characterised by logic functionLogic circuits using gas-filled tubesElectricityEngineering

Owner:RENESAS ELECTRONICS CORP

Display panel and display device

ActiveCN109493739AShow uniformImprove the display effectIdentification meansElectricityDisplay device

The invention discloses a display panel and a display device and relates to the technical field of display. In the embodiment of the invention, by arranging first connecting lines A and first connecting lines B, namely when each first grid line is electrically connected with at least one first connecting line A transmitting grid electrode scanning signals and each second grid line is electricallyconnected with at least two first connecting line B transmitting same grid electrode scanning signals, the width of the first connecting lines A is set to be smaller than that of the first connectinglines B. Therefore, decrease of load difference of first grid lines and second grid lines can be facilitated, thus the delay difference of the first grid lines and the second grid lines is decreased,display of the display panel is more uniform, and accordingly the display effect of the display panel is improved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Contention resolution for CATV with reduced waiting time variance

InactiveCN1568602AReduce latency varianceTelevision system detailsColor television detailsTelecommunicationsComputerized system

A method and system of transmitting messages include requesting to submit a first request for transmitting a first message and to submit a second request for transmitting a second message until there is no first collision detected between the submitted first and second requests upon receipt of the submitted first and second requests. Before there is no first collision detected between the submitted first and second requests, it is requested to submit a third request for transmitting a third message and to submit a fourth request for transmitting a fourth message. However, requesting to re-submit the third request for transmitting the third message and to re-submit the fourth request for transmitting the fourth message if a second collision is detected between the submitted third and the second requests upon receipt thereof is delayed until there is no first collision detected between the submitted first and second requests.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Clock signal generating circuit, display panel module, imaging device, and electronic equipment

InactiveUS7944259B2Reduce latency varianceAccurate detectionPulse automatic controlCathode-ray tube indicatorsPhase differenceDelayed time

A delay synchronization loop type clock signal generating circuit includes: a delay line for delaying a first clock signal by a set delay amount and outputting; a delay time length setting unit for setting a delay time length of the delay line, based on phase difference between a second clock signal output from an output terminal and the first clock signal; a phase relation determining unit for determining whether or not the phase relation of the first clock signal and the second clock signal are in a particular phase relation; and a phase inversion / non-inversion unit for performing phase inversion of the first clock signal on a transmission path including the delay line, at the time of detecting the particular phase relation.

Owner:JAPAN DISPLAY WEST

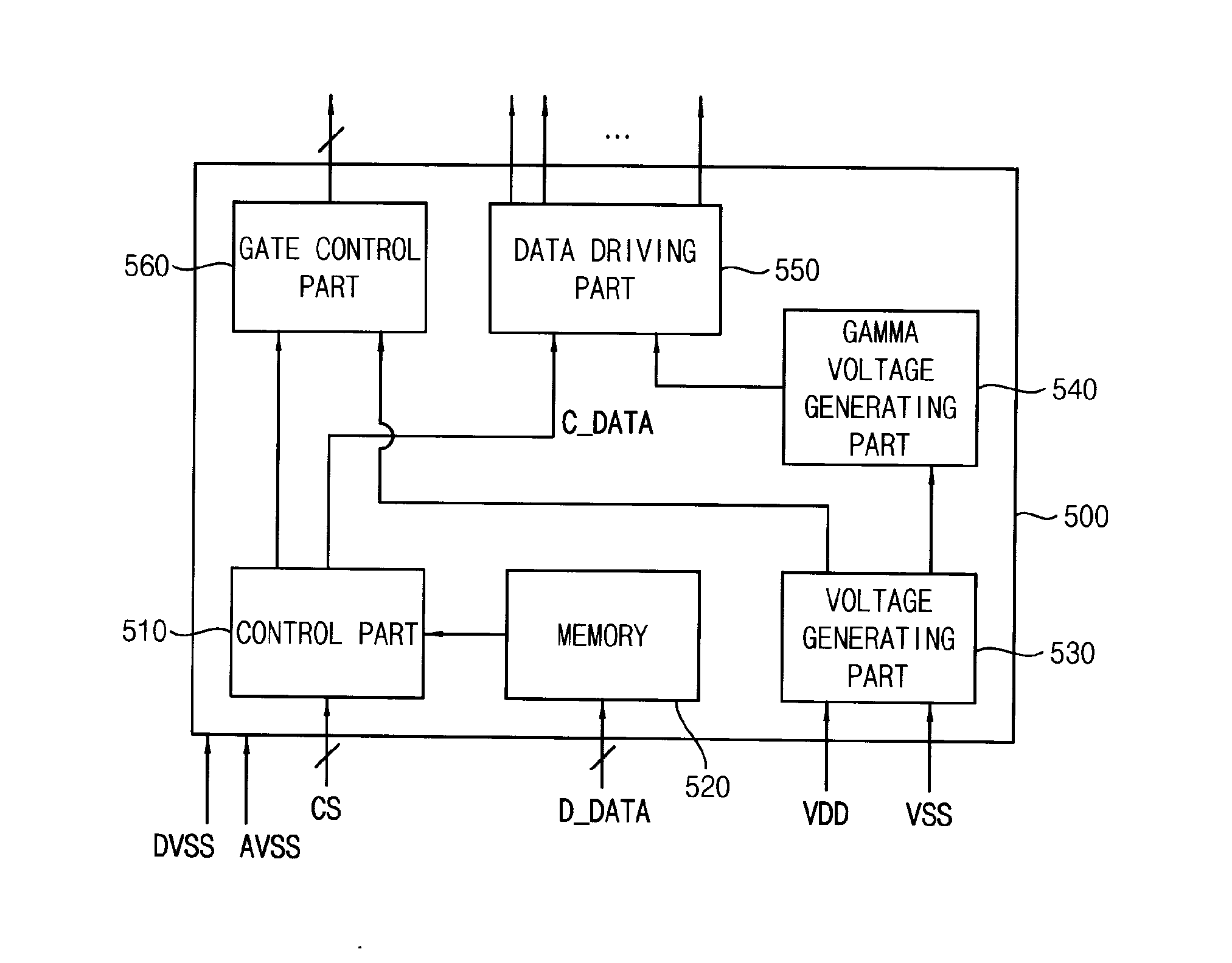

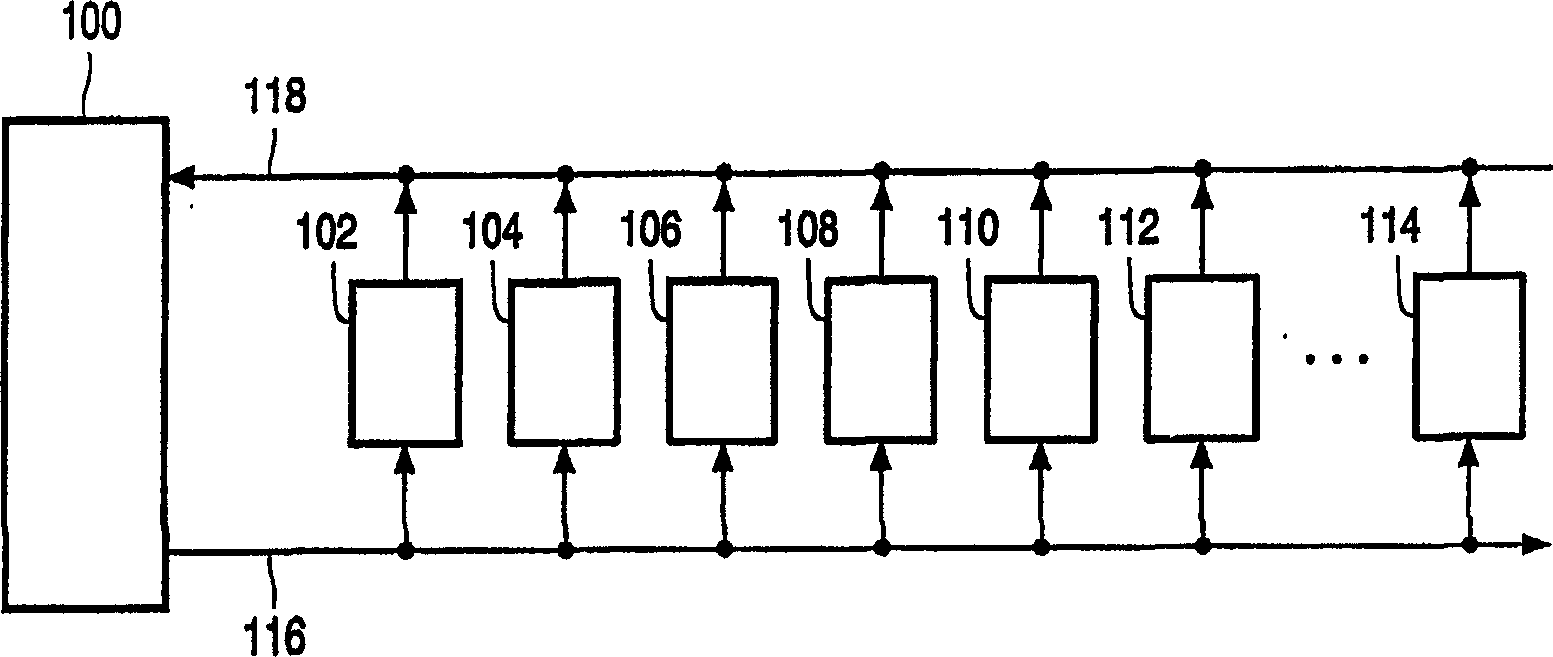

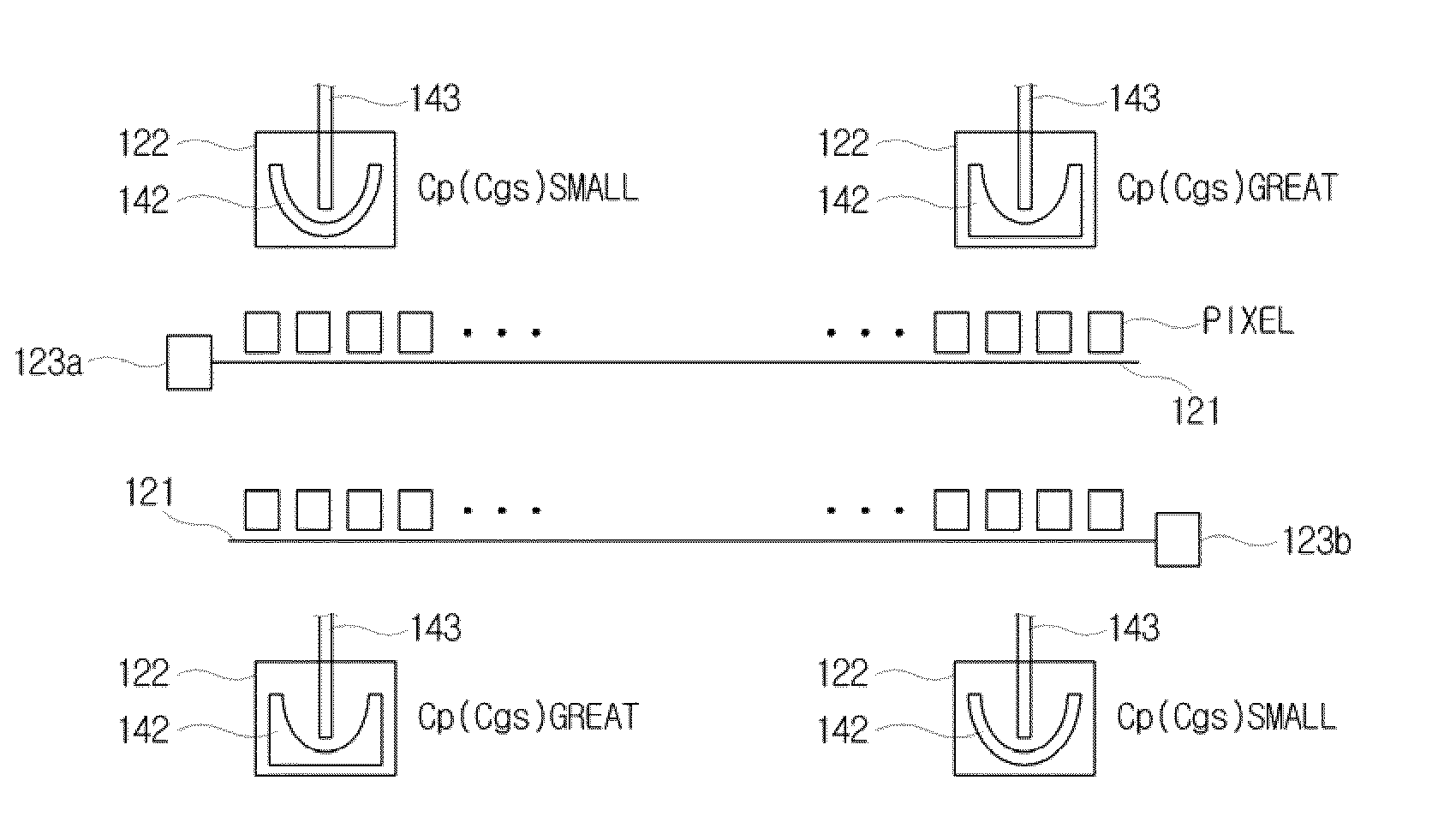

Liquid crystal display device

ActiveUS8248550B2Uniform brightnessReduce latency varianceStatic indicating devicesNon-linear opticsLiquid-crystal displayParasitic capacitance

A liquid crystal display device includes a first substrate which comprises a plurality of pixels where a thin film transistor and a pixel electrode electrically connected to the thin film transistor are formed, the first substrate including a gate line and a data line which insulatingly intersect each other; and a gate driver which applies a gate driving signal to the gate line, the thin film transistor including a gate electrode which is connected to the gate line; a source electrode which is connected to the data line; and a drain electrode which is connected to the pixel electrode, and the pixels being decreased in a value of Cp / (Cp+Clc+Cst) as going toward the gate driver (where, Cp: a sum of parasitic capacity between the gate electrode and the source electrode and parasitic capacity between the gate electrode and the drain electrode, Clc: liquid crystal capacity, and Cst: storage capacity).

Owner:SAMSUNG DISPLAY CO LTD

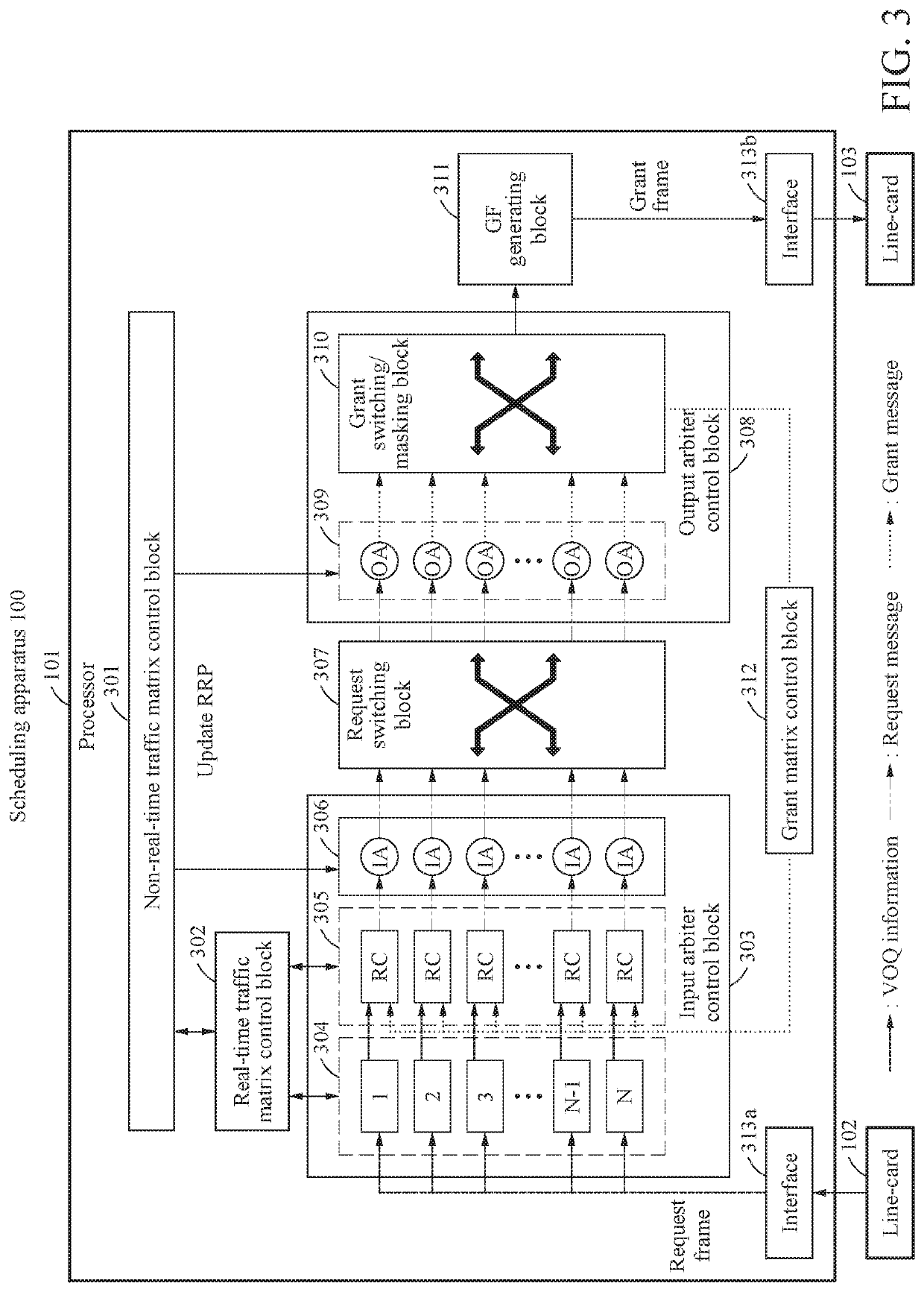

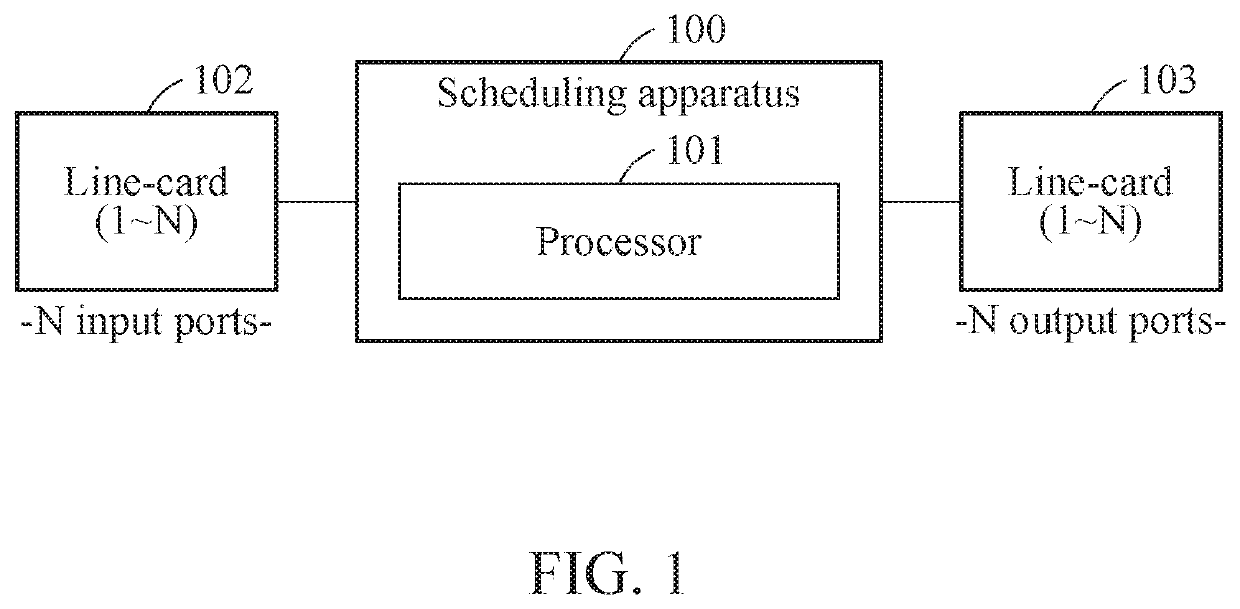

Centralized scheduling apparatus and method considering non-uniform traffic

ActiveUS20210152493A1Improve network efficiencyImproving traffic delayData switching networksComputer networkEngineering

The present disclosure relates to a centralized scheduling method and apparatus that considers non-uniform traffic and, more particularly, to a centralized scheduling method and apparatus for performing effective scheduling based on a characteristic of non-uniform traffic in consideration of a traffic distribution in a data center network.

Owner:ELECTRONICS & TELECOMM RES INST

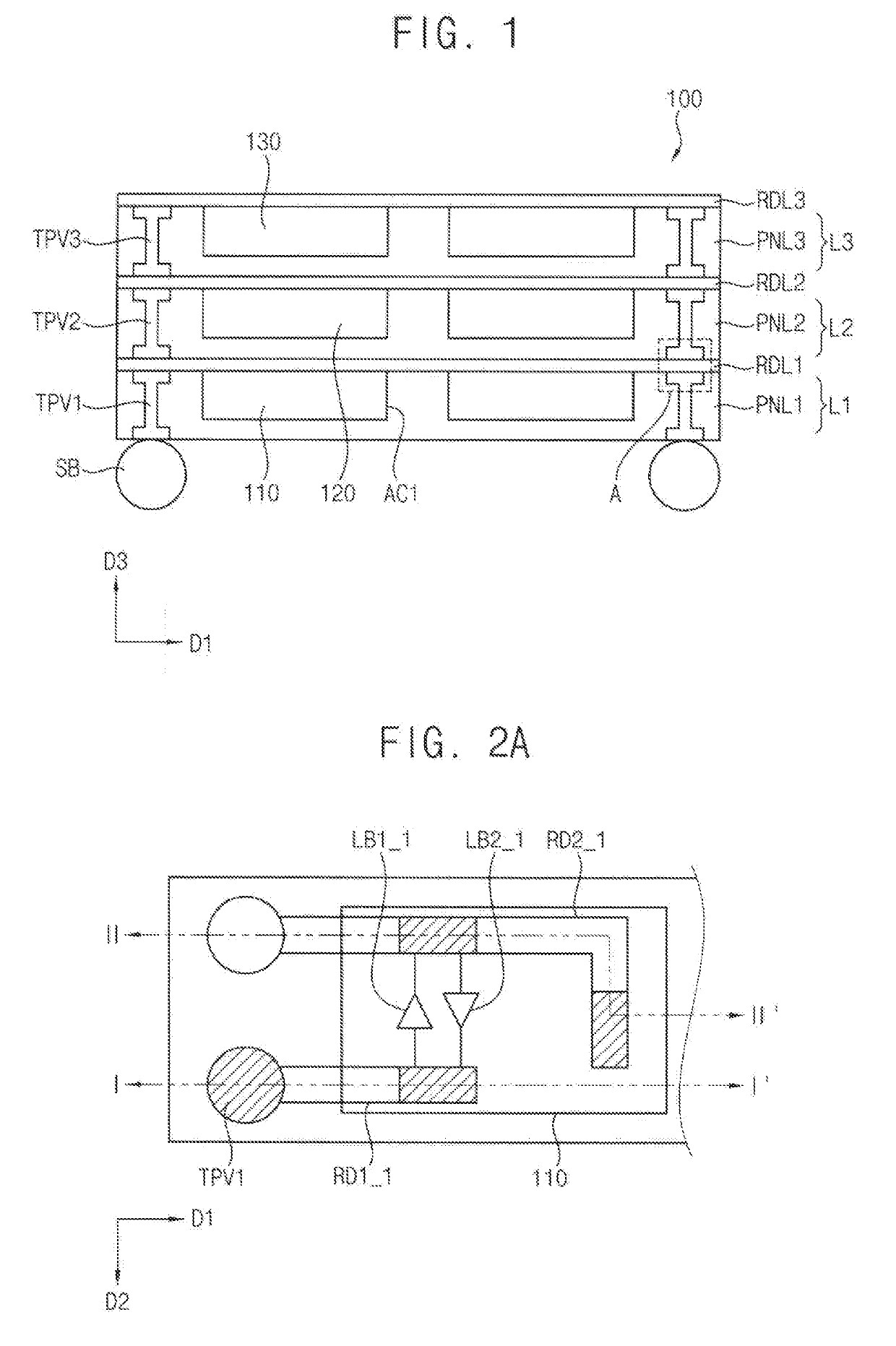

Semiconductor package and manufacturing method thereof

ActiveUS20190189592A1Reduce loadEasy loadingSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package includes a first layer including a first semiconductor chip and a first through via, a first redistribution layer disposed on a surface of the first layer, and including a first-first wiring and a second-first wiring, and a second layer including a second semiconductor chip, and stacked on the first layer. The first semiconductor chip includes a first-first buffer, and the first-first buffer is electrically connected between the first-first wiring and the second-first wiring.

Owner:SAMSUNG ELECTRONICS CO LTD

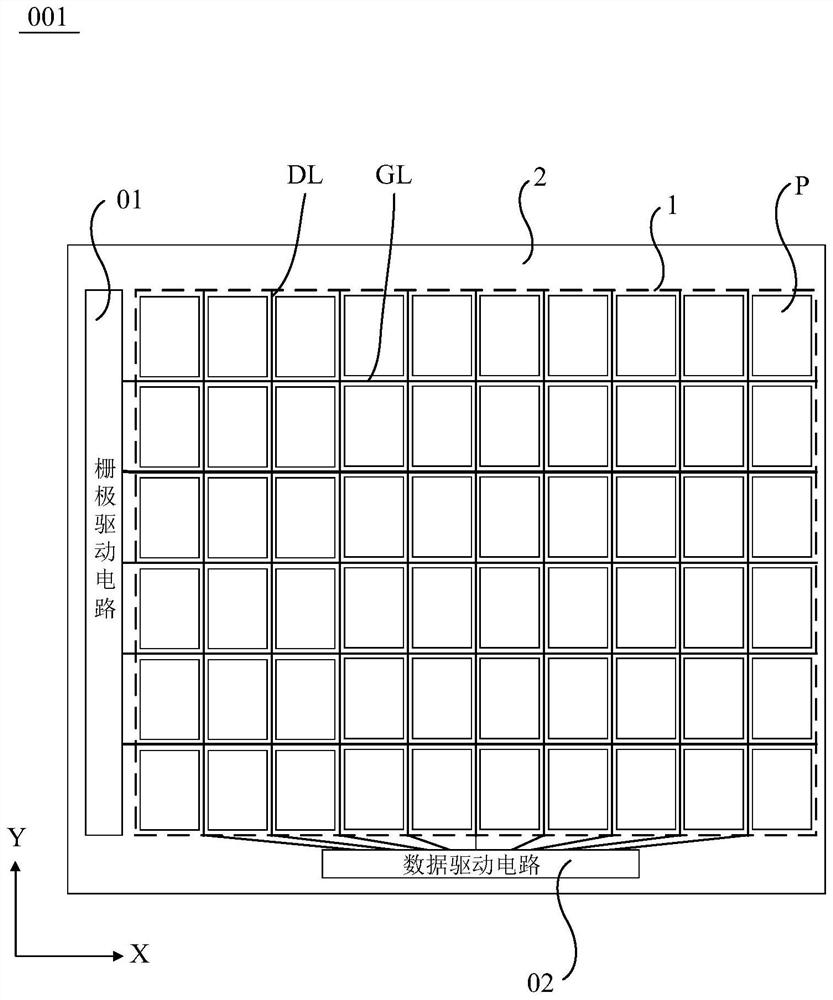

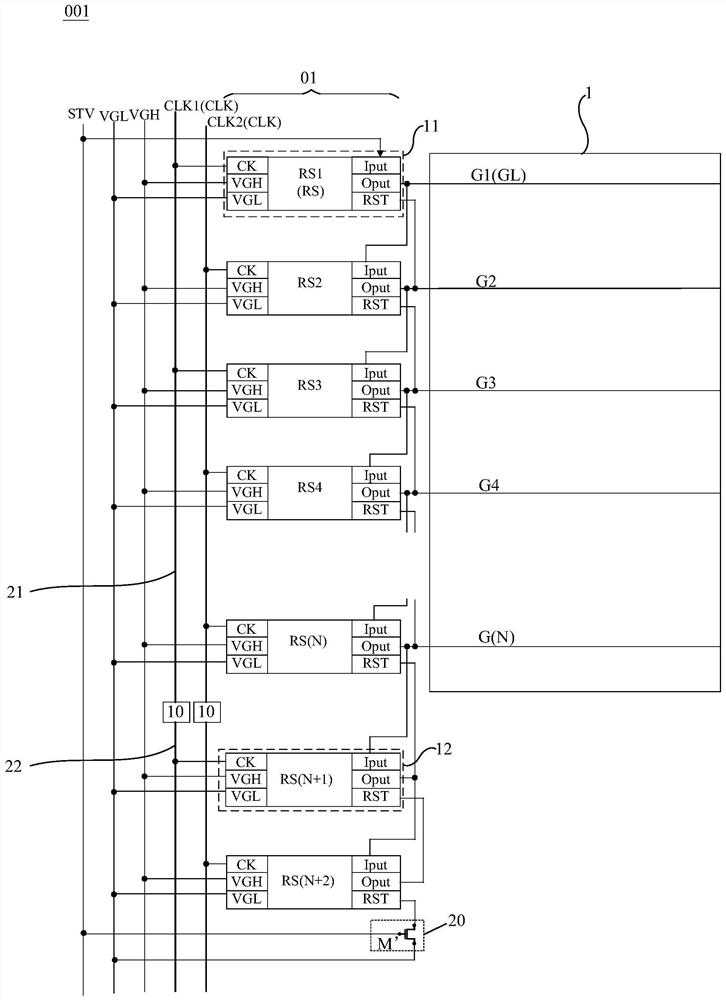

Display panel and display device

ActiveCN110189724BImprove picture qualityLower latencyStatic indicating devicesShift registerDisplay device

Embodiments of the present invention provide a display panel and a display device, which relate to the field of display technology and can reduce the delay difference between the output signal of the effective GOA unit and the output signal of the Dummy GOA unit; in the display panel, the gate drive circuit includes: The set multi-level effective shift register, and the virtual shift register after the last effective shift register; the multi-level effective shift register is connected with multiple gate lines; the clock signal line in the display panel includes: an effective clock signal line and the virtual clock signal line; the effective clock signal line is connected to the virtual clock signal through the connection control circuit; the connection control circuit is configured to: before the output scanning signal of the last effective shift register, control the effective clock signal line and the virtual clock signal The lines are disconnected; and under the control of the scanning signal output by the last effective shift register, the electrical connection between the effective clock signal line and the virtual clock signal line is controlled.

Owner:BOE TECH GRP CO LTD +1

Display substrate and display apparatus having the display substrate

ActiveUS9412326B2Reduce noiseLower resistanceStatic indicating devicesSolid-state devicesDriver circuitFlexible circuits

A display substrate includes a pixel electrode disposed in a display area, a first pad part disposed in a first area of a peripheral area which is disposed adjacent to the display area, where the first pad part is electrically connected to a driver circuit, a second pad part disposed in a second area of the peripheral area facing the first pad part, where the second pad part is electrically connected to a flexible circuit film which transfers a transmission signal to the driver circuit, and a connection line part disposed in an area between the first and second pad parts as a vertical line type, where the connection line part connects the first and second pad parts to each other.

Owner:SAMSUNG DISPLAY CO LTD

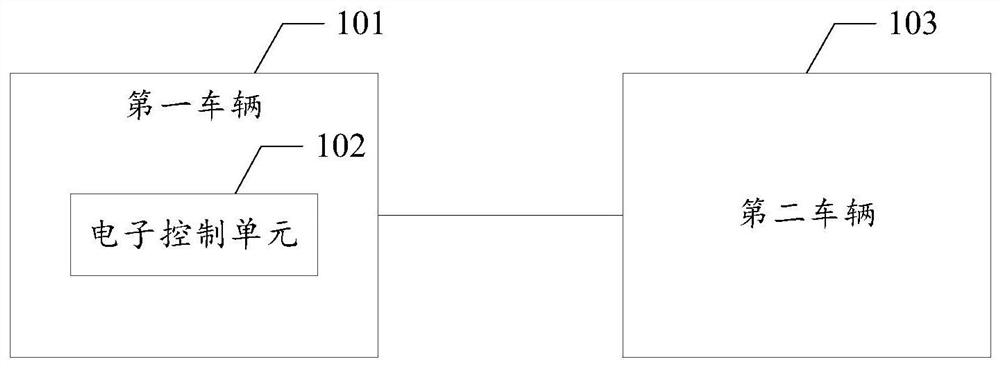

A displacement filling method and related device

ActiveCN110837089BEfficient fillingReduce latency varianceElectromagnetic wave reradiationThree-dimensional object recognitionRelative displacementPoint cloud

Owner:NEUSOFT REACH AUTOMOBILE TECH (SHENYANG) CO LTD

Centralized scheduling apparatus and method considering non-uniform traffic

The present disclosure relates to a centralized scheduling method and apparatus that considers non-uniform traffic and, more particularly, to a centralized scheduling method and apparatus for performing effective scheduling based on a characteristic of non-uniform traffic in consideration of a traffic distribution in a data center network.

Owner:ELECTRONICS & TELECOMM RES INST

light receiving circuit

ActiveCN105262548BShort transmission delayImprove output waveformElectromagnetic receiversAudio power amplifierDelayed time

A light receiving circuit is composed of 4 operational amplifiers, 8 matching resistors, output transistors, auxiliary transistors and photodiodes; after the aforementioned components are connected according to the scheme of the present invention, a main circuit and an auxiliary circuit are respectively formed, and the main circuit is used for Control the on / off of the output triode, and the auxiliary circuit is used to quickly discharge the charge stored on the base of the output triode; the beneficial technical effect of the present invention is: a light receiving circuit with a new structure is proposed, the light receiving circuit It has the performance of low transmission delay time, and at the same time, the light receiving circuit can also reduce the delay difference between the two voltage control signals through the second inverting amplifier, so that the output waveform of the light receiving circuit can be optimized.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com