Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Reduce GIDL" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

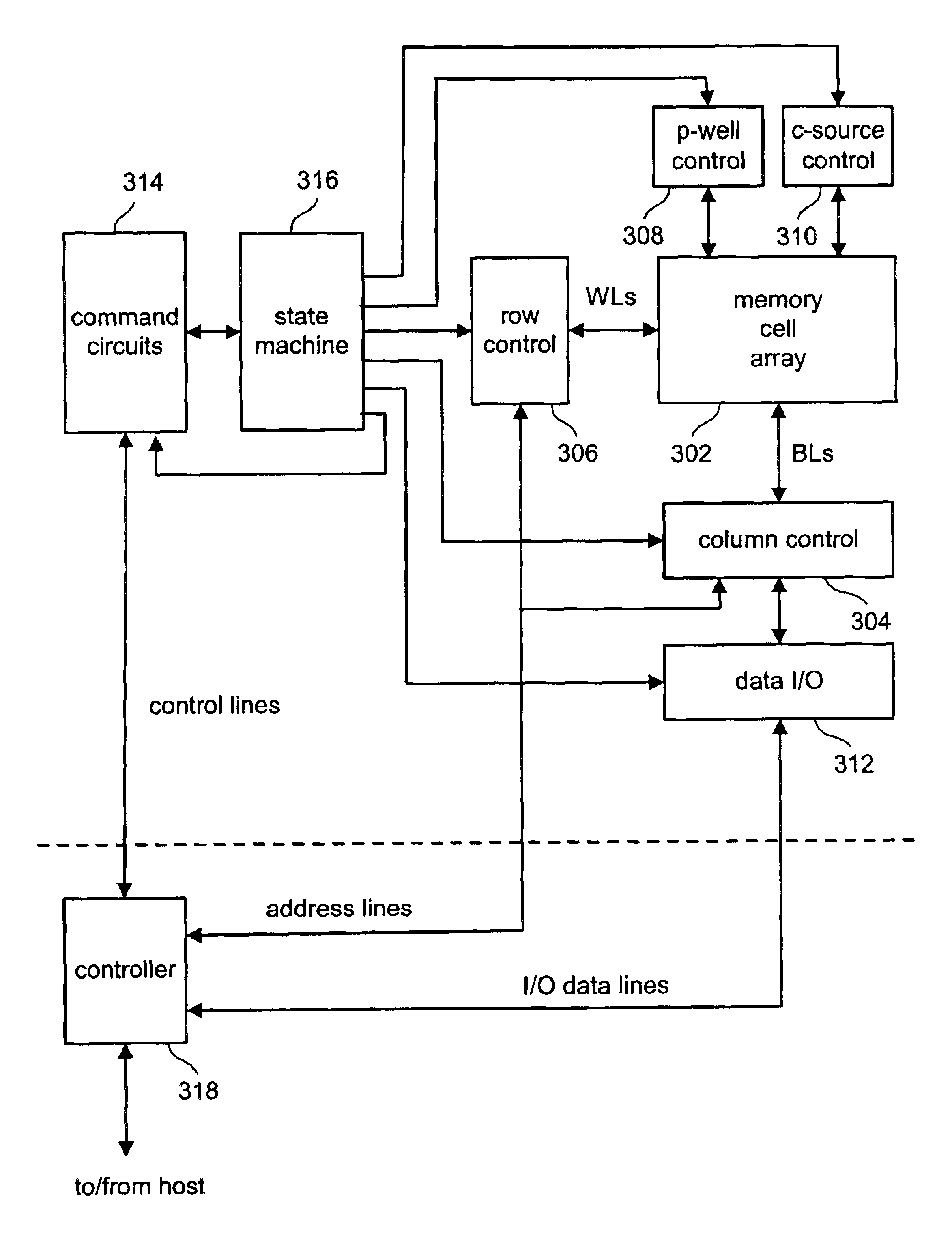

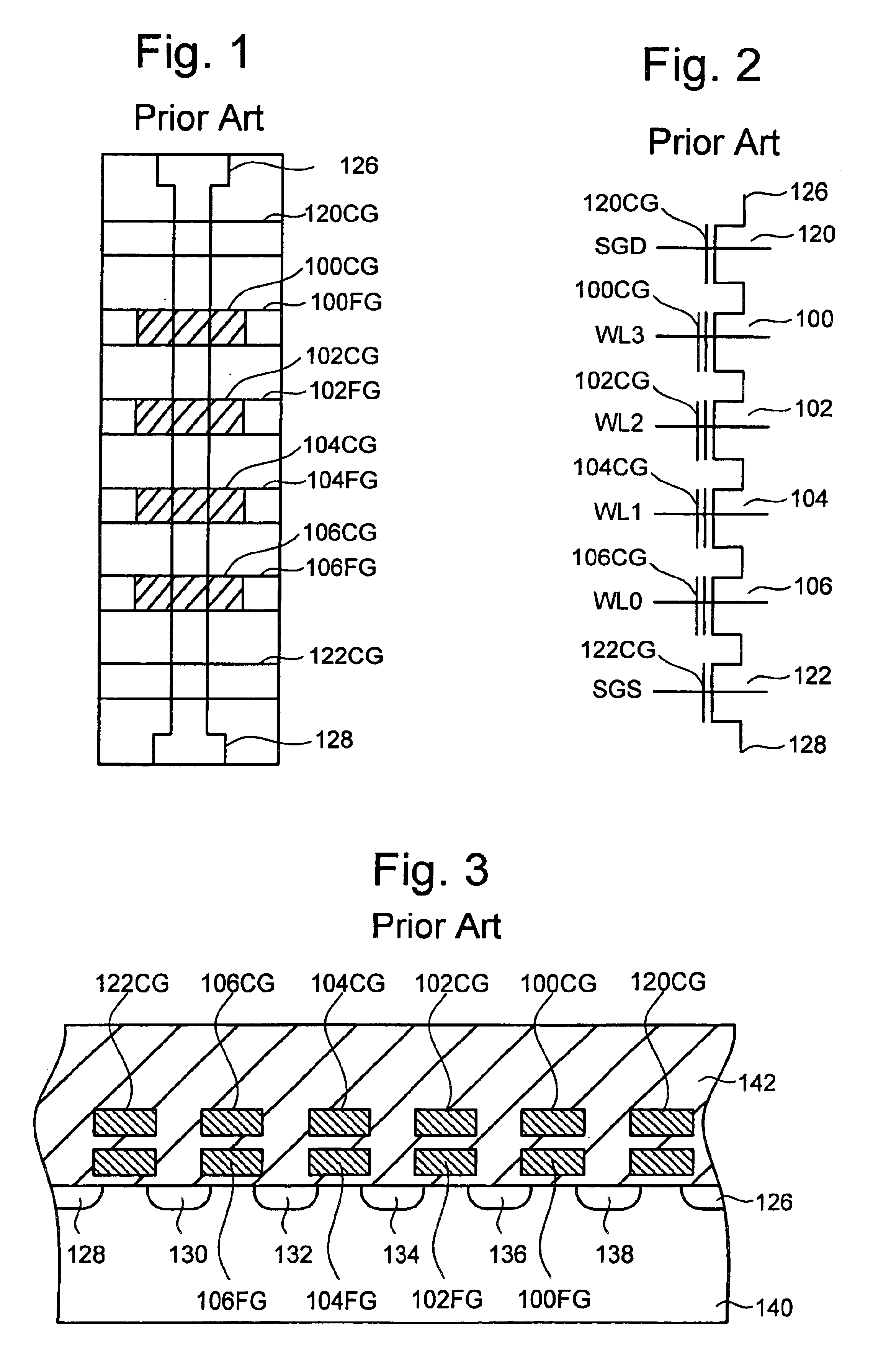

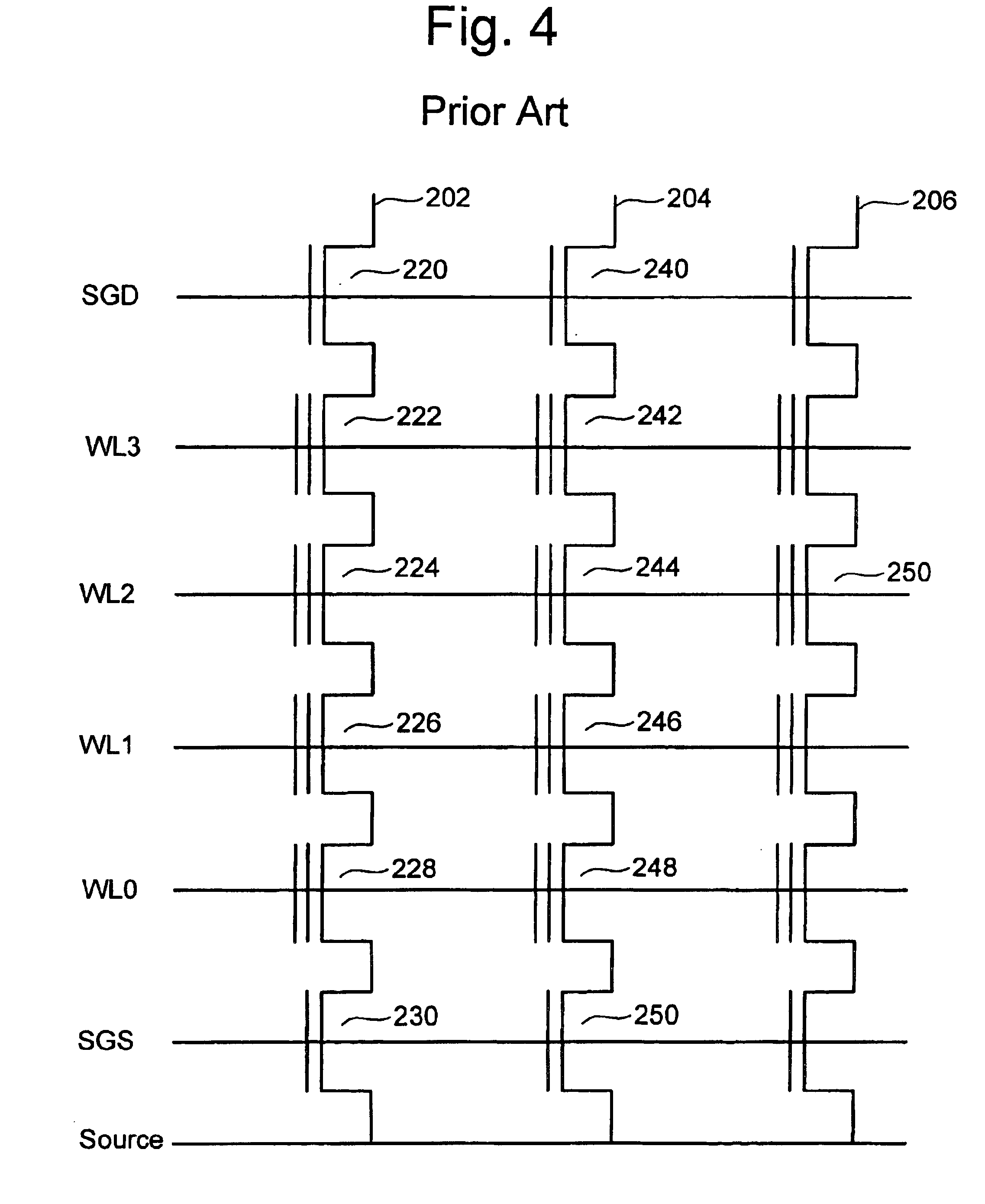

Source side self boosting technique for non-volatile memory

InactiveUS6859397B2Improve performanceMinimize program disturbRead-only memoriesDigital storagePre-chargeProgramming process

A non-volatile semiconductor memory system (or other type of memory system) is programmed in a manner that avoids program disturb. In one embodiment that includes a flash memory system using a NAND architecture, program disturb is avoided by increasing the channel potential of the source side of the NAND string during the programming process. One exemplar implementation includes applying a voltage (e.g. Vdd) to the source contact and turning on the source side select transistor for the NAND sting corresponding to the cell being inhibited. Another implementation includes applying a pre-charging voltage to the unselected word lines of the NAND string corresponding to the cell being inhibited prior to applying the program voltage.

Owner:SANDISK TECH LLC

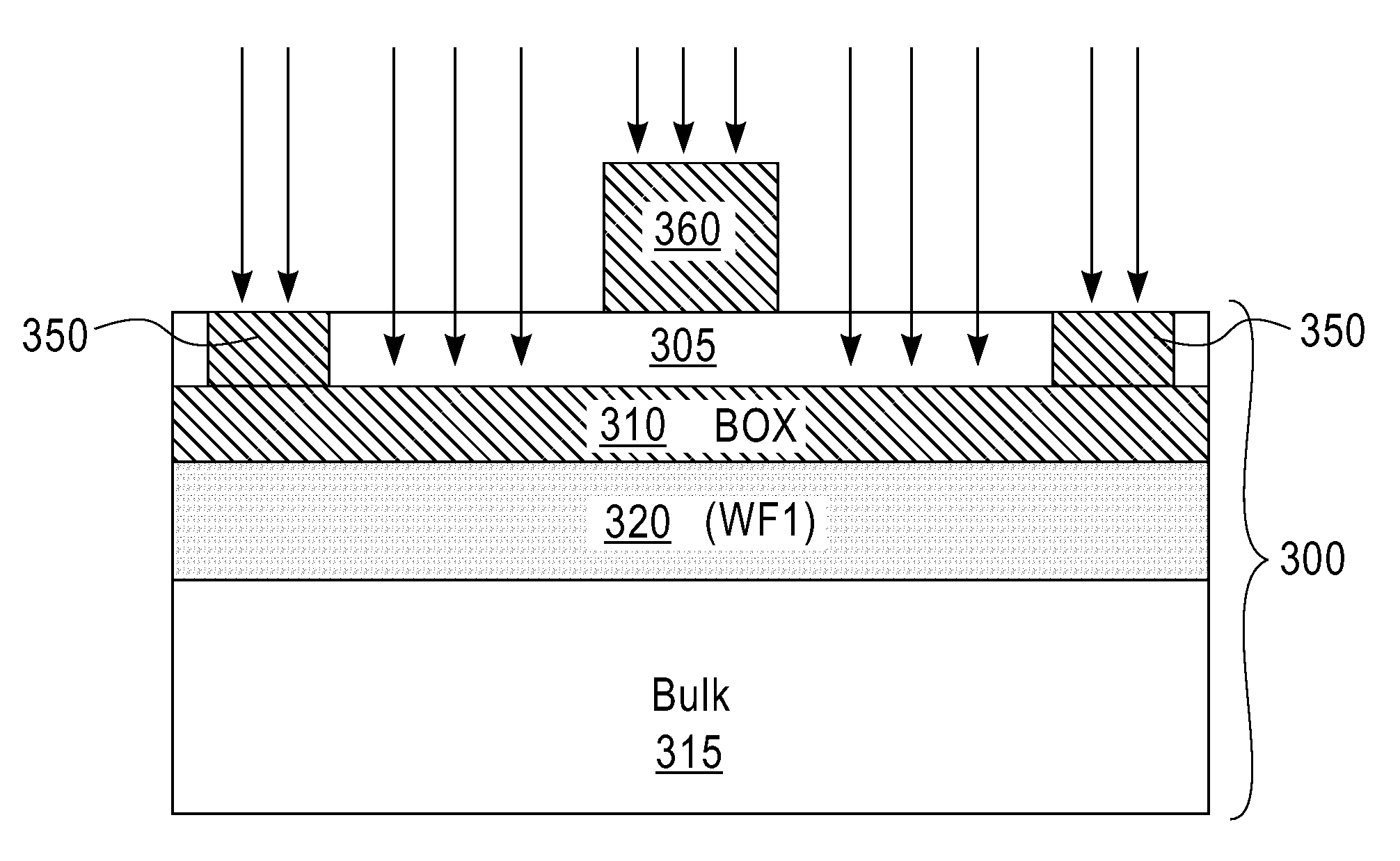

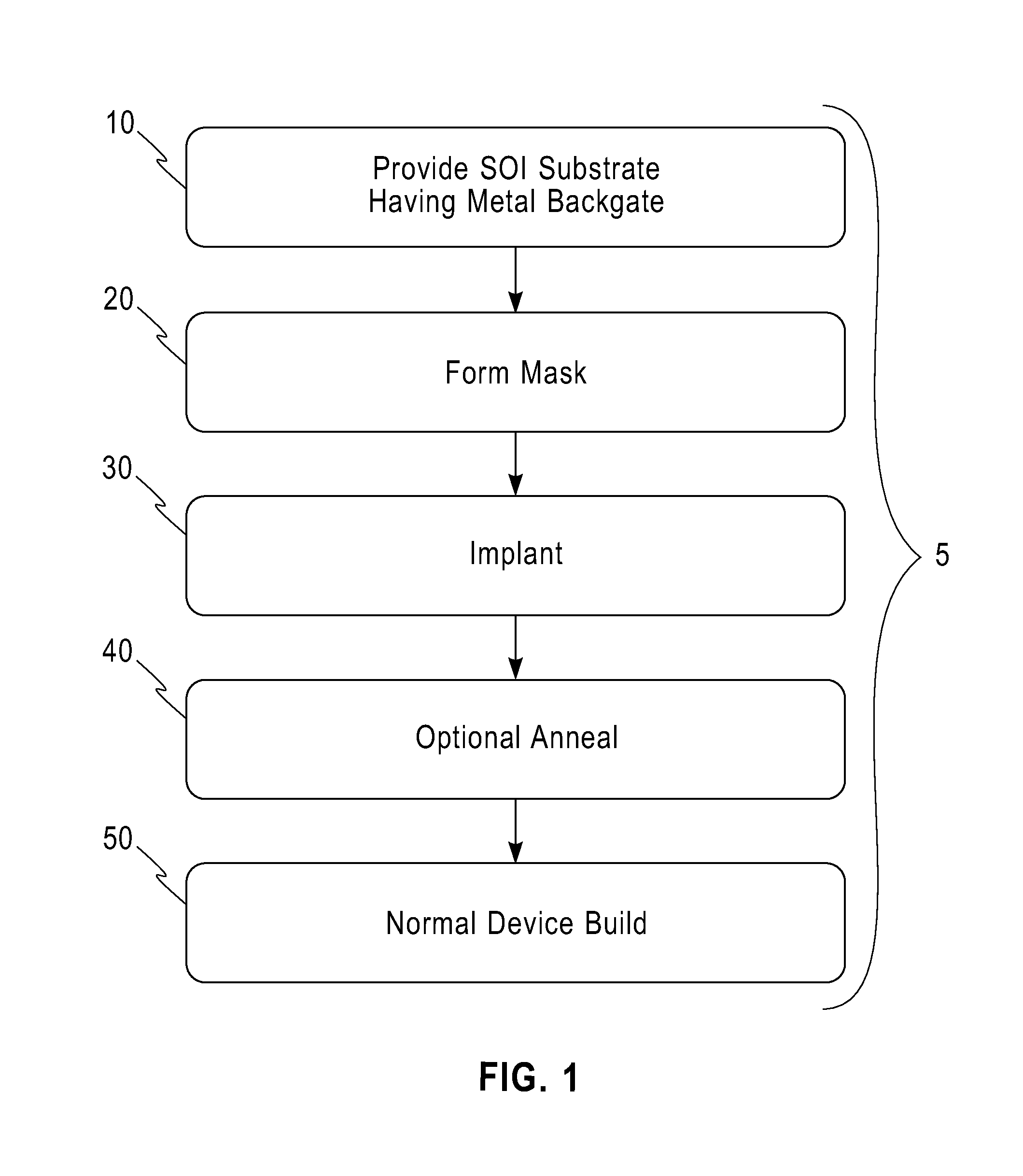

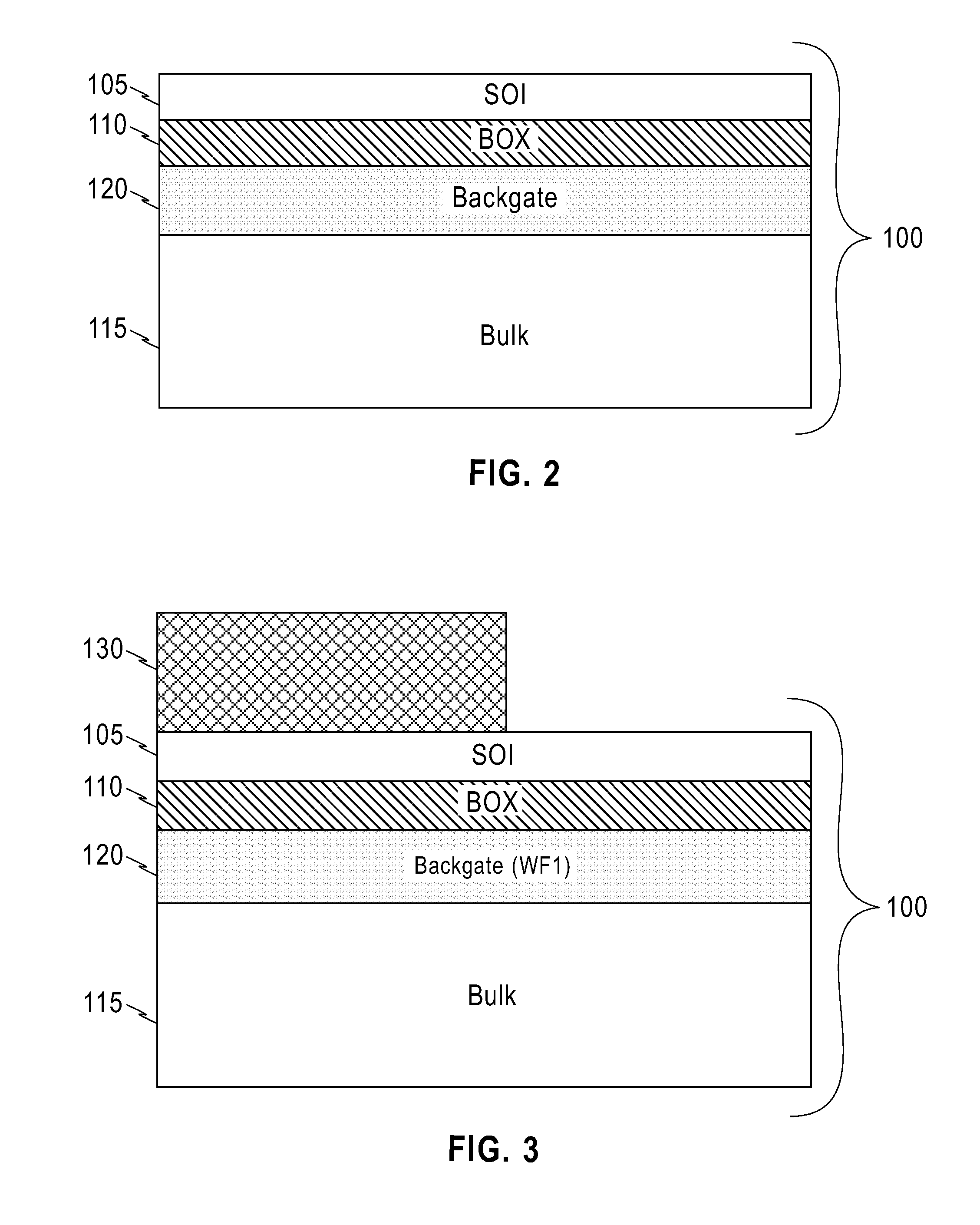

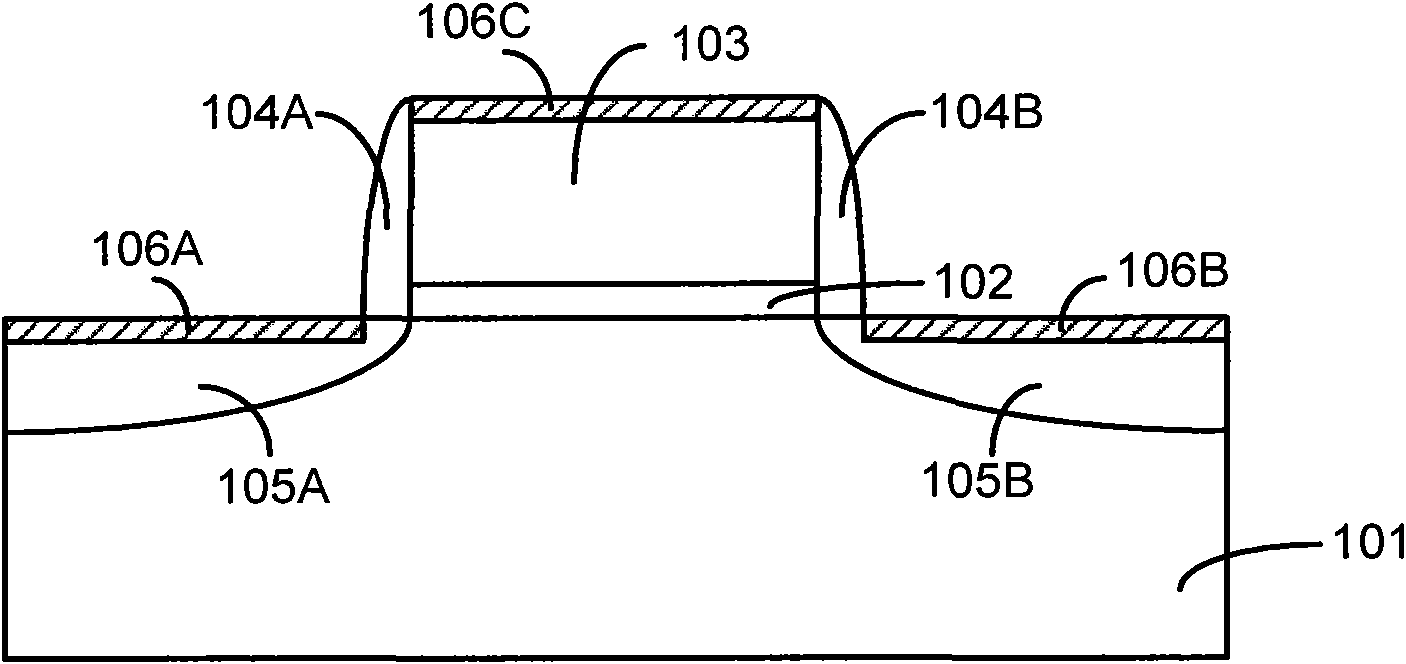

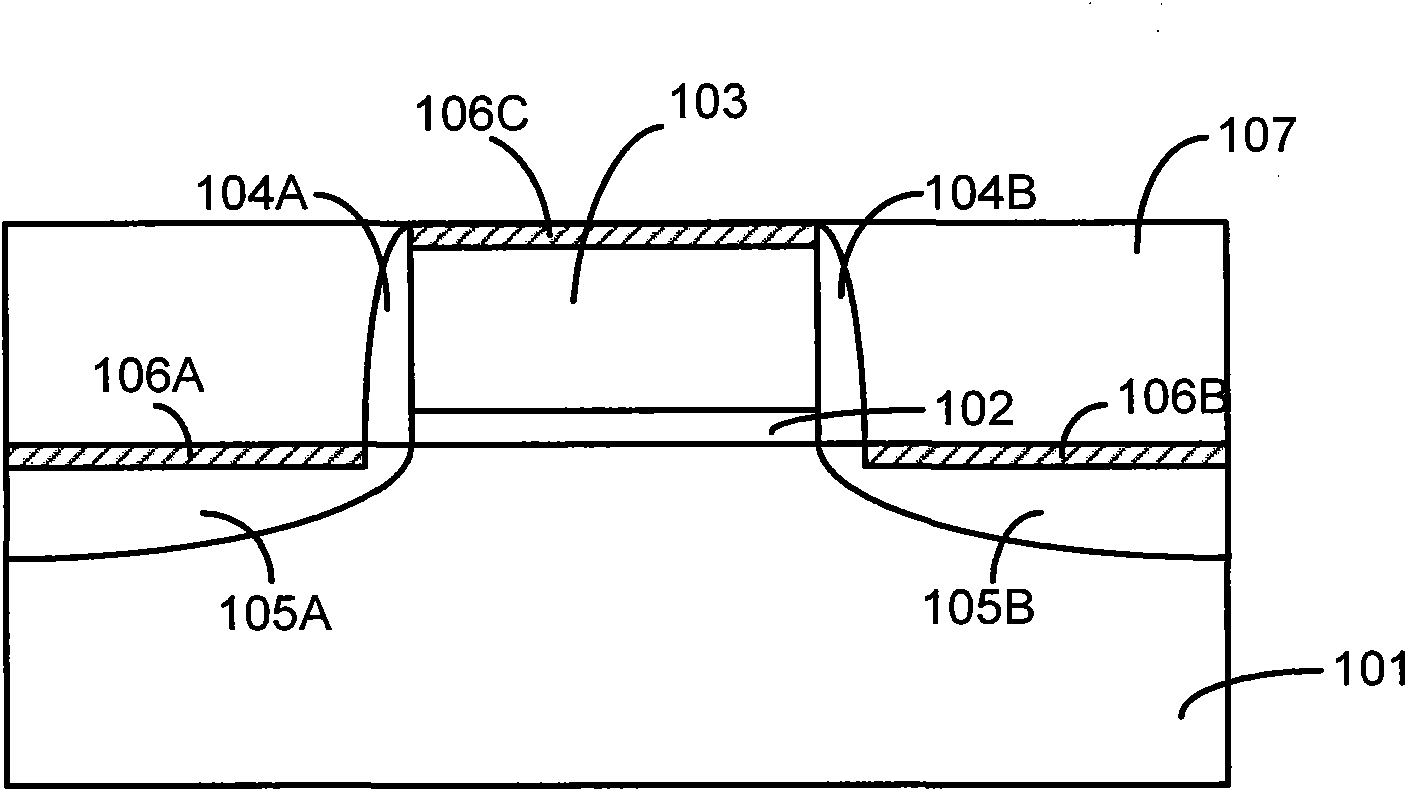

Mosfet with work function adjusted metal backgate

ActiveUS20130214356A1Limited power managementImproved backgate series resistanceTransistorSolid-state devicesMOSFETWork function

Owner:GLOBALFOUNDRIES US INC

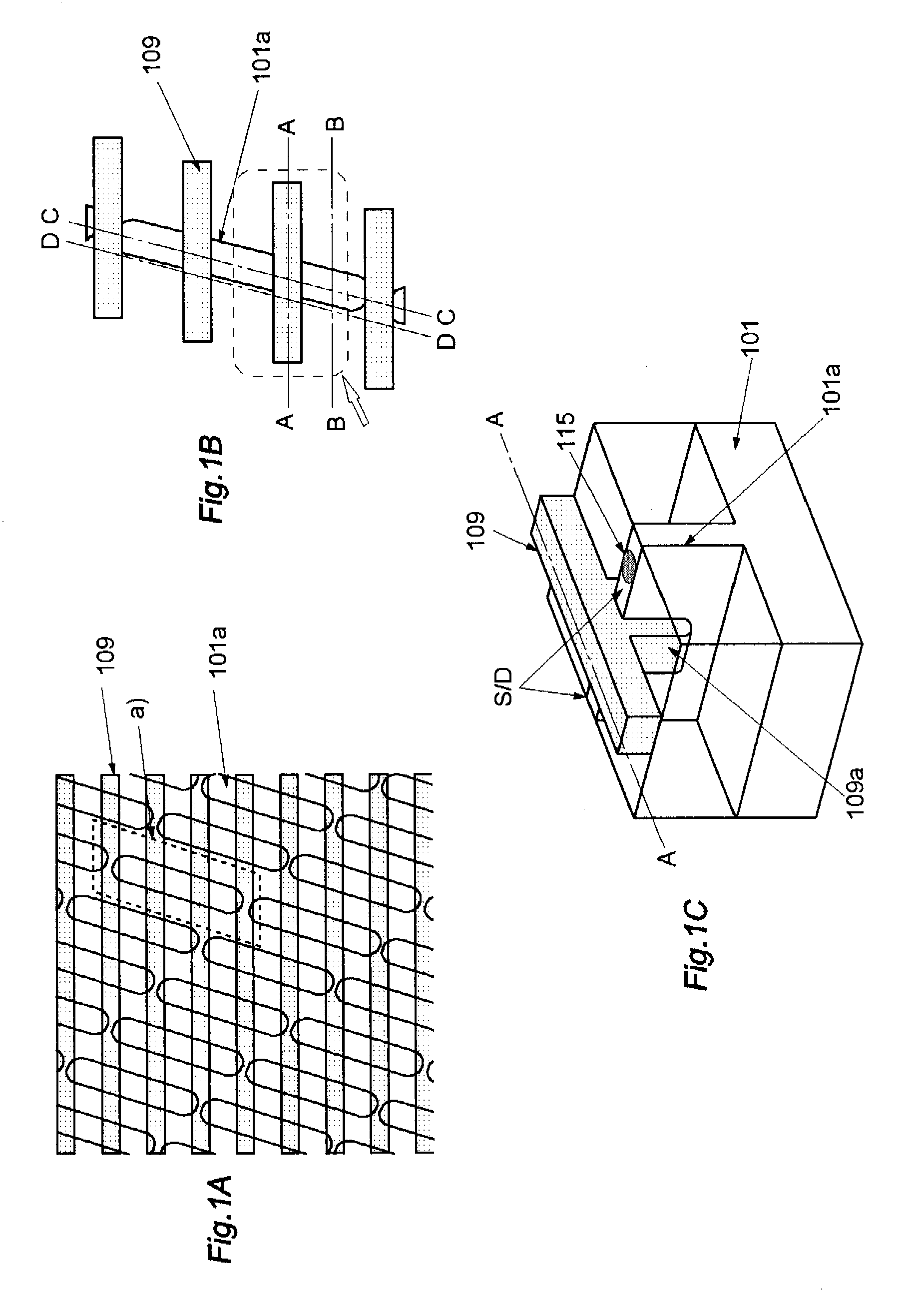

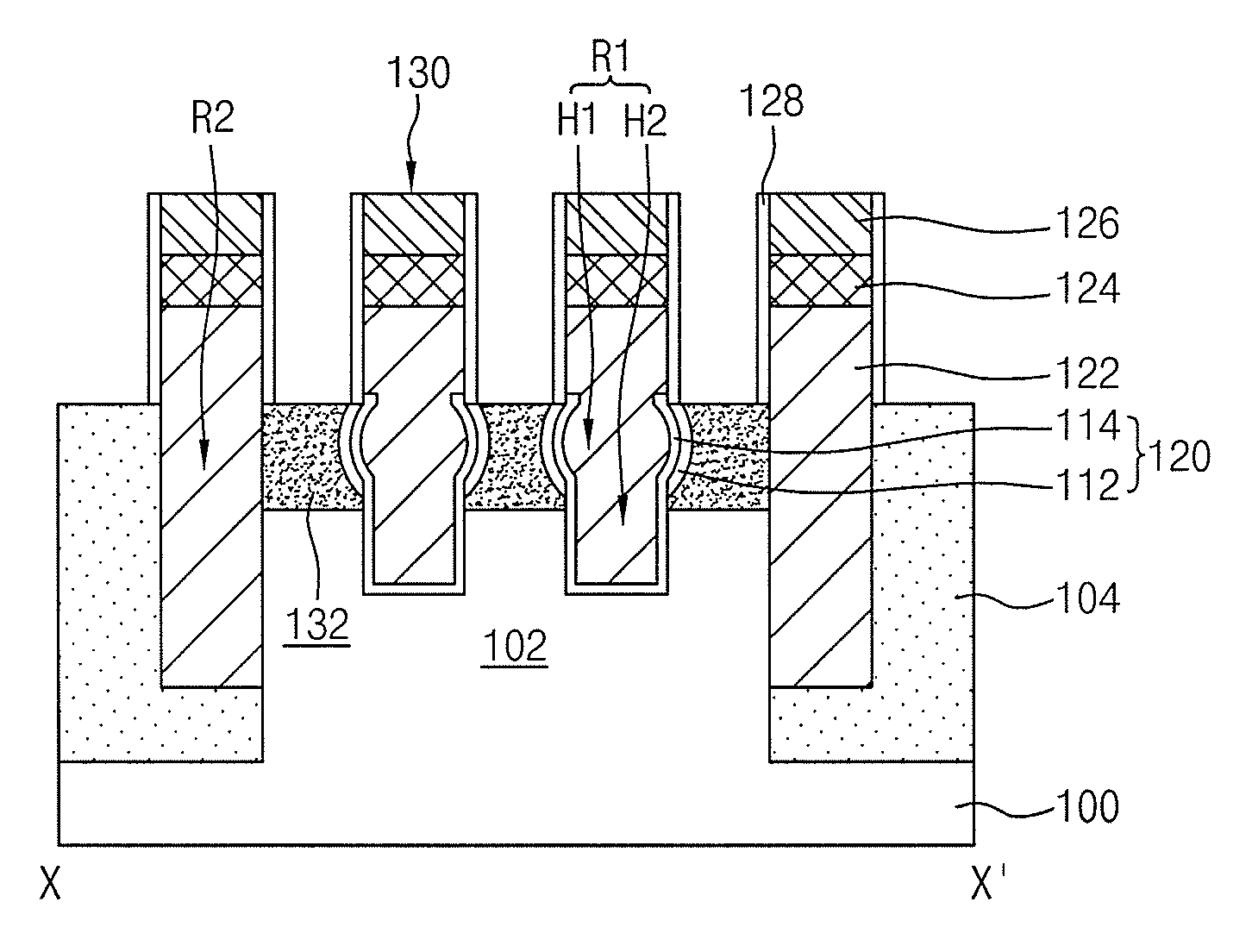

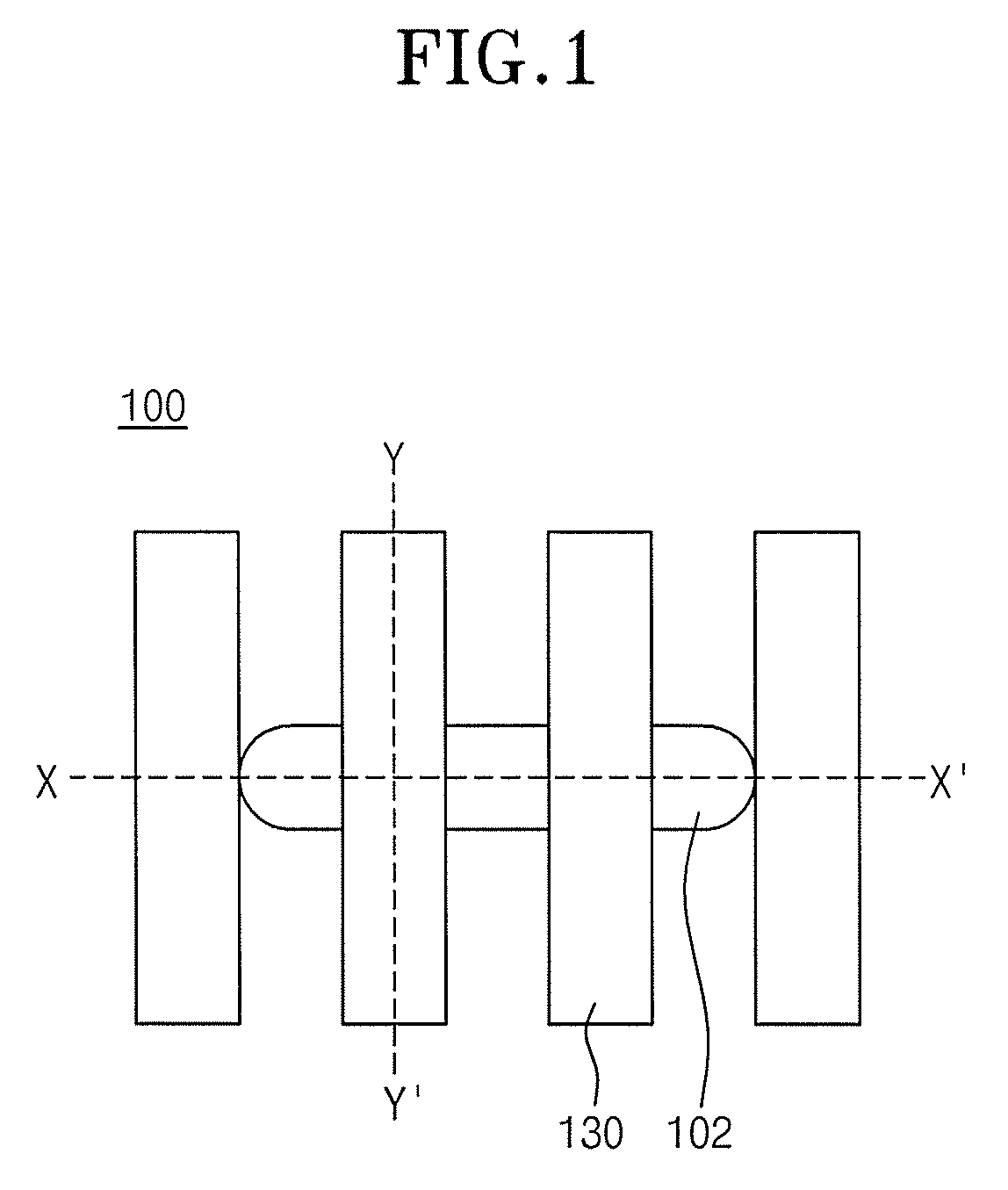

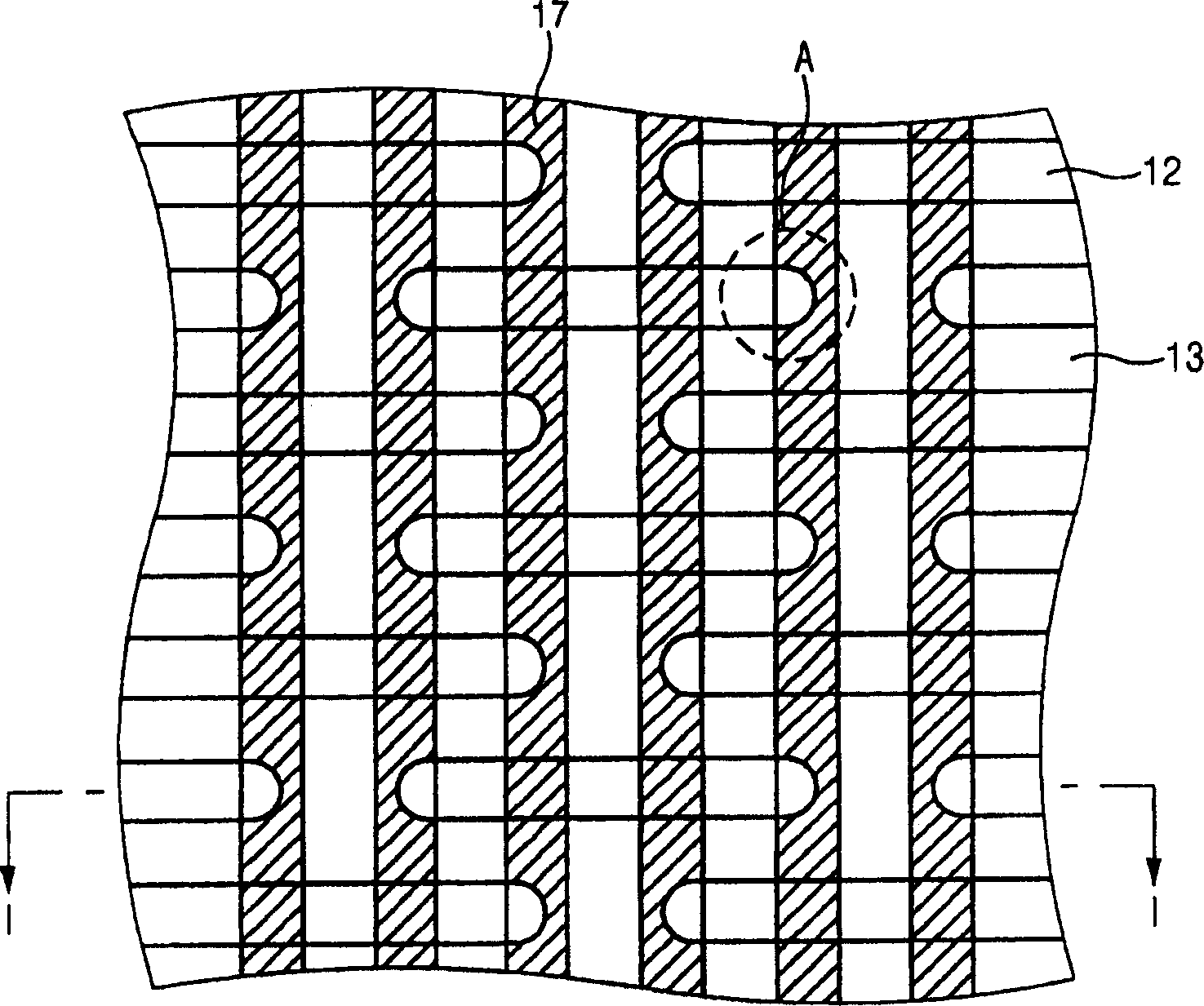

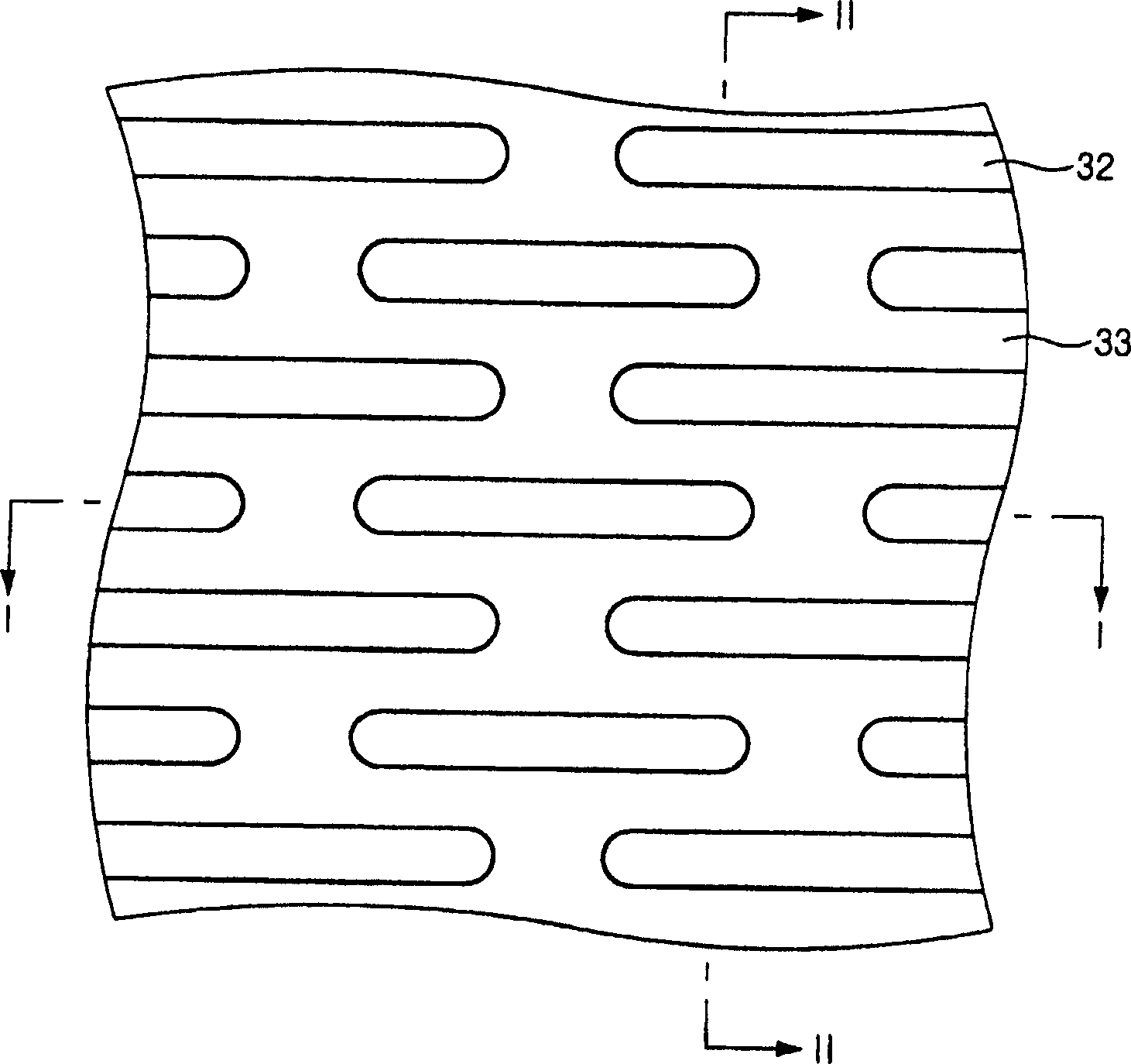

Method of manufacturing semiconductor device

InactiveUS20080242024A1Reduce diffuseImprove refresh featureSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

To provide a semiconductor device using a Fin-FET and having a contact configuration such that the GIDL is reduced while limiting an increase in contact resistance, source and drain regions of the Fin-FET are formed by solid-phase diffusion positively utilizing impurity implantation after forming of contact holes 13 and oozing-out of an impurity from polysilicon contact plugs 14. Also, contact plugs 14 are extended to side surfaces of convex semiconductor layers 101a to form side wall portions 14a, thereby increasing the contact area.

Owner:ELPIDA MEMORY INC

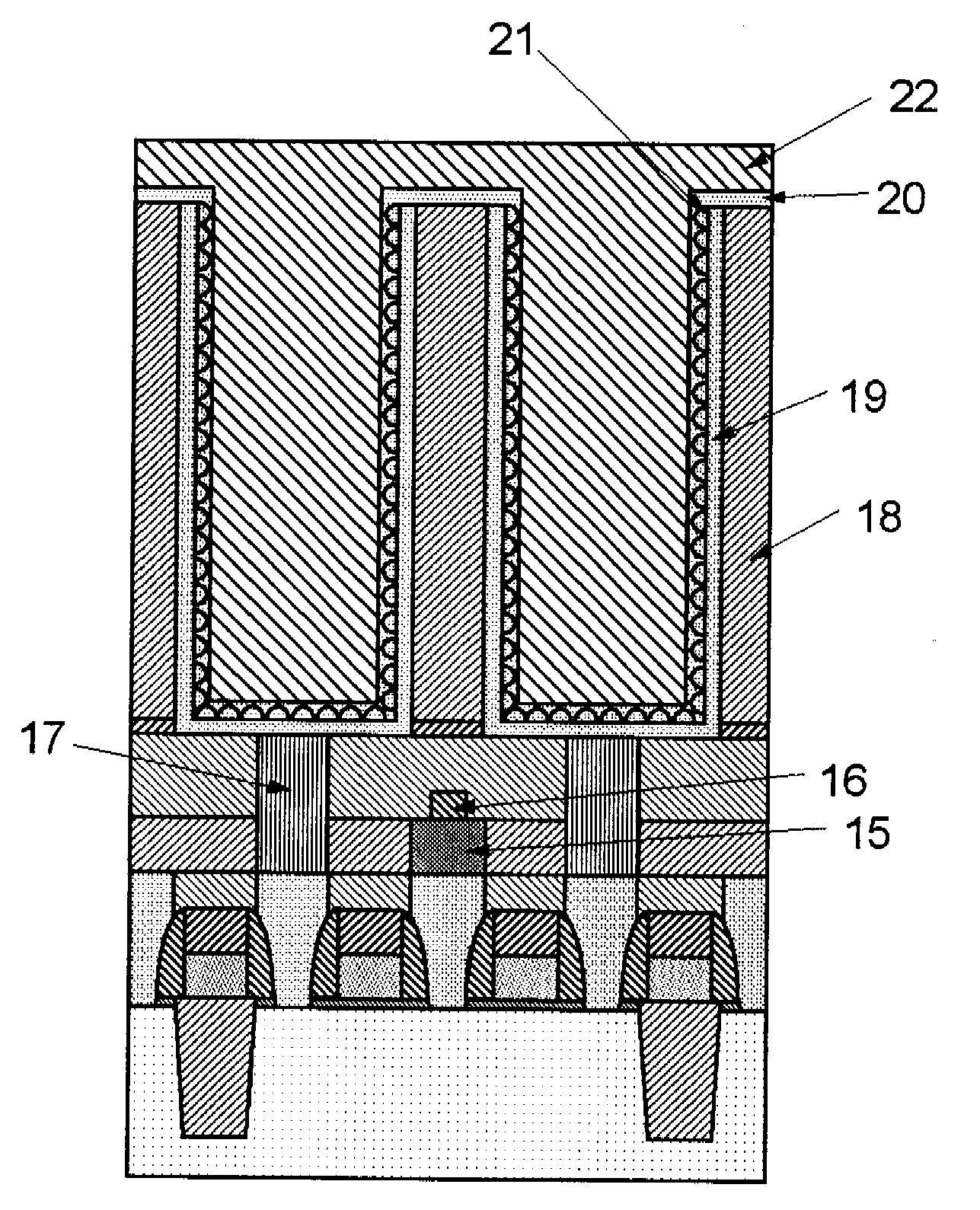

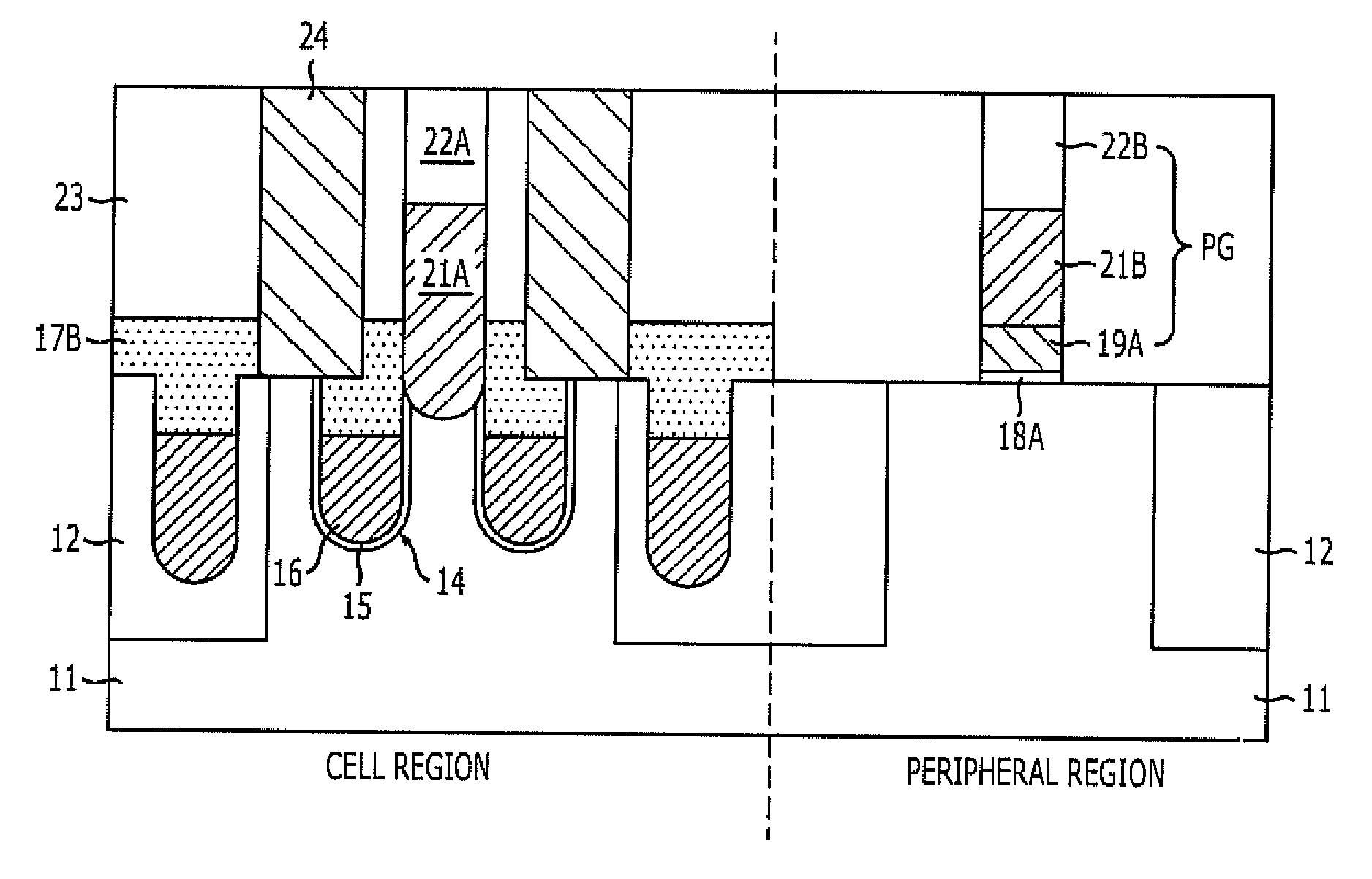

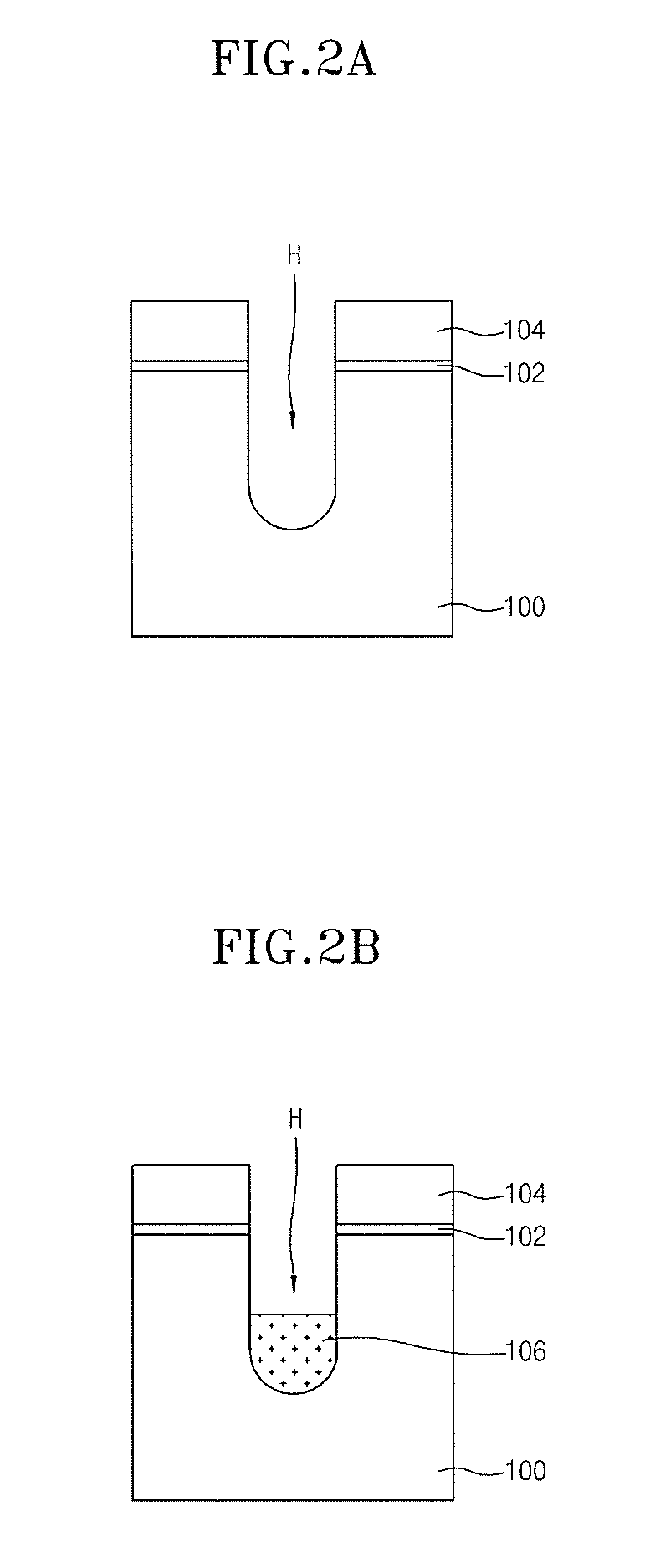

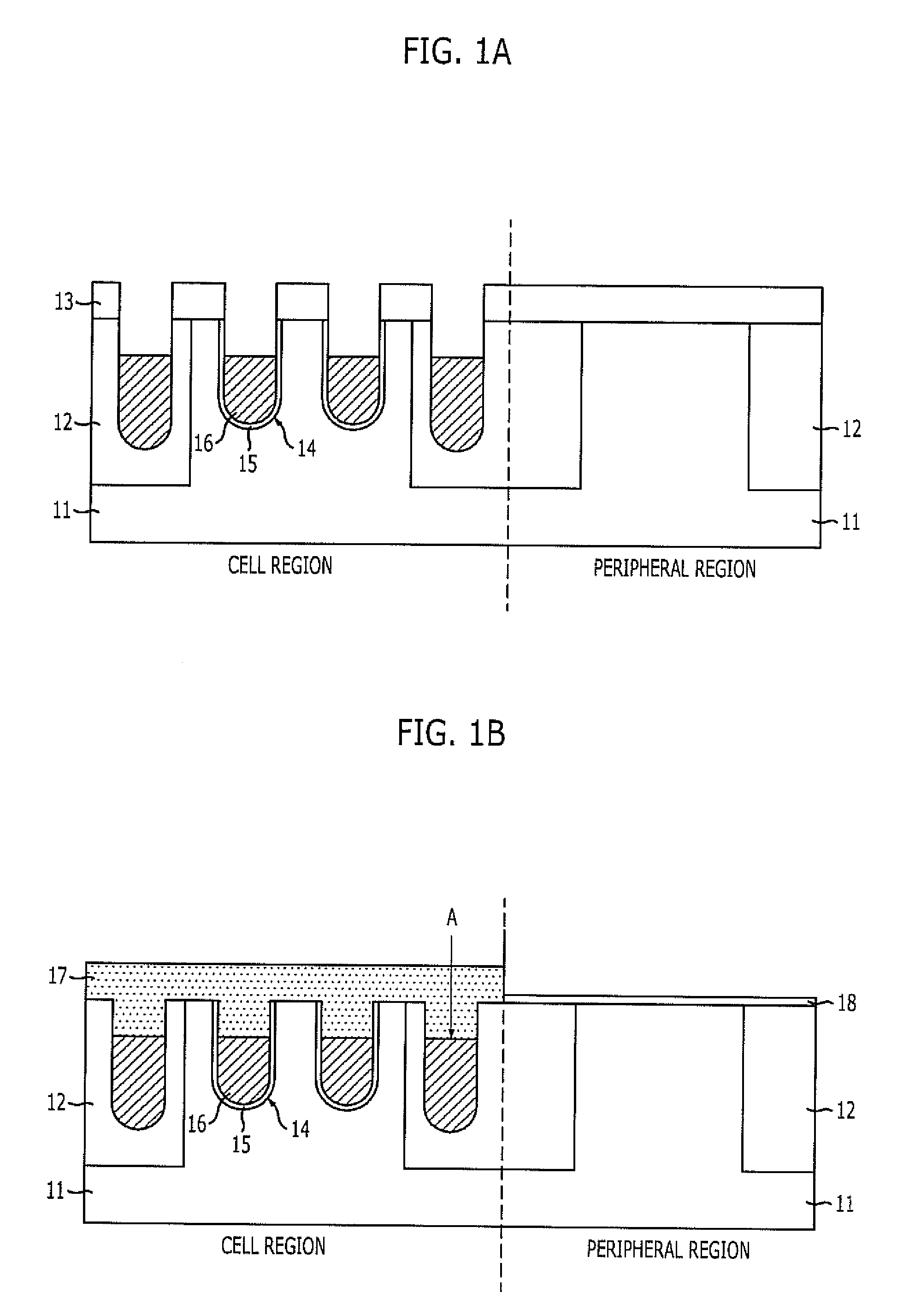

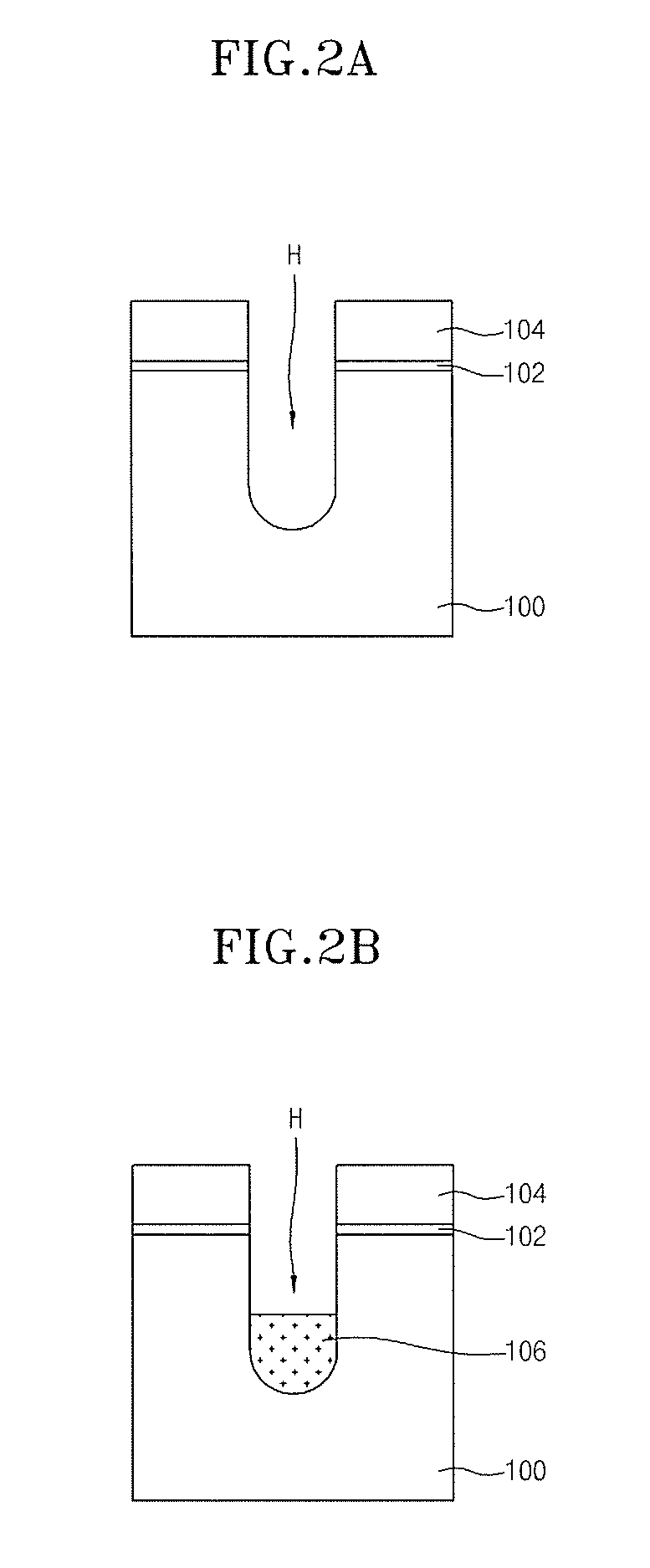

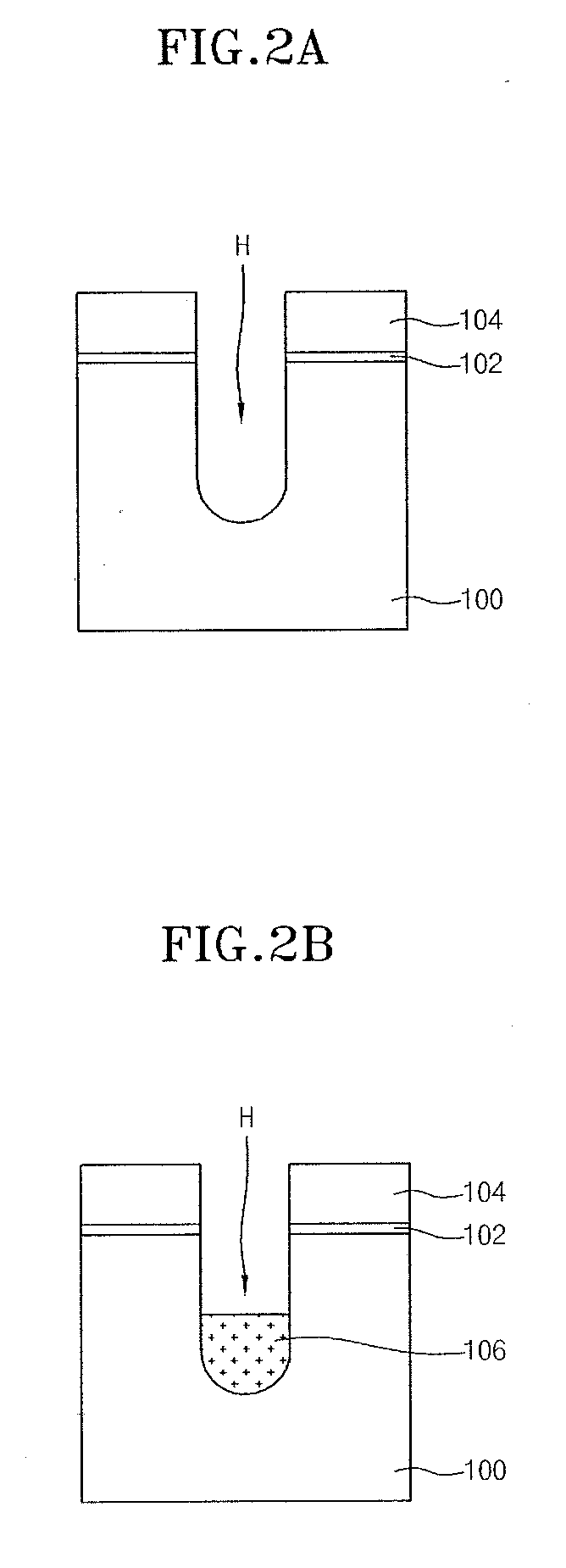

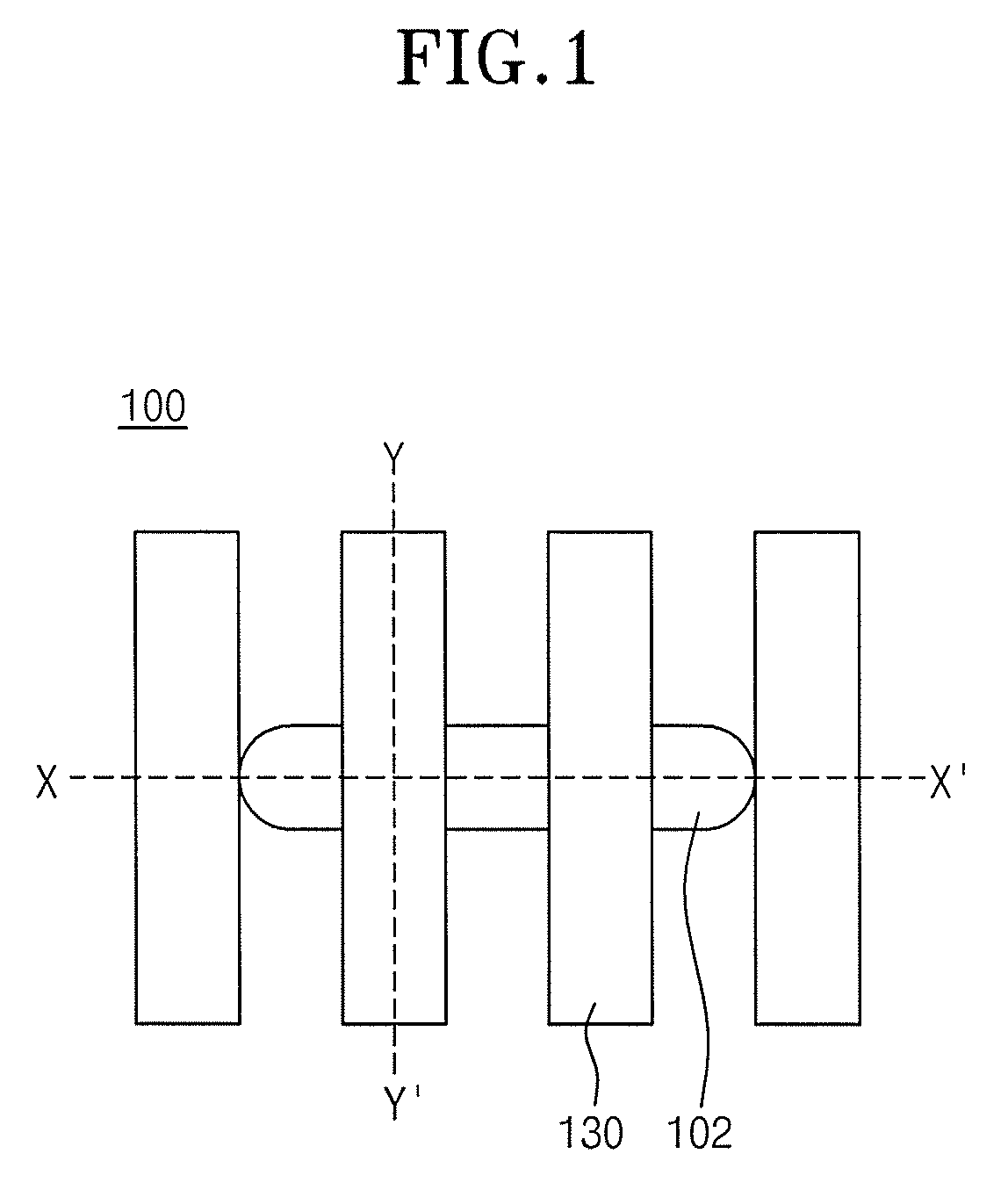

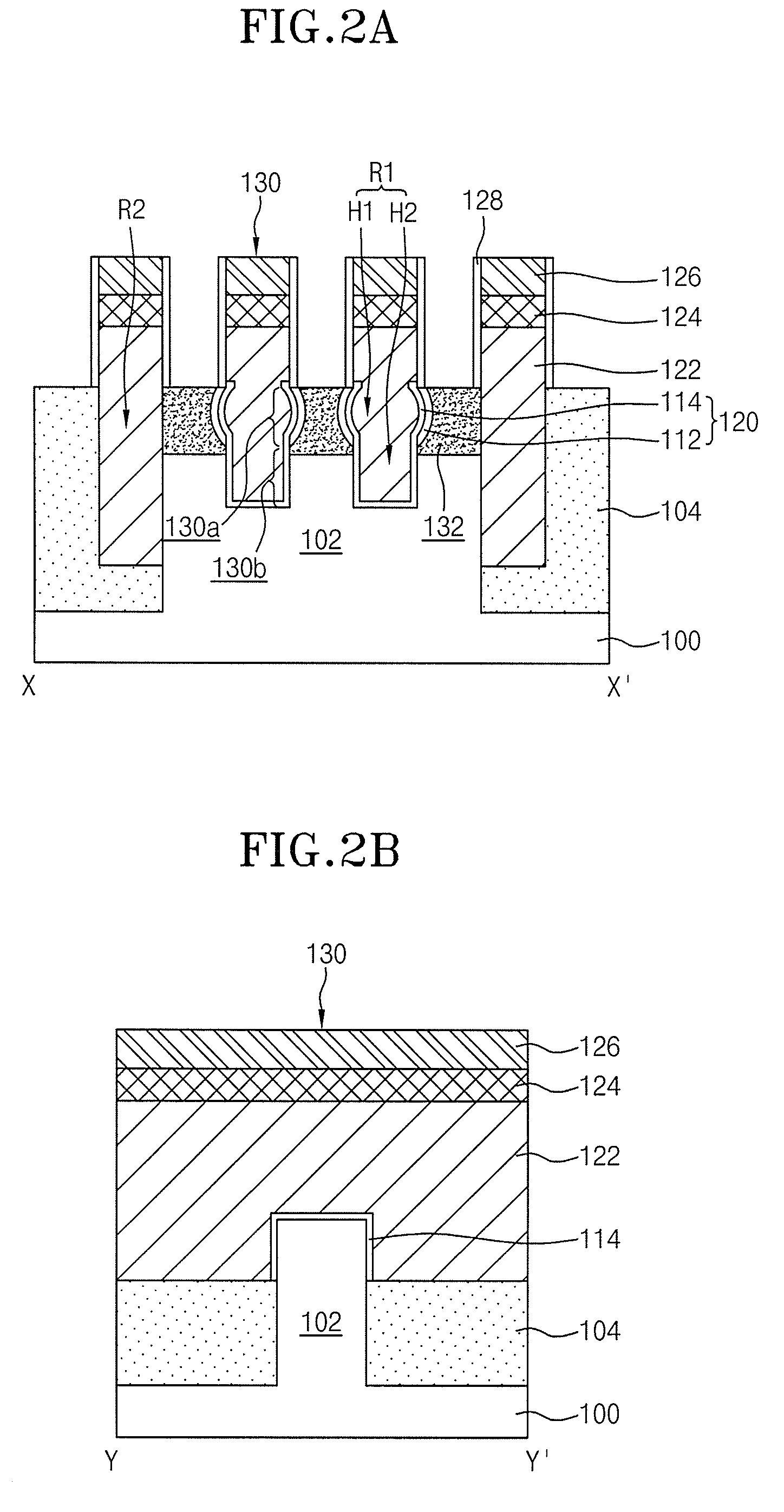

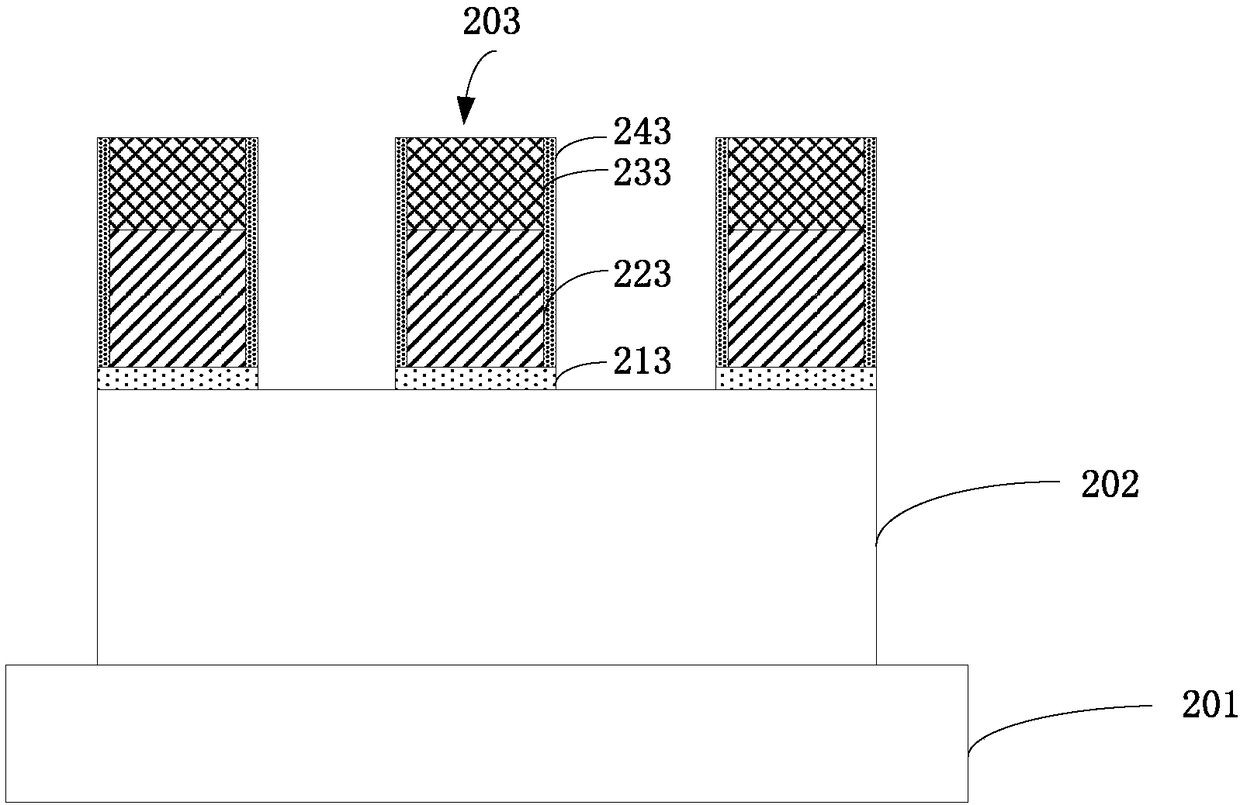

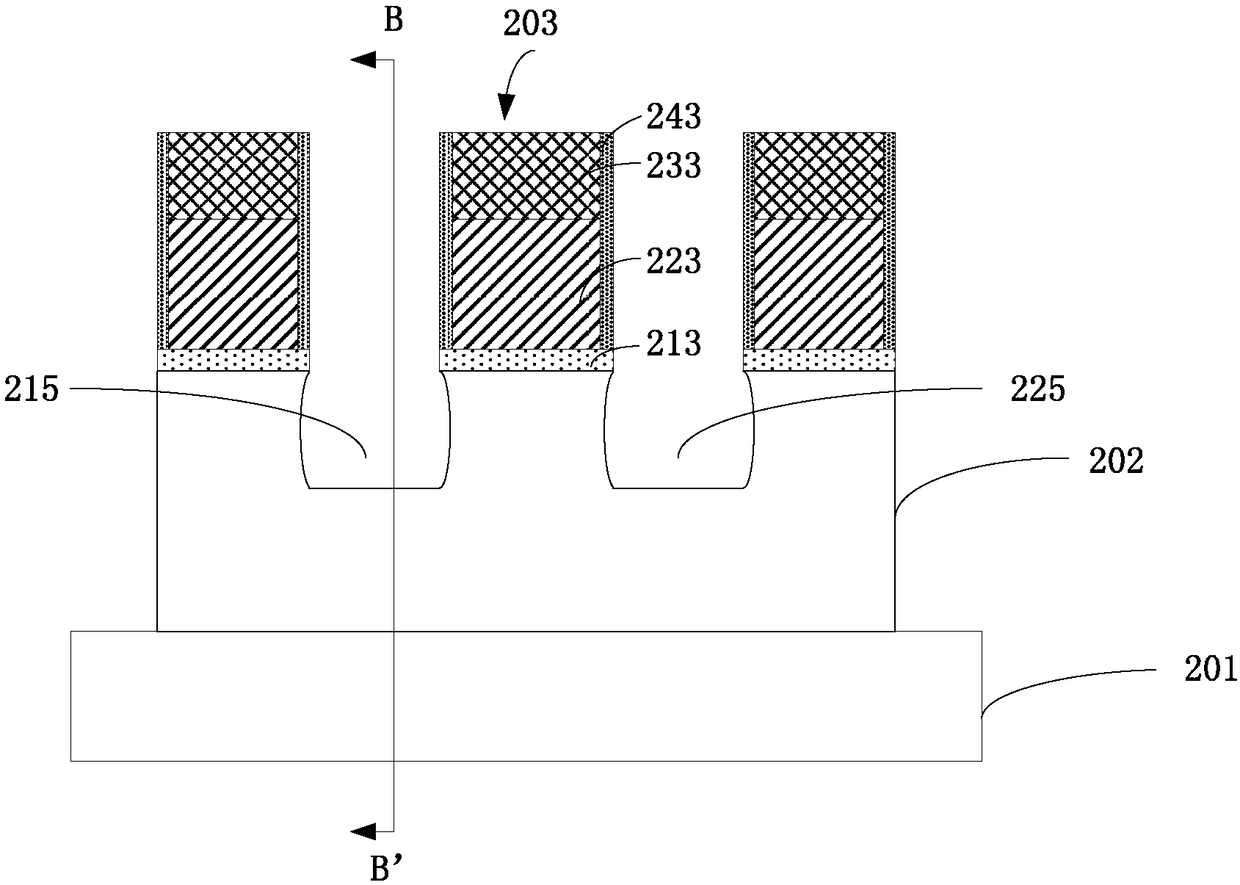

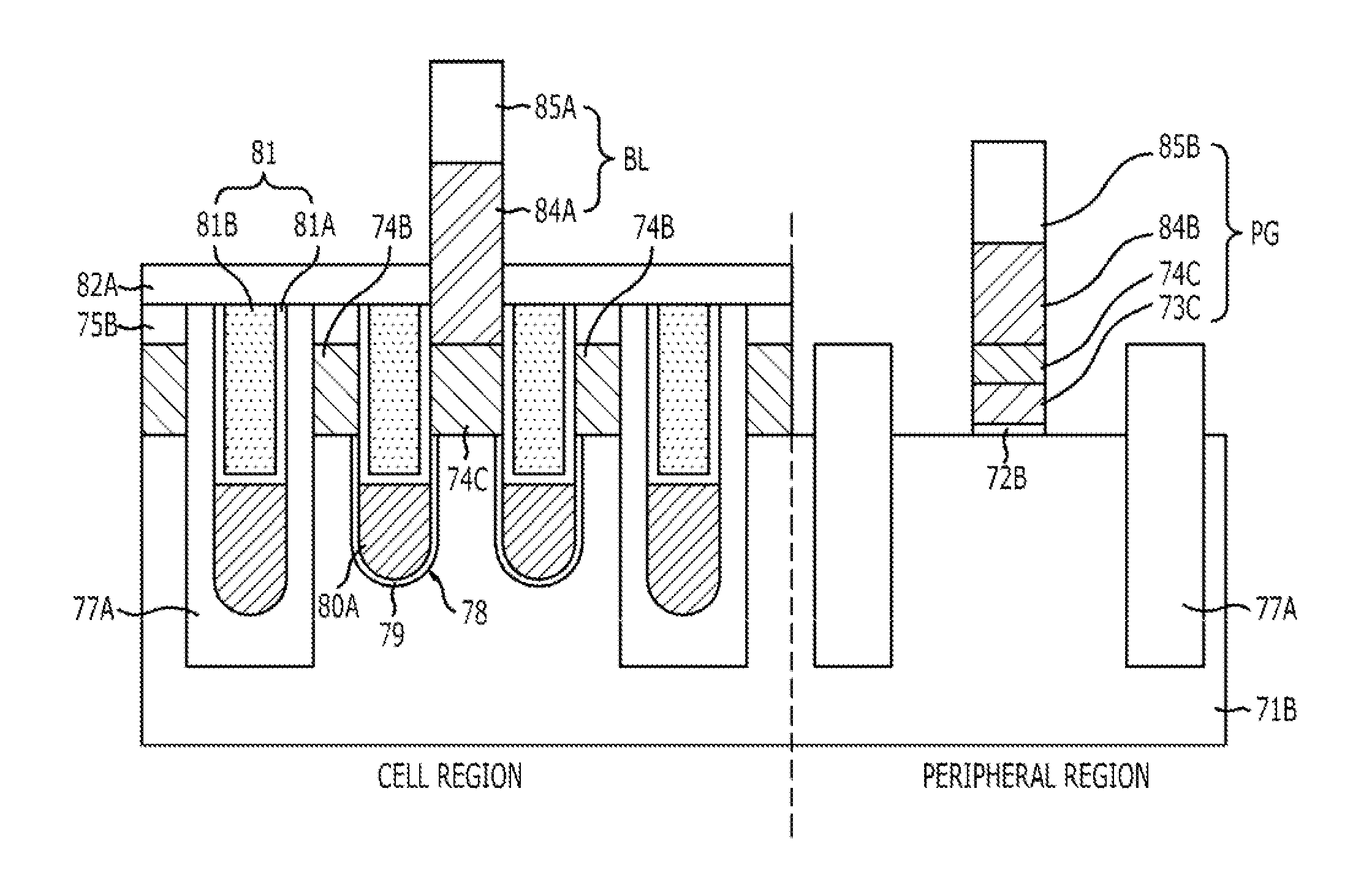

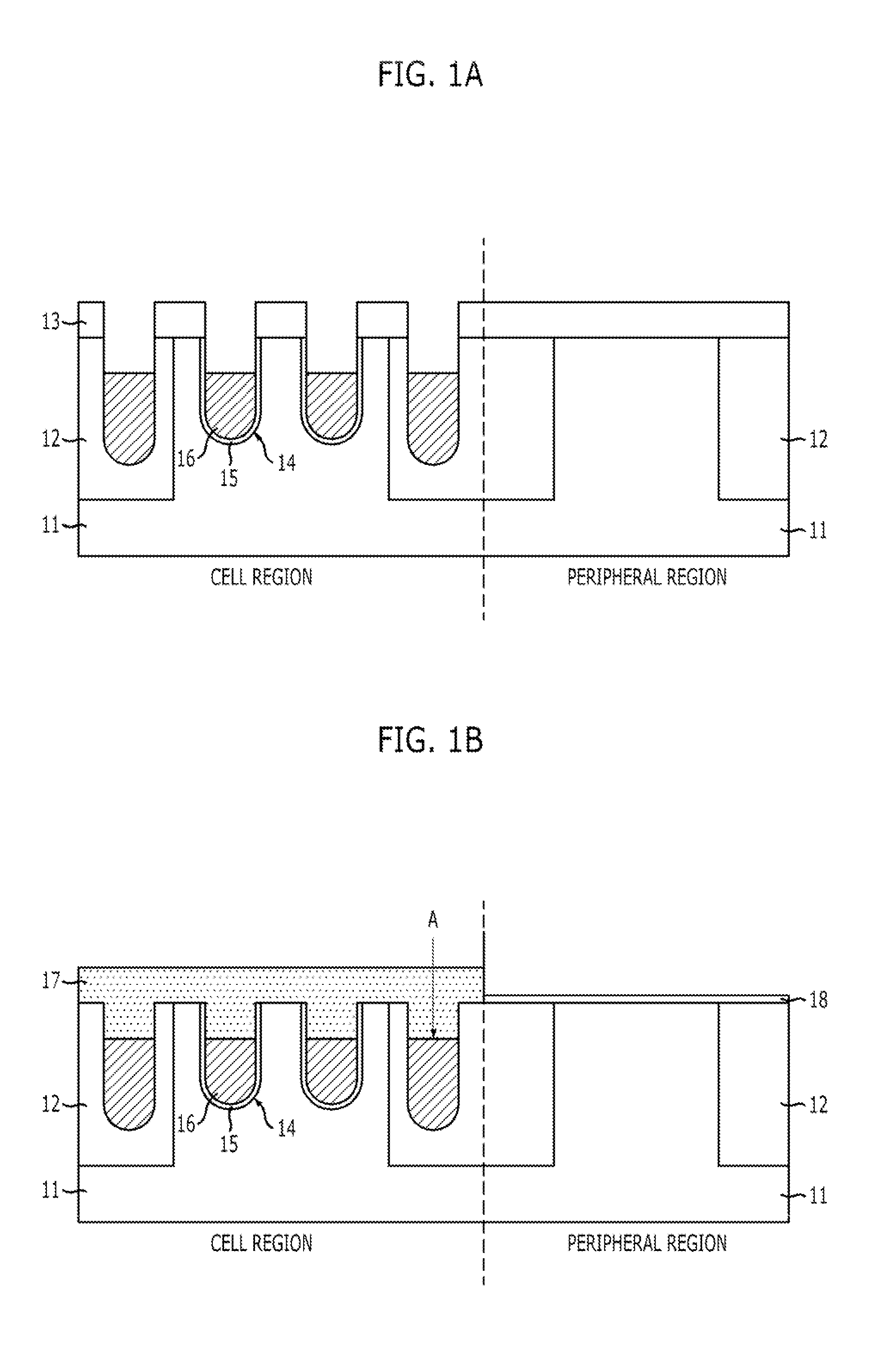

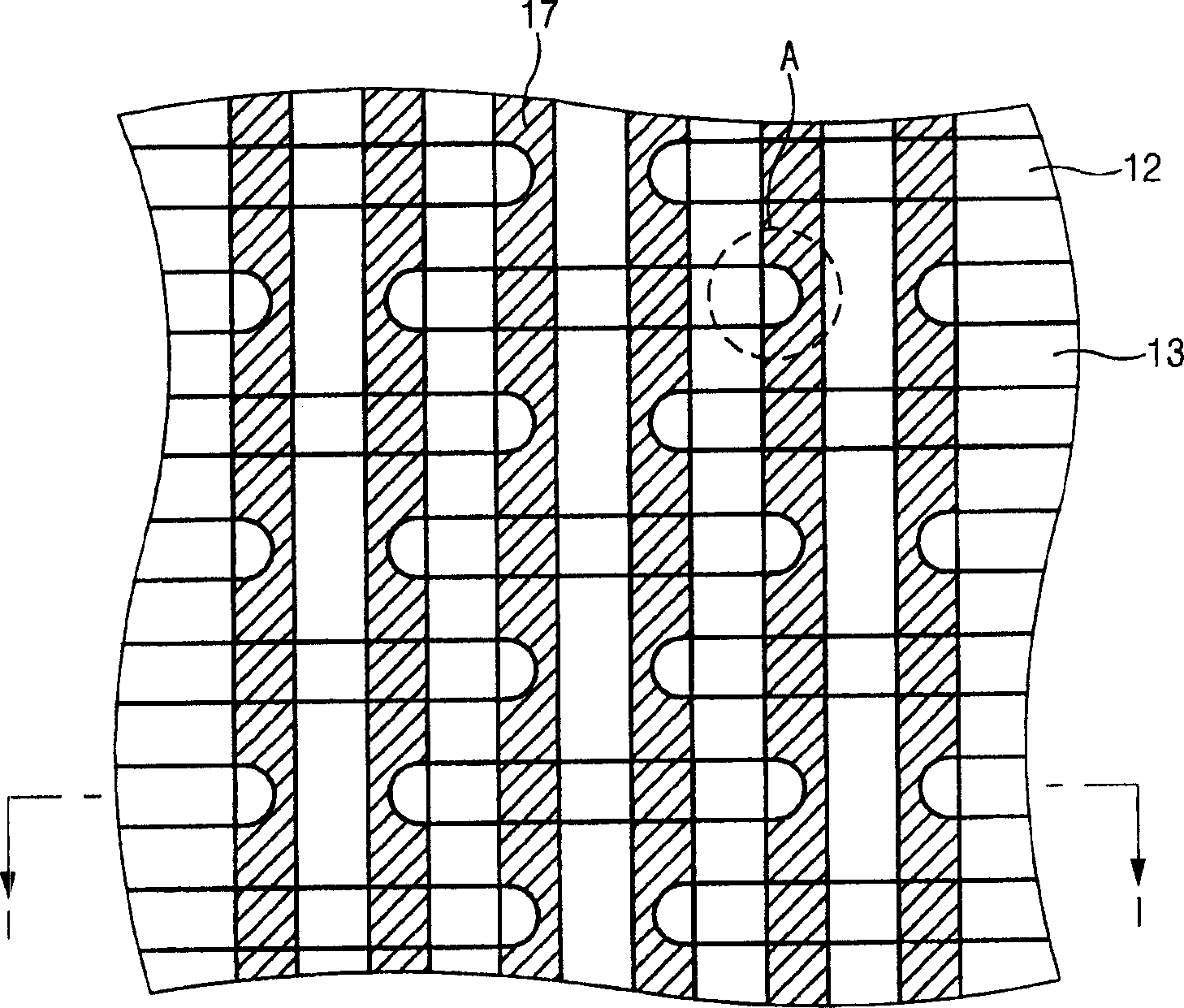

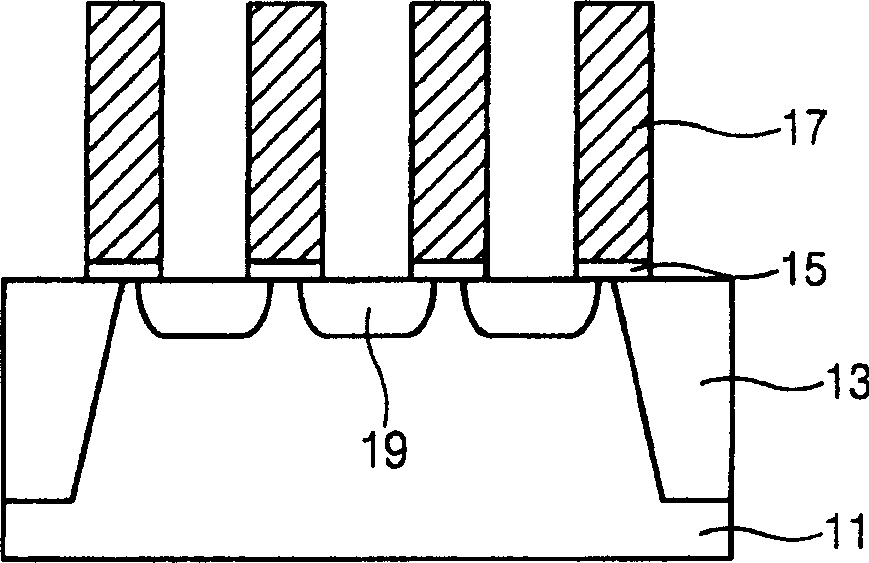

Method for fabricating buried gate using pre landing plugs

ActiveUS20110003459A1Prevent oxidationReduce contact resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorInsulation layer

A method for fabricating a semiconductor device is provided, the method includes forming a plug conductive layer over an entire surface of a substrate, etching the plug conductive layer to form landing plugs, etching the substrate between the landing plugs to form a trench, forming a gate insulation layer over a surface of the trench and forming a buried gate partially filling the trench over the gate insulation layer.

Owner:SK HYNIX INC

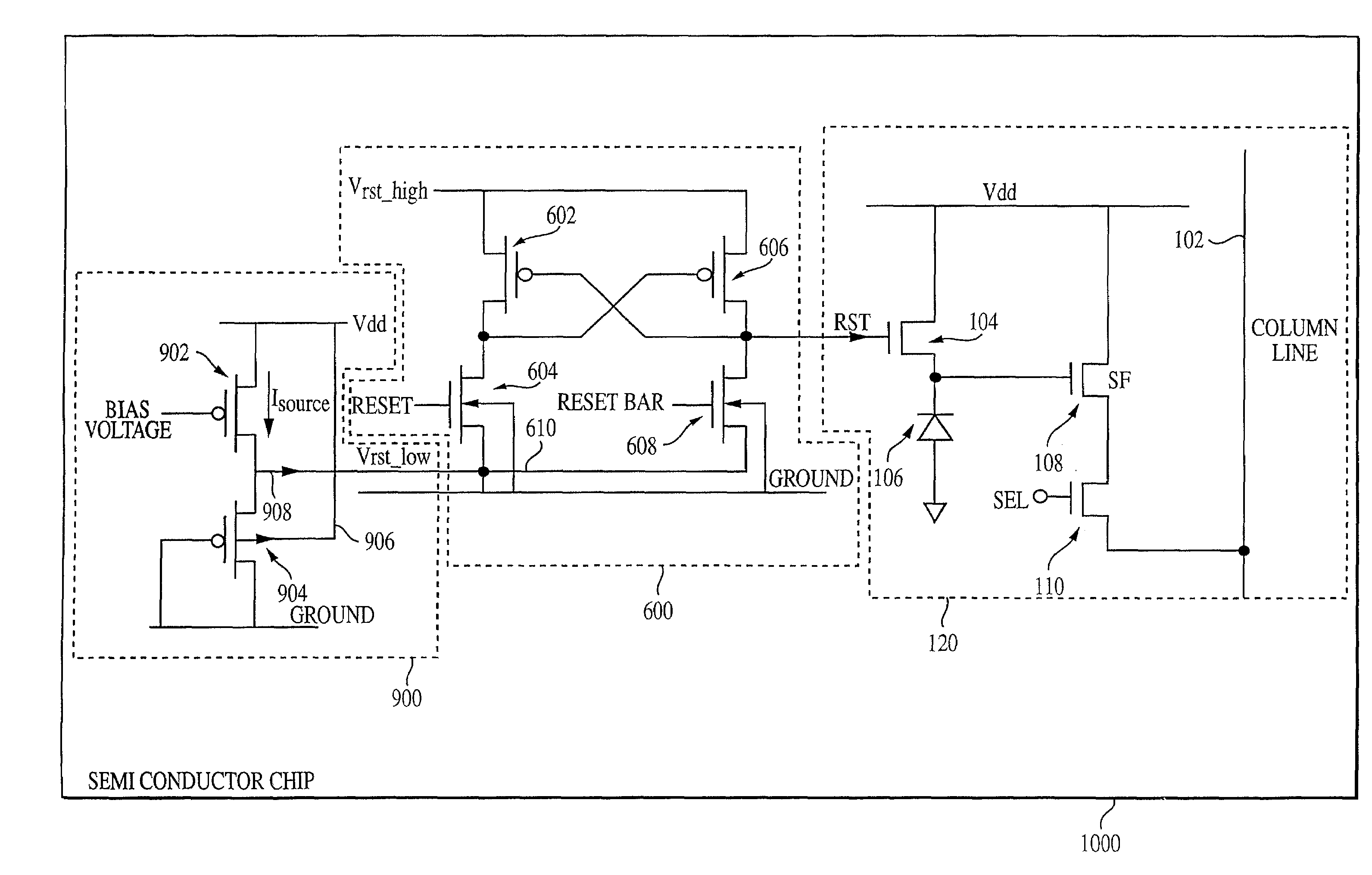

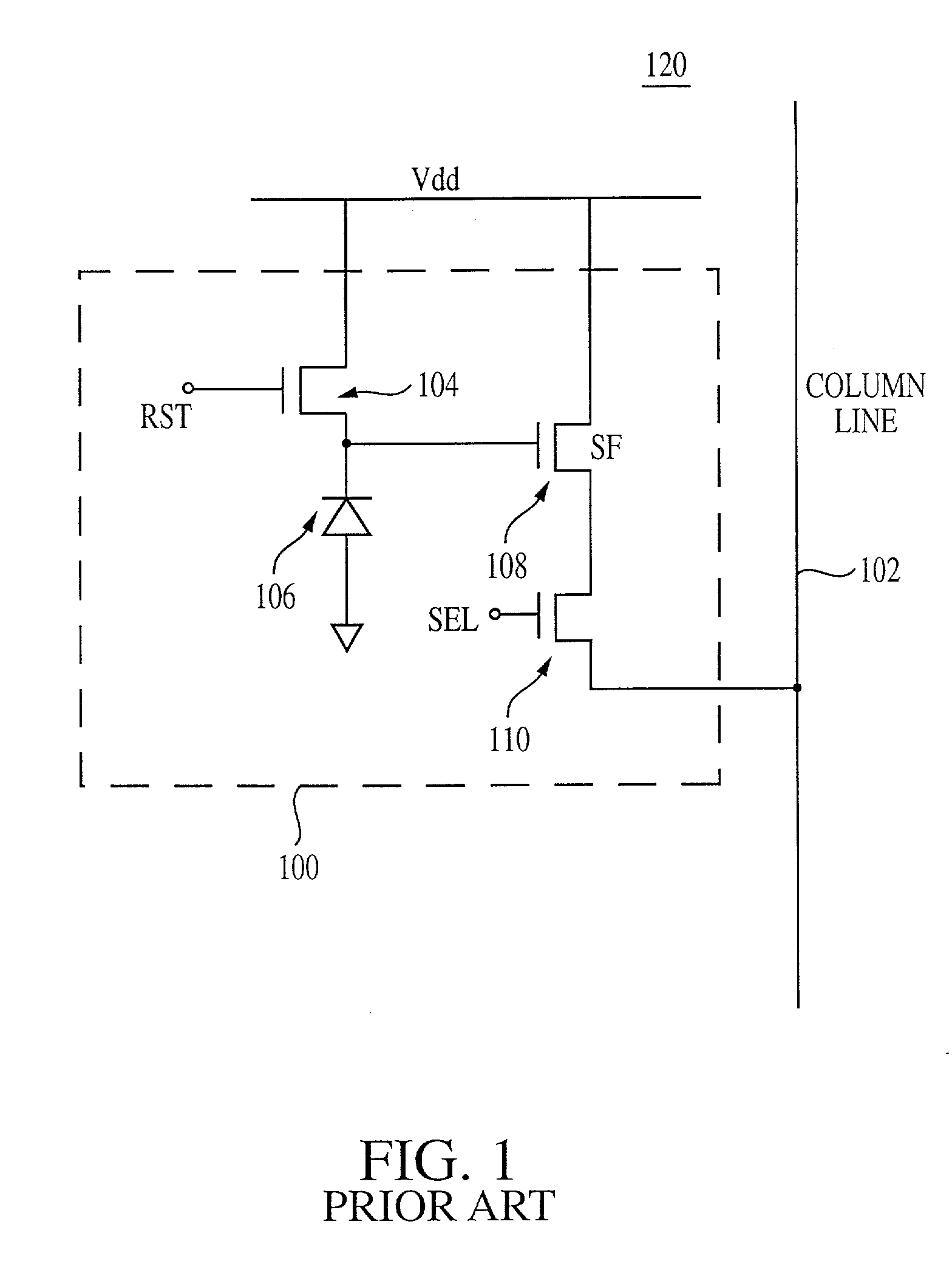

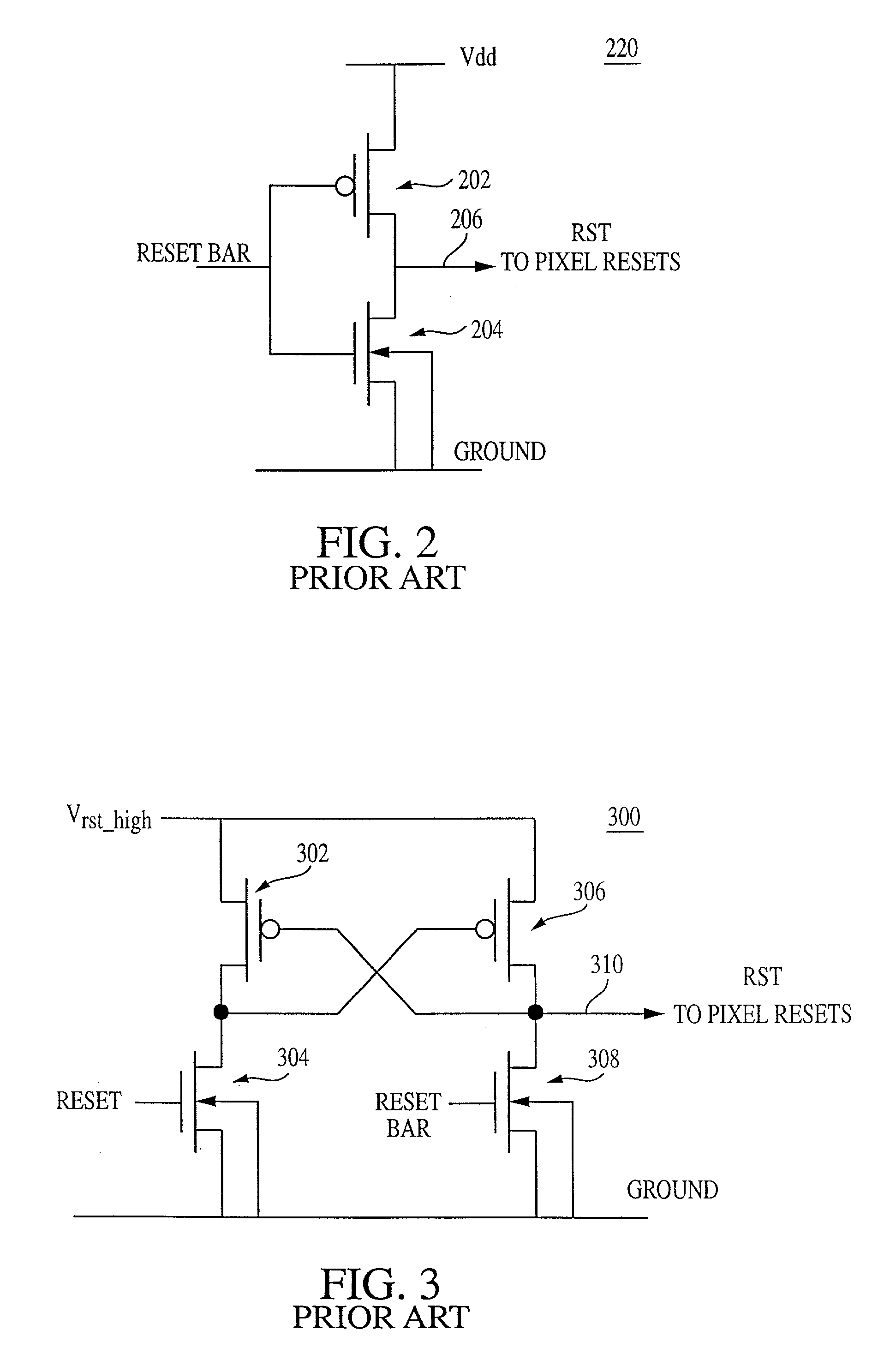

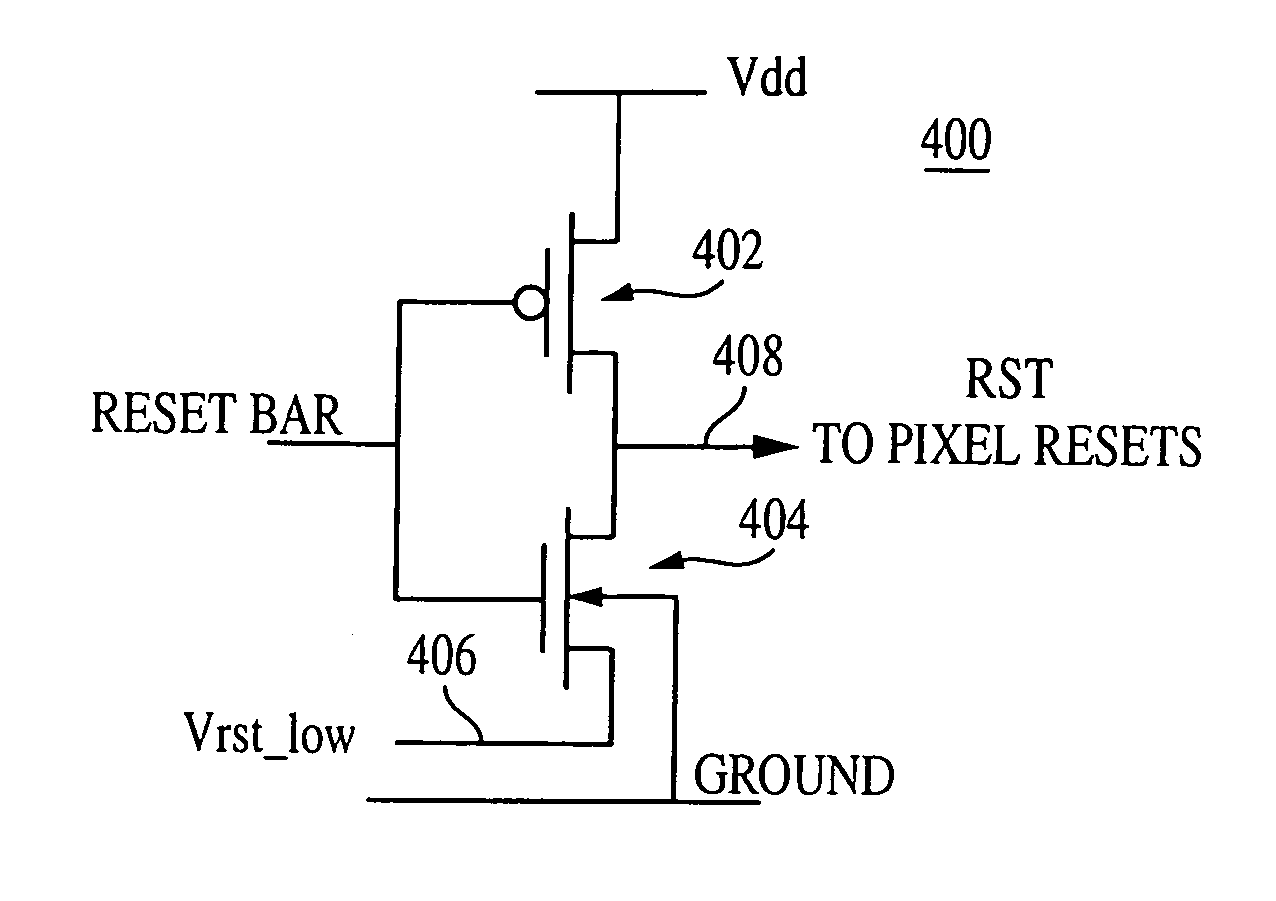

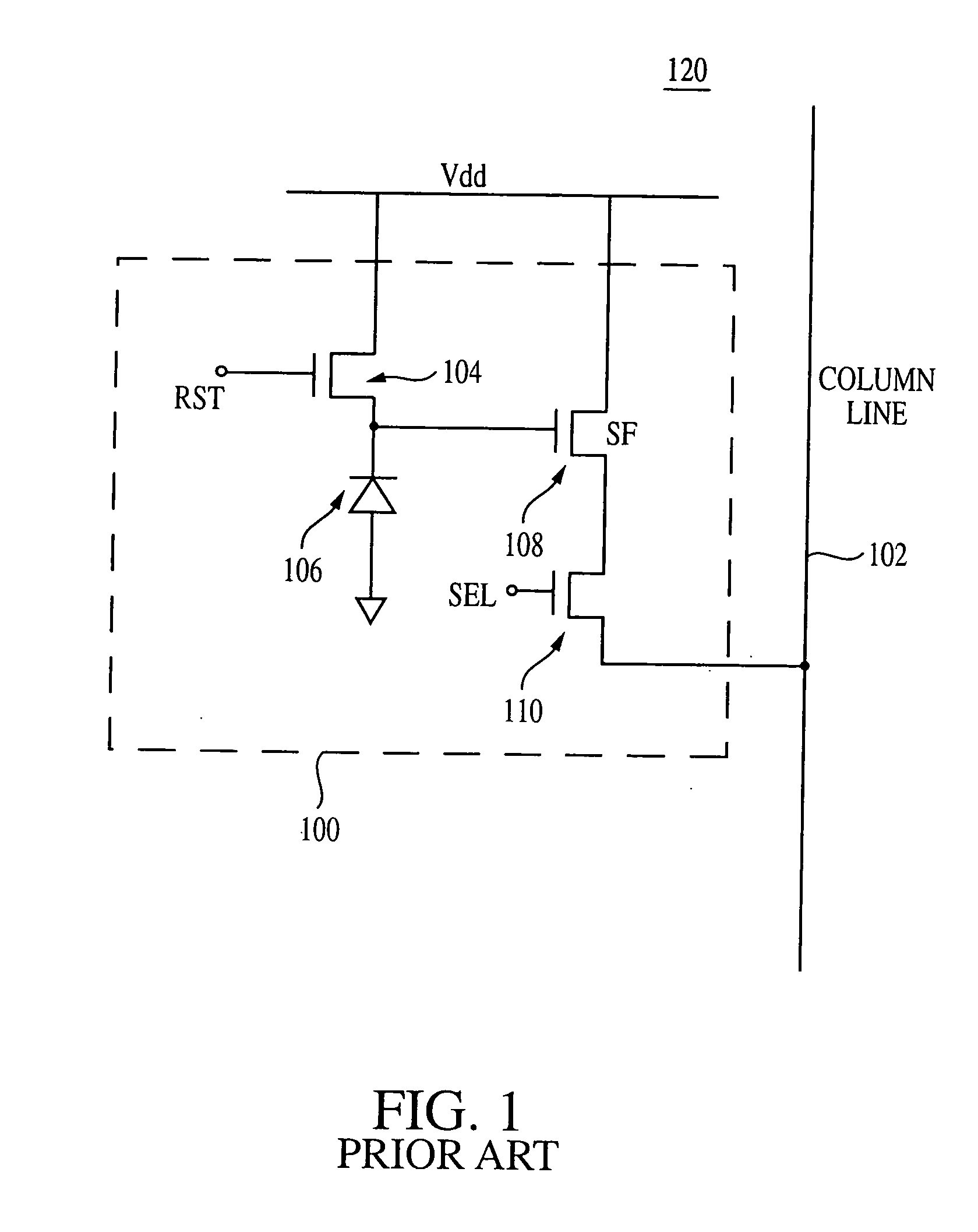

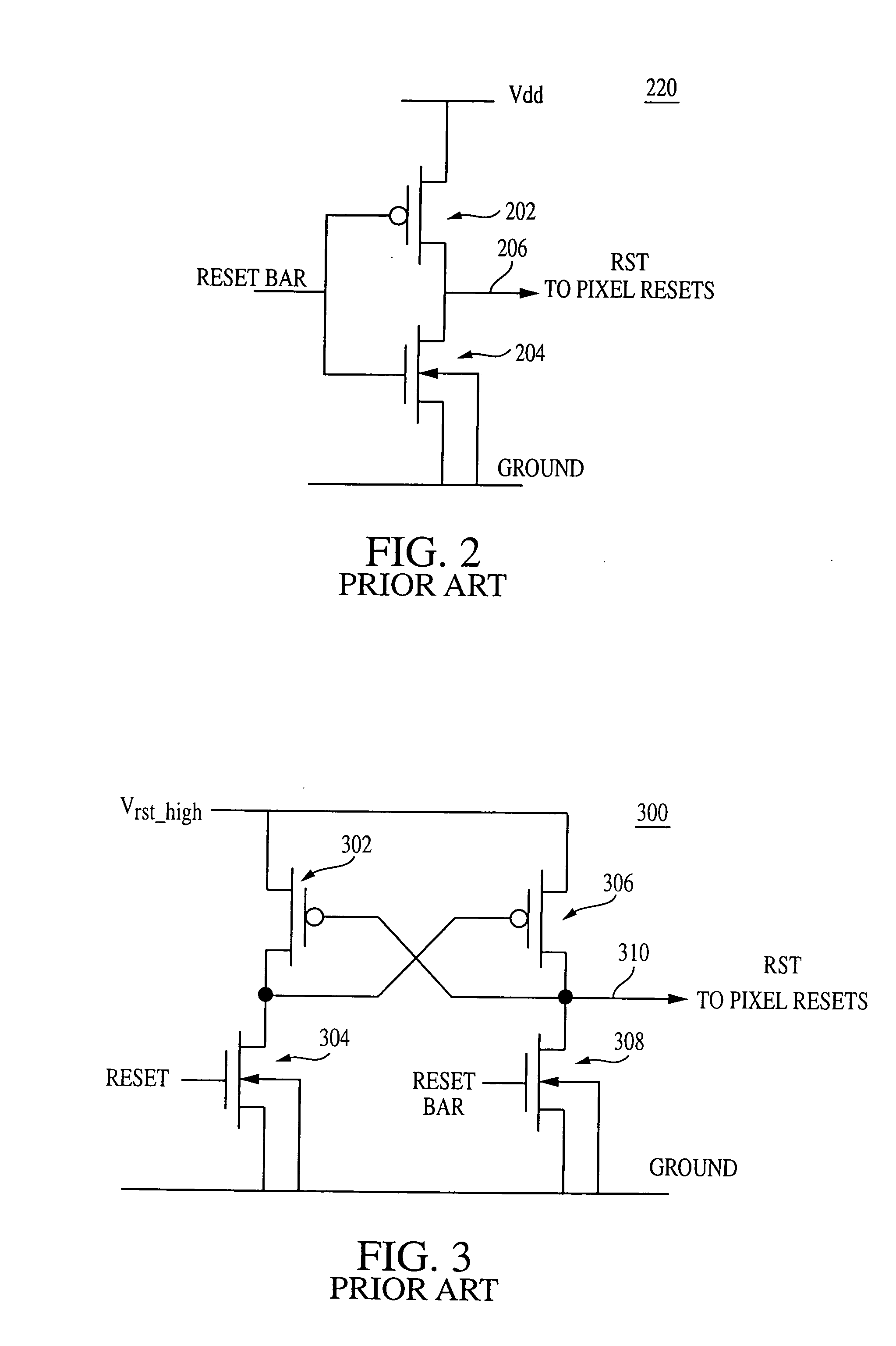

Dark current reduction circuitry for CMOS active pixel sensors

InactiveUS7015448B2Reduce GIDLMinimizing gate induced drain leakageTelevision system detailsTelevision system scanning detailsDriver circuitLow voltage

A row driver circuit is disclosed for supplying a reset voltage to a plurality of reset transistors of an active pixel sensor array while minimizing gate induced drain leakage (GIDL). The row driver circuit is configured to supply a high voltage level (e.g., Vdd or higher) to the reset transistors of the array during a reset operation. The row driver circuit is further configured to supply a low voltage level (e.g., a voltage level higher than ground) to the reset transistors of the array when the pixels are not being reset (e.g., during integration). The reduced potential difference realized between the respective gates of the reset transistors and the respective photodiodes of the pixels, when the pixels are not being reset, results in reduced GIDL.

Owner:APTINA IMAGING CORP

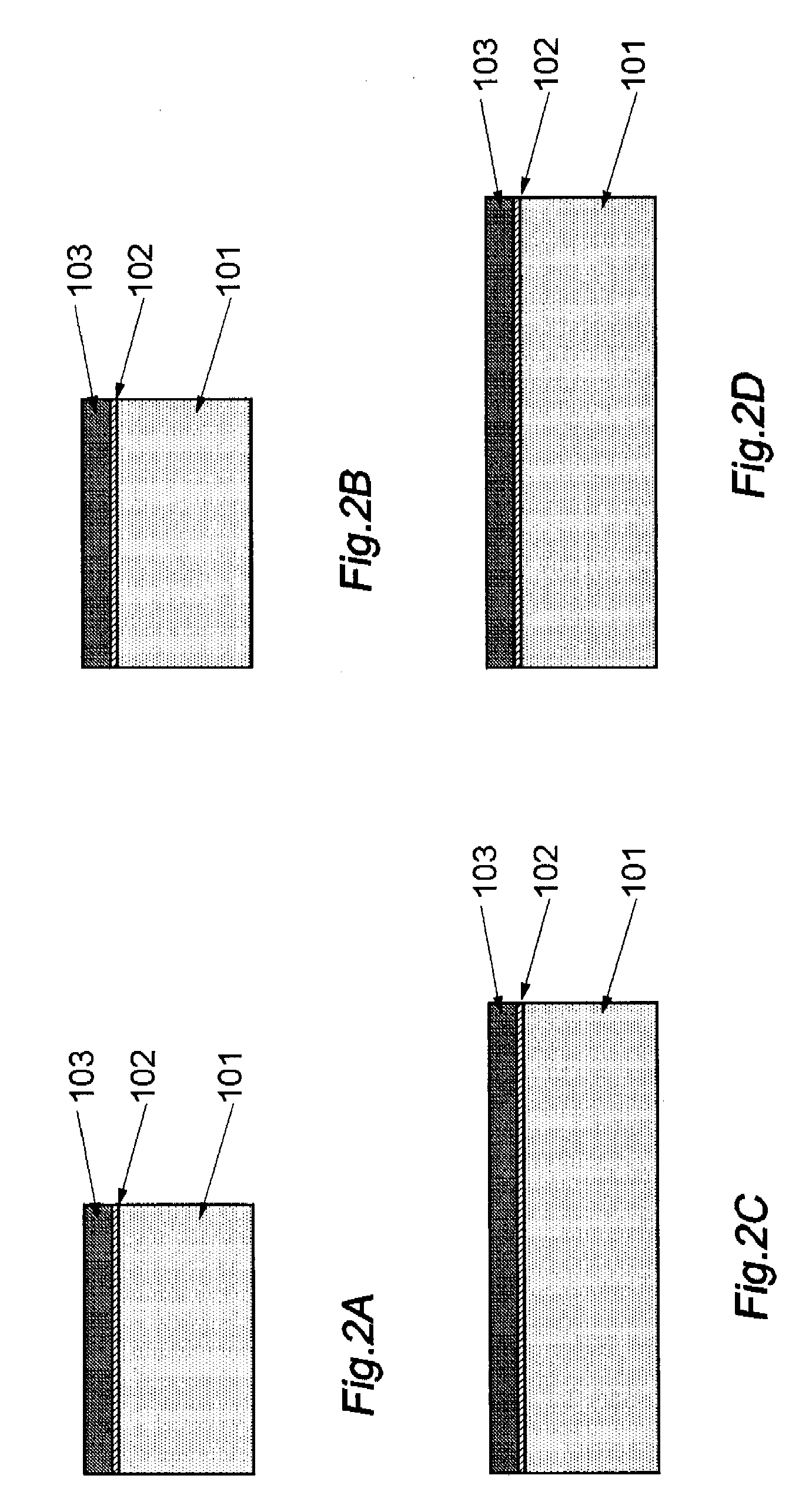

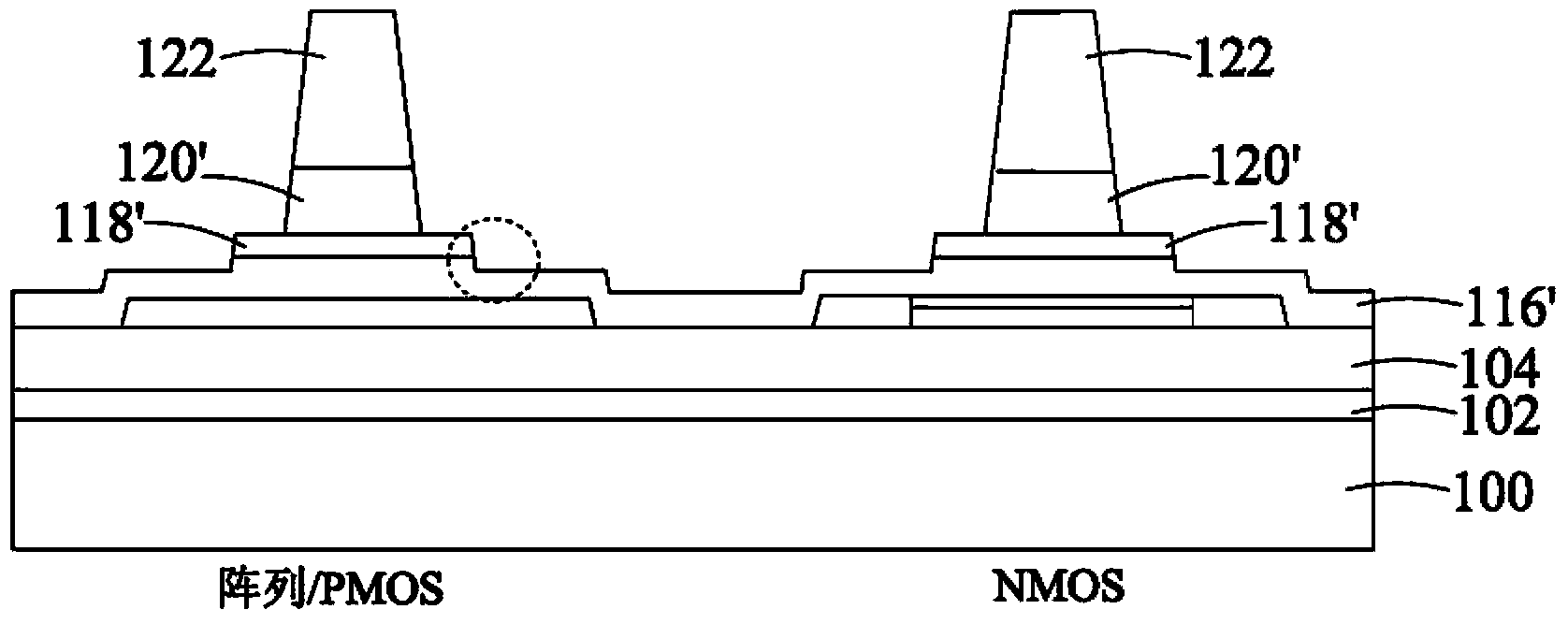

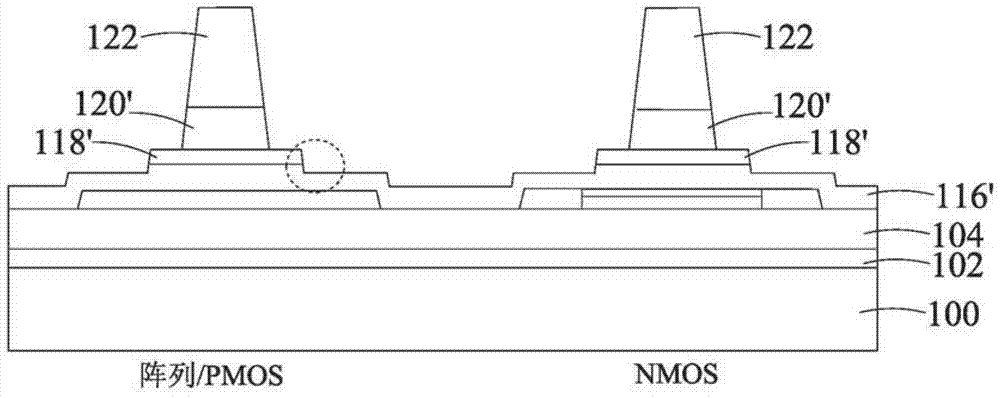

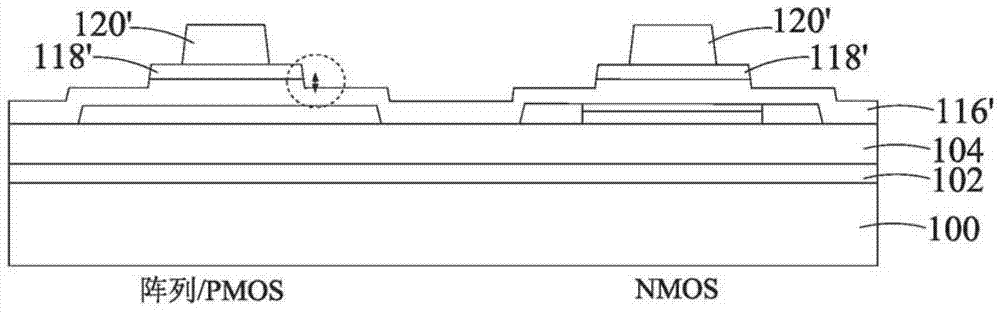

Thin film transistor, active matrix organic light emitting diode assembly and manufacturing method

ActiveCN104241389AGood injection distributionReduce lossesTransistorSolid-state devicesOxide thin-film transistorActive matrix

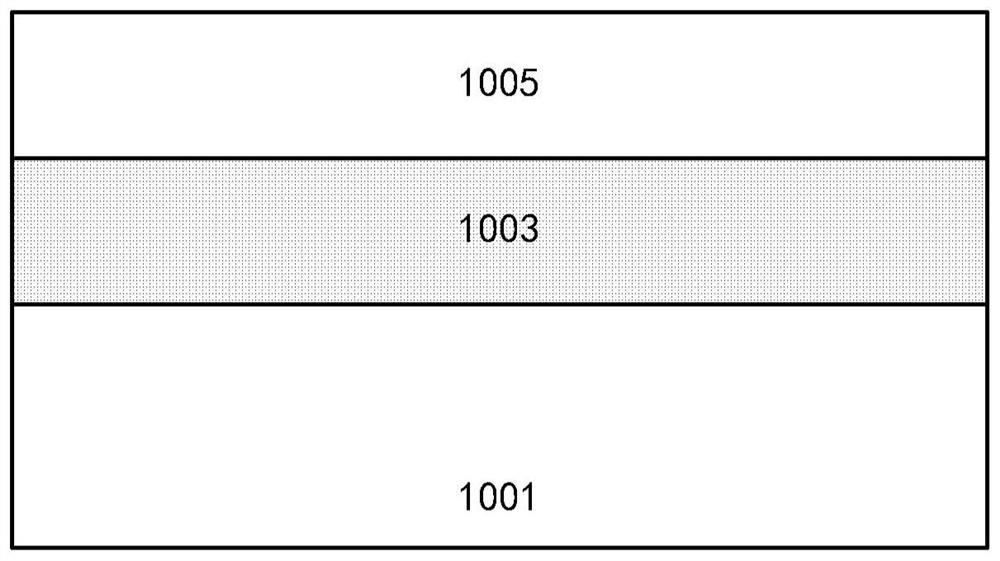

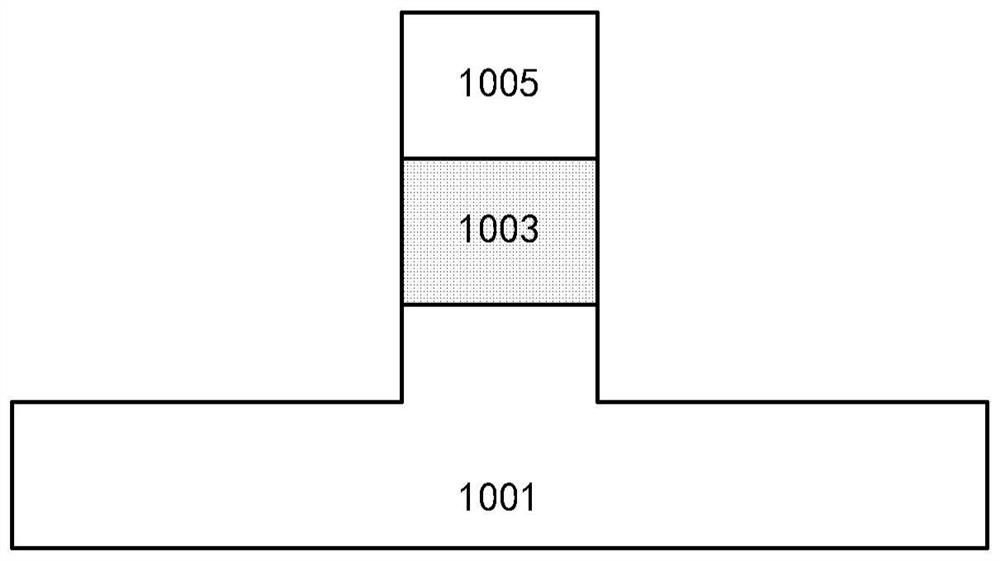

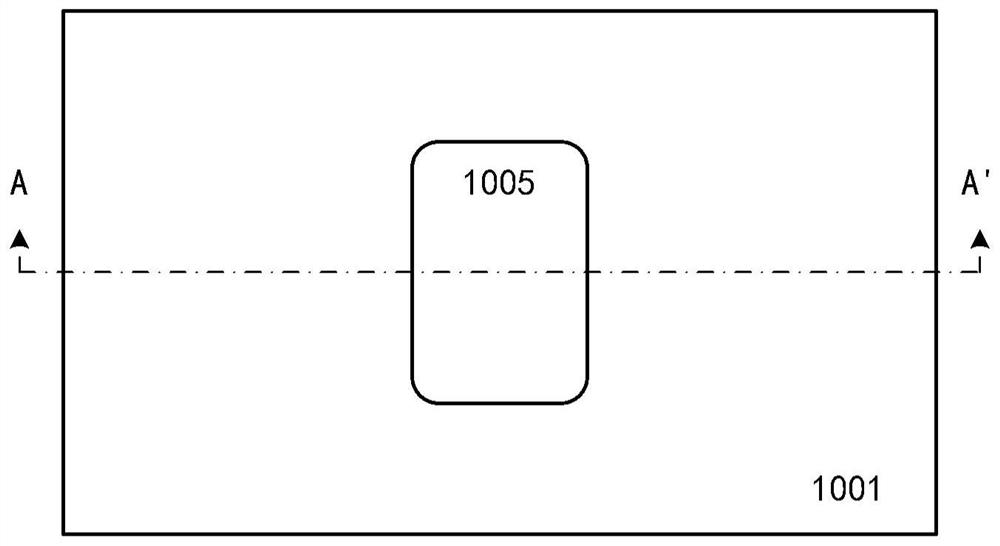

The invention provides a thin film transistor, an active matrix organic light emitting diode assembly and a manufacturing method of the thin film transistor and the active matrix organic light emitting diode assembly. The thin film transistor comprises a substrate, a buffering layer, a semiconductor layer, a first gate insulating layer, a second gate insulating layer foot and a gate electrode; wherein the buffering layer is located on the substrate; the semiconductor layer is located on the buffering layer and comprises a source region, a drain region and a channel region; the first gate insulating layer covers the semiconductor layer; the second gate insulating layer foot is located on the first gate insulating layer, and the width of the second gate insulating layer foot is smaller than that of the first gate insulating layer; the gate electrode is located on the second gate insulating layer foot. The part, located on the semiconductor layer, of the first gate insulating layer is provided with a flat upper surface.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

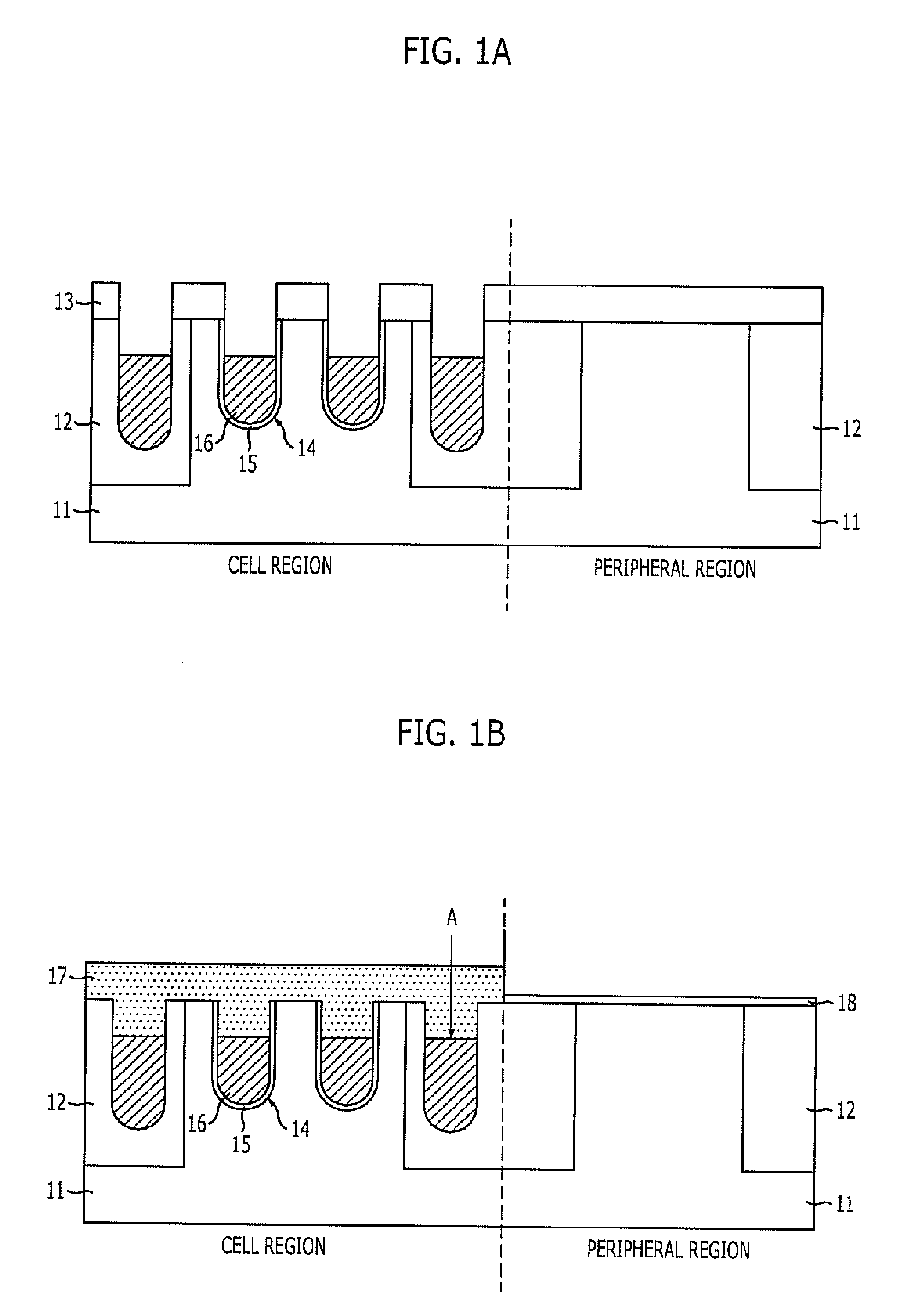

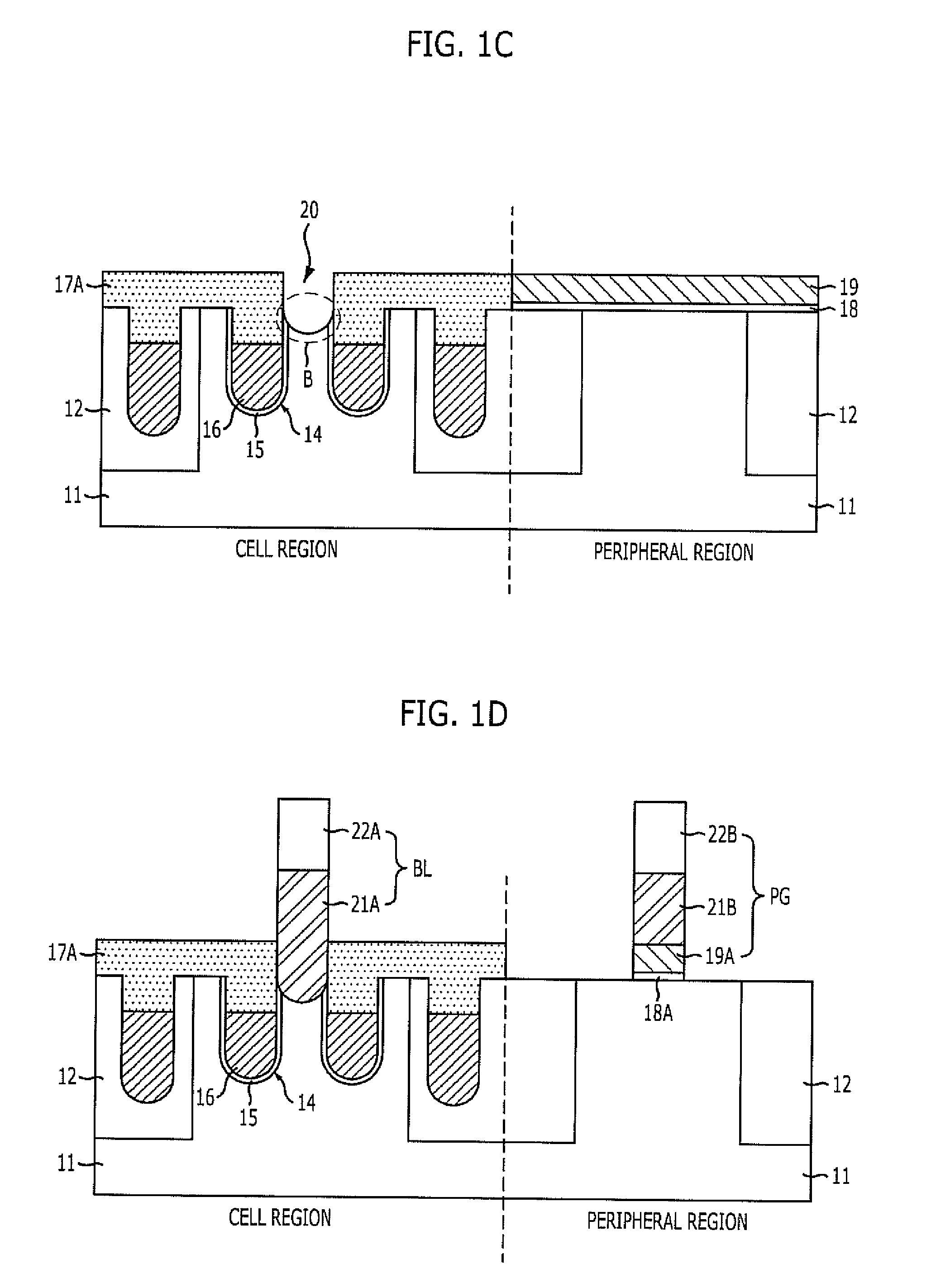

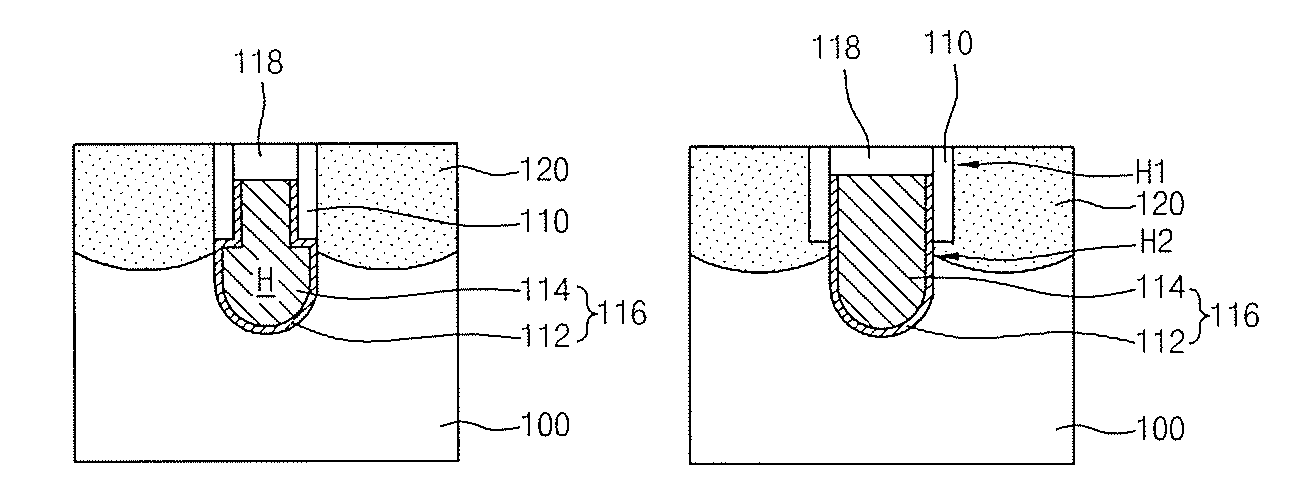

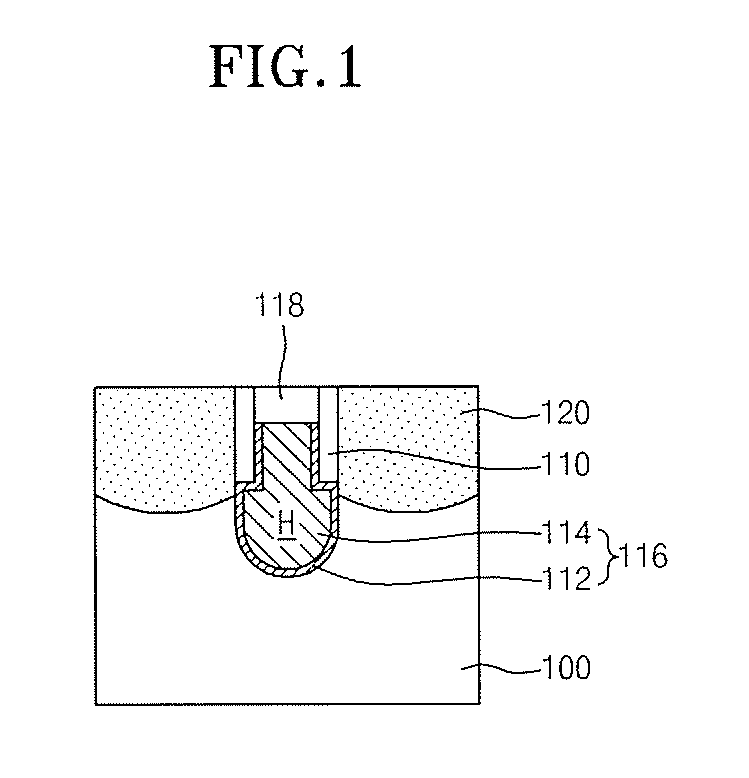

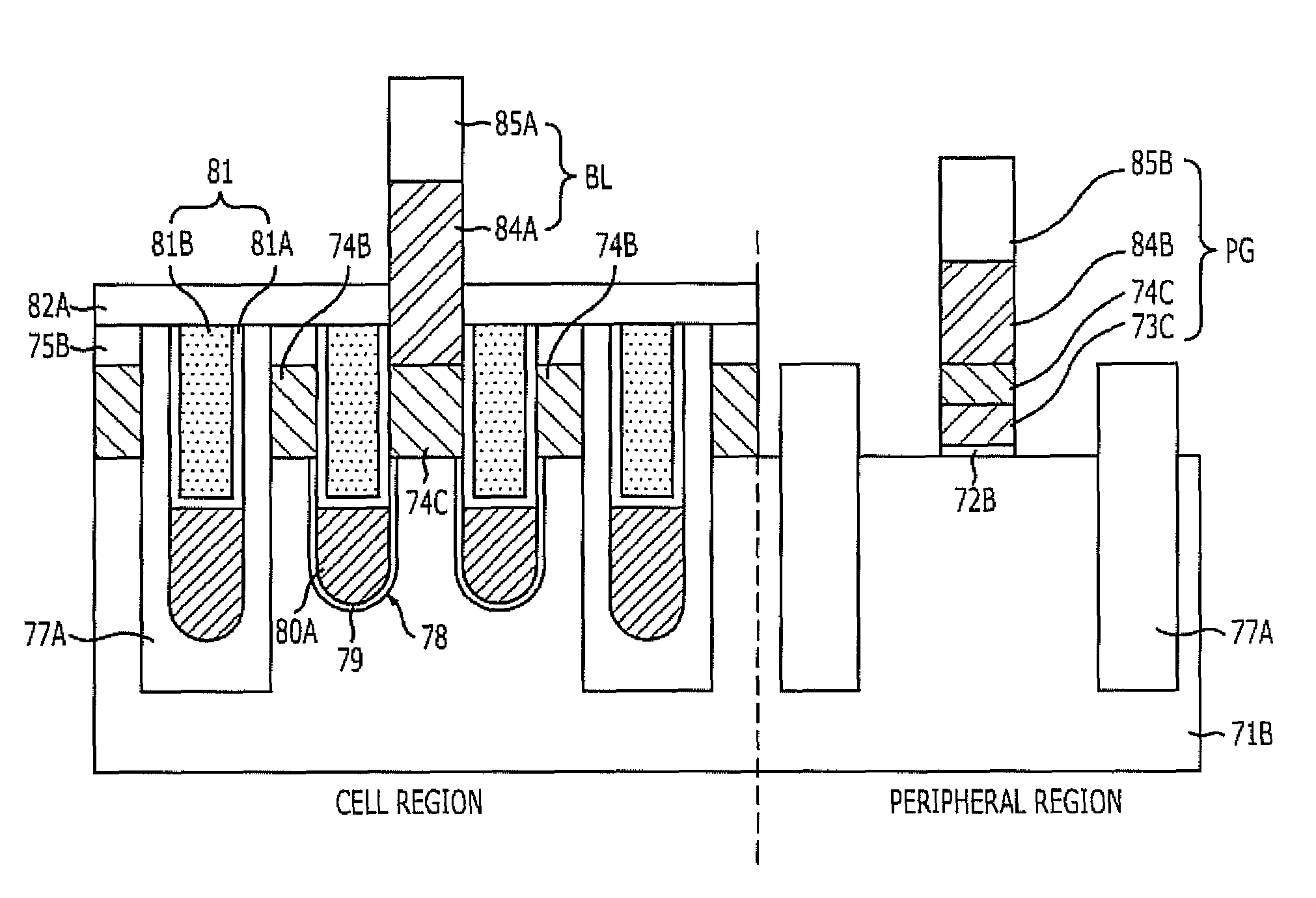

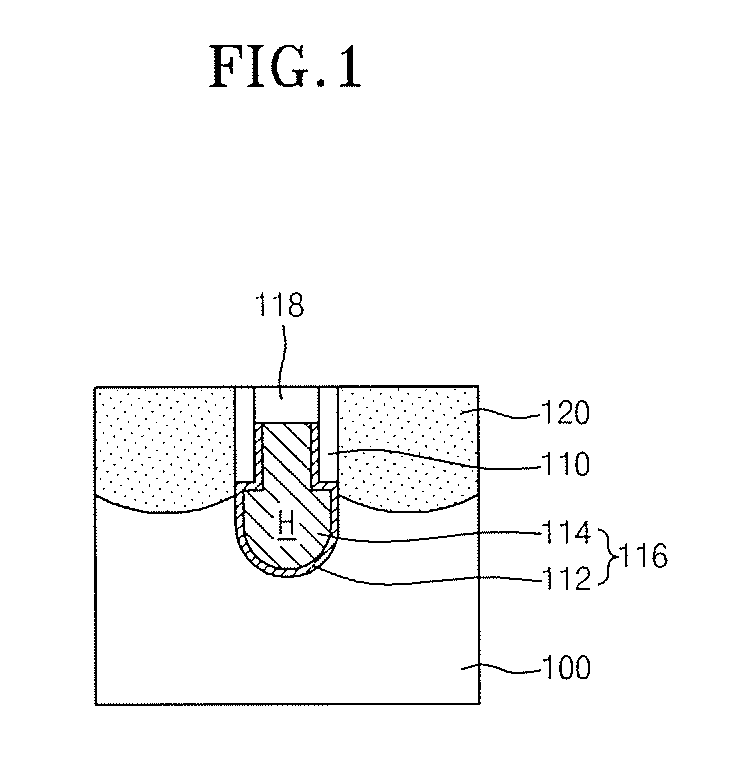

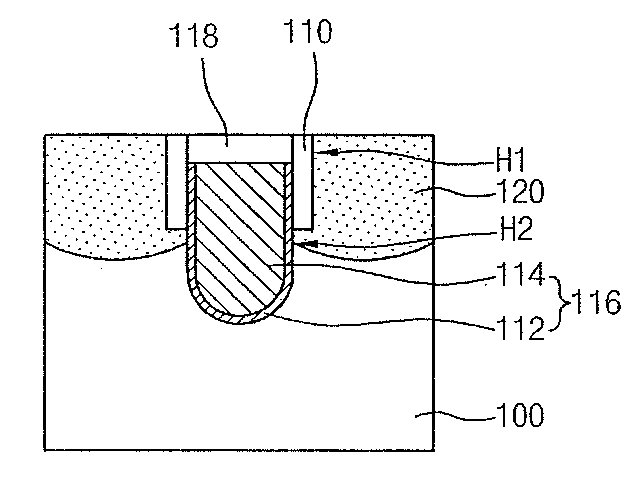

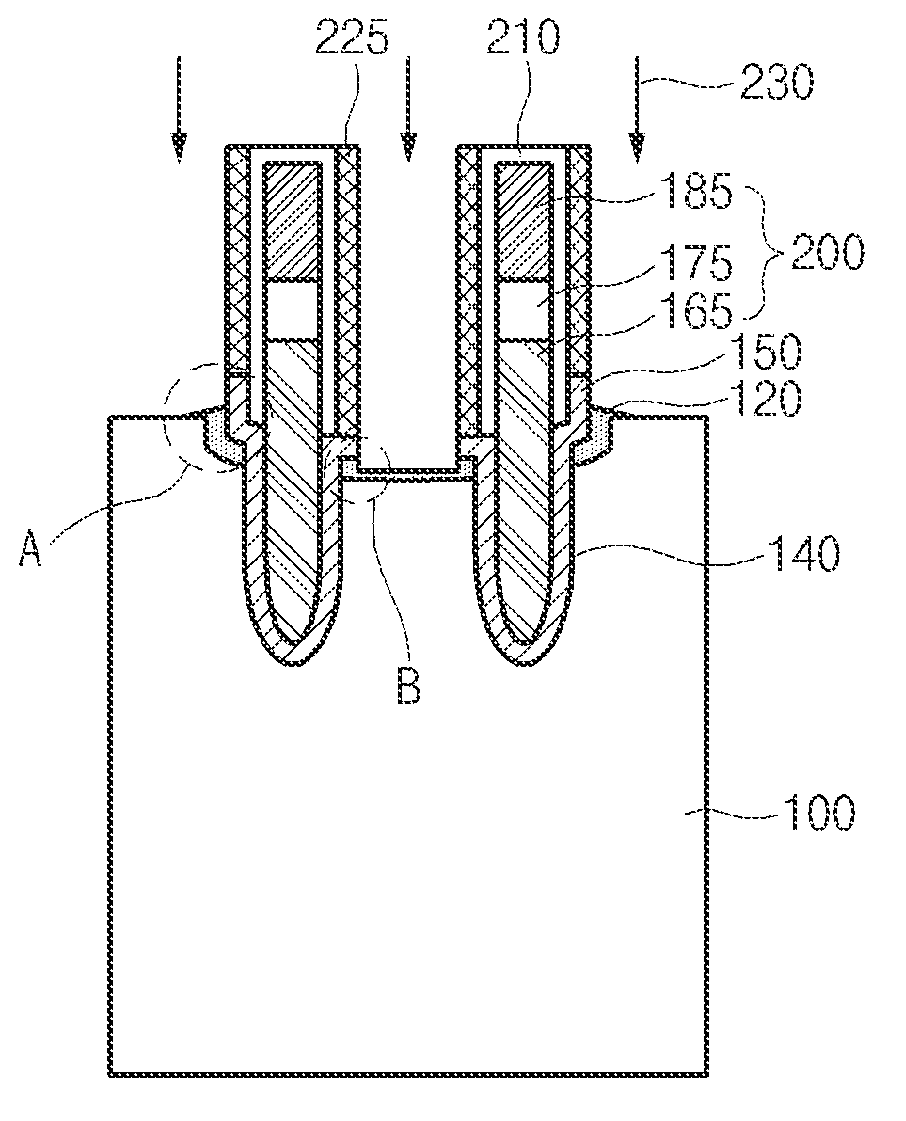

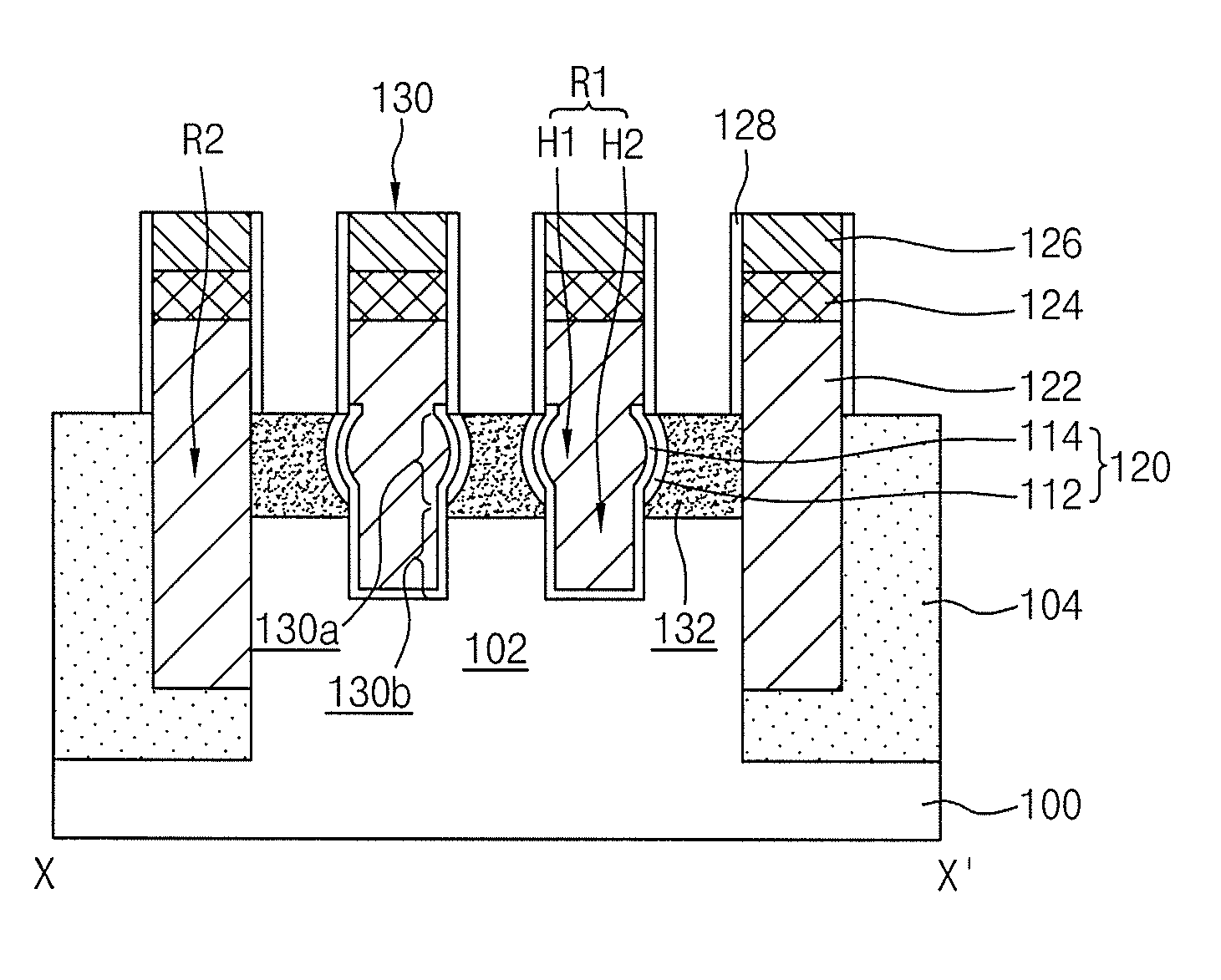

Semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage (GIDL) and method for manufacturing the same

InactiveUS8004048B2Reduce GIDLReduce leakage currentTransistorSolid-state devicesSemiconductorSemiconductor device

A semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage is presented. The semiconductor device includes a semiconductor substrate, a buried gate, and a barrier layer. The semiconductor substrate has a groove. The buried gate is formed in a lower portion of the groove and has a lower portion wider than an upper portion. The barrier layer is formed on sidewalls of the upper portion of the buried gate.

Owner:SK HYNIX INC

Method for fabricating buried gate using pre landing plugs

ActiveUS8357600B2Prevent oxidationReduce contact resistanceSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

A method for fabricating a semiconductor device is provided, the method includes forming a plug conductive layer over an entire surface of a substrate, etching the plug conductive layer to form landing plugs, etching the substrate between the landing plugs to form a trench, forming a gate insulation layer over a surface of the trench and forming a buried gate partially filling the trench over the gate insulation layer.

Owner:SK HYNIX INC

Semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage (GIDL) and method for manufacturing the same

InactiveUS20100311215A1Reduce decreaseReduce GIDLTransistorSolid-state devicesSemiconductorSemiconductor device

A semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage is presented. The semiconductor device includes a semiconductor substrate, a buried gate, and a barrier layer. The semiconductor substrate has a groove. The buried gate is formed in a lower portion of the groove and has a lower portion wider than an upper portion. The barrier layer is formed on sidewalls of the upper portion of the buried gate.

Owner:SK HYNIX INC

Semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage (GIDL) and method for manufacturing the same

ActiveUS20110275188A1Reduce GIDLReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

A semiconductor device having a buried gate that can realize a reduction in gate-induced drain leakage is presented. The semiconductor device includes a semiconductor substrate, a buried gate, and a barrier layer. The semiconductor substrate has a groove. The buried gate is formed in a lower portion of the groove and has a lower portion wider than an upper portion. The barrier layer is formed on sidewalls of the upper portion of the buried gate.

Owner:SK HYNIX INC

Dark current reduction circuitry for CMOS active pixel sensors

InactiveUS20060113461A1Minimizing gate induced drain leakageReduce GIDLTelevision system detailsTelevision system scanning detailsSensor arrayDriver circuit

A row driver circuit is disclosed for supplying a reset voltage to a plurality of reset transistors of an active pixel sensor array while minimizing gate induced drain leakage (GIDL). The row driver circuit is configured to supply a high voltage level (e.g., Vdd or higher) to the reset transistors of the array during a reset operation. The row driver circuit is further configured to supply a low voltage level (e.g., a voltage level higher than ground) to the reset transistors of the array when the pixels are not being reset (e.g., during integration). The reduced potential difference realized between the respective gates of the reset transistors and the respective photodiodes of the pixels, when the pixels are not being reset, results in reduced GIDL.

Owner:APTINA IMAGING CORP

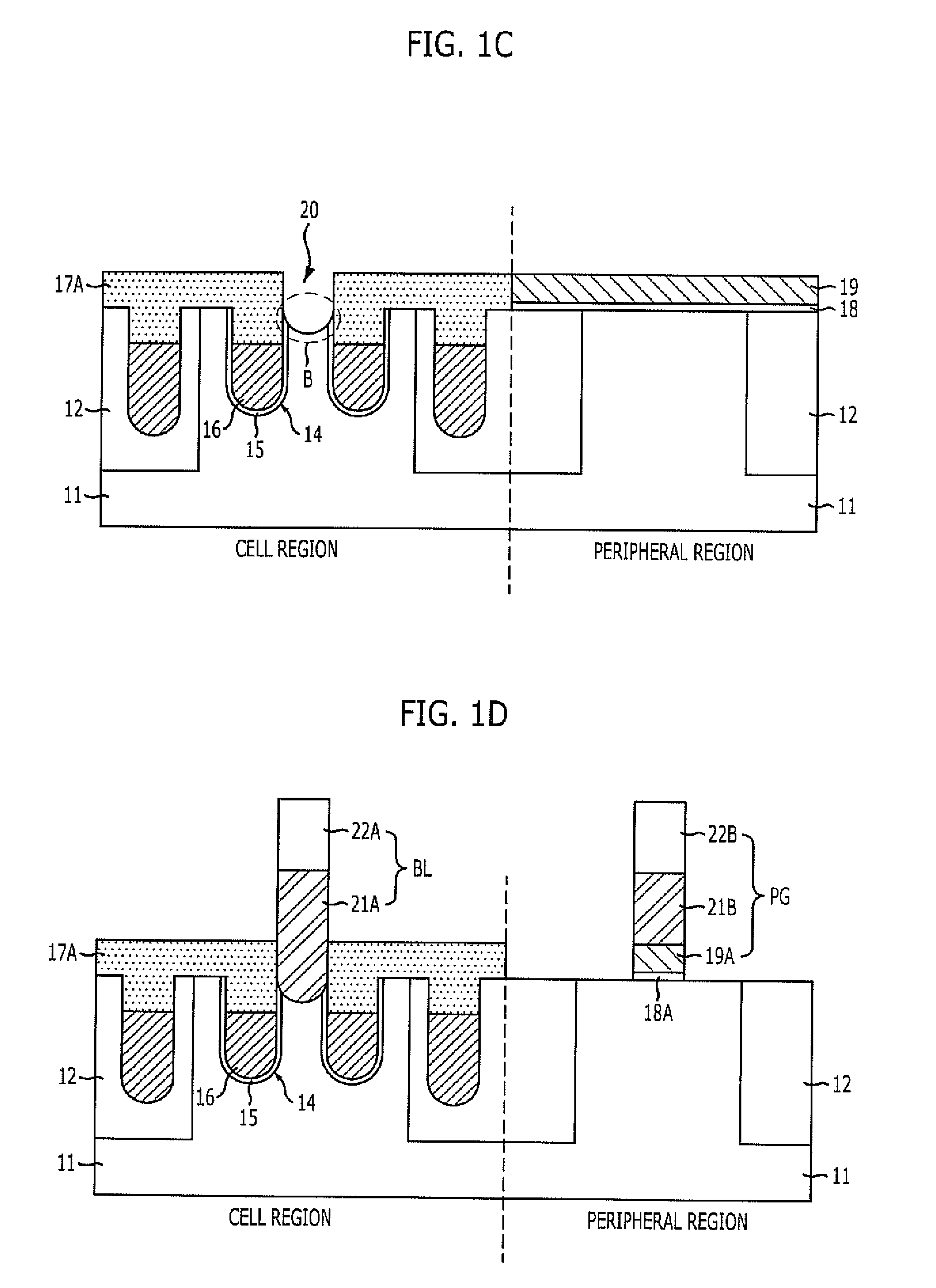

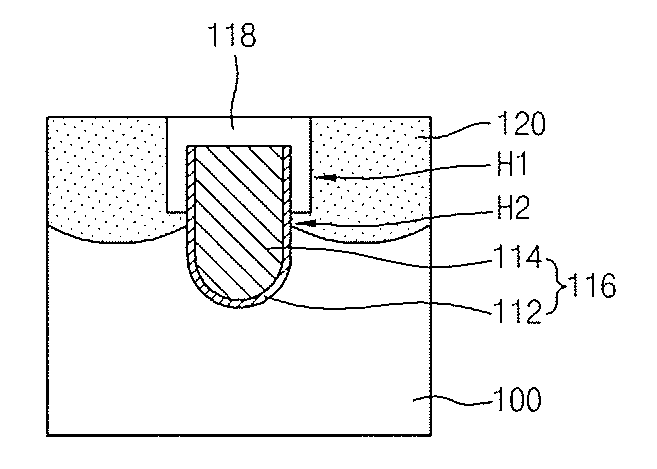

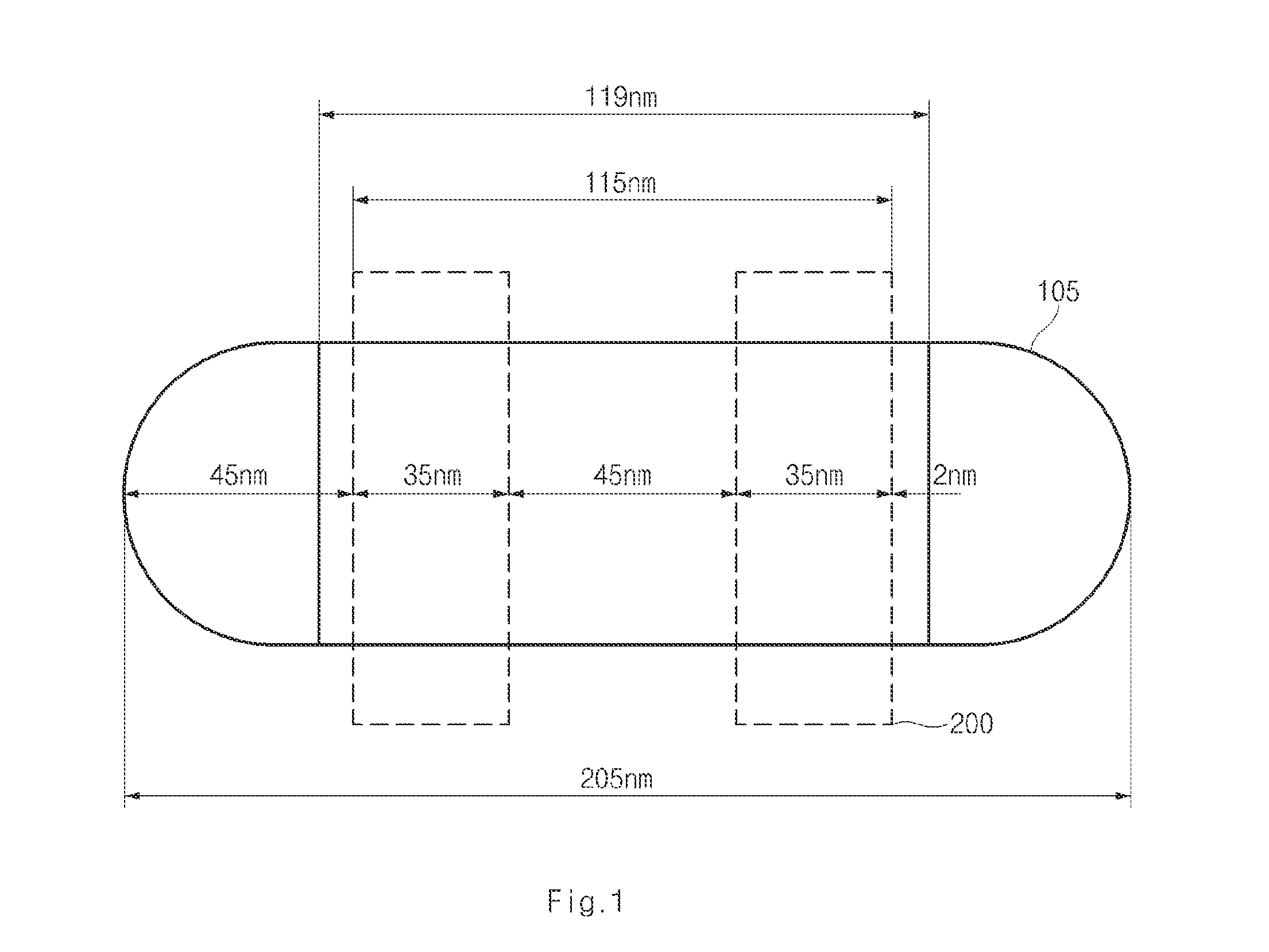

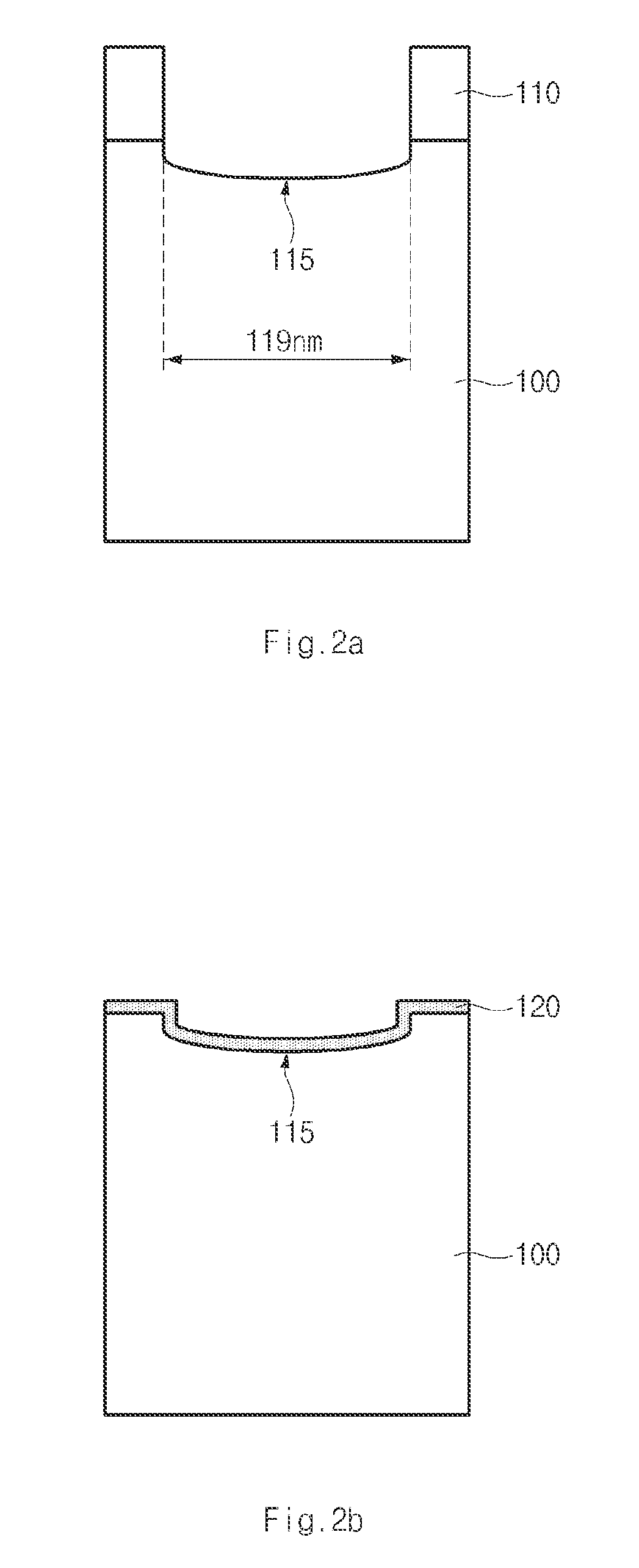

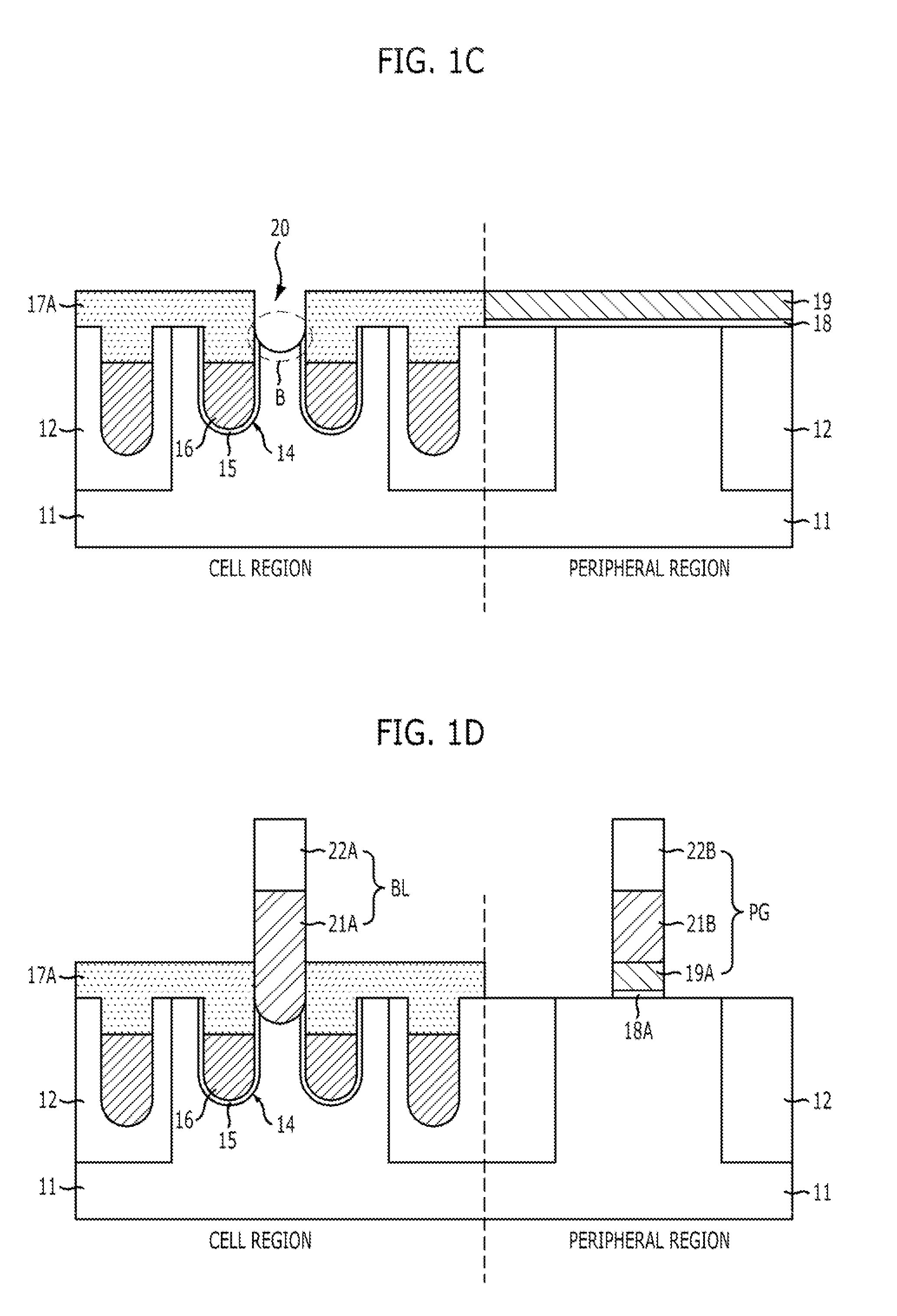

Semiconductor device with a gate having a bulbous area and a flattened area underneath the bulbous area and method for manufacturing the same

ActiveUS20100213540A1Prevent and at least minimize degradationPrevent orTransistorSolid-state devicesInsulation layerIsolation layer

A semiconductor device with a gate having a bulbous area and a flattened area underneath the bulbous are is presented. The semiconductor device includes a semiconductor substrate, an isolation layer, a gate insulation layer, and gates. The semiconductor substrate has recess parts that have first grooves which have bulbous-shaped profiles and second vertically flattened profile grooves which extend downward from the first grooves. The gates are formed in the recess parts in which the gate insulation layer is double layered in the bulbous profile areas and is single layered in the flattened profile areas.

Owner:SK HYNIX INC

Semiconductor device and method for manufacturing the same

ActiveUS20120061750A1Suppress increaseReduce GIDLSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device and a method for manufacturing the same are disclosed. A recess gate structure is formed between an overlapping region between a gate and a source / drain so as to suppress increase in gate induced drain leakage (GIDL), and a gate insulation film is more thickly deposited in a region having weak GIDL, thereby reducing GIDL and thus improving refresh characteristics due to leakage current.

Owner:SK HYNIX INC

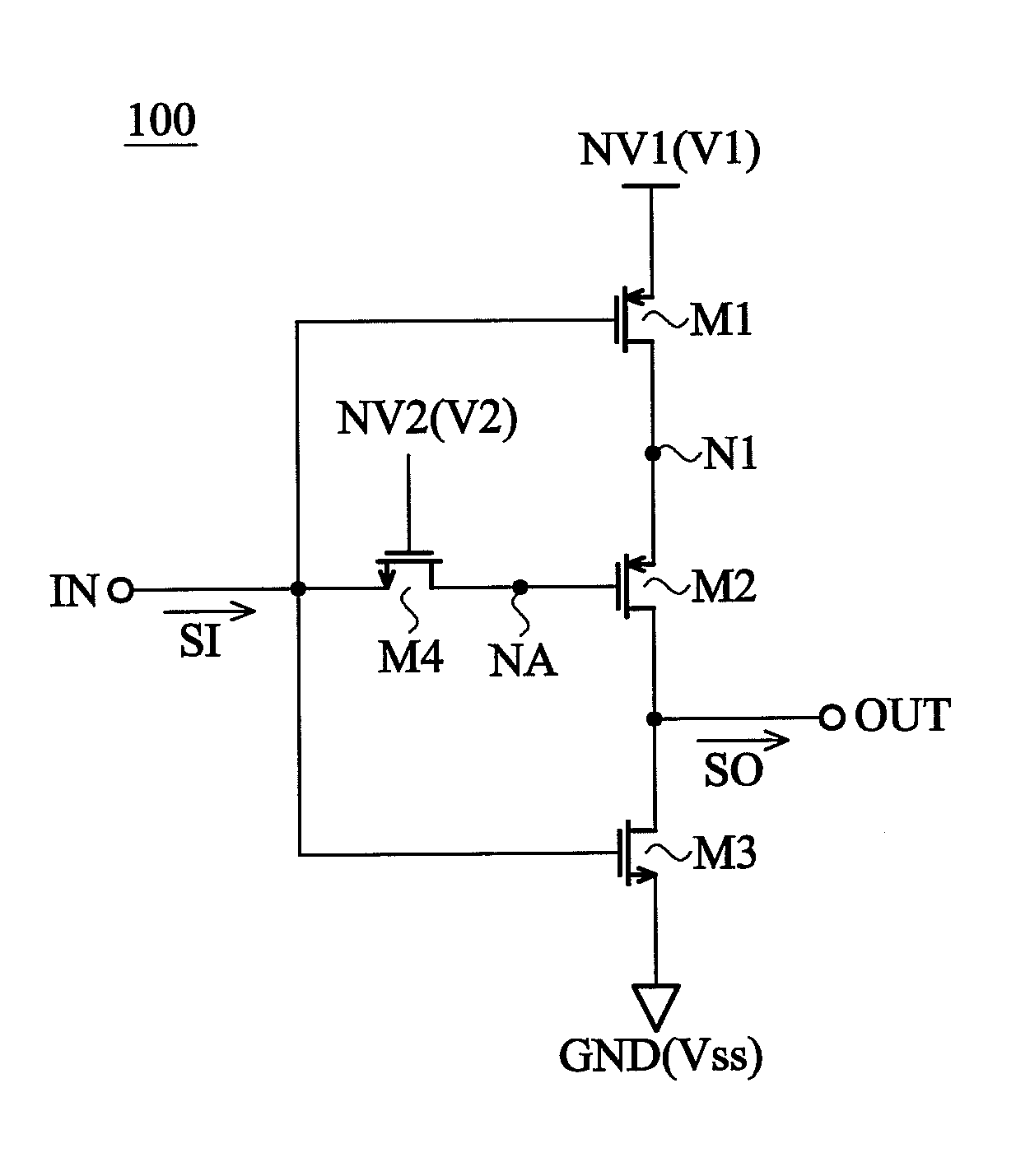

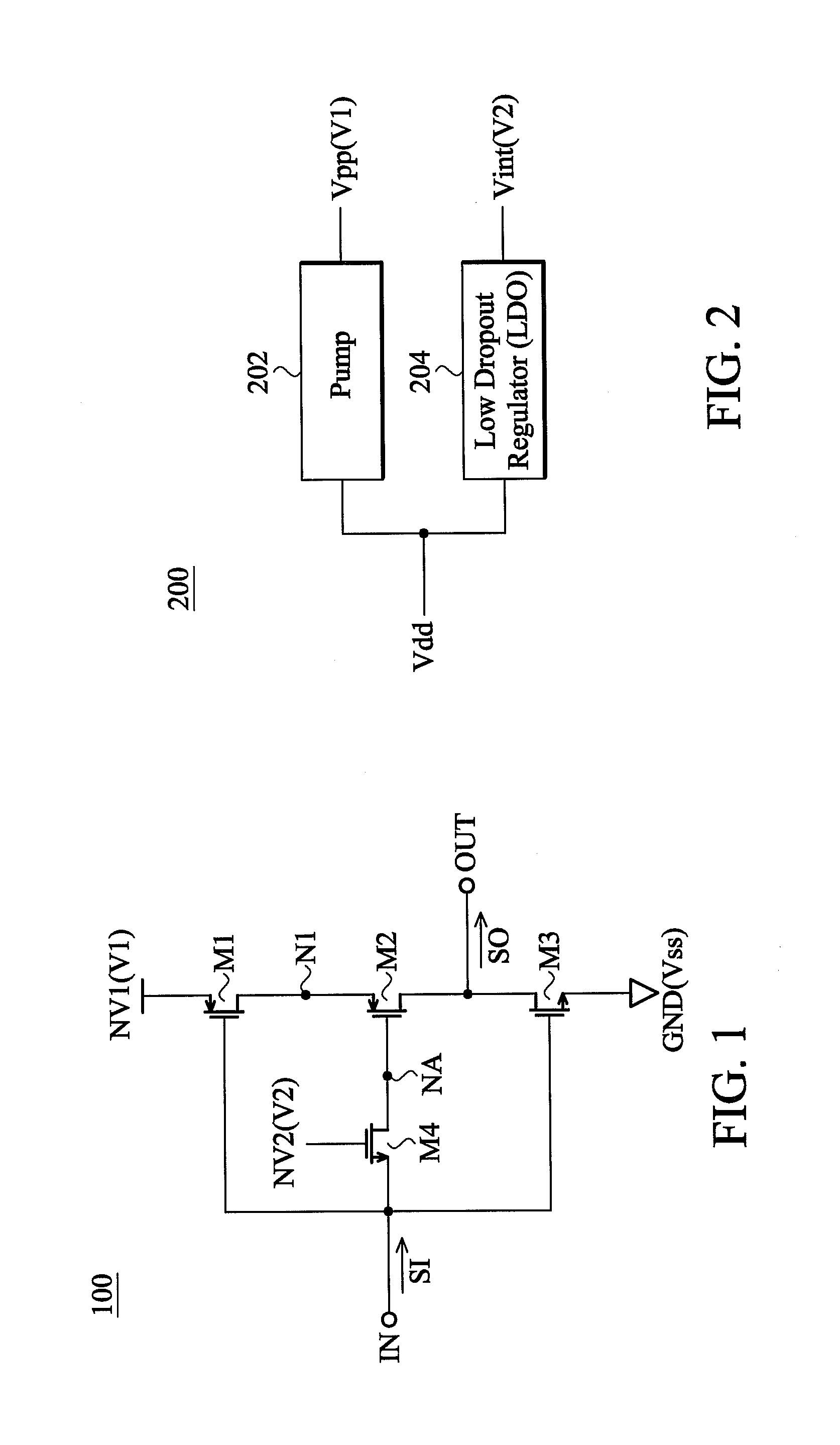

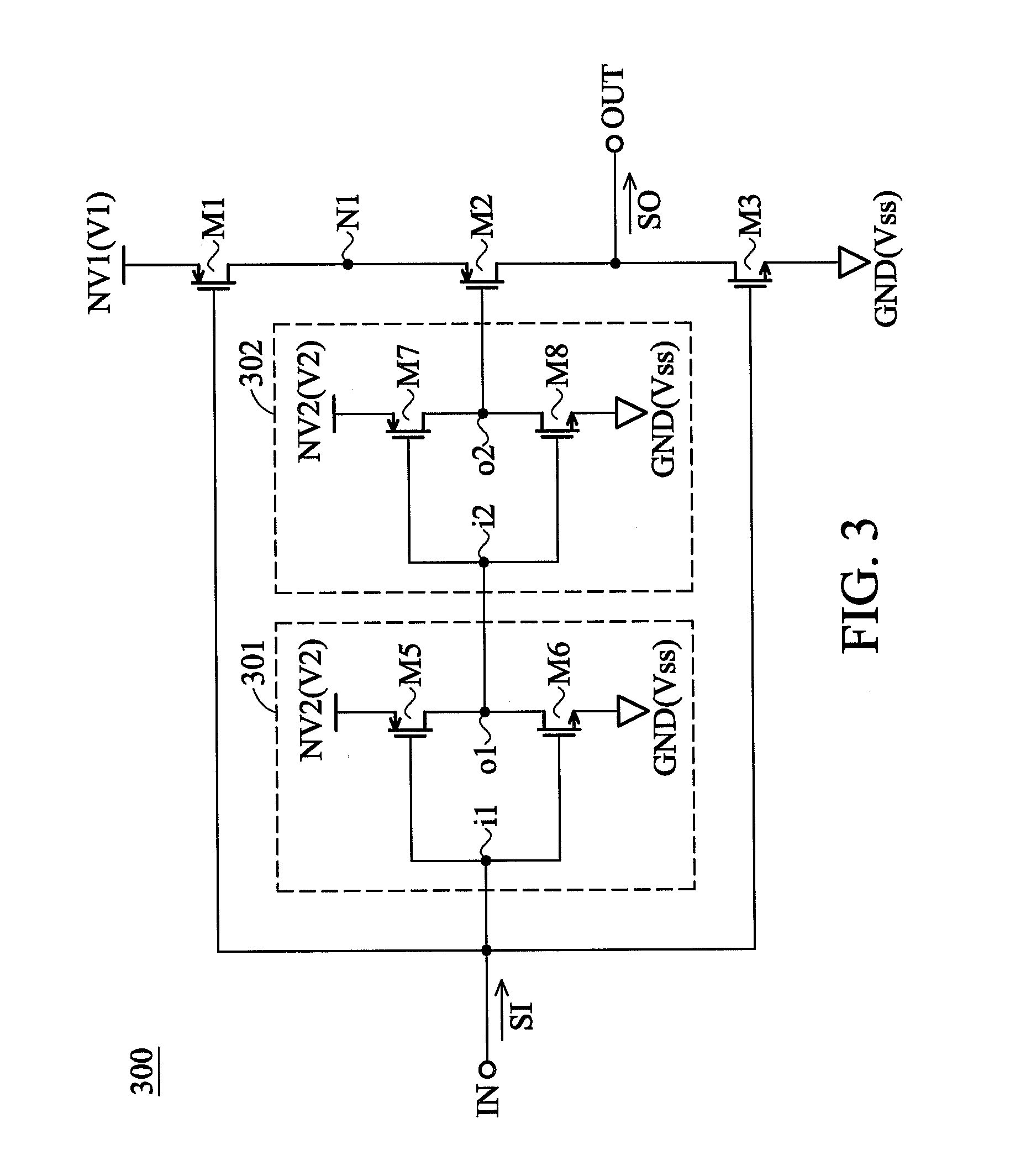

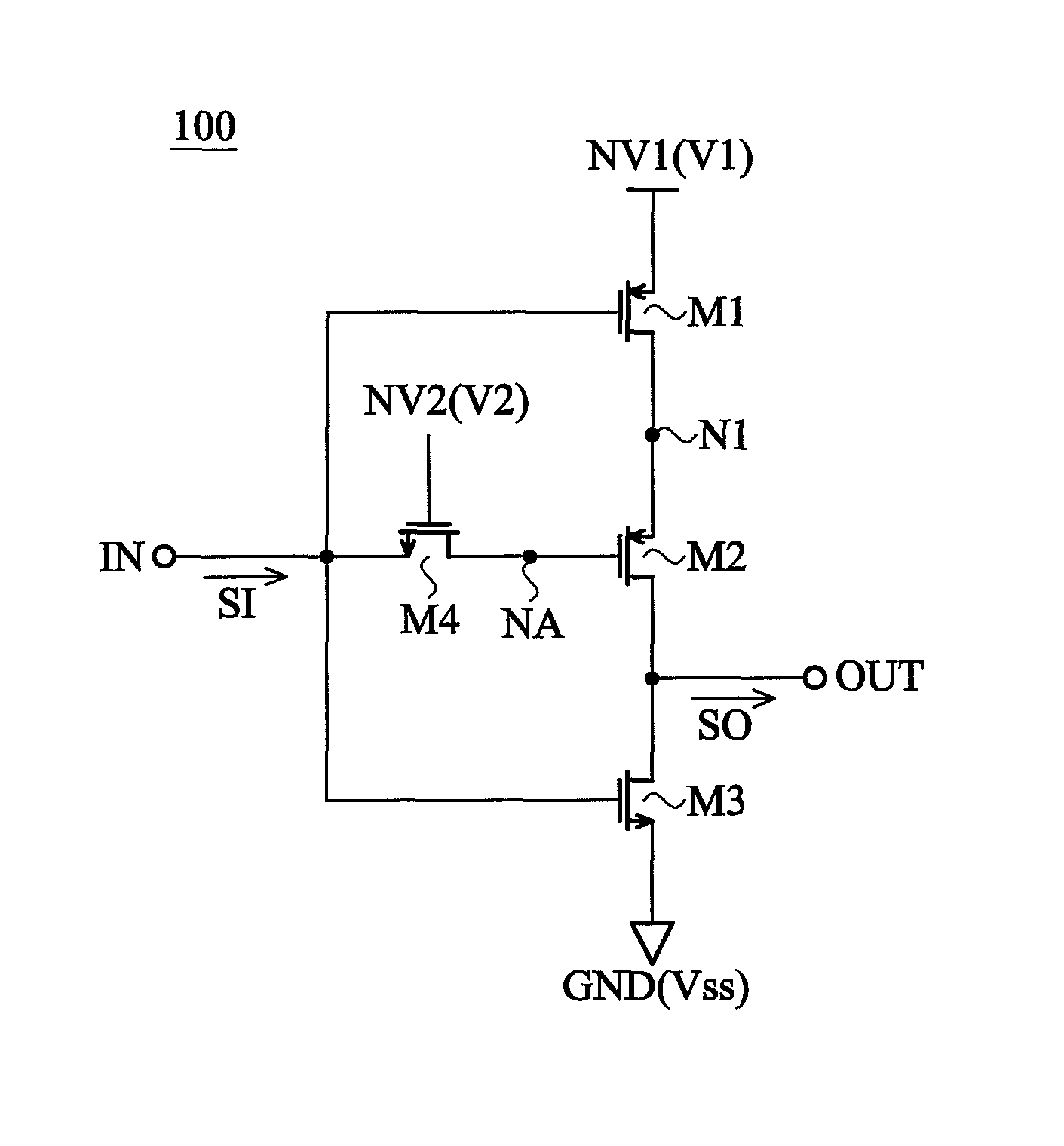

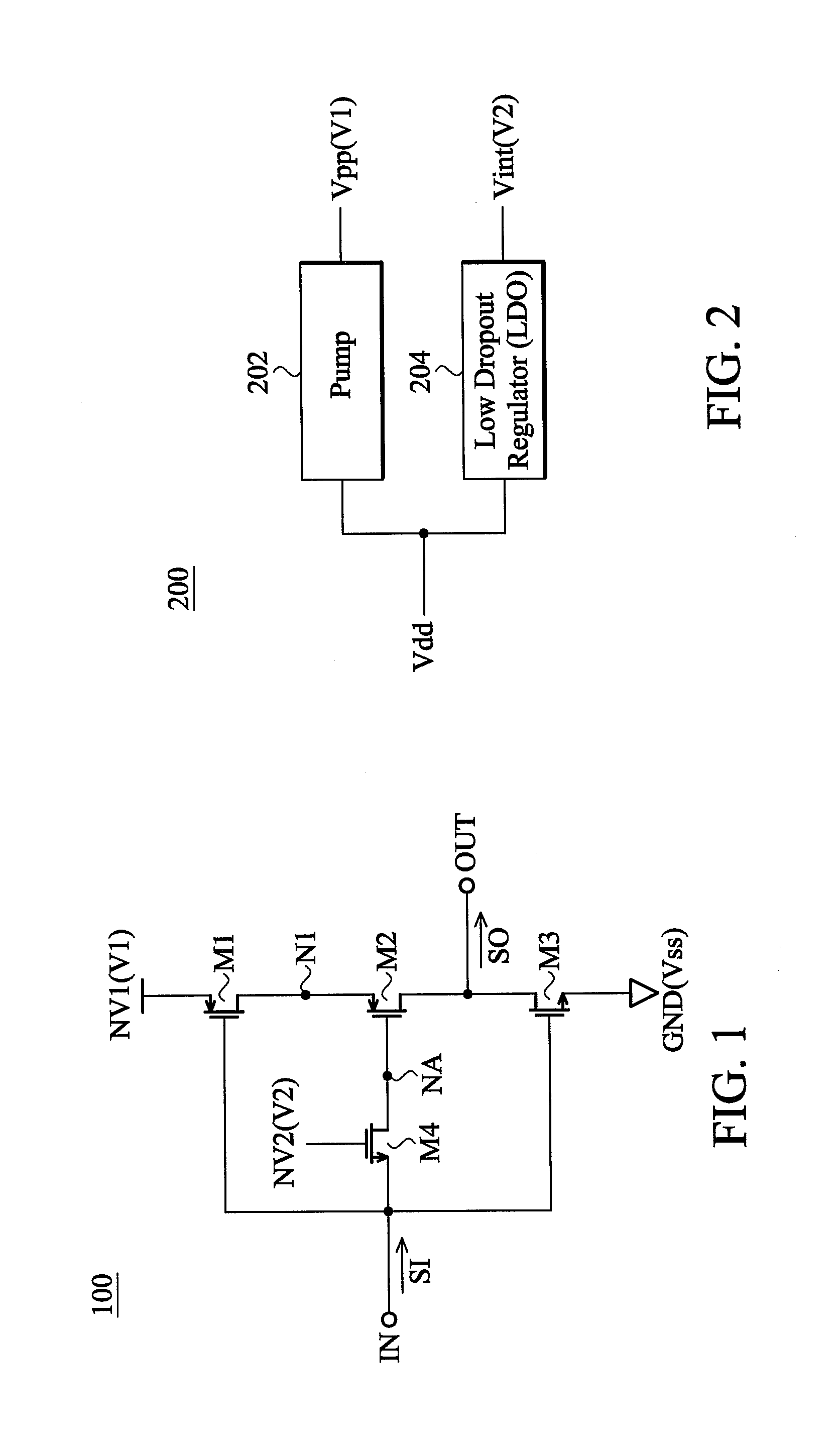

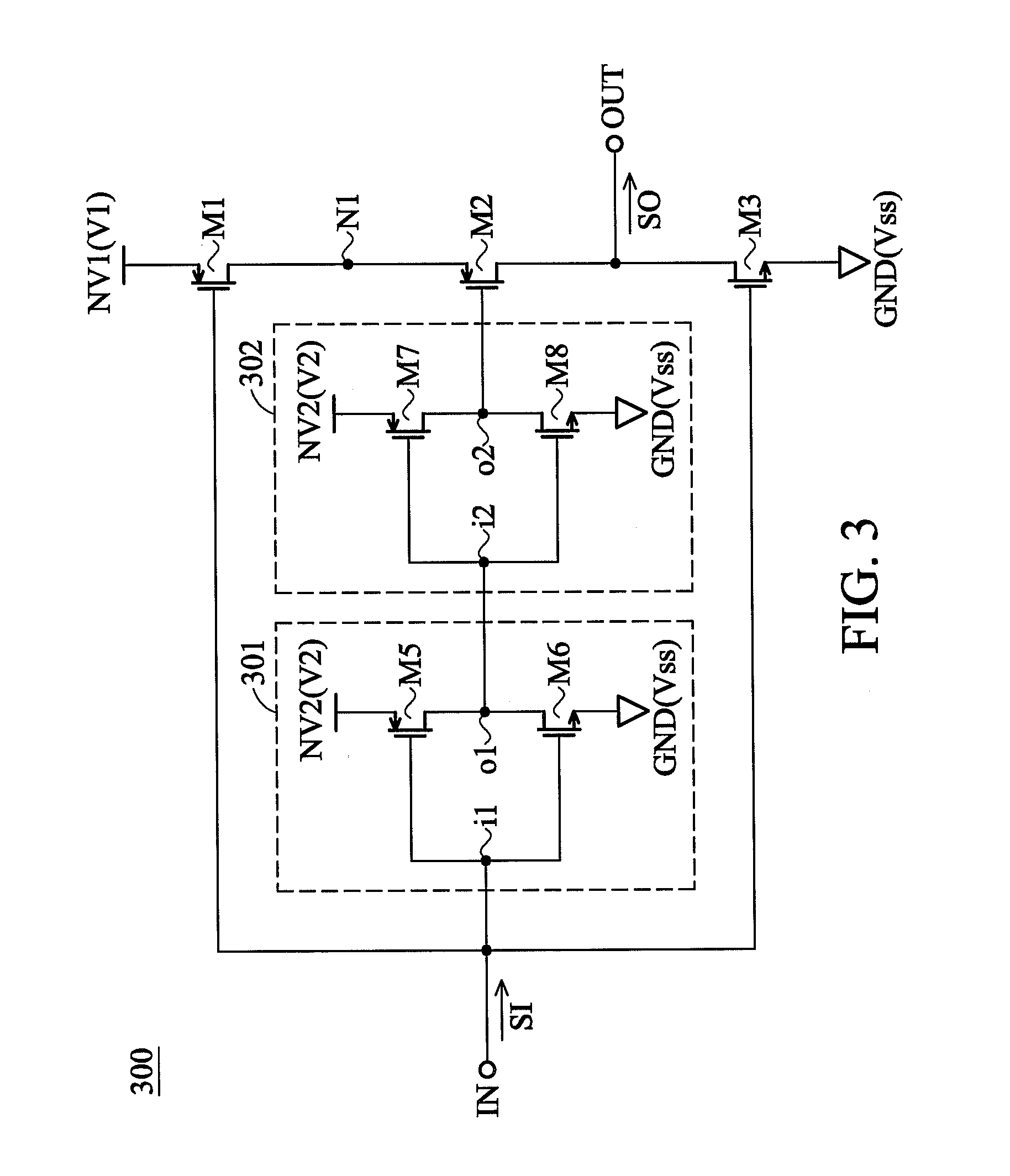

Protecting circuit and control circuit for reducing leakage current

ActiveUS20130100557A1Reduce voltage differenceReduce GIDLTransistorEmergency protective arrangements for automatic disconnectionOxide semiconductorN channel

A protecting circuit for reducing leakage currents comprises a first PMOS transistor (P-channel Metal-Oxide-Semiconductor Field-Effect Transistor), a second PMOS transistor, a first NMOS transistor (N-channel Metal-Oxide-Semiconductor Field-Effect Transistor), and a second NMOS transistor. The first PMOS transistor is coupled between a first voltage node and a node, and comprises a first gate coupled an input node. The second PMOS transistor is coupled between the node and an output node. The first NMOS transistor is coupled between the output node and a ground node, and comprises a third gate coupled to the input node. The second NMOS transistor is coupled between the input node and a second gate of the second PMOS transistor, and comprises a fourth gate coupled to a second voltage node.

Owner:WINBOND ELECTRONICS CORP

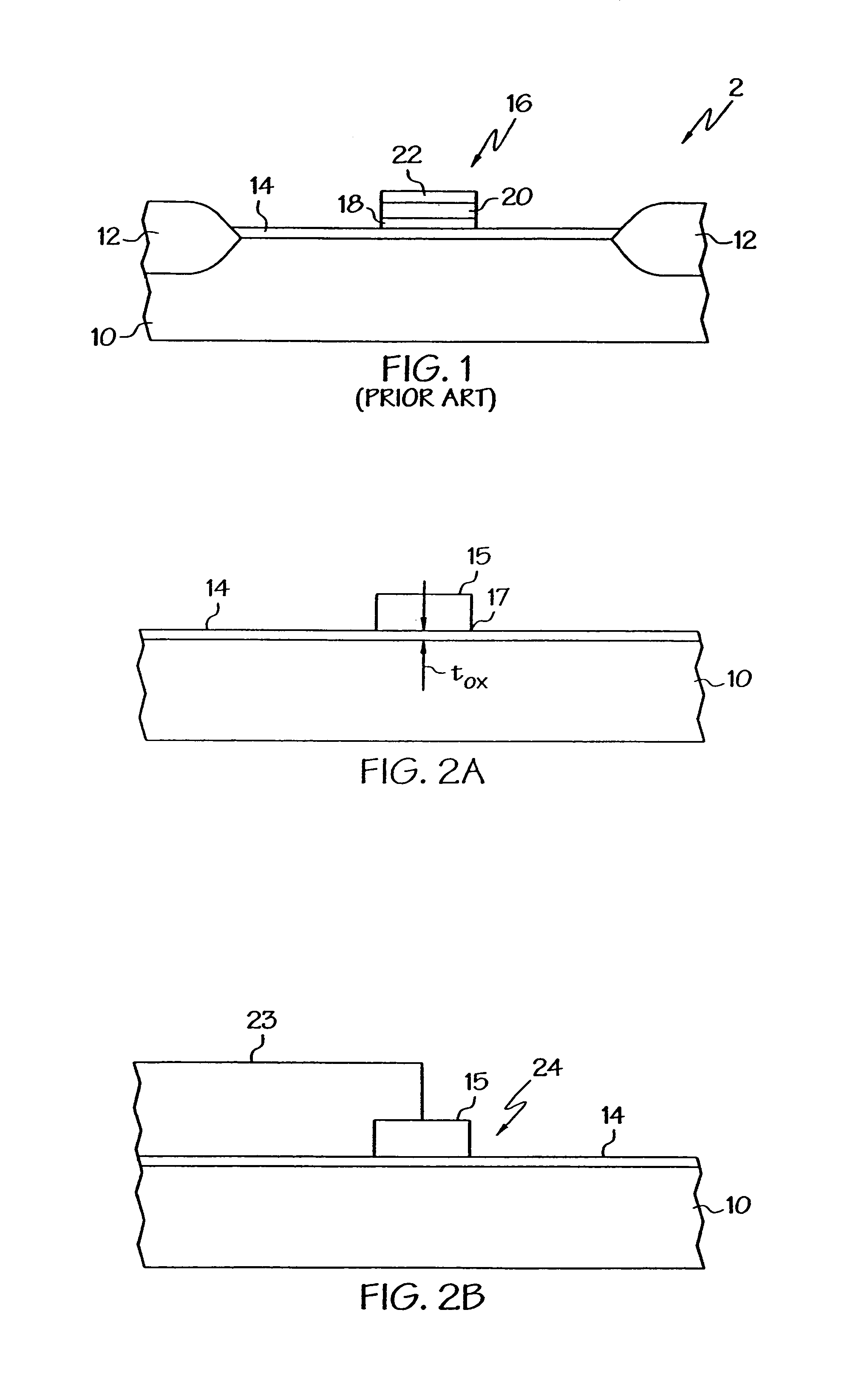

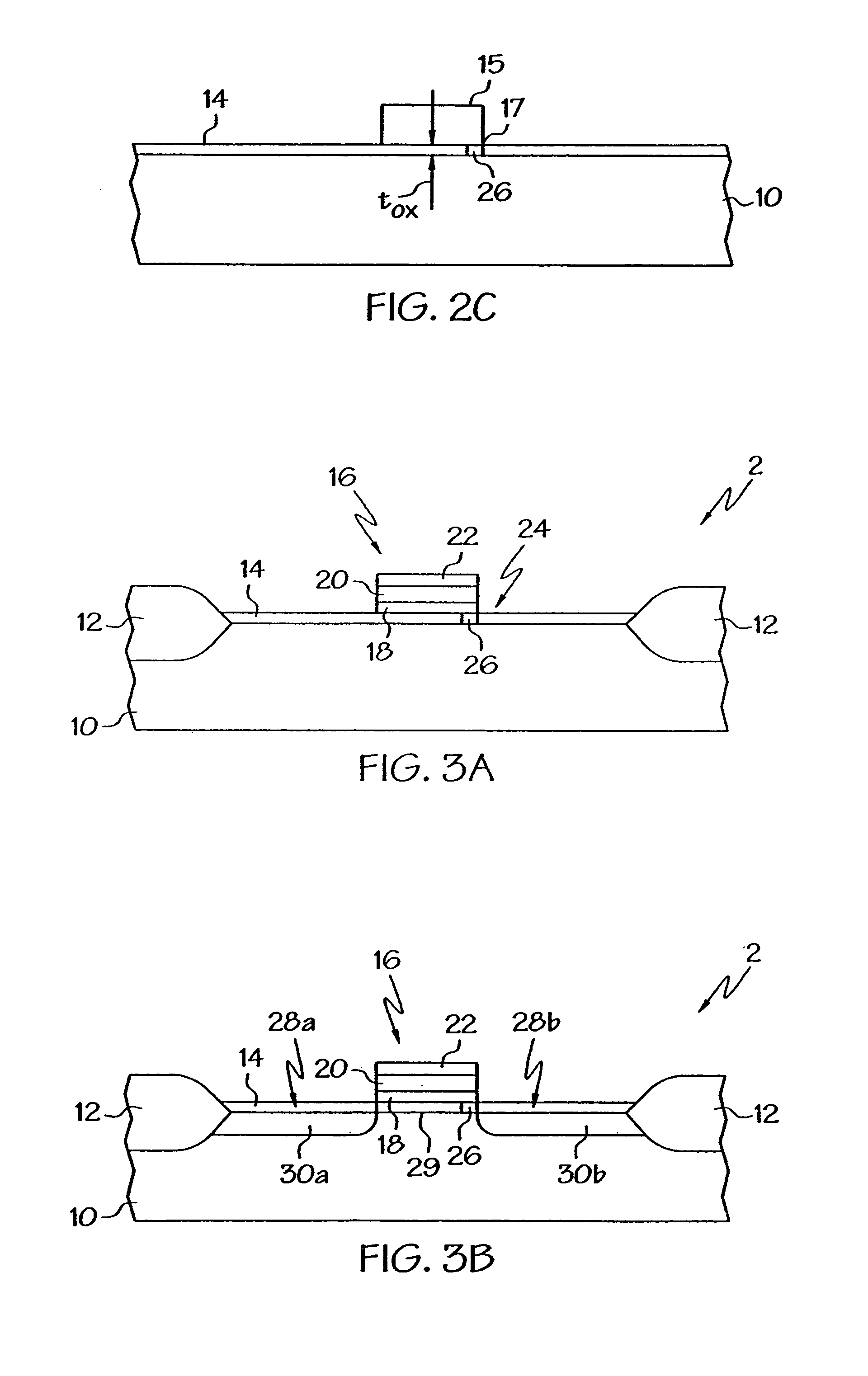

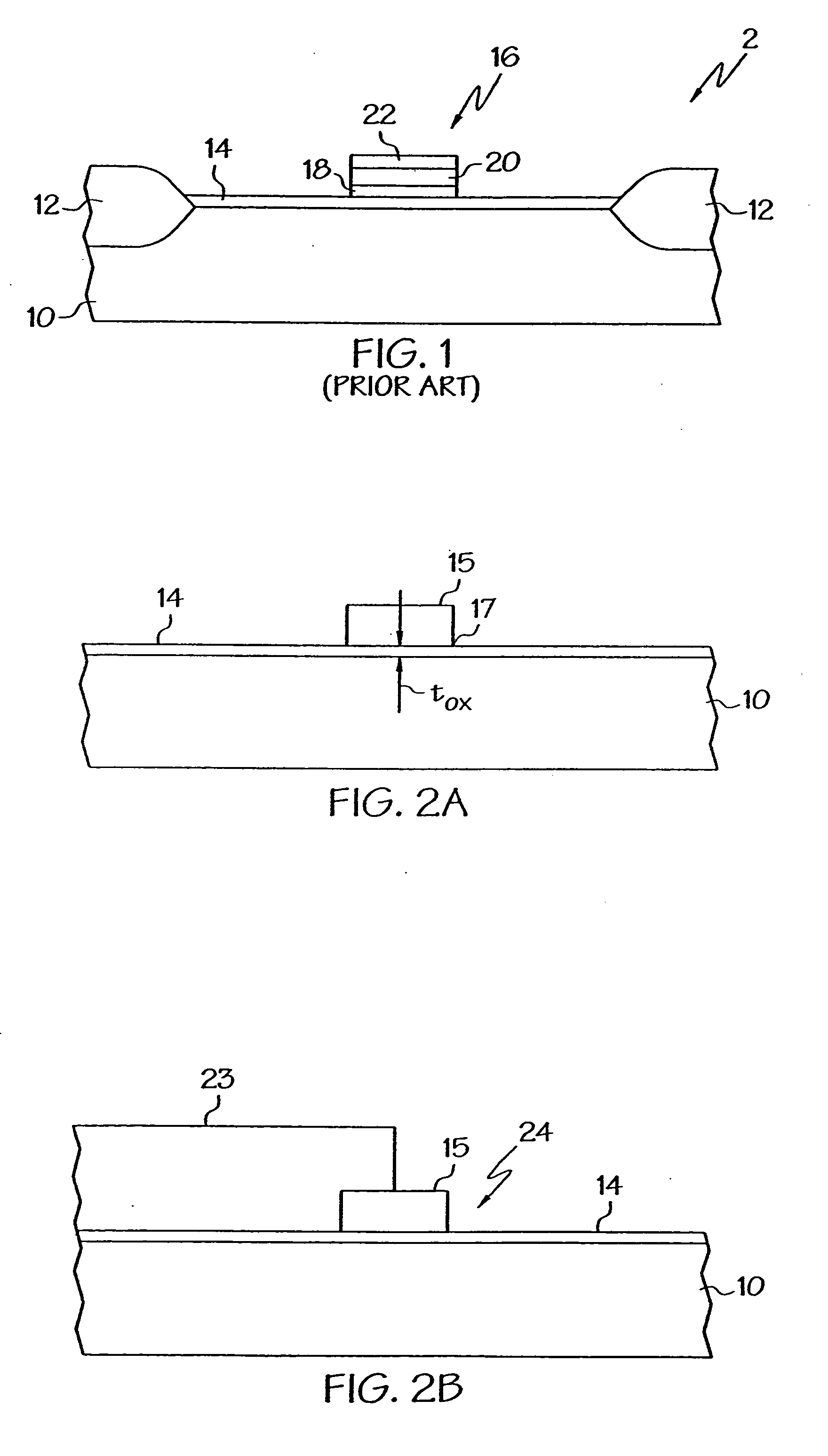

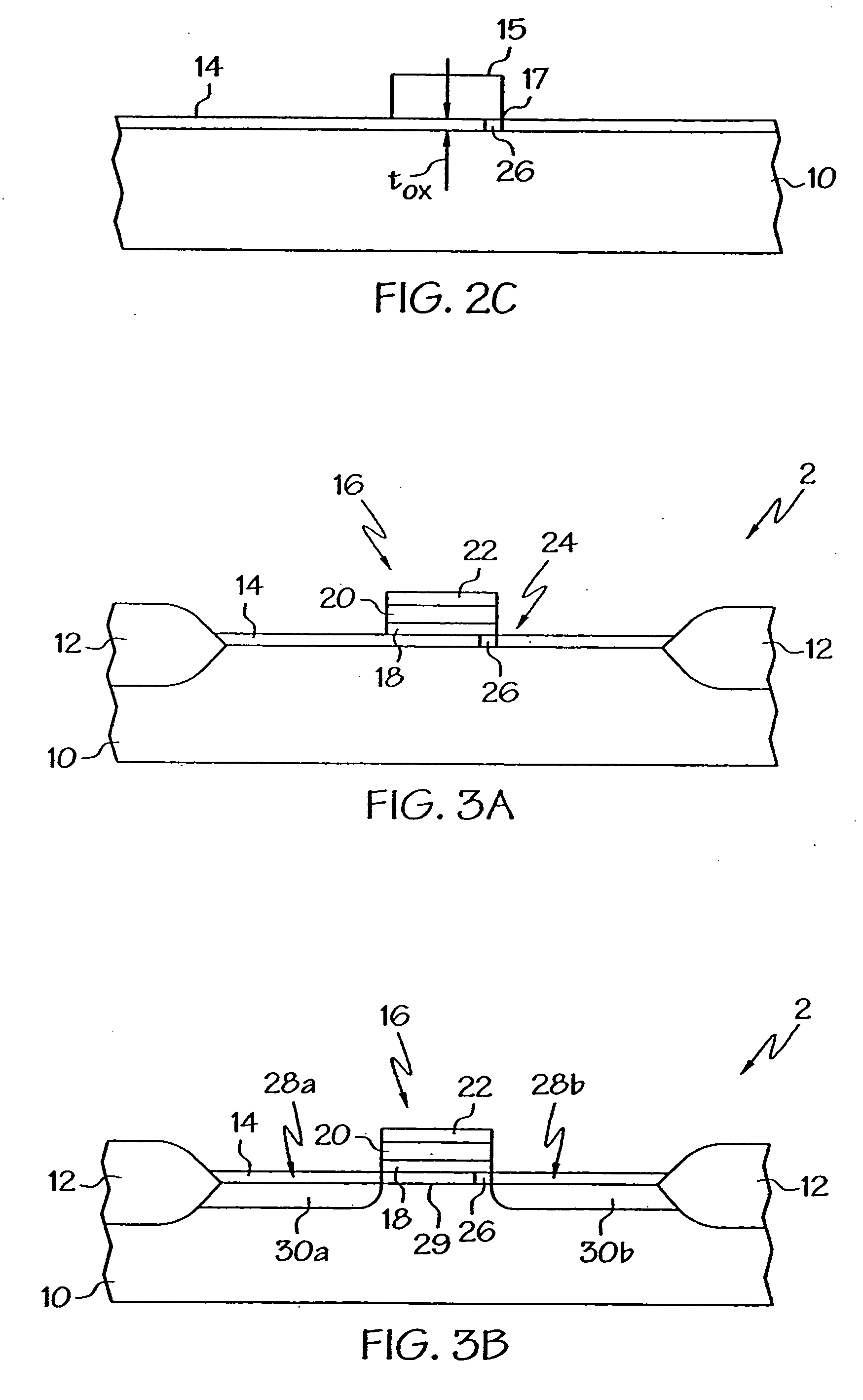

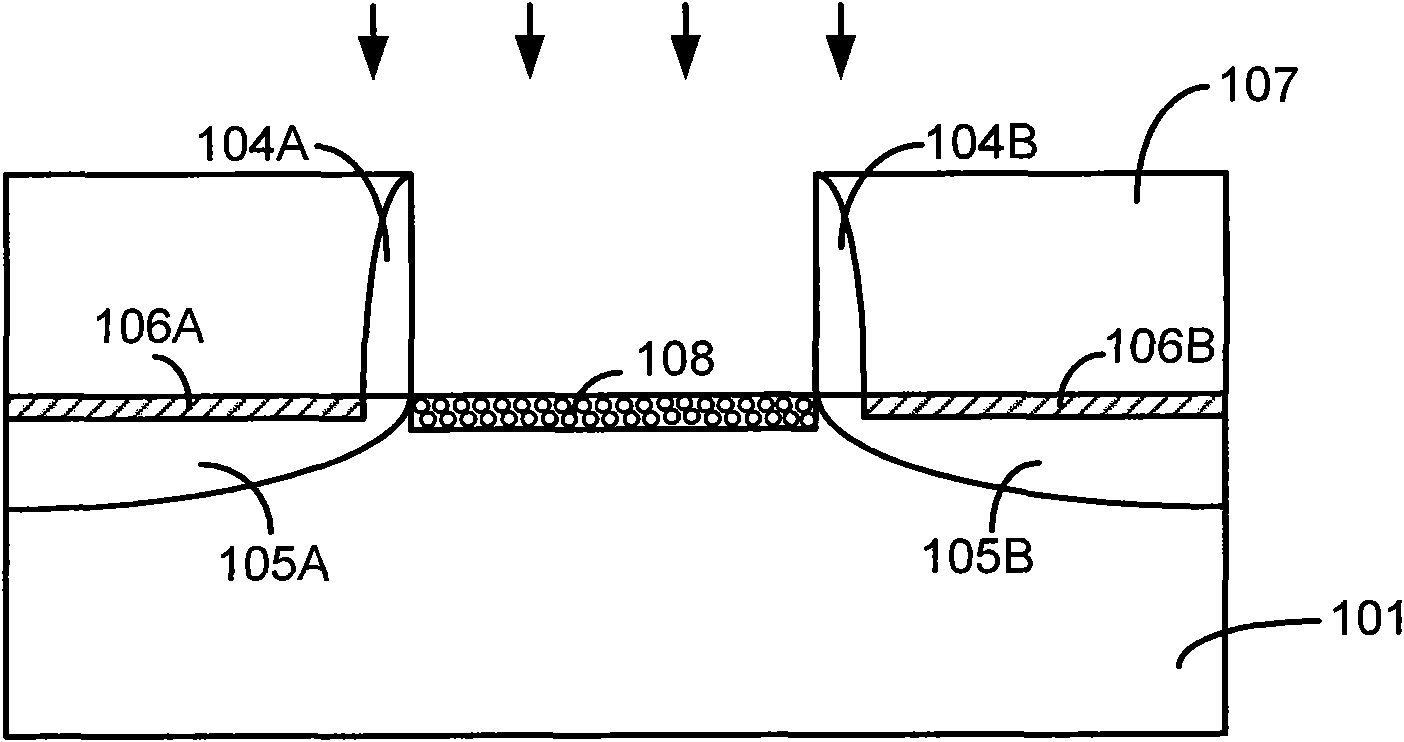

Method and device to reduce gate-induced drain leakage (GIDL) current in thin gate oxides MOSFETs

InactiveUS7247919B1Minimize GIDLReduce GIDLTransistorSemiconductor/solid-state device manufacturingHigh dosesEngineering

An integrated circuit which provides a FET device having reduced GIDL current is described. A semiconductor substrate is provided wherein active regions are separated by an isolation region and a gate oxide layer is provided on the active regions. A gate electrode is provided upon the gate oxide layer wherein beneath an edge of the gate electrode, a gate-drain overlap region having a high dose ion implant is provided.

Owner:MICRON TECH INC

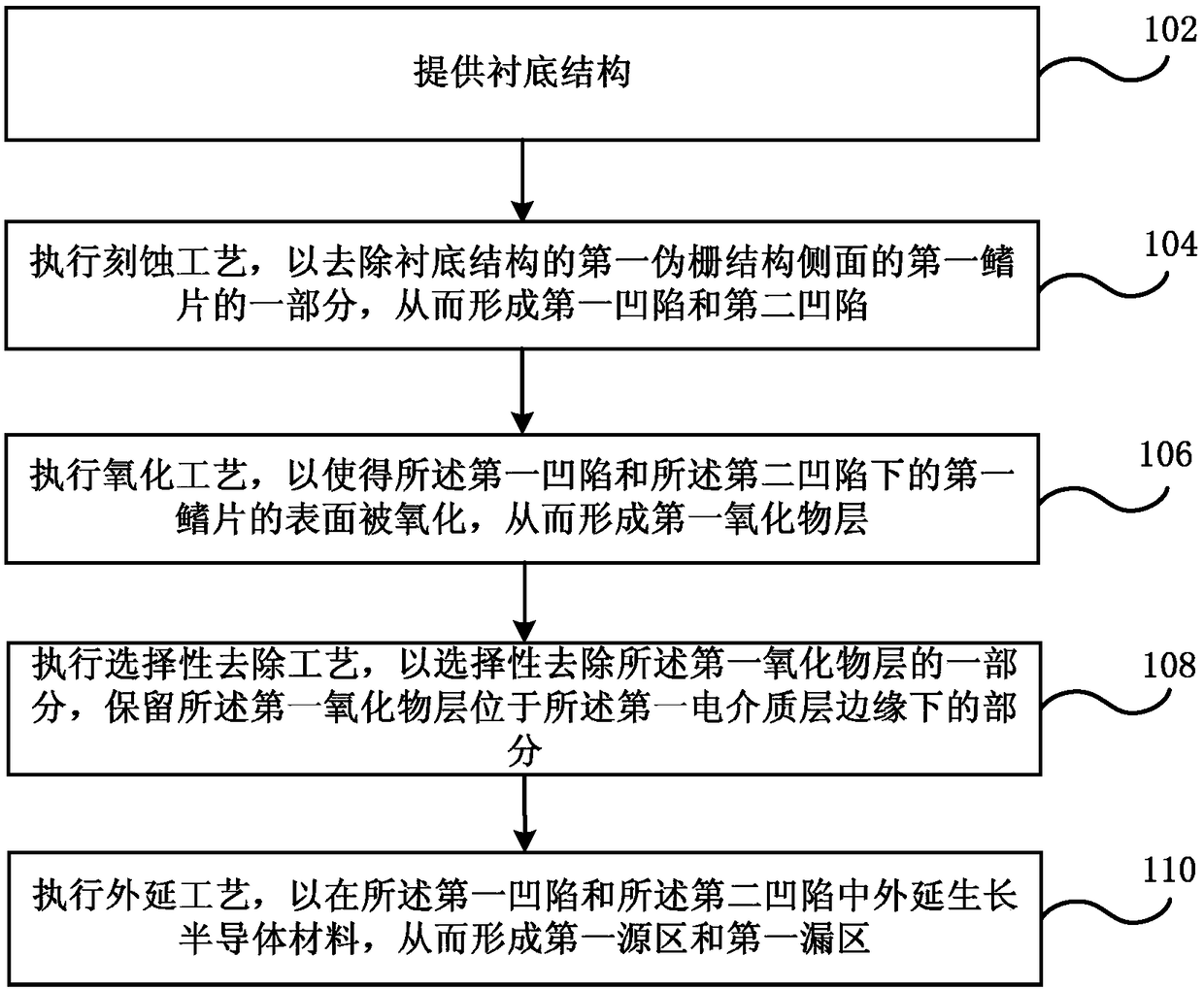

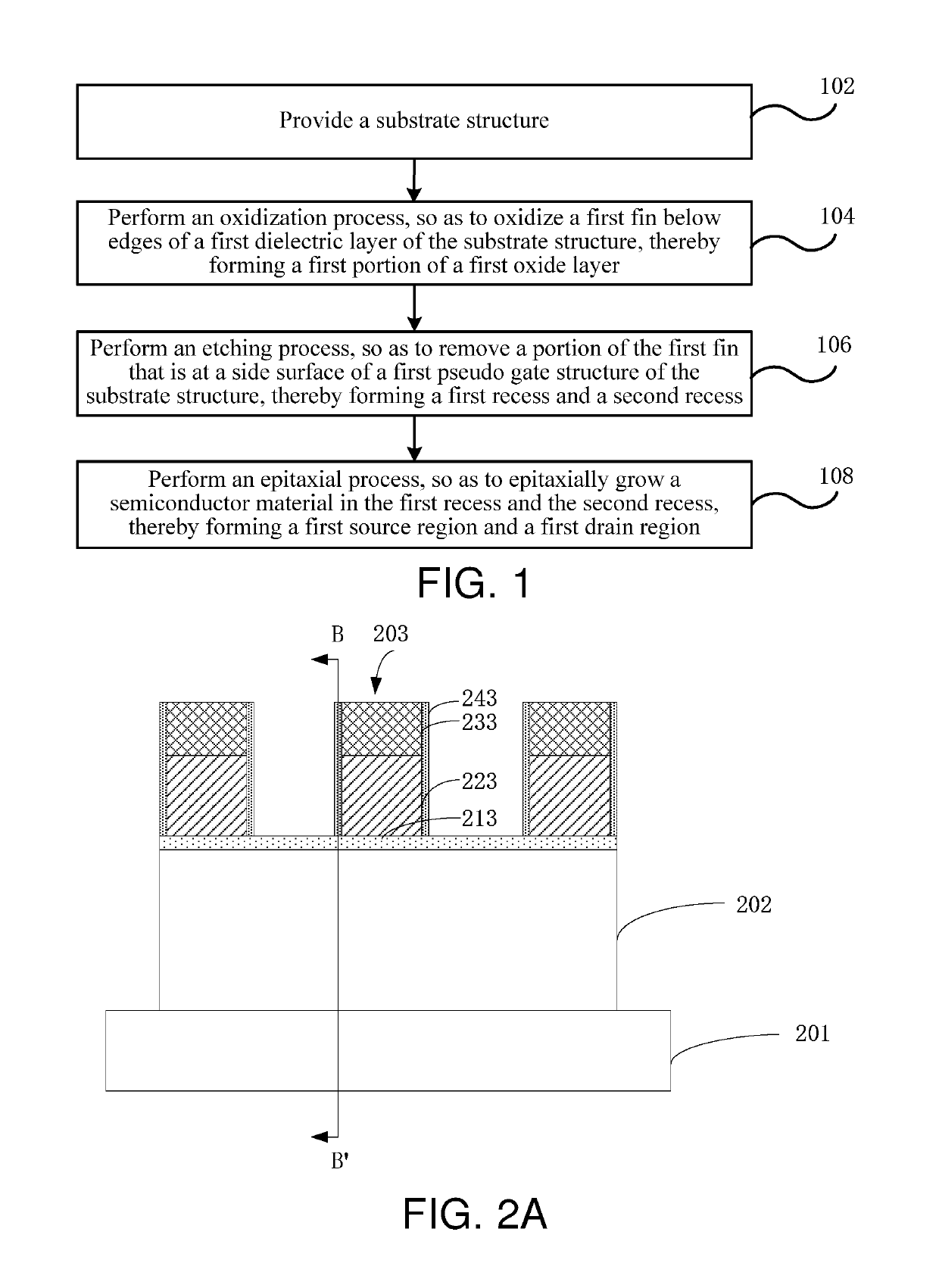

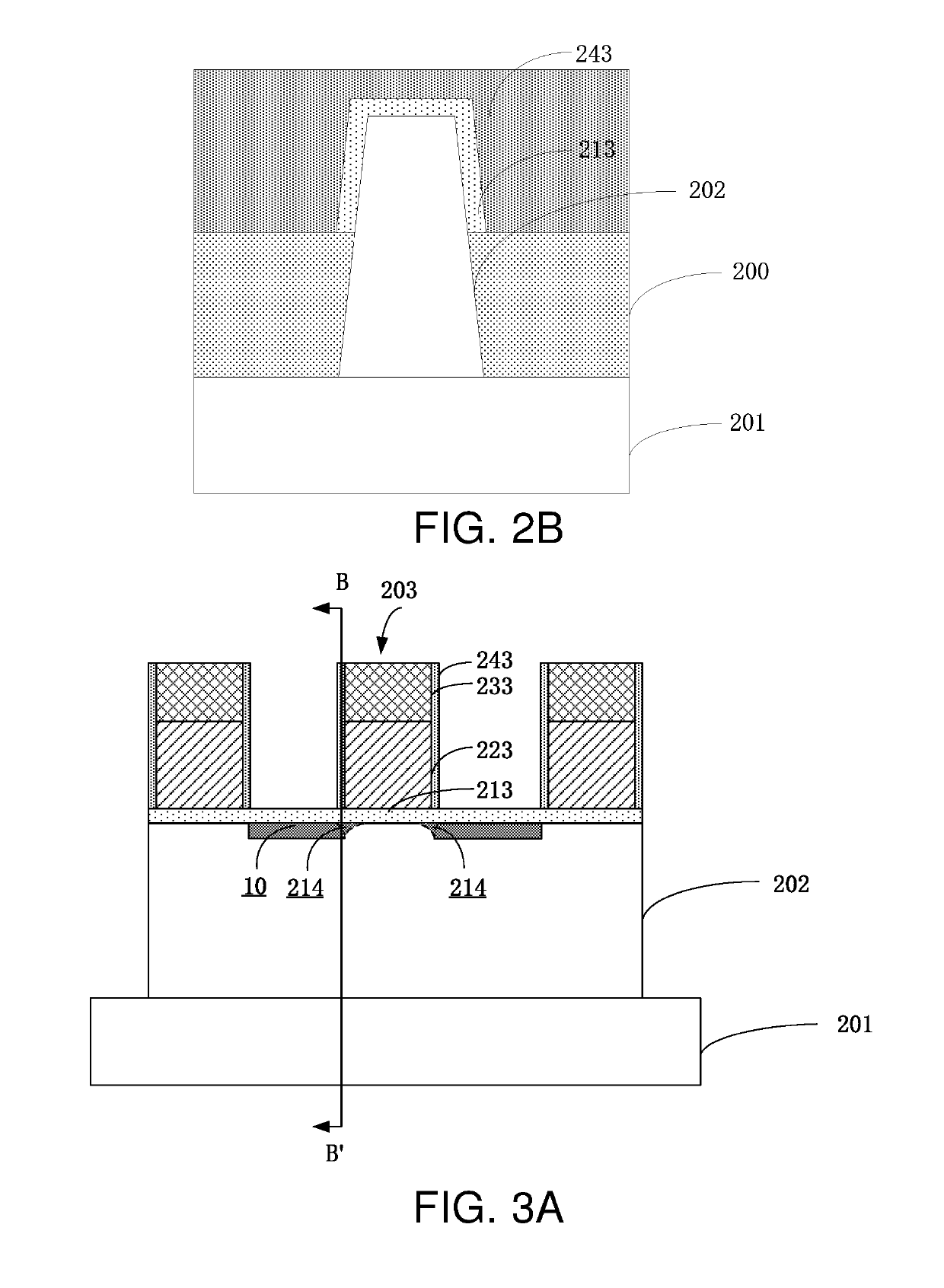

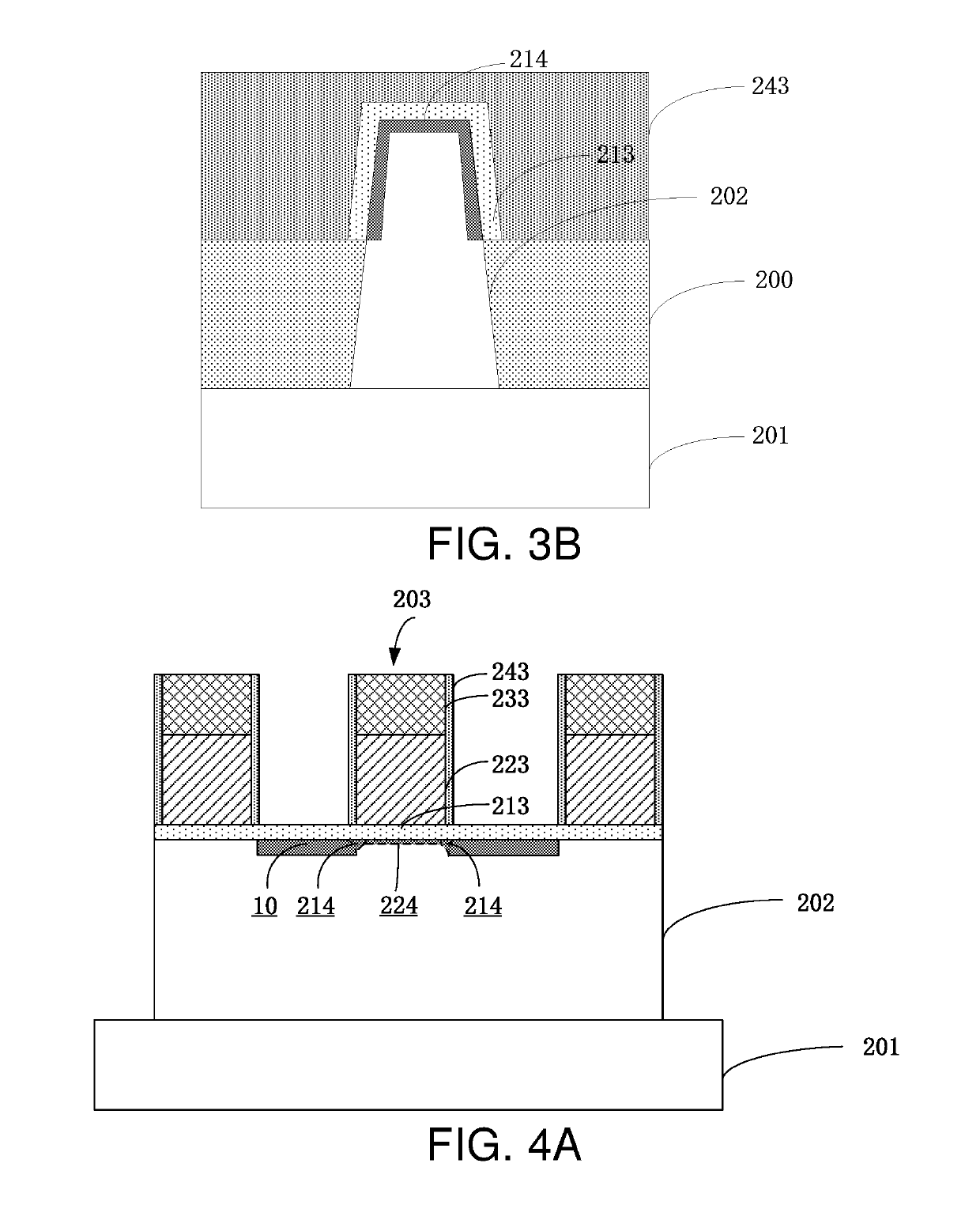

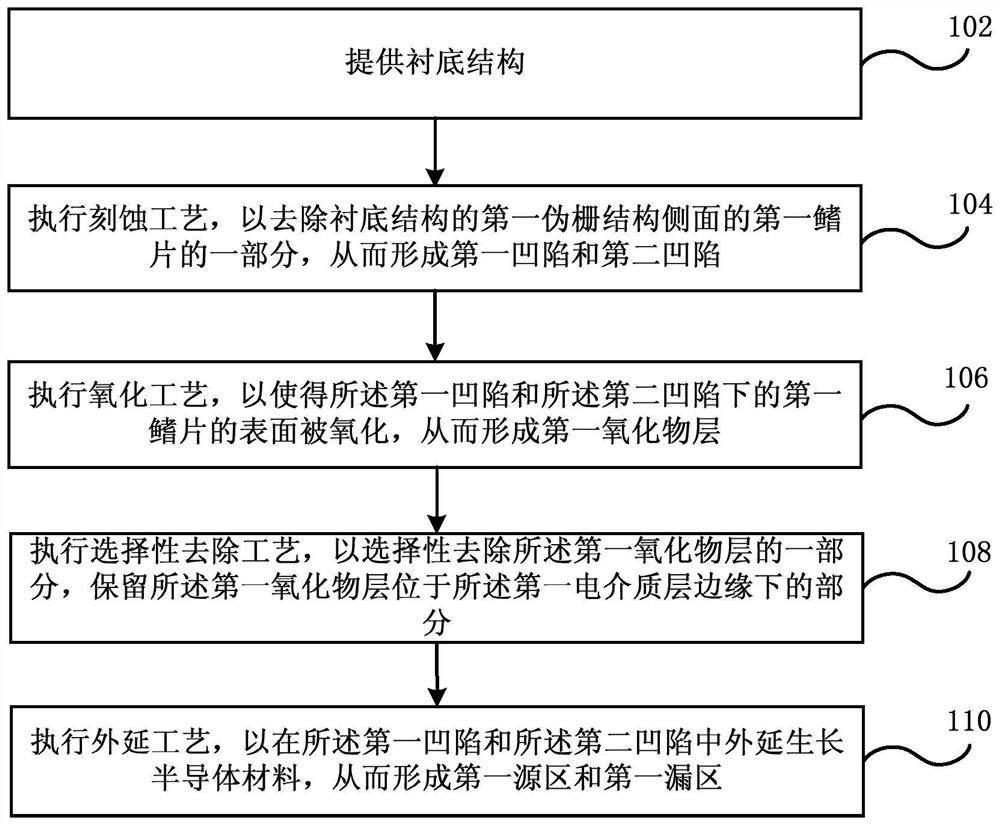

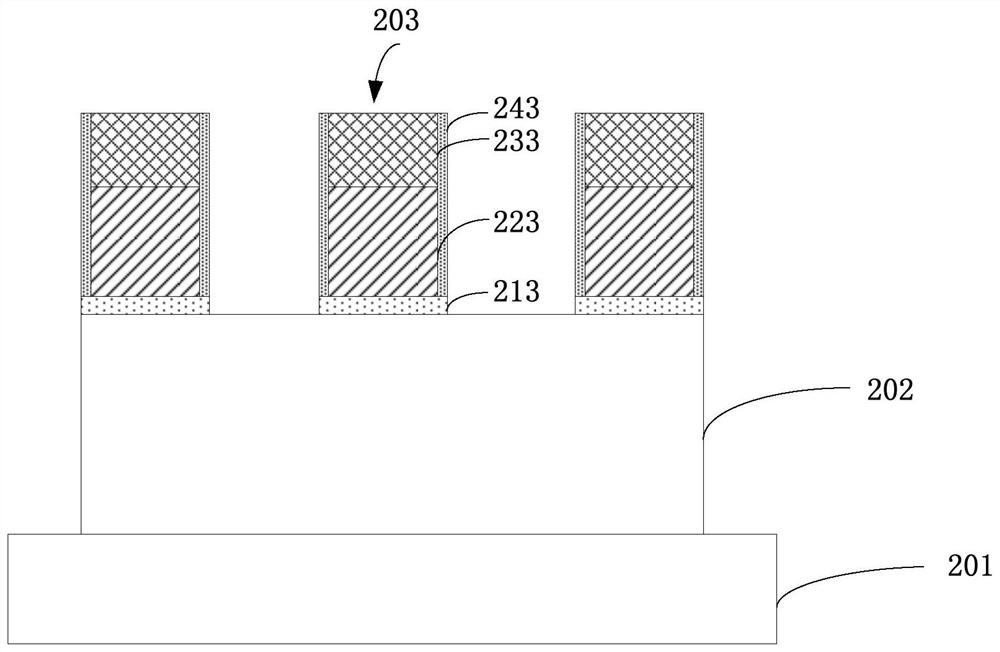

Semiconductor device and manufacturing method thereof

ActiveCN108962985AReduce the vertical electric field strengthReduce GIDLTransistorSolid-state devicesEngineeringSemiconductor device modeling

The present invention discloses a semiconductor device and a manufacturing method thereof and belongs to the semiconductor technological field. The device comprises a substrate, a first fin, a first gate structure, a first source region and a first drain region; the first fin is arranged on the substrate and is used for a first device; the first gate structure is located on a portion of the firstfin and comprises a first gate dielectric layer on a portion of the first fin and a first gate on the first gate dielectric layer; the first source region and the first drain region are arranged on two sides of the first gate structure and at least partially located in the first fin; a portion of the first gate dielectric layer, which adjoins the first drain region, is a first portion, a portion of the first gate dielectric layer, which adjoins the first source region, is a second portion; and a portion of the first gate dielectric layer, which is located between the first portion and the second portion, is a third portion, and the thickness of the first portion is greater than the thickness of the third portion. With the semiconductor device and the manufacturing method thereof of the invention adopted, the GIDL (gated-induce drain leakage) of the device can be decreased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method and device to reduce gate-induced drain leakage (GIDL) current in thin gate oxide MOSFETs

InactiveUS20060263964A1Minimize GIDLReduce GIDLTransistorSemiconductor/solid-state device manufacturingMOSFETHigh doses

A process for the fabrication of an integrated circuit which provides a FET device having reduced GIDL current is described. A semiconductor substrate is provided wherein active regions are separated by an isolation region, and a gate oxide layer is form on the active regions. Gate electrodes are formed upon the gate oxide layer in the active regions. An angled, high dose, ion implant is performed to selectively dope the gate oxide layer beneath an edge of each gate electrode in a gate-drain overlap region, and the fabrication of the integrated circuit is completed.

Owner:MOULI CHANDRA V +1

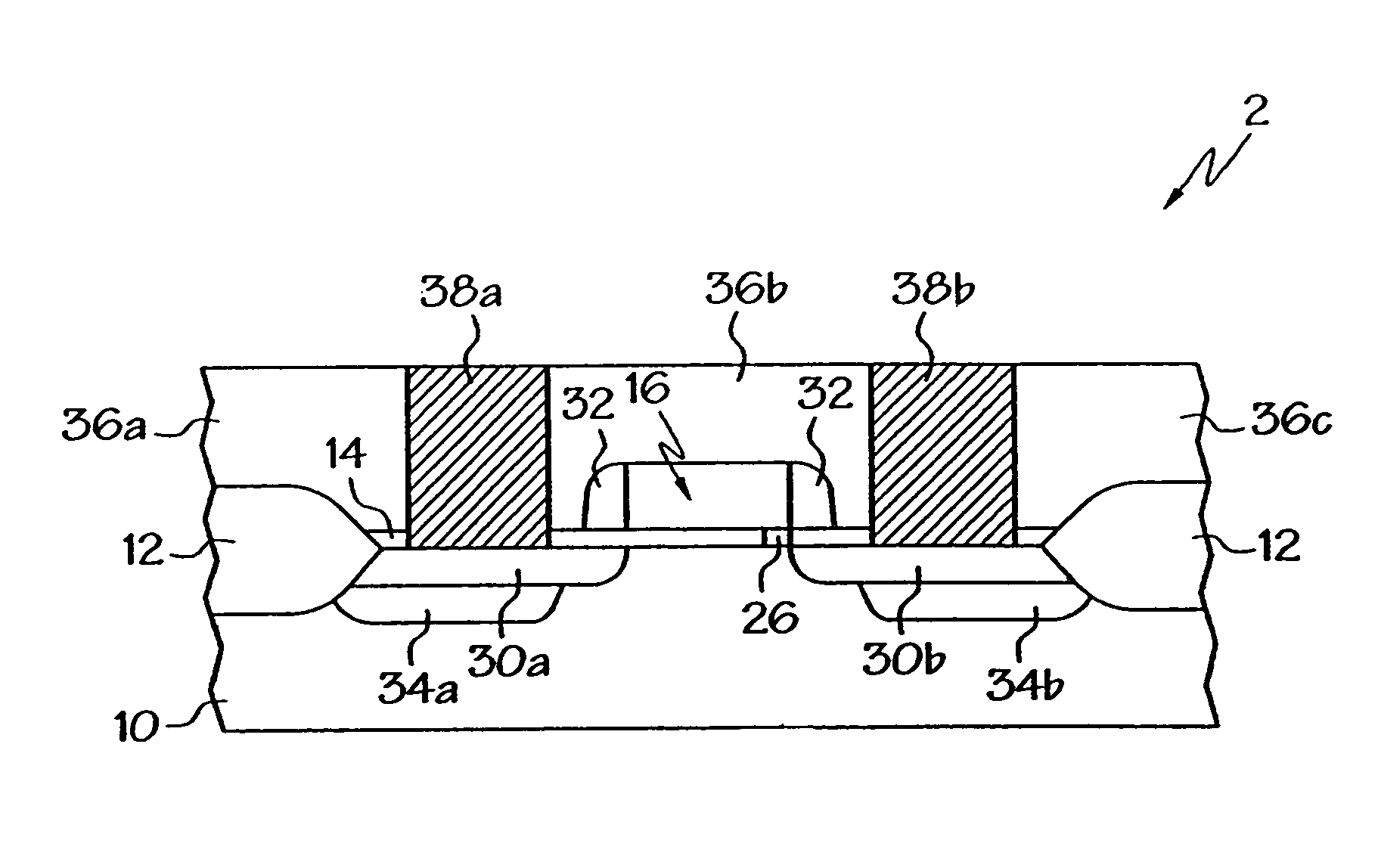

Semiconductor device and manufacturing method therefor

ActiveUS10418454B2Reduce GIDLReduced strengthTransistorSolid-state devicesGate dielectricEngineering

This disclosure relates to the technical field of semiconductors, and discloses a semiconductor device and a manufacturing method therefor. The semiconductor device may include a substrate; a first fin on the substrate for forming a first electronic component; a first gate structure on a portion of the first fin including a first gate dielectric layer on a portion of the first fin and a first gate on the first gate dielectric layer; and a first source region and a first drain region that each at one of two sides of the first gate structure and at least partially located in the first fin, where the first gate dielectric layer comprises a first region abutting against the first drain region, a second region abutting against the first source region, and a third region between the first region and the second region, and wherein thickness of the first region is greater than that of the third region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for fabricating buried gates using pre landing plugs

ActiveUS20130137258A1Reduce contact resistanceIncrease contact areaSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A method for fabricating a semiconductor device is provided, the method includes forming a plug conductive layer over an entire surface of a substrate, etching the plug conductive layer to form landing plugs, etching the substrate between the landing plugs to form a trench, forming a gate insulation layer over a surface of the trench and forming a buried gate partially filling the trench over the gate insulation layer.

Owner:SK HYNIX INC

Semiconductor device with a gate having a bulbous area and a flattened area underneath the bulbous area and method for manufacturing the same

ActiveUS8030715B2Prevent orMinimize degradationTransistorSolid-state devicesPower semiconductor deviceInsulation layer

A semiconductor device with a gate having a bulbous area and a flattened area underneath the bulbous are is presented. The semiconductor device includes a semiconductor substrate, an isolation layer, a gate insulation layer, and gates. The semiconductor substrate has recess parts that have first grooves which have bulbous-shaped profiles and second vertically flattened profile grooves which extend downward from the first grooves. The gates are formed in the recess parts in which the gate insulation layer is double layered in the bulbous profile areas and is single layered in the flattened profile areas.

Owner:SK HYNIX INC

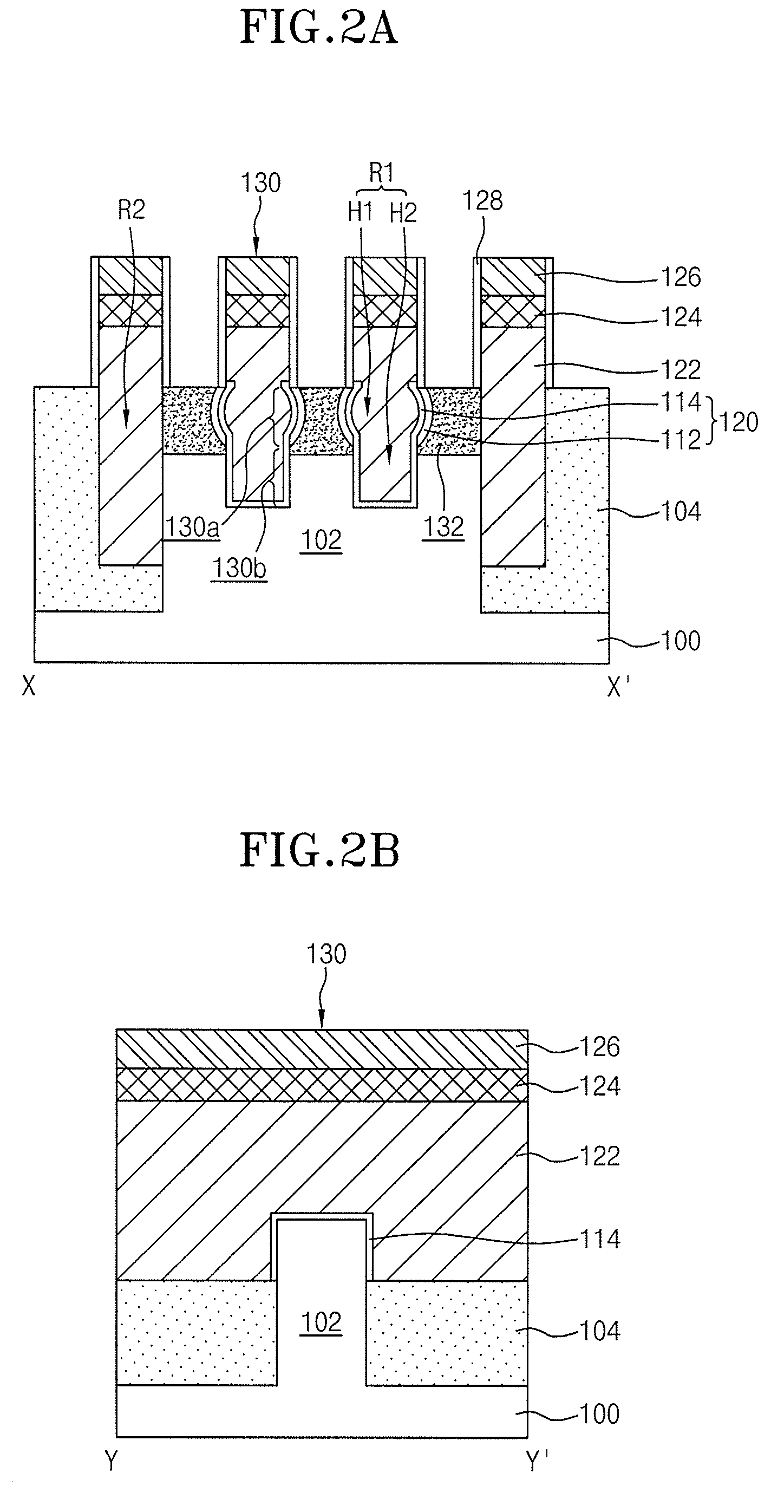

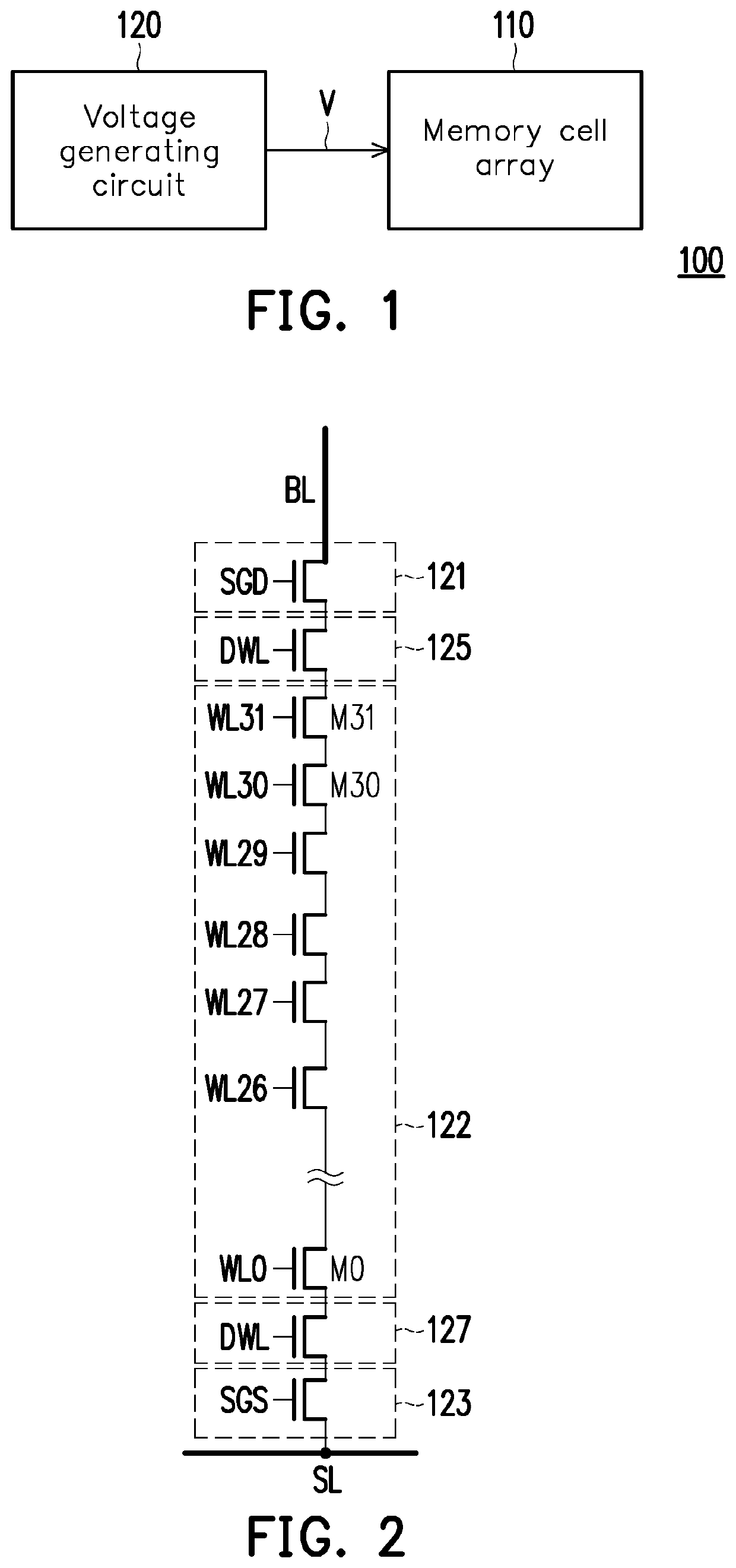

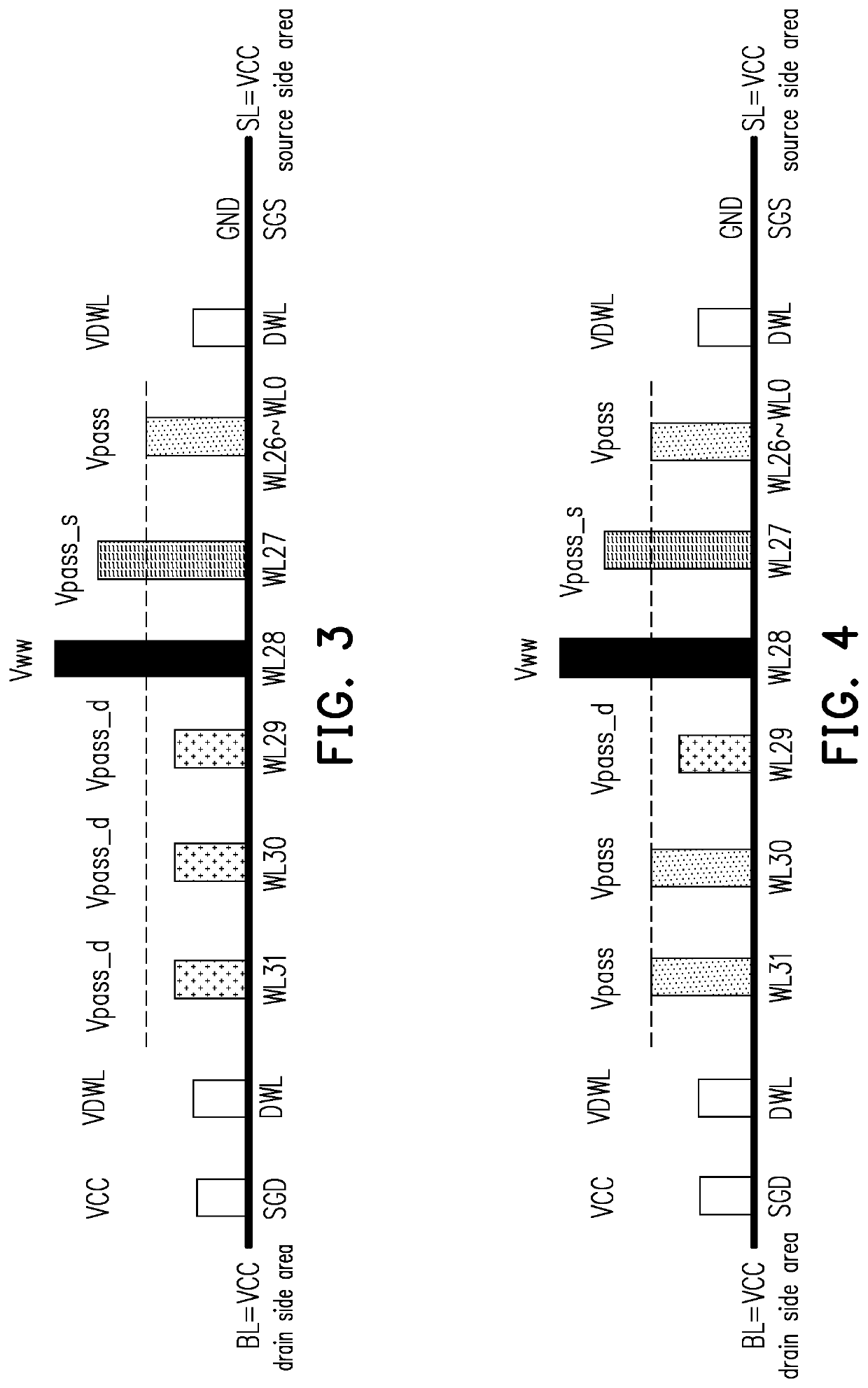

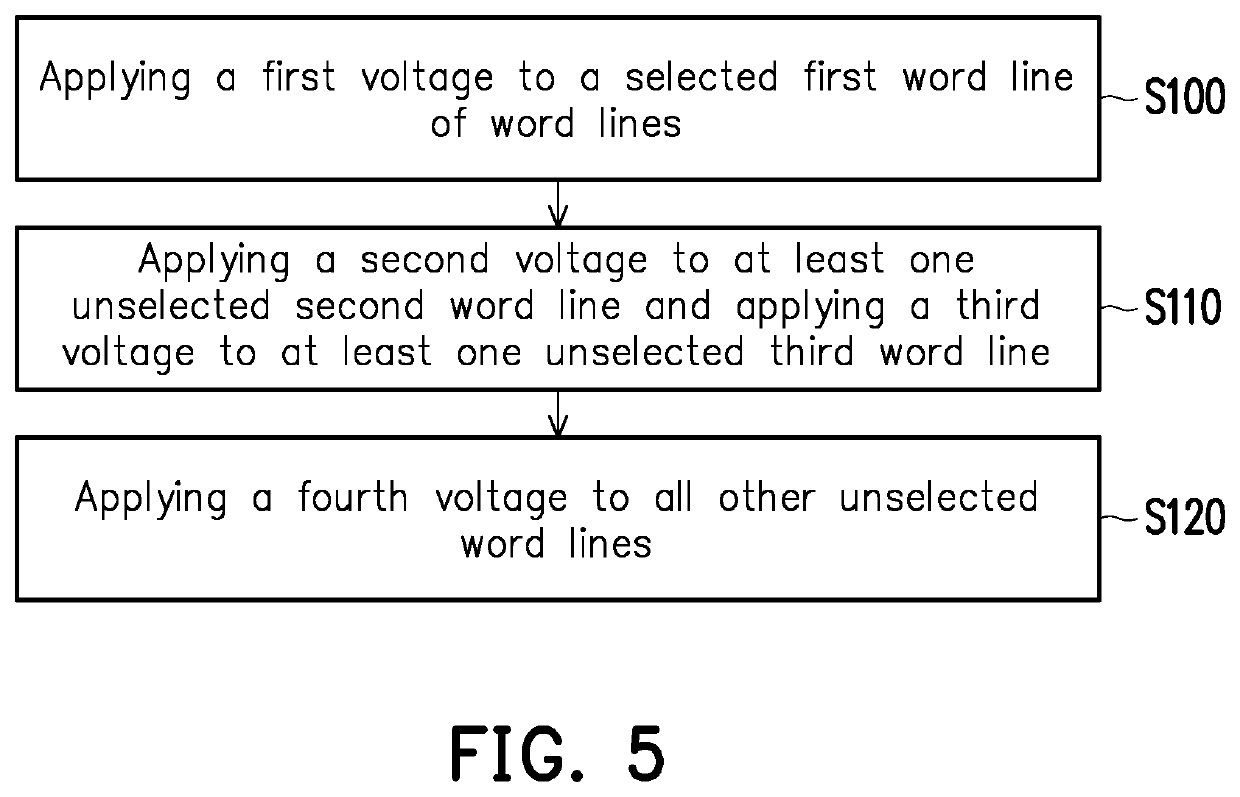

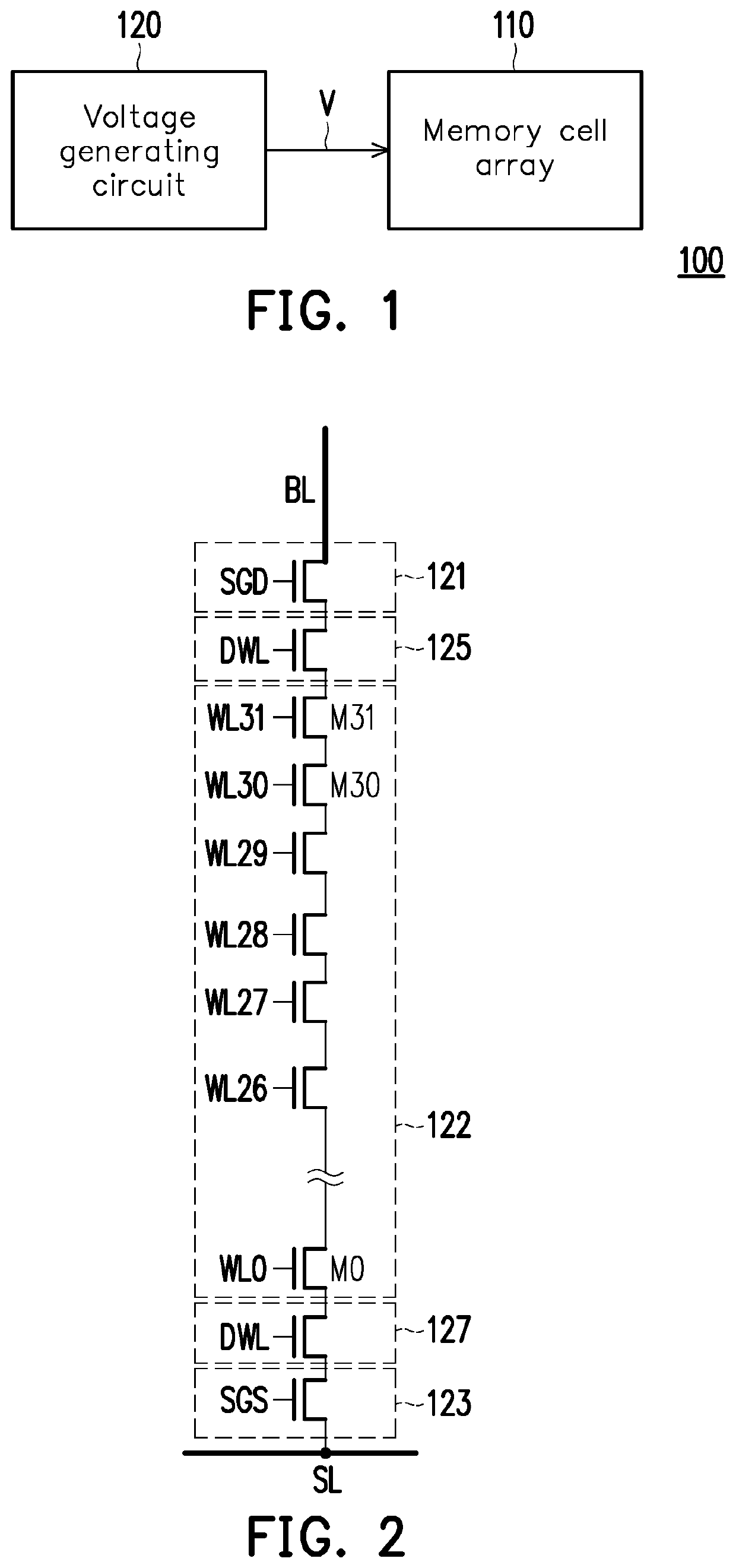

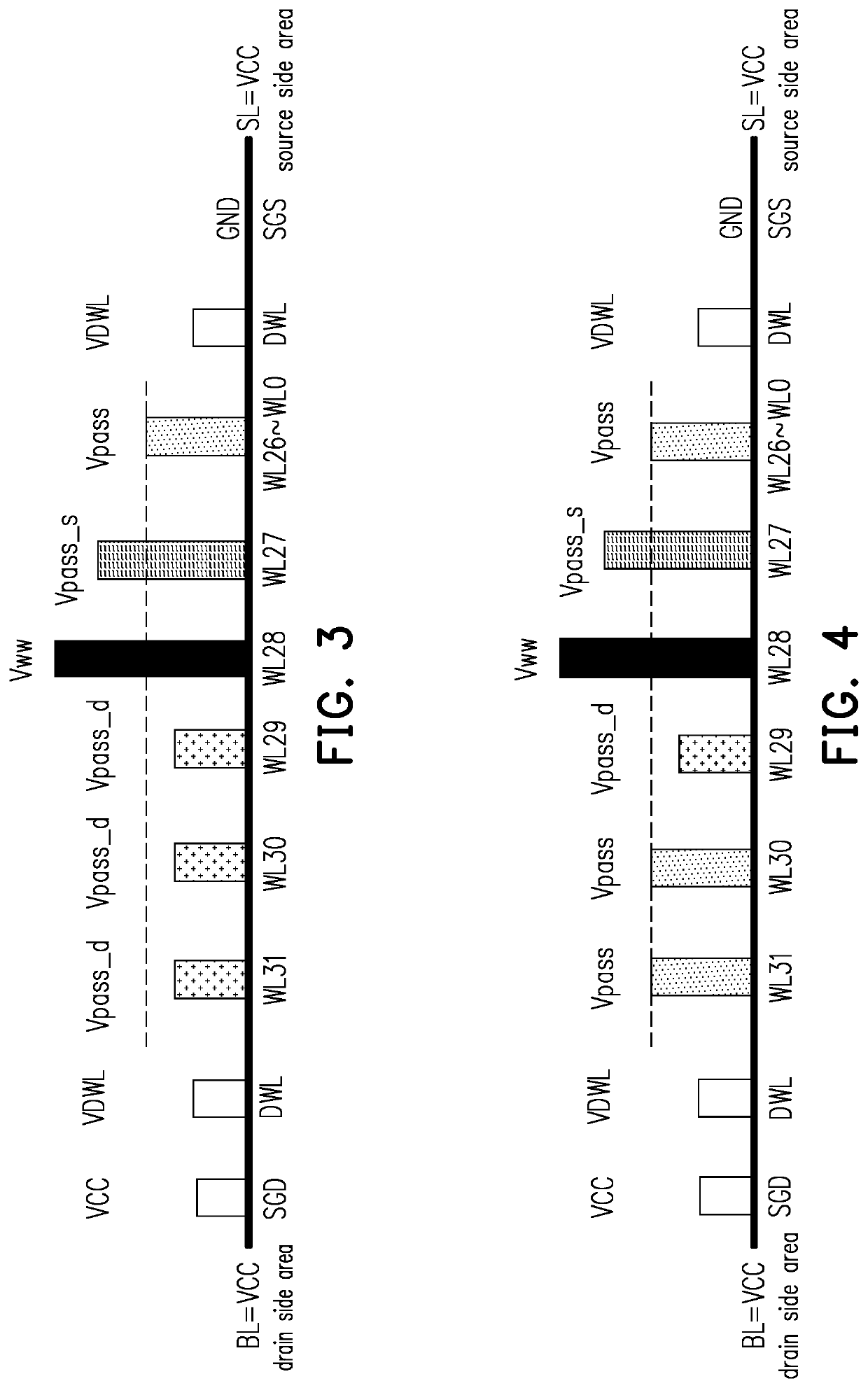

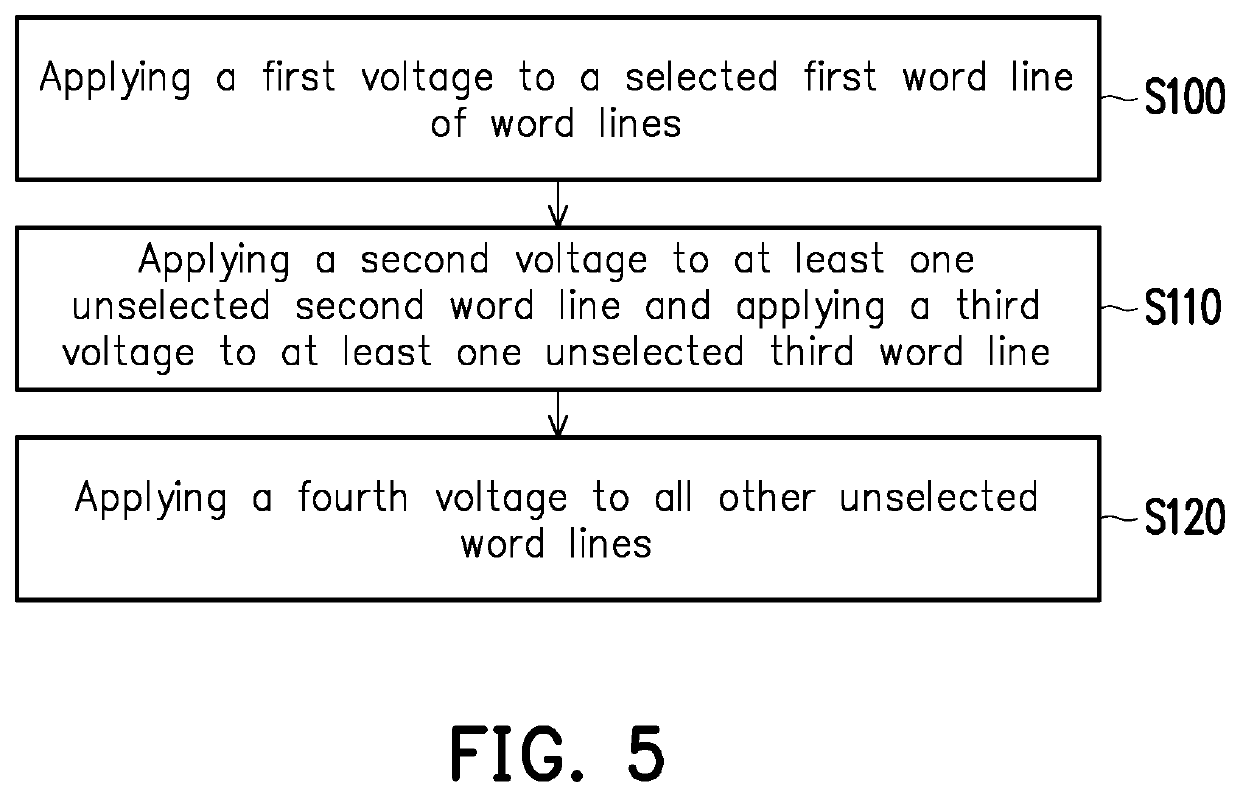

Flash memory storage apparatus and a biasing method thereof, which can reduce a gate induced drain leakage (GIDL) and improve reliability of memory cells

InactiveUS20220366963A1Improve reliabilityReduce leakageRead-only memoriesDigital storageBit lineMemory cell

A flash memory storage apparatus includes a memory cell array and a voltage generating circuit. The memory cell array includes at least one memory cell string coupled between a bit line and a source line and including memory cells; each memory cell is coupled to a corresponding word line. The voltage generating circuit is coupled to the memory cell array and configured to output a bias voltage to the word line. A first voltage is applied to a selected word line. A second voltage and a third voltage are applied to unselected second and third word lines, respectively. The first voltage is greater than the second voltage, and the second voltage is greater than the third voltage. The second word line and the third word line are located on two sides of the first word line. A biasing method of a flash memory storage apparatus is also provided.

Owner:POWERCHIP SEMICON MFG CORP

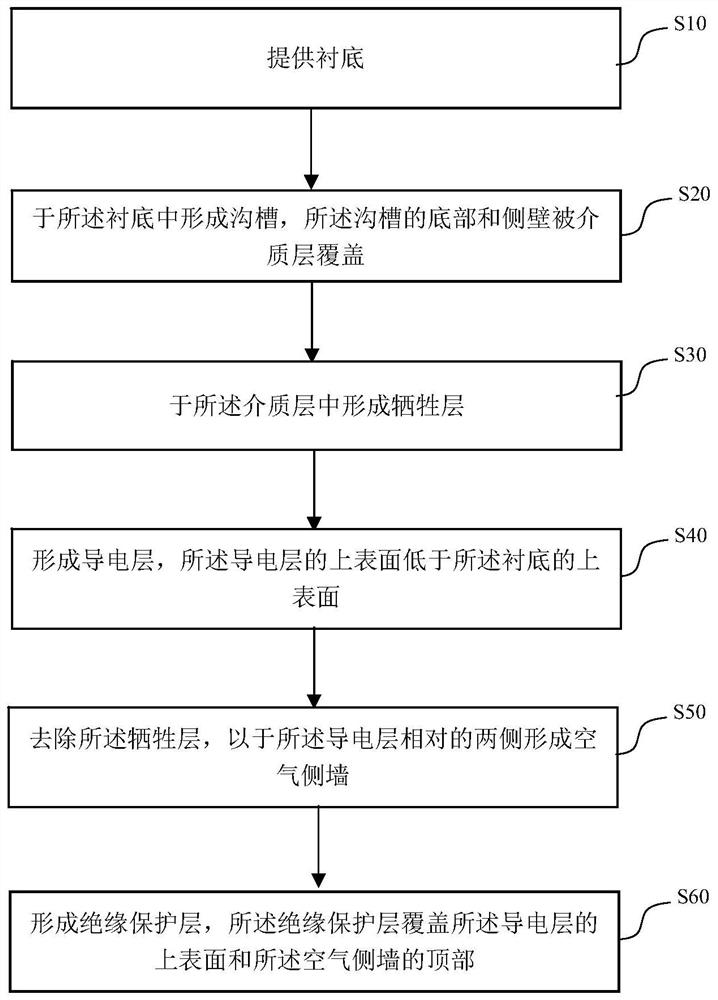

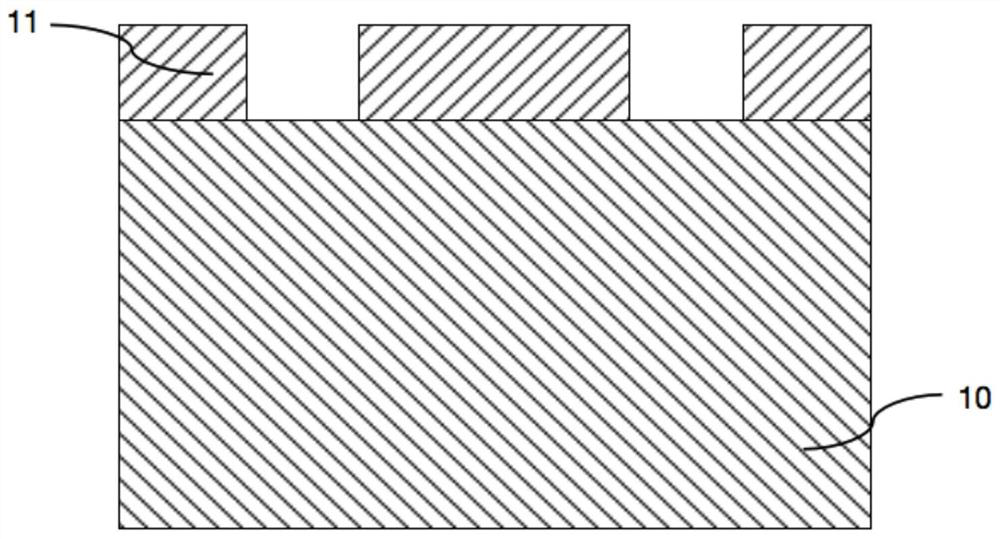

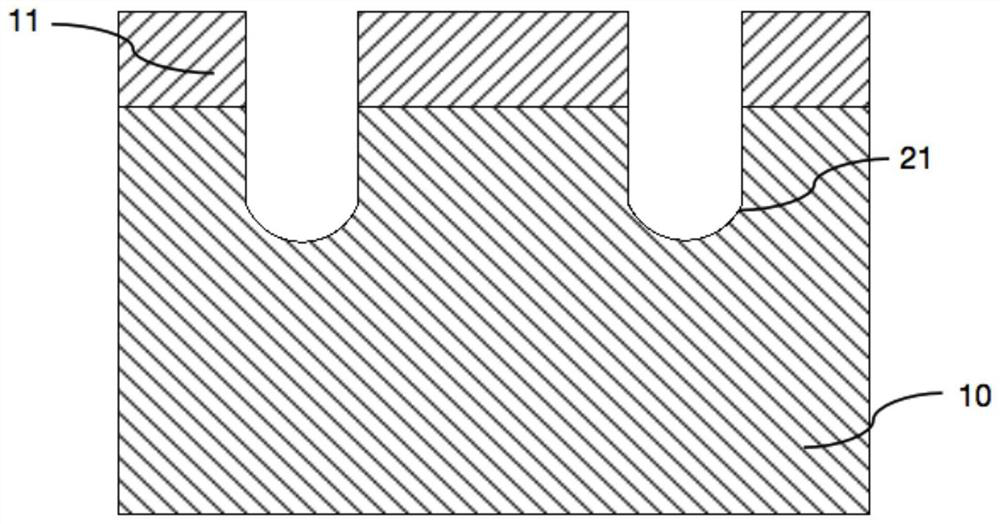

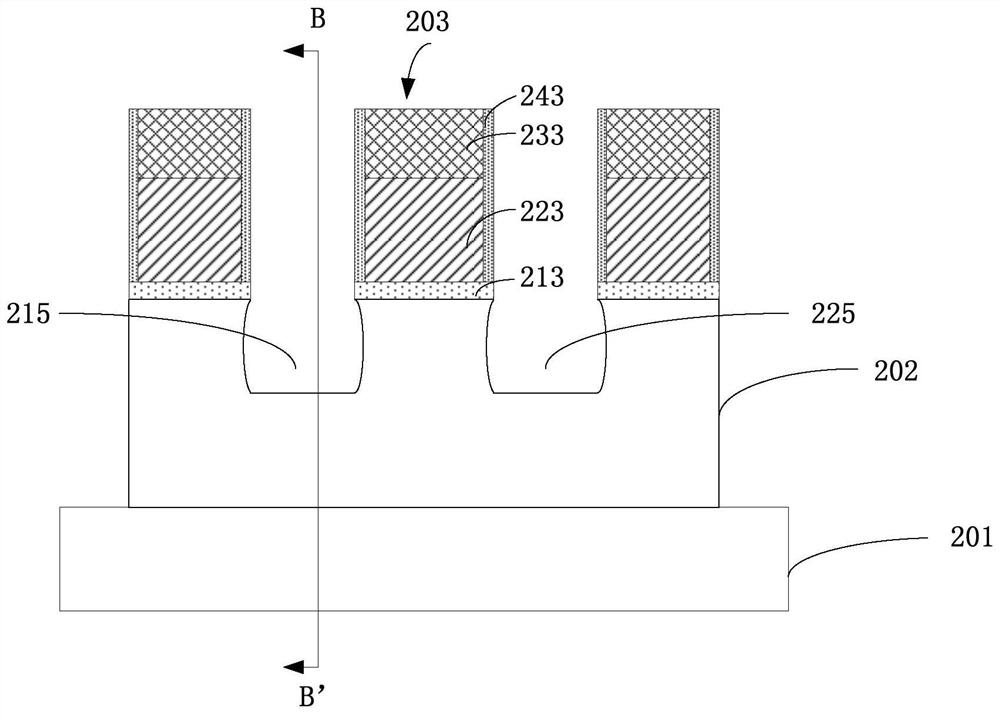

Semiconductor structure and preparation method thereof

PendingCN114725108ALower resistanceImprove reliabilityTransistorSemiconductor/solid-state device manufacturingLine resistanceSemiconductor structure

The invention relates to a semiconductor structure and a preparation method thereof. The preparation method of the semiconductor structure comprises the steps of providing a substrate; forming a groove in the substrate, wherein the bottom and the side wall of the groove are covered by the dielectric layer; forming a sacrificial layer in the dielectric layer; forming a conductive layer, wherein the upper surface of the conductive layer is lower than the upper surface of the substrate; removing the sacrificial layer to form air side walls on two opposite sides of the conductive layer; and forming an insulation protection layer, wherein the insulation protection layer covers the upper surface of the conductive layer and the top of the air side wall. According to the preparation method of the semiconductor structure, the conductive layer with relatively high height is formed in the groove, and the cross sectional area of the conductive layer can be increased under the condition that the line width of the word line structure is kept unchanged, so that the word line resistance is greatly reduced, the word line conduction current is improved, and the response speed of a transistor is improved; in addition, the air side walls are formed on the two opposite sides of the conducting layer, so that the electric field between the grid electrode and the drain electrode can be reduced, the GIDL is reduced, the crystal power consumption of the transistor is reduced, and the reliability of the transistor is improved.

Owner:CHANGXIN MEMORY TECH INC

Flash memory storage apparatus and a biasing method thereof, which can reduce a gate induced drain leakage (GIDL) and improve reliability of memory cells

InactiveUS20220246194A1Improve reliabilityReduce leakageRead-only memoriesDigital storageBit lineMemory cell

A flash memory storage apparatus includes a memory cell array and a voltage generating circuit. The memory cell array includes at least one memory cell string coupled between a bit line and a source line and including memory cells; each memory cell is coupled to a corresponding word line. The voltage generating circuit is coupled to the memory cell array and configured to output a bias voltage to the word line. A first voltage is applied to a selected word line. A second voltage and a third voltage are applied to unselected second and third word lines, respectively. The first voltage is greater than the second voltage, and the second voltage is greater than the third voltage. The second word line and the third word line are located on two sides of the first word line. A biasing method of a flash memory storage apparatus is also provided.

Owner:POWERCHIP SEMICON MFG CORP

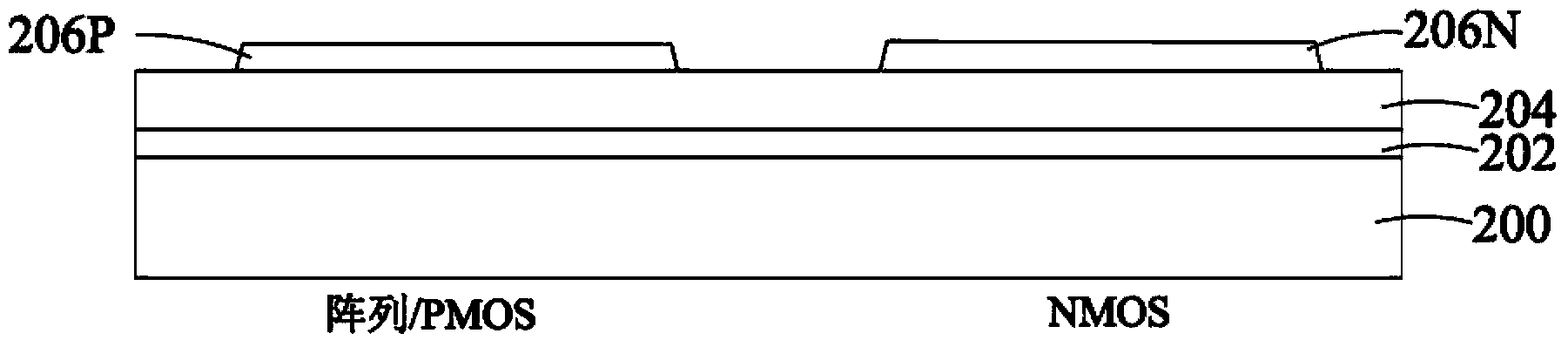

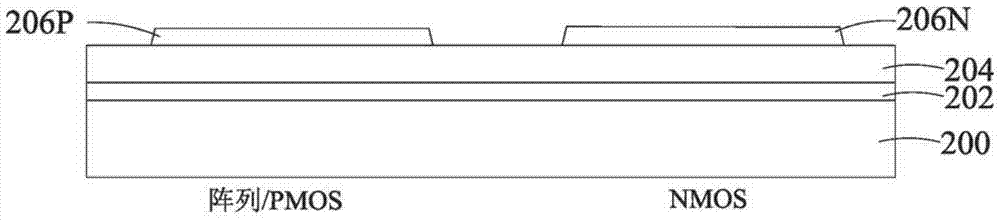

Method for forming semiconductor device with metal grid electrode

InactiveCN102386135AReduce GIDLImprove short channel effectSolid-state devicesSemiconductor/solid-state device manufacturingMetal gridShort-channel effect

The invention provides a method for forming a semiconductor device with a metal grid electrode, which comprises the steps of: providing a front-end device structure, wherein the front-end device structure is provided with a semiconductor substrate and an interlayer medium layer arranged on the semiconductor substrate, the interlayer medium layer is internally provided with an opening from which a part of the semiconductor substrate is exposed, and the semiconductor substrate which is arranged at two sides of the opening and is covered by the interlayer medium layer is internally provided with a source electrode / a drain electrode; forming a barrier layer on the front-end device structure; etching the barrier layer, so that a barrier gap wall layer is formed on the side wall of the opening; performing an ion implantation technology to the semiconductor substrate by the means that the barrier gap wall layer and the interlayer medium layer are taken as mask films, so that an unevenly-doped channel is formed; removing the barrier gap wall layer; and forming a high-k material layer in the opening, and filling with metal, so that the semiconductor device with the metal grid electrode is formed. After the semiconductor device with the metal grid electrode is formed according to the method provided by the invention, not only can the gate induced drain leakage (GIDL) be effectively reduced, but also the short channel effect can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

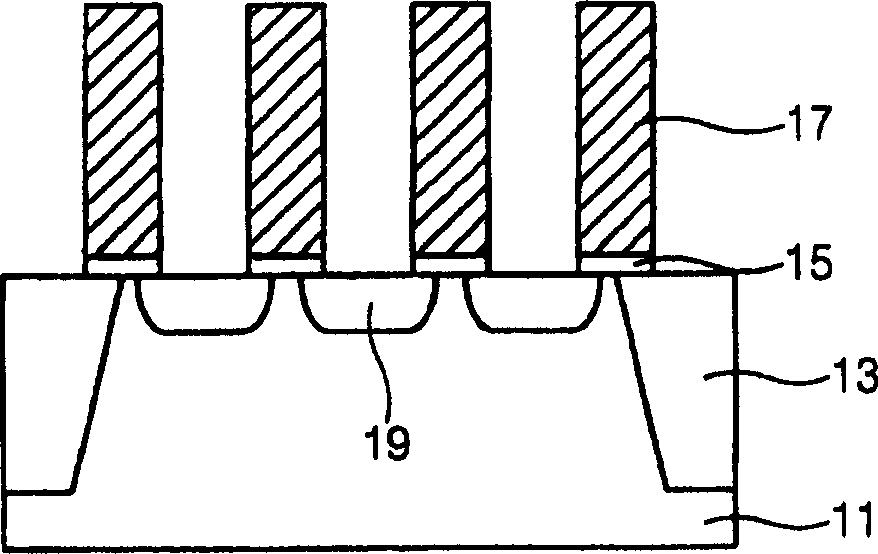

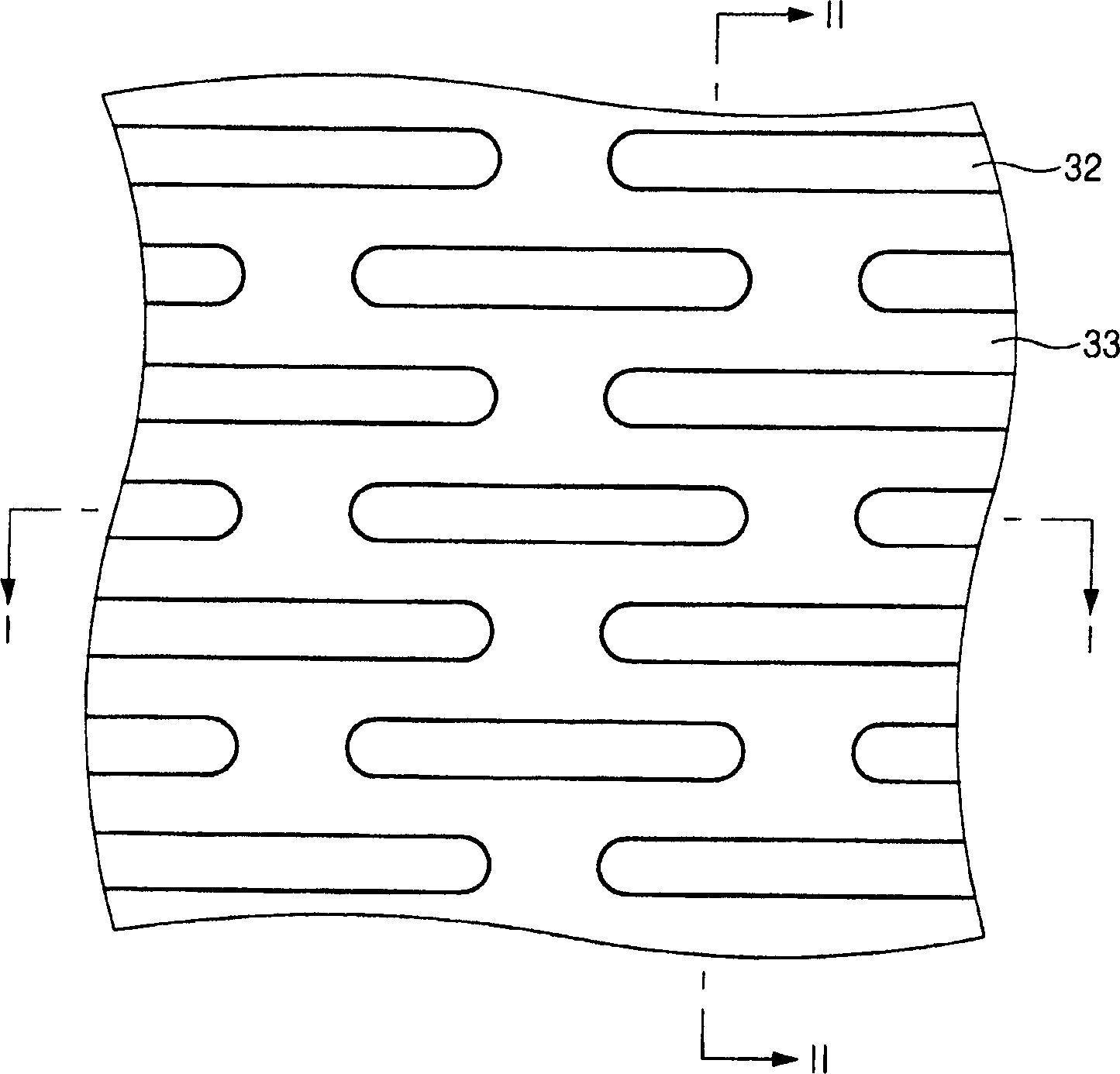

Method of forming word wire of semiconductor device

InactiveCN1263116CImprove featuresGood yieldSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideSemiconductor

A method for forming word line of semiconductor device wherein a lower portion of the word line on the channel region is a I-type and a upper portion of the word line is a line-type is disclosed. The method comprises (a) forming a sacrificial insulation film on a semiconductor substrate including an active region; (b) etching the sacrificial insulation film to form an I-type sacrificial insulation film pattern whereon a channel region is to be formed; (c) forming a source / drain region; (d) forming a first interlayer insulation film; (e) planarizing the first interlayer insulation film to expose the sacrificial insulation film pattern; (f) sequentially forming a insulation film and a second interlayer insulation film; (g) etching the second interlayer insulation film and insulation film using a word line mask; (h) removing the sacrificial insulation film pattern; (i) growing a gate oxide film; (j) forming a conductive layer; and (k) planarizing the conductive layer.

Owner:SK HYNIX INC

Method of forming word wire of semiconductor

InactiveCN1476078AImprove featuresGood yieldSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringGate oxide

A method for forming word line of semiconductor device wherein a lower portion of the word line on the channel region is a I-type and a upper portion of the word line is a line-type is disclosed. The method comprises (a) forming a sacrificial insulation film on a semiconductor substrate including an active region; (b) etching the sacrificial insulation film to form an I-type sacrificial insulation film pattern whereon a channel region is to be formed; (c) forming a source / drain region; (d) forming a first interlayer insulation film; (e) planarizing the first interlayer insulation film to expose the sacrificial insulation film pattern; (f) sequentially forming a insulation film and a second interlayer insulation film; (g) etching the second interlayer insulation film and insulation film using a word line mask; (h) removing the sacrificial insulation film pattern; (i) growing a gate oxide film; (j) forming a conductive layer; and (k) planarizing the conductive layer.

Owner:SK HYNIX INC

Protecting circuit and control circuit for reducing leakage current

ActiveUS8503136B2Reduce voltage differenceReduce GIDLTransistorEmergency protective arrangements for automatic disconnectionEngineeringDrain current

A protecting circuit for reducing leakage currents comprises a first PMOS transistor (P-channel Metal-Oxide-Semiconductor Field-Effect Transistor), a second PMOS transistor, a first NMOS transistor (N-channel Metal-Oxide-Semiconductor Field-Effect Transistor), and a second NMOS transistor. The first PMOS transistor is coupled between a first voltage node and a node, and comprises a first gate coupled an input node. The second PMOS transistor is coupled between the node and an output node. The first NMOS transistor is coupled between the output node and a ground node, and comprises a third gate coupled to the input node. The second NMOS transistor is coupled between the input node and a second gate of the second PMOS transistor, and comprises a fourth gate coupled to a second voltage node.

Owner:WINBOND ELECTRONICS CORP

Semiconductor device and manufacturing method thereof

ActiveCN108962985BIncreasing the thicknessReduce GIDLTransistorSolid-state devicesGate dielectricDevice material

The application discloses a semiconductor device and a manufacturing method thereof, which relate to the technical field of semiconductors. The apparatus comprises: a substrate; a first fin on the substrate for a first device; a first gate structure on a portion of the first fin, comprising: a first gate dielectric layer on a portion of the sheet; and a first gate on the first gate dielectric layer; and at least partially on either side of the first gate structure on the first fin The first source region and the first drain region; wherein, the part of the first gate dielectric layer adjacent to the first drain region is the first part, and the first gate dielectric layer and the first source The part adjacent to the region is a second part, the part of the first gate dielectric layer between the first part and the second part is a third part, and the thickness of the first part is greater than that of the third part. thickness. This application can reduce the GIDL of the device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Thin film transistor and active matrix organic light emitting diode component and manufacturing method

ActiveCN104241389BGood injection distributionReduce lossesTransistorSolid-state devicesActive matrixSemiconductor package

The application provides a thin film transistor, an active matrix organic light emitting diode assembly and a manufacturing method. A thin film transistor comprising: a substrate; a buffer layer on the substrate; a semiconductor layer on the buffer layer, including a source region, a drain region and a channel region; a first gate insulating layer covering the semiconductor layer; The foot of the second gate insulation layer located on the first gate insulation layer, the width of the foot of the second gate insulation layer is smaller than the width of the first gate insulation layer; the foot of the second gate insulation layer A gate electrode on the upper surface, wherein the portion of the first gate insulating layer on the semiconductor layer has a flat upper surface.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

Semiconductor device, manufacturing method thereof and electronic equipment comprising semiconductor device

PendingCN113380893AReduce GIDLSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDevice material

The invention discloses a semiconductor device, a manufacturing method thereof and electronic equipment comprising the semiconductor device. According to an embodiment, a semiconductor device may include: an active region extending substantially in a vertical direction on a substrate; the grid stack is formed around at least part of the periphery of the middle section, in the vertical direction, of the active region, and the active region comprises a channel region opposite to the grid stack, and a first source / drain region and a second source / drain region which are arranged on the two opposite sides, in the vertical direction, of the channel region respectively; the gate stack comprises a gate dielectric layer, a work function adjusting layer and a gate electrode material layer, and the work function adjusting layer is arranged between the gate electrode material layer and the channel region; and the first low-k dielectric layer extends from the first end of the work function adjusting layer to surround a first corner of the end part, close to one side of the channel region, of the gate electrode material layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com