Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Increasing number" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

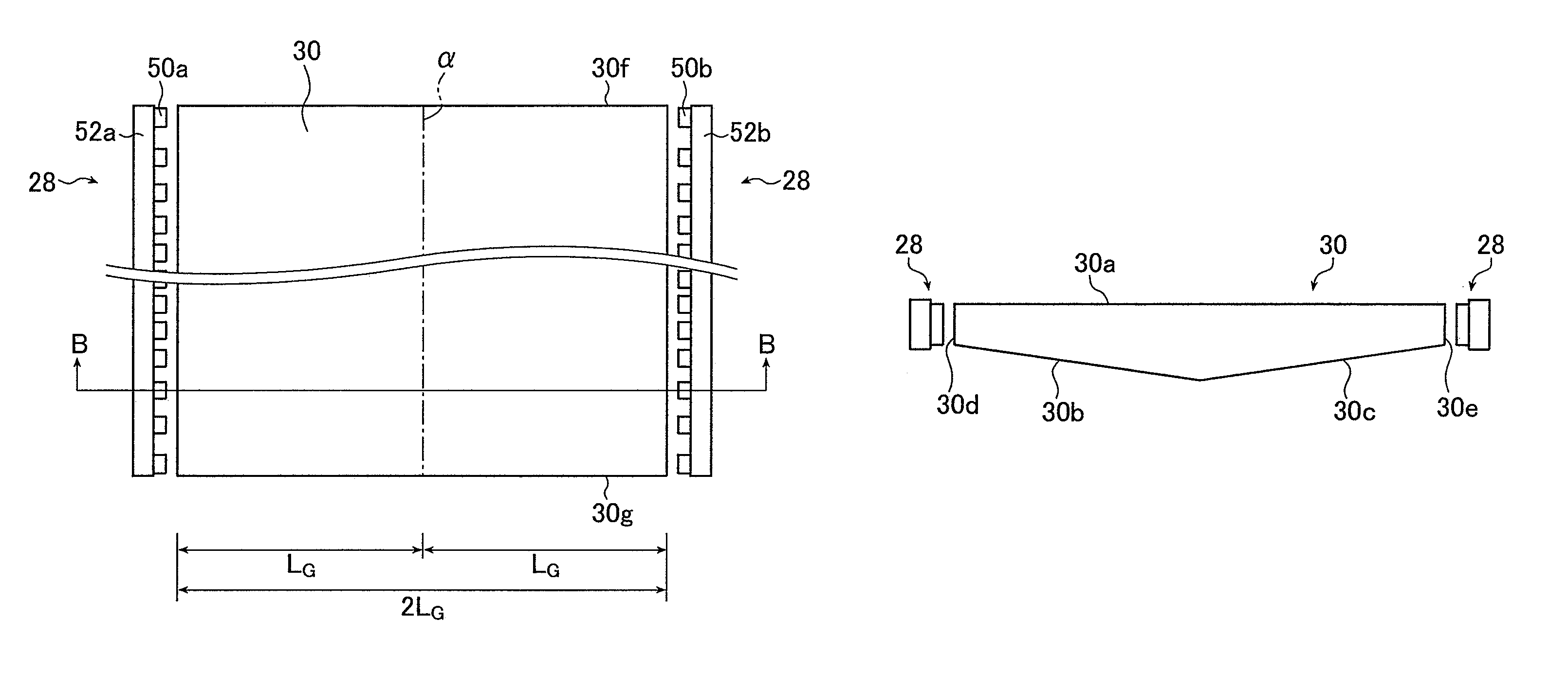

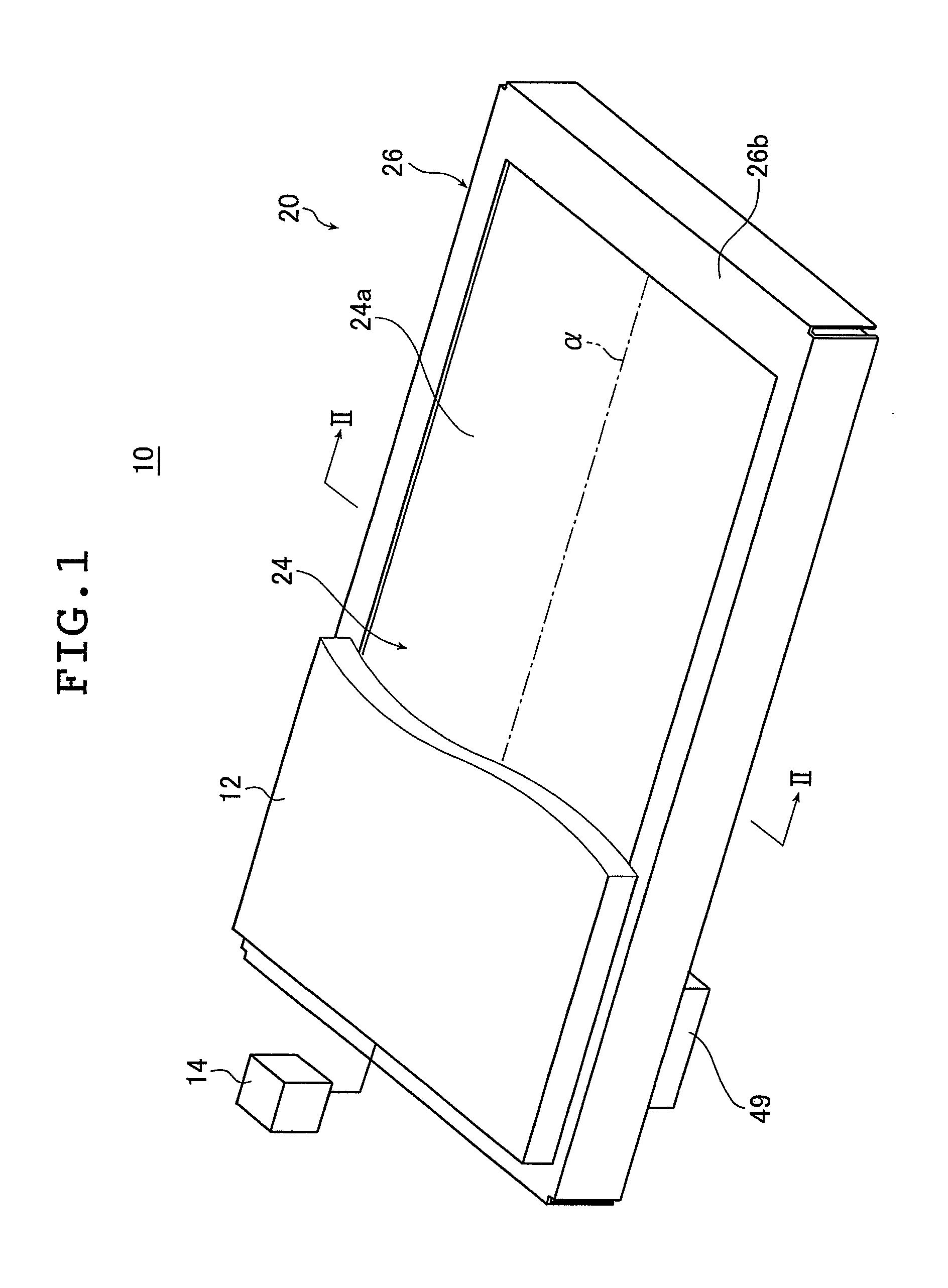

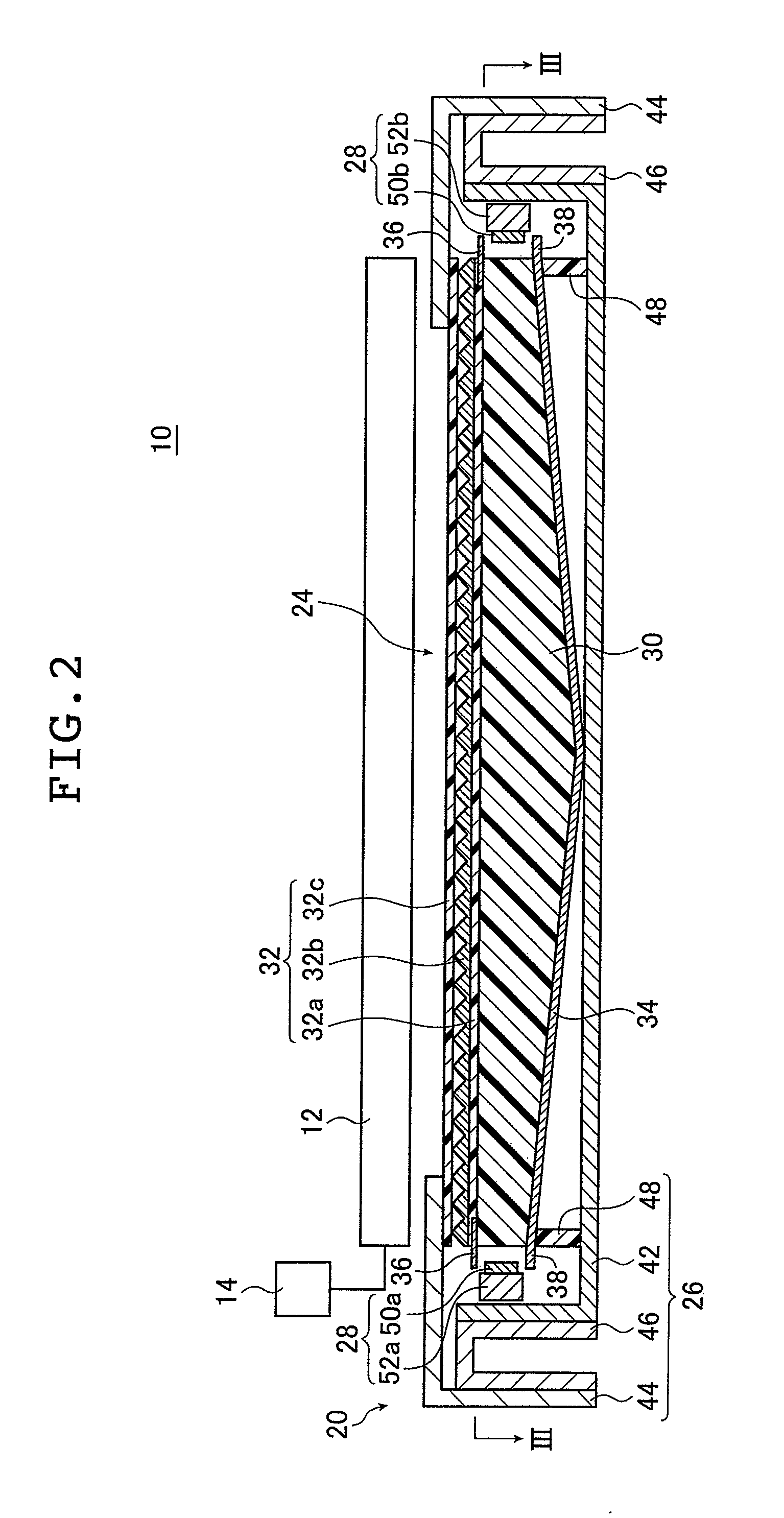

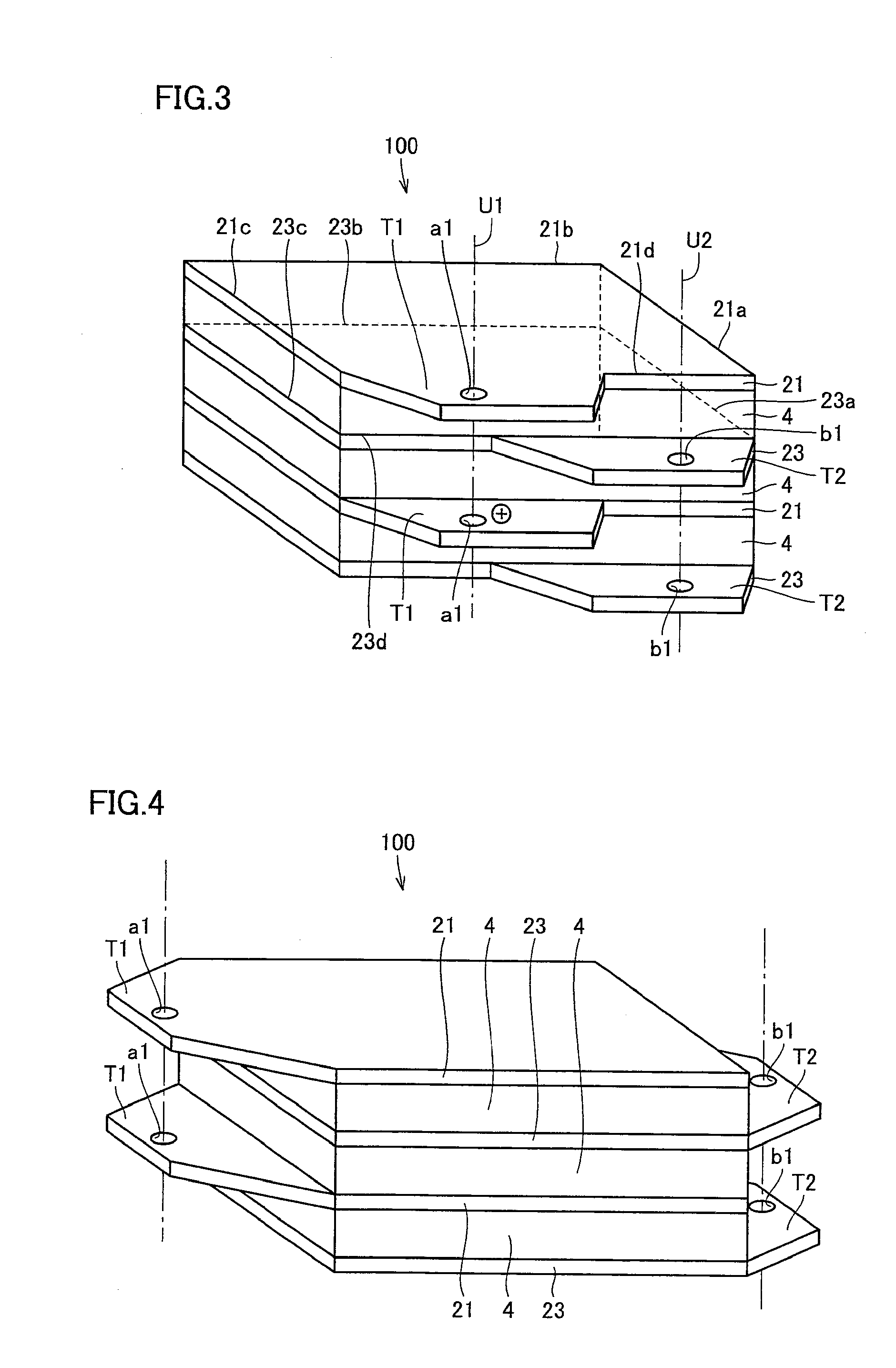

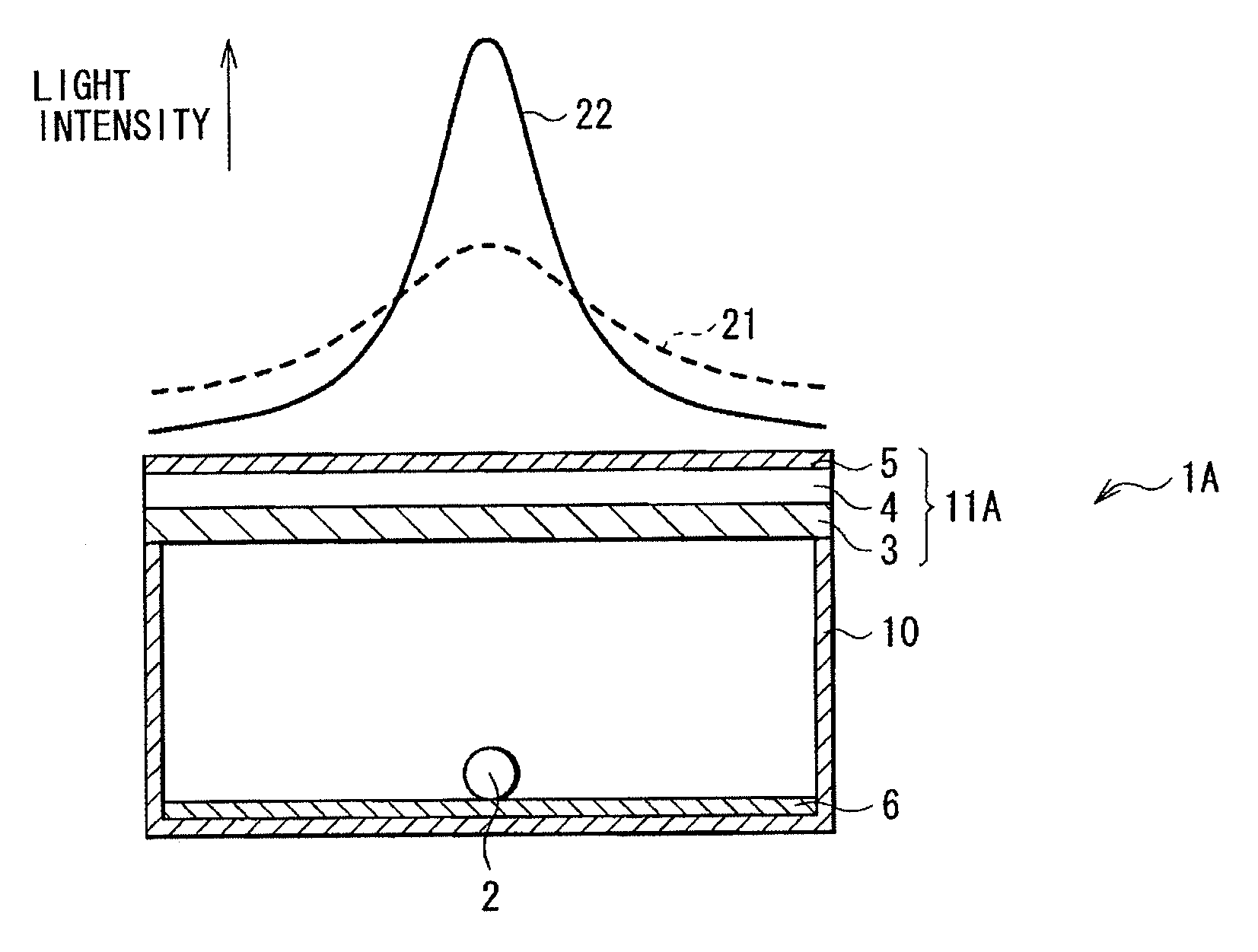

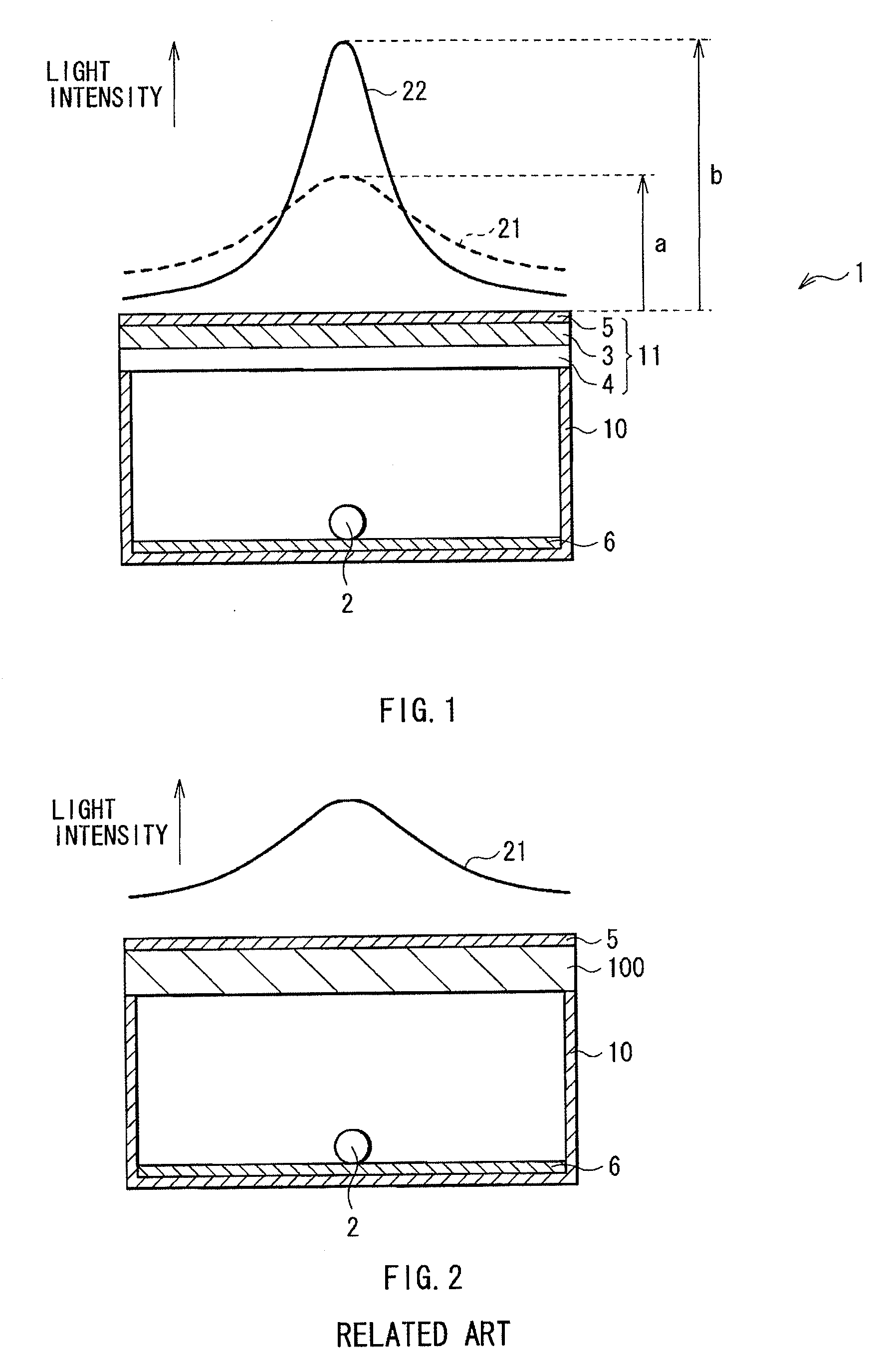

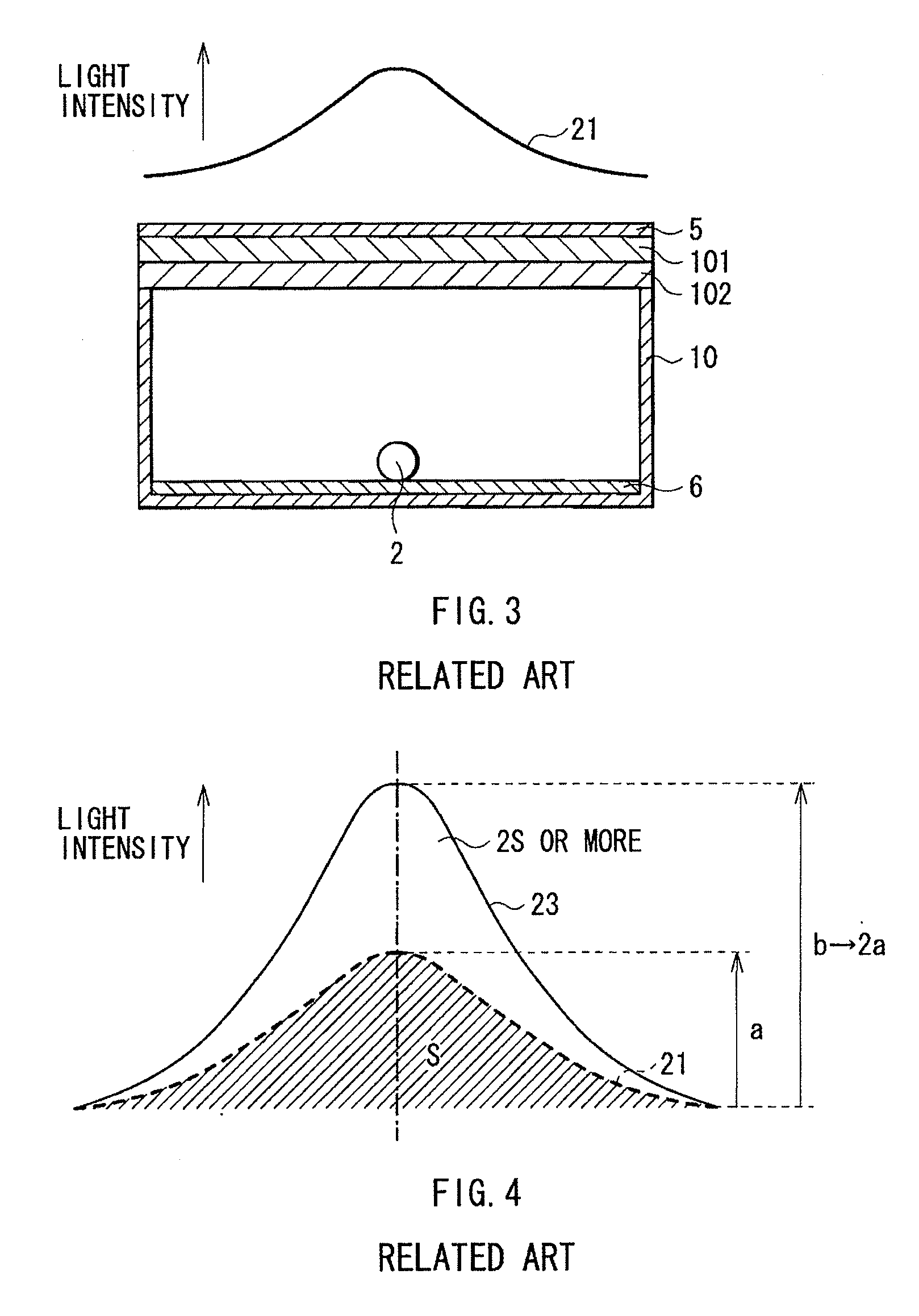

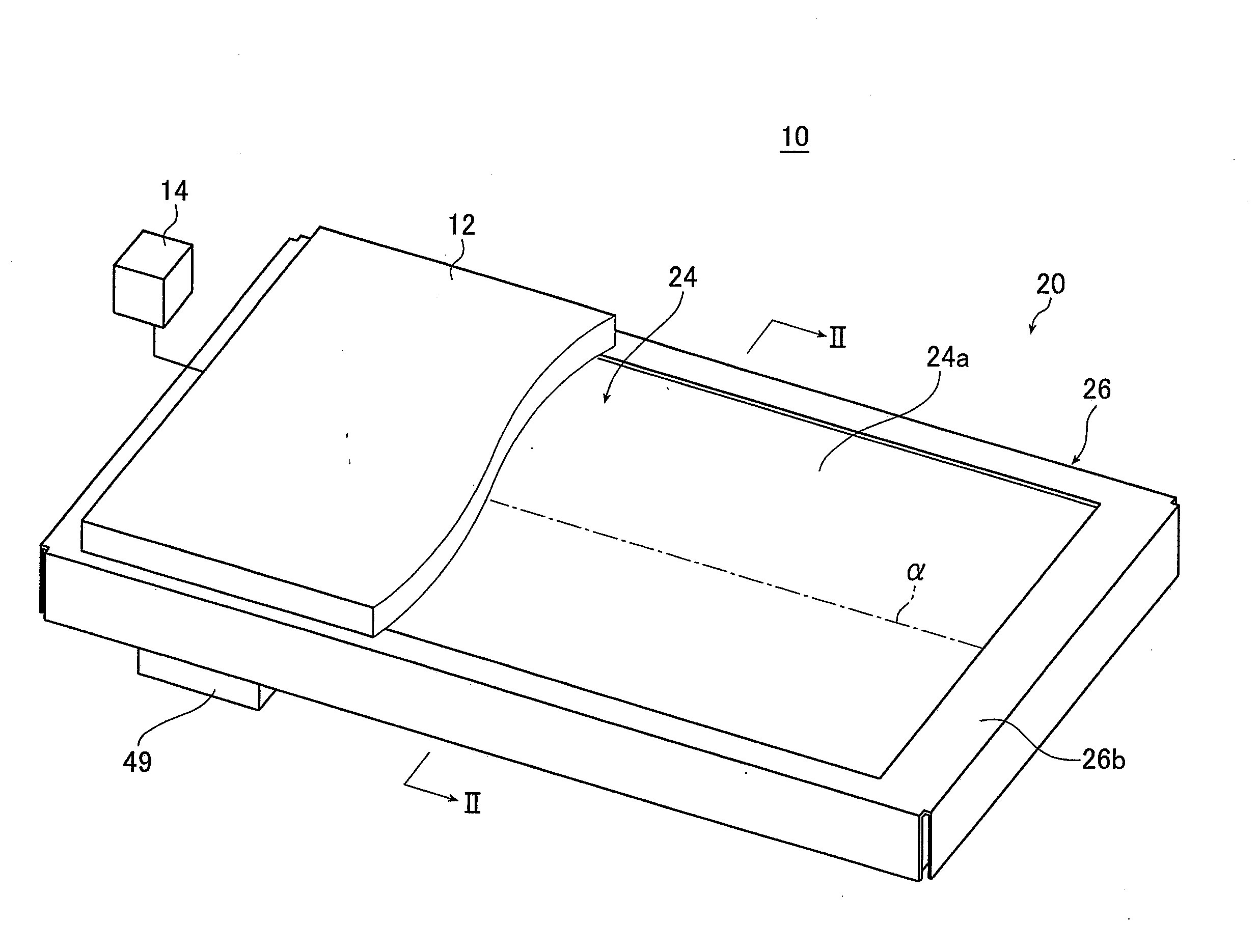

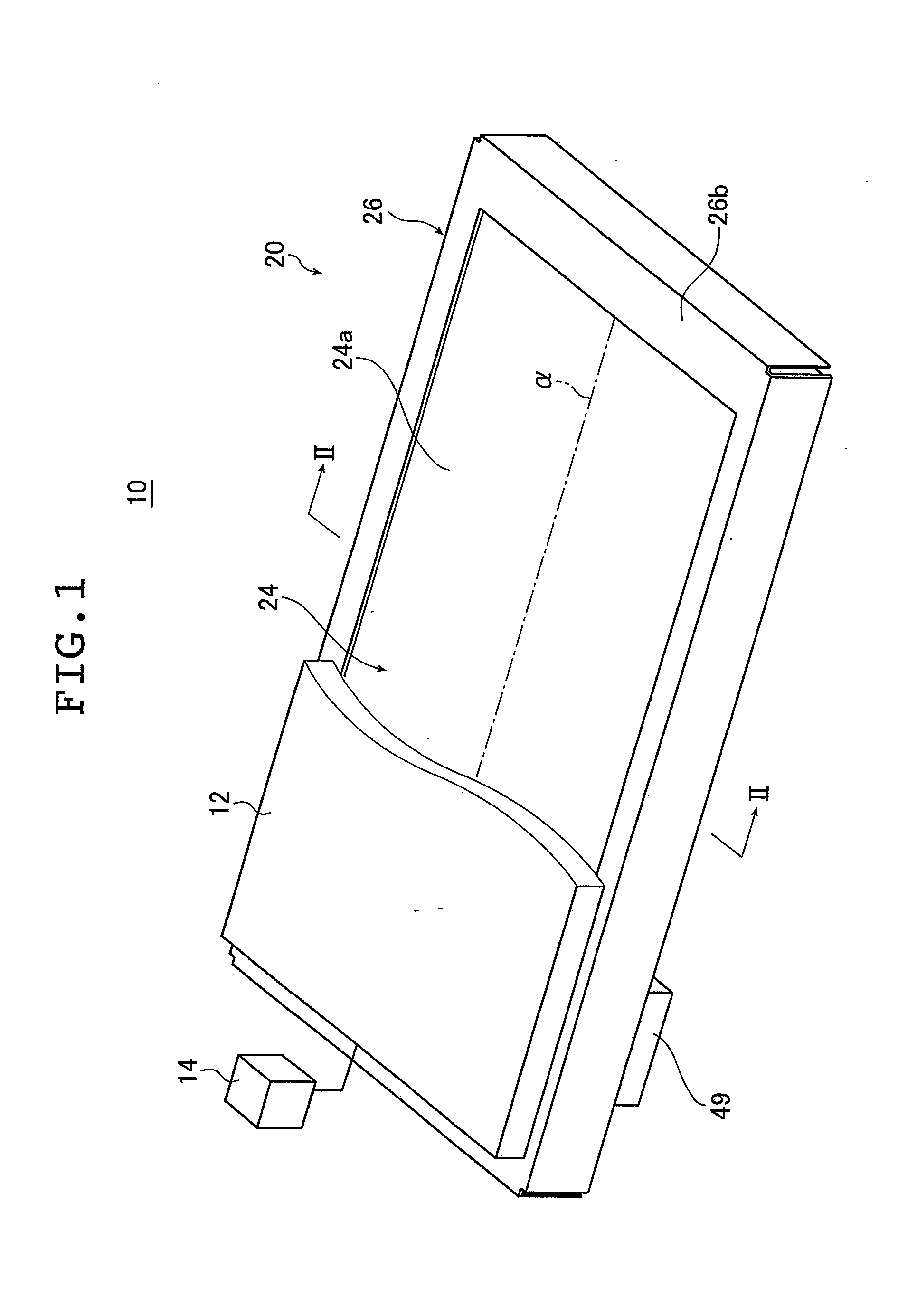

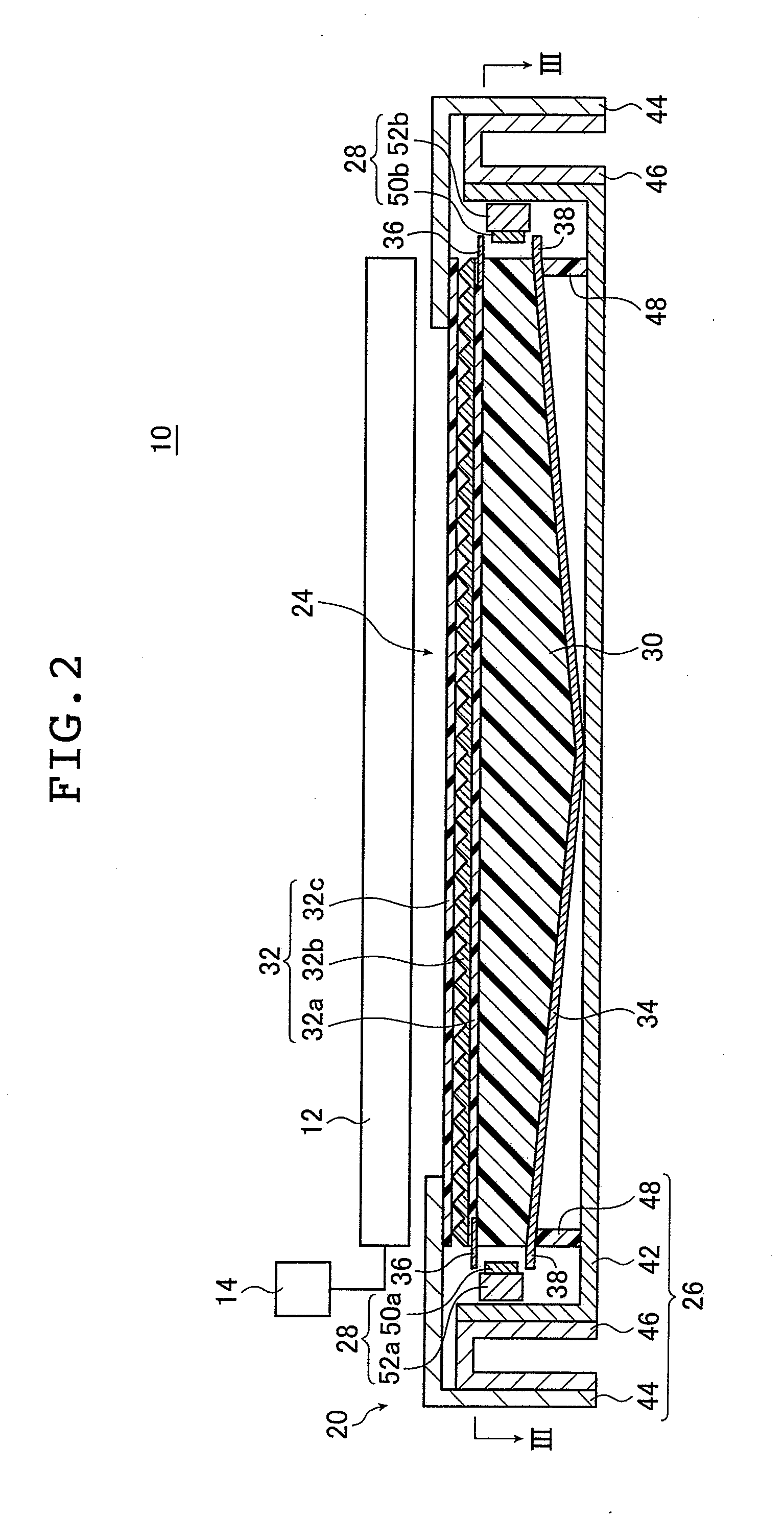

Planar lighting device

ActiveUS7771102B2Add dimensionReduce thickness and weightOptical light guidesReflectorsIlluminanceLight guide

Owner:FUJIFILM CORP

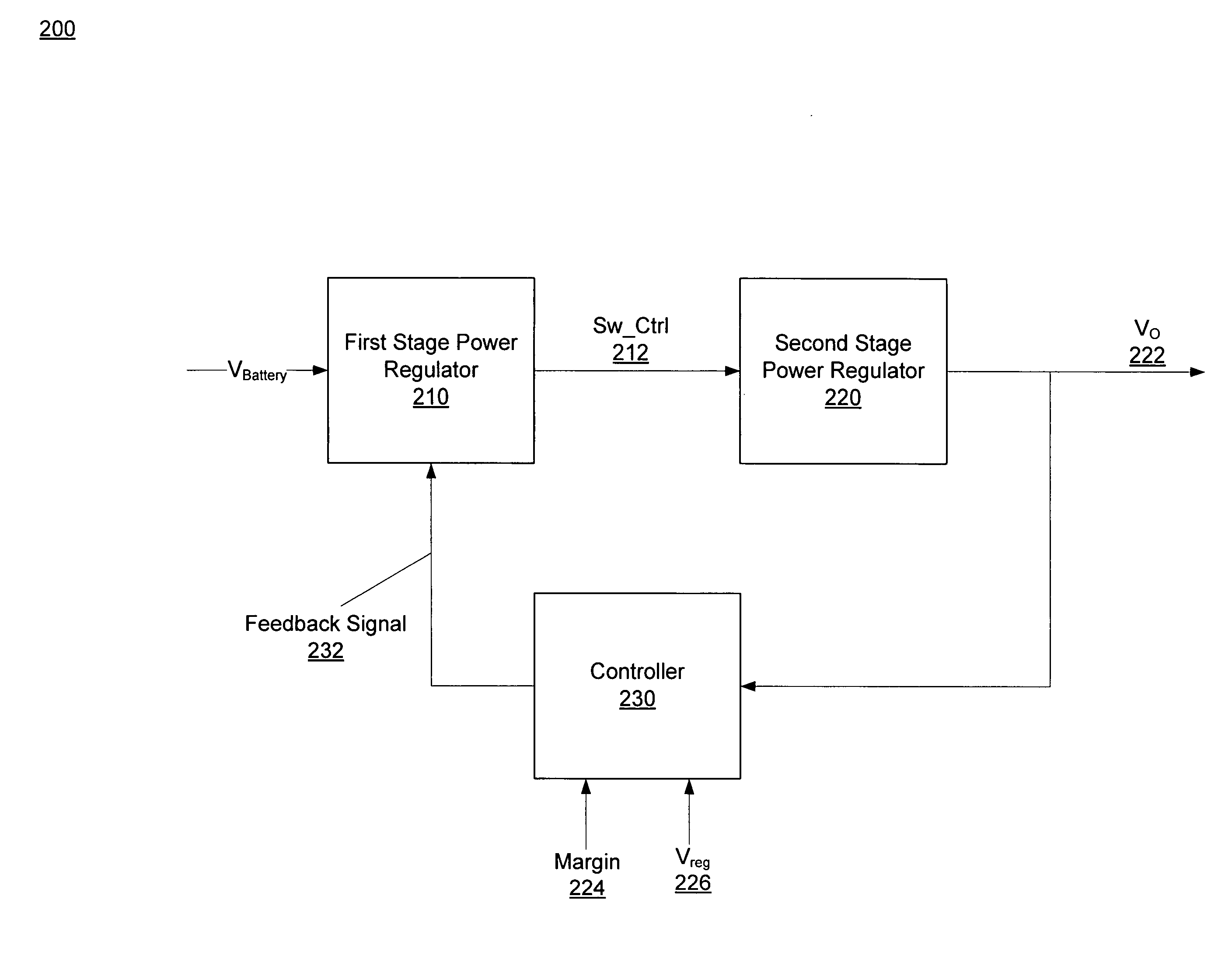

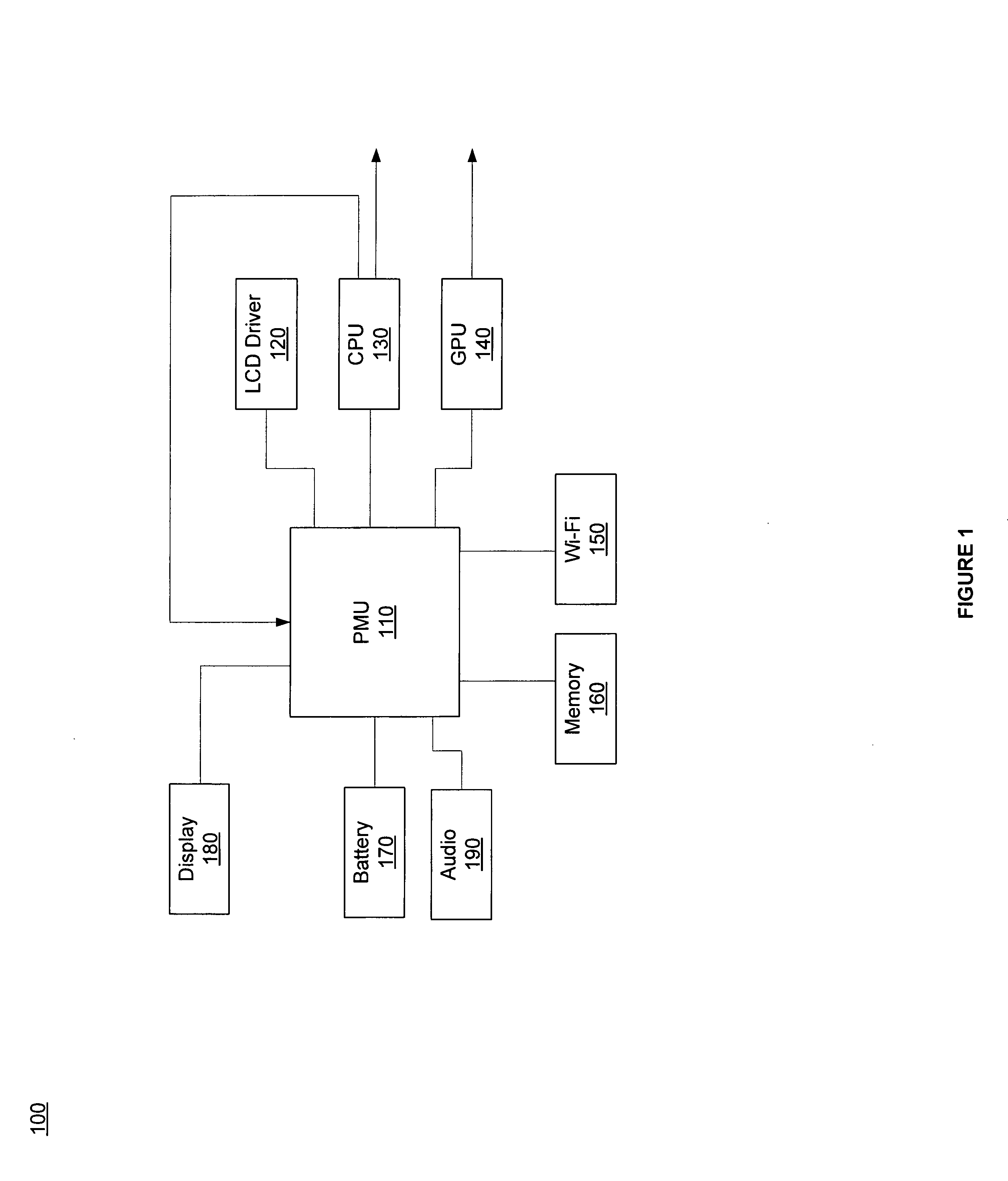

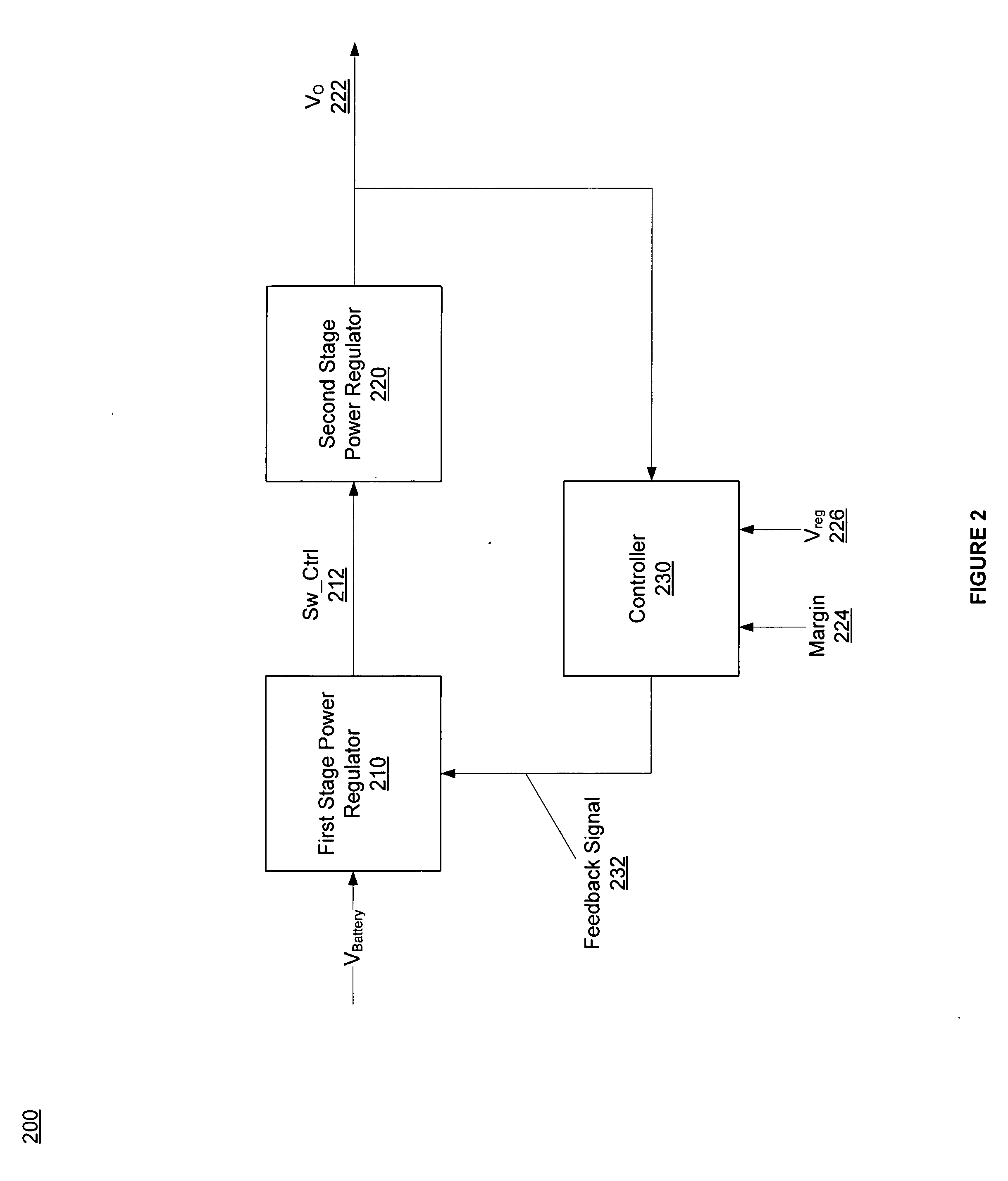

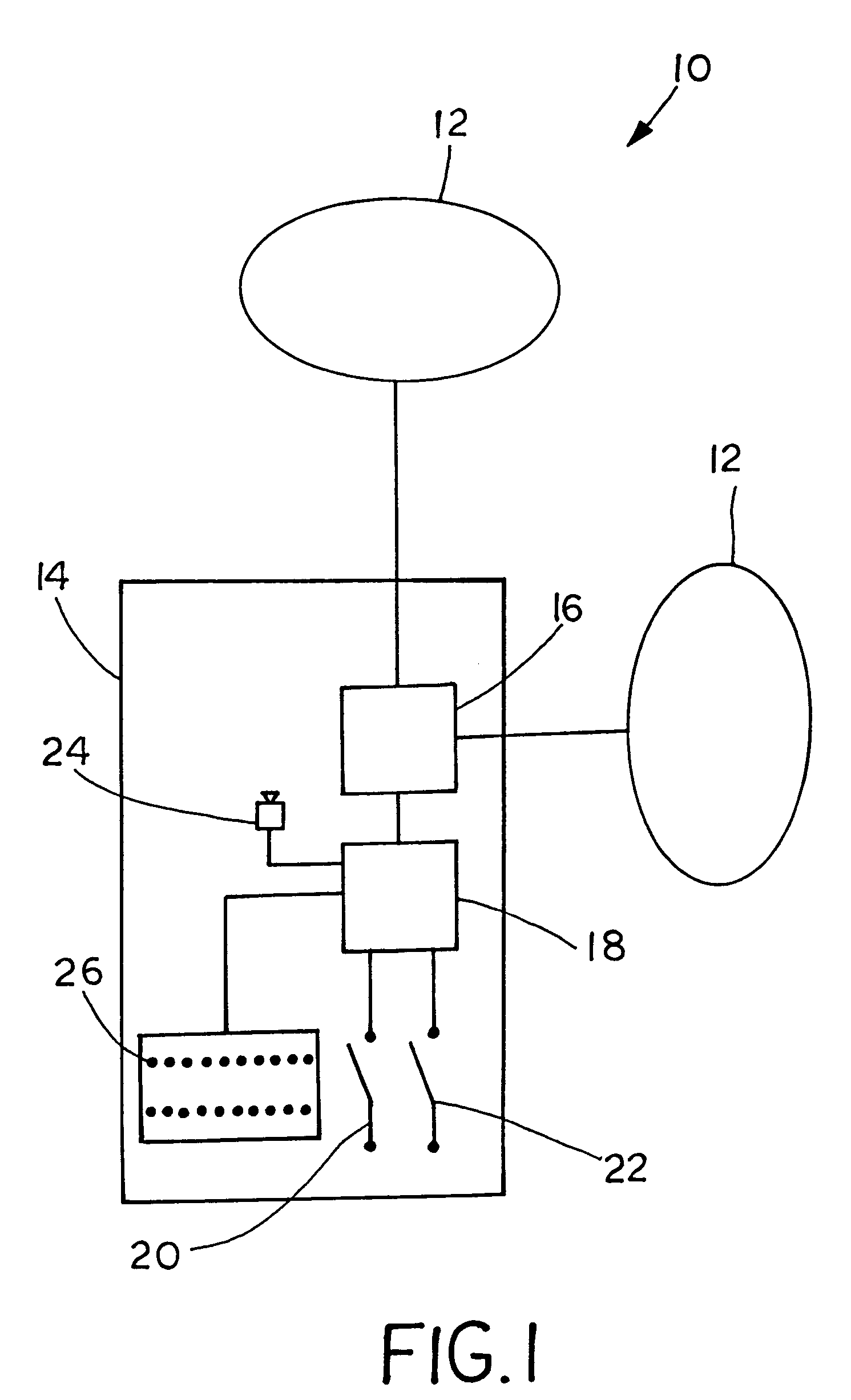

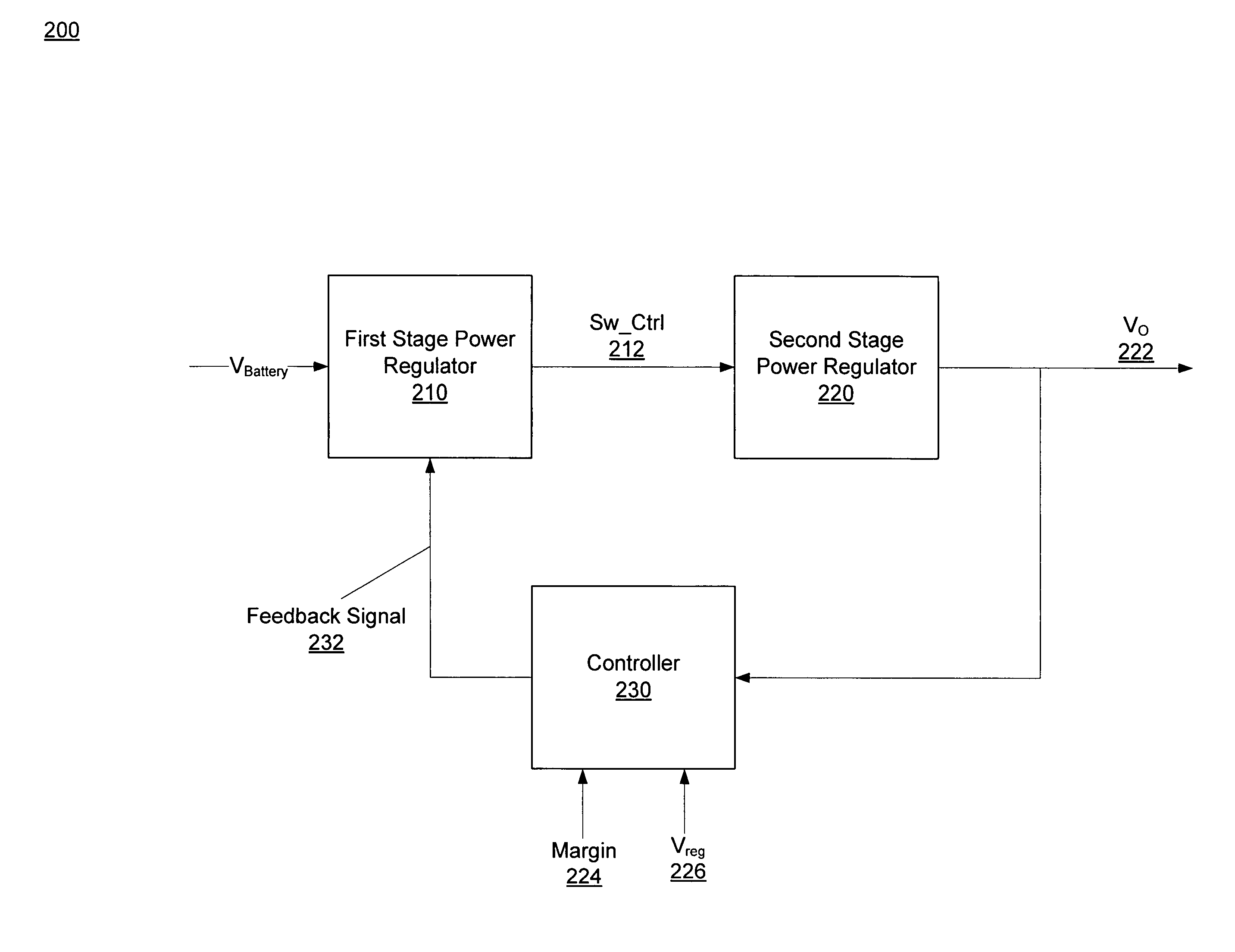

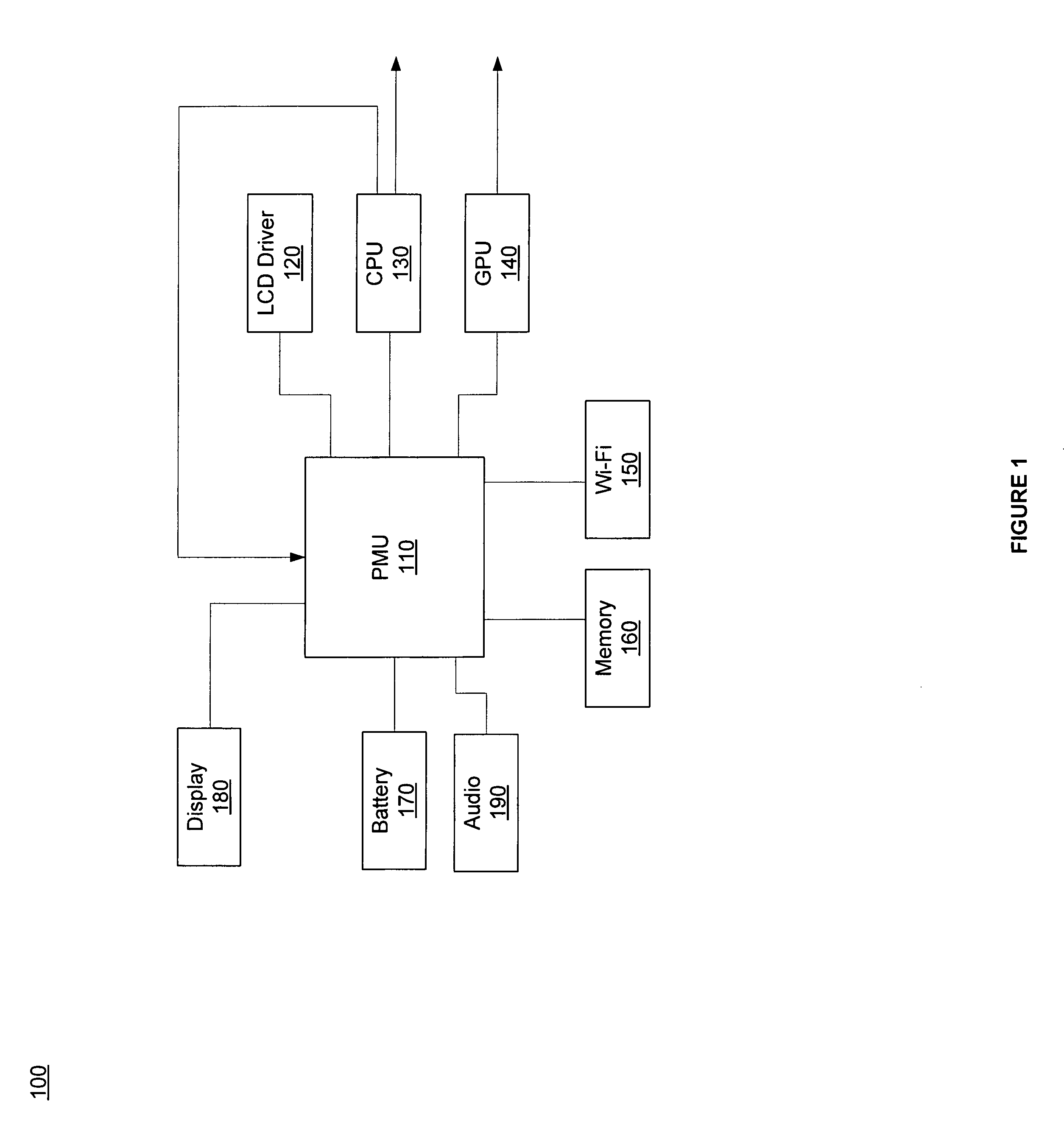

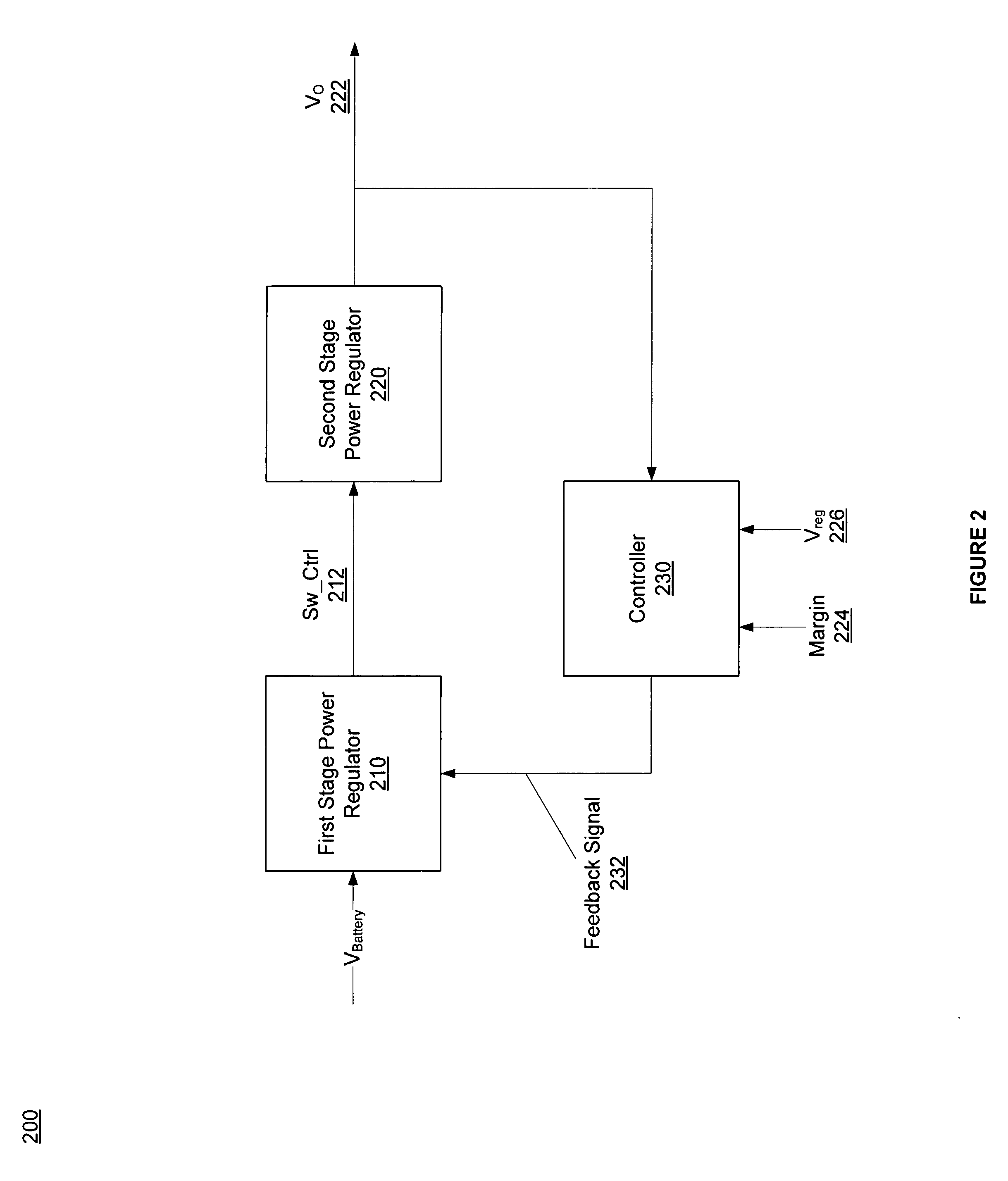

Power management efficiency using DC-DC and linear regulators in conjunction

ActiveUS20090153108A1Effective regulationIncreasing of complexityThree-or-more-wire dc circuitsApparatus with intermediate ac conversionLinear regulatorPower Management Unit

A power management unit for improving power efficiency of an electronic device. The power management unit includes a first and a second stage power regulator and a control circuitry. The first stage power regulator includes a switching regulator to efficiently adjust an input voltage based on a feedback signal. The adjusted input voltage provides the second stage power regulator that includes low dropout voltage regulators with an input voltage close to its output. Thus, power dissipation in the second stage is reduced by reducing the voltage differential between the input and desired output voltages. The second stage turns on / off power to units of the electronic device. The control circuitry generates the feedback signal based on dropout voltages of the low dropout voltages, the desired output voltage and the adjusted input voltage. The largest dropout voltage is selected and adds it to the desired output voltage to generate the feedback signal.

Owner:NVIDIA CORP

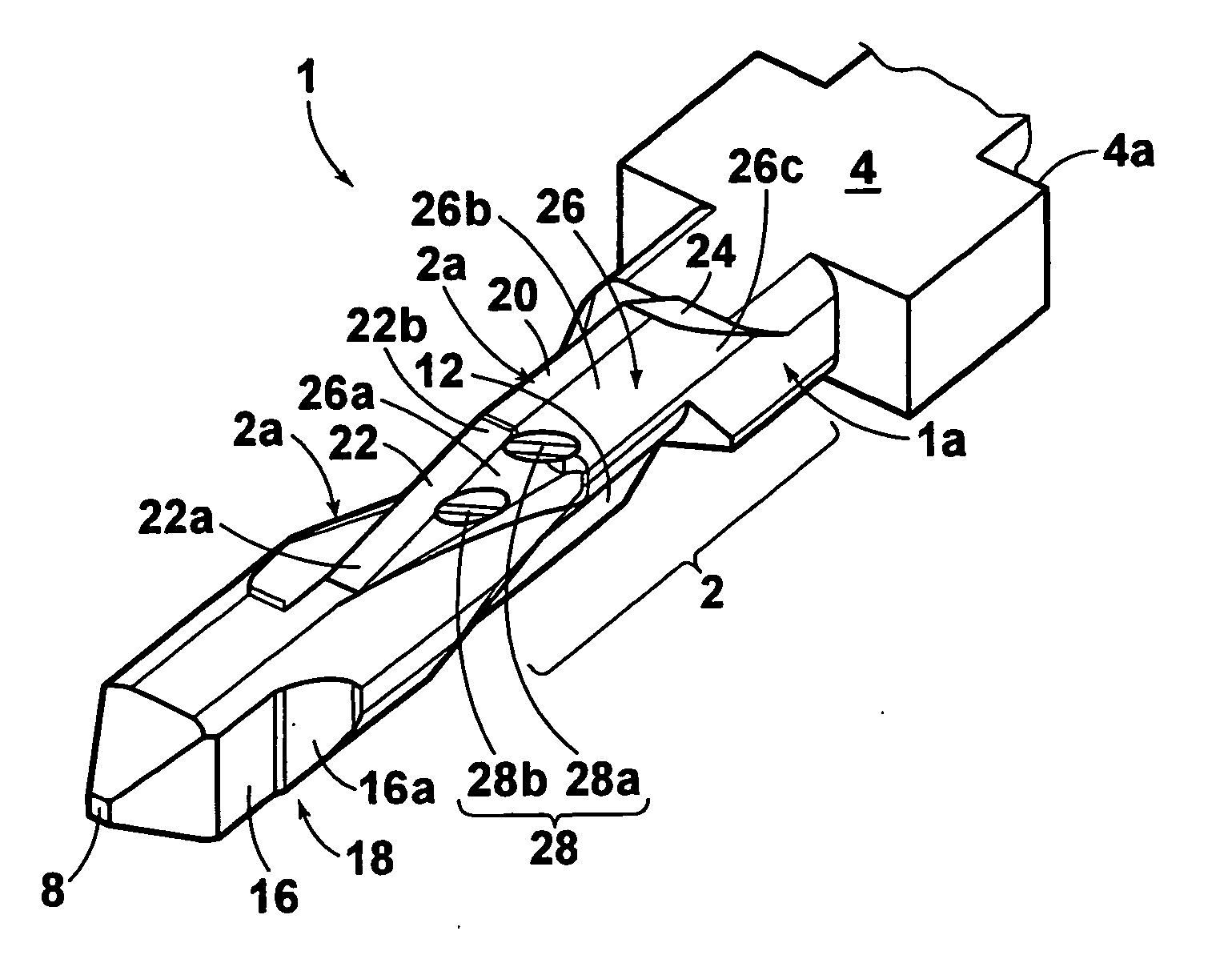

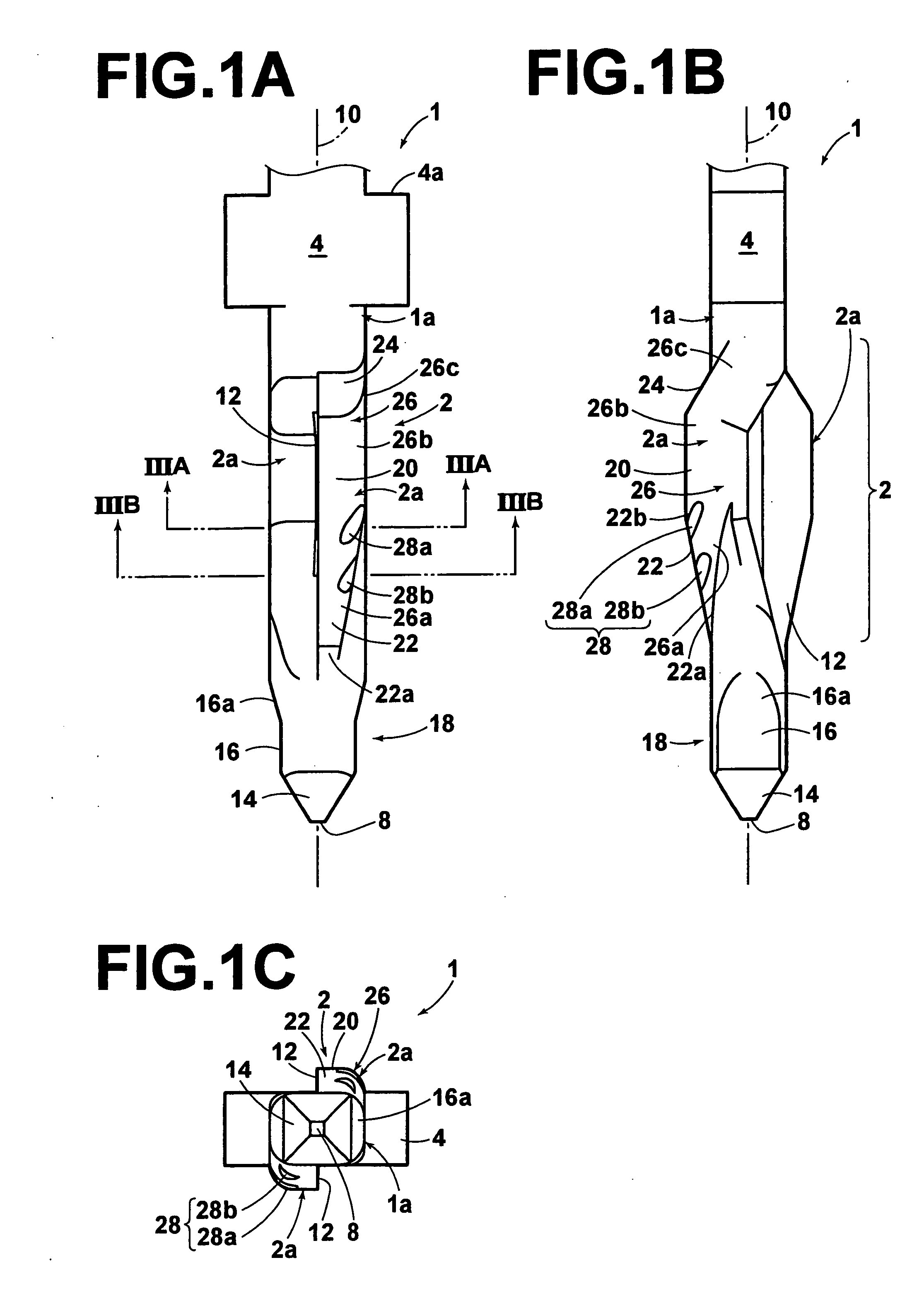

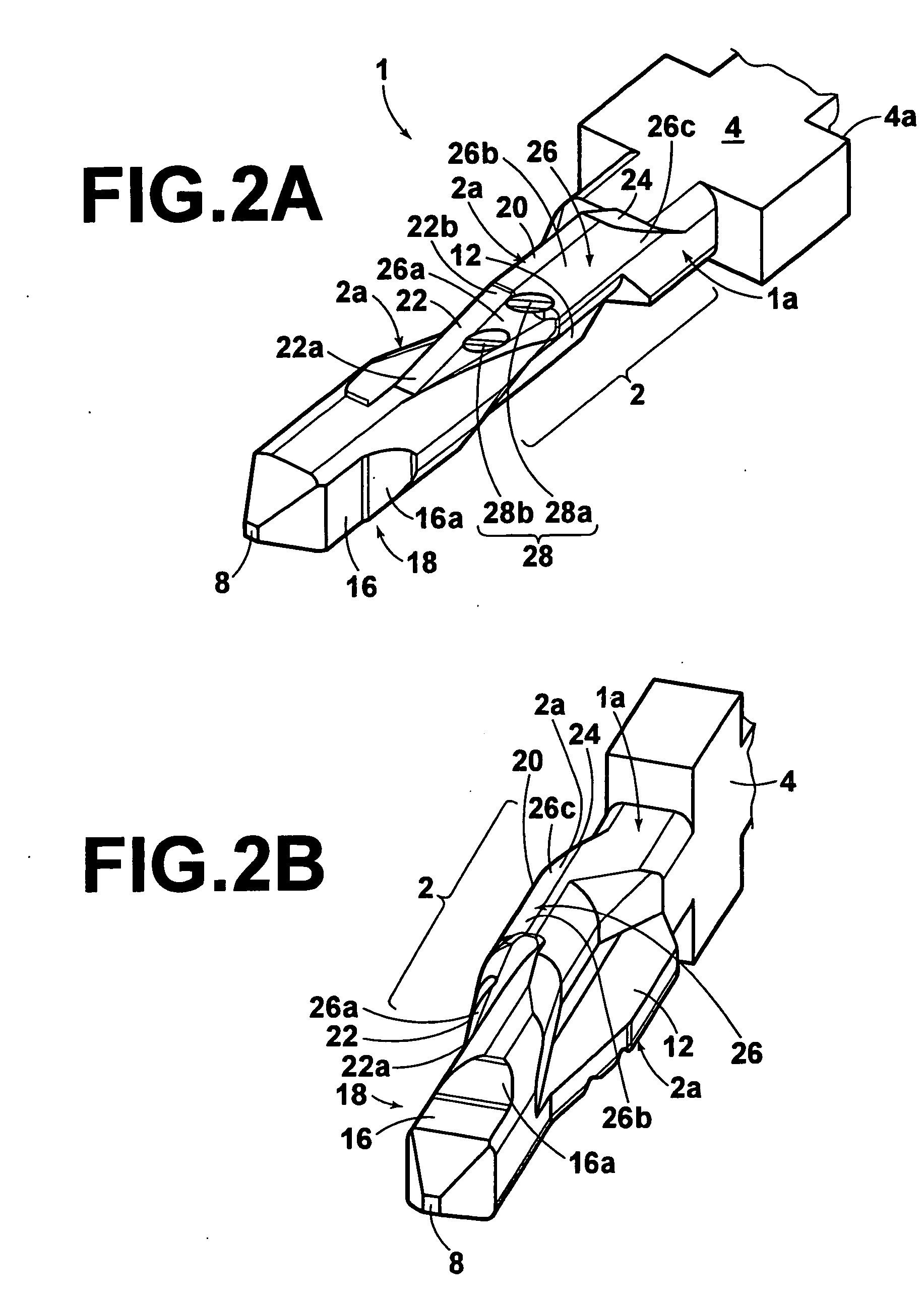

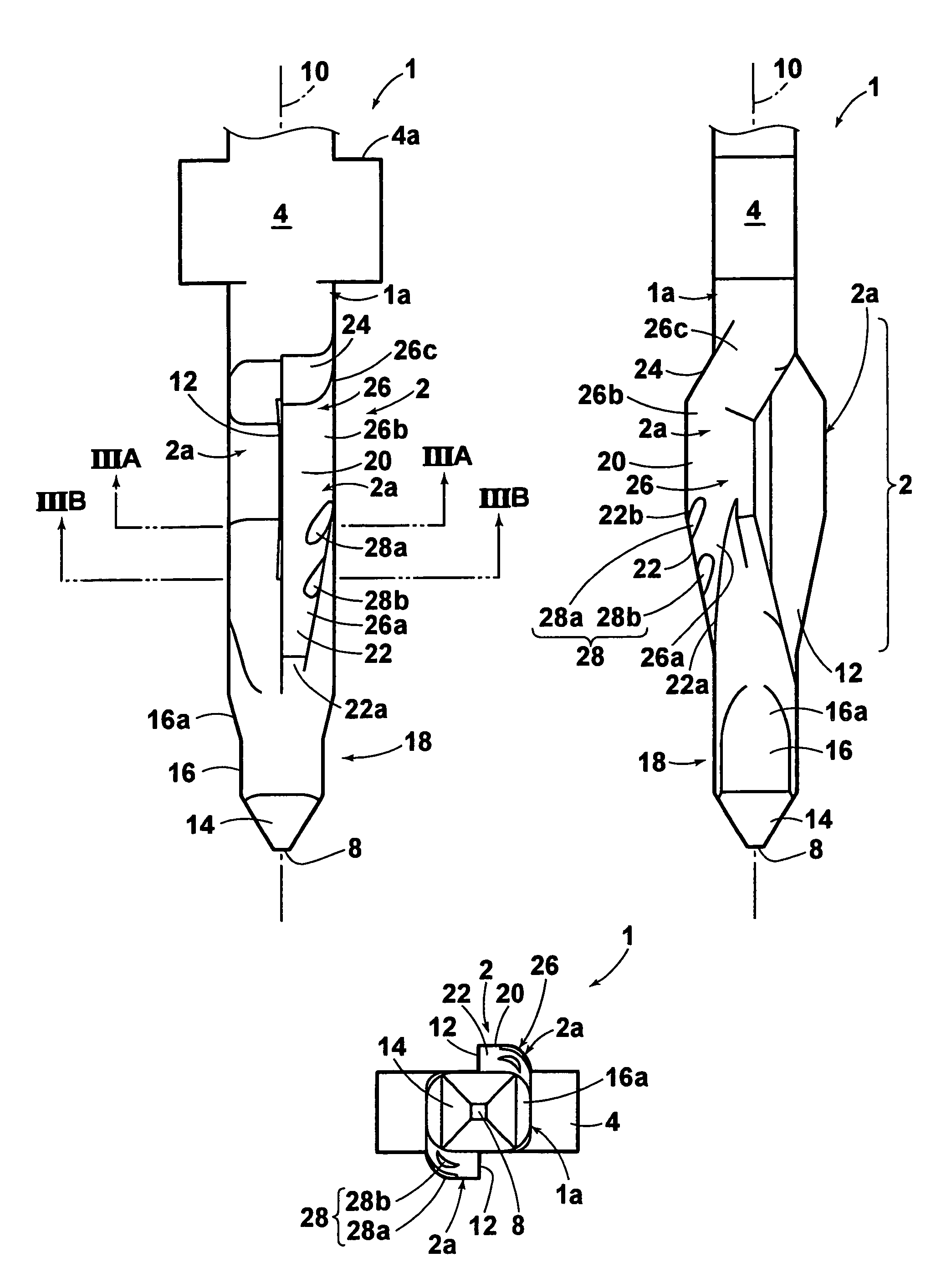

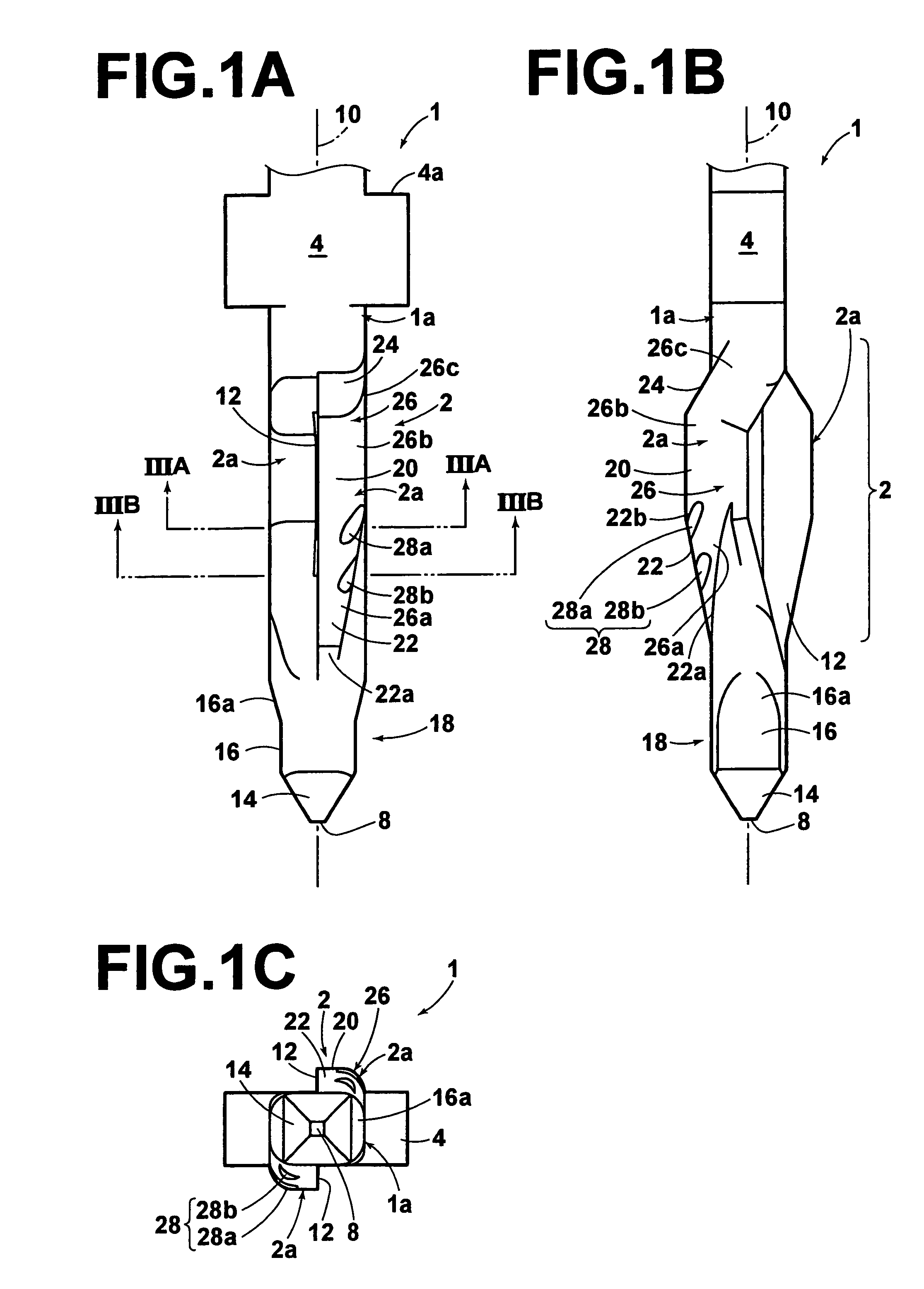

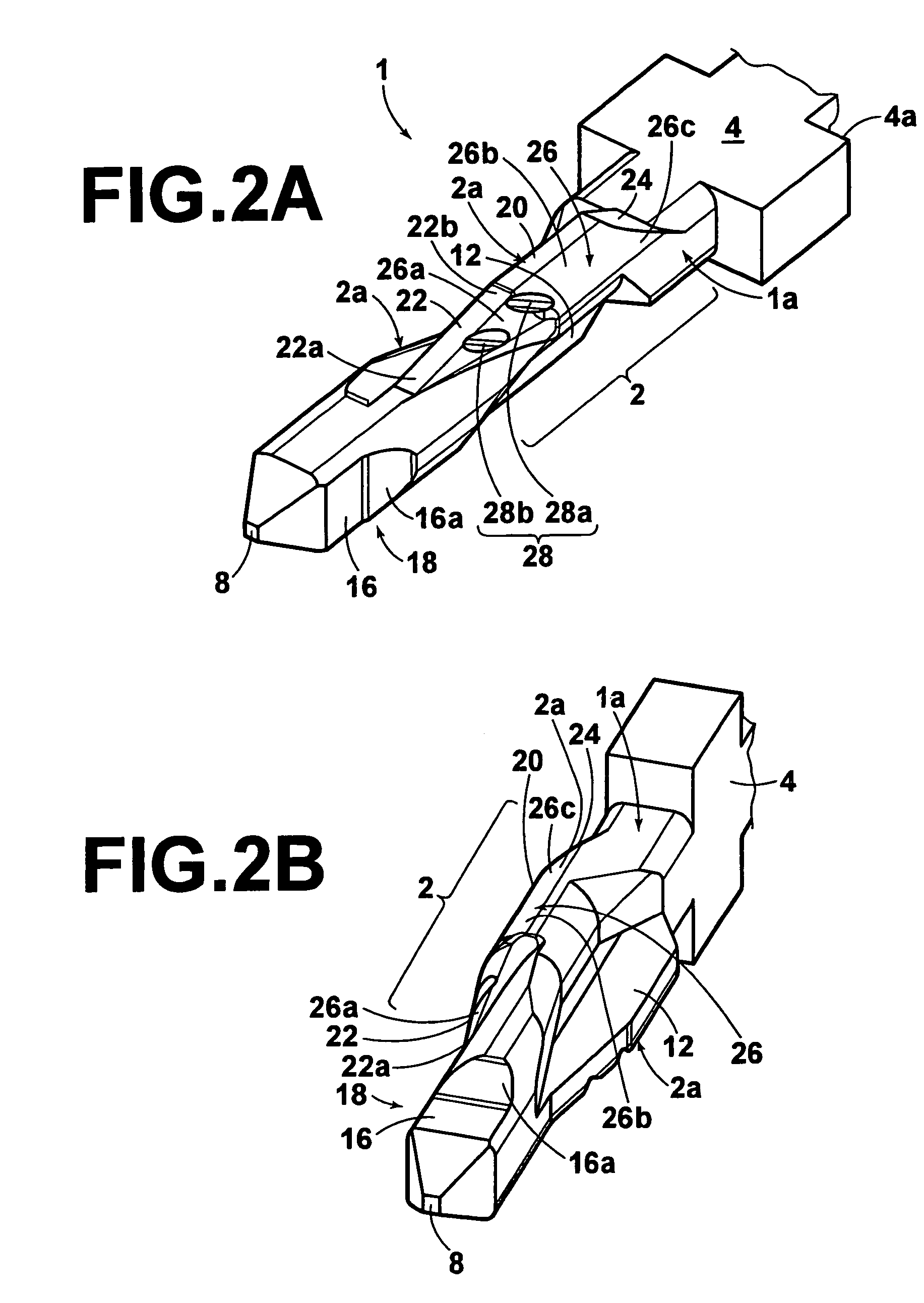

Compliant pin and electrical connector utilizing compliant pin

InactiveUS20060035535A1Reduce the amount requiredAvoid shortingSecuring/insulating coupling contact membersCoupling contact membersEngineeringMechanical engineering

Owner:TYCO ELECTRONICS JAPAN GK

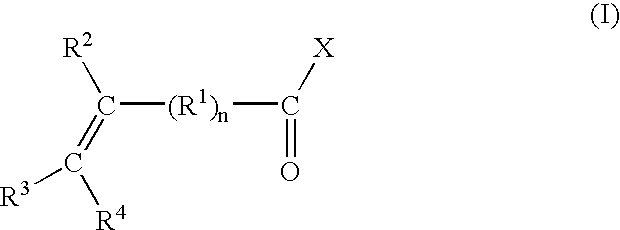

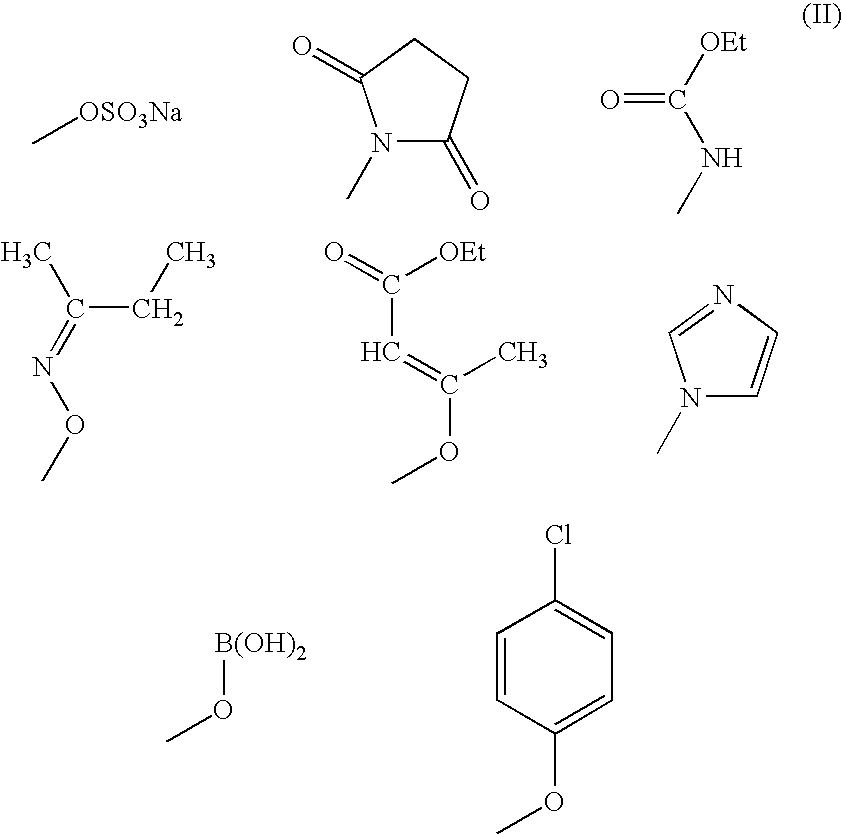

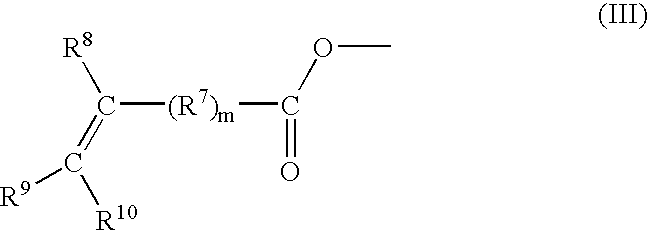

Compositions comprising functionalized polyphenylene ether resins

The invention relates to a method of forming a polyphenylene ether resin containing residual aliphatic unsaturation. A polyphenylene ether is reacted with a capping agent in a solvent to form the polyphenylene ether resin containing residual aliphatic unsaturation, which is precipitated from solution by combining the solution with an antisolvent. The precipitated polyphenylene ether resin containing residual aliphatic unsaturation has lower levels of residual impurities than the same compound isolated by devolatilization.

Owner:SABIC GLOBAL TECH BV

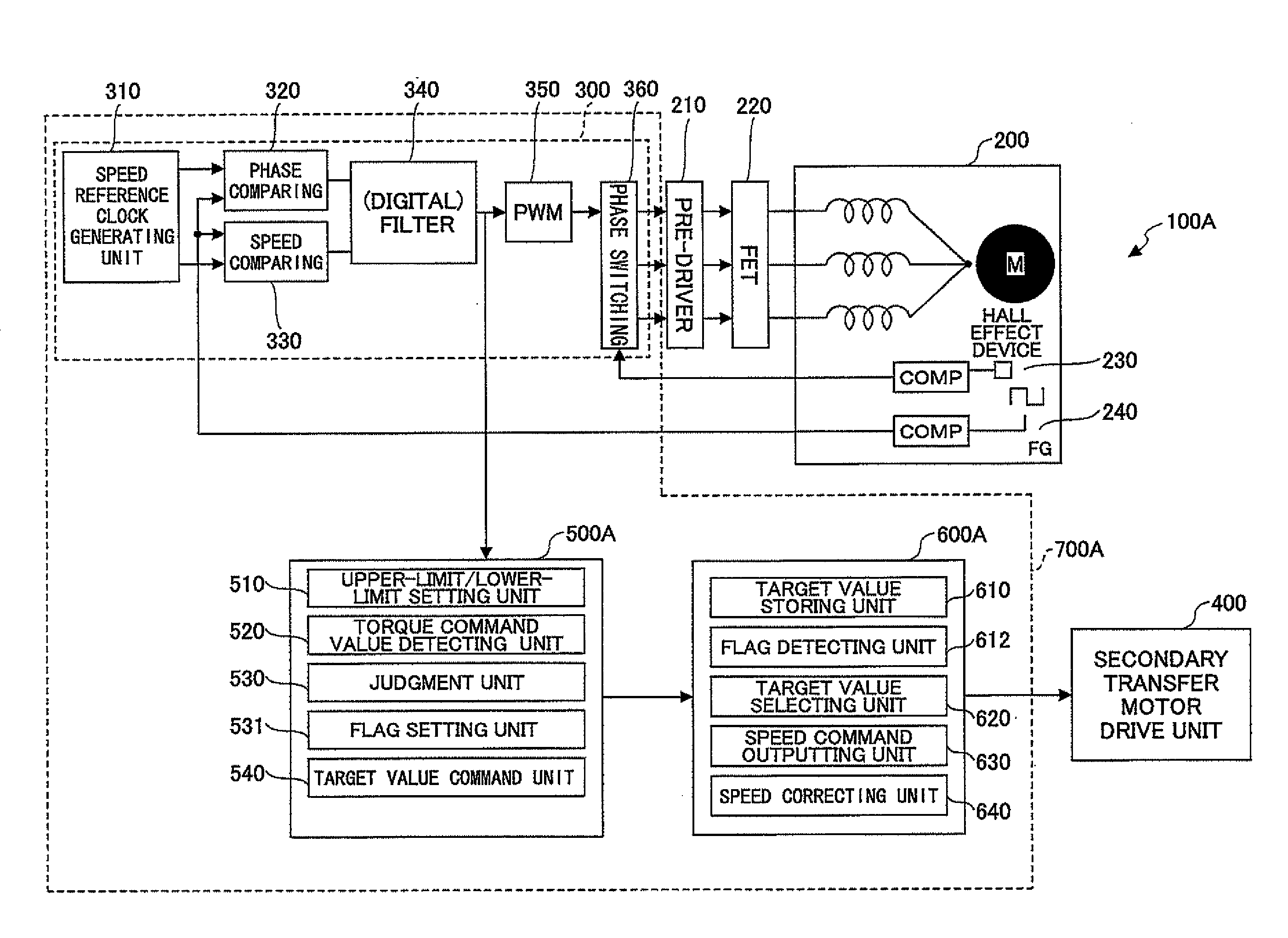

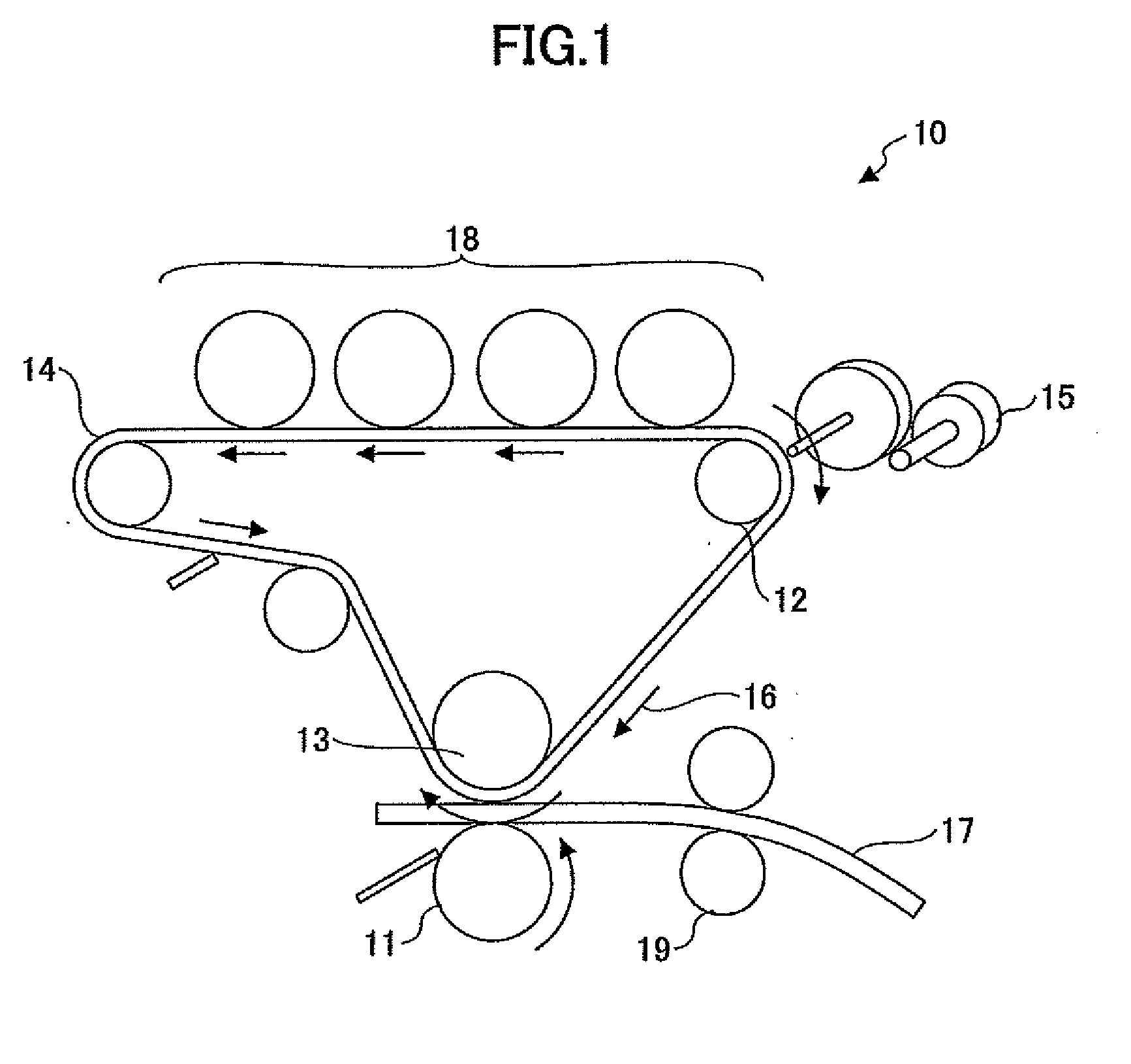

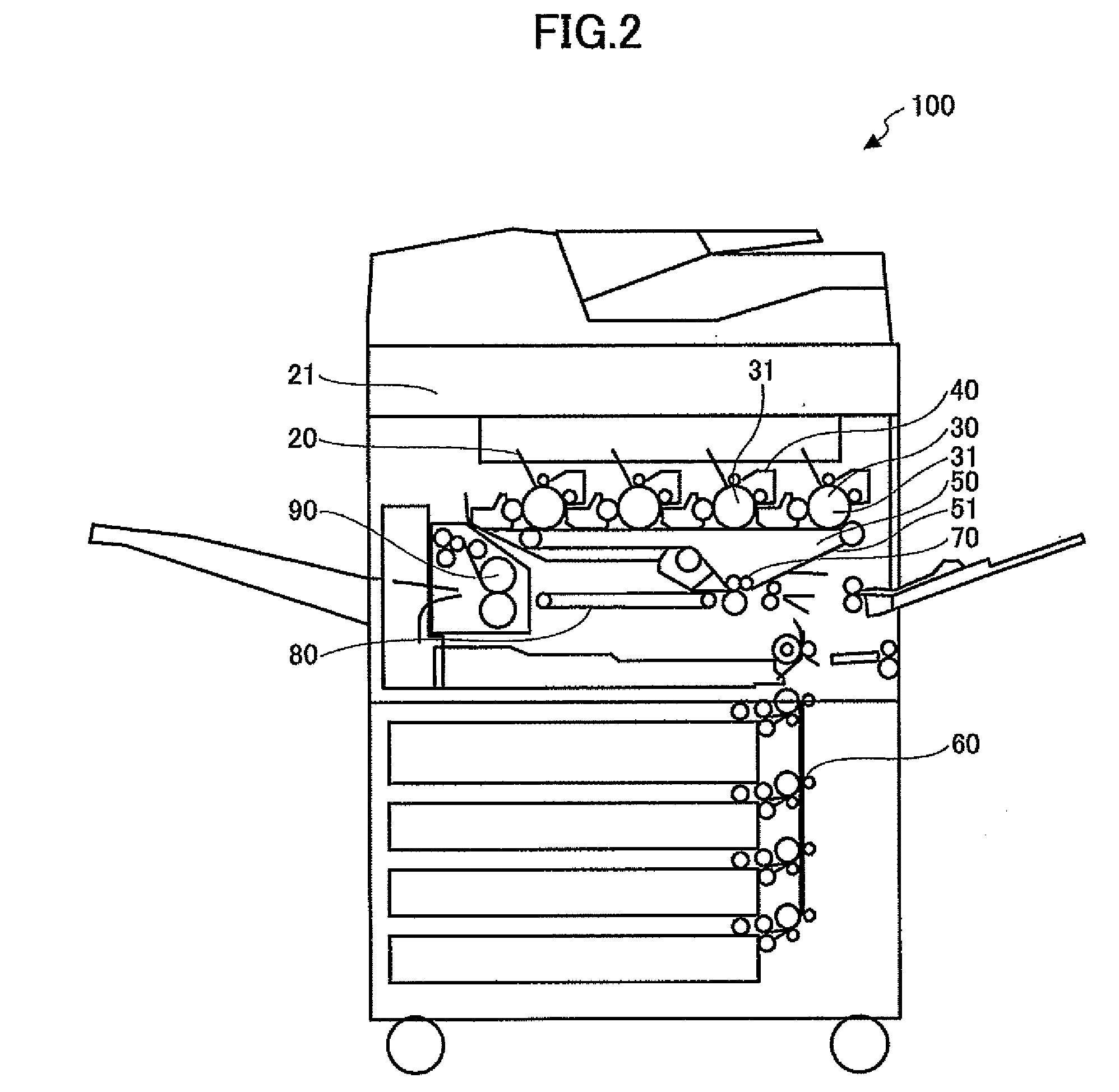

Image Forming Device and Semiconductor Device

ActiveUS20080298856A1Increasing of costIncreasing numberElectrographic process apparatusLower limitImage formation

In an image forming device including a first rotary member arranged to drive an intermediate transfer belt, a first motor arranged to rotate the first rotary member, and a second rotary member arranged to transfer a toner image formed on the intermediate transfer belt to a recording sheet, a torque command value detecting unit detects a torque command value to the first motor. A setting unit sets up a lower limit of the torque command value. A judgment unit determines whether a detected torque command value exceeds the lower limit. A control unit controls driving of the second rotary member when the detected torque command value exceeds the lower limits so that a difference between a surface speed of the intermediate transfer belt and a peripheral speed of the second rotary member falls within a predetermined range.

Owner:RICOH KK

Compliant pin and electrical connector utilizing compliant pin

InactiveUS7074094B2Increasing numberIncreasing of stepSecuring/insulating coupling contact membersCoupling contact membersEngineeringElectrical connector

Owner:TYCO ELECTRONICS JAPAN GK

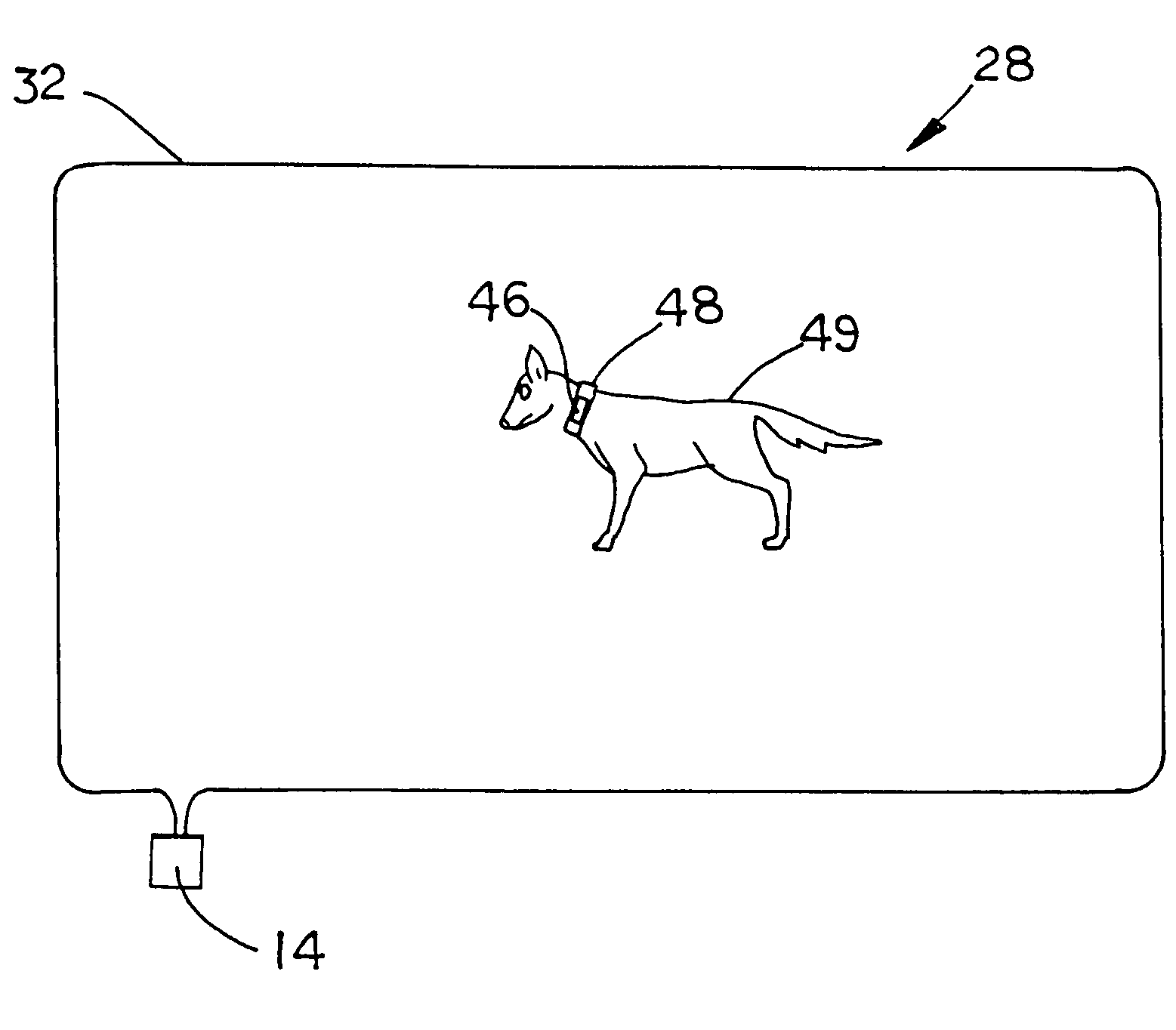

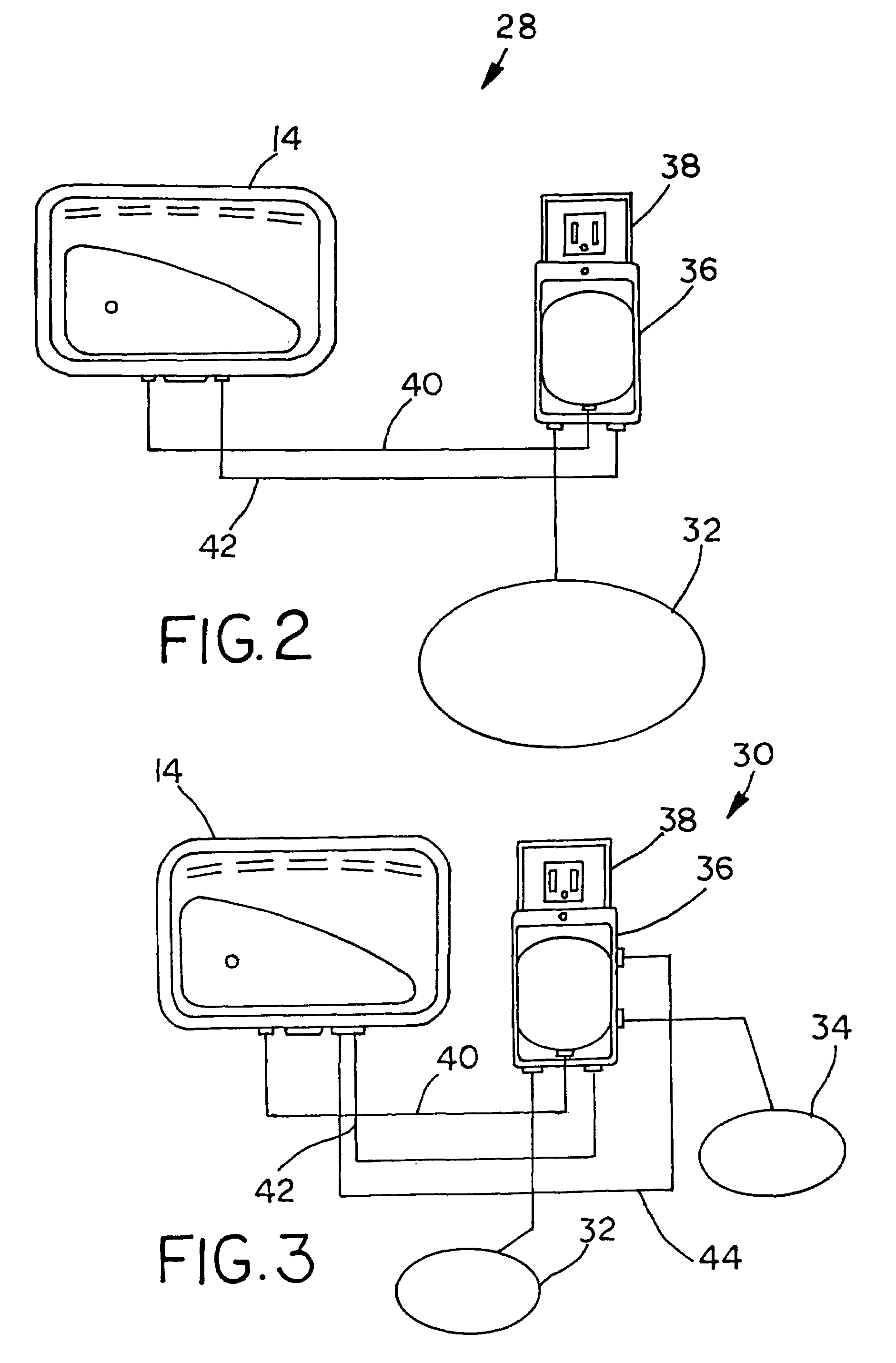

Control of animal containment system transmitter settings with minimal switches

ActiveUS7565885B2Increasing of functionIncreasing numberTaming and training devicesEngineeringAnimal training

A transmitter for an animal training system, which includes a modulator for energizing at least one antenna, and a controller connected to the modulator. A first switch is connected to the controller, and the first switch is for entering a setup mode and for selecting at least one of a plurality of setting configurations. A second switch is also connected to the controller, and the second switch is for modifying a value of a respective setting configuration.

Owner:RADIO SYST CORP

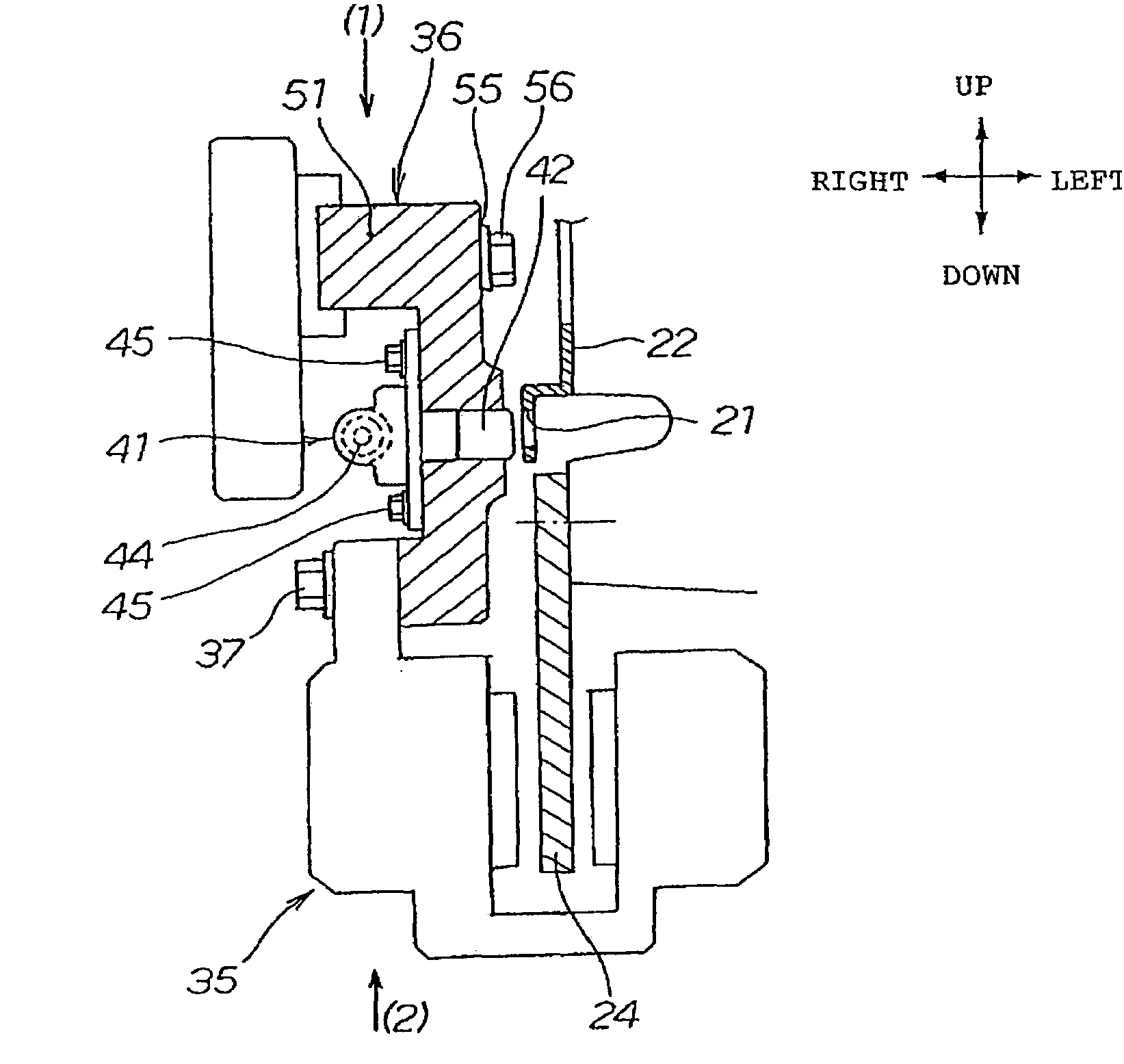

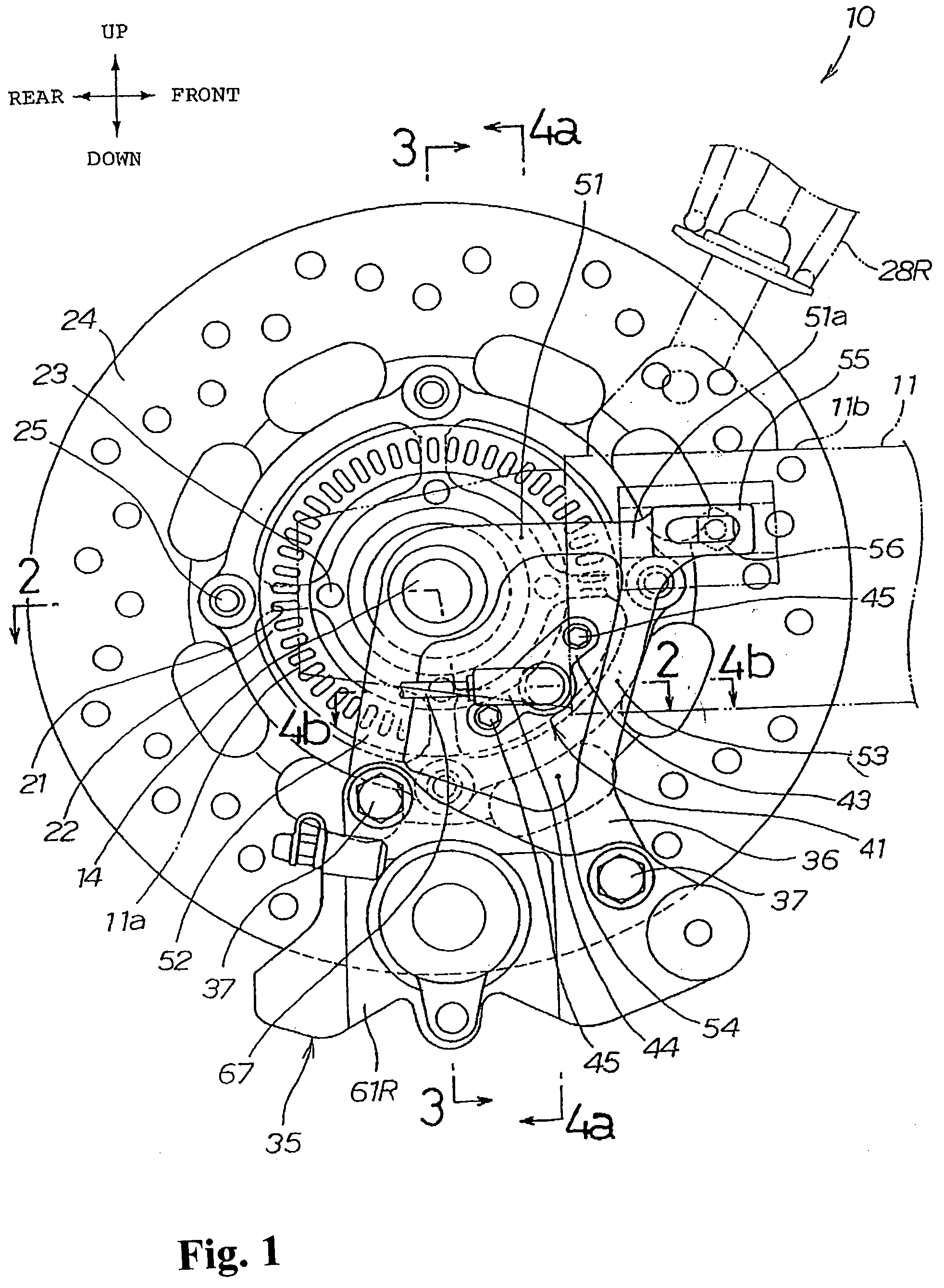

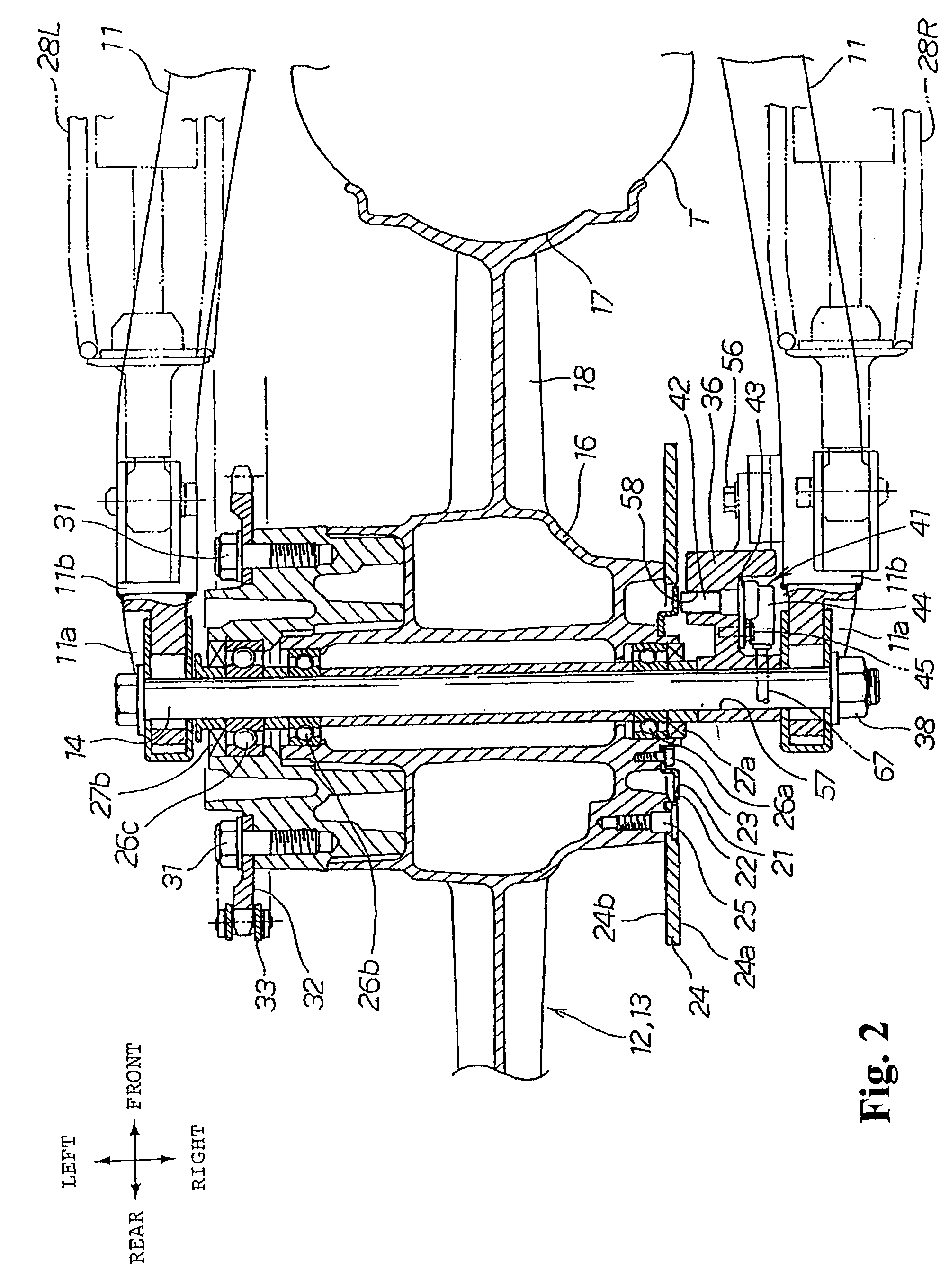

Speed sensor collision prevention device

ActiveUS20090183957A1Reduce the likelihood of a collisionIncreases weight of vehiclePassenger cyclesChildren cyclesVehicle frameWheel speed sensor

A motorcycle includes a swing arm swingably provided on a body frame, a wheel rotatably provided at an end part of the swing arm, a disk plate attached to the wheel, a caliper bracket provided on the body frame side of the vehicle, a disk brake caliper provided on the caliper bracket, and a wheel speed sensor attached to the caliper bracket. The wheel speed sensor is disposed between the swing arm and the wheel. The wheel speed sensor and the swing arm overlap one other in a side view of the vehicle.

Owner:HONDA MOTOR CO LTD

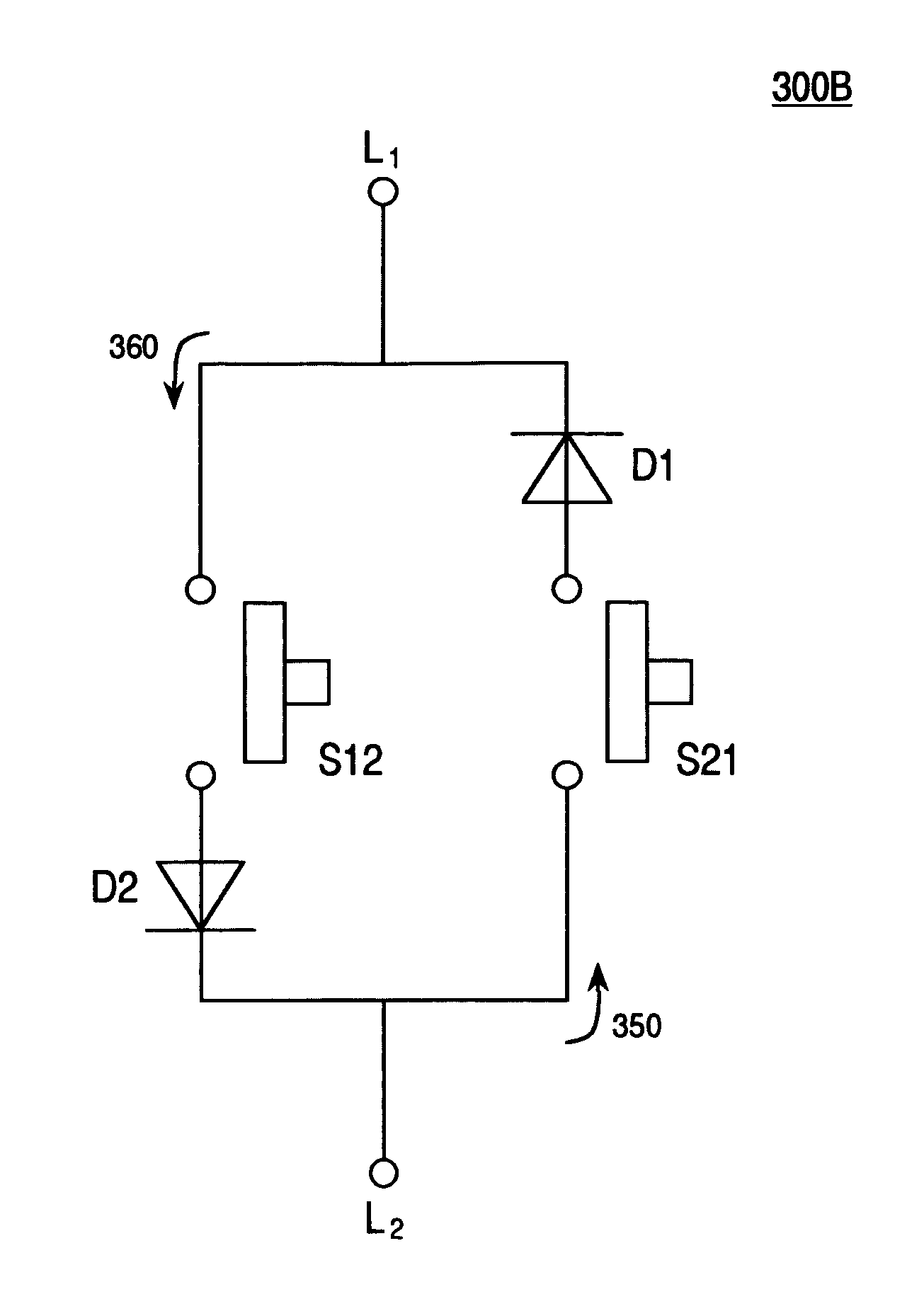

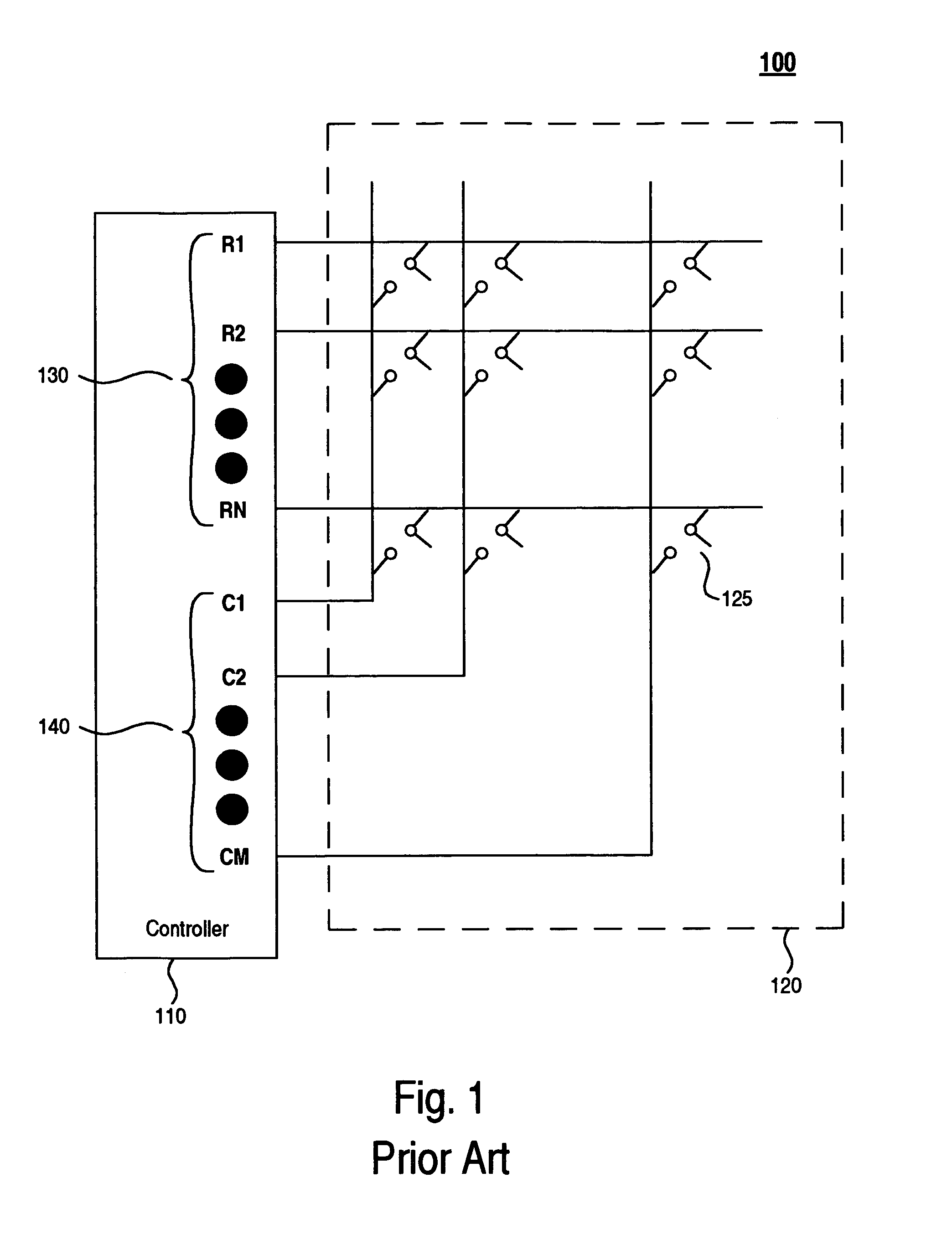

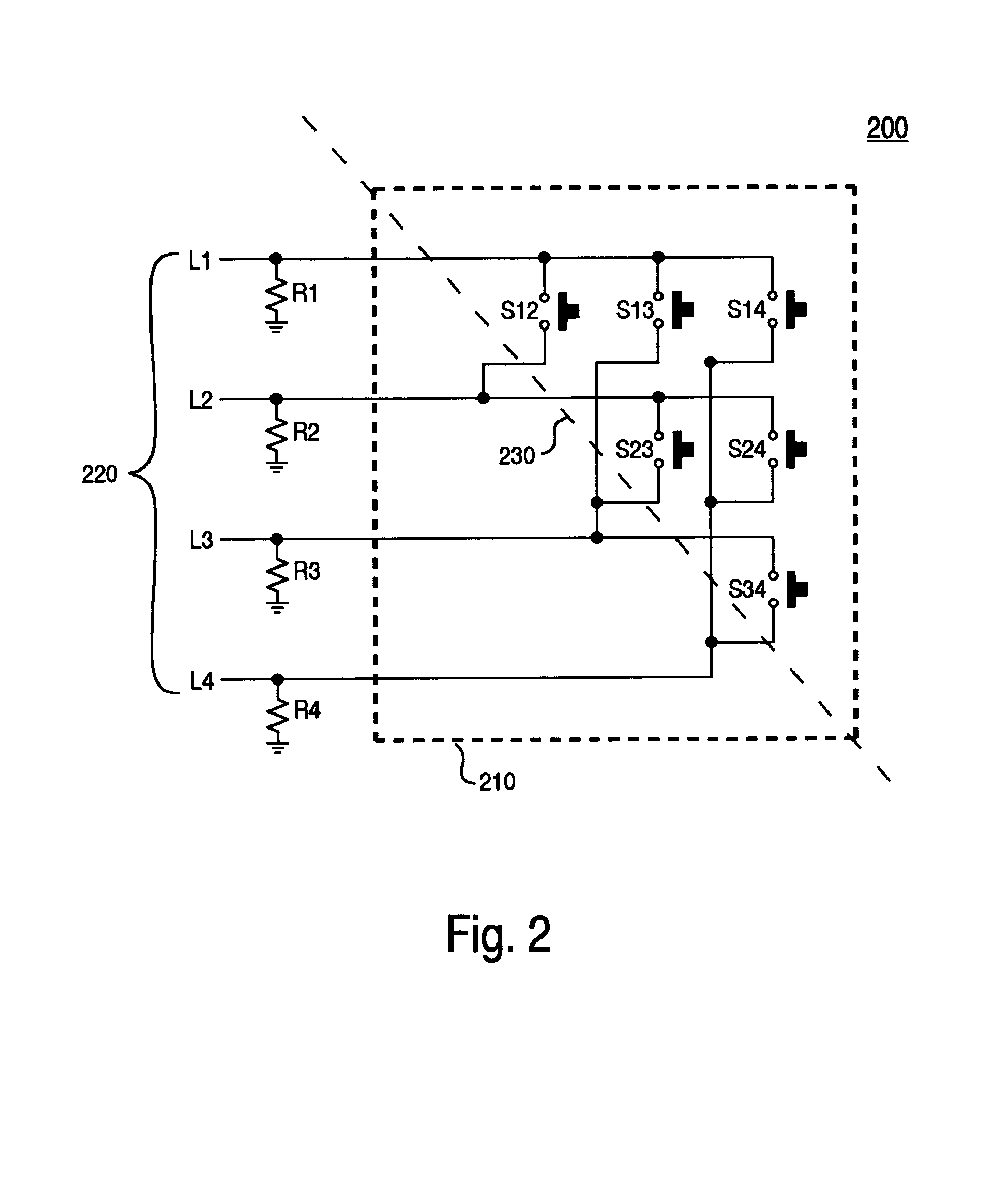

System and method for a data-input array capable of being scanned using a reduced number of signals

ActiveUS7123170B1Reduce in quantityImprove functionalityInput/output for user-computer interactionDynamic codingEngineeringInput/output

A system and method for scanning a data-input array (e.g., a keyboard or keypad) using a reduced number of signals is disclosed. Specifically, a switch array is disclosed comprising a plurality of switches and a plurality of input / output (I / O) lines. The switch array is arranged in an N*N matrix. A plurality of N I / O lines is used to scan the matrix. In one embodiment, the switches in the array are arranged in an N*(N−1) / 2 configuration. In this configuration, there is no duplication of circuit paths. In another embodiment, the switches in the array are arranged in an N(N−1) configuration. In this configuration, a plurality of diodes are used to identify an activated switch depending upon which of a plurality of signal paths is activated. The plurality of diodes is included to differentiate between pairs of switches that complete the same paths between pairs of I / O lines.

Owner:NAT SEMICON CORP

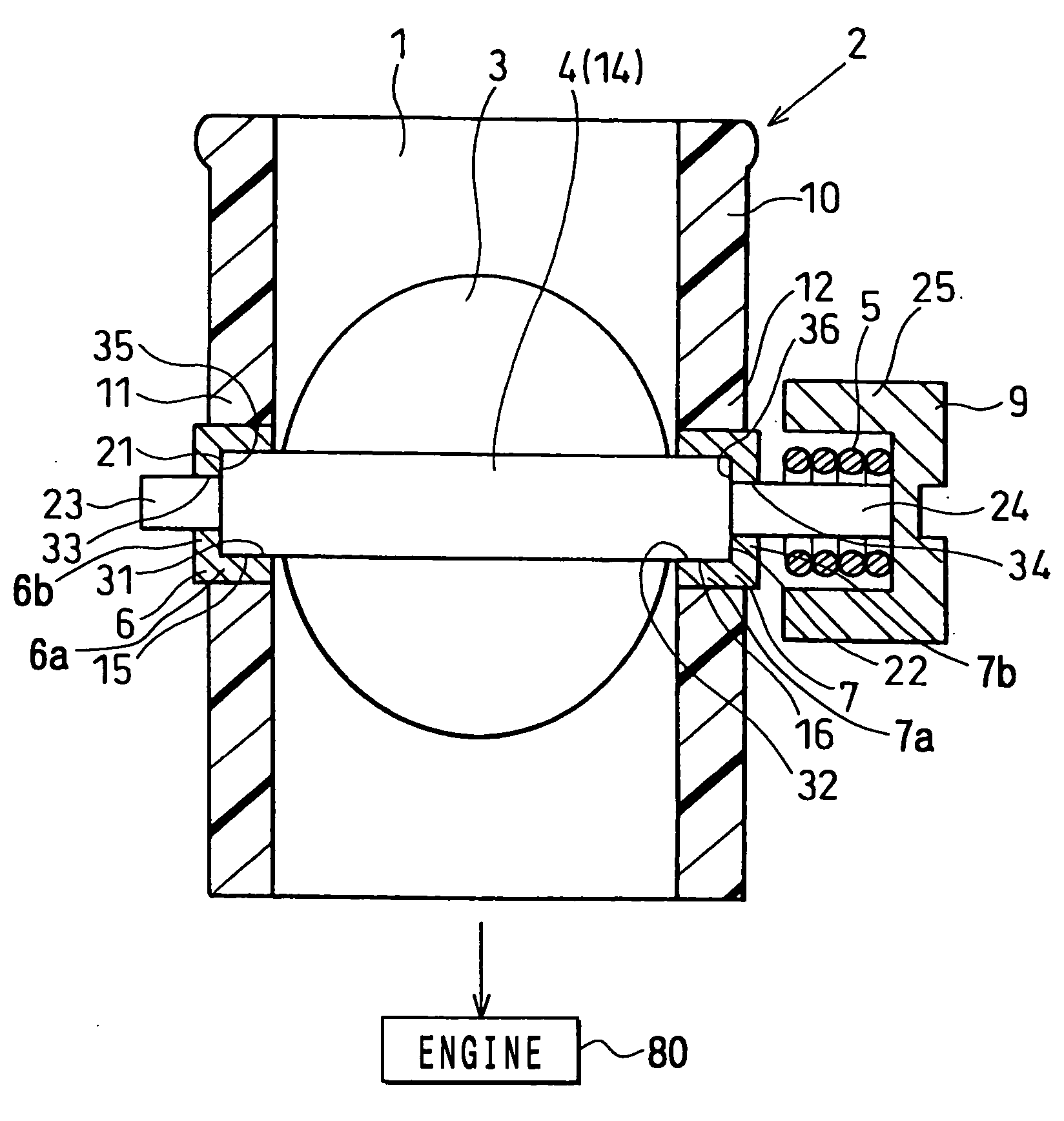

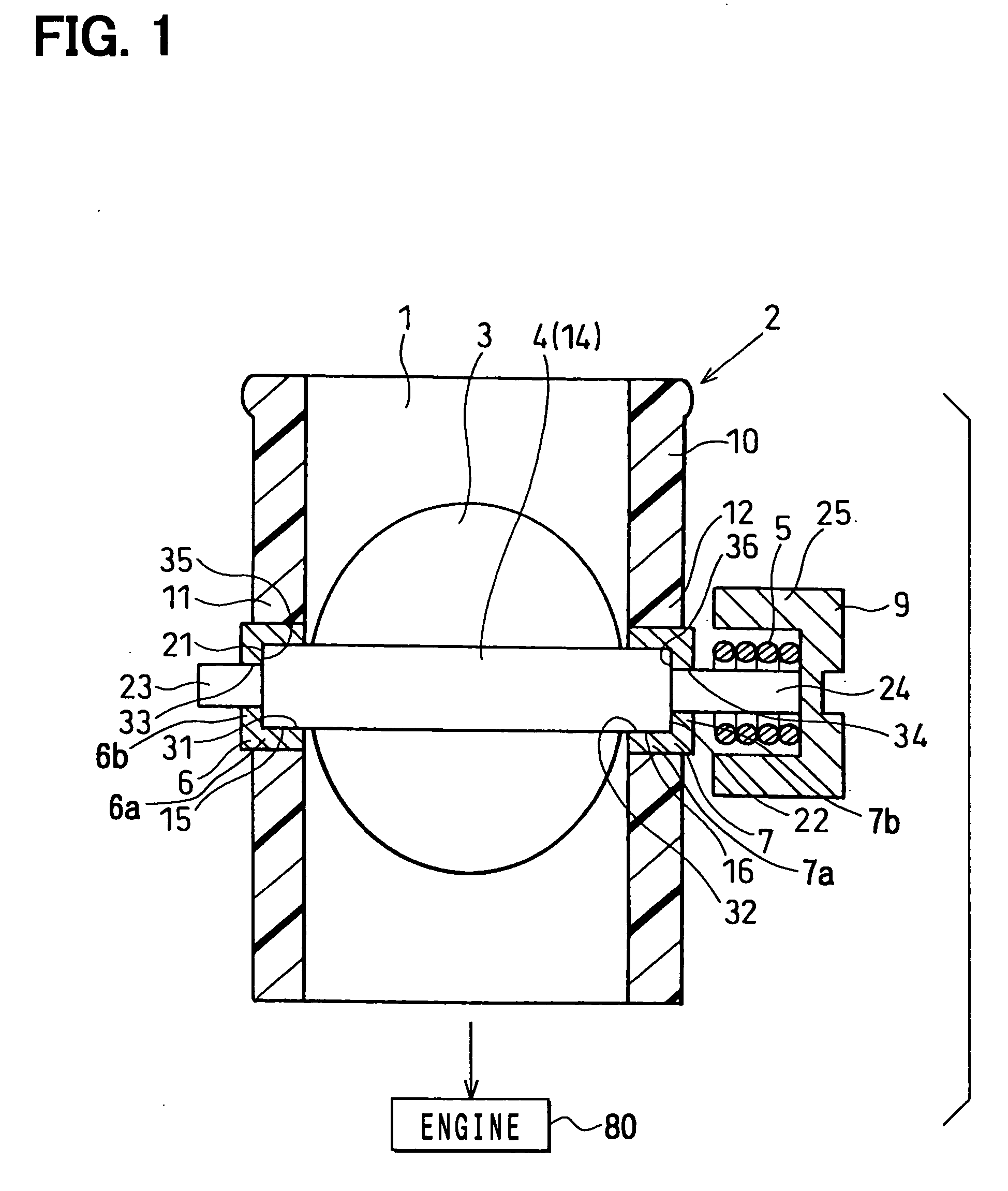

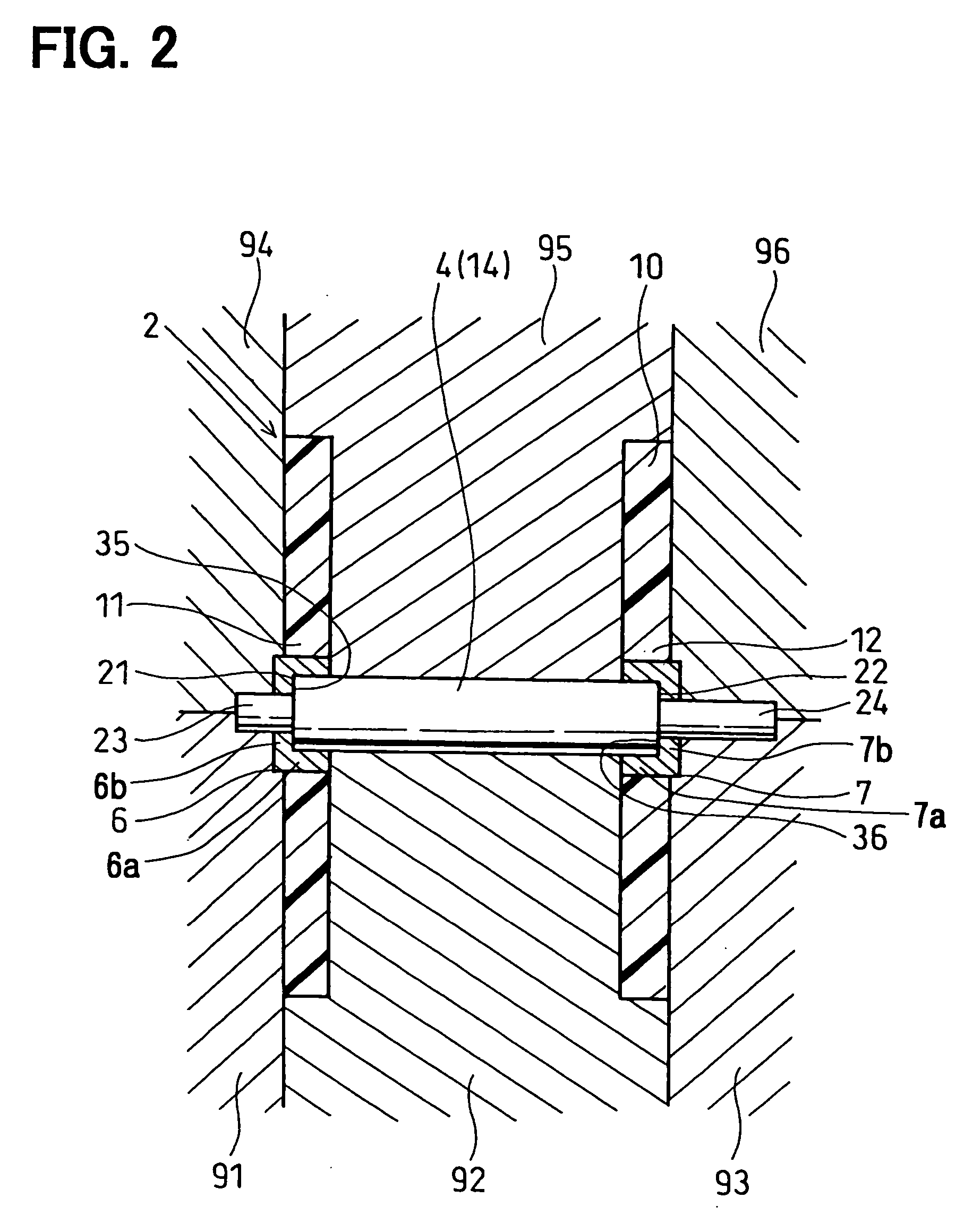

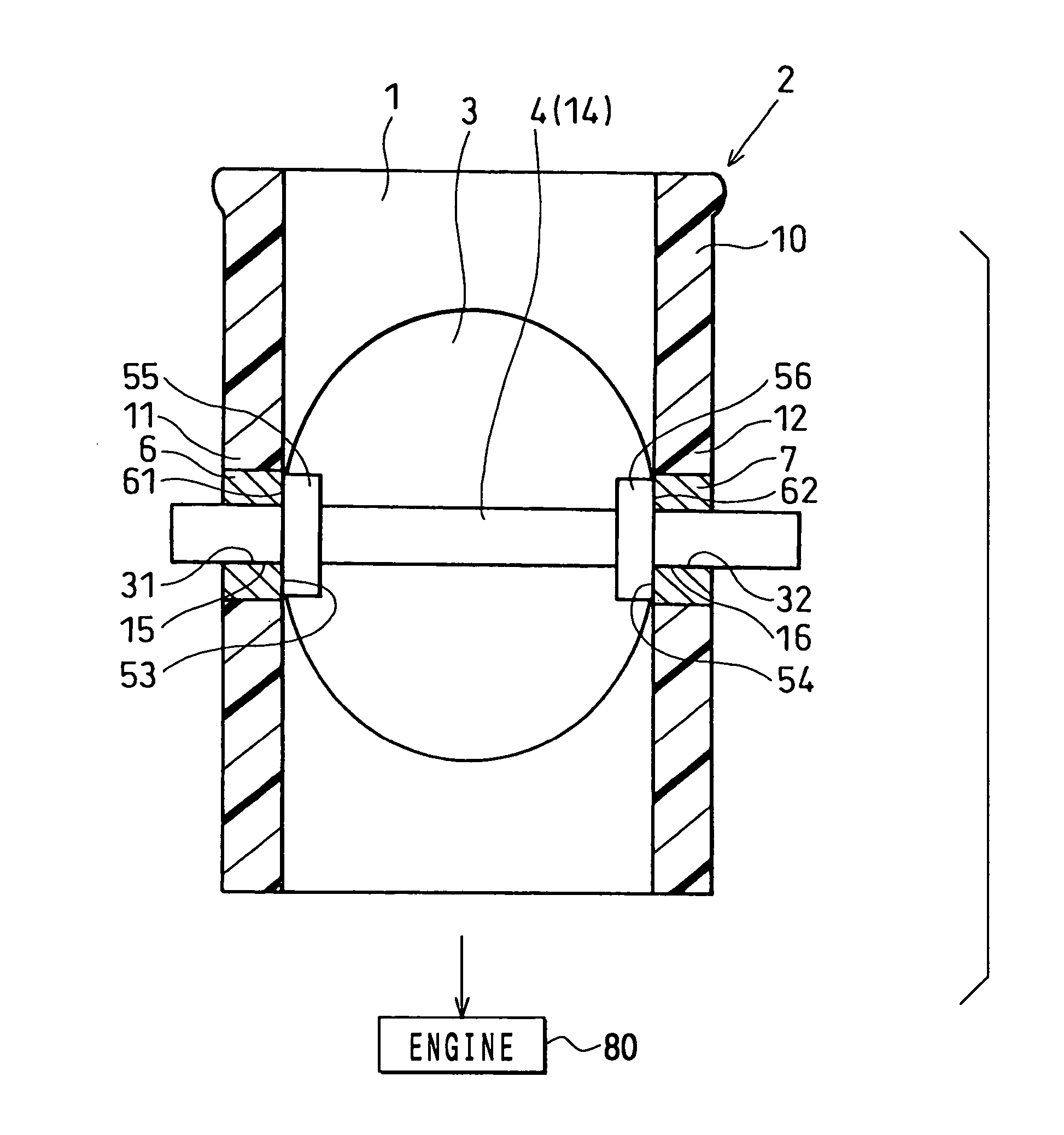

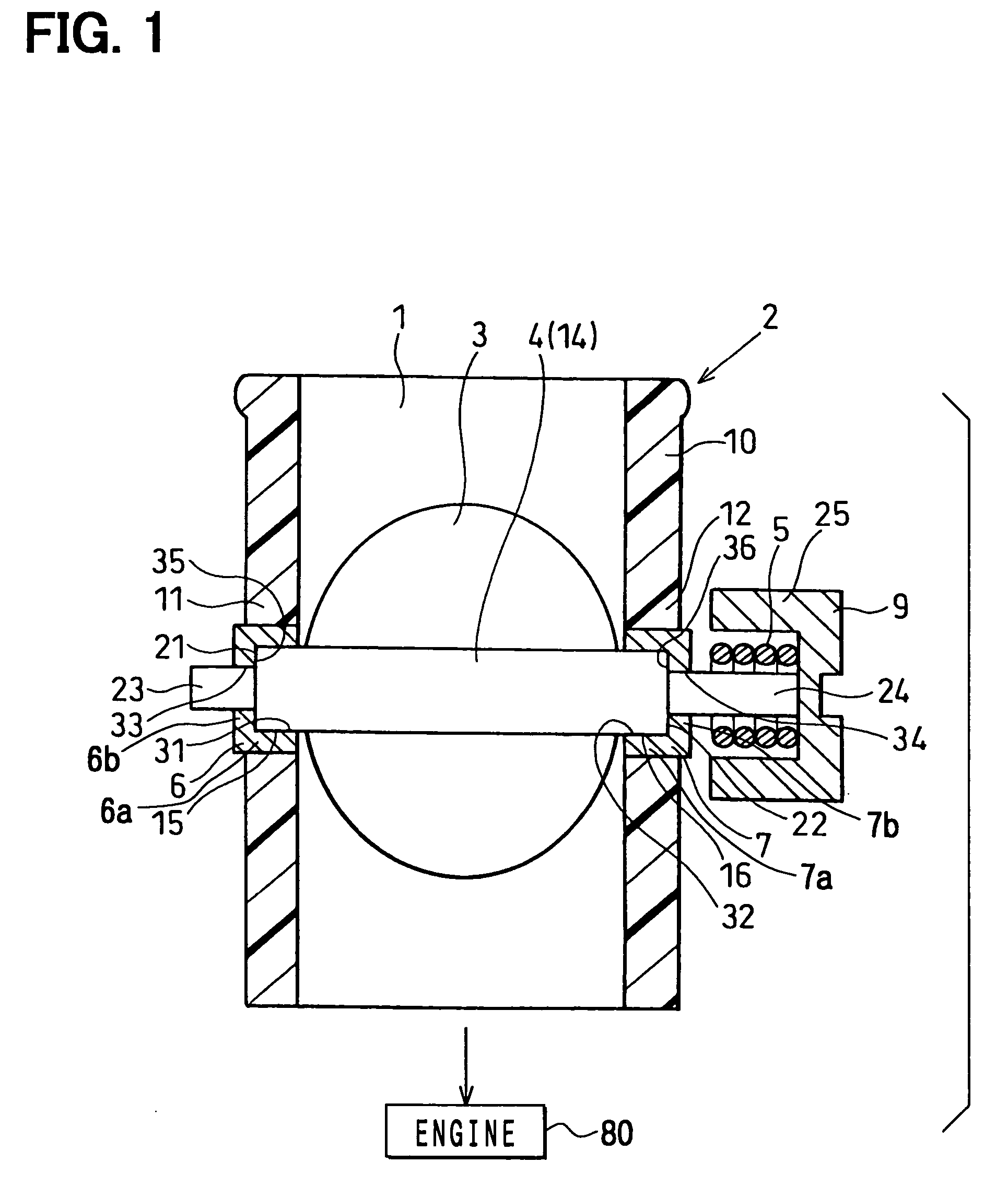

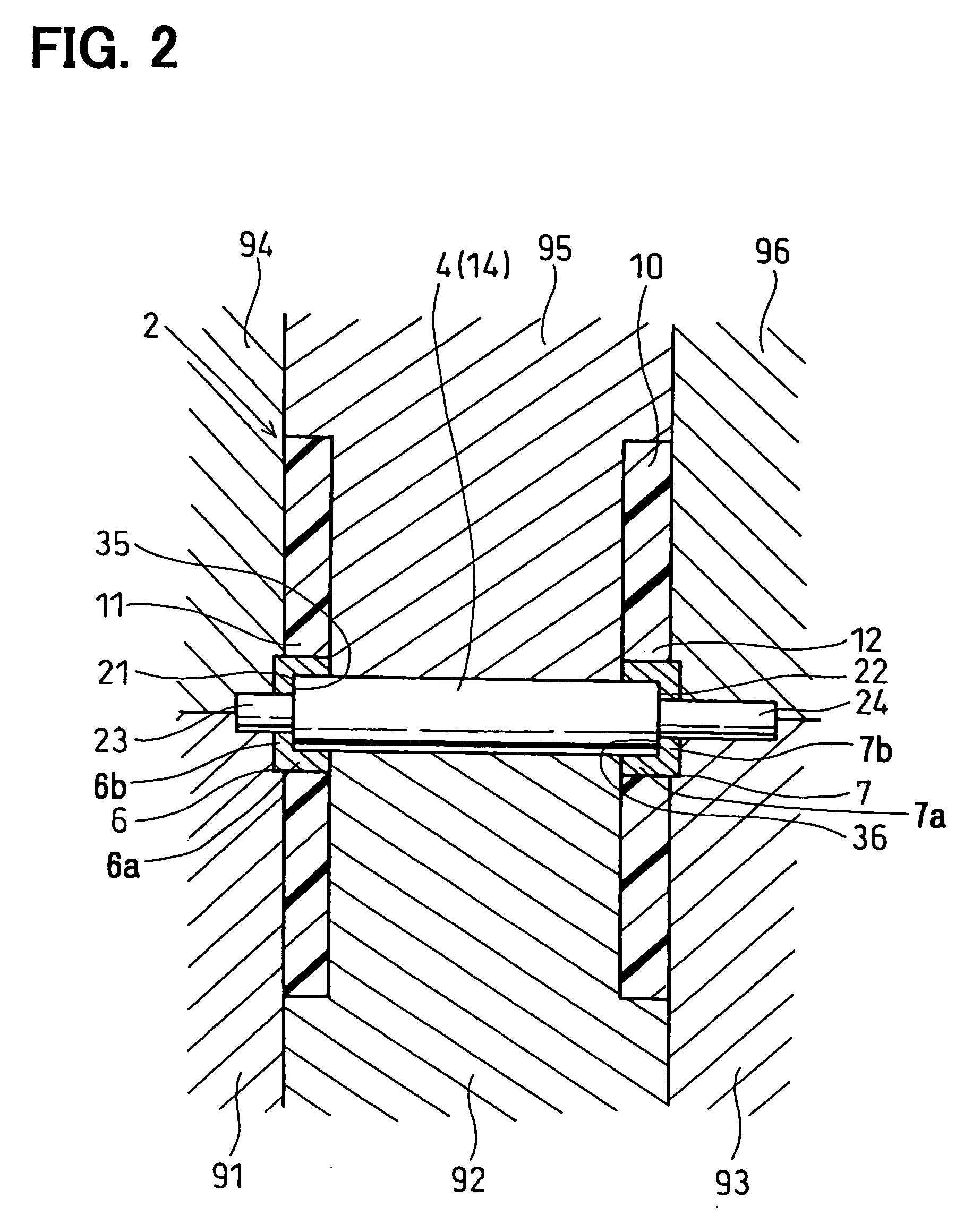

Throttle apparatus having axial displacement restricting structure

InactiveUS20050062008A1Increasing of costIncreasing numberOperating means/releasing devices for valvesBearing componentsThrottleControl theory

Owner:DENSO CORP

Throttle apparatus having axial displacement restricting structure

InactiveUS7063303B2Increasing of costIncreasing numberOperating means/releasing devices for valvesBearing componentsAxial displacementControl theory

A throttle shaft, first and second bearings, are inserted and formed in a bore wall part of a throttle body, when the throttle body is formed in the same dies. That is, when the throttle body is formed in a predetermined shape, the throttle shaft, the first and second bearings, are received in the bore wall part of the throttle body. First and second step portions, are formed in the throttle shaft, and axially inserted by first and second supporting portions, respectively formed in the first and second bearings, from both axially ends of the throttle shaft. Therefore, the throttle shaft can be restricted from moving axially, without additional thrust restricting means, such as an E-ring and a C-ring.

Owner:DENSO CORP

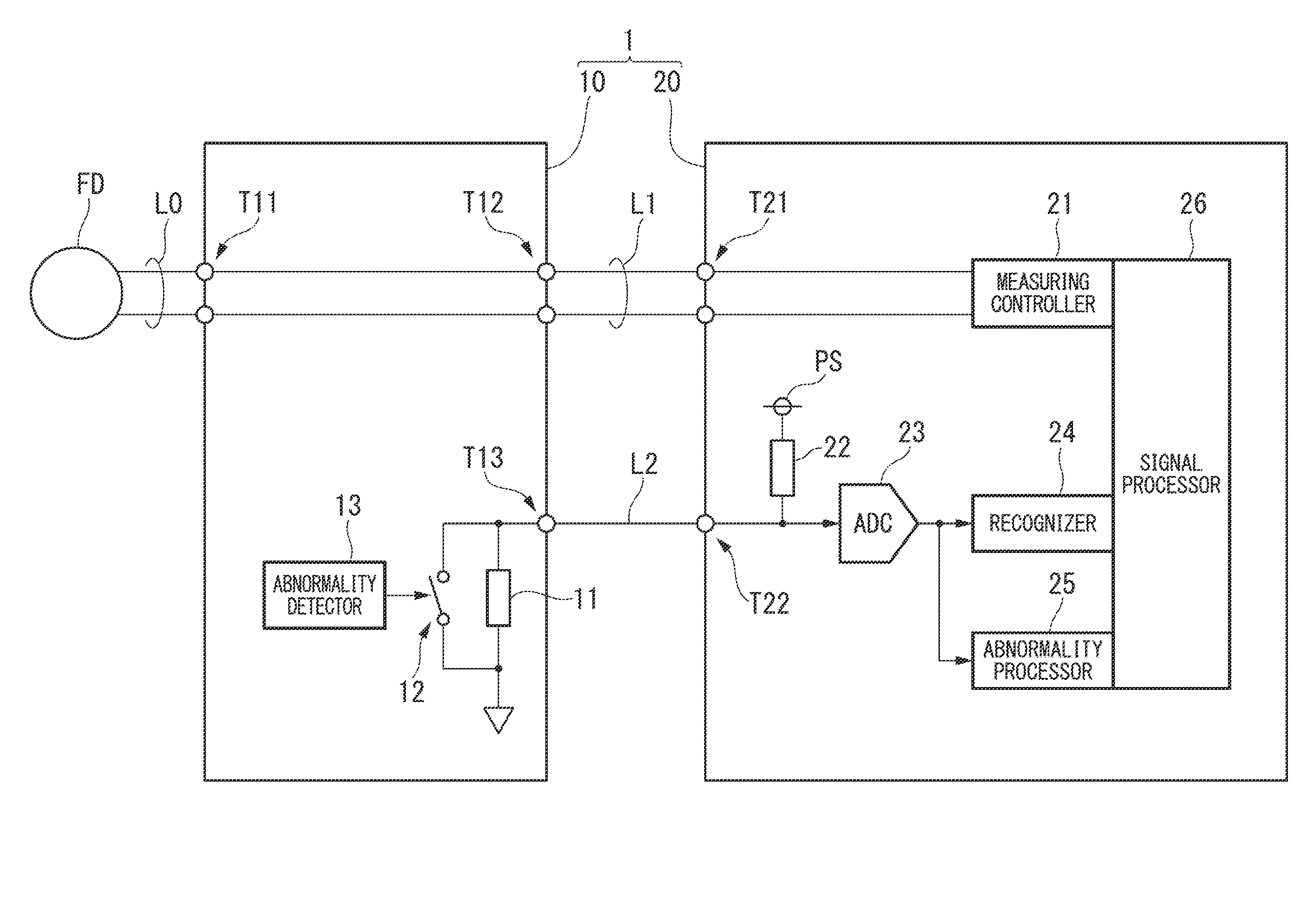

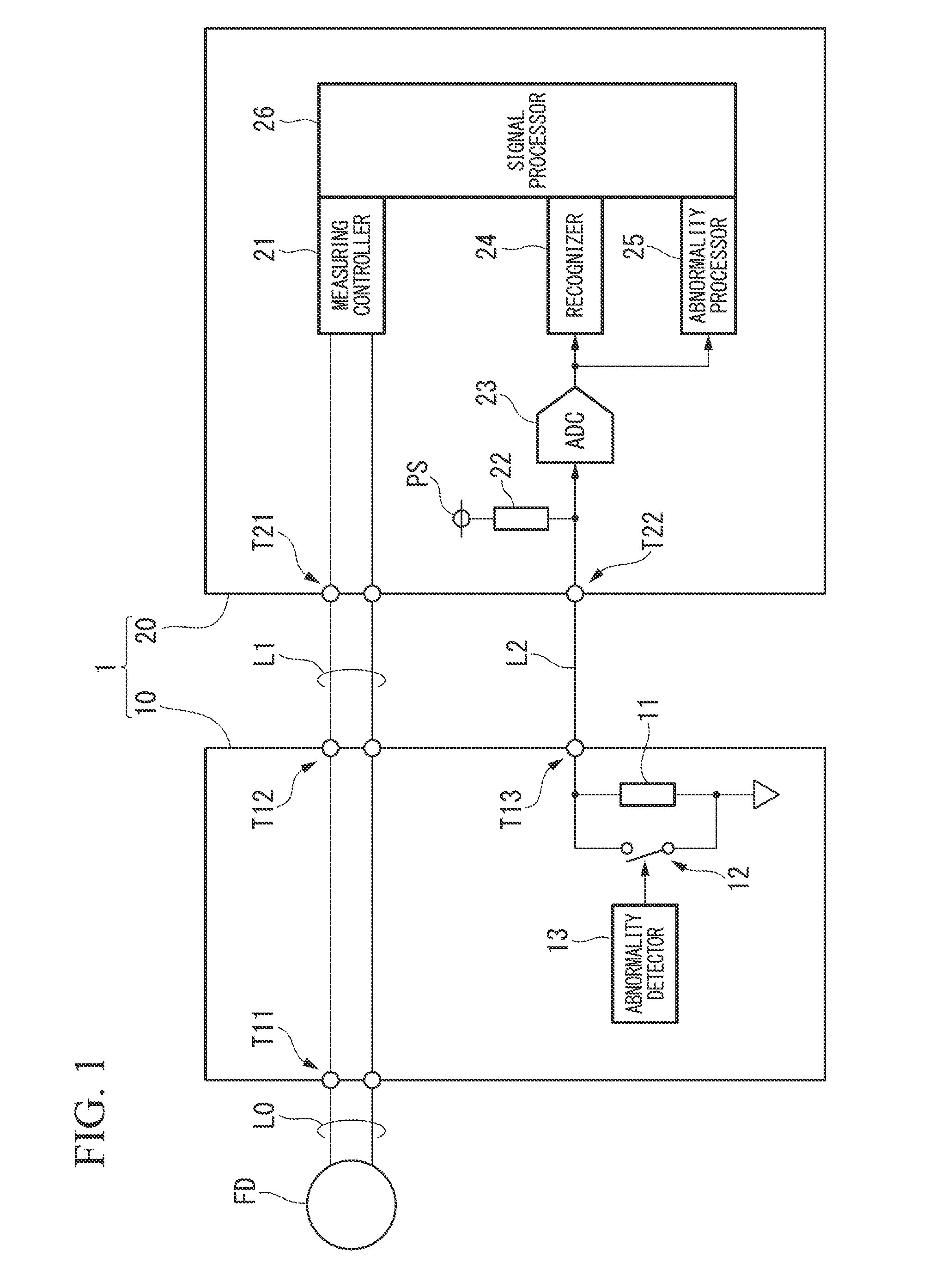

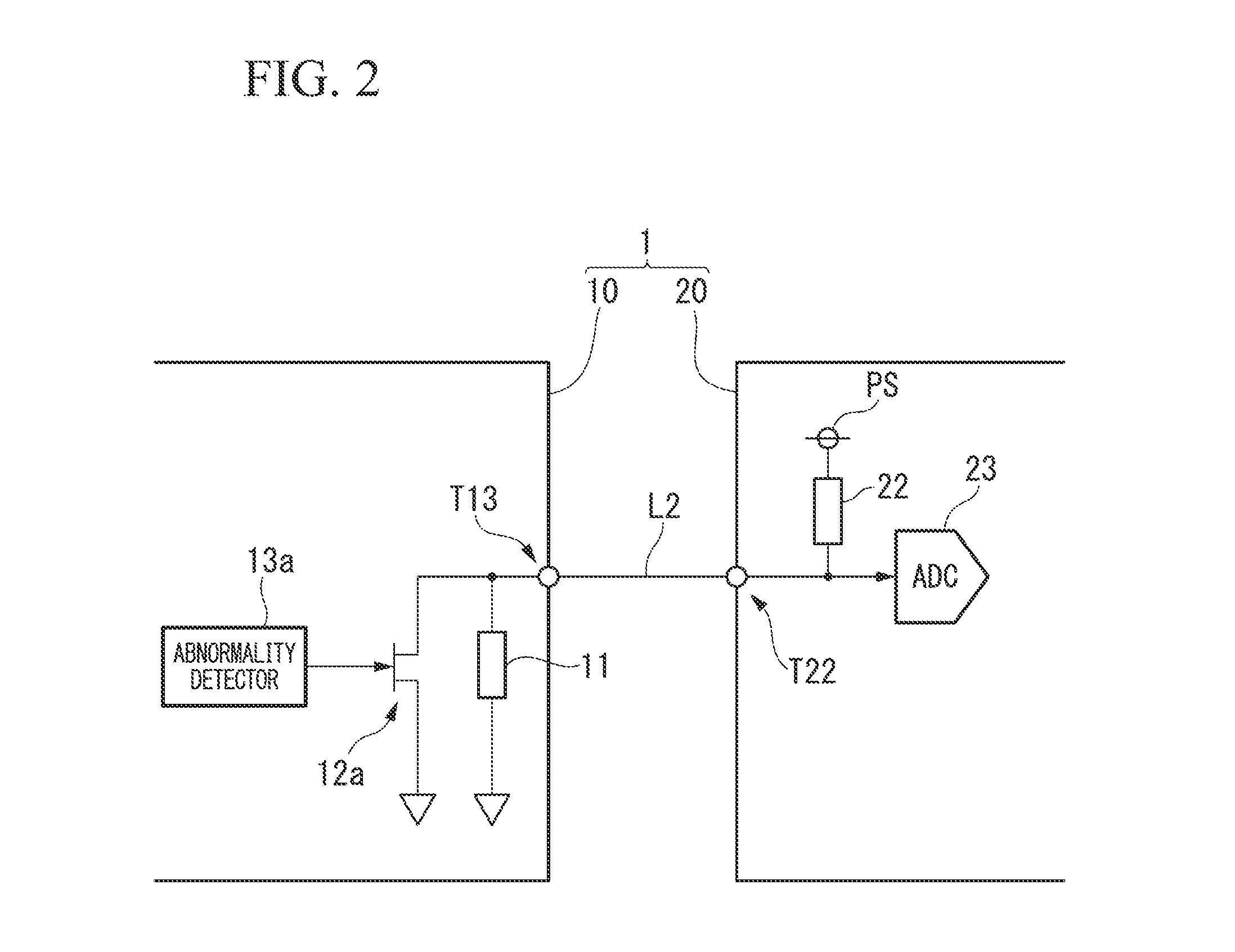

Signal processing apparatus

ActiveUS20150120004A1Increasing costIncreasing numberProgramme controlSafety arrangmentsVIT signalsPower flow

A signal processing apparatus includes an interface module and a signal processing module. The interface module includes an identification resistance for identifying the interface module, the interface module being connectable to a device configured to perform at least one of measuring of a measuring target and operating of an operation target. The signal processing module includes a first connection terminal connected to one end of the identification resistance, a first power source connected to the identification resistance via the first connection terminal, a detector configured to detect any one of voltage and electrical current at the first connection terminal, and a signal processor configured to process signals received from and transmitted to the device.

Owner:YOKOGAWA ELECTRIC CORP

Battery assembly

ActiveUS20090286141A1Increasing number of componentIncreasing of costLarge-sized flat cells/batteriesFinal product manufactureBattery cellCharge and discharge

A battery assembly of the invention includes a secondary battery formed by stacking a plurality of unit battery cells having a cathode and an anode, collector electrodes provided on respective end surfaces of the secondary battery positioned in the stacking direction of the unit battery cells; and terminal portions formed at the collector electrodes, protruded outward from a side surface of the secondary battery, to which conductive members are connected for charging and discharging. A coolant is supplied to the terminal portions to cool the terminal portions.

Owner:TOYOTA JIDOSHA KK

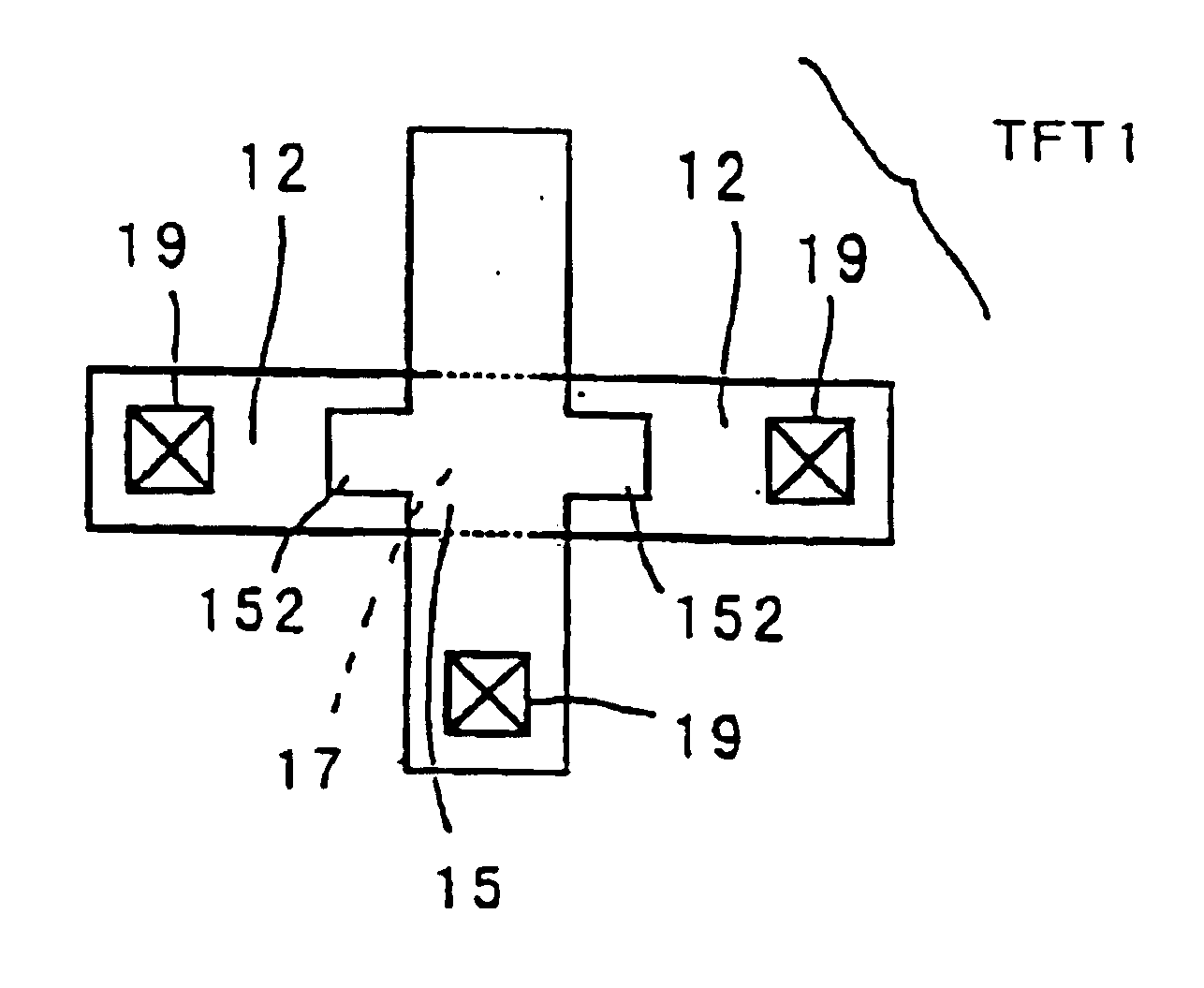

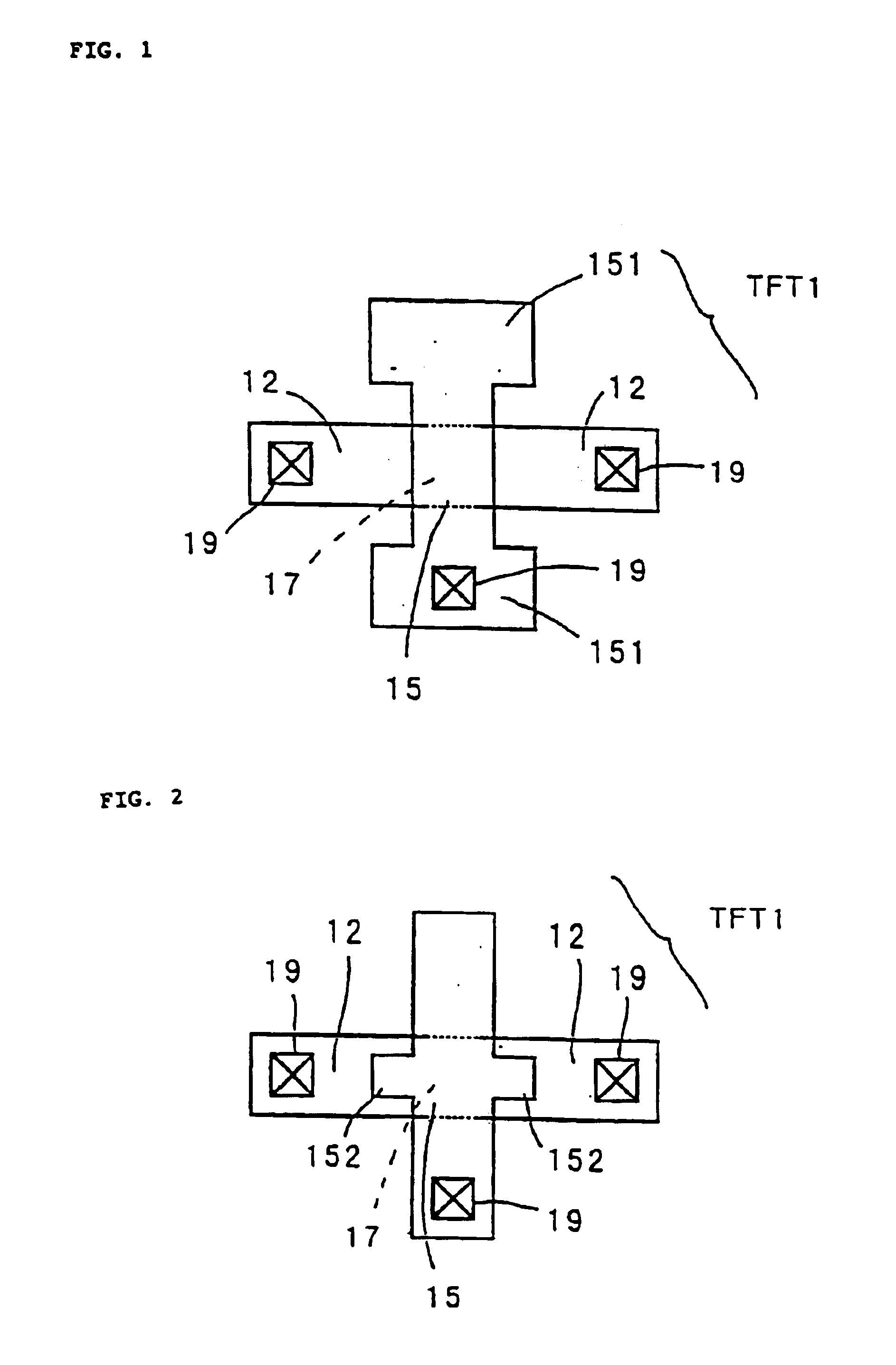

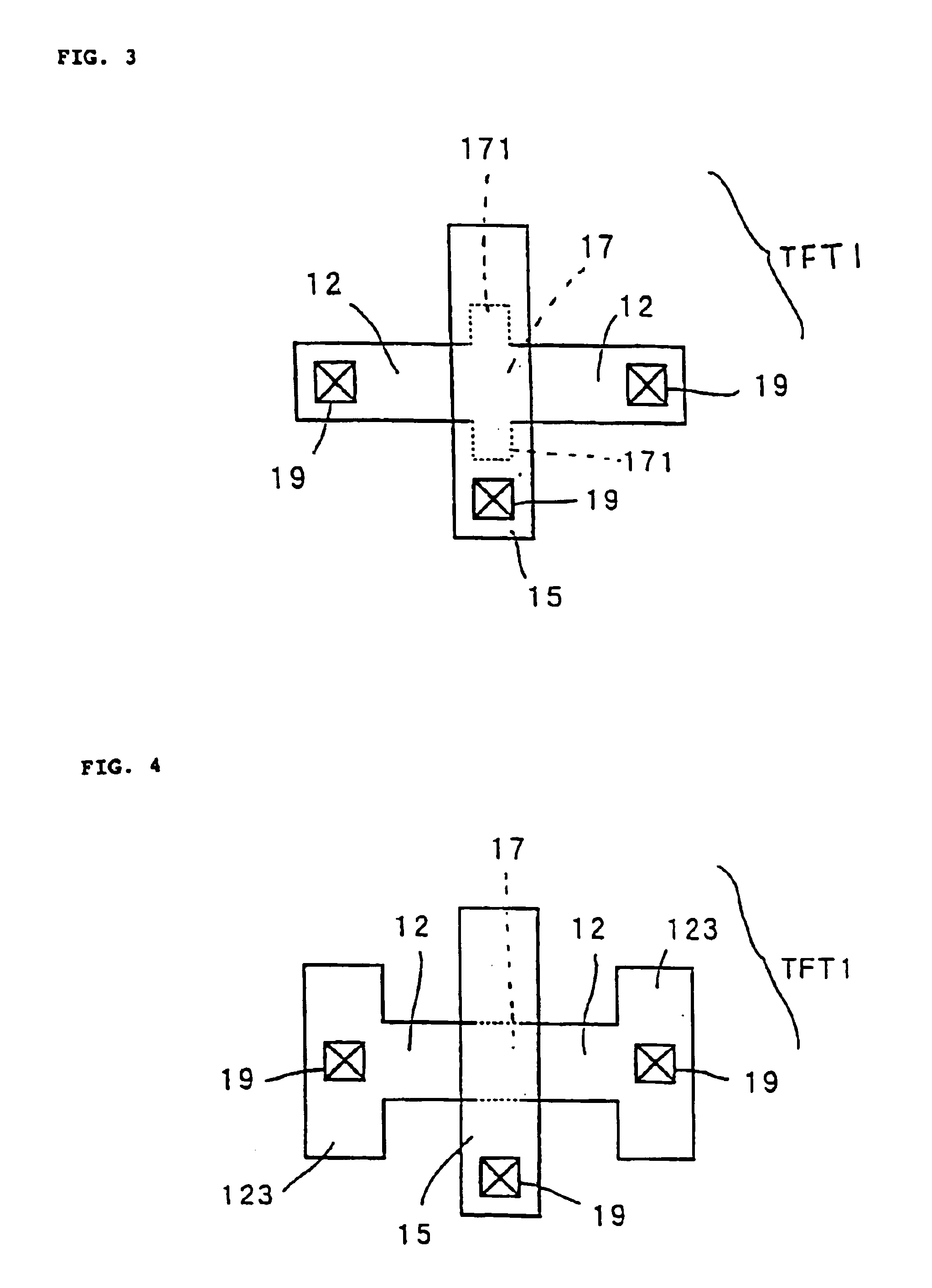

Thin film transistors, liquid crystal display device and electronic apparatus using the same

InactiveUS6933571B2Improve heat radiation efficiencyIncreasing numberTransistorSemiconductor/solid-state device detailsLiquid-crystal displayEngineering

In a TFT including on the surface side of a substrate a channel region opposed to a gate electrode, with a gate insulating film provided therebetween, and a source-drain region connected to the channel region, and a TFT including a source-drain wiring layer electrically connected to the source-drain region, and a gate wiring layer electrically connected to the gate electrode, at least one component part composed of a conductive film or a semiconductor film, among the component parts of each TFT, is provided with a heat-radiating extension extended from the component part itself for enhancing the heat-radiating efficiency from the component part.

Owner:BOE TECH GRP CO LTD

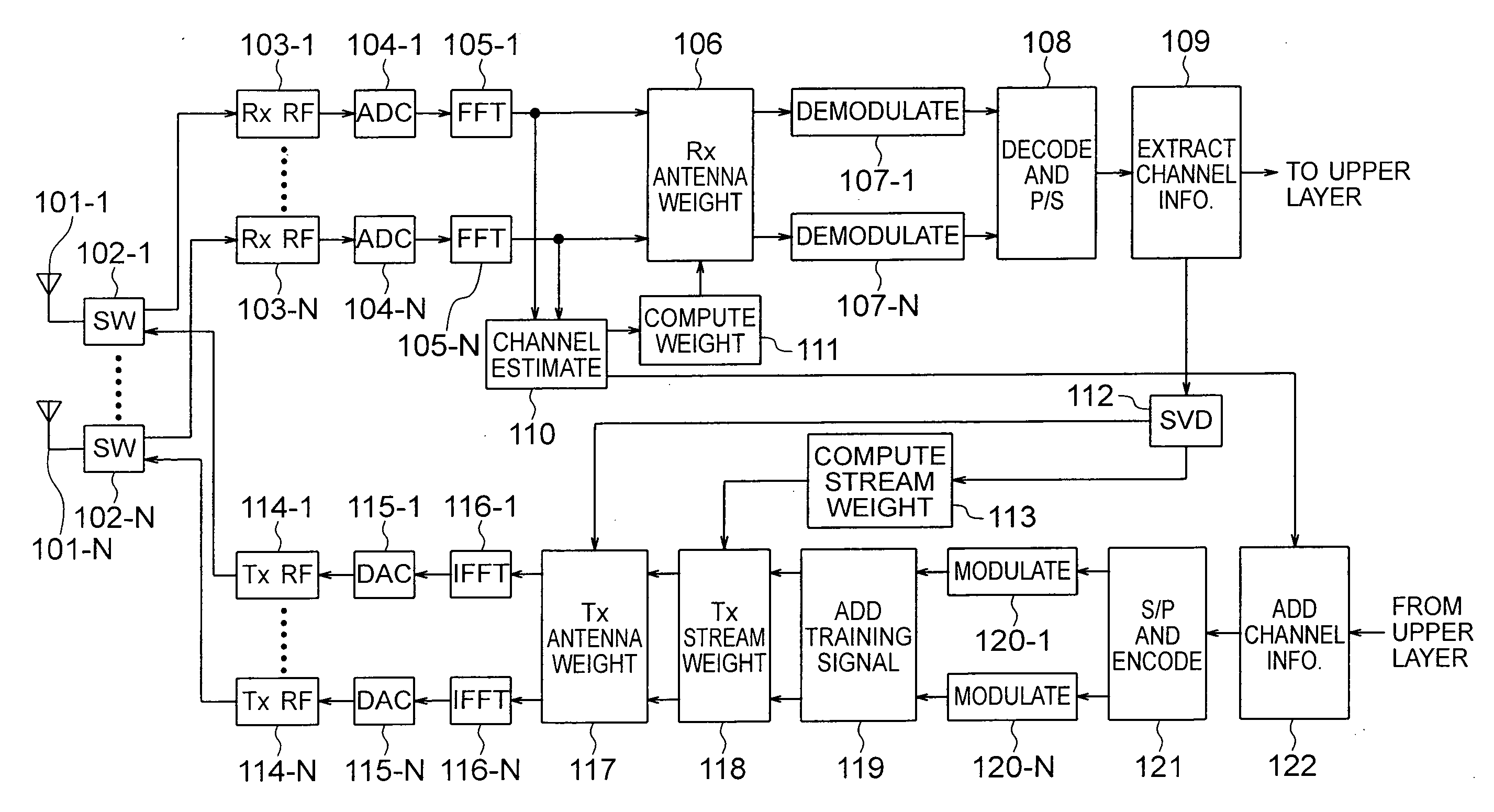

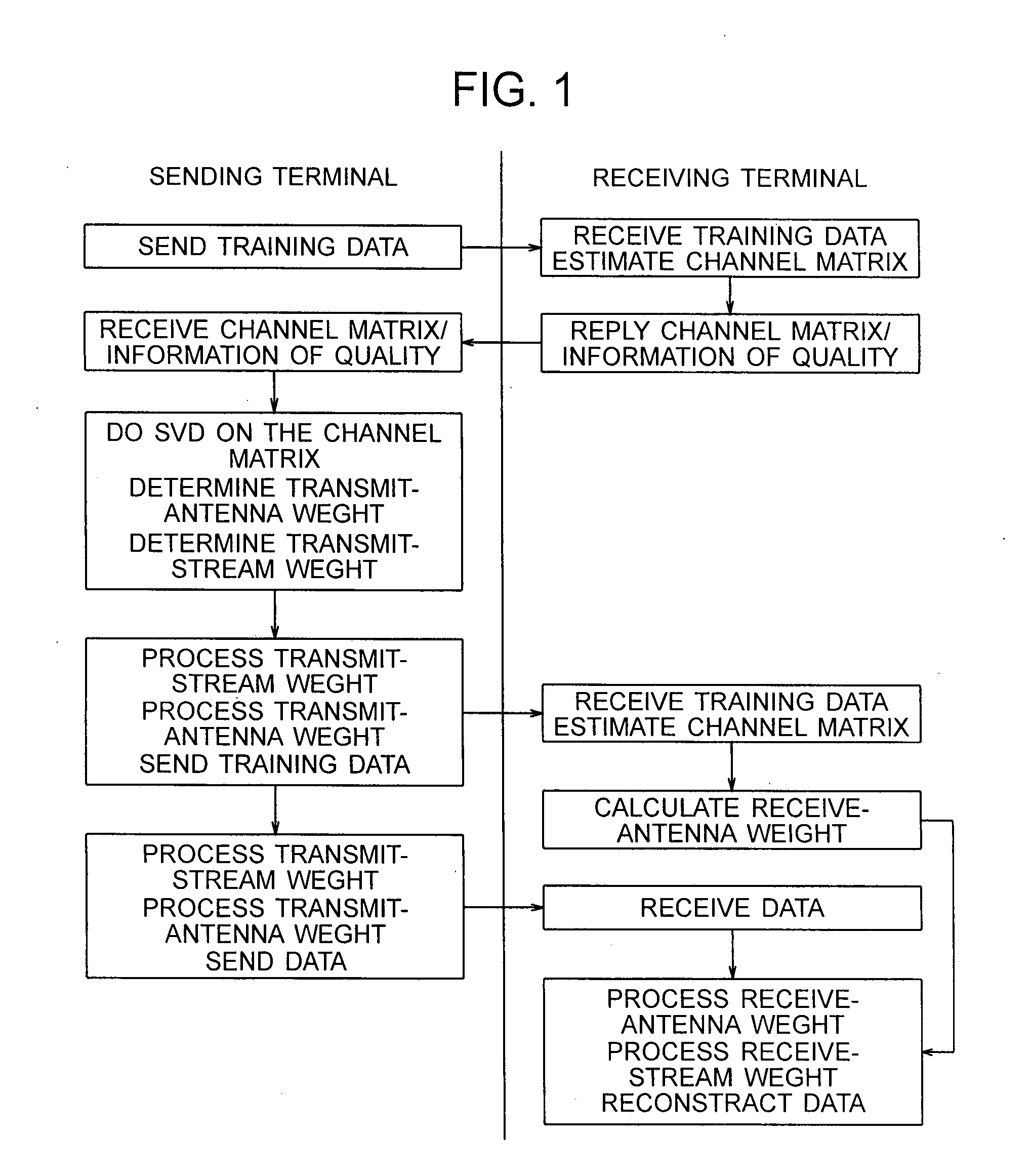

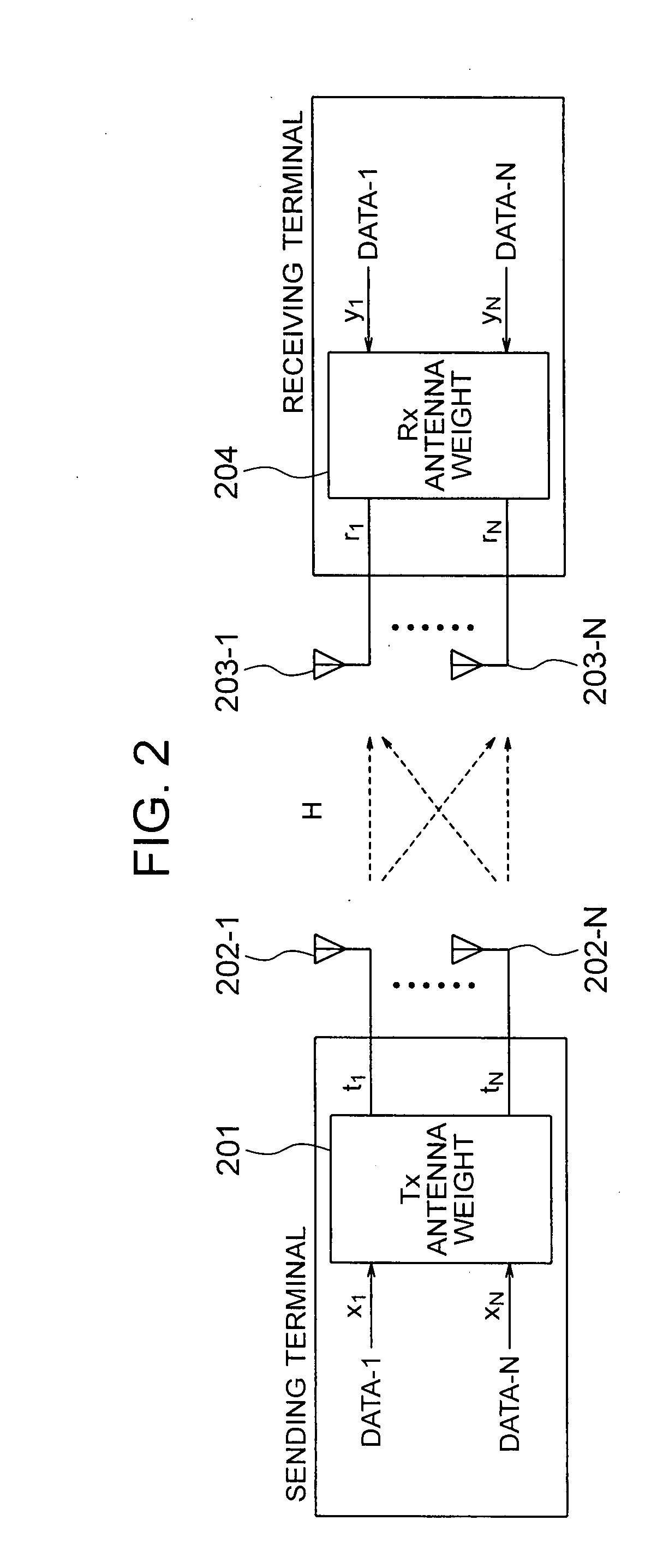

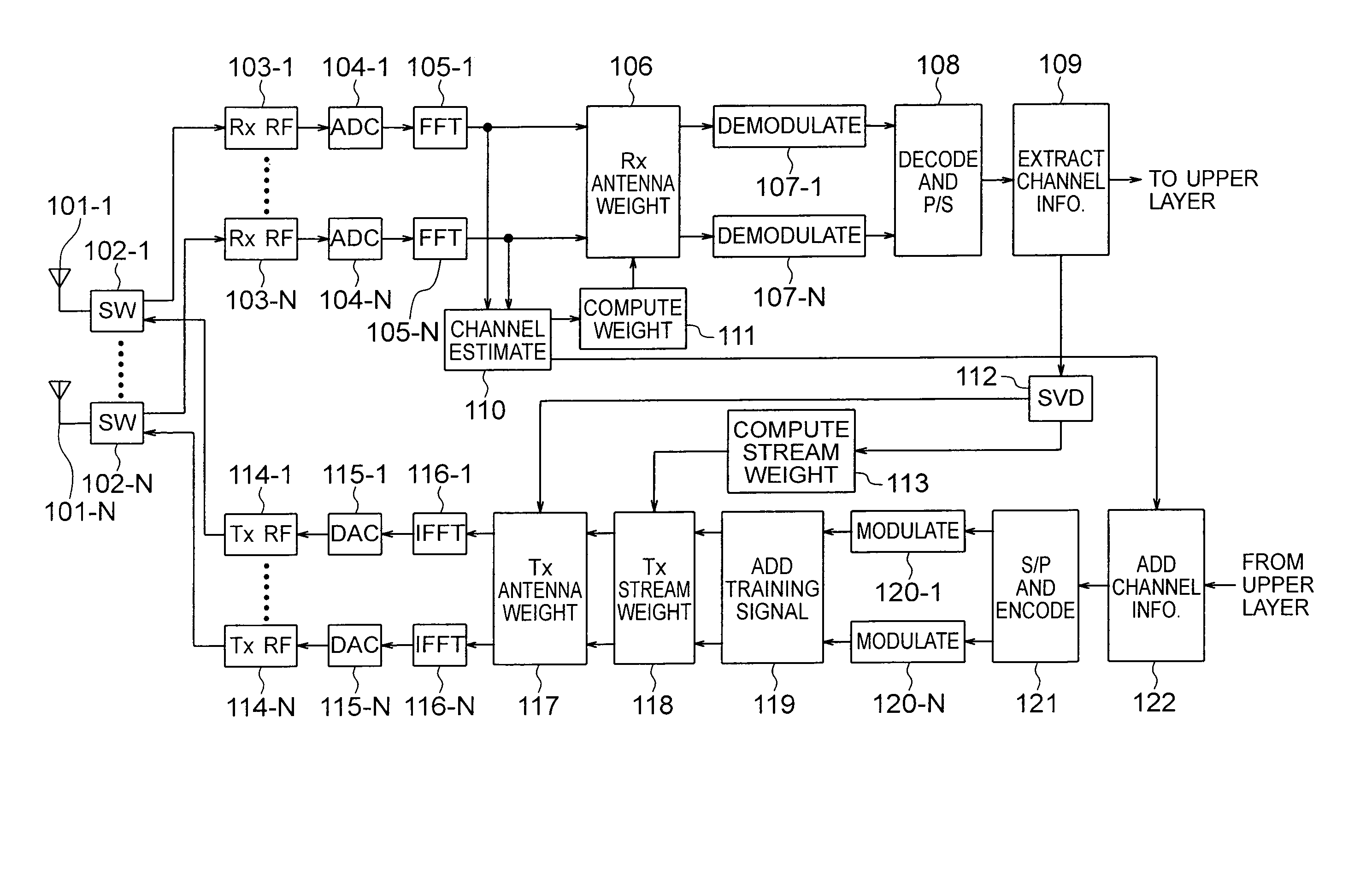

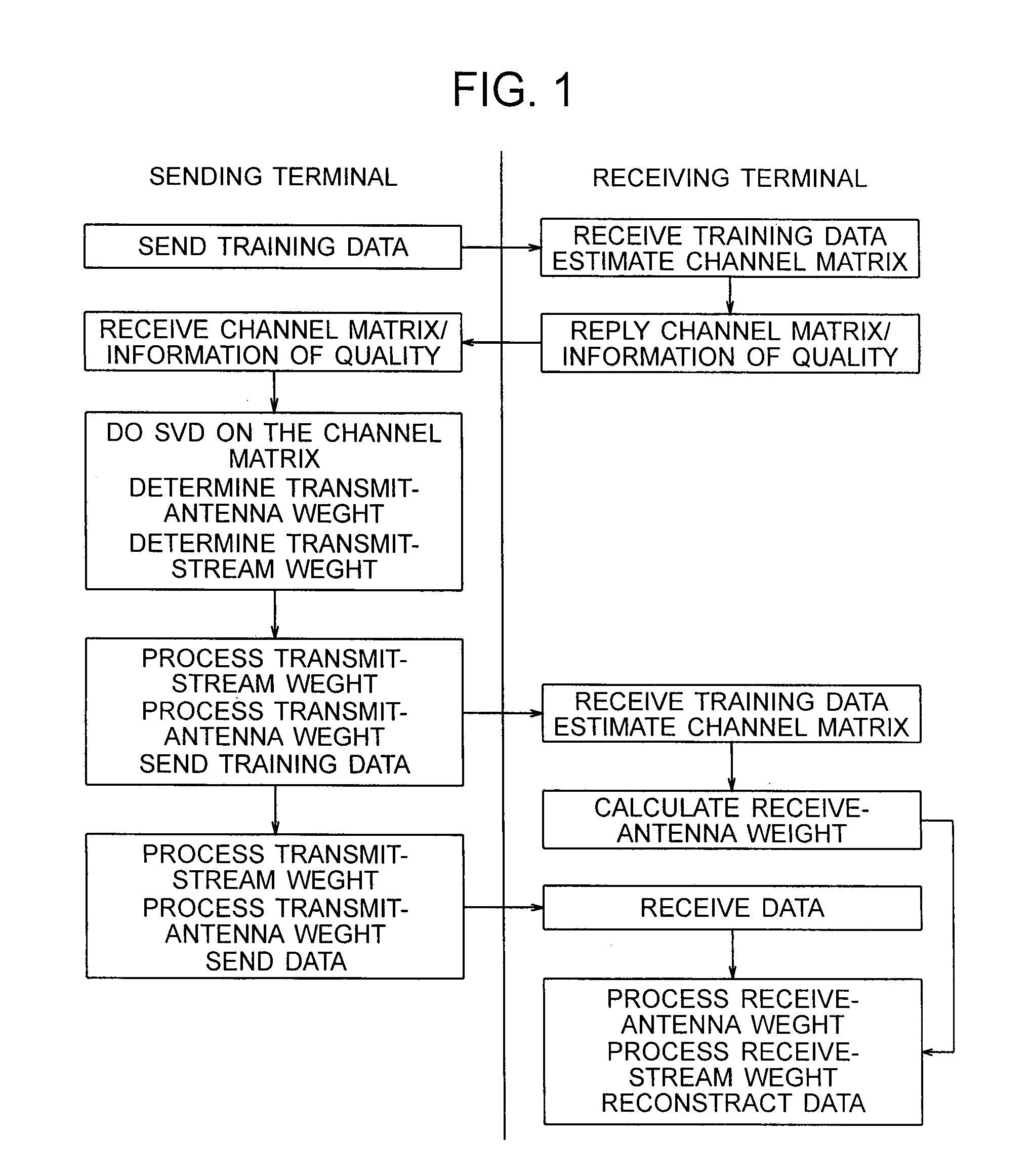

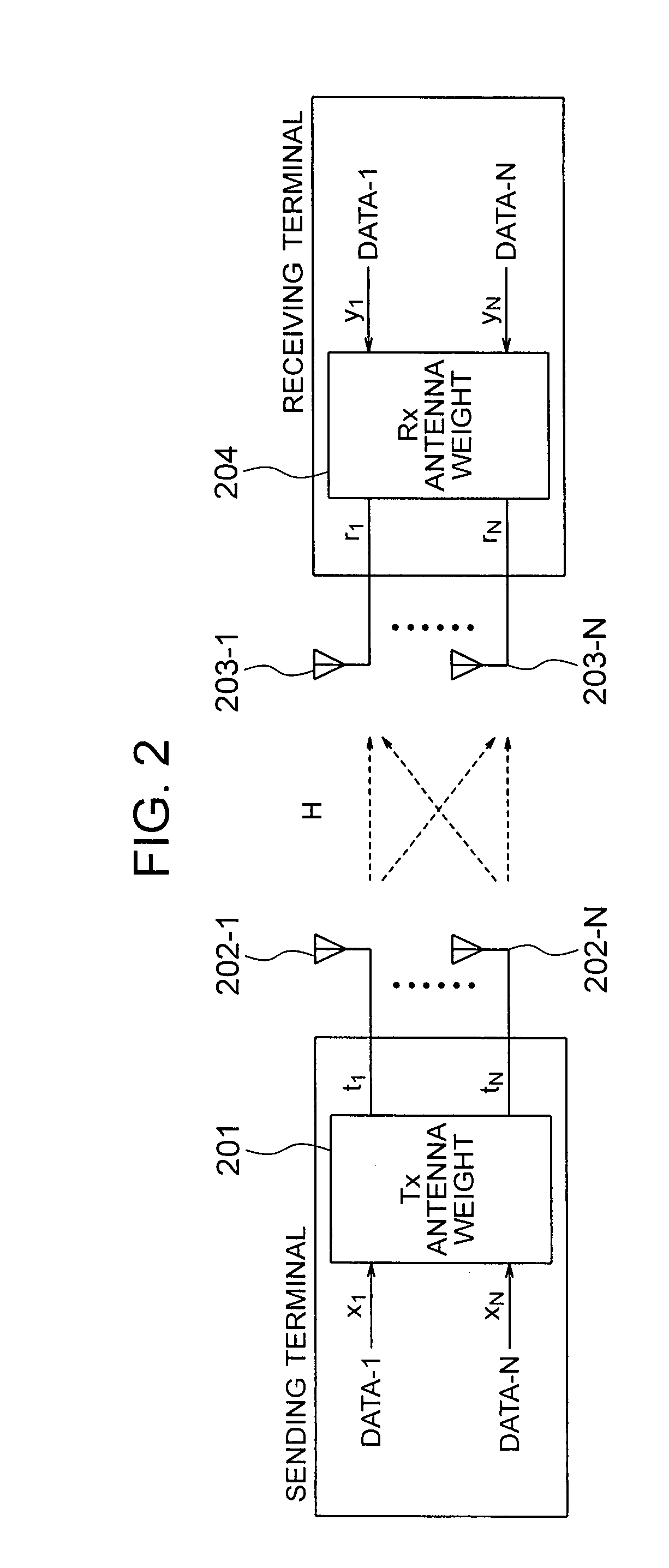

MIMO wireless data communication system, MIMO wireless data communication method and MIMO wireless data communication apparatus

InactiveUS20070263745A1Large communication capacityIncreasing numberNetwork traffic/resource managementPolarisation/directional diversityCommunications systemWireless data

In a MIMO wireless communication system, the transformation process synthesizes the eigenmodes having a large singular value (i.e. a high effective SNR) and the eigenmodes having a small singular value (i.e. a low effective SNR). Thereby, the former eigenmodes are converted into modes having suppressed effective SNR which do not require a large number of levels of modulation, and the latter eigenmodes are converted into modes having increased effective SNR instead. In a MIMO wireless communication system for eigenmode transmission, a large communication capacity is realized without increasing the number of levels of modulation even in a communication environment capable of achieving a high SNR.

Owner:HITACHI LTD

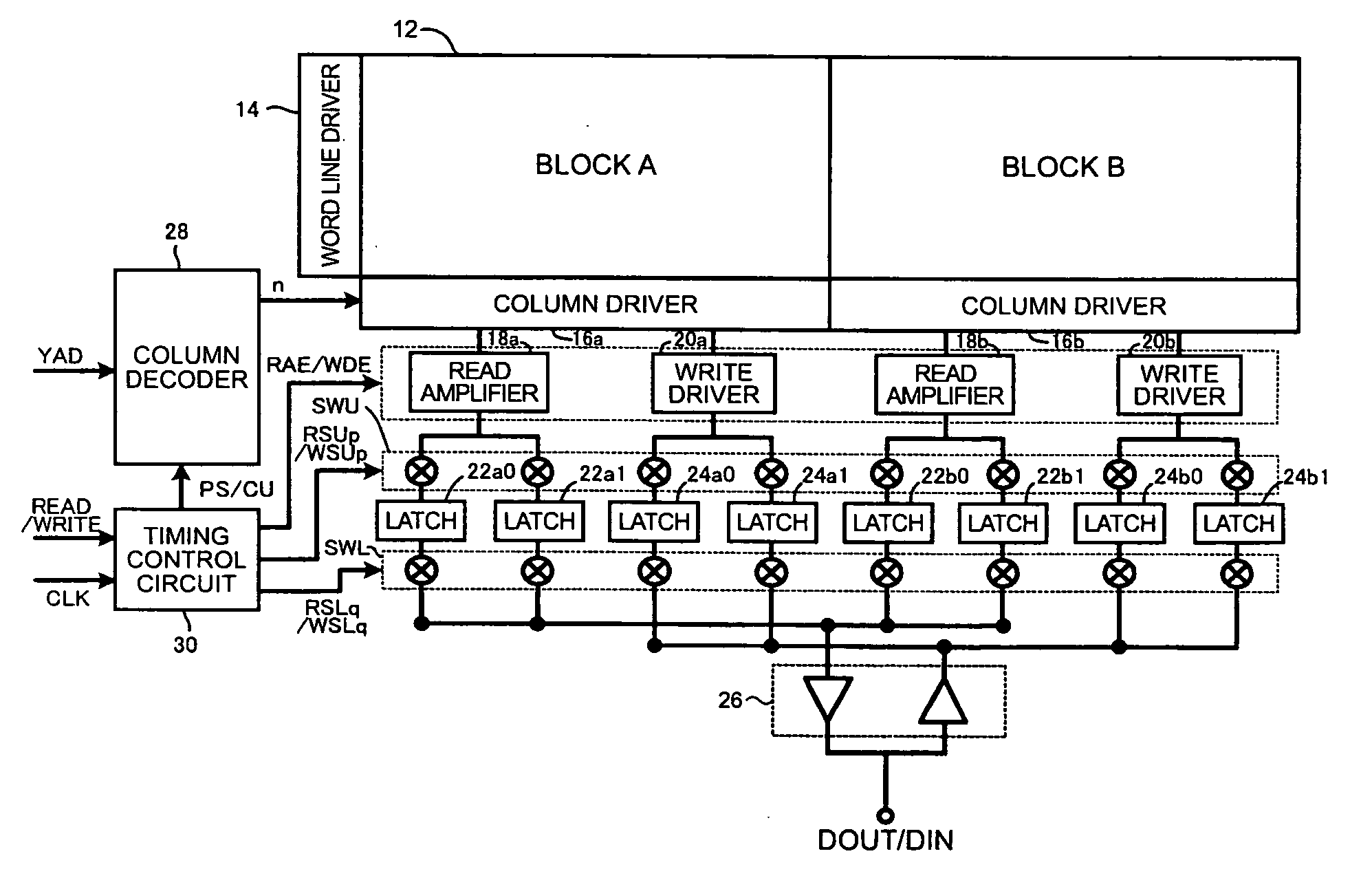

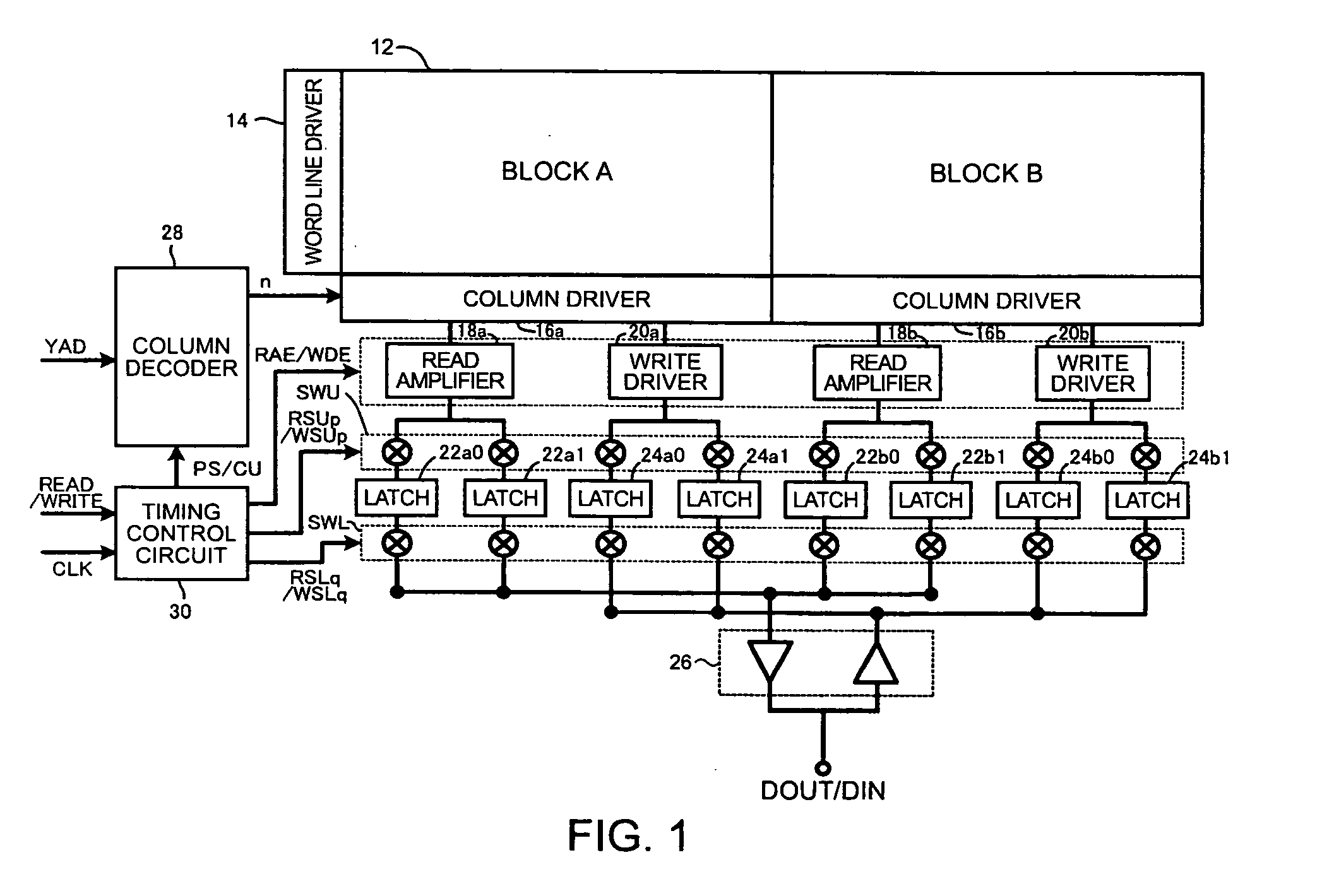

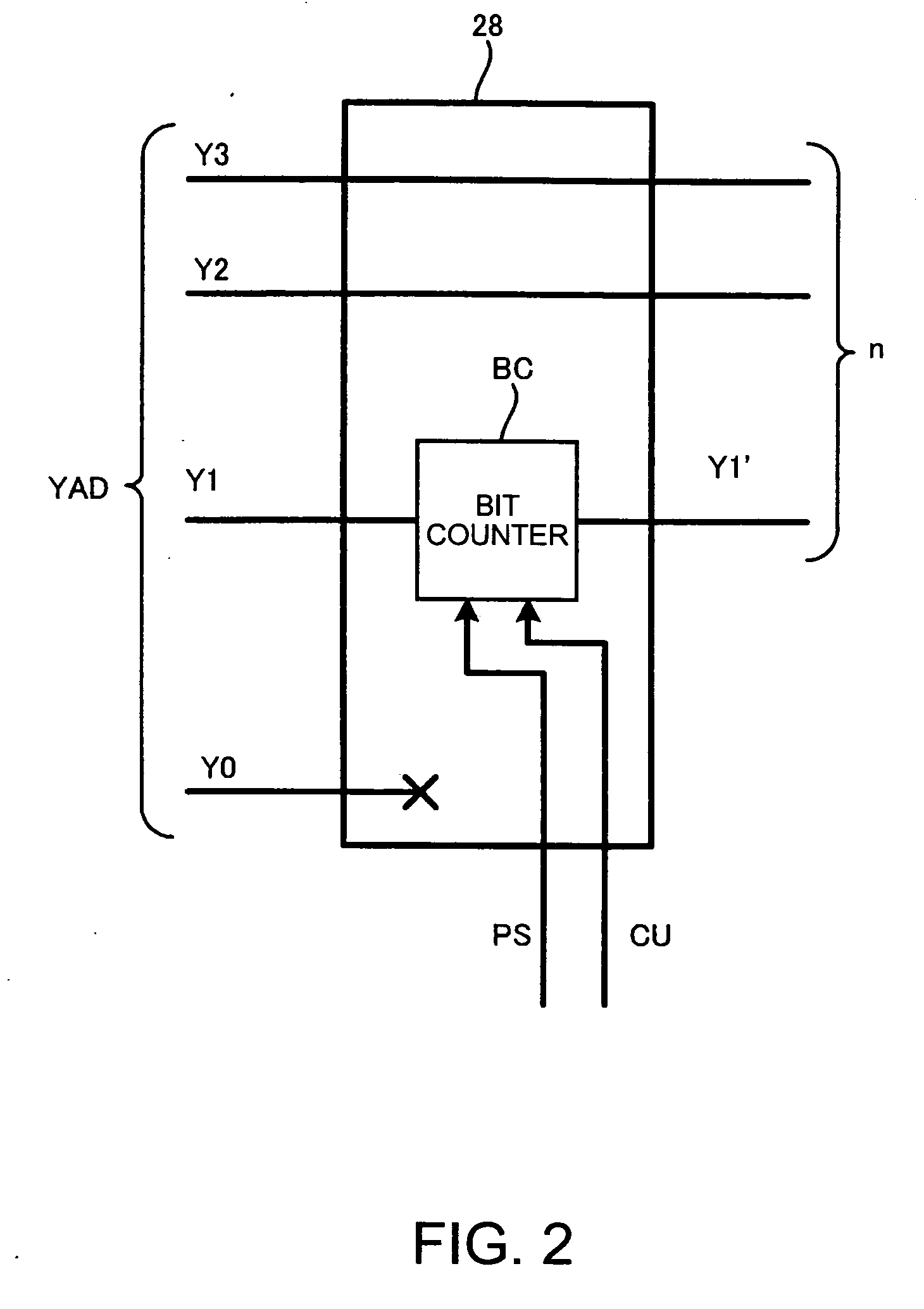

Semiconductor memory device

InactiveUS20060062071A1Increasing numberIncrease the number ofDigital storageHemt circuitsSemiconductor memory

A semiconductor memory device includes: a plurality of memory cells arranged in a matrix; a memory cell array divided into a plurality of blocks; a plurality of read amplifiers, each of which is coupled correspondingly to each of the blocks; and a plurality of latch circuits, each group of which is coupled correspondingly to each of the read amplifiers and includes two or more latch circuits coupled to one another in parallel, wherein, in order to read a plurality of data consecutively from the memory cell array, the data are firstly read from one desired memory cell for each block; the read data are secondly inputted and latched, via the read amplifier corresponding to the same block, to one of the latch circuits included in a group of latch circuits corresponding to the same read amplifier; the data are thirdly read from another desired memory cell, which is different from the memory cell from which the data are formerly read, for each block; the read data are fourthly inputted and latched, via the read amplifier corresponding to the same block, to one of the latch circuits, which is different from the latch circuit to which the data are formerly latched, included in the group of latch circuits corresponding to the same read amplifier; and the latched data are lastly outputted in a desired order from each of the latch circuits having the latched data.

Owner:SEIKO EPSON CORP

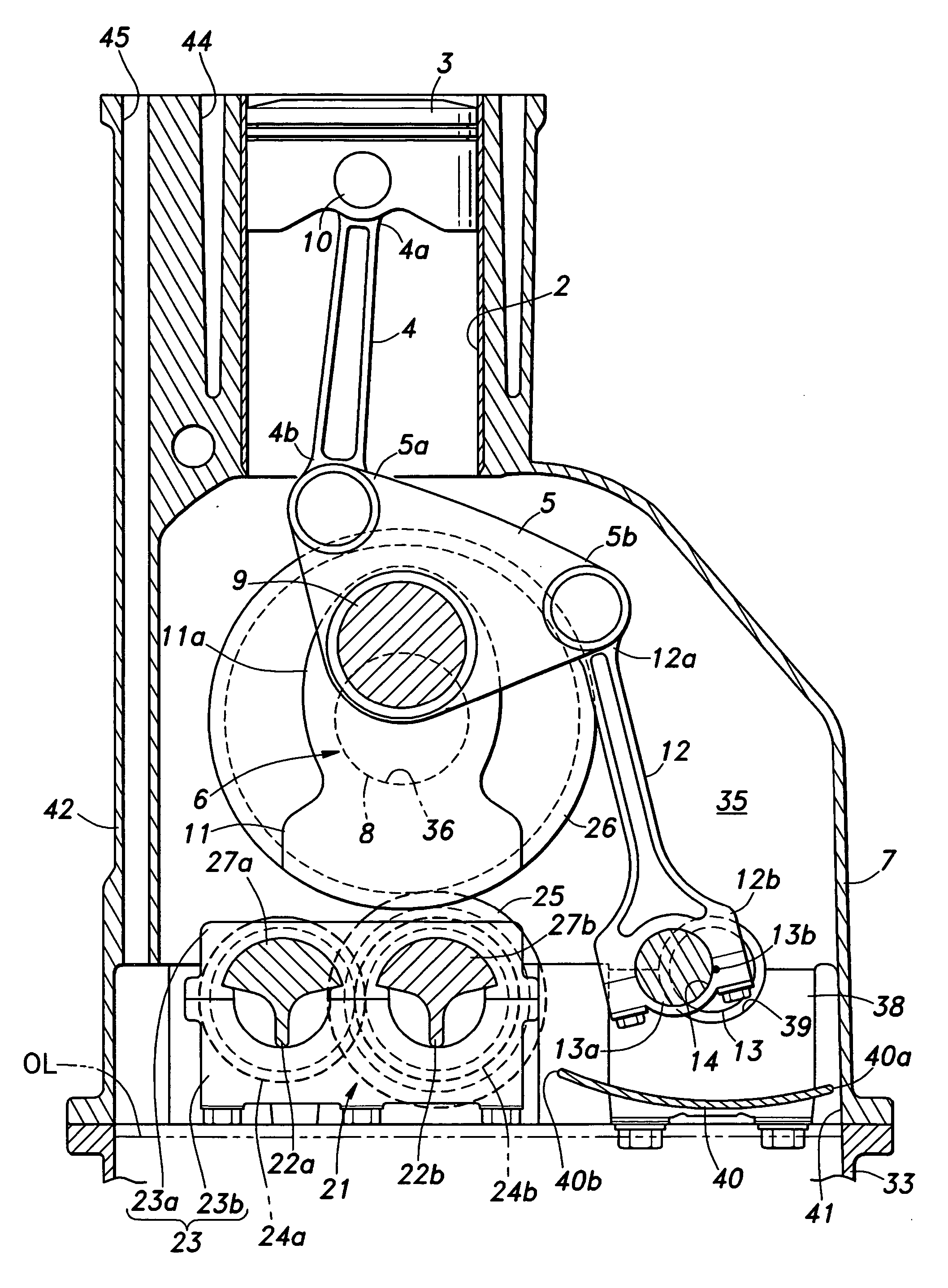

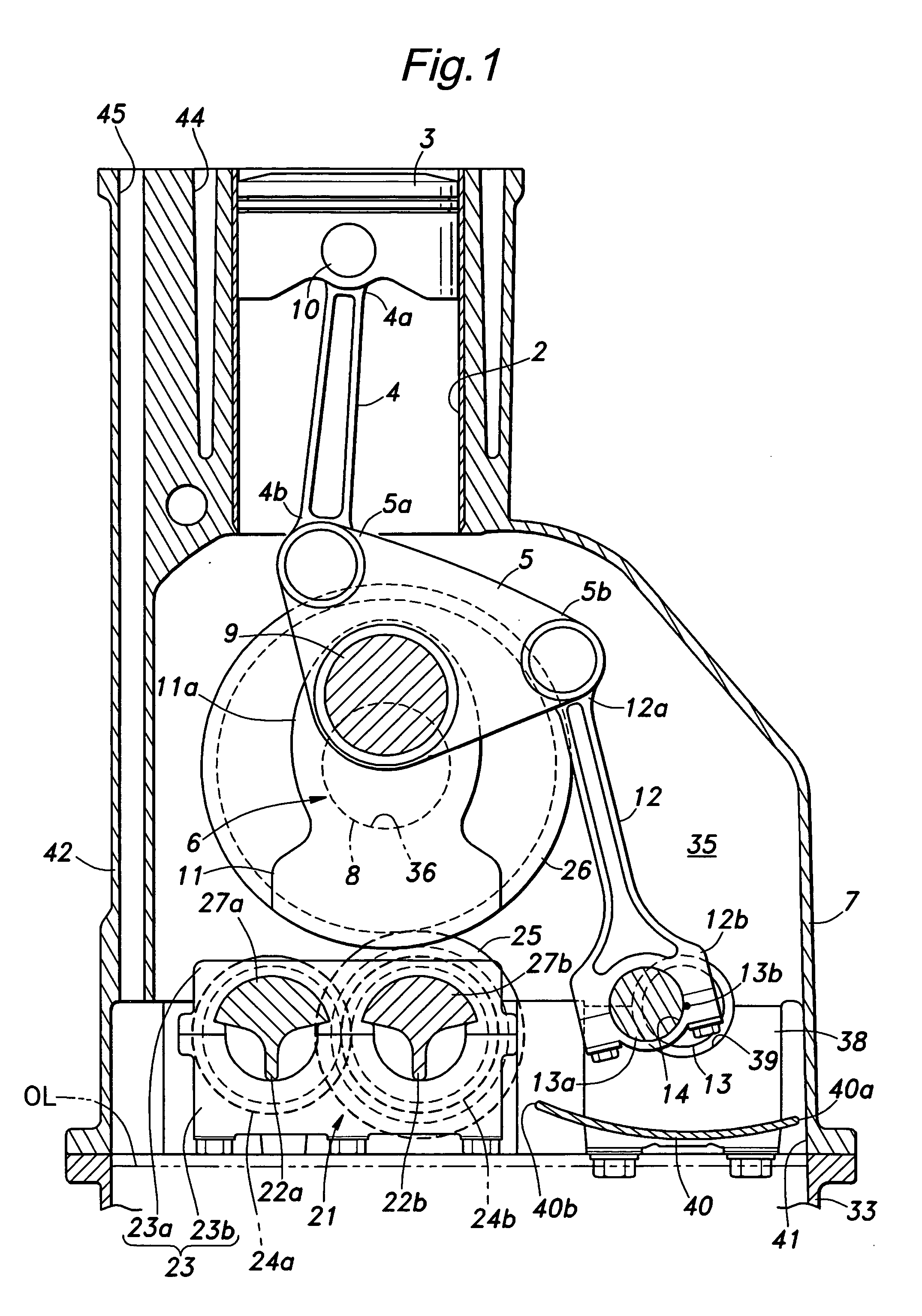

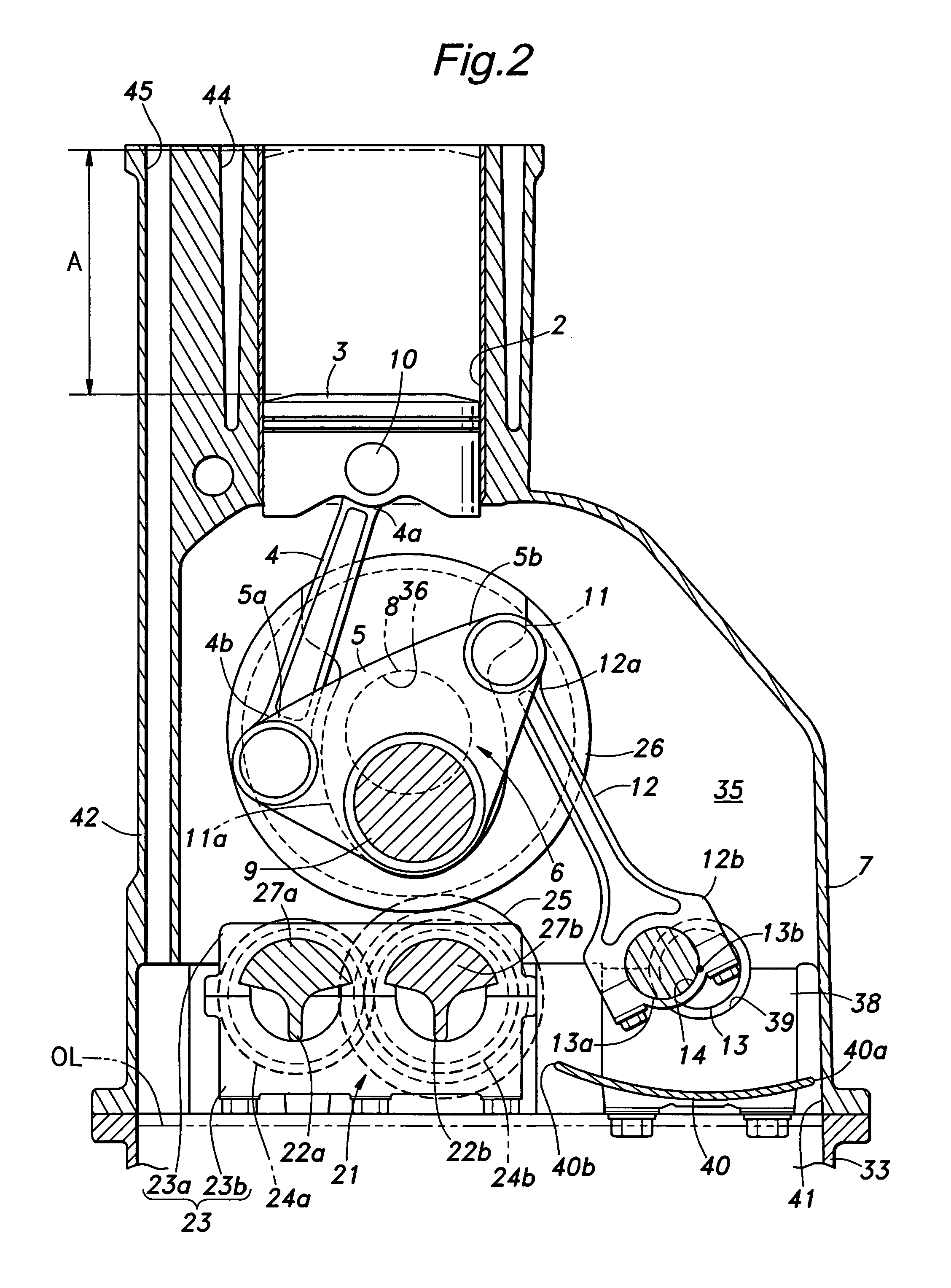

Variable stroke property engine

InactiveUS20060102116A1Increasing of amountIncreasing number of component partConnecting rodsOilsumpsEngineeringPiston

Provided is a variable stroke property engine that can prevent an increase in the resistance to the engine owing to the contact between the variable stroke piston mechanism and lubricating oil. In a variable stroke property engine equipped with a variable piston stroke mechanism consisting of a plurality of links 4, 5 and 12, a baffle plate 40 is provided between the links and the oil surface of the lubricating oil received in an oil pan so that the links may be separated from the oil surface by the baffle plate and the lubricating oil is prevented from contacting the links. Thereby, an increase to the resistance to the movement of the links can be avoided.

Owner:HONDA MOTOR CO LTD

MIMO wireless data communication system, MIMO wireless data communication method and MIMO wireless data communication apparatus

InactiveUS7817741B2Increasing numberLarge communication capacityNetwork traffic/resource managementPolarisation/directional diversityCommunications systemWireless data

In a MIMO wireless communication system, the transformation process synthesizes the eigenmodes having a large singular value (i.e. a high effective SNR) and the eigenmodes having a small singular value (i.e. a low effective SNR). Thereby, the former eigenmodes are converted into modes having suppressed effective SNR which do not require a large number of levels of modulation, and the latter eigenmodes are converted into modes having increased effective SNR instead. In a MIMO wireless communication system for eigenmode transmission, a large communication capacity is realized without increasing the number of levels of modulation even in a communication environment capable of achieving a high SNR.

Owner:HITACHI LTD

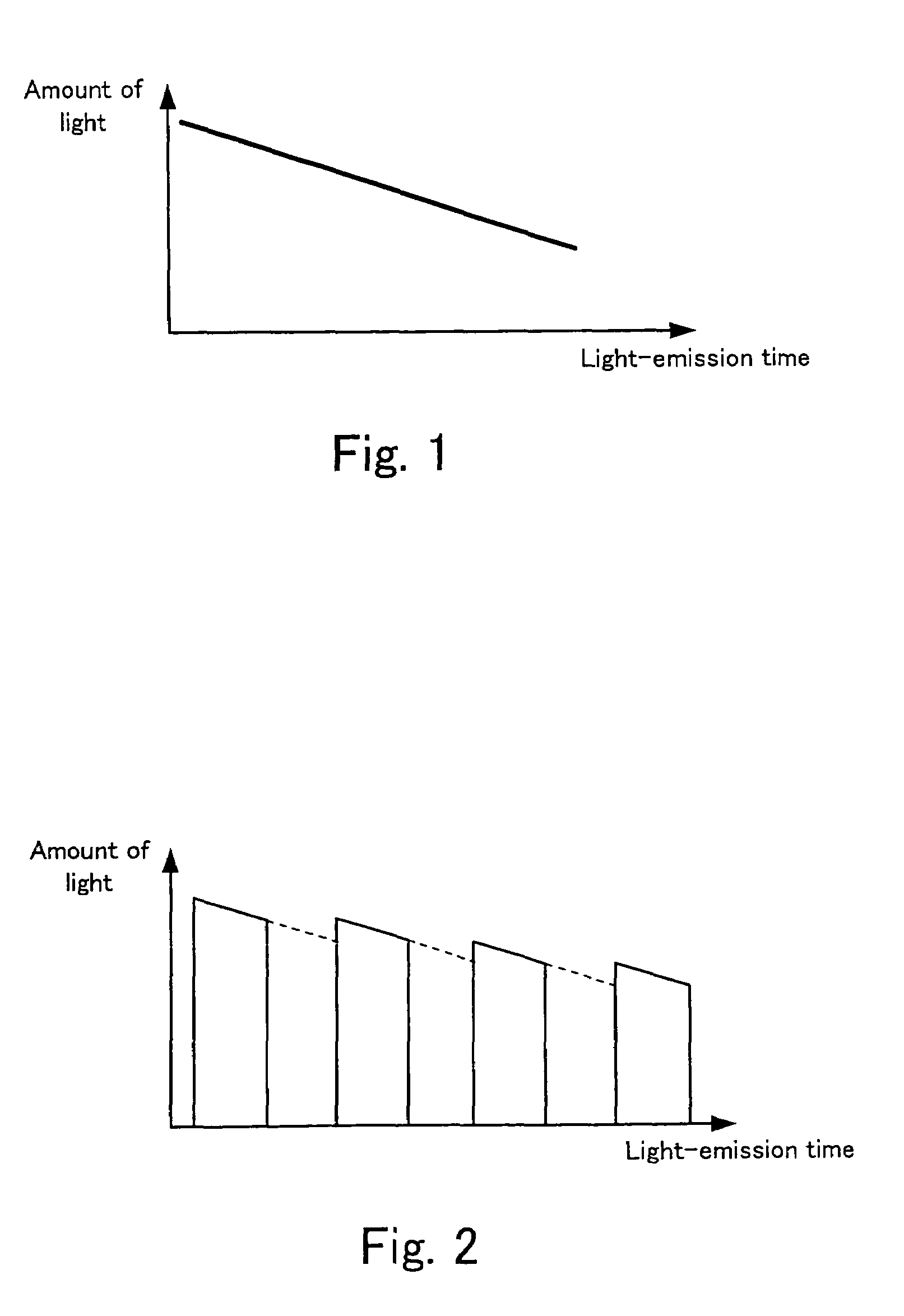

Light source system, light source device, and method of controlling light source

InactiveUS20090207613A1Increasing numberIncrease light intensityStatic indicating devicesNon-linear opticsDriving currentOptoelectronics

Light intensity may be locally increased in light intensity distribution without increasing number of light sources or drive current. A light source system includes a light source, and a diffusion unit varying diffusibility in incident light so that light intensity in a light intensity distribution in a plane, resulted from light emitted from the light source, is locally enhanced.

Owner:SONY CORP

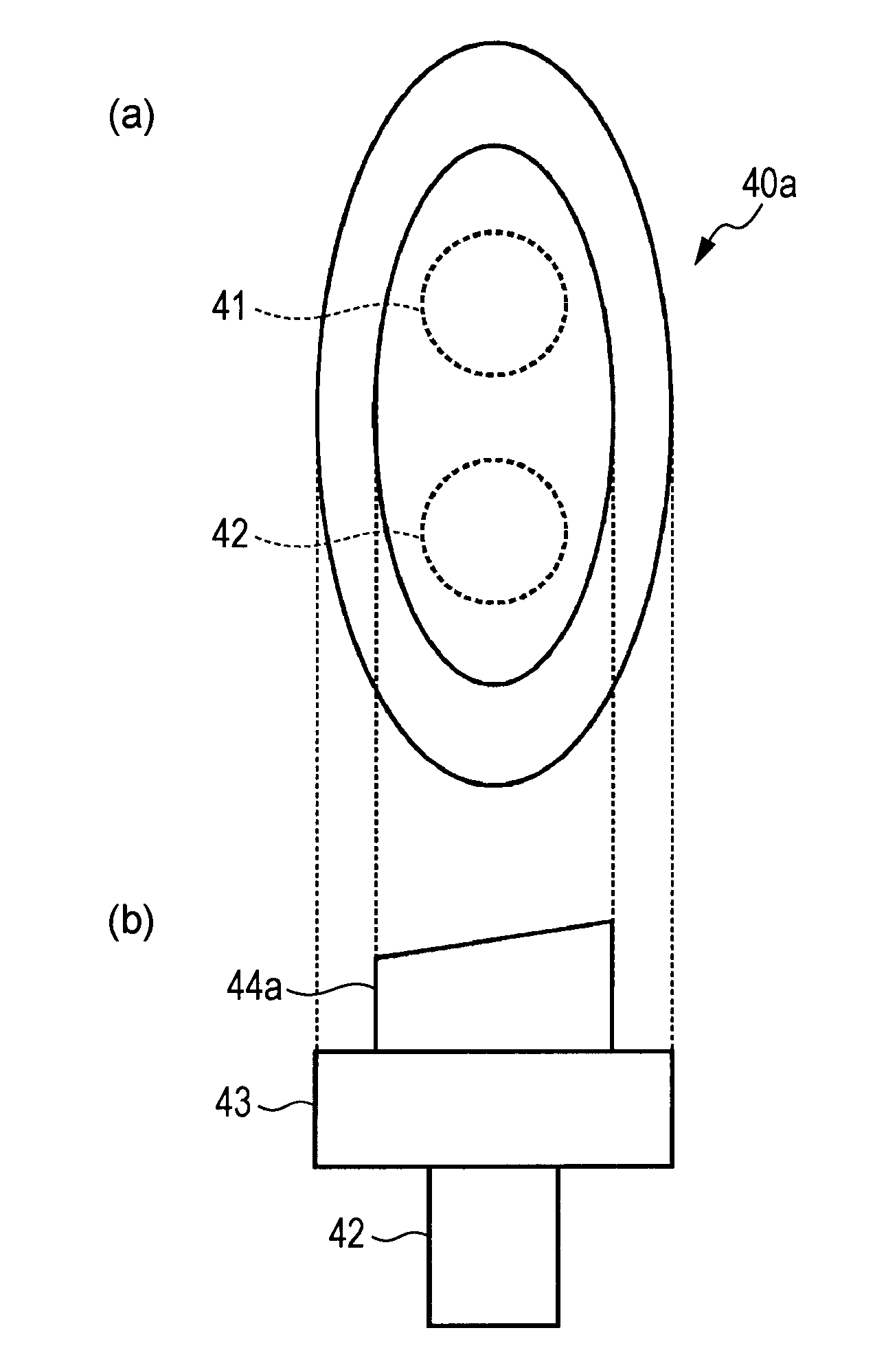

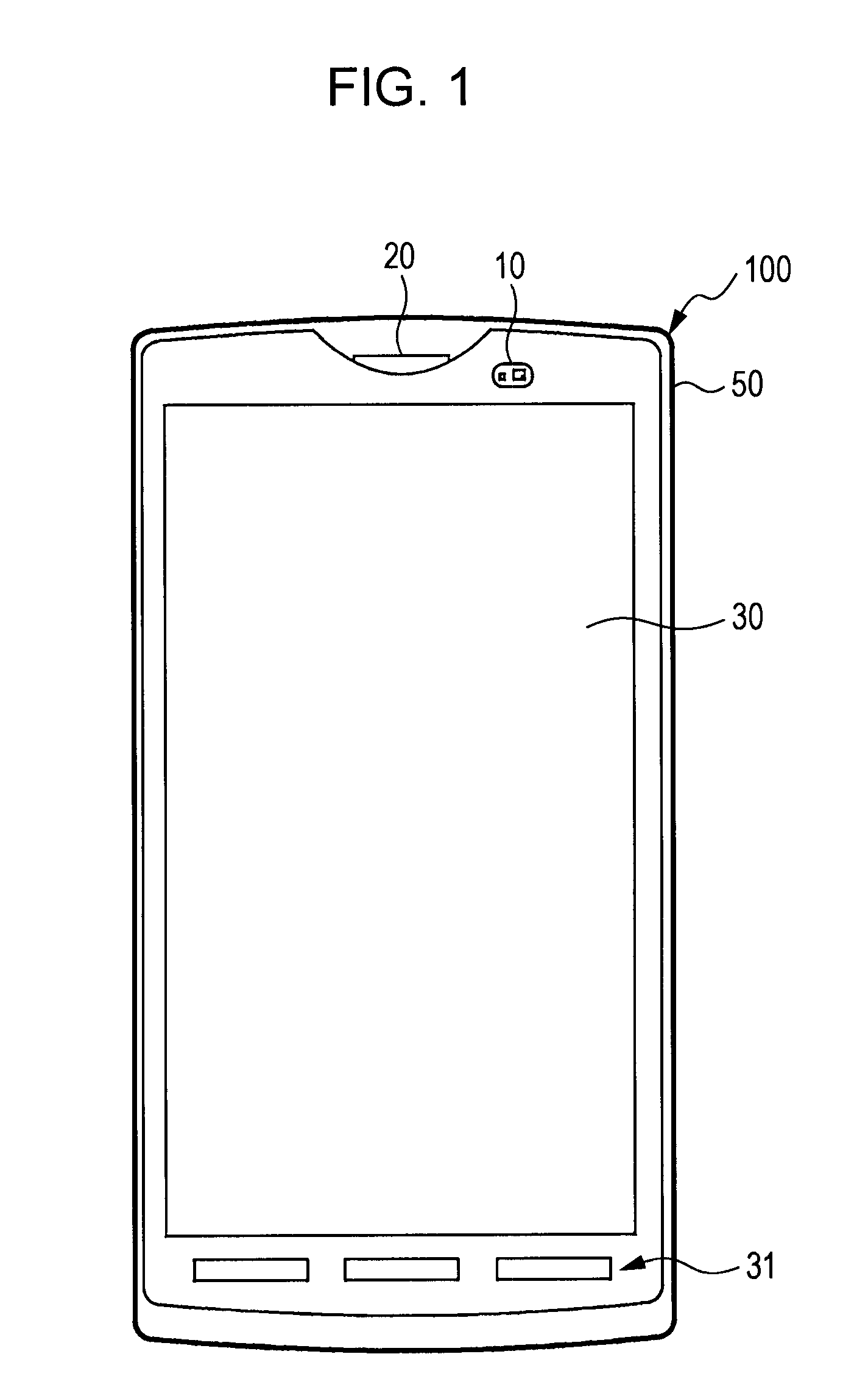

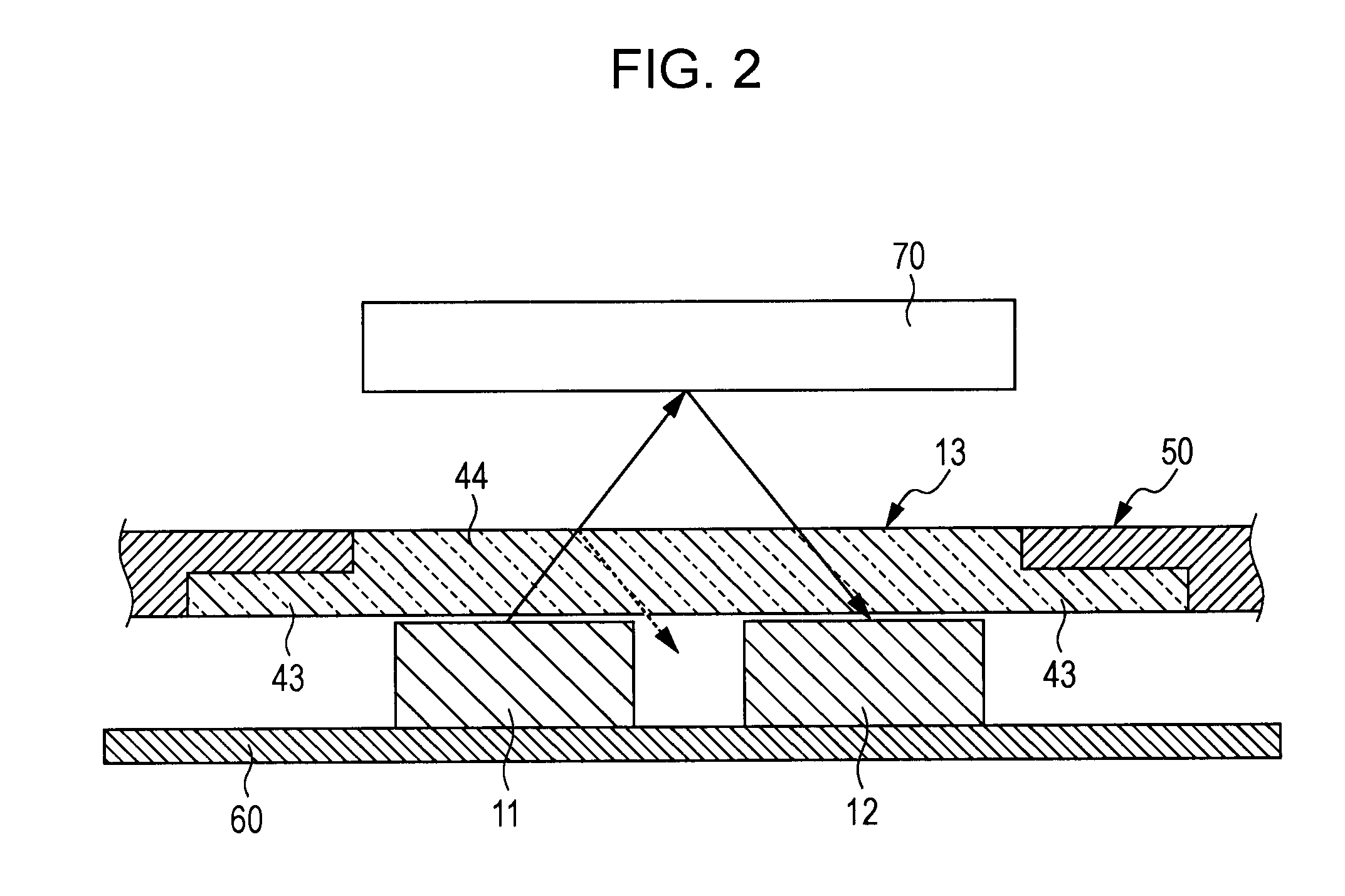

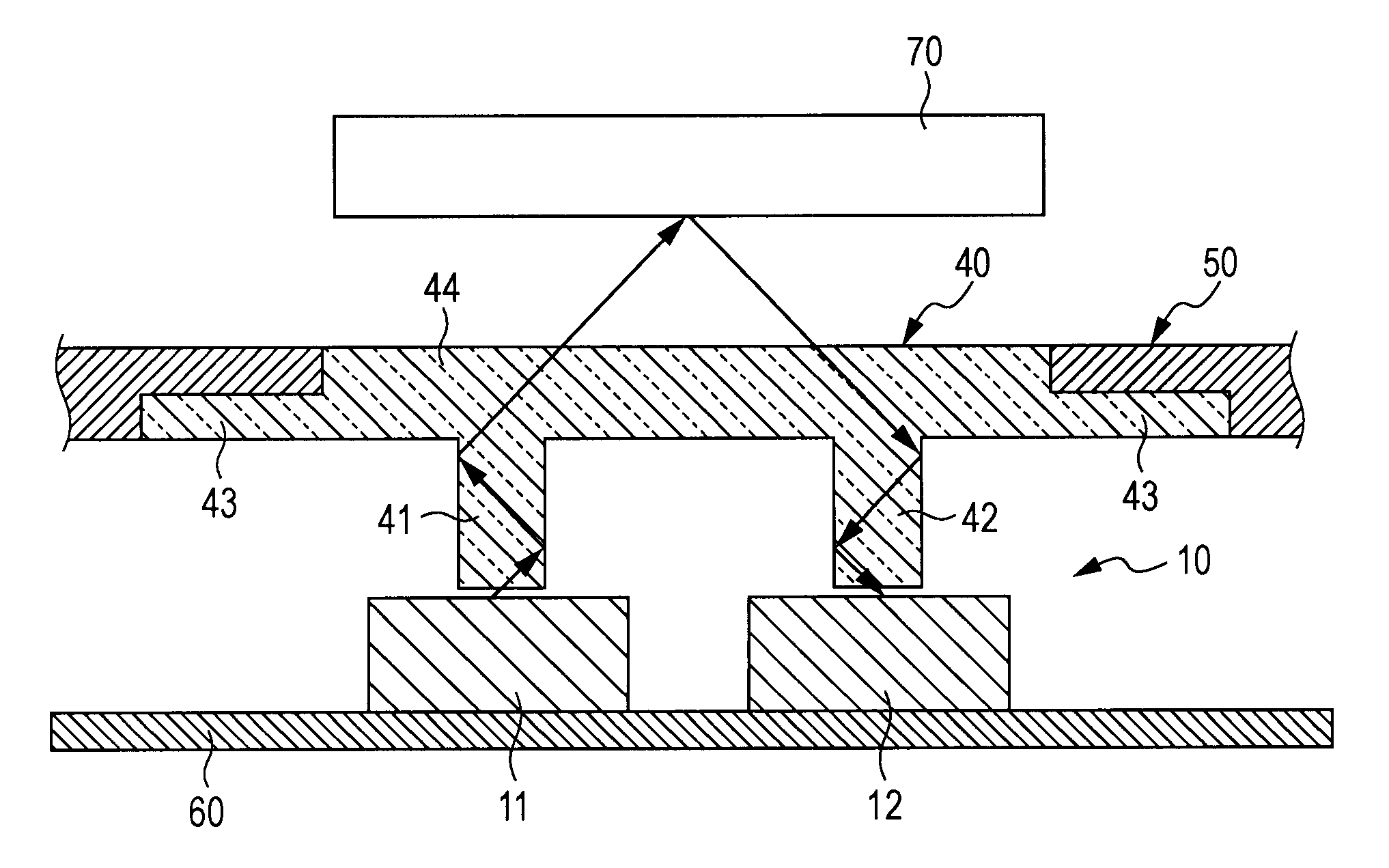

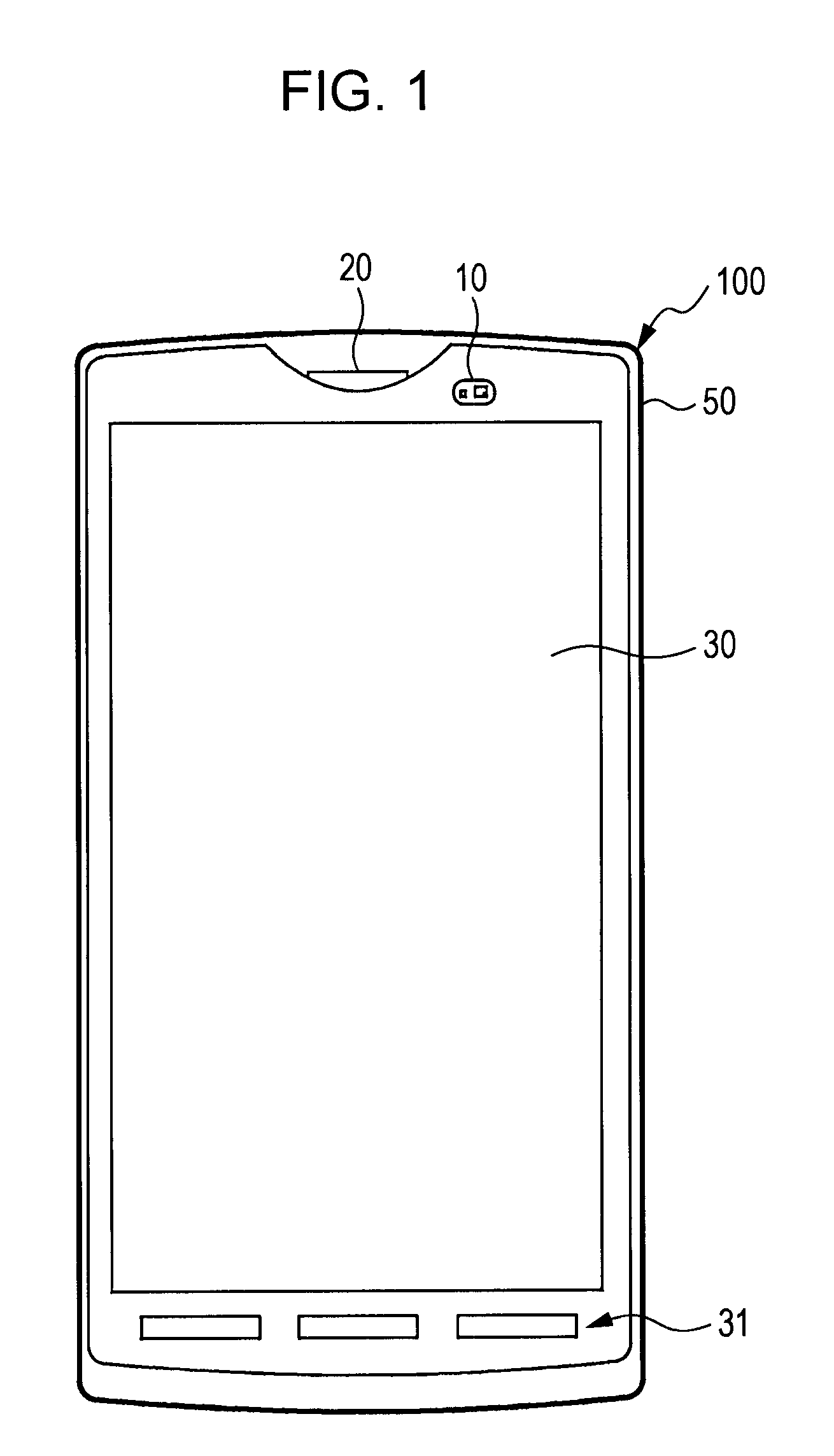

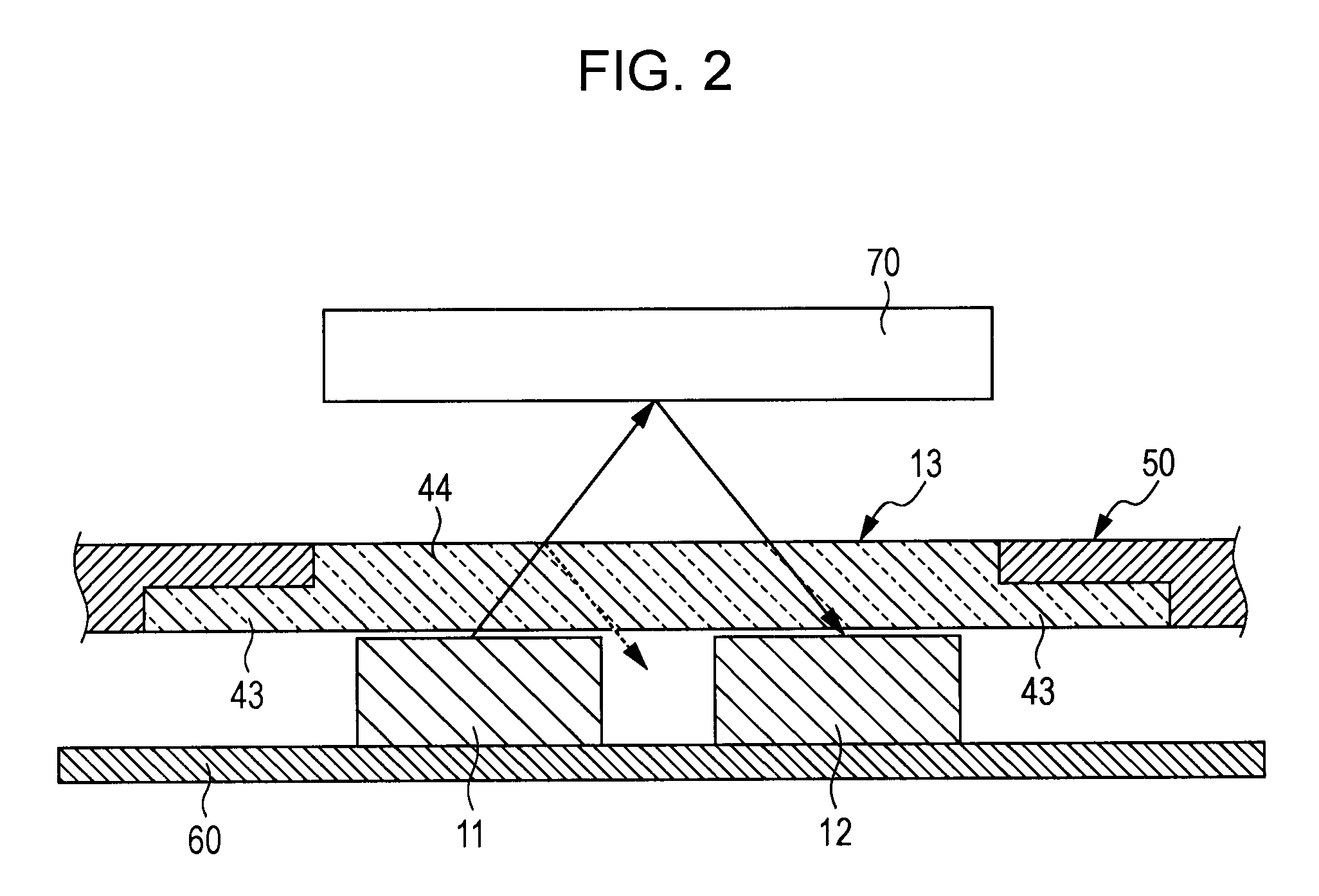

Proximity sensor and portable terminal

InactiveUS20120238320A1Prevent wrong actionPrevent improper actionElectronic switchingSubstation equipmentProximity sensorComputer terminal

A proximity sensor that includes a light emitting section that emits light; a light receiving section that detects the light emitted from the light emitting section reflected from an object; a window member that covers the light emitting section and the light receiving section; a first columnar portion disposed to extend between the light emitting section and the window member; and a second columnar portion disposed to extend between the light receiving section and the window member.

Owner:SONY CORP

Planar lighting device

ActiveUS20080304285A1Add dimensionReduce thickness and weightMechanical apparatusLight guides for lighting systemsIlluminanceLight guide

A thinner and larger planar lighting device is achieved without increasing the number of light sources and holding the power consumption to a minimum. The LED chips on the light sources are arrayed at an array density varying according to the position of each of the light entrance planes of the light guide plate such that the illuminance distribution as measured on along the middle of the light guide plate in a direction parallel to longitudinal direction of the light entrance planes represents a high-in-the-middle, bell-curve distribution.

Owner:FUJIFILM CORP

Power management efficiency using DC-DC and linear regulators in conjunction

ActiveUS9088176B2Effective regulationIncreasing of complexityThree-or-more-wire dc circuitsApparatus with intermediate ac conversionLinear regulatorPower Management Unit

A power management unit for improving power efficiency of an electronic device. The power management unit includes a first and a second stage power regulator and a control circuitry. The first stage power regulator includes a switching regulator to efficiently adjust an input voltage based on a feedback signal. The adjusted input voltage provides the second stage power regulator that includes low dropout voltage regulators with an input voltage close to its output. Thus, power dissipation in the second stage is reduced by reducing the voltage differential between the input and desired output voltages. The second stage turns on / off power to units of the electronic device. The control circuitry generates the feedback signal based on dropout voltages of the low dropout voltages, the desired output voltage and the adjusted input voltage. The largest dropout voltage is selected and adds it to the desired output voltage to generate the feedback signal.

Owner:NVIDIA CORP

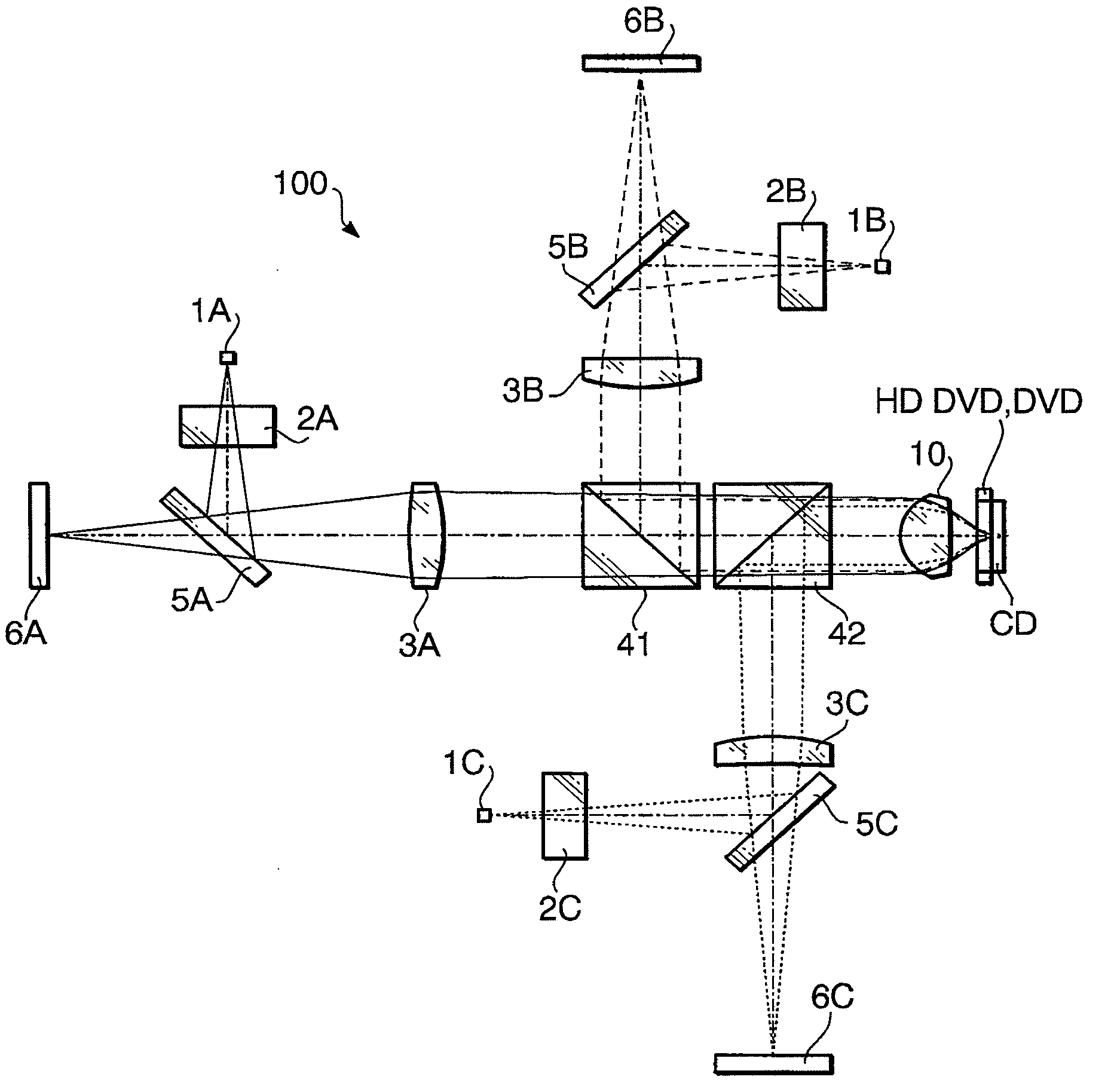

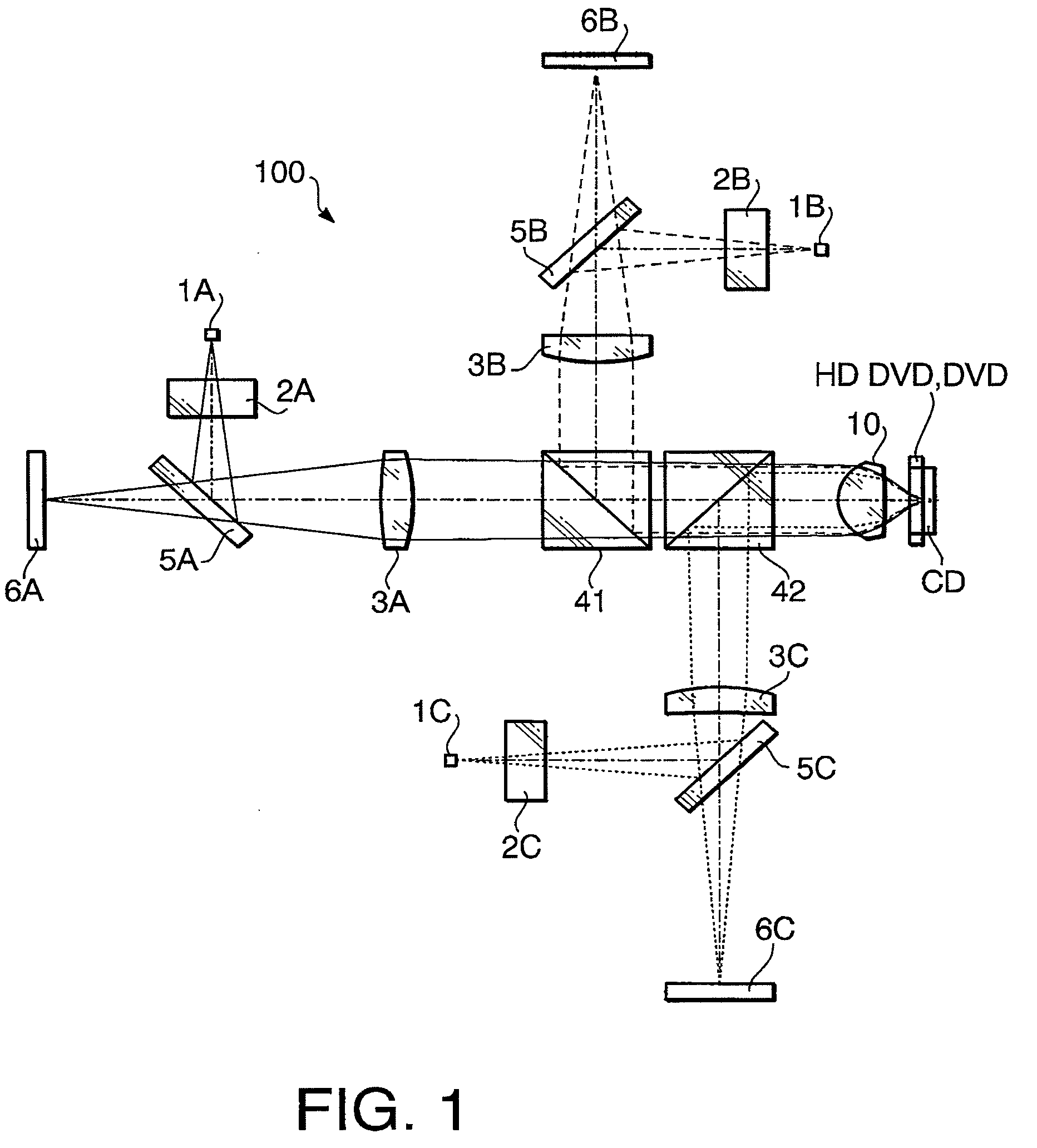

Optical pick-up

InactiveUS20090052305A1Increase the number ofImprove recording densityMechanical record carriersRecord information storageCouplingLight beam

There is provided an optical pick-up including first to third light sources respectively emitting first to third light beams, a first coupling lens, and an objective lens formed to converge each of the first, second and third light beams onto the first, second and third optical discs, respectively. The objective lens has a step structure including a plurality of concentrically formed refractive surface zones divided by steps, the step structure having a function of giving, at each step, an optical path length difference of approximately 2λ1 to the first light beam. The first coupling lens causes the first light beam to be incident on the objective lens as a converging beam. The objective lens is positioned to satisfy a condition:−0.35<f2×M2−f1×M1<−0.07 (1).

Owner:HOYA CORP

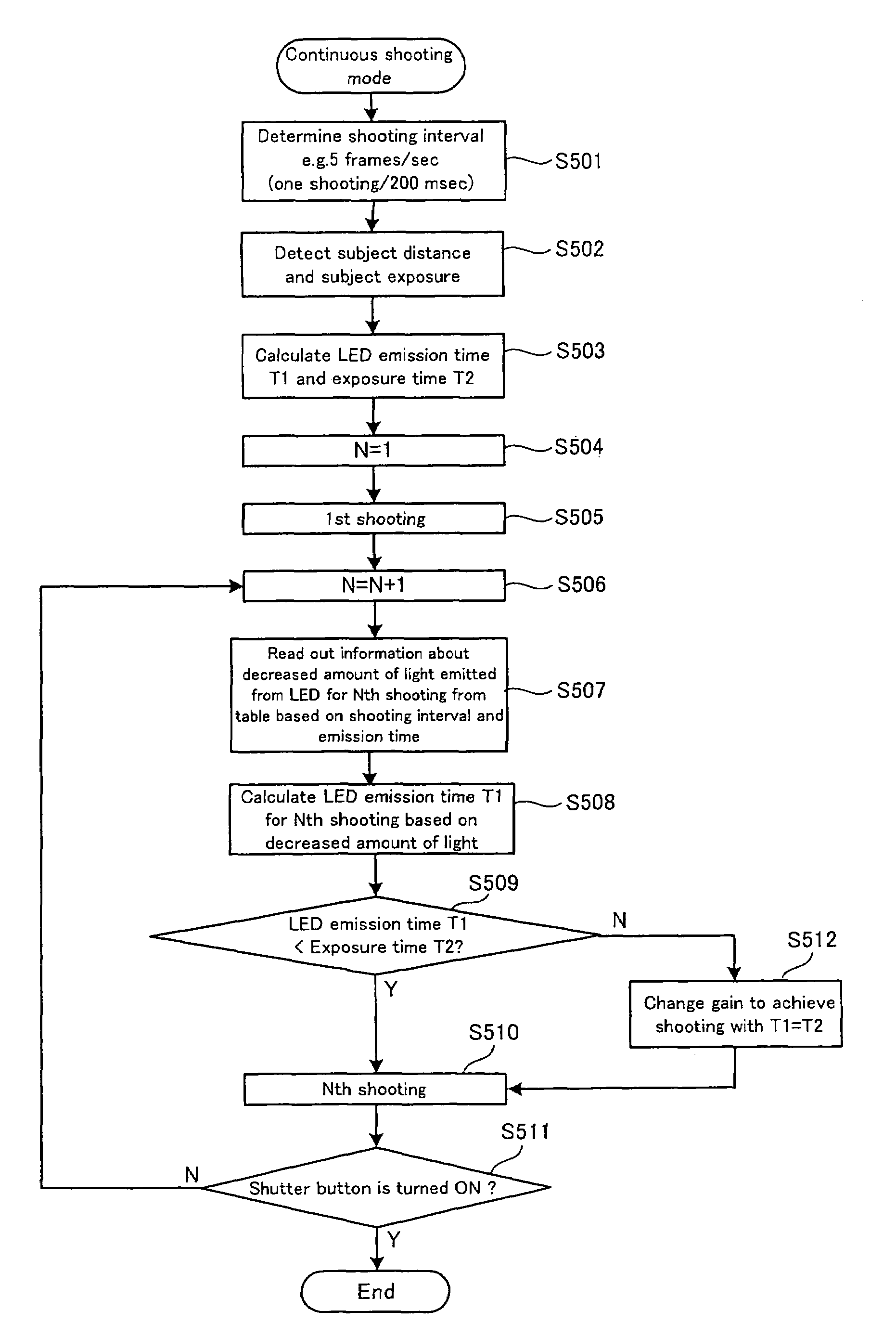

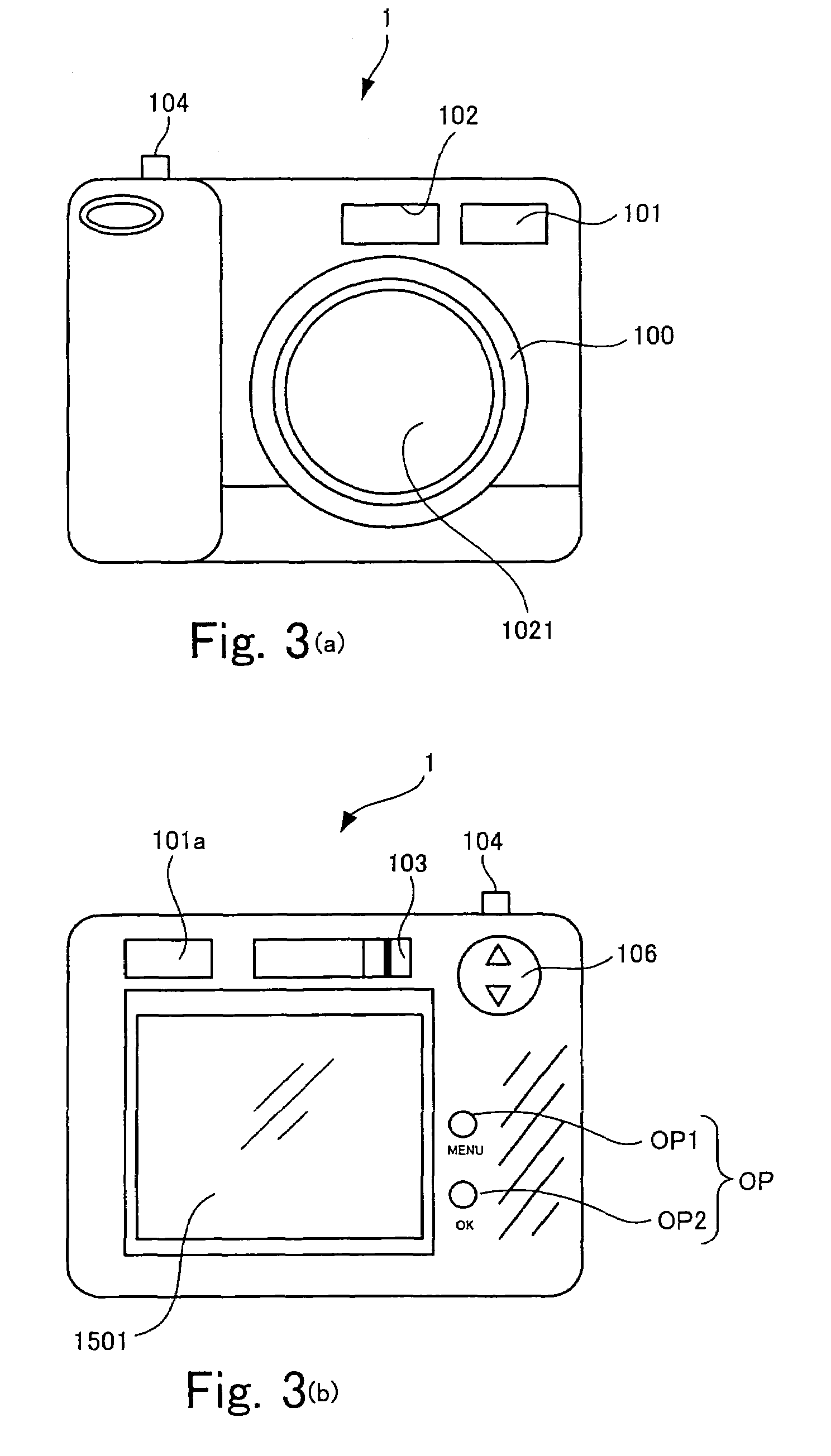

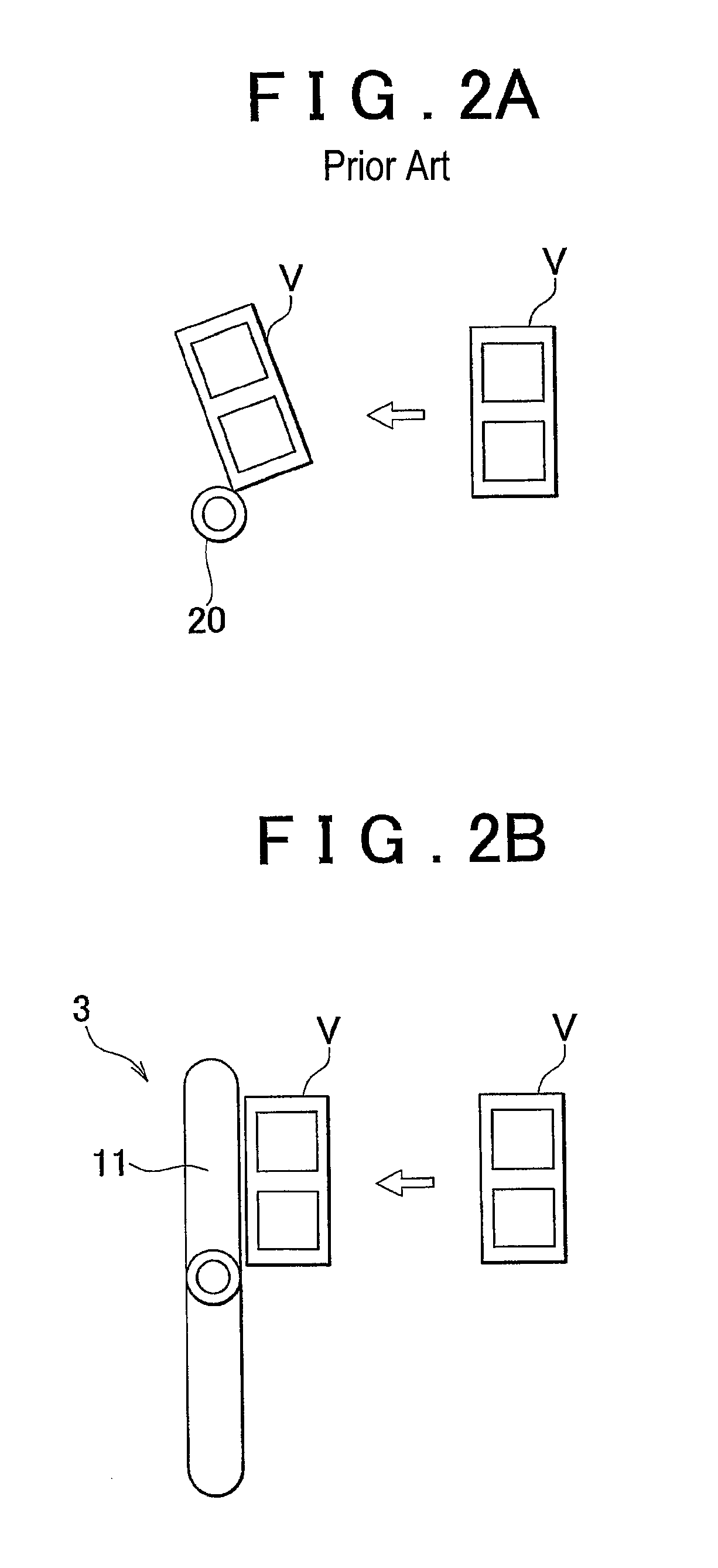

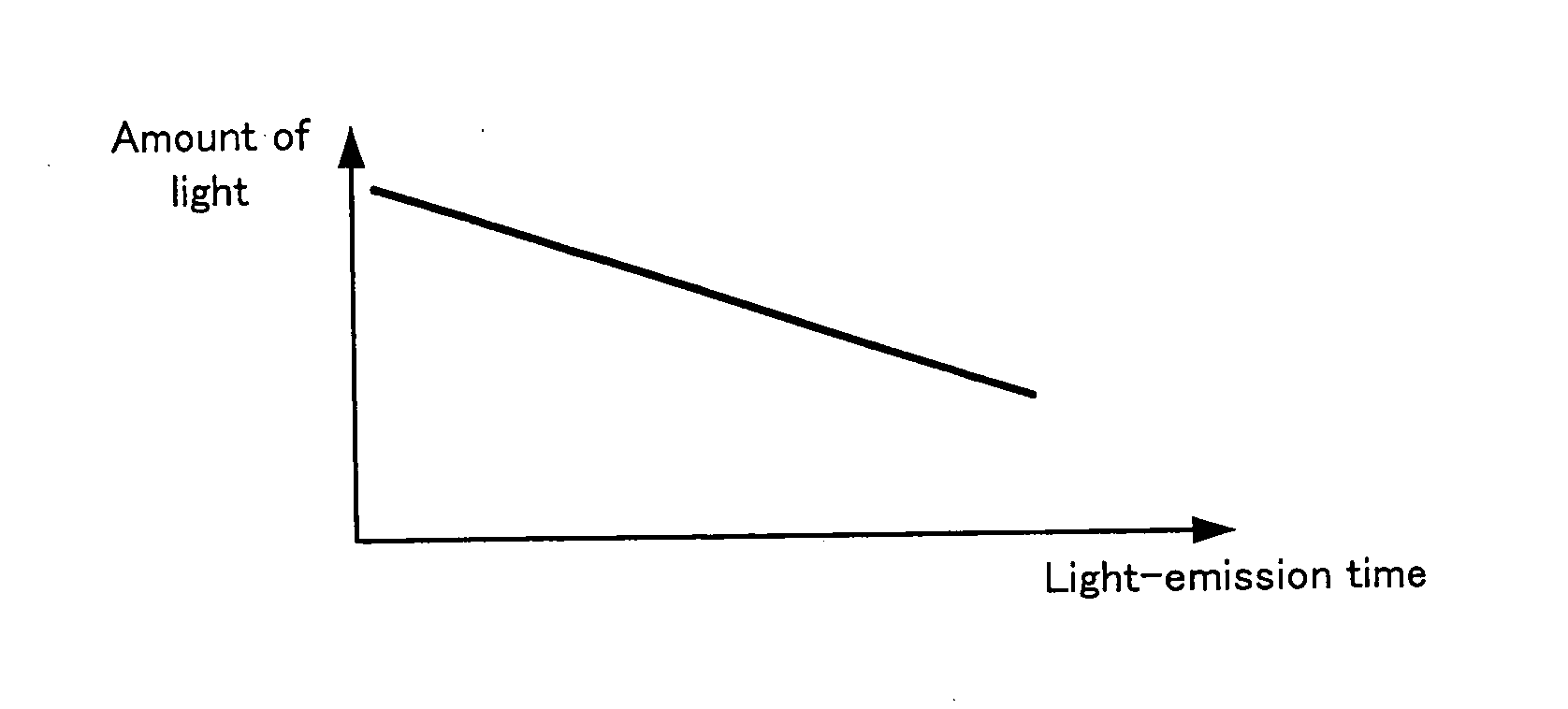

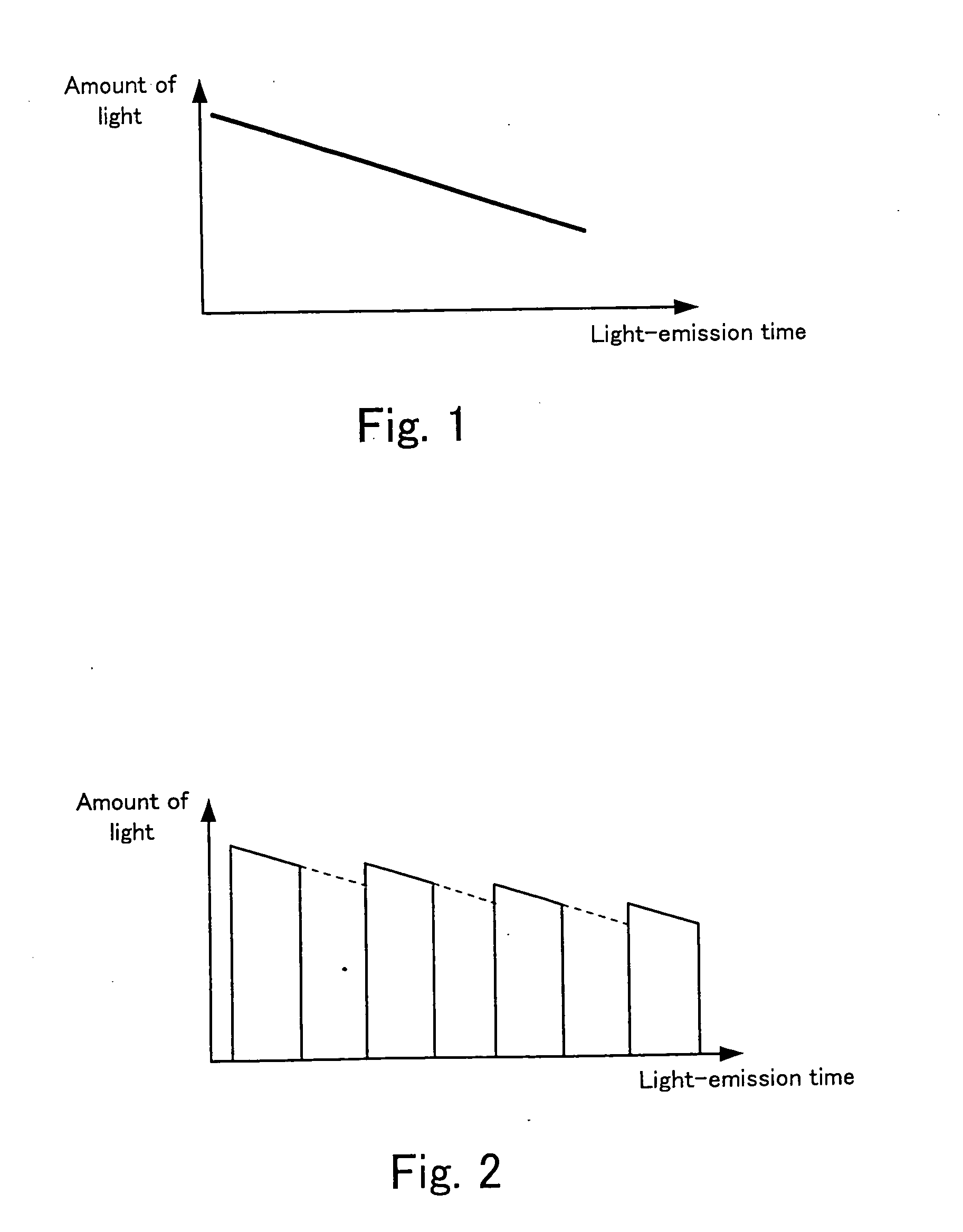

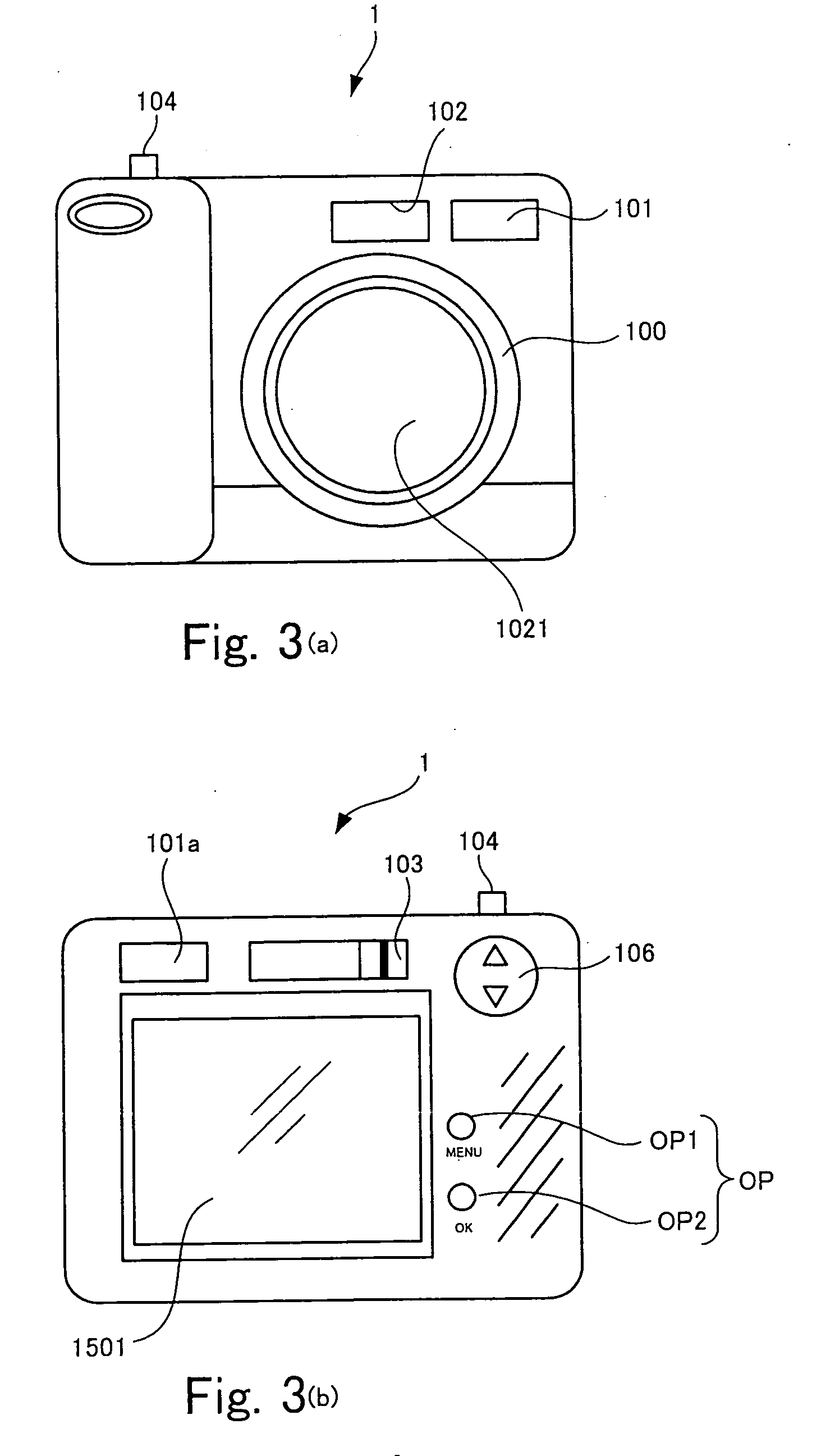

Image-taking apparatus

An image-taking apparatus includes: an A / D conversion circuit having an amplifier that is capable of amplifying image signals per shooting frame; and a gain changer that changes the gain of the amplifier. The apparatus causes the gain changer to increase the gain of the amplifier up to a level that compensates for a gradual decrease in the amount of light emitted from LEDs that occurs during continuous shooting. As a result, the amplitude level of every image signal is made constant and thus, replayed images of the same brightness shot during the continuous shooting are obtained.

Owner:FUJIFILM CORP

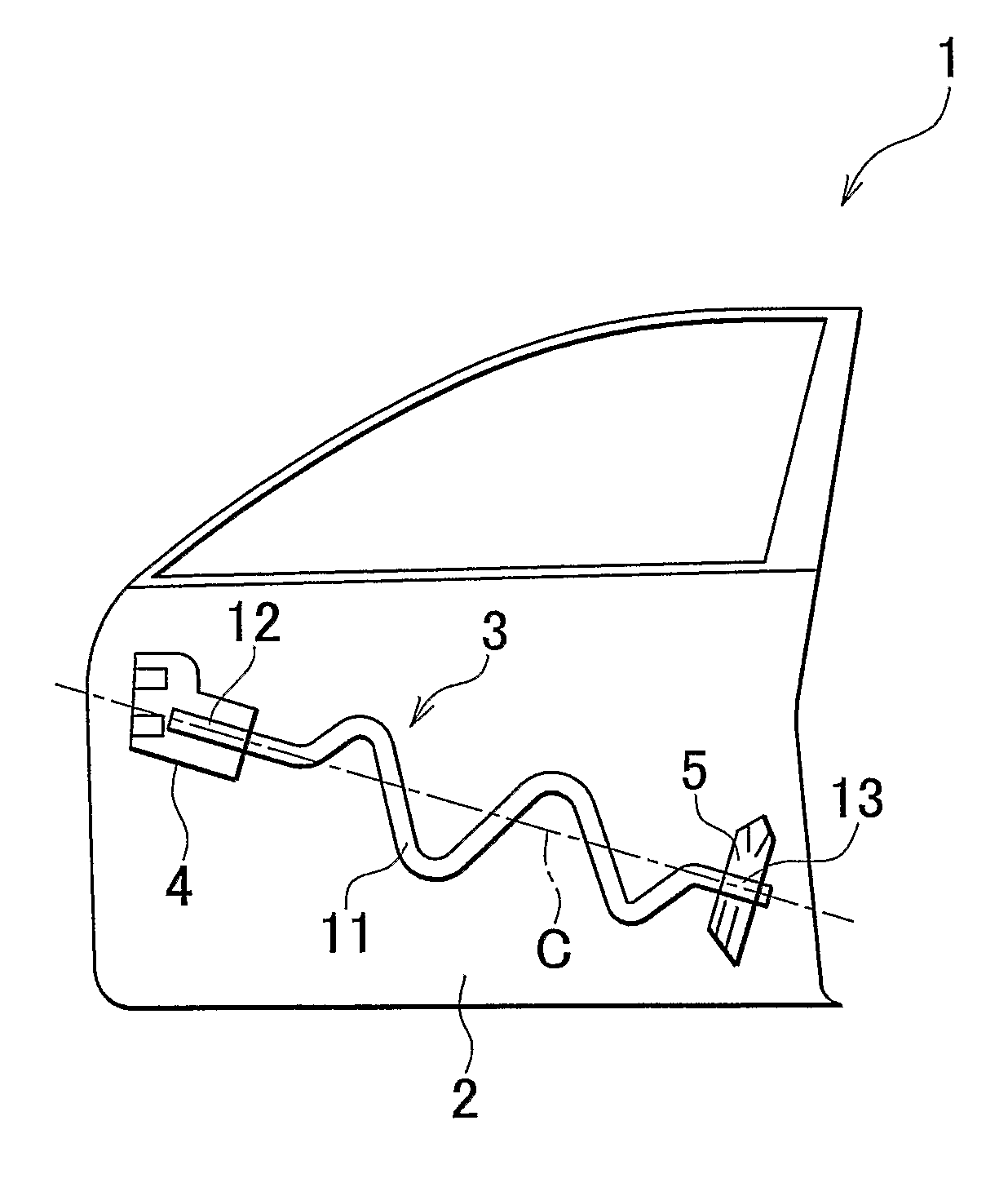

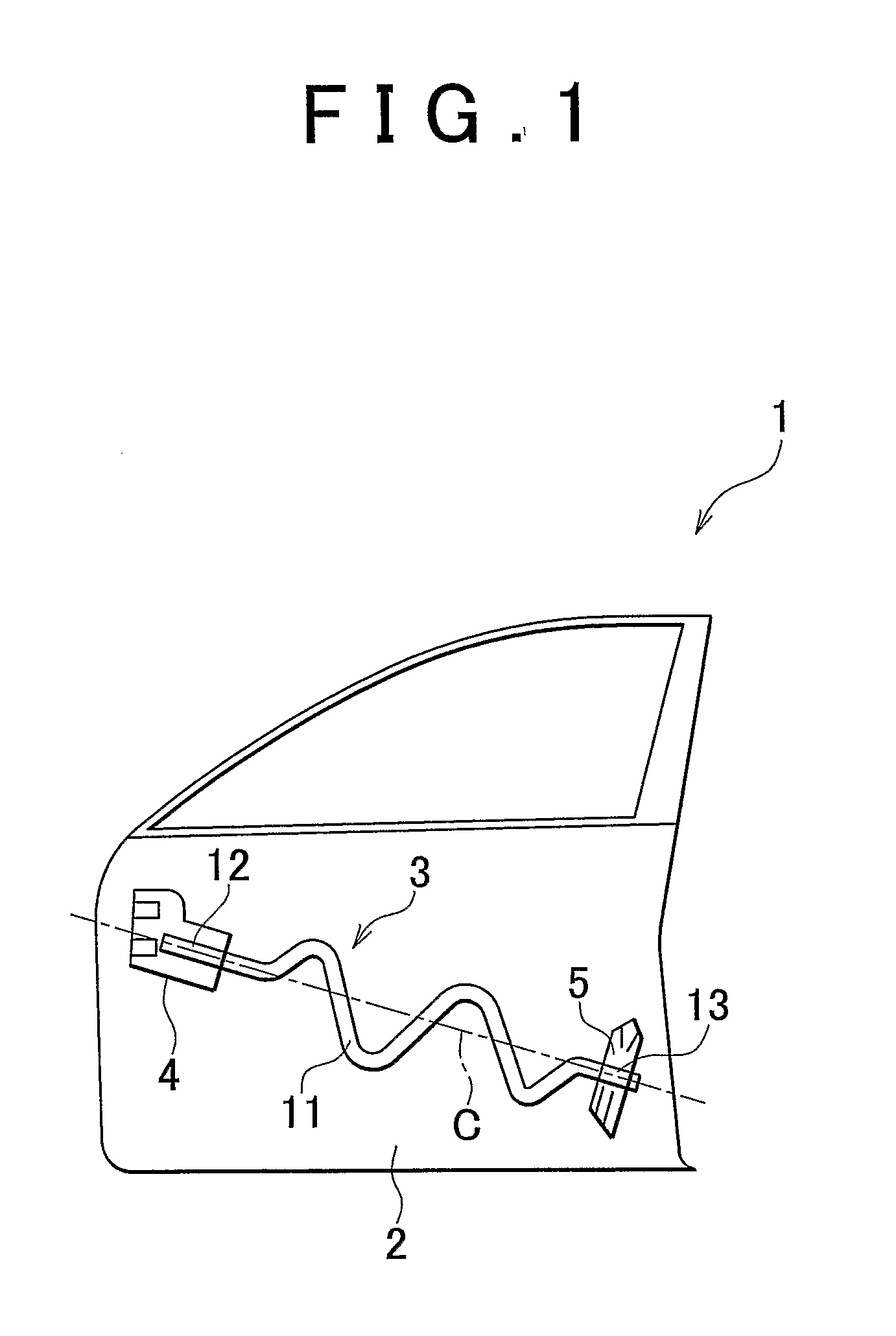

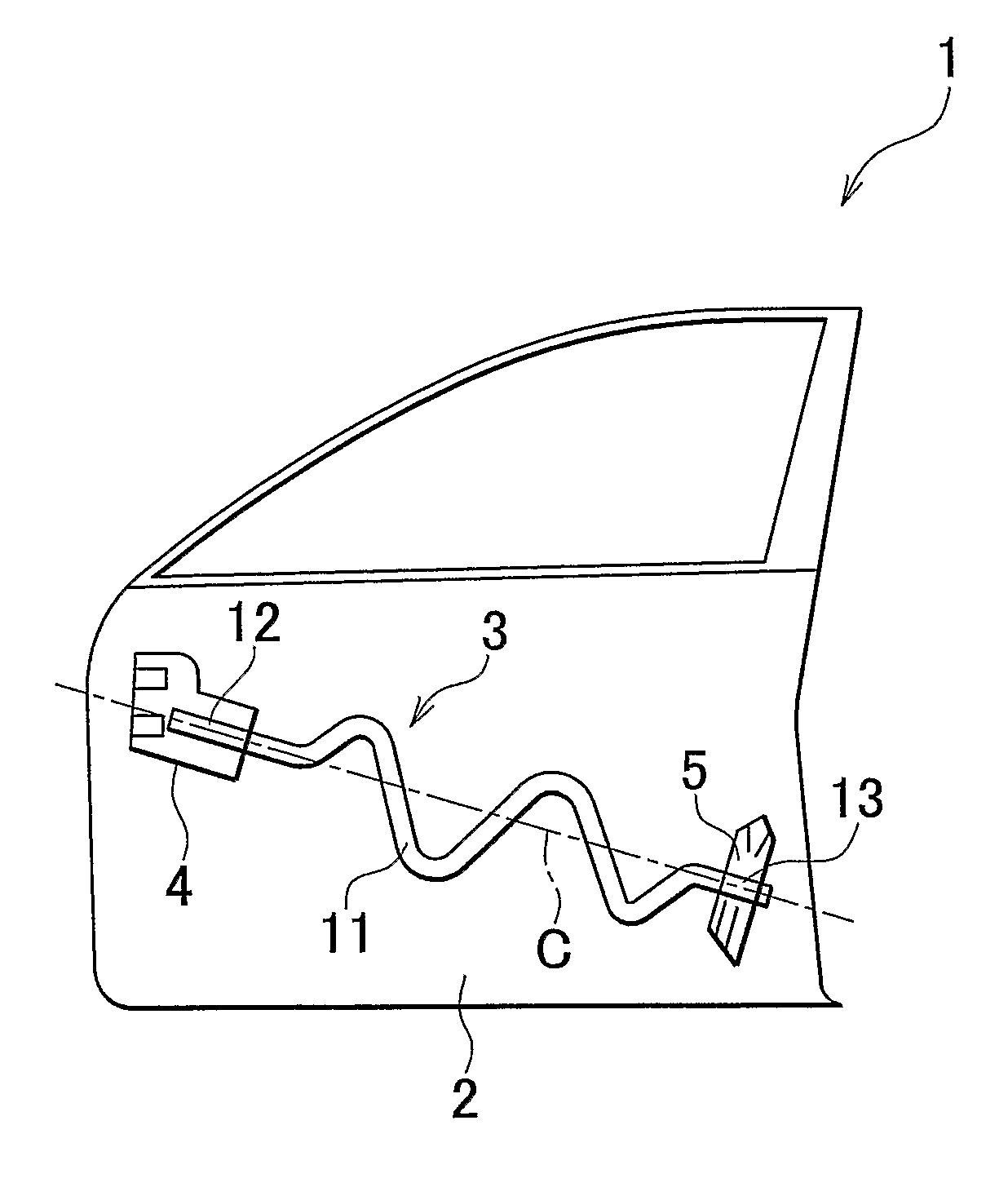

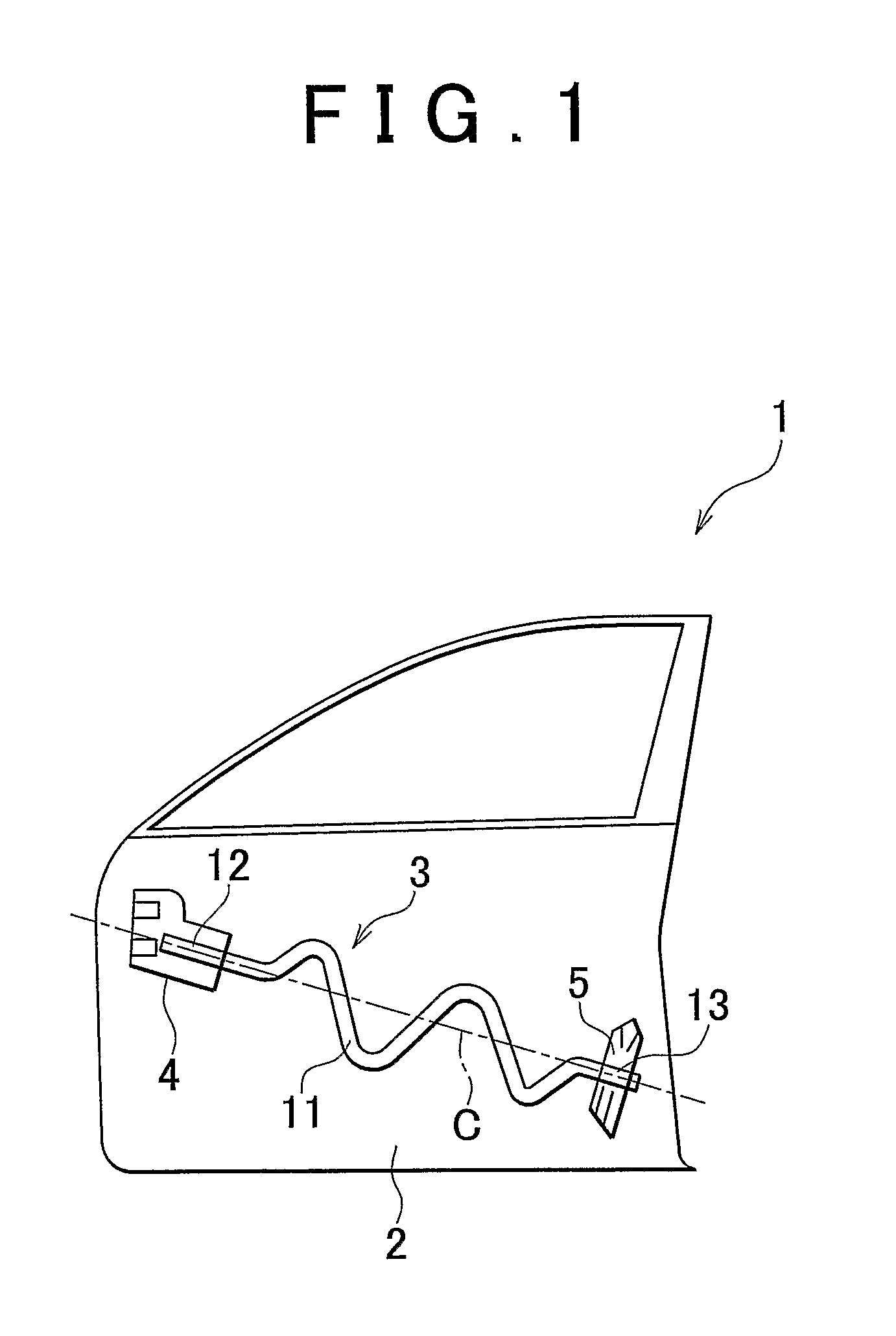

Vehicle door structure

InactiveUS20100013266A1Increasing of complexityIncreasing numberVehicle seatsEngine sealsEngineeringElectrical and Electronics engineering

An impact beam that absorbs an impact of a vehicle collision is provided in a vehicle door, at a position between an inner panel and an outer panel. The impact beam has a wavy portion that undulates in the height direction of the vehicle door. The center axis of the wavy portion extends along the longitudinal direction of a vehicle.

Owner:TOYOTA JIDOSHA KK

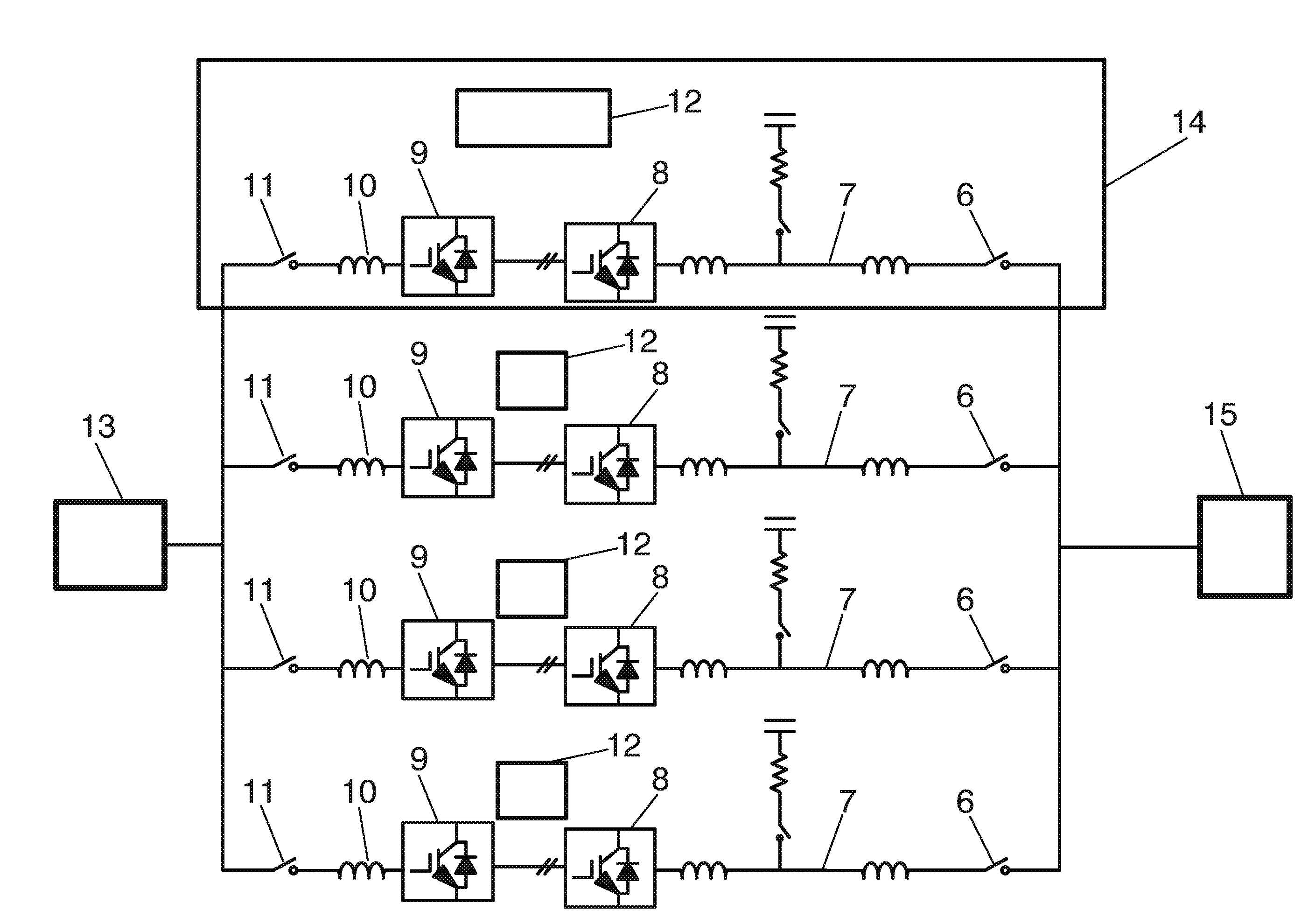

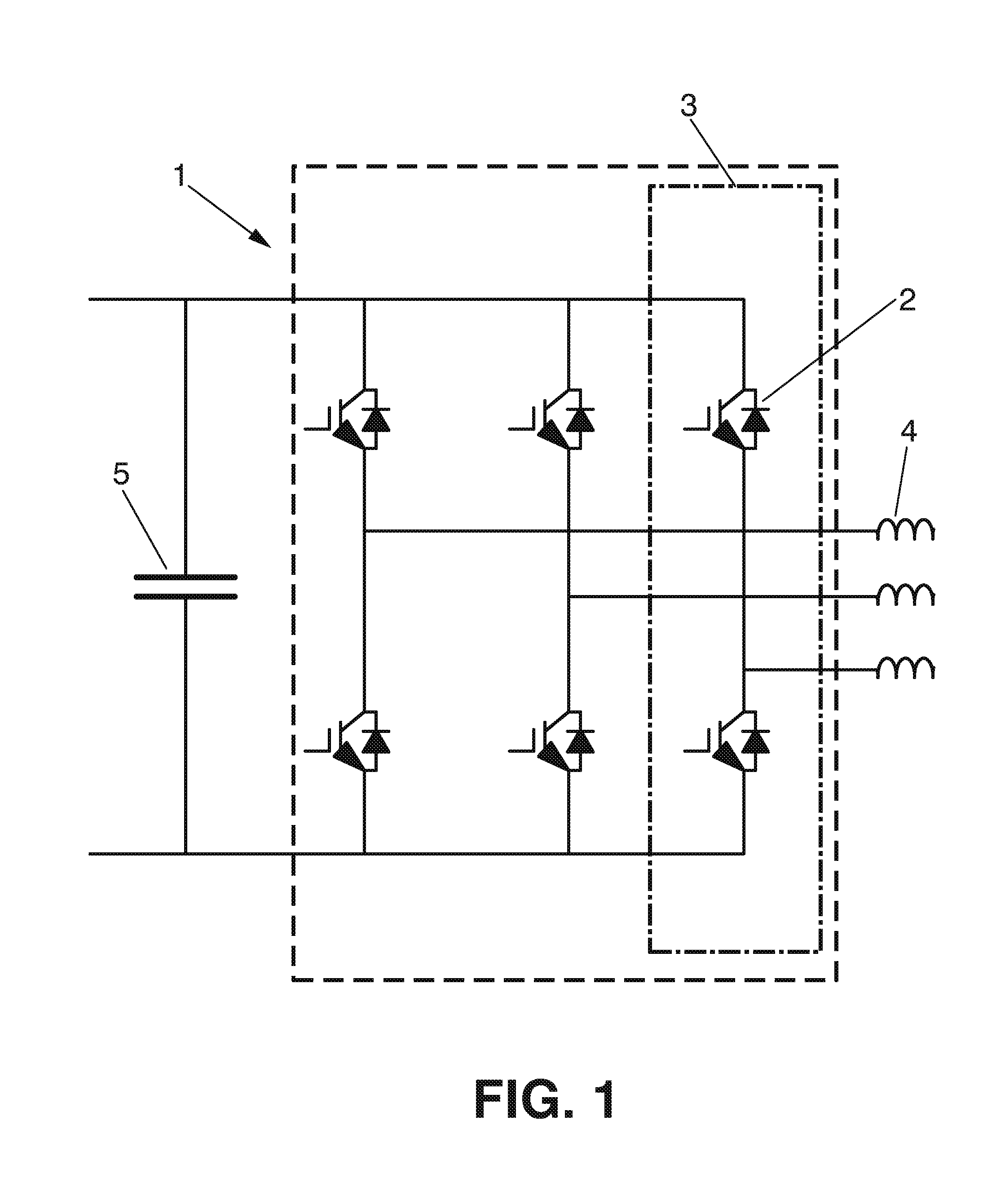

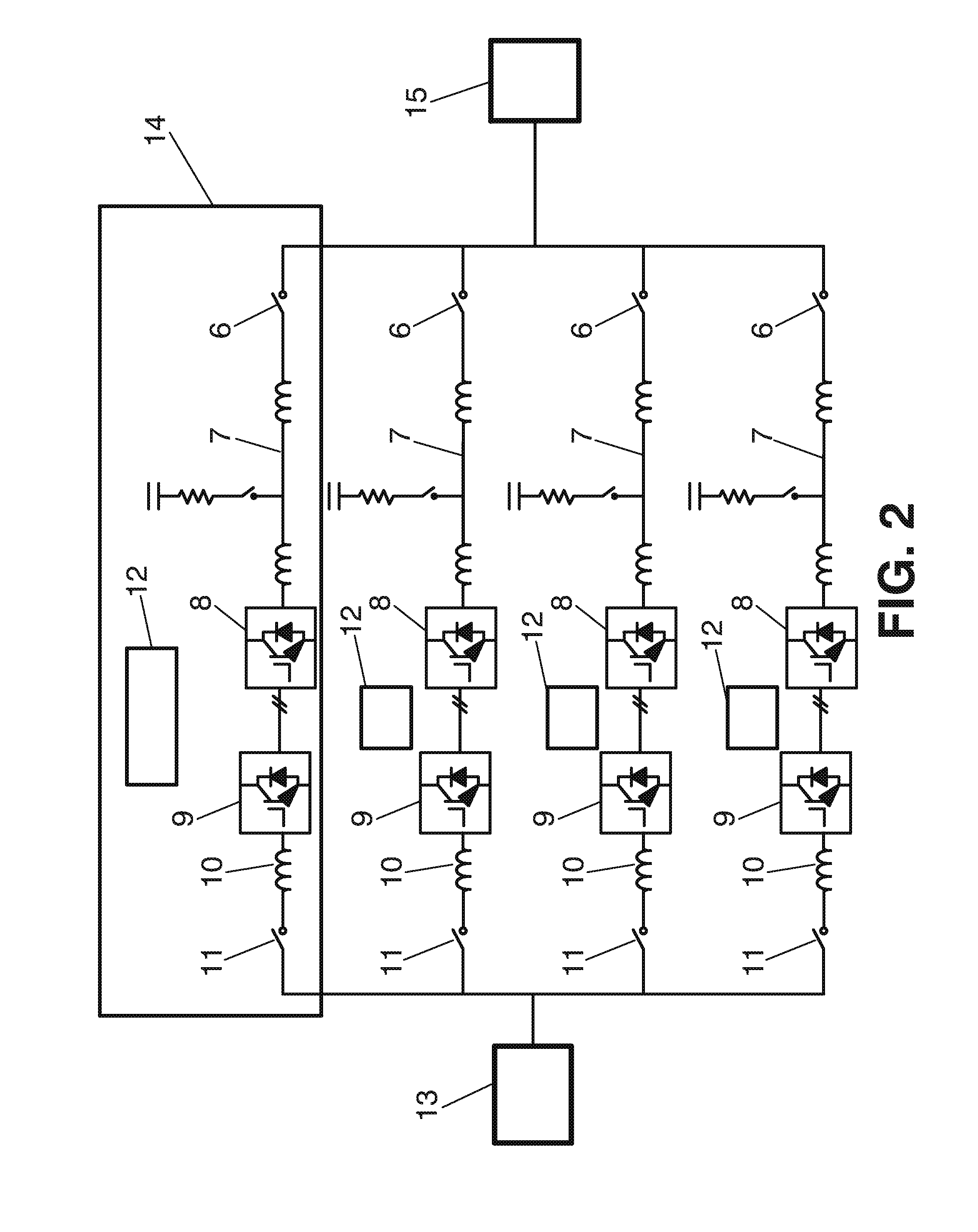

Electric power converter system with parallel units and fault tolerance

ActiveUS20140312704A1Improve availabilityIncreasing numberDc network circuit arrangementsEfficient power electronics conversionElectric energyEngineering

The present invention relates to an electric energy conversion method and system with at least two conversion units (14), comprising control means (12) establishing the maximum output current of the operative conversion modules, as well as the commutation frequency of the entire or of a sub-group of the operative conversion modules to thus increase the availability of the conversion system in the event of failures.

Owner:INGETEAM POWER TECH

Proximity sensor and portable terminal

InactiveUS8761830B2Prevent improper actionIncreasing of areaRadiation pyrometryMaterial analysis by optical meansProximity sensorComputer terminal

A proximity sensor that includes a light emitting section that emits light; a light receiving section that detects the light emitted from the light emitting section reflected from an object; a window member that covers the light emitting section and the light receiving section; a first columnar portion disposed to extend between the light emitting section and the window member; and a second columnar portion disposed to extend between the light receiving section and the window member.

Owner:SONY CORP

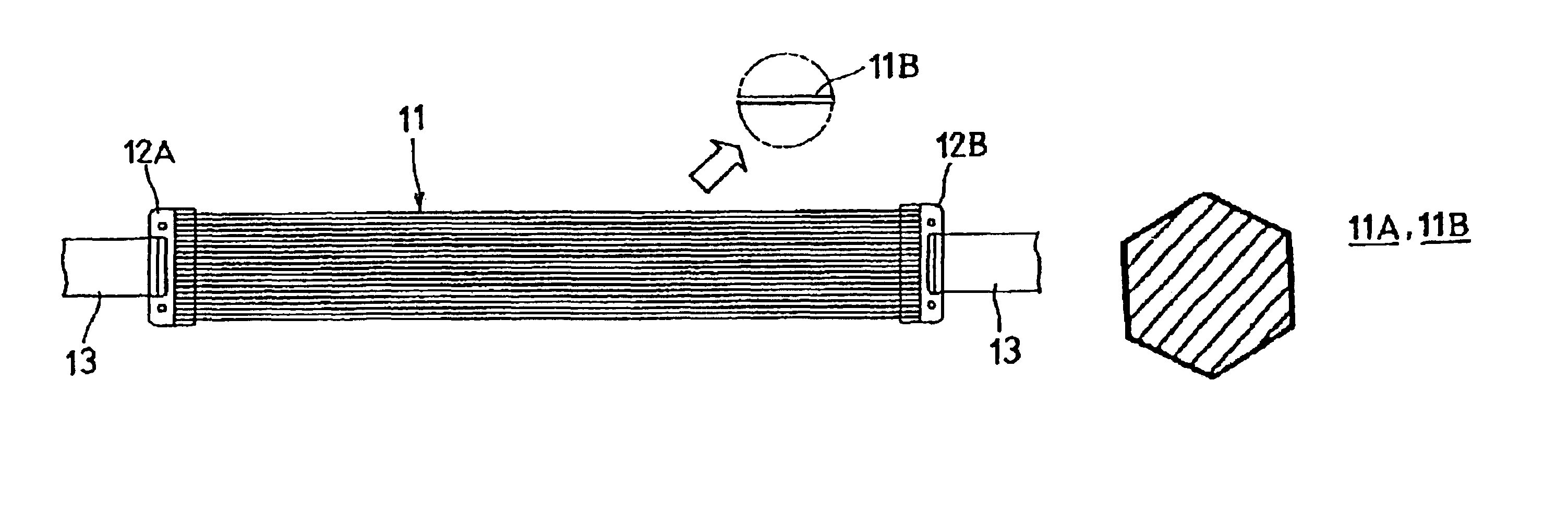

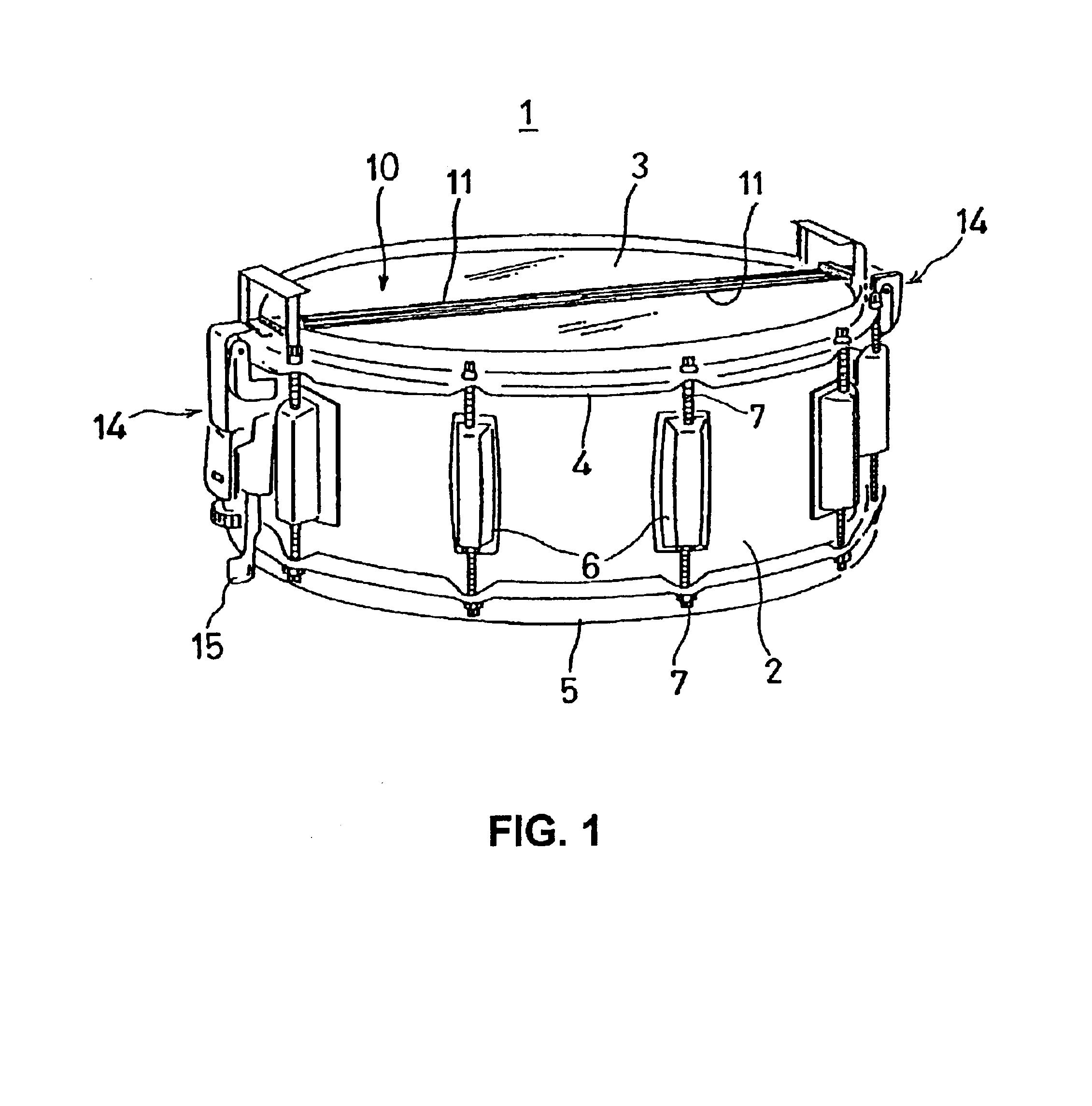

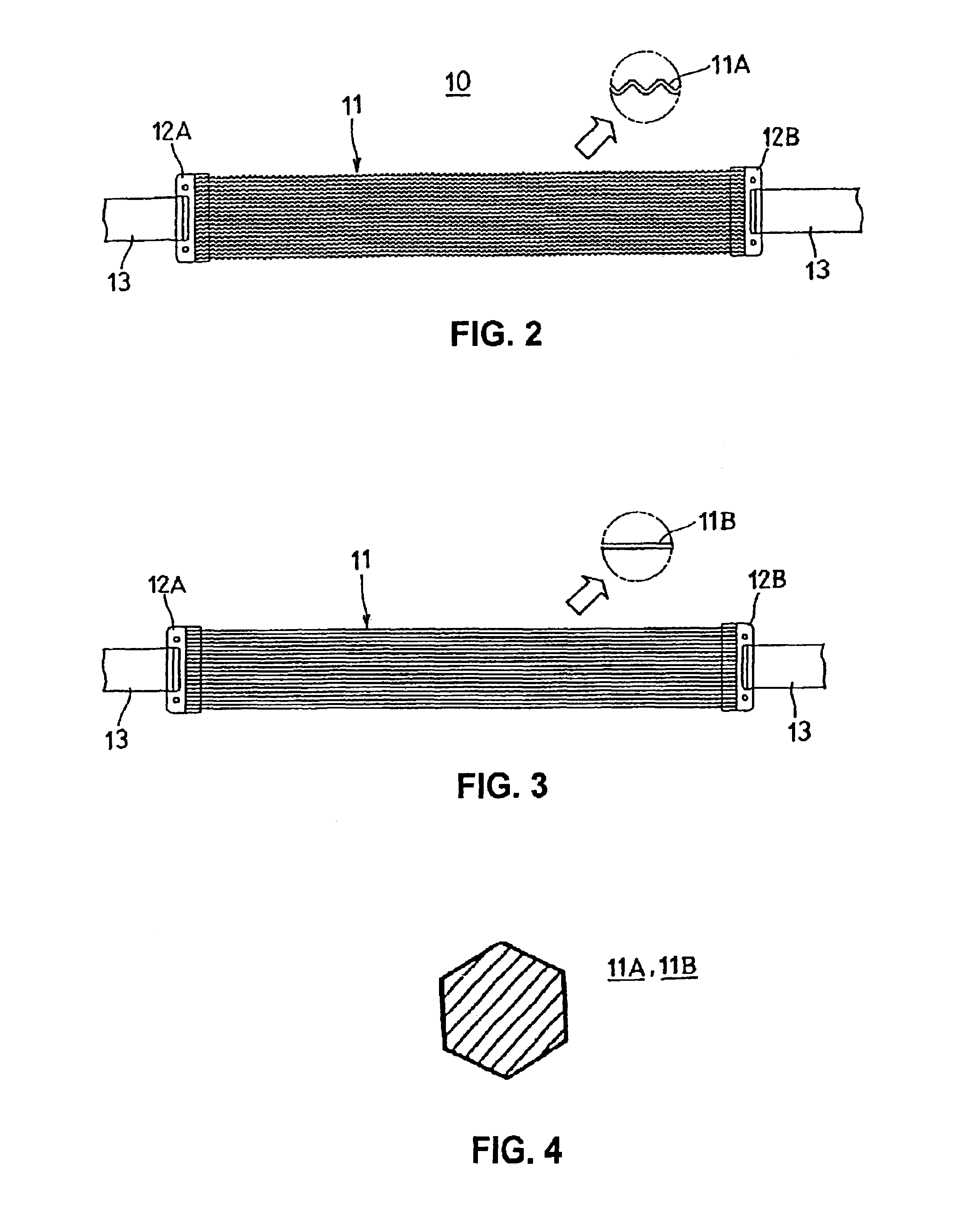

Drum acoustic wire assembly and a drum using the same

InactiveUS6849793B2Increasing numberIncreasing lengthPercussion musical instrumentsDrumheadEngineering

An acoustic wire assembly mounted on a drumhead, including a plurality of acoustic wires disposed parallel to each other so as to be brought into contact with and moved away from the drumhead in which at least some of the acoustic wires are polygonal (square, pentagonal, hexagonal and octagonal) in cross-section, and they can be in a coil shape or a straight shape.

Owner:YAMAHA CORP

Vehicle door structure

InactiveUS8226154B2Increasing of complexityIncreasing numberVehicle seatsEngine sealsElectrical and Electronics engineeringCar door

An impact beam that absorbs an impact of a vehicle collision is provided in a vehicle door, at a position between an inner panel and an outer panel. The impact beam has a wavy portion that undulates in the height direction of the vehicle door. The center axis of the wavy portion extends along the longitudinal direction of a vehicle.

Owner:TOYOTA JIDOSHA KK

Image-taking apparatus

InactiveUS20070110426A1Improve accuracyImprove precision controlShuttersExposure controlAudio power amplifierOptoelectronics

An image-taking apparatus includes: an A / D conversion circuit having an amplifier that is capable of amplifying image signals per shooting frame; and a gain changer that changes the gain of the amplifier. The apparatus causes the gain changer to increase the gain of the amplifier up to a level that compensates for a gradual decrease in the amount of light emitted from LEDs that occurs during continuous shooting. As a result, the amplitude level of every image signal is made constant and thus, replayed images of the same brightness shot during the continuous shooting are obtained.

Owner:FUJIFILM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com