Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39results about How to "Improve programming reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

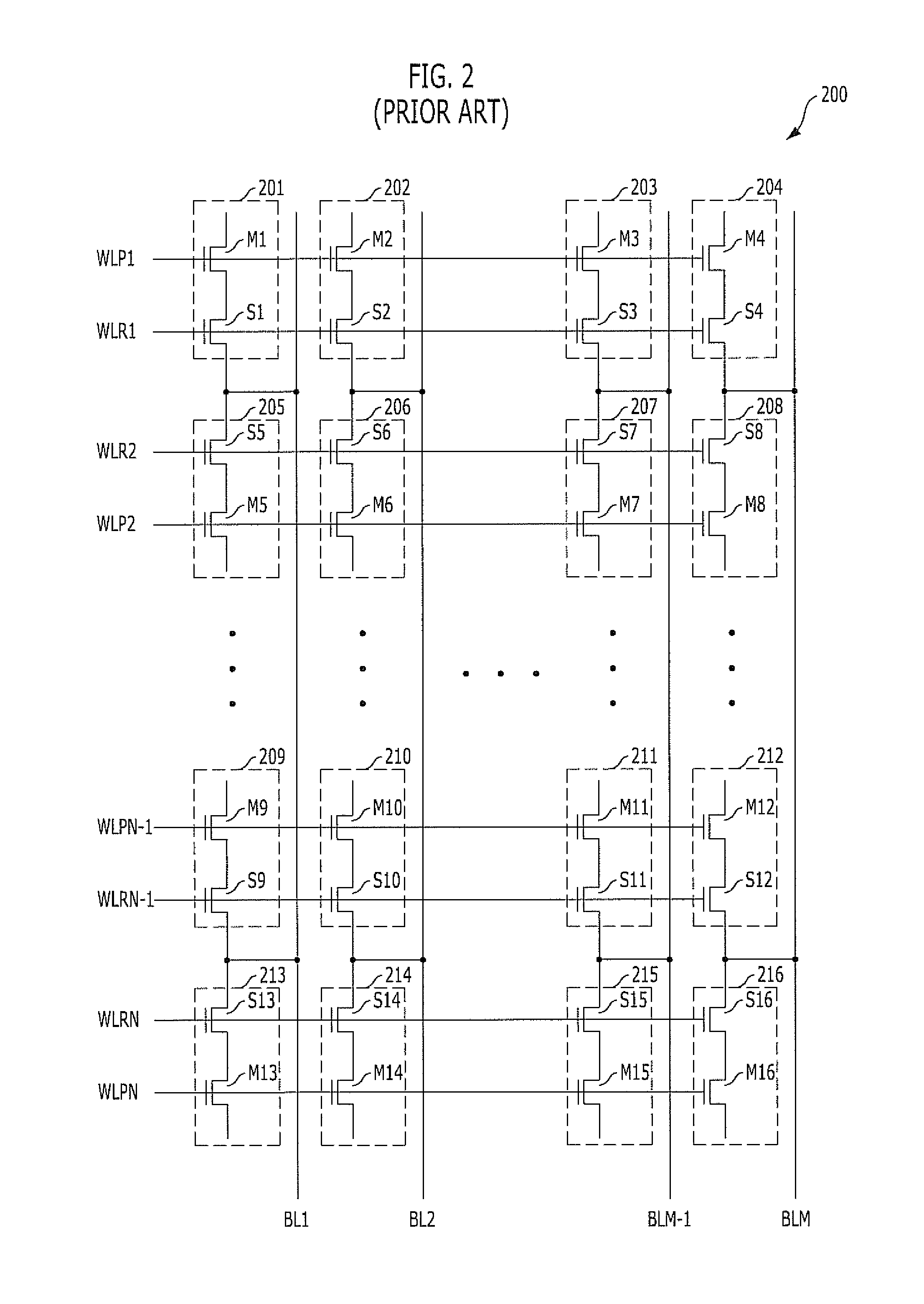

Semiconductor device and method of operating the same

ActiveUS20150023103A1Improve reliabilityImprove programming reliabilityRead-only memoriesDigital storageEngineeringControl circuit

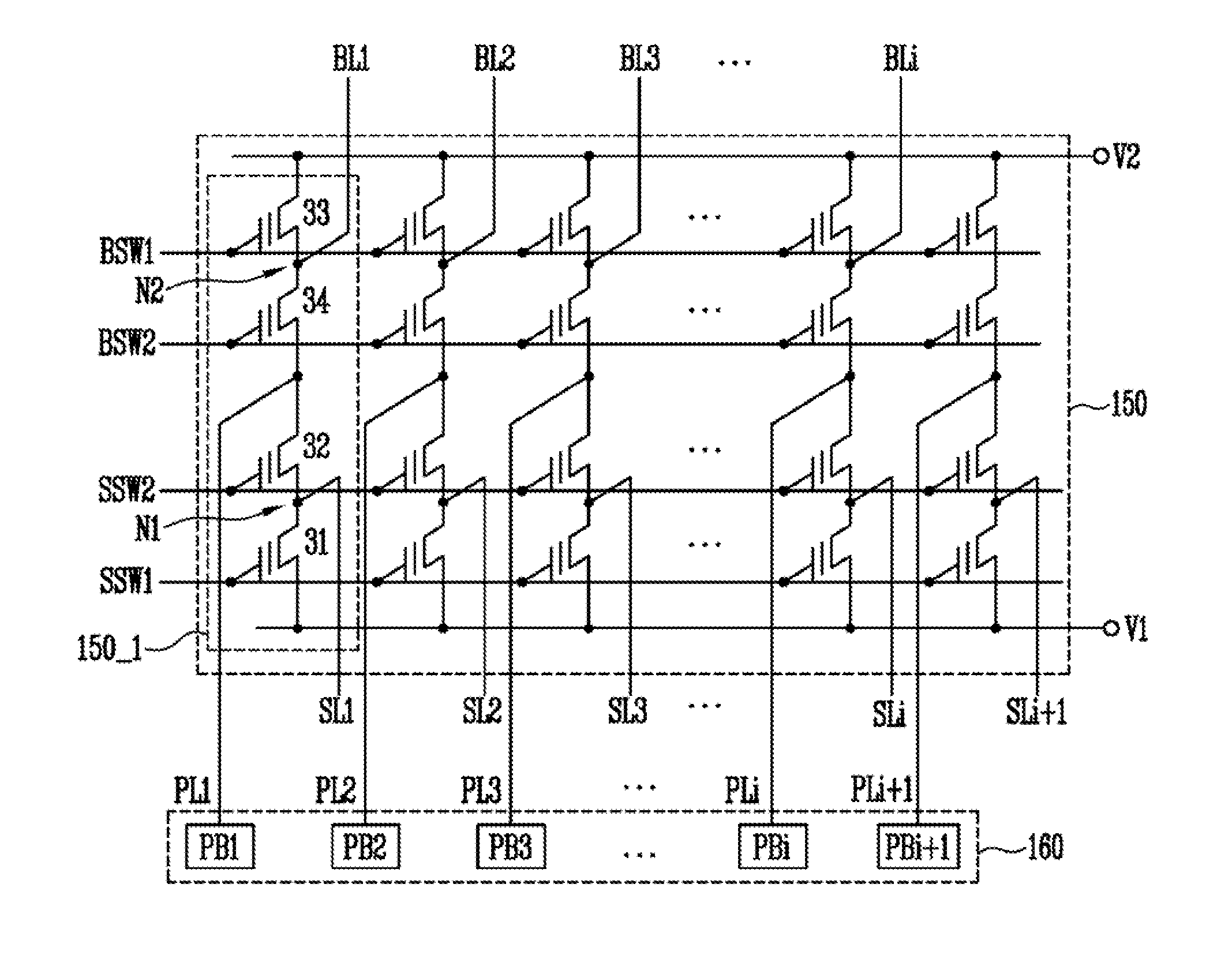

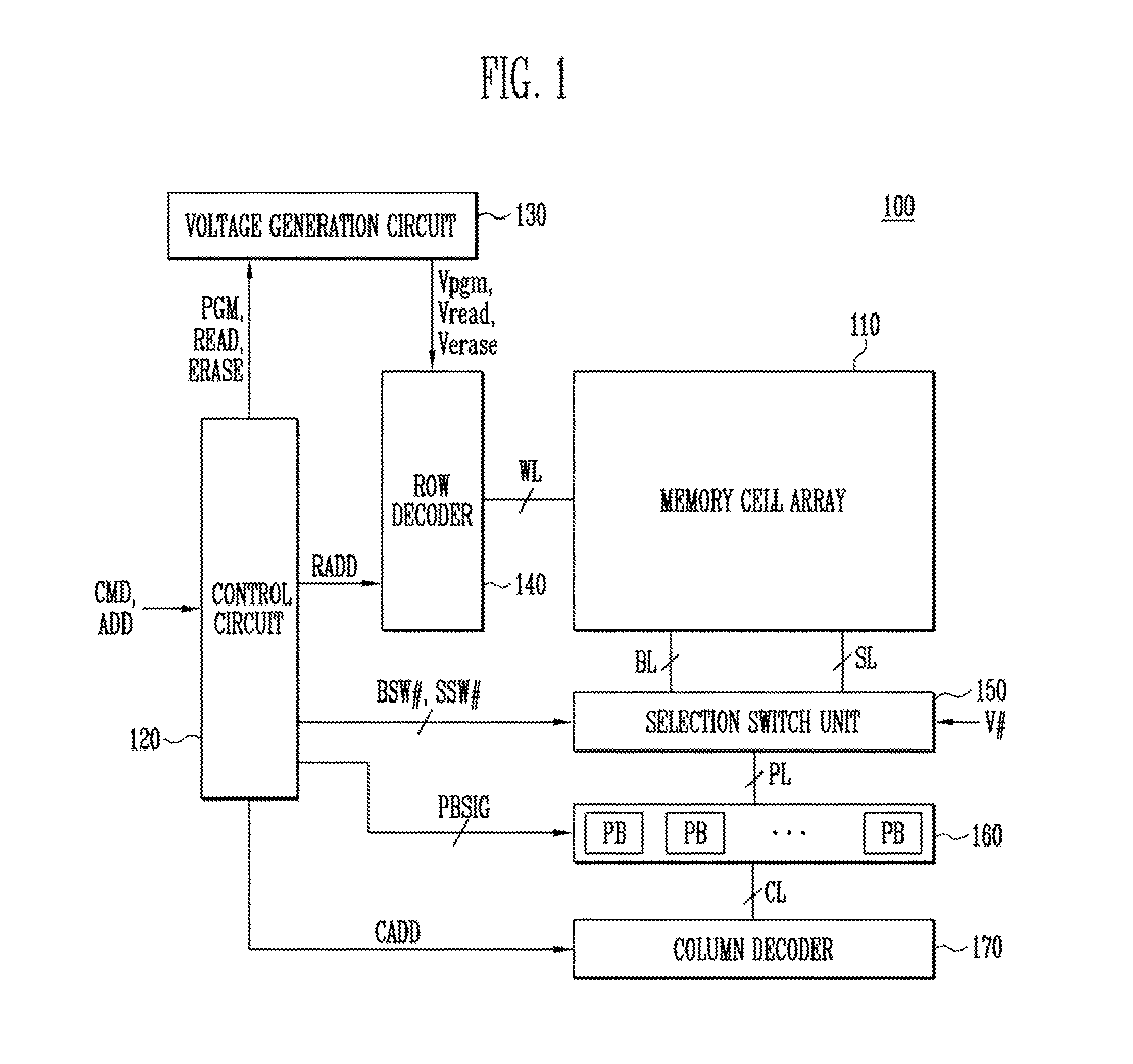

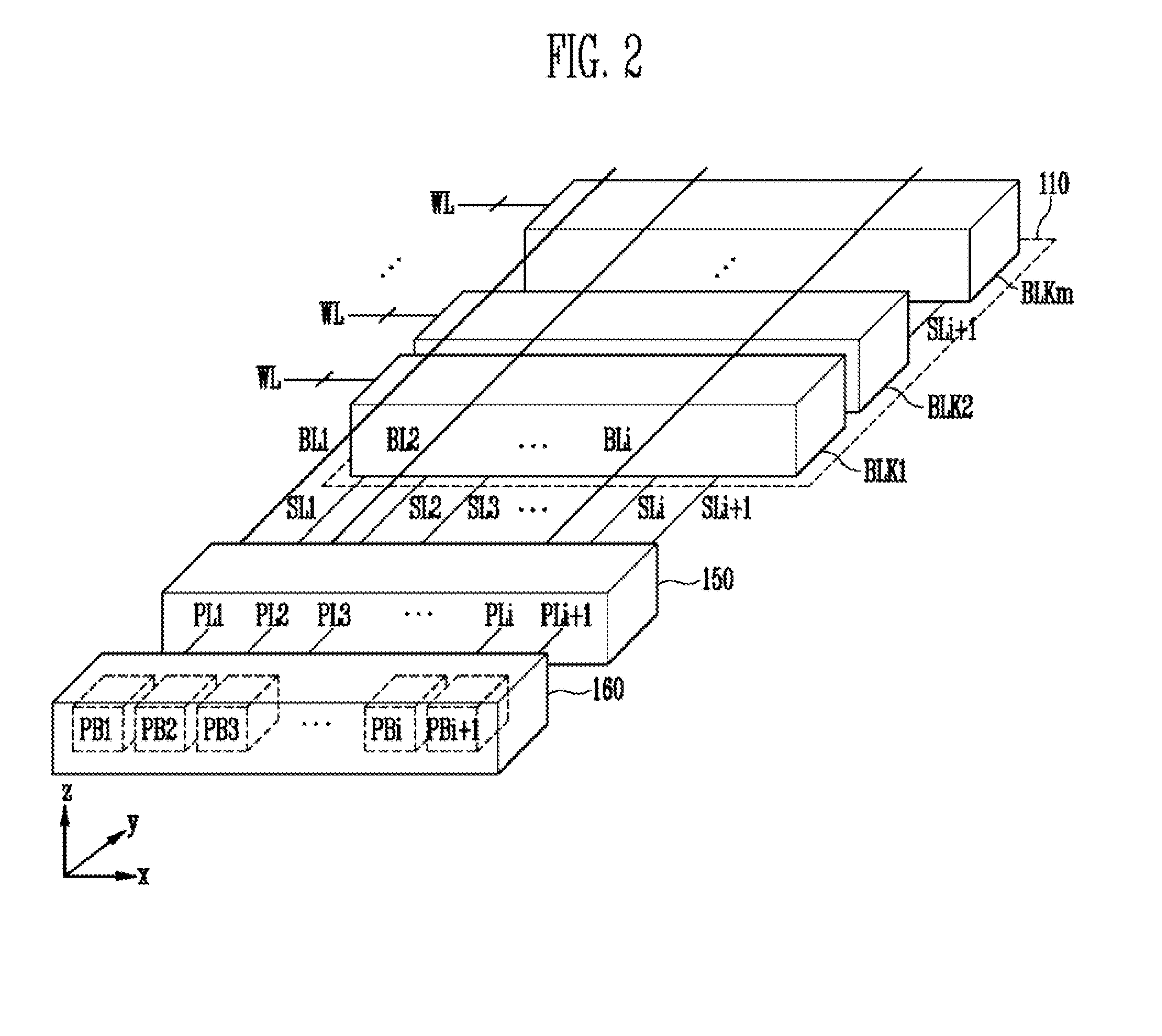

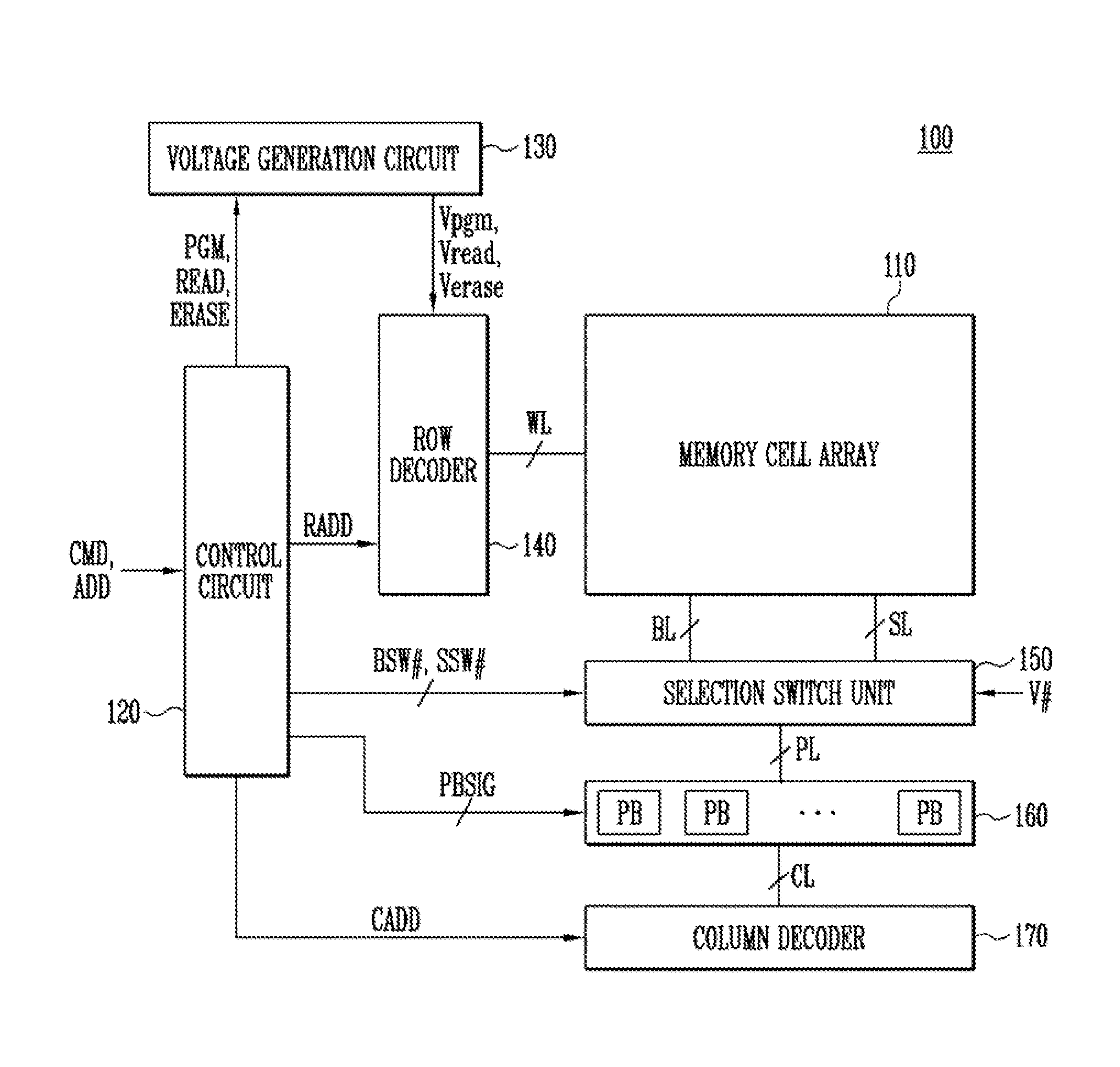

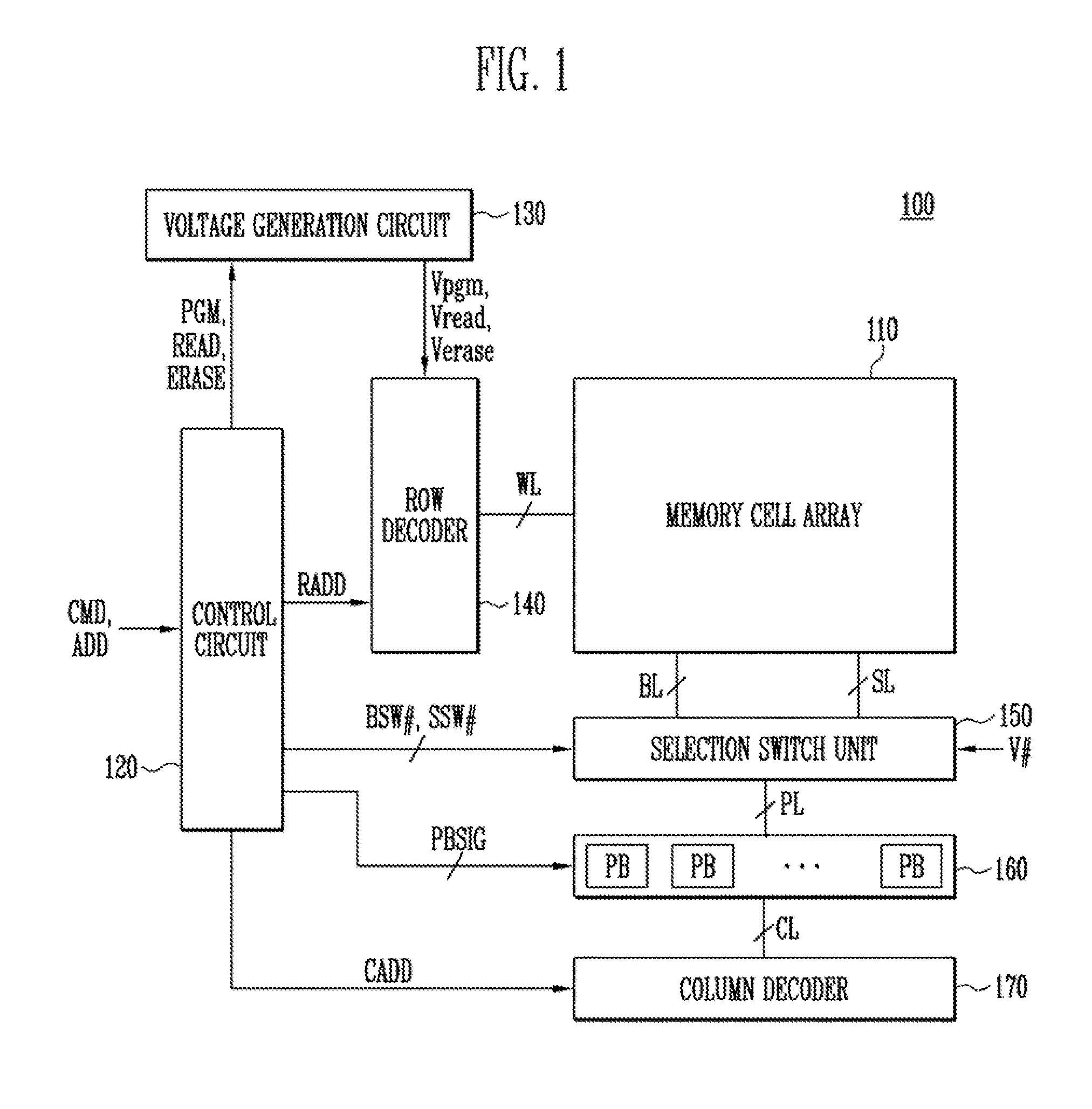

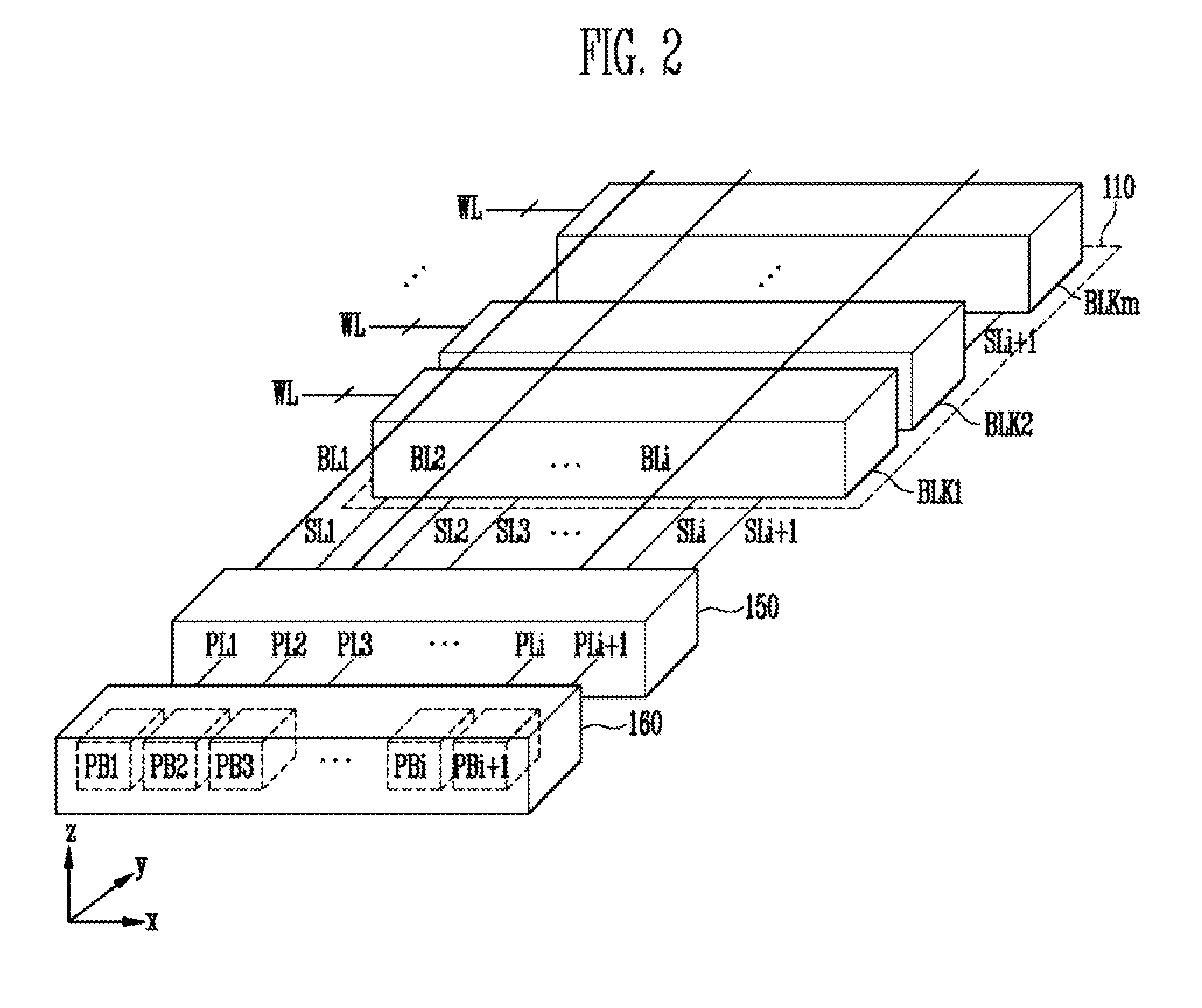

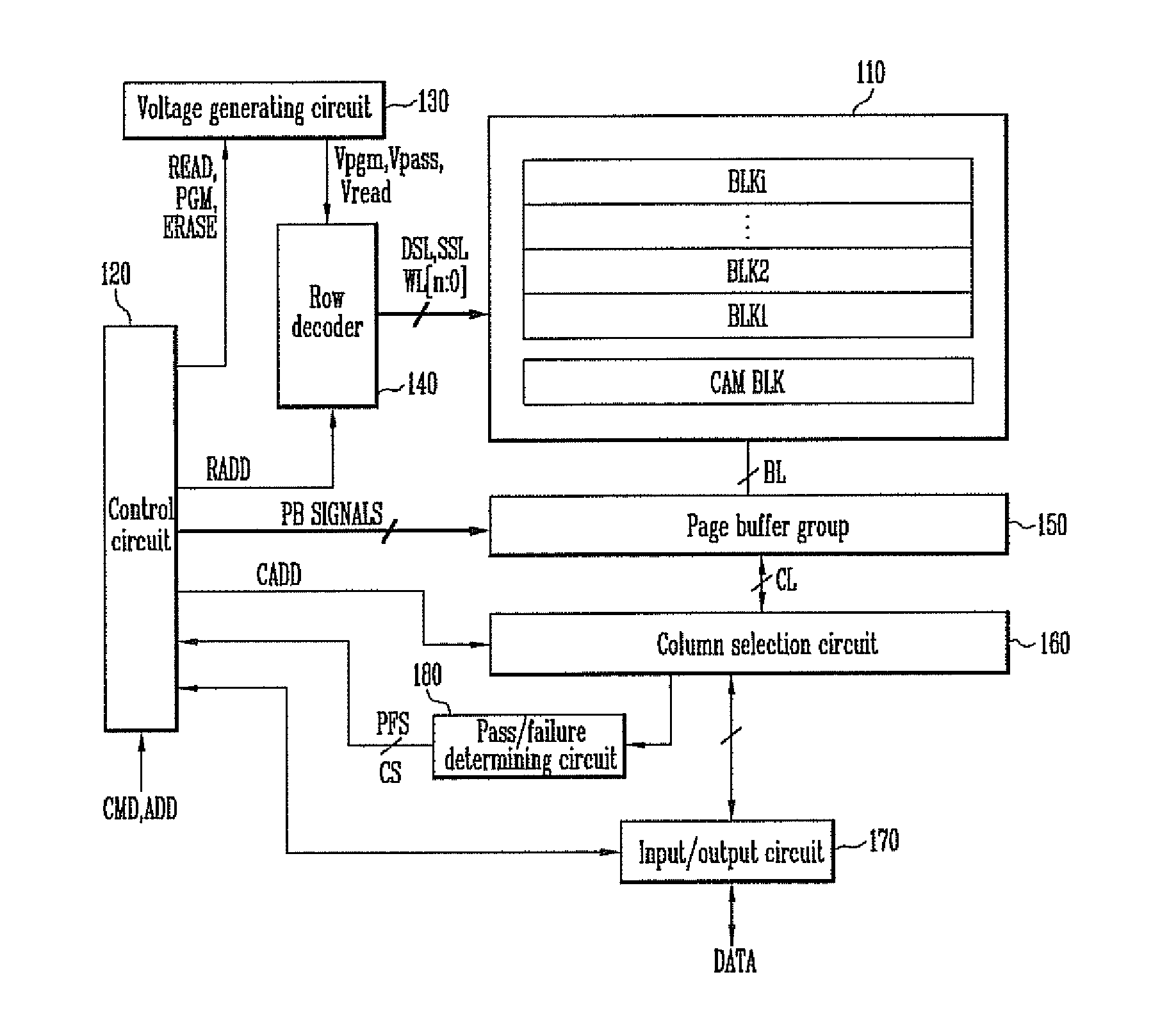

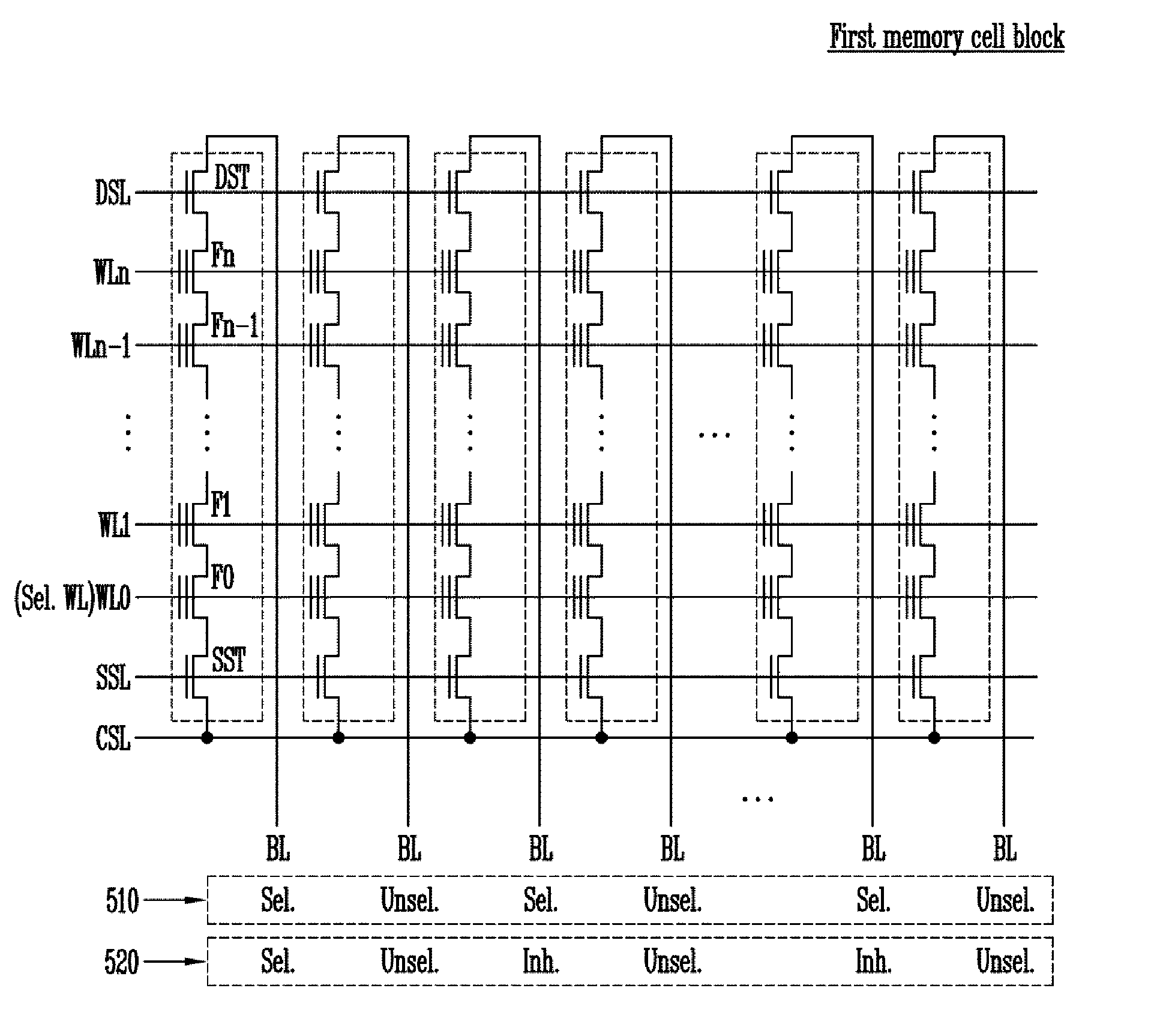

A semiconductor device includes first memory blocks arranged in a longitudinal direction, and including a plurality of strings, wherein the strings are formed along a vertical direction, and the strings adjacent to each other share bit lines or source lines with each other, each string including a drain selection transistor coupled to an odd drain selection line or an even drain selection line, memory cells coupled to word lines, and a source selection transistor coupled to an odd source selection line or an even source selection line, page buffers suitable for storing data, a selection switch unit suitable for transferring the data stored in the page buffers or various voltages supplied from an external source to the bit lines and the source lines; and a control circuit suitable for controlling the page buffers and the selection switch unit.

Owner:SK HYNIX INC

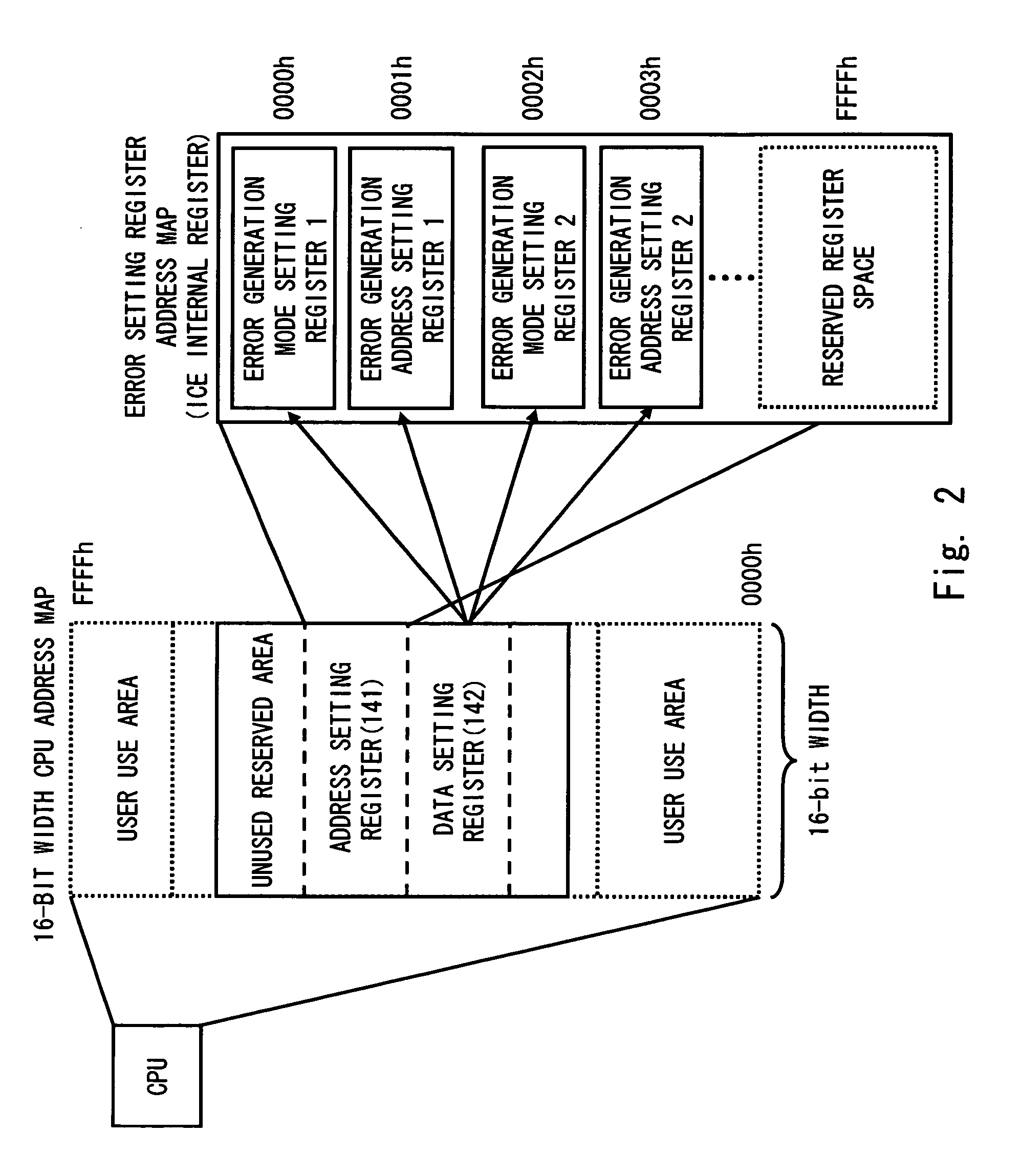

Evaluation system and method

InactiveUS20080016415A1Improve programming reliabilityError detection/correctionStatic storageMicrocomputerEvaluation system

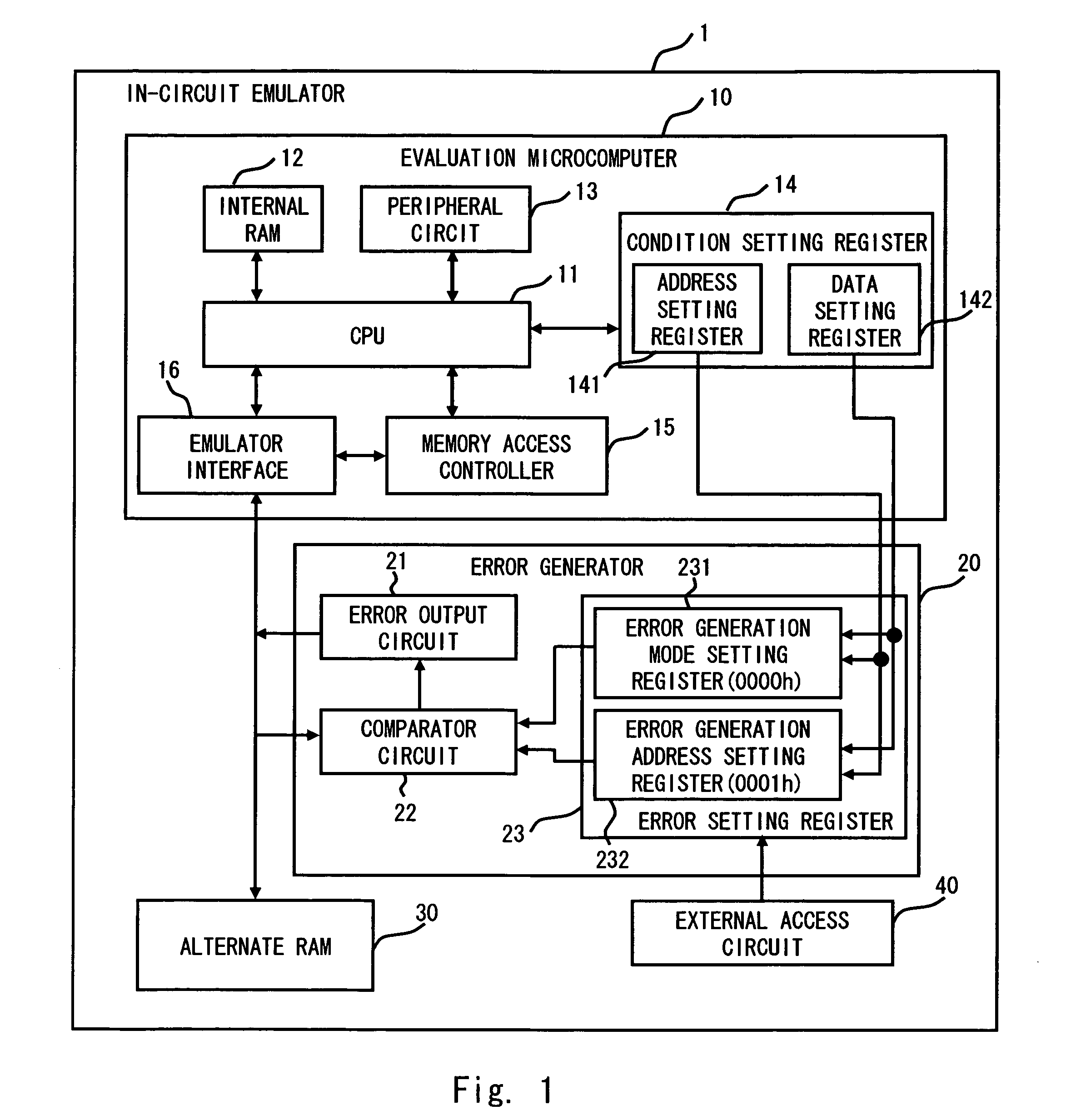

An evaluation system includes a storage unit, a microcomputer for outputting a read address to the storage unit and executing reading, and an error generator for generating an error signal based on a mode signal and the read address that are transmitted between the storage unit and the microcomputer and outputting the error signal. The microcomputer determines read data received from the storage unit as an error regardless of the read data when the error signal indicates an error in the read data.

Owner:NEC ELECTRONICS CORP

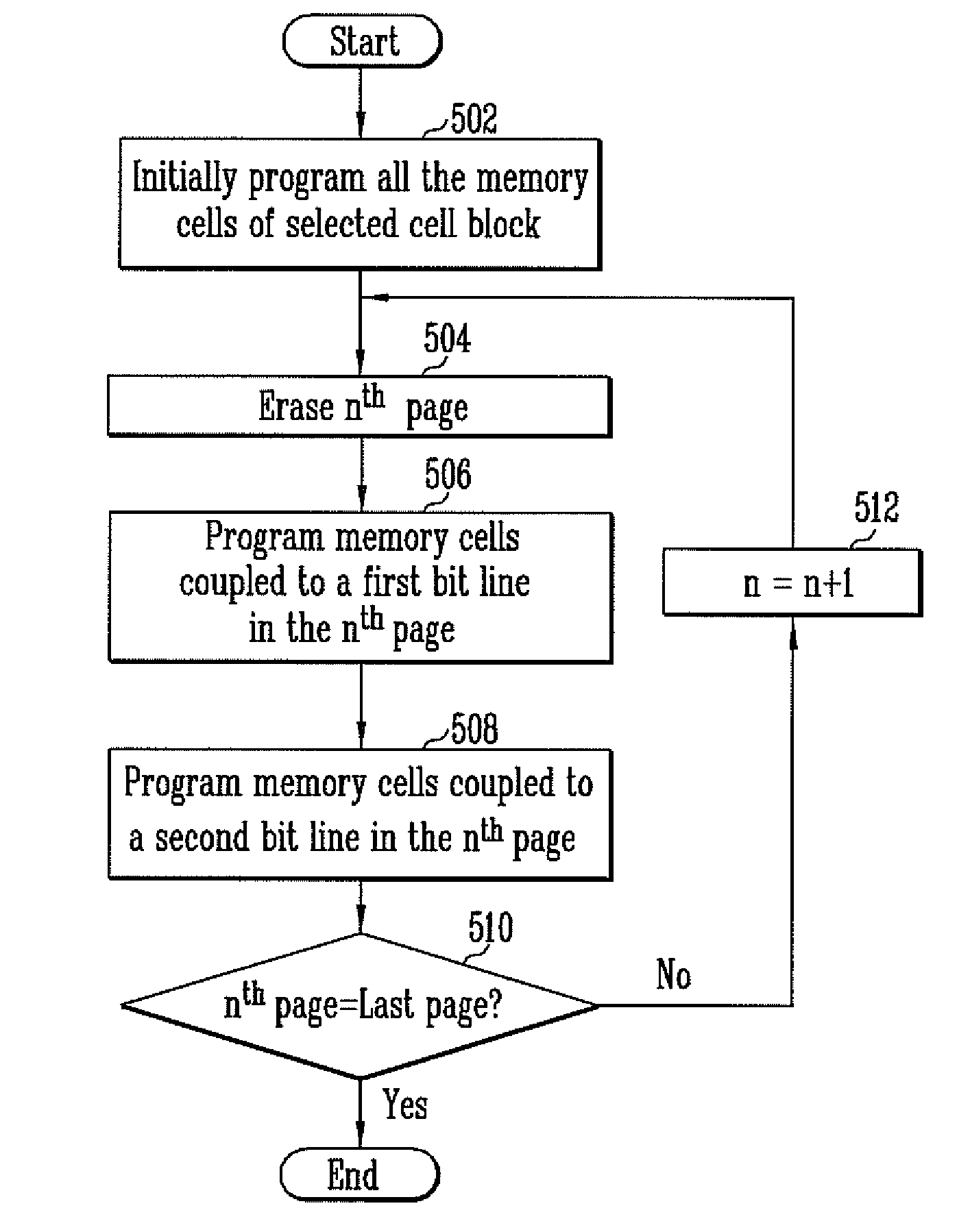

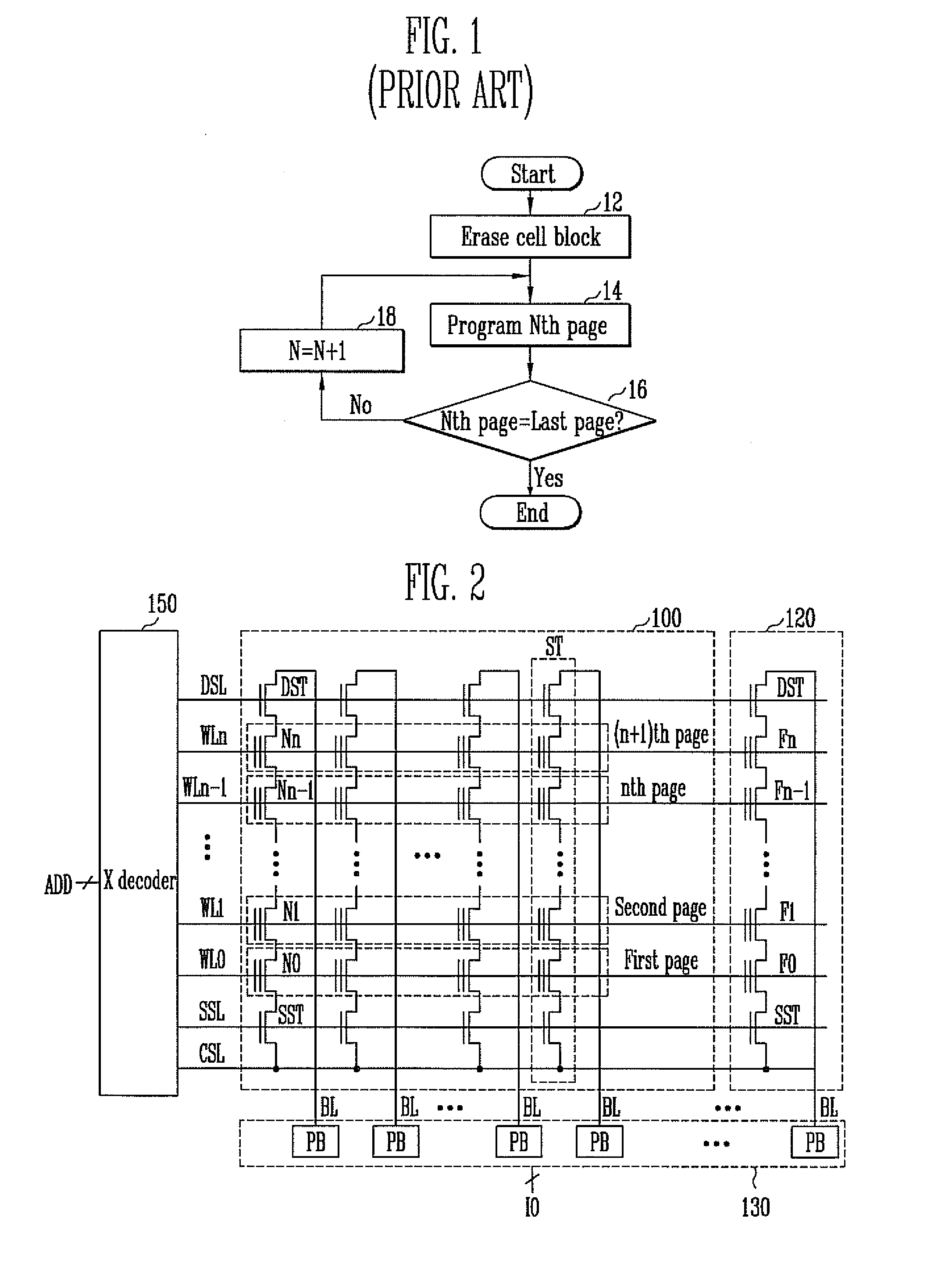

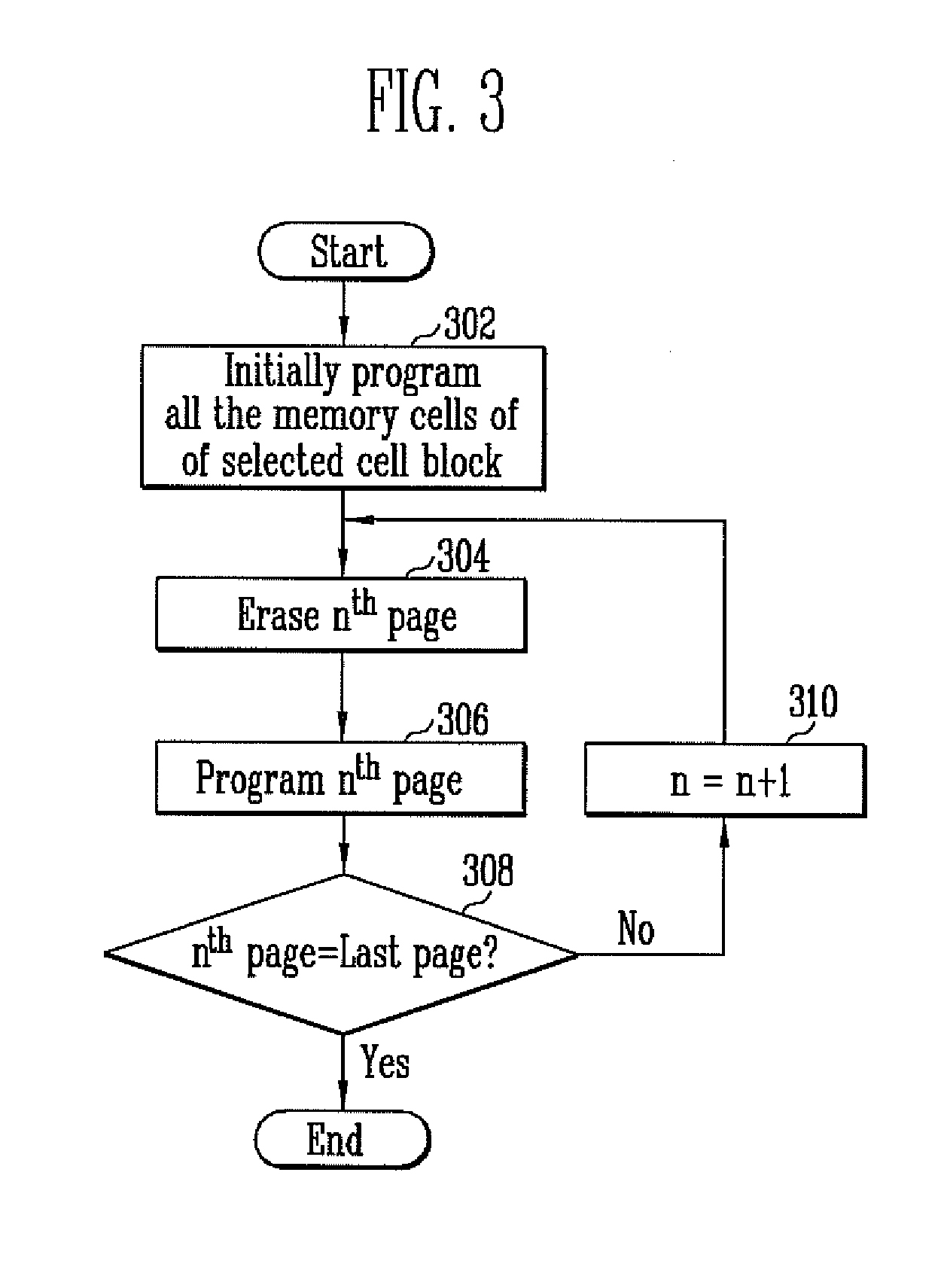

Method of programming nonvolatile memory device

InactiveUS20110292734A1Reduce interferenceInterferenceRead-only memoriesDigital storageVoltageSemiconductor

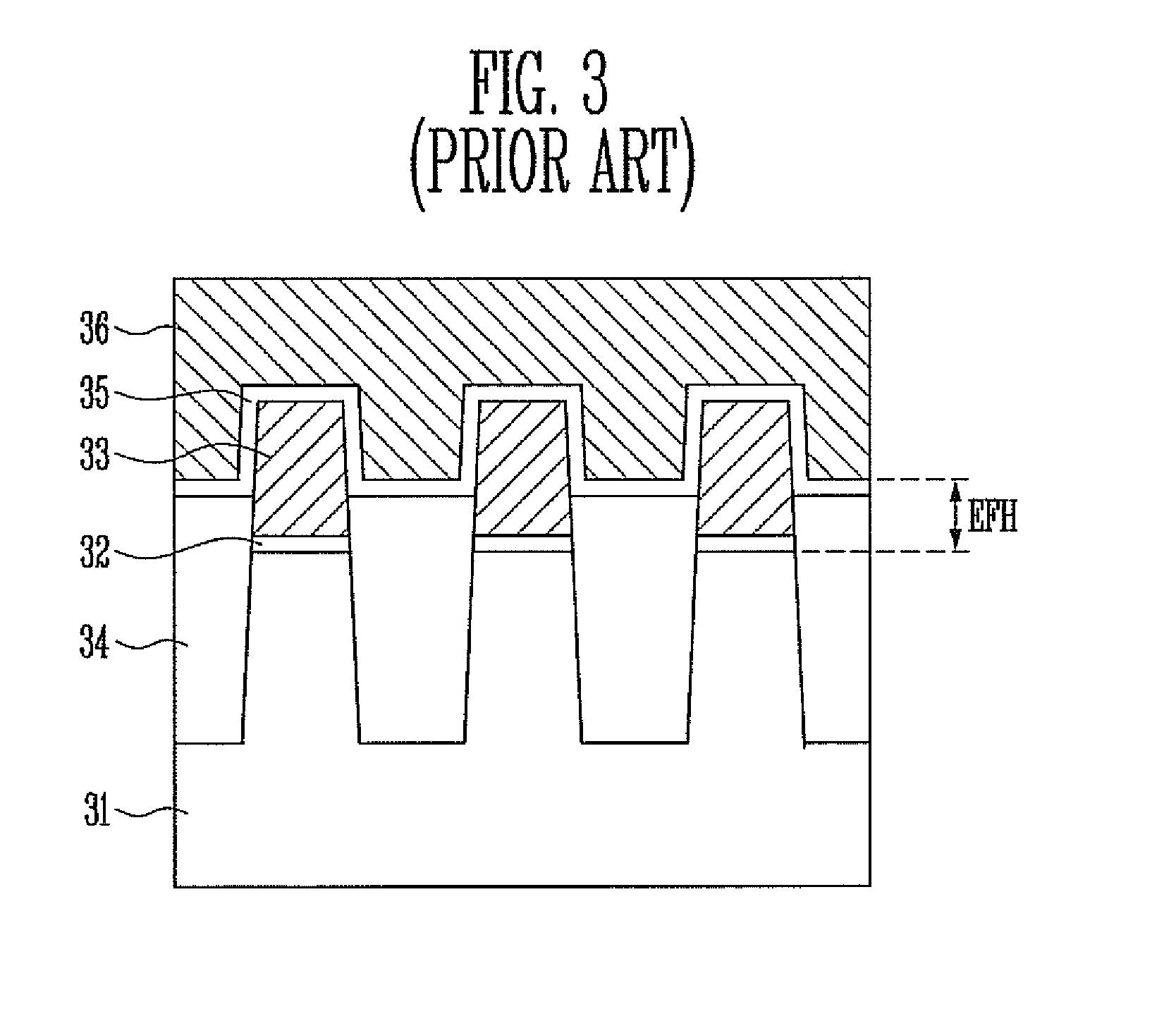

A method of programming a semiconductor device includes performing an initial program operation on all memory cells included in a selected memory cell block to set threshold voltages of all the memory cells to a voltage equal to or greater than 0 Volts, erasing memory cells of a selected page in the selected memory cell block, and programming the memory cells of the selected page.

Owner:SK HYNIX INC

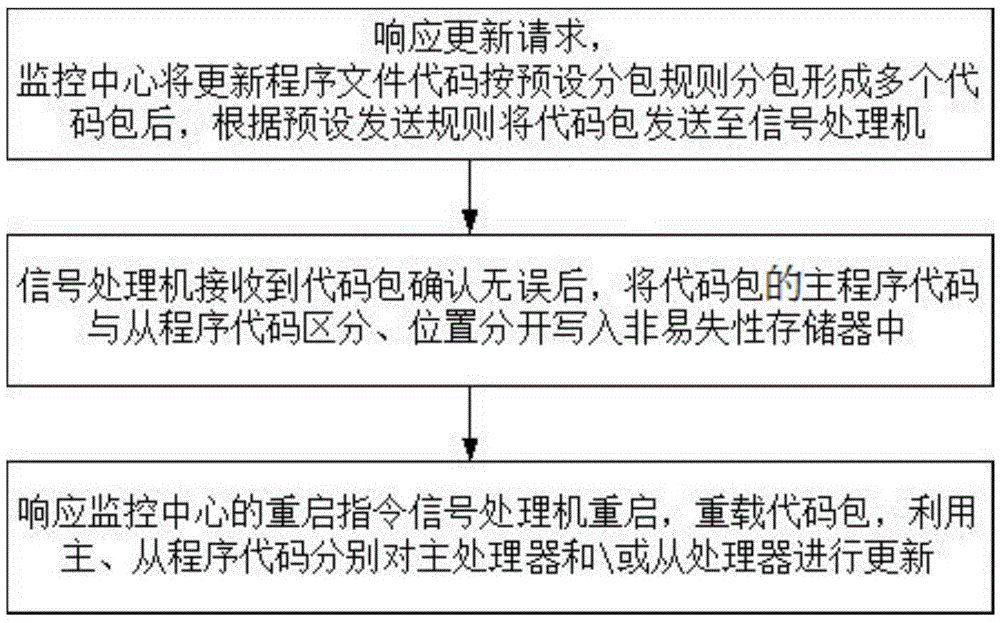

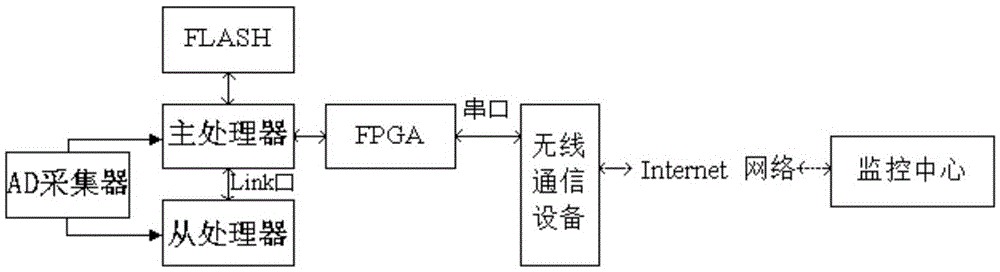

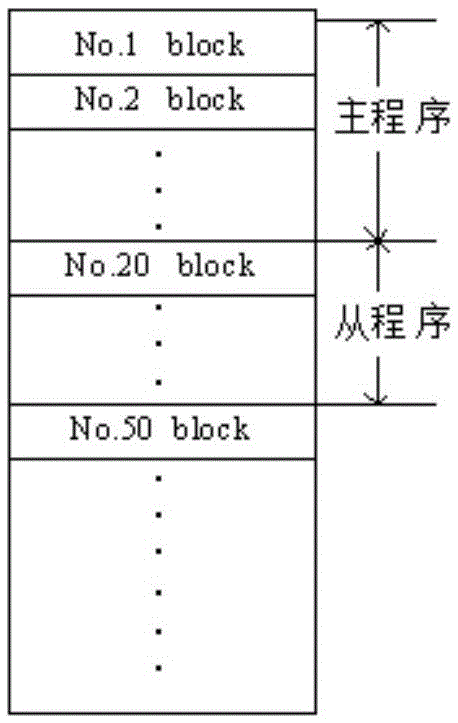

Long-distance updating method and system for embedded system software

InactiveCN105573794AThe update method is stableReliable updateProgram loading/initiatingSoftware deploymentMaster processorProgram code

The invention relates to a long-distance updating method and system for embedded system software. According to the method, updating program file codes are subpackaged to form multiple code packages through a monitor center according to a preset subpackage rule, an updating request is responded, the code packages are sent to a signal processing machine through a wireless network, and the signal processing machine receives the code packages and distinguishes master program codes from slave program codes of the code packages of the updating program file and writes the master program codes and slave program codes in a nonvolatile memory in separate positions after detecting that the code packages are correct; the signal processing machine responds to a restart instruction signal from the monitor center to be restarted after an updating program is successfully programmed, a processor reloads code packages of the updating program file, and corresponding programs of a master processor and / or a slave processor are updated respectively through the master program codes and the slave program codes. The updating method is more stable, the programming reliability is high, and updating is more reliable.

Owner:THE THIRD RES INST OF CHINA ELECTRONICS TECH GRP CORP

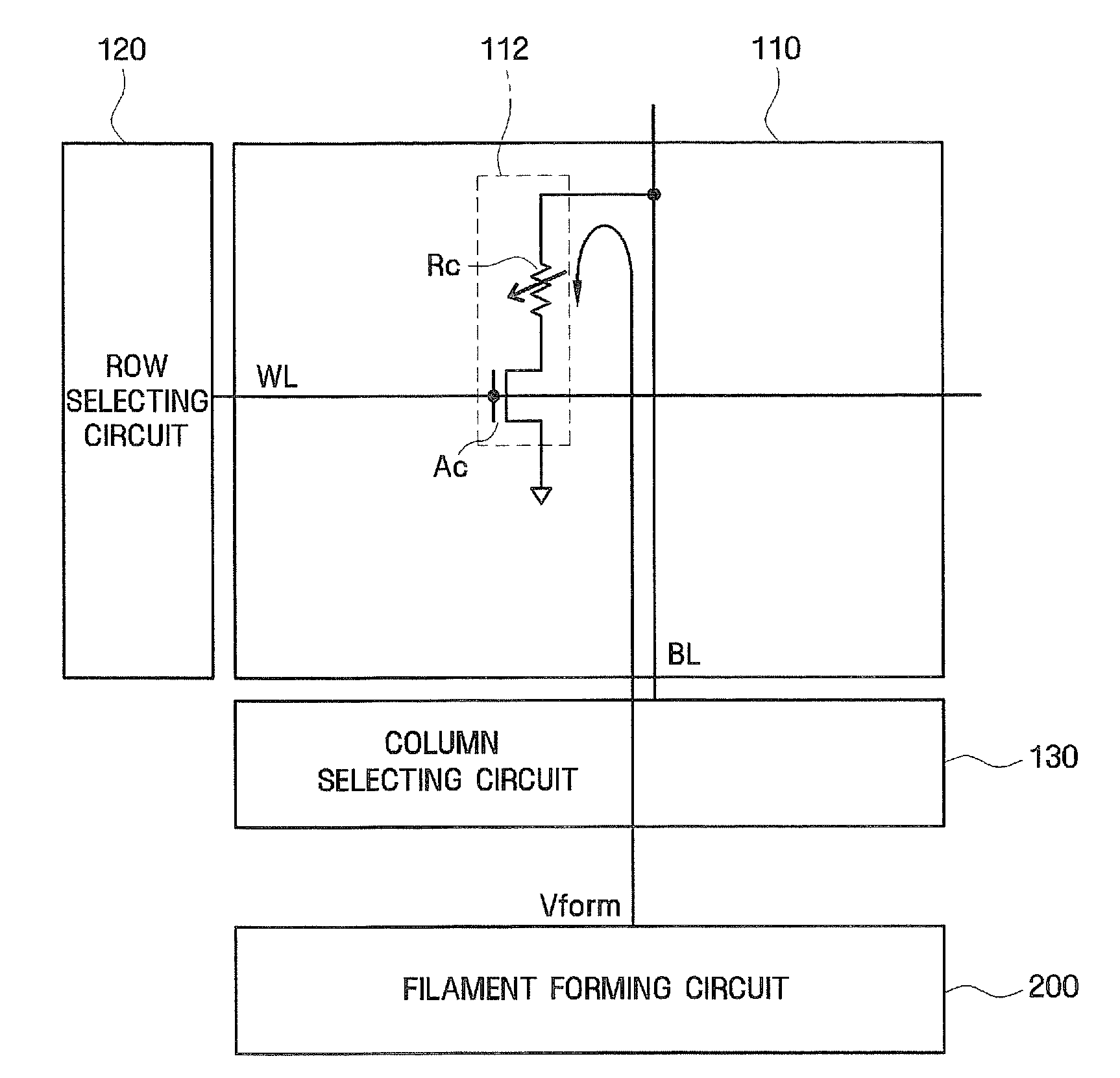

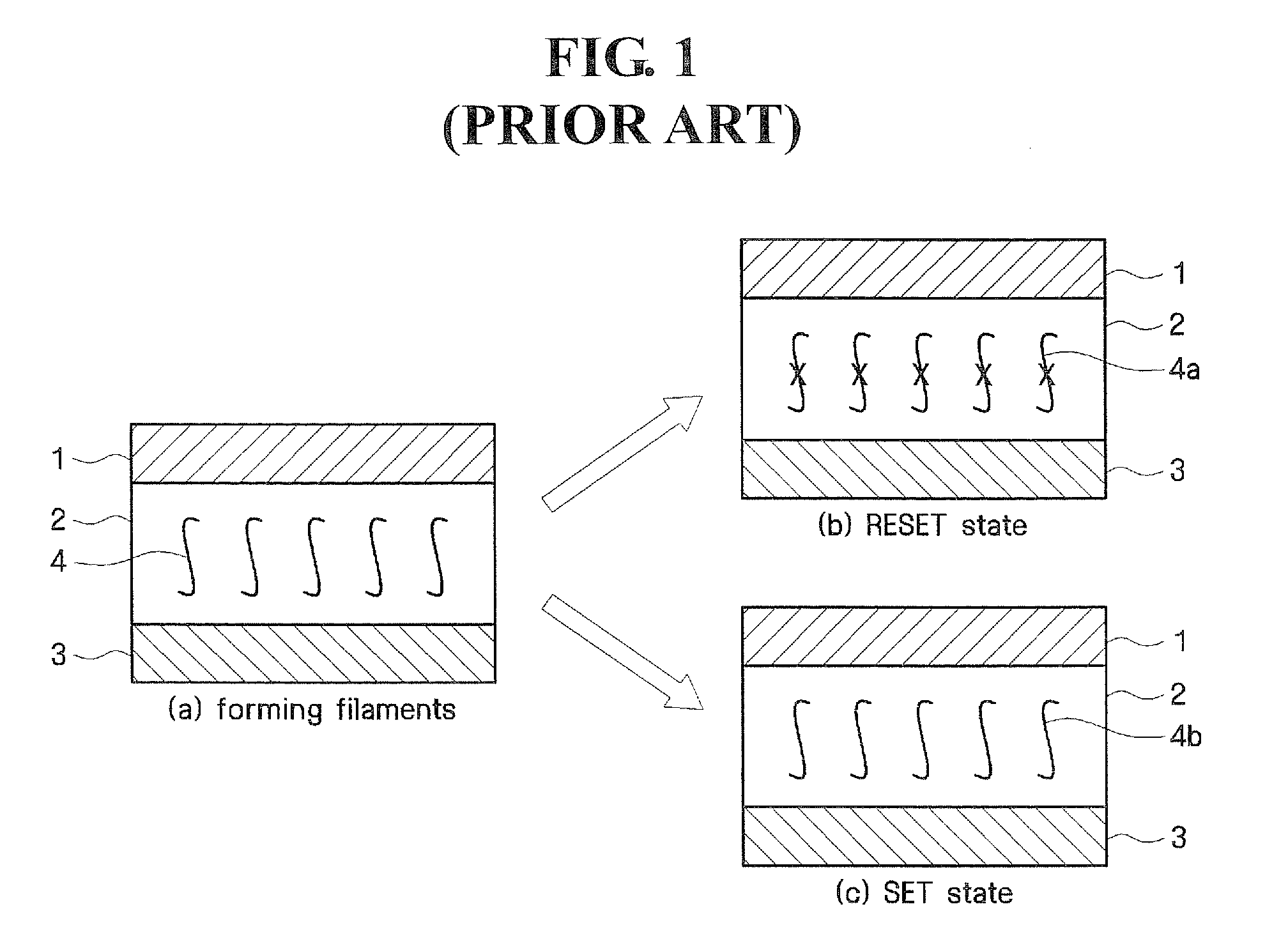

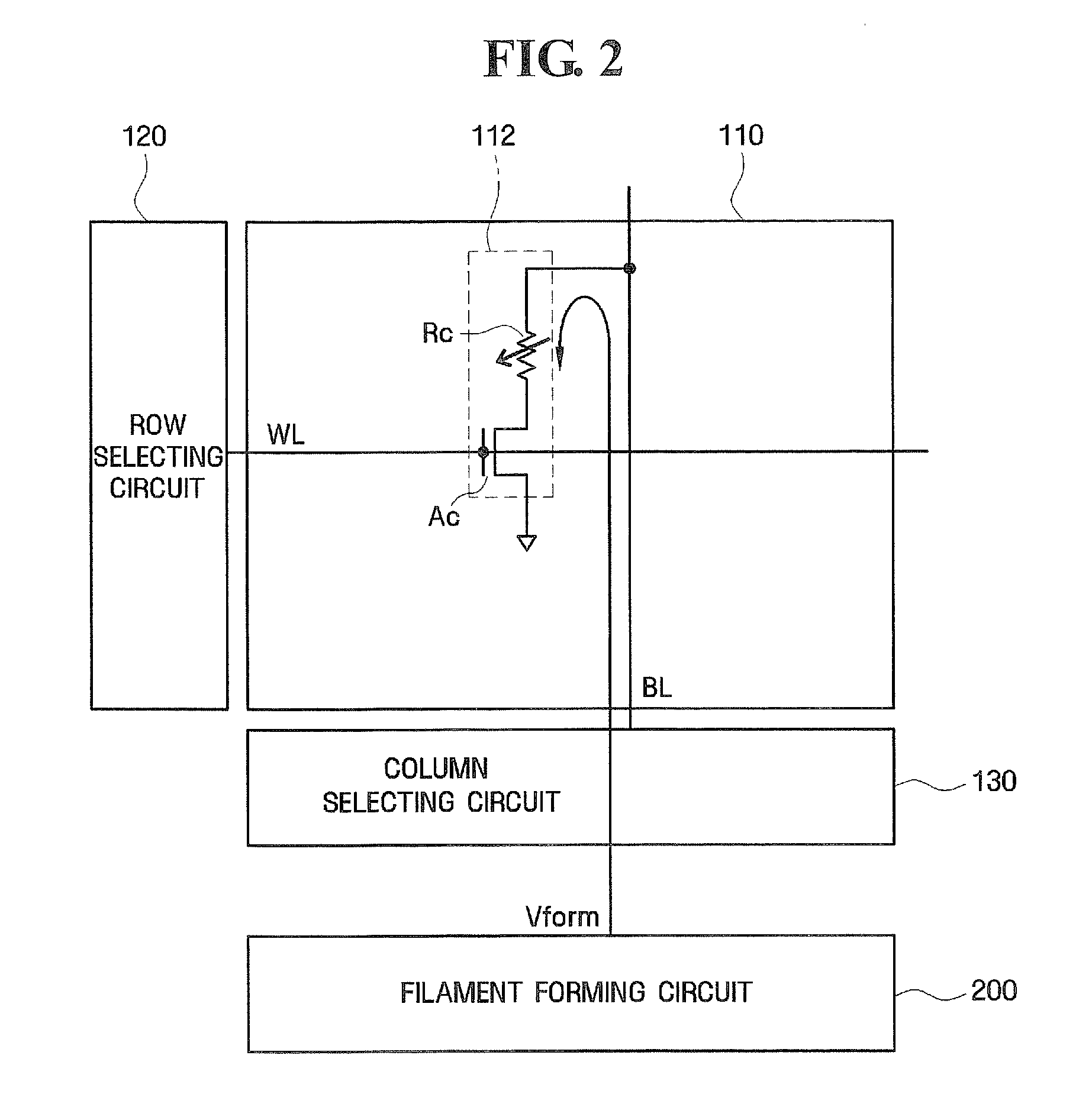

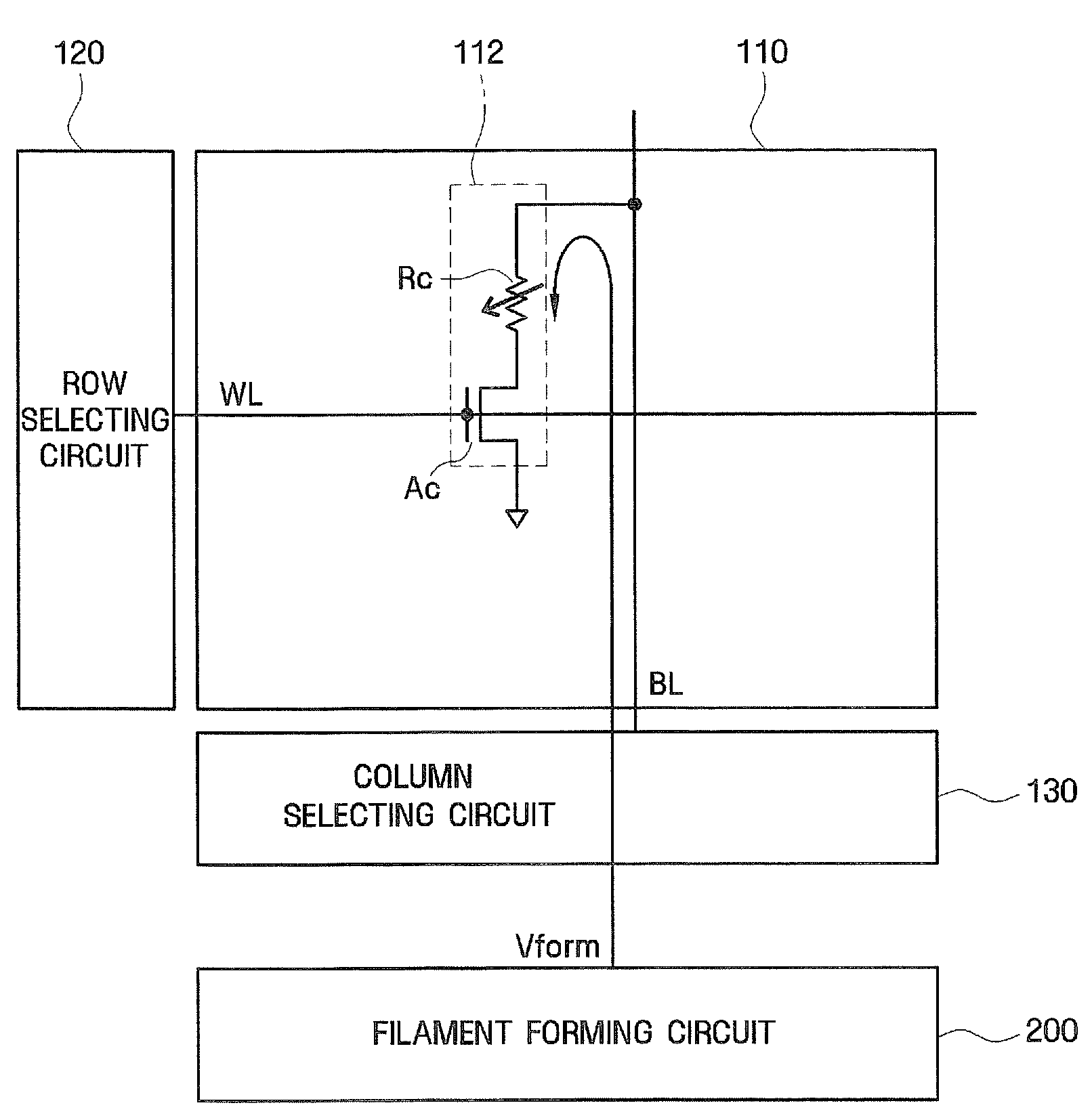

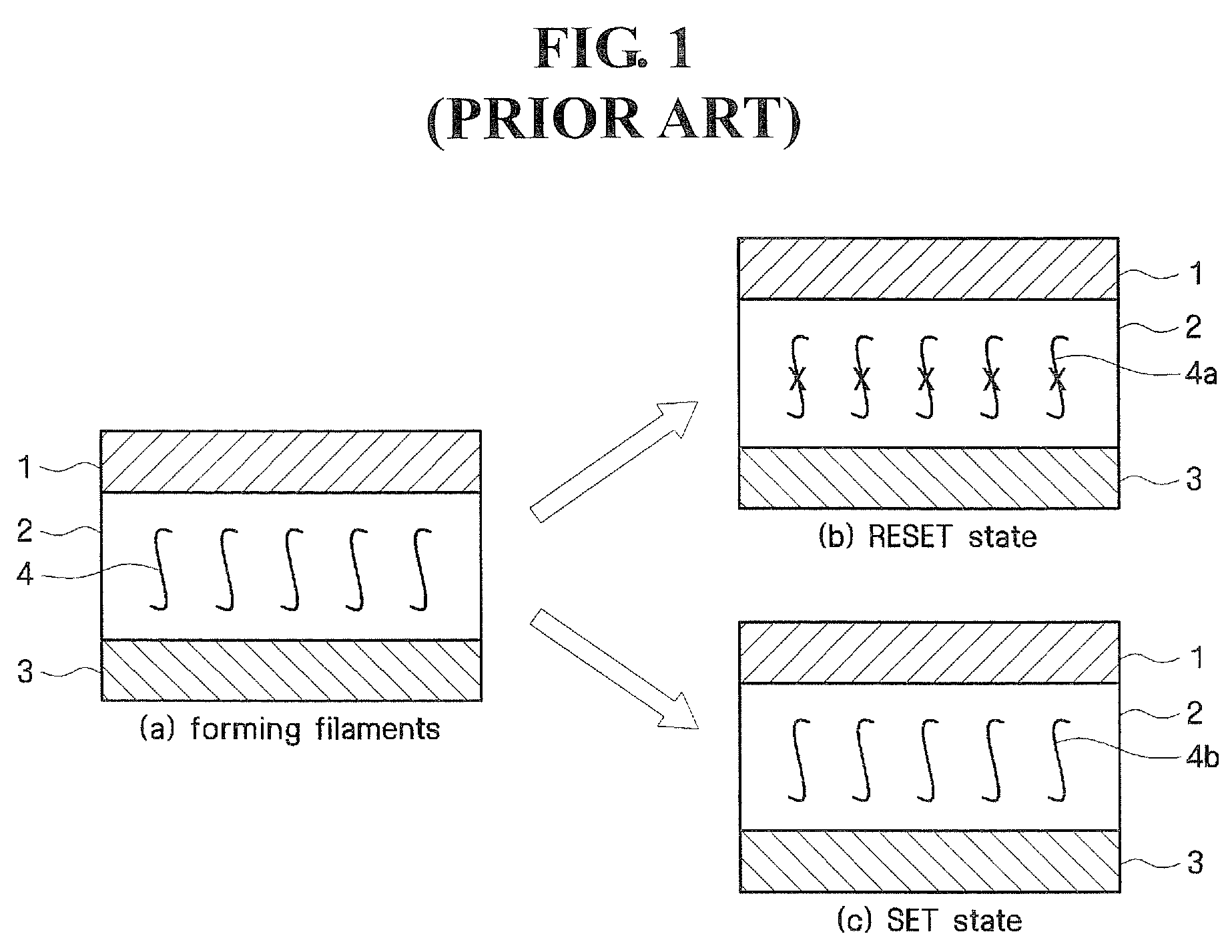

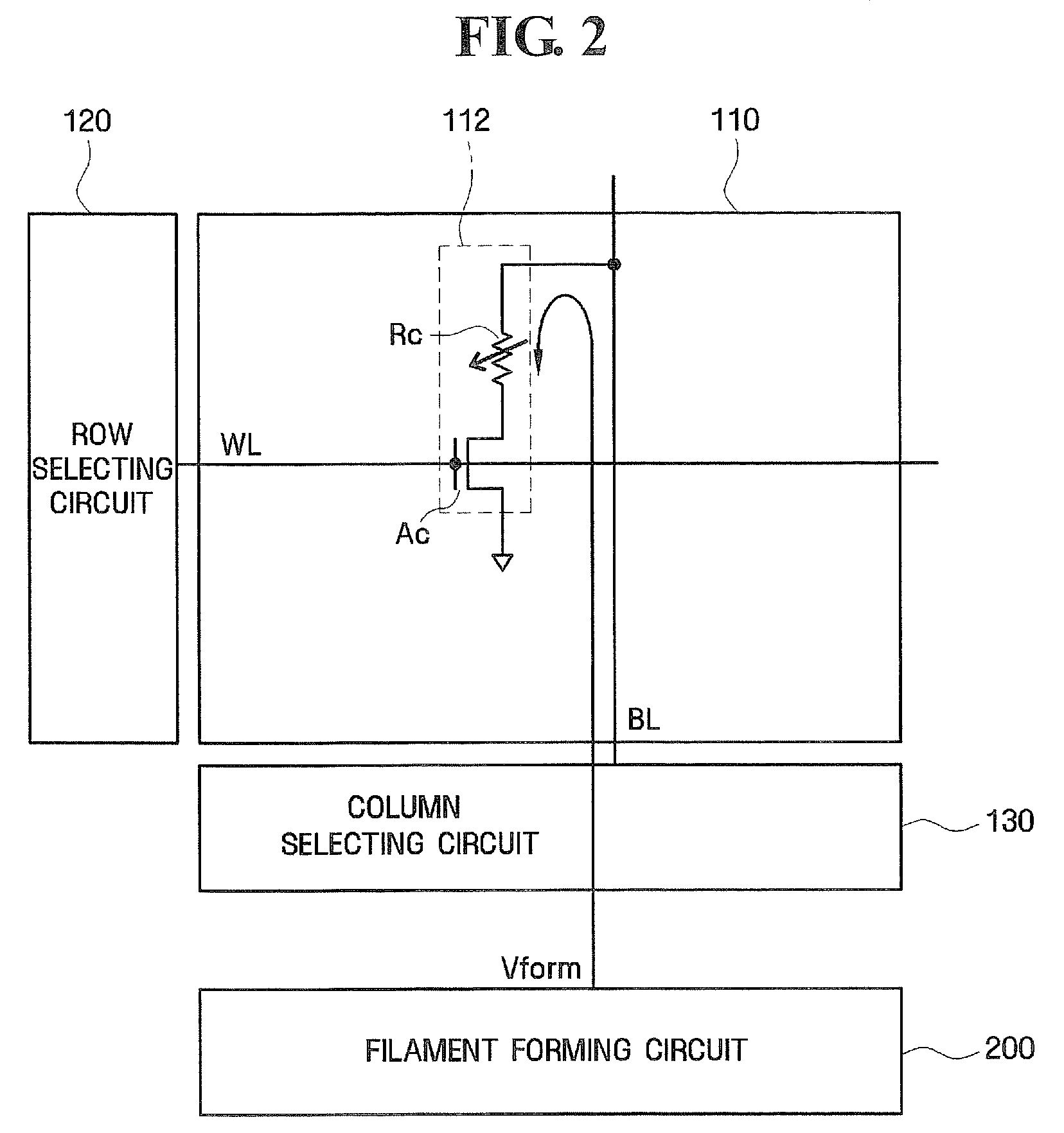

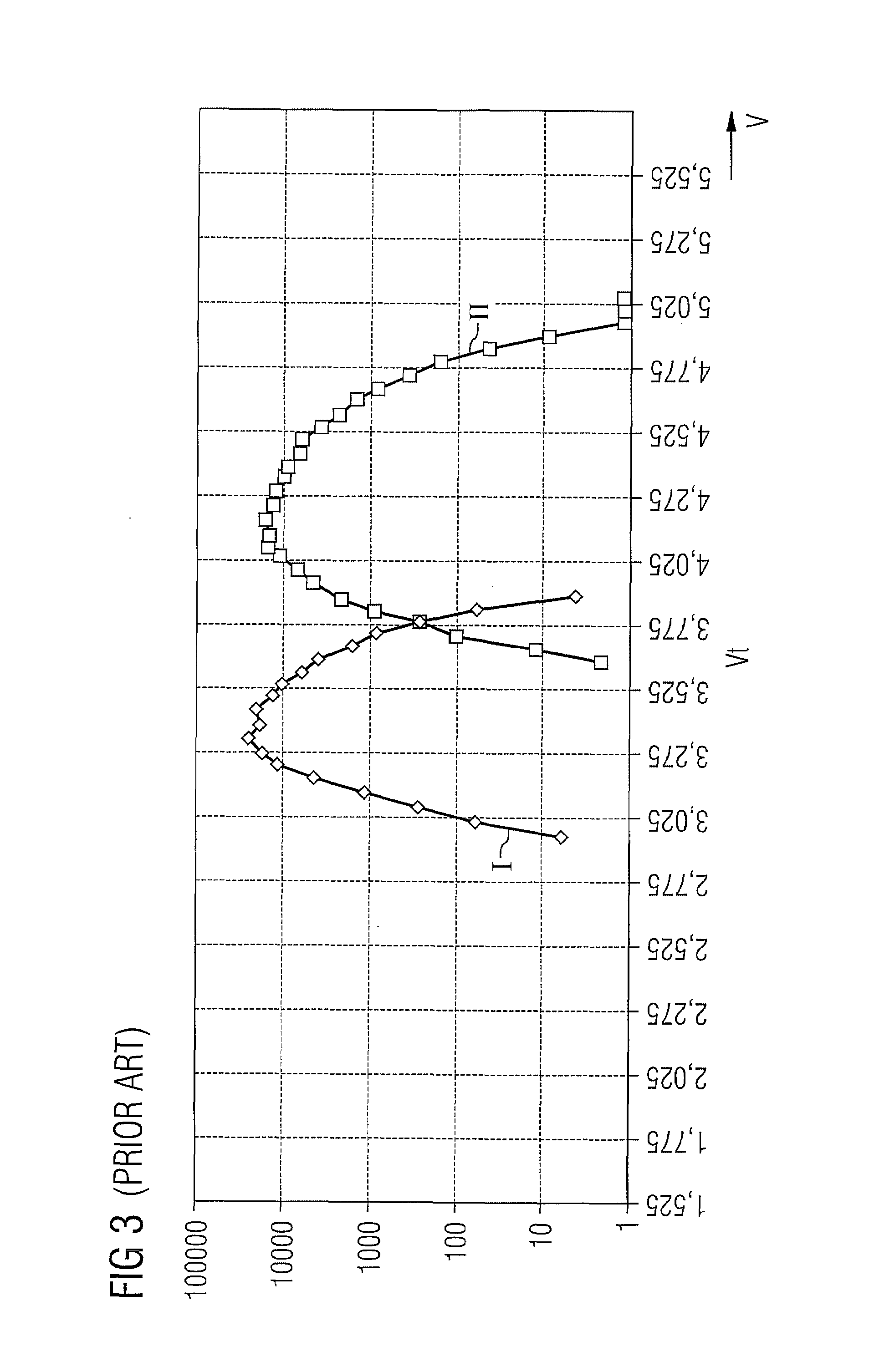

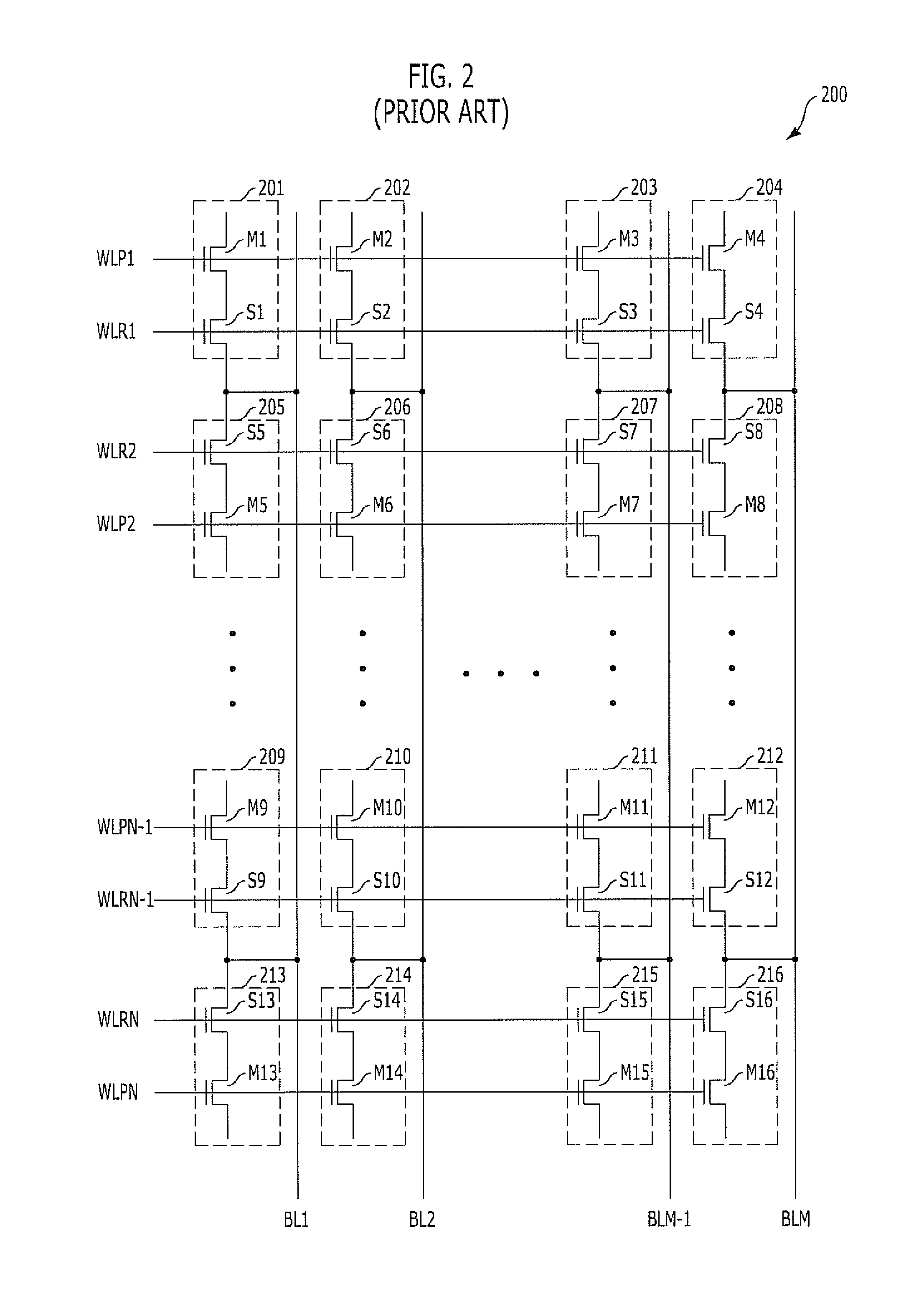

Nonvolatile memory devices having multi-filament variable resistivity memory cells therein

There is provided a resistive memory device, the device including: a plurality of word lines and a plurality of bit lines arranged such that the word lines intersect the bit lines; a plurality of resistive memory cells each having a variable resistive material coupled between the corresponding word line and the corresponding bit line and an access element; selecting circuits selecting one of the plurality of resistive memory cells; and a filament-forming circuit supplying a filament-forming voltage to the selected resistive memory cell through the bit line coupled to the selected resistive memory cell while increasing the filament-forming voltage from a predetermined voltage level until filaments having a predetermined thickness are formed in the variable resistive material of the selected resistive memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

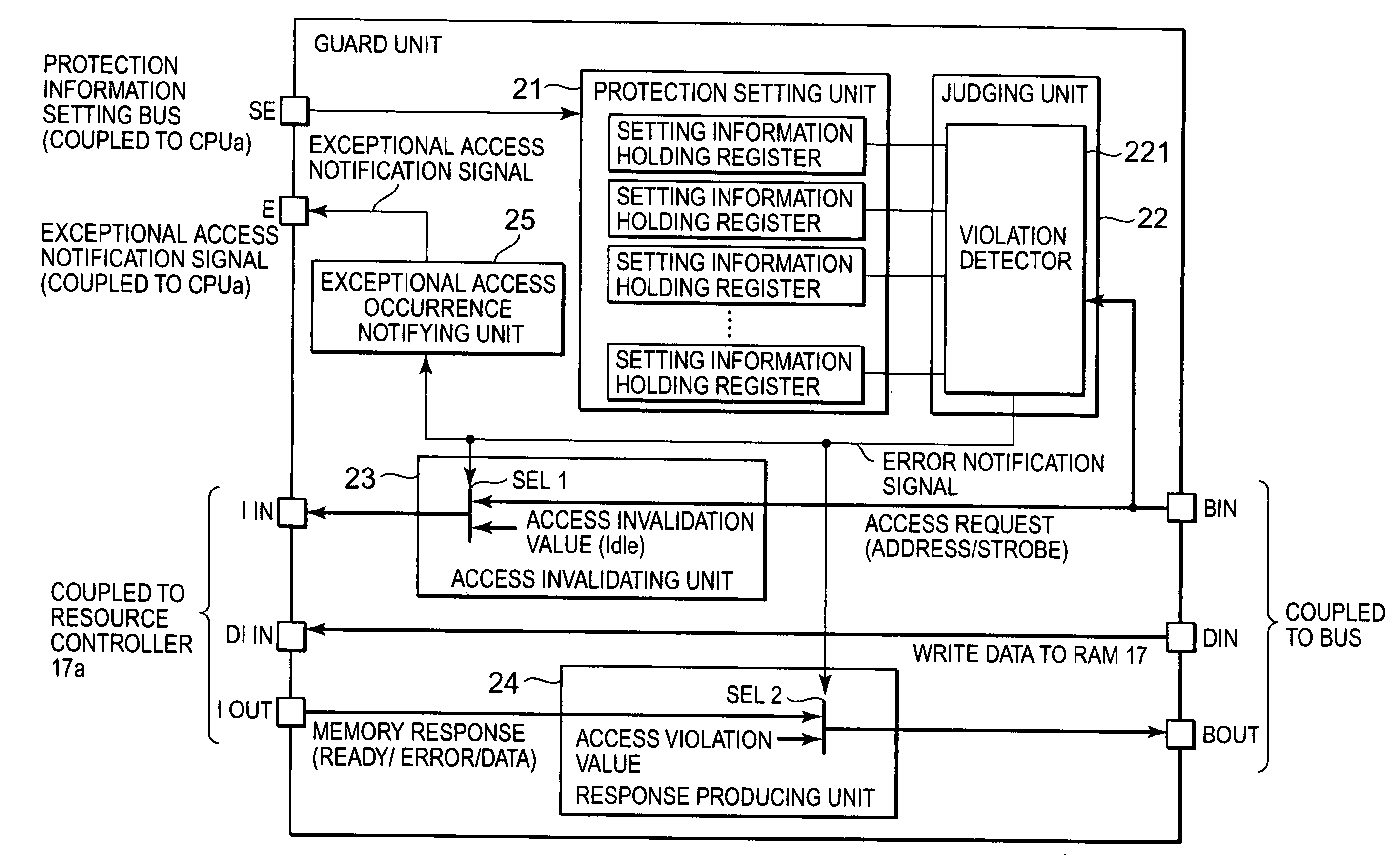

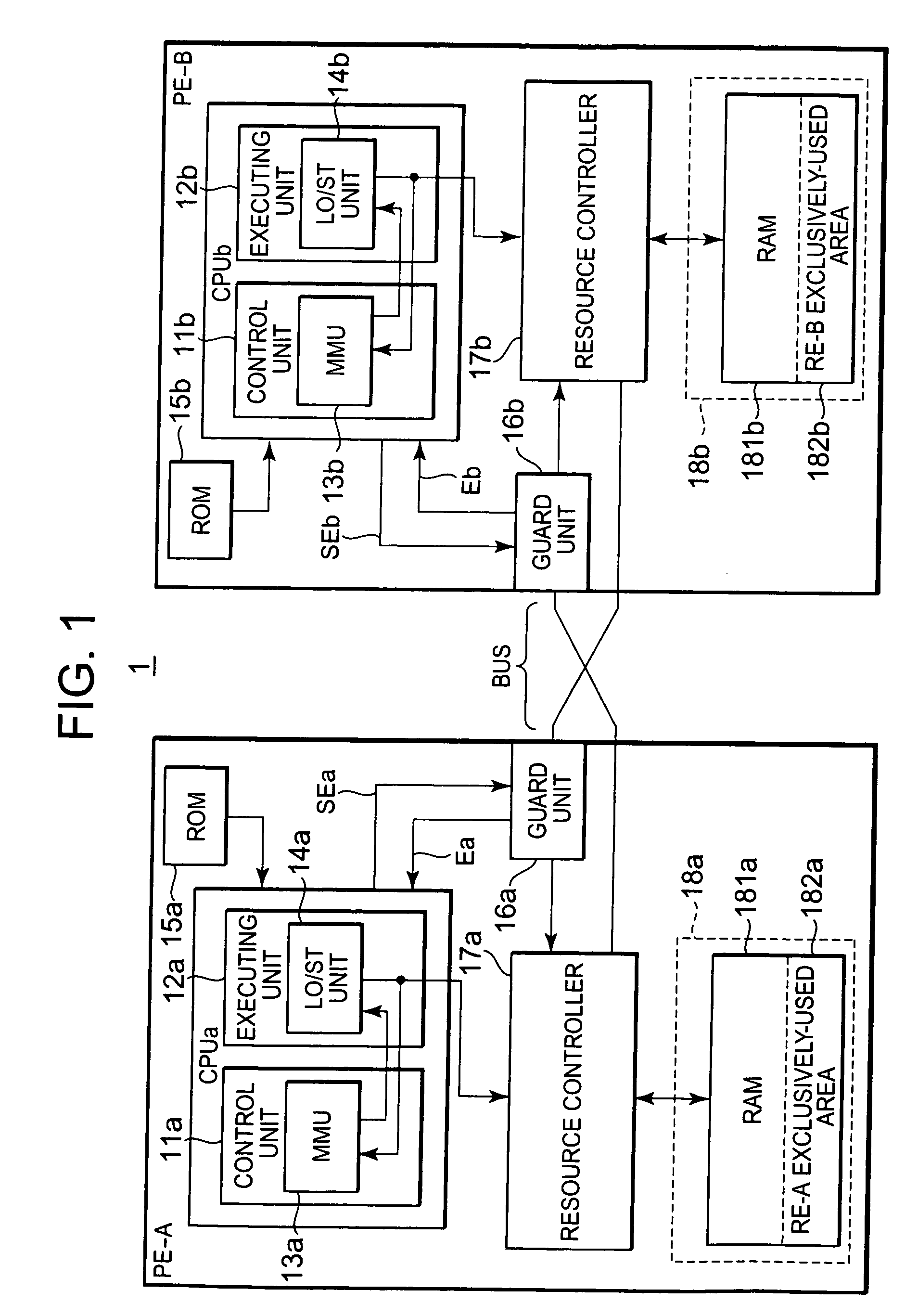

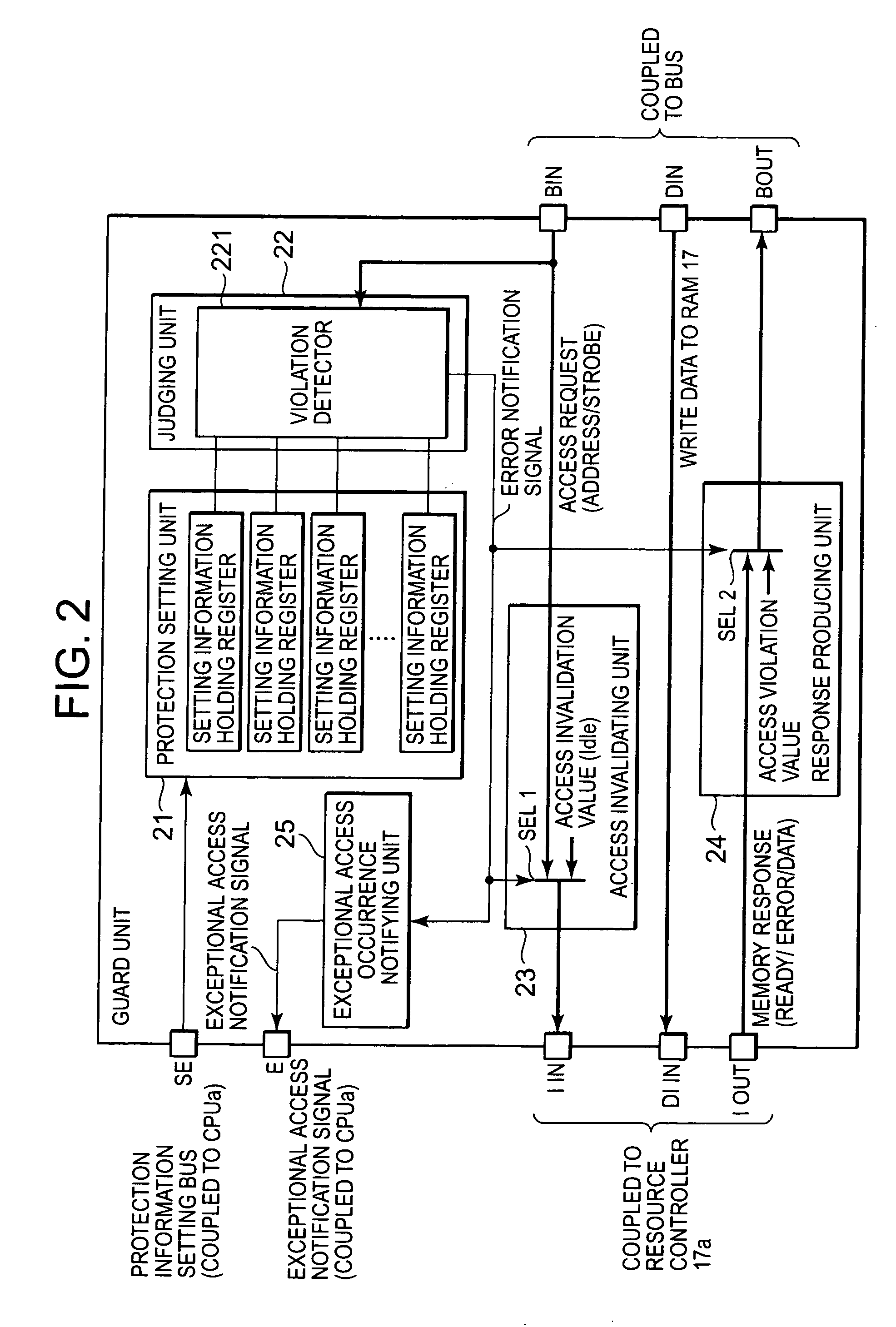

Multiprocessor system and access protection method conducted in multiprocessor system

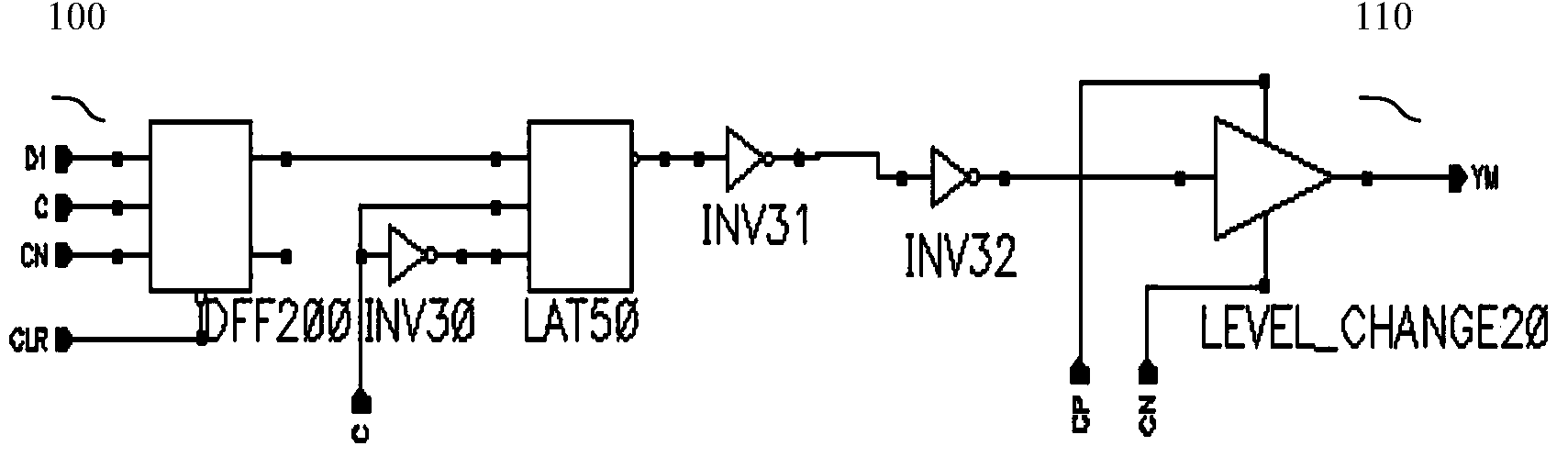

ActiveUS20080244608A1Improve programming reliabilityImprove reliabilityMemory architecture accessing/allocationSpecific access rightsProcessor elementMulti processor

In a conventional multiprocessor system, an access right with respect to a shared resource could not be changed in a flexible manner. The present invention provides a multiprocessor system having a first processor element (PE-A) and a second processor element (PE-B), the first processor element (PE-A) and the second processor element (PE-B) independently executing a program, in which the first processor element (PE-A) includes: a central processing unit (CPUa) for performing an operation processing based upon the program; a shared resource (18a) which is shared between the first processor element (PE-A) and the second processor element (PE-B); and a guard unit (16a) for restricting an access request from the second processor element (PE-B) to the shared resource (18a) based upon an access protection range setting value designated by the central processing unit (CPUa).

Owner:RENESAS ELECTRONICS CORP

Nonvolatile memory devices having multi-filament variable resistivity memory cells therein

There is provided a resistive memory device, the device including: a plurality of word lines and a plurality of bit lines arranged such that the word lines intersect the bit lines; a plurality of resistive memory cells each having a variable resistive material coupled between the corresponding word line and the corresponding bit line and an access element; selecting circuits selecting one of the plurality of resistive memory cells; and a filament-forming circuit supplying a filament-forming voltage to the selected resistive memory cell through the bit line coupled to the selected resistive memory cell while increasing the filament-forming voltage from a predetermined voltage level until filaments having a predetermined thickness are formed in the variable resistive material of the selected resistive memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

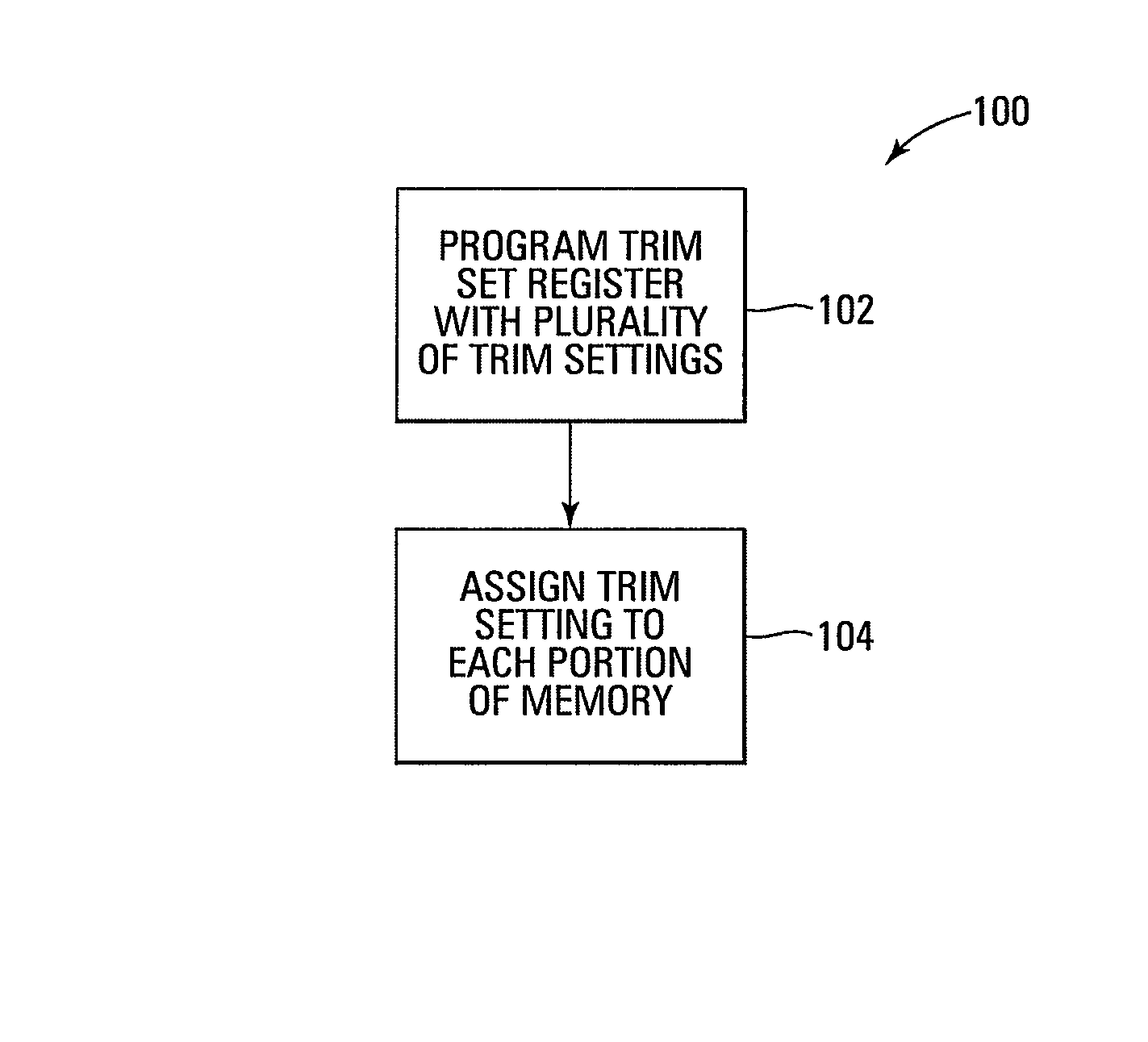

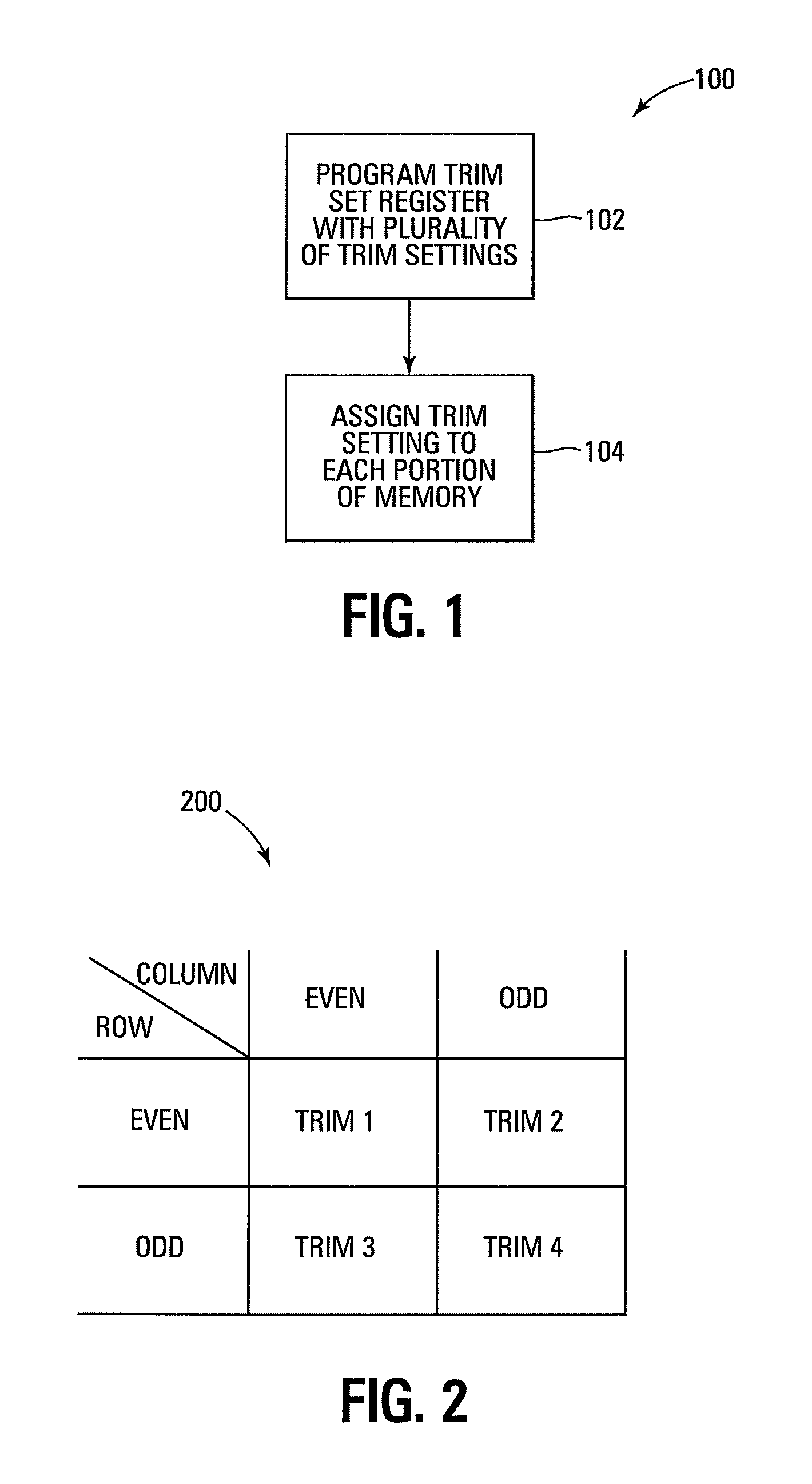

Program and read trim setting

A method and apparatus for setting trim parameters in a memory device provides multiple trim settings that are assigned to portions of the memory device according to observed or tested programming speed and reliability.

Owner:MICRON TECH INC

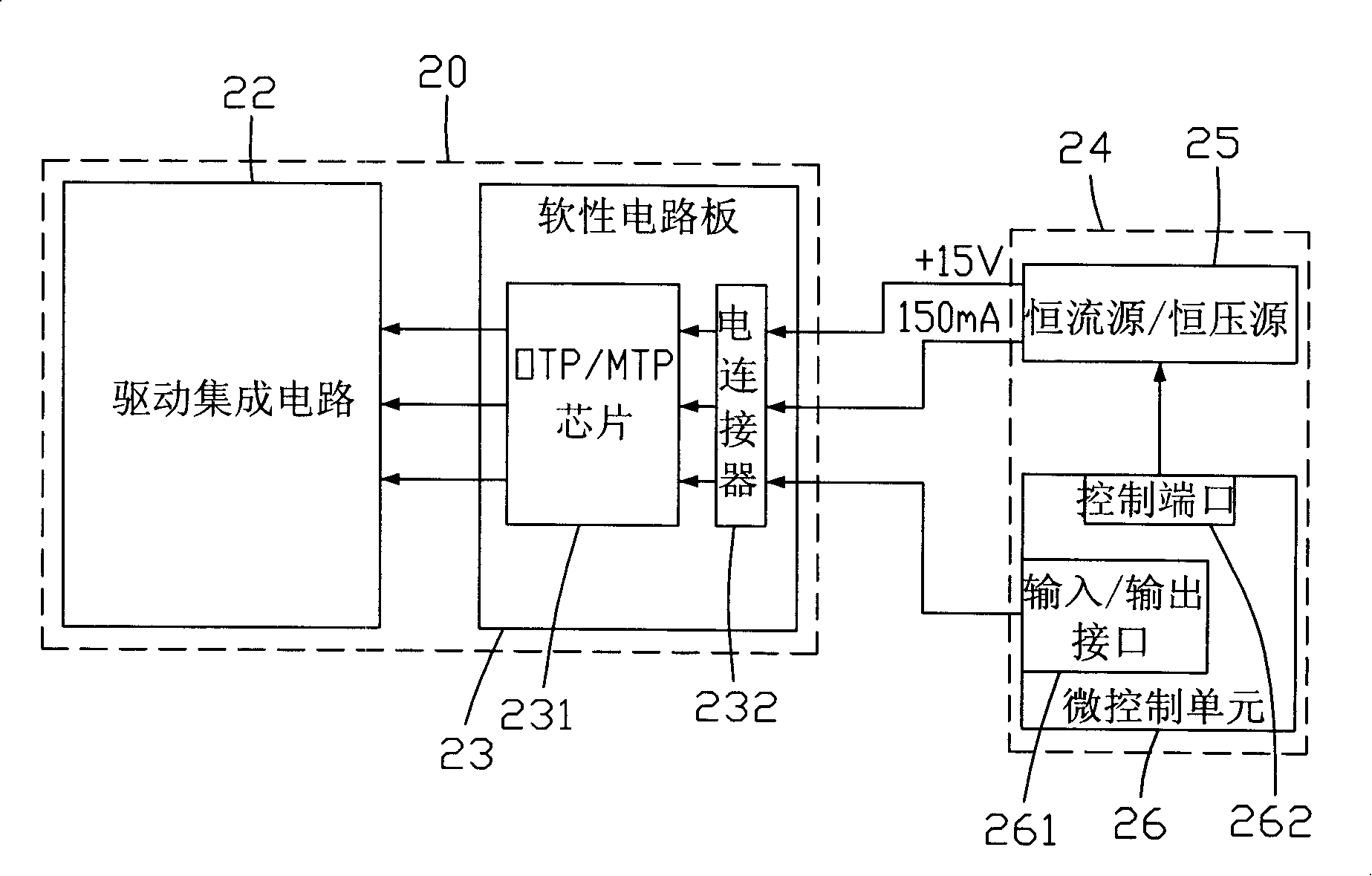

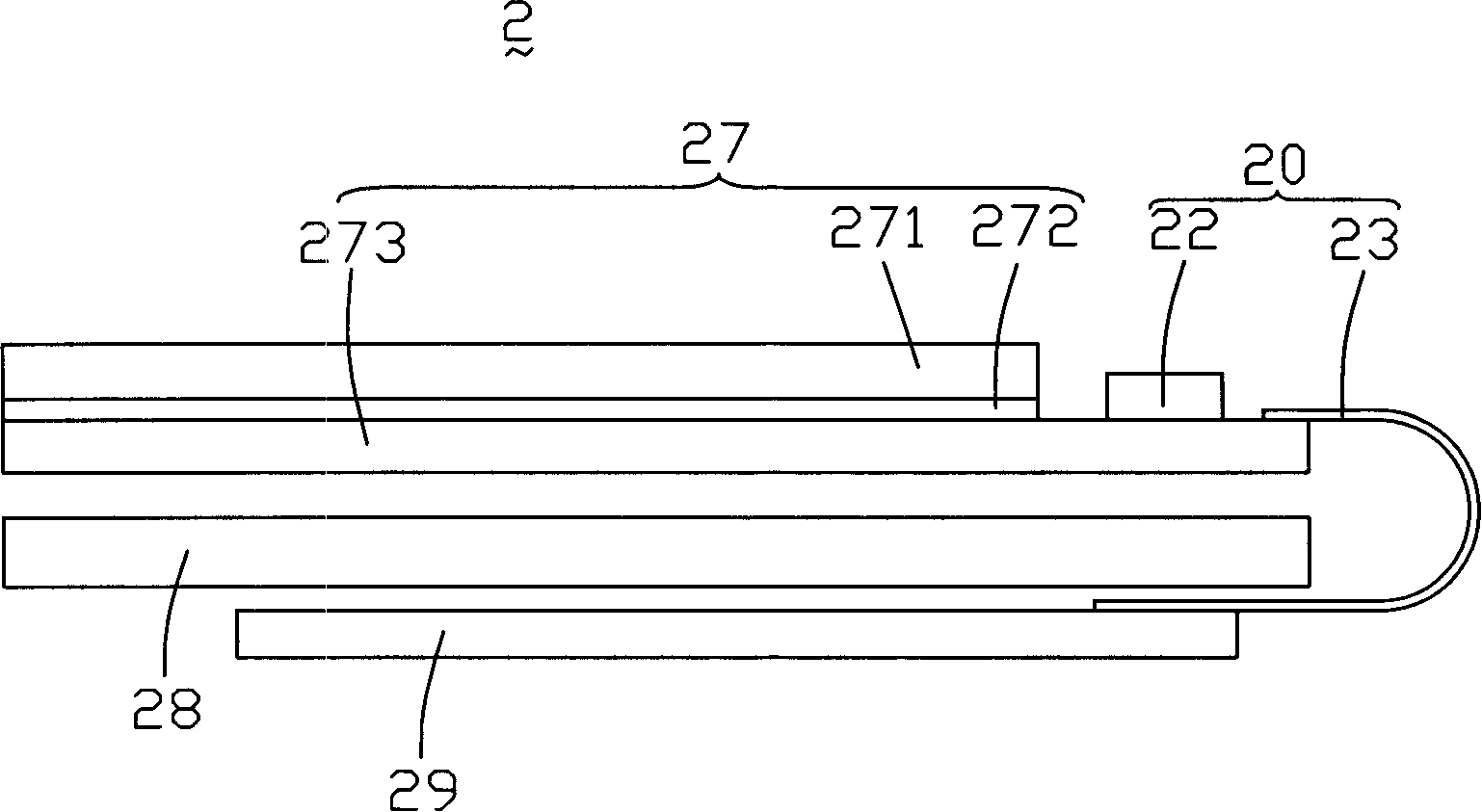

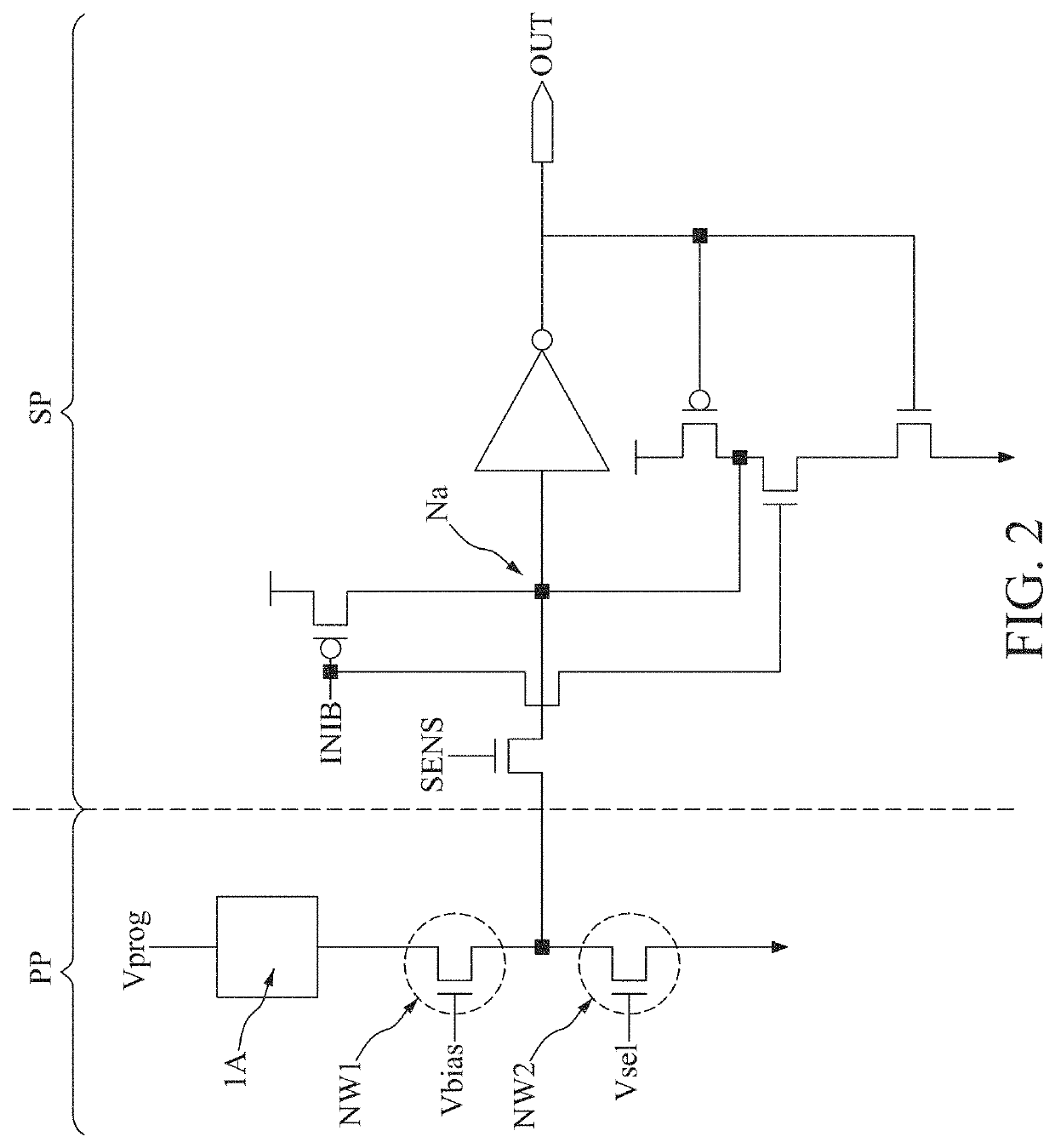

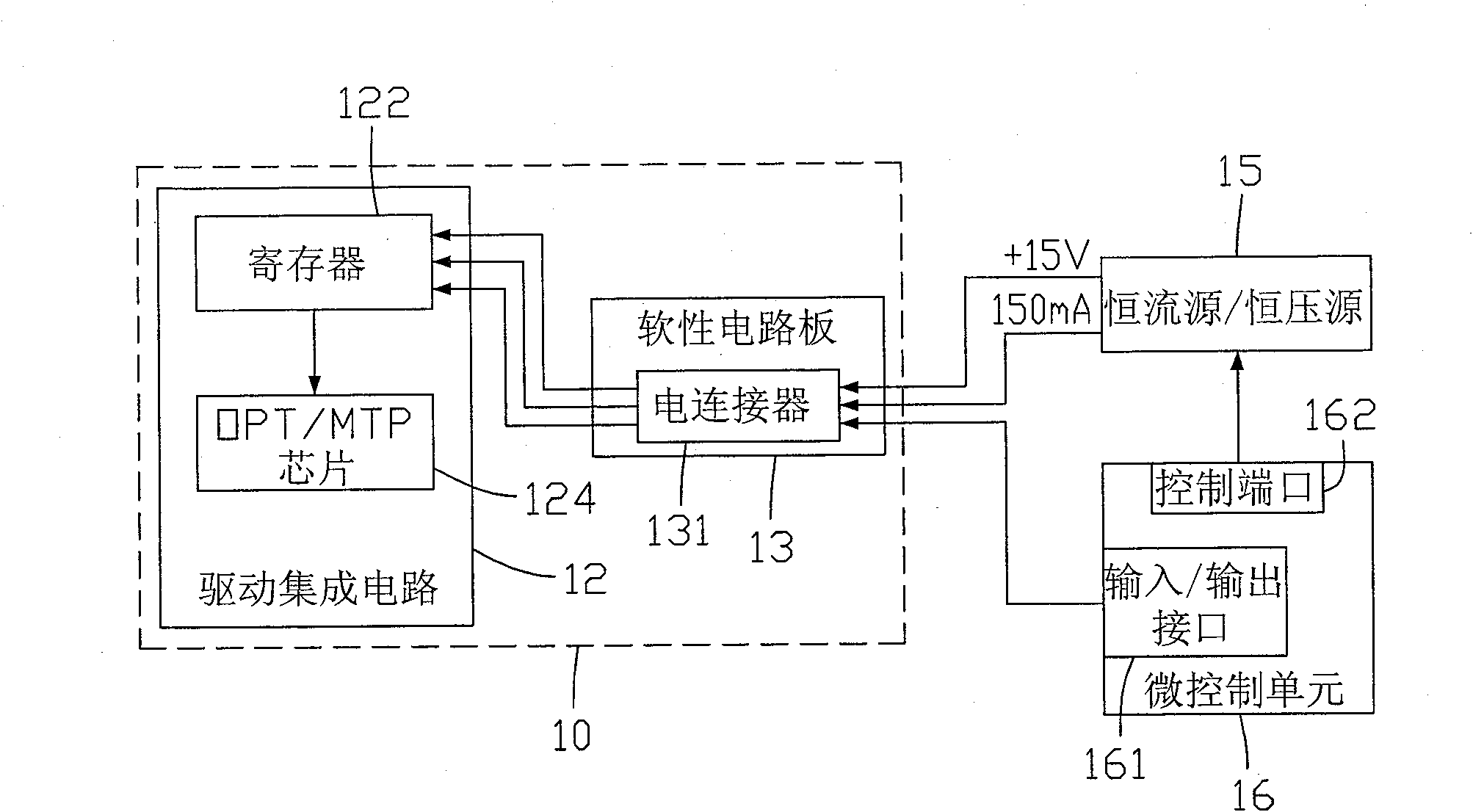

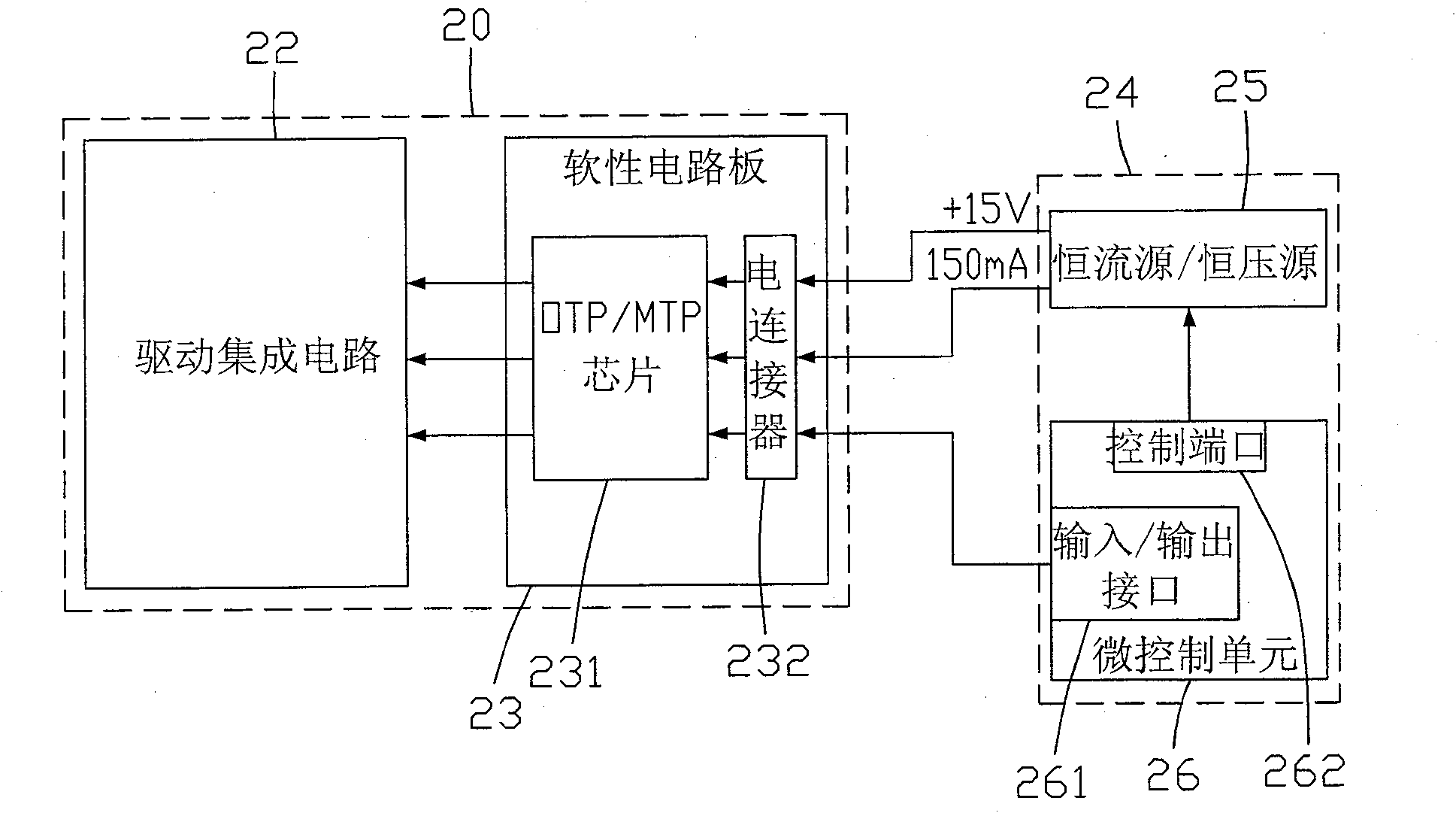

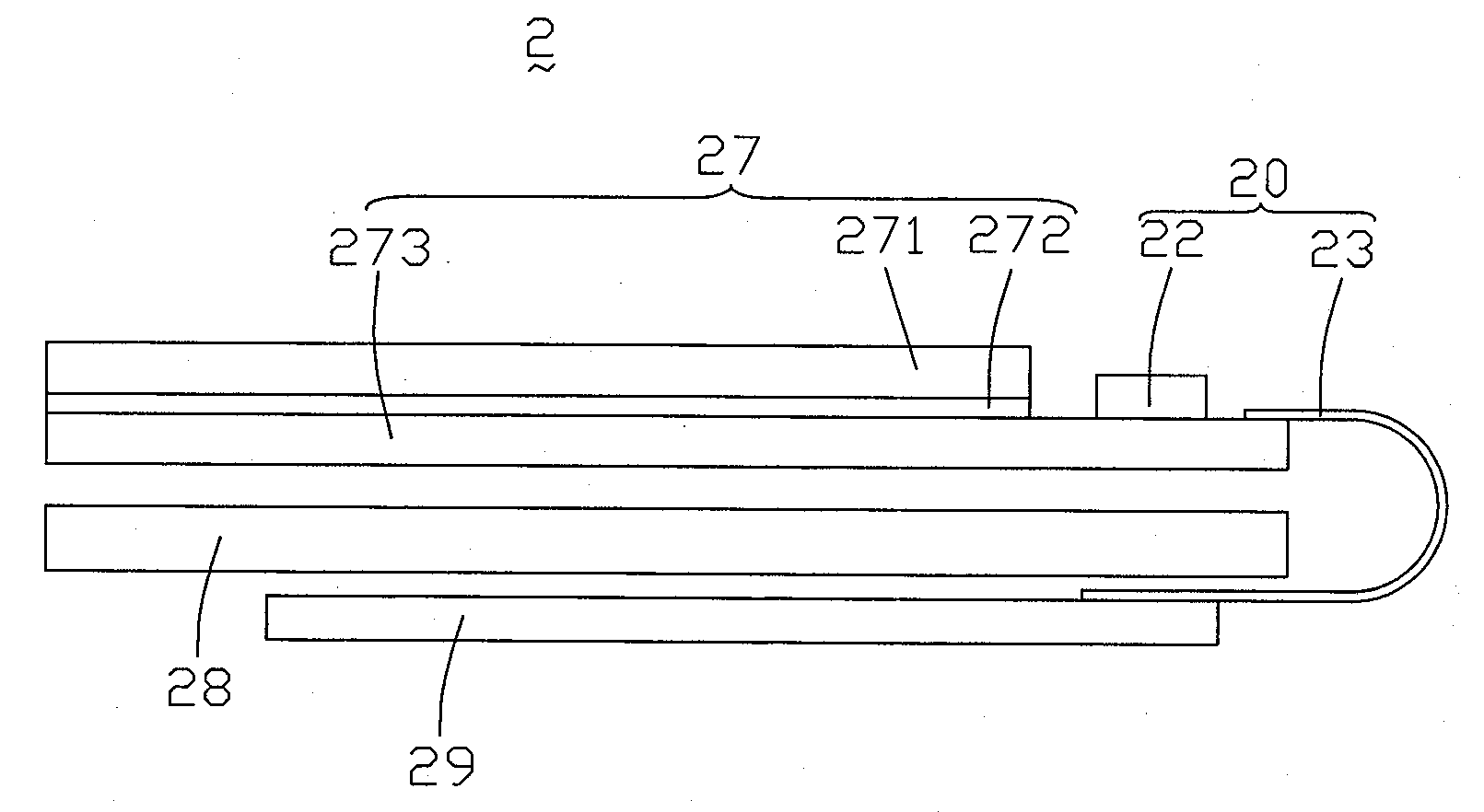

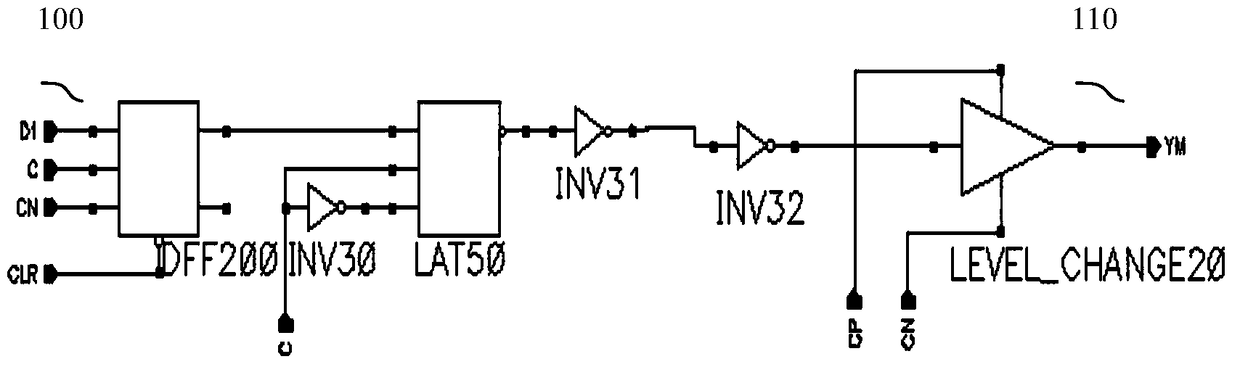

LCD panel driving circuit and LCD

InactiveCN101174037AWon't hurtImprove programming reliabilityStatic indicating devicesLiquid-crystal displayIntegrated circuit

The invention relates to a drive circuit of liquid crystal panel and a liquid crystal display. The drive circuit of liquid crystal panel comprises a drive integrated circuit and a flexible circuit board. The drive integrated circuit is used to drive the liquid crystal panel. The circuit board comprises an OTP / MTP (One Time Programmable / Multi Time Programmable) function module; the OTP / MTP function module receives the acquired imprint voltage and the imprint current for imprinting the drive integrated circuit, and stores the imprint data acquired by the drive integrated circuit. The drive integrated circuit reads imprint data from the OTP / MTP function module. The invention has an advantage of high reliability.

Owner:INNOCOM TECH SHENZHEN +1

Semiconductor device and method of operating the same

ActiveUS9042177B2Improve programming reliabilityRead-only memoriesDigital storagePower semiconductor deviceControl circuit

A semiconductor device includes first memory blocks arranged in a longitudinal direction, and including a plurality of strings, wherein the strings are formed along a vertical direction, and the strings adjacent to each other share bit lines or source lines with each other, each string including a drain selection transistor coupled to an odd drain selection line or an even drain selection line, memory cells coupled to word lines, and a source selection transistor coupled to an odd source selection line or an even source selection line, page buffers suitable for storing data, a selection switch unit suitable for transferring the data stored in the page buffers or various voltages supplied from an external source to the bit lines and the source lines; and a control circuit suitable for controlling the page buffers and the selection switch unit.

Owner:SK HYNIX INC

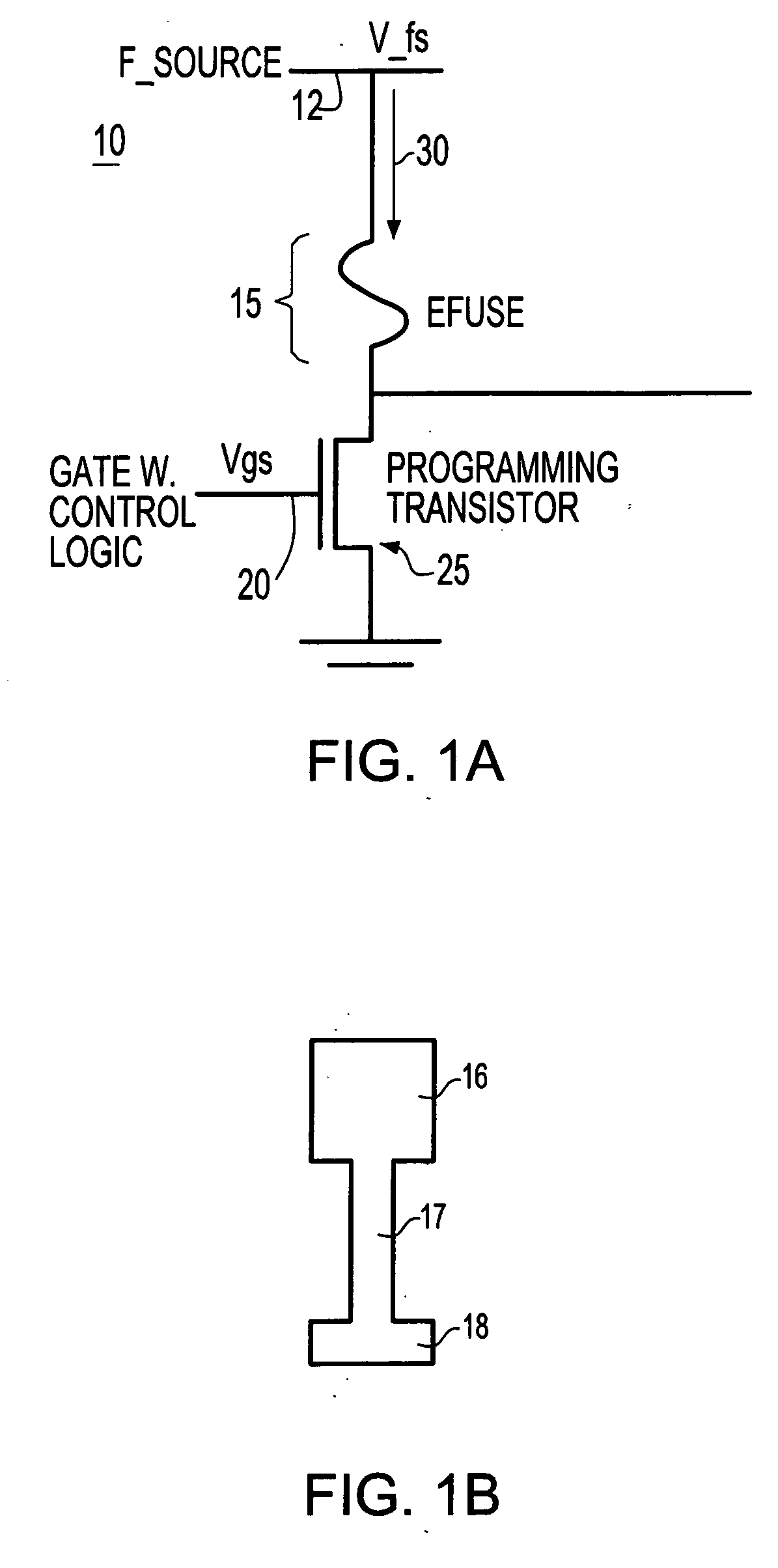

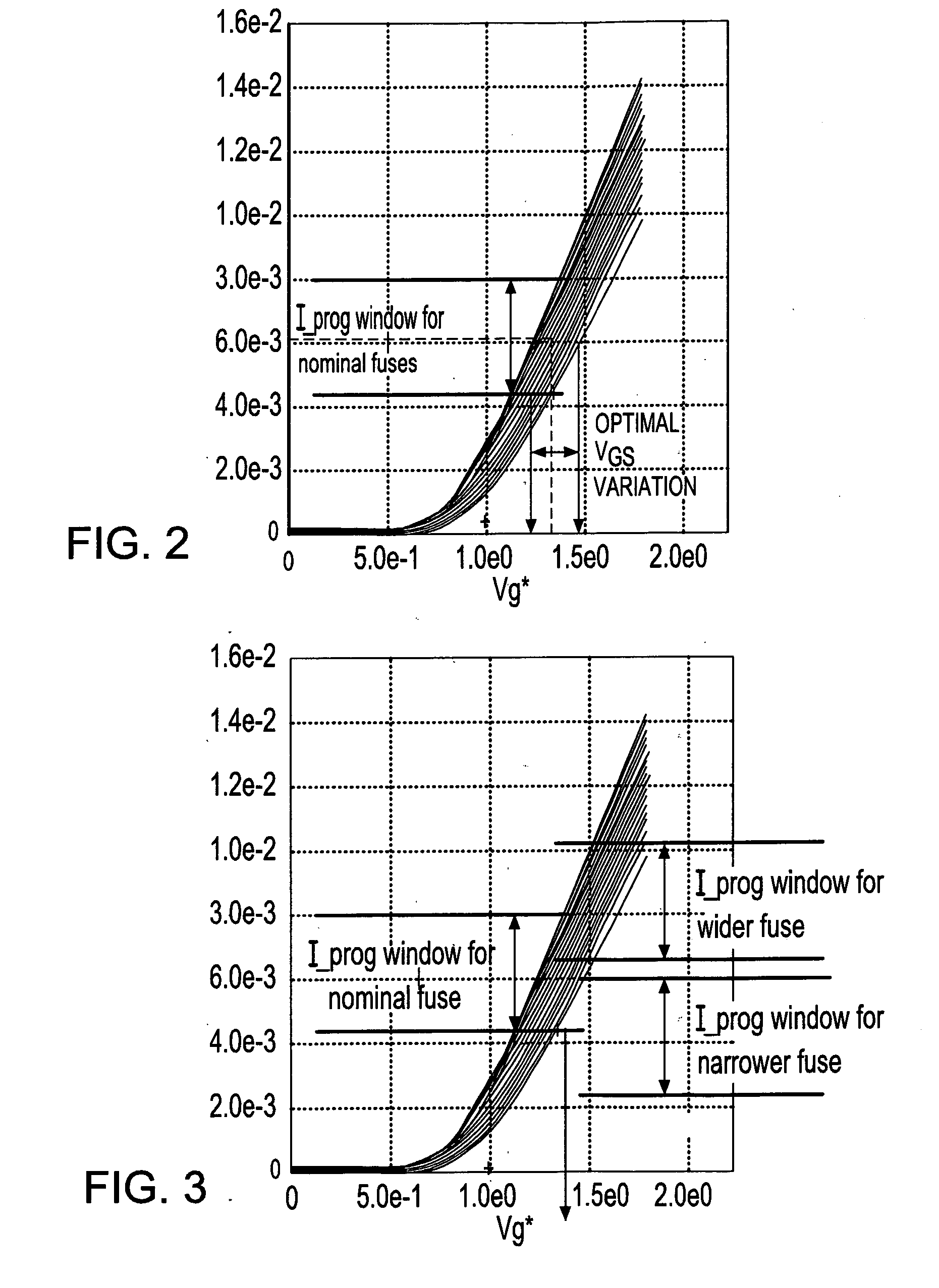

System and method for increasing reliability of electrical fuse programming

ActiveUS20070195629A1Improve programming reliabilityRead-only memoriesDigital storageCurrent rangeCode redundancy

A system and method for achieving enhanced e-fuse programming reliability. By providing an e-fuse device with redundantly coded fuse structures each with a differing fuse size dimension, reliable encoding of a fuse with a programmed bit is enhanced. That is, for each e-fuse device, each of the multiple fuse structures and a corresponding programming devices associated with each fuse structure is dimensioned to achieve the coding redundancy such that one fuse structure of the multiple fuse structures provides for a current flow of sufficient current density to ensure programming reliability of the e-fuse device. In one embodiment, each the corresponding programming transistor device is of substantially identical size and, each fuse structure of the multiple fuse structures is of a different size. Alternately, each fuse structure is of substantially identical size and each programming transistor device is of a different size, thereby ensuring reliable coding over a programmed current range.

Owner:MARVELL ASIA PTE LTD

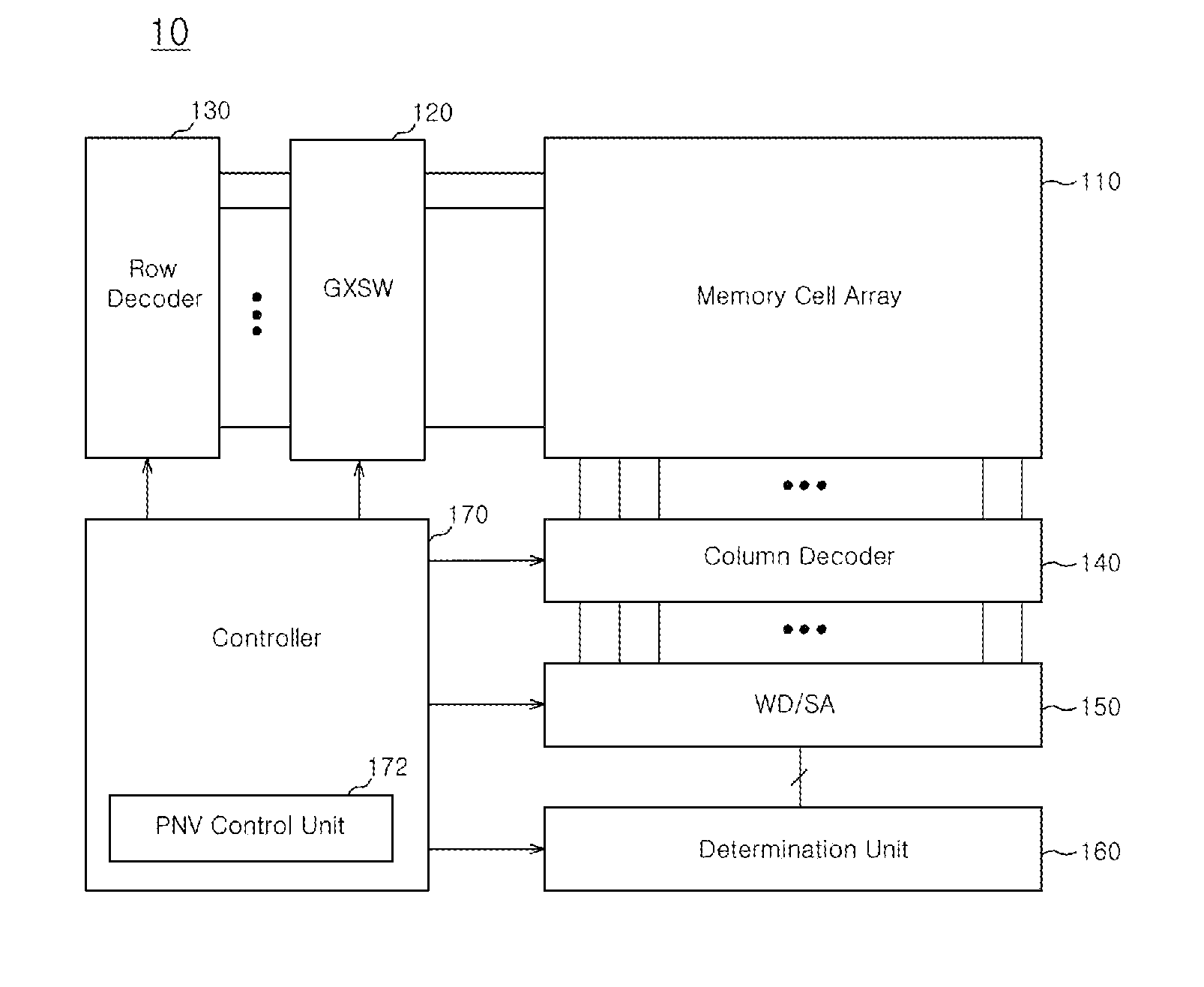

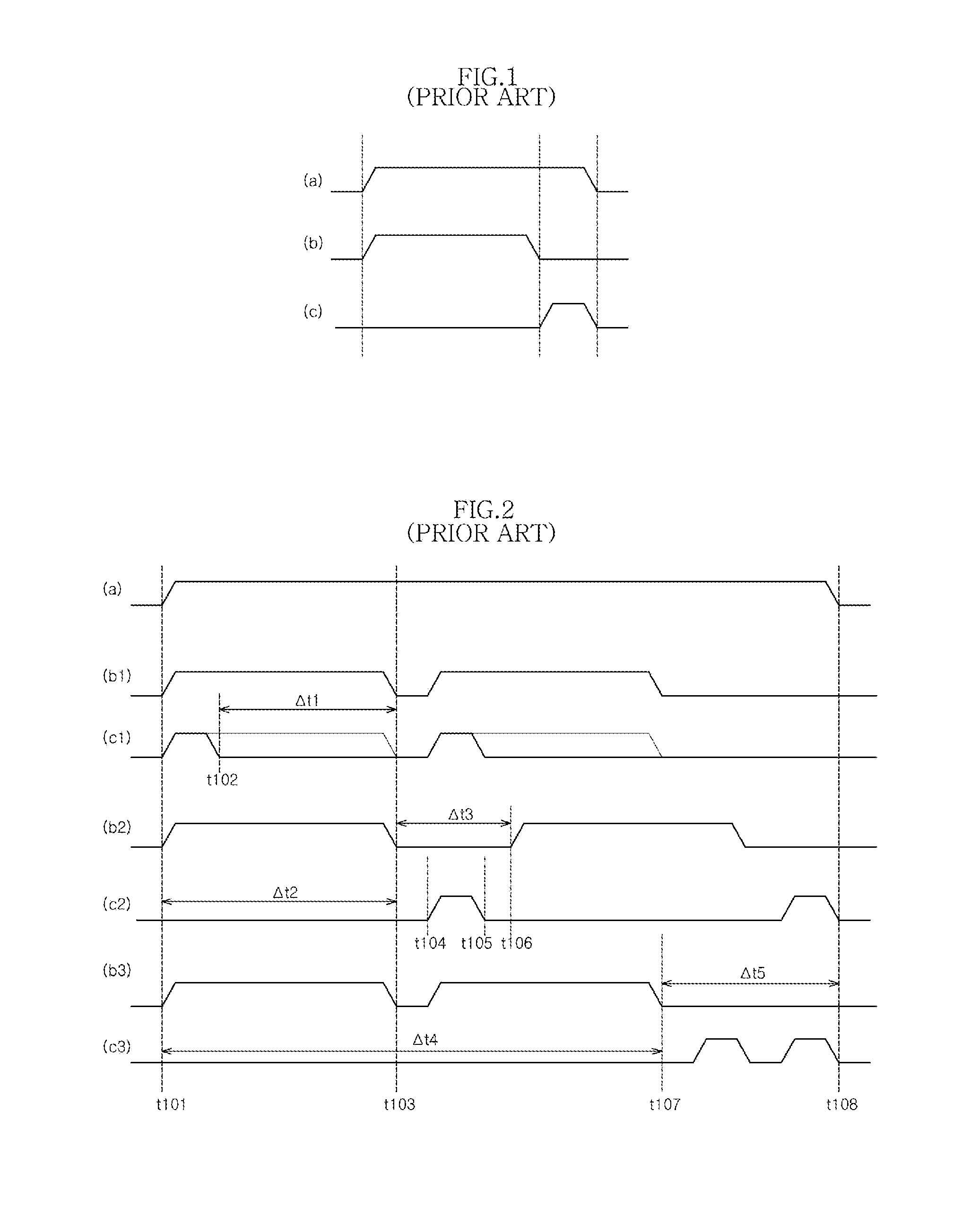

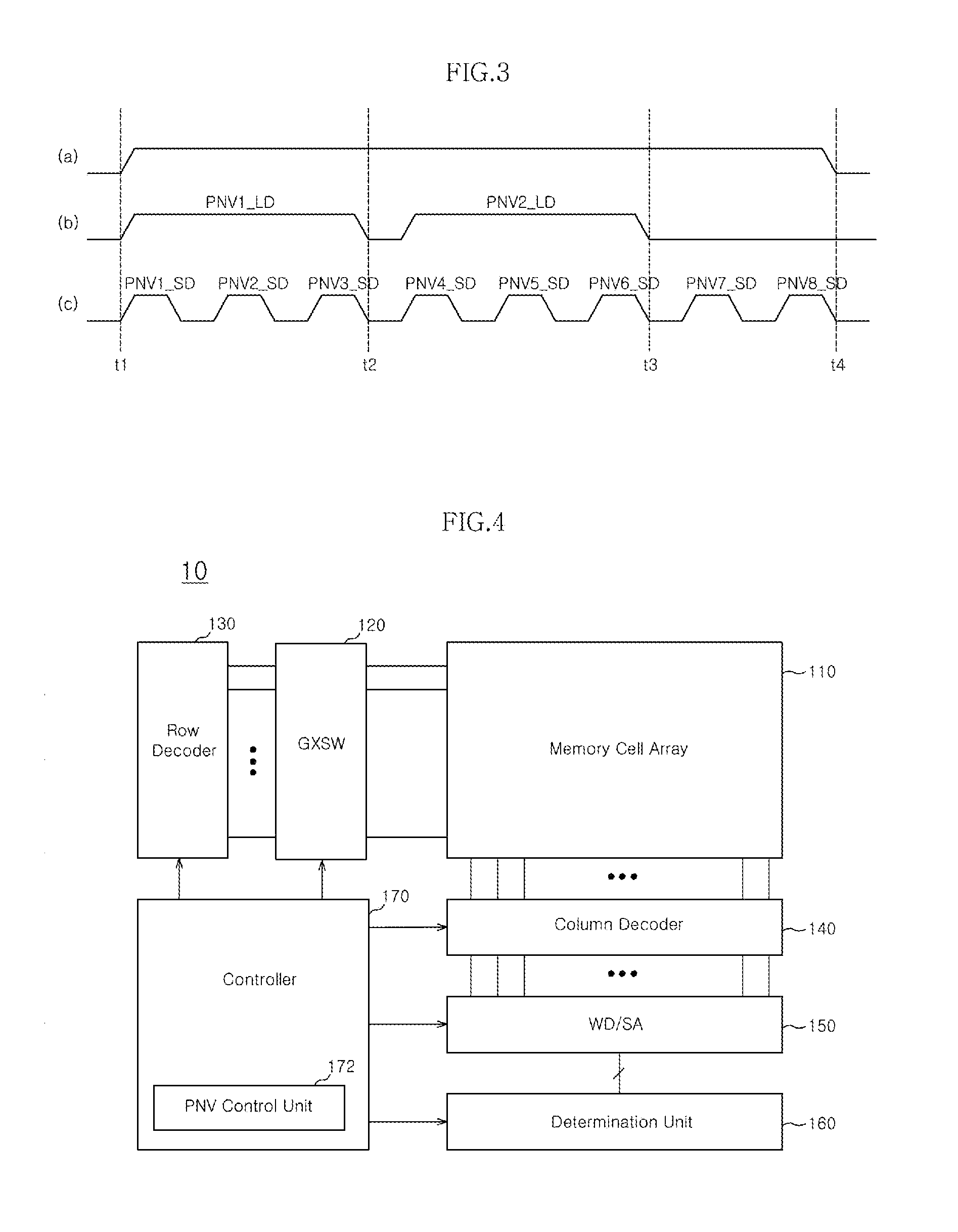

Nonvolatile memory apparatus, operating method thereof, and data processing system having the same

ActiveUS20140164682A1Shorten the timeIncrease the number ofMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemData processing

Provided is a nonvolatile memory apparatus which writes data into a memory cell according to a program and verify (PNV) operation, wherein the nonvolatile memory apparatus performs the PNV operation for first data during a first time, and performs a plurality of PNV operations for second data during the first time.

Owner:SK HYNIX INC

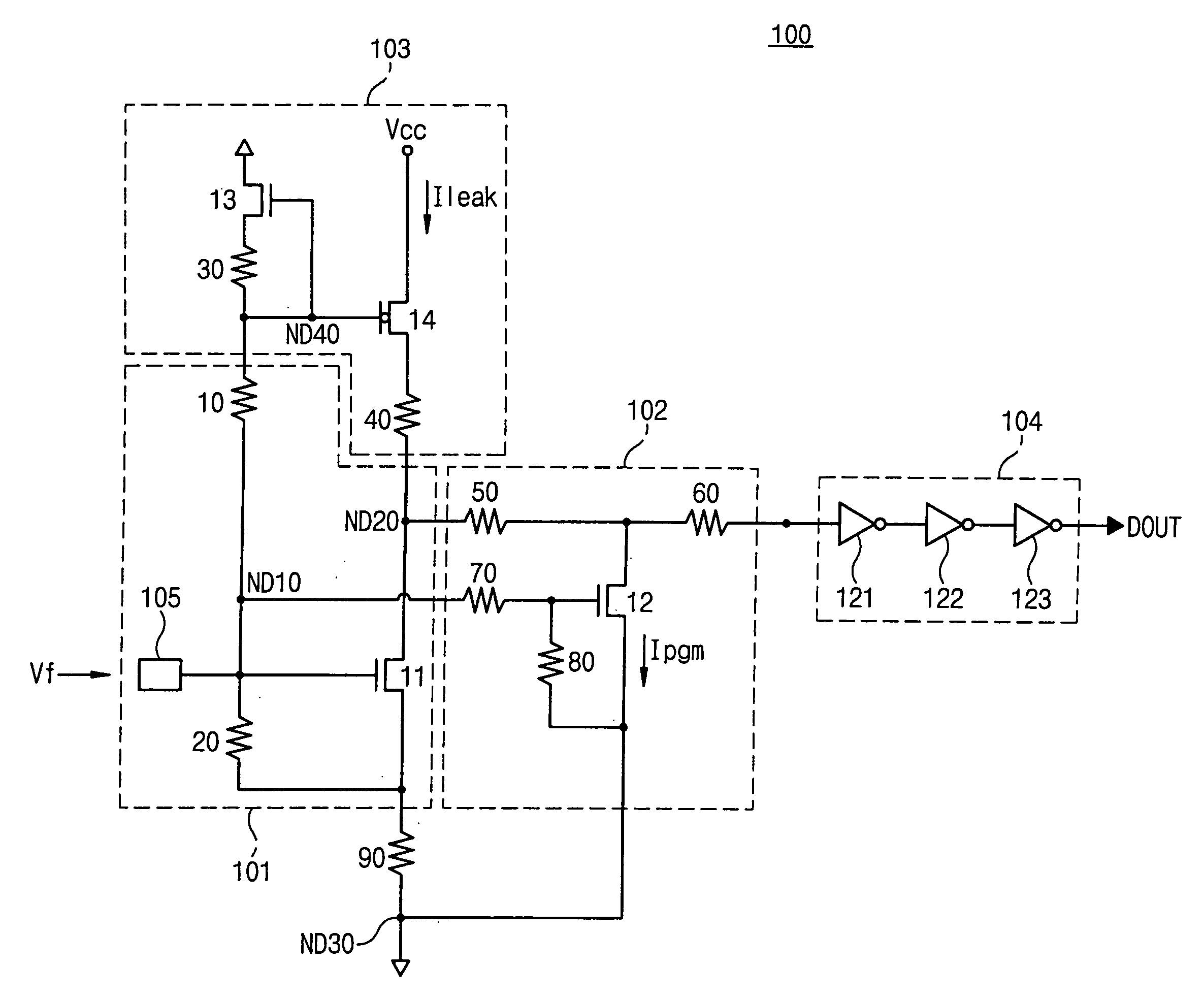

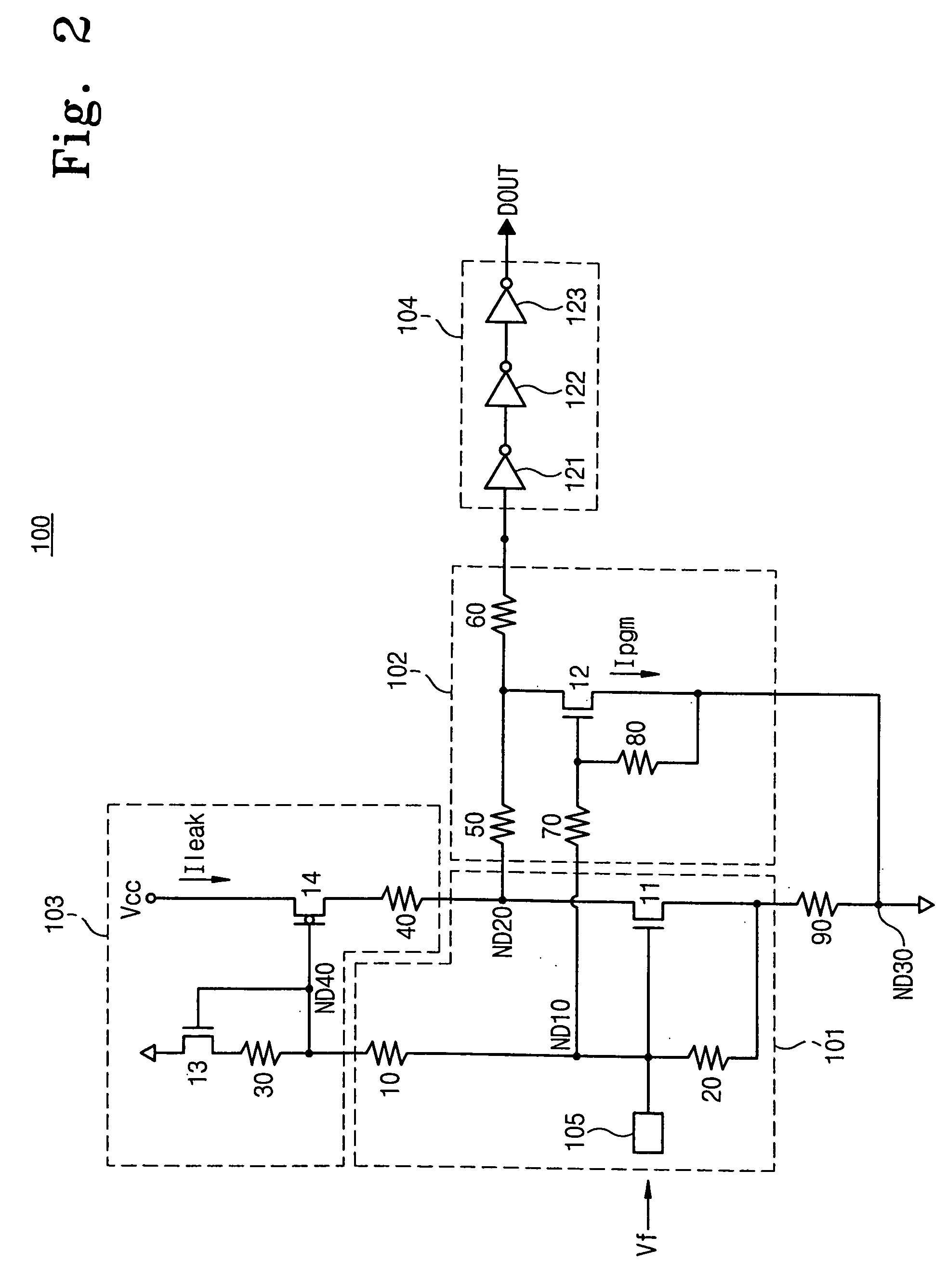

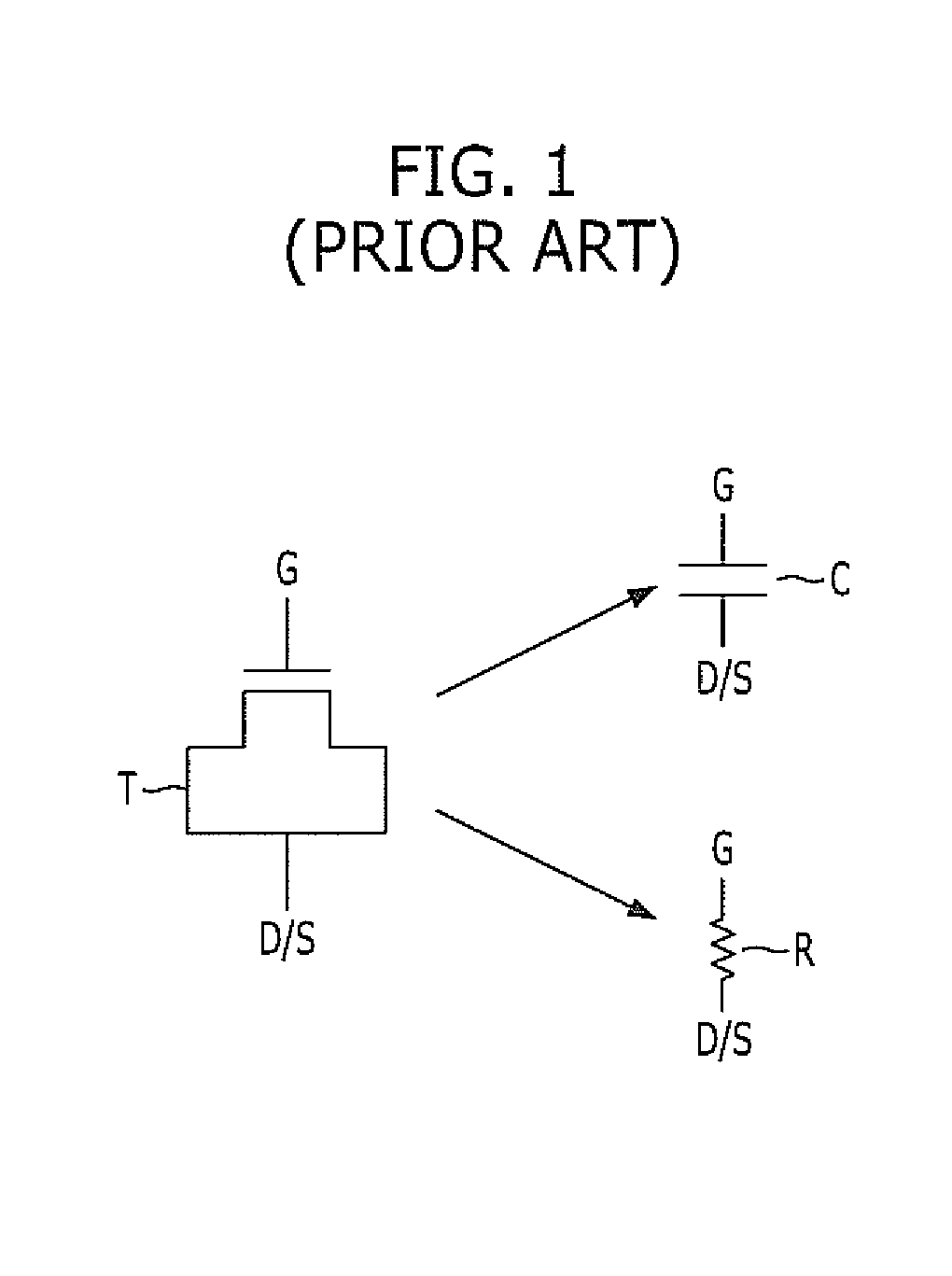

E-fuse circuit using leakage current path of transistor

InactiveUS20060244510A1Improve programming reliabilityGood reproducibilitySemiconductor/solid-state device detailsSolid-state devicesDielectricDrain current

An e-fuse adapted to indicate programming state in relation leakage current path defined by a program transistor both before and after dielectric breakdown has occurred. The e-fuse comprises: a program circuit including the program transistor, a switch circuit connected between the program circuit and ground, a current supply circuit connected to the program circuit and supplying a predetermined current to the leakage current path after the program transistor is programmed; and a sense / amplification circuit connected to a program node associated with the leakage current path and adapted to sense and output the programming state.

Owner:SAMSUNG ELECTRONICS CO LTD

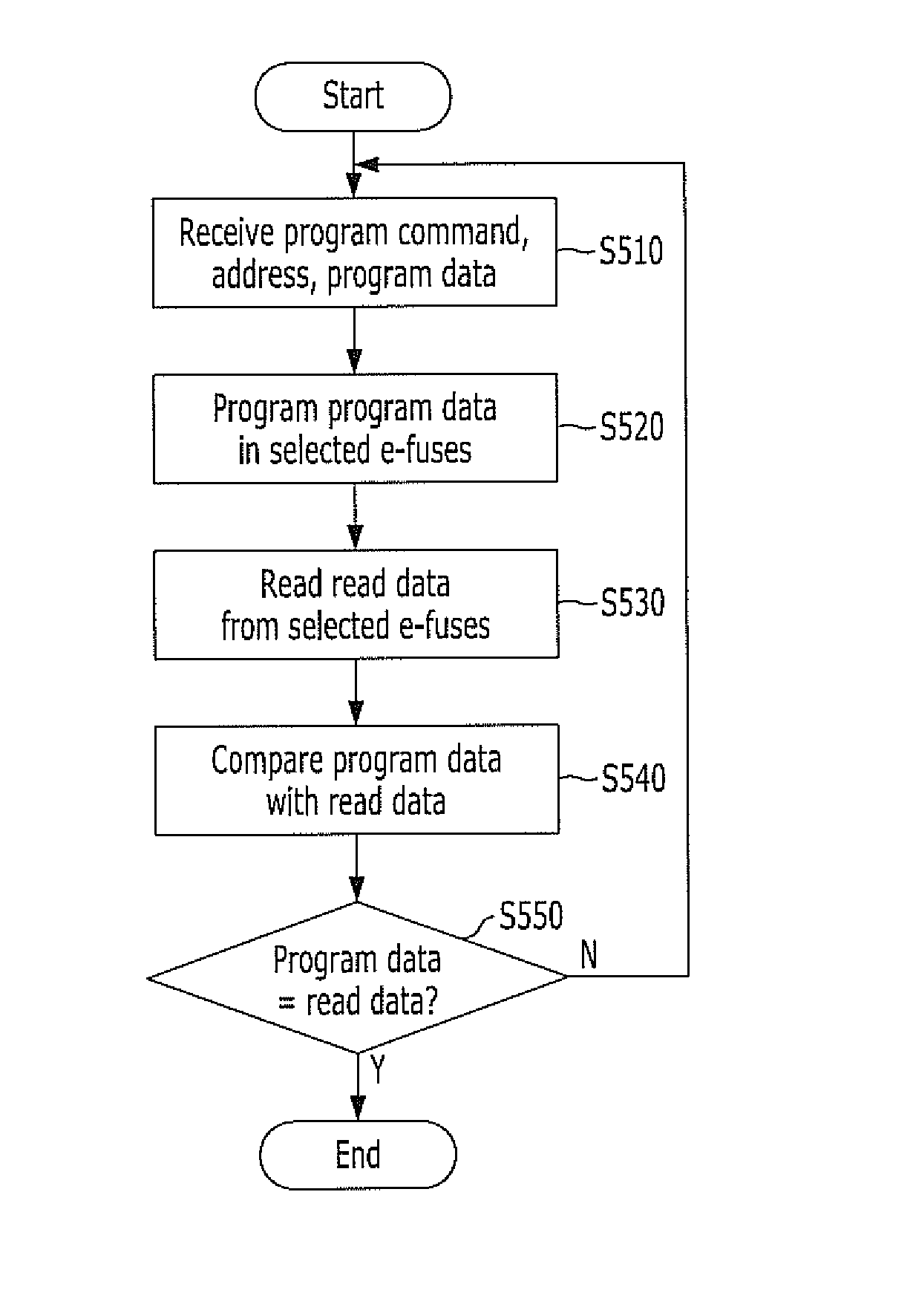

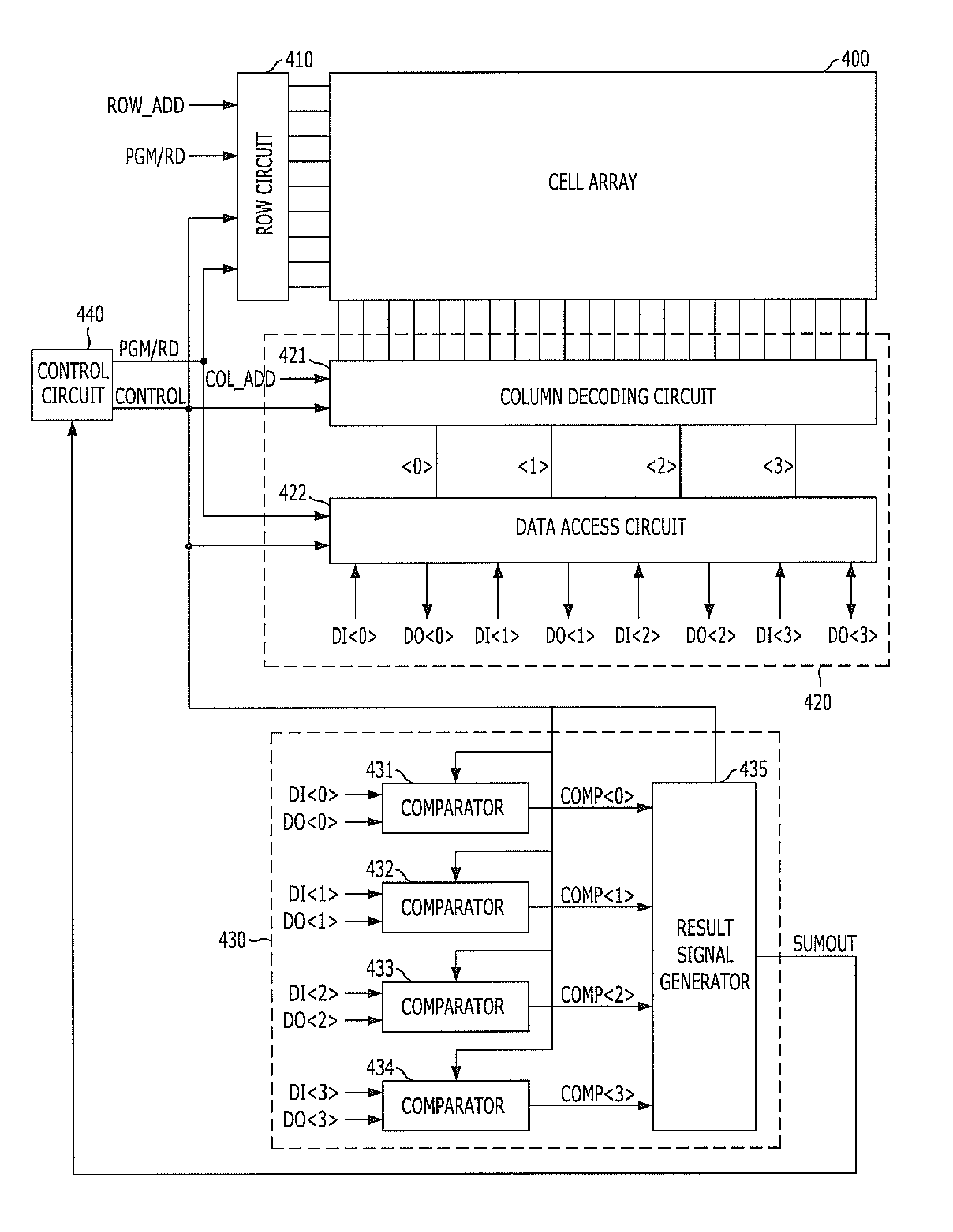

E-fuse array circuit and programming method of the same

ActiveUS20140063894A1Extension of timeImprove programming reliabilityRead-only memoriesComputer engineeringProgramming method

A program method for an e-fuse array circuit includes receiving an address and a multi-bit program data, programming the multi-bit program data in e-fuses designated by the address, reading a multi-bit read data from the e-fuses, and comparing bits of the multi-bit program data with bits of the multi-bit read data, wherein if the bits of the multi-bit program data are identical to the bits of the multi-bit read data, a program operation is terminated; and if the bits of the multi-bit read data are not identical to the bits of the multi-bit program data, then the programming of the multi-bit program data, the reading of the multi-bit read data, and the comparing of the bits are performed again.

Owner:SK HYNIX INC

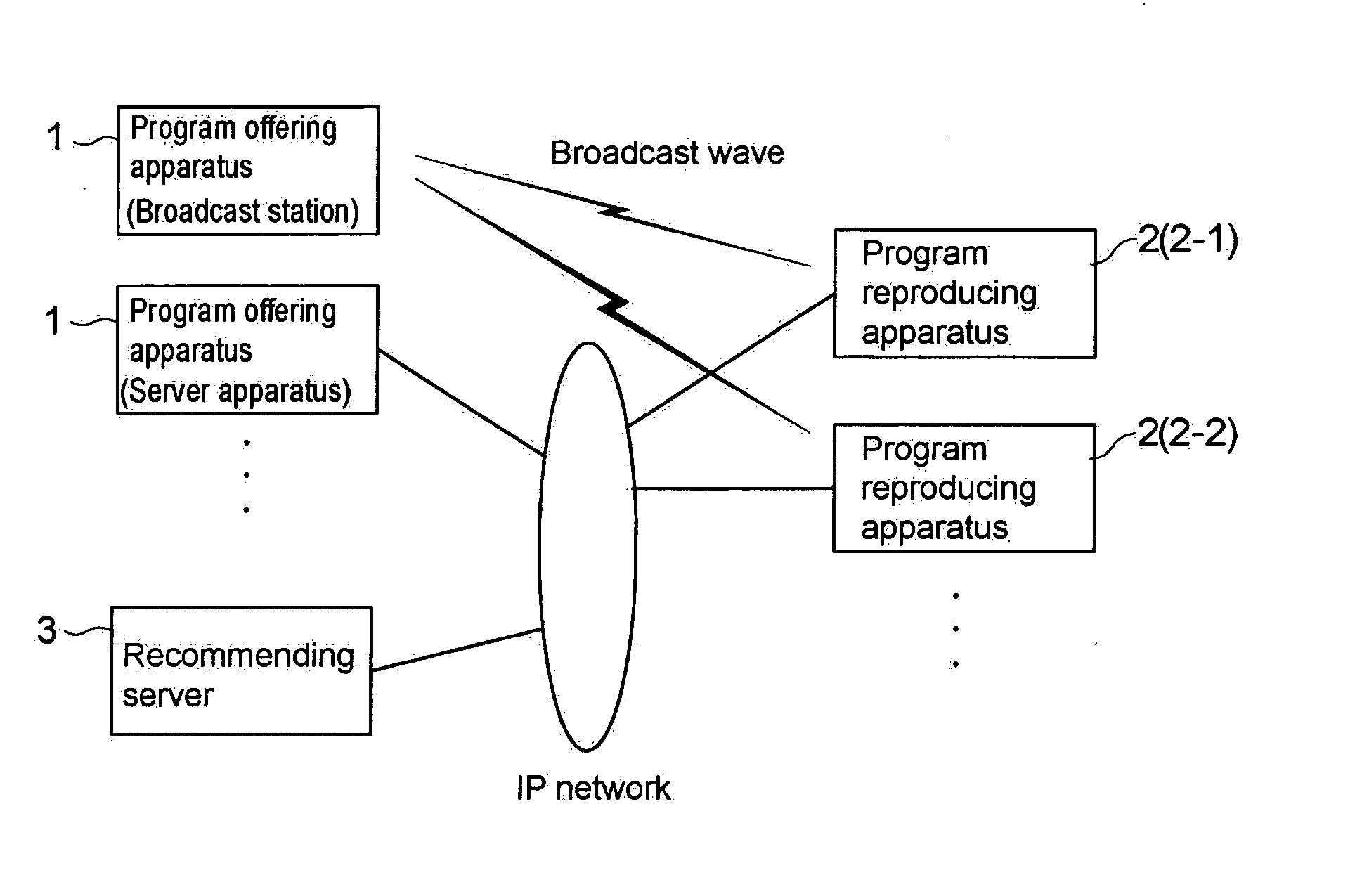

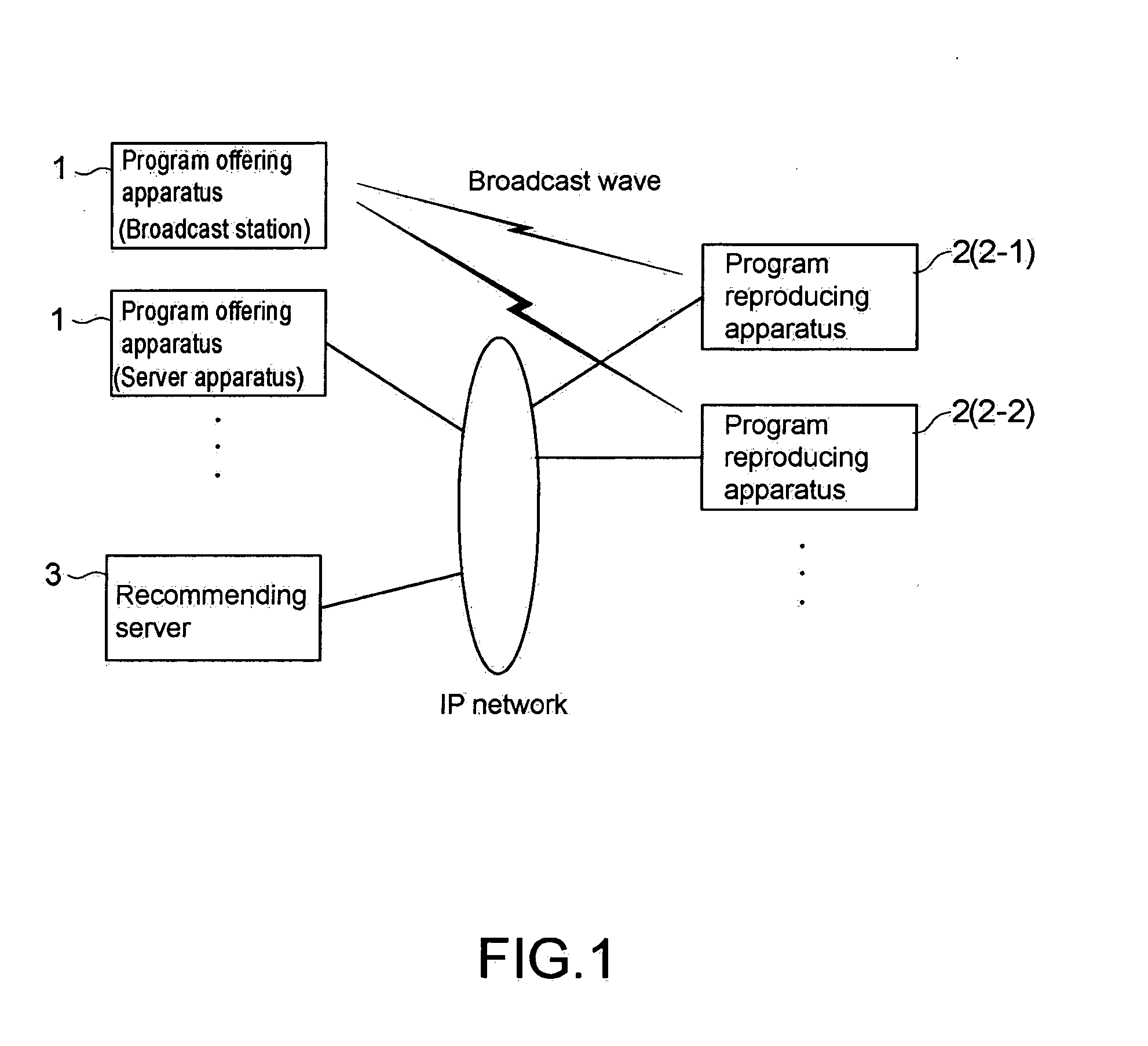

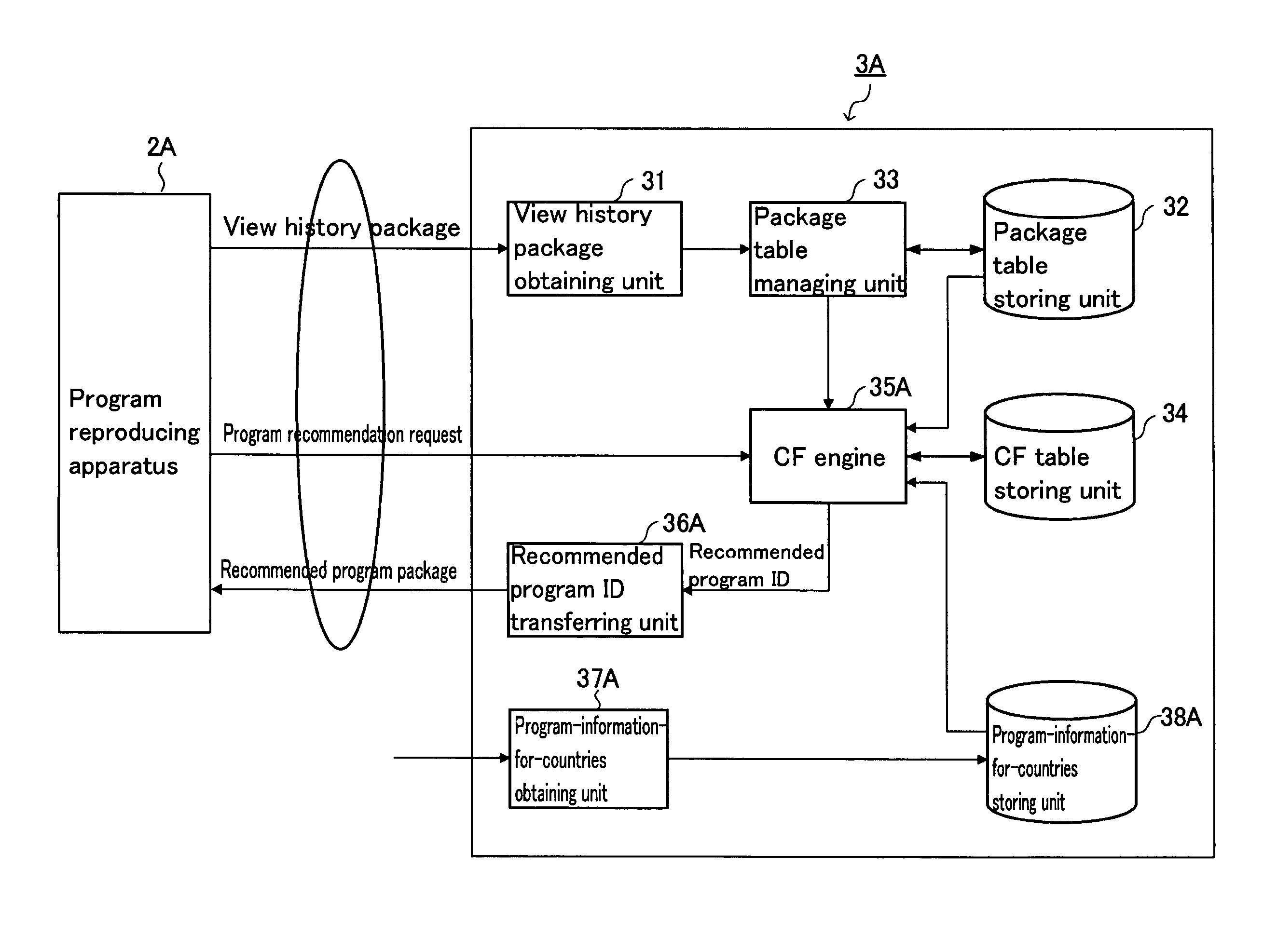

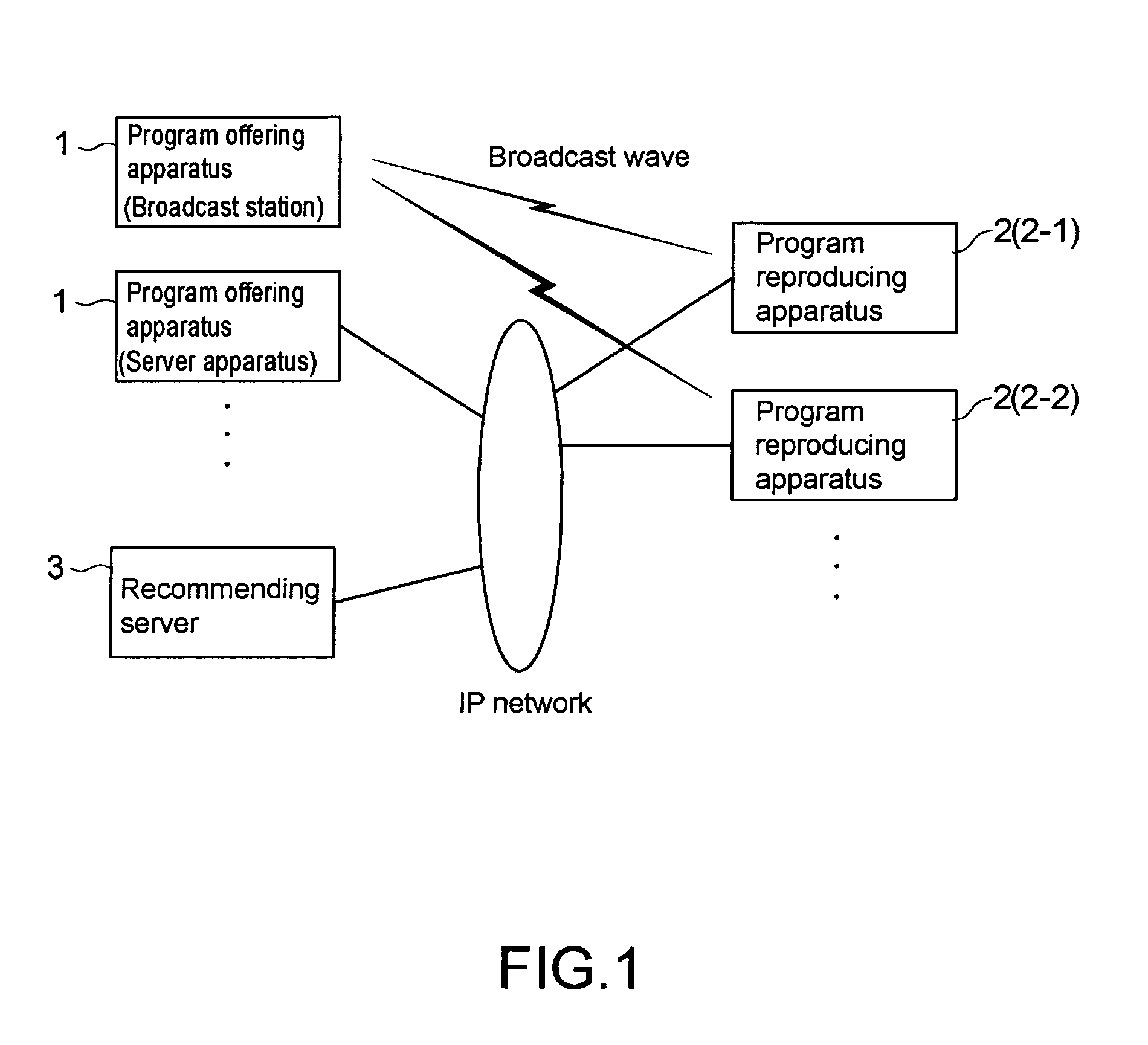

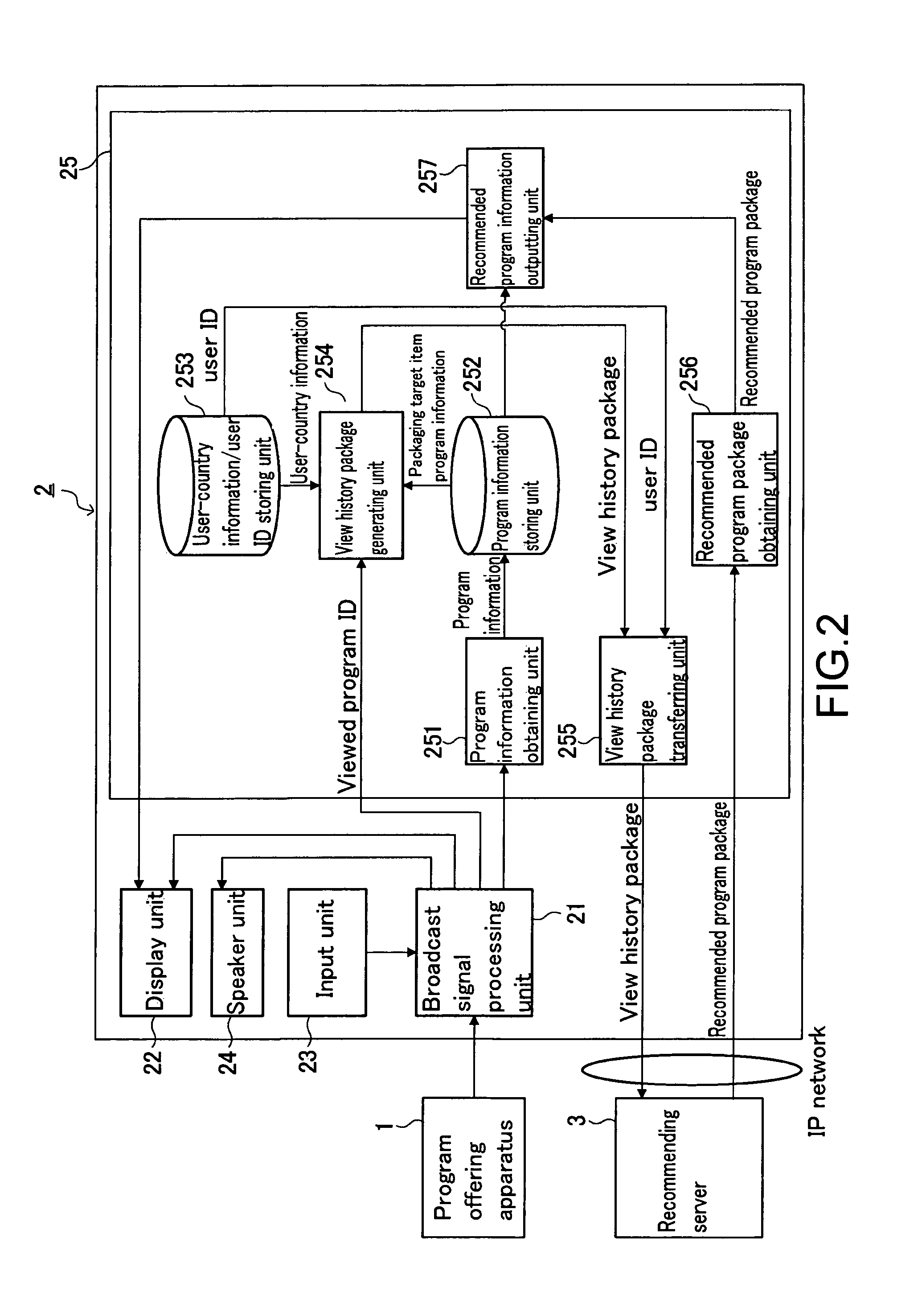

Information processing apparatus, information processing method, and program

InactiveUS20110202962A1Improve performanceSecondary useTelevision system detailsColor television detailsInformation processingUser identifier

A package identifier generating unit generates, for each unique combination of information on specific items included in a package, a package identifier identifying the combination. A first table registering unit extracts information on the specific items from the obtained package, and registers the information on the specific items, a user identifier identifying a user of a program reproducing apparatus being a transfer source of the package, and the generated package identifier in correspondence with each other, in a first table. A second table registering unit extracts a correspondence relation between the user identifier and the package identifier from the first table, and registers the package identifier corresponding to the user identifier, as a program view history for each user, in a second table. A determining unit determines the package identifier being a difference between program view histories similar to each other registered in the second table.

Owner:SATURN LICENSING LLC

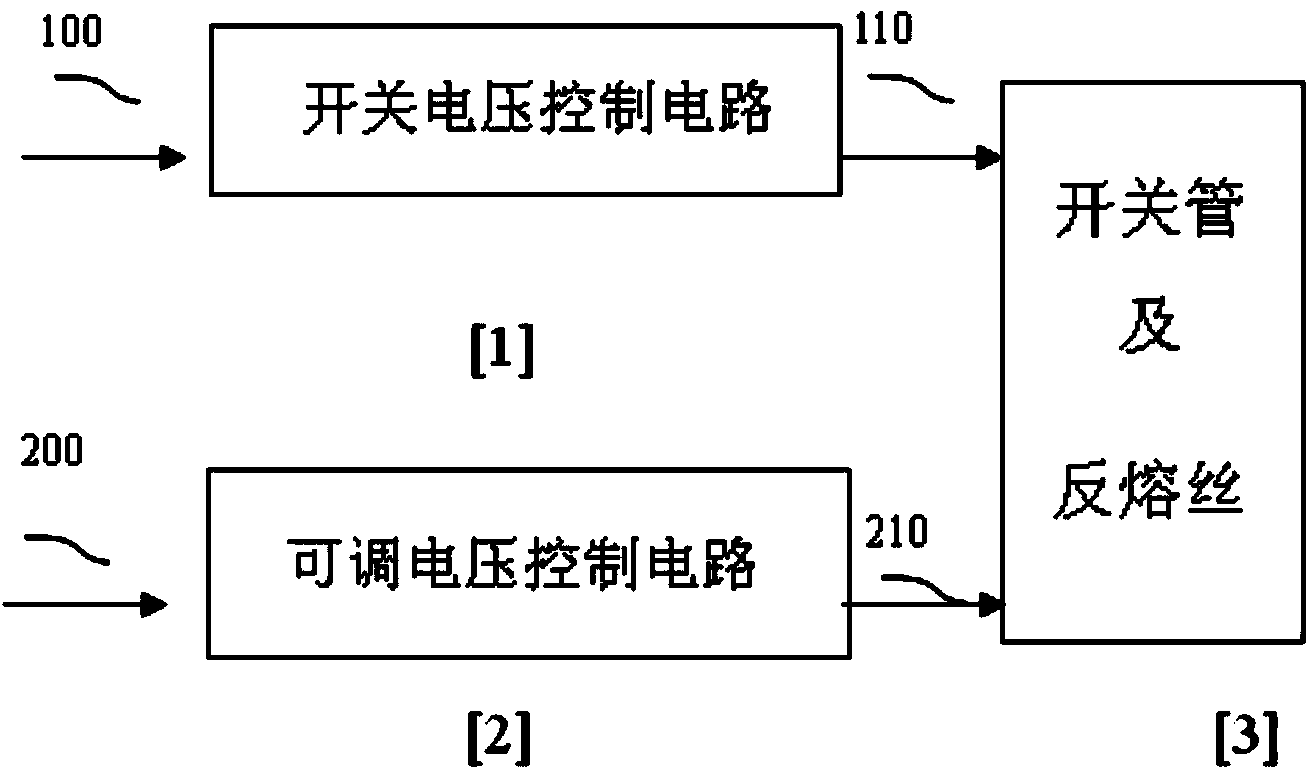

Programmed burning device for anti-fuse

ActiveCN104409100ASimple circuit structureFlexible controlRead-only memoriesElectronic switchingElectricityEngineering

The invention discloses a programmed burning device for an anti-fuse. The programmed burning device disclosed by the invention comprises a switching tube, a switching voltage control circuit and an adjustable voltage control circuit, wherein the switching tube is electrically connected with the anti-fuse; the switching voltage control circuit is connected with the switching tube and is used for providing switching voltage for the switching tube; and the adjustable voltage control circuit is connected with the switching tube and is used for providing different control voltages for the switching tube. The circuit disclosed by the invention is simple in structure, flexible to control and high in circuit speed, insufficient burning or excessive burning of the anti-fuse is avoided, the programming quality of the anti-fuse is improved, and the programming reliability of the anti-fuse is enhanced.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

Memory device and method for operating a memory device

InactiveUS7342829B2Accelerated programUnified performanceRead-only memoriesDigital storageStorage cellMemory array

A memory device (1) includes a memory array (2). The memory array (2) has at least one memory area (5) that includes a plurality of conductive lines (3) and a plurality of memory cells (4) connected to the conductive lines (3). The conductive lines (3) are arranged at positions (n) within the memory area (5). The memory cells (4) are erasable and are programmable by application of an electrical programming pulse (P) supplied via a respective conductive line (3). The memory device (1) is constructed such that for programming of a memory cell (4) an electrical programming pulse (P) is applied which has a programming pulse profile (PP) depending on the position (n) of a respective conductive line (3) to which the memory cell (4) is connected.

Owner:POLARIS INNOVATIONS LTD

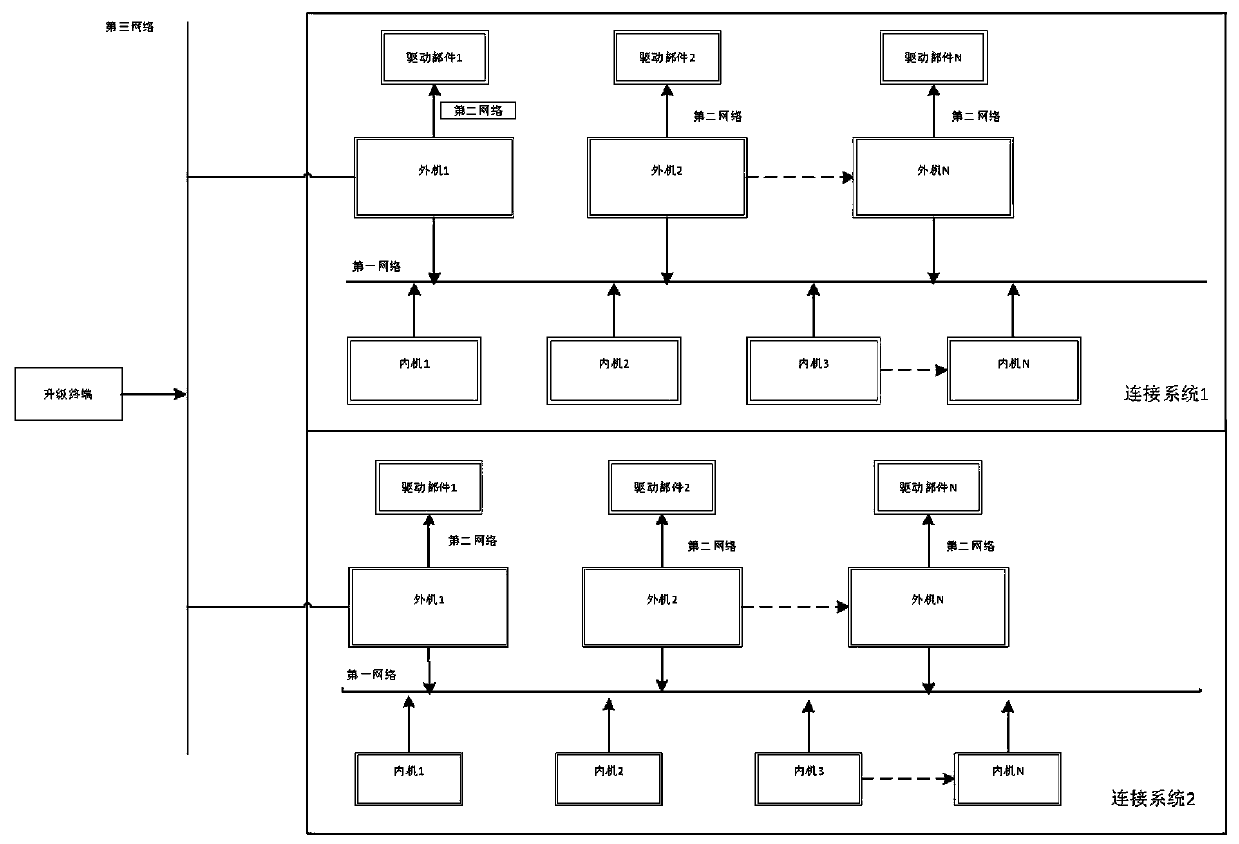

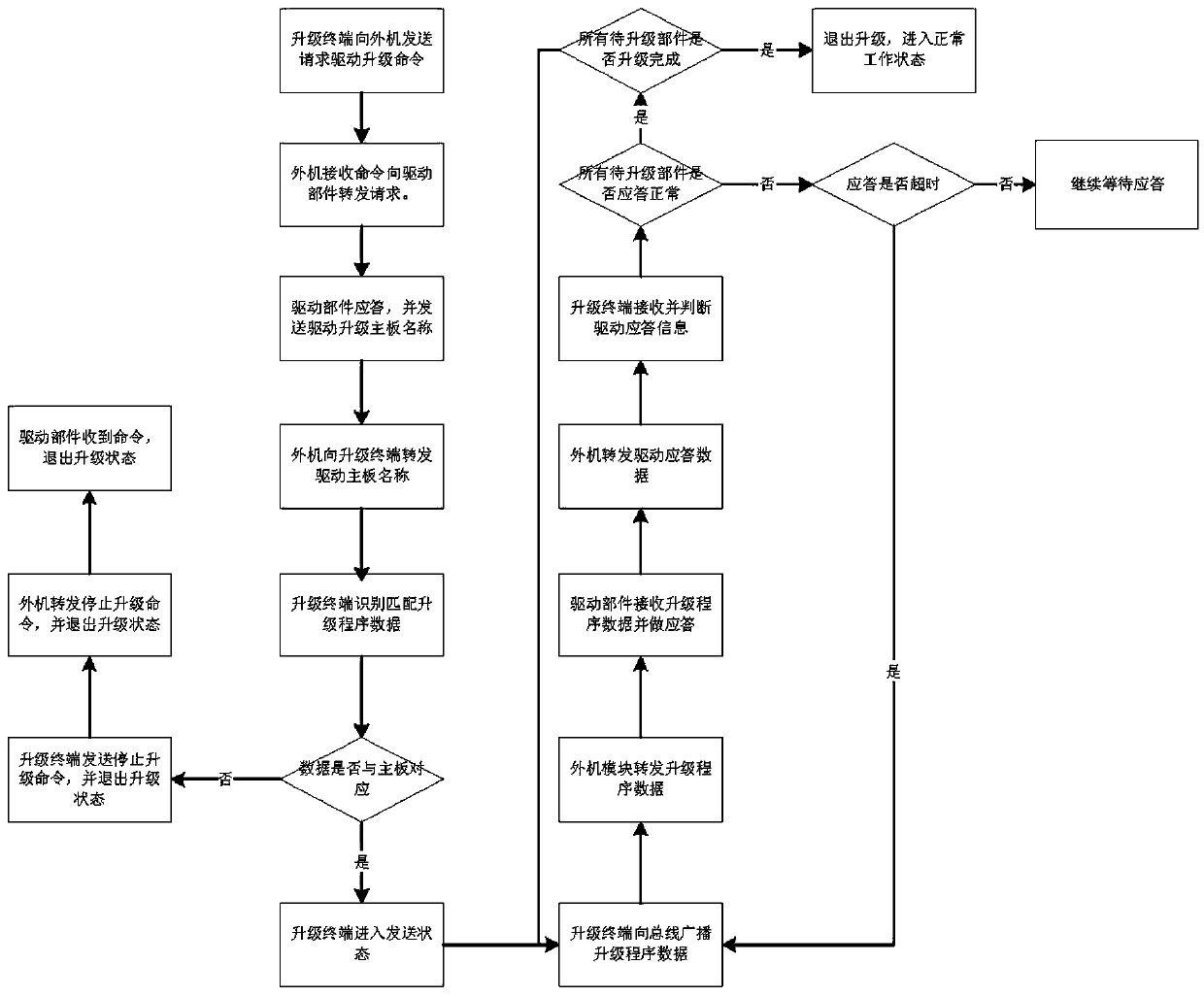

Software upgrading method of air conditioning system

InactiveCN110990040AReduce programming error rateImprove maneuverabilityTransmissionSoftware deploymentProcess engineeringAir conditioning

The invention discloses a software upgrading method of an air conditioning system. The method comprises the following steps that: an upgrading terminal loaded with upgrading program data is connectedwith the network of the air conditioning system, and the air conditioning system enters an upgrading state; the upgrading terminal acquires the identification data of a to-be-upgraded part in the airconditioning system; whether at least one piece of upgrading program data is uniquely matched with the to-be-upgraded part or not is judged, if at least one piece of upgrading program data is uniquelymatched with the to-be-upgraded part, the upgrading terminal sequentially broadcasts each piece of upgrading program data to each outdoor unit through a bus, and the upgrading program data are forwarded to the connecting parts of the outdoor units through outdoor unit protocol conversion; the to-be-upgraded part judges whether the upgrading program data are upgrading program data matched with theto-be-upgraded part, if the upgrading program data are the upgrading program data matched with the to-be-upgraded part, upgrading is conducted, and response data of successful upgrading are sent to the upgrading terminal through outdoor unit protocol conversion; and if the corresponding to-be-upgraded part is successfully upgraded, the upgrading terminal informs the air conditioning system of quitting the upgrading state. By means of the method, the multiple outdoor units of a multi-split air conditioner can be upgraded, and the upgrading process of operators is simplified.

Owner:GREE ELECTRIC APPLIANCES INC

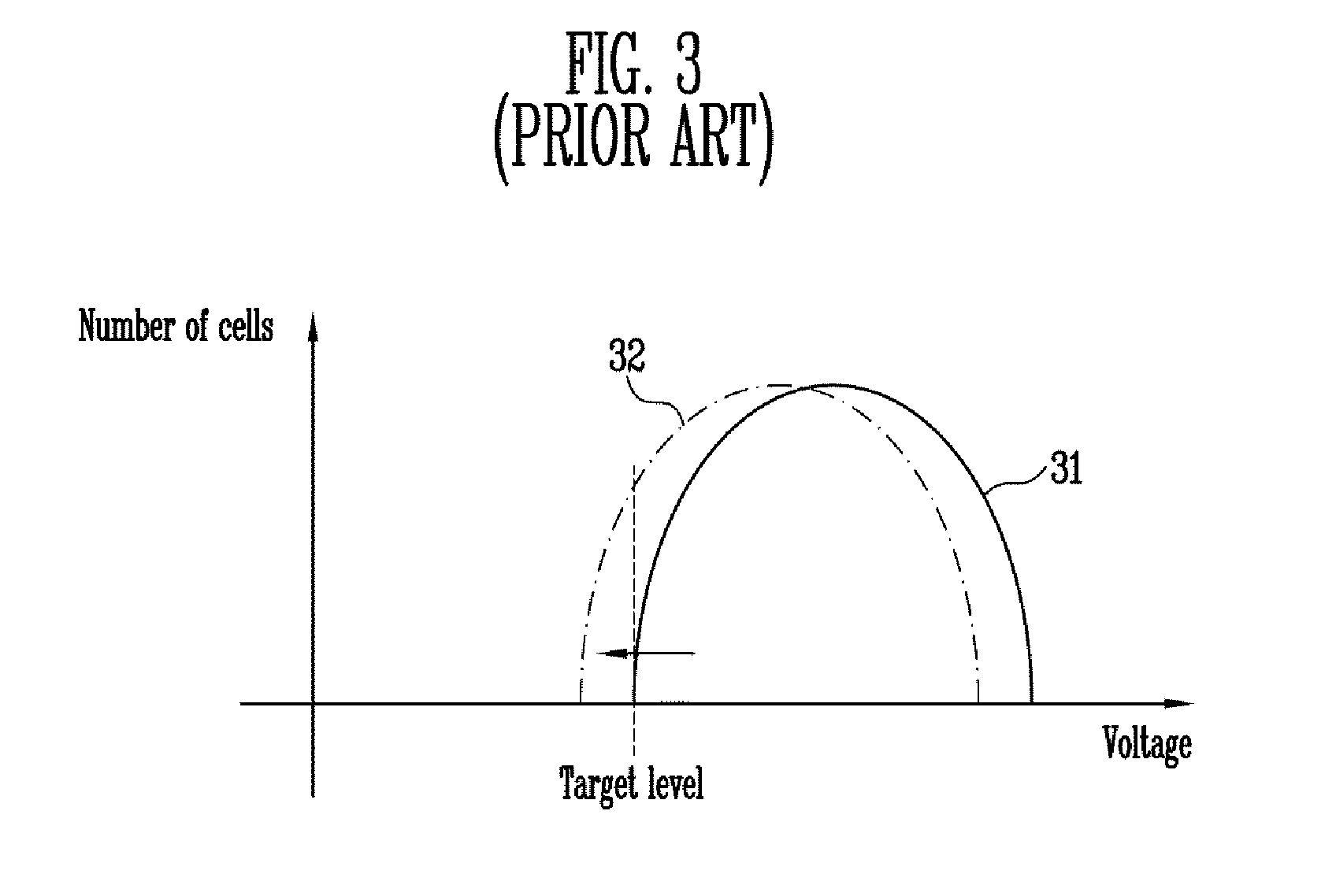

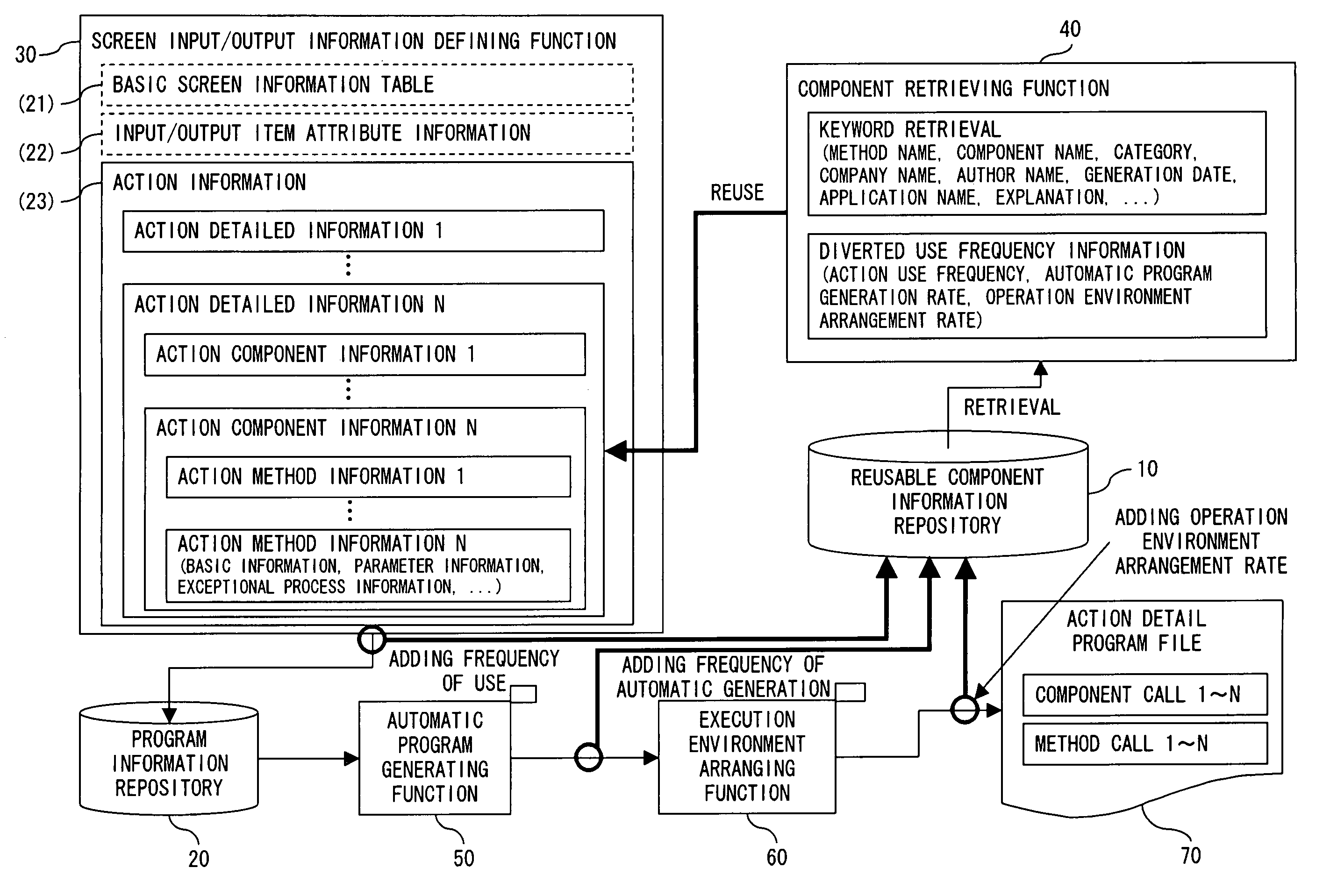

Semiconductor memory device and method of operating the same

ActiveUS8923046B2Improve programming reliabilityRead-only memoriesDigital storageHemt circuitsControl circuit

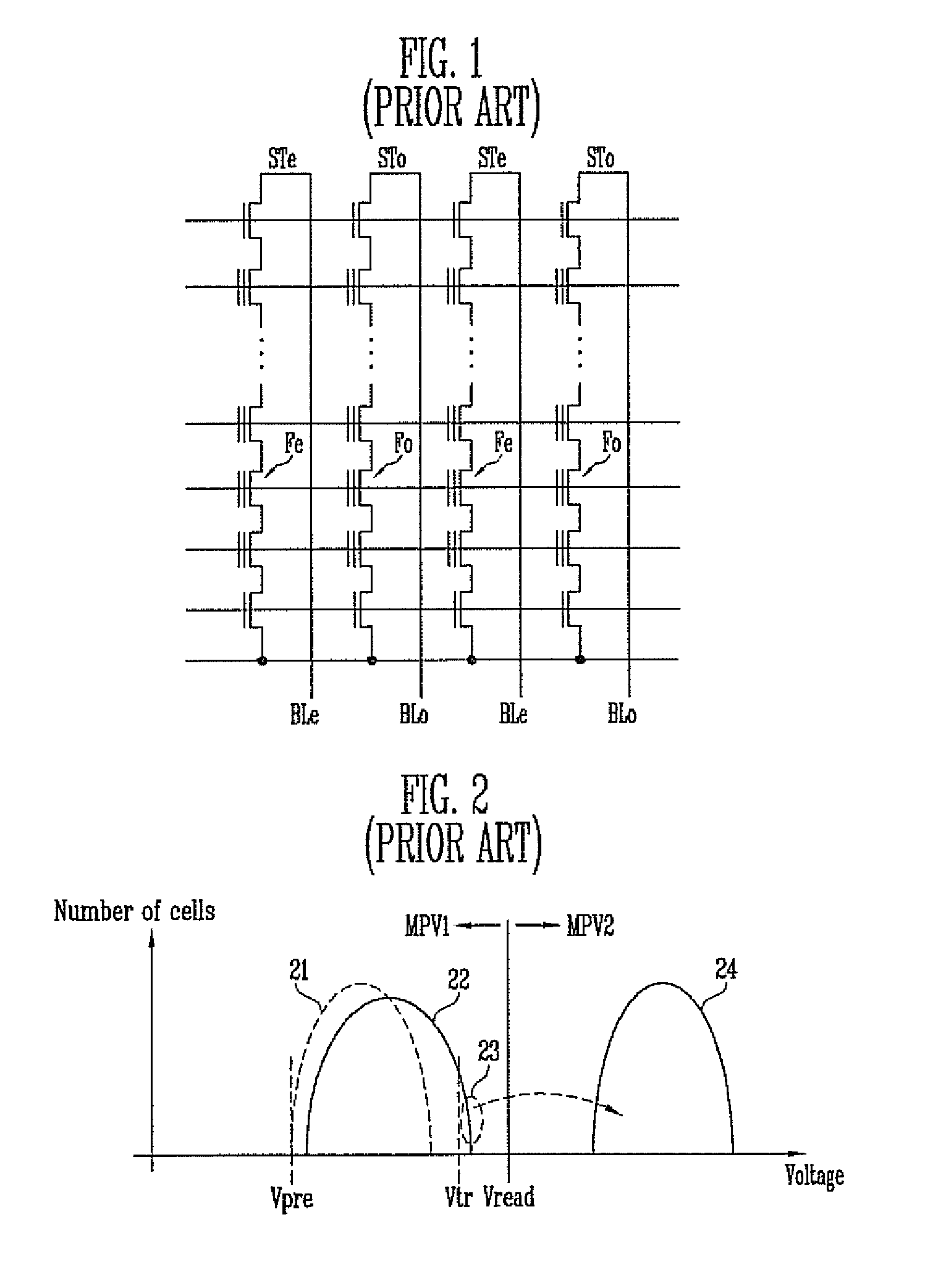

A semiconductor memory device includes a memory cell array including first memory cells and second memory cells connected to at least one word line, a circuit group configured to perform a pre-program operation on the first memory cells using a target voltage and a main program operation on the first memory cells and the second memory cells using a final target voltage, and a control circuit configured to set the target voltage depending on variations in threshold voltages of the first memory cells caused by the main program operation of the second memory cells.

Owner:SK HYNIX INC

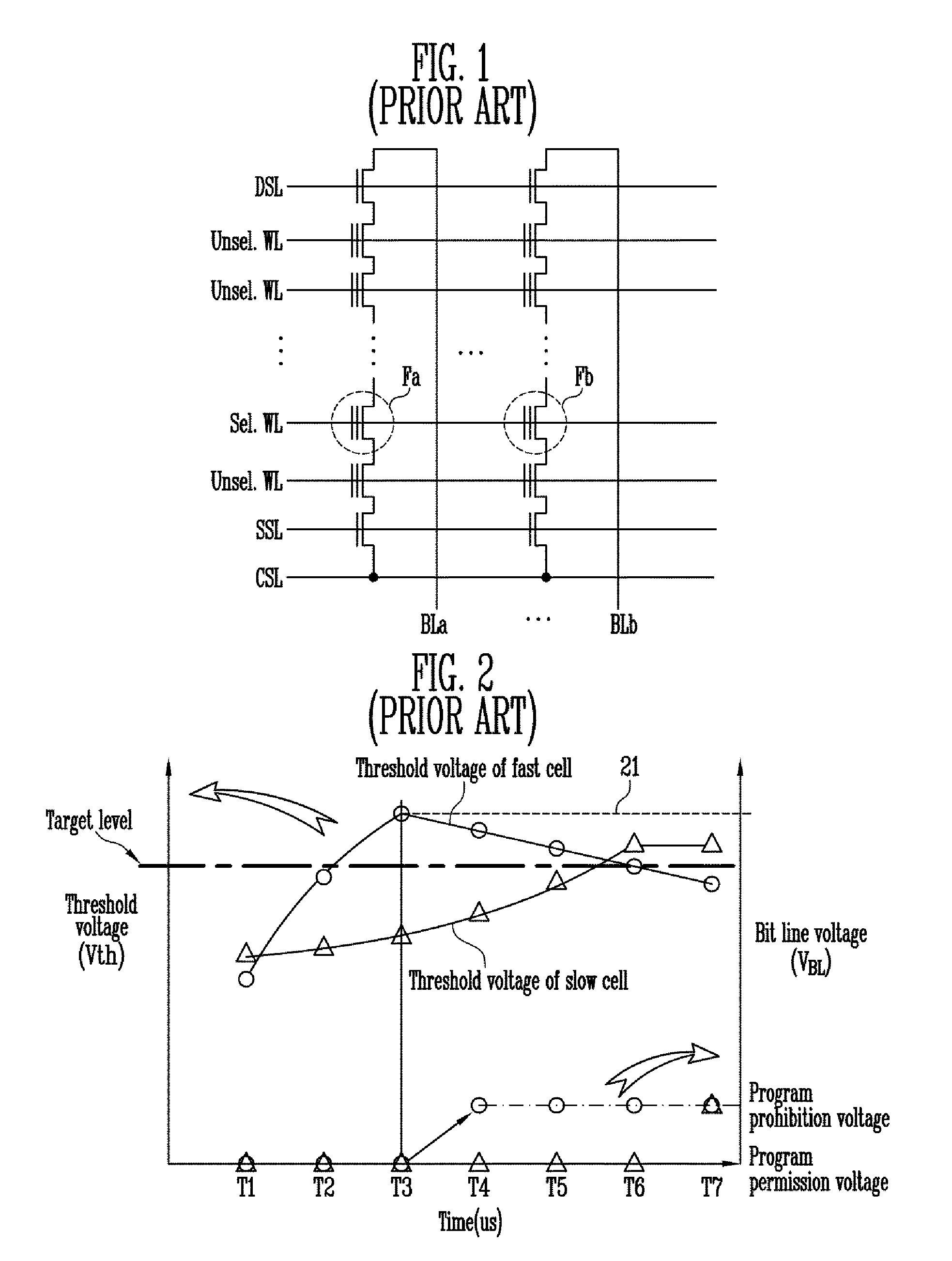

Semiconductor memory device and method of operating the same

ActiveUS20130163334A1Improve programming reliabilityRead-only memoriesDigital storageEngineeringSemiconductor

A semiconductor memory device and a method of operating the same include a circuit group configured to apply a program maintaining voltage between the program prohibition voltage and the program permission voltage to bit lines connected to programmed memory cells to prevent a decrease in threshold voltage.

Owner:SK HYNIX INC

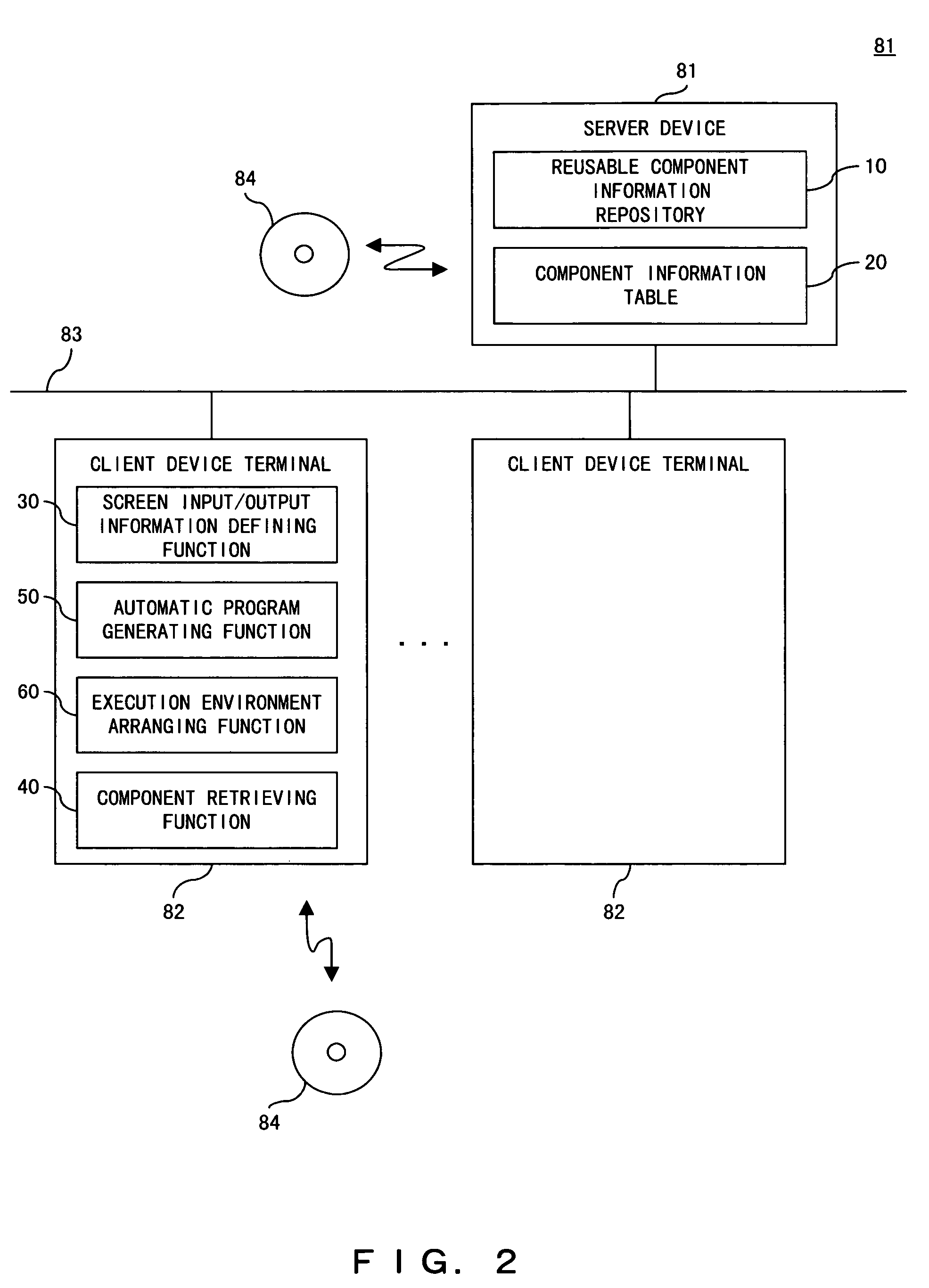

Program, program construction method, storage medium, program construction system, and terminal device

InactiveUS7539712B2Speed up the processImprove programming reliabilityDigital data processing detailsSoftware reuseInformation processingTerminal equipment

An information processing system which constructs a program by combining a plurality of functional units, has an information table for management of components, etc. each of which is a functional unit of a program, and the information table stores plural pieces of management information for individual management of the use record of each component so that the information can be referred to as the reference of reliability when the component is reused, and the management information can be sequentially updated based on the actual use record.

Owner:FUJITSU LTD

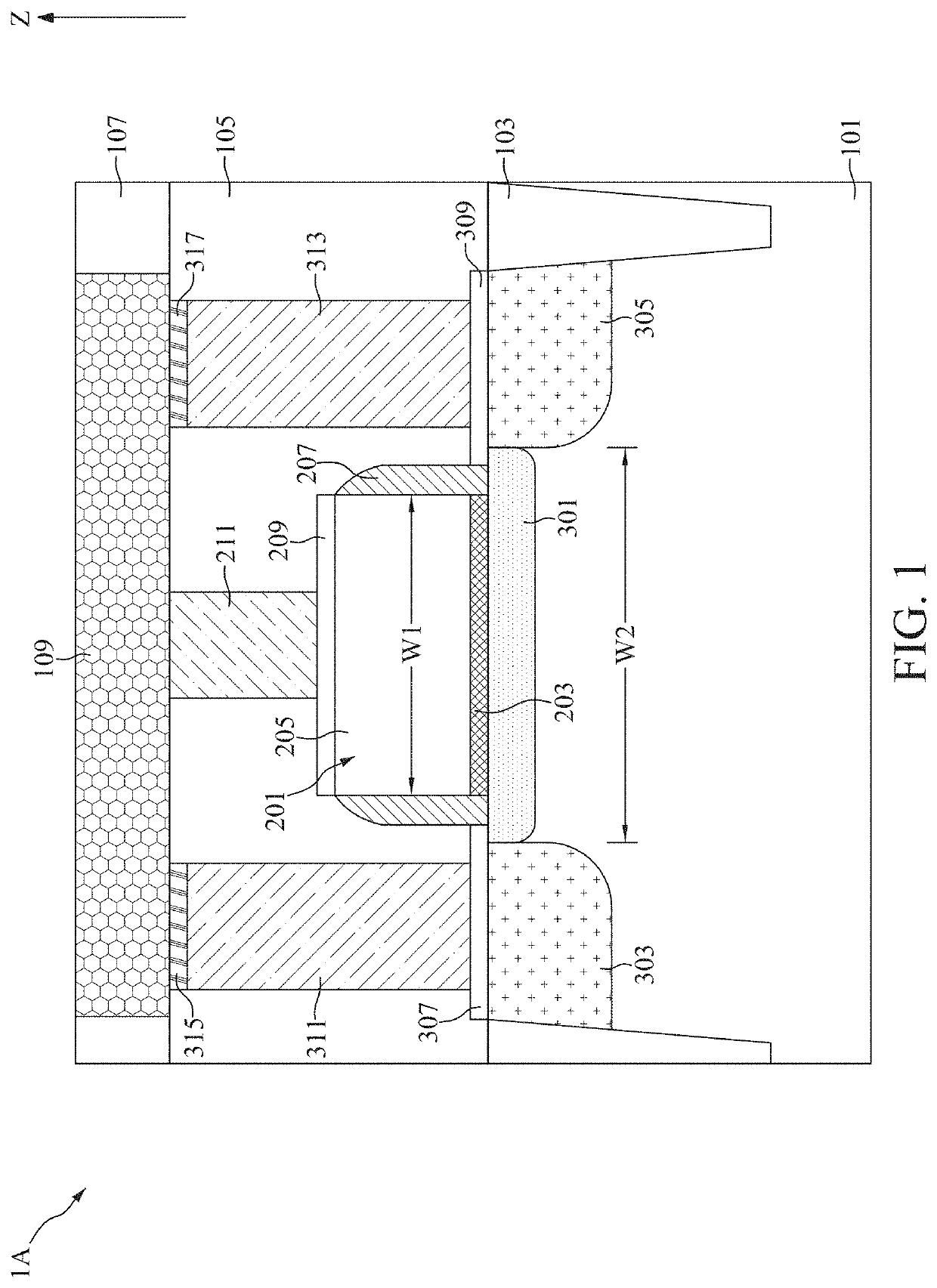

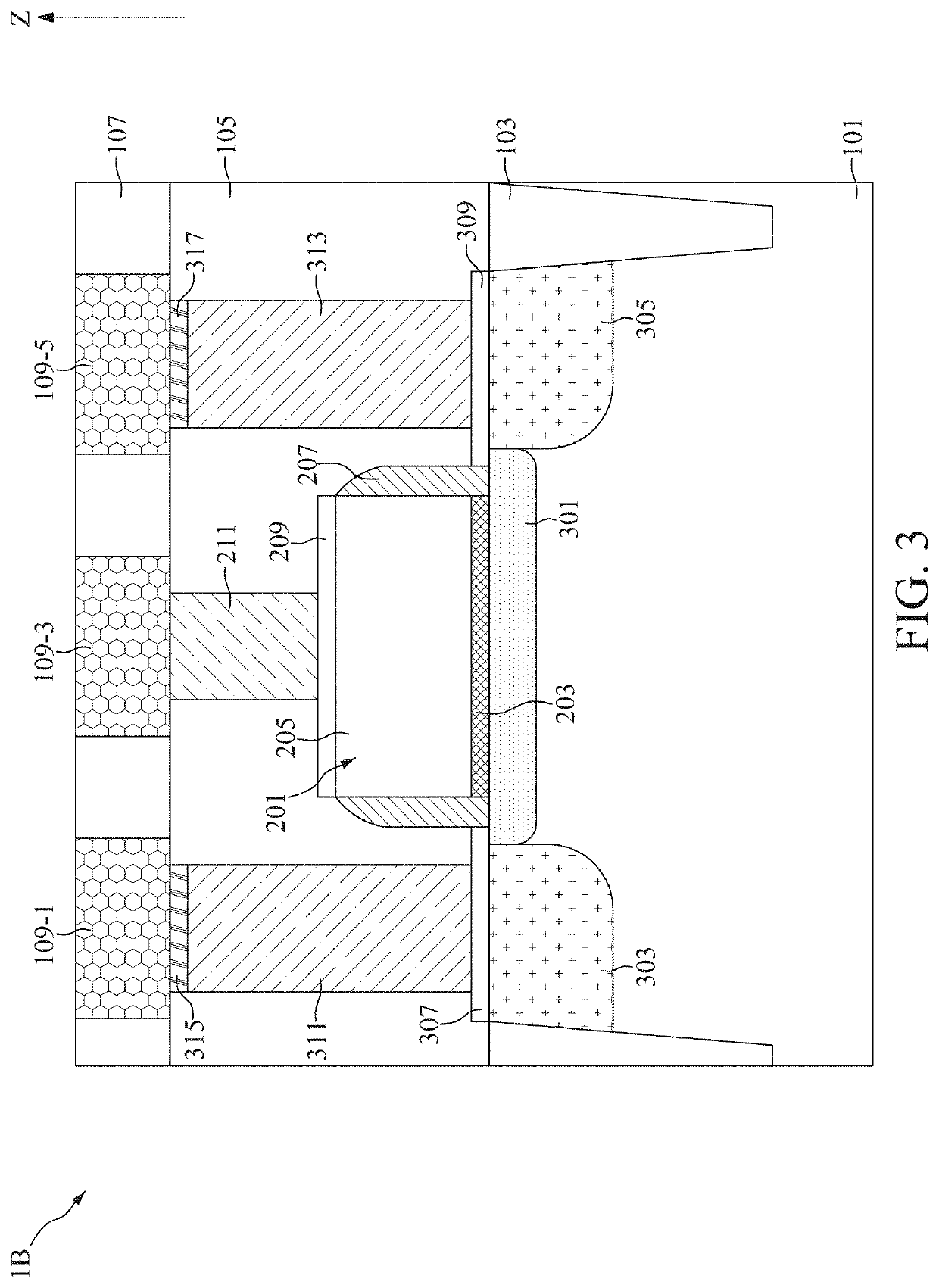

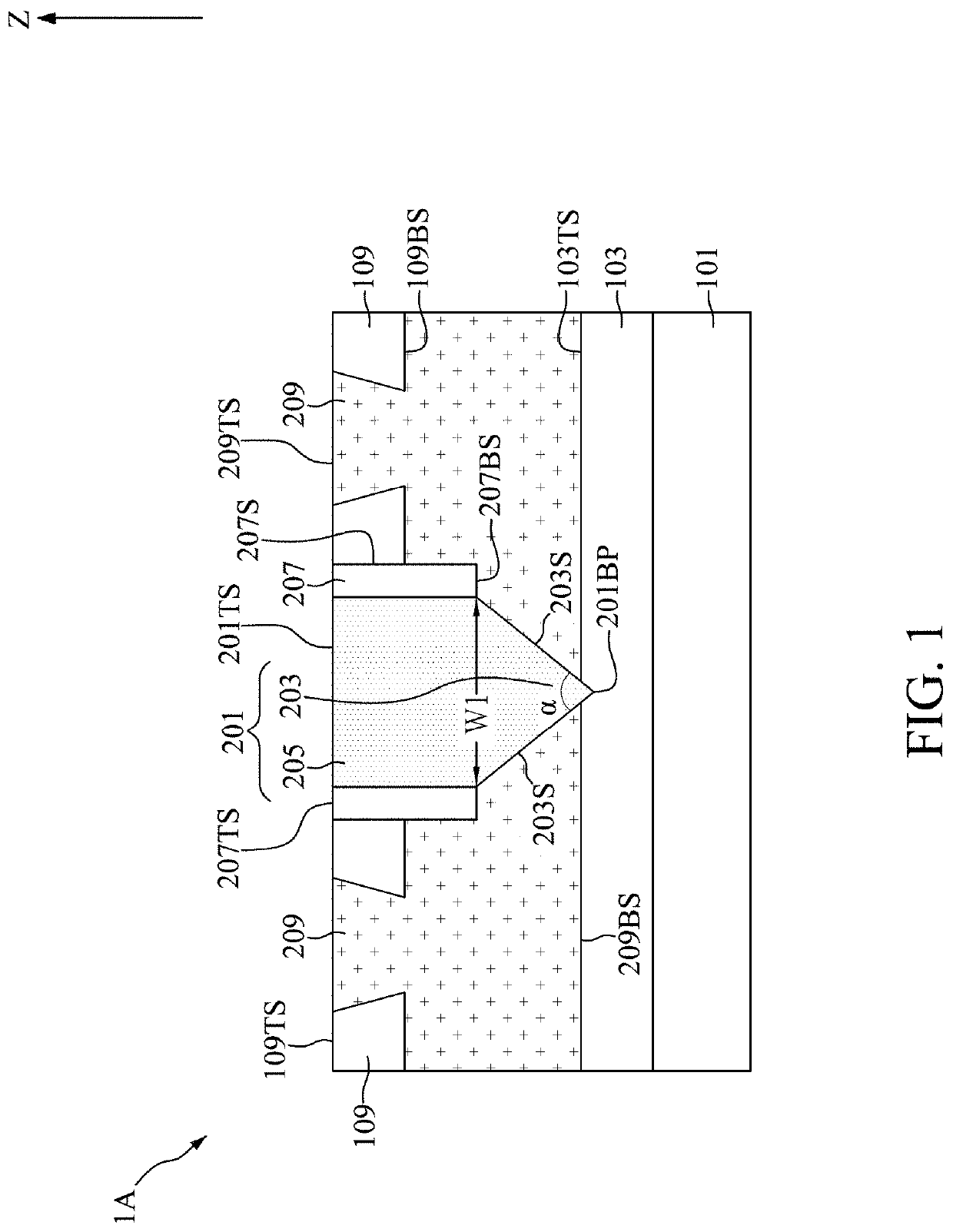

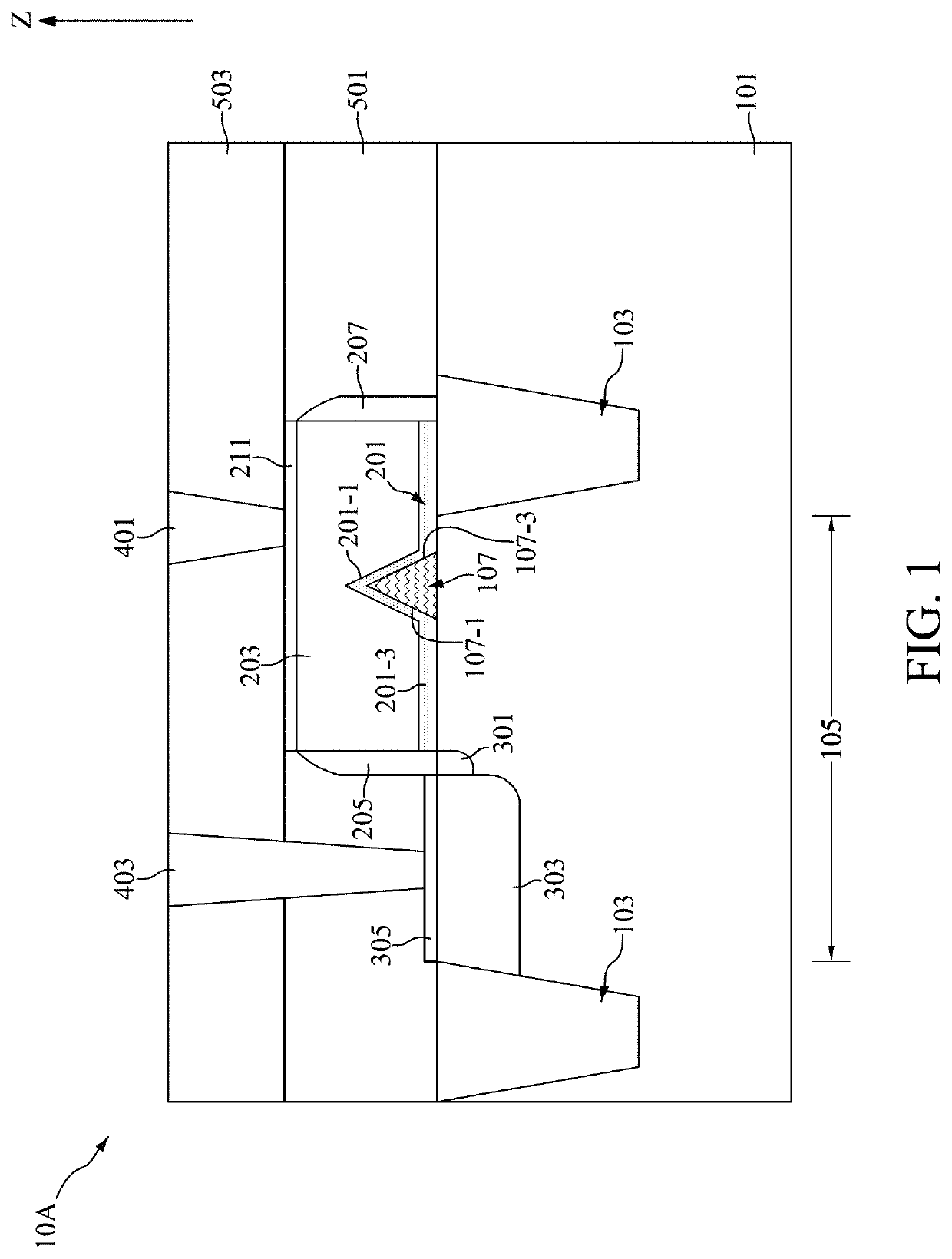

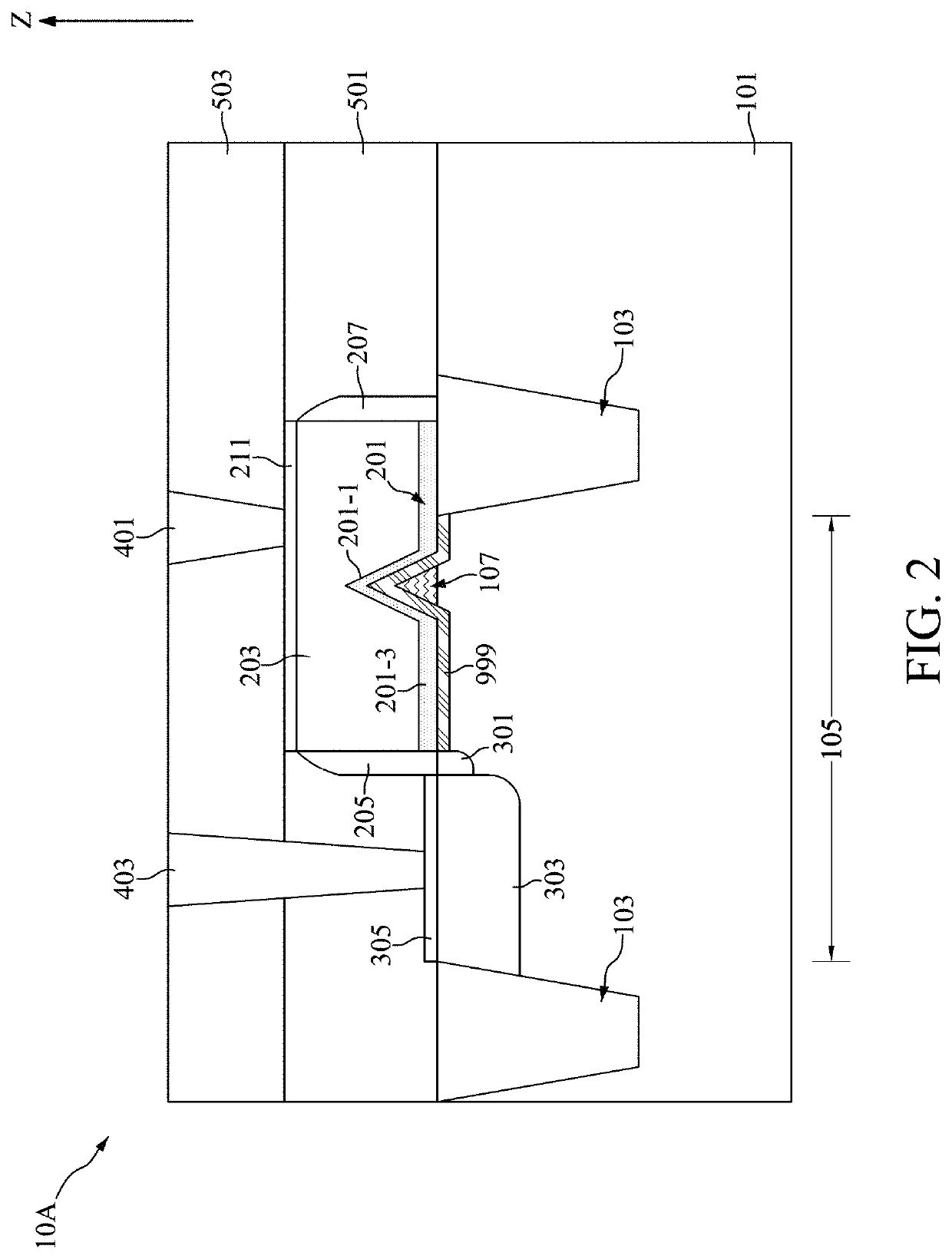

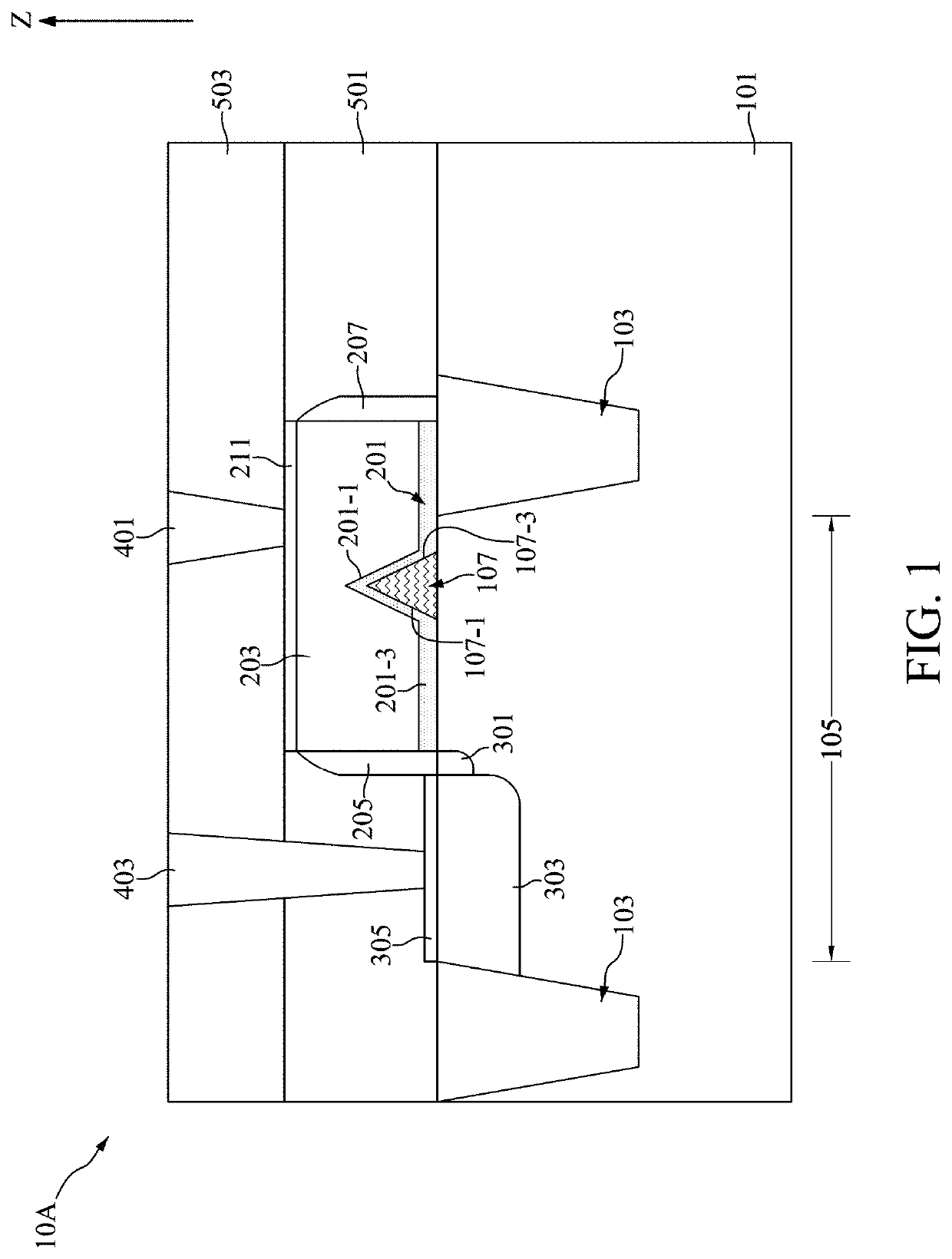

Semiconductor device with programmable element and method for fabricating the same

ActiveUS20220045212A1Increase productionImprove programming reliabilityTransistorSemiconductor/solid-state device detailsGate dielectricDevice material

The present application discloses a semiconductor device and a method for fabricating the semiconductor device. The semiconductor device includes a substrate, a channel region positioned in the substrate, first impurity regions positioned in the substrate and respectively positioned on two ends of the channel region, a gate dielectric layer positioned on the channel region, a gate bottom conductive layer positioned on the gate dielectric layer, first contacts respectively positioned on the first impurity regions, programmable insulating layers respectively positioned on the first contacts, a top conductive layer positioned on the programmable insulating layers and electrically coupled to the gate bottom conductive layer.

Owner:NAN YA TECH

LCD panel driving circuit and LCD

InactiveCN101174037BWon't hurtImprove programming reliabilityStatic indicating devicesLiquid-crystal displayFlexible circuits

Owner:INNOCOM TECH (SHENZHEN) CO LTD +1

E-fuse array circuit and programming method of the same

ActiveUS8817518B2Extension of timeImprove programming reliabilityRead-only memoriesDigital storageComputer engineering

Owner:SK HYNIX INC

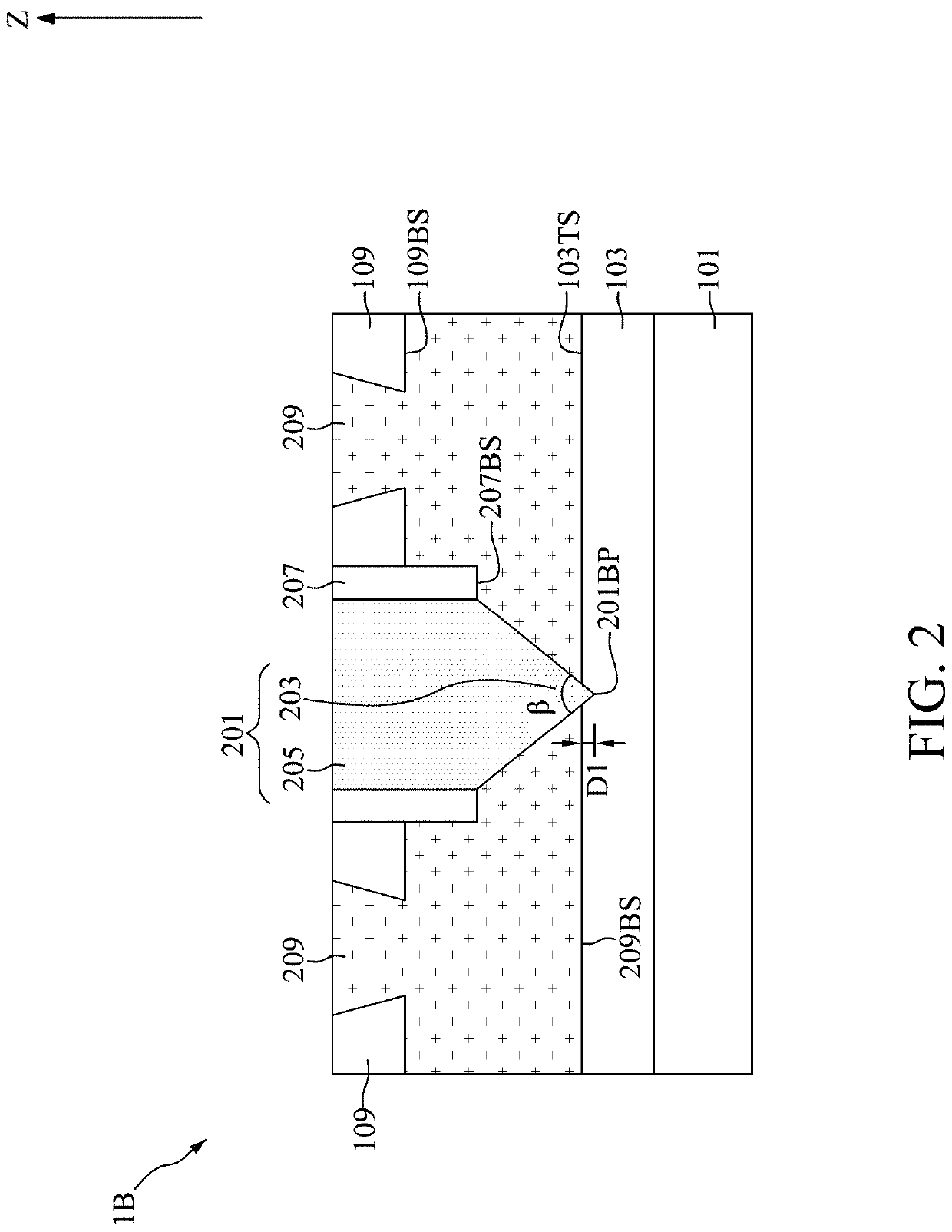

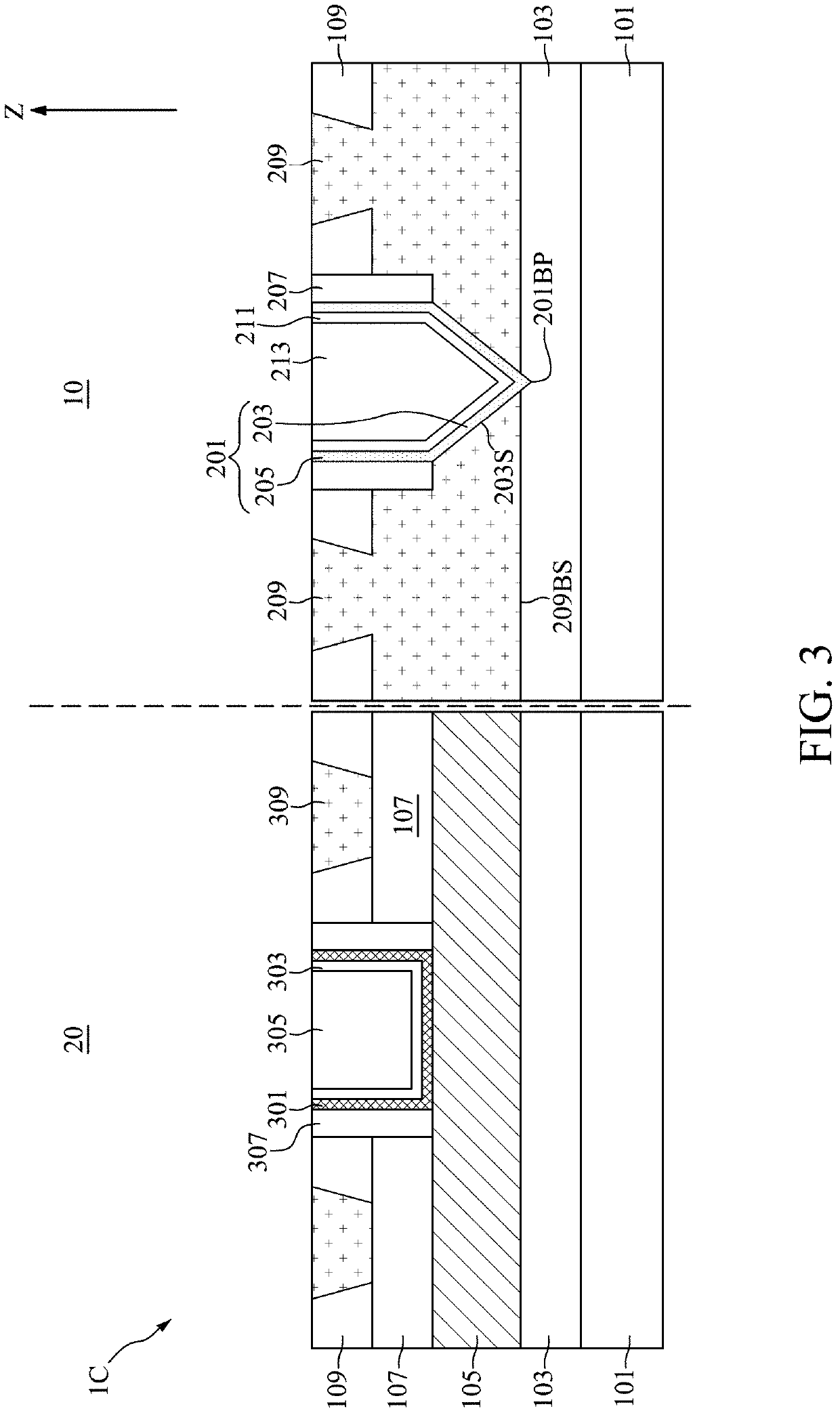

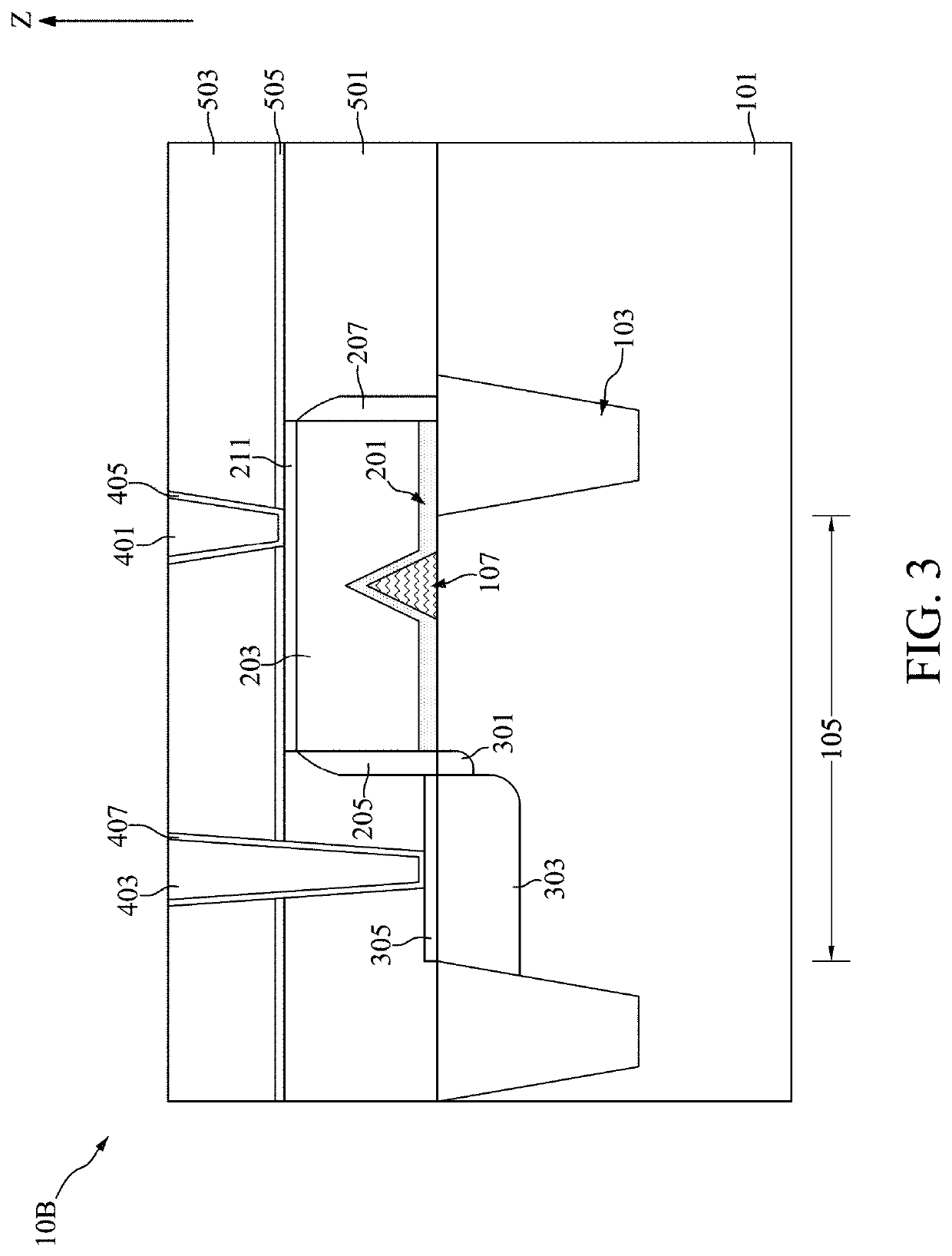

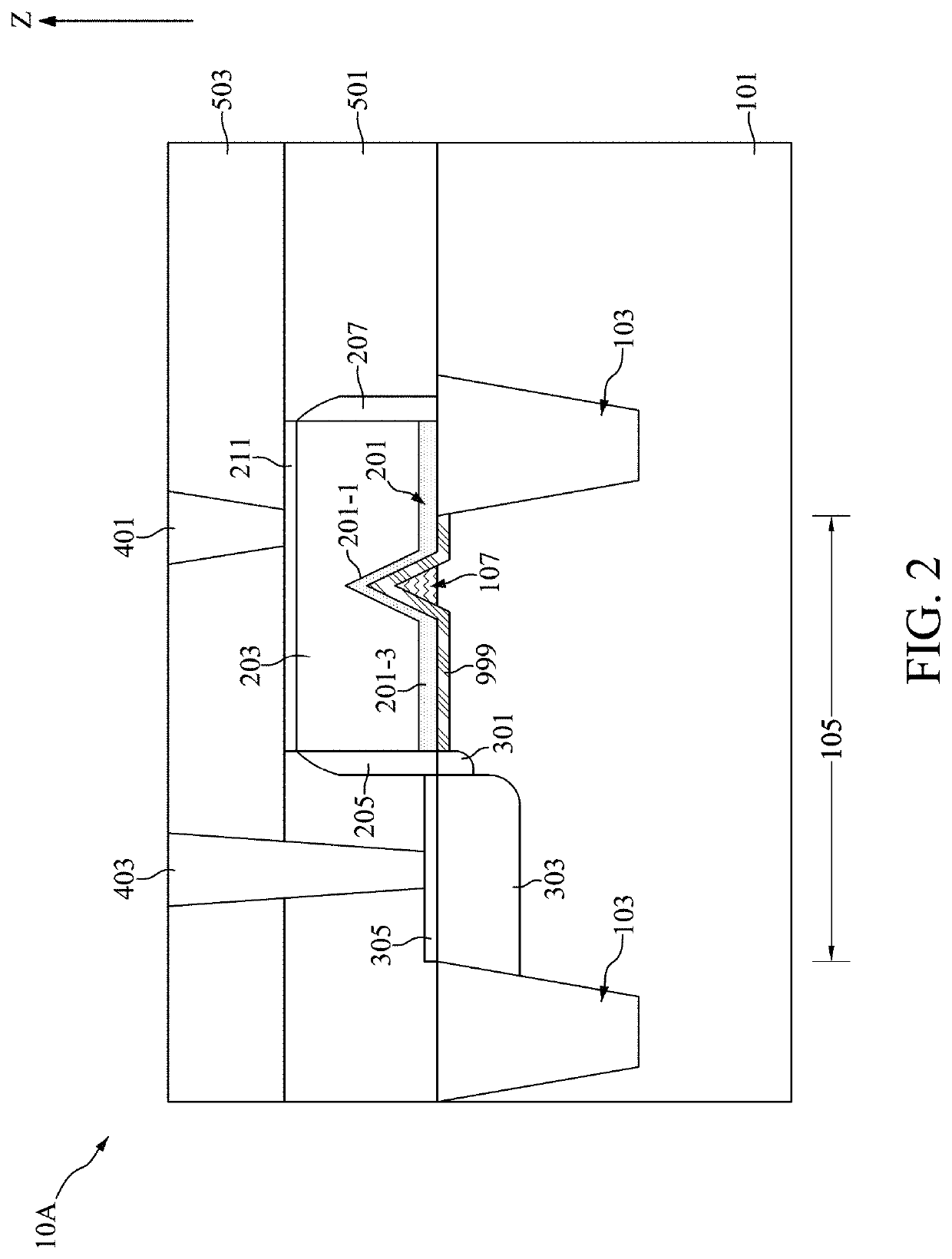

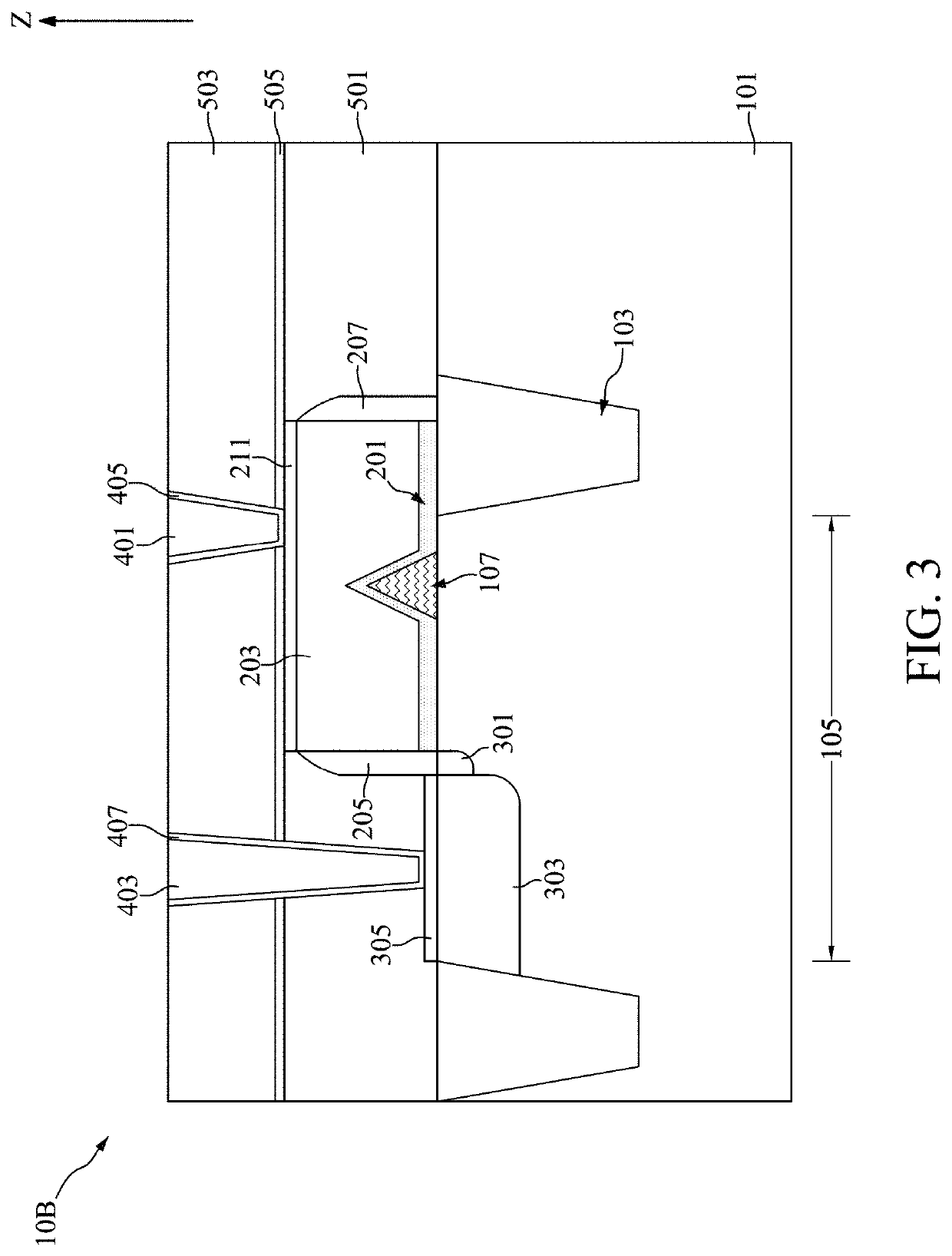

Semiconductor device with programmable feature and method for fabricating the same

ActiveUS11424346B2Reduce complexity and costImprove programming reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialAntifuse

The present application discloses a semiconductor device with a programmable feature such as anti-fuse and a method for fabricating the semiconductor device. The semiconductor device includes a first insulating layer including a peak portion and an upper portion positioned on the peak portion, and first conductive blocks positioned on two sides of the peak portion. A width of the peak portion is gradually decreased toward a direction opposite to the upper portion, and the first conductive blocks are spaced apart by the peak portion.

Owner:NAN YA TECH

Programming circuit for antifuse

ActiveCN104409100BSimple structureFlexible controlRead-only memoriesElectronic switchingElectricityEngineering

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

Information processing apparatus, information processing method, and program

InactiveUS8627372B2Reduce processing loadImprove programming reliabilityTelevision system detailsColor television detailsInformation processingUser identifier

A package identifier generating unit generates, for each unique combination of information on specific items included in a package, a package identifier identifying the combination. A first table registering unit extracts information on the specific items from the obtained package, and registers the information on the specific items, a user identifier identifying a user of a program reproducing apparatus being a transfer source of the package, and the generated package identifier in correspondence with each other, in a first table. A second table registering unit extracts a correspondence relation between the user identifier and the package identifier from the first table, and registers the package identifier corresponding to the user identifier, as a program view history for each user, in a second table. A determining unit determines the package identifier being a difference between program view histories similar to each other registered in the second table.

Owner:SATURN LICENSING LLC

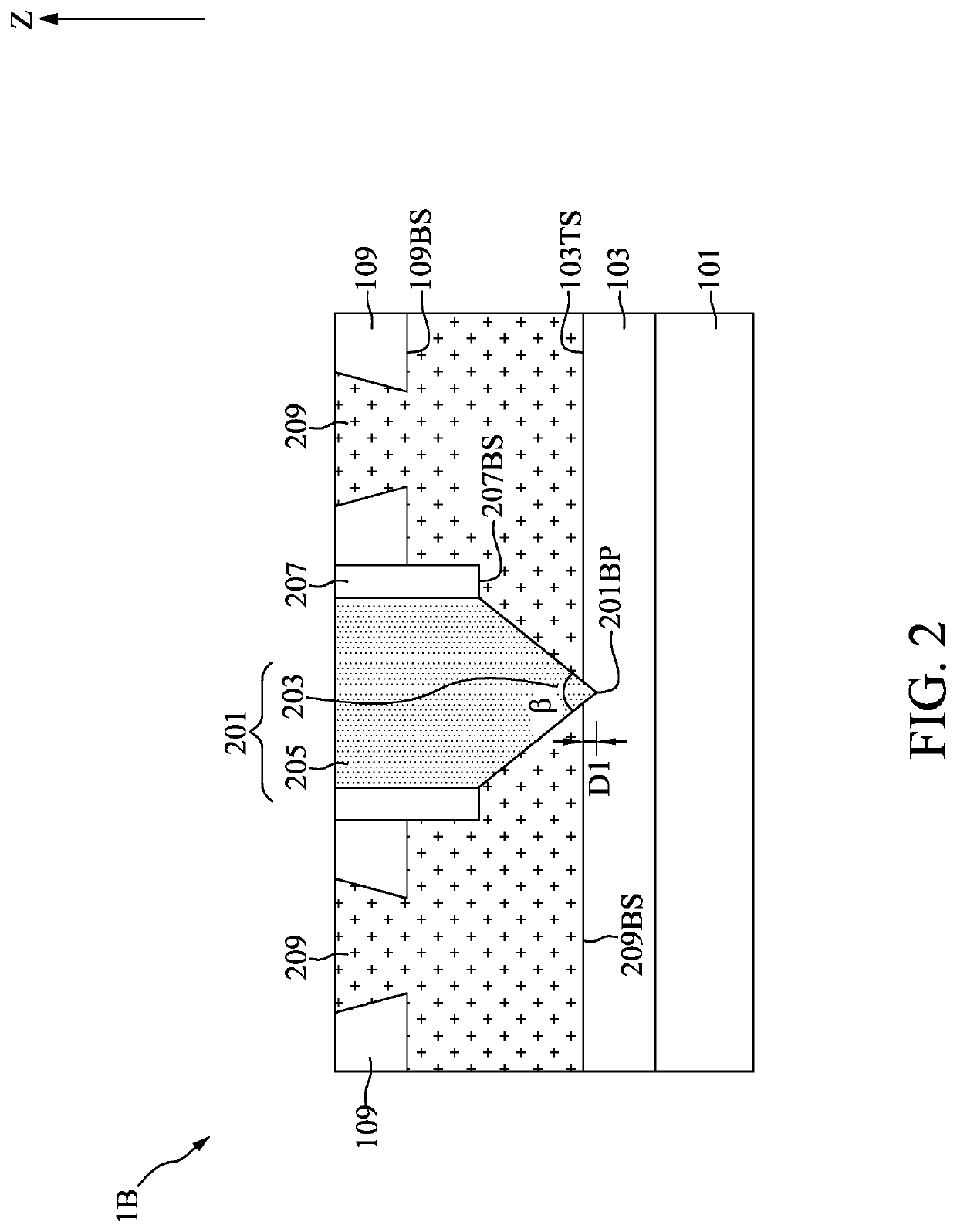

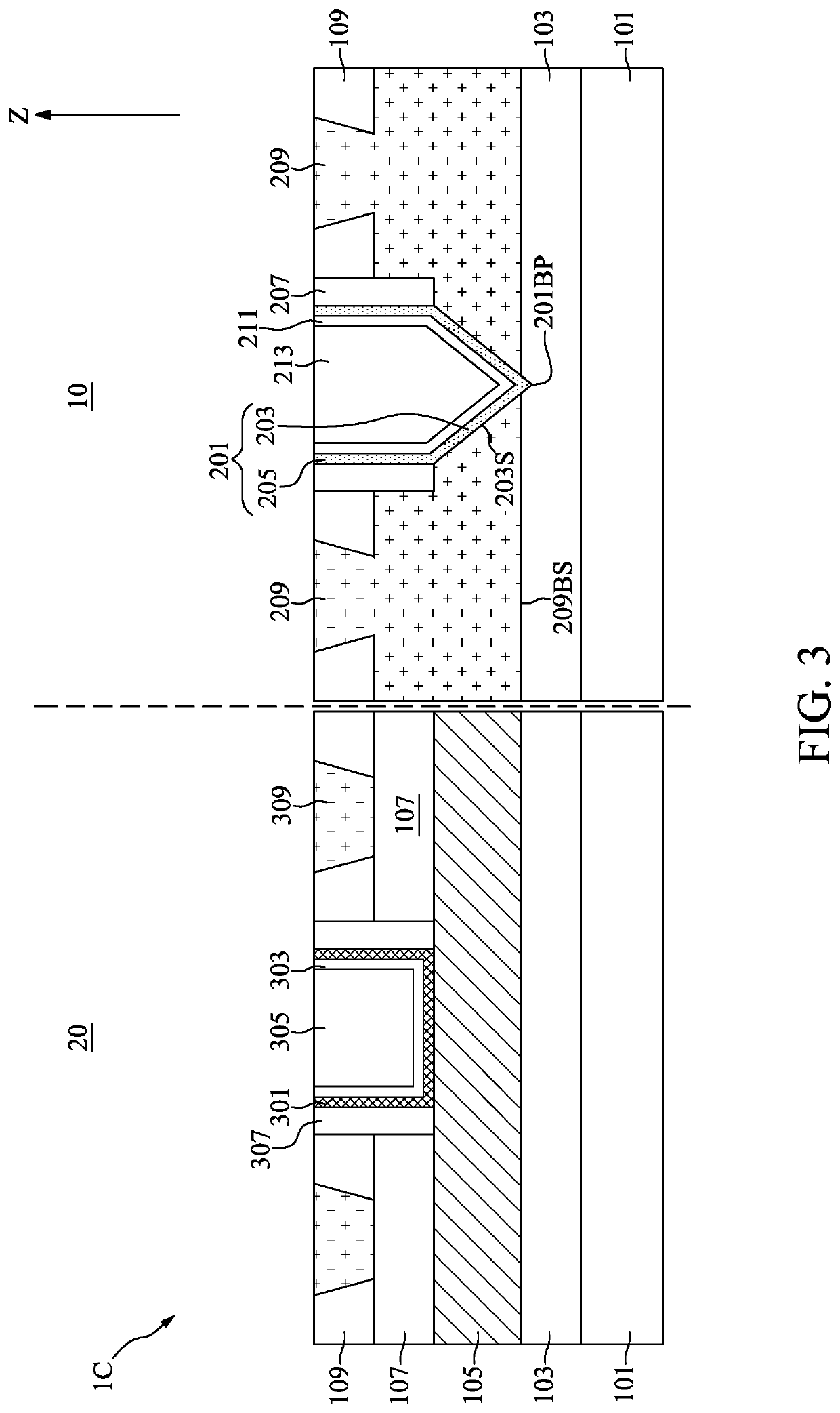

Semiconductor device with programmable anti-fuse feature and method for fabricating the same

ActiveUS11189565B2High carrier mobilityImprove programming reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present application discloses a semiconductor device and a method for fabricating the semiconductor device. The semiconductor device includes a substrate, a peak portion positioned on the substrate, a gate insulating layer positioned on the peak portion and the substrate, a gate bottom conductive layer positioned on the gate insulating layer, and a first doped region positioned in the substrate and adjacent to one end of the gate insulating layer.

Owner:NAN YA TECH

Semiconductor device with programmable Anti-fuse feature and method for fabricating the same

ActiveUS20210257297A1High carrier mobilityImprove programming reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present application discloses a semiconductor device and a method for fabricating the semiconductor device. The semiconductor device includes a substrate, a peak portion positioned on the substrate, a gate insulating layer positioned on the peak portion and the substrate, a gate bottom conductive layer positioned on the gate insulating layer, and a first doped region positioned in the substrate and adjacent to one end of the gate insulating layer.

Owner:NAN YA TECH

Method for fabricating semiconductor device with programmable feature

ActiveUS20220093769A1Reduce complexity and costImprove programming reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

The present application discloses a method for fabricating a semiconductor device with a programmable feature such as anti-fuse The method includes forming a semiconductor fin on a buried insulating layer; forming a dummy gate structure on the semiconductor fin; forming a top insulating layer over the semiconductor fin and covering the dummy gate structure; removing the dummy gate structure and concurrently forming a first trench in the top insulating layer; performing an etch process in the first trench to form a tapered pit separating the semiconductor fin; forming a first insulating layer to completely fill the first trench and the tapered pit; and replacing the semiconductor fin with first conductive blocks.

Owner:NAN YA TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com