Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "Improve bonding accuracy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

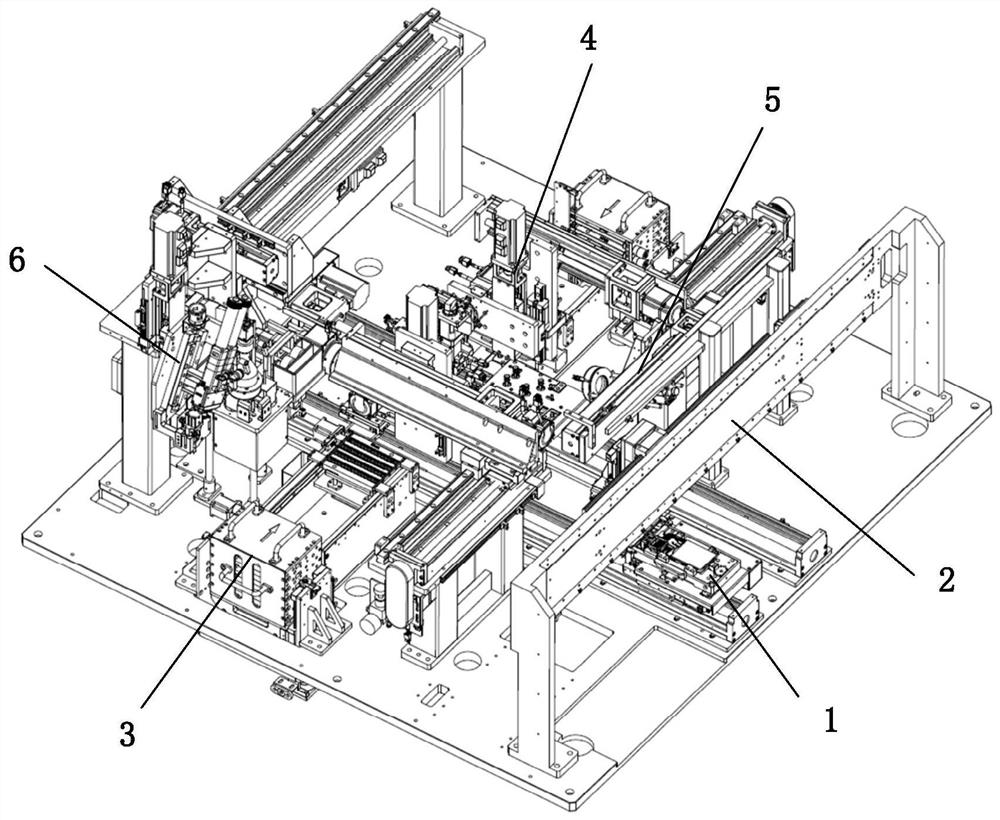

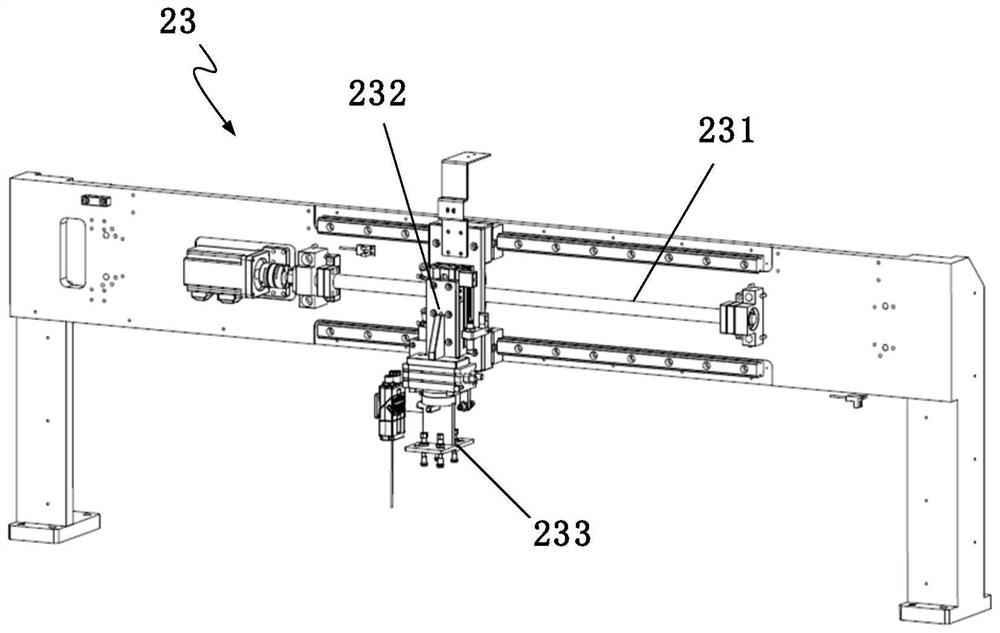

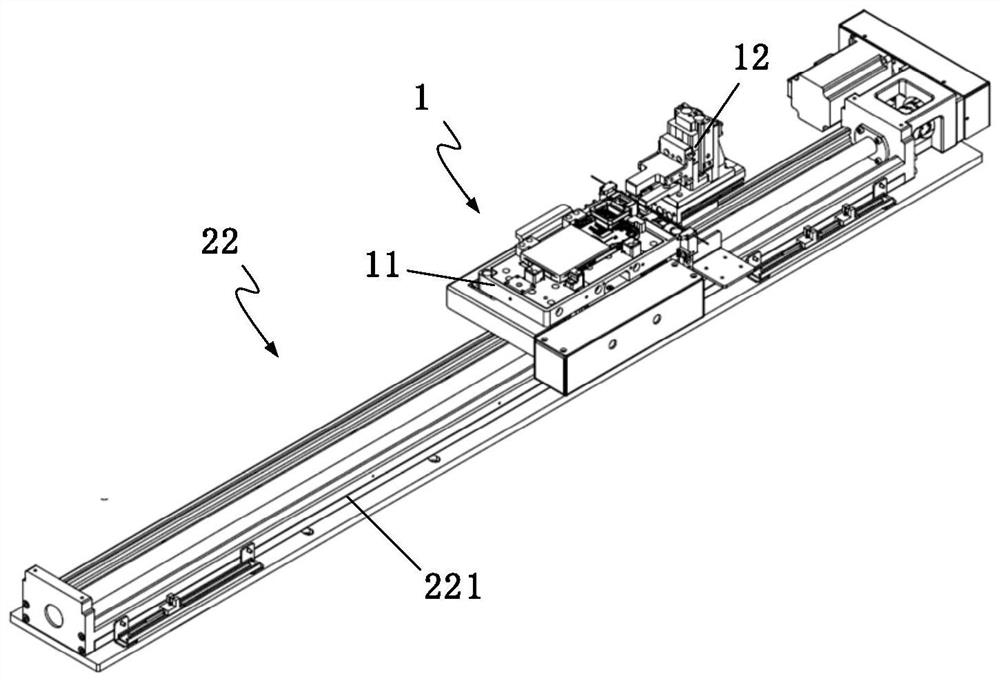

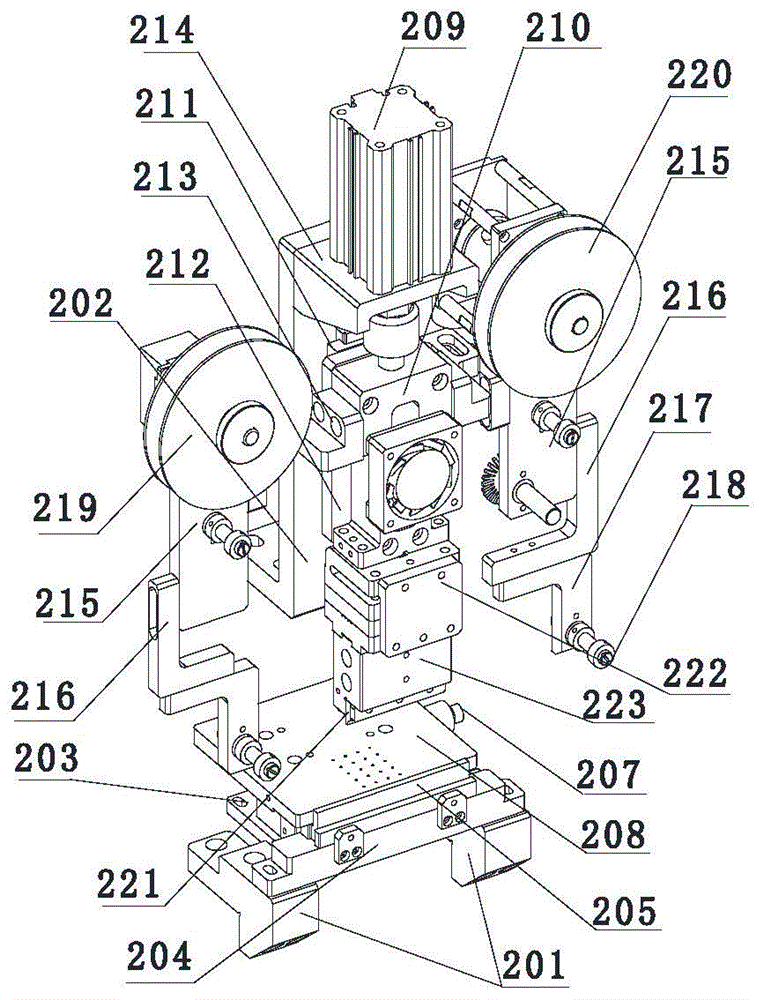

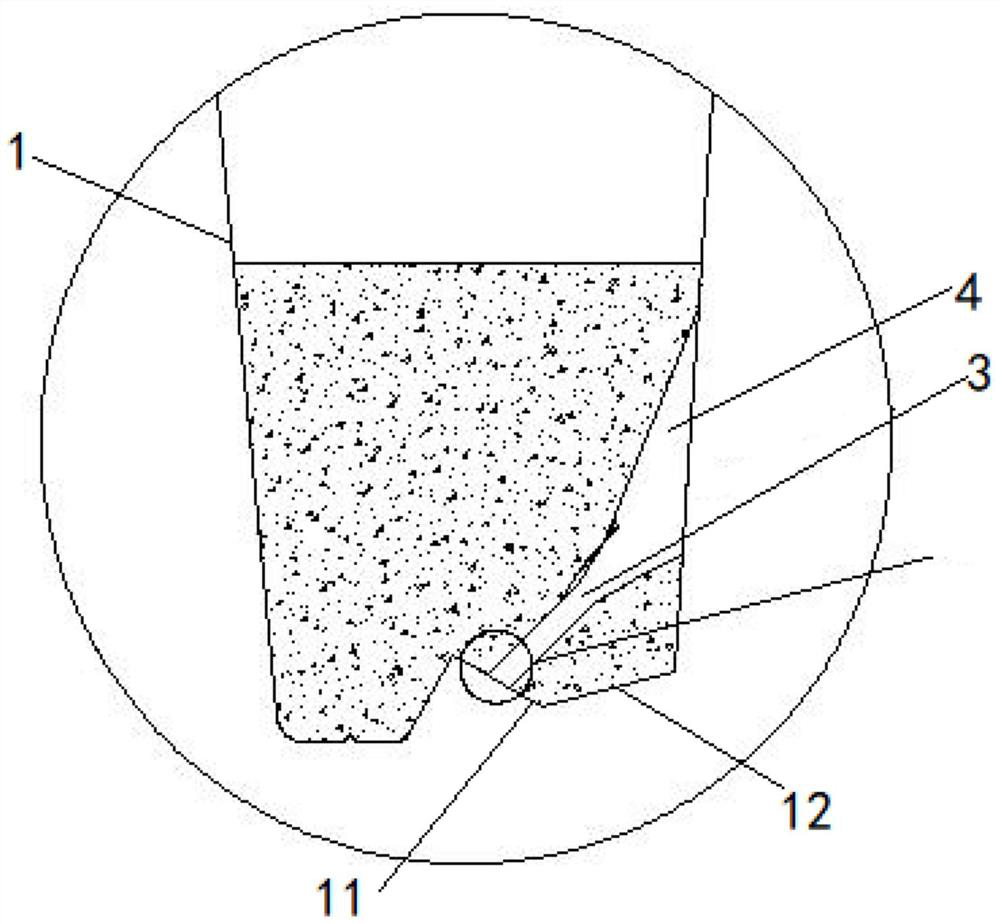

Bonding assembly equipment

InactiveCN112076947AReduce the number of targetingImprove bonding efficiencyLiquid surface applicatorsMaterial gluingEngineeringMechanical engineering

The invention belongs to the technical field of automatic assembly, and discloses bonding assembly equipment which is used for bonding assembly of a first workpiece and a second workpiece. The bondingassembly equipment comprises a jig, a first feeding device, a second feeding device, an assembling device and a glue dispensing device. The jig is configured to clamp the first workpiece. The first feeding device is configured to receive the jig input from the outside and can further transfer the jig to an assembling station and a discharging station. The second feeding device is configured to store and output the second workpiece. And the assembling device can be moved to the position among the second feeding device, the assembling station and the glue dispensing mechanism so as to pick up the second workpiece provided by the second feeding device, and after the glue dispensing device coats glue onto the bonding part of the second workpiece, the second workpiece can be bonded and assembled to the first workpiece located at the assembling station. The bonding assembly equipment provided by the invention can be used for efficiently carrying out bonding assembly operations.

Owner:BOZHON PRECISION IND TECH CO LTD

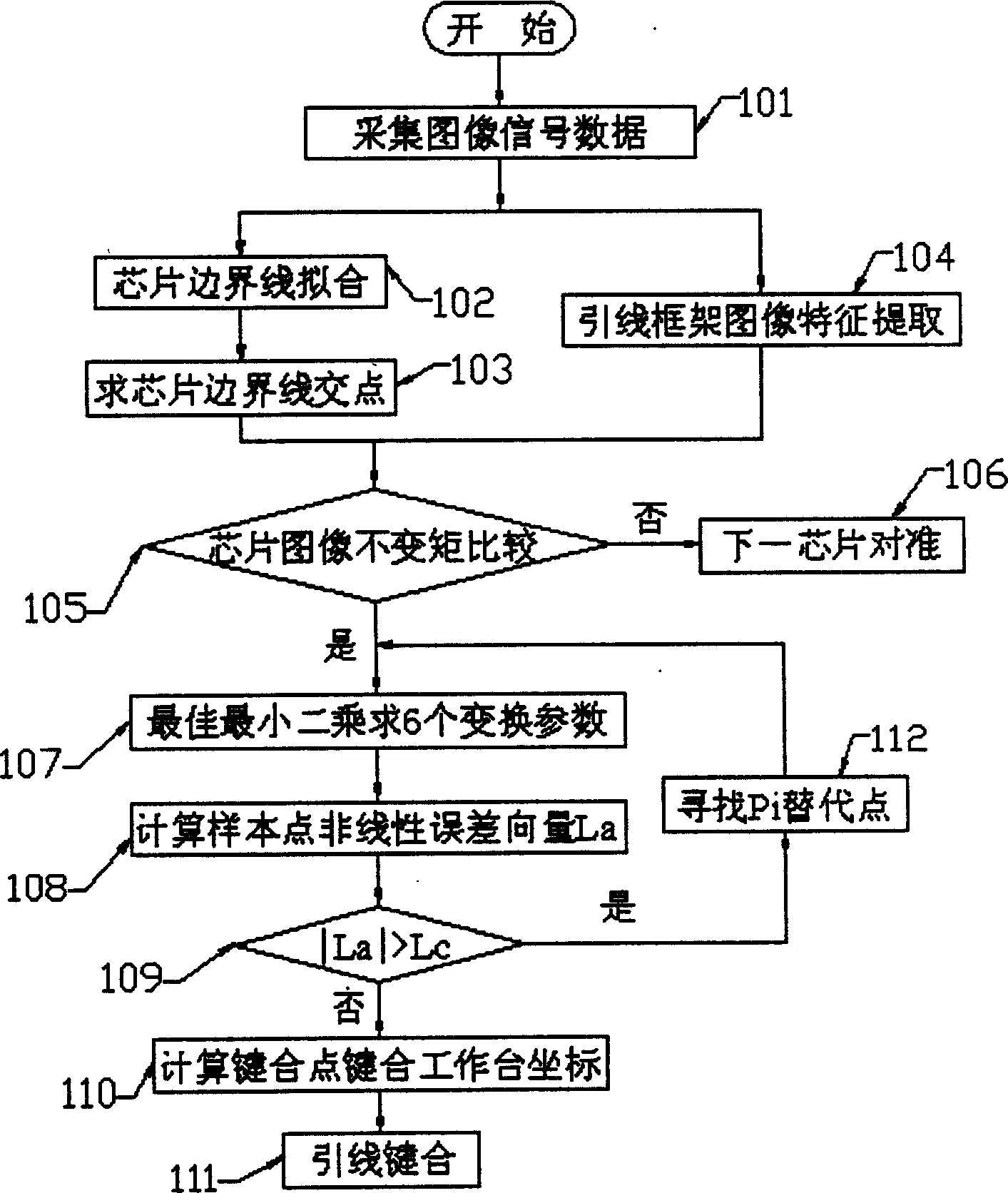

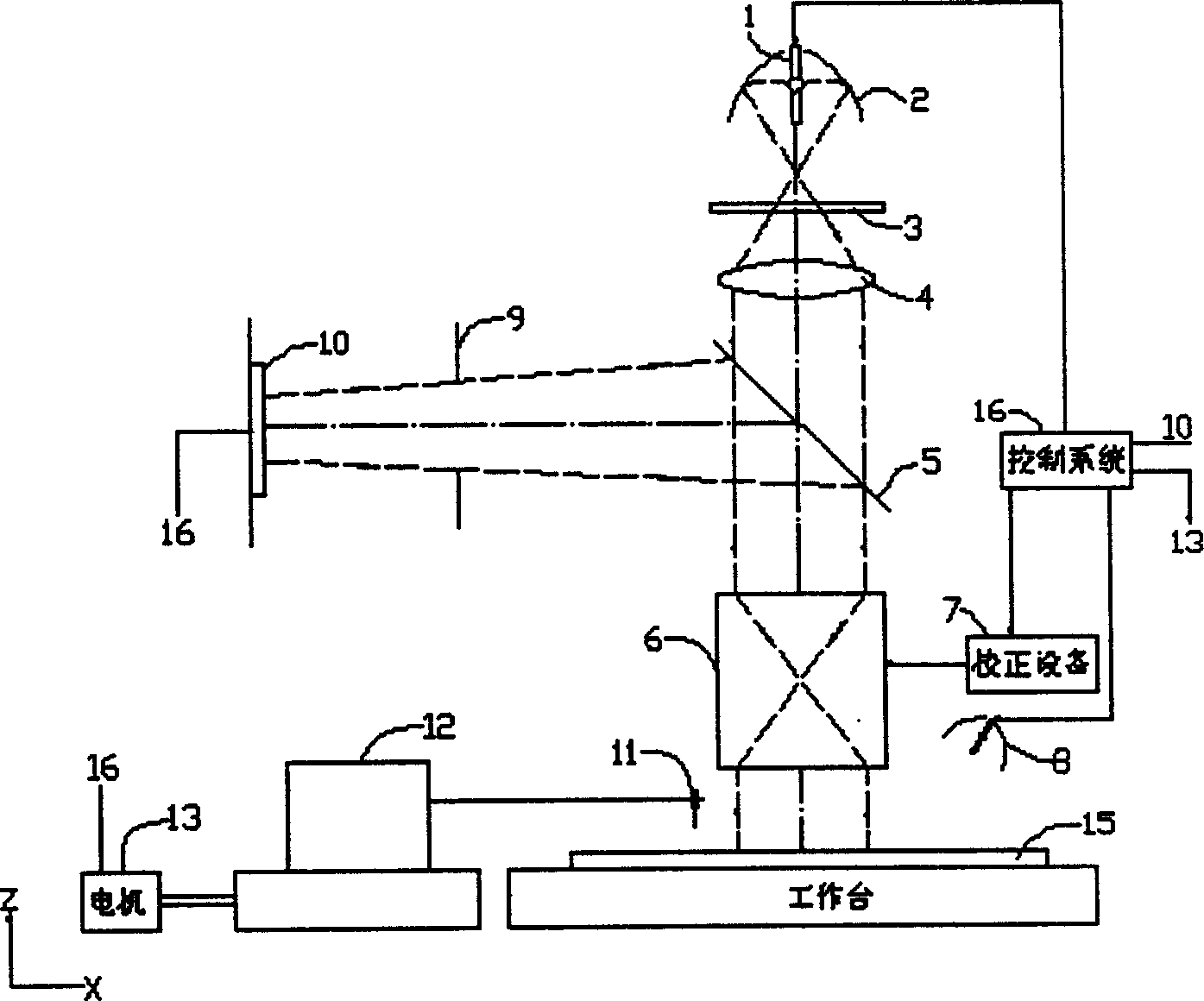

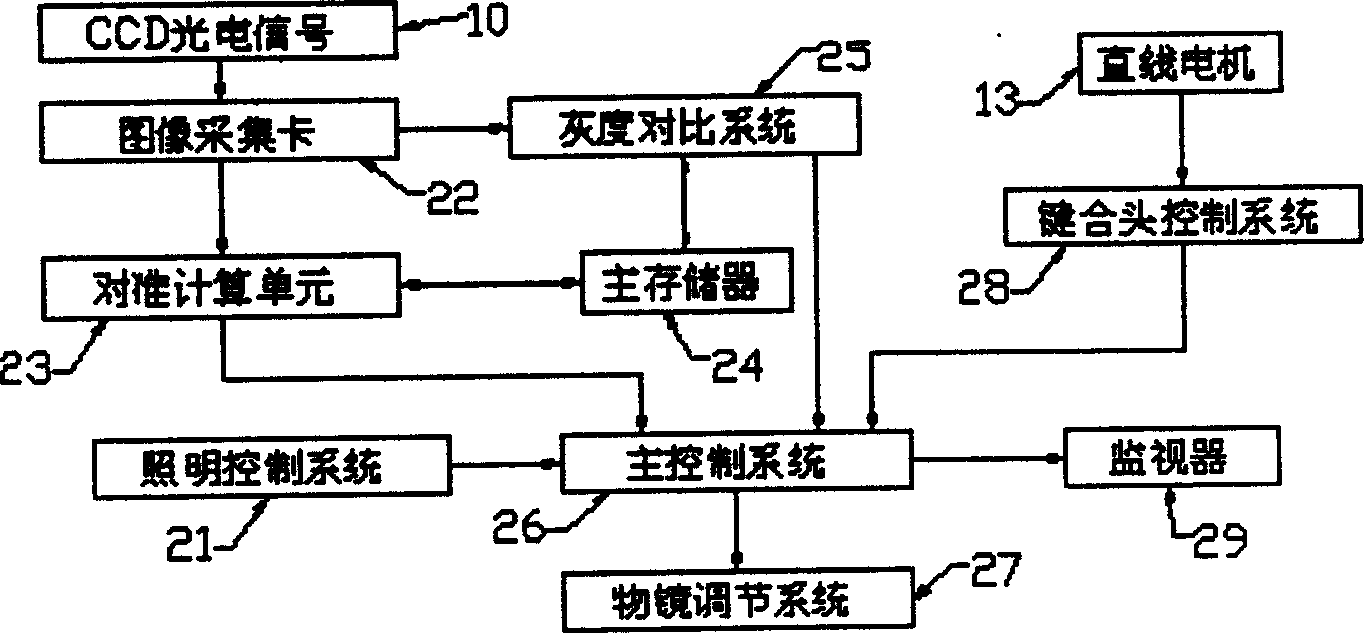

Integrated circuit chips visual aligning method

InactiveCN1604294AIncrease productivityAccurate and Efficient AlignmentSolid-state devicesSemiconductor/solid-state device manufacturingWire frameIntegrated circuit

It is an integration circuit chip vision aligning method belonging to integration circuit chip seal method, which comprises the following steps: to select sample from the lead wire frame and chip; to get the sample measurement coordinates by image process and to measure the defect chip by image constant moment; to get the chip position transformation parameters to get the coordinates; to get the sample non-linear error by minus measurement coordinates from computation coordinates till the error is within the permitted value; finally to transform the bonding arranged coordinates into bonding workbench displacement coordinates.

Owner:HUAZHONG UNIV OF SCI & TECH

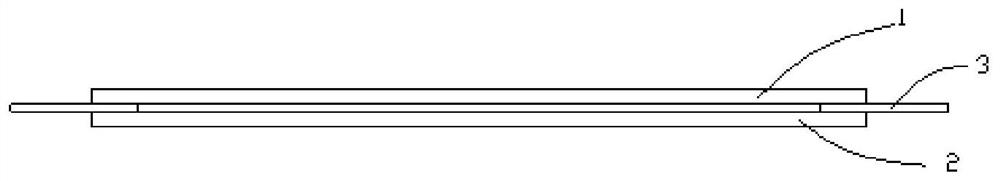

Glass circuit board based FPC (flexible printed circuit) board hot-pressing device, processing system and method

ActiveCN104582305AEfficient crawlingShorten spin timePrinted circuit assemblingAnisotropic conductive filmEngineering

The invention discloses a glass circuit board based FPC (flexible printed circuit) board hot-pressing device, processing system and method. The hot-pressing device comprises a rotating platform capable of rotating intermittently, wherein the rotating platform is provided with two layers of fixing boards which are mutually parallel and can rotate simultaneously, one layer is hot-pressing fixing board used for fixing hot-pressing assemblies, the other layer is a jig fixing board for fixing jig assemblies, the rotating platform is divided into a plurality of station areas, and one hot-pressing assembly and one jig assembly are arranged in each station area; each hot-pressing assembly comprises a lifting control mechanism, a hot-pressing head and a buffering mechanism; a loading platform, a first preset platform, an ACF (anisotropic conductive film) attachment assembly, a second preset platform, the hot-pressing device and an unloading platform are mounted on a mounting platform. The work efficiency of the hot-pressing device can be improved, the area occupied by the equipment can be reduced, and the cost is saved.

Owner:SHENZHEN LIANDE AUTOMATION EQUIP

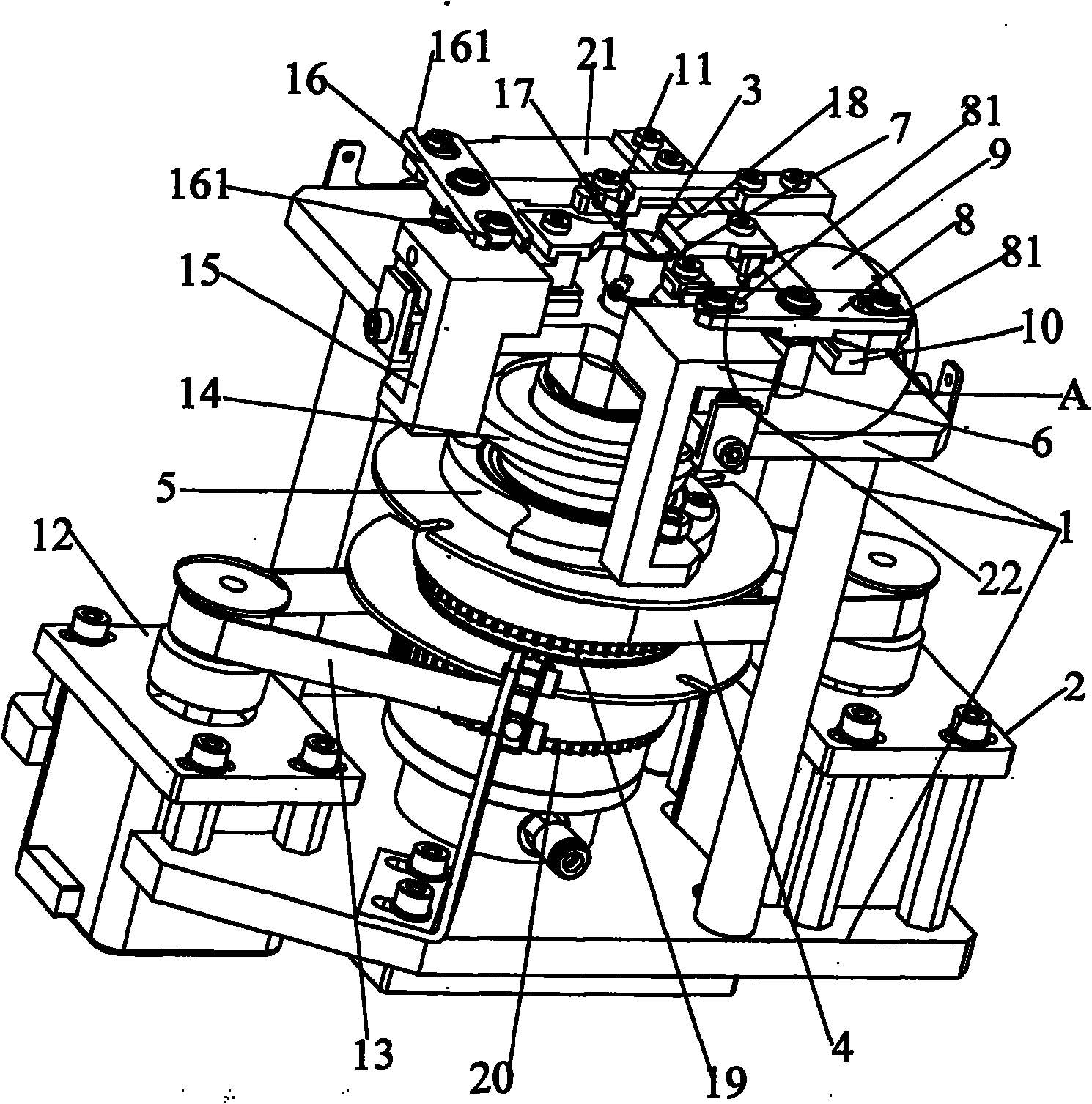

COG chip inversion bonding device

InactiveCN101714500AImprove bonding accuracyPrevent movementSemiconductor/solid-state device manufacturingDie bondingElectrical and Electronics engineering

The invention discloses a COG chip inversion bonding device which comprises a precalibration clamping device, a base plate positioning device and a delivering device, wherein the precalibration clamping device calibrates the position of a chip; the base plate positioning device positions a glass base plate bonded with the chip; the delivering device delivers the chip and the glass base plate; the precalibration clamping device and the base plate positioning device are sequentially fixed on a base; and the delivering device is respectively connected with drive parts on the precalibration clamping device and the base plate positioning device. The traditional delivering device chip is placed in the position of the precalibration clamping device, and the precalibration clamping device chip carries out precalibration; the position of the glass base plate on the base plate positioning device is calibrated by the base plate positioning device; and finally, the control device controls the clamping device to bond the chip on the glass base plate. Because the positions of the chip and the glass base plate are respectively calibrated before the chip is bonded, the bonding precision of the chip can be improved.

Owner:SUNEAST ELECTRONICS TECH SHENZHEN +1

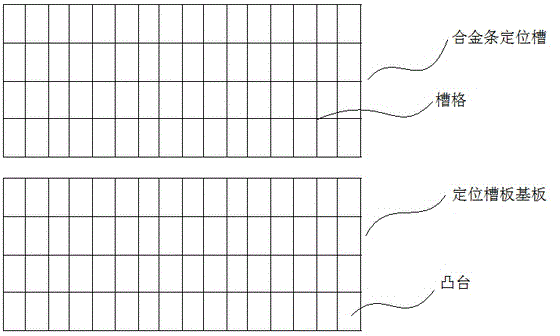

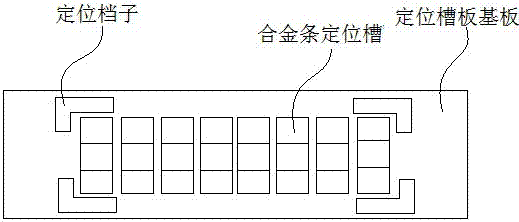

Single-face bonding method suitable for hard alloy strips in hard alloy hard-face machining process and application

ActiveCN104976201APrecise processing sizeHigh speedFastening meansWelding apparatusAdhesive beltAlloy

The invention provides a single-face bonding method suitable for hard alloy strips in a hard alloy hard-face machining process and application. A locating groove plate for bonding is scientifically designed, the hard alloy strips are placed on the locating groove plate, the hard alloy strips are bonded through punched single-face adhesive tape, and the hard alloy strips or blocks are fixed through spot welding; and then the adhesive tape is placed on a steel surface of a to-be-machined component, and through spray welding, bead weld and grinding, the steel surface is machined into a hard surface. According to the method, the aim that a large number of hard alloy strips are bonded at a time is simply and easily achieved, the bonding efficiency is greatly improved, and the conditions that due to manual operation, the bonding angles are different, and the bonding intervals are uneven are avoided; the bonding precision is improved, and wear resistance of the product hard surface can be effectively ensured and improved; and the method can be well applied to the aspect of hard-face machining of centering guides or TC bearings of drilling tools or screw drilling tools.

Owner:株洲金韦硬质合金有限公司

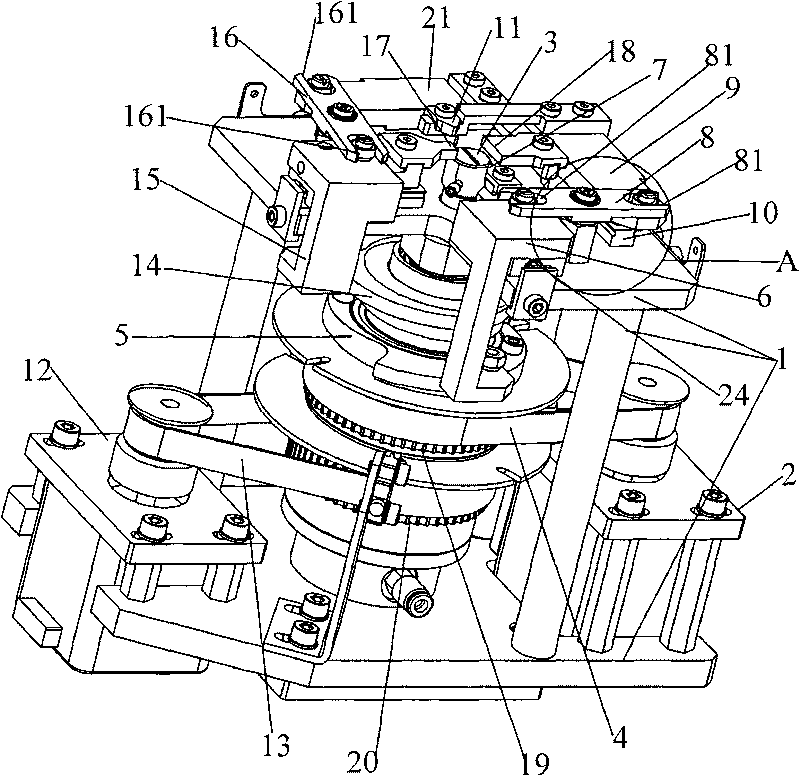

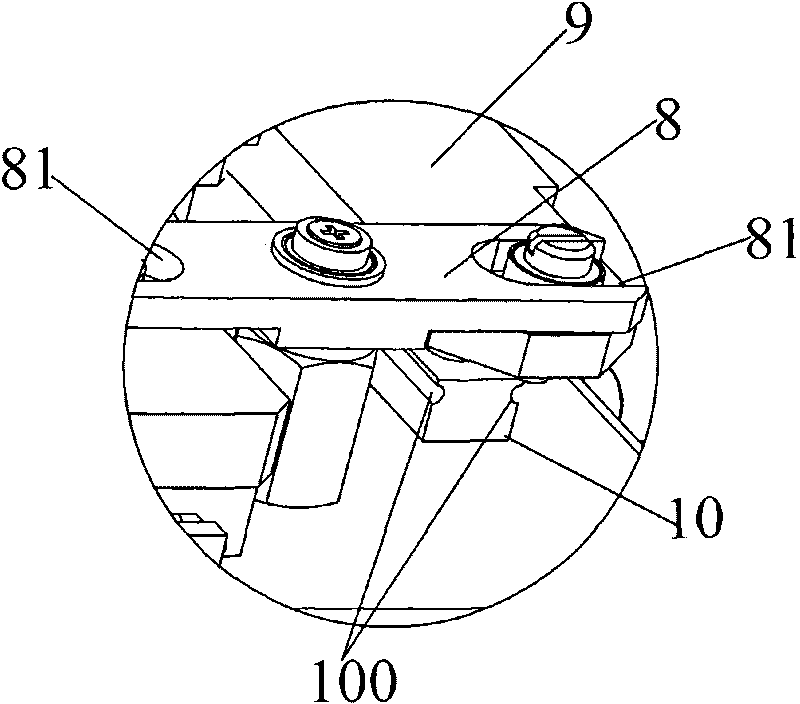

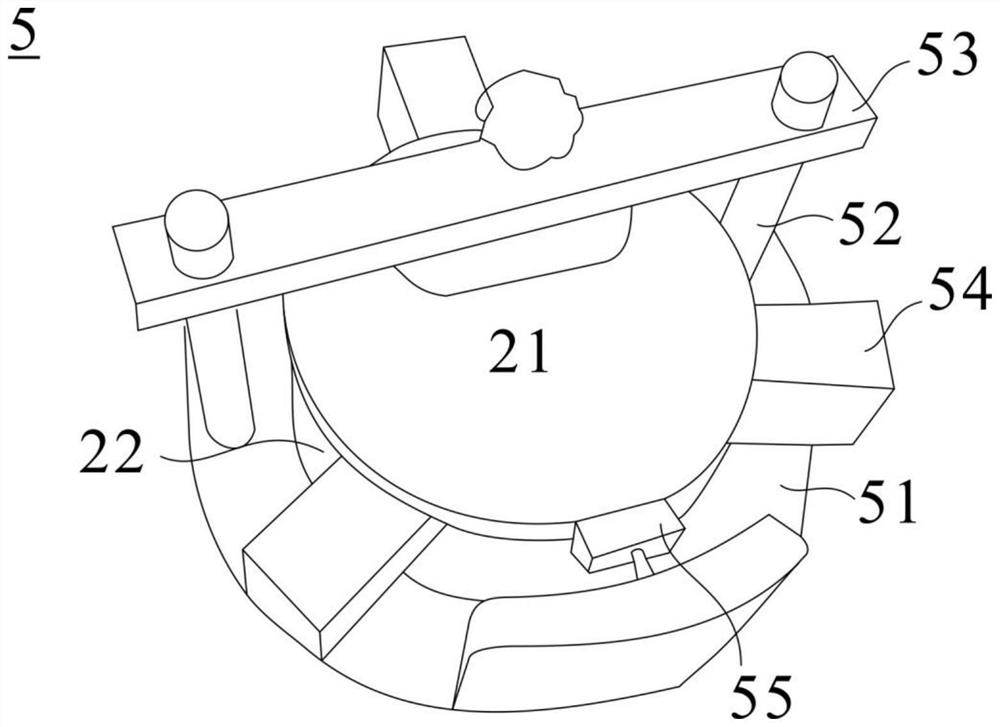

Clamping device for precalibration of COG chip

InactiveCN101710573AImprove bonding accuracySemiconductor/solid-state device manufacturingTransmission beltCam

The invention discloses a clamping device for precalibration of a COG chip, which comprises a base, a first motor and a fixing device, wherein the first motor is fixed on the base; the first motor is connected with a first rotating wheel fixed with a first rotating shaft through a first transmission belt; the first rotating shaft is connected with the base; a first cam is arranged on the first rotating shaft; a first transmission rod which is in close contact with the first cam is arranged outside the first cam; the first transmission rod which is provided with a first calibration block is connected with the base slidably; a first spring is arranged between the first transmission rod and the base; the first transmission rod is connected with a first sliding block through a first transmission piece; the first sliding block is matched with a first guide rod on the base slidably; a second calibration block is arranged on the first sliding block; and the second calibration block and the first calibration block are oppositely arranged and are respectively positioned at two sides of the fixing device. The clamping device for precalibration of the COG chip can calibrate the position of the bonded chip to improve the bonding accuracy of the chip.

Owner:SUNEAST ELECTRONICS TECH SHENZHEN +1

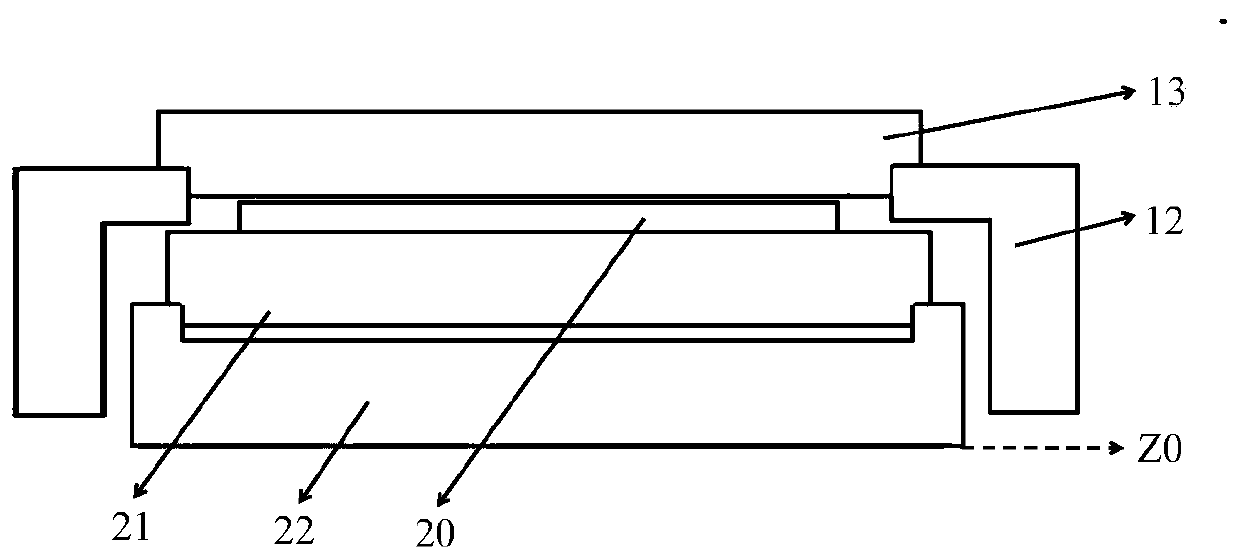

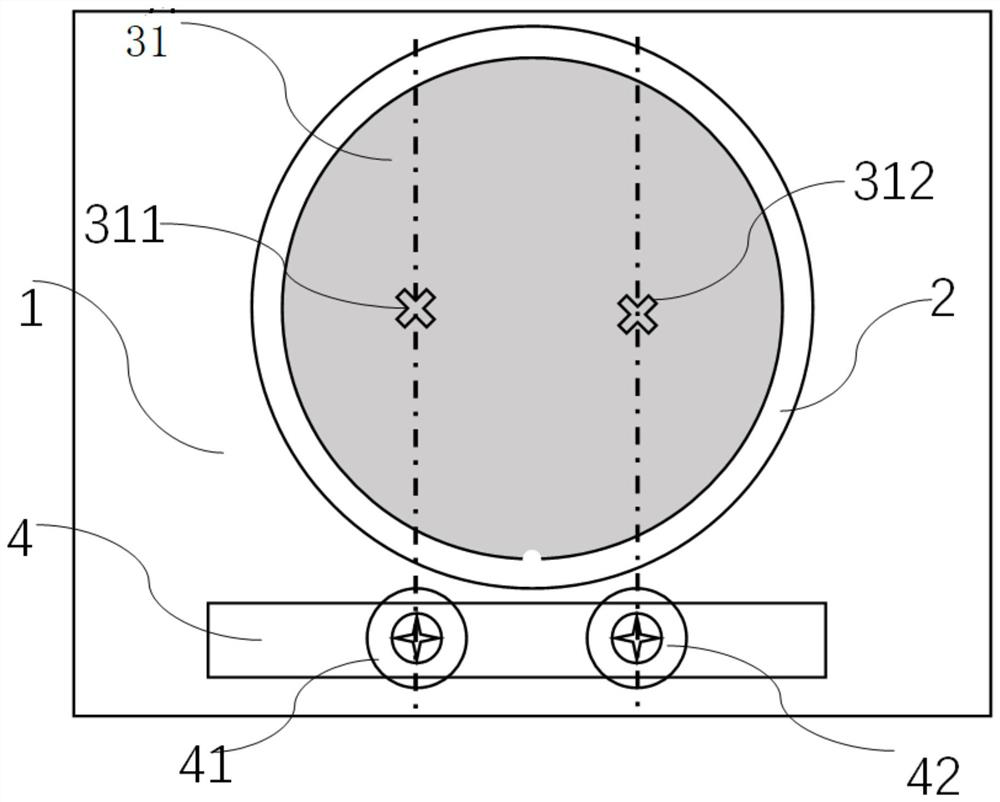

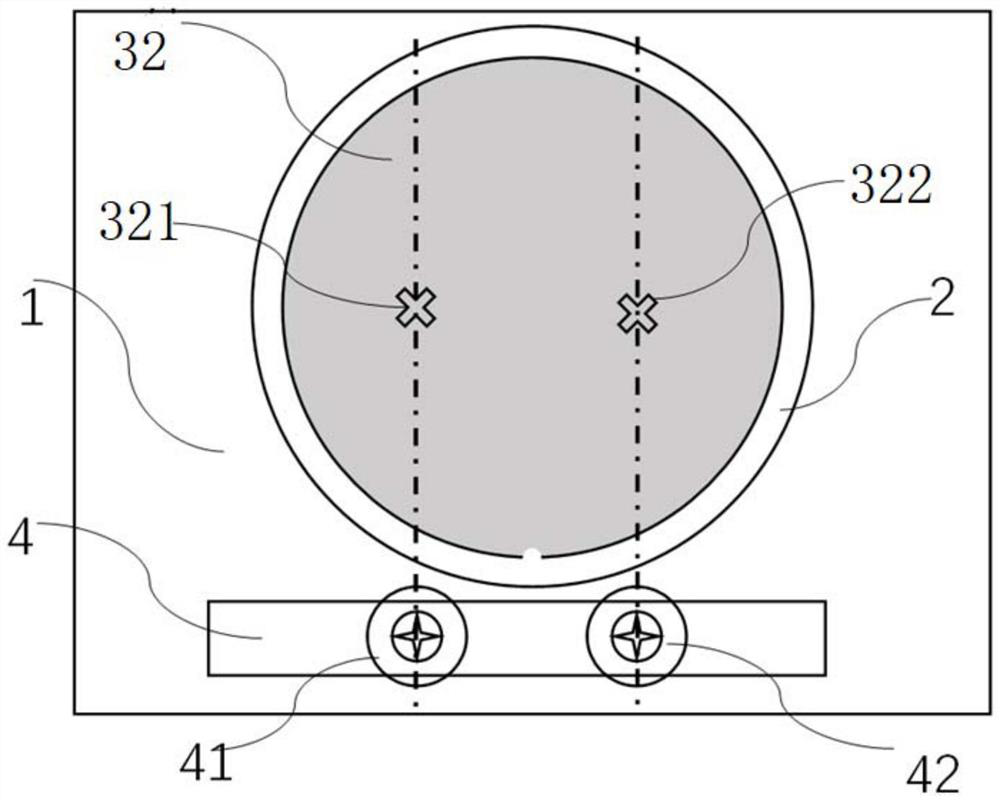

Vacuum apparatus, substrate alignment apparatus, and method of forming pre-bonded wafer

ActiveCN108122808AImprove bonding accuracySpacer structure is omittedSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

The invention provides a vacuum apparatus, a substrate alignment apparatus, and a method of forming a pre-bonded wafer. The vacuum apparatus includes an upper fixing module, a lower fixing module, anda vacuum module. The vacuum module is configured to form a vacuum cavity between the upper fixing module and the lower fixing module after an upper substrate is aligned with a lower substrate. The vacuum module includes a housing, a sealing module, and a vacuum interface. The housing has an opening and is configured to sleeve the outer sides of the upper fixing module and the lower fixing modulein a manner that the opening is arranged upwards. The sealing module is disposed between the upper fixing module and the housing to seal the upper fixing module and the housing to form a sealed cavity. The vacuum interface penetrates through the sidewall of the housing and provides a vacuum input for the sealed cavity to form a vacuum cavity. The vacuum apparatus eliminates a spacer structure between two substrates and avoids a series of alignment and bonding errors introduced by the spacer.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

BTO intelligent correction device and method of full-automatic lead bonding machine

ActiveCN113681146ARealize real-time intelligent correctionDoes not interfere with normal bonding motion operationSolid-state devicesSemiconductor/solid-state device manufacturingLead bondingOptic system

The invention relates to a BTO intelligent correction device and method of a full-automatic lead bonding machine. The full-automatic lead bonding machine comprises a workbench for bearing a chip workpiece, a bonding head provided with a chopper, and an imaging optical system. The BTO intelligent correction device comprises a basic mark point, a detector and a difference value correction system, wherein the basic mark point is arranged on the workbench and used for being aligned and identified by the imaging optical system to serve as an original point of a plane coordinate system; the detector is arranged at a theoretical BTO position, away from the basic mark point, on the workbench and used for detecting the distance between the detector and the chopper and generating an electric signal through induction when the chopper moves to an adjacent position above the detector; and the difference value correction system is used for pre-storing theoretical position coordinates when the chopper is induced, calculating a difference value between actual position coordinates and the theoretical position coordinates when the chopper is induced, obtained by the imaging optical system, and obtaining a BTO deviation value for performing compensation correction. The device is simple and small in structure, no extra equipment is added, the BTO deviation can be automatically corrected in real time, and the bonding precision of the chopper is improved.

Owner:NINGBO SHANGJIN AUTOMATION TECH CO LTD

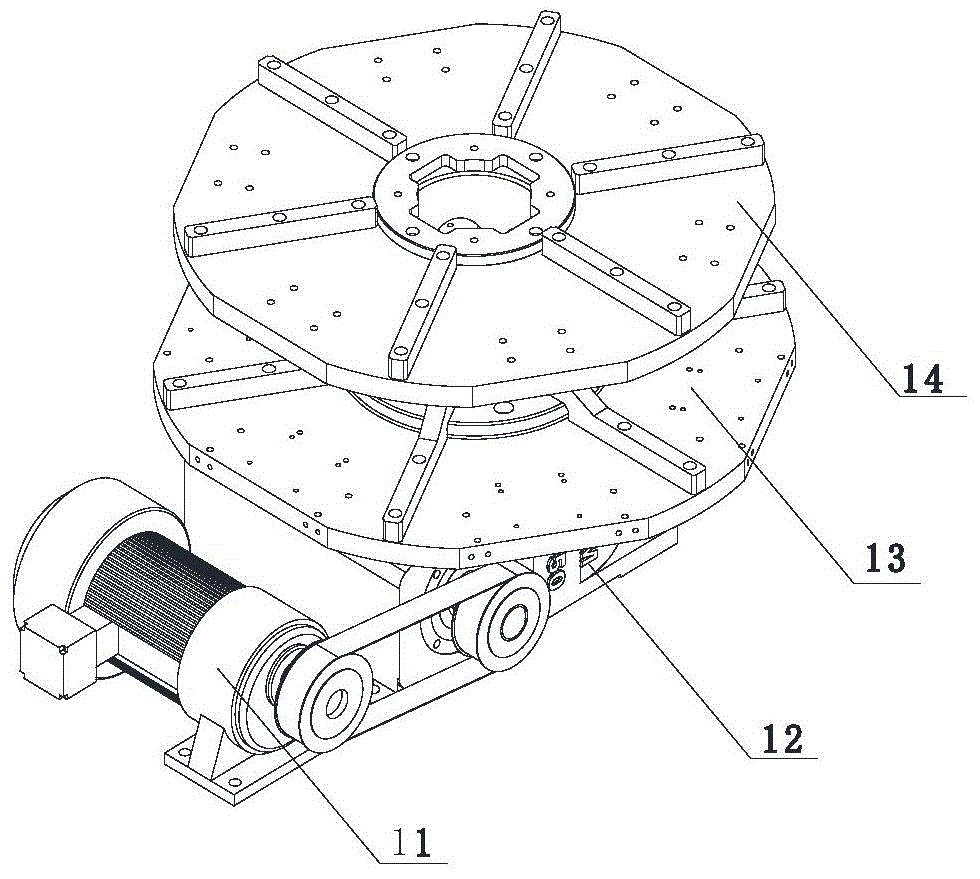

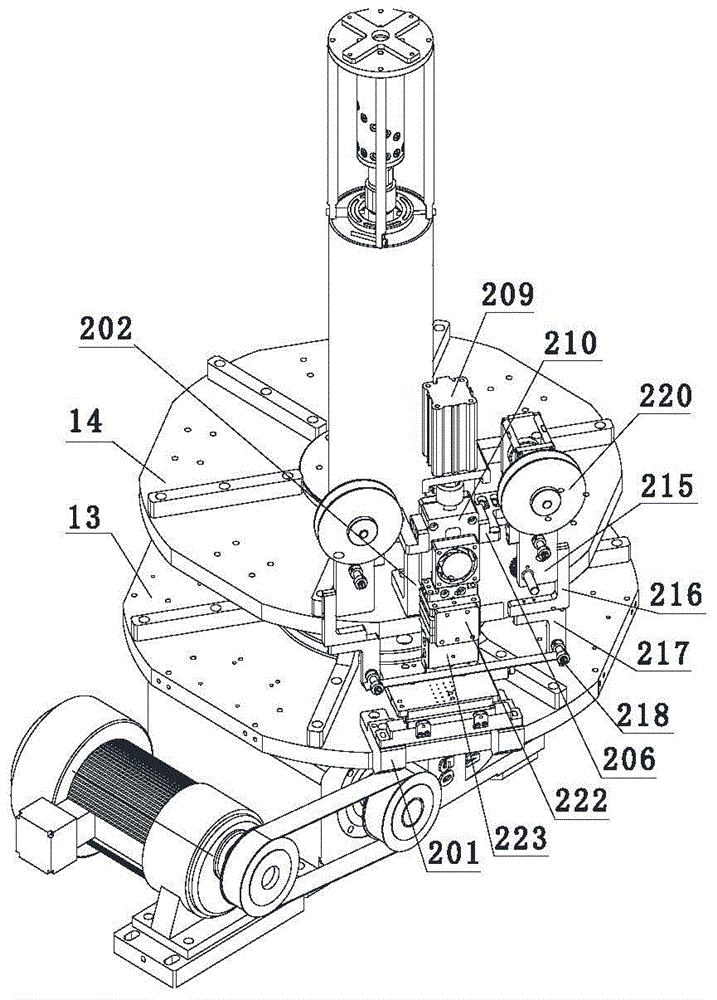

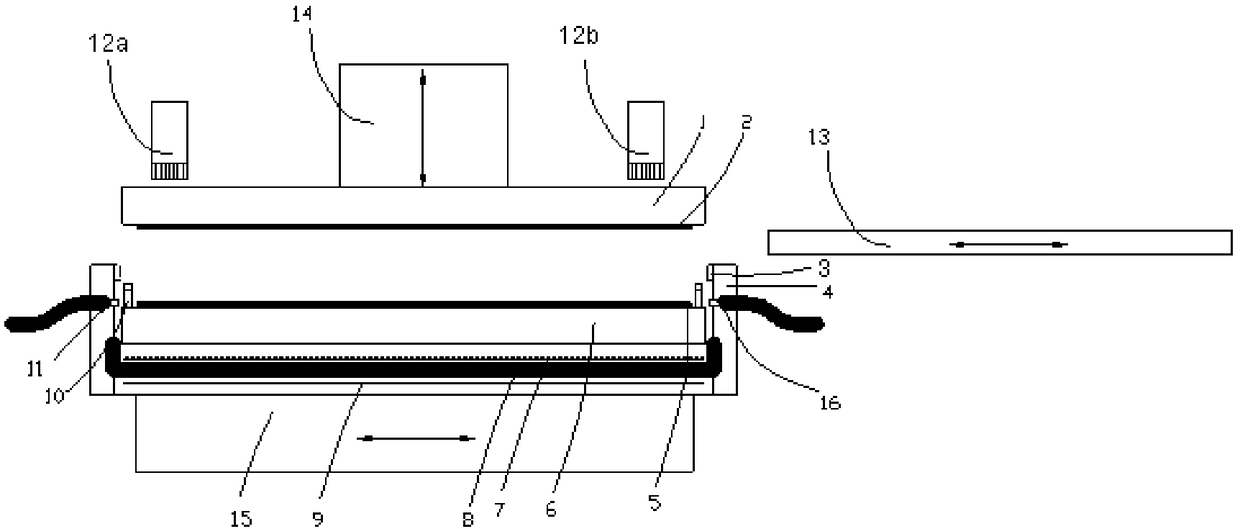

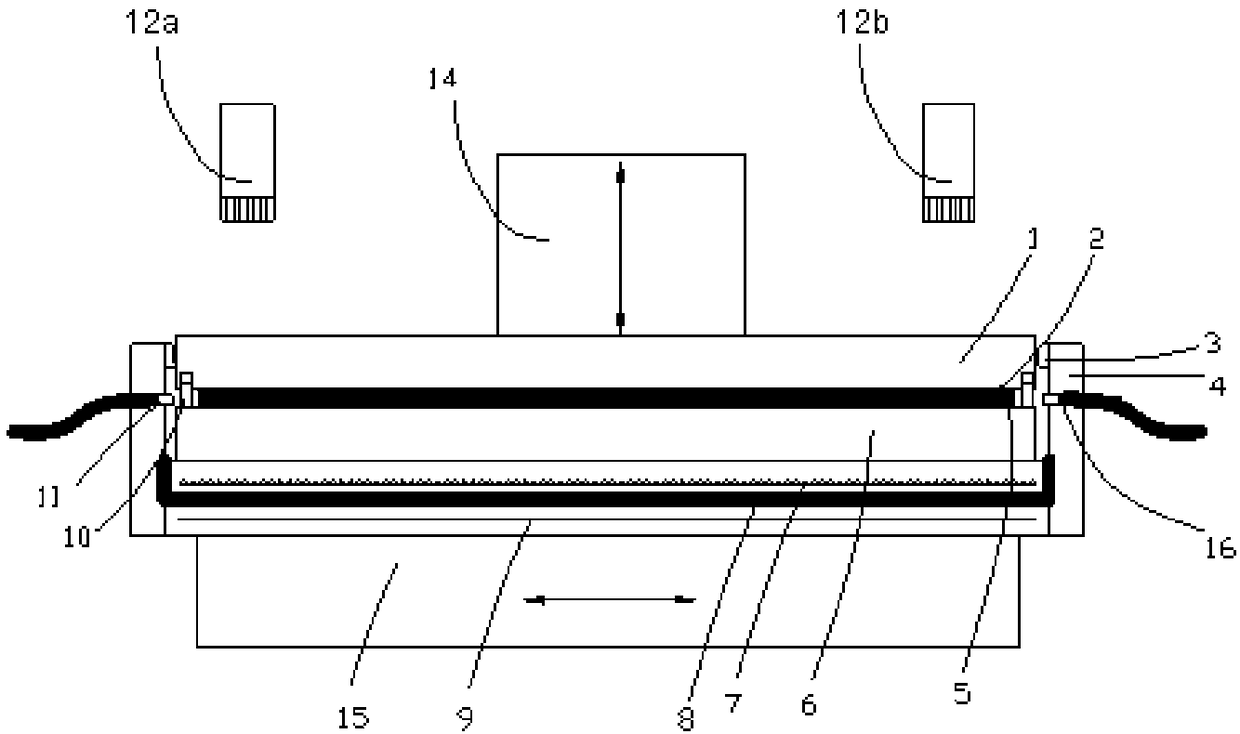

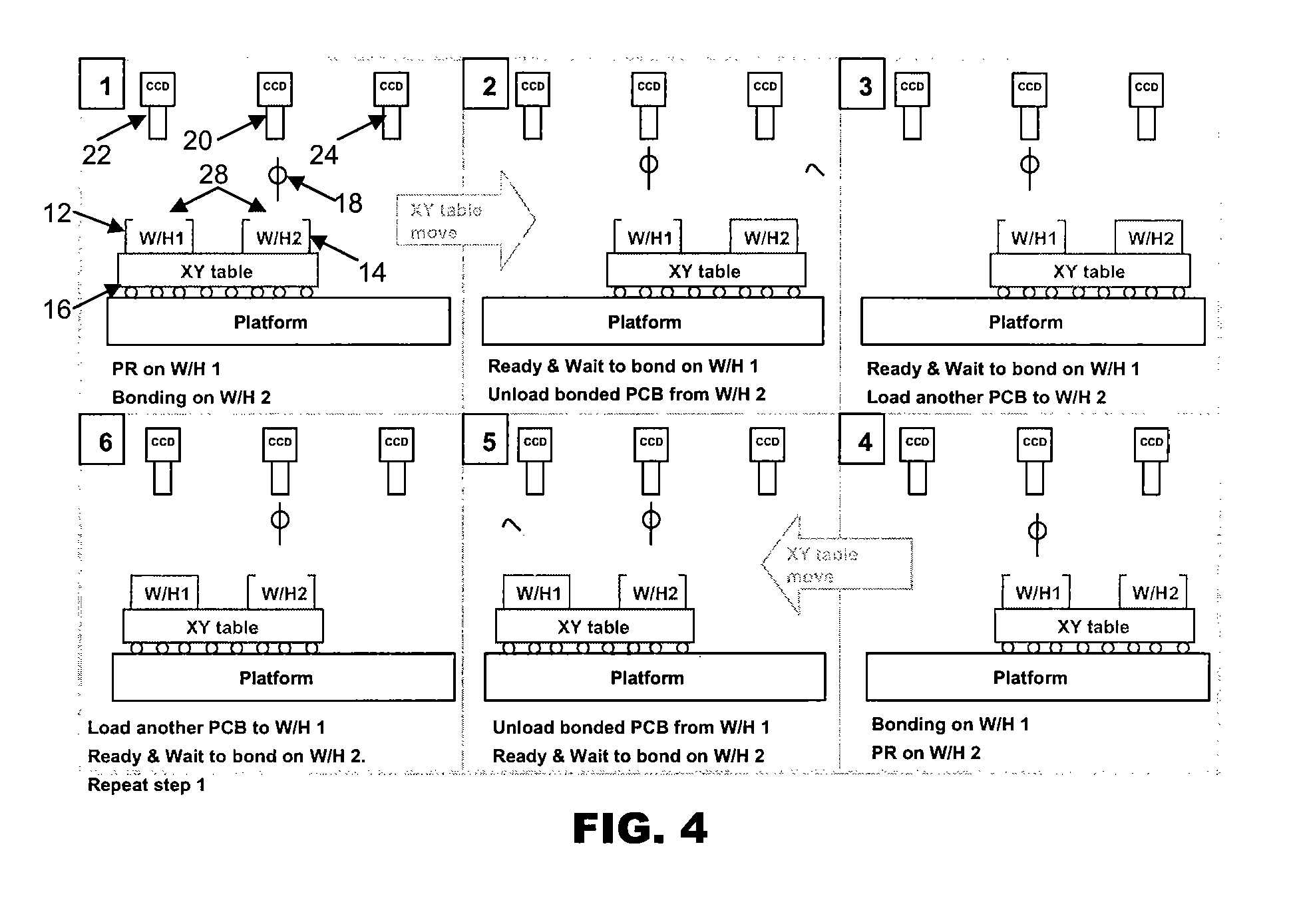

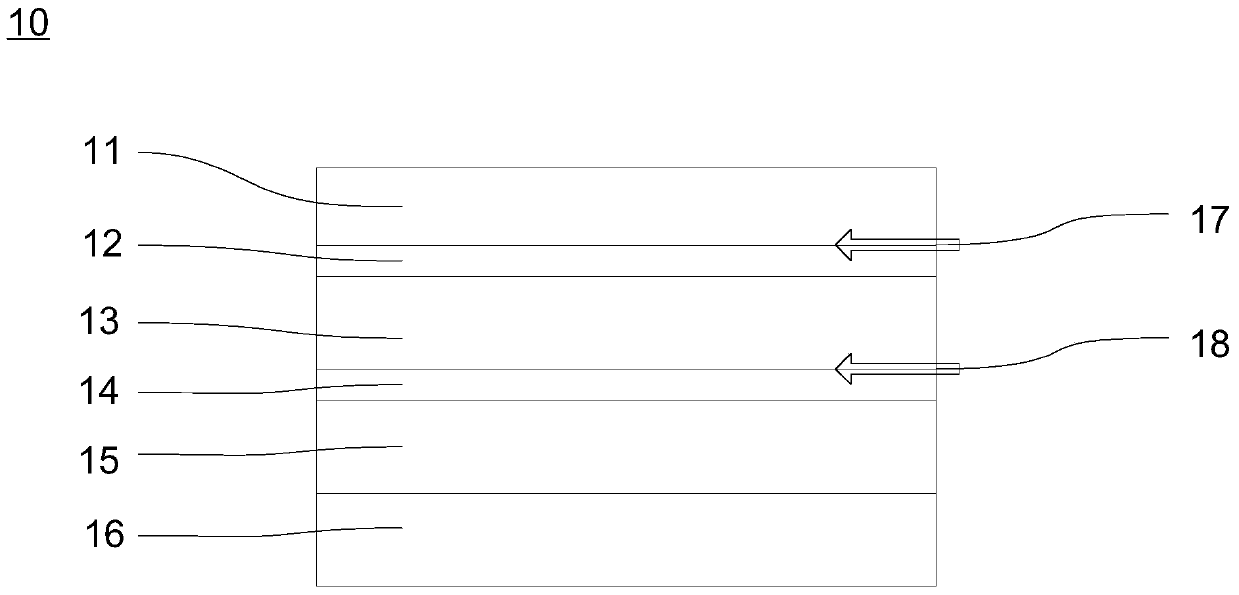

Wire bonding method and apparatus

InactiveUS20070181645A1Improve bonding accuracyImprove accuracyCooking-vessel materialsSolid-state devicesLead bondingAngular orientation

A wire bonding method and apparatus are provided for electronic components to enable PR processing and wire bonding to be carried out substantially concurrently. The apparatus comprises a bond head carrying a bonding tool for performing wire bonding and a rotary motor coupled to the bond head that is configured to change an angular orientation of the bonding tool relative to an electronic component to be bonded. There are first and second carriers for respectively mounting electronic components for wire bonding, and an optical system is arranged and configured to view bonding points on an electronic component mounted on the first carrier when the bonding tool is located over an electronic component mounted on the second carrier to perform wire bonding.

Owner:ASM ASSEMBLY AUTOMATION LTD

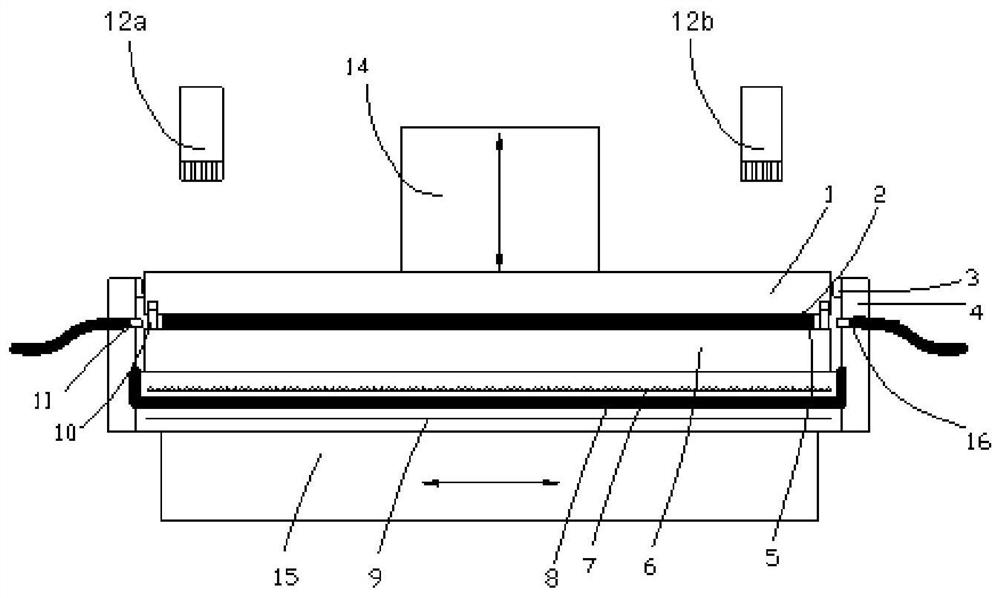

Wafer bonding device and method

ActiveCN110246771AImprove bonding accuracyClear captureSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringWafer bonding

The invention relates to the technical field of semiconductor manufacturing and particularly relates to a wafer bonding device and method. The device includes a first fixing device which is capable of moving only in the X and Y axis directions and is used for fixing a to-be-bonded first wafer on which a first calibration sign is arranged, a reference sign arranged on the first fixing device, a second fixing device which is capable of moving in the X, Y and X axis directions and is opposite to the first fixing device, a rotation device which is arranged at a surface of the second fixing device facing the first fixing device and is used for fixing a to-be-bonded second wafer on which a second calibration sign is arranged, an image acquisition device which is oppositely arranged, can synchronously move along X, Y and Z axes and is used for acquiring the first calibration sign and the second calibration sign, and a reference sign acquisition device used for reading the reference sign. The device is advantaged in that the first calibration sign and the second calibration sign can be clearly acquired by the image acquisition device, and wafer bonding accuracy is improved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

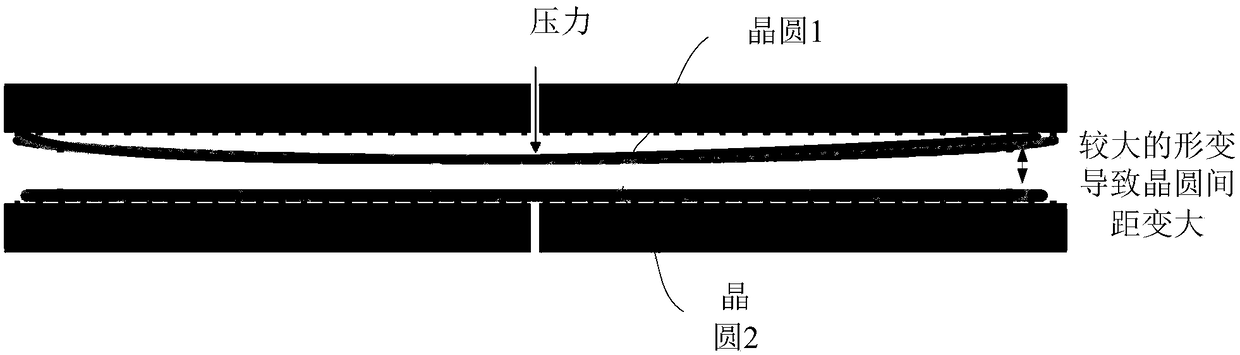

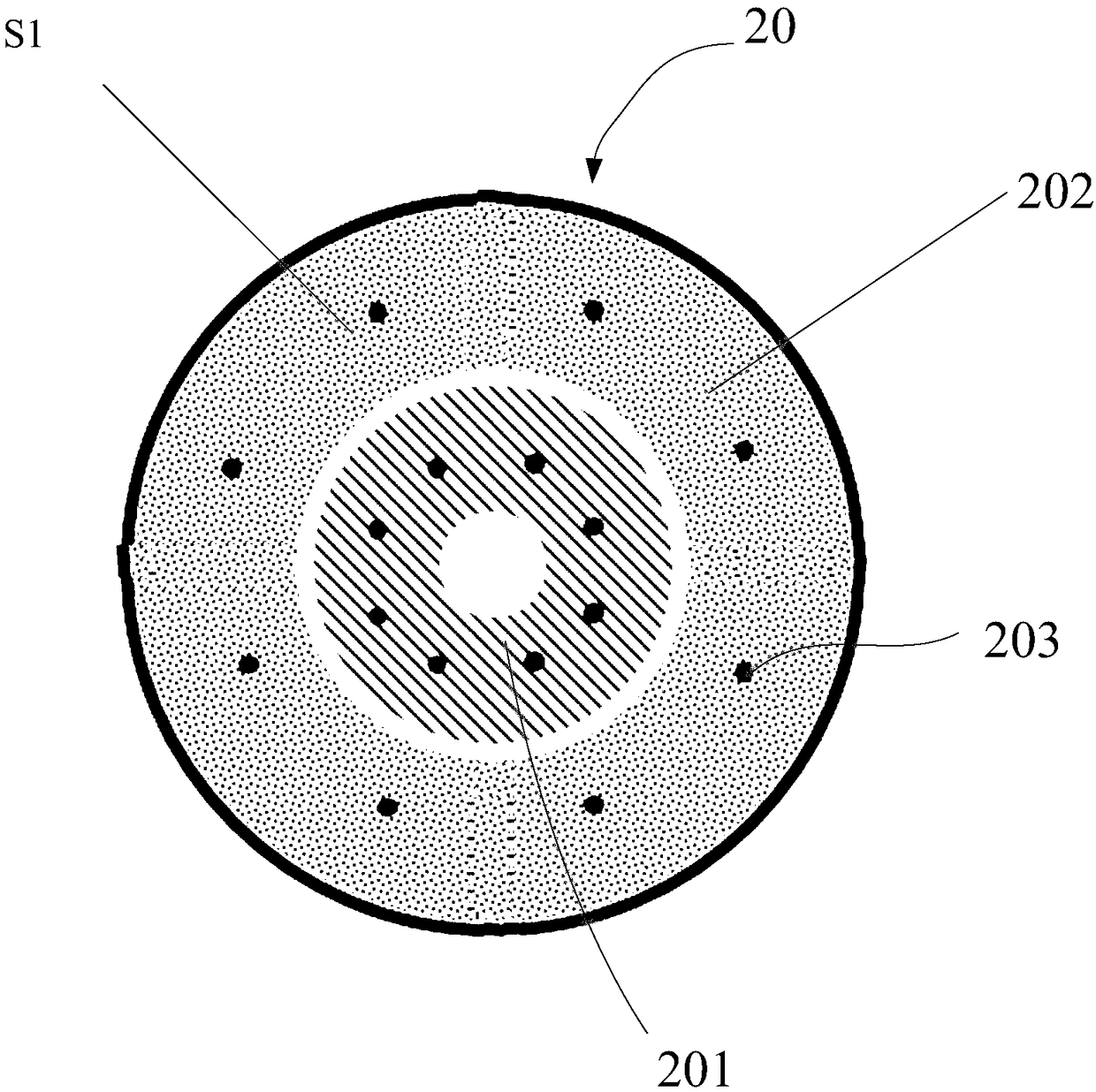

Vacuum chuck

InactiveCN109300834ADeformation will notWon't change spacingSemiconductor/solid-state device manufacturingElectrical and Electronics engineeringEngineering

The application discloses a vacuum chuck comprising a chuck body including a fixed central portion and a peripheral portion that can stretch along the radial direction of the chuck body. When a wateris attached to the chuck body, the peripheral portion is controlled to stretch along the radial direction of the chuck body; and the peripheral portion stretching along the radial direction of the chuck body can drive the attached wafer to deform along the radial direction of the chuck body, so that the wafer dimension changes. The wafer with the changed dimension matches the dimension of a to-be-bonded wafer to realize basic consistence of the dimensions of the two wafers. Moreover, the peripheral portion drives the wafer to deform along the plane direction of the wafer to prevent deformationof the wafer along other directions, so that the space between the two to-be-bonded wafers is not changed based on the wafer deformation amount controlling mode. Therefore, the vacuum chuck is able to control the deformation amount of the wafer, so that the bonding precision of wafers is improved.

Owner:YANGTZE MEMORY TECH CO LTD

Wire bonding method and apparatus

ActiveCN101026111AImprove bonding accuracySolid-state devicesSemiconductor/solid-state device manufacturingAngular orientationEngineering

A wire bonding method and apparatus are provided for electronic components to enable PR processing and wire bonding to be carried out substantially concurrently. The apparatus comprises a bond head carrying a bonding tool for performing wire bonding and a rotary motor coupled to the bond head that is configured to change an angular orientation of the bonding tool relative to an electronic component to be bonded. There are first and second carriers for respectively mounting electronic components for wire bonding, and an optical system is arranged and configured to view bonding points on an electronic component mounted on the first carrier when the bonding tool is located over an electronic component mounted on the second carrier to perform wire bonding.

Owner:ASM ASSEMBLY AUTOMATION LTD

Clamping device for precalibration of COG chip

InactiveCN101710573BImprove bonding accuracySemiconductor/solid-state device manufacturingTransmission beltCam

The invention discloses a clamping device for precalibration of a COG chip, which comprises a base, a first motor and a fixing device, wherein the first motor is fixed on the base; the first motor is connected with a first rotating wheel fixed with a first rotating shaft through a first transmission belt; the first rotating shaft is connected with the base; a first cam is arranged on the first rotating shaft; a first transmission rod which is in close contact with the first cam is arranged outside the first cam; the first transmission rod which is provided with a first calibration block is connected with the base slidably; a first spring is arranged between the first transmission rod and the base; the first transmission rod is connected with a first sliding block through a first transmission piece; the first sliding block is matched with a first guide rod on the base slidably; a second calibration block is arranged on the first sliding block; and the second calibration block and the first calibration block are oppositely arranged and are respectively positioned at two sides of the fixing device. The clamping device for precalibration of the COG chip can calibrate the position of the bonded chip to improve the bonding accuracy of the chip.

Owner:SUNEAST ELECTRONICS TECH SHENZHEN +1

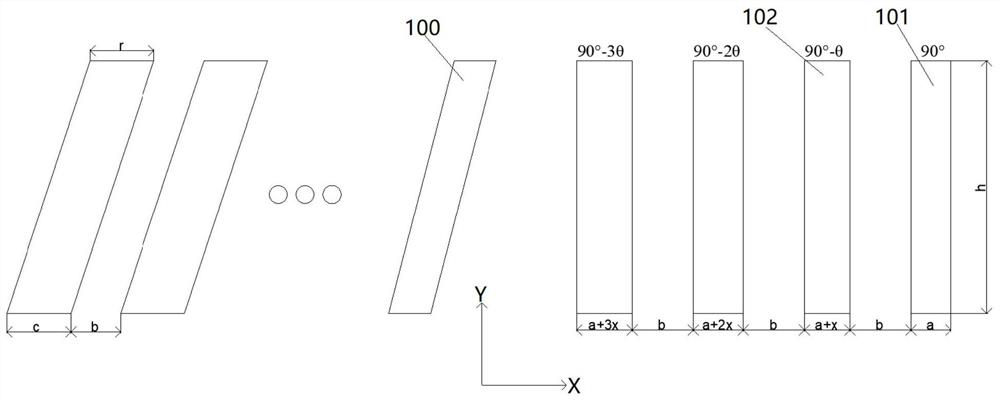

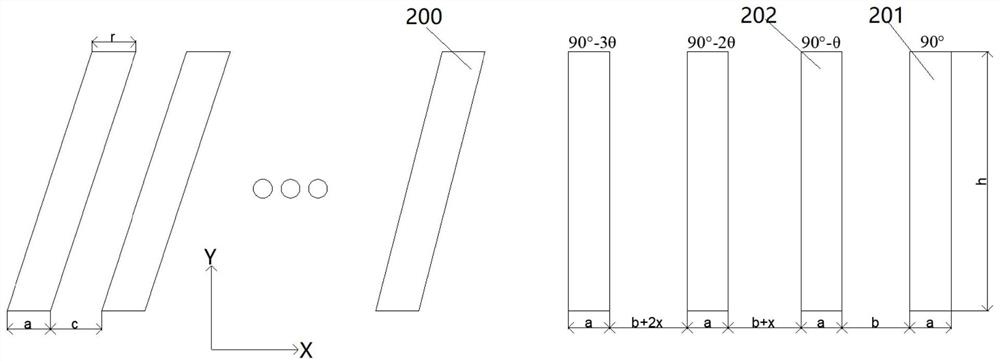

Display device and bonding method thereof, and display equipment

The invention discloses a display device and a bonding method thereof, and display equipment. The display device comprises a display panel and a driving carrier bonded with the display panel, wherein first pins on the display panel are arranged in the arrangement direction from a first center pin to two sides, first distances between adjacent edges of every two adjacent first pins are equal, and the widths of the first pins are sequentially increased; and second pins on the driving carrier are arranged in a direction from a second center pin to two sides, the widths of the second pins are equal, and second distances between the adjacent edges of every two adjacent second pins are sequentially increased. According to the display device provided by an embodiment of the invention, the distances between the pins on the display panel is not changed, the width of the pins is gradually increased from center to edge, the width of the pins on the driving carrier is not changed, the distance between the pins is gradually increased from center to edge, poor products caused by swelling amount difference are corrected, and bonding precision is improved.

Owner:BOE TECH GRP CO LTD +1

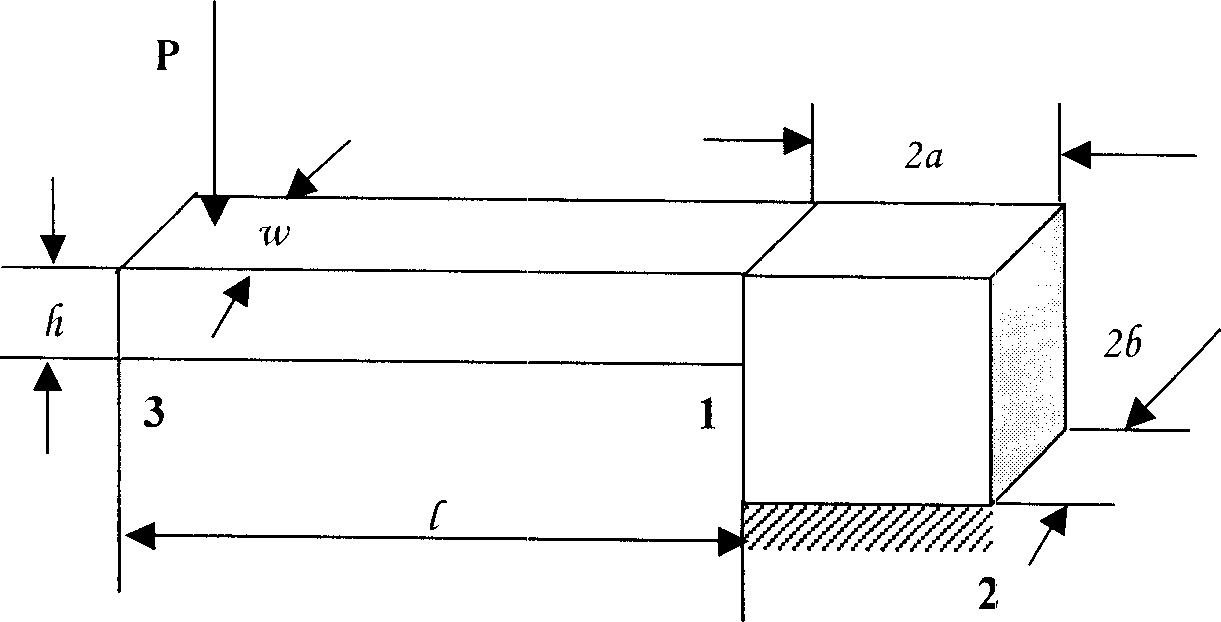

Method for detecting semiconductor micro device bonding strength

InactiveCN1828858ALower bonding temperatureGood phase adhesionSemiconductor/solid-state device testing/measurementUltimate tensile strengthSemiconductor

The present invention discloses a method for detecting semiconductor micro - device bond strength. Said method is according to formula (II) designing a group of similar press arm pattern: 8 alpha / 3 <=l <= 50000 / alpha (II), measuring bonding surface crack in one length L, then calculating or comparing bond strength. Said invented method can conveniently detecting bond strength of semiconductor micro - device.

Owner:PEKING UNIV

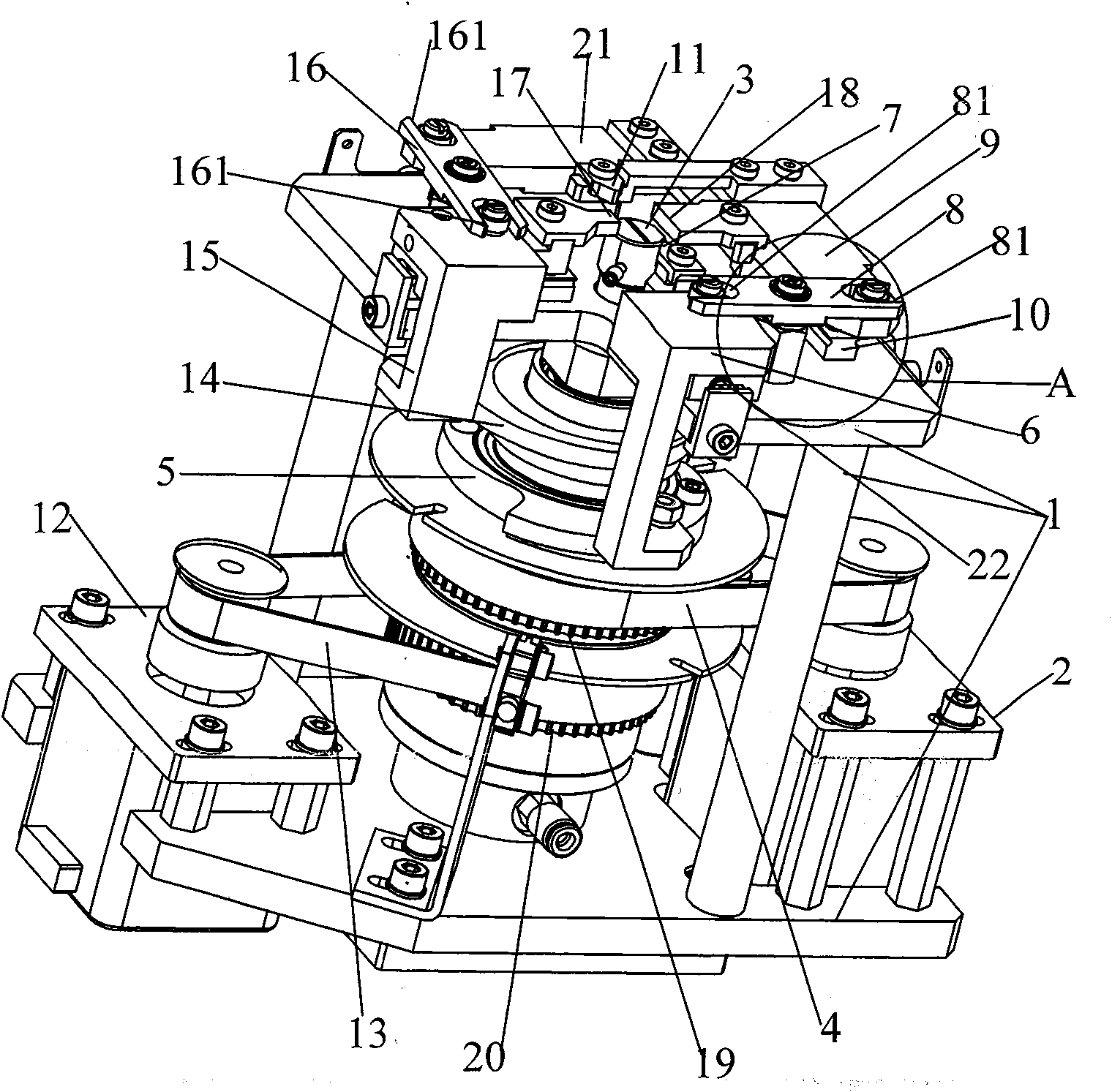

Device and method for compensating wedge-shaped error in wafer bonding

ActiveCN112053940AHigh precisionImprove bonding accuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingStructural engineeringMechanical engineering

The invention discloses a device and a method for compensating a wedge-shaped error in wafer bonding, and belongs to the field of semiconductor wafer processing. The device comprises an upper bearingtable and a lower bearing table, a first adsorption device is arranged on the lower bearing table, a gasket is arranged on the upper surface of the lower bearing table, the gasket is connected with agasket driving device, and a lifting and angle adjusting device is arranged on the lower surface of the lower bearing table; the upper bearing table comprises an inner frame and an outer frame, the edge area of the inner frame is located above the outer frame, the inner frame is connected with the outer frame in a floating mode through a gravity balance device, a plurality of capacitance sensors are arranged on the edge area of the inner frame, and a second adsorption device is arranged on the inner frame. According to the invention, the wedge-shaped error between an upper wafer and a lower wafer is eliminated by adopting a wedge-shaped error compensation method, so that the two unparallel wafers are three-dimensionally parallel, and finally, the effect of improving the wafer bonding precision is achieved.

Owner:BEIJING U PRECISION TECH

Wafer bonding equipment and method

ActiveCN110246771BImprove bonding accuracyClear captureSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringWafer bonding

The present invention relates to the technical field of semiconductor manufacturing, in particular to a wafer bonding equipment, including: a first fixing device that can only move along the X-axis and Y-axis directions, and is used to fix the first wafer to be bonded. A wafer is provided with a first calibration mark; a reference mark is set on the first fixing device; a second fixing device movable along the X axis, Y axis, and Z axis is arranged opposite to the first fixing device; the rotation device , arranged on the side of the second fixing device facing the first fixing device, for fixing a second wafer to be bonded, and a second calibration mark is provided on the second wafer; for the oppositely arranged and synchronous along the X-axis 1, Y-axis, and Z-axis moving image capture devices are respectively used to capture the first calibration mark and the second calibration mark; a reference mark capture device is used to read the reference mark. Beneficial effects: it can ensure that the image acquisition device can clearly capture the first calibration mark and the second calibration mark at the same time, thereby improving the wafer bonding precision.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Semiconductor structure and manufacturing method thereof

PendingCN113506782AReduce warpageLower resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureLead bonding

According to a semiconductor structure and a manufacturing method thereof provided by the invention, the electrical connection between the electronic component and the substrate is realized through wire bonding, and the characteristics of the bonding start point and the bonding end point are determined in real time by using wire bonding, so that the deviation caused by the precision of die bonding is compensated in a maximum allowable range, moreover, the subsequent fabrication of the fan out layer only needs to align the circuit on the substrate, and does not need to align the electronic assembly, thereby improving the yield.

Owner:ADVANCED SEMICON ENG INC

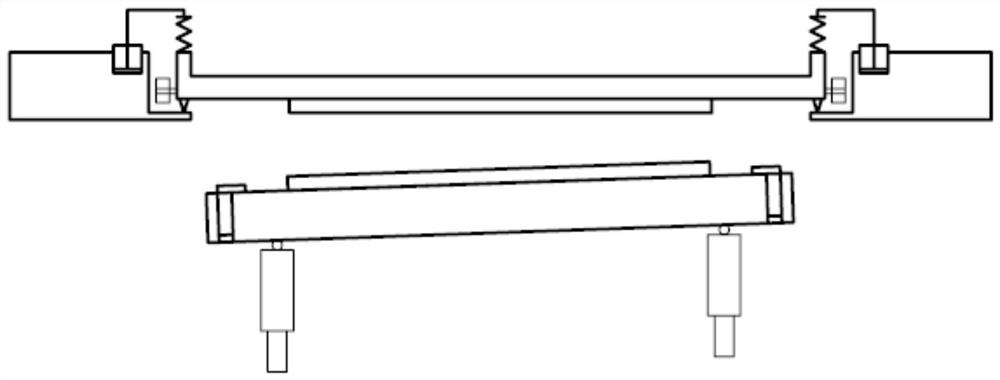

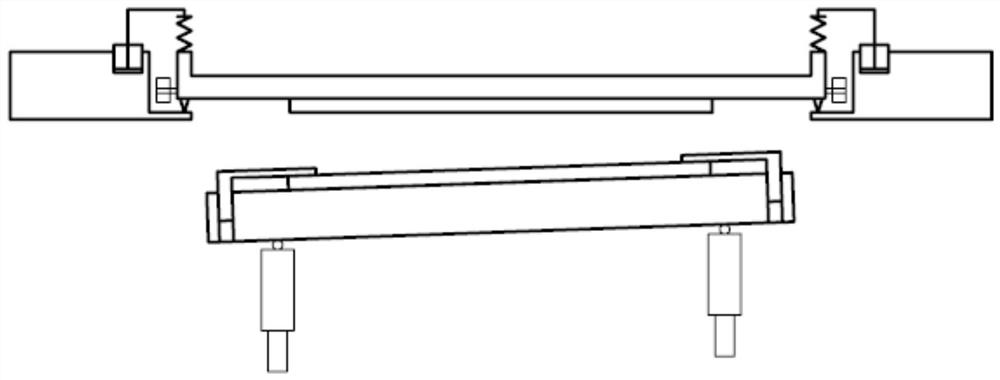

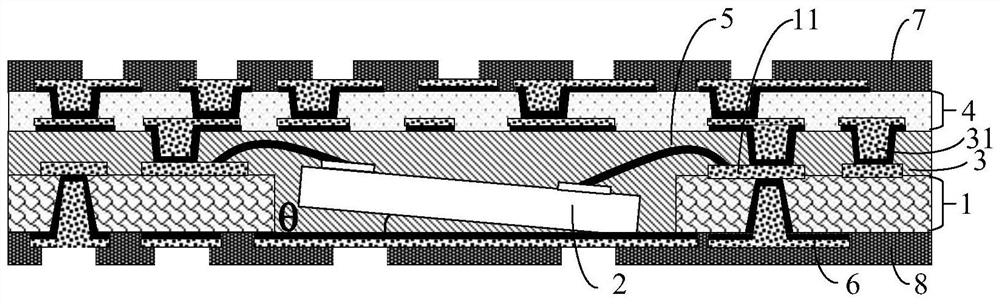

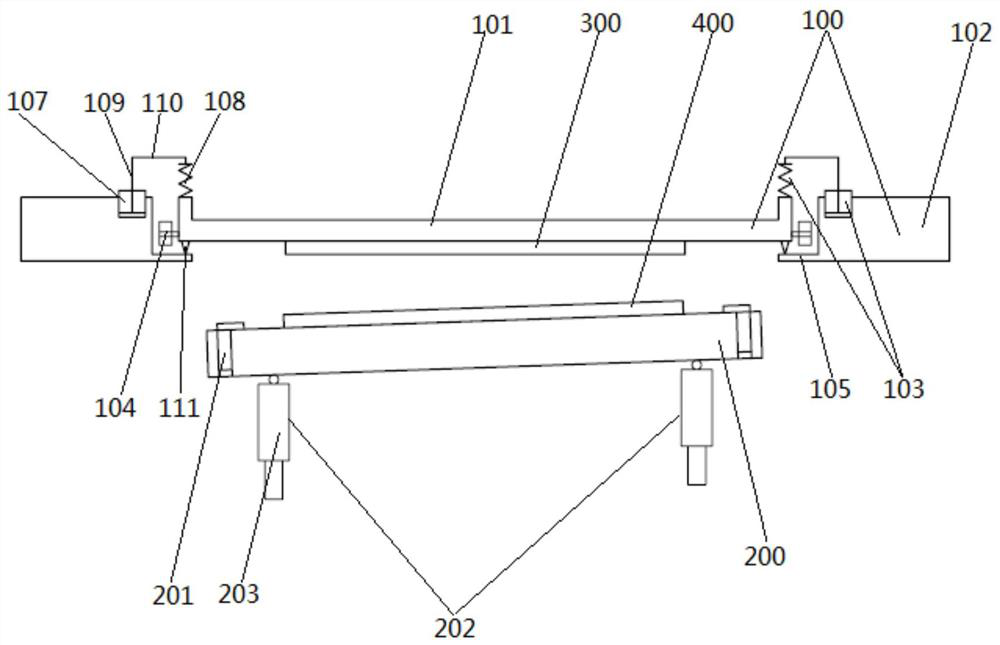

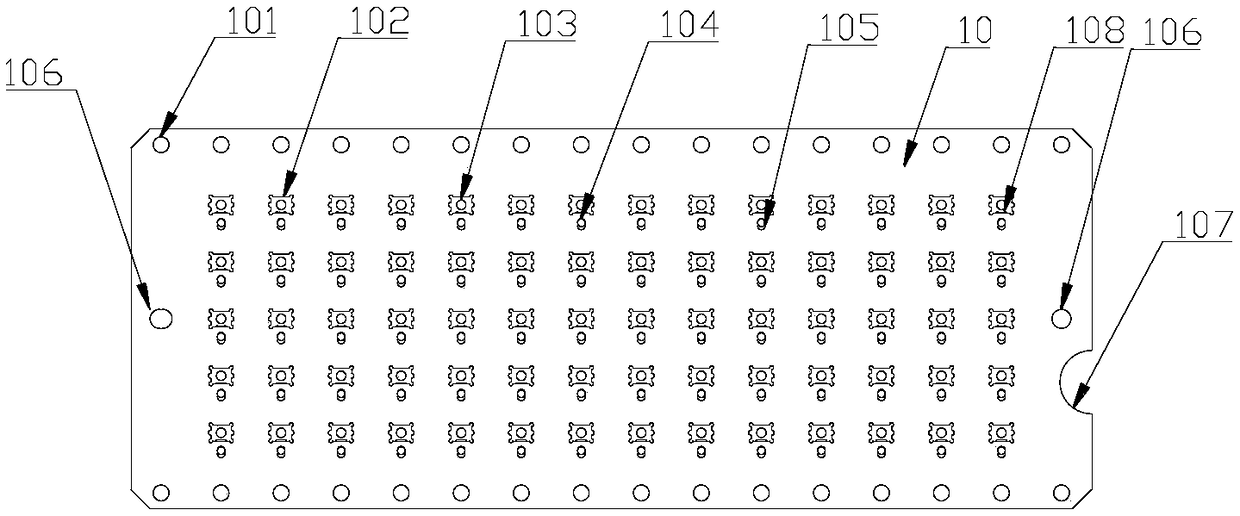

A wire bonding fixture

InactiveCN102446803BShorten pause timeRealize continuous switchingSolid-state devicesSemiconductor/solid-state device manufacturingLead bondingThree-dimensional space

Owner:BEIJING MXTRONICS CORP +1

Apparatus and method for compensating wedge errors in wafer bonding

ActiveCN112053940BImprove bonding accuracyAccurateSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingStructural engineeringWafer bonding

The invention discloses a device and a method for compensating wedge-shaped errors in wafer bonding, belonging to the field of semiconductor wafer processing. The device includes an upper bearing platform and a lower bearing platform, the lower bearing platform is provided with a first adsorption device, the upper surface of the lower bearing platform is provided with a gasket, and the gasket is connected with a gasket driving device, and the The lower surface of the lower bearing platform is provided with a lifting and angle adjustment device; the upper bearing platform includes an inner frame and an outer frame, the edge area of the inner frame is located above the outer frame, and the inner frame is connected to the outer frame through a gravity balance device. The outer frame is floatingly connected, a plurality of capacitive sensors are arranged on the edge area of the inner frame, and a second adsorption device is arranged on the inner frame. The invention adopts the method of wedge error compensation to eliminate the wedge error between the upper and lower wafers, so that two non-parallel wafers can achieve three-dimensional parallelism, and finally achieve the effect of improving wafer bonding precision.

Owner:BEIJING U PRECISION TECH

A medical device phantom, fixture and processing technology

ActiveCN109394215BControl parallelismGuaranteed accuracyMeasurement apparatus componentsWork holdersEngineeringReference line

The invention relates to a medical device phantom, fixture and processing technology. The phantom is used for correcting the accuracy of the upper moving axis of a large medical device, and the light equivalent of X-ray or nuclear magnetic resonance. The first part and the second part at the end; a reference line is set in the body, and the reference line is perpendicular to the first part and the second part respectively. A fixture comprising a base, a pair of positioning columns vertically arranged on both sides of the base; the bottom ends of the pair of positioning columns are connected to the base, and a positioning plate is connected to the top end, and the positioning plate is Describe a pair of positioning columns to do lifting motion. A processing technology for a medical device phantom mainly processes the above-mentioned medical device phantom. The structure of the mold body of the present invention is simple, and the processing procedure is simple, and the precision of each component manufactured is high, and the bonding precision, bonding fastness, bonding aesthetics, etc. between each component can effectively control the overall precision and reduce deformation. .

Owner:上海京悦机械有限公司

Flexible circuit board hot-pressing device, processing system and method based on glass circuit board

ActiveCN104582305BEfficient crawlingShorten spin timePrinted circuit assemblingAnisotropic conductive filmFlexible circuits

The invention discloses a glass circuit board based FPC (flexible printed circuit) board hot-pressing device, processing system and method. The hot-pressing device comprises a rotating platform capable of rotating intermittently, wherein the rotating platform is provided with two layers of fixing boards which are mutually parallel and can rotate simultaneously, one layer is hot-pressing fixing board used for fixing hot-pressing assemblies, the other layer is a jig fixing board for fixing jig assemblies, the rotating platform is divided into a plurality of station areas, and one hot-pressing assembly and one jig assembly are arranged in each station area; each hot-pressing assembly comprises a lifting control mechanism, a hot-pressing head and a buffering mechanism; a loading platform, a first preset platform, an ACF (anisotropic conductive film) attachment assembly, a second preset platform, the hot-pressing device and an unloading platform are mounted on a mounting platform. The work efficiency of the hot-pressing device can be improved, the area occupied by the equipment can be reduced, and the cost is saved.

Owner:SHENZHEN LIANDE AUTOMATION EQUIP

A chip bonding device and method

ActiveCN108511353BSmall footprintReduce transfer timeSolid-state devicesSemiconductor/solid-state device manufacturingDie bondingMechanical engineering

The invention discloses a chip bonding device and method. The chip bonding device comprises a chip supply unit, a chip pickup unit, a chip measurement unit, a chip temporary load-bearing unit and a chip bonding unit which are correspondingly arranged in sequence, wherein the chip temporary load-bearing unit comprises a load-bearing rotary table and bonding hands distributed on the load-bearing rotary table along the circumferential direction, the chip pickup unit picks up a chip on the chip supply unit, the chip is subjected to alignment through the chip measurement unit and then transferred to the bonding hand, and the bonding hand receives the chip and transfers the chip to a substrate borne on the chip bonding unit for bonding. The chip bonding device is applicable to a chip mounting mode with the chip facing upwards and a chip mounting mode with the chip facing downwards, and expands the application range of the equipment; the bonding hands are driven to transmit the chips throughthe load-bearing rotary table so as to save the transmission time, and the plurality of bonding hands operate simultaneously so as to improve the production rate; and the chip is aligned through the chip measurement unit, and the chip supply unit is provided with a separation detection system, so that the position of the chip is aligned, and the bonding accuracy is improved.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

Vacuum apparatus, substrate alignment apparatus and method for forming pre-bonded wafers

ActiveCN108122808BSpacer structure is omittedImprove bonding accuracySemiconductor/solid-state device manufacturingEngineeringMechanical engineering

The invention provides a vacuum apparatus, a substrate alignment apparatus, and a method of forming a pre-bonded wafer. The vacuum apparatus includes an upper fixing module, a lower fixing module, anda vacuum module. The vacuum module is configured to form a vacuum cavity between the upper fixing module and the lower fixing module after an upper substrate is aligned with a lower substrate. The vacuum module includes a housing, a sealing module, and a vacuum interface. The housing has an opening and is configured to sleeve the outer sides of the upper fixing module and the lower fixing modulein a manner that the opening is arranged upwards. The sealing module is disposed between the upper fixing module and the housing to seal the upper fixing module and the housing to form a sealed cavity. The vacuum interface penetrates through the sidewall of the housing and provides a vacuum input for the sealed cavity to form a vacuum cavity. The vacuum apparatus eliminates a spacer structure between two substrates and avoids a series of alignment and bonding errors introduced by the spacer.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

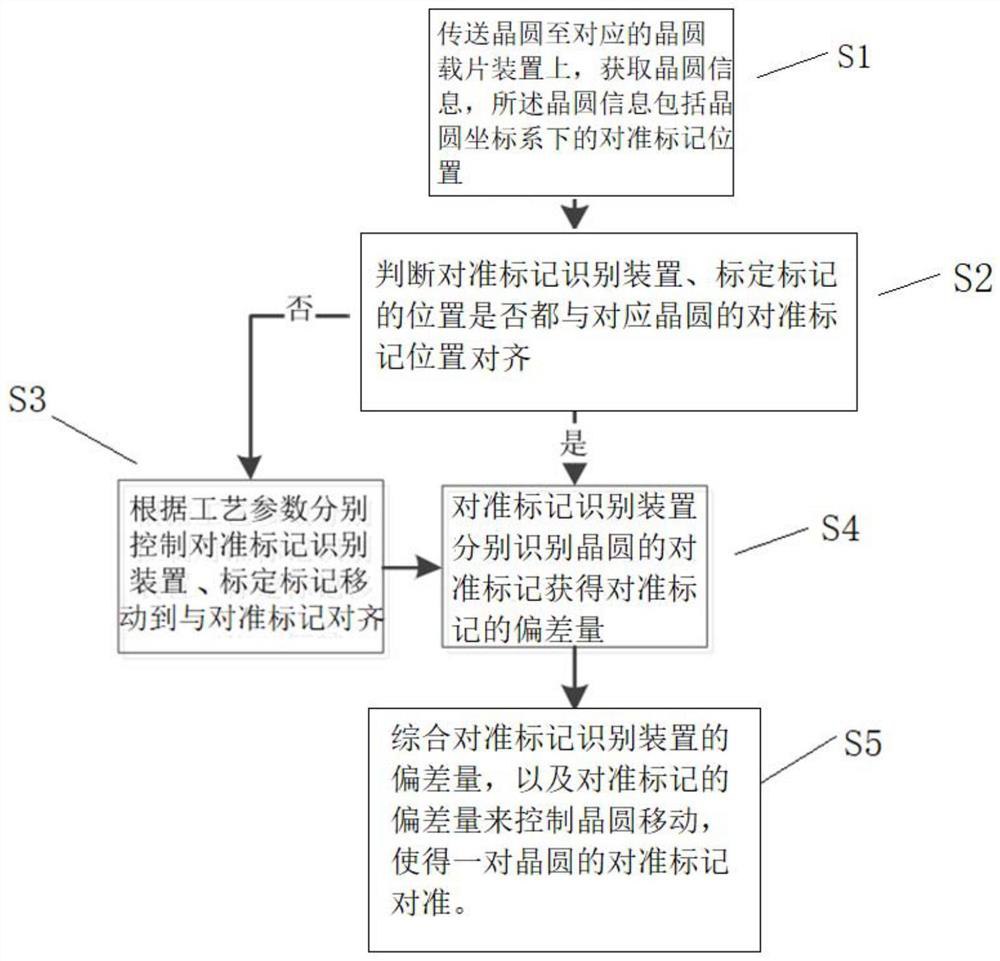

Wafer bonding dynamic calibration method and device

PendingCN114582773AReduce alignment errorImproved Wafer Bonding AccuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringIdentification device

The invention discloses a wafer bonding dynamic calibration method and device, and the method comprises the steps: transmitting a wafer to a corresponding wafer slide device, and obtaining wafer information which comprises an alignment mark position under a wafer coordinate system; whether the positions of the alignment mark recognition device and the calibration mark are aligned with the alignment mark position of the corresponding wafer or not is judged, if not, the alignment mark recognition device and the calibration mark are controlled to move to be aligned with the alignment mark of the corresponding wafer, and then the deviation value of the alignment mark recognition device is calibrated through the calibration mark; the alignment mark recognition device recognizes the alignment marks of the wafers respectively to obtain deviation values of the alignment marks, and controls the wafers to move by integrating the deviation values of the alignment mark recognition device and the deviation values of the alignment marks, so that the alignment marks of the pair of wafers are aligned. According to the invention, the calibration mark and the alignment mark identification device are synchronously moved to the same position of the alignment mark in advance, so that the alignment error can be greatly reduced, and the wafer bonding precision is improved.

Owner:BEIJING U PRECISION TECH

Bonding heating control device and method thereof

ActiveCN107293504BShorten heating timeImprove heating efficiencySolid-state devicesSemiconductor/solid-state device manufacturingThermodynamicsGlass chip

The invention provides a bonding heating control device and a method thereof. The device comprises a heating controller, two heating devices and two heating driving devices. Each heating device is used for heating and pressurizing a silicon wafer or a glass sheet. Each heating device is provided with a heater and at least two temperature sensors. The heating controller is used for measuring each temperature sensor in the two heating devices and outputting PWM opening of a heater. Each heating driving device drives the heater to work according to the PWM opening output by the heating controller. The two heating devices work independently at the same time so that heating time is saved and heating efficiency is improved. Graphite pieces are arranged on upper and lower sides of a heating disc so as to make the temperature spread evenly. Meanwhile, a heating process is divided into three stages, rapid heating in a rate heating stage shortens the heating time and increases a yield; and adjustable power in a heating rate stage is realized and more process parameters are provided for a bonding process.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

Wedge-shaped chopper structure for improving lead bonding precision

ActiveCN113787250AImprove bonding accuracyAvoid cable jamsSemiconductor/solid-state device detailsSolid-state devicesPhysicsEngineering

The invention relates to the technical field of microelectronic packaging, and particularly discloses a wedge-shaped chopper structure for improving lead bonding precision. The wedge-shaped chopper structure for improving lead bonding precision comprises a chopper handle and a chopper head connected with one end of the cutter handle; the chopper head is provided with a bonding lead via hole; and the bonding lead via hole comprises a guide hole and an elliptical through hole, wherein the guide hole is formed in the side surface of the chopper head and an elliptical through hole communicating with the guide hole. According to the wedge-shaped chopper structure for improving the lead bonding precision, the movable range of the bonding lead in the horizontal direction is effectively limited, and the bonding lead is prevented from deviating in the bonding lead via hole; the bonding lead can be always located in the center of the end face of the chopper head in the bonding process; and the bonding precision of the bonding lead is effectively improved.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

Wafer assembly

PendingCN113421874AImprove recognition efficiency and accuracyImprove bonding accuracySemiconductor/solid-state device detailsSolid-state devicesPhysicsMechanical engineering

The invention provides a wafer assembly. The wafer assembly comprises a first wafer and a first alignment mark located on the first wafer, a second wafer and a second alignment mark located on the second wafer. At least one of the first alignment mark and the second alignment mark extends from an intersection area of the cutting channels to a non-intersection area on the wafer where the first alignment mark and the second alignment mark are located. The length of a pattern (such as a strip-shaped pattern) in the first alignment mark and / or the second alignment mark can be larger than the width of the cutting channel and is not limited by the width of the cutting channel any more. On the basis of an existing wafer bonding machine and process conditions, large-size alignment marks can be made under the condition that the width of a cutting channel is fixed, and the wafer bonding recognition efficiency and precision are improved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

One-side bonding method and application of cemented carbide strips suitable for cemented carbide hard surface processing

The invention provides a single-face bonding method suitable for hard alloy strips in a hard alloy hard-face machining process and application. A locating groove plate for bonding is scientifically designed, the hard alloy strips are placed on the locating groove plate, the hard alloy strips are bonded through punched single-face adhesive tape, and the hard alloy strips or blocks are fixed through spot welding; and then the adhesive tape is placed on a steel surface of a to-be-machined component, and through spray welding, bead weld and grinding, the steel surface is machined into a hard surface. According to the method, the aim that a large number of hard alloy strips are bonded at a time is simply and easily achieved, the bonding efficiency is greatly improved, and the conditions that due to manual operation, the bonding angles are different, and the bonding intervals are uneven are avoided; the bonding precision is improved, and wear resistance of the product hard surface can be effectively ensured and improved; and the method can be well applied to the aspect of hard-face machining of centering guides or TC bearings of drilling tools or screw drilling tools.

Owner:株洲金韦硬质合金有限公司

Bonding fixture for small component

PendingCN109302838ASimple structureEffectively fixedElectrical componentsPiezoelectric quartzBonding process

The invention, which relates to the field of electronic component manufacturing, particularly discloses a bonding fixture for a small component. The bonding fixture comprises a carrying piece; a plurality of station slots are formed in the carrying piece; and at least one elastic mechanism is arranged at the side of each station slot. When components are placed in the station slots, the elastic mechanisms extrude the sides of the components to fix the components in the station slots. With the bonding fixture with a simple structure, fixation of a small device is realized and thus the device isprevented from being offset during the bonding process and is protected from being polluted, so that the quality of the piezoelectric quartz device is improved substantially and the yield of the piezoelectric quartz device is enhanced. Meanwhile, the bonding fixture has advantages of low manufacturing cost, low manufacturing difficulty and low cost, so that the manufacturing cost of the piezoelectric quartz device is lowered.

Owner:GUANGZHOU JINGYOU ELECTRONICS TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com