Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "High impedance state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

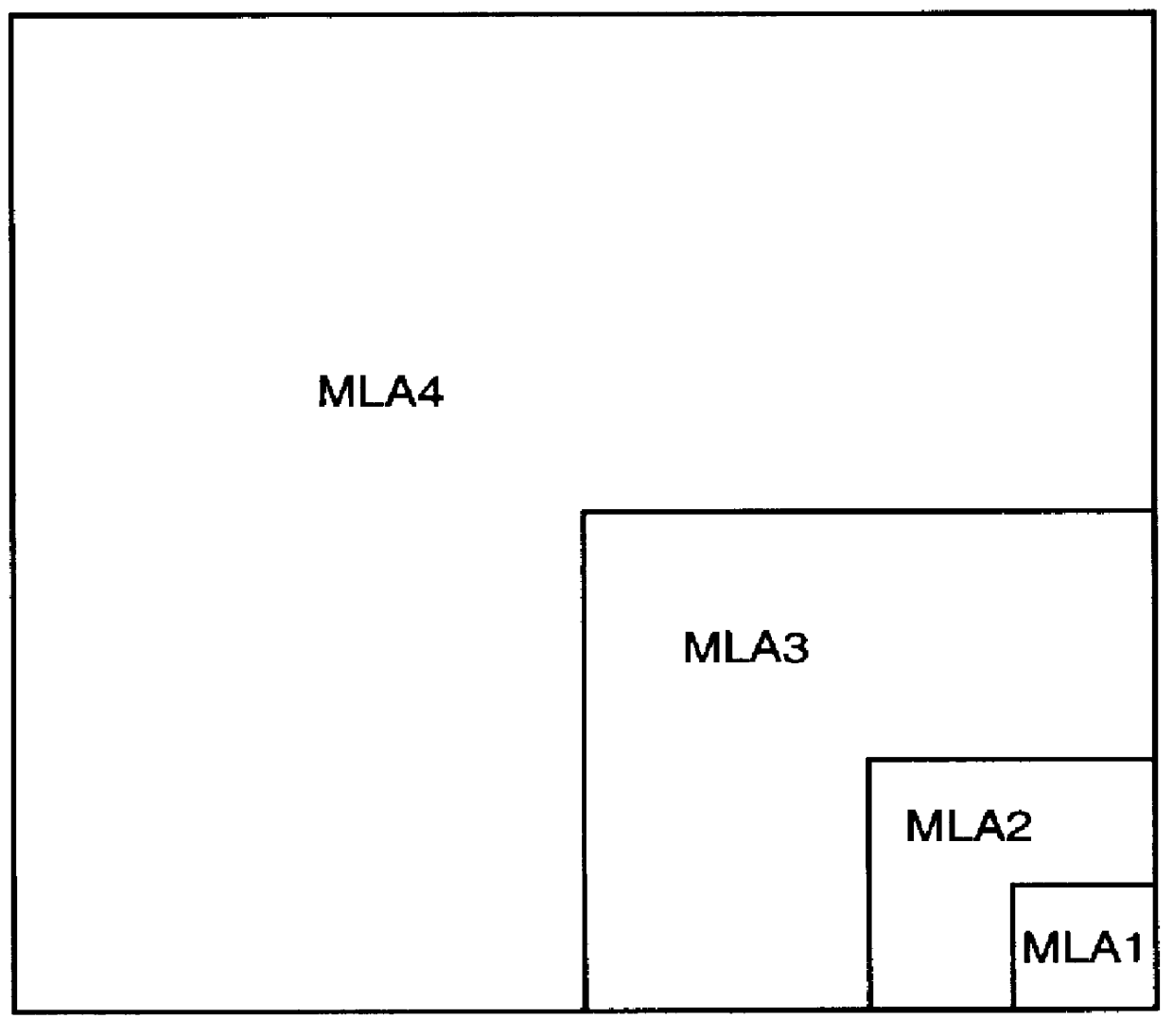

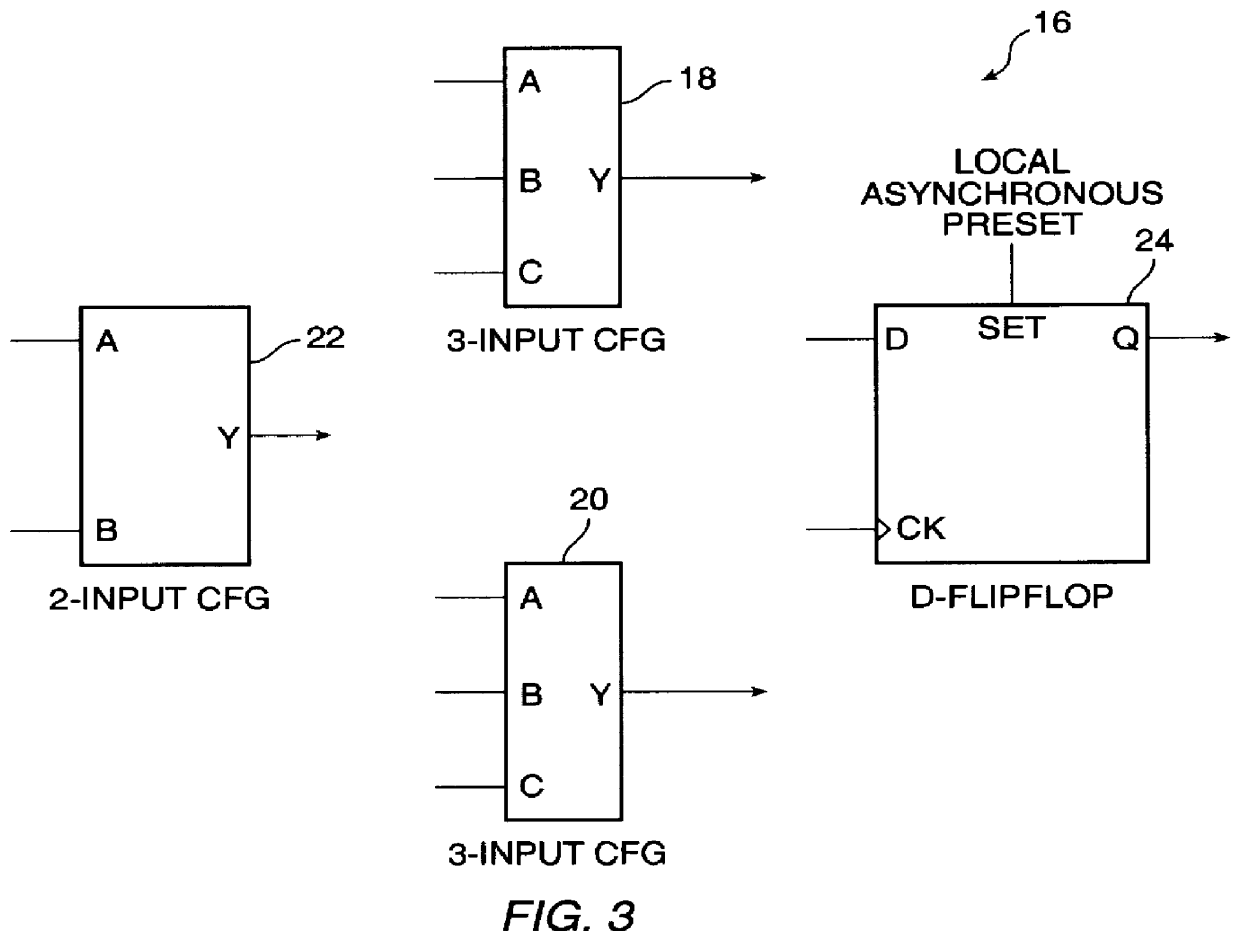

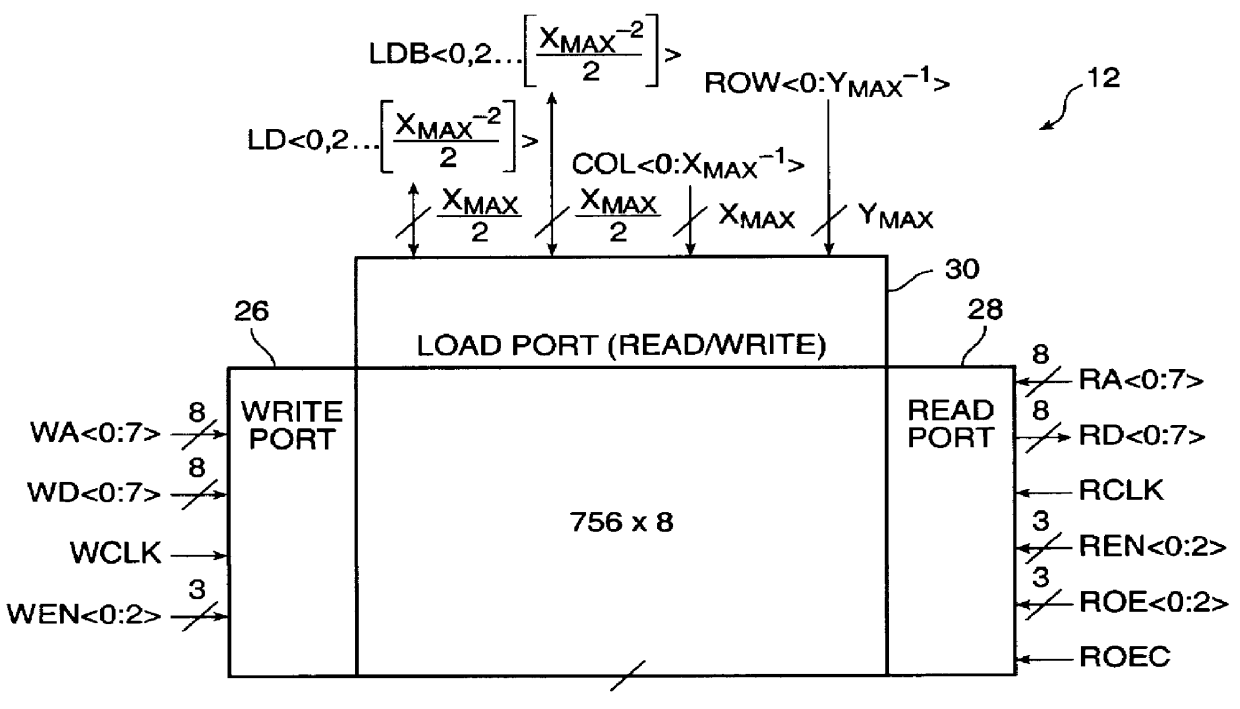

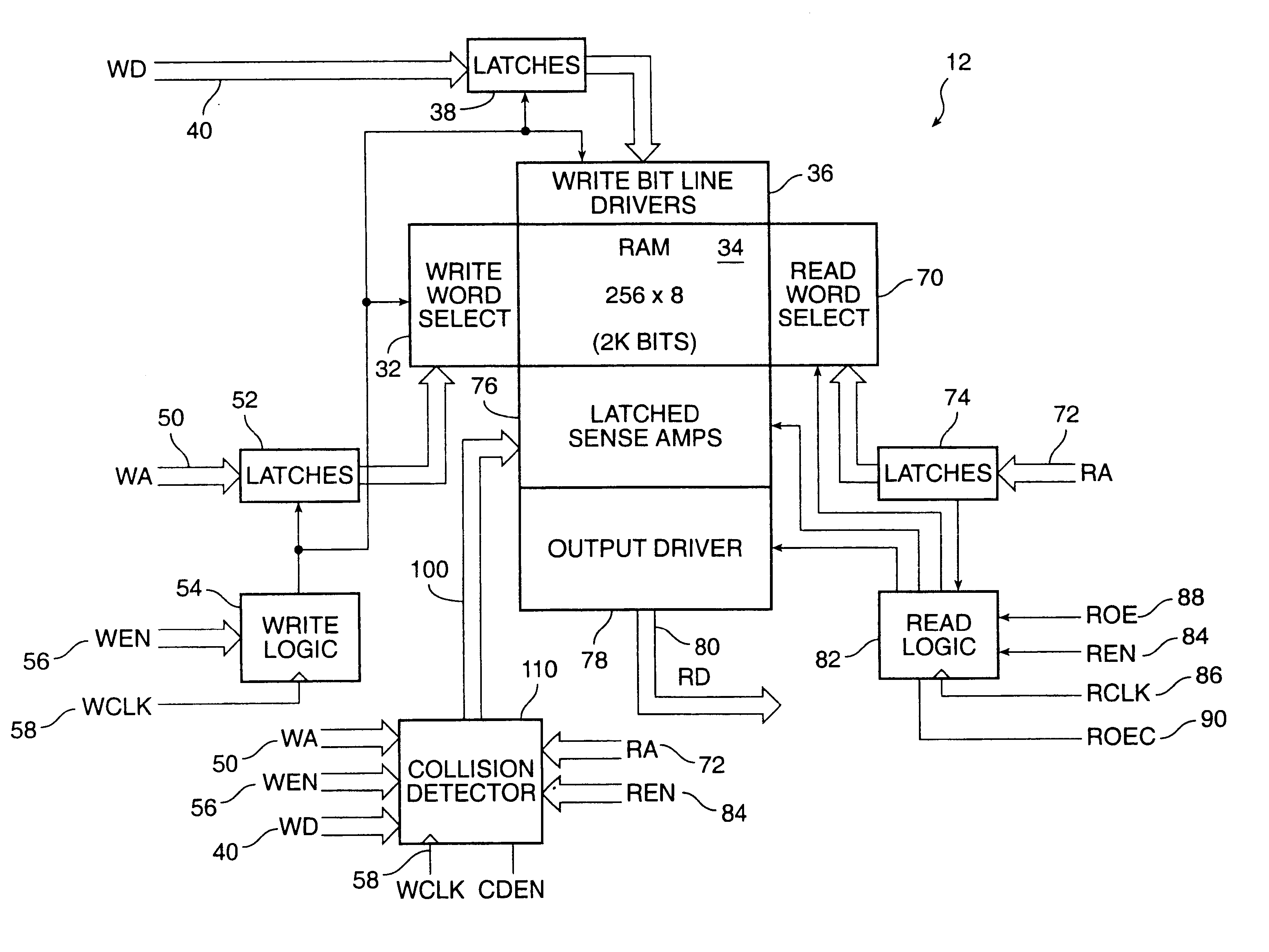

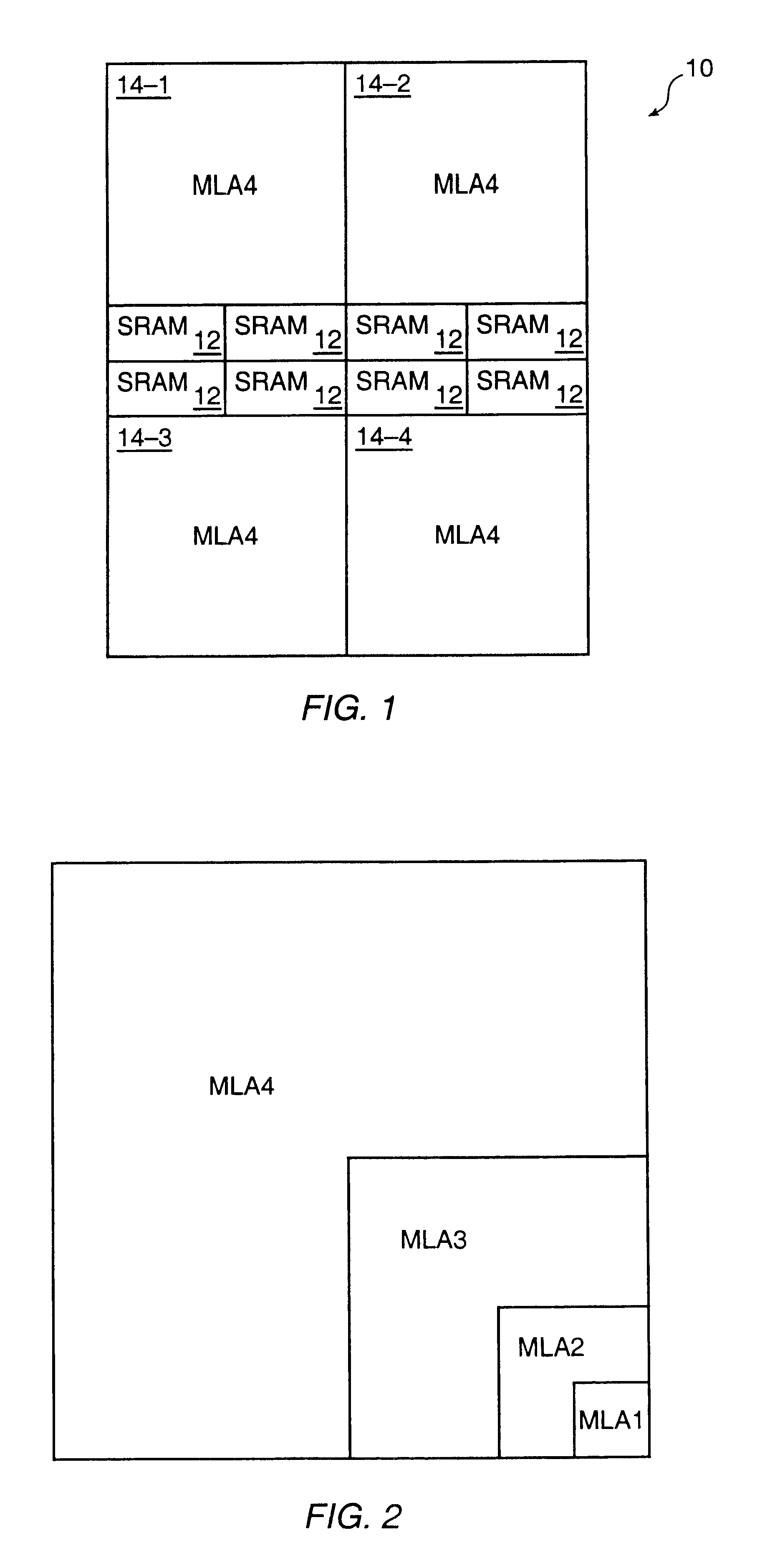

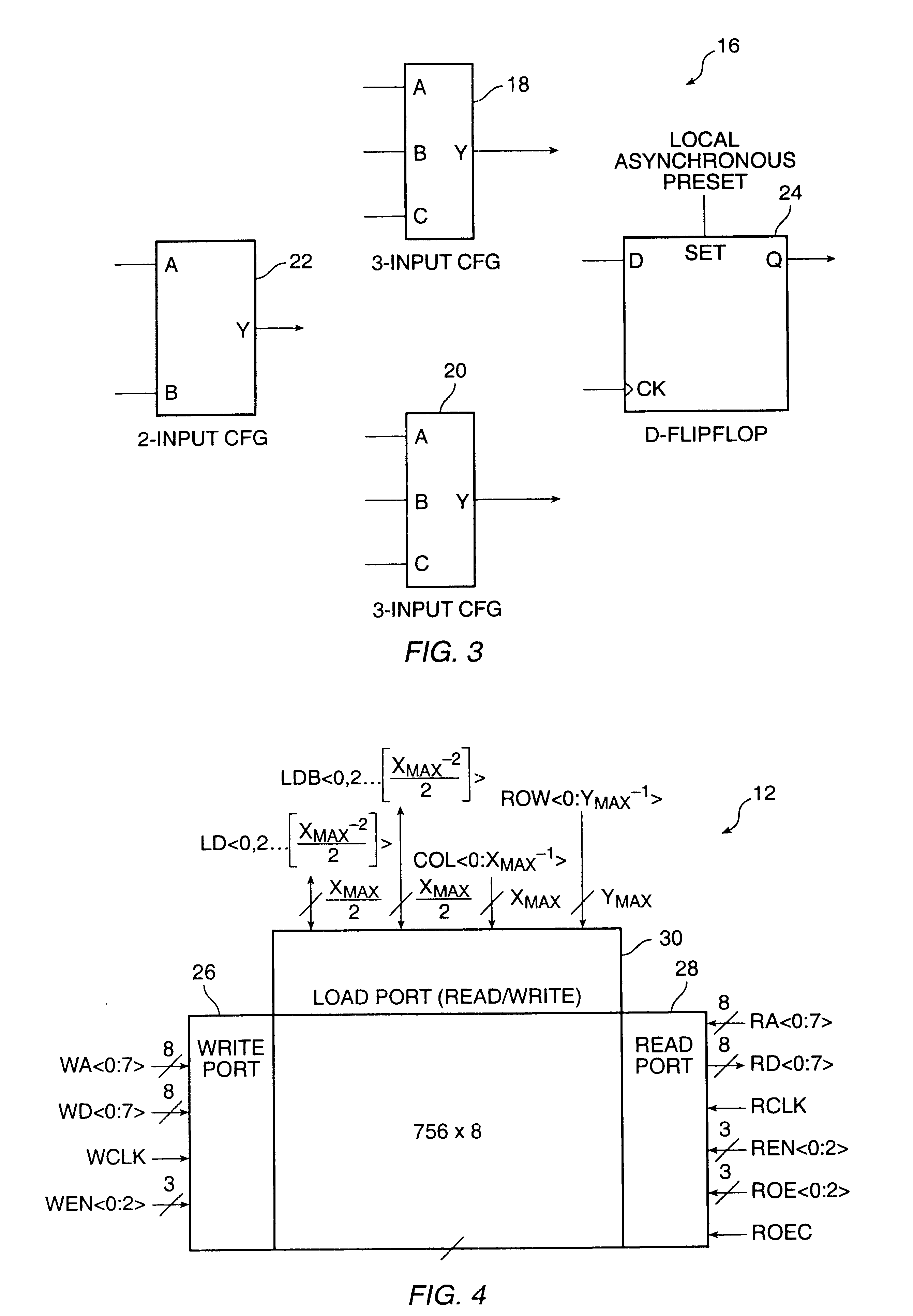

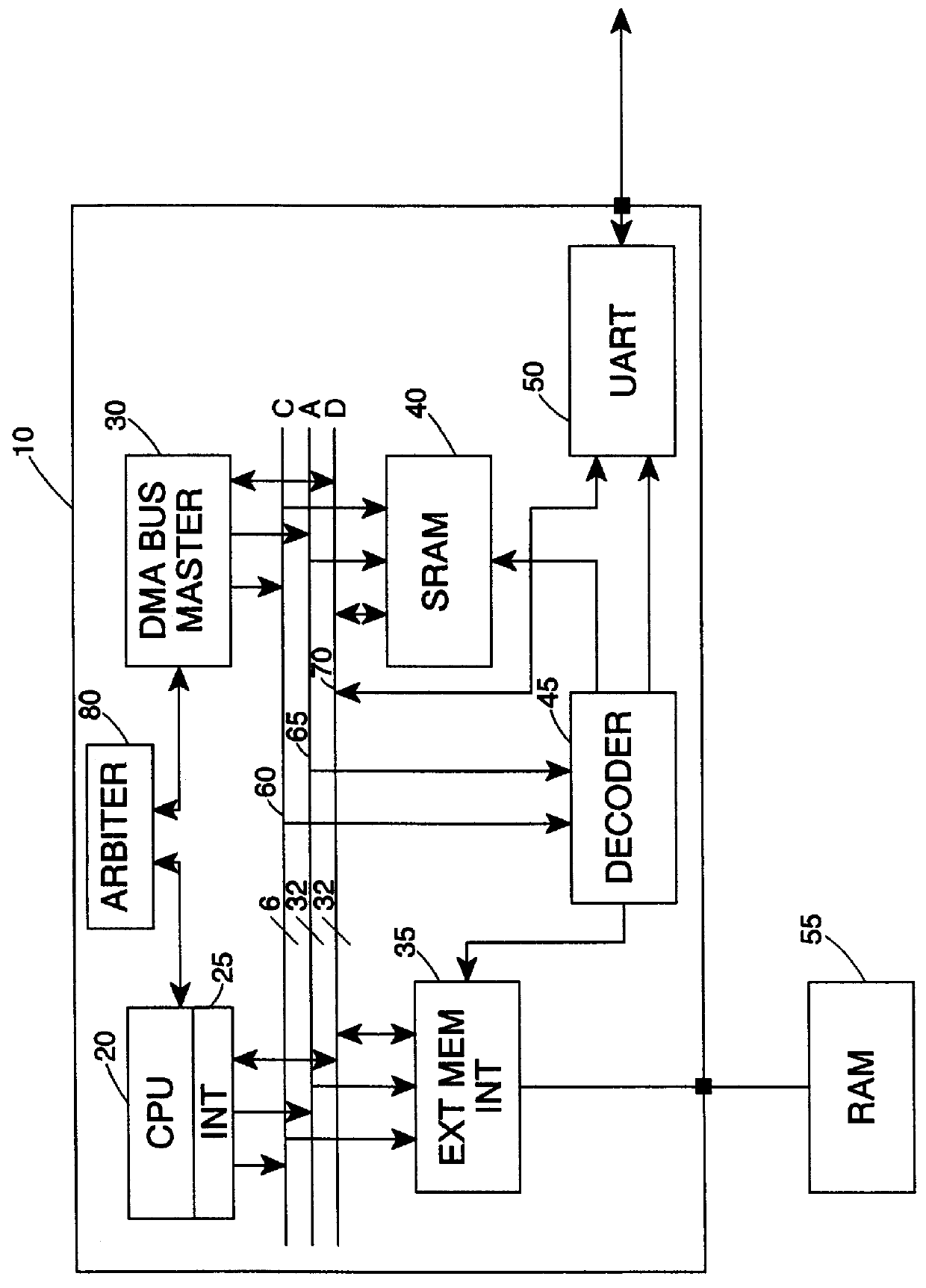

Embedded static random access memory for field programmable gate array

InactiveUS6049487AHigh impedance stateSolve conflictsDetecting faulty hardware by configuration testRead-only memoriesStatic random-access memoryRandom access memory

A dual ported (simultaneous read / write) SRAM block with an additional load port that interacts with the circuitry employed in the loading and testing of the configuration data of the FPGA core is disclosed. Each SRAM block contains circuits in both the read port and the write port that permit the SRAM blocks to be connected into deeper and wider configurations by without any additional logic as required by the prior art. An address collision detector is provided such that when both read and write ports in the SRAM block access the same address simultaneously a choice between the data being read can be made between the data presently in the SRAM block or the new data being written to the SRAM block.

Owner:MICROSEMI SOC

Embedded static random access memory for field programmable gate array

InactiveUS6430088B1High impedance stateSolve conflictsDetecting faulty hardware by configuration testRead-only memoriesStatic random-access memoryRandom access memory

A dual ported (simultaneous read / write) SRAM block with an additional load port that interacts with the circuitry employed in the loading and testing of the configuration data of the FPGA core is disclosed. Each SRAM block contains circuits in both the read port and the write port that permit the SRAM blocks to be connected into deeper and wider configurations by without any additional logic as required by the prior art. An address collision detector is provided such that when both read and write ports in the SRAM block access the same address simultaneously a choice between the data being read can be made between the data presently in the SRAM block or the new data being written to the SRAM block.

Owner:MICROSEMI SOC

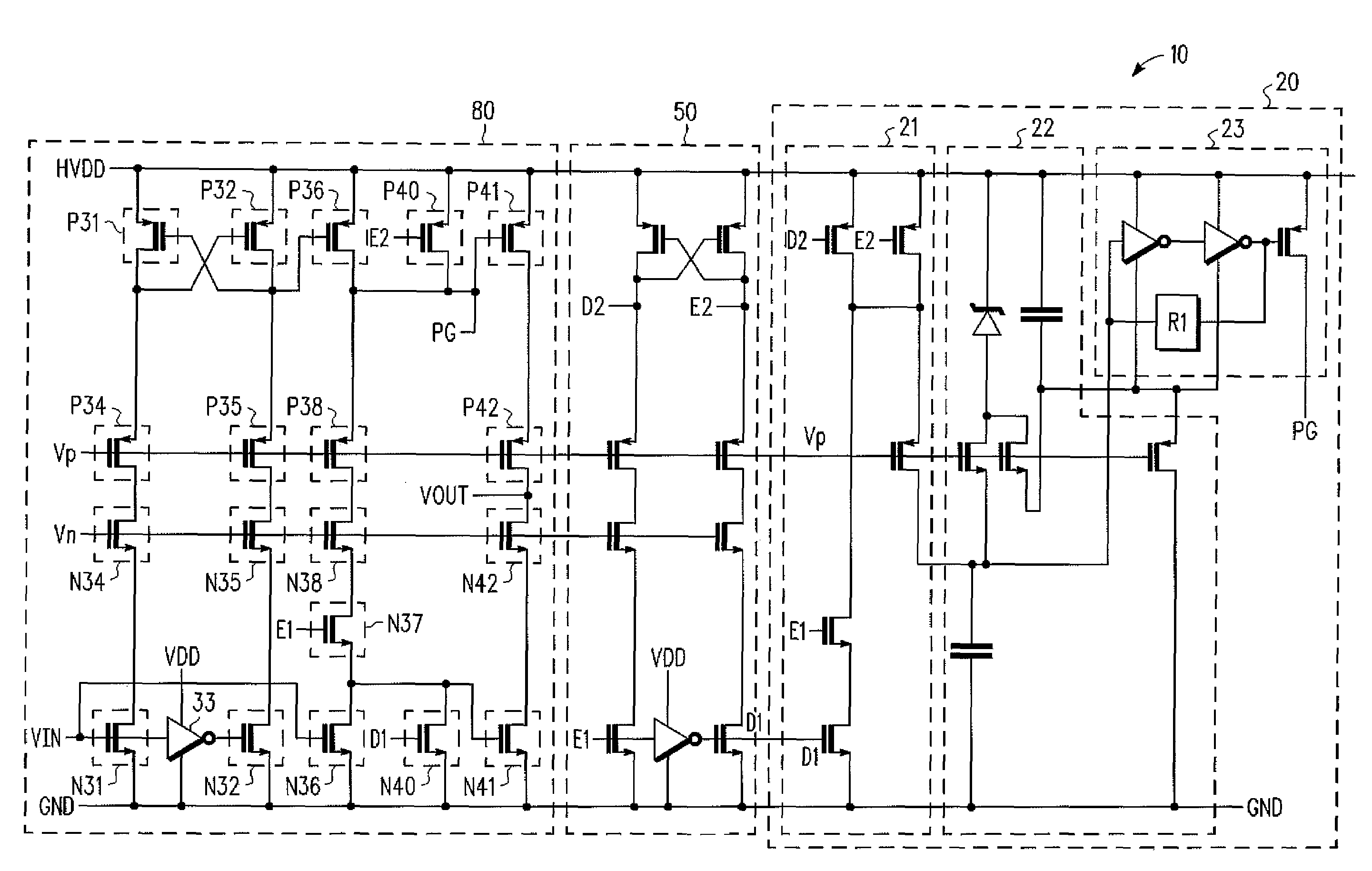

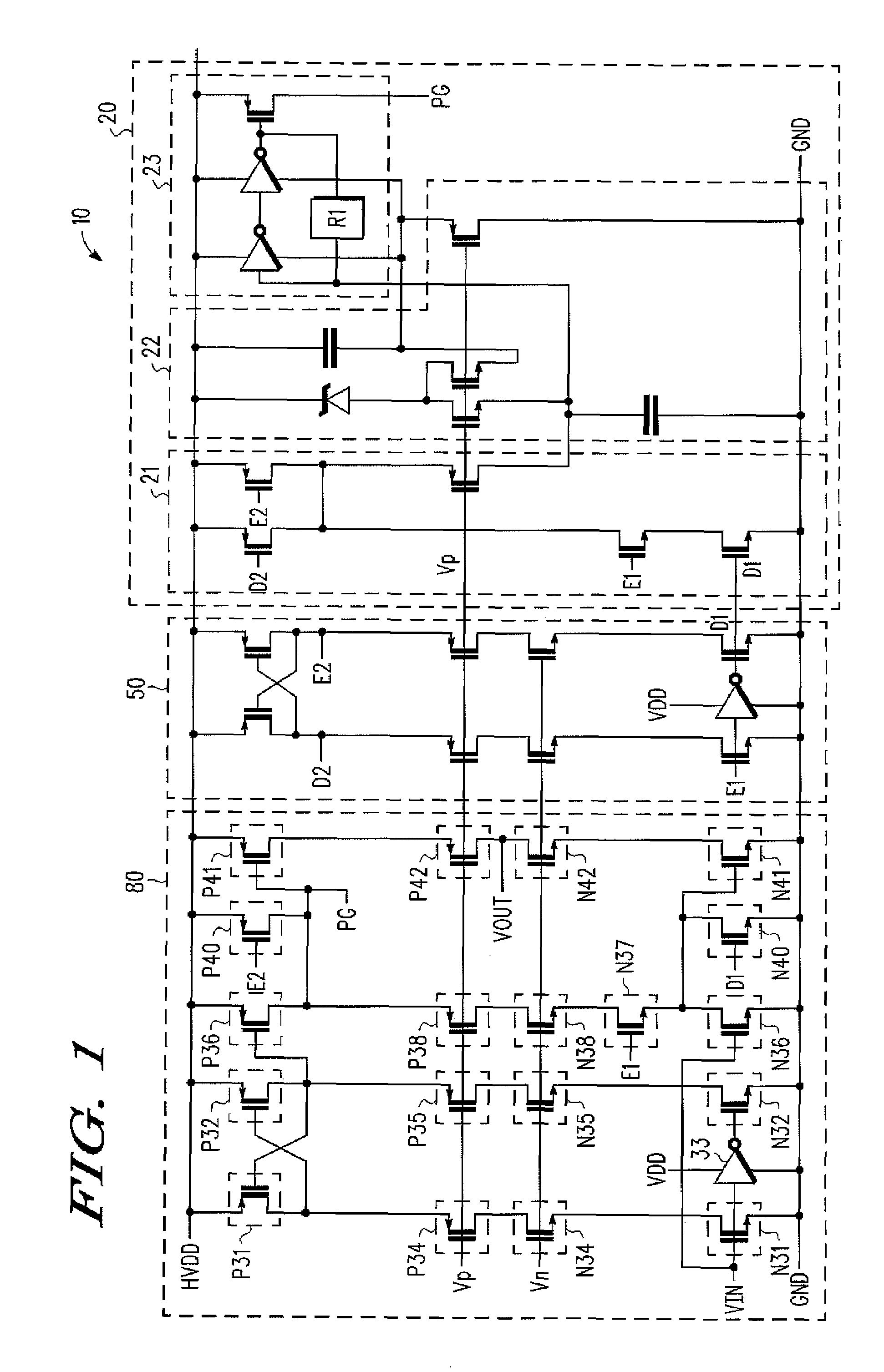

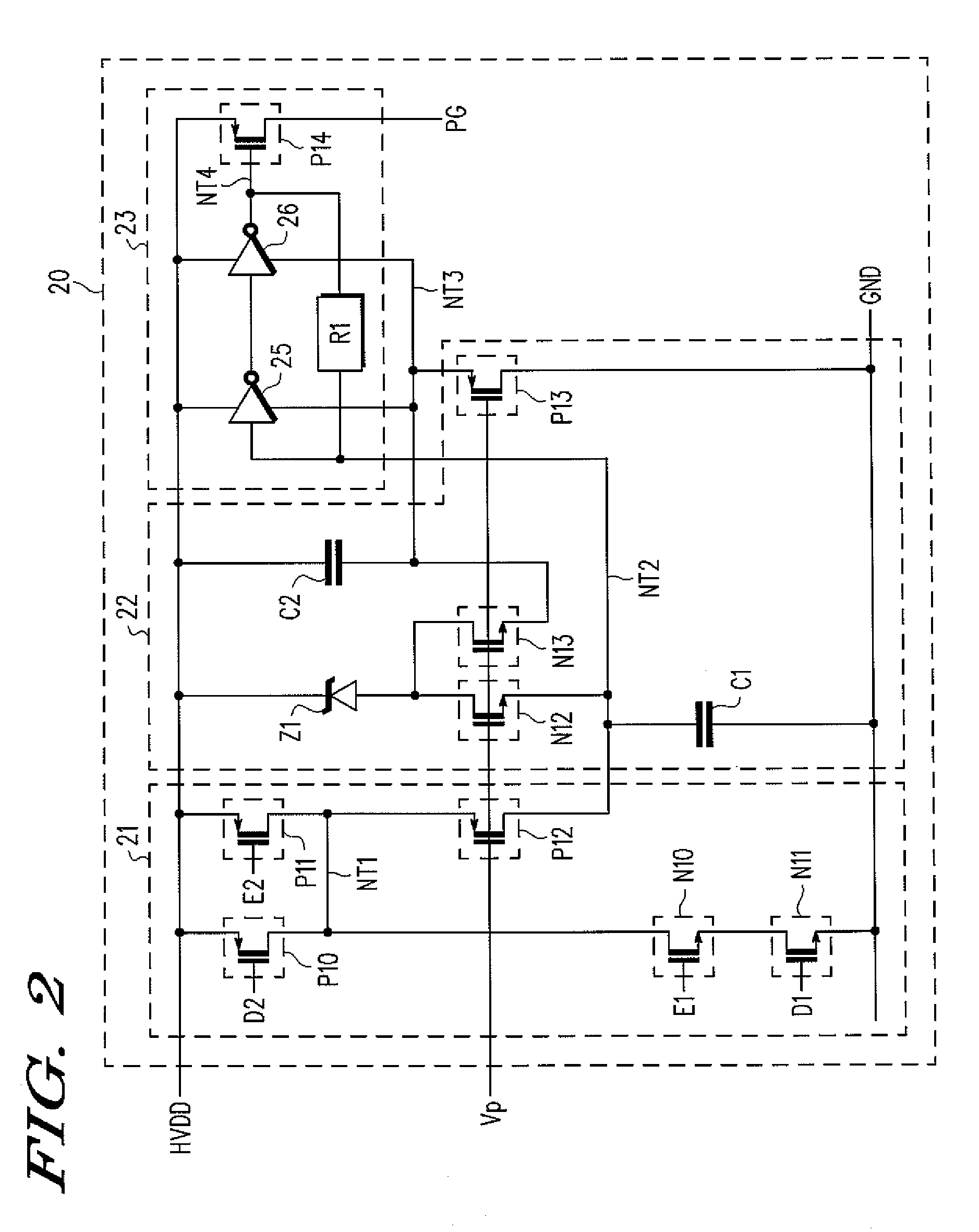

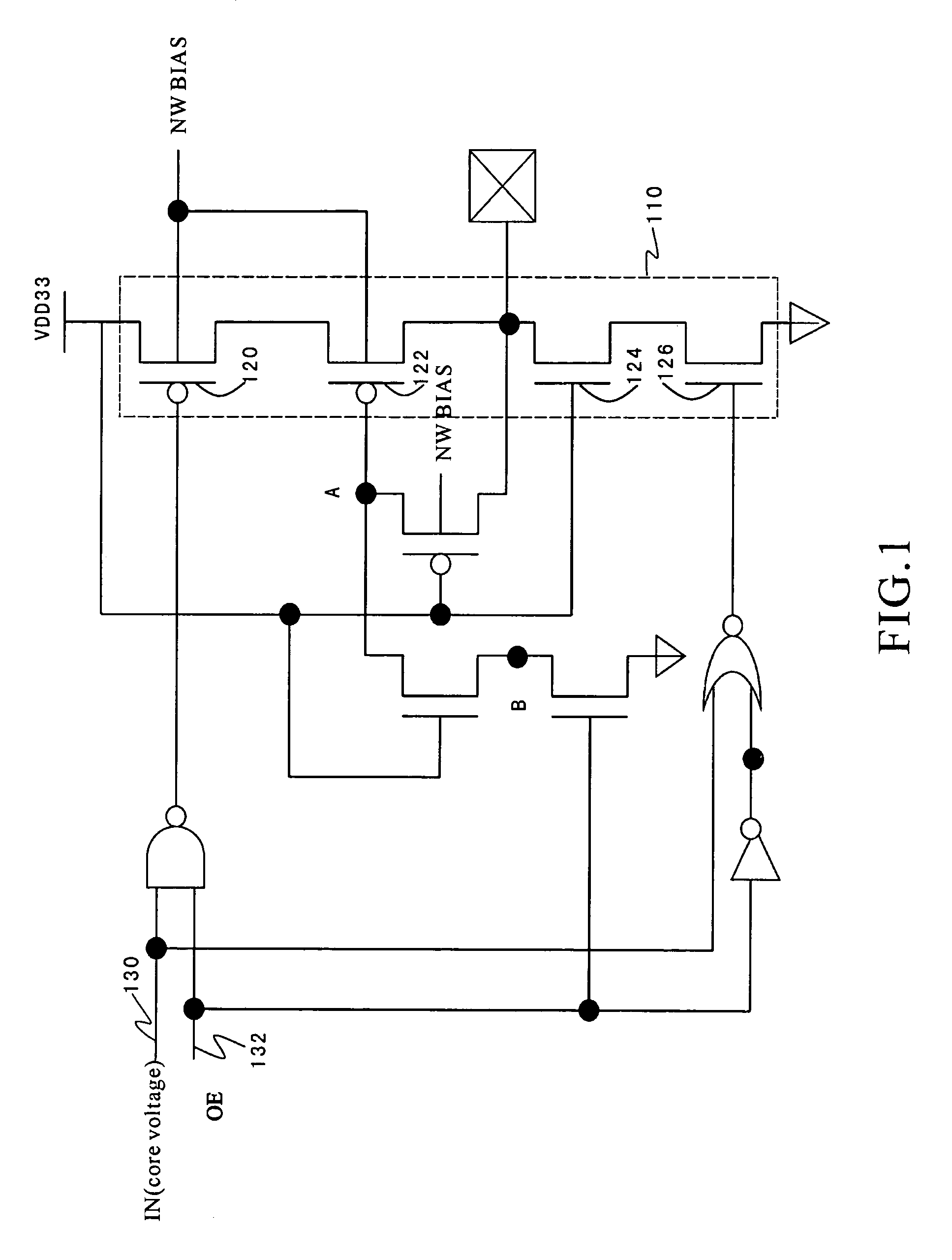

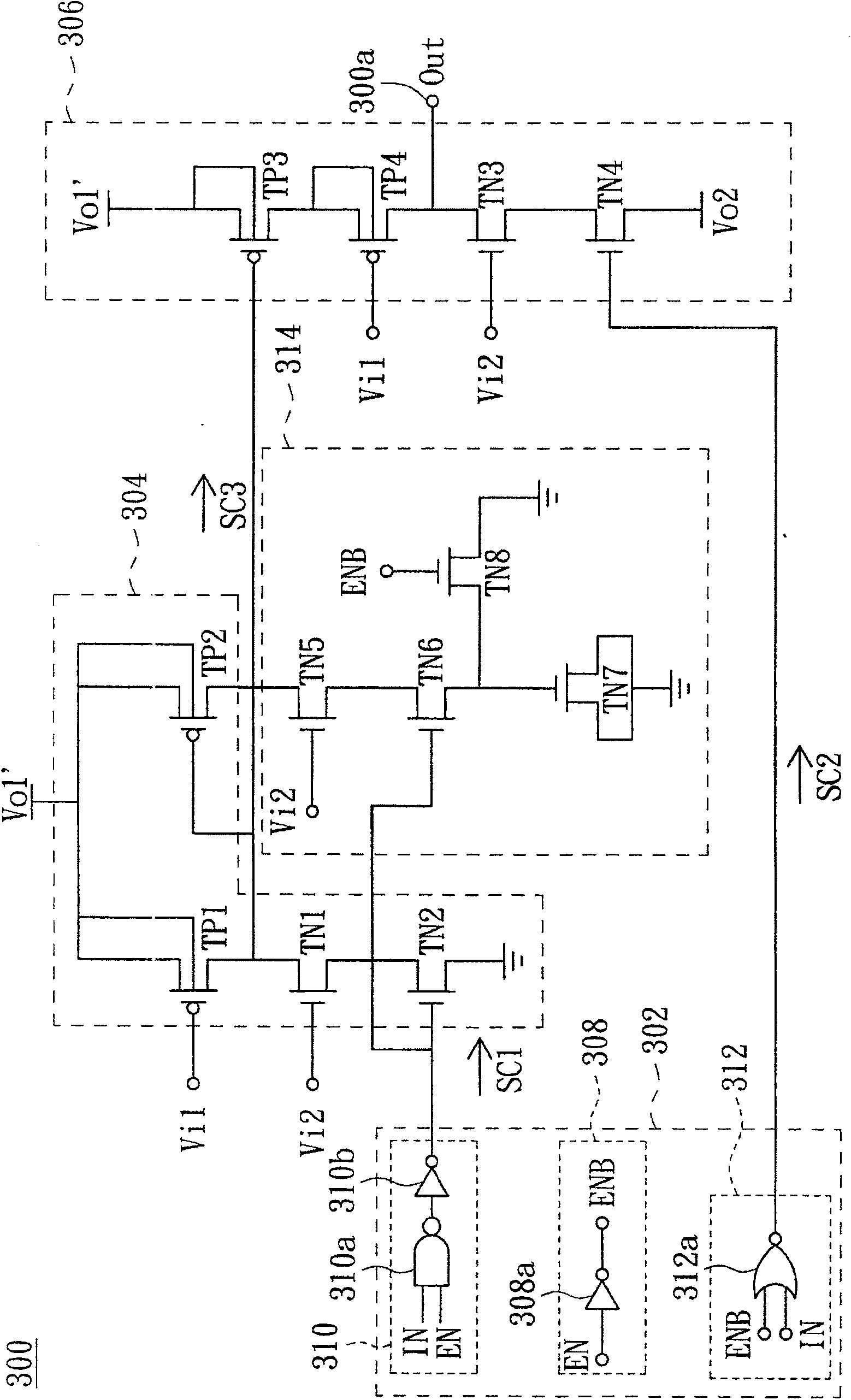

Level shifter circuit

InactiveUS7382158B2High impedance stateReduce power consumptionLogic circuit coupling/interface arrangementsEngineeringP channel

A level shifter circuit for ensuring a high impedance state even in a transitional period such as when activating an external power supply while reducing power consumption. A latch circuit is set to a low level by a set circuit when a high potential power supply voltage increases. When the high potential power supply voltage exceeds a threshold voltage, a p-channel MOS transistor of the latch circuit is activated and the high potential power supply voltage is applied to a first transistor via a connection node. When a high potential enable signal having normal high level signal voltage is provided to a second transistor, which is connected to the first transistor, the reset circuit provides the high level signal to the latch circuit and stops the voltage application to the first transistor via the connection node.

Owner:NORTH STAR INNOVATIONS

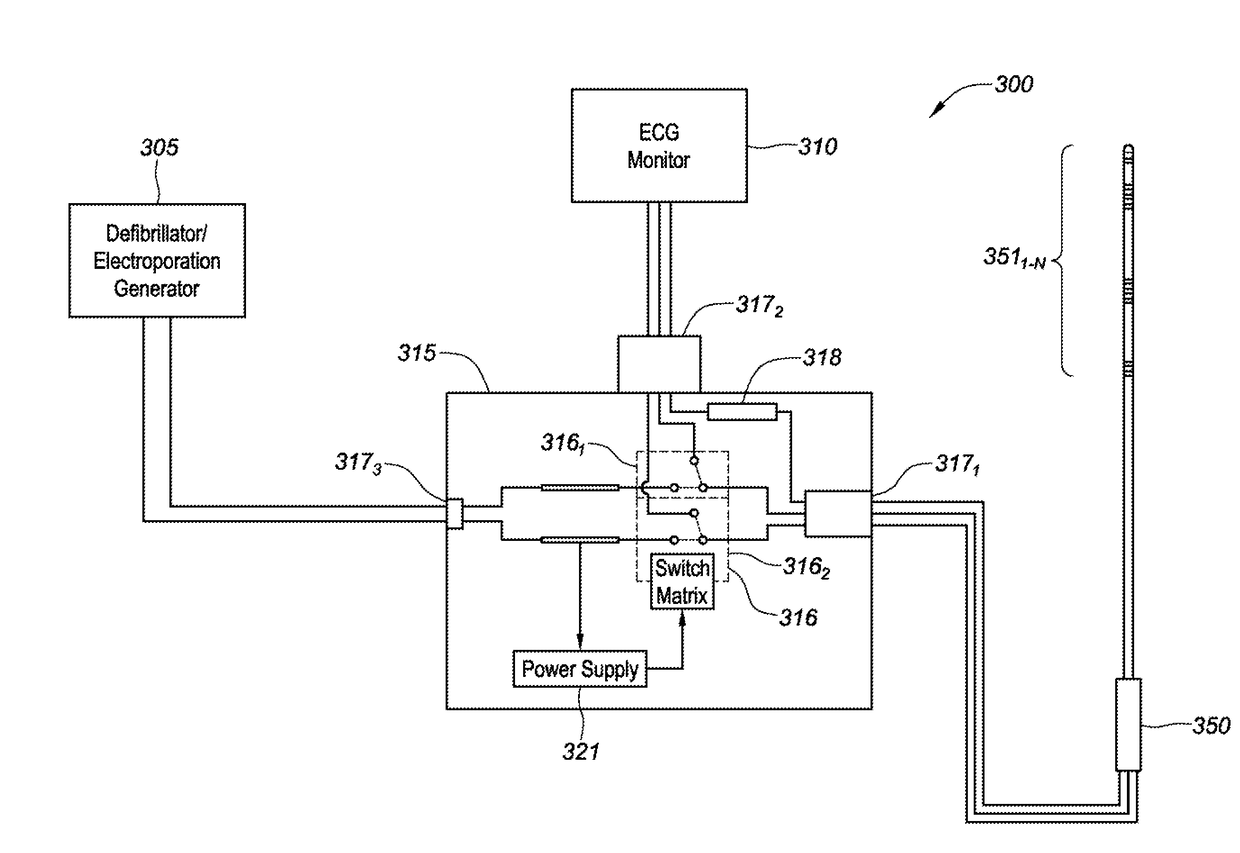

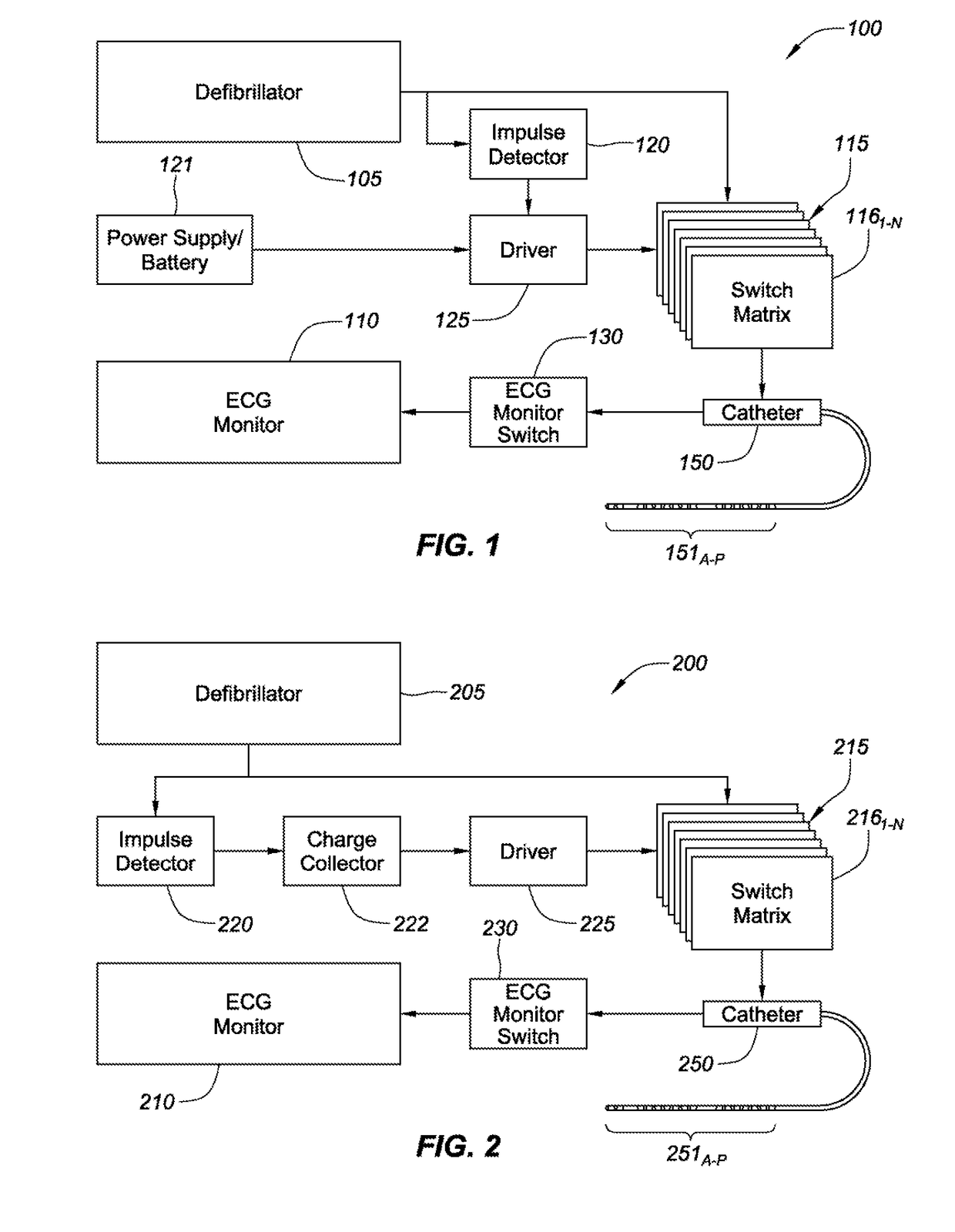

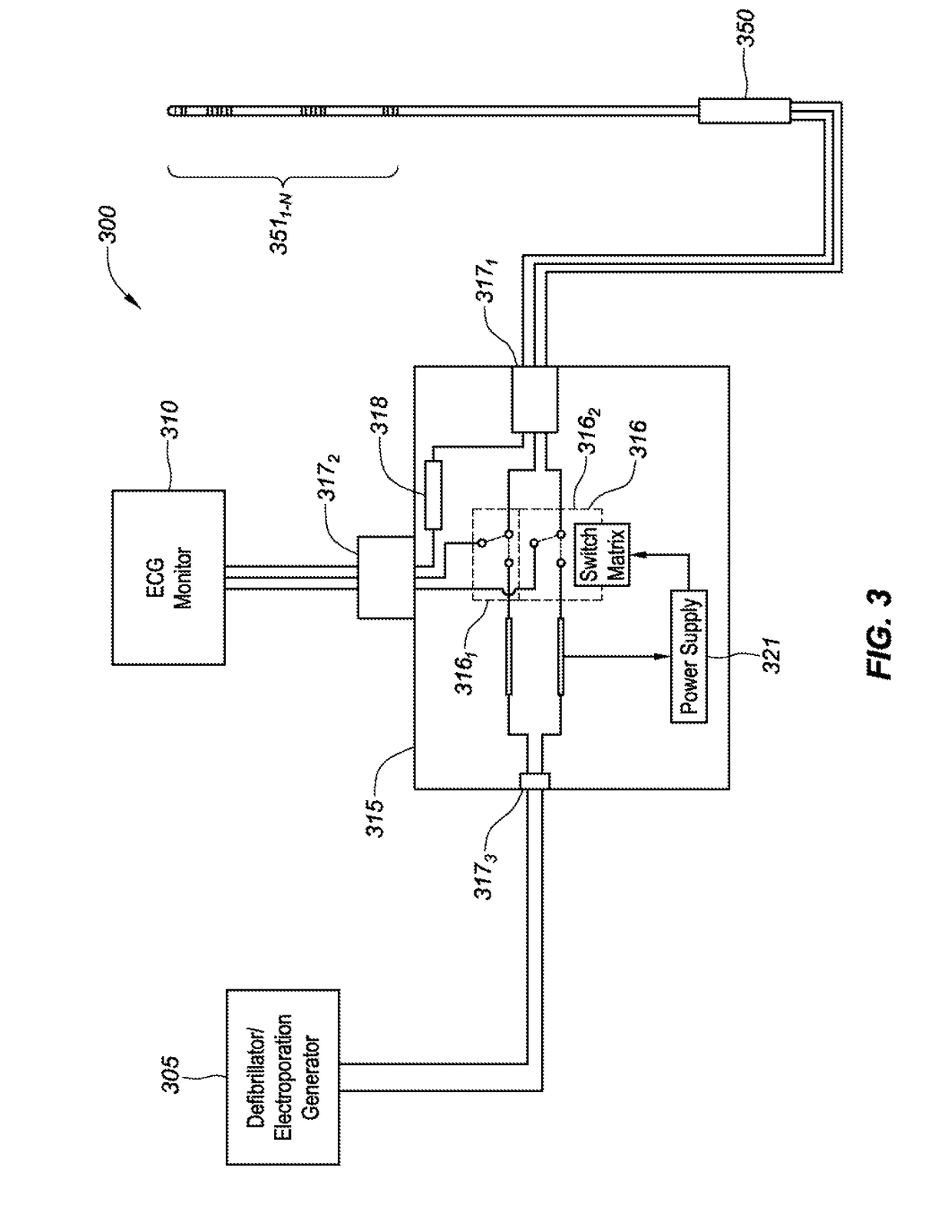

Electronic switchbox

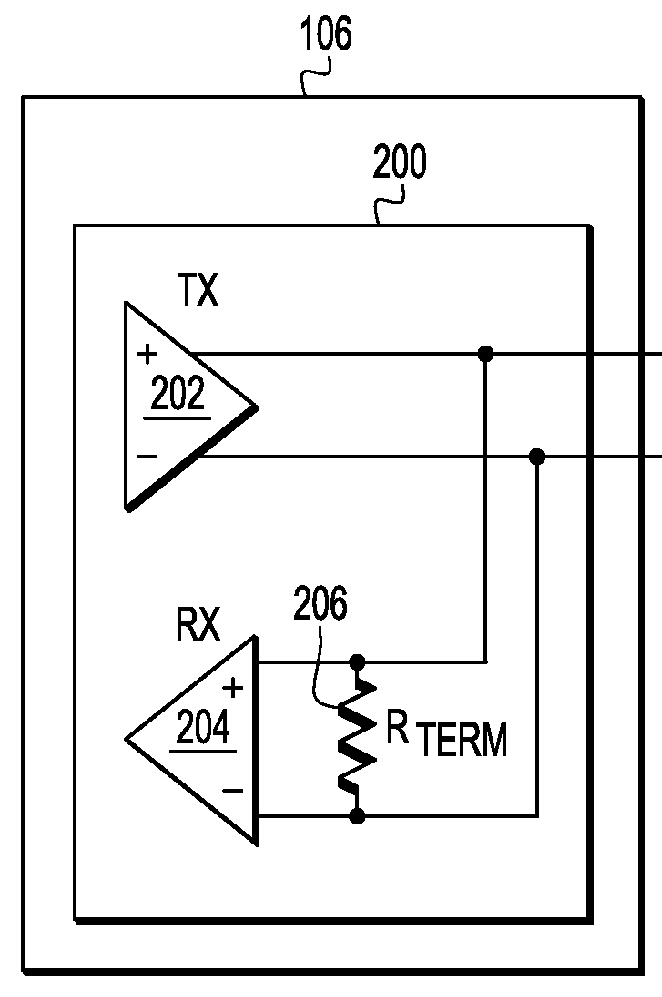

ActiveUS20180221085A1High impedance stateElectrocardiographyHeart defibrillatorsTelecommunicationsCardioversion

Aspects of the present disclosure are directed to an electronic switchbox for automatically switching between receive and transmit functionalities. In one embodiment, an electronic switchbox automatically switches between receiving electrocardiograph signals and transmitting cardioversion impulses.

Owner:ST JUDE MEDICAL CARDILOGY DIV INC

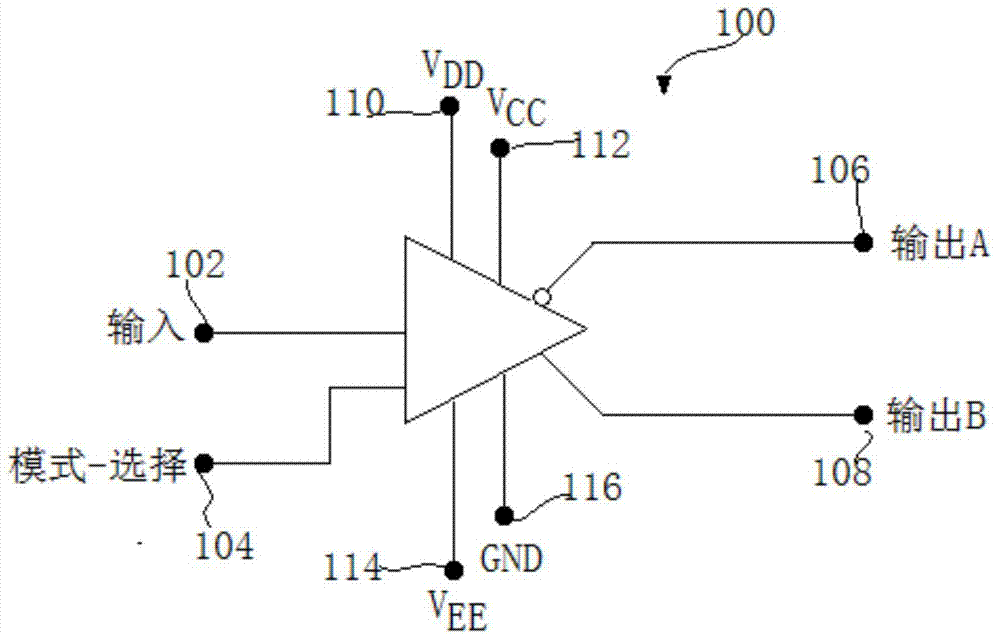

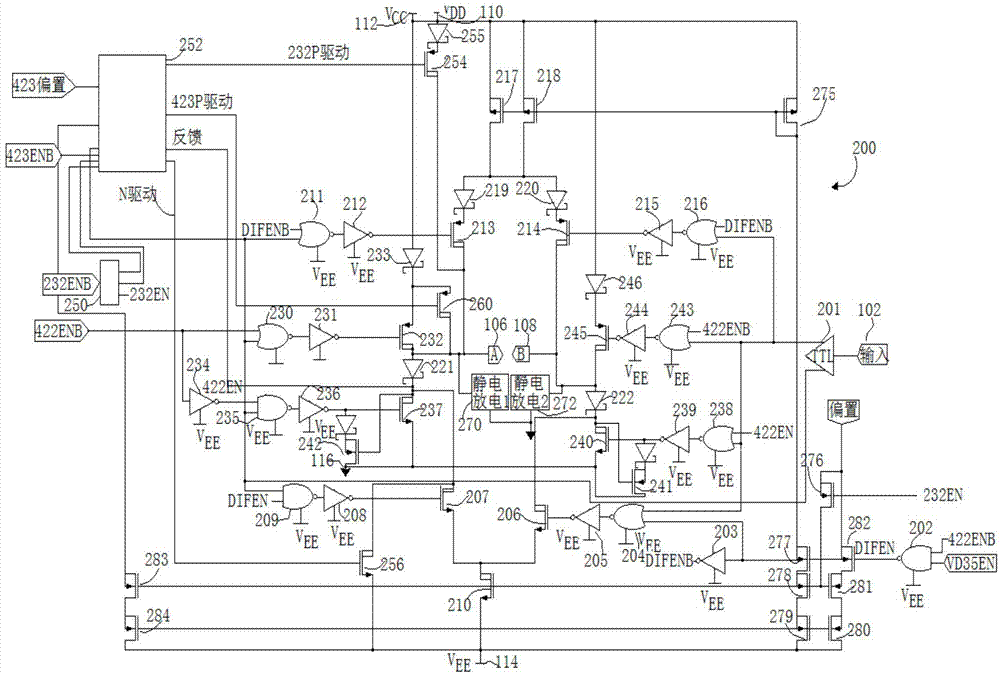

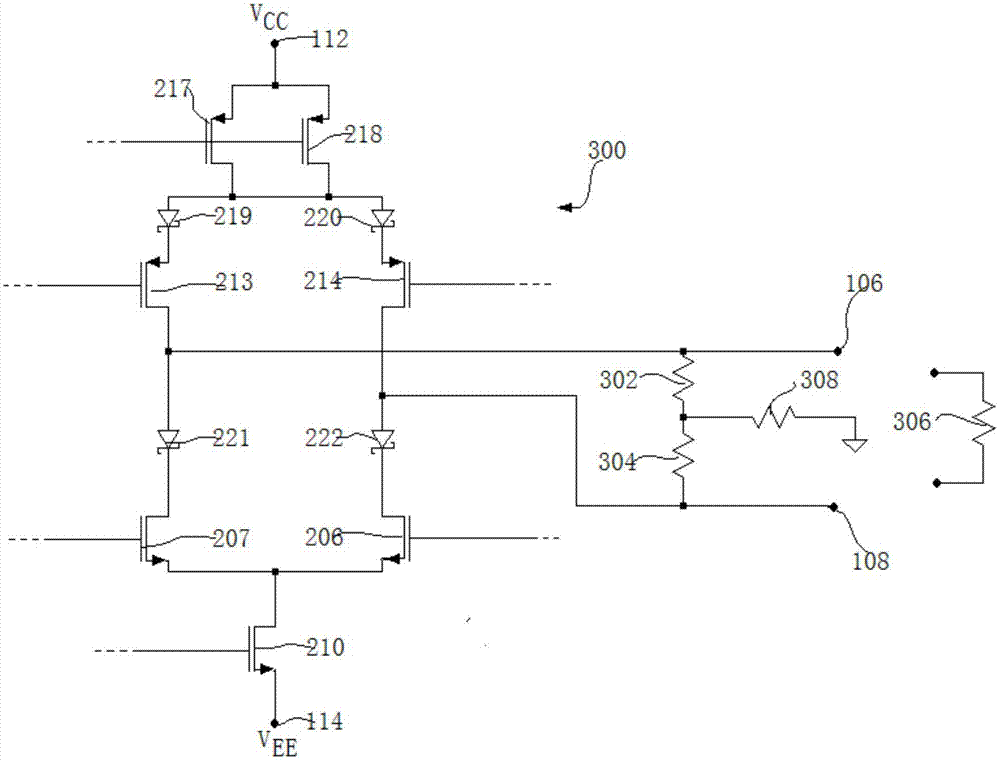

Mixed-mode multi-protocol serial interface driver

InactiveCN103618536AHigh impedance stateLogic circuit coupling/interface arrangementsInterface standardEngineering

Provided is a mixed-mode multi-protocol serial interface driver. The driver can work in the current mode or the voltage mode or work in the two modes at the same time. The driver comprises a circuit used for making an output signal conform to one of a series of selectable electrical interface standards including the CCITT / EIA standards V.35, V.11 / RS-422, V.28 / RS-232 and V.10 / RS-423. When the specific standard is selected for an input signal through mode selection, a proper portion in the circuit can start response. Part of the circuit can not be placed in a high-impedance state, and the part of the circuit is prevented from interfering with the portion, starting the response, of the circuit.

Owner:SUZHOU BATELAB MICROELECTRONICS

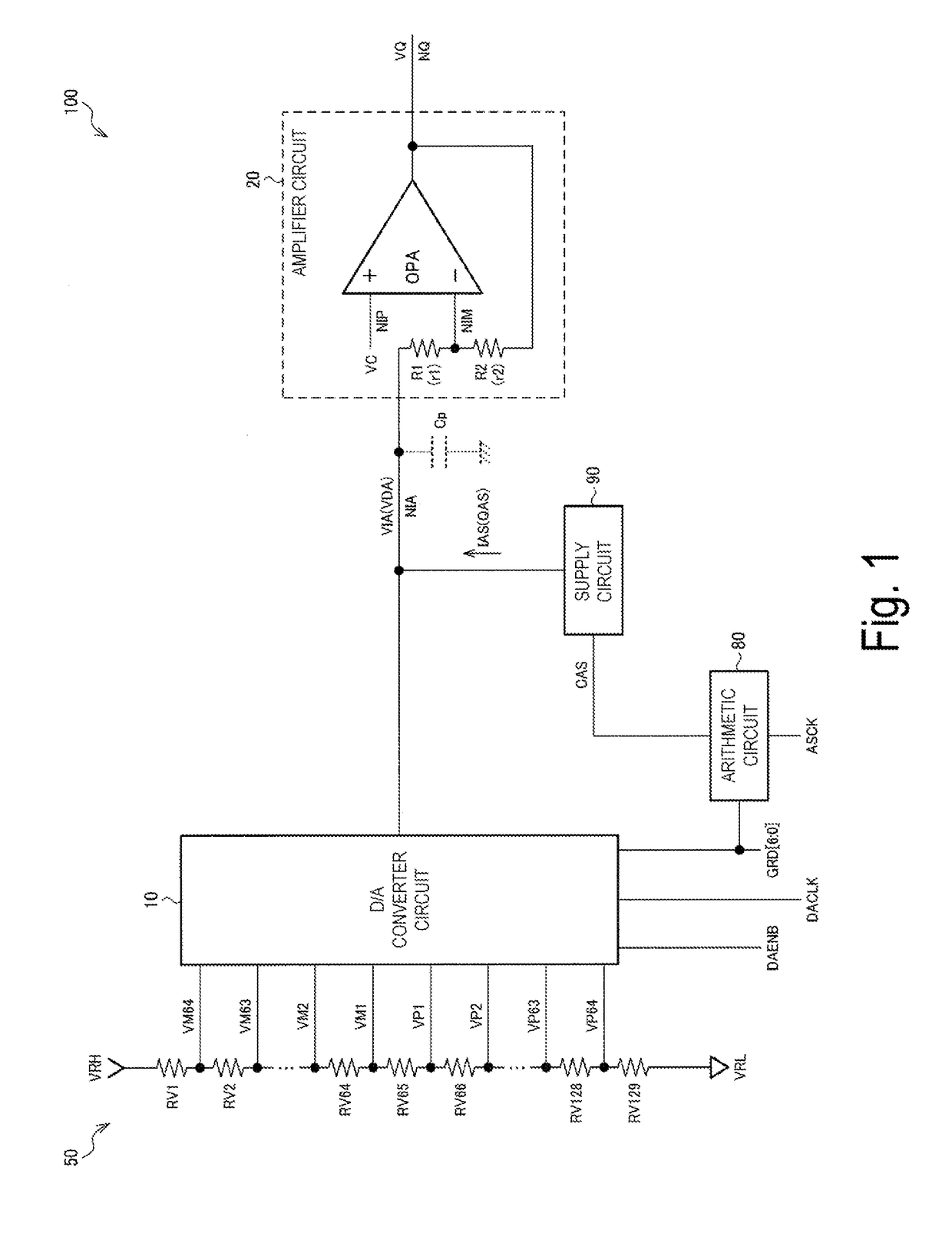

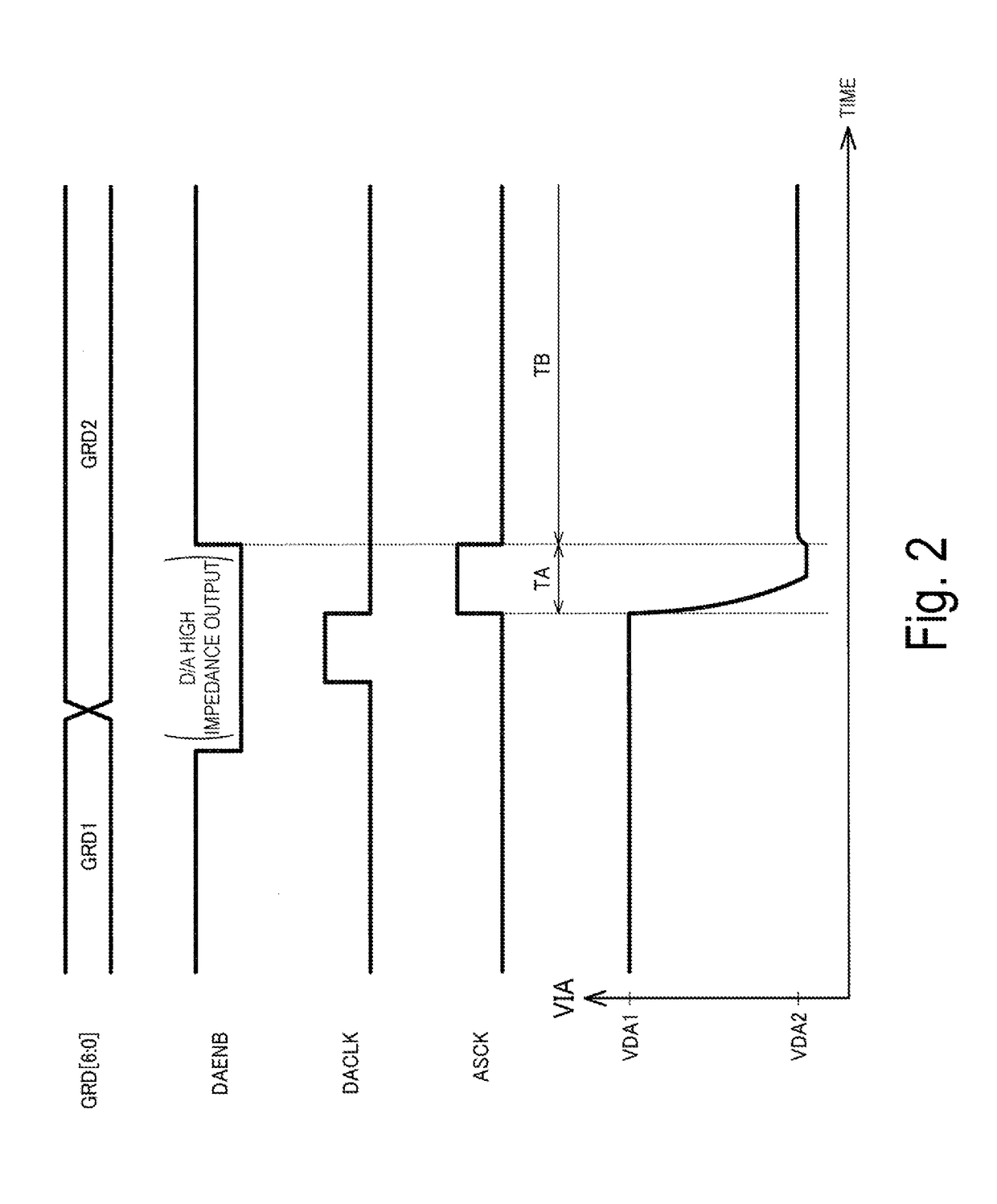

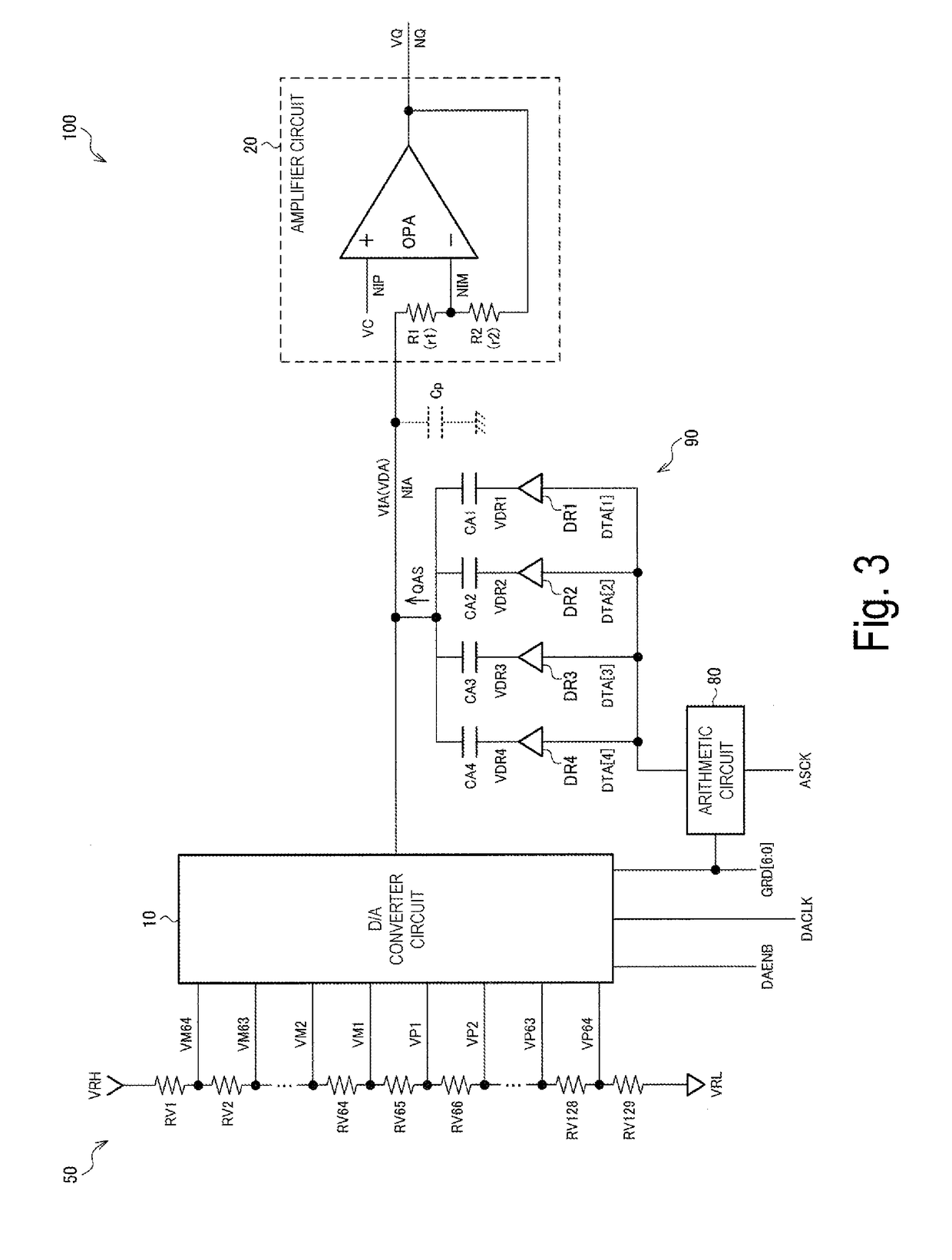

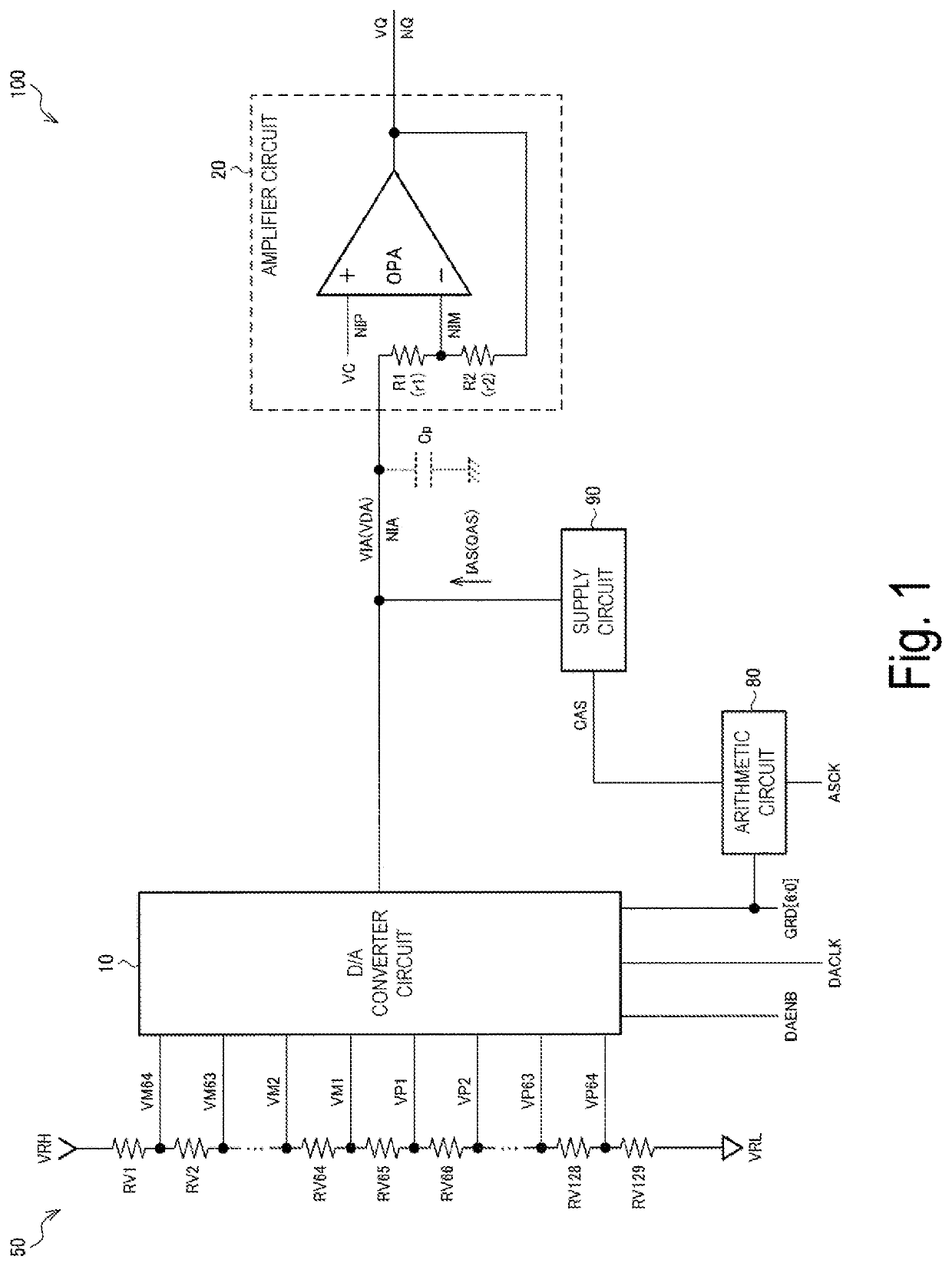

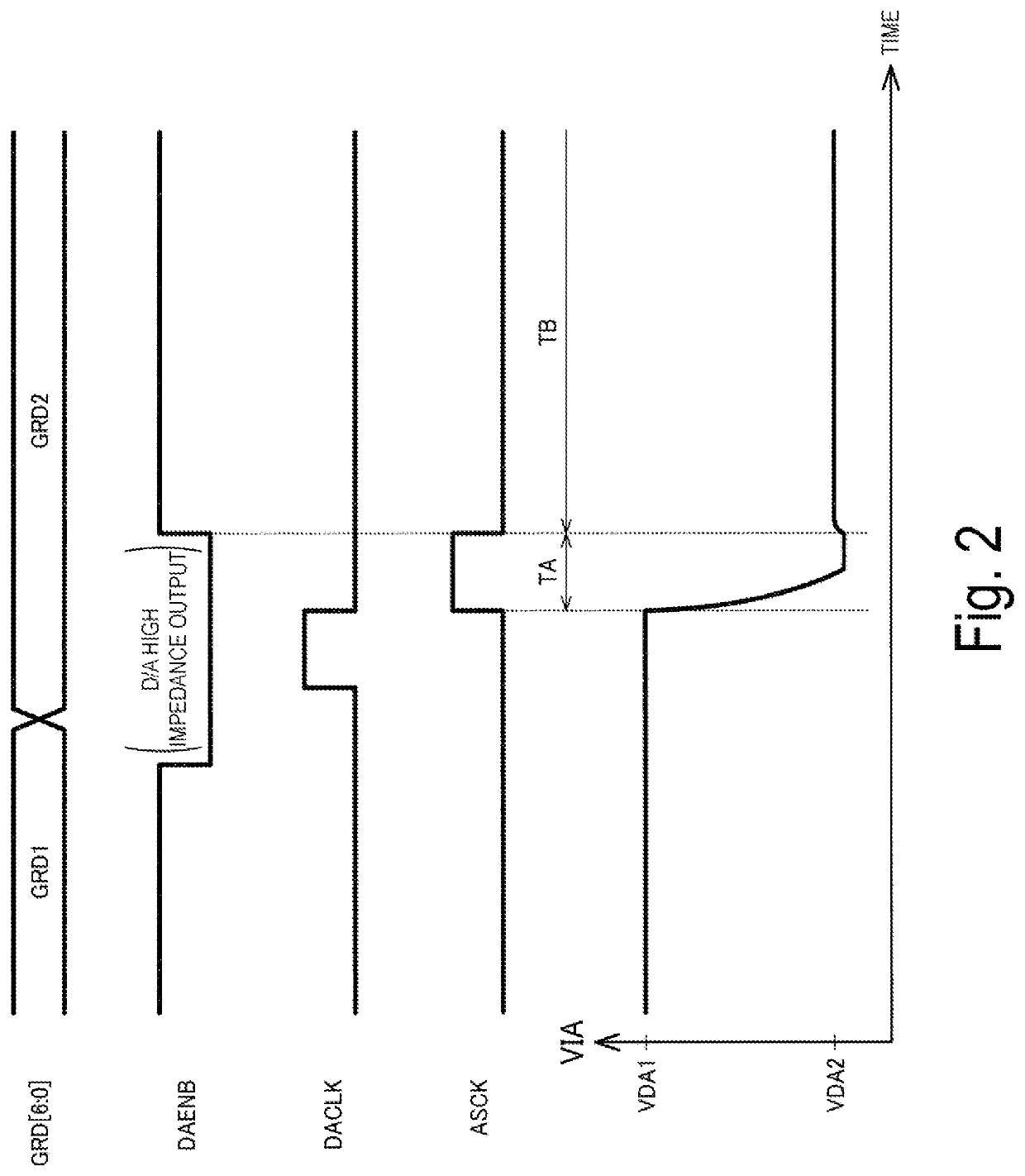

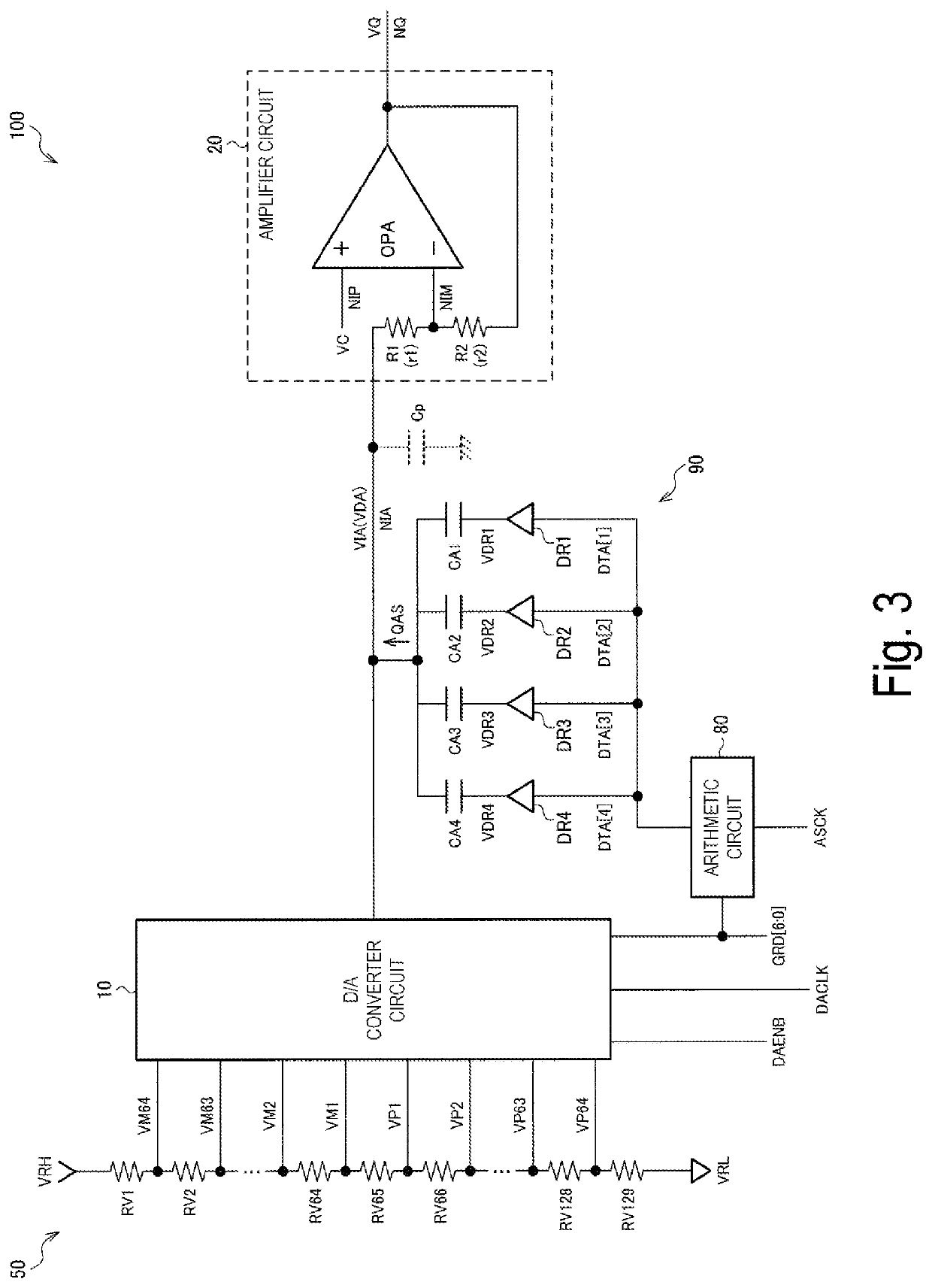

Display driver, electro-optical device, and electronic apparatus

ActiveUS20190088229A1Voltage changeSensitive highStatic indicating devicesPower flowAudio power amplifier

A display driver includes a D / A converter circuit configured to convert display data into a gradation voltage, an amplifier circuit including an input node to which the gradation voltage is input and configured to output data voltage, and a supply circuit configured to supply an auxiliary current or an auxiliary electrical charge to the input node of the amplifier circuit. In an auxiliary period, an output of the D / A converter circuit is in a high impedance state, and the supply circuit supplies the auxiliary current or the auxiliary electrical charge to the input node of the amplifier circuit. In a non-auxiliary period after the auxiliary period, the D / A converter circuit outputs the gradation voltage to the input node of the amplifier circuit.

Owner:SEIKO EPSON CORP

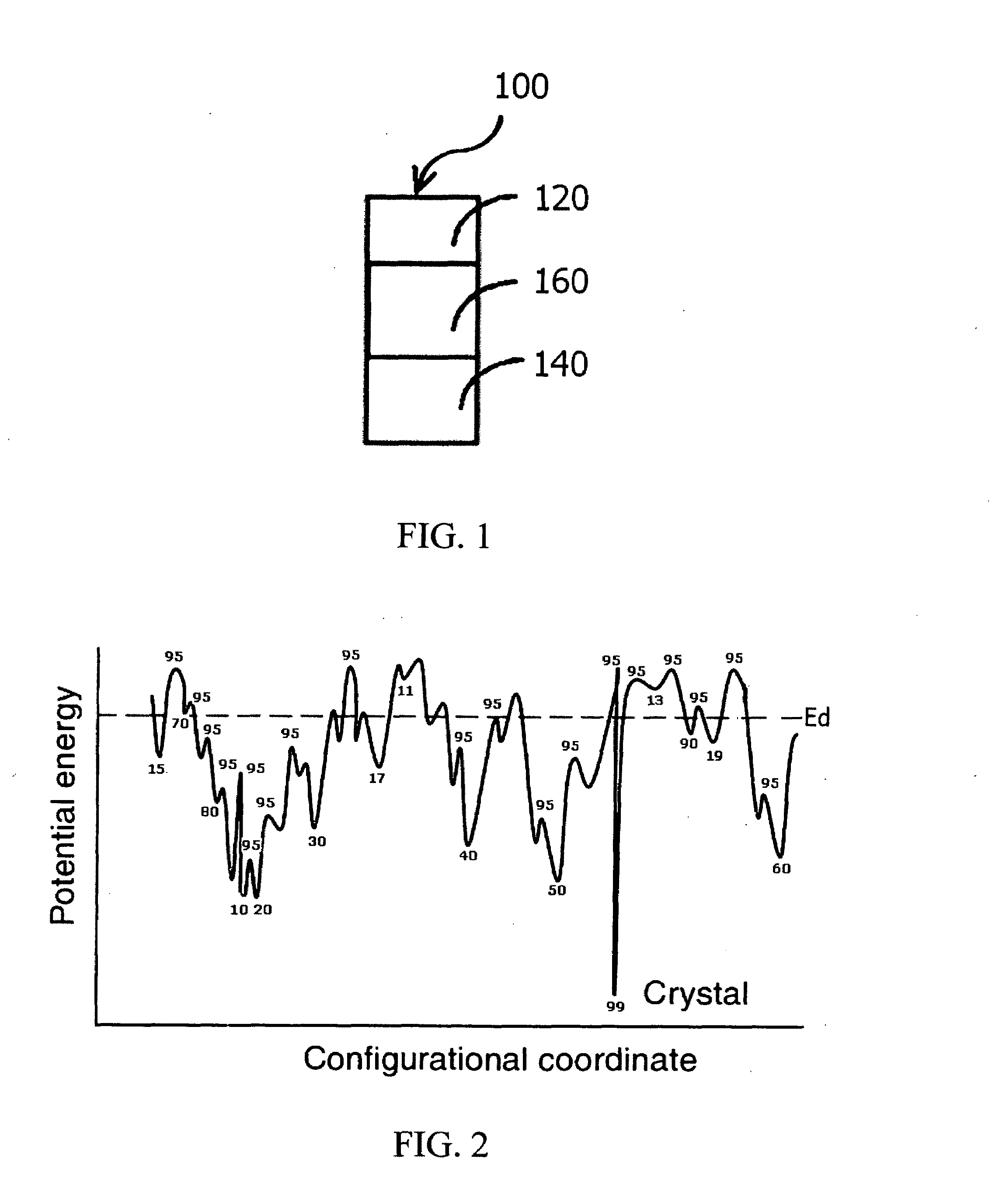

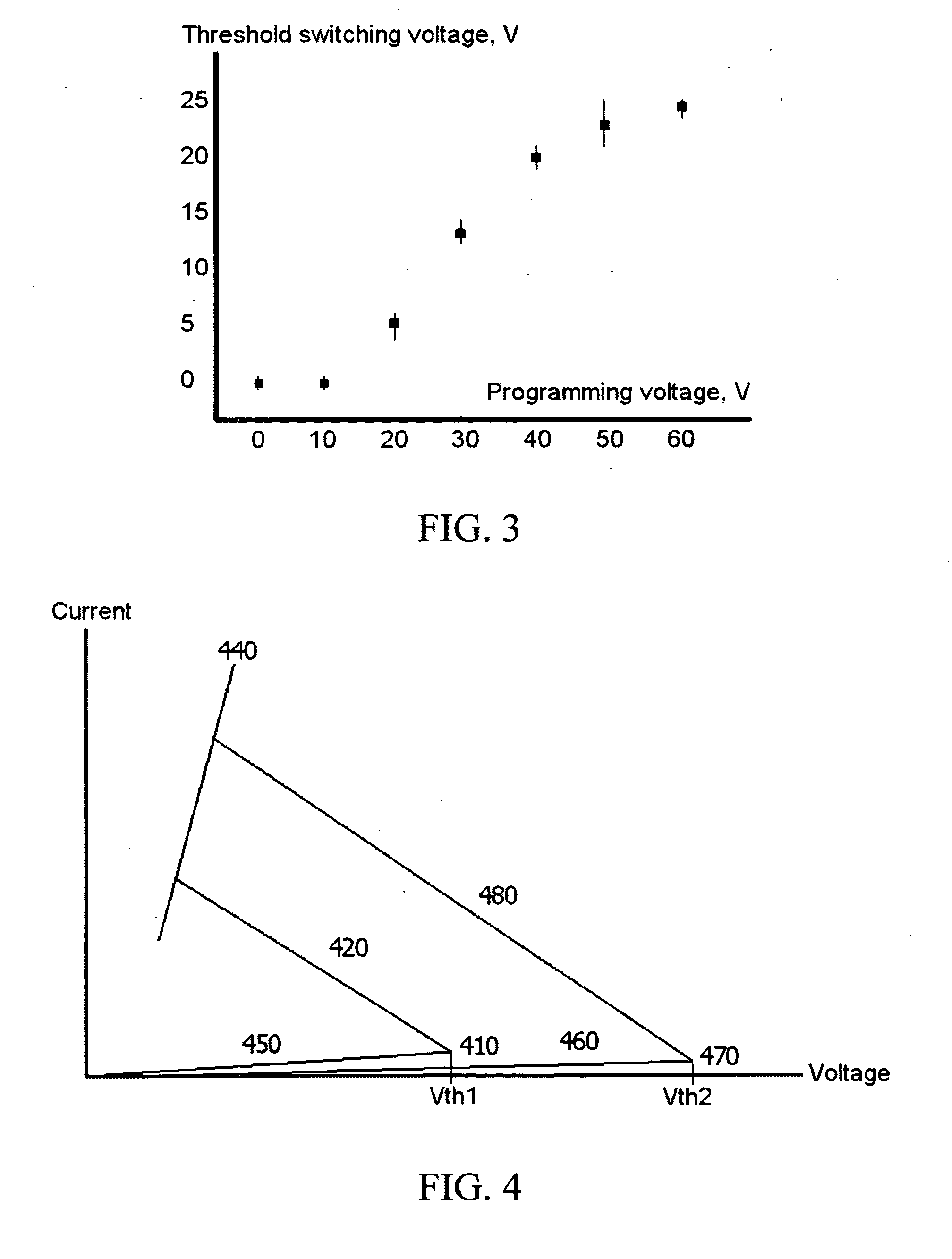

Nanoscale electrical device

InactiveUS20100090189A1High impedanceHigh impedance stateSolid-state devicesBulk negative resistance effect devicesElectrical devicesEngineering

A device consists a disordered relaxation insulator or / and a polyamorphous solid between two or more electrodes. Invented devices can perform passive, logic and memory functions in an electronic integrated circuit.

Owner:SAVRANSKY SEMYON D

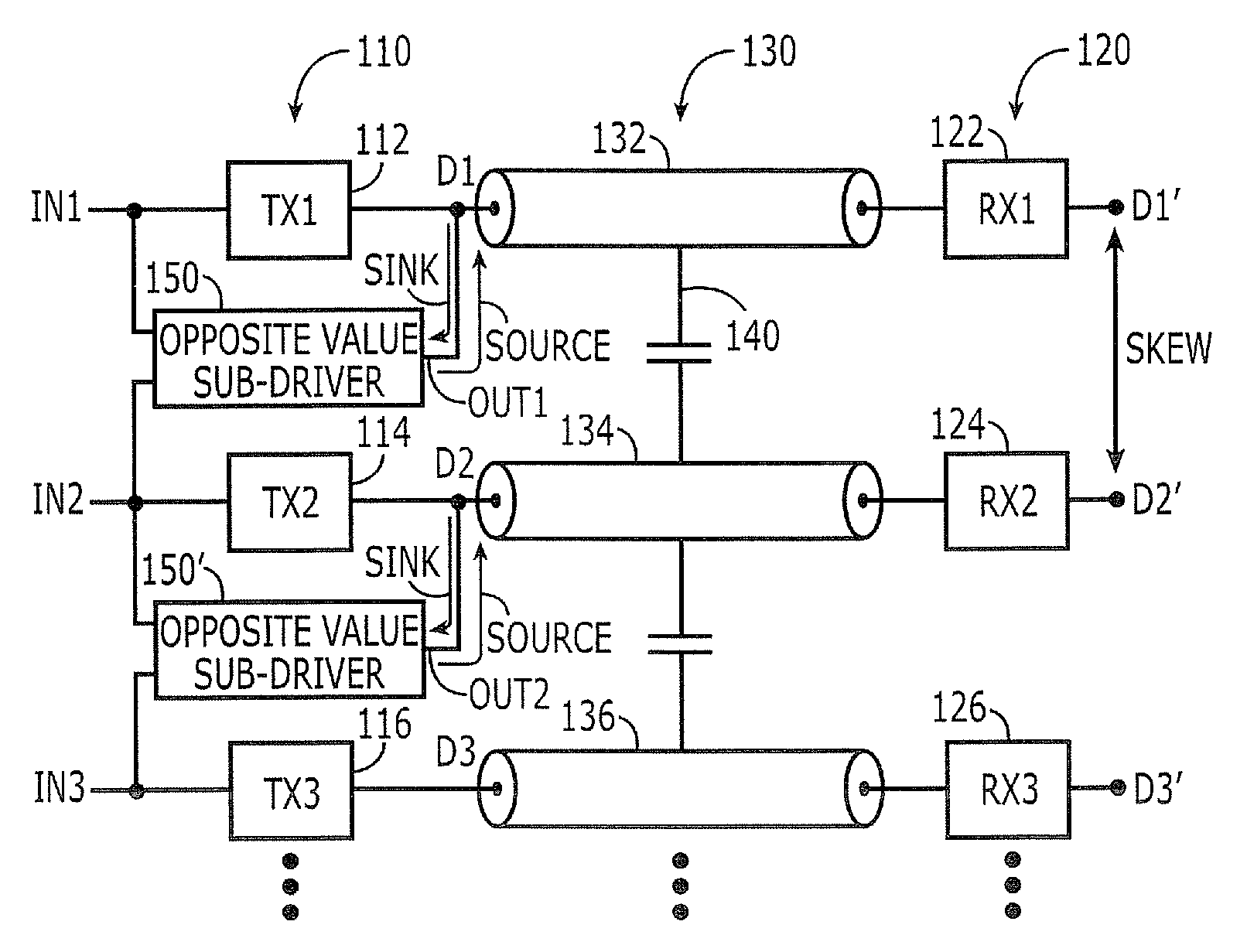

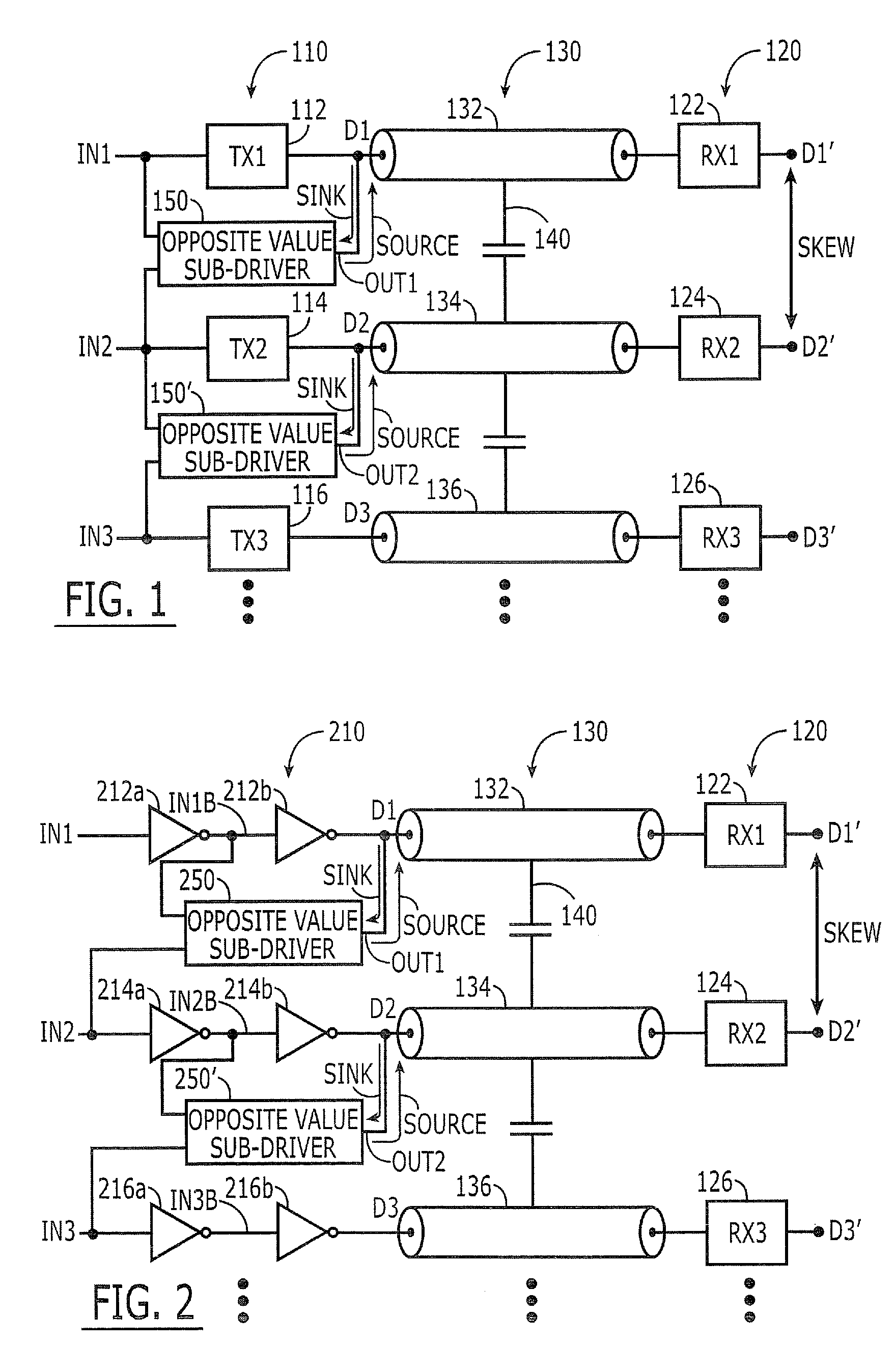

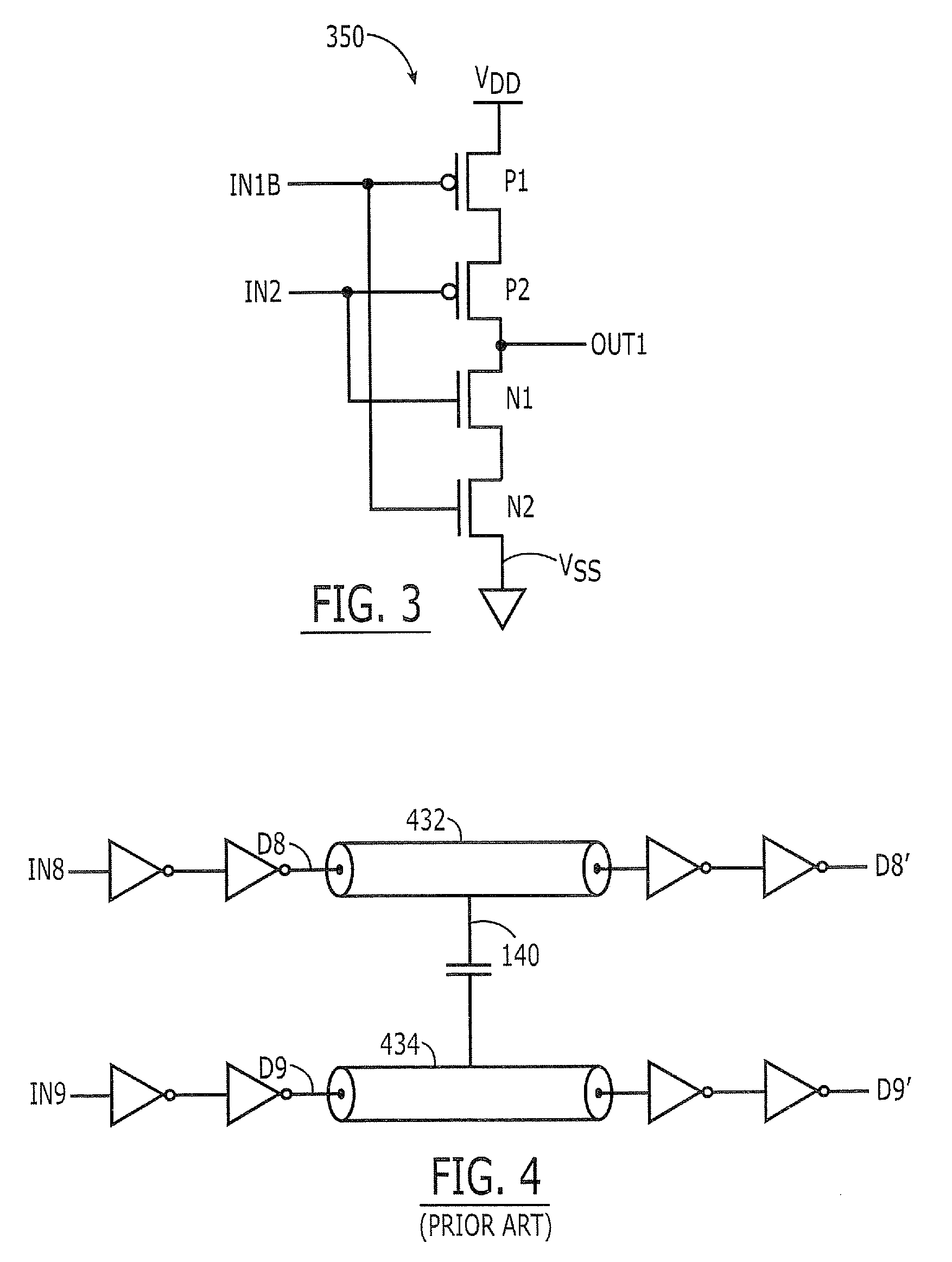

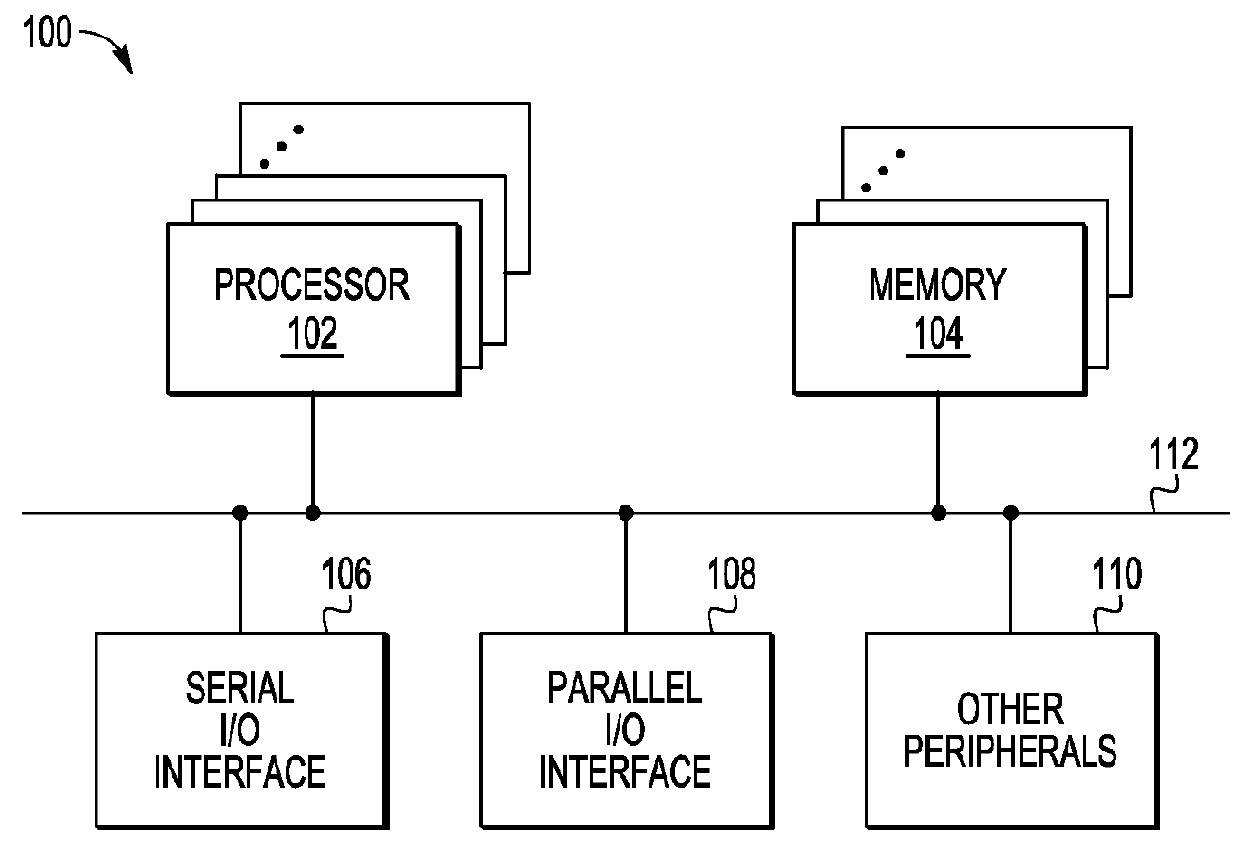

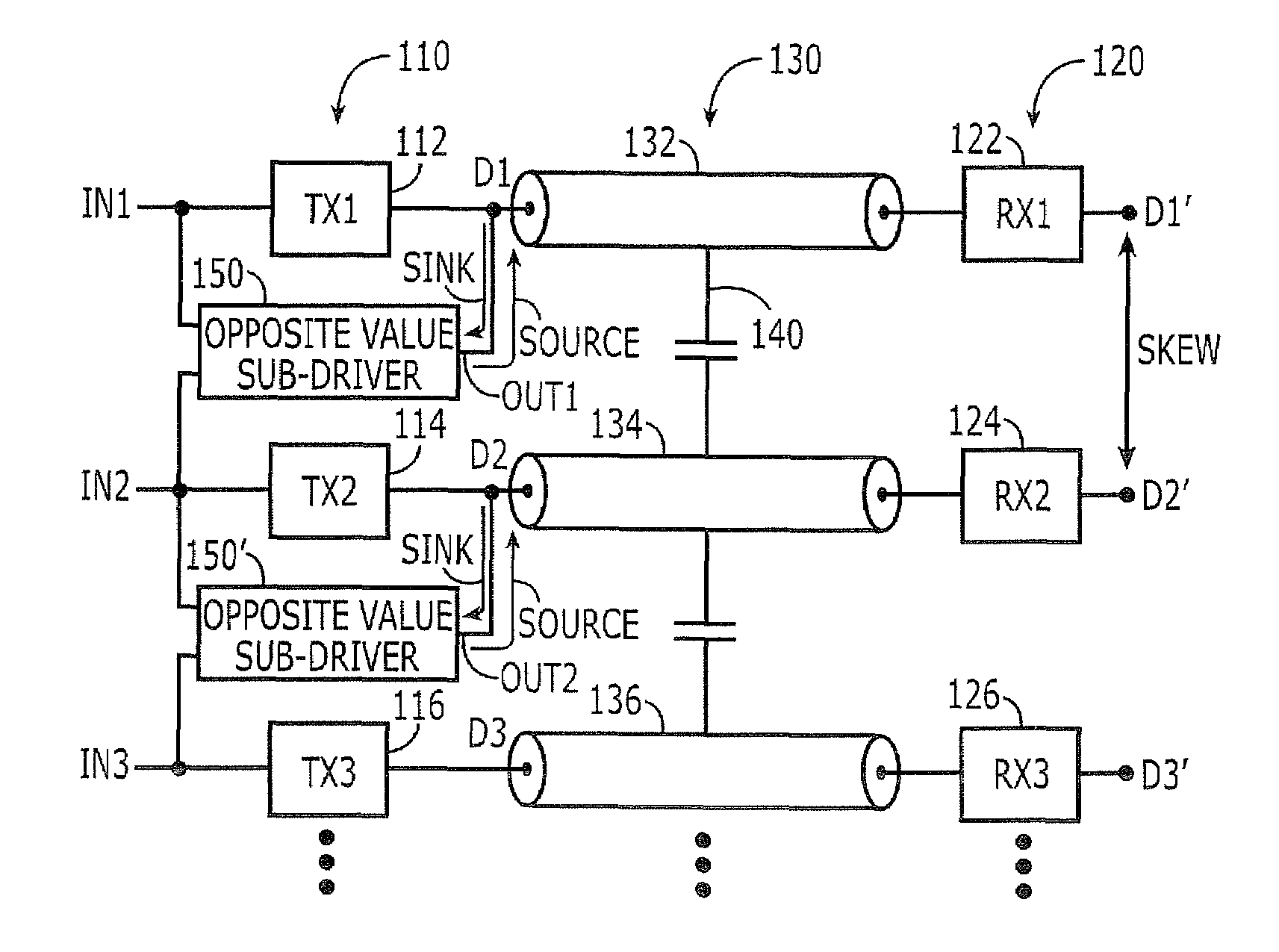

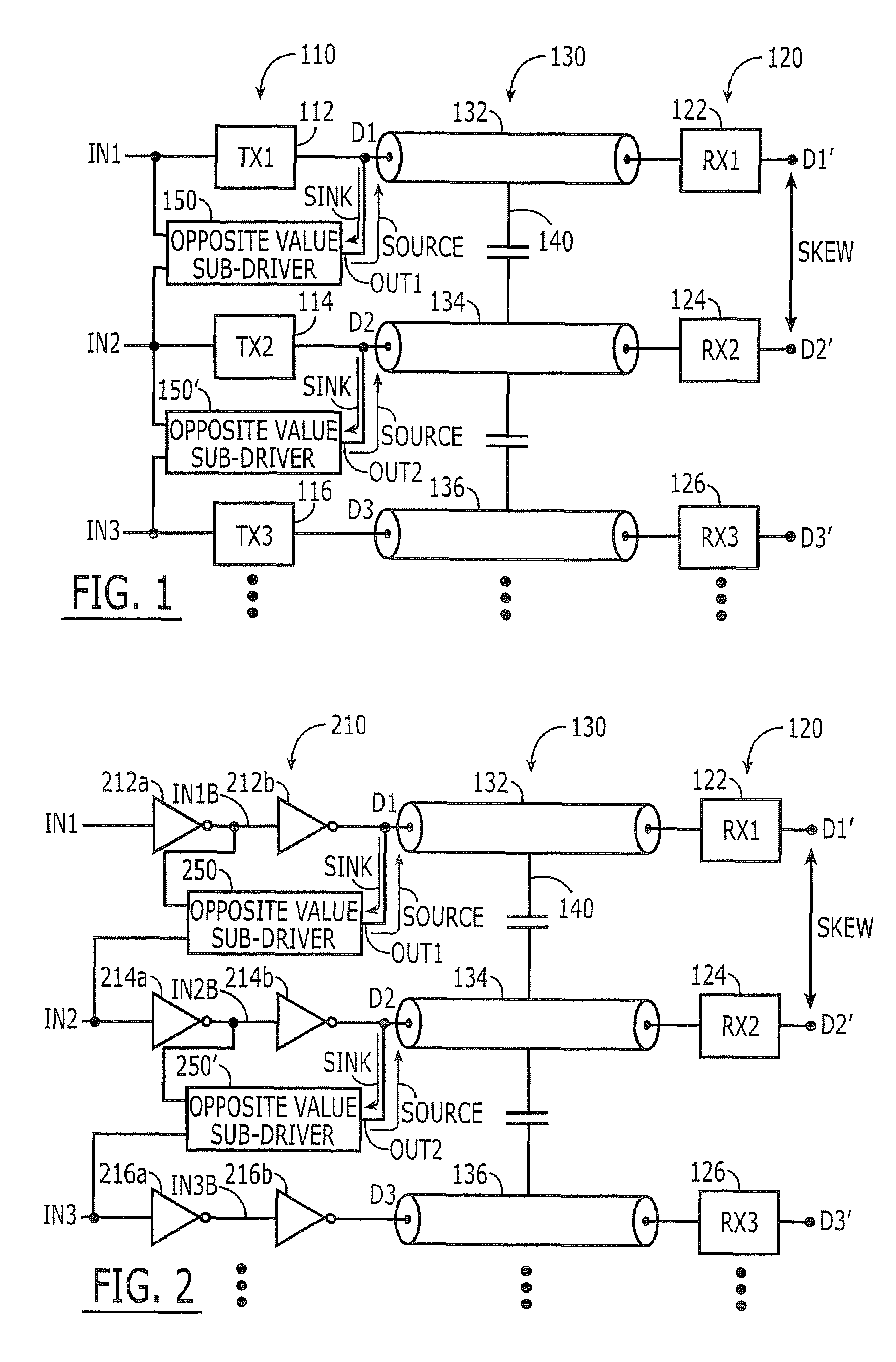

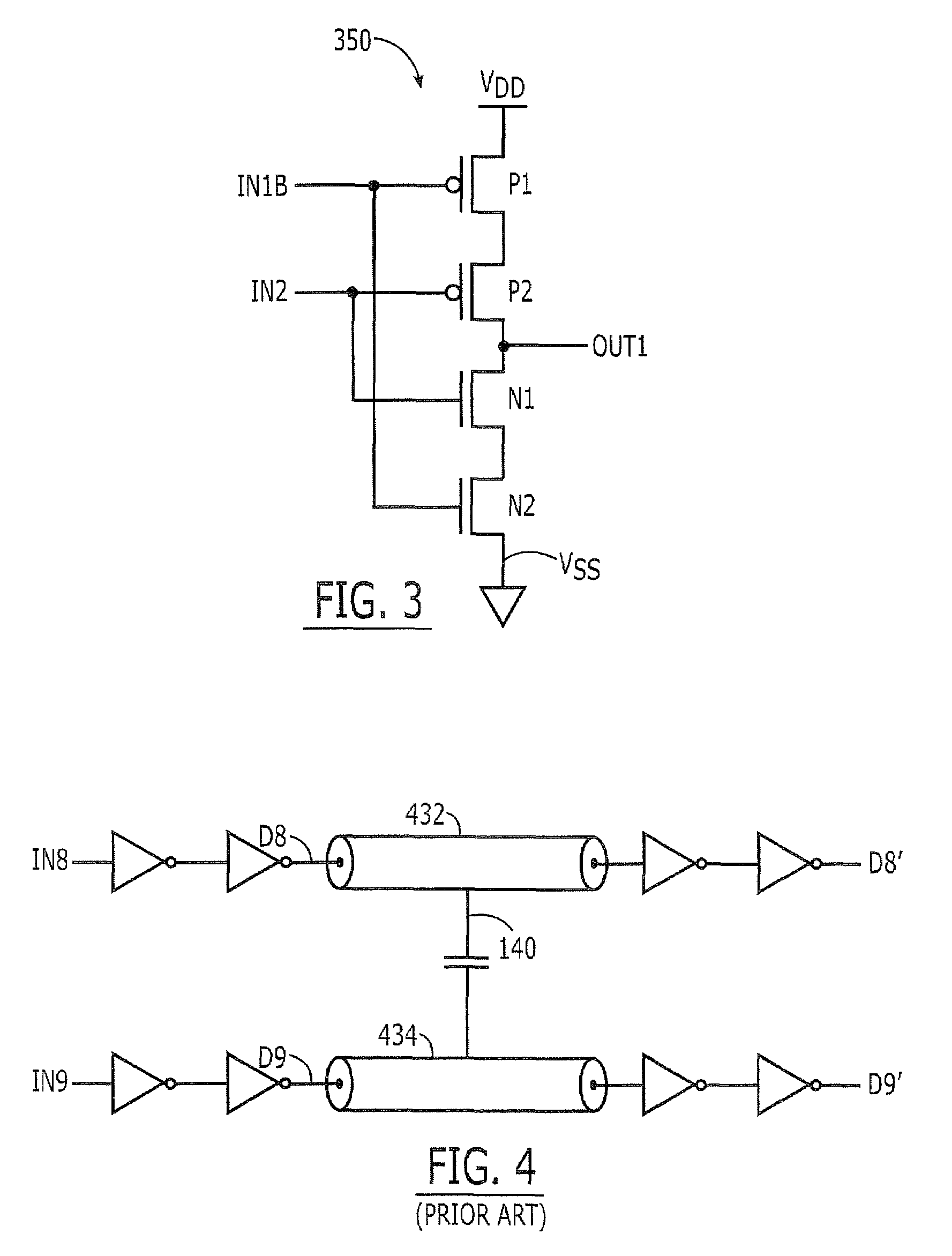

Skew-reducing signal line sub-driver circuits, methods and systems

ActiveUS20080024331A1Reduce skewHigh impedance stateTransmission control/equlisationCode conversionDriver circuitEngineering

Circuits, methods and systems are provided to reduce skew between a first digital signal that is transmitted by a first driver circuit over a first signal line, and a second digital signal that is transmitted by a second driver circuit over a second signal line. Skew may be reduced by sourcing or sinking additional current to or from the first signal line in response to the first digital signal and the second digital signal transitioning to opposite logical values, and otherwise refraining from sourcing or sinking the additional current to or from the first signal line. Skew may also be reduced between the first digital signal that is transmitted by the first driver circuit over the first signal line and a third digital signal that is transmitted by a third driver circuit over a third signal line by sourcing or sinking additional current to or from the first signal line in response to the first digital signal and the third digital signal transitioning to opposite logical values, and to otherwise refrain from sourcing or sinking the additional current to or from the first signal line.

Owner:SAMSUNG ELECTRONICS CO LTD

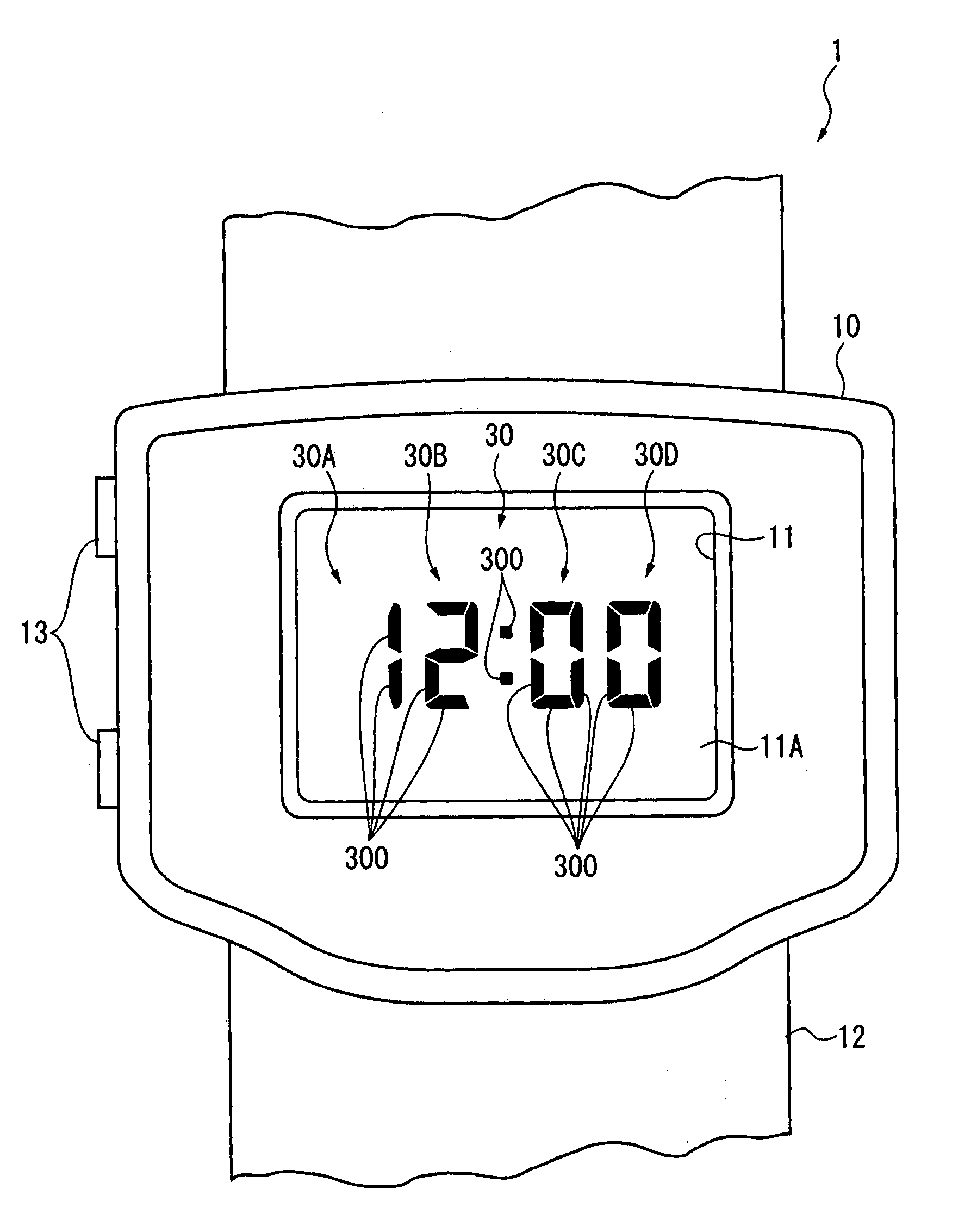

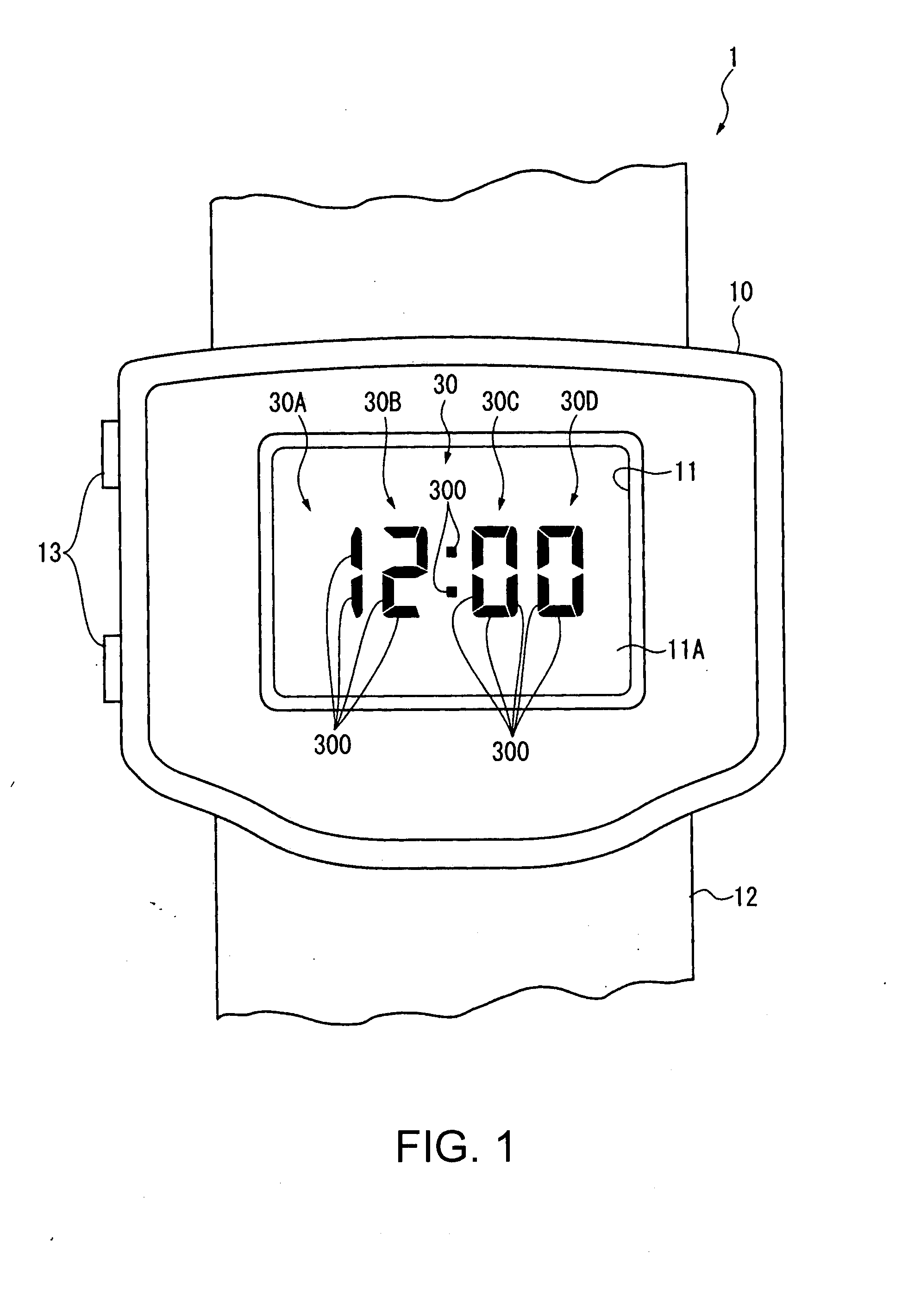

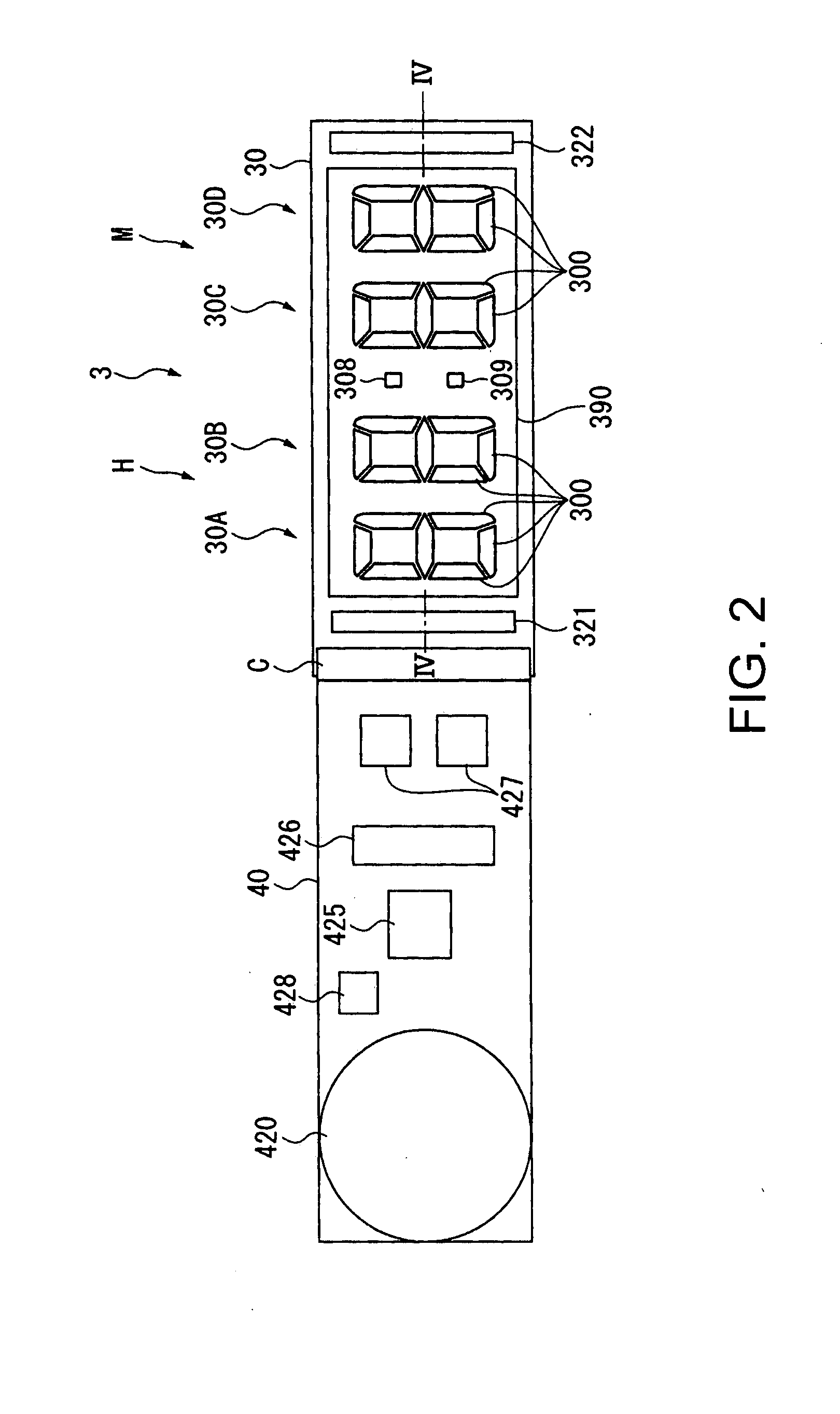

Drive method and a drive device for an electrophoretic display panel, an electrophoretic display device, and an electronic device

InactiveUS20080024431A1Avoid display qualityIncrease contrastVisual indicationsCathode-ray tube indicatorsPotential changeElectrophoresis

A drive method for an electrophoretic display panel having one electrode as a common electrode and another electrode divided into a plurality of segment electrodes, the drive method having steps of: applying pulses that change between two different potential levels to the common electrode; applying pulses at one of the two potential levels to the segment electrode of a segment that changes display state to produce a potential difference to the pulse applied to the common electrode; applying pulses of the same phase and potential as the pulses applied to the common electrode to the segment electrode of a segment that holds the same display state; and inserting a high impedance state to the pulses applied to the common electrode and the pulses applied to the segment electrode of the segment that holds the same display state when the pulse potential changes.

Owner:SEIKO EPSON CORP

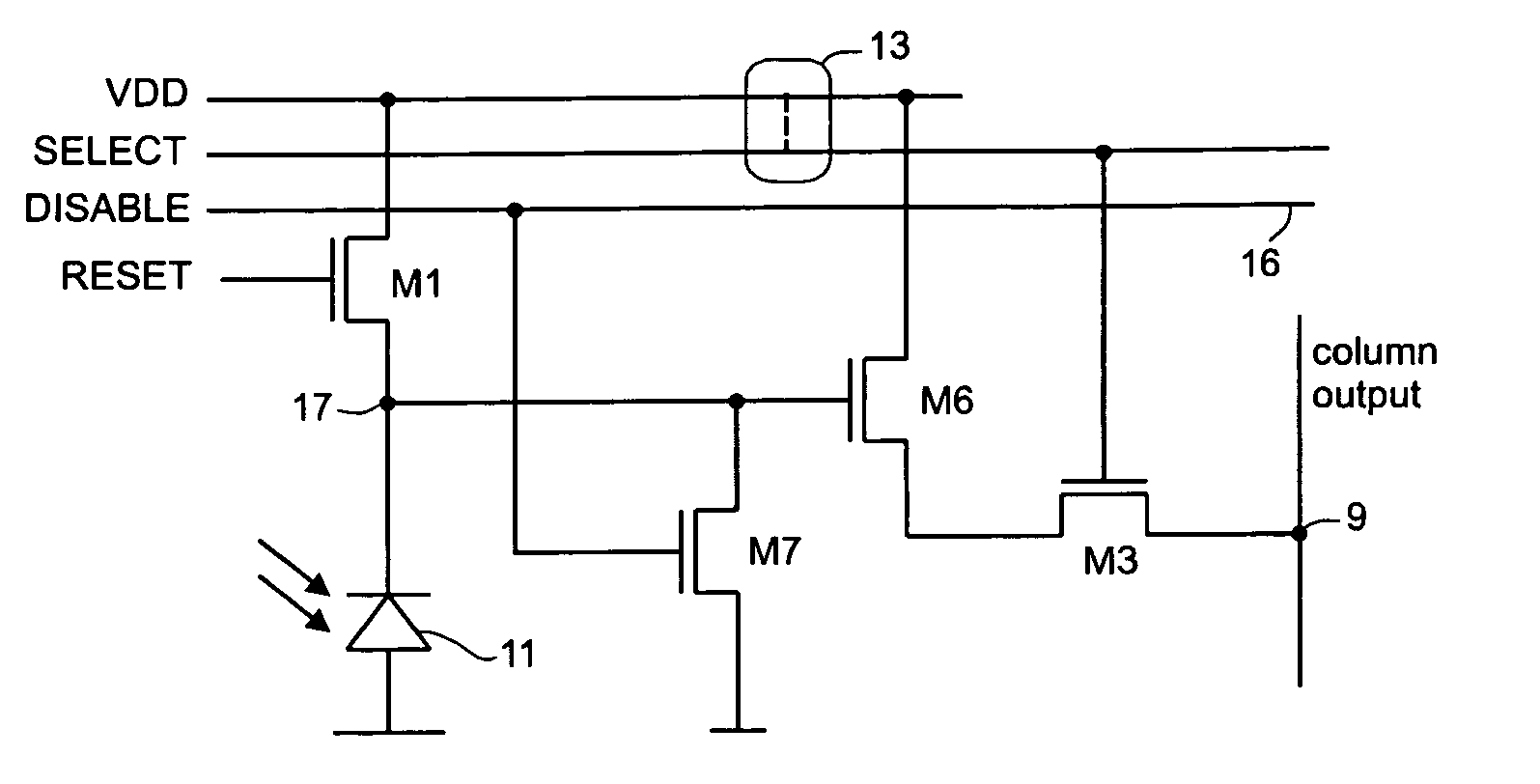

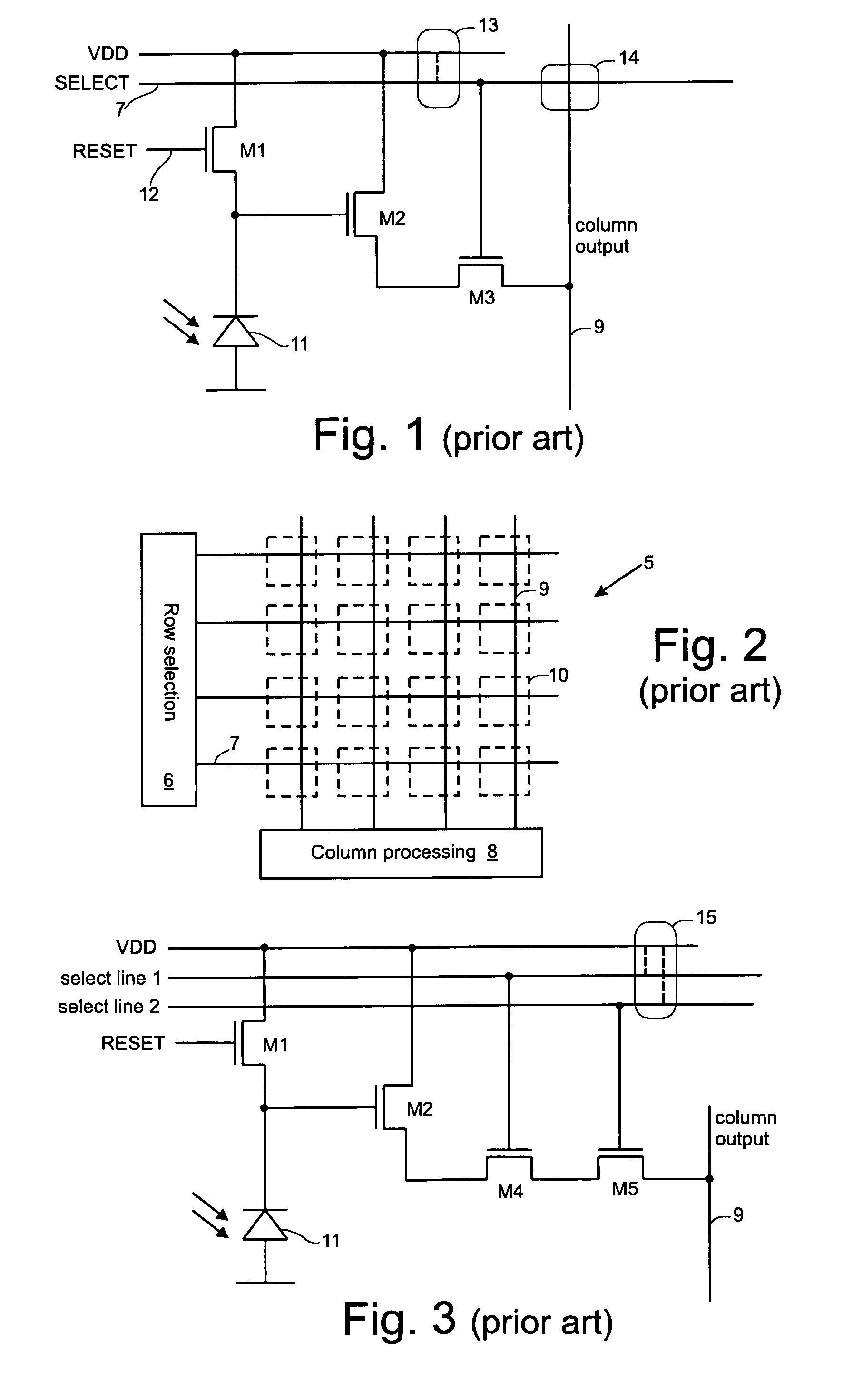

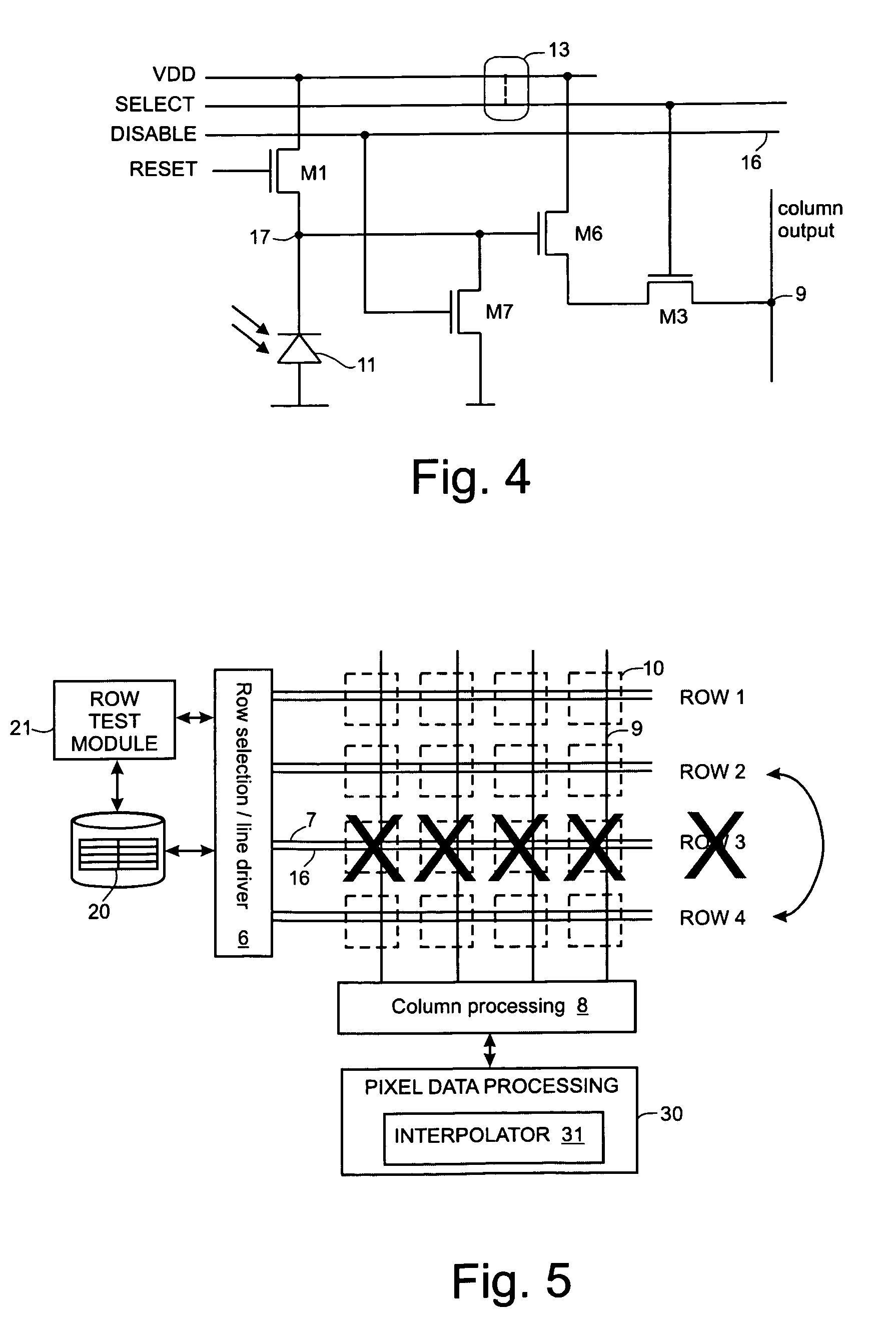

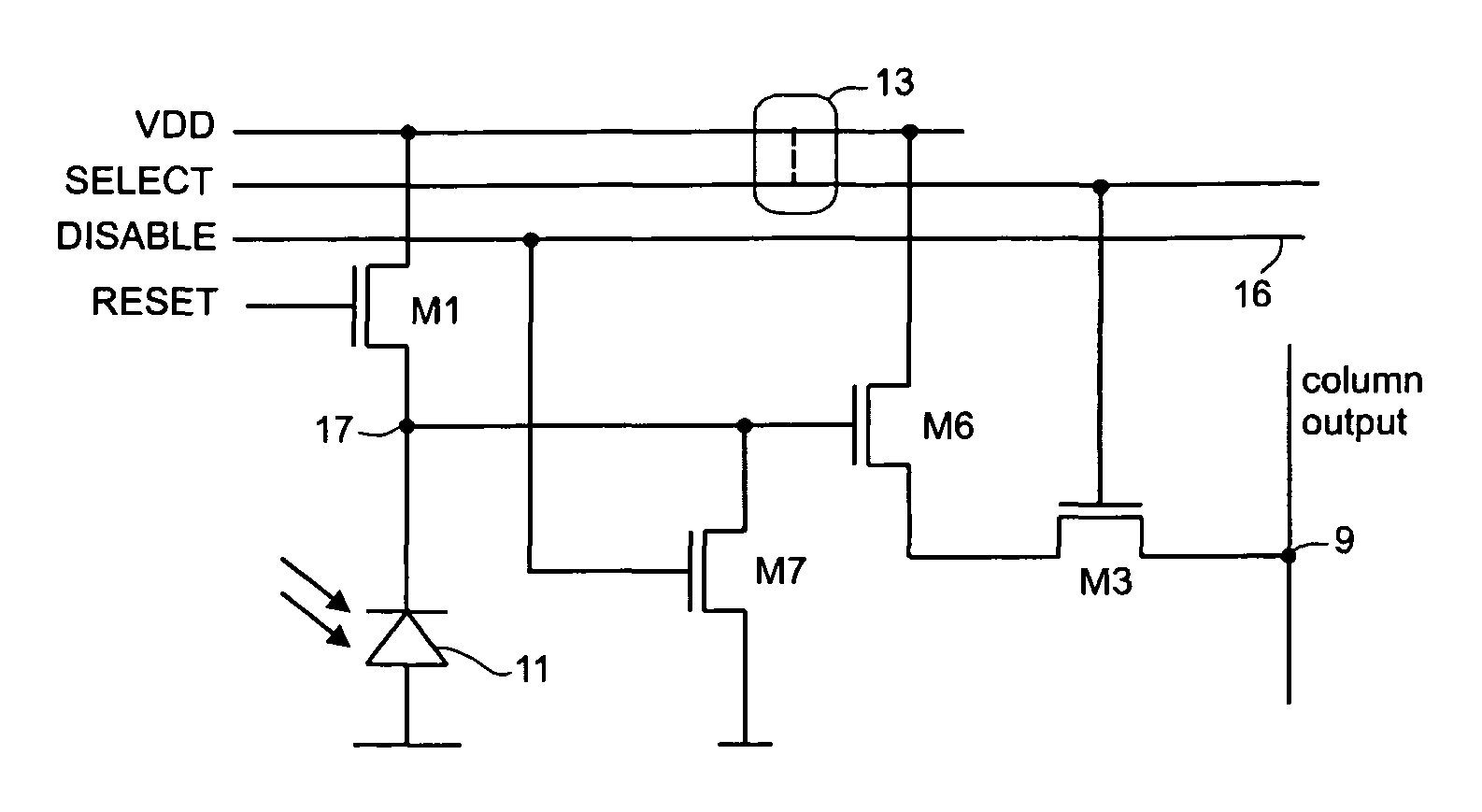

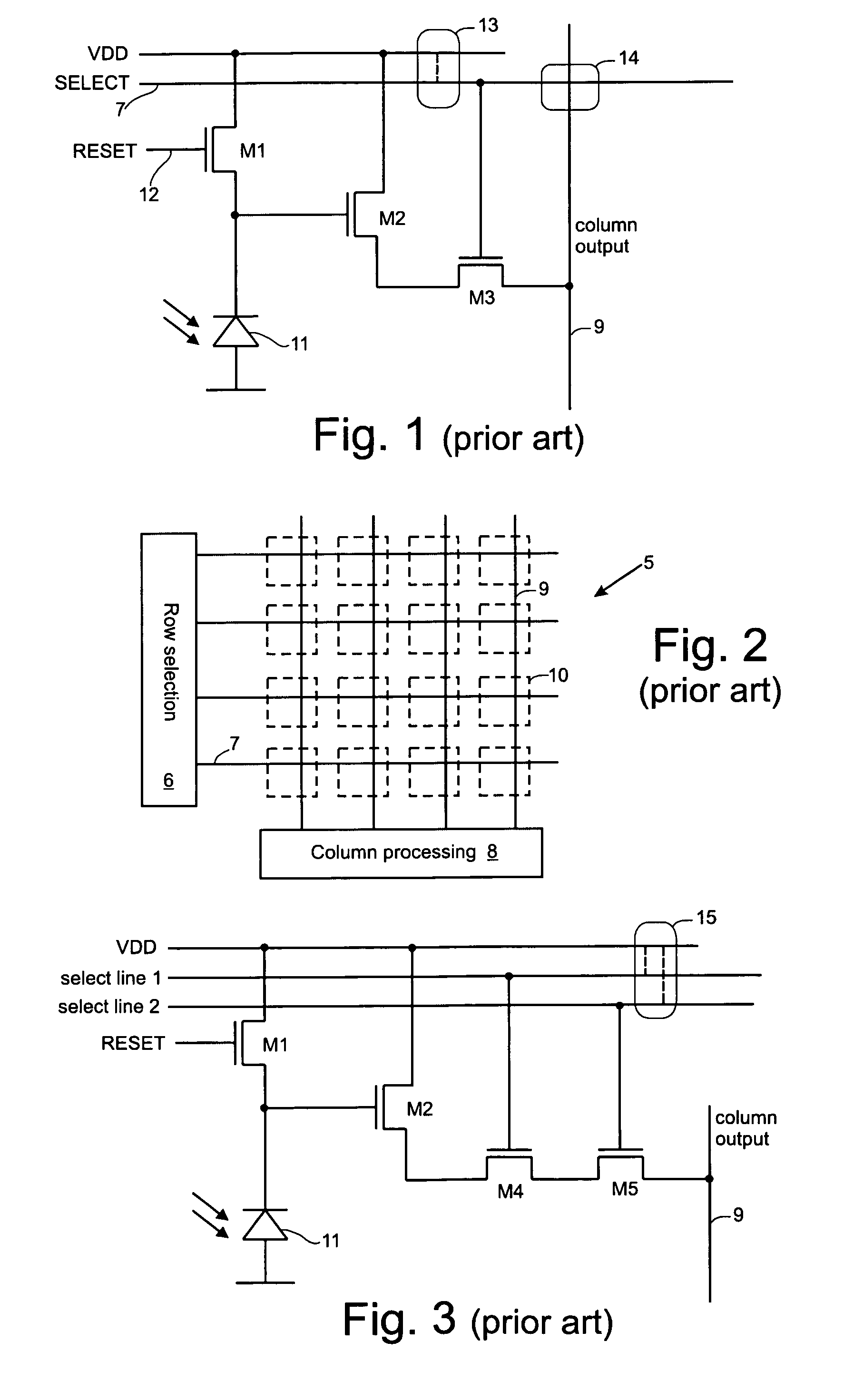

Pixel array with reduced sensitivity to defects

ActiveUS20090160752A1Increase productionHigh impedance stateTelevision system detailsColor signal processing circuitsAudio power amplifierLow voltage

An array of active pixels comprises rows of pixels and row select lines for selecting rows of pixels. Each active pixel comprises a buffer amplifier for buffering an output of a photo-sensitive element. An output of the buffer amplifier can be selectively put into a high impedance state, by control of the input of the buffer amplifier, when there is a defect in the row select line for that pixel. This allows other rows, which are defect-free, to remain operating as normal. A disable line can be provided for a row of pixels and each pixel can have a switch connected to the disable line. Alternatively, a first supply line powers a row of pixels. Each pixel comprises a reset switch connected between a photo-sensitive element and the first supply line for resetting the photo-sensitive element. The array is configured such that, in the event of a defect in a row select line, the first supply line is set to ground, or a low voltage, and the reset switch is turned on to put the buffer amplifier into the high impedance state.

Owner:CMOSIS

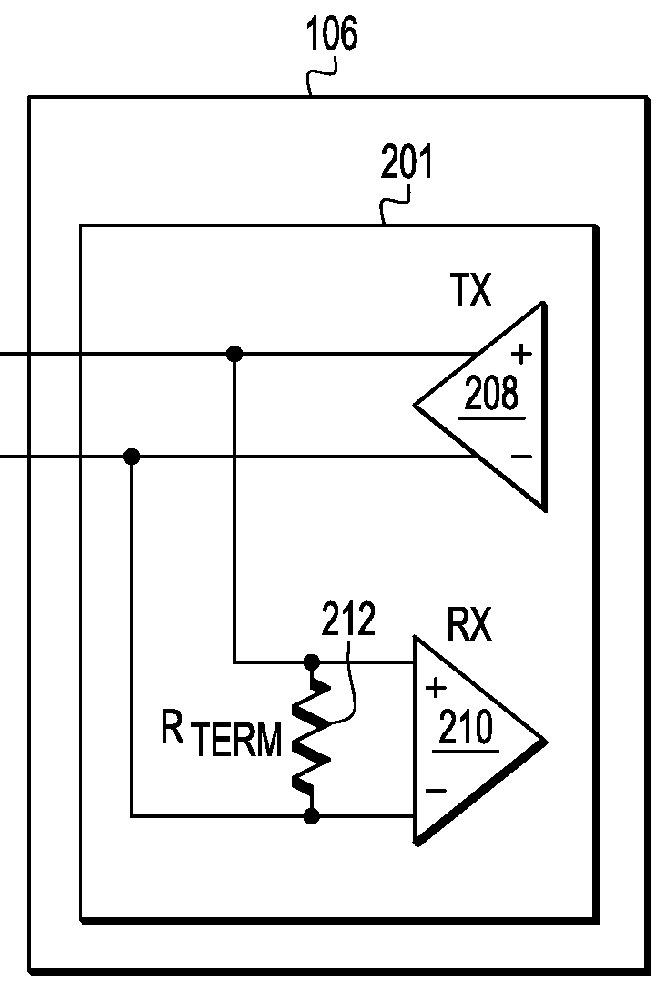

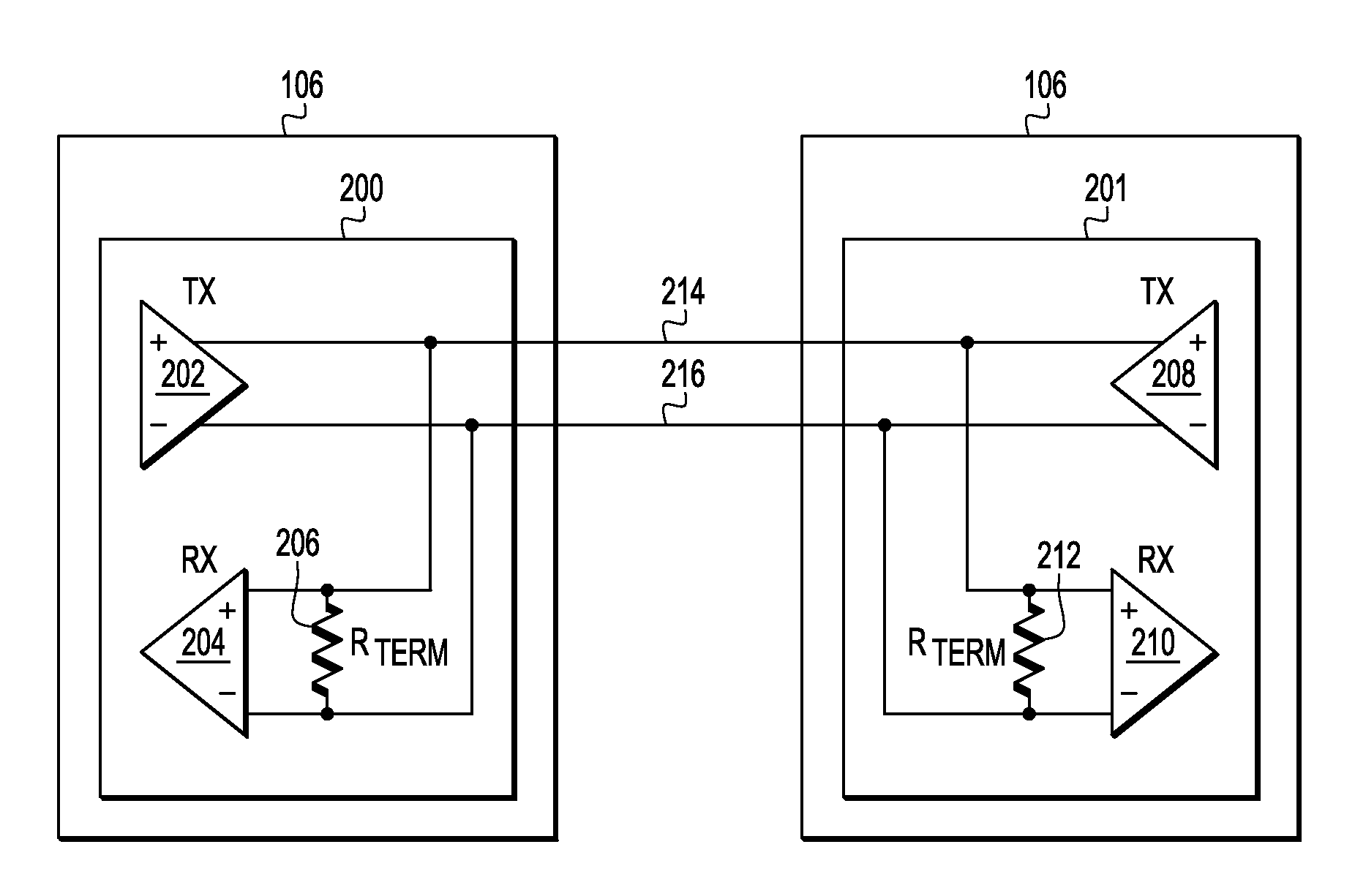

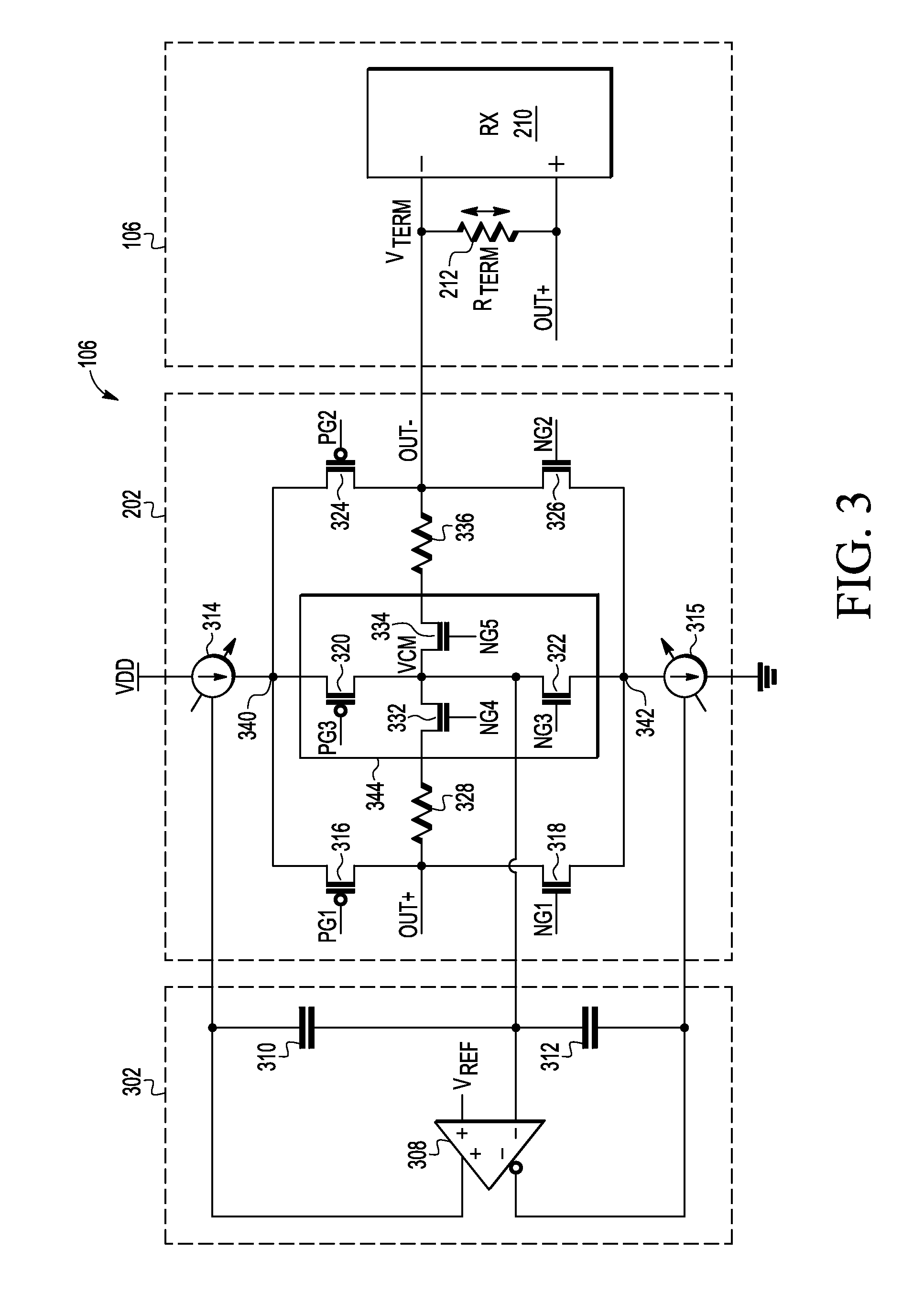

LVDS with idle state

ActiveUS9362915B1Reduce start-up delayShorten the timeElectric pulse generatorBaseband systemsPower flowDifferential signaling

A low voltage differential signaling generating circuit, which comprises a current source a pair of output nodes for providing a differential signal by virtue of a voltage difference therebetween, first and second differential switch circuitries and a bypass circuitry. The first differential switch circuitry selectively connects the current source to the first output node based on a control signal to cause a current flow from the first output node to the second one. The second differential switch circuitry selectively connects the current source to the second output node based on the control signal to cause a current flow from the second output node to the first one. The bypass circuitry is arranged in parallel to the first and second differential switch circuitries and is selectively switched based on an idle mode signal to prevent a current between the output nodes.

Owner:NXP USA INC

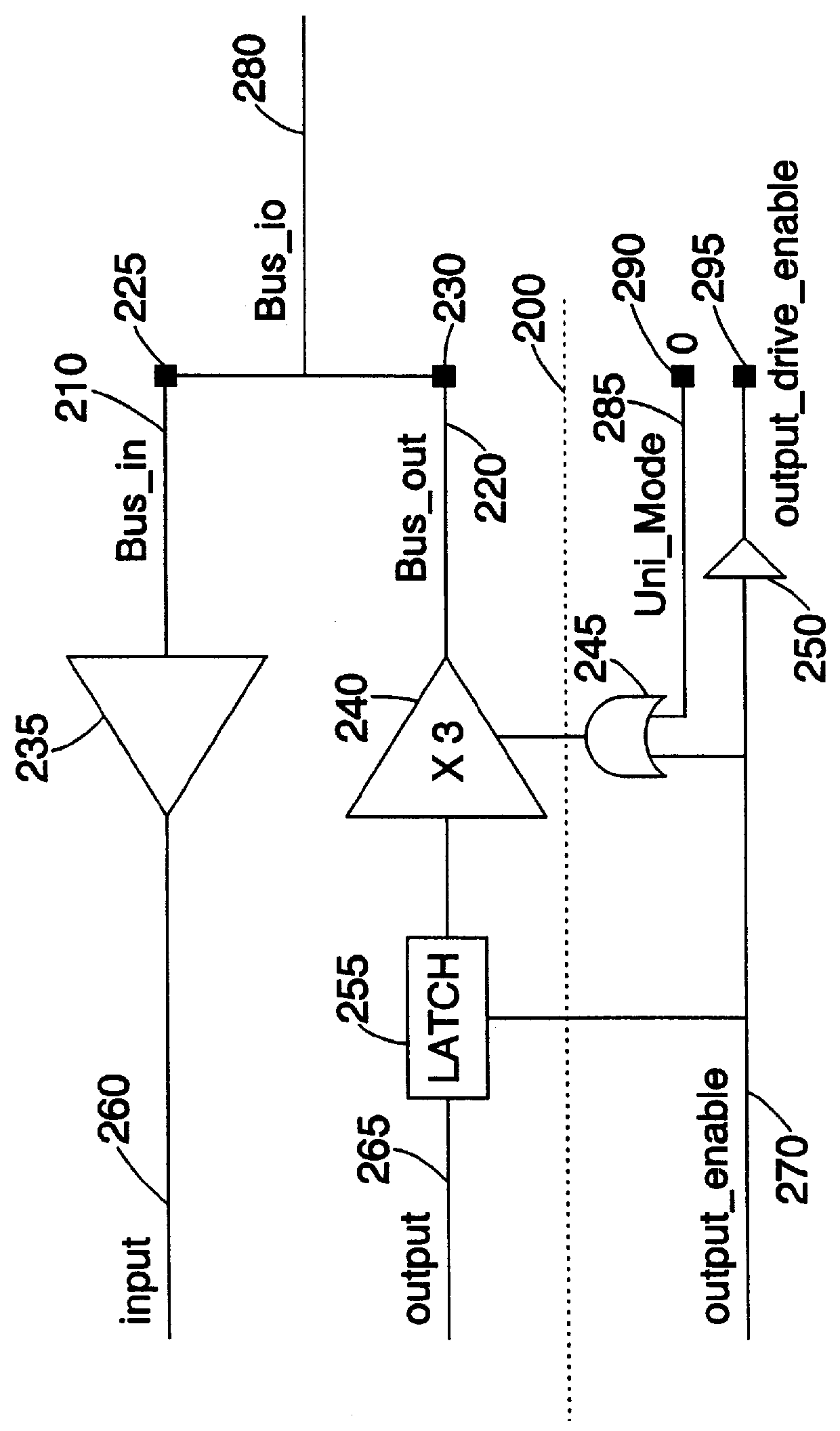

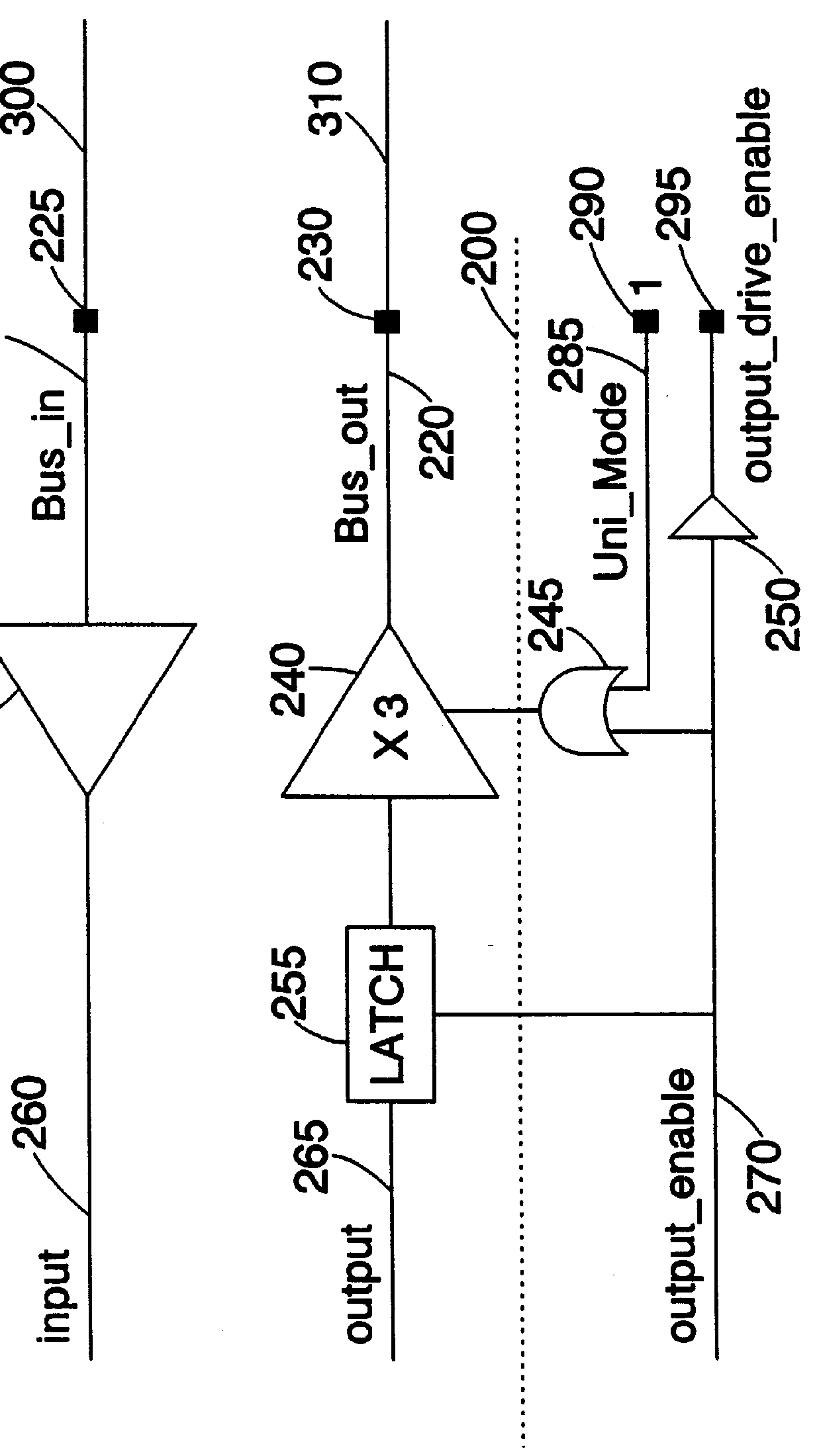

Macrocell for data processing circuit

InactiveUS6034545AHigh impedance stateLogic circuits using elementary logic circuit componentsLogic circuit coupling/interface arrangementsMacrocellComputer science

The present invention provides a macrocell for a data processing circuit, comprising macrocell logic, and an interface for connecting the macrocell logic to a bus of the data processing circuit. The interface comprises: an input bus connected to an input bus terminal, an output bus connected to an output bus terminal, and a buffering circuit for buffering the output bus from the macrocell logic. Further, the interface has a mode input terminal for receiving a mode value, the mode value being arranged to control the buffering circuit. The buffering circuit is responsive to a first mode value to enter an inactive state when no data is being output from the macrocell, and is responsive to a second mode value to permanently drive the output bus. Hence, to enable the macrocell to be coupled to a unidirectional bus on the data processing circuit, the second mode value is supplied to the mode input terminal, whilst to enable the macrocell to be coupled to a bidirectional bus on the data processing circuit, the input bus terminal and output bus terminal are connected together externally to the macrocell, and the first mode value is supplied to the mode input terminal.

Owner:ARM LTD

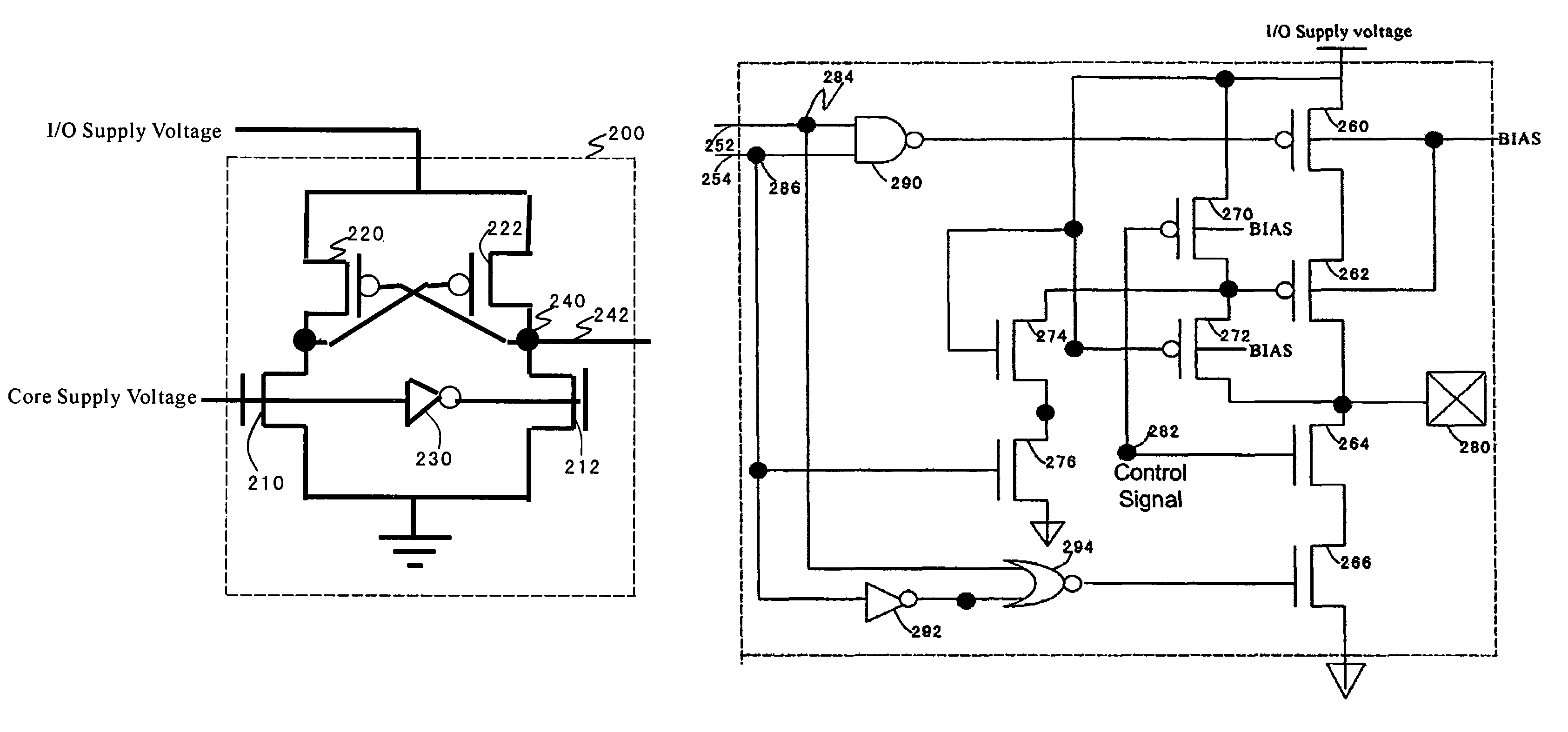

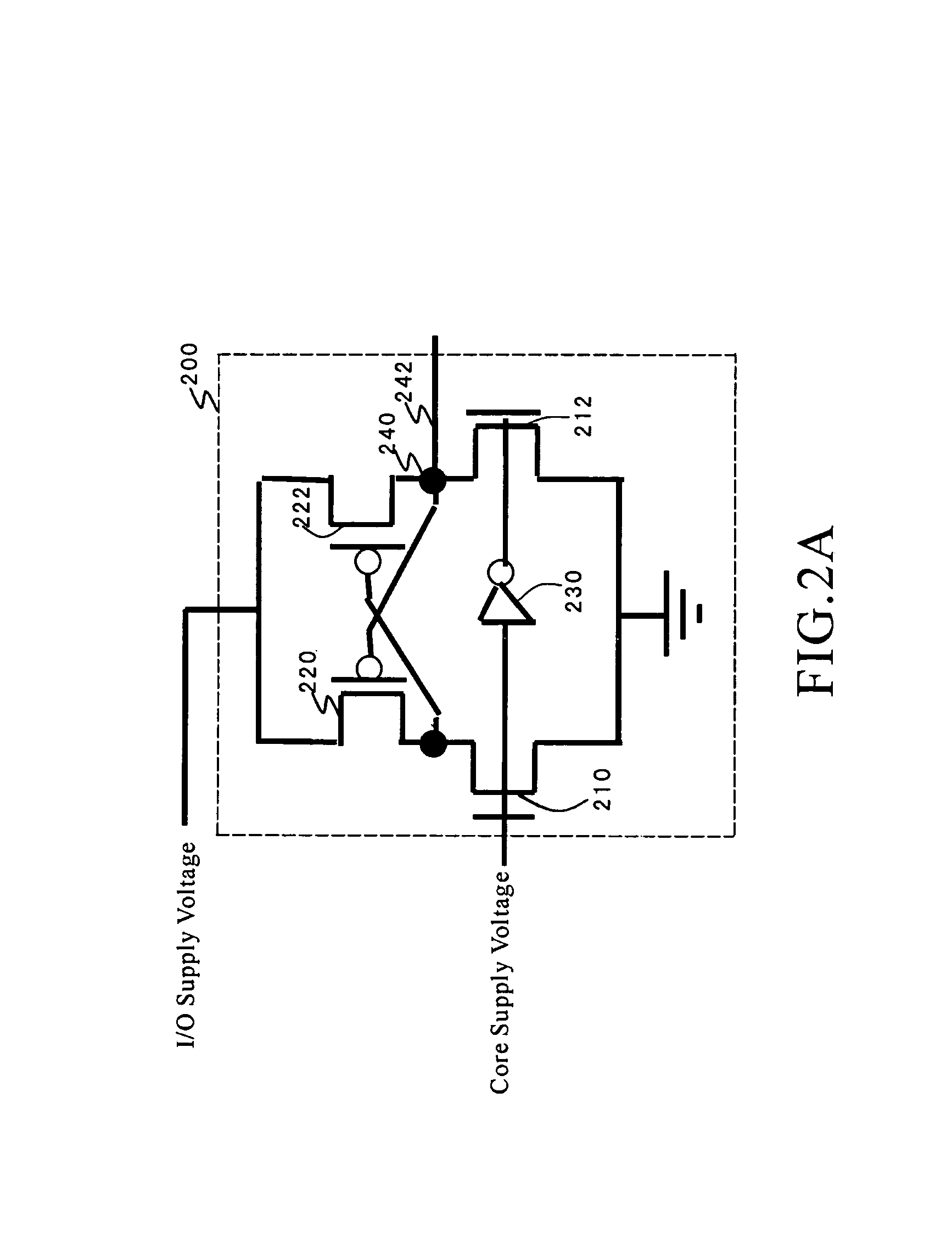

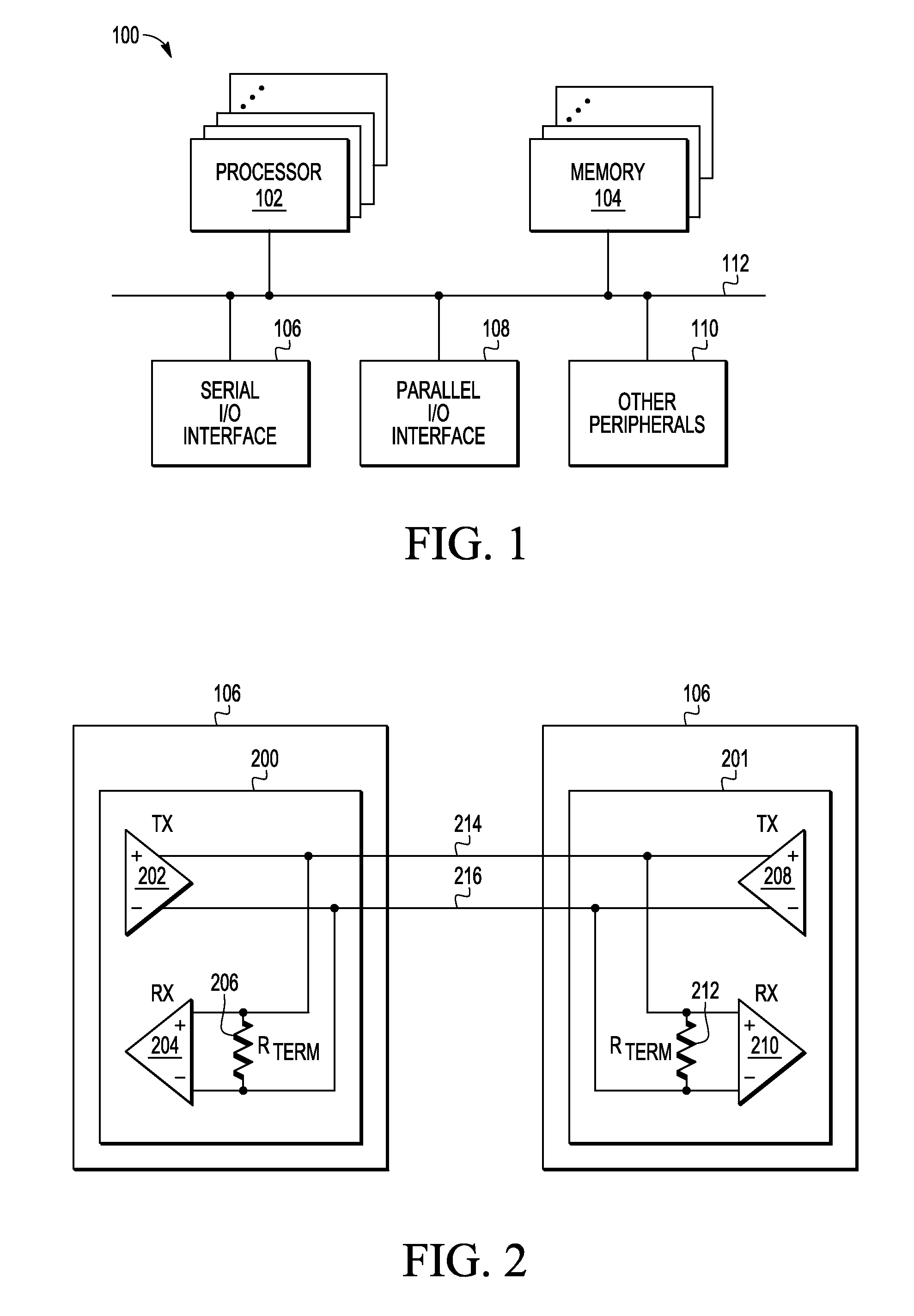

System and method for power-on control of input/output drivers

ActiveUS7239186B2Reduce or eliminate high input/output crowbar currentReduce and eliminate congestionReliability increasing modificationsElectric pulse generatorElectricityControl signal

A system and method for controlling an input / output driver. The system includes a control system configured to receive a first supply voltage and a second supply voltage and generate a control signal, and a first transistor including a first gate, a first terminal, and a second terminal. The first gate is configured to receive the control signal, and the first terminal is configured to receive the first supply voltage. Additionally, the system includes a second transistor including a second gate, a third terminal, and a fourth terminal, and the second gate is coupled to the second terminal. Moreover, the system includes a third transistor including a third gate, a fifth terminal, and a sixth terminal, and the third gate is configured to receive the control signal. Also, the system includes an input / output pad coupled to the fourth terminal and the fifth terminal.

Owner:SEMICON MFG INT (SHANGHAI) CORP

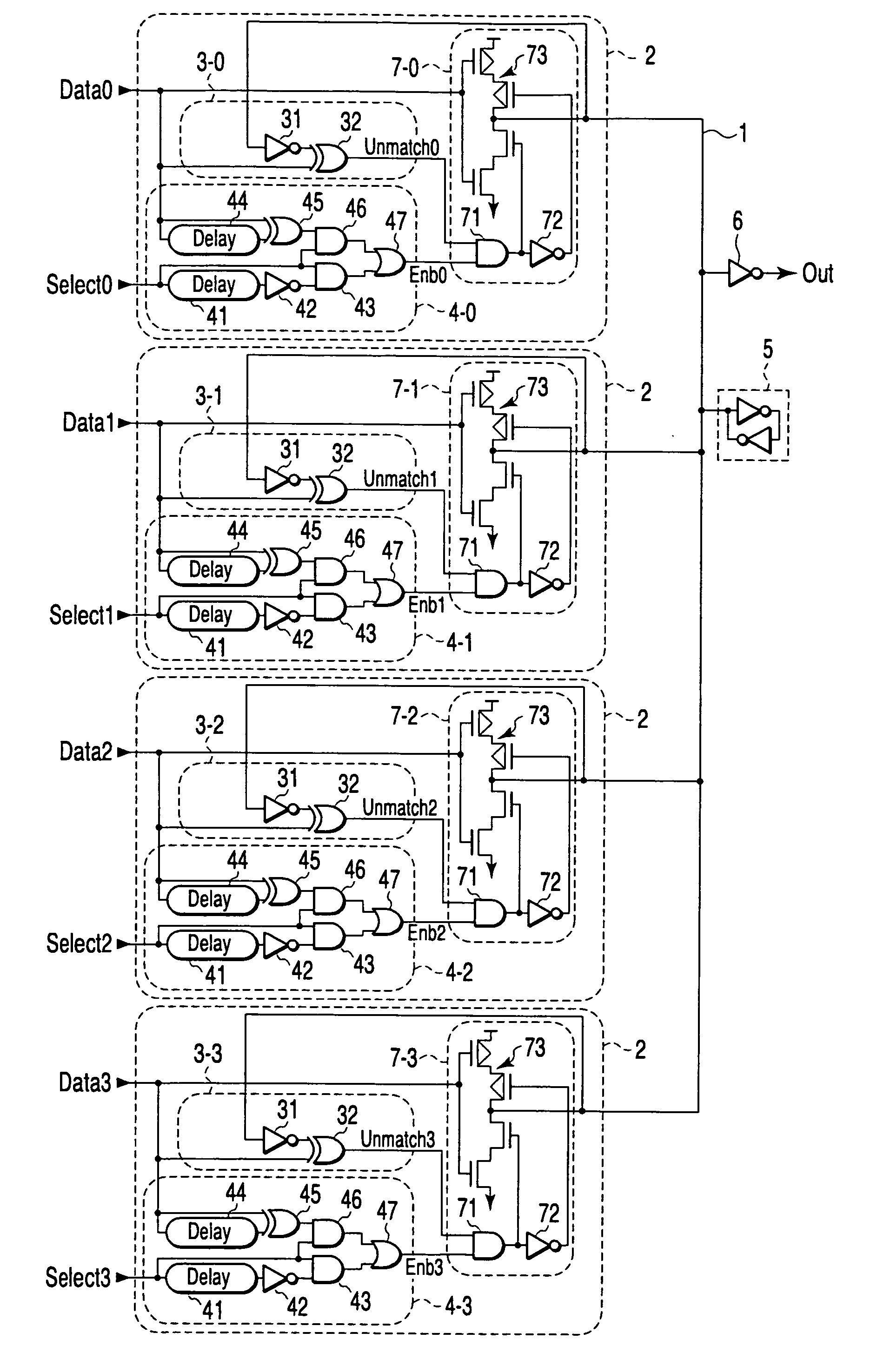

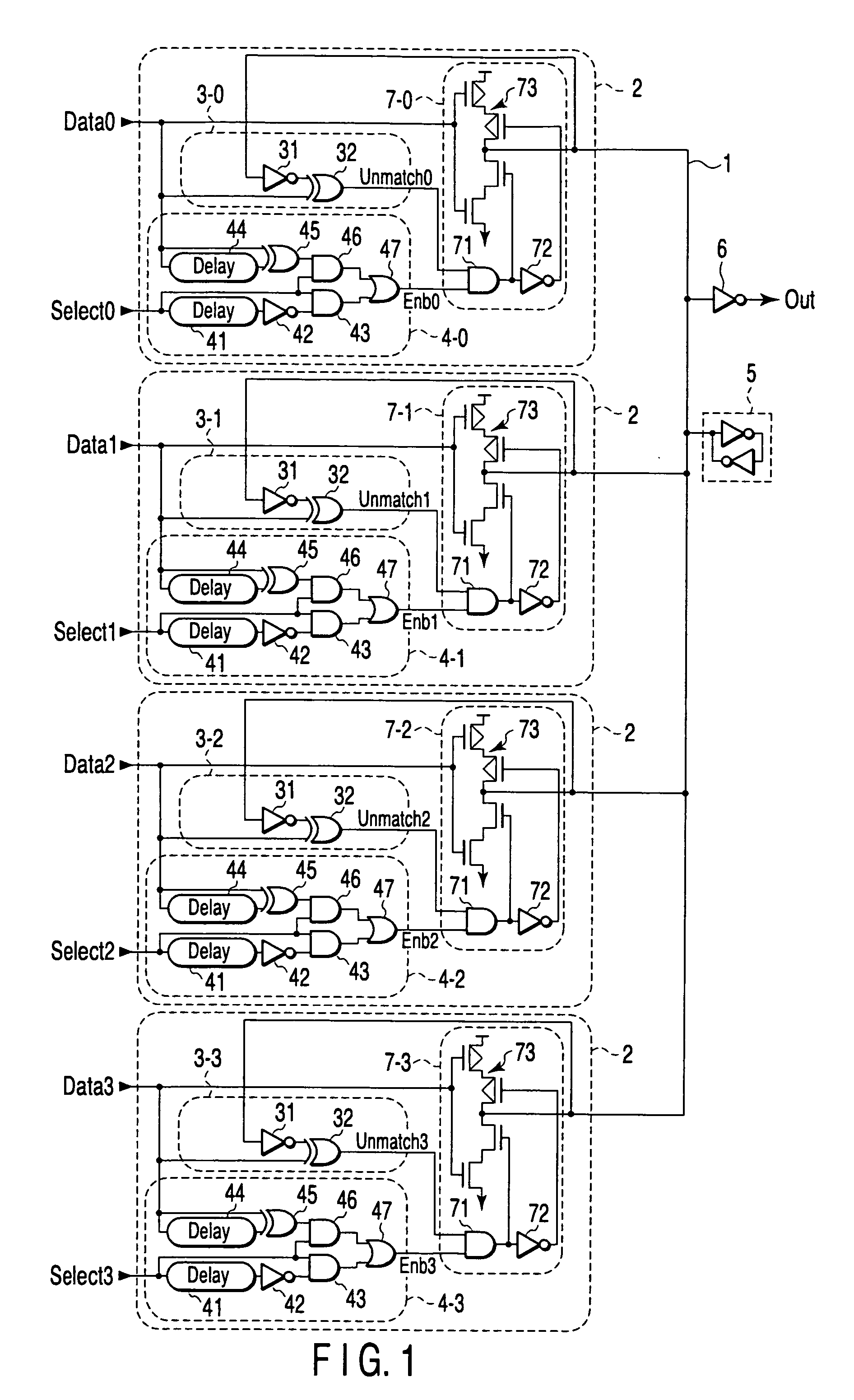

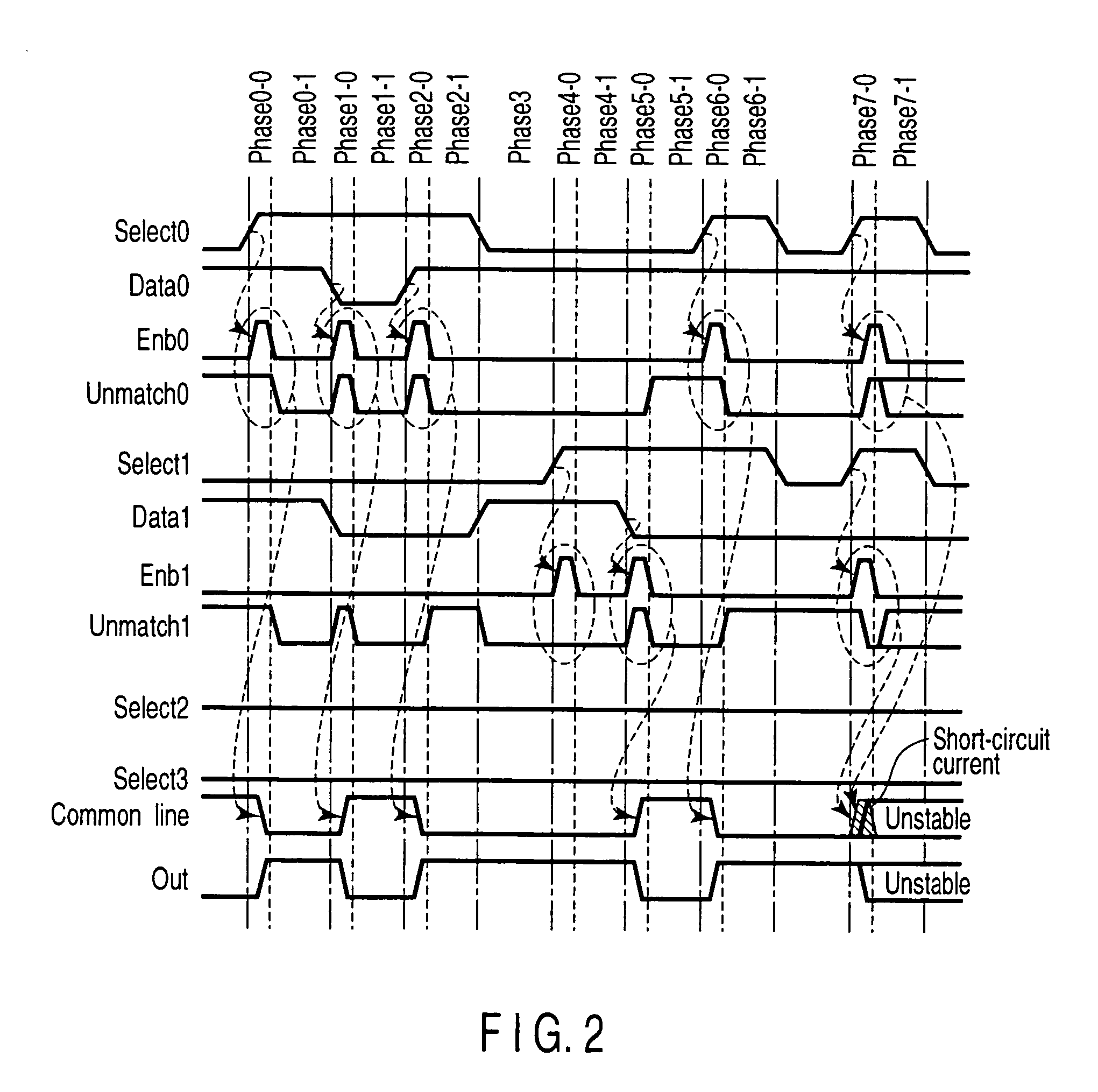

Multiple-select multiplexer circuit, semiconductor memory device including a multiplexer circuit and method of testing the semiconductor memory device

InactiveUS20050213394A1High impedance stateElectronic circuit testingElectronic switchingElectricityMultiplexer

A multiplexer circuit is composed of several basic unit circuits, which are each supplied with a data signal and select signal. Each output terminal of several basic unit circuits is connected to a common line. Each basic unit circuit is composed of an unmatch detection circuit detecting an unmatch state of the common line and the data signal, a control circuit controlling drive timing of the common line when receiving a state transition of the select signal, and a tri-state buffer driving the common line according to a state of the data signal when an output of the unmatch detection circuit and an output of the control circuit are both in an active state while holds high impedance state when the state other than above is given.

Owner:KK TOSHIBA

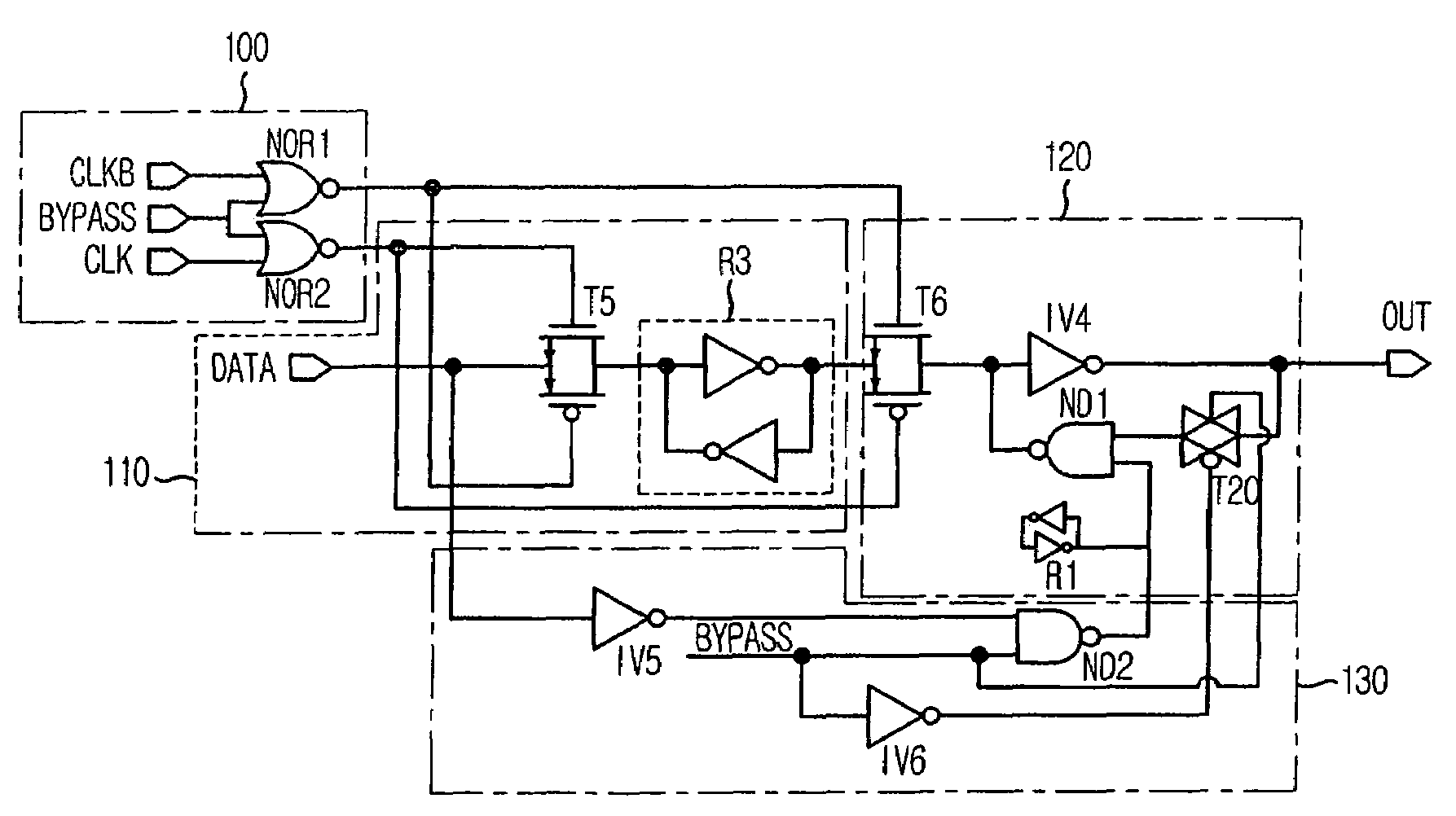

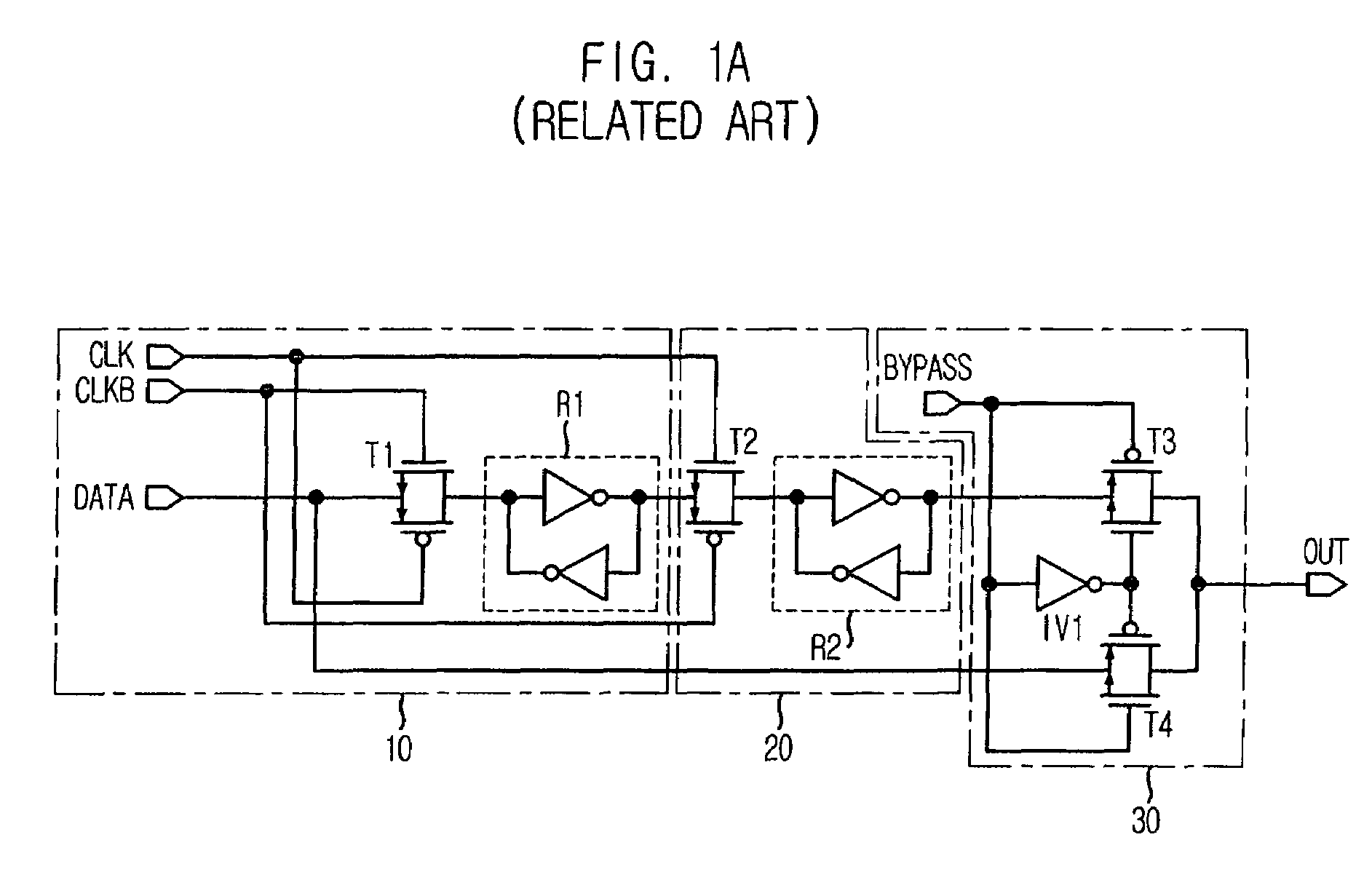

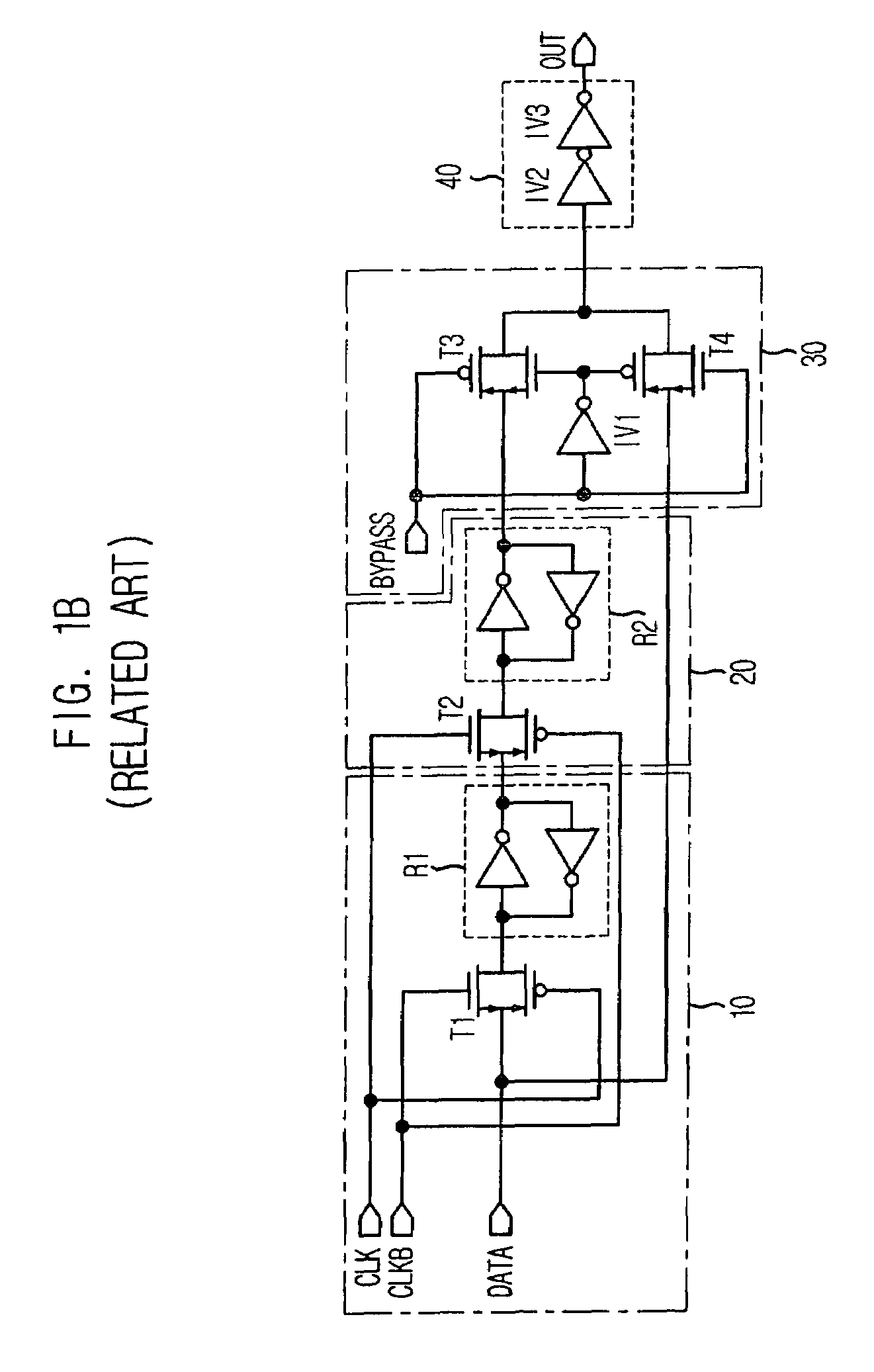

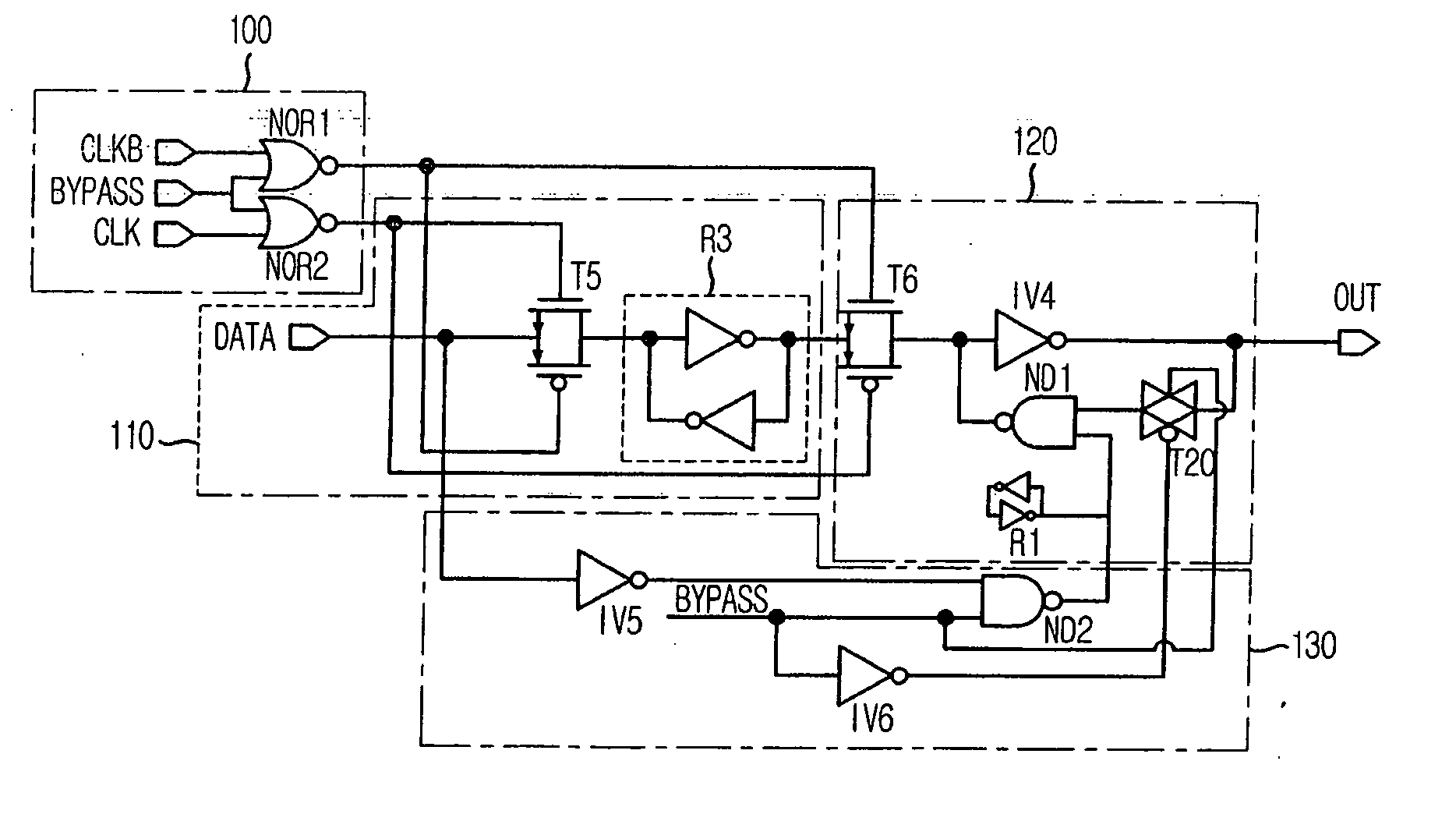

Flip-flop circuit

ActiveUS7427875B2High impedance stateElectric pulse generatorLogic circuits using elementary logic circuit componentsDelay marginEngineering

Signal delivery delay margin of a bypass flip-flop circuit is stabilized during high-frequency operation. An input controller for logically operating a bypass signal and a clock produces first and second output signals having different states depending on whether or not the bypass signal is activated. A latch circuit latches input data based on the first and second output signals. A latch controller logically operates the bypass signal and input data to generate a third output signal having a different state depending on whether or not the bypass signal is activated. An output controller is switched in response to the states of the first and second output signals for logically combining an output signal selected from the latch circuit and the third output signal to provide the output signal.

Owner:SK HYNIX INC

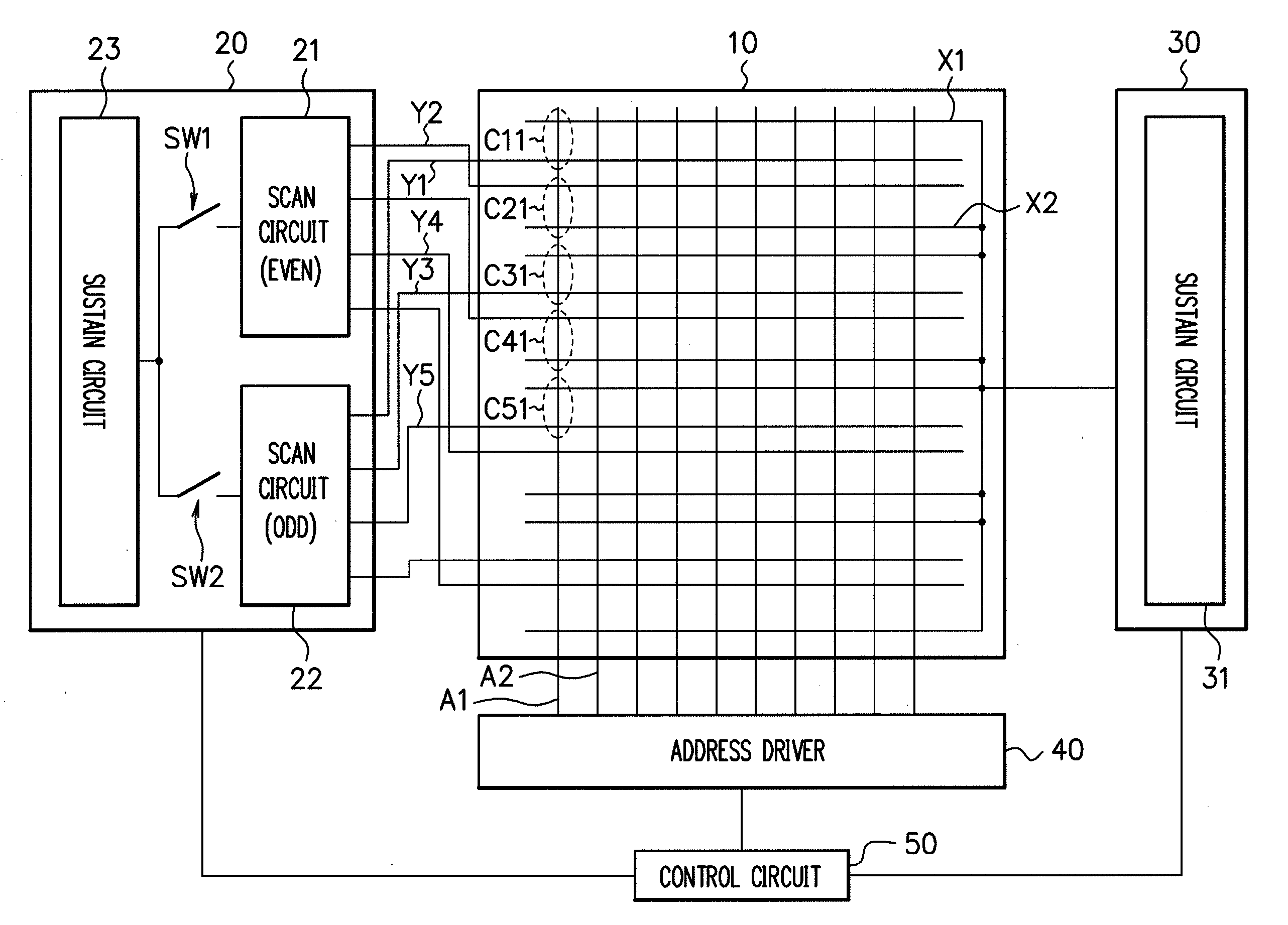

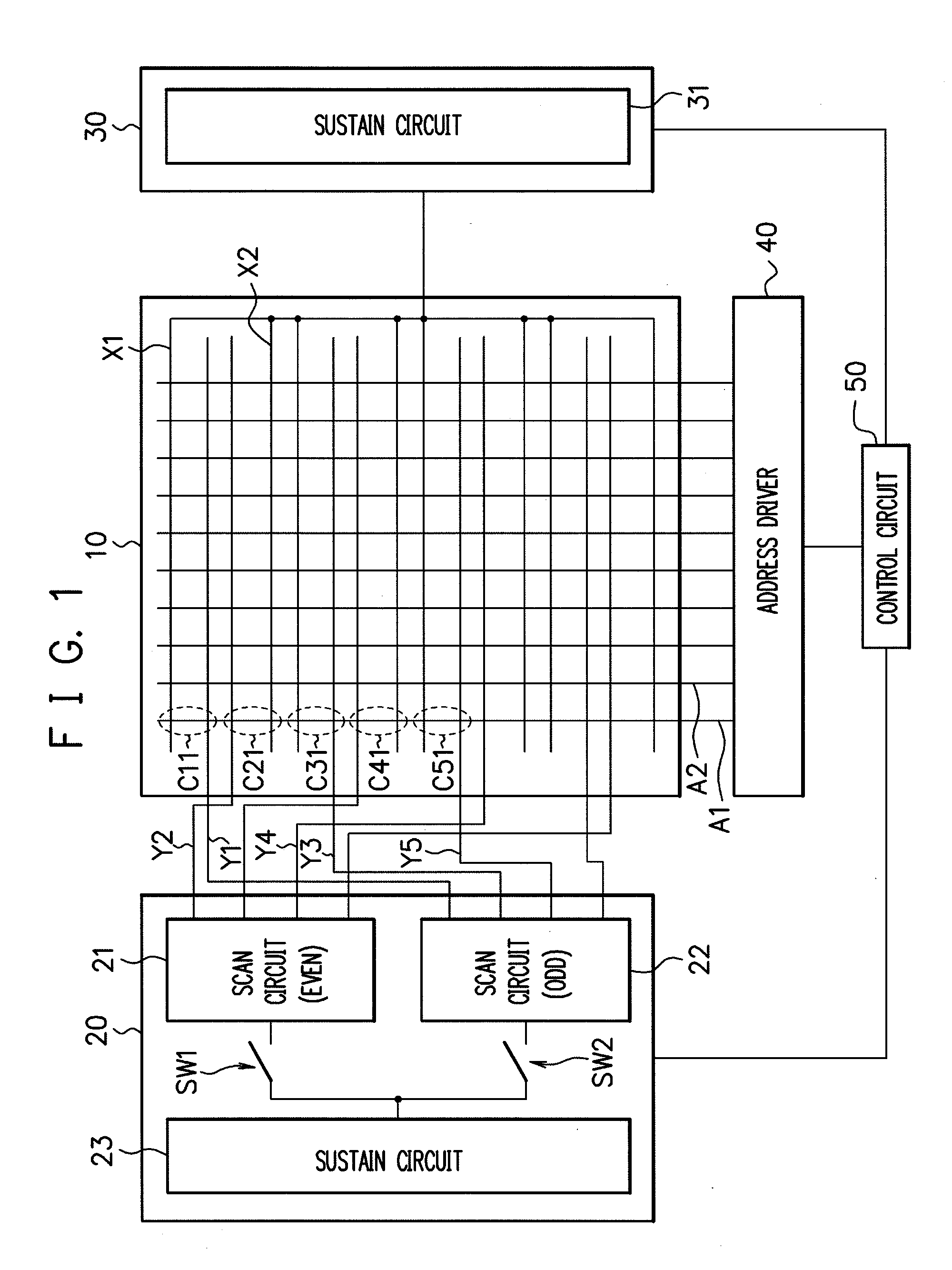

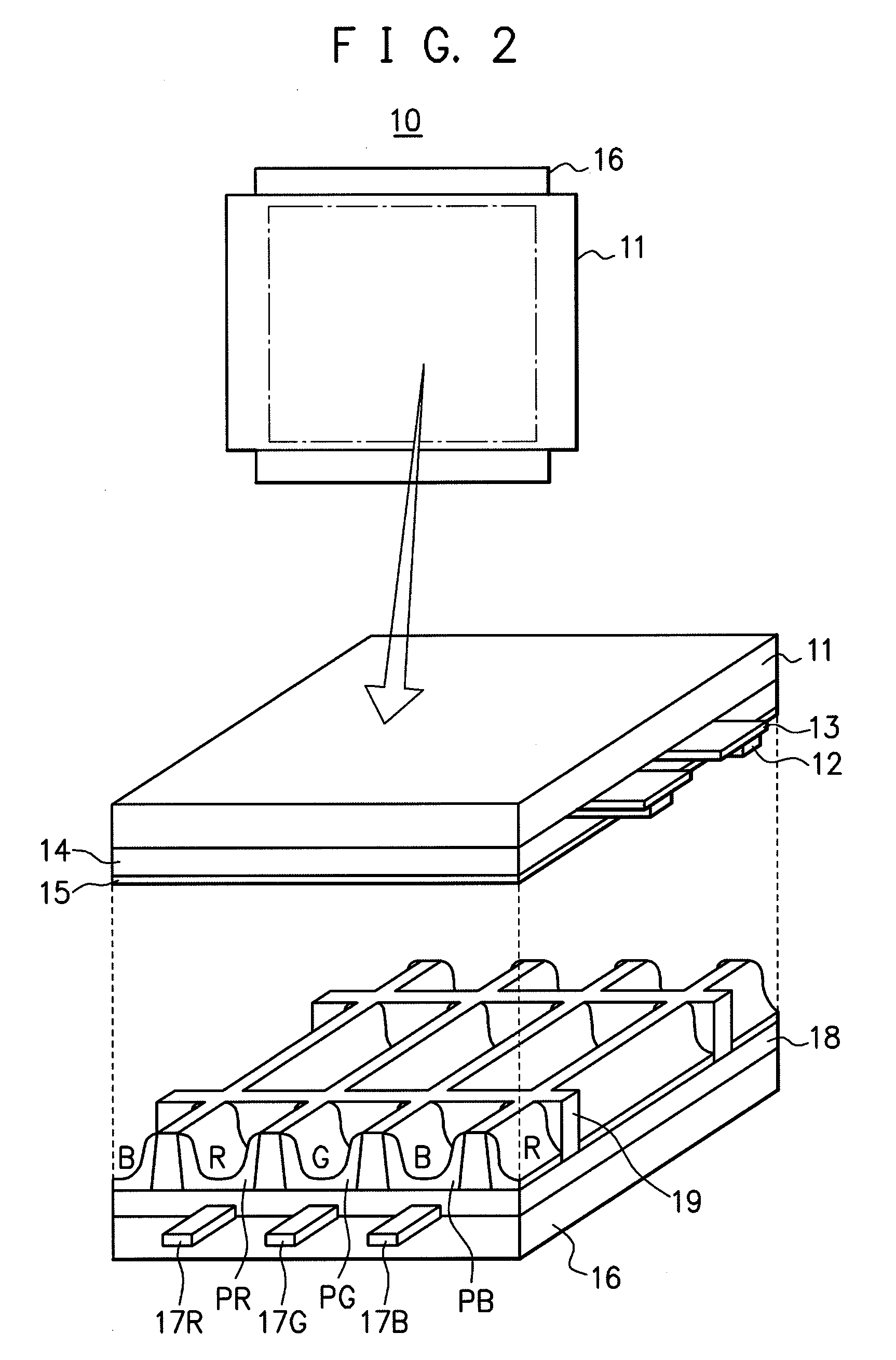

Plasma Display Device

InactiveUS20090058765A1Simple circuit configurationHigh impedance stateStatic indicating devicesScan circuitsPlasma display

Between a sustain circuit outputting a sustain pulse and a scan circuit (even) driving a Y electrode of an even display line, there is provided a first switch capable of making the Y electrode of the even display line be in a high impedance state, and between the sustain circuit and a scan circuit (odd) driving a Y electrode of an odd display line, there is provided a second switch capable of making the Y electrode of the odd display line be in the high impedance state. By first and second switches, the Y electrode of the even display line and the Y electrode of the odd display line can be independently controlled to be in the high impedance states, whereby discharge of the even display line can be restrained in a sustain period of an odd frame, while a discharge of the odd display line can be restrained in a sustain period of an even frame, thereby realizing an interlace drive without complicating a circuit configuration.

Owner:HITACHI LTD

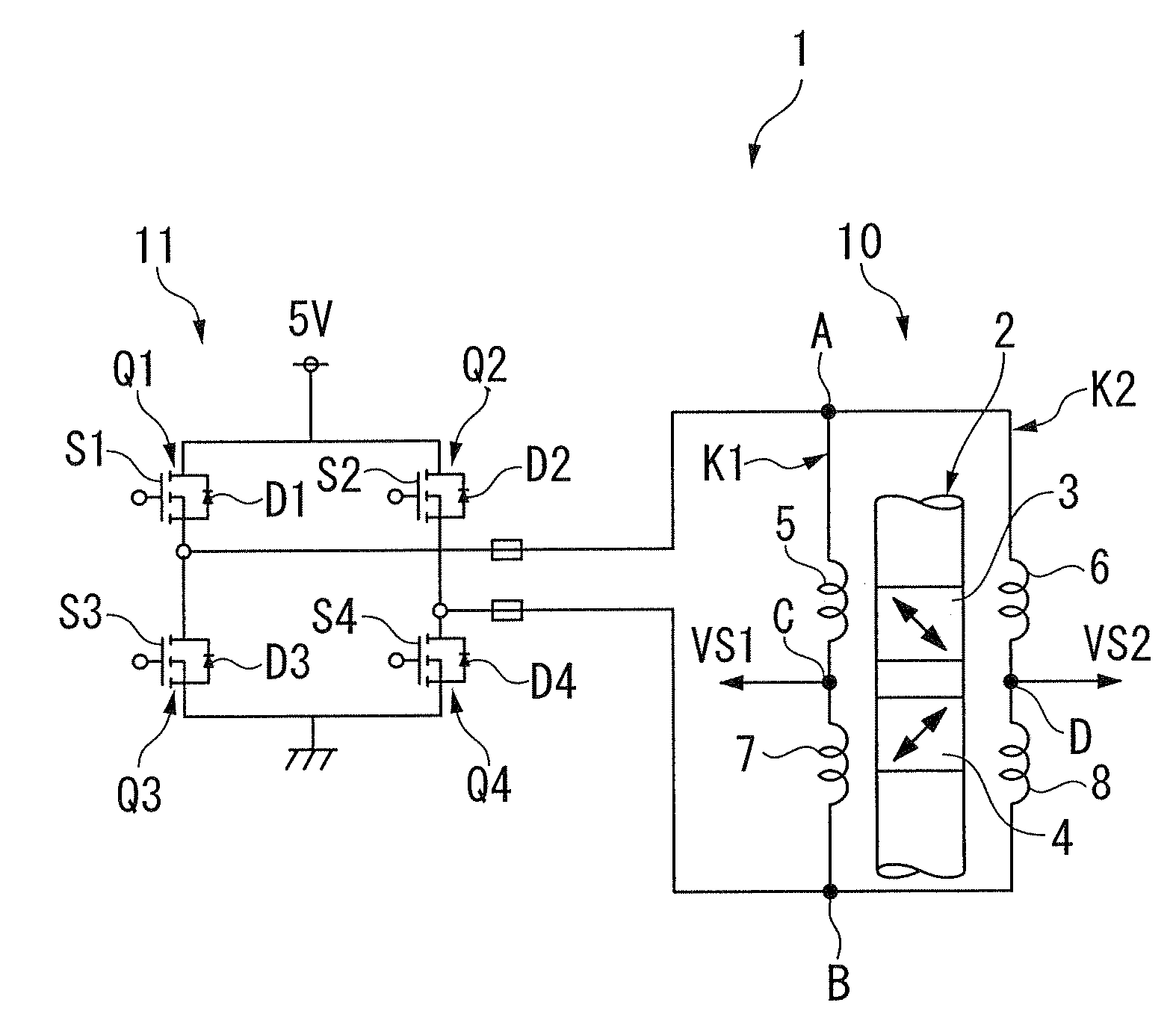

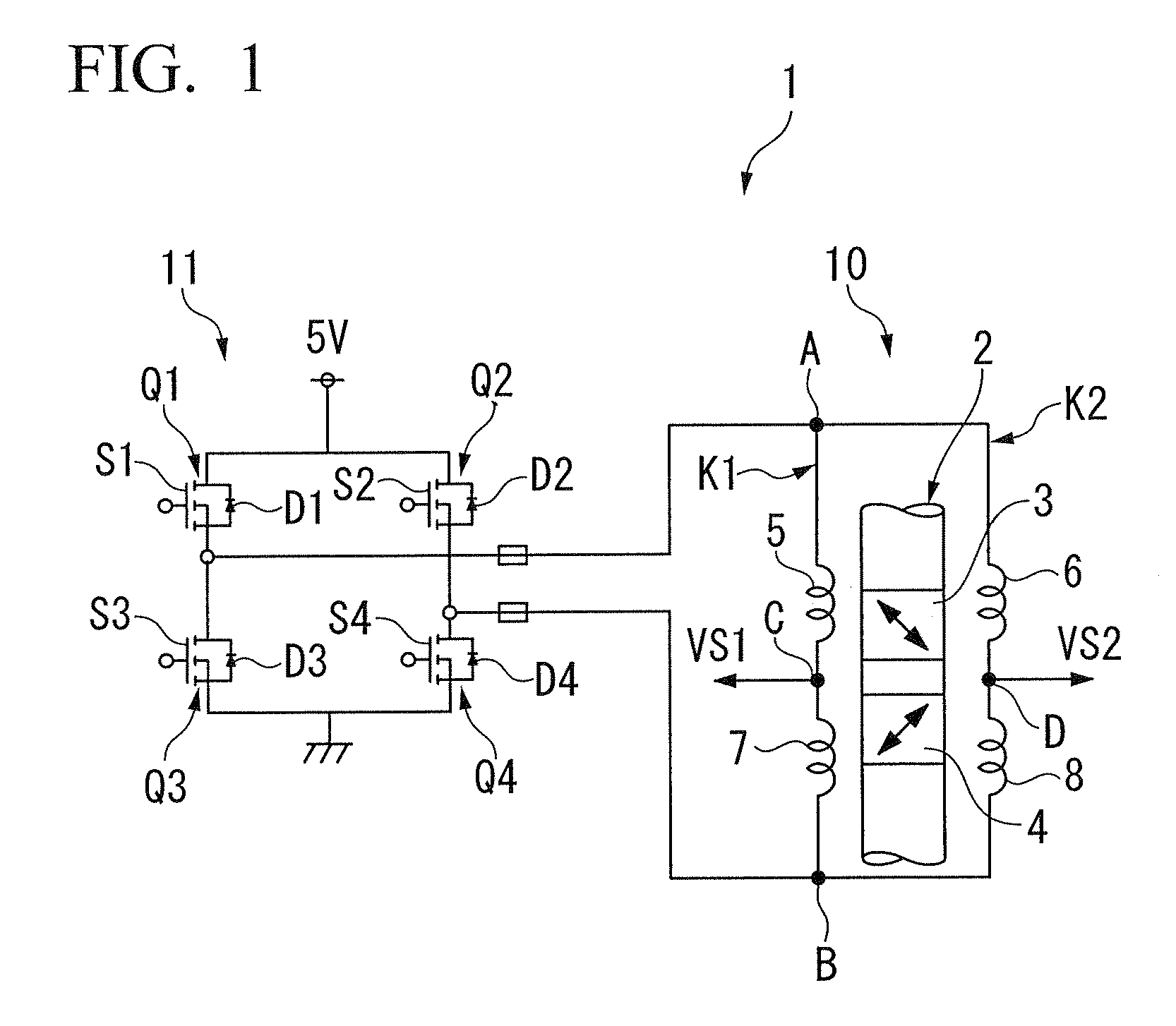

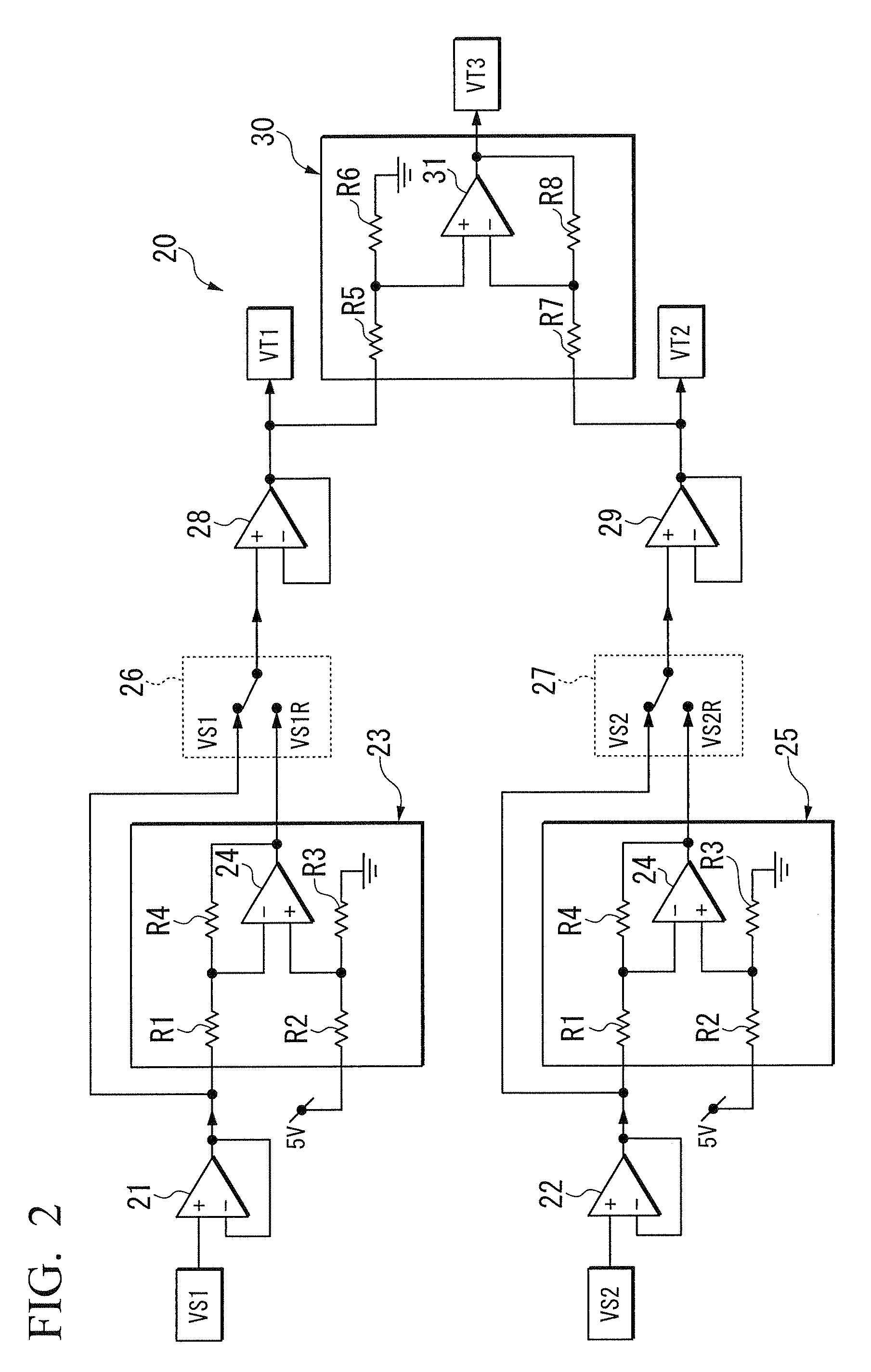

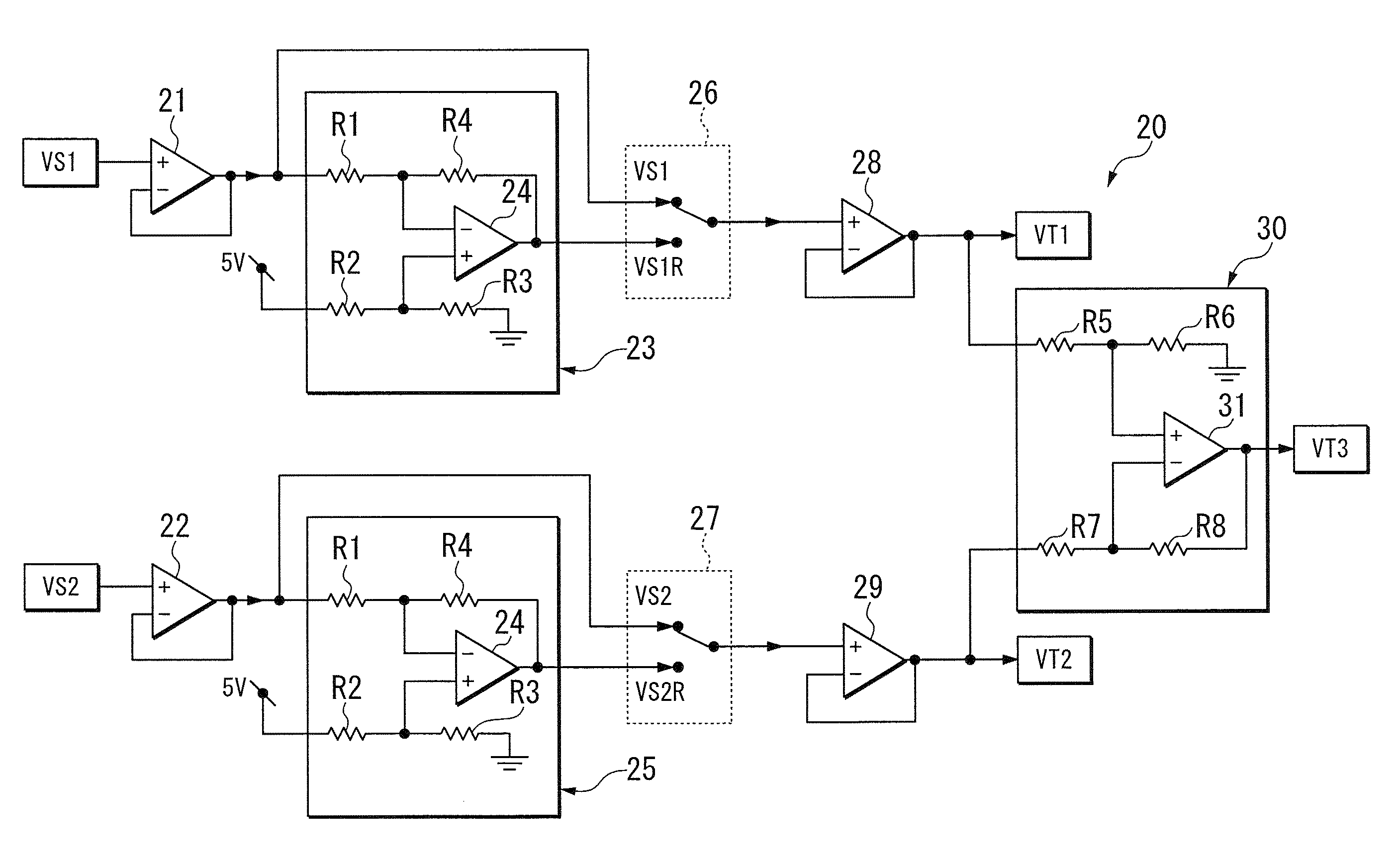

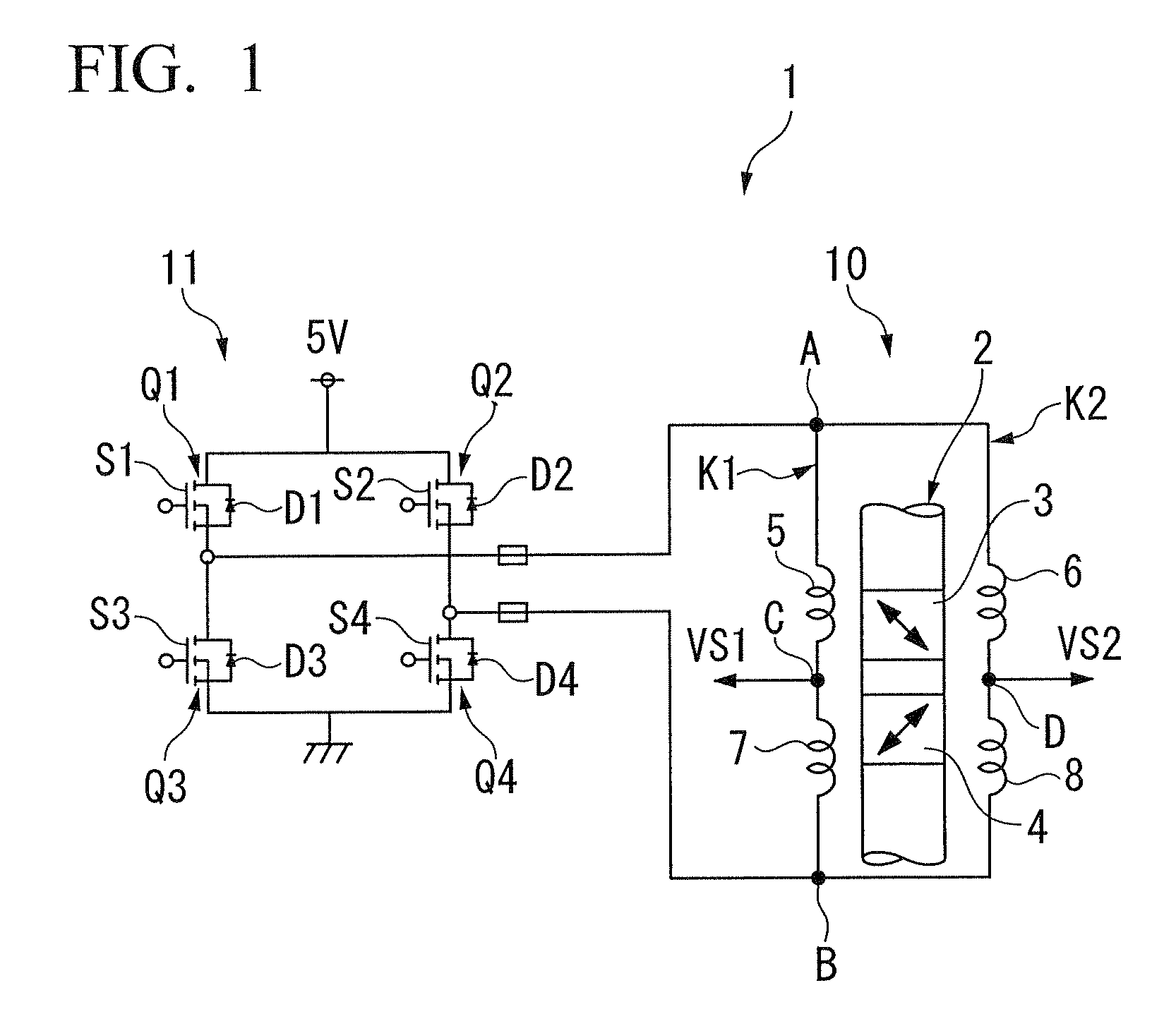

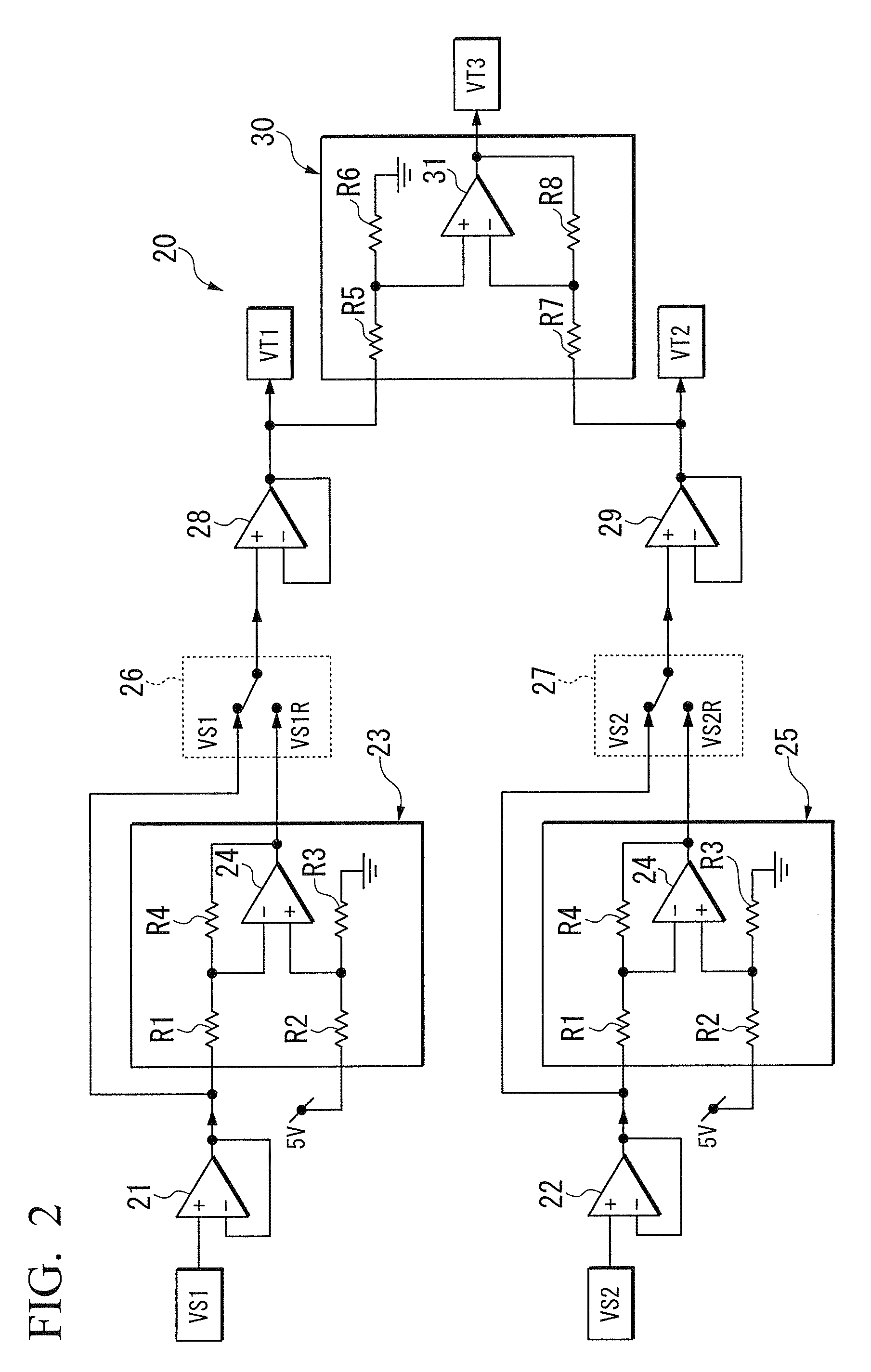

Magnetostrictive Torque Sensor

ActiveUS20090049931A1Reduce sensitivityHigh impedanceMagnetic field measurement using flux-gate principleWork measurementEngineeringControl theory

A magnetostrictive torque sensor of the present invention is provided with: a magnetostrictive film; a detection coil; a current direction switching device; and an inversion device, wherein: when the current flows in a direction from one side to another side of the detection coil by the current direction switching device, the torque reacted to the shaft is detected based on the input signal of the inversion device; and when the current flows in a inverse direction from another side to one side of the detection coil by the current direction switching device, the torque reacted to the shaft is detected based on the output signal of the inversion device.

Owner:HONDA MOTOR CO LTD

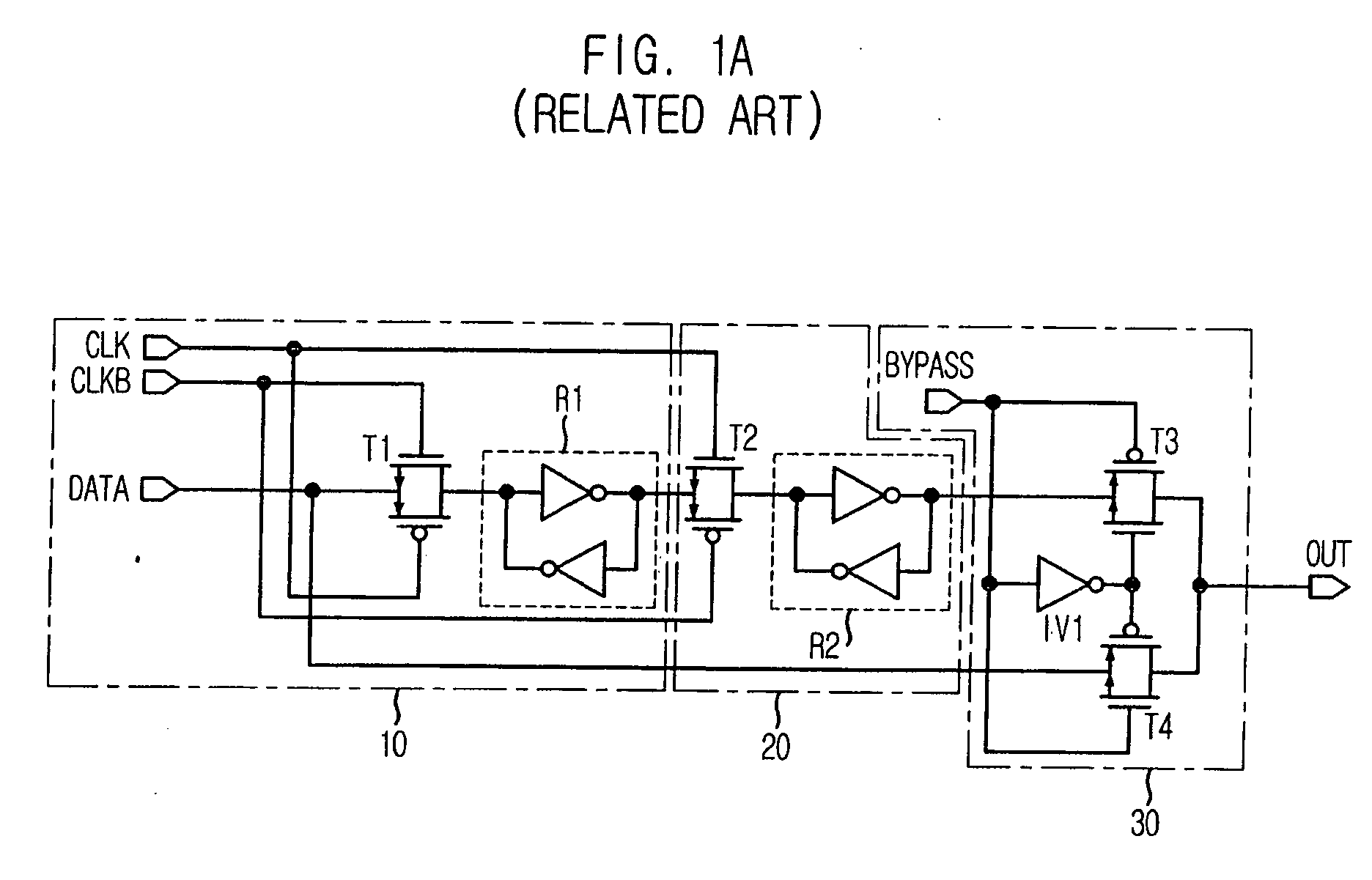

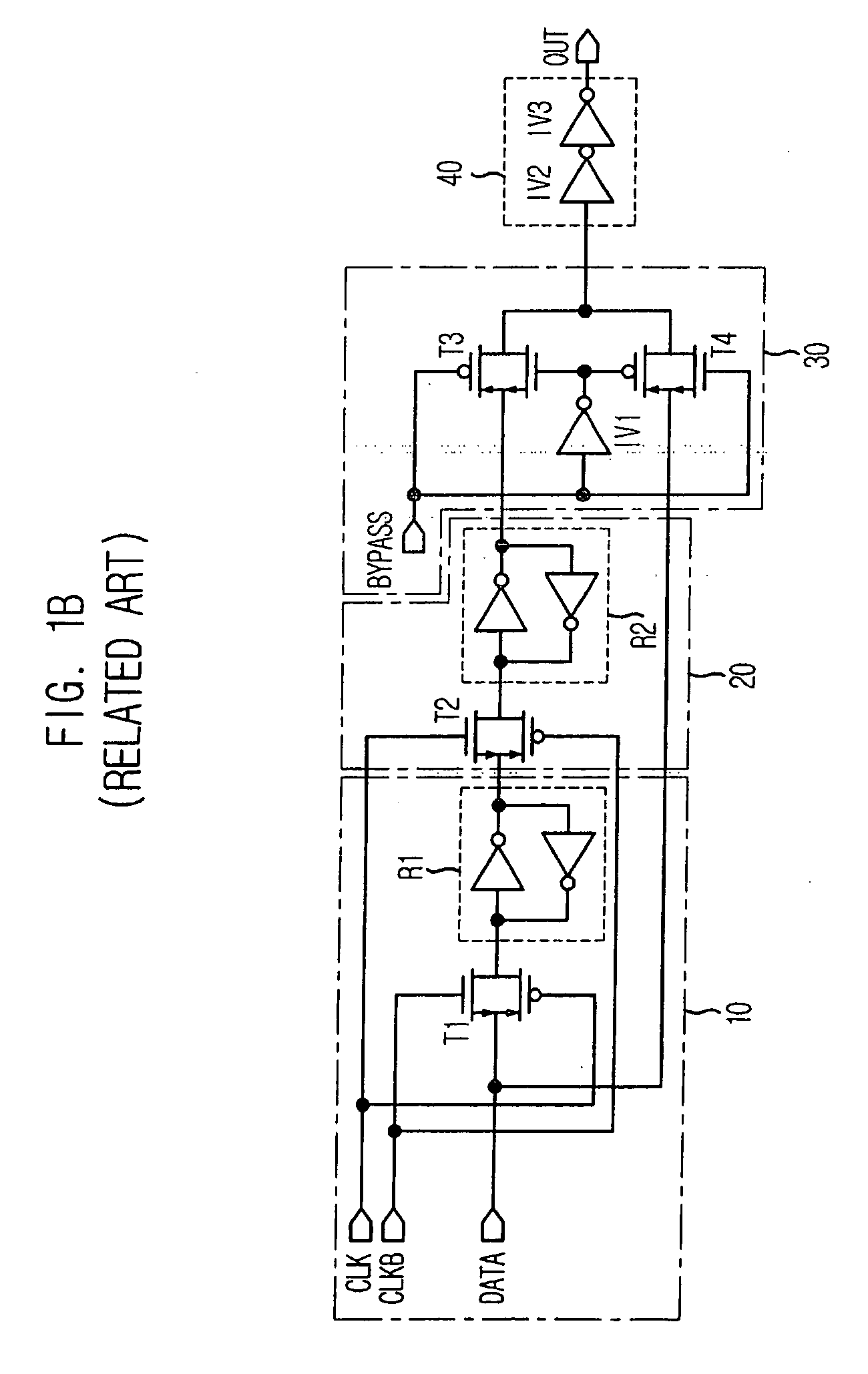

Flip-flop circuit

ActiveUS20070080714A1High impedance stateElectric pulse generatorLogic circuits using elementary logic circuit componentsDelay marginEngineering

Signal delivery delay margin of a bypass flip-flop circuit is stabilized during high-frequency operation. An input controller for logically operating a bypass signal and a clock produces first and second output signals having different states depending on whether or not the bypass signal is activated. A latch circuit latches input data based on the first and second output signals. A latch controller logically operates the bypass signal and input data to generate a third output signal having a different state depending on whether or not the bypass signal is activated. An output controller is switched in response to the states of the first and second output signals for logically combining an output signal selected from the latch circuit and the third output signal to provide the output signal.

Owner:SK HYNIX INC

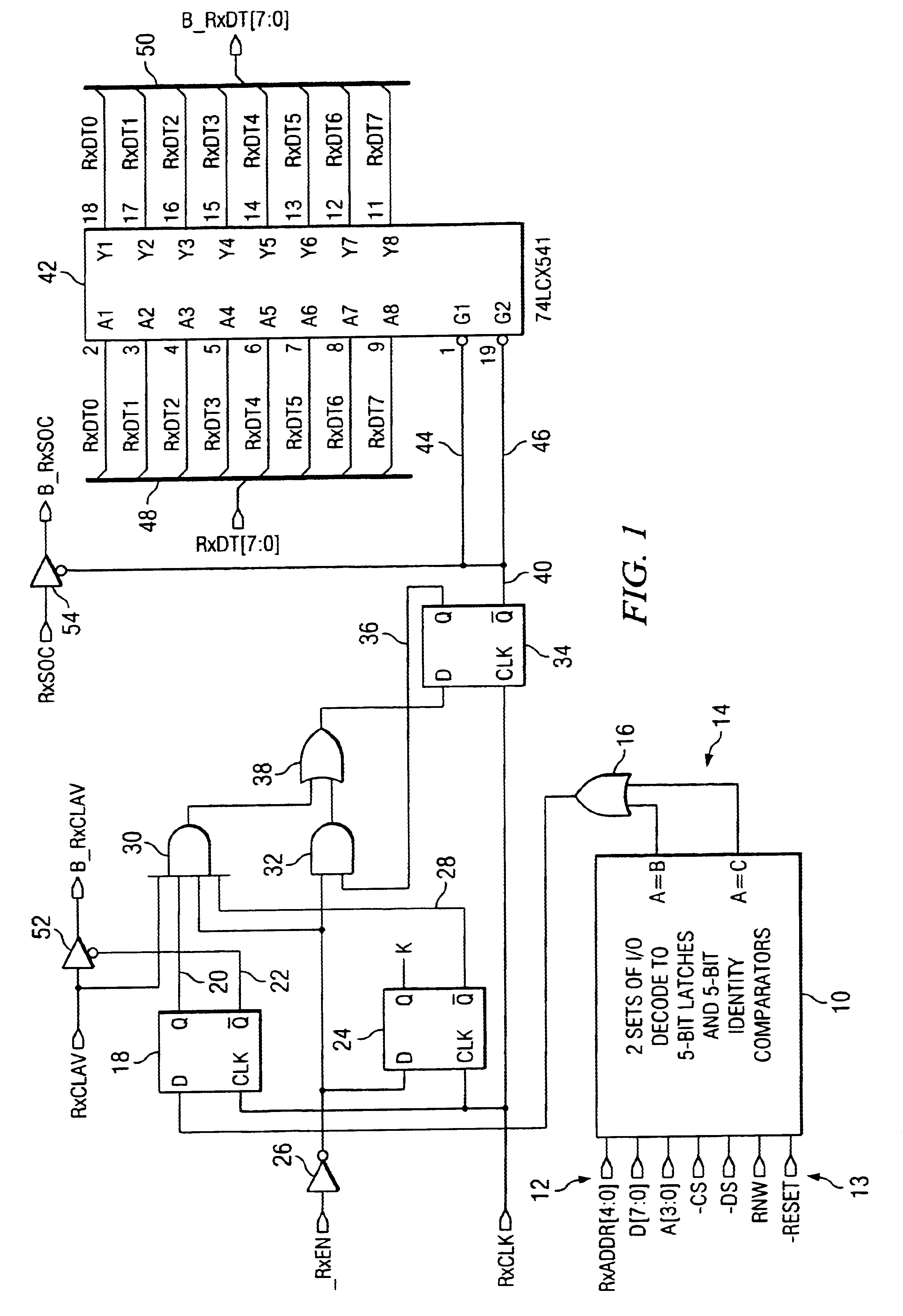

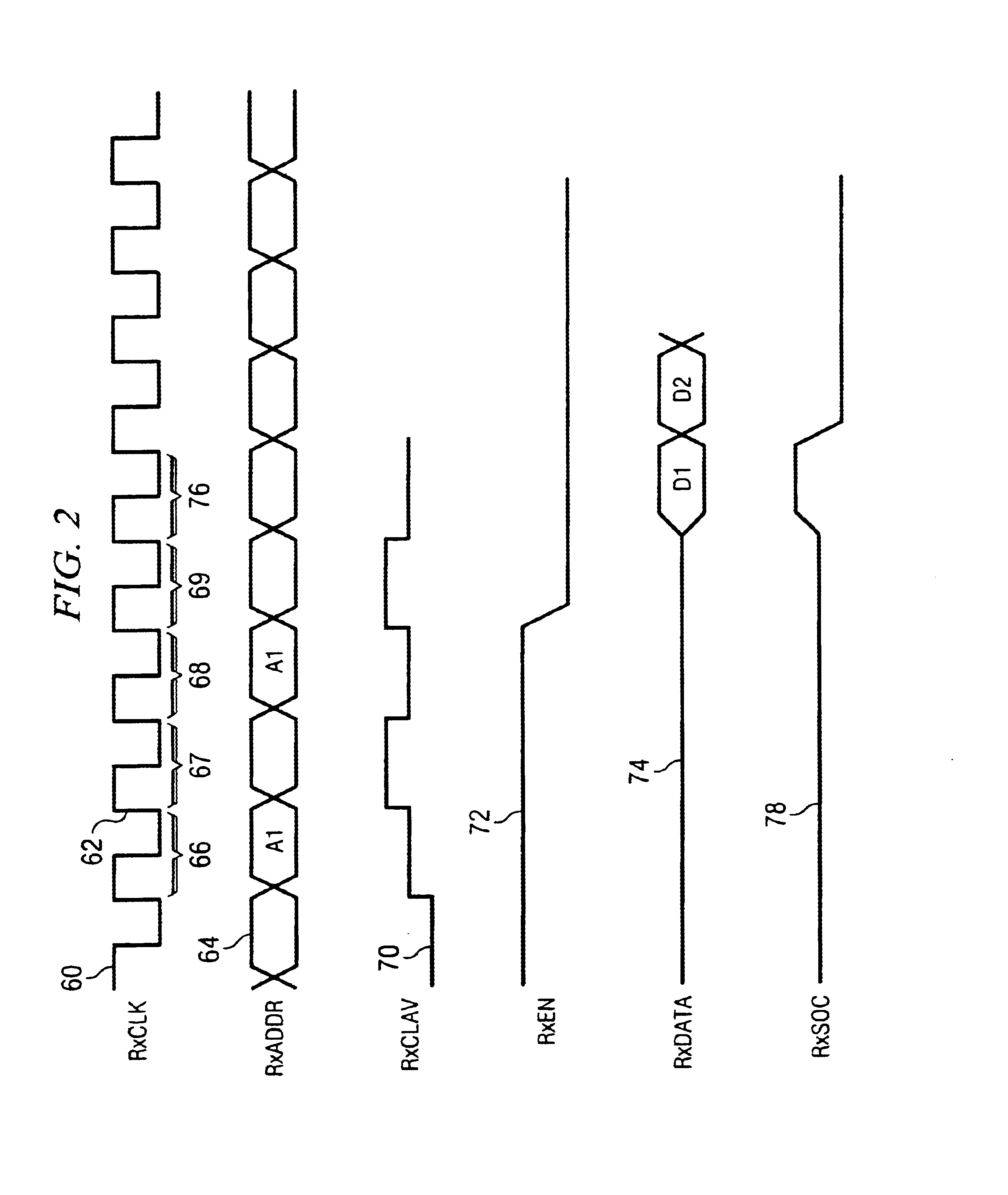

Backplane utopia bus

InactiveUS6850535B1High impedance stateData switching by path configurationData bufferEmbedded system

The present invention discloses a system for buffering the outputs of peripheral devices operating in UTOPIA protocol to allow devices on separate circuit boards connected through long buses, such as backplanes, to communicate with the system controller. Address detection logic stores the peripheral device address and compares it to the UTOPIA bus address signal. When the correct address is recognized in a first clock cycle, a flip flop stores the information for the next cycle. A second flip flop stores the state of the read enable signal. An AND gate detects when the correct address was found and the read enable was de-asserted during the first clock cycle and the read enable and read cell available signals are positive during the current clock cycle and provides a high signal to a third flip flop. On a third clock cycle the third flip flop enables the outputs of a data buffer which then drives the peripheral device data signals on to the read data bus. The third flip flop output and the read enable signal are provided to a second AND gate which feeds back to the third flip flop to maintain its state until the read enable signal is de-asserted. The first flip flop is also used to control a buffer for the read cell available signal from the peripheral device. The third flip flop is also used to control a buffer for the read start of cell signal from the peripheral device.

Owner:SPRINT CORPORATION

Display driver, electro-optical device, and electronic apparatus

A display driver includes a D / A converter circuit configured to convert display data into a gradation voltage, an amplifier circuit including an input node to which the gradation voltage is input and configured to output data voltage, and a supply circuit configured to supply an auxiliary current or an auxiliary electrical charge to the input node of the amplifier circuit. In an auxiliary period, an output of the D / A converter circuit is in a high impedance state, and the supply circuit supplies the auxiliary current or the auxiliary electrical charge to the input node of the amplifier circuit. In a non-auxiliary period after the auxiliary period, the D / A converter circuit outputs the gradation voltage to the input node of the amplifier circuit.

Owner:SEIKO EPSON CORP

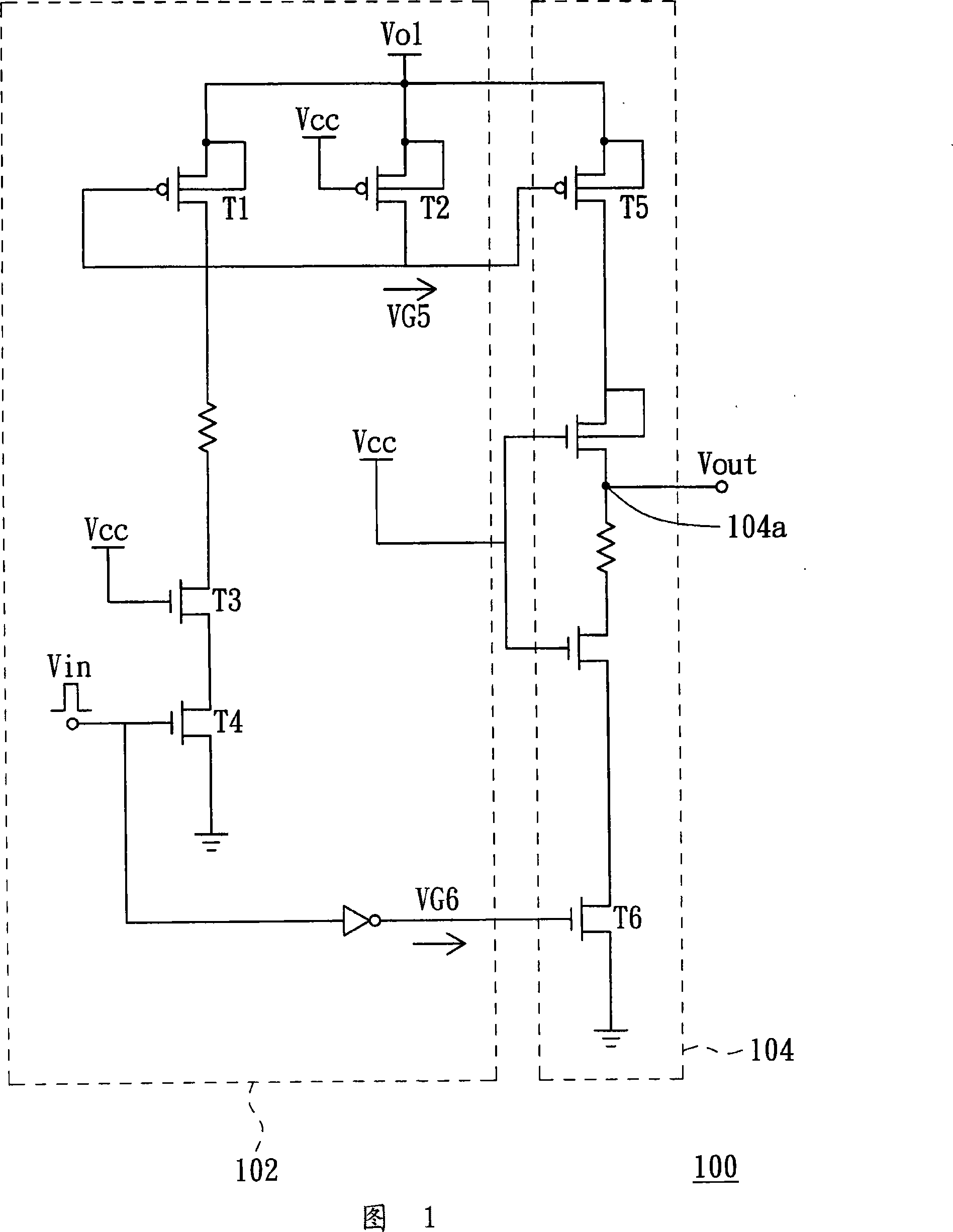

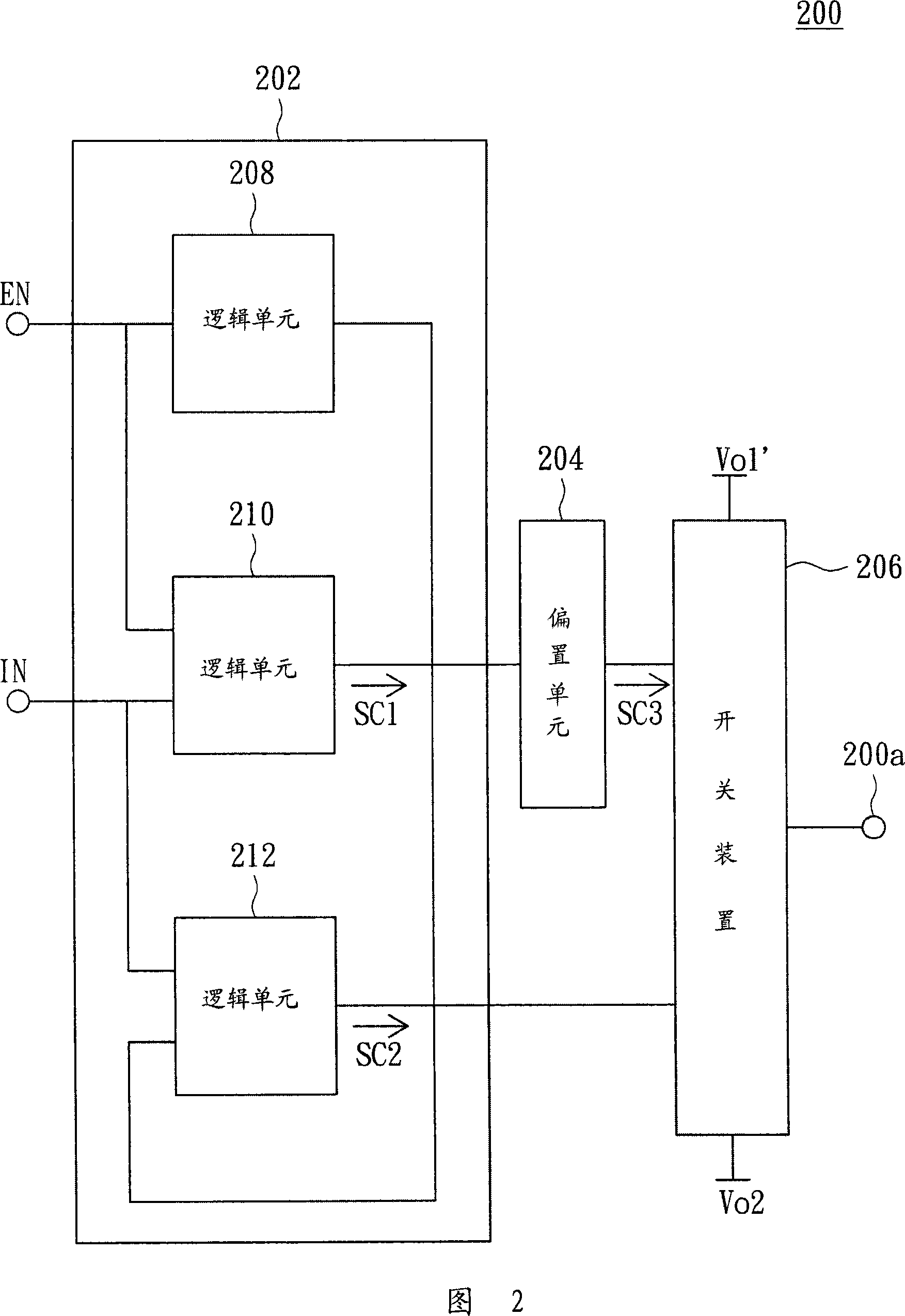

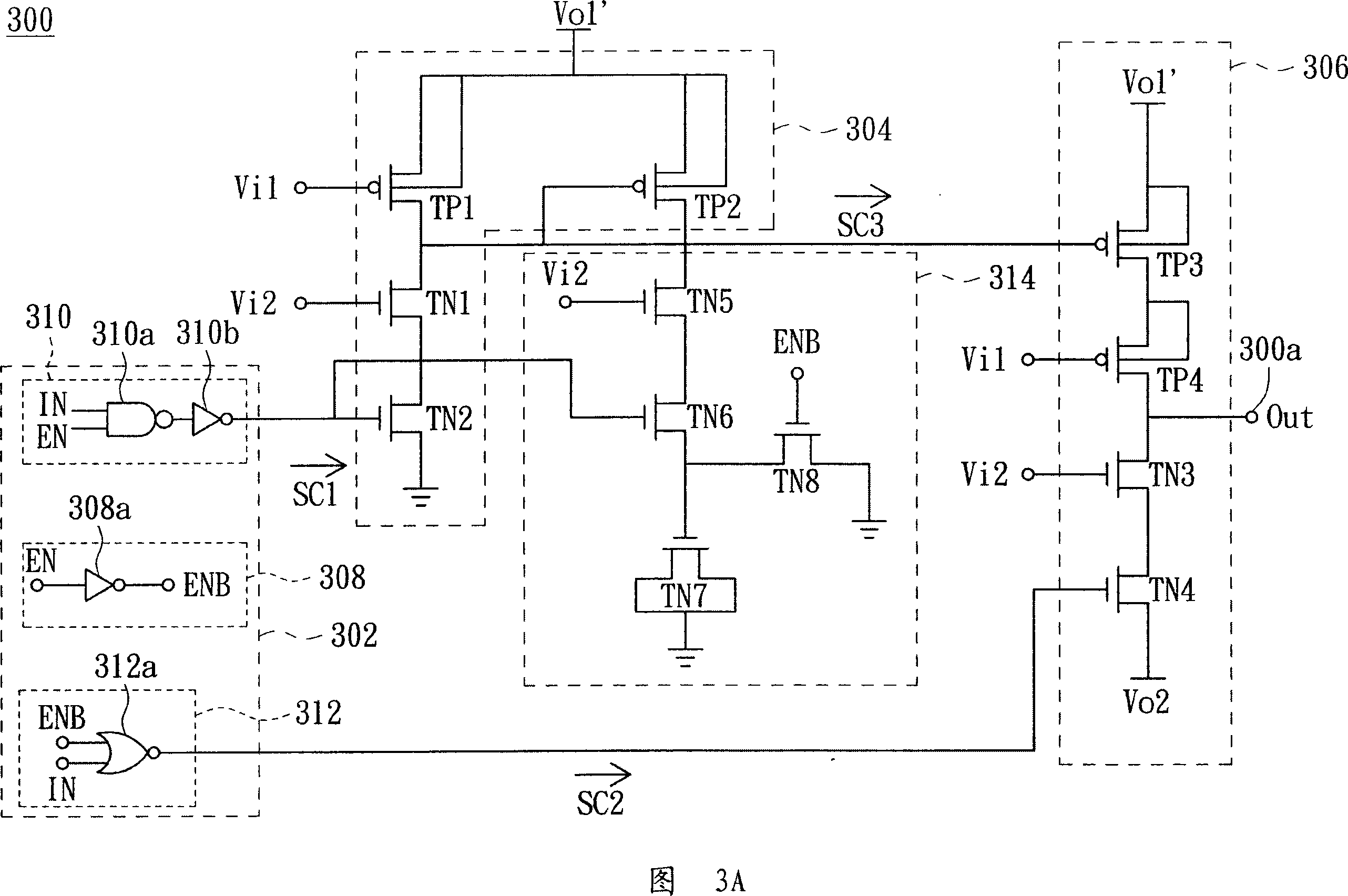

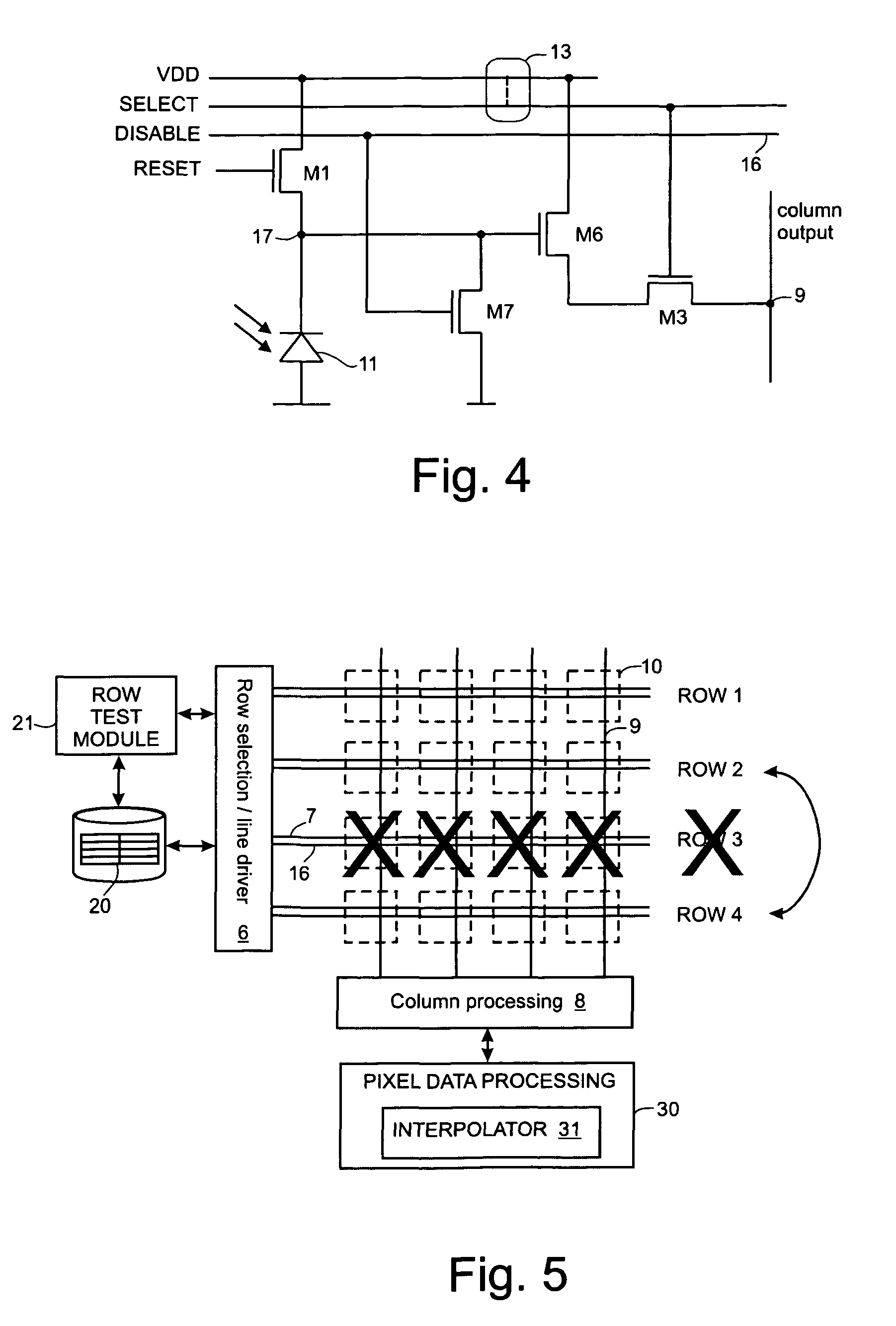

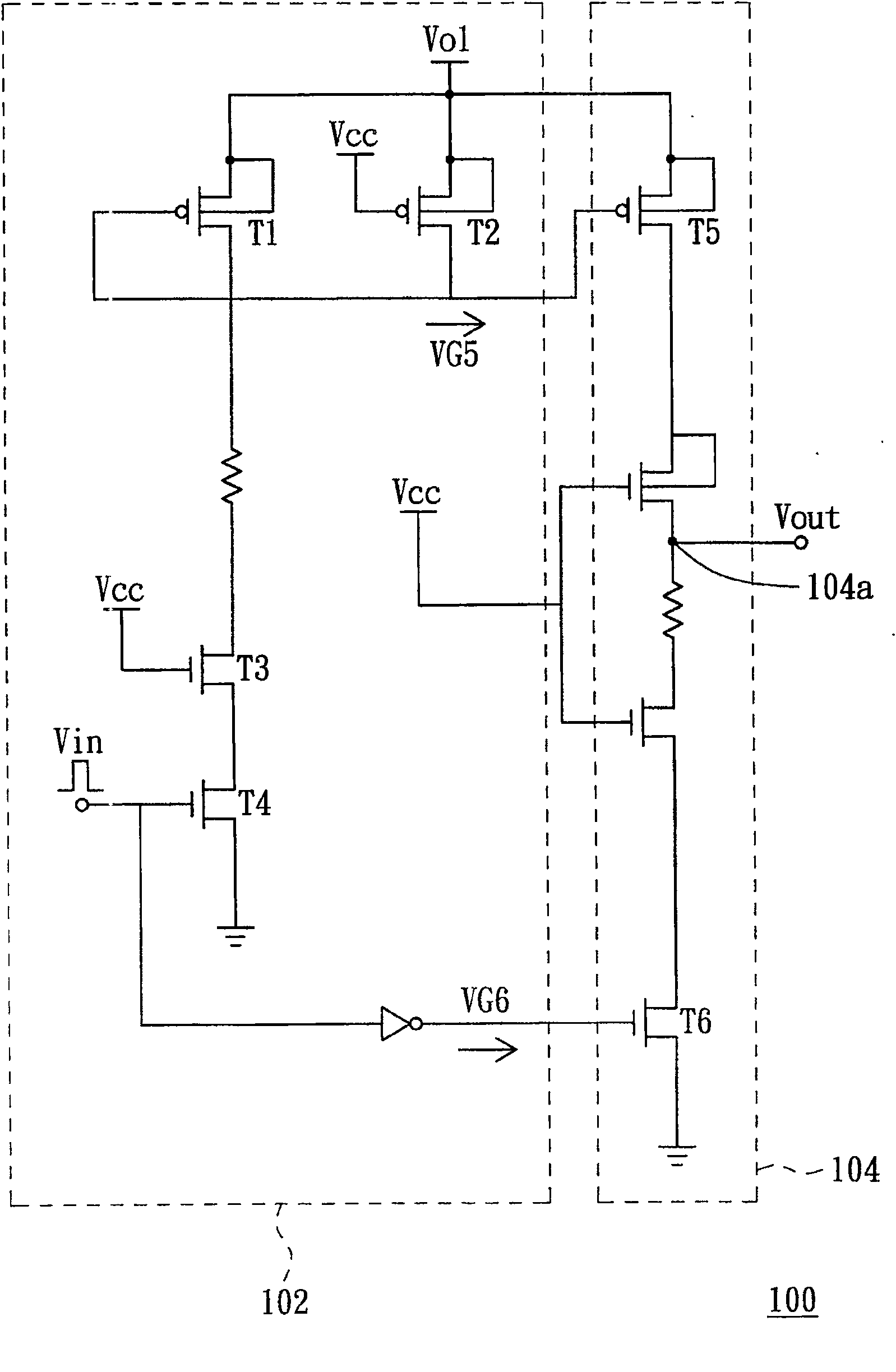

Low voltage complementary metal oxide semiconductor process tri-state buffer

ActiveCN101174830AAvoid power consumptionHigh impedance stateLogic circuits coupling/interface using field-effect transistorsOxide semiconductorCMOS

A tri-state buffer made of low voltage complementary metal oxide semiconductor (CMOS) includes a logic device, a biasing device and a switch device. The logic device receives an input signal and an enable signal and generates a first control signal and a second control signal. The biasing device receives the first control signal and thus controls a voltage level of a third control signal. The switch device receives the second and third control signals and respectively couples an output terminal to a first external voltage source and a second external voltage source when the second and third control signals are enabled. When the enable signal is disabled, the second and third control signals are simultaneously disabled so that the output terminal is floating with respect to the first and second external voltage sources and the output terminal is held in a high impedance state.

Owner:MACRONIX INT CO LTD

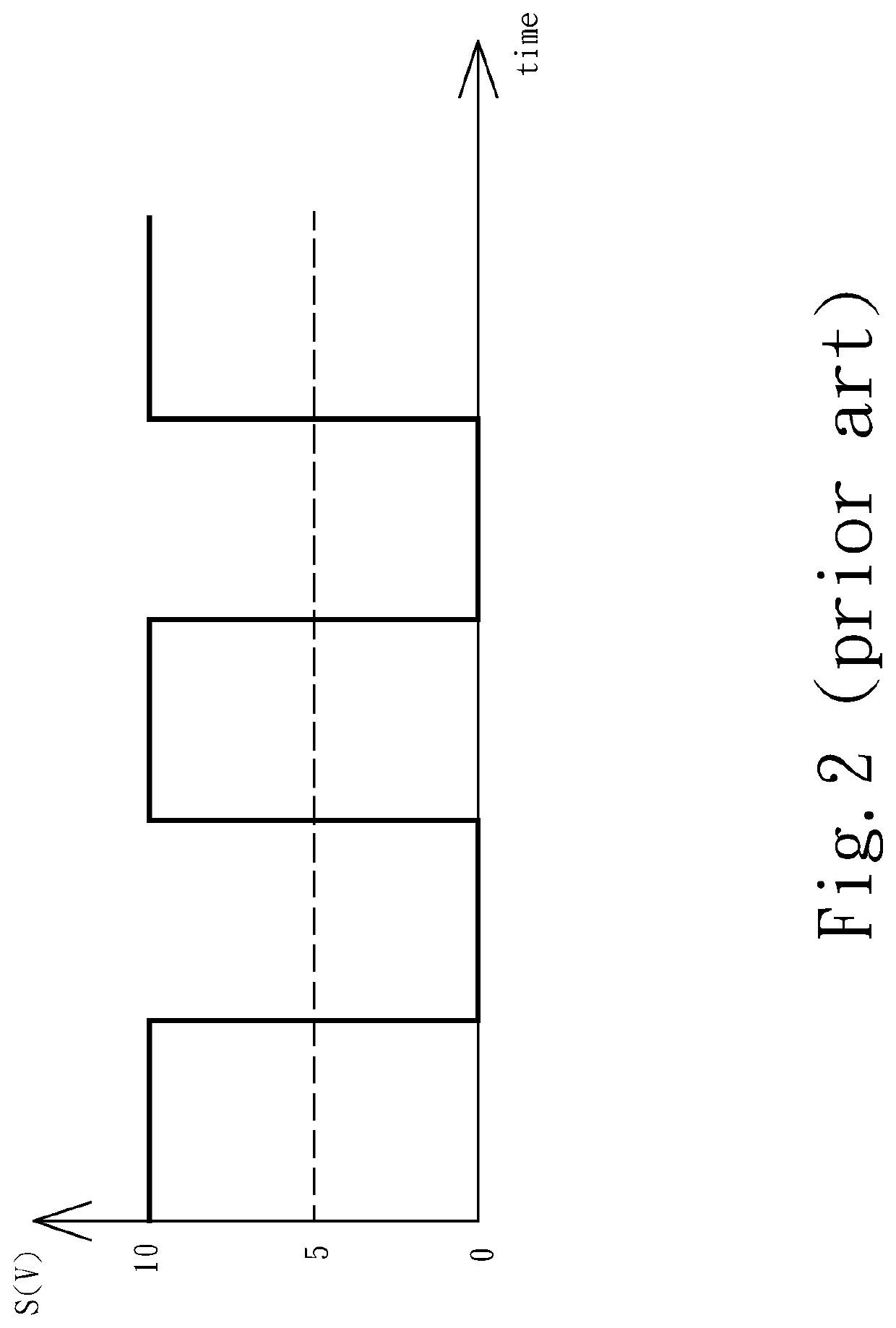

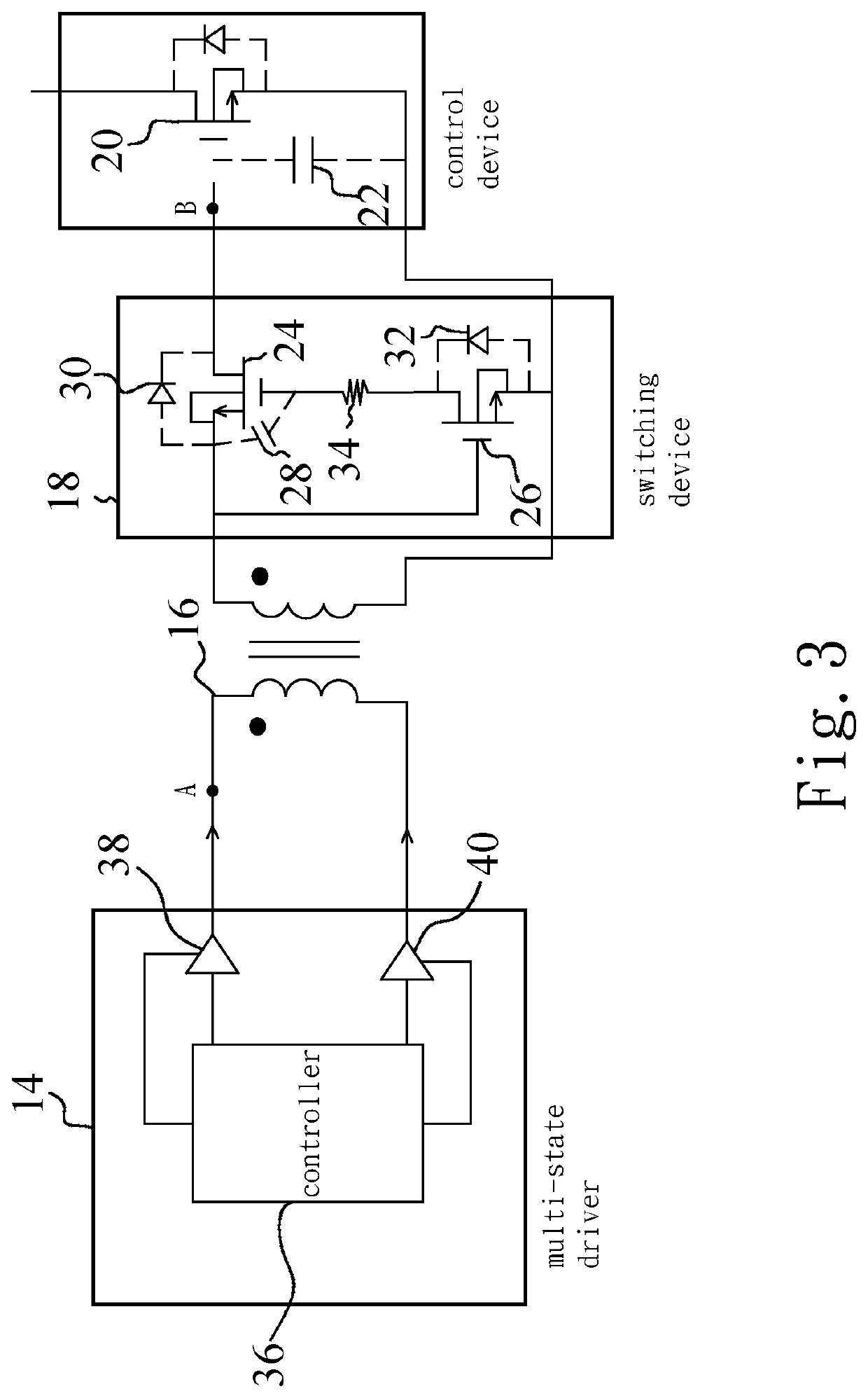

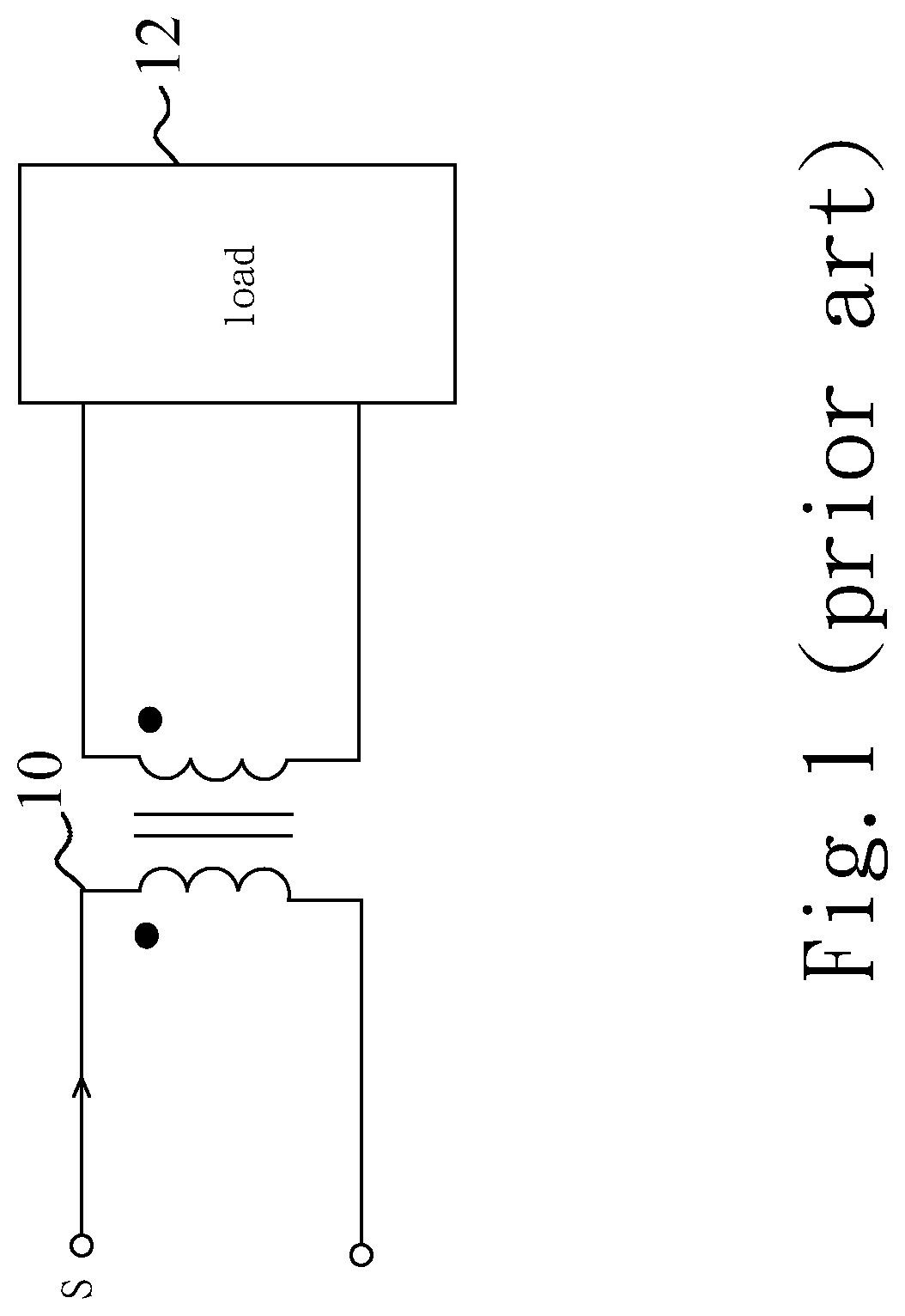

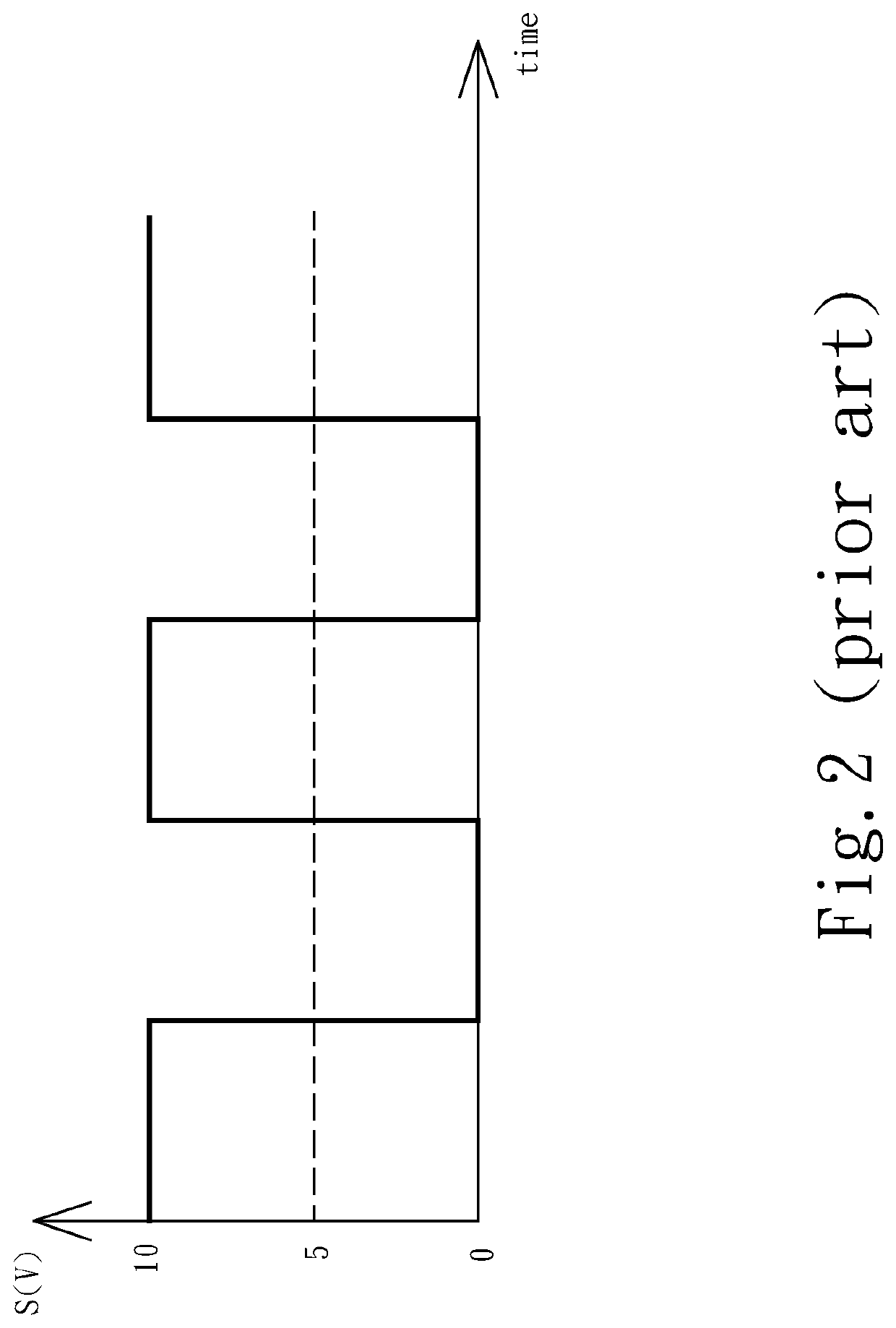

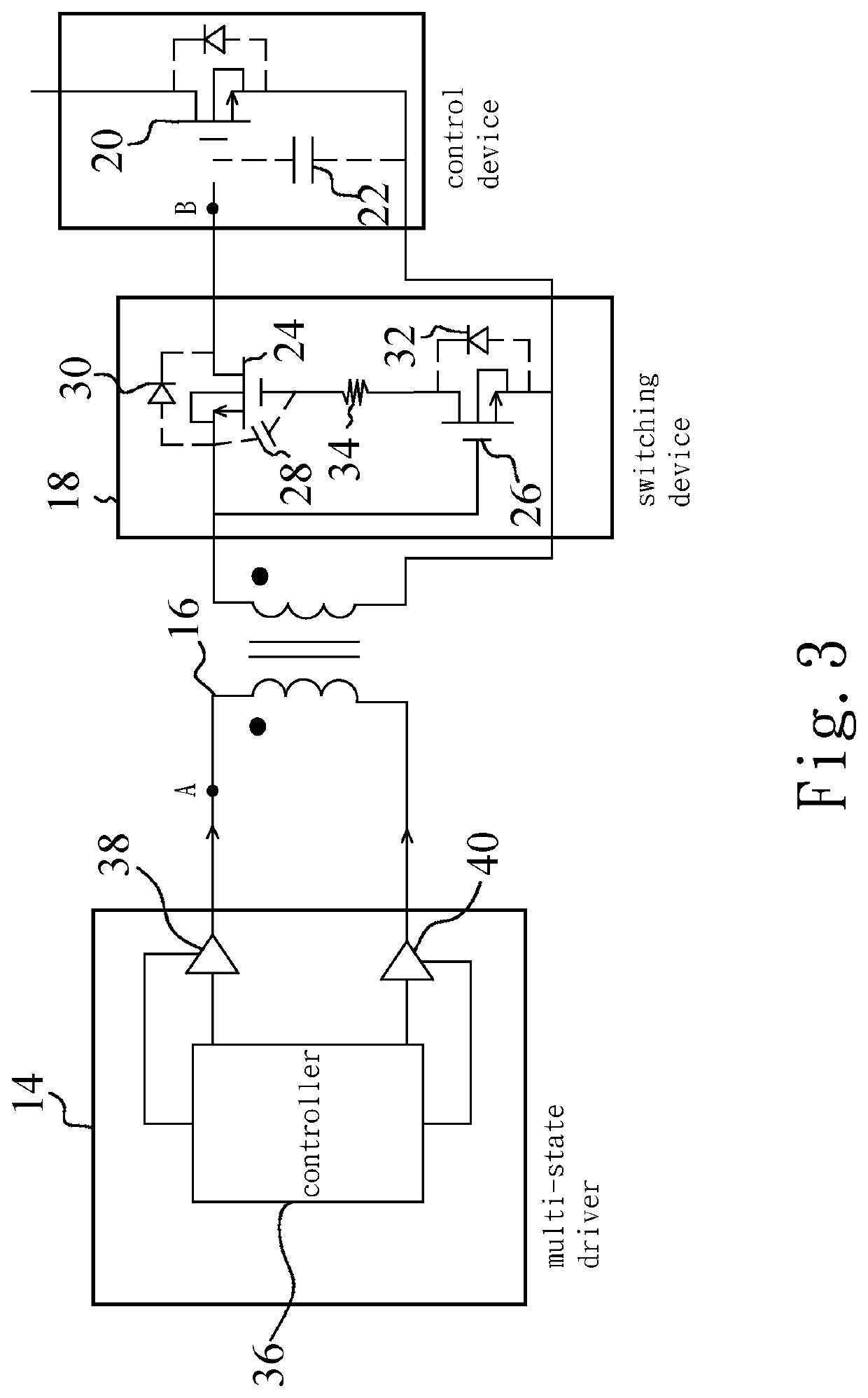

Driving method and driving device using the same

ActiveUS20210152173A1Avoid disadvantagesErroneous operationTransformers/inductances coils/windings/connectionsDc-dc conversionCharge (electrical)Electrical connection

A driving method and a driving device using the same are disclosed. The driving method controls a pulse transformer. The secondary winding of the pulse transformer is electrically connected to a control device. Firstly, positive charging electrical energy is delivered to the primary winding, thereby charging the control device. Then, the control device is disconnected from the secondary winding while the primary winding is in a high-impedance state. Finally, negative discharging electrical energy is delivered to the primary winding and the control device is electrically connected to the secondary winding, thereby discharging the control device, and the primary winding is in a low-impedance state after the step of delivering the negative discharging electrical energy to the primary winding.

Owner:SYNC POWER CORP

Magnetostrictive torque sensor

ActiveUS7658120B2Reduce sensitivityHigh impedanceMagnetic field measurement using flux-gate principleWork measurementControl theoryElectrical current

A magnetostrictive torque sensor of the present invention is provided with: a magnetostrictive film; a detection coil; a current direction switching device; and an inversion device, wherein: when the current flows in a direction from one side to another side of the detection coil by the current direction switching device, the torque reacted to the shaft is detected based on the input signal of the inversion device; and when the current flows in a inverse direction from another side to one side of the detection coil by the current direction switching device, the torque reacted to the shaft is detected based on the output signal of the inversion device.

Owner:HONDA MOTOR CO LTD

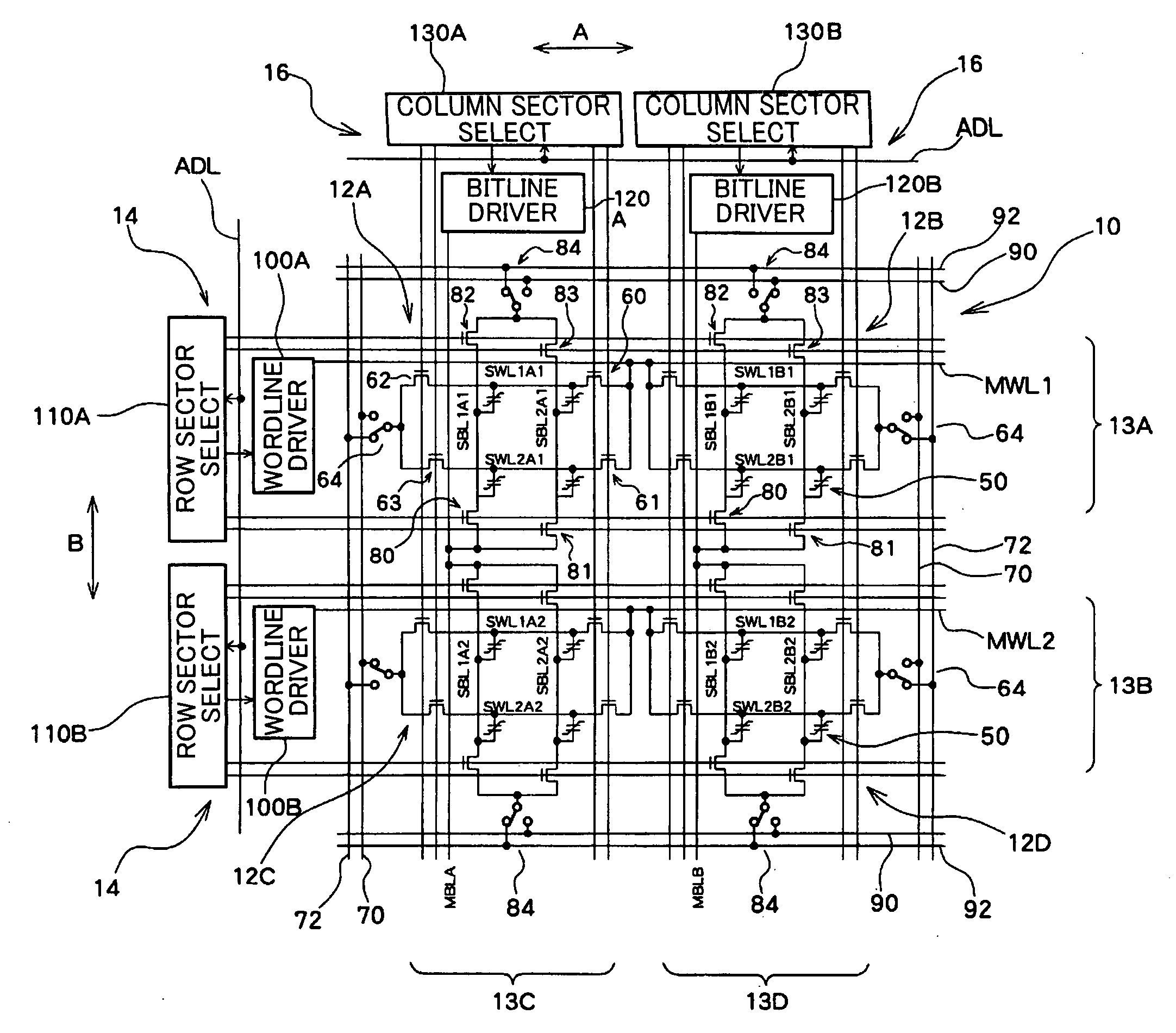

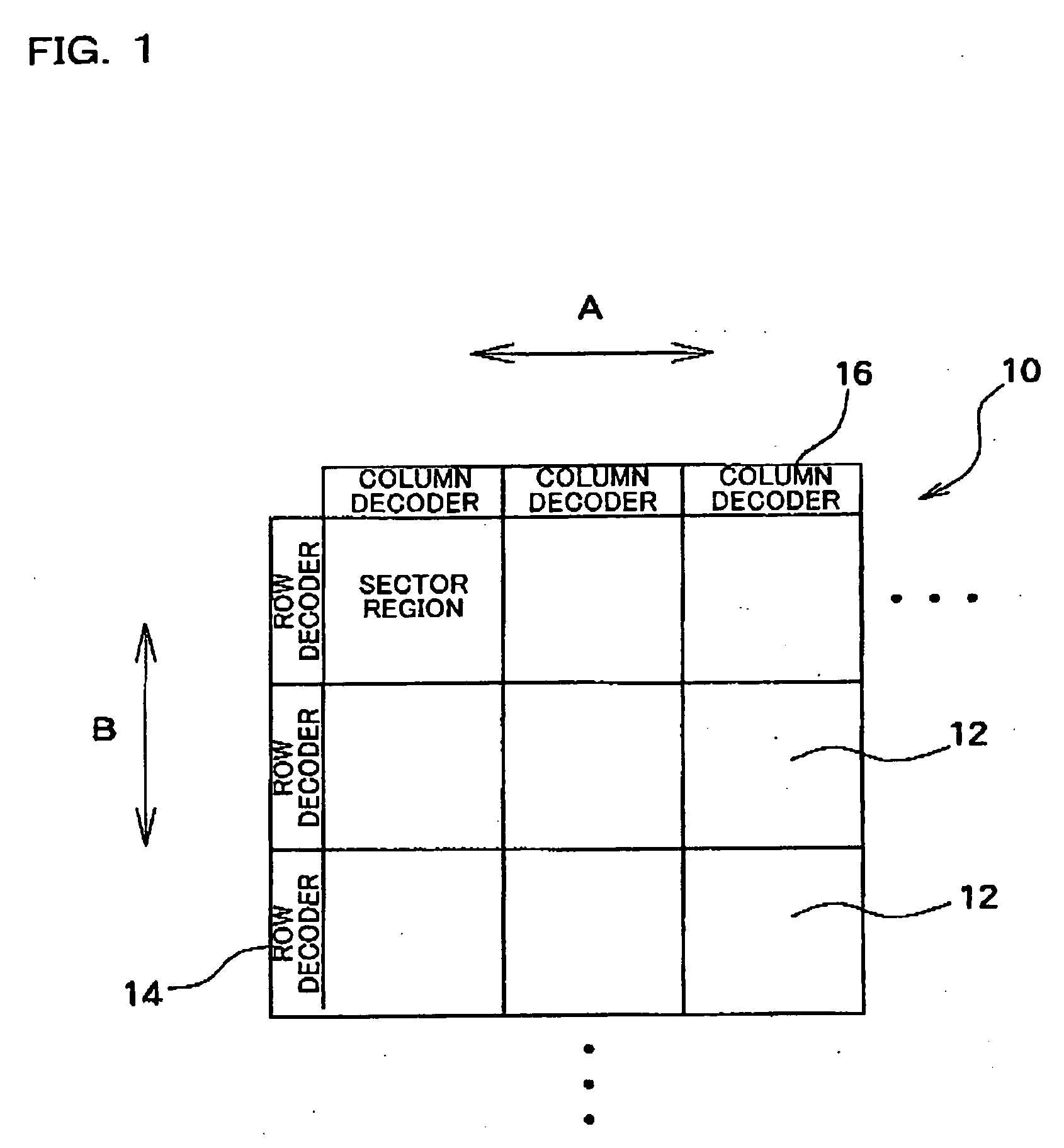

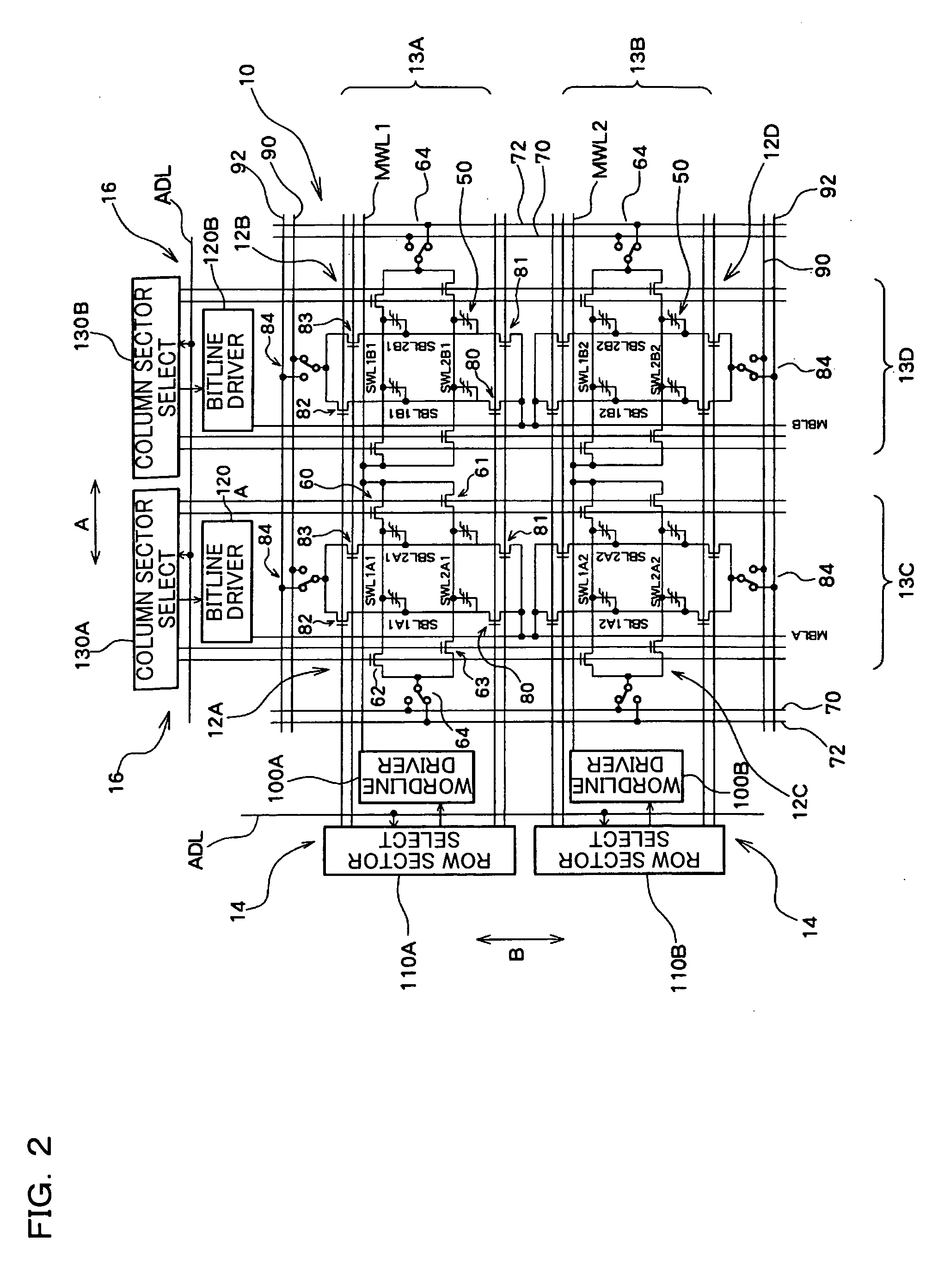

Ferroelectric memory device

A ferroelectric memory device, in which wordlines and bitlines are hierarchized and influence of disturbance-noise is reduced, includes: first sub-wordline select switches, each of which are disposed between one of the main-wordlines and one end of one of the sub-wordlines provided for the one main-wordline; first sub-bitline select switches, each of which are disposed between one of the main-bitlines and one end of one of the sub-bitlines provided for the one main-bitline; second sub-wordline select switches, each of which are disposed between the other end of one of the sub-wordlines and the unselected wordline potential supply line; and second sub-bitline select switches, each of which are disposed between the other end of one of the sub-bitlines and the unselected bitline potential supply line, each of the first and second sub-wordline select switches and first and second sub-bitline select switches being driven independently at least in one of the sector regions.

Owner:SEIKO EPSON CORP

Skew-reducing signal line sub-driver circuits, methods and systems

ActiveUS7498853B2Reduce skewHigh impedance stateTransmission control/equlisationCode conversionDriver circuitDigital signal

Circuits, methods and systems are provided to reduce skew between a first digital signal that is transmitted by a first driver circuit over a first signal line, and a second digital signal that is transmitted by a second driver circuit over a second signal line. Skew may be reduced by sourcing or sinking additional current to or from the first signal line in response to the first digital signal and the second digital signal transitioning to opposite logical values, and otherwise refraining from sourcing or sinking the additional current to or from the first signal line. Skew may also be reduced between the first digital signal that is transmitted by the first driver circuit over the first signal line and a third digital signal that is transmitted by a third driver circuit over a third signal line by sourcing or sinking additional current to or from the first signal line in response to the first digital signal and the third digital signal transitioning to opposite logical values, and to otherwise refrain from sourcing or sinking the additional current to or from the first signal line.

Owner:SAMSUNG ELECTRONICS CO LTD

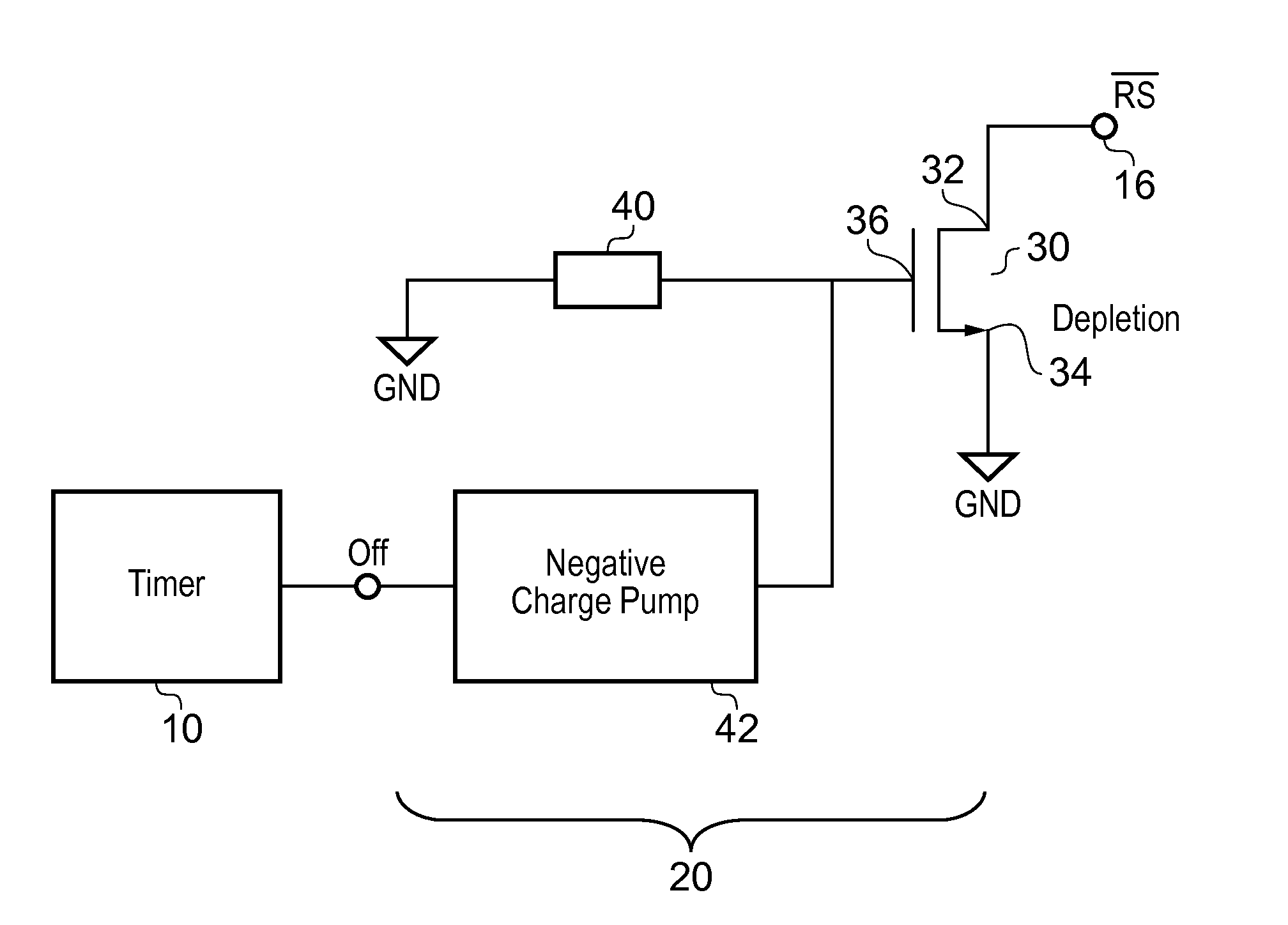

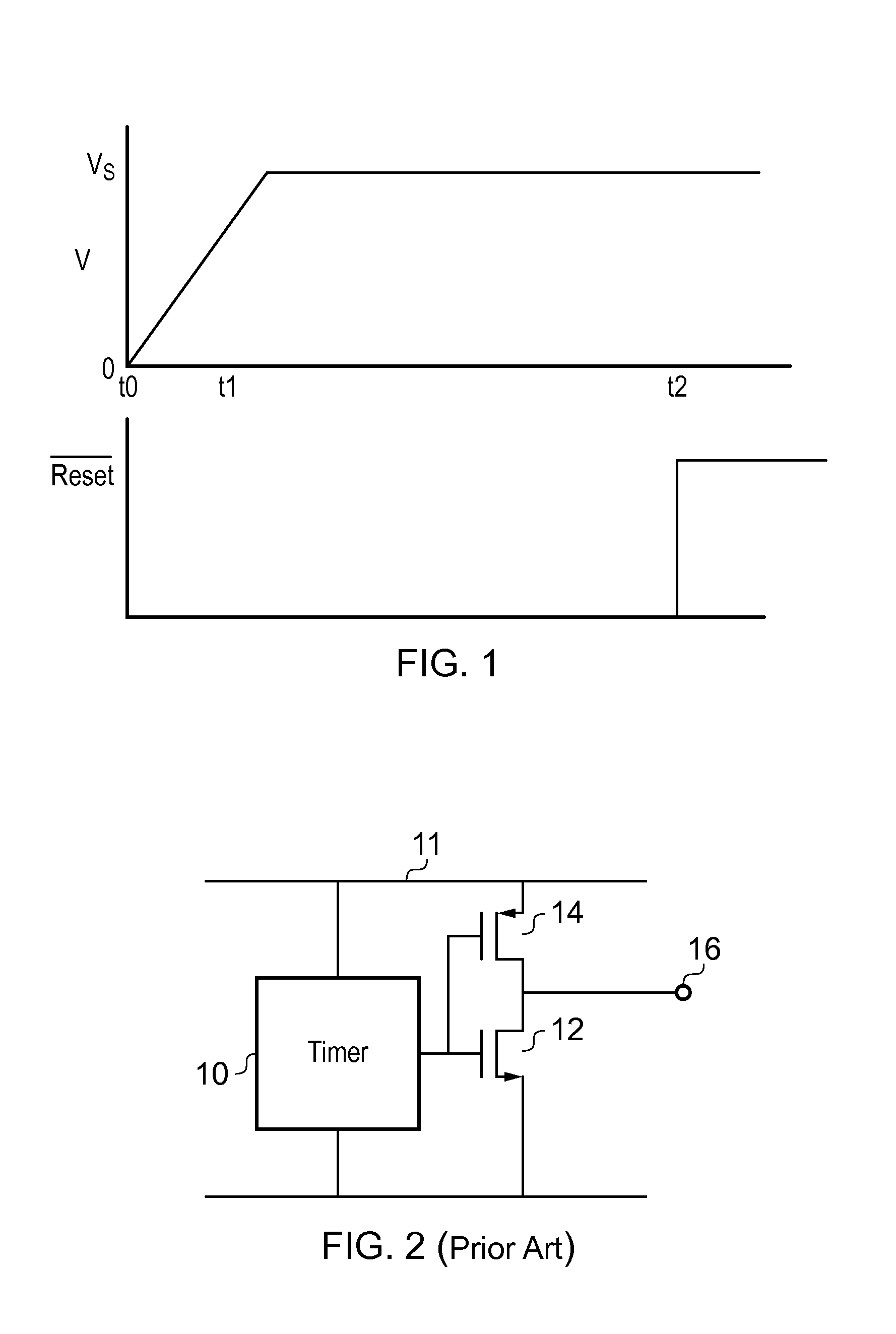

Reset generator

ActiveUS20130082749A1High impedance stateTransistorPulse automatic controlHigh impedanceControl circuit

A reset circuit comprising: a first depletion mode device having a first terminal coupled to a node at a reset voltage and a second terminal for providing a reset signal to at least one device; and a control circuit arranged to switch the first depletion mode device into a high impedance state after a first predetermined period.

Owner:ANALOG DEVICES INC

Lvds with idle state

ActiveUS20160173091A1Reduce start-up delayShorten the timeElectric pulse generatorOscillations generatorsPower flowDifferential signaling

A low voltage differential signaling generating circuit, which comprises a current source a pair of output nodes for providing a differential signal by virtue of a voltage difference therebetween, first and second differential switch circuitries and a bypass circuitry. The first differential switch circuitry selectively connects the current source to the first output node based on a control signal to cause a current flow from the first output node to the second one. The second differential switch circuitry selectively connects the current source to the second output node based on the control signal to cause a current flow from the second output node to the first one. The bypass circuitry is arranged in parallel to the first and second differential switch circuitries and is selectively switched based on an idle mode signal to prevent a current between the output nodes.

Owner:NXP USA INC

Driving method and driving device using the same

ActiveUS11146266B2Avoid disadvantagesErroneous operationTransformers/inductances coils/windings/connectionsDc-dc conversionCharge (electrical)Electrical connection

A driving method and a driving device using the same are disclosed. The driving method controls a pulse transformer. The secondary winding of the pulse transformer is electrically connected to a control device. Firstly, positive charging electrical energy is delivered to the primary winding, thereby charging the control device. Then, the control device is disconnected from the secondary winding while the primary winding is in a high-impedance state. Finally, negative discharging electrical energy is delivered to the primary winding and the control device is electrically connected to the secondary winding, thereby discharging the control device, and the primary winding is in a low-impedance state after the step of delivering the negative discharging electrical energy to the primary winding.

Owner:SYNC POWER CORP

Pixel array with reduced sensitivity to defects

ActiveUS8259199B2Increase productionReduce in quantityTelevision system detailsTelevision system scanning detailsAudio power amplifierLow voltage

An array of active pixels comprises rows of pixels and row select lines for selecting rows of pixels. Each active pixel comprises a buffer amplifier for buffering an output of a photo-sensitive element. An output of the buffer amplifier can be selectively put into a high impedance state, by control of the input of the buffer amplifier, when there is a defect in the row select line for that pixel. This allows other rows, which are defect-free, to remain operating as normal. A disable line can be provided for a row of pixels and each pixel can have a switch connected to the disable line. Alternatively, a first supply line powers a row of pixels. Each pixel comprises a reset switch connected between a photo-sensitive element and the first supply line for resetting the photo-sensitive element. The array is configured such that, in the event of a defect in a row select line, the first supply line is set to ground, or a low voltage, and the reset switch is turned on to put the buffer amplifier into the high impedance state.

Owner:CMOSIS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com