Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39results about How to "Correct logic function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

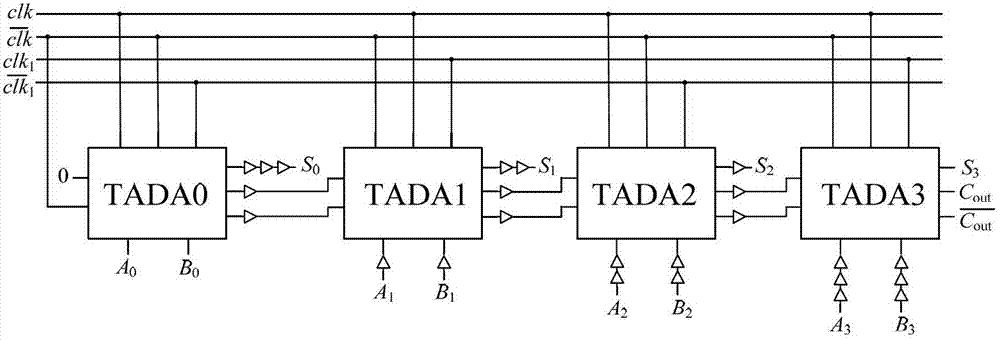

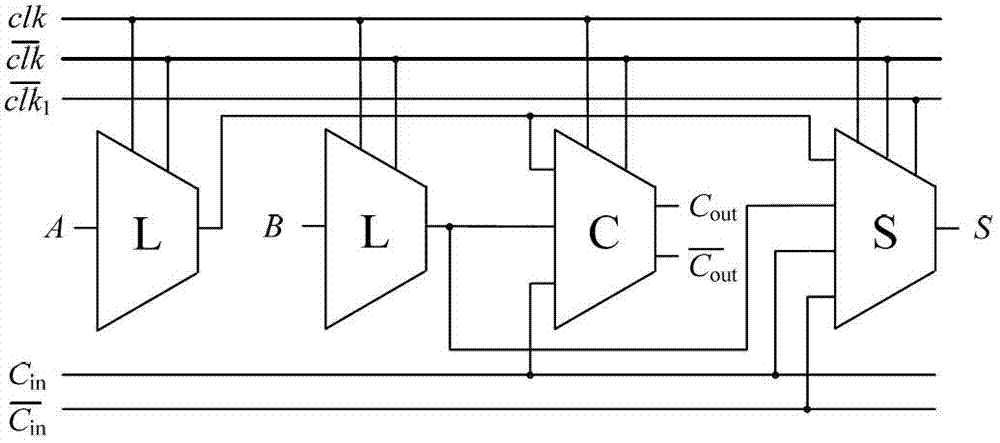

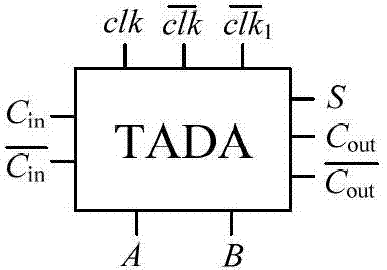

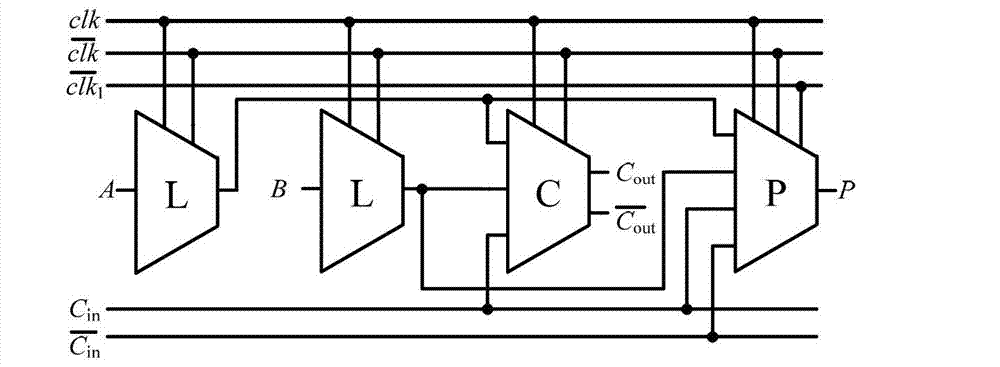

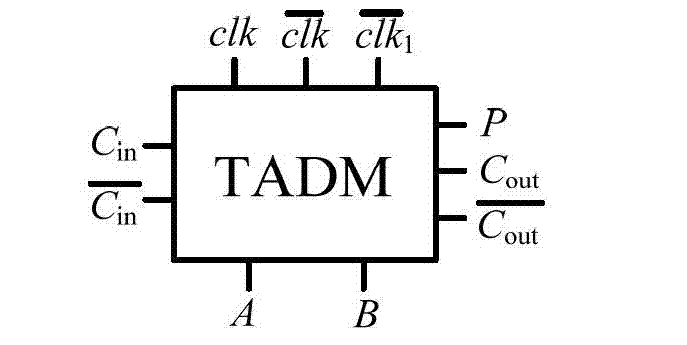

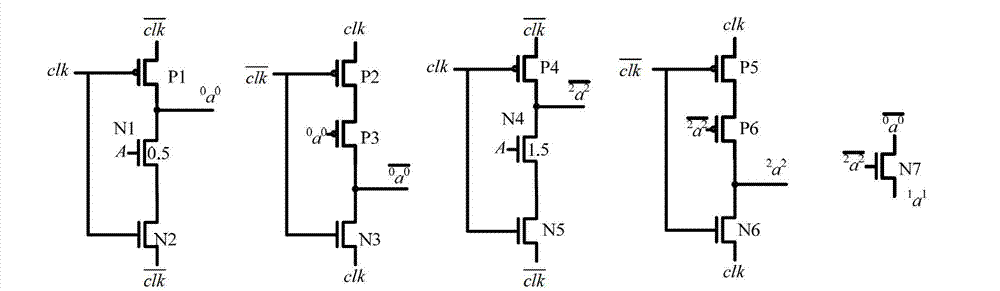

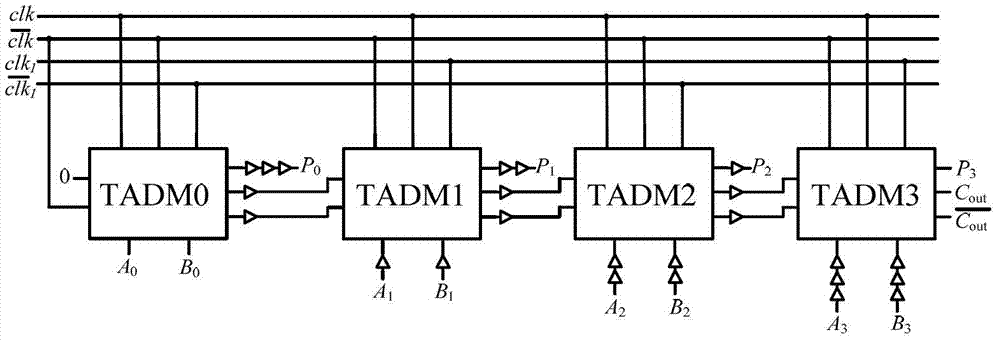

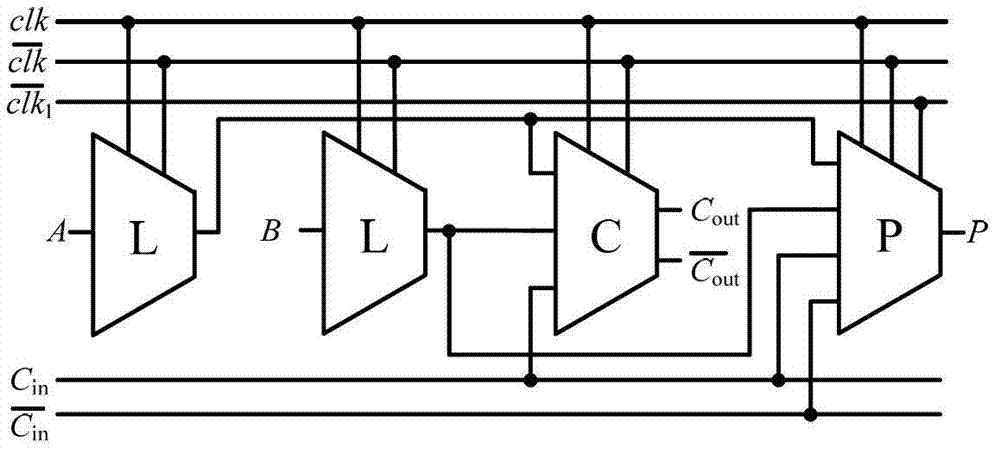

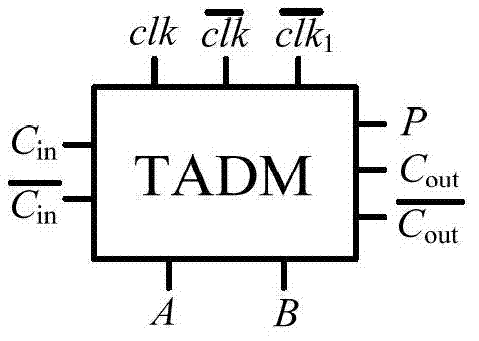

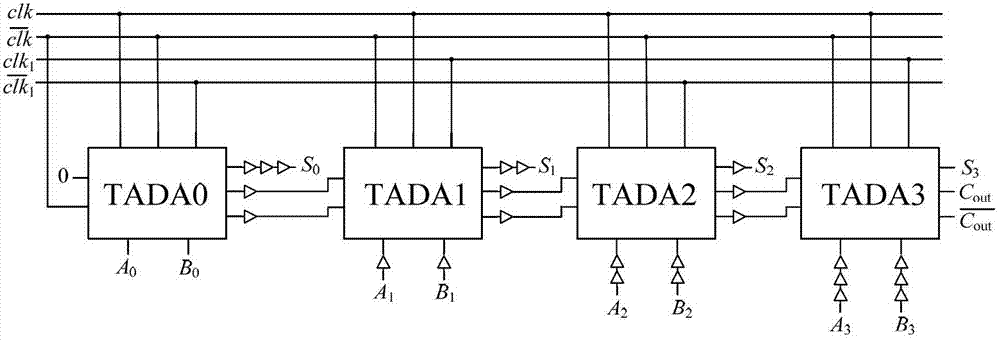

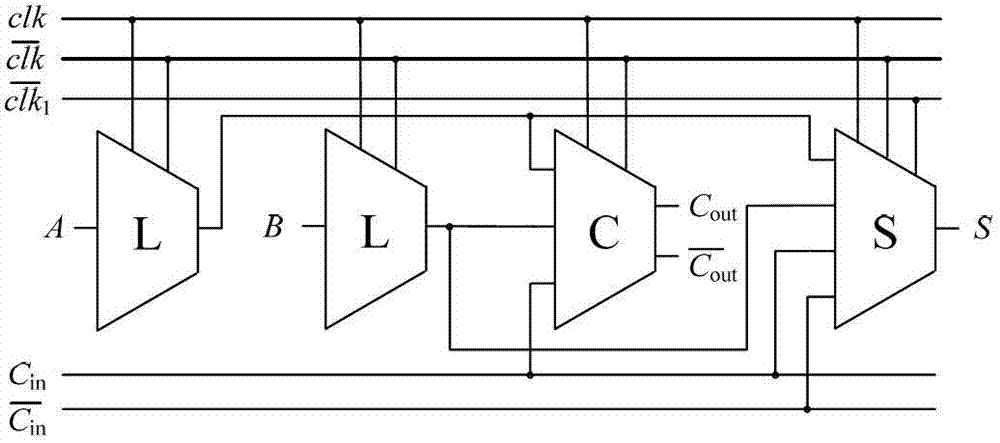

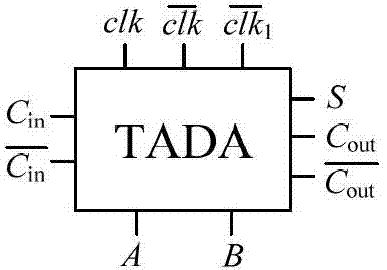

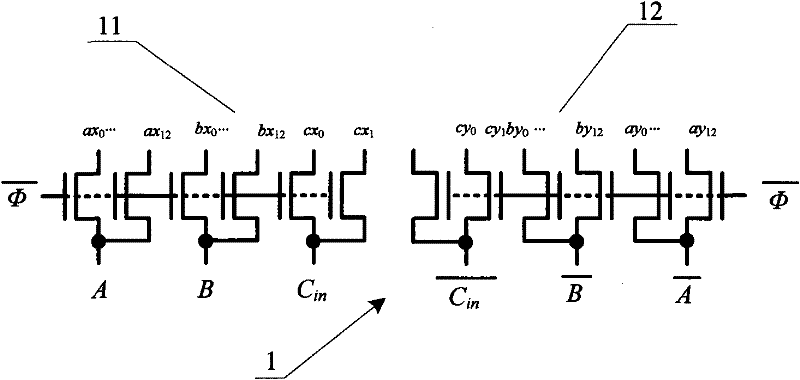

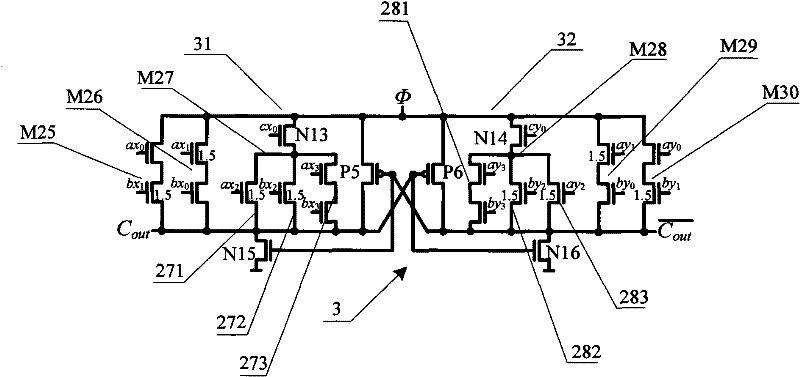

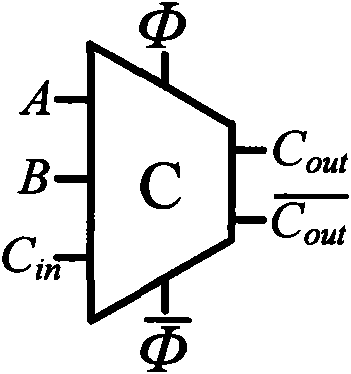

Tri-valued, thermal-insulating and low-power adder unit and adder

InactiveCN101833432ACorrect logic functionReduce power consumptionComputation using non-contact making devicesEngineeringEnergy recovery

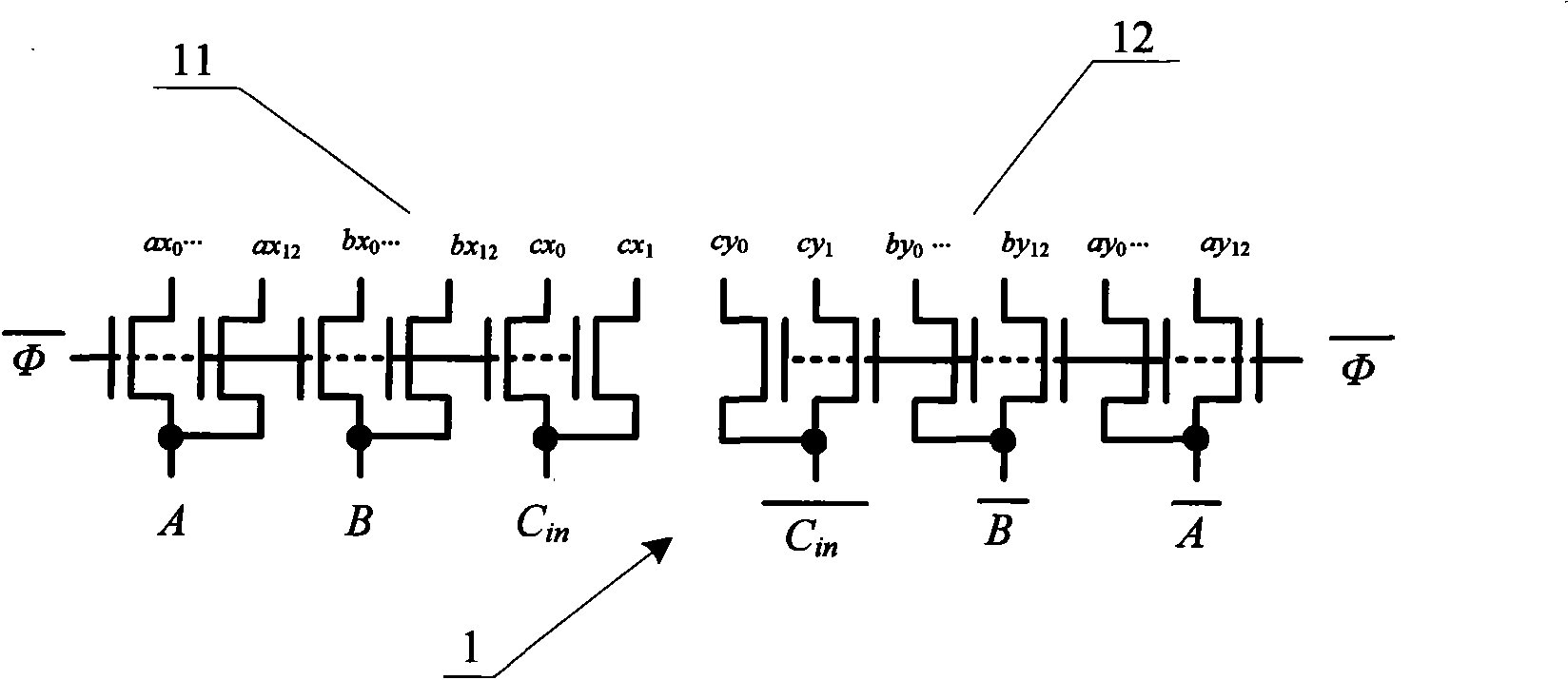

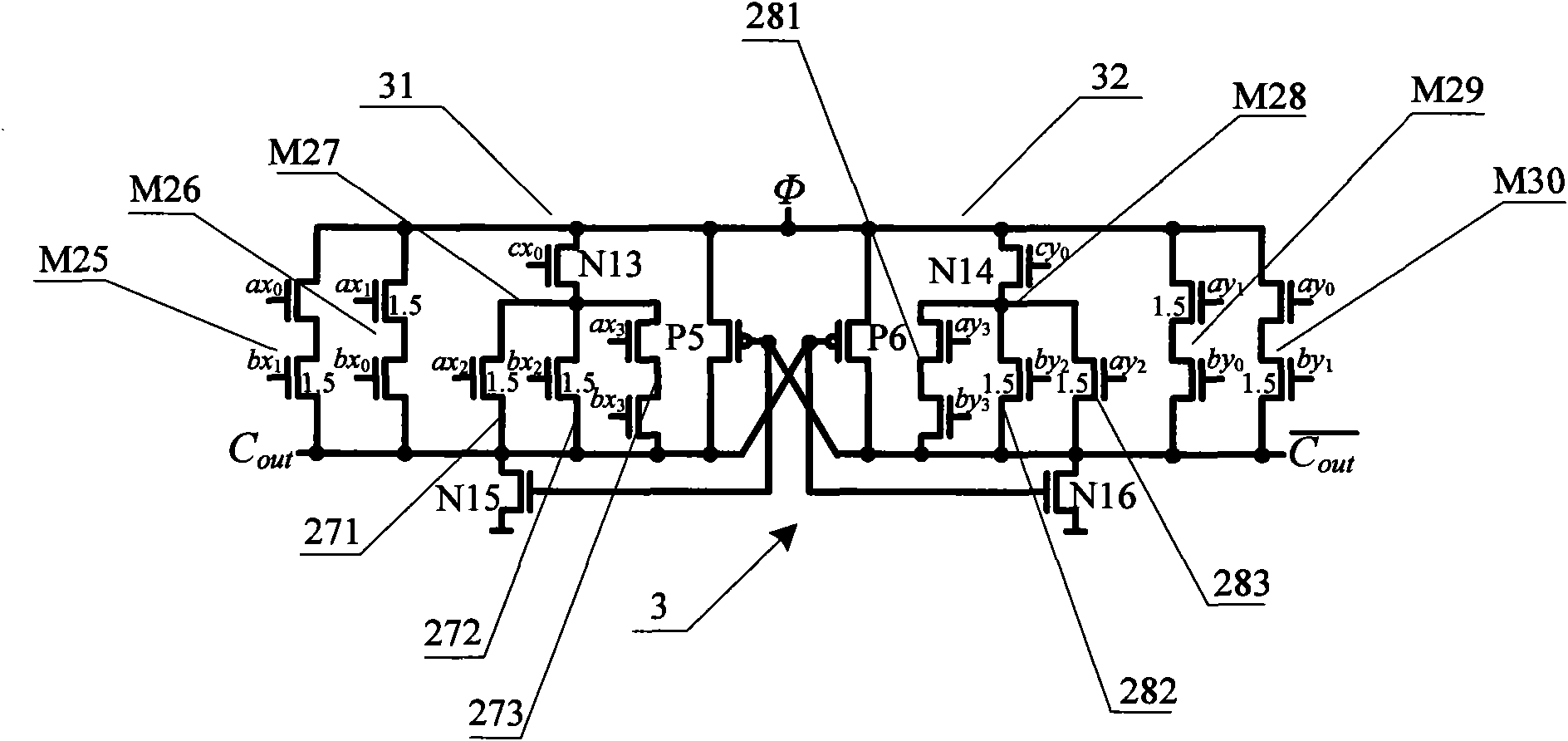

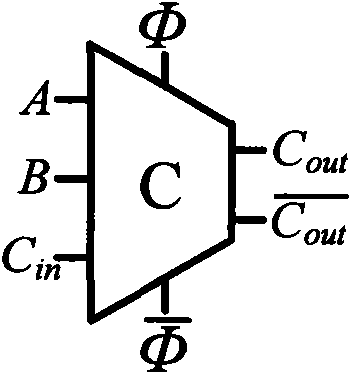

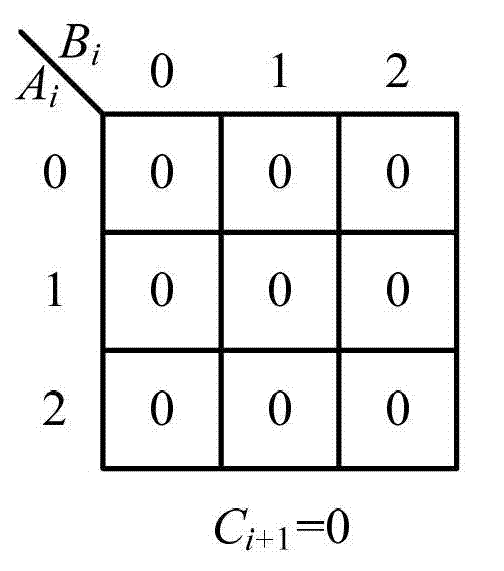

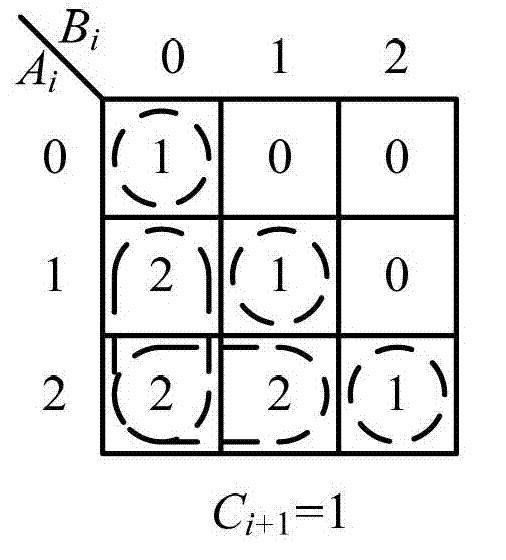

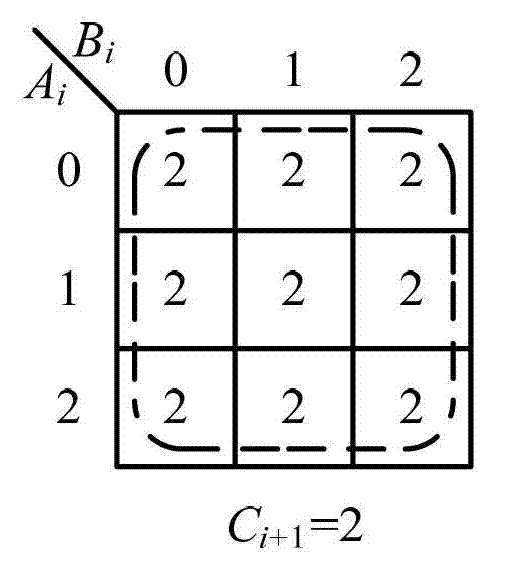

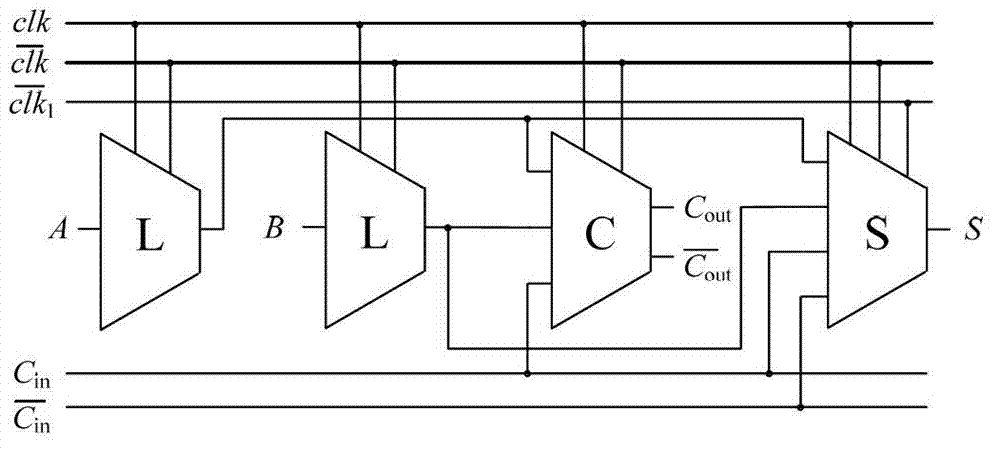

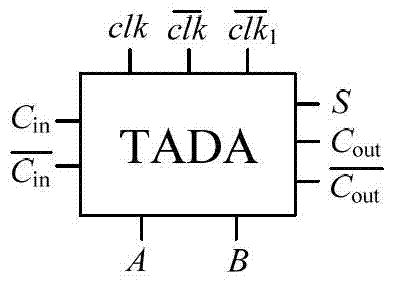

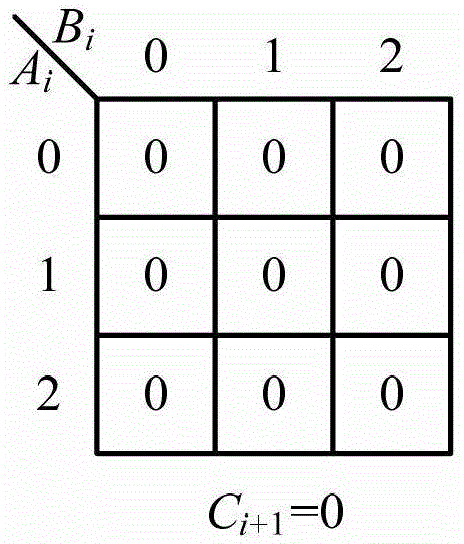

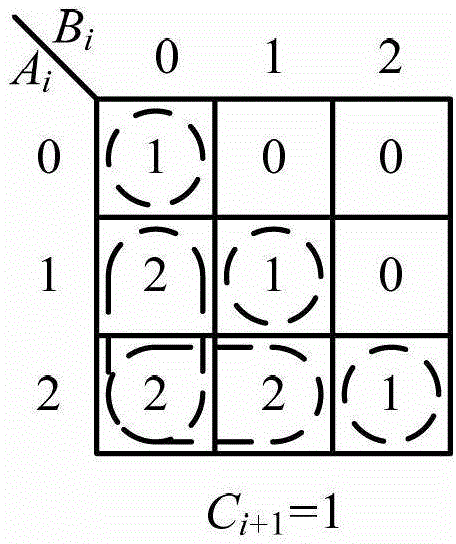

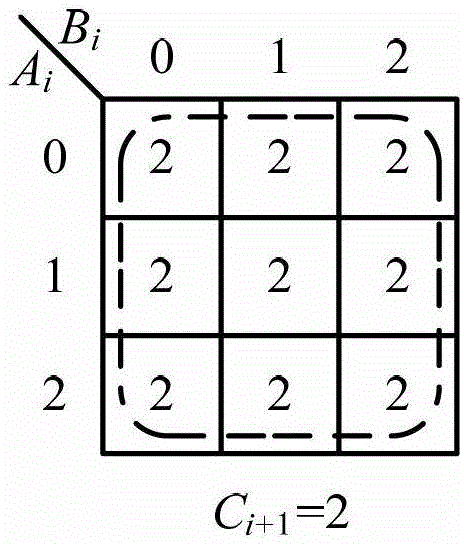

The invention discloses a tri-valued, thermal-insulating and low-power adder unit and an adder. The adder unit controls each NMOS tube in an input signal sampling circuit to sample input signals by using a clock-controlled clock signal; four corresponding summing circuit modules and carry output circuits with cross storage-type structures are constructed by sampled values according to required realized addition logic relationship through the bootstrap operation of the NMOS tube; power clocks phi1 and phi complete the evaluation and energy recovery of the output load to realize correct logic function; and compared with a DPL tri-valued adder, the four-digit tri-valued thermal-insulating and low-power adder can save energy consumption by about 90 percent in 0.9 microsecond, and has distinct low-power characteristics.

Owner:NINGBO UNIV

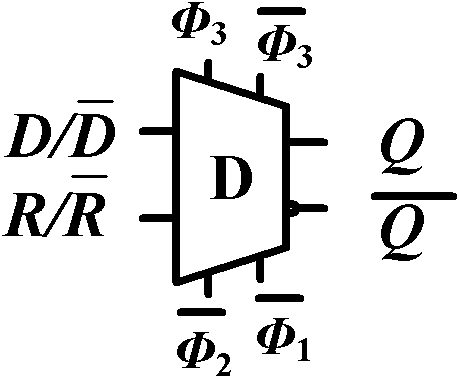

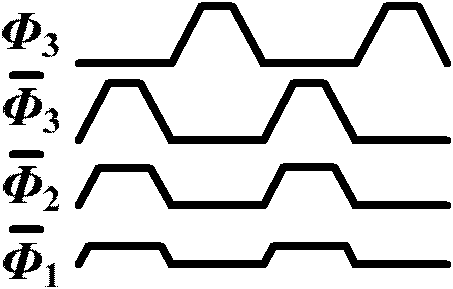

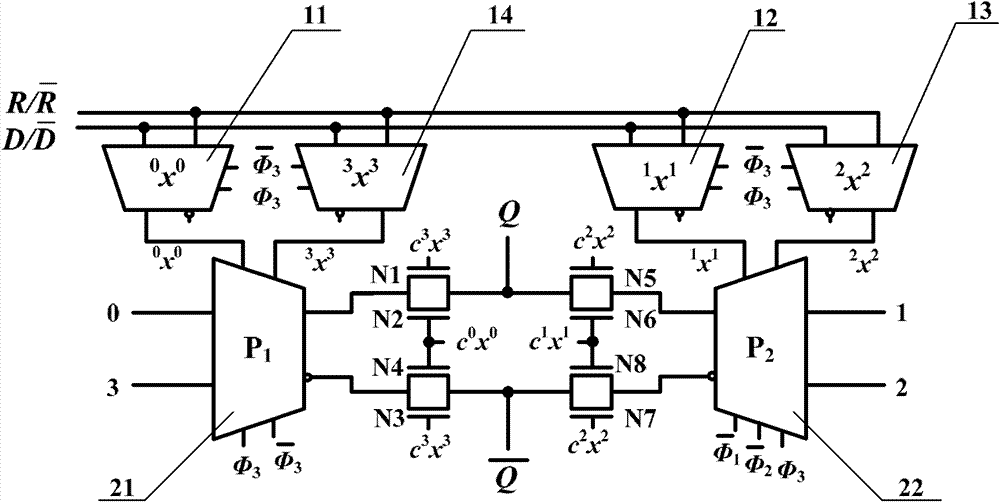

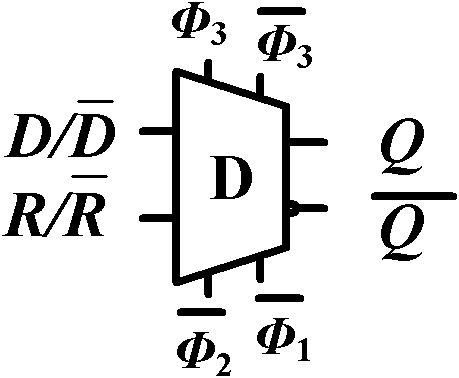

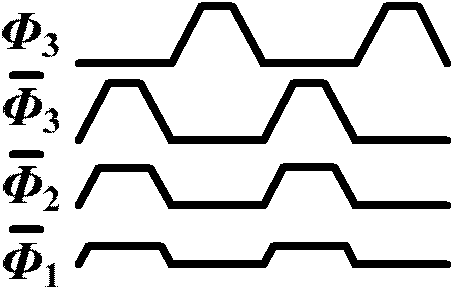

Four-value heat-insulating dynamic D trigger

InactiveCN101969301ACorrect logic functionHigh working reliabilityElectric pulse generatorSampling circuitsFour-valued logic

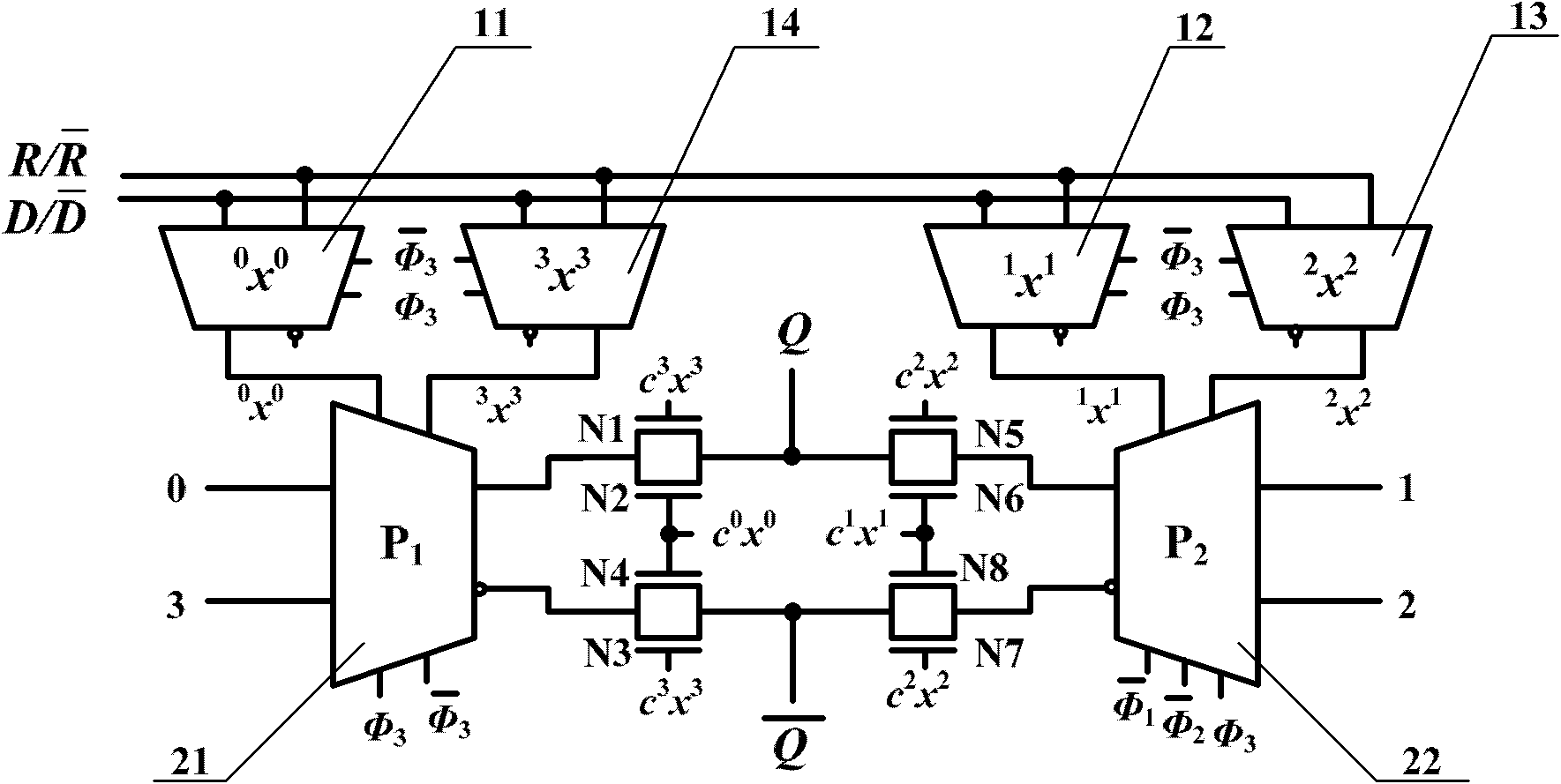

The invention discloses a four-value heat-insulating dynamic D trigger. The D trigger comprises a character computing circuit, a character sampling circuit and a logic signal generating circuit, wherein the character computing circuit mainly comprises first, second, third and fourth sub-character computing circuits; and the logic signal generating circuit mainly comprises a 0-3 logic signal generating circuit and a 1-2 logic signal generating circuit. The trigger is characterized in that: the four-value heat-insulating dynamic D trigger designed through clocked heat insulation technology and multi-threshold MOS tube control technology mainly comprises the character computing circuit and the logic signal generating circuit; and the logic signal generating circuit is controlled by the character computing circuit to generate a four-value logic signal. The circuits of the D trigger sample the input signal through a clocked NMOS tube, and the output load realizes assignment and energy through a sampling value, the bootstrap-operated NMOS tube and a follow power clock with a cross storage type structure. The D trigger effectively reduces the power consumption and improves working reliability of the circuit on the premise of guaranteeing the correct logic function of the circuits.

Owner:NINGBO UNIV

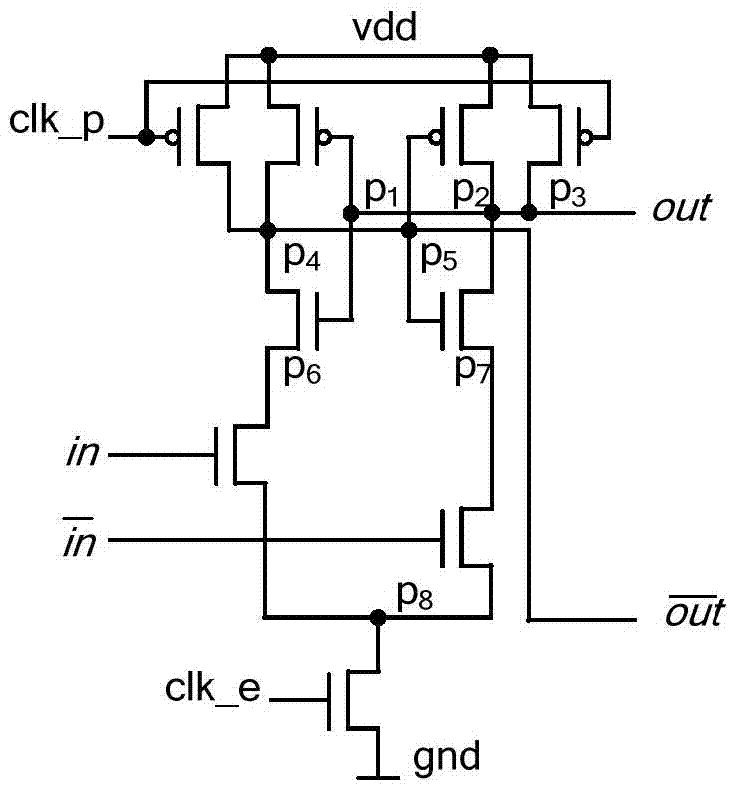

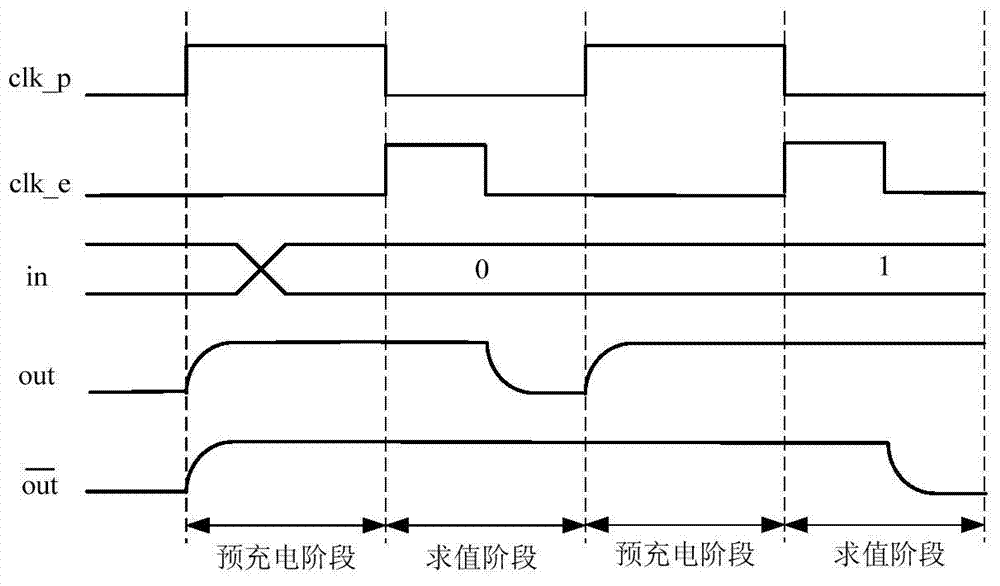

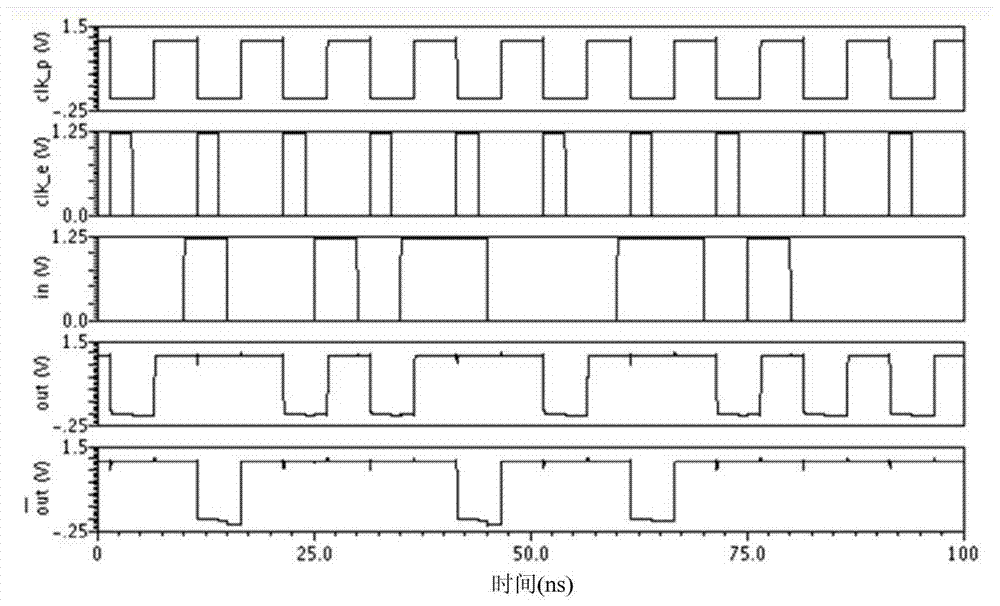

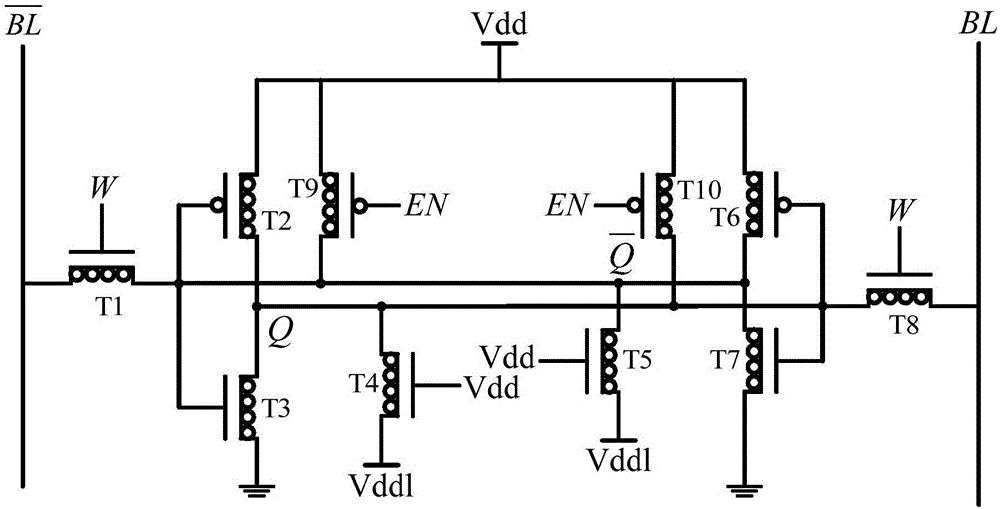

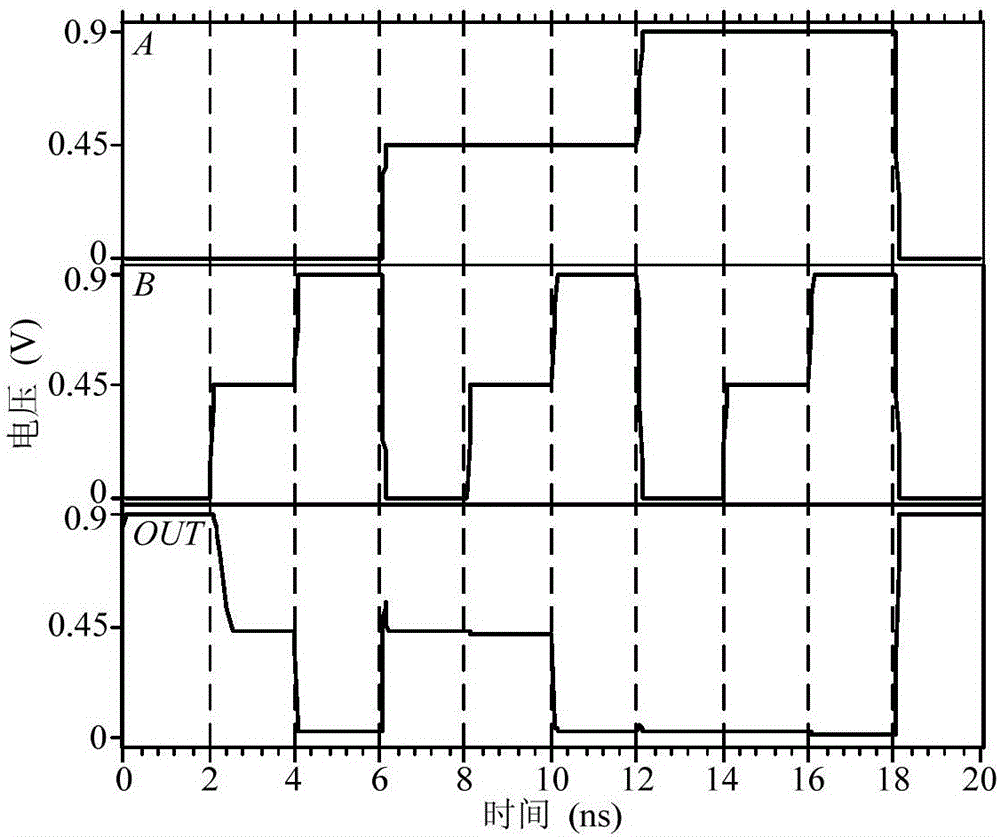

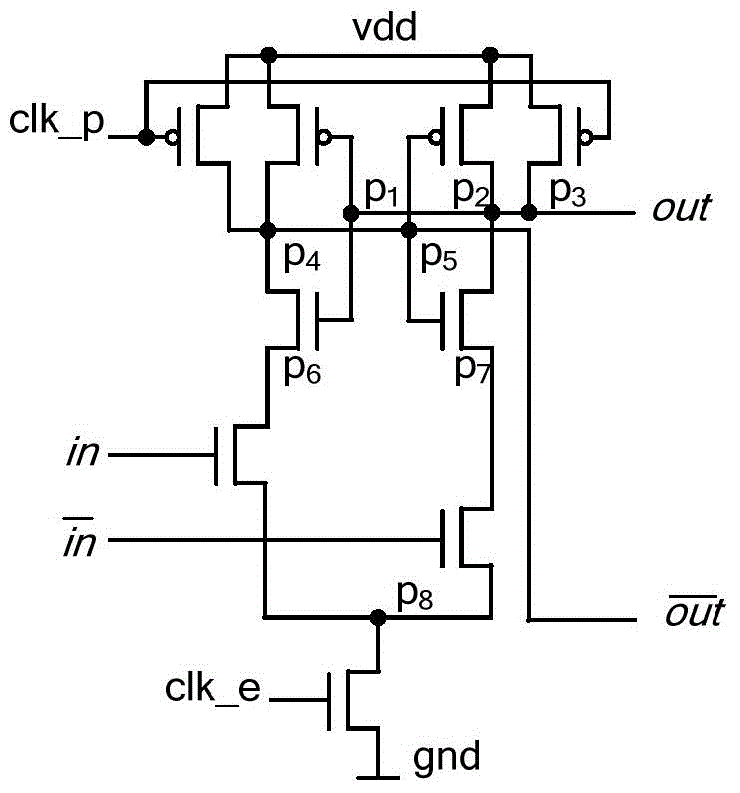

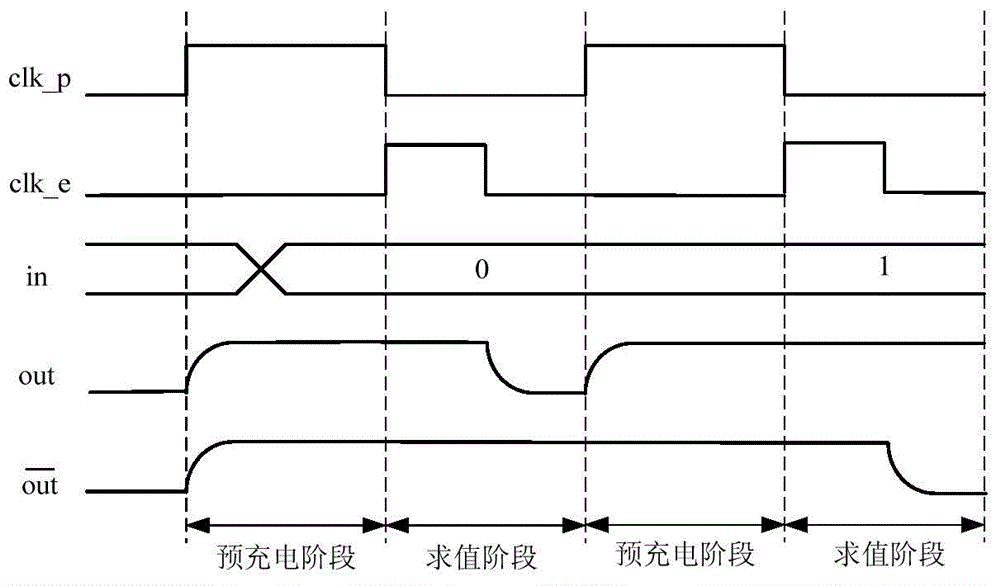

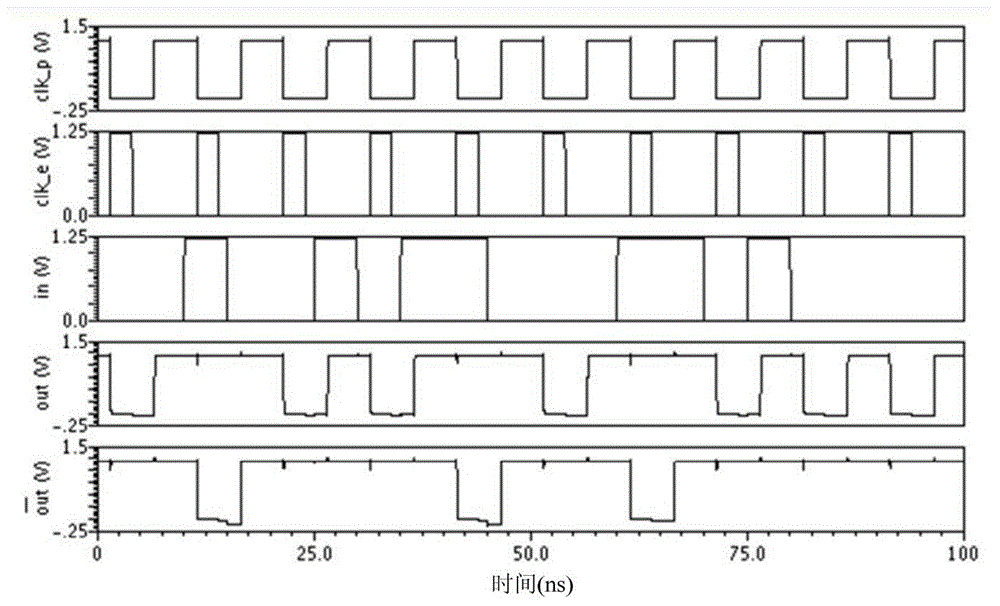

Double-edge D flip-flop based on N type SABL logic

InactiveCN103595371ACorrect logic functionConstant power consumptionElectric pulse generator circuitsCMOSTransmission gate

The invention discloses a double-edge D flip-flop based on N type SABL logic. The double-edge D flip-flop comprises a first transmission gate, a second transmission gate, a third transmission gate, a fourth transmission gate, a fifth transmission gate, a sixth transmission gate and two N type SABL logical units. The double-edge D flip-flop has the advantages that the two N type SABL logical units and the six transmission gates are adopted for designing the double-edge D flip-flop, in the Cadence environment, by the adoption of a TSMC 0.13-micrometer CMOS technology, analog simulation is performed on the double-edge D flip-flop based on the N type SABL logic, an analog result shows that a circuit has a correct logical function, by analyzing power consumption curves of the double-edge D flip-flop based on the N type SABL logic, it can be known that in every clock period, the power consumption curves of the double-edge D flip-flop are the same, power consumption is constant, and the double-edge D flip-flop has a power balance characteristic and achieves the characteristic of resisting to bypass attacks.

Owner:NINGBO UNIV

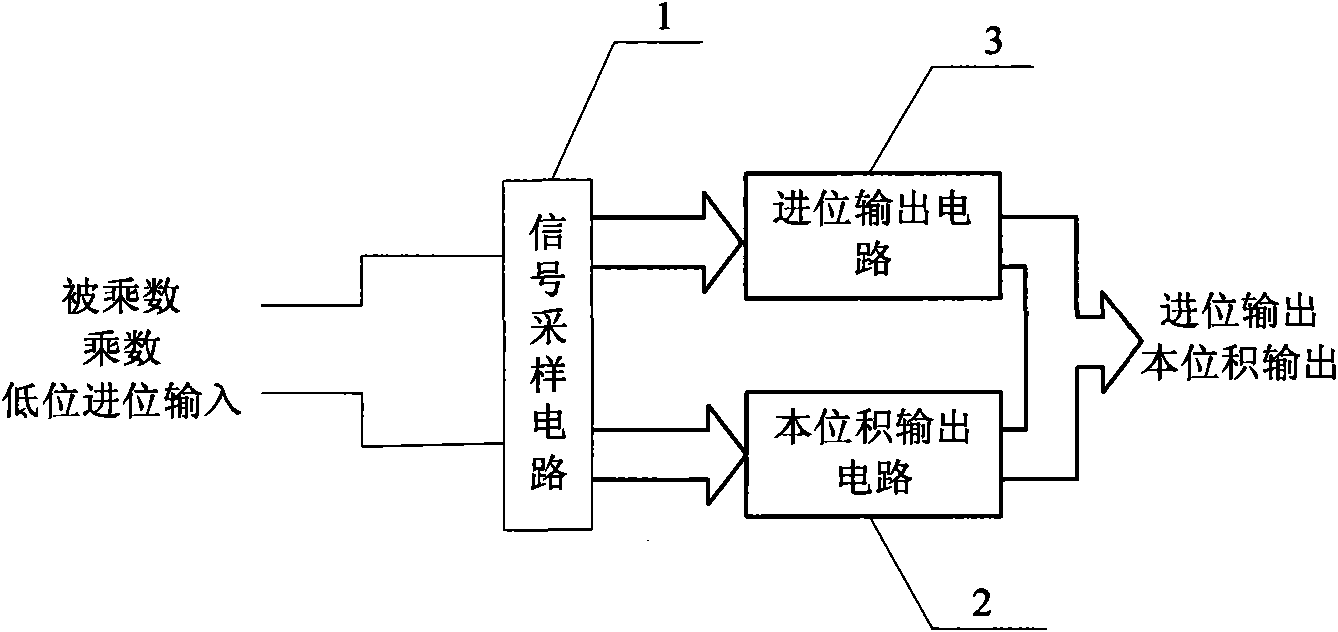

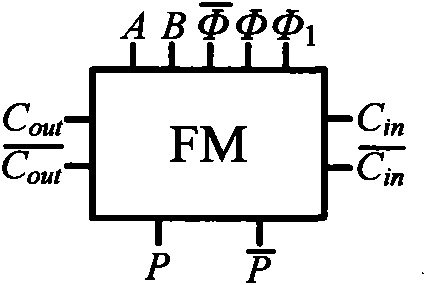

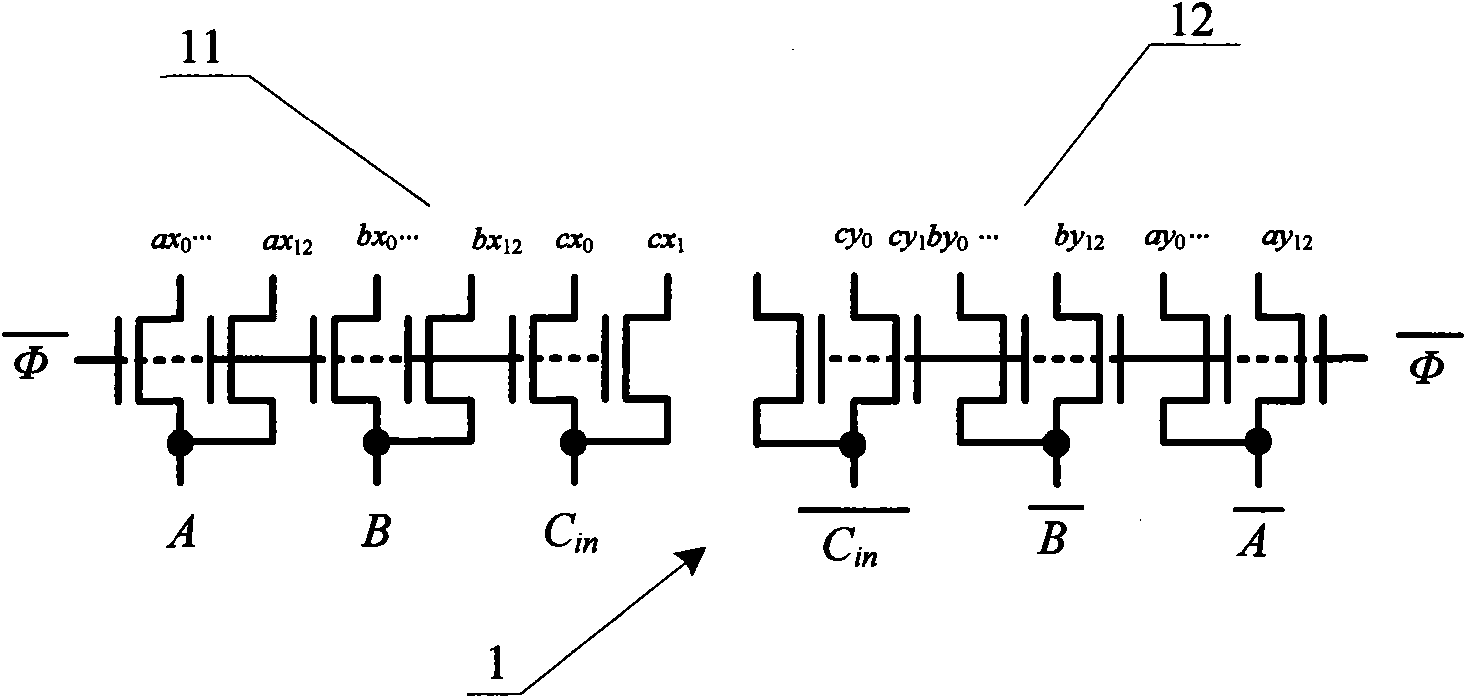

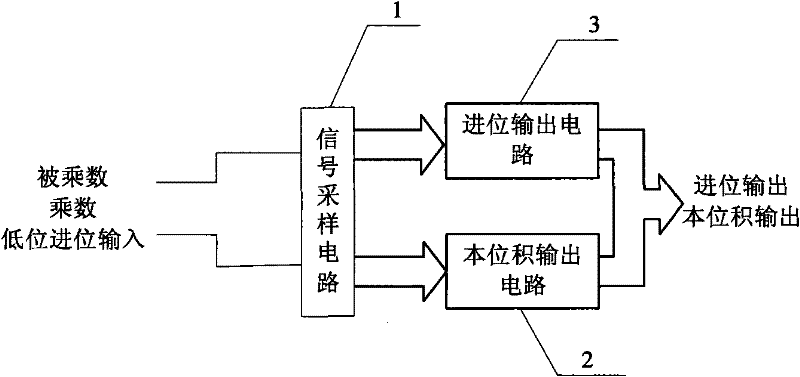

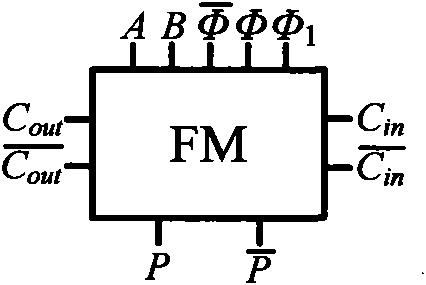

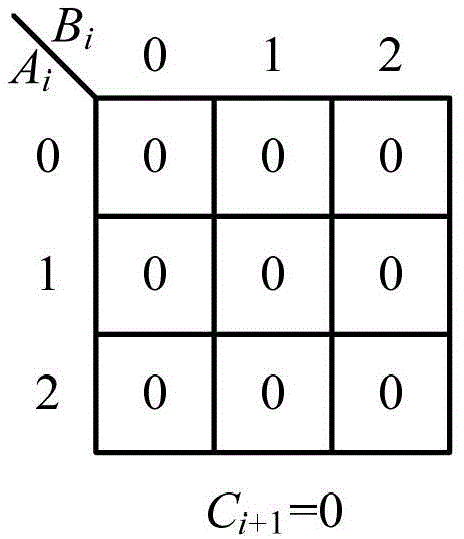

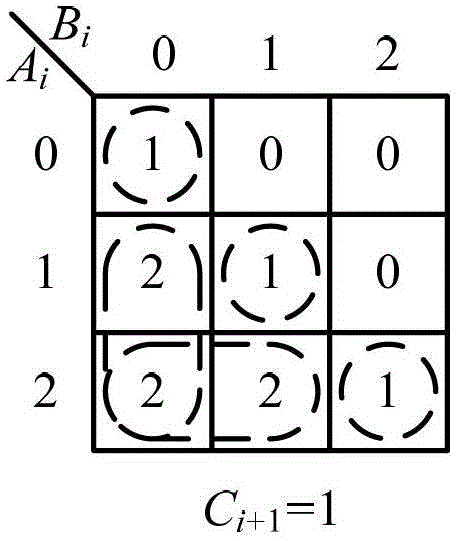

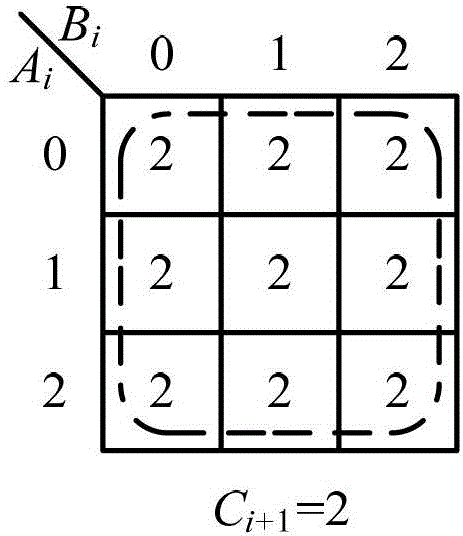

Tri-valued, thermal-insulating and low-power multiplier unit and multiplier

InactiveCN101833433ACorrect logic functionLow Power FeaturesComputation using non-contact making devicesBinary multiplierEngineering

The invention discloses a tri-valued, thermal-insulating and low-power multiplier unit and a multiplier. The multiplier unit controls each NMOS tube in an input signal sampling circuit to sample input signals by using a clock-controlled clock signal; four corresponding integrating circuit modules and carry output circuits with cross storage-type structures are constructed by sampled values according to required realized multiplication logic relationship through the bootstrap operation of the NMOS tube; power clocks phi1 and phi complete the evaluation and energy recovery of the output load to realize correct logic function; and compared with a DPL tri-valued multiplier, the four-digit tri-valued thermal-insulating and low-power multiplier can save energy consumption by about 91 percent in 0.9 microsecond and has distinct low-power characteristics.

Owner:NINGBO UNIV

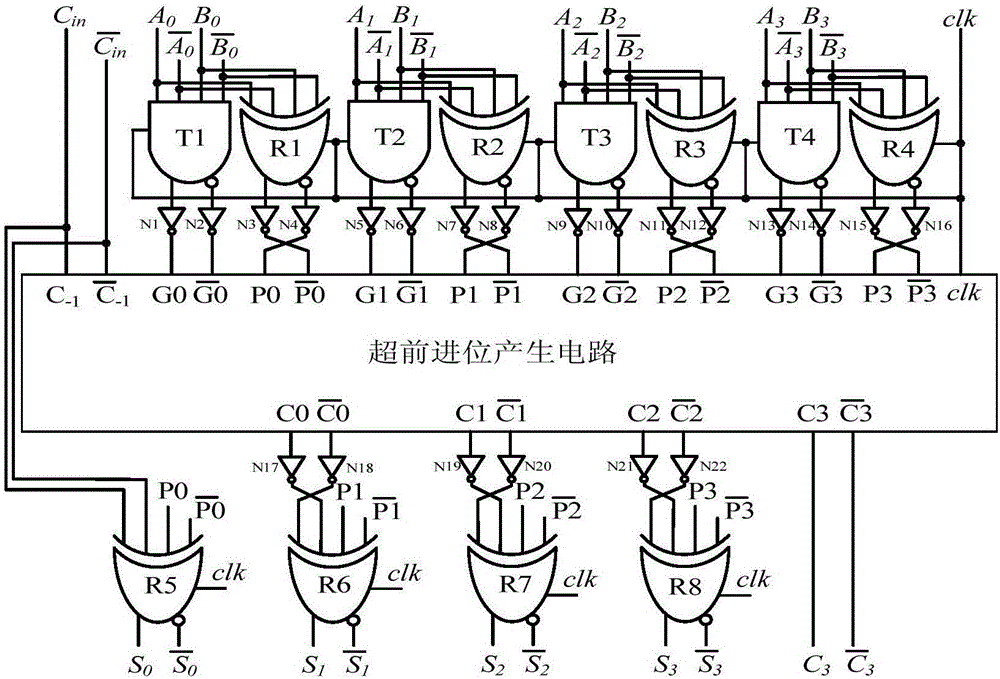

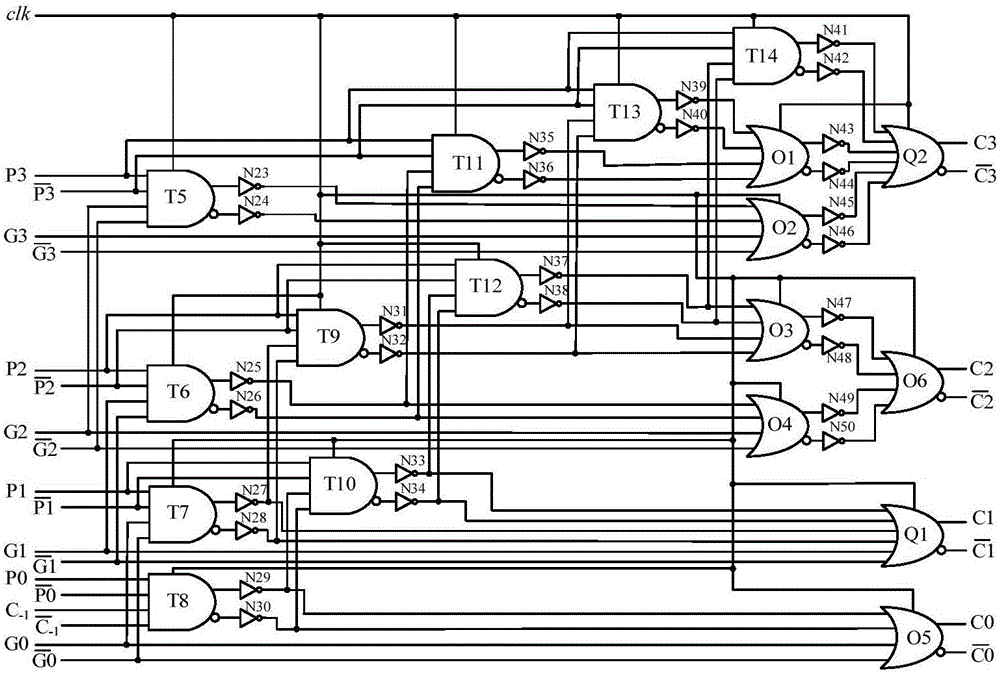

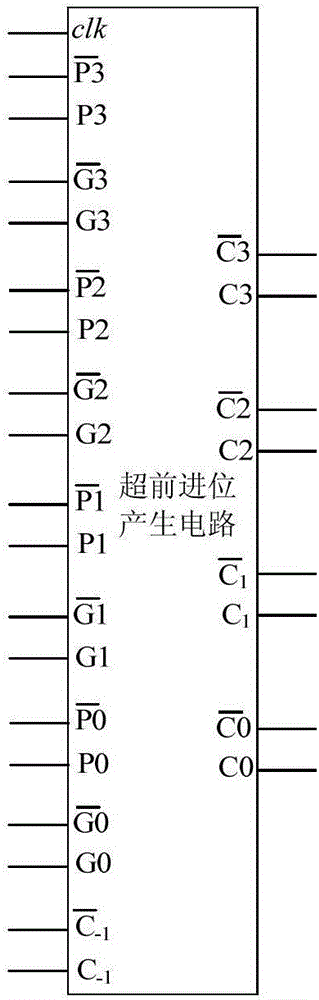

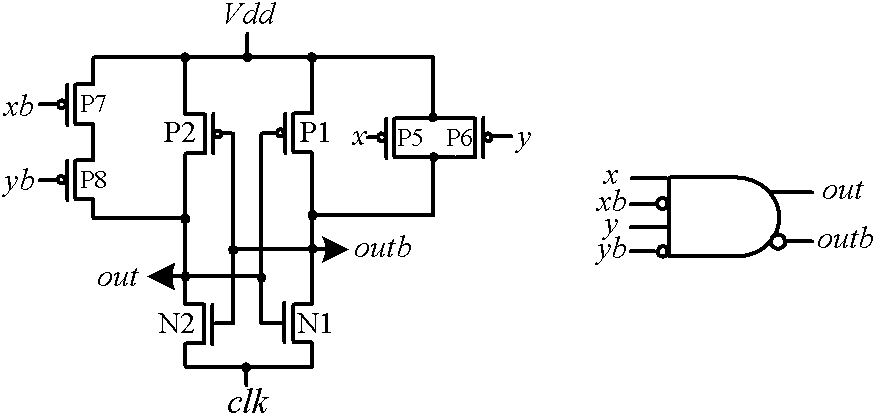

Differential power analysis defense adder employing sense amplifier based logic

ActiveCN106547513ACorrect logic functionPower independent performance improvementExclusive-OR circuitsComputation using non-contact making devicesPower analysisCMOS

The invention discloses a differential power analysis defense adder employing sense amplifier based logic. The adder consists of four two-input not and / and gates, eight two-input exclusive or / nor gates, twenty-two inverters and a carry look-ahead generation circuit. The adder has the advantages that a TSMC 65nm CMOS technology is adopted; simulation analysis is performed on the circuit by a Spectre tool; an experimental result indicates that the adder has a correct logic function; compared with the traditional adder circuit, the adder has the advantage that the power independence can be improved by 97%; and differential power analysis can be effectively defended.

Owner:NINGBO UNIV

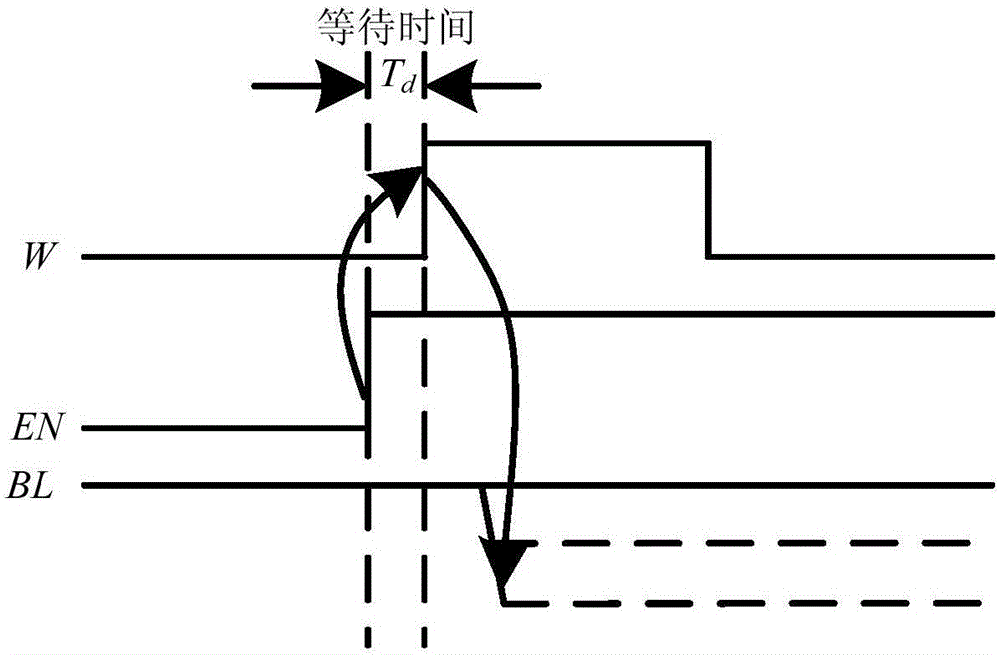

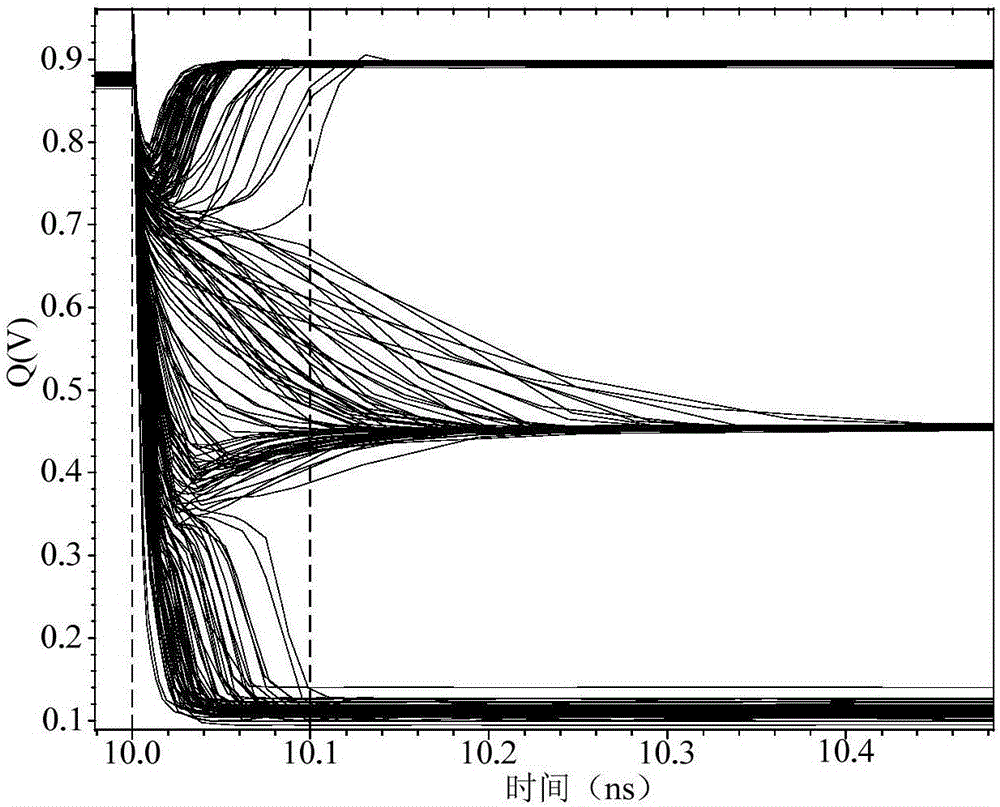

Three-value PUF unit and circuit realized by using CNFET

ActiveCN106850227AReduce areaStrong randomnessSemiconductor/solid-state device detailsUser identity/authority verificationElectrical and Electronics engineeringMatrix form

Owner:NINGBO UNIV

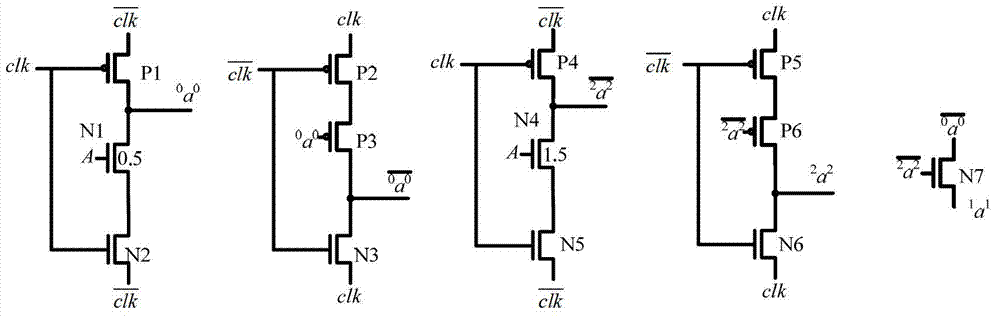

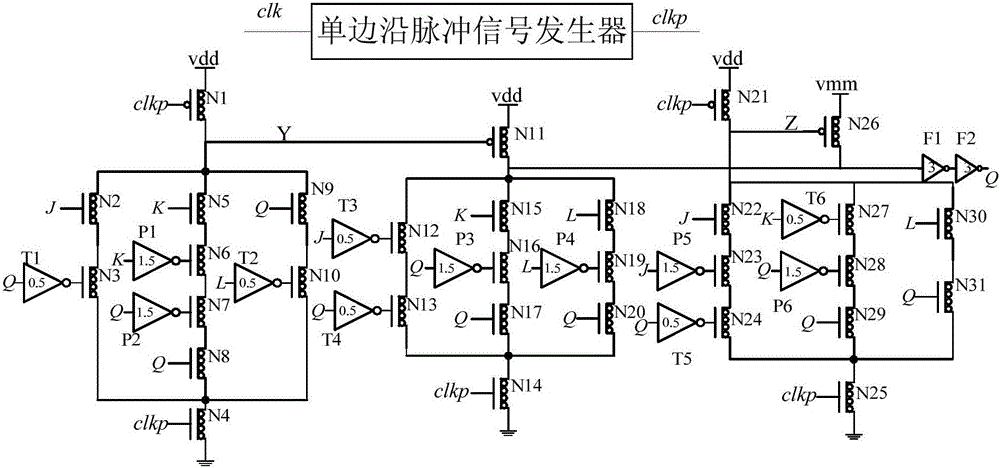

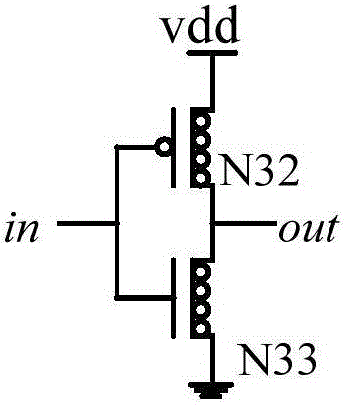

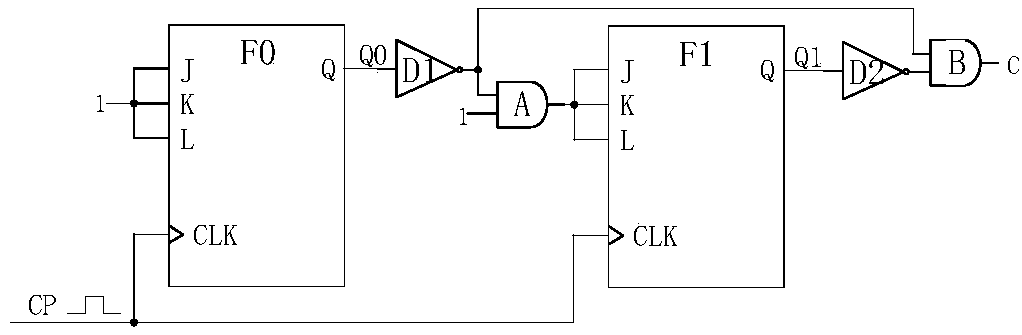

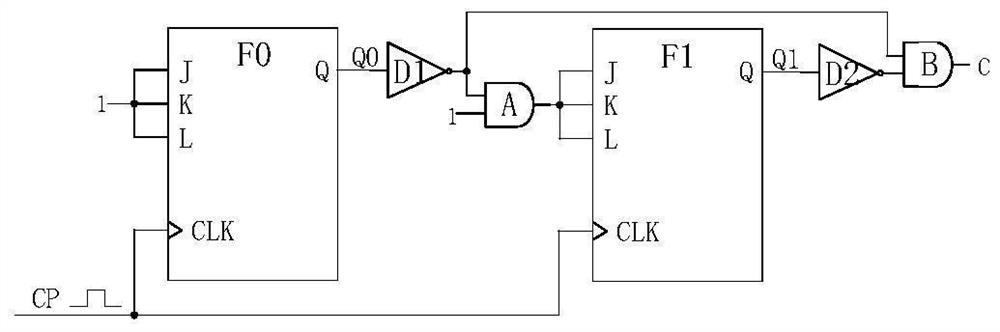

CNFET type double-edge pulse type JKL trigger

ActiveCN106100611AIncrease work rateCorrect circuit logicElectric pulse generatorMulti valuedEngineering

The invention discloses a carbon nanotube field effect transistor (CNFET) type double-edge pulse type JKL trigger. The CNFET type double-edge pulse type JKL trigger comprises a double-edge pulse signal generator, thirty-first CNFET tubes, six NTI gate circuits with the same circuit structure, six PTI gate circuit with the same circuit structure, a first ternary phase inverter and a second ternary phase inverter, wherein the first ternary phase inverter and the second ternary phase inverter have the same circuit structure. The CNFET type double-edge pulse type JKL trigger has the advantages: a clock signal is generated by utilizing the double-edge pulse signal generator; by combining switching operation of a multi-value logic circuit and high-speed low-power features of CNFET, a purpose of reducing the power consumption is achieved when the working speed of the JKL trigger is improved; and based on experiment results, the JKL trigger provided by the invention has a correct logic function and remarkable characteristic of low power consumption.

Owner:NINGBO UNIV

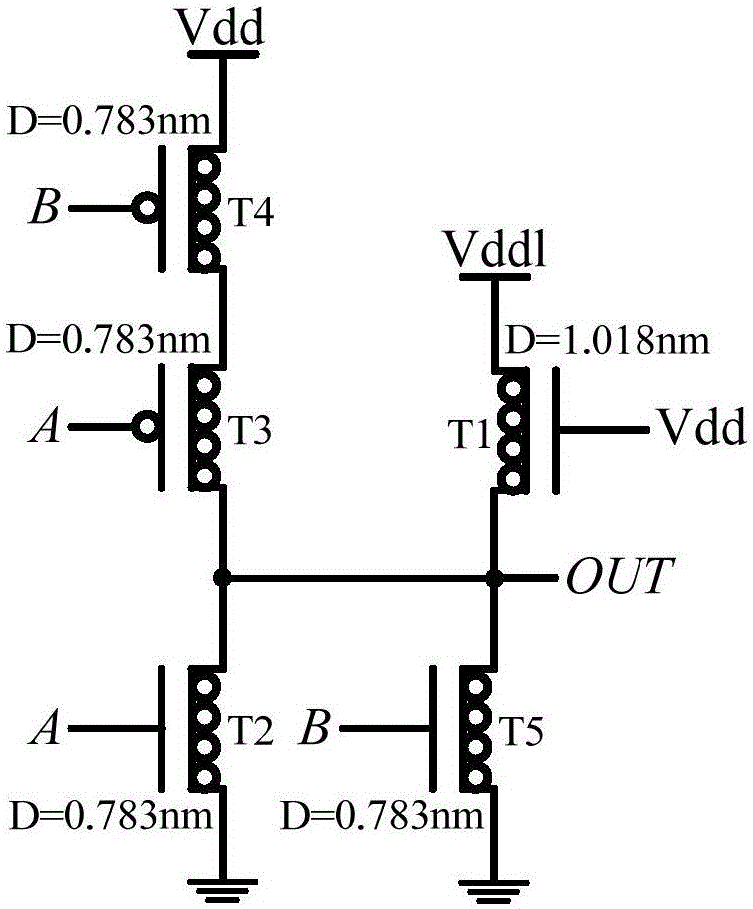

CNFET-based (carbon nanotube field effect transistor-based) three-valued NOR gate and three-valued 1-3 line address decoder

The invention discloses a CNFET-based (carbon nanotube field effect transistor-based) three-valued NOR gate and a three-valued 1-3 line address decoder. The CNFET-based three-valued NOR gate comprises a first CNFET, a second CNFET, a third CNFET, a fourth CNFET, and a fifth CNFET, and the CNFET-based three-valued 1-3 line address decoder comprises a first CNFET, a second CNFET, a third CNFET, a fourth CNFET, a fifth CNFET, a sixth CNFET, a seventh CNFET, an eighth CNFET, a ninth CNFET, a tenth CNFET, and an eleventh CNFET. The invention has the advantages of low power consumption and short delay.

Owner:NINGBO UNIV

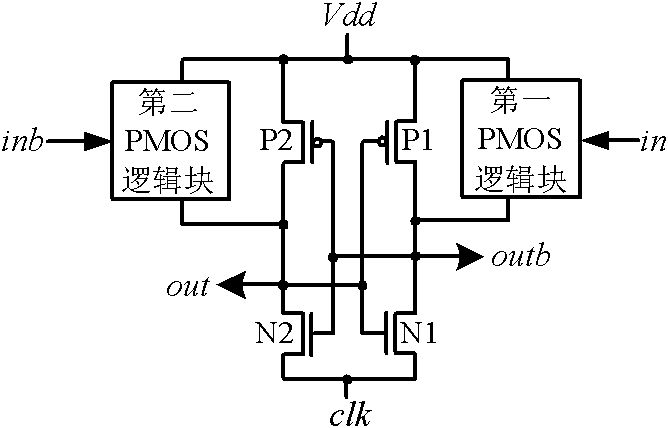

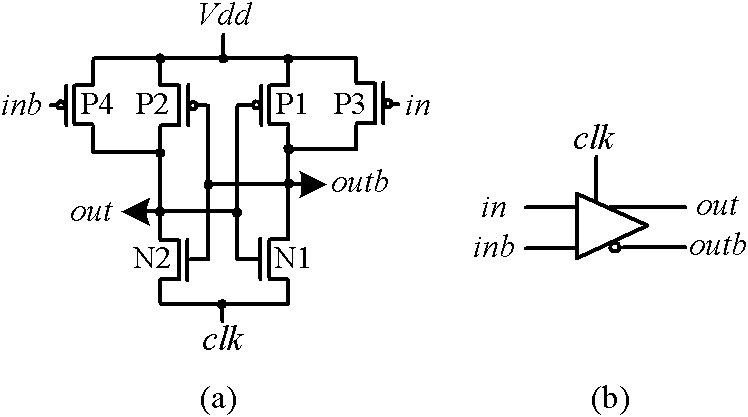

Novel adiabatic logic gating circuit

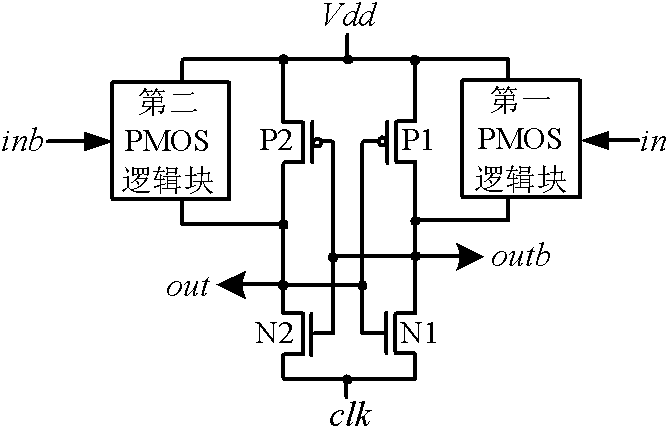

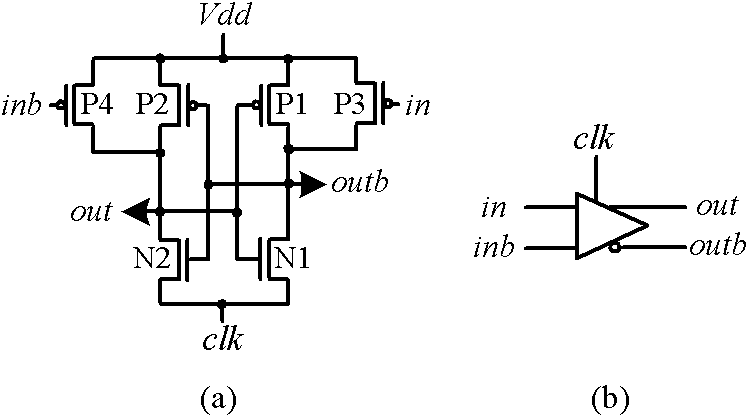

InactiveCN101977050AReduce power consumptionReduce consumptionLogic circuitsAdiabatic logicPMOS logic

The invention discloses a novel adiabatic logic gating circuit. A first p-channel metal oxide semiconductor (PMOS) tube, a second PMOS tube, a first n-channel metal oxide semiconductor (NMOS) tube, and a second NMOS tube form an energy recovery circuit with a cross-coupled structure, the source electrode of the first PMOS tube and the drain electrode of the second PMOS tube are parallelly connected to the positive terminal of a power source, the source electrode of the first NMOS tube and the drain electrode of the second NMOS tube are parallelly connected to a clock signal terminal, a first PMOS logic block is bridged between the source electrode of the first PMOS tube and the drain electrode of the first PMOS tube, a second PMOS logic block is bridged between the drain electrode of the second PMOS tube and the source electrode of the second PMOS tube, the first PMOS logic block is provided with at least one positive input signal connecting terminal, and the second PMOS logic block is provided with at least one inverted input signal connecting terminal. The invention has the advantages that: an adiabatic circuit of which the functional characteristics are completely opposite to those of the traditional adiabatic logic circuit is provided, and the first PMOS logic block and the second PMOS logic block consists of PMOS tubes, so that the circuit power consumption can be greatly reduced.

Owner:NINGBO UNIV

Low power consumption multiposition three-valued Domino adder

The invention discloses a low power consumption multiposition three-valued Domino adder. The adder comprises n-numbered positions of three-valued heat insulation Domino adding units, wherein the k position of three-valued heat insulation Domino adding unit is connected with the low-position carry signal output end of the (k+1) position of three-valued heat insulation Domino adding unit by a heat insulation Domino buffer; the k position of three-valued heat insulation Domino adding unit is also connected with the complementary low-position carry signal output end of the (k+1) position of three-valued heat insulation Domino adding unit by a heat insulation Domino buffer; the ipso position and the signal output end of the j position of three-valued heat insulation Domino adding unit are connected with (n-j)-numbered heat insulation Domino buffers in sequence; the addend signal input end and augend signal input end of the j position of three-valued heat insulation Domino adding unit are connected with (j-1)-numbered heat insulation Domino buffers in sequence; k is equal to 1, 2,......, n-1; j is equal to 1, 2,......, n; and m is equal to 1, 2,......, n-1. The adder has the following advantage: the power consumption is reduced by about 61% compared with that of the conventional three-valued Domino adder adopting the direct-current power source.

Owner:智创控安(杭州)科技有限公司

Ternary low-power-consumption domino comparison unit

ActiveCN102891668ACorrect logic functionSimple structureMultiple input and output pulse circuitsEngineeringControl circuit

The invention discloses a ternary low-power-consumption domino comparison unit. The ternary low-power-consumption domino comparison unit comprises a first control circuit, a second control circuit and a comparison signal generation circuit, wherein the first control circuit and the second control circuit are respectively used for controlling generation of signals of logics 2 and 1. A comparator comprises at least two ternary low-power-consumption domino comparison units, wherein a comparison result of a first complementary value signal and a second complementary value signal, which are output from a high-order ternary low-power-consumption domino comparison unit, serves as a complementary high-order comparison output signal which is connected to a low-order ternary low-power-consumption domino comparison unit. The ternary low-power-consumption domino comparison unit has the advantages of correct logic function and simple structure. Compared with the conventional ternary domino value comparison unit adopting a direct current power supply, the comparator has the obvious characteristic of low power consumption, and the power consumption is saved by about 60 percent.

Owner:NINGBO UNIV

Three-value adiabatic domino addition unit

ActiveCN102832928AReduce power consumptionReduce in quantityLogic circuits characterised by logic functionComputer scienceDirect current

The invention discloses a three-value adiabatic domino addition unit, comprising a first three-value adiabatic domino text operational circuit, a second three-value adiabatic domino text operational circuit, a carry signal generating circuit and a standard and signal generating circuit, wherein the first three-value adiabatic domino text operational circuit is connected with the carry signal generating circuit and the standard and signal generating circuit respectively; the second three-value adiabatic domino text operational circuit is connected with the carry signal generating circuit and the standard and signal generating circuit respectively; and a low carry signal input end of the carry signal generating circuit is connected with that of the standard and signal generating circuit. The unit has the following advantages: the unit has a simple structure on the prime of ensuring the correct logic function; compared with the three-value routine domino adder unit using a direct current power, the unit can save about 54% of energy; and compared with the three-value addition unit based on a DTCTGAL circuit, the transistor quantity of the unit can be reduced around 47%.

Owner:智创控安(杭州)科技有限公司

CNFET type single-edge pulse JKL trigger

ActiveCN106100612AIncrease work rateCorrect circuit logicElectric pulse generatorSignal generatorLogical Function

The invention discloses a CNFET type single-edge pulse JKL trigger. The CNFET type single-edge pulse JKL trigger comprises a single-edge pulse signal generator, thirty one CNFETs, six NTI gate circuits with identical circuit structure, six PTI gate circuits with identical circuit structure, and a first ternary inverter and a second ternary inverter with identical circuit structure. The CNFET type single-edge pulse JKL trigger has the advantages that the JKL trigger generates a clock signal through the single-edge pulse signal generator, and in combination with switch operation of a multiple-valued logical circuit and characteristics of high speed and low power consumption of the CNFETs, working speed of the JKL trigger is improved, and an aim of reducing power consumption is also achieved; and an experimental result shows that the JKL trigger provided by the invention has correct logical functions and remarkable characteristic of low power consumption.

Owner:NINGBO UNIV

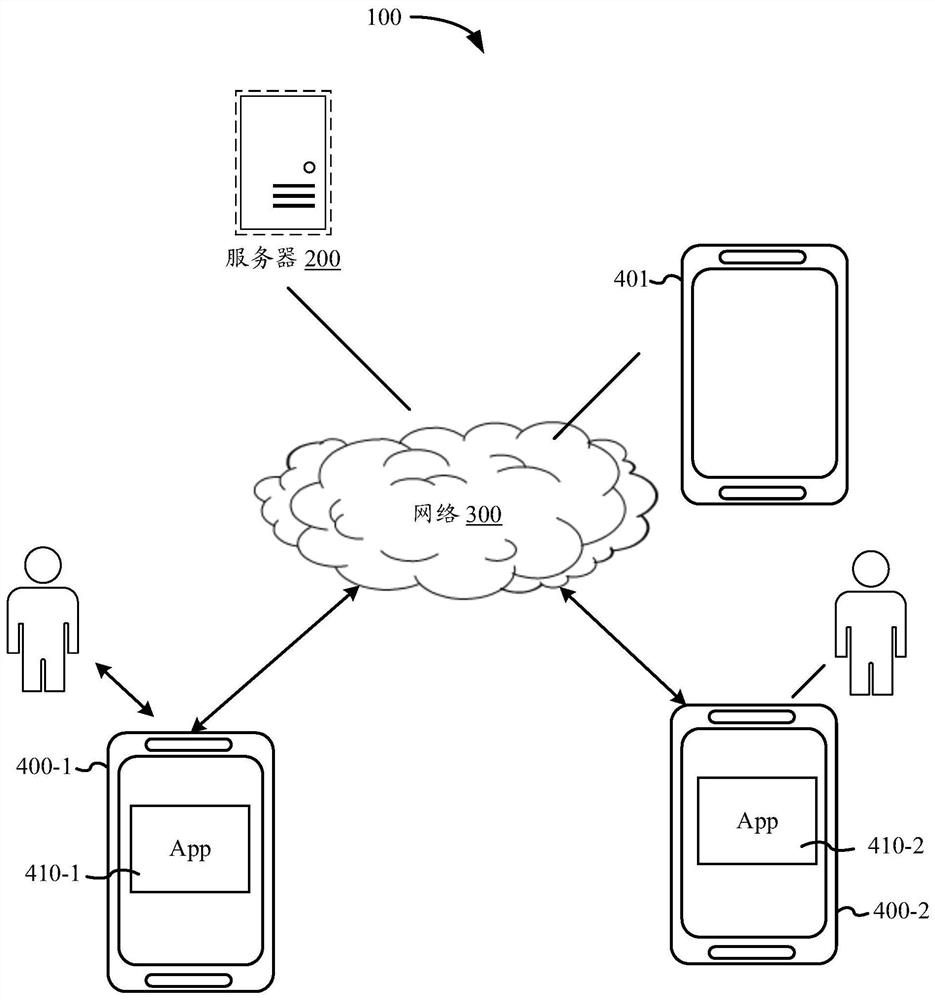

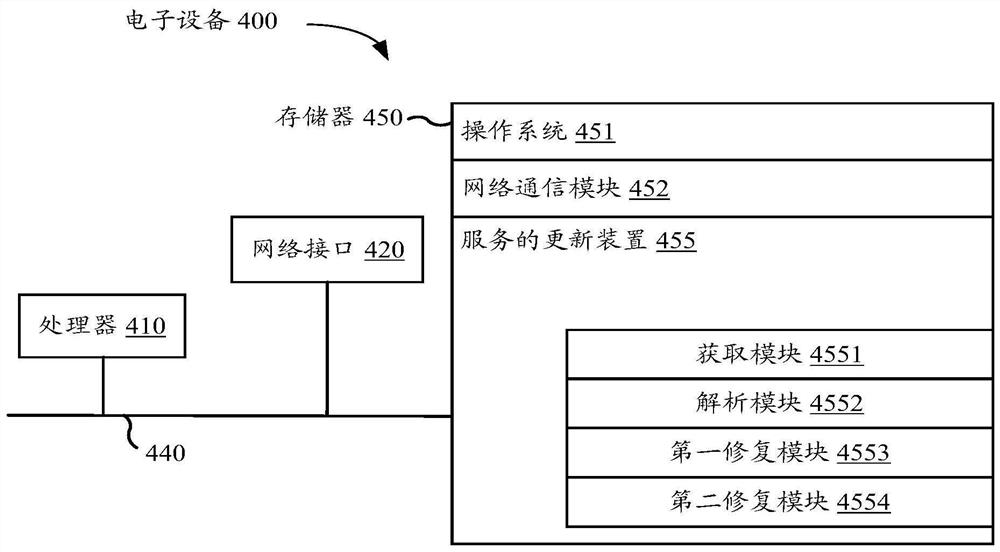

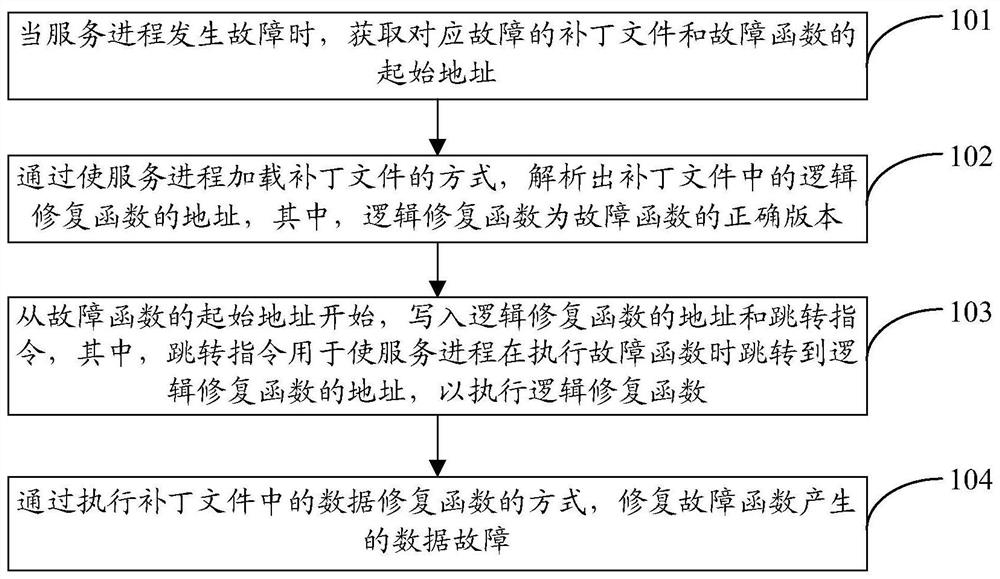

Service updating method and device and computer readable storage medium

ActiveCN113342389AFix logic errorsFix data errorsVersion controlNon-redundant fault processingLogisimOperating system

The invention provides a service updating method and device and a computer readable storage medium. The method comprises the following steps: when a service process has a fault, acquiring a patch file corresponding to the fault and an initial address of a fault function; analyzing the address of a logic repair function in the patch file in the mode that the service process loads the patch file, wherein the logic repair function is the correct version of the fault function; writing an operation instruction from the initial address of the fault function, wherein the operation instruction is used for writing the address of the logic repair function into the register and enabling the service process to jump to the address of the logic repair function when executing the fault function so as to execute the logic repair function; and repairing the data fault generated by the fault function by executing the data repairing function in the patch file. According to the method and the device, the fault of the service process can be efficiently repaired under the condition that the service process does not need to be restarted, and the capability of solving the emergency online fault is effectively improved.

Owner:SHENZHEN TENCENT NETWORK INFORMATION TECH CO LTD

Ternary adiabatic domino multiplication unit

ActiveCN102902508AReduce power consumptionReduce in quantityDigital data processing detailsTransmission gateTransistor count

The invention discloses a ternary adiabatic domino multiplication unit. The unit comprises a first ternary adiabatic domino literal arithmetic circuit, a second ternary adiabatic domino literal arithmetic circuit, a carry signal generating circuit and a standard product signal generating circuit, wherein the first ternary adiabatic domino literal arithmetic circuit is connected with the carry signal generating circuit and the standard product signal generating circuit respectively, the second ternary adiabatic domino literal arithmetic circuit is connected with the carry signal generating circuit and the standard product signal generating circuit respectively, and the low order carry signal input end of the carry signal generating circuit is connected with the low order carry signal input end of the standard product signal generating circuit. The unit has the advantages that the structure is simple under the guarantee of the correct logic function, compared with the conventional ternary domino multiplication unit in which a direct current power supply is adopted, the power consumption of the unit is saved by about 54%, and compared with a ternary multiplication unit based on design of a double power clock ternary clocked transmission gate adiabatic logic (DTCTGAL) circuit, the amount of transistors is reduced by about 31%.

Owner:NINGBO UNIV

Multidigit three-valued low power consumption domino multiplying unit

ActiveCN102891677AReduce in quantityCorrect logic functionLogic circuitsAdiabatic logicTransmission gate

The invention discloses a multidigit three-valued low power consumption domino multiplying unit which comprises a first three-valued heat-insulating domino text operating circuit, a second three-valued heat-insulating domino text operating circuit, a carry signal generating circuit and an original standard signal generating circuit; the first three-valued heat-insulating domino text operating circuit is respectively in circuit connection with the carry signal generating circuit and the original standard signal generating circuit; the second three-valued heat-insulating domino text operating circuit is respectively in circuit connection with the carry signal generating circuit and the original standard signal generating circuit; a low-bit carry signal input end of the carry signal generating circuit is connected with a low-bit carry signal input end of the original standard signal generating circuit. The multidigit three-valued low power consumption domino multiplying unit has the following advantages that the multiplying unit is simple in structure on the basis of guaranteeing correct logic function; in comparision with a regular three-valued domino multiplying unit adopting a direct current source, the power consumption is saved by about 54%; in comparison with the three-valued multiplying unit designed on the basis of double power clock ternary clocked transmission gate adiabatic logic (DTCTGAL), the number of transistors is reduced by about 31%.

Owner:NINGBO UNIV

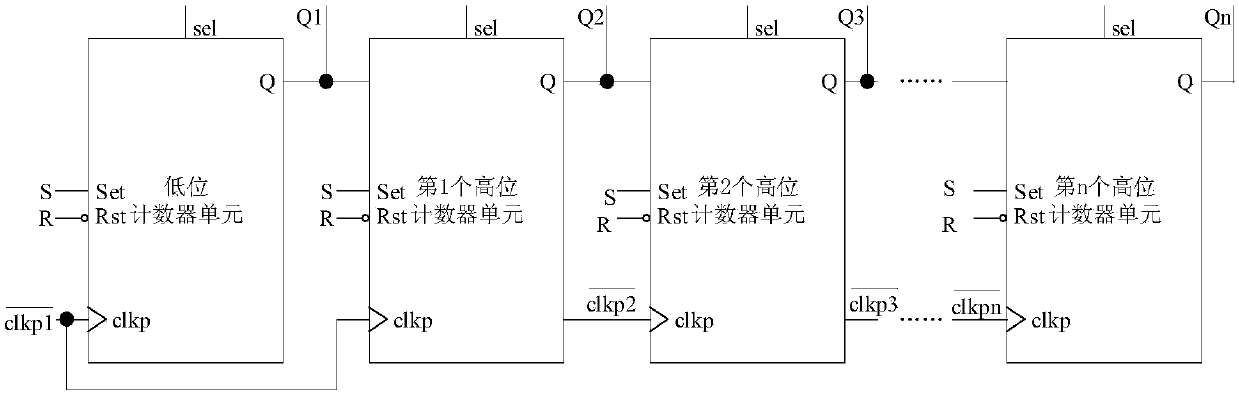

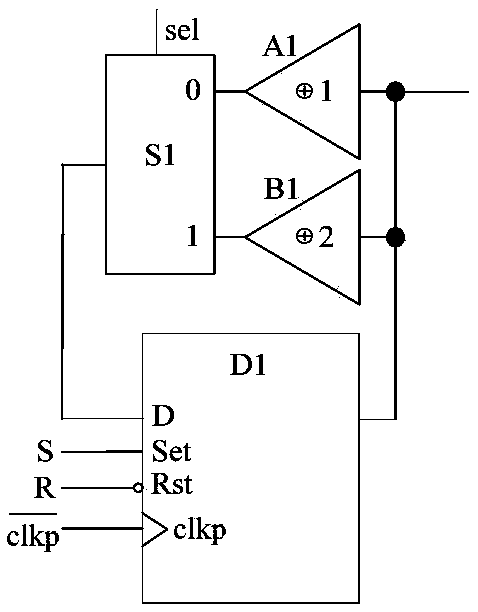

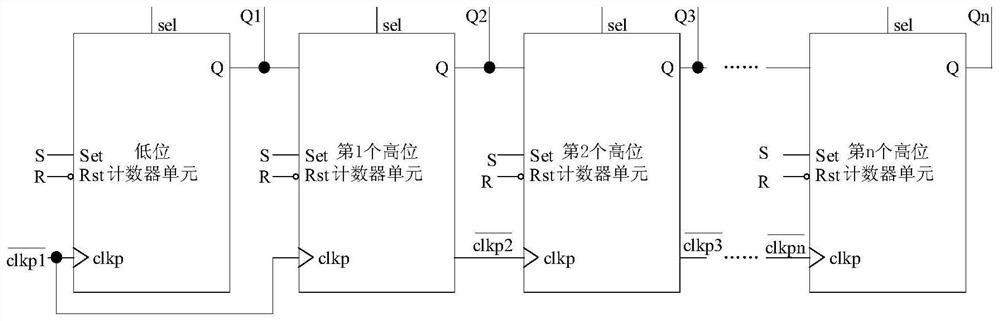

Three-valued reversible counter using carbon nano-field effect transistor

ActiveCN107682006AReduce redundant jumpsReduce dynamic power consumptionCounting chain pulse counters using semiconductor devicesCounting chain reversible pulse countersField-effect transistorComputer science

The invention discloses a three-valued reversible counter using a carbon nano-field effect transistor. The three-valued reversible counter comprises a low-bit counting unit and n high-bit counting units with the same circuit structure, wherein the low-bit counting unit comprises a three-valued pulse type D trigger, a first alternative selector, a first modulo-1 circuit, and a first modulo-2 circuit; the high-bit counting unit comprises a second three-valued pulse type D trigger, a second alternative selector, a second modulo-1 circuit, a second modulo-2 circuit and a carry / borrow circuit. Thethree-valued reversible counter disclosed by the invention has the advantage that the clock signal of each level of counting unit is input after the clock signal of the former level of counting unit is processed through the carry / borrow circuit, thereby guaranteeing that each level of counting unit only needs to receive the clock signal in the counting time, the redundancy hop of the counter produced by the change of the clock signal is reduced, and the dynamic power consumption of the circuit is lowered.

Owner:NINGBO UNIV

Novel adiabatic logic gating circuit

InactiveCN101977050BReduce power consumptionReduce consumptionLogic circuitsAdiabatic logicPMOS logic

The invention discloses a novel adiabatic logic gating circuit. A first p-channel metal oxide semiconductor (PMOS) tube, a second PMOS tube, a first n-channel metal oxide semiconductor (NMOS) tube, and a second NMOS tube form an energy recovery circuit with a cross-coupled structure, the source electrode of the first PMOS tube and the drain electrode of the second PMOS tube are parallelly connected to the positive terminal of a power source, the source electrode of the first NMOS tube and the drain electrode of the second NMOS tube are parallelly connected to a clock signal terminal, a first PMOS logic block is bridged between the source electrode of the first PMOS tube and the drain electrode of the first PMOS tube, a second PMOS logic block is bridged between the drain electrode of the second PMOS tube and the source electrode of the second PMOS tube, the first PMOS logic block is provided with at least one positive input signal connecting terminal, and the second PMOS logic block is provided with at least one inverted input signal connecting terminal. The invention has the advantages that: an adiabatic circuit of which the functional characteristics are completely opposite to those of the traditional adiabatic logic circuit is provided, and the first PMOS logic block and the second PMOS logic block consists of PMOS tubes, so that the circuit power consumption can be greatlyreduced.

Owner:NINGBO UNIV

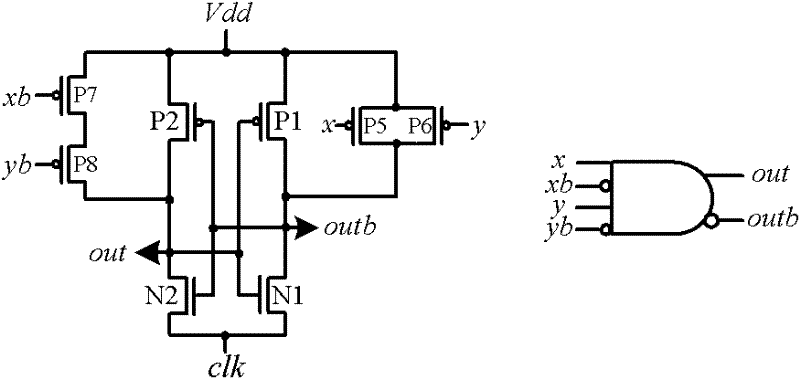

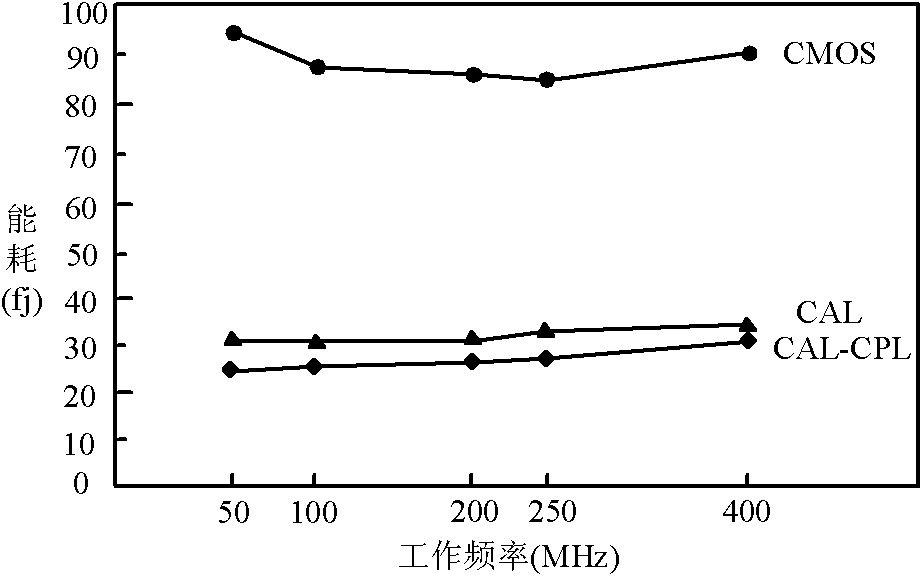

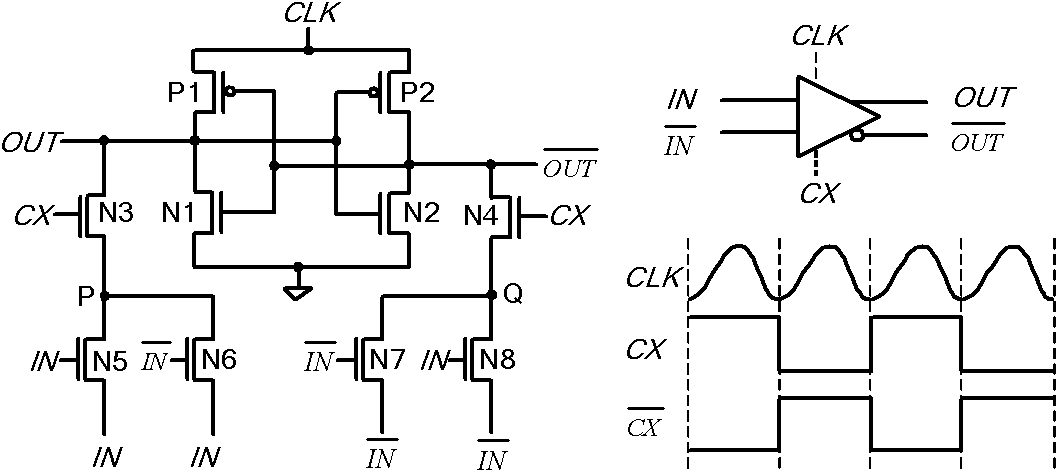

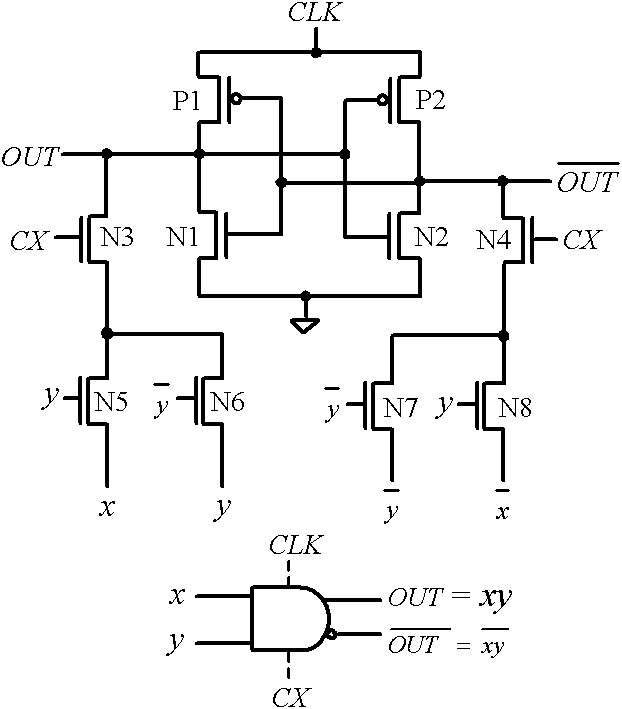

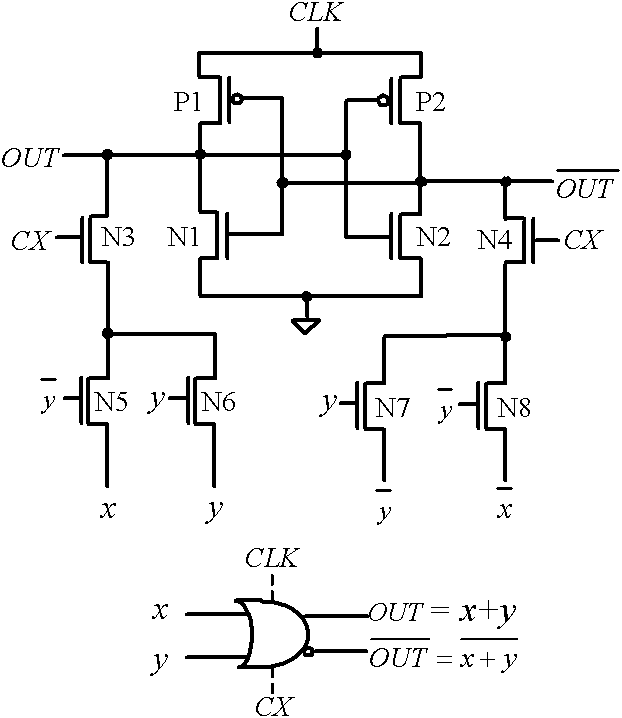

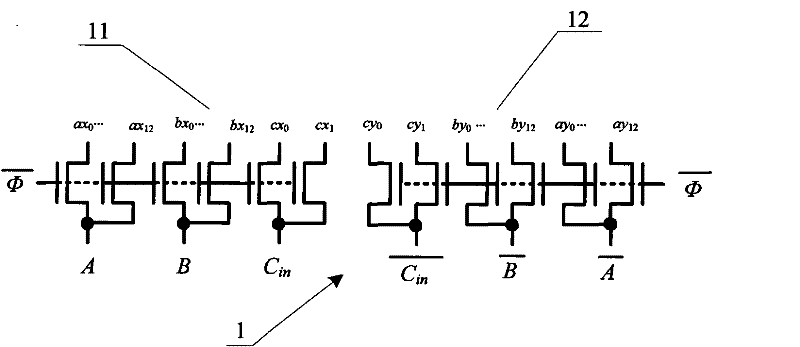

Single-phase clock pass transistor adiabatic logic circuit, full adder and 5-2 compressor

InactiveCN101951256AReduce complexityReduce areaLogic circuits using semiconductor devicesAdiabatic logicEnergy regeneration

The invention discloses a single-phase clock pass transistor adiabatic logic circuit. The circuit is characterized by comprising a logic assignment circuit and an energy regeneration circuit, wherein the energy regeneration circuit consists of two pMOS transistors, namely a first pMOS transistor and a second pMOS transistor; the source of the first pMOS transistor and the source of the second pMOS transistor are connected in parallel with a power clock end; and the logic assignment circuit consists of four nMOS pass transistors, namely, a fifth nMOS pass transistor, a sixth nMOS pass transistor, a seventh nMOS pass transistor and an eighth nMOS pass transistor. The circuit has the advantages of combining the advantages of the single-phase power clock adiabatic logic (CAL) and complementary pass transistor logic (CPL), only one power clock CLK is needed, an auxiliary clock (CX and CX') alternately controls each stage of logic circuit, and the frequency of the circuit is half that of the power clock CLK; the single-phase power clock is used by a full adder on the basis, so that complexity of the clock circuit is reduced, the clock circuit is easier to generate, and the area of the circuit is greatly reduced; and a 5-2 compressor only consists of the full adder and has a simple and normative circuit structure and can compress more digits at one time.

Owner:NINGBO UNIV

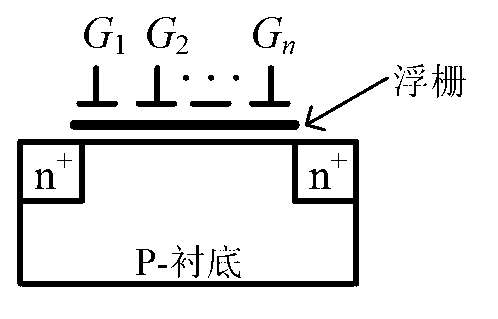

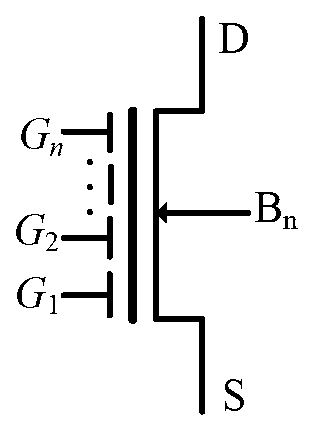

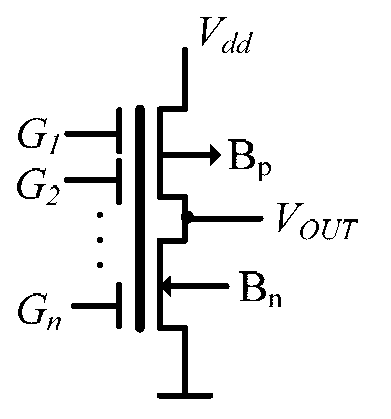

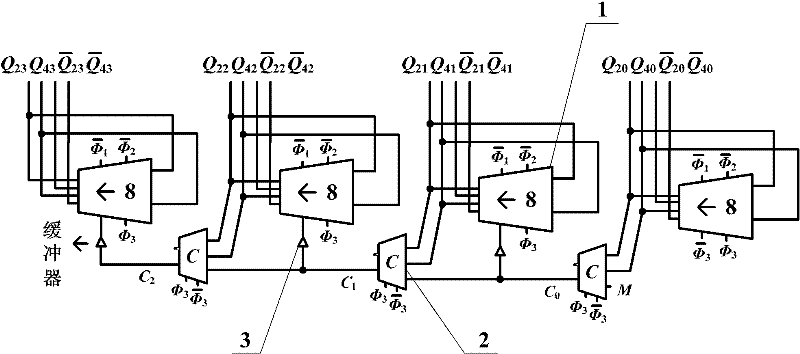

Multiple-valued counter unit based on nerve MOS tube and multi-digit multiple-valued counter

InactiveCN101777139BLow costReduce power consumptionCounting mechanisms/objectsSemiconductor devicesInput controlEngineering

The present invention discloses a neuron MOS based multi-valued counter unit. The counter unit includes a neuron MOS source follower and at least a control gate connected the neuron MOS source follower. The control gate includes a first dual-value D flip-flop, a second dual-value D flip-flop, an AND gate, and an OR gate. The present invention utilizes the neuron MOS to replace the complicated threshold value operations of the multi-value logic. The current invention implements the true multi-value logic and a multi-base multi-value counter by increasing the number of the dual-value D flip-flop, and connecting the dual-value D flip-flop to the input control gate of the neuron MOS follower. Comparing to the conventional multi-value counter, the present invention reduces the necessary components in constructing the counter, and it also reduces the cost and power consumption. The present invention applies the asynchronous carry-over concept to implement the multi-digit multi-value counter, and it also has been verified by the simulation of P Simulation Program with Integrated Circuit Emphasis (SPICE).

Owner:NINGBO UNIV

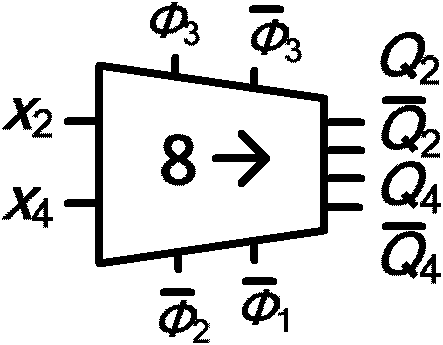

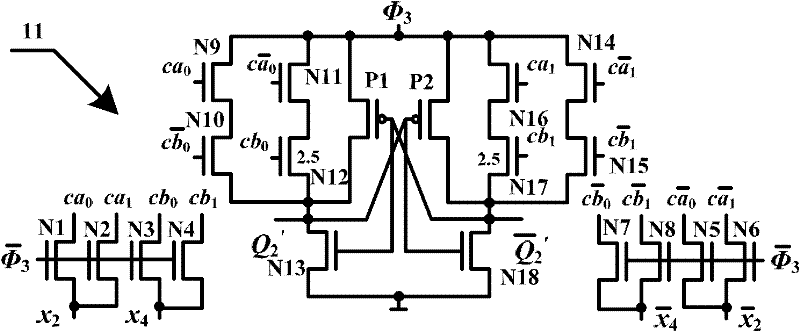

Mixed-value based eight-value heat-insulation addition and subtraction counter

InactiveCN101968733BCorrect logic functionHigh Information Density FeaturesComputations using residue arithmeticEngineeringEnergy recovery

The invention discloses a mixed-value based eight-value heat-insulation addition and subtraction counter, which adopts mixed value technology, multi-threshold MOS pipe control technology and clocked heat insulation technology. The counter mainly comprises an eight-value trigger type positive circulating gate and an eight-value heat insulation carry / borrow circuit, wherein the eight-value trigger type heat insulation positive circulating ate consists of a two-value heat insulation positive circulating circuit and a four-value heat insulation positive circulating circuit, a text operation circuit of the four-value heat insulation positive circulating circuit controls a logic signal generating circuit to generate a four-value logic signal. The counter samples an input signal by utilizing a clocked NMOS pipe, ensures that the output load realizes logical assignment and energy reclamation along with a power clock through a sampling value, a bootstrapped NMOS pipe and a cross storage structure, effectively reduces the power consumption on the premise of ensuring the circuit has correct logical function, and improves the work reliability of the integrated circuit.

Owner:NINGBO UNIV

Low power consumption multiposition three-valued Domino adder

The invention discloses a low power consumption multiposition three-valued Domino adder. The adder comprises n-numbered positions of three-valued heat insulation Domino adding units, wherein the k position of three-valued heat insulation Domino adding unit is connected with the low-position carry signal output end of the (k+1) position of three-valued heat insulation Domino adding unit by a heat insulation Domino buffer; the k position of three-valued heat insulation Domino adding unit is also connected with the complementary low-position carry signal output end of the (k+1) position of three-valued heat insulation Domino adding unit by a heat insulation Domino buffer; the ipso position and the signal output end of the j position of three-valued heat insulation Domino adding unit are connected with (n-j)-numbered heat insulation Domino buffers in sequence; the addend signal input end and augend signal input end of the j position of three-valued heat insulation Domino adding unit are connected with (j-1)-numbered heat insulation Domino buffers in sequence; k is equal to 1, 2,......, n-1; j is equal to 1, 2,......, n; and m is equal to 1, 2,......, n-1. The adder has the following advantage: the power consumption is reduced by about 61% compared with that of the conventional three-valued Domino adder adopting the direct-current power source.

Owner:智创控安(杭州)科技有限公司

Tri-valued, thermal-insulating and low-power multiplier unit and multiplier

InactiveCN101833433BCorrect logic functionLow Power FeaturesComputation using non-contact making devicesBinary multiplierHemt circuits

The invention discloses a tri-valued, thermal-insulating and low-power multiplier unit and a multiplier. The multiplier unit controls each NMOS tube in an input signal sampling circuit to sample input signals by using a clock-controlled clock signal; four corresponding integrating circuit modules and carry output circuits with cross storage-type structures are constructed by sampled values according to required realized multiplication logic relationship through the bootstrap operation of the NMOS tube; power clocks phi1 and phi complete the evaluation and energy recovery of the output load torealize correct logic function; and compared with a DPL tri-valued multiplier, the four-digit tri-valued thermal-insulating and low-power multiplier can save energy consumption by about 91 percent in0.9 microsecond and has distinct low-power characteristics.

Owner:NINGBO UNIV

Multi-order ternary double-track domino comparator

ActiveCN102891667BCorrect logic functionSimple structureMultiple input and output pulse circuitsControl circuitComparator

The invention discloses a multi-order ternary double-track domino comparator. The multi-order ternary double-track domino comparator consists of at least two-order ternary low-power-consumption domino comparison units; each comparison unit comprises a first control circuit, a second control circuit and a comparison signal generation circuit; and the first control circuit and the second control circuit are respectively used for controlling generation of signals of logics 2 and 1. A comparison result of a high-order ternary low-power-consumption domino comparison unit serves as a high-order comparison output signal which is connected to a low-order ternary low-power-consumption domino comparison unit, a complementary comparison result of the high-order ternary low-power-consumption domino comparison unit serves as a complementary high-order comparison output signal which is connected to the low-order ternary low-power-consumption domino comparison unit, and the high-order comparison output signal and the complementary high-order comparison output signal, which are connected to the highest-order ternary low-power-consumption domino comparison unit, are the logic 1. The multi-order ternary double-track domino comparator has the advantages of correct logic function and simple structure. Compared with the conventional multi-order ternary domino comparator, the multi-order ternary double-track domino comparator has the obvious characteristic of low power consumption, and about 71.4 percent of power consumption is saved.

Owner:智创控安(杭州)科技有限公司

Four-value heat-insulating dynamic D trigger

InactiveCN101969301BCorrect logic functionHigh working reliabilityElectric pulse generatorEnergy recoveryFour-valued logic

The invention discloses a four-value heat-insulating dynamic D trigger. The D trigger comprises a character computing circuit, a character sampling circuit and a logic signal generating circuit, wherein the character computing circuit mainly comprises first, second, third and fourth sub-character computing circuits; and the logic signal generating circuit mainly comprises a 0-3 logic signal generating circuit and a 1-2 logic signal generating circuit. The trigger is characterized in that: the four-value heat-insulating dynamic D trigger designed through clocked heat insulation technology and multi-threshold MOS tube control technology mainly comprises the character computing circuit and the logic signal generating circuit; and the logic signal generating circuit is controlled by the character computing circuit to generate a four-value logic signal. The circuits of the D trigger sample the input signal through a clocked NMOS tube, and the output load realizes assignment and energy through a sampling value, the bootstrap-operated NMOS tube and a follow power clock with a cross storage type structure. The D trigger effectively reduces the power consumption and improves working reliability of the circuit on the premise of guaranteeing the correct logic function of the circuits.

Owner:NINGBO UNIV

Single-phase clock pass transistor adiabatic logic circuit, full adder and 5-2 compressor

InactiveCN101951256BReduce complexityReduce areaLogic circuits using semiconductor devicesAdiabatic logicClock rate

Owner:NINGBO UNIV

Tri-valued, thermal-insulating and low-power adder unit and adder

InactiveCN101833432BCorrect logic functionReduce power consumptionComputation using non-contact making devicesCircuit delayHemt circuits

The invention discloses a tri-valued, thermal-insulating and low-power adder unit and an adder. The adder unit controls each NMOS tube in an input signal sampling circuit to sample input signals by using a clock-controlled clock signal; four corresponding summing circuit modules and carry output circuits with cross storage-type structures are constructed by sampled values according to required realized addition logic relationship through the bootstrap operation of the NMOS tube; power clocks phi1 and phi complete the evaluation and energy recovery of the output load to realize correct logic function; and compared with a DPL tri-valued adder, the four-digit tri-valued thermal-insulating and low-power adder can save energy consumption by about 90 percent in 0.9 microsecond, and has distinctlow-power characteristics.

Owner:NINGBO UNIV

A double-edge d flip-flop based on n-type sabl logic

InactiveCN103595371BCorrect logic functionWith power balance featureElectric pulse generator circuitsCMOSTransmission gate

Owner:NINGBO UNIV

A Three-value Reversible Counter Using Carbon Nano Field-Effect Transistor

ActiveCN107682006BReduce redundant jumpsReduce dynamic power consumptionCounting chain pulse counters using semiconductor devicesCounting chain reversible pulse countersHemt circuitsFlip-flop

The invention discloses a three-valued reversible counter using a carbon nano-field effect transistor. The three-valued reversible counter comprises a low-bit counting unit and n high-bit counting units with the same circuit structure, wherein the low-bit counting unit comprises a three-valued pulse type D trigger, a first alternative selector, a first modulo-1 circuit, and a first modulo-2 circuit; the high-bit counting unit comprises a second three-valued pulse type D trigger, a second alternative selector, a second modulo-1 circuit, a second modulo-2 circuit and a carry / borrow circuit. Thethree-valued reversible counter disclosed by the invention has the advantage that the clock signal of each level of counting unit is input after the clock signal of the former level of counting unit is processed through the carry / borrow circuit, thereby guaranteeing that each level of counting unit only needs to receive the clock signal in the counting time, the redundancy hop of the counter produced by the change of the clock signal is reduced, and the dynamic power consumption of the circuit is lowered.

Owner:NINGBO UNIV

Ternary low-power-consumption domino comparison unit

ActiveCN102891668BCorrect logic functionSimple structureMultiple input and output pulse circuitsEngineeringControl circuit

The invention discloses a ternary low-power-consumption domino comparison unit. The ternary low-power-consumption domino comparison unit comprises a first control circuit, a second control circuit and a comparison signal generation circuit, wherein the first control circuit and the second control circuit are respectively used for controlling generation of signals of logics 2 and 1. A comparator comprises at least two ternary low-power-consumption domino comparison units, wherein a comparison result of a first complementary value signal and a second complementary value signal, which are output from a high-order ternary low-power-consumption domino comparison unit, serves as a complementary high-order comparison output signal which is connected to a low-order ternary low-power-consumption domino comparison unit. The ternary low-power-consumption domino comparison unit has the advantages of correct logic function and simple structure. Compared with the conventional ternary domino value comparison unit adopting a direct current power supply, the comparator has the obvious characteristic of low power consumption, and the power consumption is saved by about 60 percent.

Owner:NINGBO UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com