Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

470 results about "Object system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

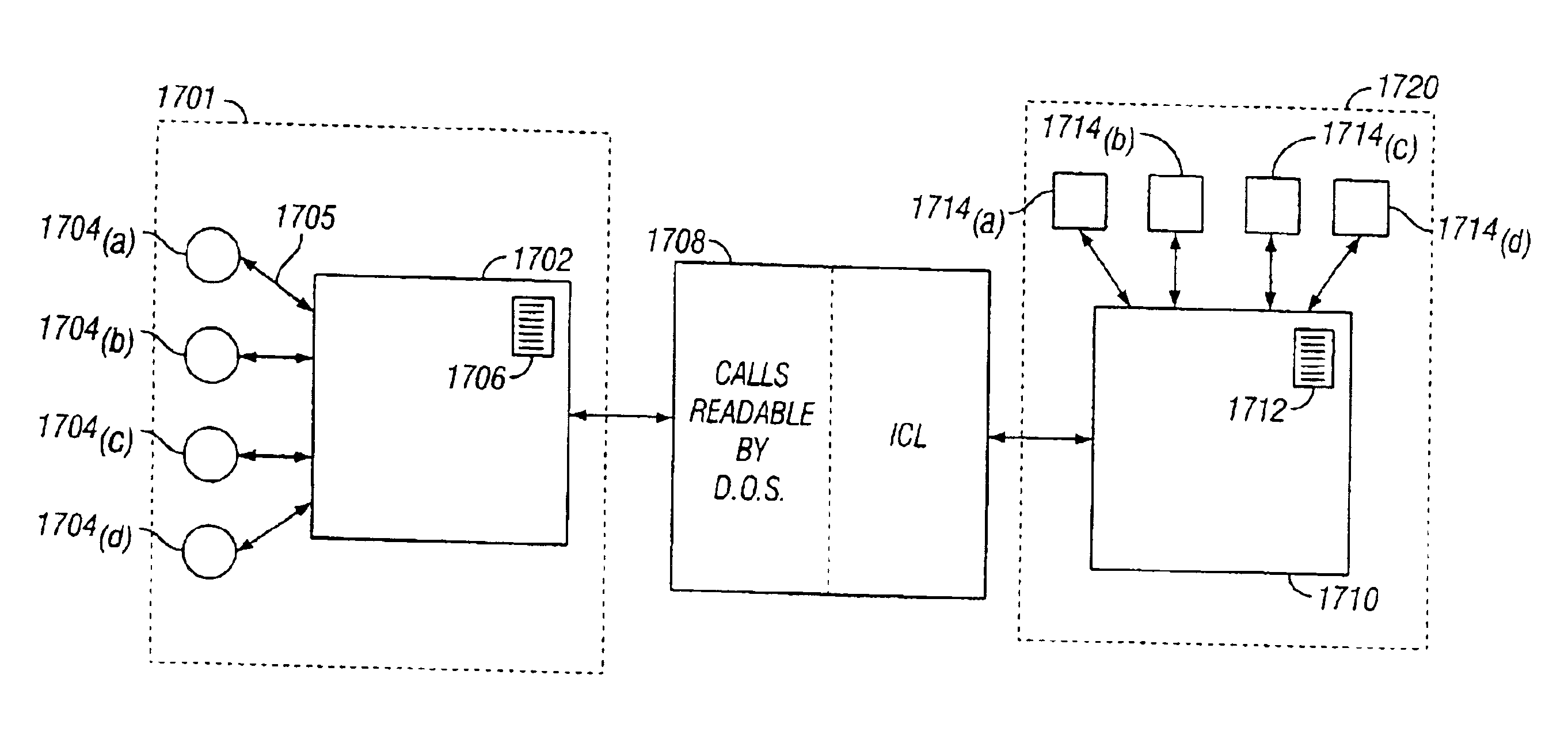

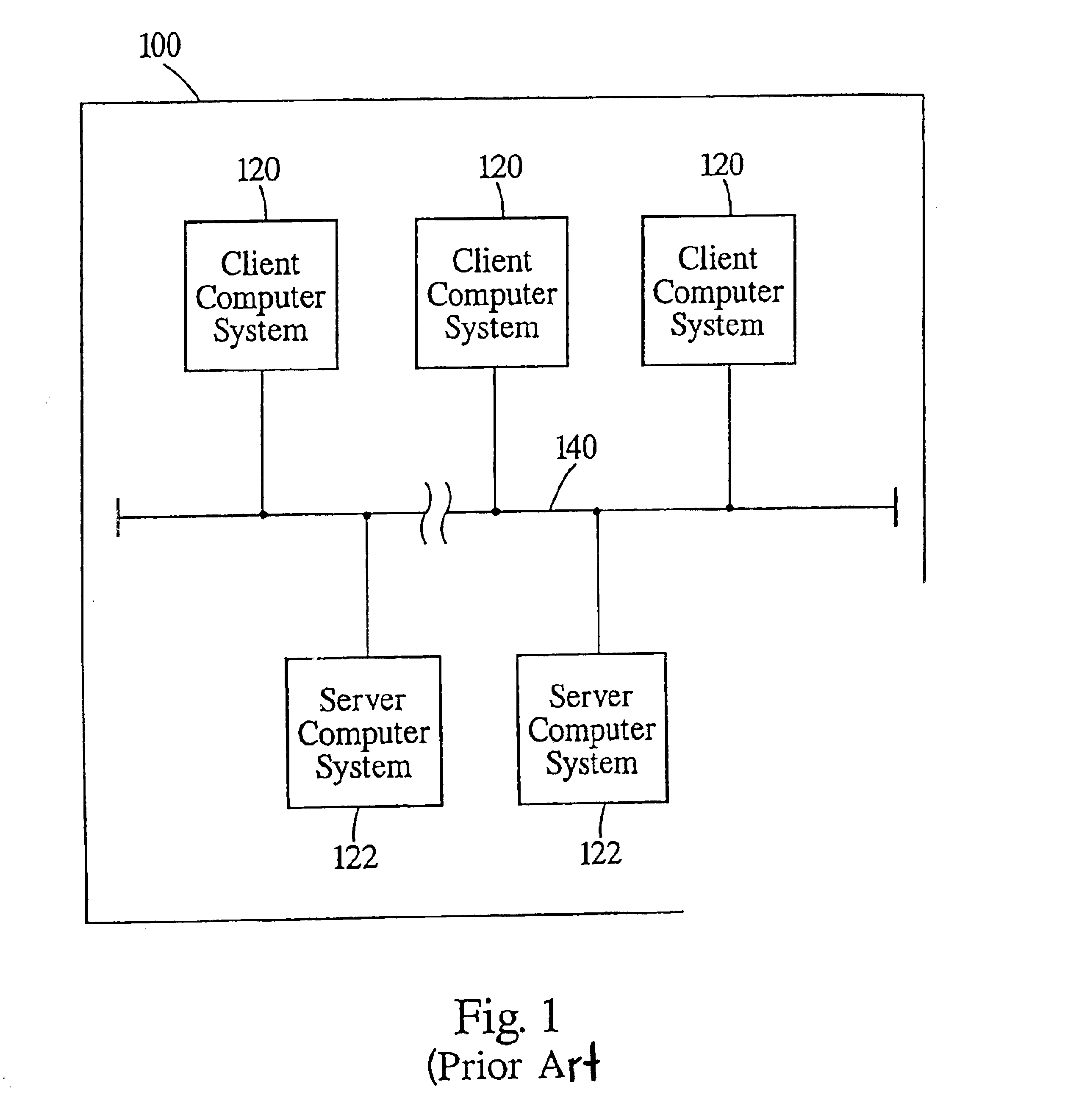

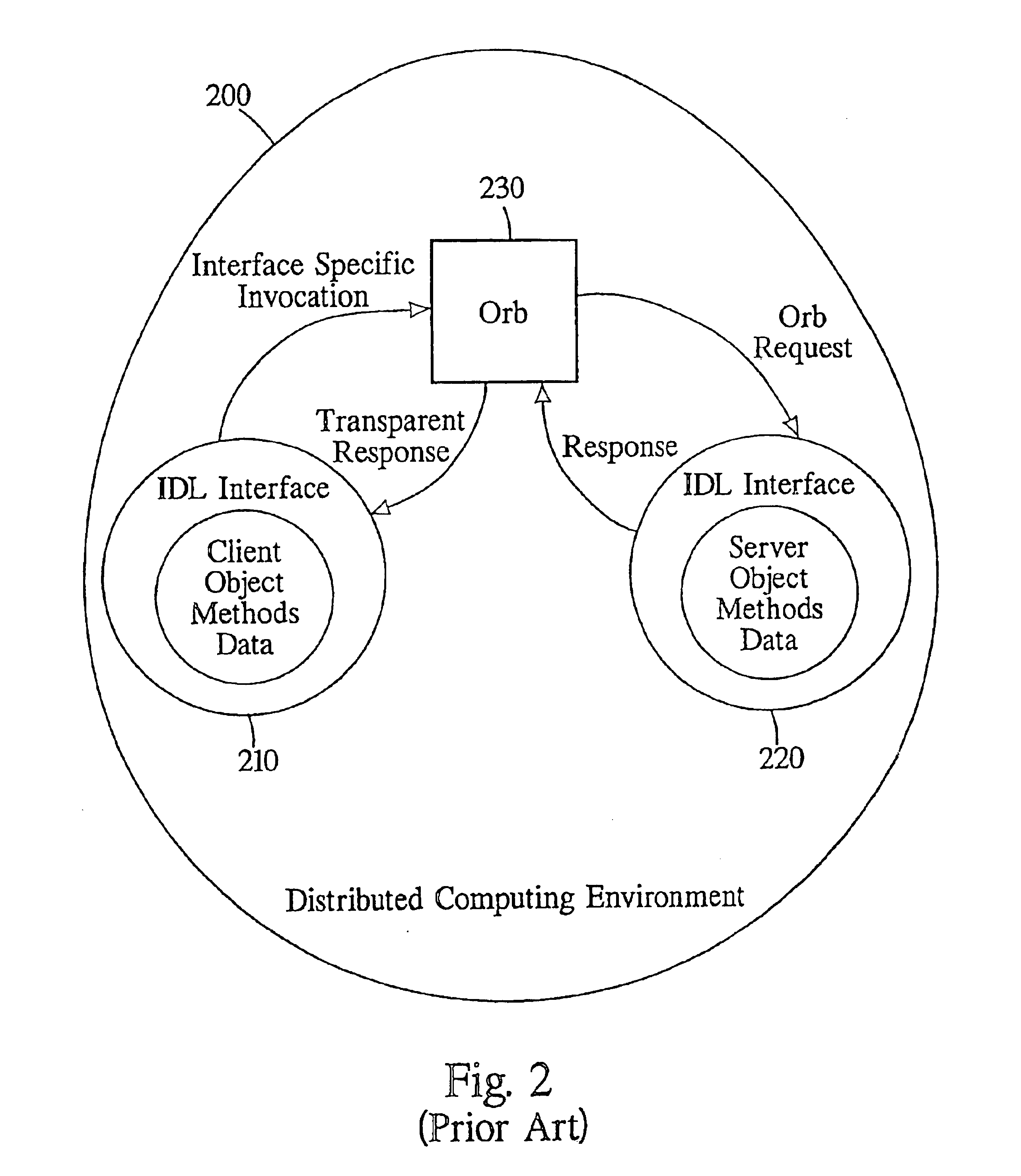

Extensible software-based architecture for communication and cooperation within and between communities of distributed agents and distributed objects

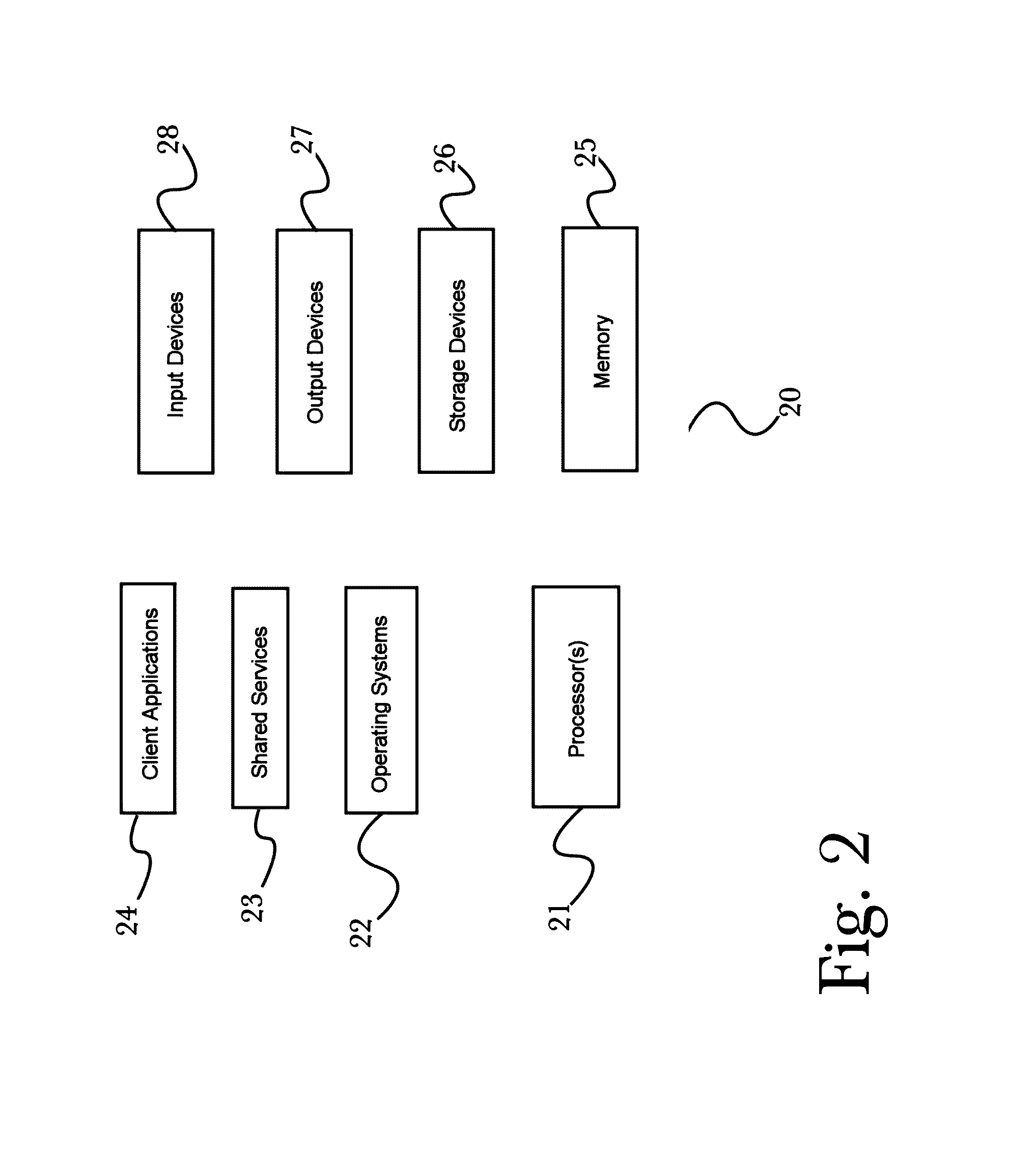

InactiveUS6859931B1Minimal effortIncrease flexibilityDigital data information retrievalInterprogram communicationIntelligent planningDistributed object systems

A distributed agent community is able to dynamically interact with alternative sofware technologies that manage distributed objects. The leveraging of capabilities of distributed object systems greatly expands the flexibility and capabilites of the distributed agent community. Through access to distributed object systems, the distributed agent community can draw on the capabilites of all the objects managed by the distributed object systems. The access to distributed systems by the distributed agent community allows for collaboration and intelligent planning that the distributed object systems do not themsleves provide.

Owner:IPA TECH INC

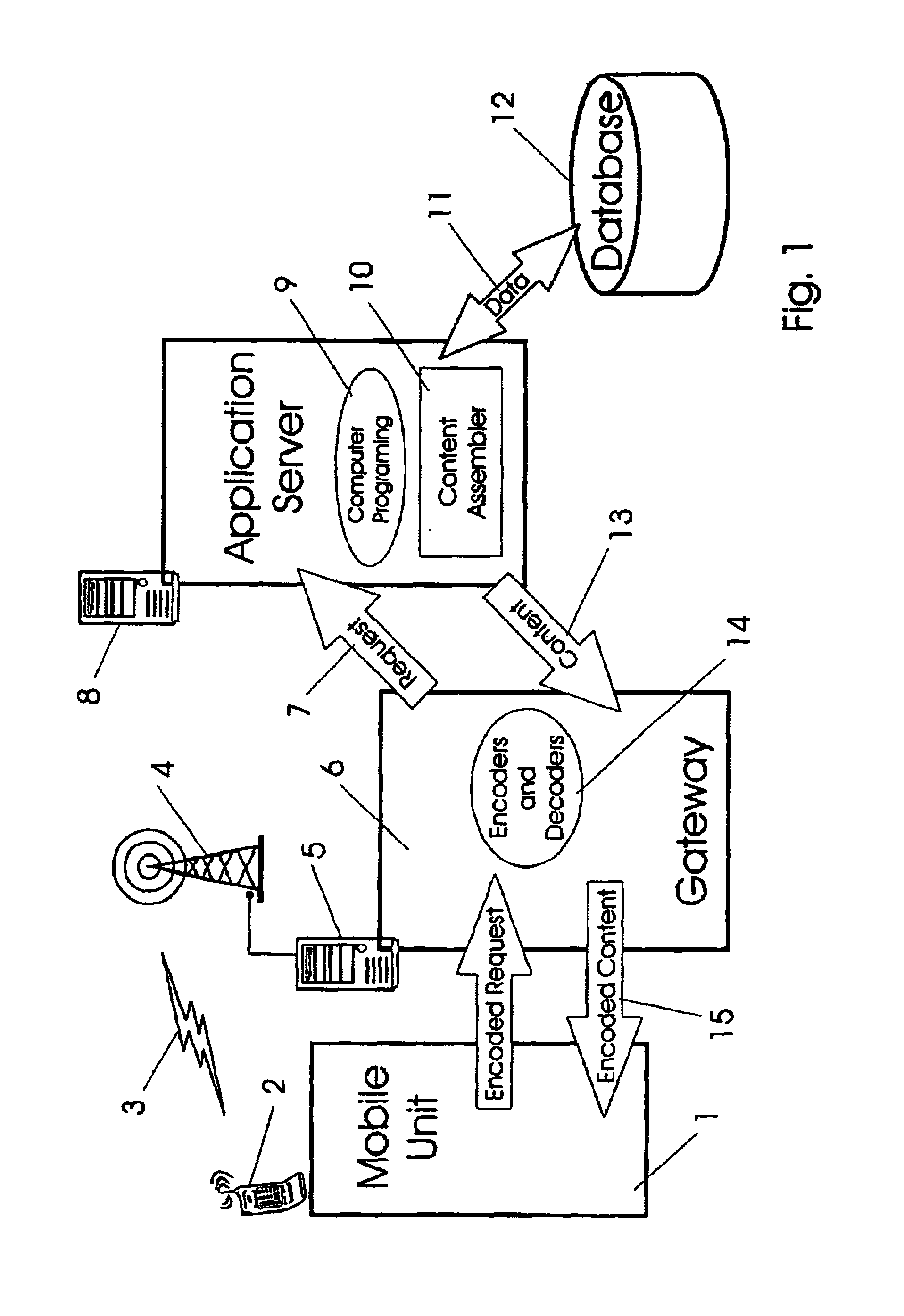

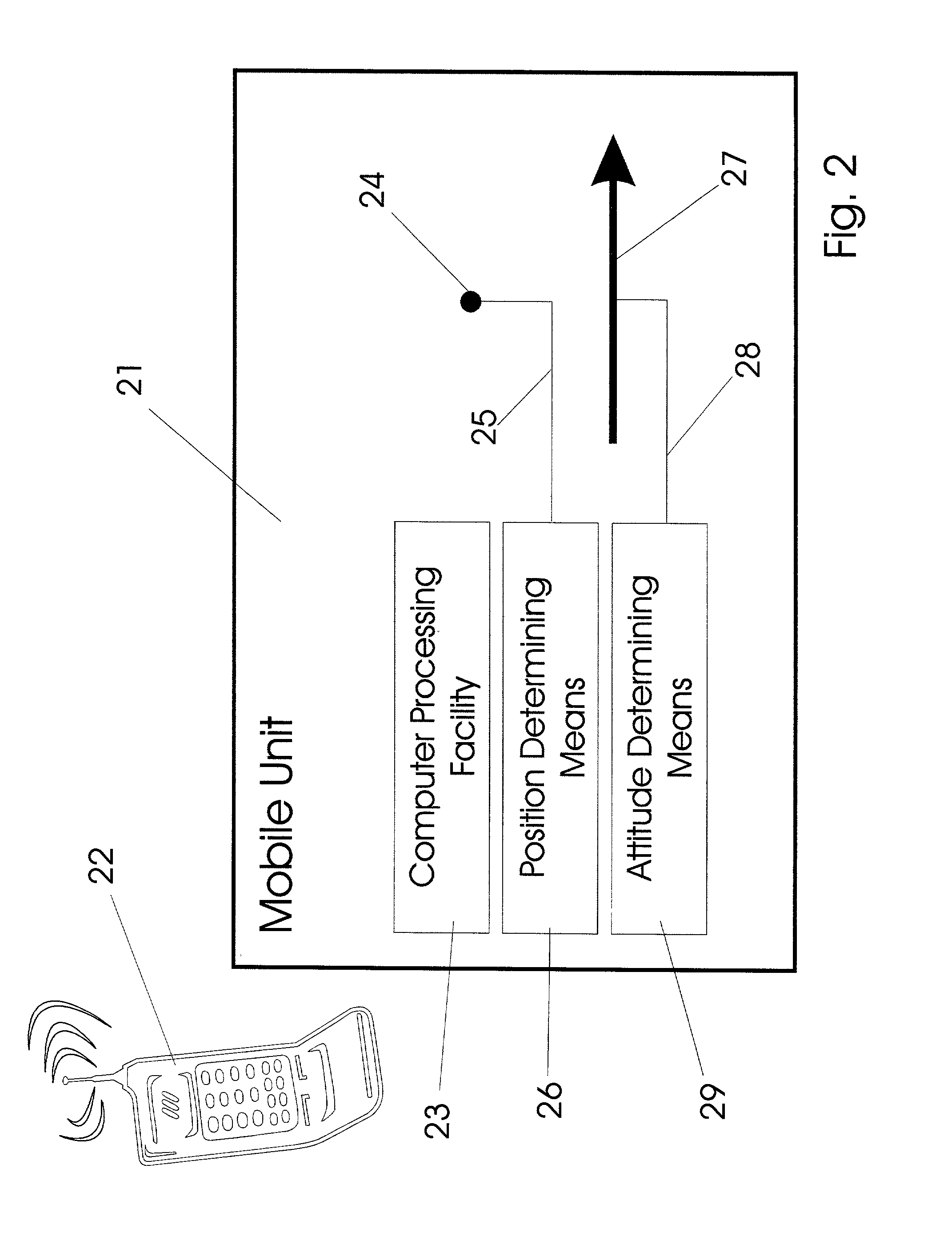

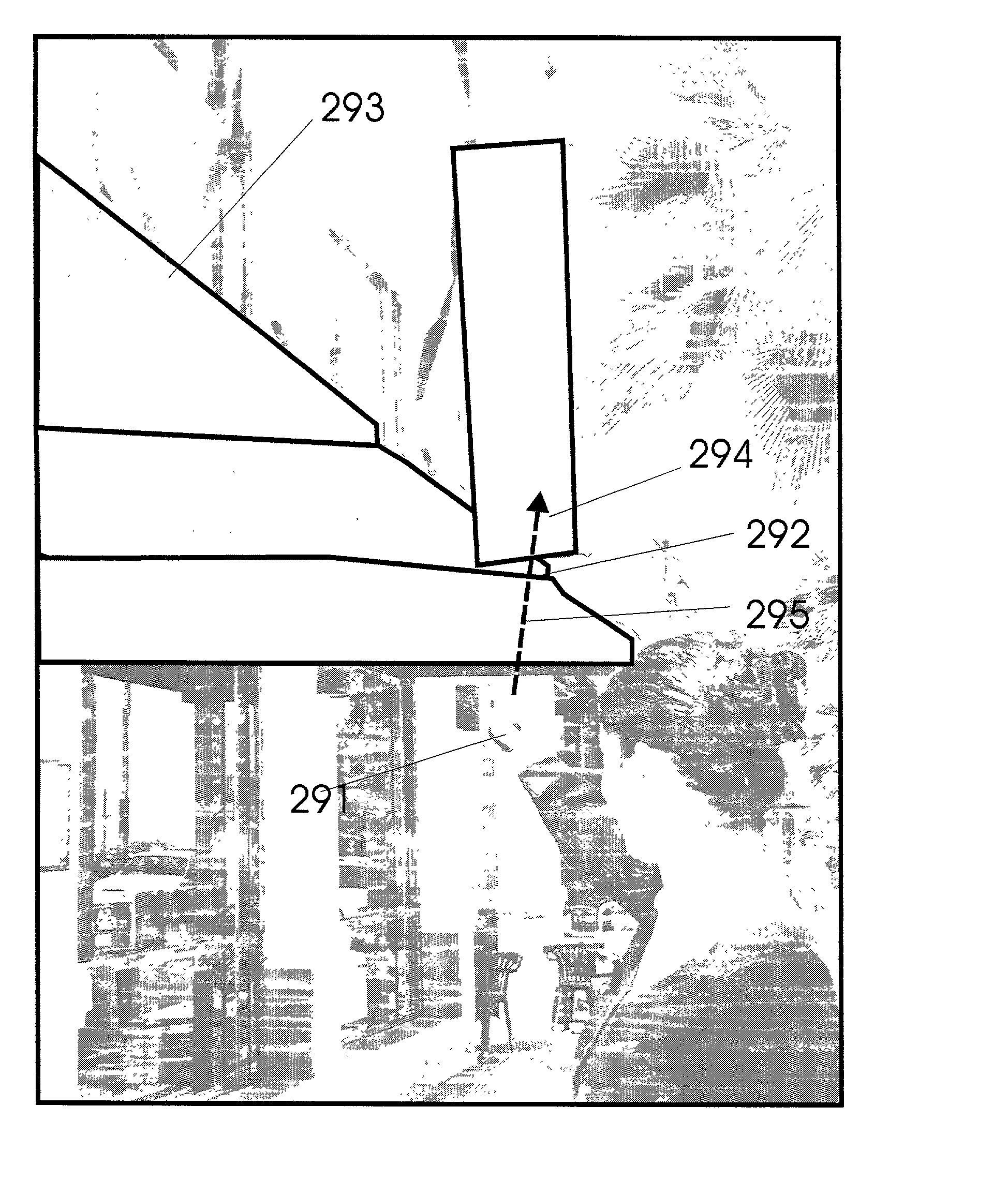

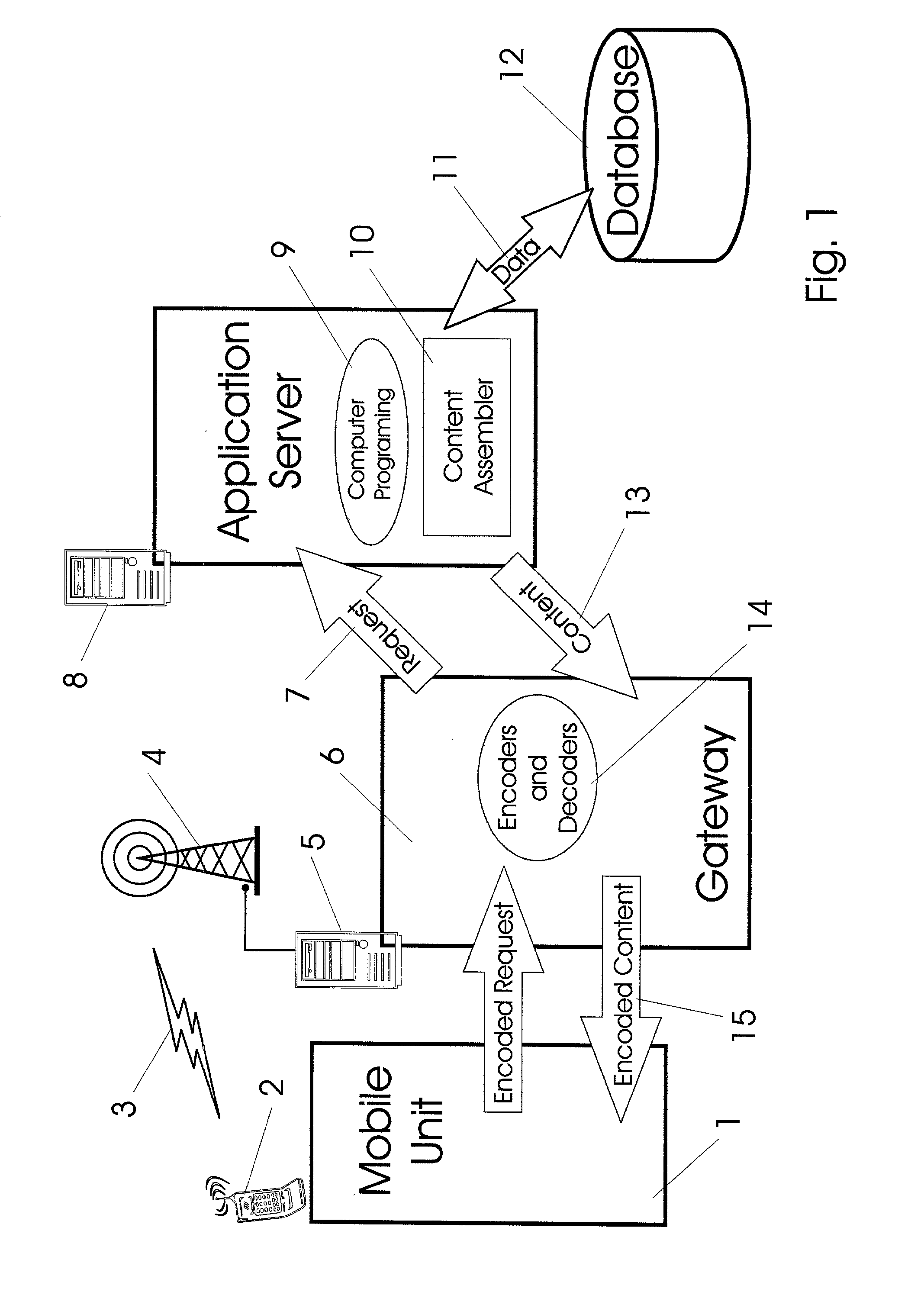

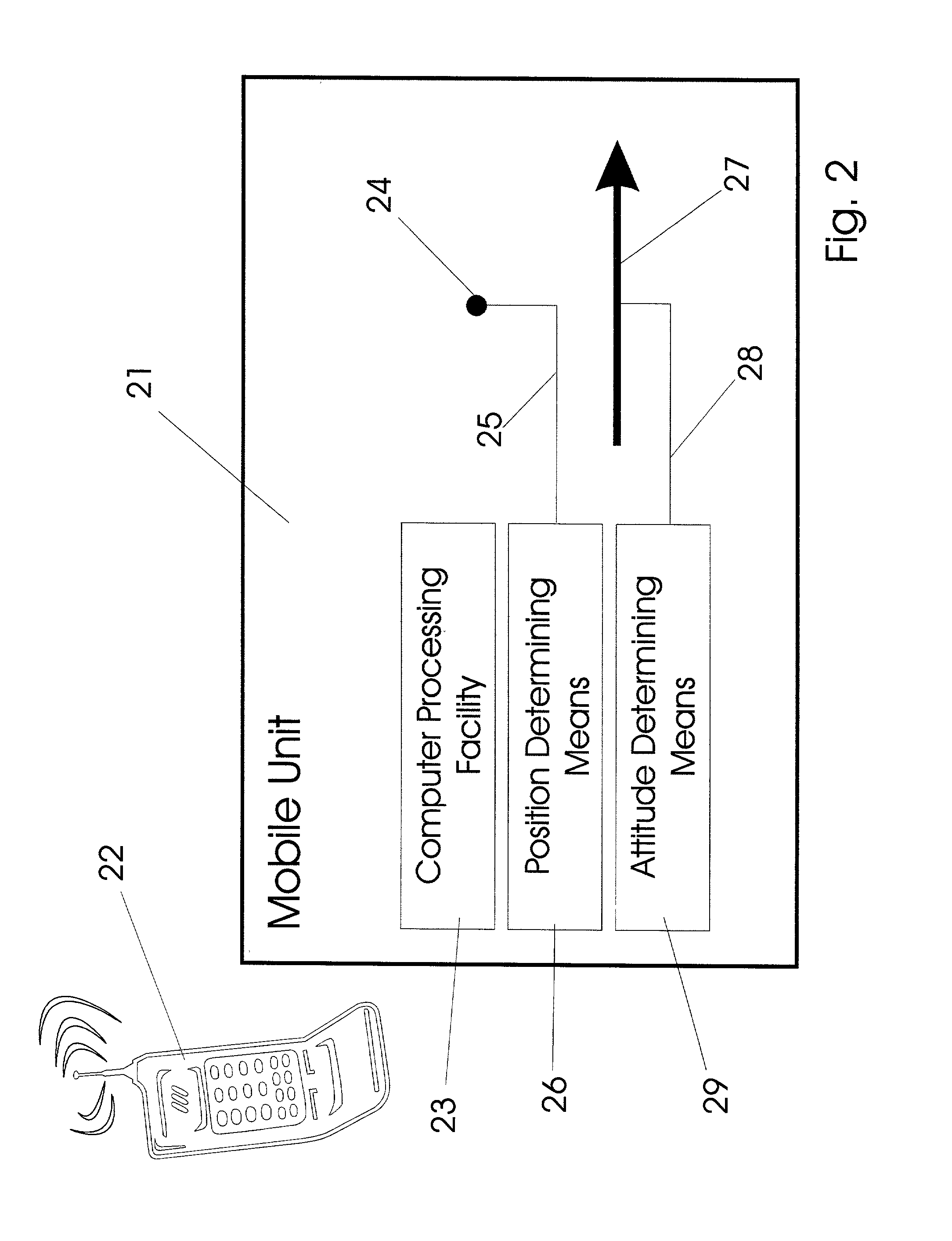

Pointing systems for addressing objects

InactiveUS7031875B2Navigational calculation instrumentsDigital data processing detailsHand heldHand held devices

Systems are arranged to provide a user information which relates to objects of interest. A user may point a hand held device toward an object to address it. The device determines which objects are being addressed by making position and attitude measurements and further a reference and search of a database containing preprogrammed information relating to objects. Information relating to objects determined as objects presently being addressed is thereafter presented at a user interface. Devices of these systems include a point reference, a direction reference, a position determining support, attitude determining support, a computer processor and database, and a user interface. Methods of systems include the steps of addressing an object, determining position and attitude, searching a database, and presenting information to a user.

Owner:GEOVECTOR

Pointing systems for addressing objects

InactiveUS20020140745A1Quickly availableNavigational calculation instrumentsDigital data processing detailsHand heldHand held devices

Systems are arranged to provide a user information which relates to objects of interest. A user may point a hand held device toward an object to address it. The device determines which objects are being addressed by making position and attitude measurements and further a reference and search of a database containing preprogrammed information relating to objects. Information relating to objects determined as objects presently being addressed is thereafter presented at a user interface. Devices of these systems include a point reference, a direction reference, a position determining support, attitude determining support, a computer processor and database, and a user interface. Methods of systems include the steps of addressing an object, determining position and attitude, searching a database, and presenting information to a user.

Owner:GEOVECTOR

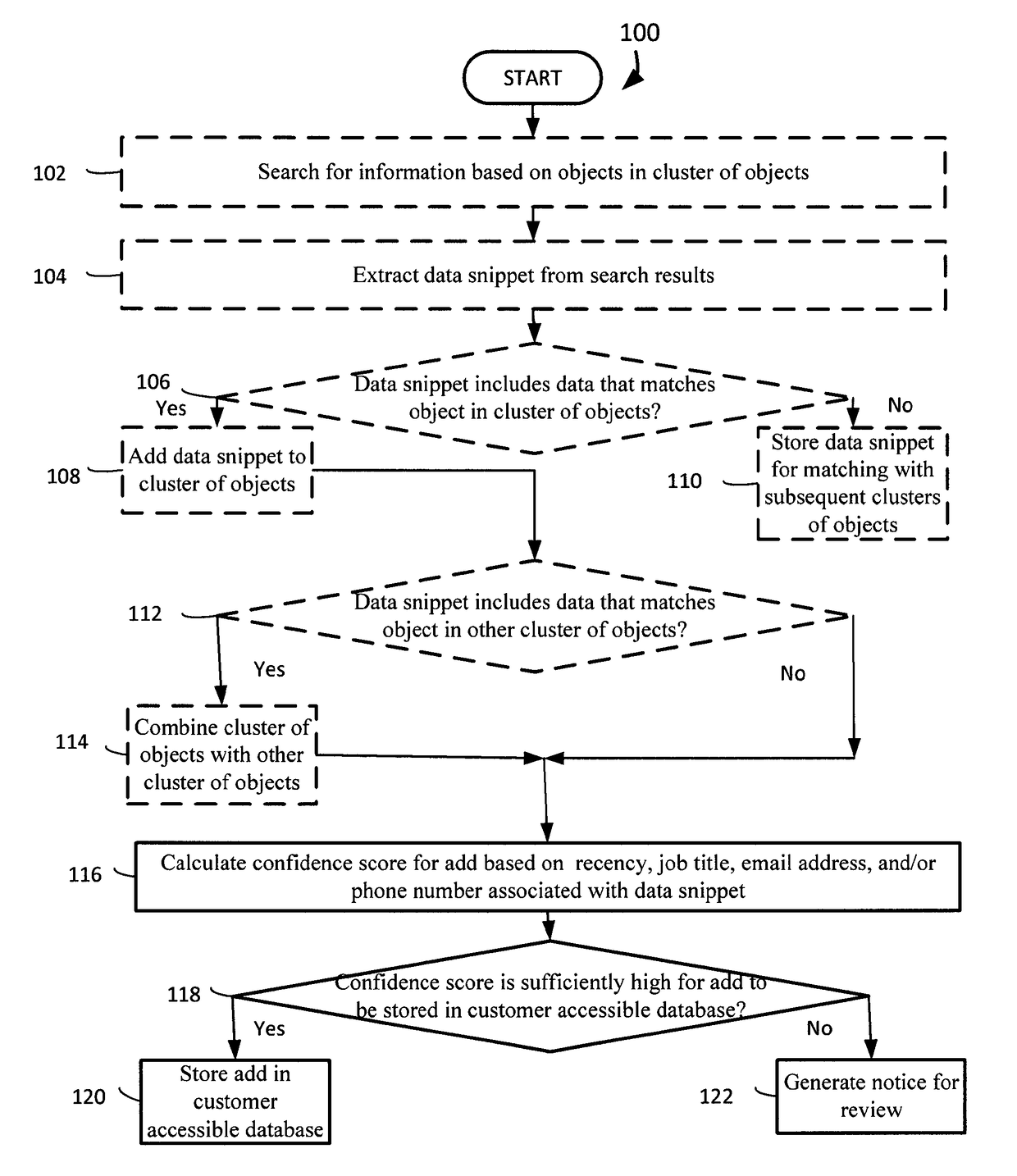

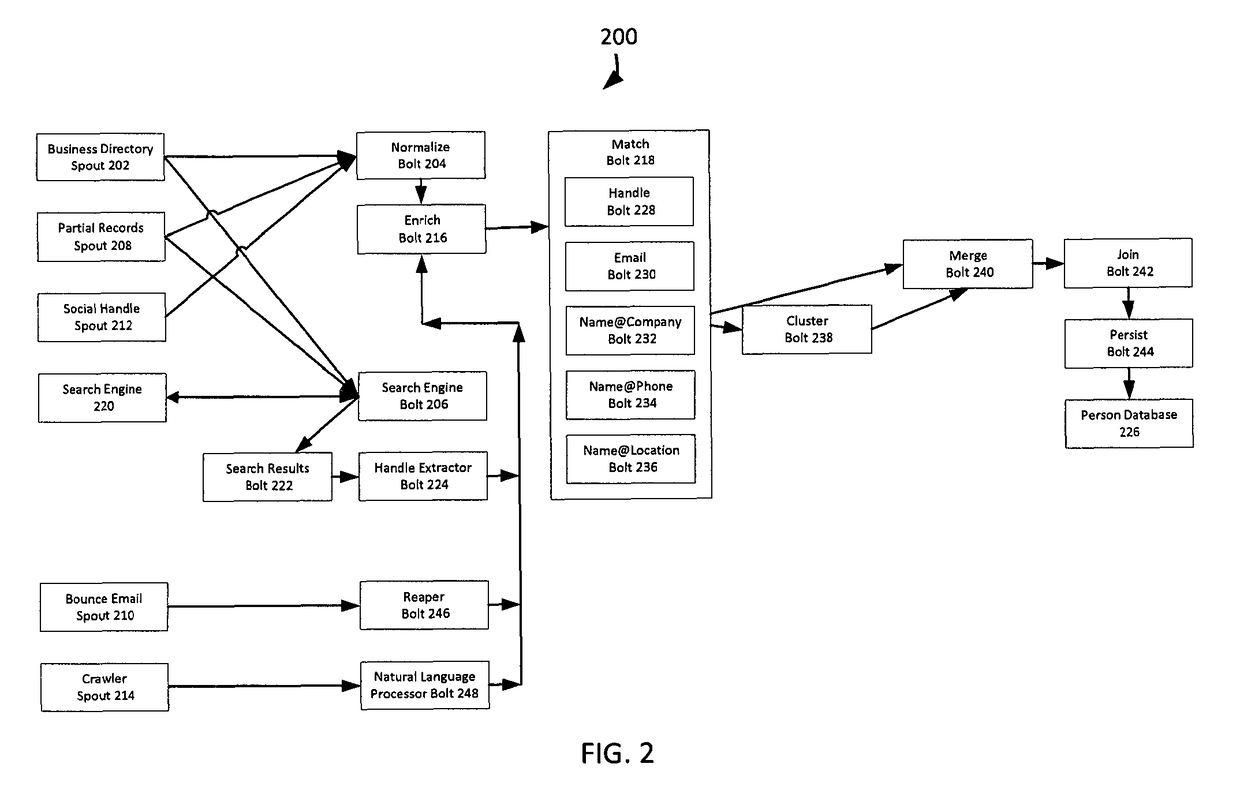

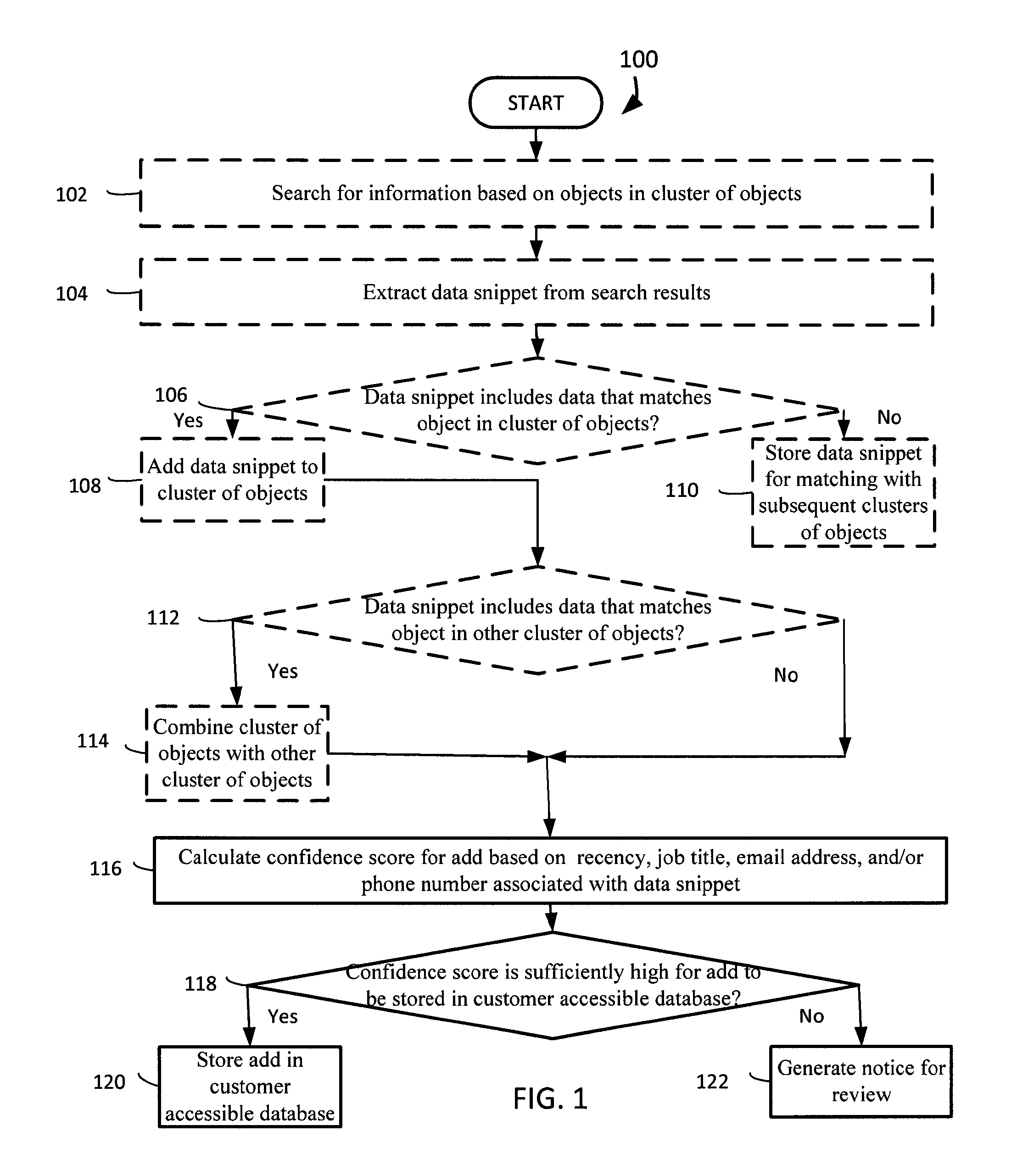

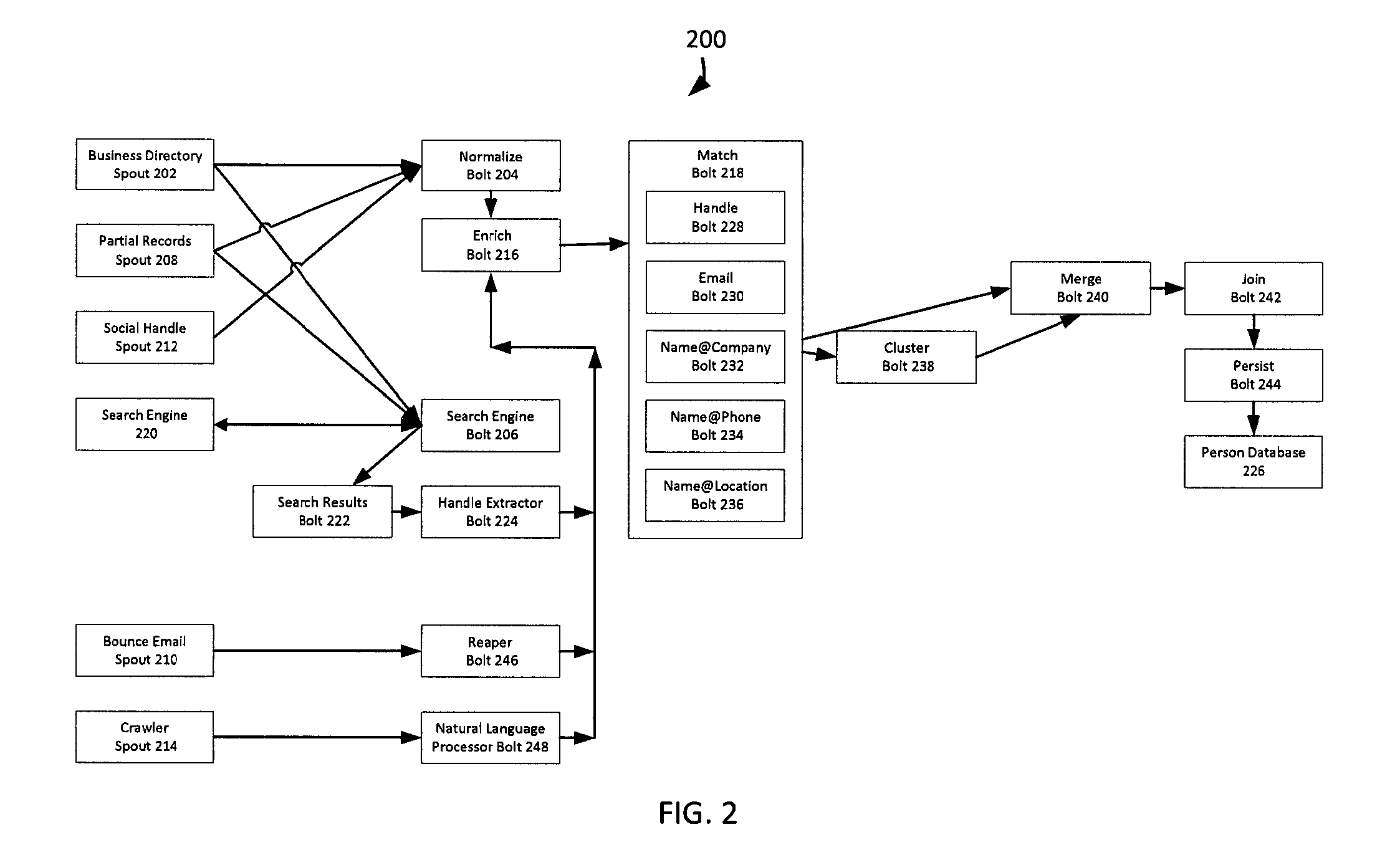

Confidently adding snippets of search results to clusters of objects

ActiveUS9760620B2Quality improvementMetadata text retrievalRelational databasesEmail addressData mining

Systems and methods are provided for matching snippets of search results to clusters of objects. A system adds a data snippet of a search result to a cluster of objects. The system calculates a confidence score for the add based on the recency, a job title, an email address, and / or a phone number associated with the data snippet. The system stores the add in the customer accessible database if the confidence score is sufficiently high for the add to be stored in the customer accessible database. The system generates a notice for review if the confidence score is not sufficiently high for the add to be stored in the customer accessible database.

Owner:SALESFORCE COM INC

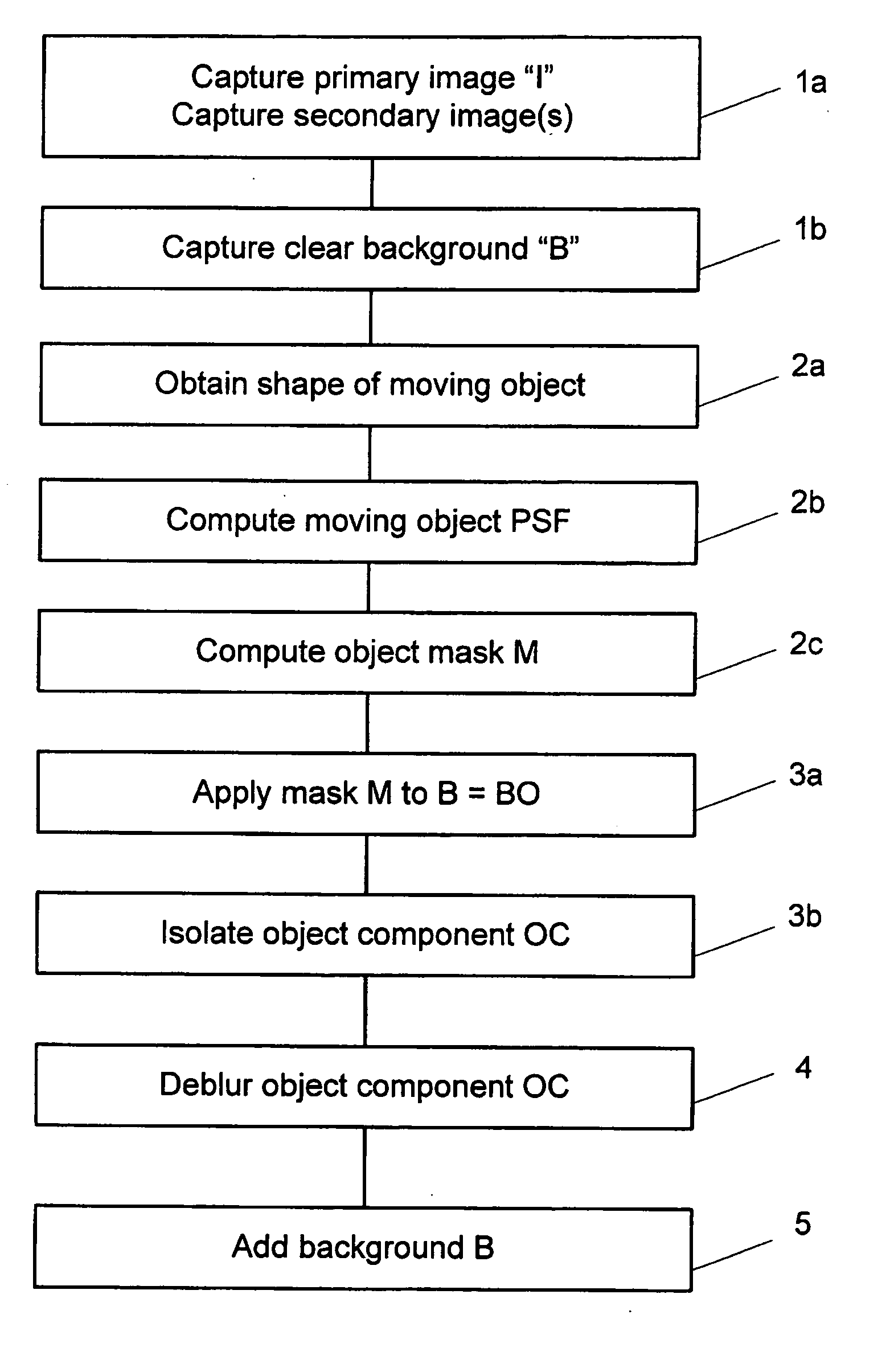

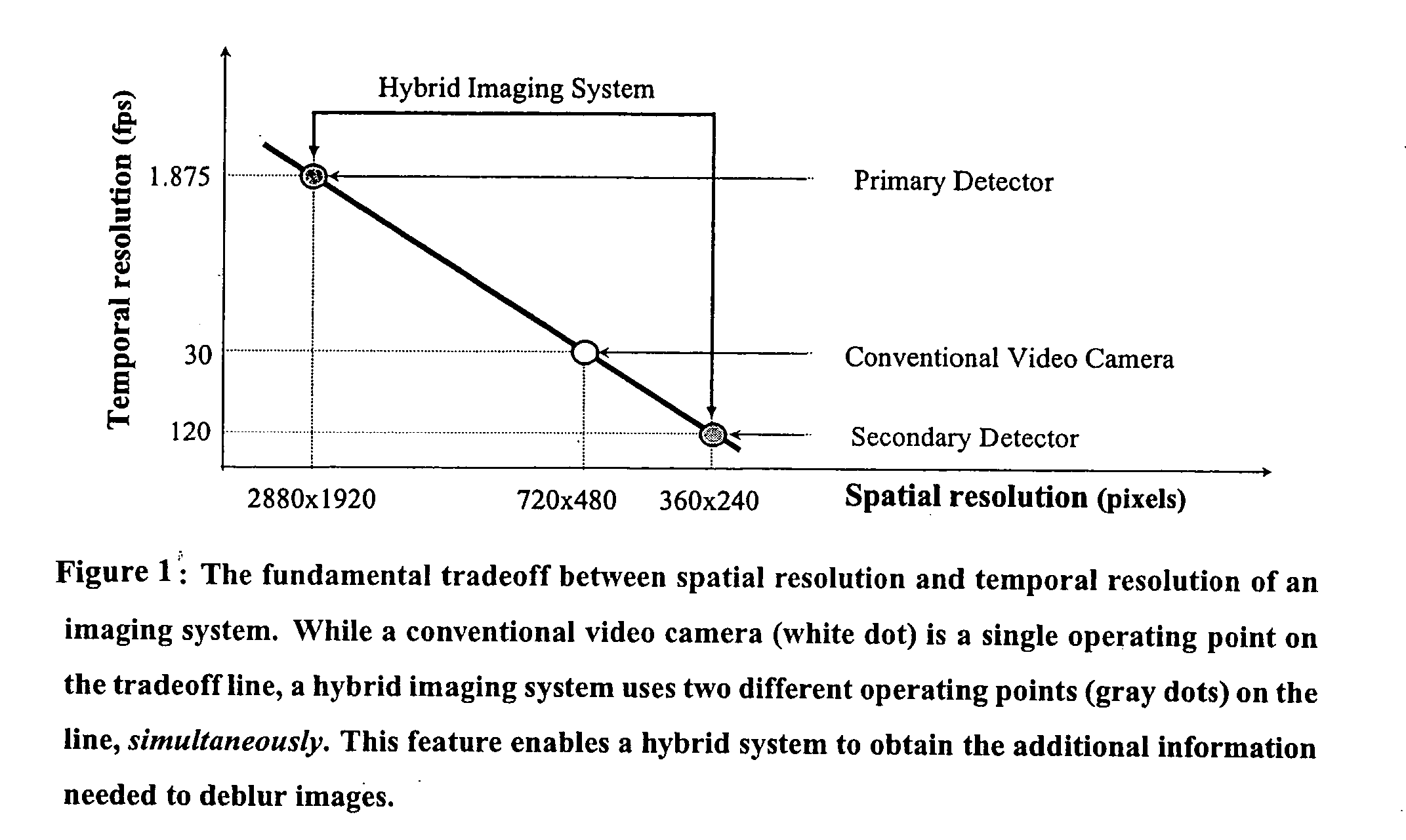

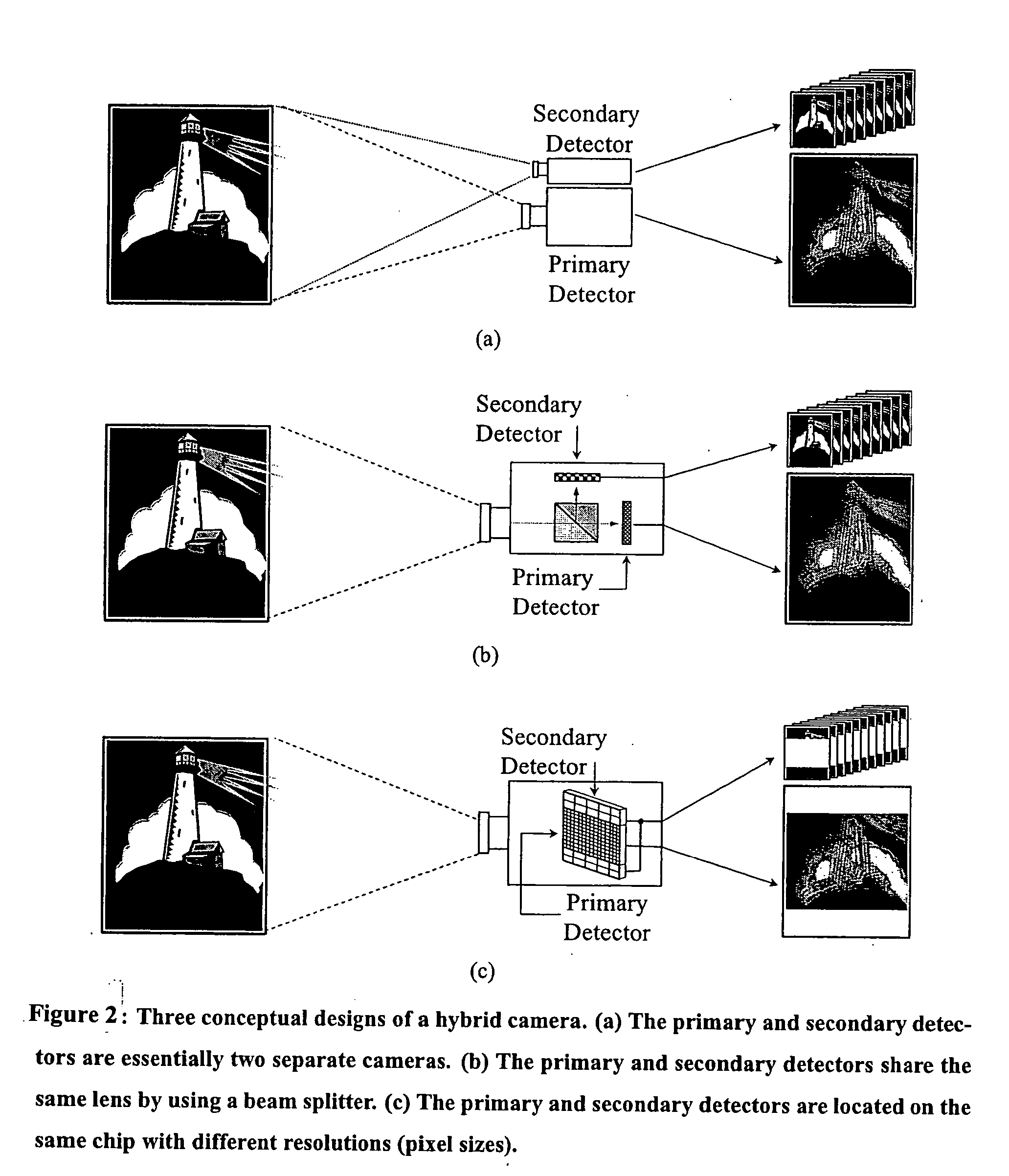

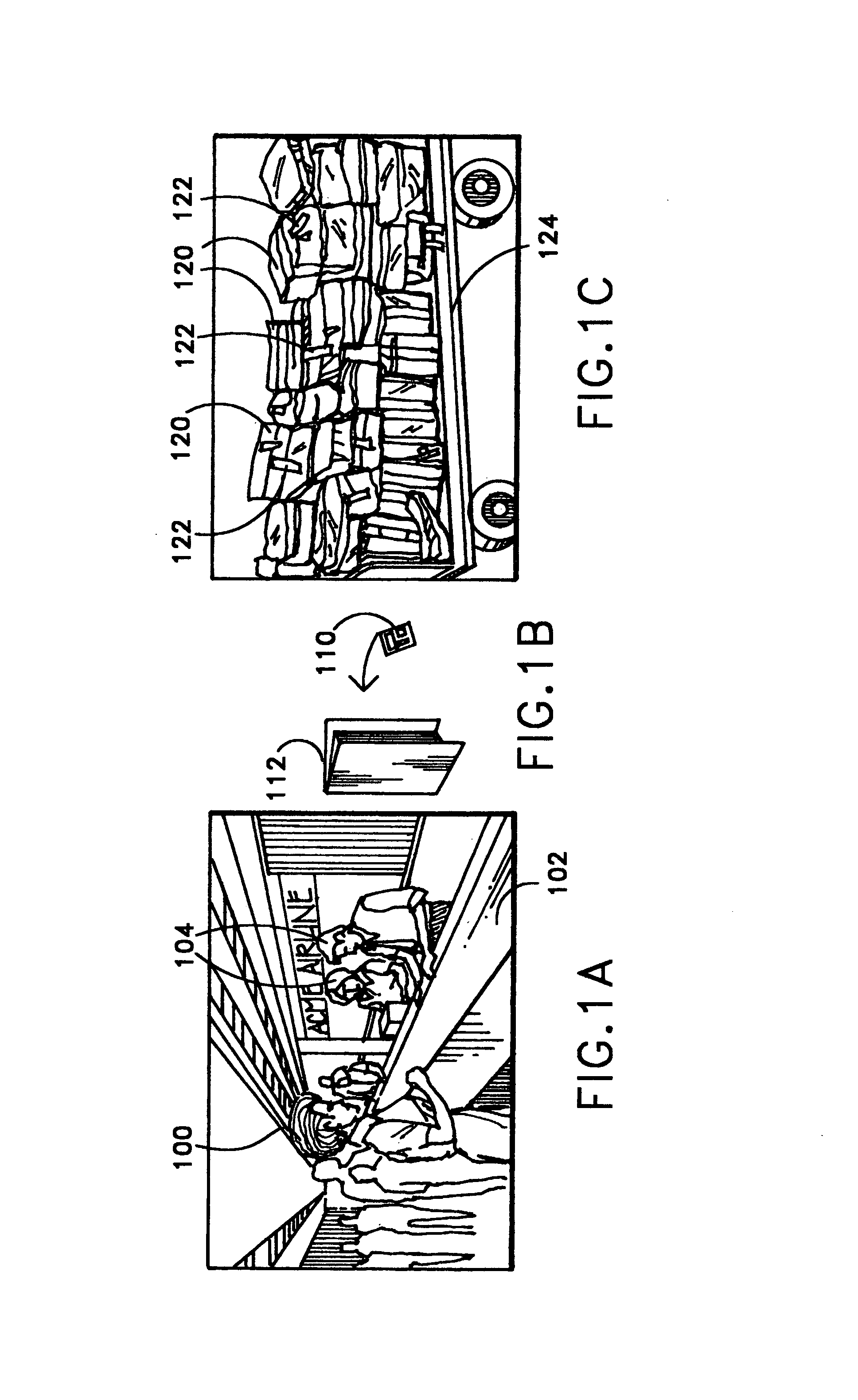

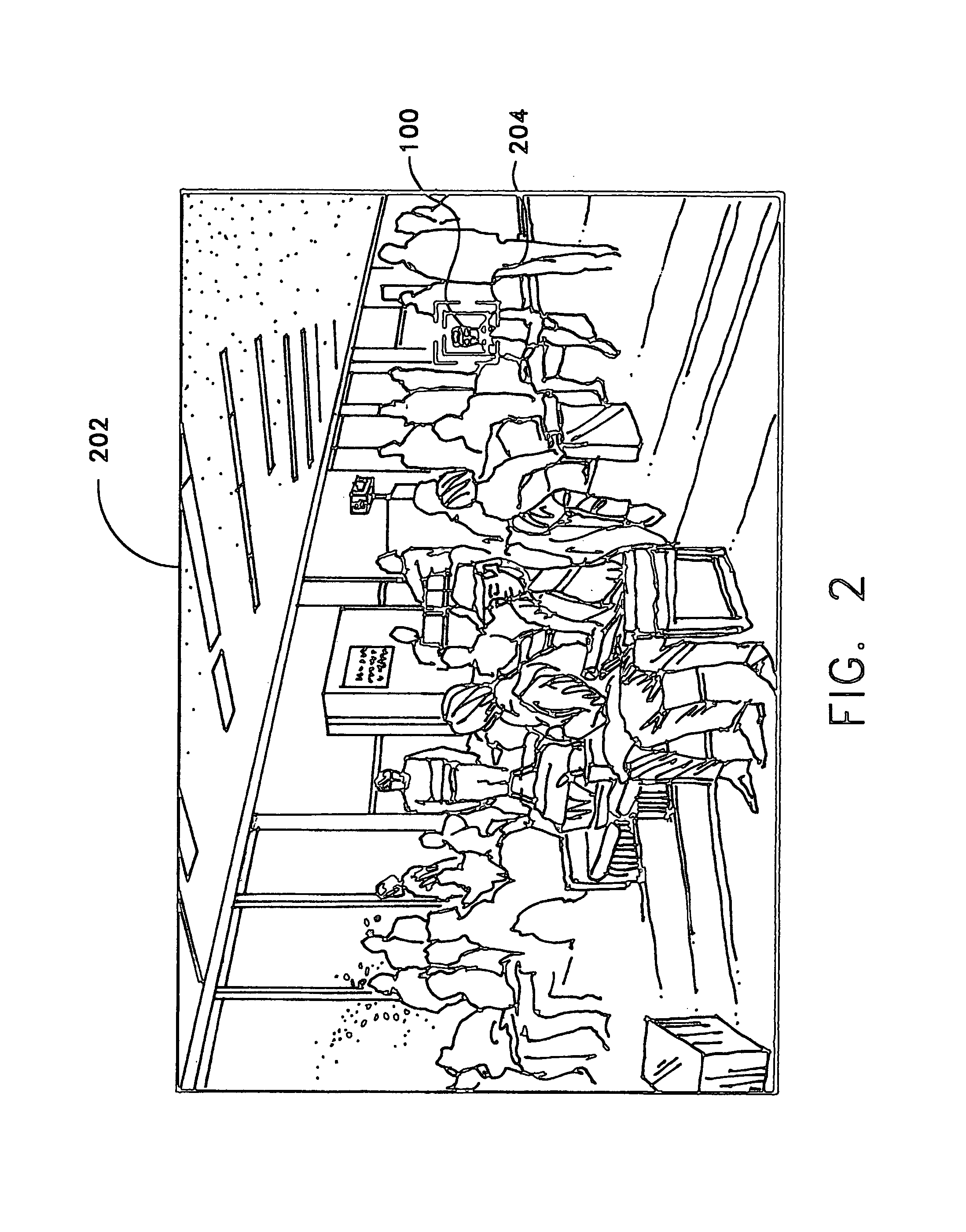

Method for de-blurring images of moving objects

ActiveUS20050047672A1Reduce spatial resolutionImage enhancementTelevision system detailsImaging processingObject system

Systems and methods for providing methods are provided for deblurring images, which are blurred due to the movement of objects in the imaged scene. The systems and methods involve separating a moving object component from a static or background component of a primary image. The moving object component is deblurred using suitable image processing algorithms, and then superimposed on the static or background component to obtain a deblurred primary image.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Synthesizing training data for broad area geospatial object detection

A system for broad area geospatial object recognition, identification, classification, location and quantification, comprising an image manipulation module to create synthetically-generated images to imitate and augment an existing quantity of orthorectified geospatial images; together with a deep learning module and a convolutional neural network serving as an image analysis module, to analyze a large corpus of orthorectified geospatial images, identify and demarcate a searched object of interest from within the corpus, locate and quantify the identified or classified objects from the corpus of geospatial imagery available to the system. The system reports results in a requestor's preferred format.

Owner:MAXAR INTELLIGENCE INC

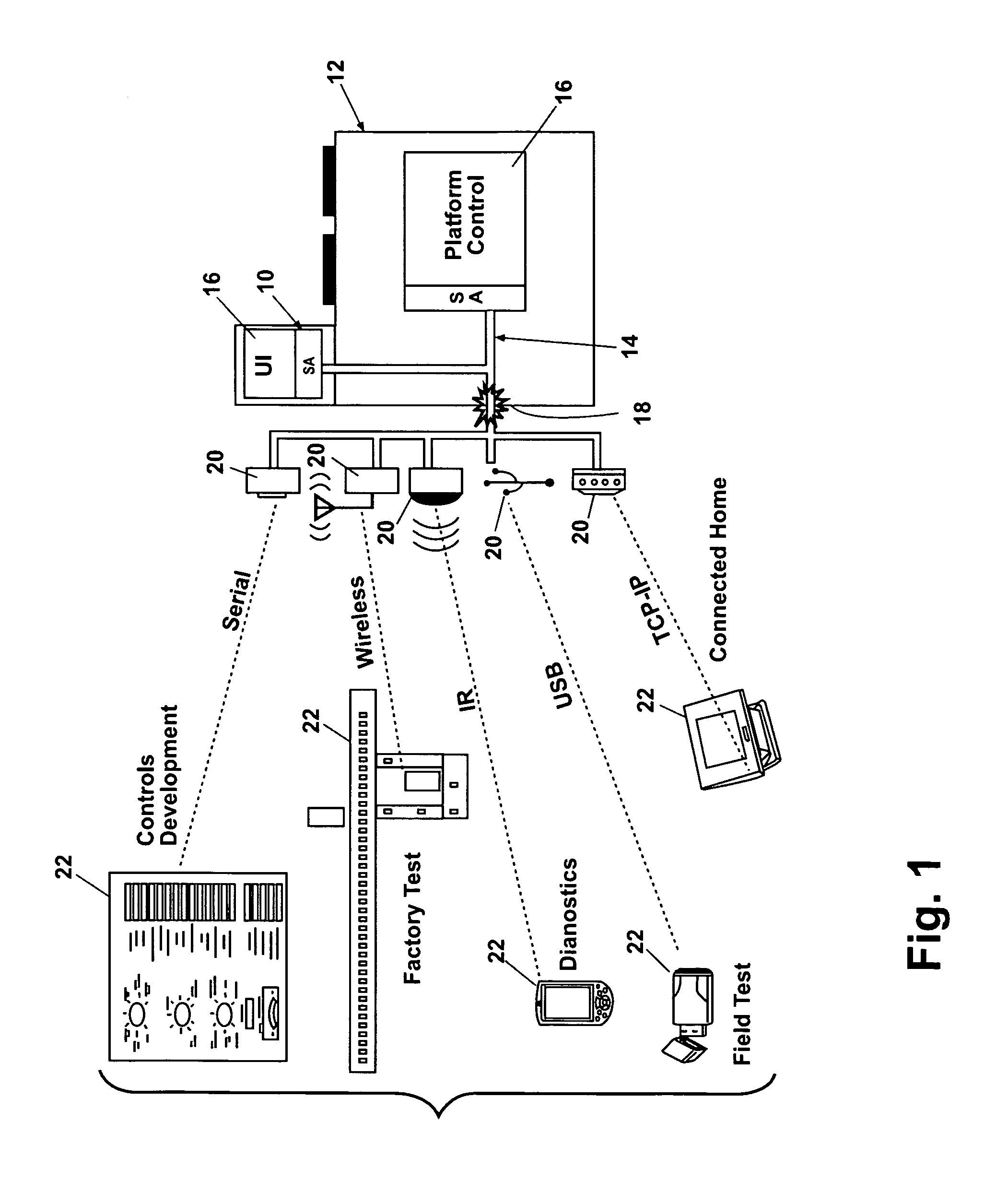

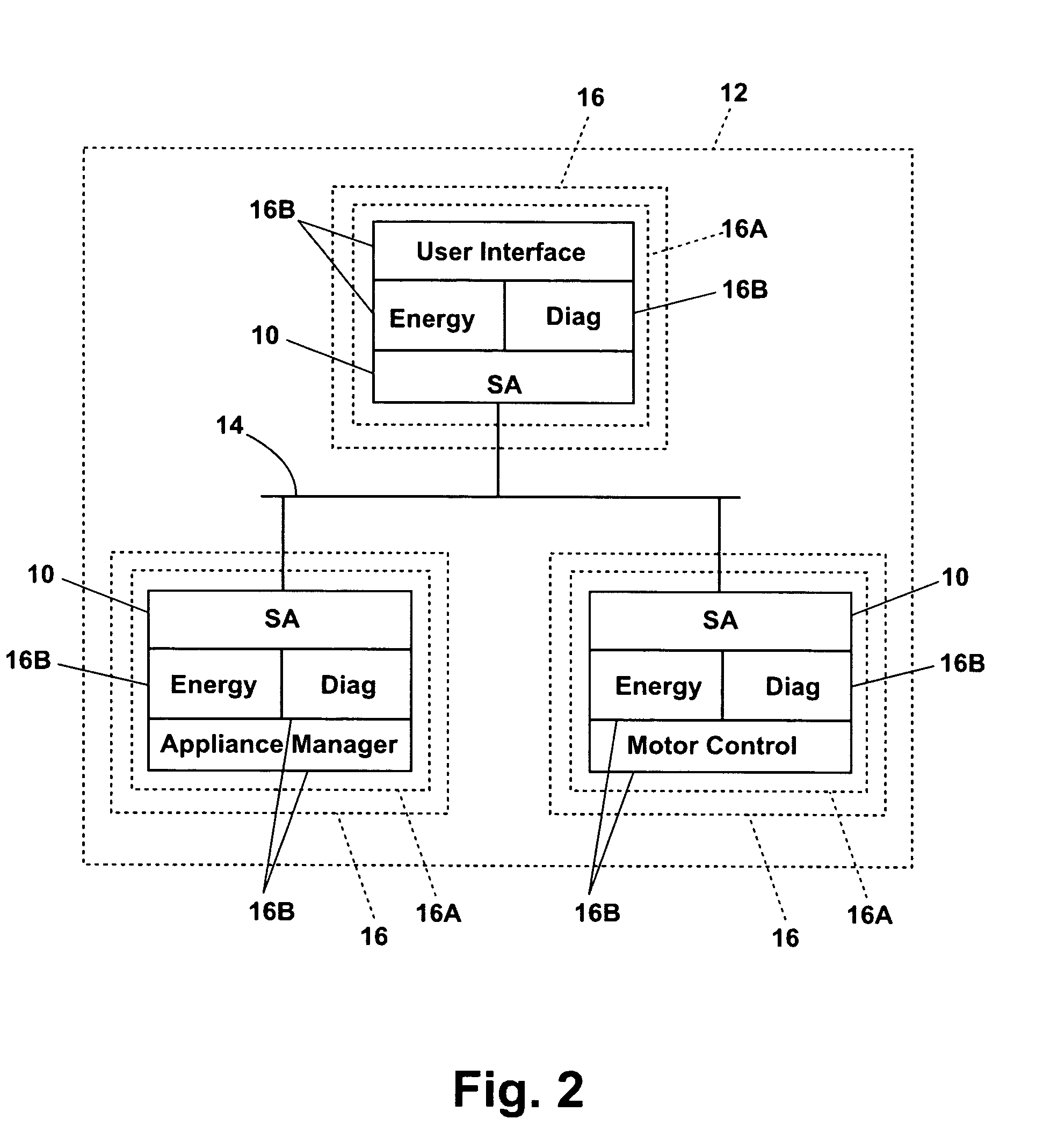

Distributed object-oriented appliance control system

InactiveUS20080188963A1Error detection/correctionInterprogram communicationDistributed objectControl system

The invention relates to an object-oriented control system for an appliance, configurable by a configuration mechanism in selective operable communication with a plurality of object oriented control systems using a packet protocol for constructing messages comprising identifiers from a plurality of namespaces associated with the building blocks of object-oriented systems. The meaning of each unique identifier within class library namespace is uniquely meaningful throughout a universe of appliances.

Owner:WHIRLPOOL CORP

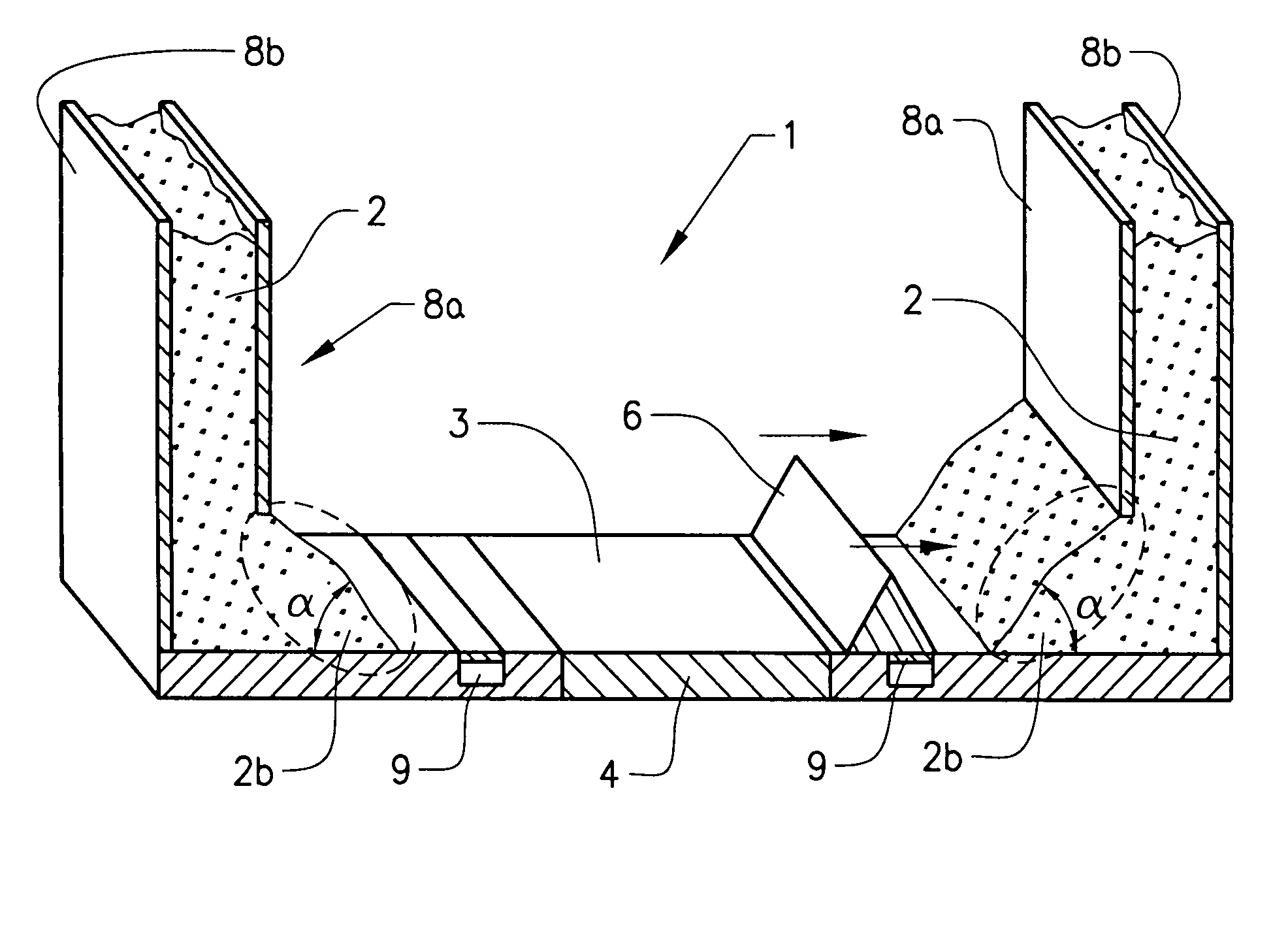

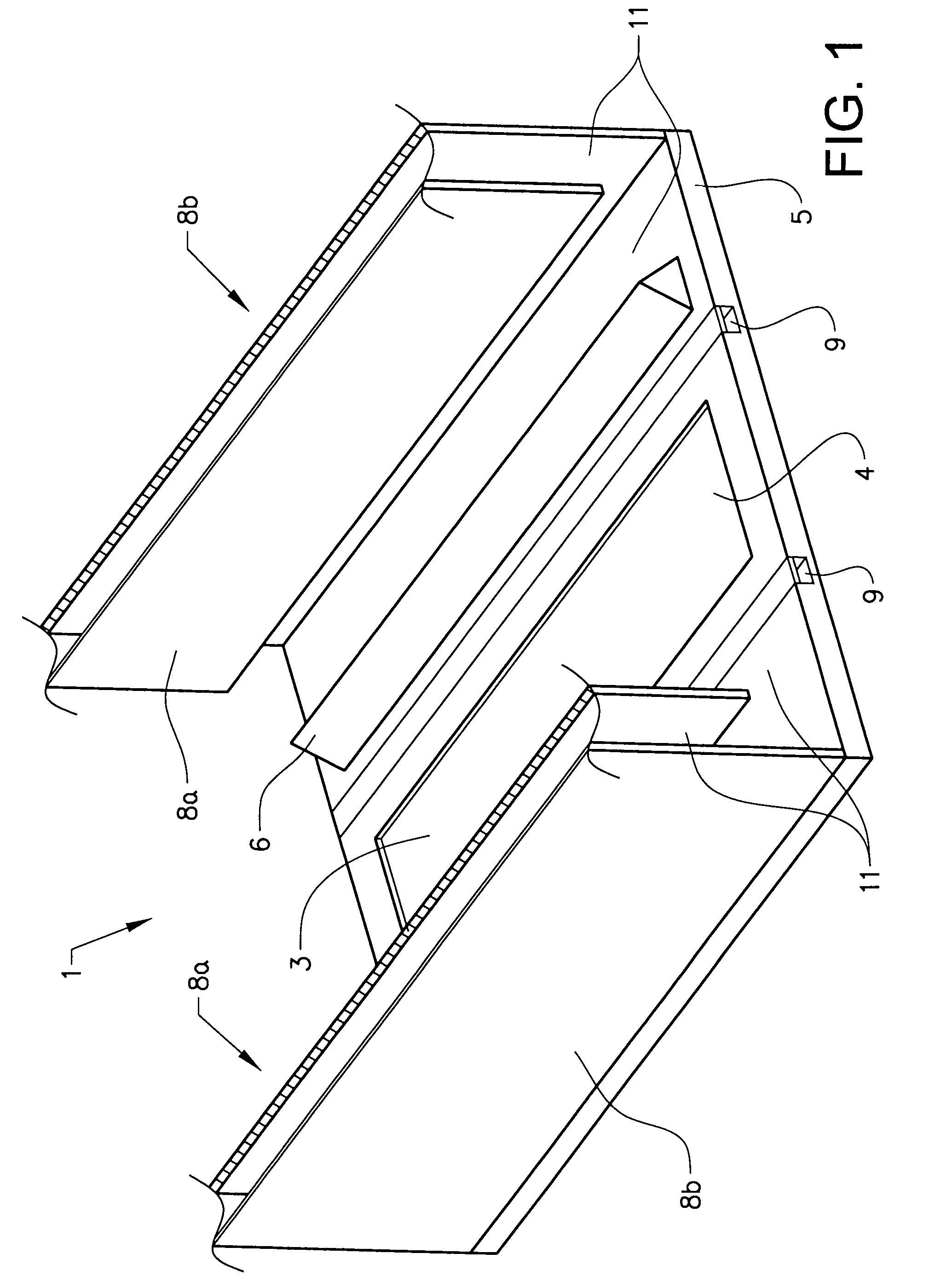

Systems, apparatus, and methods to feed and distribute powder used to produce three-dimensional objects

ActiveUS7871551B2Mechanically reliableMechanically simplerAdditive manufacturing apparatusConfectioneryObject systemMaterials science

Systems, apparatus, and methods feed and distribute a powder over a working area used for producing three-dimensional objects. A powder storage unit contains a supply of powder, and a distribution member is arranged to be moveable across the working area to distribute a portion of powder onto the working area. In an embodiment, the distribution member is, in a first step, moveable a predetermined distance into a supply of powder placed in the powder storage unit, said distance being sufficiently long to bring about a transfer of a portion of powder from the powder supply at one side of the distribution member to another side of the distribution member facing the working area, and the distribution member is, in a second step, moveable towards and across the working area to distribute the portion of powder onto the working area. Other embodiments are disclosed.

Owner:ARCAM AB

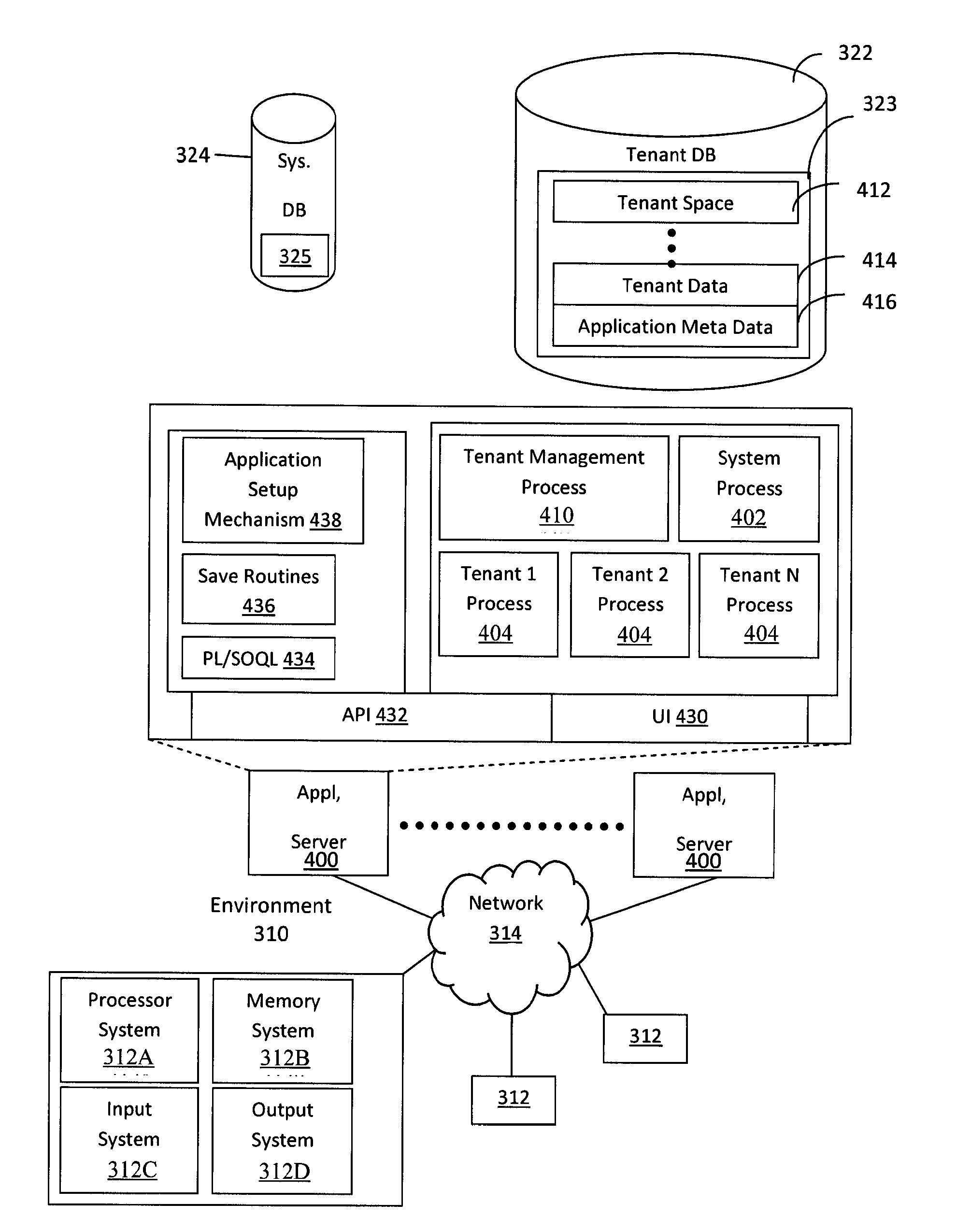

Confidently adding snippets of search results to clusters of objects

ActiveUS20150032738A1Quality improvementMetadata text retrievalDigital data processing detailsEmail addressData mining

Systems and methods are provided for matching snippets of search results to clusters of objects. A system adds a data snippet of a search result to a cluster of objects. The system calculates a confidence score for the add based on the recency, a job title, an email address, and / or a phone number associated with the data snippet. The system stores the add in the customer accessible database if the confidence score is sufficiently high for the add to be stored in the customer accessible database. The system generates a notice for review if the confidence score is not sufficiently high for the add to be stored in the customer accessible database.

Owner:SALESFORCE COM INC

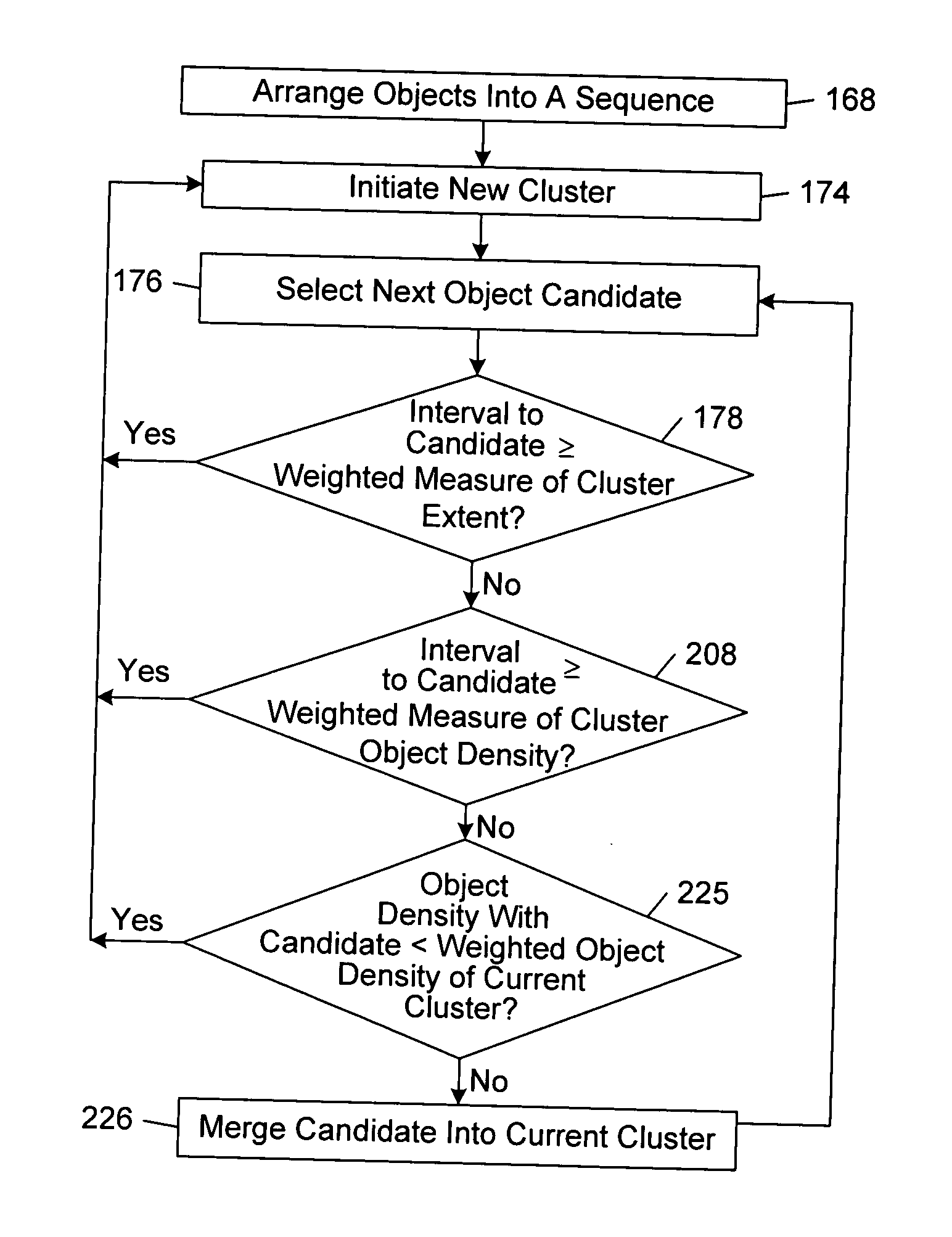

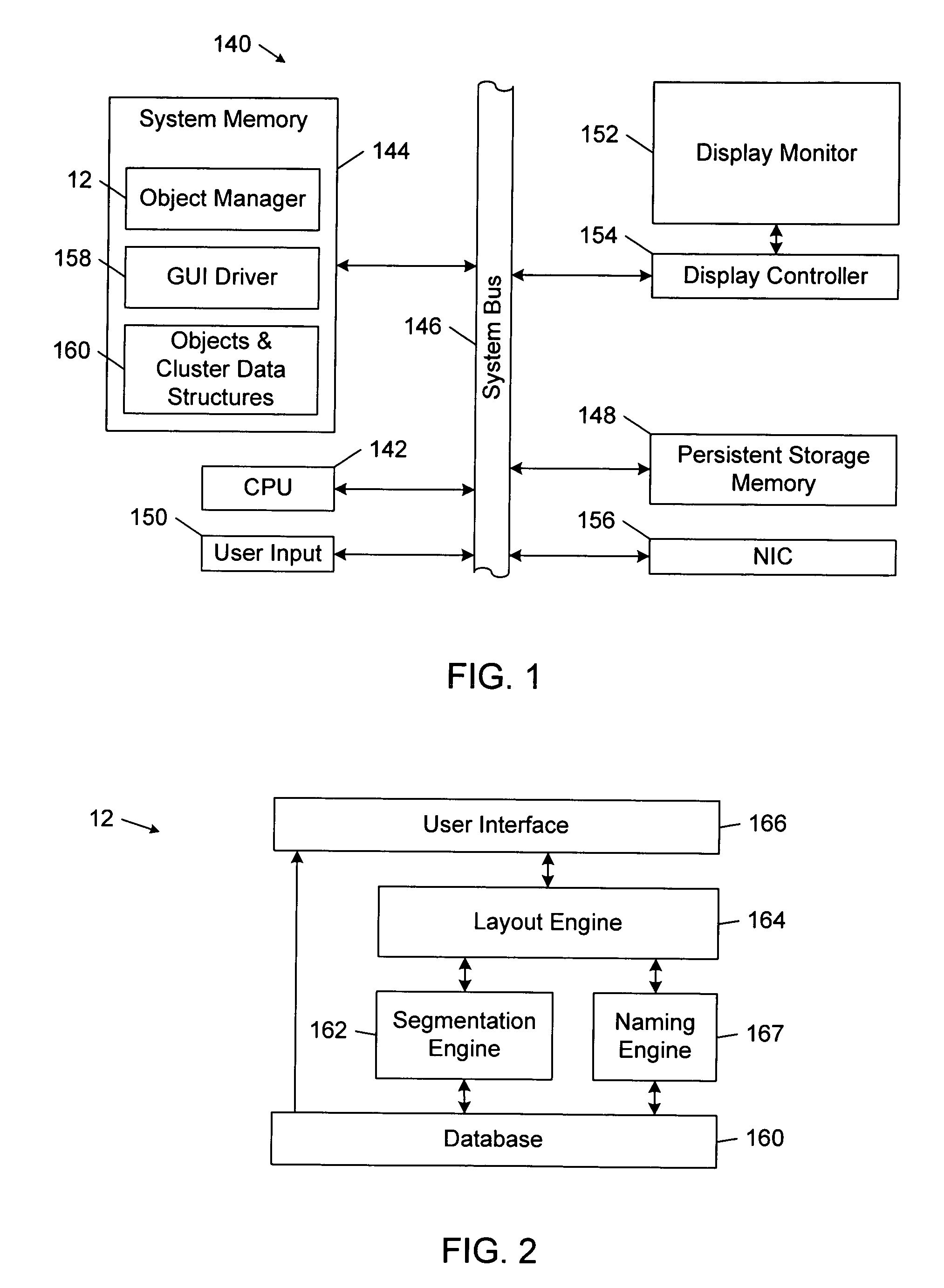

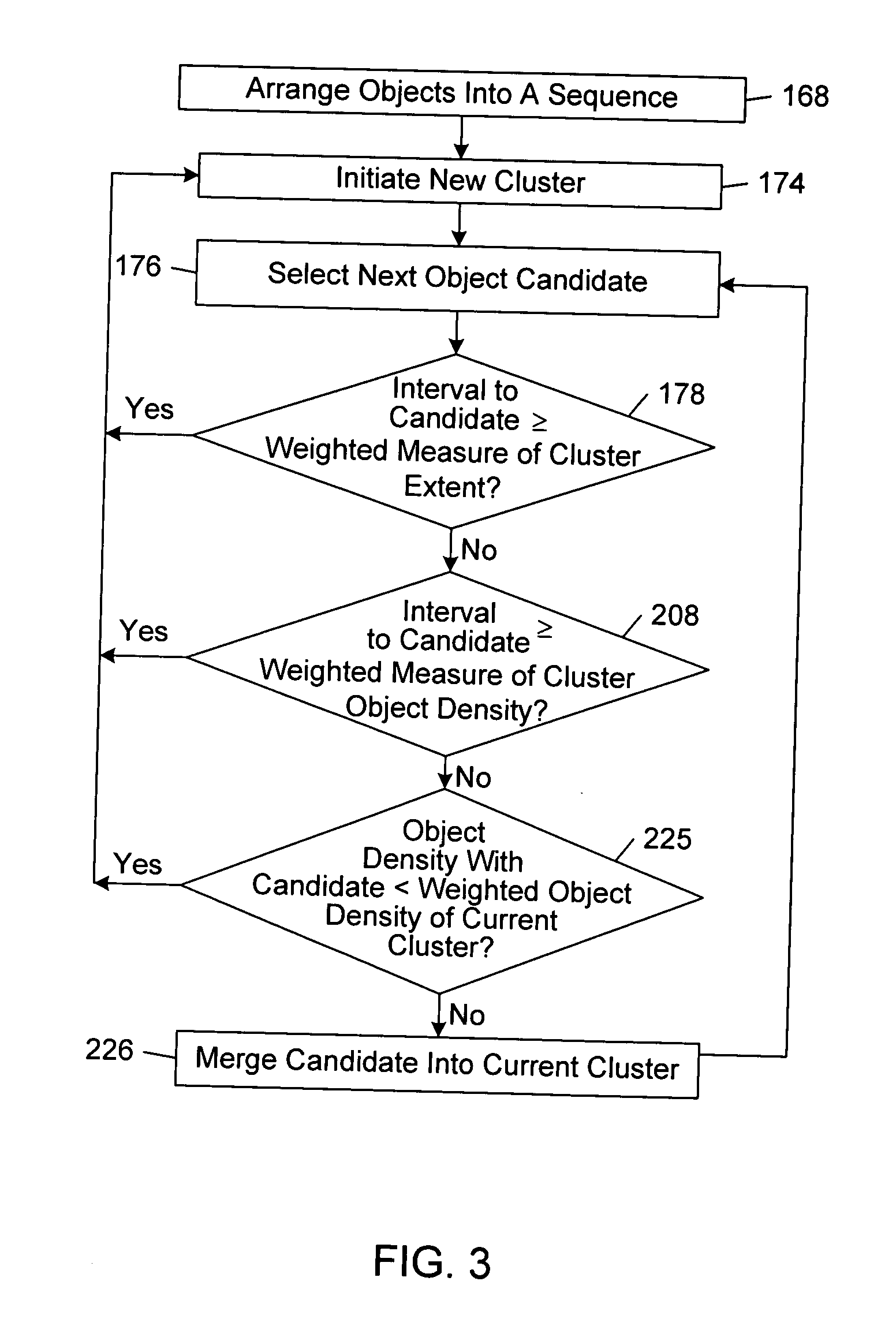

Organizing a collection of objects

InactiveUS20050027712A1Reduce quality problemsTransforming corporations, markets, and the global economyDigital data processing detailsStill image data browsing/visualisationGraphicsArtificial intelligence

Owner:HEWLETT PACKARD DEV CO LP

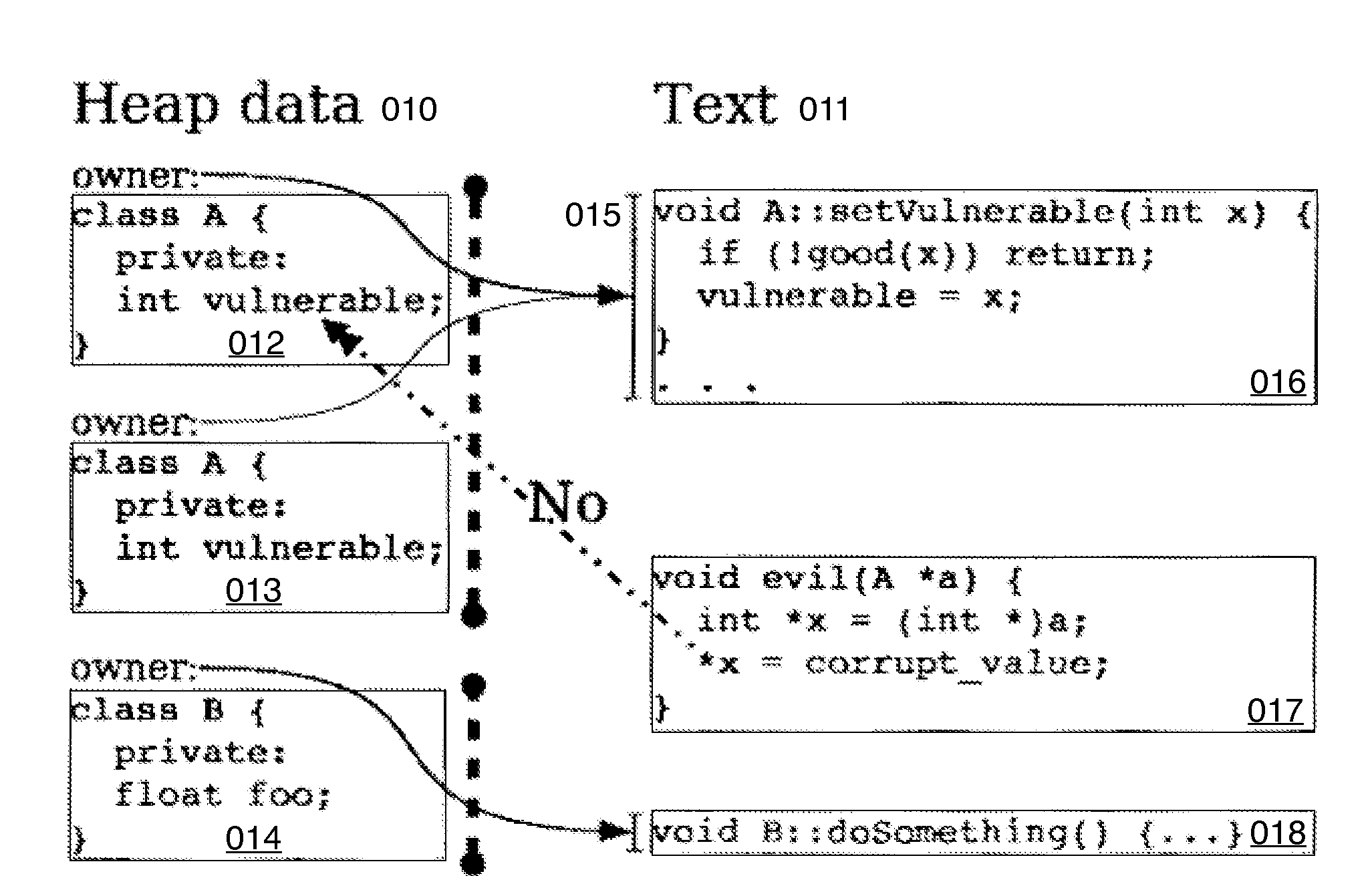

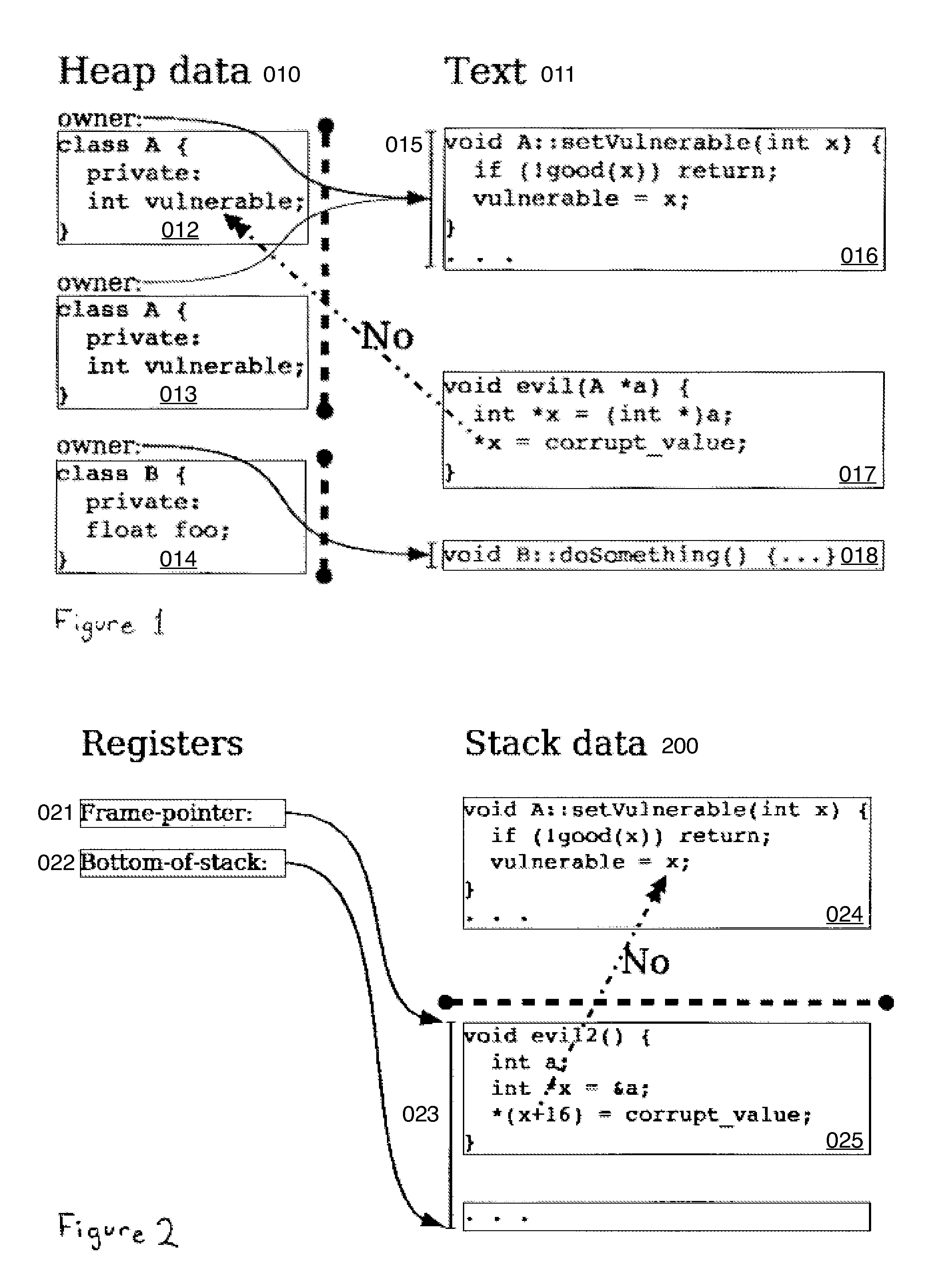

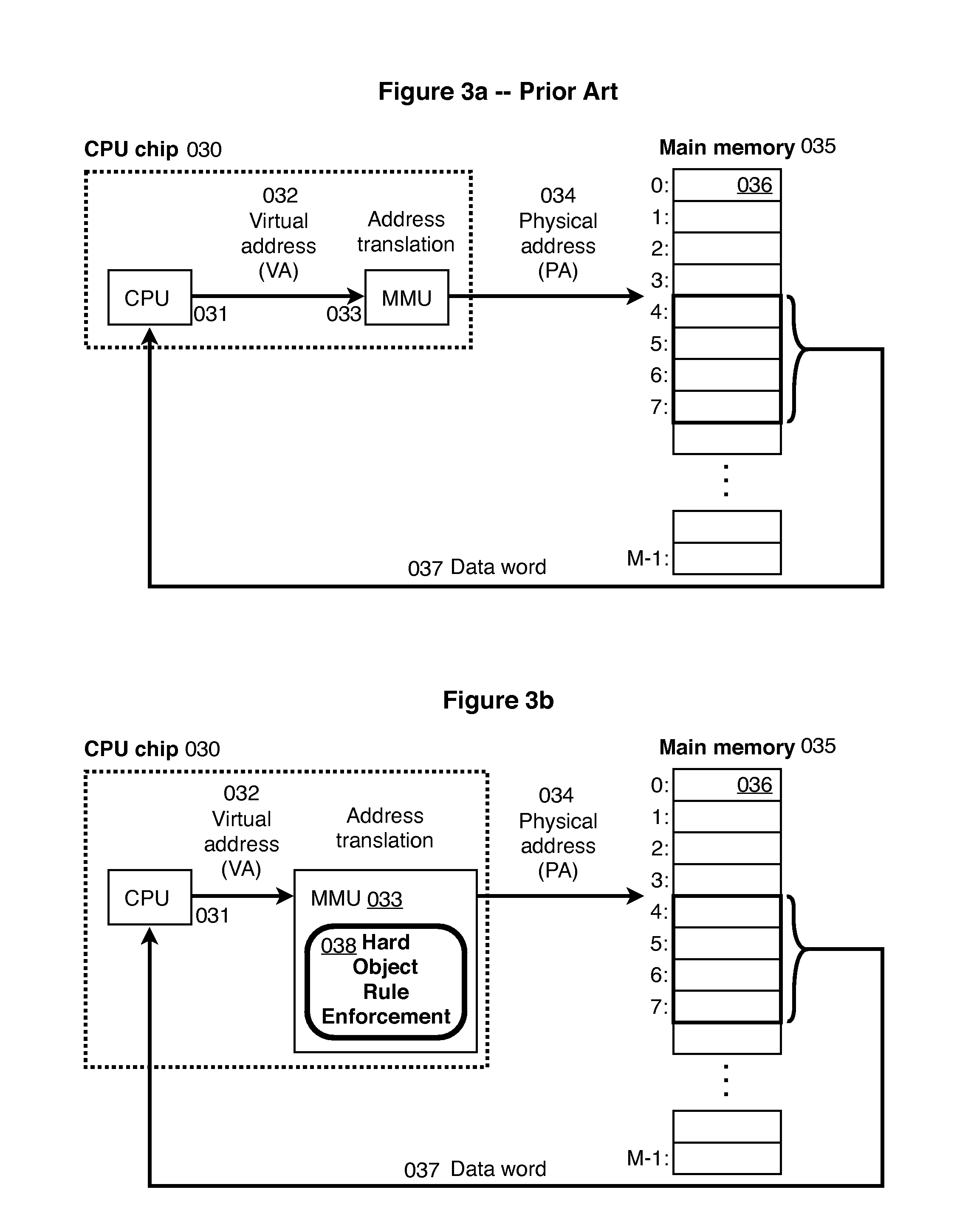

Hard Object: Hardware Protection for Software Objects

ActiveUS20080222397A1Efficiently implement enforceable separation of programDigital computer detailsAnalogue secracy/subscription systemsProcessor registerPhysical address

In accordance with one embodiment, additions to the standard computer microprocessor architecture hardware are disclosed comprising novel page table entry fields 015 062, special registers 021 022, instructions for modifying these fields 120 122 and registers 124 126, and hardware-implemented 038 runtime checks and operations involving these fields and registers. More specifically, in the above embodiment of a Hard Object system, there is additional meta-data 061 in each page table entry beyond what it commonly holds, and each time a data load or store is issued from the CPU, and the virtual address 032 translated to the physical address 034, the Hard Object system uses its additional PTE meta-data 061 to perform memory access checks additional to those done in current systems. Together with changes to software, these access checks can be arranged carefully to provide more fine-grain access control for data than do current systems.

Owner:WILKERSON DANIEL SHAWCROSS +1

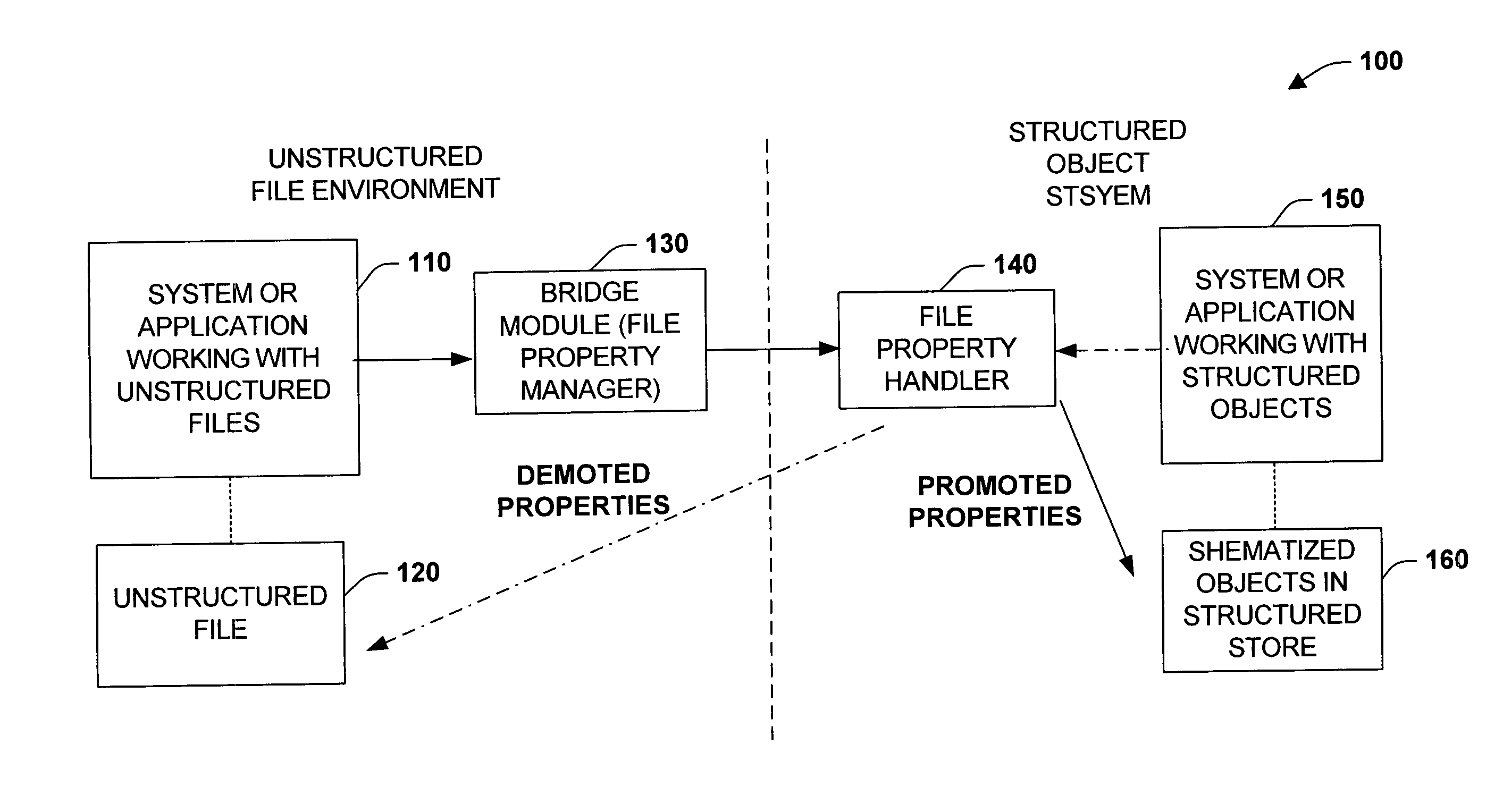

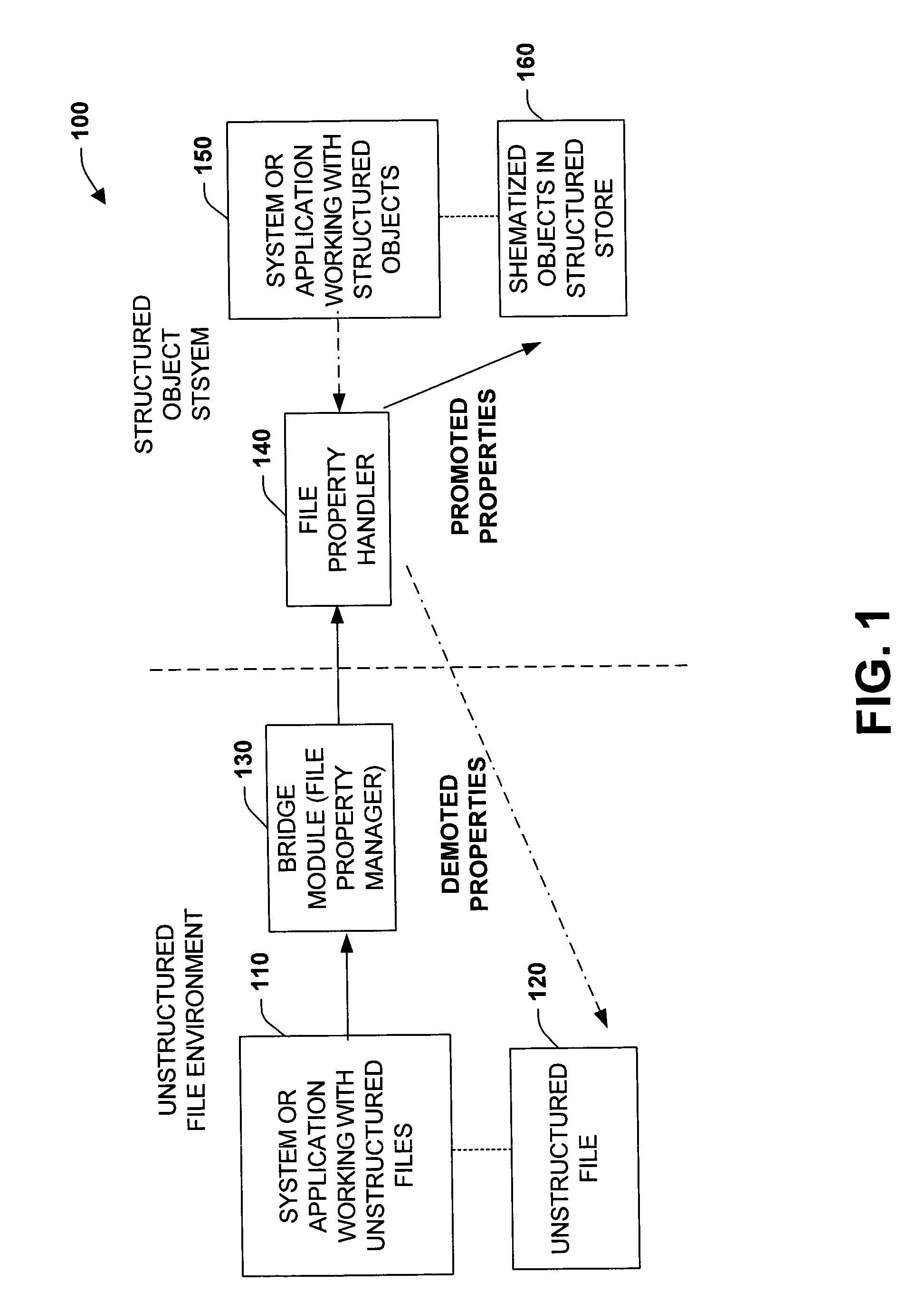

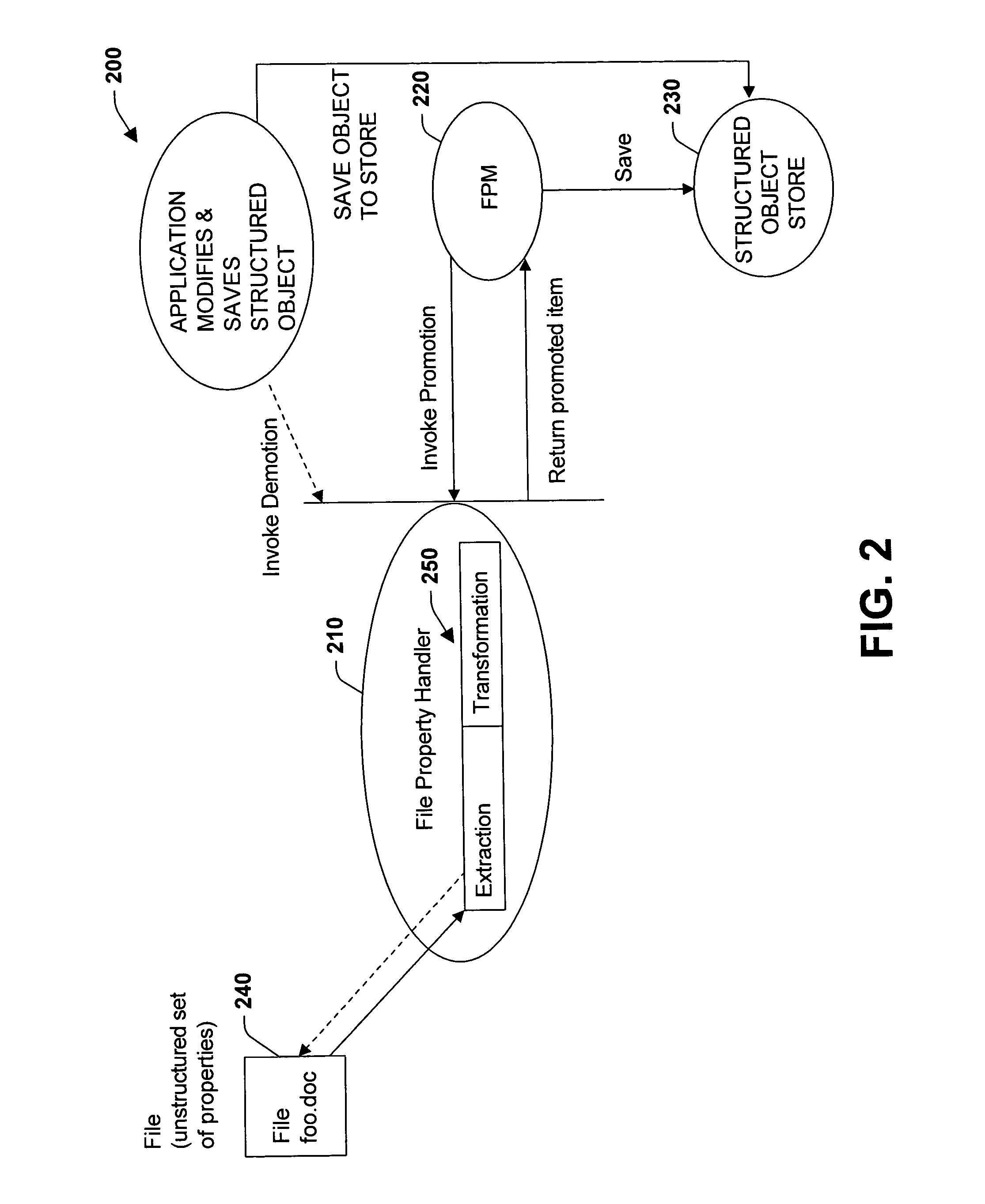

Promotion and demotion techniques to facilitate file property management between object systems

ActiveUS20050091285A1Facilitate file manipulationAchieve consistencyAcutation objectsData processing applicationsComputer compatibilityObject store

The present invention relates to a system and methodology to facilitate interoperability and compatibility between disparate data systems. In one aspect, a file transformation system is provided having at least one file associated with one or more unstructured properties. A file property handler manipulates the unstructured properties in accordance with one or more structured properties associated with a structured object store environment. If an unstructured file is to be operated in the context of a structured object store environment, a promotion operation is performed to update unstructured properties in the file with structured properties suitable for operation in the structured object store environment. If a promoted item were to be manipulated in the structured object store environment, a demotion operation or reverse transformation is performed to update properties in the file.

Owner:MICROSOFT TECH LICENSING LLC

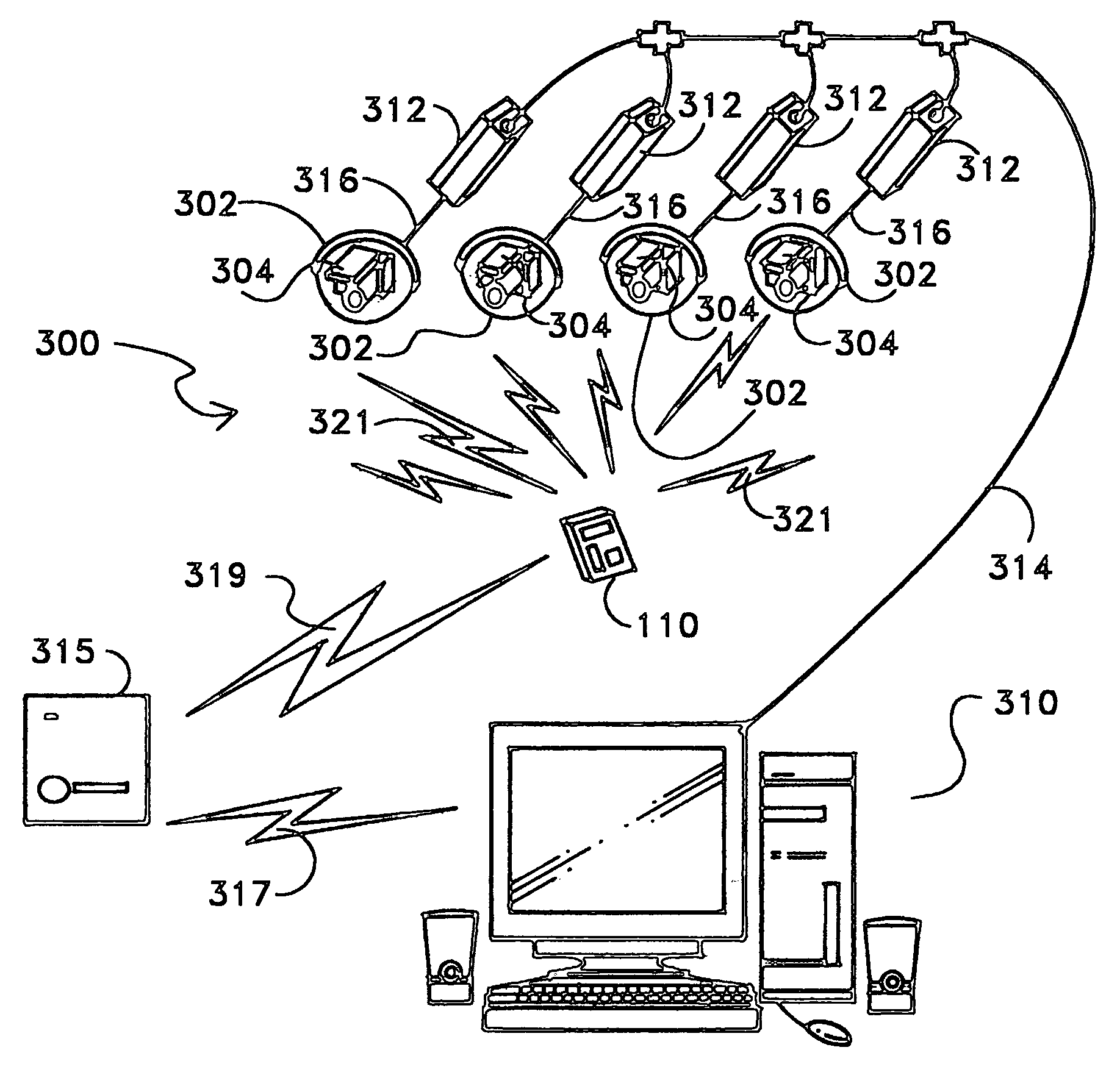

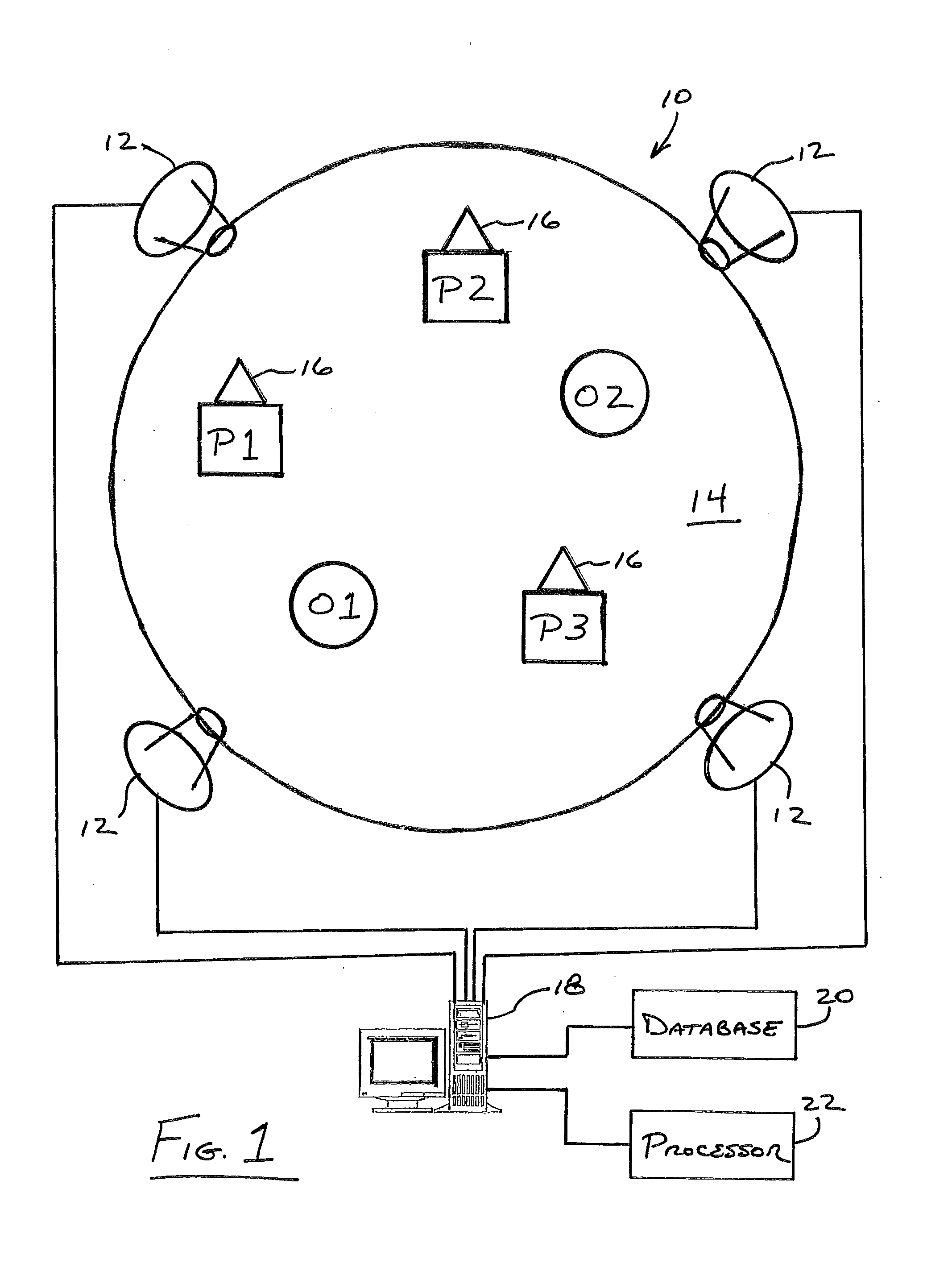

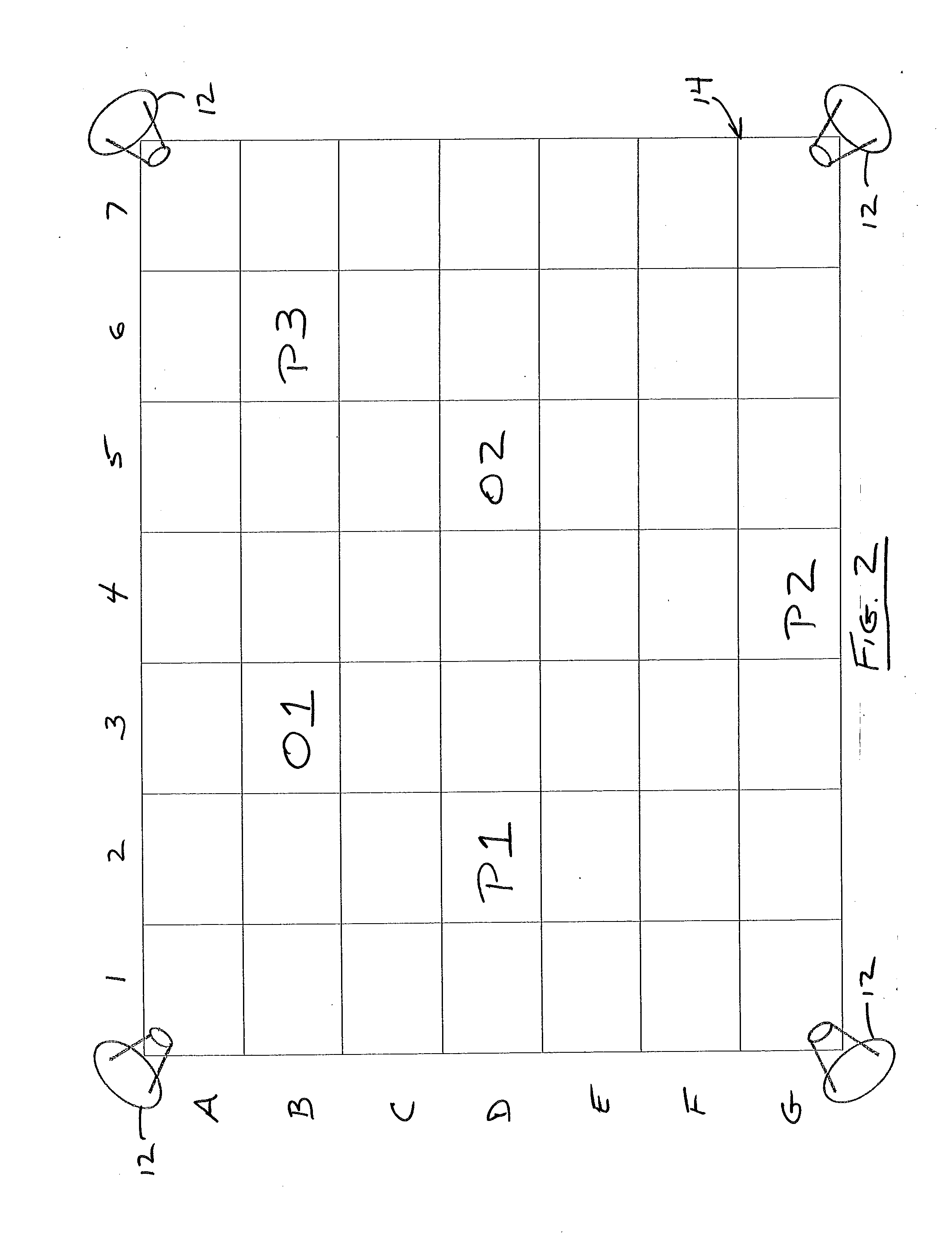

Systems and methods for location of objects

ActiveUS7151454B2Easy to handleTelevision system detailsColor television detailsObject systemCable television

Systems and methods that may be employed to visually locate and / or track objects equipped with active RFID tags. The disclosed systems and methods may employ an articulated camera / s, such as closed circuit television (“CCTV”) or other suitable type of articulated camera / s, that is equipped with an antenna array.

Owner:UTC FIRE & SECURITY AMERICAS CORPORATION INC

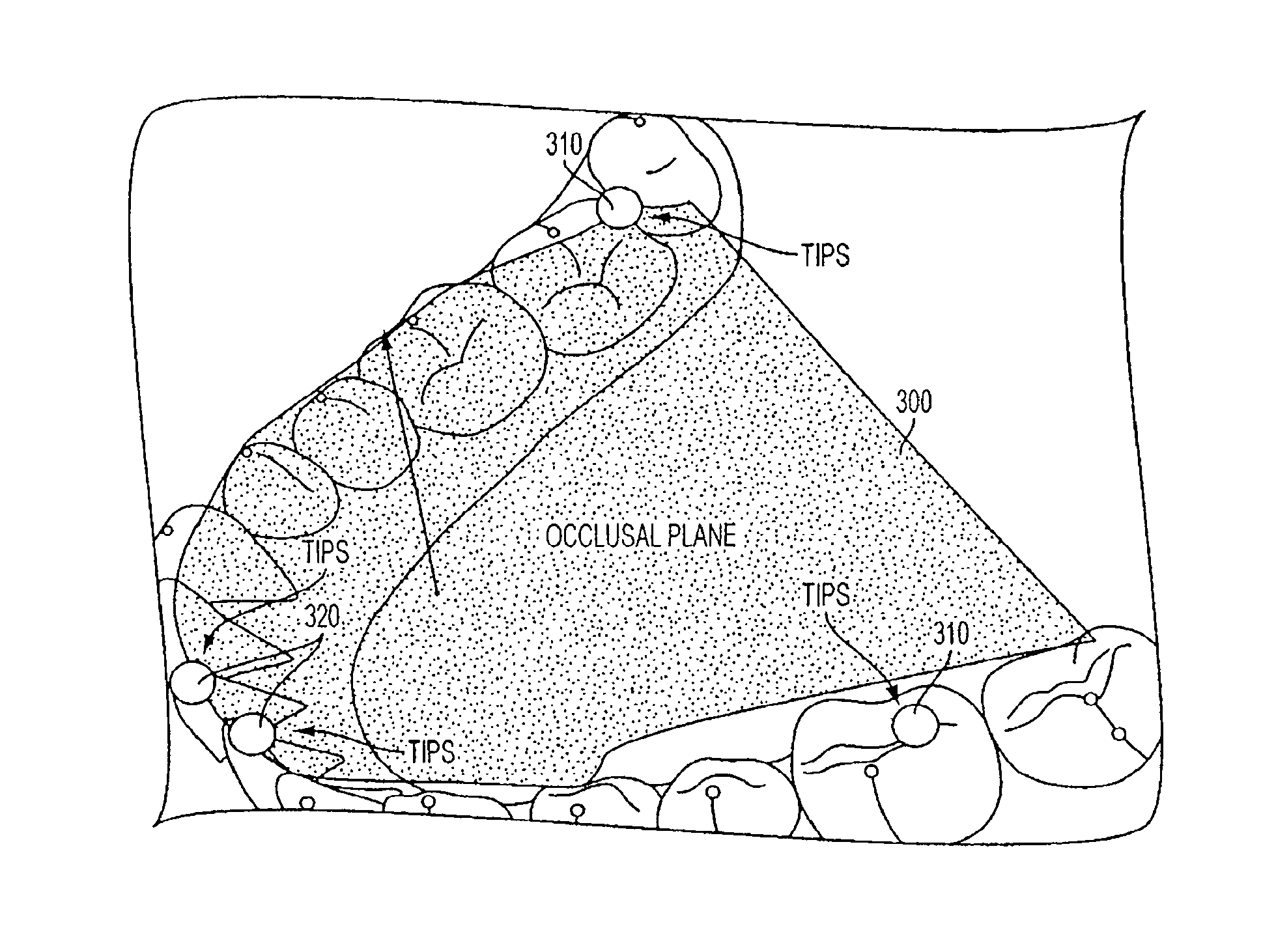

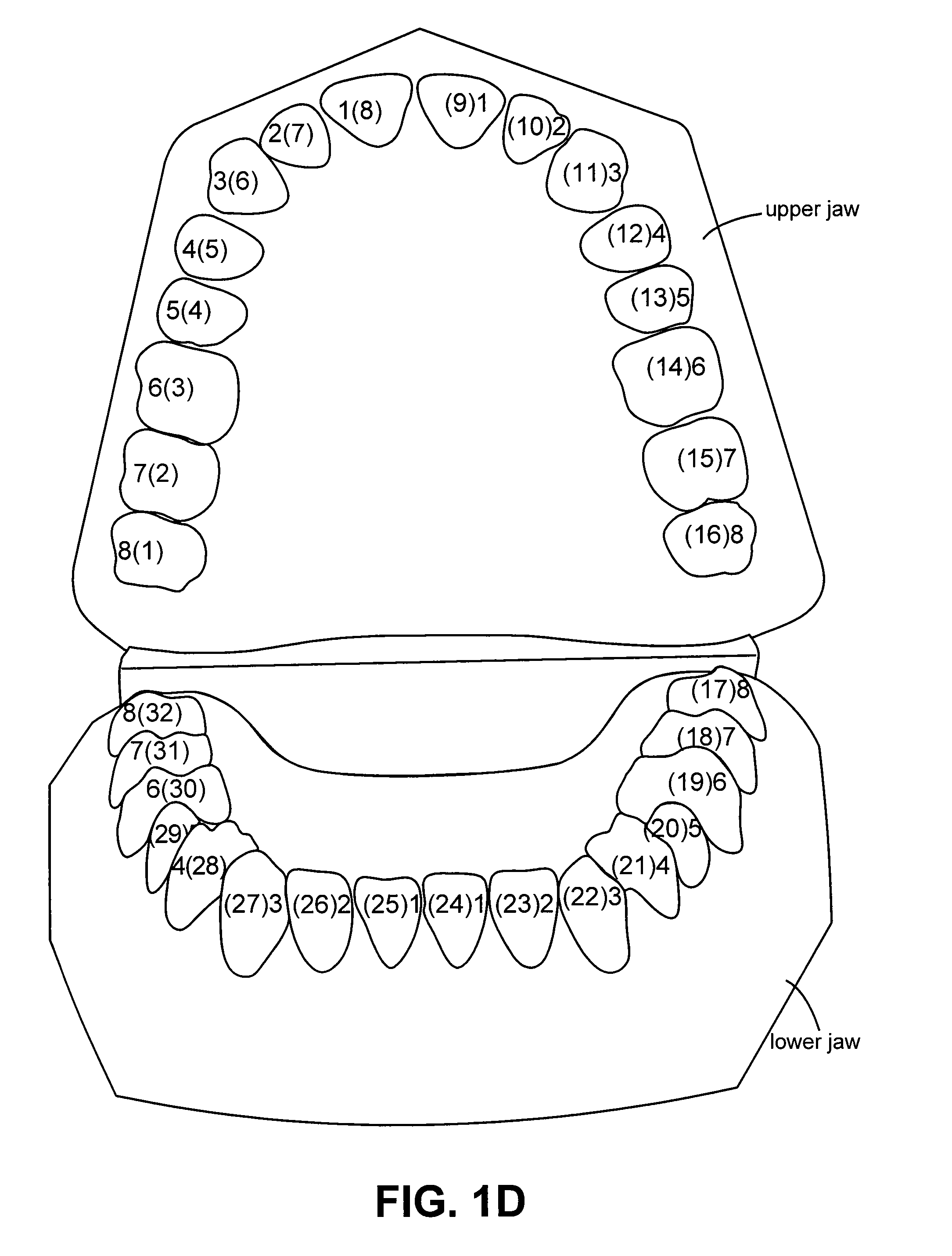

System and method for automatic construction of orthodontic reference objects

System and method for automatic construction of orthodontic reference objects, such as the occlusal plane, arch form, and the local occlusal plane for a patient's teeth are disclosed. In accordance with an exemplary embodiment, a computer-implemented system and method for automatic construction of orthodontic reference objects comprises receiving three dimensional data for the teeth, setting an initial direction for a normal of the occlusal plane, determining tips for selected teeth, calculating a plane that matches the determined tip, and determining a new normal for the calculated plane.

Owner:ALIGN TECH

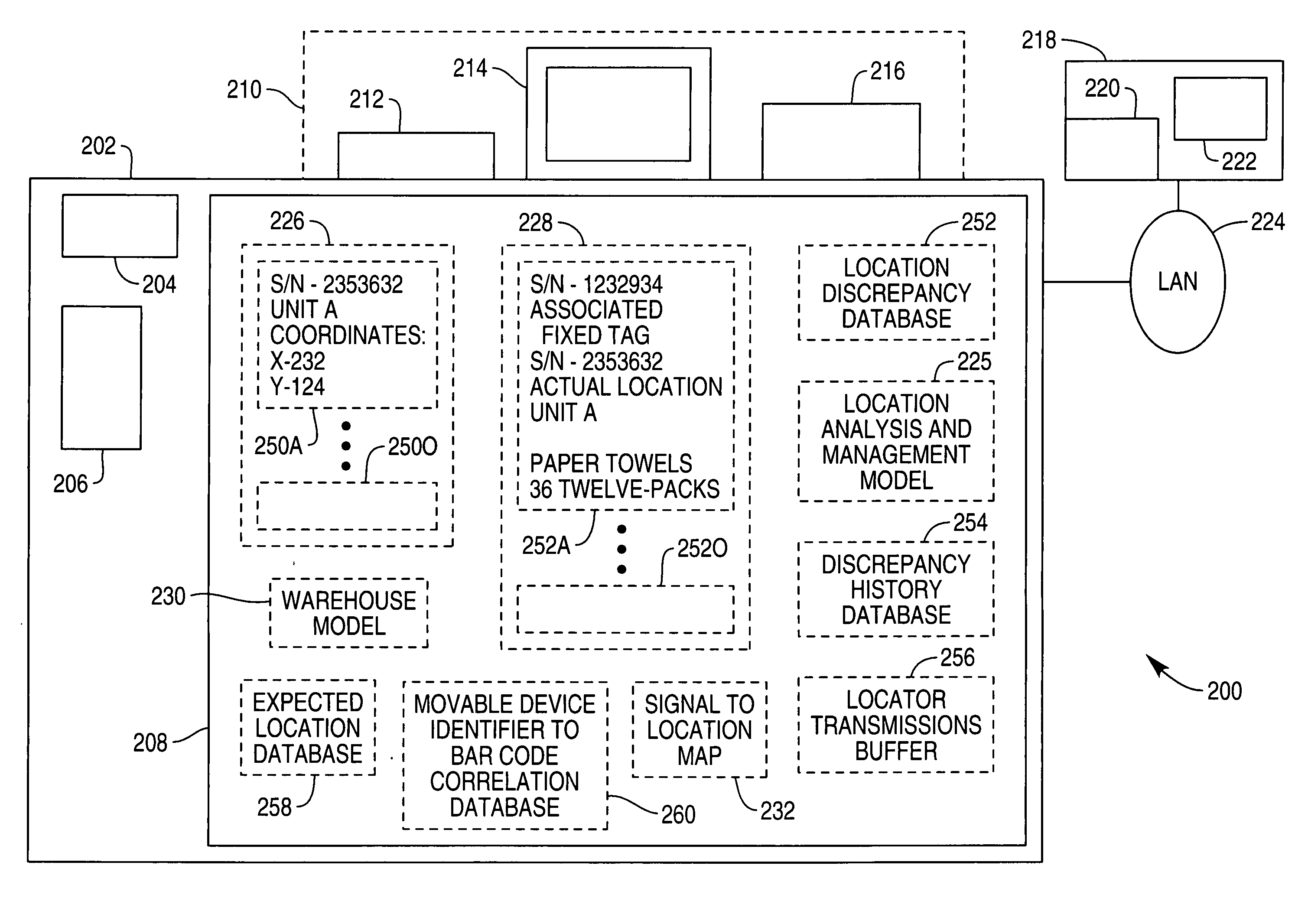

Methods and apparatus for managing location information for movable objects

ActiveUS20070136152A1High precisionDigital data processing detailsSatellite radio beaconingLocation detectionEngineering

Systems and techniques for locating stored goods. A plurality of fixed contactless identification devices are deployed in an area. Each fixed device exhibits a fixed device identifier that can be read from a distance. Locations within the area are identified through mapping to combinations of fixed device identifiers detected at the location. In addition, a plurality of movable contactless identification devices are associated with goods to be stored and retrieved. Each movable device exhibits a movable device identifier, and movable contactless identification devices are located by identifying a combination of fixed device identifiers received when a movable device identifier is received. The location information may be used independently, or as a supplement to expected location information obtained through other means.

Owner:NCR CORP

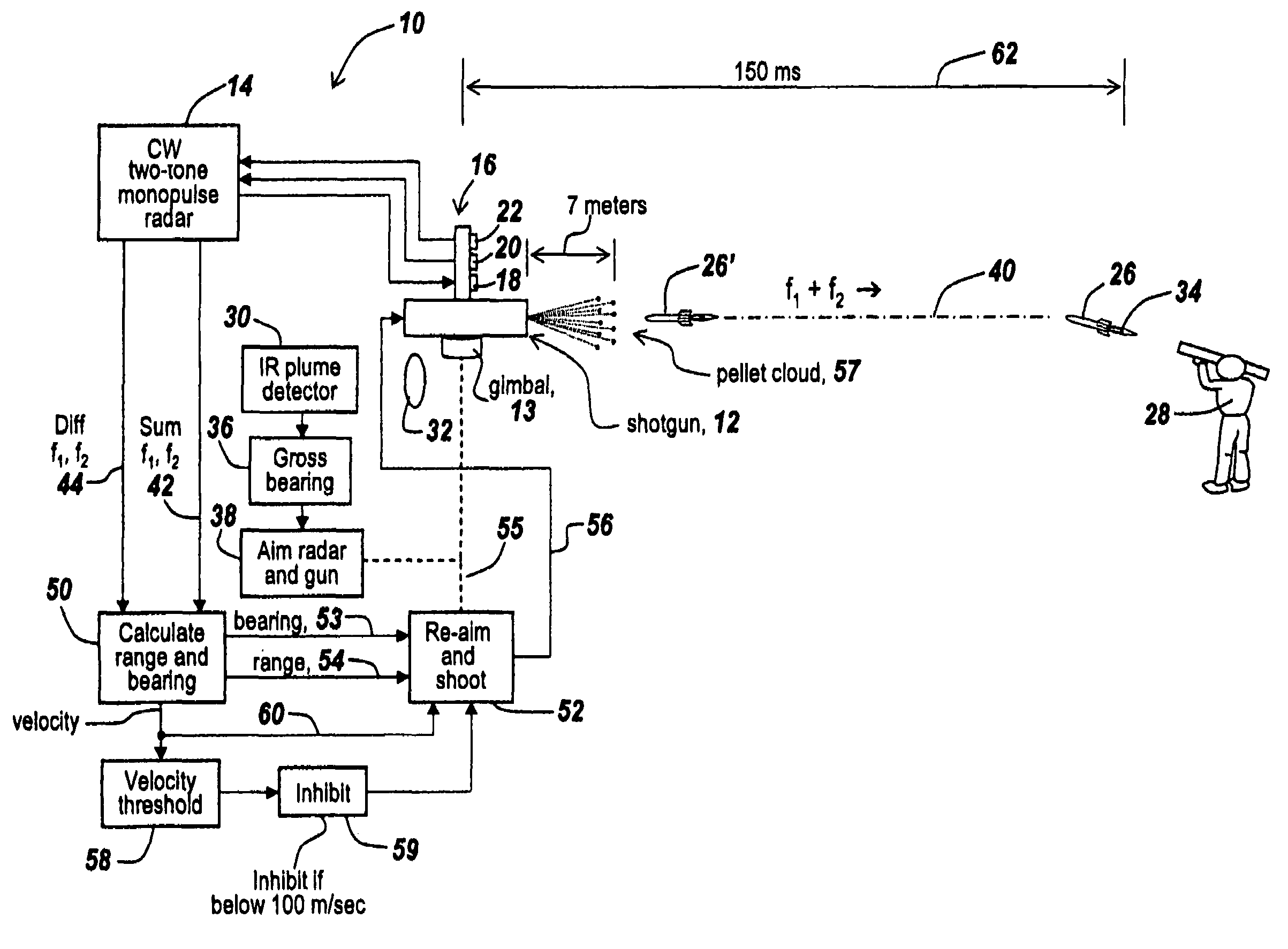

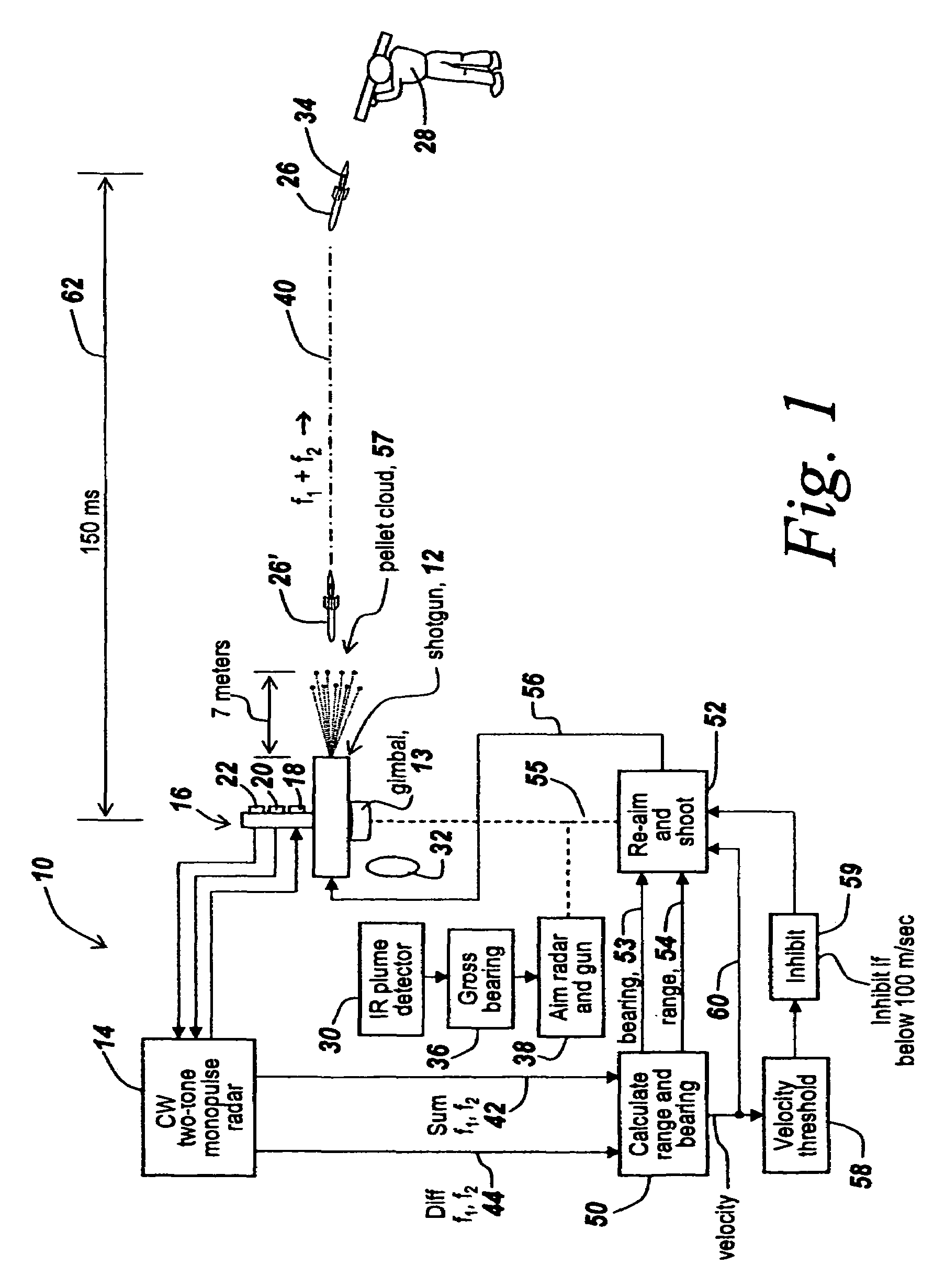

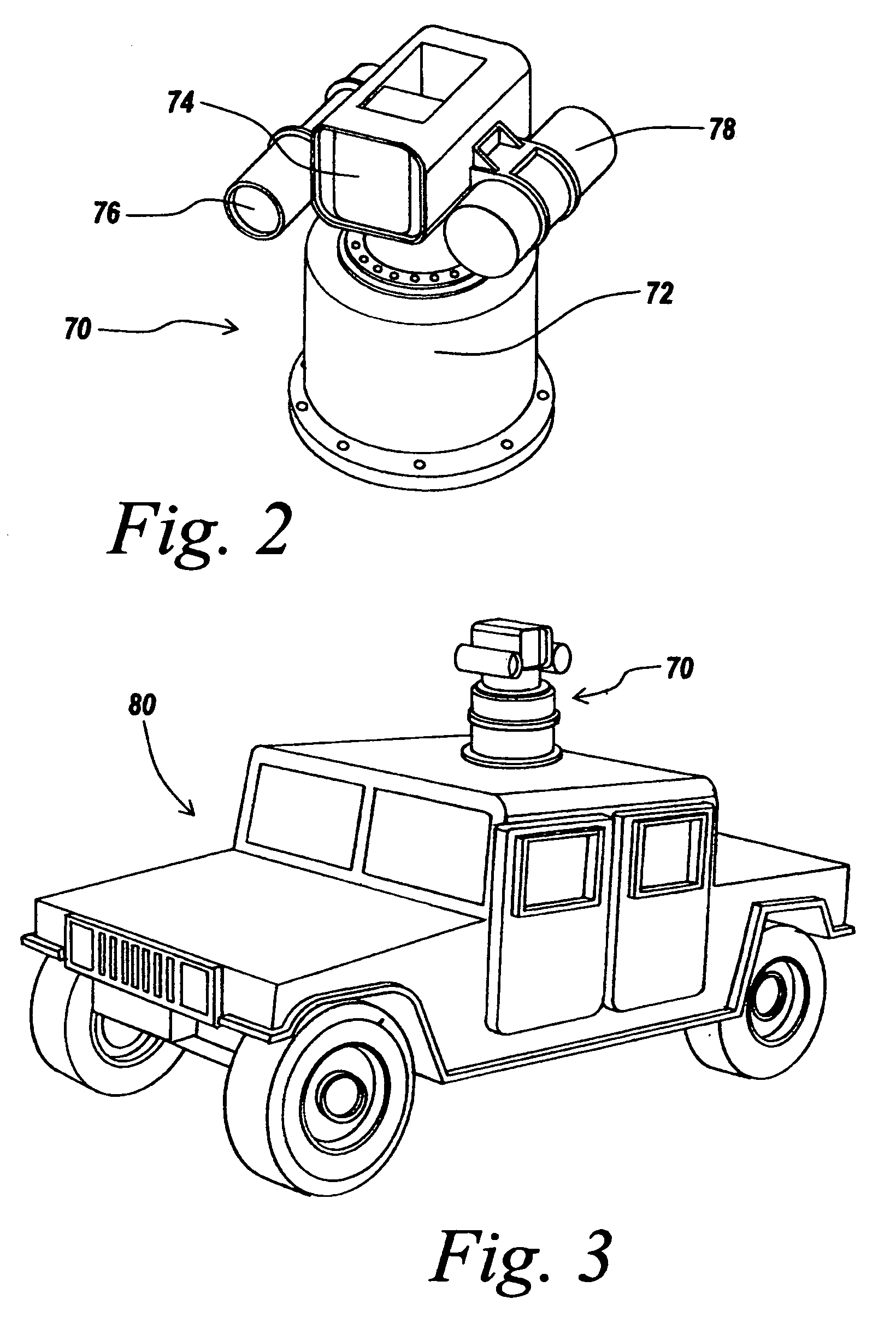

Method and apparatus for improved determination of range and angle of arrival utilizing a two tone CW radar

ActiveUS7205932B2Double accuracyImprove noiseRadio wave reradiation/reflectionSingular value decompositionFire-control system

An improved system is provided for aiming a shotgun-based or other countermeasure system so as to be able to countermeasure incoming rockets or projectiles. In one embodiment a shotgun aimed and controlled by the subject system projects a pattern of pellets to intercept a rocket-propelled grenade or incoming projectile. The fire control system uses a CW two-tone monopulse radar to derive range and angle of arrival within 150 milliseconds, with range and angle of arrival measurements having approximately twice the accuracy of prior CW two-tone monopulse radars. The improvement derives from using all of the information in the returned radar beams and is the result of the recognition that one can use the Sum and Difference signals to assemble a two-by-two Rank One matrix that permits using singular value decomposition techniques to generate range and angle of arrival matrices in which all available information is used and in which noise is eliminated.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

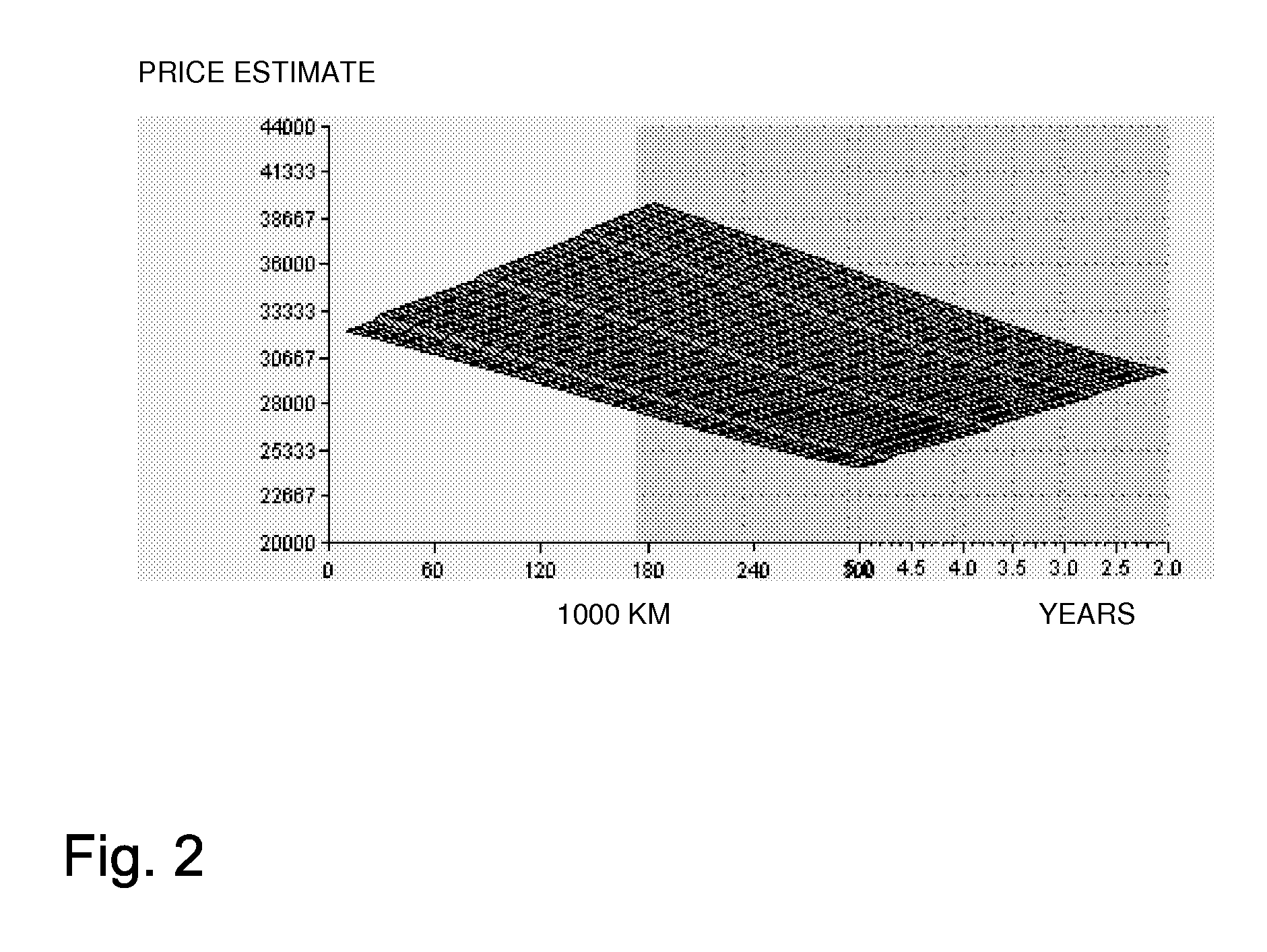

Systems and methods for providing price quotes for 3D objects

ActiveUS20140279177A1Quickly and easily costCost of productionAdditive manufacturing apparatusBuying/selling/leasing transactionsComputer graphics (images)Price quote

Systems and methods for providing price quotes for 3D objects are described herein. In one embodiment, costs related to generating a 3D object molded from a 3D printer mold may be based on various parameters. The process for generating a price quote may include uploading an initial file to a server and converting that file into a 3D CAD file. The method may also include selecting units, materials, a finish, and / or a quantity of objects to be made. Based on the selections, the server may generate a price quote to produce the one or more objects, and a checkout option may be provided allowing the user to purchase the one or more objects.

Owner:KEMEERA INC

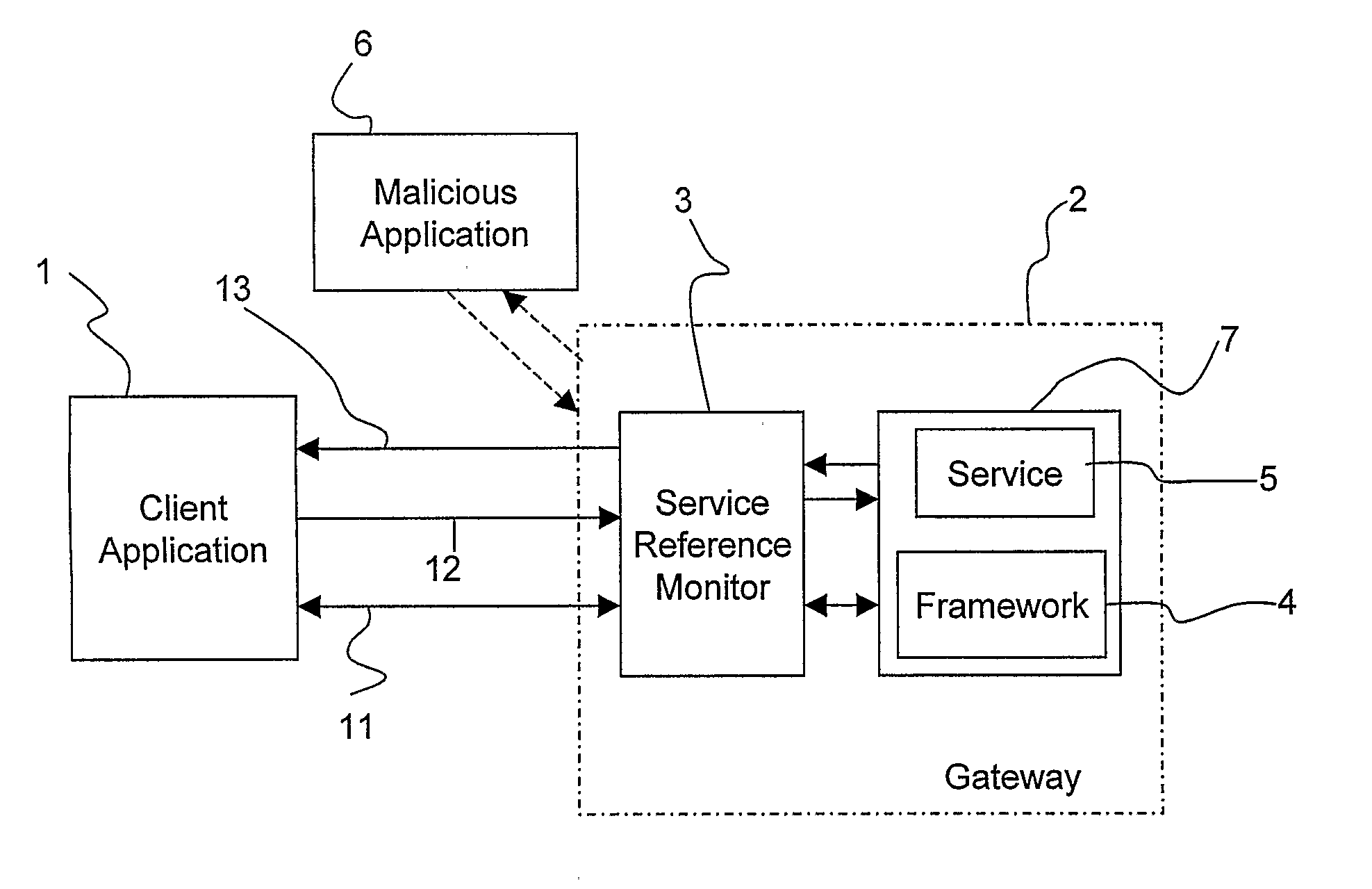

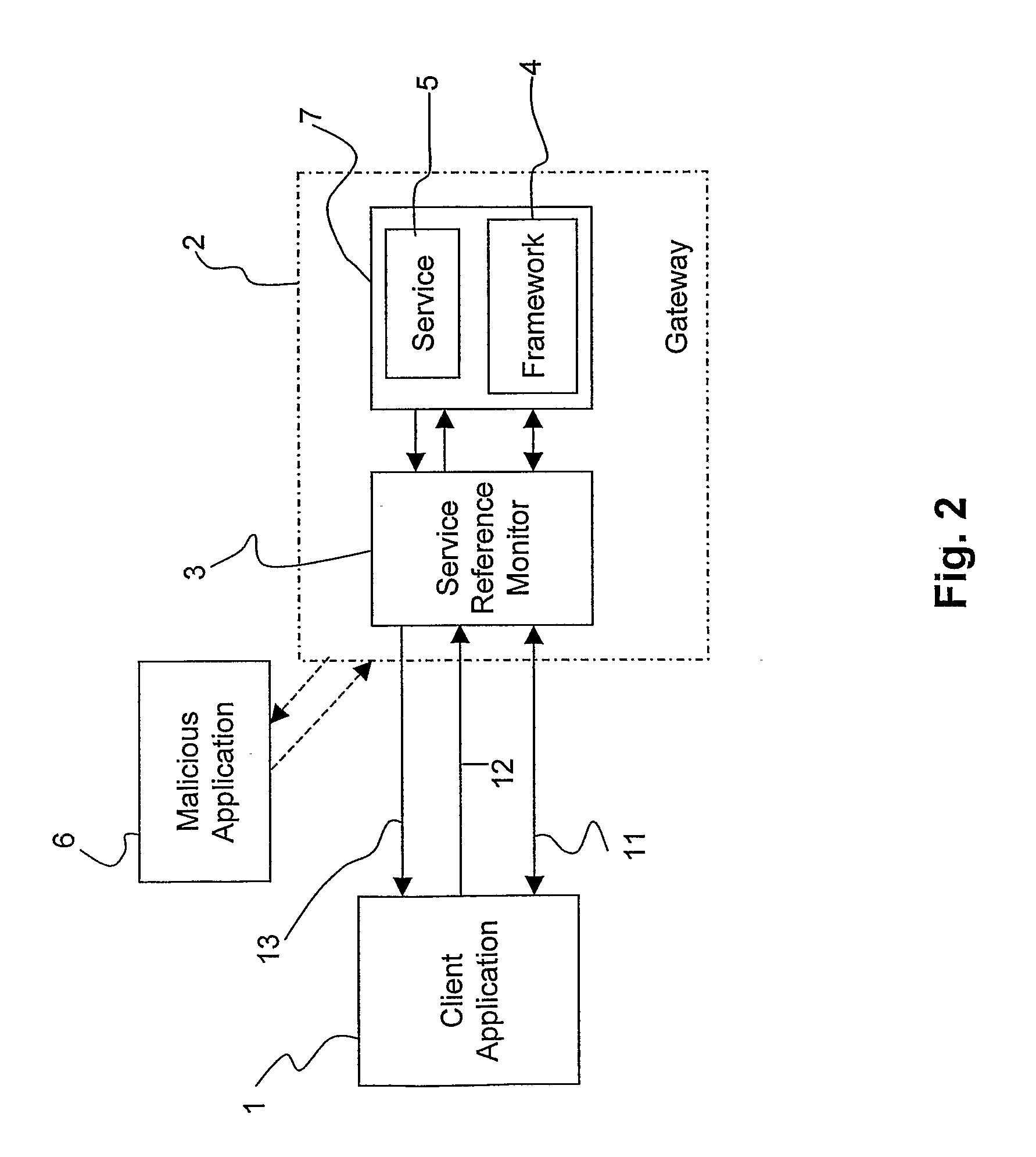

Method and System for Access Control in Distributed Object-Oriented Systems

InactiveUS20070233883A1Reduce probabilityMultiple digital computer combinationsTransmissionEntity linkingLimited access

A method and a system for accessing services provided by network resources in communication networks. Access to service capabilities is controlled at the application level by controlling the access through a gateway wherein an object-oriented service architecture based on abstracted application programming interfaces is implemented. Preferably, the service architecture is defined in OSA / Parlay standards. Access control is carried out by means of a logical entity, the service reference monitor, which is linked to the gateway and configured so that it intercepts all the communications passing between the client applications and the gateway. The service reference monitor captures the object reference to the service capability and assigns to the object reference a lifetime. At the expiration of the lifetime, the service reference monitor destroys the service capability. The probability of a malicious attack is lowered by limiting the time window of the life of access to a service.

Owner:TELECOM ITALIA SPA

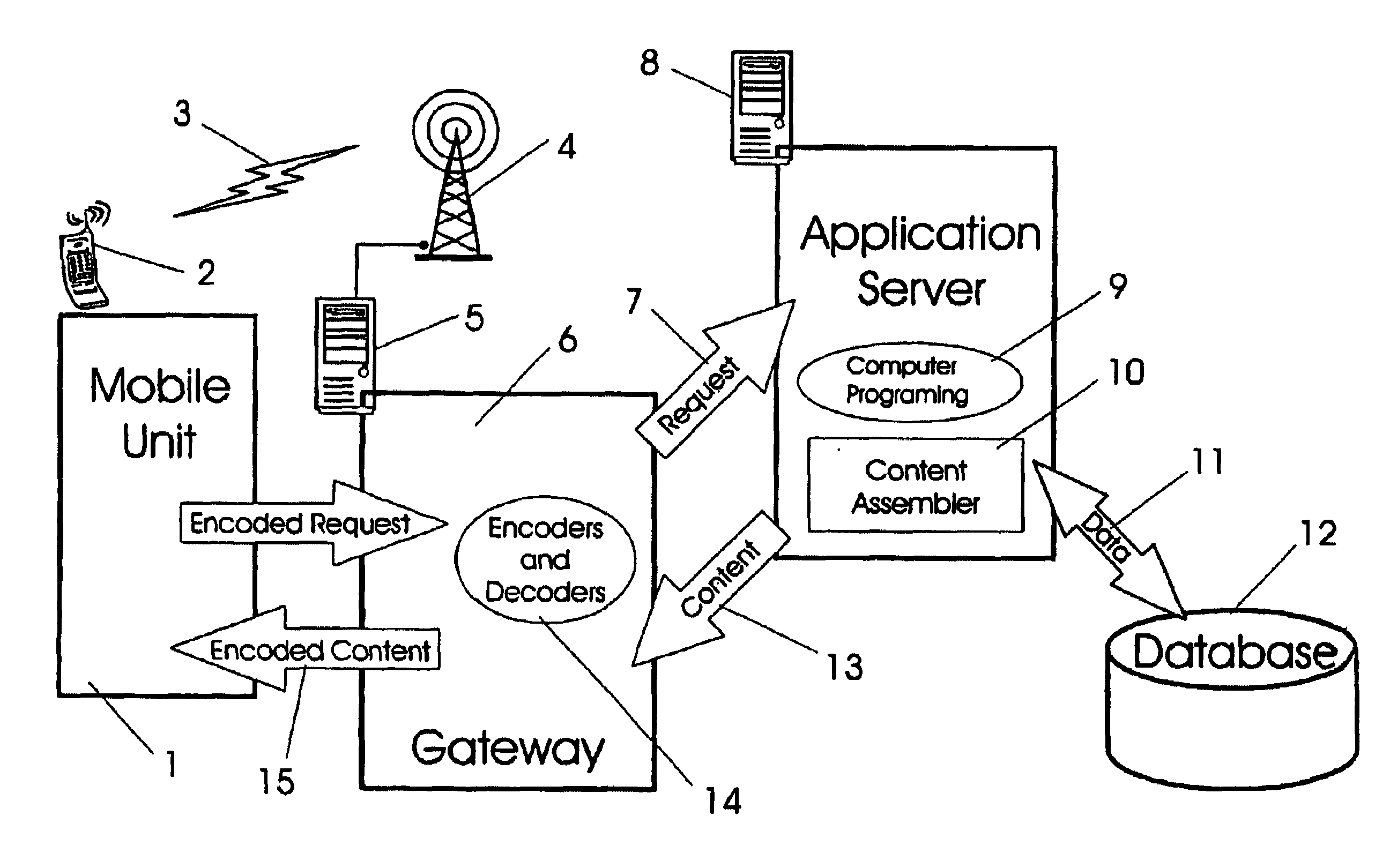

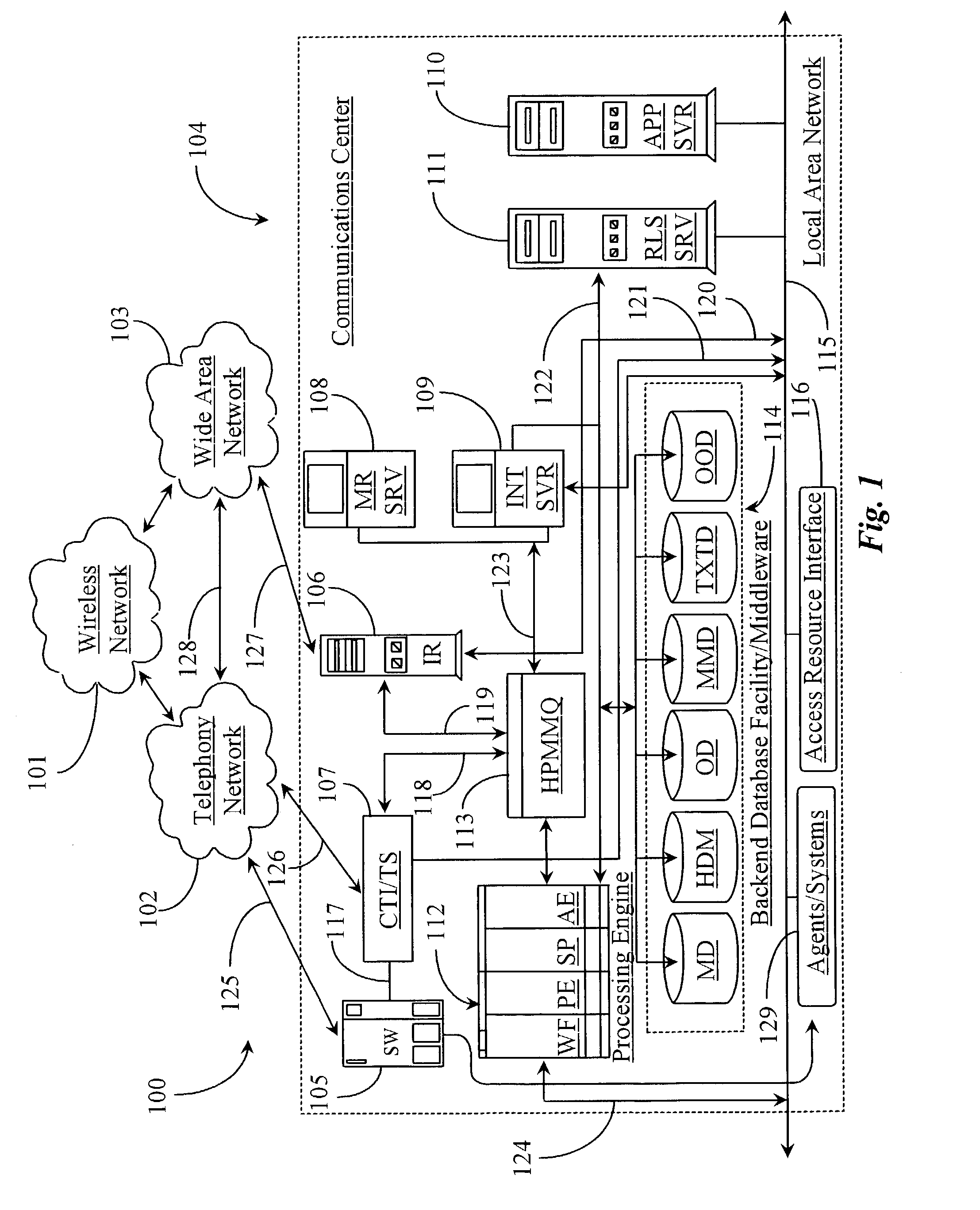

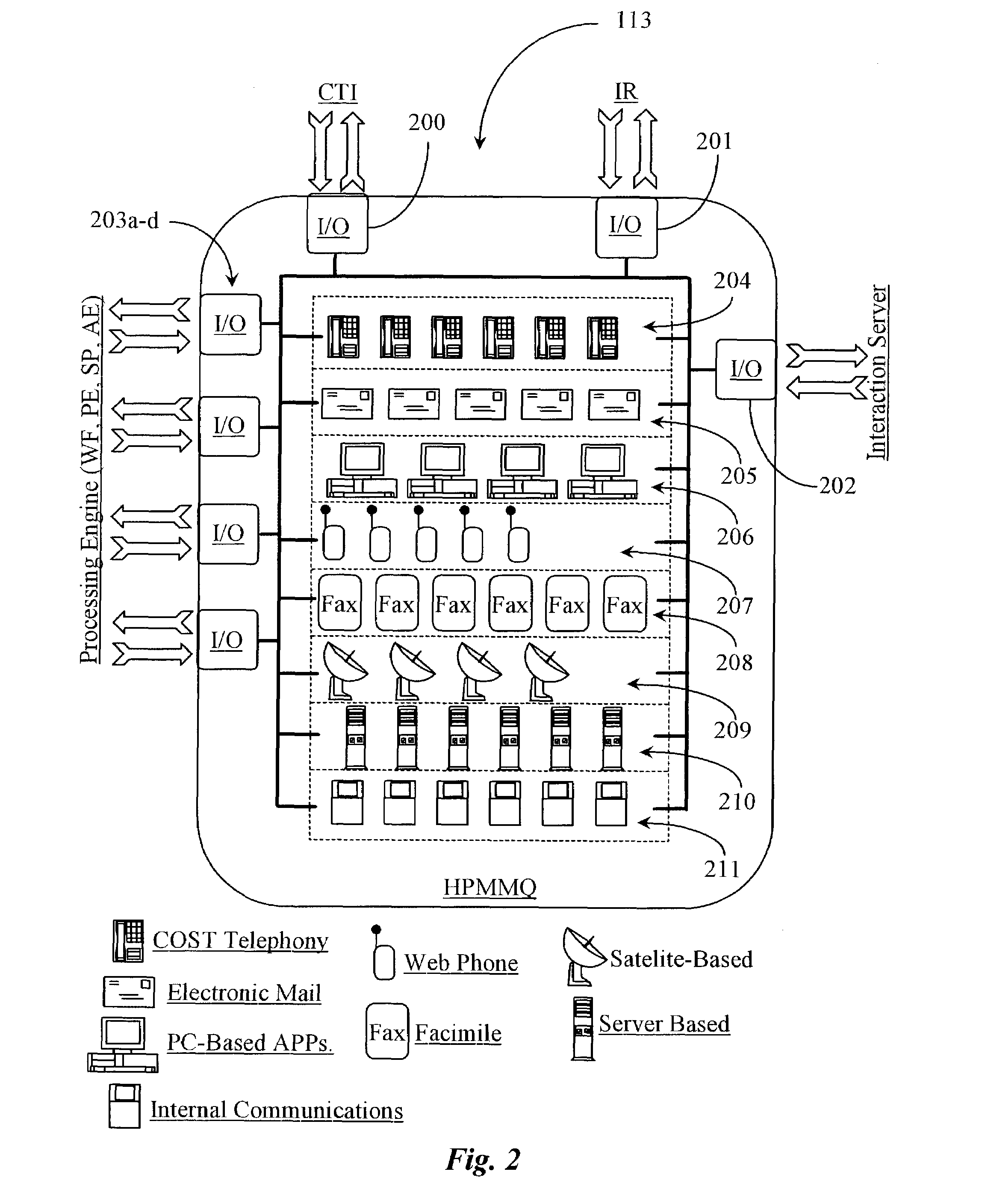

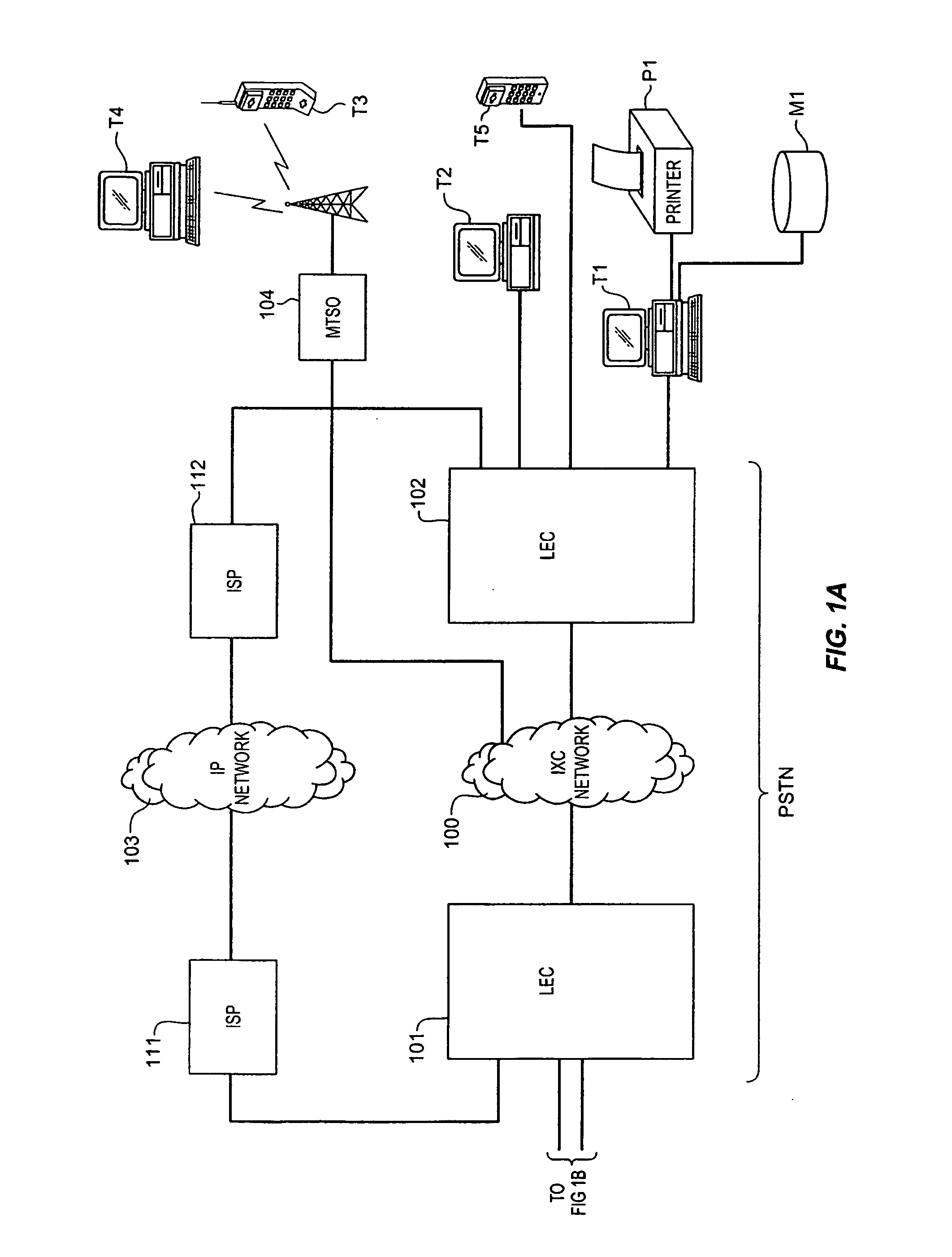

Method and system for providing adaptive and proactive interaction management for multiple types of business interactions occurring in a multimedia communications environment

ActiveUS7373410B2Multiprogramming arrangementsData switching by path configurationEvent typeMedia type

An object-oriented system for managing multiple media types in a communication center environment has a multimedia queuing system, a processor for processing events in the queue, an interaction server for selecting media type or event types, a resource manager for reporting availability of a resource access point, and a data store for storing client information about media types available to the client and historical information about success of past use of those media types. In a preferred application, the system processes and routes incoming events of known media type to access points defined as systems or agents based in part on media channel availability of the access point, and wherein the system selects a media channel or channels for certain events in queue that are not pre-dedicated as specific media type events but are generated outbound or internal proactive contact events. For proactive contact events, the system automatically selects a media channel for each event based on a combination of set preferences and predictions based on historical channel information relating to success channel connections to that client.

Owner:GENESYS TELECOMMUNICATIONS LABORATORIES INC

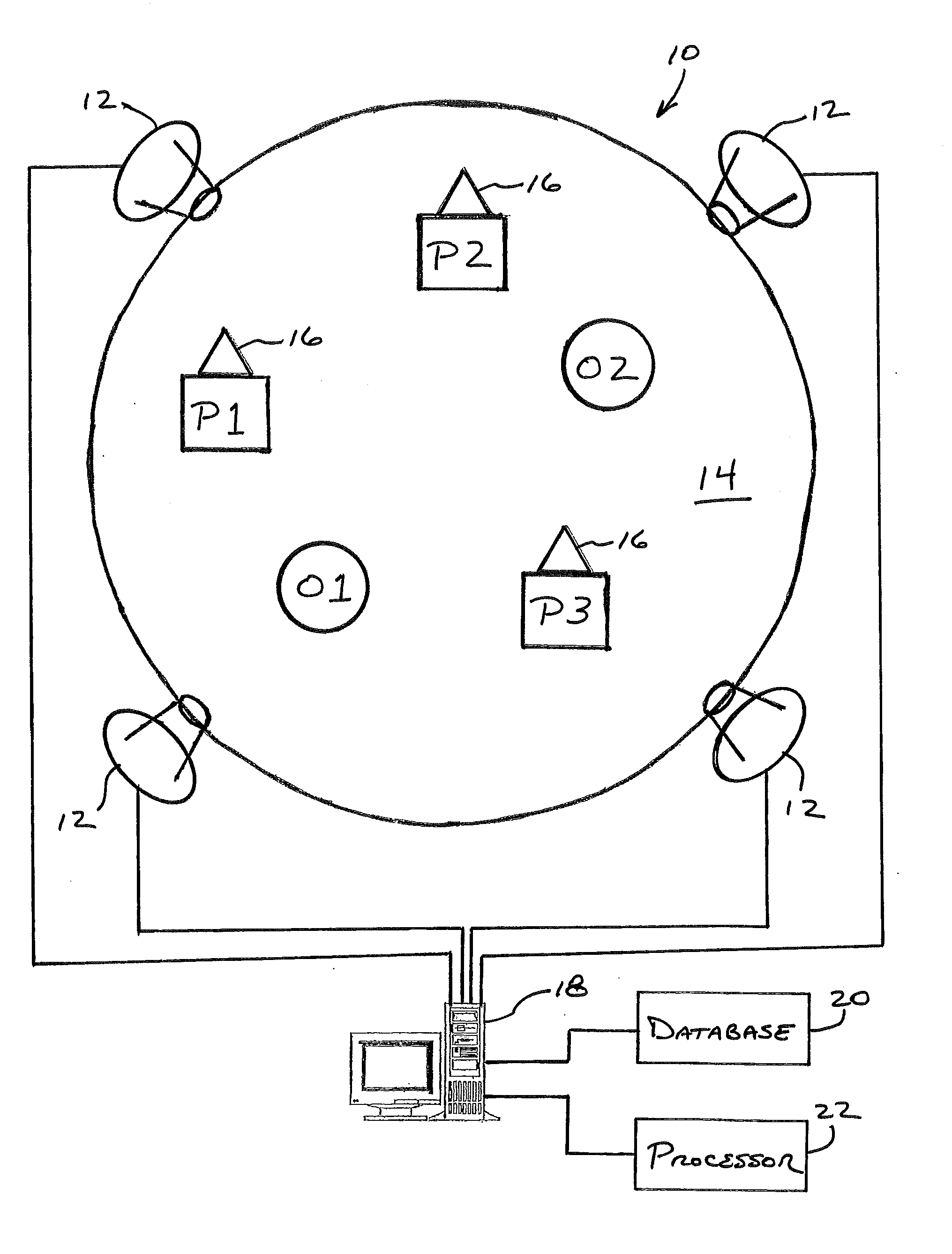

System and Method for Tracking, Monitoring and Deriving the Location of Transient Objects by Monitoring the Location of Equipment Used to Move the Objects

System and method combining a Dock Automation (“DA”) system with a Real Time Locating System (“RTLS”) to achieve automated accuracy relating to the location of shipment components. An RTLS system is used to track the position of assets which move shipment components over time. When any action is performed on a shipment component in the DA system, the time of the action and the RTLS device ID of the asset (piece of equipment or person) performing the action would be used in conjunction with the RTLS database, providing the location at which the event took place. Knowing the location of the asset performing an action on a component implies knowing the location of the component being acted upon. At any time, the component should be wherever the last asset interacted with it.

Owner:HAMMEL

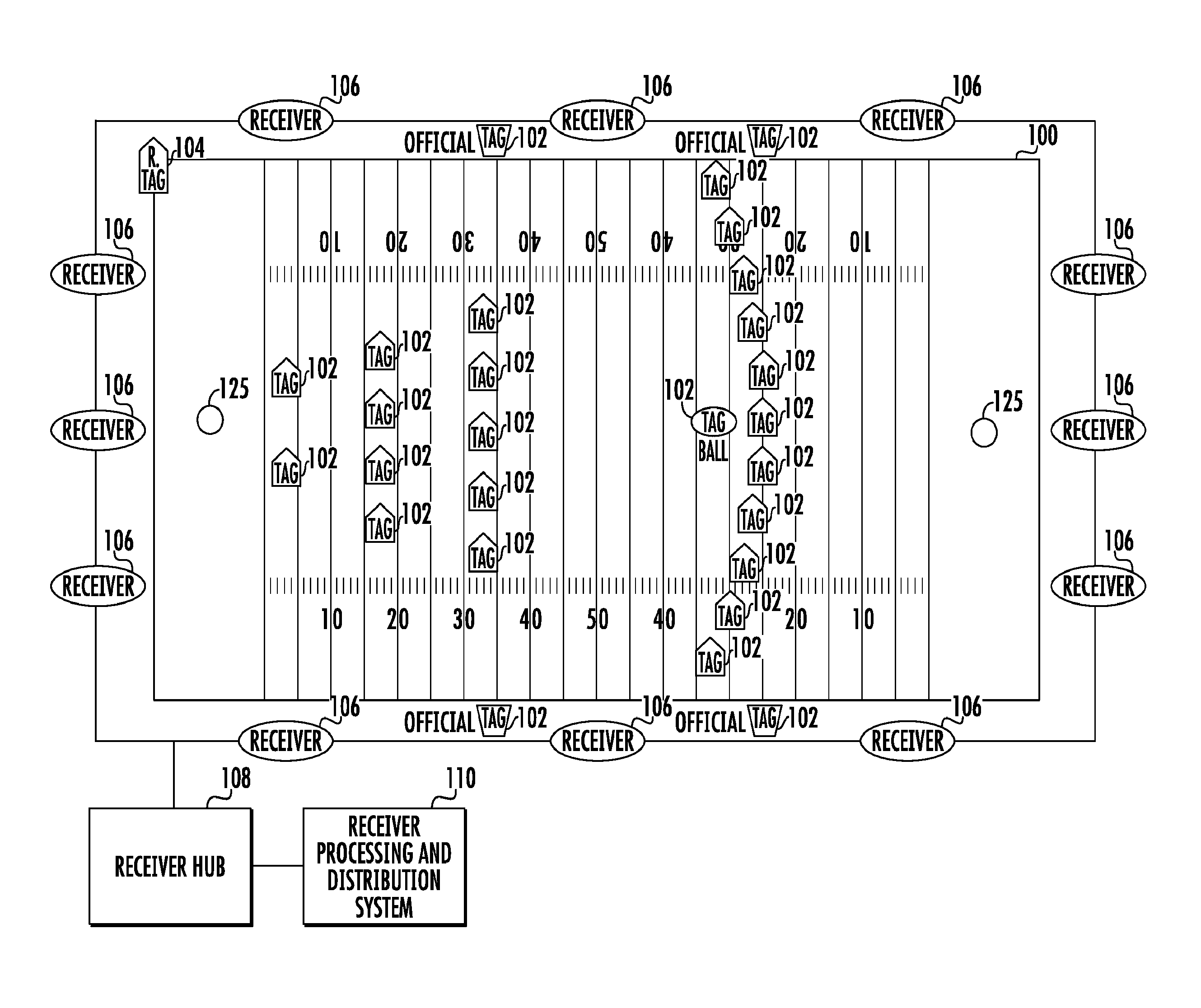

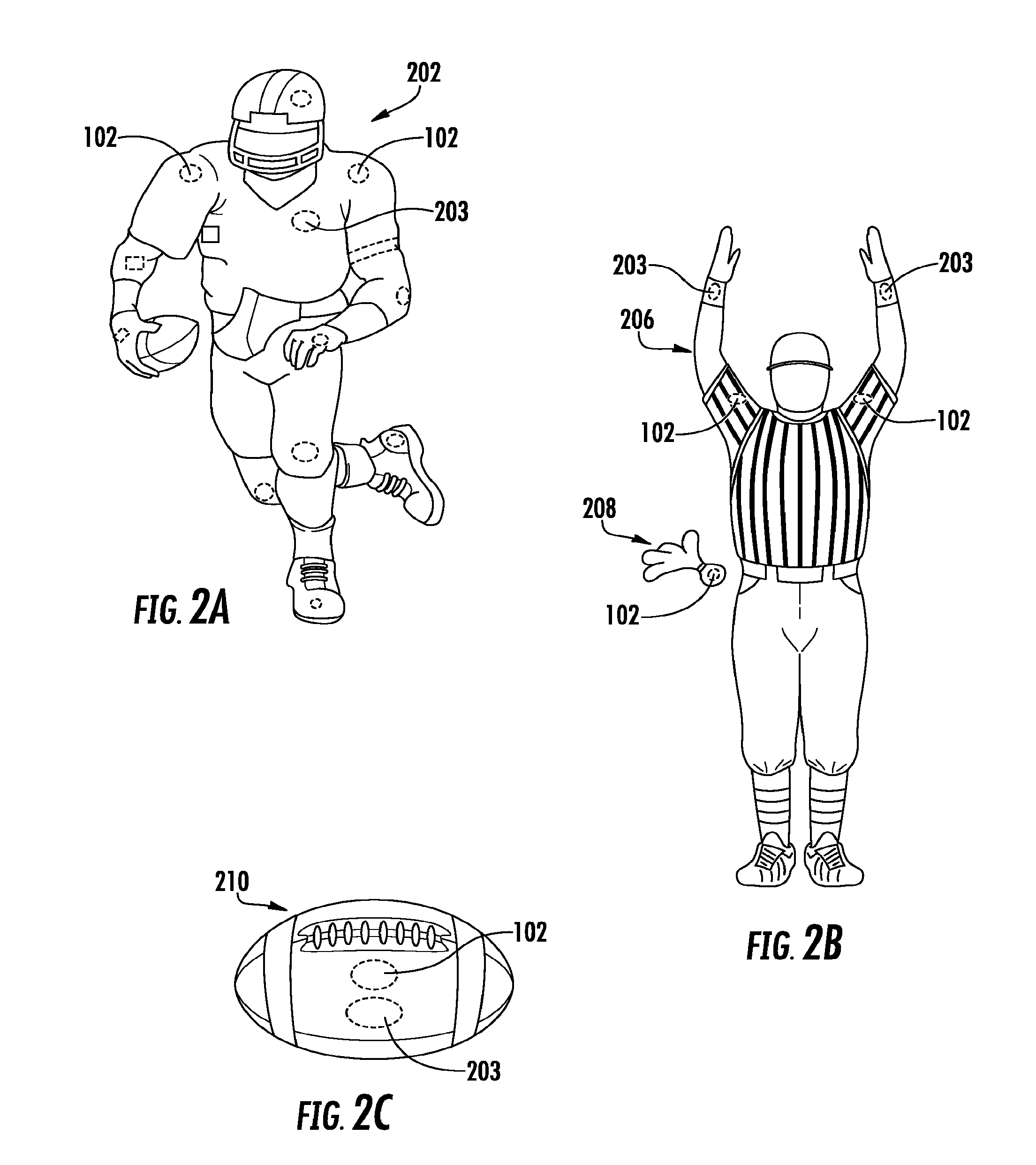

Performance analytics based on real-time data for proximity and movement of objects

ActiveUS8989880B2Gymnastic exercisingCharacter and pattern recognitionReal-time dataComputer science

Systems, methods, apparatuses, and computer readable media are disclosed for providing performance analytics using dynamics / kinetics models based on role data or weather data and real time data on movement and proximity of tagged objects. In one embodiment, a method is provided for monitoring a participant that at least includes correlating at least one tag to the participant; receiving blink data transmitted by the at least one tag; and determining tag location data based on the blink data. The method further includes receiving participant role data; comparing the tag location data to participant dynamics / kinetics models based at least in part on the participant role data; and determining participant location data based on the comparing the tag location data to the participant dynamics / kinetics models.

Owner:ZEBRA TECH CORP

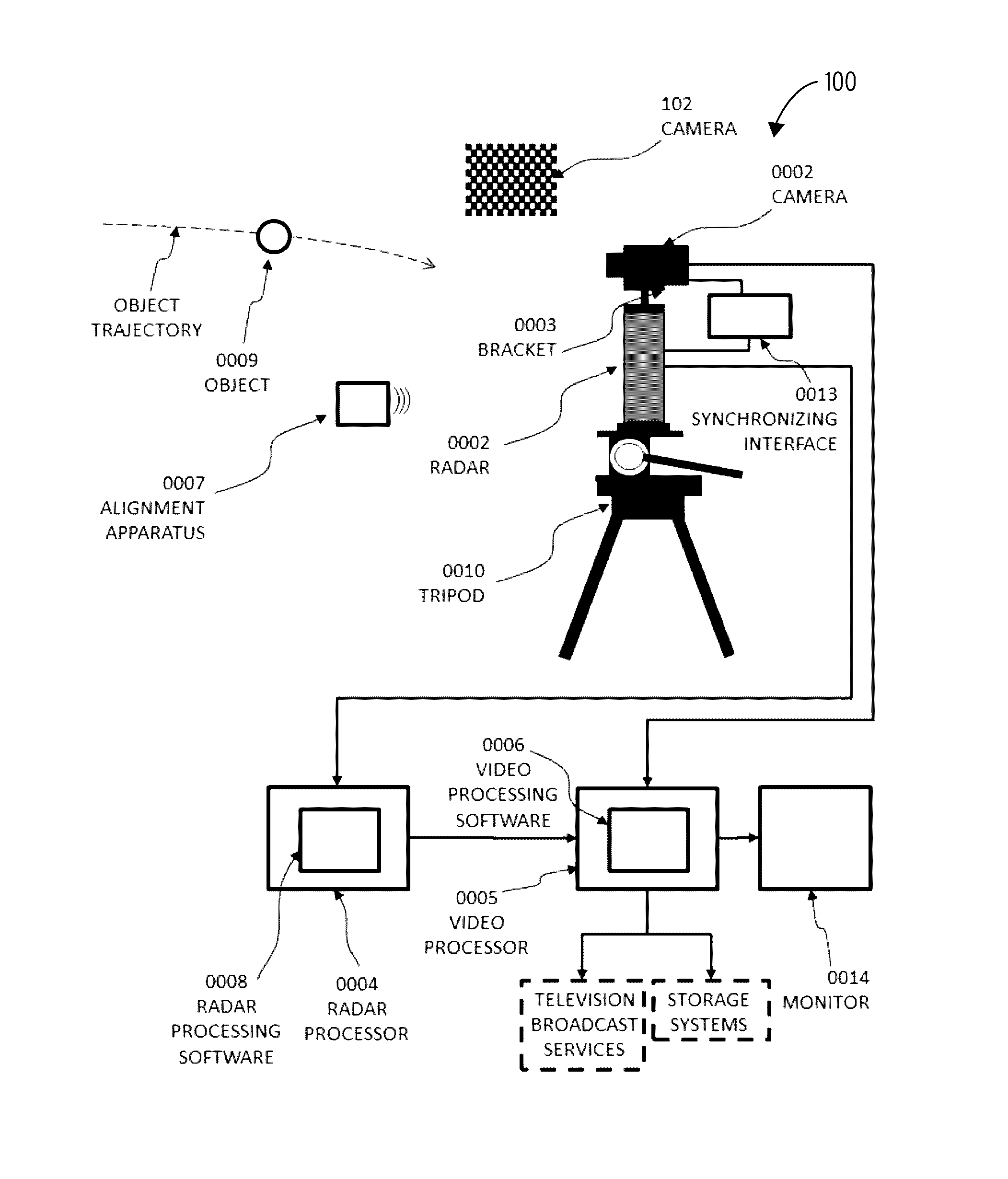

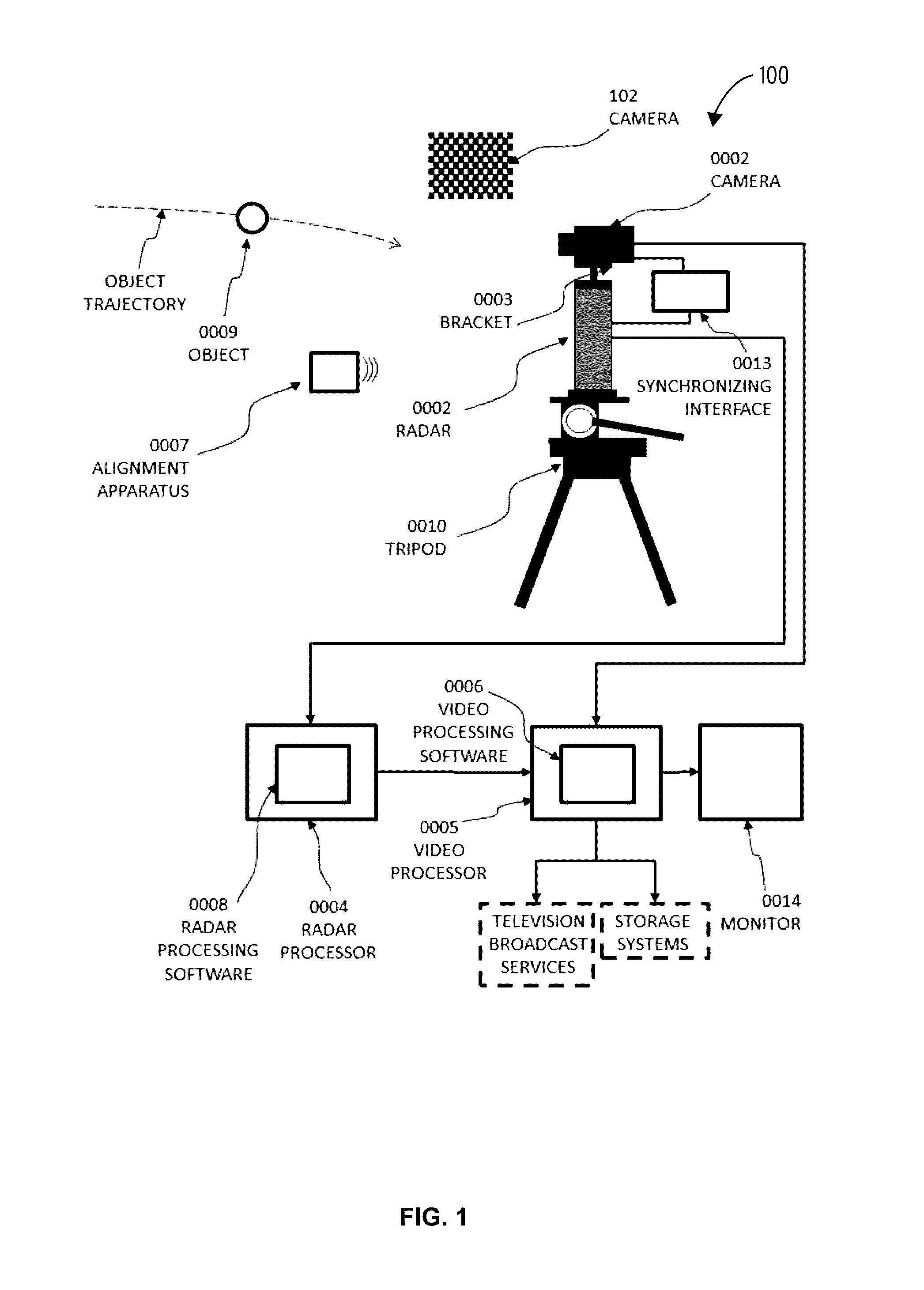

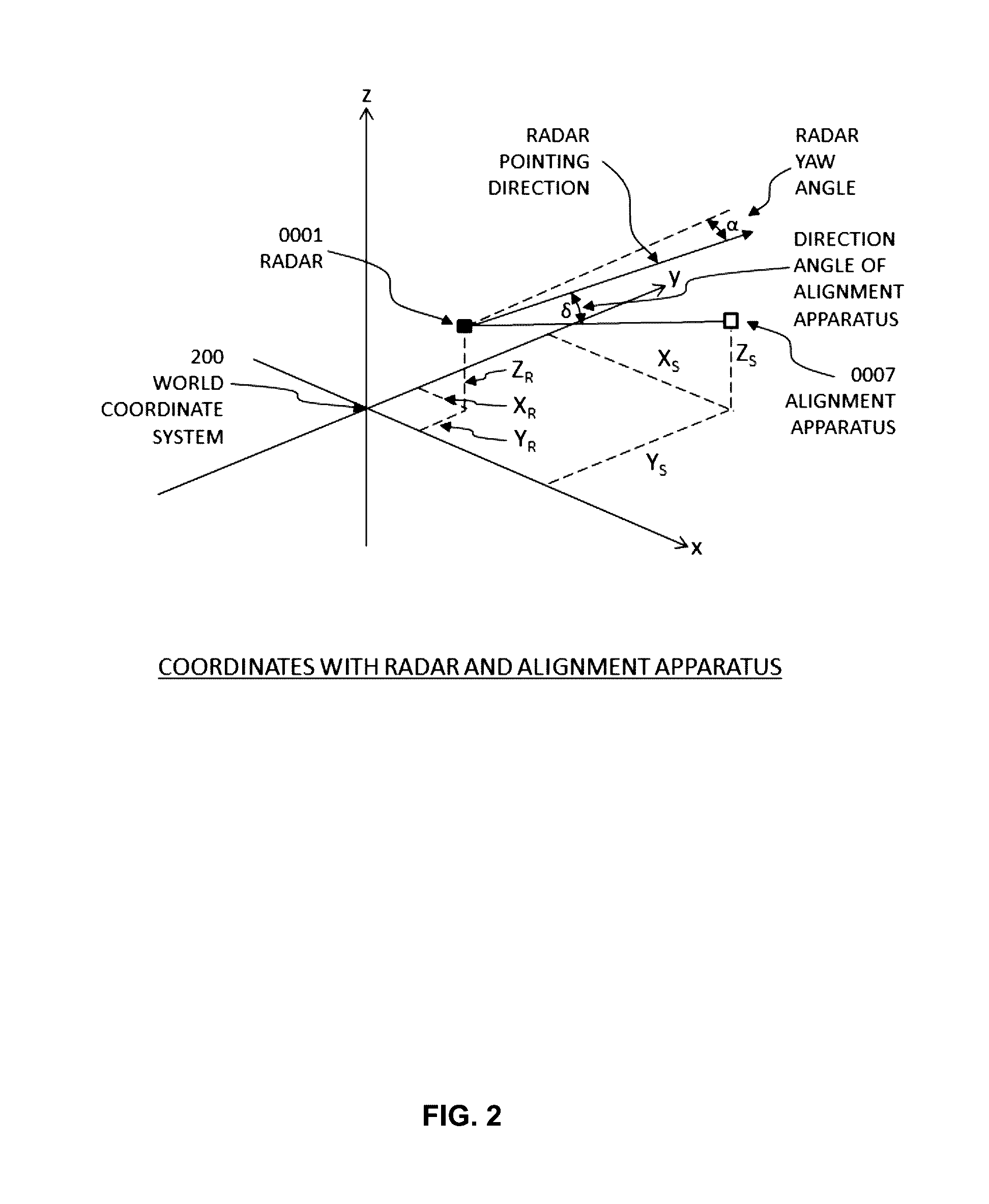

Systems to track a moving sports object

ActiveUS20160320476A1Improve depth measurement accuracyEasy to measureImage enhancementImage analysisRadarDoppler measurements

Systems, methods and computer-readable media are provided for tracking a moving sports object. In one example, a method of tracking a moving sports object includes calibrating a perspective of an image of a camera to a perspective of a Doppler radar for simultaneous tracking of the moving sports object, and tracking the moving sports object simultaneously with the camera and Doppler radar. The method may further comprise removing offsets or minimizing differences between simultaneous camera measurements and Doppler radar measurements of the moving sports object. The method may also include combining a camera measurement of an angular position of the moving sports object with a simultaneous Doppler measurement of a radial distance, speed or other measurement of the moving sports object.

Owner:EDH US

Graphical Application Integration with MPEG Objects

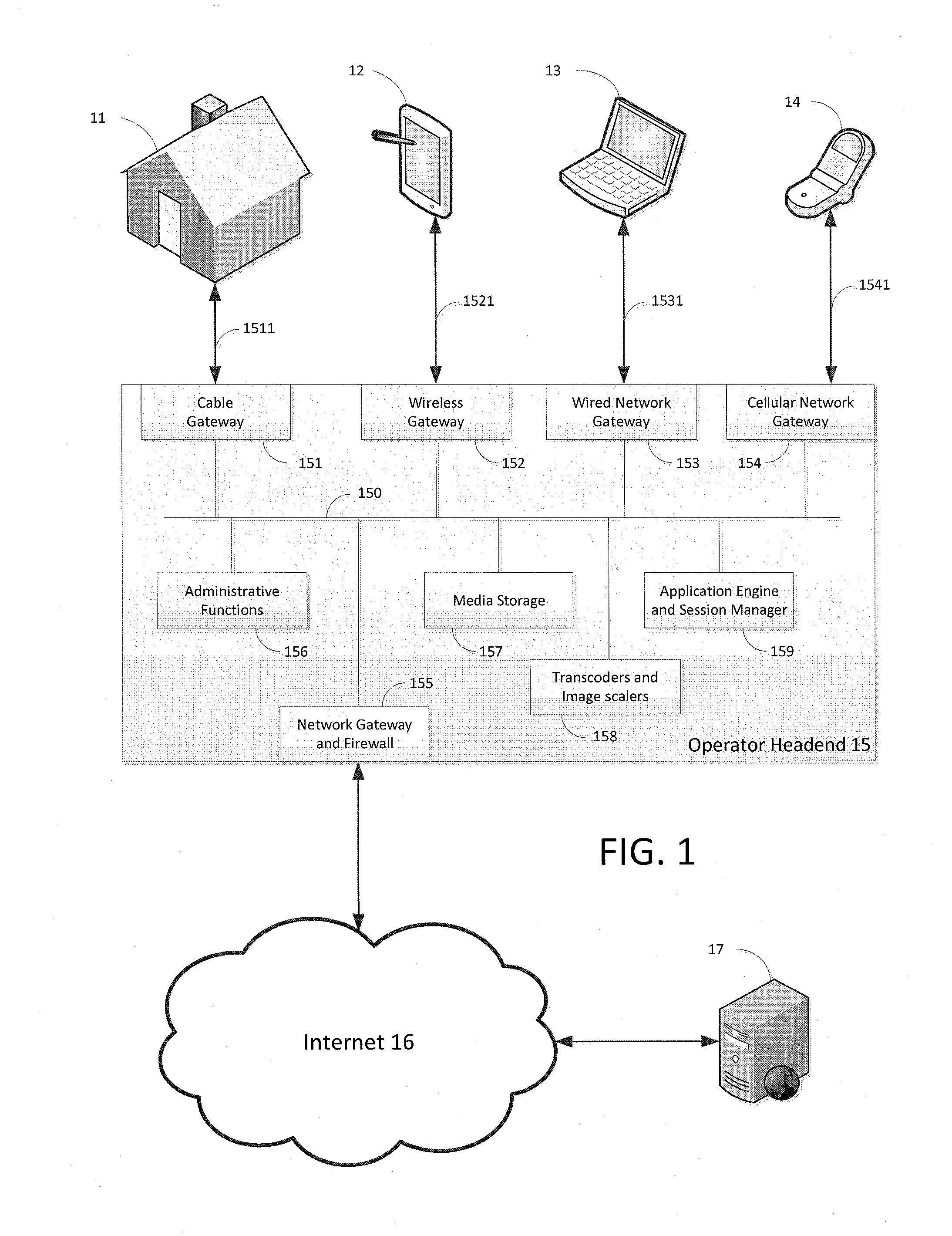

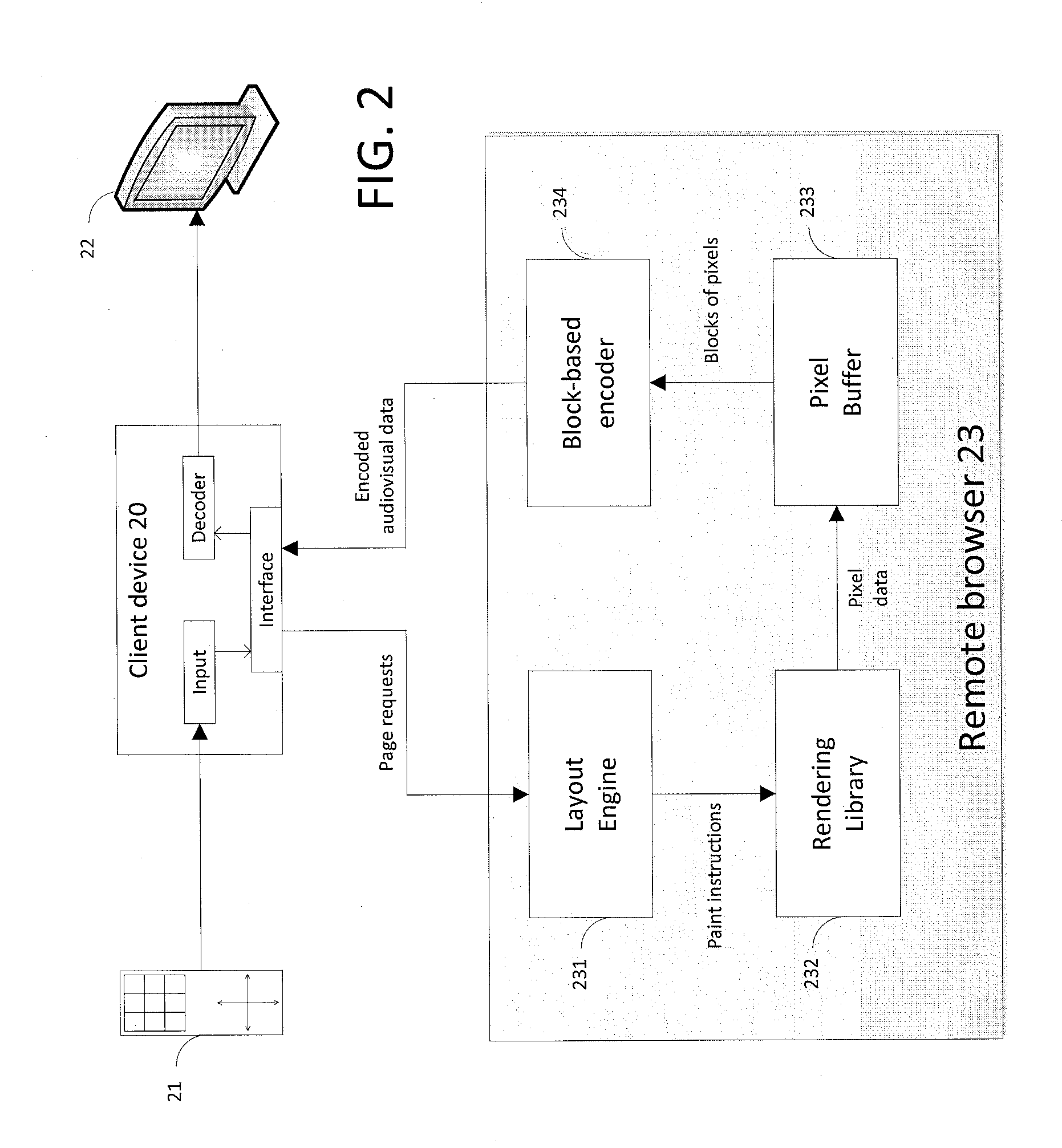

ActiveUS20130272394A1Efficient inter-encodingImprove efficiencyPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningGraphicsData stream

System and methods are provided to cache encoded graphical objects that may be subsequently combined with other encoded video data to form a data stream decodable by a client device according to a format specification. Paint instructions relating to a graphical object are sent from a layout engine to a rendering library. A shim intercepts these instructions and determines whether the graphical object already has been rendered and encoded. If so, a cached copy of the object is transmitted to the client device. If not, the shim transparently passes the instructions to the rendering library, and the object is rendered, encoded, and cached. Hash values are used for efficiency. Methods are disclosed to detect and cache animations, and to cut and splice cached objects into encoded video data.

Owner:ACTIVE VIDEO NETWORKS INC

System and method for assessing and managing objects

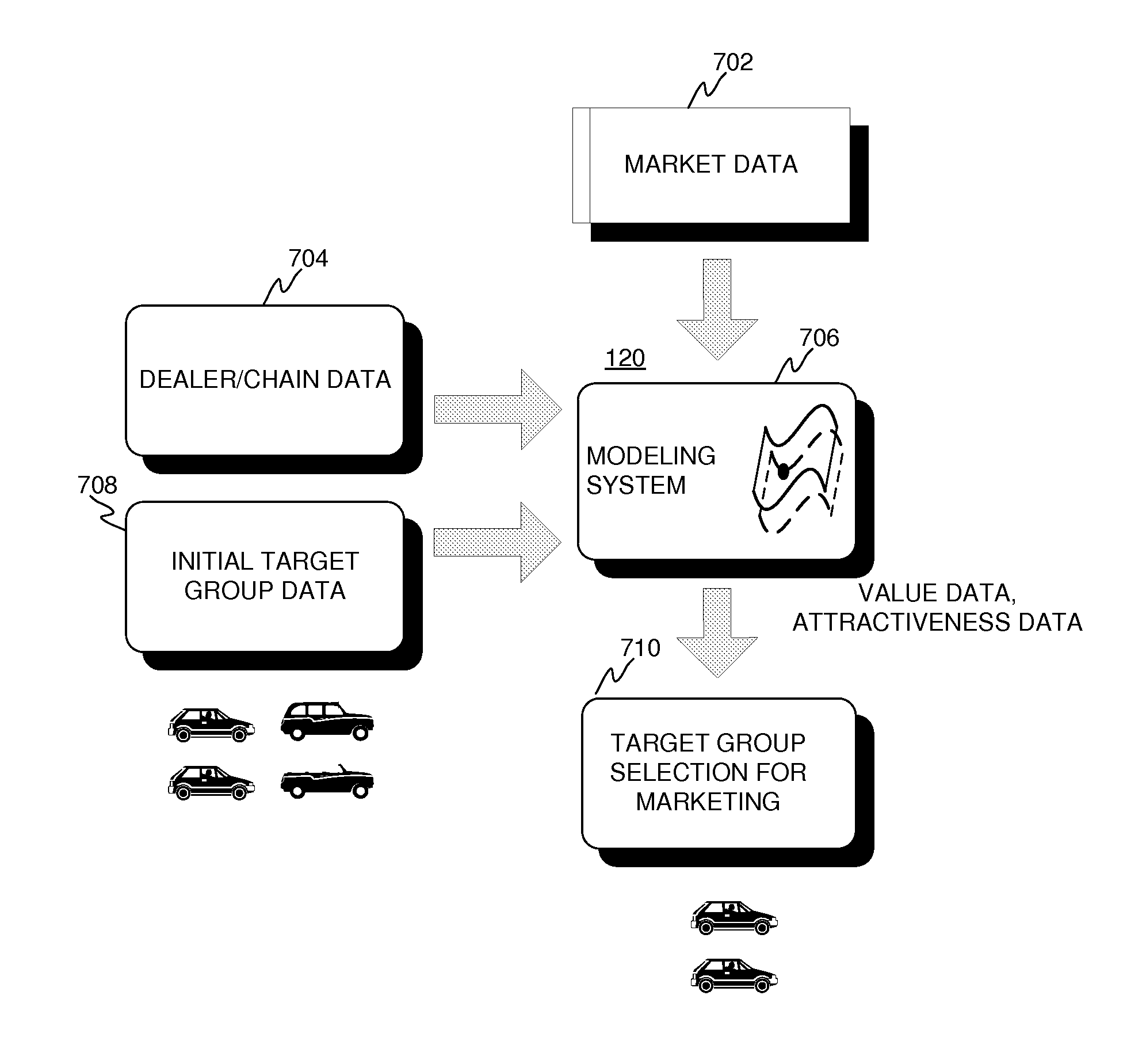

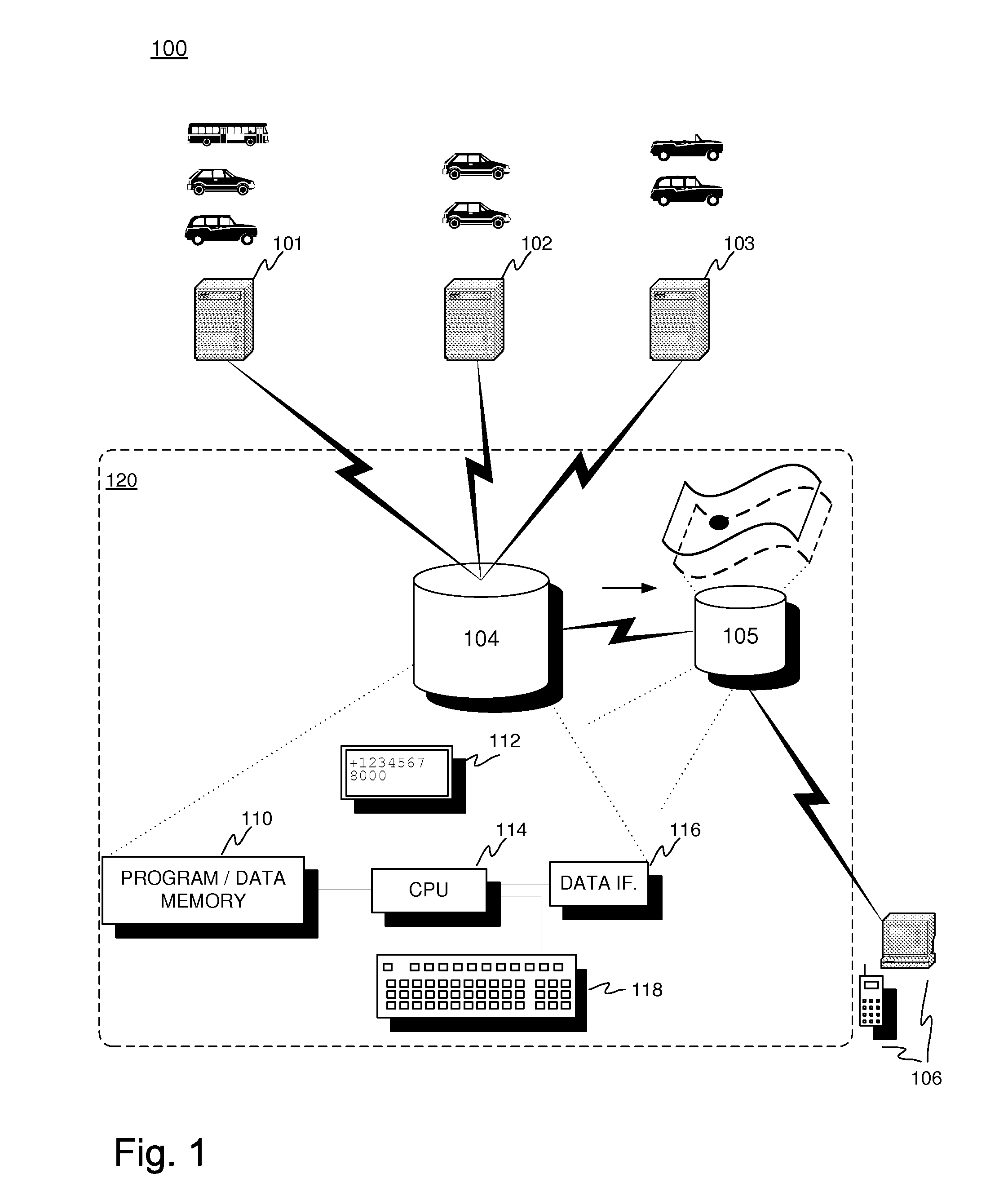

InactiveUS20100179861A1Reliable valueKept detailed and accurateMarket predictionsProduct appraisalManagement objectComputer science

System and method for assessing objects such as vehicles, wherein a value estimation model is determined for vehicles on a basis of data representing characteristics of a plurality of vehicles, the model including a plurality of parameters to be determined and a plurality of explanatory variables associated with the parameters and defined on the basis of the characteristics, wherein age and / or mileage of vehicles is configured to affect the value estimate, the value estimate being a dependent variable in the model, and wherein a unit for producing a value estimate for a target vehicle on the basis of the model is configured to perform an action (508, 510, 512, 513, 518, 524, 604, 710) to facilitate comparison of the value estimate to other valuation information related to the particular target vehicle or some other vehicle.

Owner:GREY HEN

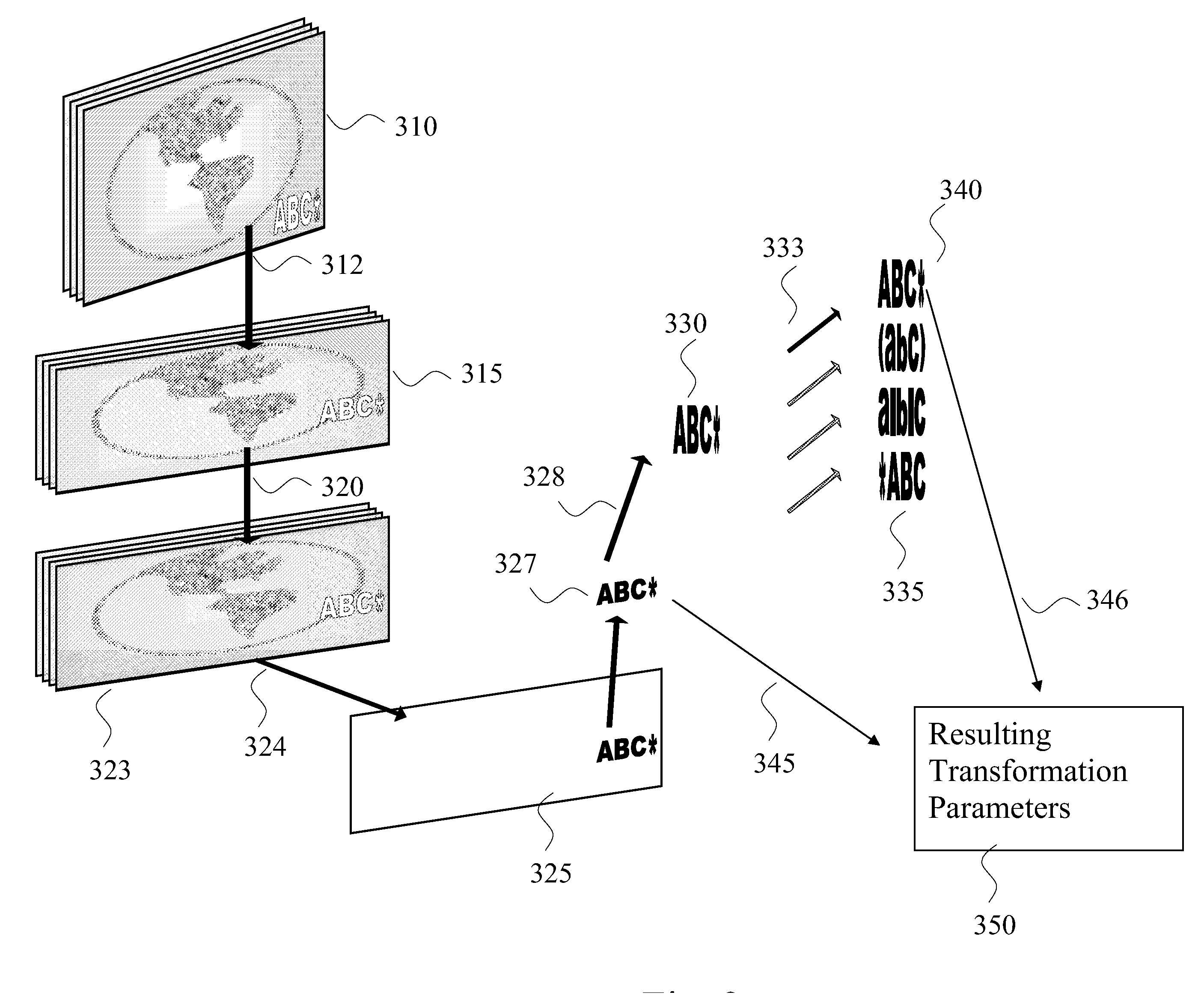

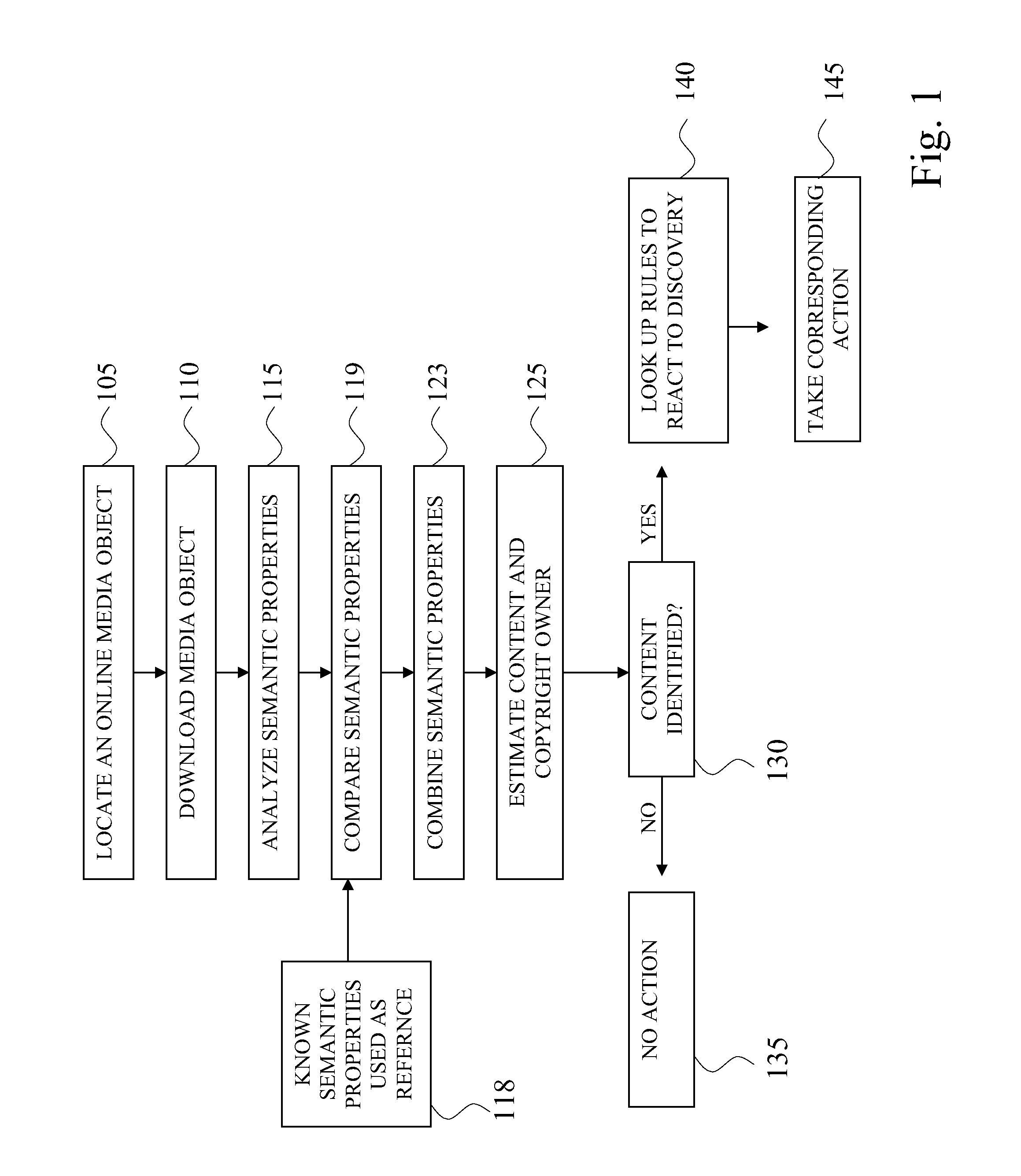

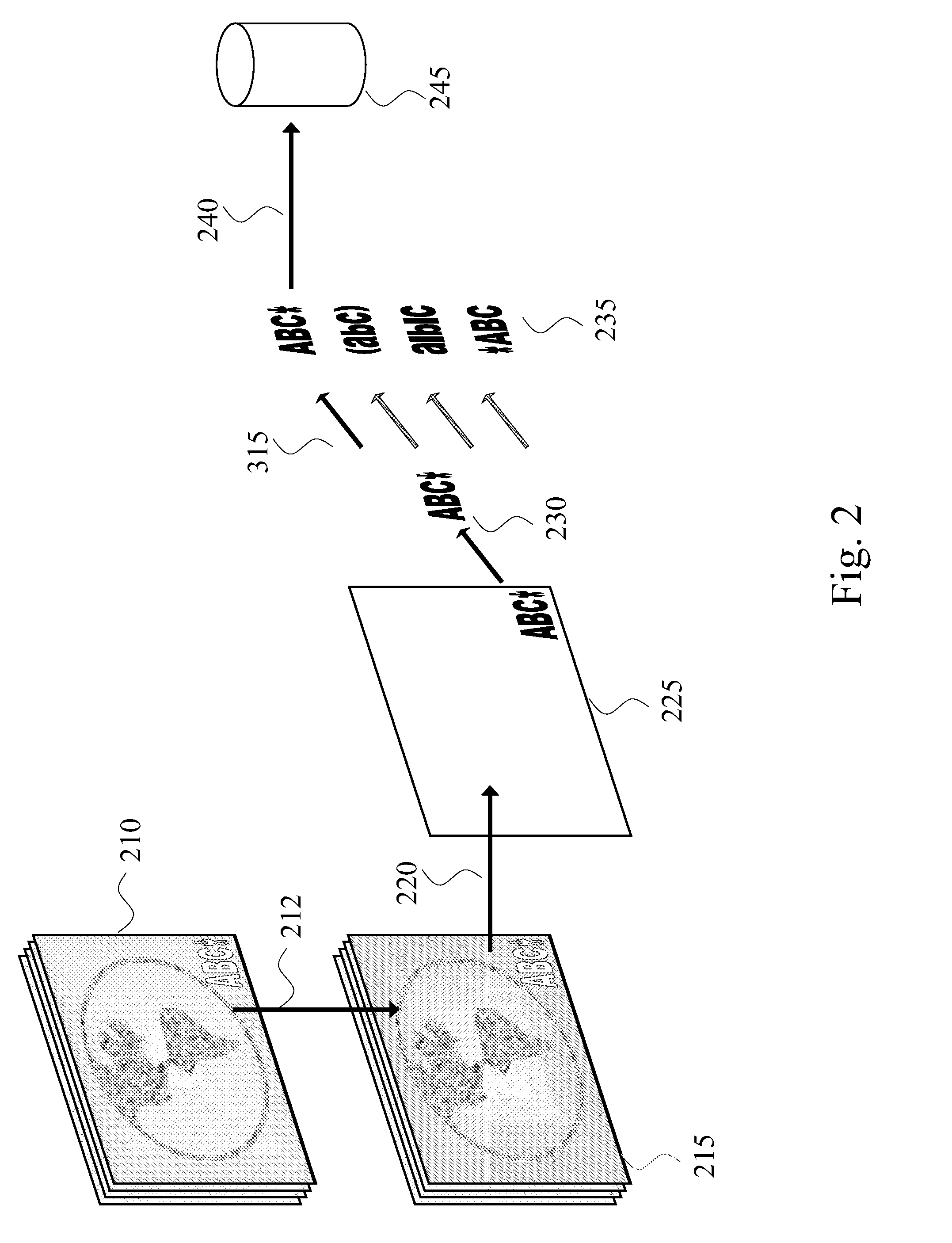

Systems and methods for performing semantic analysis of media objects

ActiveUS20130097625A1Television system detailsColor television signals processingWorld Wide WebObject system

System and method for identification of ownership to media objects through analysis of semantic information in the media objects are disclosed Semantic information is a term that can be used to describe aspects of the content of a media object that are apparent to a human viewing or listening to the content One embodiment of the invention includes extracting semantic information from a specified media object, matching said semantic information of the specified media object against known semantic information of known media objects, and taking action based on the result of the companson.

Owner:VERIMATRIX INC

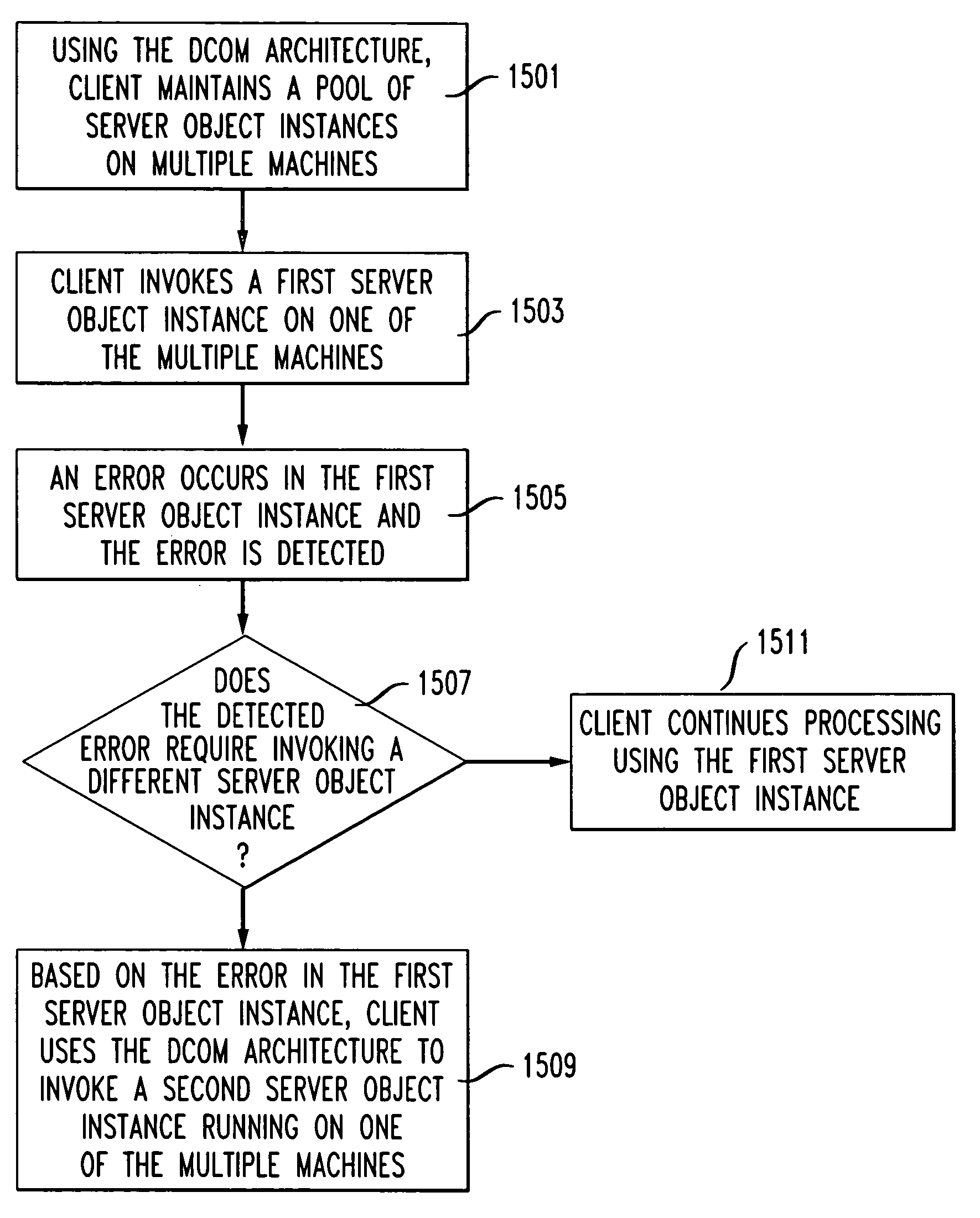

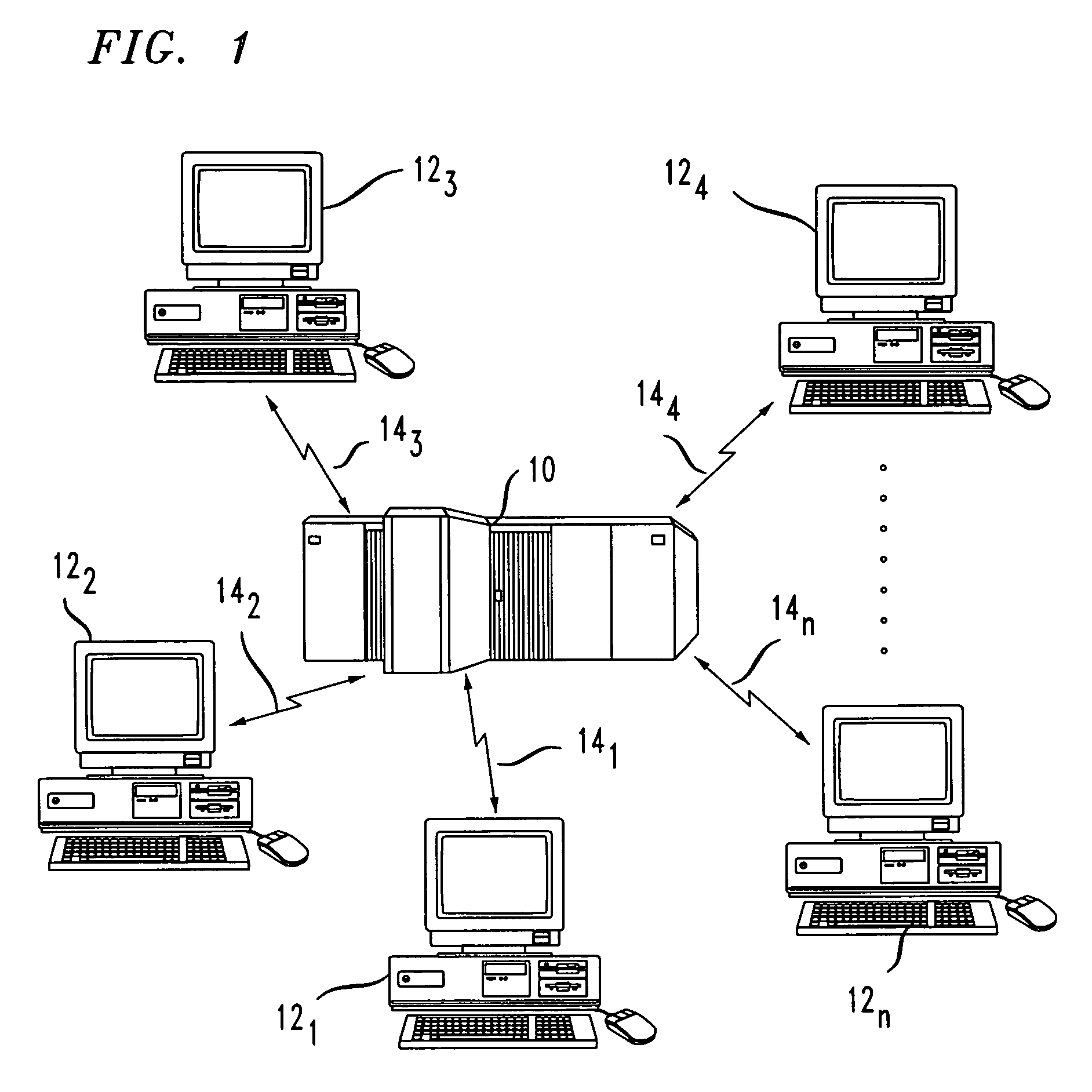

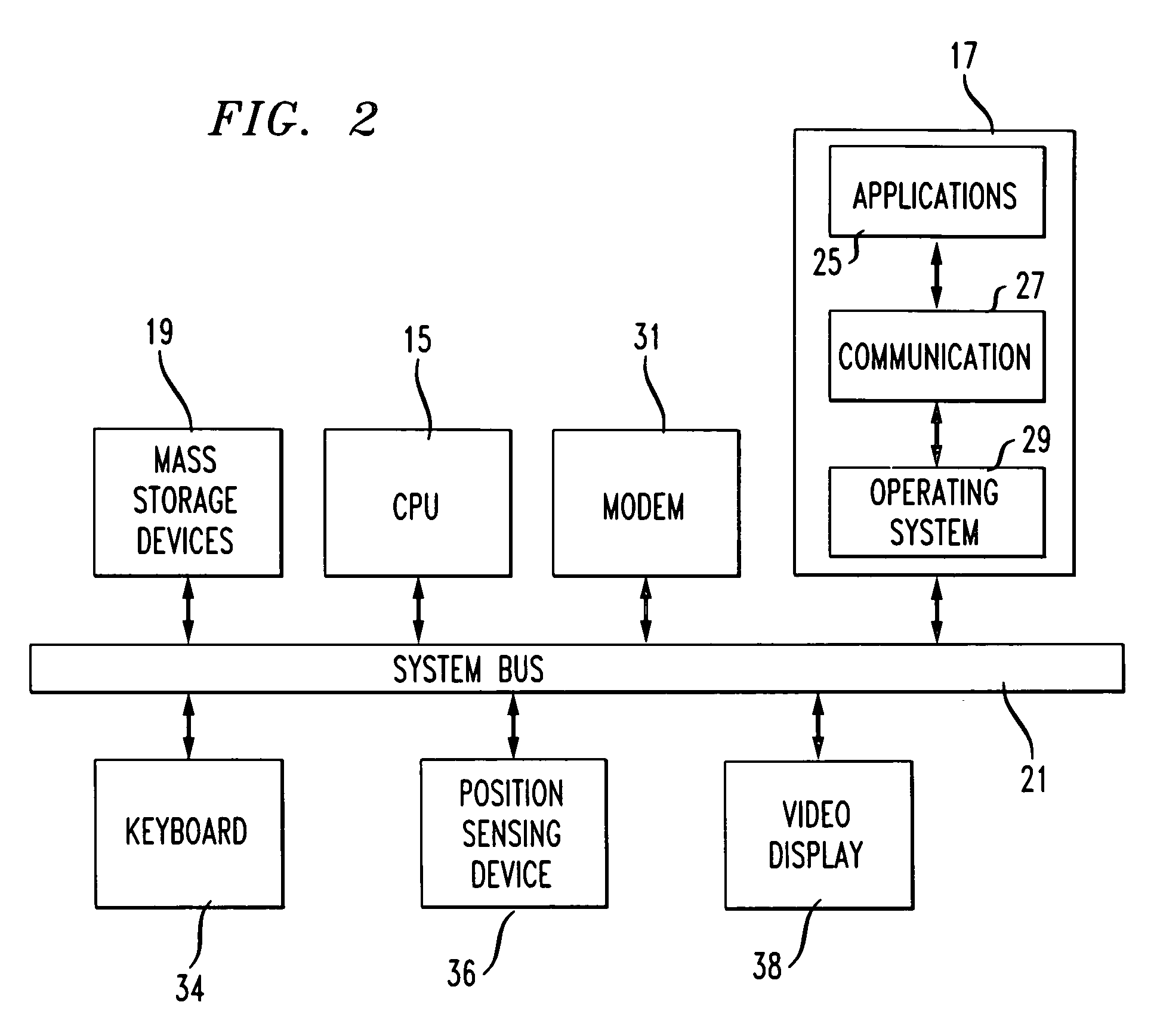

Method and system for providing reliability and availability in a distributed component object model (DCOM) object oriented system

InactiveUS7082553B1Improve reliabilityImprove availabilityError detection/correctionDistributed Component Object ModelFailover

A method and system for improving reliability and availability in distributed computer applications. The method and system may be used in the context of primary-backup, failover recovery. The method involves software-fault tolerance using technique of structured storage; referral components; and wrappers. The method and system exploit the platform and operating system independence of component object models to allow the dynamic linkage of different component objects, the objects being resident on different inter-linked machines, based on the application requirements at any given point in time.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

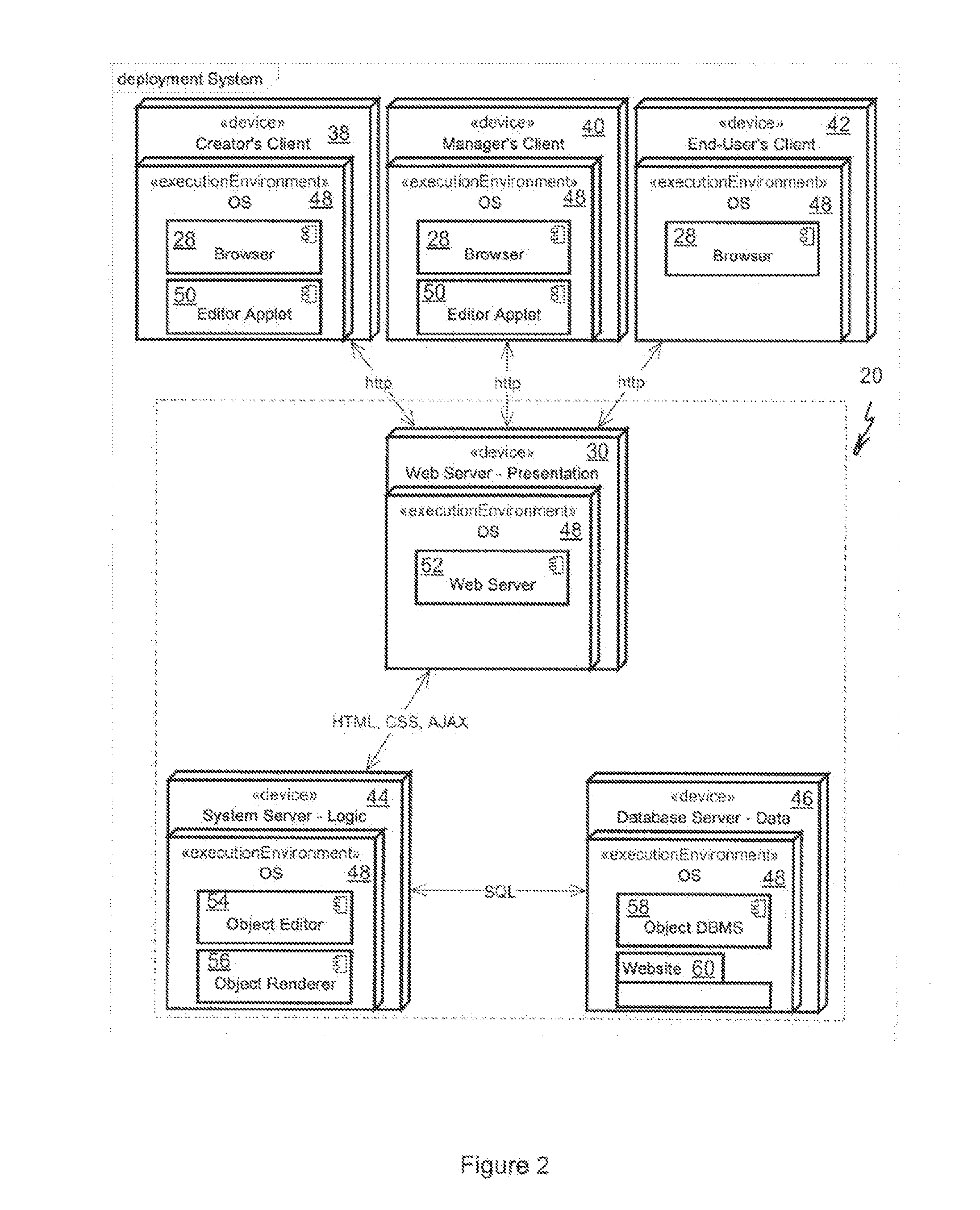

Object-oriented system for creating and managing websites and their content

The invention teaches a method for creating and managing a website as an object oriented system, comprising: providing on a system server a plurality of hierarchical classes of objects, each of the classes representing one aspect of the storage, presentation and logic of a website; providing on a web server an interface operable to present representations of objects instantiating the plurality of hierarchical classes and receive commands meant to one of: instantiate a new object, destroy a presented object, and change a property of a presented object; and storing on a database server objects as a traversable tree in accordance with the plurality of hierarchical classes.

Owner:SALESFORCE COM INC

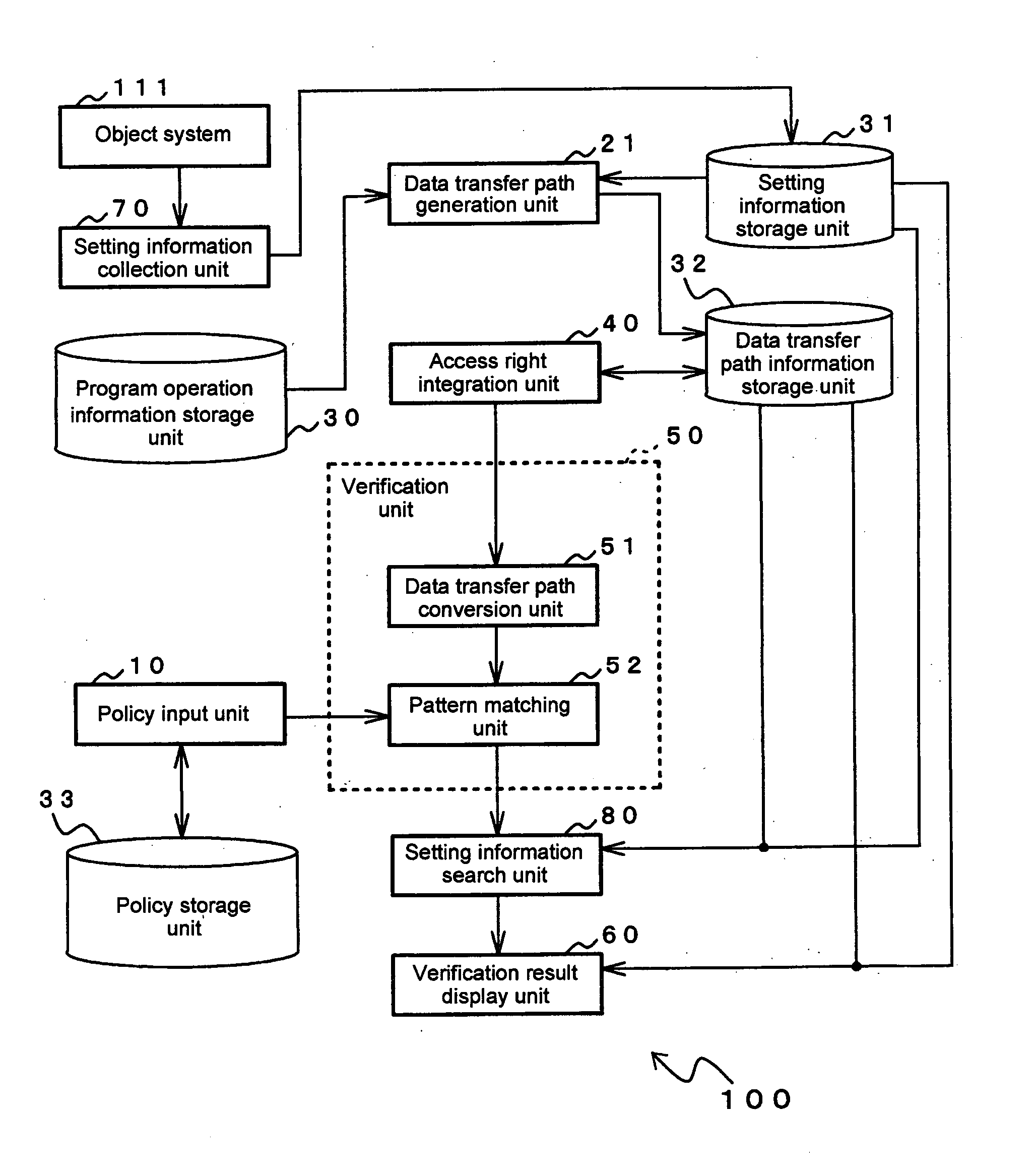

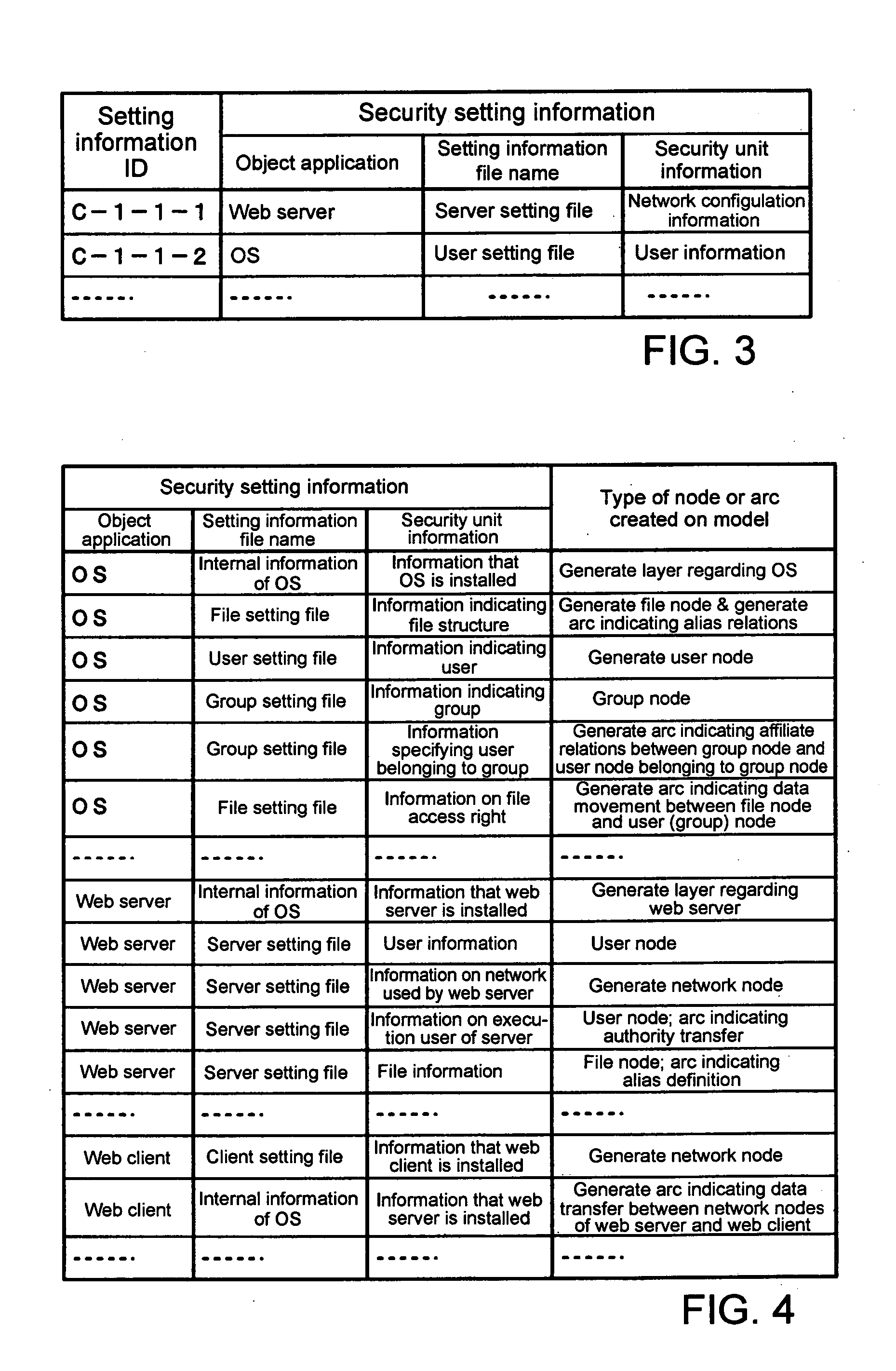

Security verification method and device

InactiveUS20050144475A1Rigorously verifying security settingRigorously verifying security settingsDigital data processing detailsDigital computer detailsData transmissionSecurity validation

A security verification method for verifying whether improper settings that indicate composite errors of security settings exist in an object system, which is an object of examination, includes steps of: reading data transfer paths that represent data movement in the object system and that are generated based on program operation information that describes operations of a program that is used in the object system, integrating the access rights of data transfer paths that have been read; and searching for improper paths among the data transfer paths for which access rights have been integrated based on security verification policies in which improper paths, which are paths of data movement that are improper from the standpoint of security, have been set in advance.

Owner:NEC CORP

Common point authoring system for the complex sharing of hierarchically authored data objects in a distribution chain

InactiveUS20070061360A1Reduction of burden costImprove connectivityDigital data processing detailsComputer security arrangementsInterconnectivityInformation object

The Common Point Authoring system functions to provide Livestock Informational Objects via the use of a centralized repository of uniquely identified, immutable Livestock Informational Objects. This system automates the authoring, maintenance, and distribution of the Livestock Informational Objects by using an Internet-based paradigm and a centralized repository of uniquely-identified, immutable Data Elements. The Common Point Authoring system provides a set of software modules that the manufacturers can use to author, maintain, and distribute Livestock Informational Objects and their customers, as Members of the system of Livestock Informational Objects, can use to retrieve, maintain, and distribute the Livestock Informational Objects. The system's interconnectivity allows for the use of an Internet-based paradigm for the purchase and sale among Members of the system of Livestock Informational Objects as commodities, and for reducing the burden costs among Members of compliance with government regulations.

Owner:PARDALIS TECH LICENSING LLC

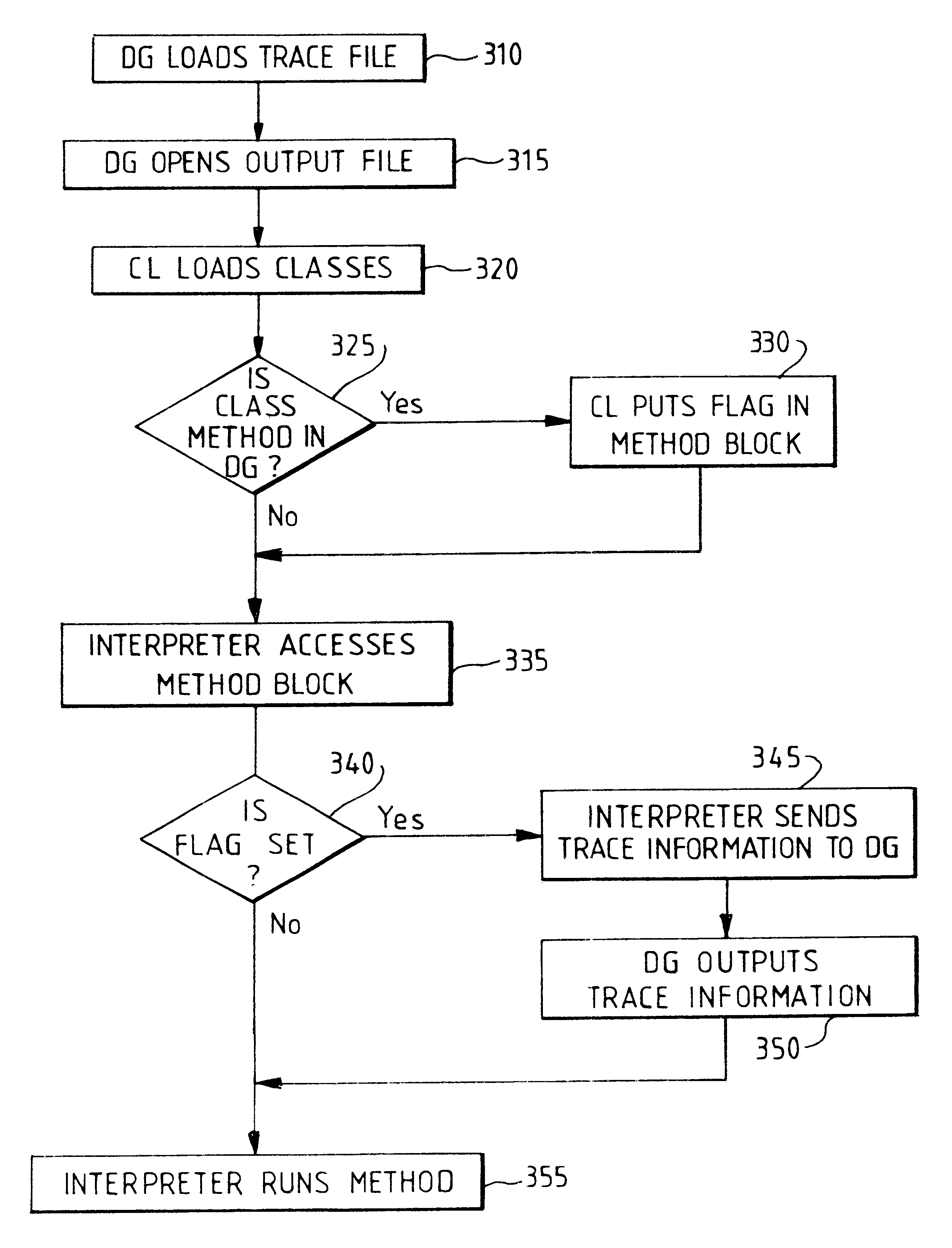

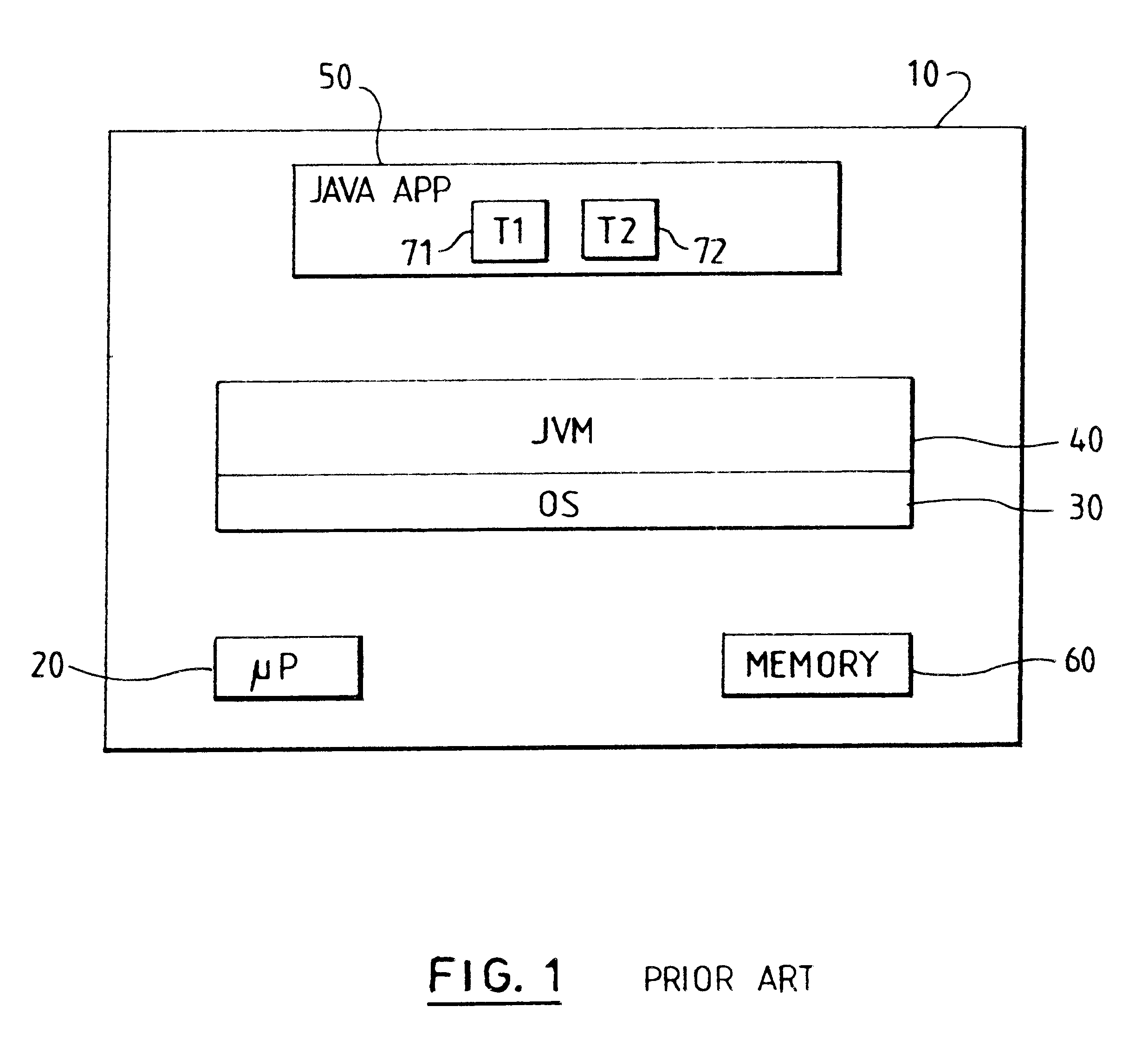

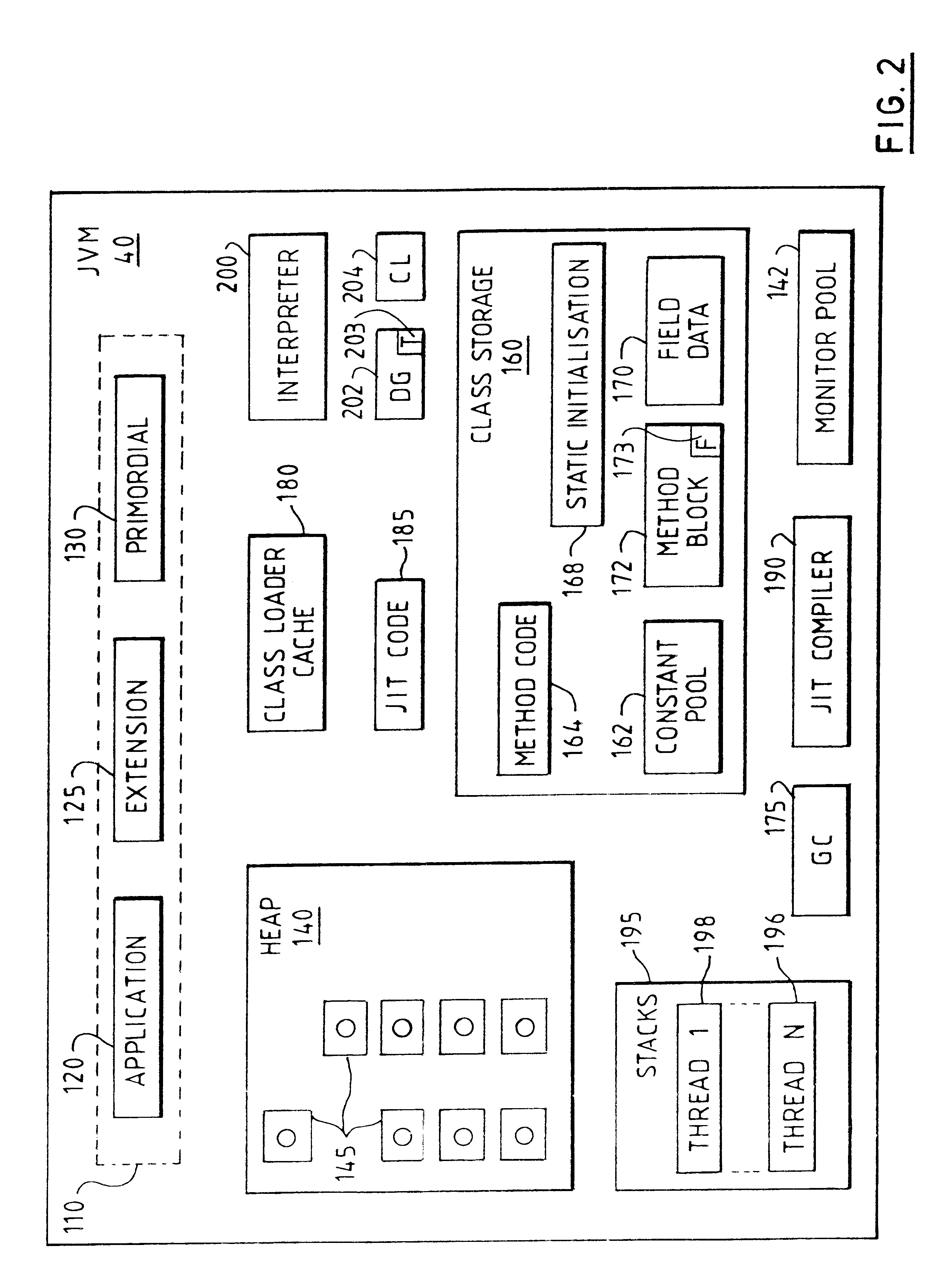

Trace information in a virtual machine

InactiveUS6738965B1Increase valueAssisting in performanceSoftware testing/debuggingSpecific program execution arrangementsObject systemUser defined

A virtual machine in an object-oriented system includes an interpreter. In order to provide trace information from a program about specific method calls, a user defines a selection of methods to be traced. As the program runs on the interpreter, it is determined, whether or not the method is included within the selection to be traced. For those methods included within the selection, trace information about the method call is outputted. A method block is associated with each method and is used by the interpreter to invoke the method. For each method within the user-defined selection, a flag is set within the method block associated with the method. The status of this flag is checked when the interpreter invokes a method, in order to determine whether or not the method is included within the selection.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com