Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

69 results about "Fast interrupt request" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fast Interrupt Requests (FIQs) are a specialized type of Interrupt Request, a standard technique used in computer CPUs to deal with events which need to be processed as they occur such as receiving data from a network card, or keyboard or mouse actions. FIQs are specific to the ARM CPU architecture, which supports two types of interrupts; FIQs for fast, low latency interrupt handling and Interrupt Requests (IRQs), for more general interrupts.

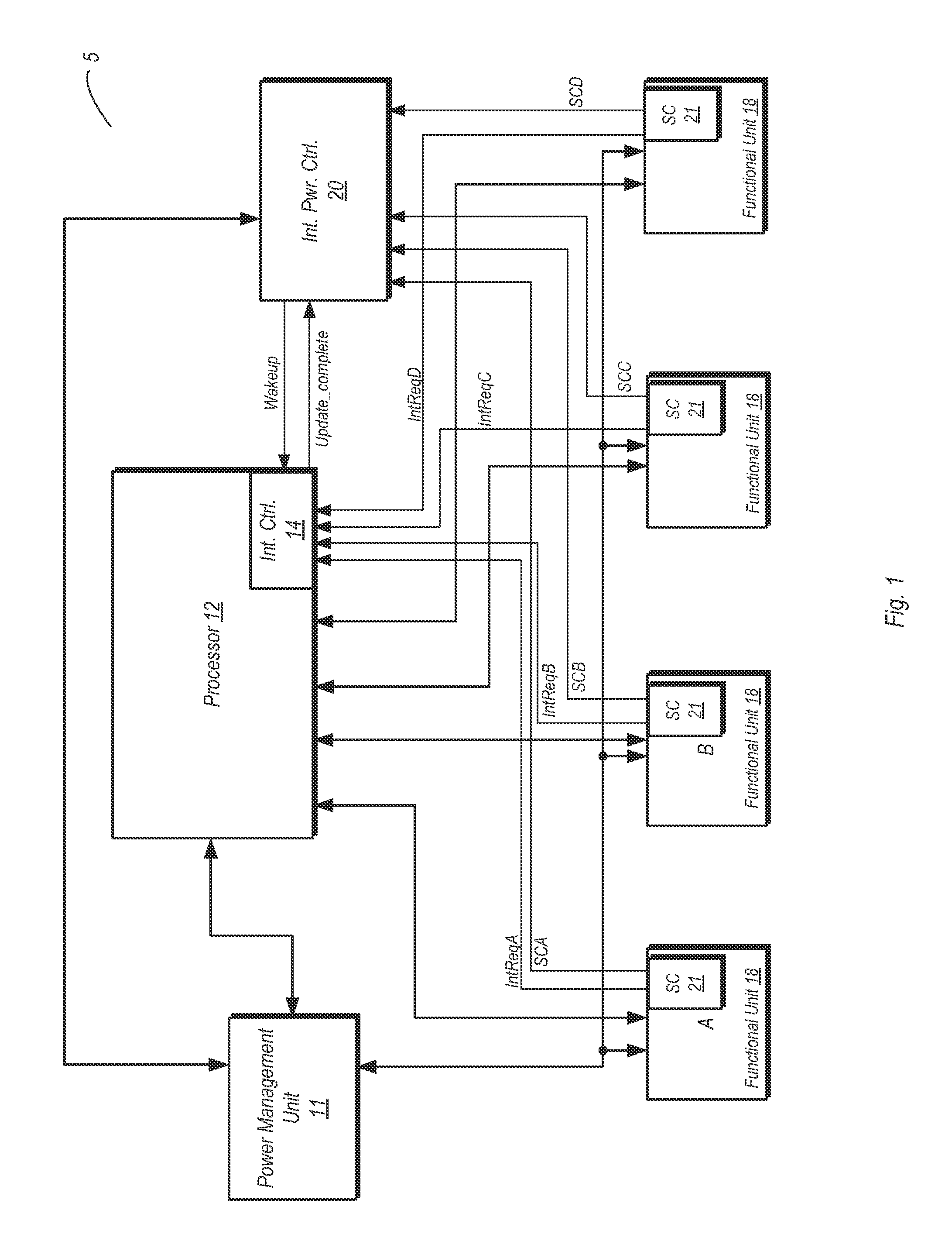

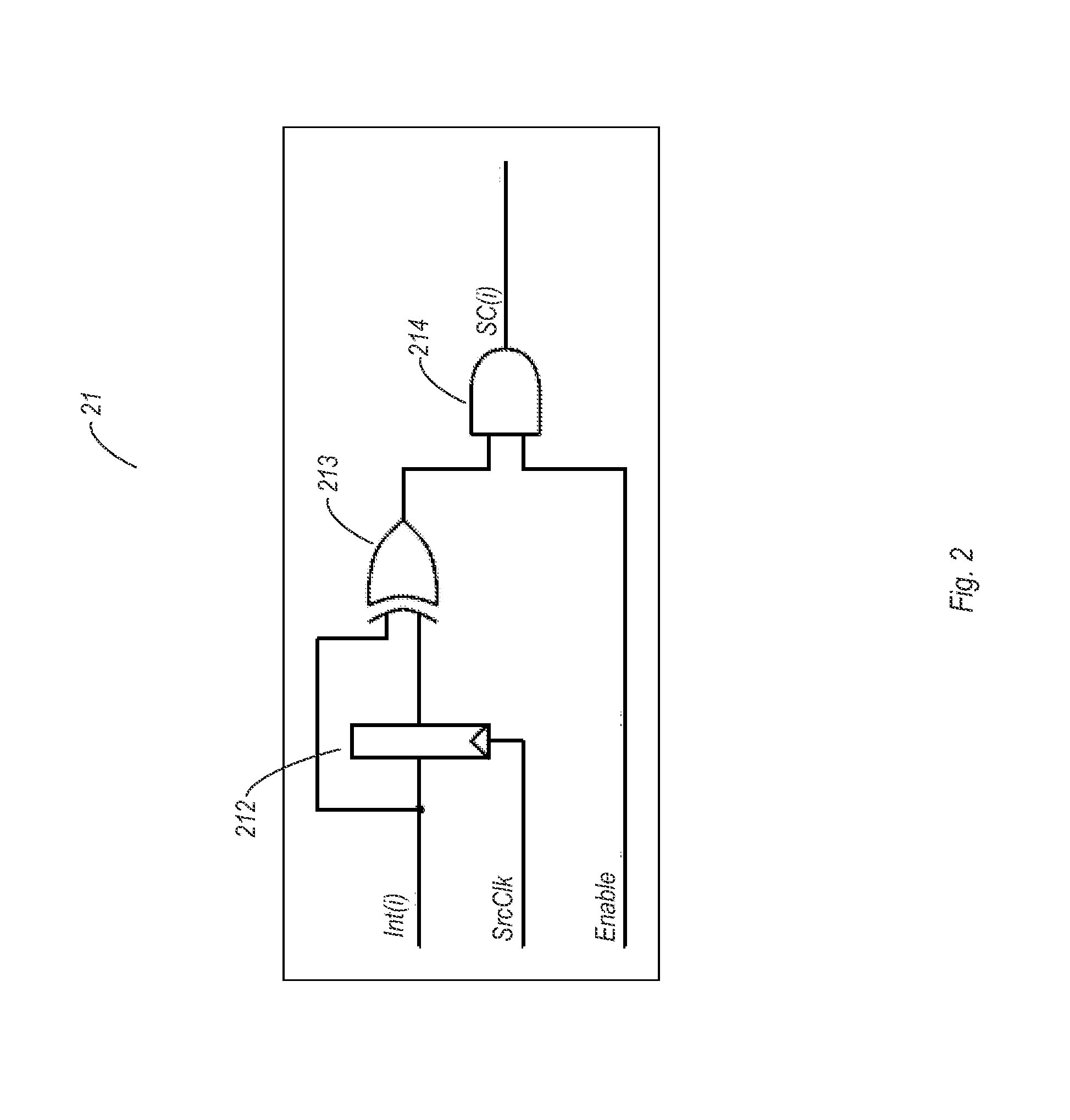

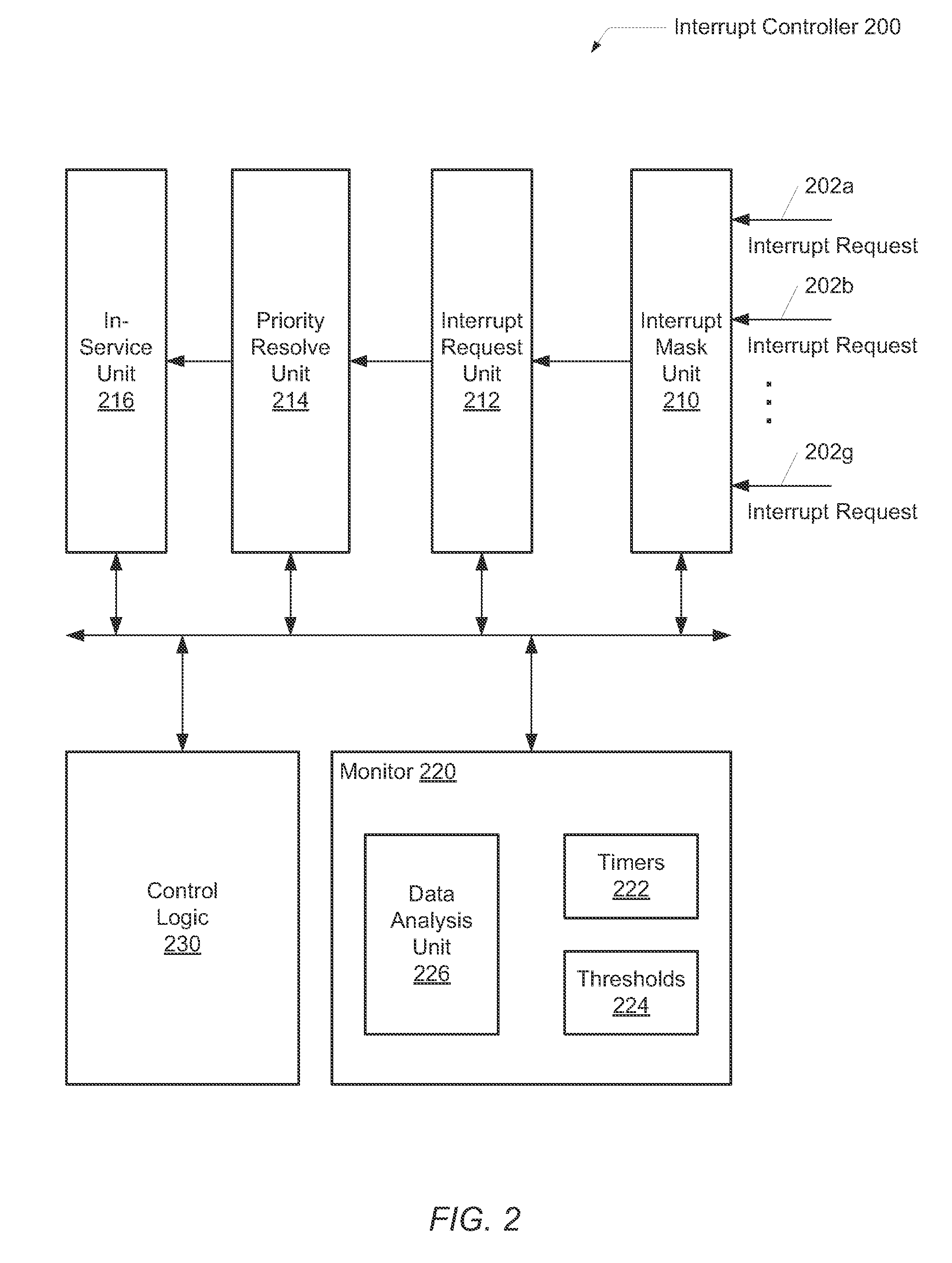

Interrupt controller

ActiveUS7624215B2Increase powerStatic power consumption of the interrupt controller can be reducedEnergy efficient ICTVolume/mass flow measurementPower modeControl circuit

Owner:ARM LTD

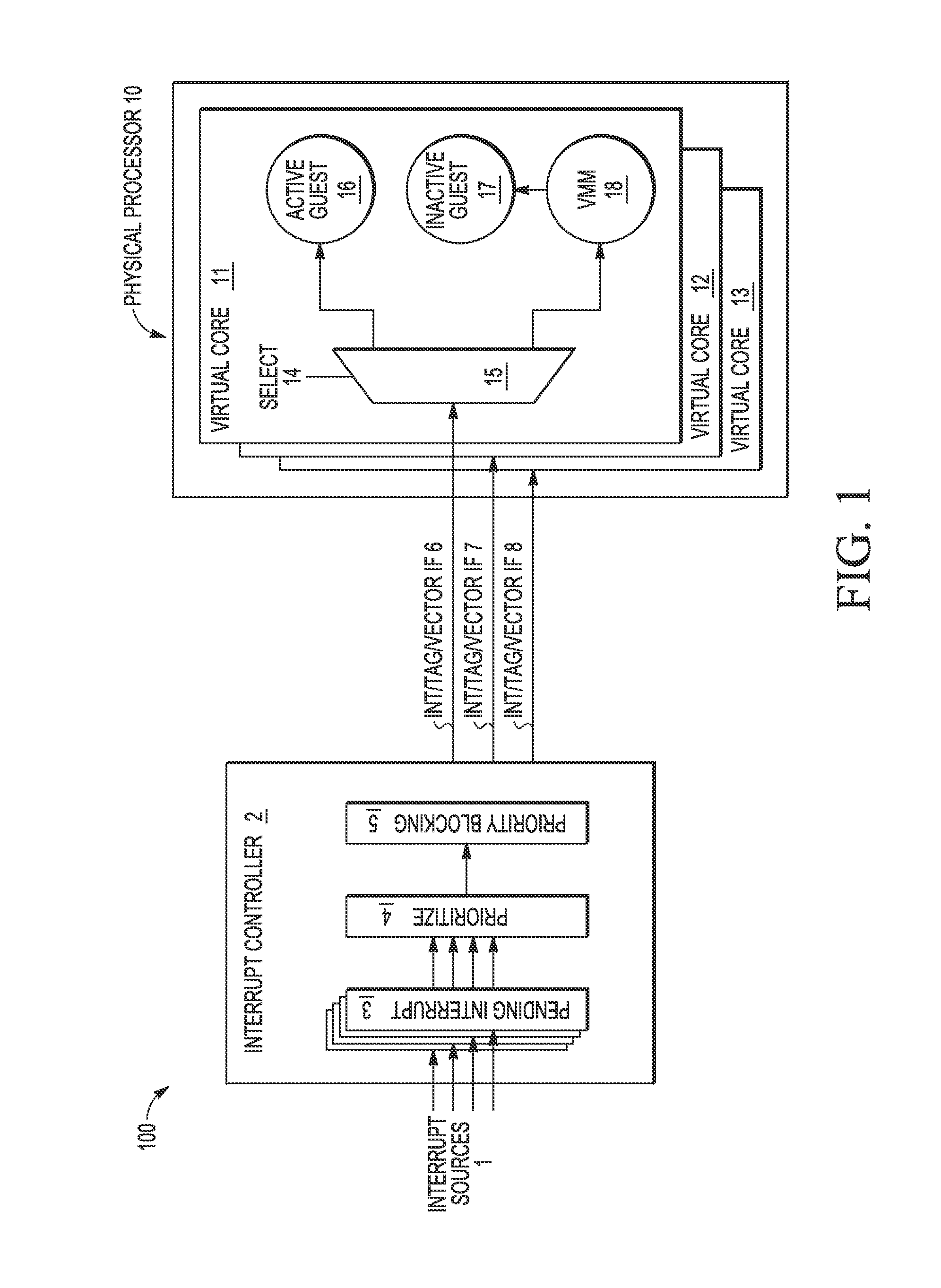

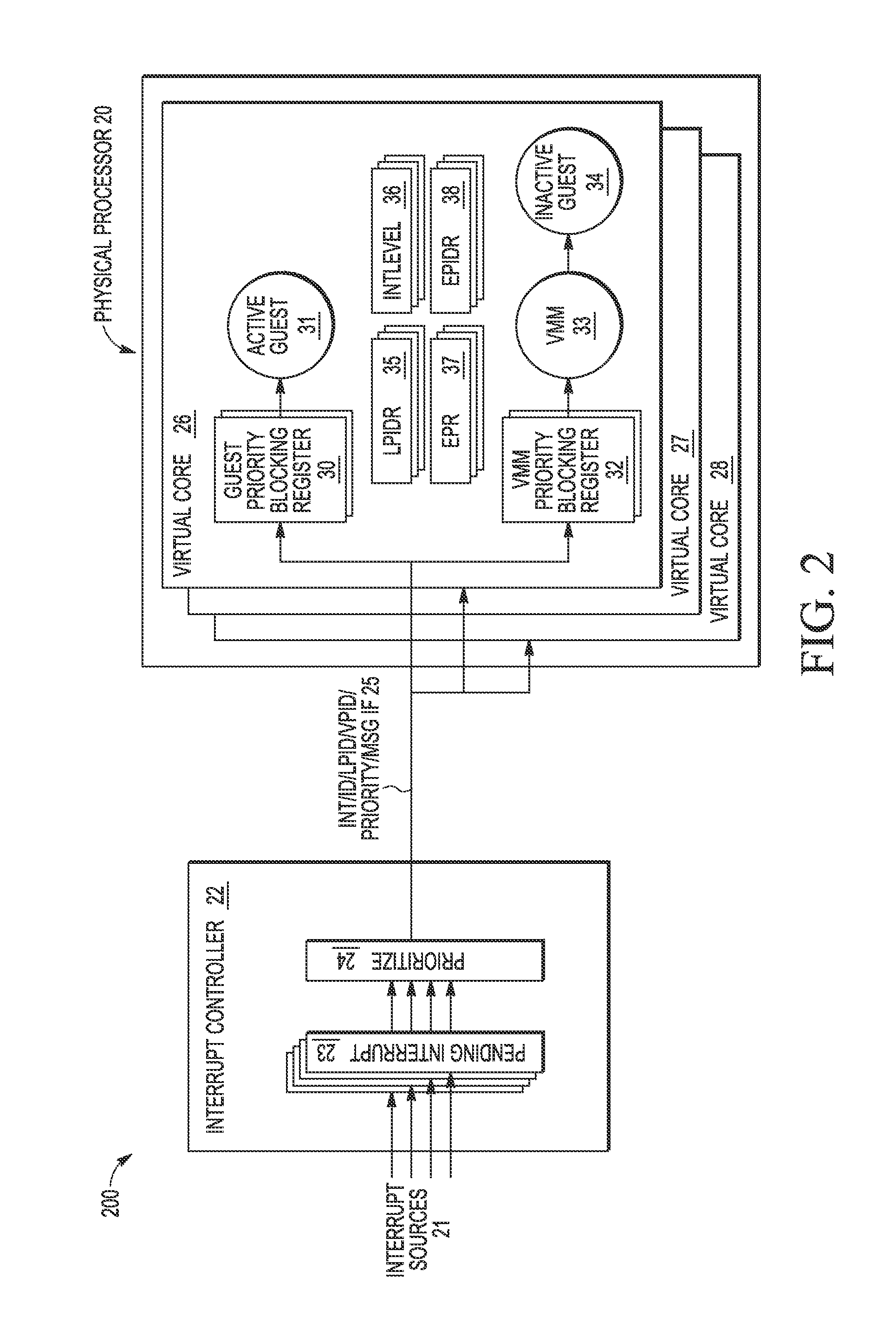

Processor Interrupt Interface with Interrupt Partitioning and Virtualization Enhancements

A method and circuit for a data processing system (200) provide a processor-based partitioned priority blocking mechanism by storing interrupt identifiers, partition identifiers, thread identifiers, and priority levels associated with accepted interrupt requests in special purpose registers (35-38) located at the processor core (26) to enable quick and efficient interrupt priority blocking on a partition basis.

Owner:NXP USA INC

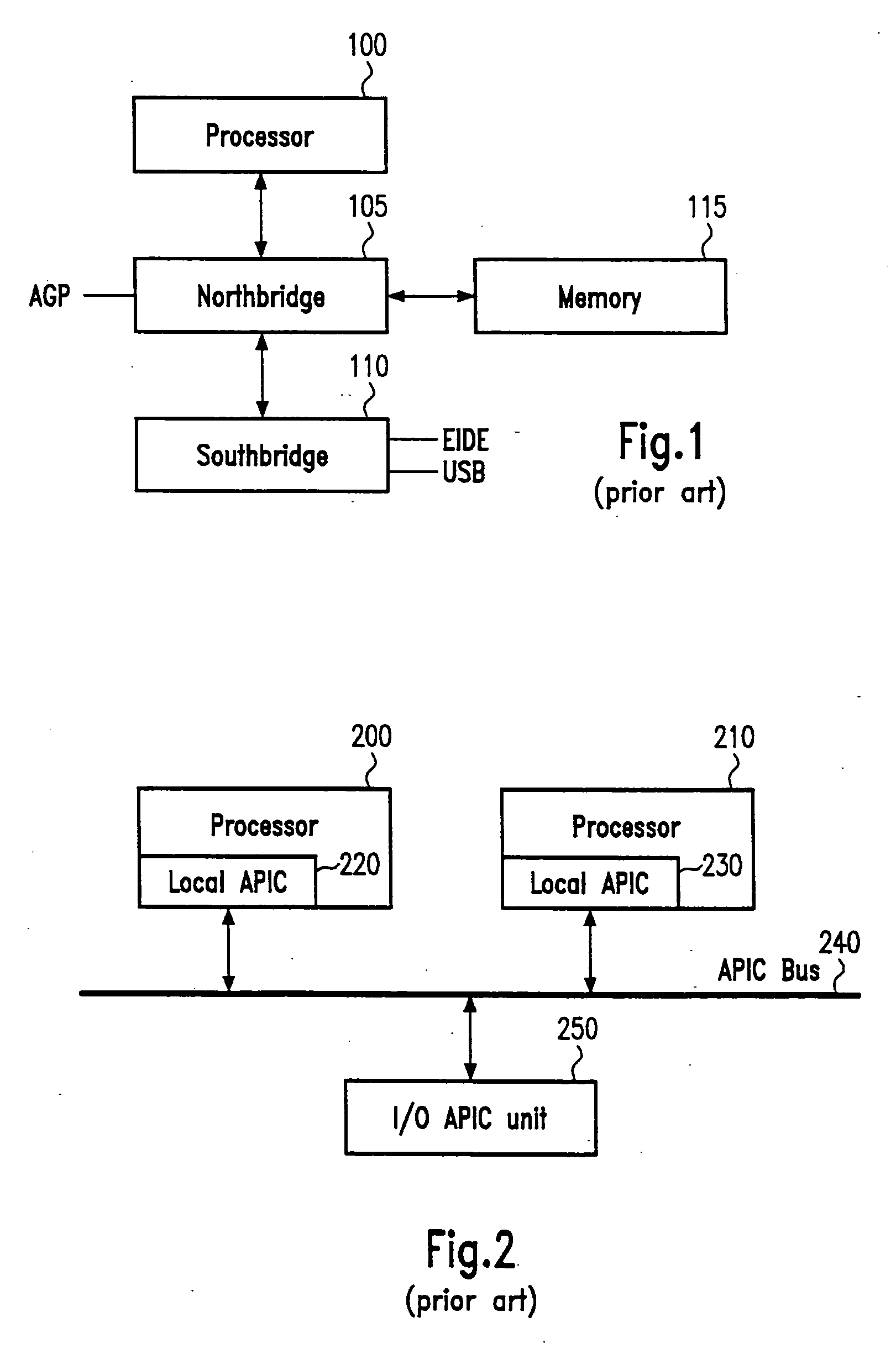

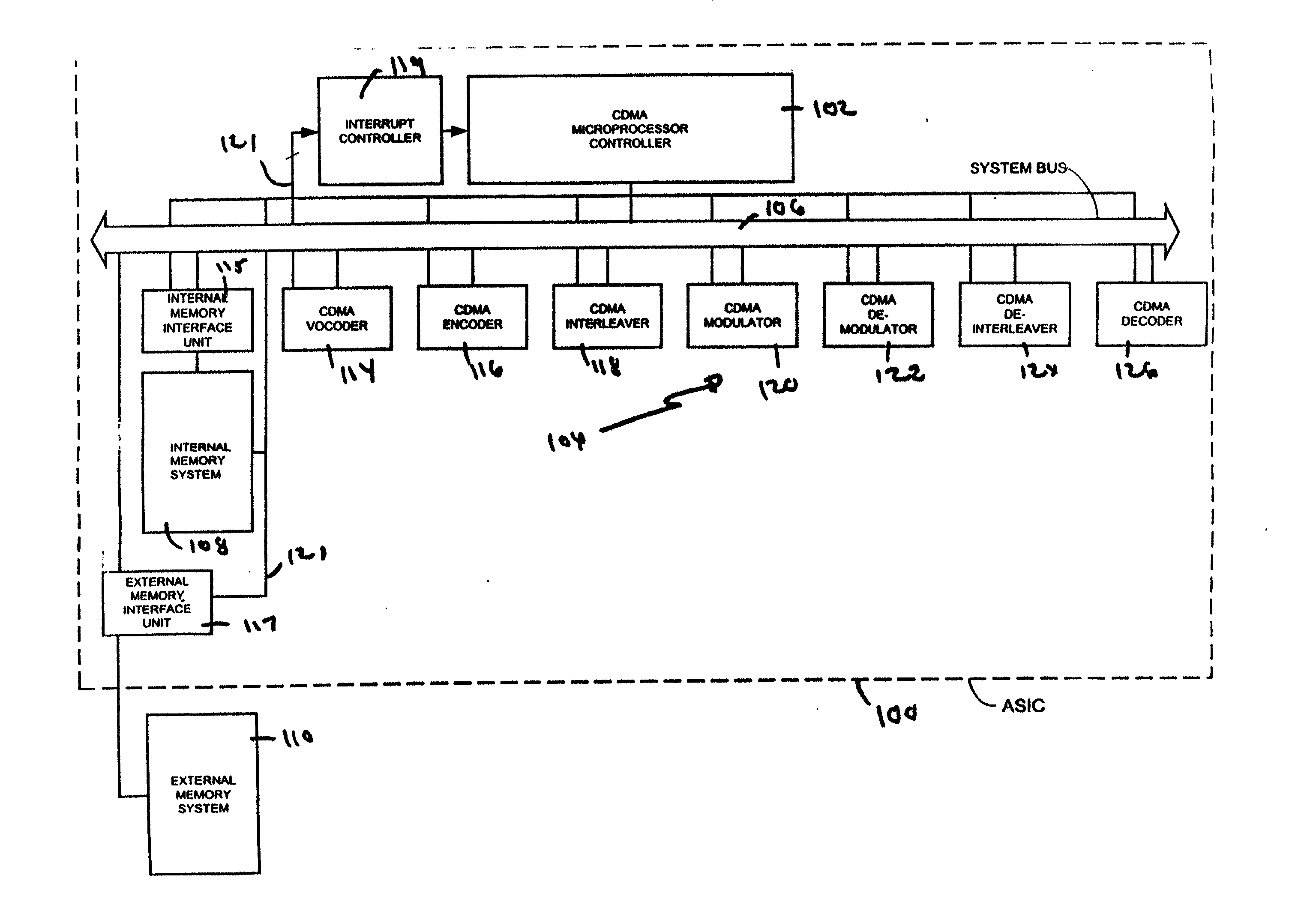

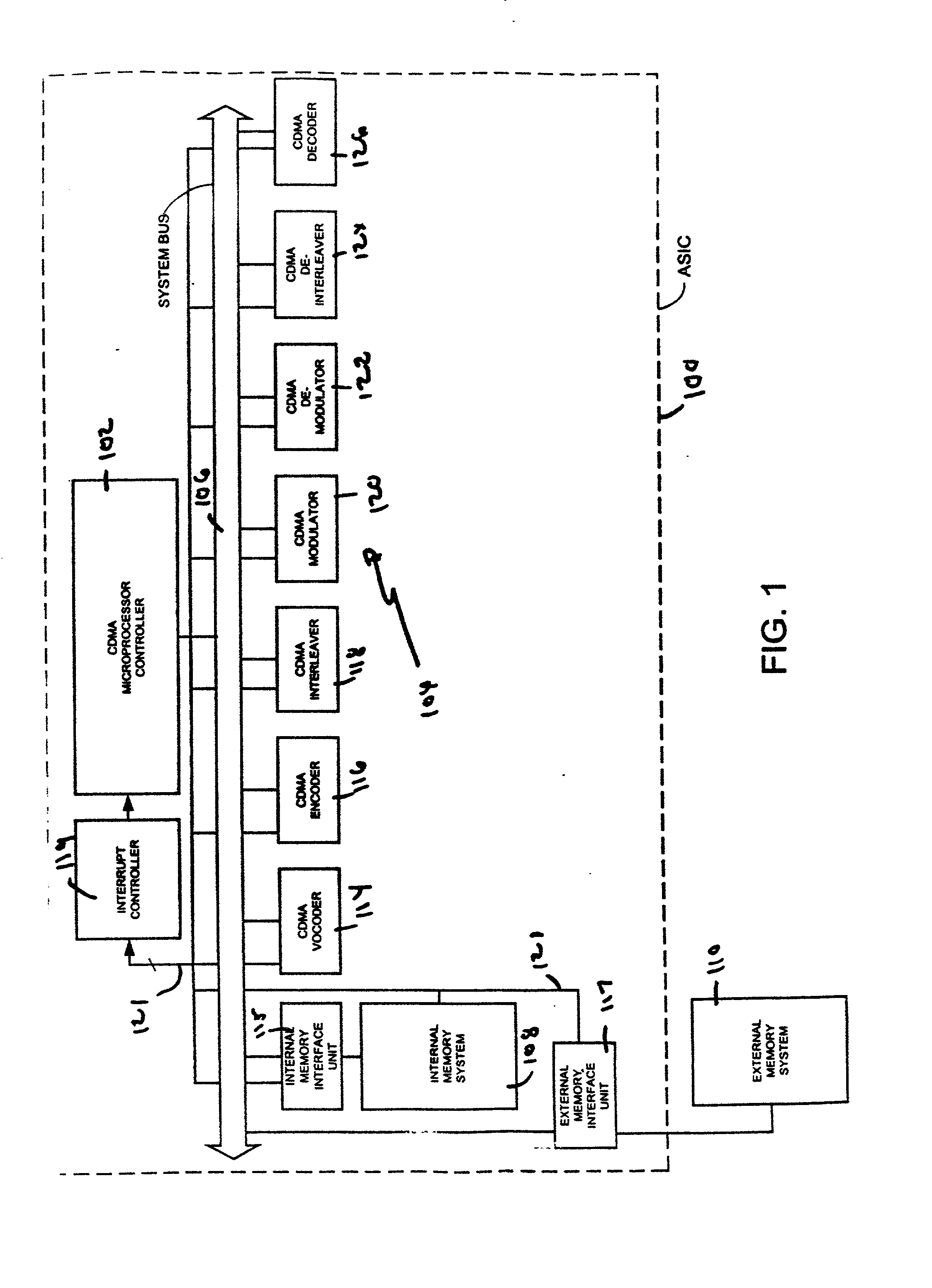

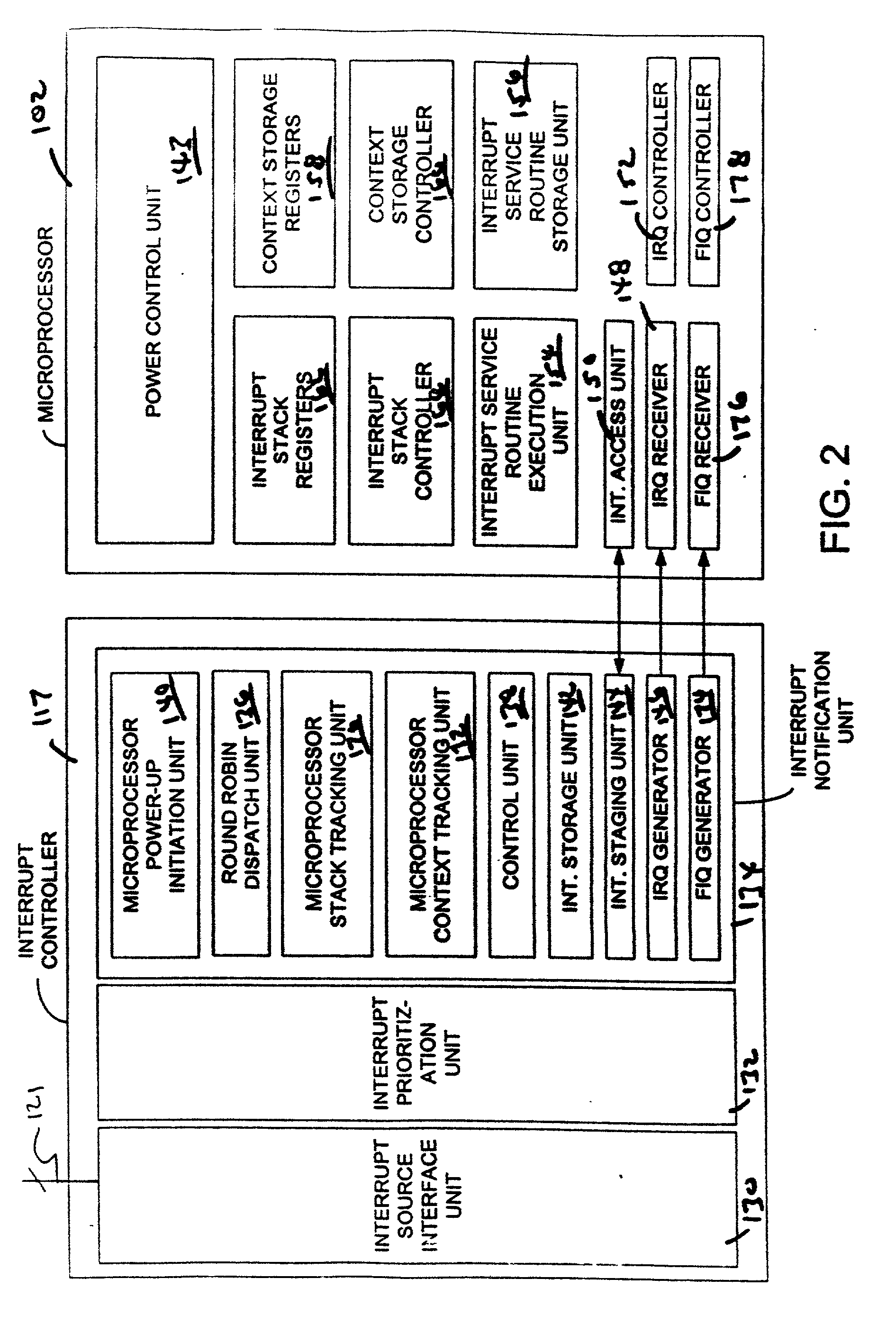

Mobile communication device having a prioritized interrupt controller

InactiveUS6807595B2Energy efficient ICTEnergy efficient computingProgrammable Interrupt ControllerComputer science

A microprocessor system having an interrupt controller is provided for use in a mobile communications device. Peripheral processing units generate interrupt requests for sending to the microprocessor. The microprocessor has components for responding to interrupt requests by interrupting current processing and performing an interrupt service routine associated with the interrupt request. The interrupt controller receives interrupt requests directed to the microprocessor from the peripheral processing units and for prioritizes the interrupt requests on behalf of the microprocessor. By providing an interrupt controller for prioritizing interrupt requests on behalf of the microprocessor, the microprocessor therefore need not devote significant internal resources to prioritizing the interrupt request signals.

Owner:QUALCOMM INC

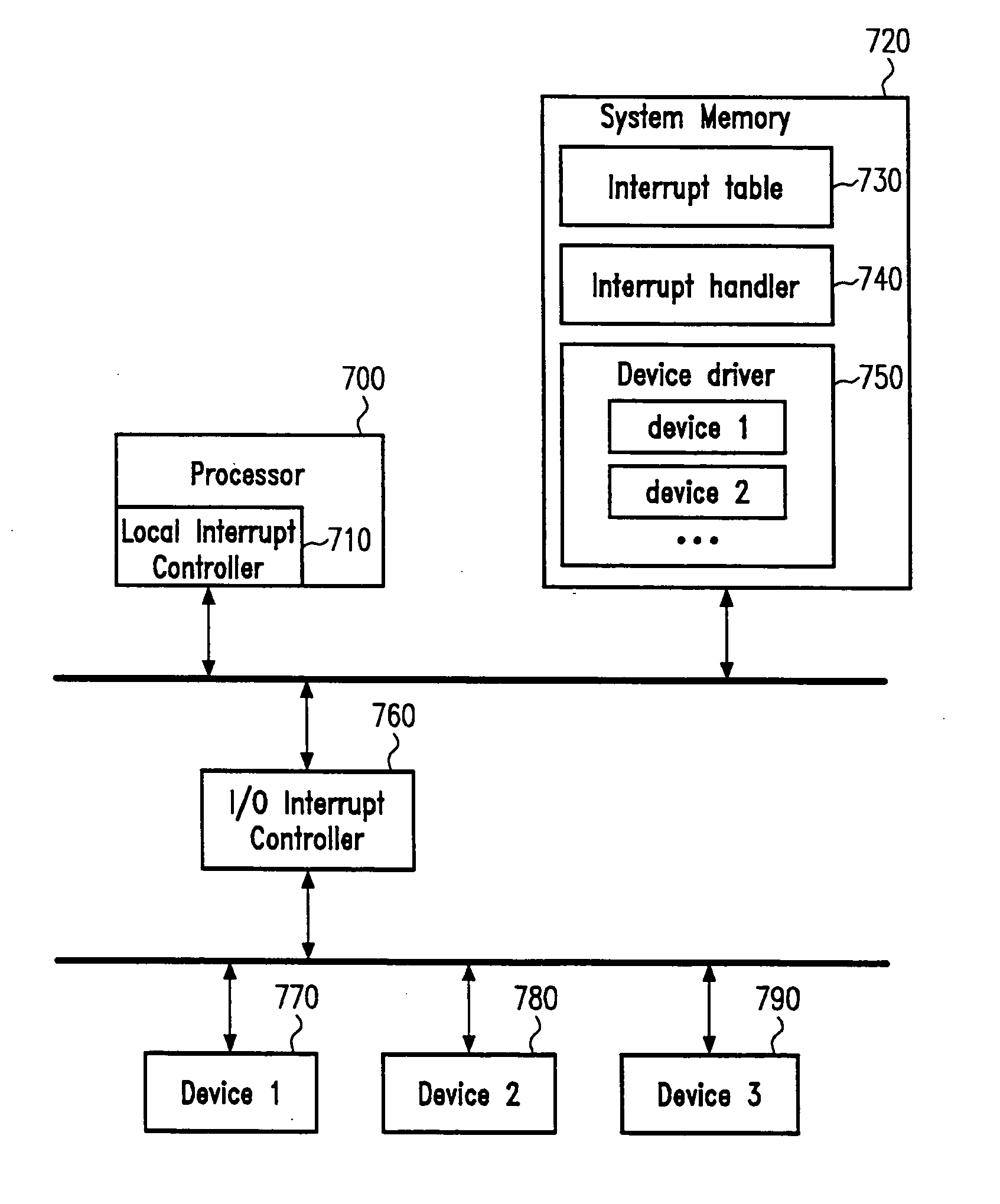

Message based interrupt table

InactiveUS20060047877A1Reduce Interrupt LatencyHigh speedElectric digital data processingMemory addressInterrupt vector table

An interrupt processing technique is provided where an interrupt message is sent to an interrupt controller of a processor in response to an interrupt request from an individual device. The interrupt message comprises a memory address and interrupt status information. The memory address is specifically allocated to the device that has issued the interrupt request. The interrupt status information indicates an interrupt status of the device. An interrupt table that is stored in the memory is updated by the interrupt controller using the interrupt status information comprised in the interrupt message. The interrupt table holds device specific interrupt statuses. Updating the interrupt table comprises addressing the memory using the memory address in the interrupt message.

Owner:GLOBALFOUNDRIES INC

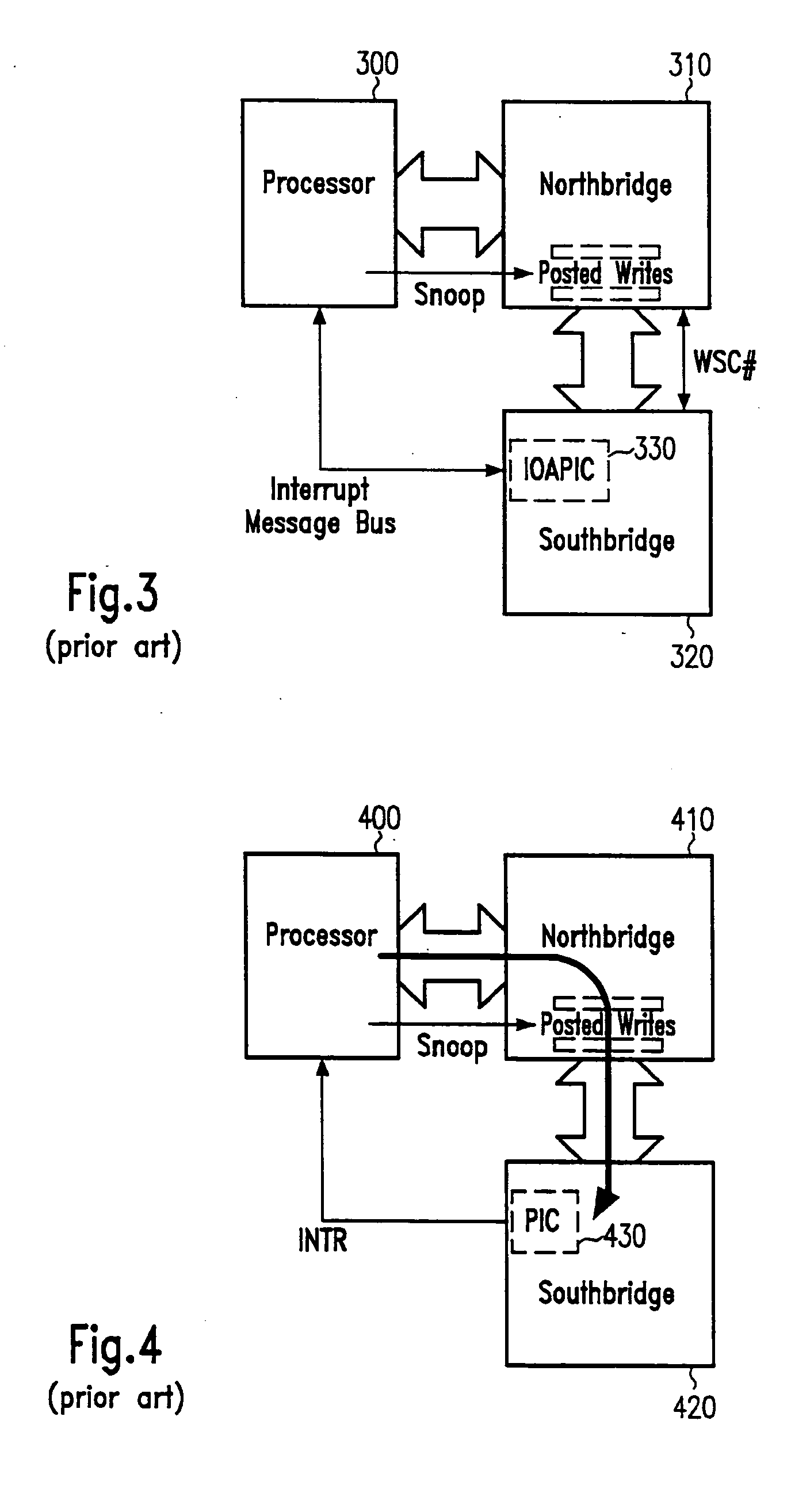

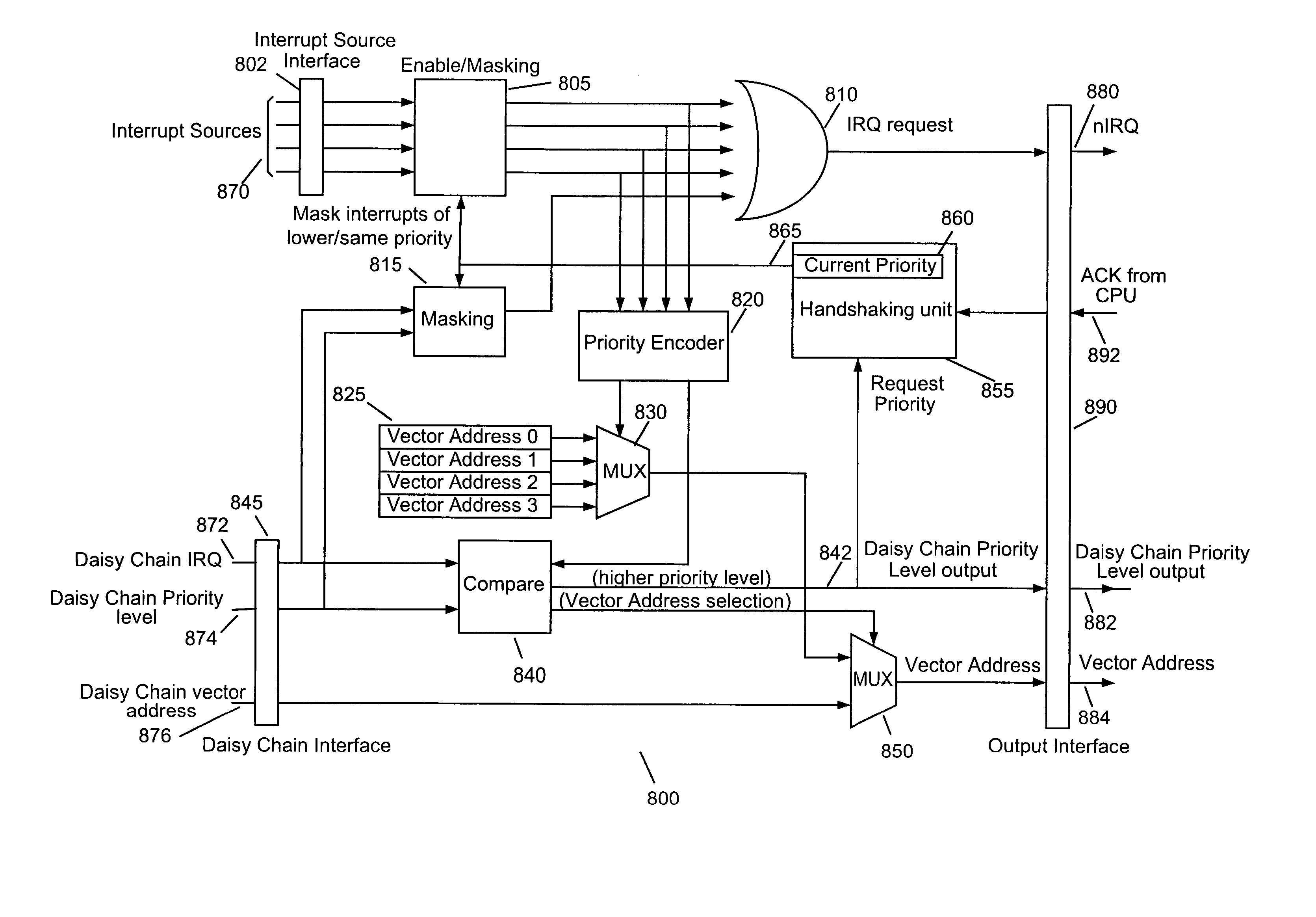

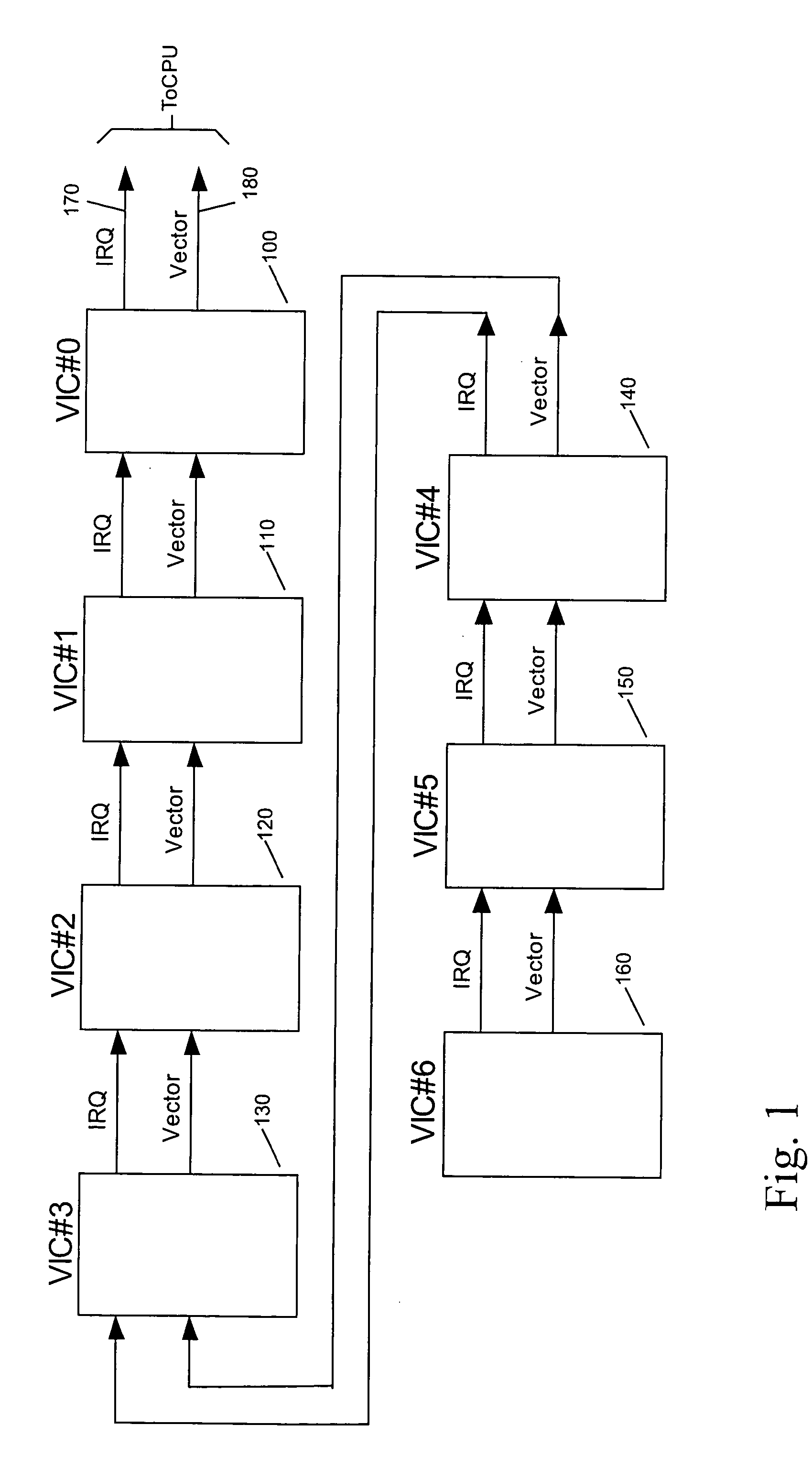

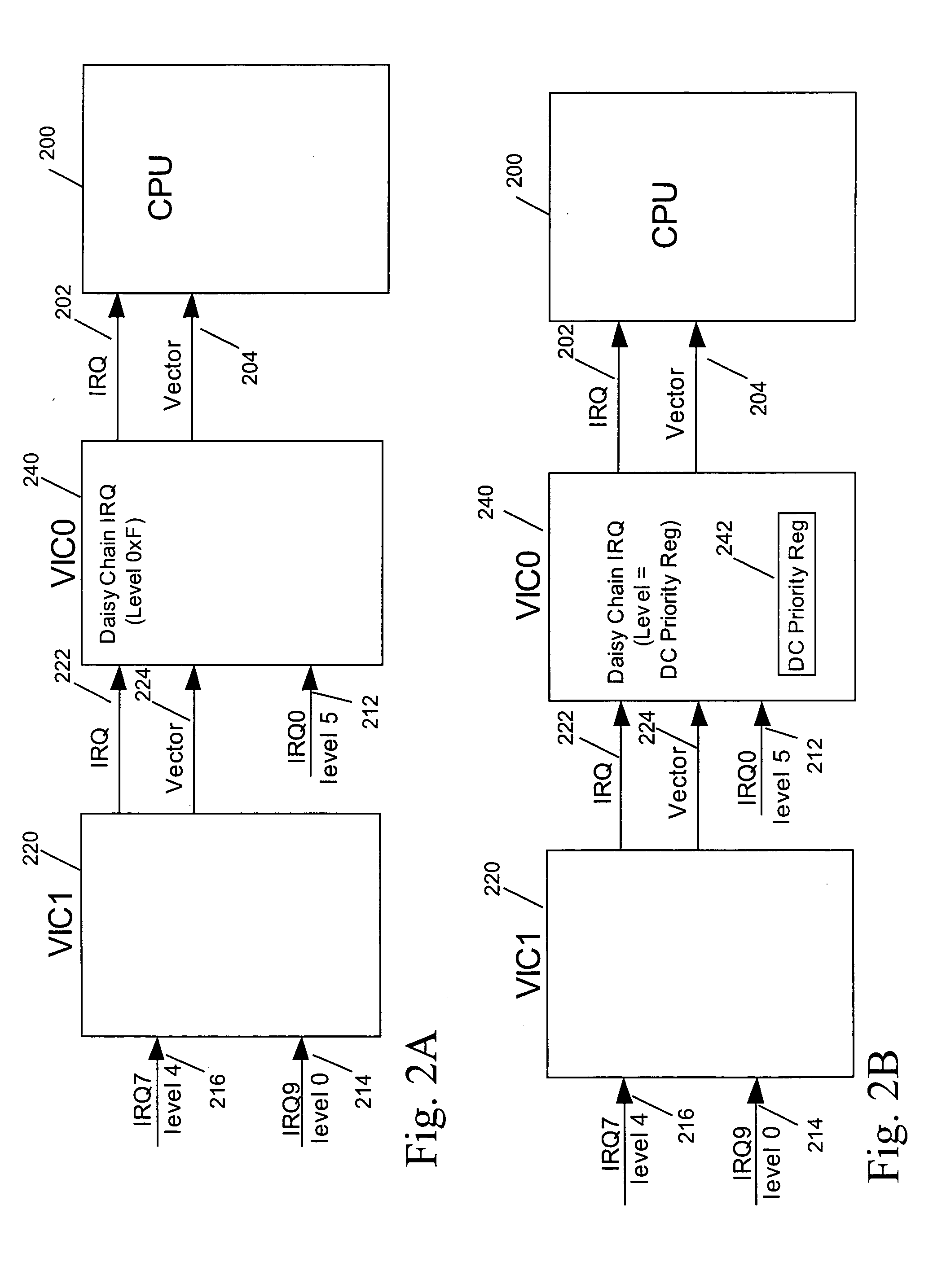

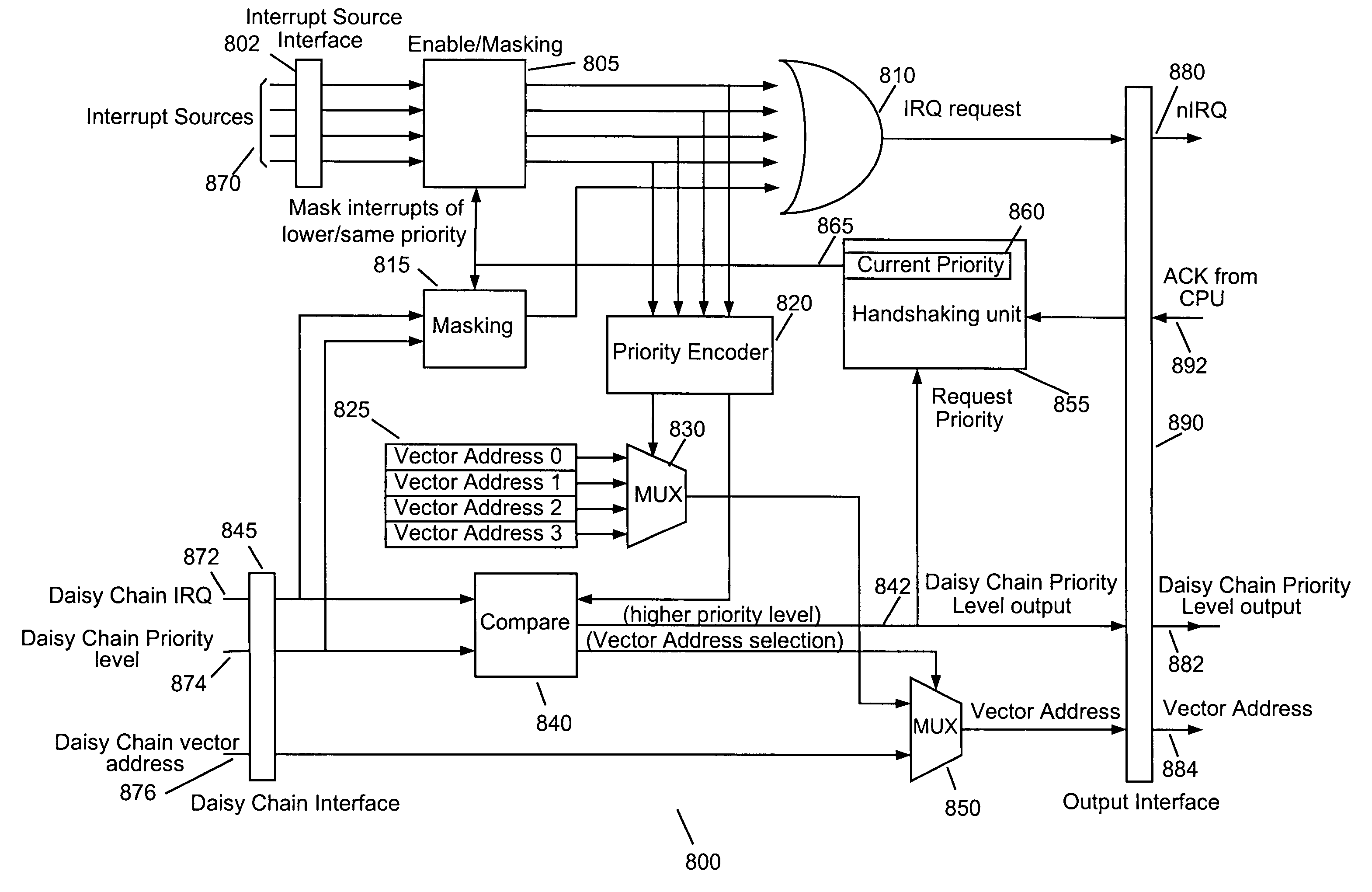

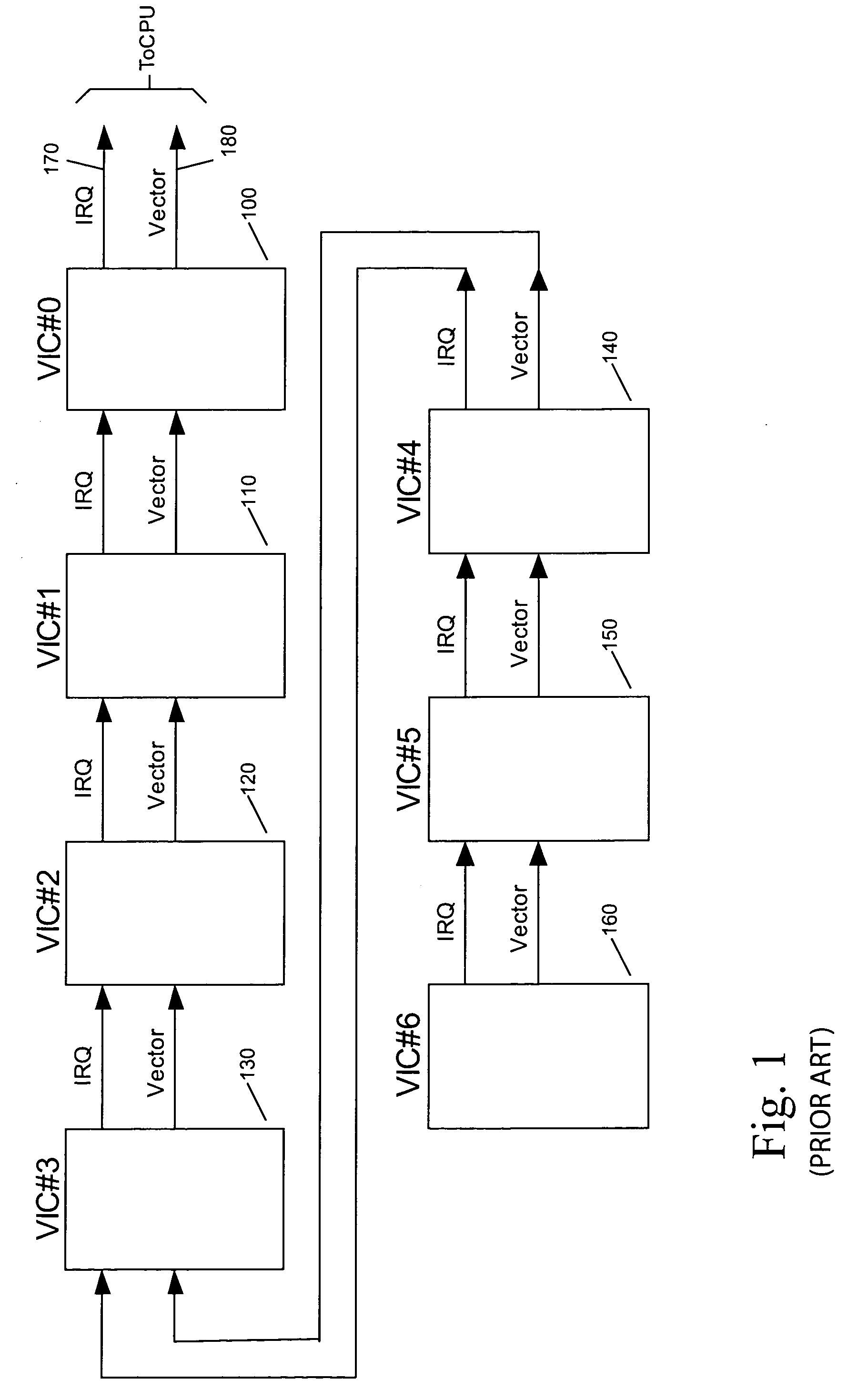

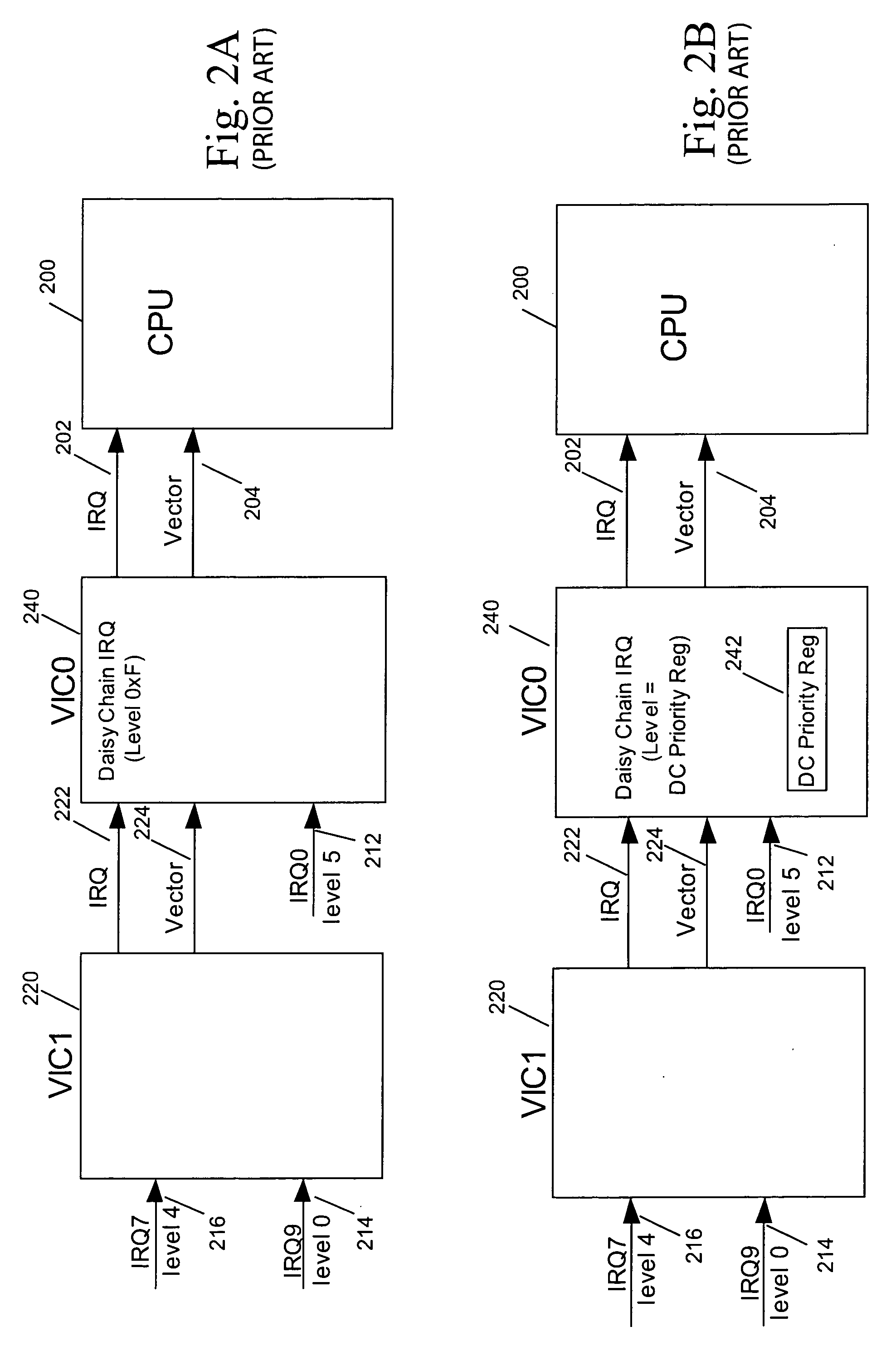

Interrupt controller and interrupt controlling method for prioritizing interrupt requests generated by a plurality of interrupt sources

An interrupt controller and interrupt controlling method are provided for prioritizing interrupt requests generated by a plurality of interrupt sources. The interrupt controller comprises an interrupt source interface operable to receive interrupt requests generated by a first plurality of interrupt sources, and a daisy chain interface operable to receive a daisy chain interrupt request output by a further interrupt controller based on a second plurality of interrupt requests generated by a second plurality of interrupt sources. The daisy chain interface includes a priority input operable to receive a daisy chain priority signal indicating a priority associated with the daisy chain interrupt request. Prioritization logic is operable to receive the daisy chain priority signal and to apply predetermined prioritisation criteria to determine the highest priority interrupt request selected from the daisy chain interrupt request and the interrupt request generated by the first plurality of interrupt sources. An output interface is operable to output the highest priority interrupt request, the output interface including a priority output operable to provide an output priority signal indicating a priority associated with the highest priority interrupt request.

Owner:ARM LTD

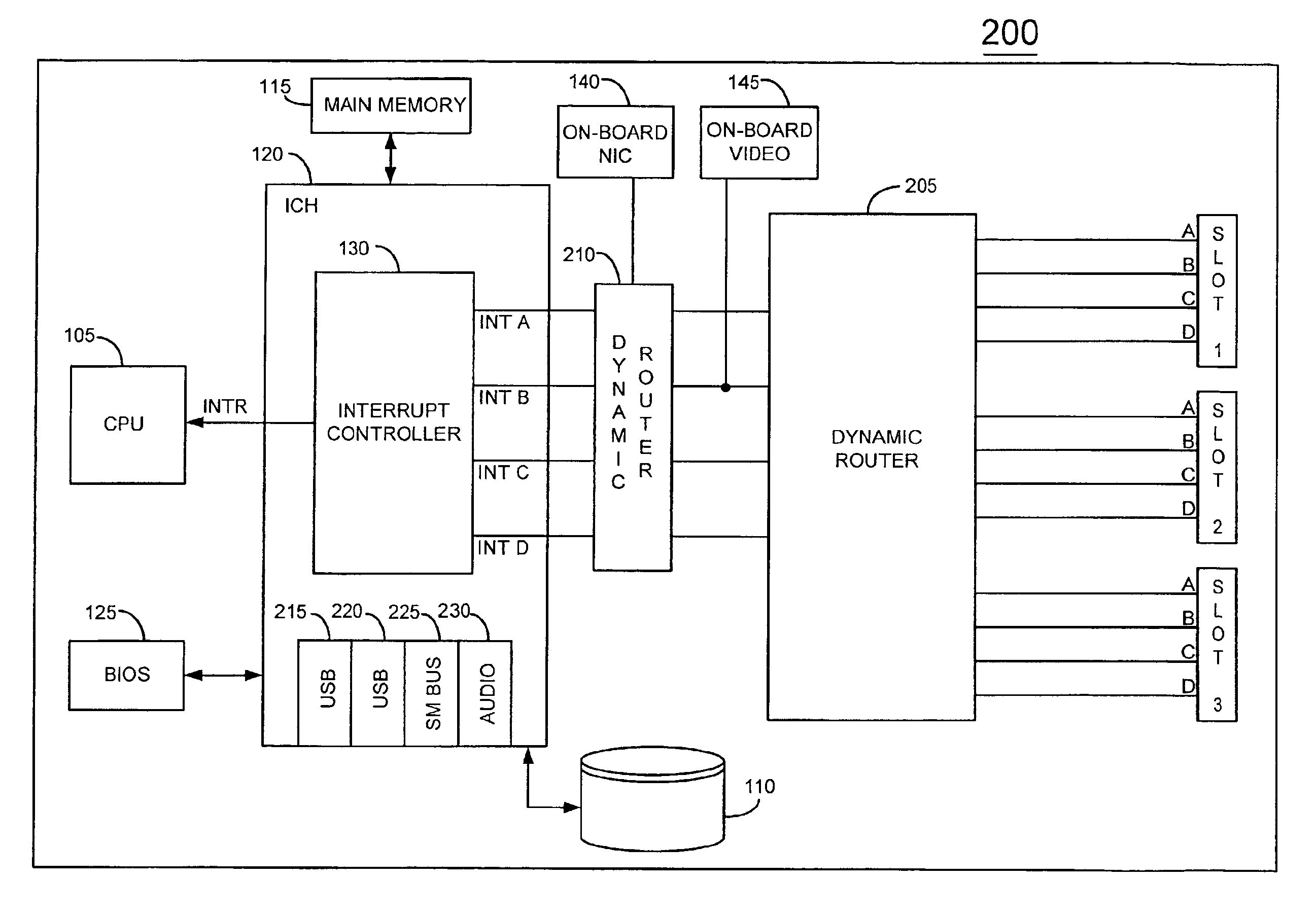

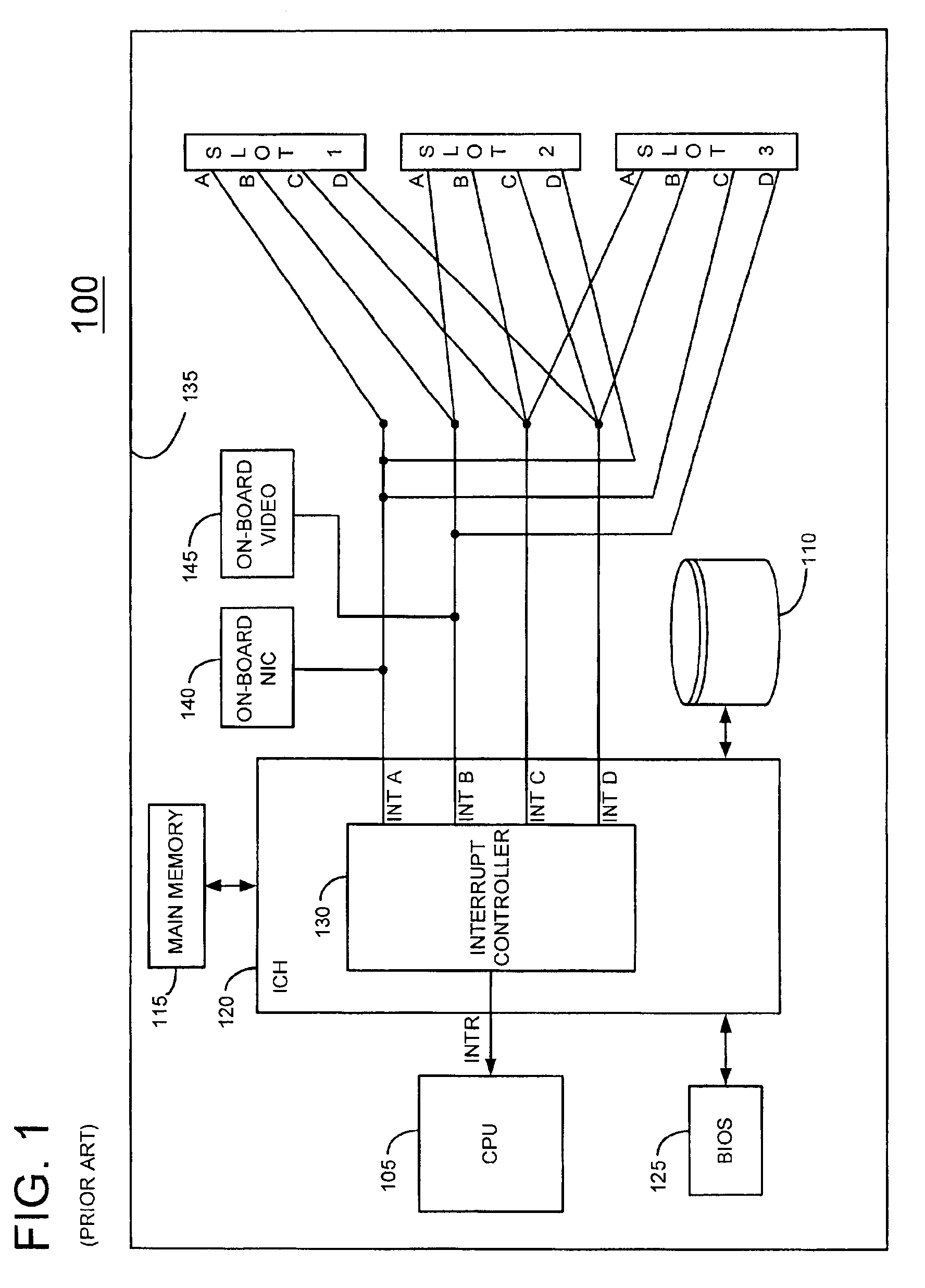

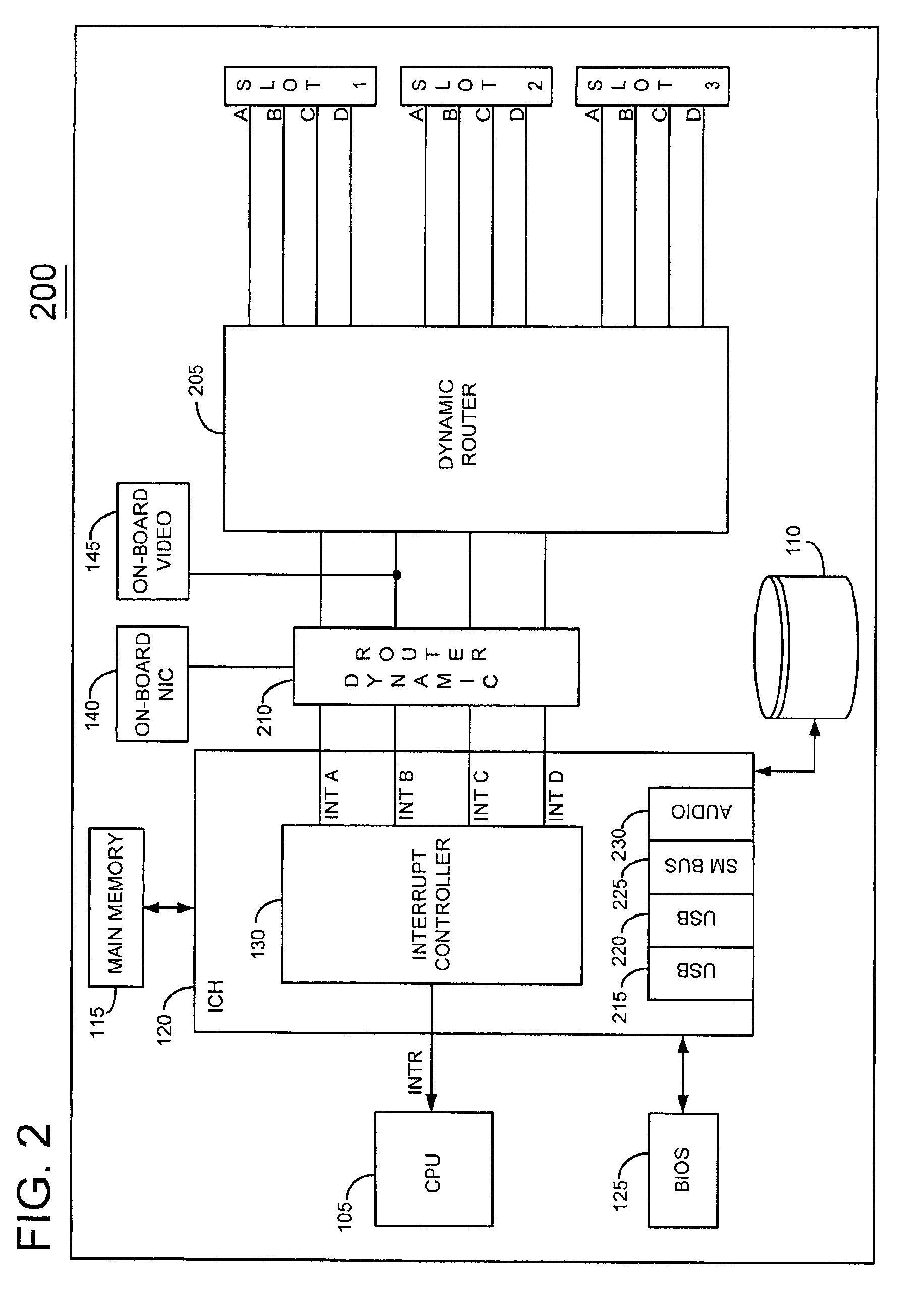

Information handling system with dynamic interrupt allocation apparatus and methodology

InactiveUS6877057B2More balancedUniform distribution of interruptElectric digital data processingHandling systemInformation handling system

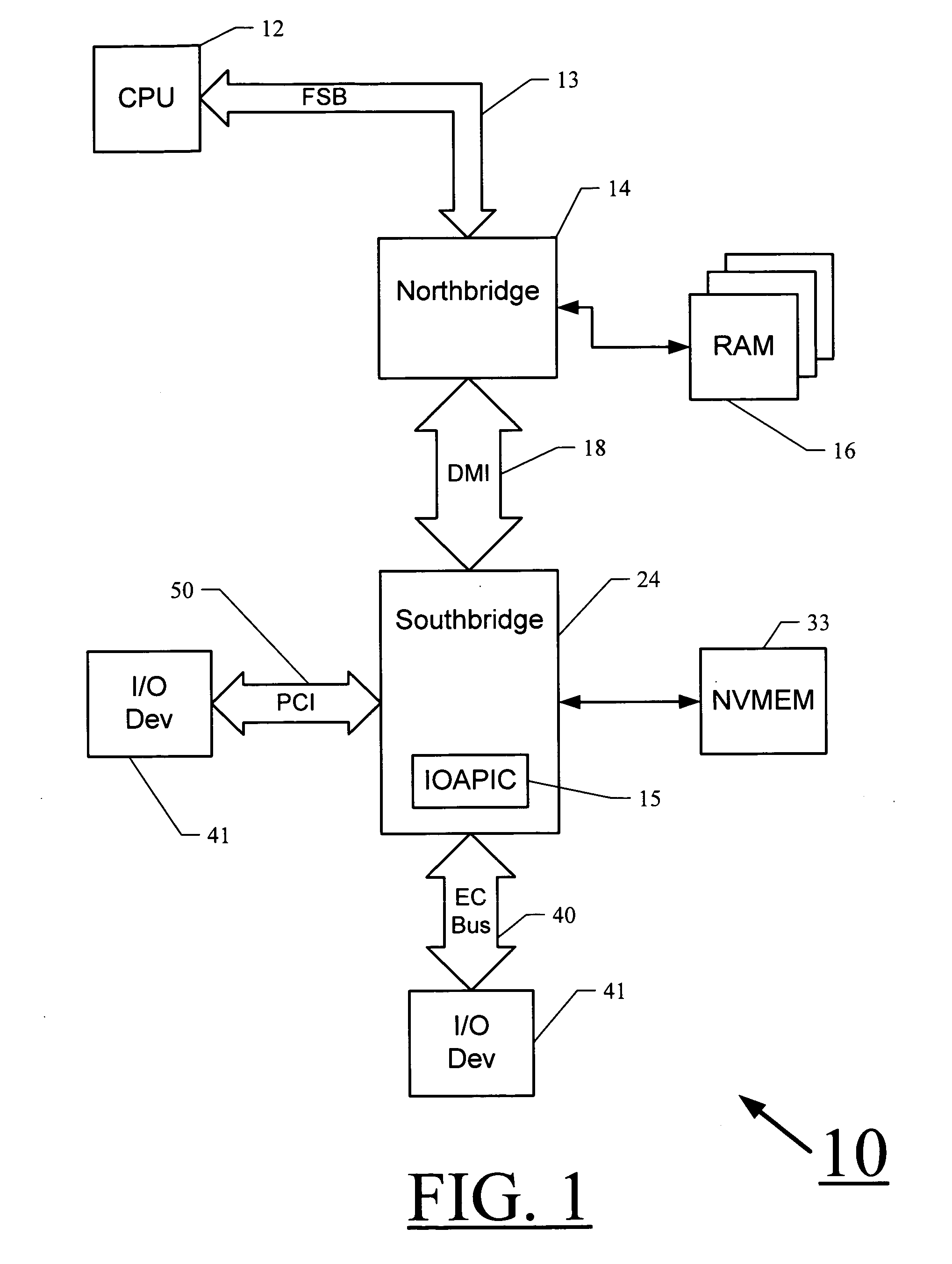

An information handling system is provided which includes a dynamic interrupt router for balancing interrupt assignments among a plurality of devices requesting interrupt assignments. The system balances interrupt assignments among both fixed devices mounted on the processor board and interrupt assignments to devices situated in expansion slots. When the system is populated with a large number of devices relative to the number of available interrupts, improved interrupt sharing is desirably achieved by causing a device which generates a large number of interrupt requests to share a common interrupt with a device which generates a lower number of interrupts.

Owner:DELL PROD LP

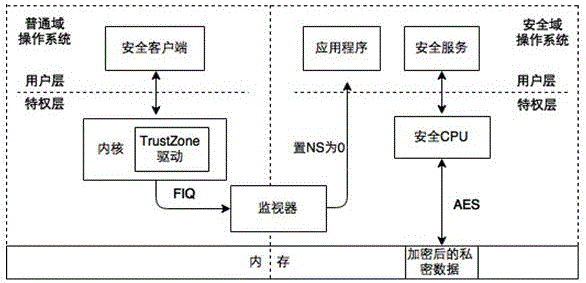

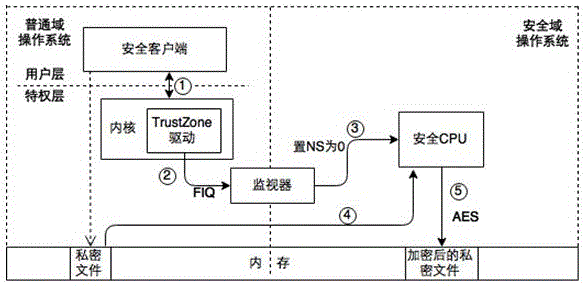

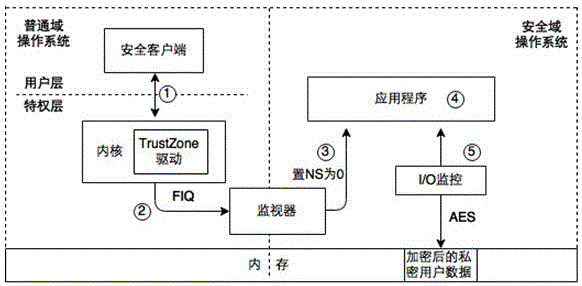

Cell phone private information safe box based on ARM Trust Zone

InactiveCN104992122AProtection securityAchieve isolationDigital data protectionInternal/peripheral component protectionMonitor modeProcessor register

The invention discloses a cell phone private information safe box based on an ARM Trust Zone. The cell phone private information safe box comprises a common zone operating system (Rish OS) and a security zone operating system (Security OS); when the common region zone operating system is switched to the security zone operating system, a monitor mode provided by the ARM Trust Zone is needed; a user sends a fast interrupt request (FIQ) through the common zone operating system to enter the monitor mode; under the monitor mode, an NS site of a security configuration register (SCR) of an ARM processor is modified and is set to be 0, so that a CPU status is switched to the security zone operating system; and a user of a security zone can selectively carry out a security operating procedure or store a cell phone private document, and utilizes an encryption function provided by the CPU of the ARM Trust Zone to carry out encryption and decryption on the security zone. According to the cell phone private information safe box provided by the invention, the cell phone private document and software with high-security requirements are preserved in the security region by a user of a common zone through simple operation, and the private document of the user in the security zone is encrypted and decrypted; and meanwhile, the user can safely operate application programs with high-security requirements.

Owner:WUHAN UNIV

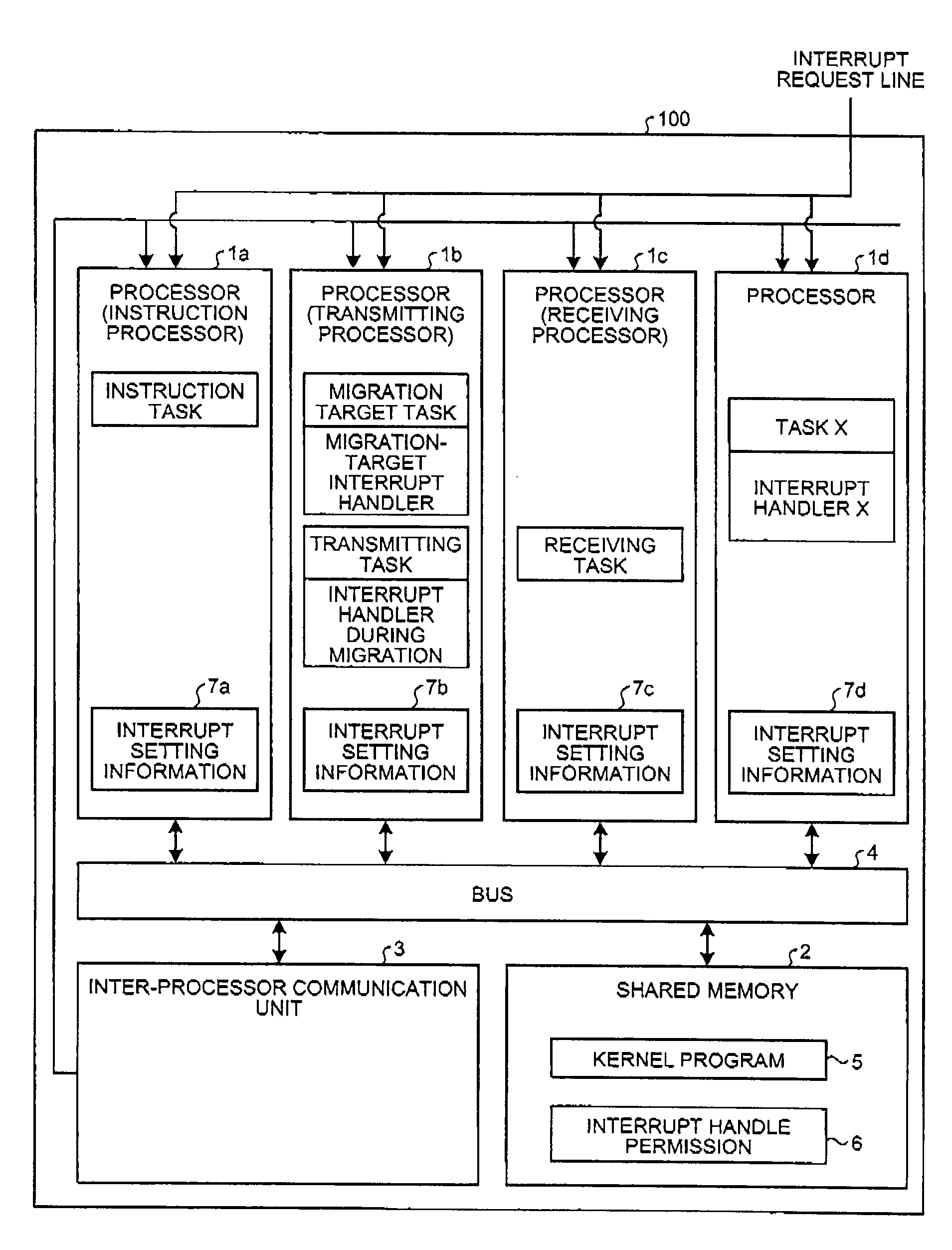

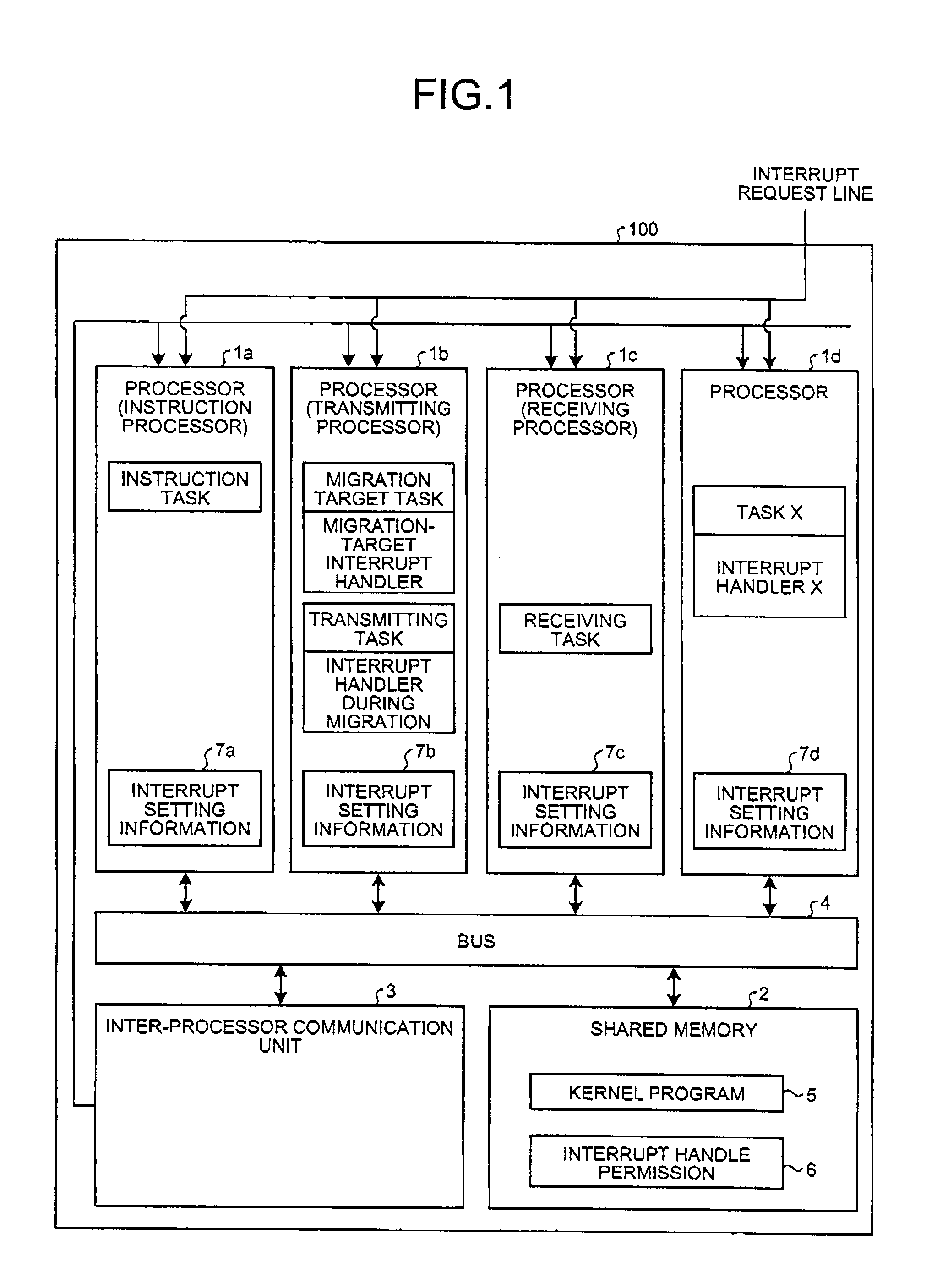

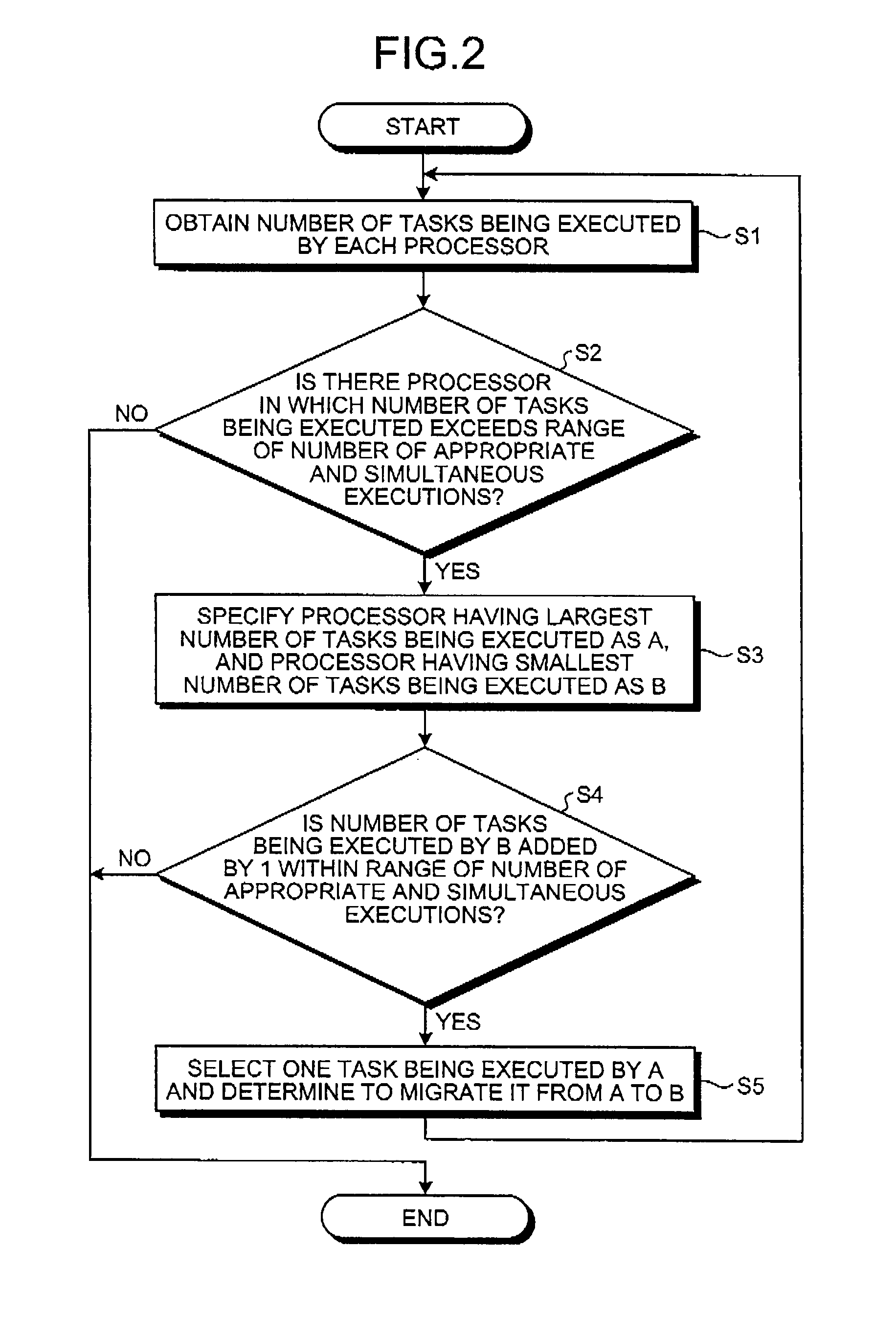

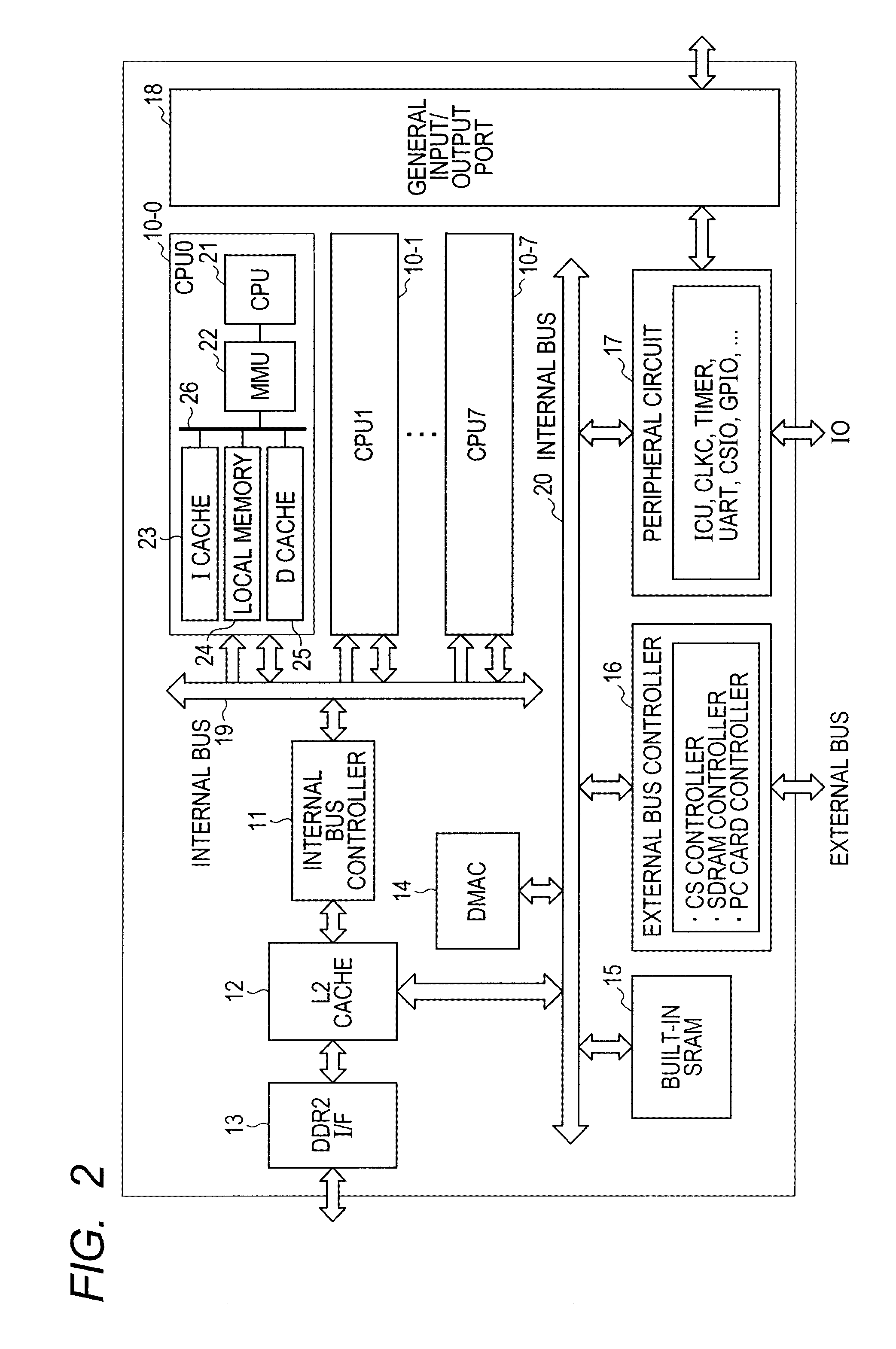

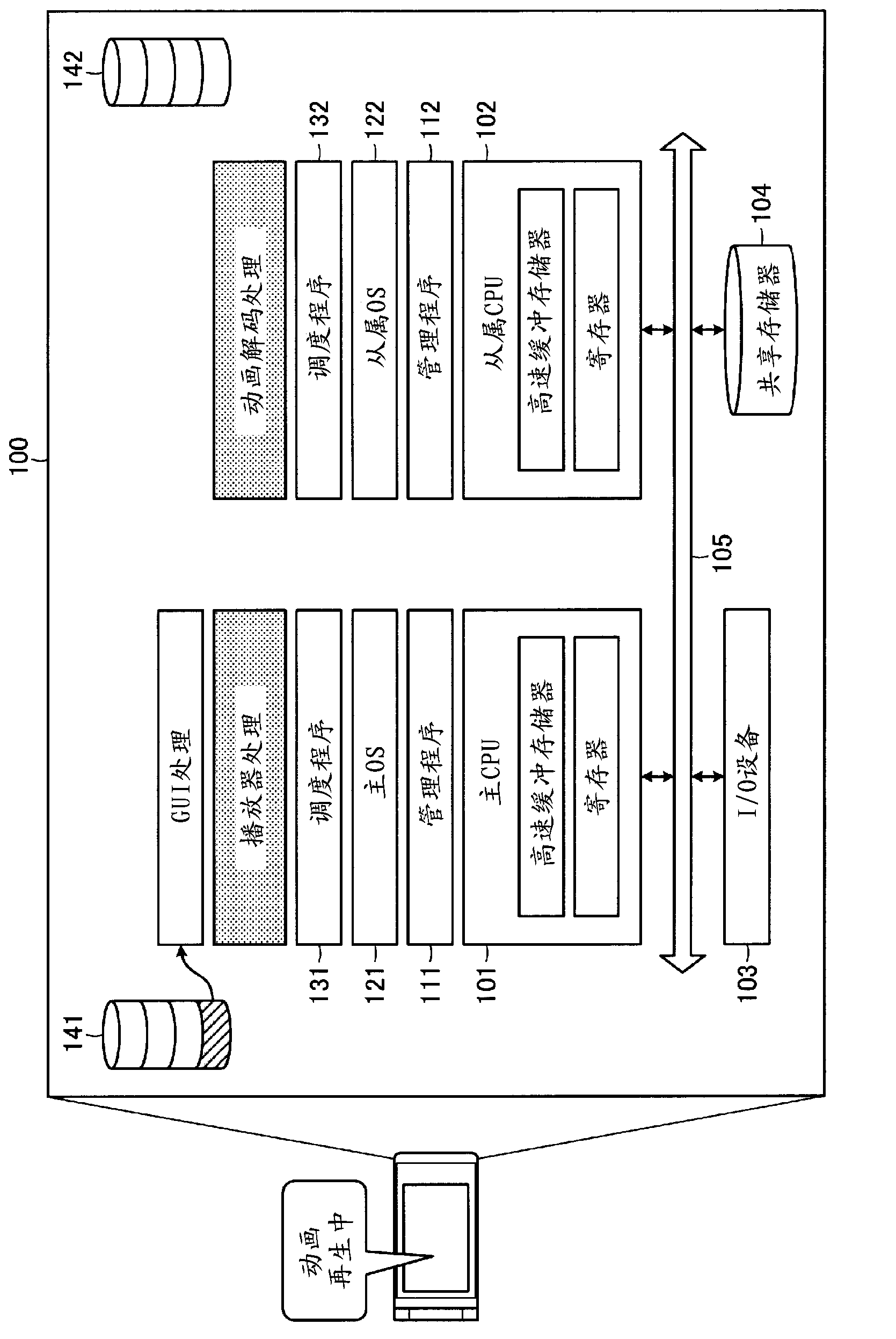

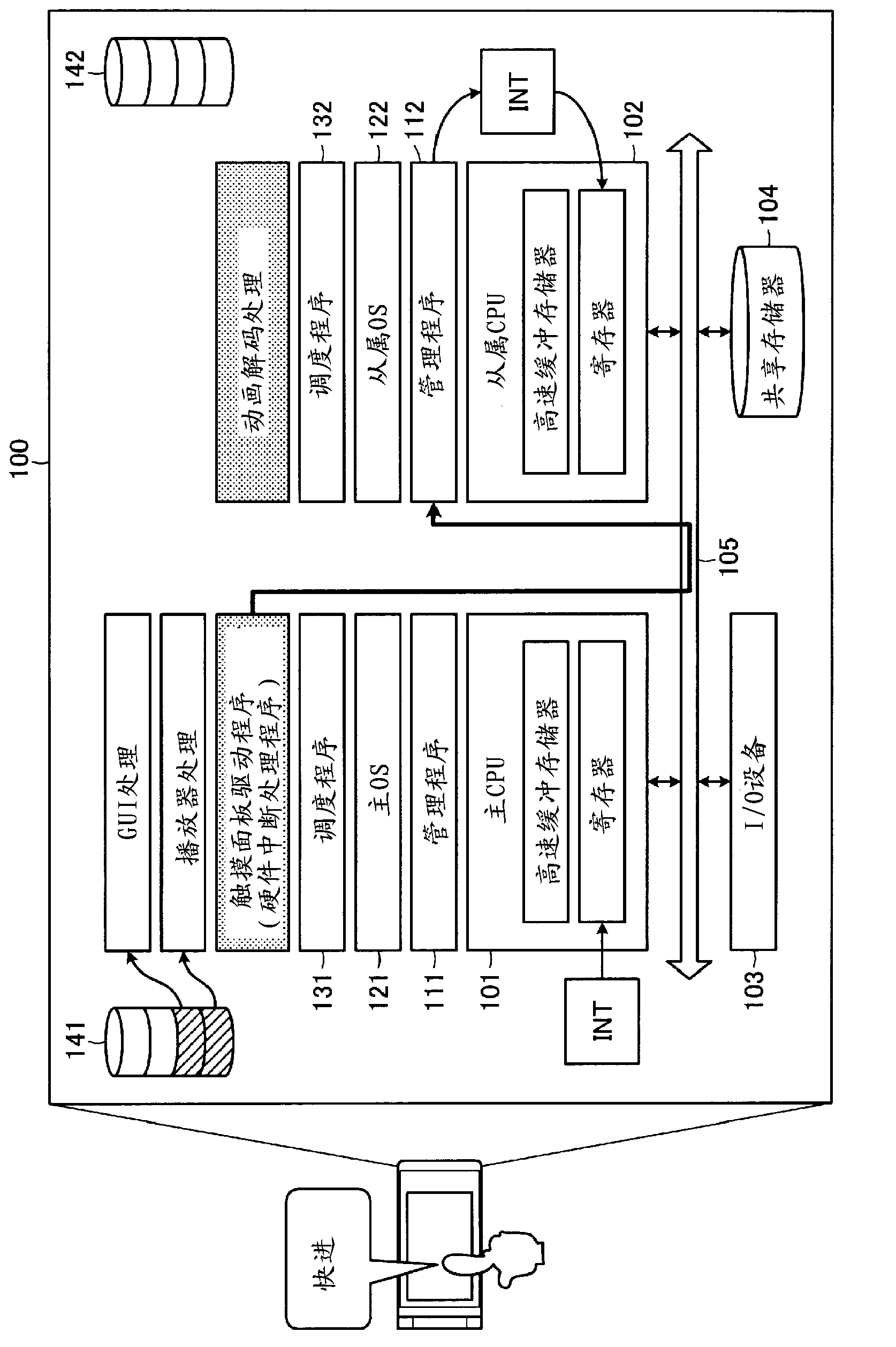

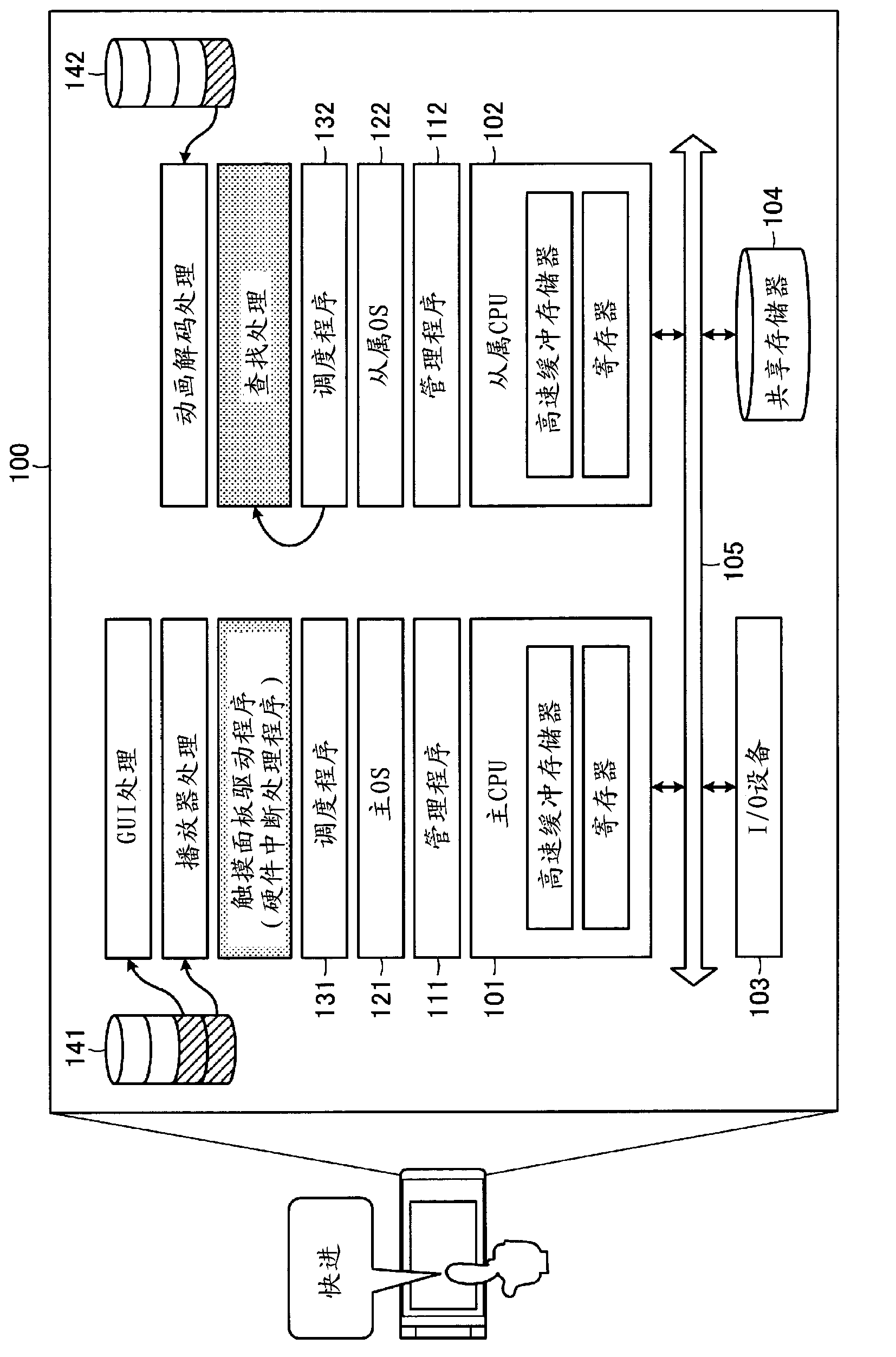

Multiprocessor system and computer program product

InactiveUS20100299472A1Energy efficient ICTMultiprogramming arrangementsMulti processorInterrupt handler

In a multiprocessor system including a plurality of processors, the processors execute, at a time of migration a task operating in own processor to another processor, a transmitting task for transmitting the migration target task to a destination processor, and when an interrupt request to be received and executed by an interrupt handler accompanying the migration target task is generated during transmission of the migration target task, the transmitting task receives the interrupt request instead of the interrupt handler and starts the interrupt handler.

Owner:KK TOSHIBA

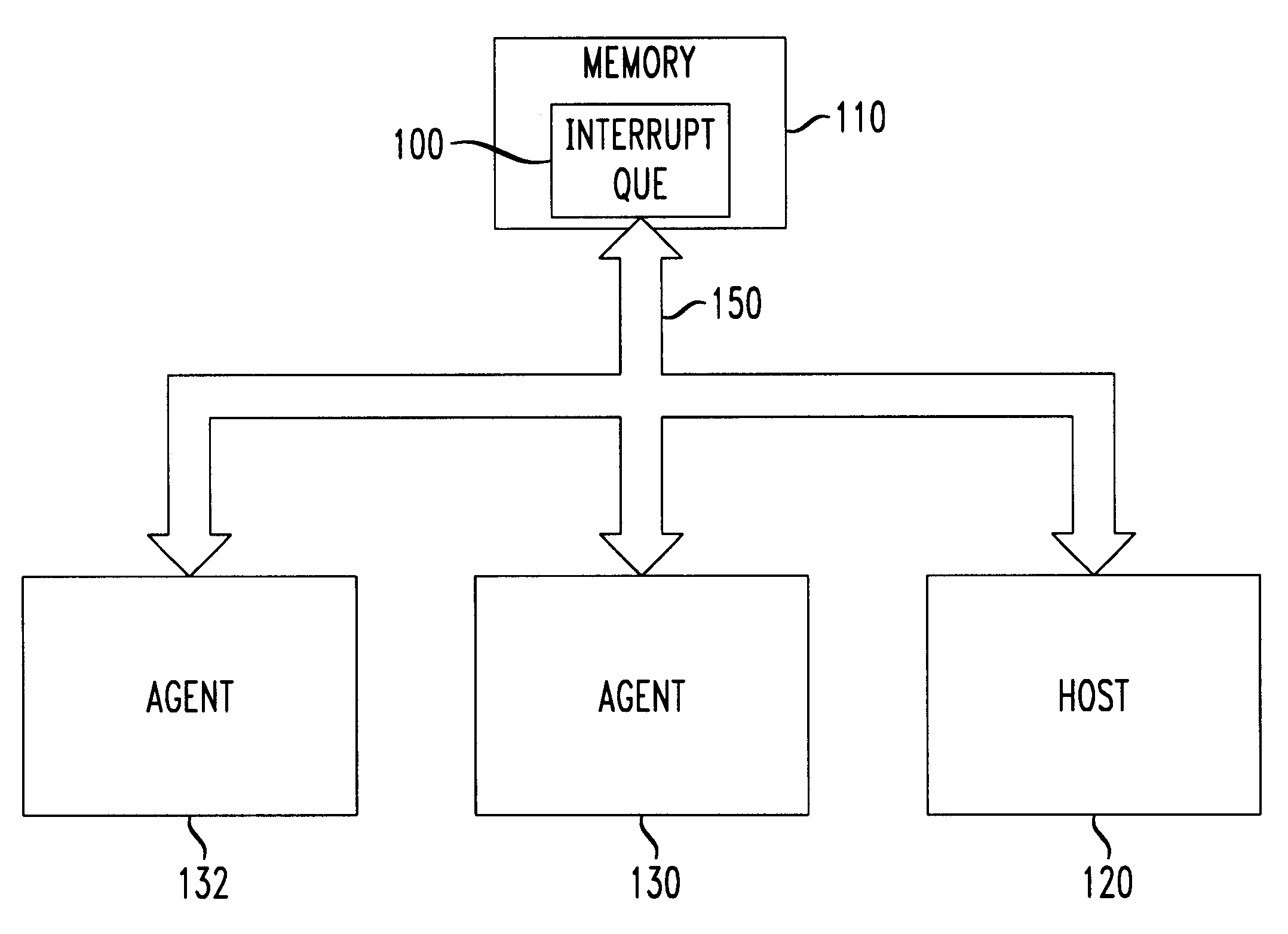

System for memory based interrupt queue in a memory of a multiprocessor system

InactiveUS6240483B1Memory adressing/allocation/relocationHardware monitoringMulti processorStatus register

An interrupt mechanism which reduces or eliminates the need for an interrupt status register while at the same time provides suitable information to a host or other processor with respect to the cause and parameters surrounding an interrupt signal. An interrupt queue is maintained in shared memory accessible by both a host and an interrupting agent. The interrupt queue has a capacity or two or more separate interrupt requests, either from a same interrupting agent or from two different interrupting agents. As interrupting agents write to the interrupt queue, an agent current interrupt pointer (ACIP) is incremented to a next position in the interrupt queue. As the host services interrupts, the current host pointer is incremented to clear the serviced interrupt request entry.

Owner:LUCENT TECH INC

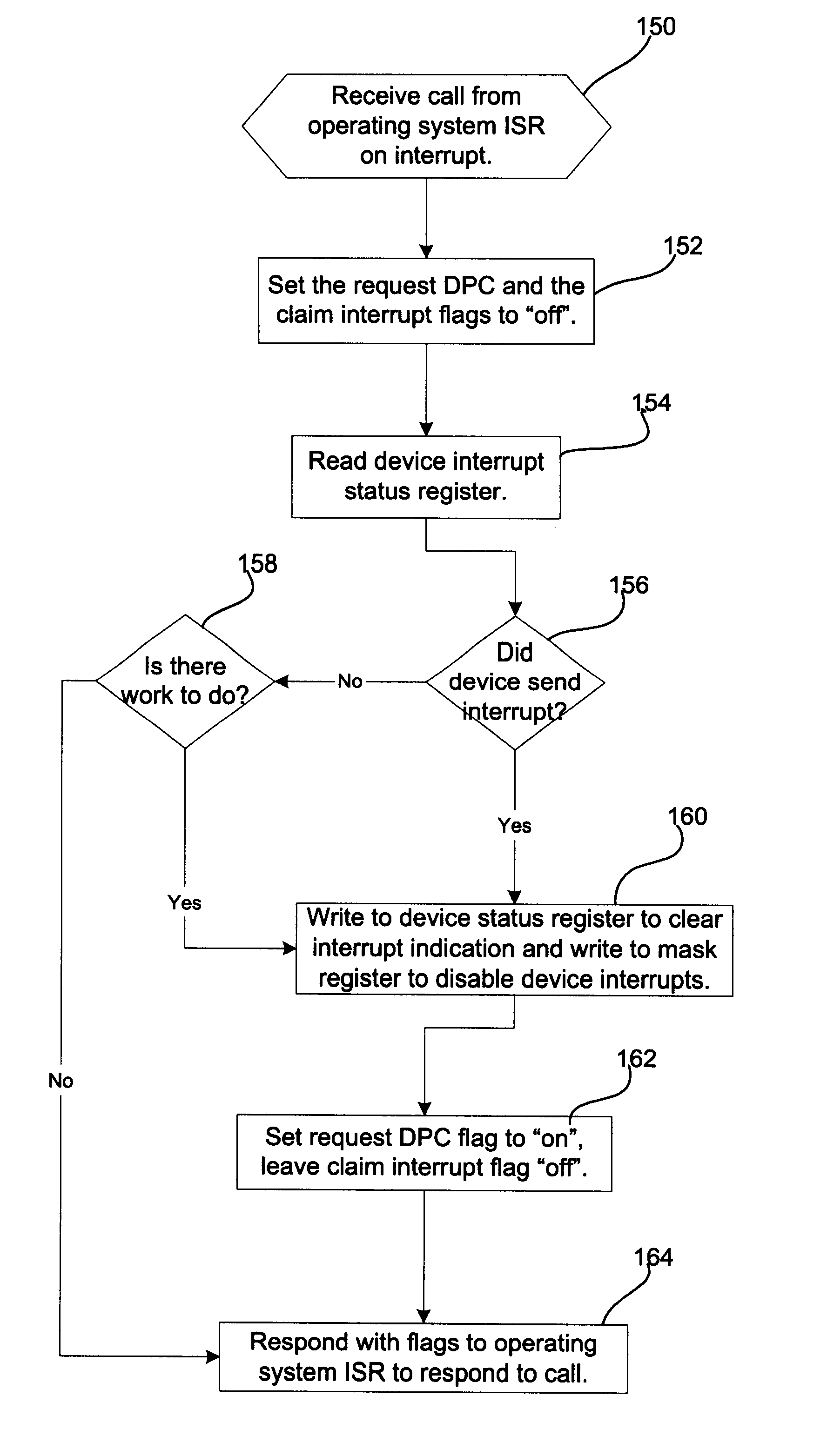

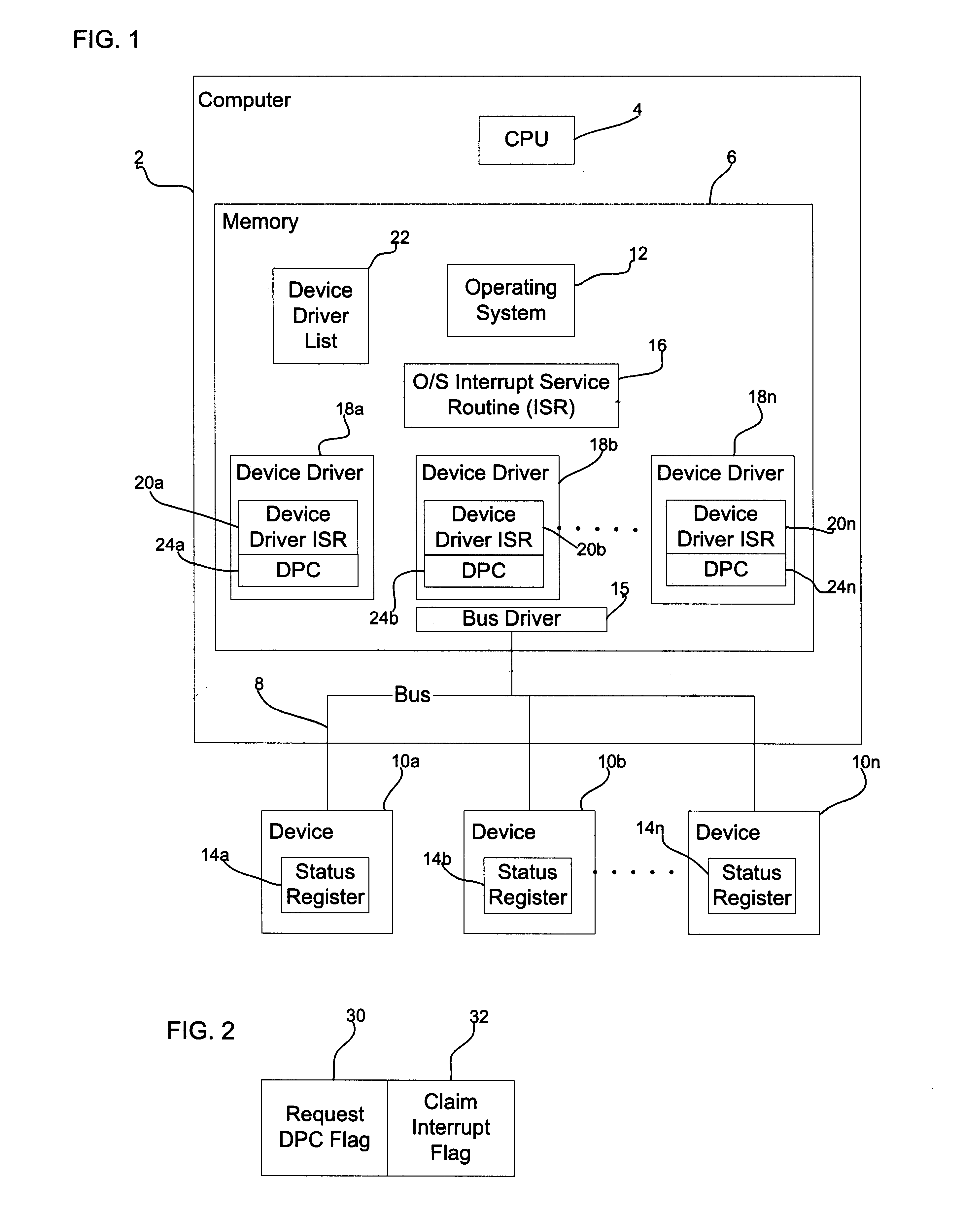

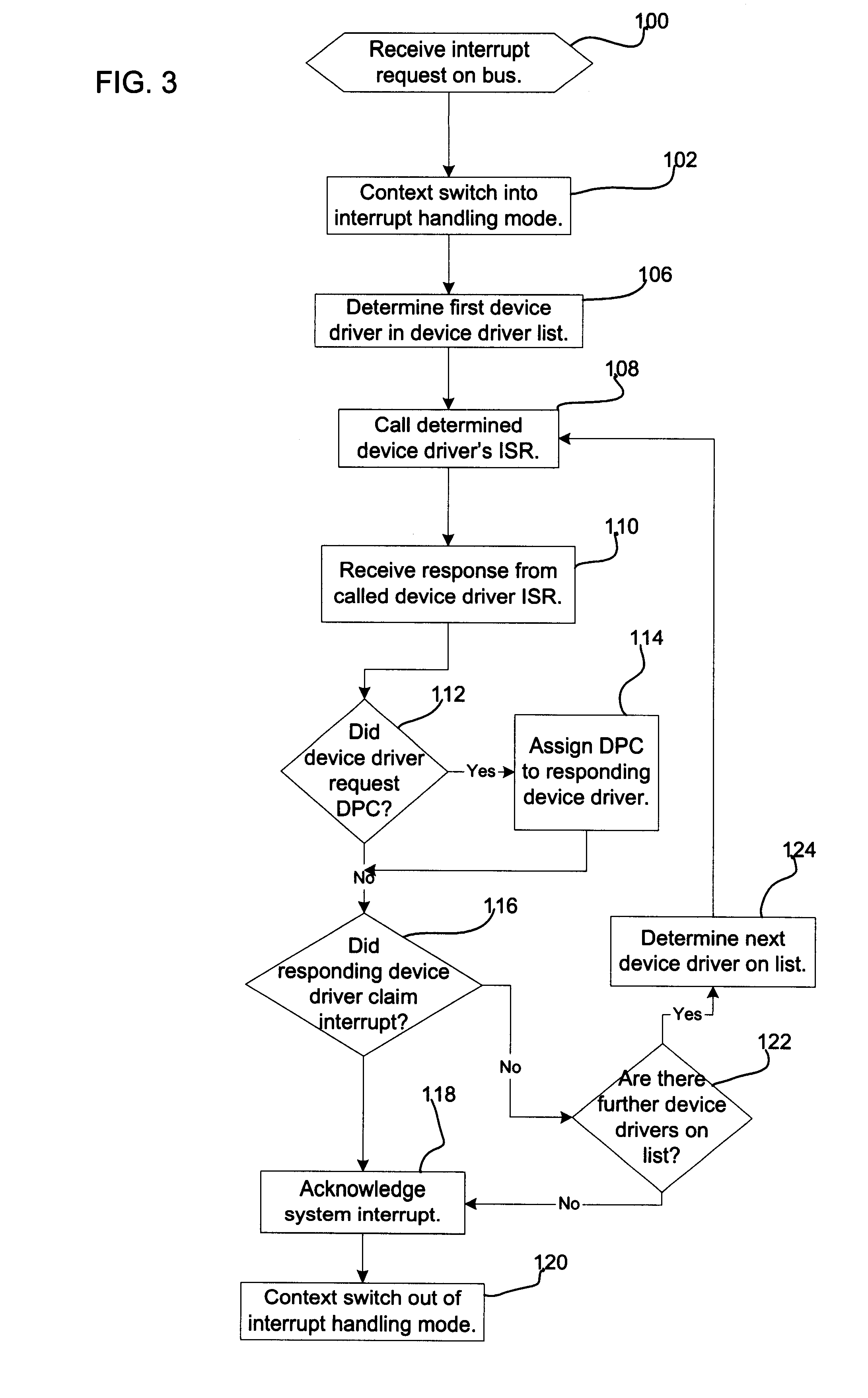

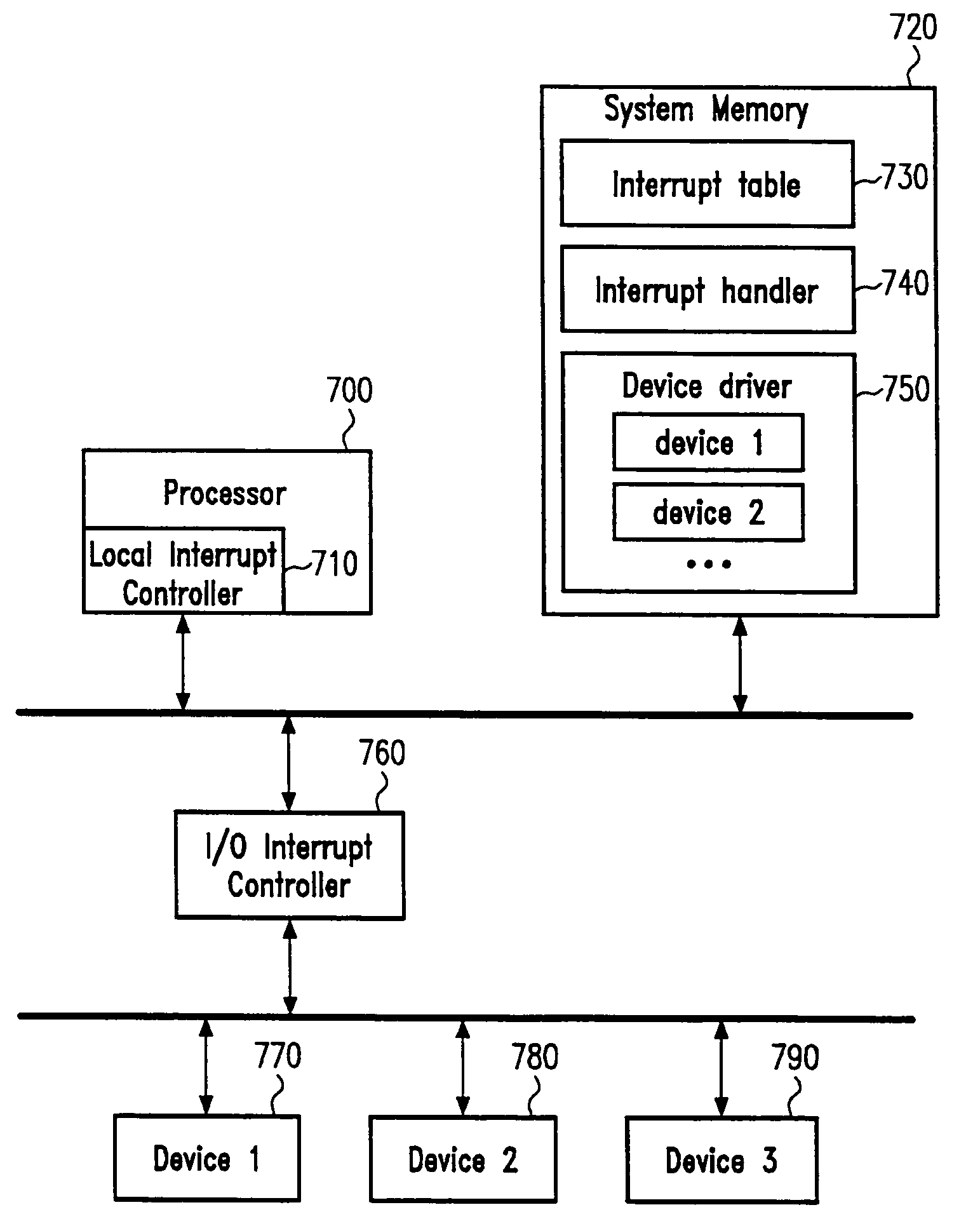

Method, system, and program for handling interrupt requests

InactiveUS6789142B2Input/output processes for data processingData conversionComputer scienceEmbedded system

Owner:INTEL CORP

Message based interrupt table

InactiveUS7257658B2Reduce Interrupt LatencyHigh speedElectric digital data processingMemory addressInterrupt vector table

An interrupt processing technique is provided where an interrupt message is sent to an interrupt controller of a processor in response to an interrupt request from an individual device. The interrupt message comprises a memory address and interrupt status information. The memory address is specifically allocated to the device that has issued the interrupt request. The interrupt status information indicates an interrupt status of the device. An interrupt table that is stored in the memory is updated by the interrupt controller using the interrupt status information comprised in the interrupt message. The interrupt table holds device specific interrupt statuses. Updating the interrupt table comprises addressing the memory using the memory address in the interrupt message.

Owner:GLOBALFOUNDRIES INC

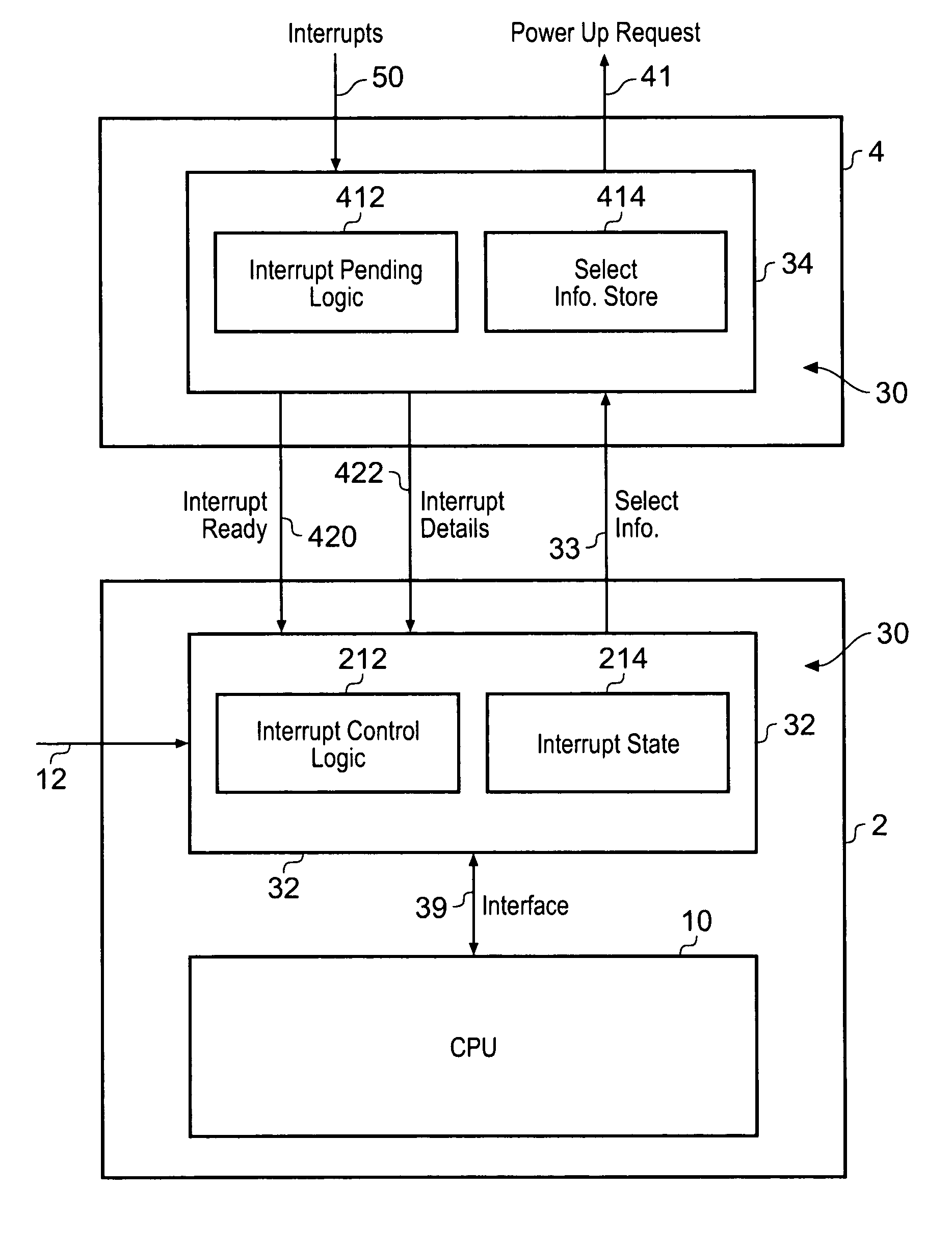

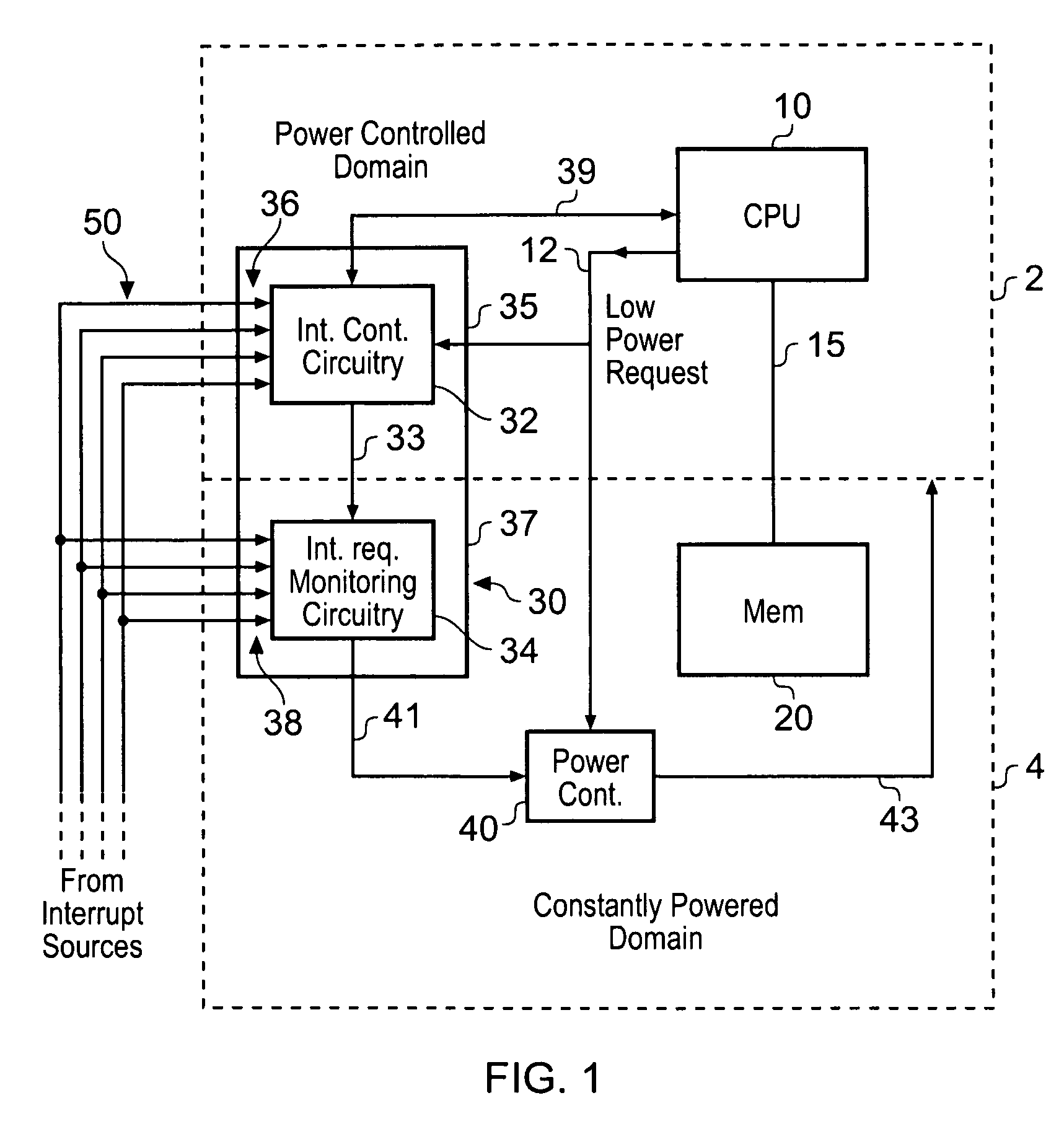

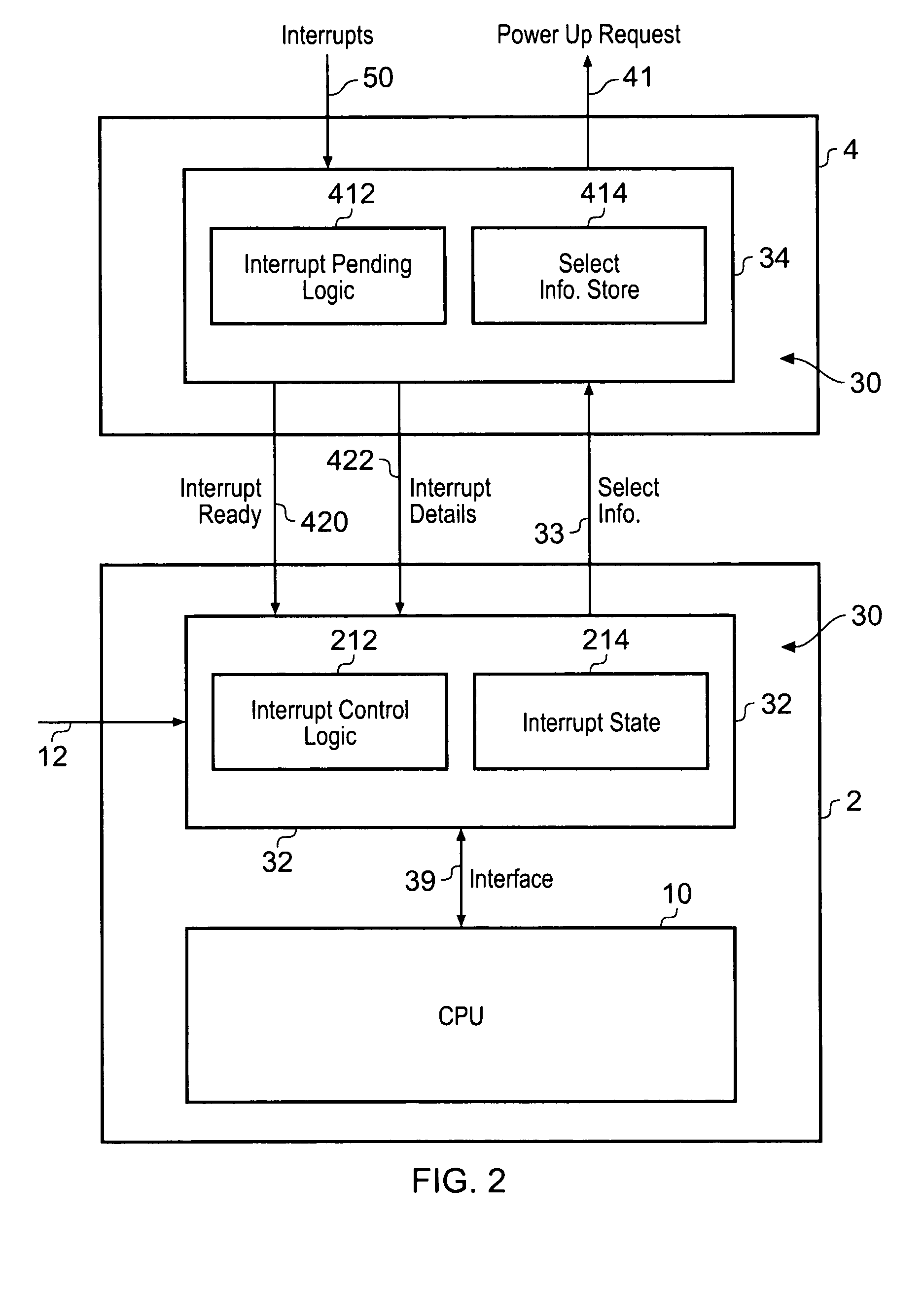

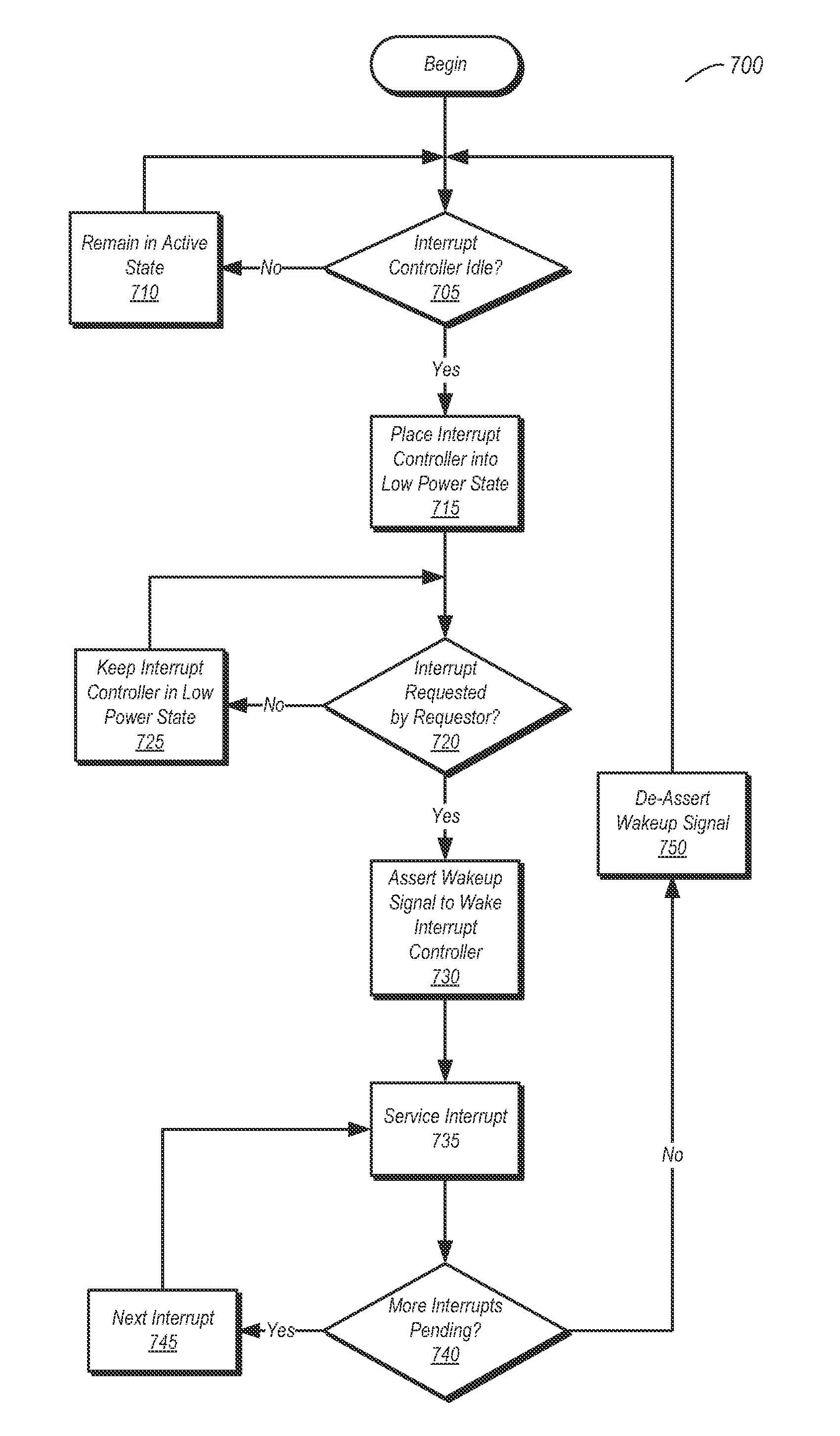

Interrupt Based Power State Management

ActiveUS20140310540A1Volume/mass flow measurementPower supply for data processingState managementInterrupt handler

A method and apparatus for power managed interrupt handling is disclosed. In one embodiment, a system includes one or more agents that may invoke an interrupt request. An interrupt controller is configured to receive and process the interrupt requests. When idle, the interrupt controller may be placed in a low power state. The system also includes an interrupt power control circuit coupled to receive interrupt request indications from each of the one or more agents that may invoke interrupts. The interrupt power control circuit is configured to assert a wakeup signal responsive to receiving an indication of an interrupt request from one of the agents. If the interrupt controller is in a low power state, it may exit the state and resume operation in an active state responsive to assertion of the wakeup signal.

Owner:APPLE INC

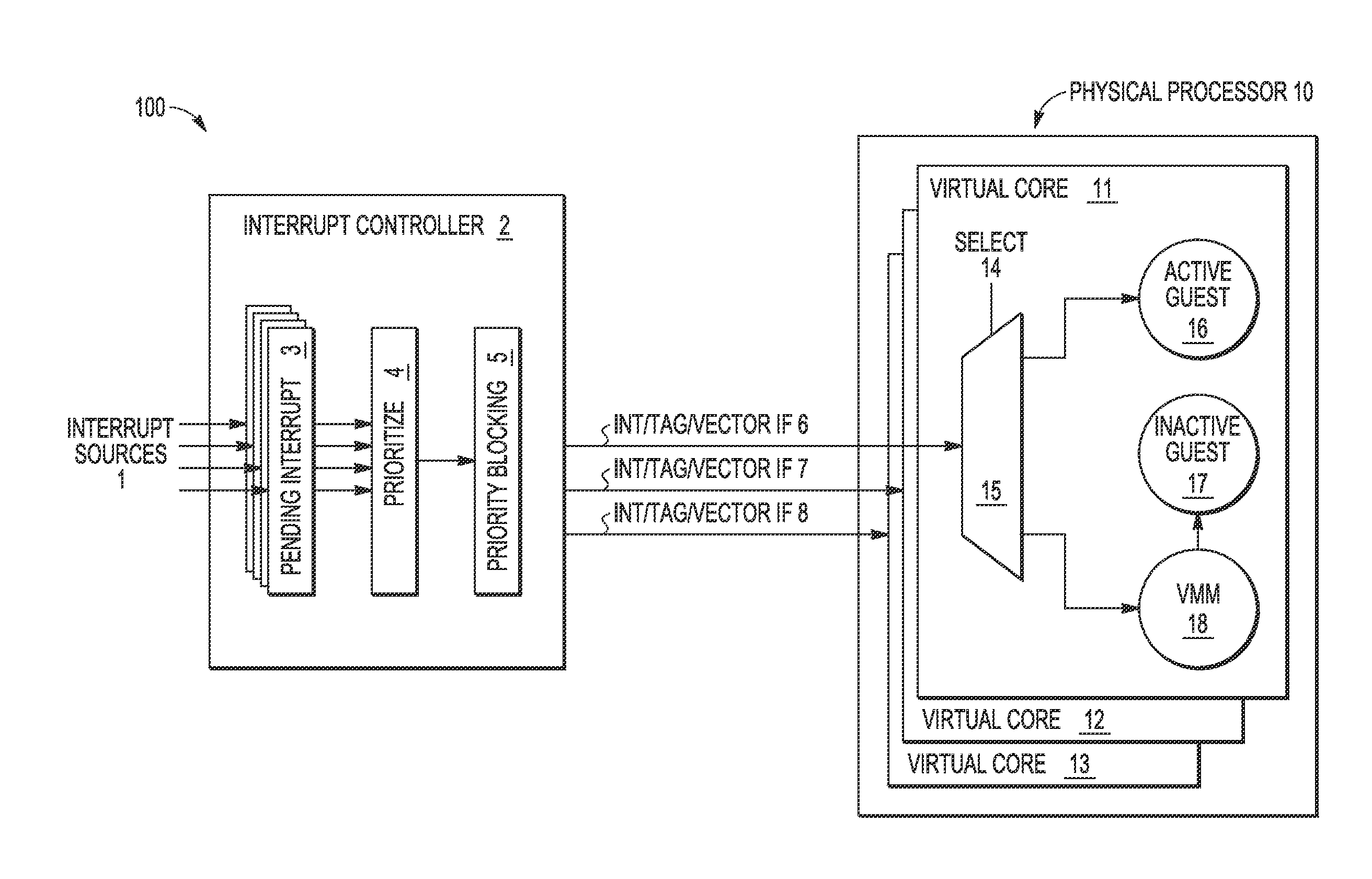

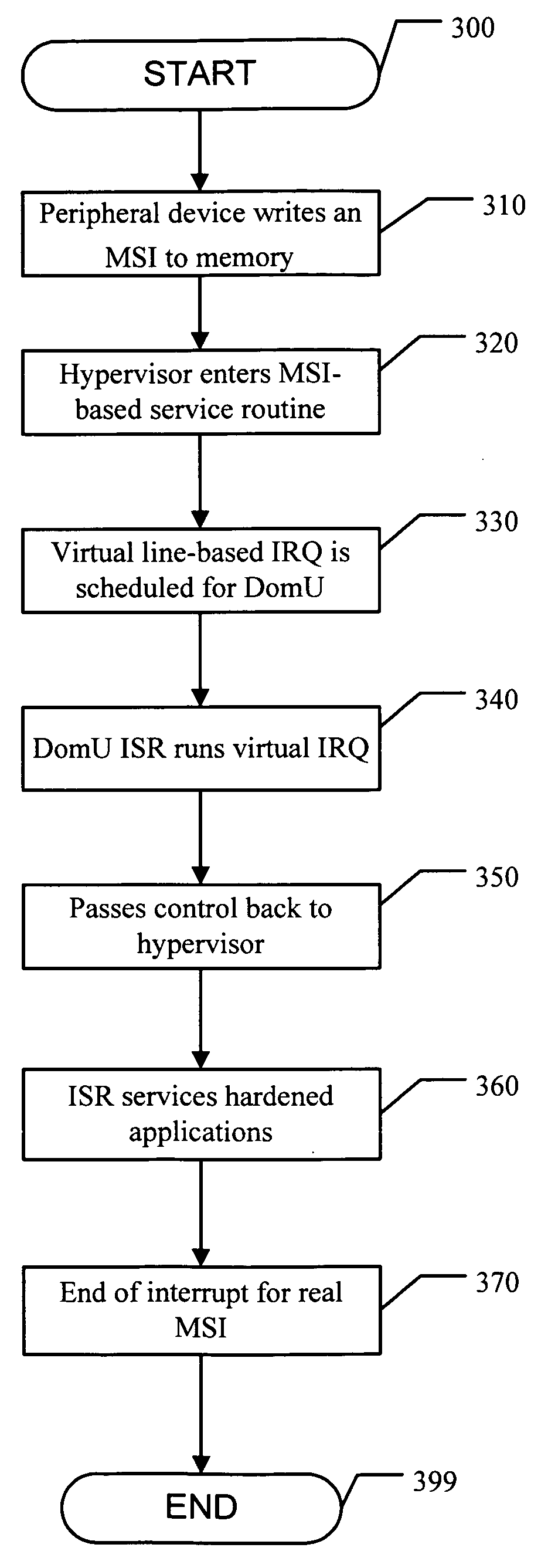

Interrupt request and message signalled interrupt logic for passthru processing

InactiveUS20100161864A1Enables interrupt sharingProgram controlMessage Signaled InterruptsDevice status

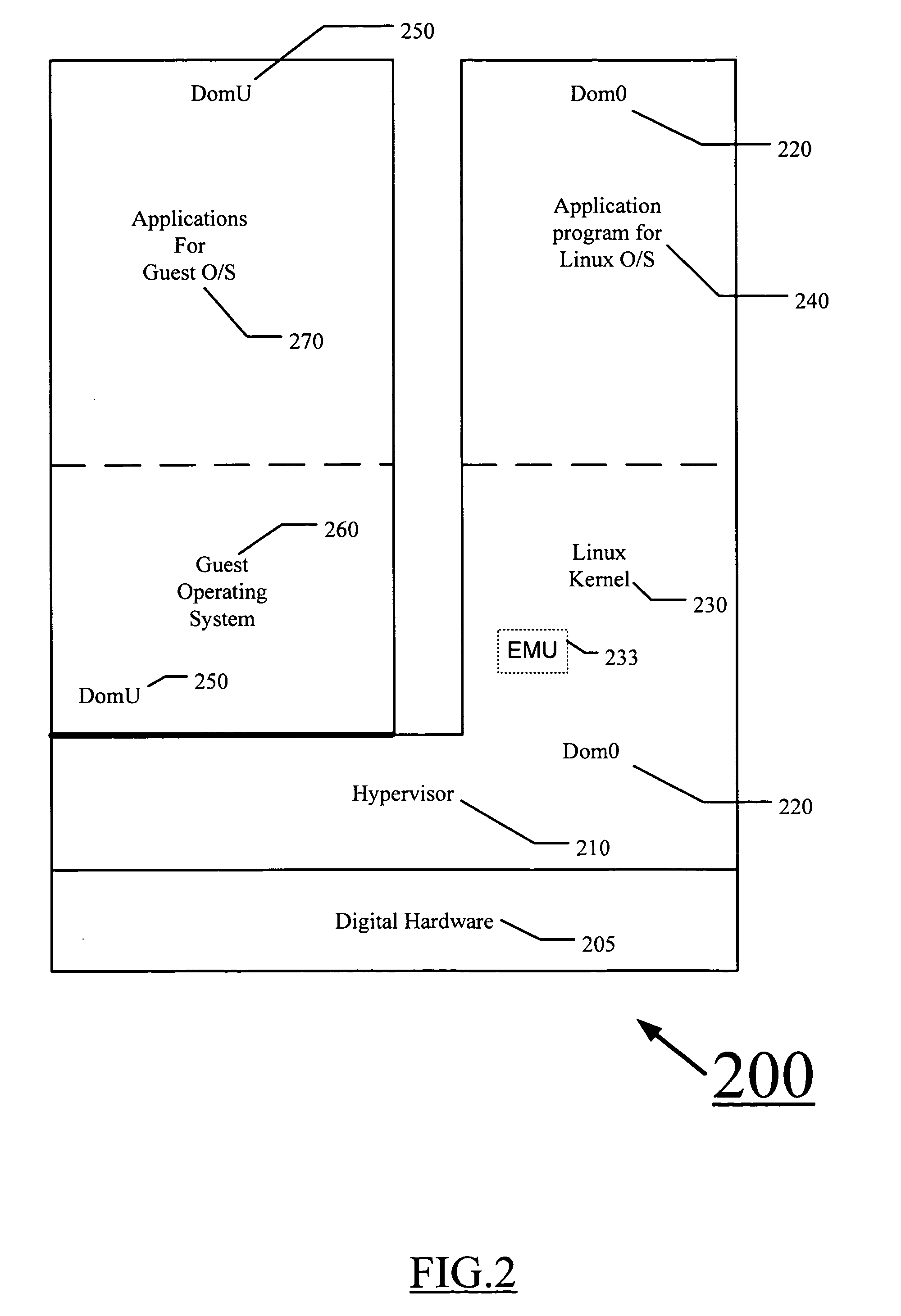

Methods, systems, apparatuses and program products are disclosed for managing interrupt services in hypervisor and hypervisor-related environments in Message Signaled Interrupts are emulated as other type(s) of interrupt.According to an aspect of the present invention, a method of executing a program includes receiving a MSI (message signaled interrupt). Responsively, a virtual interrupt is generated and an ISR (interrupt service routine) is invoked that handles a line-based virtual interrupt transaction. A surrogate or virtual peripheral device status may also be provided and may be associated with the virtual interrupt. A single device interrupt event may, in certain circumstances, be serviced both as a line-based interrupt and also as an MSI, or as either responsive to run-time context.Embodiments of the present invention enable superior tradeoffs in regards to the interrupt sharing to a greater and more flexible extent than with previous implementations. Moreover, it makes possible interrupt sharing using an ISR that was not expressly designed for interrupt sharing.

Owner:HEWLETT PACKARD CO

Method and device for executing non-maskable interrupt

ActiveCN105279021AImplement the NMI processProgram initiation/switchingData resettingNon-maskable interruptComputer science

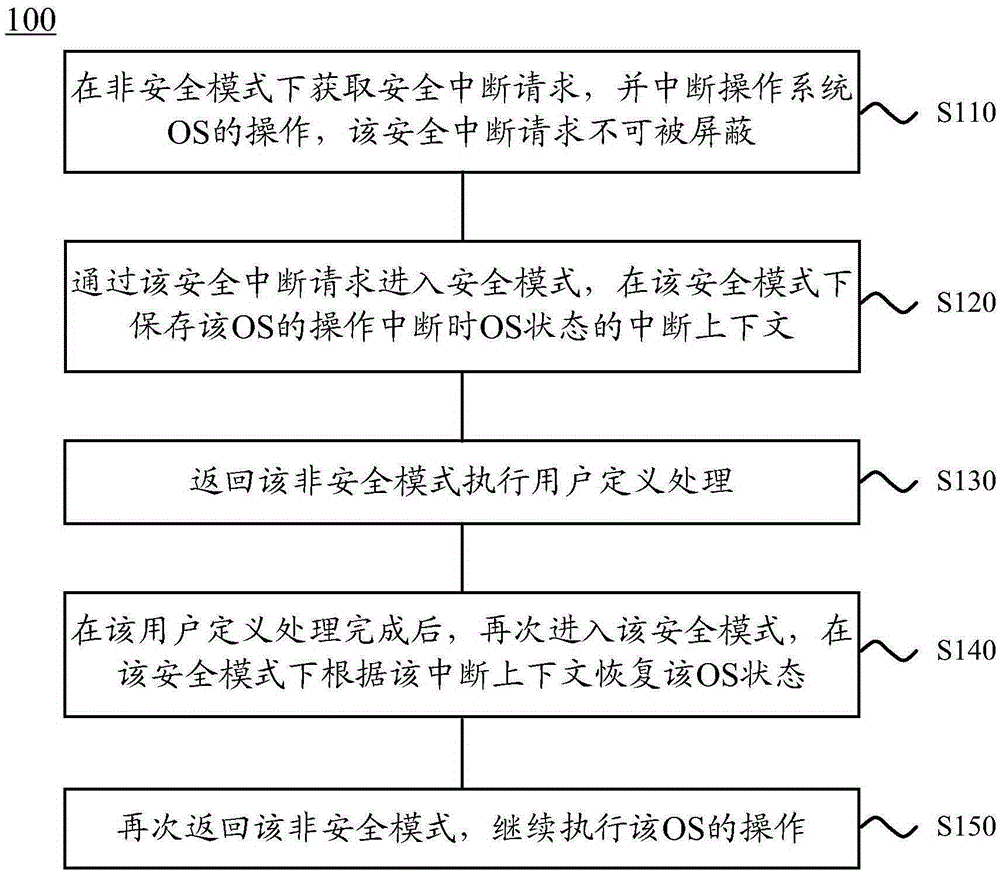

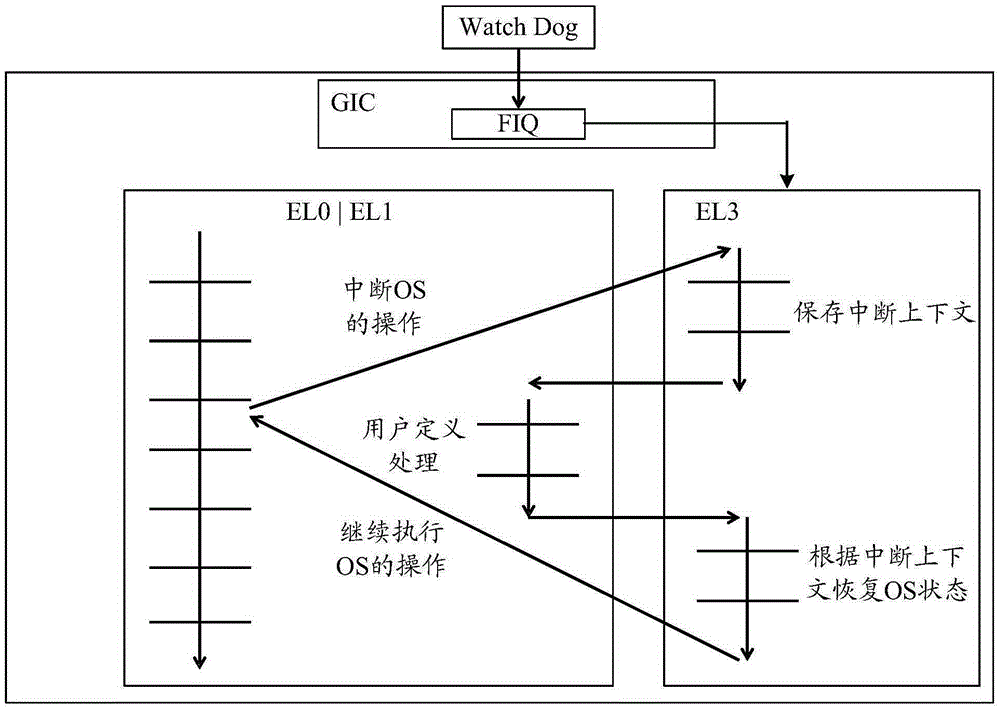

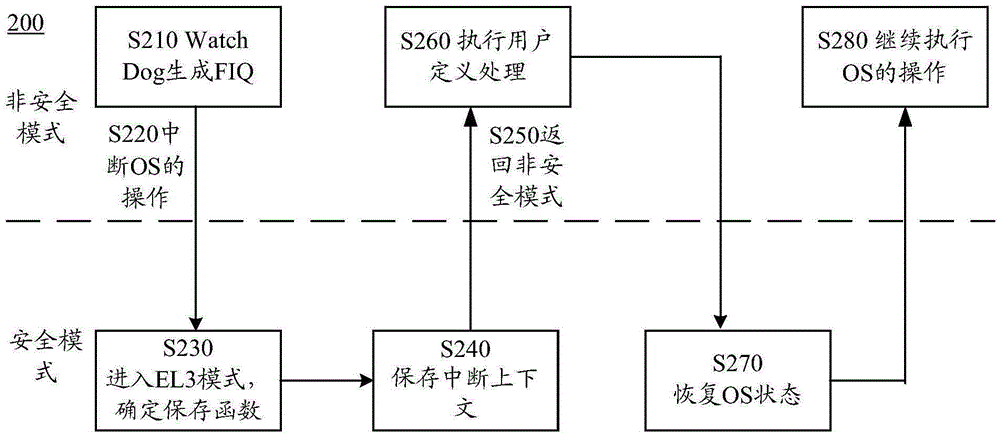

The invention discloses a method and device for executing non-maskable interrupt. The method comprises the following steps: obtaining a safe interrupt request under an unsafe mode and interrupting the operation of an operating system OS, wherein the safe interrupt request is non-maskable; entering a safe mode through the safe interrupt request, and storing the interrupt context of the OS state when the operation of the OS is interrupted under the safe mode; returning to the unsafe mode to execute user defined processing; after the user defined processing is finished, entering the safe mode again and restoring the OS state according to the interrupt context under the safe mode; and returning to the unsafe mode again and continuing to execute the operation of the OS. According to the method and device for executing non-maskable interrupt, the NMI can be simply realized without hardware.

Owner:HUAWEI TECH CO LTD

Programmable interrupt controller

InactiveCN1547082AFlexible configurationProgramme control in sequence/logic controllersProgrammable logic controllerProgrammable Interrupt Controller

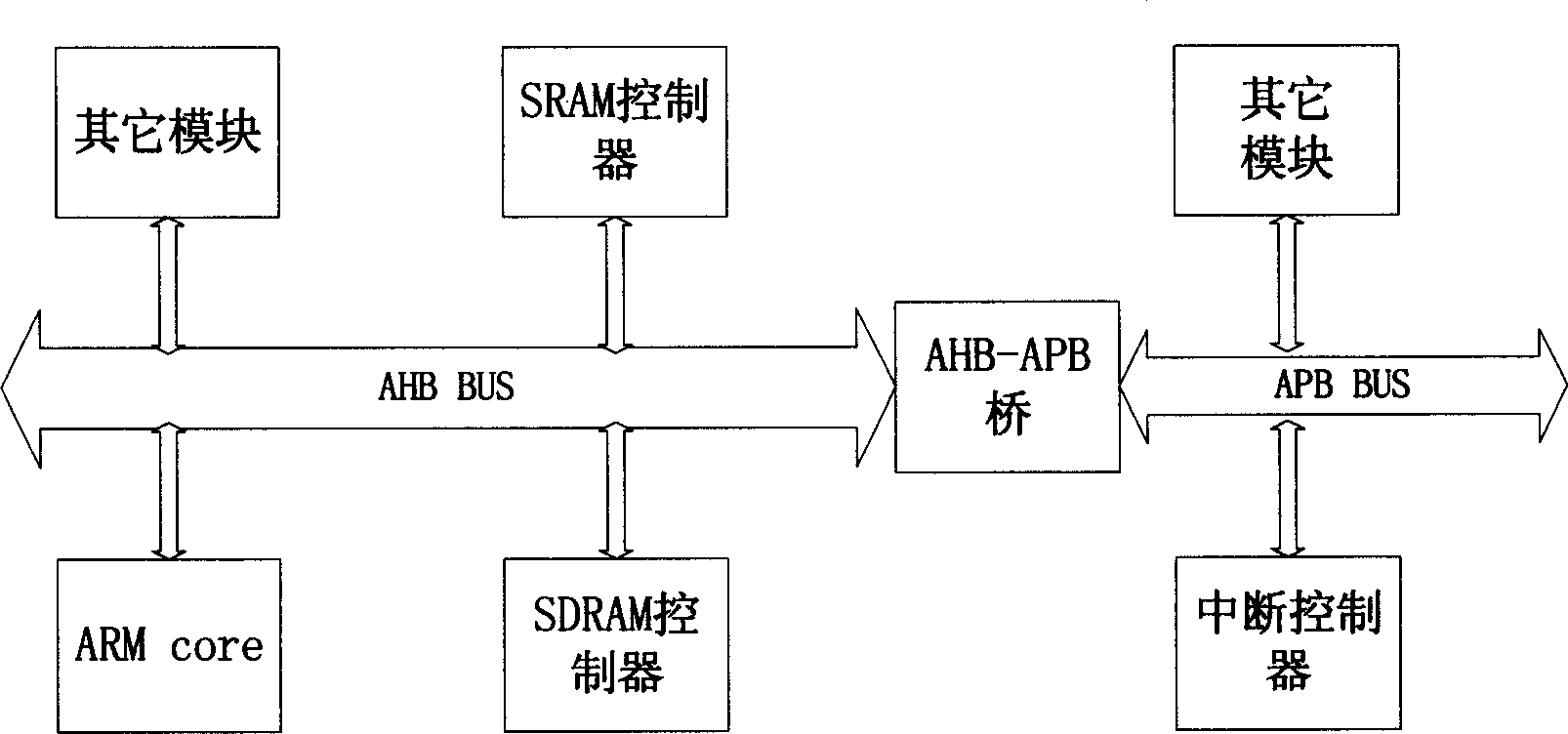

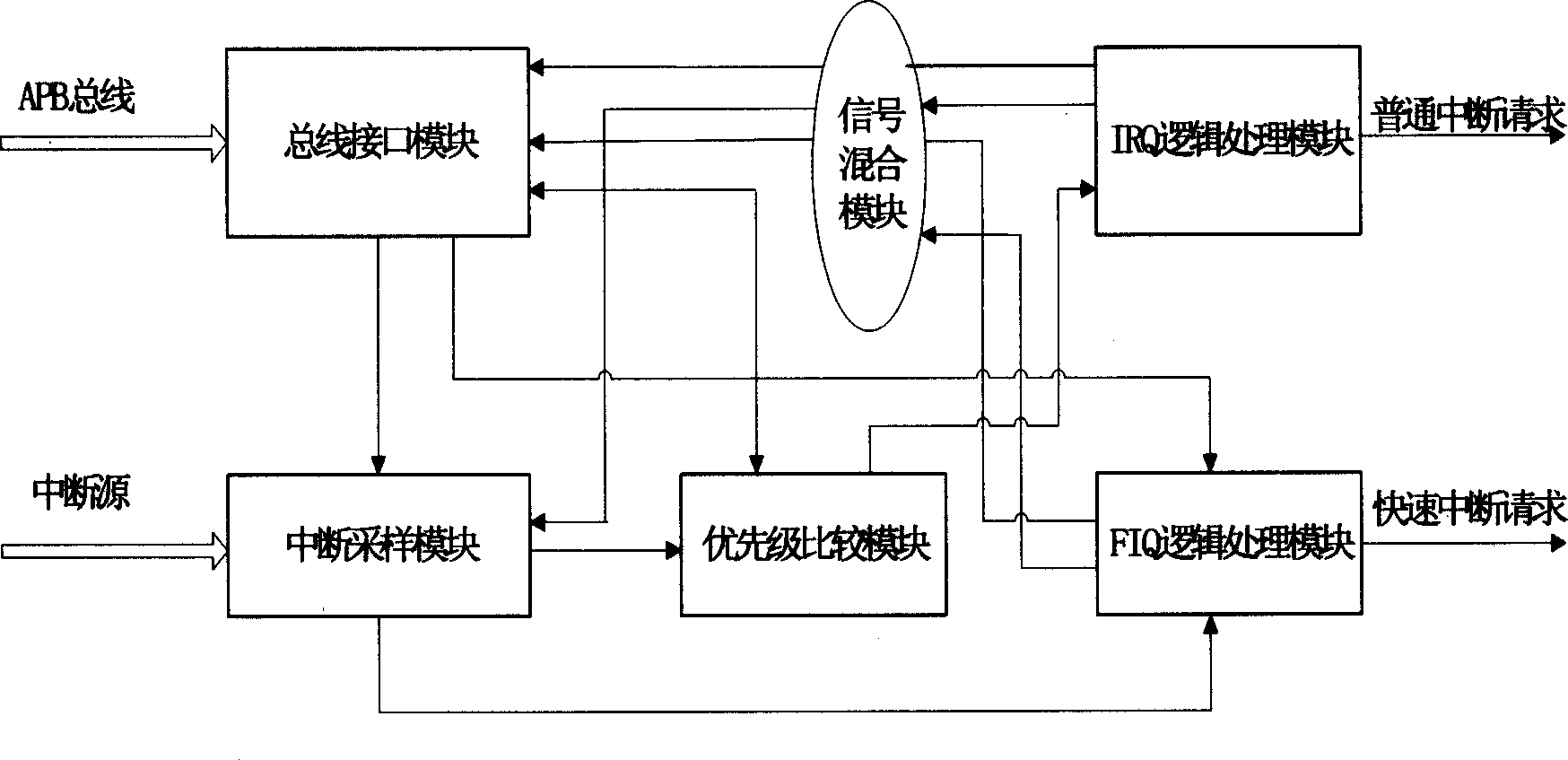

The invention is a kind of programmable interrupt controller, which refers to a kind of interrupt controller which can select the interrupt with the highest priority from the primary device interrupt, the salve device interrupt, the soft interrupt and the outer interrupt, and sends out interrupt application to the processor core (ARM core). The device includes a bus interface model, an interrupt sampling model, an iRQ (normal interrupt quest) logic processing model, a FIQ (fast interrupt quest) logic processing model, priority comparing model and signal blending model. The controller can solve the problem that the function is single, the configuration is inflexible, and the repeatability is bad in the current technology.

Owner:SANECHIPS TECH CO LTD

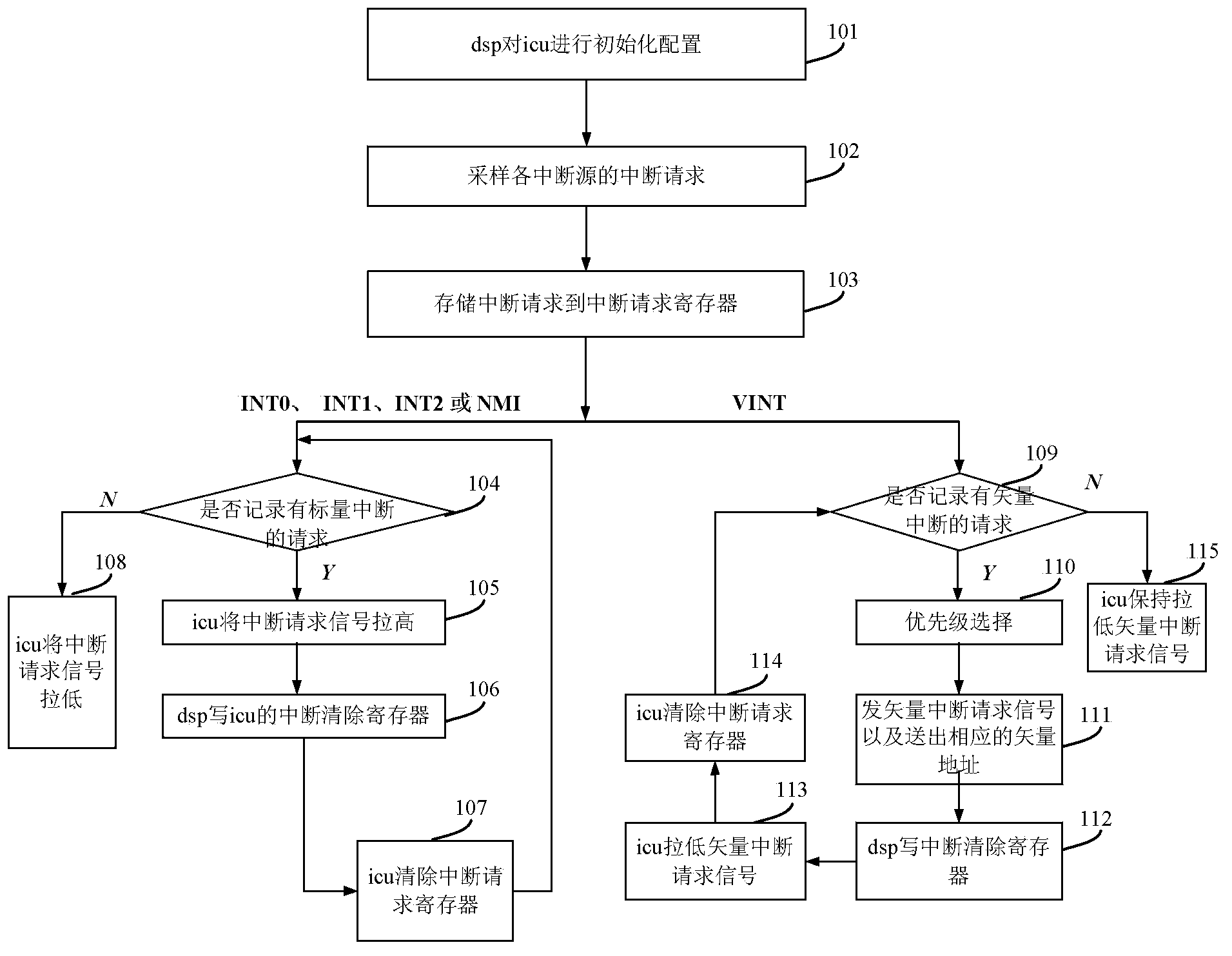

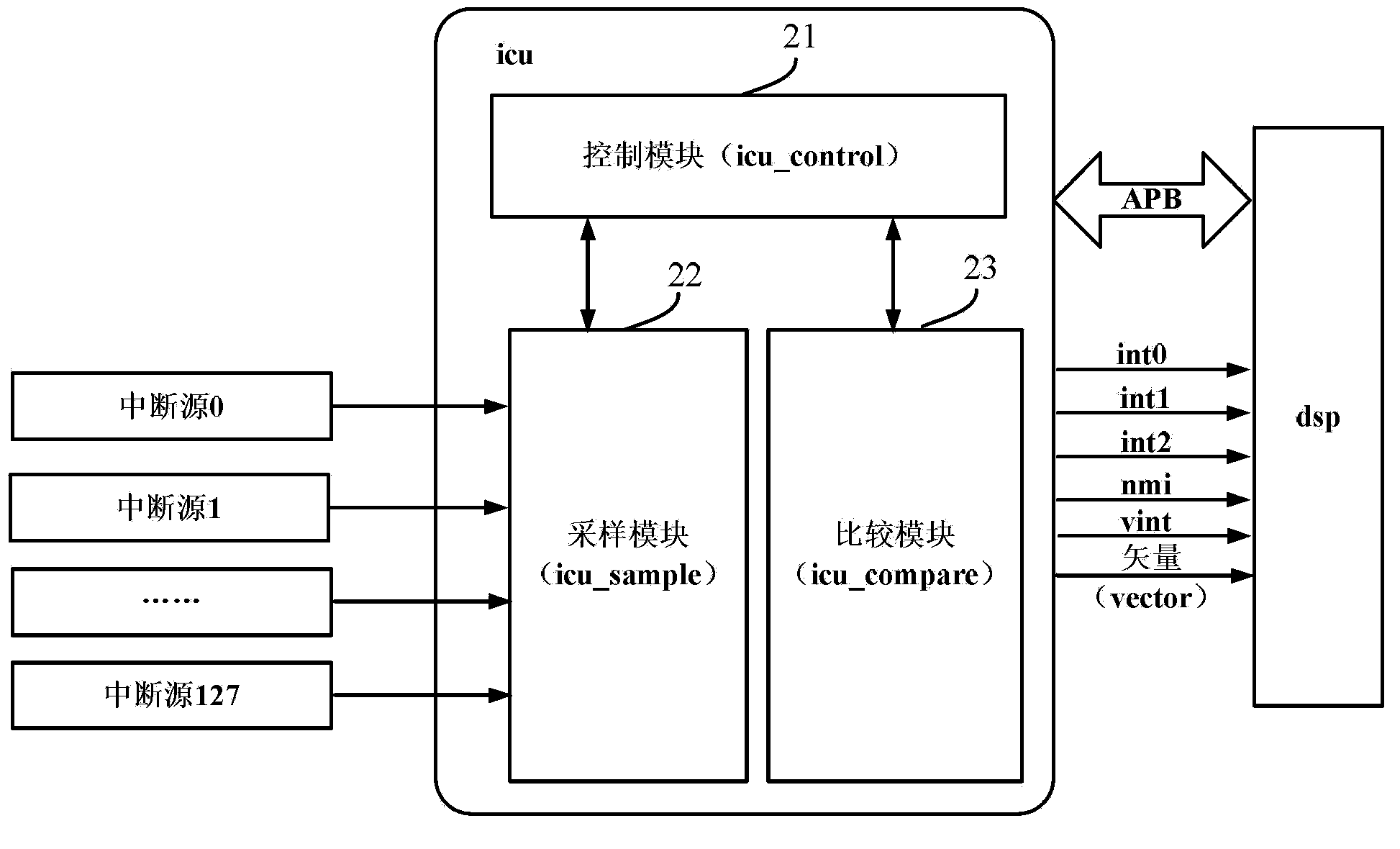

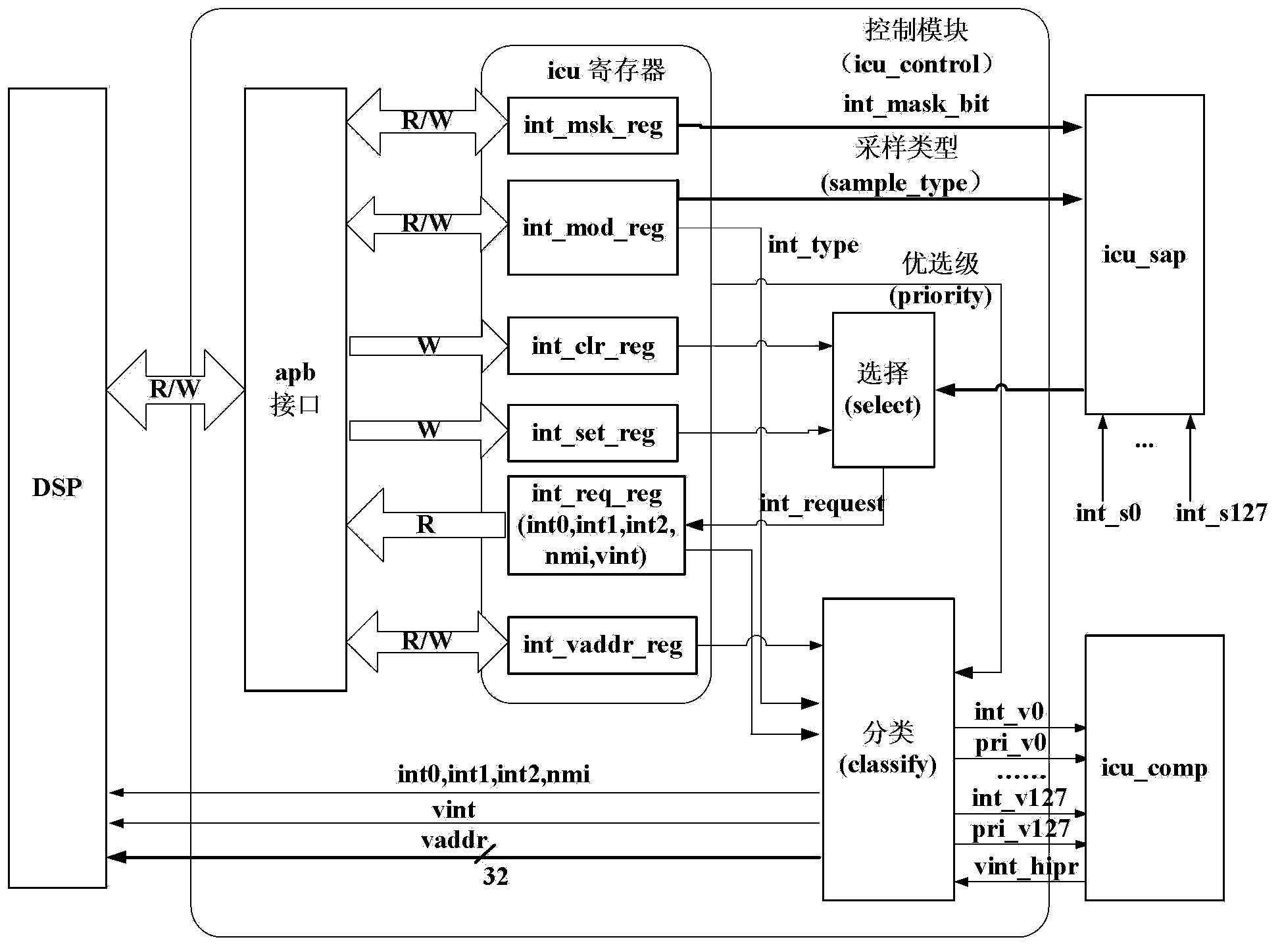

Interrupt control method, interrupt processing method, interrupt controller and processor

ActiveCN103544125AImprove processing efficiencyElectric digital data processingControl signalComputer science

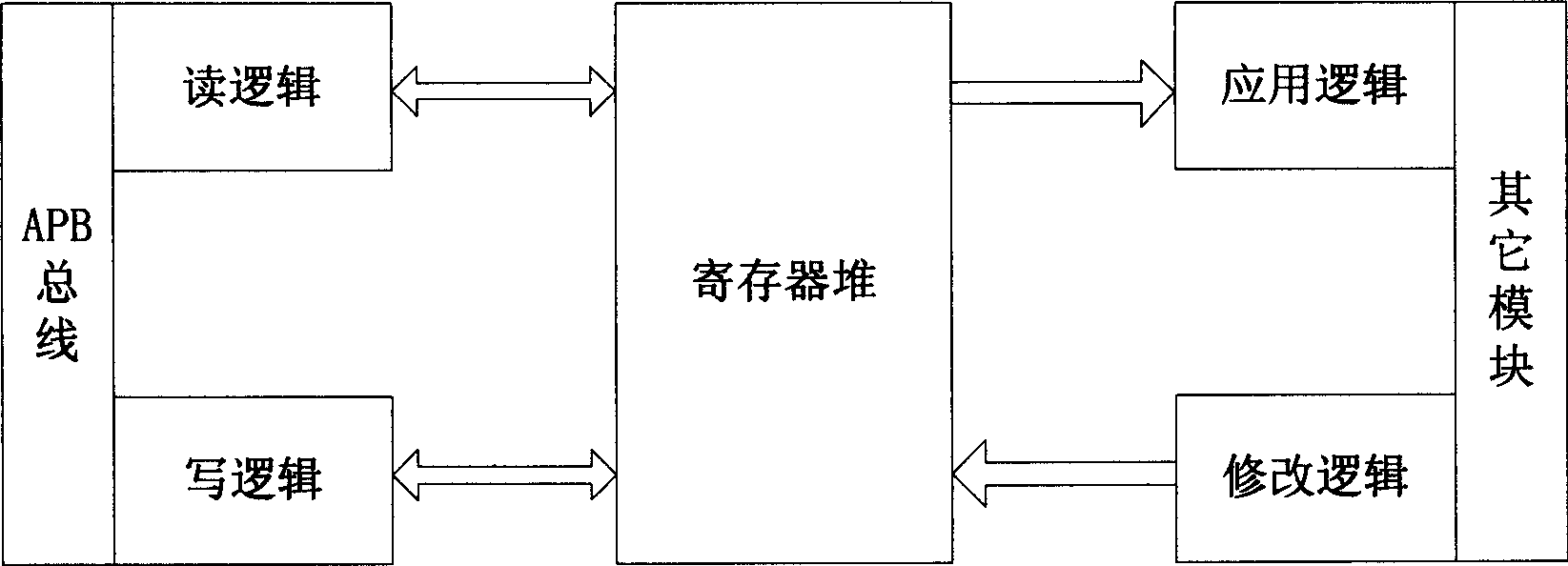

The invention provides an interrupt control method, an interrupt processing method, an interrupt controller and a processor. The interrupt control method comprises the steps that interrupt requests of all interrupt sources are sampled according sampling information and the interrupt requests are stored to corresponding interrupt request registers with a group as a unit according to the interrupt types; if the fact that an interrupt request exists in the current interrupt request register is determined, a control signal is sent to the processor so that the processor can execute all the interrupt requests in the interrupt group where the interrupt request belongs according to the control signal. According to the interrupt control method, the interrupt processing method, the interrupt controller and the processor, interrupt grouping configuration is conducted so that the processor can process the interrupt requests with a group as a unit in a batch mode, the interrupt request processing efficiency of the processor is improved, and therefore the processing efficiency of a whole system is improved.

Owner:SANECHIPS TECH CO LTD

Mobile communication device having a prioritized interrupt controller

InactiveUS20020184423A1Energy efficient ICTEnergy efficient computingProgrammable Interrupt ControllerCommunication device

A microprocessor system having an interrupt controller is provided for use in a mobile communications device. Peripheral processing units generate interrupt requests for sending to the microprocessor. The microprocessor has components for responding to interrupt requests by interrupting current processing and performing an interrupt service routine associated with the interrupt request. The interrupt controller receives interrupt requests directed to the microprocessor from the peripheral processing units and for prioritizes the interrupt requests on behalf of the microprocessor. By providing an interrupt controller for prioritizing interrupt requests on behalf of the microprocessor, the microprocessor therefore need not devote significant internal resources to prioritizing the interrupt request signals.

Owner:QUALCOMM INC

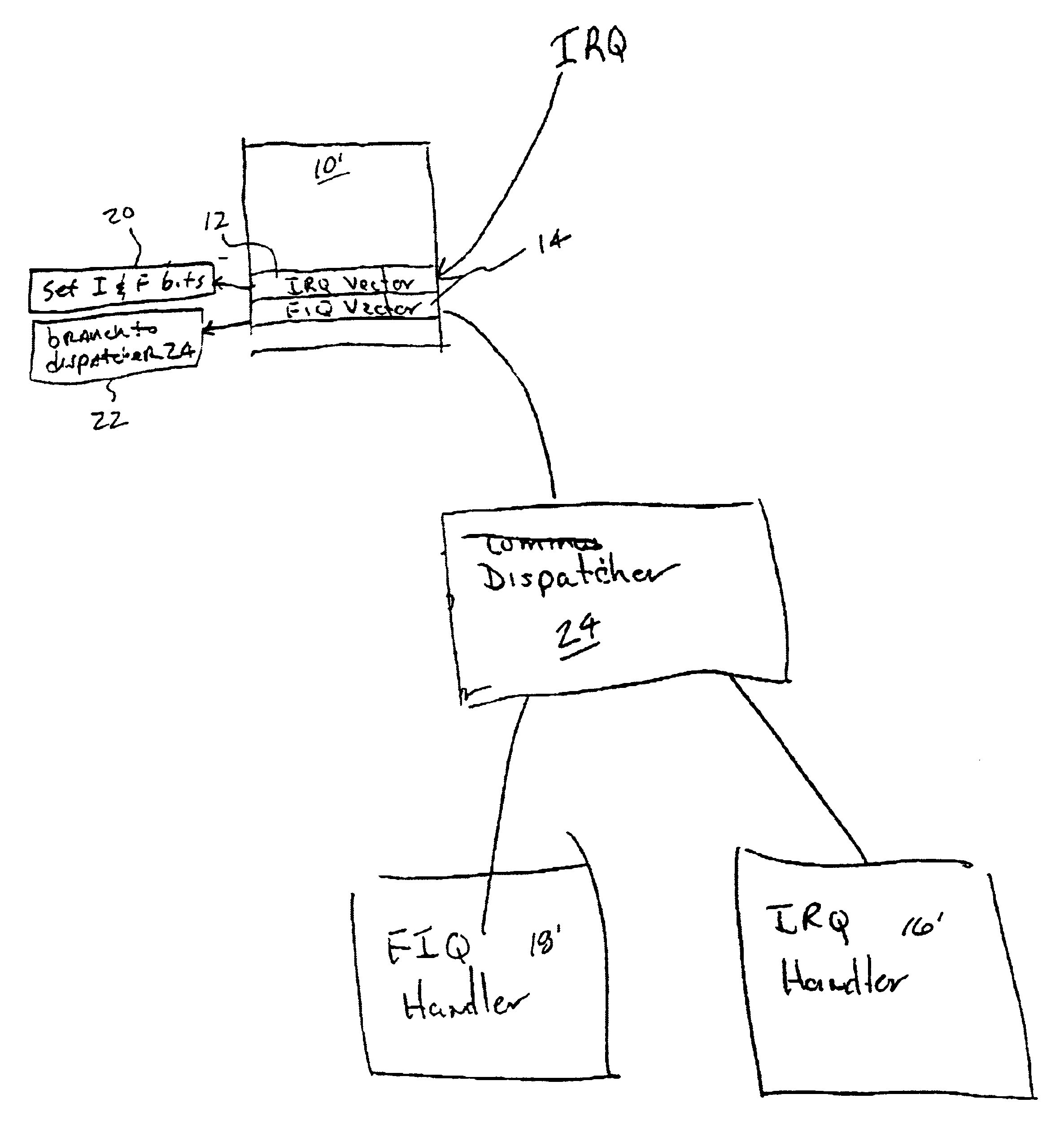

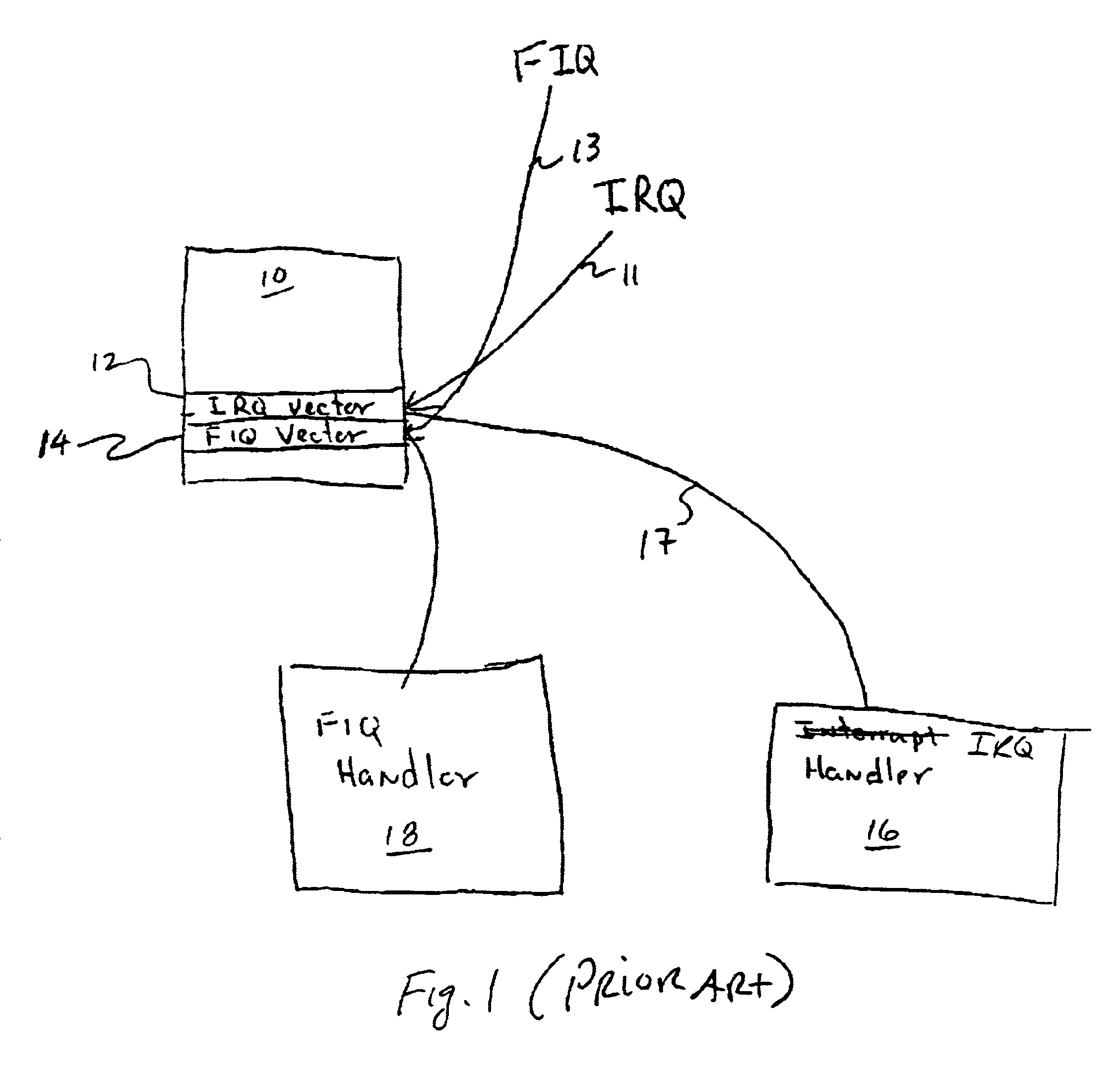

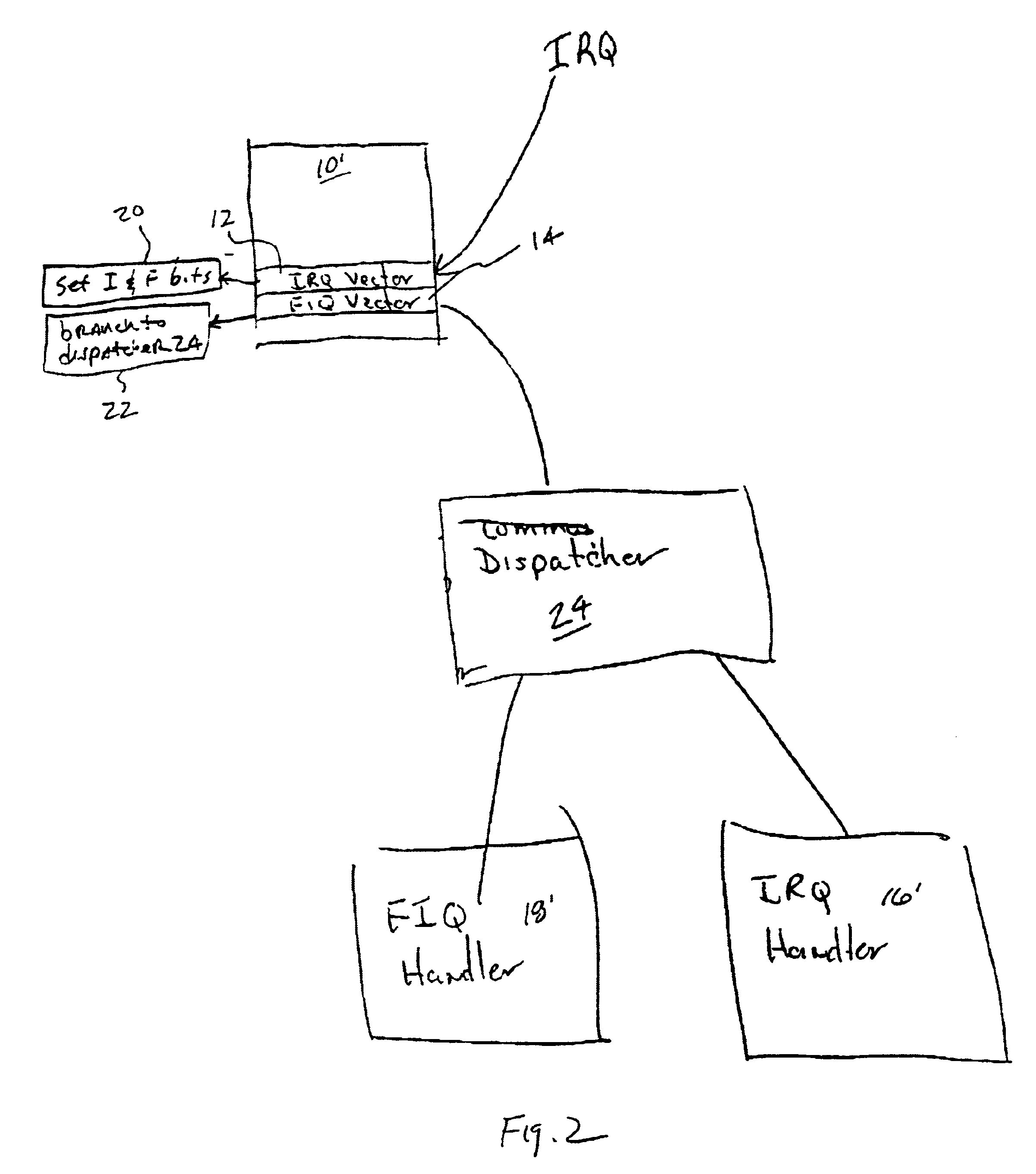

Unified exception handling for hierarchical multi-interrupt architectures

A unified interrupt handling system and method is provided for an embeddable processor having multiple interrupt types. An instruction is inserted into the first vector address that disables the second interrupt mode. At the second vector address, an other instruction is inserted that branches to a common interrupt dispatcher. The common interrupt dispatcher is provided with an interrupt routine that processes the interrupt, and then re-enables the second interrupt modes. Interrupt requests are then processed by the common interrupt dispatcher without interruption.

Owner:WIND RIVER SYSTEMS

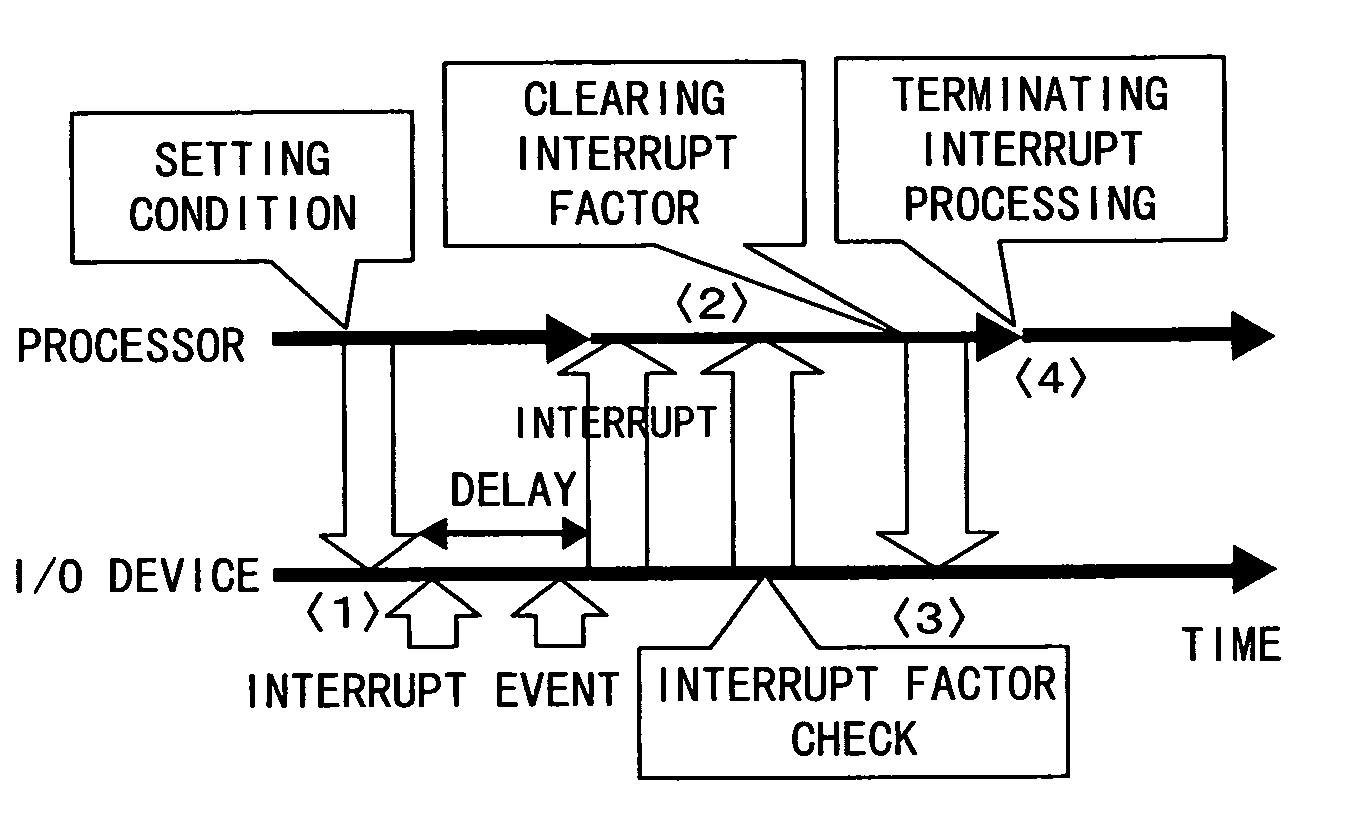

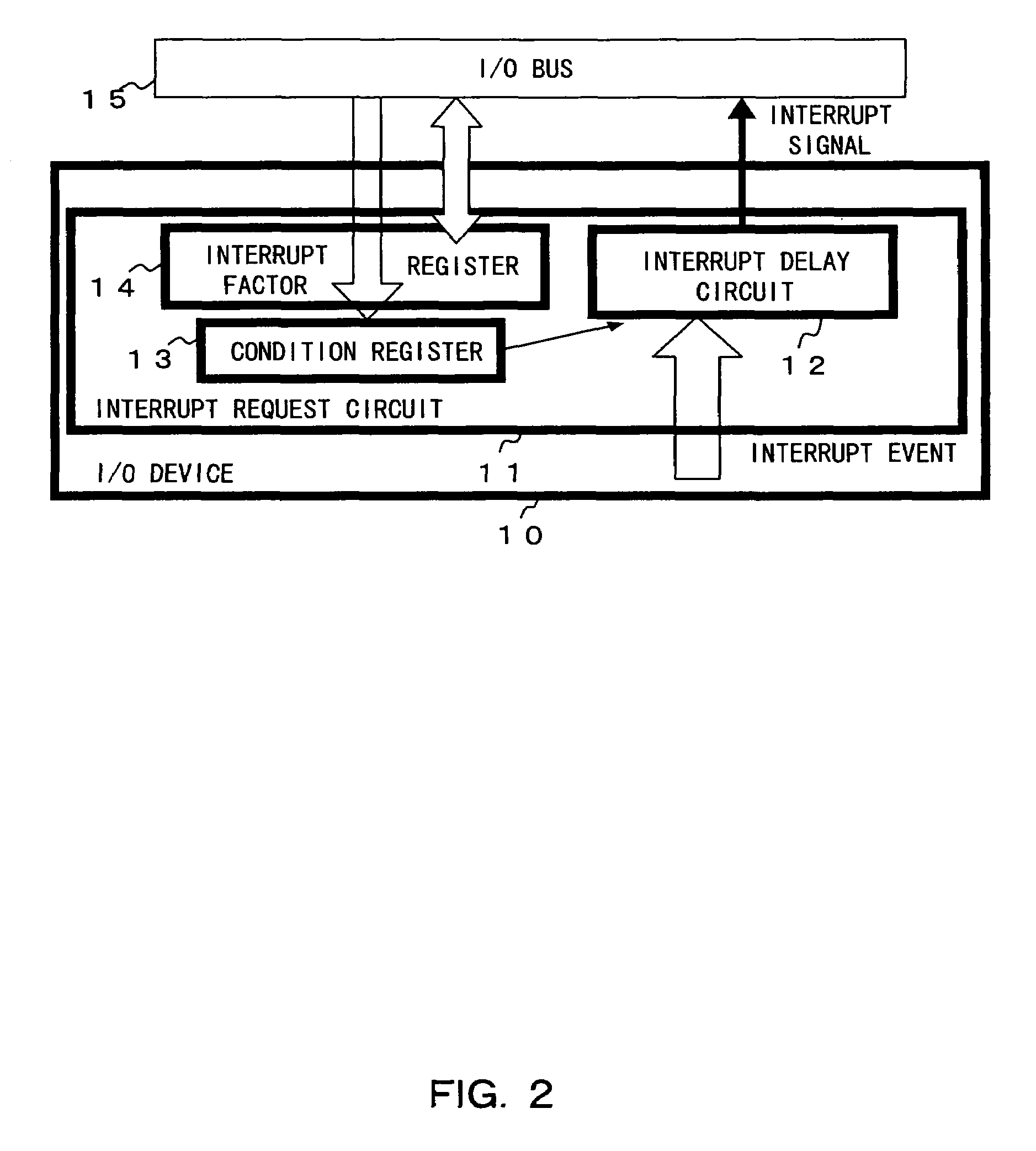

Computer for dynamically determining interrupt delay

InactiveUS7415561B2Program initiation/switchingInput/output processes for data processingDelayed timeEmbedded system

In a computer having a unit for outputting an interrupt request to a processor, a delay condition from occurrence of an interrupt event to issue of an interrupt request to the processor can be dynamically determined depending on the processor load status, etc. The interrupt request output unit includes a unit for obtaining a determination factor of a delay condition from the occurrence of an interrupt event to the issue of an interrupt request to the processor, and a unit for determining a delay condition corresponding to the obtained determination factor. For example, a time up to a read of an interrupt factor by the processor is obtained as a determination factor, and is multiplied by a coefficient, thereby determining a delay time as a delay condition.

Owner:FUJITSU LTD

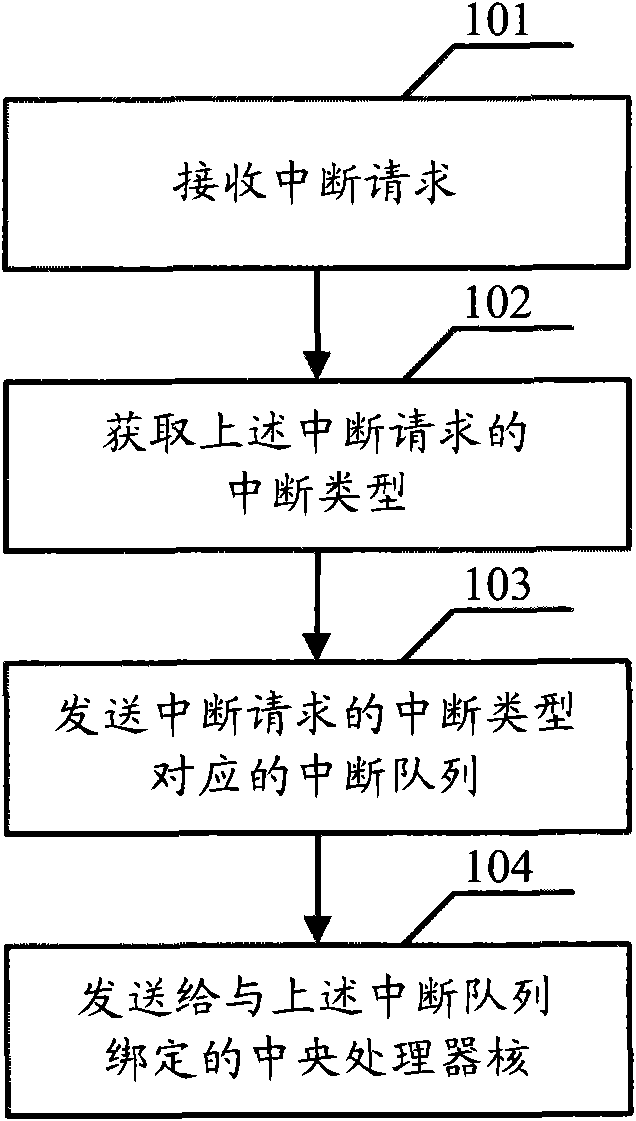

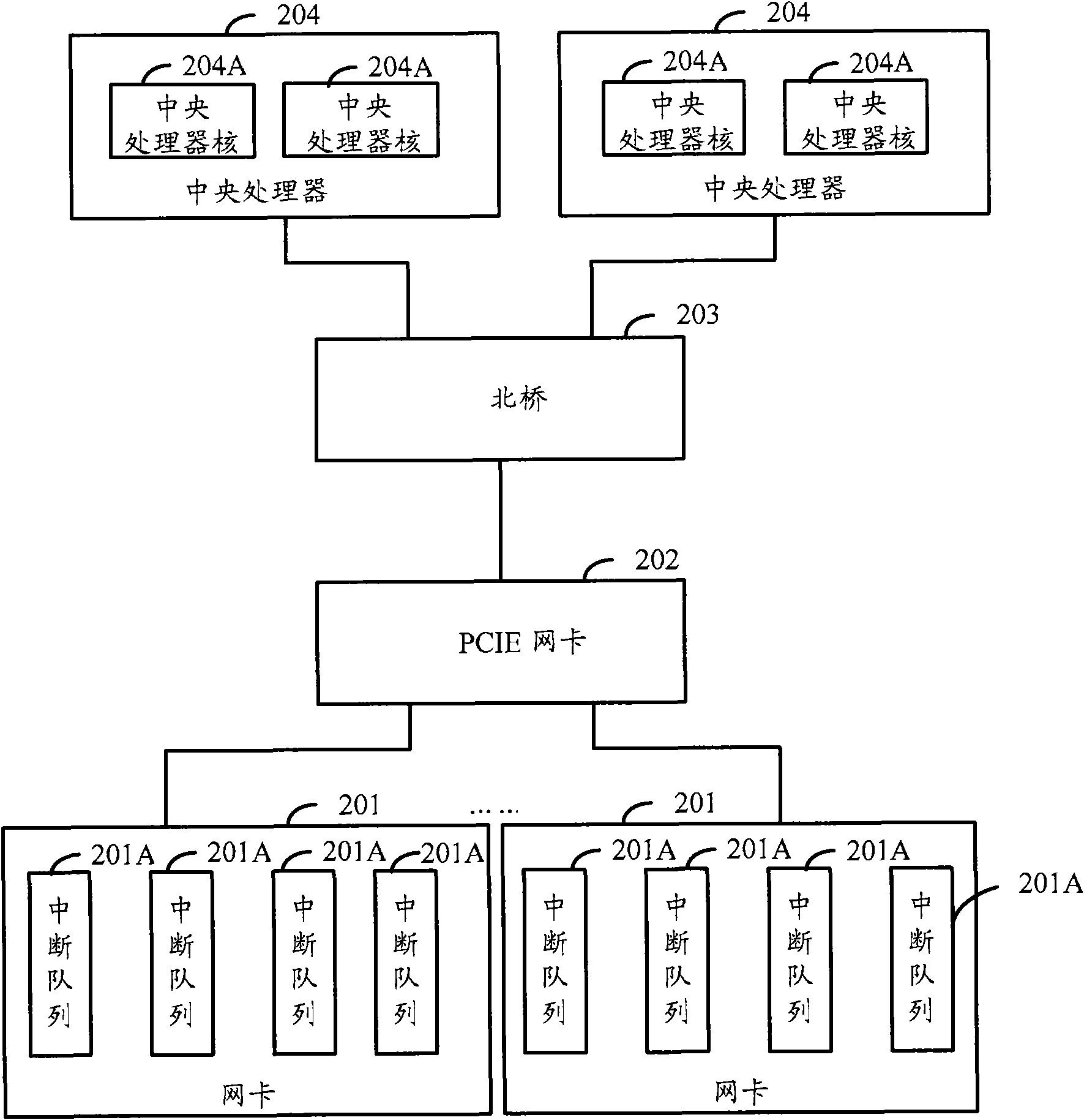

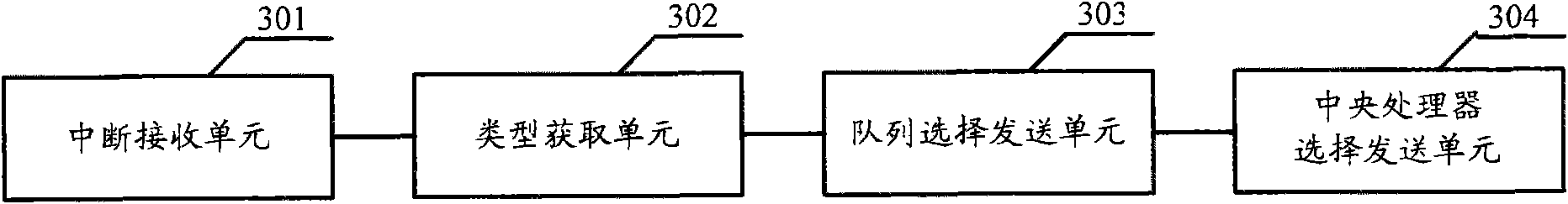

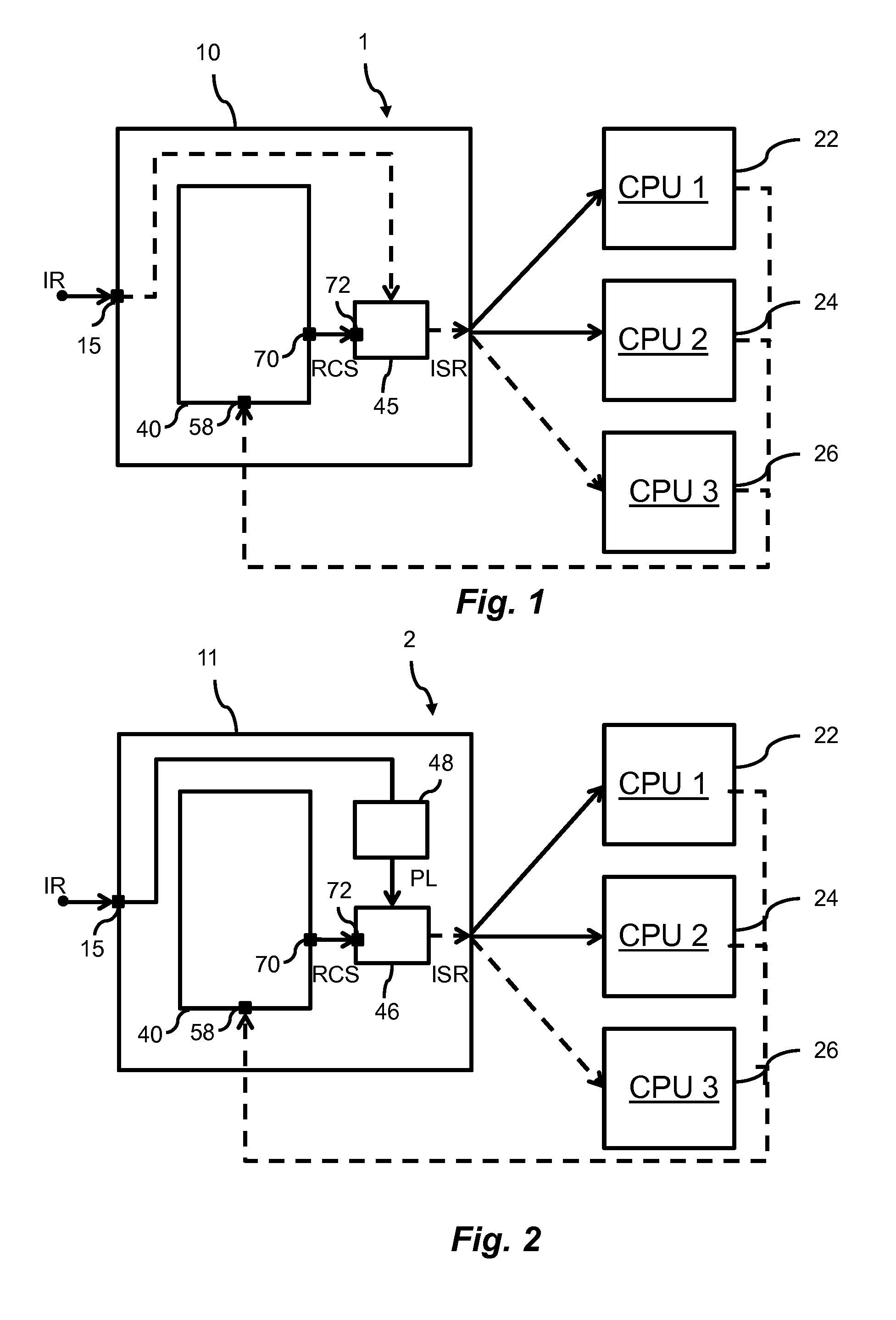

Method, device and system for processing multiple interrupt types

InactiveCN101634974AReduce processing timeImprove efficiencyElectric digital data processingComputer scienceEmbedded system

The invention discloses a method, a device and a system for processing multiple interrupt types. The method comprises the following steps: receiving interrupt requests and obtaining the interrupt types of the interrupt requests; sending the interrupt requests to an interruption queue which corresponds to the interrupt types; and sending the interrupt requests in the interruption queue to a central processing unit (CPU) core bound to the interruption queue. In the technical scheme, the interrupt types of the interrupt requests are identified before the interrupt requests enter the interruption queue, and then the interrupt requests are sent to the interruption queue which corresponds to the interrupt types. The interrupt requests in the interruption queue have the same types, therefore, the CPU core does not need to judge the interrupt types before processing the interrupt requests so as to save the processing time of the CPU and enhance the efficiency of the CPU. In addition, one CPU processes one type of interrupt requests so as to avoid the mutually exclusive operation among the CPU cores, improve the concurrent processing performance of the CPU and enhance the efficiency of the CPU.

Owner:HUAWEI DIGITAL TECH (CHENGDU) CO LTD

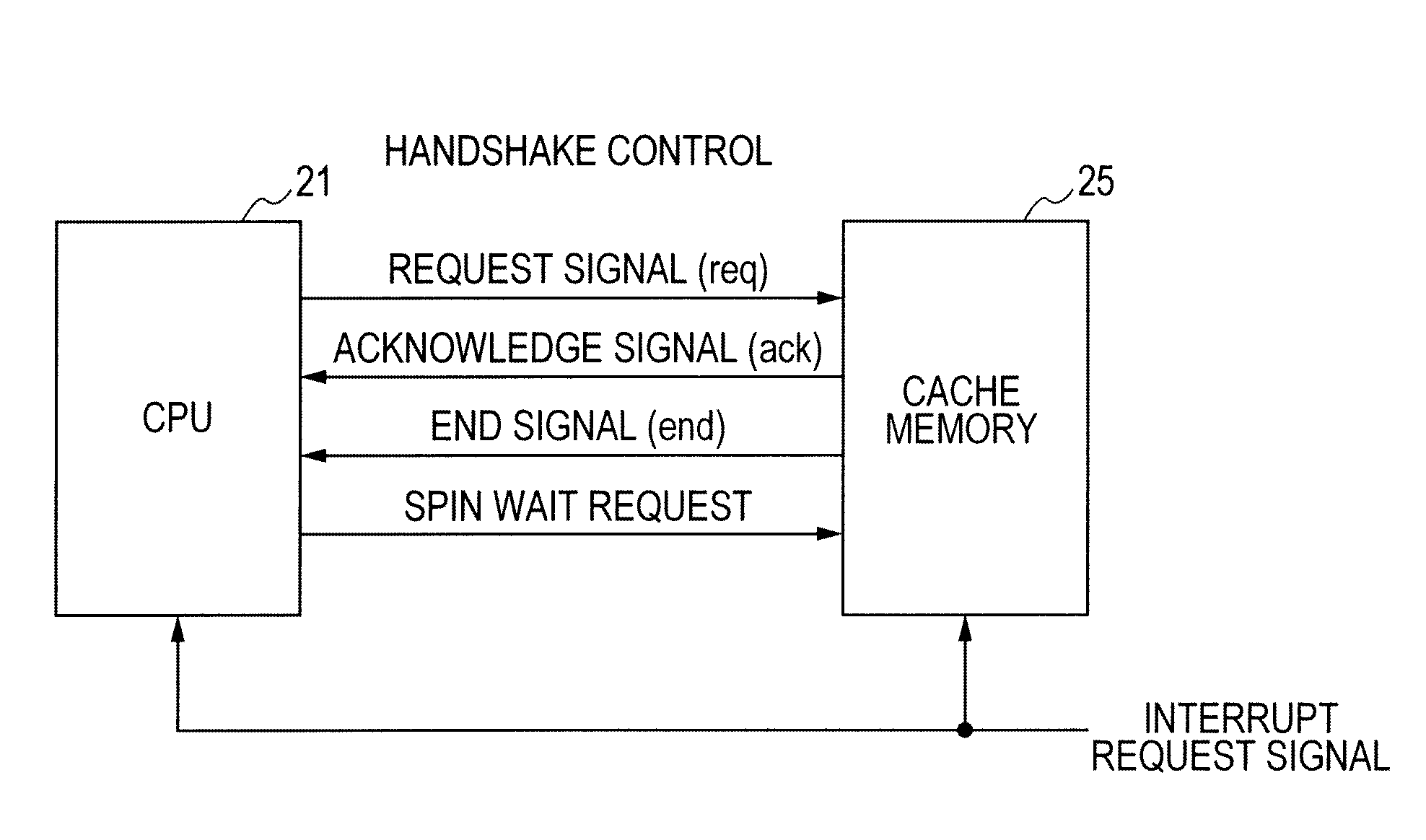

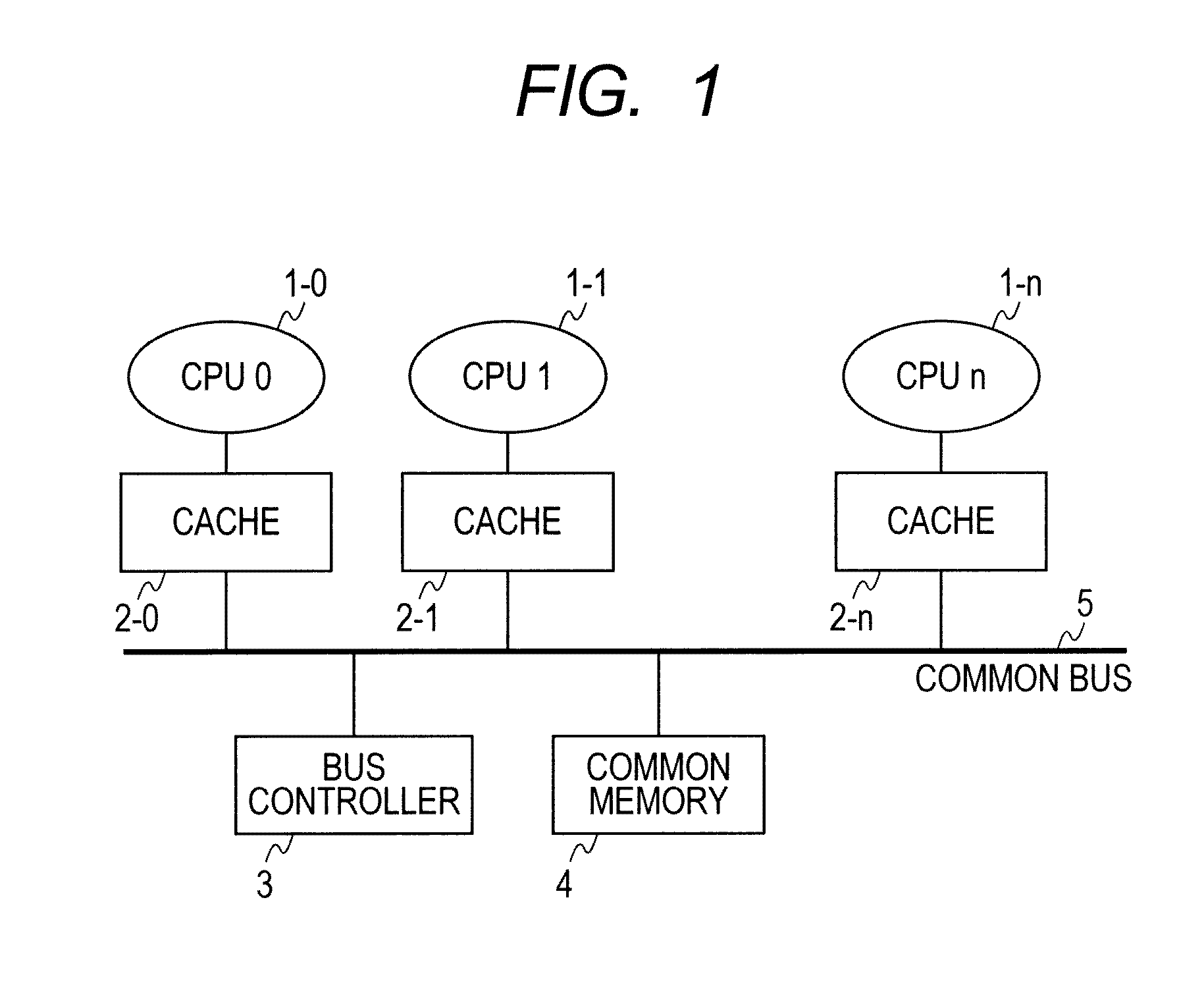

Data processor

ActiveUS20110179226A1Reduce power consumptionEnergy efficient ICTMemory adressing/allocation/relocationLoad instructionParallel computing

The present invention provides a data processor capable of reducing power consumption at the time of execution of a spin wait loop for a spinlock. A CPU executes a weighted load instruction at the time of performing a spinlock process and outputs a spin wait request to a corresponding cache memory. When the spin wait request is received from the CPU, the cache memory temporarily stops outputting an acknowledge response to a read request from the CPU until a predetermined condition (snoop write hit, interrupt request, or lapse of predetermined time) is satisfied. Therefore, pipeline execution of the CPU is stalled and the operation of the CPU and the cache memory can be temporarily stopped, and power consumption at the time of executing a spin wait loop can be reduced.

Owner:RENESAS ELECTRONICS CORP

Interrupt controller and interrupt controlling method for prioritizing interrupt requests generated by a plurality of interrupt sources

An interrupt controller and interrupt controlling method are provided for prioritizing interrupt requests generated by a plurality of interrupt sources. The interrupt controller comprises an interrupt source interface operable to receive interrupt requests generated by a first plurality of interrupt sources, and a daisy chain interface operable to receive a daisy chain interrupt request output by a further interrupt controller based on a second plurality of interrupt requests generated by a second plurality of interrupt sources. The daisy chain interface includes a priority input operable to receive a daisy chain priority signal indicating a priority associated with the daisy chain interrupt request. Prioritization logic is operable to receive the daisy chain priority signal and to apply predetermined prioritisation criteria to determine the highest priority interrupt request selected from the daisy chain interrupt request and the interrupt request generated by the first plurality of interrupt sources. An output interface is operable to output the highest priority interrupt request, the output interface including a priority output operable to provide an output priority signal indicating a priority associated with the highest priority interrupt request.

Owner:ARM LTD

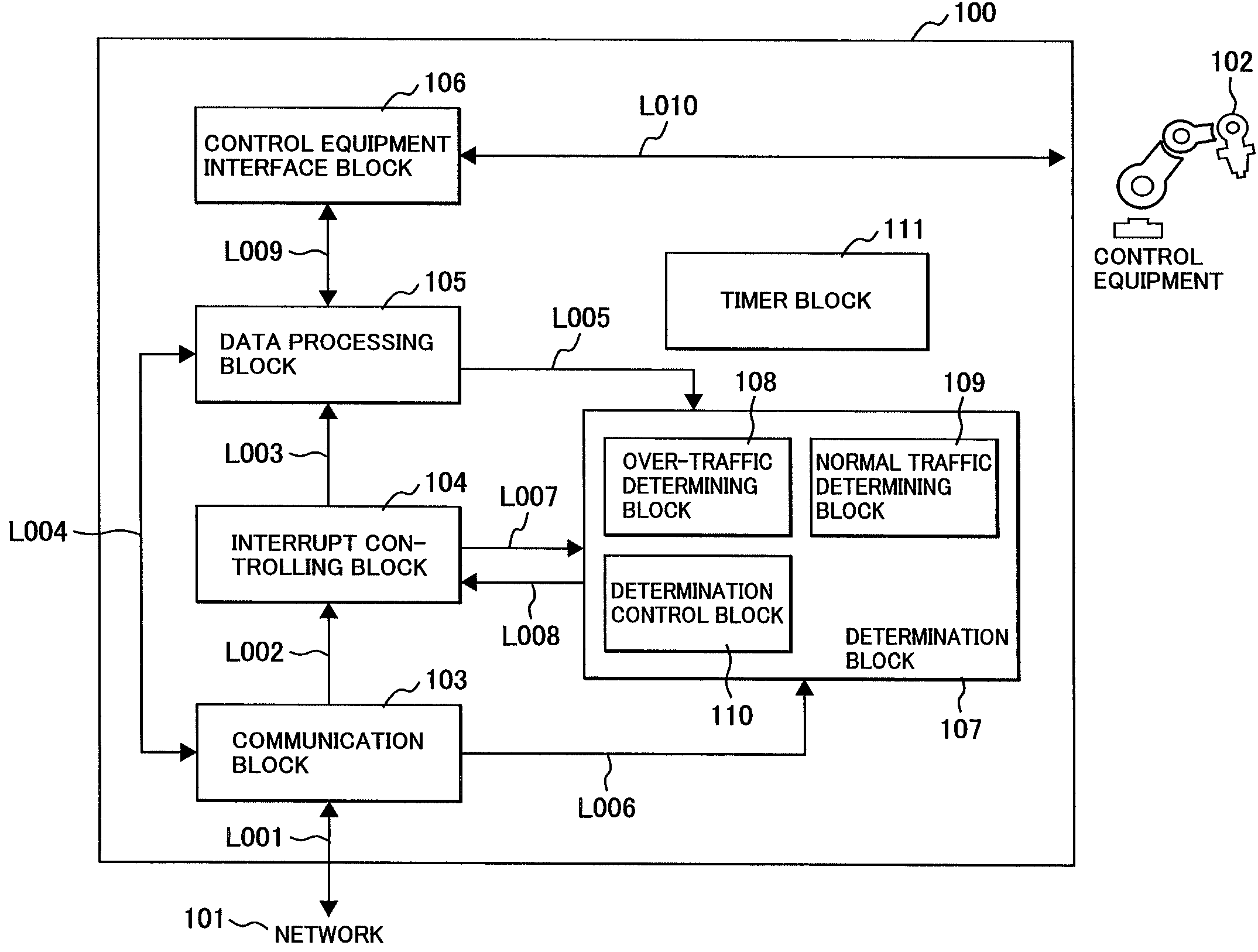

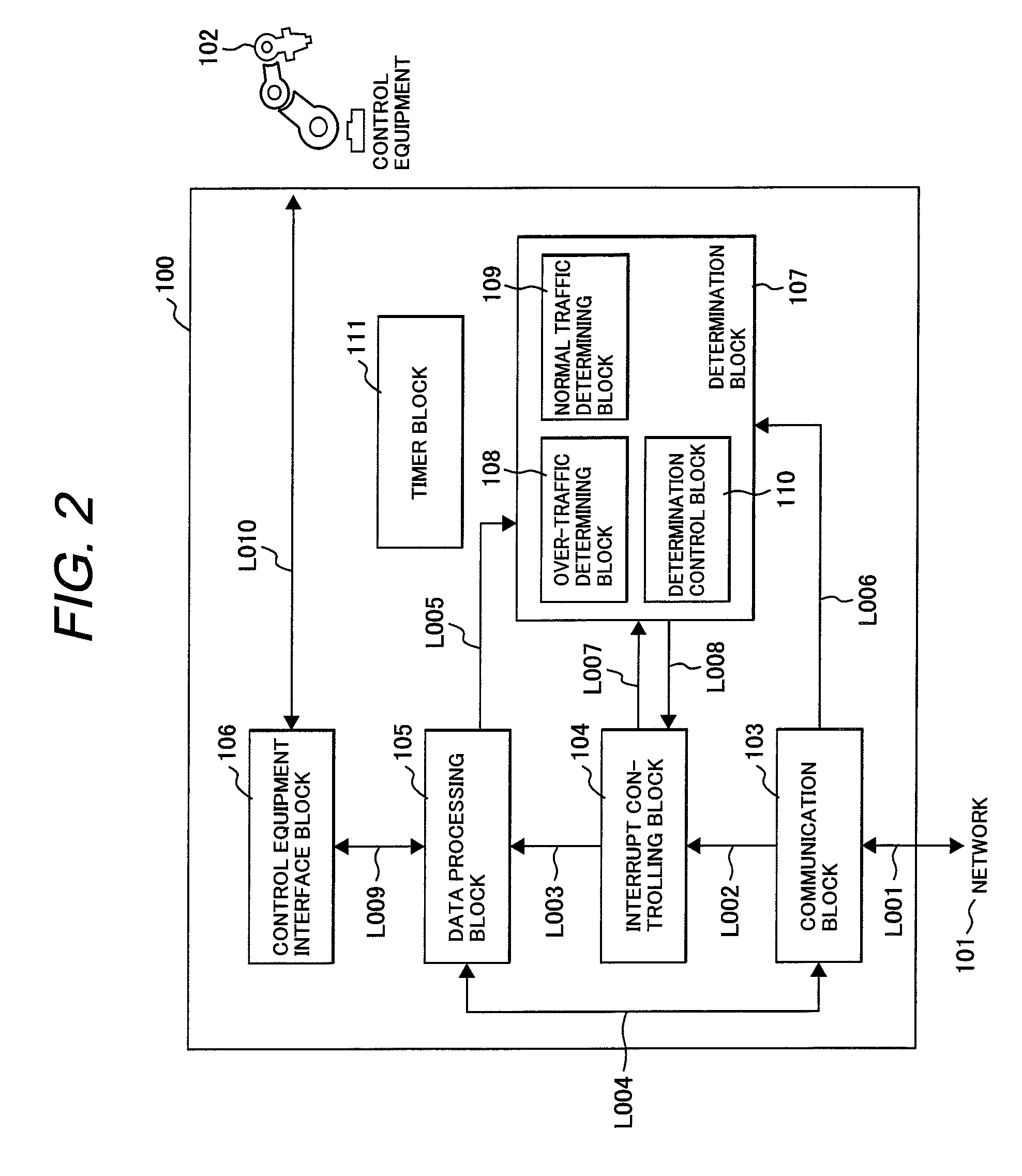

Information processor deactivates communication processing function without passing interrupt request for processing when detecting traffic inbound is in over-traffic state

ActiveUS7814224B2Avoid communicationReduce riskMultiple digital computer combinationsPlatform integrity maintainanceTraffic capacityInformation processor

An information processor disclosed herein prevents adverse impacts on higher priority processing due to extremely frequent receive processing when inbound traffic from a network is over-traffic state (under a DoS attack). The information processor attached to a network collects information about traffic state and, if it is determined that over-traffic state is present, deactivates the communication processing function without passing an interrupt request due to communication to the data processing block. In this state, the information processor continues to collect information about traffic state and, when it is determined that over-traffic state has terminated, starts to transfer an interrupt request to the data processing block and makes the communication processing function recover.

Owner:HITACHI IND EQUIP SYST CO LTD

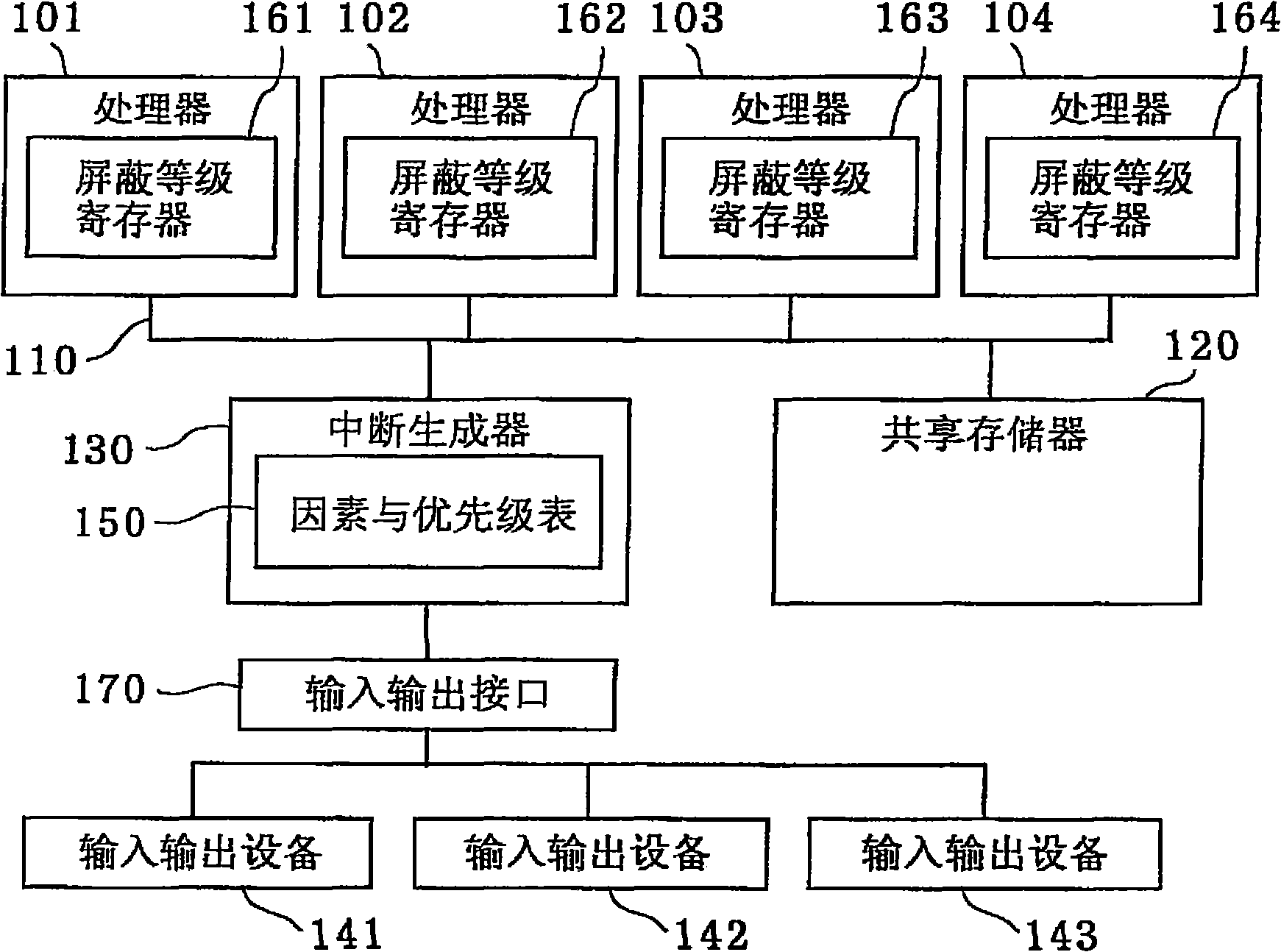

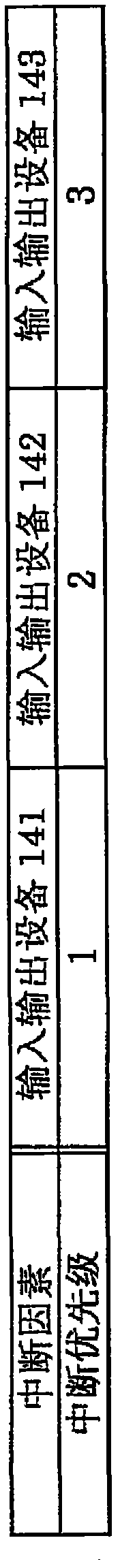

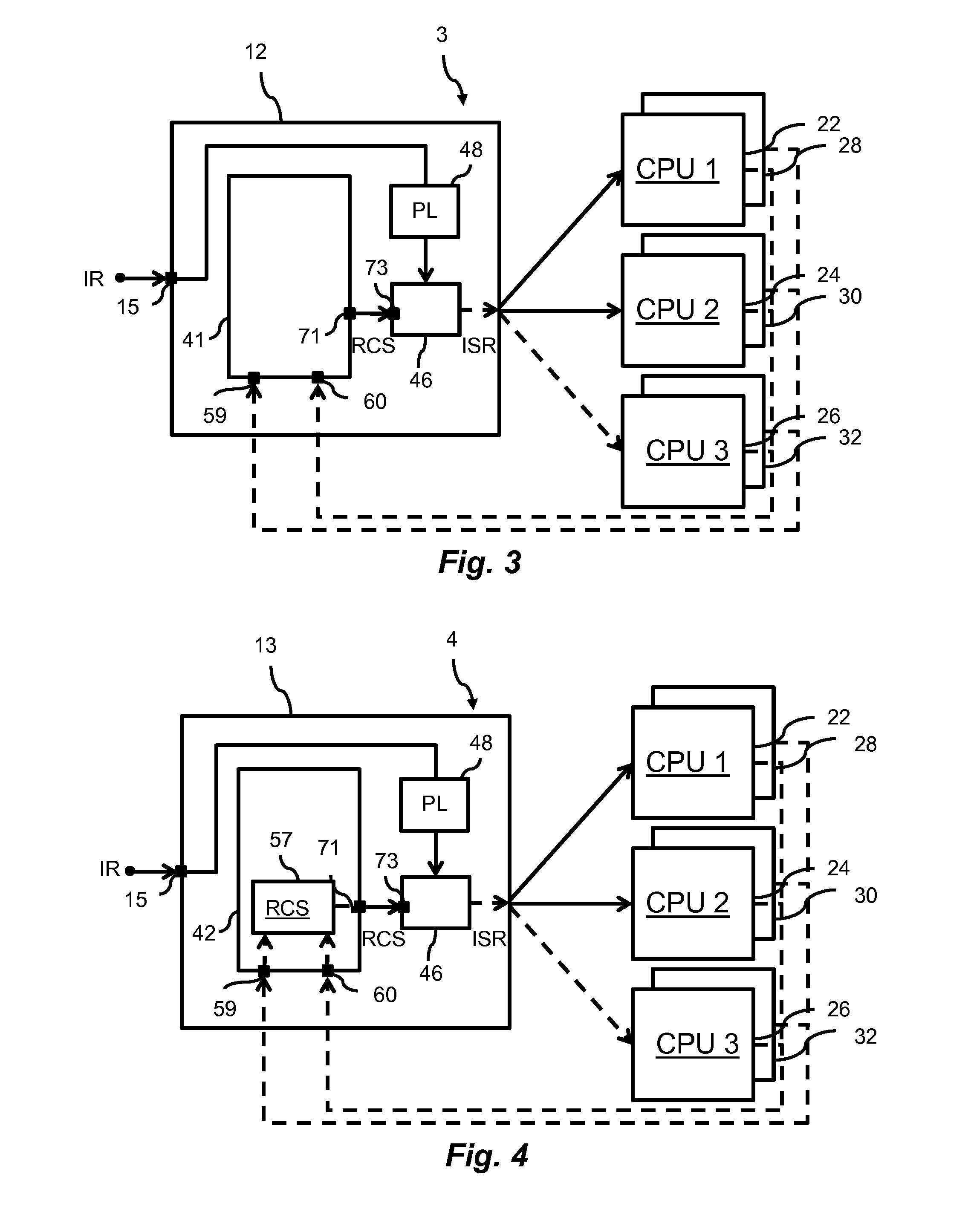

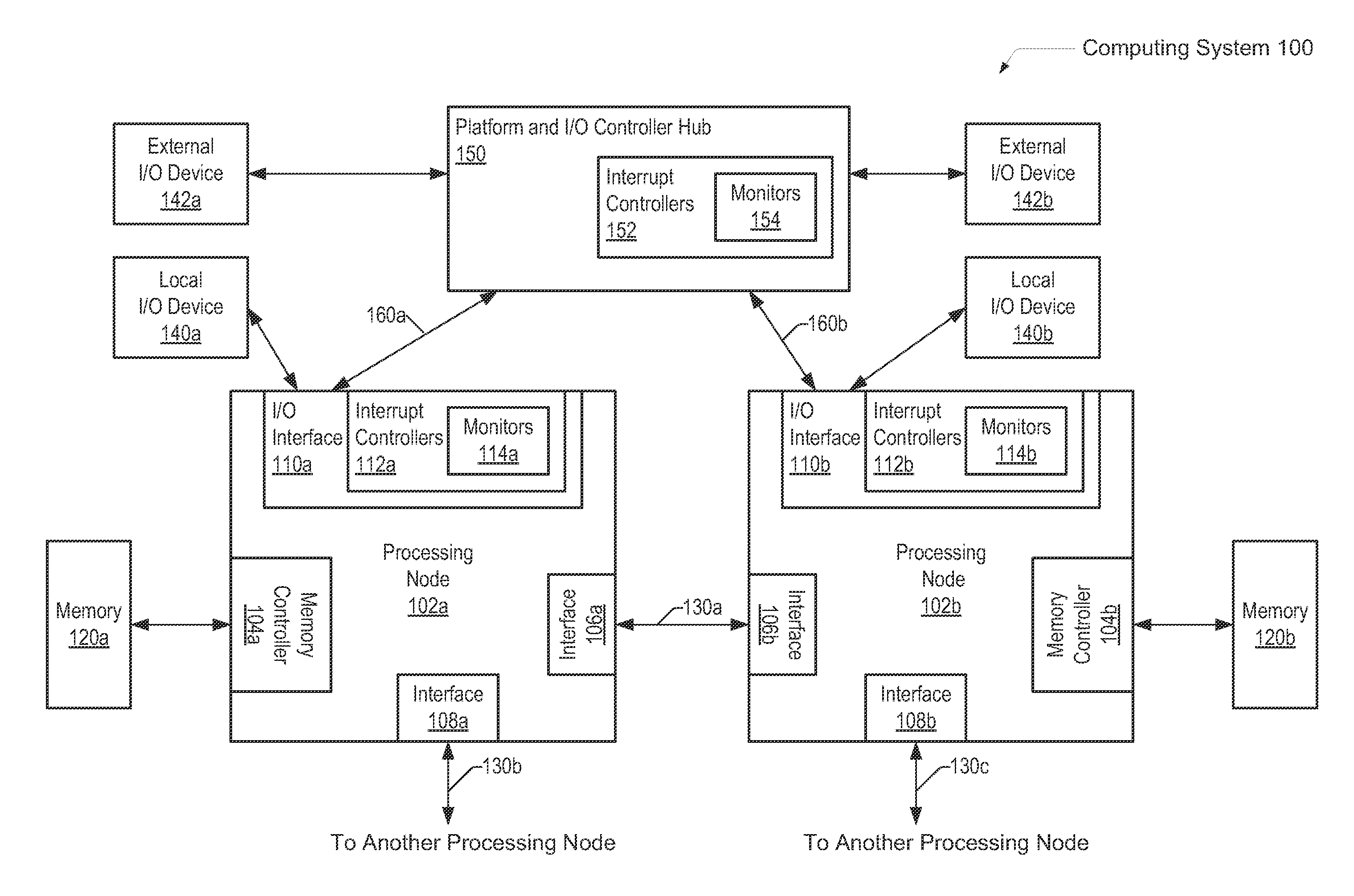

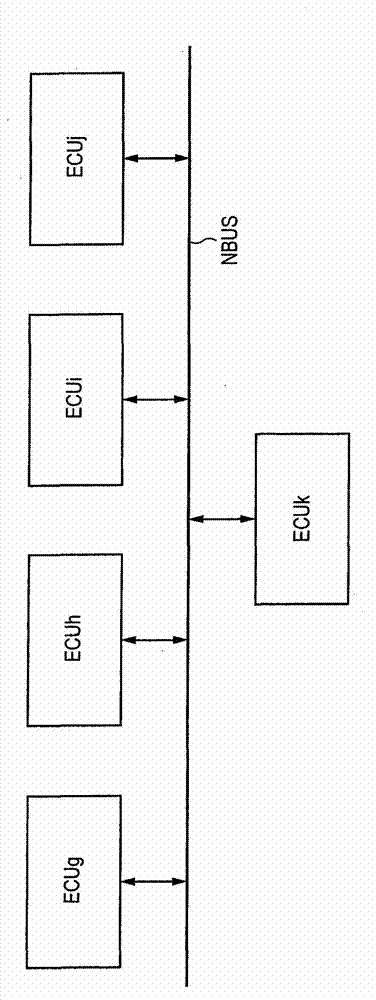

Multiprocessor system and multiprocessor system interrupt control method

InactiveCN102099797AProper interrupt responsivenessImprove processing efficiencyElectric digital data processingProcessor registerMulti processor

A multiprocessor system can improve the entire system processing efficiency while assuring an appropriate interrupt response based on an interrupt priority. The multiprocessor system includes: a plurality of processors each having a register; a plurality of I / O devices; and an interrupt generator. An interrupt control method includes: a setting step in which a corresponding processor sets an interrupt allowance degree in a register; a report step in which the interrupt generator which has caused a storage unit to store the interrupt priority indicating a priority for an interrupt from each of I / O devices receives an interrupt request from an I / O device and reports the interrupt request to a plurality of processors together with the interrupt priority of the I / O device; and an interrupt acceptance step in which the interrupt request is accepted by any one of the processors having the register in which a lower interrupt allowance degree is stored as compared to the interrupt priority.

Owner:PANASONIC CORP

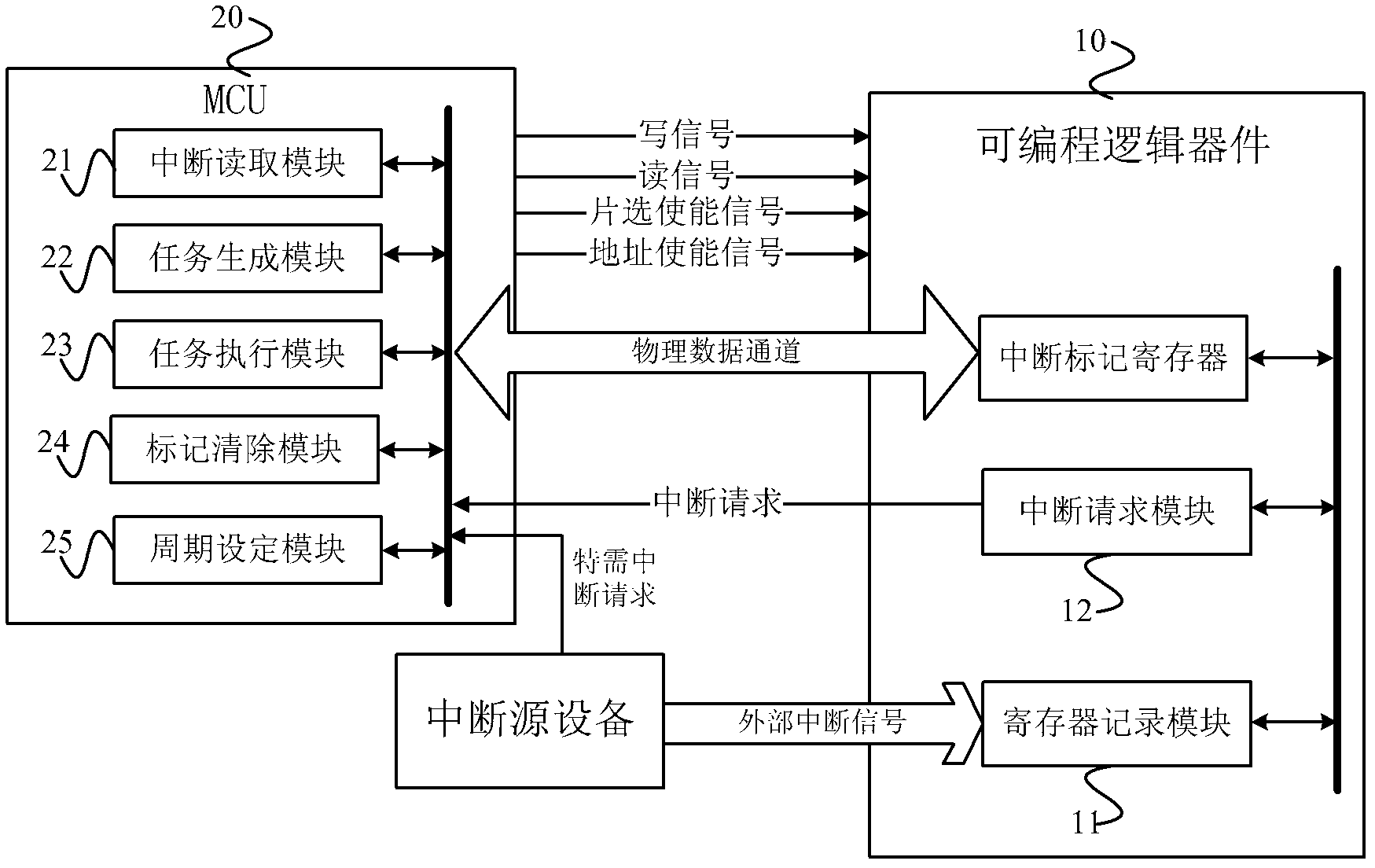

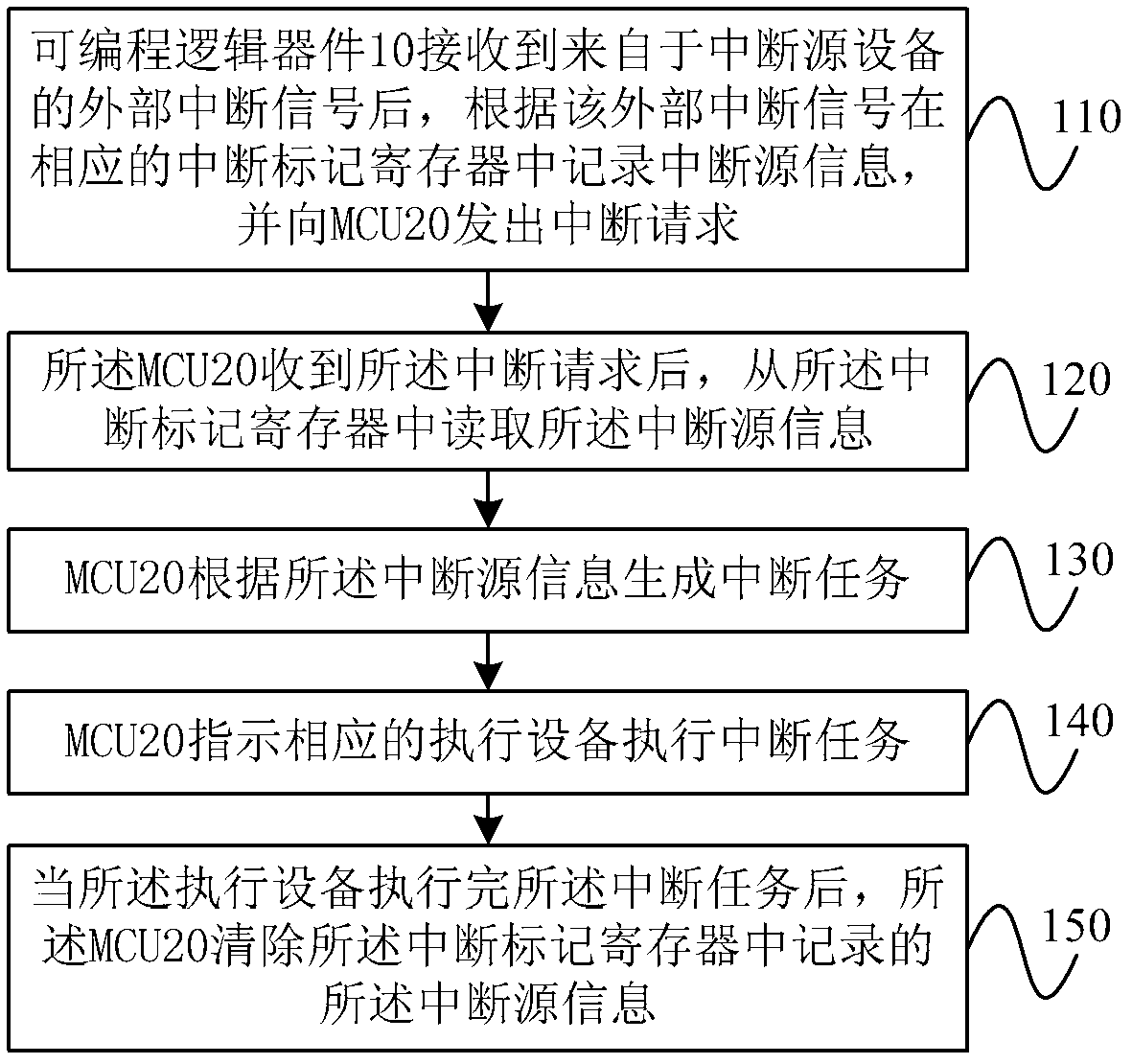

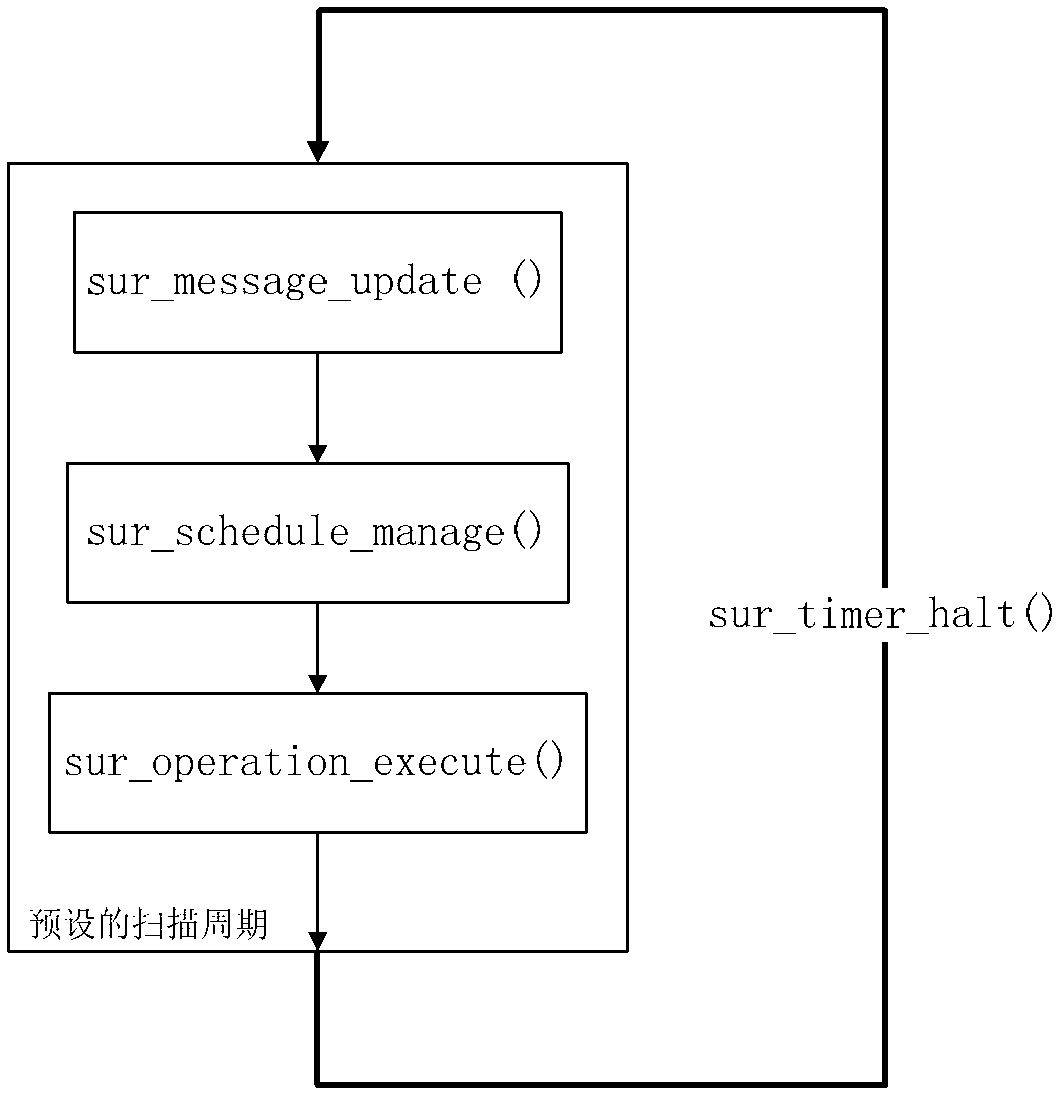

Interrupt control method and interrupt control unit

InactiveCN103077137AReduce resource usageOvercoming Quantitative LimitationsElectric digital data processingExtensibilityProgrammable logic device

The invention provides an interrupt control method and an interrupt control unit. The method comprises the following steps that after an MCU (micro control unit) receives an interrupt request, the MCU reads interrupt source information from an interrupt marker register of a programmable logic device, wherein the interrupt source information is the information recorded in the interrupt marker register according to an external interrupt signal after the programmable logic device receives the external interrupt signal of interrupt source equipment; the MCU generates an interrupt task according to the interrupt source information; and the MCU indicates corresponding execution equipment to execute the interrupt task. By a cooperative work means between the programmable logic device and the MCU, the interrupt control is realized, the expandability of the interrupt control unit is improved, and the resource occupancy on the MCU is reduced.

Owner:BEIJING DAHAO TECH

Multi-core processor sytem, control program, and control method

InactiveCN102822802ARaise prioritySpeed up response timeProgram initiation/switchingInterrupt handlerMulti-core processor

Owner:FUJITSU LTD

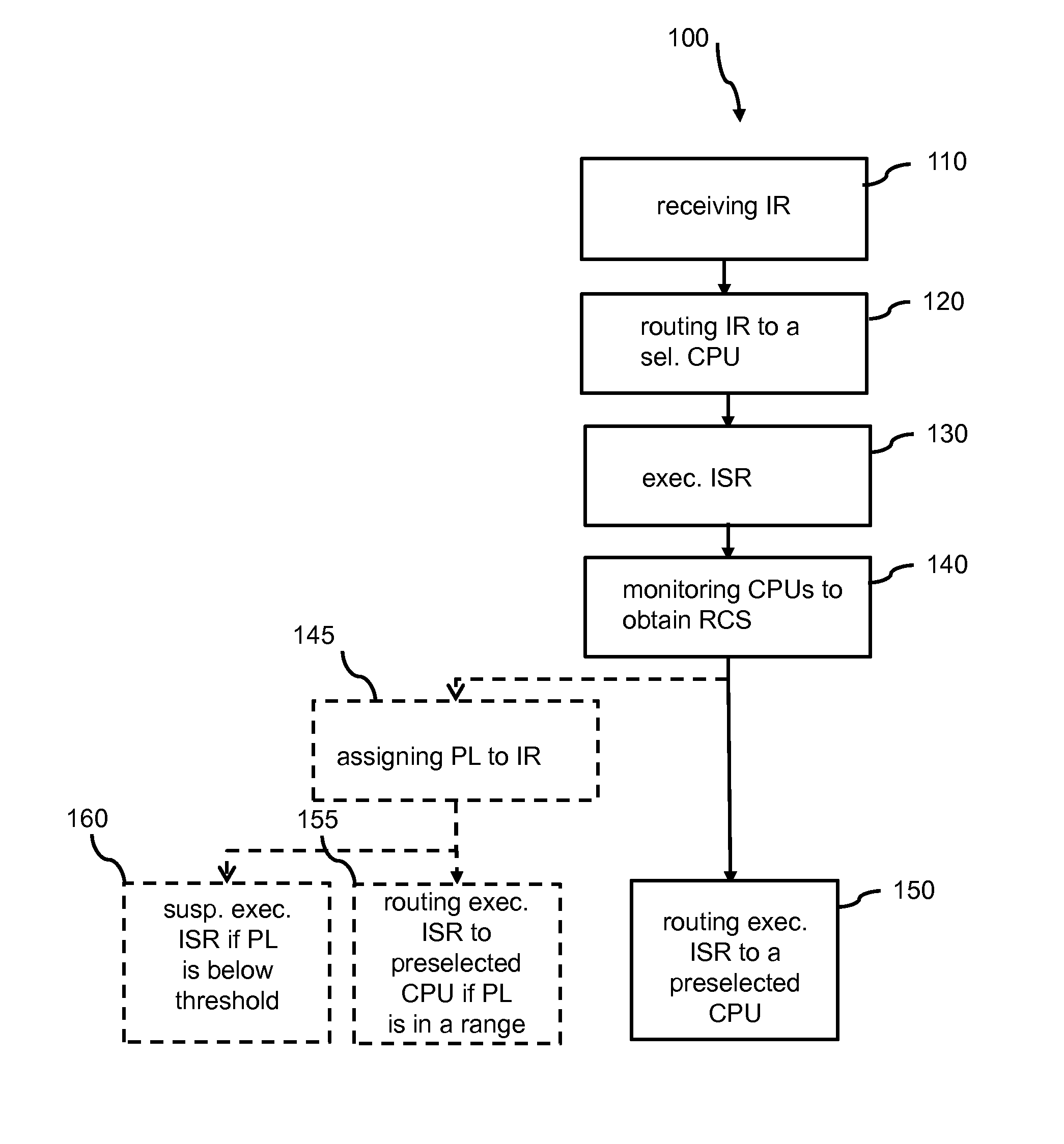

Interrupt controller and a method of controlling processing of interrupt requests by a plurality of processing units

An interrupt controller for controlling processing of interrupt requests by a plurality of processing units. The processing units have at least two modes: an active mode and an inactive mode. The interrupt controller comprises a controller input, an interrupt router coupled to the controller input and a monitoring unit. The monitoring unit outputs a routing change signal to the interrupt router if it determines that a selected processing unit, to which, in response to a received interrupt request, an execution of an interrupt service routine was initially routed, is in inactive mode while a preselected one is in the active mode. The interrupt router reroutes the execution of the interrupt service routine to the preselected processing unit.

Owner:NXP USA INC

Interrupt latency performance counters

ActiveUS20140115198A1Input/output processes for data processingData conversionRelevant informationLong latency

A system and method for finding the sources of increased interrupt latencies. An interrupt controller includes monitoring logic for measuring and storing latencies for servicing interrupt requests. The interrupt controller determines a measured latency is greater than an associated threshold and in response sends an indication of a long latency. The interrupt controller may send the indication to firmware, a device driver, or other software. The interrupt controller stores associated information with the measured latency for debug purposes. Additionally, the monitoring logic may perform statistical analysis in place of, or in addition to, software.

Owner:ADVANCED MICRO DEVICES INC

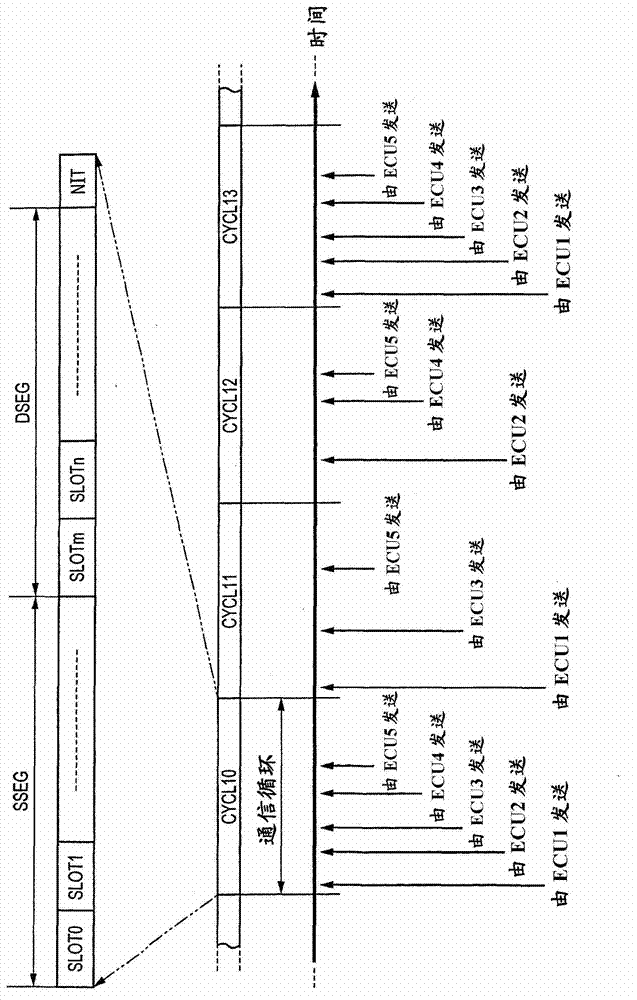

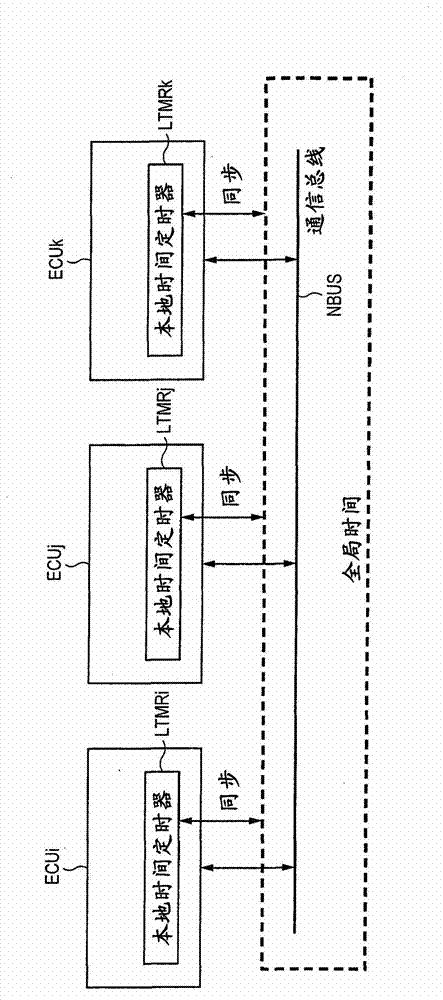

Semiconductor data processing device, time-triggered communication system, and communication system

The variation of the timing of starting interrupt processing in response to a timer interrupt request is reduced regardless of the condition of processing of other interrupts. A semiconductor data processing device incorporated in each of plural electronic control devices coupled to a network for time-triggered communication system is provided with a central processing unit, a communication control circuit and an interrupt control circuit. The communication control circuit has a local time timer for use in time-triggered communication and issues, based on time counting by the local time timer, a timer interrupt request for time-triggered communication. When a timer interrupt request for time-triggered communication is received, the interrupt control circuit performs control to cause the central processing unit to delay, by a predetermined reservation time, starting the interrupt processing to be performed in response to the timer interrupt request.

Owner:RENESAS ELECTRONICS CORP

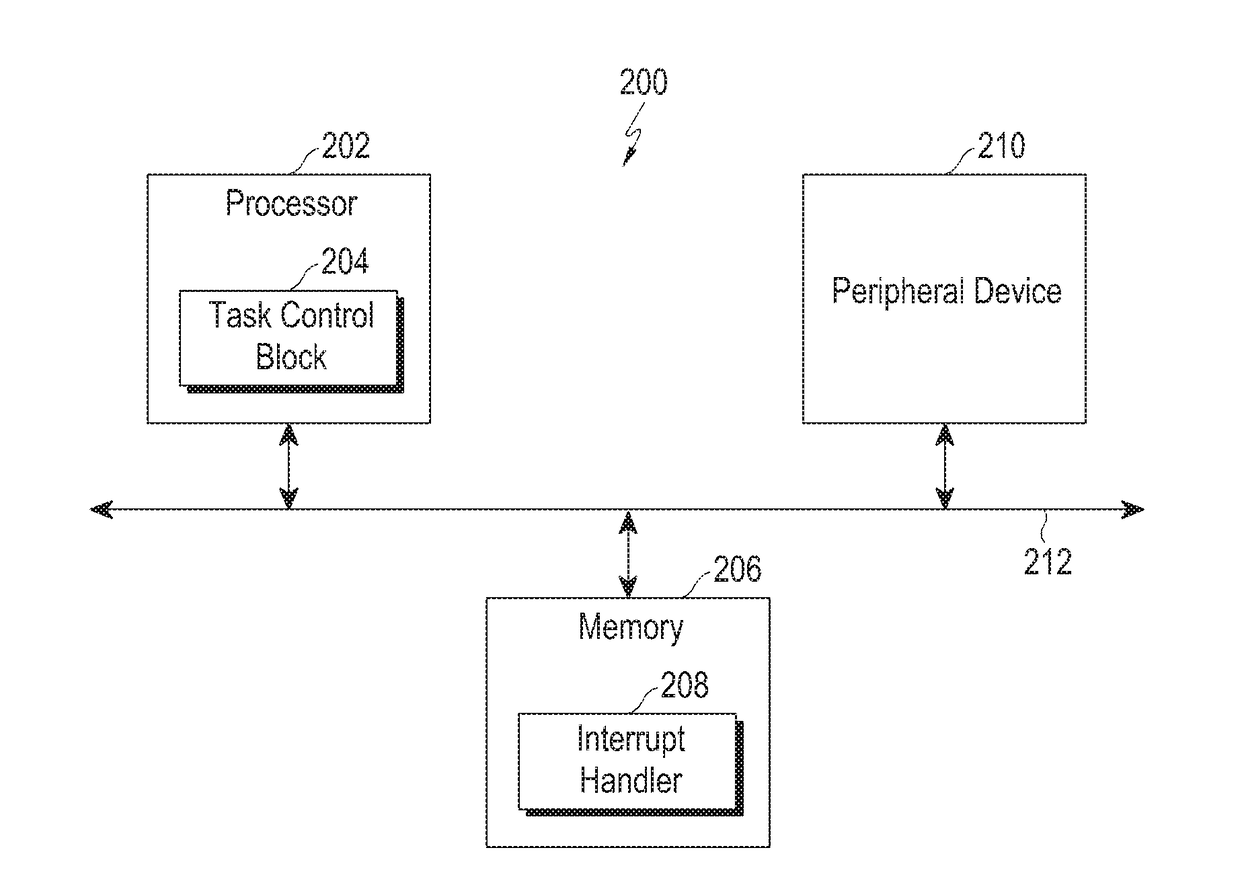

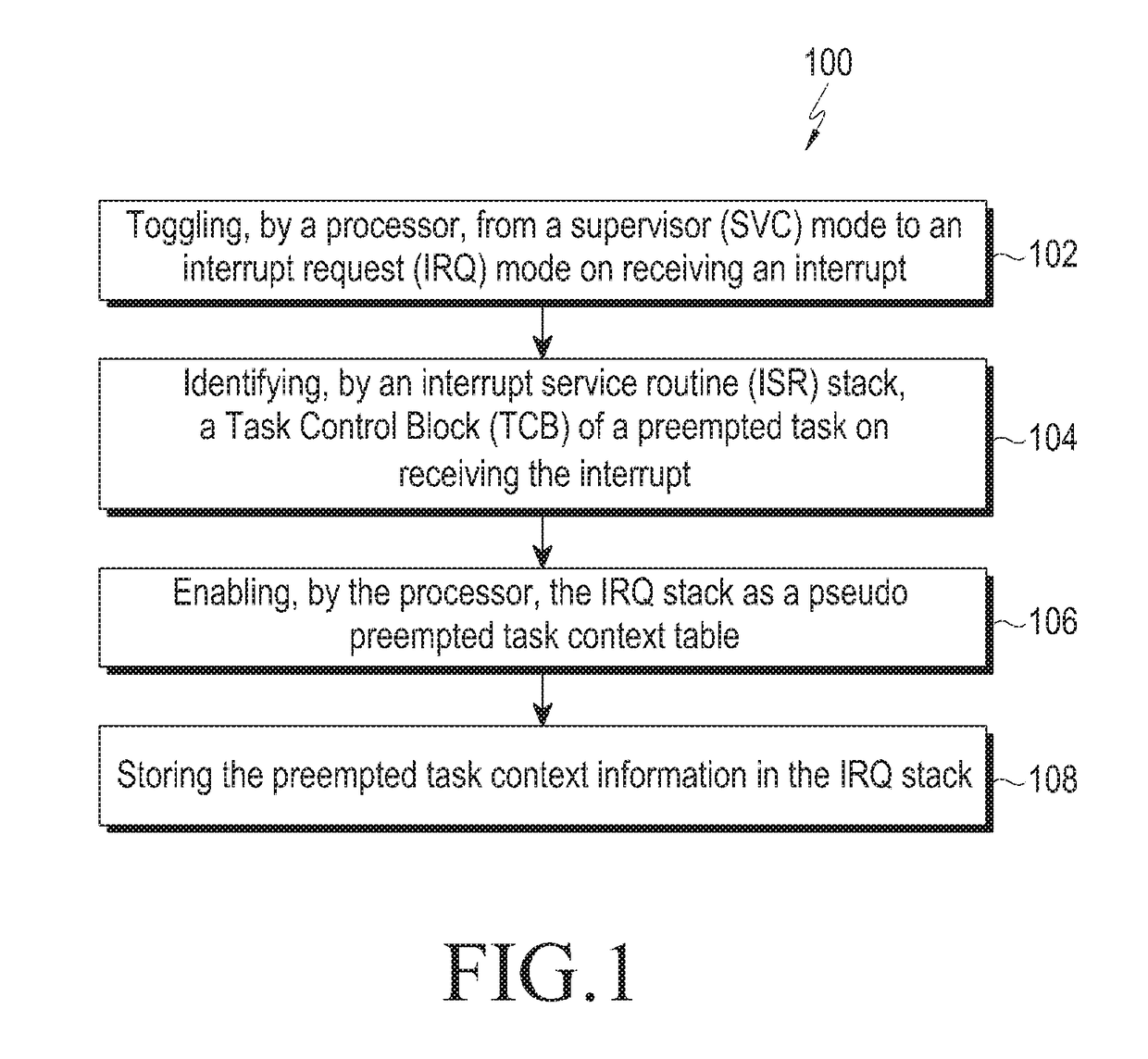

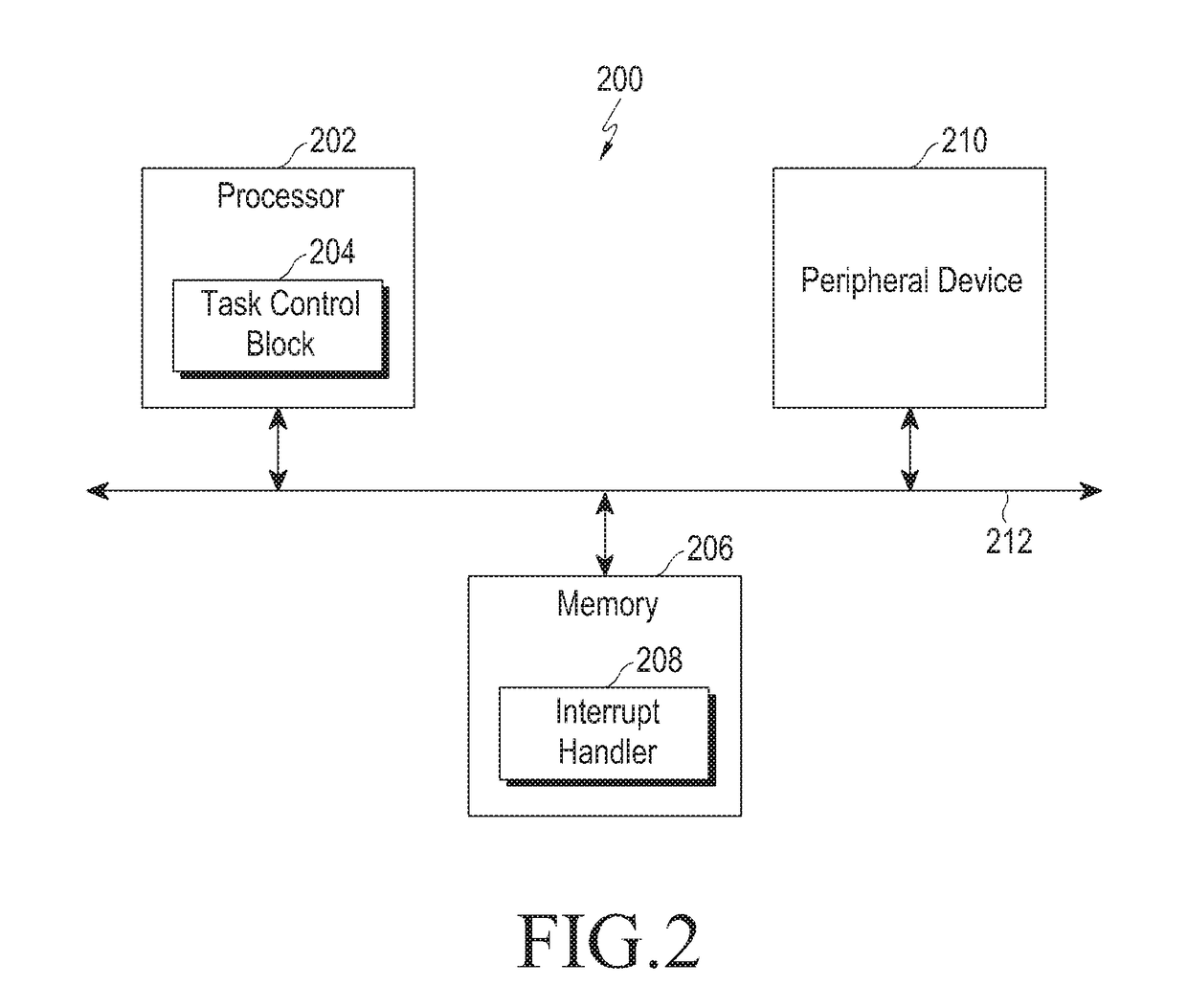

Method for reducing interrupt latency in embedded systems

ActiveUS20180203722A1Reduce Interrupt LatencyProgram initiation/switchingProgram saving/restoringProcessor registerTask control

The various embodiments of the present invention disclose a method for reducing interrupt latency in embedded systems. According to at least one example embodiment of the inventive concepts, the method for reducing interrupt latency in embedded systems, the method comprises steps of toggling, by a processor, from a supervisor (SVC) mode to an interrupt request (IRQ) mode on receiving an interrupt, identifying, by the processor, a Task Control Block (TCB) of a preempted task on receiving the interrupt, enabling, by the processor, the IRQ stack as a pseudo preempted task context table, and storing the preempted task context information in the IRQ stack, wherein a register set is stored in IRQ stack before processing the received interrupt.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com