Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

44 results about "Message Signaled Interrupts" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

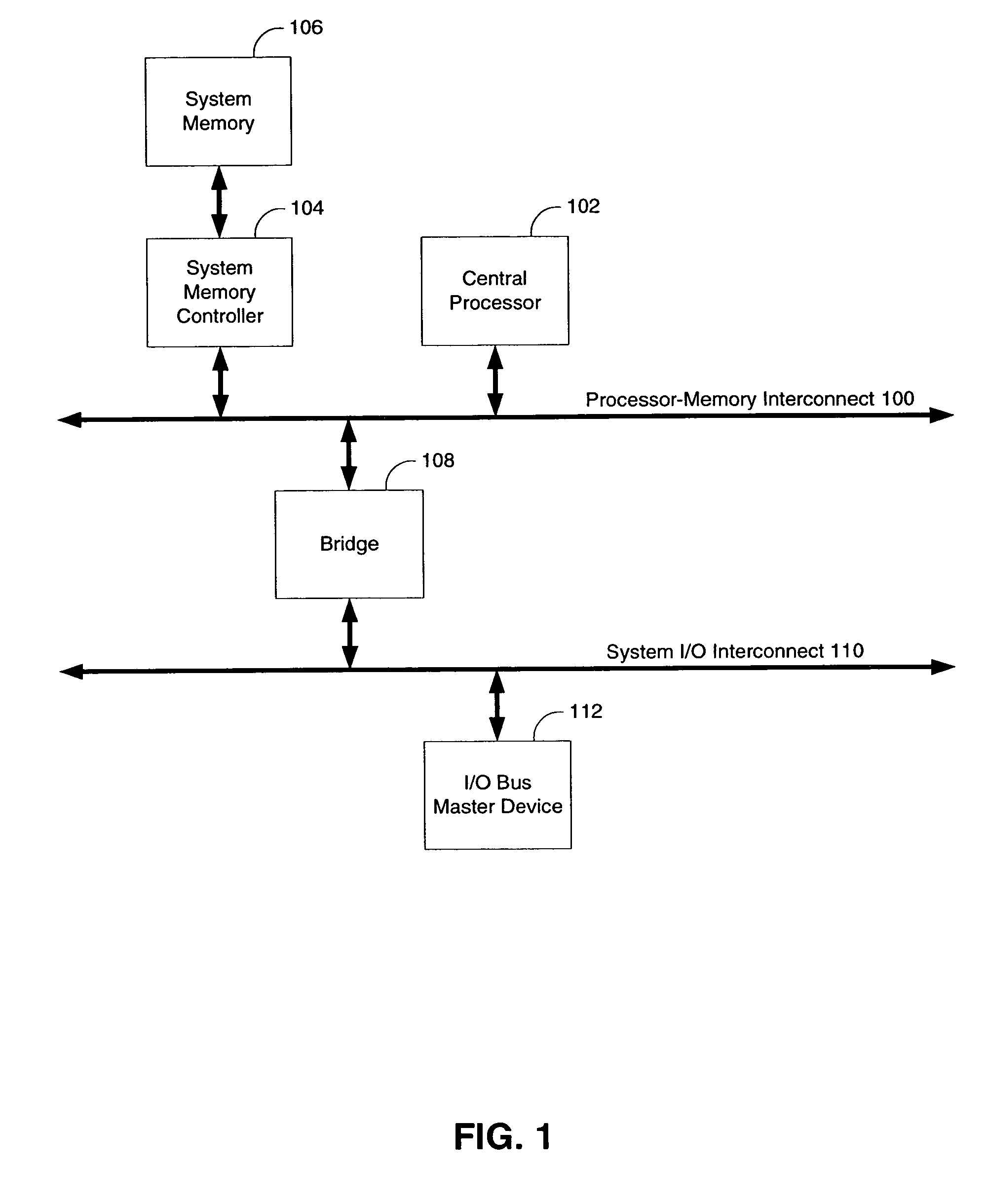

Message Signaled Interrupts (MSI) are an alternative in-band method of signaling an interrupt, using special in-band messages to replace traditional out-of-band assertion of dedicated interrupt lines. While more complex to implement in a device, message signaled interrupts have some significant advantages over pin-based out-of-band interrupt signaling.

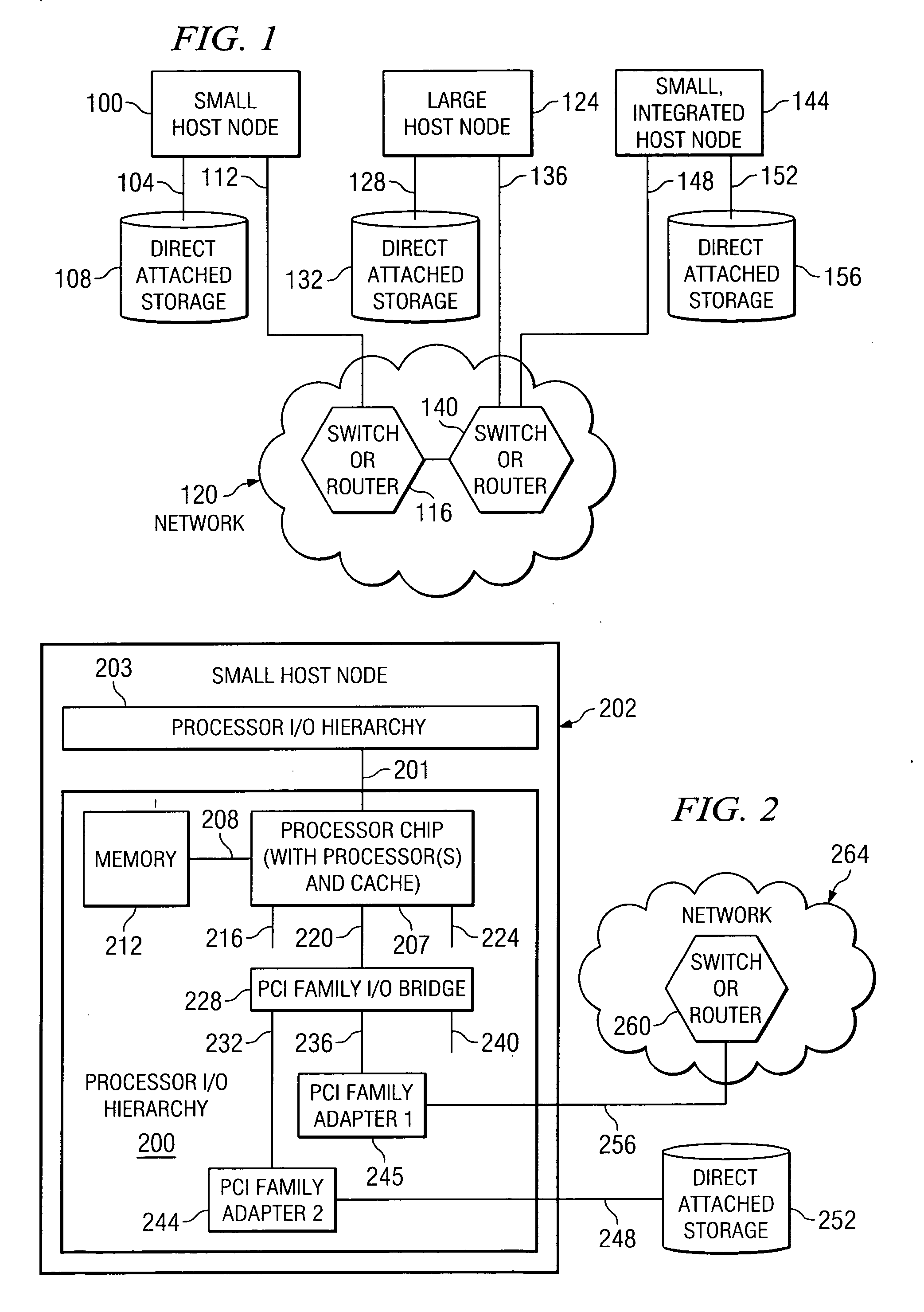

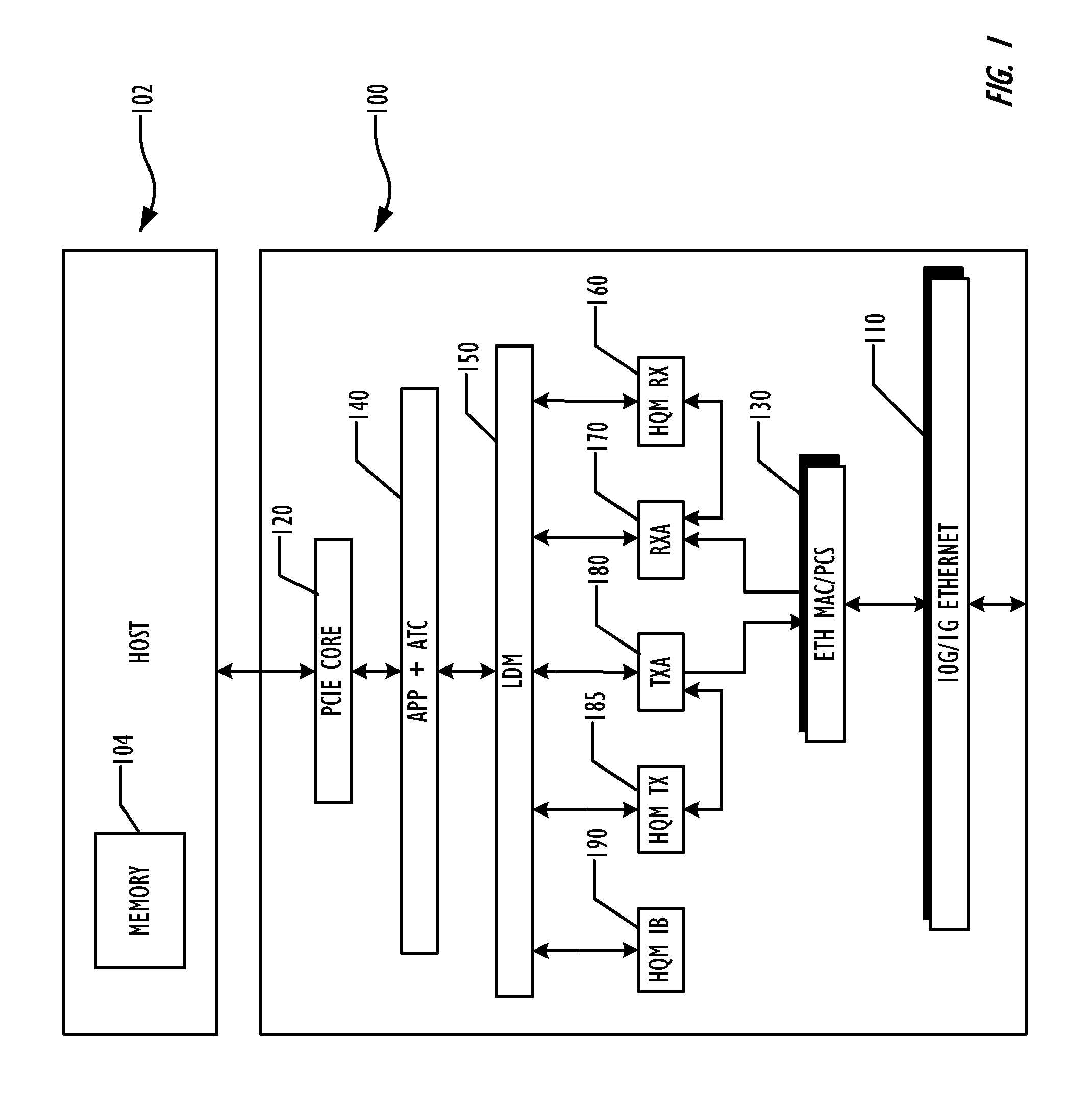

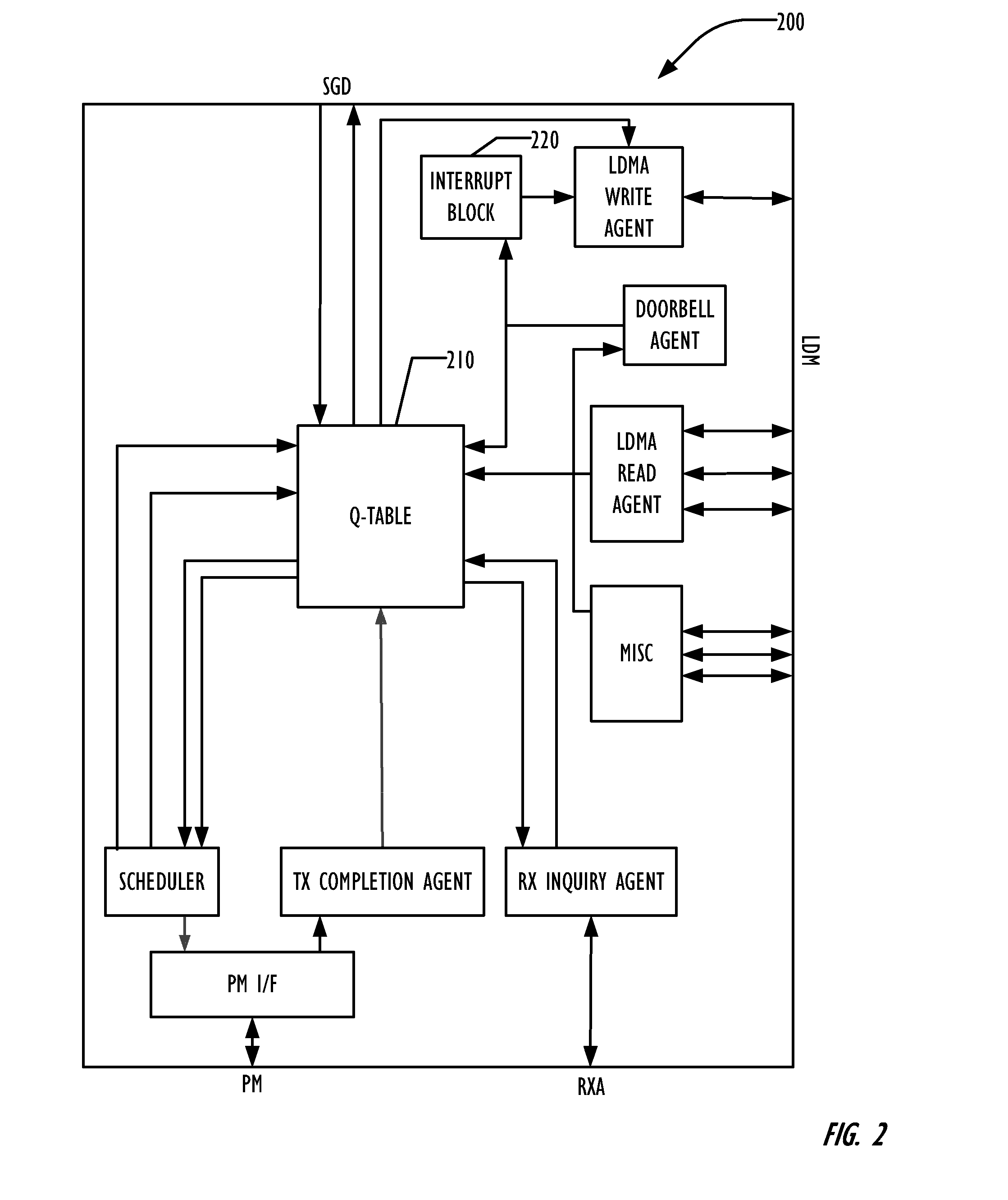

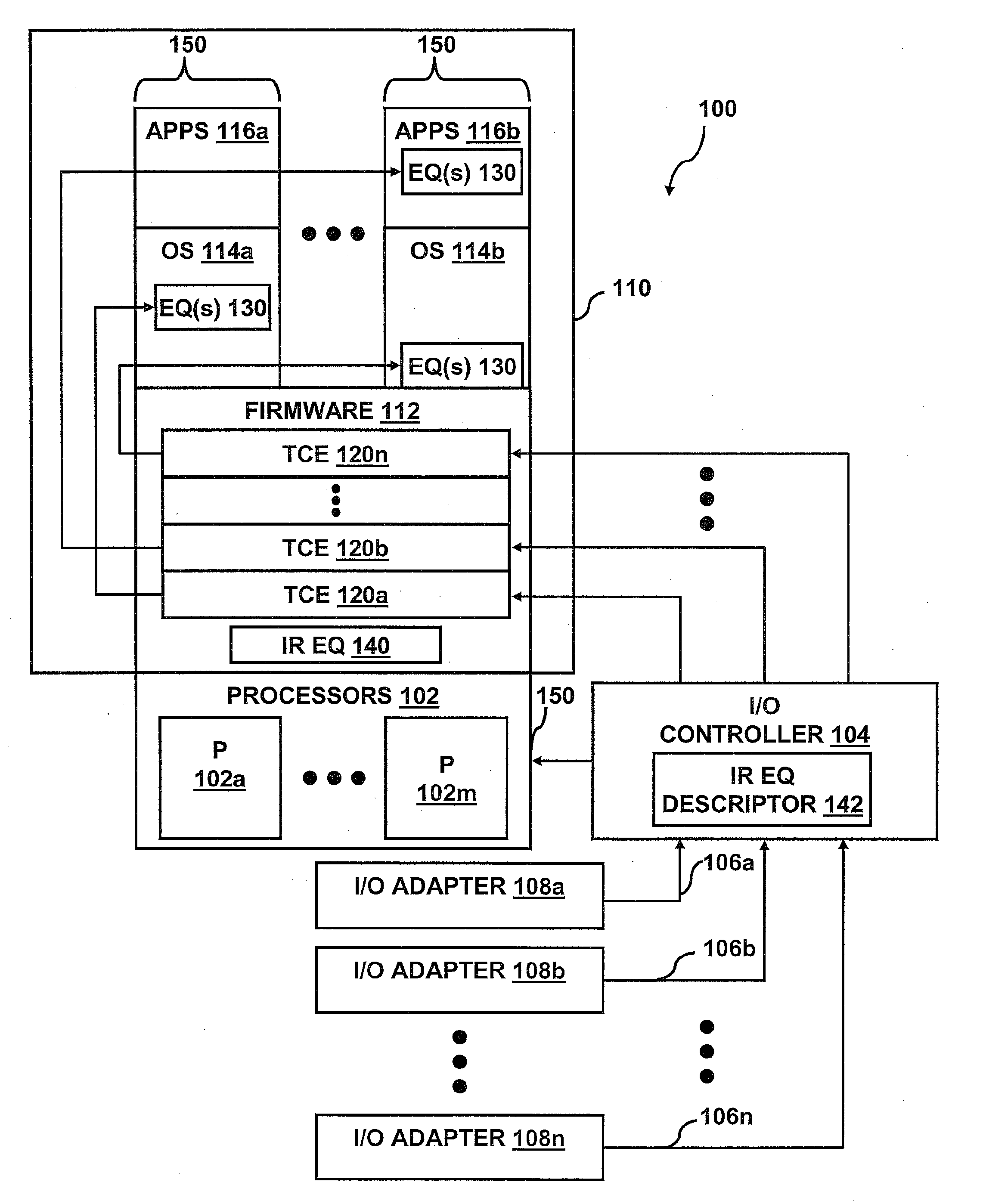

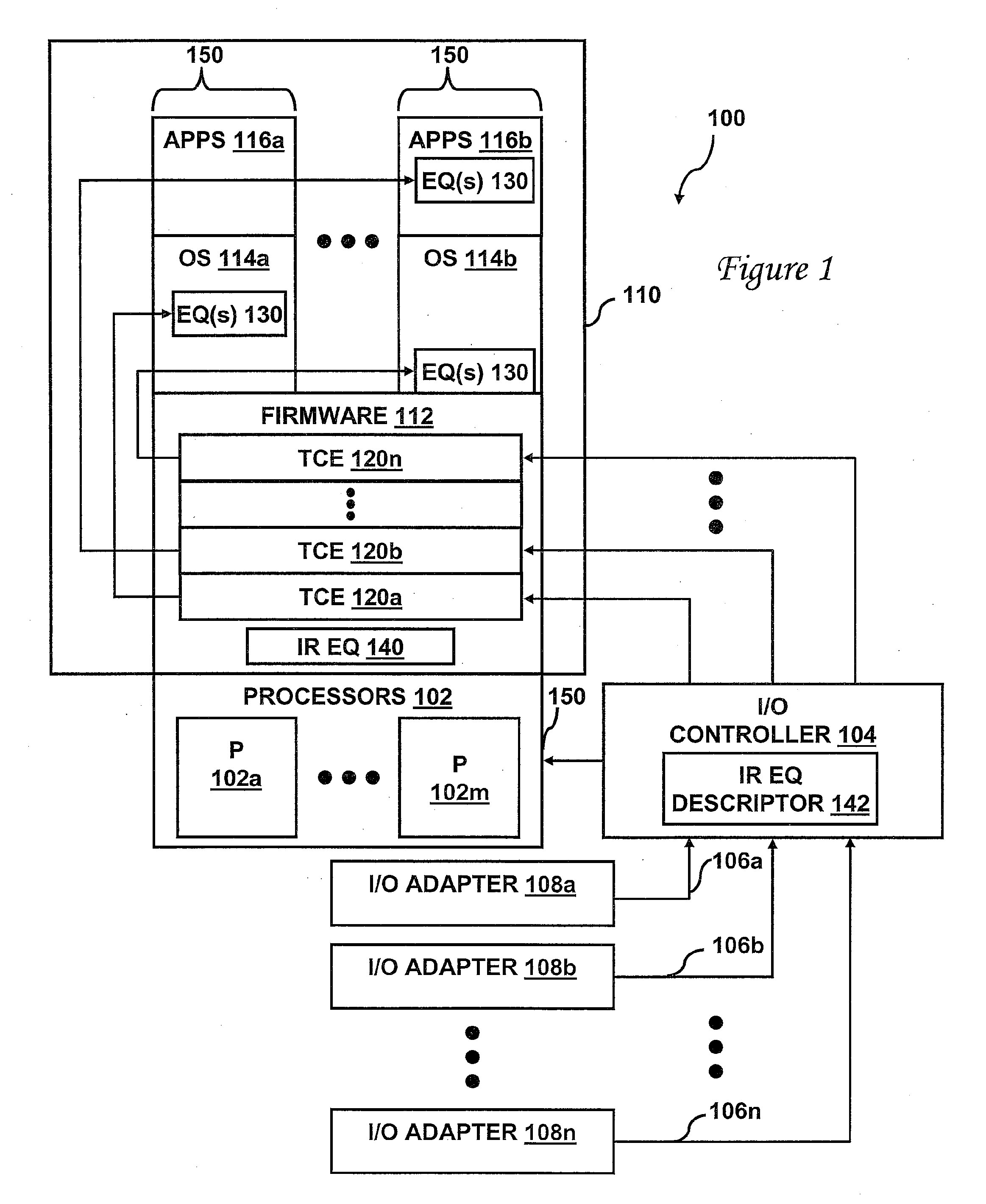

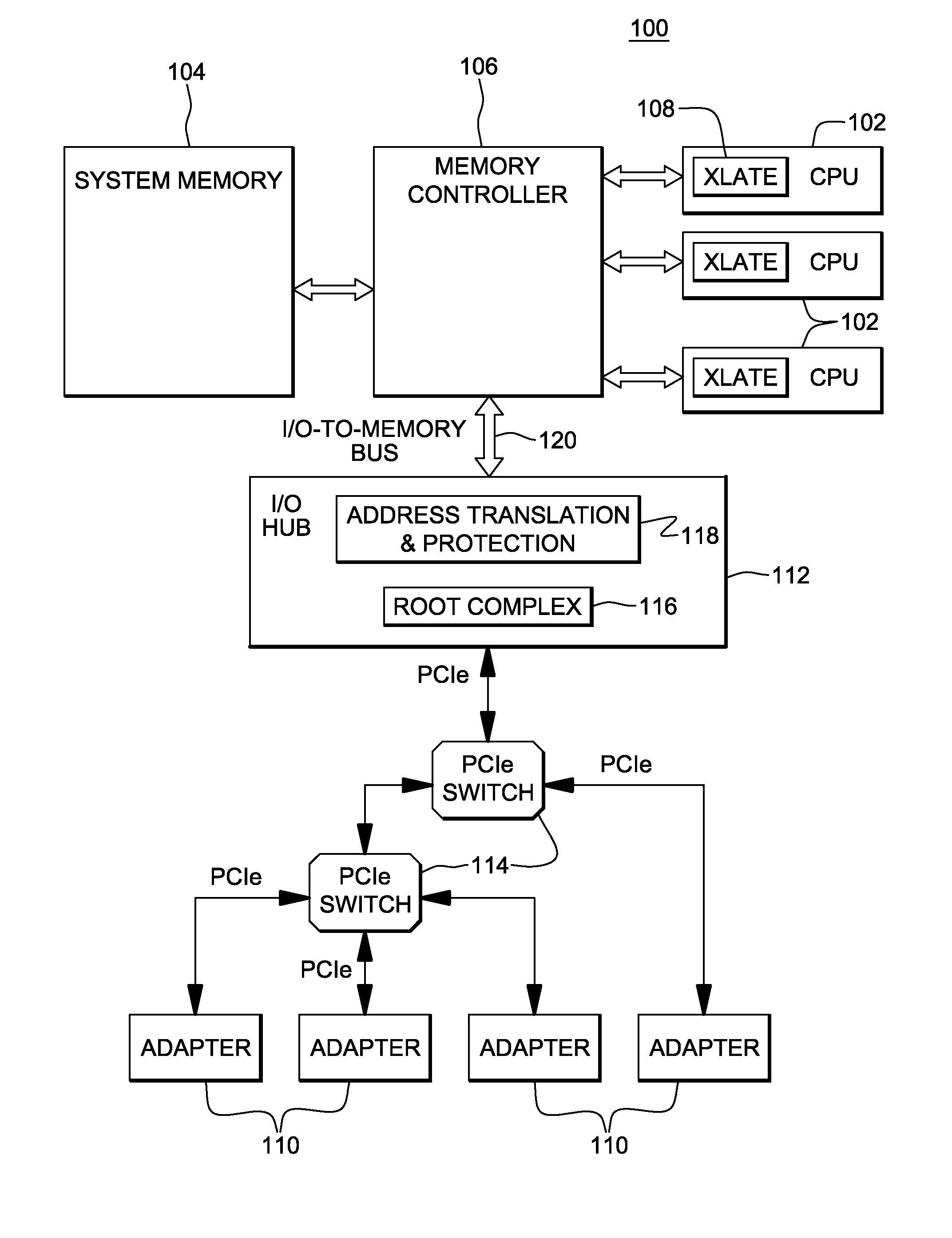

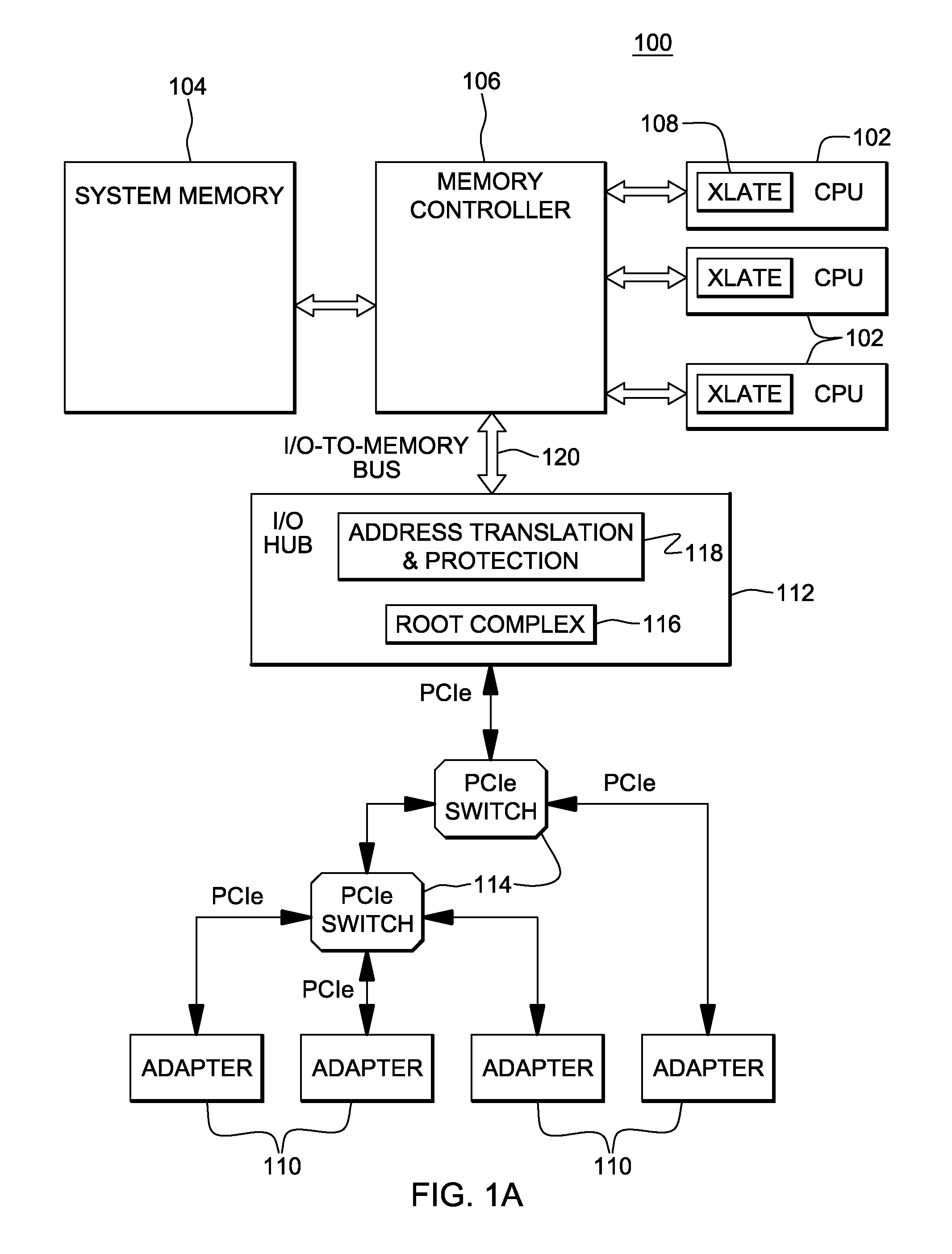

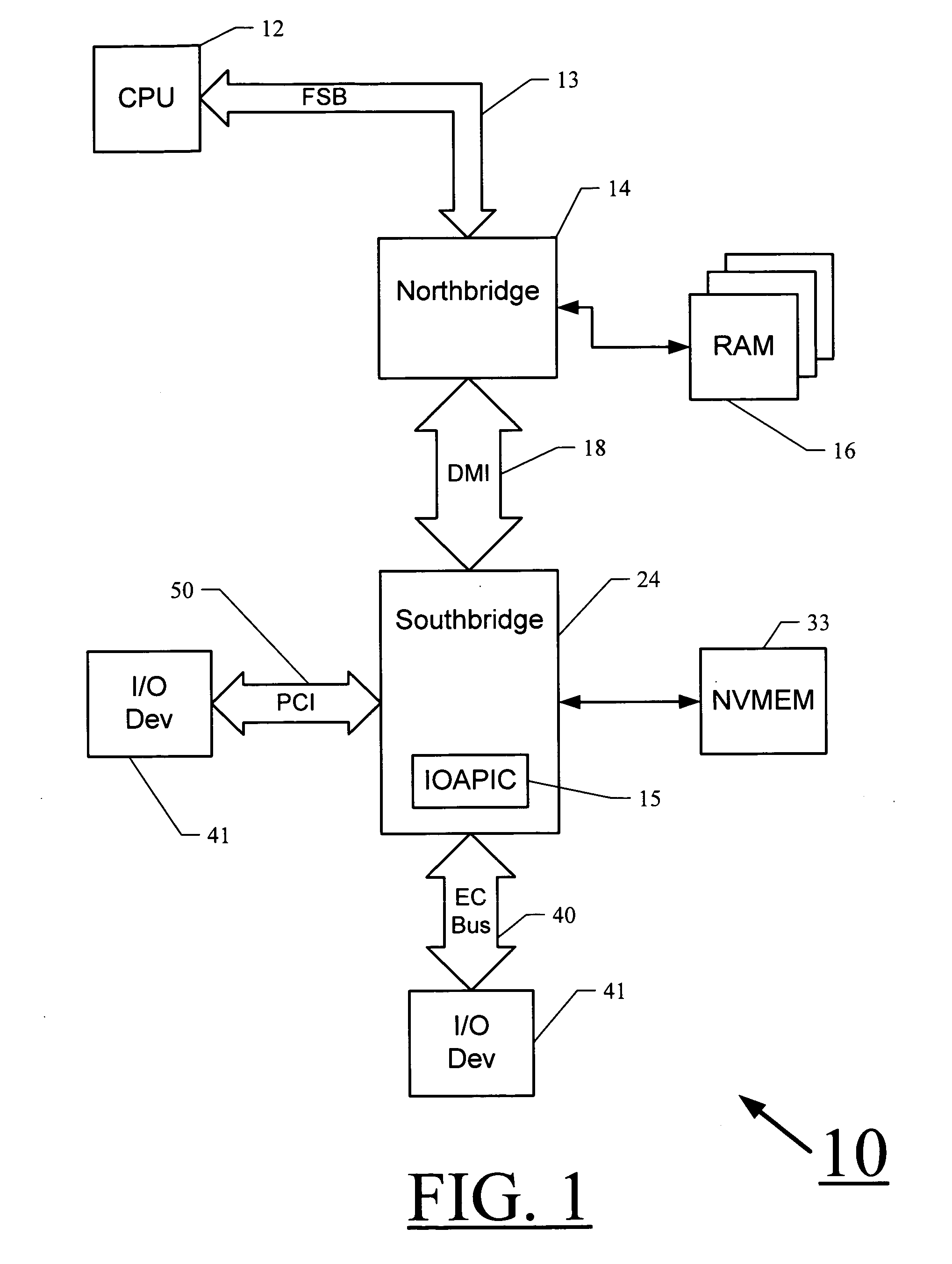

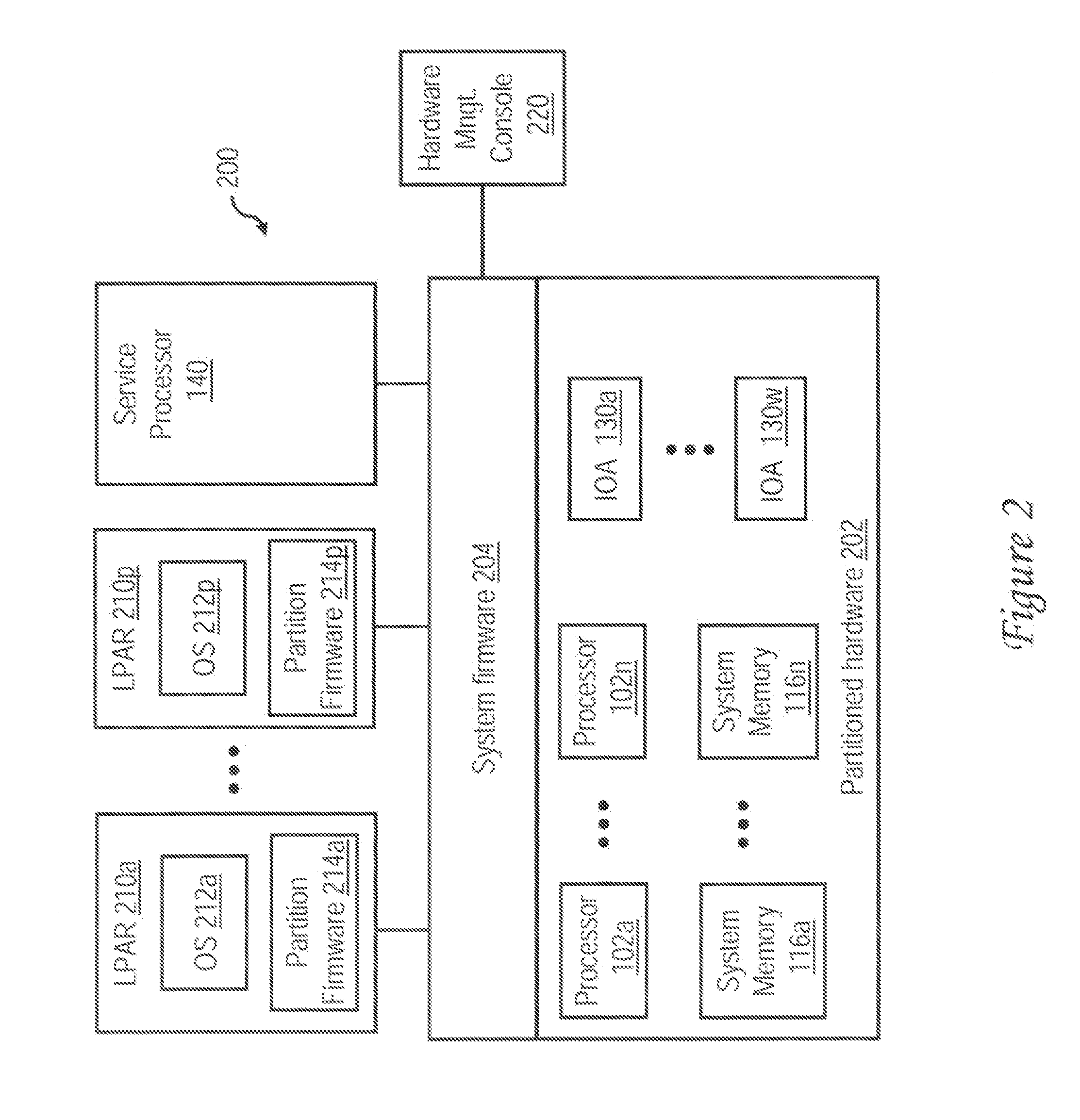

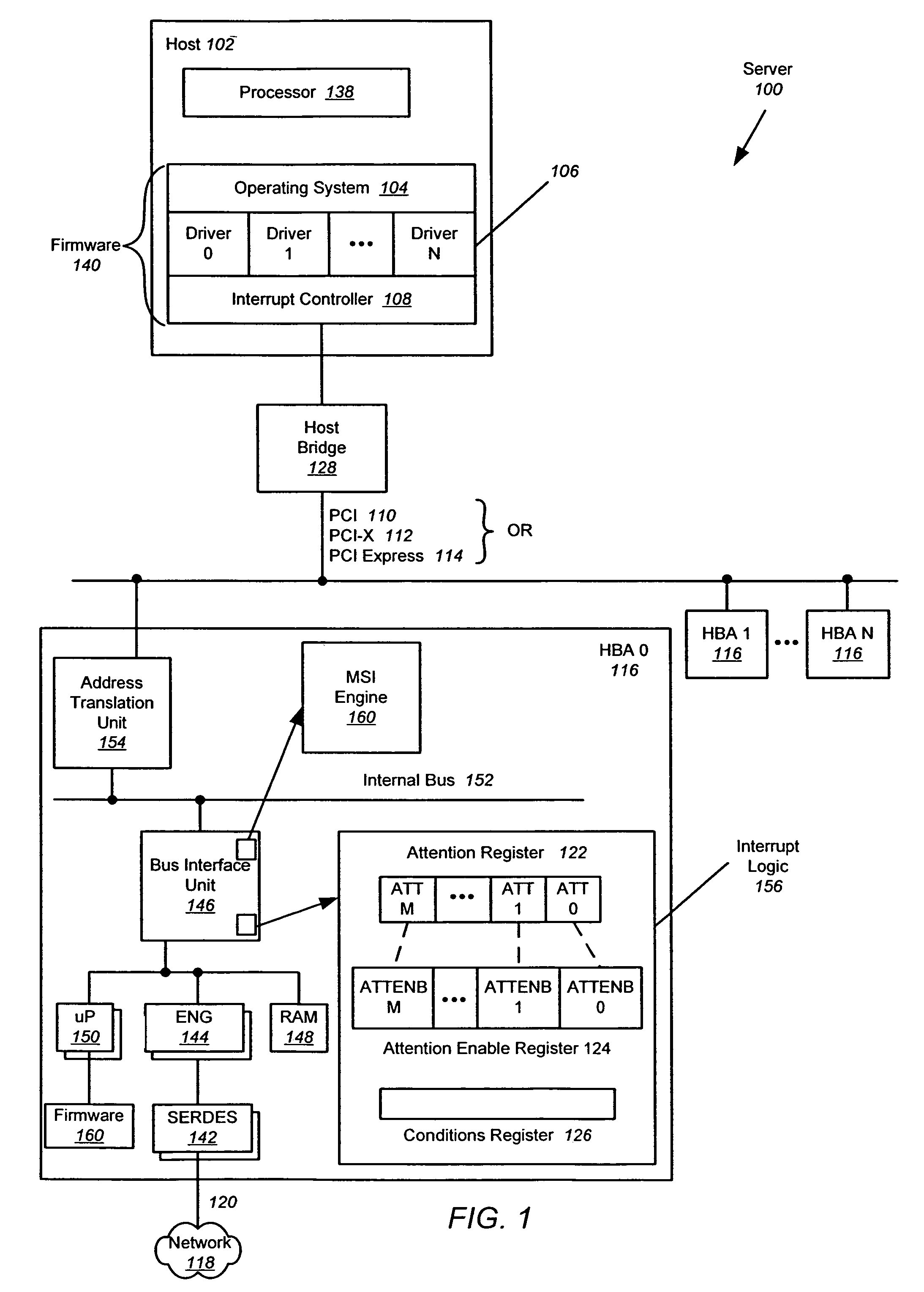

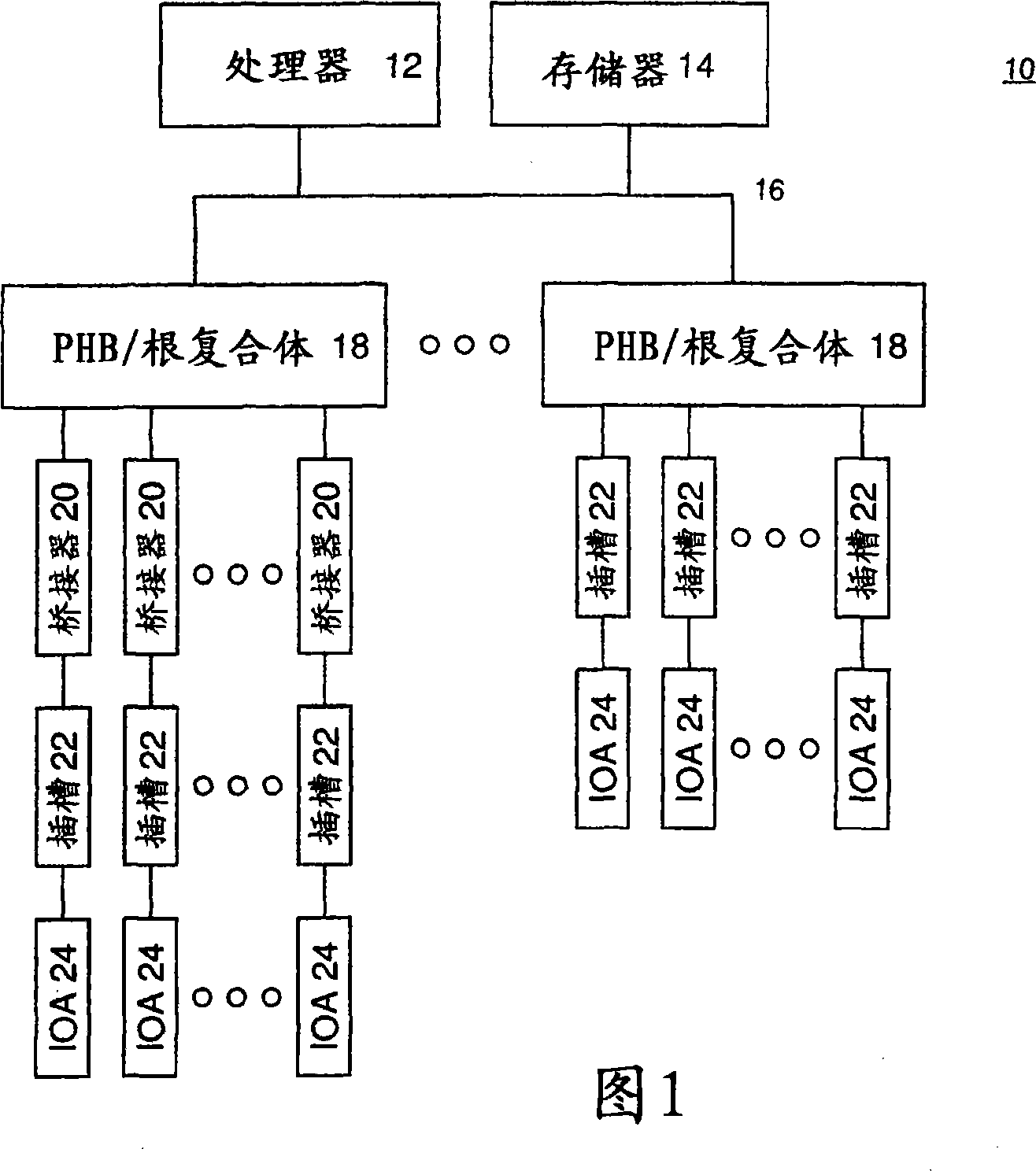

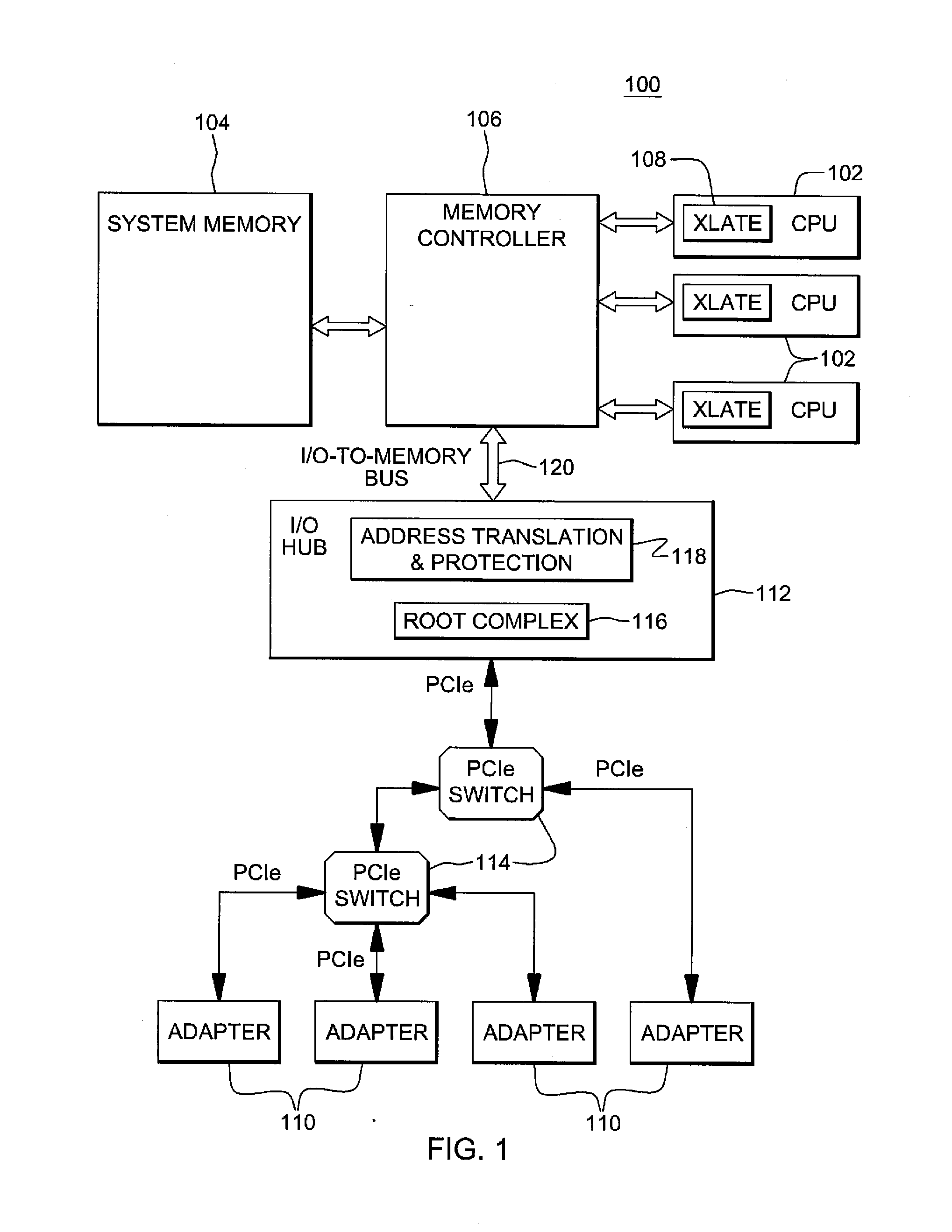

Virtualized I/O adapter for a multi-processor data processing system

InactiveUS20060195663A1Unauthorized memory use protectionGeneral purpose stored program computerData processing systemSCSI

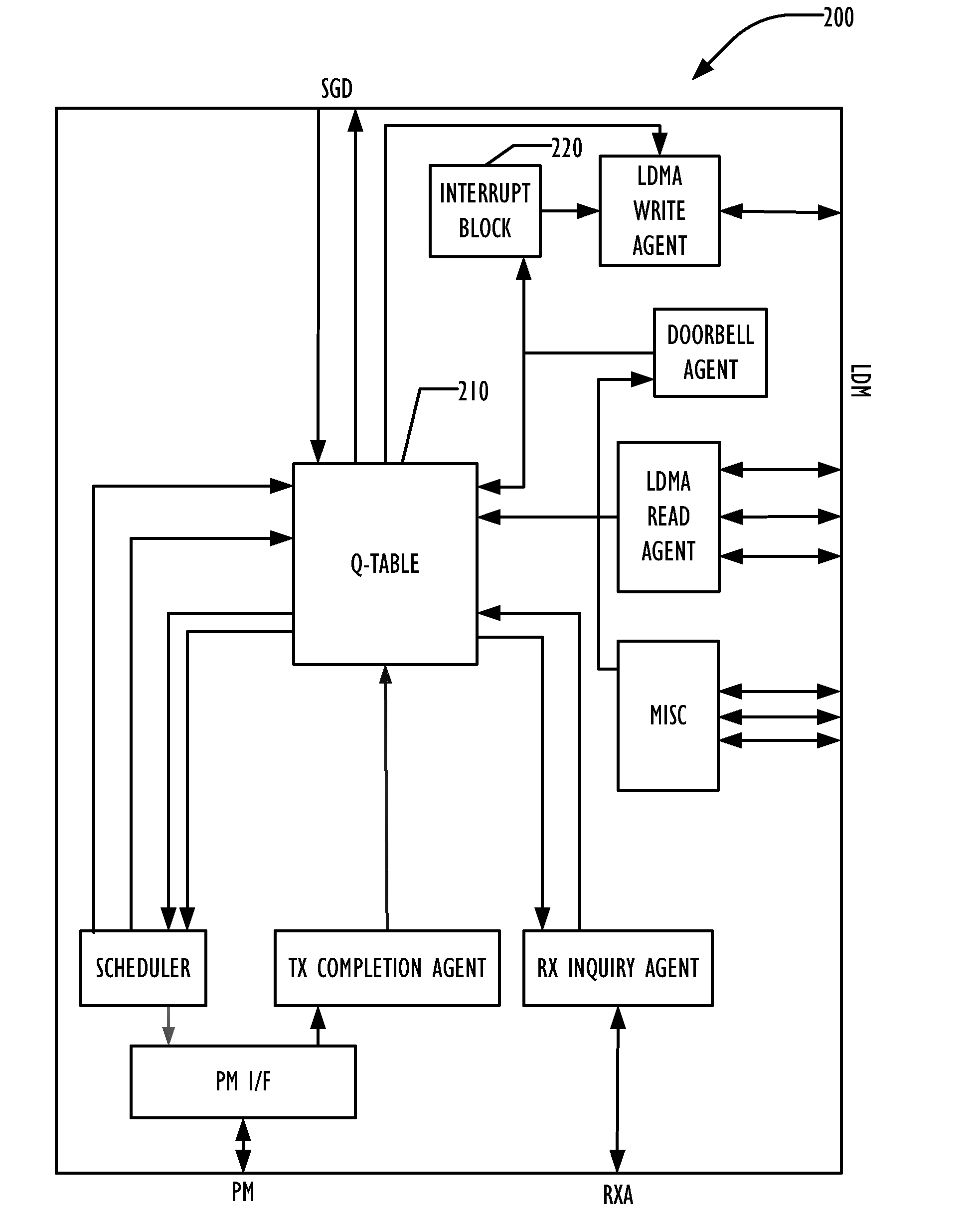

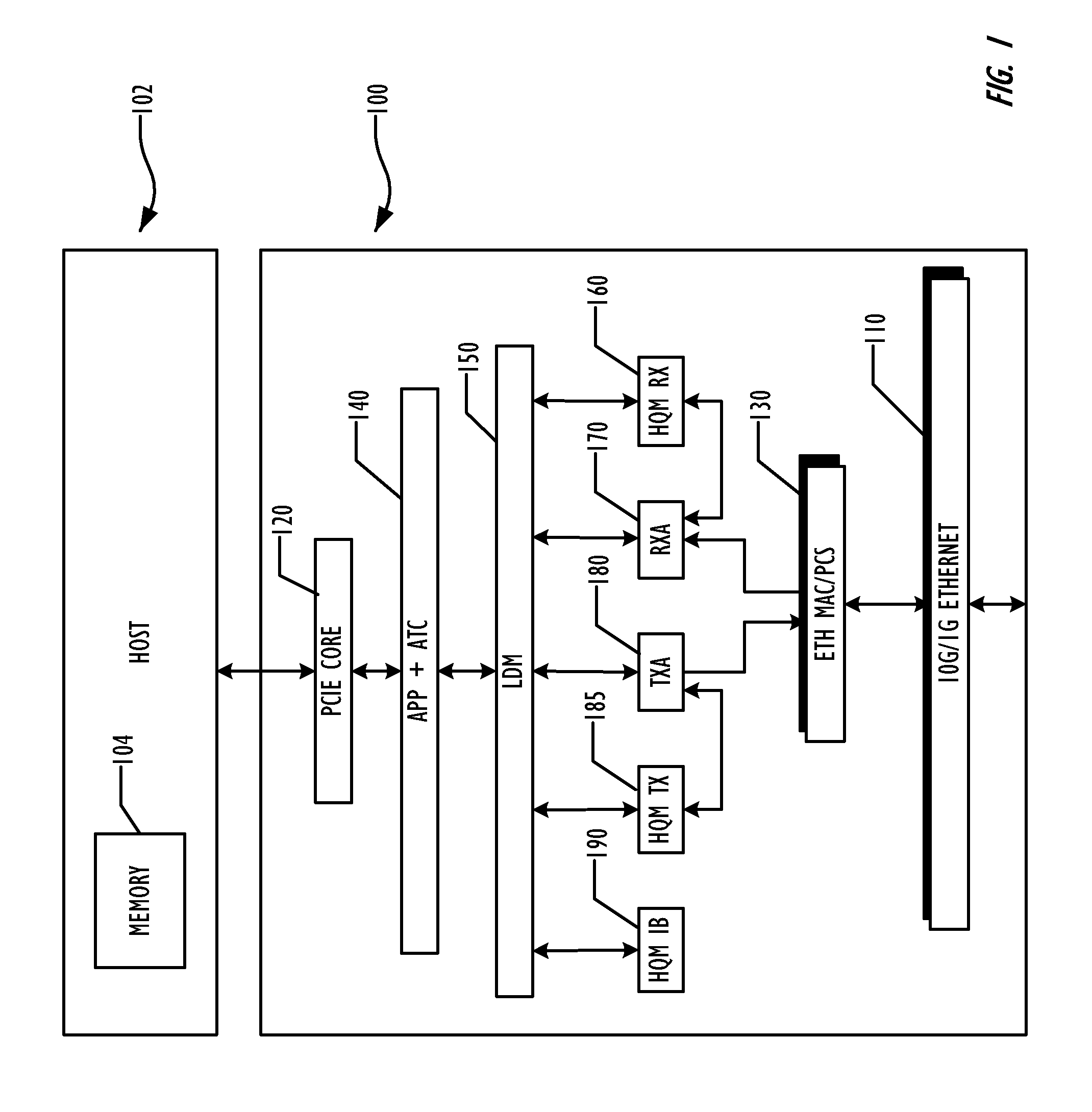

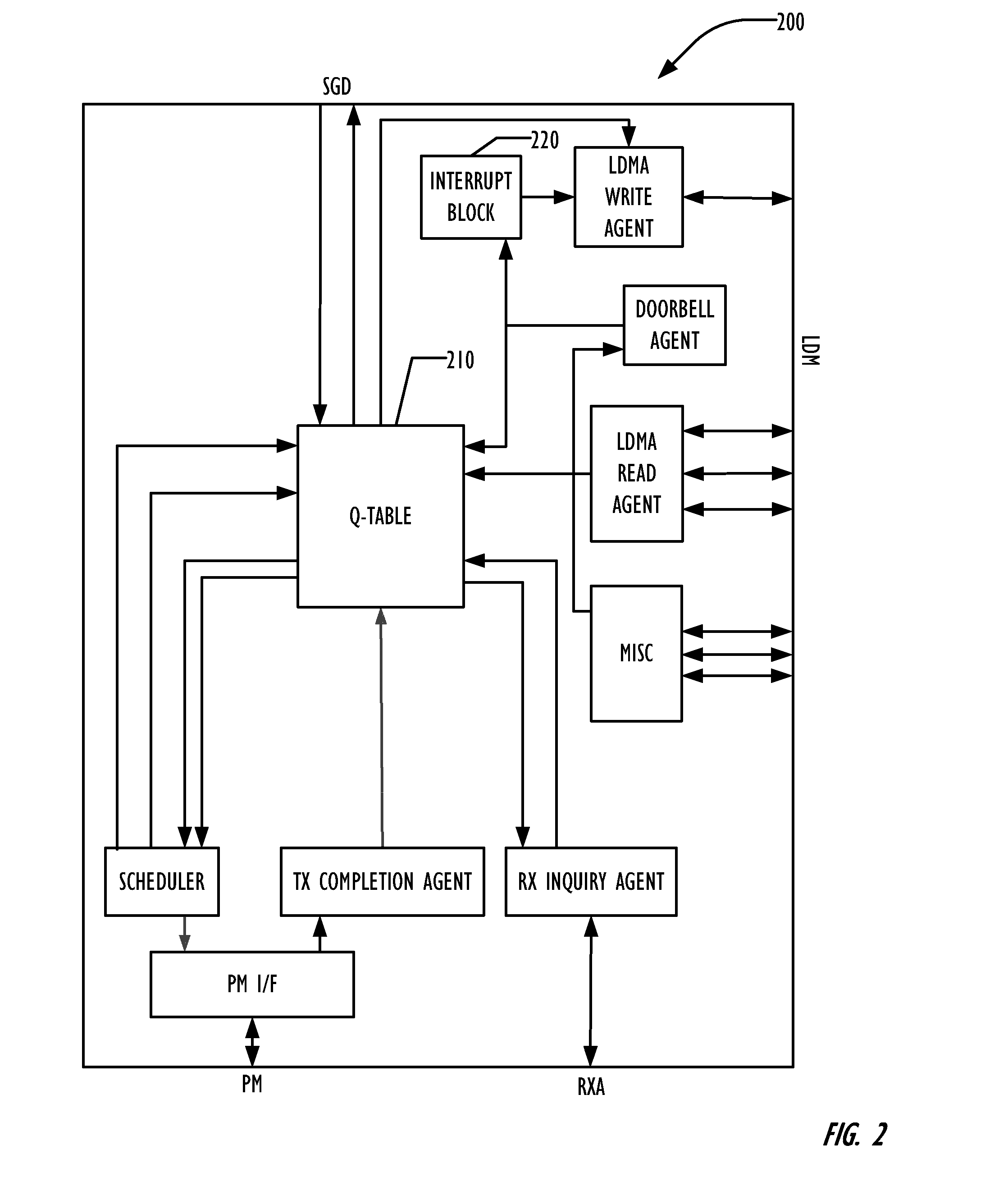

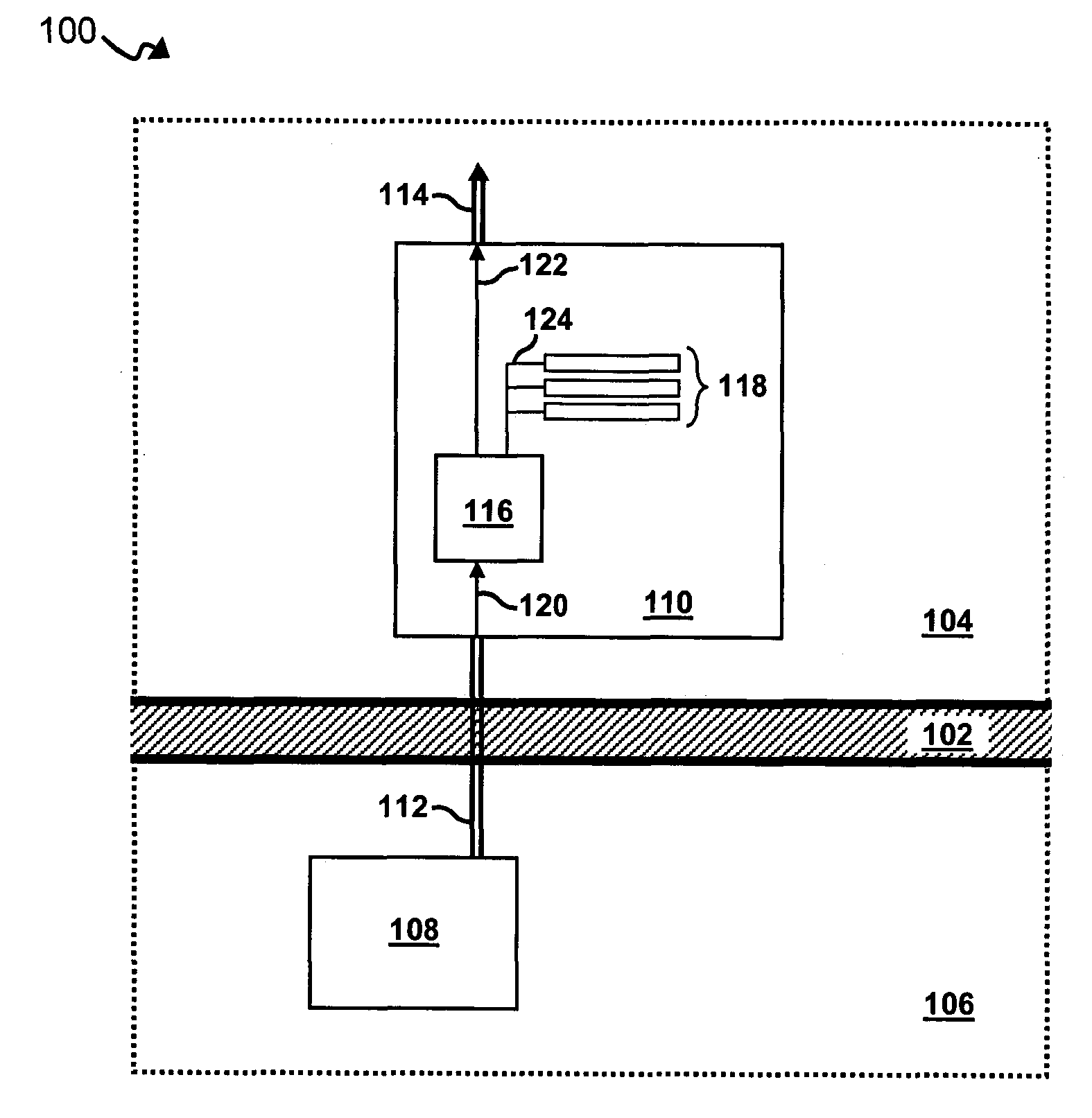

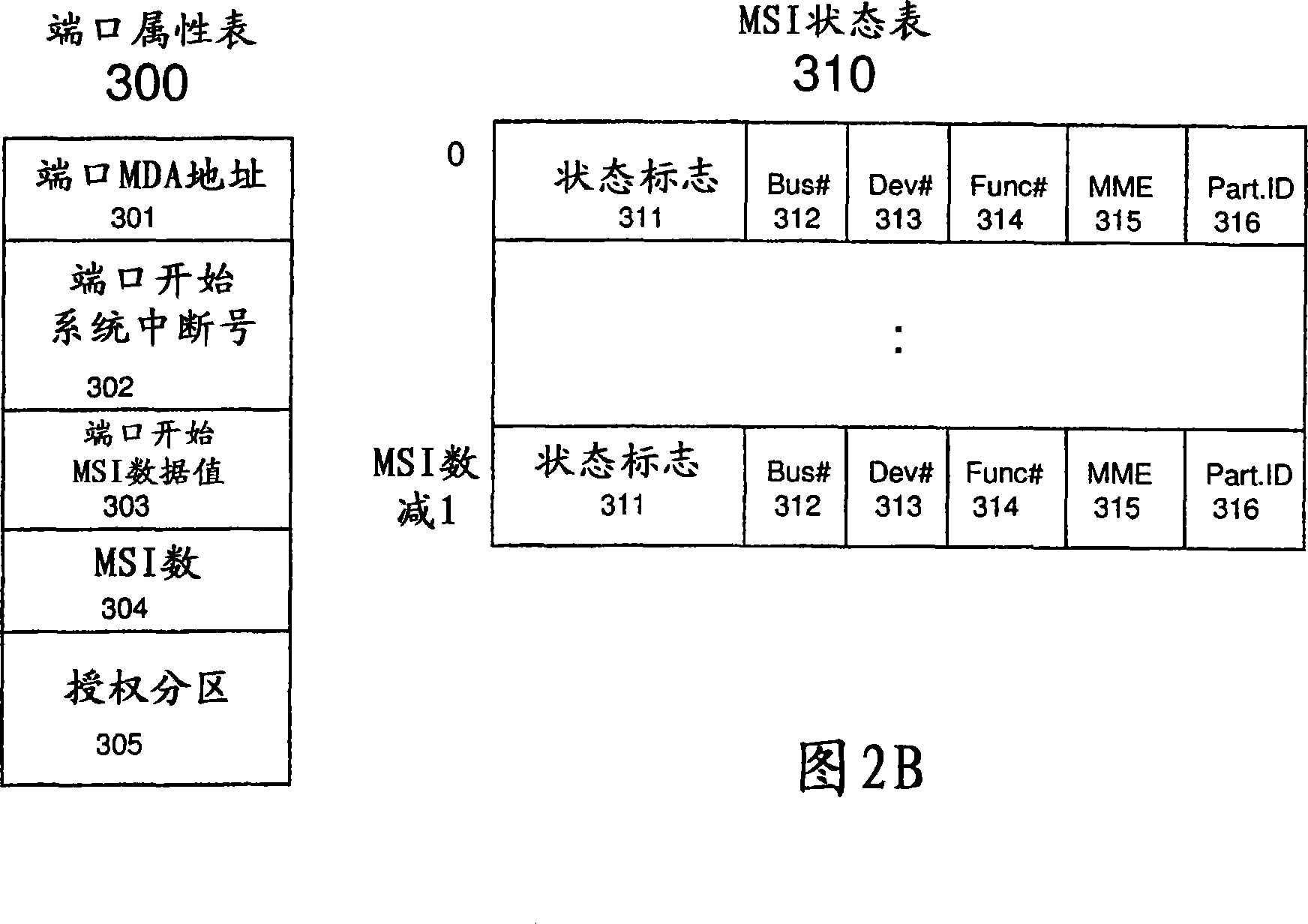

An enhanced SCSI storage adapter with multiple queues for use by different server processors or partitions. For a non-partitioned server, the operating system (OS) owns the SCSI storage adapter, controls the adapter queues, both creation of and changes to the queues, and updates the queue table(s) in the storage adapter with queue address information, device list, message signaled interrupt (MSI) information and optional queue priorities. An OS operator can specify that one or more SCSI devices can be accessed by a specific processor or group of processors. The processor or group of processors is given an adapter queue to access the SCSI device or devices. For a partitioned server, one partition, which may be a hosting partition, owns the SCSI storage adapter, controls the adapter queues, both creation of and changes to the queues, and updates the queue table(s) in the storage adapter with queue address information, device list, message signaled interrupt (MSI) information and optional queue priorities. A system operator can assign one or more SCSI devices under a storage adapter to a partition. Each partition that has access to a SCSI device(s) under a SCSI adapter is given an adapter queue to access the device(s).

Owner:IBM CORP

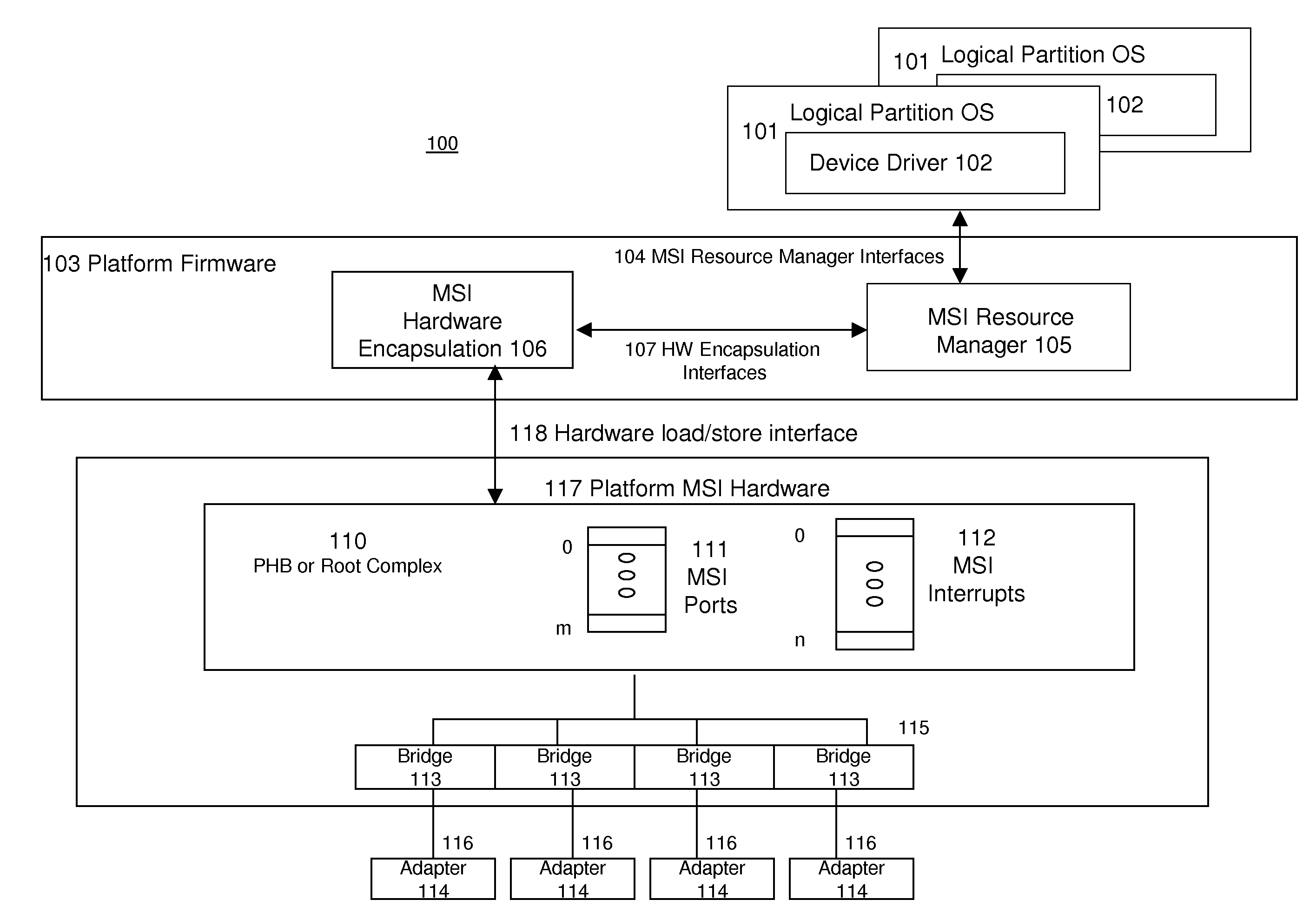

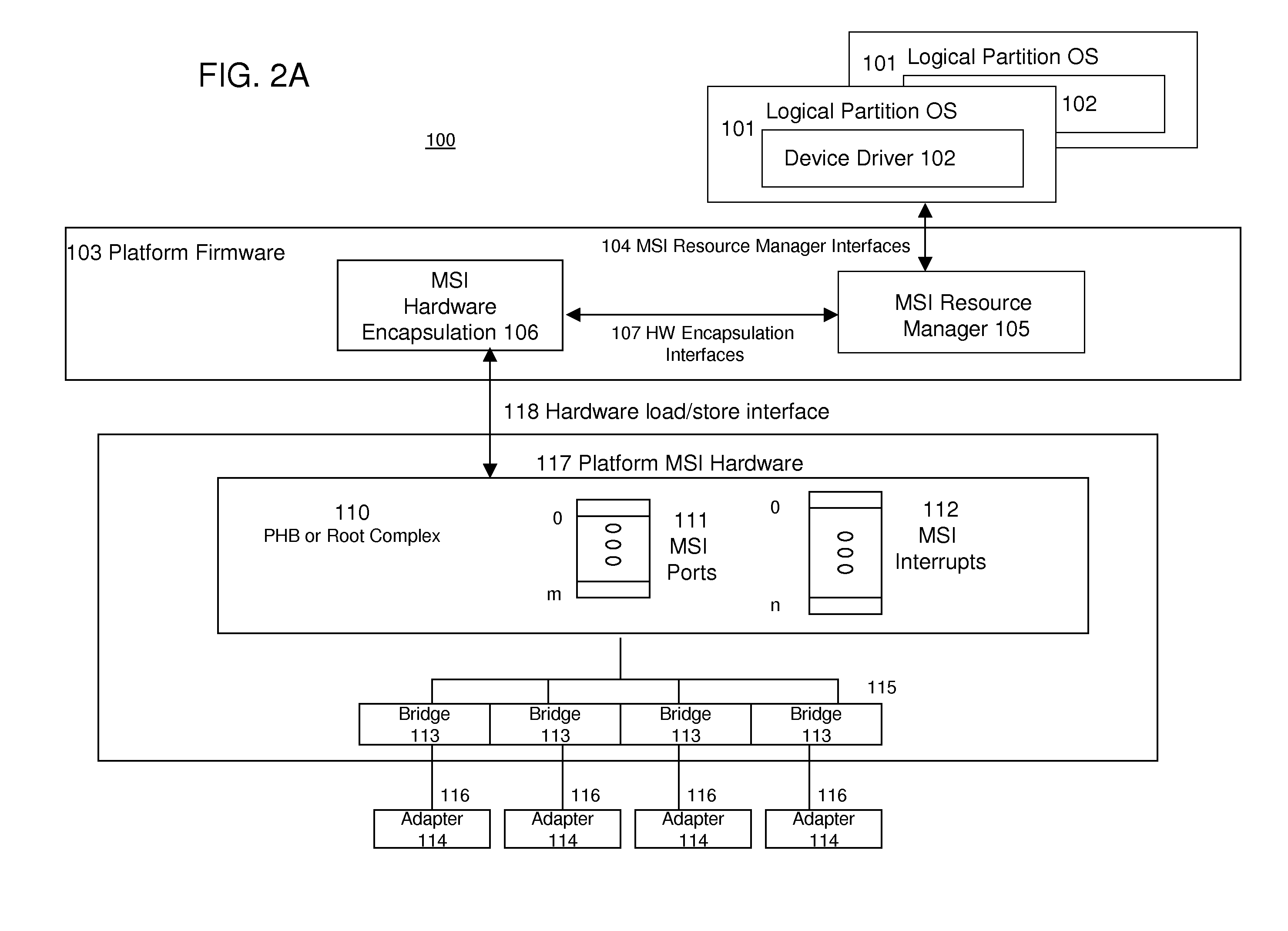

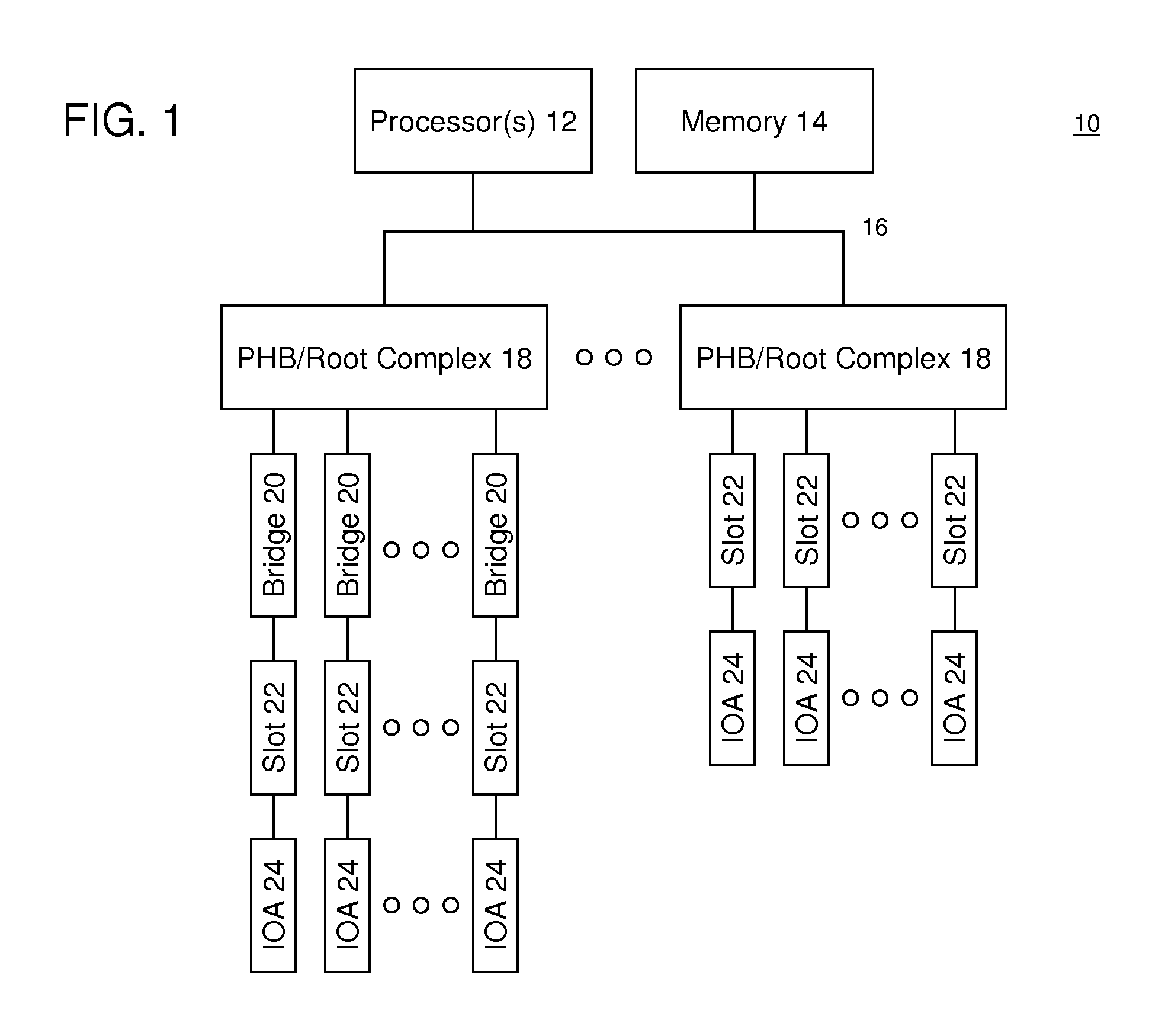

Message Signaled Interrupt Management for a Computer Input/Output Fabric Incorporating Platform Independent Interrupt Manager

ActiveUS20080126648A1Easy to useElectric digital data processingMessage Signaled InterruptsClient-side

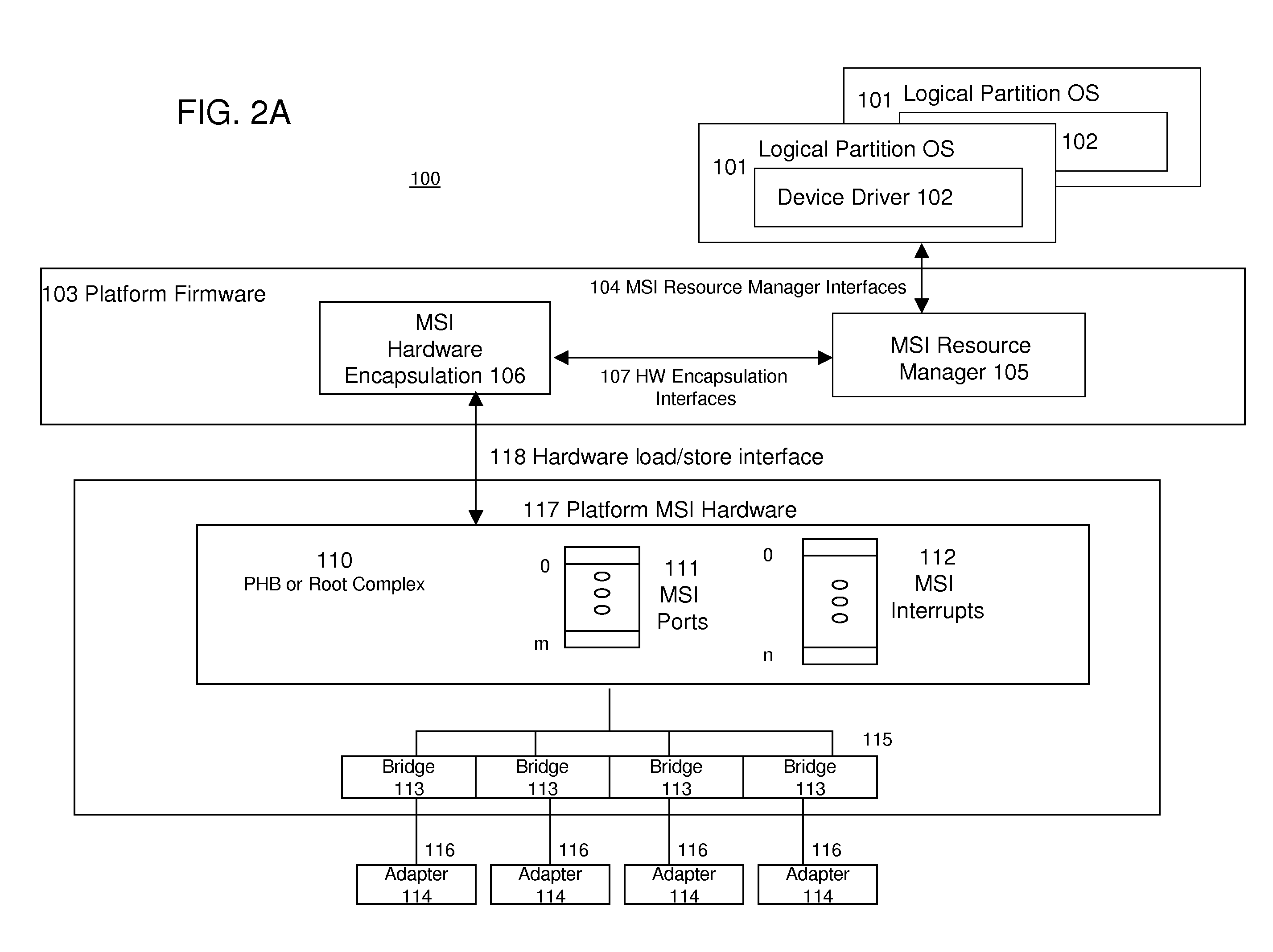

An apparatus, program product and method dynamically bind Message Signaled Interrupt (MSI) resources shared by a plurality of clients to an interrupt facility in an MSI-capable computer. In addition, management of such bindings may be implemented using a platform independent interrupt manager capable of managing multiple MSI bindings between MSI resources to an interrupt facility, and interfaced with an underlying hardware platform of a computer through platform-specific encapsulation program code.

Owner:IBM CORP

Circuitry to selectively produce MSI signals

InactiveUS20050289271A1Electric digital data processingElectrical conductorMessage Signaled Interrupts

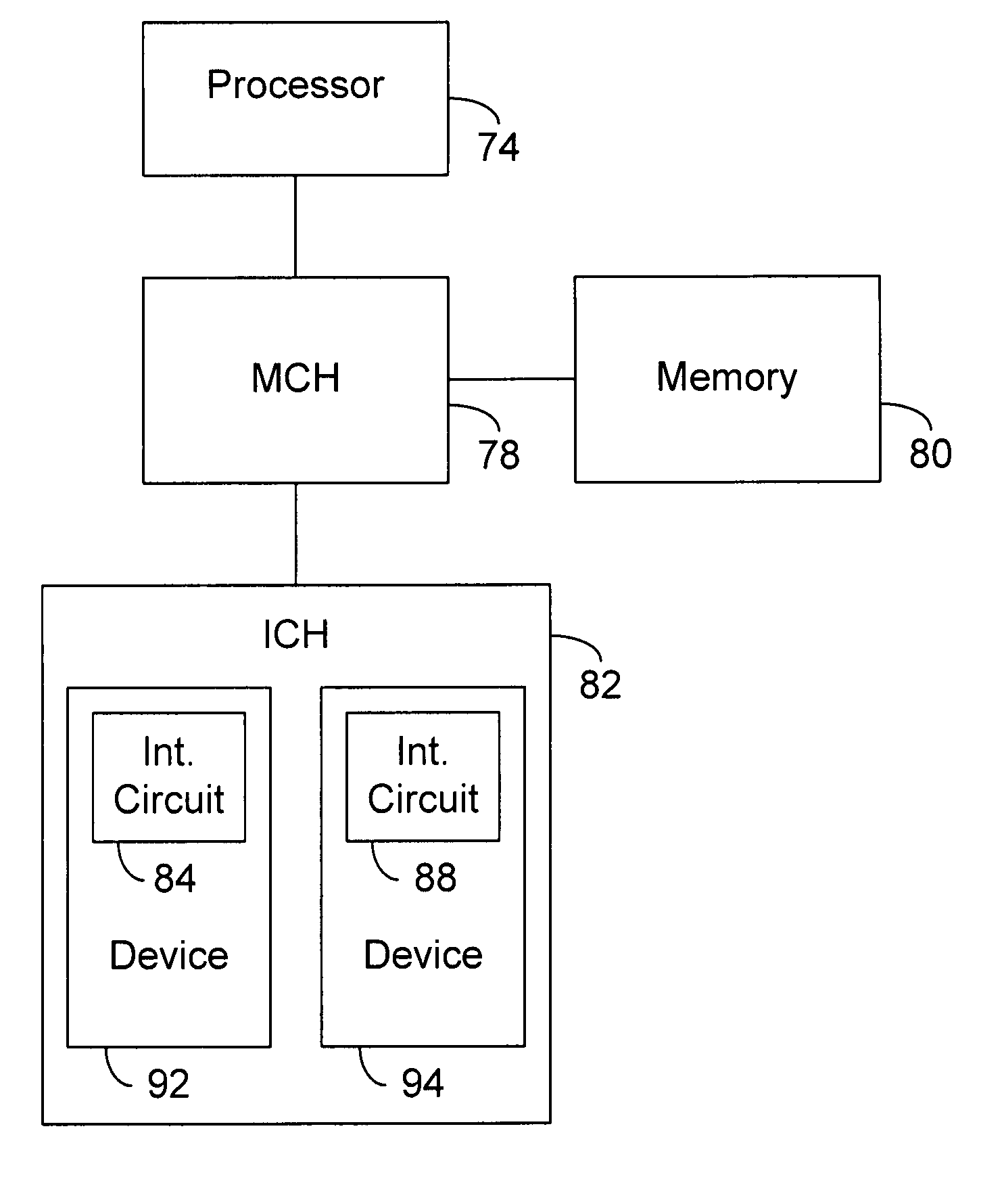

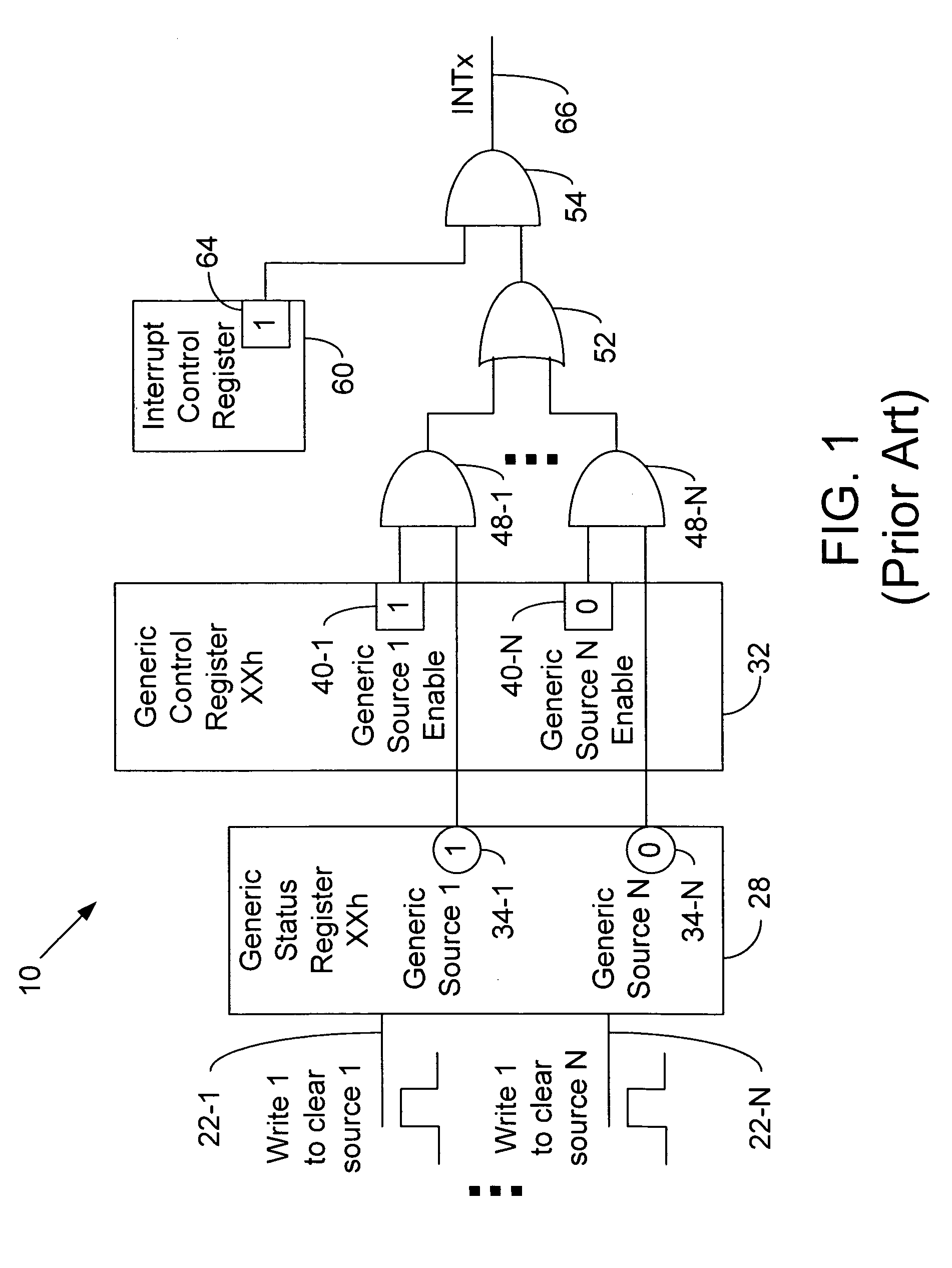

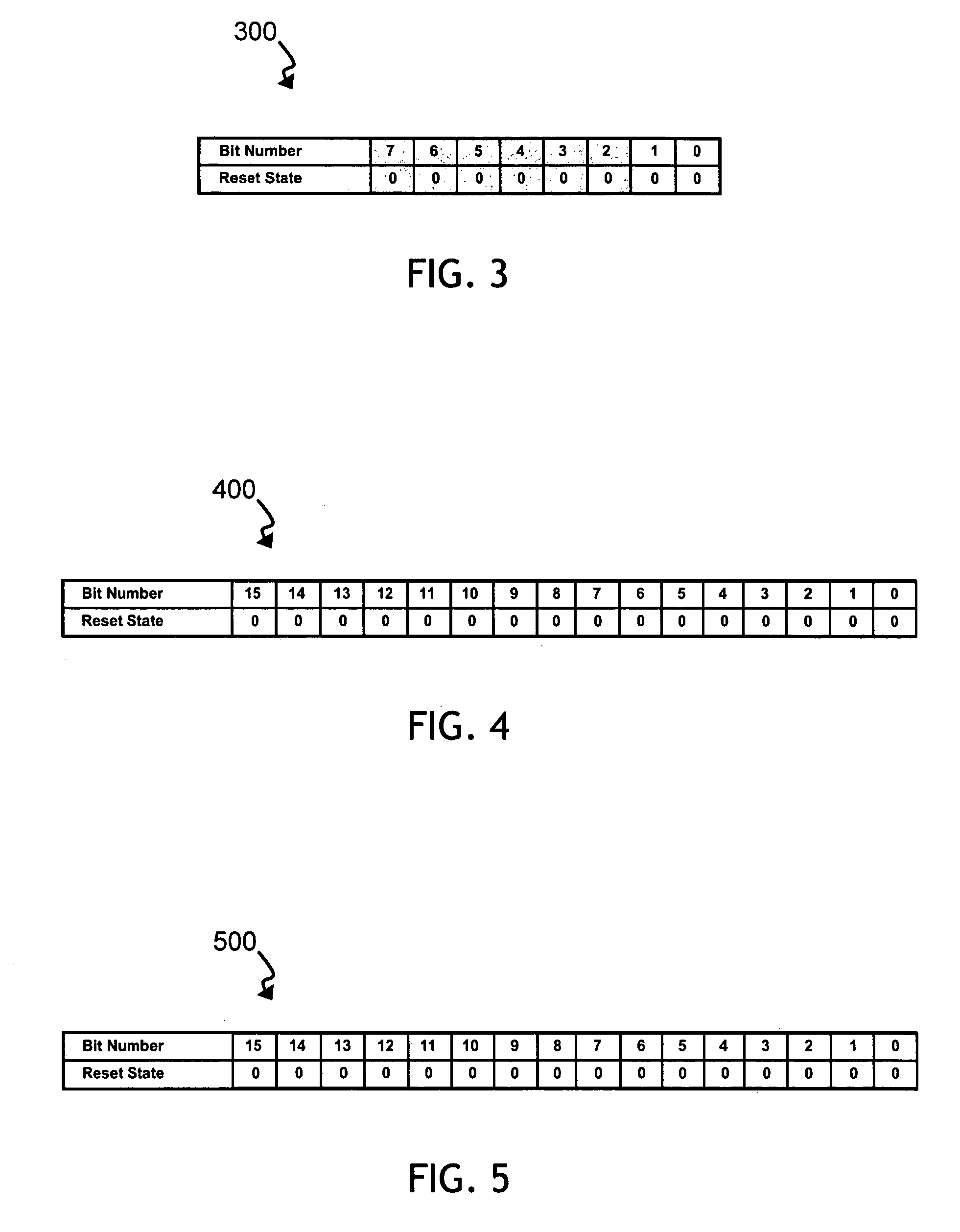

In some embodiments, the inventions include a chip having a status register circuit coupled to conductors to receive interrupt event signals to provide source signals corresponding to the interrupt event signals. The chip also includes a control register circuit to provide source enable signals for selective ones of the interrupt sources, and a re-arming logic circuit coupled to the conductors to receive the interrupt event signals and provide a re-arming signal. The chip further includes first logic circuit to receive the source signals, the source enable signals, and the re-arming signal to provide an initial interrupt signal, and message signaled interrupt (MSI) signal pulse generation logic to receive the initial interrupt signal and provide an MSI signal in response thereto. Other embodiments are described and claimed.

Owner:INTEL CORP

System for signaling serialized interrupts using message signaled interrupts

ActiveUS20050033895A1Expands legacy system support capabilityCost-effectiveElectric digital data processingMessage Signaled InterruptsPCI Express

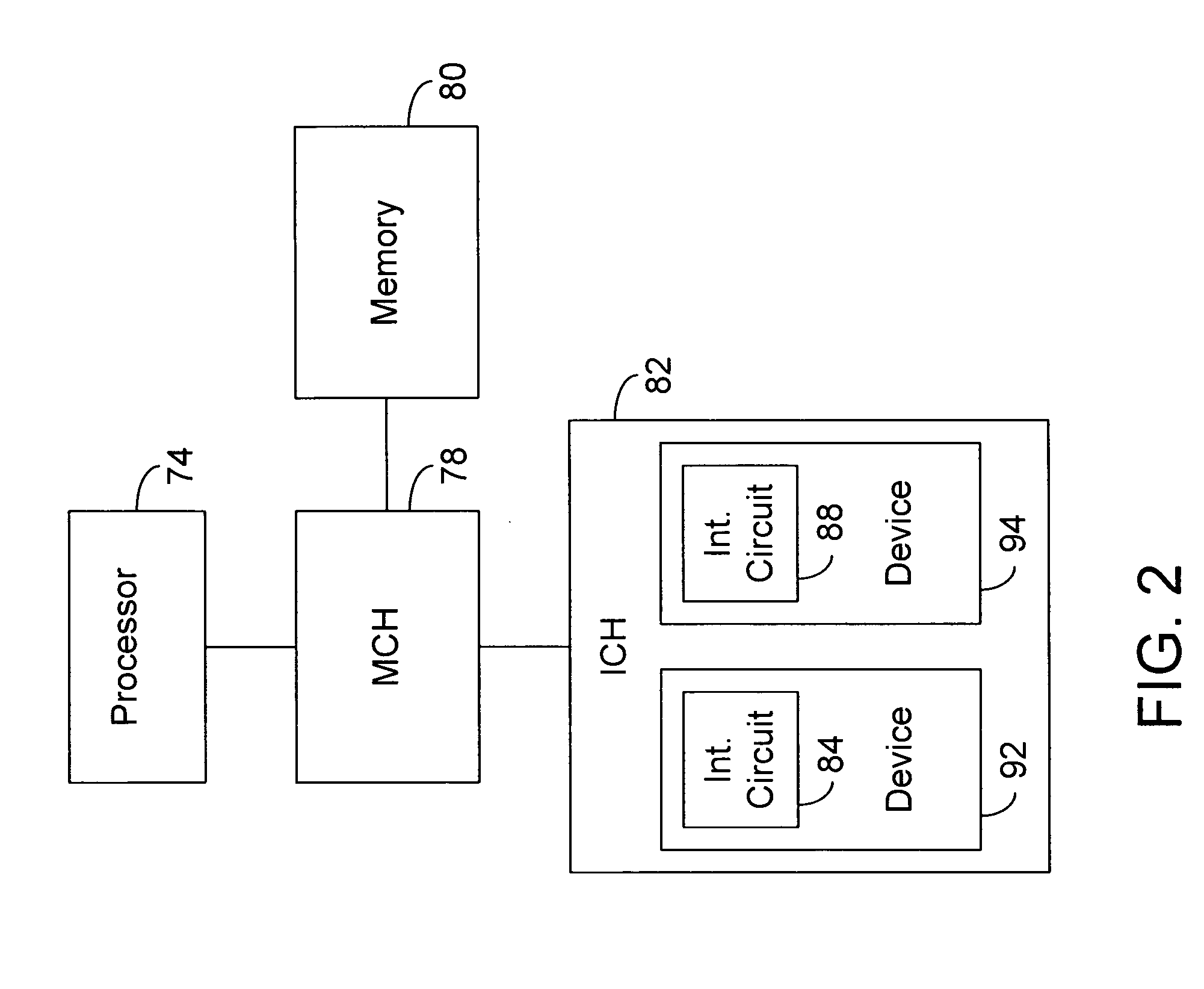

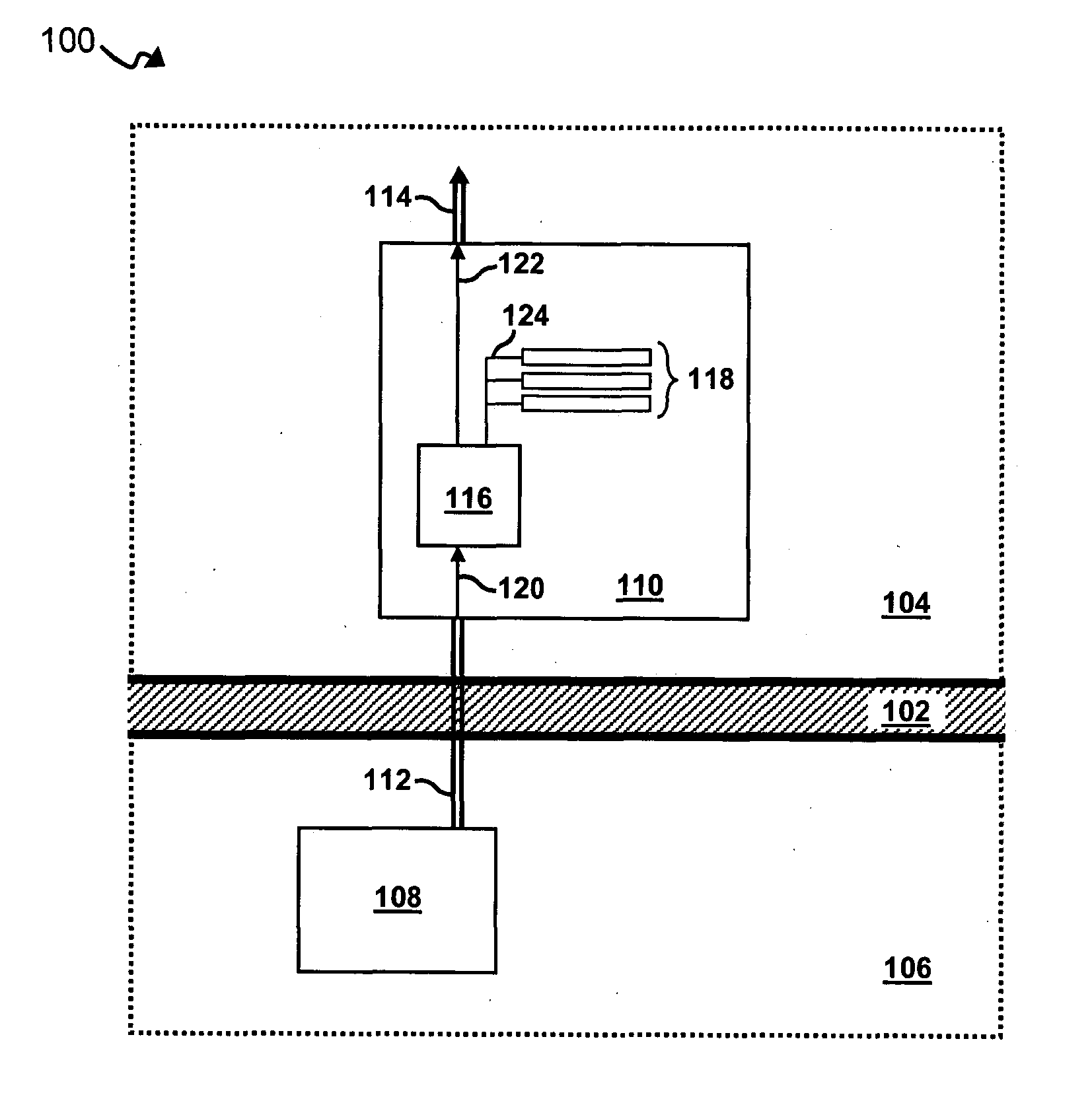

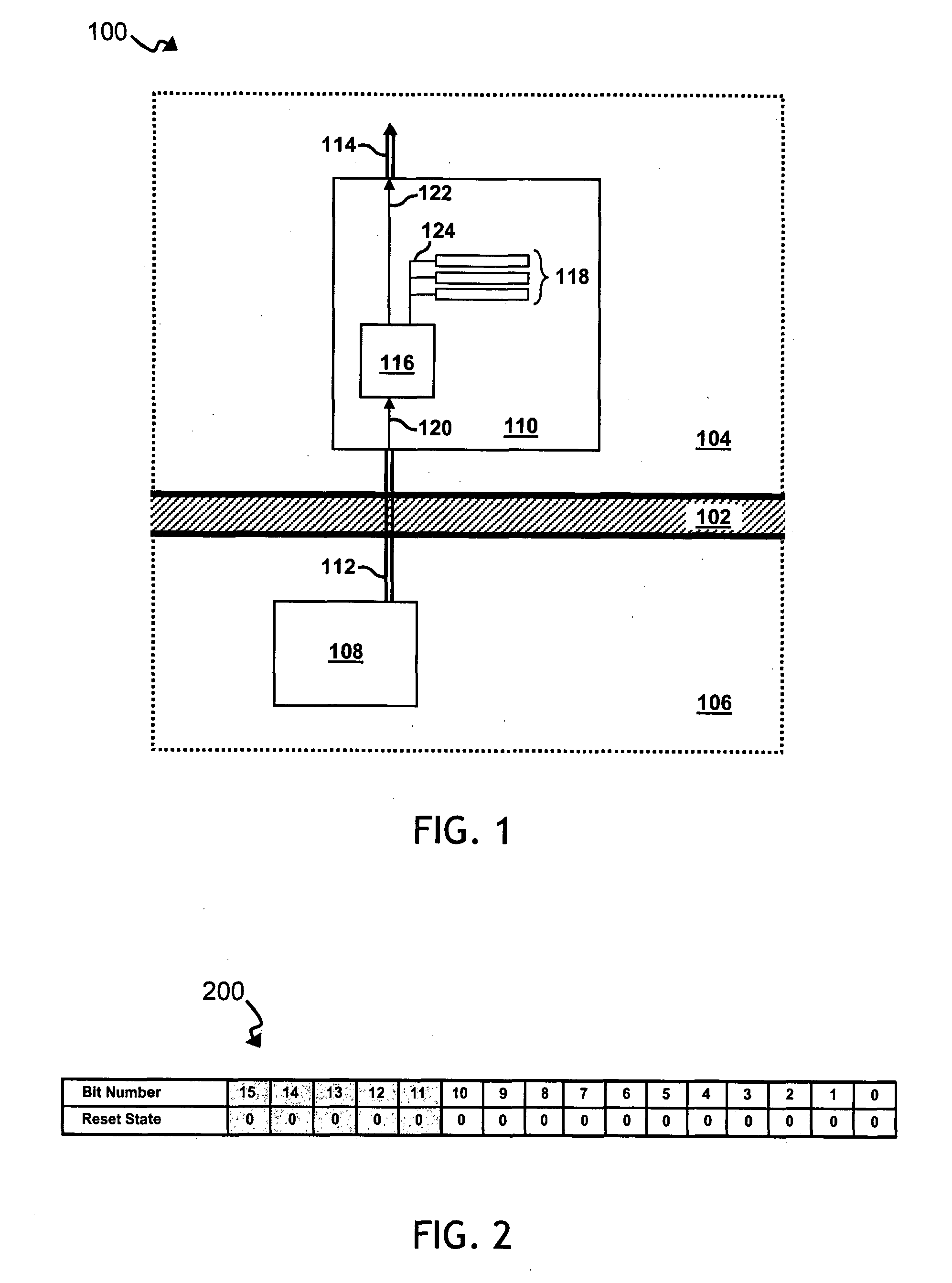

The present invention provides a system for signaling legacy serialized interrupts within a PCI-Express environment, using message signaled interrupts. The system provides structures and methods that interface a PCI environment (106) with a PCI-Express environment (104). The present invention provides a PCI to PCI-Express bridge device (110) that is communicatively linked (112, 114) to the PCI and PCI-Express environments. The bridge device comprises a translation function (116) that is communicatively linked (120, 122) to the PCI and PCI-Express environments. A serialized interrupt is signaled from the PCI environment, and the translation function generates a message signaled interrupt within the PCI-Express environment based on that serialized interrupt.

Owner:TEXAS INSTR INC

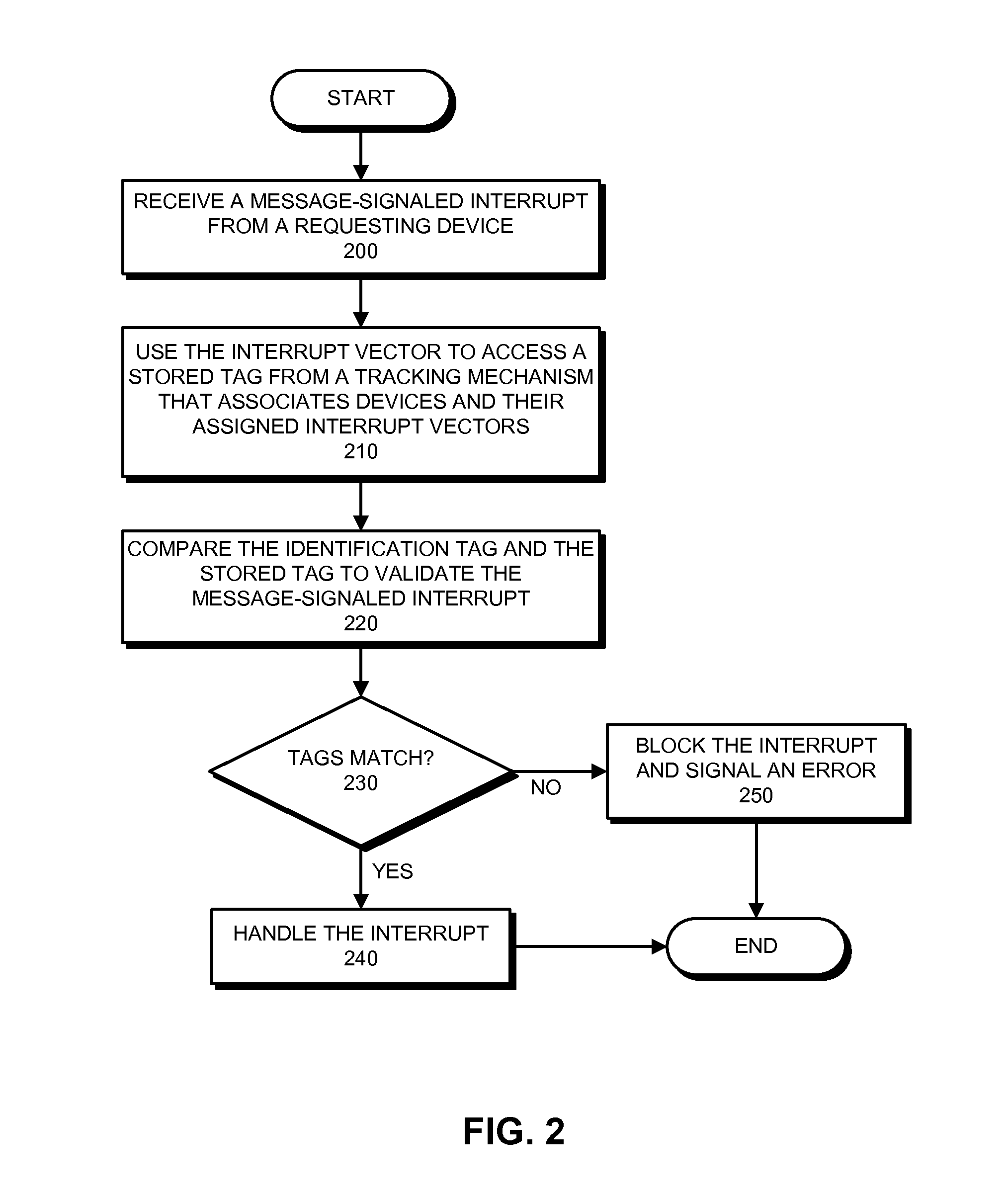

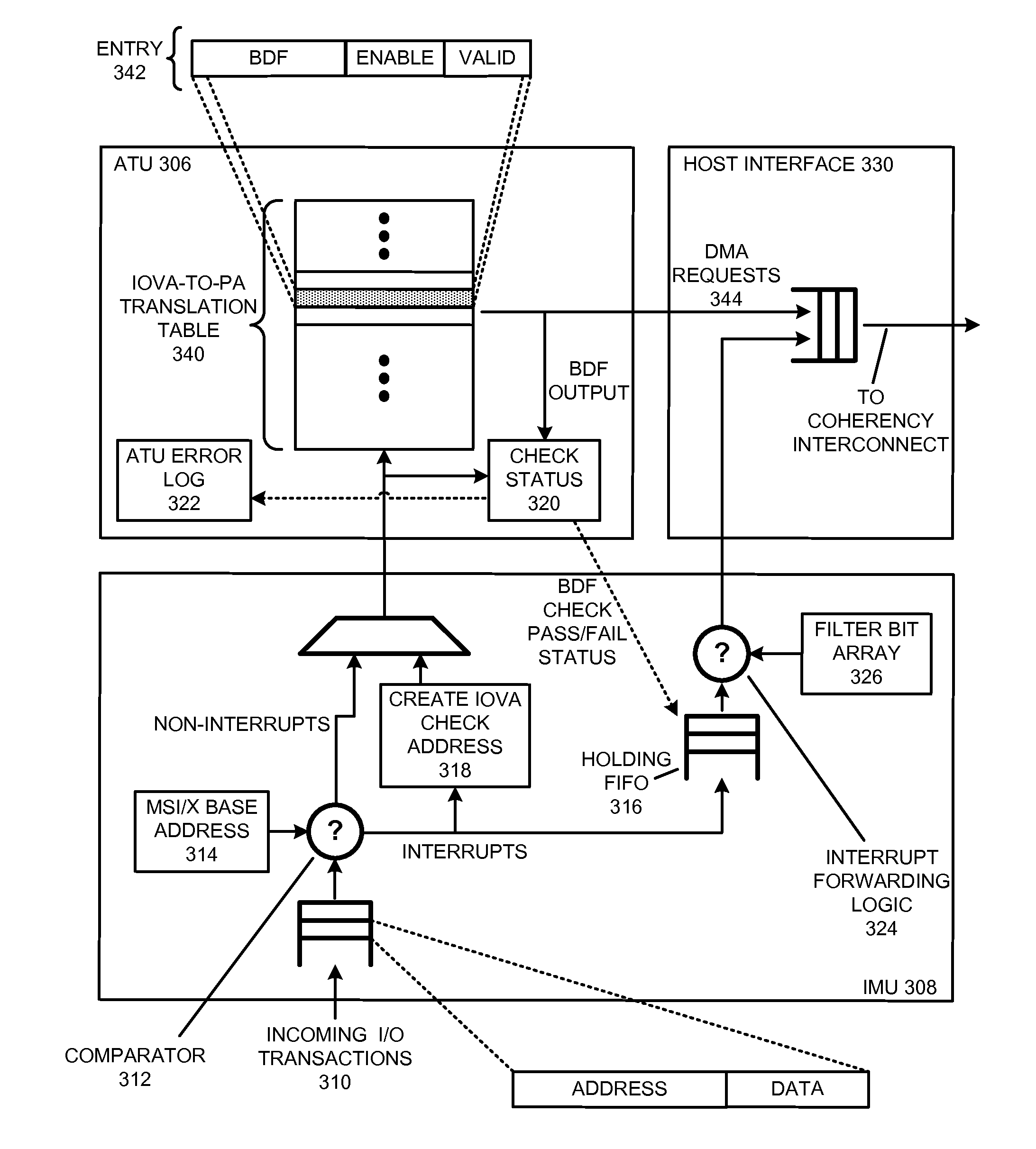

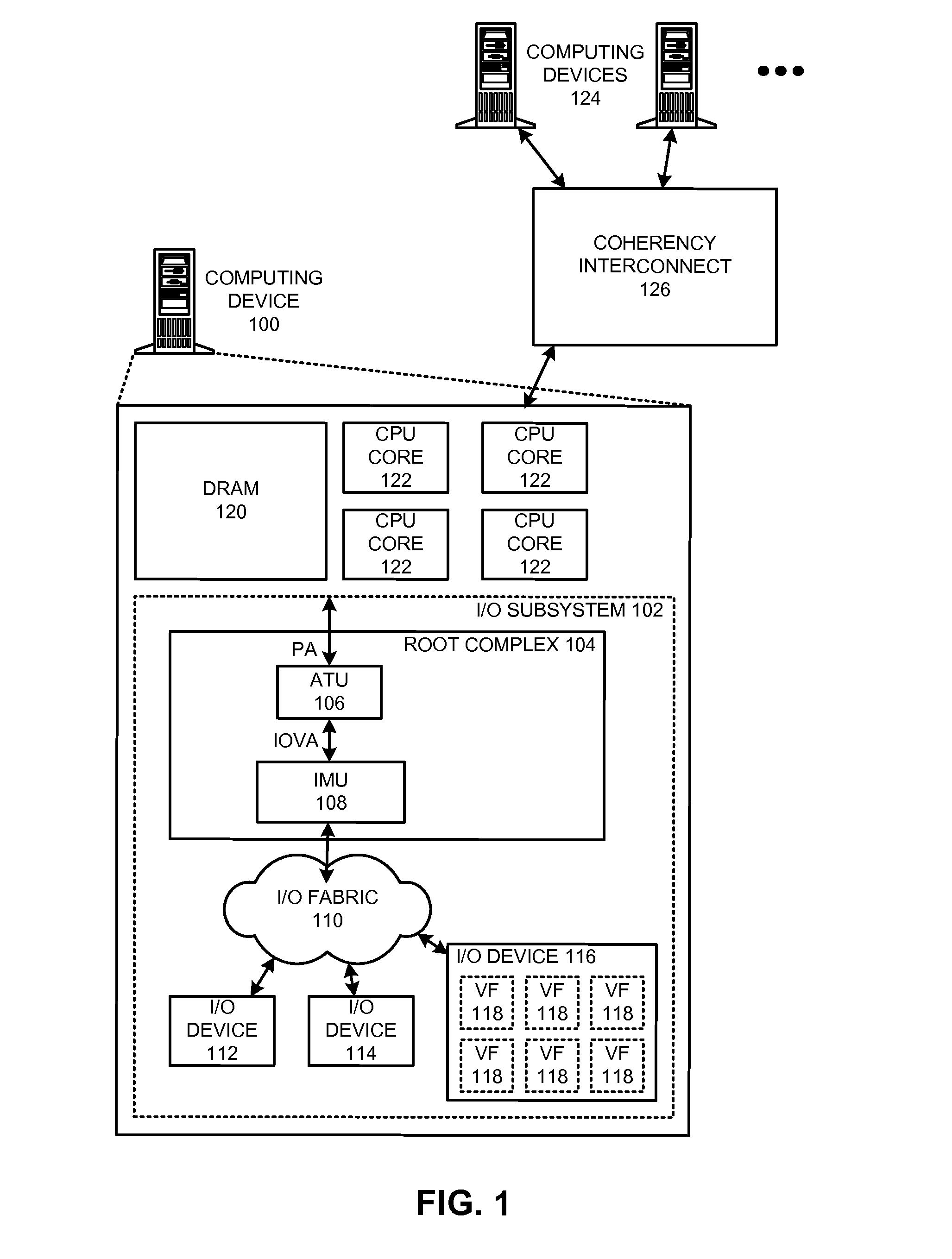

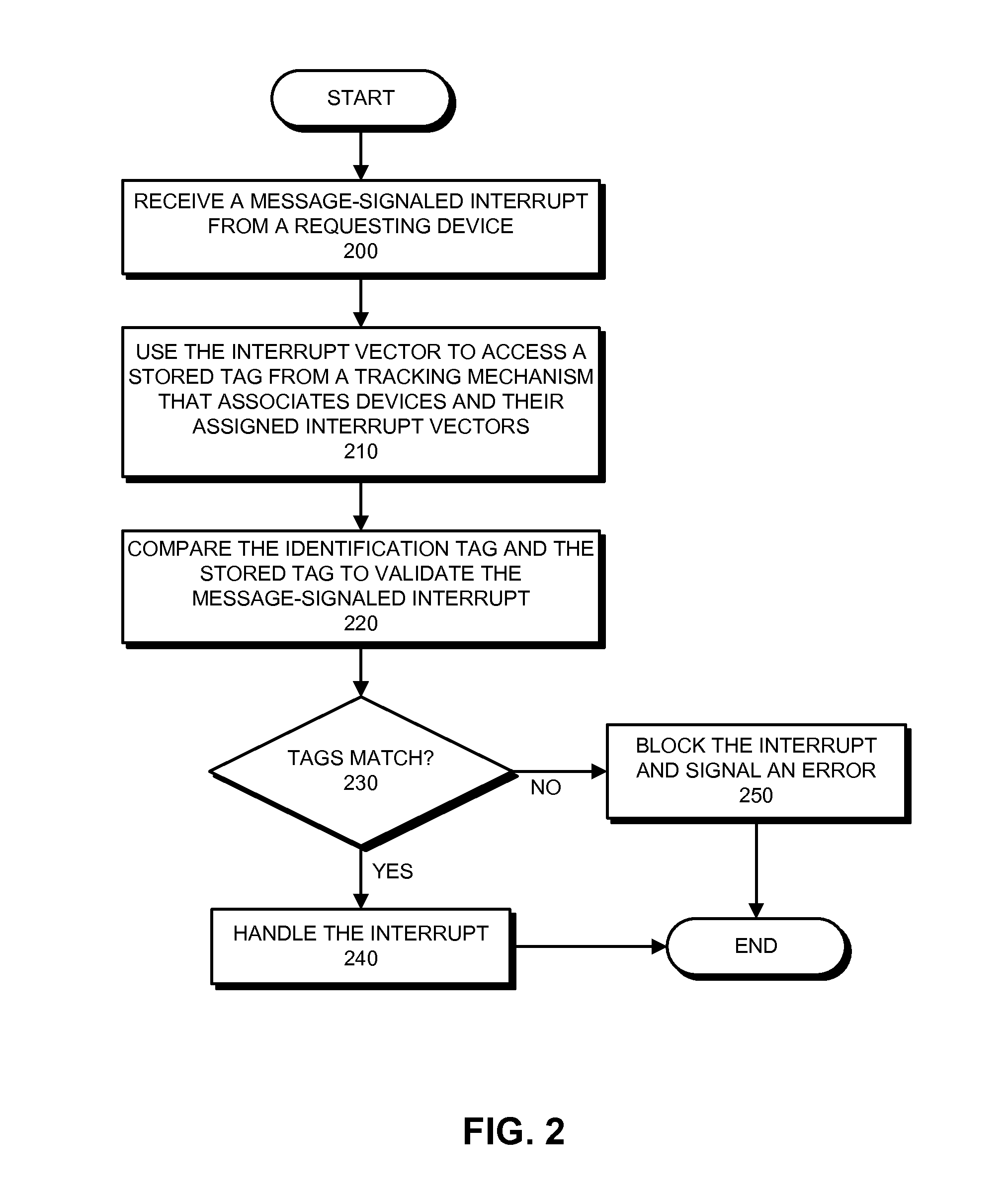

Validating message-signaled interrupts

ActiveUS20130080673A1Interrupt usePlatform integrity maintainanceMessage Signaled InterruptsSystem usage

The disclosed embodiments provide a system that validates message-signaled interrupts. During operation, the system receives a message-signaled interrupt from a requesting device. This message-signaled interrupt includes an interrupt vector that identifies an interrupt, and is accompanied by an identification tag that identifies the source of the interrupt. The system uses the interrupt vector to access a stored tag from a tracking mechanism that associates source devices with their assigned interrupt vector(s). The system then compares the identification tag and the stored tag to validate the message-signaled interrupt.

Owner:ORACLE INT CORP

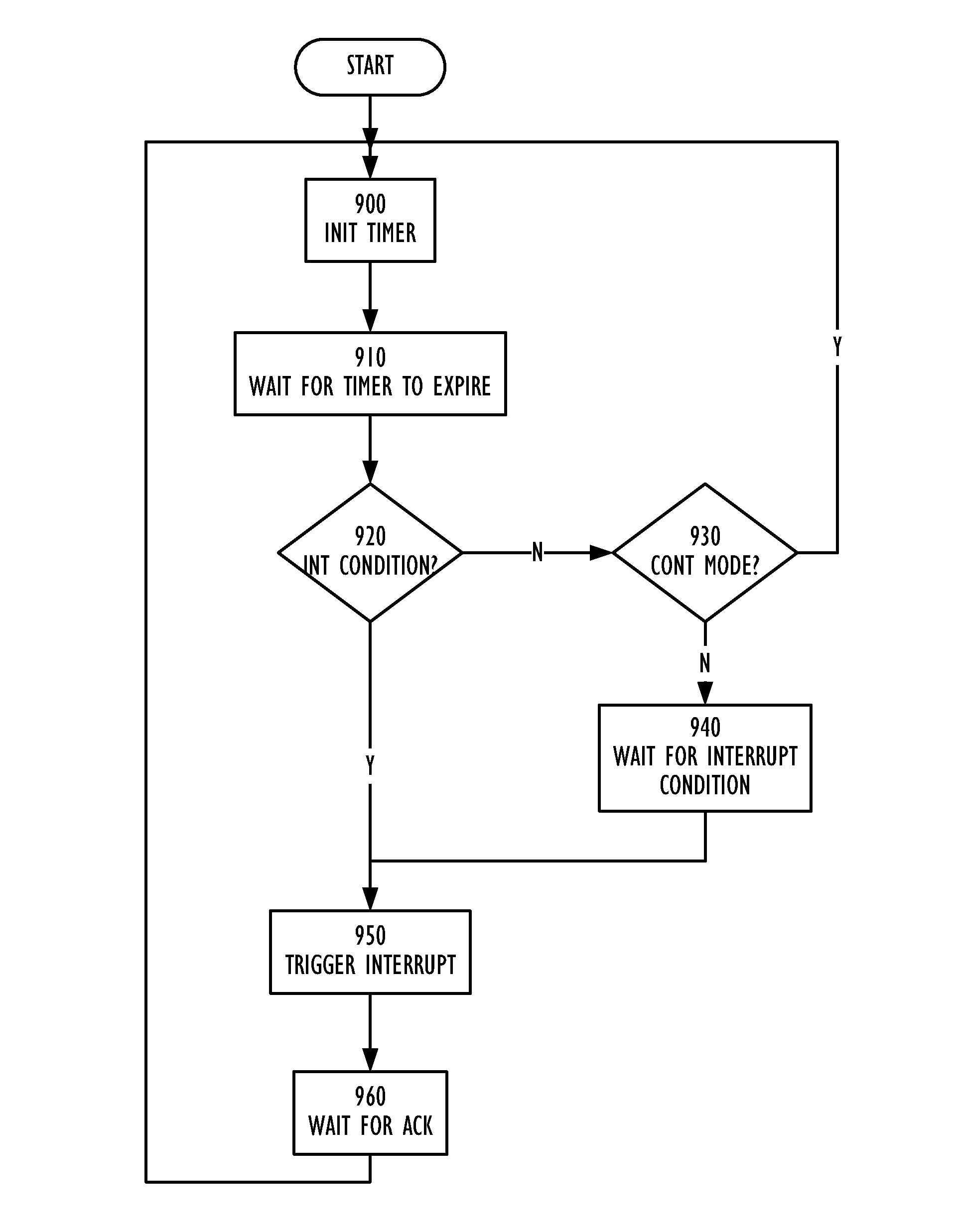

Interrupt moderation

A technique for interrupt moderation allows coalescing interrupts from a device into groups to be processed as a batch by a host processor. Receive and send completions may be processed differently. When the host is interrupted for receive completions, it may check for send completions, reducing the need for interrupts related to send completions. Timers and a counter allow coalescing interrupts into a single interrupt that can be used to signal the host to process multiple completions. The technique is suitable for both dedicated interrupt line and message-signaled interrupts.

Owner:AVAGO TECH INT SALES PTE LTD

Interrupt Moderation

A technique for interrupt moderation allows coalescing interrupts from a device into groups to be processed as a batch by a host processor. Receive and send completions may be processed differently. When the host is interrupted for receive completions, it may check for send completions, reducing the need for interrupts related to send completions. Timers and a counter allow coalescing interrupts into a single interrupt that can be used to signal the host to process multiple completions. The technique is suitable for both dedicated interrupt line and message-signaled interrupts.

Owner:AVAGO TECH INT SALES PTE LTD

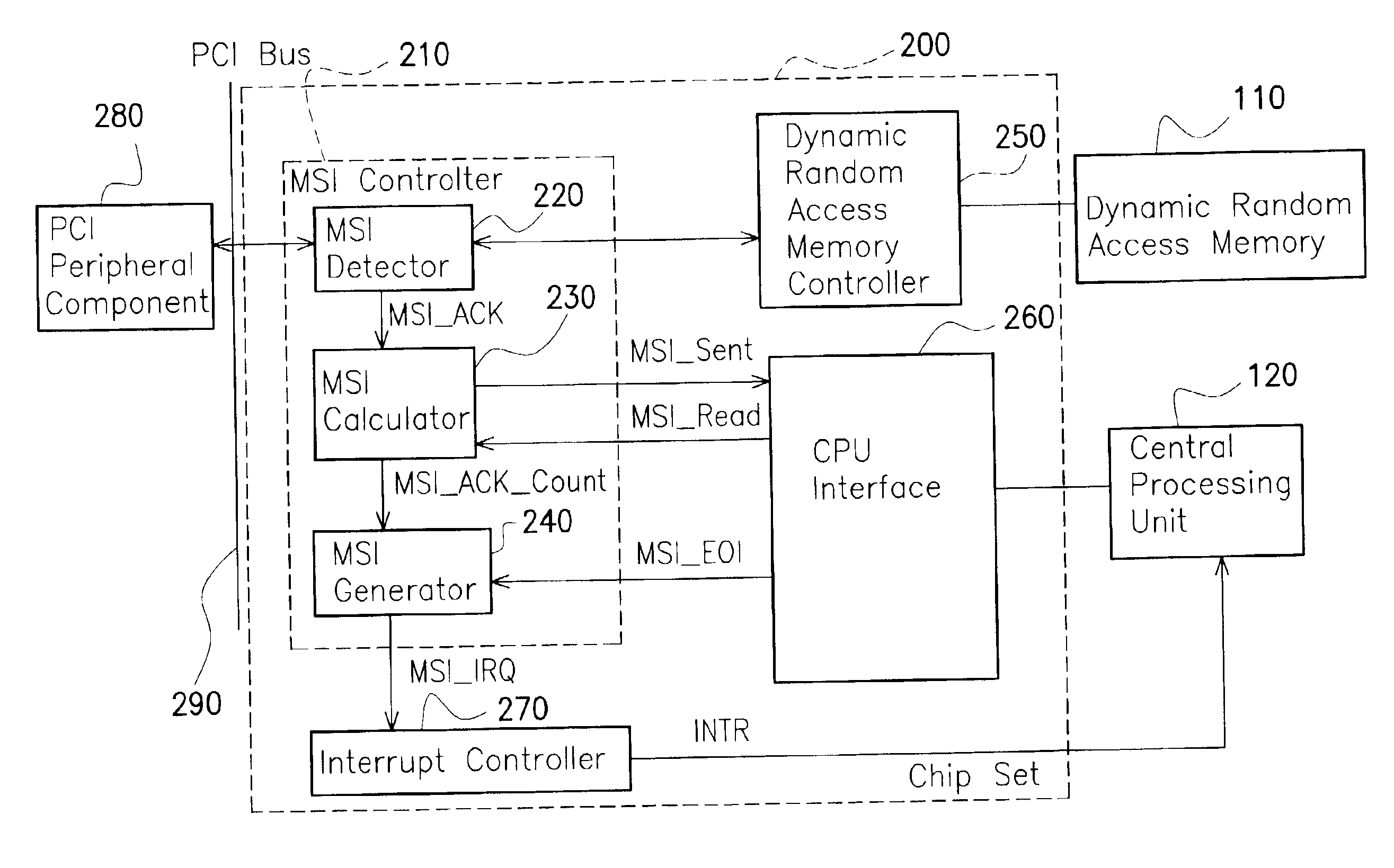

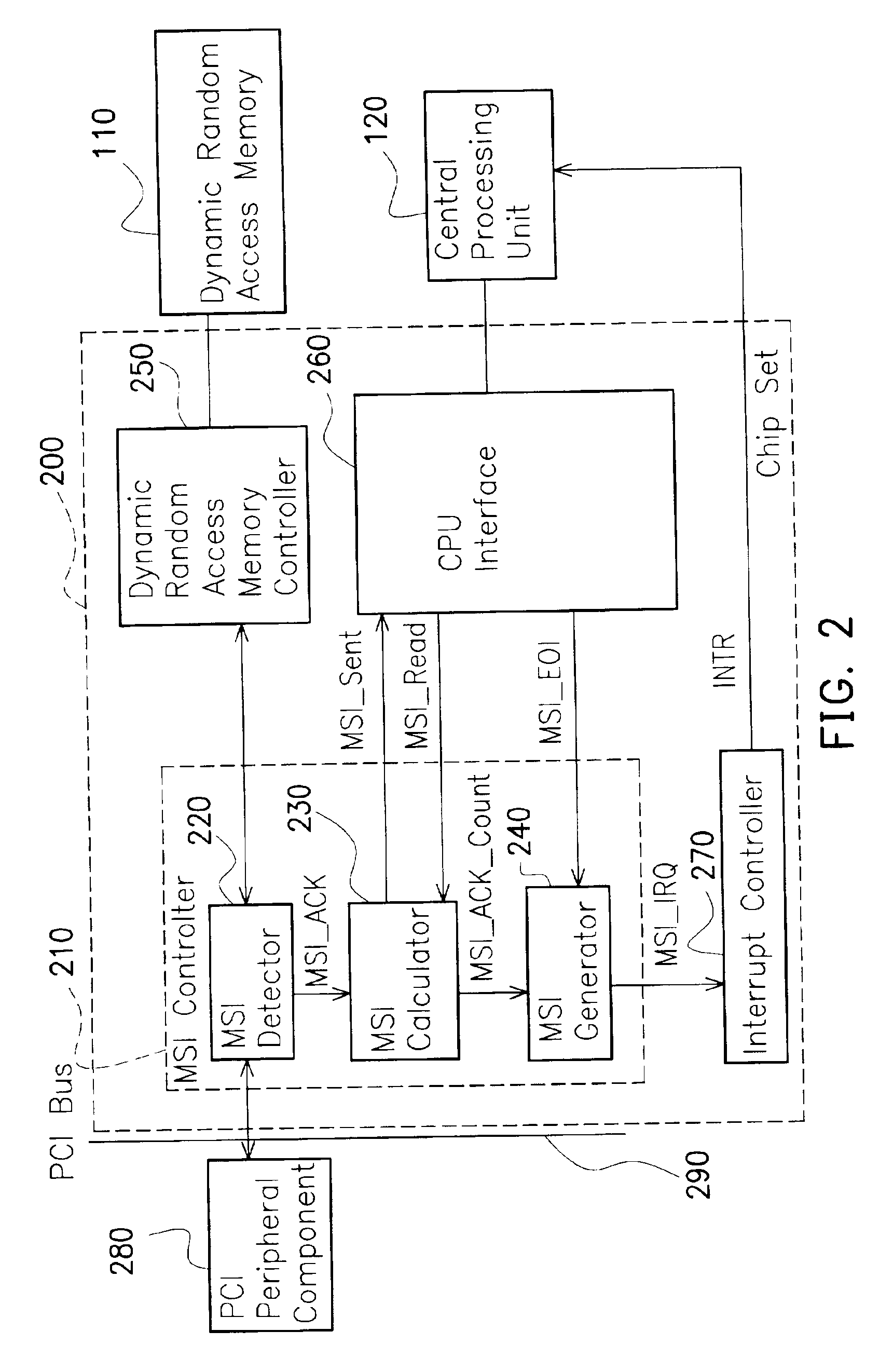

Processing method, chip set and controller for supporting message signaled interrupt

InactiveUS6941398B2Interrupt occurrenceElectric digital data processingWrite bufferMessage Signaled Interrupts

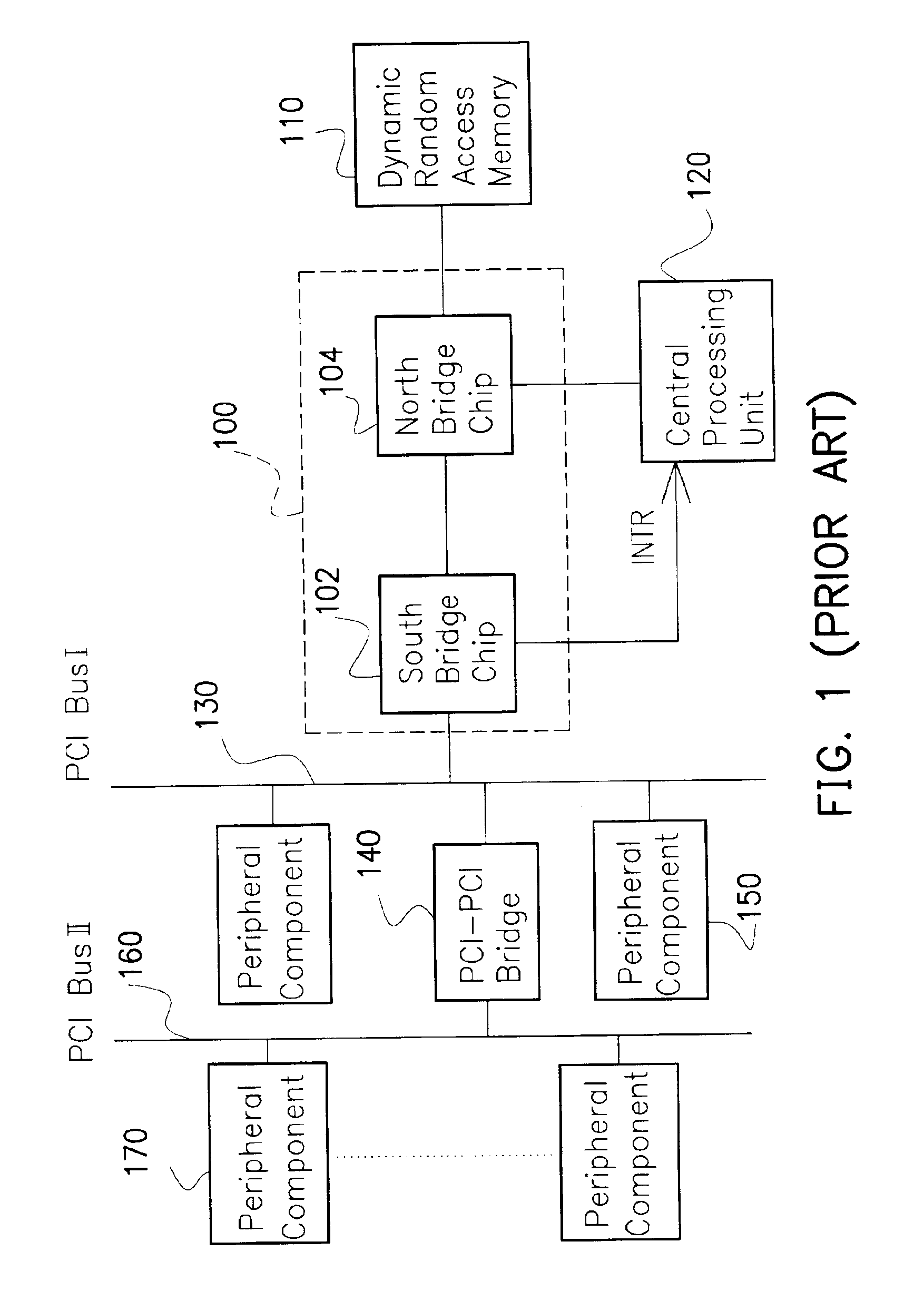

A processing method, a chip set and a controller for supporting message signaled interrupt. A memory write transaction on a PCI bus is monitored. When the address of the system memory specified in the interrupt message of the write transaction is located at a range of a reserved interrupt address, the interrupting service sequence is performed. The reserved interrupt address is located in an address of a system memory. Thus, the data to be processed and the system-specified message are written in the buffer and arranged in sequence. The problem of “write buffer latency” is resolved, and is irrelevant to the level of the PCI bus. Many system specified messages can be stored in the system memory, so that multiple system message signaled interrupts issue from different peripheral components can be processed in the same interrupt service routine.

Owner:VIA TECH INC

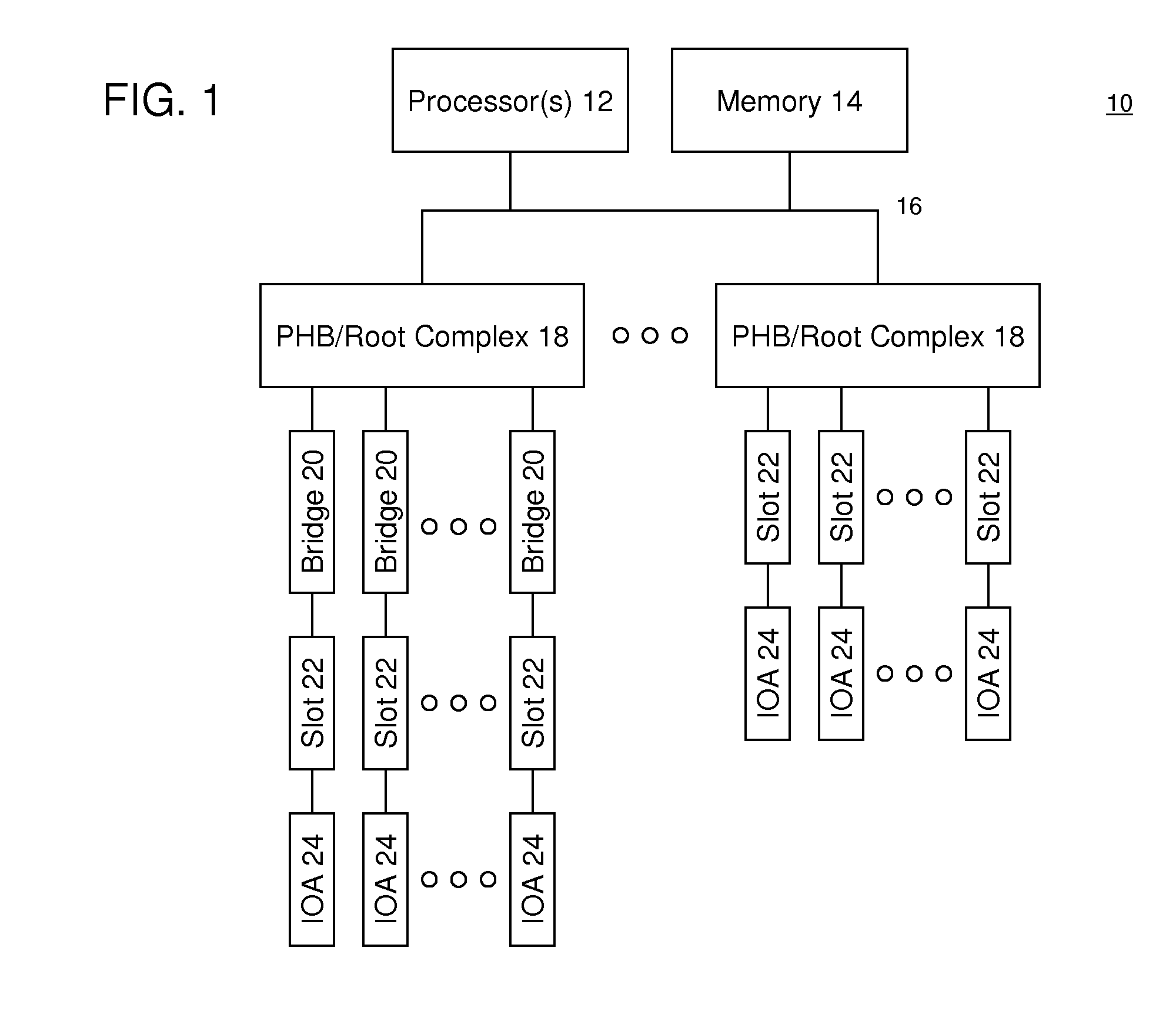

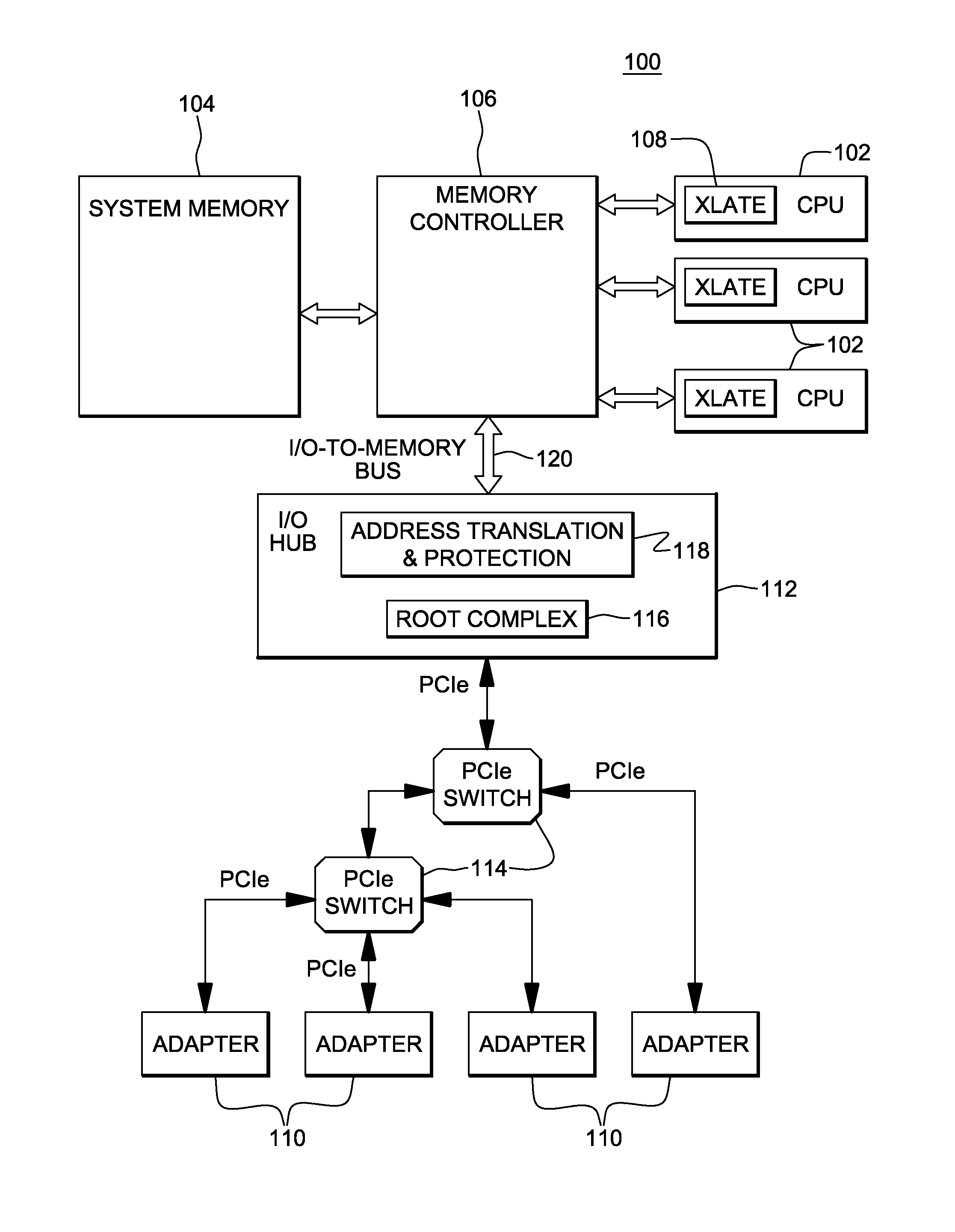

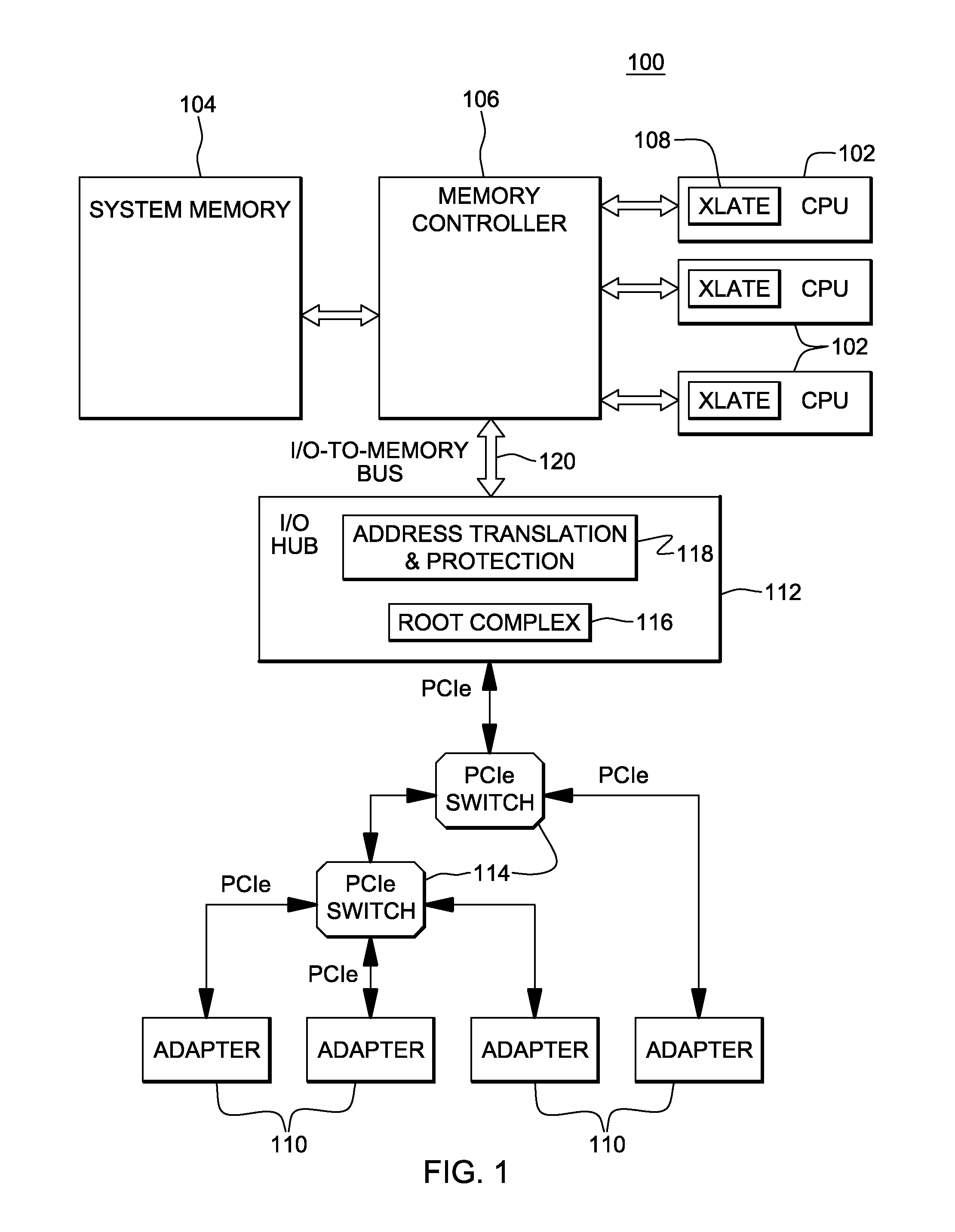

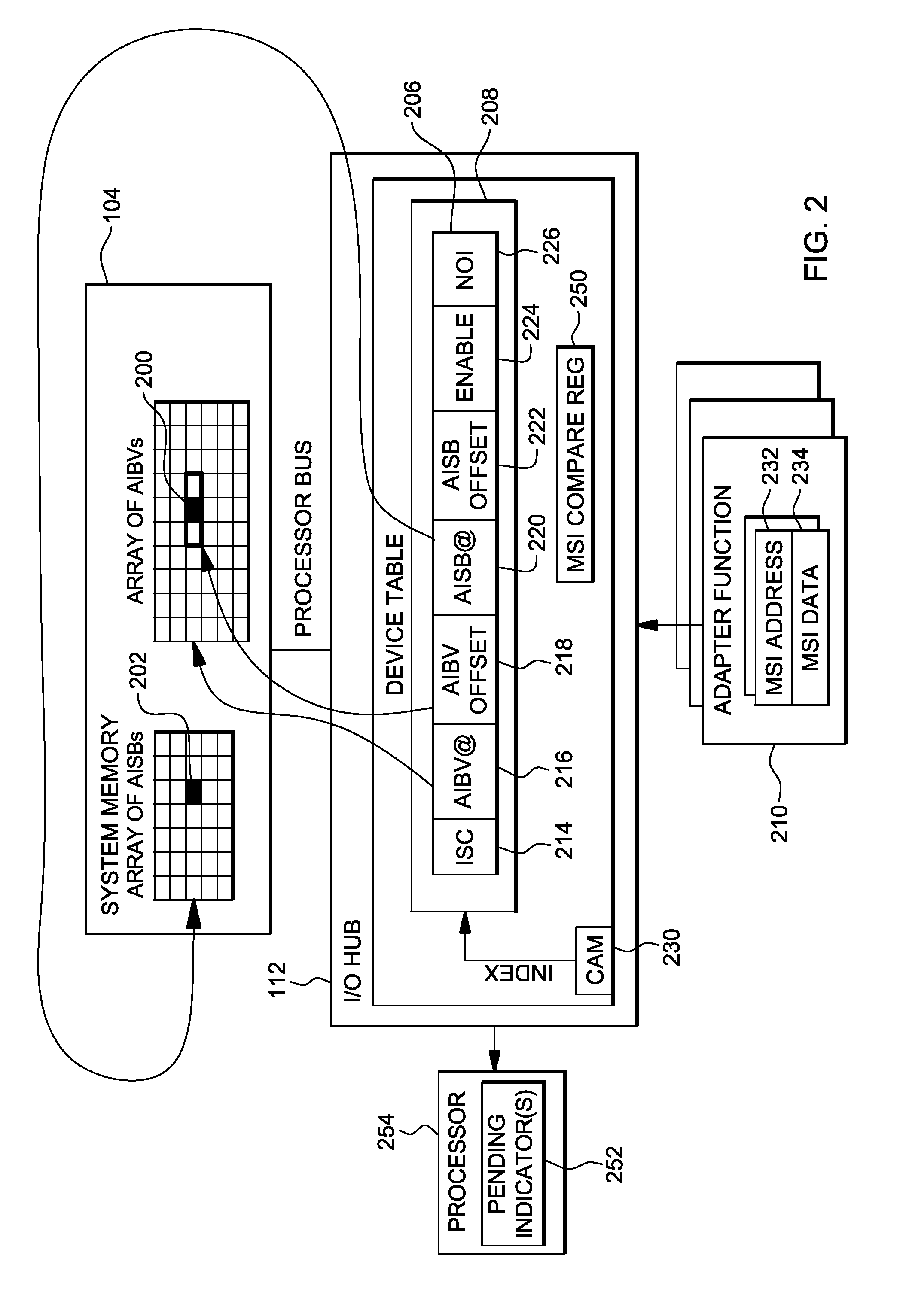

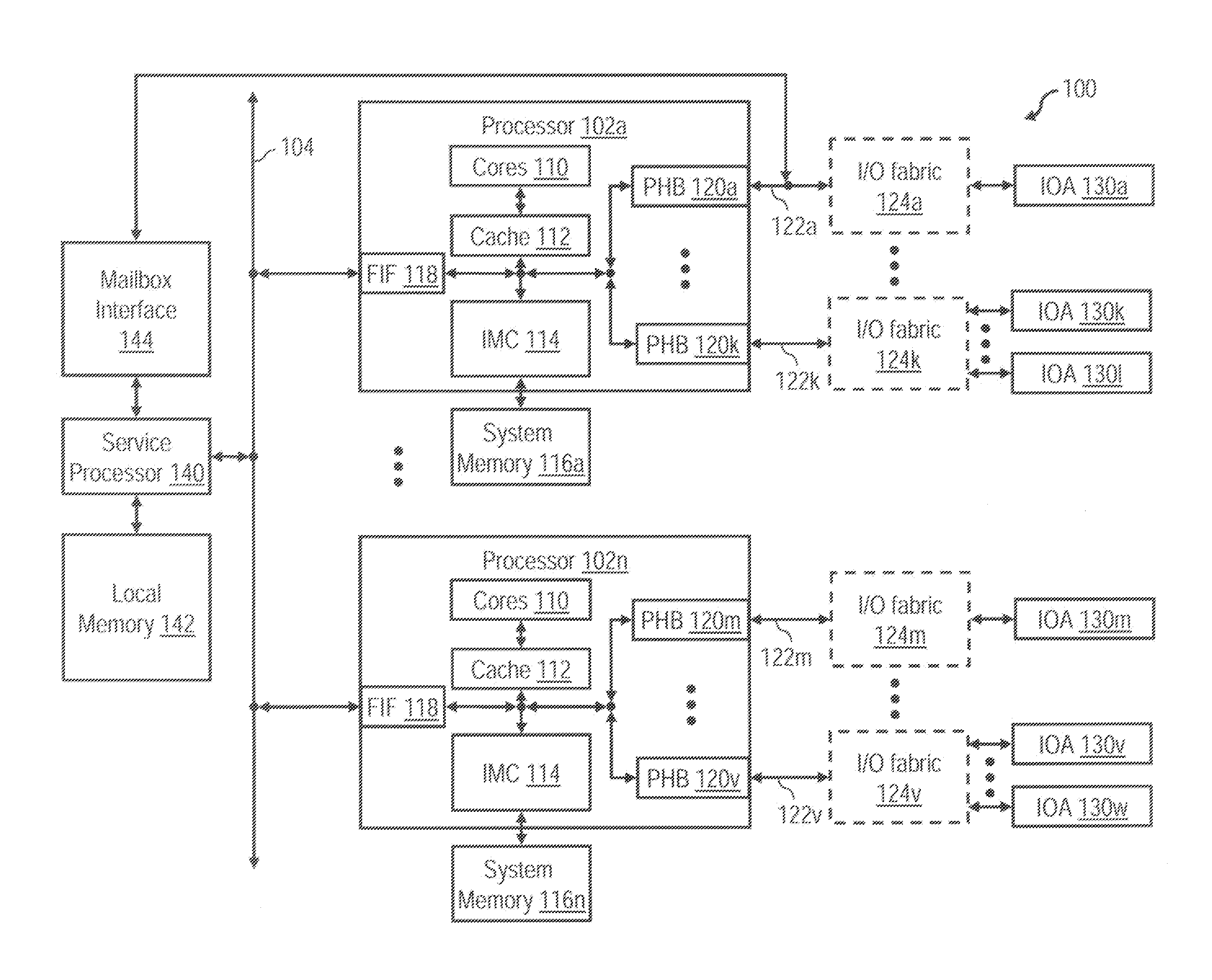

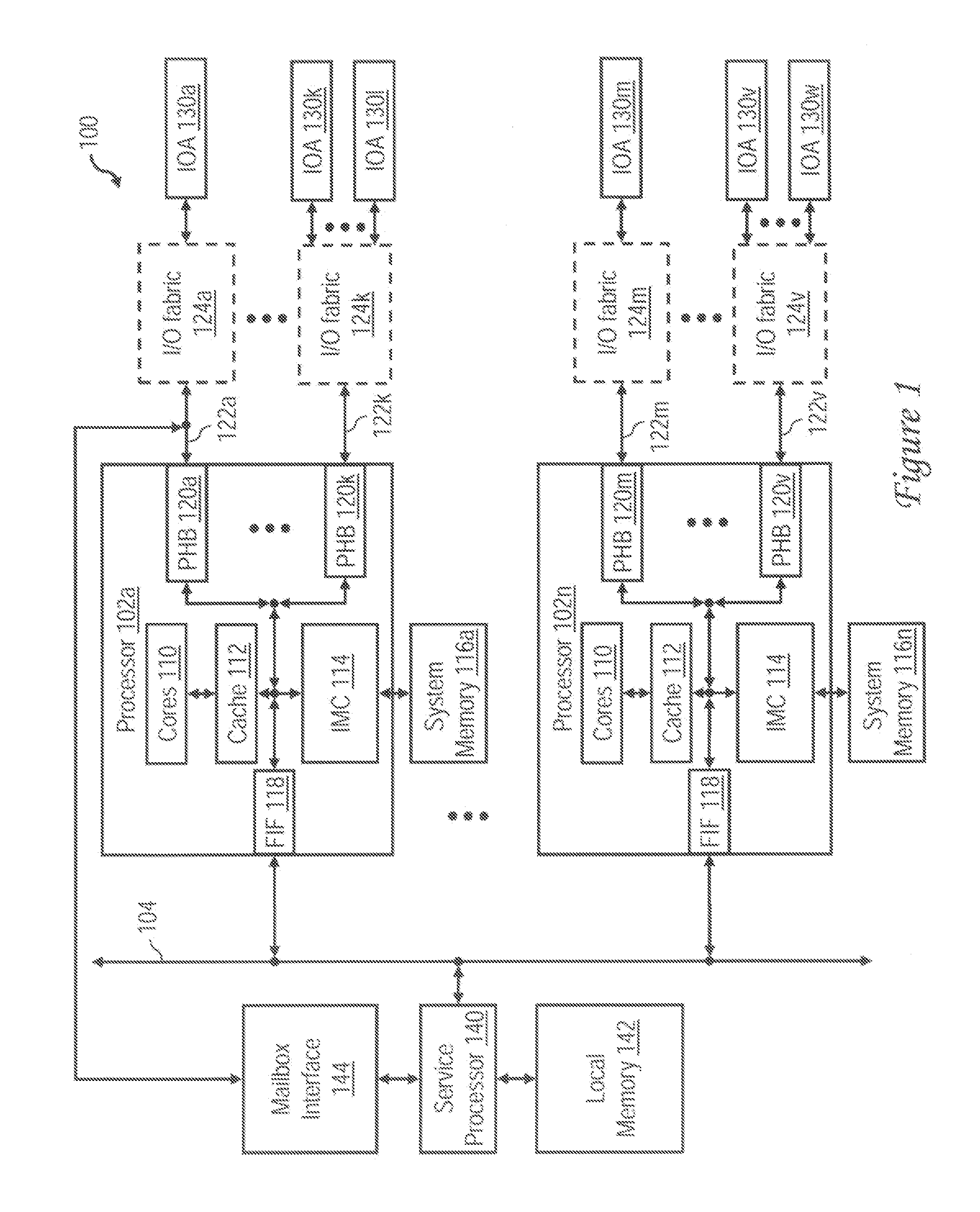

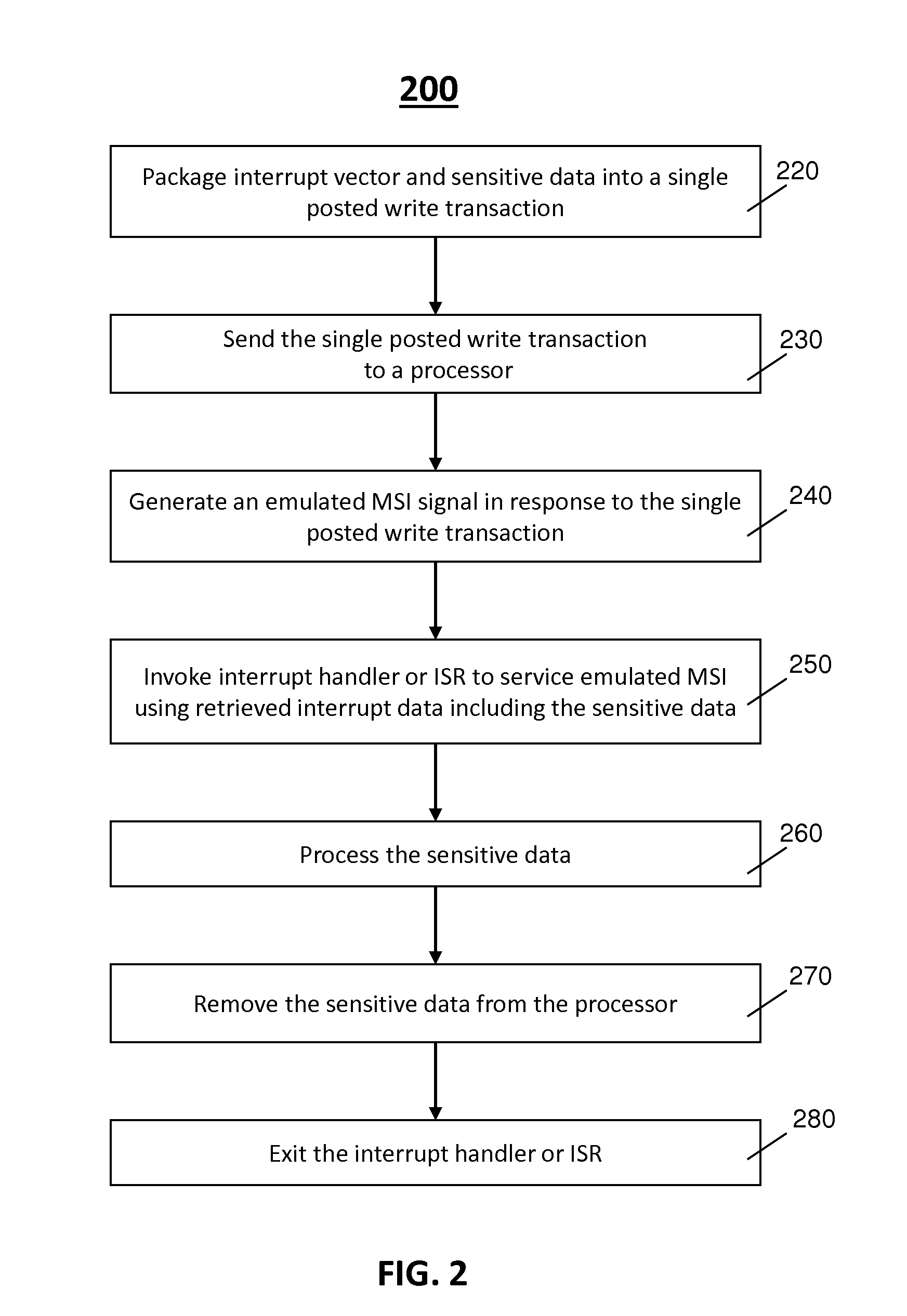

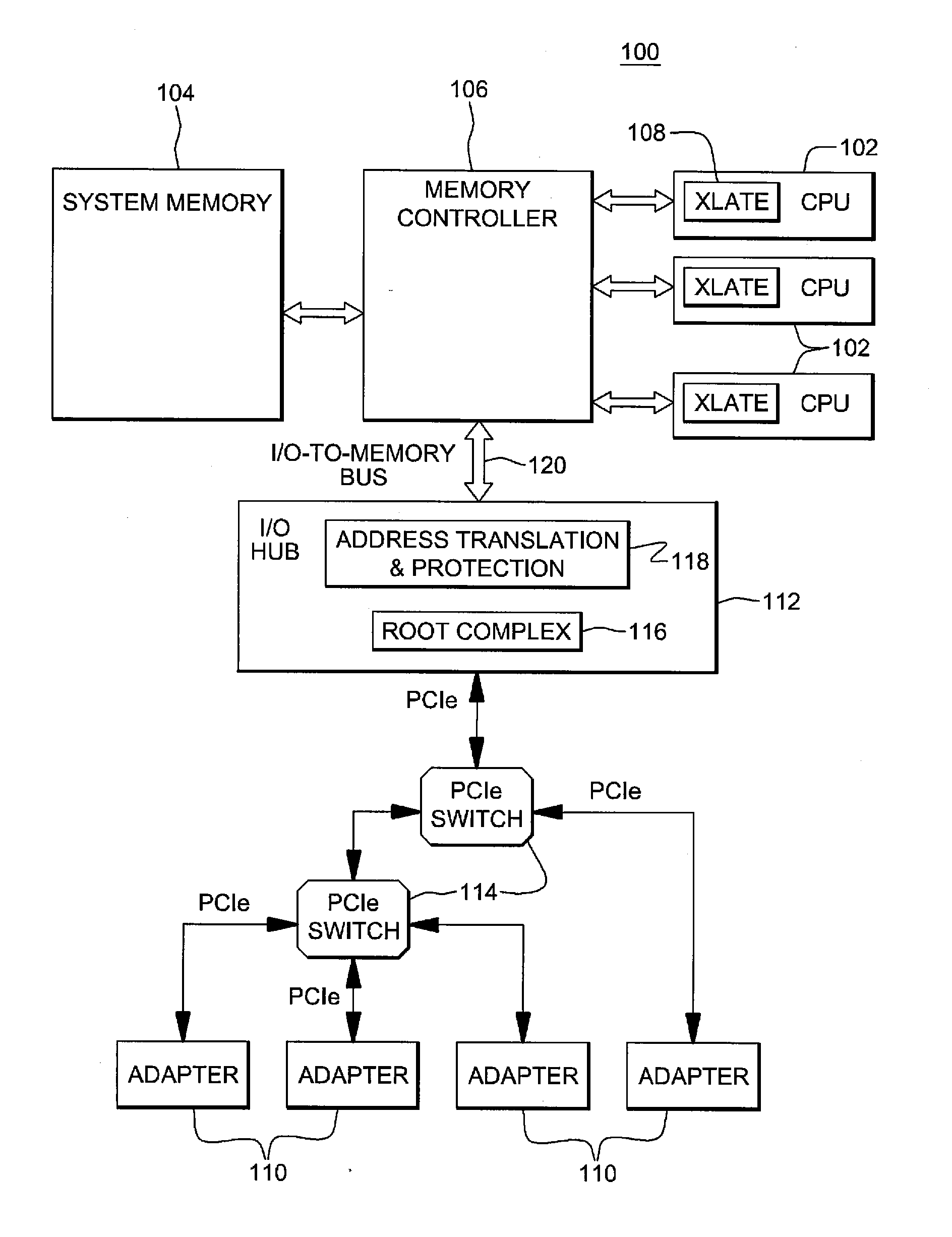

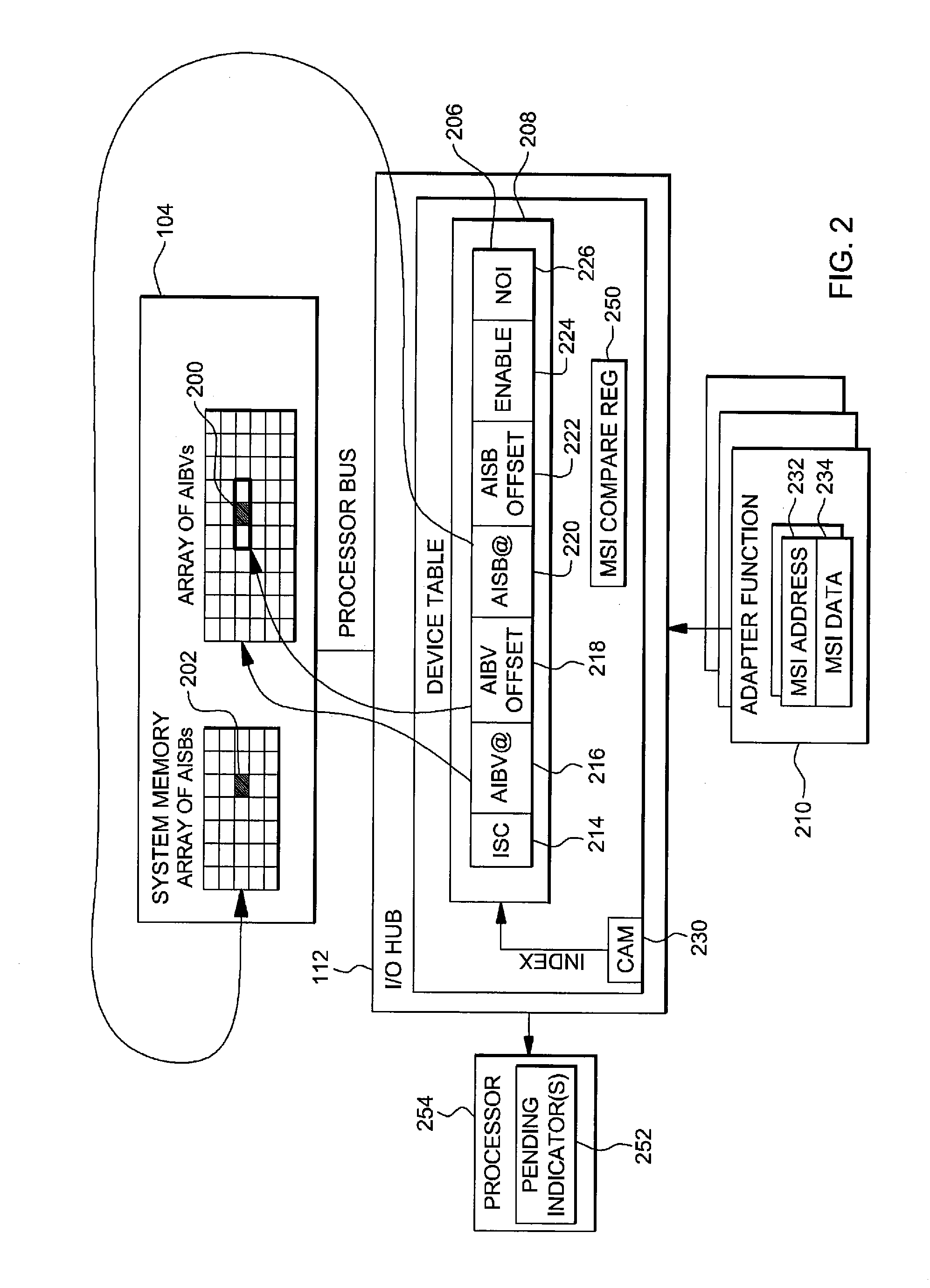

Converting a message signaled interruption into an I/O adapter event notification

ActiveUS20110321061A1Easy to manageProgram initiation/switchingSpecific program execution arrangementsMessage Signaled InterruptsComputer science

One or more message signaled interruption requests from one or more input / output (I / O) adapters are converted to I / O adapter event notifications. Each I / O adapter event notification includes the setting of one or more specific indicators in system memory and an interruption request, the first of which results in a pending I / O adapter interruption request. While a request for an I / O adapter interruption is pending, subsequent message signaled interruption requests are converted to I / O adapter event notifications, but do not result in additional requests for I / O adapter interruptions.

Owner:IBM CORP

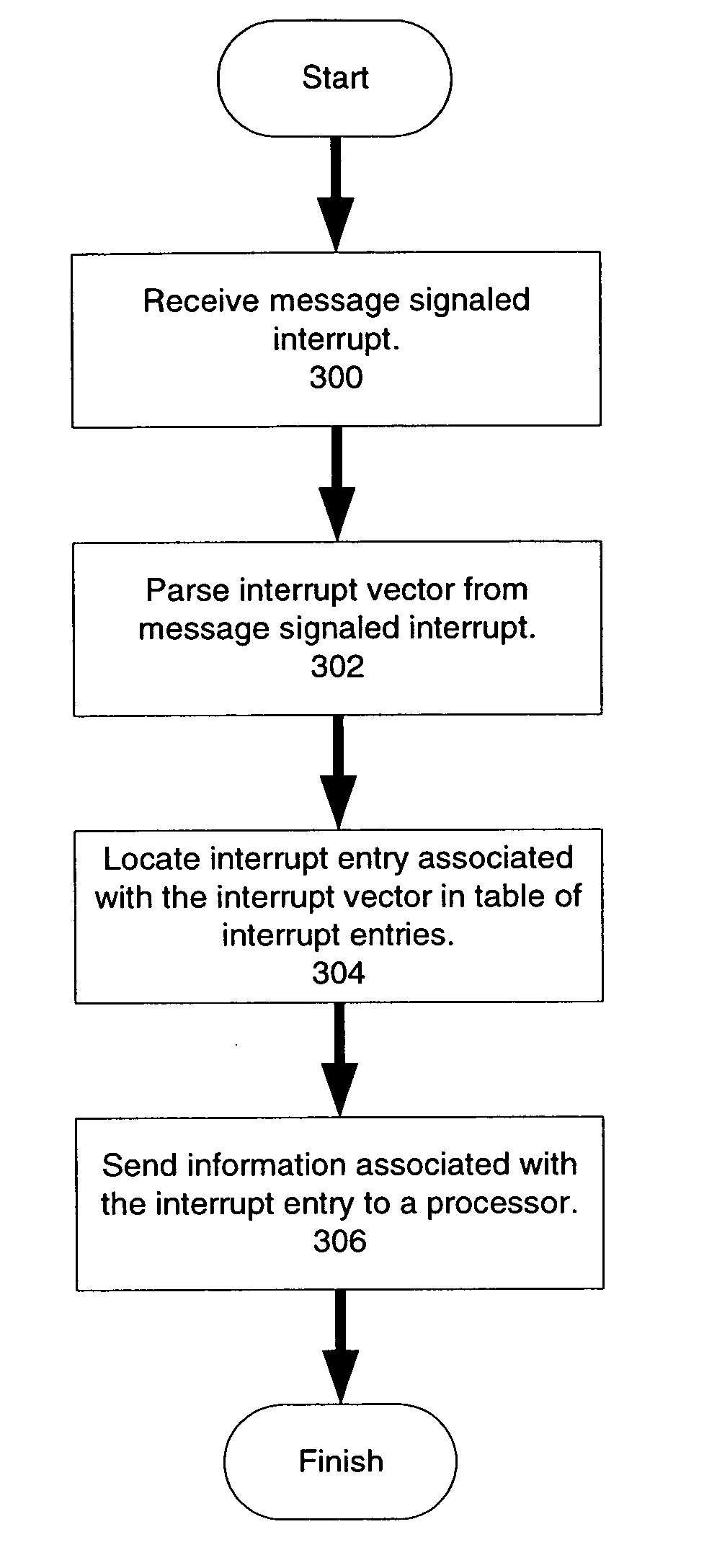

Message signaled interrupt redirection

A method, device, and system are disclosed. In one embodiment, the method comprises receiving a message signaled interrupt, parsing an interrupt vector from the message signaled interrupt, locating an interrupt entry associated with the interrupt vector in a table of interrupt entries, and sending information associated with the interrupt entry to a processor.

Owner:INTEL CORP

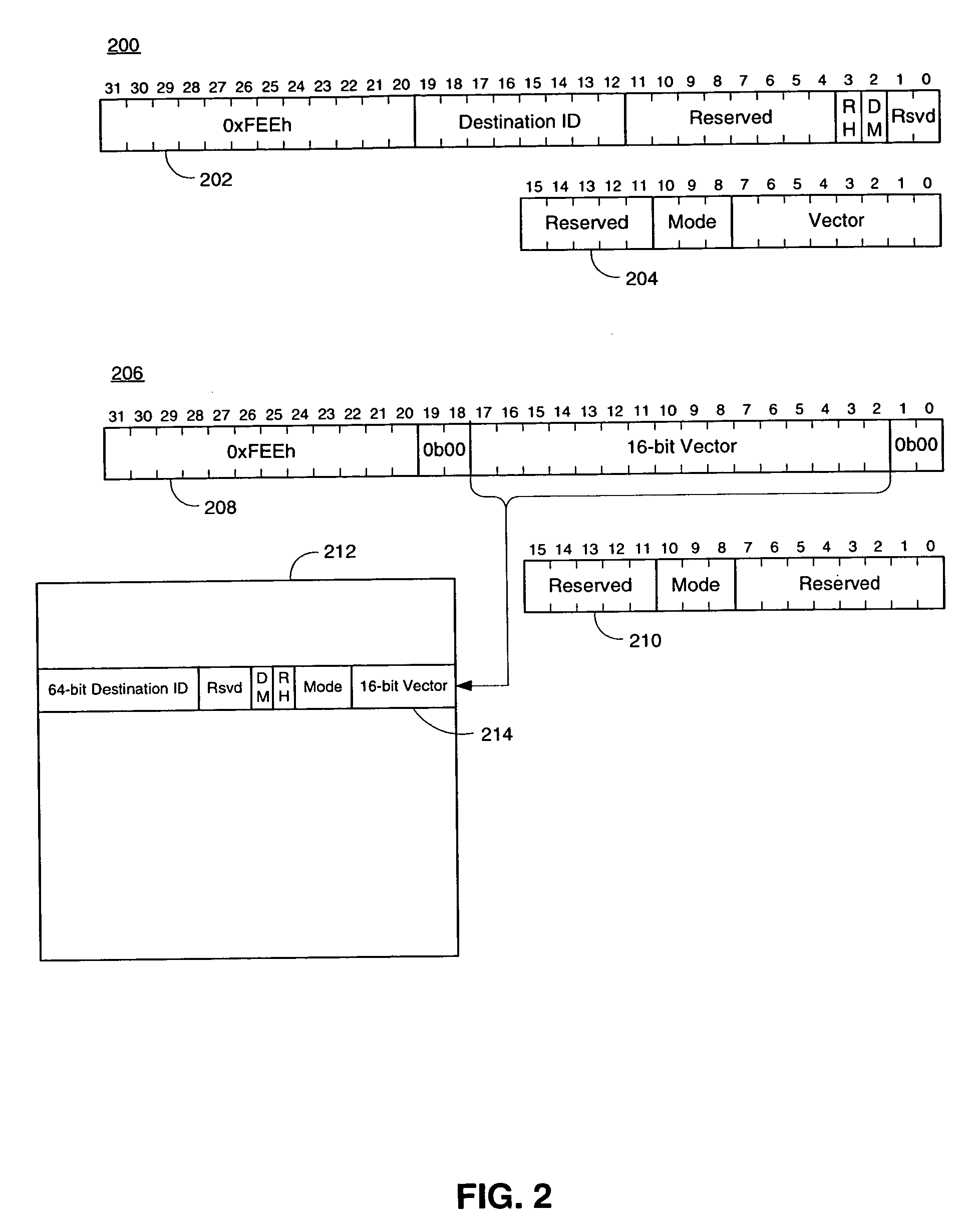

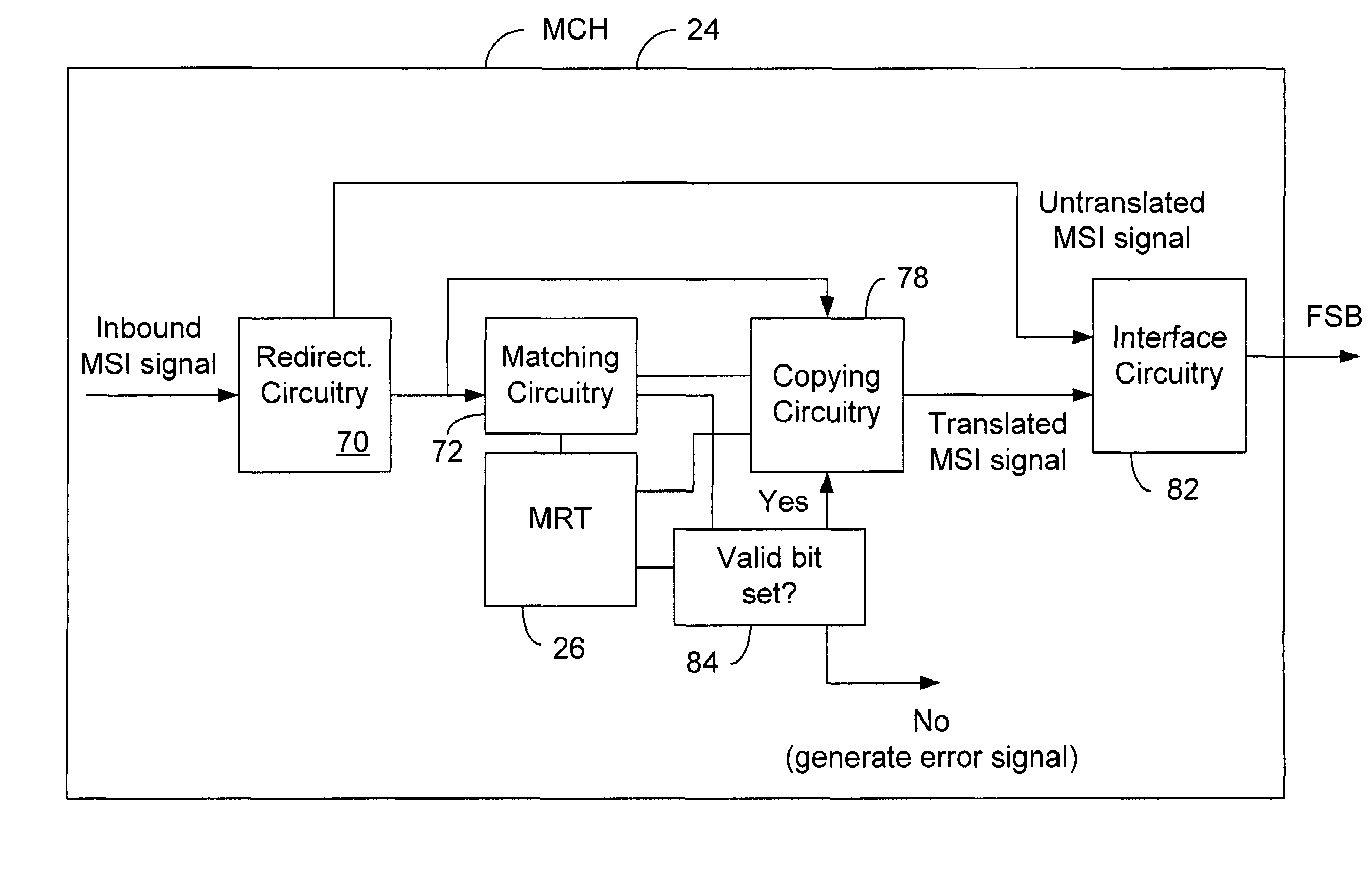

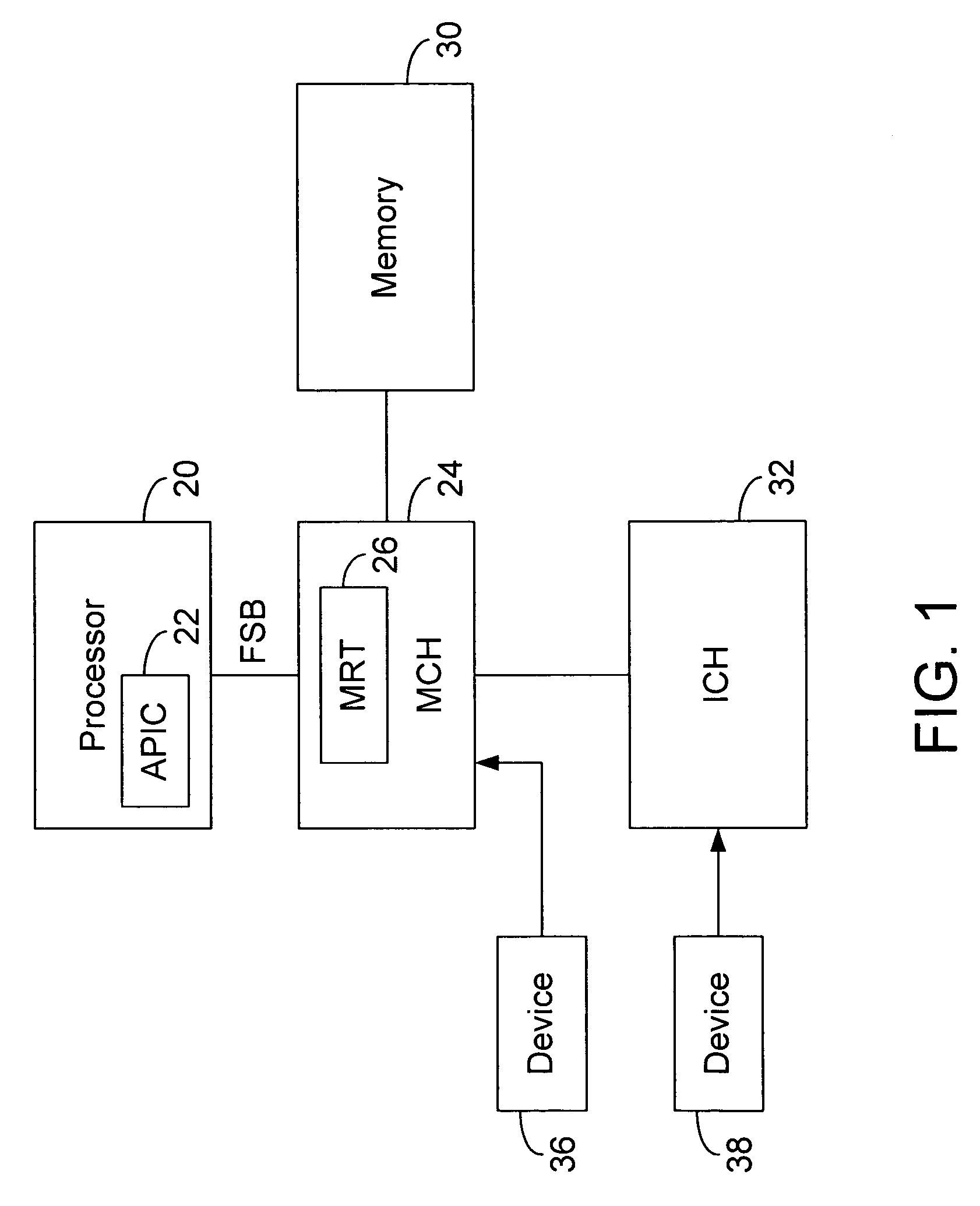

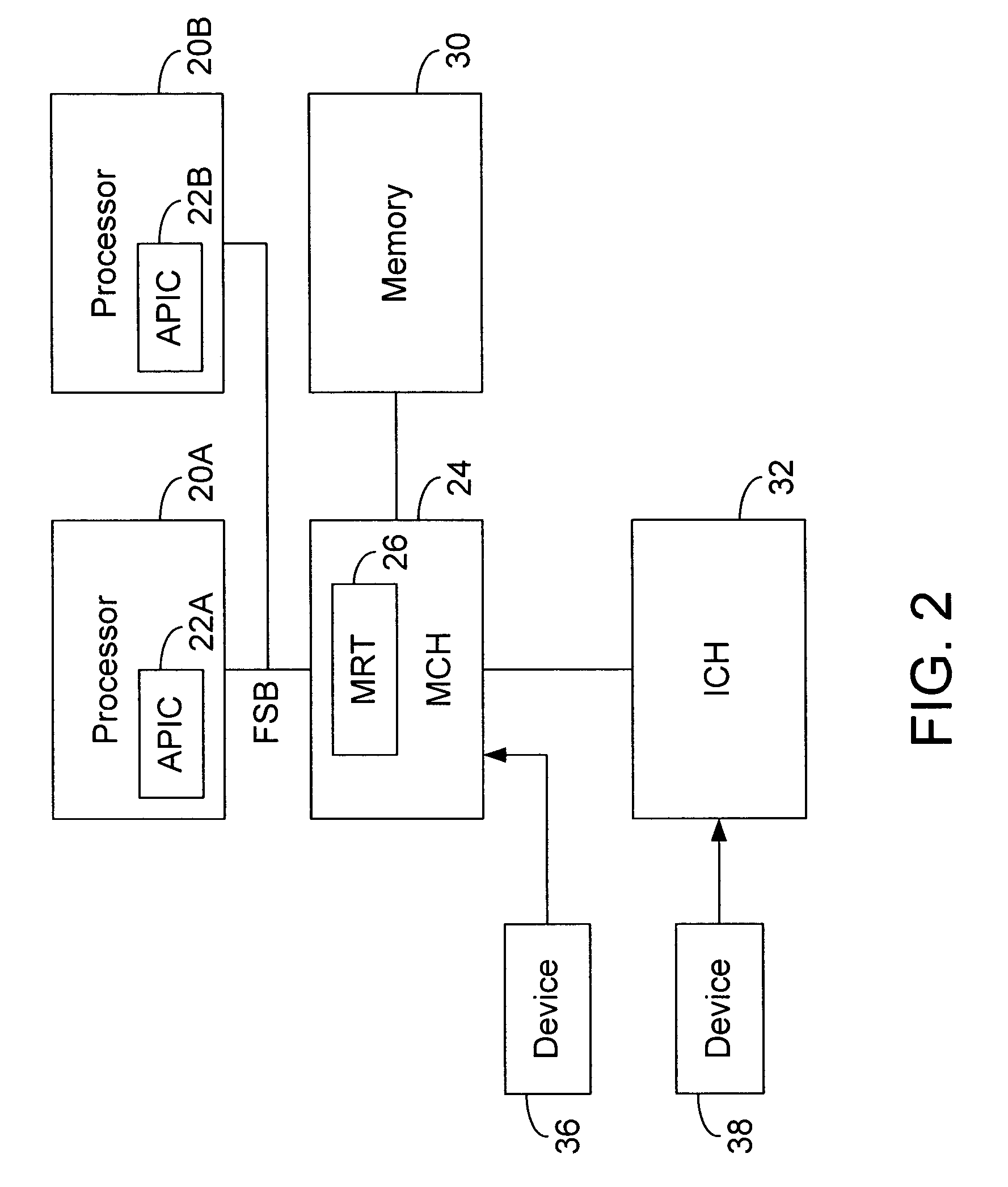

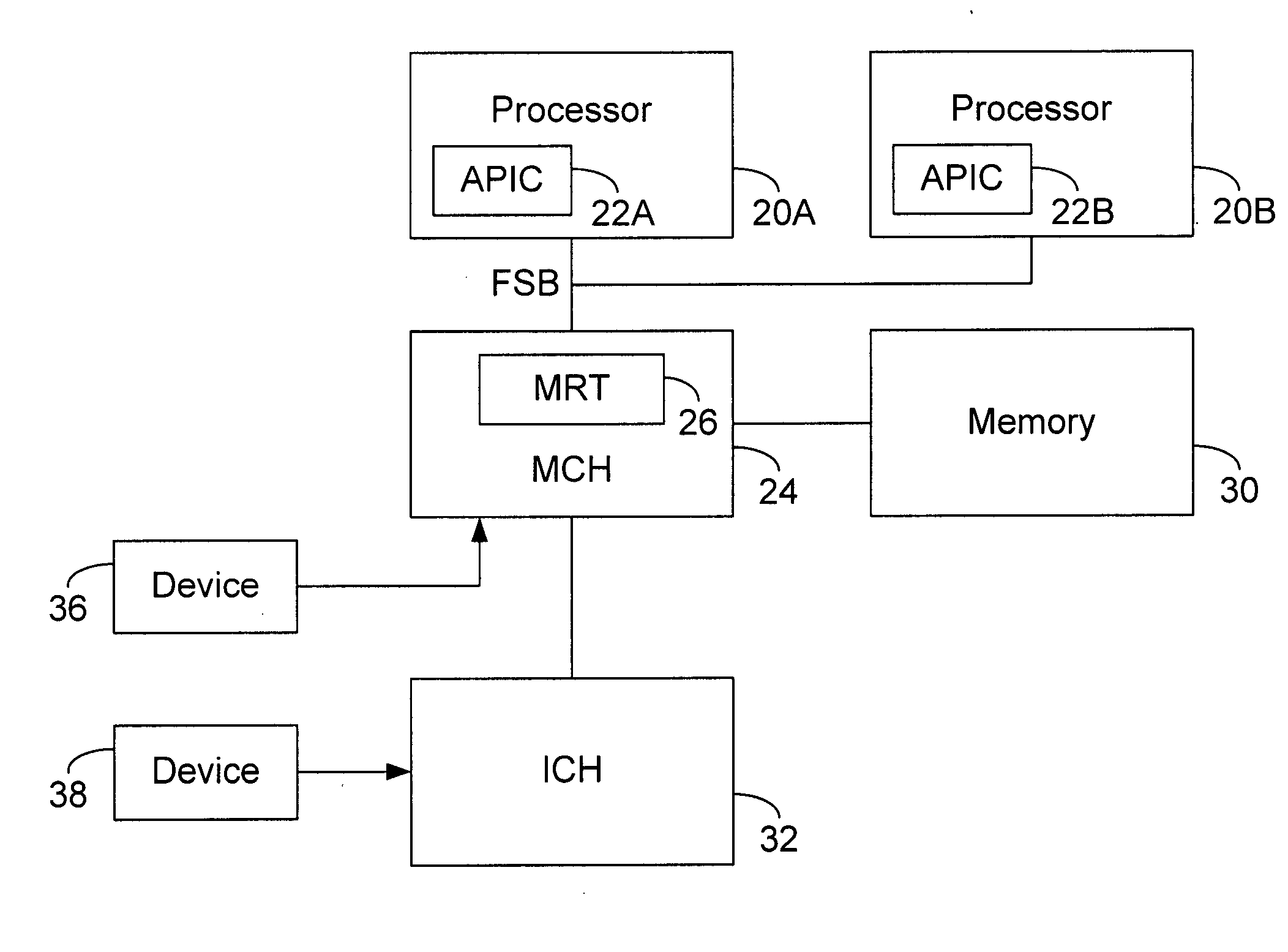

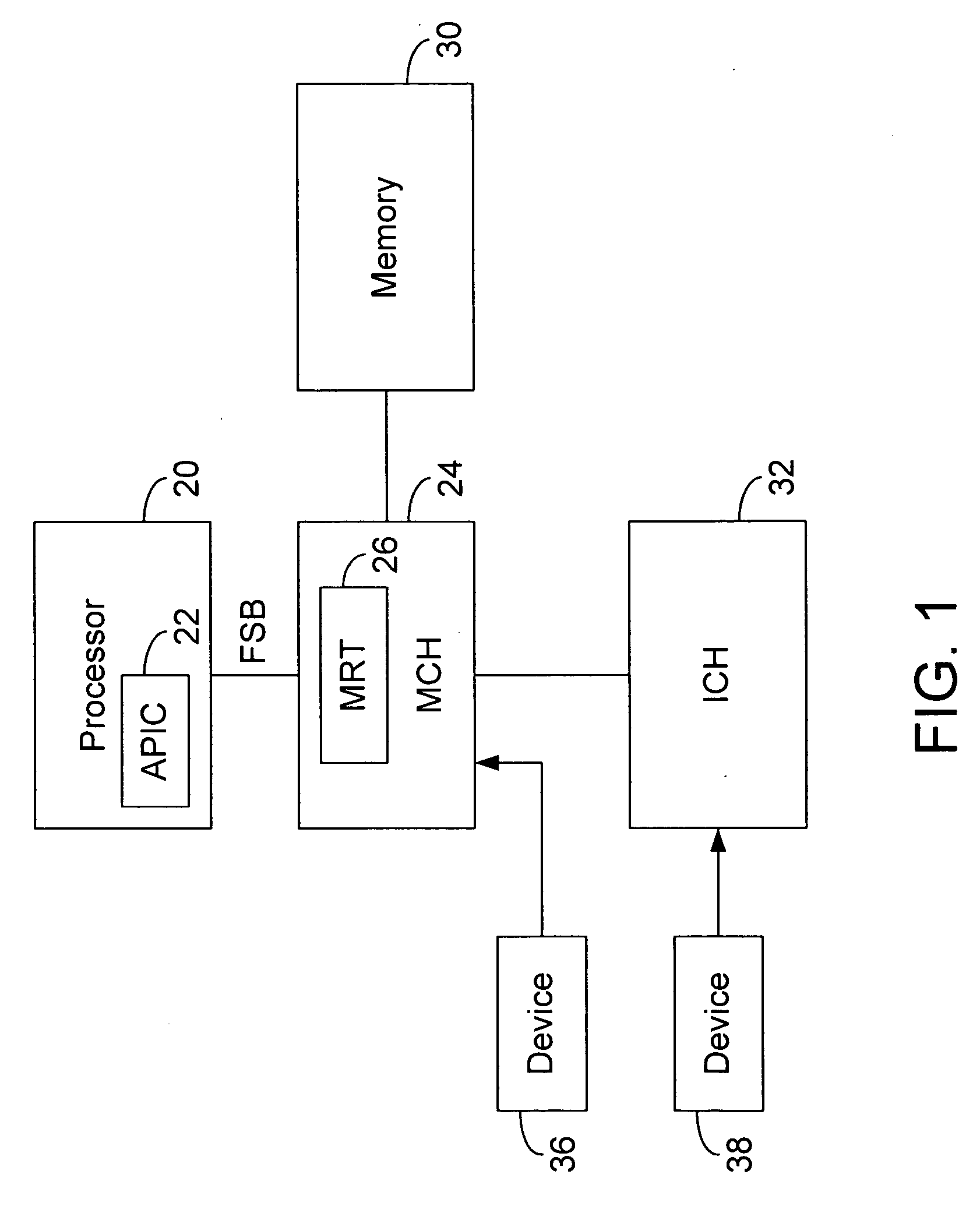

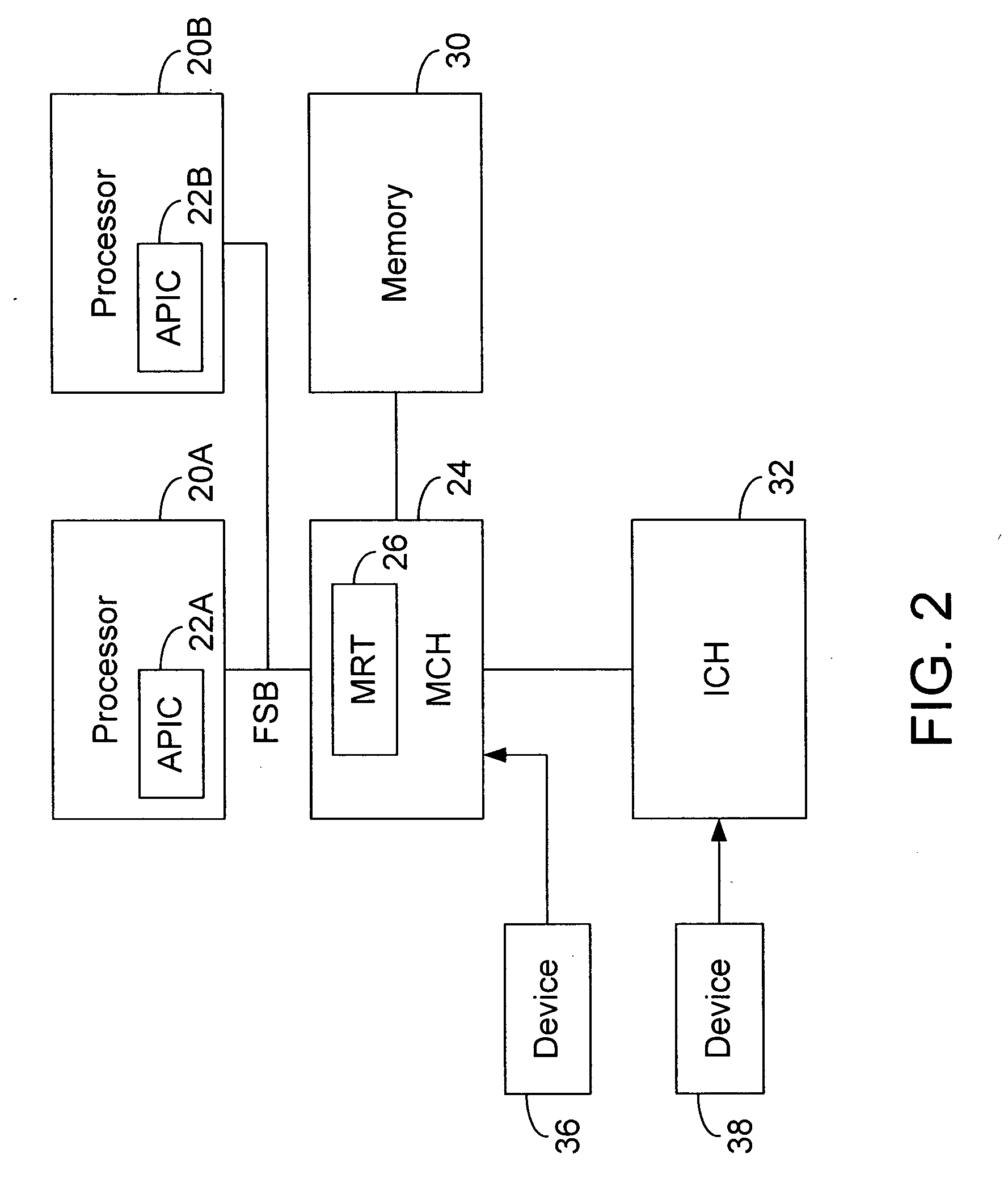

Message signaled interrupt redirection table

In some embodiments, the inventions include a chip having a message signaled interrupt redirection table (MRT) that contains entries including an address field and a data field. The chip also includes translation circuitry to translate an address field and a data field of a message signaled interrupt (MSI) signal by copying contents of the address field and data field of an entry in the MRT into the address field and data field of the MSI. Other embodiments are described and claimed.

Owner:INTEL CORP

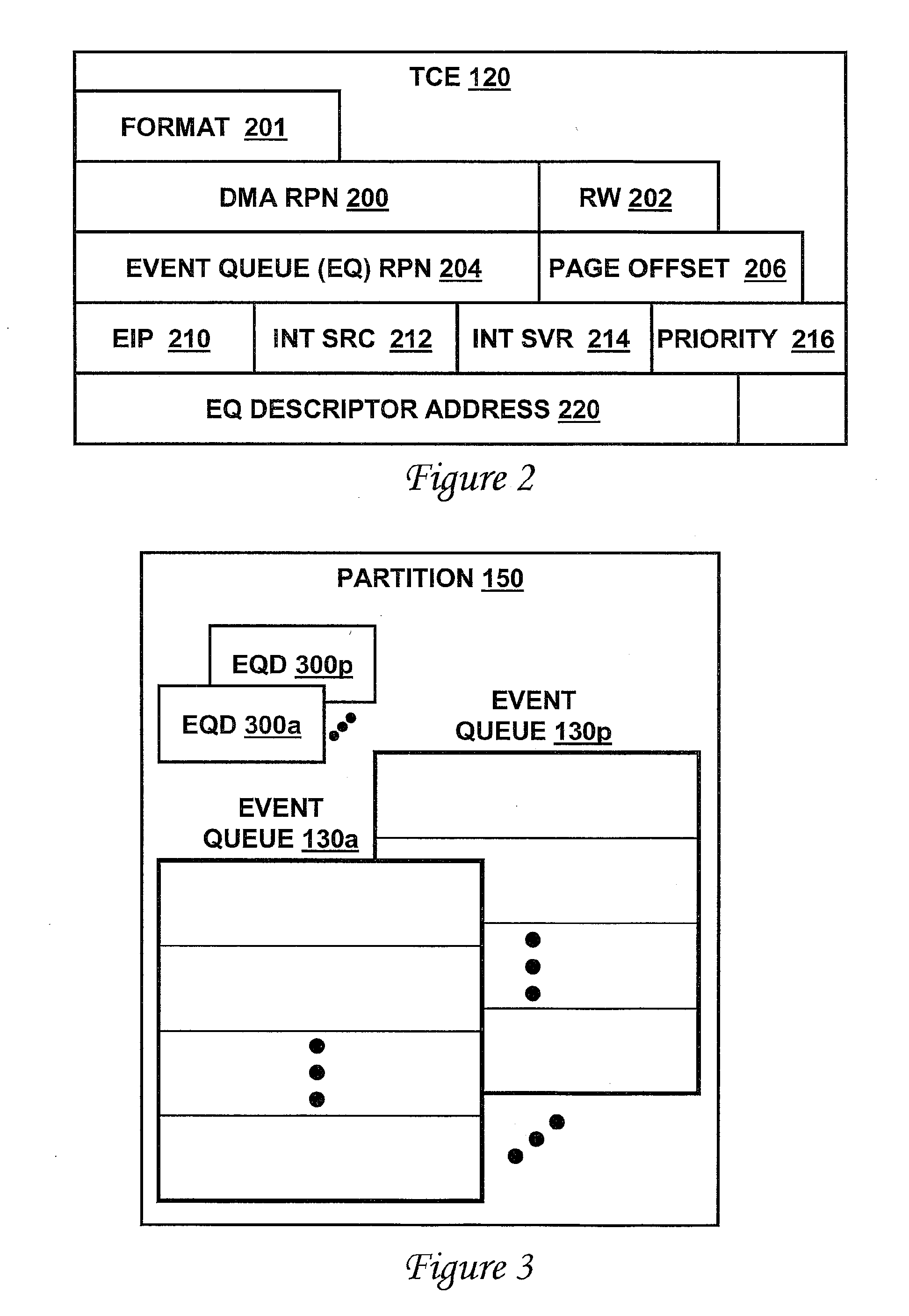

Method, system, and apparatus for enhanced management of message signaled interrupts

InactiveUS20080109564A1Input/output processes for data processingMemory addressMessage Signaled Interrupts

A message signaled interrupt (MSI) specifying an input / output (I / O) address in I / O address space is received. In response to receipt of the MSI, a translation data structure is accessed and the I / O address is translated into a physical memory address by reference to the translation data structure. The MSI is then enqueued in an event queue at the physical memory address for subsequent servicing.

Owner:IBM CORP

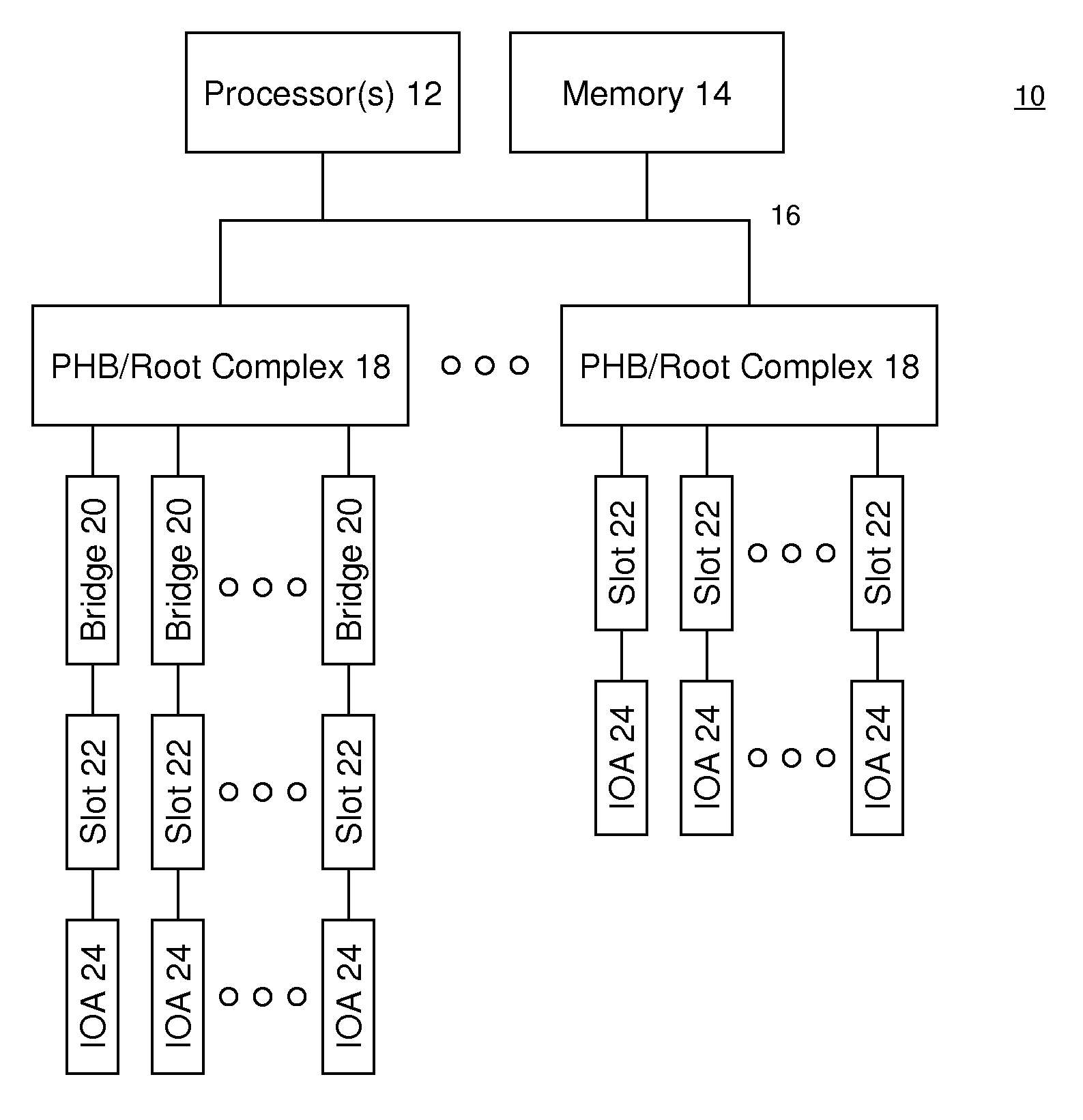

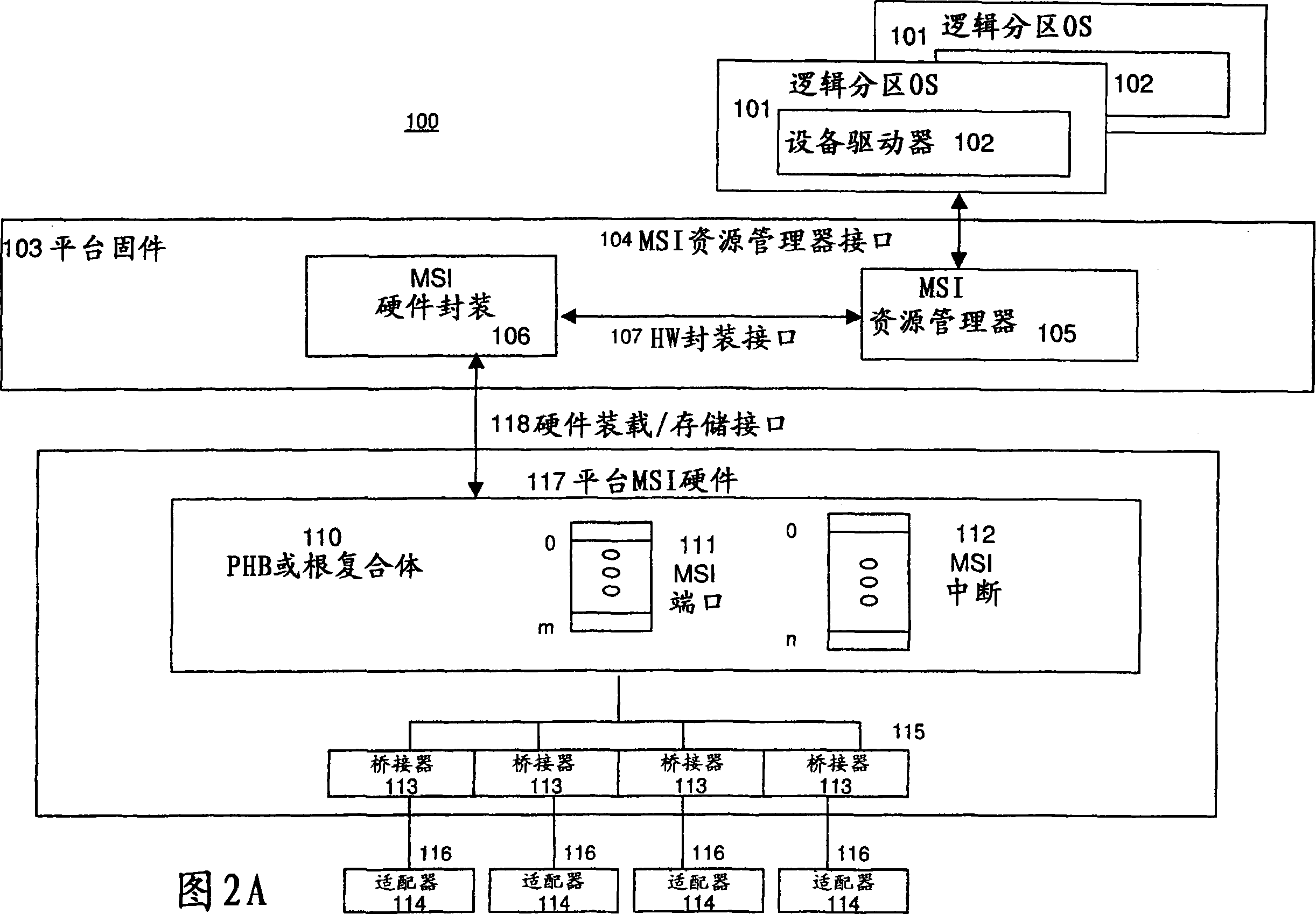

Message Signaled Interrupt Management for a Computer Input/Output Fabric Incorporating Dynamic Binding

InactiveUS20080126617A1Program controlInput/output processes for data processingMessage Signaled InterruptsClient-side

An apparatus, program product and method dynamically bind Message Signaled Interrupt (MSI) resources shared by a plurality of clients to an interrupt facility in an MSI-capable computer. In addition, management of such bindings may be implemented using a platform independent interrupt manager capable of managing multiple MSI bindings between MSI resources to an interrupt facility, and interfaced with an underlying hardware platform of a computer through platform-specific encapsulation program code.

Owner:IBM CORP

Message signaled interrupt redirection table

In some embodiments, the inventions include a chip having a message signaled interrupt redirection table (MRT) that contains entries including an address field and a data field. The chip also includes translation circuitry to translate an address field and a data field of a message signaled interrupt (MSI) signal by copying contents of the address field and data field of an entry in the MRT into the address field and data field of the MSI. Other embodiments are described and claimed.

Owner:INTEL CORP

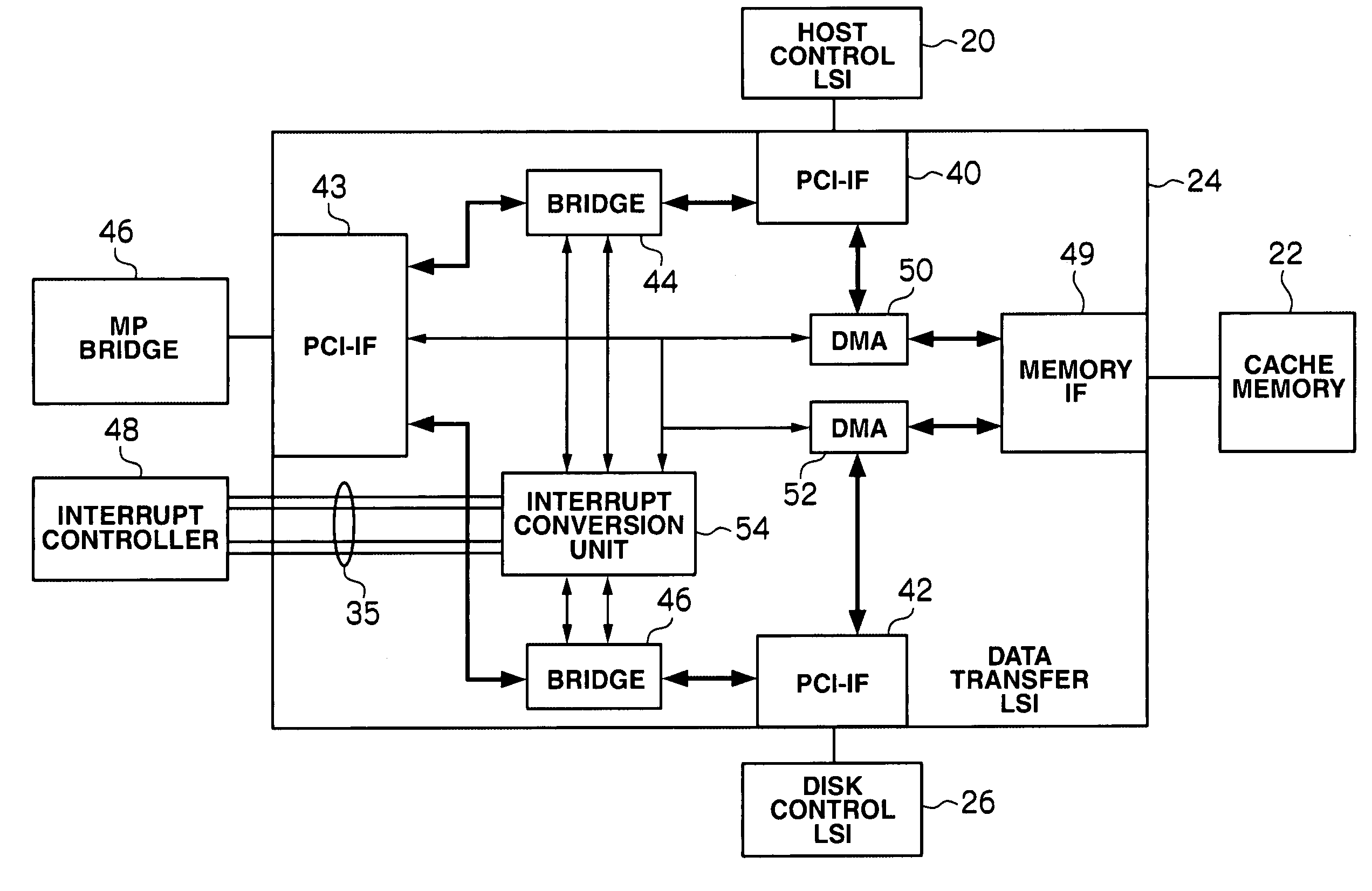

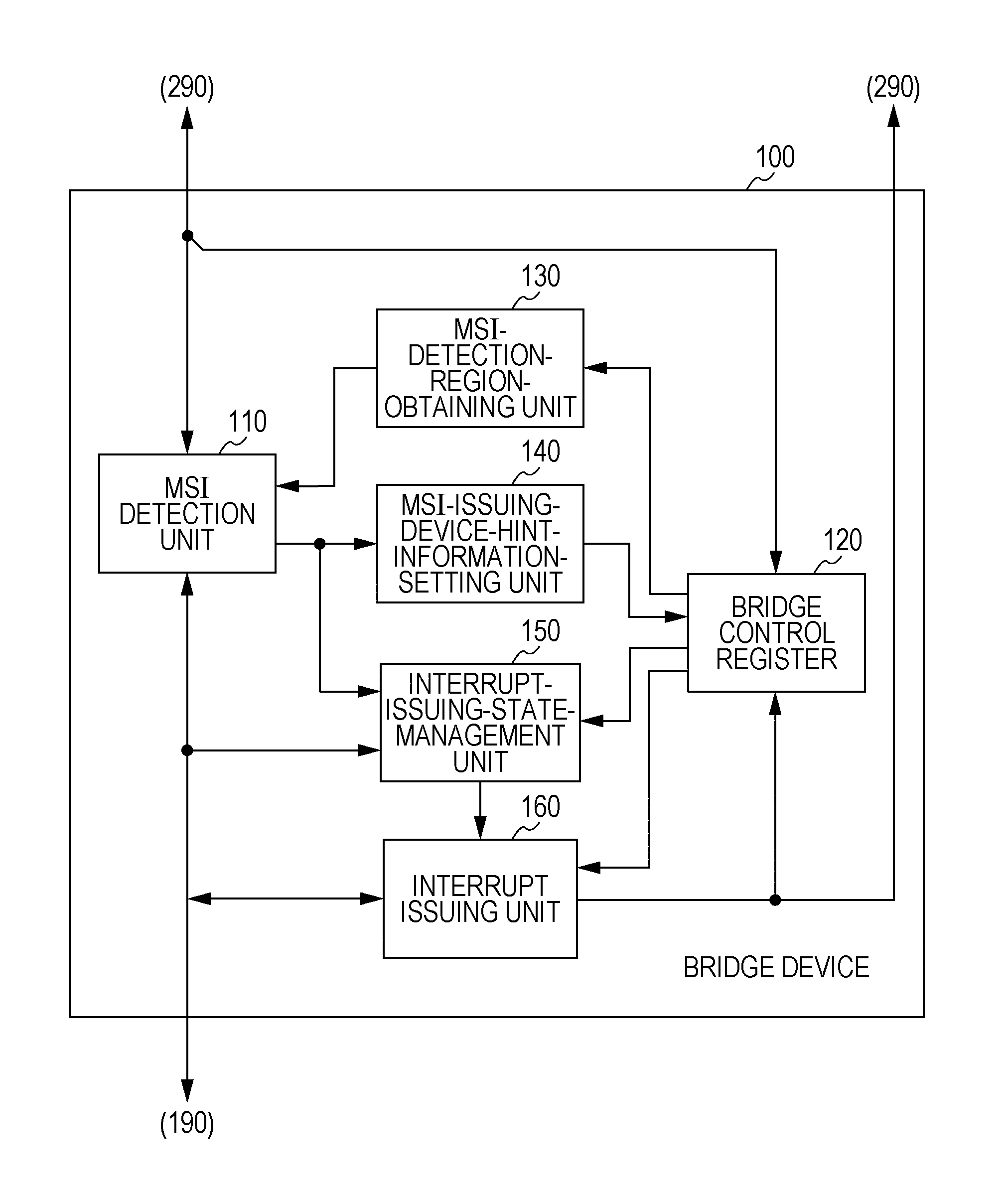

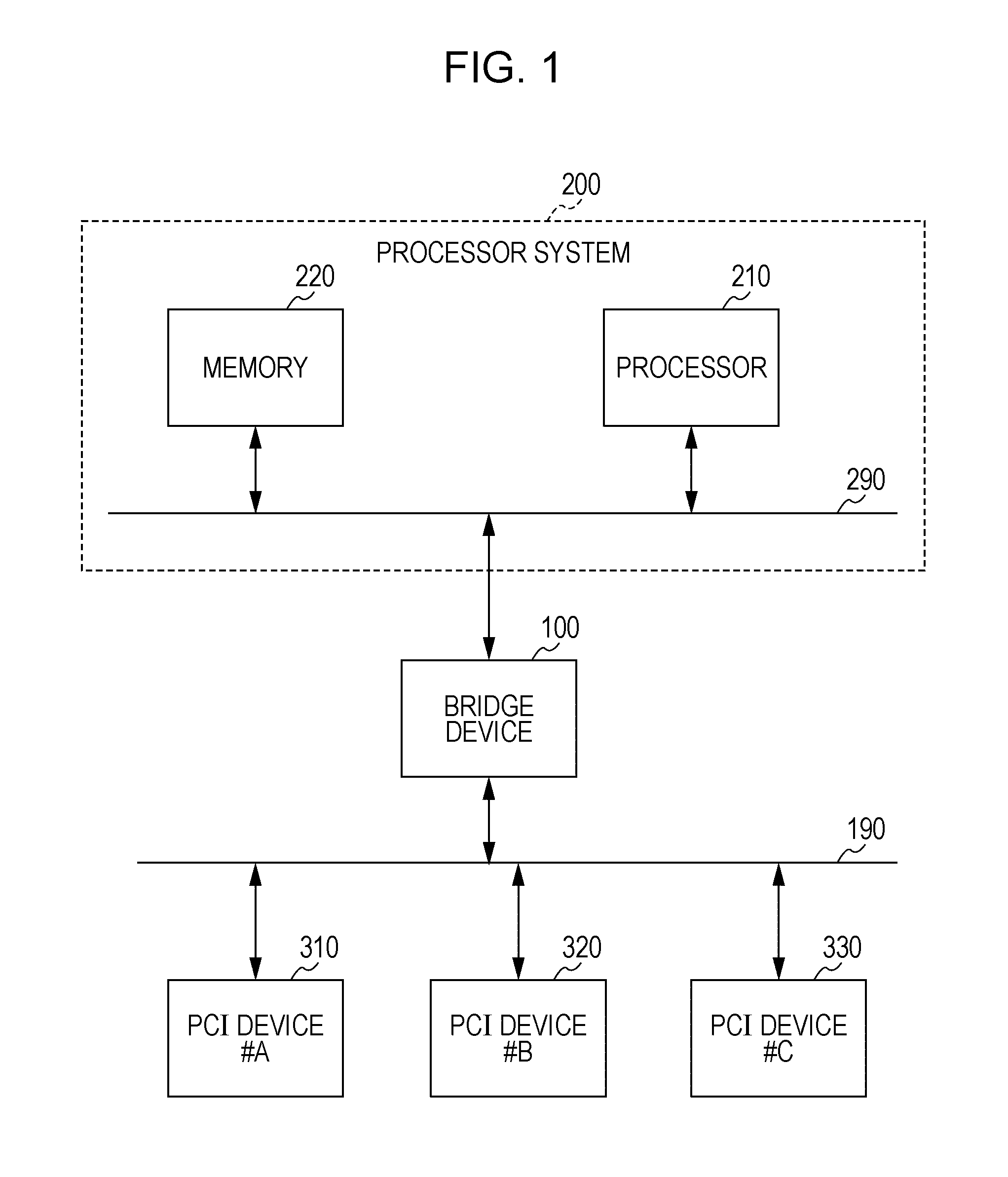

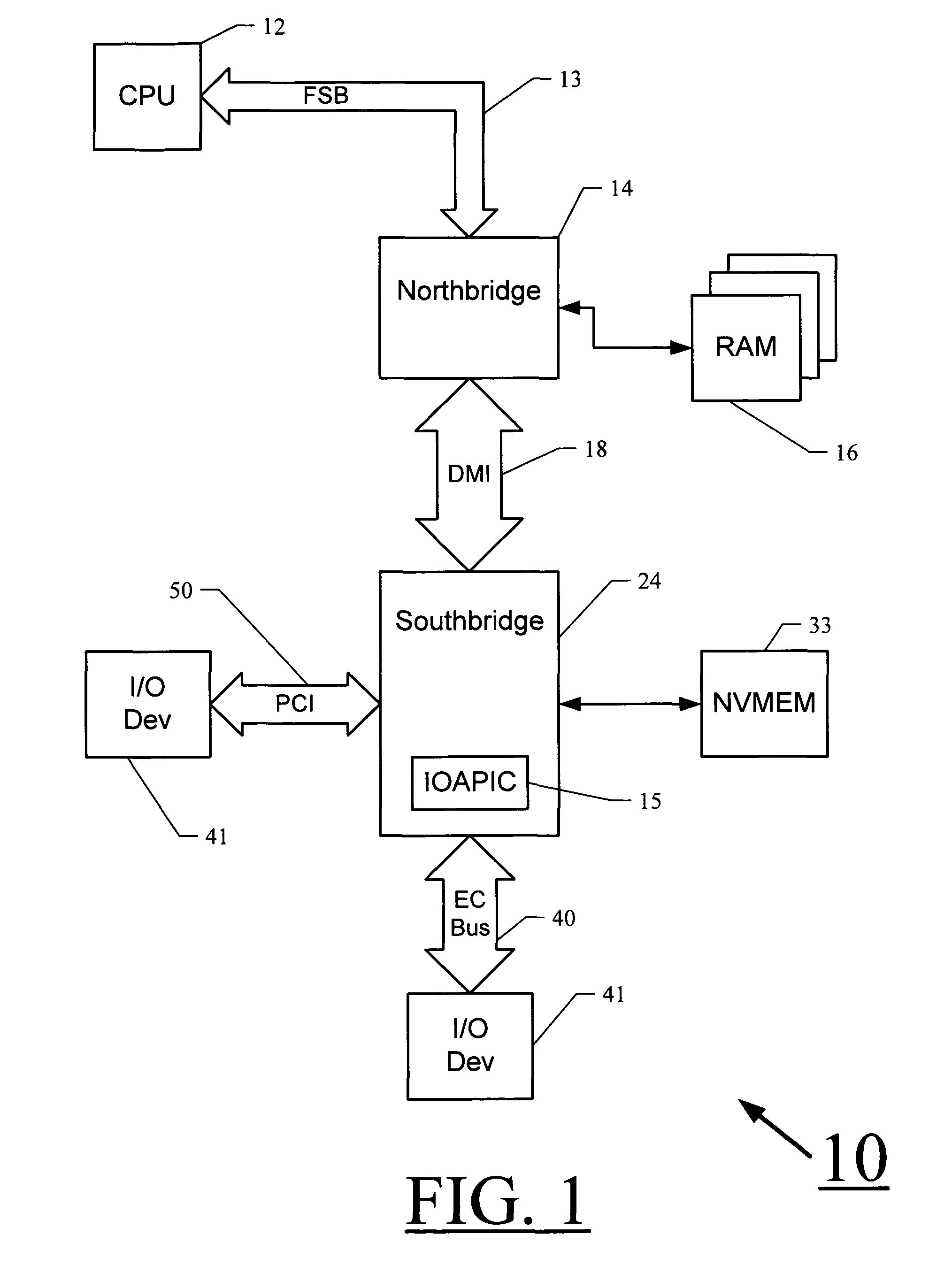

Interrupt control system and storage control system using the same

ActiveUS7526592B2Effective installationImprove efficiencyElectric digital data processingControl breakPci interface

An interrupt control system is provided where a signal-line-based interrupt system can be incorporated into interrupt control using MSIs (Message Signal Interrupts). The interrupt control system includes a first PCI interface, a second PCI interface, a PCI bridge serving as a bridge between the first PCI interface and the second PCI interface, and a control circuit for controlling an interrupt signal. The PCI bridge recognizes a message signal interrupt issued from the first PCI interface to the second PCI interface and transfers the message signal interrupt to the control circuit, and the control circuit is provided with an interrupt conversion unit for converting the message signal interrupt into an interrupt signal and outputting it via a signal line.

Owner:GOOGLE LLC

Validating message-signaled interrupts by tracking interrupt vectors assigned to devices

ActiveUS8631181B2Interrupt usePlatform integrity maintainanceMessage Signaled InterruptsComputer science

Owner:ORACLE INT CORP

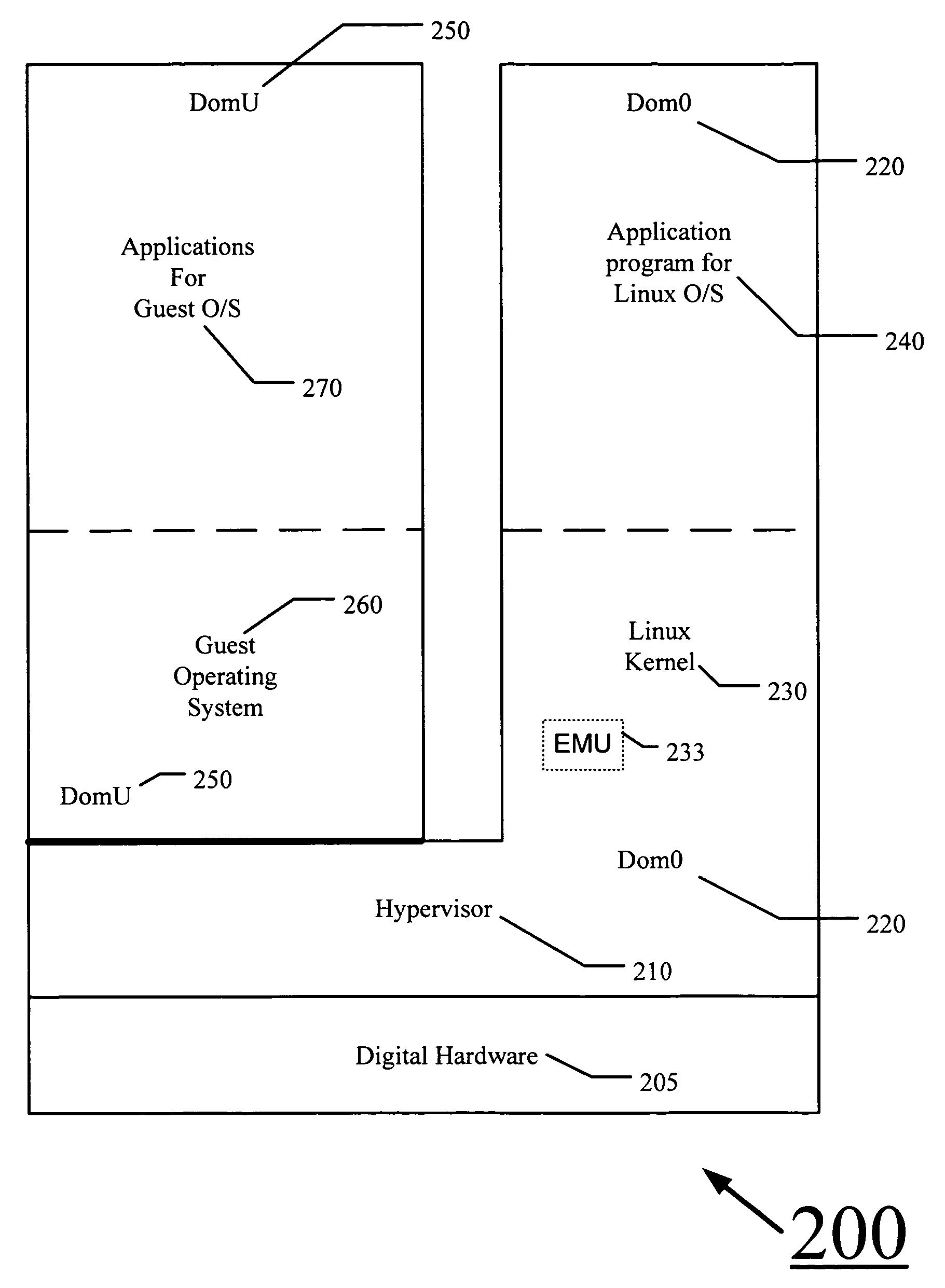

Converting a message signaled interruption into an I/O adapter event notification to a guest operating system

Owner:IBM CORP

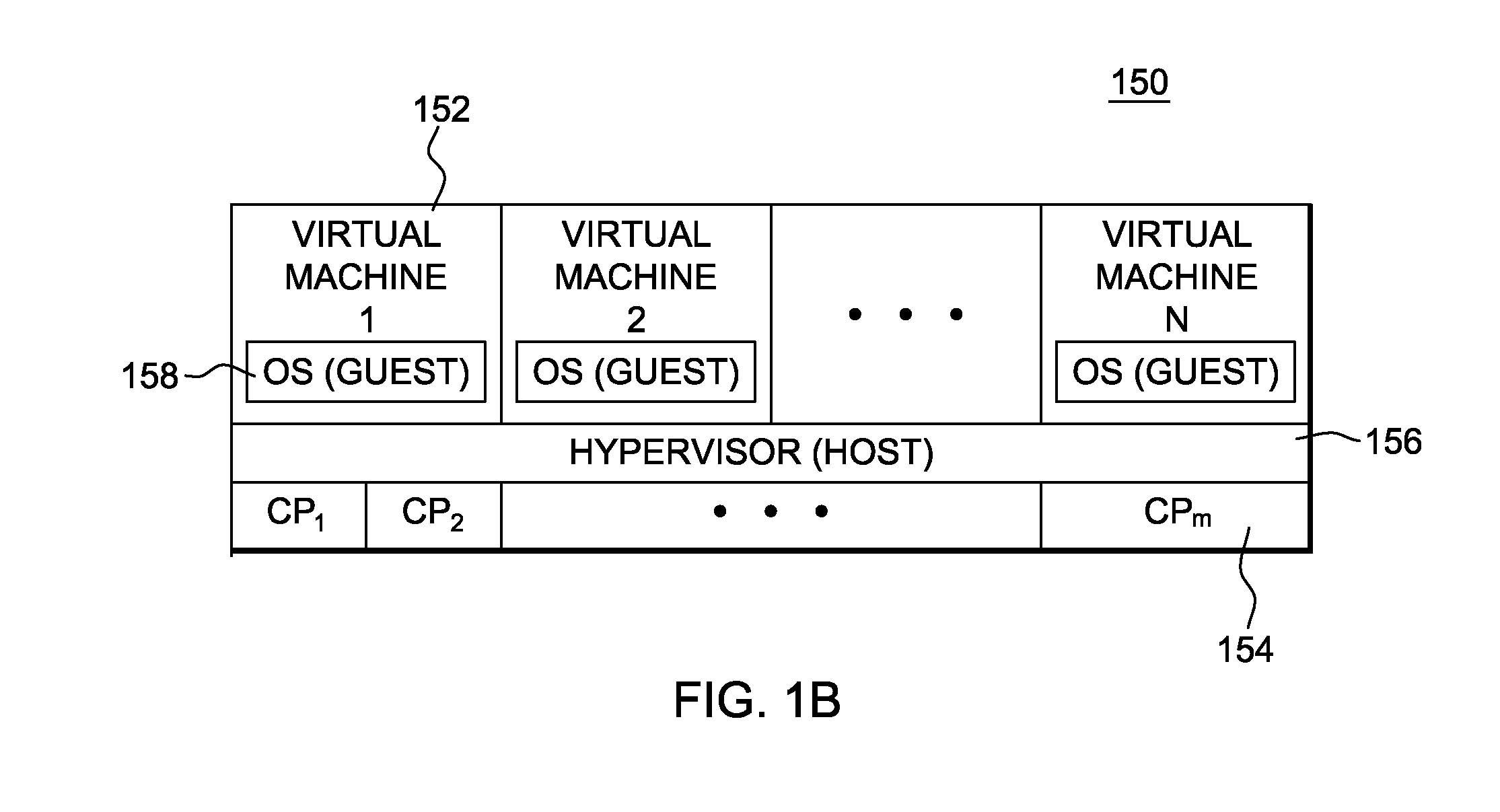

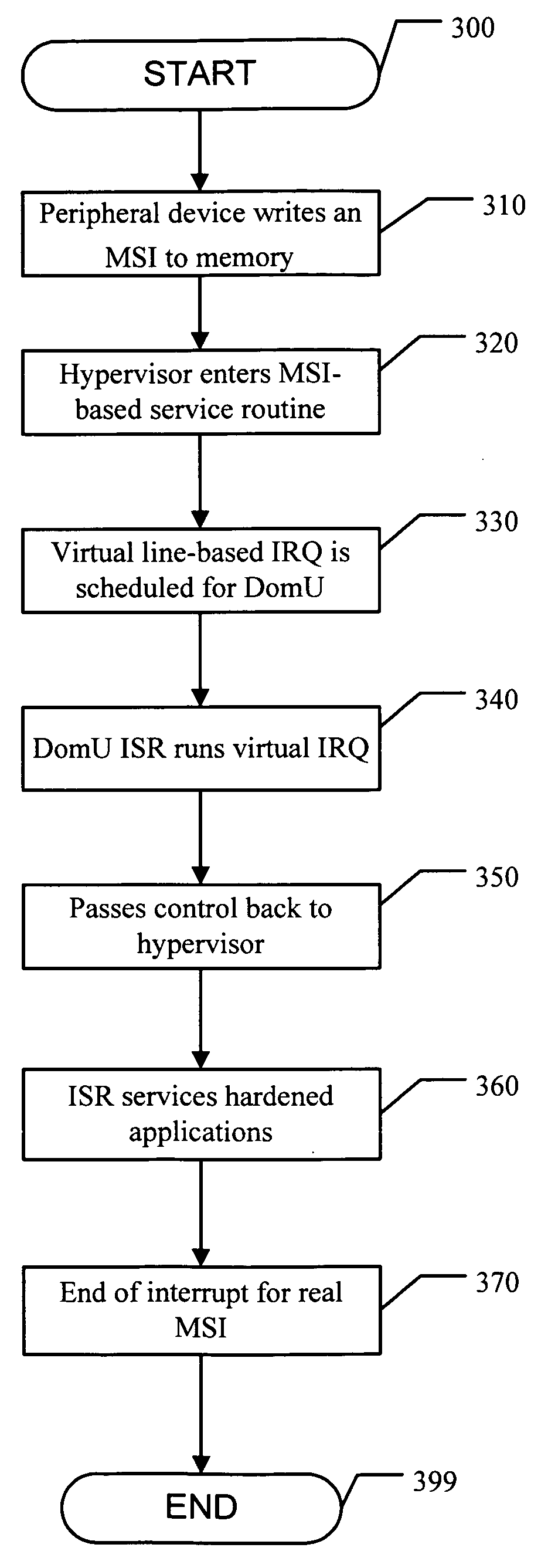

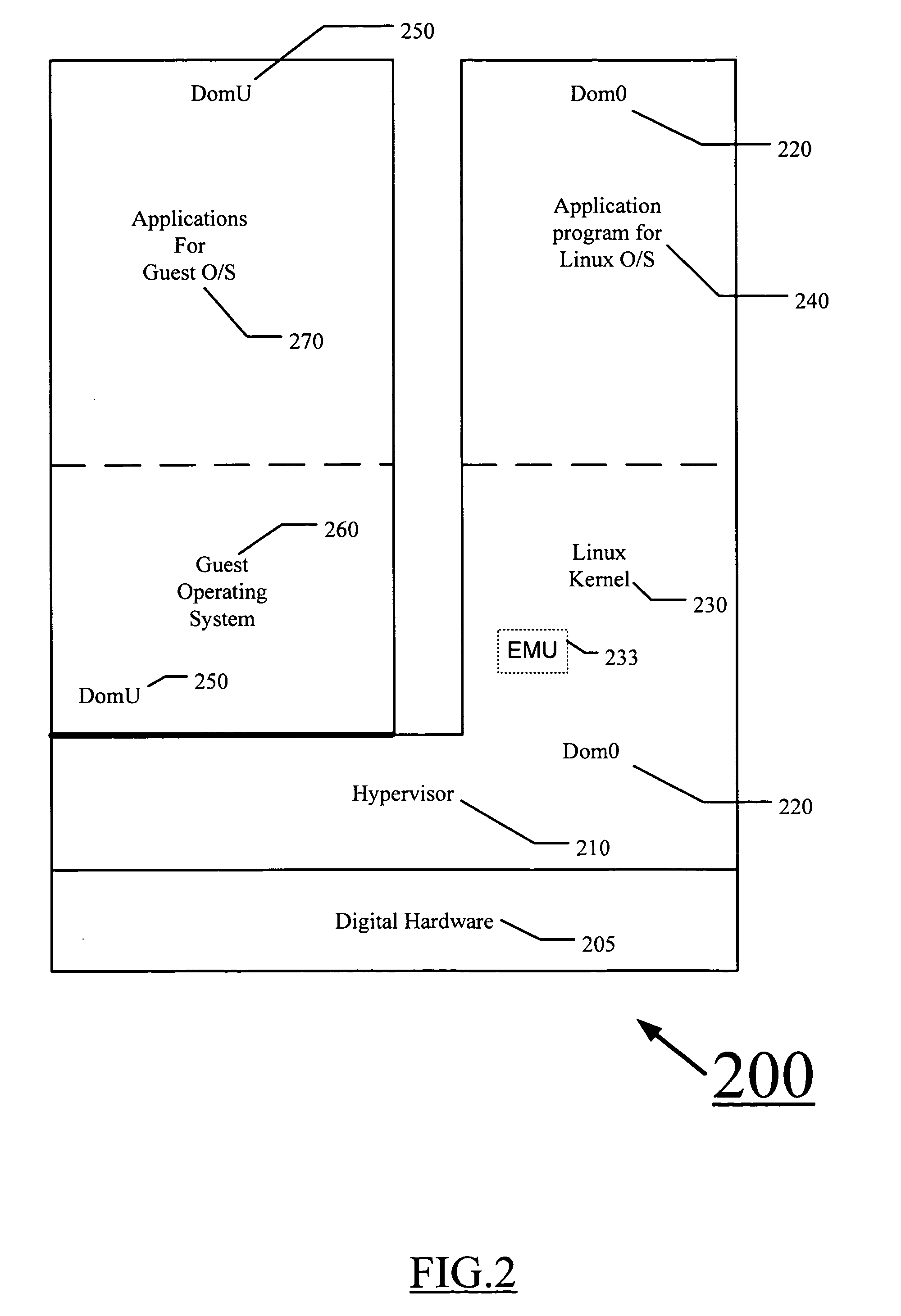

Interrupt request and message signalled interrupt logic for passthru processing

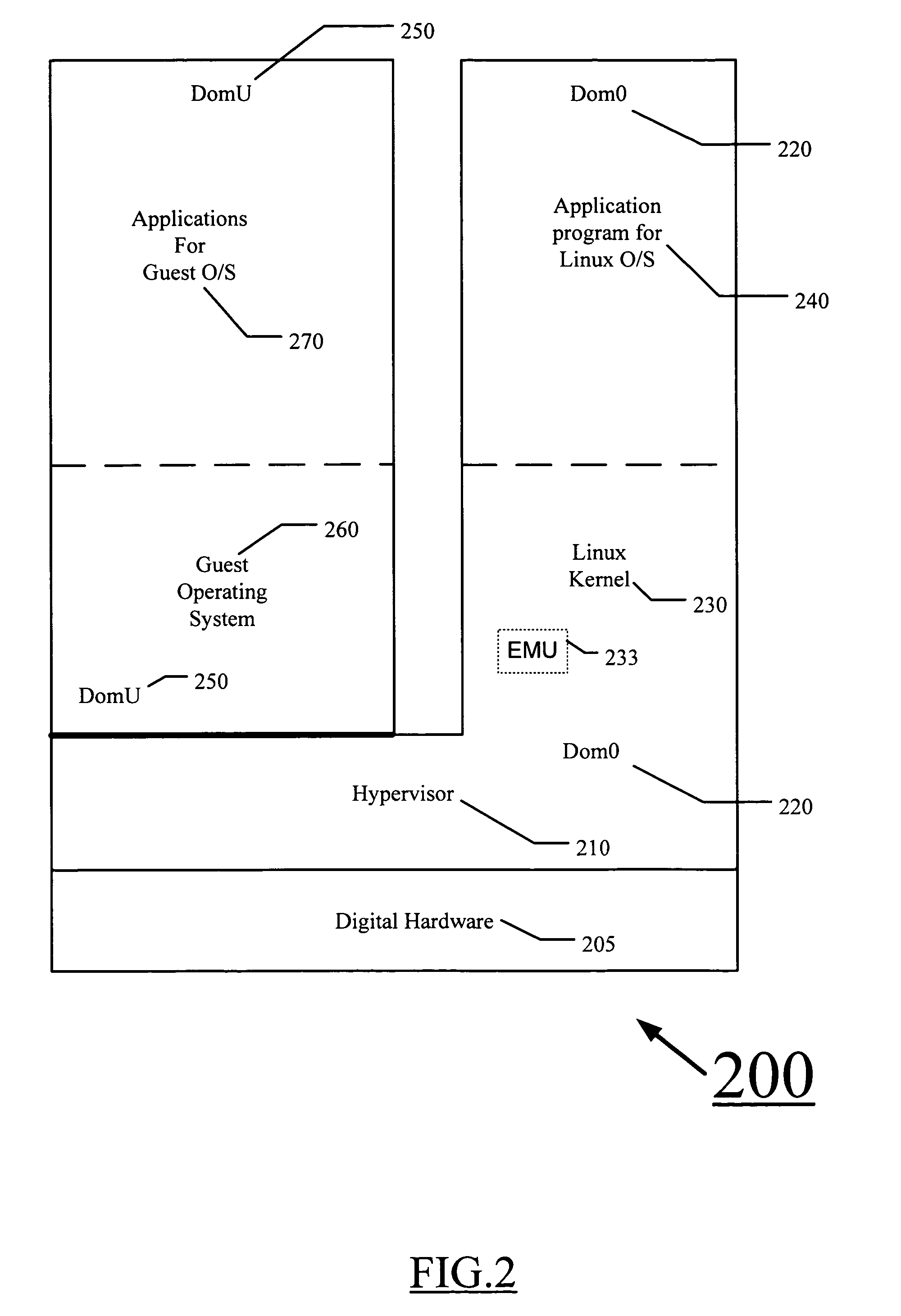

InactiveUS20100161864A1Enables interrupt sharingProgram controlMessage Signaled InterruptsDevice status

Methods, systems, apparatuses and program products are disclosed for managing interrupt services in hypervisor and hypervisor-related environments in Message Signaled Interrupts are emulated as other type(s) of interrupt.According to an aspect of the present invention, a method of executing a program includes receiving a MSI (message signaled interrupt). Responsively, a virtual interrupt is generated and an ISR (interrupt service routine) is invoked that handles a line-based virtual interrupt transaction. A surrogate or virtual peripheral device status may also be provided and may be associated with the virtual interrupt. A single device interrupt event may, in certain circumstances, be serviced both as a line-based interrupt and also as an MSI, or as either responsive to run-time context.Embodiments of the present invention enable superior tradeoffs in regards to the interrupt sharing to a greater and more flexible extent than with previous implementations. Moreover, it makes possible interrupt sharing using an ISR that was not expressly designed for interrupt sharing.

Owner:HEWLETT PACKARD CO

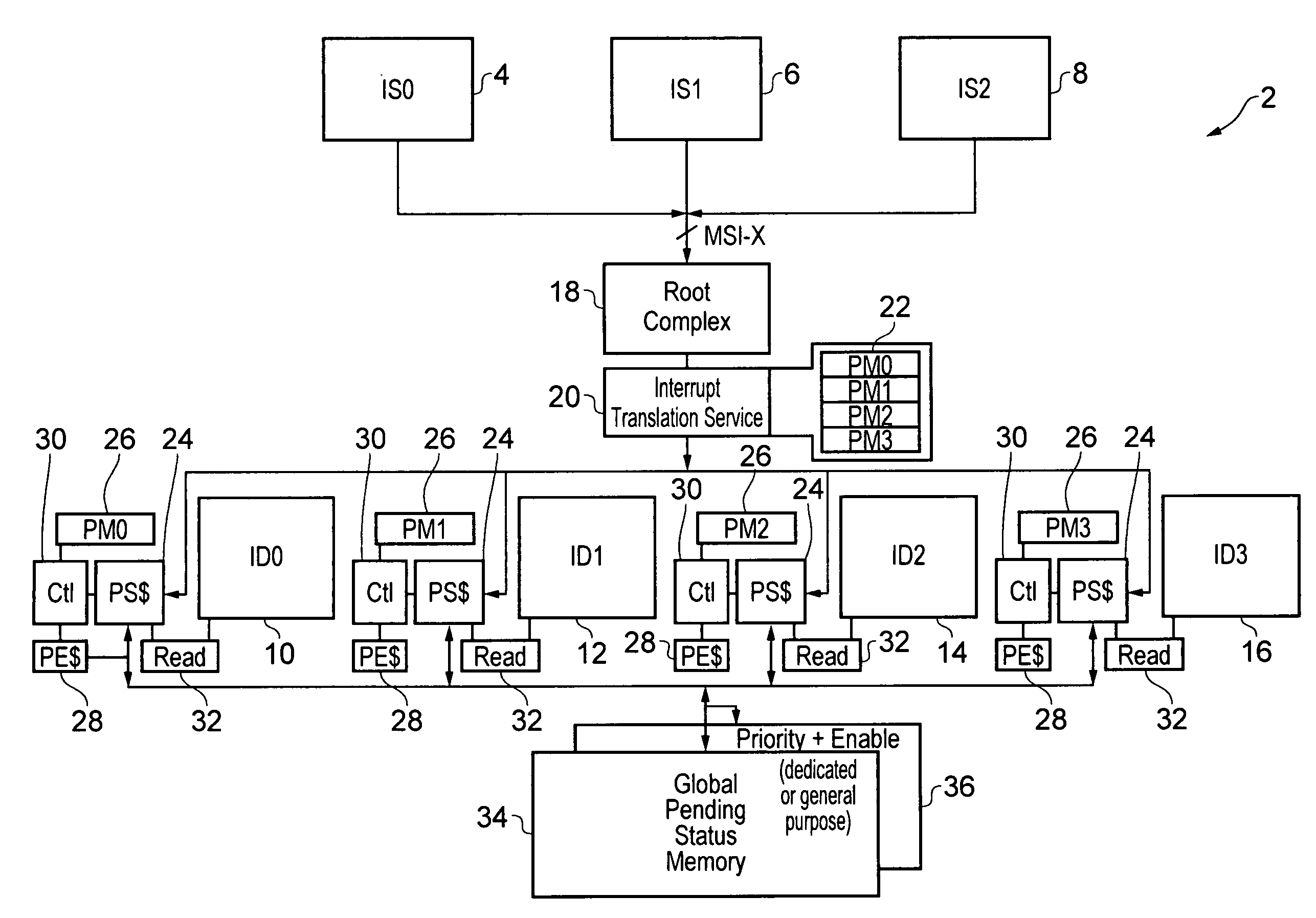

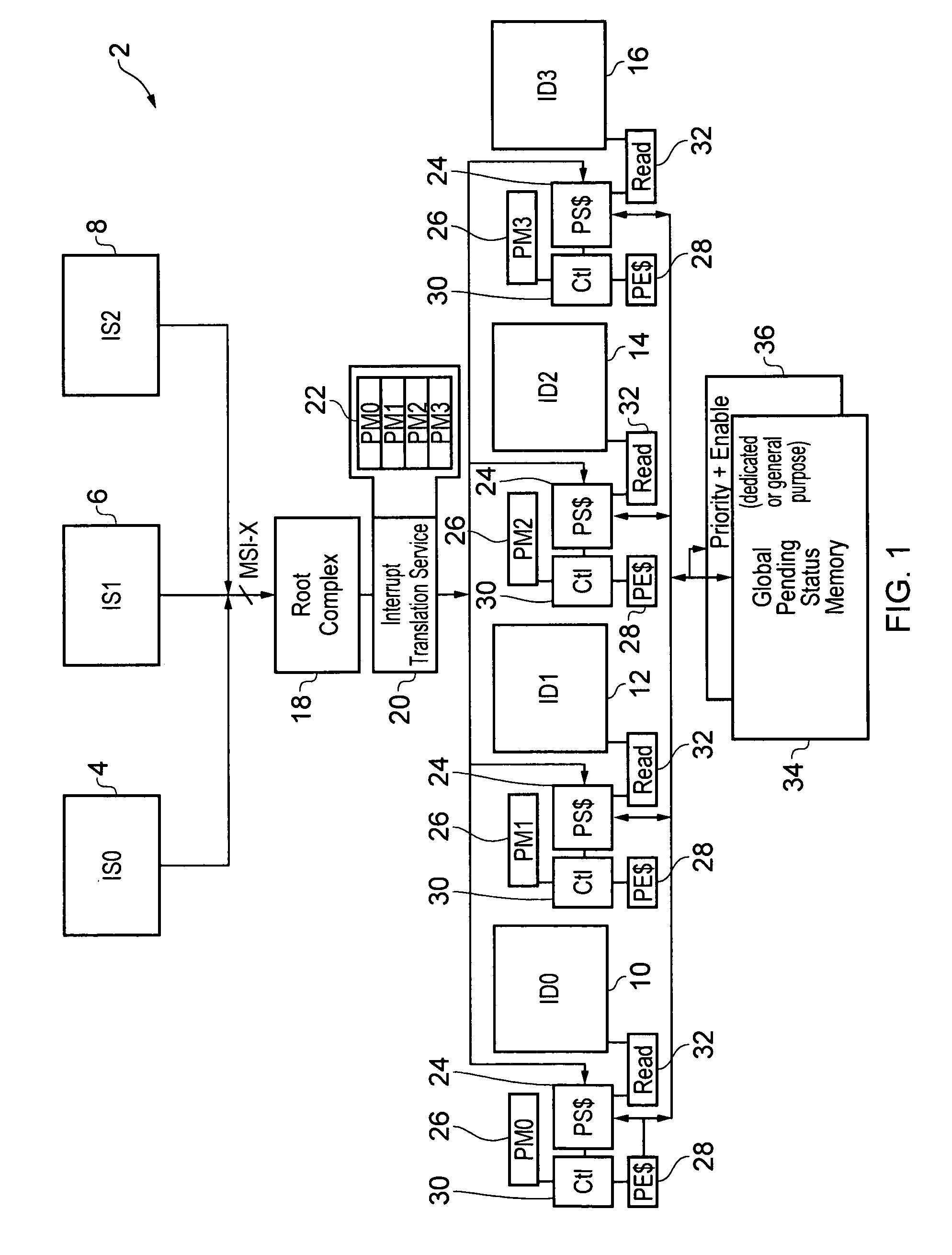

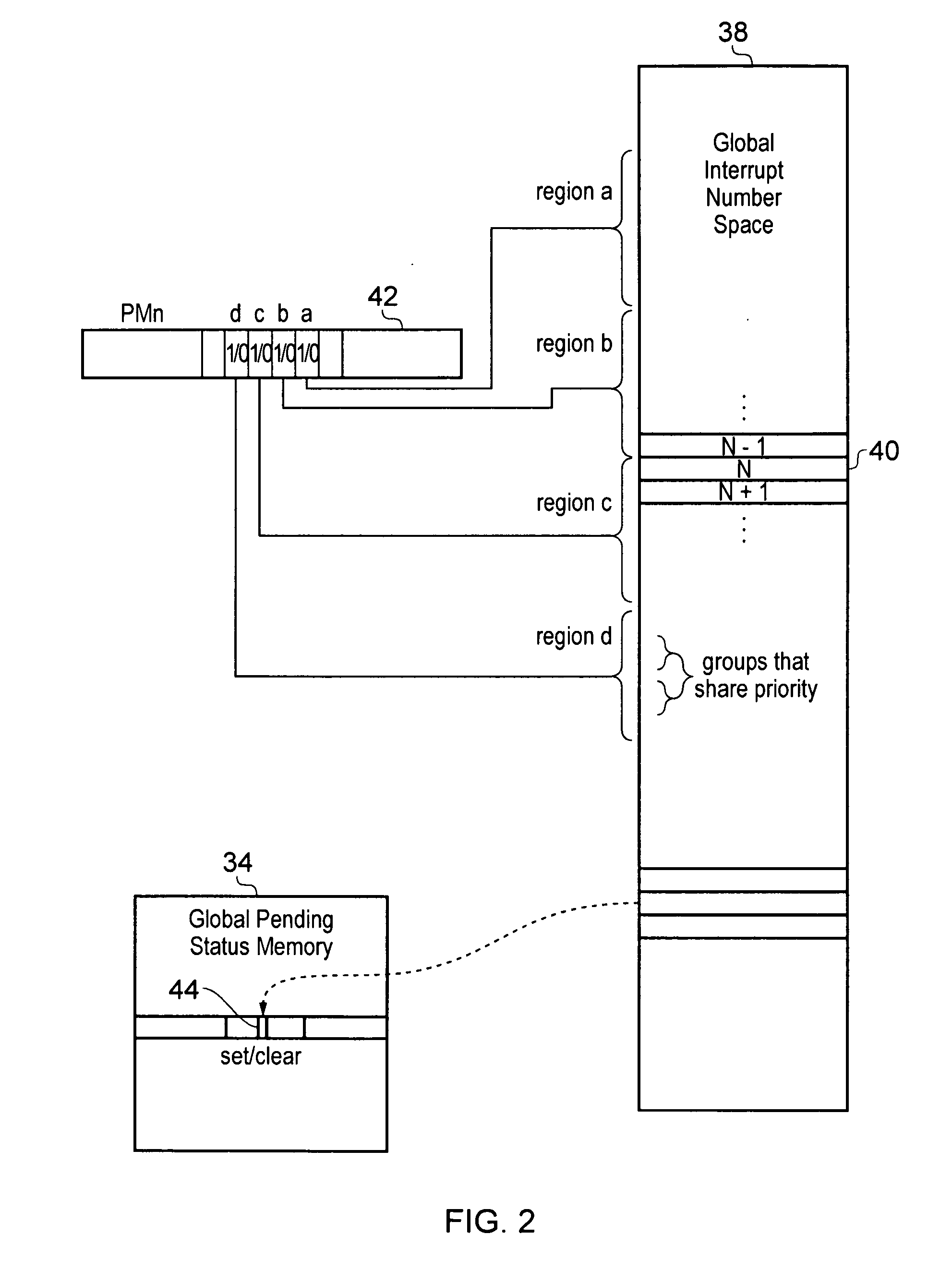

Interrupt source controller with scalable state structures

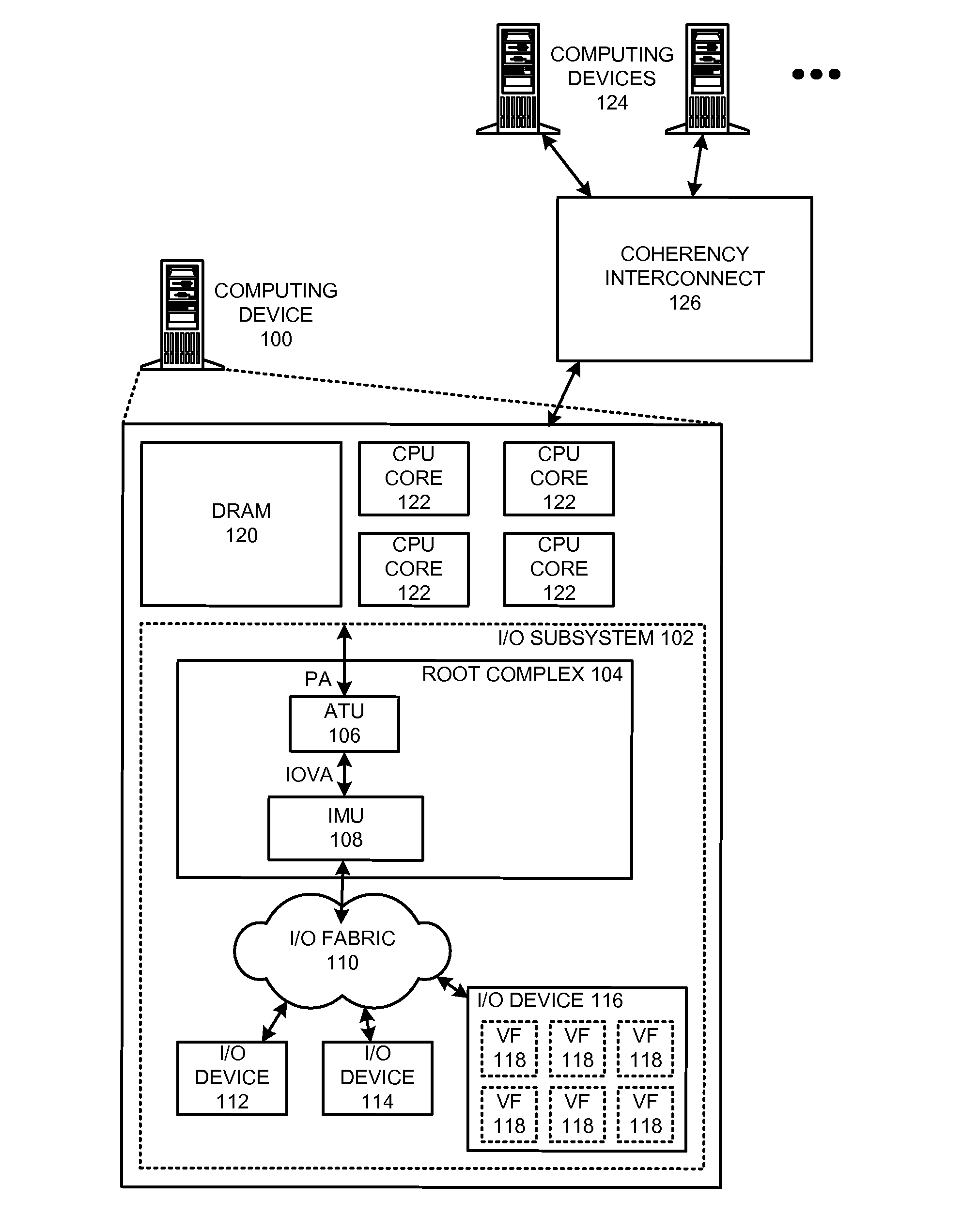

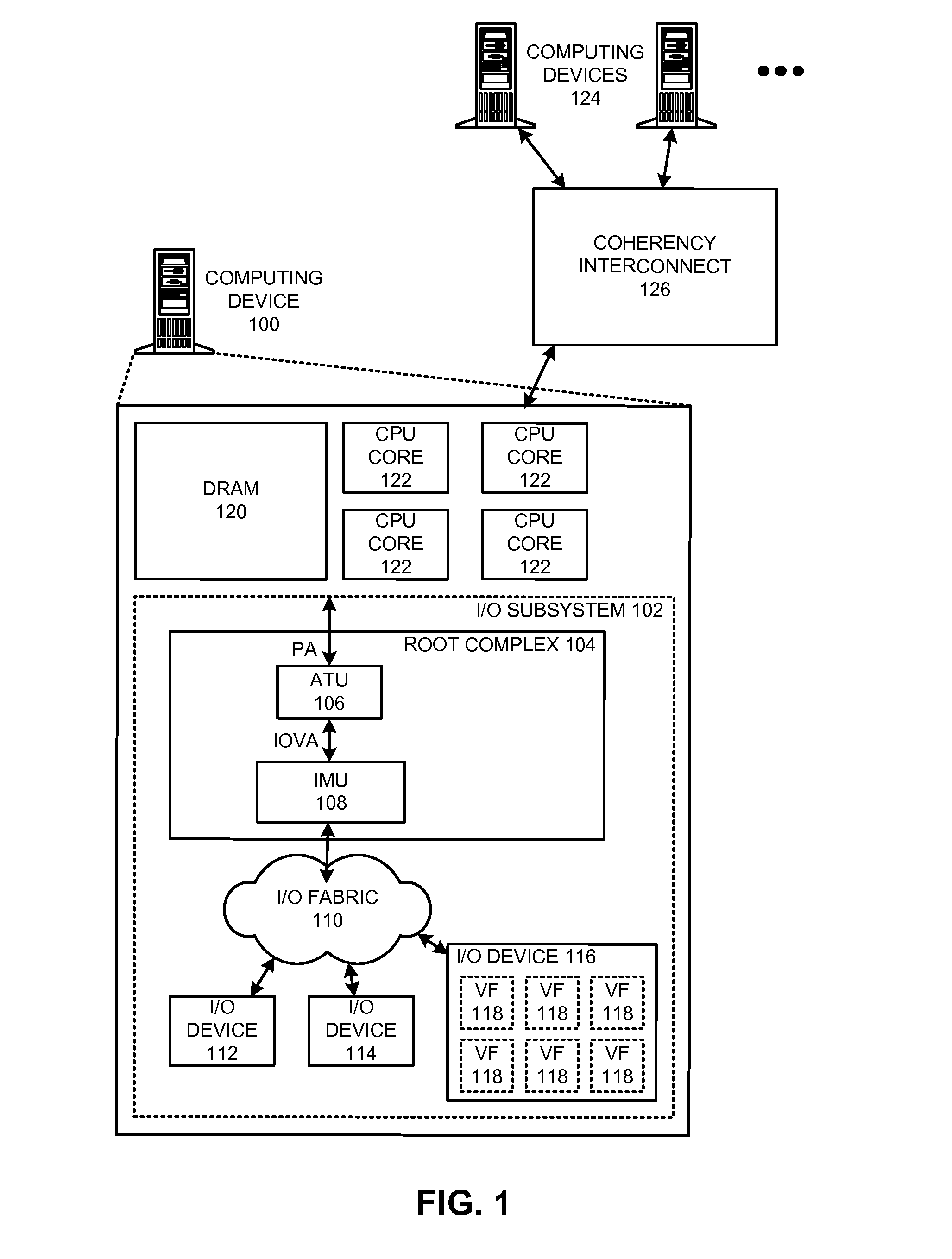

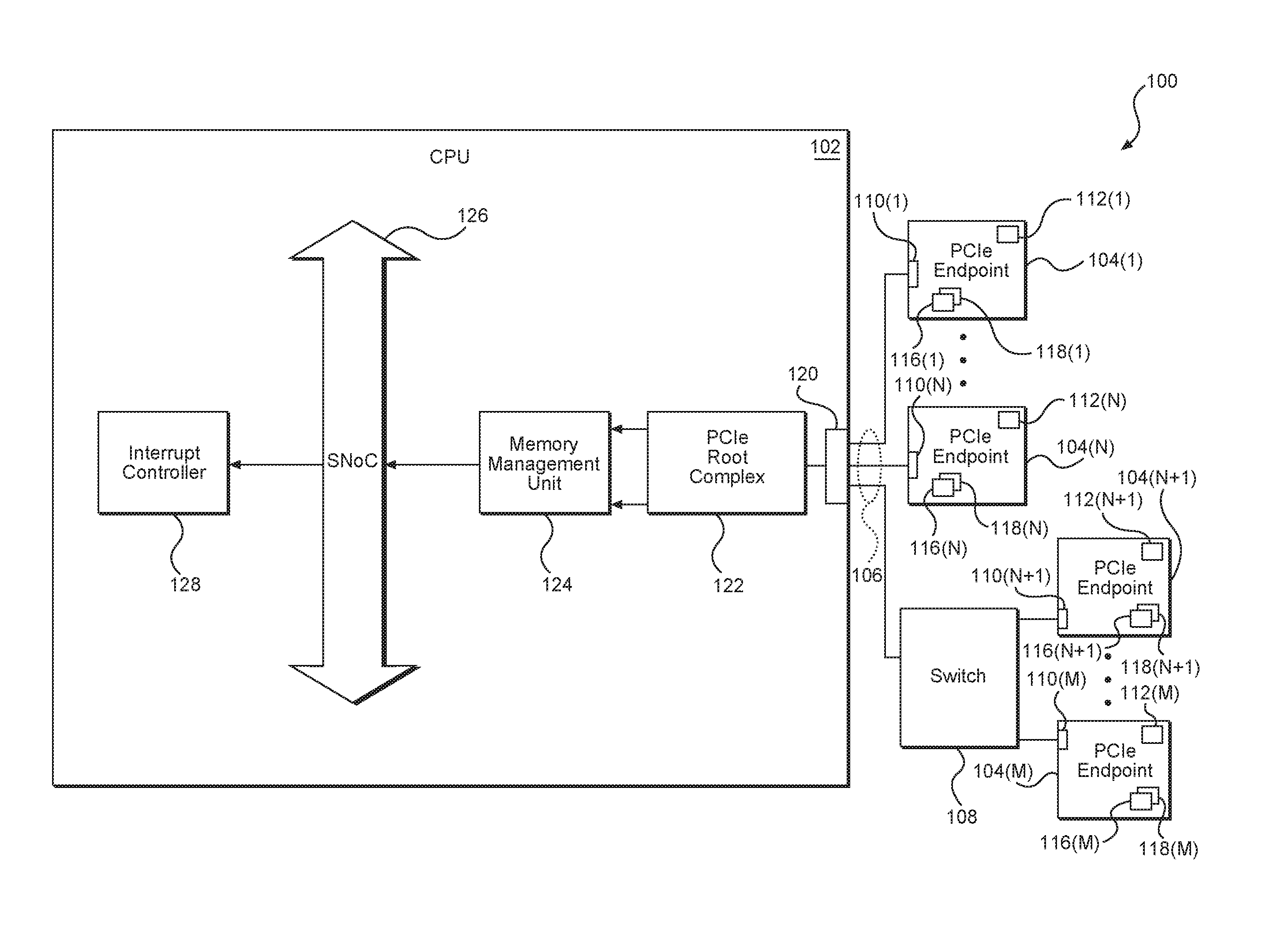

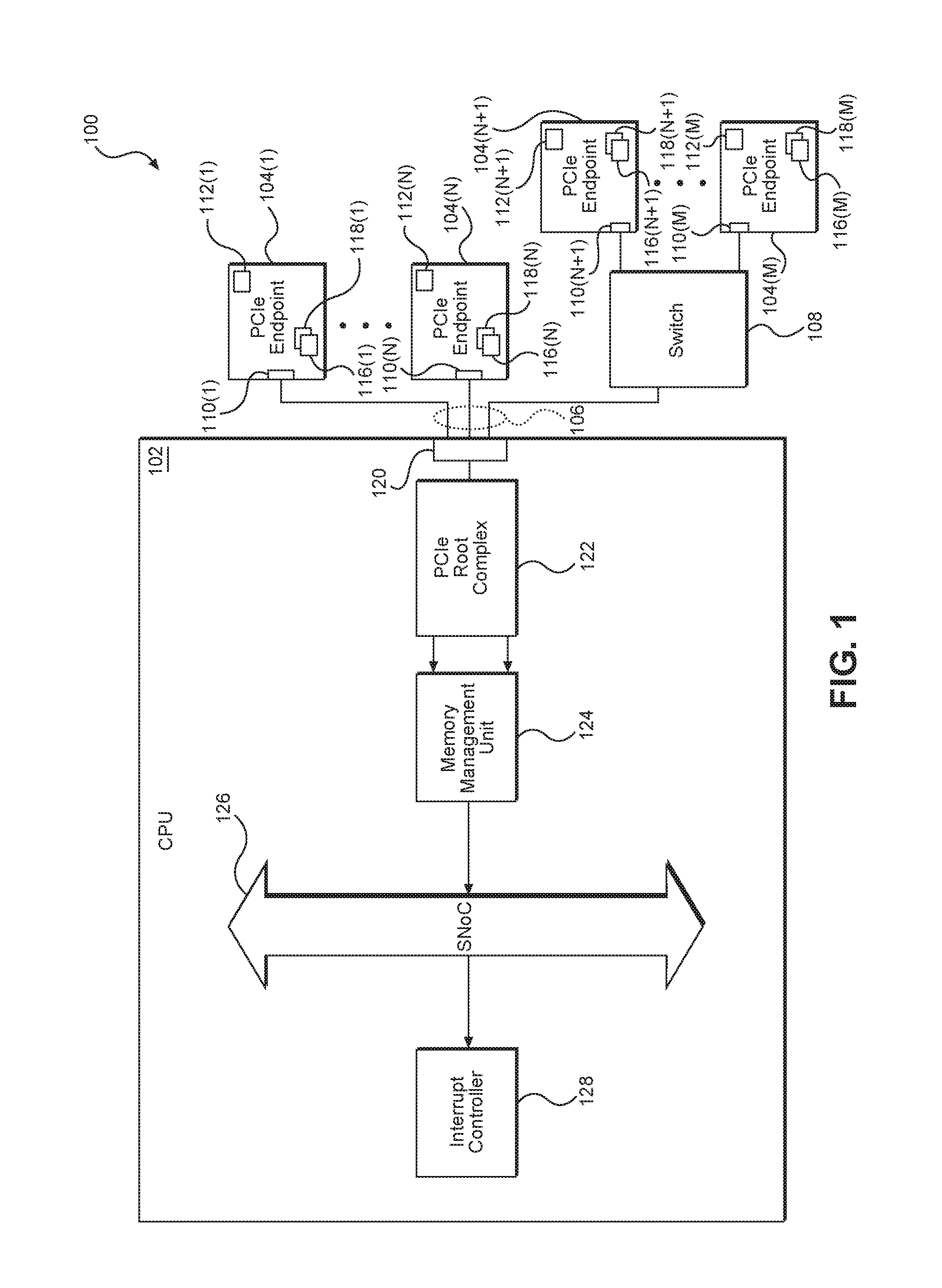

A data processing system includes a processor core, a system memory, coupled to the processor core, that includes an interrupt data structure including a plurality of entries each associated with a respective one of a plurality of interrupts. An input / output (I / O) subsystem including at least one I / O host bridge and a plurality of partitionable endpoints (PEs) each having an associated PE number. The I / O host bridge, responsive to receiving a message signaled interrupt (MSI) including at least a message address, determines from the message address a system memory address of a particular entry among the plurality of entries in the interrupt data structure, accesses the particular entry, and, based upon contents of the particular entry, validates authorization of an interrupt source to issue the MSI and presents an interrupt associated with the particular entry for service.

Owner:IBM CORP

Communication of message signalled interrupts

ActiveUS20140122760A1Easy to handleImprove efficiencyDigital data processing detailsDigital computer detailsPending - statusMessage Signaled Interrupts

Owner:ARM LTD

System for signaling serialized interrupts using message signaled interrupts

The present invention provides a system for signaling legacy serialized interrupts within a PCI-Express environment, using message signaled interrupts. The system provides structures and methods that interface a PCI environment (106) with a PCI-Express environment (104). The present invention provides a PCI to PCI-Express bridge device (110) that is communicatively linked (112, 114) to the PCI and PCI-Express environments. The bridge device comprises a translation function (116) that is communicatively linked (120, 122) to the PCI and PCI-Express environments. A serialized interrupt is signaled from the PCI environment, and the translation function generates a message signaled interrupt within the PCI-Express environment based on that serialized interrupt.

Owner:TEXAS INSTR INC

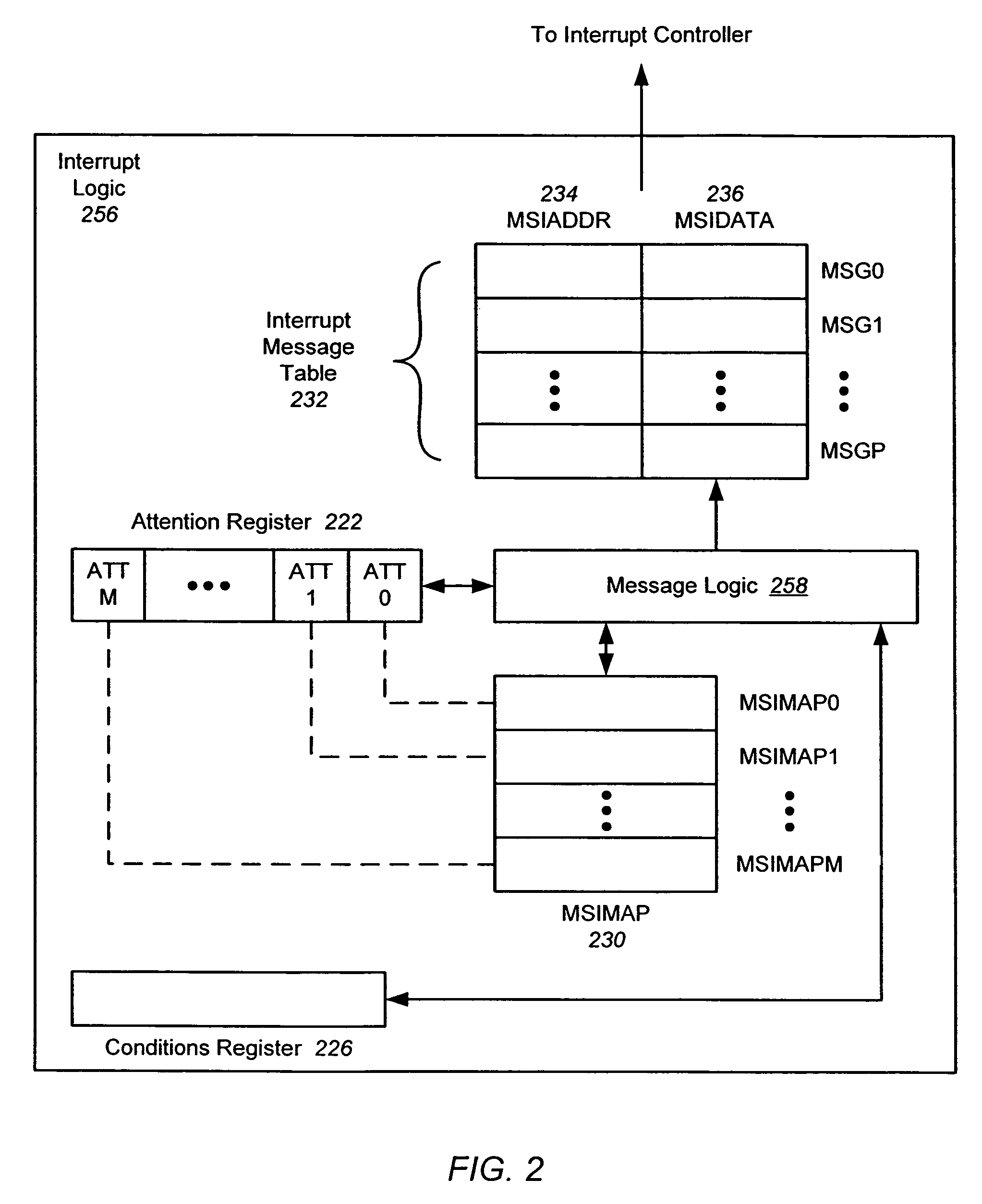

Message signaled interrupt extended (MSI-X) auto clear and failsafe lock

InactiveUS7565471B2Improve performanceAvoid adjustmentMemory systemsMessage Signaled InterruptsFail-safe

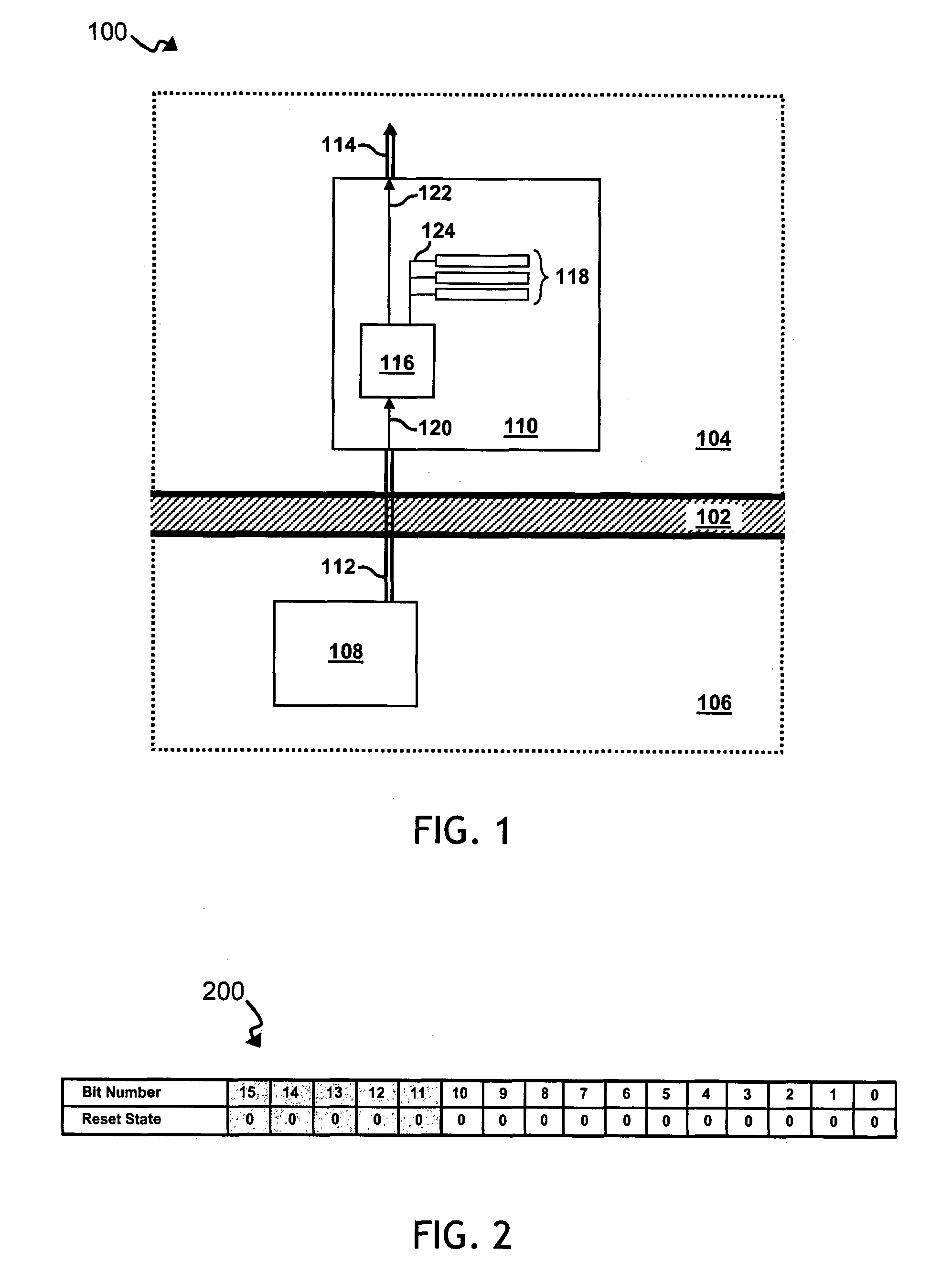

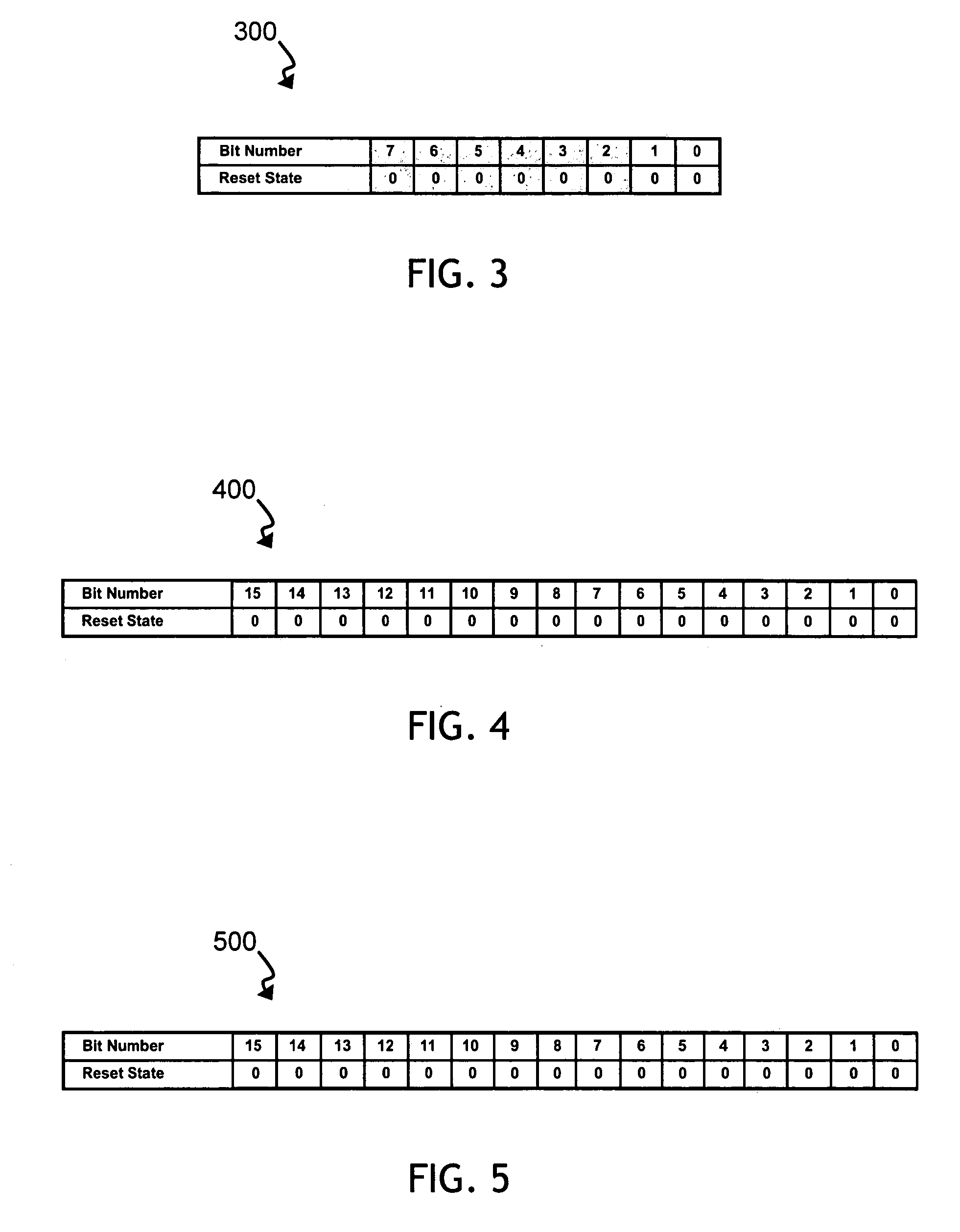

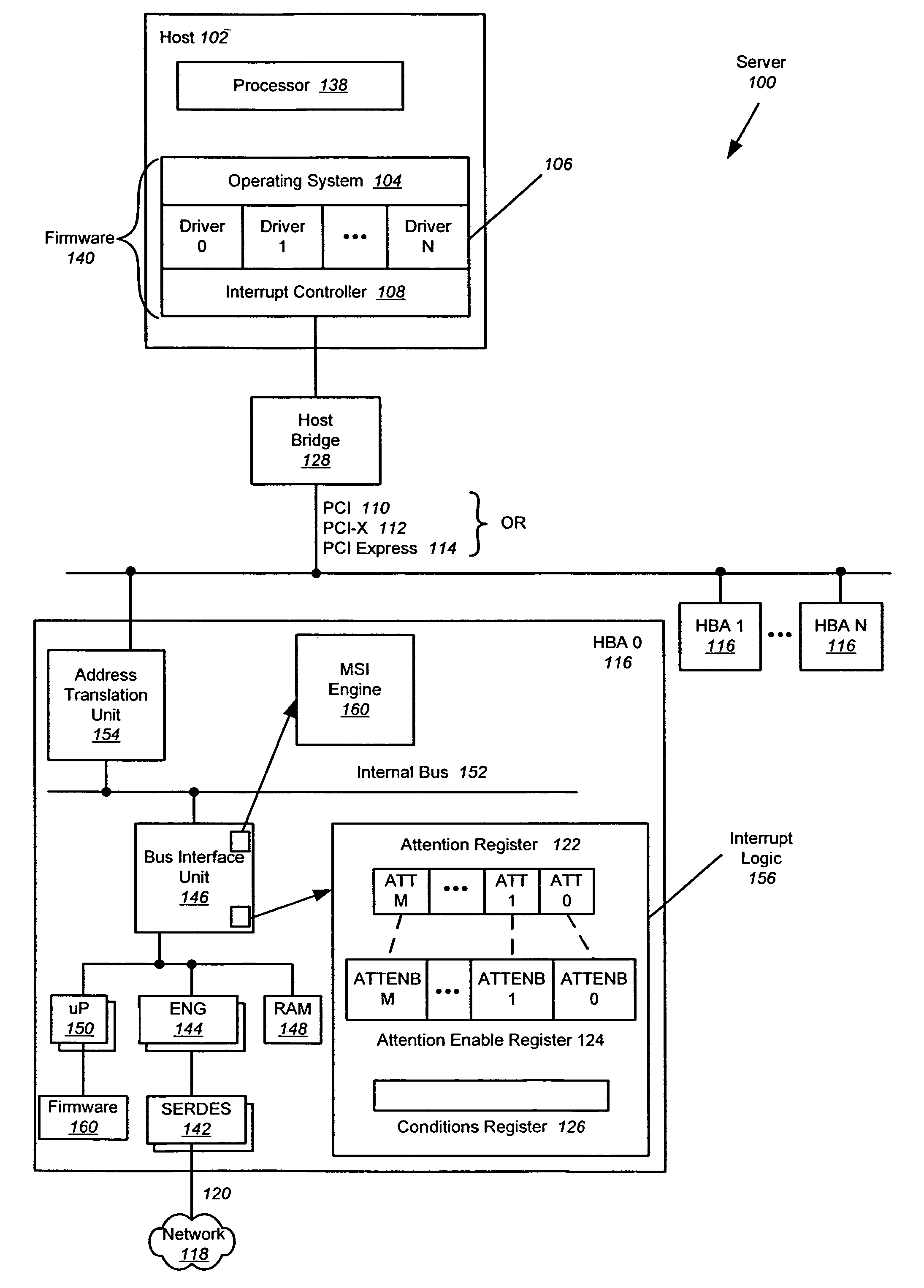

A method and apparatus is disclosed for improving the MSI and MSI-X specifications by implementing an efficient delivery and clearing mechanism for interrupt conditions to increase performance between the driver and hardware / firmware interface while ensuring that no interrupts are lost in the process. In particular, an auto clear function is employed to eliminate the need for drivers in the host to send writes over the PCI-based bus to deassert and assert attention enable register bits and clear down attention register bits, and a fail safe mechanism is utilized to prevent lost interrupts.

Owner:AVAGO TECH INT SALES PTE LTD

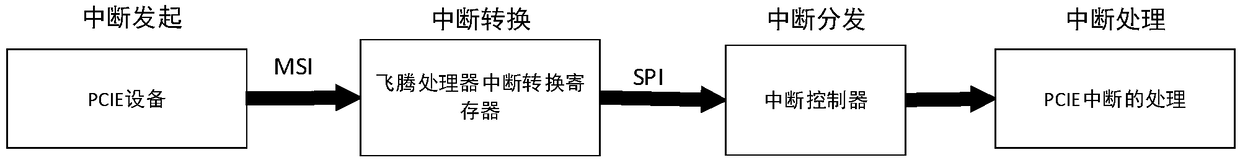

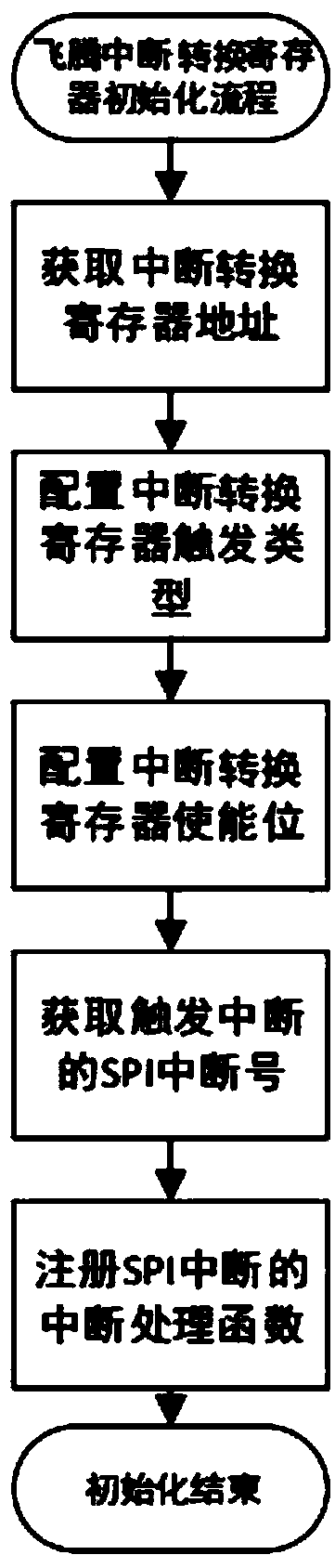

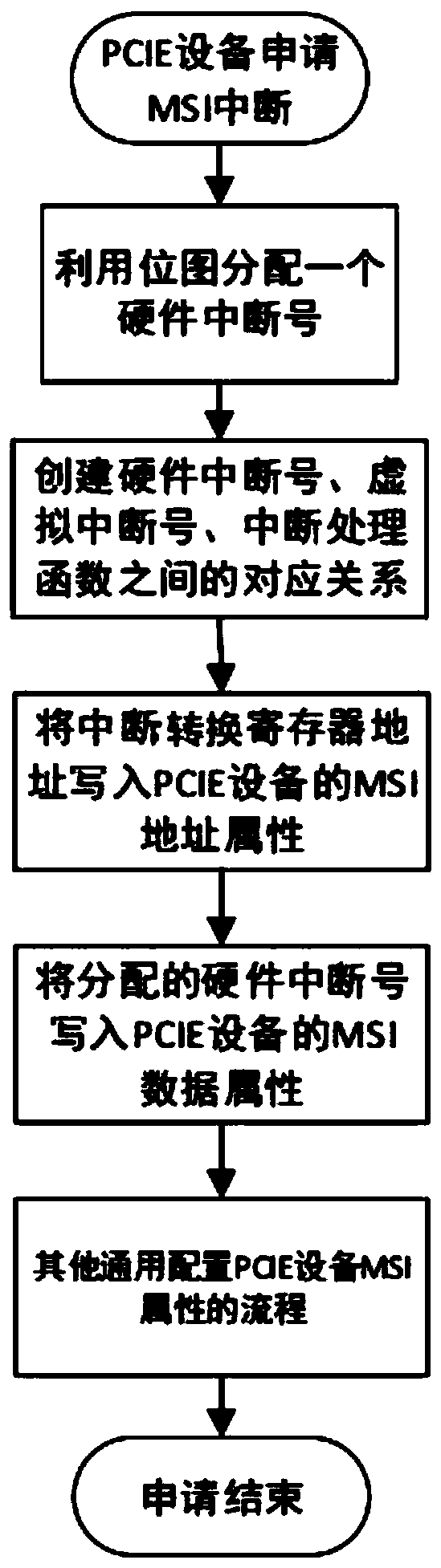

Implementation method of interruption conversion mechanism based on soar platform

PendingCN108628782AElectric digital data processingEnergy efficient computingMessage Signaled InterruptsConfiguration space

The invention discloses an implementation method of an interruption conversion mechanism based on a soar platform. The method includes the steps of interruption issuing, wherein a PCIE device issues an MSI interruption request and issues a message for writing a hardware interruption number to an interruption conversion register of the soar platform according to the MSI property of the configuration space; interruption converting, wherein the PCIE device transmits the hardware interruption number to the interruption conversion register to cause shared peripheral interruption; interruption distributing, wherein the shared peripheral interruption is distributed to a central processing unit through an interruption controller; interruption processing, wherein the shared peripheral interruptionis received by the central processing unit, a shared peripheral interruption processing function is triggered, the hardware interruption number is read from the interruption conversion register, and the interruption of the PCIE device is processed. By means of the method, the conversion from the message signal interruption to the shared peripheral interruption of the PCIE device is realized, and the interruption issuing, interruption converting, interruption distributing and interruption processing of the soar platform using a GICV2 controller and supporting a PCIE bus controller are realized.

Owner:KYLIN CORP

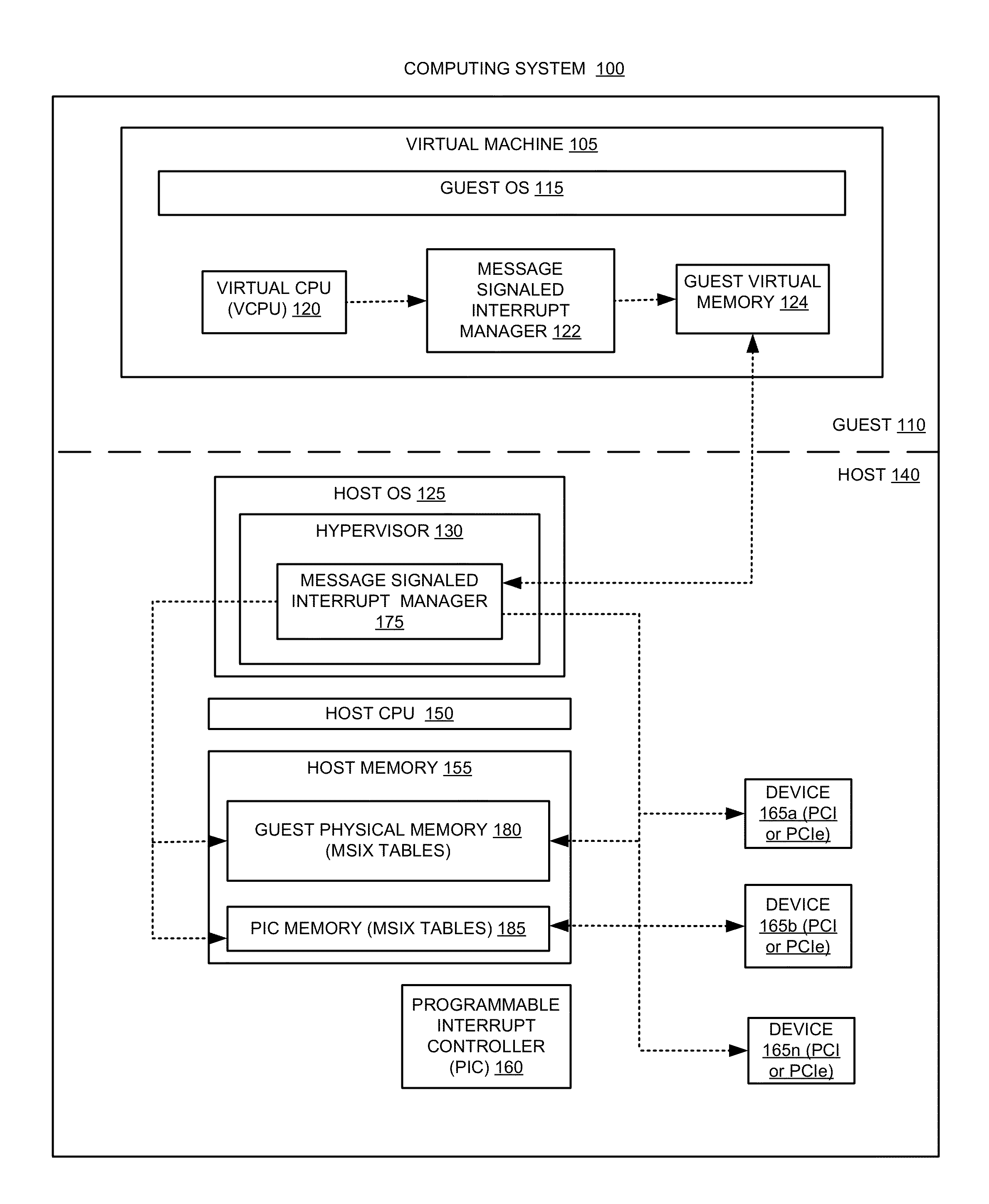

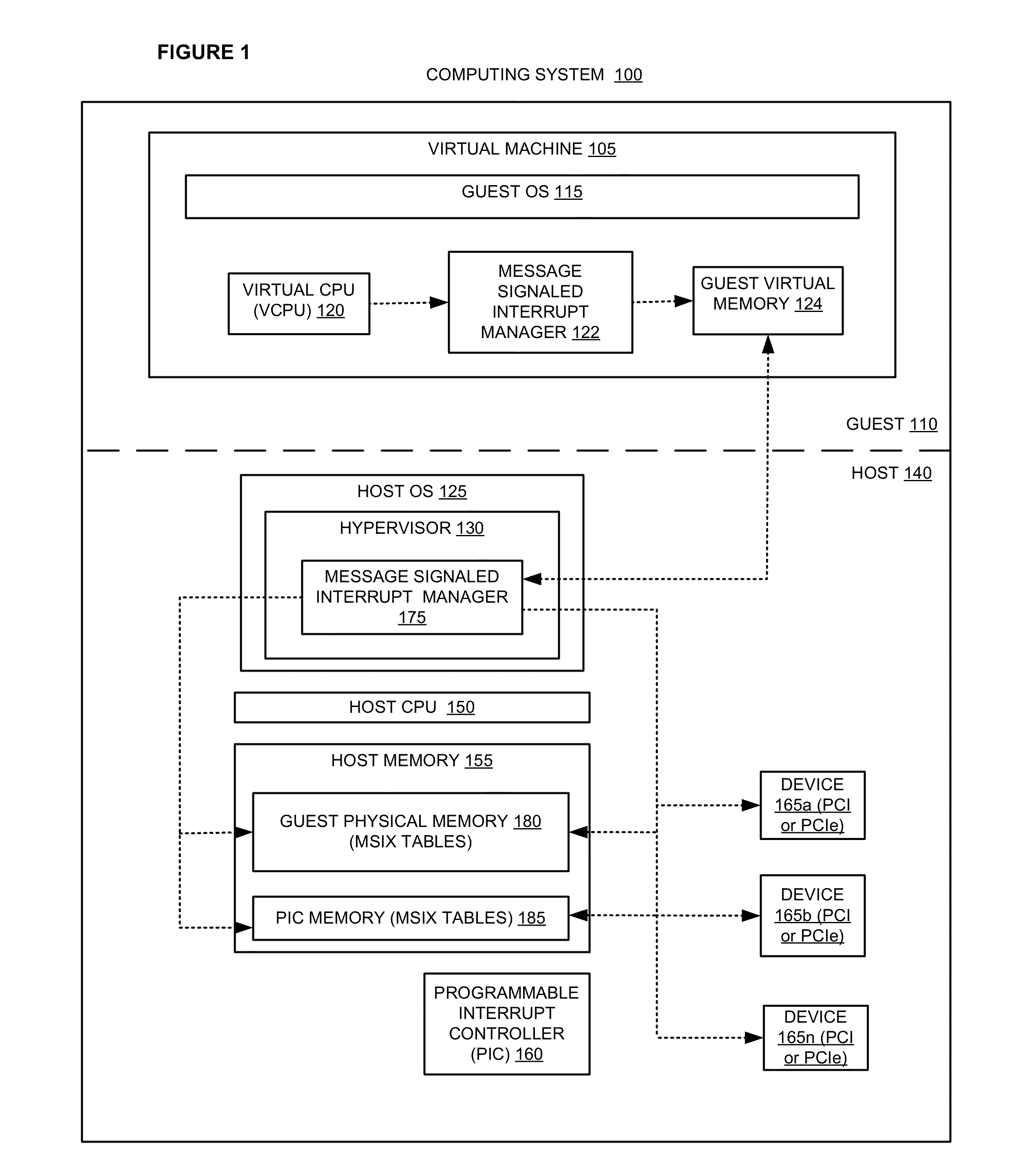

Direct mapping of MSI-x registers using paravirtualized memory monitoring

A method and system for permitting a guest to program a message-signaled interrupt-based device is disclosed. A hypervisor of a host detects a request by a guest to map an address range of memory of the guest to a message signaled-interrupt capability table associated with a device. The hypervisor maps the message signaled-interrupt capability table from a message signaled-interrupt capability register of a programmable interrupt controller associated with the host to the address range of memory of the guest. The hypervisor detects an attempt by the guest to program the device with the message-signaled interrupt configuration located in the address range of memory of the guest. The hypervisor programs the device with the message-signaled interrupt configuration specified by the guest in the address range of memory of the guest.

Owner:RED HAT ISRAEL

Processing and forwarding of message-signaled interrupts

Owner:SONY CORP

Method and device for managing information transmission interruption resources

An apparatus, program product and method dynamically bind Message Signaled Interrupt (MSI) resources shared by a plurality of clients to an interrupt facility in an MSI-capable computer. In addition, management of such bindings may be implemented using a platform independent interrupt manager capable of managing multiple MSI bindings between MSI resources to an interrupt facility, and interfaced with an underlying hardware platform of a computer through platform-specific encapsulation program code.

Owner:INT BUSINESS MASCH CORP

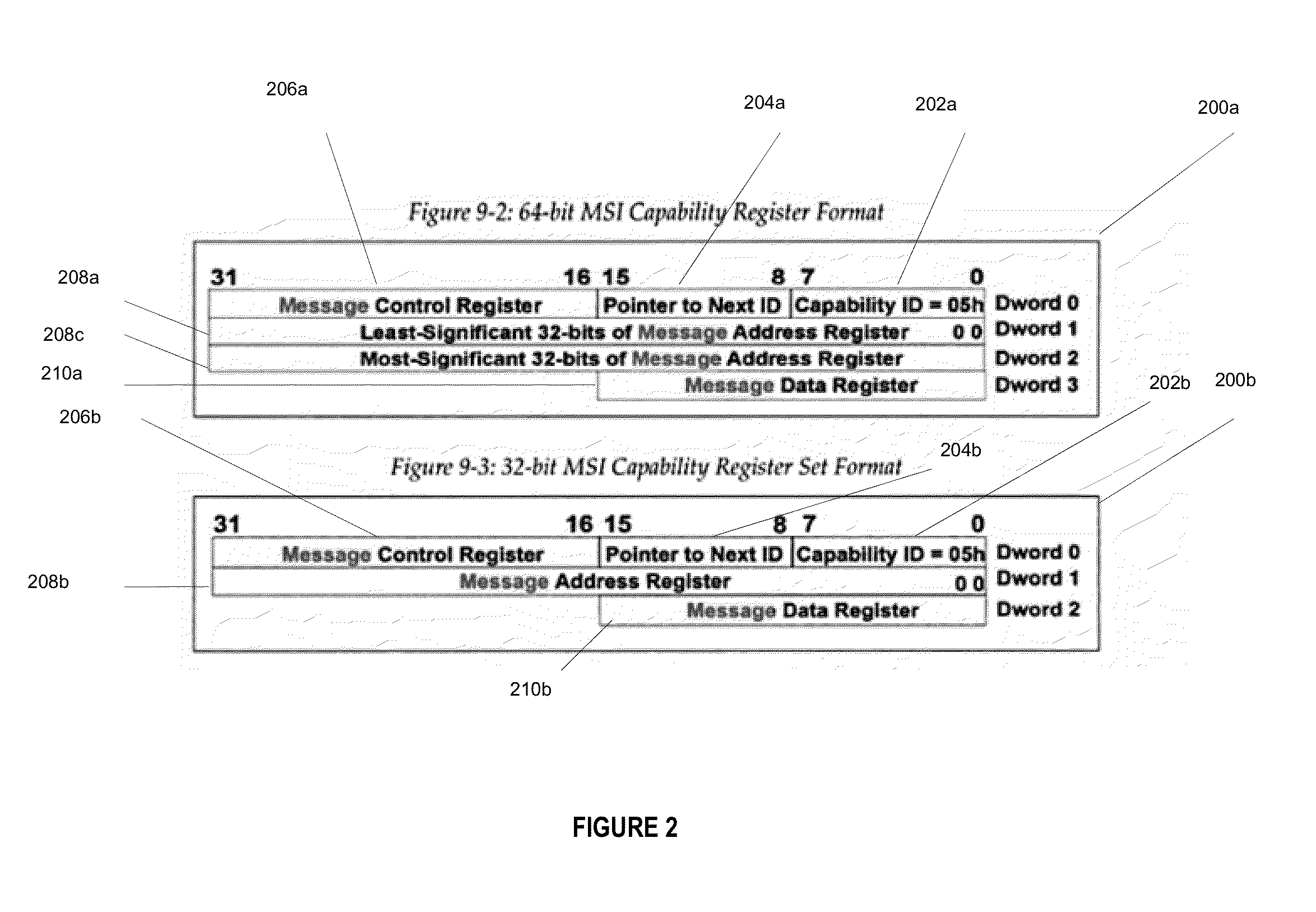

Extended message signaled interrupts (MSI) message data

ActiveUS20160371208A1Easy wiringReduce power consumptionEnergy efficient computingElectric digital data processingComputer hardwareMessage Signaled Interrupts

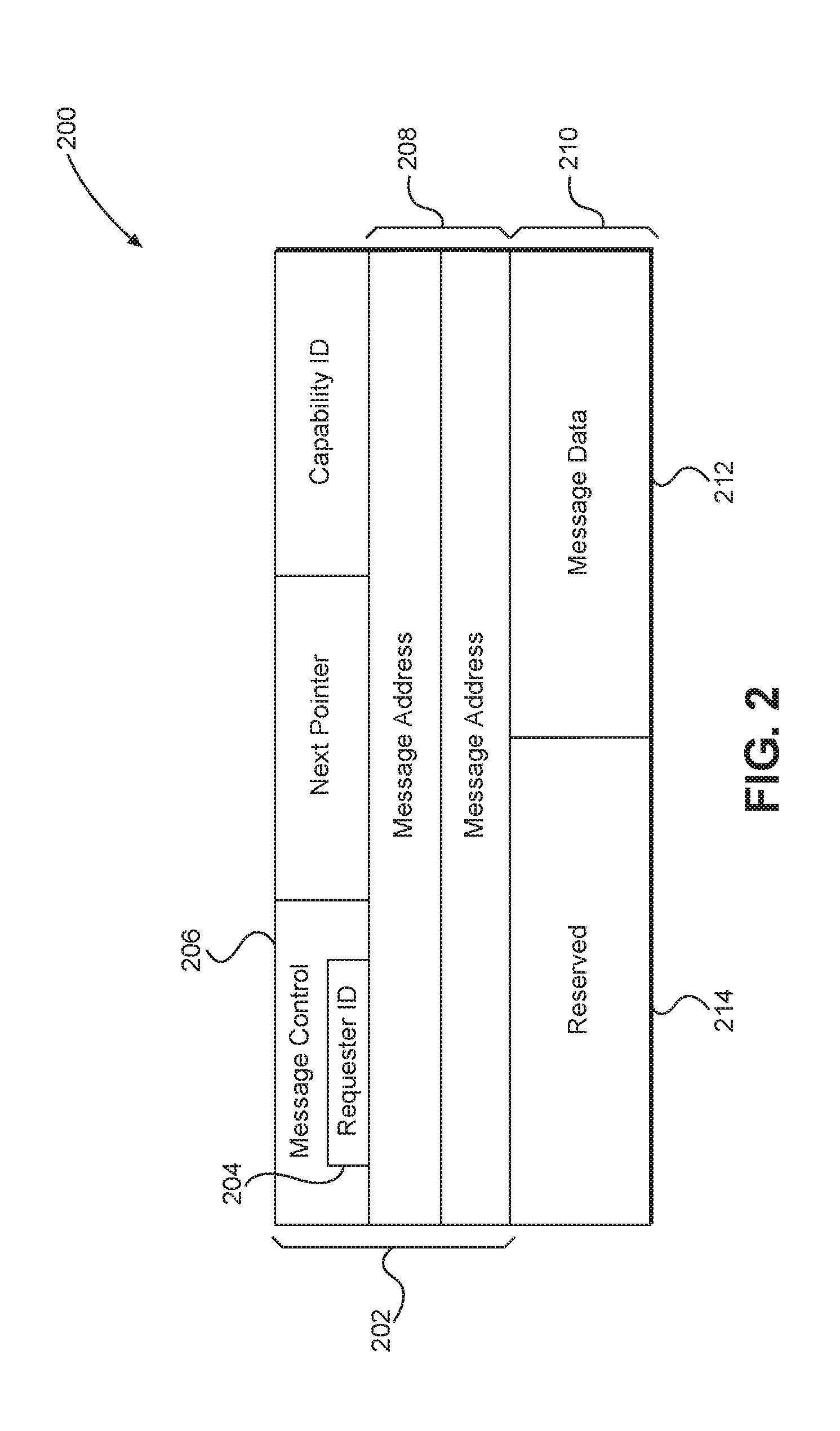

Extended message signaled interrupts (MSI) data are disclosed. In one aspect, MSI bits are modified to include a system level identifier. In an exemplary aspect, an upper sixteen bits of the MSI message data are modified to be the system level identifier. By providing the system level identifier within the MSI message data, an interrupt controller can verify the interrupt source.

Owner:QUALCOMM INC

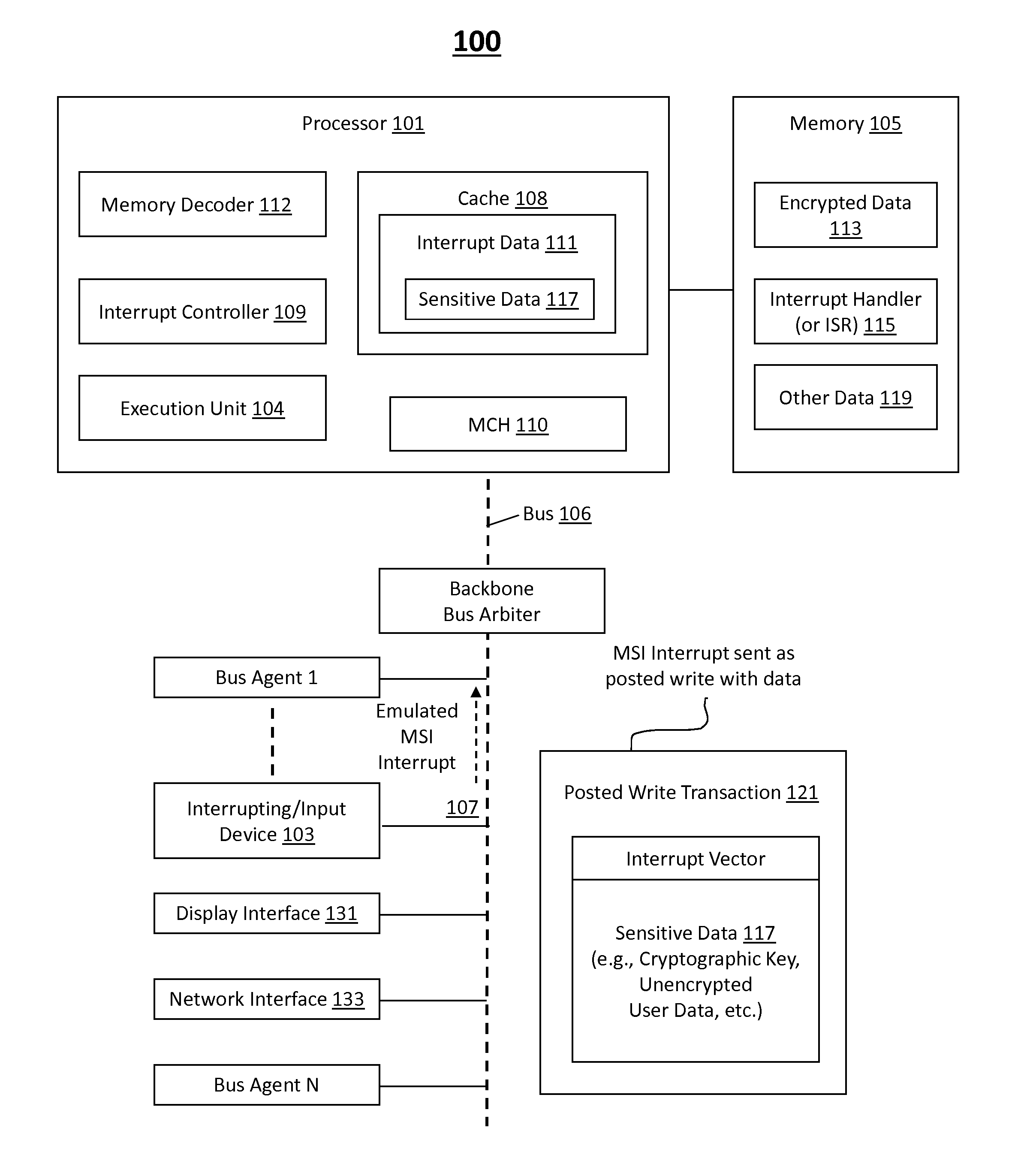

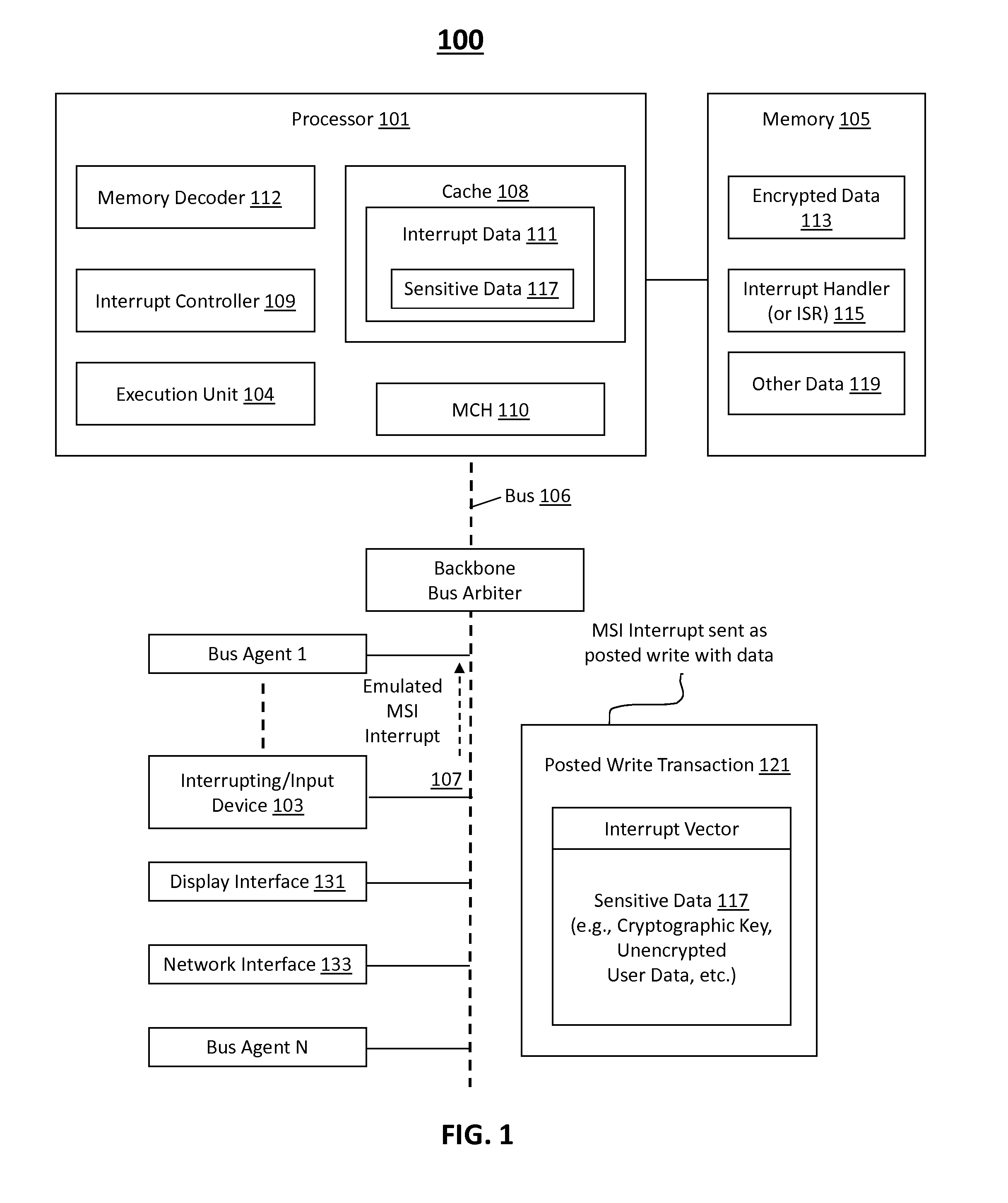

Method for implementing secure data channel between processor and devices

ActiveUS20140068129A1TransmissionElectric digital data processingMessage Signaled InterruptsInterrupt handler

Apparatuses, systems, and methods are directed to securely store, transfer, and / or process data especially sensitive data sent from input devices to processors. In one embodiment, sensitive data may be packaged with at least one interrupt vector to provide a single posted write transaction initiated by an input device. The single posted write transaction may then be directly sent to a predetermined memory block allocated from a processor. In response to the single posted write transaction, a memory decoder associated with the processor may generate an emulated message signaled interrupt (MSI) signal to invoke an interrupt handler or an interrupt service routine (ISR) to service the emulated MSI using interrupt data, including the sensitive data, retrieved from the predetermined memory block. Once the sensitive data are processed by the processor, they may be removed from the processor before the processor exits the interrupt handler.

Owner:INTEL CORP

Converting a message signaled interruption into an I/O adapter event notification

ActiveUS20120221757A1Program initiation/switchingInput/output processes for data processingMessage Signaled InterruptsInput/output

One or more message signaled interruption requests from one or more input / output (I / O) adapters are converted to I / O adapter event notifications. Each I / O adapter event notification includes the setting of one or more specific indicators in system memory and an interruption request, the first of which results in a pending I / O adapter interruption request. While a request for an I / O adapter interruption is pending, subsequent message signaled interruption requests are converted to I / O adapter event notifications, but do not result in additional requests for I / O adapter interruptions.

Owner:INT BUSINESS MASCH CORP

Emulating a line-based interrupt transaction in response to a message signaled interrupt

Methods, systems, apparatuses and program products are disclosed for managing interrupt services in hypervisor and hypervisor-related environments in Message Signaled Interrupts are emulated as other type(s) of interrupt.According to an aspect of the present invention, a method of executing a program includes receiving a MSI (message signaled interrupt). Responsively, a virtual interrupt is generated and an ISR (interrupt service routine) is invoked that handles a line-based virtual interrupt transaction. A surrogate or virtual peripheral device status may also be provided and may be associated with the virtual interrupt. A single device interrupt event may, in certain circumstances, be serviced both as a line-based interrupt and also as an MSI, or as either responsive to run-time context.Embodiments of the present invention enable superior tradeoffs in regards to the interrupt sharing to a greater and more flexible extent than with previous implementations. Moreover, it makes possible interrupt sharing using an ISR that was not expressly designed for interrupt sharing.

Owner:HEWLETT PACKARD CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com