Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60 results about "Data bus inversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

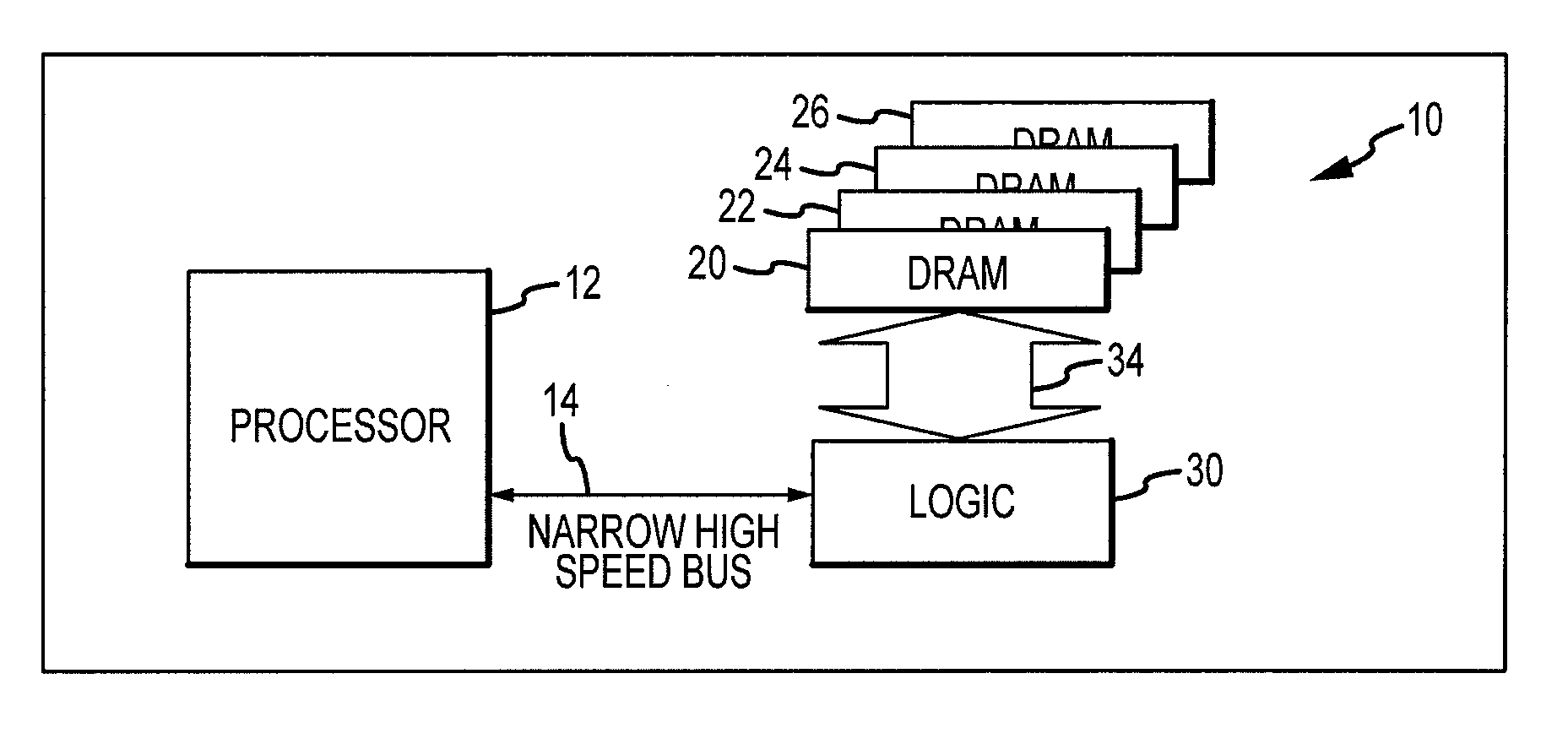

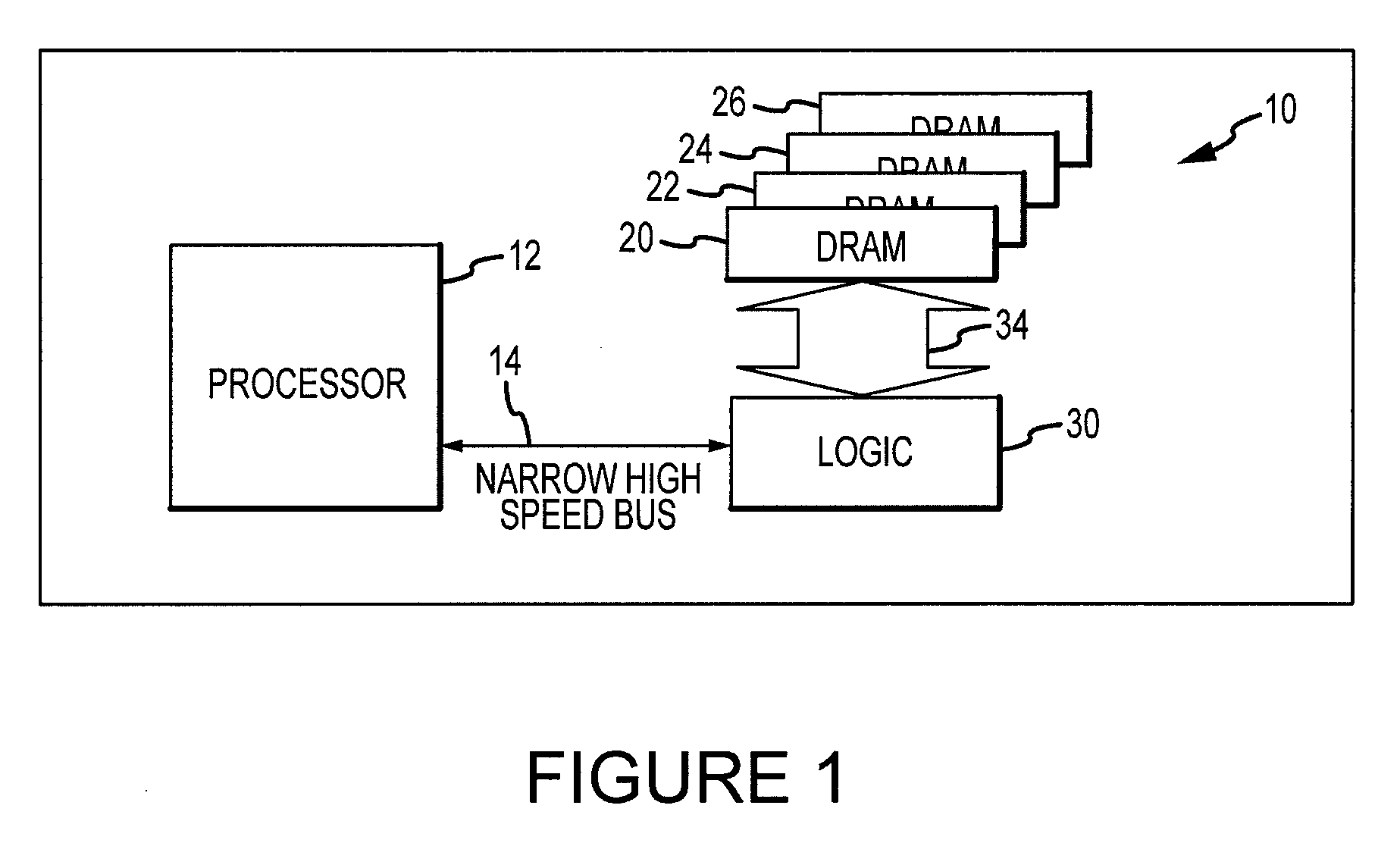

Memory system and method using a memory device die stacked with a logic die using data encoding, and system using the memory system

A memory system and method using at least one memory device die stacked with and coupled to a logic die by interconnects, such as through silicon vias. One such logic die includes an ECC system generating error checking and correcting (“ECC) bits corresponding to write data. The write data are transmitted to the memory device dice in a packet containing a serial burst of a plurality of parallel data bits. The ECC bits are transmitted to the memory device dice using through silicon vias that are different from the vias through which data are coupled. Such a logic die could also include a data bus inversion (“DBI”) system encoding the write data using a DBI algorithm and transmitting to the memory device dice DBI bits indicating whether the write data have been inverted. The DBI bits are transmitted using through silicon vias that are shared with the ECC bits when they are unused for transferring the ECC bits.

Owner:MICRON TECH INC

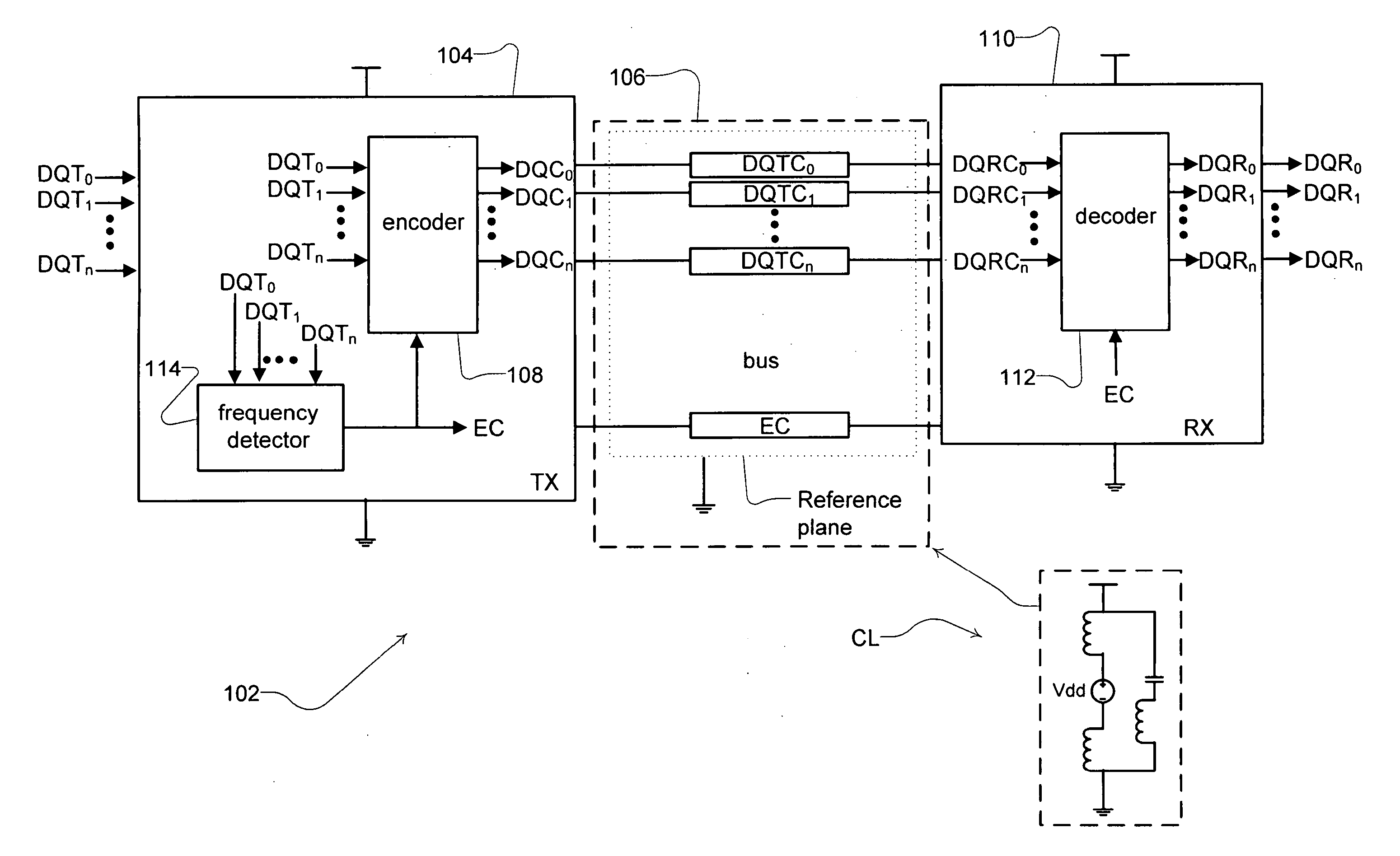

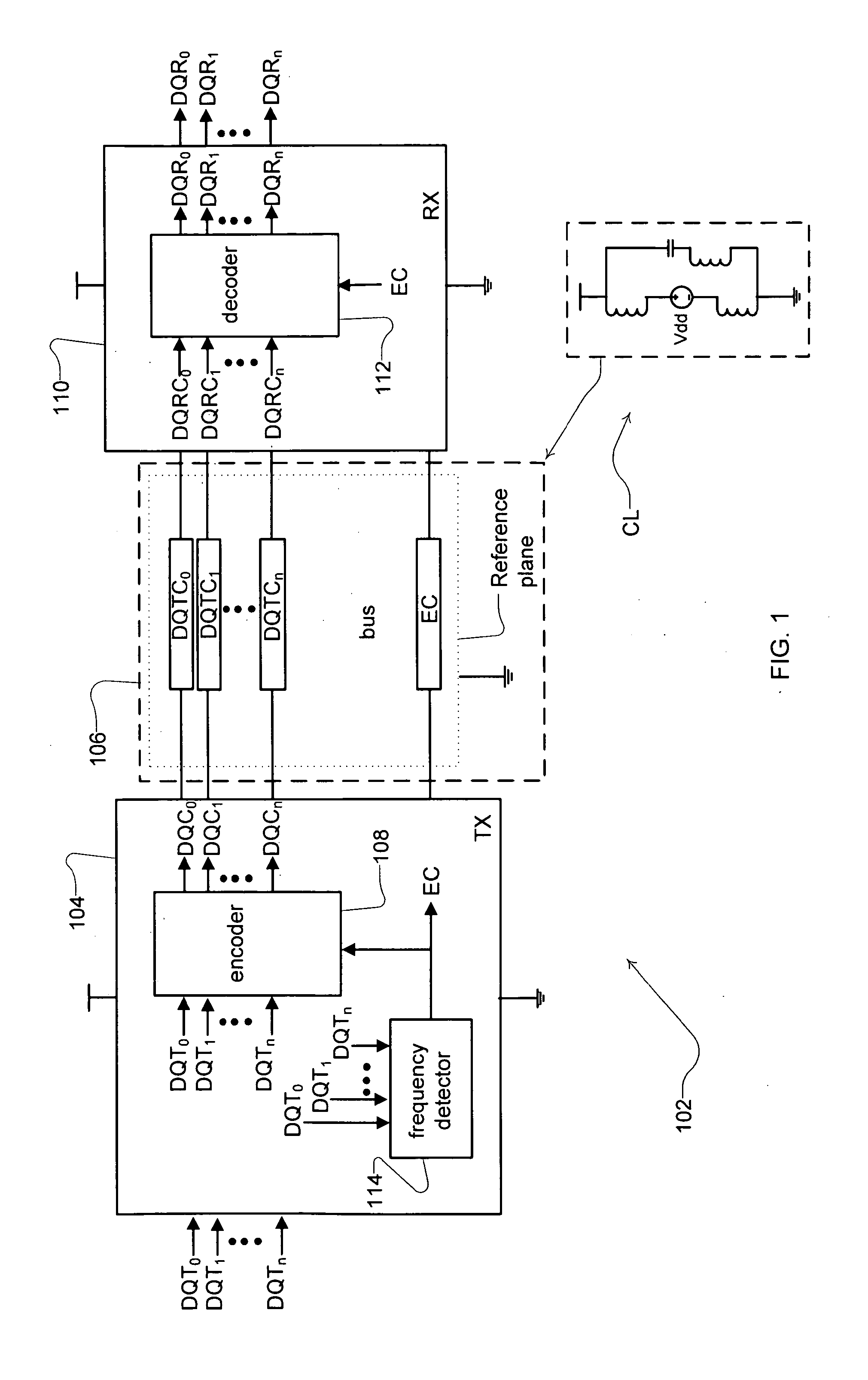

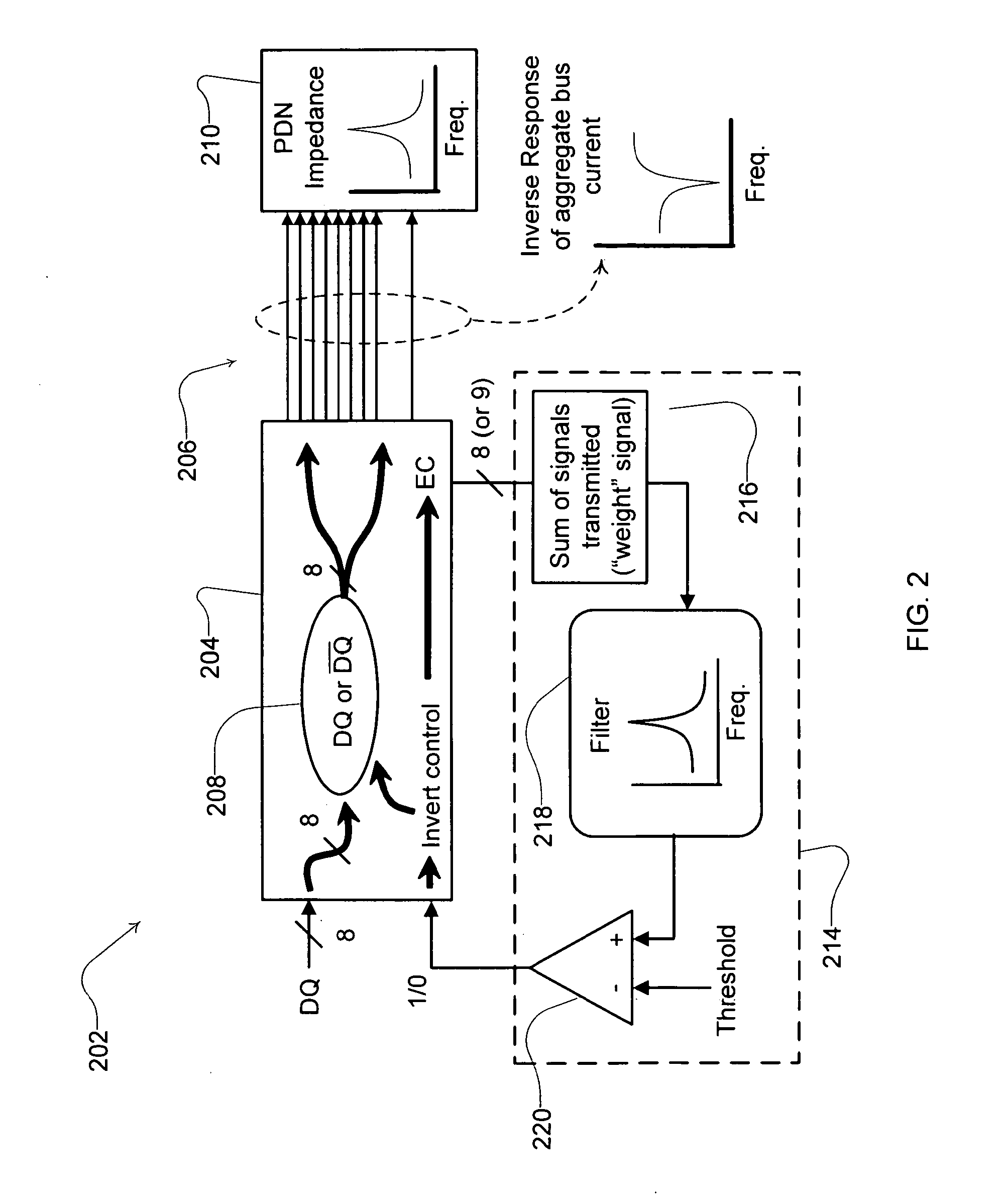

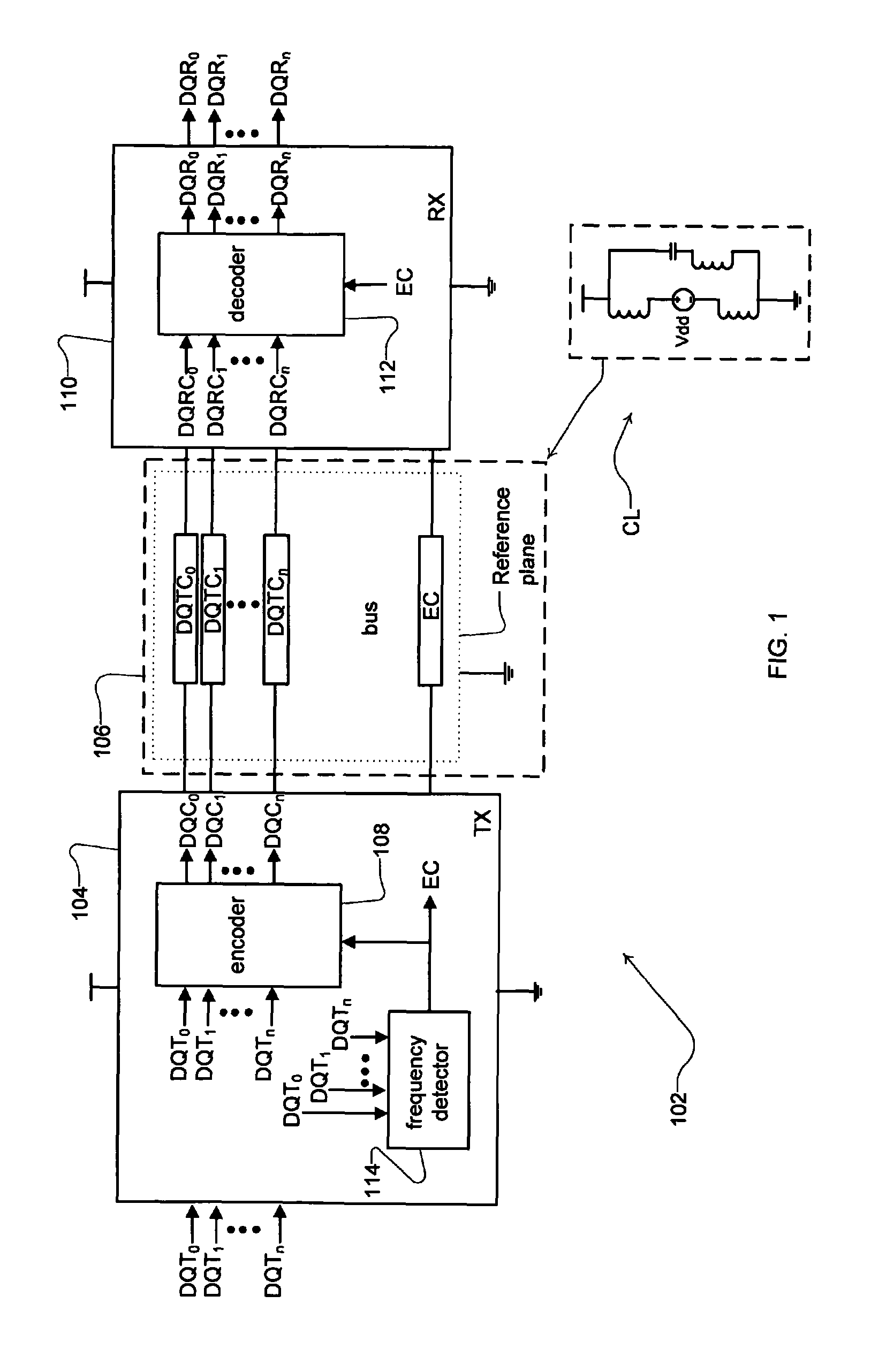

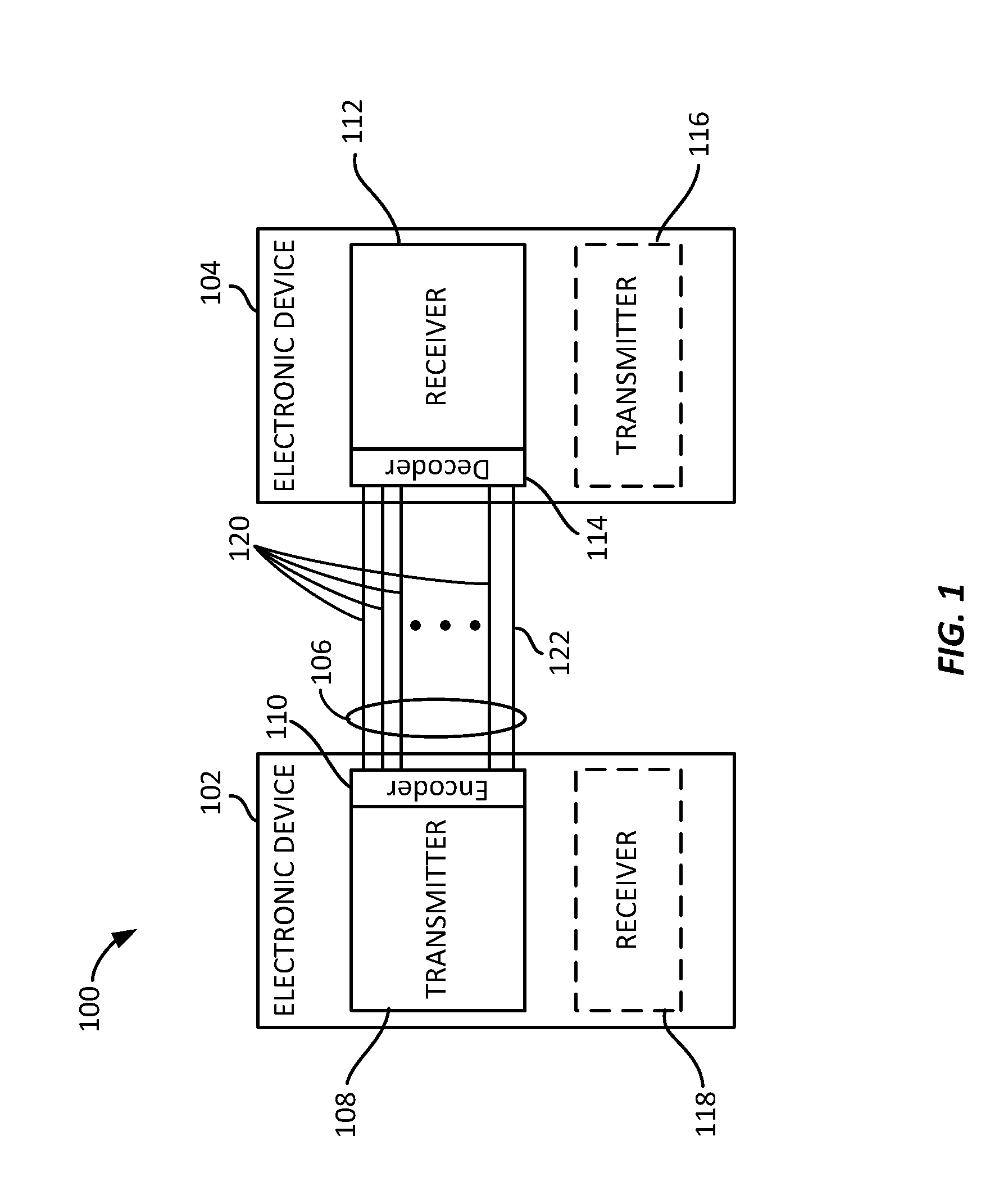

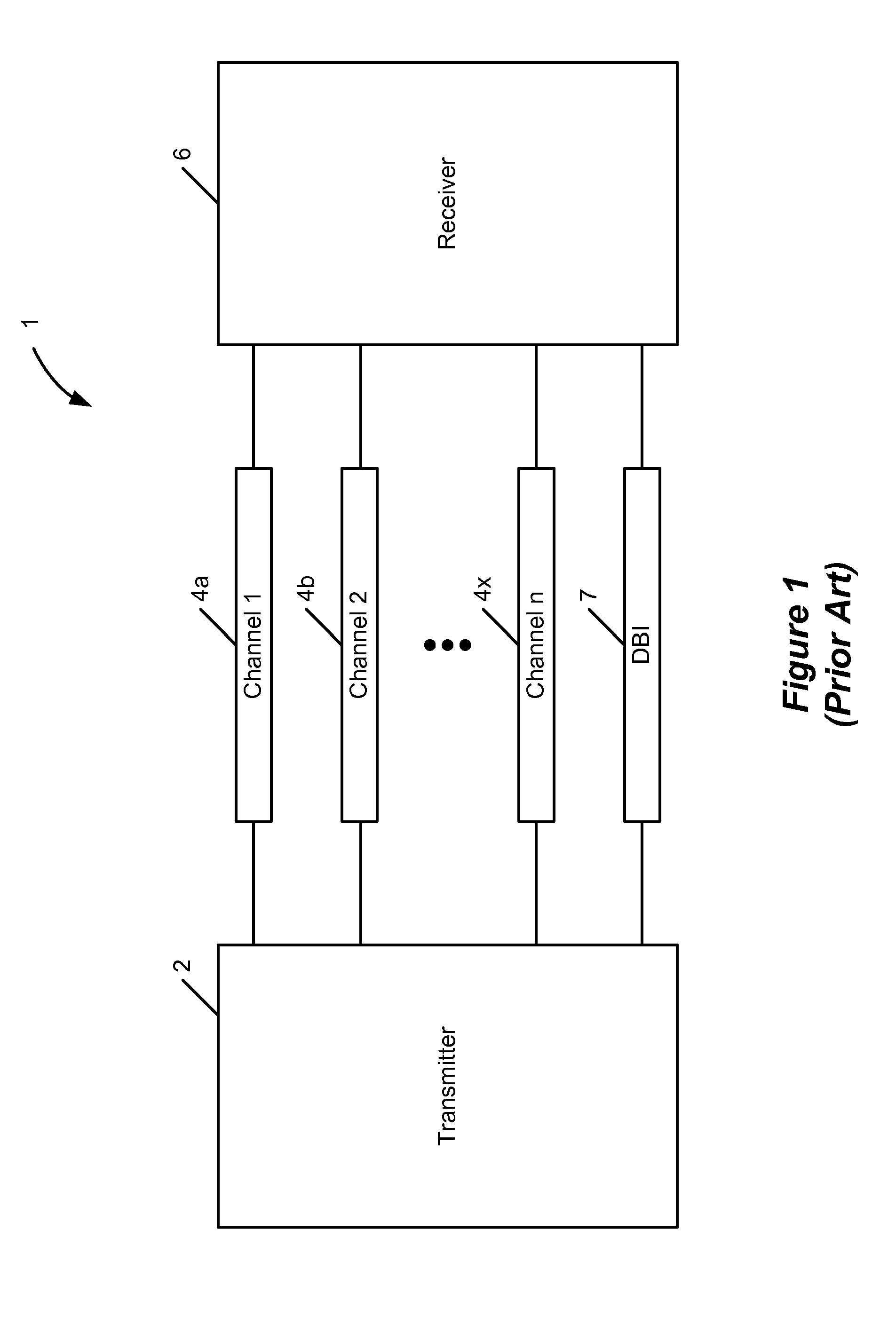

Frequency responsive bus coding

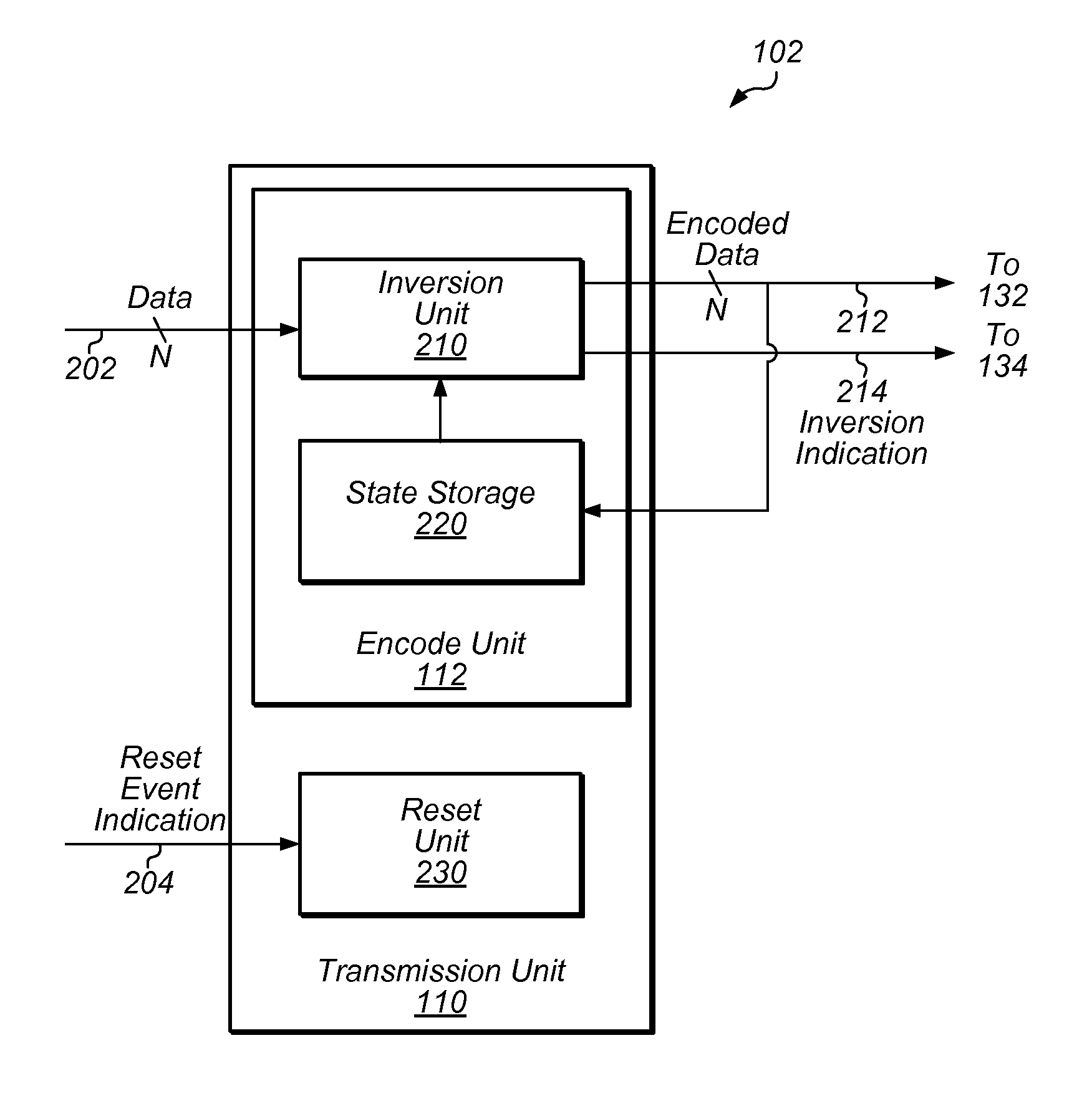

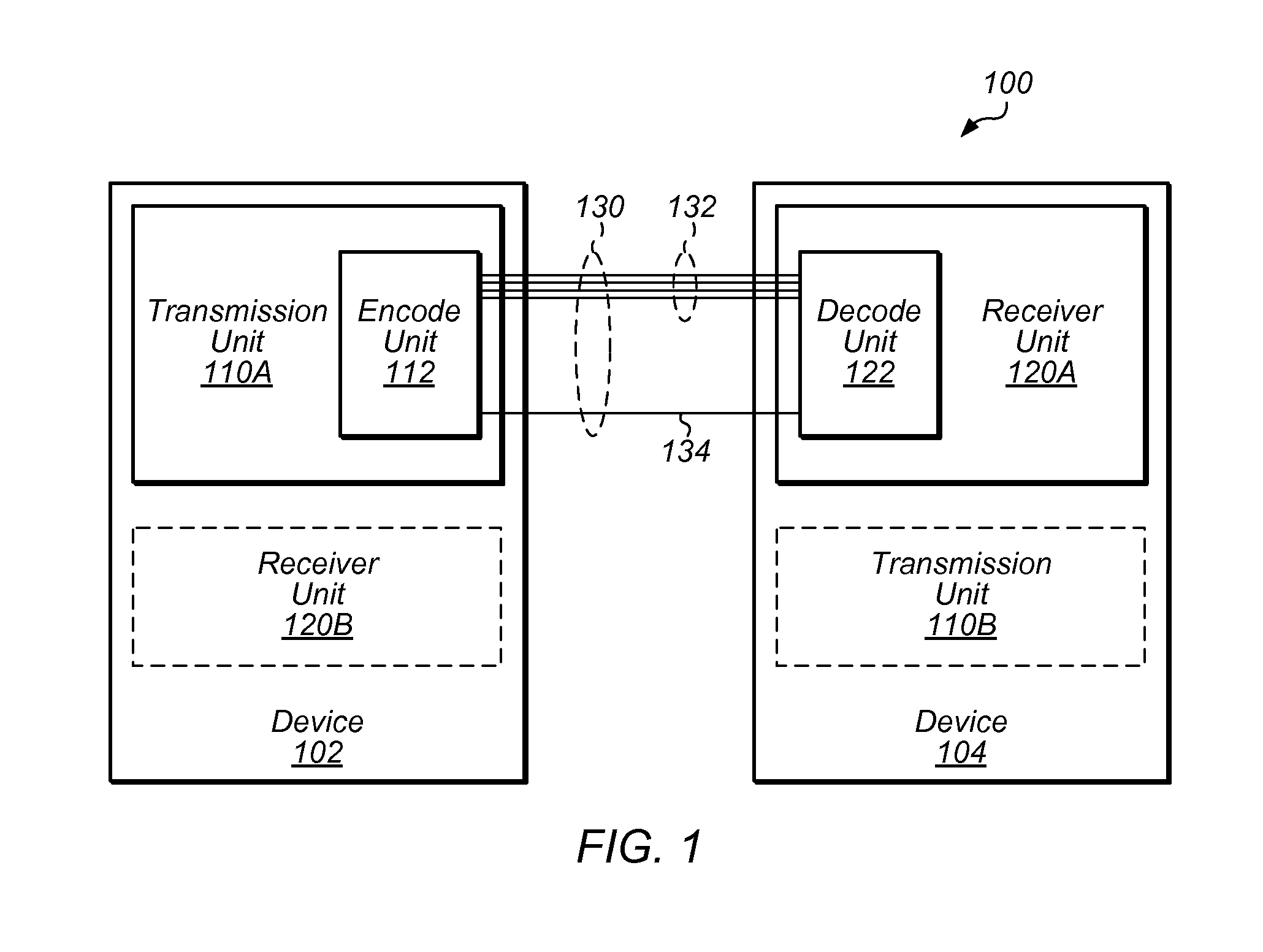

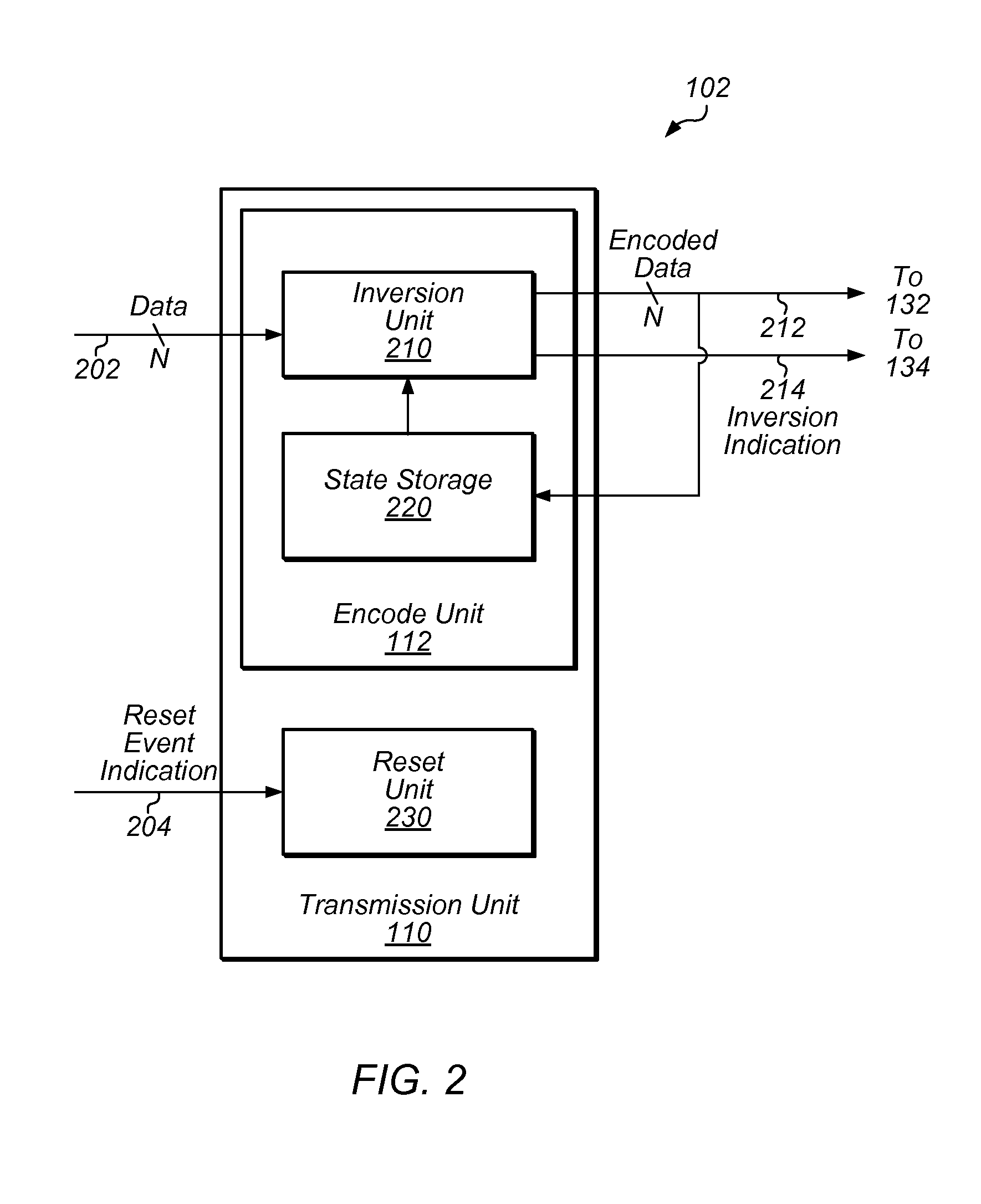

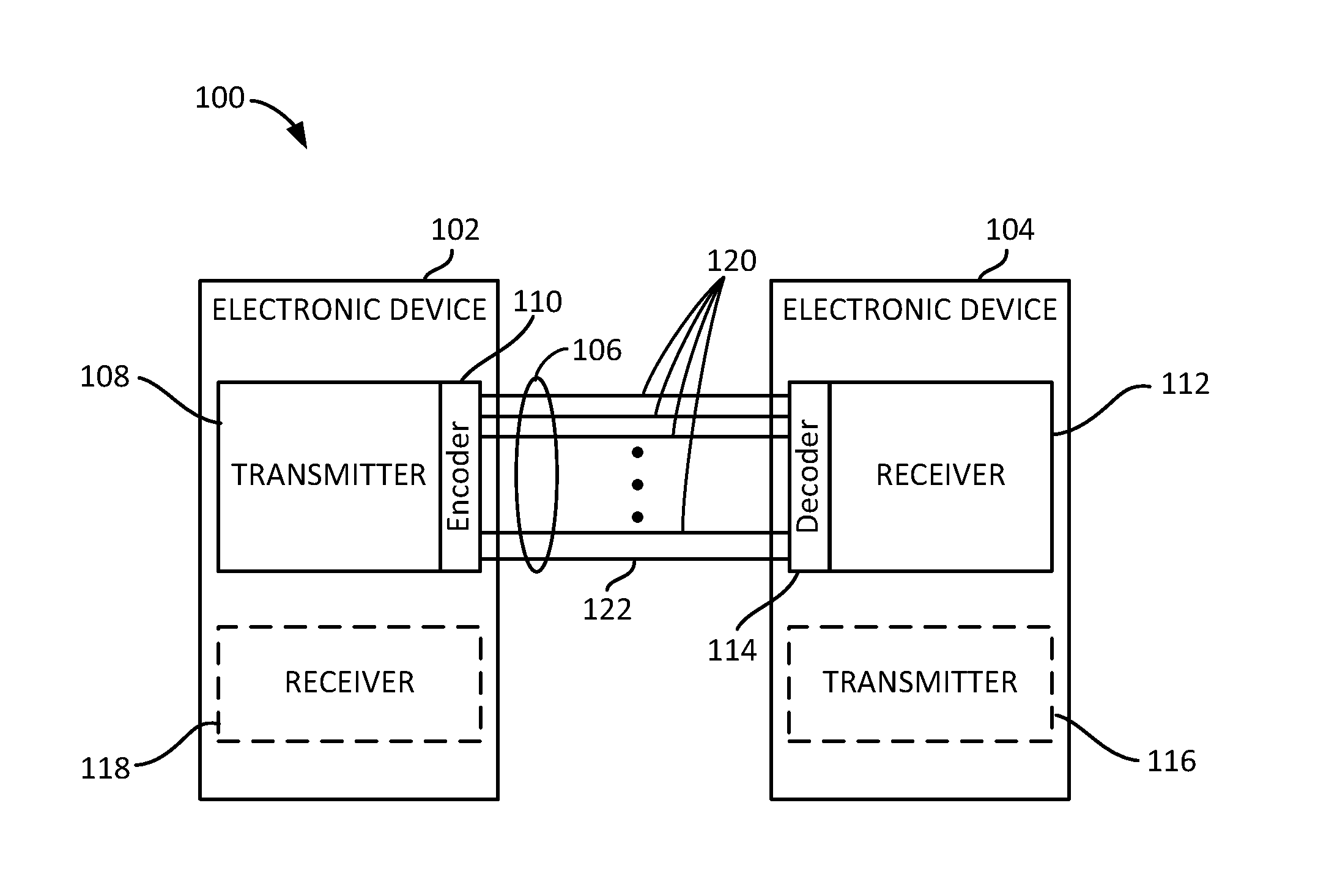

A data system 102 permits bus encoding based on frequency of the bus; an encoding scheme may be implemented to avoid undesirable frequency conditions such as a resonant condition that may lead to degradation in system performance. The device or integrated circuit will typically include an encoder; in one embodiment, the encoder is a data bus inversion (DBI) circuit that selectively inverts all lines of a data bus. A detector that may include a band-pass or stop-band filter that, for example, evaluates data for transmission on the bus to detect frequency, for example, a predetermined frequency or a frequency range. The detector provides a control signal for the encoder to selectively apply an encoding scheme as a function of frequency.

Owner:RAMBUS INC

Frequency responsive bus coding

A data system 102 permits bus encoding based on frequency of the bus; an encoding scheme may be implemented to avoid undesirable frequency conditions such as a resonant condition that may lead to degradation in system performance. The device or integrated circuit will typically include an encoder; in one embodiment, the encoder is a data bus inversion (DBI) circuit that selectively inverts all lines of a data bus. A detector that may include a band-pass or stop-band filter that, for example, evaluates data for transmission on the bus to detect frequency, for example, a predetermined frequency or a frequency range. The detector provides a control signal for the encoder to selectively apply an encoding scheme as a function of frequency.

Owner:RAMBUS INC

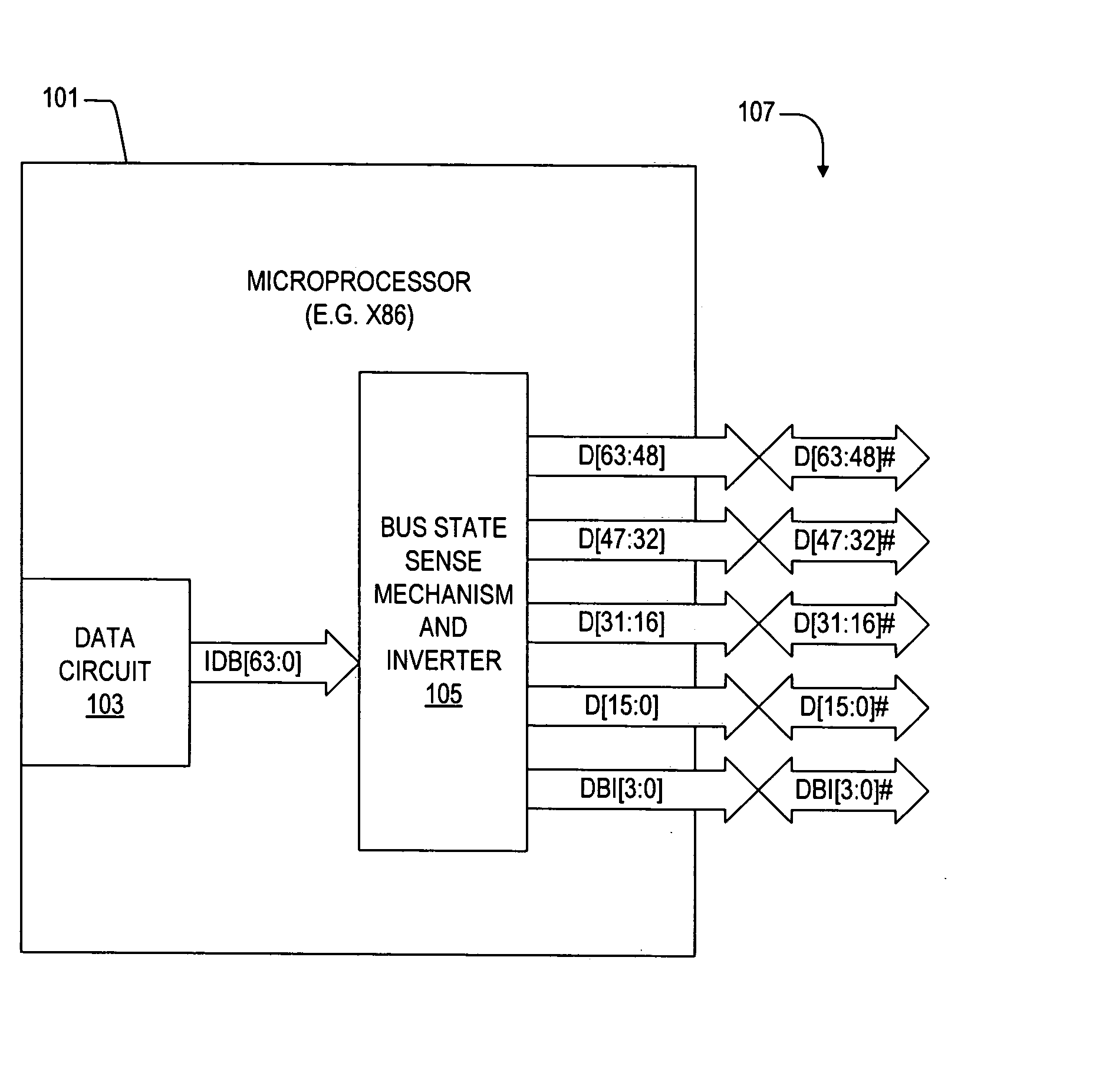

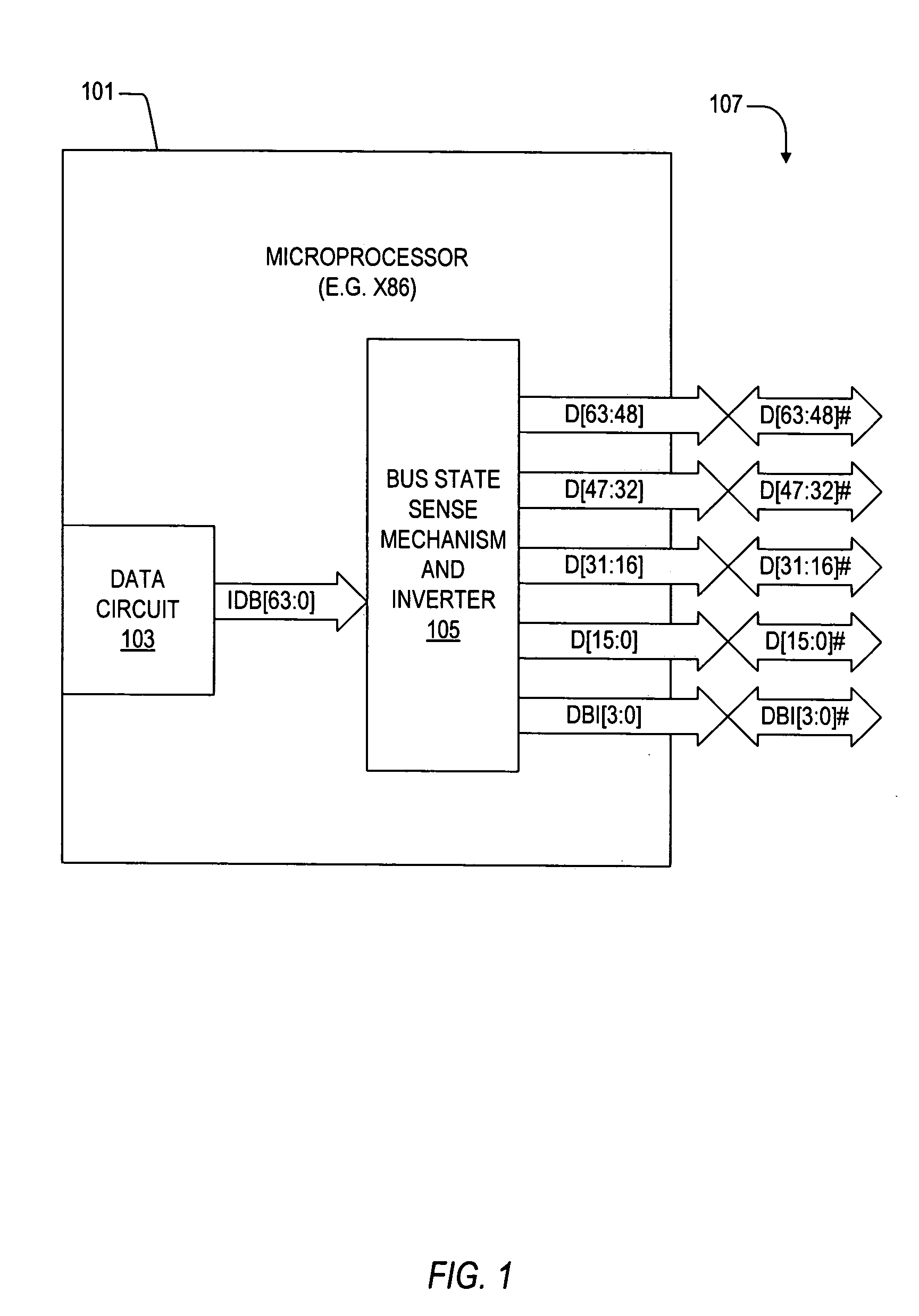

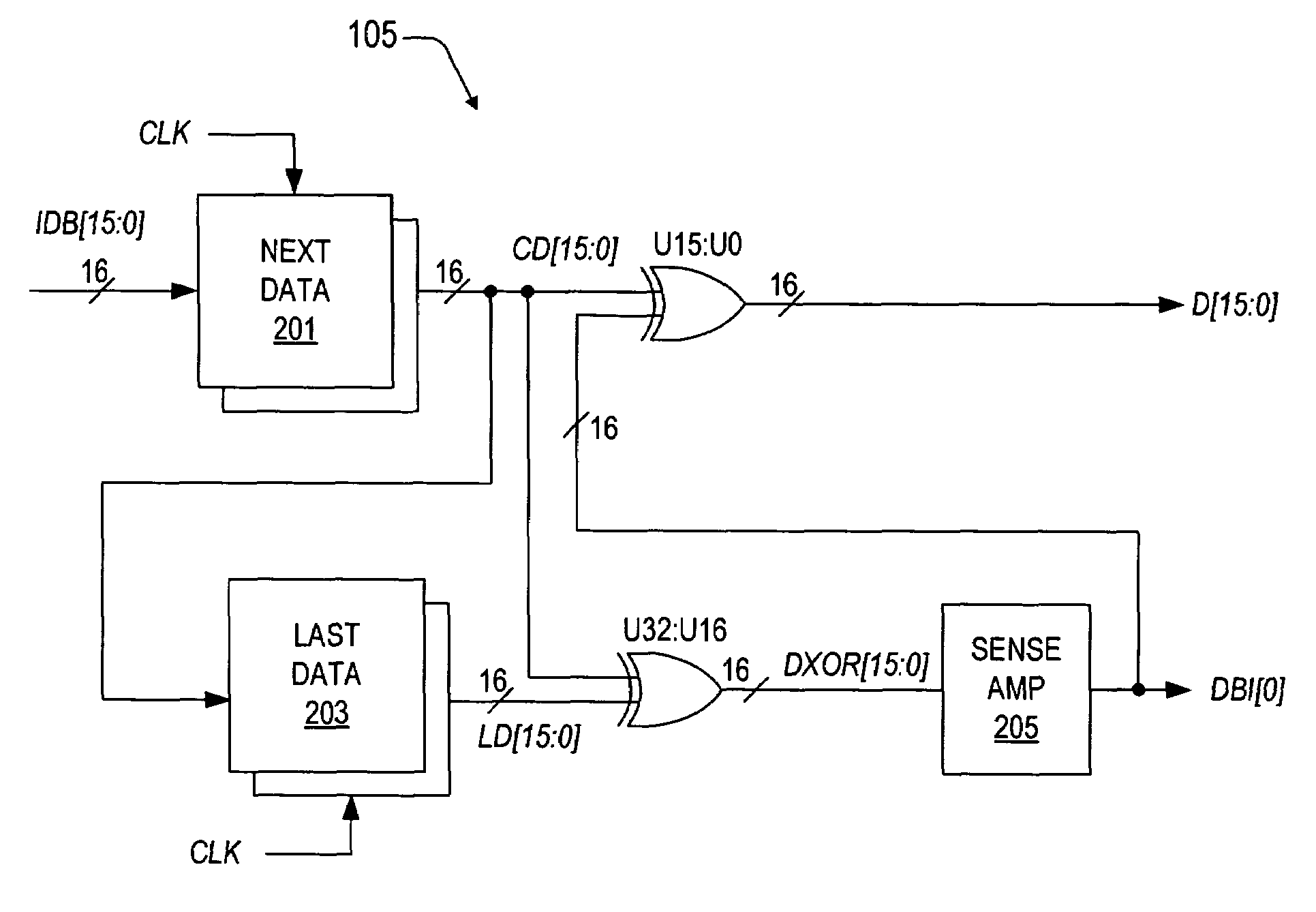

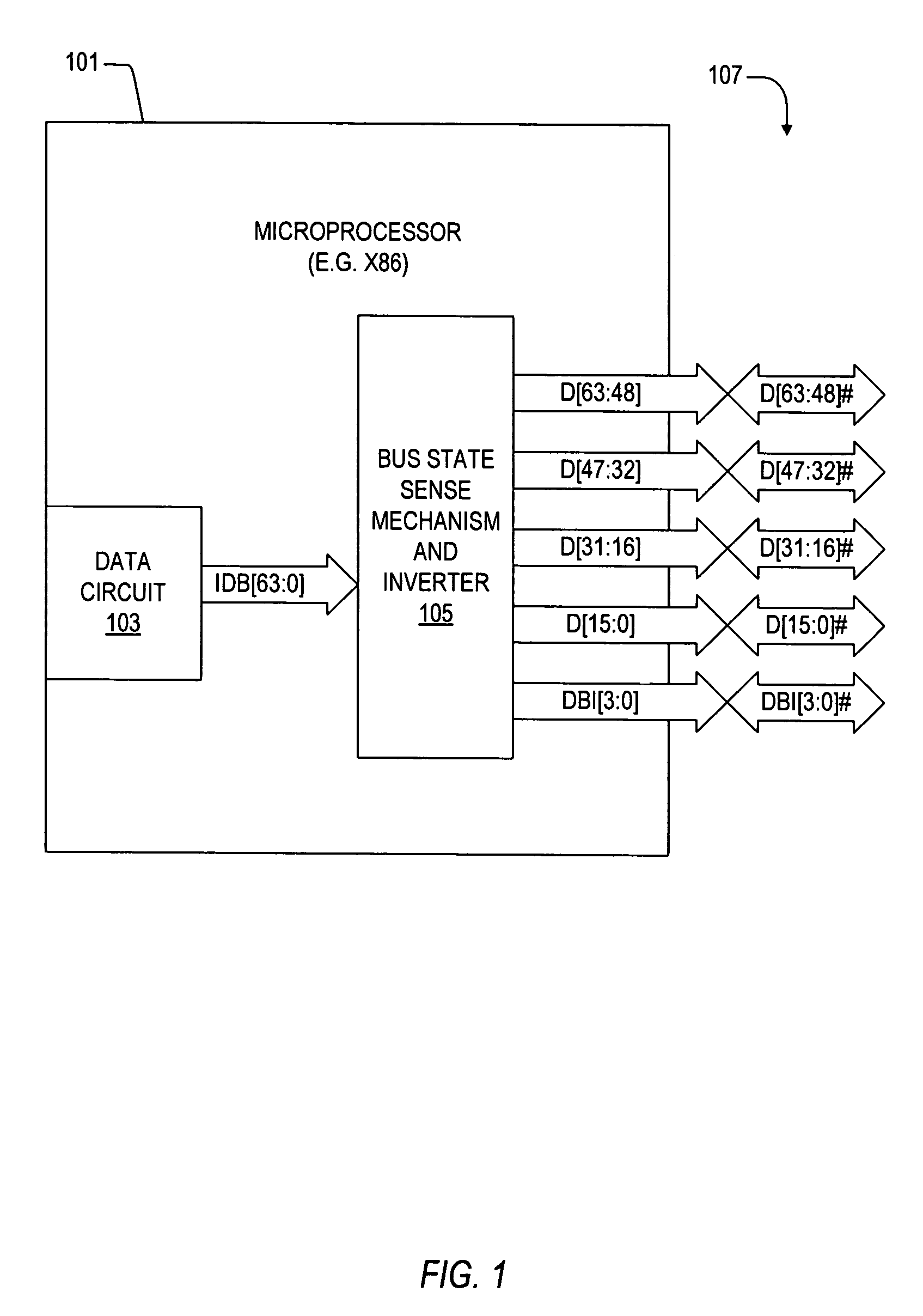

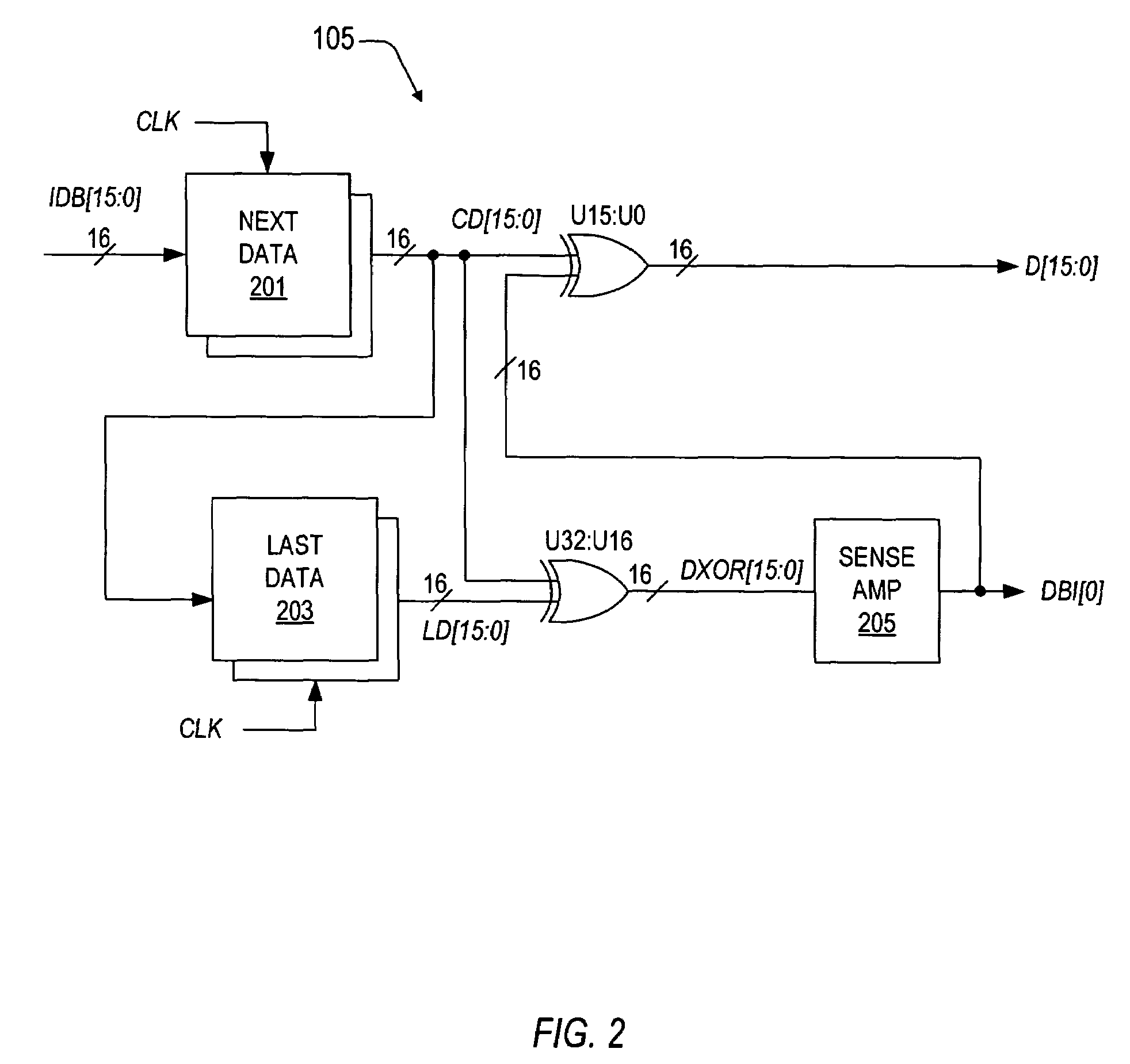

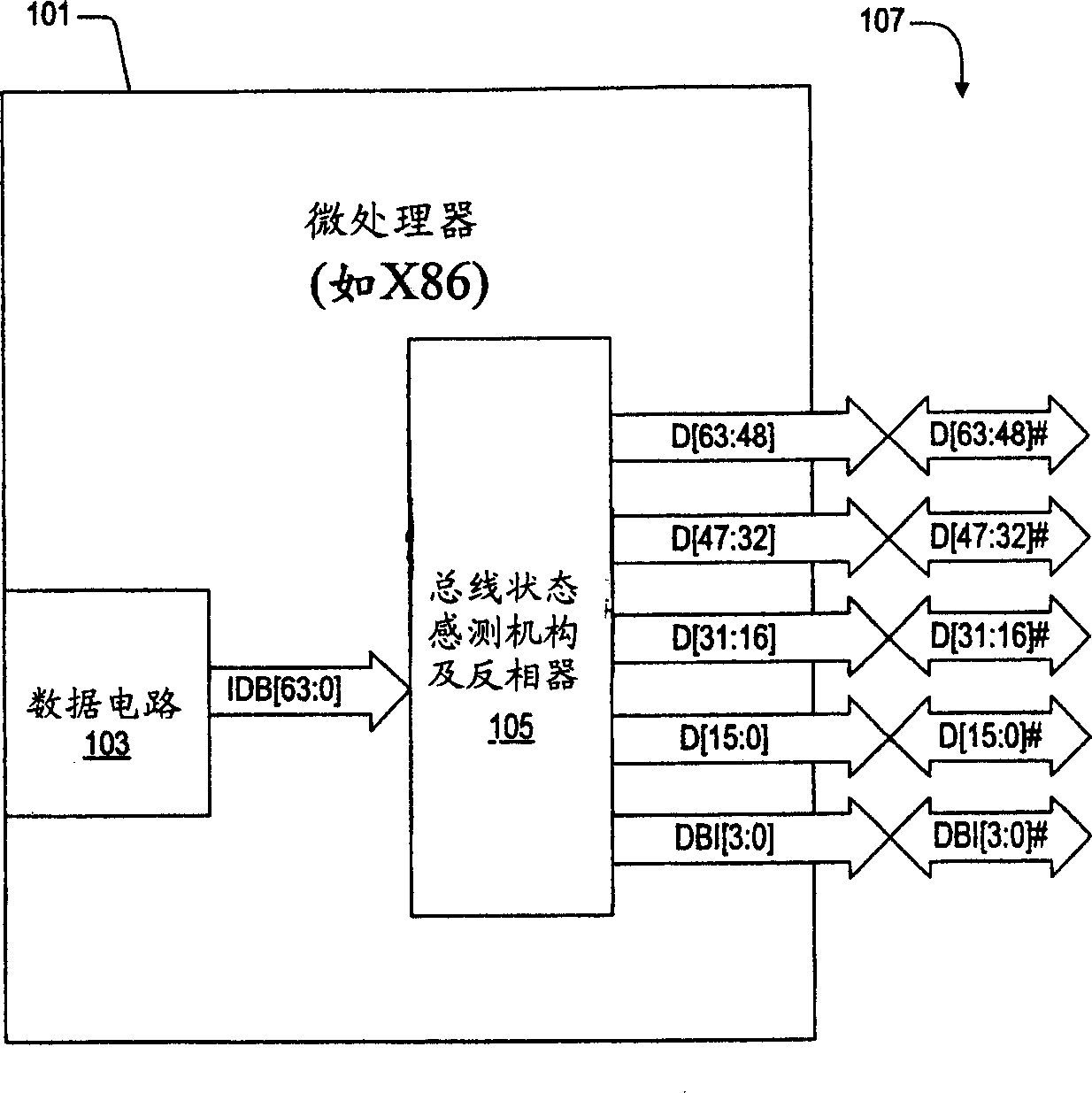

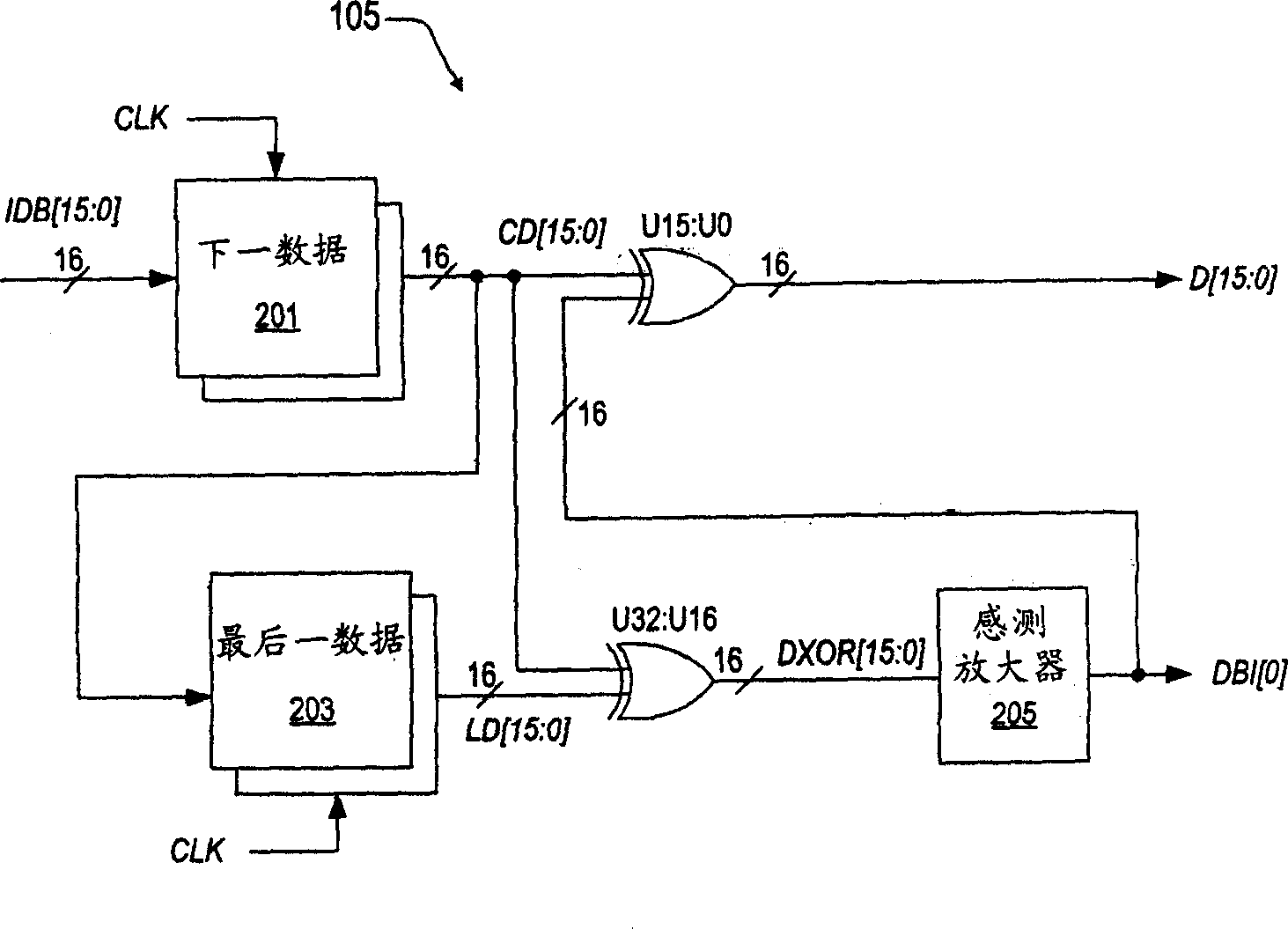

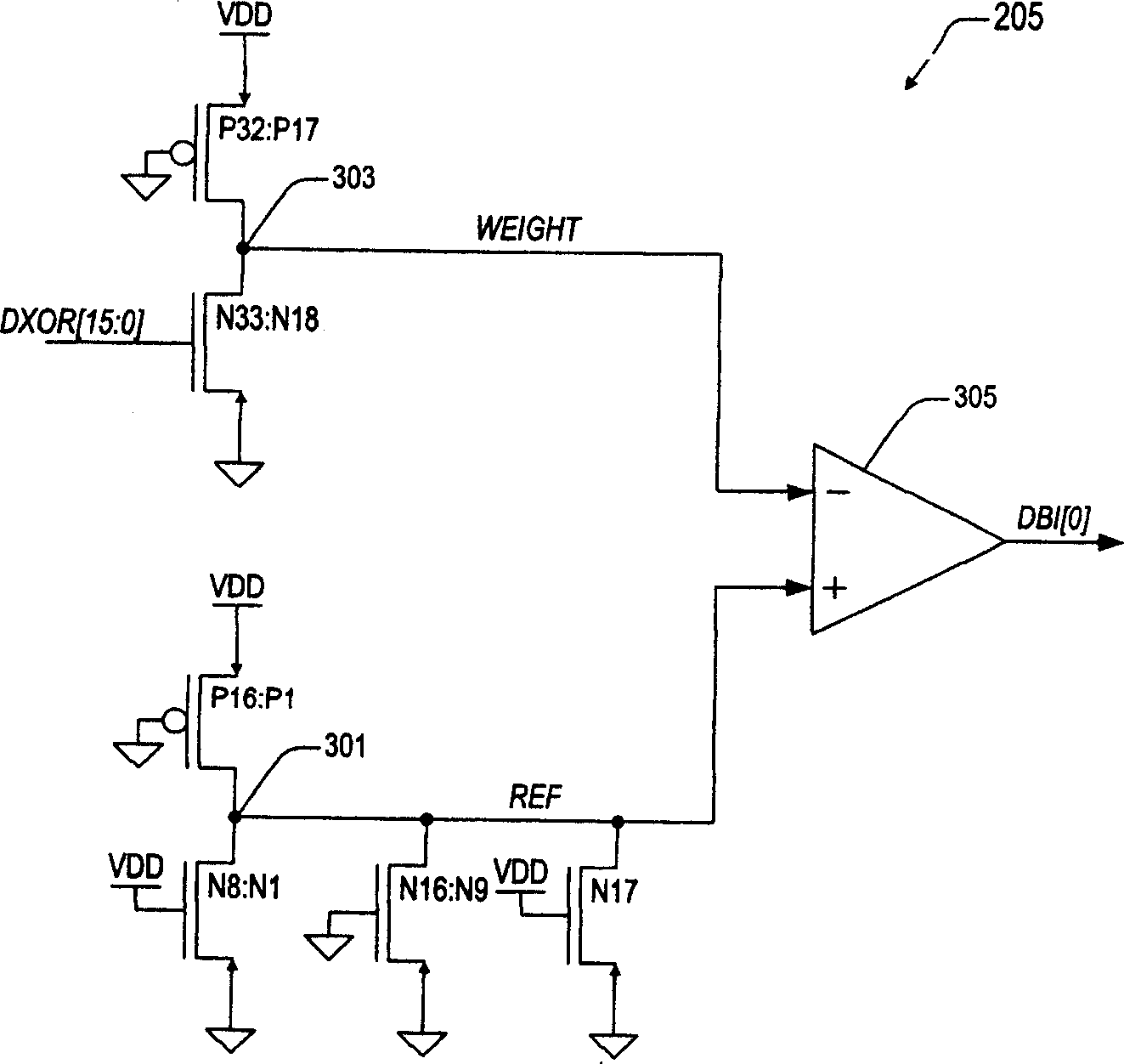

Sense mechanism for microprocessor bus inversion

ActiveUS20050216630A1Digital storageElectric digital data processingData bus inversionMicroprocessor

A sense mechanism for data bus inversion including a first memory device and an analog adder. The first memory device stores bits of the bus in a previous bus cycle. The analog adder compares the bits of the bus in the previous bus cycle with bits of the bus in a current bus cycle and provides a data inversion signal indicative of whether more than half of the bits of the bus have changed state. The analog adder operates as a bus state change sense device which rapidly evaluates bus state changes from one bus cycle to the next. The data inversion signal is used for selectively inverting the data bits of the bus and indicating bus inversion according to data bus inversion operation, such as according to X86 microprocessor protocol.

Owner:VIA TECH INC

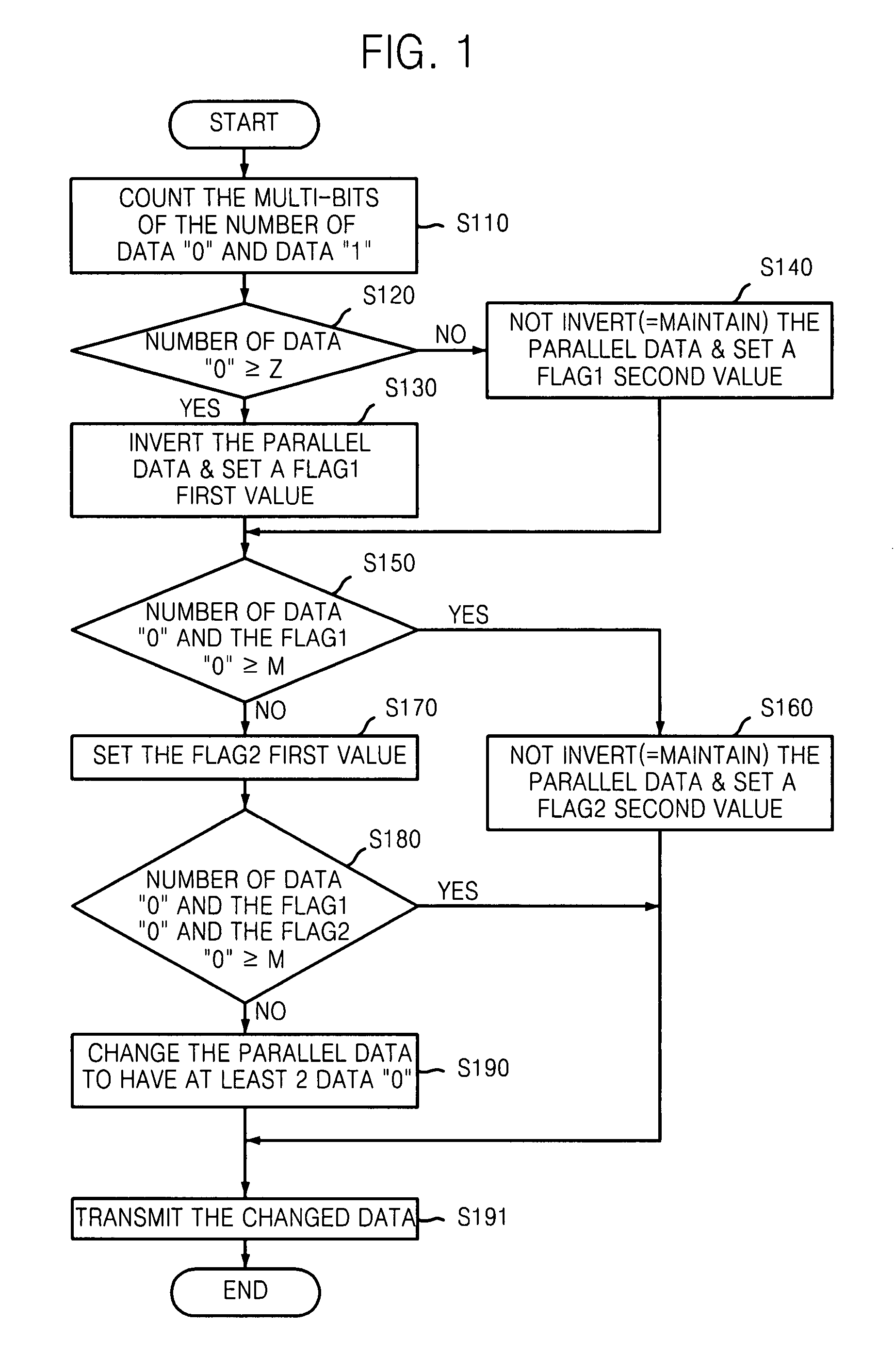

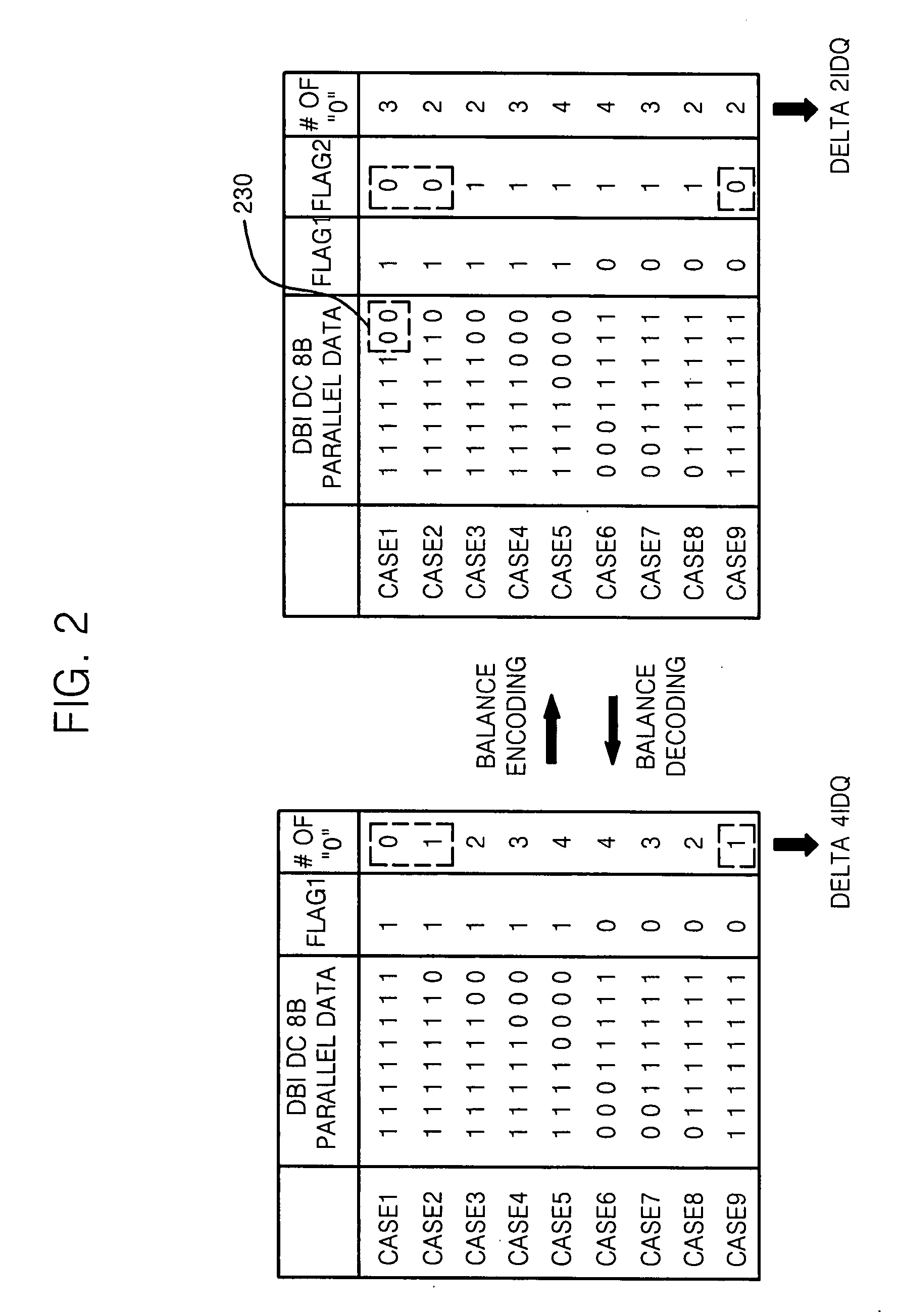

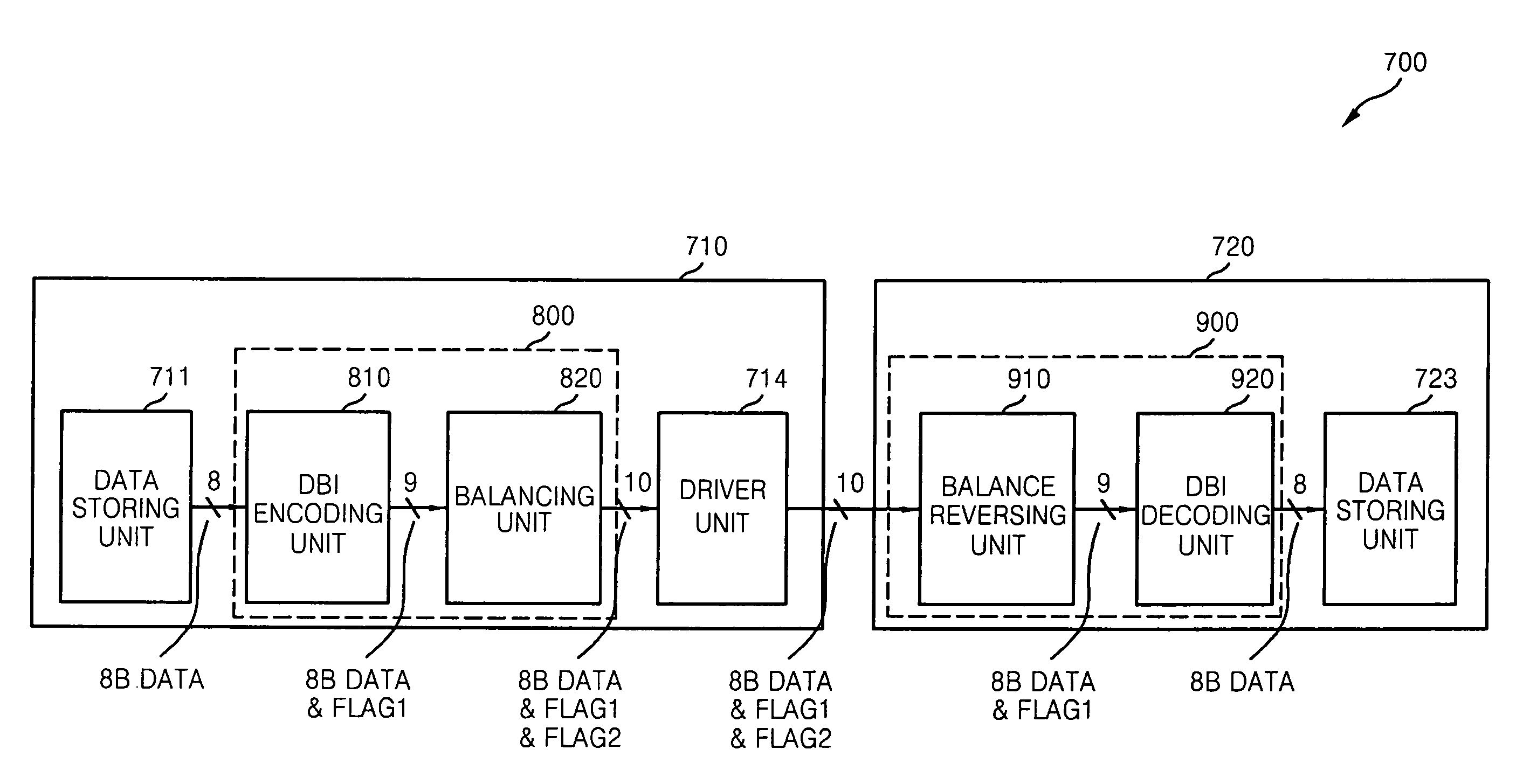

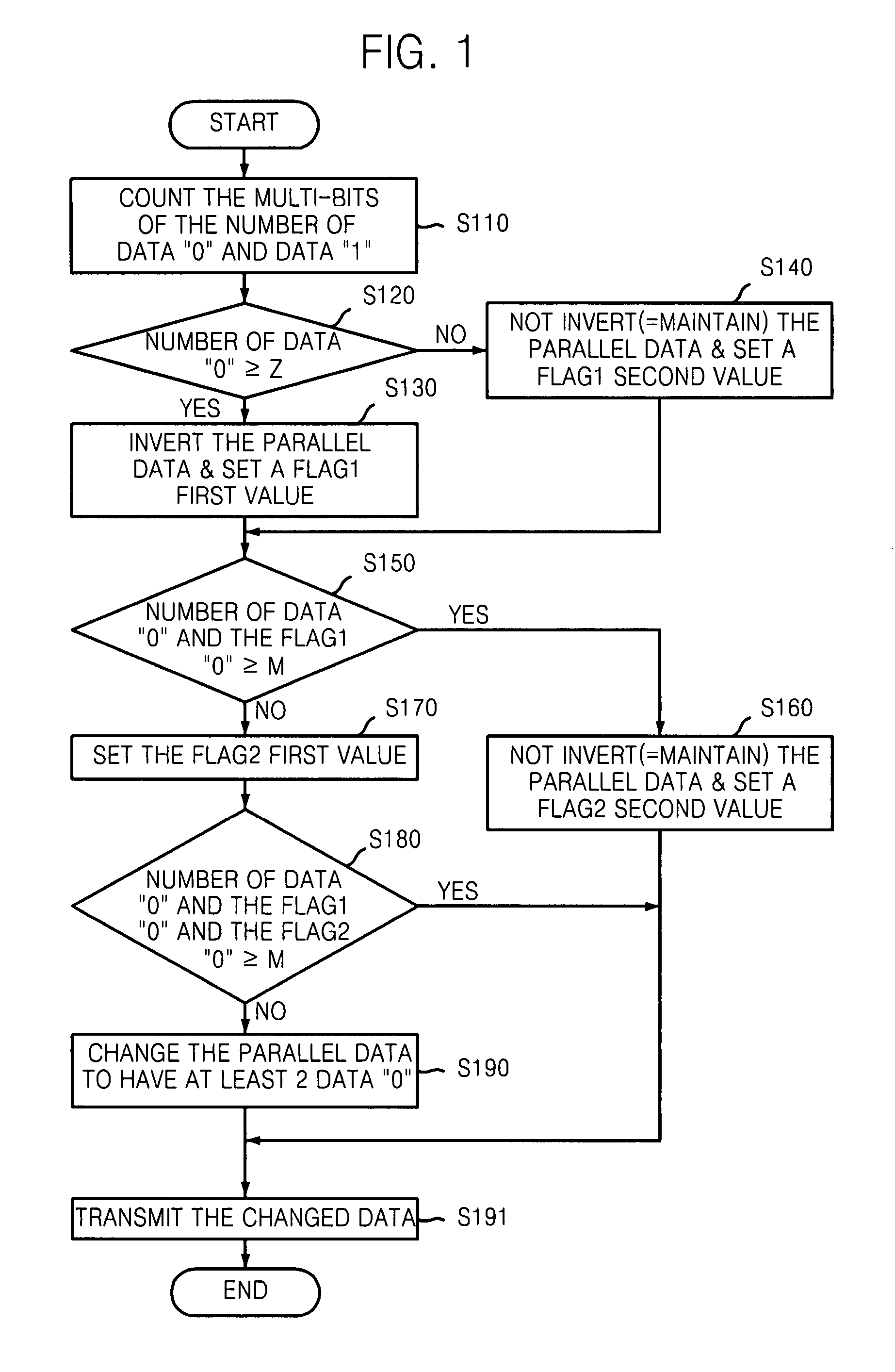

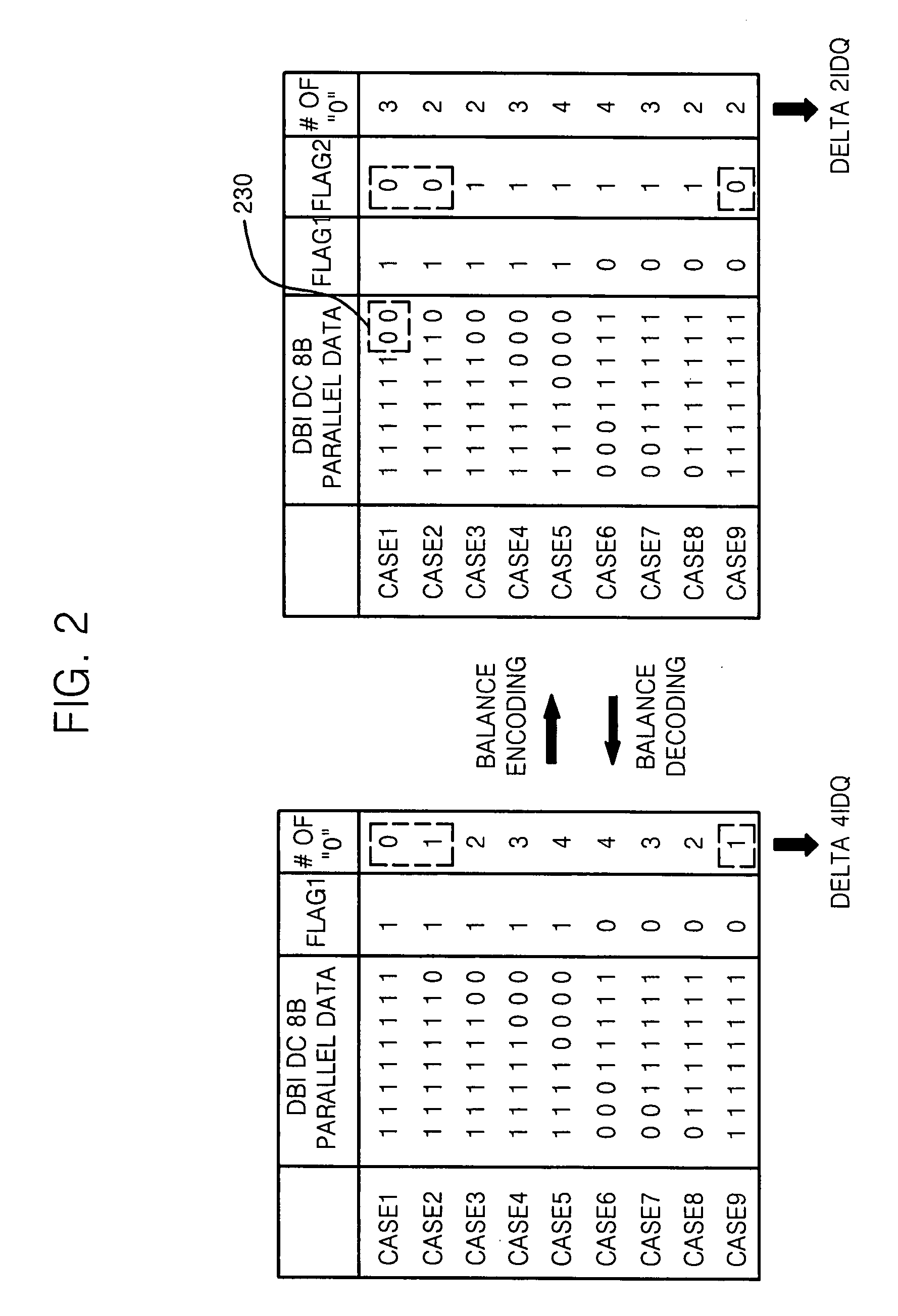

Low power balance code using data bus inversion

ActiveUS20070242508A1Reduce power consumptionReduce noiseIndividual digits conversionDigital storageComputer hardwarePower Balance

A method and apparatus for reducing power consumption needed to refresh a memory may receive data having been encoded using data bus inversion (DBI), the DBI data having a first delta between a number of zeros for different cases between zero and a DBI maximum, balance code the DBI data to balance the number of zeros across the DBI data, and output data having a number of zeros for different cases between a minimum number greater than zero and less than or equal to the DBI maximum and a maximum number equal to the minimum number plus a second delta, the second delta being less than the first delta.

Owner:SAMSUNG ELECTRONICS CO LTD

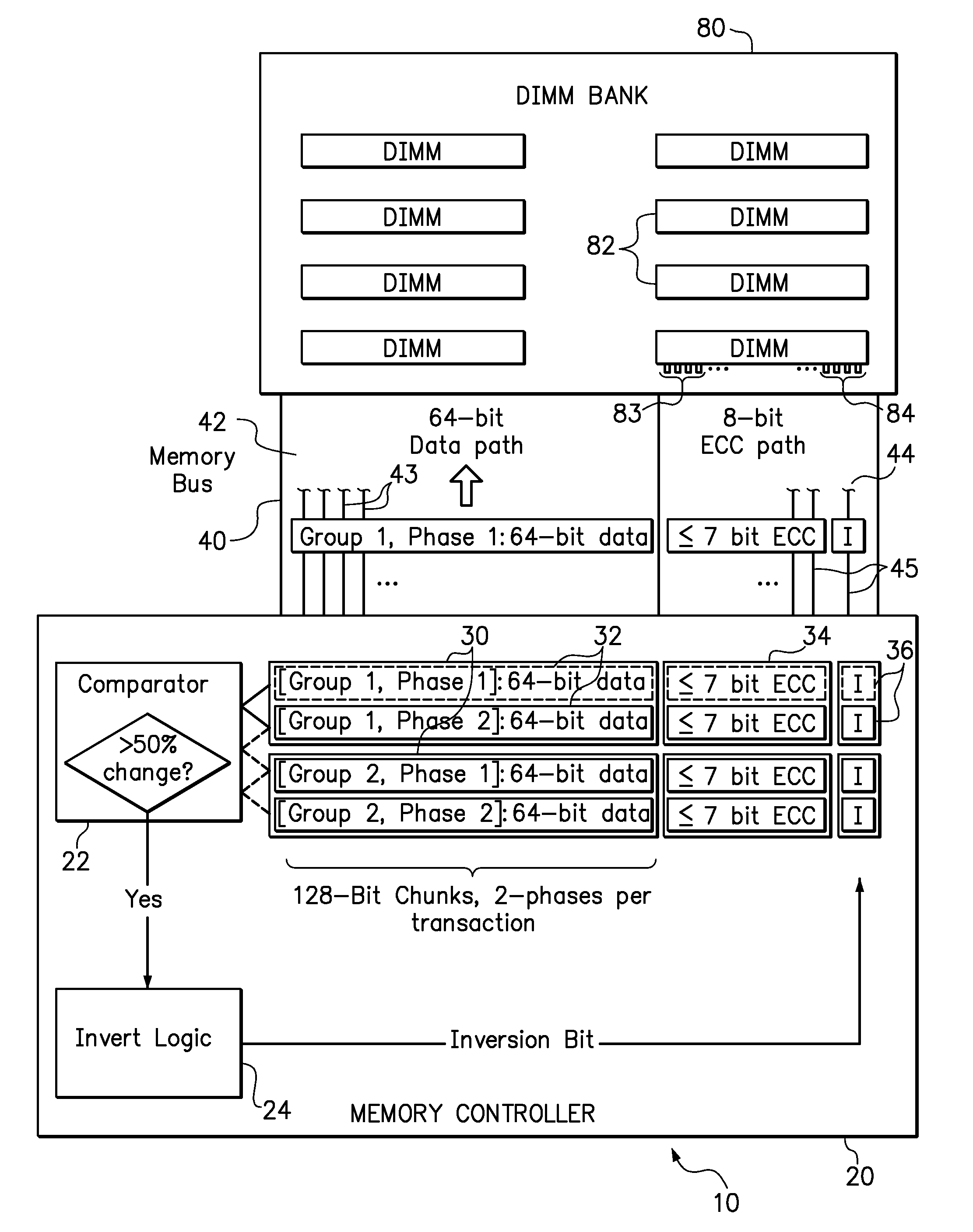

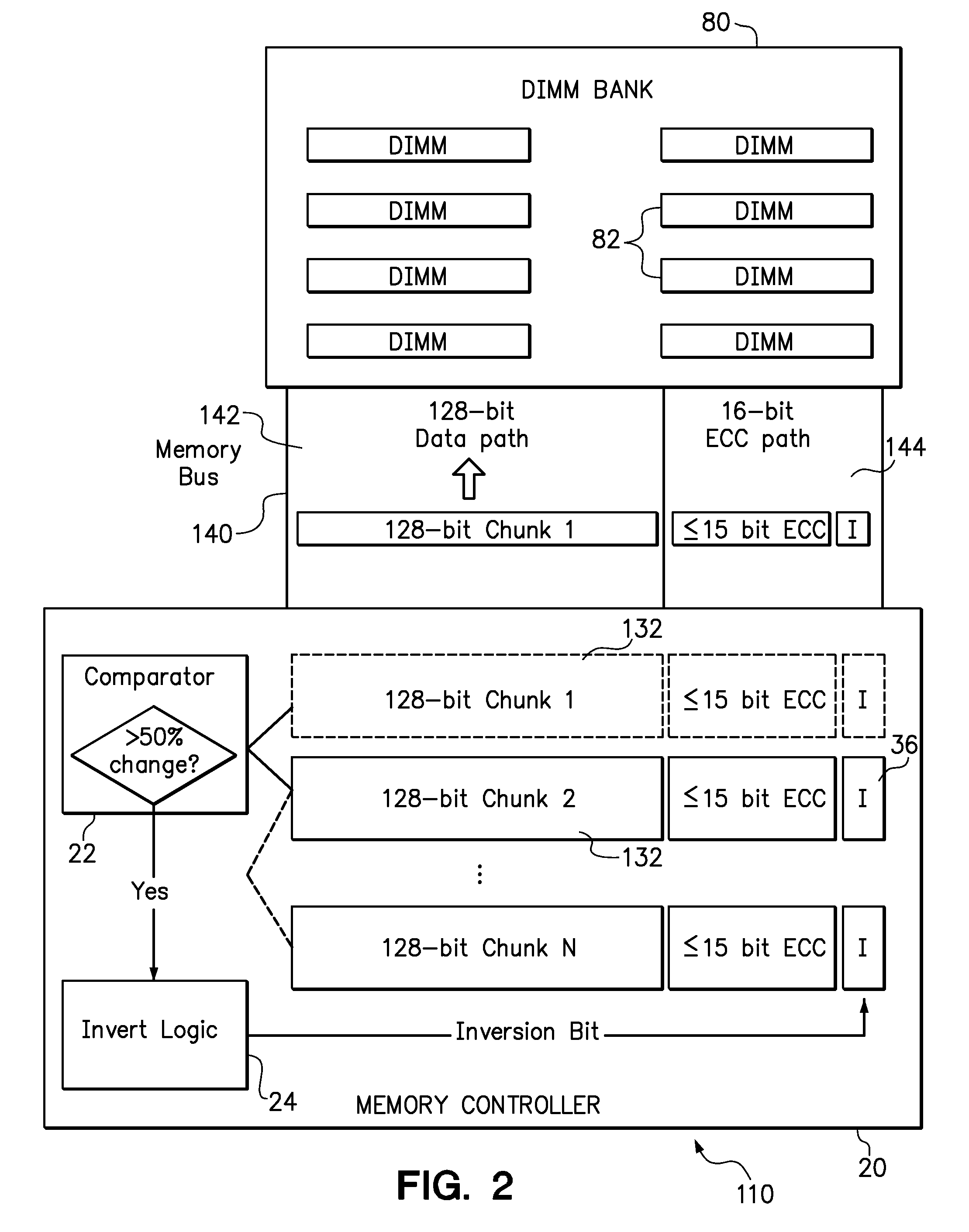

Data bus inversion using spare error correction bits

In a memory system, a spare error correction bit is produced by processing data to be stored in sufficiently large chunks that the number of error correction bits required to protect each chunk are fewer than the available error correction signal lines on a memory bus and storage device. The spare bit is then used for an inversion bit in a parallel data bus inversion scheme, wherein data is selectively inverted to minimize bus switching. The transmission of data and error correction bits are spread over multiple phases, wherein parallel data bus inversion is applied to each phase. Alternatively, the transmission of data and error correction bits may be transmitted and stored in a single transaction. In either case, the spare bit is transmitted on a conventional memory bus and stored in a conventional memory module along with data and error correction bits.

Owner:LENOVO GLOBAL TECH INT LTD

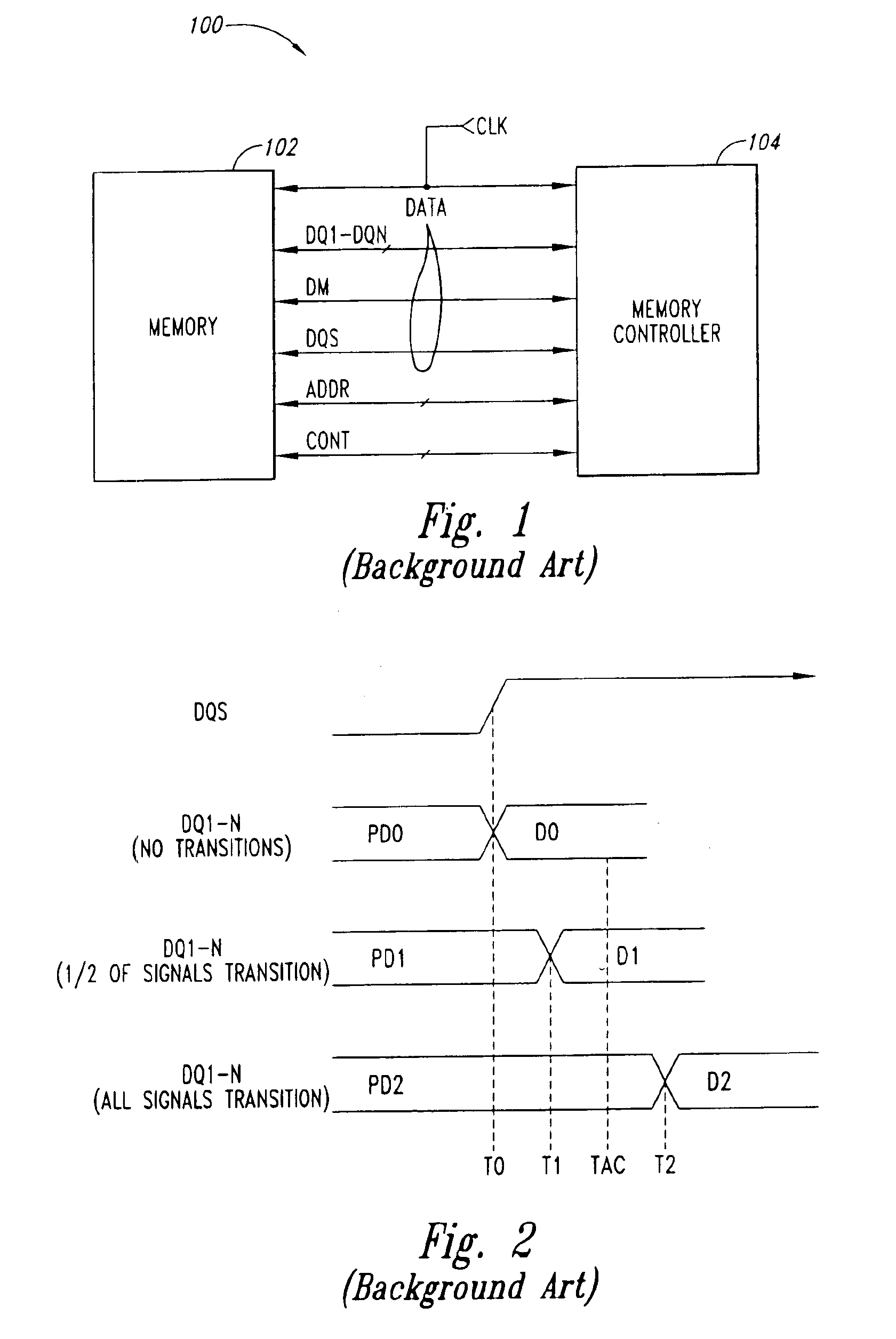

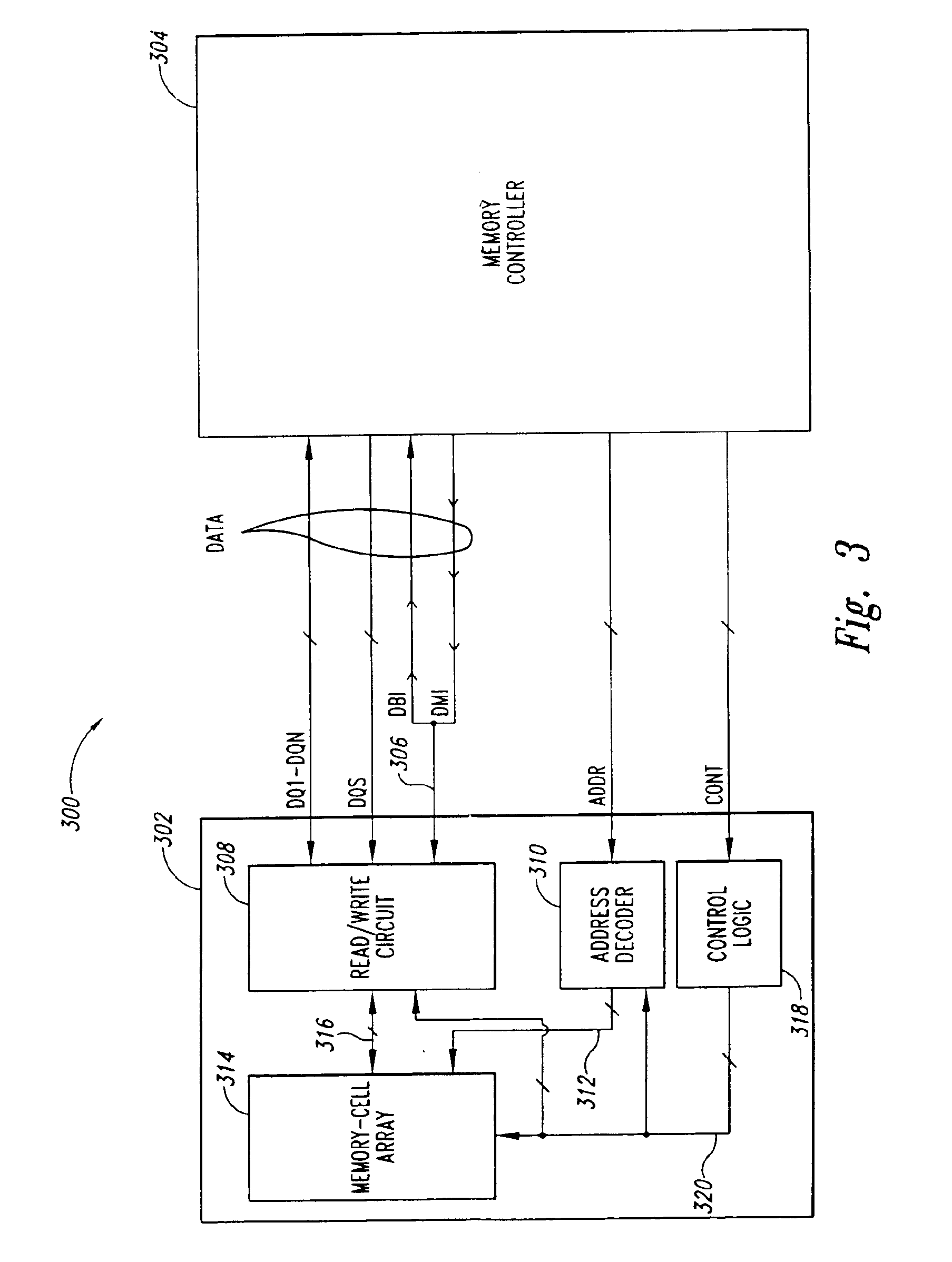

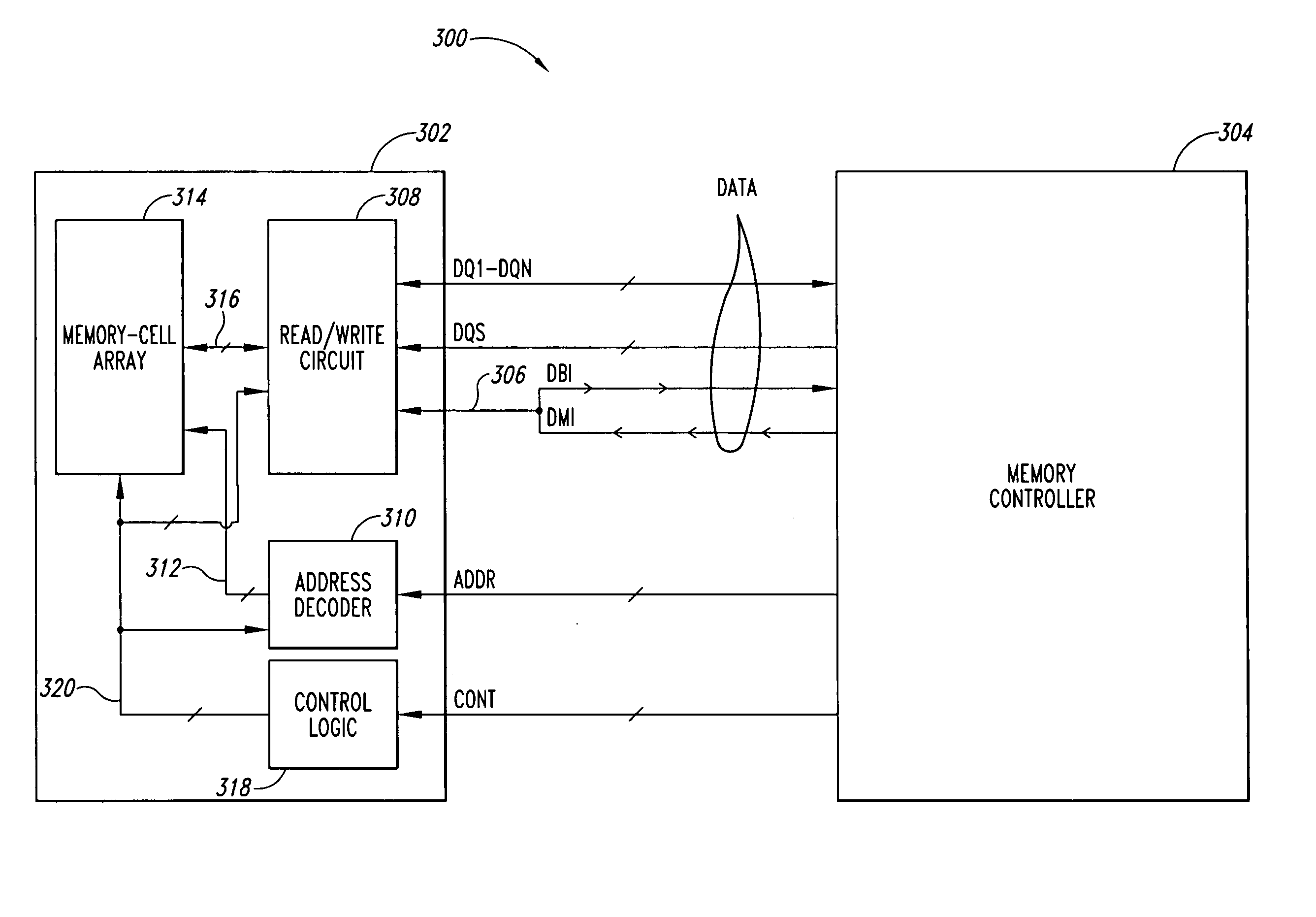

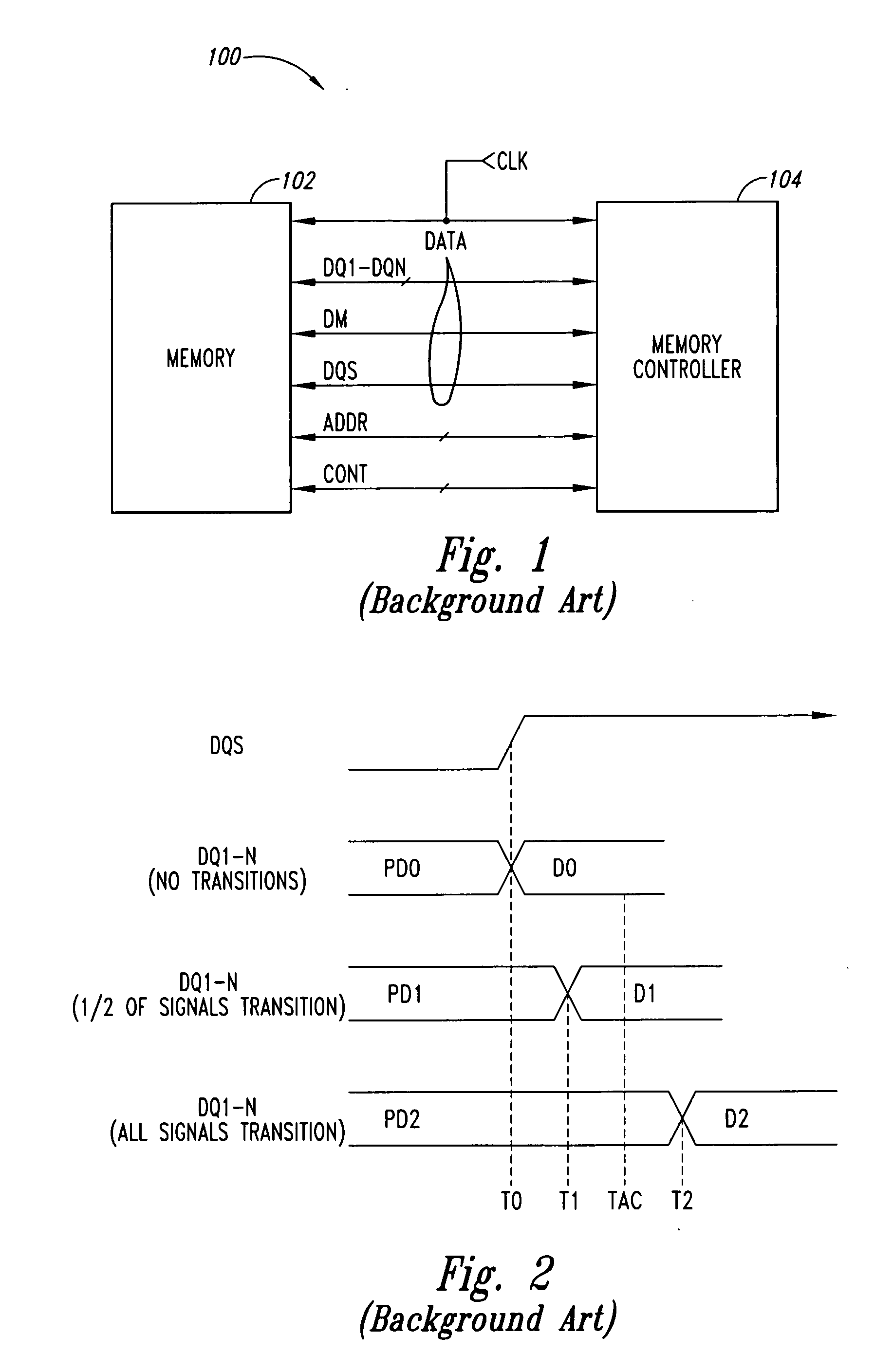

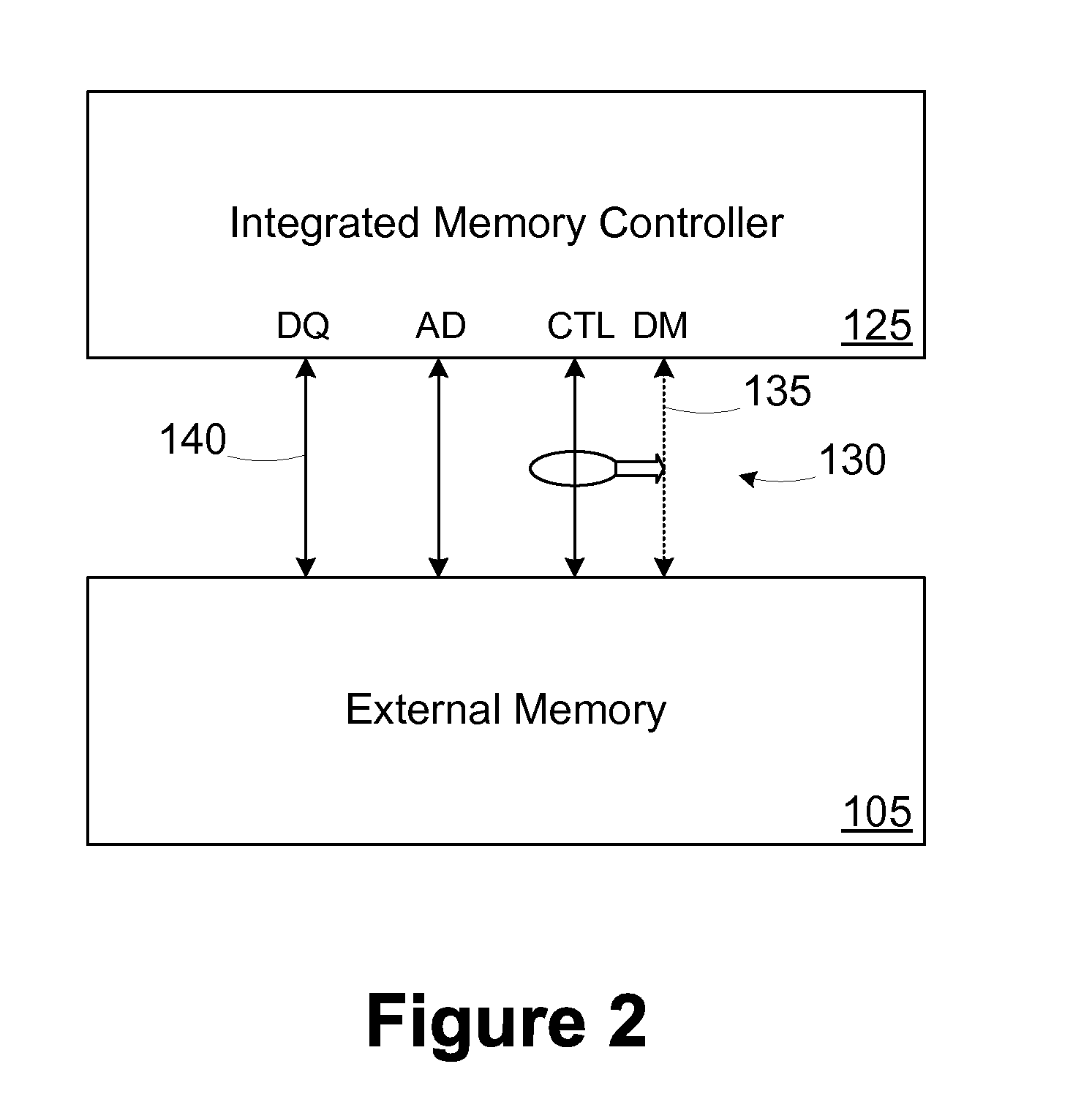

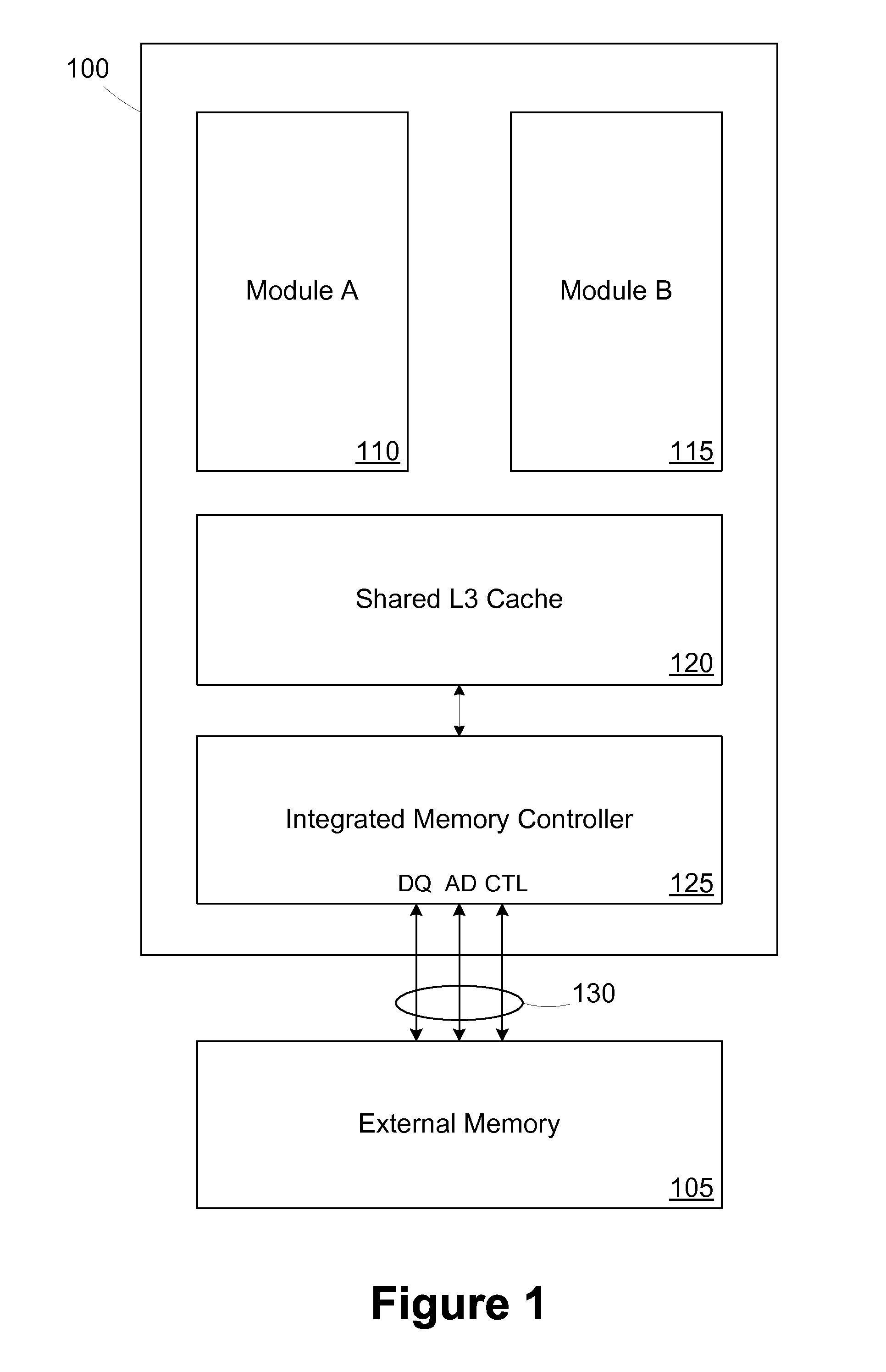

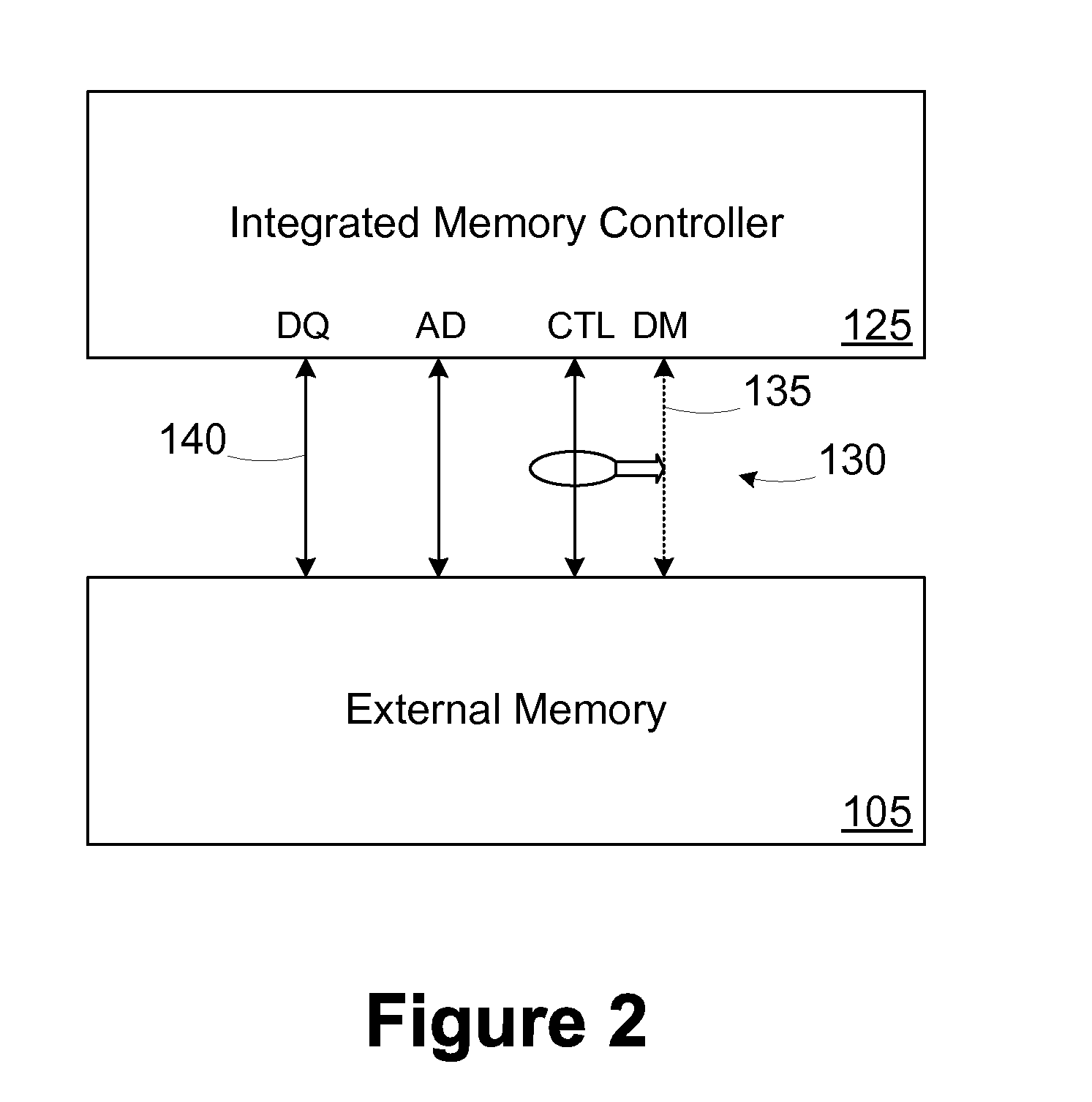

Memory bus polarity indicator system and method for reducing the affects of simultaneous switching outputs (SSO) on memory bus timing

A method and system transfer read data from a memory device having a data bus and a data masking pin adapted to receive a masking signal during write operations of the memory device. The method includes placing a sequence of read data words on the data bus and applying a data bus inversion signal on the data masking pin, the data bus inversion signal indicating whether the data contained each read data word has been inverted. Another method and system transfer data over a data bus. The method includes generating a sequence of data words, at least one data word including data bus inversion data. The sequence of data words is applied on the data bus and is thereafter stored. The data bus inversion data is applied to invert or not invert the data contained in the stored data words.

Owner:MICRON TECH INC

Data bus inversion coding

ActiveUS20130159584A1Energy efficient ICTEnergy efficient computingData transmissionInterface circuits

Techniques are disclosed relating to data inversion encoding. In one embodiment, an apparatus includes an interface circuit. The interface circuit is configured to perform first and second data bursts that include respective pluralities of data transmissions encoded using an inversion coding scheme. In such an embodiment, the initial data transmission of the second data burst is encoded using the final data transmission of the first data burst. In some embodiments, the first and second data bursts correspond to successive write operations or successive read operations to a memory module from a memory PHY.

Owner:ADVANCED MICRO DEVICES INC

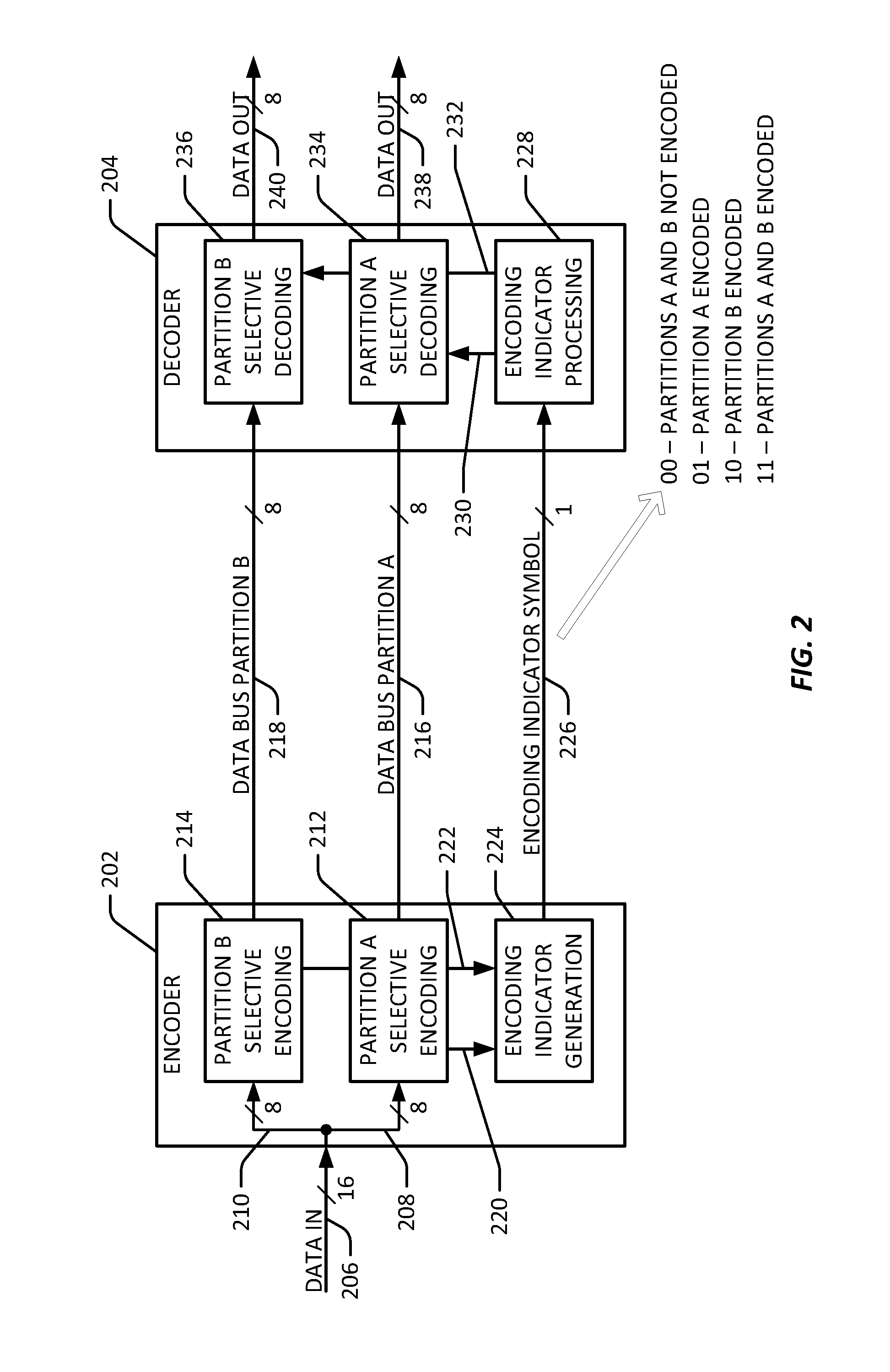

Encoding for partitioned data bus

InactiveUS20150229325A1Reduce power consumptionImprove efficiencyPulse conversionEnergy efficient computingData transmissionData bus inversion

A data bus is split into partitions and encoding is independently applied to data transmitted over each bus partition to improve power and / or throughput efficiency. The encoding can be data bus inversion or any other suitable type of encoding. An encoding indicator symbol transmitted in conjunction with the data indicates which bus partition is encoded, if any. In some implementations, encoding is selectively applied to each bus partition during each data transfer cycle of a parallel data bus. In some implementation, the encoding indicator symbol is a multi-level signal where each level of the multi-level signal represents at least two bits of information indicative of, for a corresponding bus partition, whether encoding is applied to the data to be transmitted over the bus partition. Advantageously, the encoding indicator symbol can be transmitted over a single, dedicated bus line.

Owner:QUALCOMM INC

Low power balance code using data bus inversion

ActiveUS7495587B2Reduce power consumptionReduce noiseIndividual digits conversionDigital storageComputer hardwarePower Balance

A method and apparatus for reducing power consumption needed to refresh a memory may receive data having been encoded using data bus inversion (DBI), the DBI data having a first delta between a number of zeros for different cases between zero and a DBI maximum, balance code the DBI data to balance the number of zeros across the DBI data, and output data having a number of zeros for different cases between a minimum number greater than zero and less than or equal to the DBI maximum and a maximum number equal to the minimum number plus a second delta, the second delta being less than the first delta.

Owner:SAMSUNG ELECTRONICS CO LTD

Sense mechanism for microprocessor bus inversion

A sense mechanism for data bus inversion including a first memory device and an analog adder. The first memory device stores bits of the bus in a previous bus cycle. The analog adder compares the bits of the bus in the previous bus cycle with bits of the bus in a current bus cycle and provides a data inversion signal indicative of whether more than half of the bits of the bus have changed state. The analog adder operates as a bus state change sense device which rapidly evaluates bus state changes from one bus cycle to the next. The data inversion signal is used for selectively inverting the data bits of the bus and indicating bus inversion according to data bus inversion operation, such as according to X86 microprocessor protocol.

Owner:VIA TECH INC

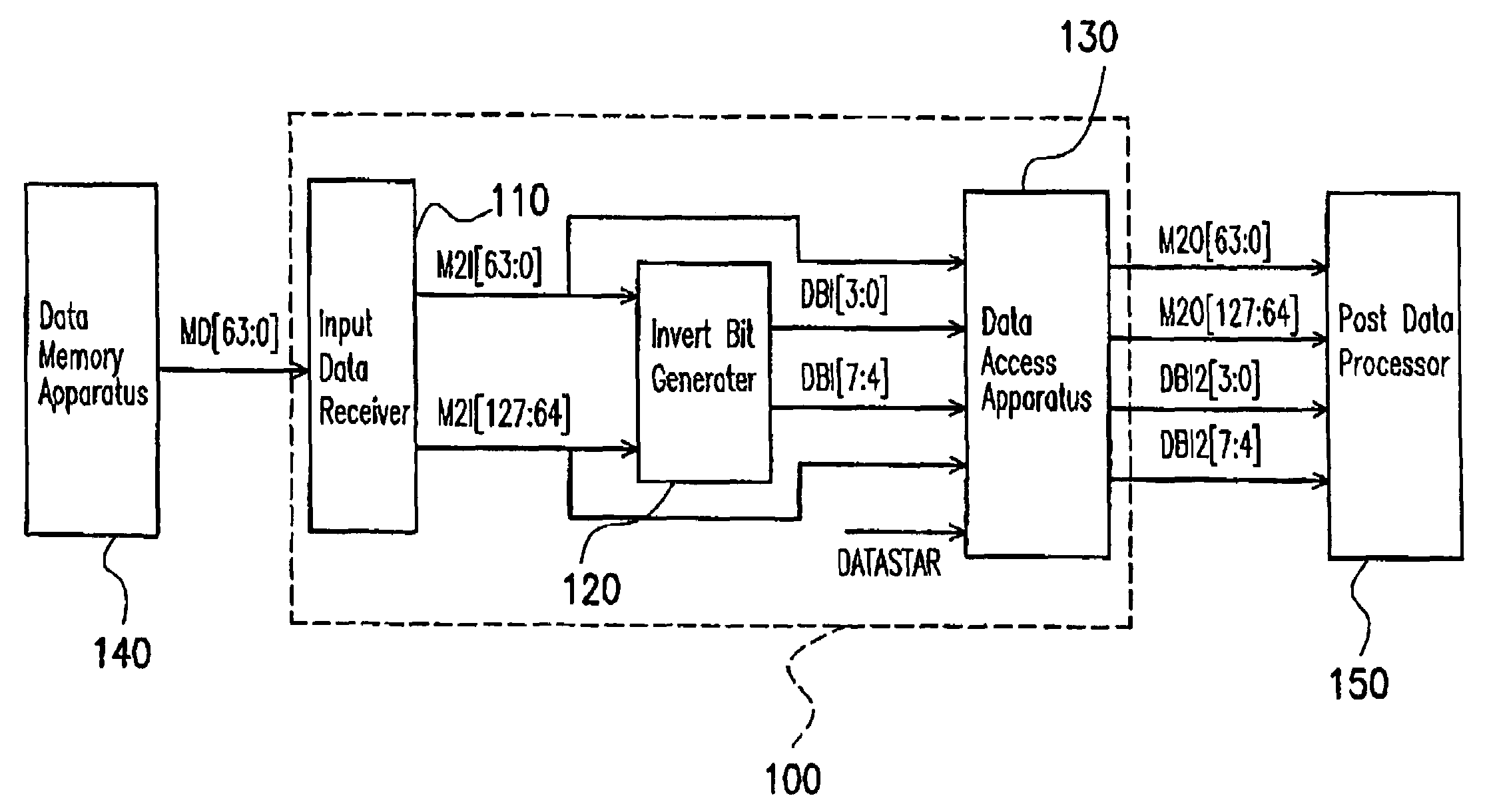

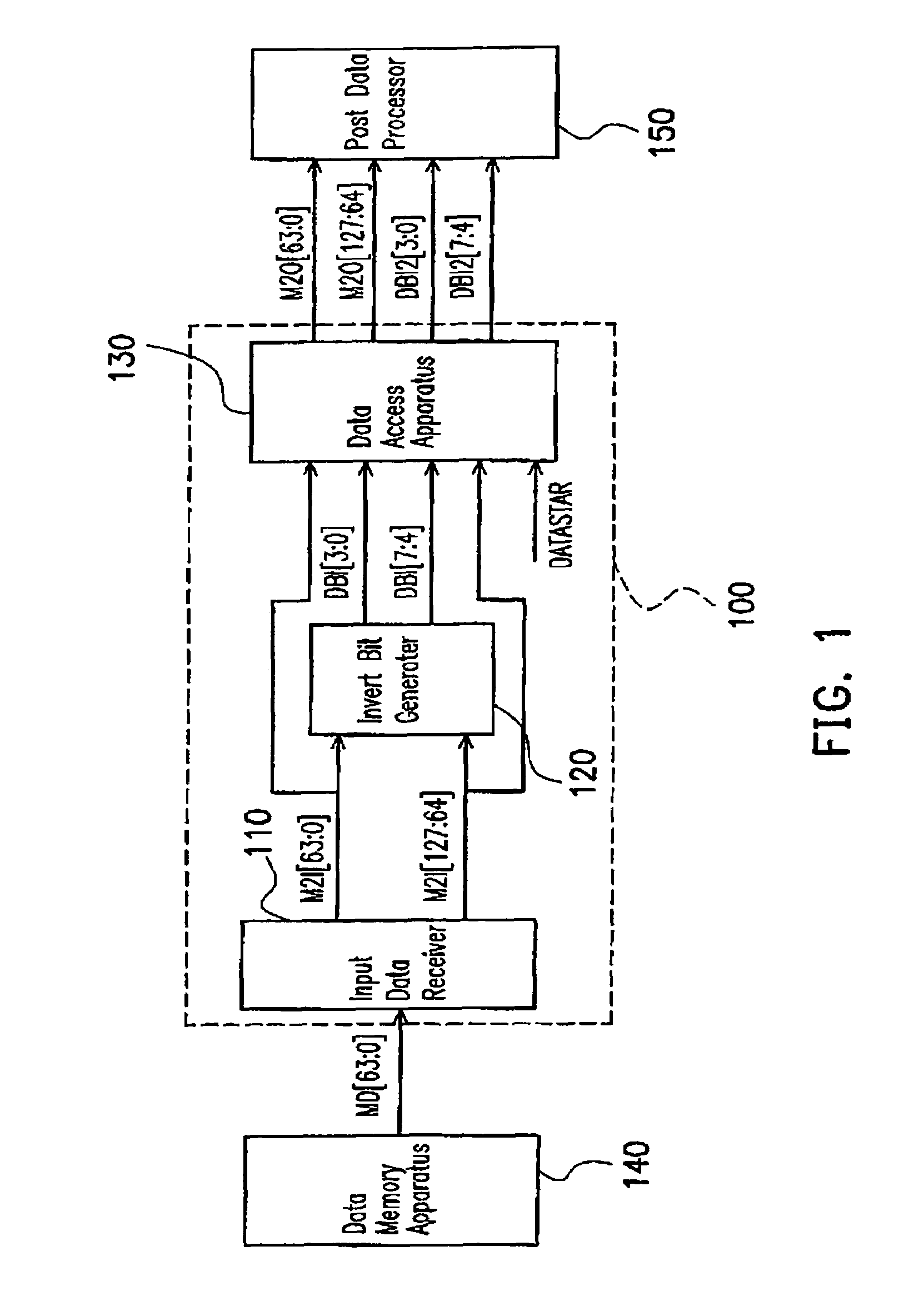

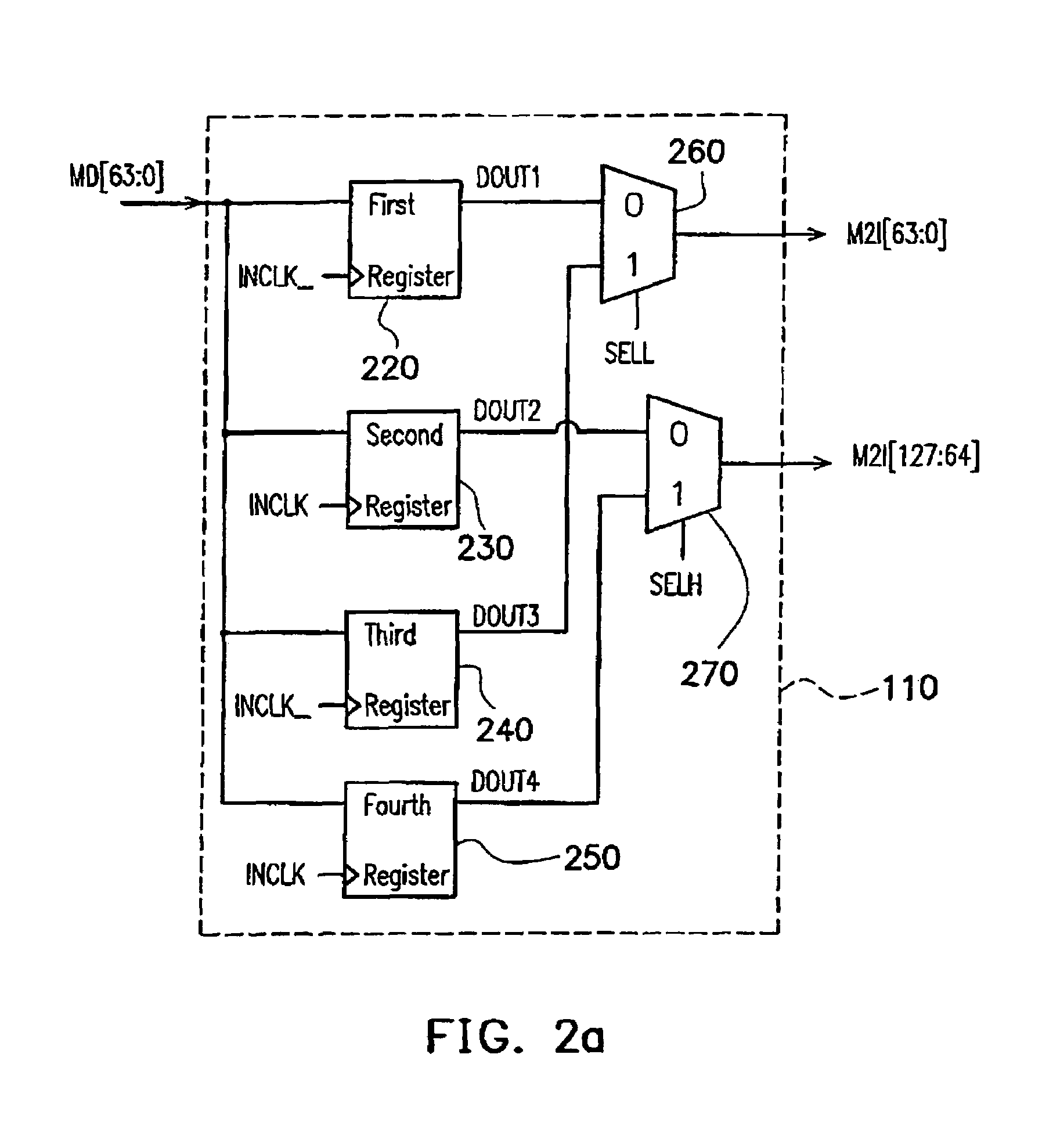

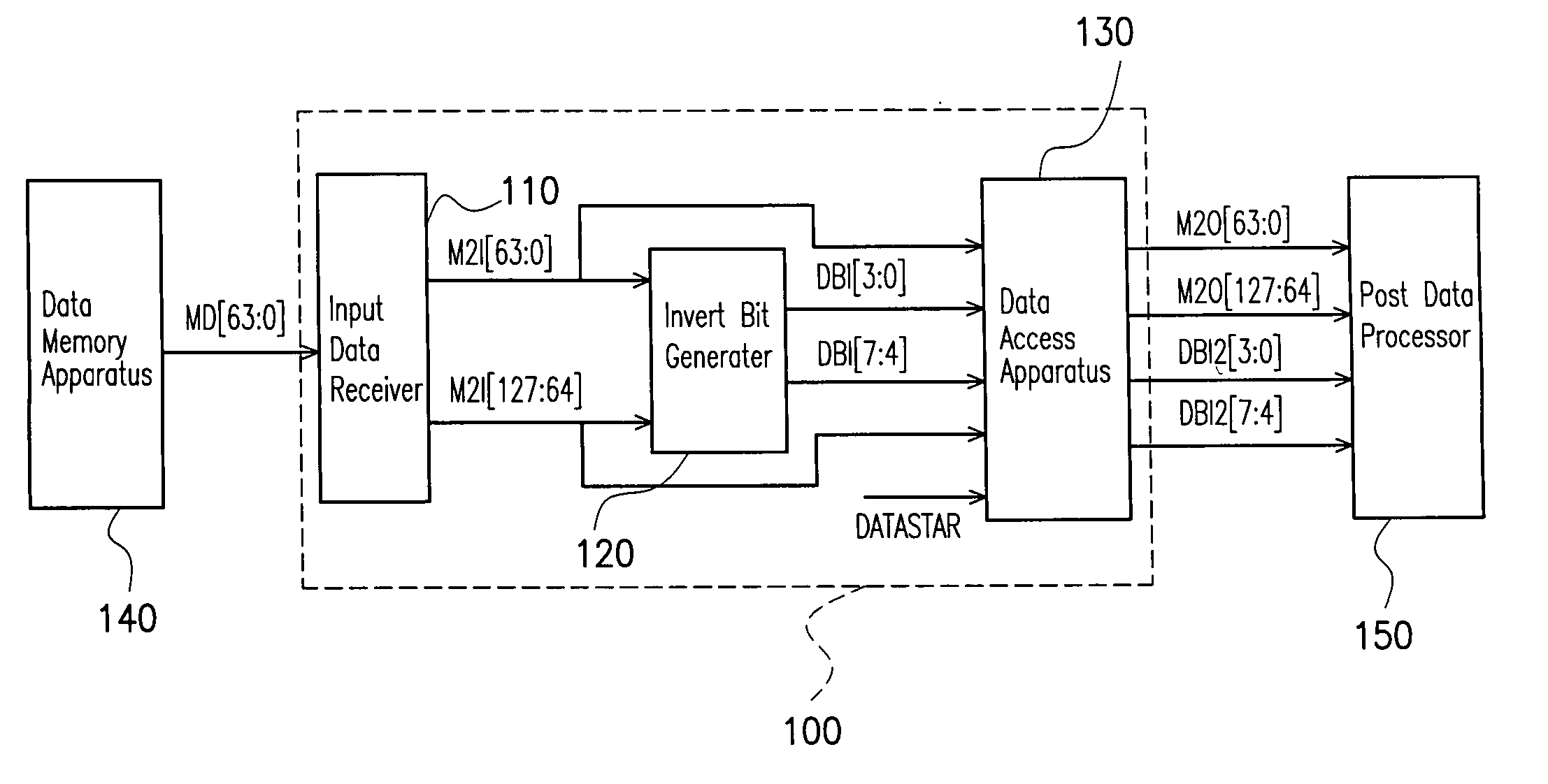

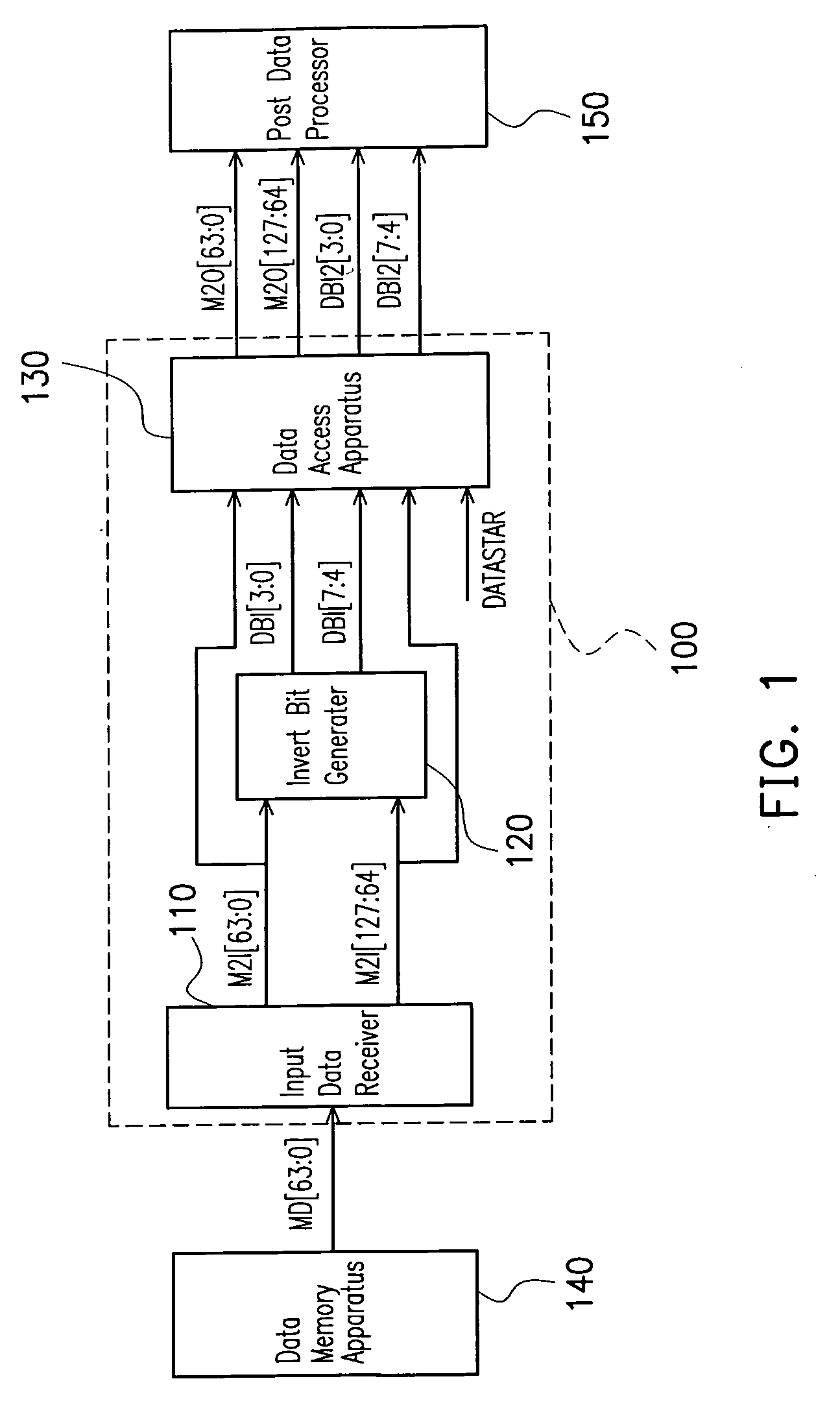

Data memory controller that supports data bus invert

InactiveUS7082489B2Extension of timeReduce variationEnergy efficient ICTPower supply for data processingTiming marginFrequency reduction

The present invention provides a data memory controller that supports for the invert of data bus. Data transmitted from a memory is received in a chip set, which further transmits the data to a data processing apparatus. While receiving the memory data, the chip set doubles the bandwidth and reduces the frequency, such that the time margin for processing data is increased. In addition, after outputting data to the data processing apparatus, a first frame of data is compared to bus idle state to further reduce frequency of data invert and power consumption.

Owner:VIA TECH INC

Memory bus polarity indicator system and method for reducing the affects of simultaneous switching outputs (SSO) on memory bus timing

A method and system transfer read data from a memory device having a data bus and a data masking pin adapted to receive a masking signal during write operations of the memory device. The method includes placing a sequence of read data words on the data bus and applying a data bus inversion signal on the data masking pin, the data bus inversion signal indicating whether the data contained each read data word has been inverted. Another method and system transfer data over a data bus. The method includes generating a sequence of data words, at least one data word including data bus inversion data. The sequence of data words is applied on the data bus and is thereafter stored. The data bus inversion data is applied to invert or not invert the data contained in the stored data words.

Owner:MICRON TECH INC

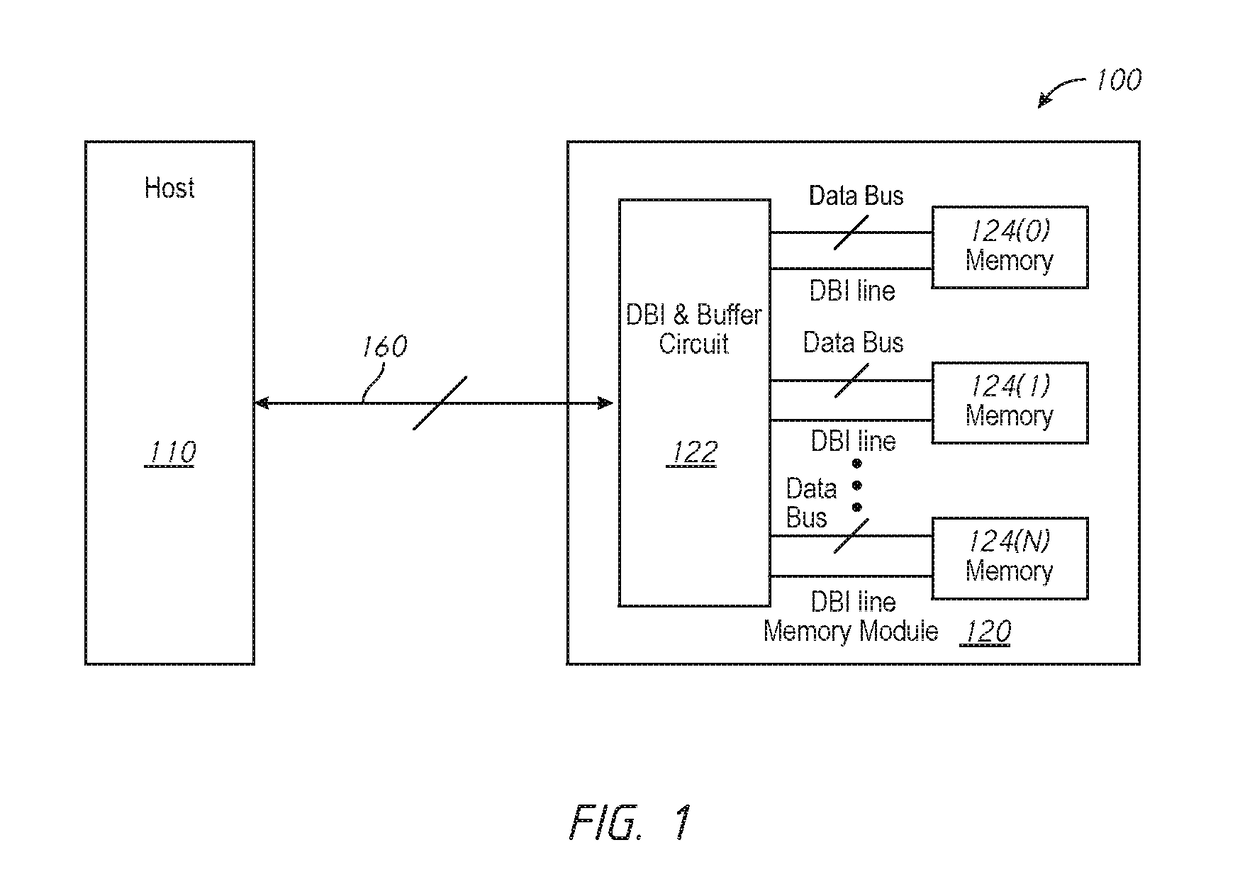

Apparatuses and methods for performing intra-module databus inversion operations

ActiveUS20170337951A1Digital storageElectric digital data processingComputer scienceData bus inversion

Apparatuses, memory modules, and methods for performing intra-module data bus inversion operations are described. An example apparatus include a memory module comprising a data bus inversion (DBI) and buffer circuit and a plurality of memories. The DBI and buffer circuit configured to encode a block of data received by the memory module and to provide DBI data and a corresponding DBI bit to a respective memory of the plurality of memories.

Owner:MICRON TECH INC

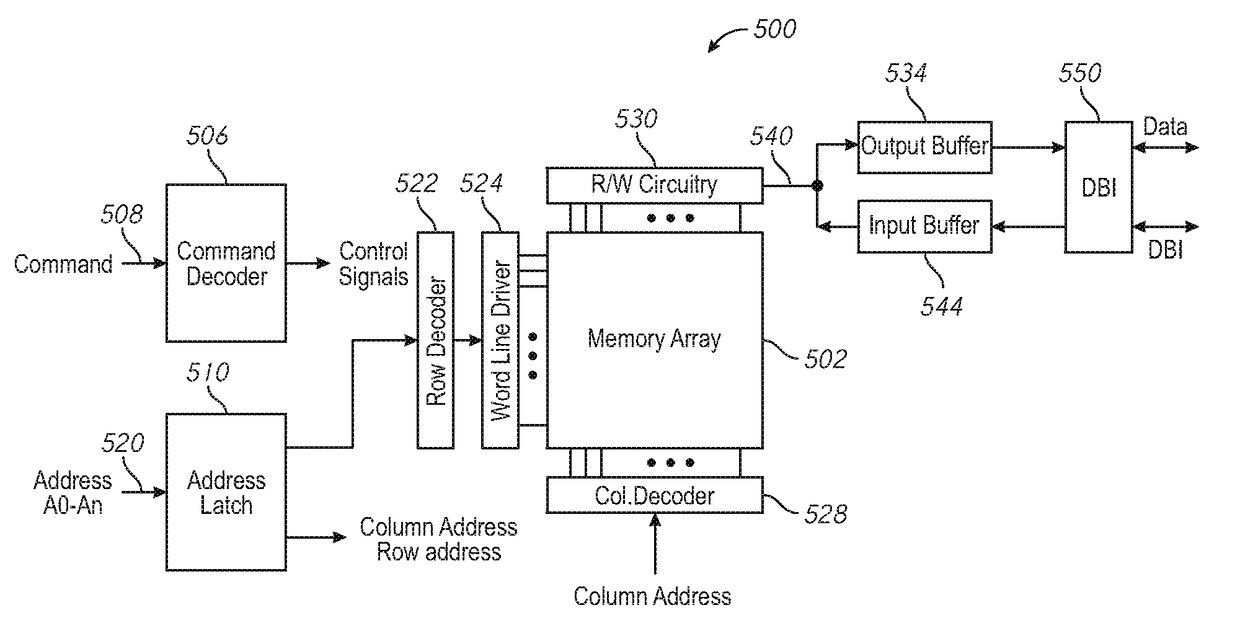

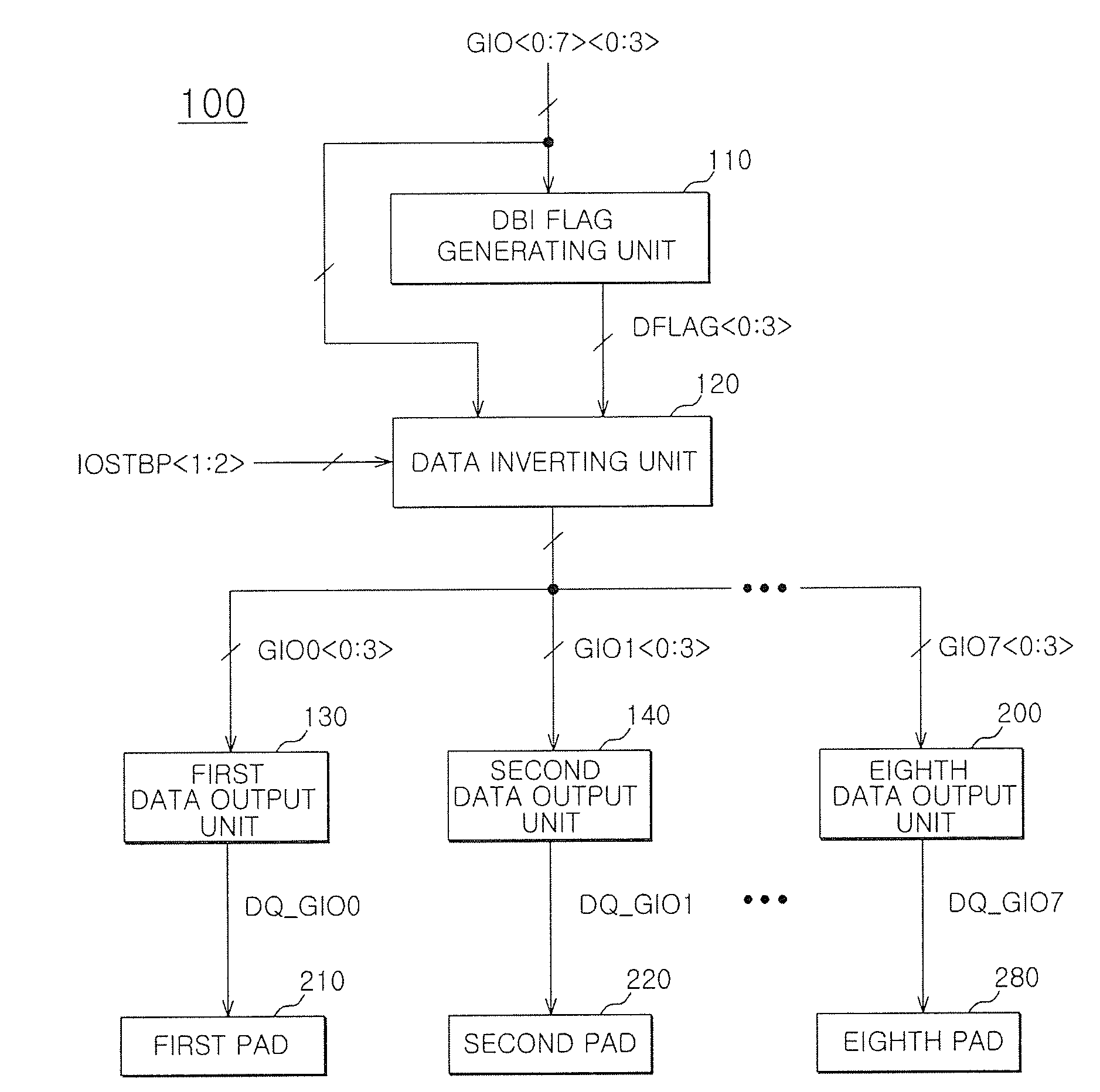

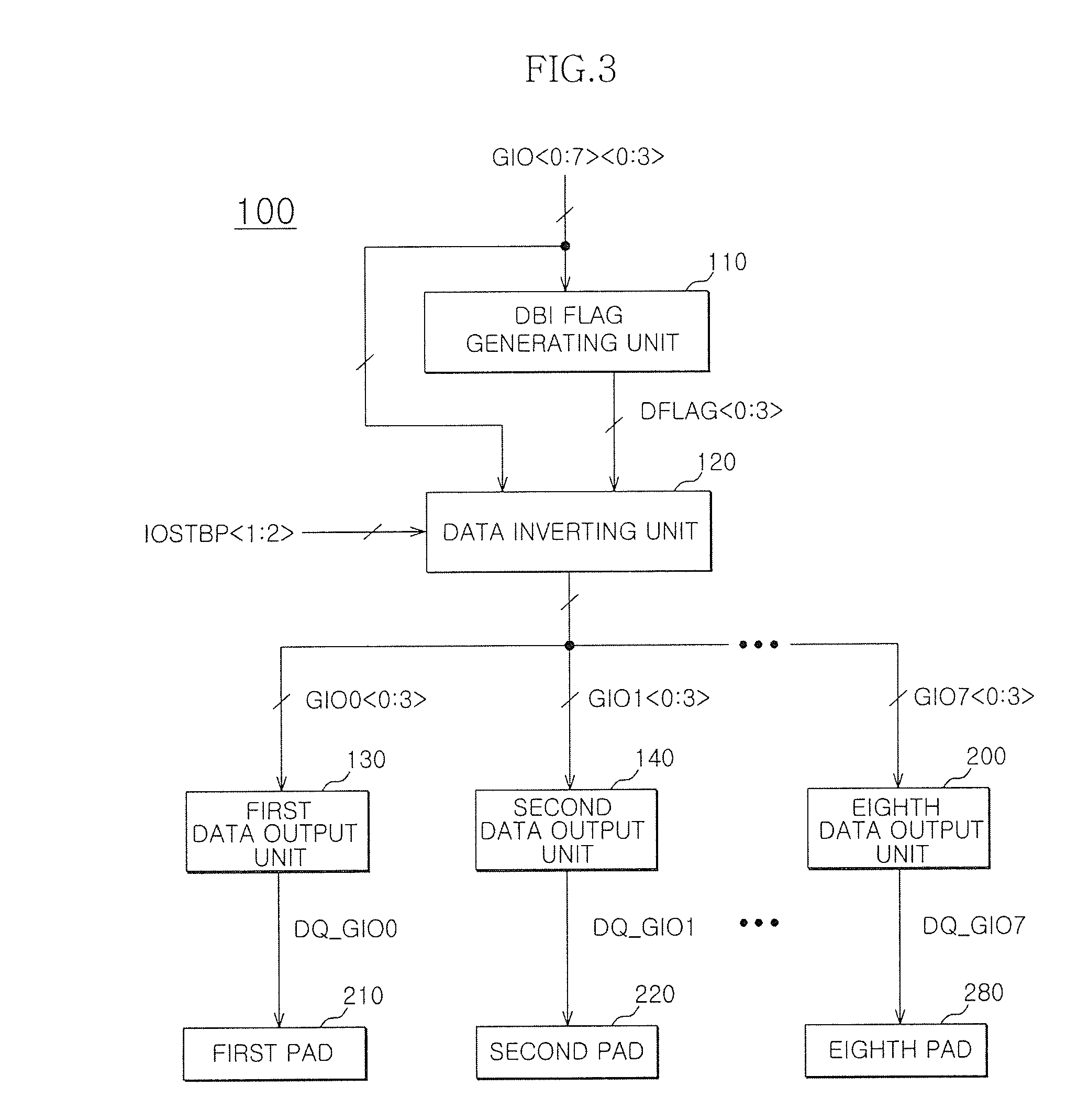

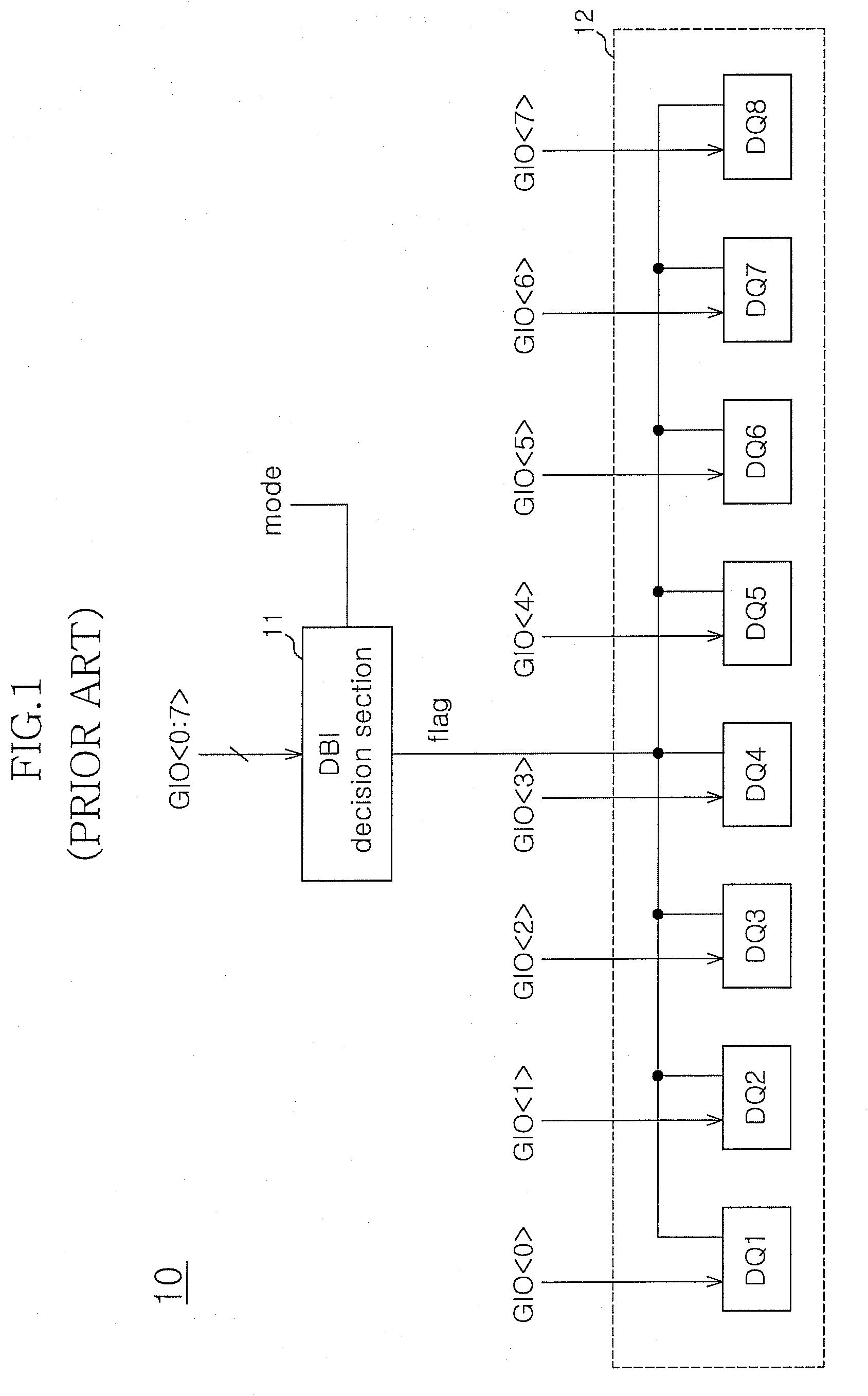

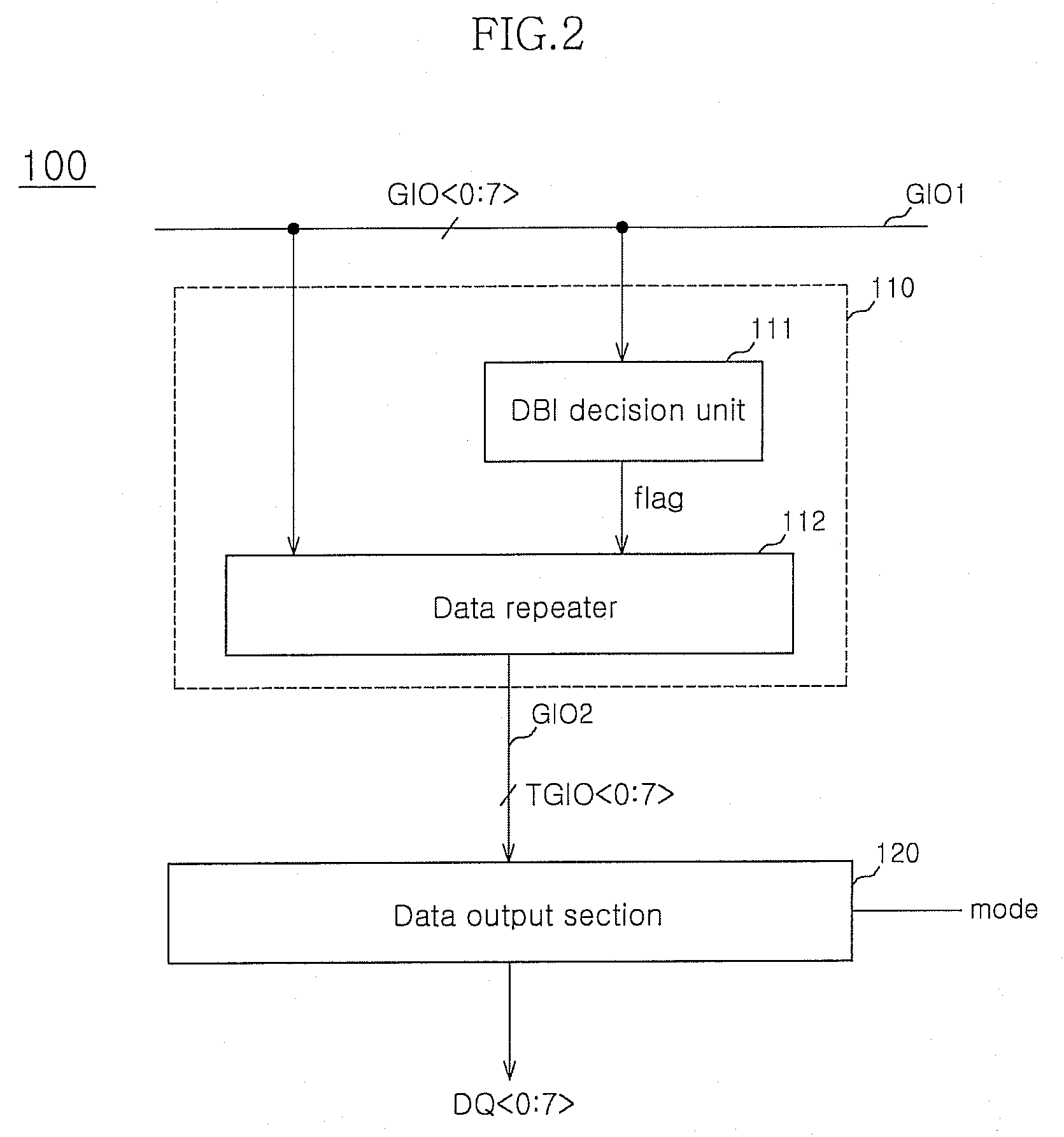

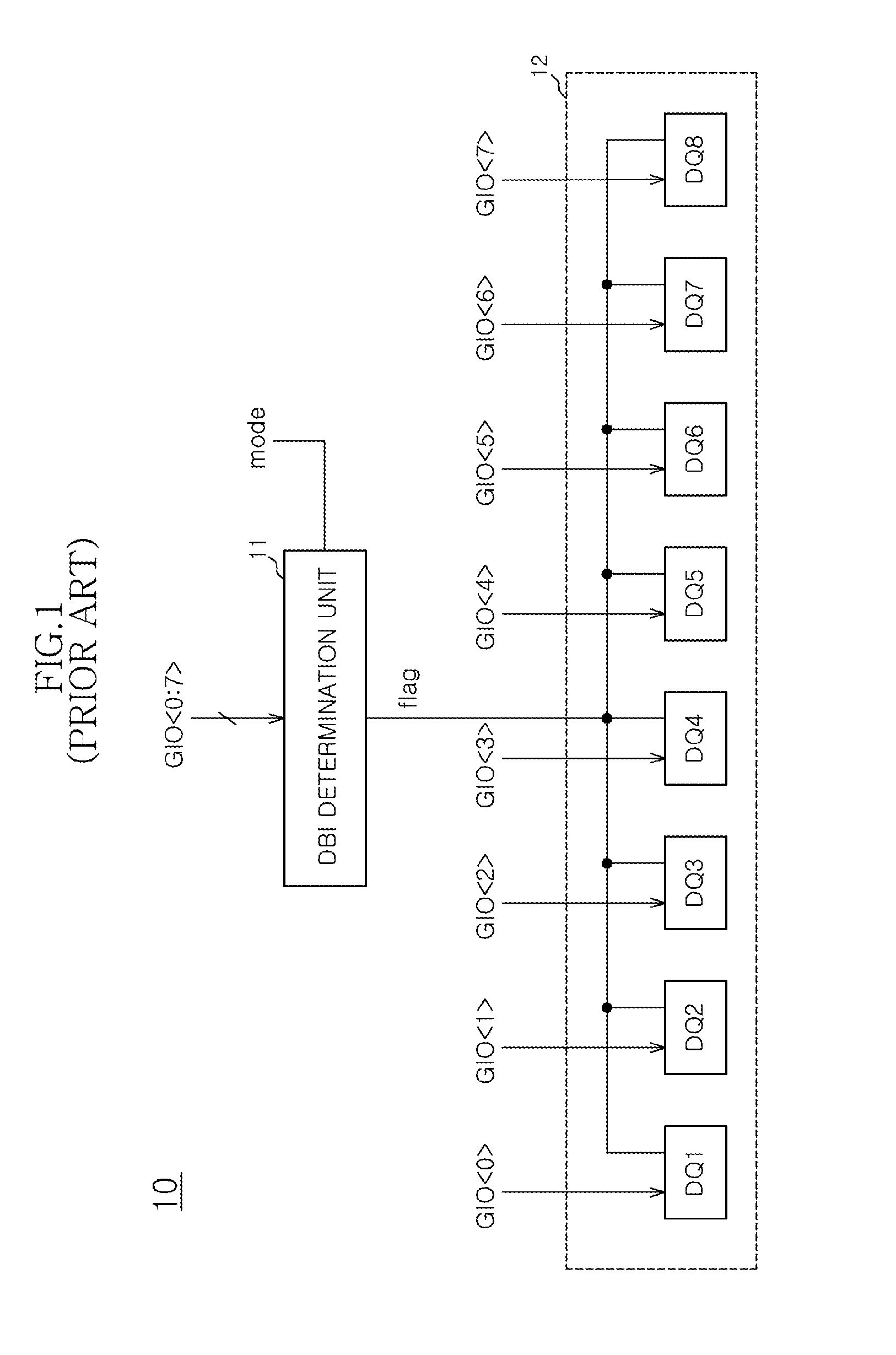

Semiconductor integrated circuit with data bus inversion function

A semiconductor integrated circuit includes a data bus inversion (DBI) flag generating unit to generate DBI flag signals using a plurality of output data sets, a data inverting unit to invert the plurality of output data sets according to the DBI flag signals and transmit the plurality of output data sets through global transmission lines, and a plurality of data output units to output the plurality of output data sets, which are transmitted through the global transmission lines by pads.

Owner:SK HYNIX INC

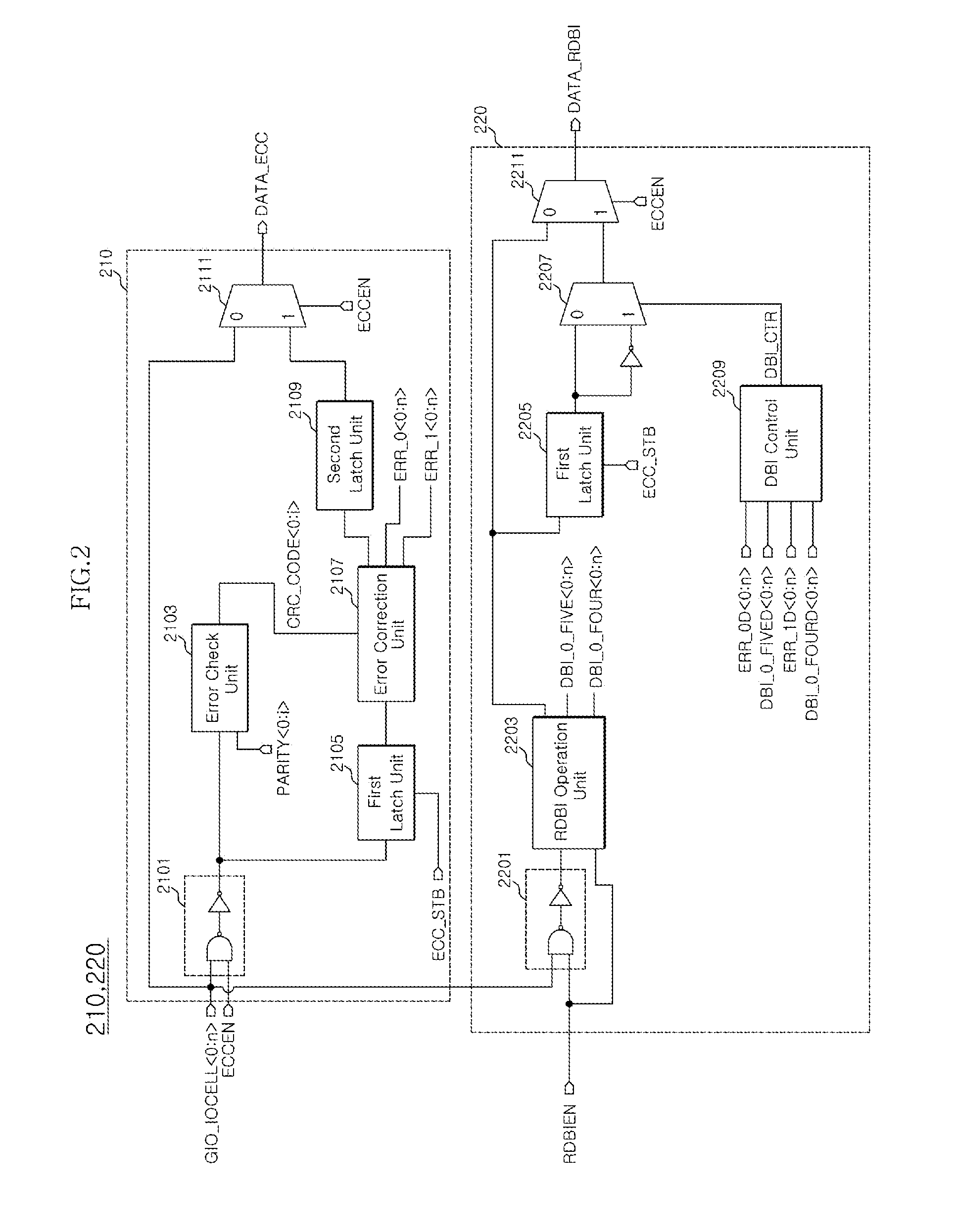

Semiconductor memory apparatus and operating method thereof

A semiconductor memory apparatus may include an error check and correction circuit block configured to receive a plurality of cell data, and output error-checked data and error data discrimination signals after receiving an error check enable signal; and a data bus inversion circuit block configured to receive the plurality of cell data, and output the plurality of cell data by inverting or non-inverting the cell data after receiving a read data bus inversion enable signal, the error check enable signal and the error data discrimination signals.

Owner:SK HYNIX INC

Reducing simultaneous switching outputs using data bus inversion signaling

ActiveUS20110252171A1Volume/mass flow measurementIndividual digits conversionData transmissionComputer science

An apparatus includes a plurality of data lines defining a data bus for communicating data. A controller is operable to communicate a plurality of data transfers over the data bus using a plurality of data time slots, wherein for at least a subset of the data time slots the controller is operable to communicate an associated data bus inversion indicator indicating that bits communicated during the associated data time slot are inverted, the data bus inversion indicators for the subset of the data transfers are grouped into a data bus inversion vector, and the controller is operable to communicate a global data bus inversion indicator indicating an inversion of the data bus inversion vector.

Owner:ADVANCED MICRO DEVICES INC

Reducing simultaneous switching outputs using data bus inversion signaling

ActiveUS8260992B2Volume/mass flow measurementIndividual digits conversionData transmissionData bus inversion

An apparatus includes a plurality of data lines defining a data bus for communicating data. A controller is operable to communicate a plurality of data transfers over the data bus using a plurality of data time slots, wherein for at least a subset of the data time slots the controller is operable to communicate an associated data bus inversion indicator indicating that bits communicated during the associated data time slot are inverted, the data bus inversion indicators for the subset of the data transfers are grouped into a data bus inversion vector, and the controller is operable to communicate a global data bus inversion indicator indicating an inversion of the data bus inversion vector.

Owner:ADVANCED MICRO DEVICES INC

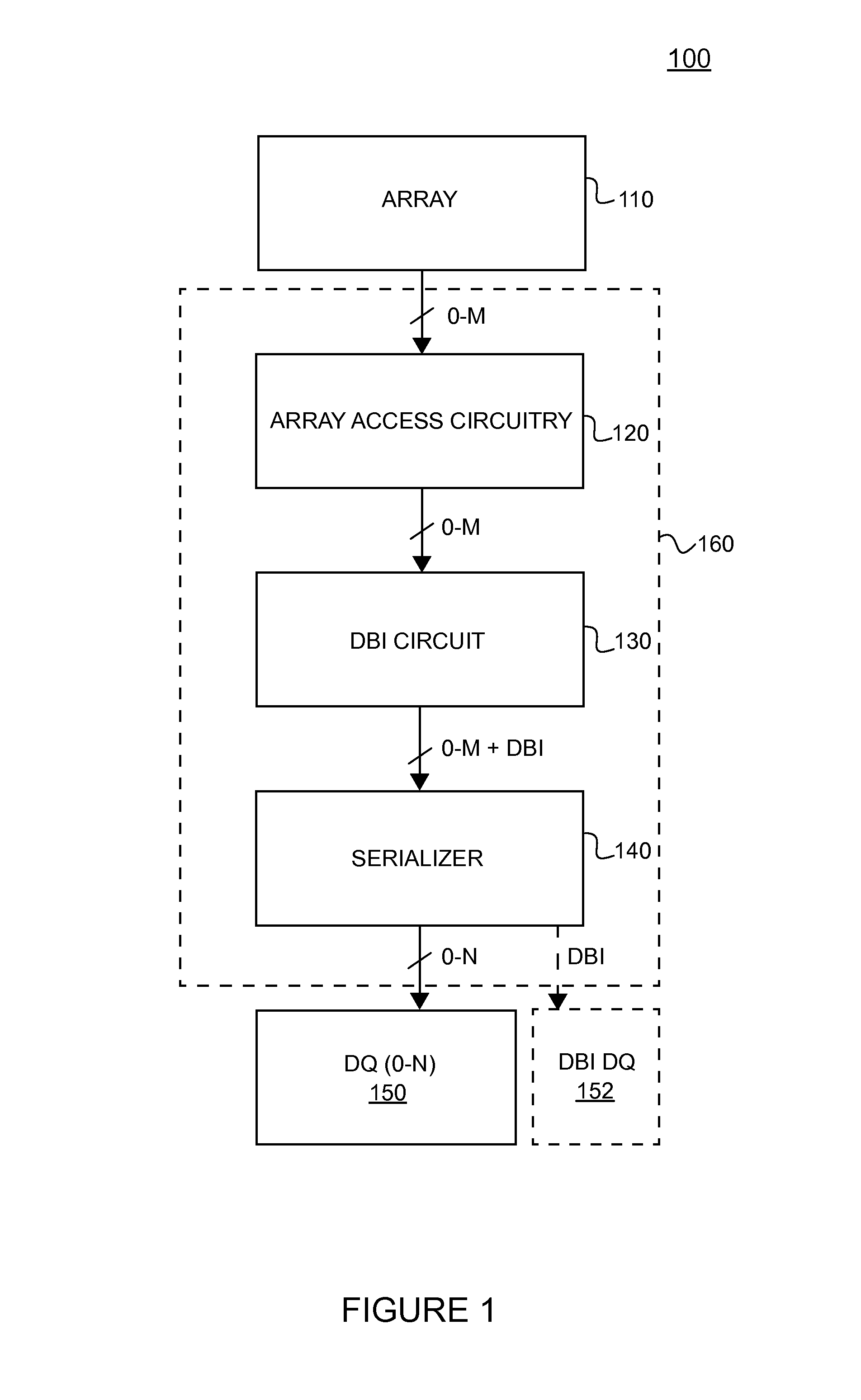

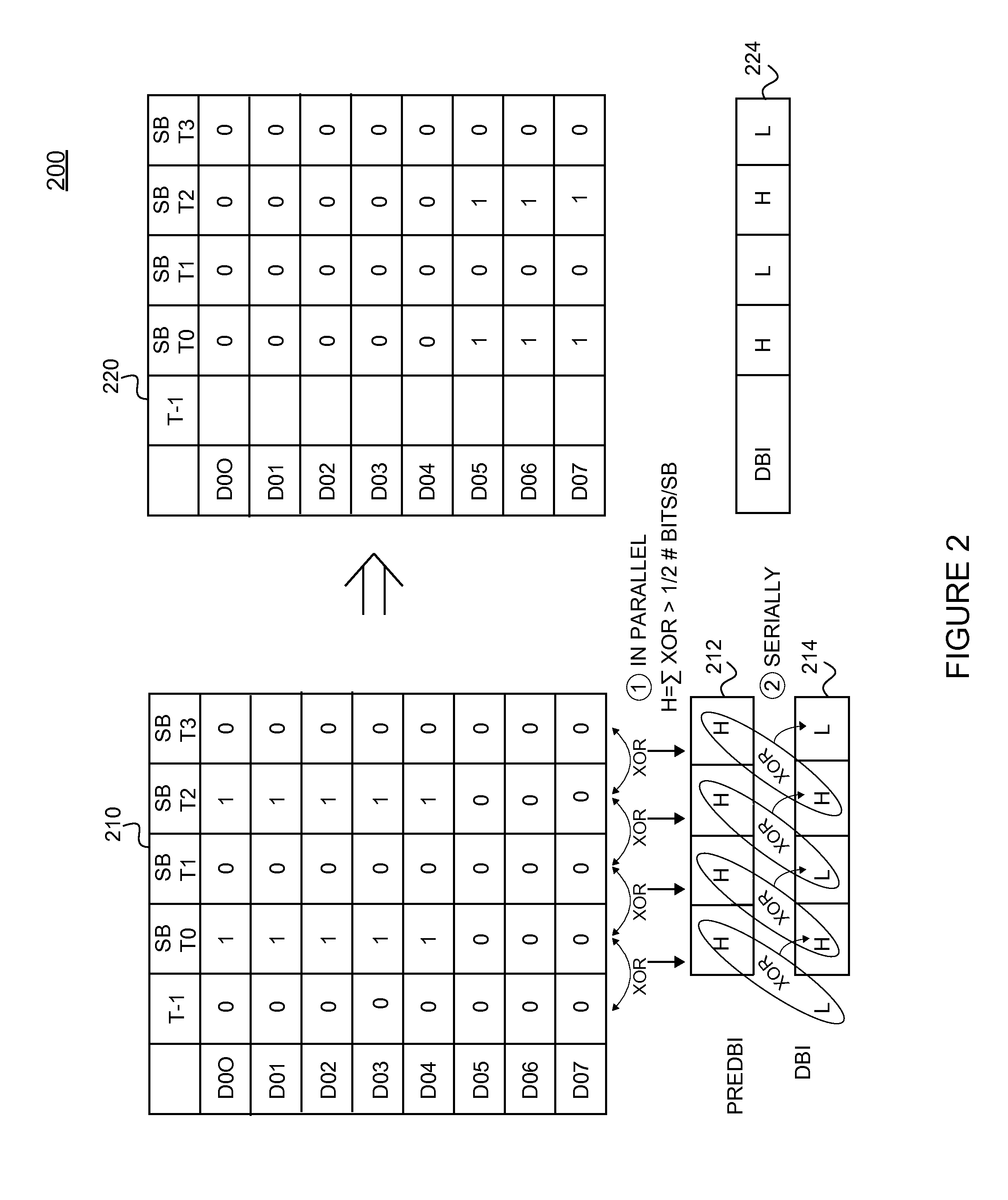

Apparatuses and methods for performing a databus inversion operation

ActiveUS9405721B2Individual digits conversionError correction/detection using block codesComputer hardwareData bus inversion

Apparatuses and methods for performing a data bus inversion operation (DBI) are described. An example apparatus includes a DBI circuit configured to, in parallel, determine preliminary DBI bits based on a block of data. Individual preliminary DBI bits are associated with respective sub-blocks of the block of data. The DBI circuit is further configured to serially determine DBI bits based on the preliminary DBI bits. Individual ones of the DBI bits are associated with respective ones of the sub-blocks. The DBI circuit is further configured to invert bits of individual sub-blocks responsive to the respective associated DBI bits having a particular logical value to provide DBI data. The apparatus further includes data outputs configured to serially output sub-blocks of the DBI data and the DBI bits.

Owner:MICRON TECH INC

Semiconductor memory apparatus and a method for reading data stored therein

ActiveUS20100157696A1Reduce current consumptionSolve problemsDigital storageData storingComputer science

A semiconductor memory apparatus includes a data bus inversion (DBI) section configured to receive a plurality of input data and decide whether to invert or output, without an inversion, the plurality of input data depending upon logic levels of the plurality of data, and further configured to generate a plurality of inversion data based on the decision; and a data output section configured to receive the plurality of inversion data, invert or output, without an inversion the plurality of inversion data in response to a mode signal, and generate a plurality of output data.

Owner:SK HYNIX INC

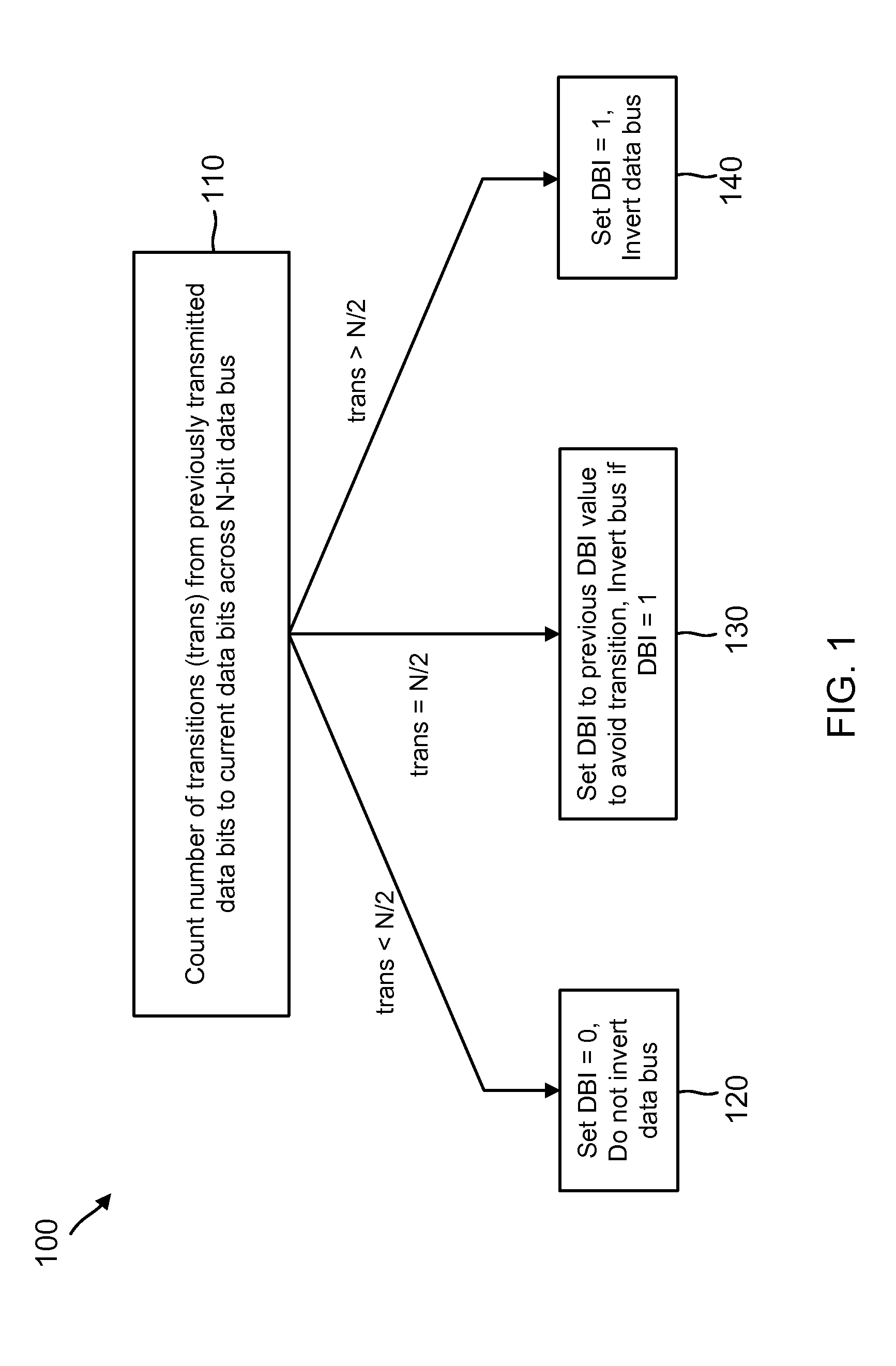

Systems and methods for transition-minimized data bus inversion

ActiveUS20160019179A1Increase powerImprove power integrityIndividual digits conversionElectric digital data processingEmbedded systemData bus inversion

Circuits and methods for Data Bus Inversion (DBI) are provided. In one example, the immediately previous value of the DBI bit affects the next value of the DBI bit. Specifically, in some instances, the value of the DBI bit is held to the immediately previous value of the DBI bit to limit the total number of transitions on a data bus.

Owner:QUALCOMM INC

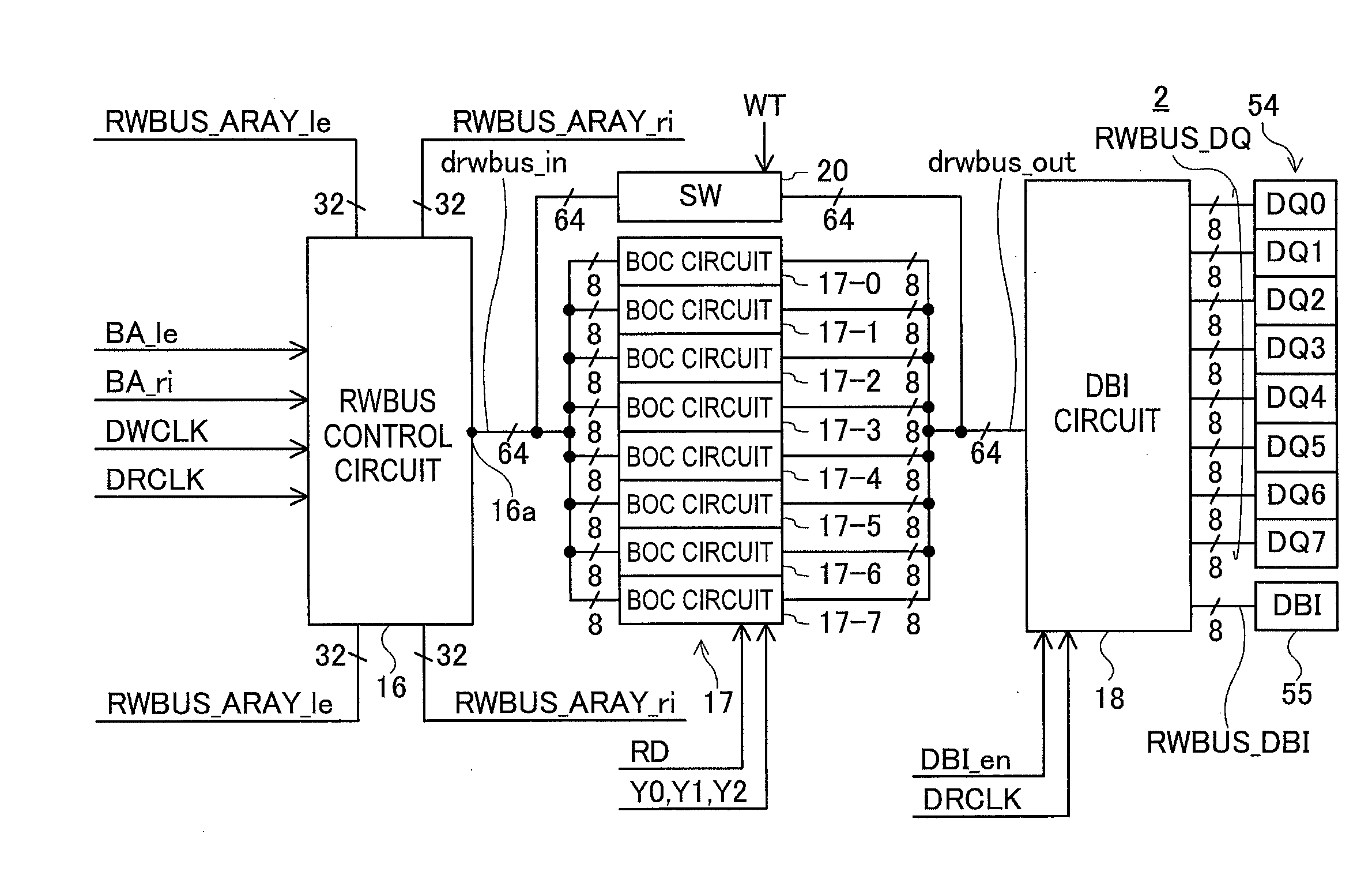

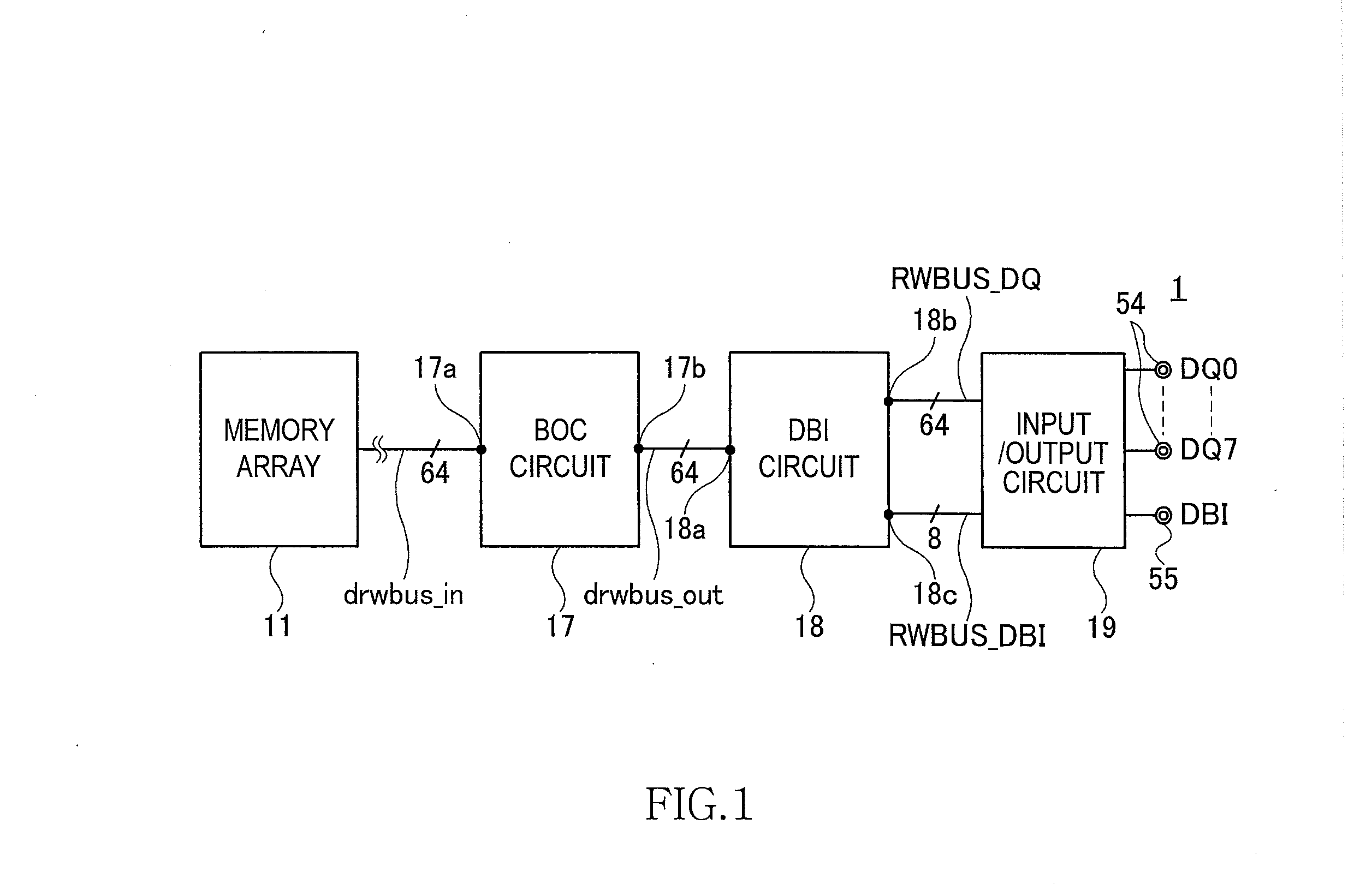

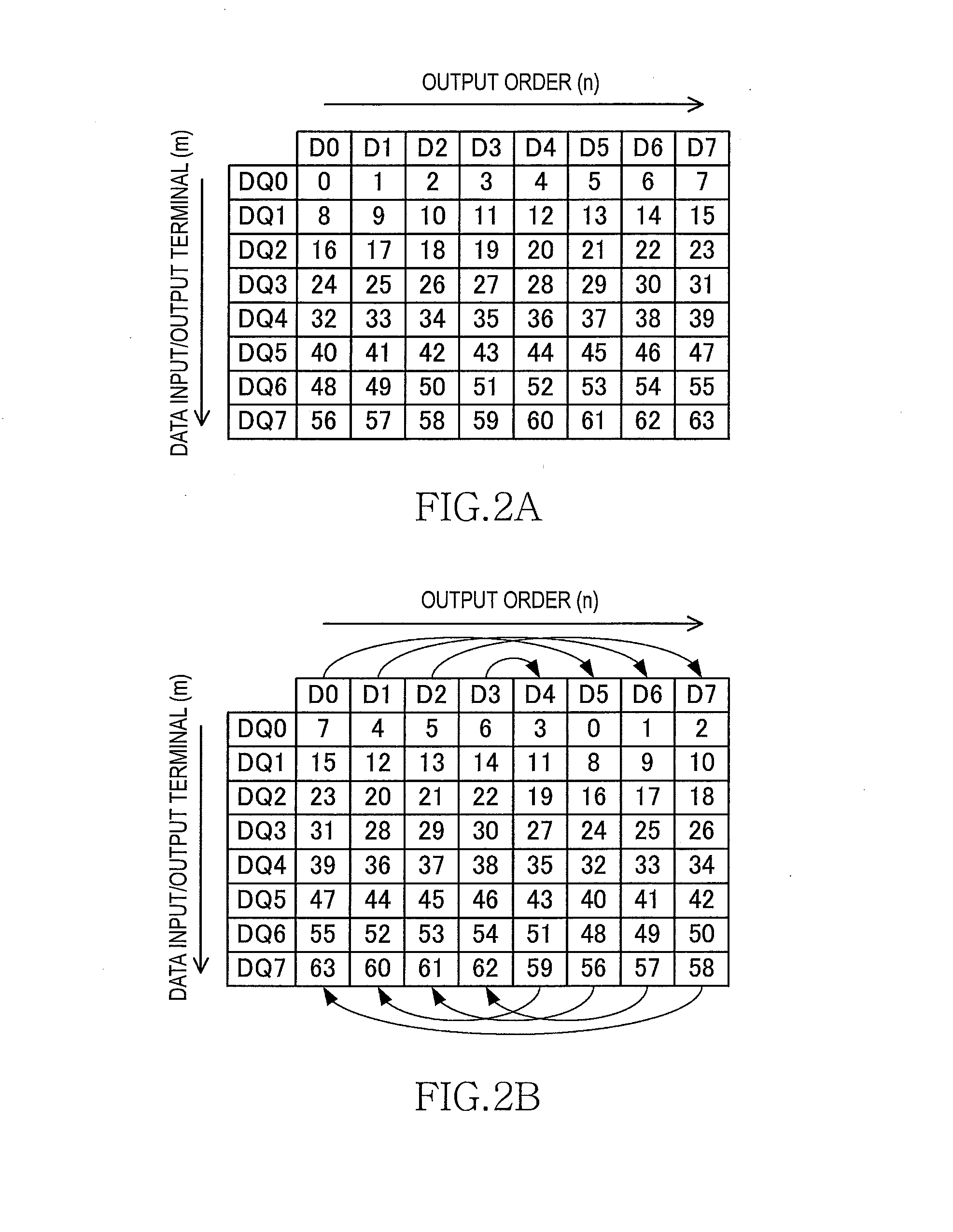

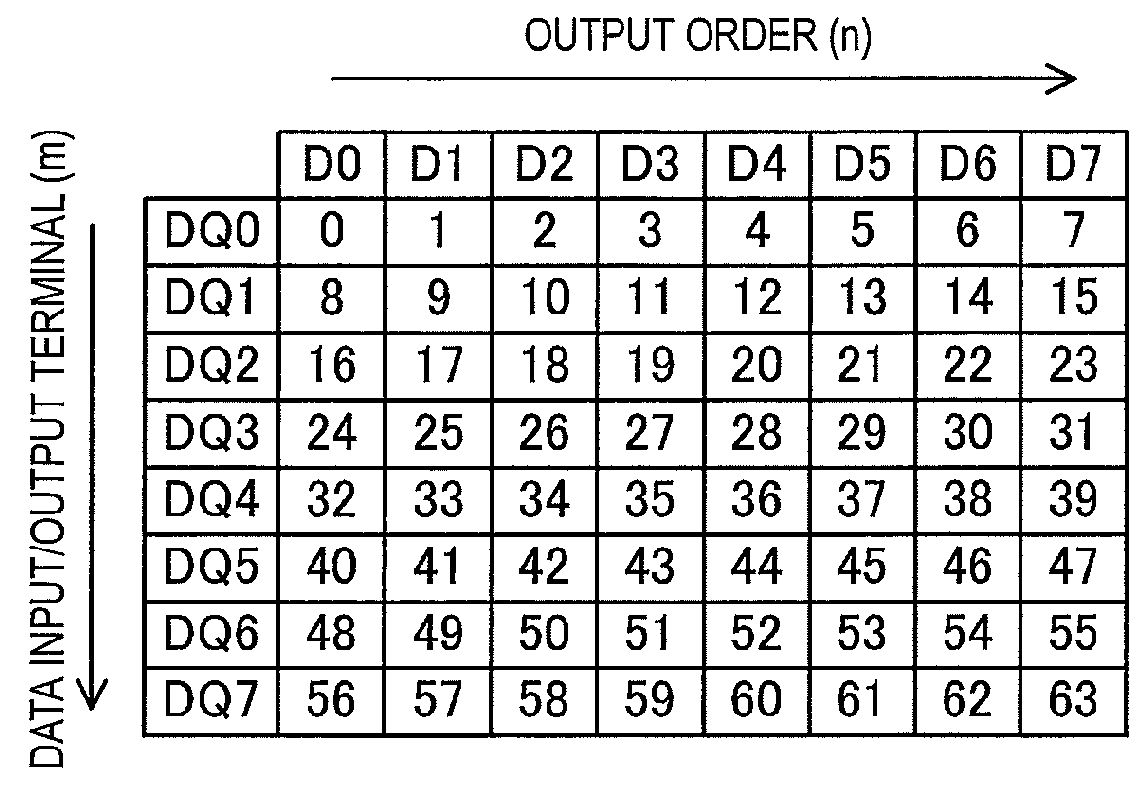

Semiconductor device performing burst order control and data bus inversion

Disclosed herein is a device that a device including first data lines transmitting a plurality of sequential first data bits, respectively, second data lines transmitting a plurality of sequential second data bits, respectively, third data lines transmitting a plurality of sequential third data bits, respectively, a BOC circuit rearranging order of the plurality of first data bits supplied from the plurality of first data lines in accordance with address information, the BOC circuit supplying the resultant to the plurality of second data lines as the plurality of second data bits, and a DBI circuit performing inversion or non-inversion of the plurality of second data bits supplied from the plurality of second data lines independently of each other in accordance with a predetermined condition, the DBI circuit supplying the resultant to the plurality of third data lines as the plurality of third data bits.

Owner:LONGITUDE LICENSING LTD

Data bus inversion using spare error correction bits

In a memory system, a spare error correction bit is produced by processing data to be stored in sufficiently large chunks that the number of error correction bits required to protect each chunk are fewer than the available error correction signal lines on a memory bus and storage device. The spare bit is then used for an inversion bit in a parallel data bus inversion scheme, wherein data is selectively inverted to minimize bus switching. The transmission of data and error correction bits are spread over multiple phases, wherein parallel data bus inversion is applied to each phase. Alternatively, the transmission of data and error correction bits may be transmitted and stored in a single transaction. In either case, the spare bit is transmitted on a conventional memory bus and stored in a conventional memory module along with data and error correction bits.

Owner:LENOVO GLOBAL TECH INT LTD

Integrated circuit chip and memory device

InactiveUS20130339641A1Abnormal operationAbnormal operation due to erroneous settings may be preventedMemory adressing/allocation/relocationDigital storageComputer scienceData masking

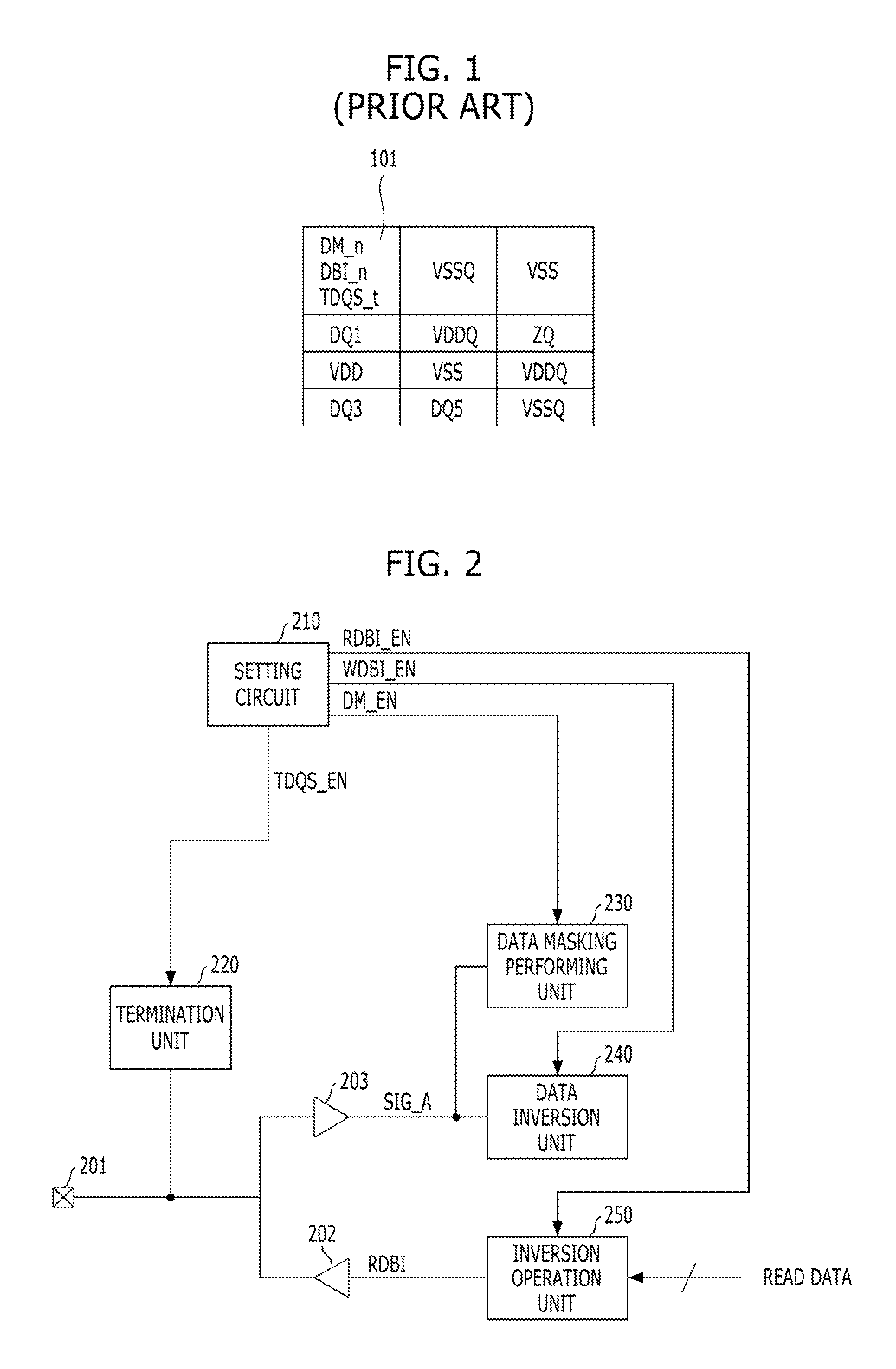

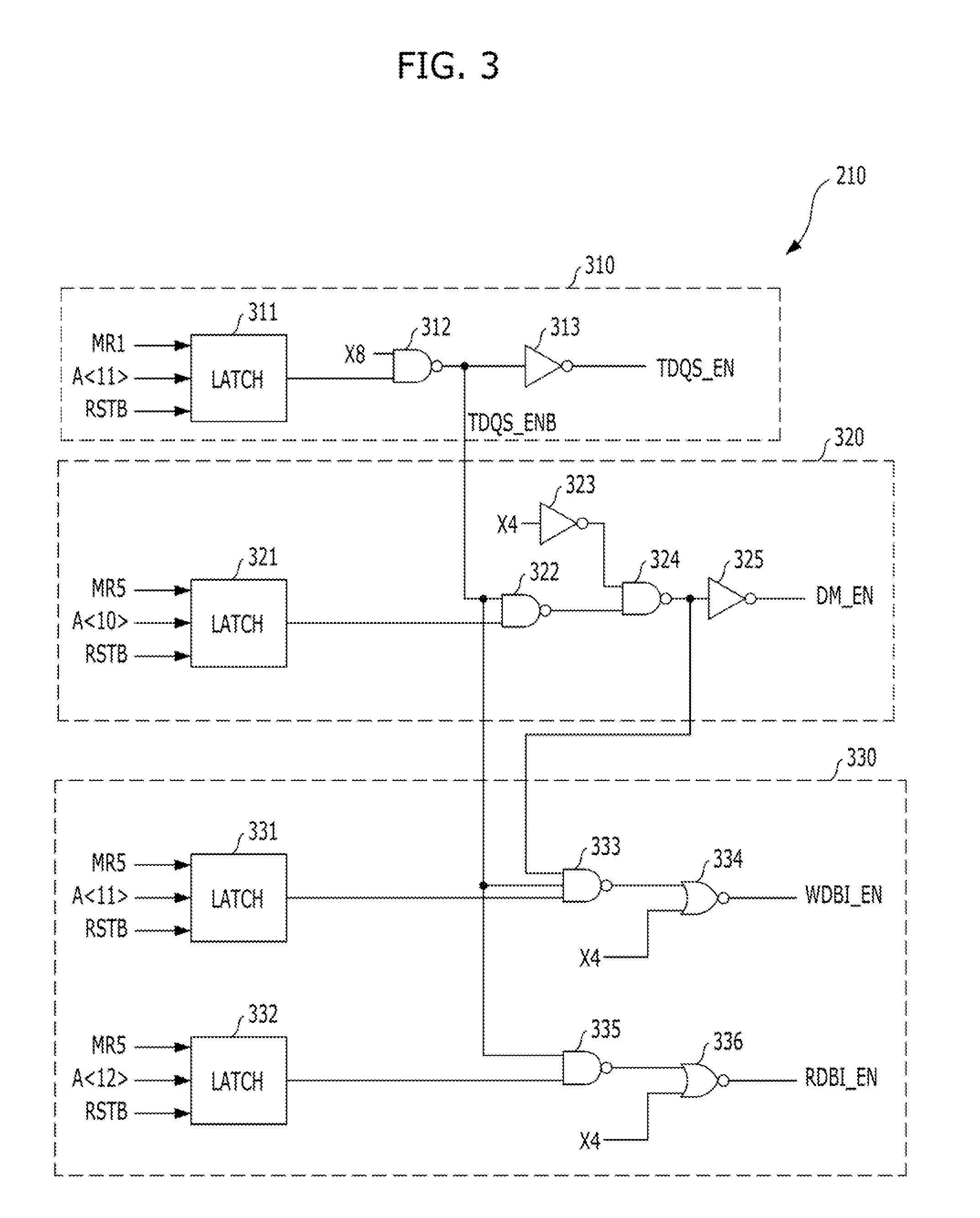

A memory device includes a pad that provides an interface with an exterior, a first setting unit that generates a termination setting signal for setting the pad for a purpose of termination data strobe using a first specific code of a mode register set operation, a second setting unit that generates a mask setting signal for setting the pad for a purpose of data mask using a second specific code of the mode register set operation, and a third setting unit that generates a write inversion setting signal for setting the pad for a purpose of write data bus inversion using third specific code of the mode register set operation. When a setting signal with a higher priority is activated, a setting signal with a lower priority is deactivated regardless of a value of the corresponding code.

Owner:SK HYNIX INC

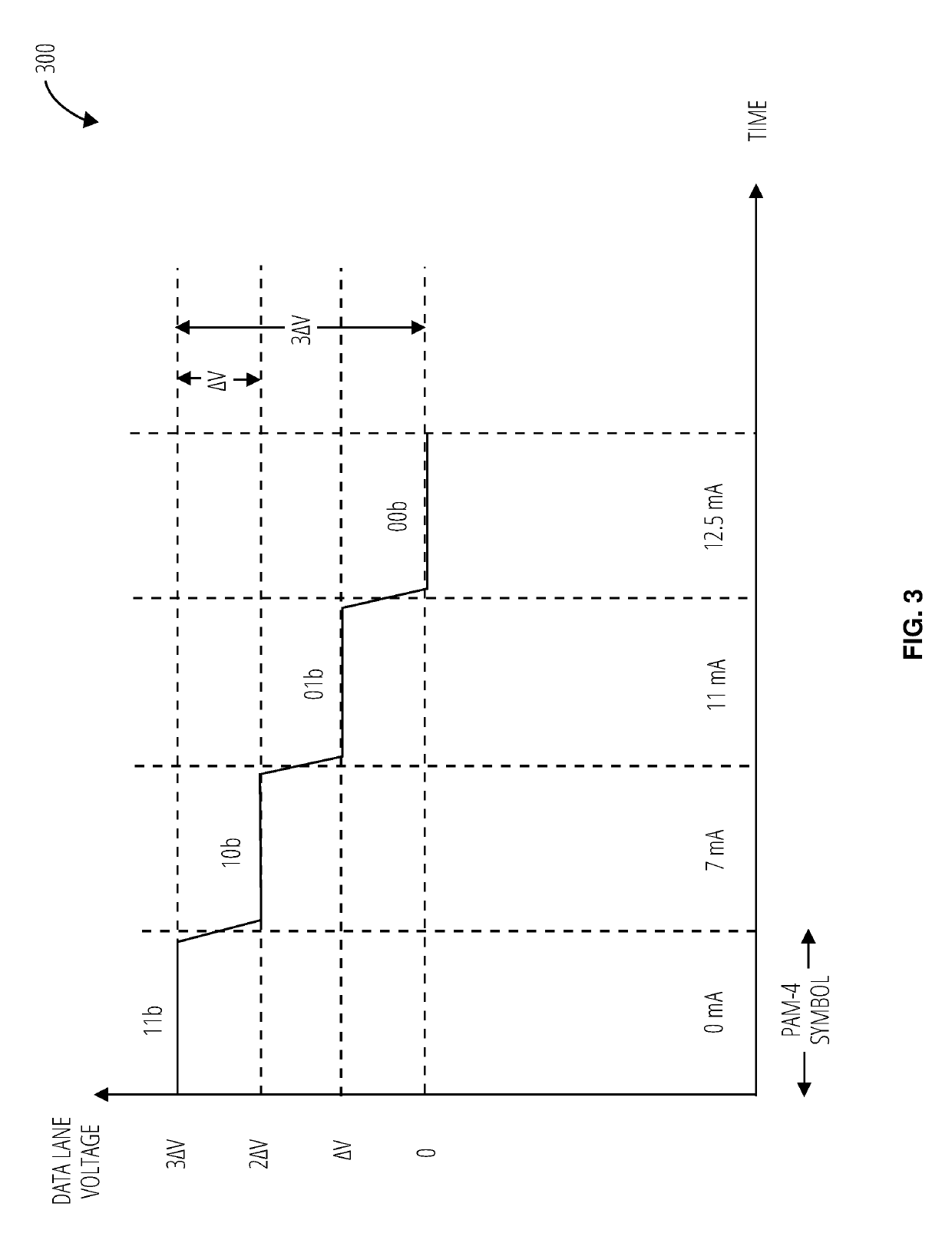

Data bus inversion (DBI) on pulse amplitude modulation (PAM) and reducing coupling and power noise on pam-4 I/O

ActiveUS20190305765A1Dc level restoring means or bias distort correctionIndividual digits conversionCommunications systemCoupling

Mechanisms to reduce noise and / or energy consumption in PAM communication systems, utilizing conditional symbol substitution in each burst interval of a multi-data lane serial data bus.

Owner:NVIDIA CORP

Data memory controller that supports data bus invert

InactiveUS20060184757A1Extension of timeReduce variationEnergy efficient ICTEnergy efficient computingTiming marginData memory

The present invention provides a data memory controller that supports for the invert of data bus. Data transmitted from a memory is received in a chip set, which further transmits the data to a data processing apparatus. While receiving the memory data, the chip set doubles the bandwidth and reduces the frequency, such that the time margin for processing data is increased. In addition, after outputting data to the data processing apparatus, a first frame of data is compared to bus idle state to further reduce frequency of data invert and power consumption.

Owner:VIA TECH INC

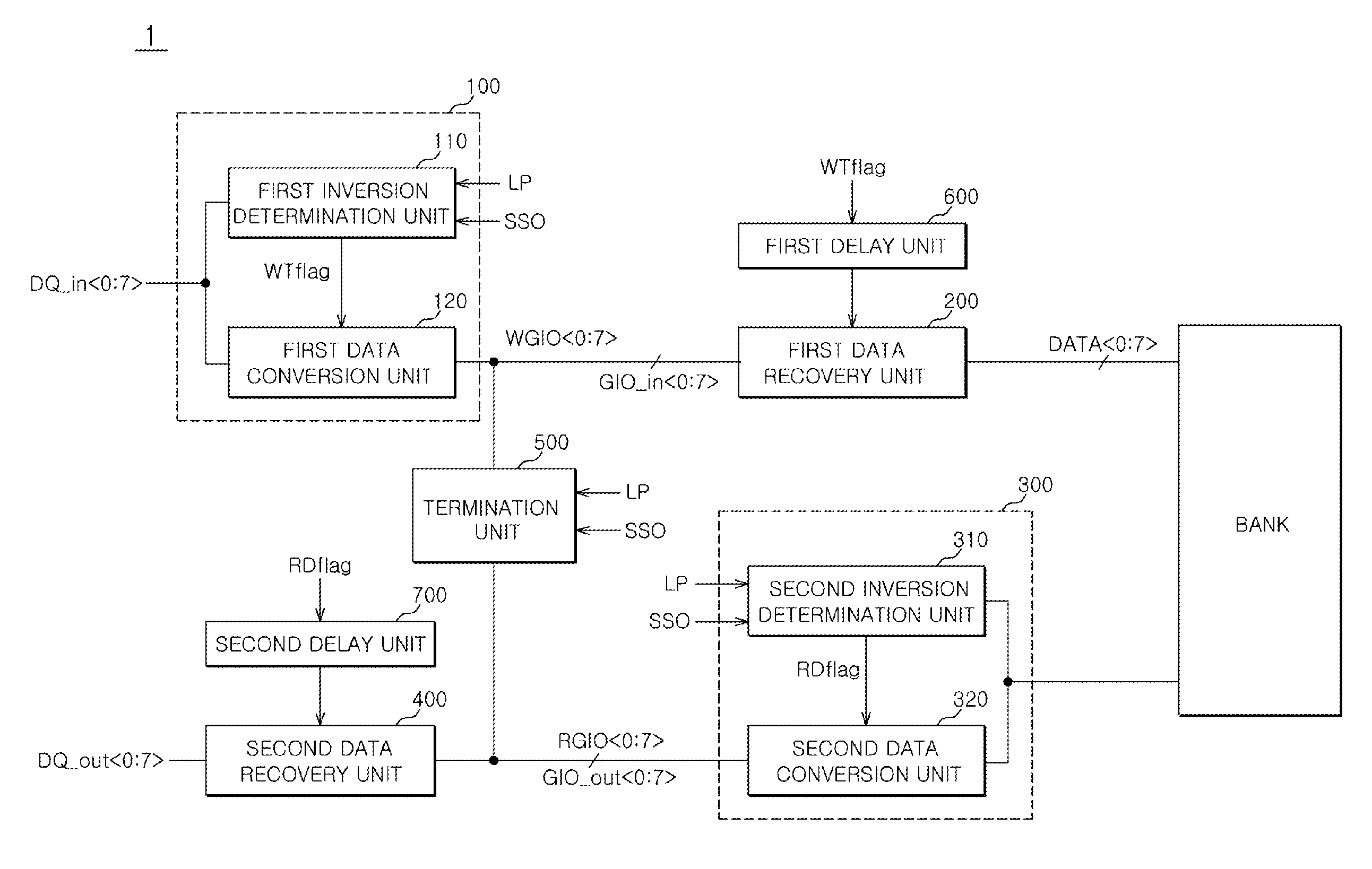

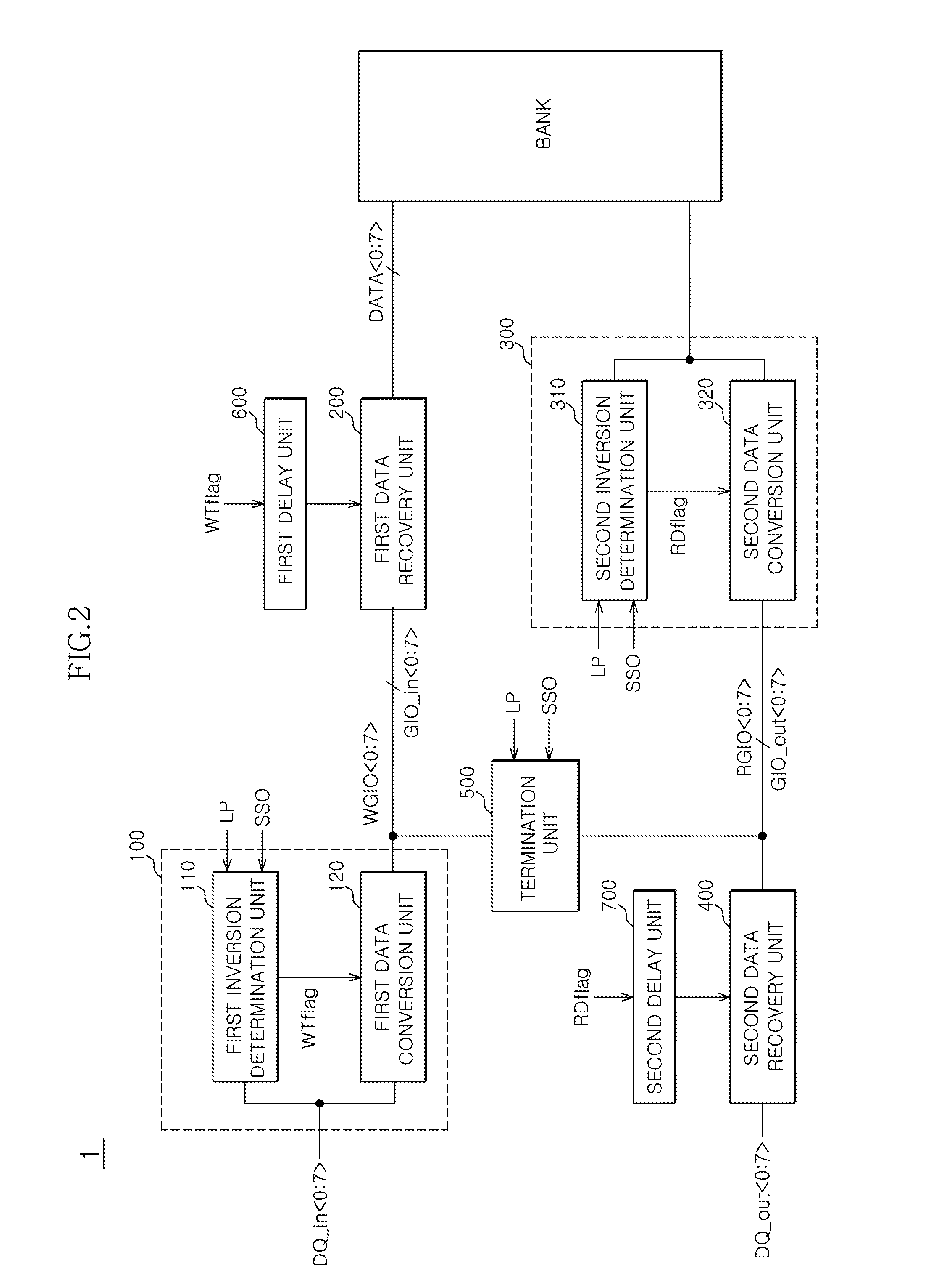

Semiconductor memory apparatus and data input and output method thereof

A semiconductor memory apparatus includes an input data bus inversion unit, a data input line, a termination unit, a data recovery unit and a memory bank. The input data bus inversion unit determines whether or not to invert a plurality of input data based on an operation mode signal and the plurality of input data and generates a plurality of conversion data. The data input line transmits the plurality of conversion data. The termination unit terminates the data input line in response to the operation mode signal. The data recovery unit receives the plurality of conversion data and generates a plurality of storage data. The memory bank configured to store the plurality of storage data.

Owner:SK HYNIX INC

Data bus inversion usable in a memory system

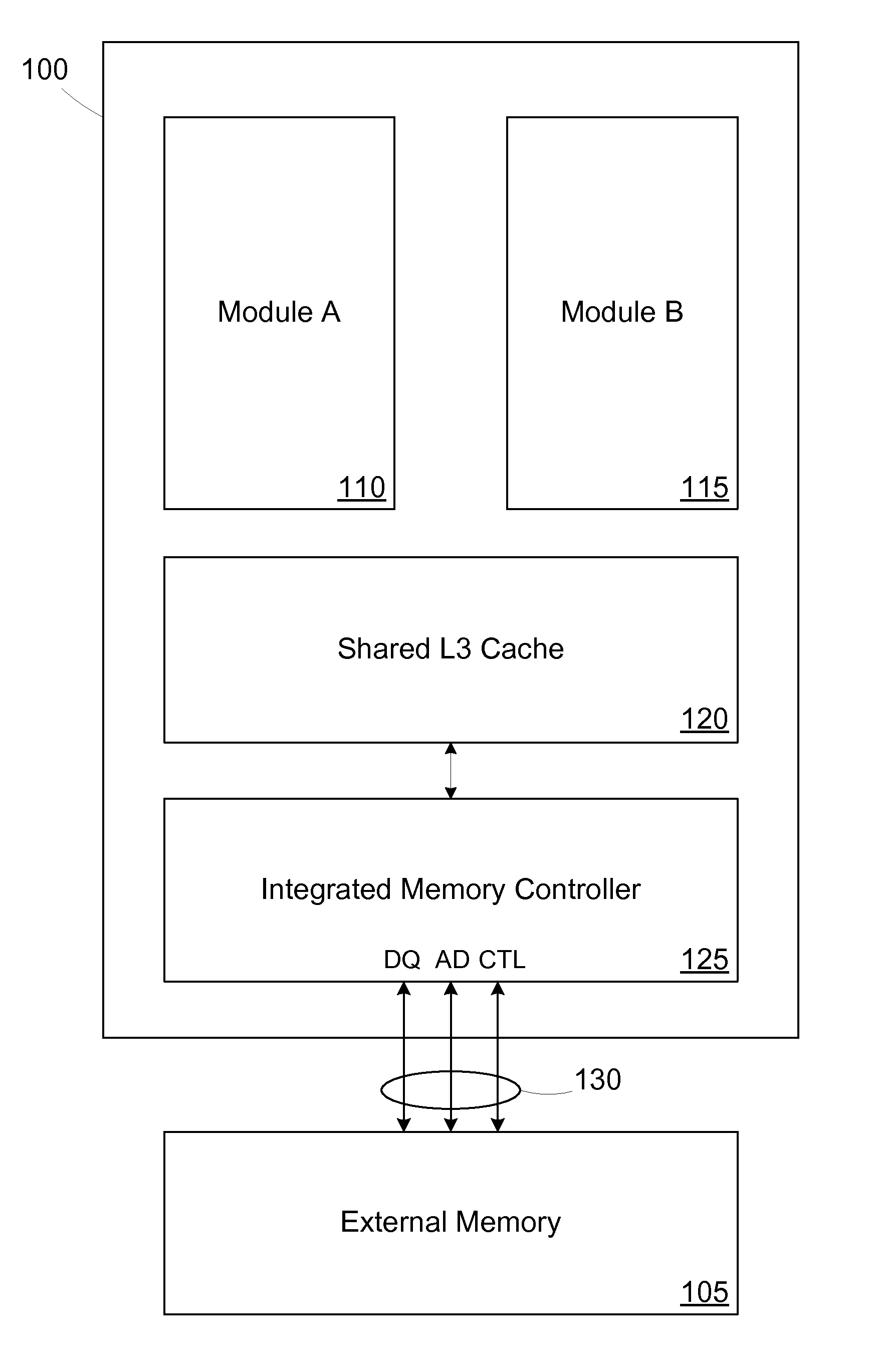

ActiveUS20150363260A1Static storageRedundant data error correctionRandom access memoryMemory controller

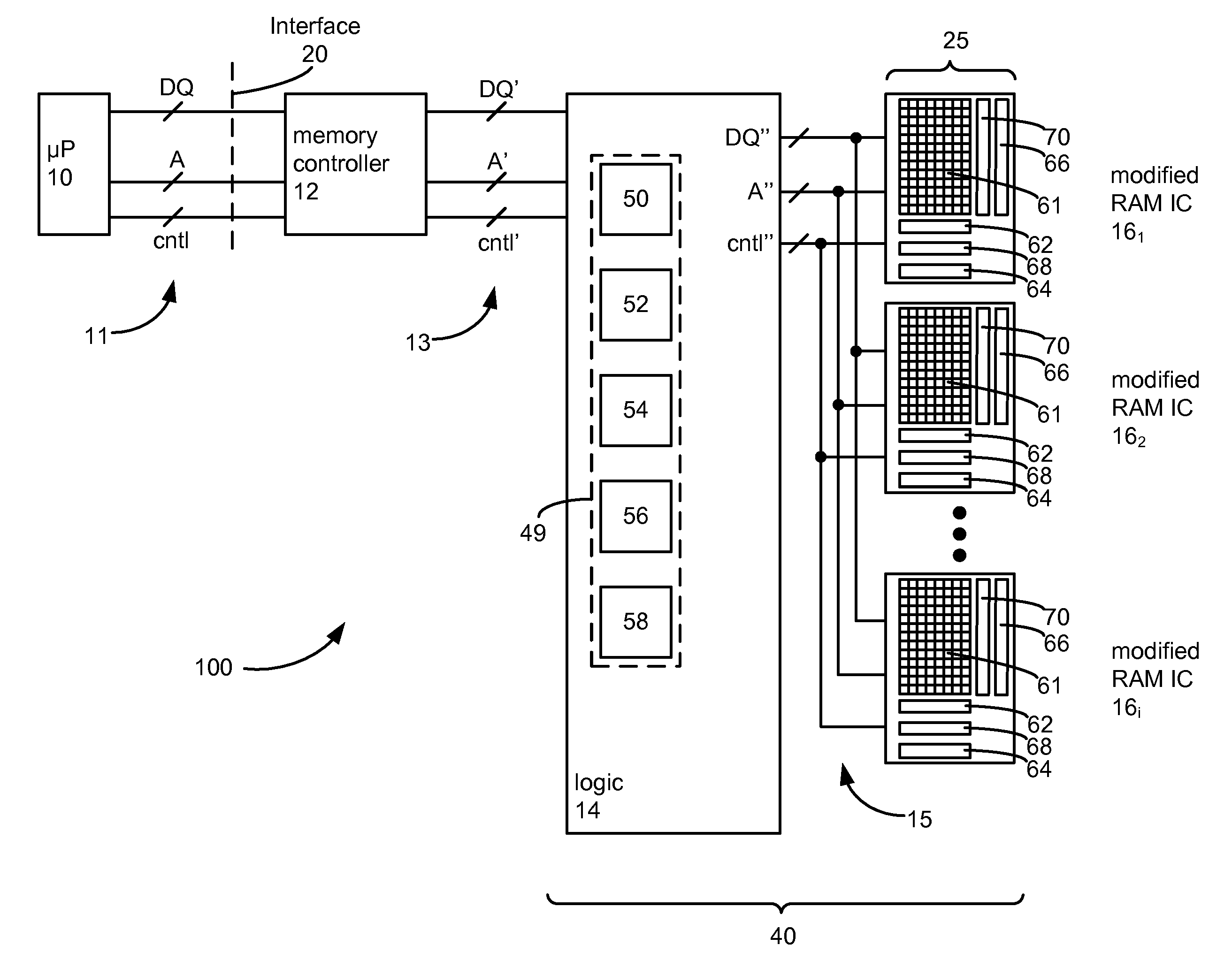

Implementations of Data Bus Inversion (DBI) techniques within a memory system are disclosed. In one embodiment, a set of random access memory (RAM) integrated circuits (ICs) is separated from a logic system by a bus. The logic system can contain many of the logic functions traditionally performed on conventional RAM ICs, and accordingly the RAM ICs can be modified to not include such logic functions. The logic system, which can be a logic integrated circuit intervening between the modified RAM ICs and a traditional memory controller, additionally contains DBI encoding and decoding circuitry. In such a system, data is DBI encoded and at least one DBI bit issued when writing to the modified RAM ICs. The RAM ICs in turn store the DBI bit(s) with the encoded data. When the encoded data is read from the modified RAM ICs, it is transmitted across the bus in its encoded state along with the DBI bit(s). The logic integrated circuit then decodes the data using the DBI bit(s) to return it to its original state.

Owner:MICRON TECH INC

Semiconductor device performing burst order control and data bus inversion

Disclosed herein is a device that a device including first data lines transmitting a plurality of sequential first data bits, respectively, second data lines transmitting a plurality of sequential second data bits, respectively, third data lines transmitting a plurality of sequential third data bits, respectively, a BOC circuit rearranging order of the plurality of first data bits supplied from the plurality of first data lines in accordance with address information, the BOC circuit supplying the resultant to the plurality of second data lines as the plurality of second data bits, and a DBI circuit performing inversion or non-inversion of the plurality of second data bits supplied from the plurality of second data lines independently of each other in accordance with a predetermined condition, the DBI circuit supplying the resultant to the plurality of third data lines as the plurality of third data bits.

Owner:LONGITUDE LICENSING LTD

Sense mechanism for microprocessor bus inversion

A sense mechanism for data bus inversion including a first memory device and an analog adder. The first memory device stores bits of the bus in a previous bus cycle. The analog adder compares the bits of the bus in the previous bus cycle with bits of the bus in a current bus cycle and provides a data inversion signal indicative of whether more than half of the bits of the bus have changed state. The analog adder operates as a bus state change sense device which rapidly evaluates bus state changes from one bus cycle to the next. The data inversion signal is used for selectively inverting the data bits of the bus and indicating bus inversion according to data bus inversion operation, such as according to X86 microprocessor protocol.

Owner:VIA TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com