Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

44 results about "Clock shift" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

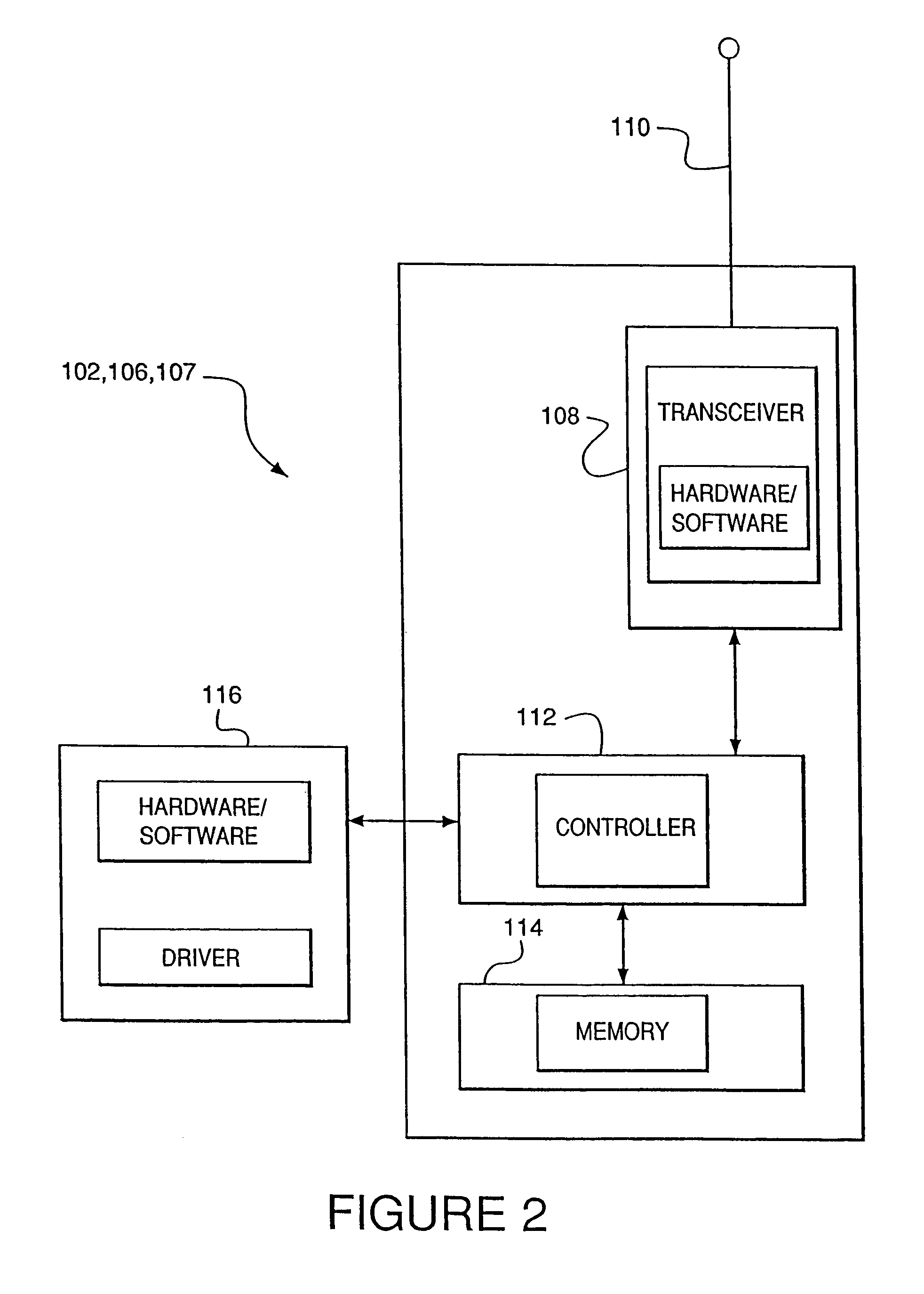

System and method for correcting the clock drift and maintaining the synchronization of low quality clocks in wireless networks

A system and method for establishing and maintaining node clock synchronization in a wireless network. The system and method calculates the clock shift, clock drift and propagation delay values using a series of message exchanges and control algorithms between a selected reference node and a client node in a wireless network, then uses these values to synchronize the client node clock to the reference node clock.

Owner:ARRIS ENTERPRISES LLC

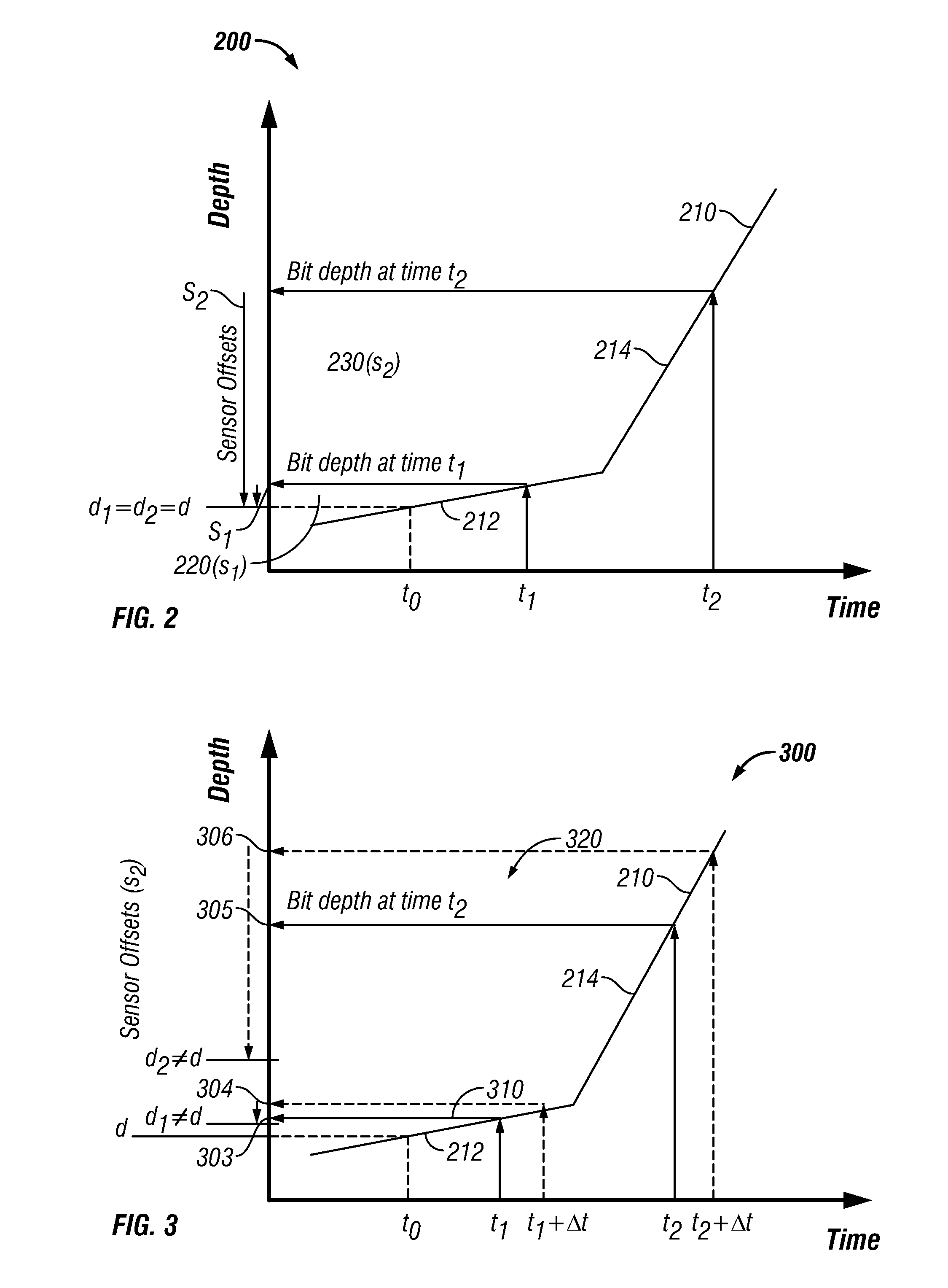

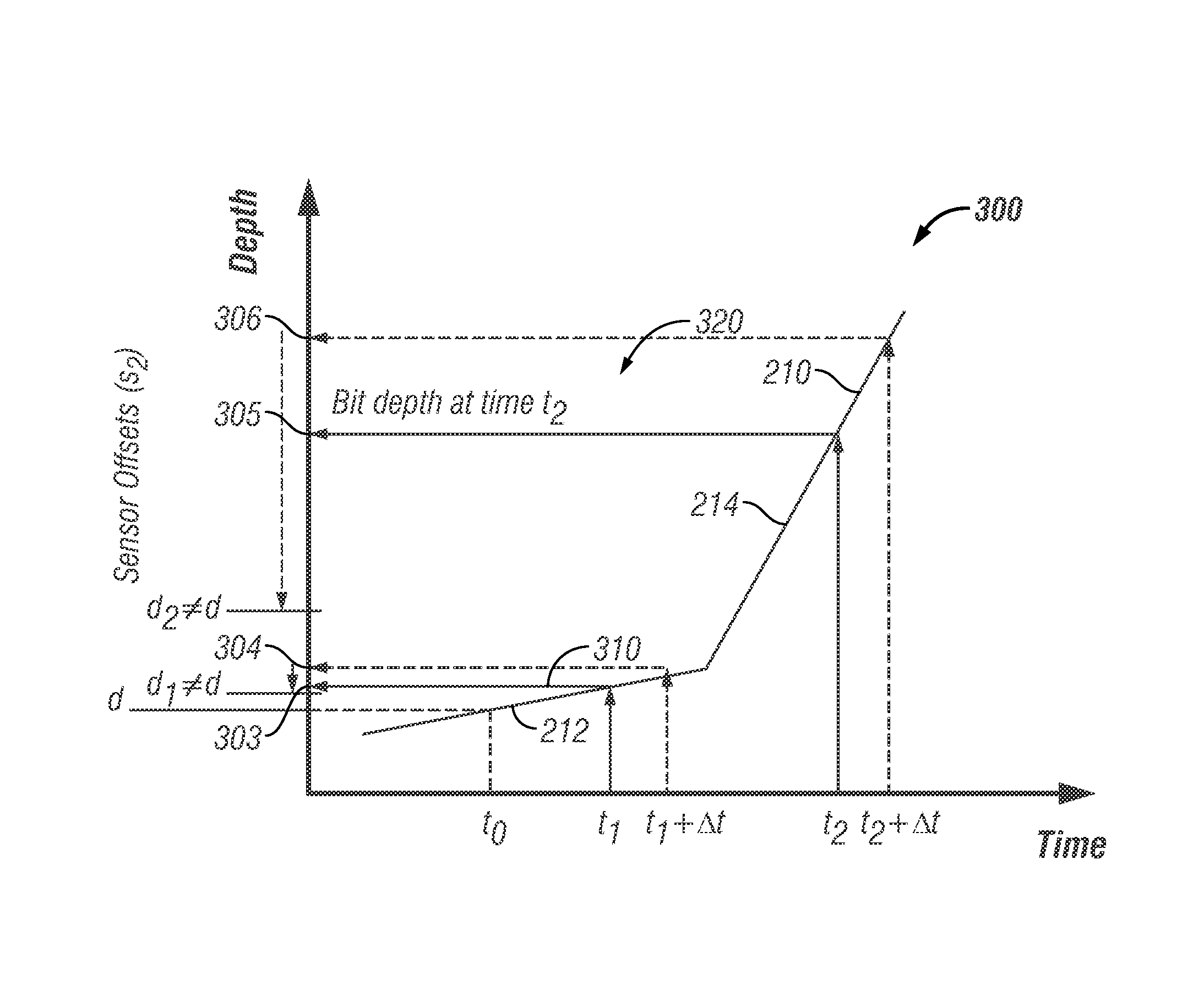

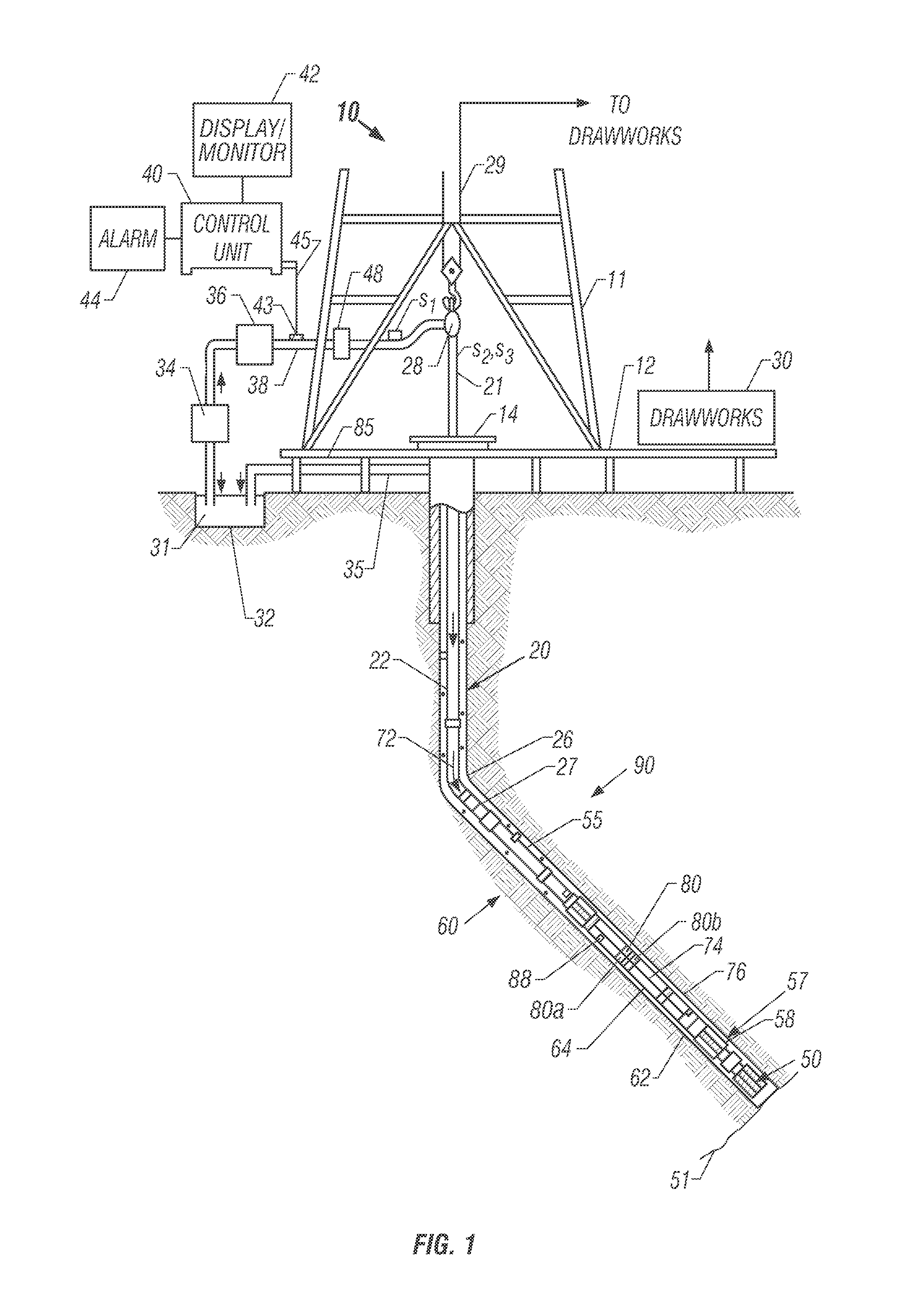

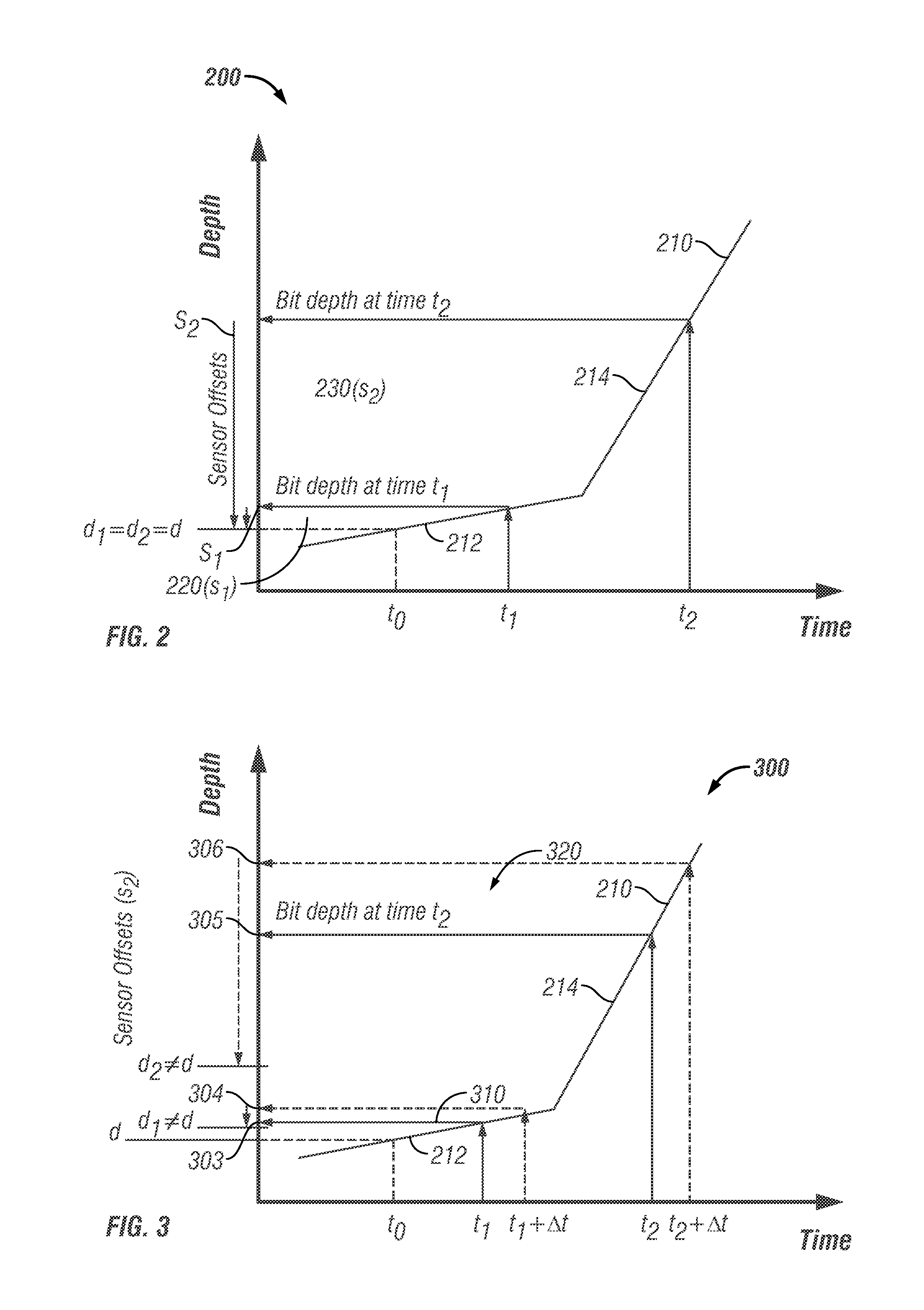

Apparatus and Method for Clock Shift Correction for Measurement-While-Drilling Measurements

The disclosure provides a method which includes transmitting signals over a time period between a downhole location and a surface location during drilling of a wellbore; recording the time of each signal at the surface using a surface clock and the time of each signal downhole using a downhole clock; and correcting the downhole measurements using the recorded times.

Owner:BAKER HUGHES INC

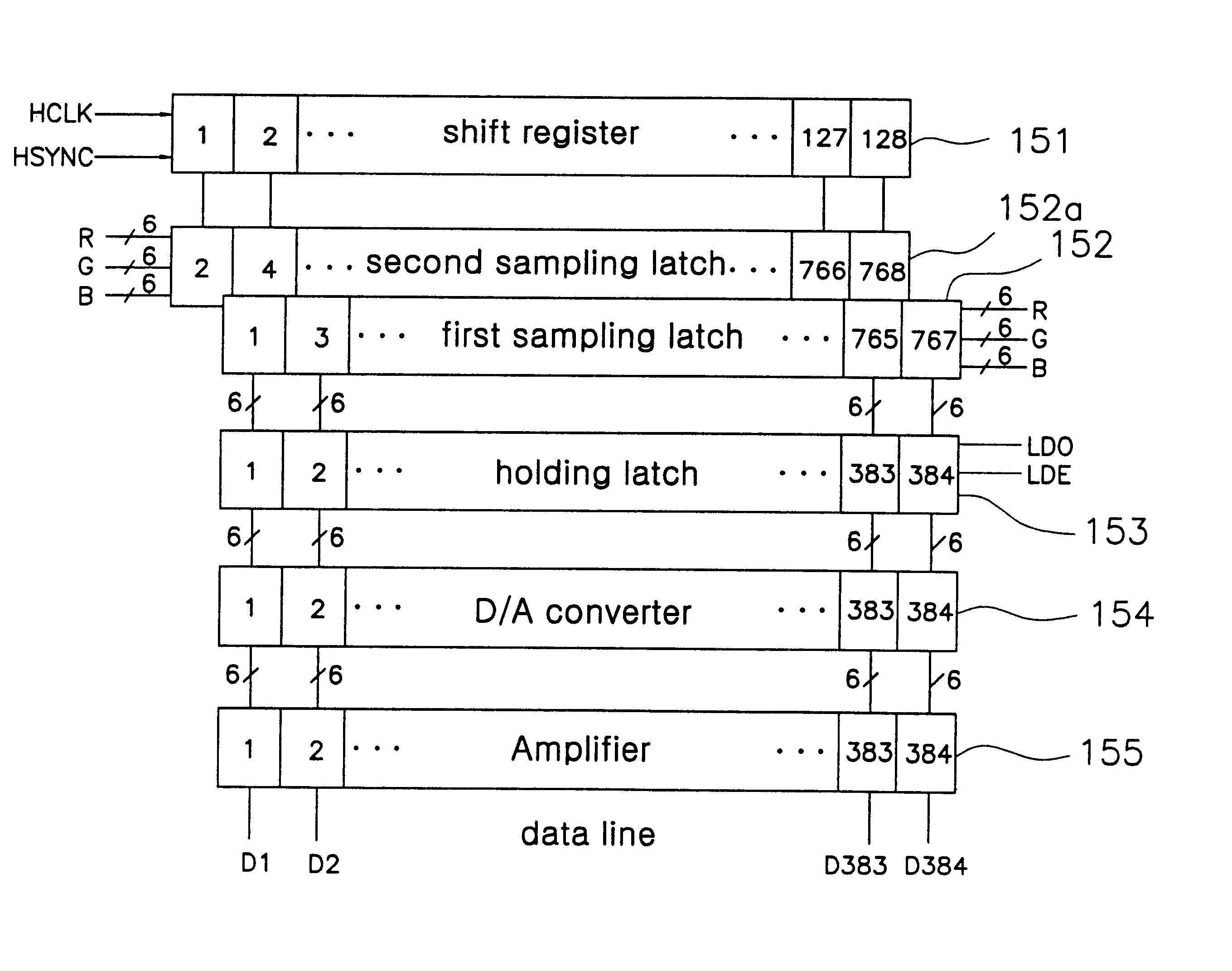

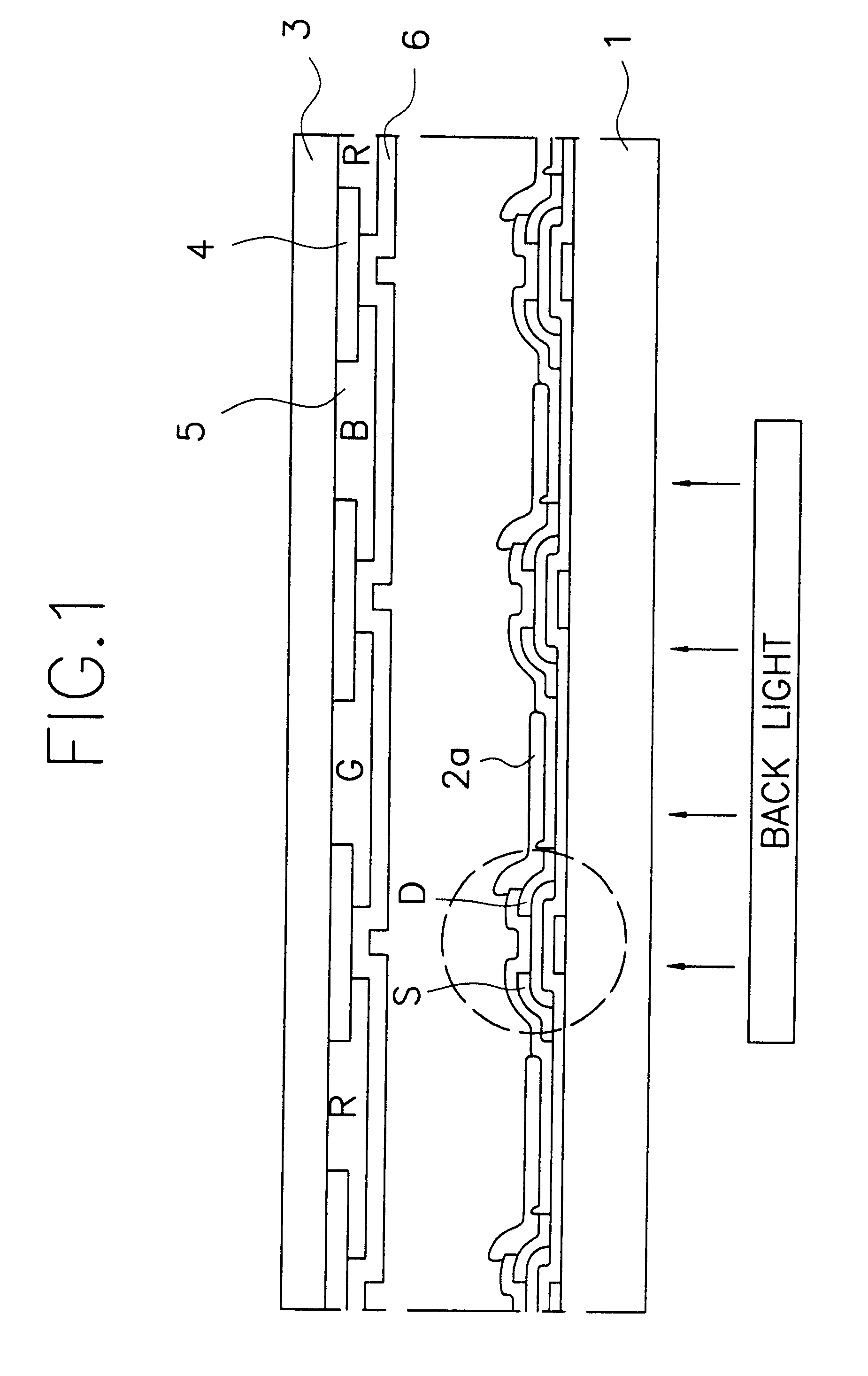

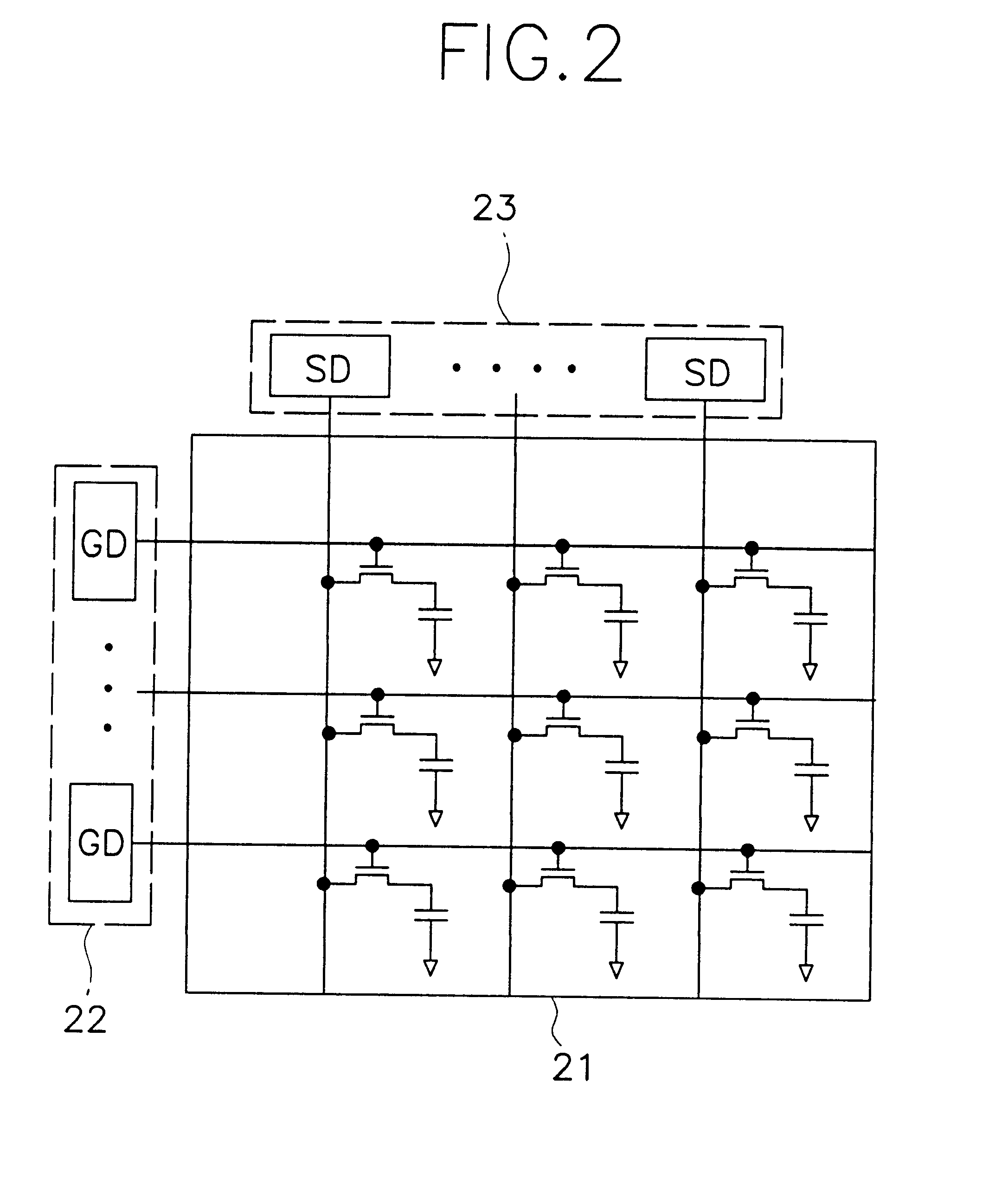

Driver of liquid crystal display

InactiveUS6525710B1Reduce in quantityStatic indicating devicesNon-linear opticsDigital videoShift register

Owner:SAMSUNG ELECTRONICS CO LTD

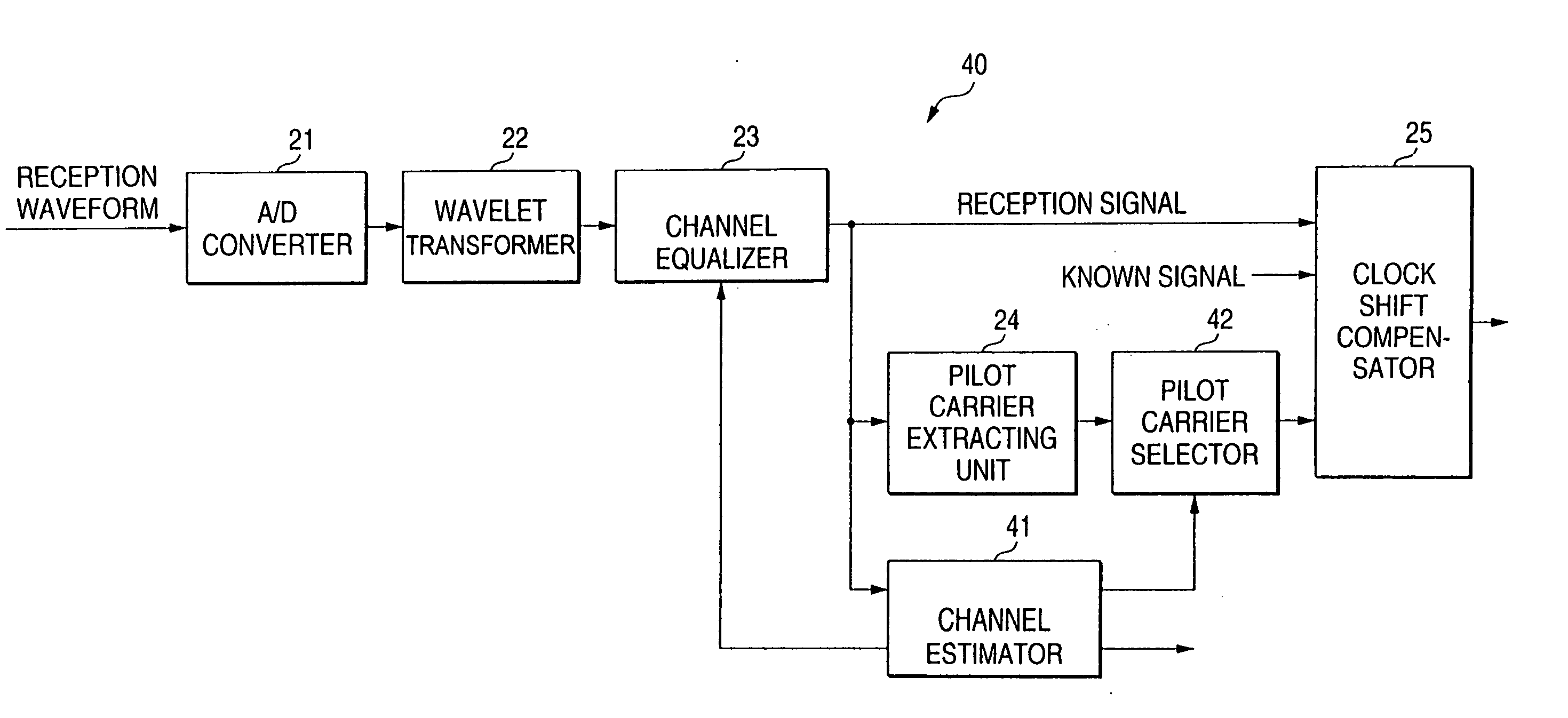

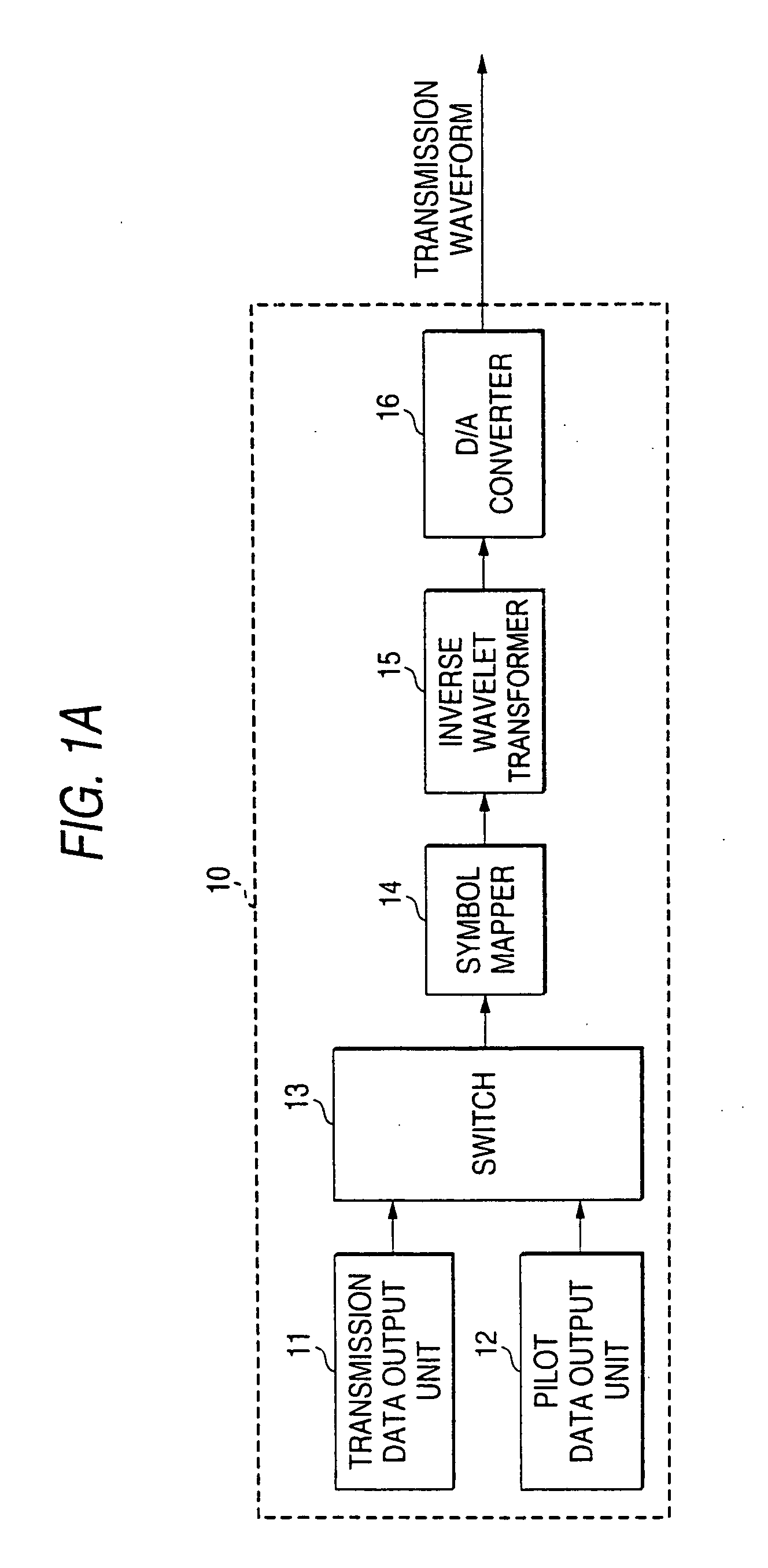

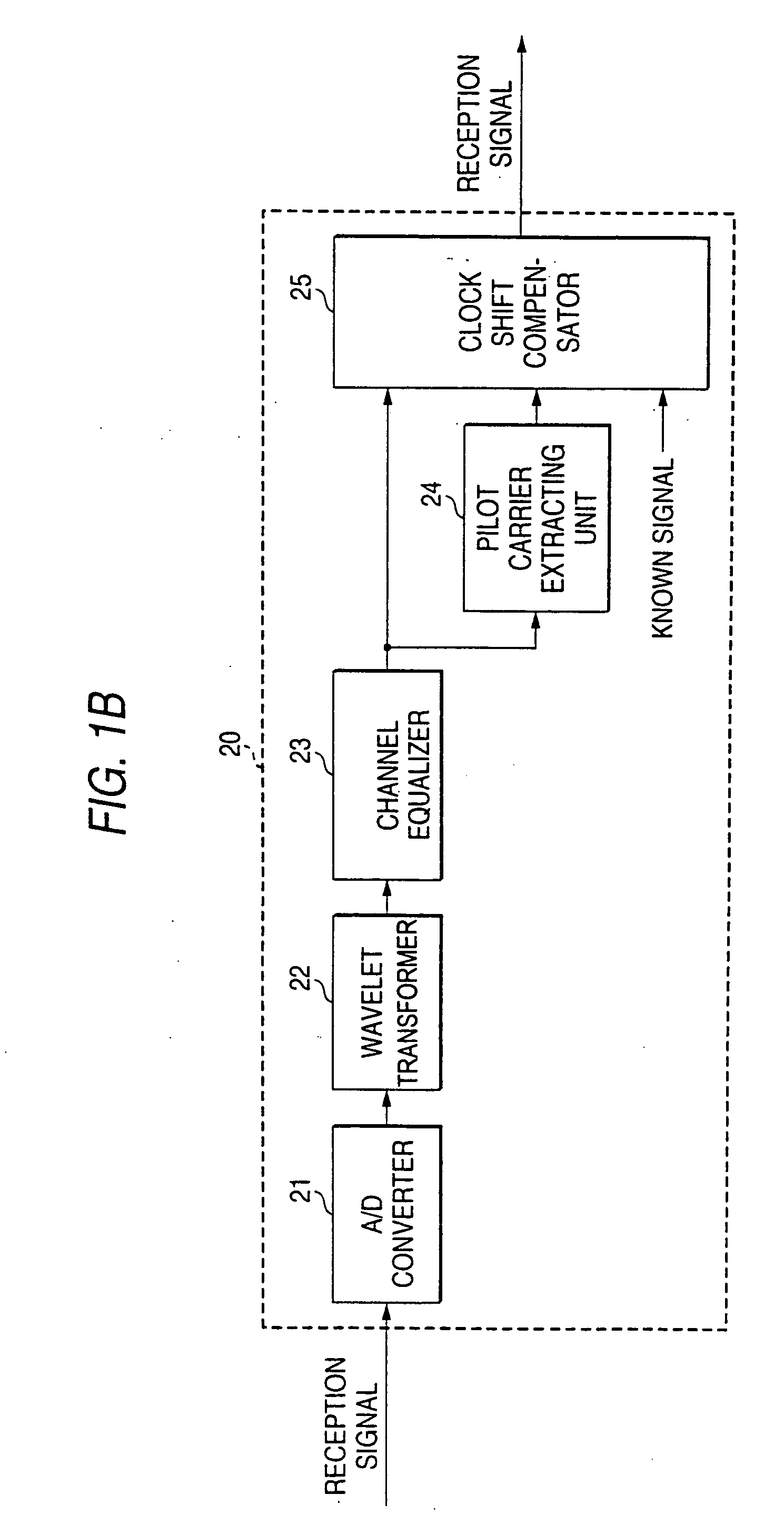

Communication apparatus and communication method using digital wavelet multi carrier transmission system

InactiveUS20050238109A1Modulated carrier system with waveletsTransmission control/equalisingCarrier signalData transmission

When a pilot carrier is provided in data transmission according to the DWMC transmission system, continuous identical data are given in a sub-carrier pair having predetermined adjacent two sub-carriers as a unit in plural sub-carriers on a frequency axis, whereby pilot carriers P1, P2, . . . to be sine wave signals are formed. It is possible to perform clock shift compensation or the like between a transmitter and a receiver according to complex information obtained from the pilot carriers by transmitting a transmission signal using the pilot carriers between the transmitter and the receiver.

Owner:PANASONIC CORP

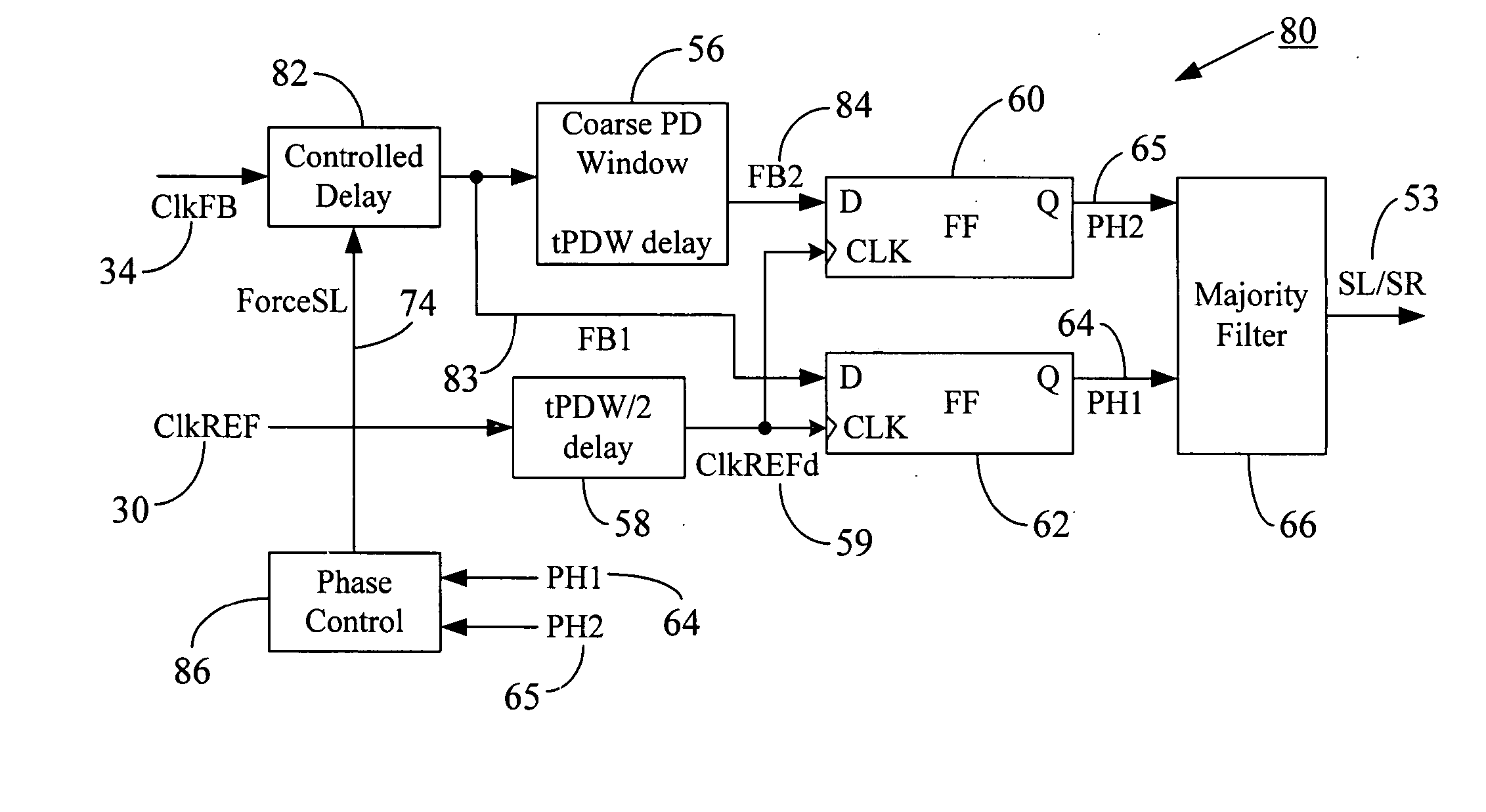

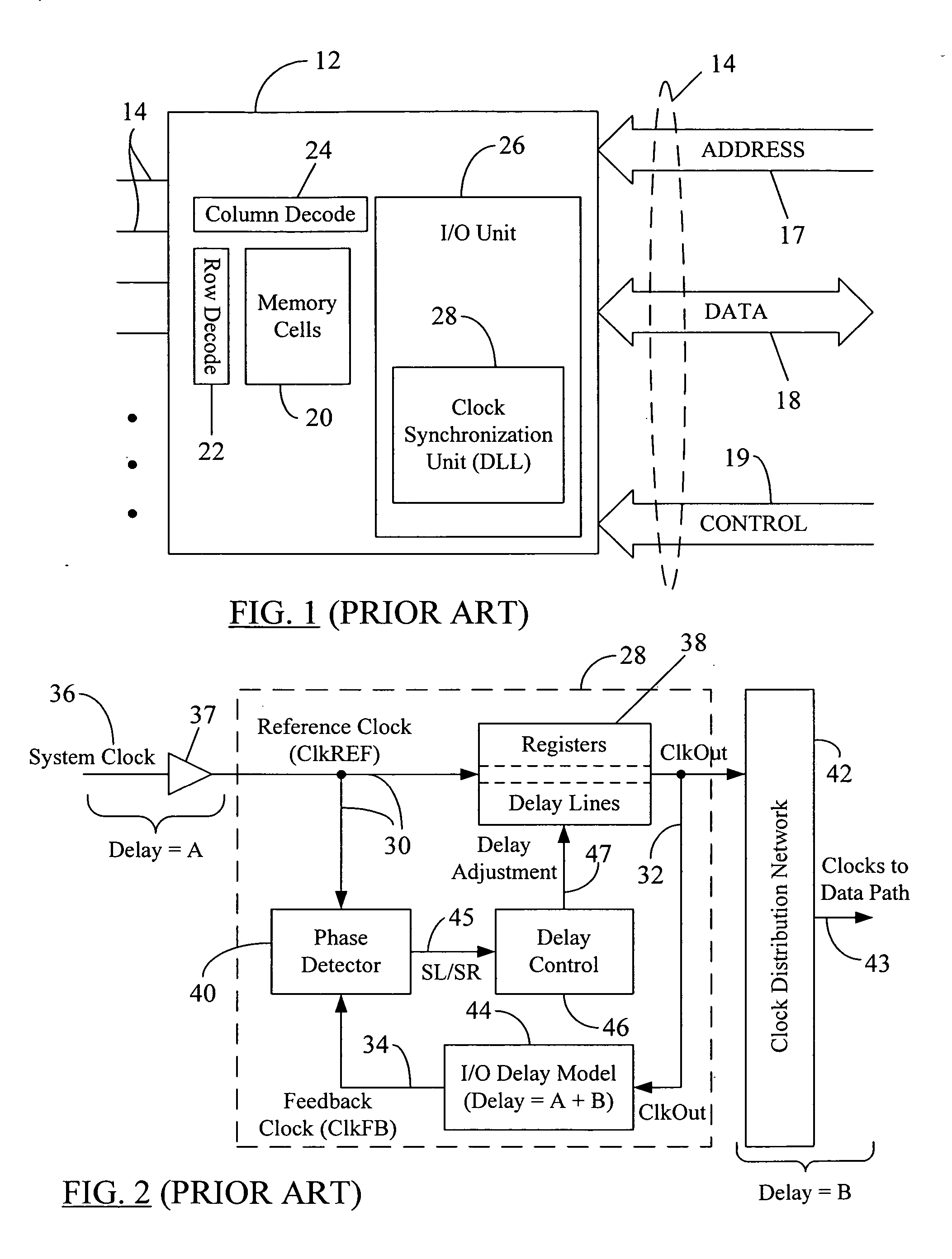

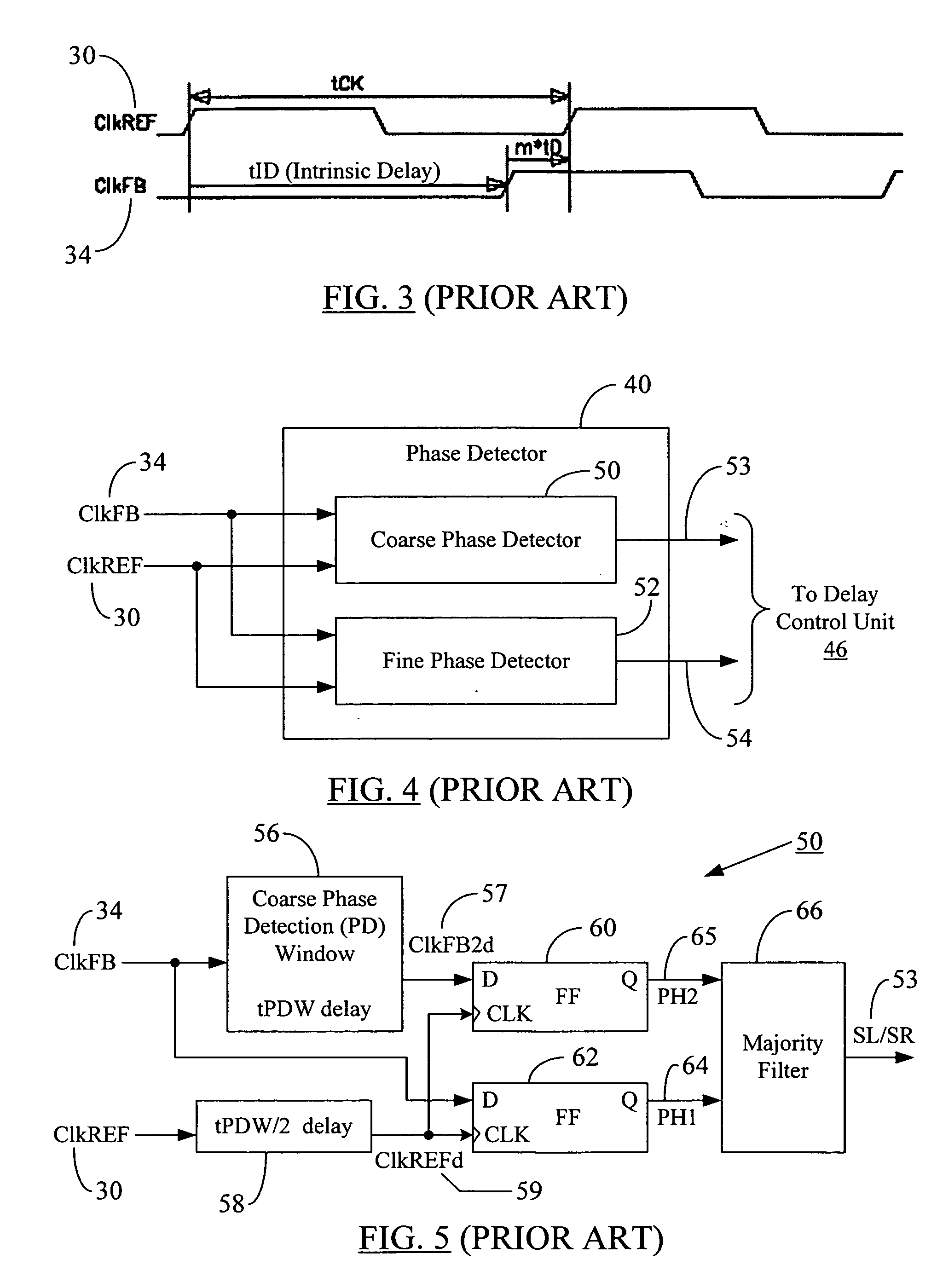

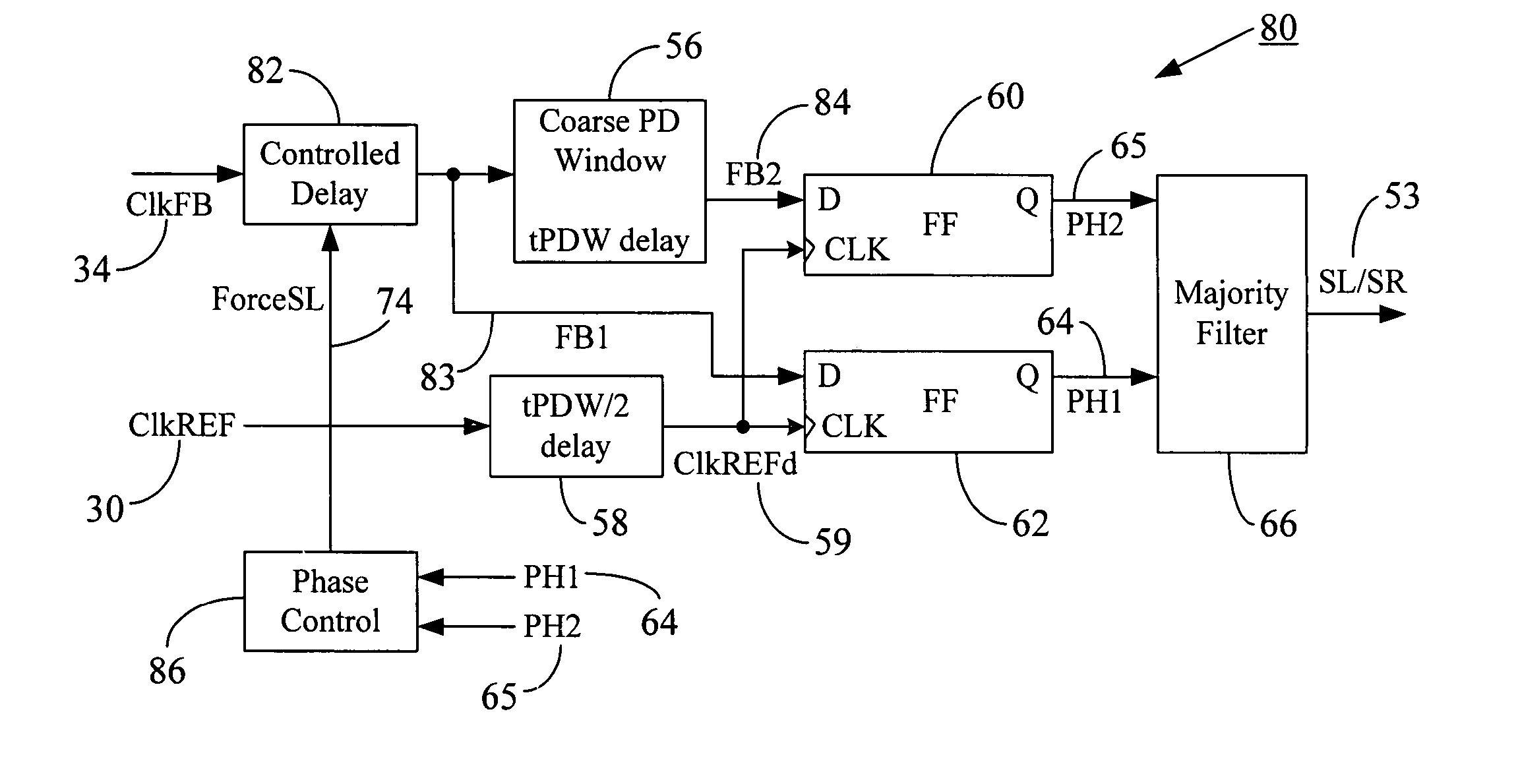

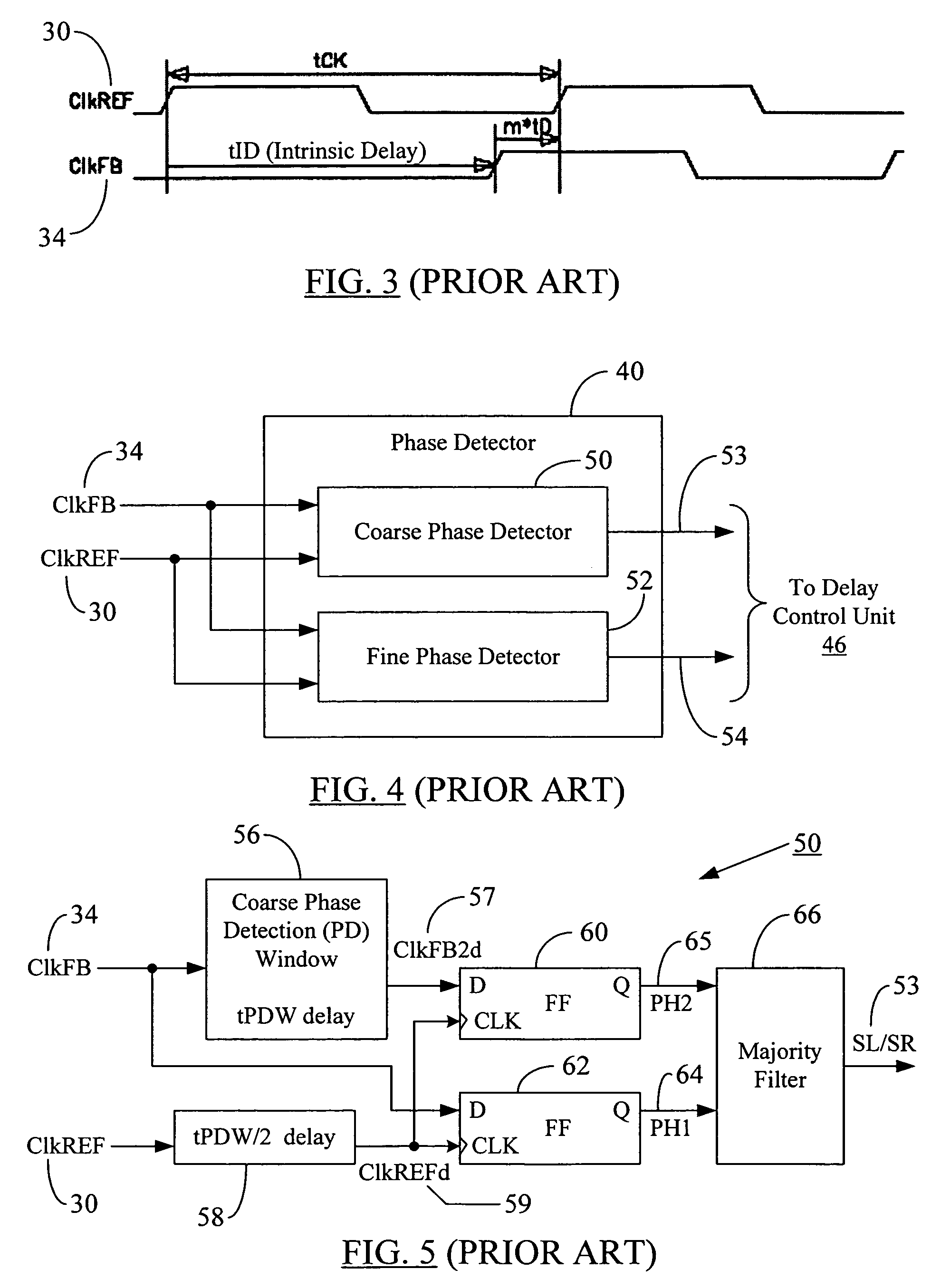

DLL phase detection using advanced phase equal

ActiveUS20050262373A1Faster DLL locking timeFast locking timePulse automatic controlError detection/correctionPhase detectorDelay-locked loop

A system and method are disclosed to generate and terminate clock shift modes during initialization of a synchronous circuit (e.g., a delay-locked loop or DLL). Upon initialization, the DLL is entered into a ForceSL (Force Shift Left) mode and an On1x mode (i.e., left shifting on each clock cycle). The feedback clock that tracks the phase of the reference clock (which, in turn, is derived from the system clock) is initially delayed in a coarse phase detector prior to applying it to the coarse phase detection window. Two delayed versions of the feedback clock are sampled by the reference clock to generate a pair of phase information signals, which are then used to establish an advanced phase equal (APHEQ) signal. The APHEQ signal advances onset of the PHEQ (phase equalization) phase and is used to terminate the ForceSL and On1x modes, thereby preventing wrong ForceSL exit due to clock jitter or feedback path overshooting during On1x exit. The avoidance of wrong ForceSL exit and On1x overshooting problems further results in faster DLL locking time.

Owner:MICRON TECH INC

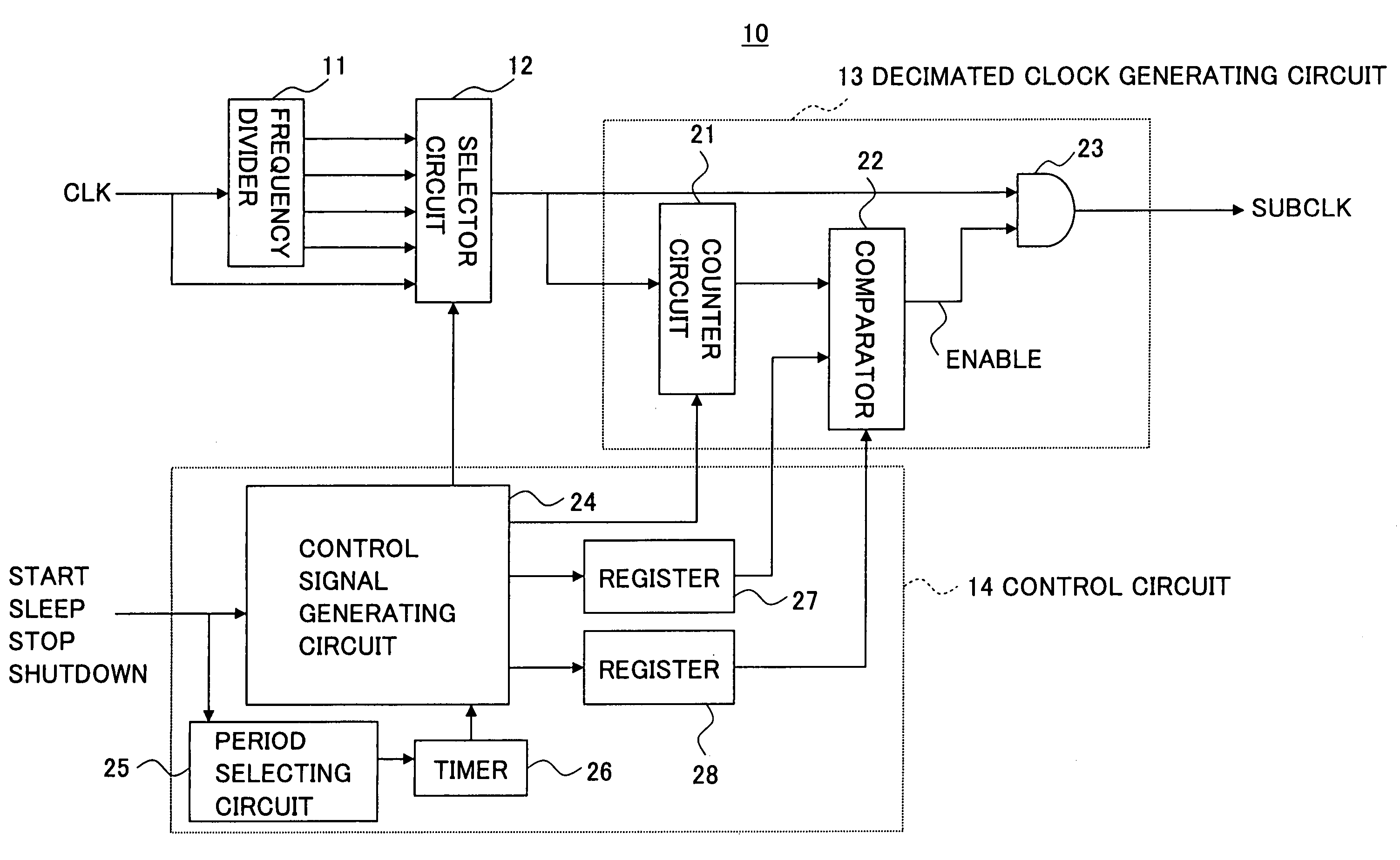

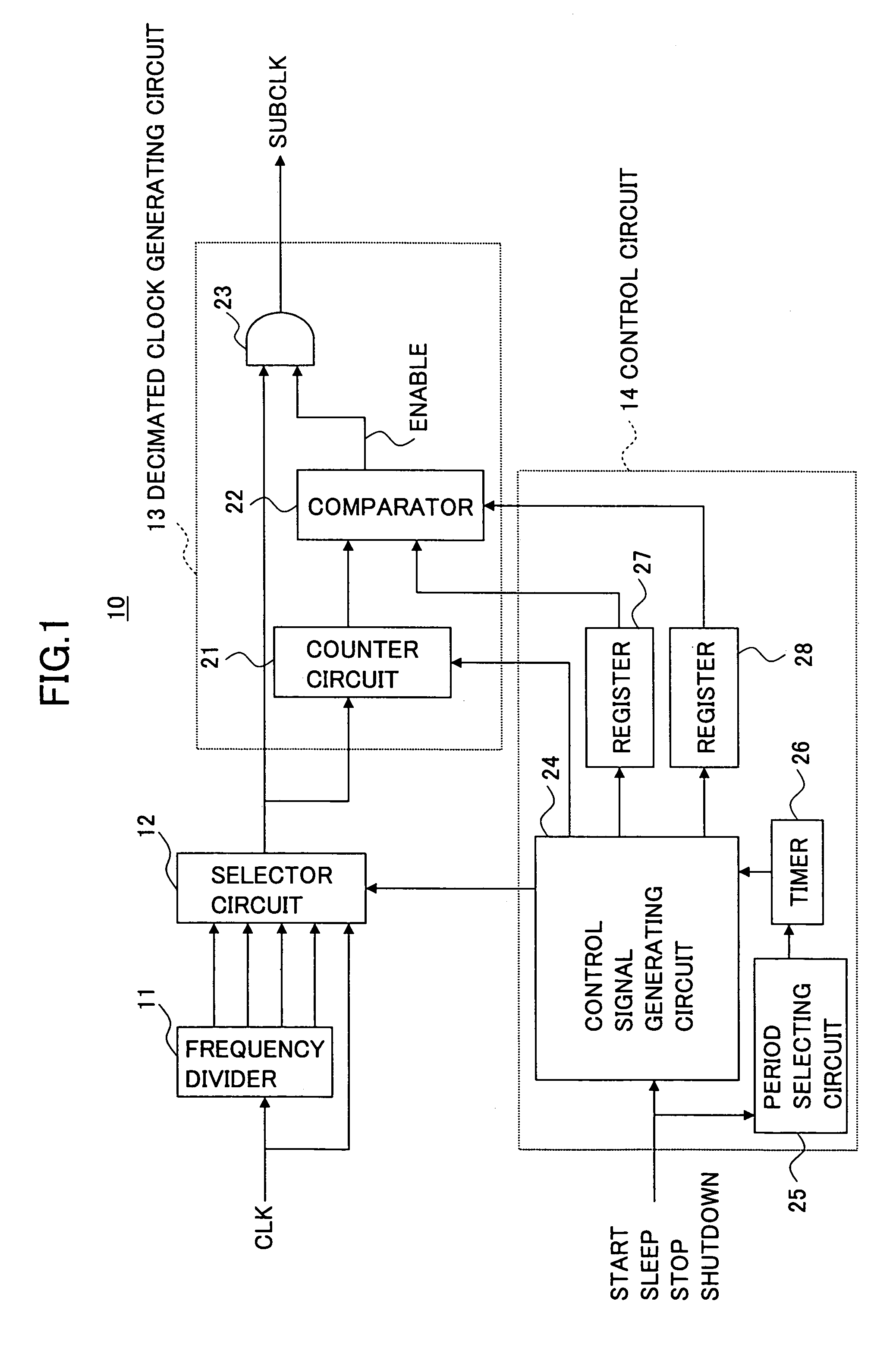

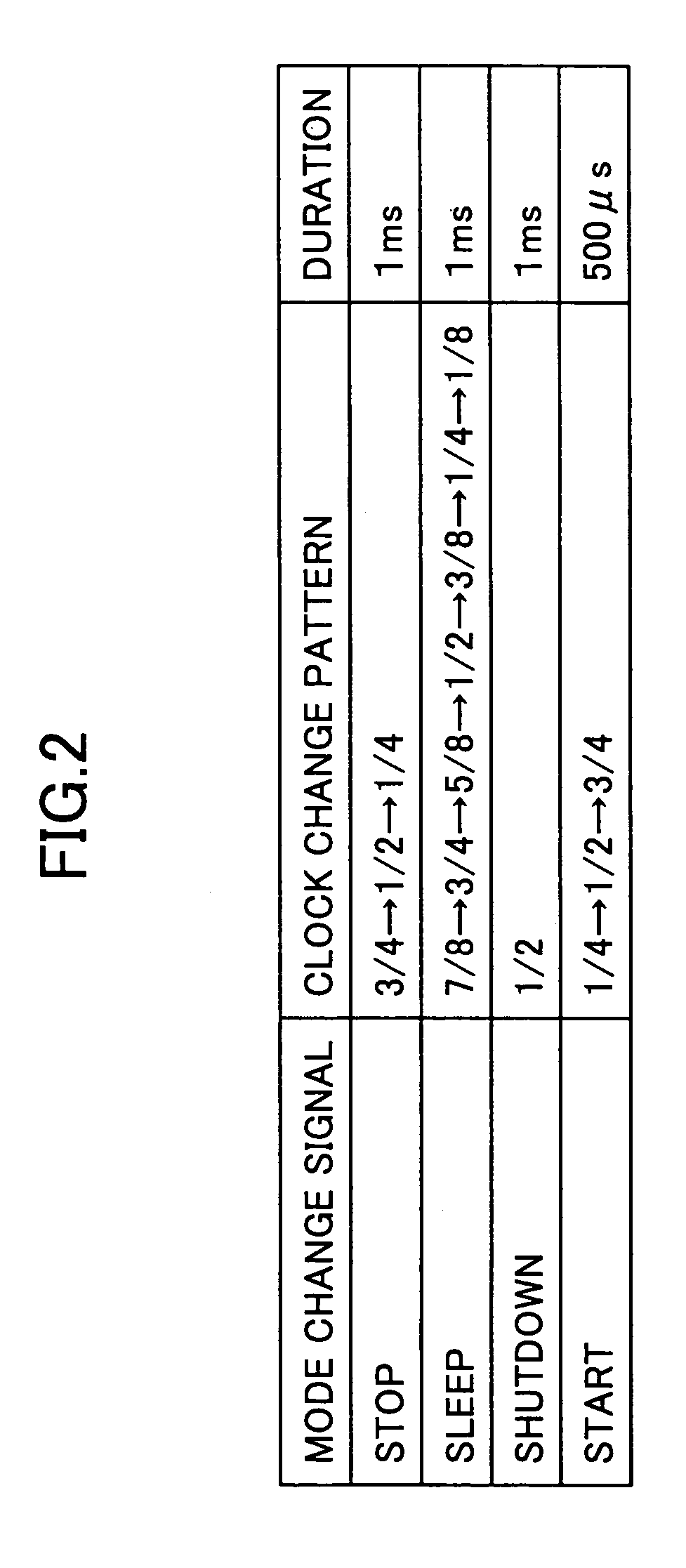

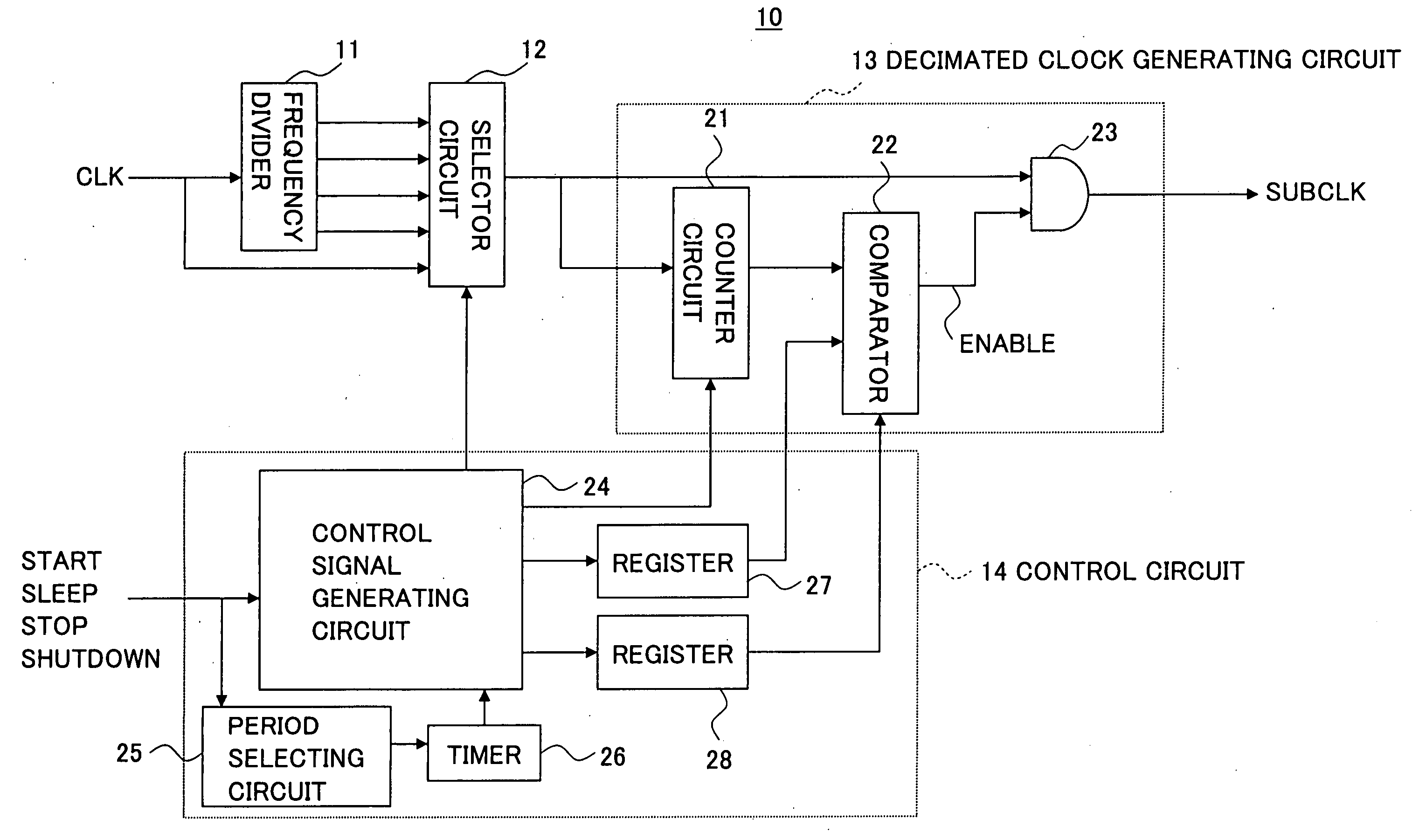

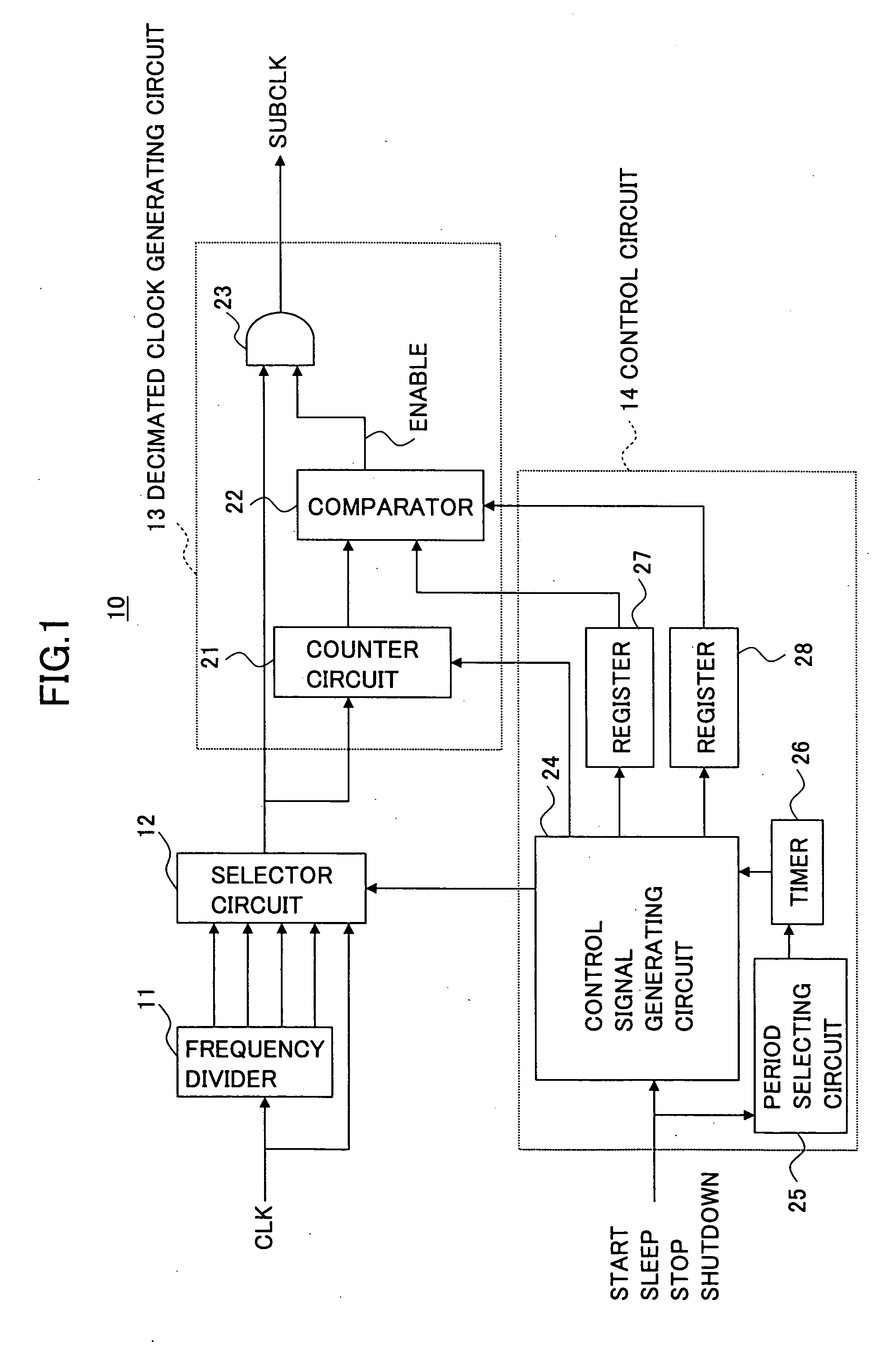

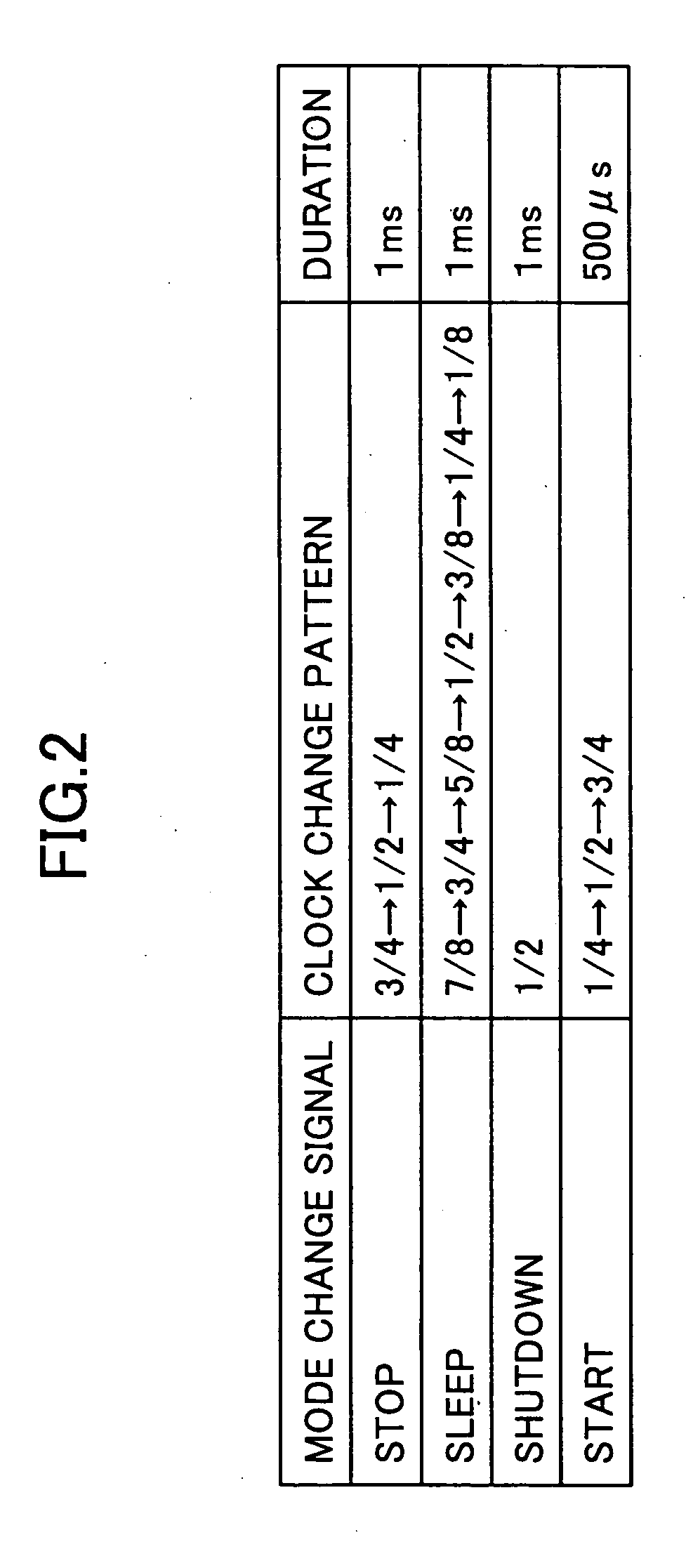

Clock shift circuit for gradual frequency change

ActiveUS7012454B2Reduce in quantityIncrease the number ofDelay line applicationsElectric pulse generatorOperation modeEngineering

Owner:MONTEREY RES LLC

Clock shift circuit for gradual frequency change

ActiveUS20050083098A1Reduce in quantityIncrease the number ofDelay line applicationsElectric pulse generatorEngineeringOperation mode

A circuit for changing clocks includes a clock generating circuit which generates an output clock signal by controlling a frequency of an original clock signal, and a control circuit which controls the clock generating circuit in response to an operation mode change signal indicative of a change from a first operation mode to a second operation mode of an external circuit operating based on the output clock signal, thereby changing the output clock signal from a first frequency corresponding to the first operation mode to an intervening frequency and then from the intervening frequency to a second frequency corresponding to the second operation mode, the intervening frequency having a frequency between the first frequency and the third frequency.

Owner:MONTEREY RES LLC

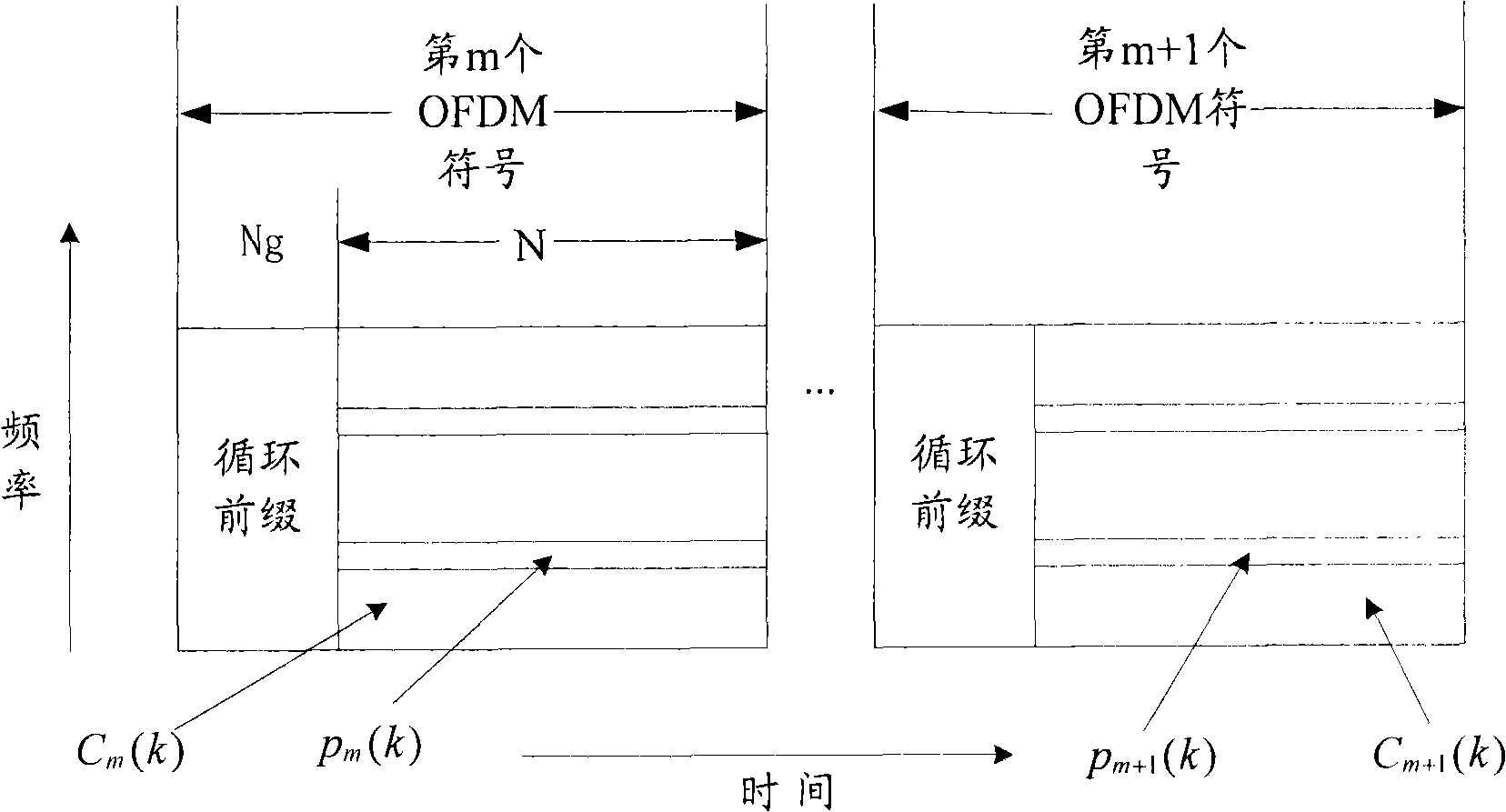

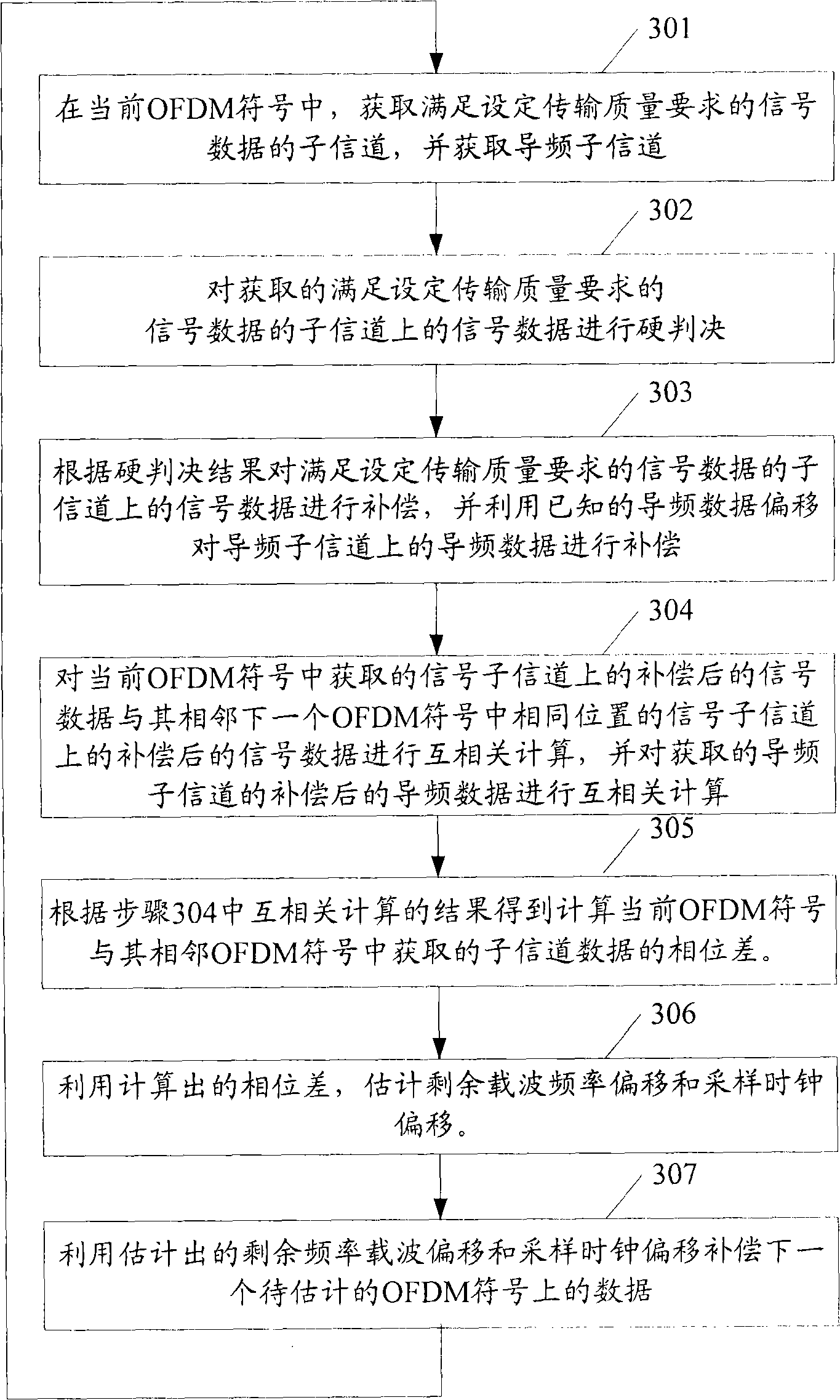

Synchronous estimation method and system for orthogonal frequency division multiplexing technique

InactiveCN101299737AAvoid the effects of bit errorsHigh precisionRadio transmission for post communicationMulti-frequency code systemsMutual correlationEstimation methods

The invention provides an in-phase estimation method and a system of the orthogonal frequency division multiplexing (OFDM) technology, wherein the method includes: obtaining the sub-channels which satisfy the given transmission quality in the OFDM symbols; computing the phase offset between the data on the obtained sub-channels and the data on the sub-channels with the same position in the adjacent OFDM symbols; estimating the residual carrier frequency shift and the sampling clock shift of the current OFDM symbols. The method and the system estimates the residual carrier frequency shift and the sampling clock shift through the mutual correlation data on the sub-channels which satisfy the given transmission quality, overcomes the effect of the sub-channel with bad quality to generate the error code, advances the precision of the in-phase estimation to a great extent.

Owner:HUAWEI TECH CO LTD +1

DLL phase detection using advanced phase equalization

ActiveUS7421606B2Fast locking timePulse automatic controlError detection/correctionPhase detectorDelay-locked loop

A system and method are disclosed to generate and terminate clock shift modes during initialization of a synchronous circuit (e.g., a delay-locked loop or DLL). Upon initialization, the DLL is entered into a ForceSL (Force Shift Left) mode and an On1x mode (i.e., left shifting on each clock cycle). The feedback clock that tracks the phase of the reference clock (which, in turn, is derived from the system clock) is initially delayed in a coarse phase detector prior to applying it to the coarse phase detection window. Two delayed versions of the feedback clock are sampled by the reference clock to generate a pair of phase information signals, which are then used to establish an advanced phase equal (APHEQ) signal. The APHEQ signal advances onset of the PHEQ (phase equalization) phase and is used to terminate the ForceSL and On1x modes, thereby preventing wrong ForceSL exit due to clock jitter or feedback path overshooting during On1x exit. The avoidance of wrong ForceSL exit and On1x overshooting problems further results in faster DLL locking time.

Owner:MICRON TECH INC

Data transmission system and data transmission apparatus

InactiveUS20050111572A1Reduce circuit sizeReduce power consumptionSynchronisation information channelsSynchronisation signal speed/phase controlClock shiftComparator

A data transmission system having a clock shift compensating function is designed for a reduced circuit scale and reduced electric power consumption. A data transmission D flip-flop in a transmitter is supplied with a clock signal for transmitting data from a clock delay. A transmitter has a data reception D flip-flop, a clock supply, a divide-by-n frequency divider for frequency-dividing a clock signal, and a metastability avoider for removing a metastable state from a clock signal received via the clock delay. The transmitter also has a phase comparator for comparing output signals from the metastability avoider and a modulo-m counter, and a clock edge deleter for controlling the number of pulses or edges of the clock signal from the clock supply depending on an output signal from the phase comparator. Pulses of the clock signal from the clock edge deleter are counted by the counter and supplied to the data reception D flip-flop.

Owner:SONY CORP

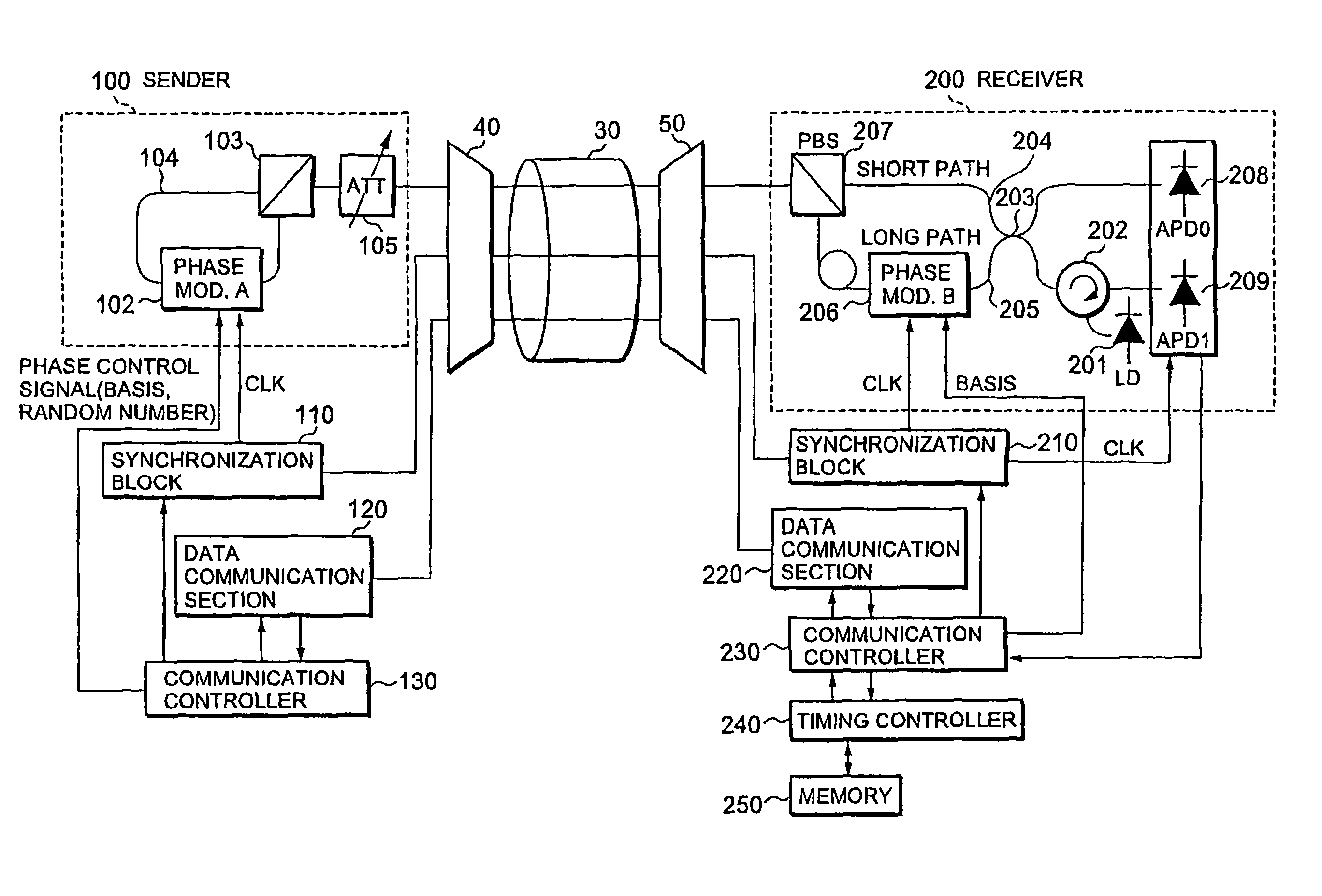

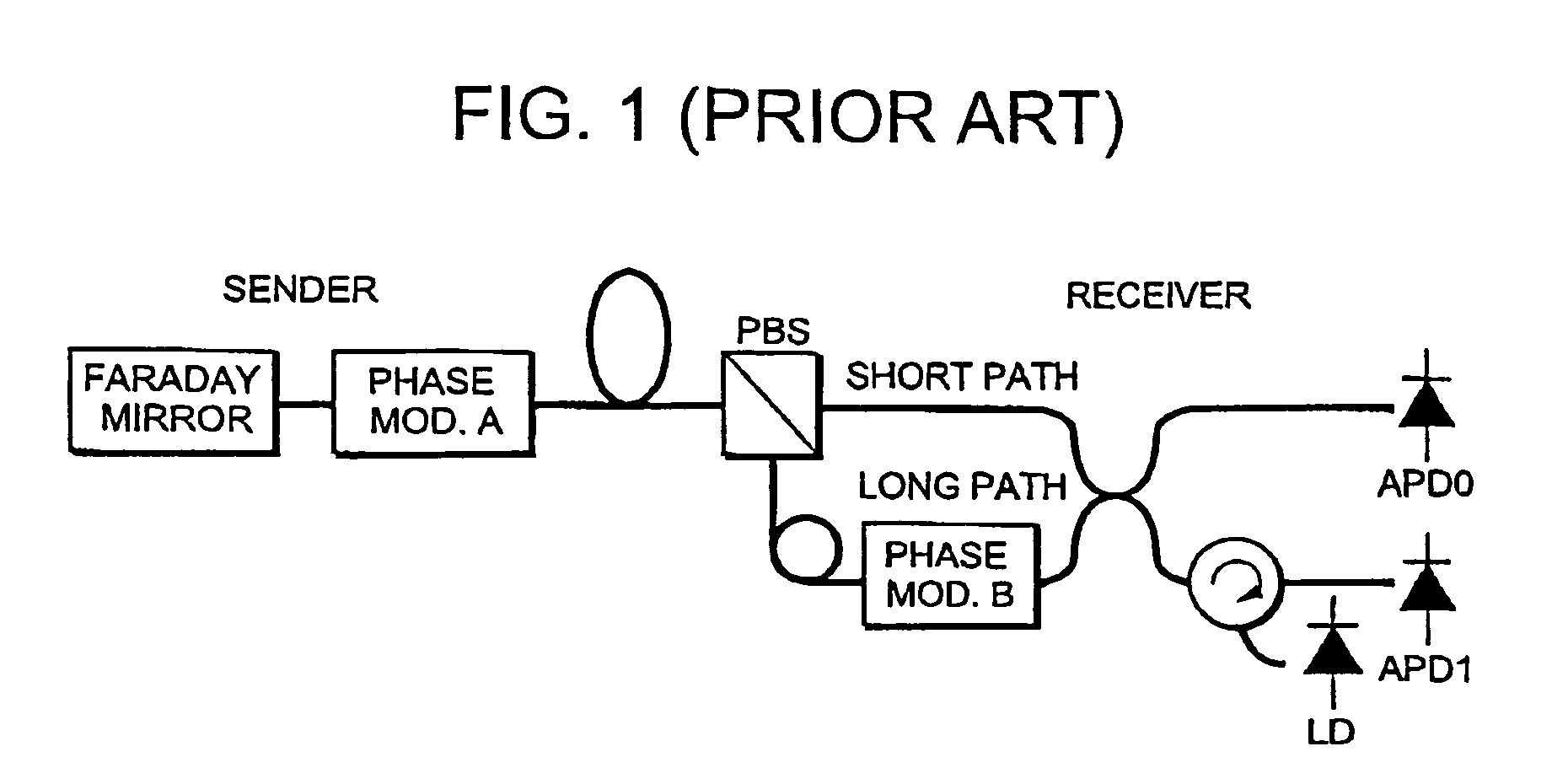

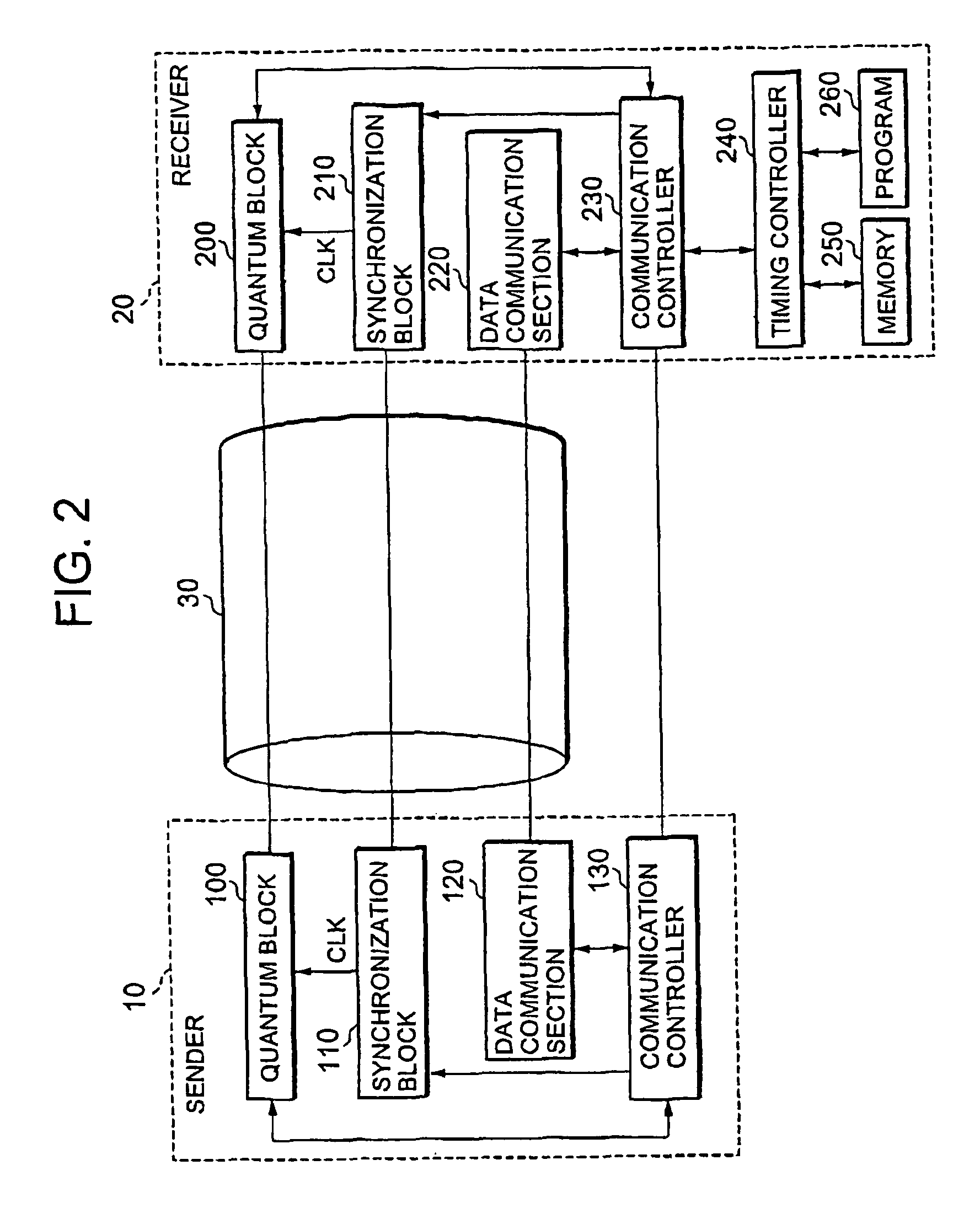

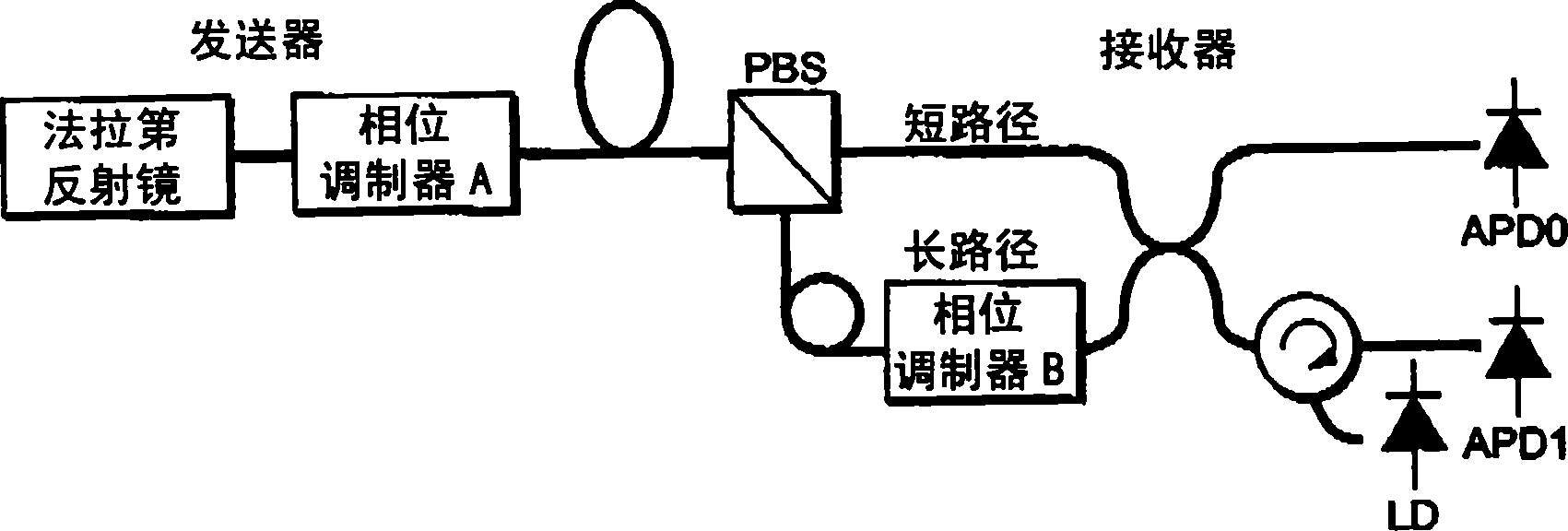

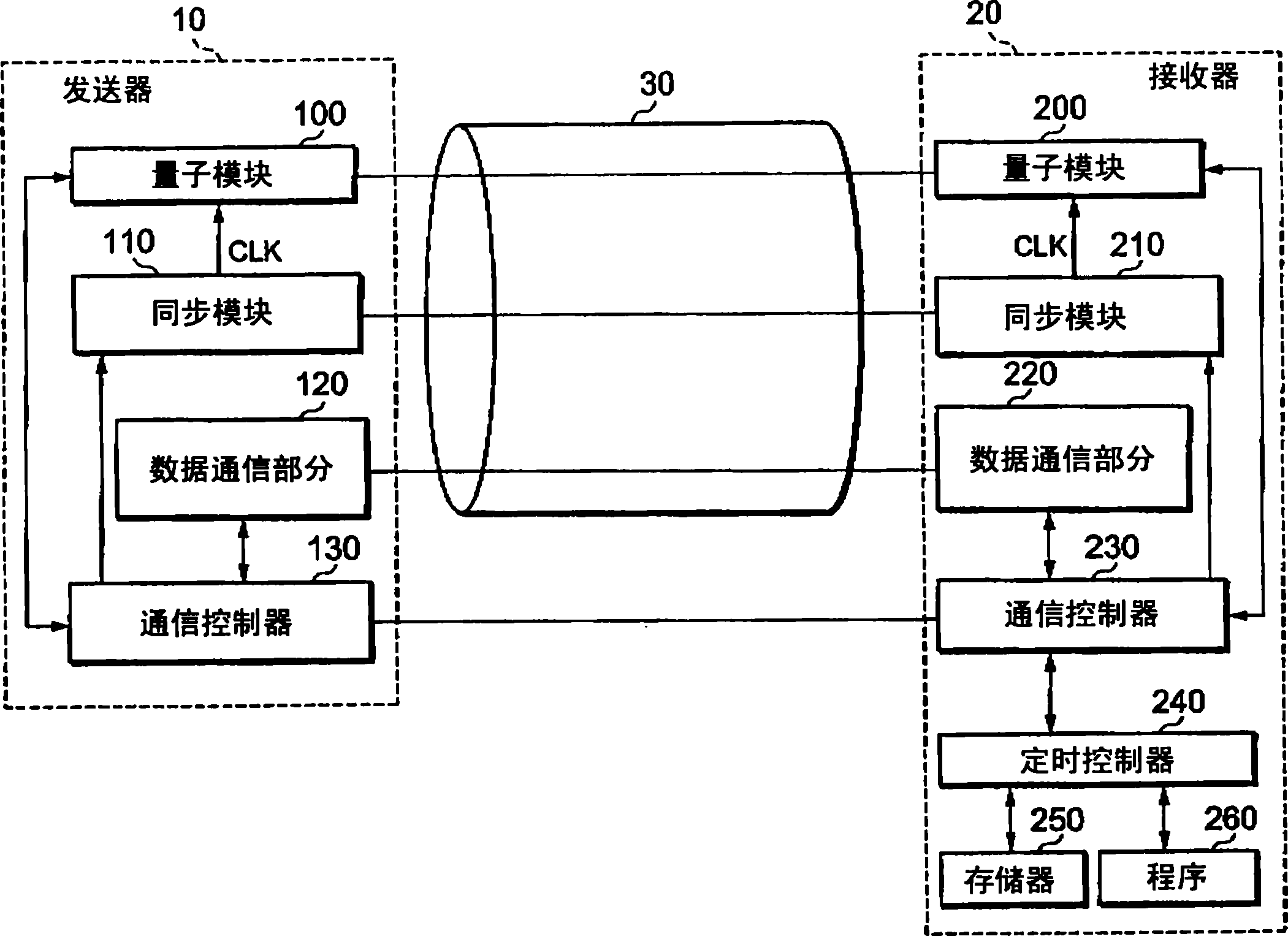

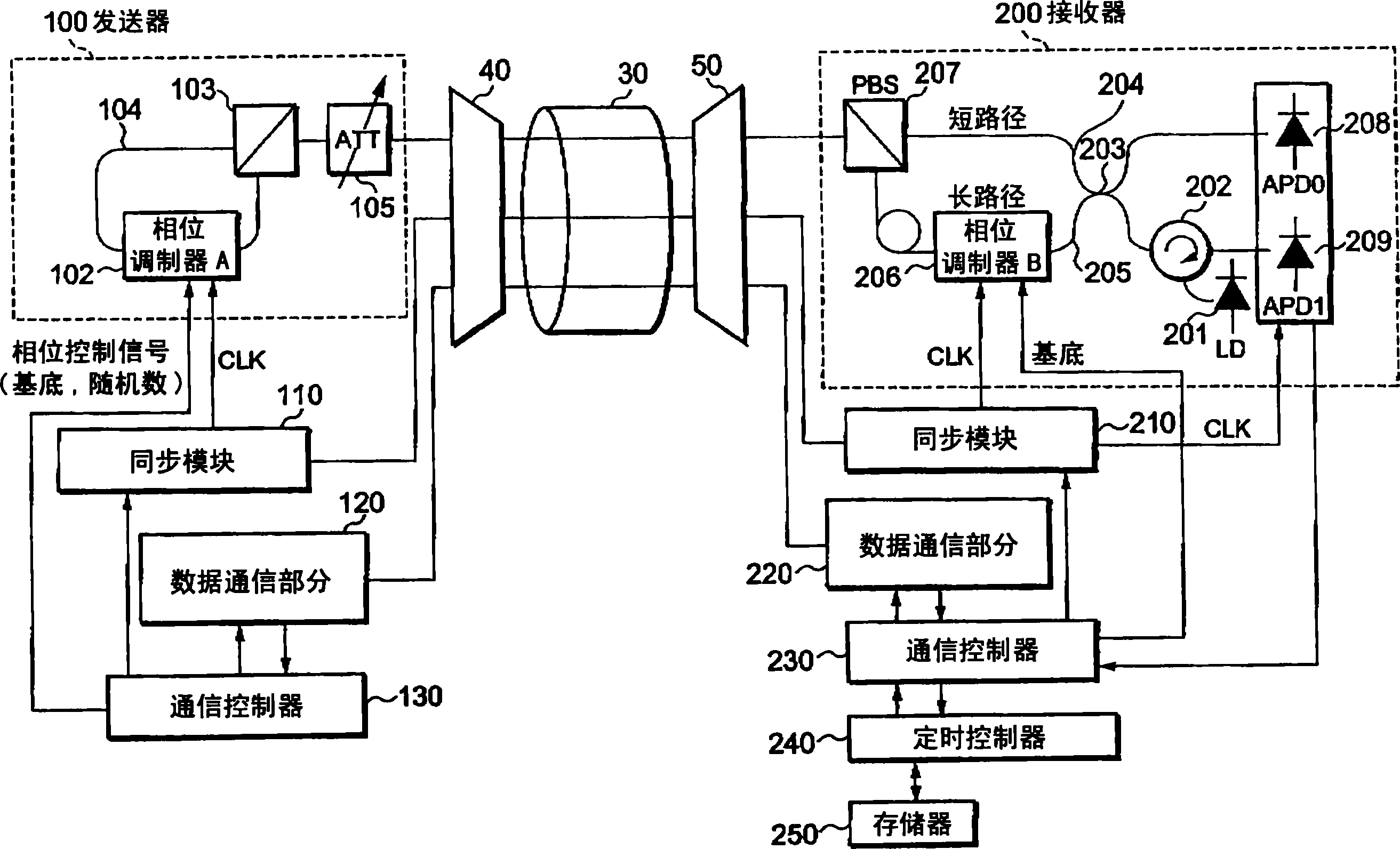

Communication system and timing control method

ActiveUS8184989B2Convenient timeEvenly distributedKey distribution for secure communicationSecret communicationCommunications systemGroup velocity dispersion

A communication system and a timing control method are proposed that optimize timing in a sender and thereby enable information to be stably transmitted at the right timing. Under instructions from a timing controller in a receiver, the timing of driving a phase modulator in a sender is shifted by one step after another, and the then amount of clock shift and result of interference are monitored at the receiver and stored in a memory. The optimum timing is determined based on the stored data. Thus, a clock for driving the phase modulator in the sender can be set at the right timing. This is equivalent to compensating for group velocity dispersion due to wavelength dispersion that occurs when an optical signal channel and a clock signal channel are transmitted by wavelength division multiplexing transmission.

Owner:NEC CORP

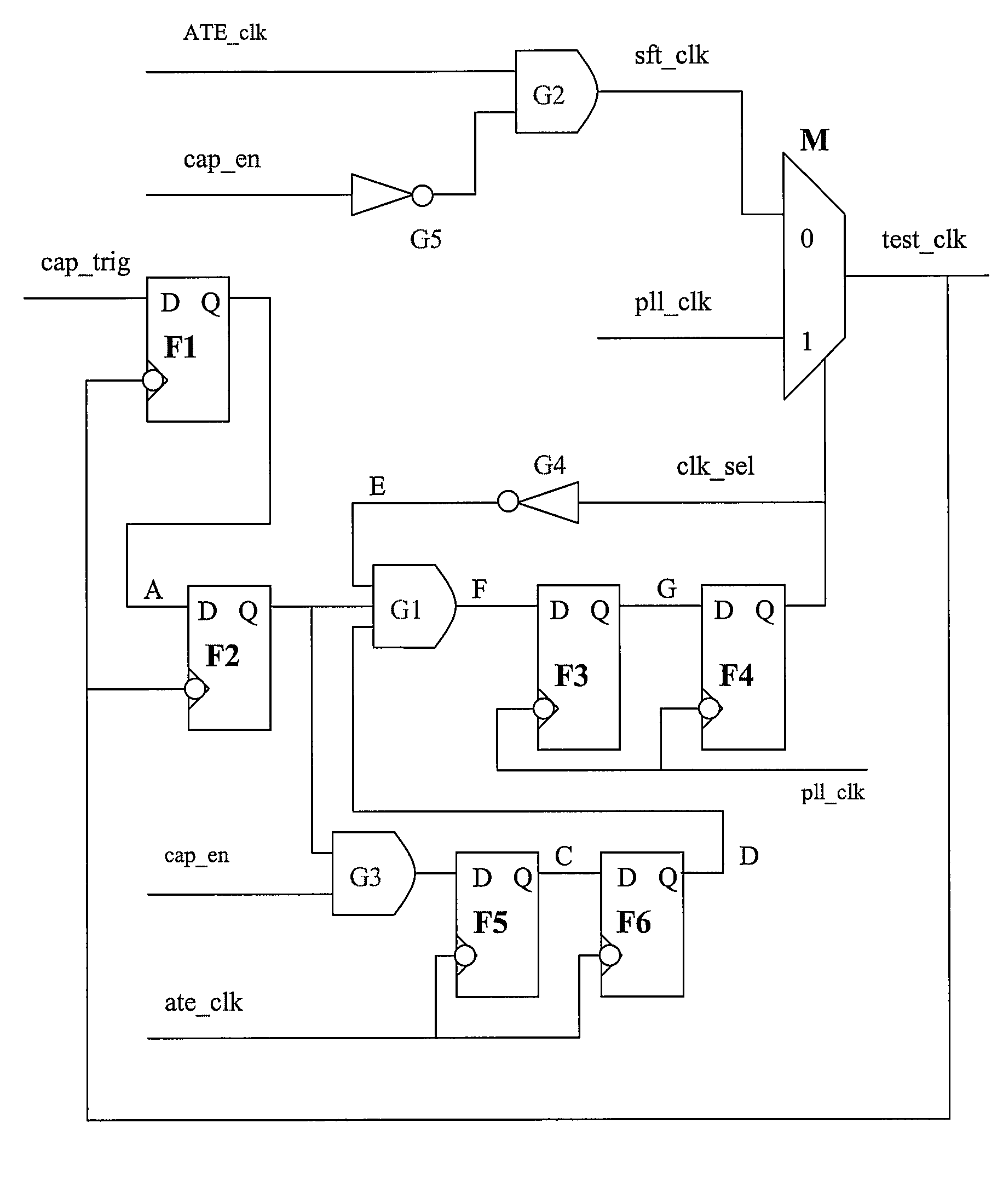

System and method for generating self-synchronized launch of last shift capture pulses using on-chip phase locked loop for at-speed scan testing

Presented herein are system(s) and method(s) for generating self-synchronized launch of last shift capture pulses using on-chip phase locked loop for at-speed scan testing. In one embodiment, there is presented a system for scan testing. The system comprises an ATE clock and a phase lock loop. The ATE clock shifts scan data. The phase lock loop generates capture pulses. The ATE clock or the capture pulses are selected based on an external synchronization signal.

Owner:AVAGO TECH INT SALES PTE LTD

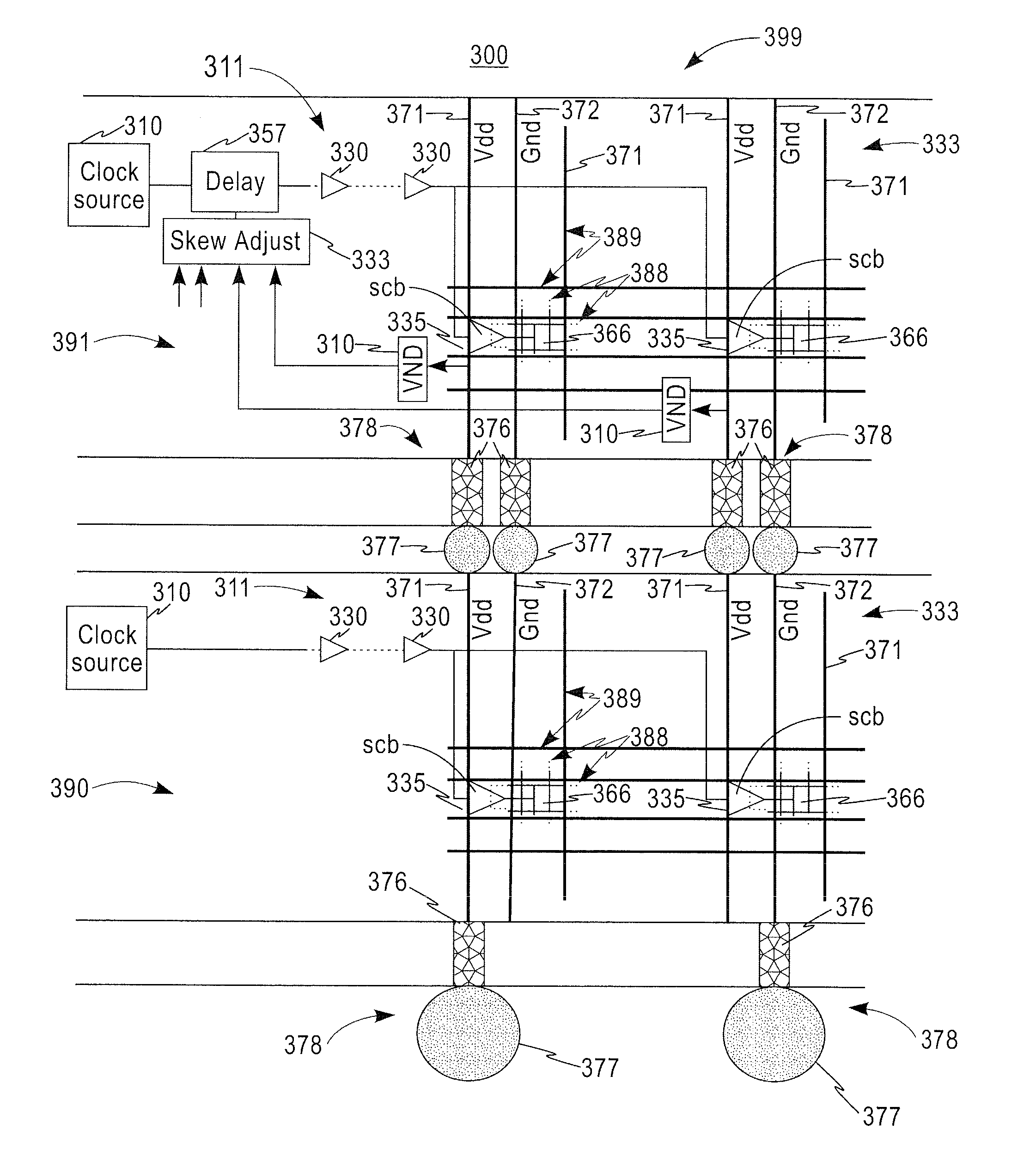

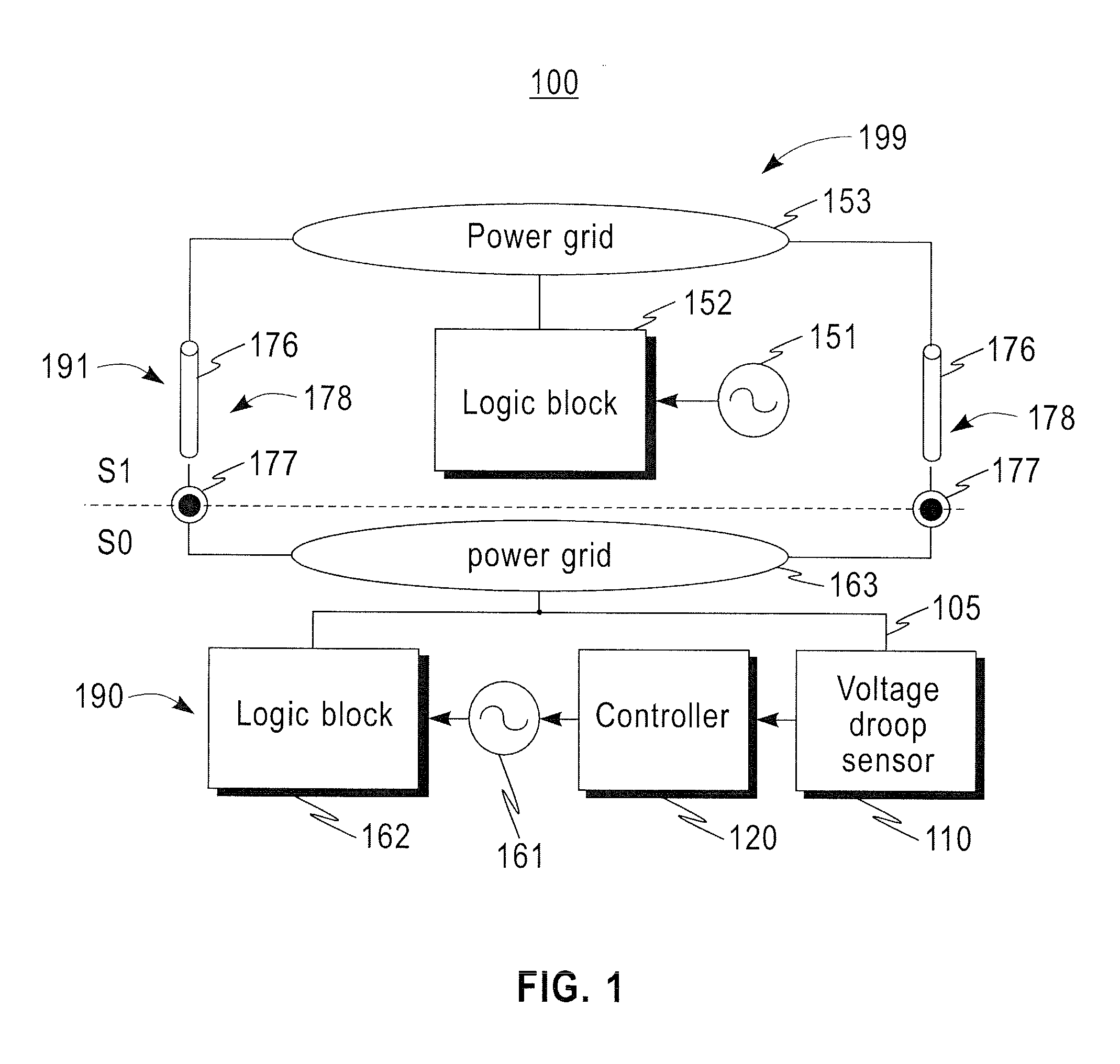

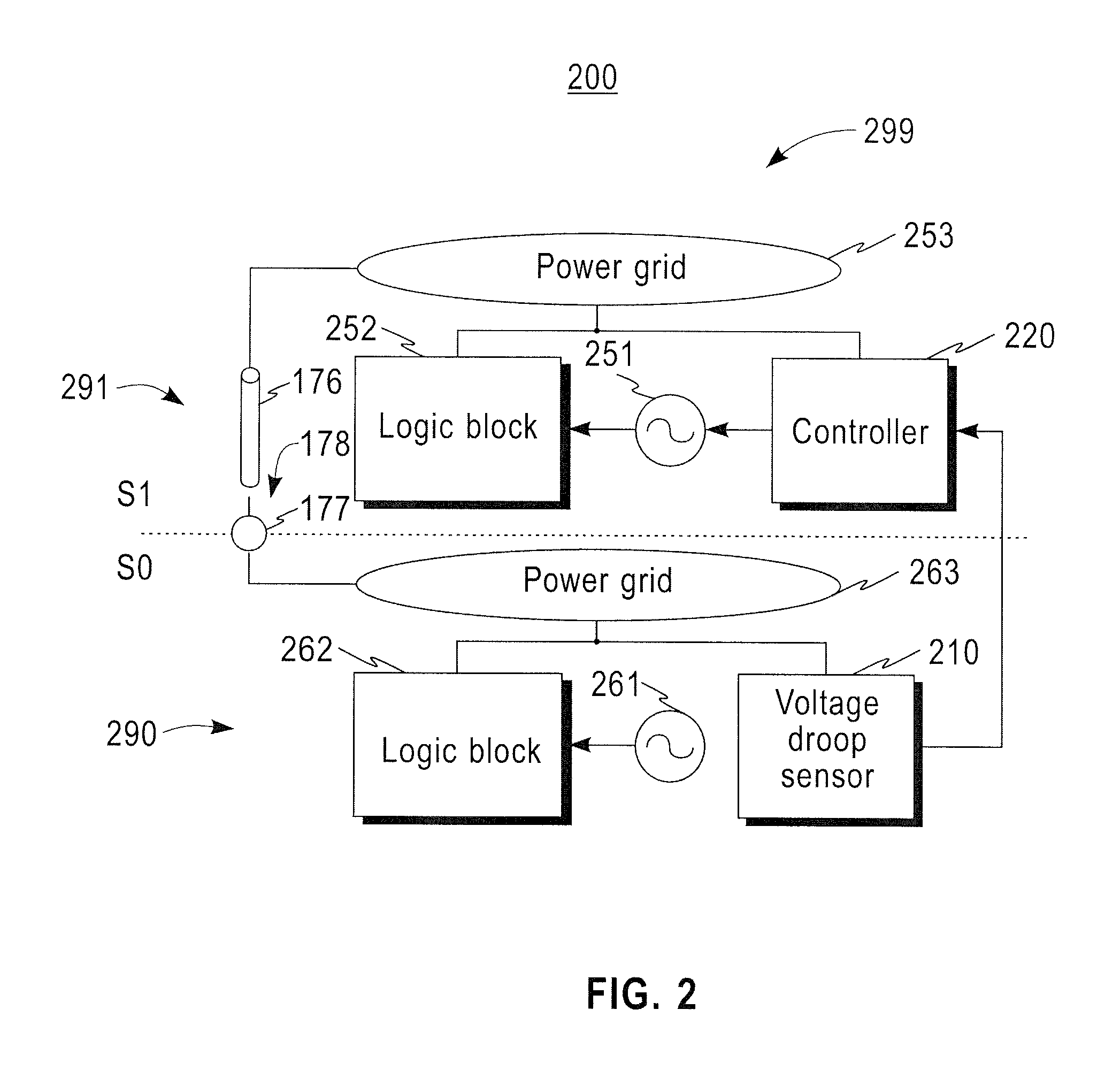

Ac supply noise reduction in a 3D stack with voltage sensing and clock shifting

ActiveUS20130049828A1Reduced alternating current supply noiseReducing alternating current supply noisePulse automatic controlSolid-state devicesReducerEngineering

There is provided an alternating current supply noise reducer for a 3D chip stack having two or more strata. Each of the strata has a respective one of a plurality of power distribution circuits and a respective one of a plurality of clock distribution circuits arranged thereon. The alternating current supply noise reducer includes a plurality of voltage droop sensors and a plurality of skew adjustors. The plurality of voltage droop sensors is for detecting alternating current supply noise in the plurality of power distribution circuits. One or more voltage droop sensors are respectively arranged on at least some of the strata. The plurality of skew adjusters are for delaying one or more clock signals provided by the plurality of clock distribution circuits responsive to an amount of the alternating current supply noise. Each skew adjuster is respectively arranged on the at least some of the strata.

Owner:GLOBALFOUNDRIES US INC

Apparatus and method for clock shift correction for measurement-while-drilling measurements

The disclosure provides a method which includes transmitting signals over a time period between a downhole location and a surface location during drilling of a wellbore; recording the time of each signal at the surface using a surface clock and the time of each signal downhole using a downhole clock; and correcting the downhole measurements using the recorded times.

Owner:BAKER HUGHES INC

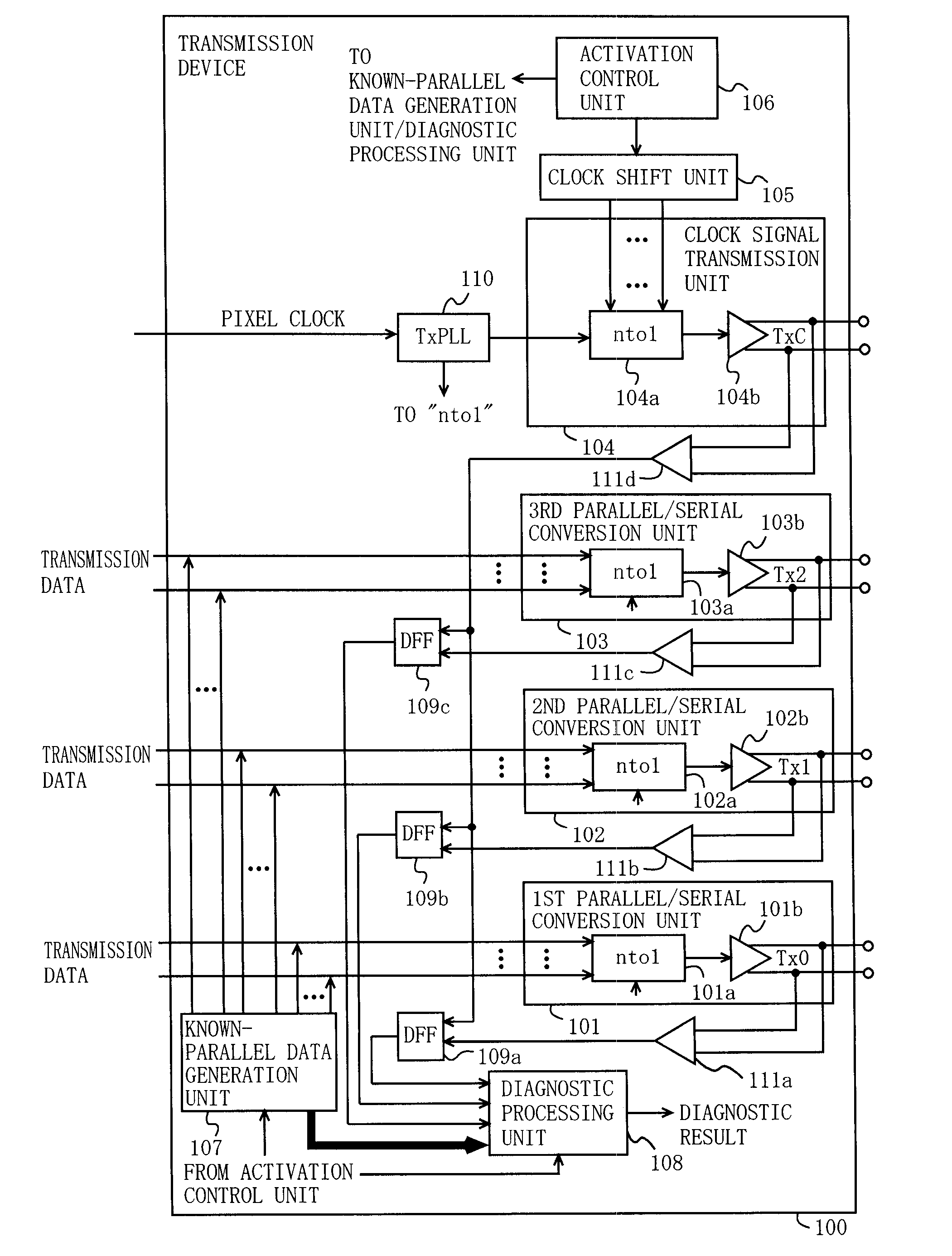

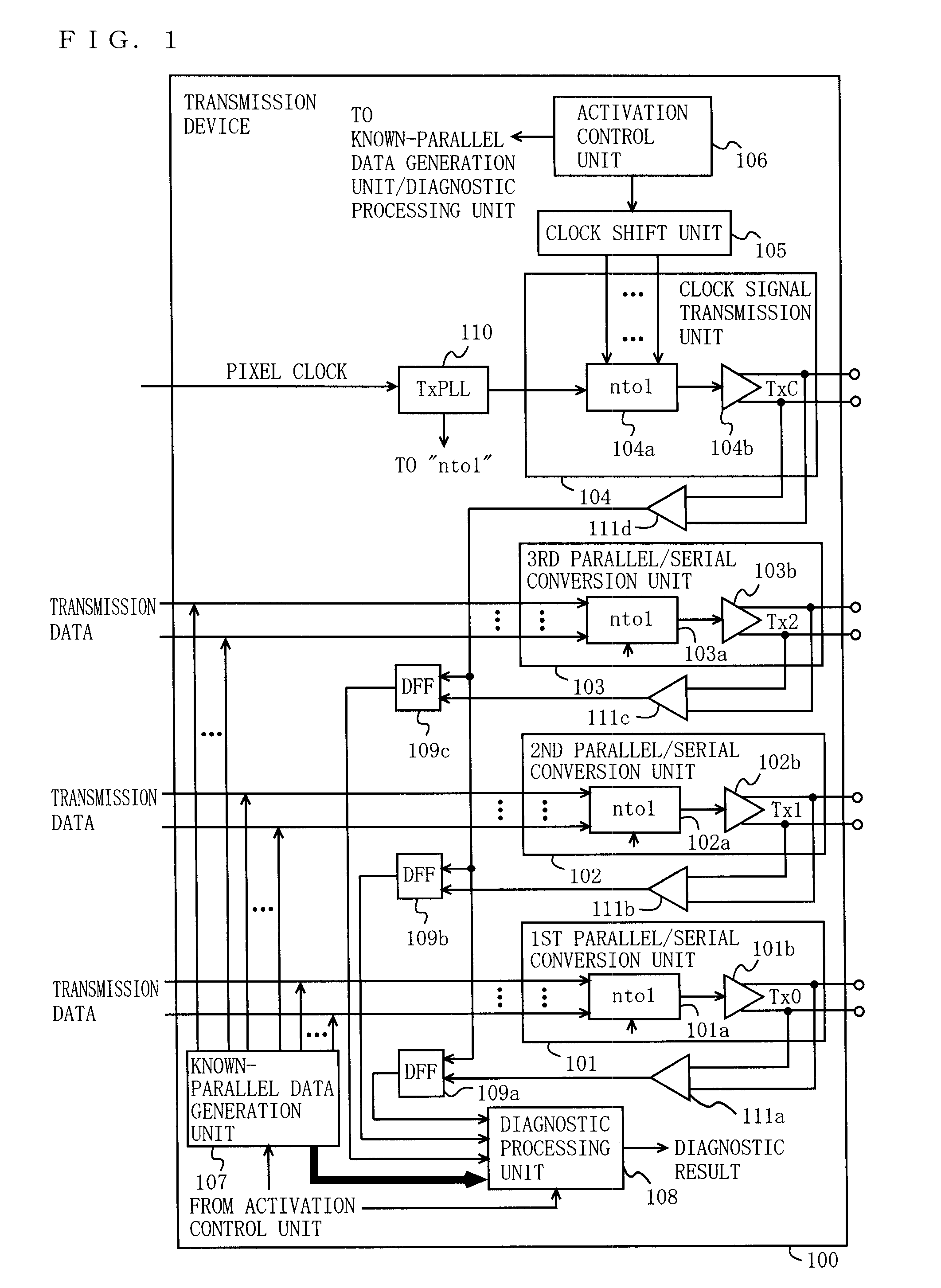

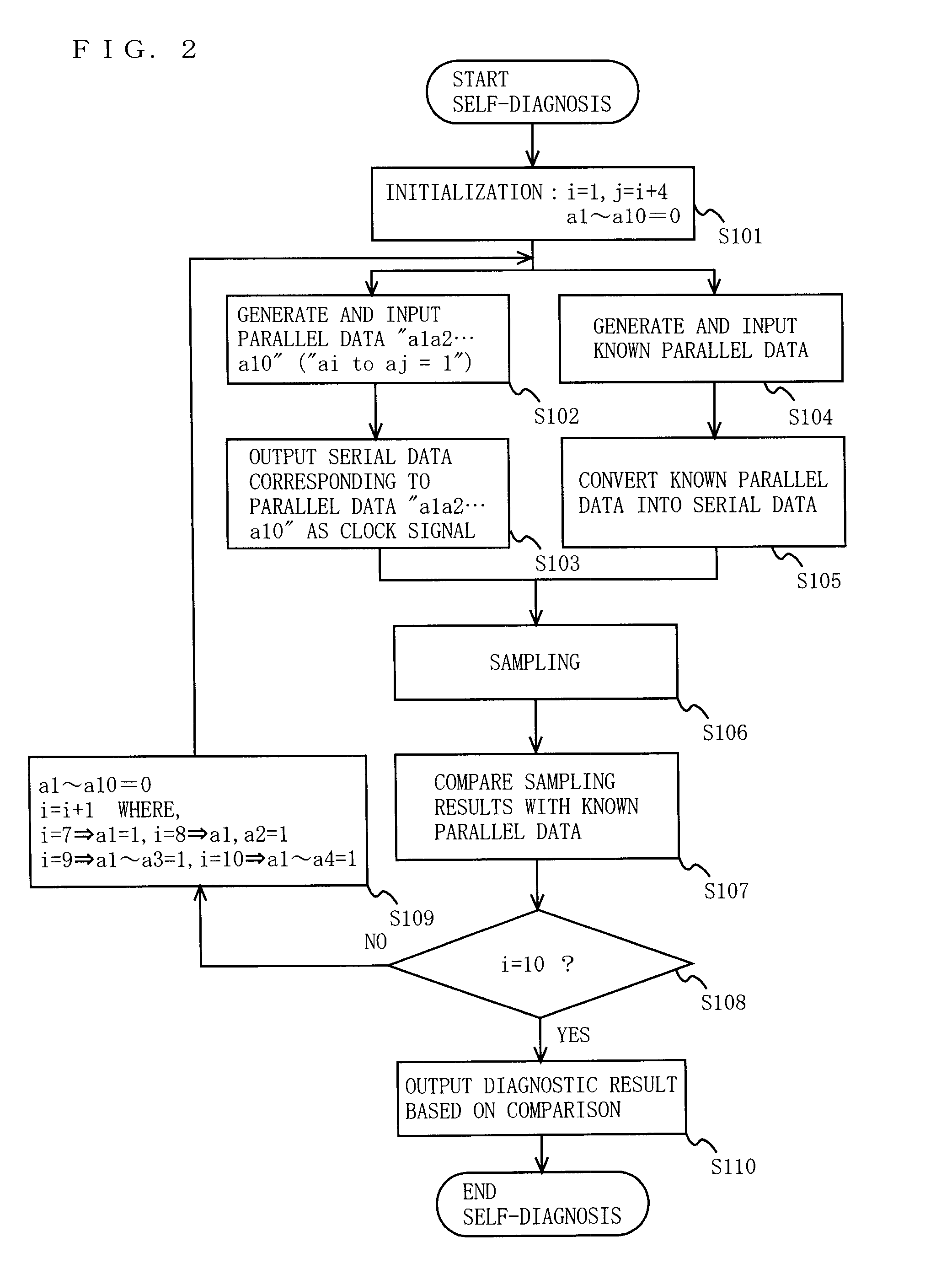

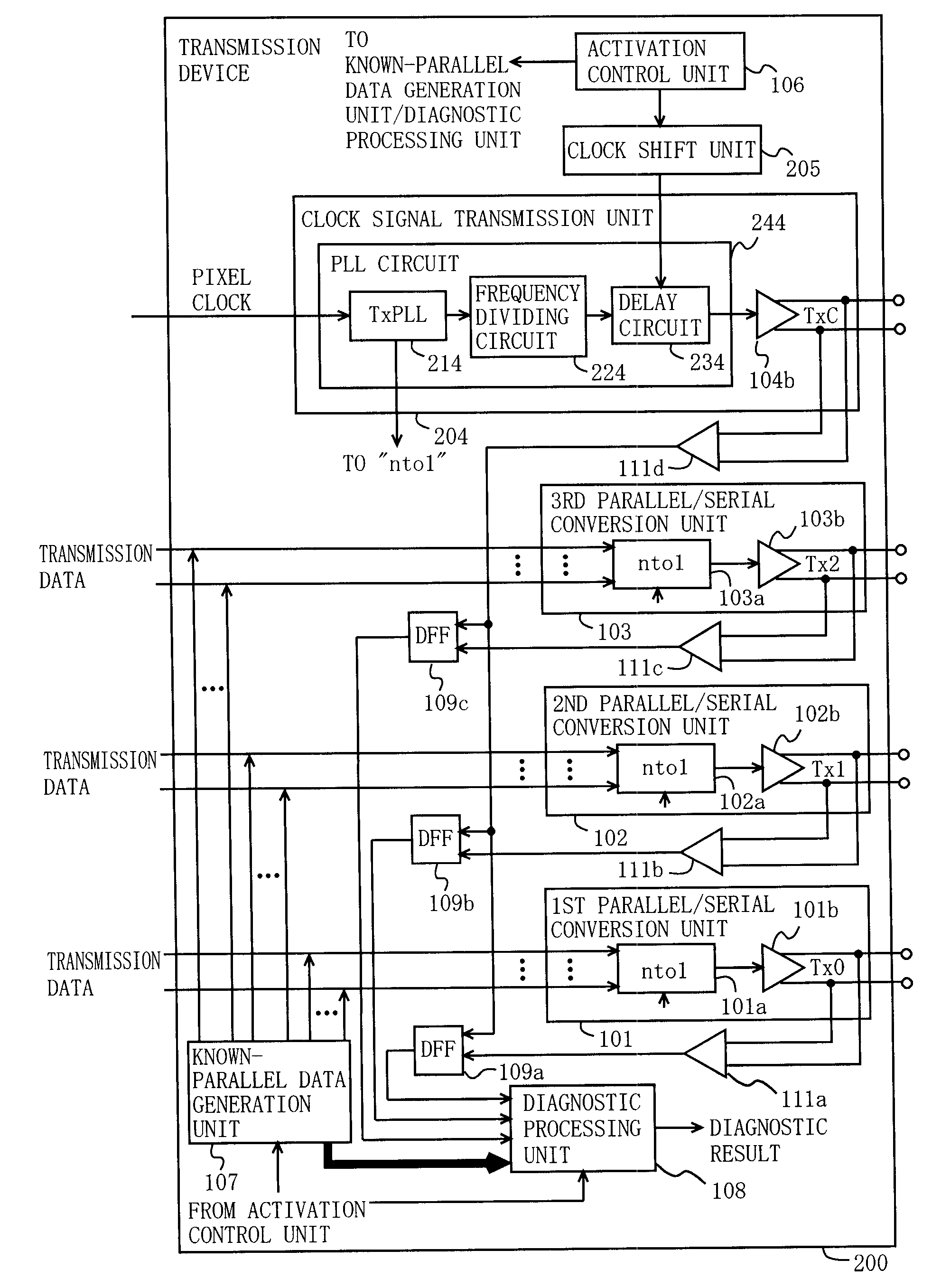

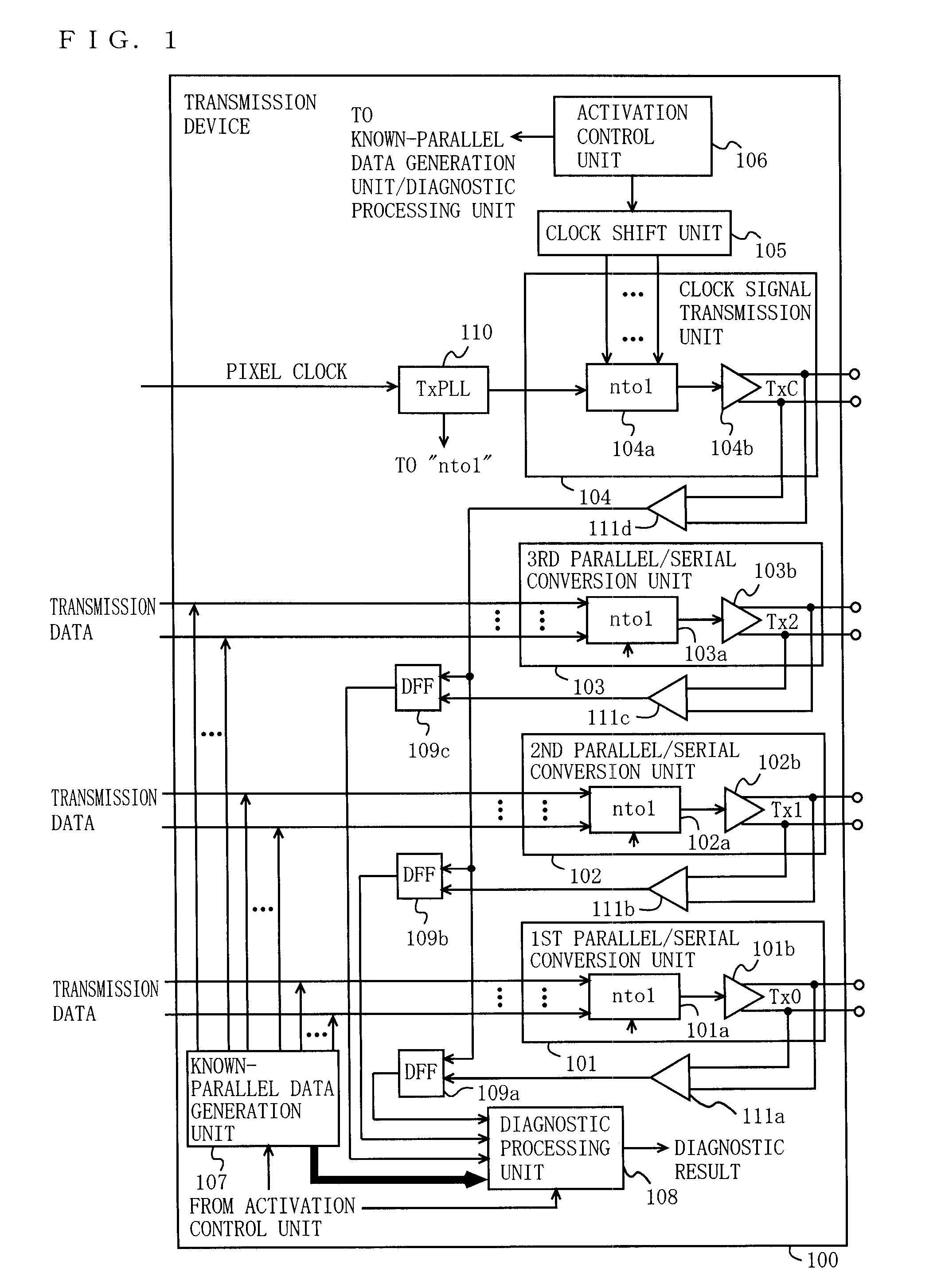

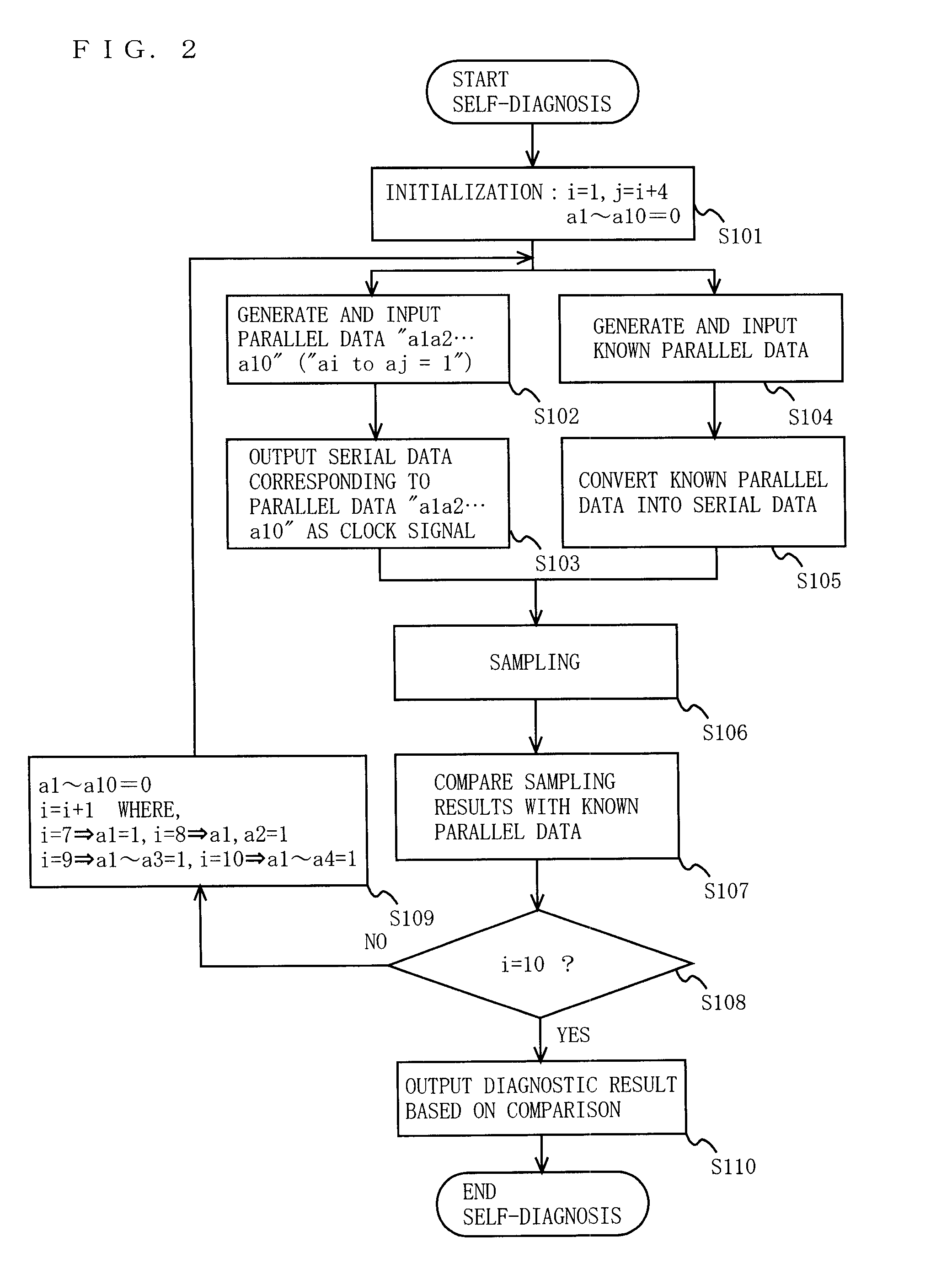

Transmission device and electronic apparatus with self-diagnostic function, and self-diagnostic method for use therein

A transmission device includes: parallel / serial conversion units; a clock signal transmission unit; a known-parallel data generation unit for inputting known-parallel data to the parallel / serial conversion units; a clock shift unit for sequentially shifting a clock signal, which is outputted from the clock signal transmission unit, by 1 UI of a data signal; sampling units for sampling data signals obtained by serializing the known-parallel data, in accordance with the clock signal shifted by 1 UI; and a diagnostic processing unit for making a diagnosis as to whether the transmission device is operating normally by comparing sampling results with the known-parallel data, and outputting a result of the diagnosis.

Owner:SILICON LIBRARY

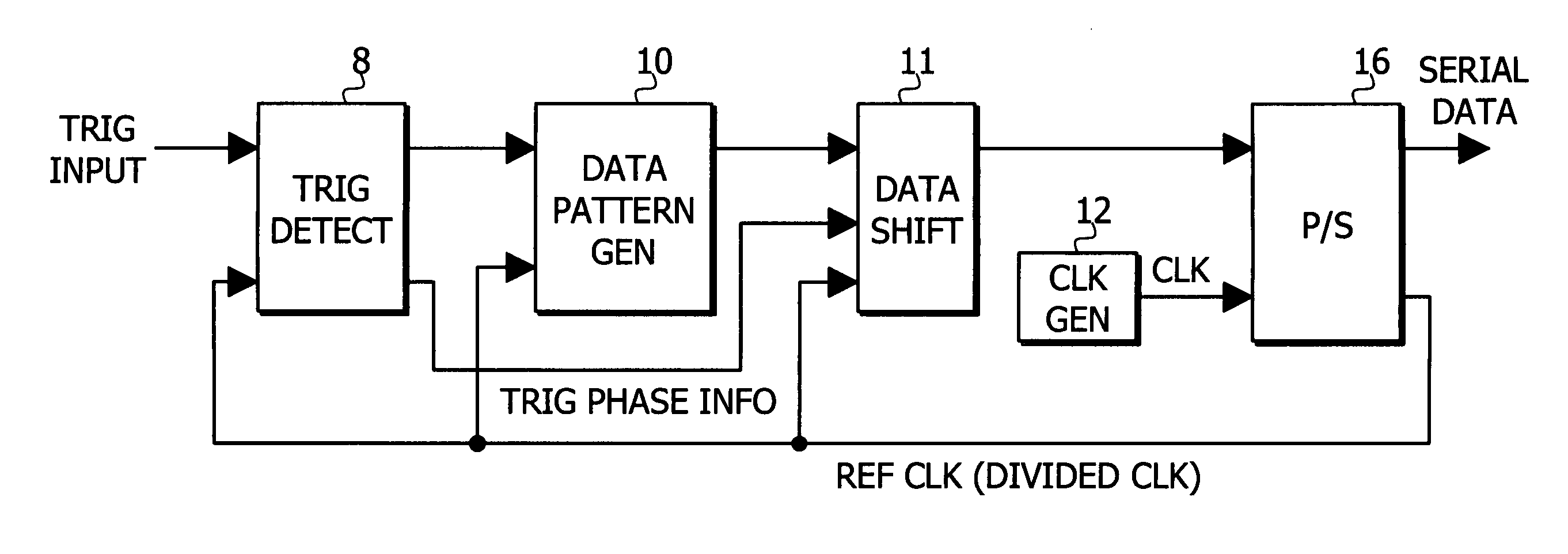

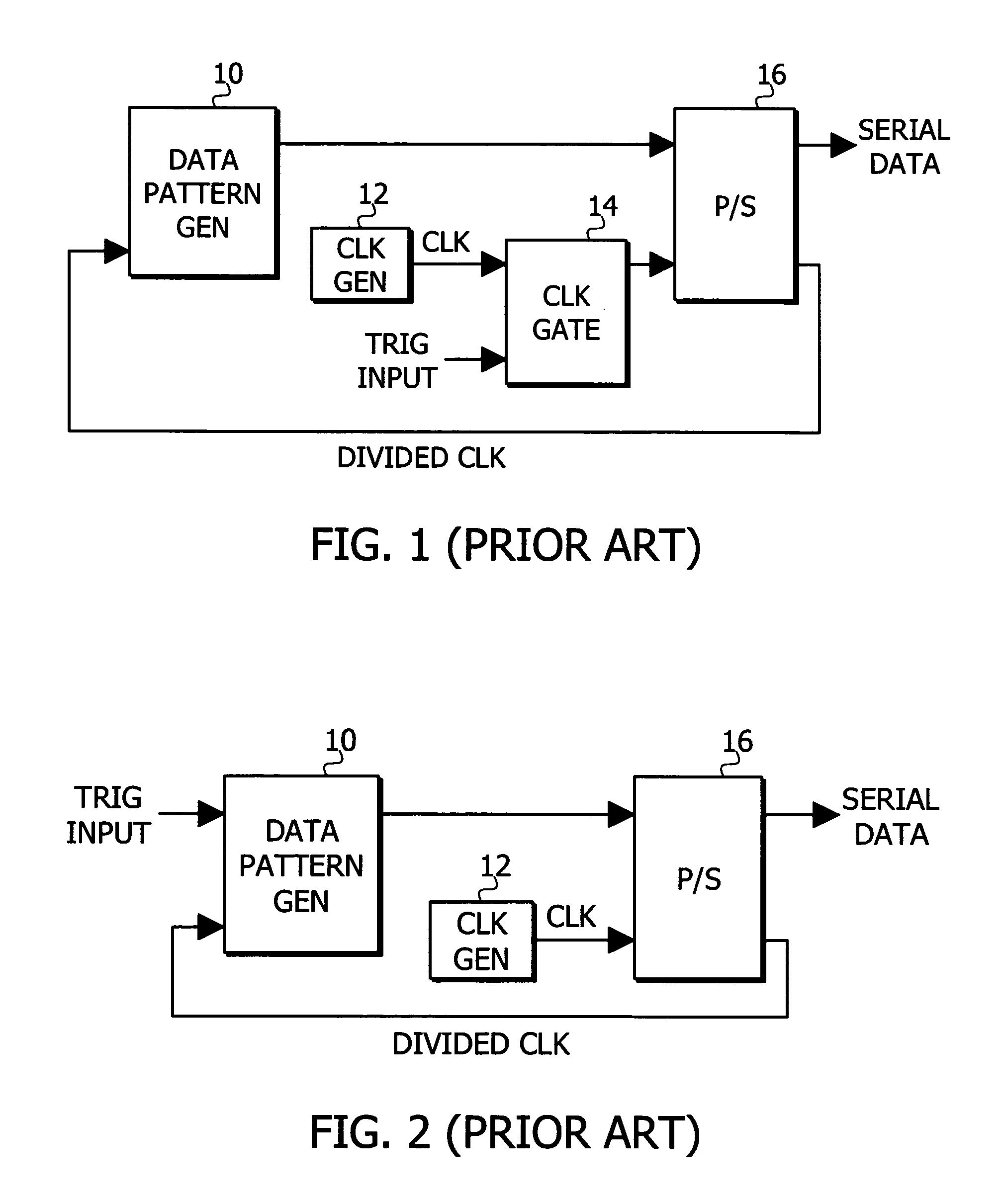

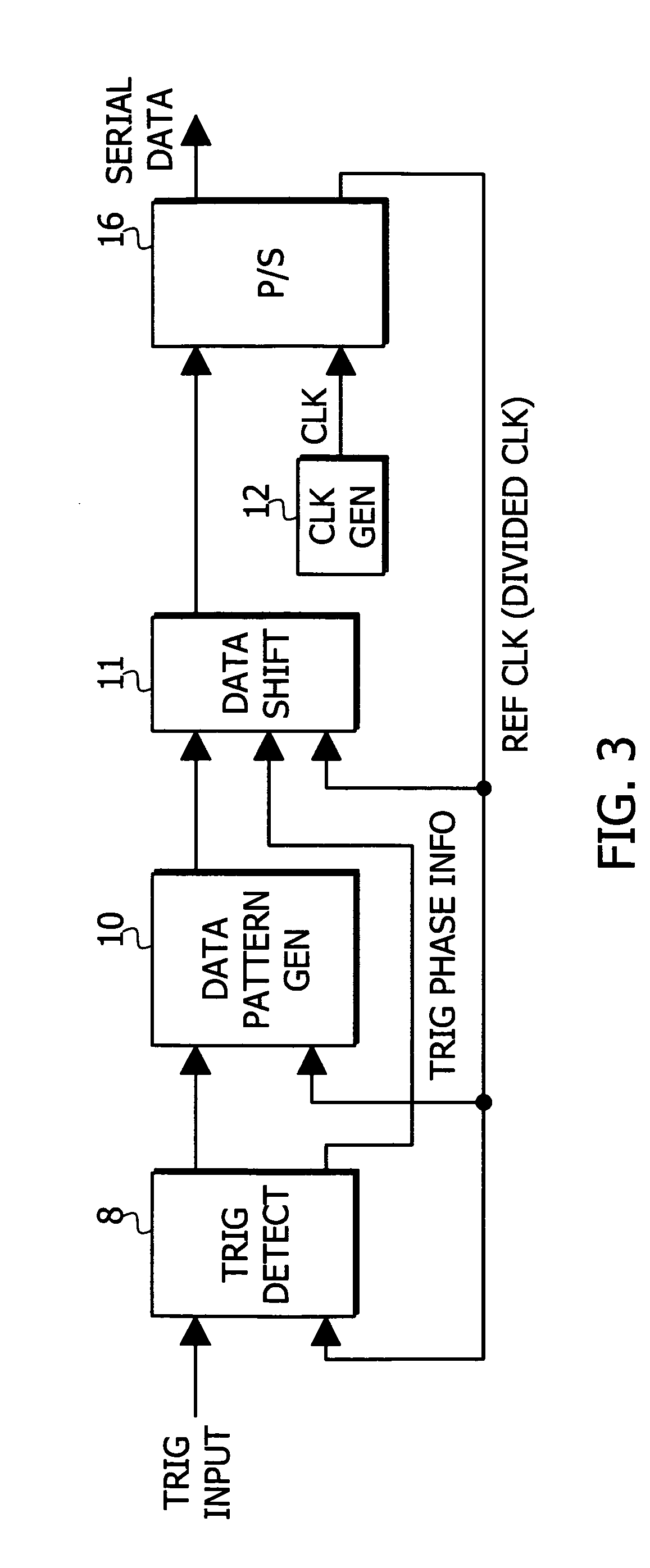

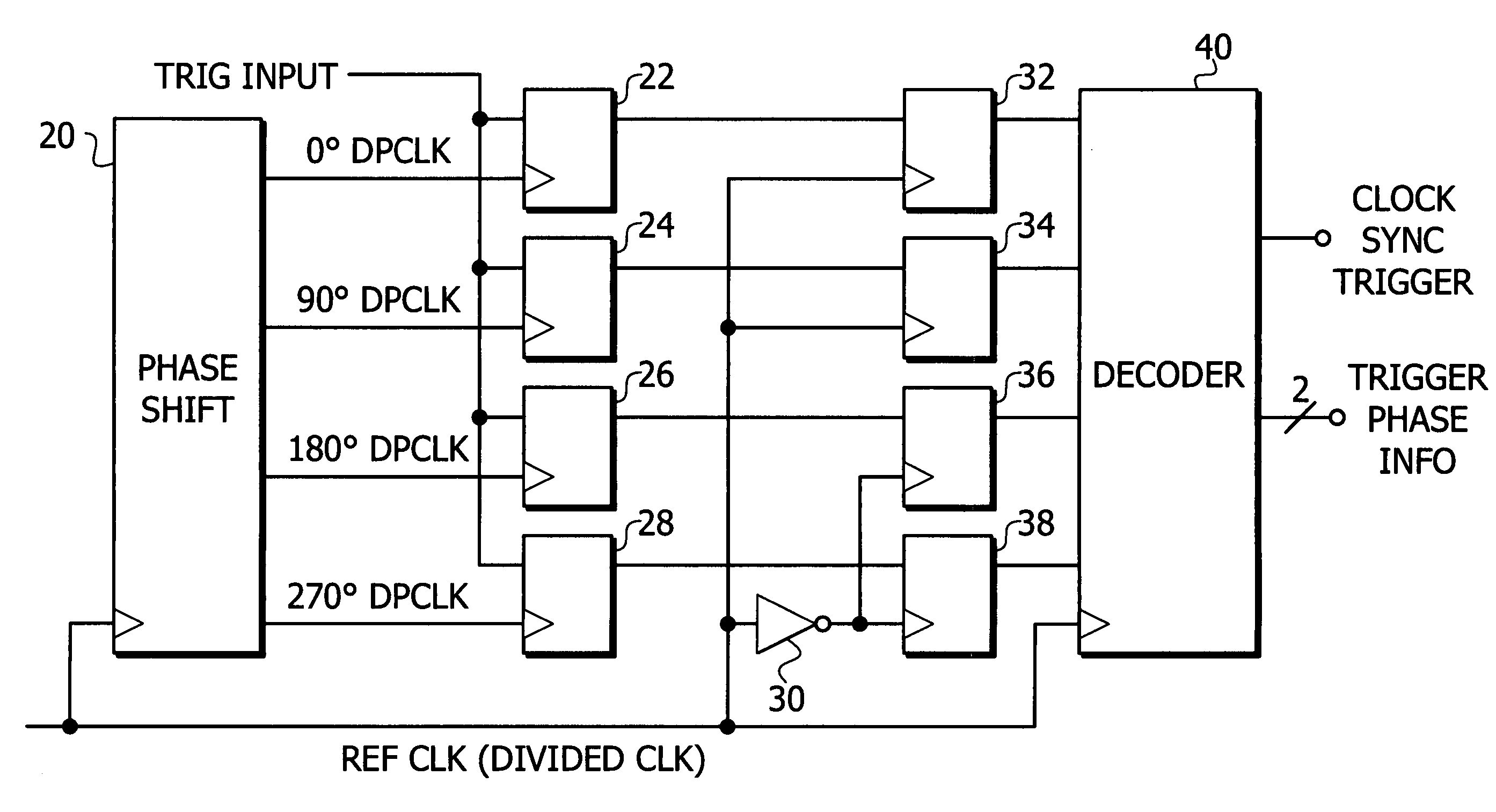

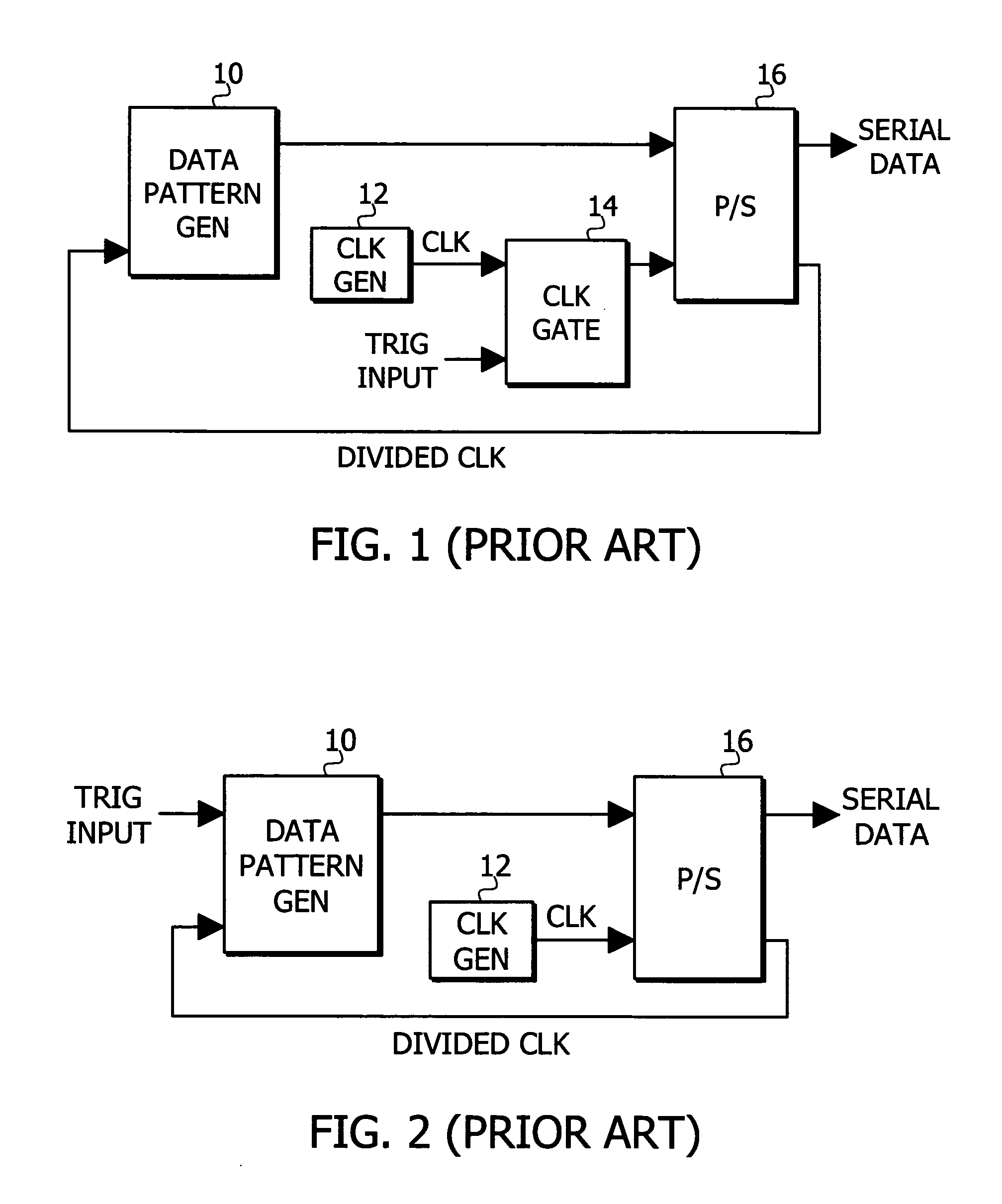

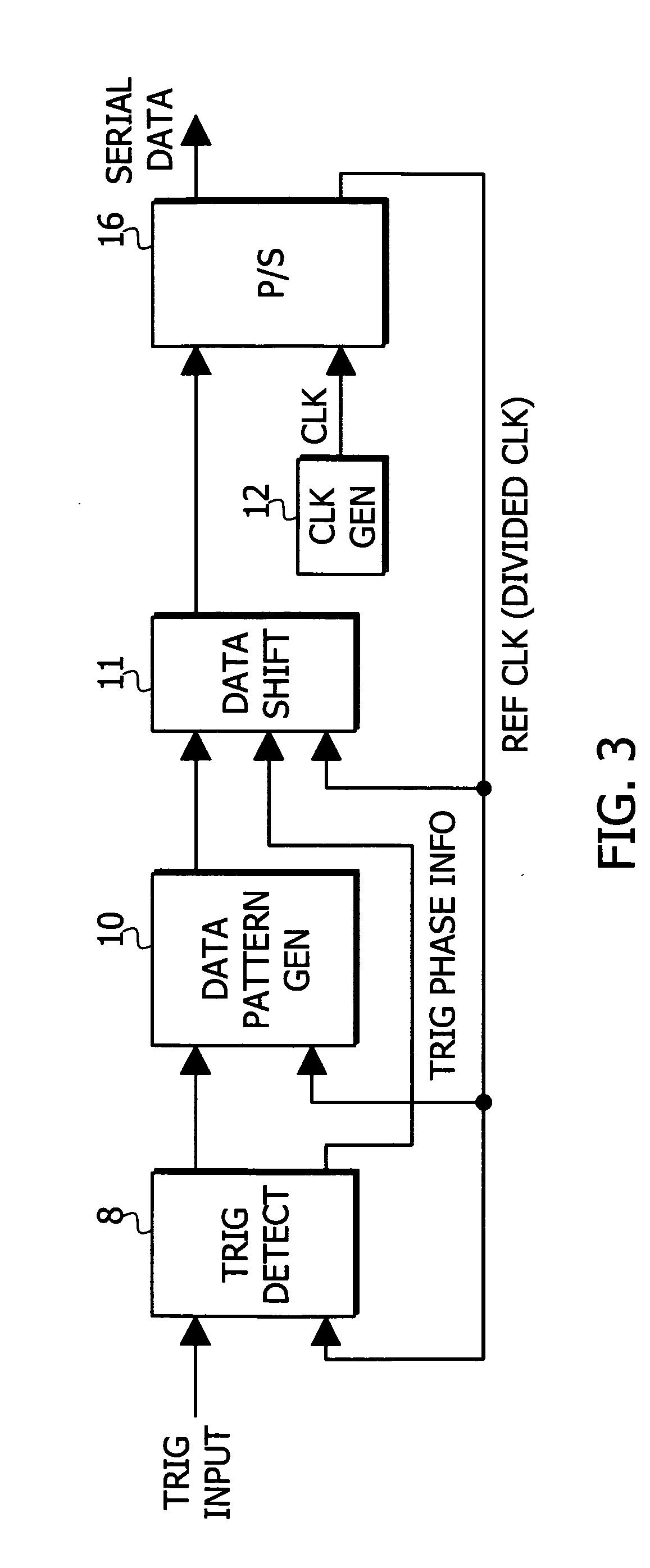

Triggered data generator

ActiveUS7295139B2Reduce uncertaintyShort delayParallel/series conversionDigital data processing detailsClock shiftComputer science

A triggered data generator reduces timing jitter at the start of serial data output from arrival of a trigger signal. A trigger detecting circuit 8 produces trigger phase information indicating the phase relationship between the trigger signal and a reference clock. A data pattern generating circuit 10 generates parallel data bits according to the reference clock in response to the trigger signal. A data shifting circuit 11 rearranges the parallel data bits in a predetermined order to produce shifted parallel data bits in which data bit order is shifted relative to the reference clock as a function of the trigger phase information. A parallel to serial converter 16 converts the shifted parallel data bits into serial data bits.

Owner:TEKTRONIX INC

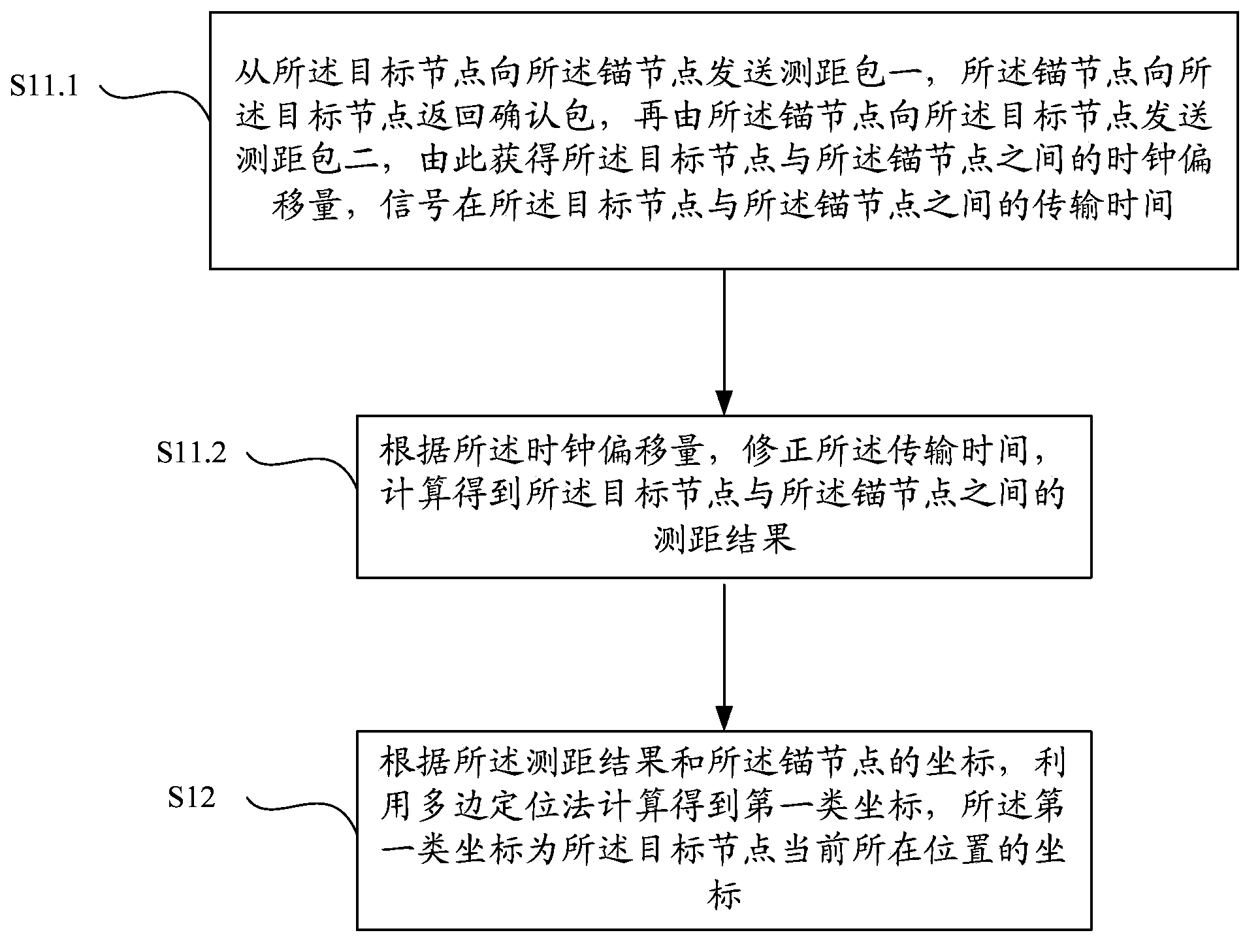

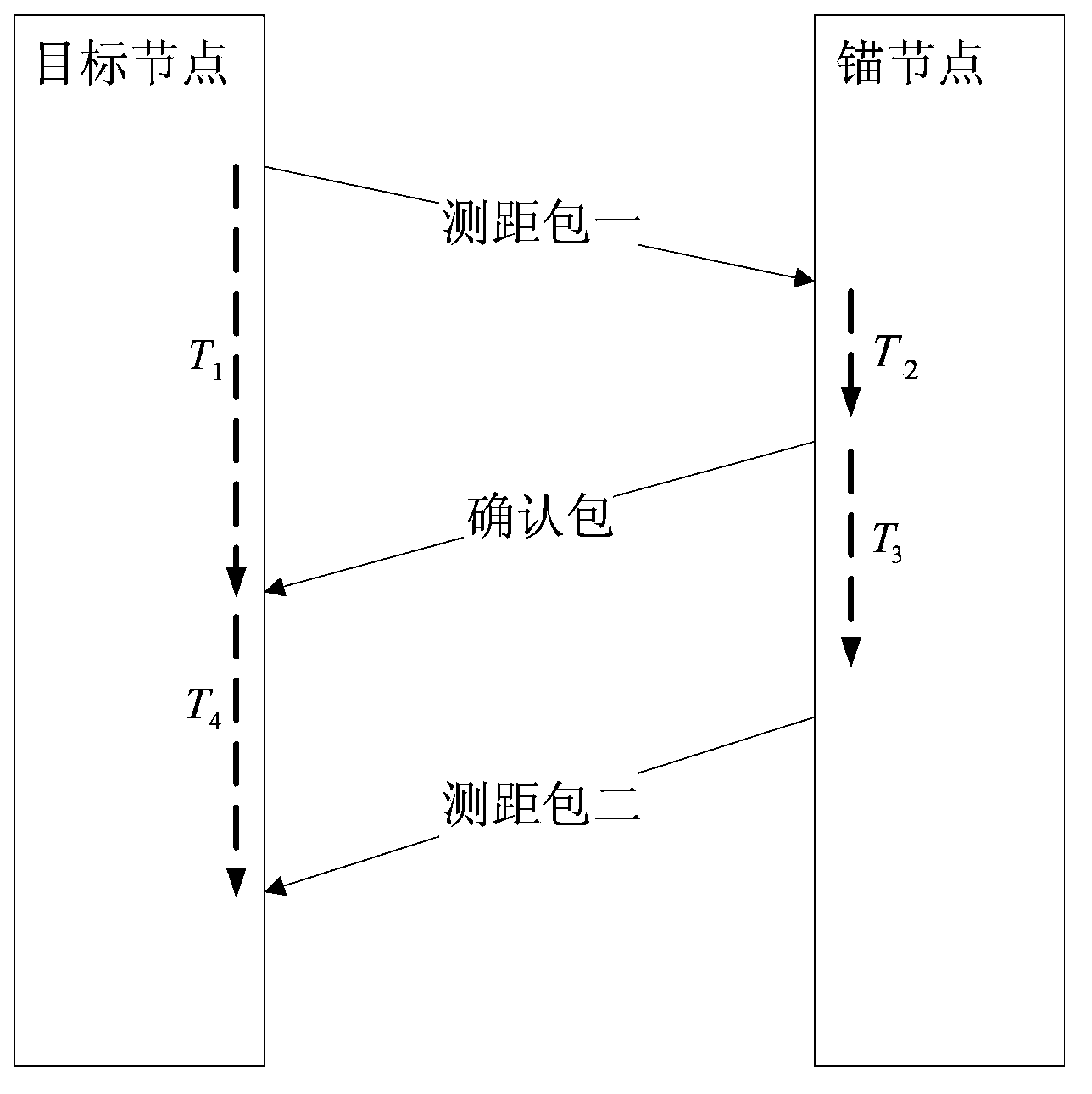

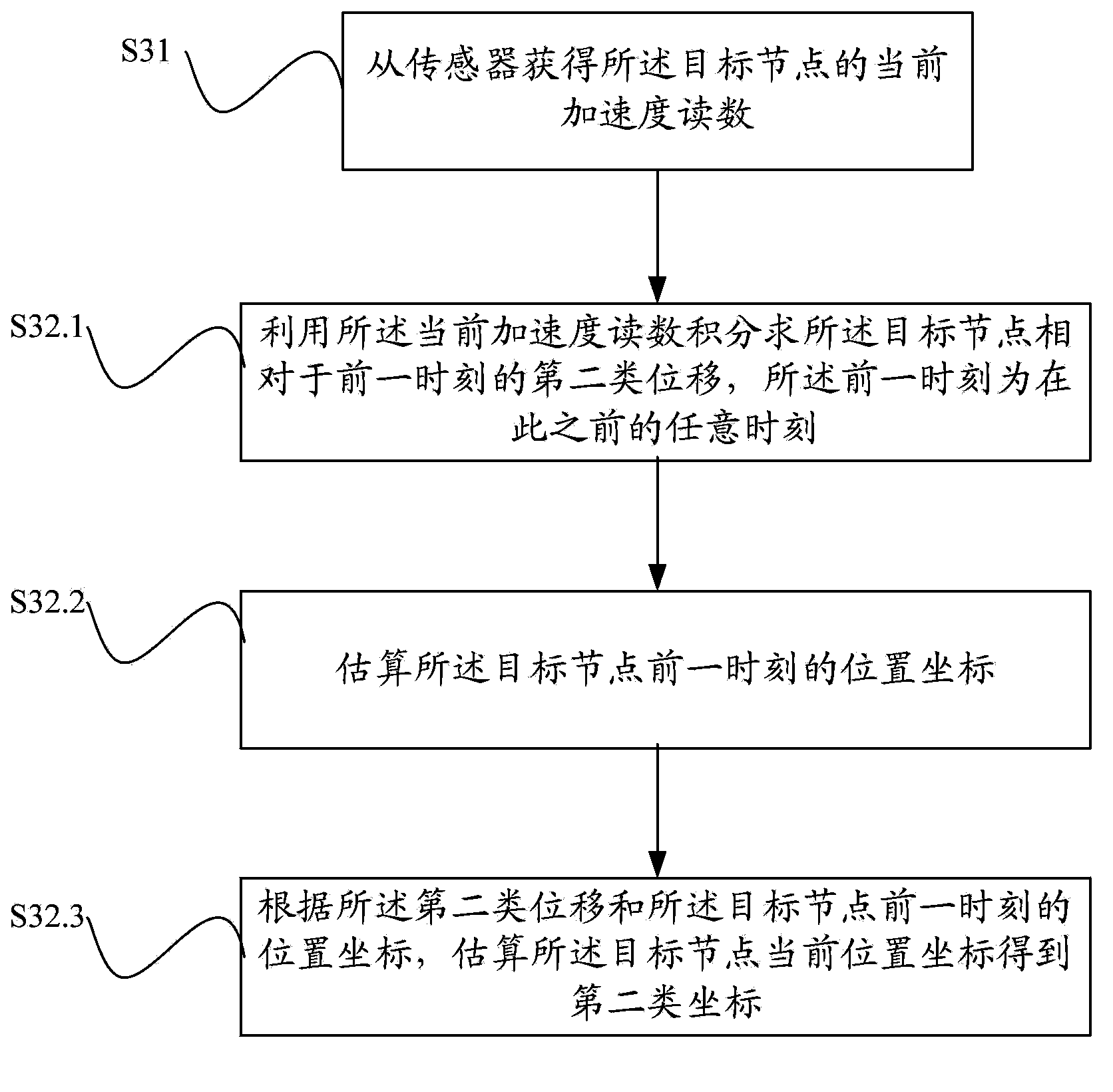

Method and device for realizing wireless sensing network node positioning

The invention discloses a method and a device for realizing wireless sensing network node positioning. According to the invention, high-precision ranging can be realized only through three-time one-way communication in the ranging step, so that communication process is saved and ranging expense is reduced compared with a current ranging agreement; moreover, high-precision time synchronization is not required, so that the node cost is reduced. The influence of clock shift between two nodes on the ranging precision is more considered, and the ranging precision is improved as the time shift problem during the ranging calculation process is solved. In addition, compared with a common method for obtaining an average result through repeated measurement, a more precise ranging result is obtained by allowing the obtained ranging results between a goal node and an anchor node to be subjected to weighting process by utilizing a minimum optimization principle. Moreover, sensor reading can be adopted to estimate the goal node coordinates so as to correct the goal node coordinates obtained by utilizing the ranging results, and as a result, the node positioning accuracy is further improved.

Owner:THE PLA INFORMATION ENG UNIV

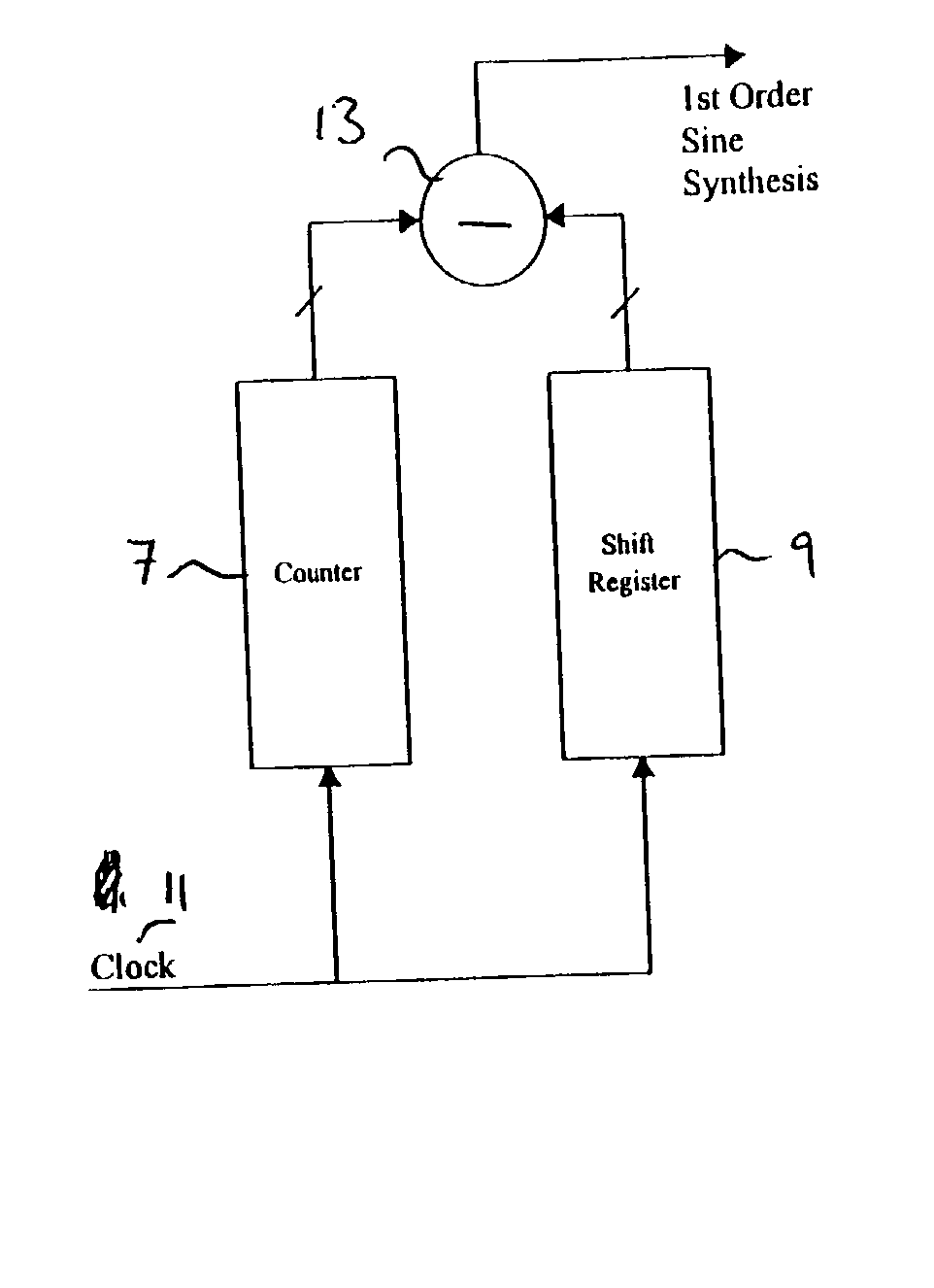

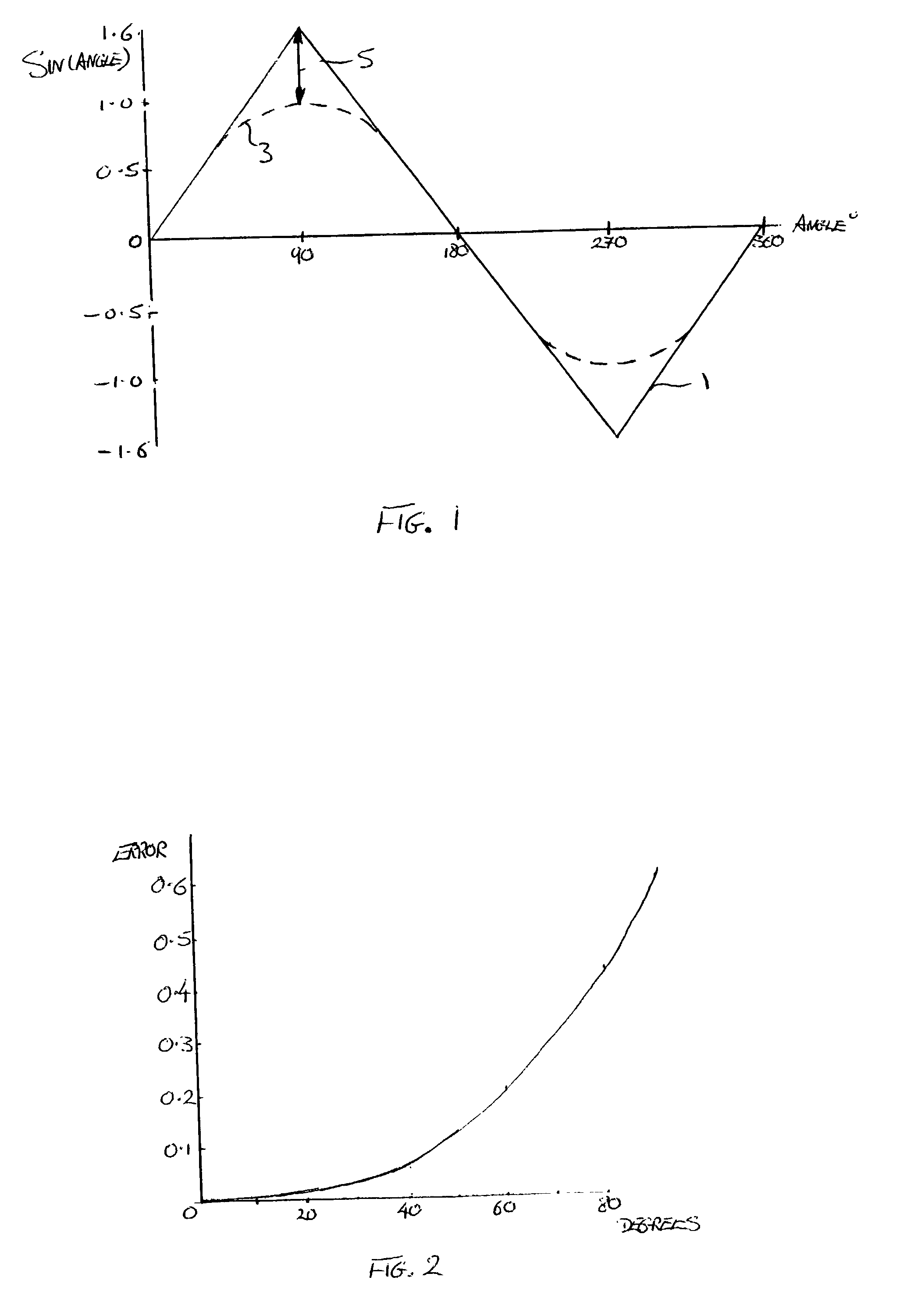

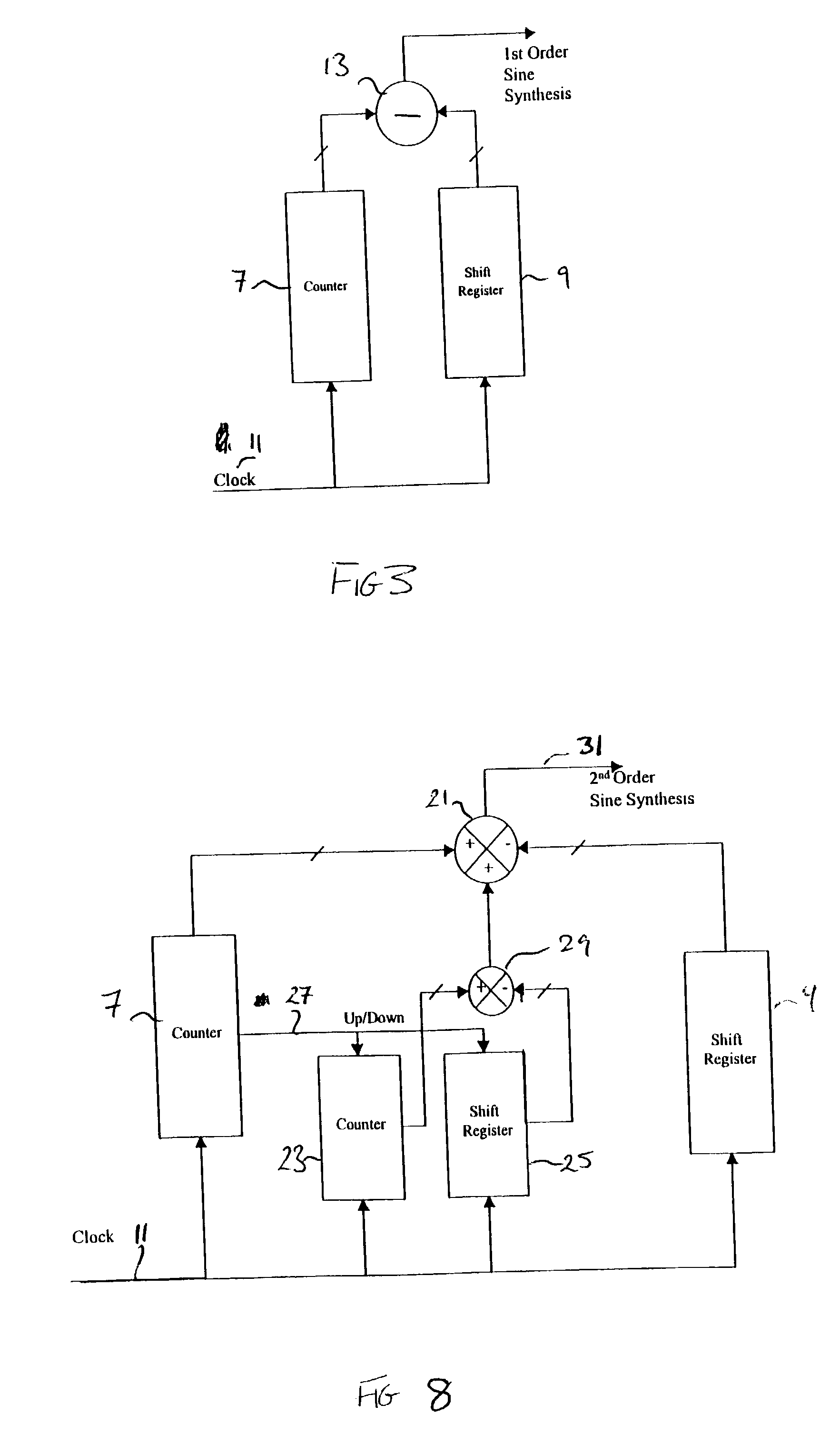

Sinusoid synthesis

An approximate sinusoid is synthesised by subtracting the error between a periodic signal, for example a triangle wave, and a true sinusoid. The periodic signal is produced using a counter circuit, while the error signal is generated using a shift register circuit, both circuits being clocked by a common clock signal. An improved approximation to the sine wave may be achieved by further generating an error signal approximating to the error between the first generated approximate sine wave and a true sine wave, approximate error signal being generated in the same fashion using a counter circuit and shift register clocked from a common clock signal, the second error signal being combined with approximate sine wave to produce an improved sine wave.

Owner:GOODRICH CONTROL SYST LTD

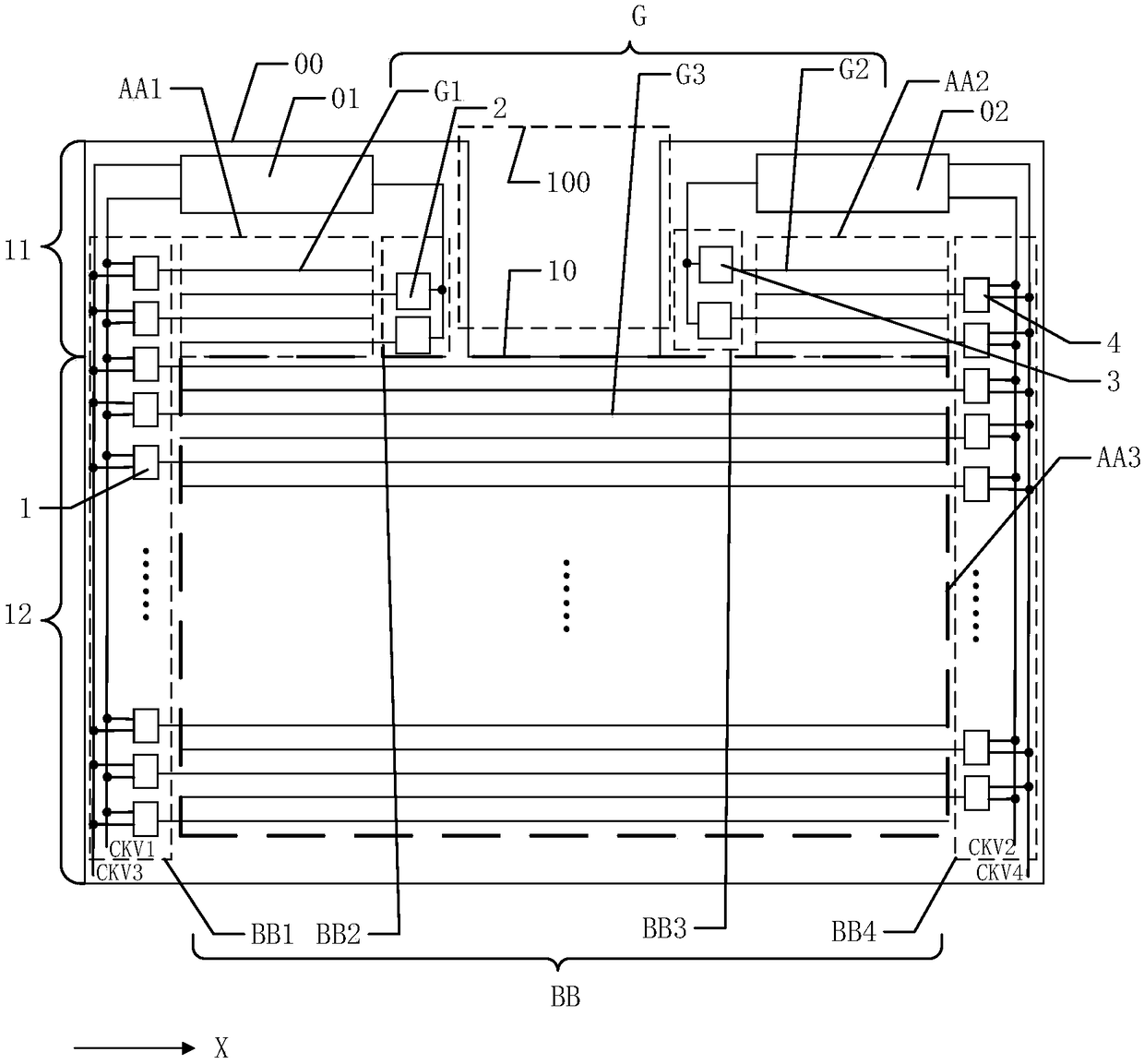

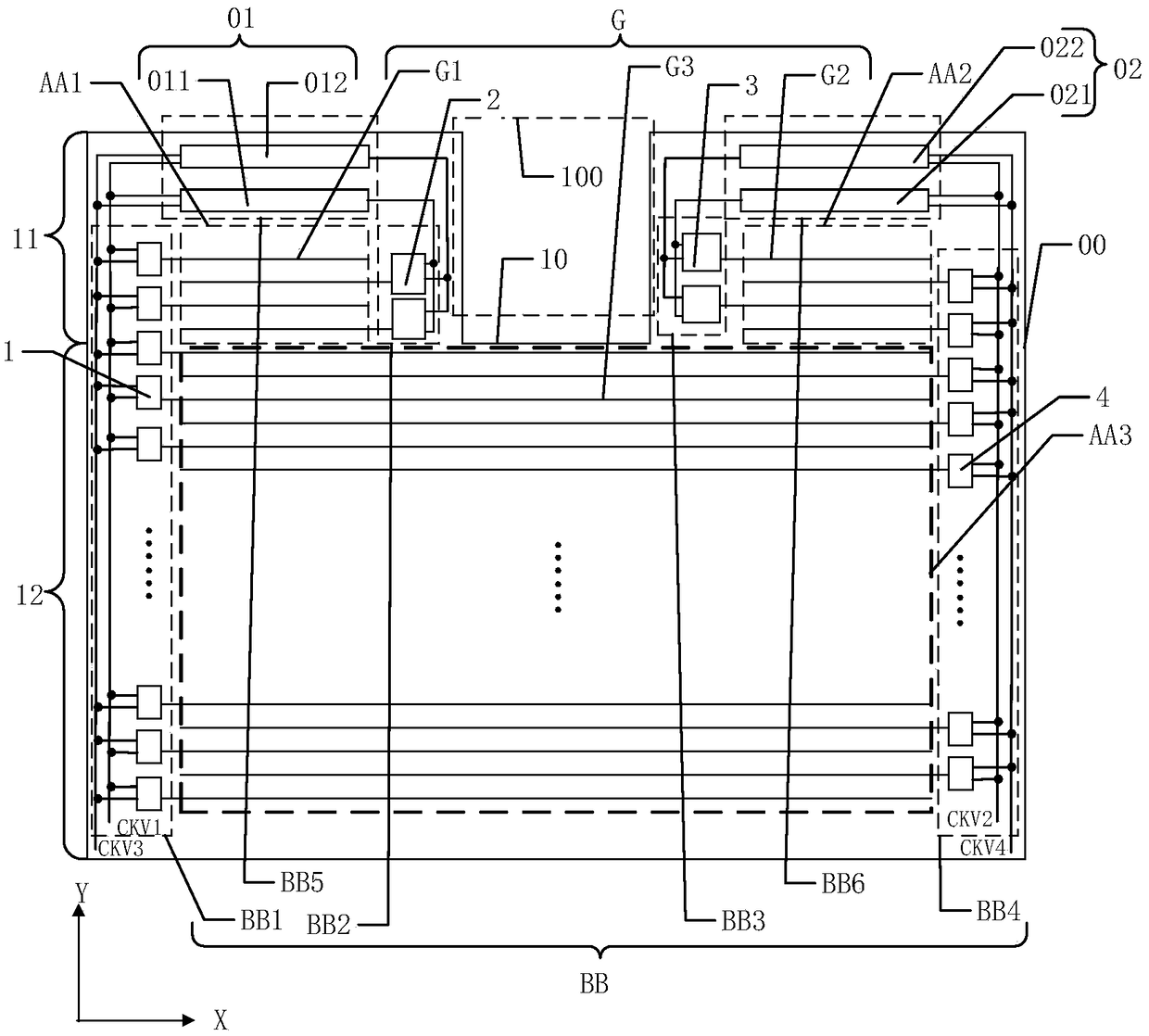

Display panel and display device

ActiveCN108665845AReduce border widthAchieving Narrow BezelsStatic indicating devicesShift registerDisplay device

The invention discloses a display panel and a display device. The display panel comprises an array substrate, multiple scanning lines which are located on the array substrate and extend in the first direction, multiple cascaded first shifting register units electrically connected with odd-numbered lines of scanning lines, multiple cascaded second shifting register units electrically connected witheven-numbered lines of scanning lines, a first clock signal line, a third clock signal line and a first clock shift circuit group; an input end of the first clock shift circuit group is connected with the first clock signal line and the third clock signal line, and an output end of the first clock shift circuit group is connected with signal input ends of the second shifting register units. The display device comprises the display panel. Accordingly, the signal synchronization and stabilization effects are achieved, the display quality is improved, and the problems that due to signal delay, the image display quality is poor is avoided; the proportion of the width of a display panel non-display area signal line can be reduced, and then display panel narrow bezel is achieved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Triggered data generator

ActiveUS20060202875A1Reduce uncertaintyShort delayParallel/series conversionDigital data processing detailsComputer scienceClock shift

A triggered data generator reduces timing jitter at the start of serial data output from arrival of a trigger signal. A trigger detecting circuit 8 produces trigger phase information indicating the phase relationship between the trigger signal and a reference clock. A data pattern generating circuit 10 generates parallel data bits according to the reference clock in response to the trigger signal. A data shifting circuit 11 rearranges the parallel data bits in a predetermined order to produce shifted parallel data bits in which data bit order is shifted relative to the reference clock as a function of the trigger phase information. A parallel to serial converter 16 converts the shifted parallel data bits into serial data bits.

Owner:TEKTRONIX INC

Transmission device and electronic apparatus with self-diagnostic function, and self-diagnostic method for use therein

A transmission device includes: parallel / serial conversion units; a clock signal transmission unit; a known-parallel data generation unit for inputting known-parallel data to the parallel / serial conversion units; a clock shift unit for sequentially shifting a clock signal, which is outputted from the clock signal transmission unit, by 1 UI of a data signal; sampling units for sampling data signals obtained by serializing the known-parallel data, in accordance with the clock signal shifted by 1 UI; and a diagnostic processing unit for making a diagnosis as to whether the transmission device is operating normally by comparing sampling results with the known-parallel data, and outputting a result of the diagnosis.

Owner:SILICON LIBRARY

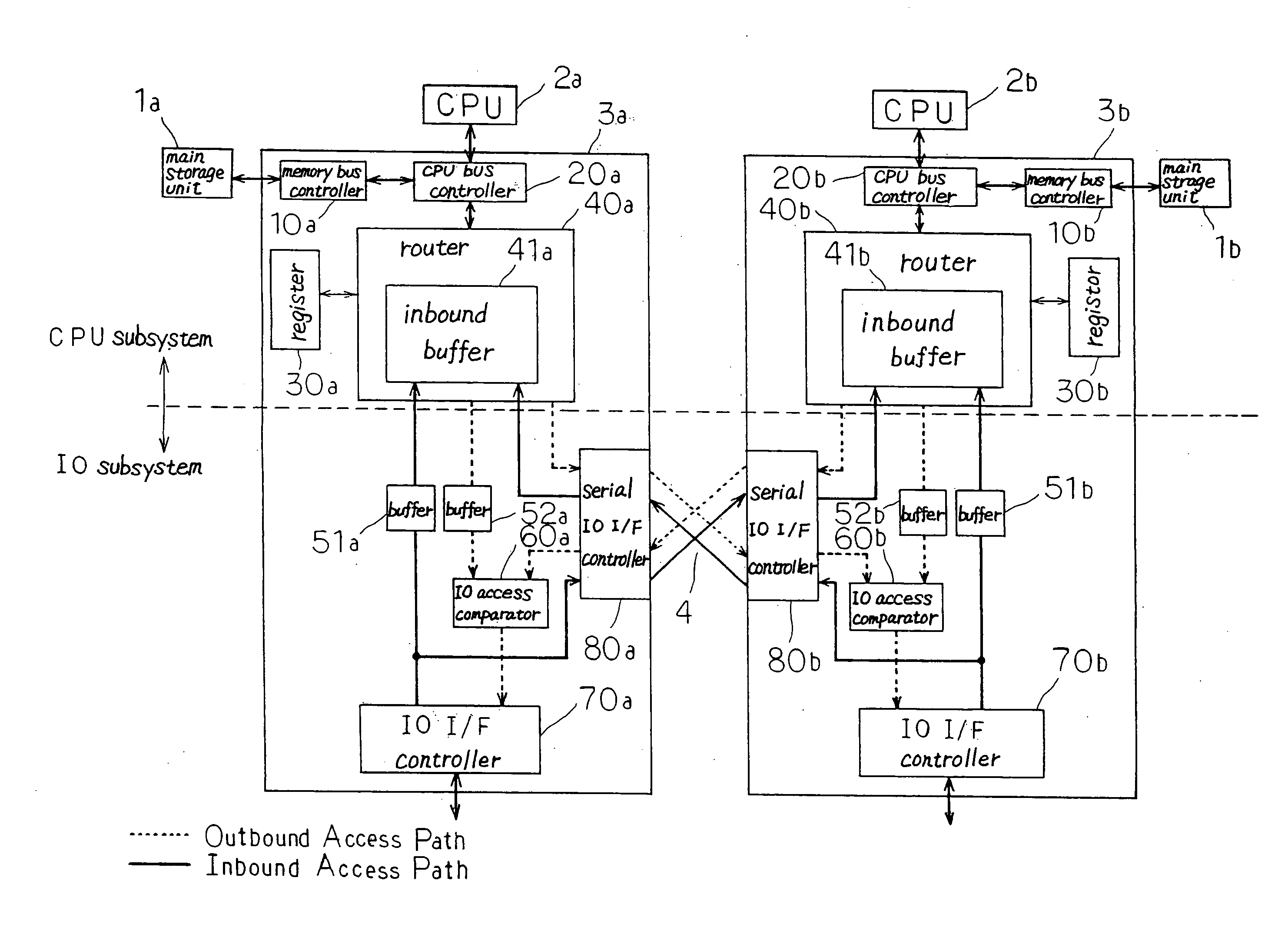

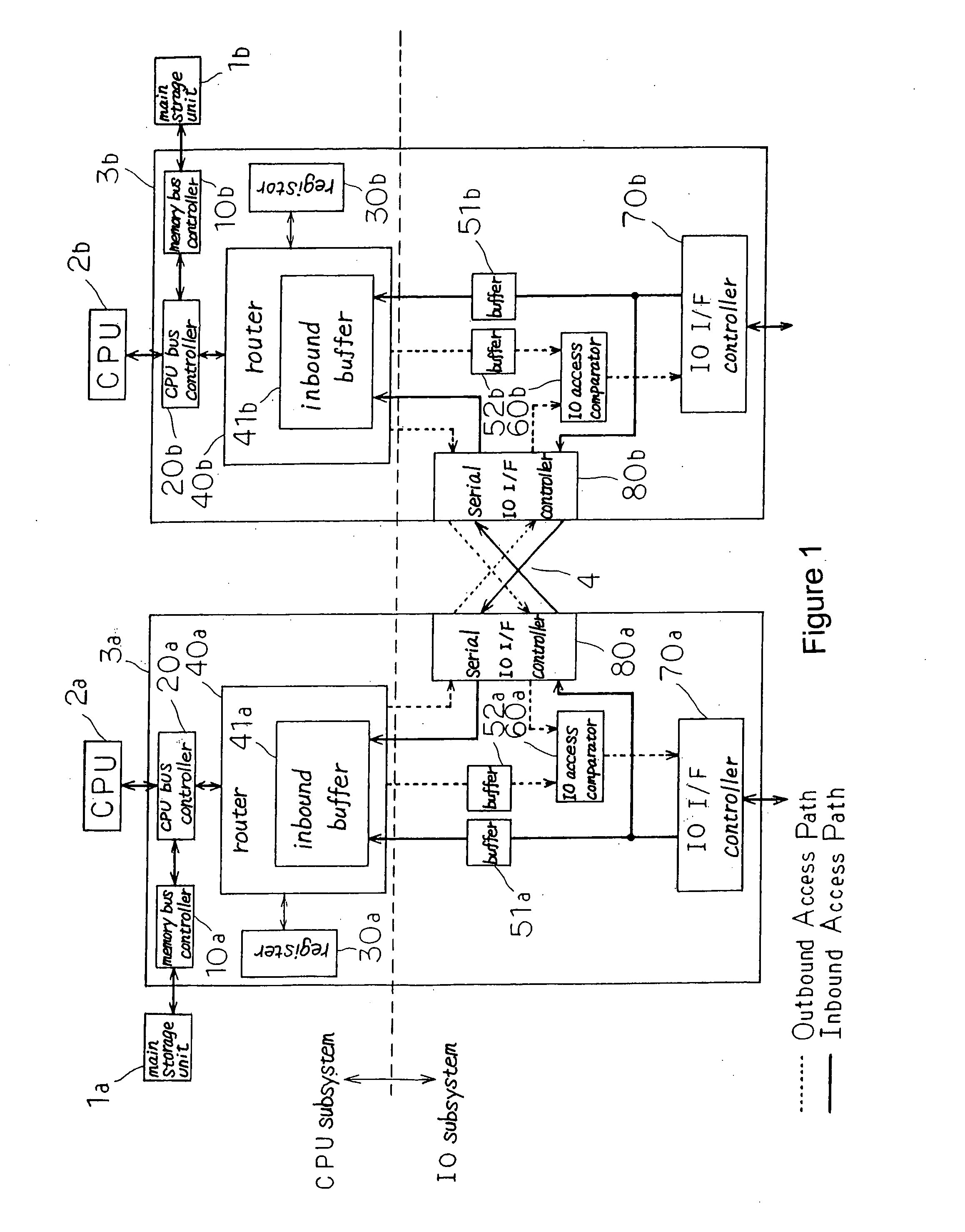

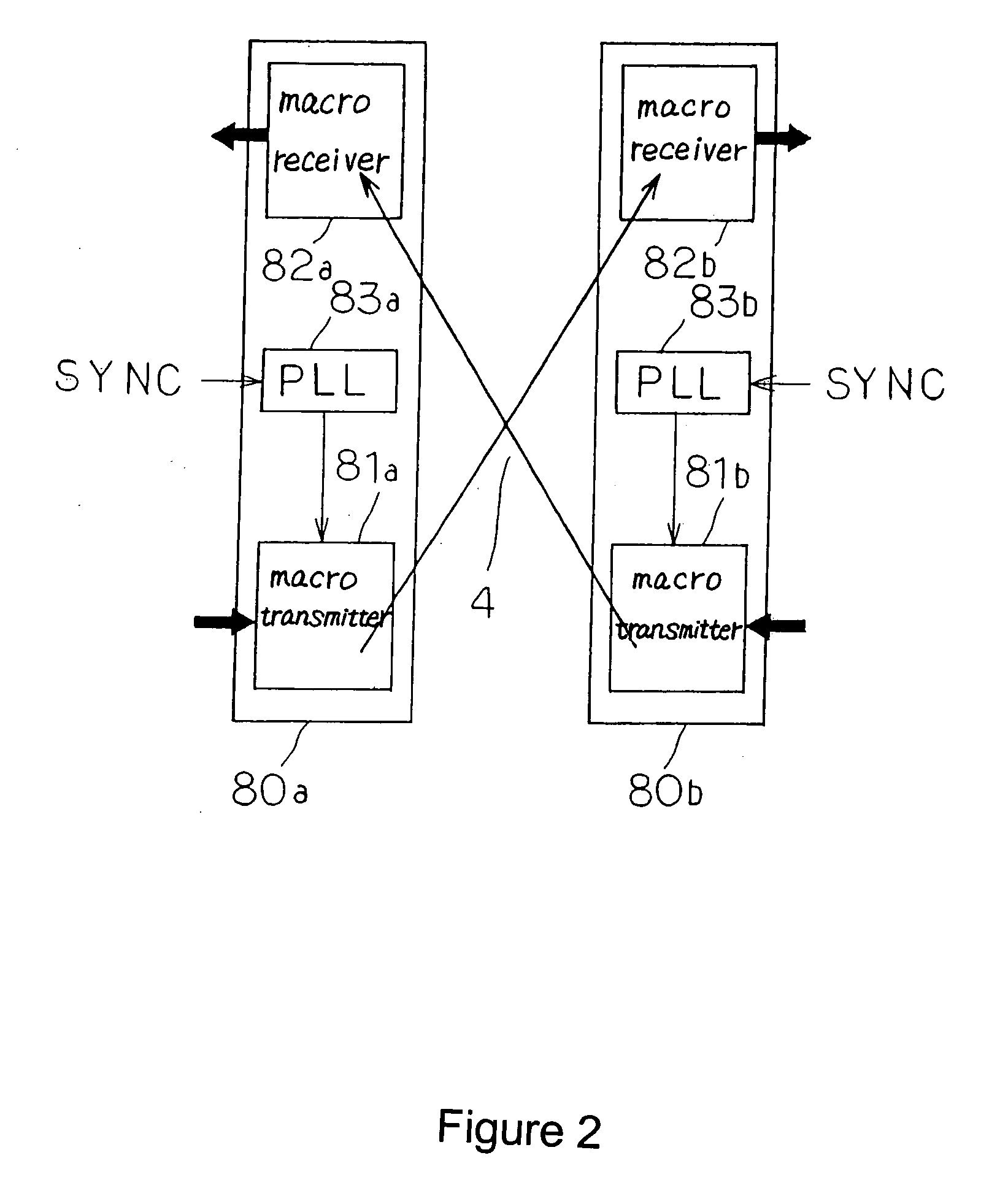

Fault-tolerant computer and method of controlling same

A fault-tolerant computer has duplex systems each comprising a CPU subsystem for controlling access to a CPU and a storage unit, and an IO subsystem for controlling data which are input to the IO subsystem from an external circuit and output from the IO subsystem to the external circuit. Data with a transmission time assigned thereto is transmitted from one of the IO subsystems to the other IO subsystem, and is received asynchronously by the other IO subsystem. The other IO subsystem records a reception time of the data, and calculates an ideal reception time using the transmission time assigned to the data. A clock shift in the other IO subsystem with respect to the one IO subsystem is calculated from the calculated ideal reception time and the recorded reception time. Thereafter, the counter in the other IO subsystem is changed based on the calculated clock shift, and data is received using the changed counter.

Owner:NEC CORP

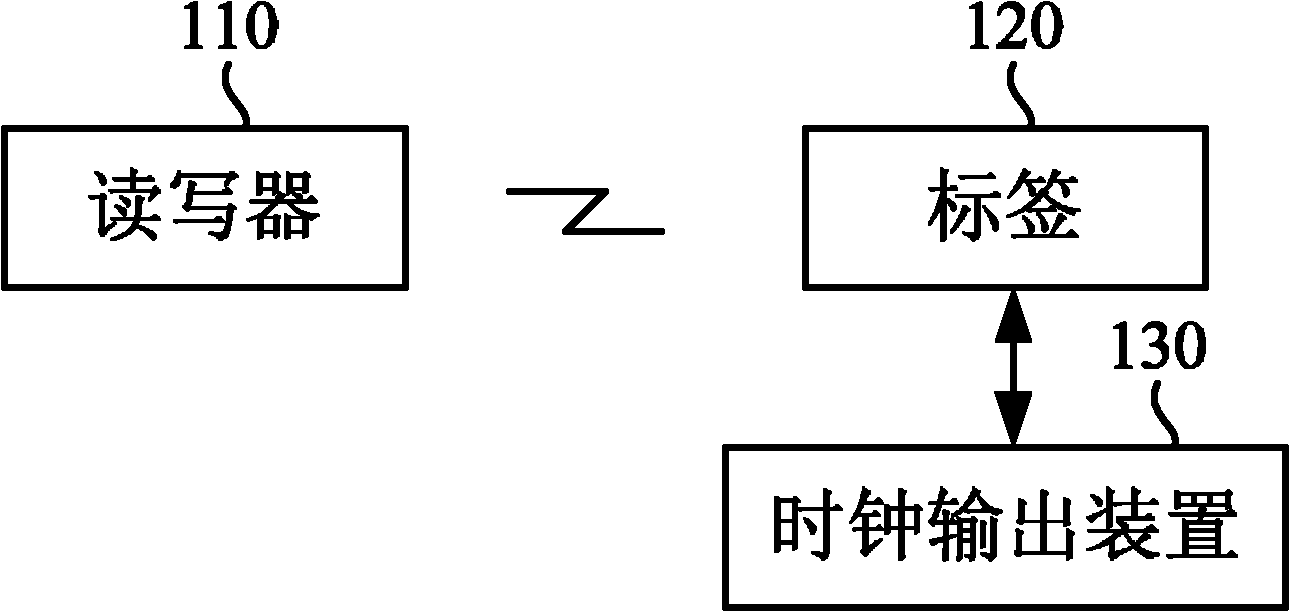

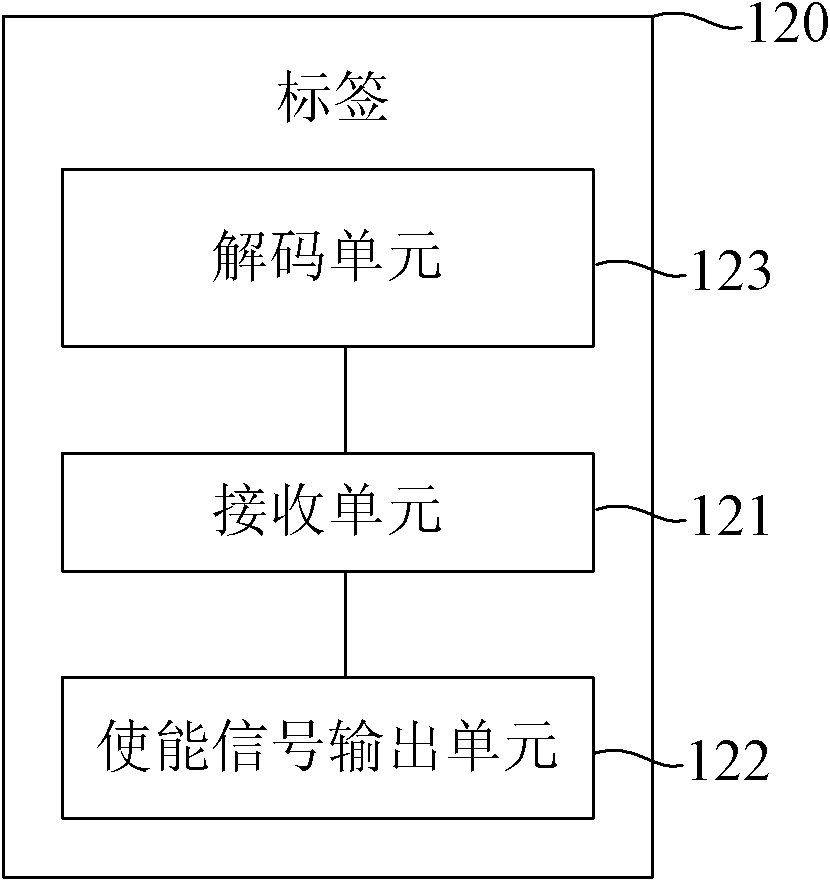

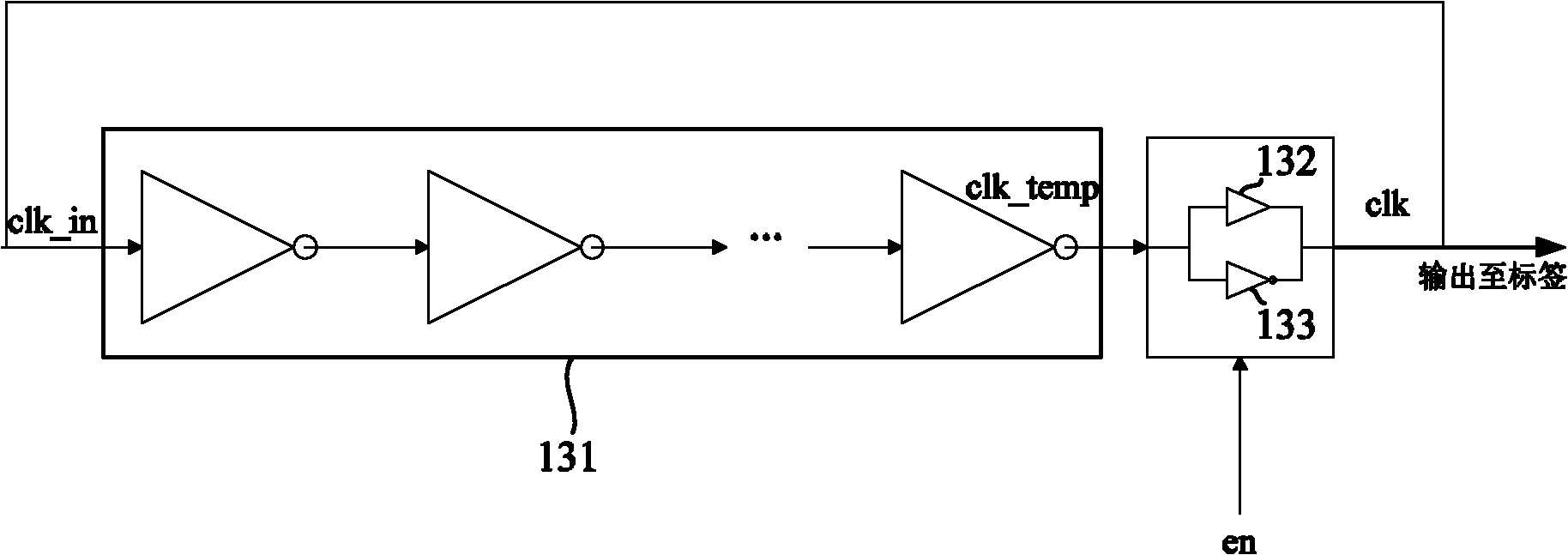

Synchronous injection decoding method and system for RFID system

ActiveCN102129588AAvoid decoding errorsCo-operative working arrangementsDecoding methodsOutput device

The embodiment of the invention provides a synchronous injection decoding method and a synchronous injection decoding system for an RFID (Radio Frequency Identification) system, wherein the method comprises the steps of: receiving mmc-encoded input data; taking the jumping of the input data as an enabling signal of a clock output data along a generated pulse signal in order to generate a clock signal clk with variable duty ratio and invariable cycle; and performing sampling decoding on the input data by using the clock signal generated by the clock output device. In the embodiment of the invention, stable synchronous clock signal is obtained based on phase locking method and decoding is implemented in accordance with the clock signal, thereby effectively avoiding erroneous mmc decoding derived from clock shift.

Owner:中国电子技术标准化研究所 +1

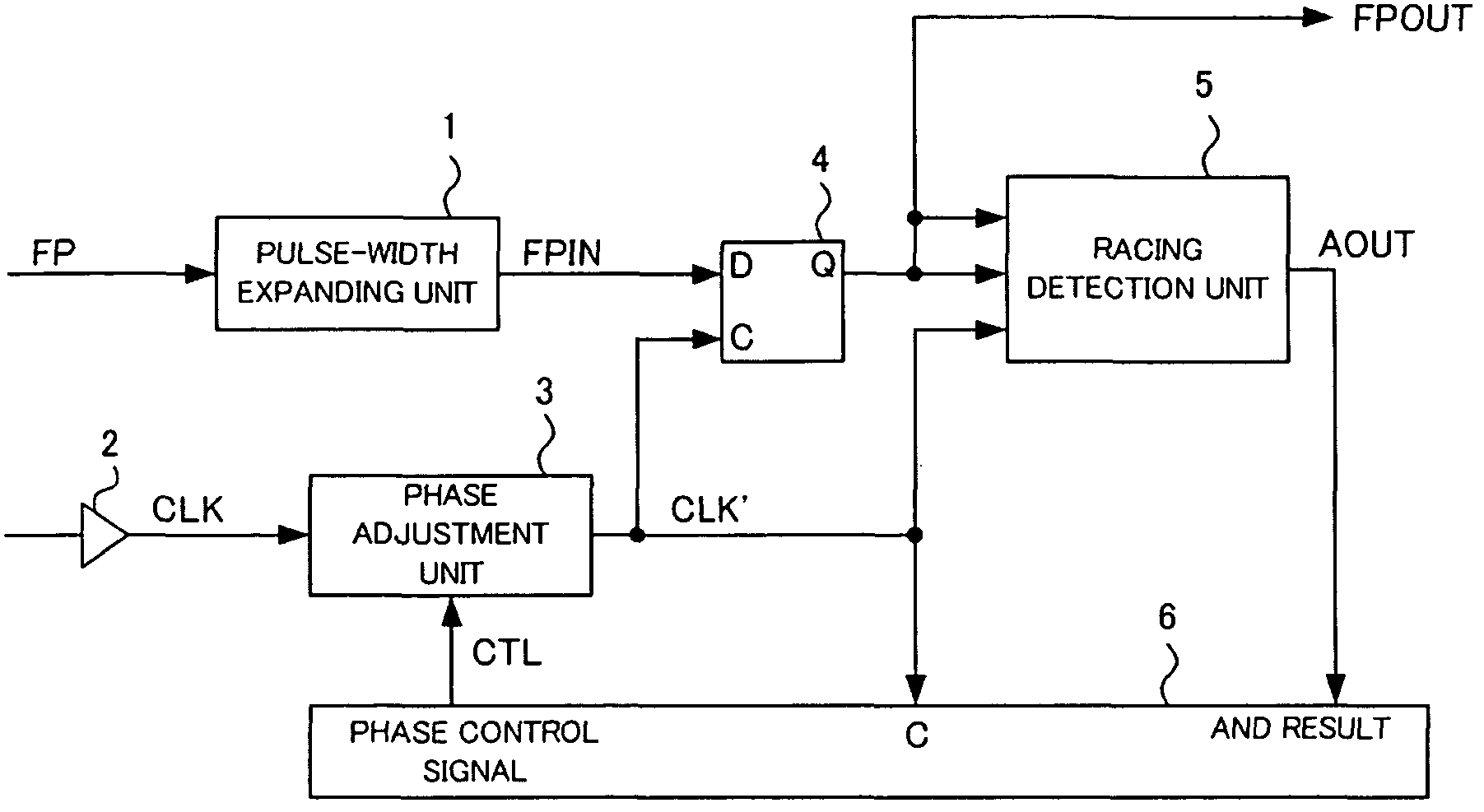

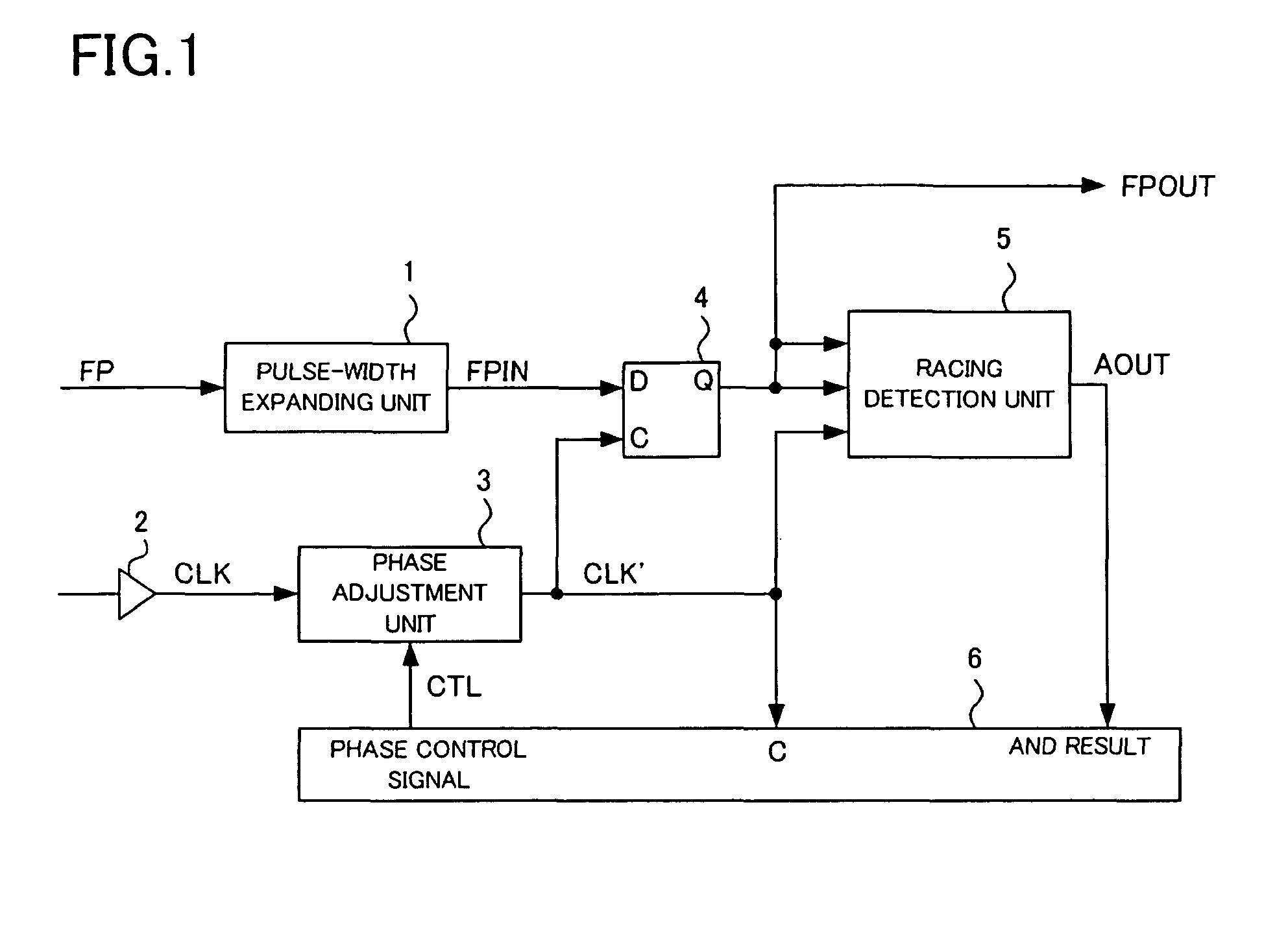

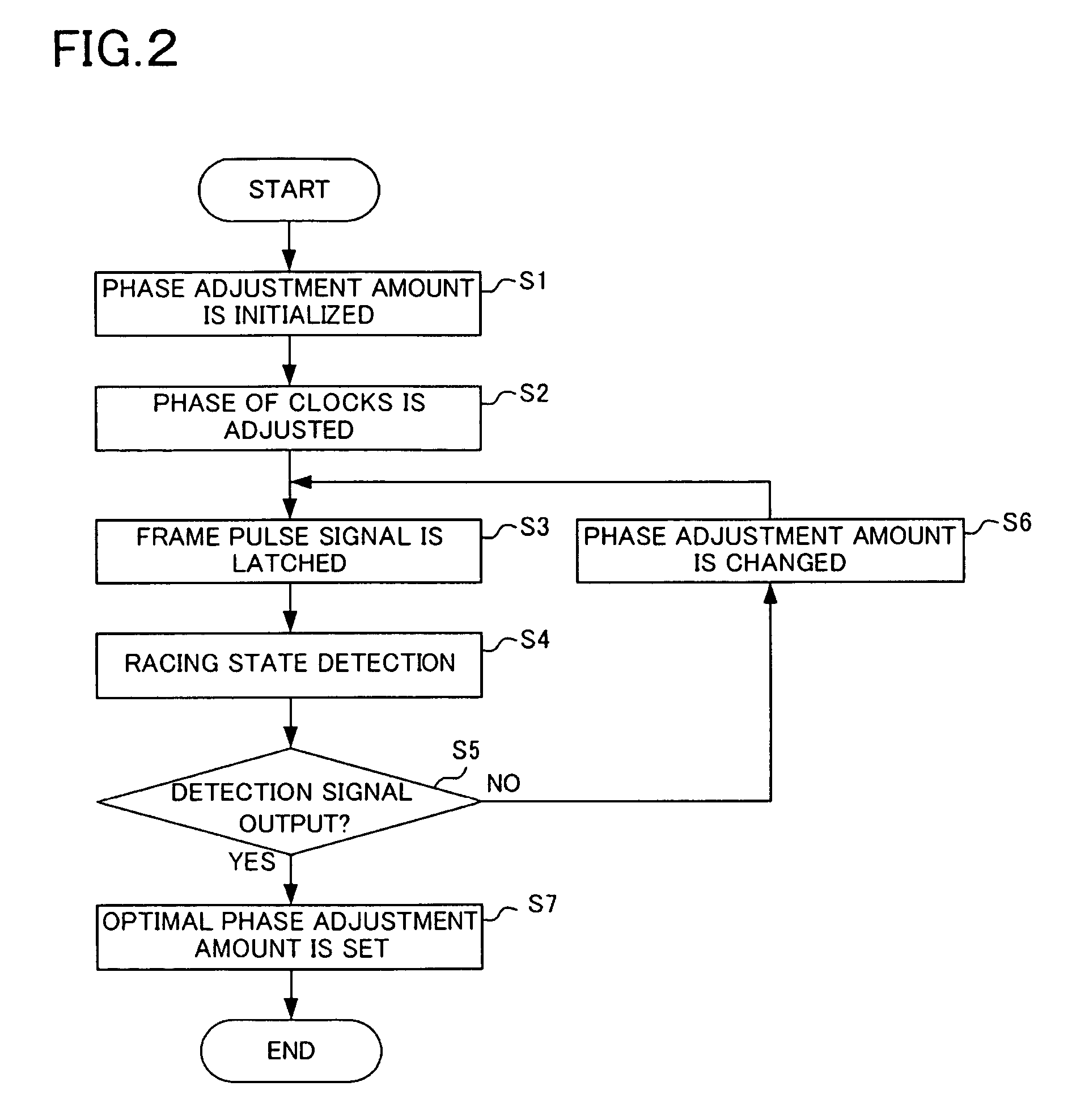

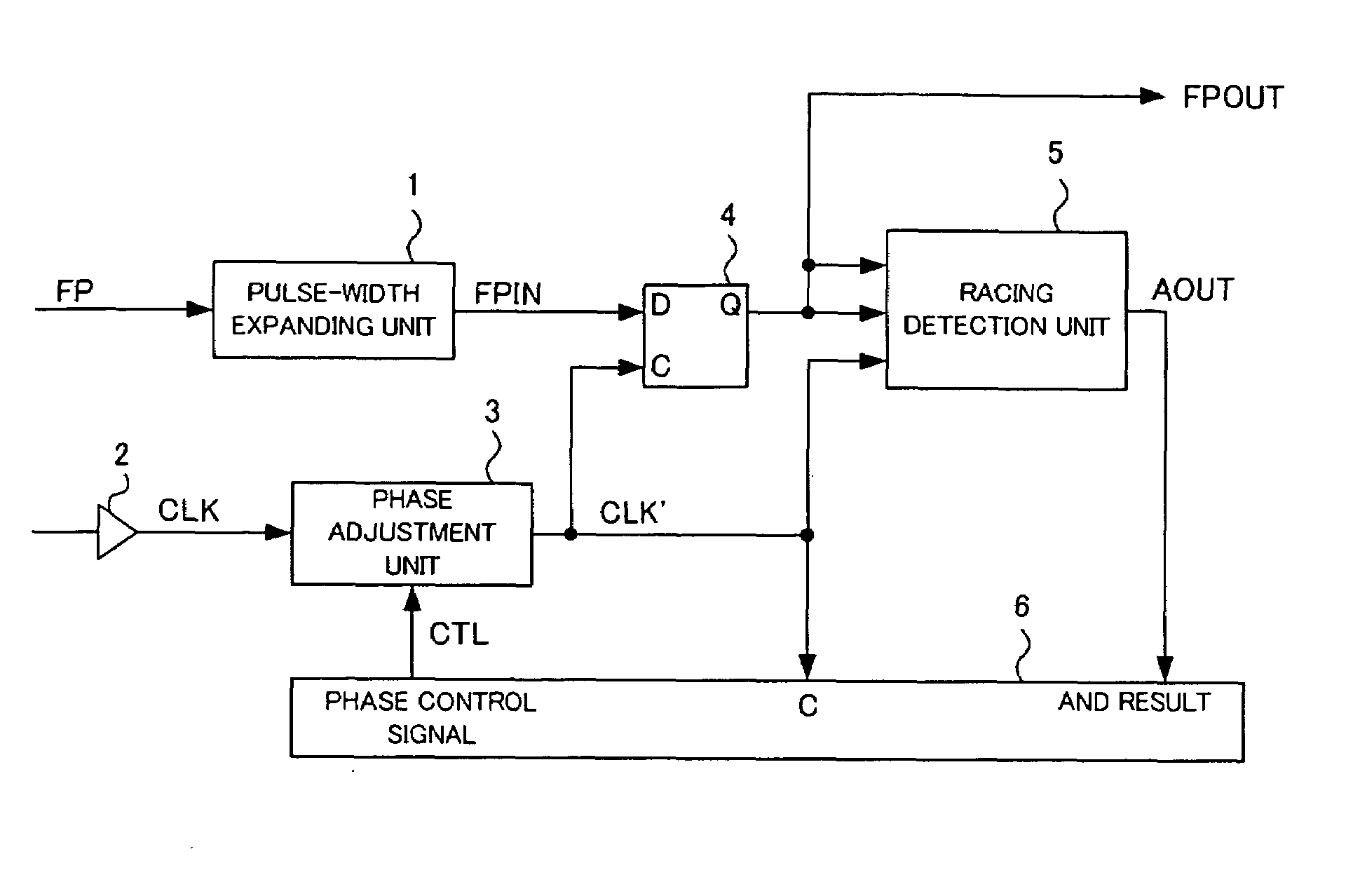

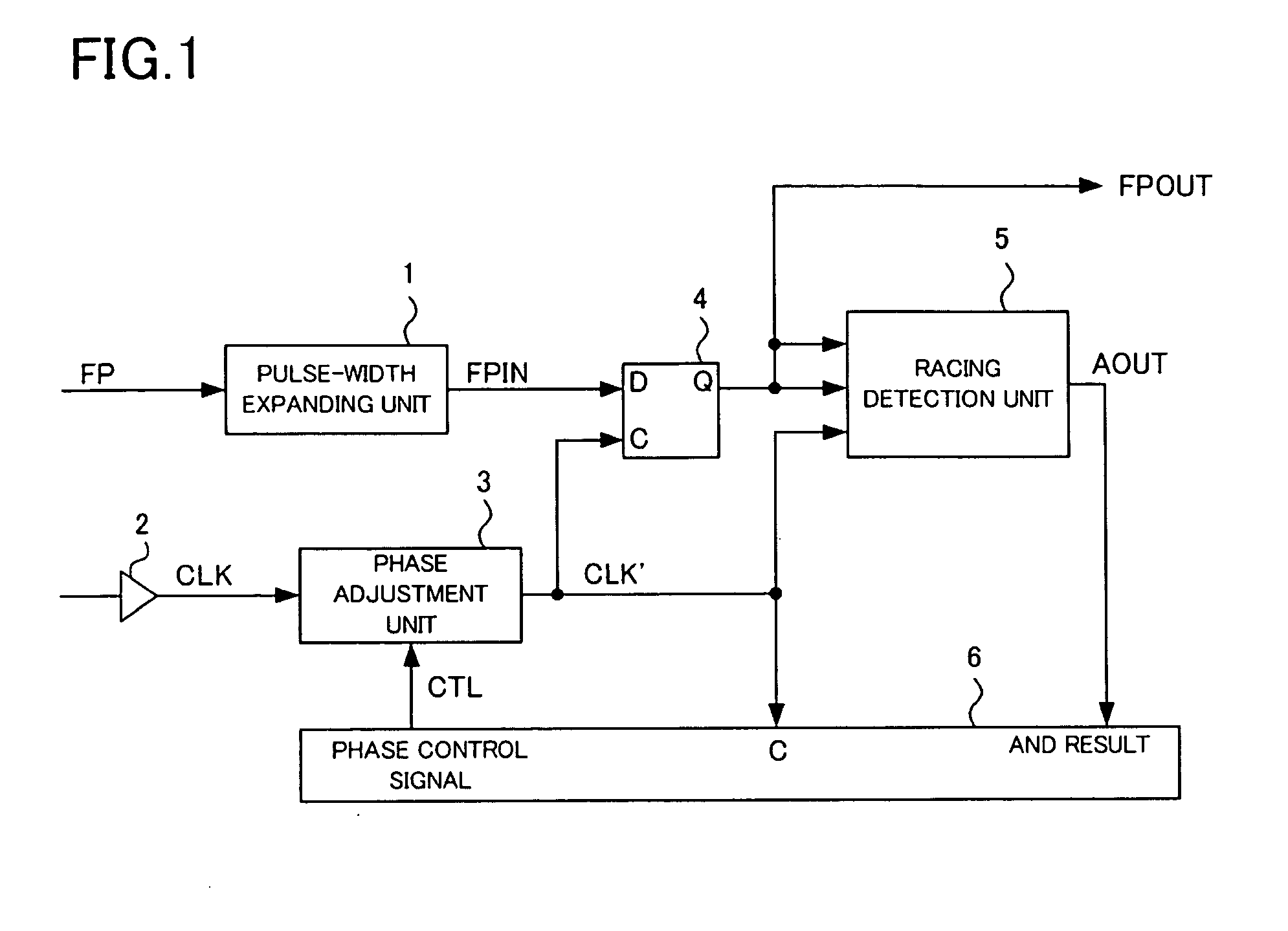

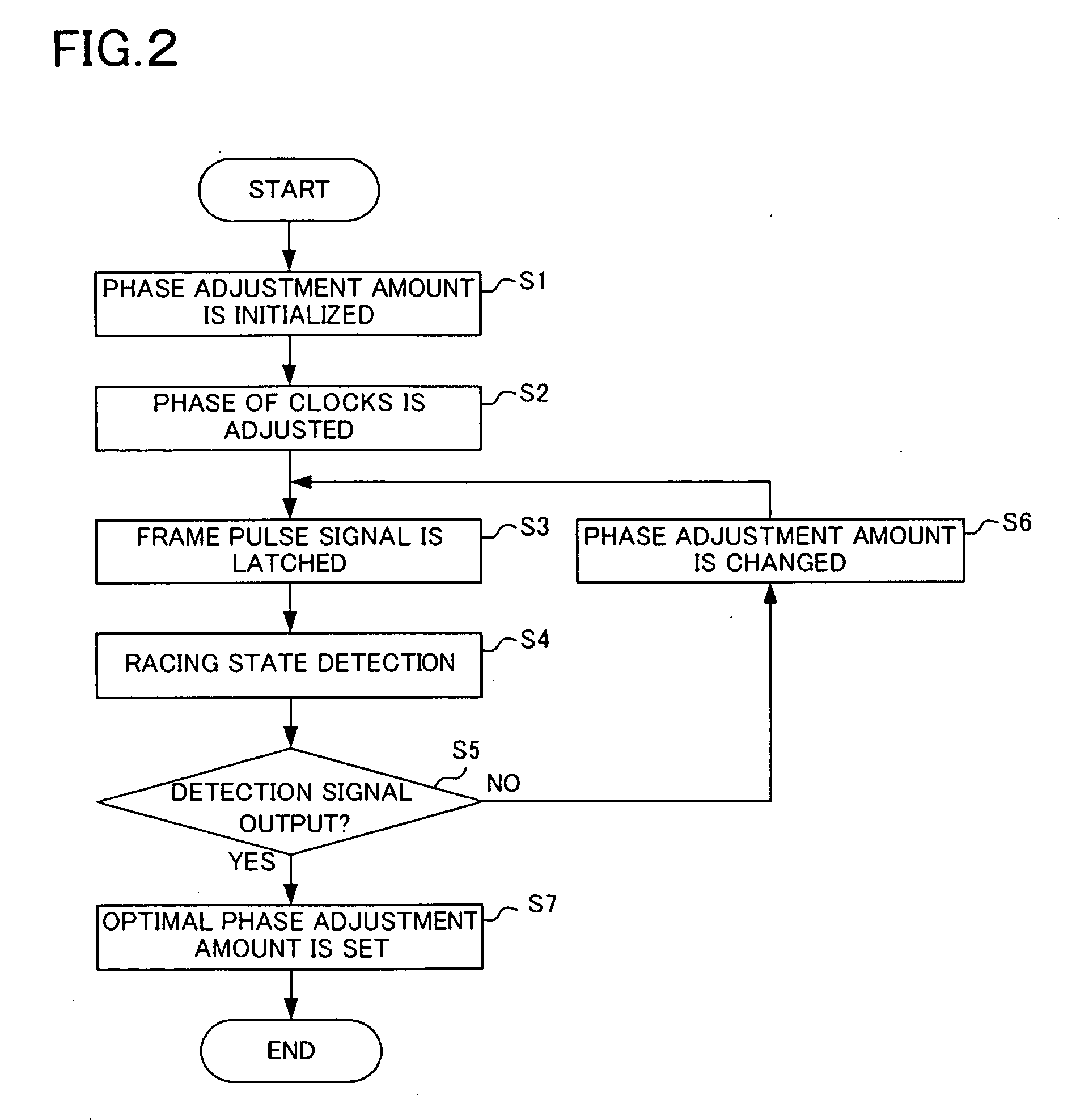

Frame pulse signal latch circuit and phase adjustment method

A frame pulse signal latch circuit has: a pulse-width expanding unit which outputs a frame pulse signal FPIN having a pulse width longer than a m-clock cycle; a phase adjustment unit which generates a phase-adjusted output clock CLK′; a flip-flop which latches the frame pulse signal FPIN; a racing detection unit which generates signals, which are shifted by one to m clocks with respect to a frame pulse signal FPOUT, and detects a racing state based on a result of an AND operation of the frame pulse signal FPOUT and the clock-shifted signals; and a control unit which sequentially selects and directs different phase adjustment amounts to the phase adjustment unit, determines an optimal phase adjustment amount based on a worst phase adjustment amount of the case in which the racing state is detected, and gives a direction about the optimal phase adjustment amount to the phase adjustment unit.

Owner:NEC CORP

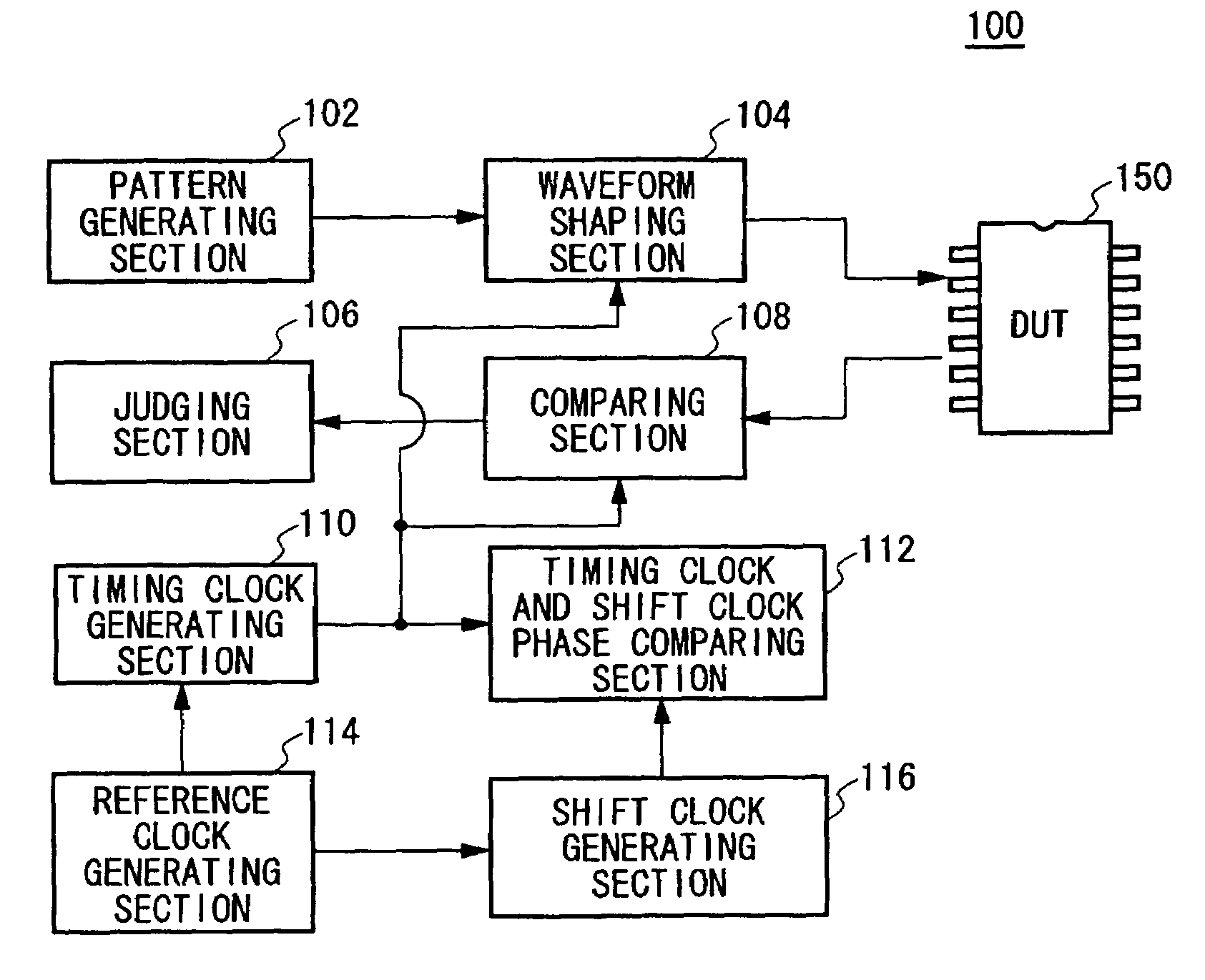

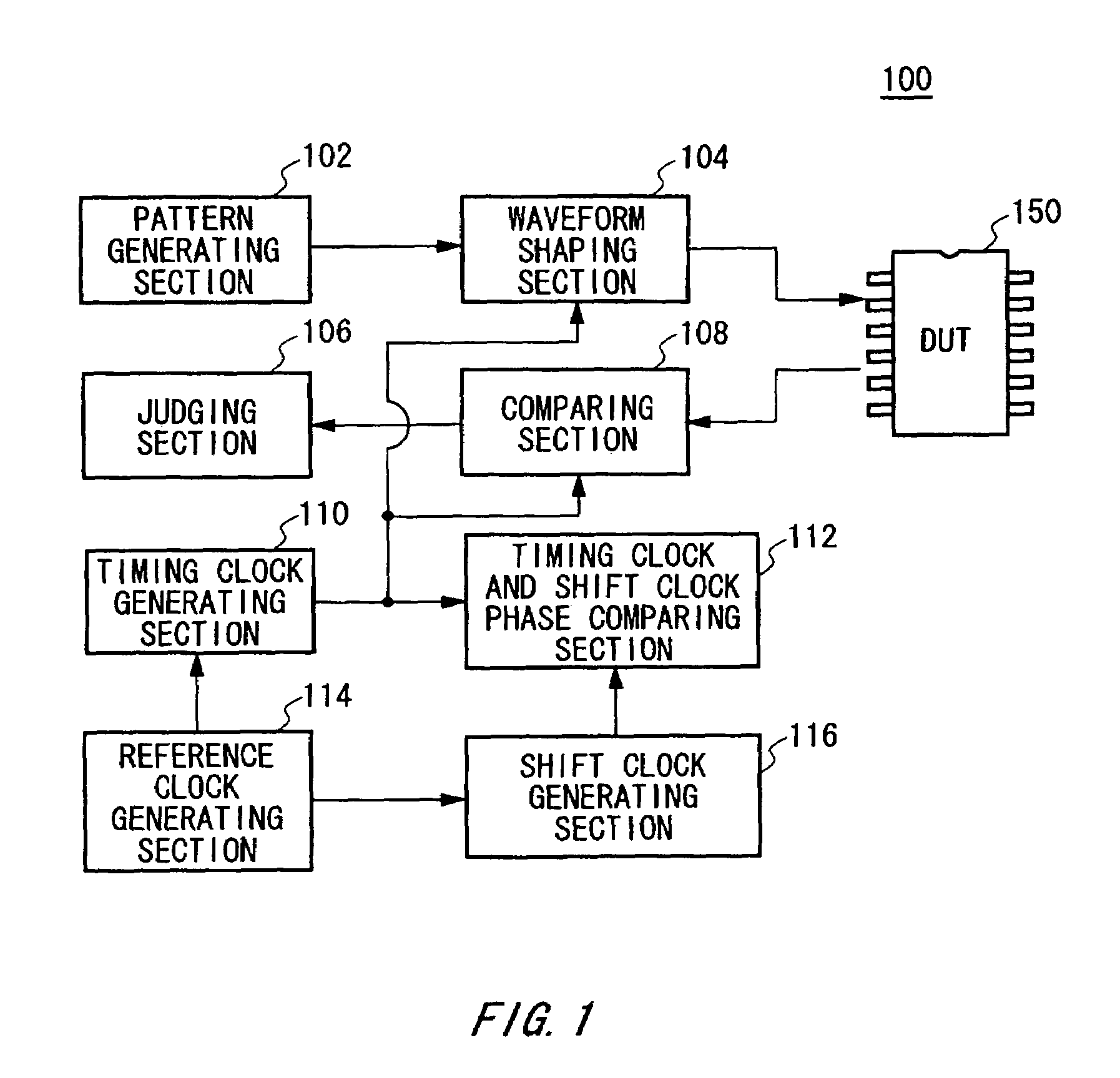

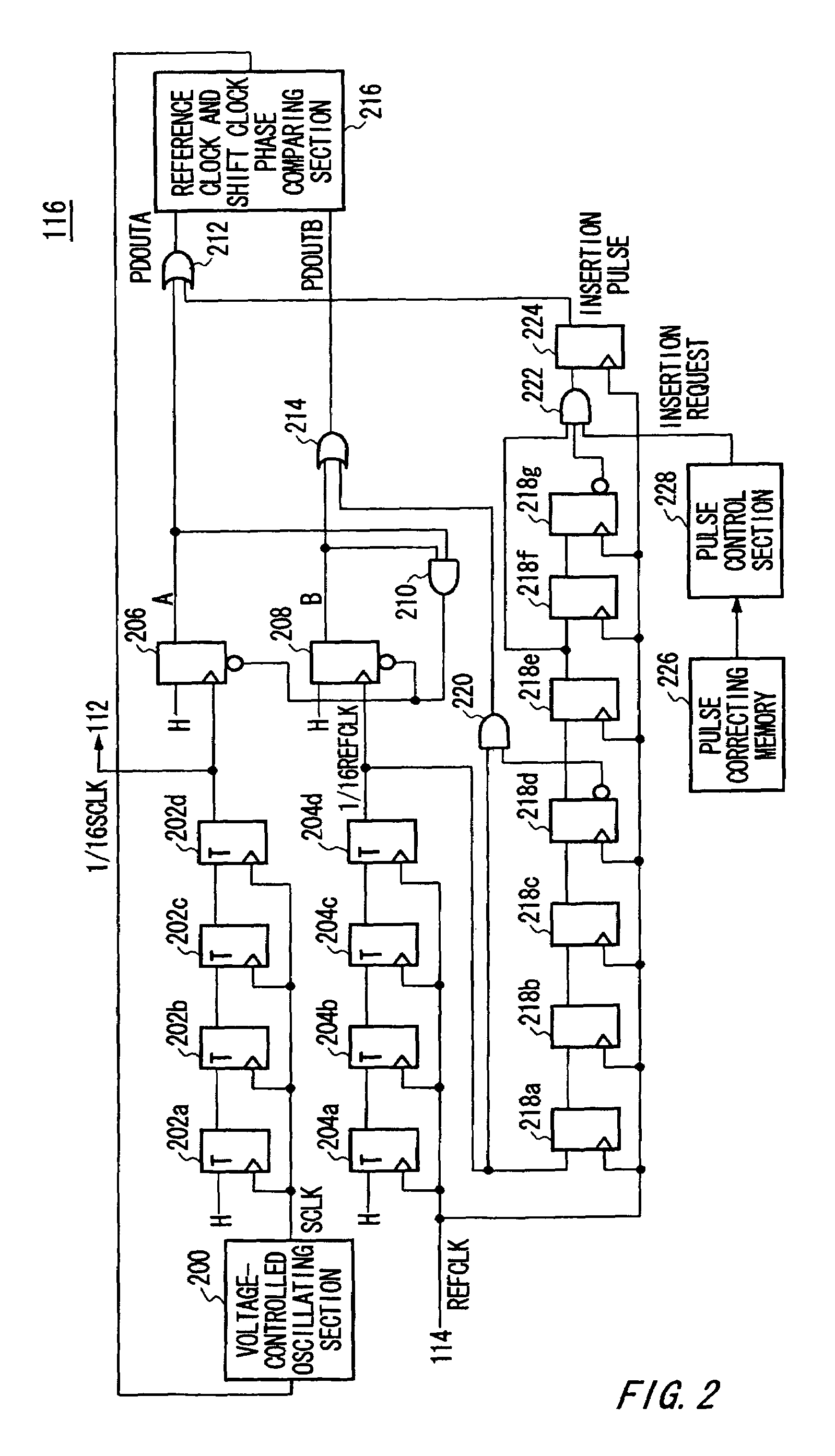

Method for calibrating timing clock

InactiveUS7190174B2High precisionShort timeDigital circuit testingFrequency analysisClock shiftElectrical and Electronics engineering

A method for calibrating a timing clock is provided. The method includes the steps of calibrating a shift amount of an edge of a shift clock by using a period of the timing clock as a reference by detecting an edge of the timing clock more than once while changing the shift amount of the edge of the shift clock; shifting and generating the edge of the shift clock by a predetermined shift amount by the calibrated shift clock generating section; and calibrating a required delay amount for delaying the timing clock by time corresponding to the predetermined shift amount by detecting the edge of the shift clock shifted by the predetermined amount while changing a delay amount of the timing clock.

Owner:ADVANTEST CORP

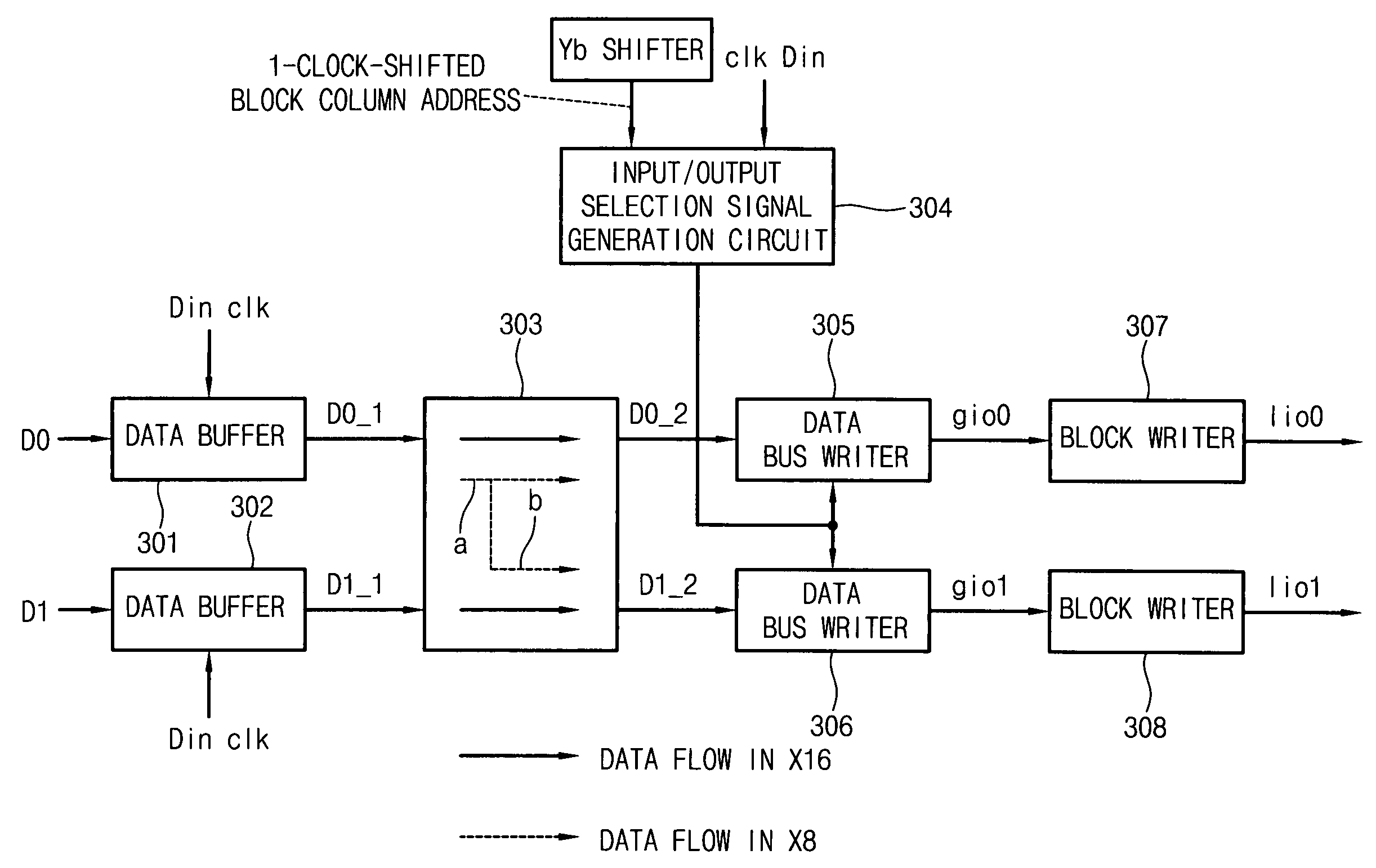

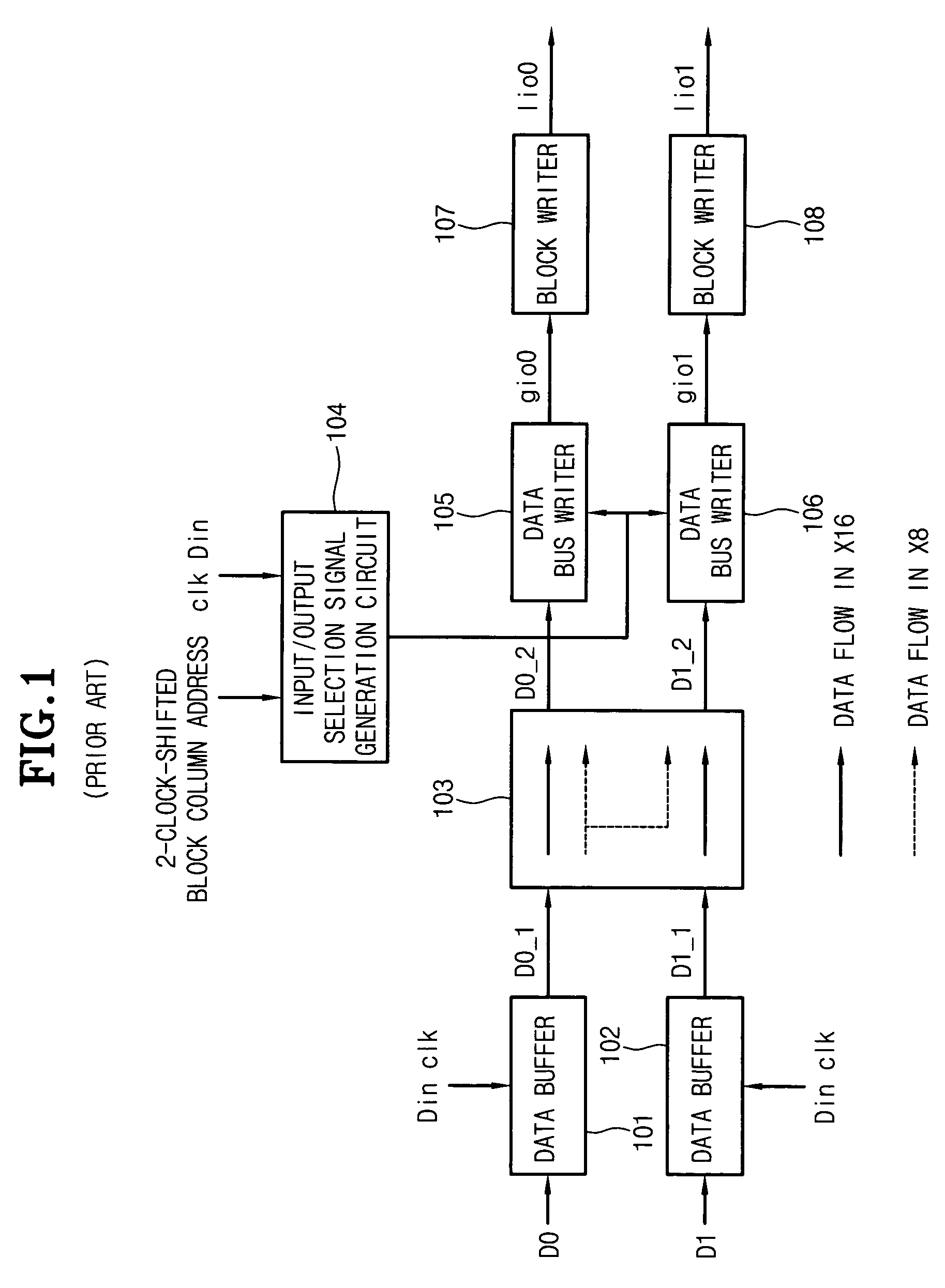

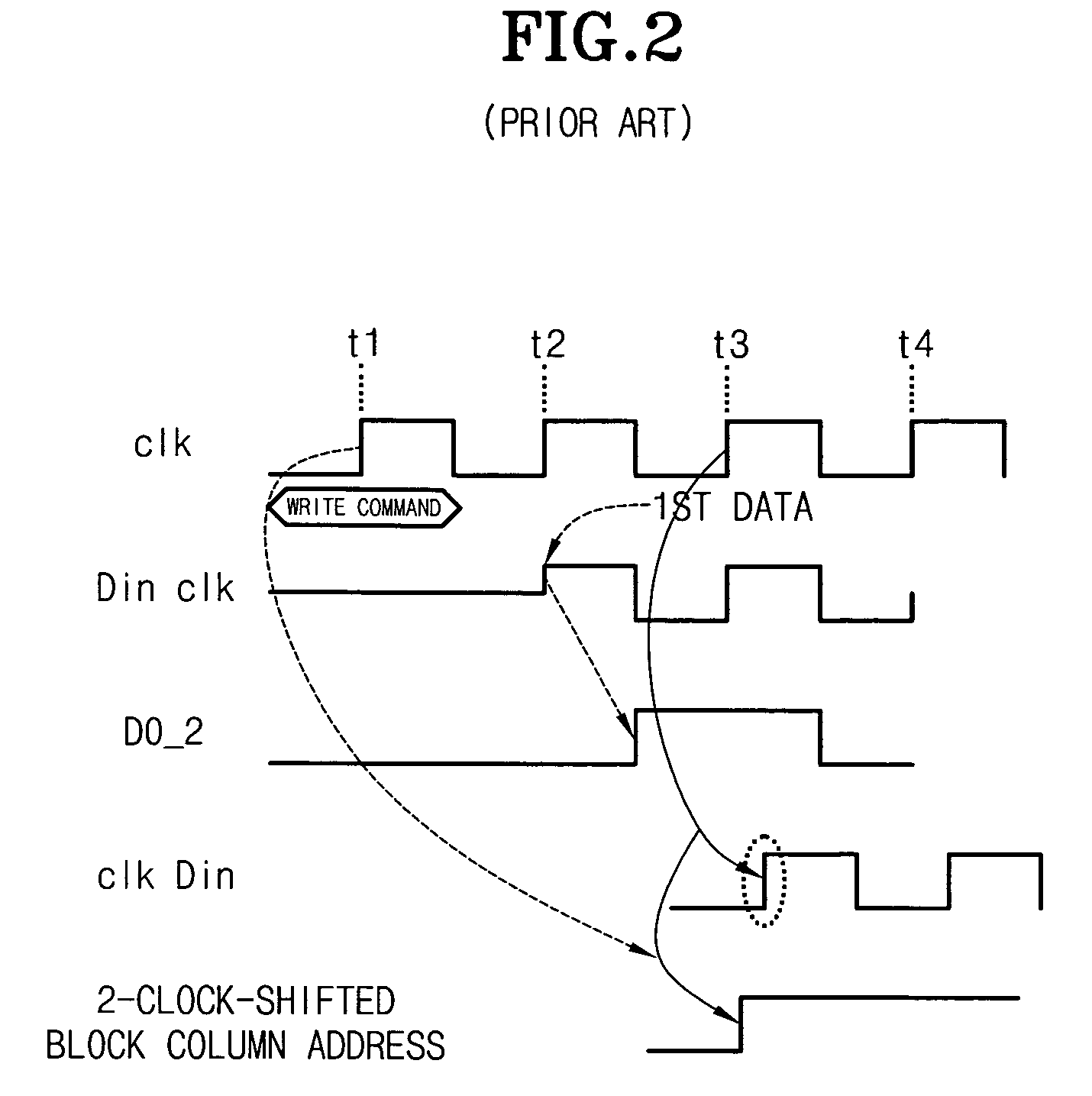

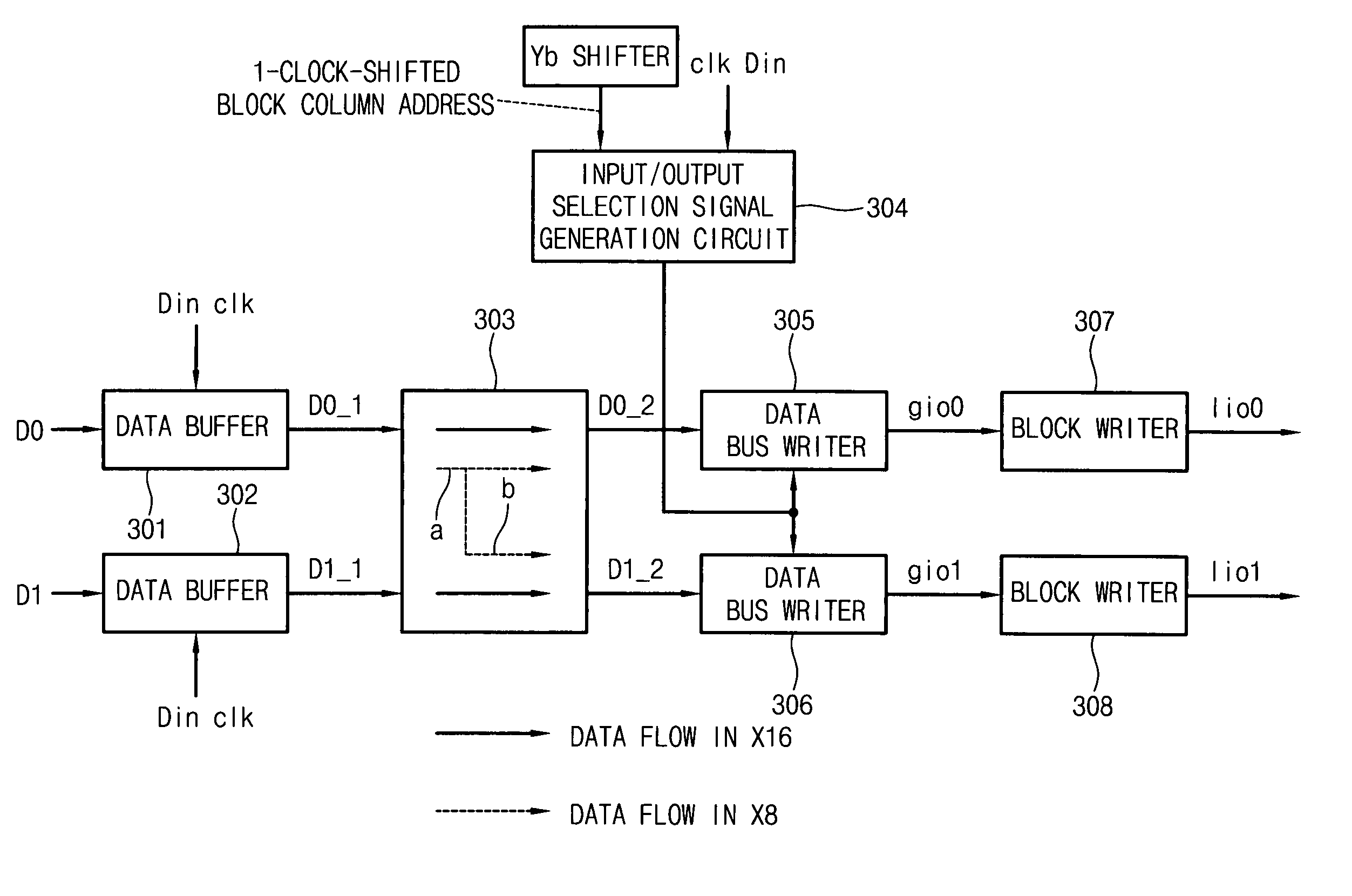

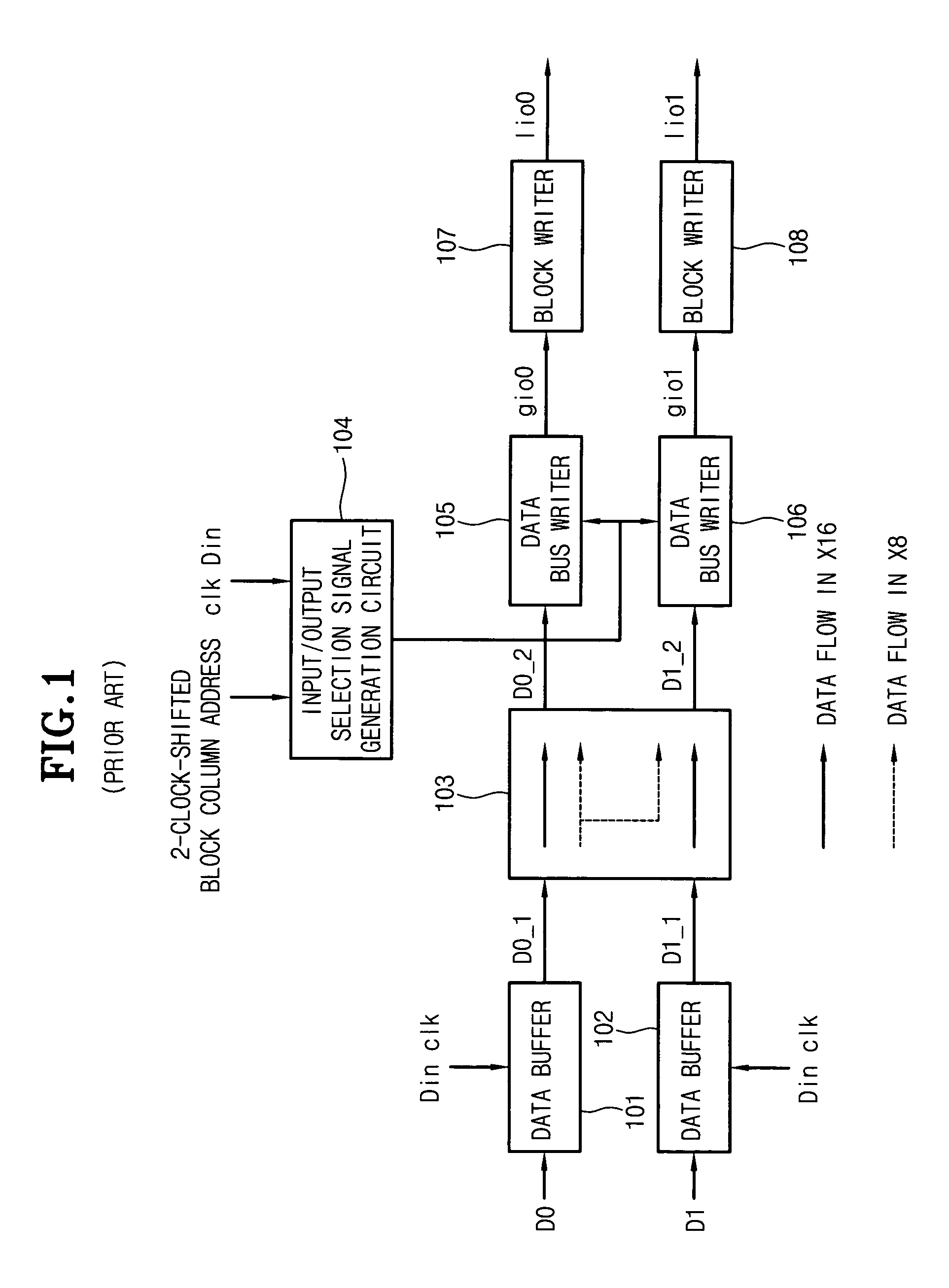

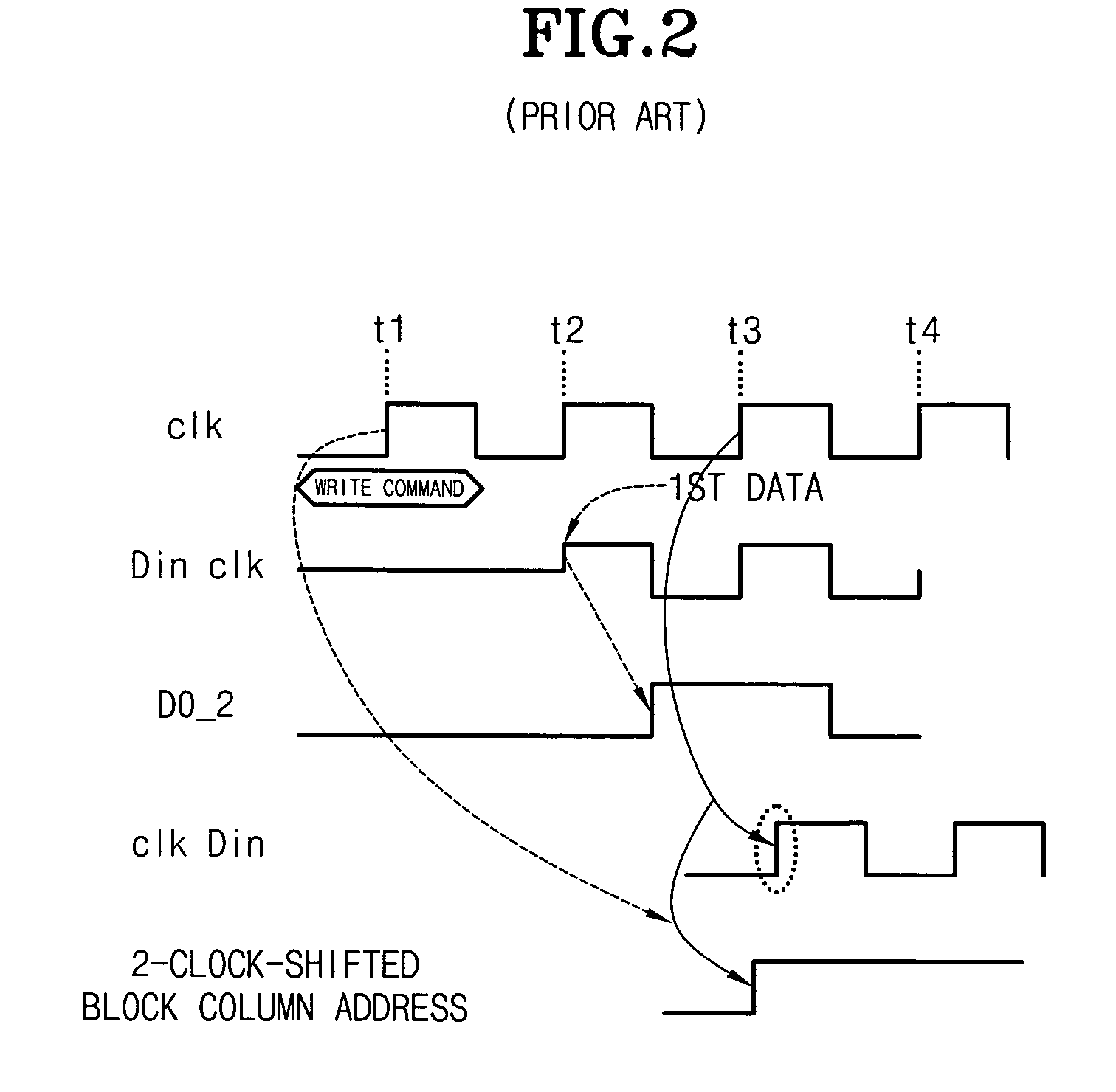

Input circuit for memory device

ActiveUS7184325B2Accelerating the operation time point of a data bus writerImprove processing speedSurgical instrument detailsDigital storageSemiconductor storage devicesHemt circuits

An input circuit for a semiconductor memory device is disclosed. The input circuit controlling transmission paths for data having passed through a data input buffer by using a 1-clock shifted block column address is provided. In particular, a data input apparatus improving a data processing speed by advancing an operation time point of a data bus writer is provided.

Owner:SK HYNIX INC

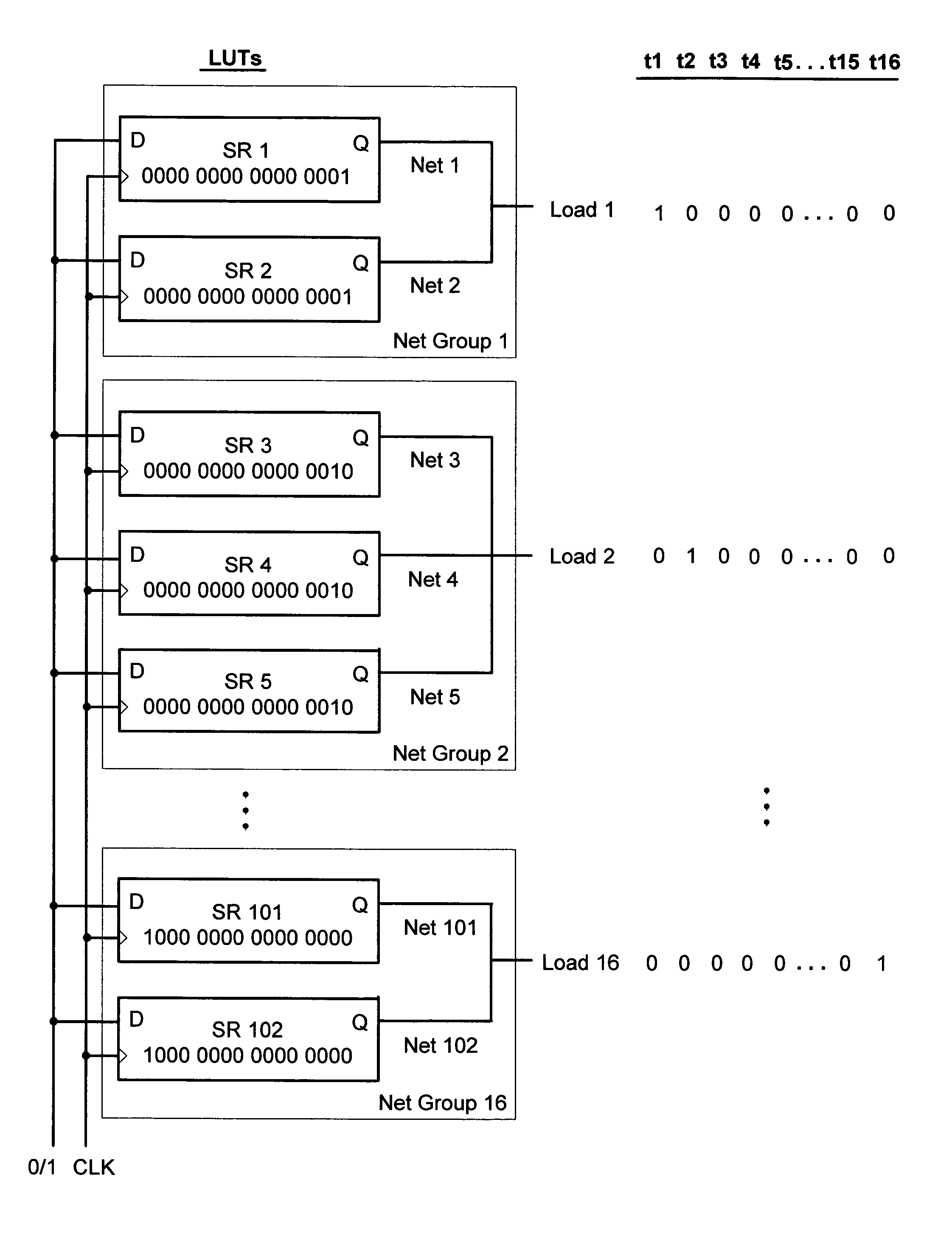

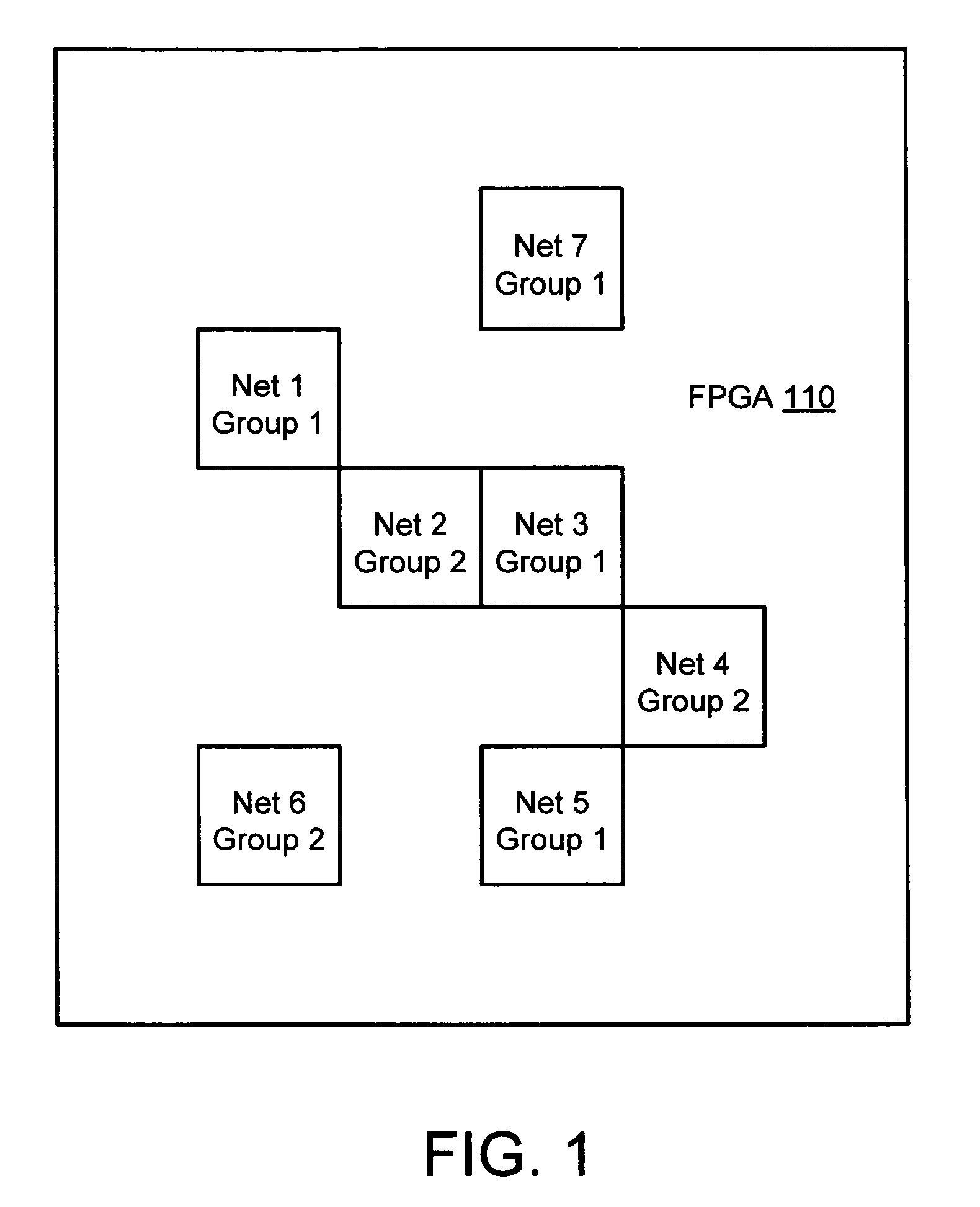

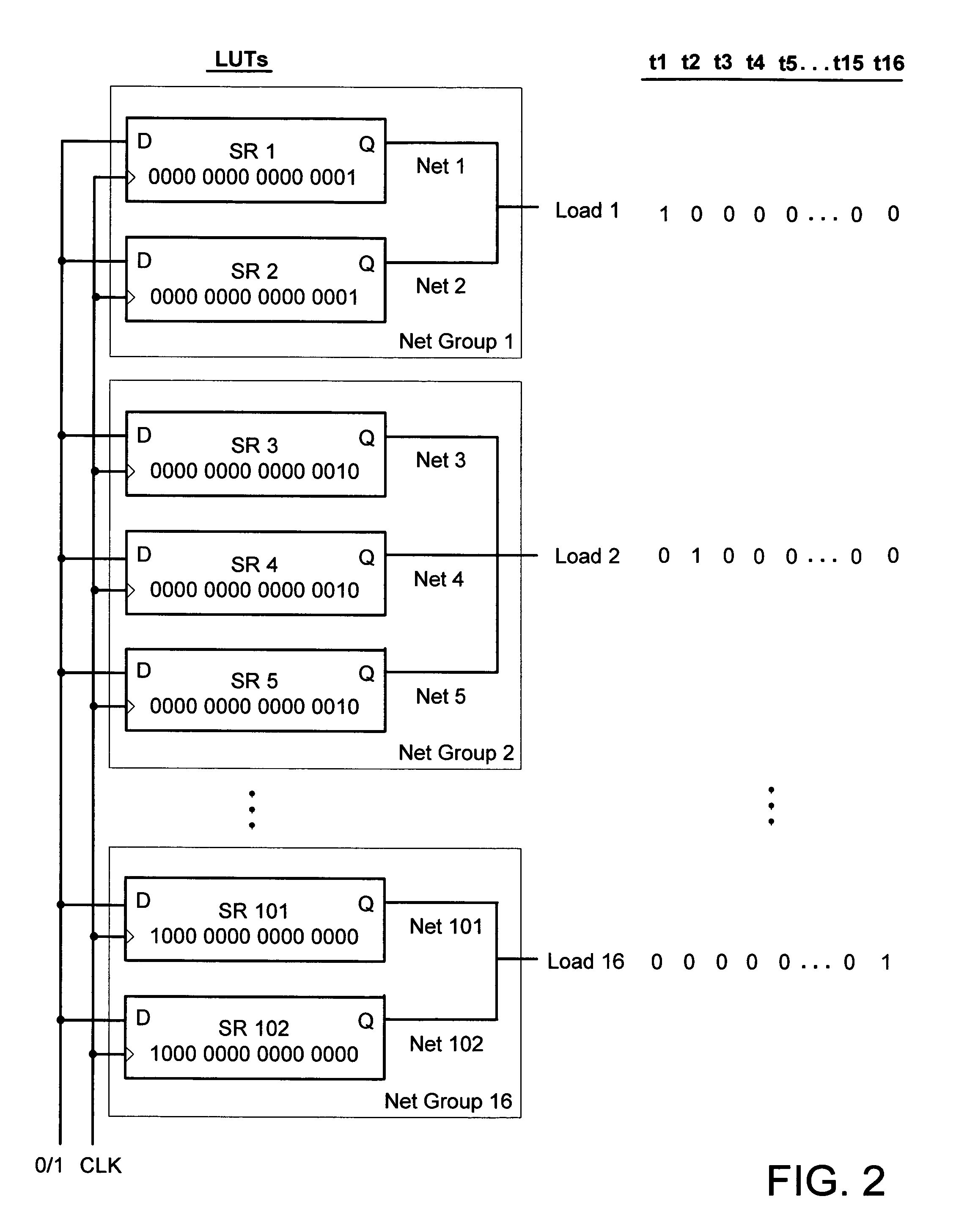

Testing for bridge faults in the interconnect of programmable integrated circuits

InactiveUS7614022B1Detecting faulty computer hardwareElectrical testingShift registerIntegrated circuit interconnect

Apparatus and methods of testing for bridge faults in nets of the interconnect of a programmable integrated circuit. Each net is sourced by a function generator (e.g., a look up table) configured as a clocked shift register. For each net group, shift registers connecting nets in the group are initialized identically to one value and are initialized to a different unique value from shift registers connecting nets of other net groups. Each shift register stores one bit with a value one and zeros in all other bits. When the shift register is clocked, it provides a single one on one clock cycle and provides zeros in all other clock cycles. At the end of n clock cycles, where n is the length of the shift register, if the load on any net has a value that is different from the value provided by the net's corresponding shift register, a short is detected.

Owner:XILINX INC

Frame pulse signal latch circuit and phase adjustment method

A frame pulse signal latch circuit has: a pulse-width expanding unit which outputs a frame pulse signal FPIN having a pulse width longer than a m-clock cycle; a phase adjustment unit which generates a phase-adjusted output clock CLK′; a flip-flop which latches the frame pulse signal FPIN; a racing detection unit which generates signals, which are shifted by one to m clocks with respect to a frame pulse signal FPOUT, and detects a racing state based on a result of an AND operation of the frame pulse signal FPOUT and the clock-shifted signals; and a control unit which sequentially selects and directs different phase adjustment amounts to the phase adjustment unit, determines an optimal phase adjustment amount based on a worst phase adjustment amount of the case in which the racing state is detected, and gives a direction about the optimal phase adjustment amount to the phase adjustment unit.

Owner:NEC CORP

Input circuit for memory device

ActiveUS20050243641A1Improve processing speedSurgical instrument detailsDigital storageHemt circuitsAddress control

An input circuit for a semiconductor memory device is disclosed. The input circuit controlling transmission paths for data having passed through a data input buffer by using a 1-clock shifted block column address is provided. In particular, a data input apparatus improving a data processing speed by advancing an operation time point of a data bus writer is provided.

Owner:SK HYNIX INC

Communication system and timing control method

ActiveCN1885764AModulation Timing OptimizationFast and stable distributionKey distribution for secure communicationWavelength-division multiplex systemsCommunications systemGroup velocity dispersion

A communication system and a timing control method are proposed that optimize timing in a sender and thereby enable information to be stably transmitted at the right timing. Under instructions from a timing controller in a receiver, the timing of driving a phase modulator in a sender is shifted by one step after another, and the then amount of clock shift and result of interference are monitored at the receiver and stored in a memory. The optimum timing is determined based on the stored data. Thus, a clock for driving the phase modulator in the sender can be set at the right timing. This is equivalent to compensating for group velocity dispersion due to wavelength dispersion that occurs when an optical signal channel and a clock signal channel are transmitted by wavelength division multiplexing transmission.

Owner:NEC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com