Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32 results about "Branch trace" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Branch trace is a computer program debugging tool or analysis technique. It is an abbreviated instruction trace in which only the successful branch instructions are recorded. On IBM System/360 this was implemented as part of Program-Event Recording (PER) but was seldom used at the application programming level. Program Event Recording hardware was used and due to the overhead of this tool, it was removed from customer-available MVS systems.

Software debugging tool

ActiveUS7401322B1Raise completelyIncrease heightError detection/correctionSpecific program execution arrangementsTest caseProgram control

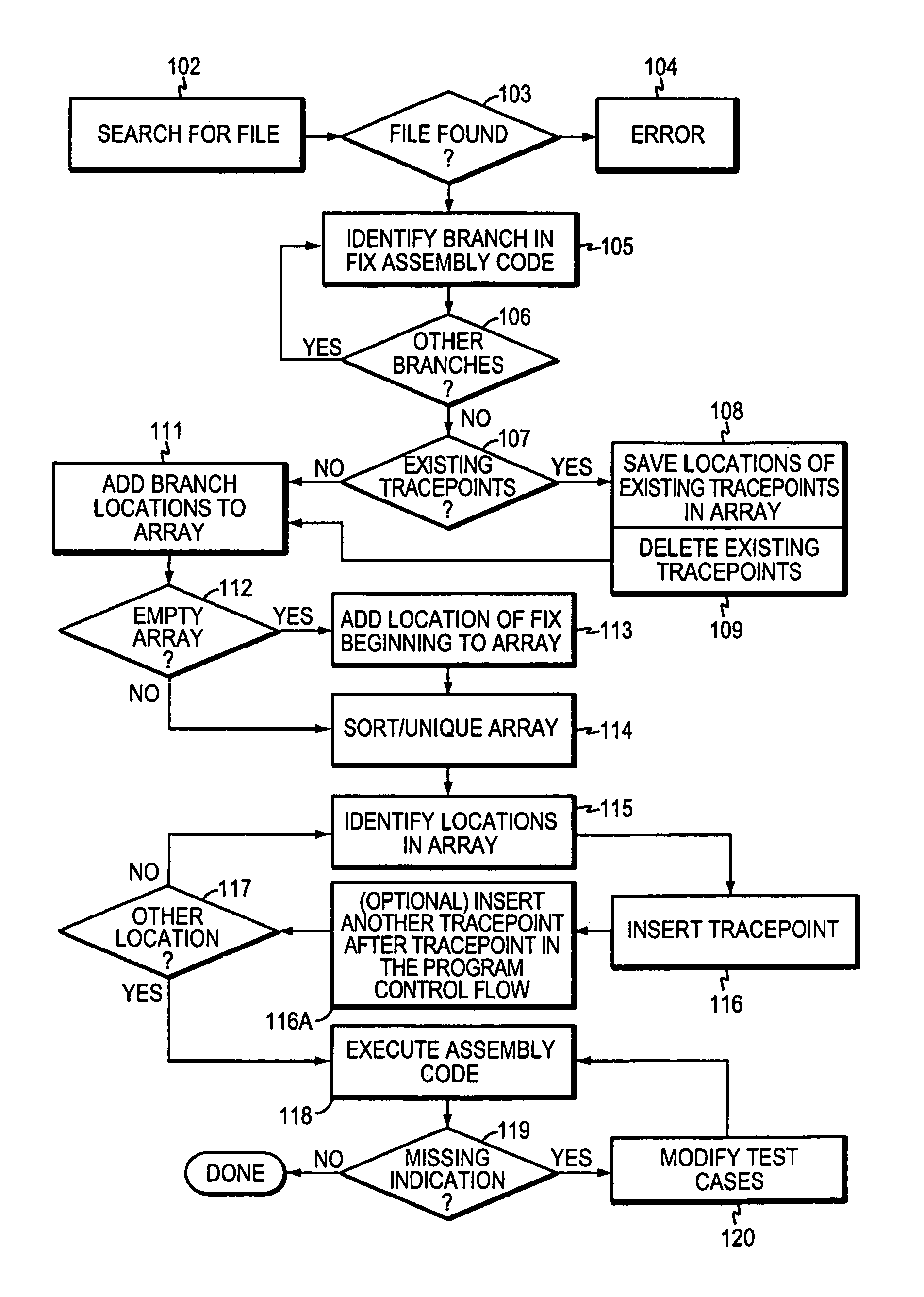

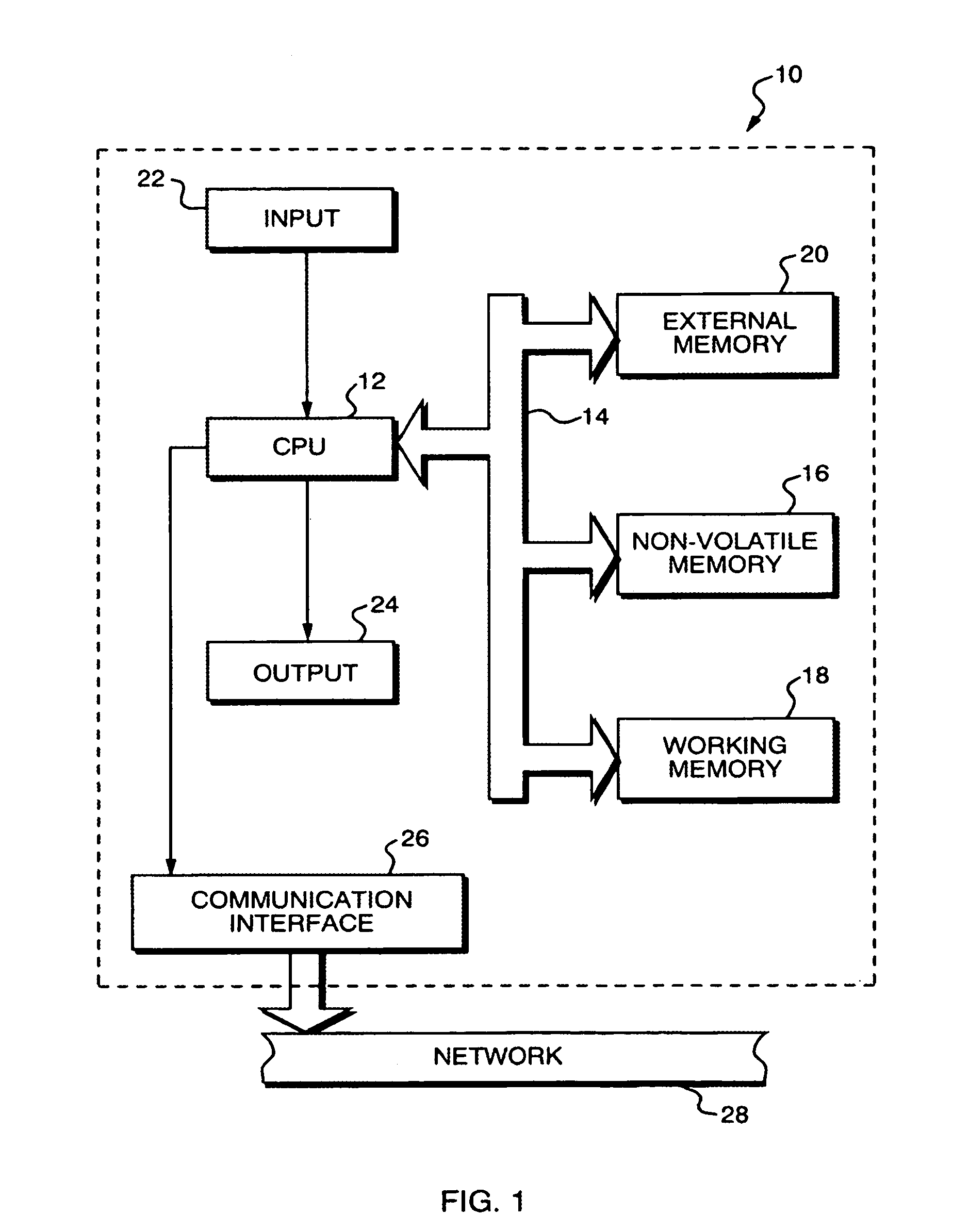

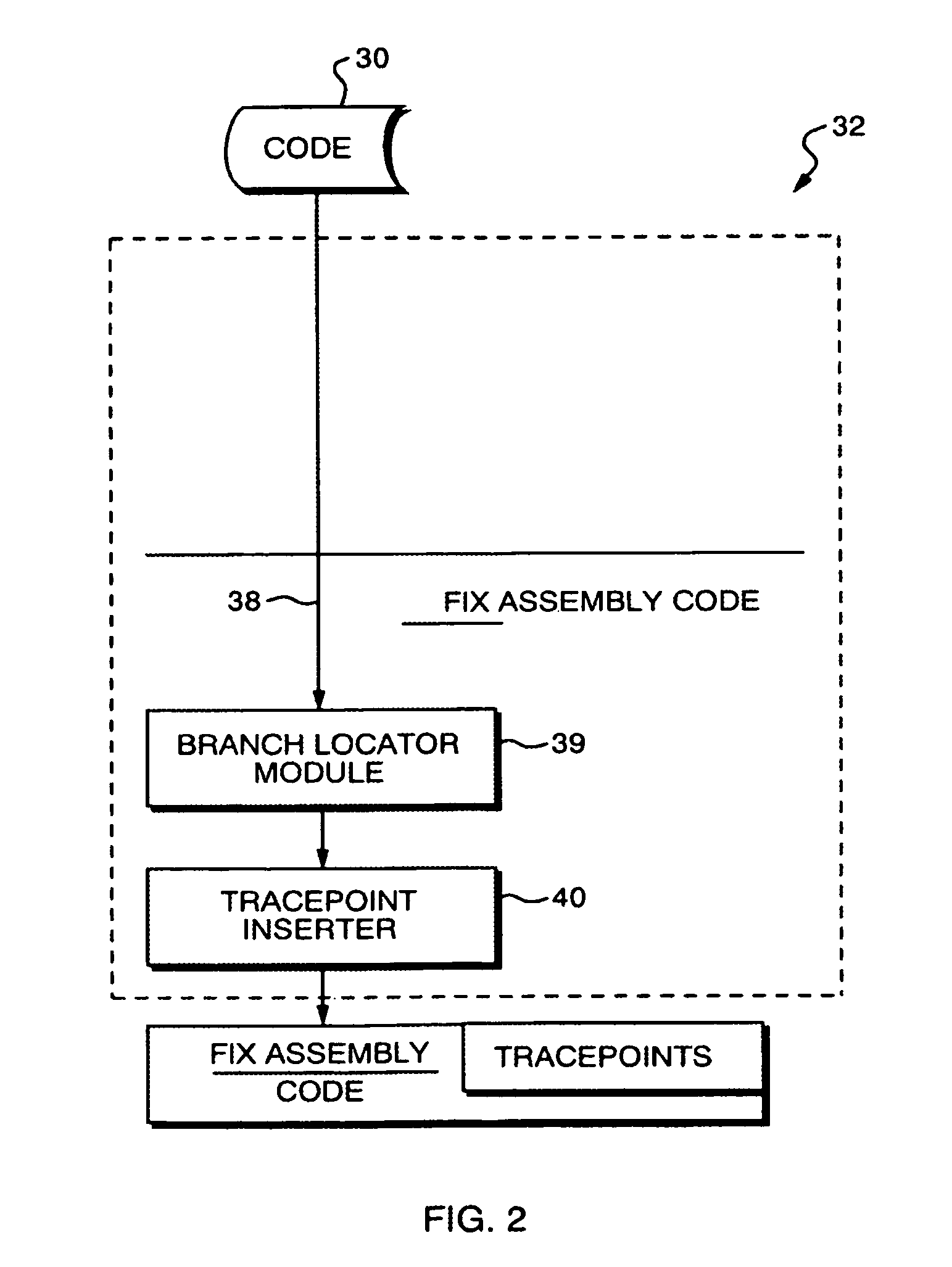

In a method for testing computer code, each branch that occurs within the machine-readable code is located. A first tracepoint is placed immediately after the beginning of the branch and a second tracepoint at the target address of each branch, each tracepoint generating an indicator. When the machine-readable code with the tracepoints is executed on the target computer, the method identifies those indicators that have been generated by their corresponding tracepoints, thereby permitting determination of those branches that the program control flow has not passed through. The test cases are modified to exercise the previously omitted branches, and the converted code is re-executed, until all branches have been properly exercised. The tracepoints are automatically eliminated after they have performed their intended function.

Owner:WILSON PENELOPE S +1

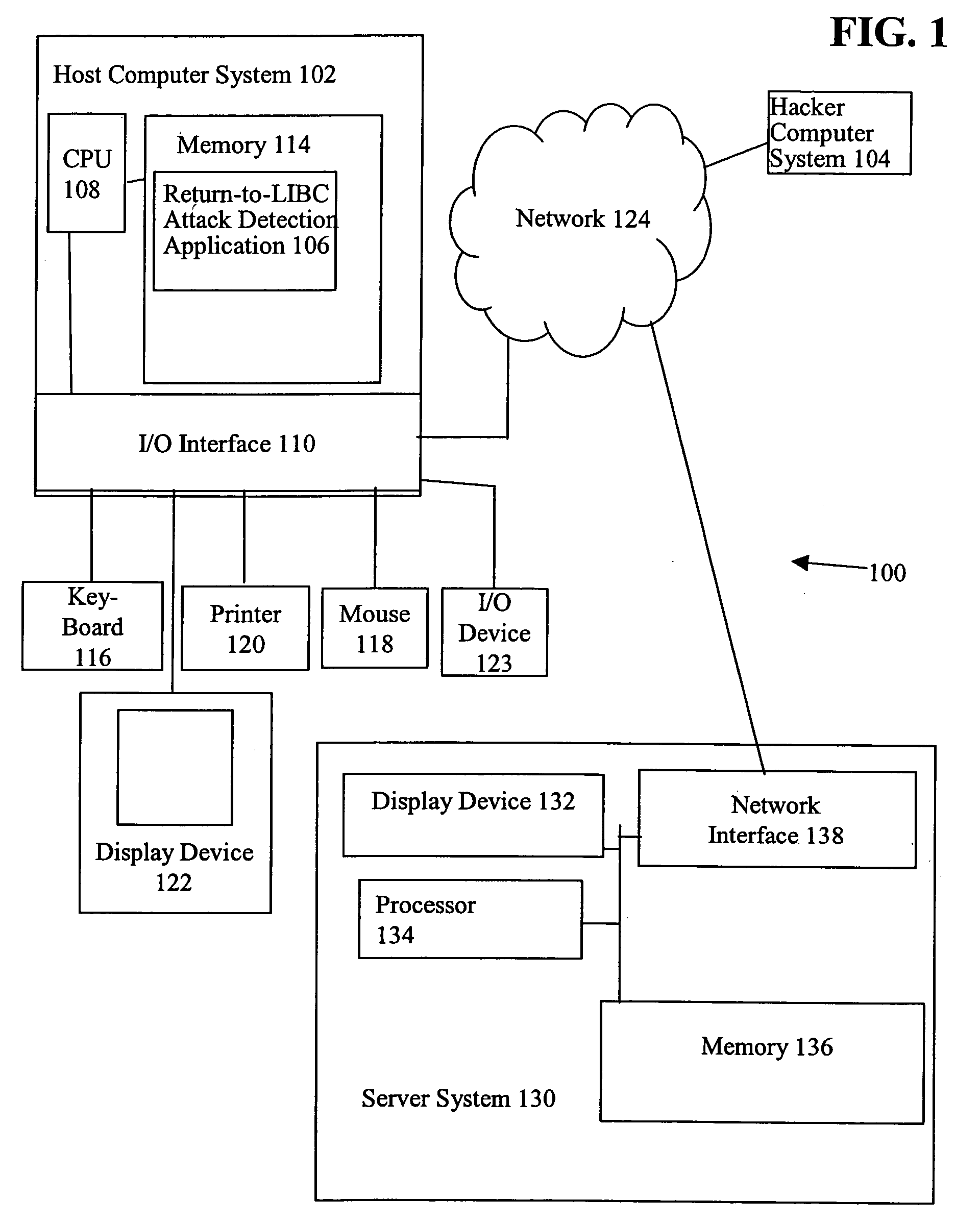

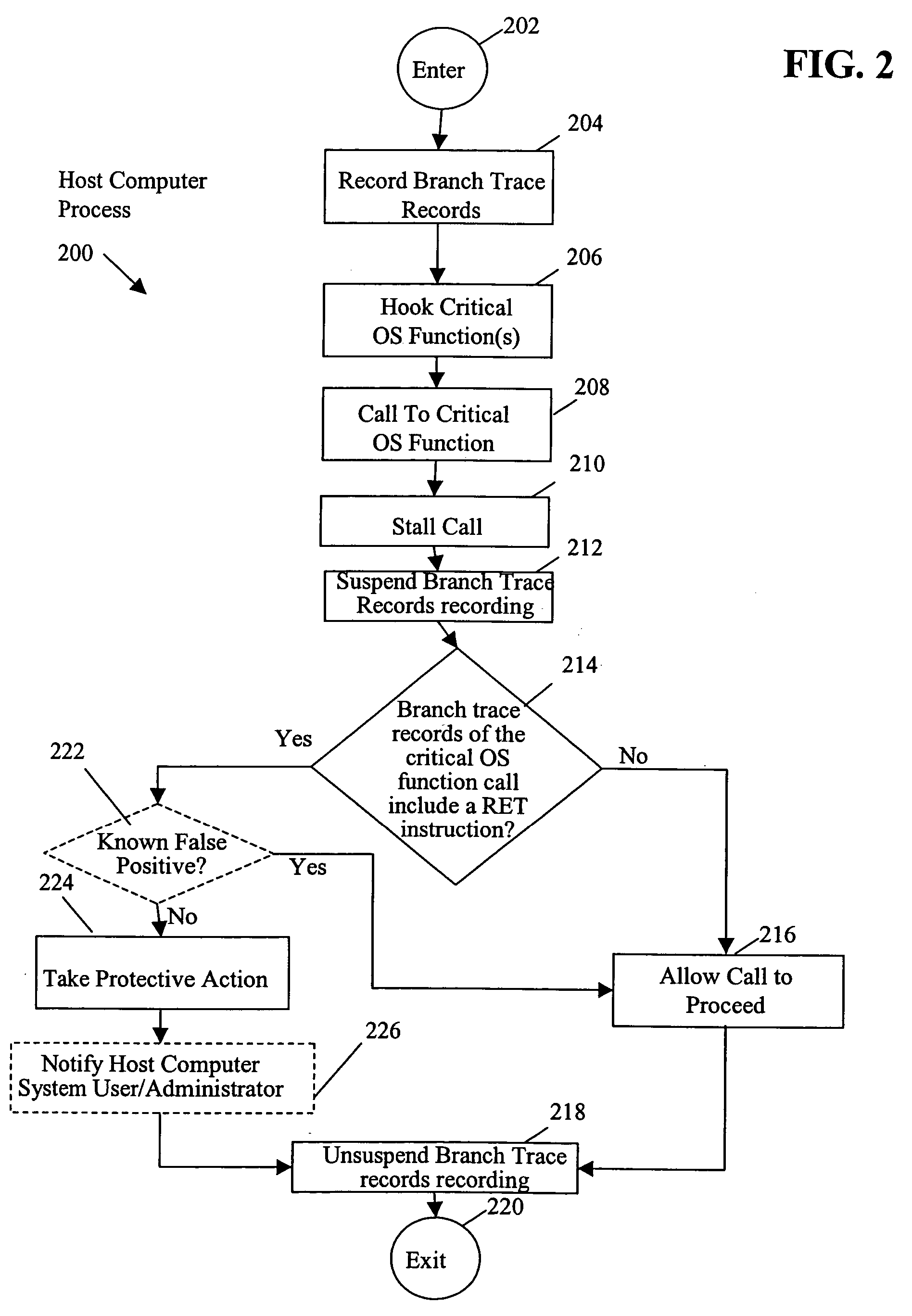

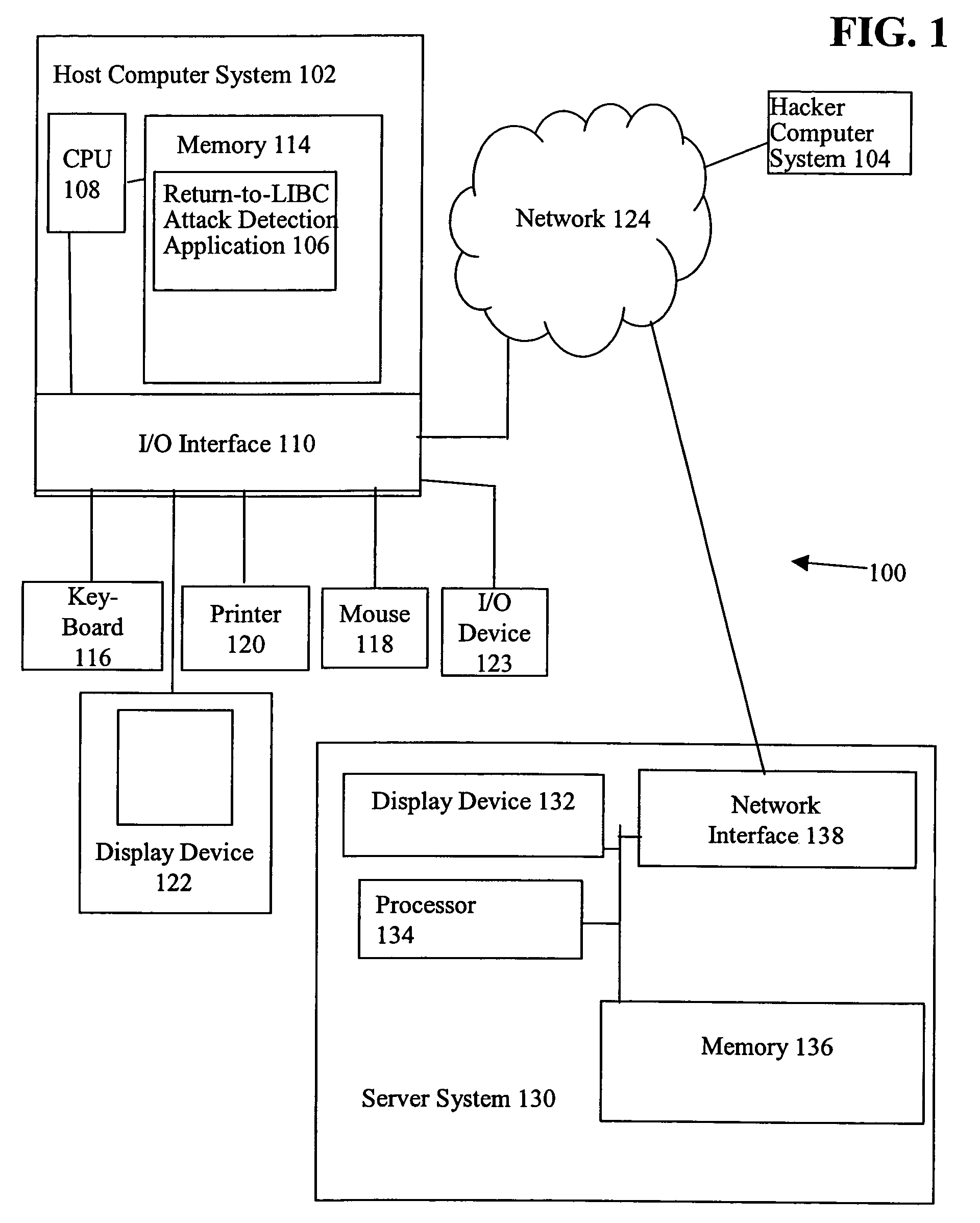

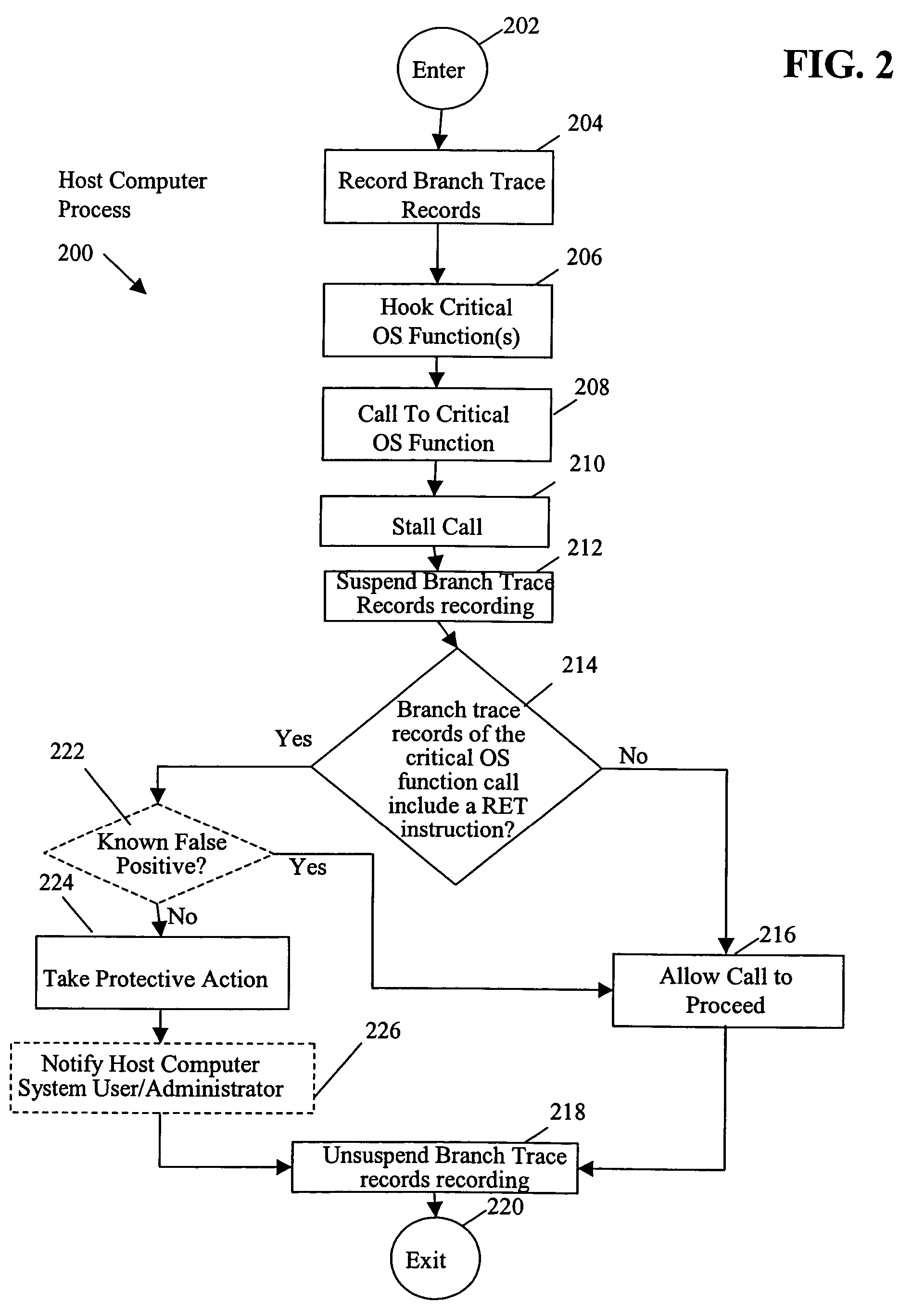

Return-to-LIBC attack detection using branch trace records system and method

ActiveUS20050166001A1Memory loss protectionDigital data processing detailsOperational systemBranch trace

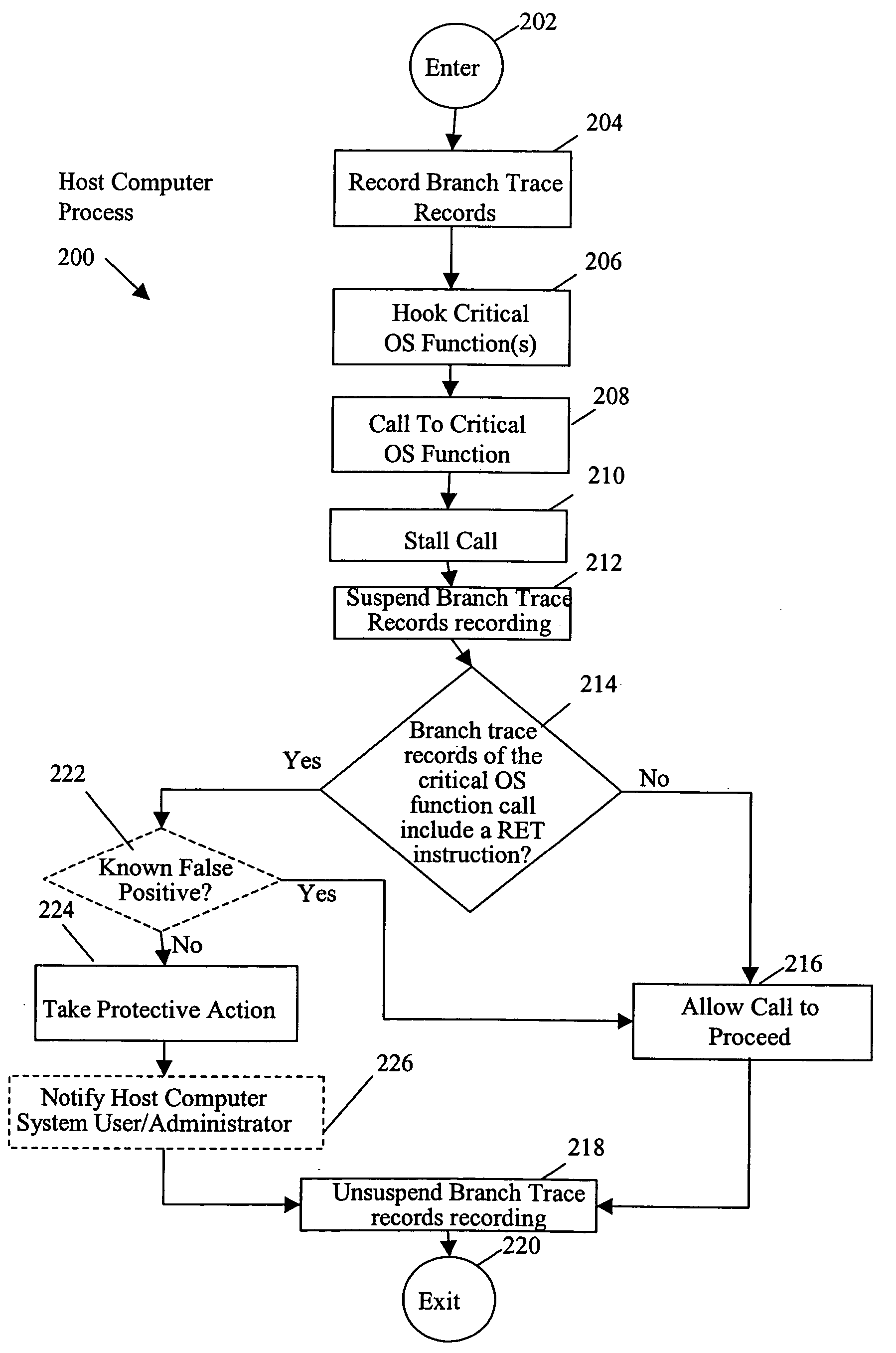

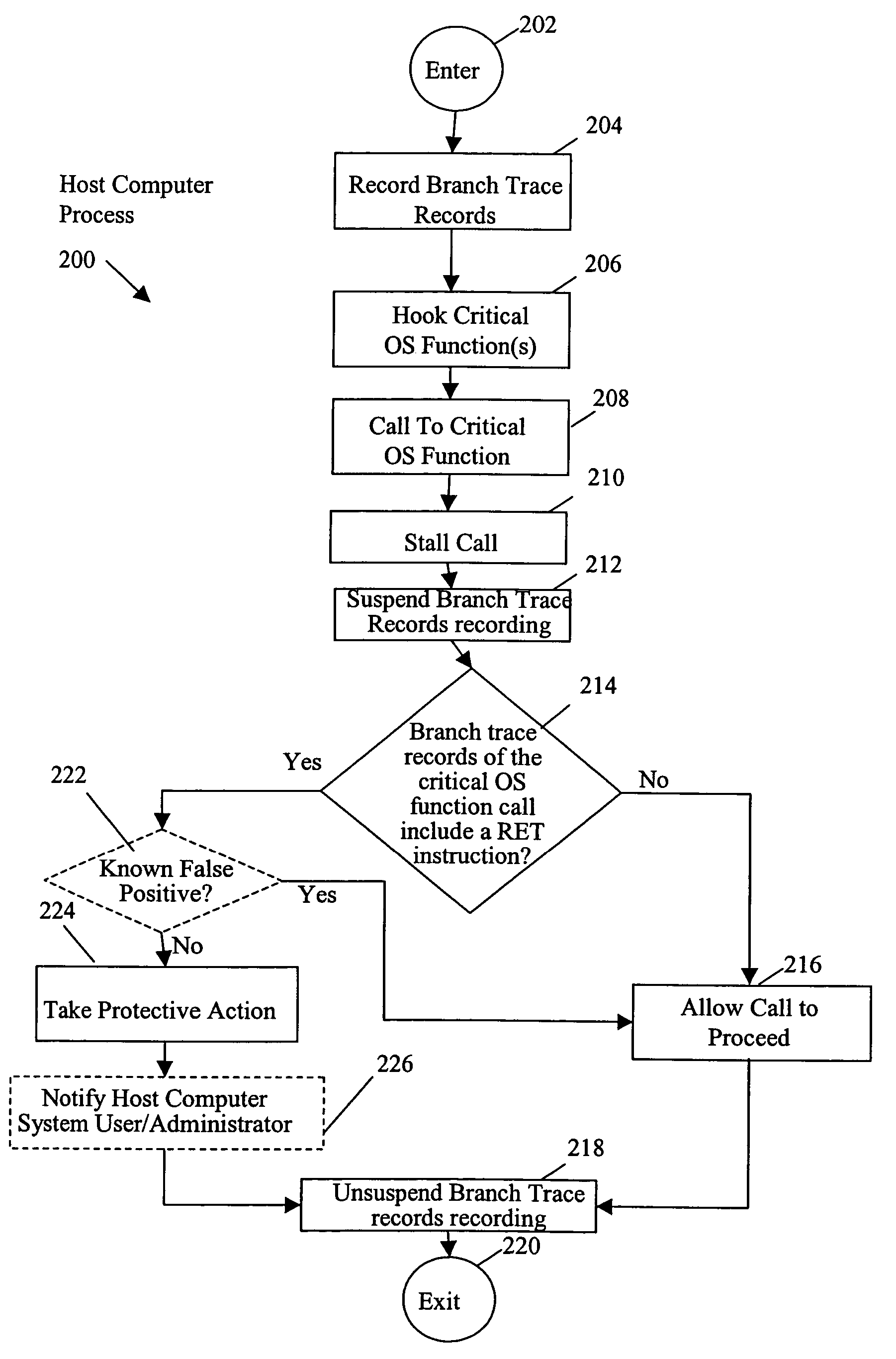

A method includes stalling a call to a critical operating system (OS) function and determining whether branch trace records of the call include a return instruction. Upon a determination that the branch trace records of the call do include a return instruction, the method further includes taking protective action to protect a computer system.

Owner:CA TECH INC

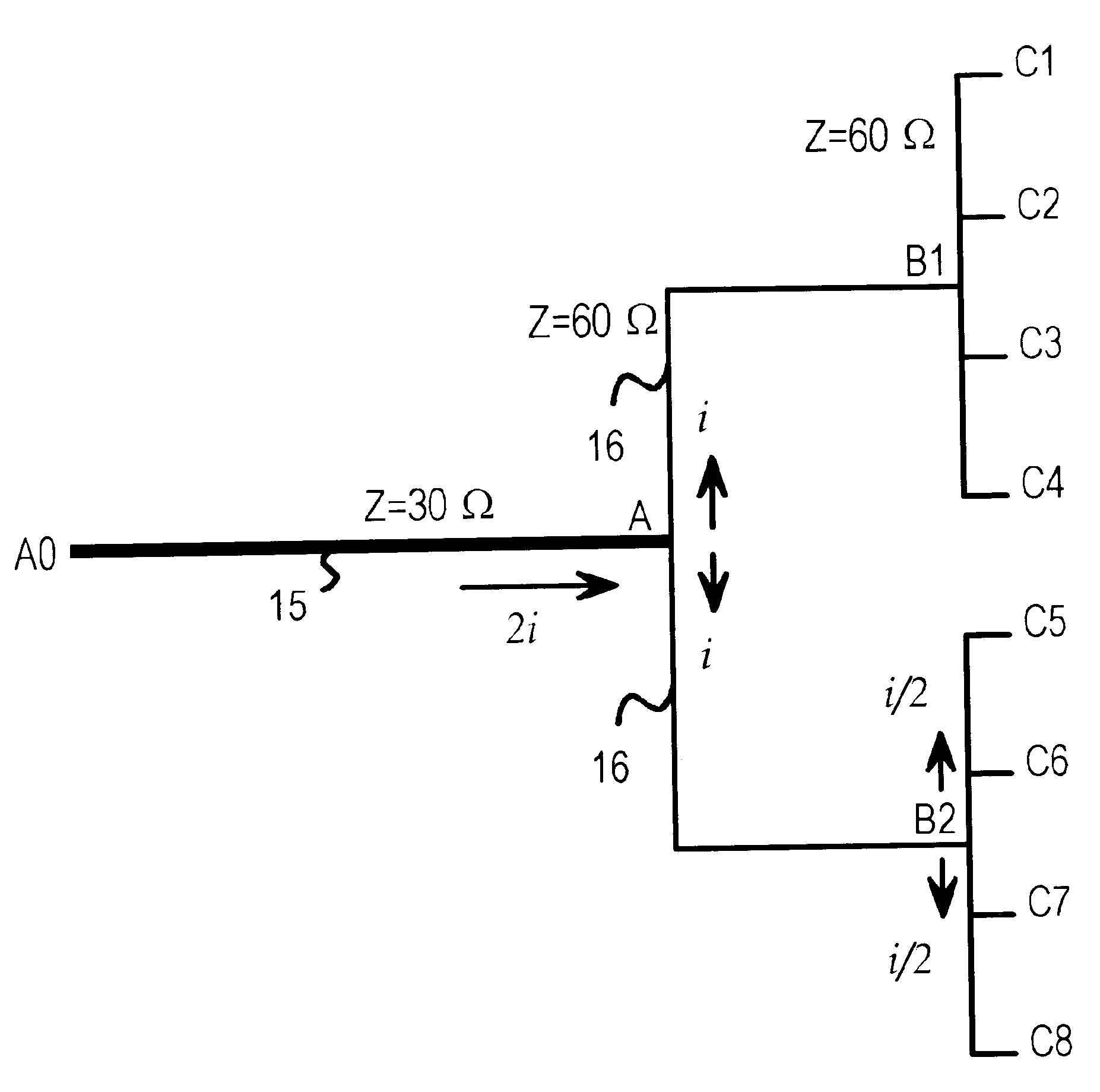

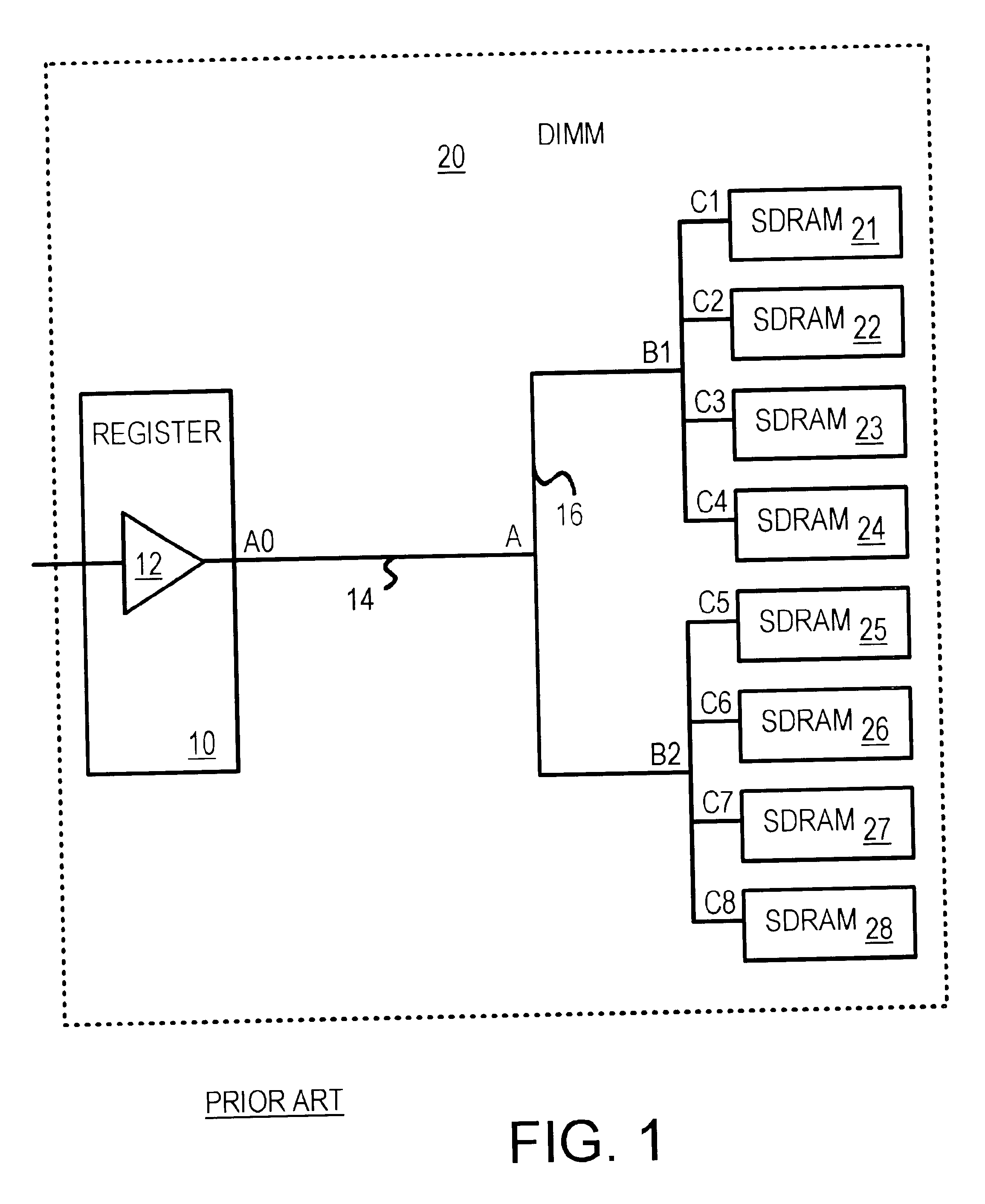

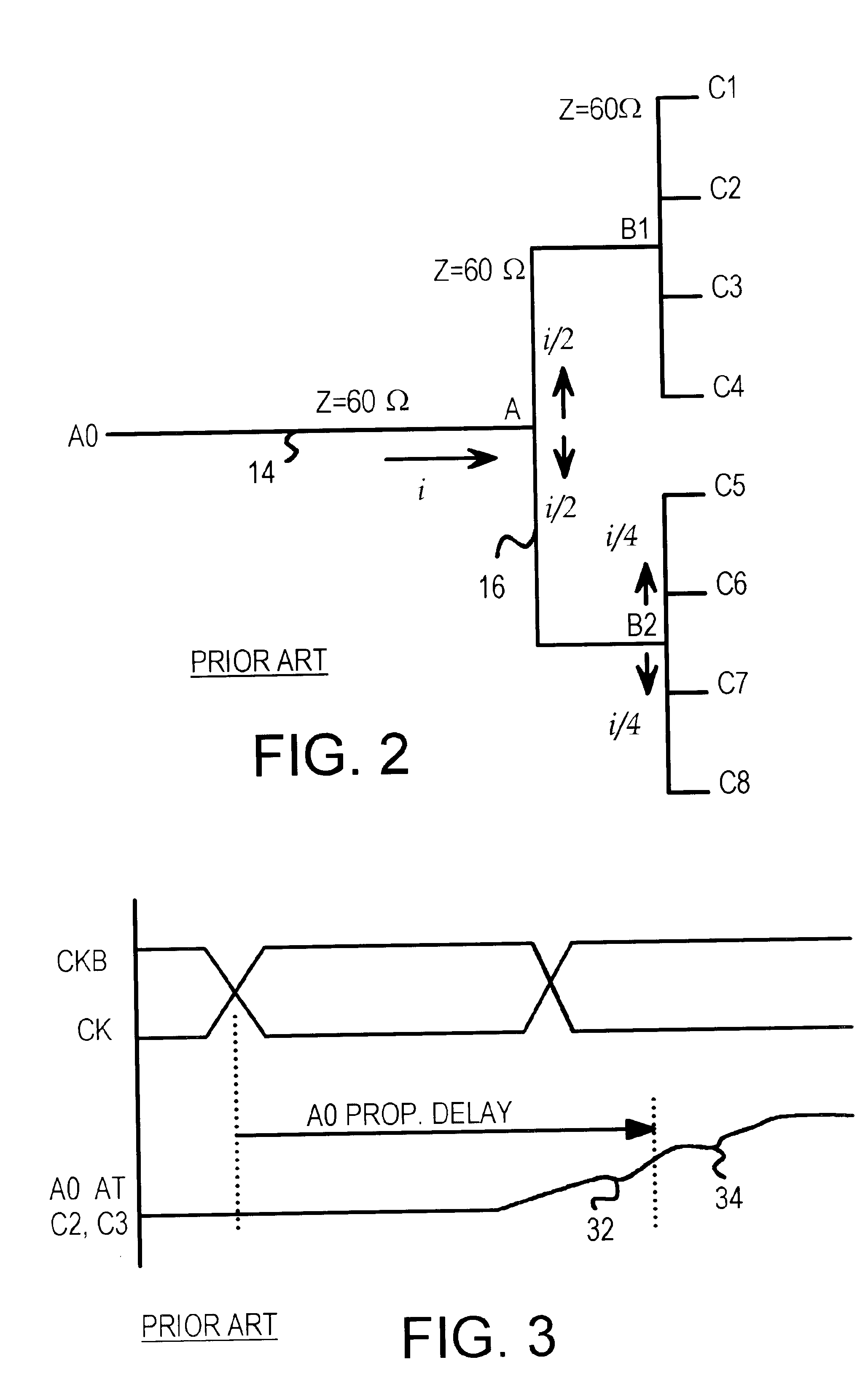

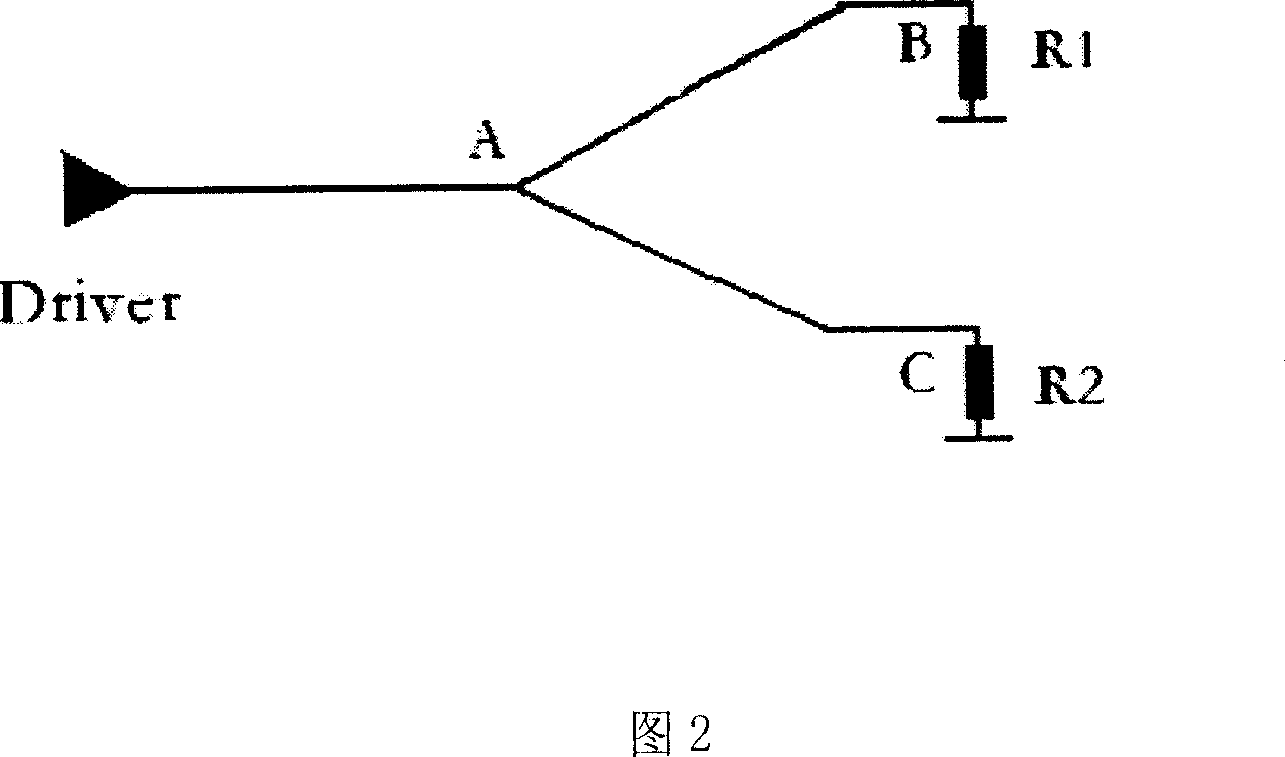

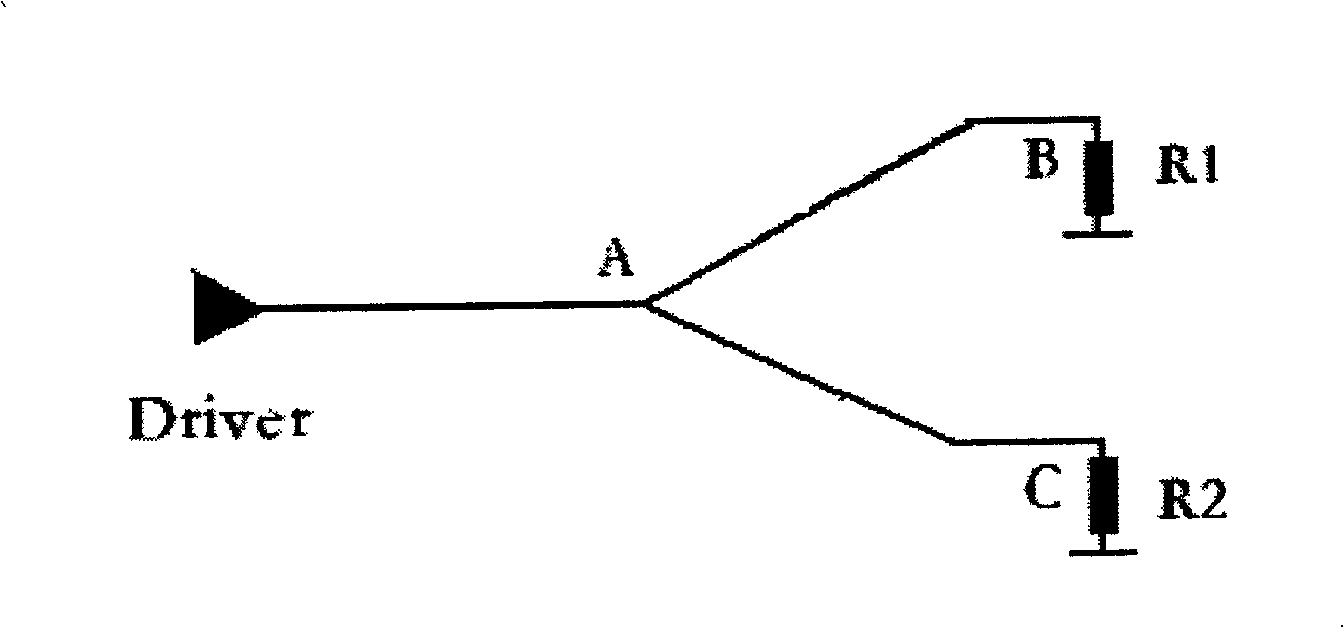

Trace-impedance matching at junctions of multi-load signal traces to eliminate termination

A module board has trace impedances that are matched at trace junctions. An input line that drives a signal to a junction has its impedance adjusted to match the equivalent impedance of branch traces output from the junction. Since input and output impedances match, reflections caused by the junction are minimized or eliminated. The input impedance can match by being within 20% of the equivalent impedance of the branch lines. The equivalent impedance of branches is the reciprocal of the sum of the individual branch lines' reciprocal impedance. Termination can be eliminated when such junctions are impedance-matched. Secondary junctions can also be impedance-matched, allowing for a variety of trace topologies. Such trace-impedance matching is especially useful for memory modules.

Owner:DIODES INC

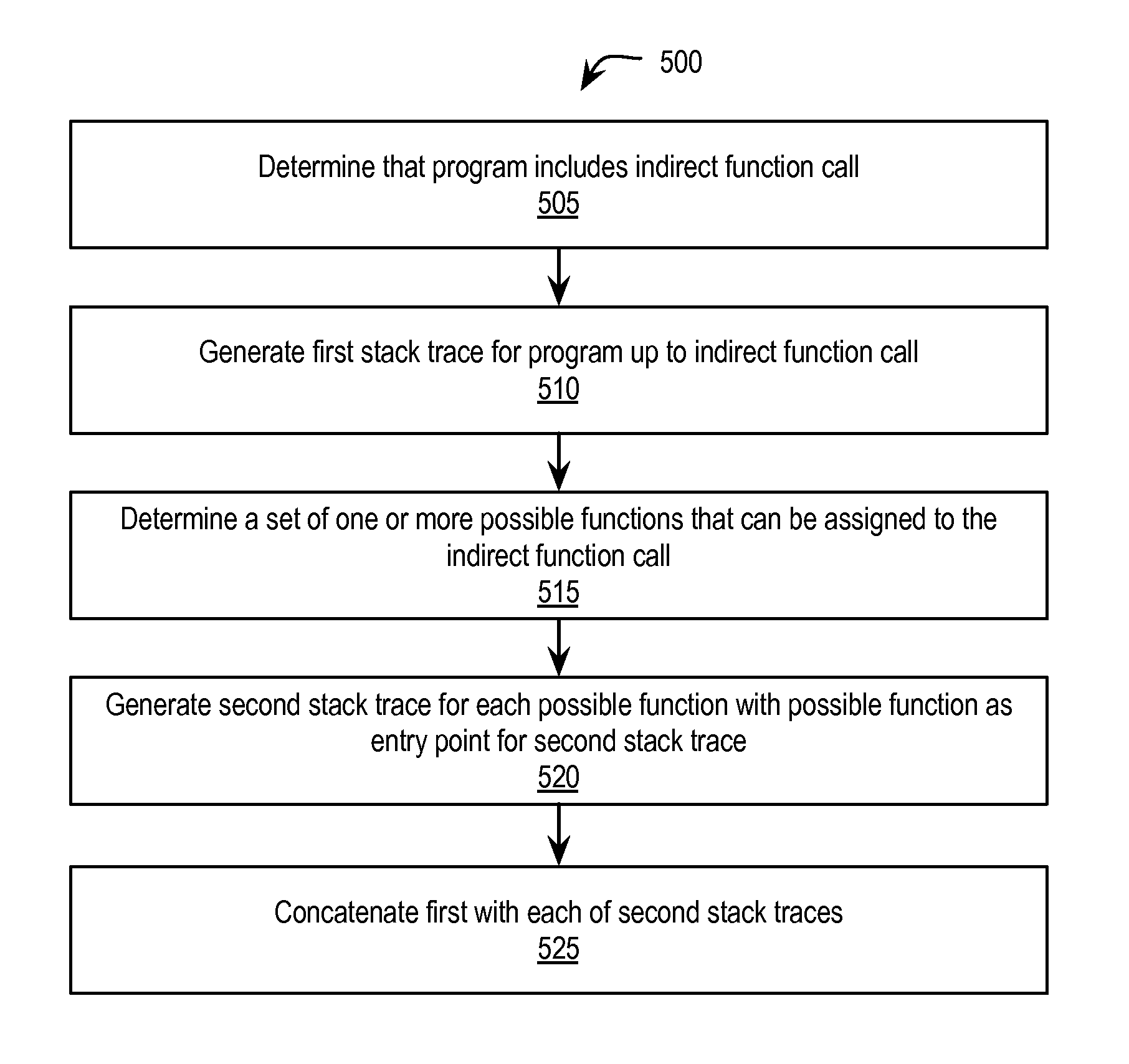

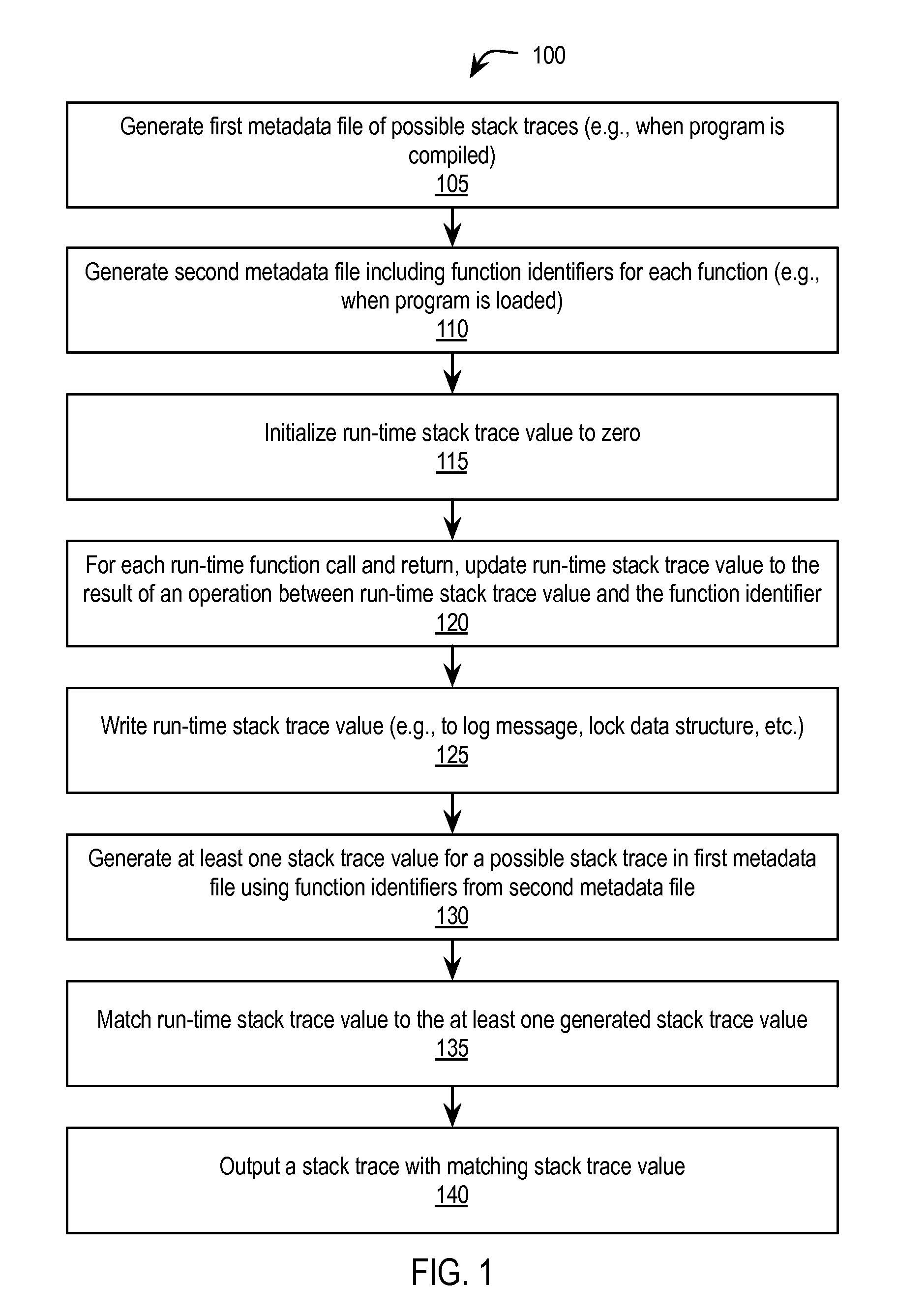

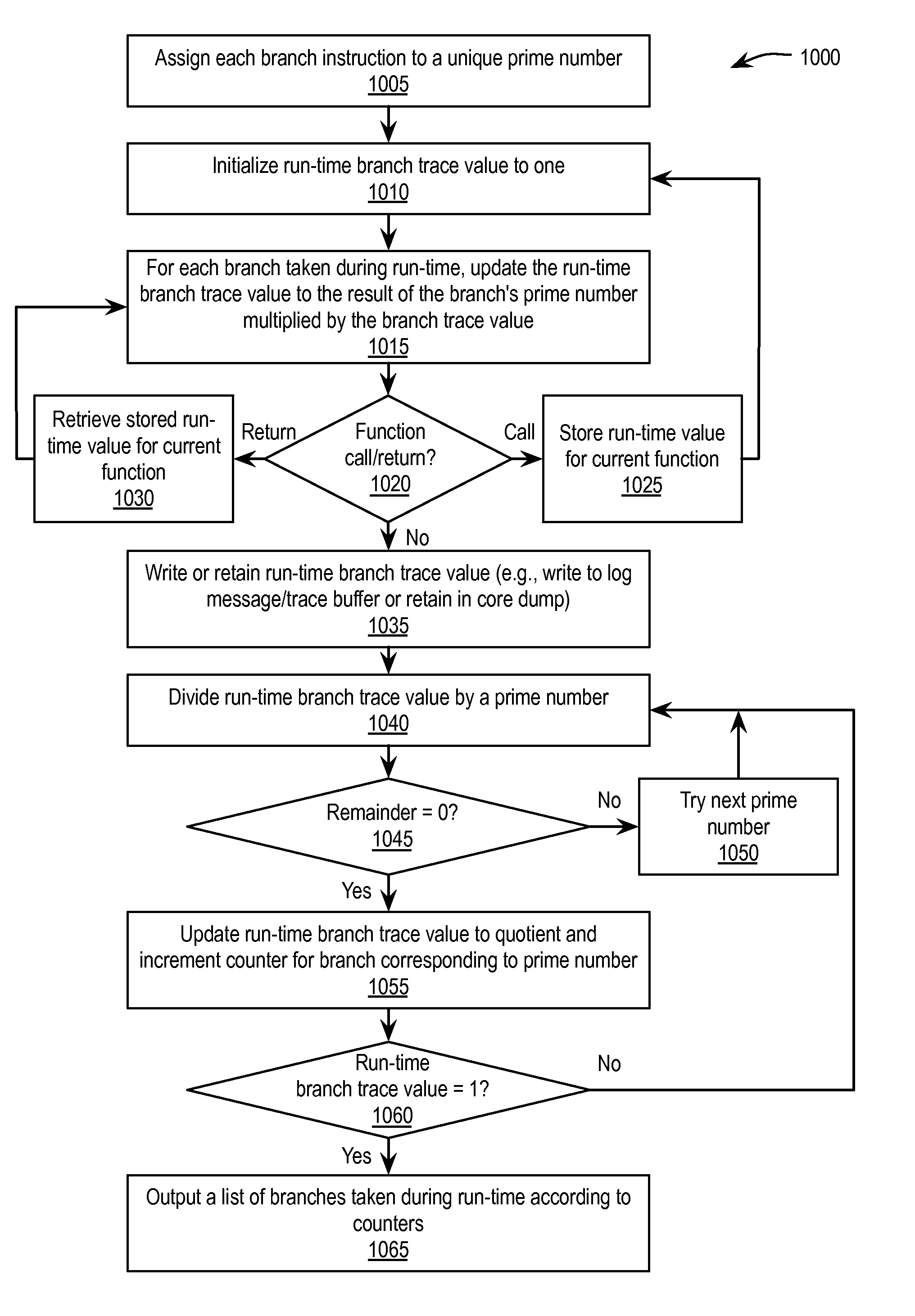

Branch trace compression

Exemplary methods, apparatuses, and systems assign a plurality of branch instructions within a computer program to a plurality of prime numbers. Each branch instruction is assigned a unique prime number within the plurality of prime numbers. A run-time branch trace value is determined to be divisible, without a remainder, by a first prime number of the plurality of prime numbers. The run-time branch trace value was generated during execution of the computer program. An output is generated indicating that a first branch instruction assigned to the first prime number was executed.

Owner:VMWARE INC

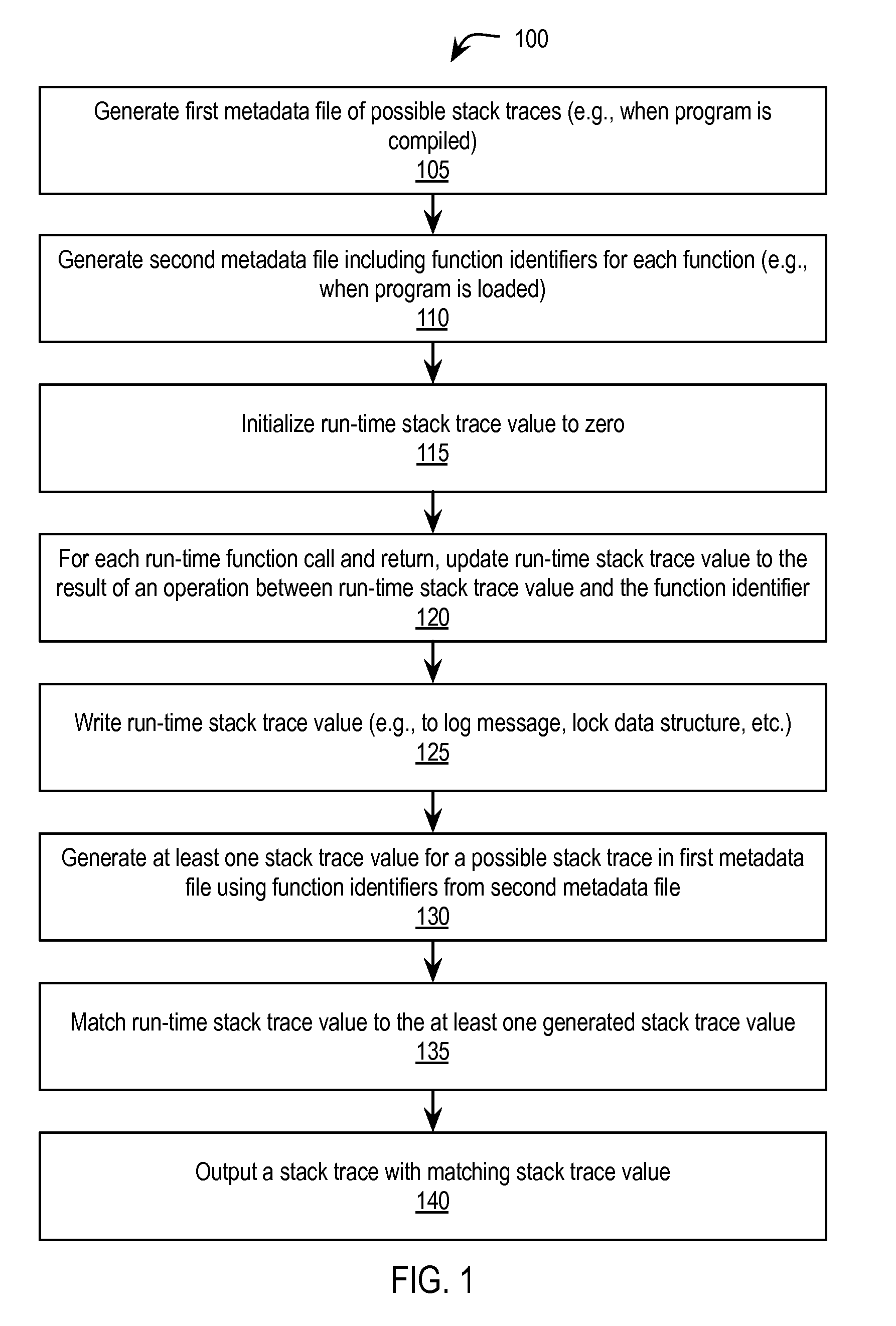

Branch trace compression

ActiveUS20150058606A1Error detection/correctionDigital computer detailsLogical operationsBranch trace

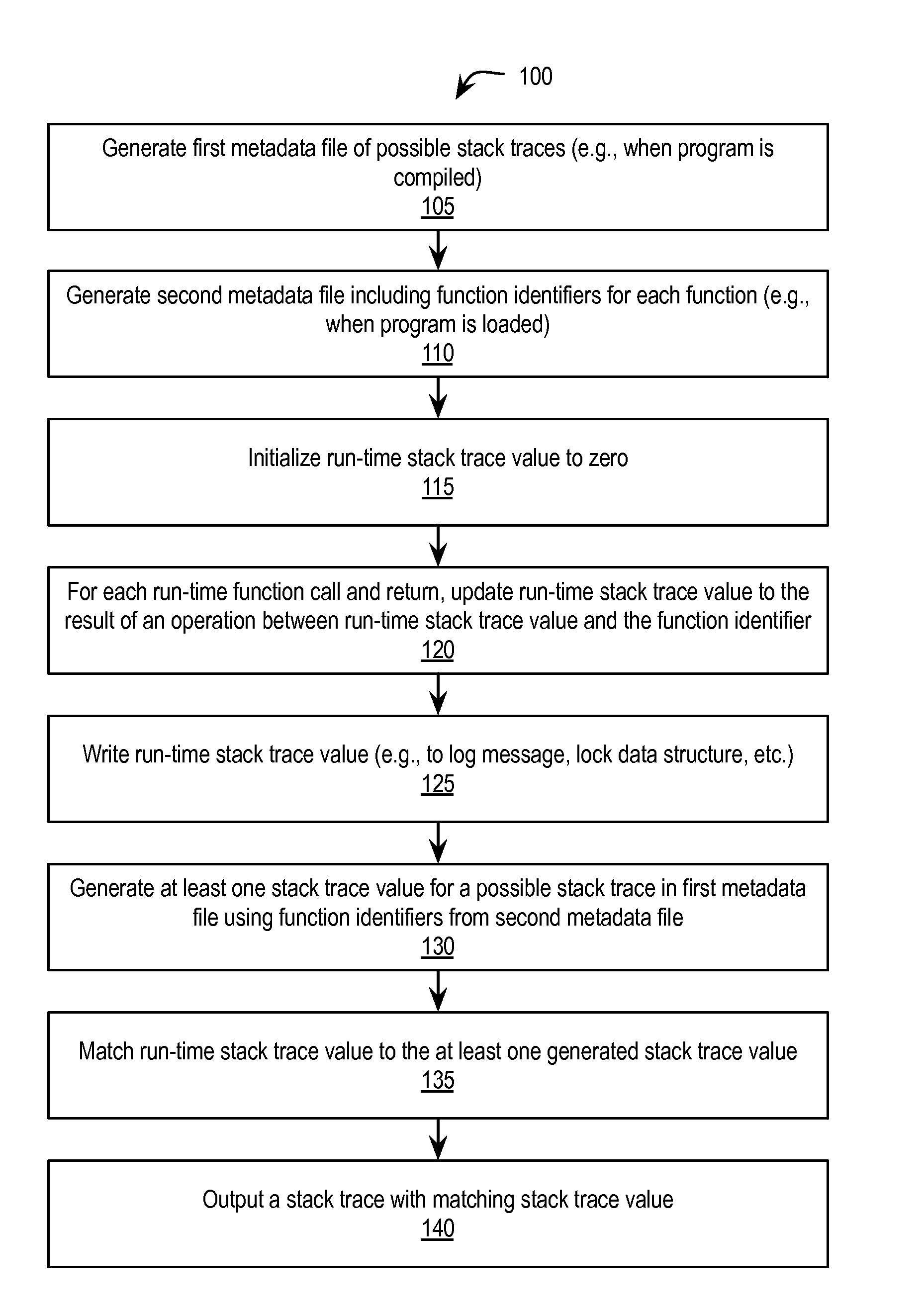

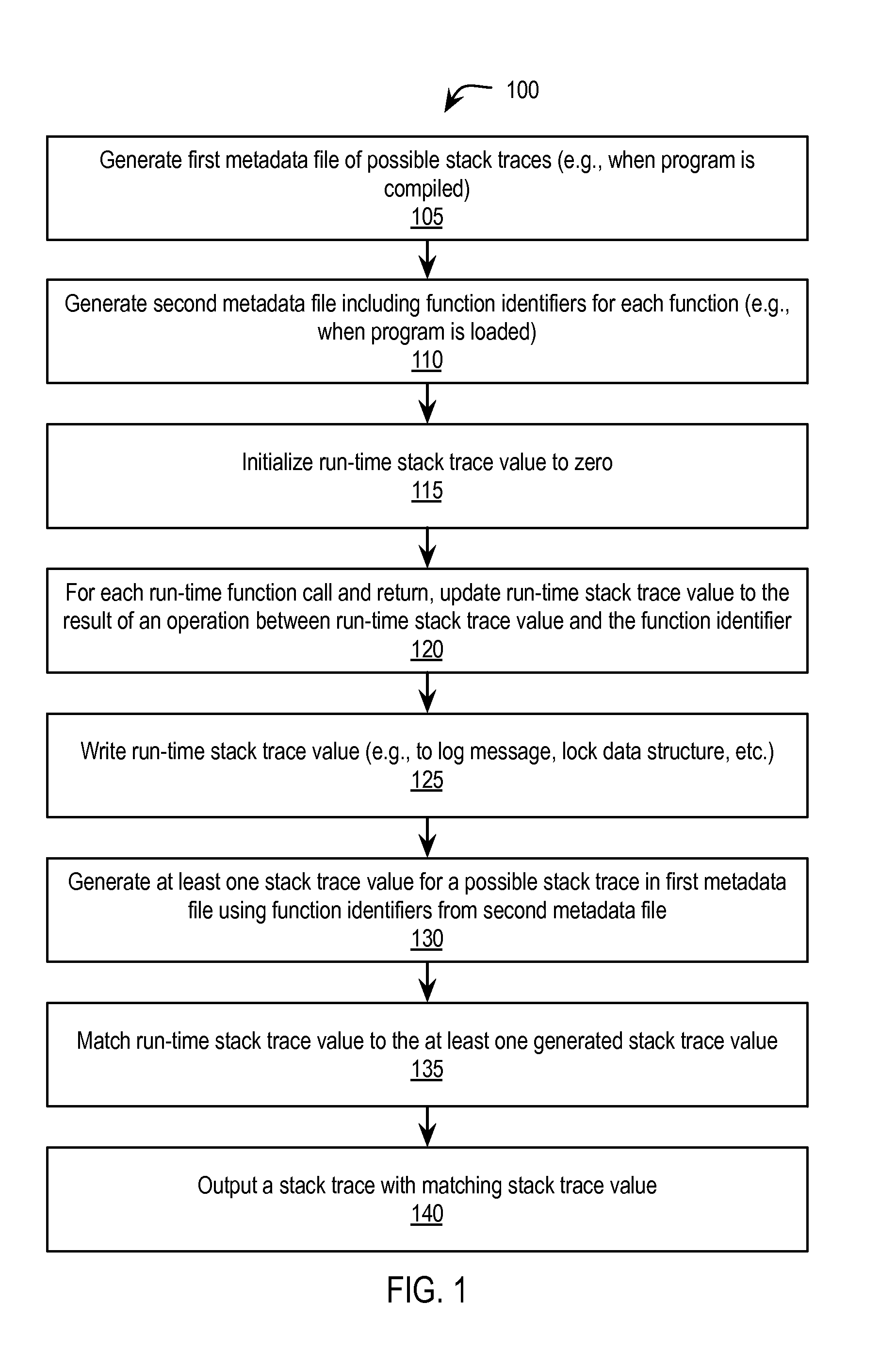

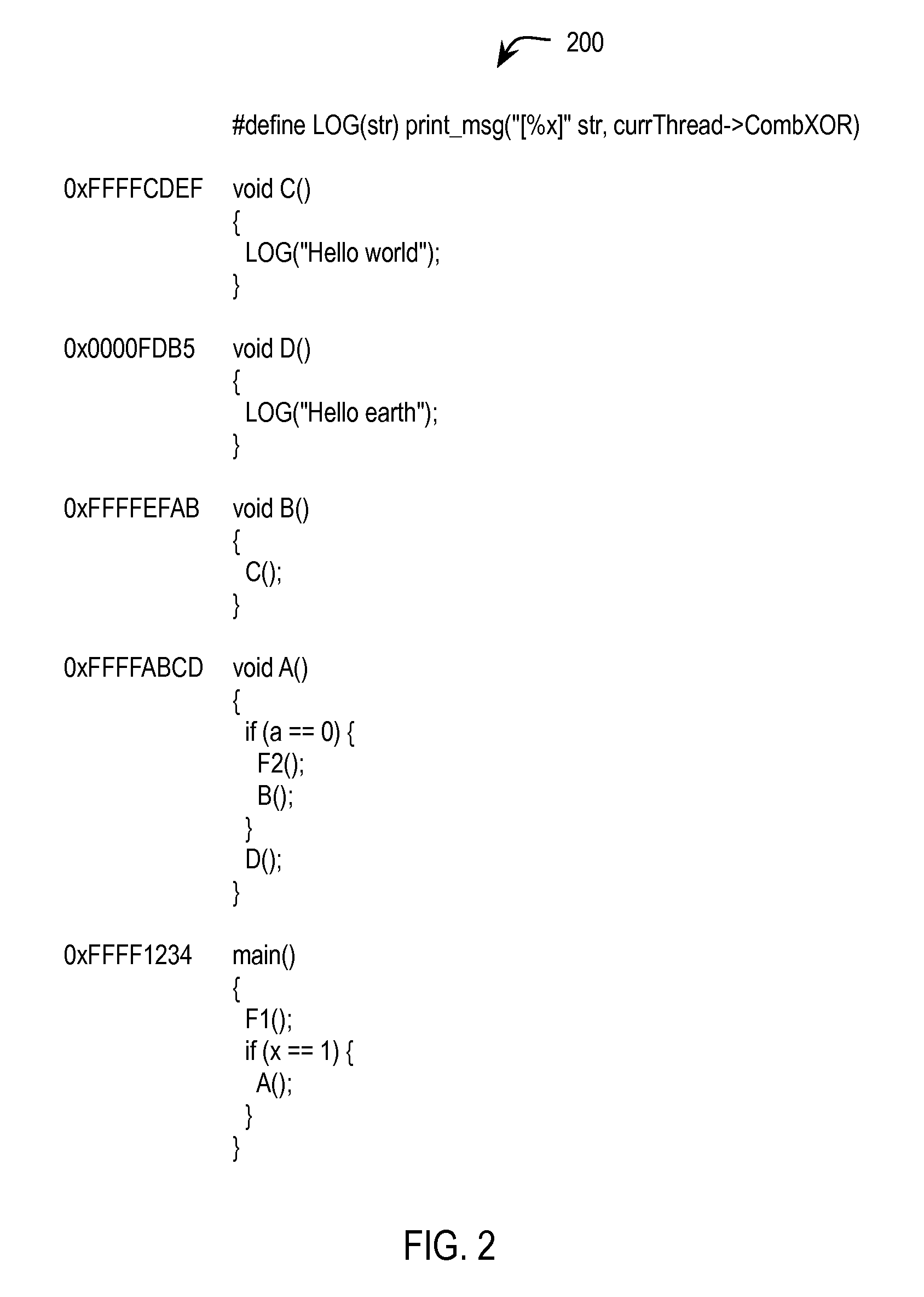

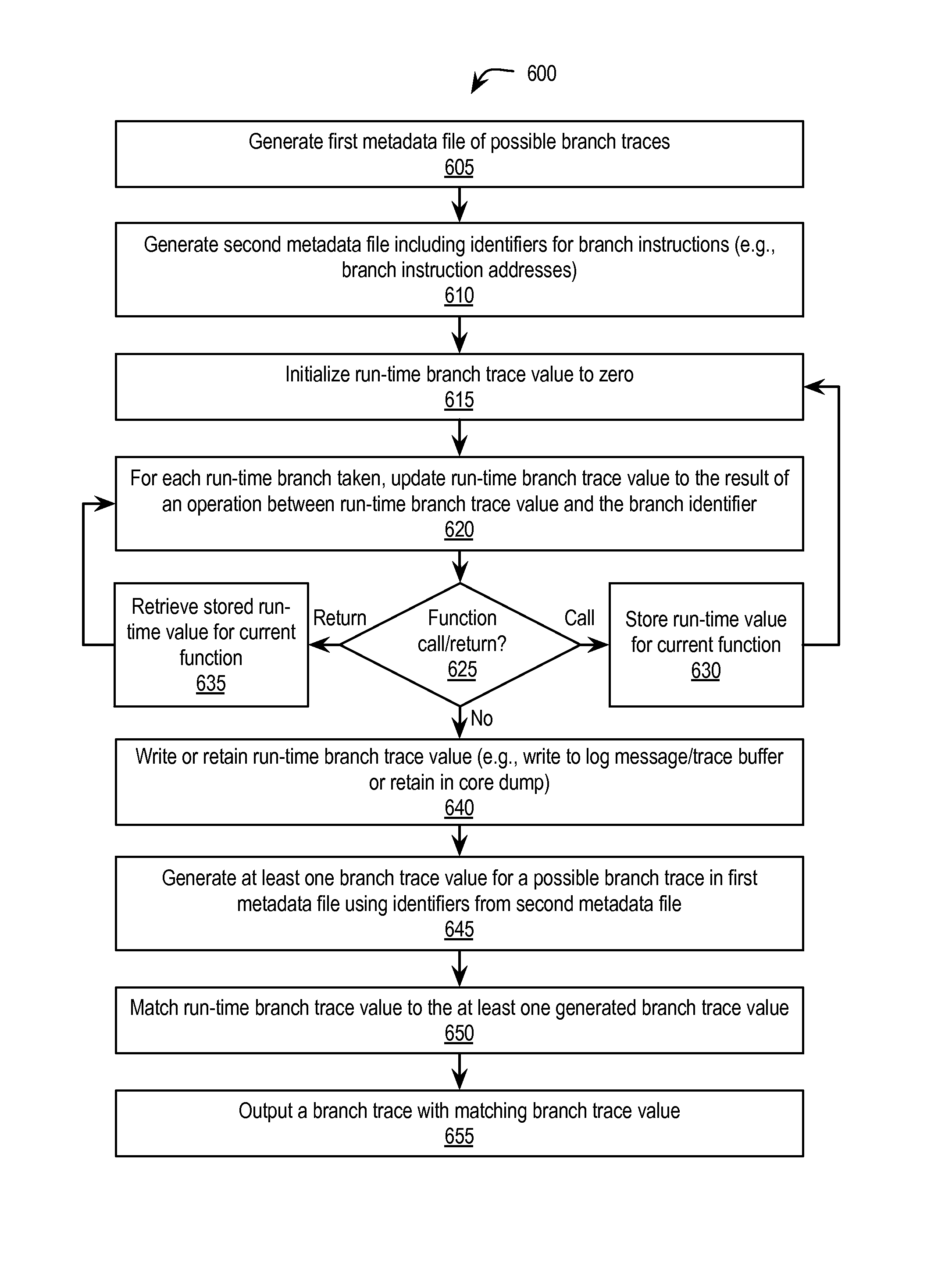

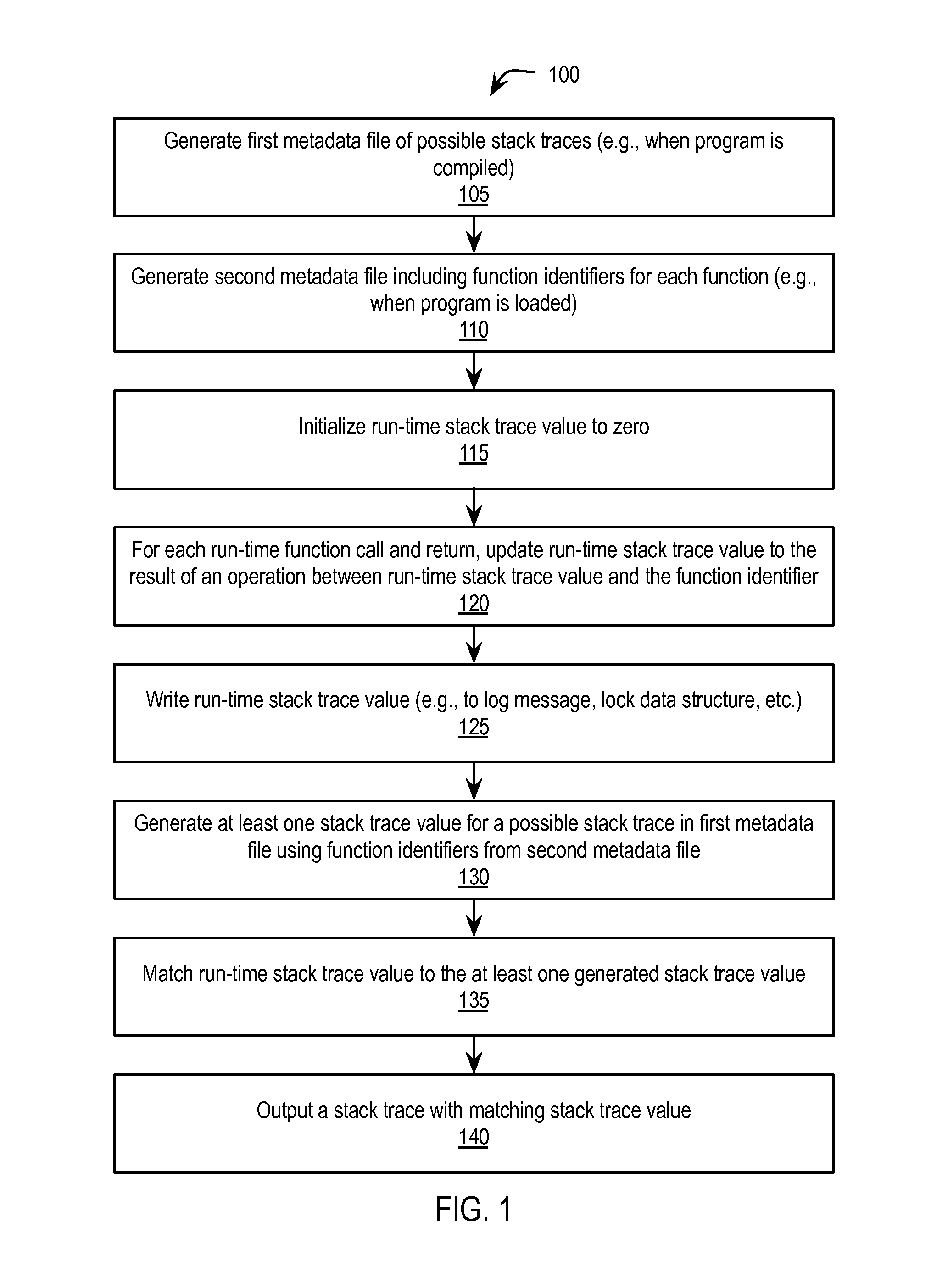

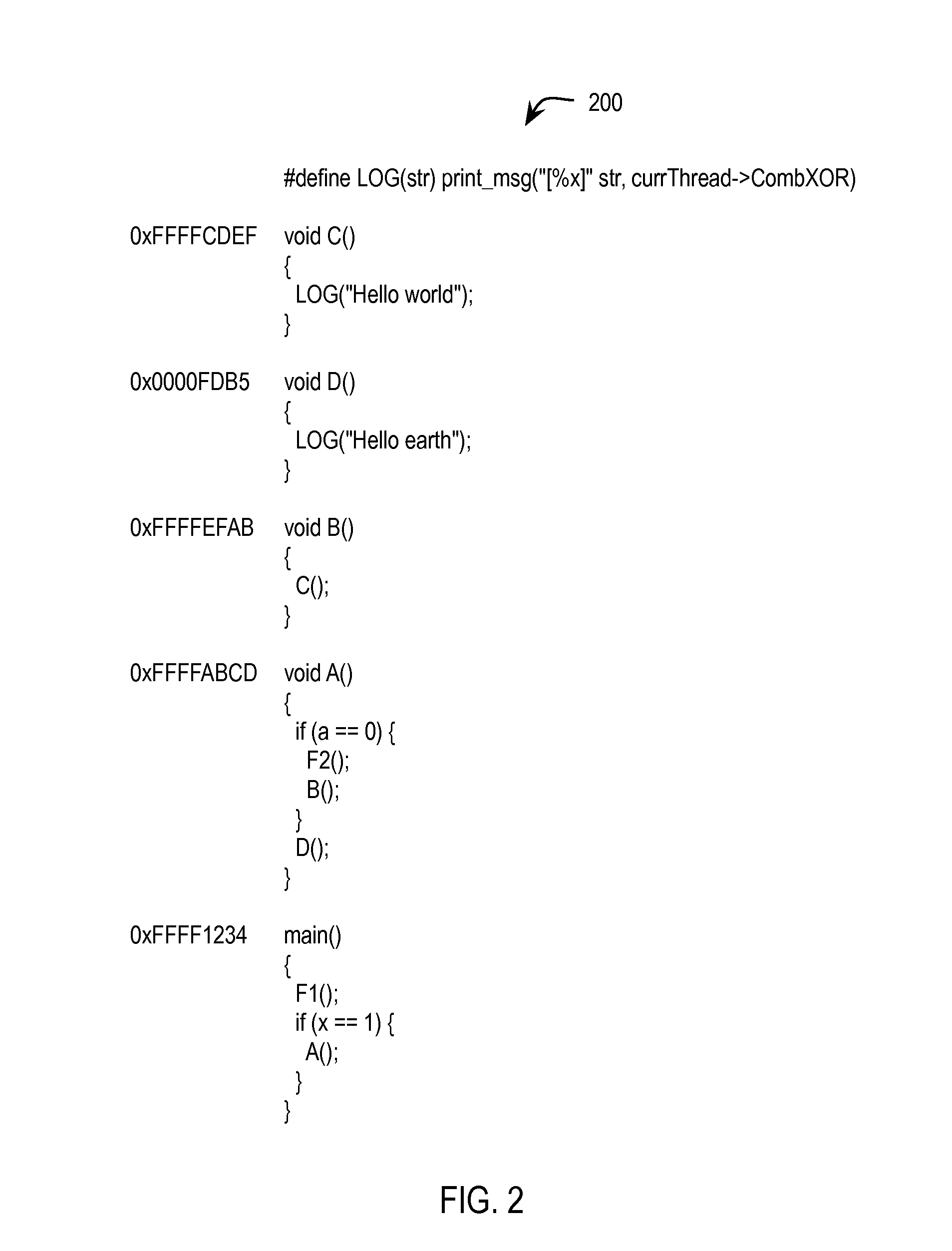

Exemplary methods, apparatuses, and systems generate a plurality of possible branch traces for a computer program. Each possible branch trace represents different sequences of branch instructions that may be executed while the computer program is running. Each branch instruction has a corresponding identifier. A branch trace value is generated for at least one of the plurality of possible branch traces. Generating the branch trace value includes performing a mathematical or logical operation between a first identifier and each subsequent identifier of the possible branch trace to obtain the branch trace value. An output including a branch trace is generated based upon a match between a run-time branch trace value and the at least one generated branch trace value.

Owner:VMWARE INC

Return-to-LIBC attack detection using branch trace records system and method

ActiveUS7284276B2Memory loss protectionDigital data processing detailsOperational systemBranch trace

A method includes stalling a call to a critical operating system (OS) function and determining whether branch trace records of the call include a return instruction. Upon a determination that the branch trace records of the call do include a return instruction, the method further includes taking protective action to protect a computer system.

Owner:CA TECH INC

Branch trace compression

Exemplary methods, apparatuses, and systems generate a plurality of possible branch traces for a computer program. Each possible branch trace represents different sequences of branch instructions that may be executed while the computer program is running. Each branch instruction has a corresponding identifier. A branch trace value is generated for at least one of the plurality of possible branch traces. Generating the branch trace value includes performing a mathematical or logical operation between a first identifier and each subsequent identifier of the possible branch trace to obtain the branch trace value. An output including a branch trace is generated based upon a match between a run-time branch trace value and the at least one generated branch trace value.

Owner:VMWARE INC

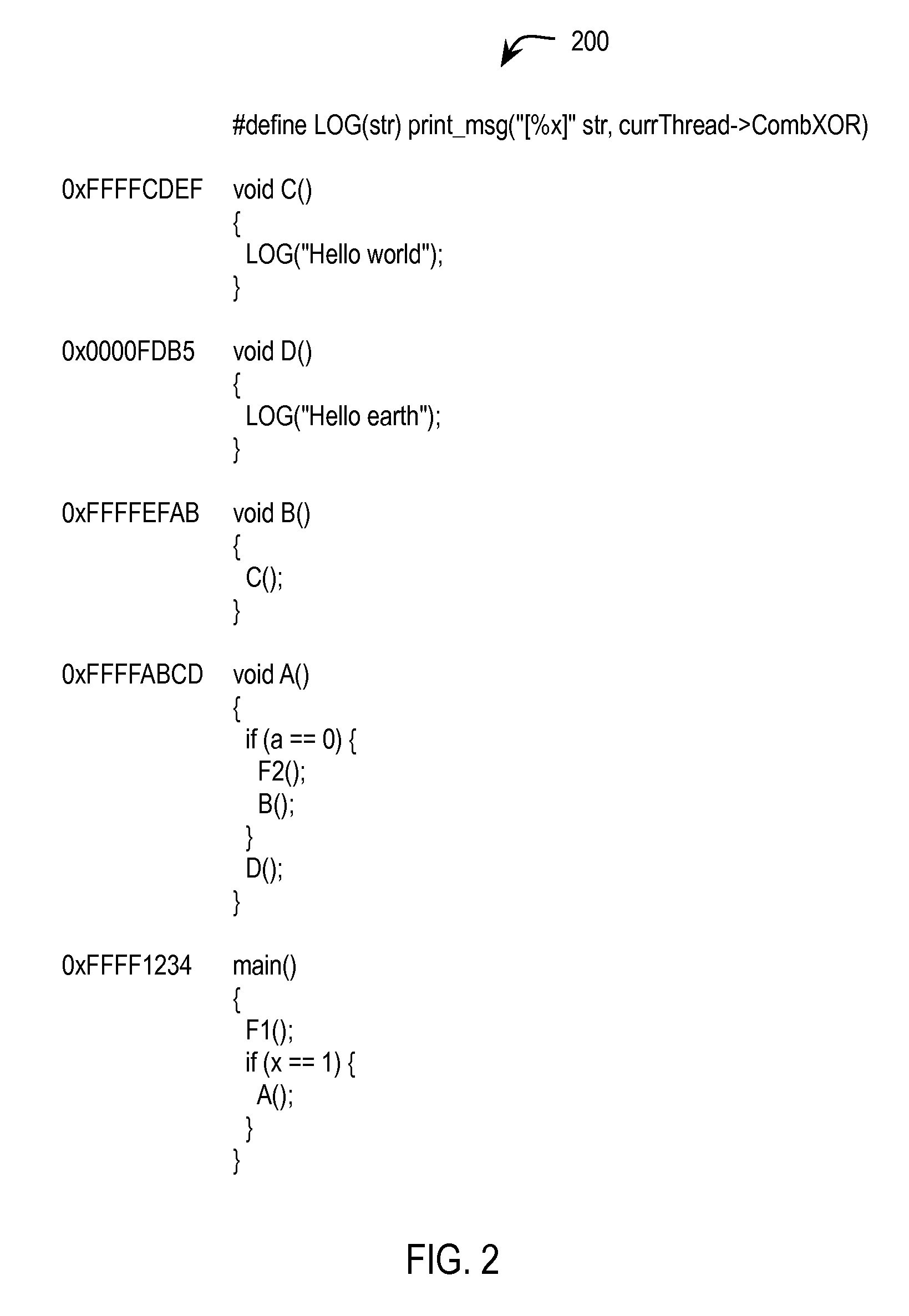

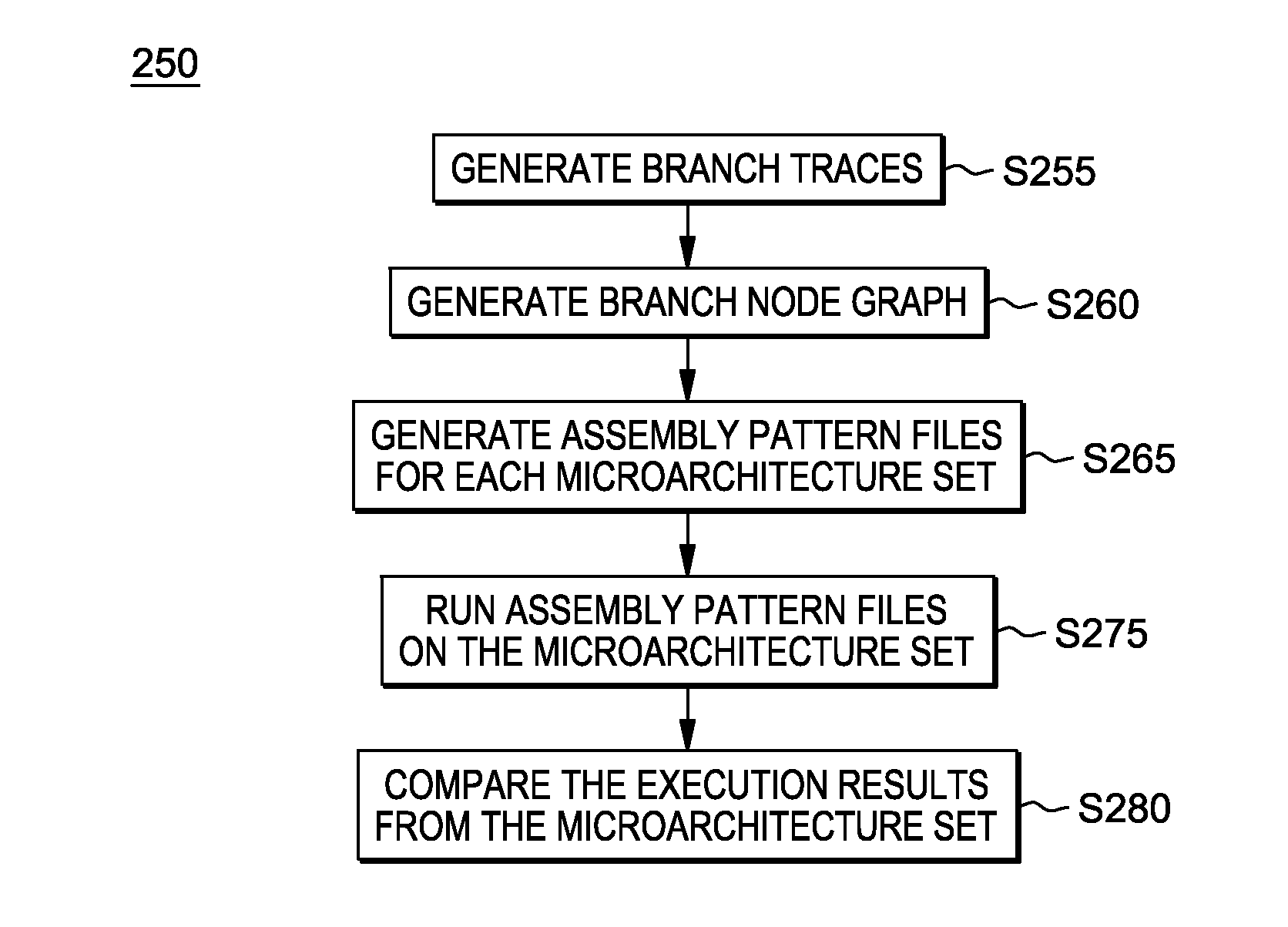

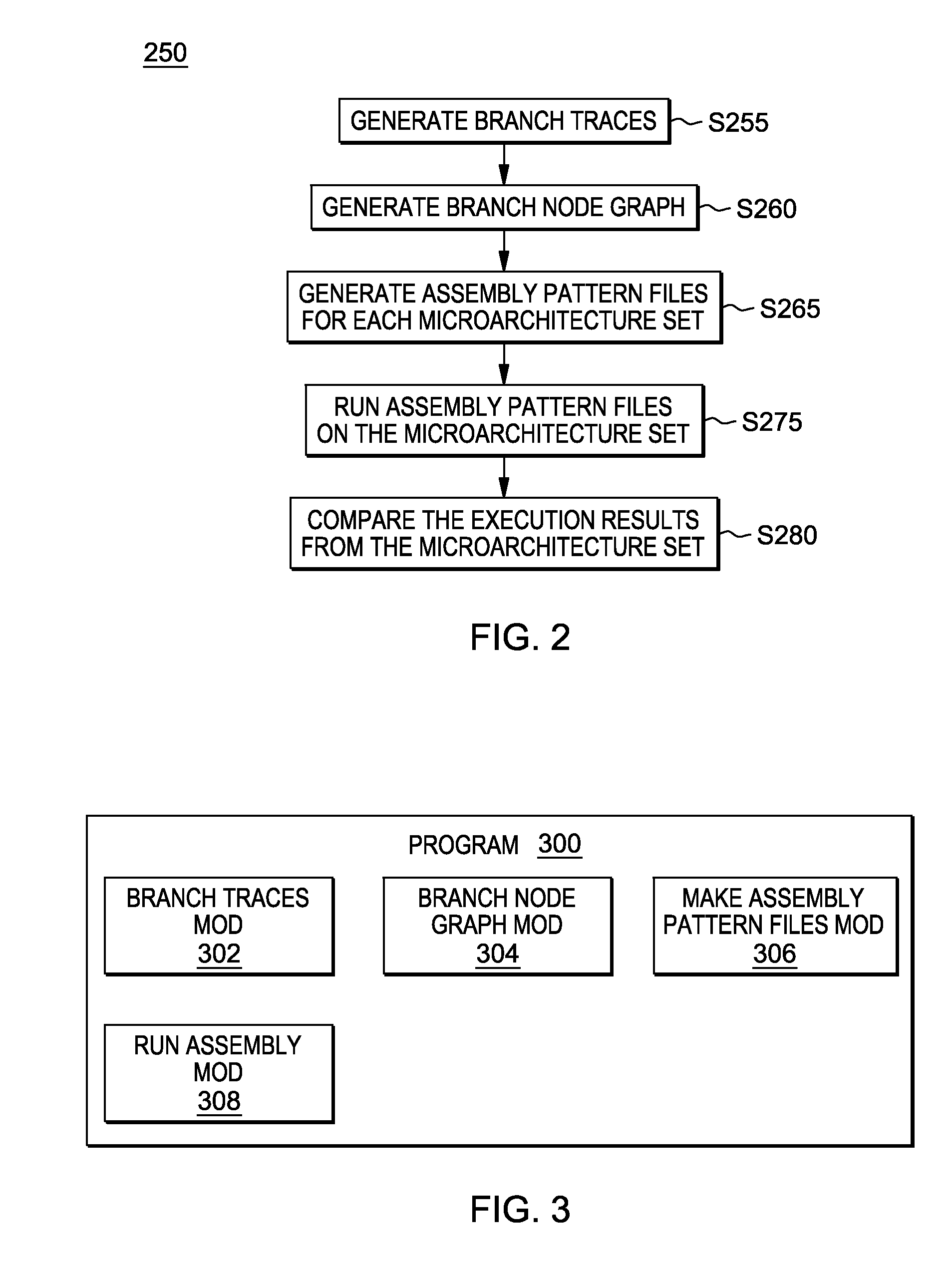

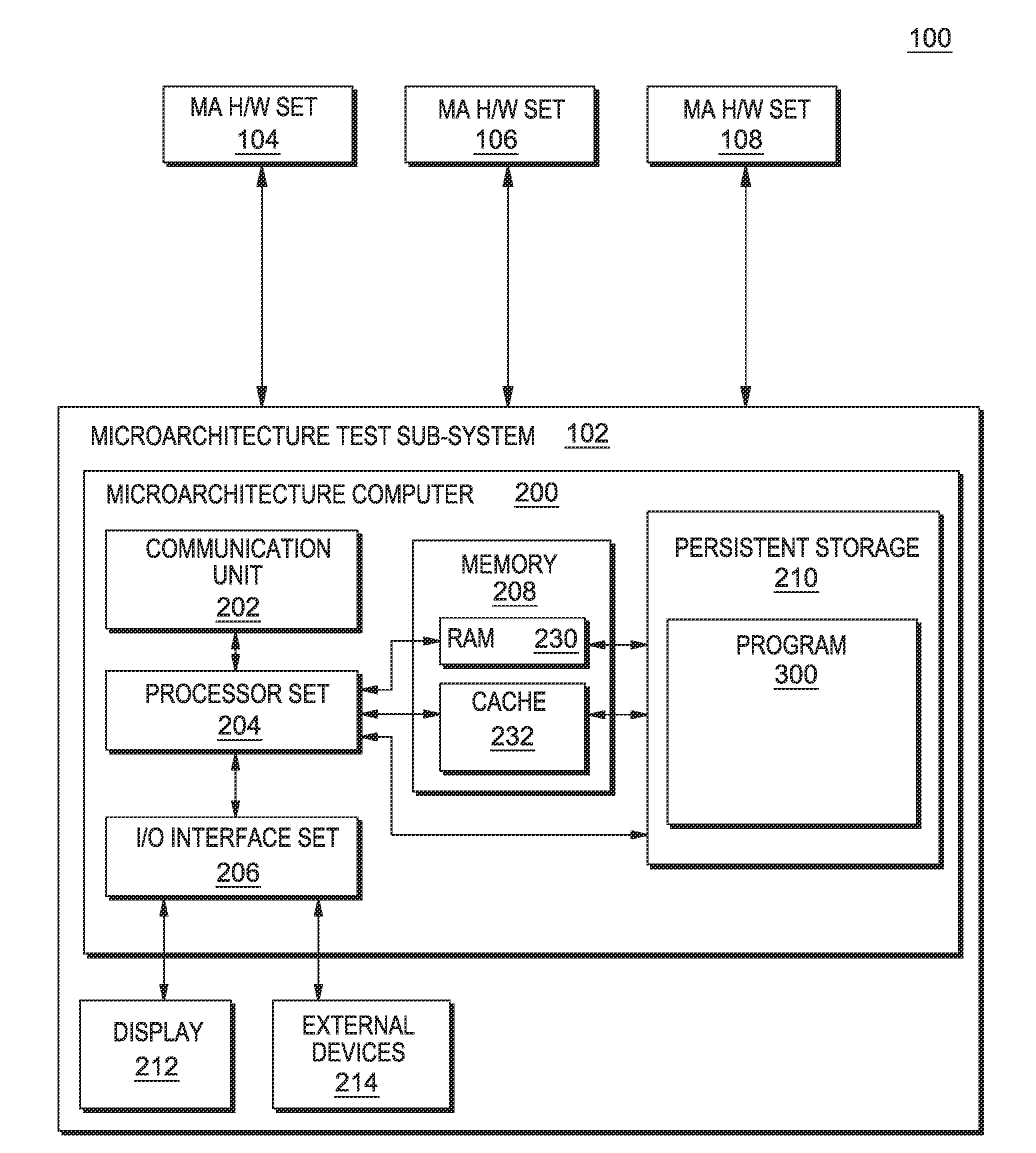

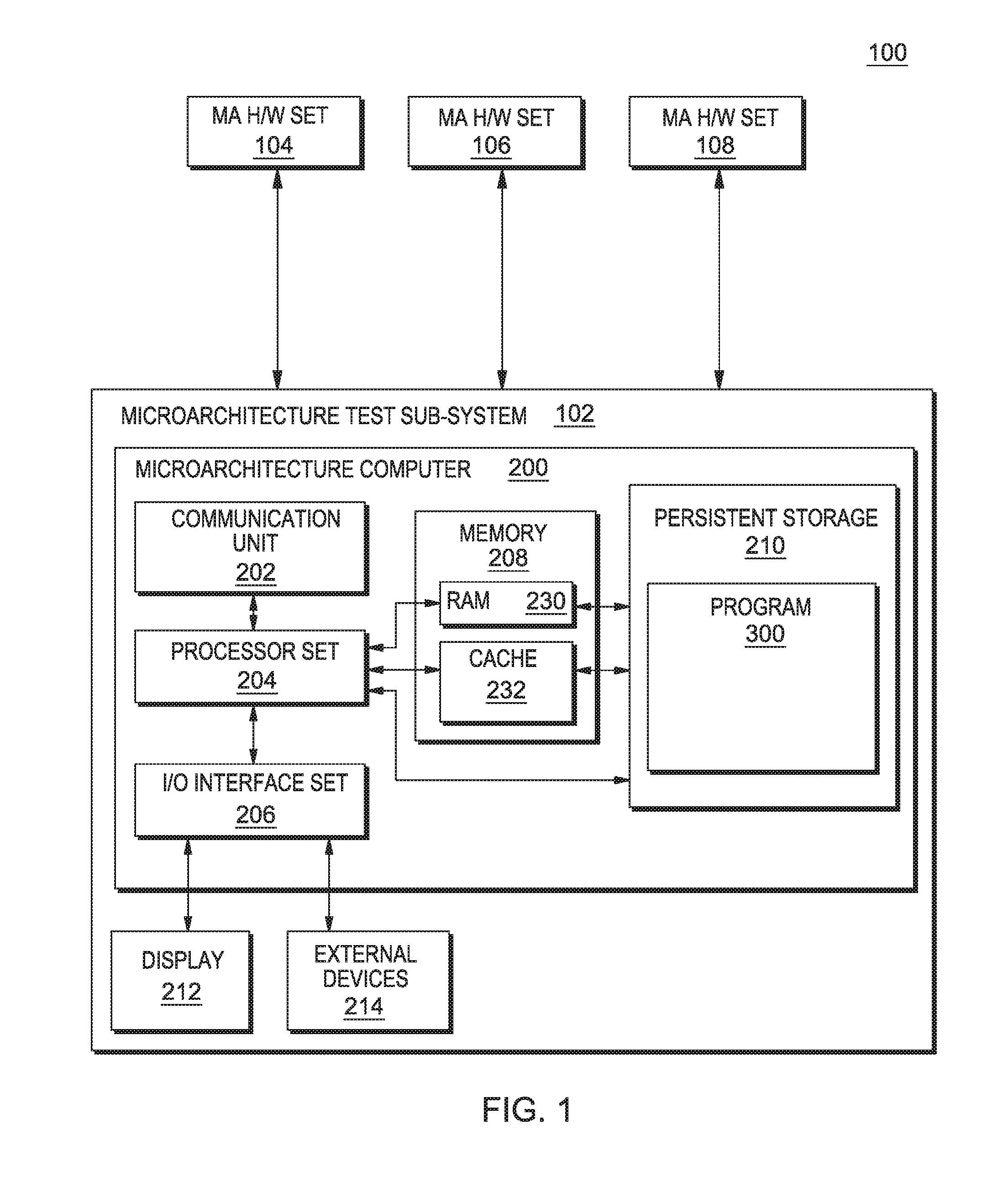

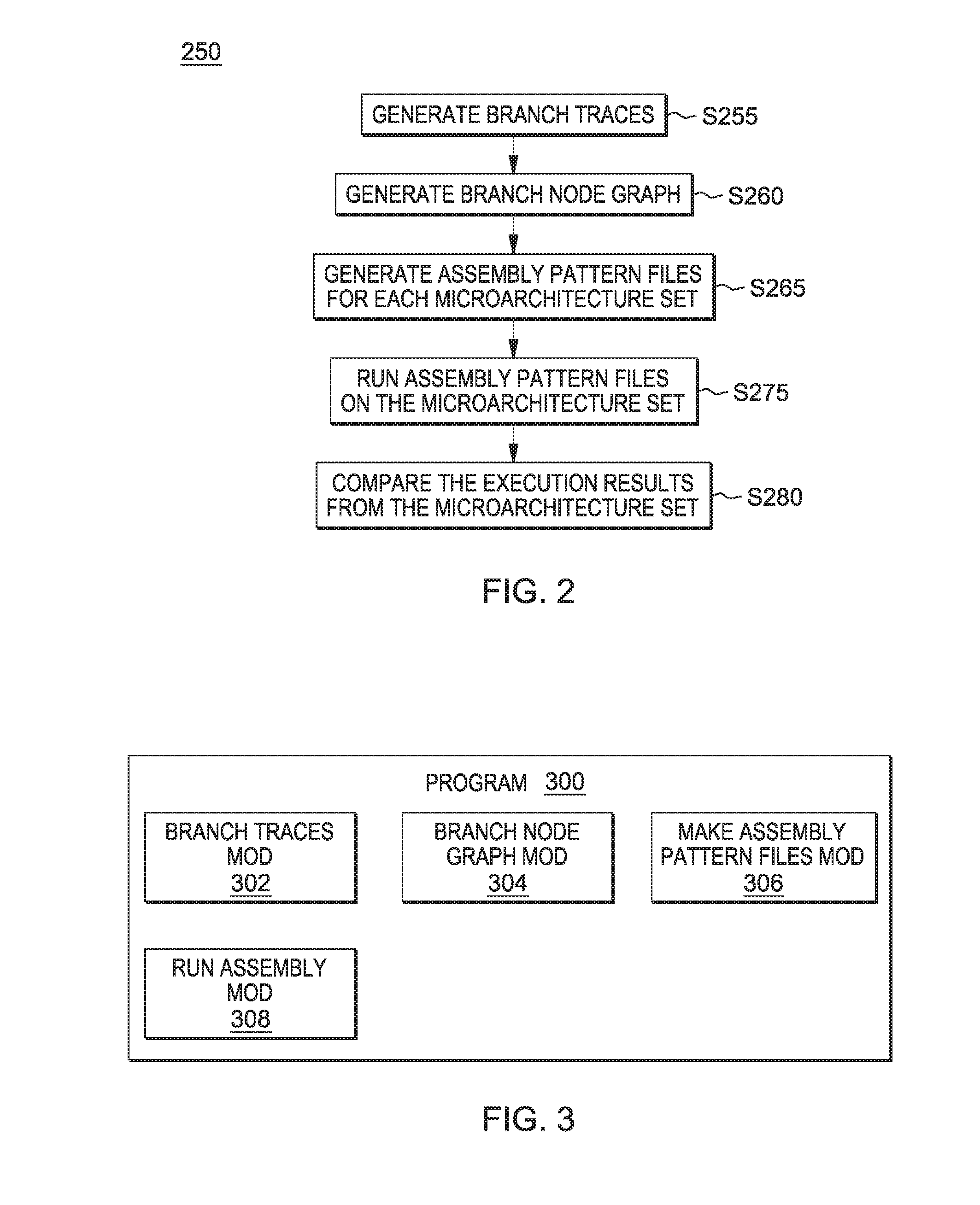

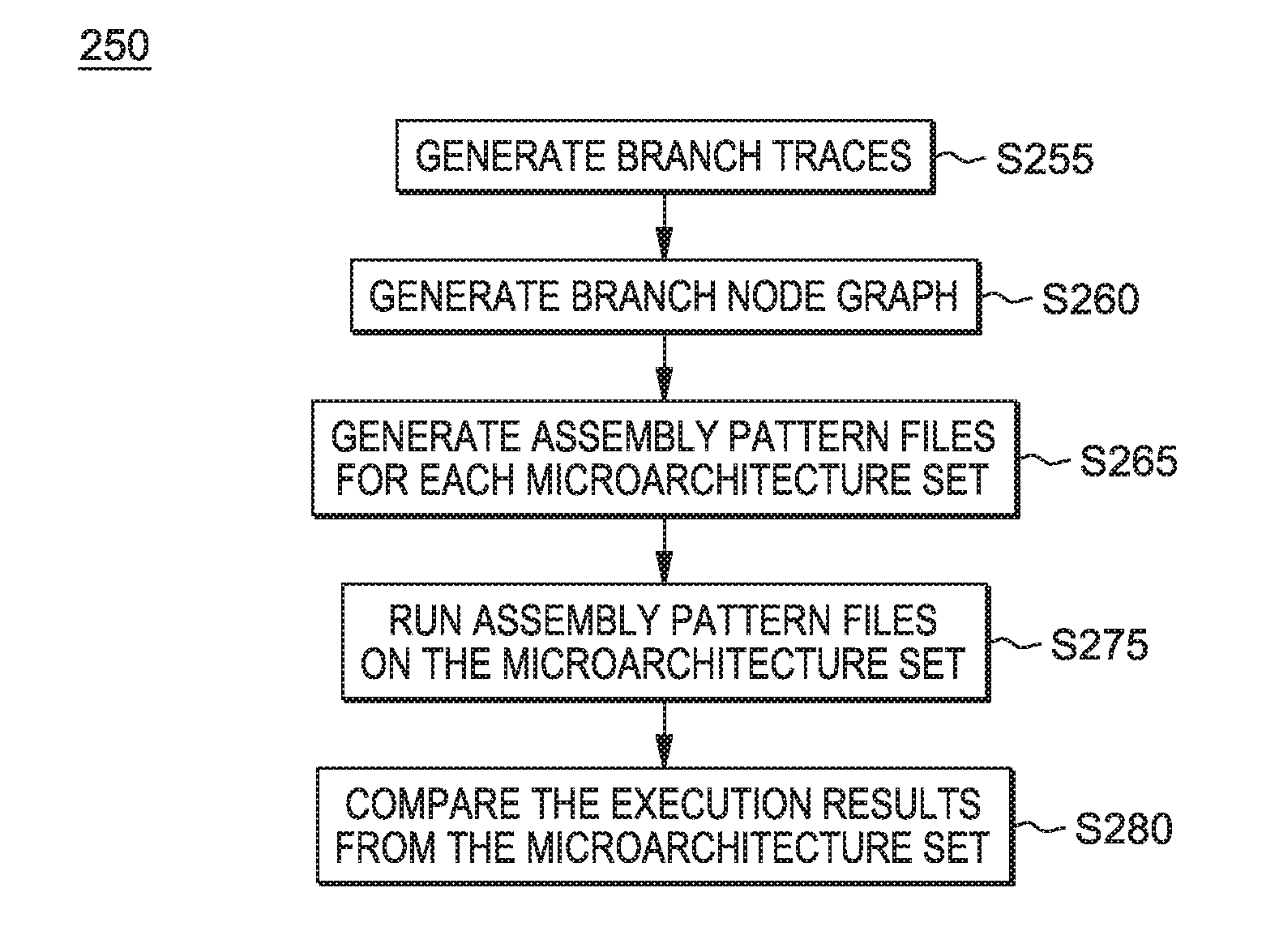

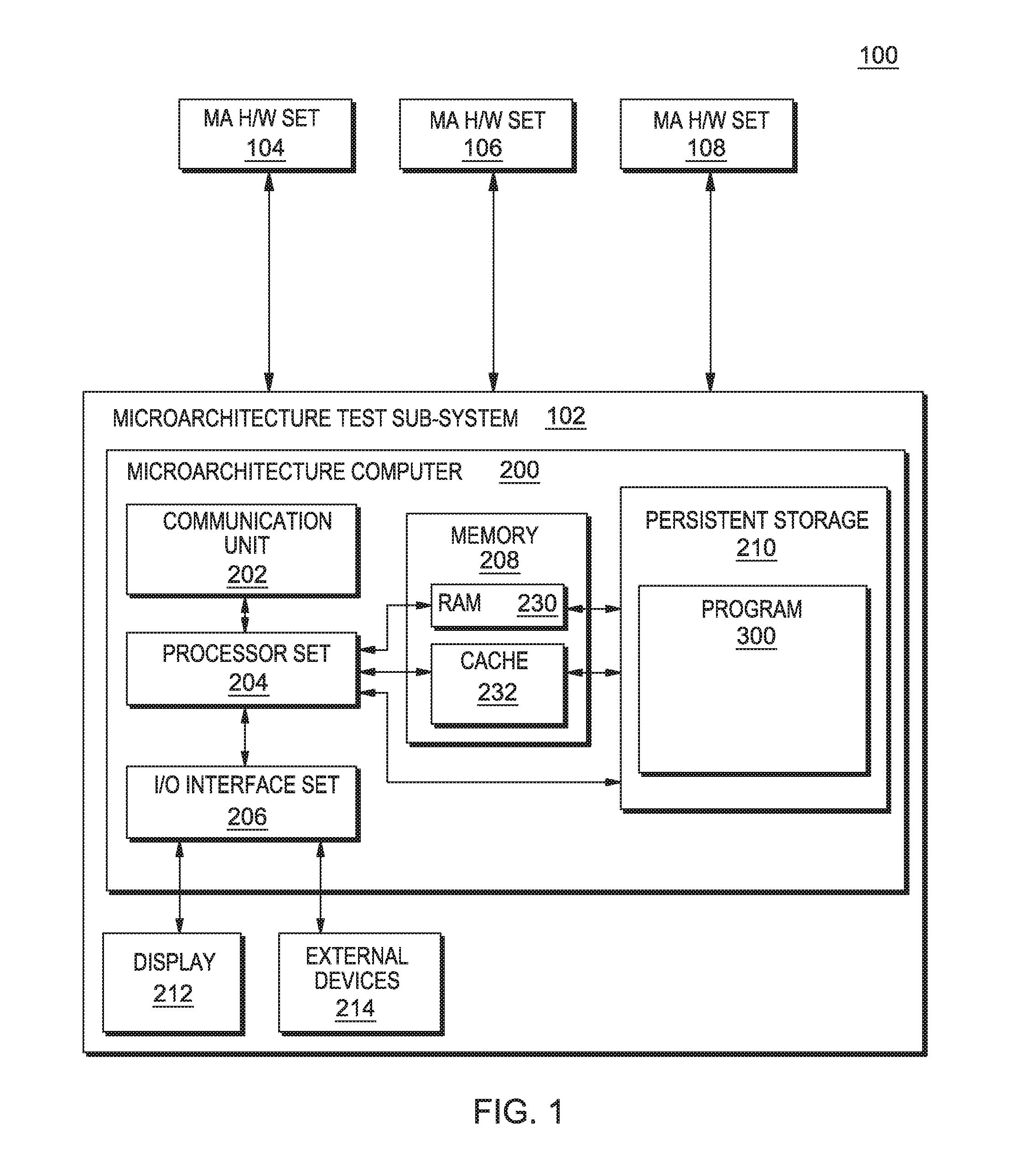

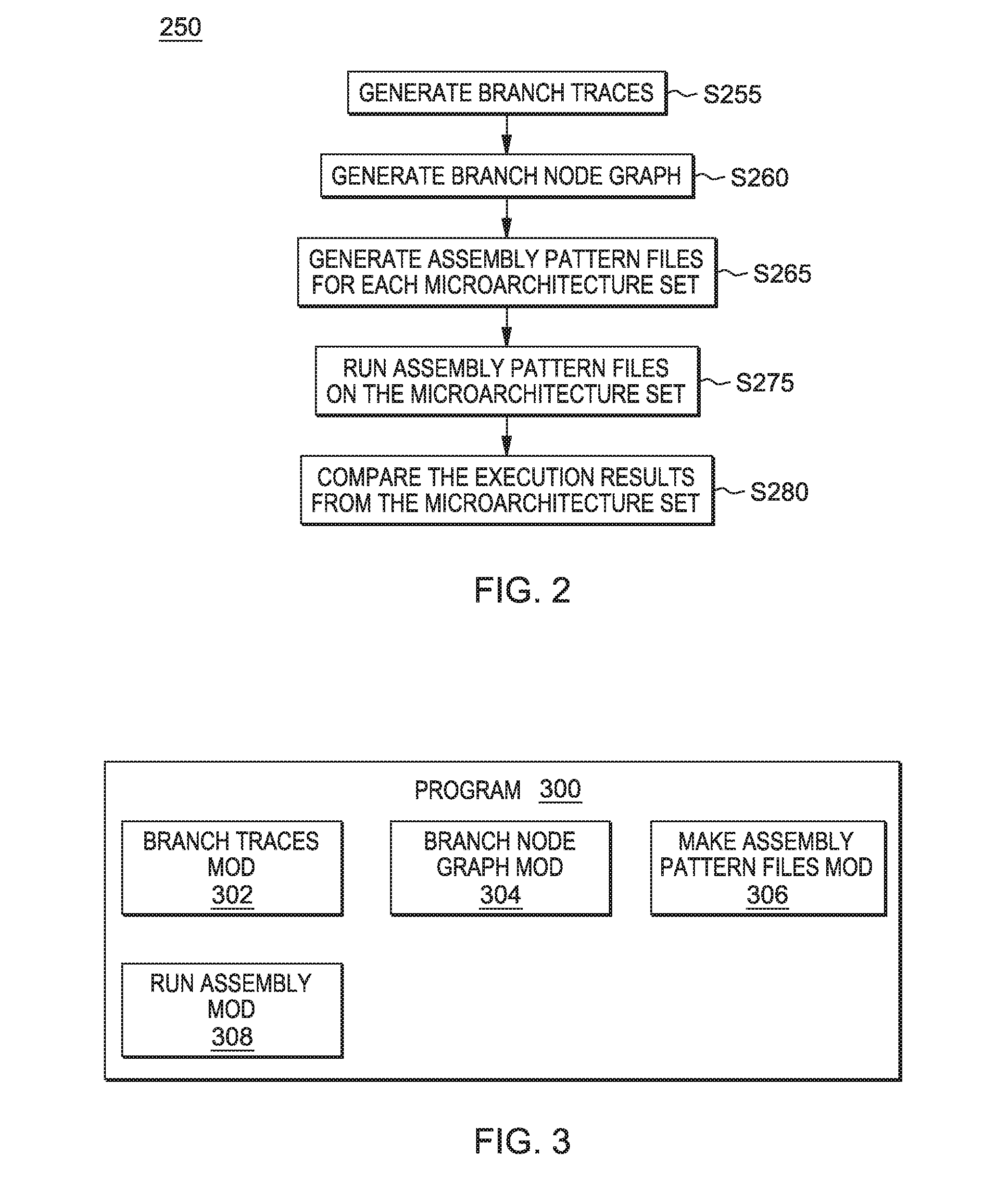

Branch synthetic generation across multiple microarchitecture generations

Branch sequences for branch prediction performance test are generated by performing the following steps: (i) generating a branch node graph, by a branch node graph generator machine logic set, based, at least in part, upon a set of branch traces of a workload or benchmark code; (ii) generating a first assembly pattern file, for use with a first instruction set architecture (ISA) / microarchitecture set, by an assembly pattern generator machine logic set, based, at least in part, upon the branch node graph so as to mimic the control-flow pattern of the workload or benchmark code; and (iii) running the assembly pattern file on the first ISA / microarchitecture set to obtain first execution results.

Owner:IBM CORP

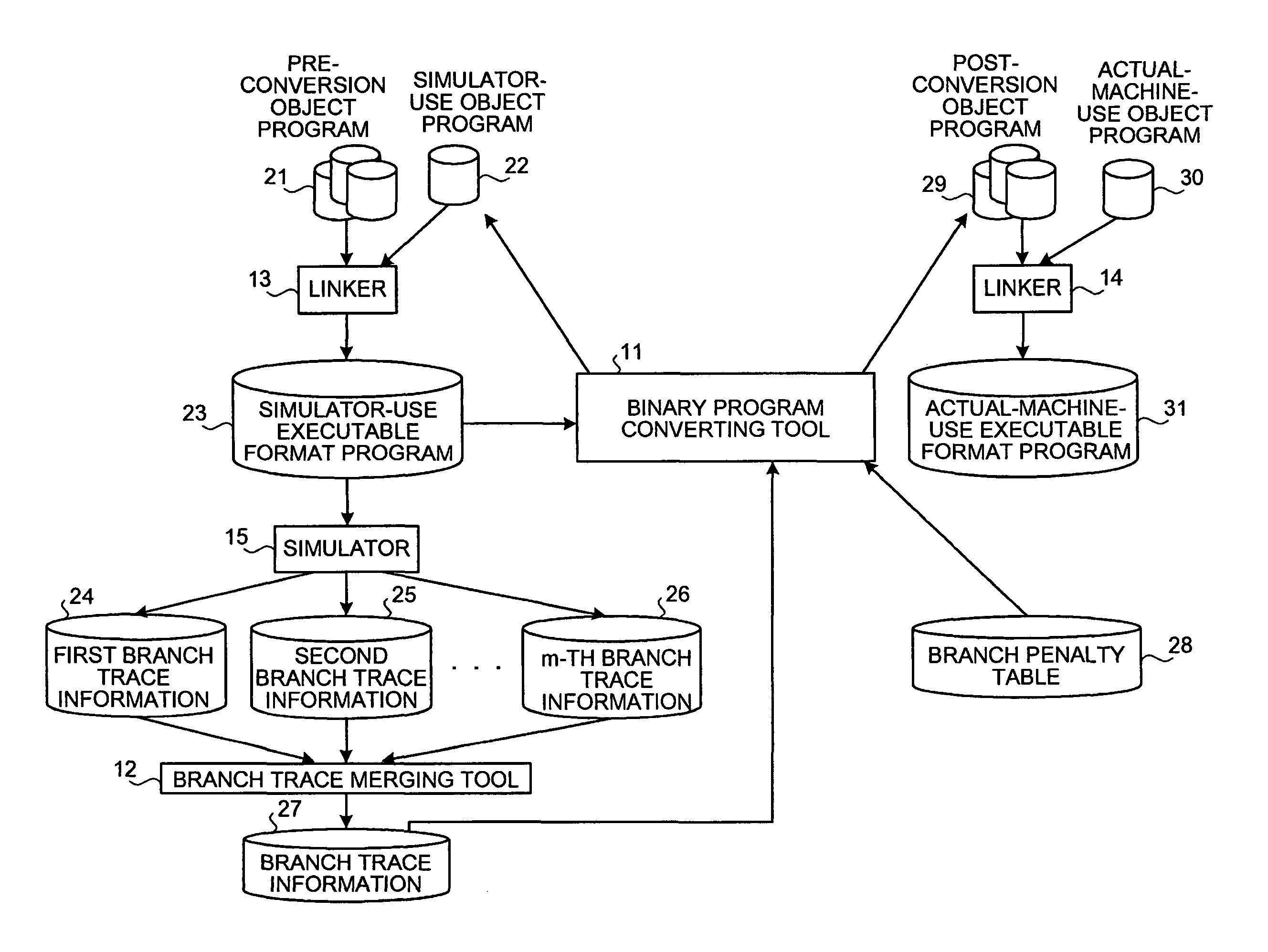

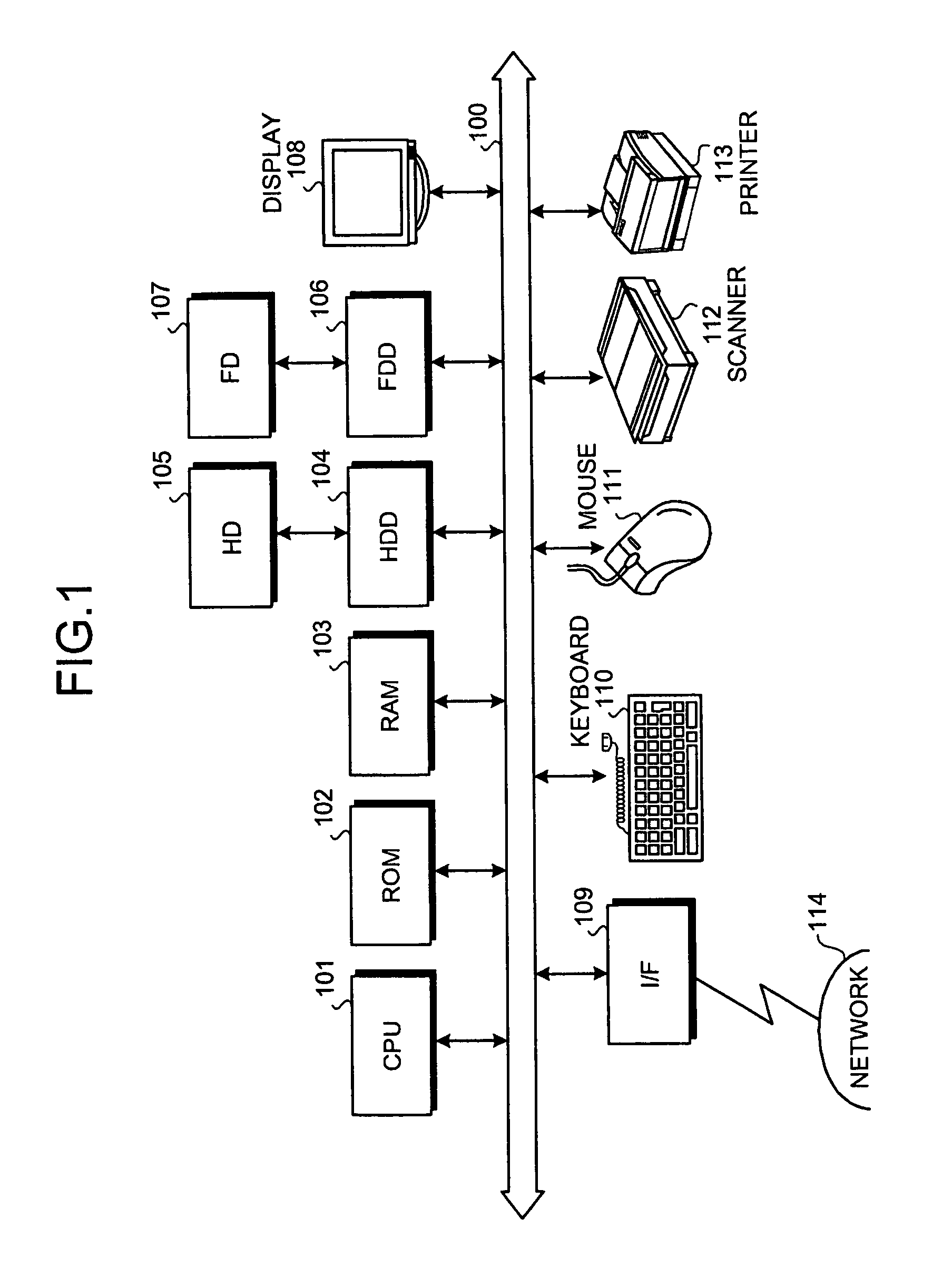

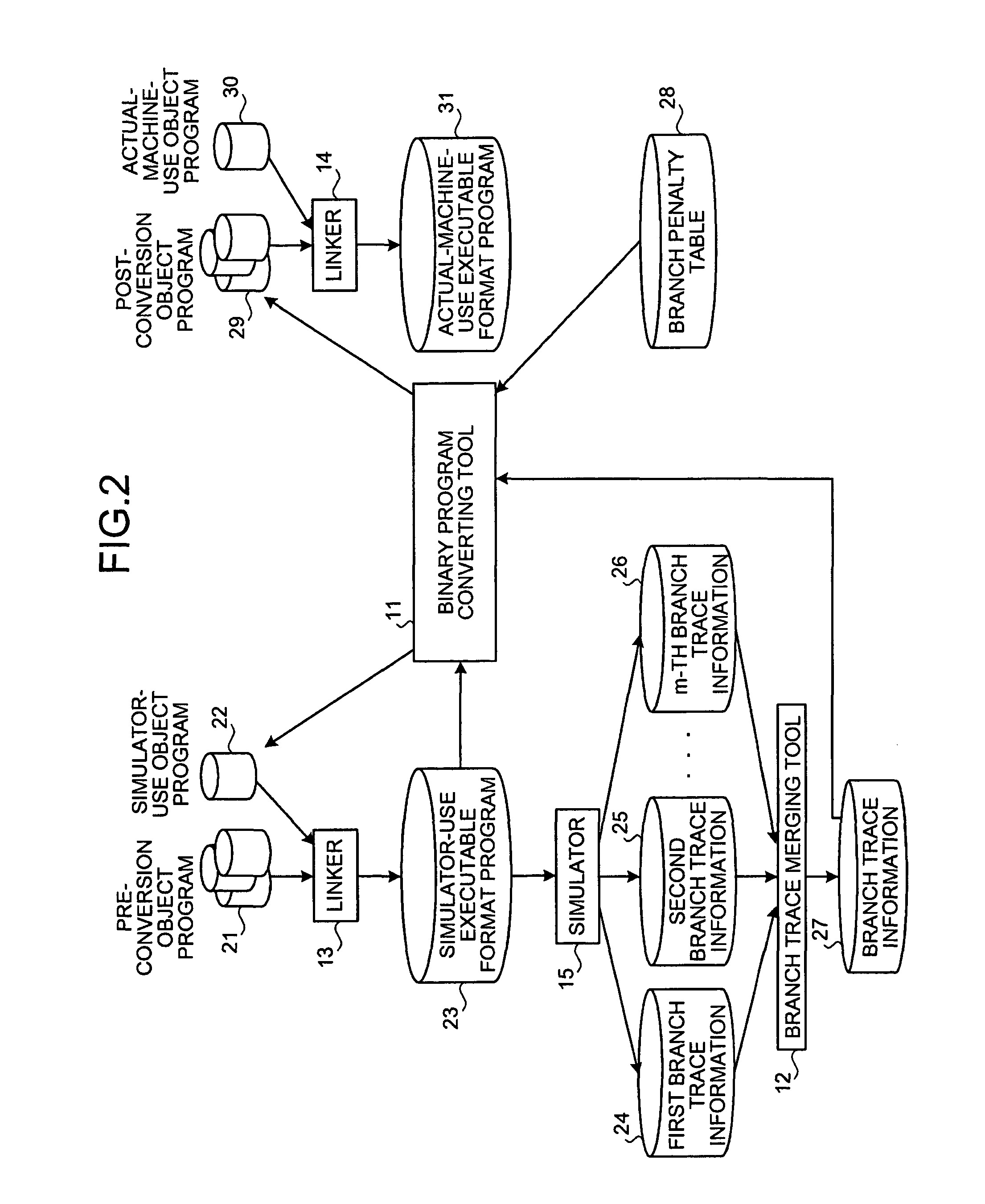

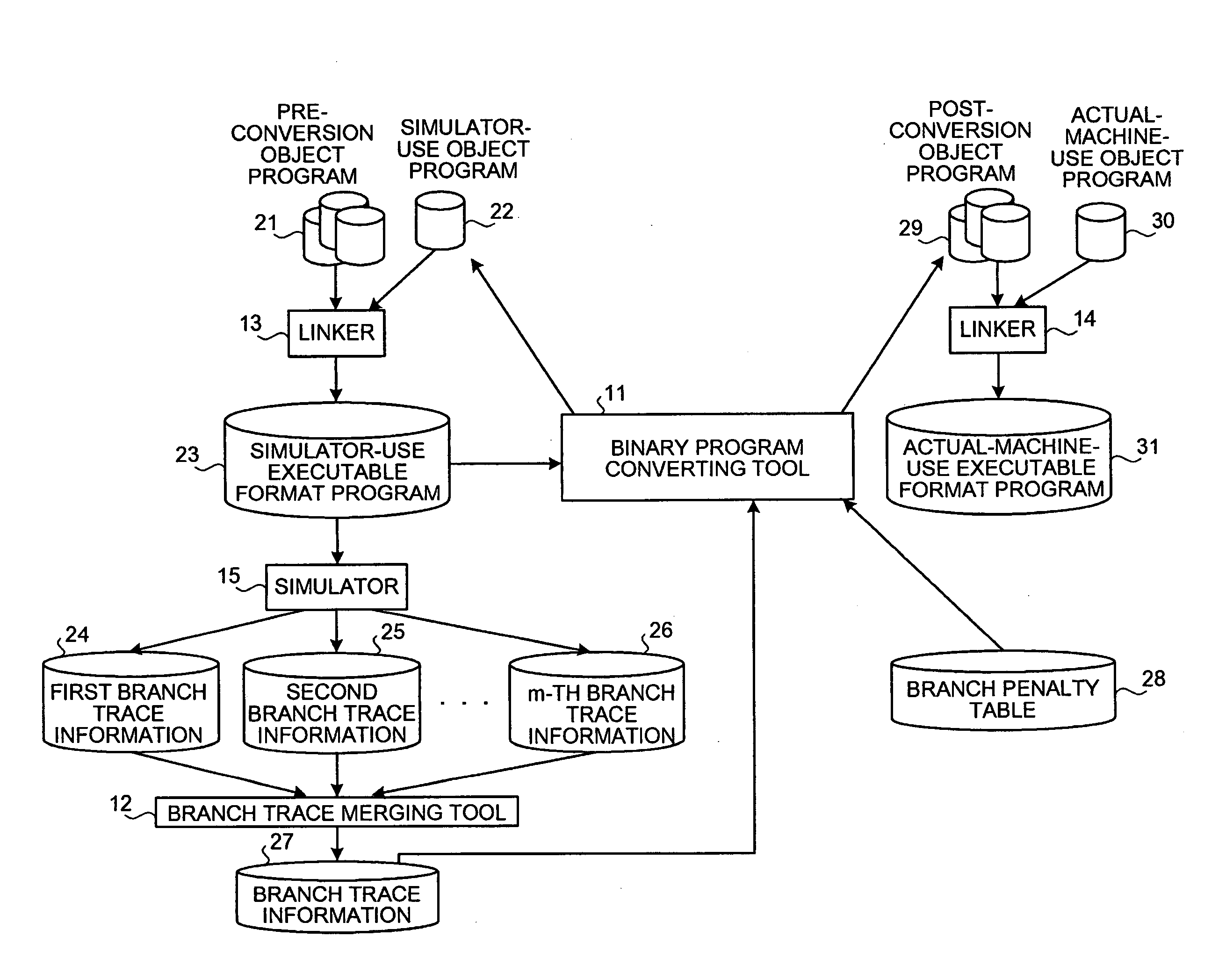

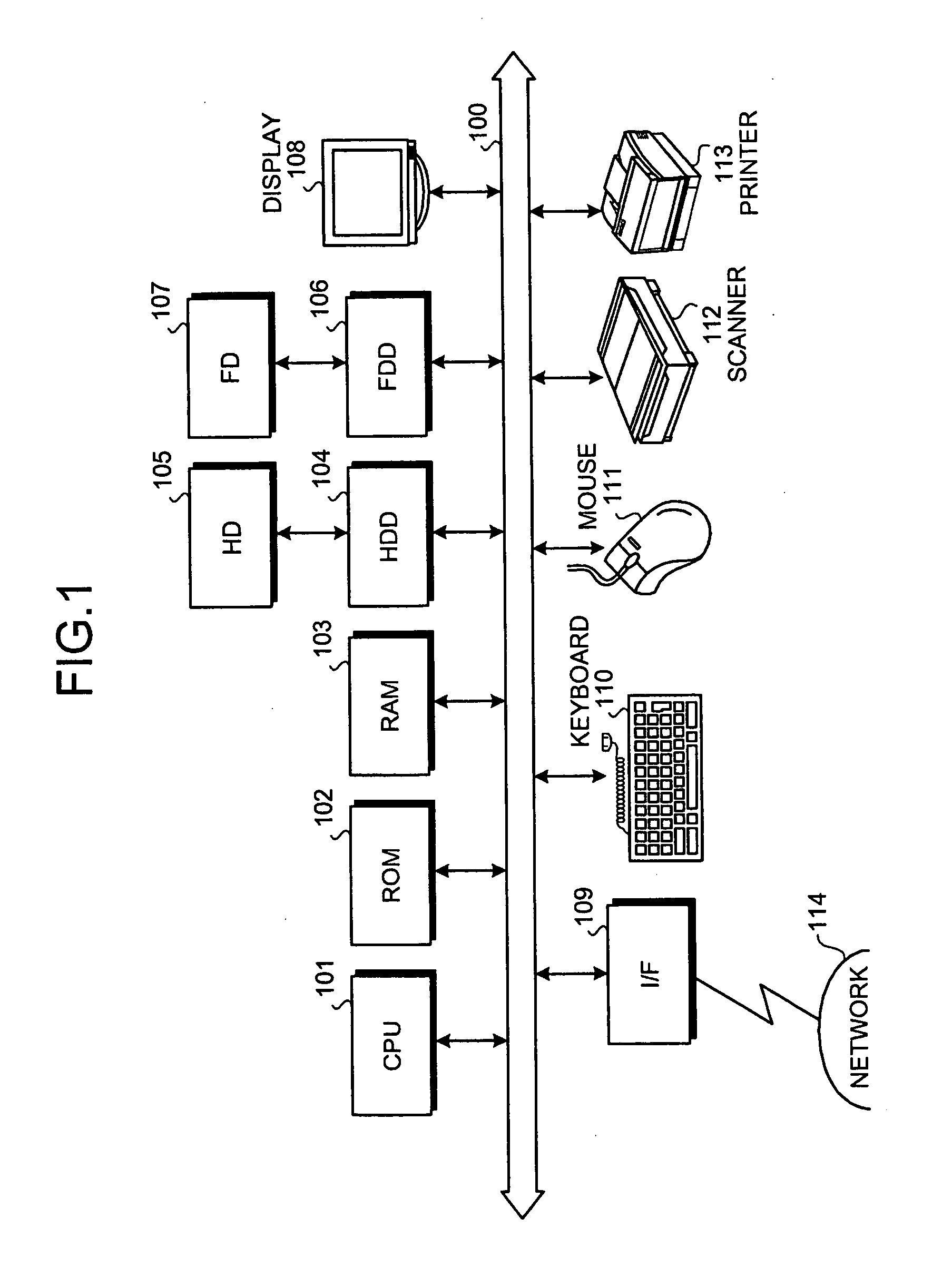

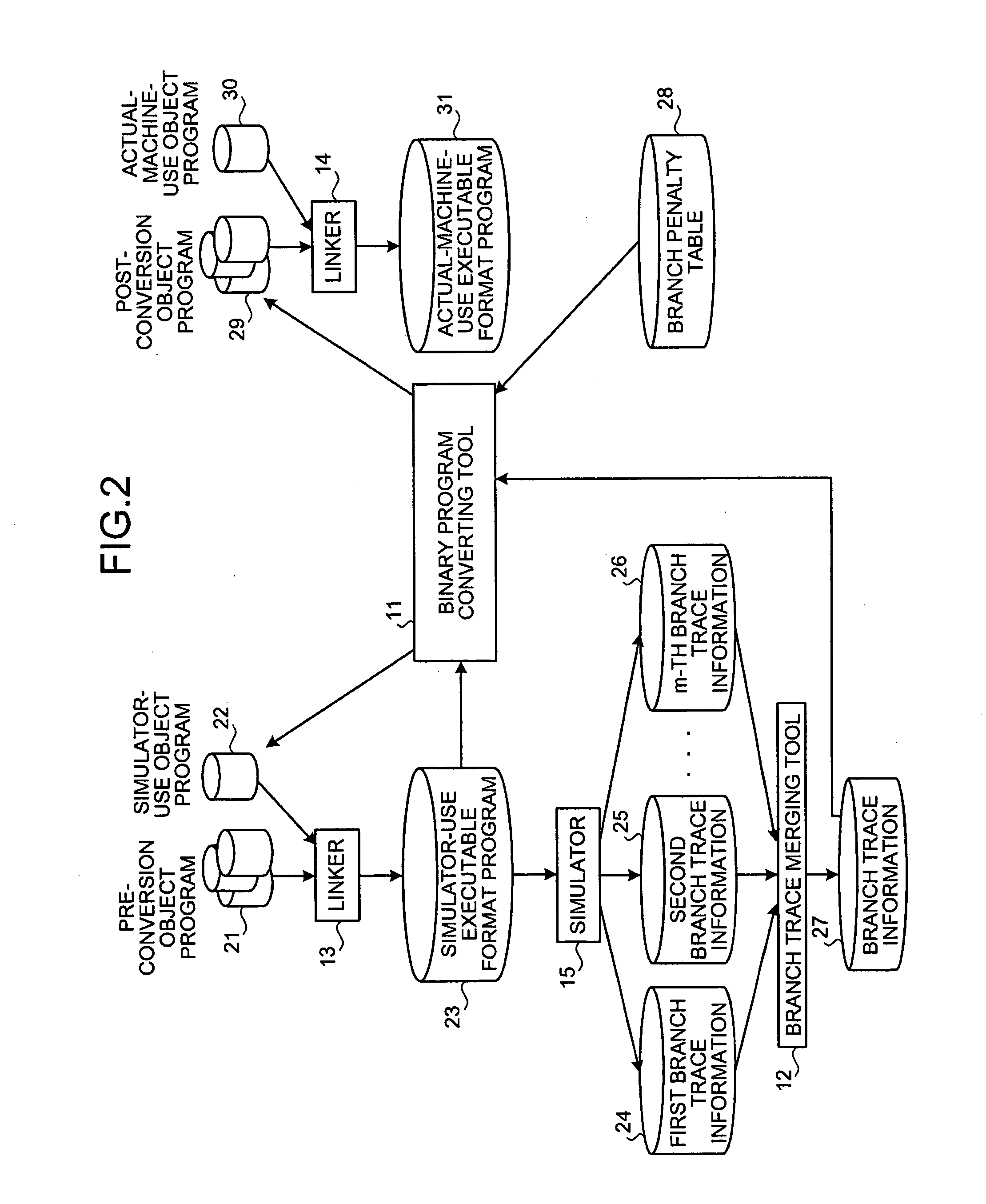

Program conversion apparatus, program conversion method, and computer product

A linker generates a simulator-use executable format program from a pre-conversion object program and a simulator-use object program. A simulator executes the simulator-use object program and acquires branch trace information. A binary program converting tool, based on the branch trace information and a branch penalty table, generates a post-conversion object program having a rewritten branching prediction bit of the pre-conversion object program. Another linker generates an actual-machine-use executable format program from the post-conversion object program and an actual-machine-use object program.

Owner:SOCIONEXT INC

Process for controlling particle size of nano calcium carbonate for sulfur fixation by alternating magnetic field

InactiveCN105948094ANarrow particle size distributionGood dimensional stabilityCalcium/strontium/barium carbonatesMaterial nanotechnologyCALCIUM HYDROXIDE SOLUTIONSulfur

The invention discloses a process for controlling particle size of nano calcium carbonate for sulfur fixation by an alternating magnetic field and relates to the technical field of technologies. The process comprises the steps: additionally arranging the alternating magnetic field outside a reactor; enabling a calcium hydroxide solution to flow through the alternating magnetic field at the rate of 12m / s to 15m / s, and meanwhile, enabling a branch trace solution to enter a microscope observation range from a main passage of the calcium hydroxide solution; slowly introducing CO2 gas into the calcium hydroxide solution, controlling the flow rate of introduced CO2 gas by a flowmeter, and observing the moment when microscopic crystals appear, i.e., appropriate CO2 gas flow; and maintaining the CO2 gas flow until crystallization is completed. According to the process for controlling the particle size of the nano calcium carbonate for sulfur fixation by the alternating magnetic field, disclosed by the invention, by the alternating magnetic field, the agglomeration among calcium carbonate grains is controlled, the dimensional stability is improved, and the phase interfacial tension is lowered, so that the sulfur fixation reaction performance of the nano calcium carbonate is improved, the nano calcium carbonate can have relatively good sulfur fixation capability under the condition of low use level, and thus the field of application of the nano calcium carbonate is widened.

Owner:深圳市第四能源科技有限公司

Program conversion apparatus, program conversion method, and comuter product

A linker generates a simulator-use executable format program from a pre-conversion object program and a simulator-use object program. A simulator executes the simulator-use object program and acquires branch trace information. A binary program converting tool, based on the branch trace information and a branch penalty table, generates a post-conversion object program having a rewritten branching prediction bit of the pre-conversion object program. Another linker generates an actual-machine-use executable format program from the post-conversion object program and an actual-machine-use object program.

Owner:SOCIONEXT INC

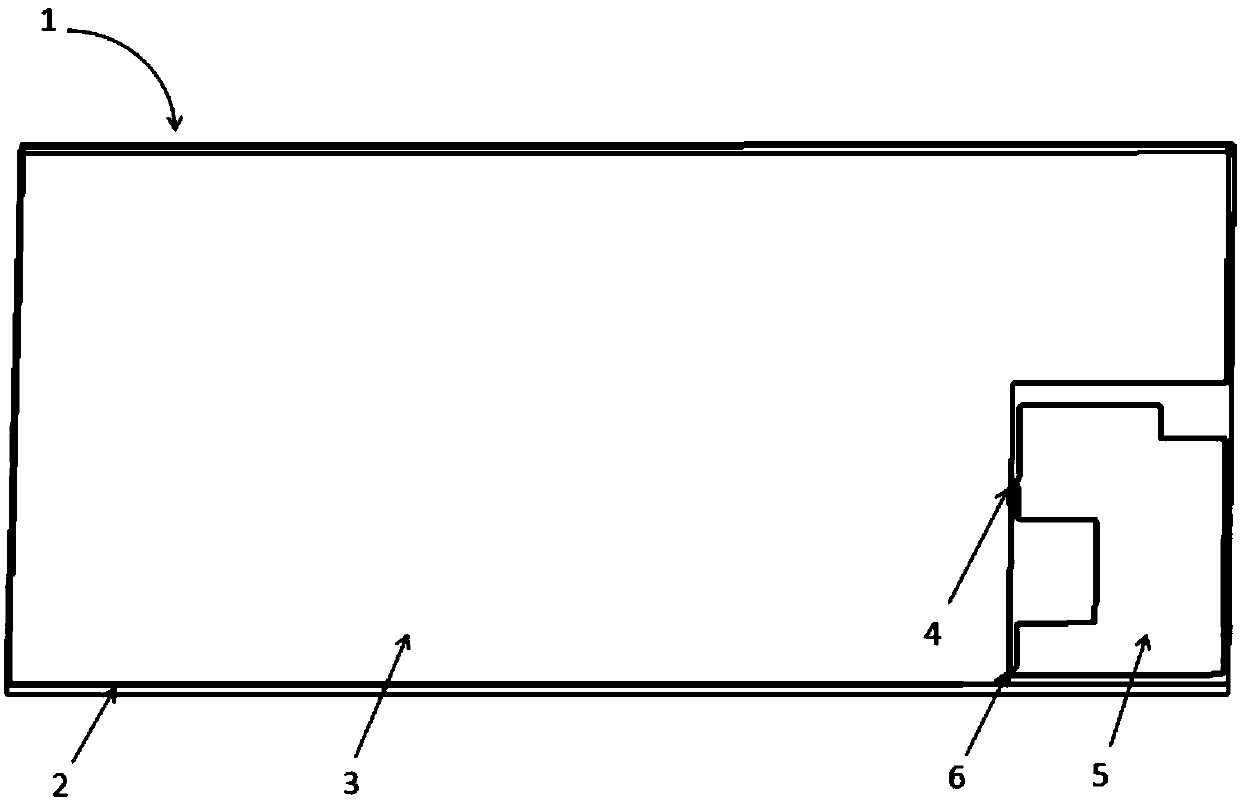

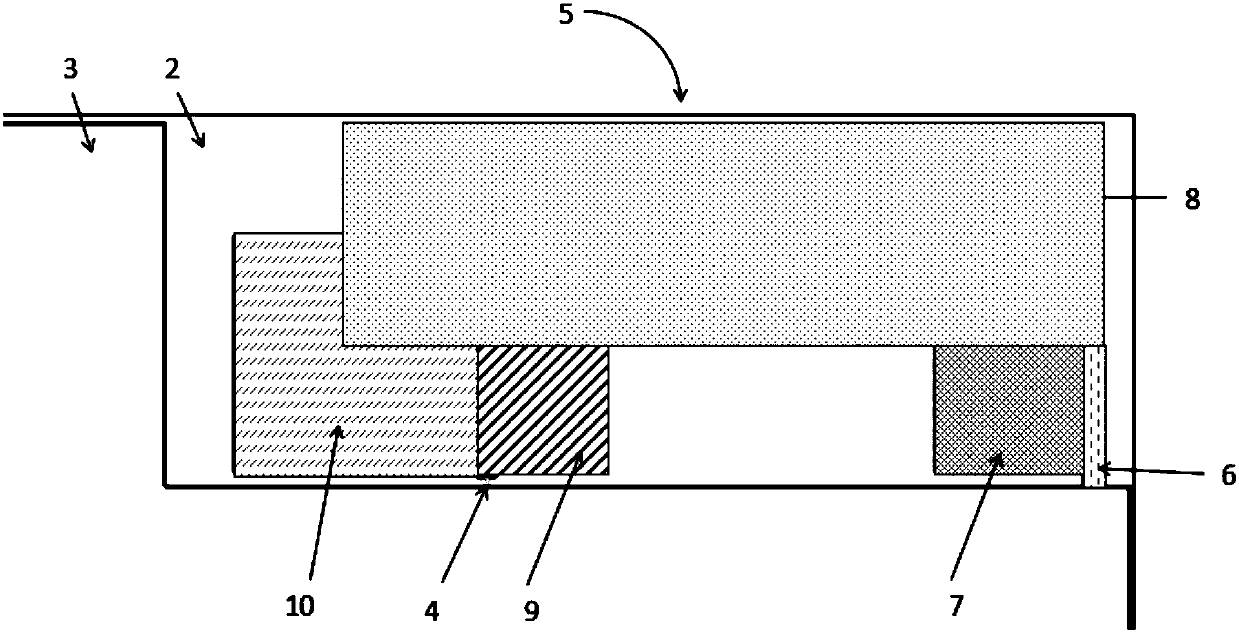

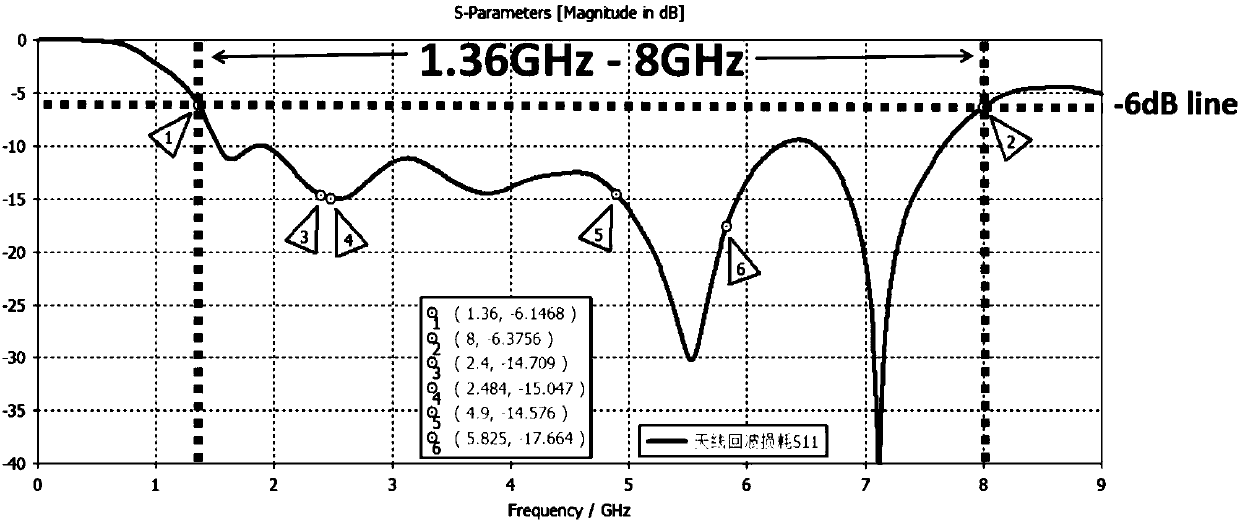

Novel broadband PCB antenna suitable for Wireless Local Area Network (WLAN)

PendingCN107946748AEffective radiationHigh bandwidthSimultaneous aerial operationsRadiating elements structural formsBranch traceEngineering

The invention relates to a novel broadband PCB antenna suitable for a Wireless Local Area Network (WLAN). The novel broadband PCB antenna includes a printed circuit board and an antenna radiation unit, the antenna radiation unit is located on the printed circuit board, the antenna radiation unit and the printed circuit board serve as antenna system, a grounding wire is located on an edge of the antenna radiation unit and the printed circuit board, a first radiating body is arranged beside the grounding wire, and a second radiating body, the grounding wire and a third radiating body form a broadband loop antenna; the third radiating body is coupled to a lower side metal floor plate; a fourth radiating body serves as a branch line of an antenna radiating body and is located at an included angle position of two side faces of the metal floor plate. Three principles of forming the loop antenna, antenna branch line and antenna ground coupling are utilized to realize broadband radiation impedance, thereby realizing antenna effective radiation in an ultra-wide range of 1.36GHz to 8GHz, covering a WLAN 2.4GHz frequency band and a 5GHz frequency band, and having very high robustness to surrounding environment of the antenna.

Owner:SHANGHAI RADIATE COMM ELECTRONICS

Branch synthetic generation across multiple microarchitecture generations

Branch sequences for branch prediction performance test are generated by performing the following steps: (i) generating a branch node graph, by a branch node graph generator machine logic set, based, at least in part, upon a set of branch traces of a workload or benchmark code; (ii) generating a first assembly pattern file, for use with a first instruction set architecture (ISA) / microarchitecture set, by an assembly pattern generator machine logic set, based, at least in part, upon the branch node graph so as to mimic the control-flow pattern of the workload or benchmark code; and (iii) running the assembly pattern file on the first ISA / microarchitecture set to obtain first execution results.

Owner:IBM CORP

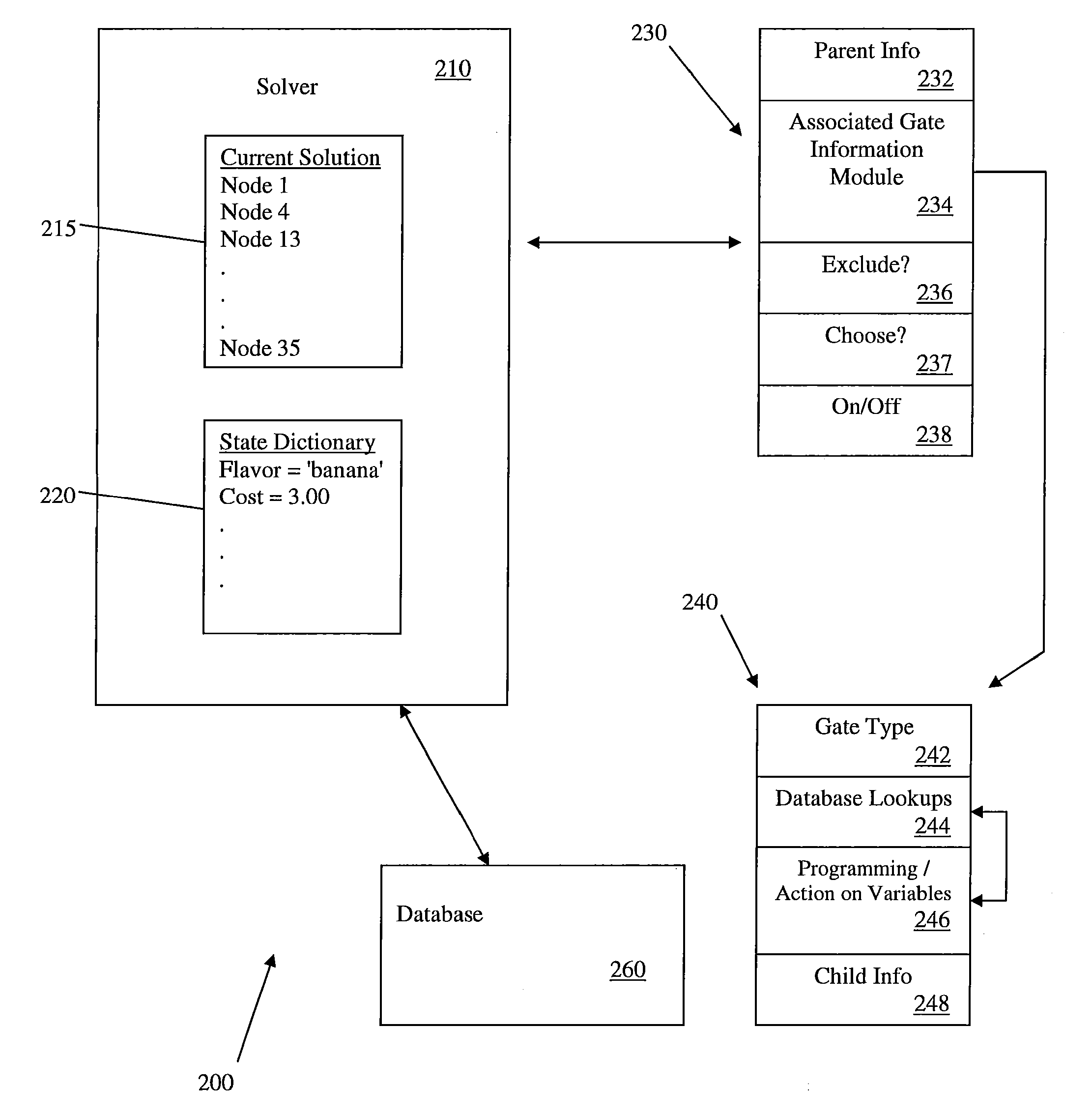

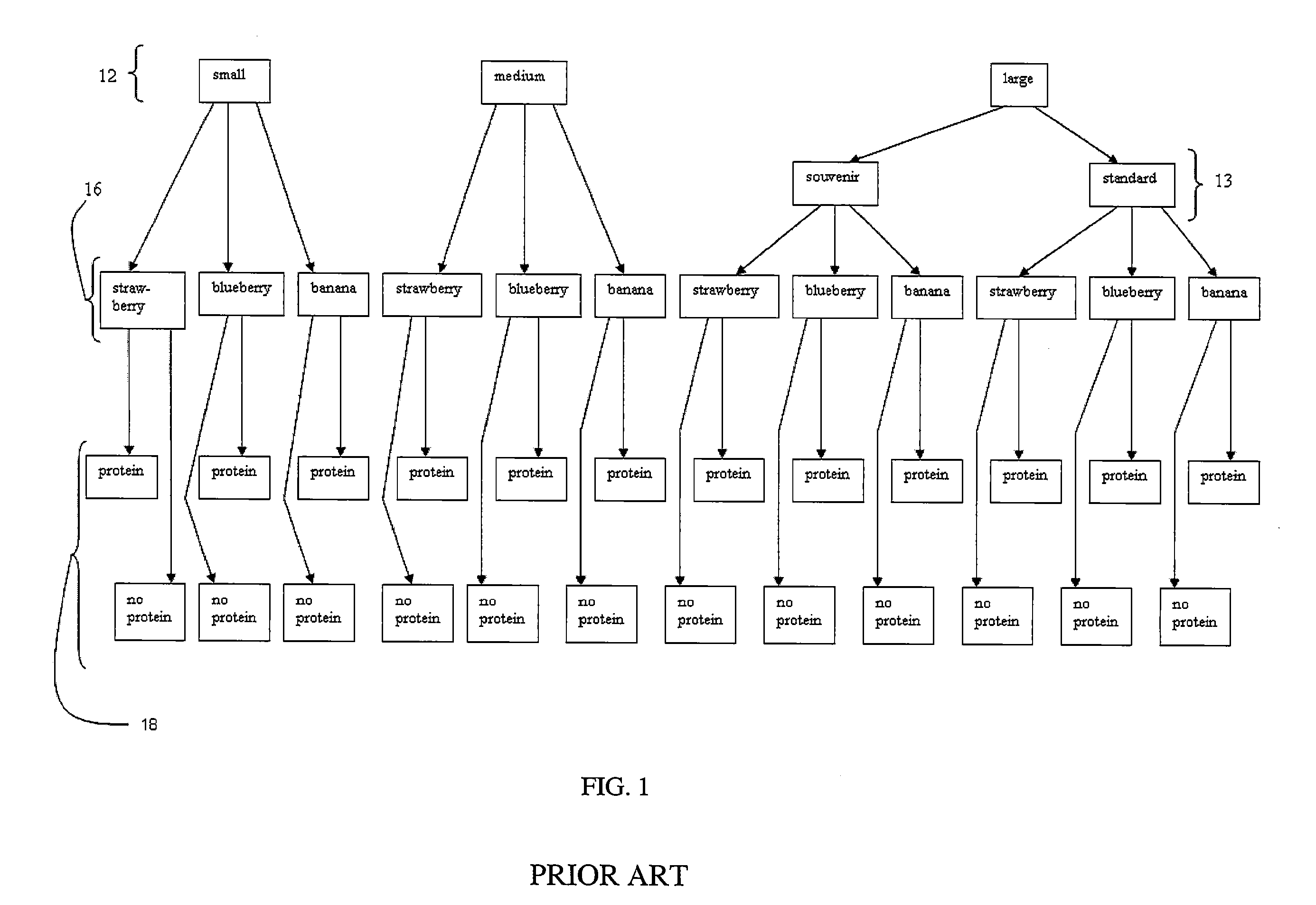

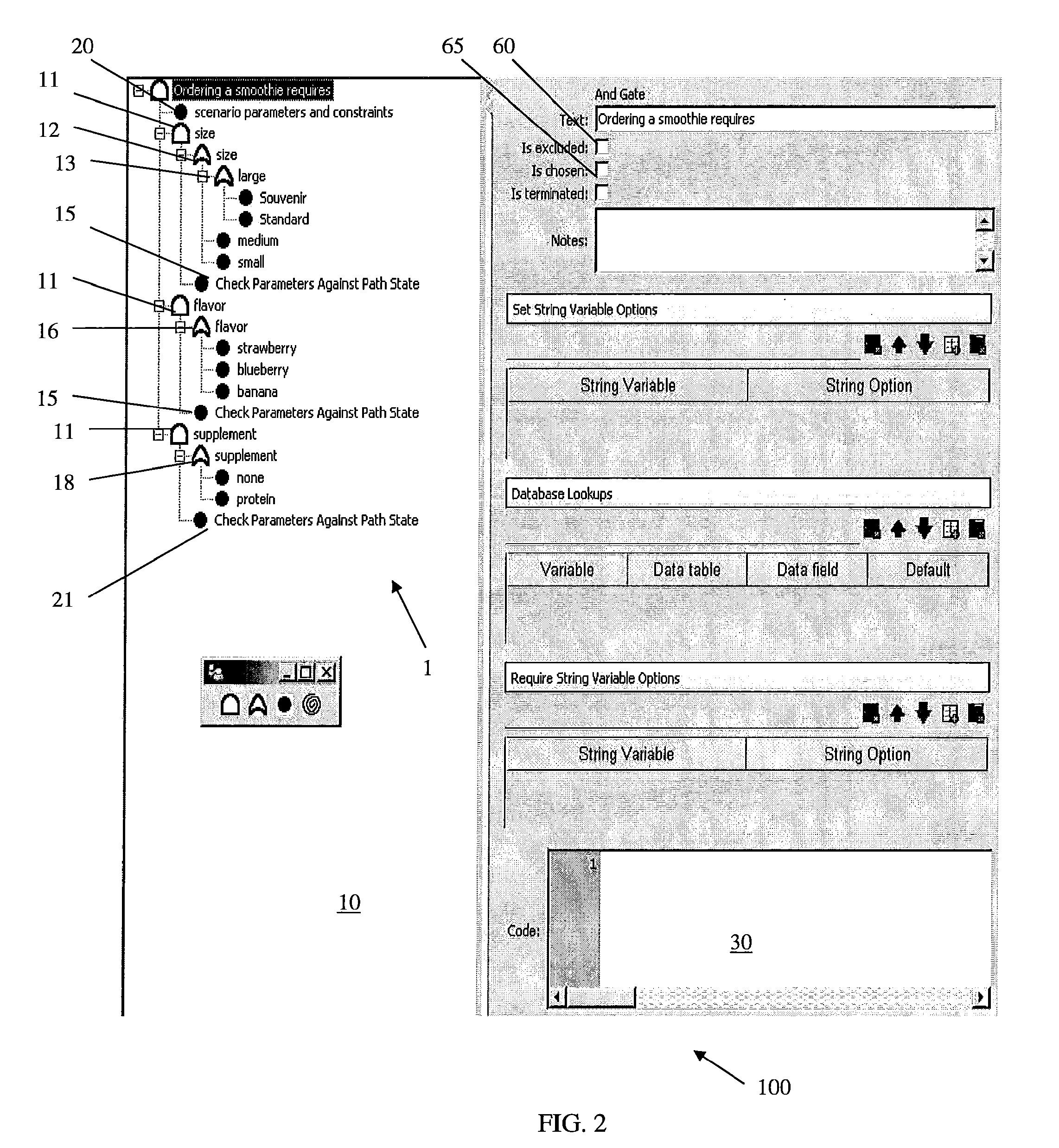

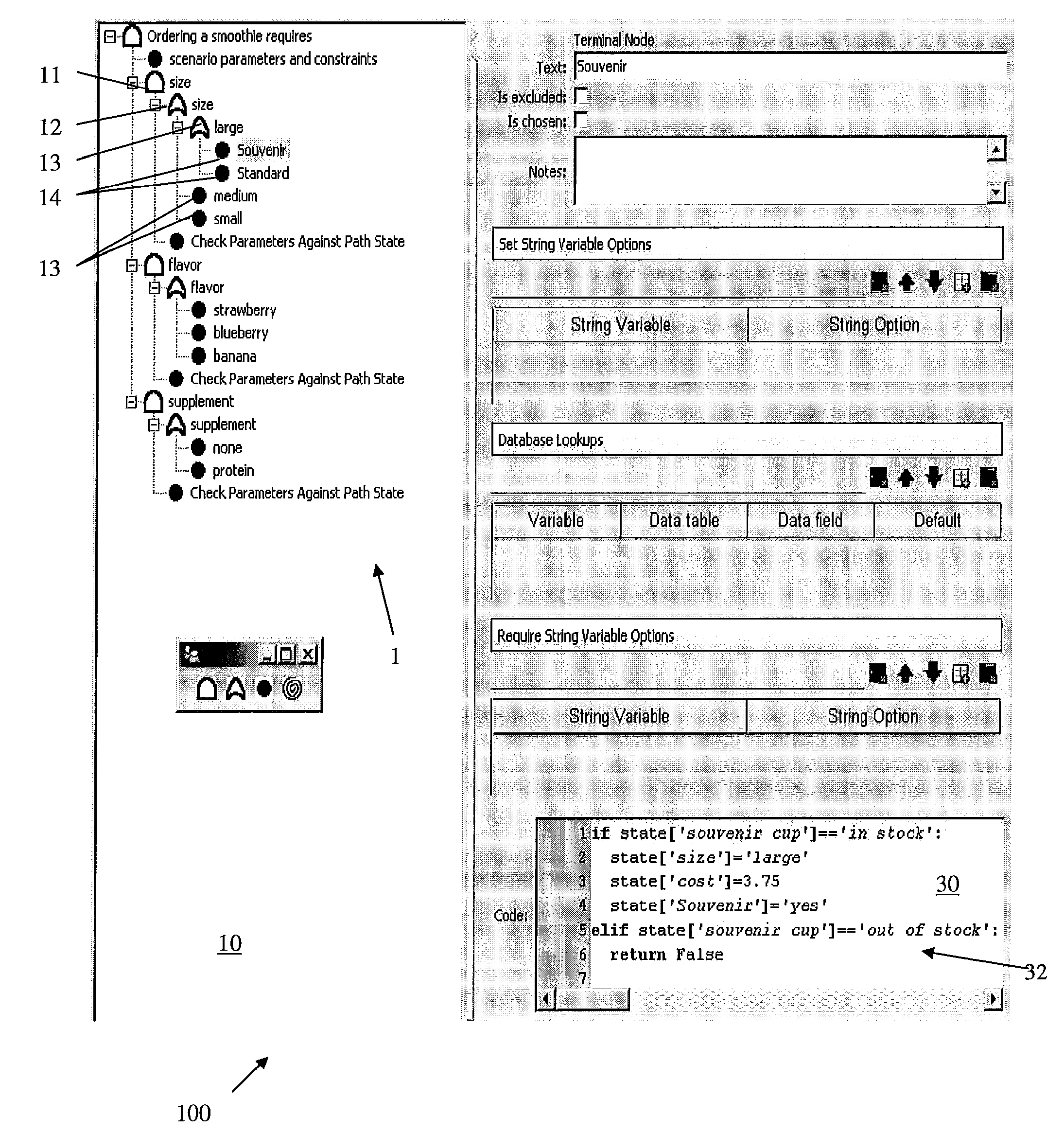

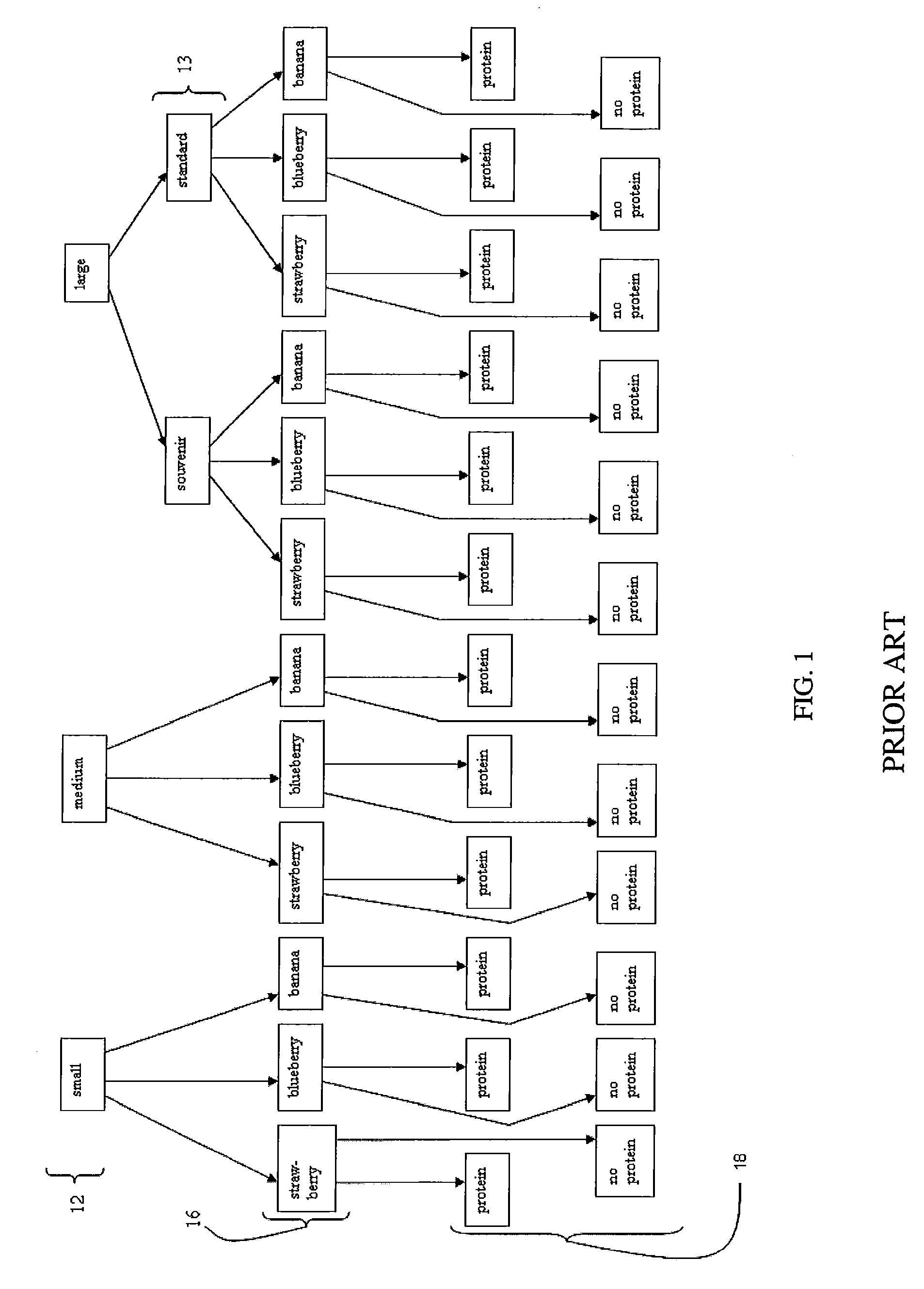

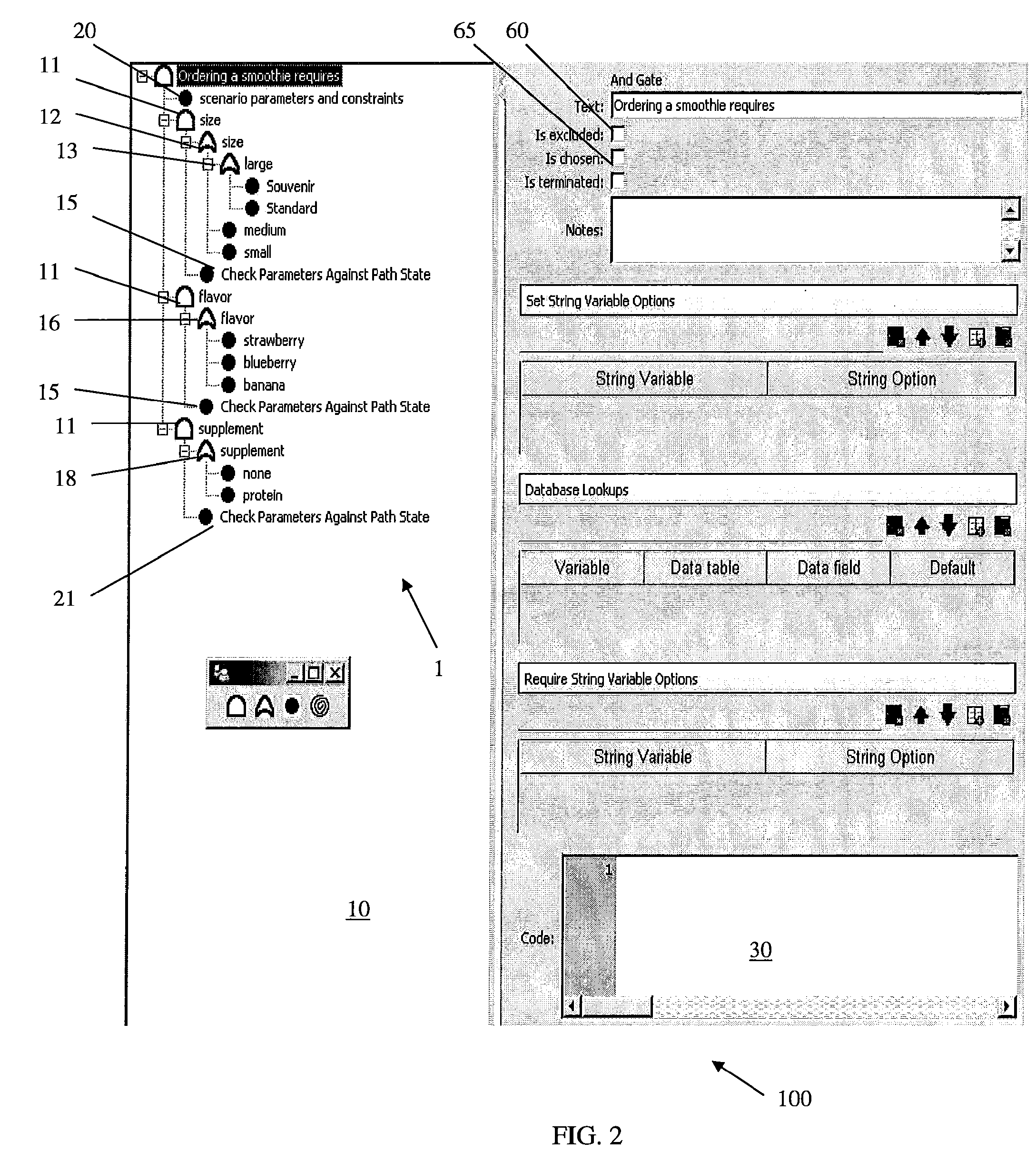

System and method for modeling and analyzing complex scenarios

InactiveUS20110066621A1Reduces power necessaryShorten the timeDigital data processing detailsKnowledge representationProcessor elementTheoretical computer science

An embodiment of the present invention includes a method for analyzing and solving possibility tree. A possibility tree having a plurality of programmable nodes is constructed and solved with a solver module executed by a processor element. The solver module executes the programming of said nodes, and tracks the state of at least a variable through a branch. When a variable of said branch is out of tolerance with a parameter, the solver disables remaining nodes of the branch and marks the branch as an invalid solution. The valid solutions are then aggregated and displayed as valid tree solutions.

Owner:TRIAD NAT SECURITY LLC

Branch trace compression

Owner:VMWARE INC

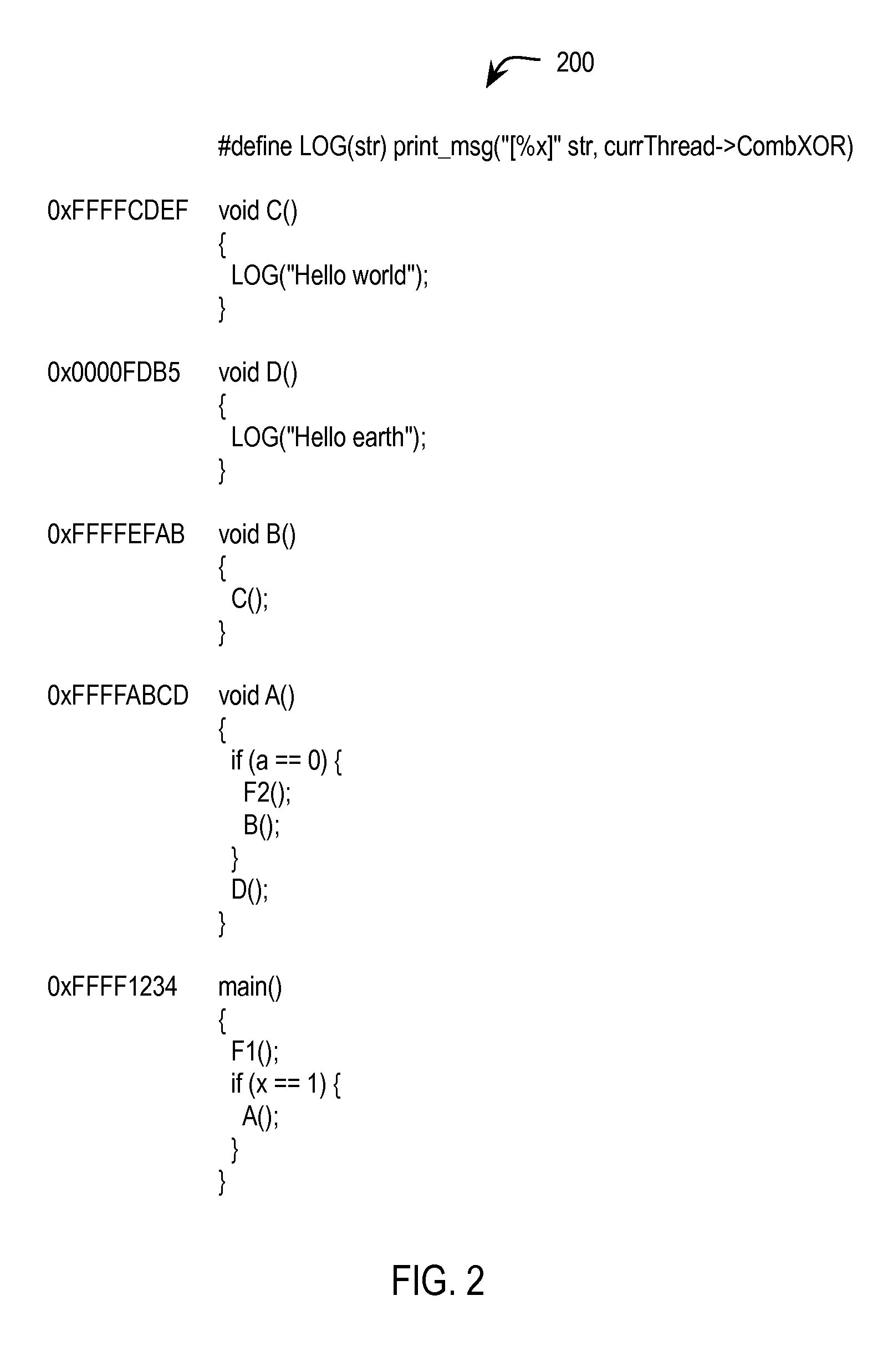

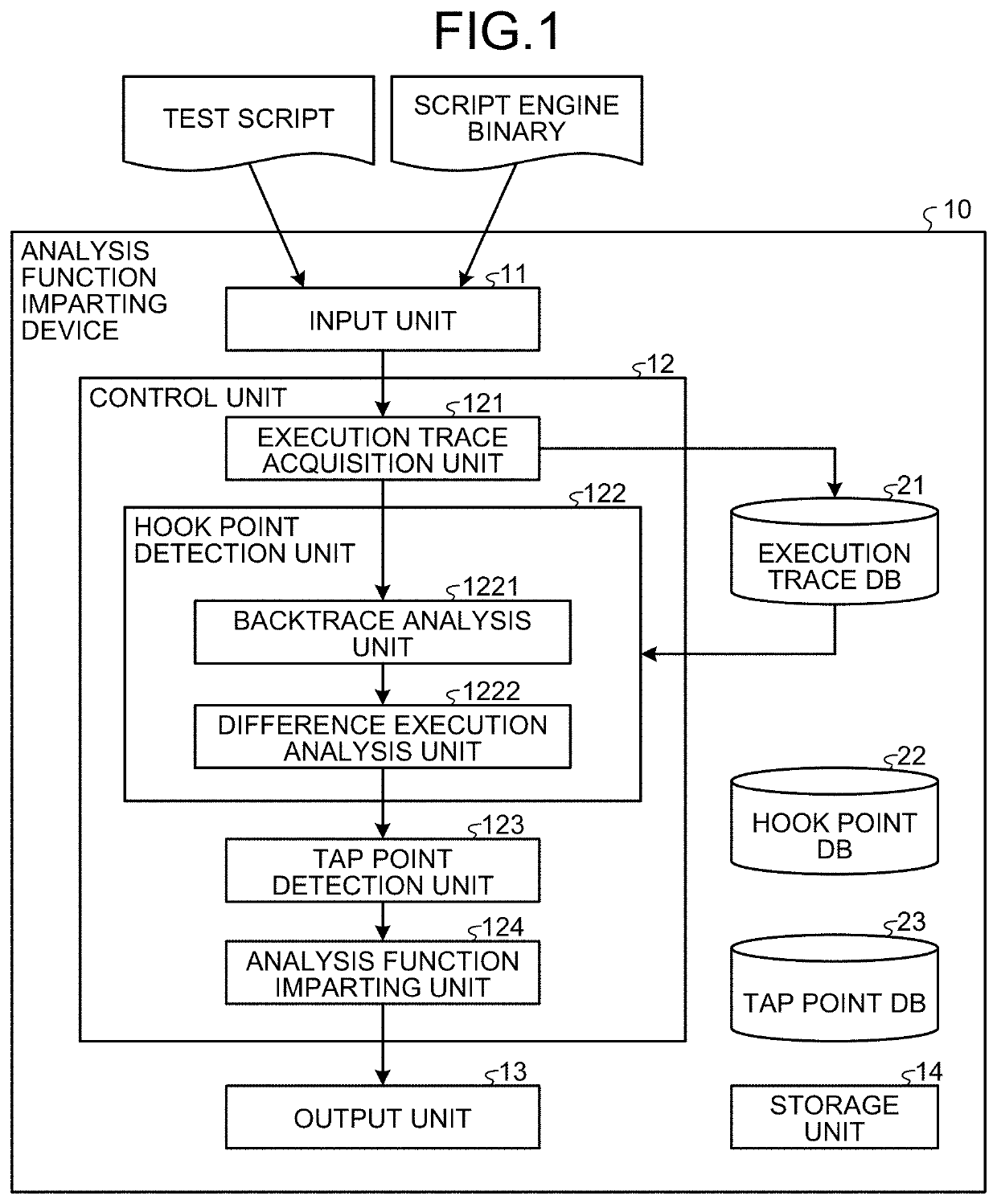

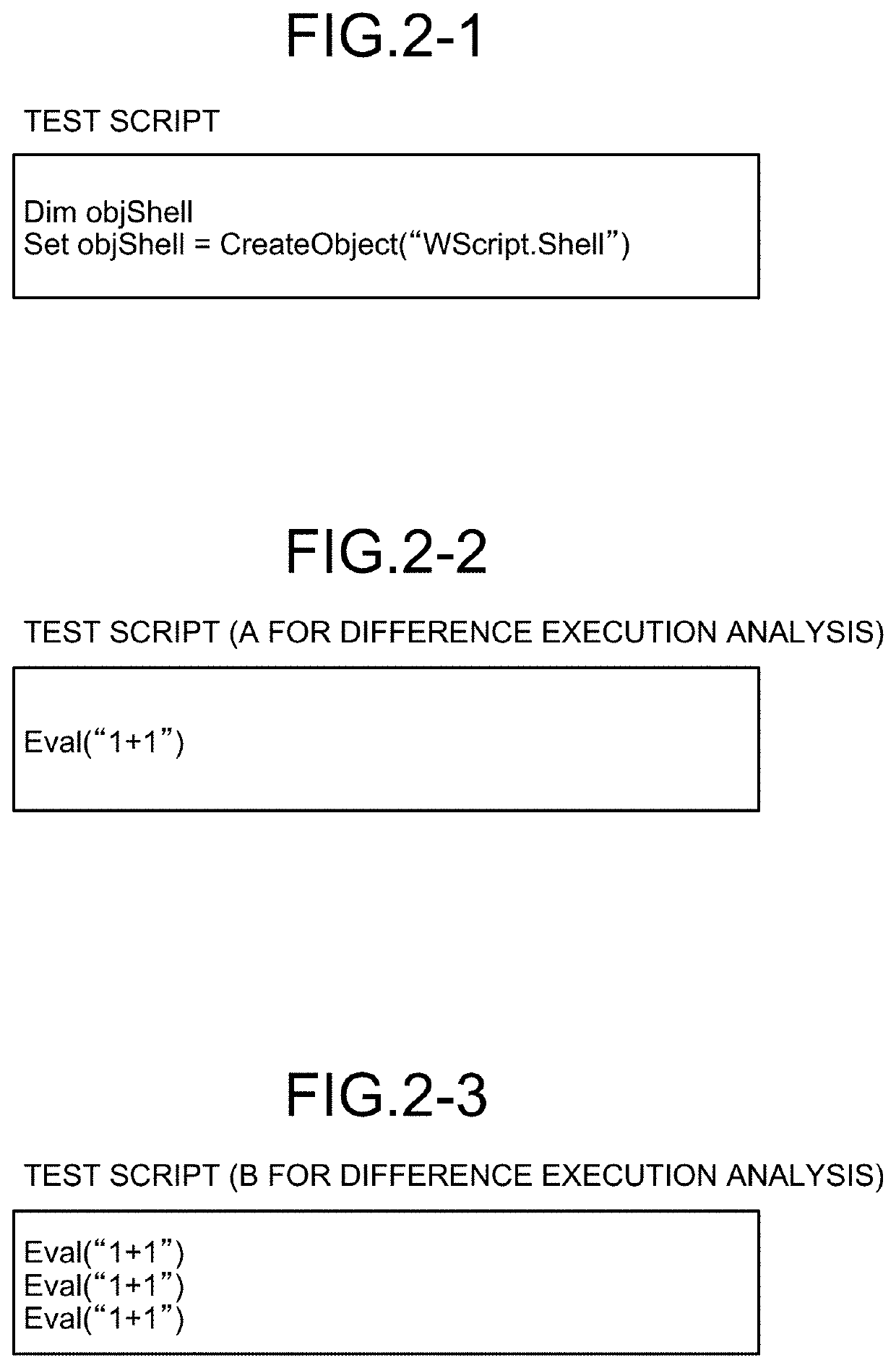

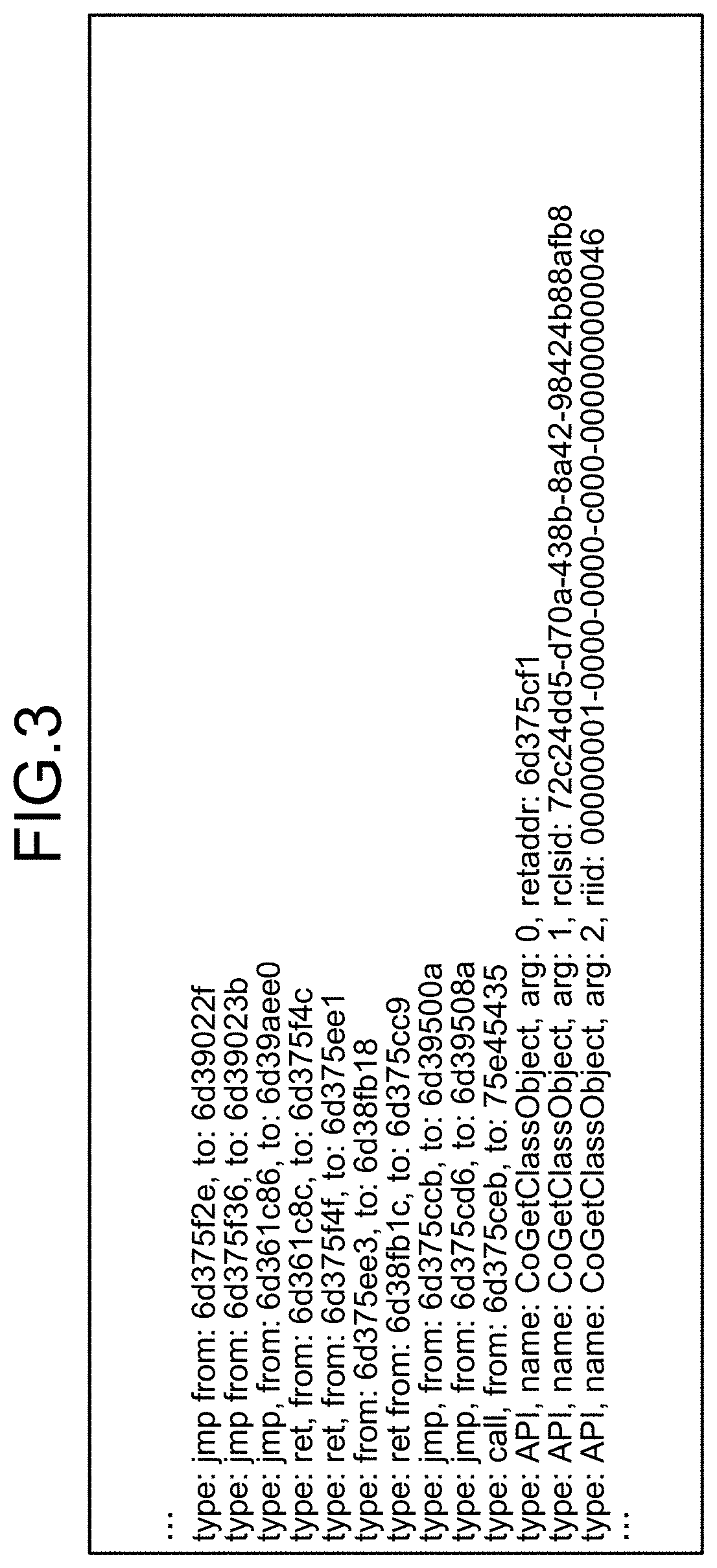

Analysis function imparting device, analysis function imparting method, and recording medium

PendingUS20210390183A1Interprogram communicationPlatform integrity maintainanceComputer hardwareApplication programming interface

An analysis function imparting device according to the present invention includes processing circuitry configured to execute a script engine while monitoring the script engine to acquire an execution trace including an application programming interface (API) trace and a branch trace, analyze the execution trace, and detect a hook point that is a location to which a hook is applied and a code for analysis is inserted, detect, based on monitoring at the hook point, a tap point that is a memory monitoring location at which the code for analysis outputs a log, and apply a hook to the script engine to impart an analysis function to the script engine based on the hook point and the tap point.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

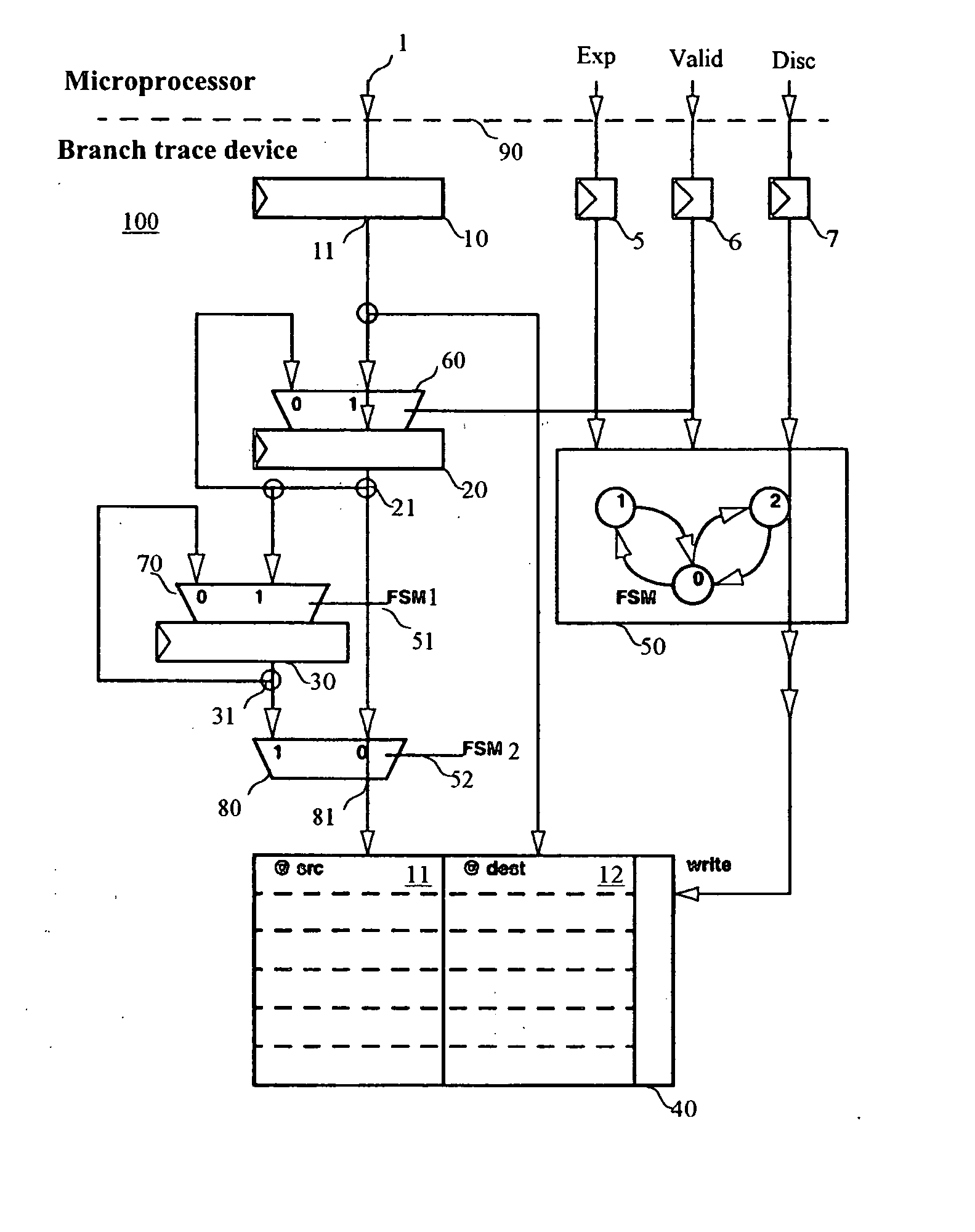

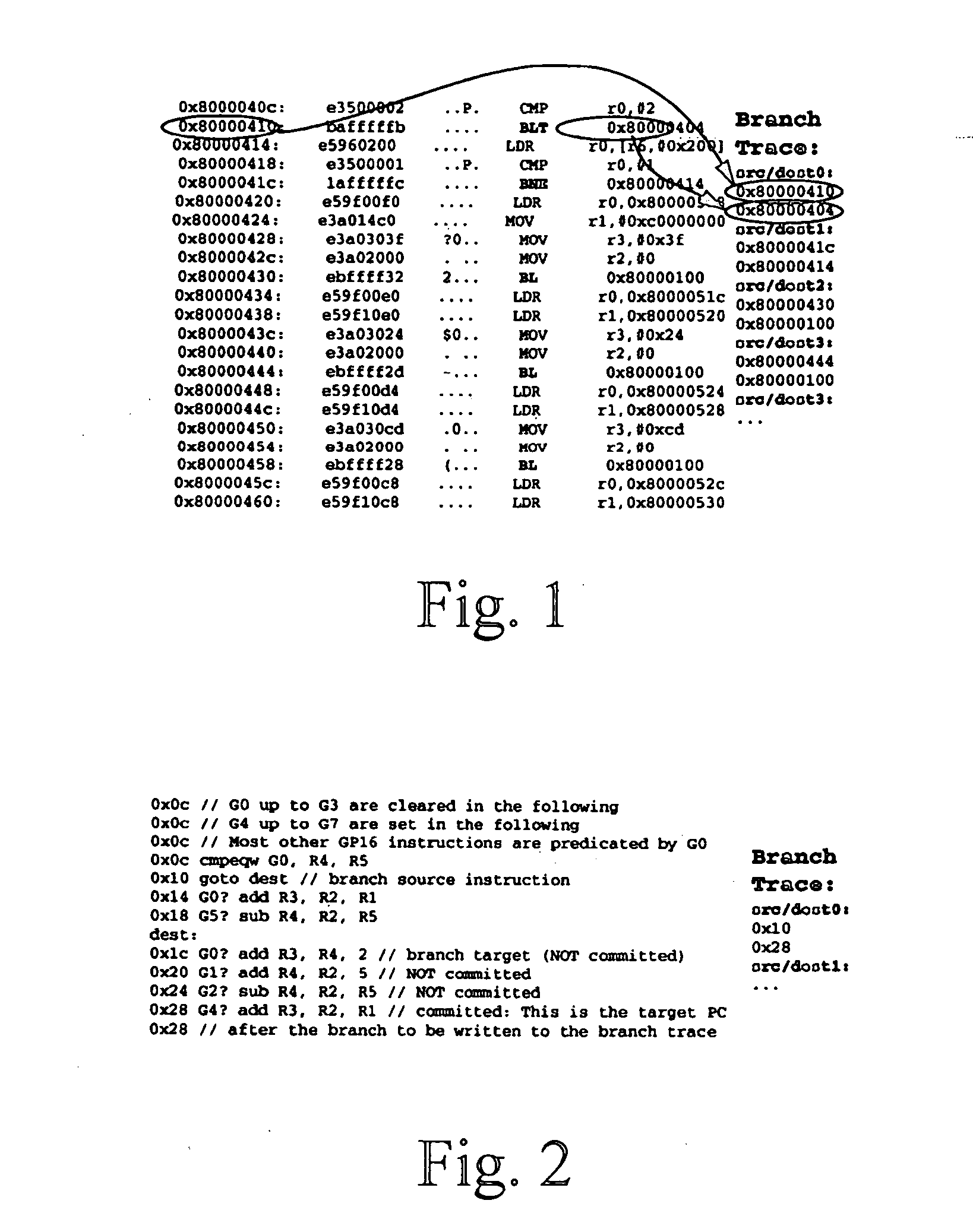

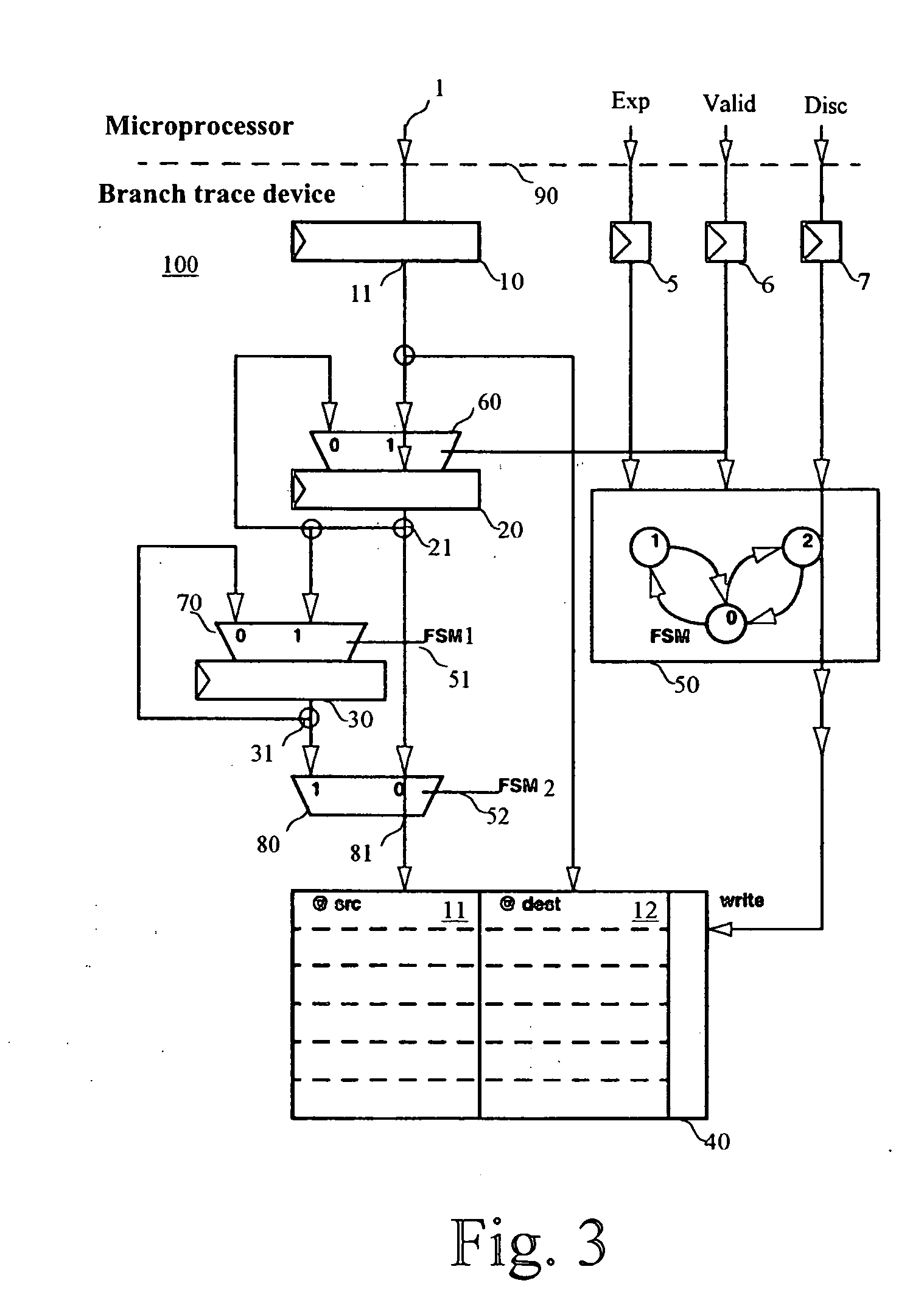

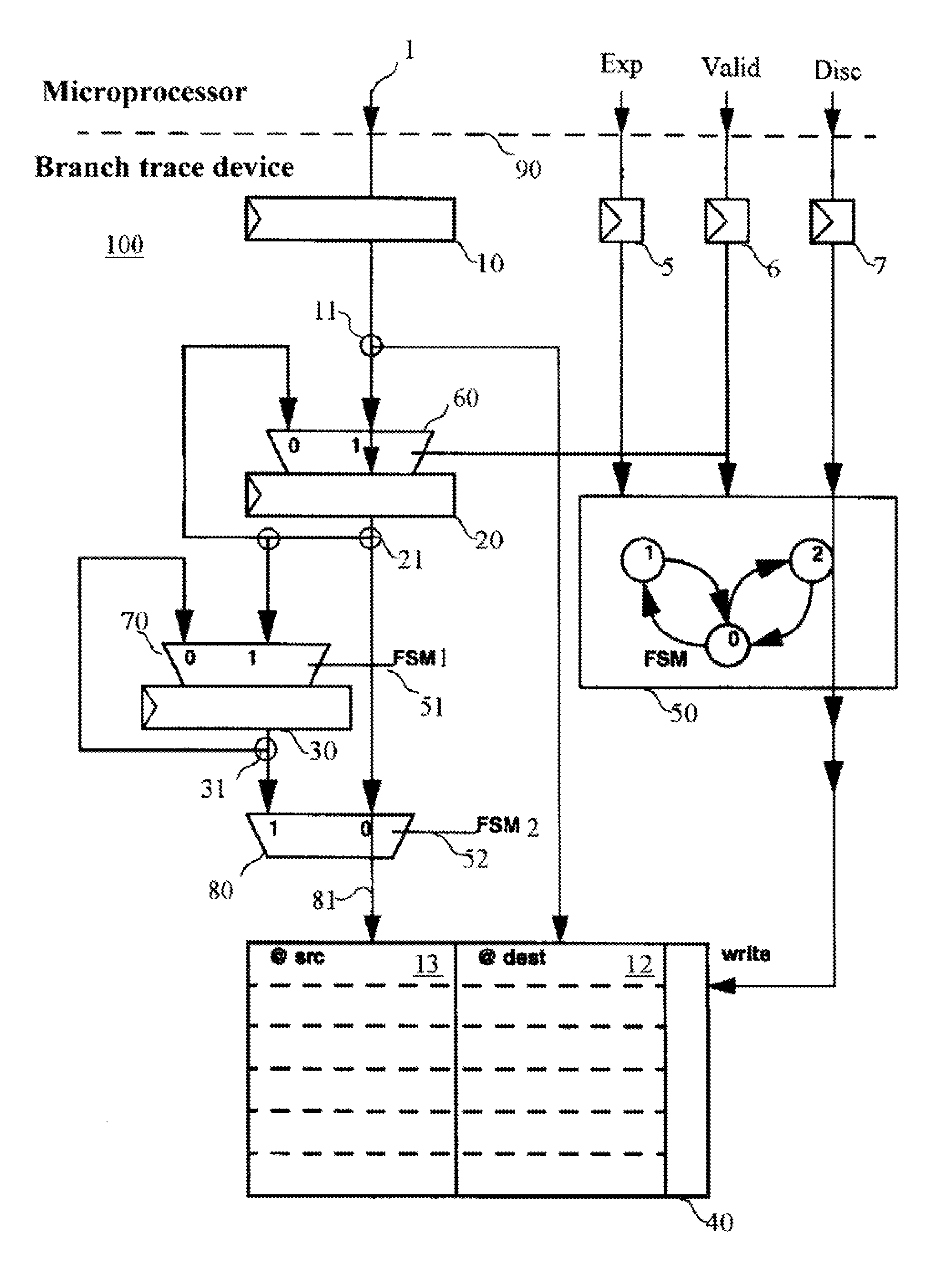

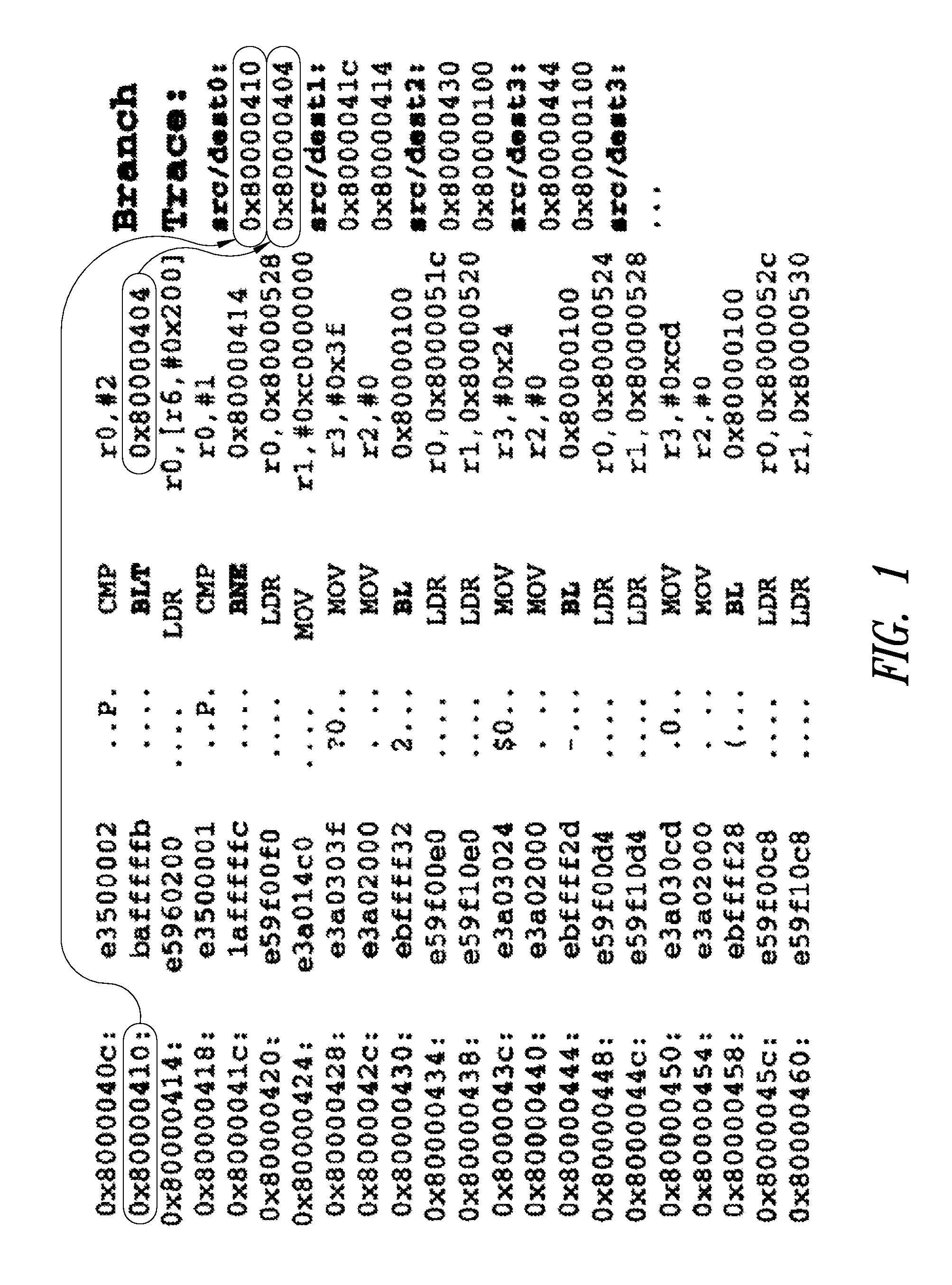

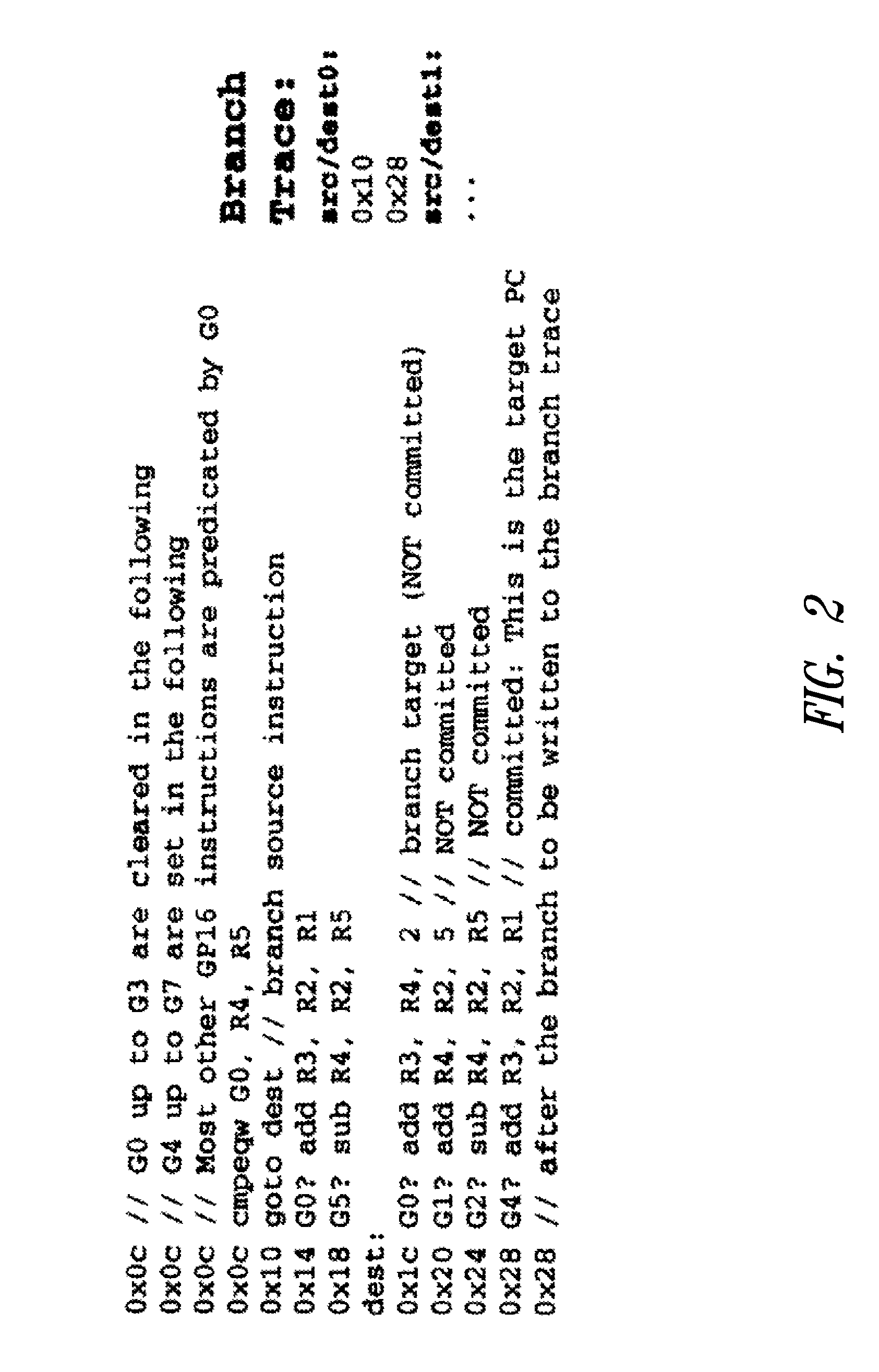

Branch tracing generator device for a microprocessor and microprocessor equipped with such a device

ActiveUS20060224868A1Efficient mechanismError detection/correctionDigital computer detailsMicrocontrollerBranch trace

A device for generating an address branch trace for a microcontroller unit, a microprocessor or a data processing unit having a set of instructions including at least one predicated instruction and at least one instruction of the expanded type, said device including: means for receiving a first signal representative of an actually executed instruction; means for receiving a second signal representative of an expanded instruction; means for receiving a third signal representative of a discontinuity branch between a source address and a destination address of a program executed by said microcontroller, microprocessor or data processing unit; means for storing consecutive addresses pointed by a program counter; means for processing said first, second and third signals in order to determine a pair comprised of a source address and a destination address for an address branch, when appropriate; and means for storing said address pair.

Owner:STMICROELECTRONICS SRL

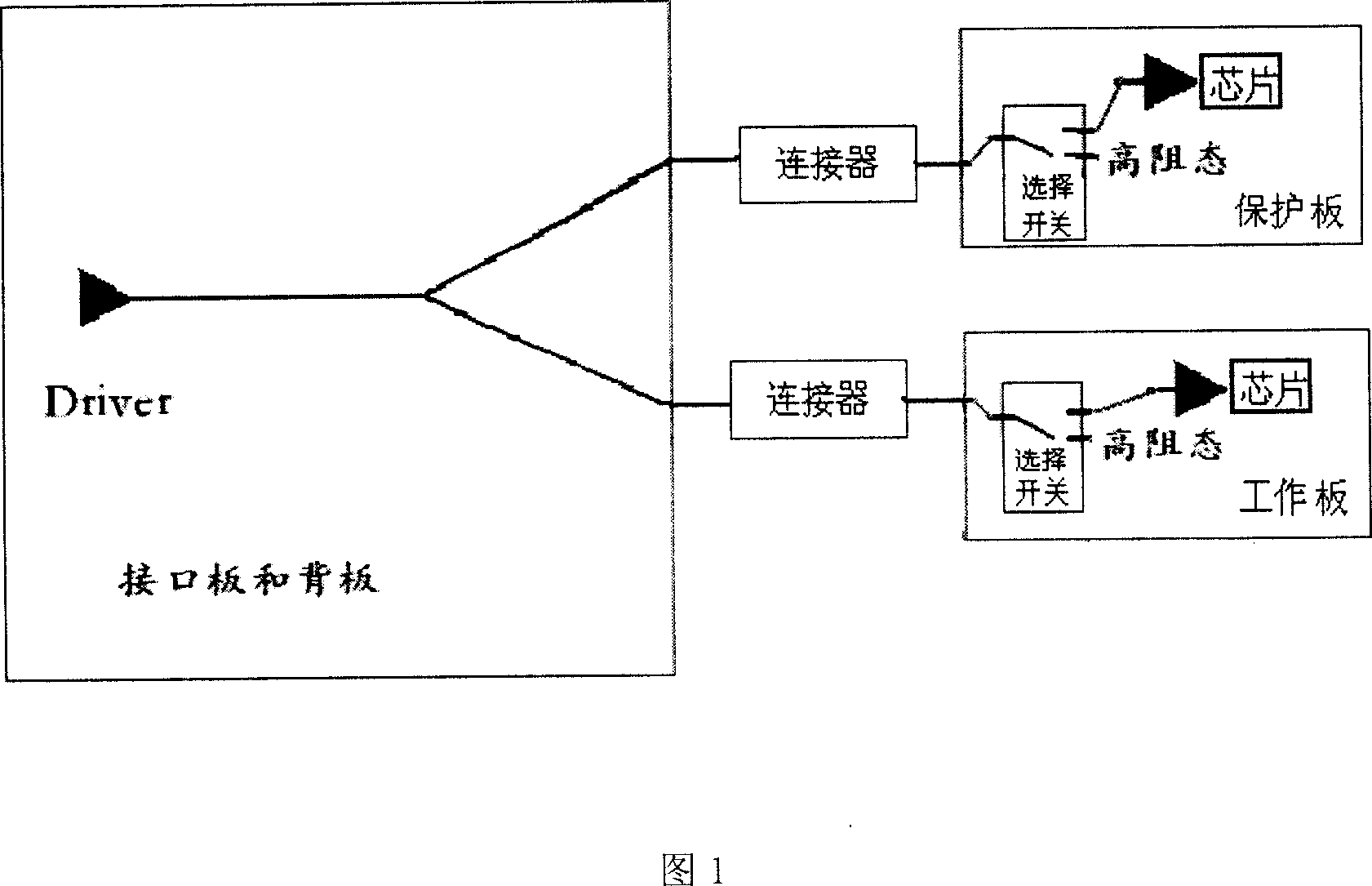

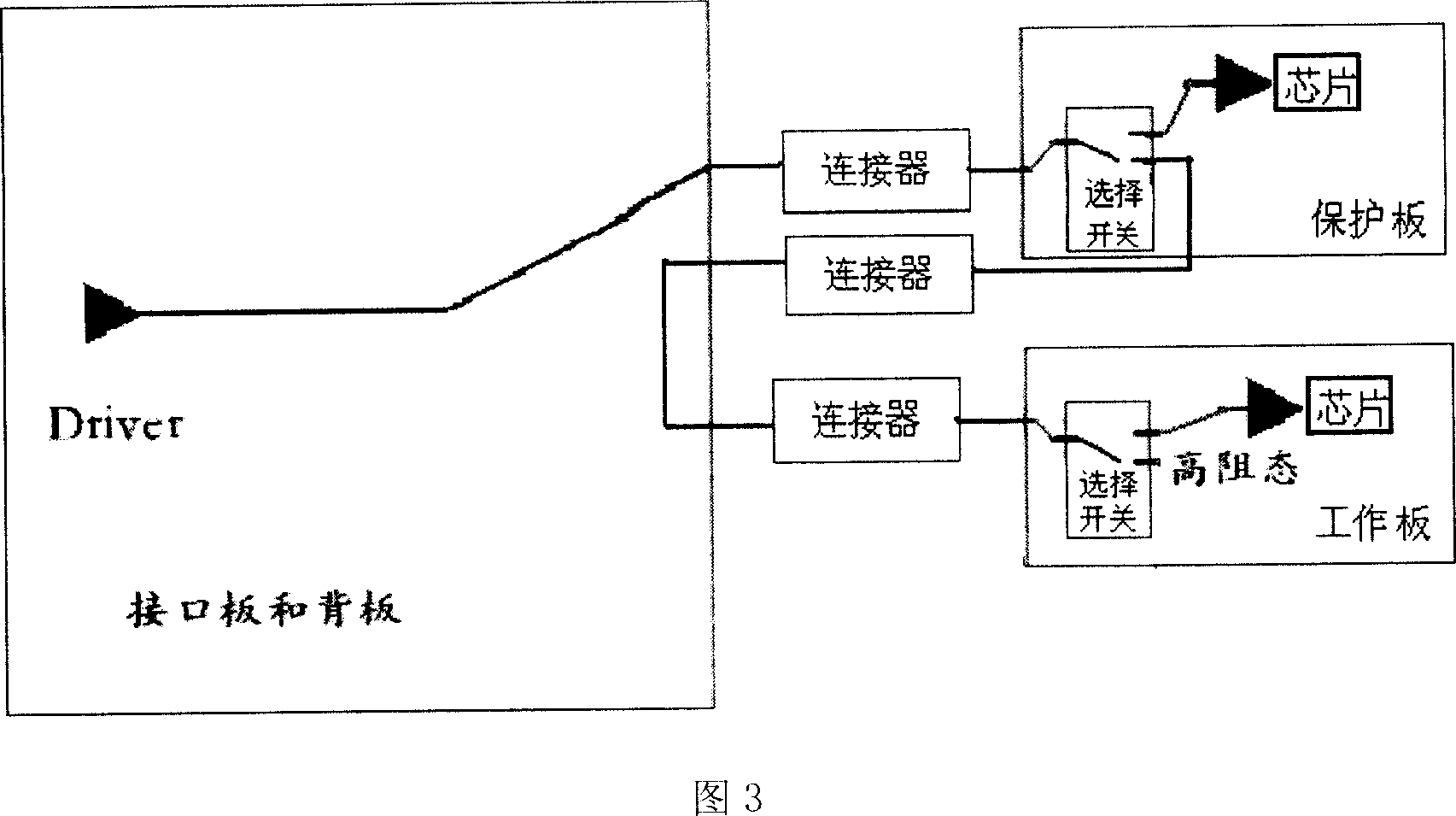

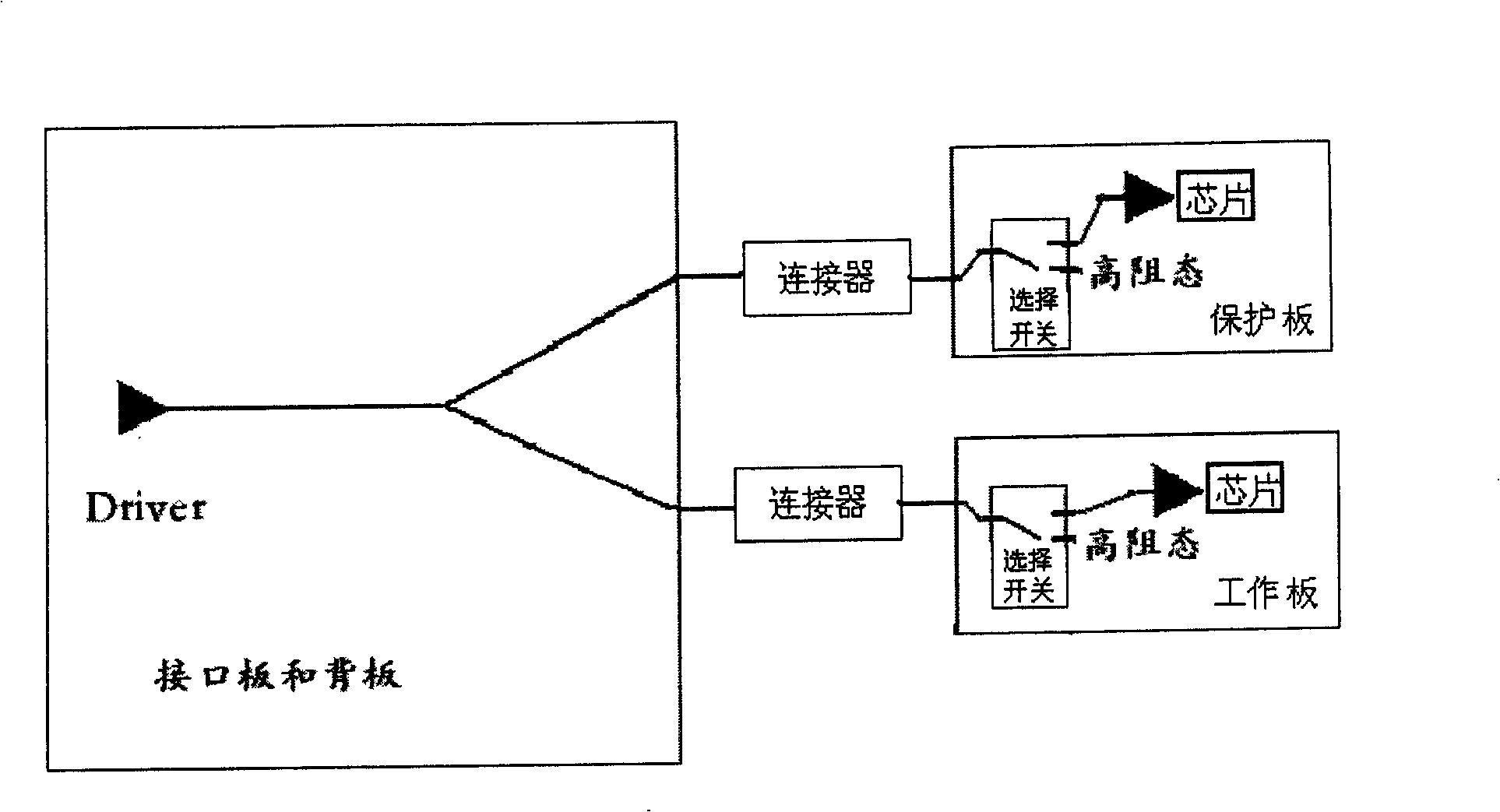

Branch protection negater circuit

InactiveCN1949721AImprove protectionProtection circuits are easier to implement with easyTime-division multiplexData switching networksBranch traceEngineering

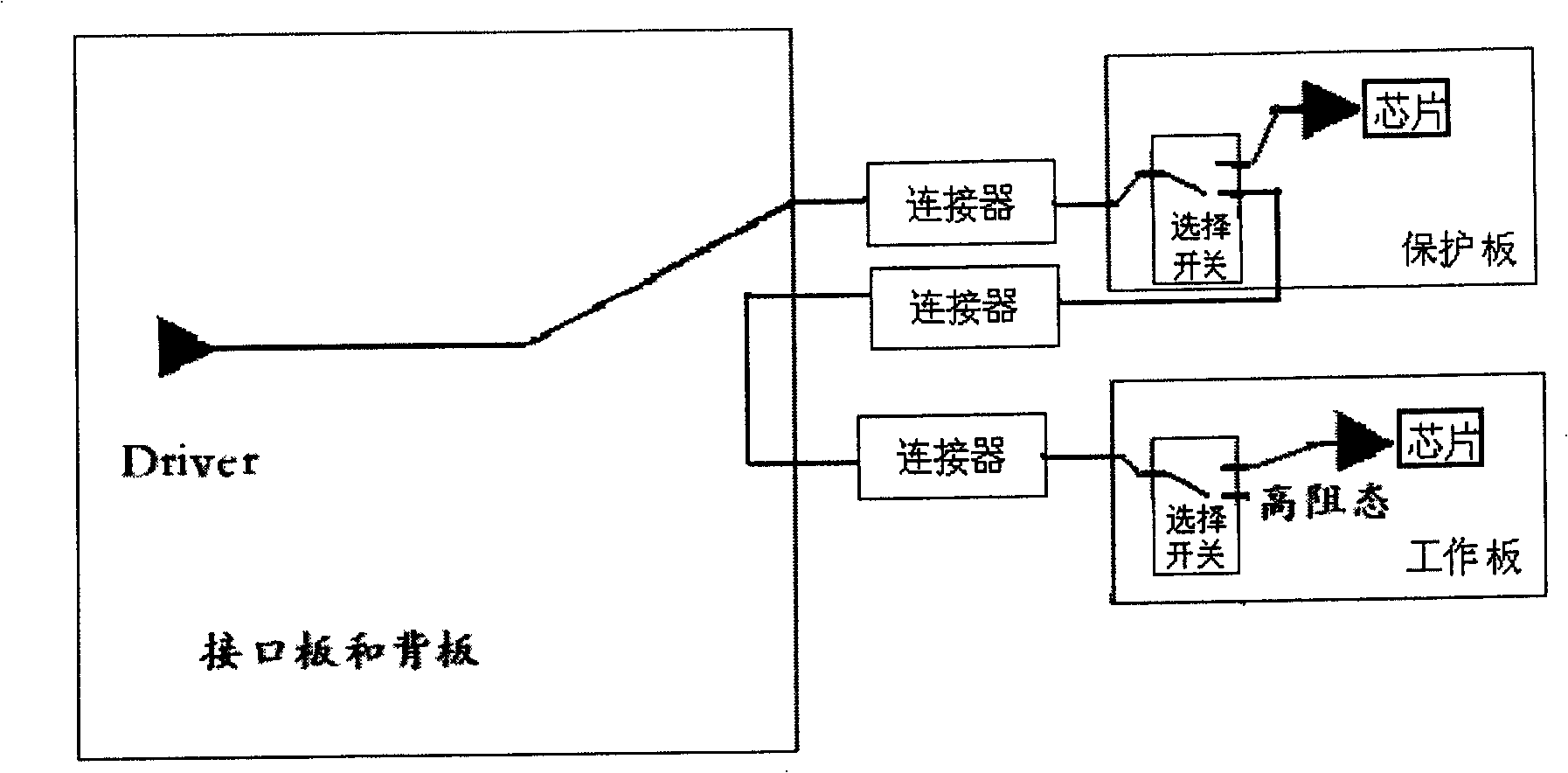

The invention discloses a branch protection switching circuit, relating to a network equipment protection circuit. And the branch protection switching circuit comprises driving end, at least a working plate and at least a protection plate, where the working plate and the protection plate are equipped with switch and processing chip, respectively, the driving end is branched into at least two branches which are connected through the switch with the processing chip; and also comprises at least two impedance matching networks whose first ends are connected to the said branches, respectively and whose second ends are connected to power supply VCC or ground. And it can improve signal transmission quality of interconnected systems with longer branched traces, and implement reliable protection for the interconnected systems.

Owner:HUAWEI TECH CO LTD

System and method for modeling and analyzing complex scenarios

InactiveUS8412708B2Remove the burdenReduce total powerDigital data processing detailsKnowledge representationProcessor elementTheoretical computer science

An embodiment of the present invention includes a method for analyzing and solving possibility tree. A possibility tree having a plurality of programmable nodes is constructed and solved with a solver module executed by a processor element. The solver module executes the programming of said nodes, and tracks the state of at least a variable through a branch. When a variable of said branch is out of tolerance with a parameter, the solver disables remaining nodes of the branch and marks the branch as an invalid solution. The valid solutions are then aggregated and displayed as valid tree solutions.

Owner:TRIAD NAT SECURITY LLC

Branch synthetic generation across multiple microarchitecture generations

Branch sequences for branch prediction performance test are generated by performing the following steps: (i) generating a branch node graph, by a branch node graph generator machine logic set, based, at least in part, upon a set of branch traces of a workload or benchmark code; (ii) generating a first assembly pattern file, for use with a first instruction set architecture (ISA) / microarchitecture set, by an assembly pattern generator machine logic set, based, at least in part, upon the branch node graph so as to mimic the control-flow pattern of the workload or benchmark code; and (iii) running the assembly pattern file on the first ISA / microarchitecture set to obtain first execution results.

Owner:INT BUSINESS MASCH CORP

Branch tracing generator device and method for a microprocessor supporting predicated instructions and expanded instructions

ActiveUS7404069B2Error detection/correctionDigital computer detailsMicrocontrollerProcessor register

A device generates an address branch trace for a microcontroller unit, a microprocessor or a data processing unit having a set of instructions including at least one predicated instruction and at least one instruction of the expanded type. The device includes: a first block to receive a first signal representative of an actually executed instruction; a second block to receive a second signal representative of an expanded instruction; a third block to receive a third signal representative of a discontinuity branch between a source address and a destination address of a program executed by the microcontroller, microprocessor or data processing unit; at least one register to store consecutive addresses pointed to by a program counter; a fourth block to process the first, second and third signals in order to determine a pair having a source address and a destination address for an address branch, when appropriate; and a storage unit to store said address pair.

Owner:STMICROELECTRONICS SRL

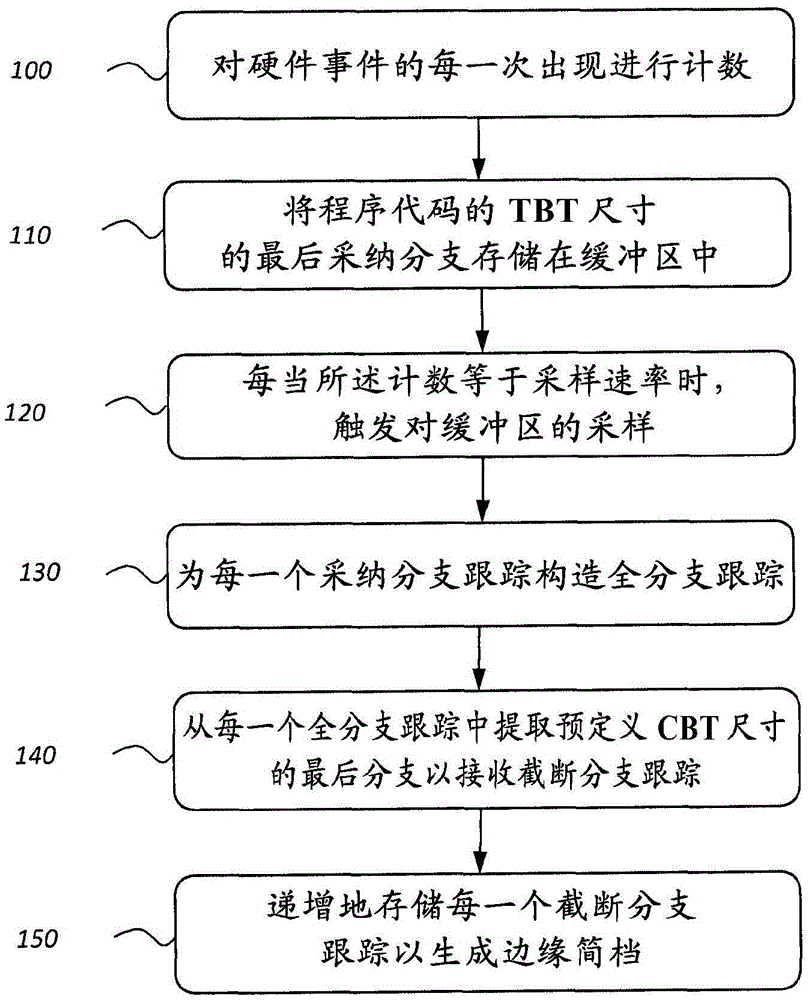

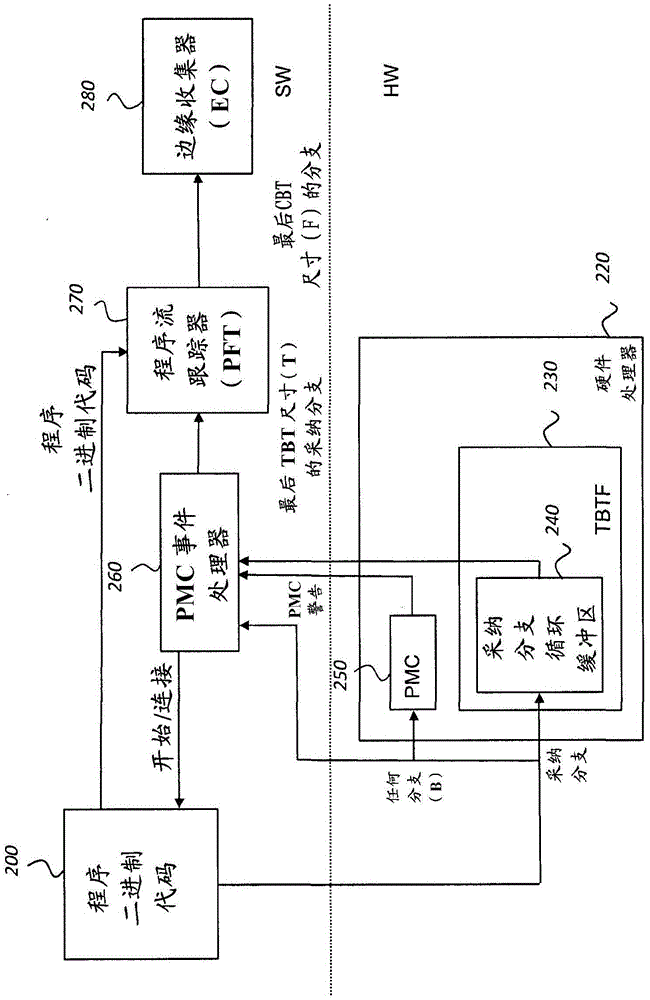

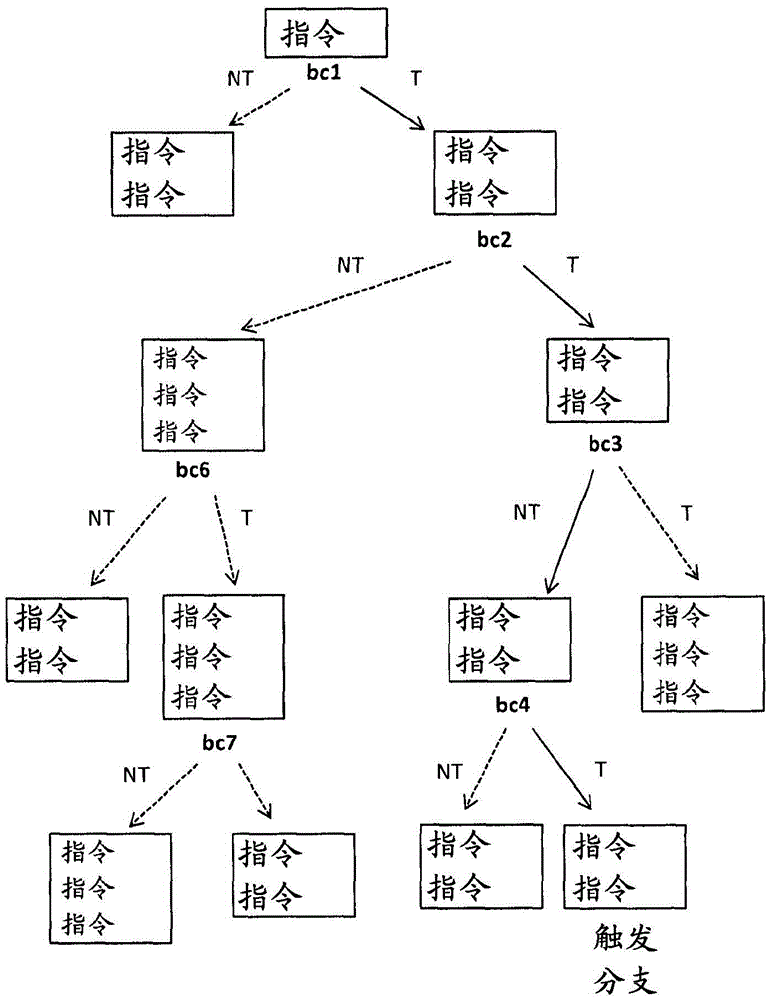

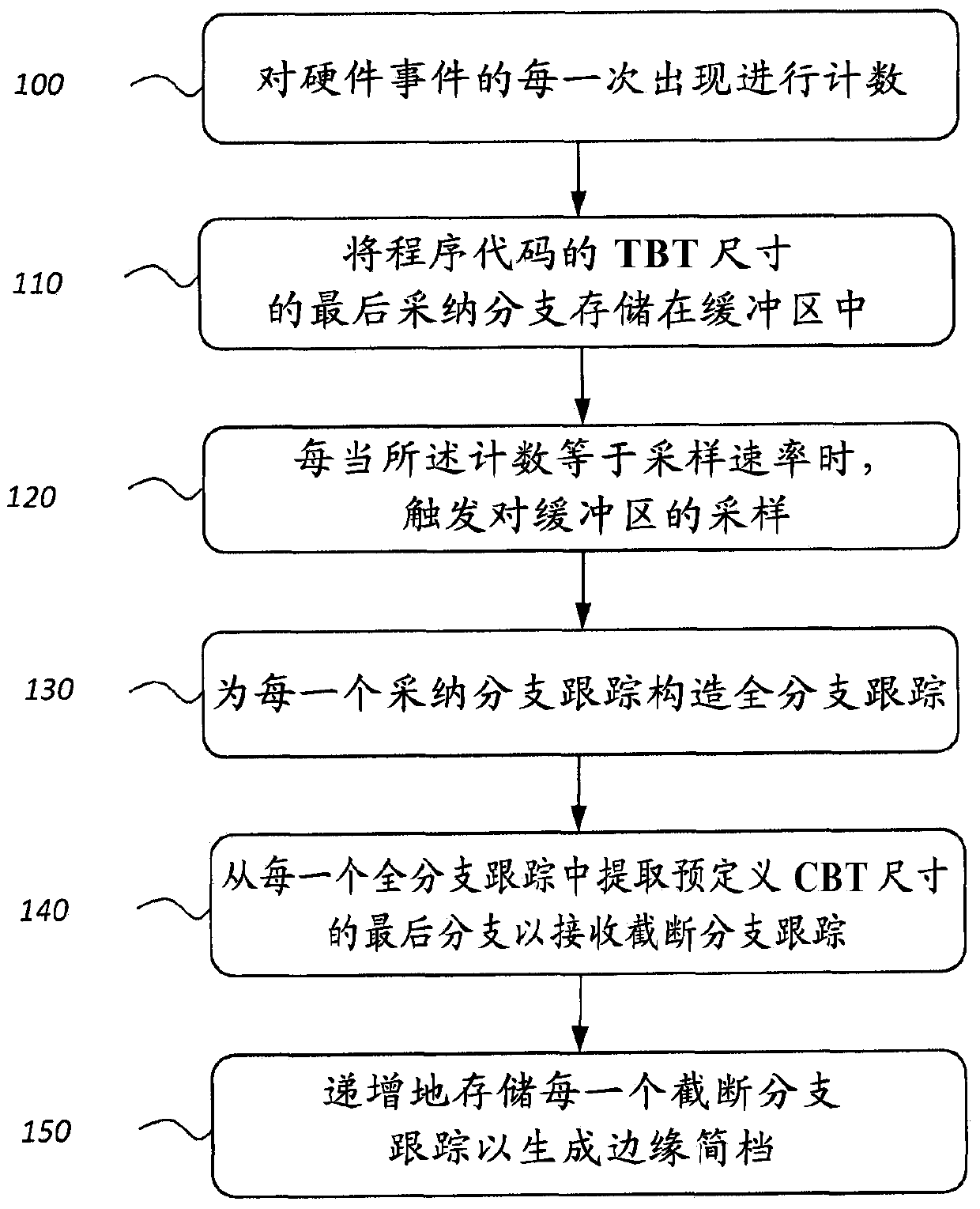

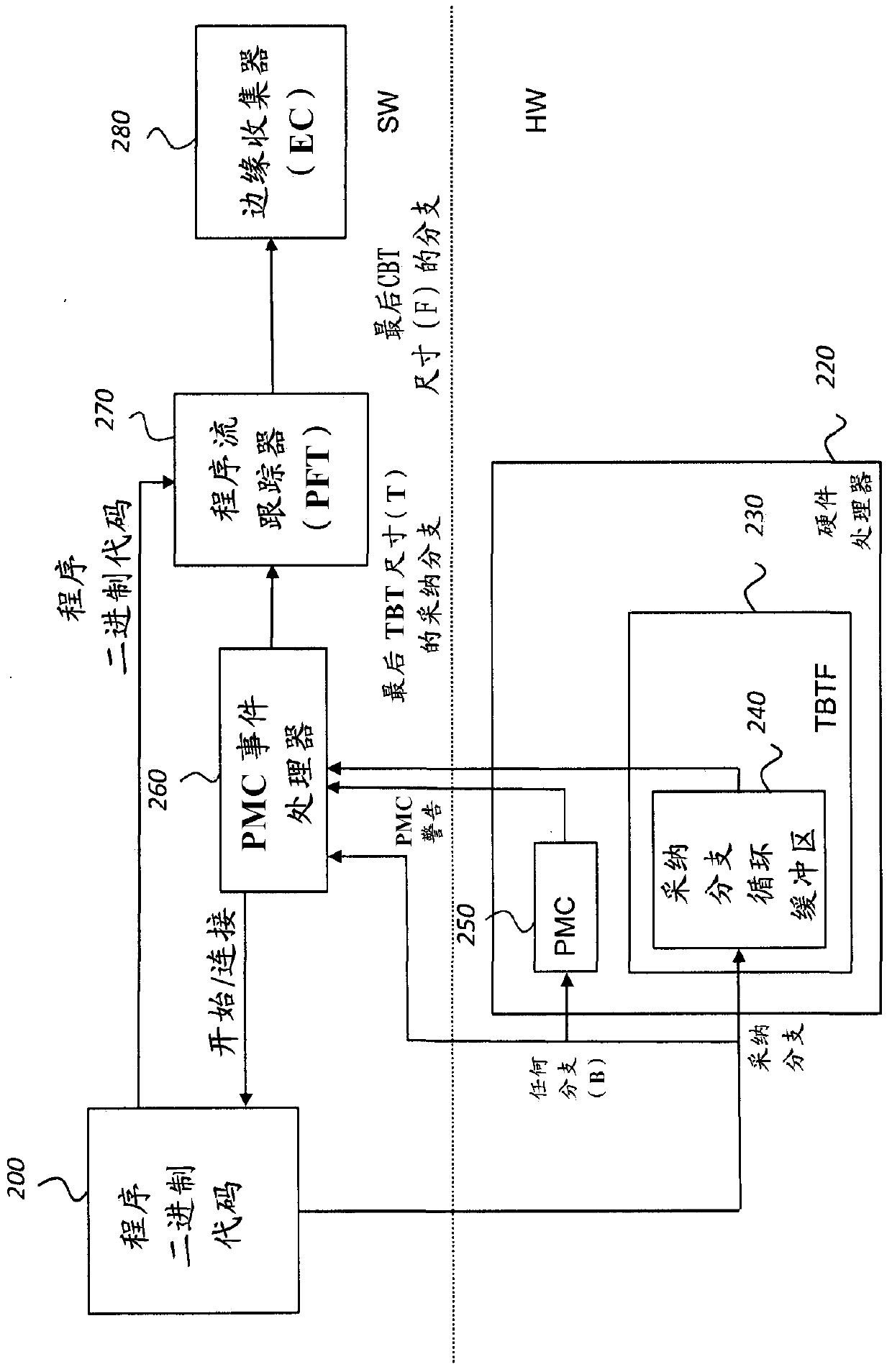

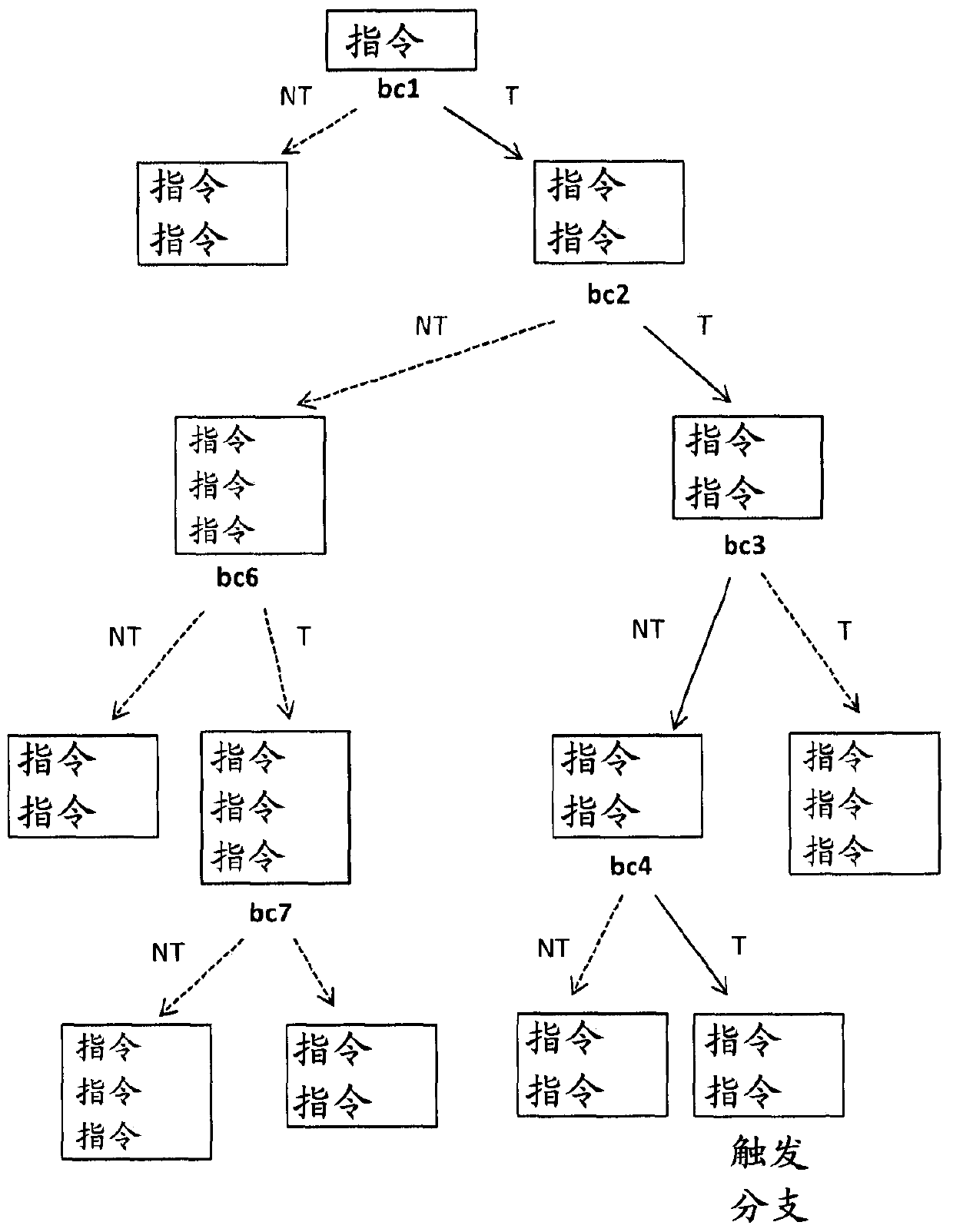

Hardwave-based edge profiling method and system

The present invention relates to a hardwave-based edge profiling method and system. The method comprising: counting each occurrence of a hardware event by a Performance Monitoring Counter of a hardware processor during the execution of a target program code; orderly and continuously storing in a buffer of a Taken Branch Trace (TBT) Facility of said hardware processor a predefined TBT size of last taken branches of said target program code during its execution; every time said counting equals a sampling rate, triggering sampling of said buffer, to receive a TBT comprising current said predefined TBT size of last taken branches; constructing a full branch trace for each said TBT based on said target program code; extracting a predefined Chopped Branch Trace (CBT) size of last branches from each said full branch trace, to receive a chopped branch trace for said each TBT; and incrementally storing each said chopped branch trace to generate an edge profile of said target program code.

Owner:IBM CORP

Branch protection negater circuit

InactiveCN100450029CImprove protectionProtection circuits are easier to implement with easyTime-division multiplexData switching networksBranch traceImpedance matching

The invention discloses a branch protection switching circuit, relating to a network equipment protection circuit. And the branch protection switching circuit comprises driving end, at least a working plate and at least a protection plate, where the working plate and the protection plate are equipped with switch and processing chip, respectively, the driving end is branched into at least two branches which are connected through the switch with the processing chip; and also comprises at least two impedance matching networks whose first ends are connected to the said branches, respectively and whose second ends are connected to power supply VCC or ground. And it can improve signal transmission quality of interconnected systems with longer branched traces, and implement reliable protection for the interconnected systems.

Owner:HUAWEI TECH CO LTD

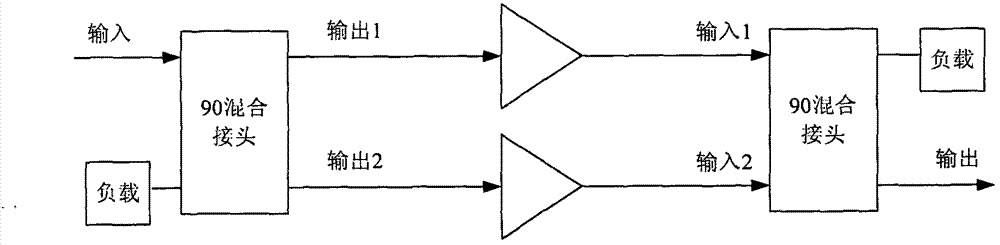

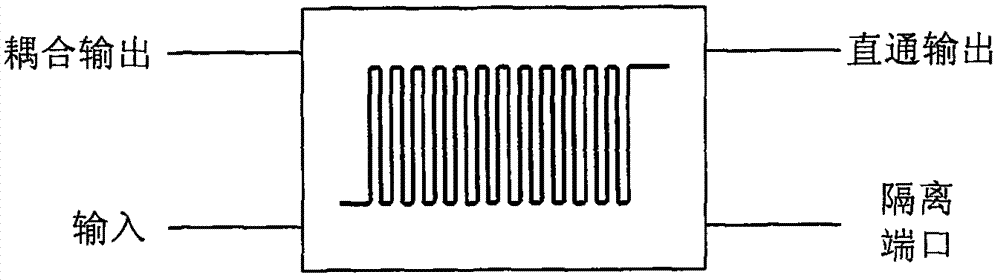

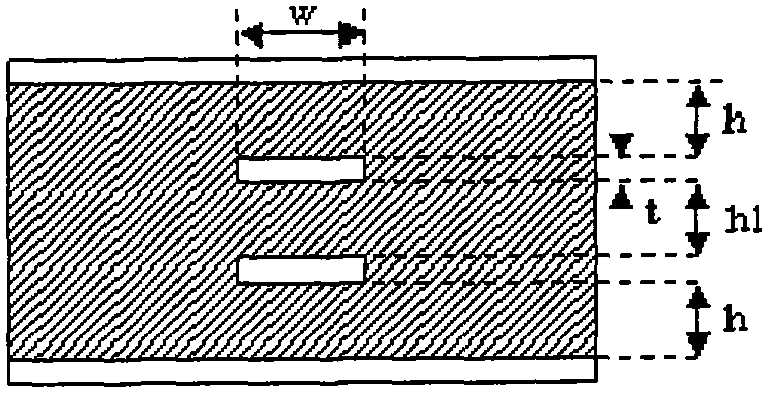

A Stripline 90° Hybrid Joint

InactiveCN104538720BAppropriate aspect ratioImprove reliabilityCoupling devicesRibbon cableBranch trace

The invention belongs to the technical field of 90° hybrid joints, and discloses a stripline 90° hybrid joint. The stripline 90° hybrid joint of the present invention includes two layers of parallel signal transmission lines, the bottom signal transmission line is a straight-through signal line, and the two ends of the straight-through signal line are respectively the input end and the straight-through end of the stripline 90° hybrid joint, and the upper layer signal The transmission line is a coupled line, and the two ends of the coupled signal line are striplines. The 90° hybrid connector is the coupled end and the isolated end; the straight-through signal line and the coupled signal line adopt serpentine routing, and the distance between two adjacent single-branch wires is equal to 2 times the width of the signal transmission line. The volume of the invention is small, the proportion of length and width is appropriate, the invention is more solid and reliable.

Owner:NO 63 RES INST HEADQUARTERS OF THE GENERAL STAFF PLA

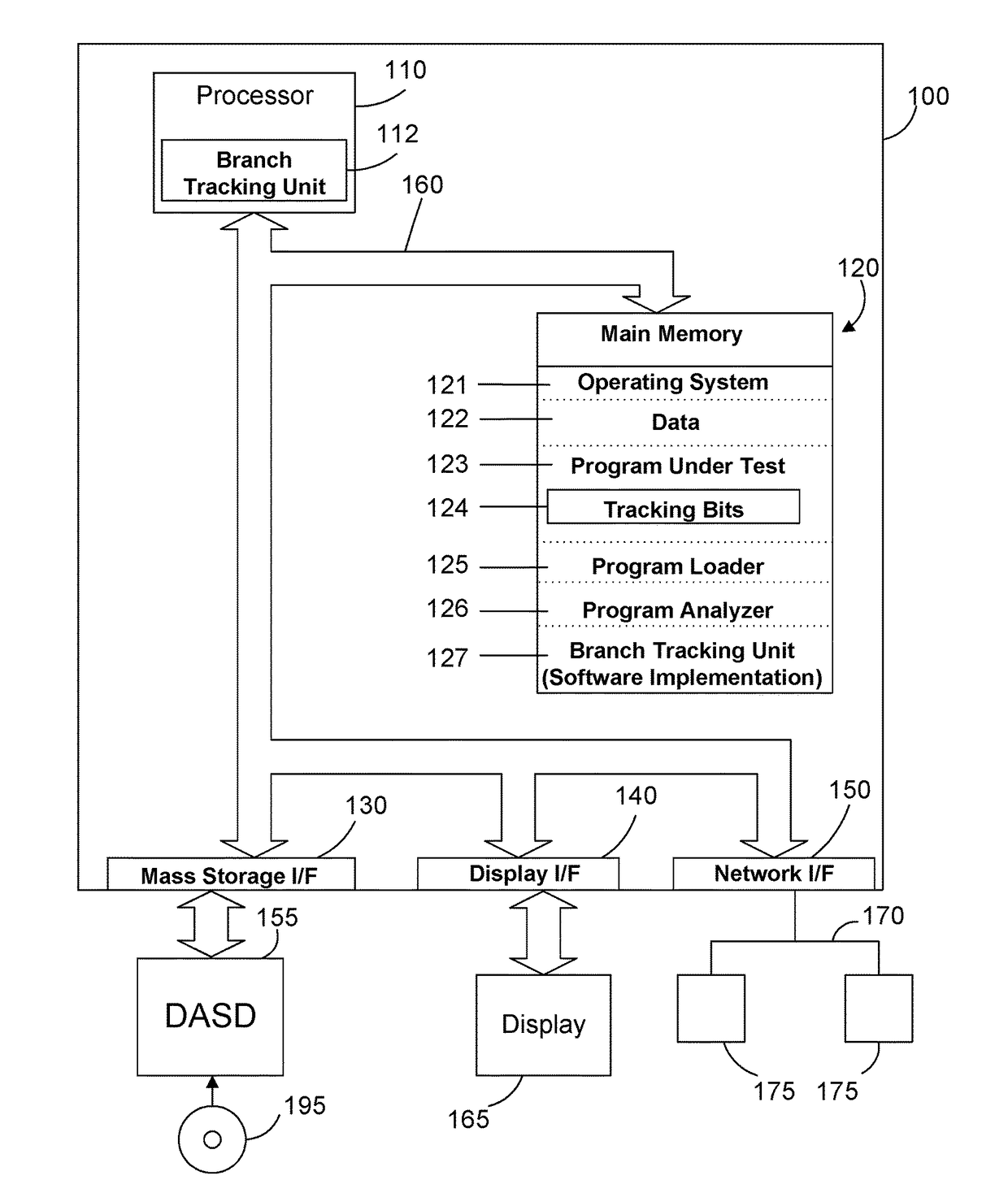

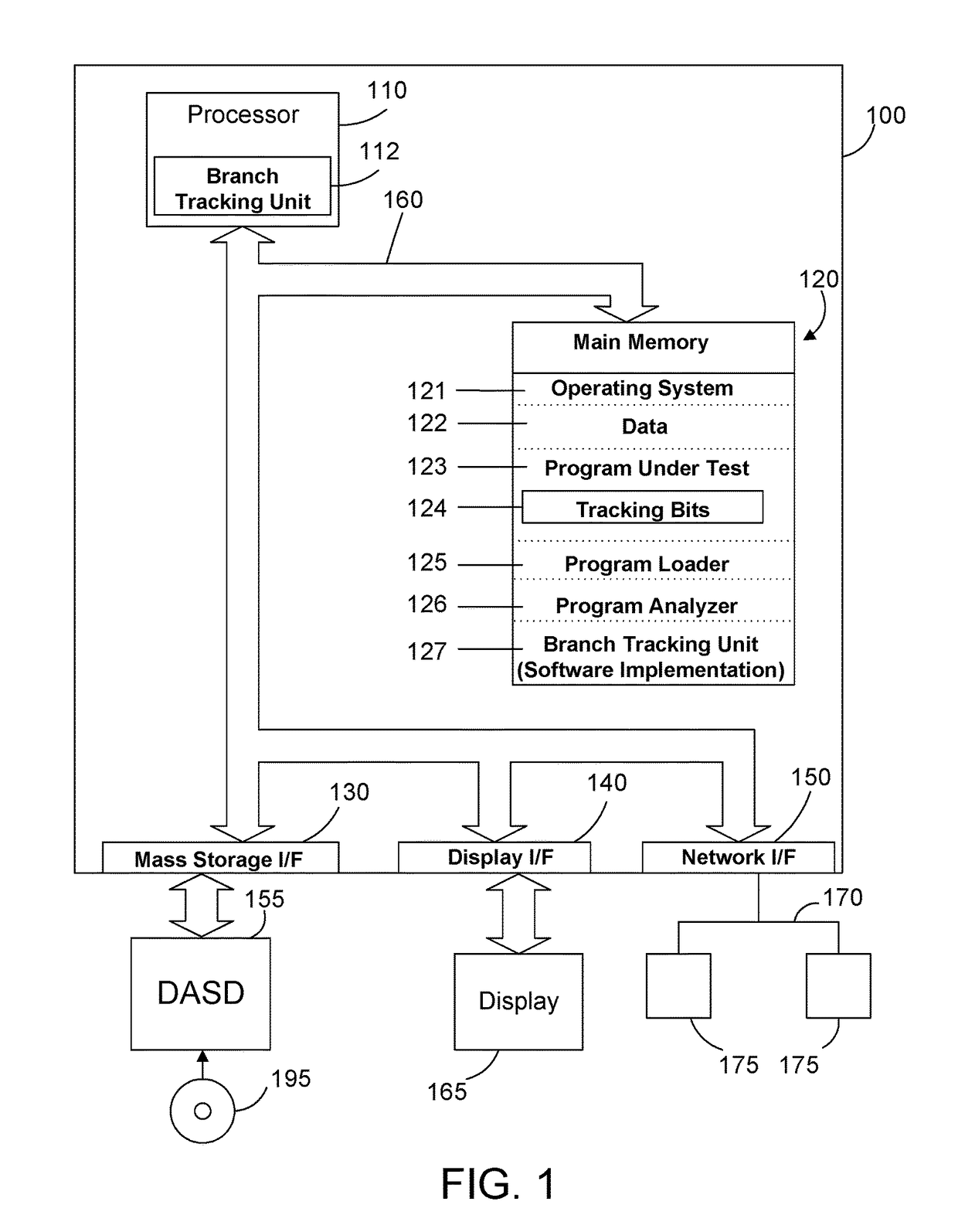

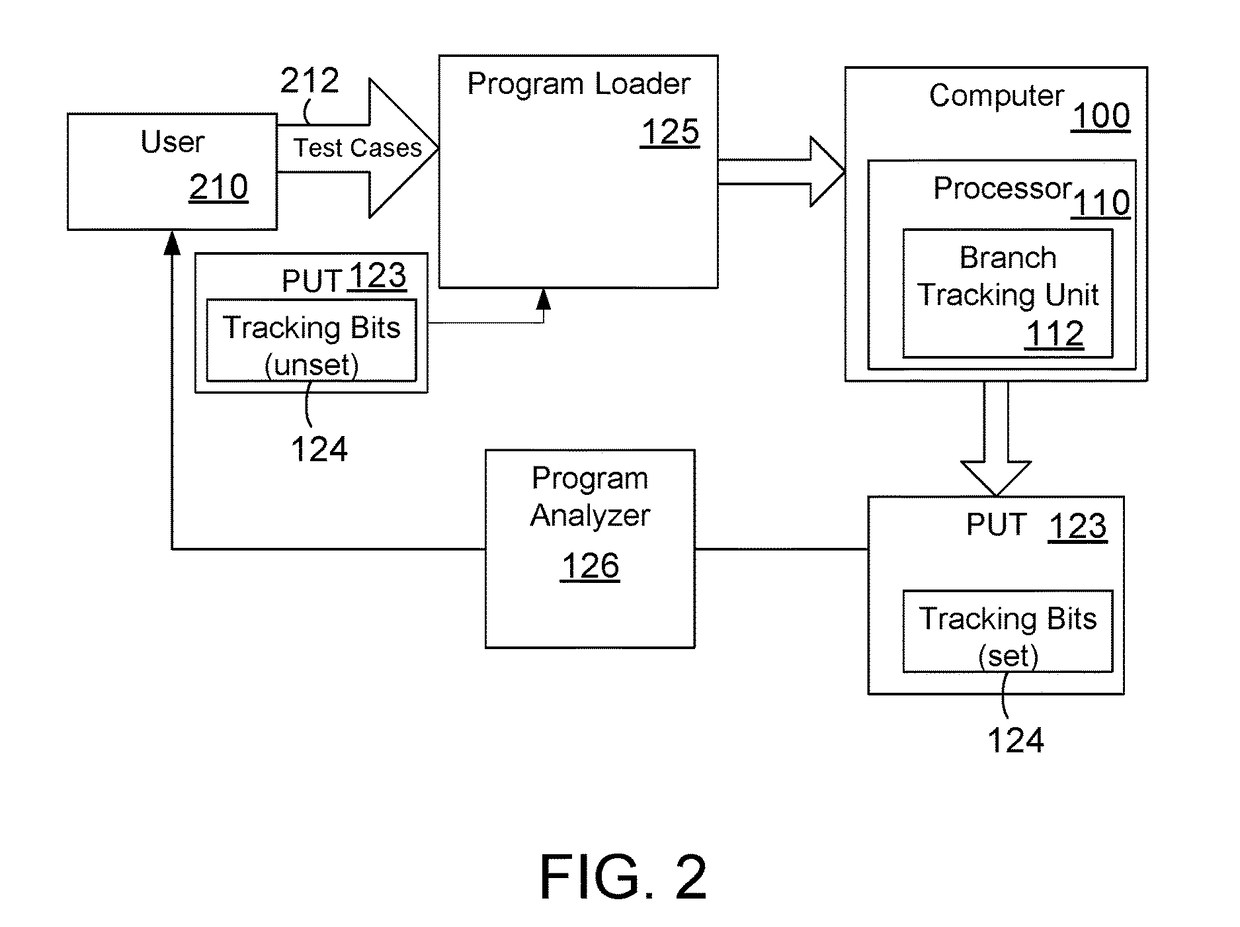

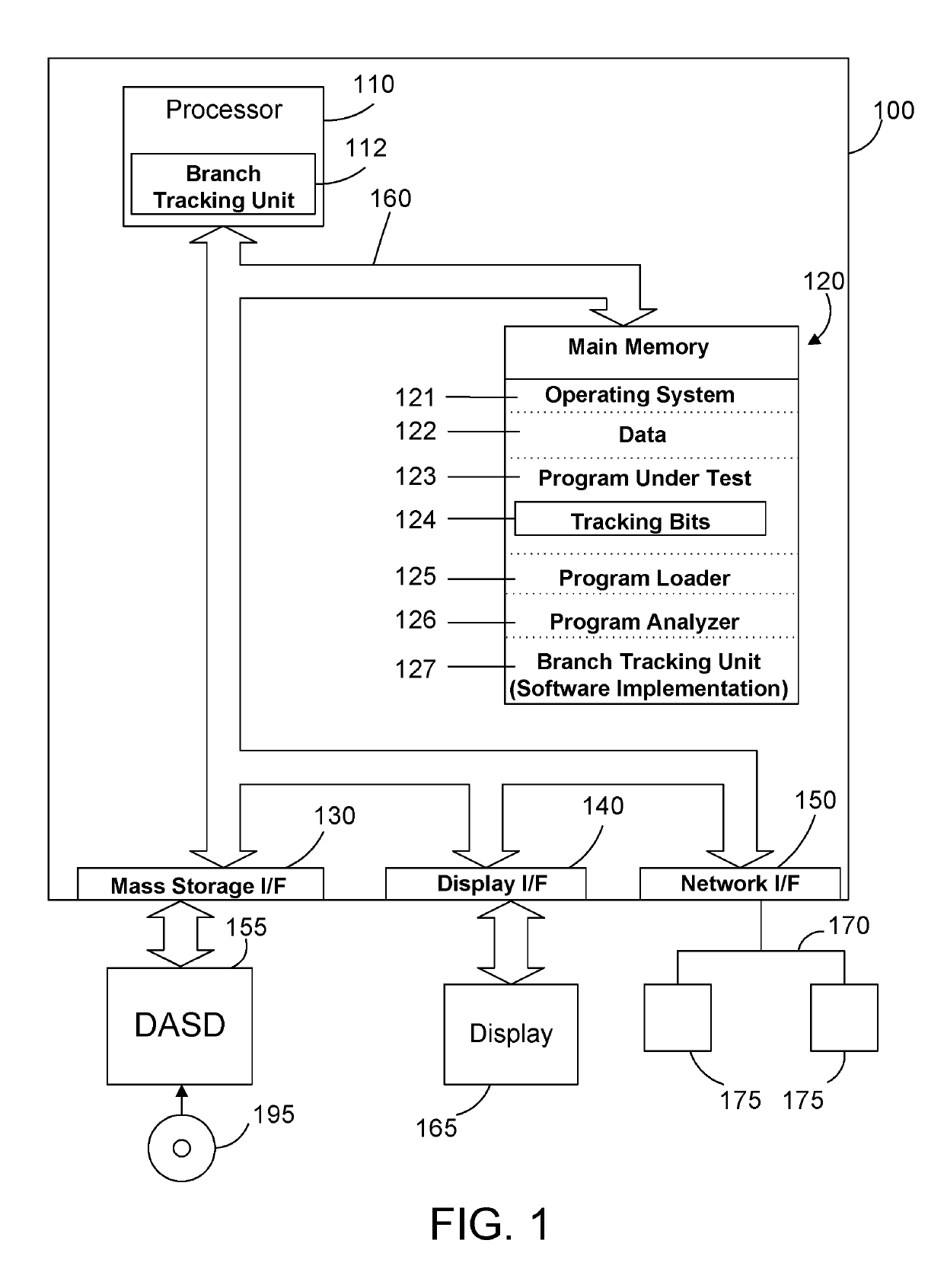

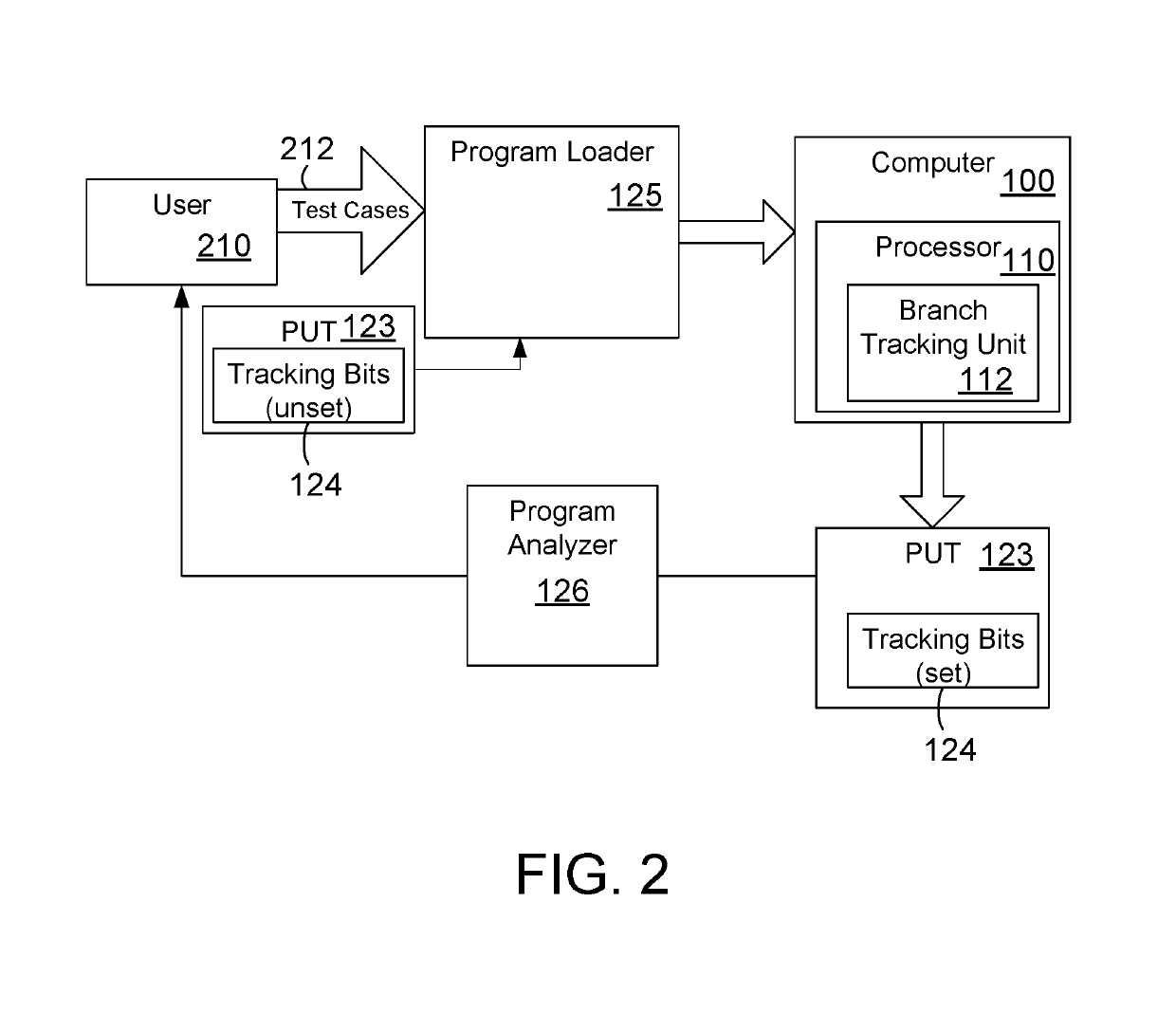

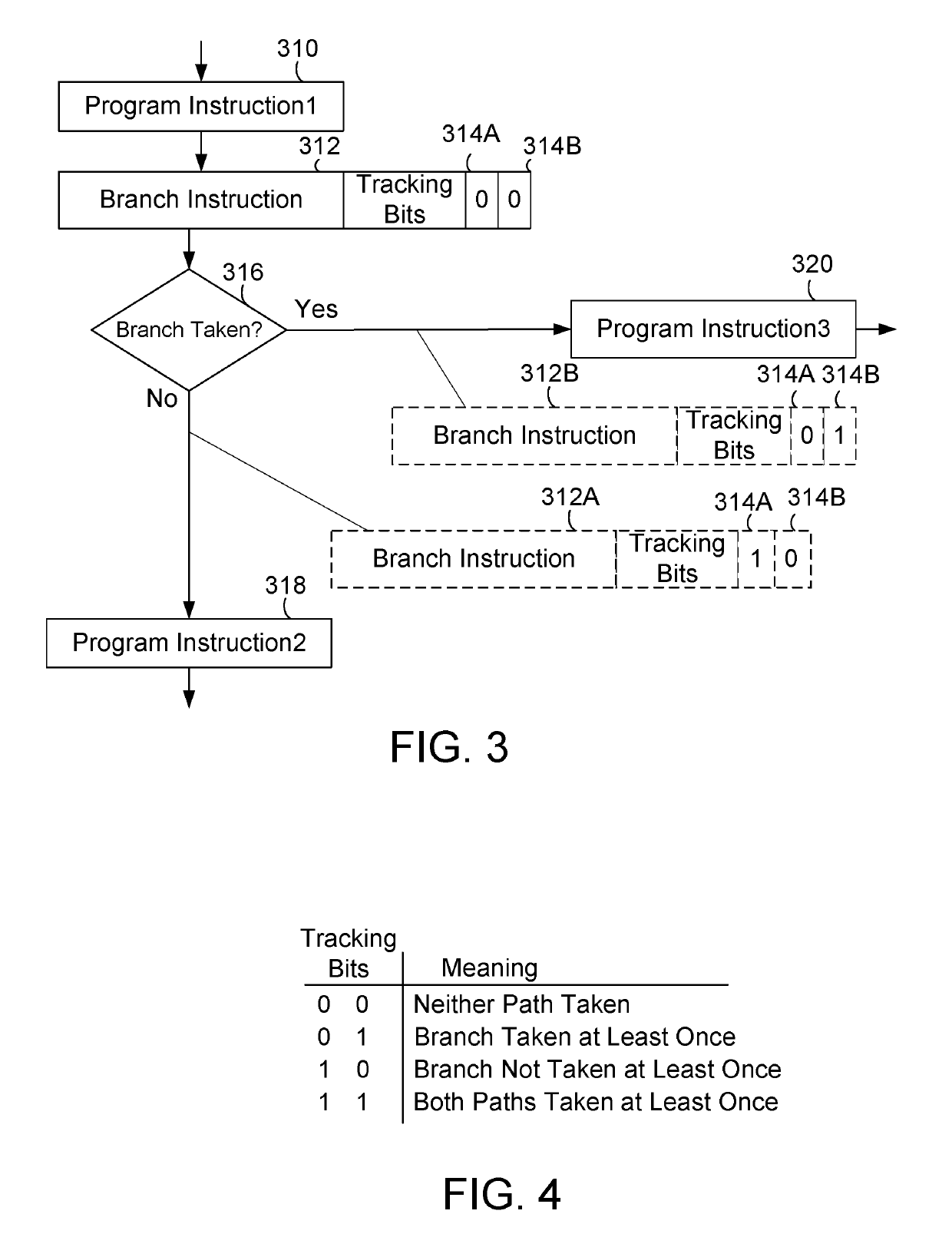

Testing computer software using tracking bits

A system and method tests computer software using tracking bits in branch instructions to track portions of the software that have been tested. The tracking bits are bits of a branch programming instruction and may be repurposed hint bits used in the prior art to control pre-fetch of instructions. A branch tracking unit sets bits in a branch instruction of an application or program being tested. The branch tracing unit sets a first bit if a branch is taken and sets a second tracking bit if the branch is not taken. The modified program instructions can be analyzed after running the test inputs to determine if any branches in the software have not been exercised by the test inputs.

Owner:IBM CORP

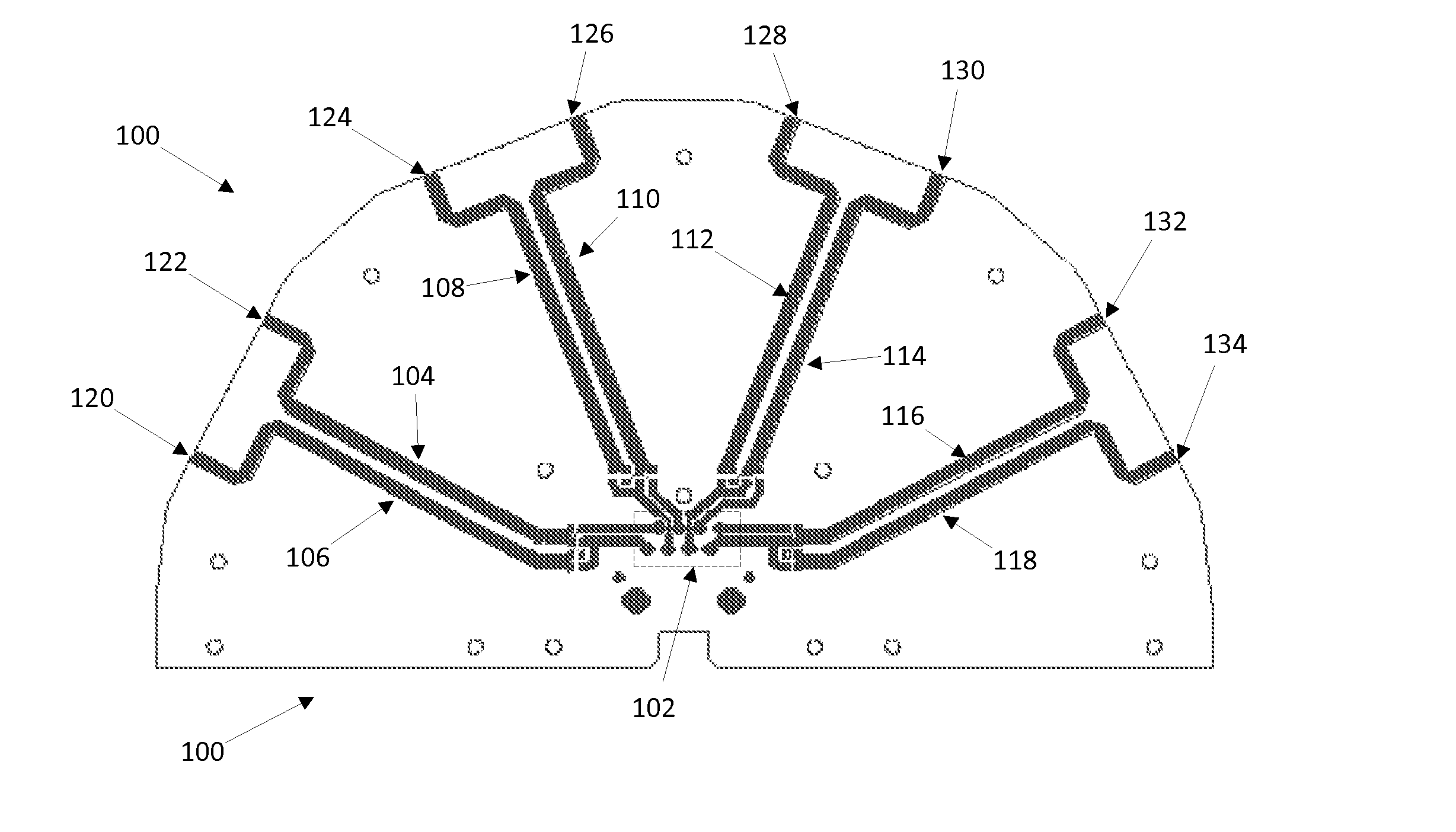

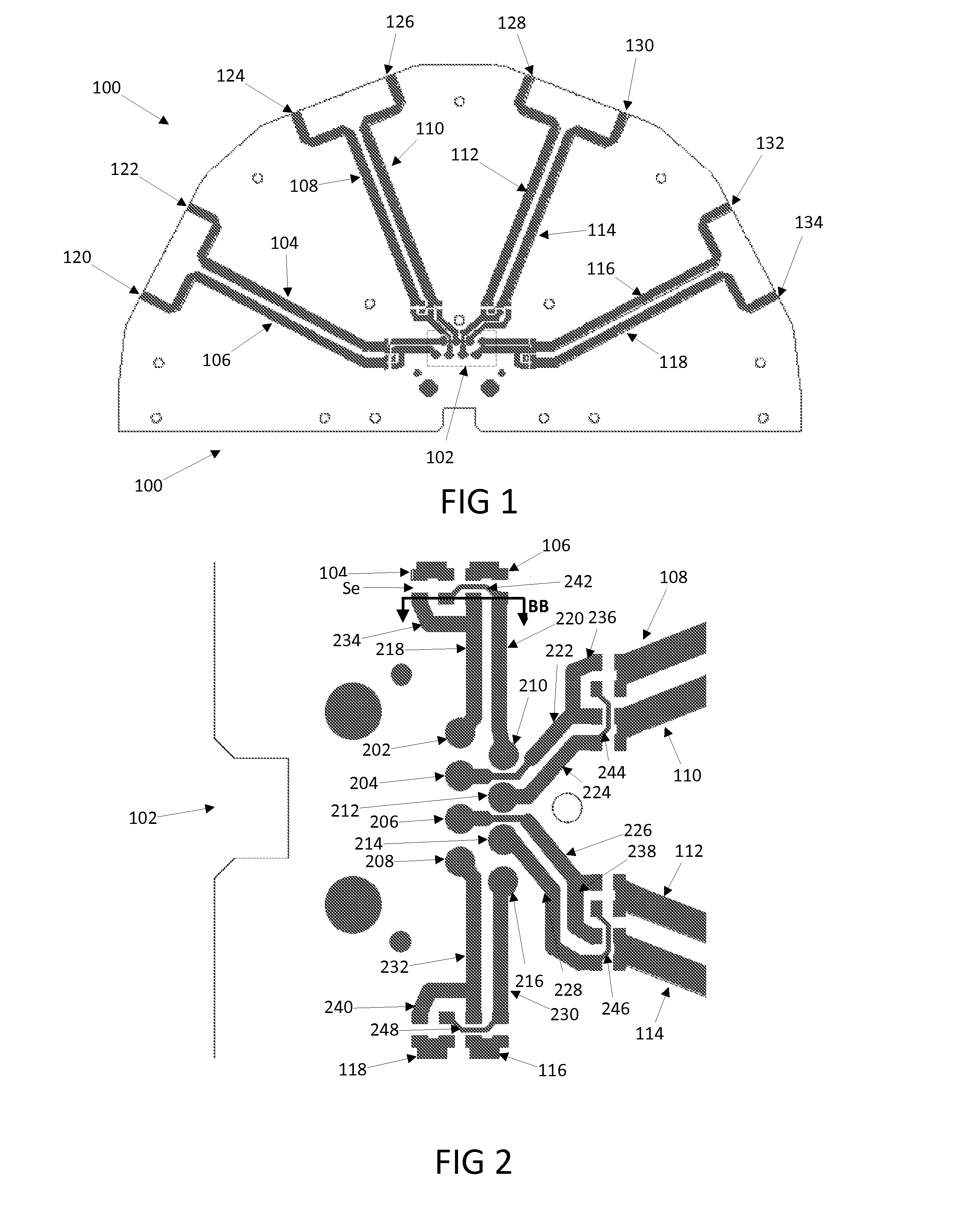

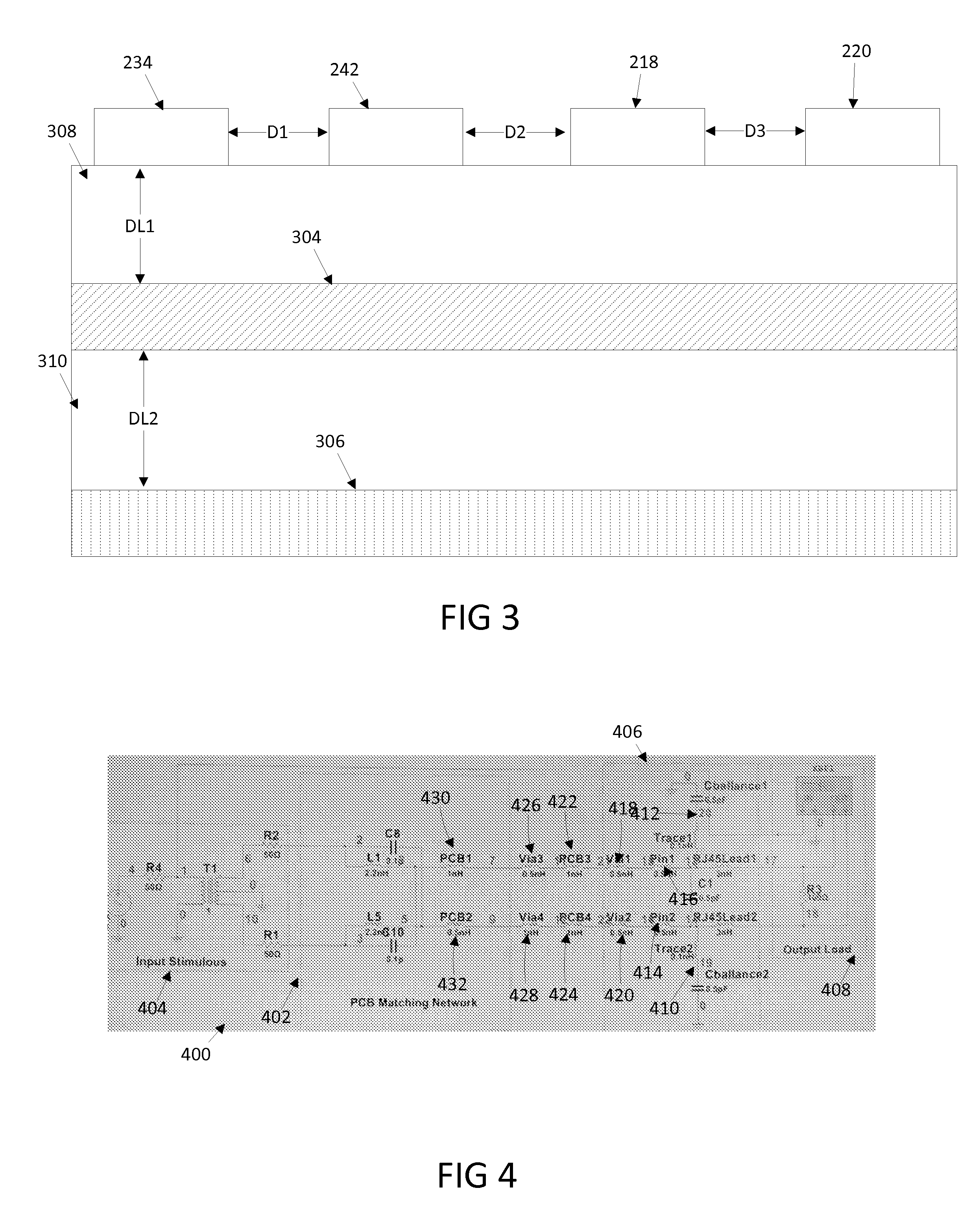

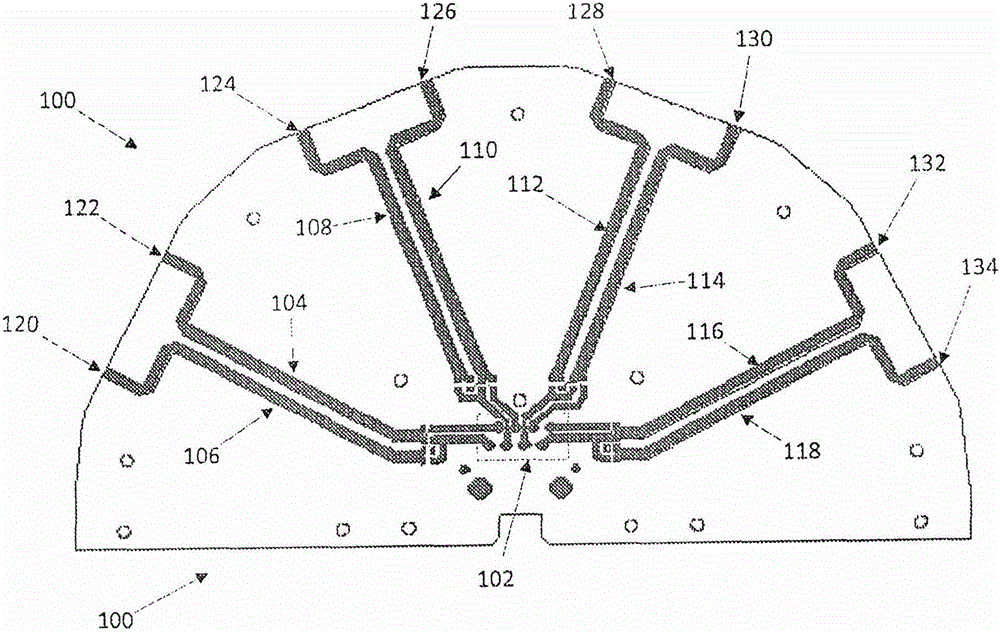

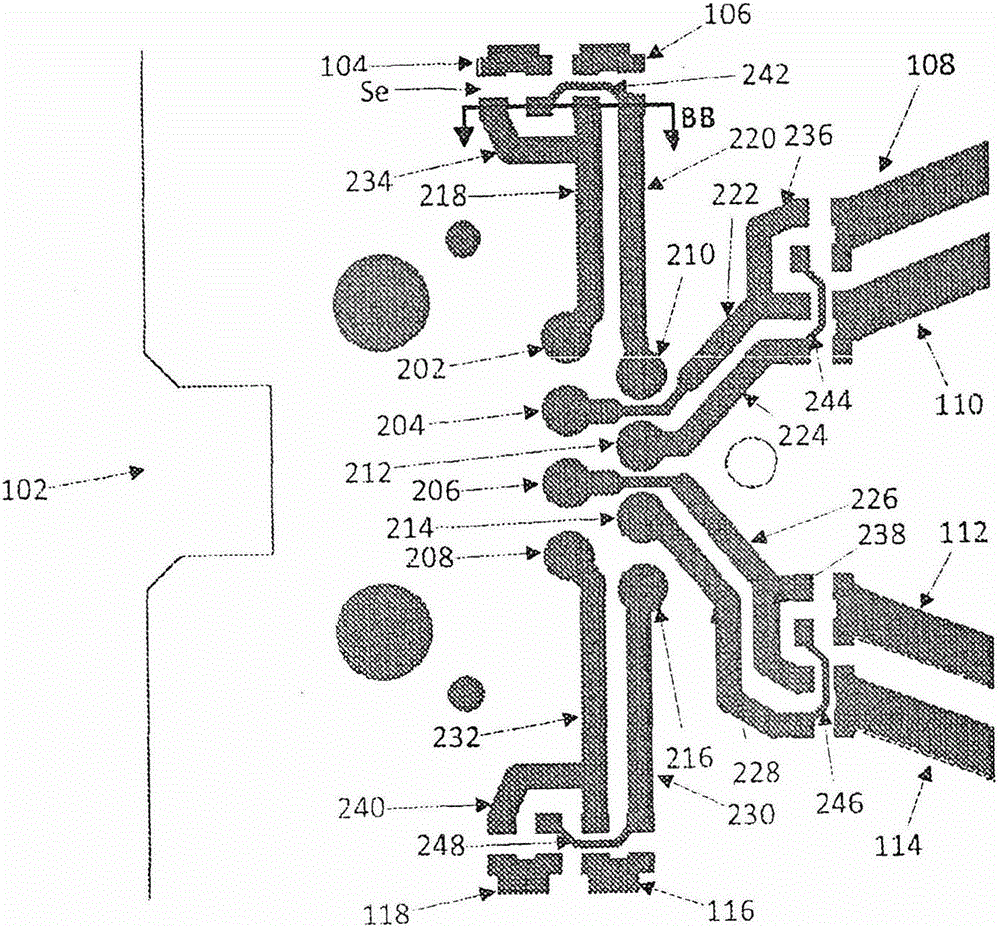

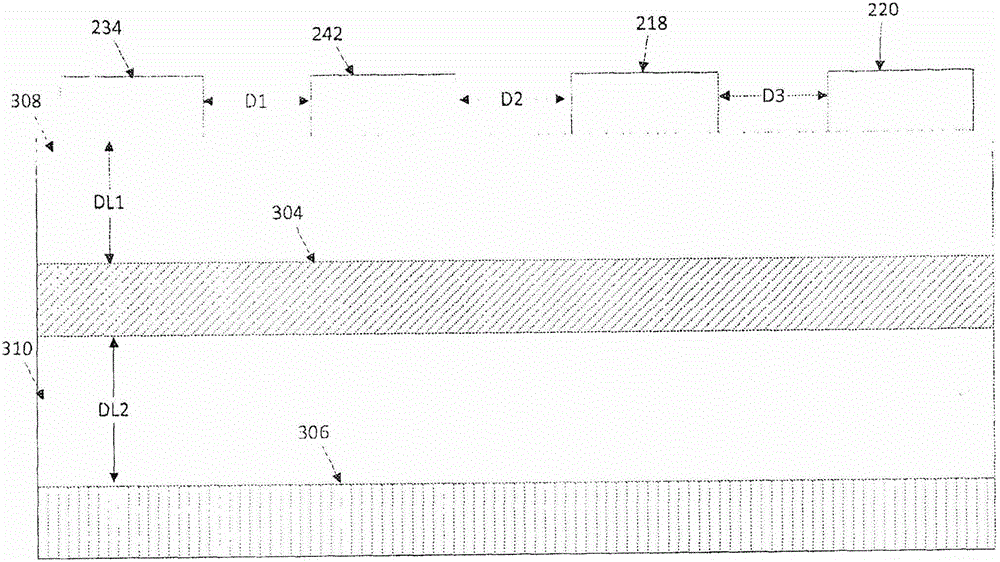

Testing apparatus for a high speed communications jack and methods of operating the same

ActiveUS20140204788A1Substation/switching arrangement detailsCorrect operation testingBranch traceEngineering

A testing unit including a substrate, a plurality of vias located in the substrate, a plurality of pin traces having a height and a width and each extending from a respective via towards an edge of the substrate, a plurality of end traces having a height and a width with each end trace extending from an end of a respective pin trace towards the edge of the substrate, a plurality of branch traces having a height and a width and each extending from a side of a respective pin trace, a plurality of traces extending from the end of a respective end trace, branch trace or pin trace to the edge of the substrate, where each end trace is adjacent to a respective branch trace, each end trace is adjacent to a respective branch trace on one side and a pin trace on the opposite side, and each pin trace is adjacent to another pin trace on one side.

Owner:SENTINEL CONNECTOR SYST

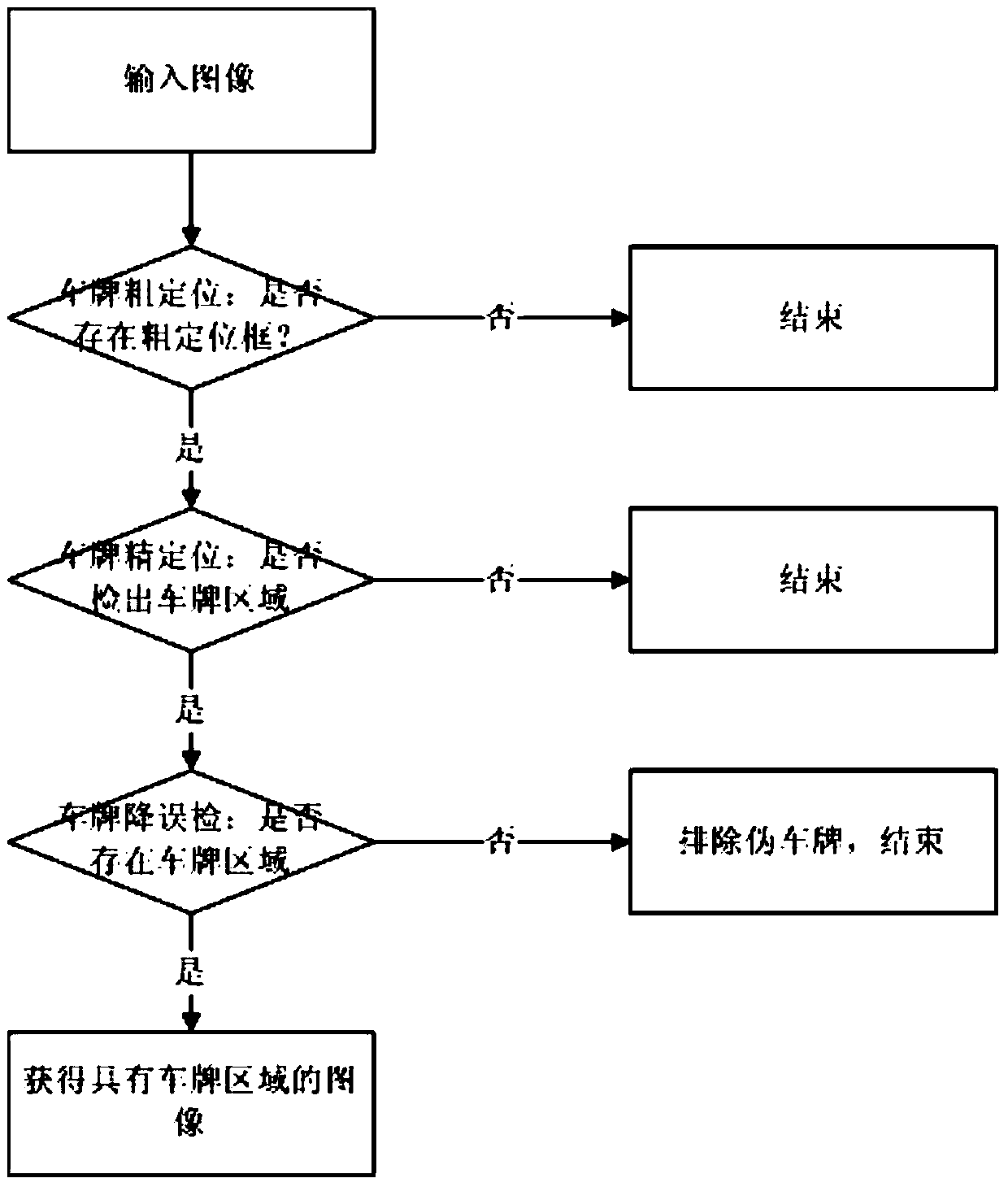

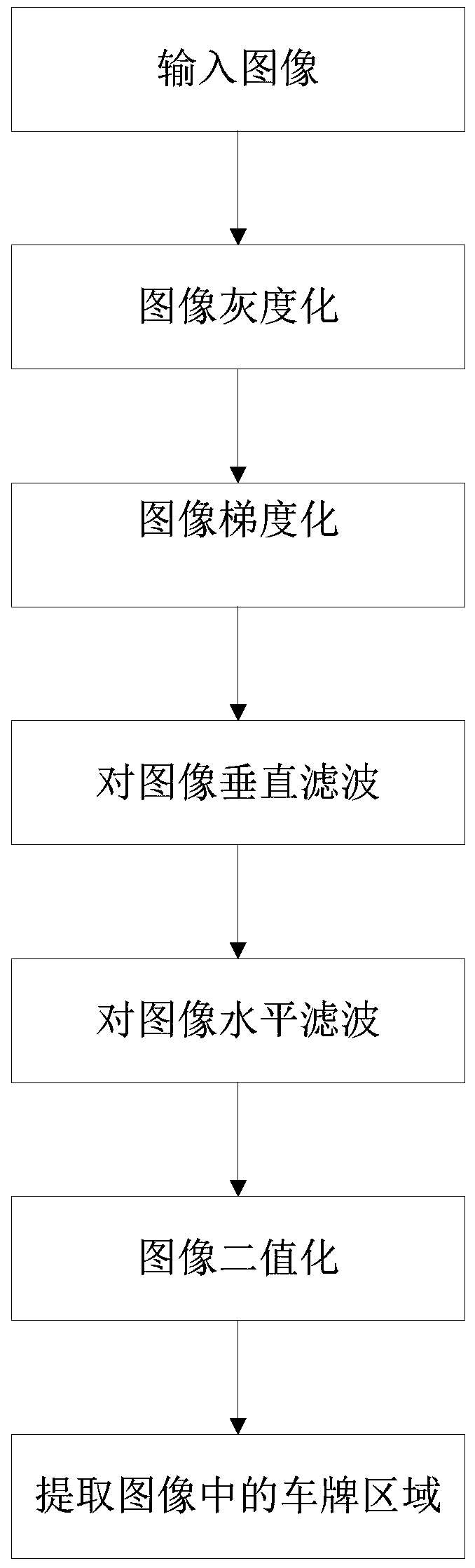

License plate detection method and device in complex scenes

ActiveCN106257494BGuaranteed detection rateReduce false detection rateCharacter and pattern recognitionBranch traceComplex field

The invention discloses a license plate detection method in a complex scene, which includes: performing rough positioning on an input image, the rough positioning includes horizontal filtering and binarization processing, and using a trained fine positioning classifier to classify areas with rough positioning The license plate area detection is performed on the image of the license plate area, which also includes: the image of the license plate area is detected through the false detection classifier obtained by branch training to exclude the image of the falsely detected license plate area, and obtain the final image containing the license plate area. The invention also includes a license plate detection device. Compared with the existing methods, the license plate detection method and device adopted by the present invention have the outstanding advantages of low false detection rate and faster speed than the existing methods on the basis of ensuring the correct detection rate of the license plate.

Owner:ZHEJIANG UNIVIEW TECH CO LTD

Testing apparatus for a high speed communications jack and methods of operating the same

The disclosure relates to a testing apparatus for a high speed communications jack and methods of operating the same. A testing unit including a substrate, a plurality of vias located in the substrate, a plurality of pin traces having a height and a width and each extending from a respective via towards an edge of the substrate, a plurality of end traces having a height and a width with each end trace extending from an end of a respective pin trace towards the edge of the substrate, a plurality of branch traces having a height and a width and each extending from a side of a respective pin trace, a plurality of traces extending from the end of a respective end trace, branch trace or pin trace to the edge of the substrate, where each end trace is adjacent to a respective branch trace.

Owner:SENTINEL CONNECTOR SYST

Method and system for hardware-based edge profiling

Methods and systems for hardware-based edge profiling are related. A method comprising: counting each occurrence of a hardware event by a performance monitoring counter in a hardware processor during execution of object program code; The taken branches are sequentially and continuously stored in a buffer of the hardware processor's taken branch tracking (TBT) facility; each time the count is equal to the sampling rate, the sampling of the buffer is triggered to receive the TBT of the last adopted branch of the predefined TBT size; construct a full branch trace of each of the TBTs based on the target program code; extract the last branch trace of a predefined truncated branch trace (CBT) size from each of the full branch traces branching to receive said truncated branch trace for each TBT; and incrementally store each of said truncated branch traces to generate an edge profile for said object program code.

Owner:IBM CORP

Testing computer software using tracking bits

A system and method tests computer software using tracking bits in branch instructions to track portions of the software that have been tested. The tracking bits are bits of a branch programming instruction and may be repurposed hint bits used in the prior art to control pre-fetch of instructions. A branch tracking unit sets bits in a branch instruction of an application or program being tested. The branch tracing unit sets a first bit if a branch is taken and sets a second tracking bit if the branch is not taken. The modified program instructions can be analyzed after running the test inputs to determine if any branches in the software have not been exercised by the test inputs.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com