Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Little space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

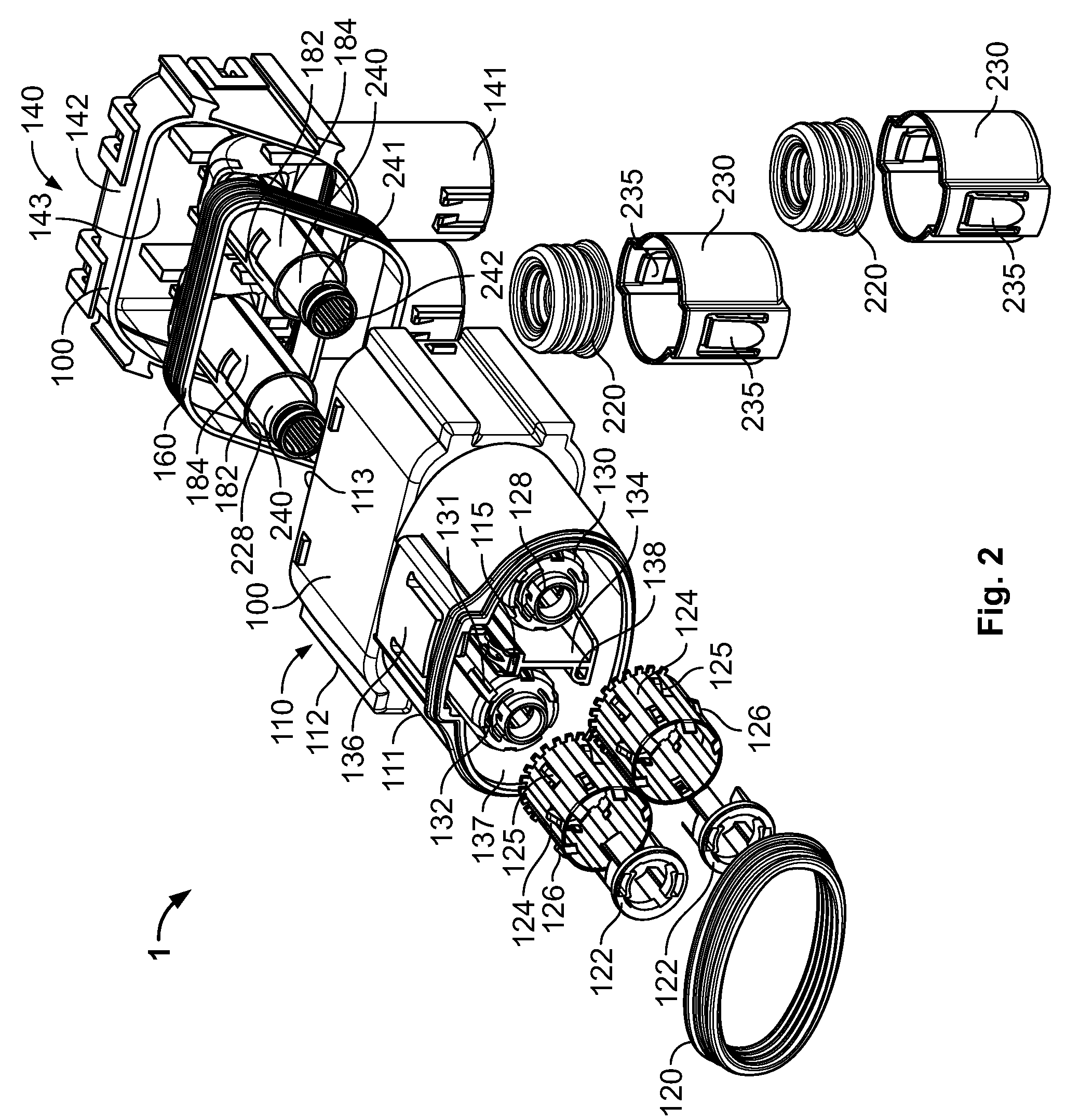

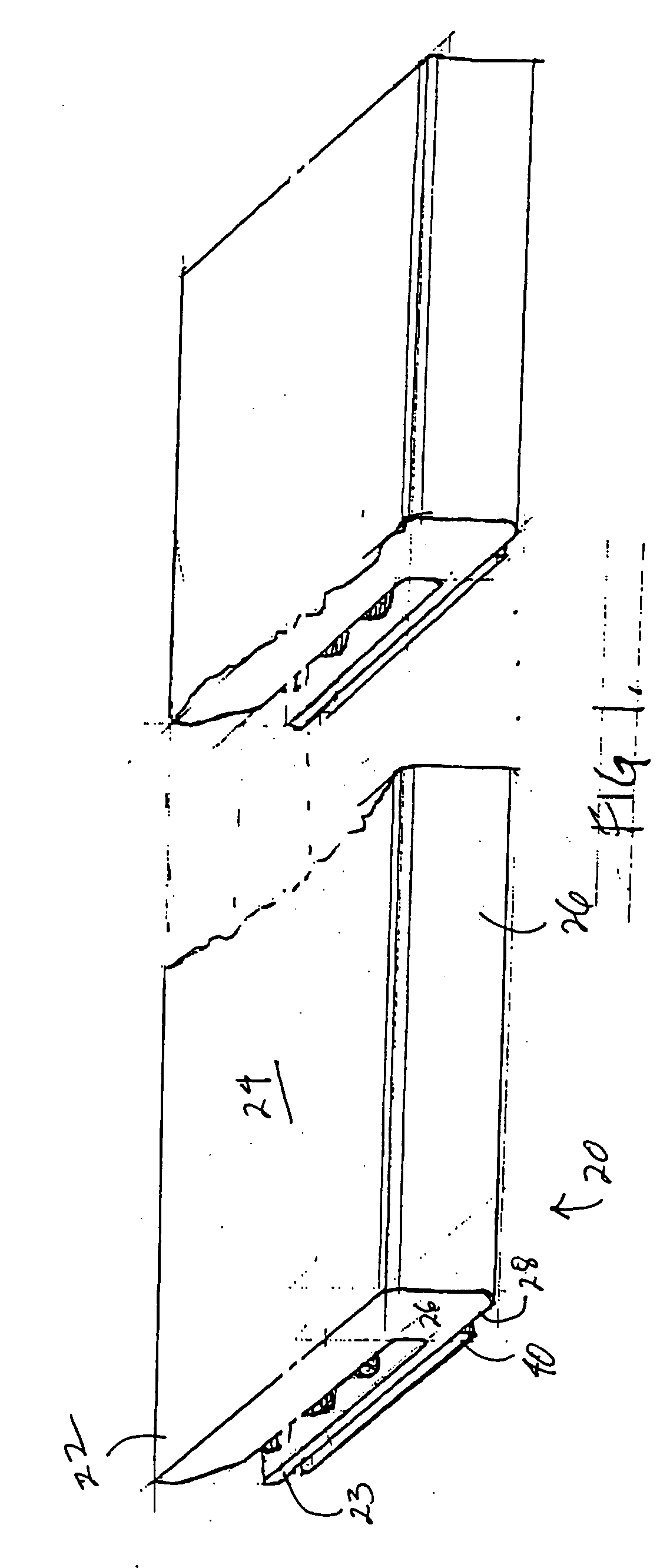

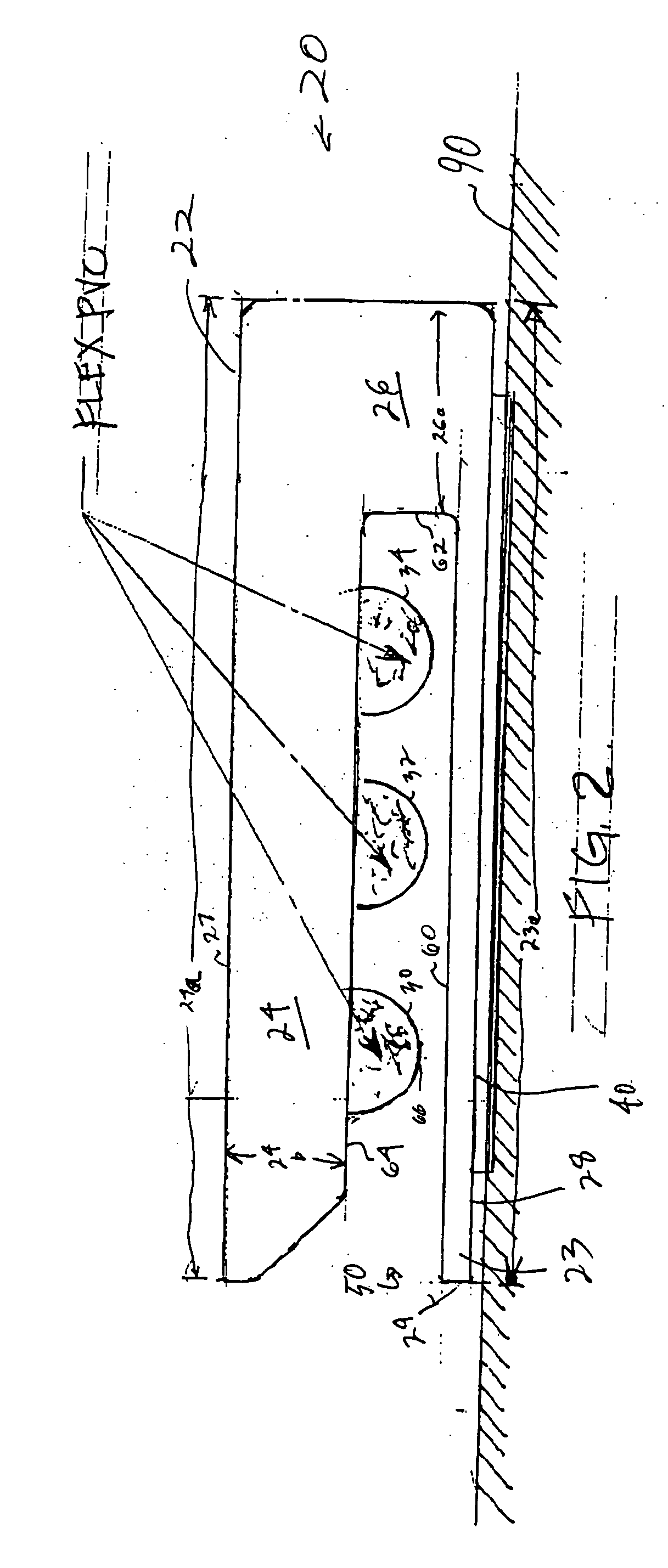

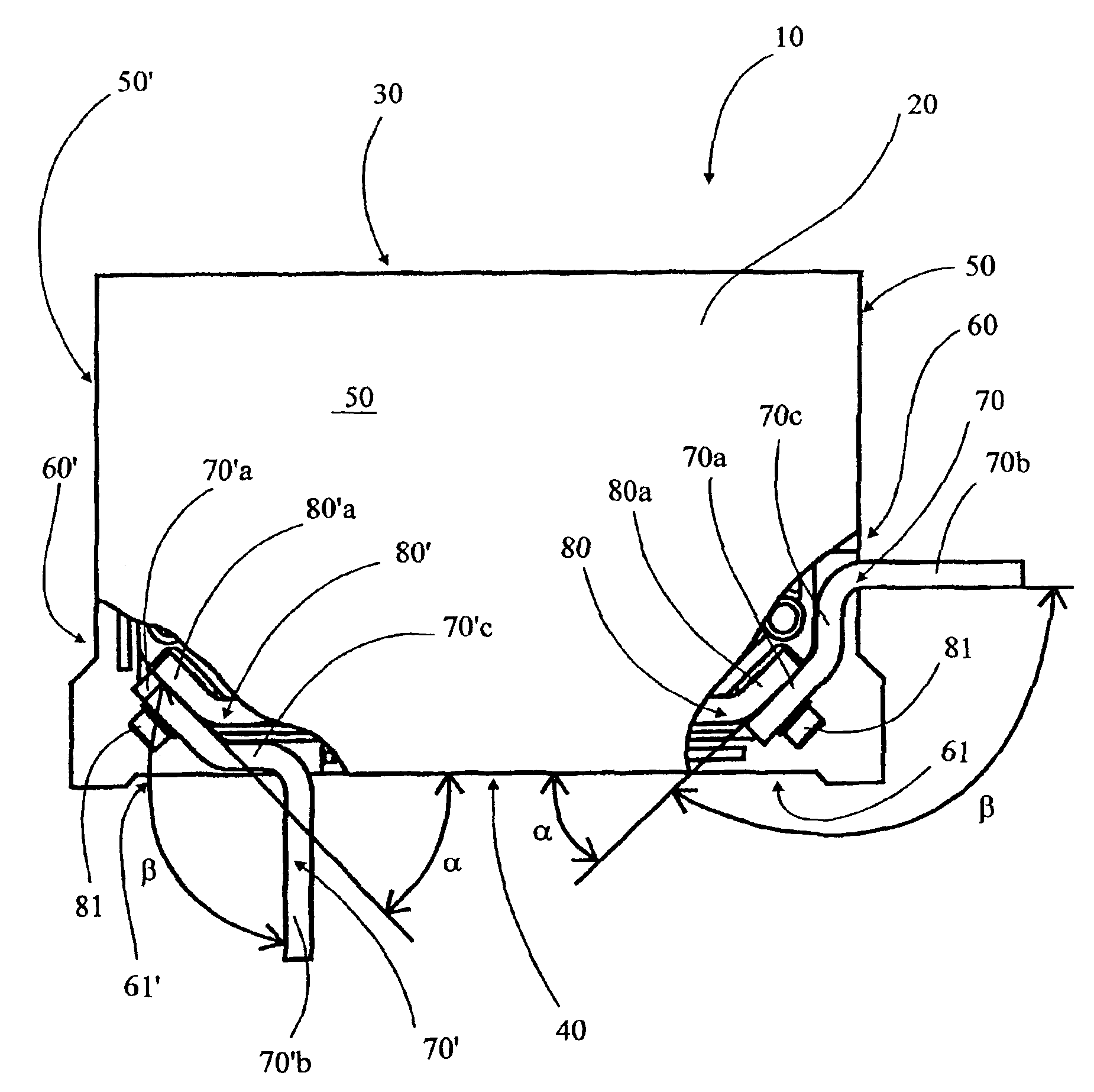

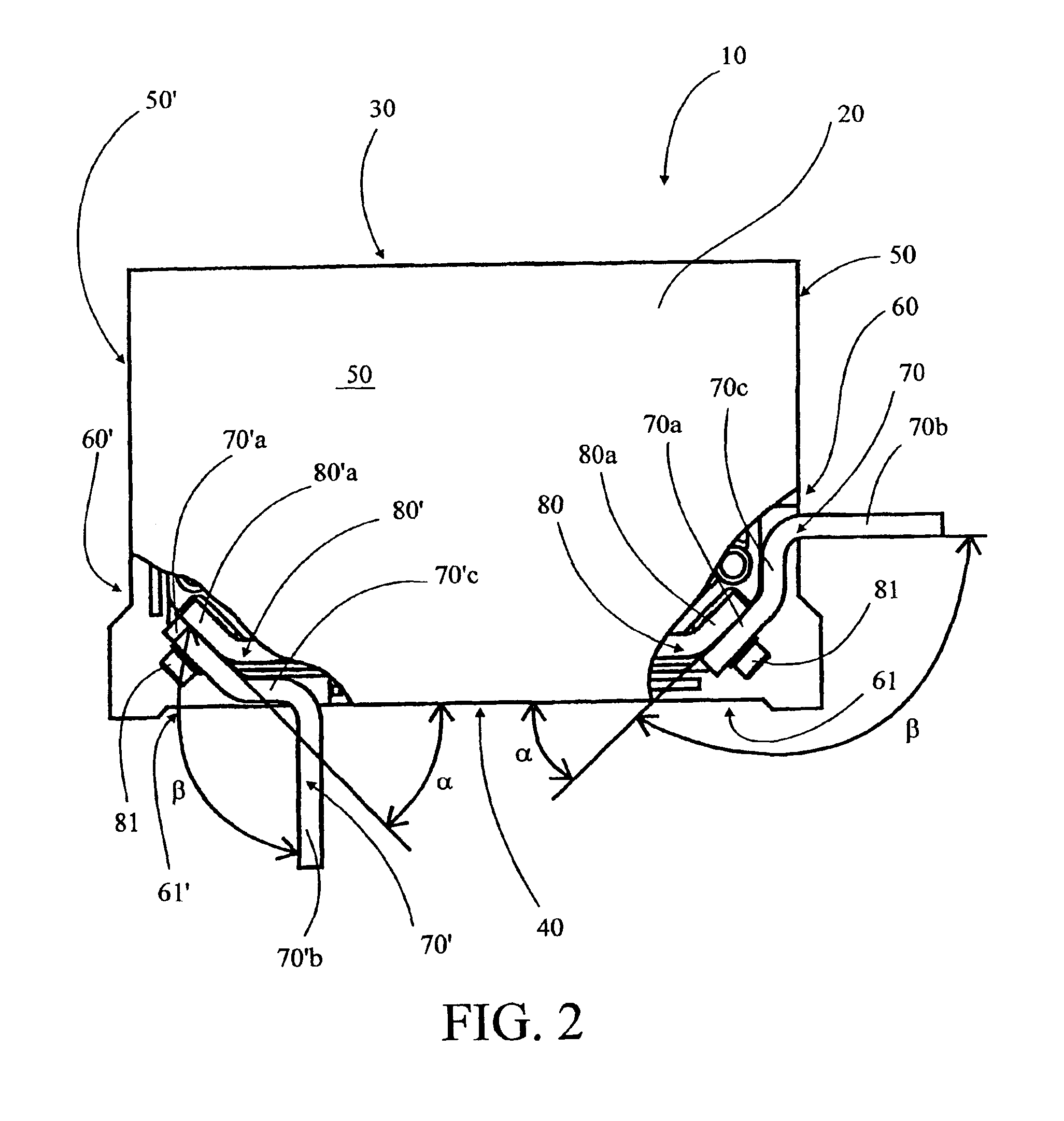

Electrical connector

InactiveUS7540772B2Simply constructedLittle spaceIncorrect coupling preventionTwo-part coupling devicesEngineeringElectrical and Electronics engineering

An electrical connector having a housing having a body and a plug tip, a cable raceway having a raceway riser configured to receive a cable, the cable raceway being configured for attachment to the body, wherein the plug tip of the housing is angled with respect to a raceway riser when the cable raceway is attached to the body is disclosed.

Owner:TYCO ELECTRONICS AMP ITAL +1

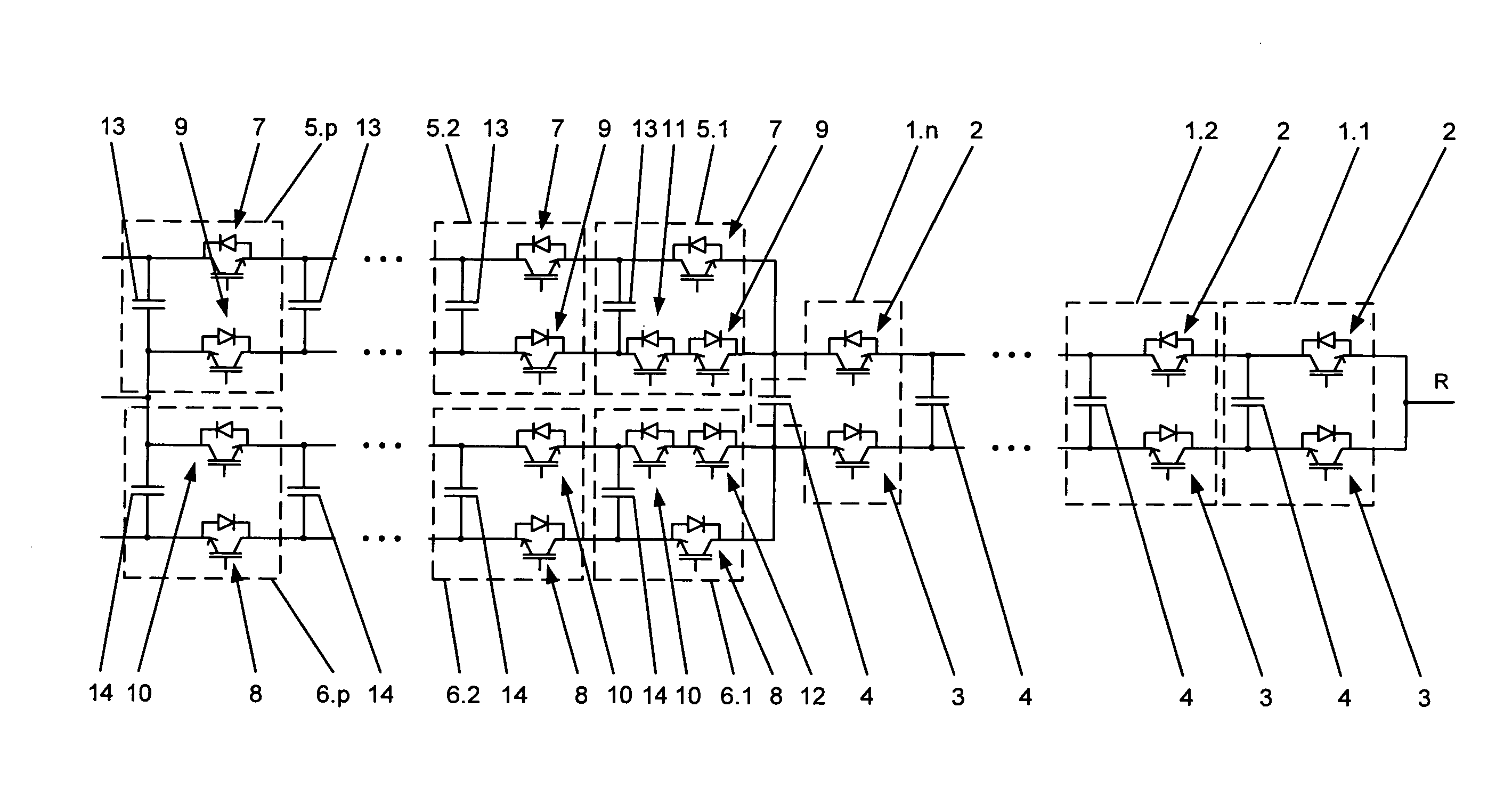

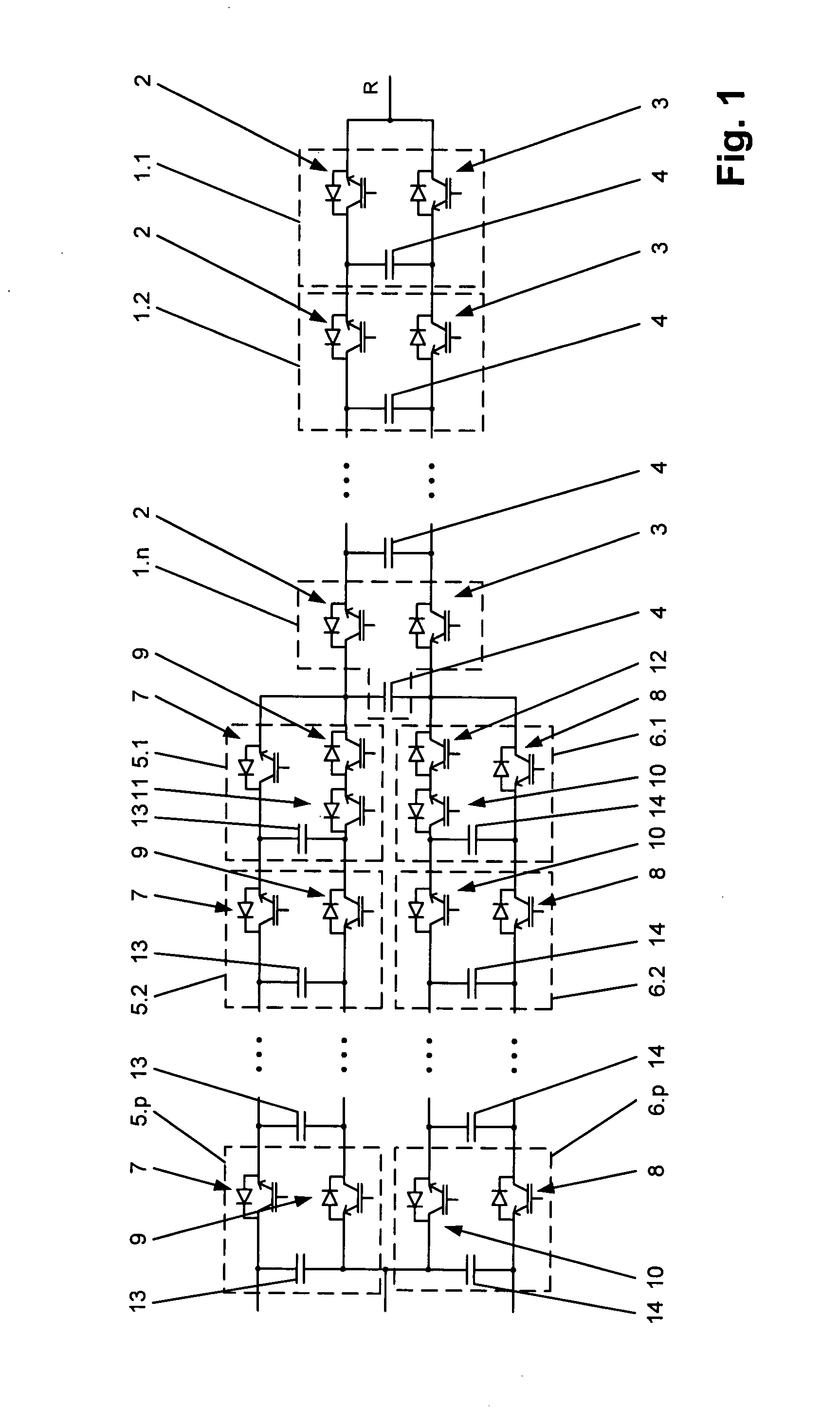

Converter circuit for switching of a multiplicity of switching voltage levels

InactiveUS20070235293A1Reduce amountLittle spaceConversion with intermediate conversion to dcDc-dc conversionElectric energyTransverter

A converter circuit is specified for switching of a multiplicity of switching voltage levels, which have n first switching groups (1.1, . . . , 1.n) for each phase (R, S, T), with the n-th first switching group (1.n) being formed by a first drivable bidirectional power semiconductor switch (2) and a second drivable bidirectional power semiconductor switch (3), and with the first first switching group (1.1) to the (n−1)-th switching group (1.(n−1)) each being formed by a first drivable bidirectional power semiconductor switch (2) and a second drivable bidirectional power semiconductor switch (3), and by a capacitor (4) which is connected to the first and second drivable bidirectional power semiconductor switches (2, 3) with each of the n first switching groups (1.1, . . . , 1.n) being connected in a linked form to the respectively adjacent first switching group (1.1, . . . , 1.n), and with the first and the second drivable bidirectional power semiconductor switches (2, 3) in the first first switching group (1.1) being connected to one another. In order to reduce the stored electrical energy in the converter circuit, n≧1, and p second switching groups (5.1, . . . , 5.p) and p third switching groups (6.1, . . . , 6.p) are provided, which each have a first drivable bidirectional power semiconductor switch (7, 8), a second drivable bidirectional power semiconductor switch (9, 10) and a capacitor (13, 14), where p≧1. Each of the p second switching groups (5.1, . . . , 5.p) is connected in a linked form to the respectively adjacent second switching group (5.1, . . . , 5.p), and each of the p third switching groups (6.1, . . . , 6.p) is connected in a linked form to the respectively adjacent third switching group (6.1, . . . , 6.p). Furthermore, the first second and the first third switching group (5.1, 6.1) each have a third drivable bidirectional power semiconductor switch (11, 12) which is connected back-to-back in series with the respective second drivable bidirectional power semiconductor switch (9, 10), with the first second switching group (5.1) being connected to the first drivable bidirectional power semiconductor switch (2) in the n-th first switching group (1.n), and with the first third switching group (6.1) being connected to the second drivable bidirectional power semiconductor switch (3) in the n-th first switching group (1.n), and the capacitor (13) in the p-th second switching group (5.p) is connected in series with the capacitor (14) in the p-th third switching group (6.p).

Owner:ABB RES LTD

Restraining and/or retaining apparatus for portable devices

InactiveUS6036068ALittle spaceEconomical to manufactureTravelling sacksTravelling carriersEngineeringWrap around

A restraining and / or retaining apparatus 18 consisting of an elastic band 19 and retaining loops 21A, 21B for restraining and retaining multiple neck-suspended and / or unsuspended devices at the same time. The elastic band 19 wraps around the back and sides of the user and then encircles the neck strap, cord, lanyard or string 34 of a portable device 40 suspended at the chest or abdomen, and restricts its movement while walking, running, bending over or to the side. When the portable device 40 is used, the elasticity of the elastic band 19 allows it to be moved to any position from the chest to the face with little resistance and without detaching it. The retaining loops 21A, 21B hold and / or restrain other neck suspended or unsuspended devices at the same time for quick and convenient access.

Owner:CARTMELL STEVEN D

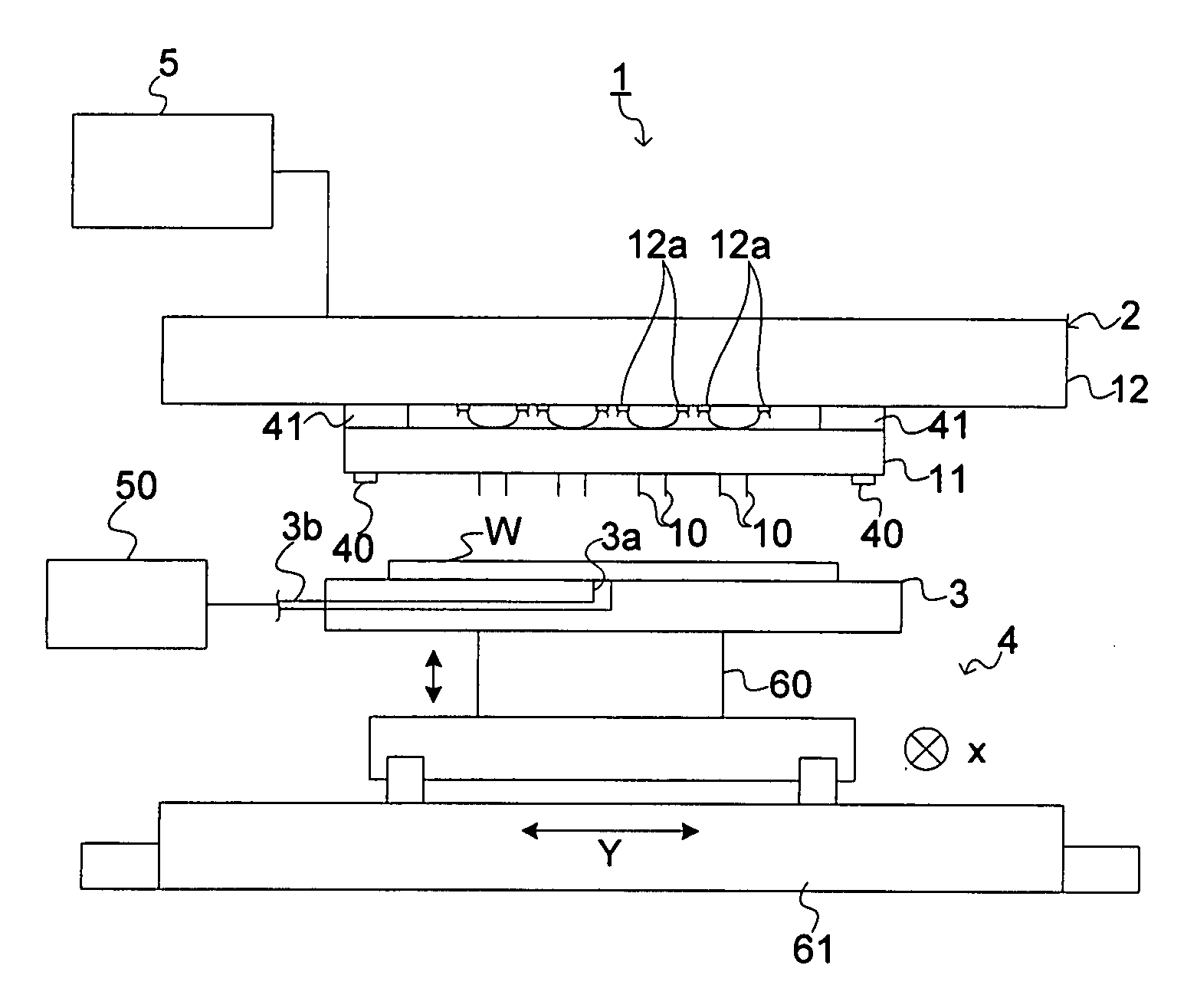

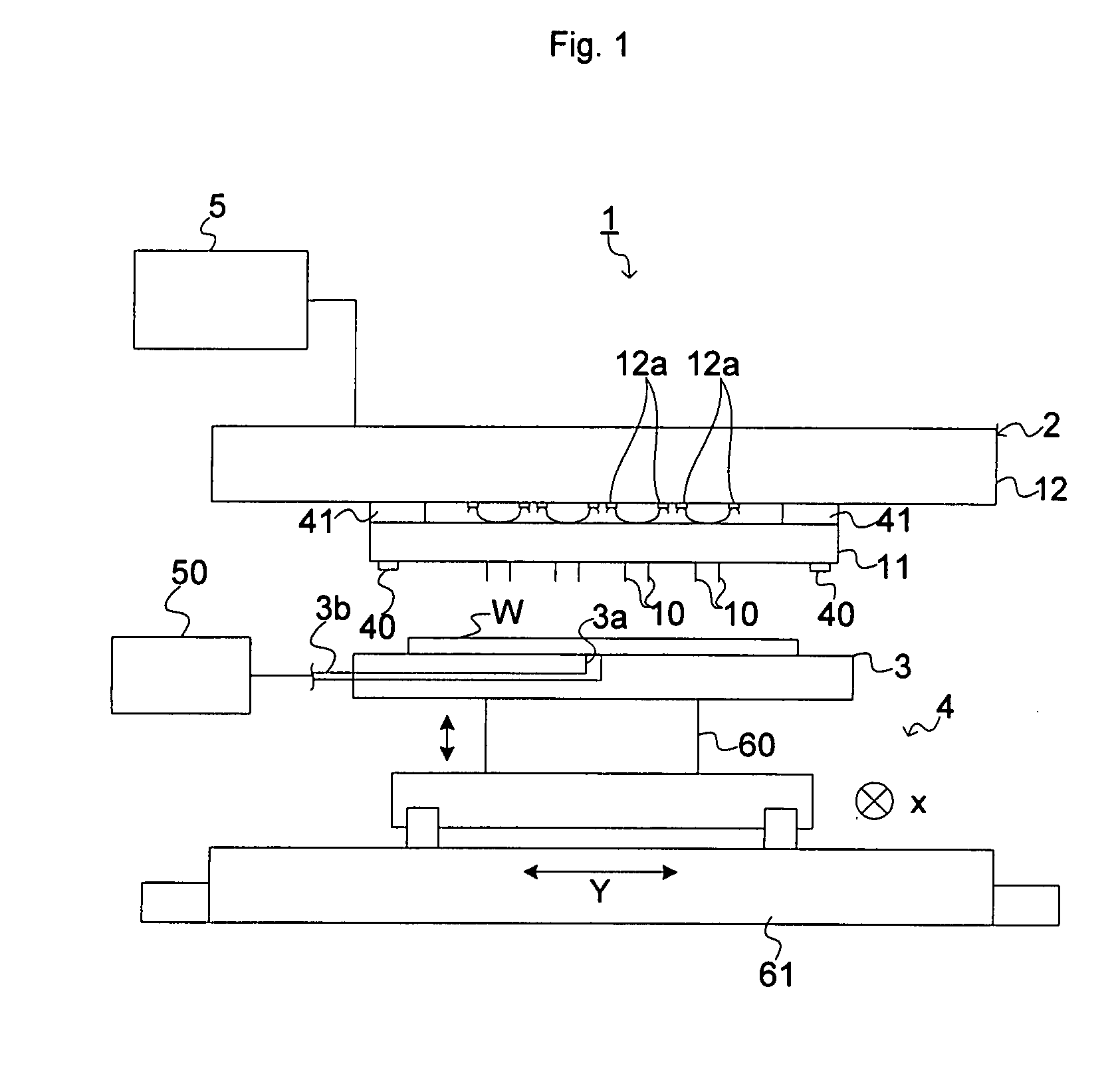

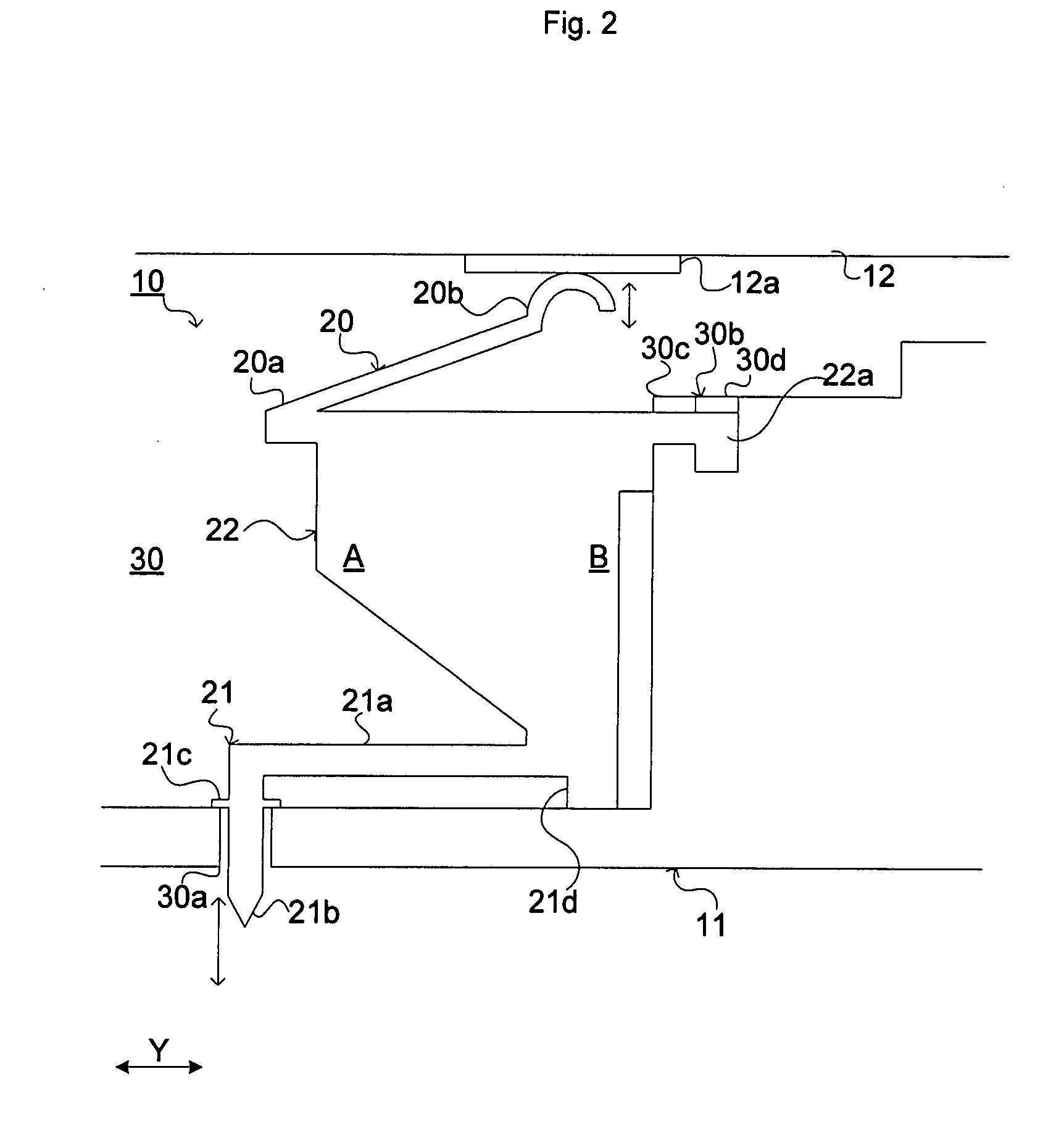

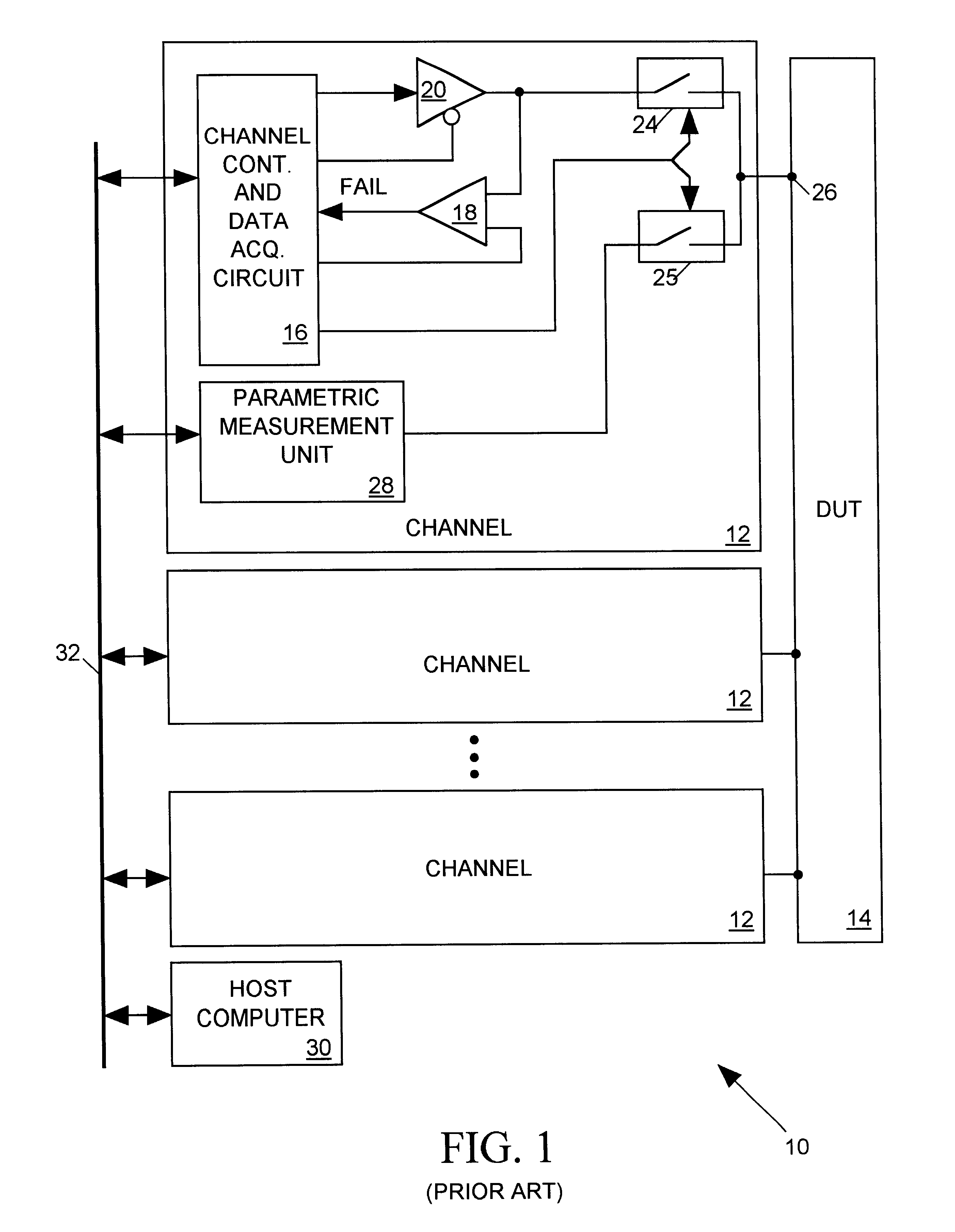

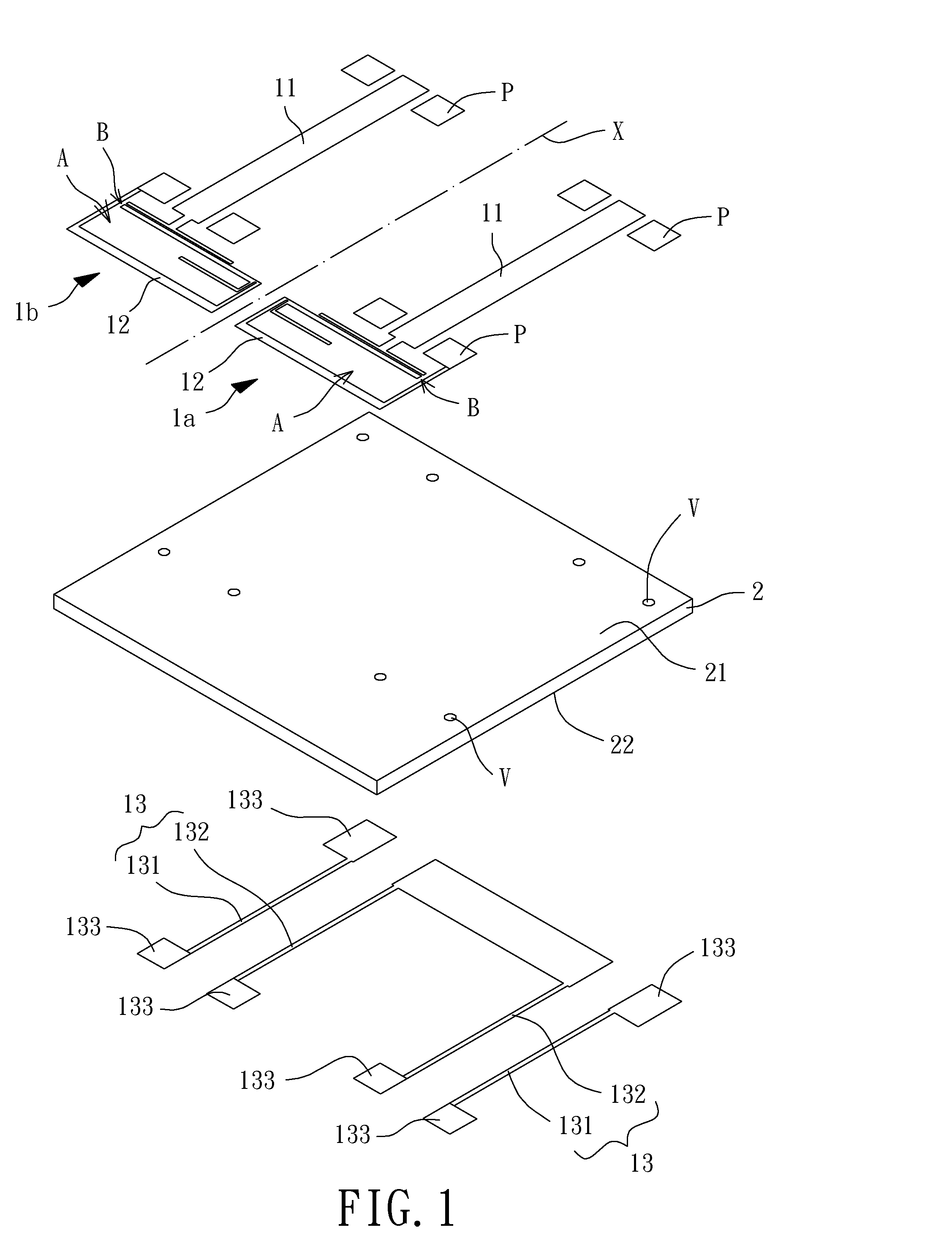

Probe card

InactiveUS20070290698A1Easy and inexpensive to manufactureLittle spaceElectrical measurement instrument detailsSolid-state devicesEngineeringLower face

The present invention provides a probe card that can examine an object with small electrode spacing. A probe supporting plate is provided to a lower face side of a printed wiring board of a probe card. A plurality of probes are supported by the probe supporting plate. The probes comprise an upper contact, a lower contact, and a main body portion. An upper end portion of the upper contact protrudes toward an upper side of the probe supporting plate and contacts a terminal of the printed wiring board. A lower end portion of the lower contact protrudes toward a lower side of the probe supporting plate. On the probe supporting plate, a through-hole and a concave portion are formed to lock the probes, and the probes can be inserted and removed freely against the probe supporting plate from above.

Owner:TOKYO ELECTRON LTD

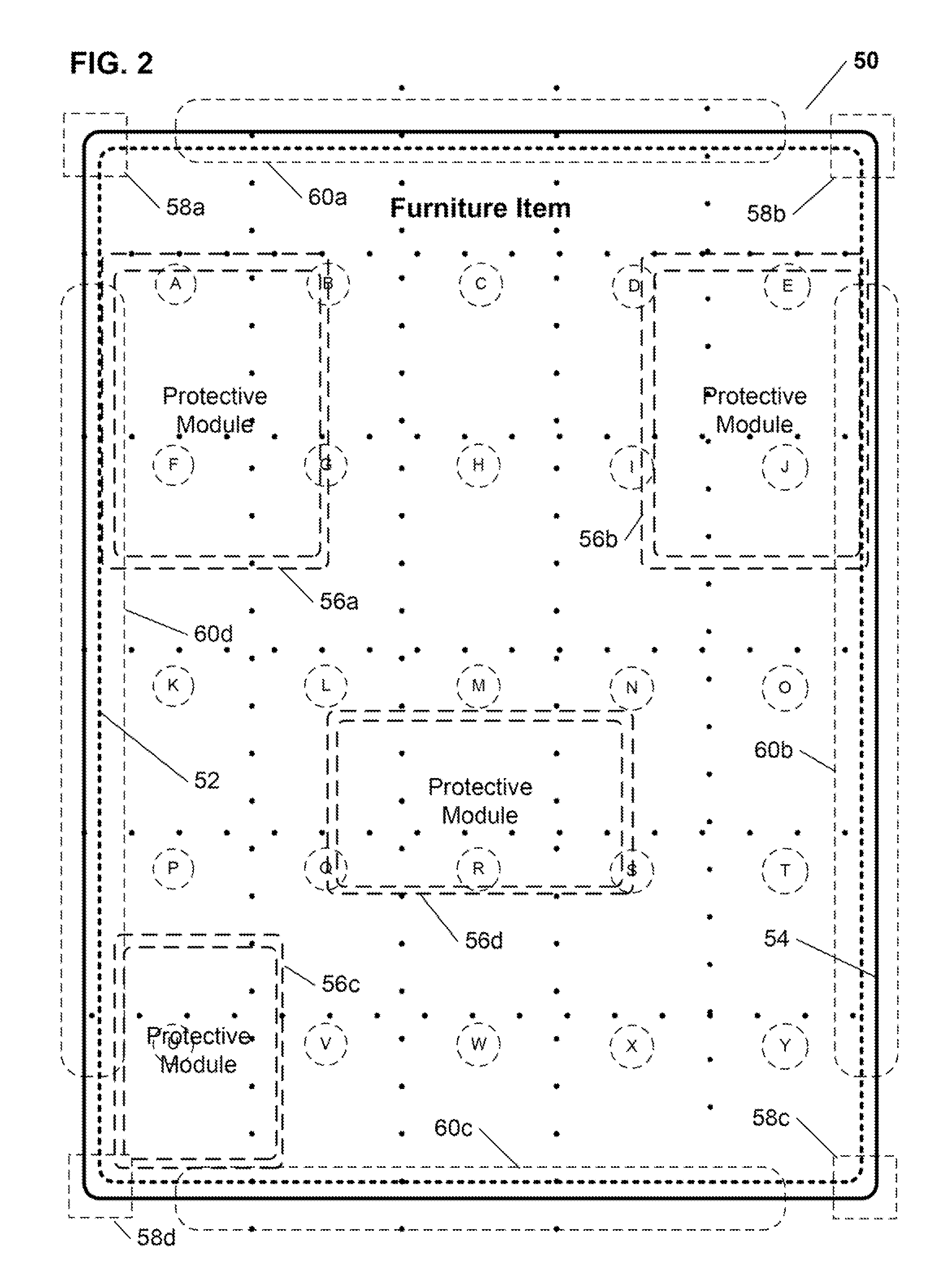

Modular Baby Safety System for On-Furniture Deployment

The present invention relates generally to products for safeguarding children, and more particularly to modular safety systems, operable to be readily mounted on any conventional flat top surface furniture items, or for deployment on any other substantially flat and stable surface, to secure the child within a predefined controlled area therein, and to provide protection from falling and accidental injuries to infants and toddlers positioned therein, during sleep, rest, interaction, and other activities thereof.

Owner:CUDABY

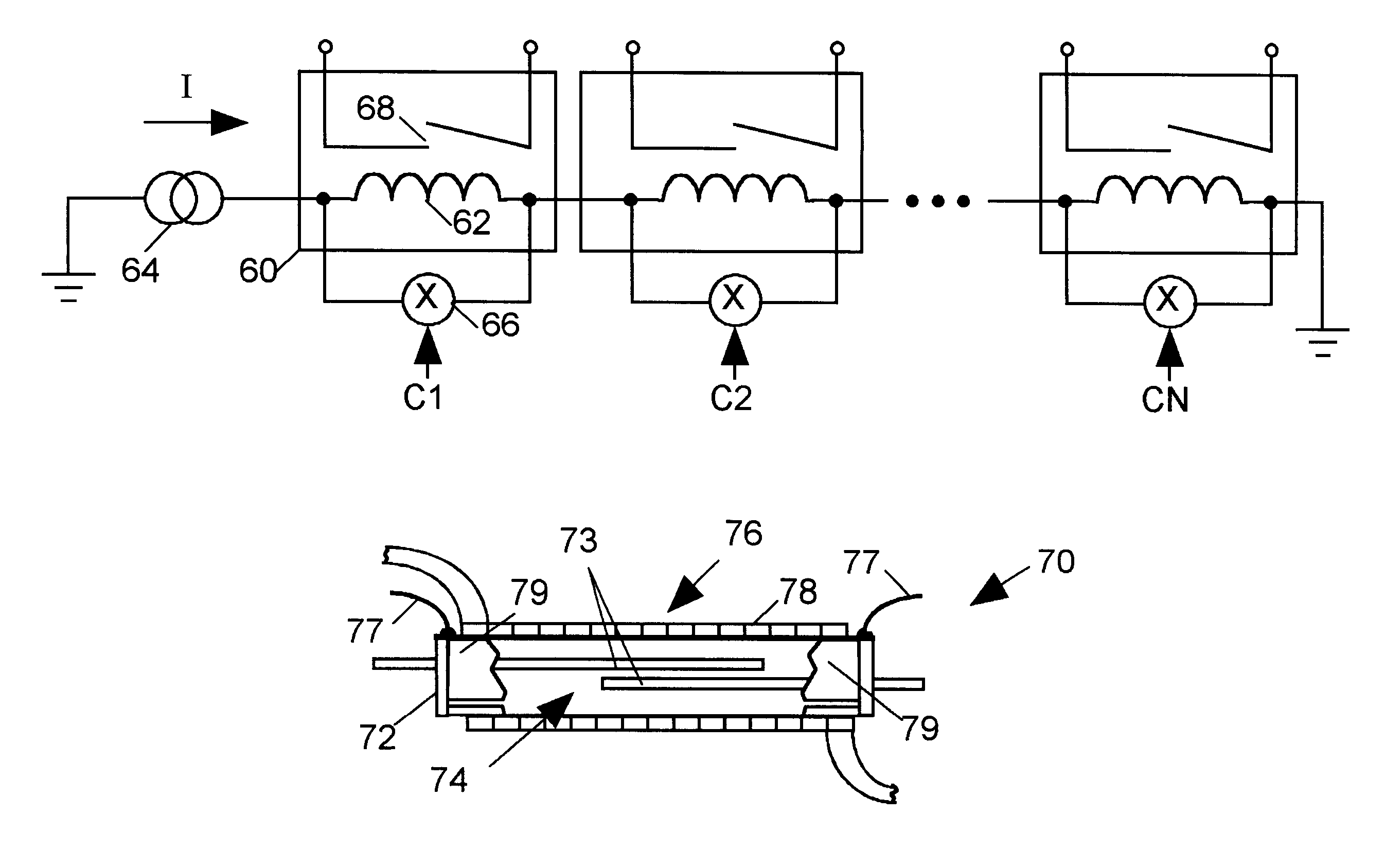

Low profile, current-driven relay for integrated circuit tester

InactiveUS6329892B1Little spaceDigital circuit testingMagnetic/electric field switchesIntegrated circuitMagnetic flux

A relay includes contacts residing within a glass tube. A coil surrounding the tube and a switch are connected in parallel between two terminals of the relay. A current source supplies a current to the coil and switch. When the switch is open, substantially all of the current passes through the coil and the coil produces a sufficient amount of magnetic flux to close the relay's contacts. When the switch closes, it shunts a sufficient amount of the current away from the coil to reduce the magnetic flux it produces below the level needed to keep the contacts closed. The current source is sized so that the coil requires relatively few turns, thereby allowing the relay to be relatively thin. The coil is formed by a conductor embedded in an insulating substrate surrounding the tube.

Owner:CREDENCE SYSTEMS

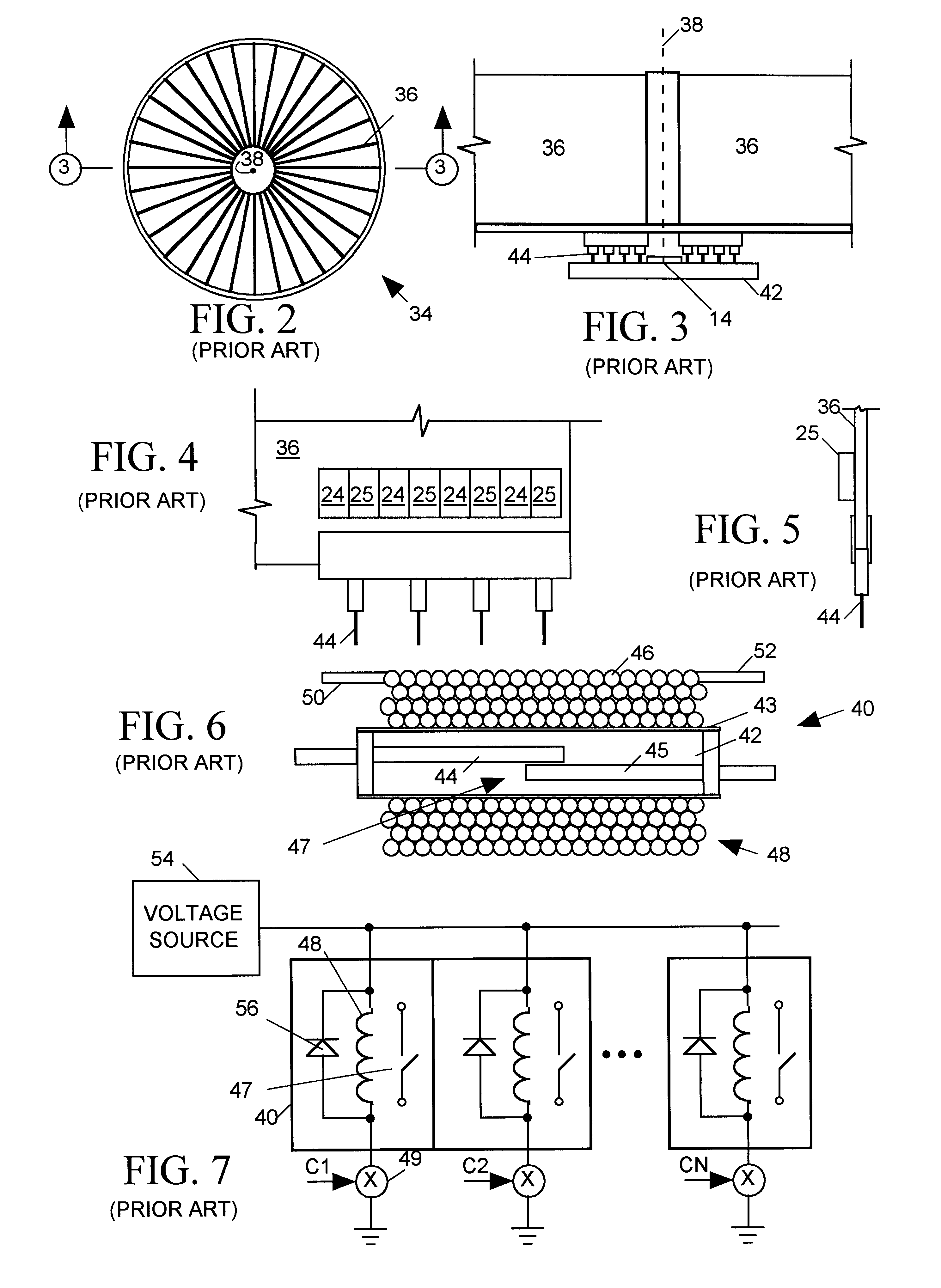

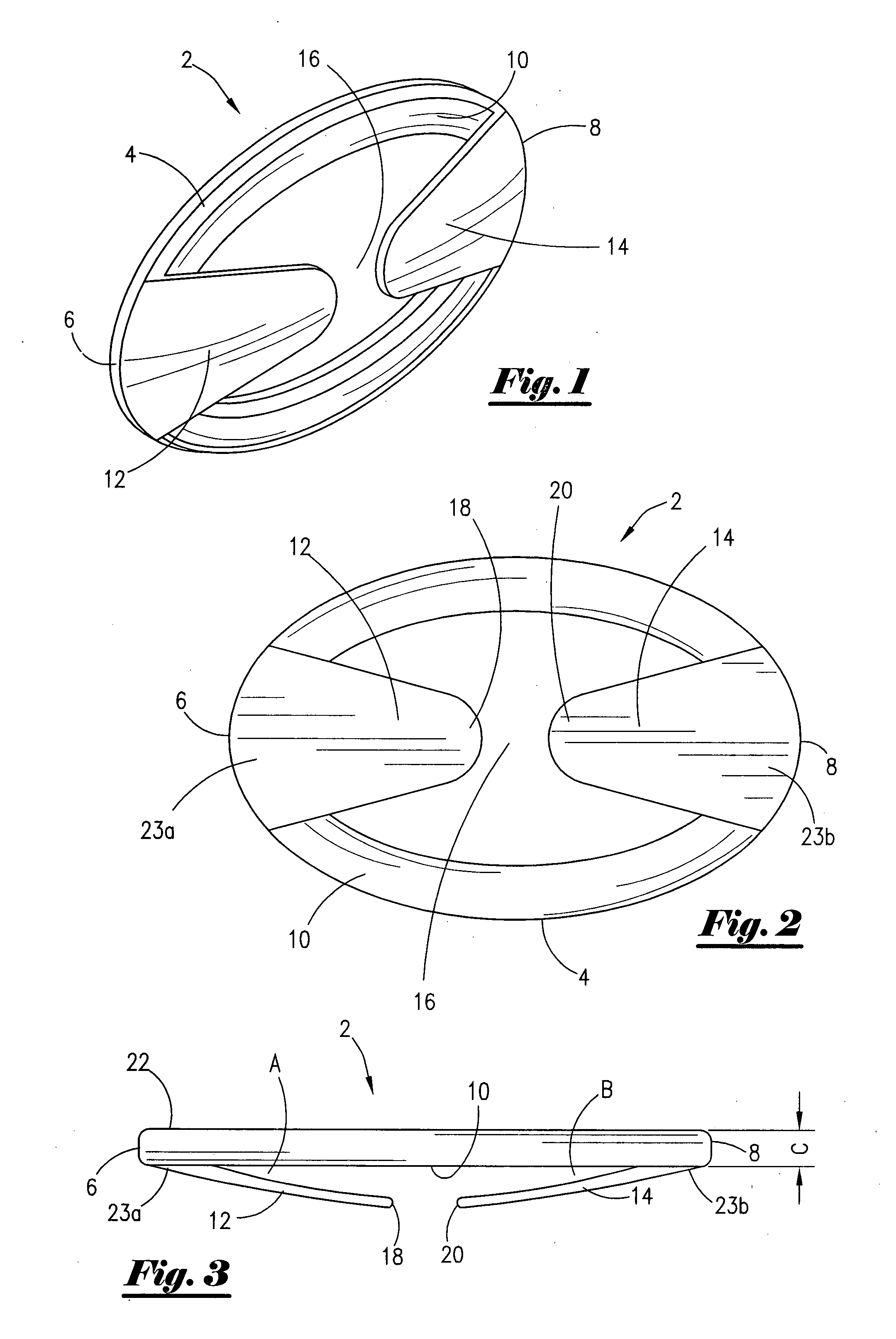

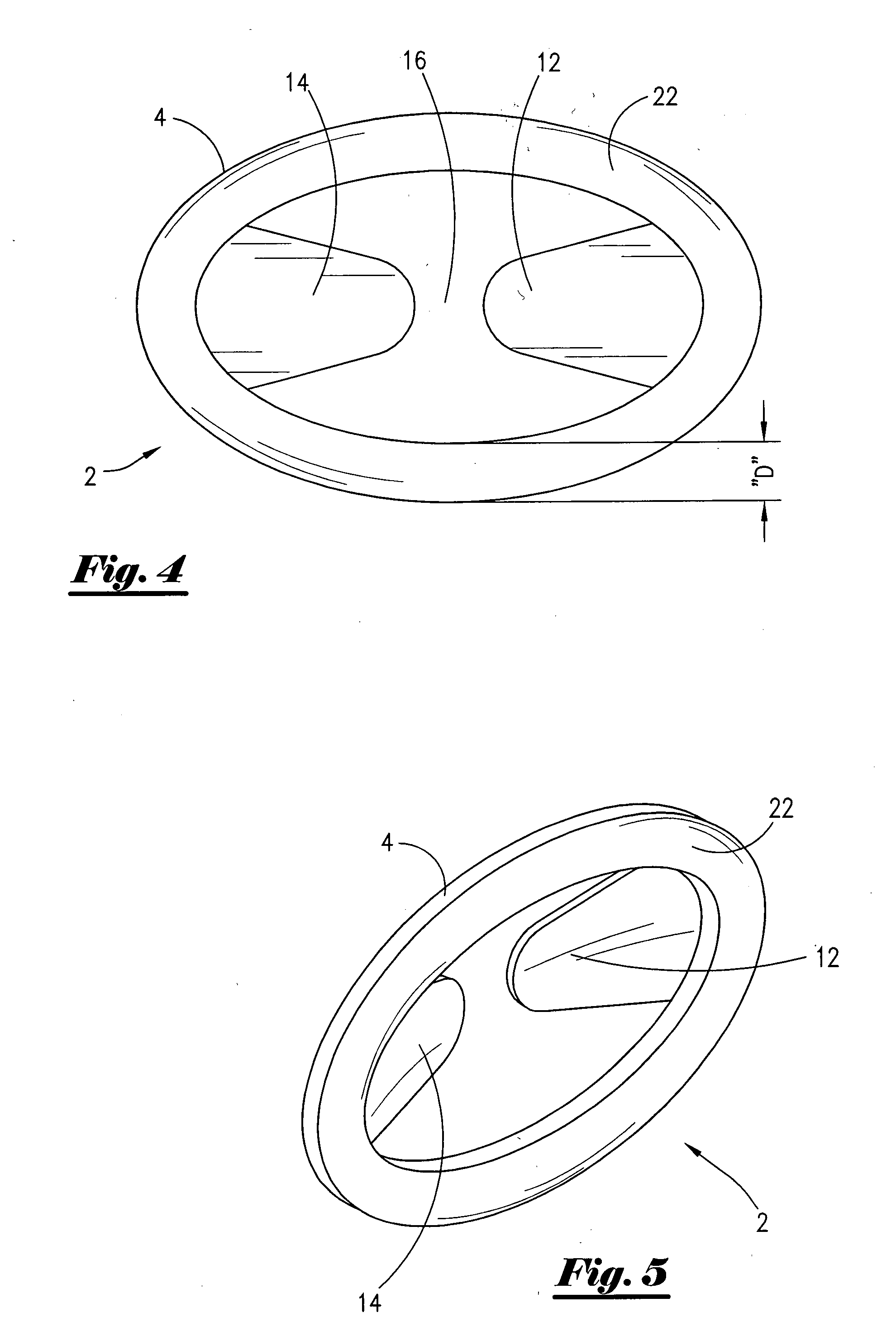

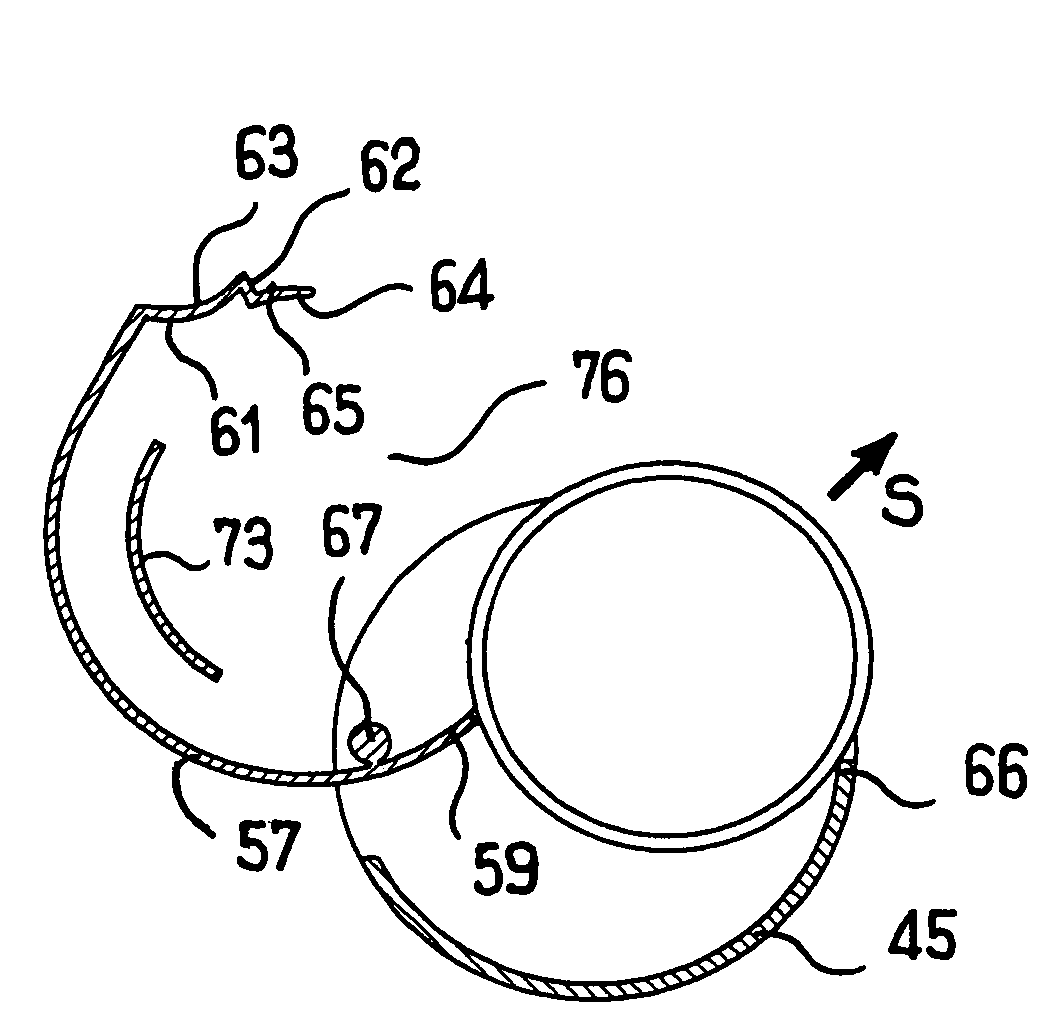

Apparatus for enhancing cleavage and method

InactiveUS20090126163A1Little spaceEconomical to manufactureSnap fastenersShoulder strapLeft shoulderEngineering

A device and method used with a woman's garment, including a brassiere. The device comprises a ring member having a first segment and a second segment, a front side and a back side, and wherein the ring member has a mid-way point between the first and second segment. The device further comprises a first prong extending from the first end of the ring member, with the first prong having a length terminating at a distance less than the mid-way point of the ring member, and a second prong extending from the second end of the ring member, with the second prong having a length terminating at a distance less than the mid-way point of the ring member. In the most preferred embodiment, the center portion allows for passage of the right shoulder strap and the left shoulder.

Owner:CLEAVAGE CLIP

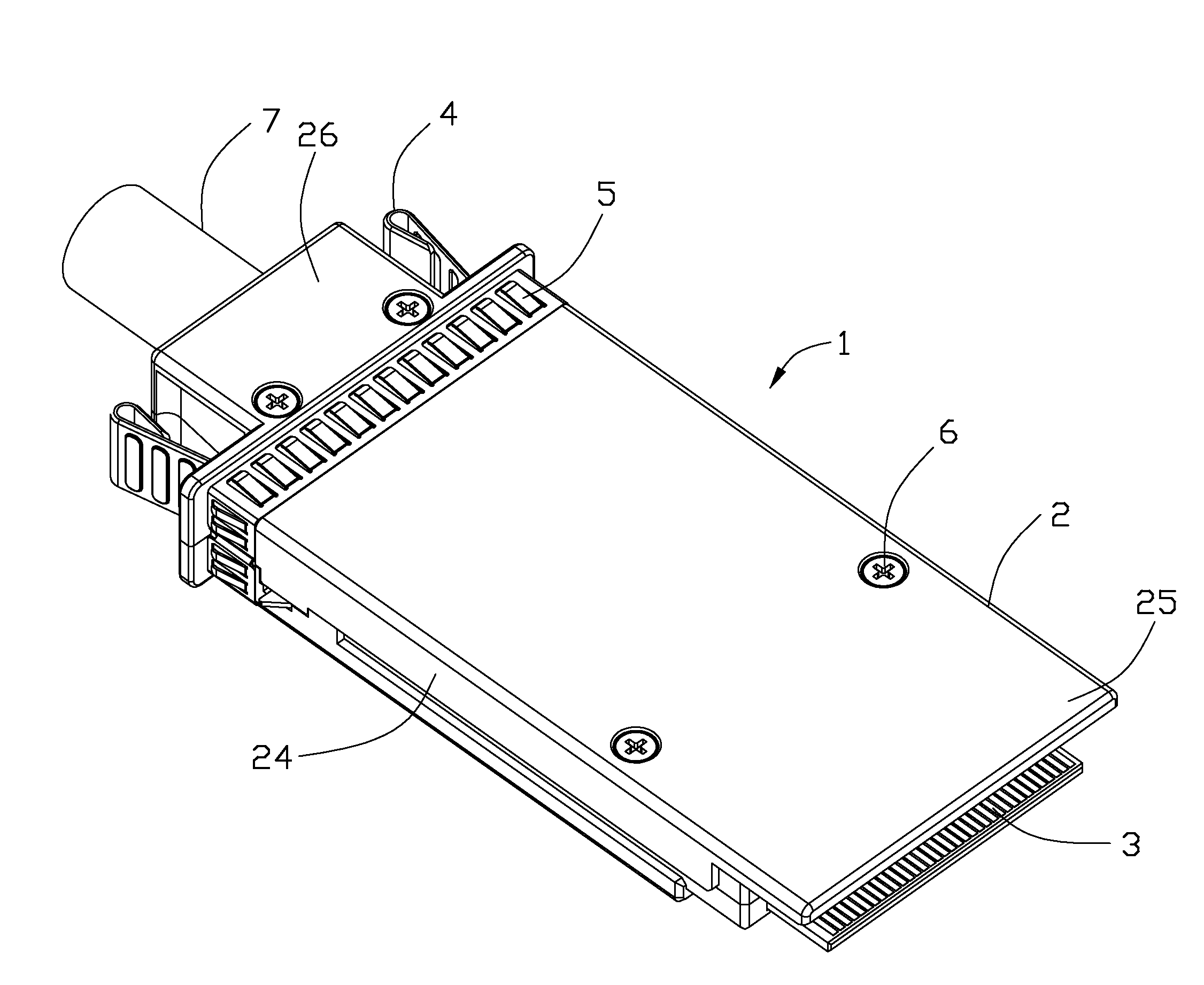

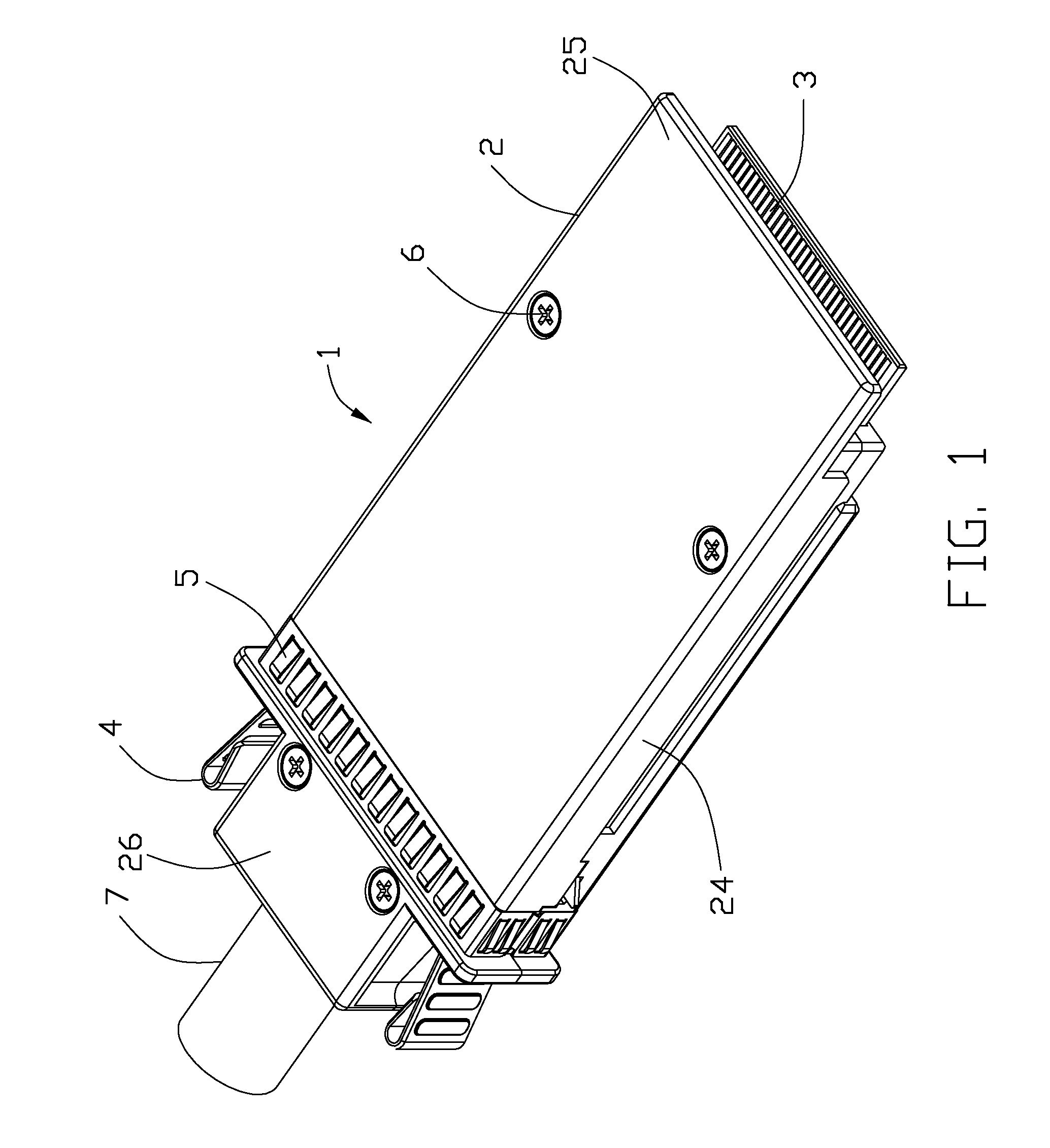

Electrical connector assembly wth improved latching mechanism

InactiveUS20100285682A1Improved latching mechanismLittle spaceElectrically conductive connectionsCoupling device detailsPrinted circuit boardHOLDING CHAMBER

An electrical connector assembly (1) for connecting with a cable (7), comprises a metallic housing (2) defining a receiving room (23), a pair of receiving spaces disposed at two sides of the receiving room and a pair of slits formed at two sides of the housing and respectively communicated with the pair of receiving spaces. A printed circuit board (3) is received into the receiving room and has a mating portion (31) extending forwardly from a front surface of the housing. A pair of latches (4) received into the corresponding receiving spaces, each latch having a base portion (41) disposed in the receiving space, an engaging portion (42) formed at a front end thereof and engaged with the housing and a pressing portion (43) extending rearwardly from the base portion and out of the housing, a latching portion (411) extending outwardly from the base portion and passing through the slit for latching with a complementary connector, an elastic portion (412) extending inwardly and rearwardly from the base portion to urge the latching portion extending out of the housing.

Owner:HON HAI PRECISION IND CO LTD

Switch, in particular for an electric parking brake

ActiveUS20130213787A1Little spaceLow costSwitches with three operating positionsTumbler/rocker switch detailsElectric parking brakeElectrical and Electronics engineering

Owner:TRW AUTOMOTIVE ELECTRONICS & COMPONENTS

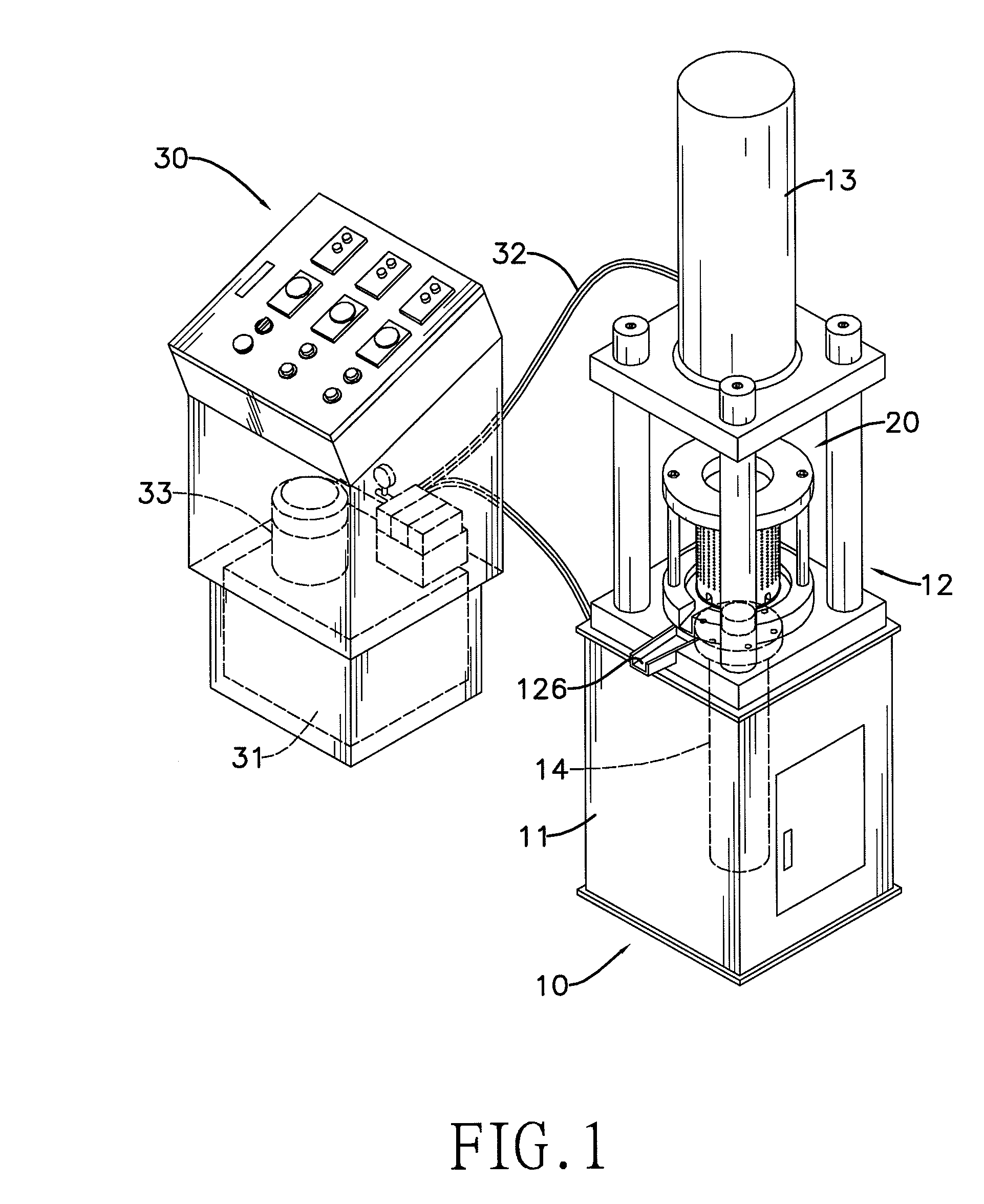

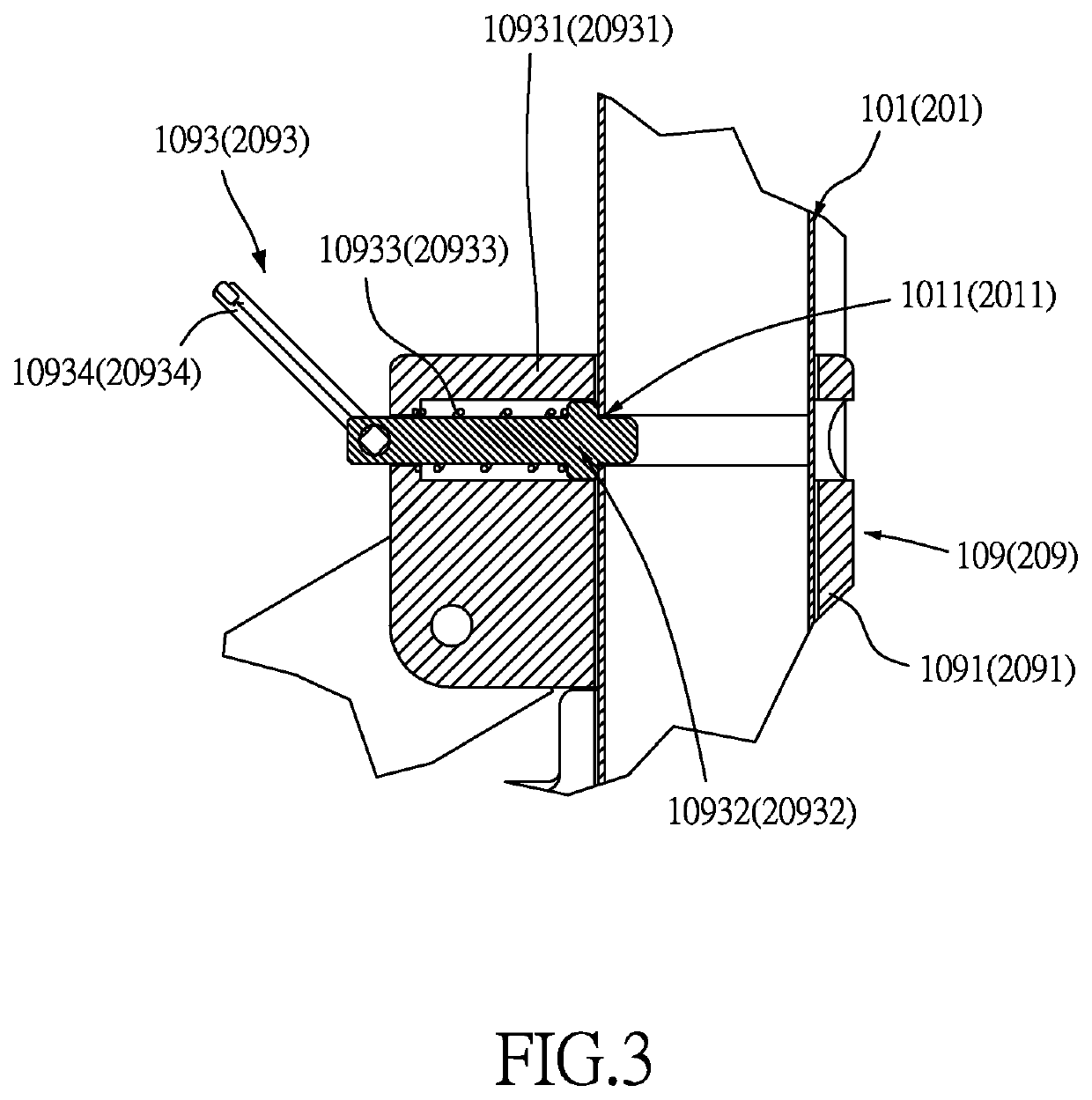

Oil expeller

An oil expeller has a stand with an upper cylinder and a lower cylinder, an oil filter mounted on the stand and a control device controlling the upper and lower cylinders. The oil filter has a filter tank and two pressing panels mounted in the filter tank. Raw materials are disposed between the pressing panels. Thus, the upper cylinder presses a corresponding pressing panel and the raw materials to extract oil from the raw materials. The lower cylinder pushes a corresponding pressing panel and waste product out of the filter tank. The oil expeller takes up little space, operates easily and extracts oil from the raw materials 40 and removes the waste product alternately. Moreover, the user is allowed to provide fresh oil based on his needs when extracting oil from a suitable amount of raw materials.

Owner:GOLDEN FLOWER TEA OIL PRODN

Universal support element for universal shelf divider, label and sign holder

InactiveUS20050204965A1Little spaceMaximize lengthSnap fastenersStampsEngineeringMechanical engineering

An improved support element for a shelf divider, label, and sign holder system. The support element includes a substantially U-shaped rigid plastic shell which may be adhesively affixed to the upper surface of a shelf to support a shelf divider. The support element includes elongated flexible ridges or beads within a support element channel, the free ends of which are spaced from and face the interior surface that defines the channel. The ridges are compressible to exert a gripping force on the item to be retained. The support element can also be part of a label and sign holder system. Both a single and double-facing support element is provided to interact with a label holder locking strip.

Owner:FAST INDS

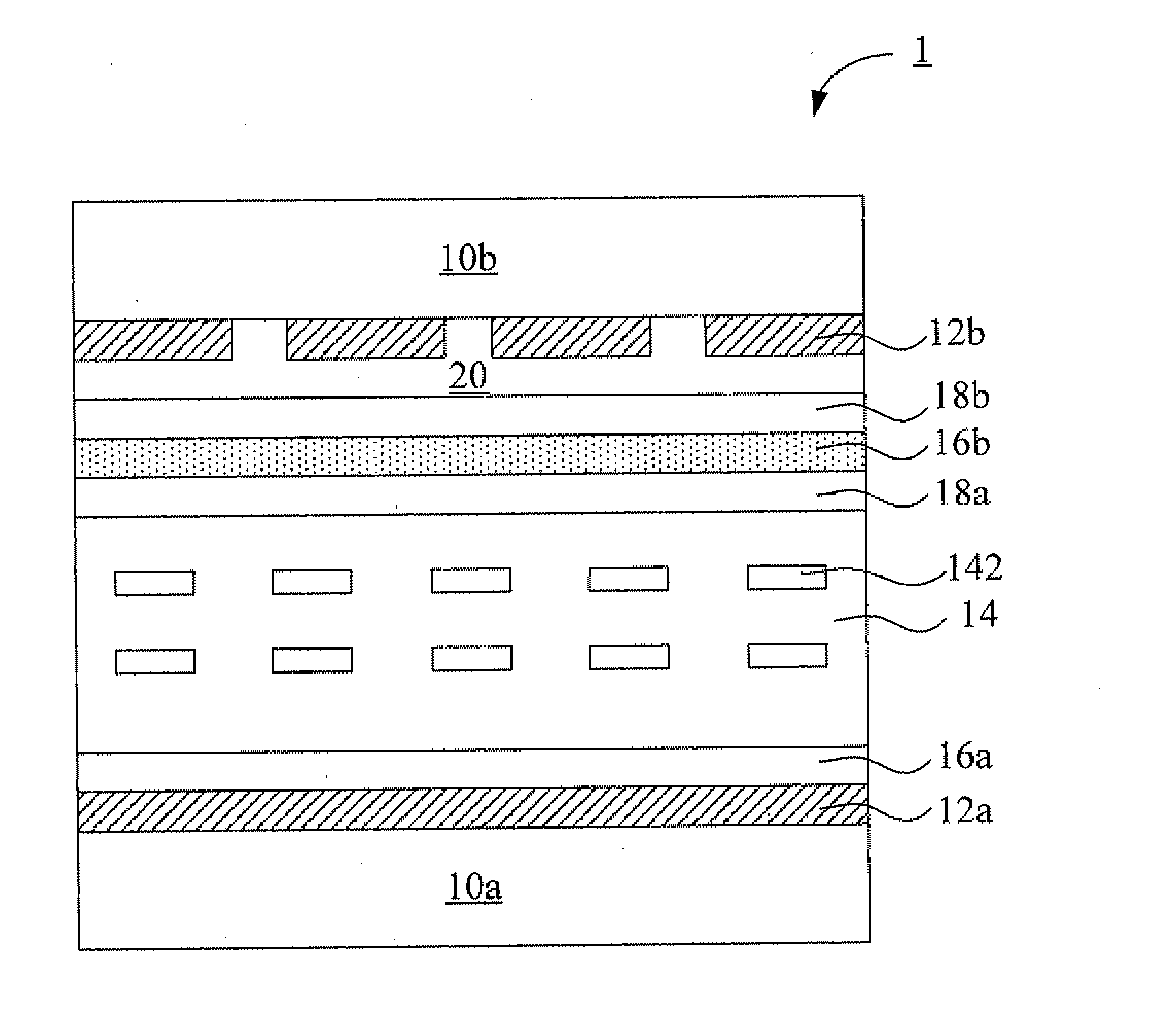

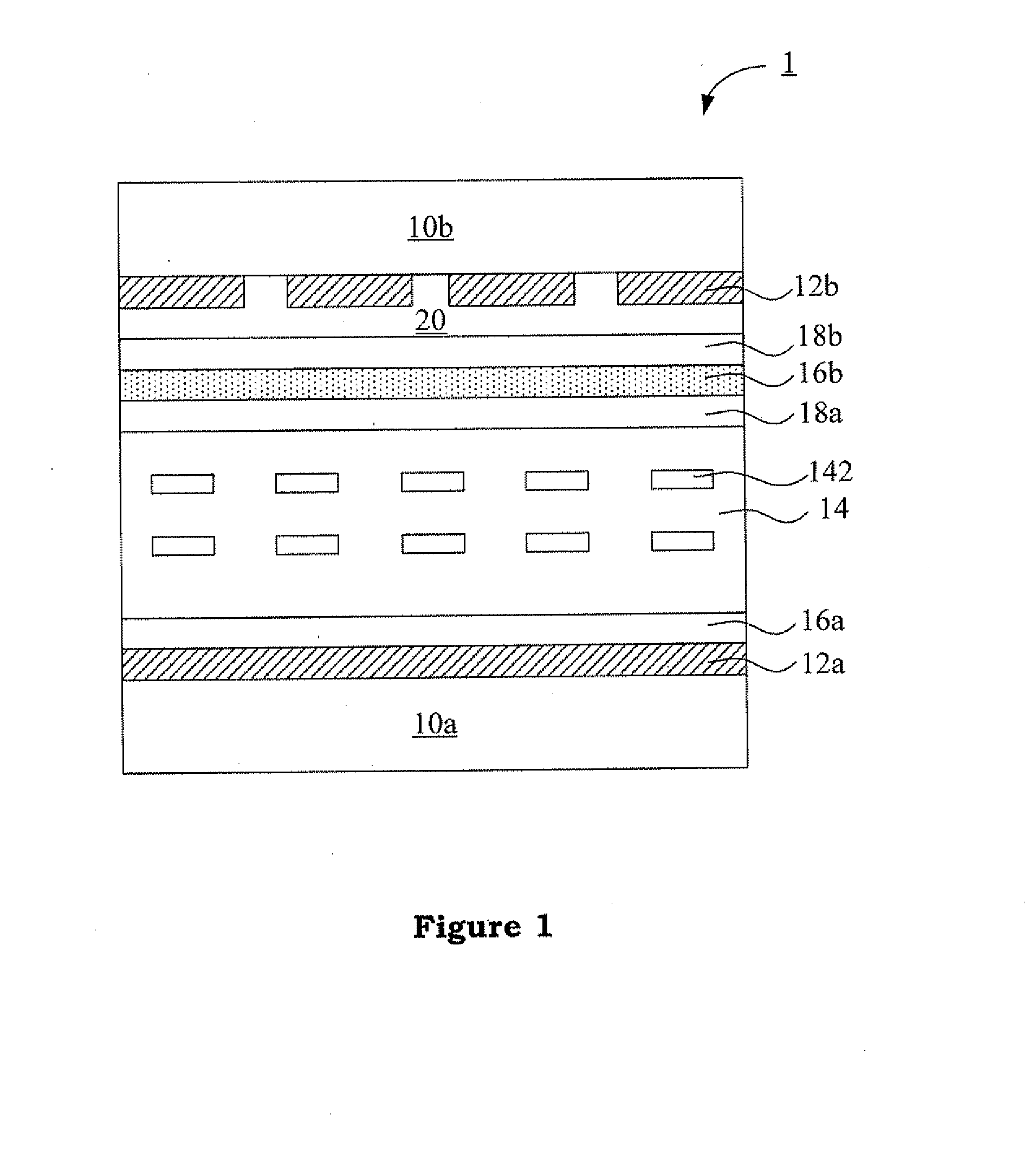

Controllable optical device and the forming method thereof

A controllable optical device comprises a first substrate, a first conductive layer, a liquid crystal layer, a semiconductor conductive layer, a second conductive layer, and a second substrate. The first conductive layer is formed on the first substrate, the liquid crystal layer is formed on the first conductive layer, the semiconductor conductive layer is formed on the liquid crystal layer, the second conductive layer is formed on the semiconductor layer, and the second substrate is formed on the second conductive layer.

Owner:NATIONAL CHIAO TUNG UNIVERSITY

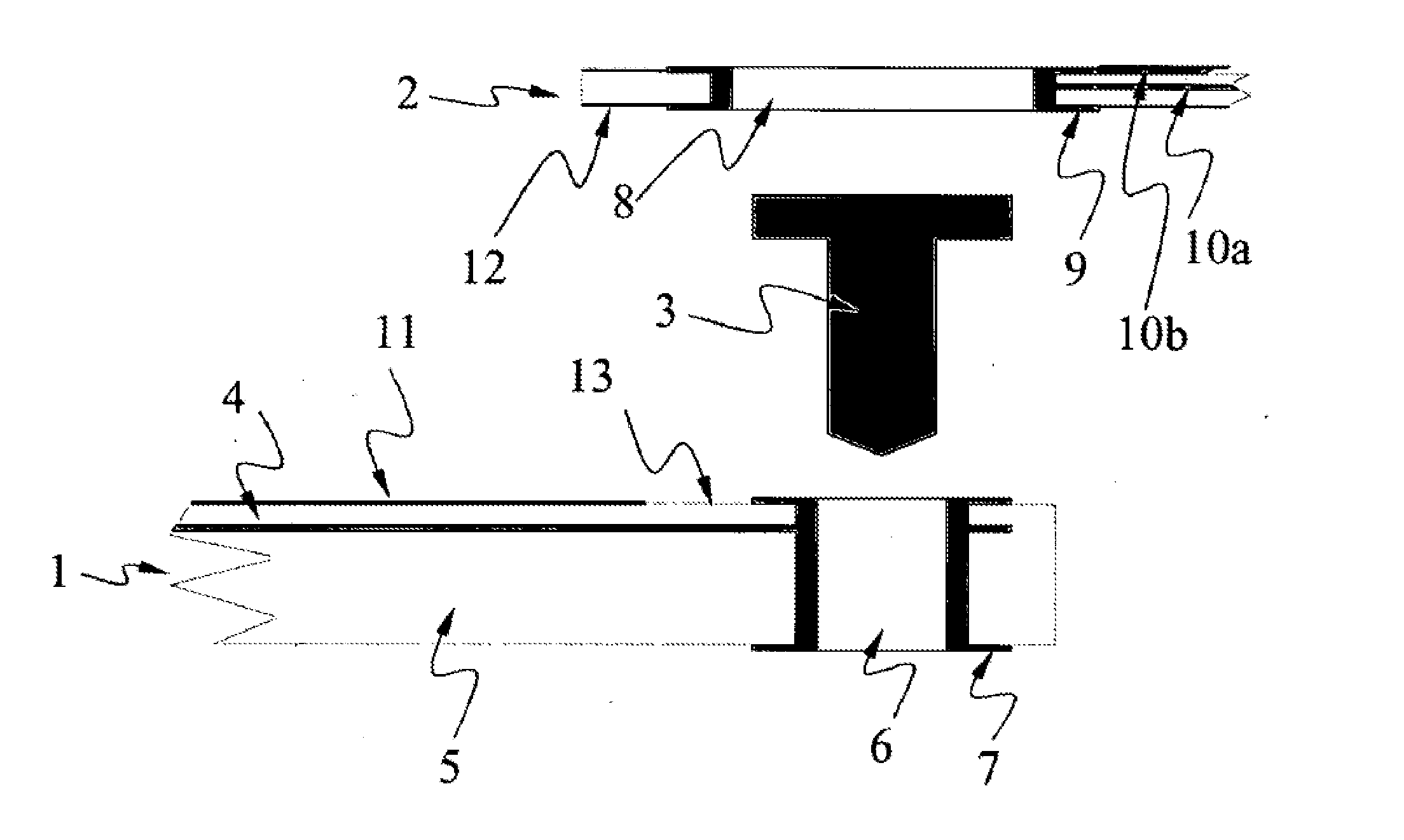

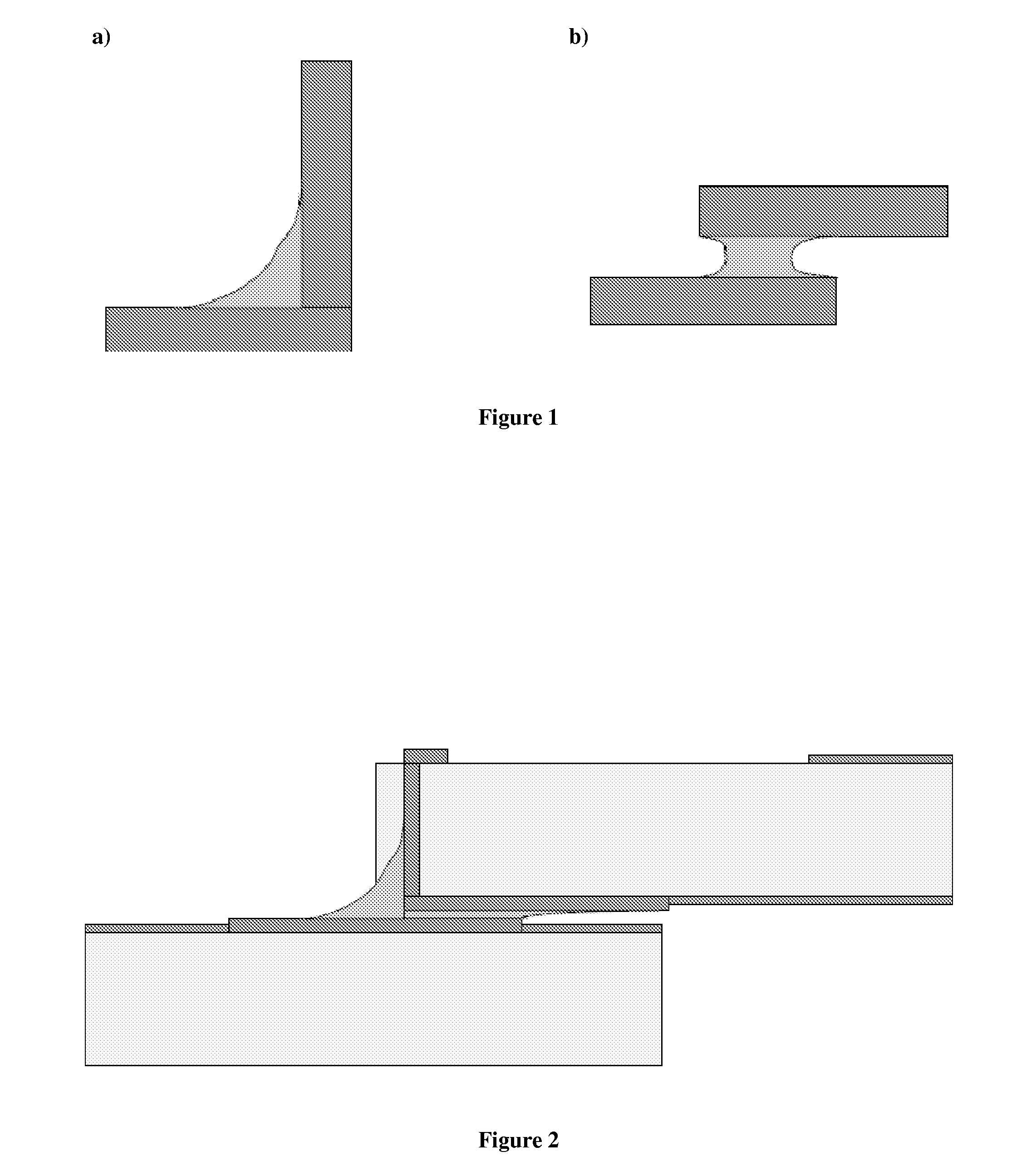

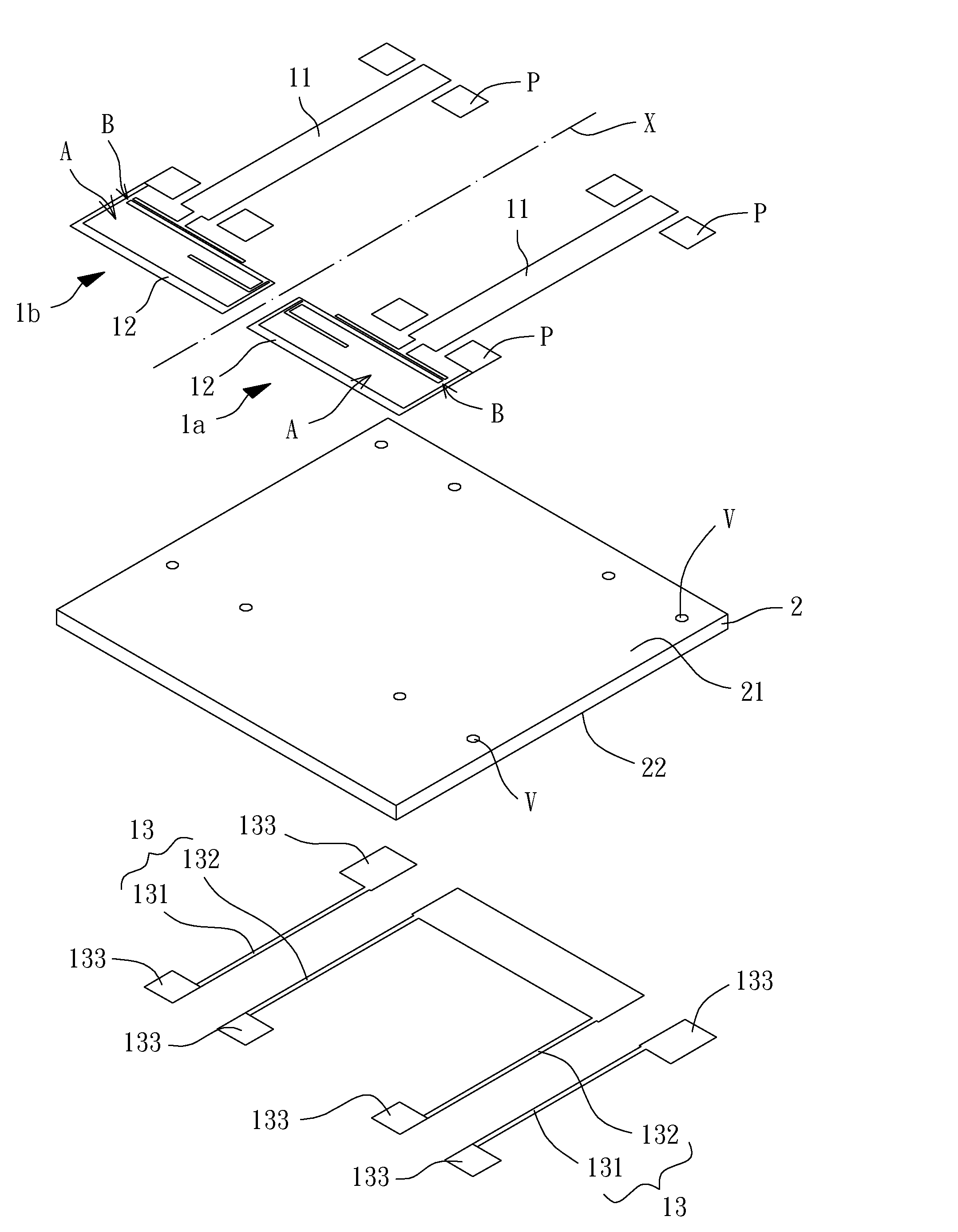

Termination apparatus and method for planar components on printed circuit boards

InactiveUS20100118505A1Little spaceLow-resistance connectionPrinted circuit assemblingSoldered/welded conductive connectionsSolder maskElectricity

The disclosure involves the efficient termination of a winding PCB of a planar inductive component to a main PCB, using relatively little space and providing a low-resistance connection. The disclosed methods are especially suitable for planar structures where several winding PCBs, and / or winding PCBs and a main PCB, are all enclosed by the magnetic path components. The methods allow for a winding PCB to simply rest on the main PCB, or other winding PCBs, without any clearance. The disclosure employs mating sets of conductive annular rings with an optional interlocking terminal pin that allows two PCBs to be fixedly coupled together, while preserving a minimum distance between the solder-mask layers of the two PCBs in order to prevent the formation of unwanted electrical connections between the two PCBs. Solder is used to ensure effective coupling in each assembly of mating annular rings and optional terminal pin.

Owner:BATTERY BIZ

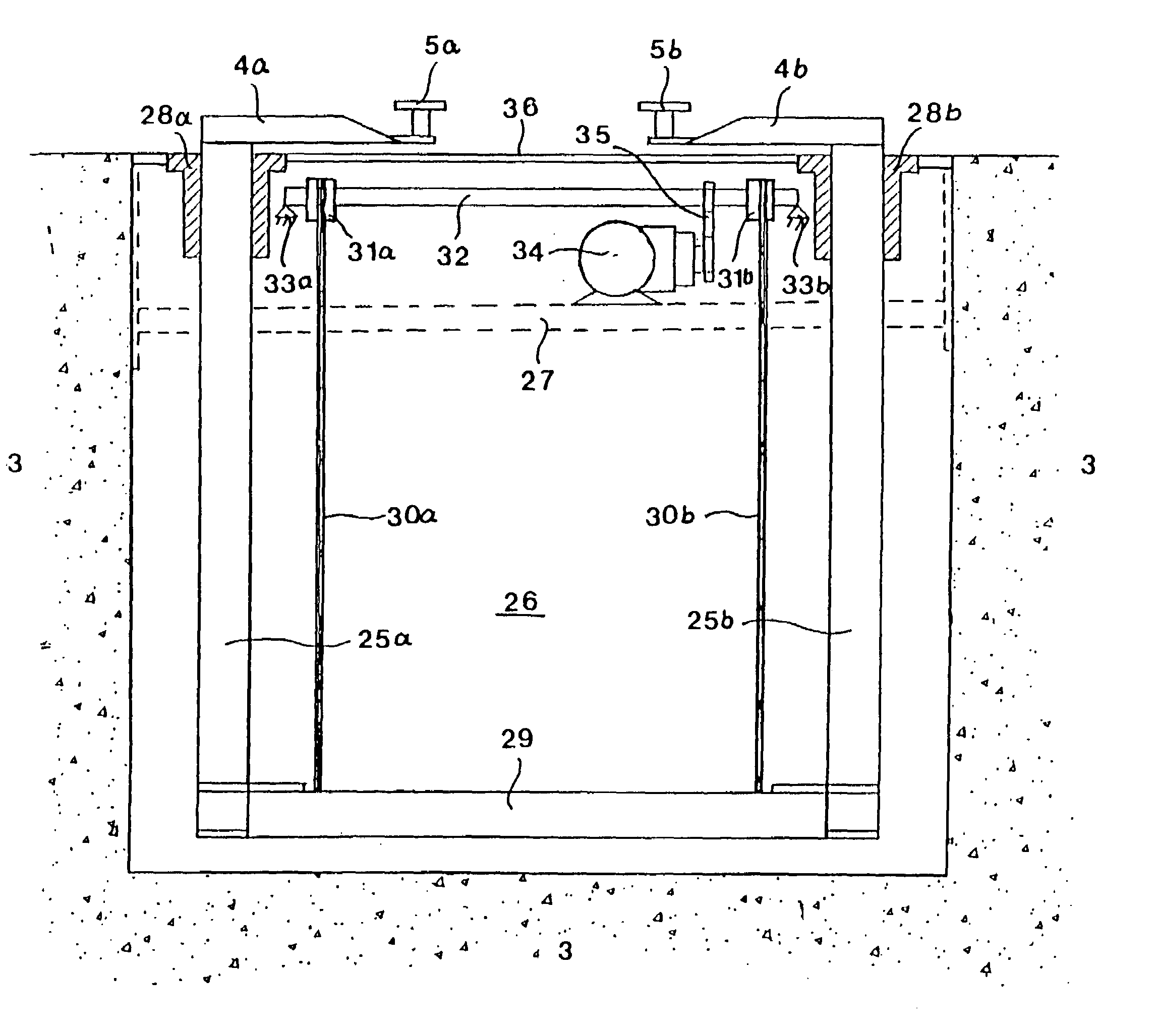

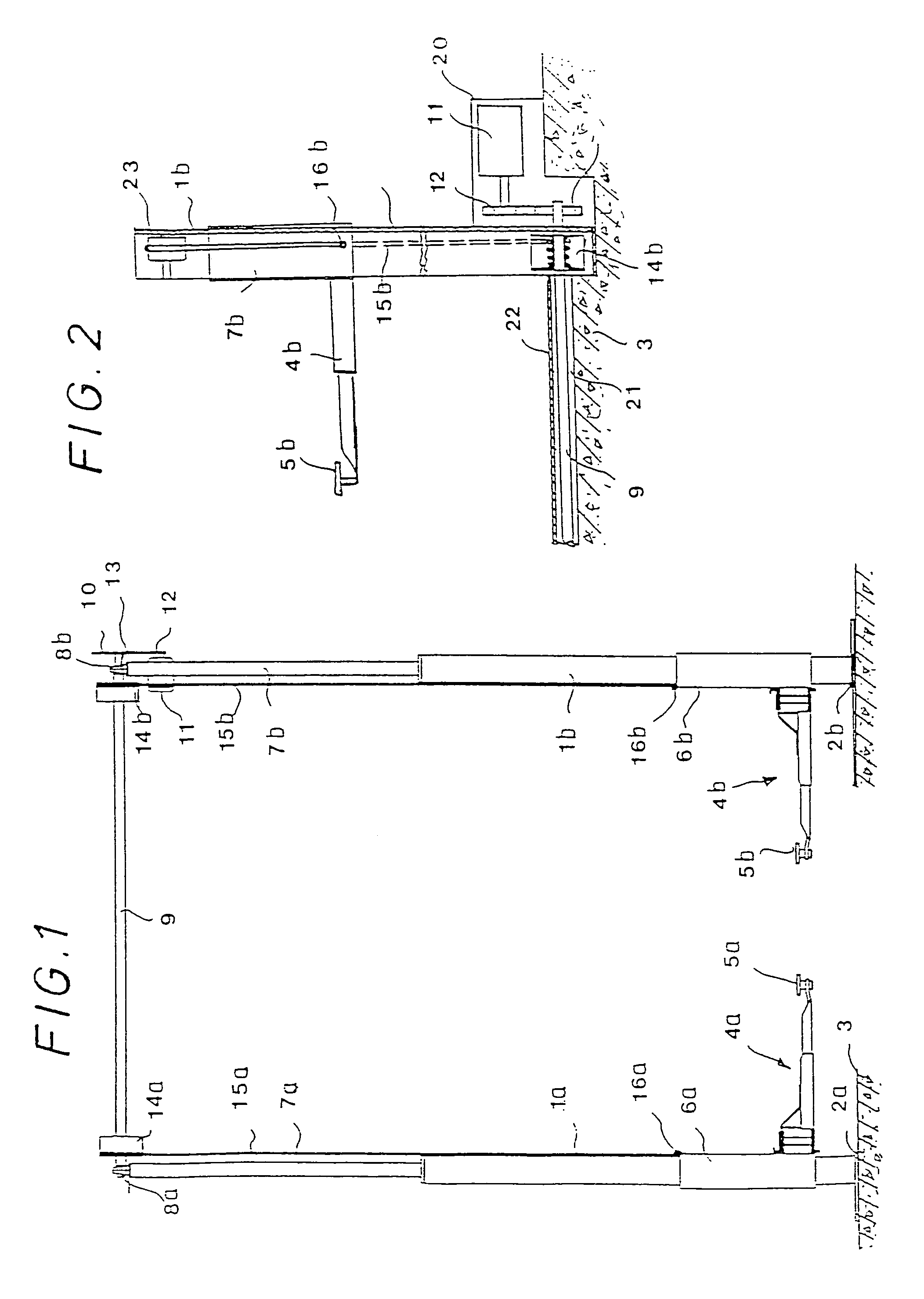

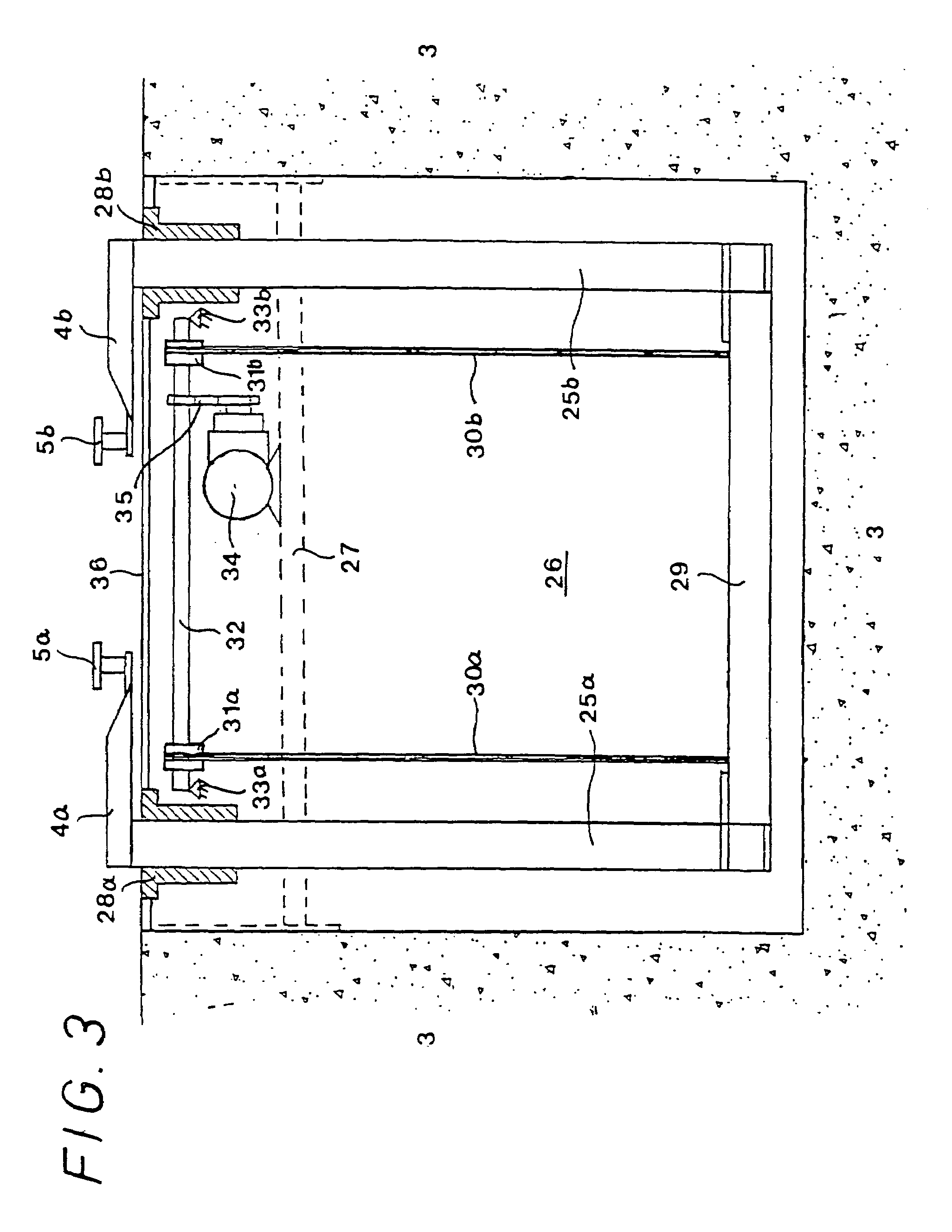

Vehicle lifting platform

A lifting platform for vehicles having at least one column, at least one support arm shiftable on the column by vertical guides and having supports. The lifting platform also includes a prime mover having switching and control elements and a transmission disposed between the prime mover and the associated support arm, the transmission having at least one flexible traction cable coupled to a rotating member positioned at the upper end of the respective column and to the associated support arm.

Owner:MASCHENBAU HALDENWANG

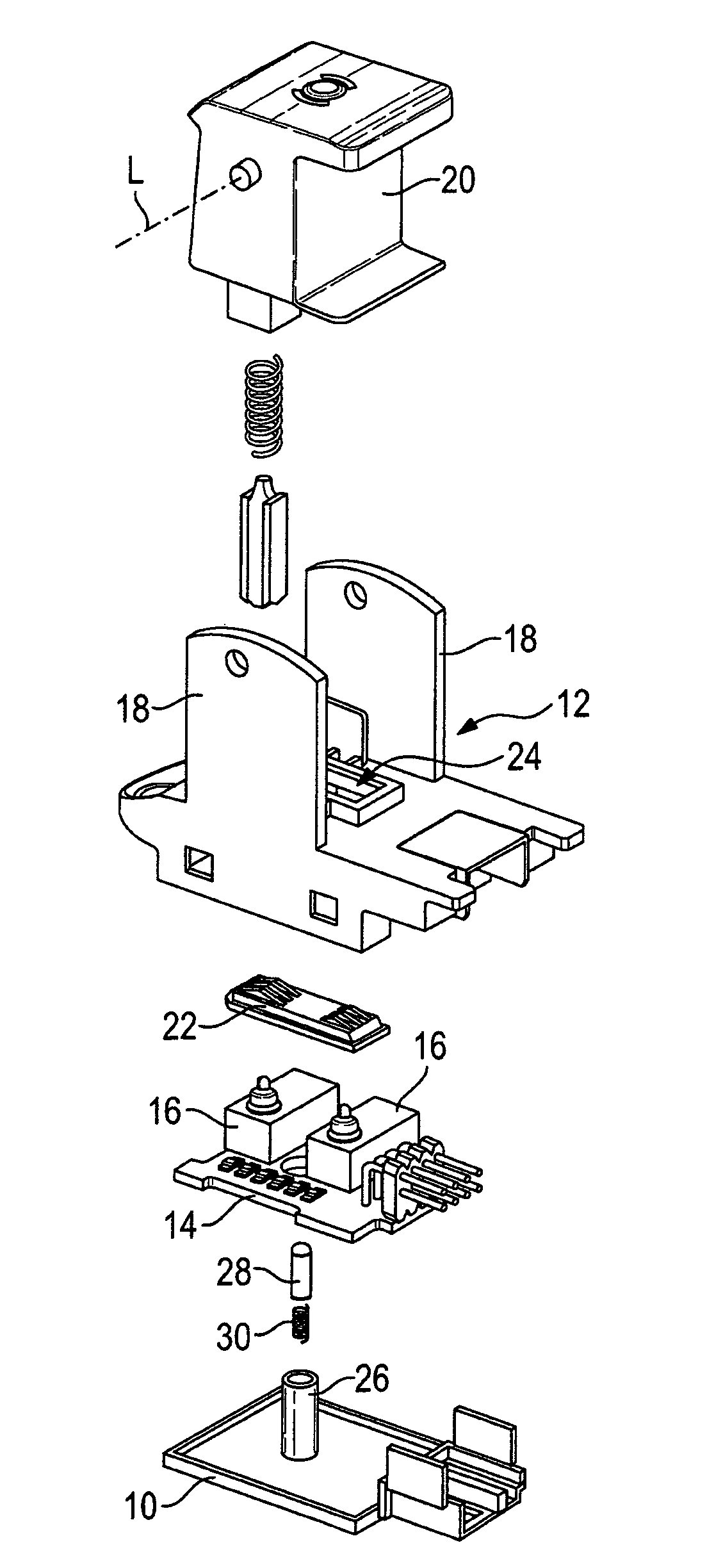

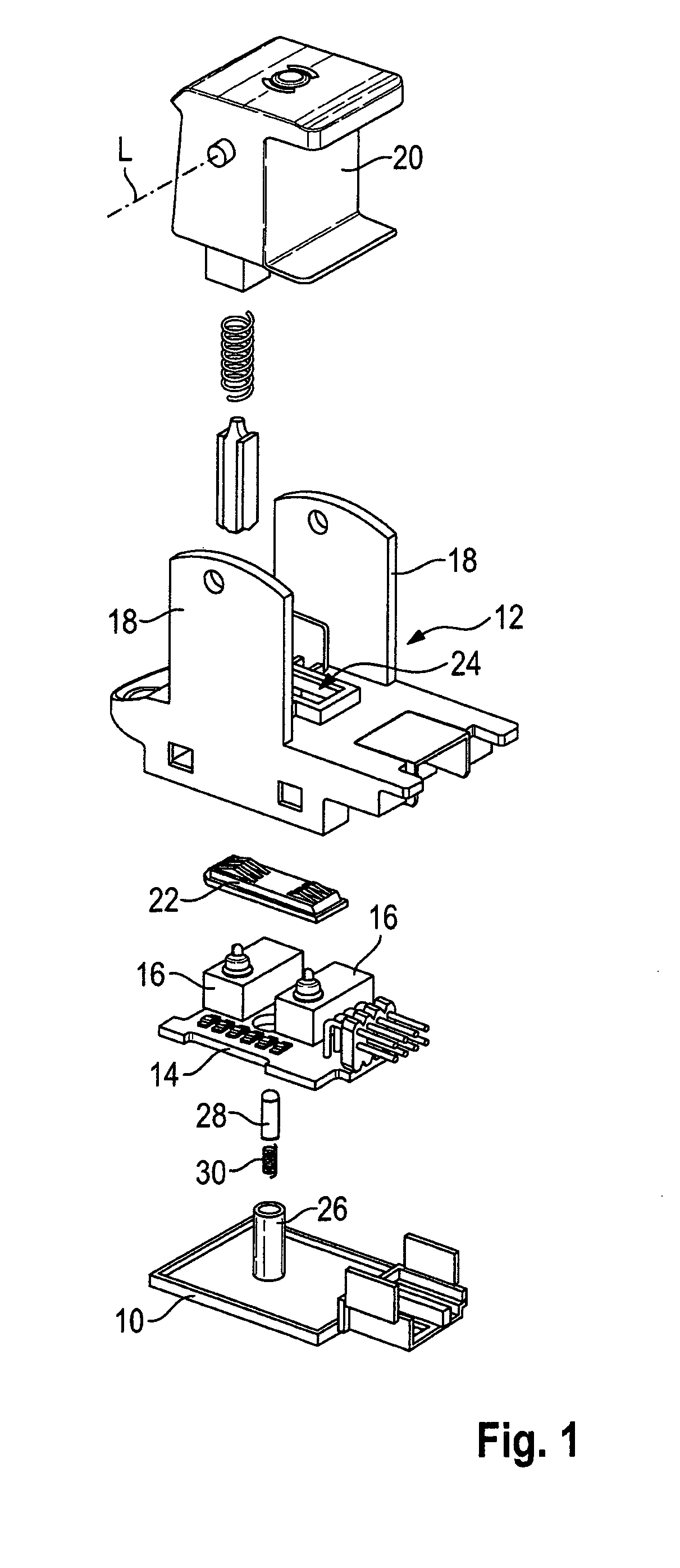

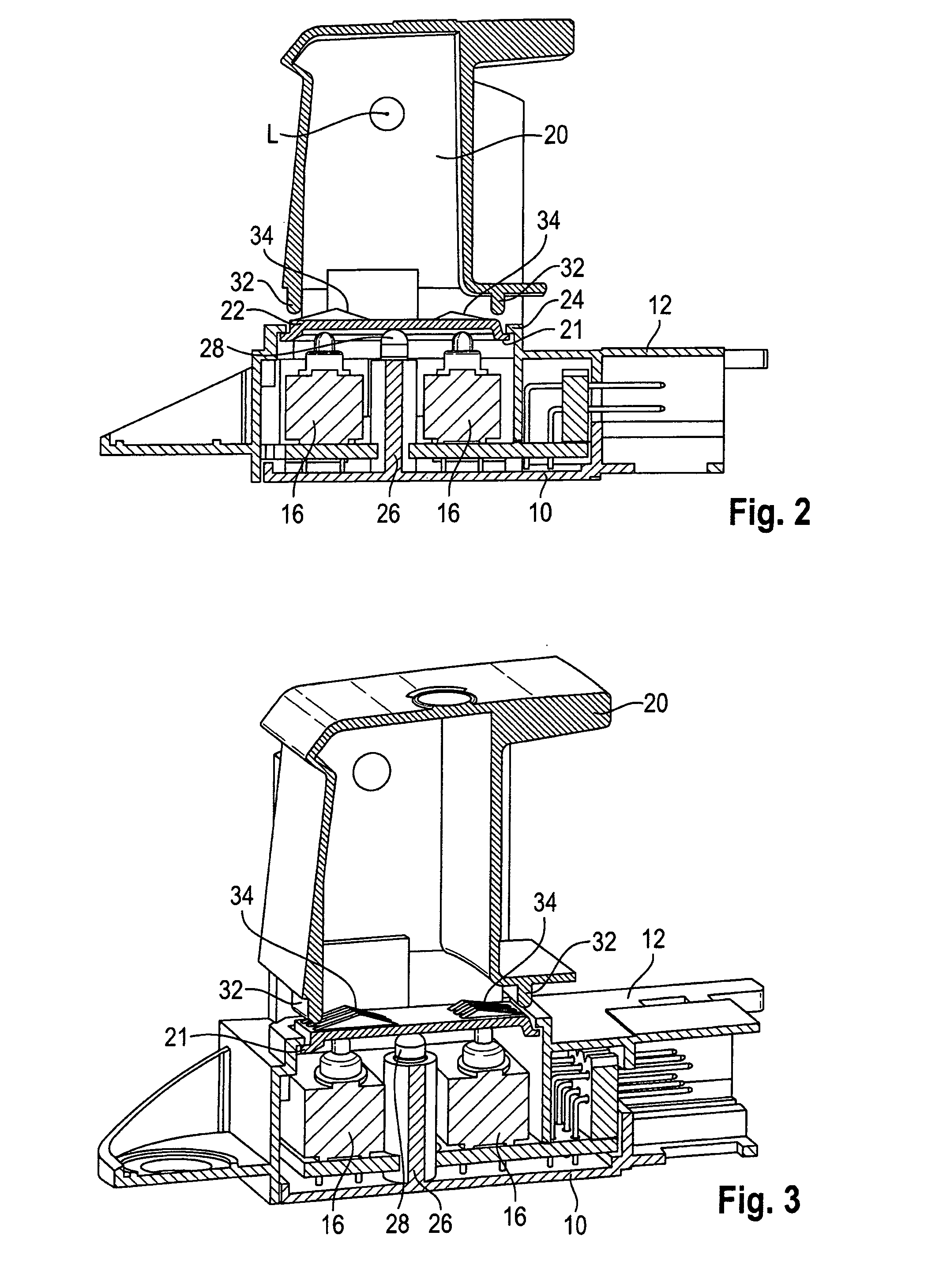

Electrical apparatus intended for mounting on a subframe

ActiveUS6923680B2Simple to manufacture and useLittle spaceElectrically conductive connectionsCoupling parts mountingEngineeringMechanical engineering

Owner:SOCOMEC

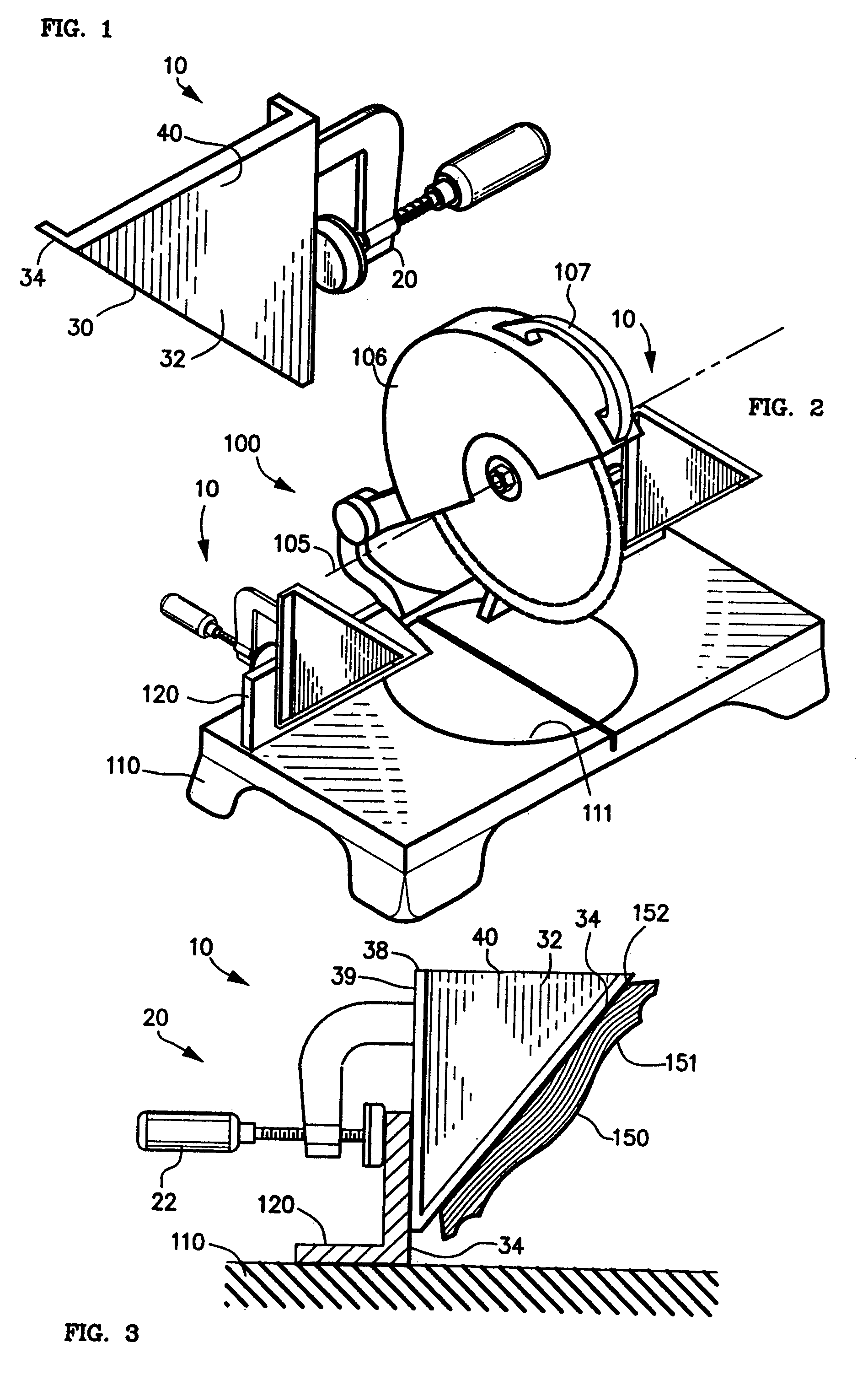

Attachment for a saw

InactiveUS20060230901A1Little spaceReduce chanceGuide fencesShearing machinesRight triangleEngineering

Attachment for a saw simplifies cutting of crown molding by supporting molding at “spring” angle during cutting. Attachment includes clamp for removably mounting attachment on saw fence, and a right triangle having a hypotenuse congruent with “spring” angle. Attachment makes possible cutting of compound angle using only miter adjustment of saw.

Owner:FIGURSKI ADAM J

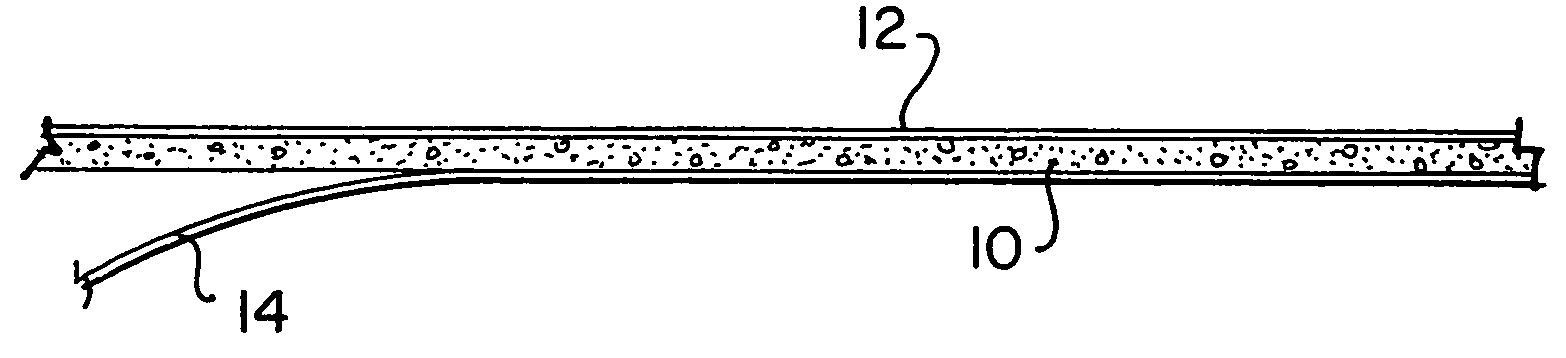

Insulated packaging material

InactiveUS20070110986A1Little spaceEasy to assembleSynthetic resin layered productsLaminationFoamcoreEngineering

A packaging material for making insulated containers, comprises a foam core and a radiant barrier layer laminated to at least one side of the foam core. Preferably, the radiant barrier layer comprises a plastic film metallized on at least one side bonded to a paper substrate. The paper substrate of the radiant barrier layer may be bonded to the foam core by the application of heat and pressure.

Owner:NIELSEN & BAINBRIDGE LLC

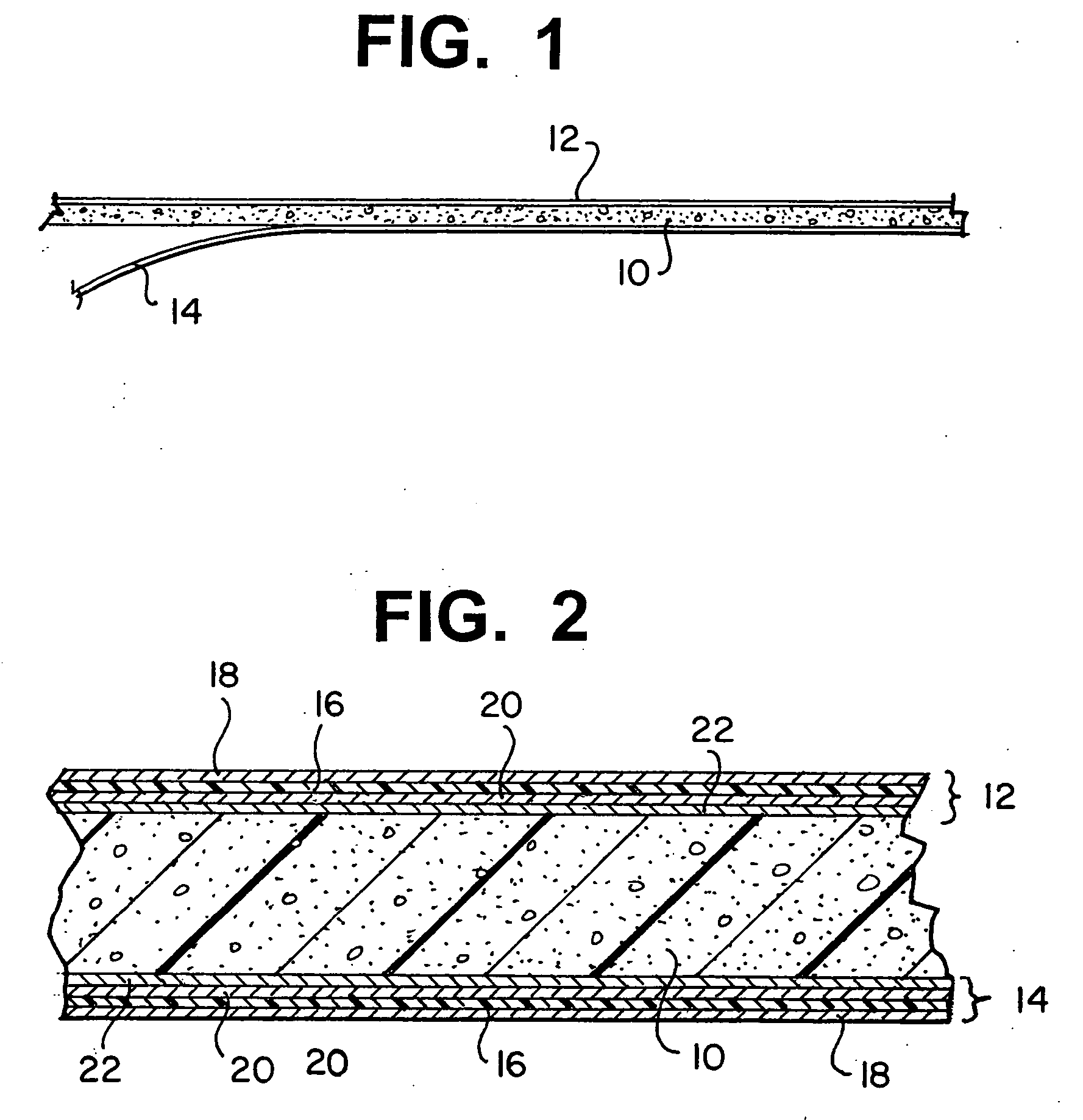

Device for adjusting circuits before encapsulation

InactiveUS6953971B2Little spaceSpace minimizationTransistorSemiconductor/solid-state device detailsVoltage referenceEngineering

A device for adjusting an integrated circuit before encapsulation includes a first MOS transistor having a gate and a source connected together, and a body connected to a voltage reference. A first resistor is connected in parallel with the first MOS transistor. A second MOS transistor is connected in series with the first MOS transistor. The second MOS transistor has a gate and a source connected together, and a body connected to the voltage reference. A second resistor is connected in parallel with the second MOS transistor. A first terminal is connected to the source of the first MOS transistor, and a second terminal is connected to the source of the second MOS transistor. The first terminal is accessible externally after the integrated circuit has been encapsulated.

Owner:STMICROELECTRONICS SRL

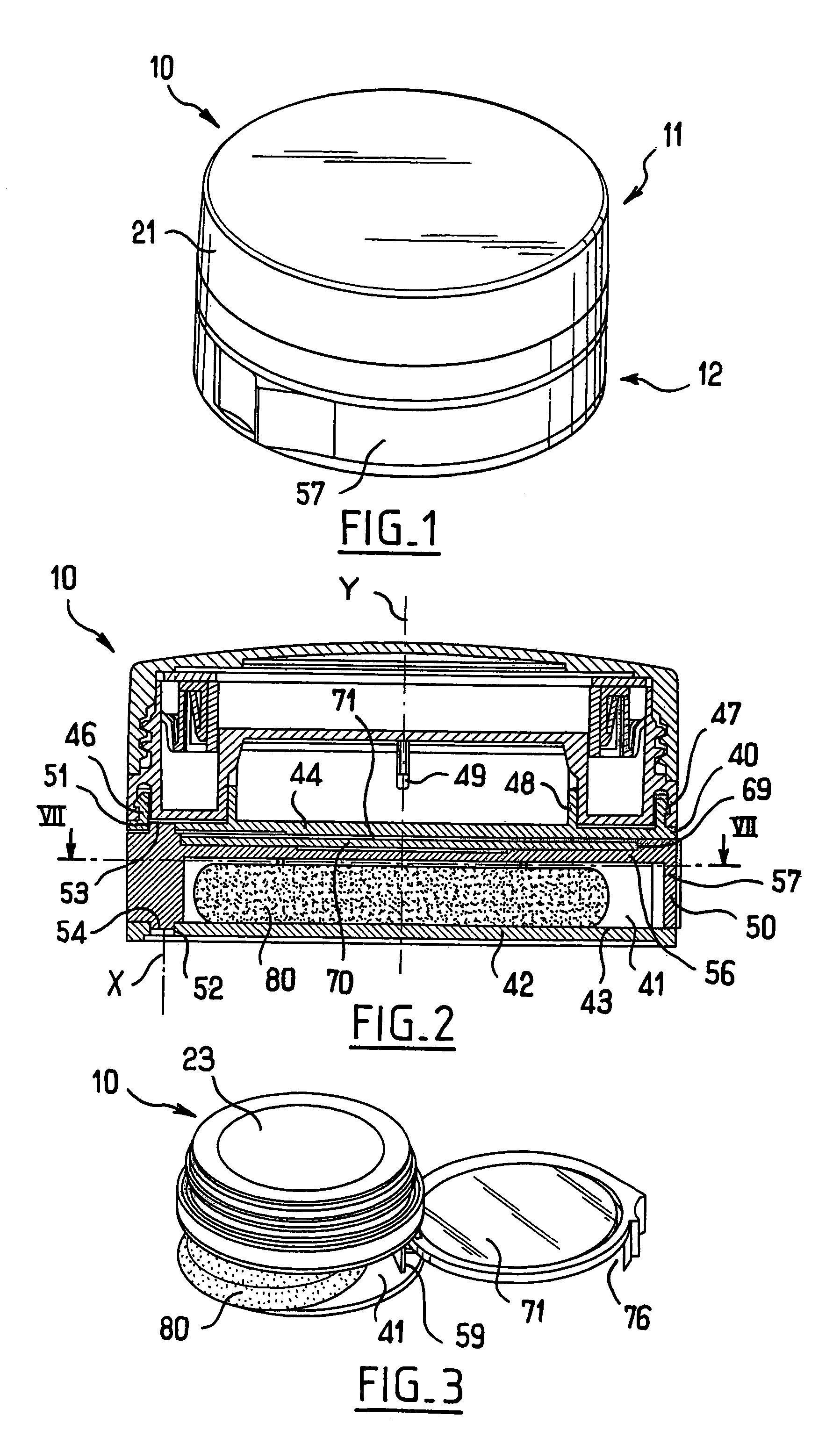

Device for packaging and applying a substance such as a cosmetic or another care product

InactiveUS7350525B2Little spaceReliable in operationPackaging toiletriesPackaging cosmeticsBiomedical engineering

Owner:LOREAL SA

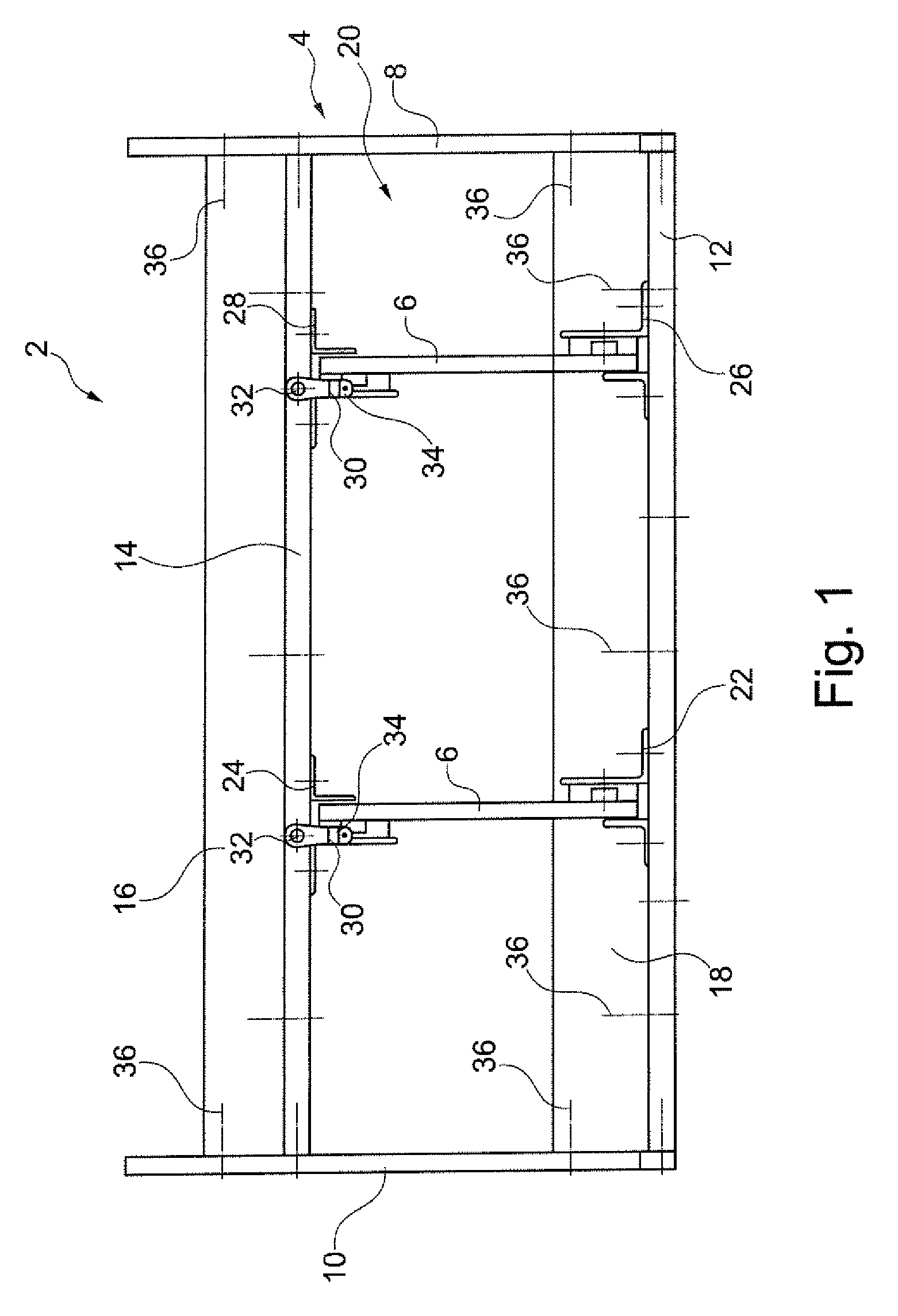

Assembly for storing objects in the cabin of a vehicle

ActiveUS20090294585A1Little spaceMinimizes maintenance and installationLuggage compartmentEmergency oxygen systemsEngineeringMechanical engineering

The invention relates to an assembly for storing objects in the cabin of a vehicle, comprising at least one frame with attachment means, and at least one holding device for mounting the objects, wherein the frame has a contour that, at least in some regions, essentially corresponds to the interior contour of a storage container so that the frame can be arranged in the storage container and can be attached in the storage container with the use of the attachment means, and wherein the holding device can be removably stored in the frame. The assembly according to the invention can be placed in a pre-assembled state in the vehicle, thus reducing the time required for installation and maintenance, while at the same time making better use of the available space.

Owner:AIRBUS OPERATIONS GMBH

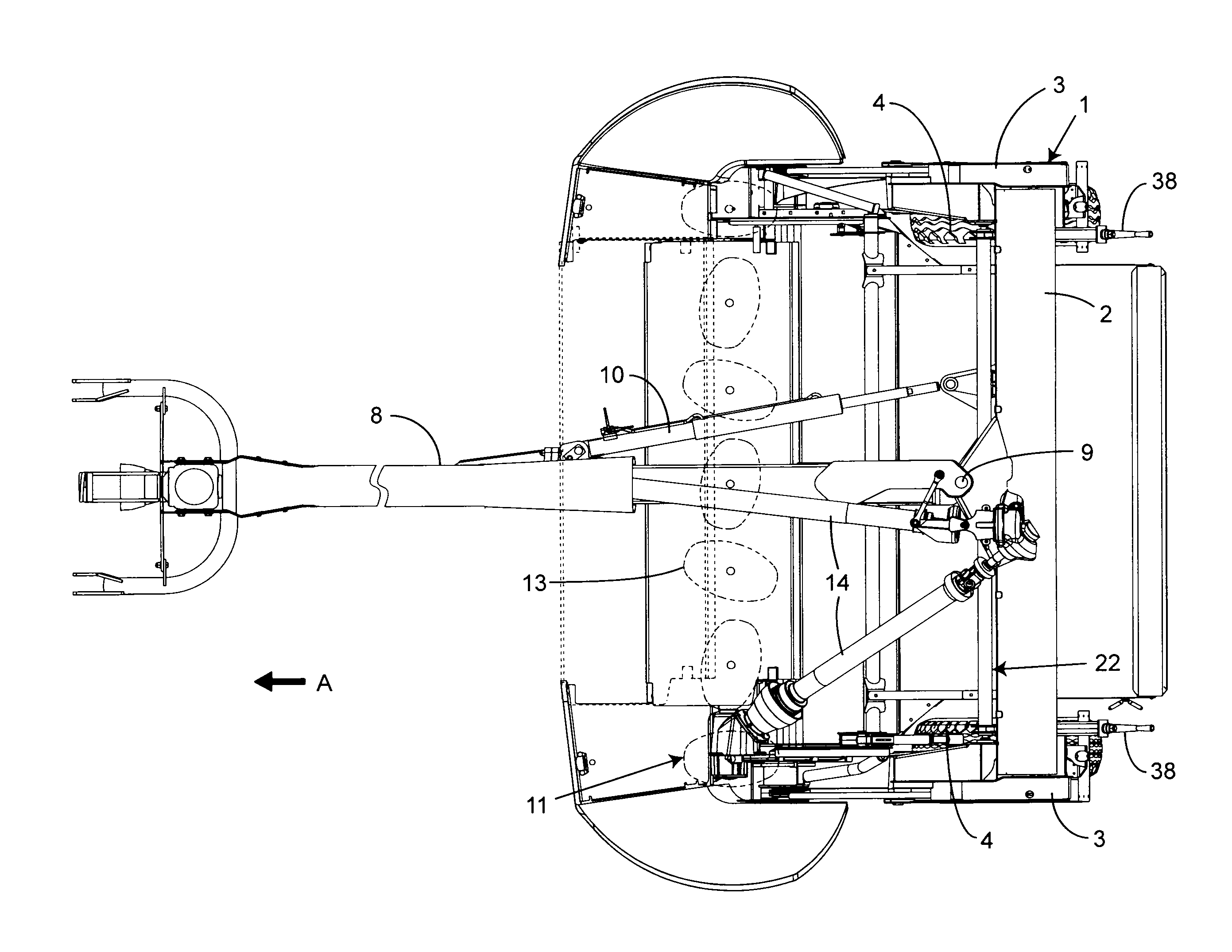

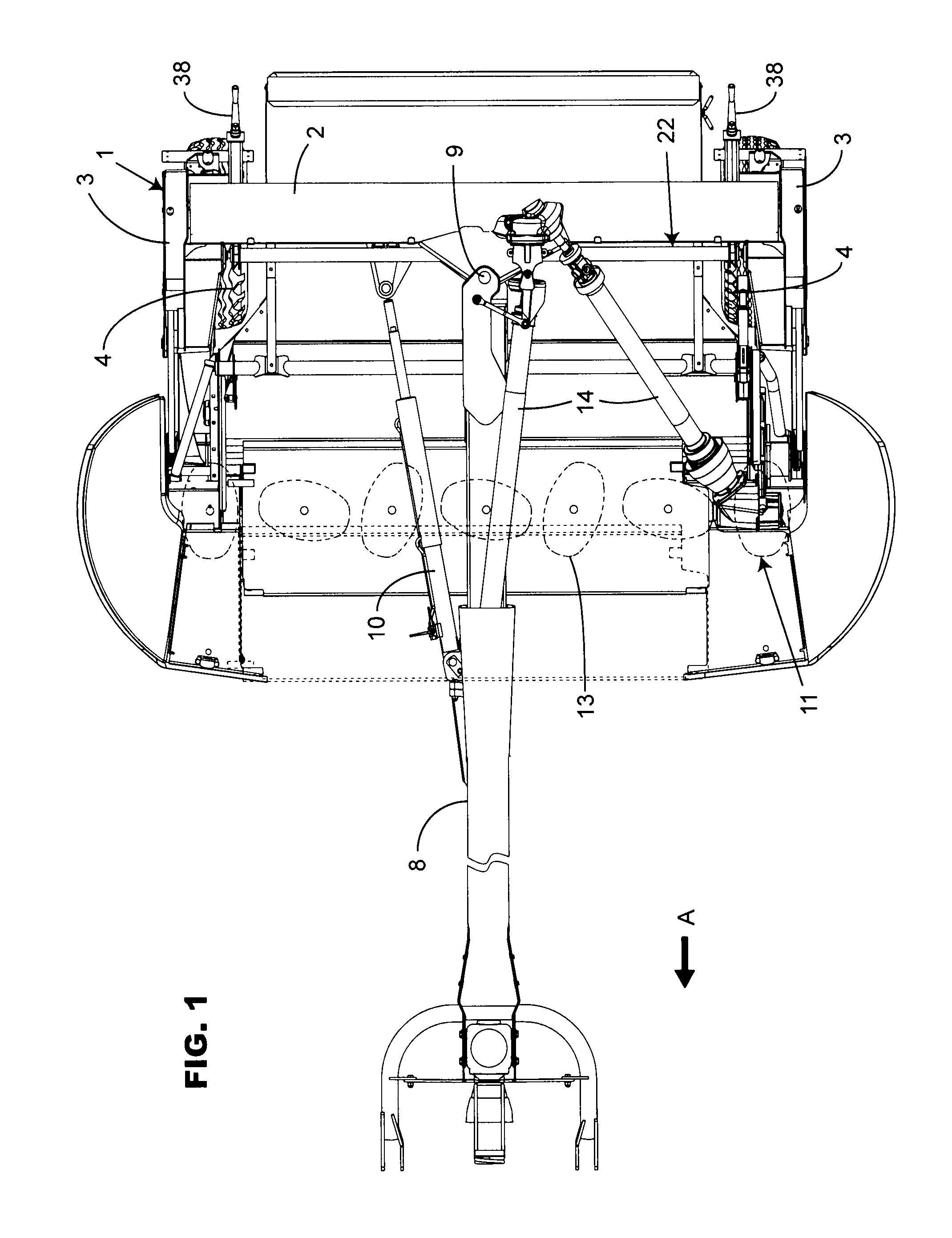

Mower with an improved lightening device

A mower comprising a chassis carrying at least one harvesting mechanism and a lightening device of said harvesting mechanism.The lightening device is constituted by at least one torsion bar which is connected to a transverse beam of the chassis and which carries a lever on one of the ends of which a rod is articulated which is directed towards the harvesting mechanism and which is itself articulated on said harvesting mechanism or its suspension device.

Owner:KUHN SA

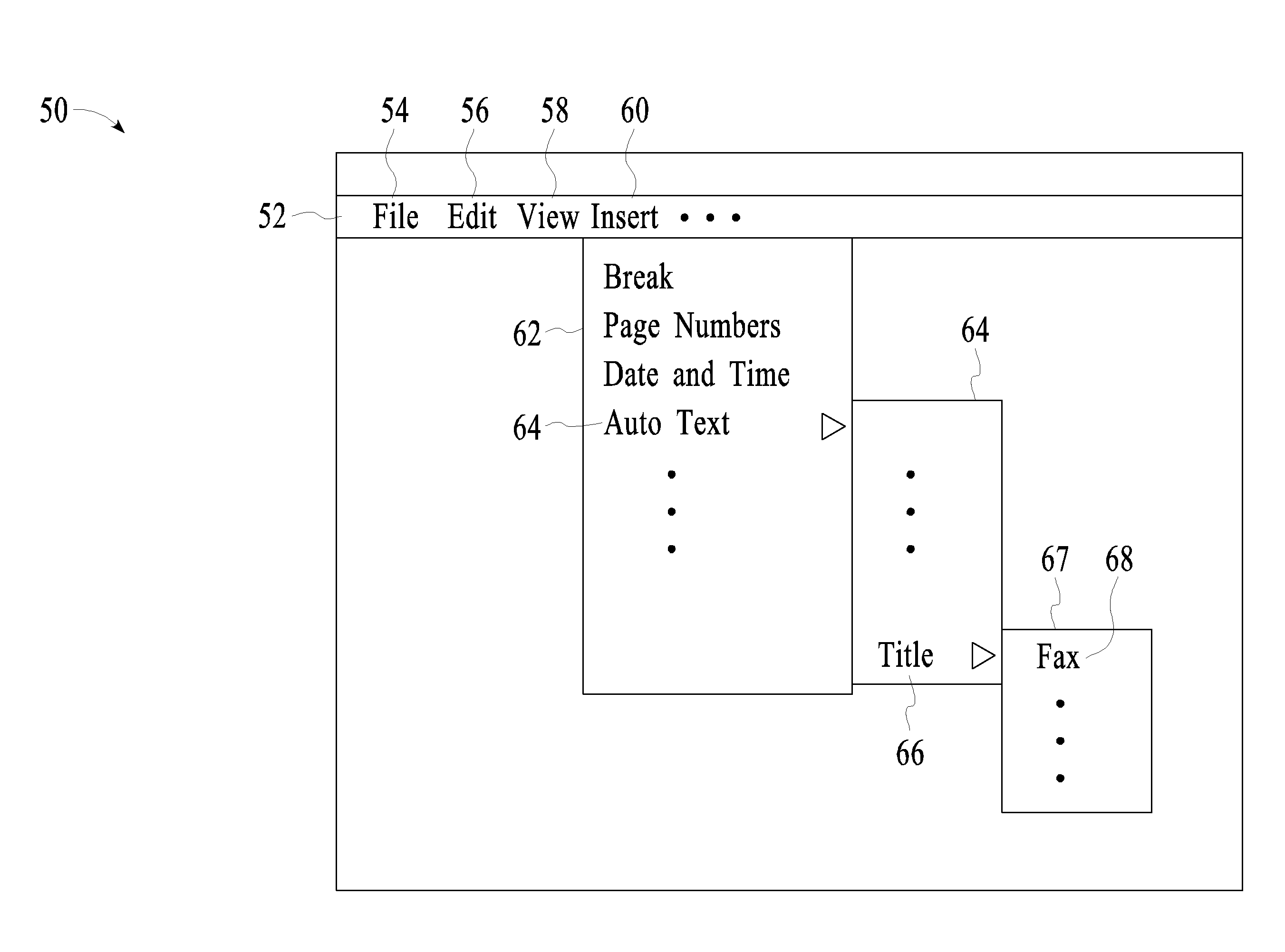

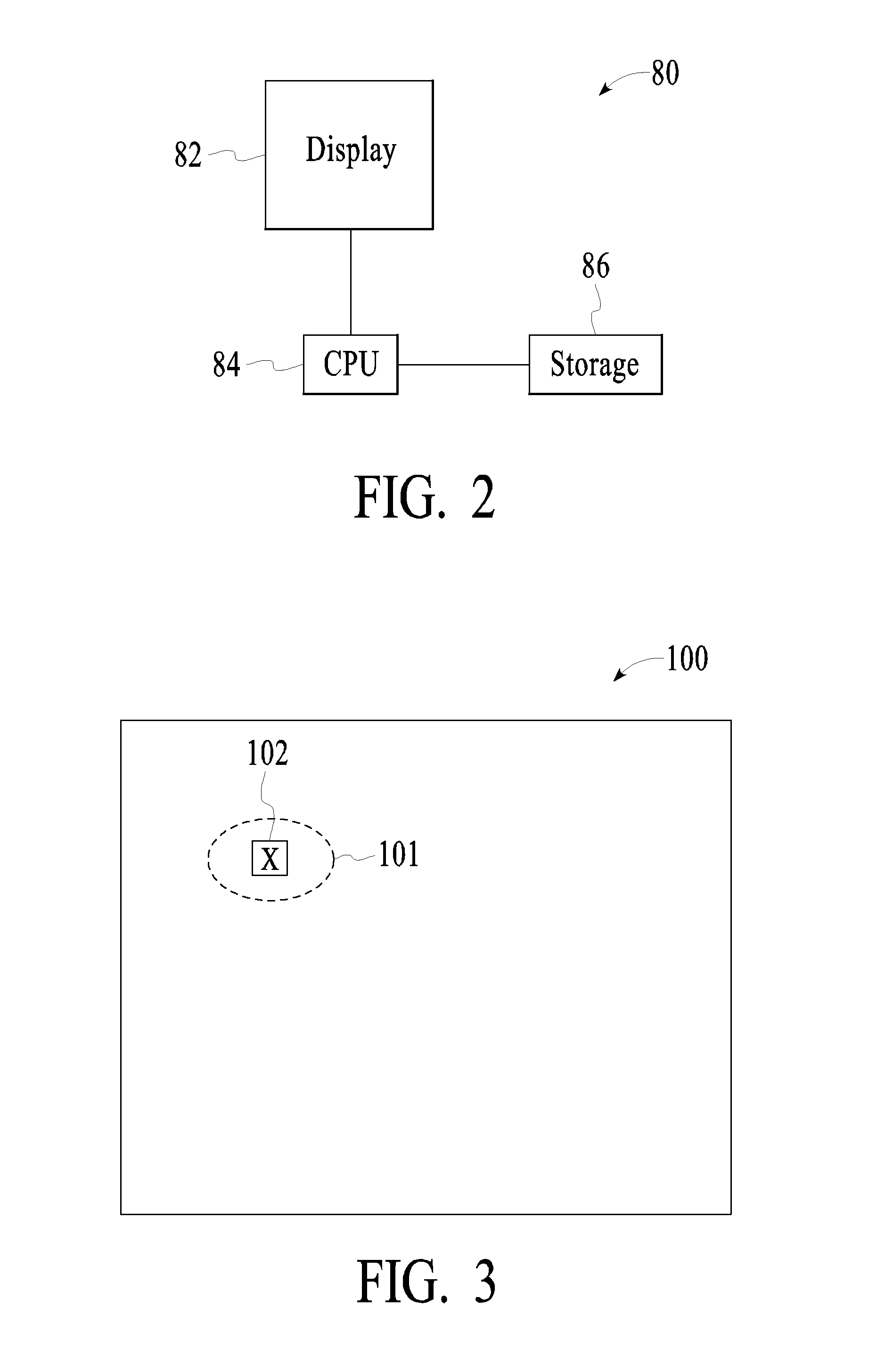

System for consolidated associated buttons into easily accessible groups

InactiveUS20080216019A1Little spaceQuickly and conveniently selectCathode-ray tube indicatorsInput/output processes for data processingScreen spaceHuman engineering

A system for consolidating associated buttons on a screen into easily accessible groups includes: a control button and at least one other button that appears when the control button is selected, where the at least one other button is contiguous with the control button. A user can quickly and conveniently select buttons. Furthermore, a significant amount of on-screen real estate is saved because the buttons used are small and square rather than long and rectangular. Further, the configuration of nested menus is such that it takes up little space on the screen. In addition, the menu is ergonomic because the buttons are contiguous, and as such selections can be made without the mouse pointer needing to move very far across the screen.

Owner:TOSHIBA GLOBAL COMMERCE SOLUTIONS HLDG

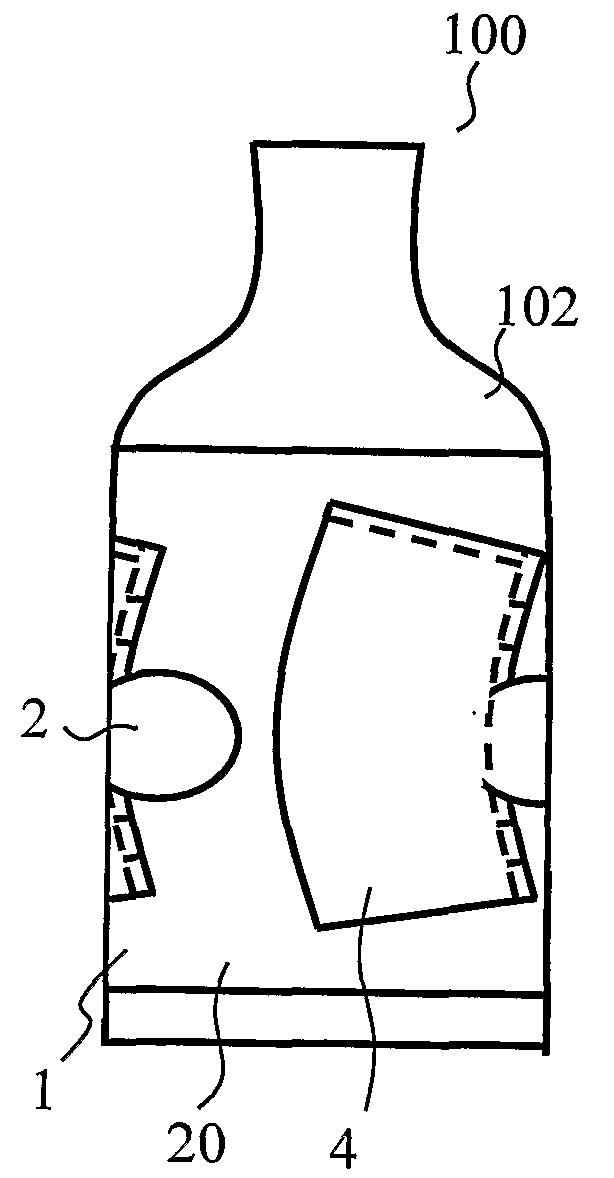

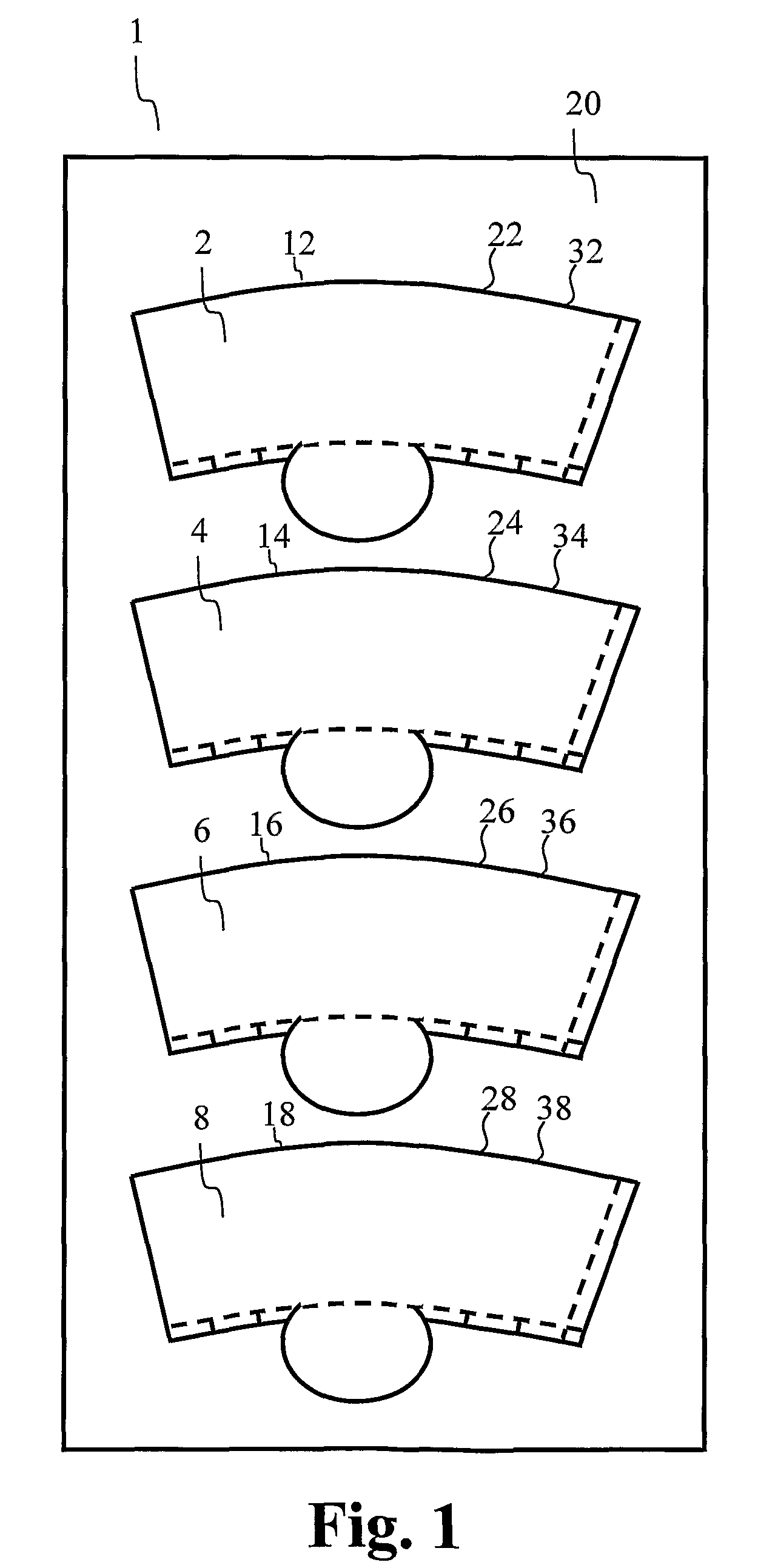

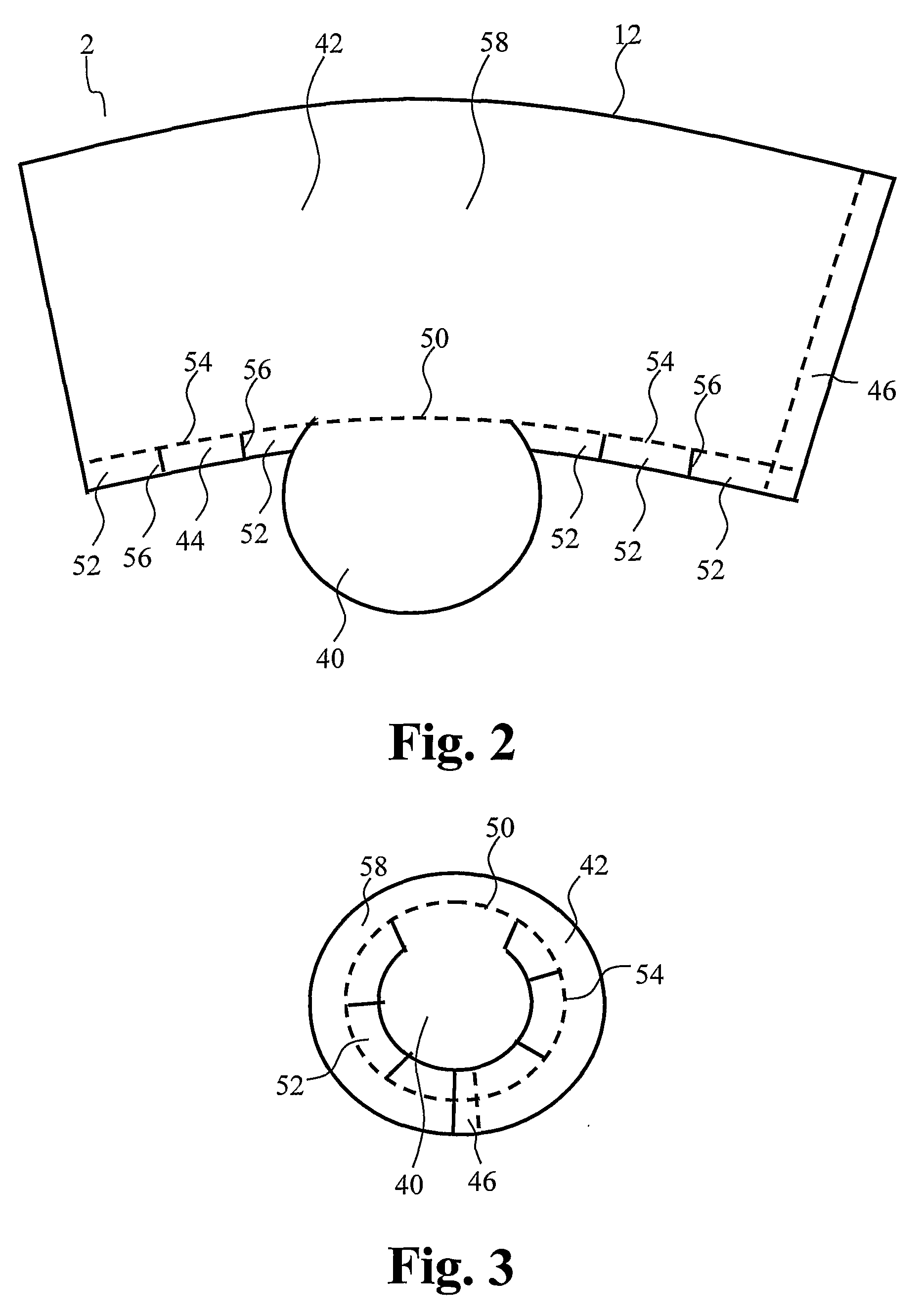

Label with a formable cup

The present invention relates to a label (1) comprising at least one formable cup in the form of at least one cup sheet (2), and to a drinking system (100) comprising a container (102) with a label comprising at least one cup sheet (2). The label (1) comprises at least one cup sheet (2), each cup sheet (2) having an outer edge (12), a first surface, and a second surface (58), wherein the at least one cup sheet (2) is detachable from the label (1) and formable such that the at least one cup sheet (2) can be formed into at least one cup.

Owner:RIIS MOGENS +1

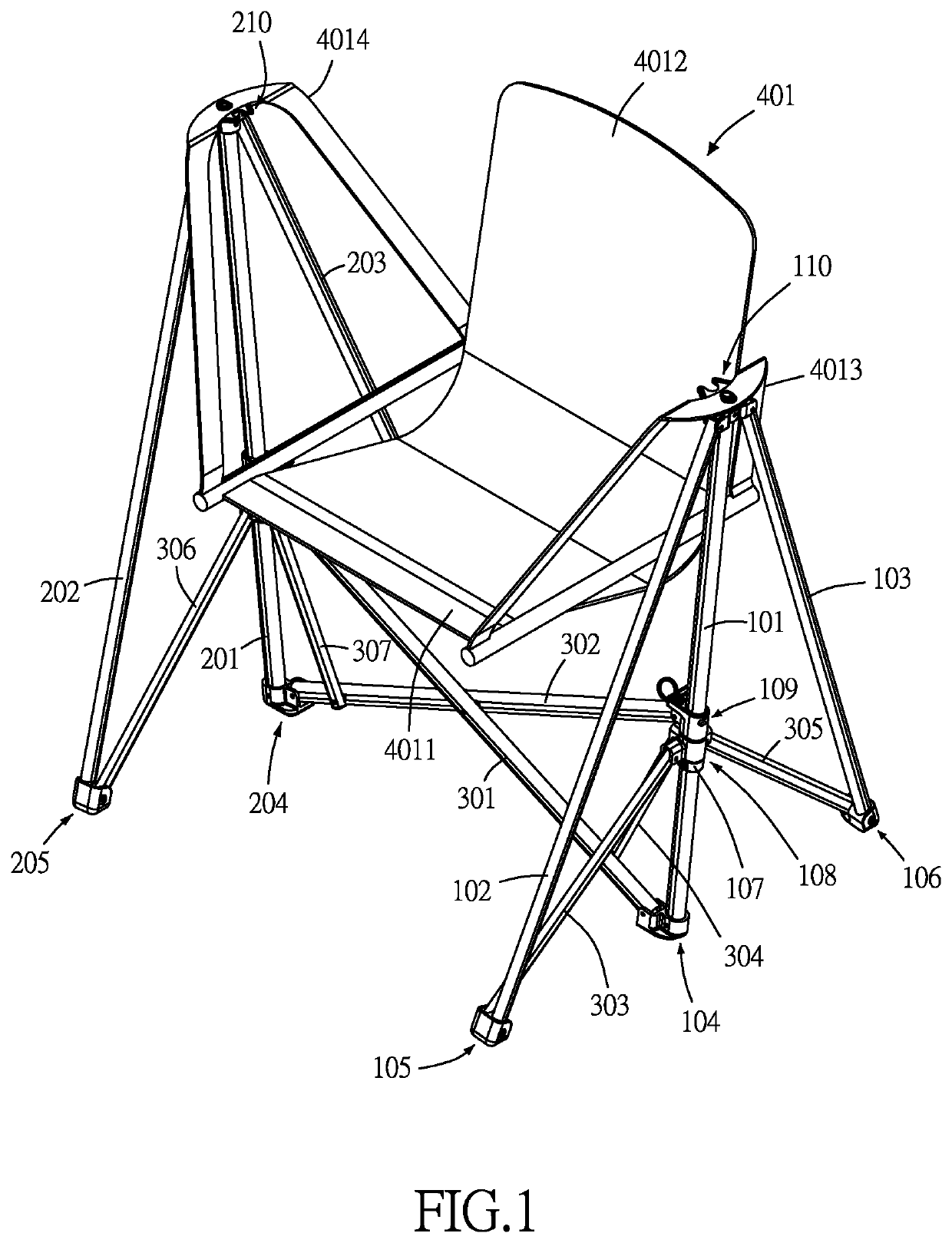

Folding chair

ActiveUS11330906B1Little spaceHigh stabilityDismountable chairsFoldable chairsMechanical engineeringWeight-bearing ability

A folding chair includes a left central support rod, left front support rod, left rear support rod, left central leg terminal, left front leg terminal, left rear leg terminal, left limiting element, left sliding element, left limiting sliding element, left connecting element, right central support rod, right front support rod, right rear support rod, right central leg terminal, right front leg terminal, right rear leg terminal, right limiting element, right sliding element, right limiting sliding element, right connecting element, first connecting rod, second connecting rod, third connecting rod, fourth connecting rod, fifth connecting rod, sixth connecting rod, seventh connecting rod, eighth connecting rod and weight-bearing unit. The folding chair can be folded up like an umbrella and thus takes up little space and is portable and can be unfolded to demonstrate high stability and high load-bearing capability.

Owner:SPORT DIVERSIONS INC

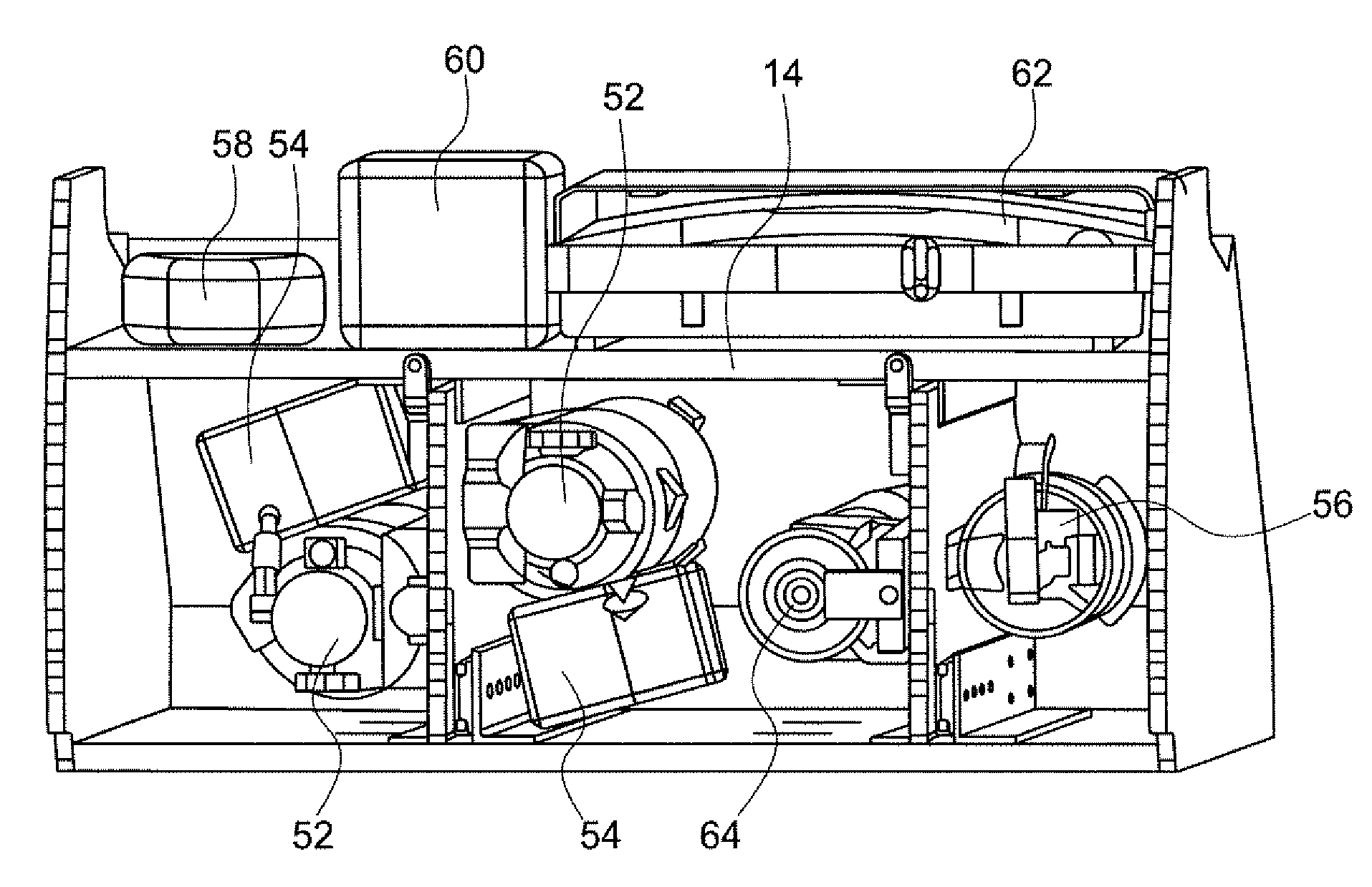

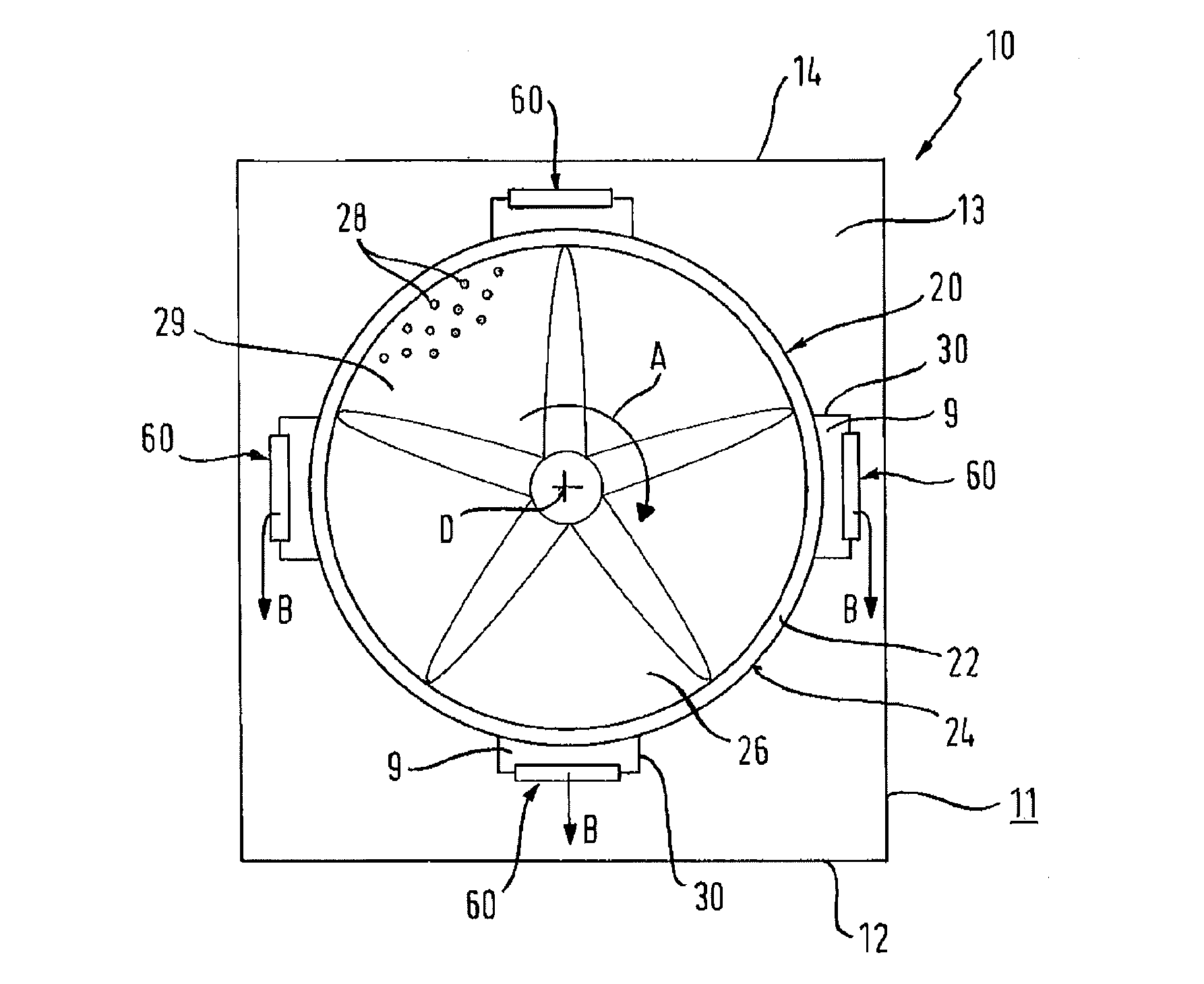

Tumble dryer with automatic fire extinguishing system

ActiveUS20130167400A1Reduce out circumferenceLittle spaceDrying gas arrangementsOther washing machinesLaundryEngineering

A tumble dryer, in particular a household tumble dryer, includes a housing, a drum intended for laundry to be dried, which is supported rotatably in the housing, and a container positioned on an outer face of the lateral surface of the drum and holding an extinguishing agent. The container has a first temperature-activated release facility which automatically releases the extinguishing agent into a space outside the drum, in the presence of a temperature produced by a fire.

Owner:BSH BOSCH & SIEMENS HAUSGERAETE GMBH

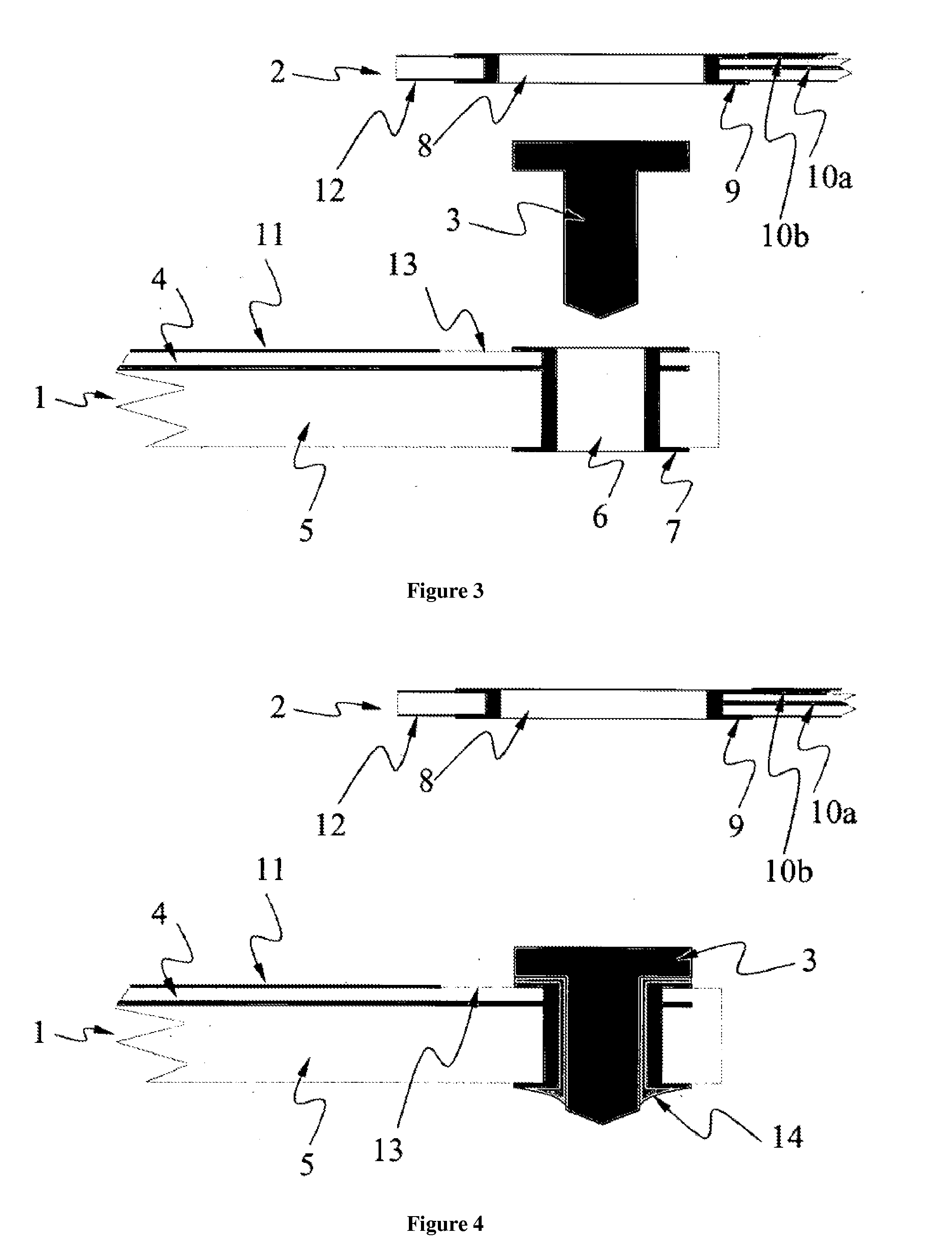

MIMO antenna device, antenna and antenna package

ActiveUS20130321234A1Little spaceImprove isolationSolid-state devicesAntenna earthingsRadiationElectrical and Electronics engineering

A multi-input and multi-output antenna device is disclosed. The MIMO antenna device comprises two antennas symmetrically disposed on a substrate. Each antenna comprises a T-shaped feeding unit, a radiation unit and a ground unit. The T-shaped feeding unit and the radiation unit are disposed on a first surface of the substrate. The T-shaped feeding unit forms a strip portion and a top portion. The radiation unit has first and second ends. The radiation unit extends from the first end to the second end to form a rectangular region and a spacing. The first end extends parallel to the top portion. The ground unit is disposed along two sides of the strip portion and electrically coupled to the second end. The two strip portions of the two T-shaped feeding units are parallel to and aligned with each other. The two ground units are electrically connected to each other.

Owner:NAT SUN YAT SEN UNIV

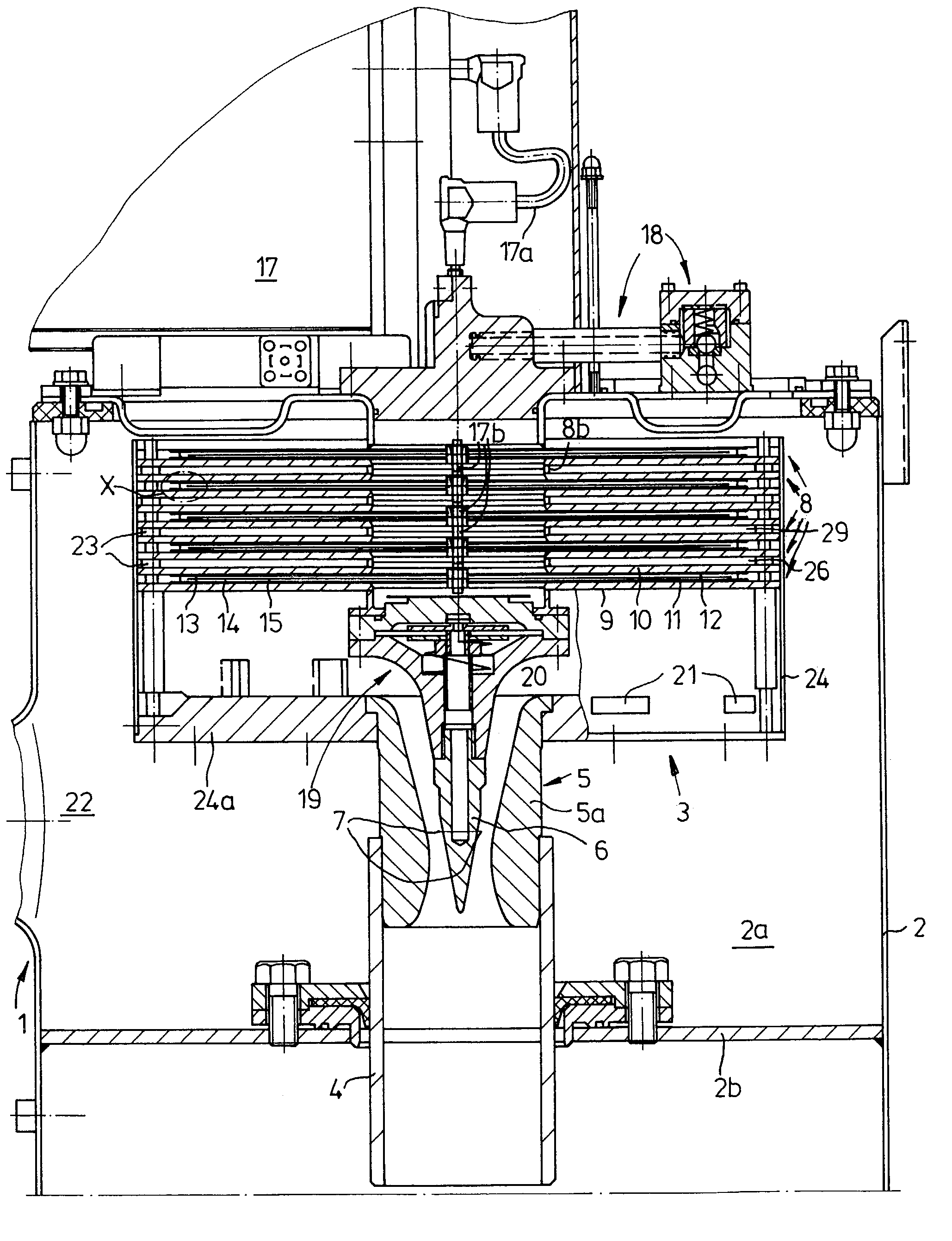

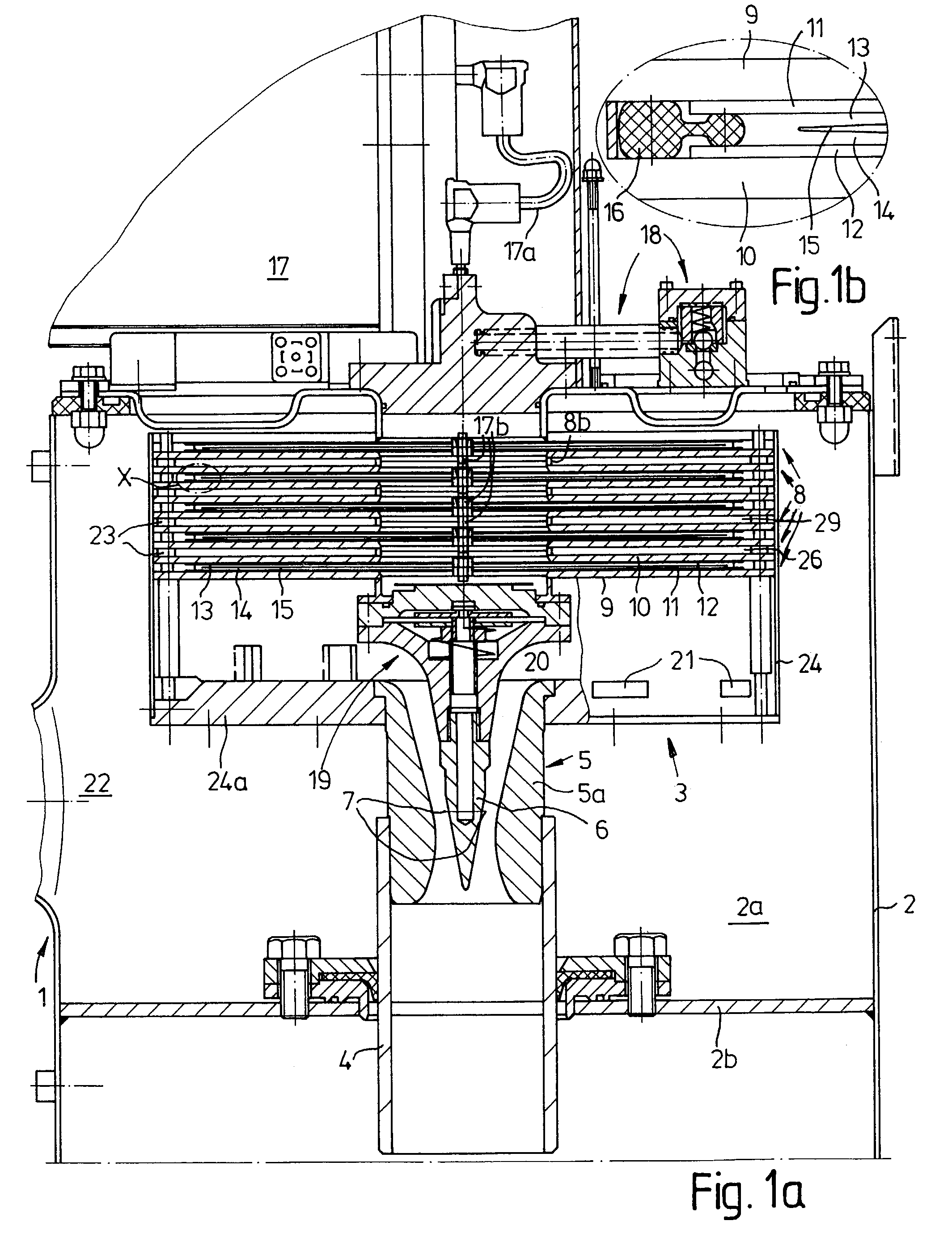

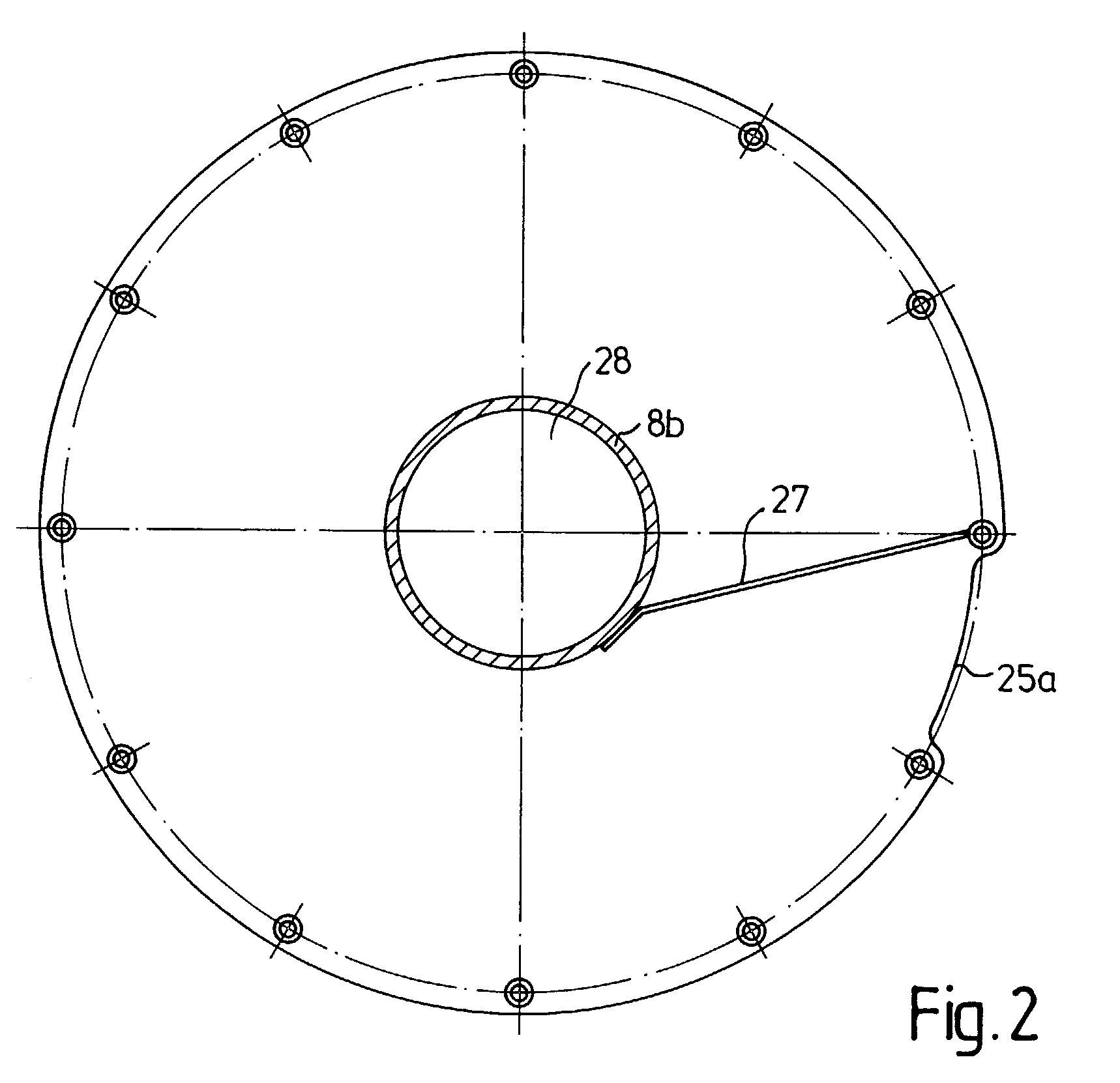

Ozone generator

InactiveUS6967009B2High ozone generation rateLittle spaceElectrical discharge ozone preparationEnergy based chemical/physical/physico-chemical processesOzone generatorsOzone

An ozone generator is proposed which comprises a plurality of plate-like ozone generating elements, stacked one on top of the other, which are in at least partial contact with a process water stream, each of the ozone generating elements having at least one plate-like, electrically insulated inner electrode and at least one likewise plate-like counterelectrode, between which a space is provided for a gas discharge. According to the invention, the ozone generating elements are situated at a distance from one another, perpendicular to their plate-like extension, in such a way that process water is able to flow between the ozone generating elements over substantial surface regions of the plate-like ozone generating elements.

Owner:HYDRO ELEKTRIK

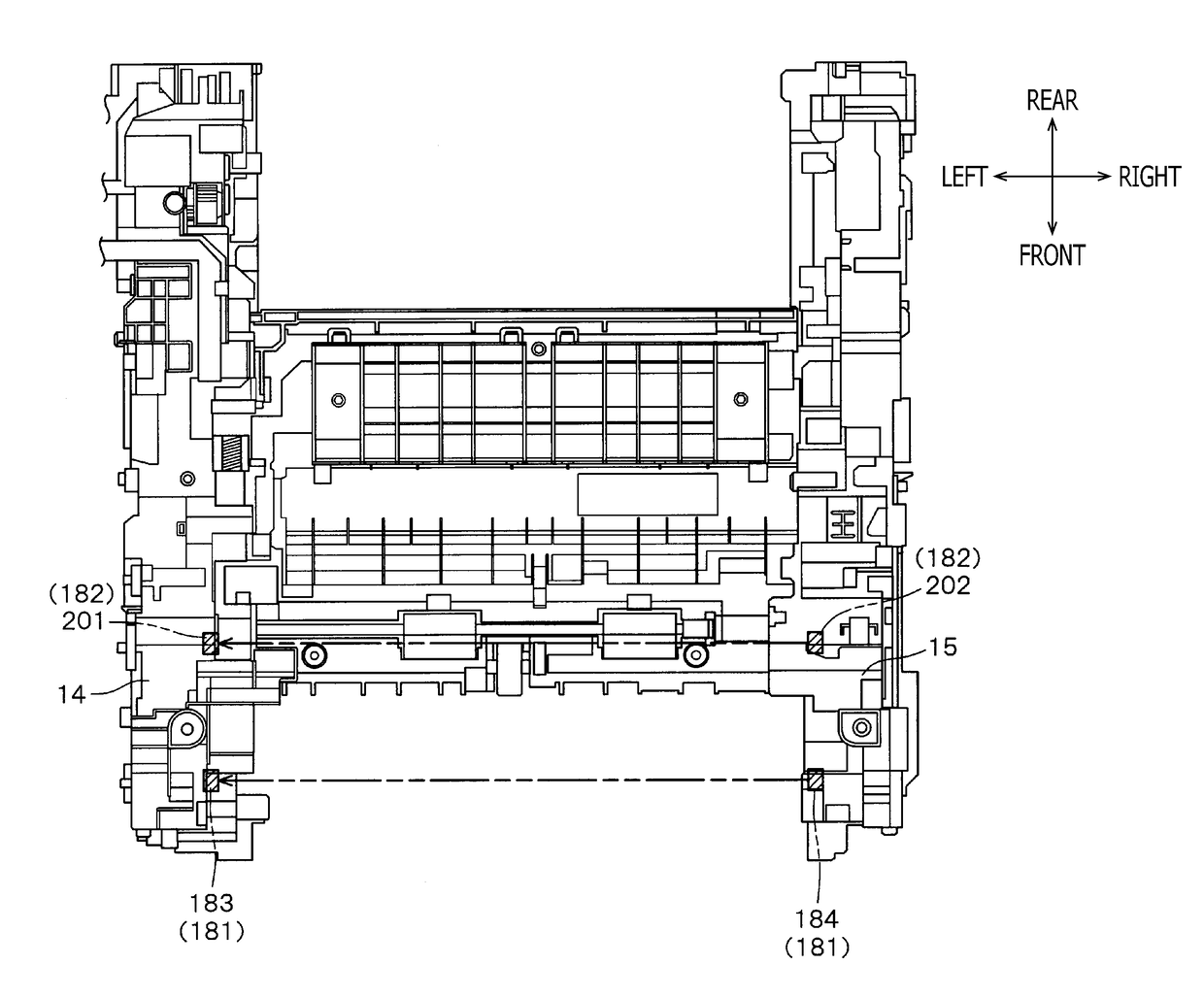

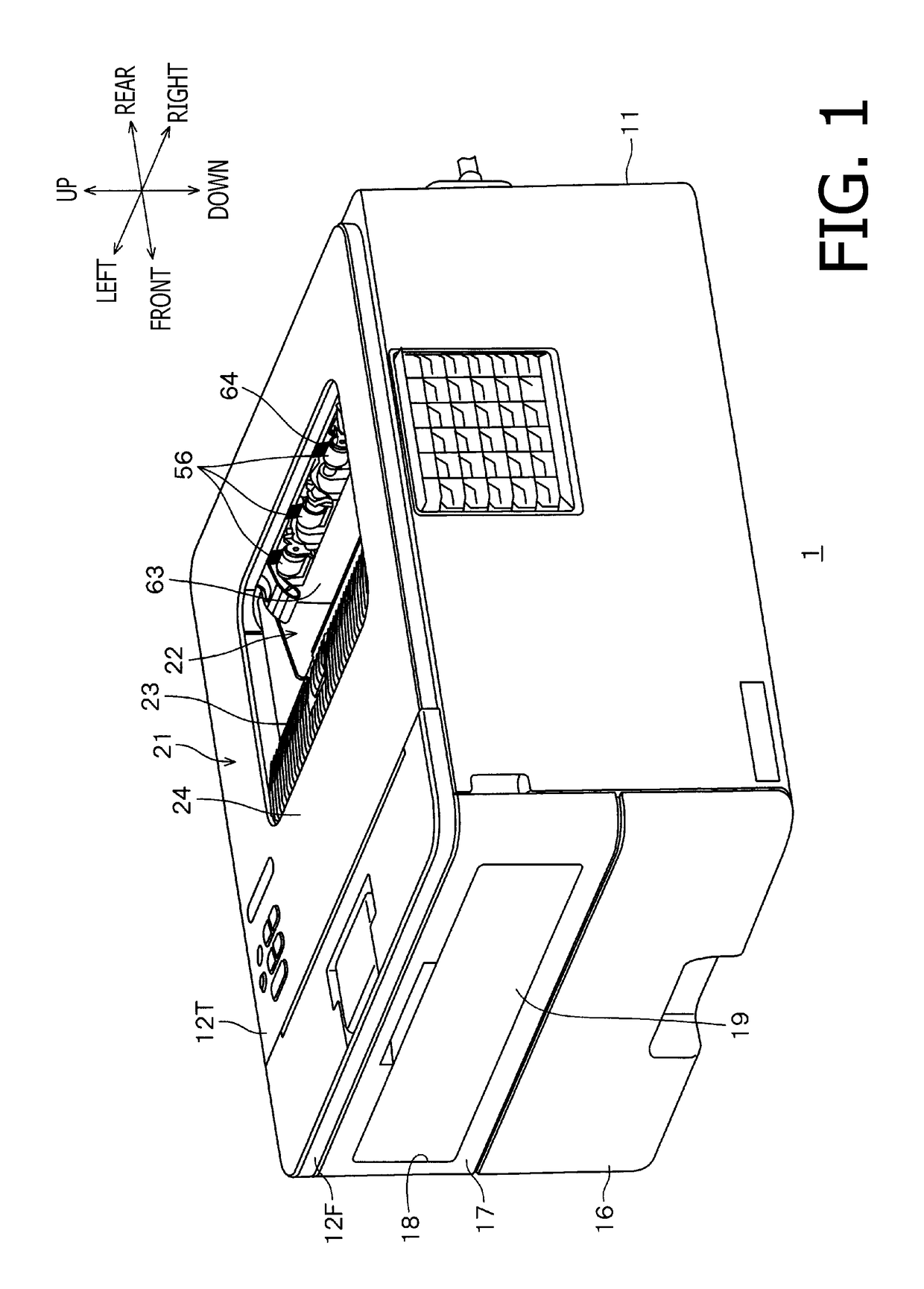

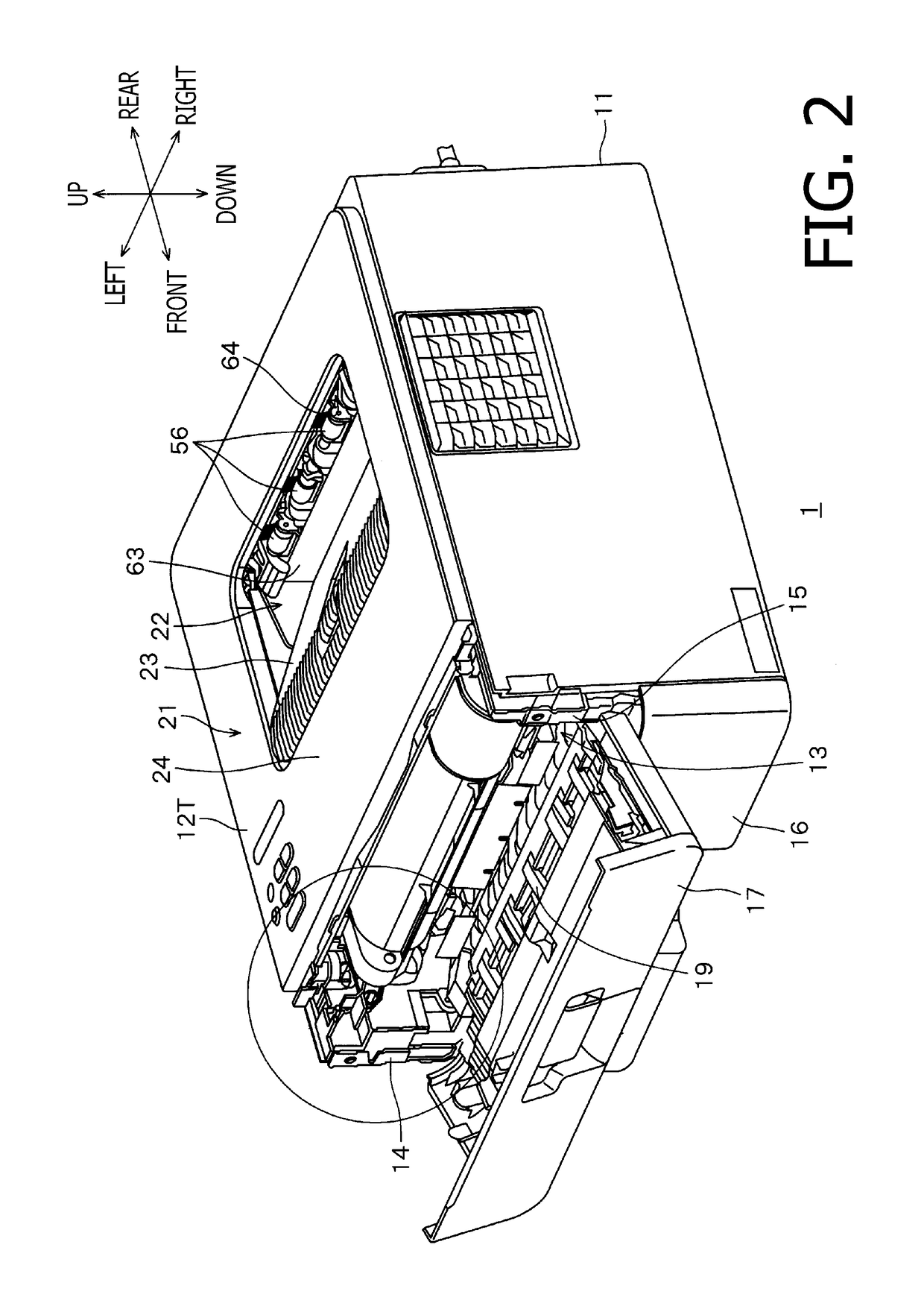

Image forming apparatus

ActiveUS20180335750A1Small distanceLittle spaceElectrographic process apparatusEngineeringElectrical and Electronics engineering

An image forming apparatus has a first opening on a side surface of the casing, first and second frames, a cartridge detachably attached through the first opening, and light receiver and light emitter respectively provided to the first and second frames. The cartridge shields the light from the light emitted when attached to an attachment position. The first and second frames face across the attachment position. The light reaches the light receiver when the cartridge is detached from the casing. A door is movably secured to the casing between closing and opening positions, and a second opening allowing a sheet to pass through is formed on the door. External light entering through the second opening and directed toward the light receiver is shielded by a light shielding part provided to the first frame, which also serves as a guiding part to guide attachment of the cartridge.

Owner:BROTHER KOGYO KK

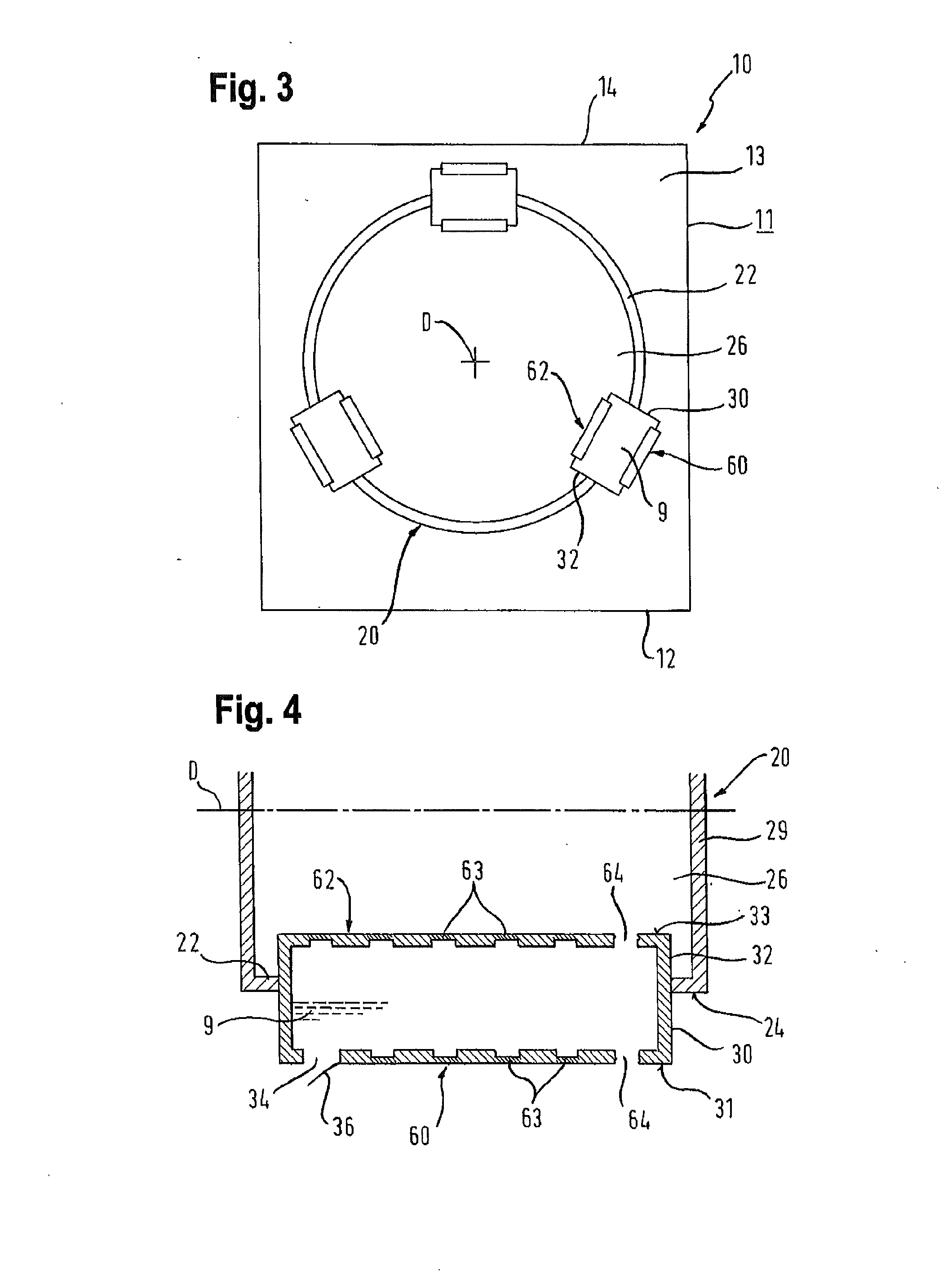

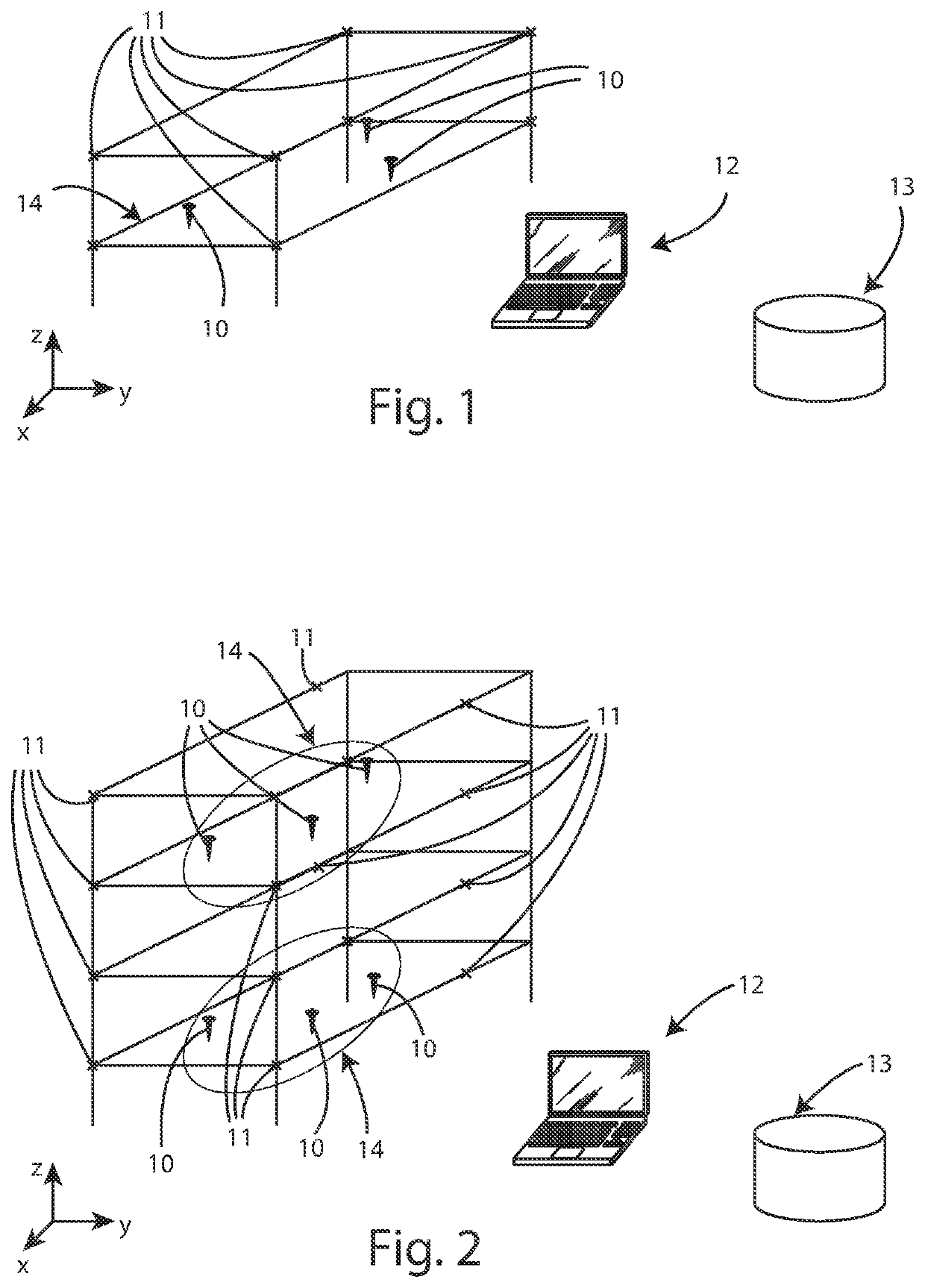

Tracking and communication system for microphones

PendingUS20220345819A1Little spaceEasily designPublic address systemsLocation information based serviceRadio unitTransceiver

A tracking and communication system for microphones (10), comprising a plurality of microphones (10) installed in one or more zones (14) of contiguous or separate environments. Each microphone (10) is equipped with a radio unit which is connected to the microphone (10). The tracking and communication system comprises also a network of radio transceivers (11), which are positioned in said one or more zones (14) and which are connected wirelessly or through one or more cable one to each other, being configured to receive signals from said microphones (10) and to transmit to them a plurality of data, and a command and control unit (12), to which said radio transceivers (11) are connected wirelessly or via cables.

Owner:WISYCOM

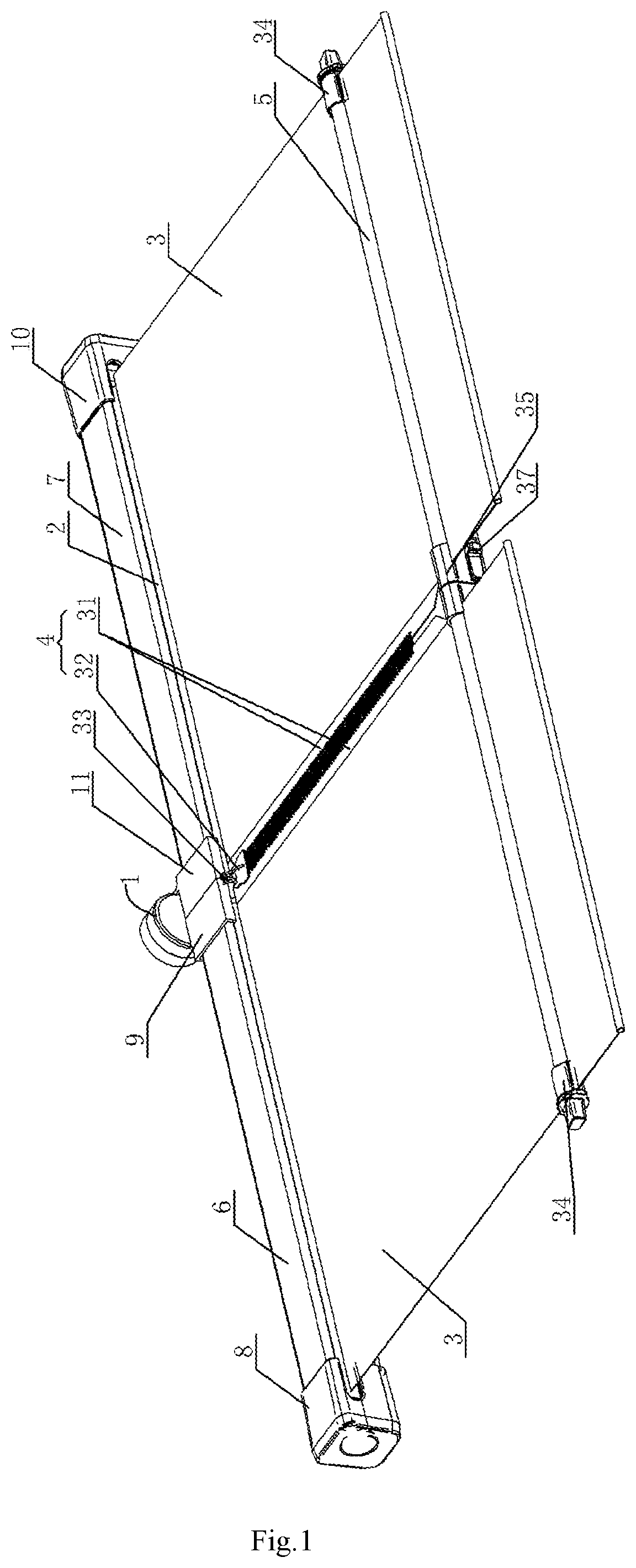

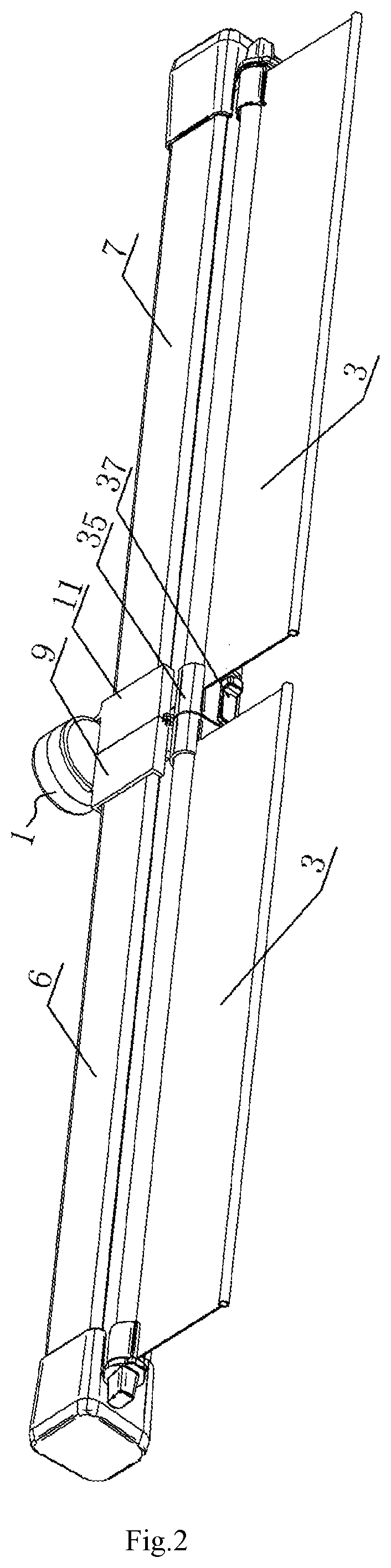

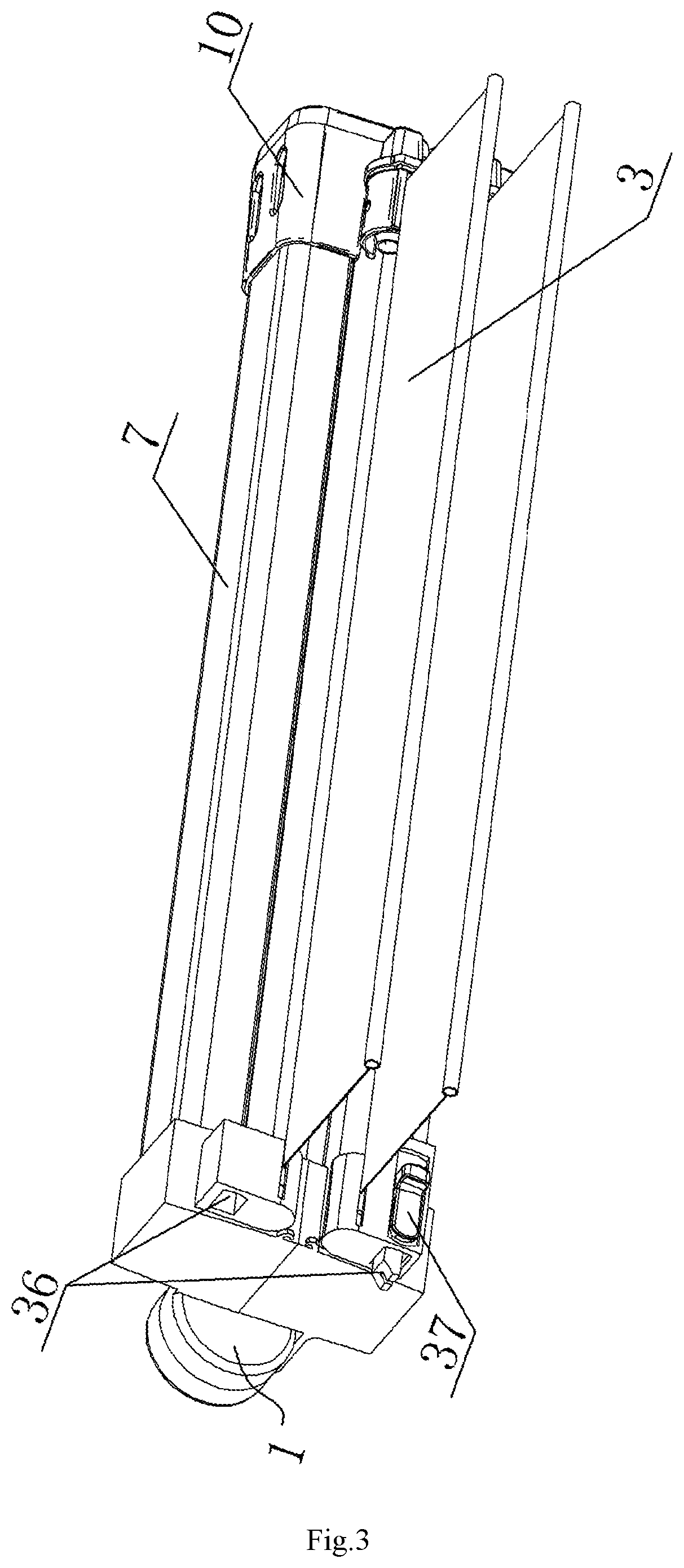

Foldable and recyclable covering curtain

PendingUS20210046879A1Little spaceEasy to storeVehicle componentsStructural engineeringMechanical engineering

Disclosed is a foldable and retractable covering curtain, which includes: two outer tubes; inner ends of the two outer tubes in a length direction are connected by a rotating structure, the two outer tubes are folded or unfolded into a straight line structure by the rotating structure; a corresponding spacing groove is provided at one side of each outer tube in the length direction; a curtain fabric that is capable of being rolled up is provided inside each outer tube, and each curtain fabric extends outside of the corresponding outer tube by the corresponding spacing groove; and when the curtain fabric is in an expanded state, facing sides of the two curtain fabrics are in closed connection by a zipper mechanism, and when the curtain fabric is in a retracted state, the zipper mechanism is opened.

Owner:YUQIU MOLD PLASTICS CO LTD OF KUNSHAN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com