Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

189 results about "Processor assignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for measuring timing of signals received from multiple base stations in a CDMA communication system

InactiveUS6697629B1Improve usabilityDirection finders using radio wavesPosition fixationTime segmentComputer terminal

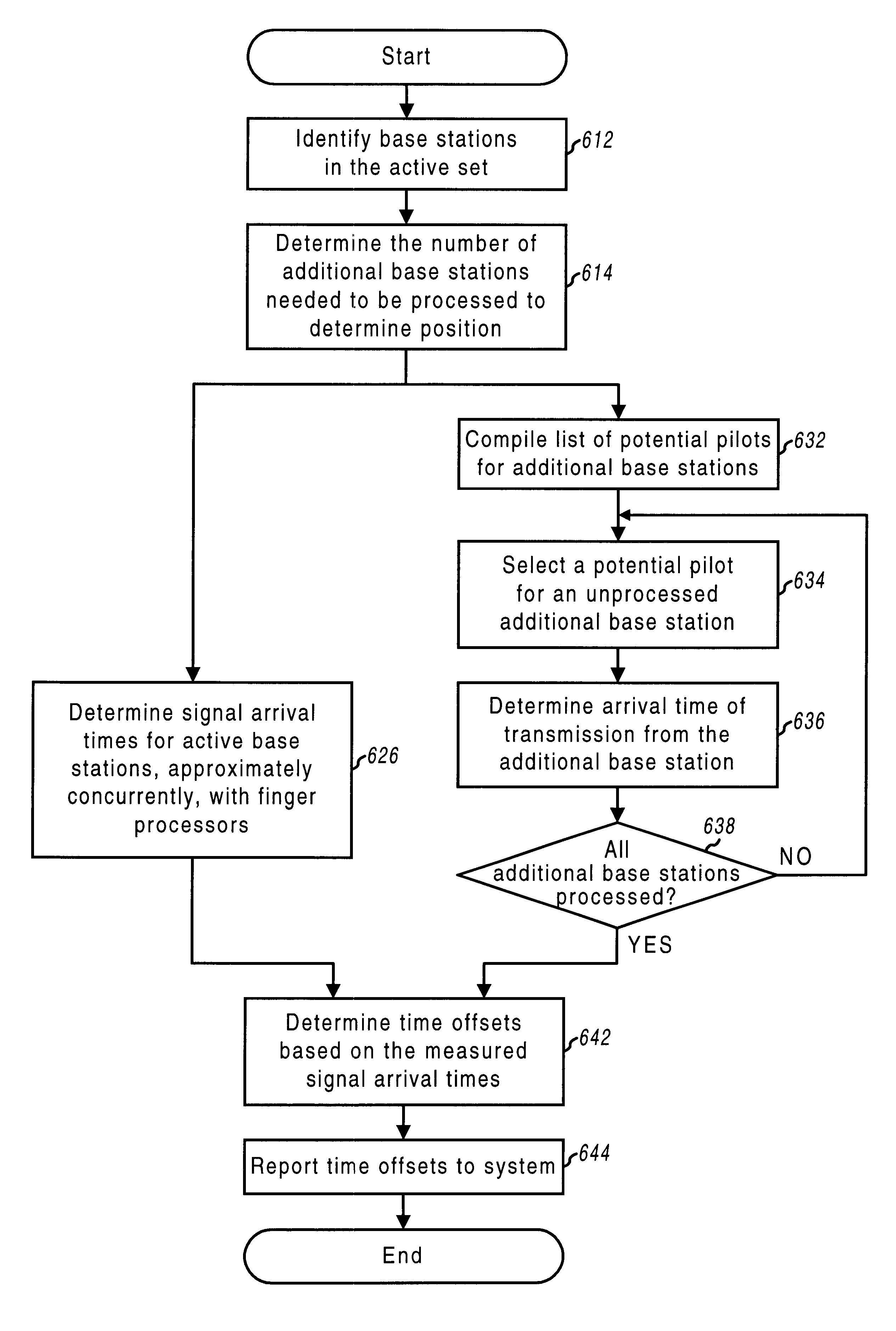

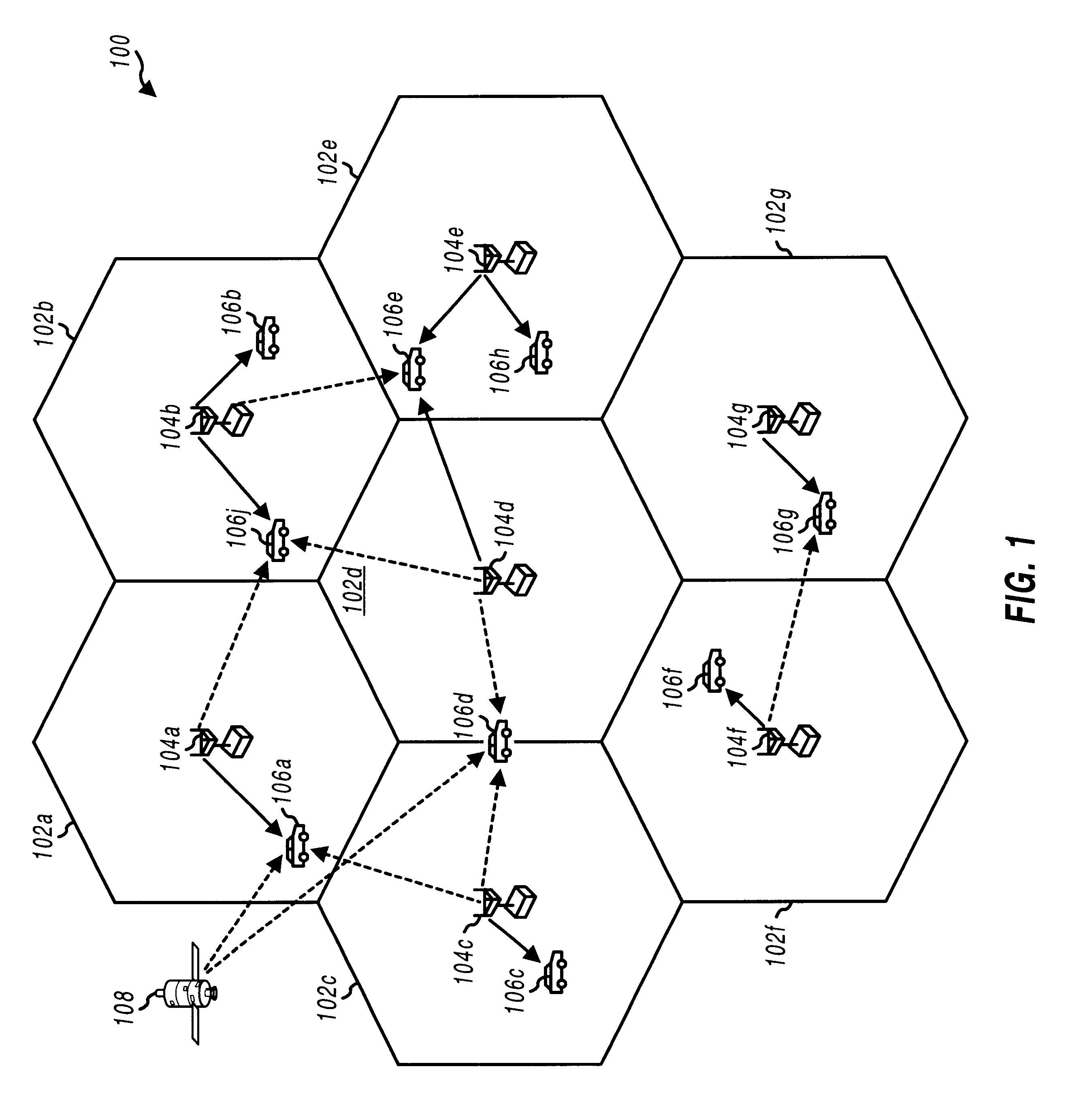

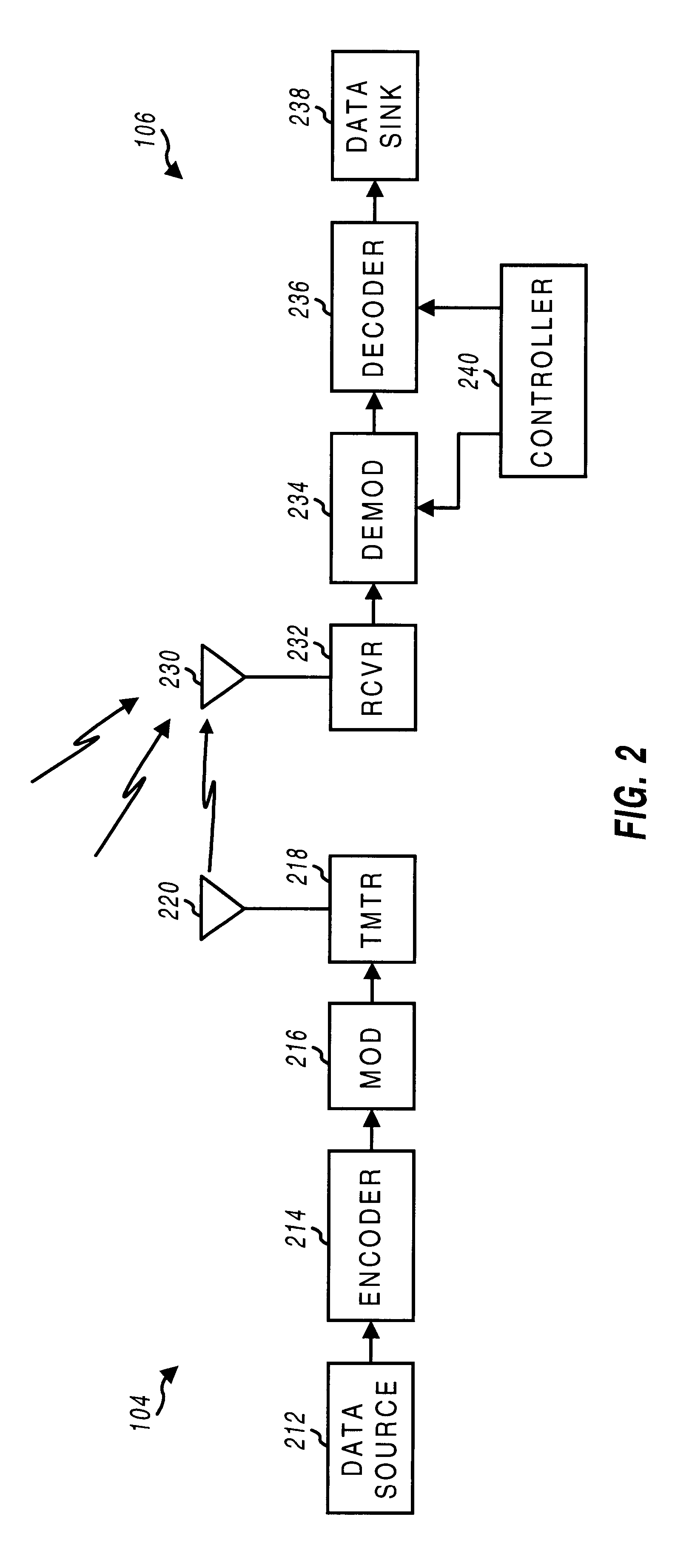

Techniques to more accurately measure the arrival times of transmissions received at a remote terminal from a number of base stations. In one aspect, unassigned finger processors are used to process and measure the arrival times of transmissions from base stations not in the active set. In another aspect, if no finger processors are available for assignment, the arrival times can be measured in the time period between updates of a reference oscillator used for the measurements. In accordance with a method for determining a position of a remote terminal, a first set of one or more base stations in active communication with the remote terminal is identified and each base station in the first set is assigned at least one finger processor. A second set of one or more base stations not in active communication with the remote terminal is also identified and an available finger processor is assigned to each of at least one base station in the second set. A (signal arrival) time measurement is then performed for each base station, and outputs indicative of the measurements are provided for further processing. To improve accuracy, the measurements can be performed within a narrow time window.

Owner:QUALCOMM INC

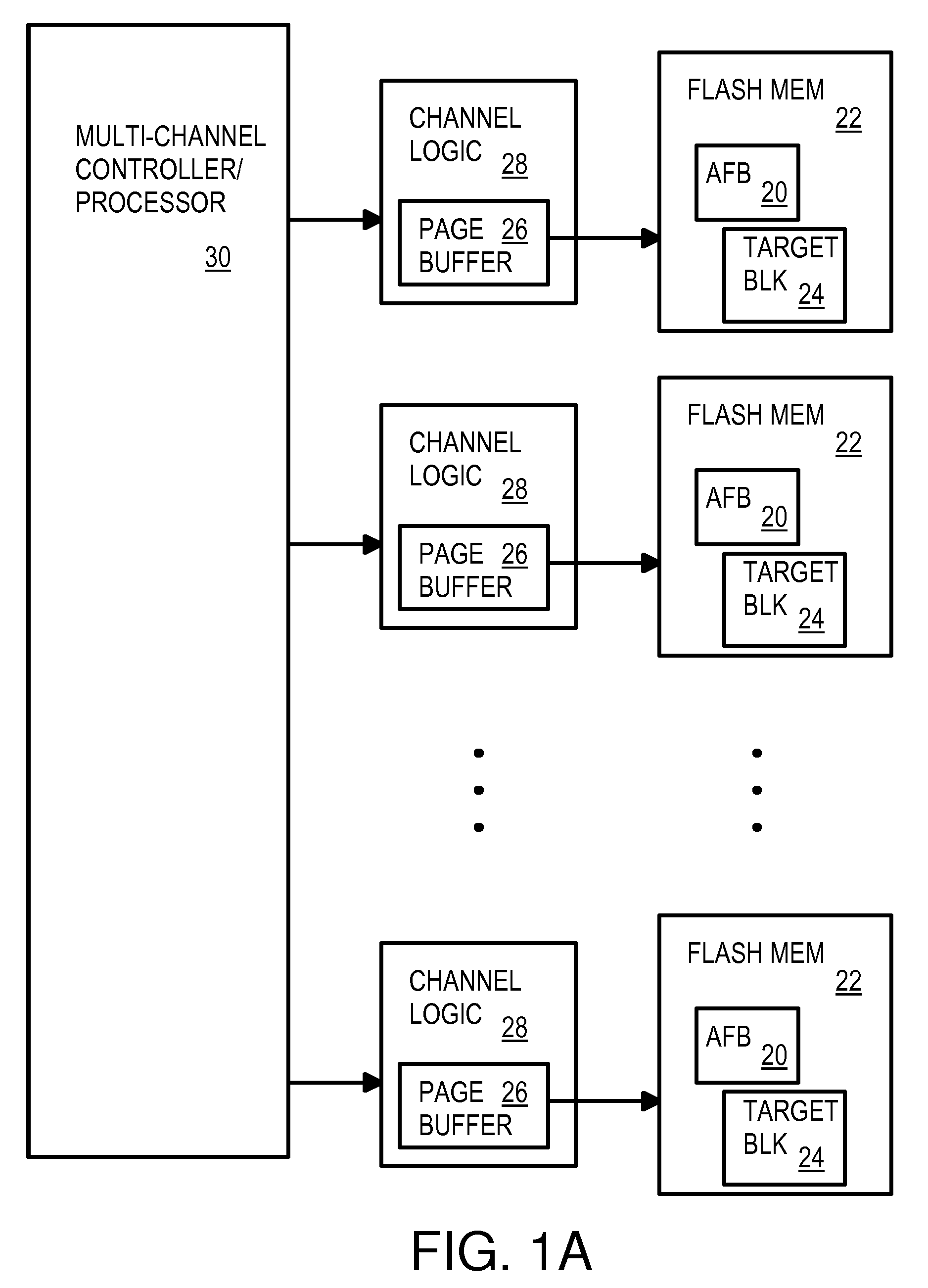

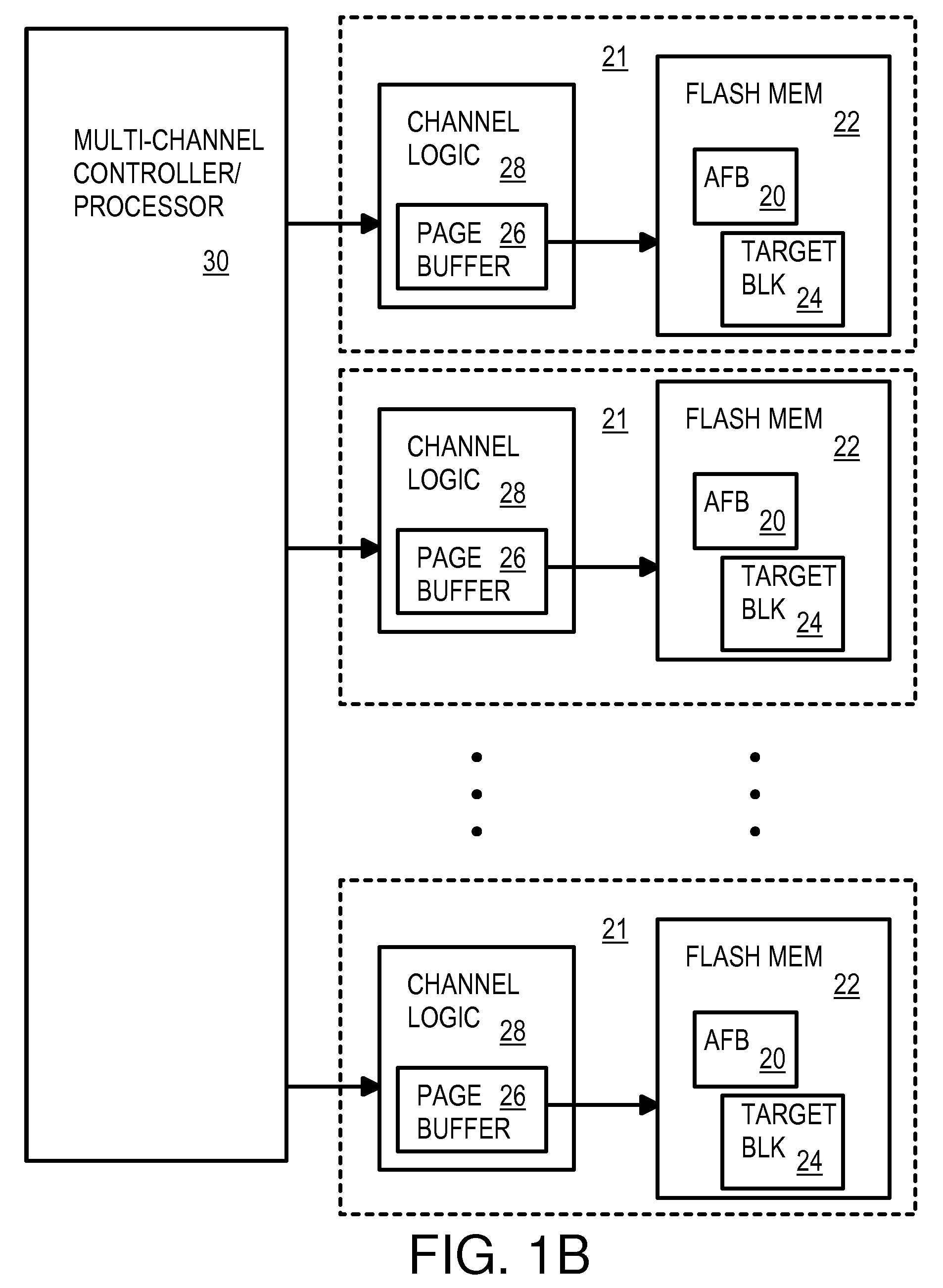

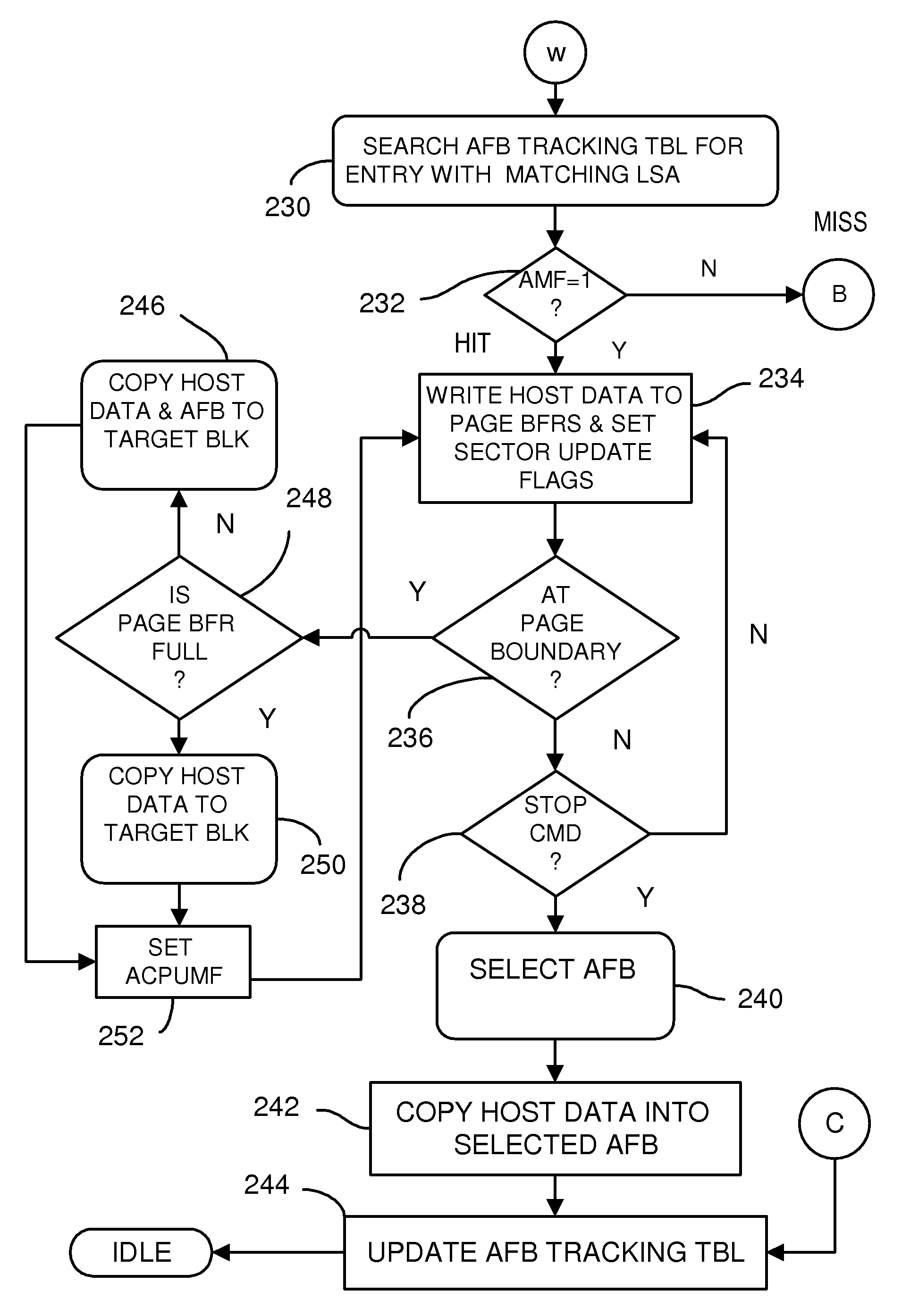

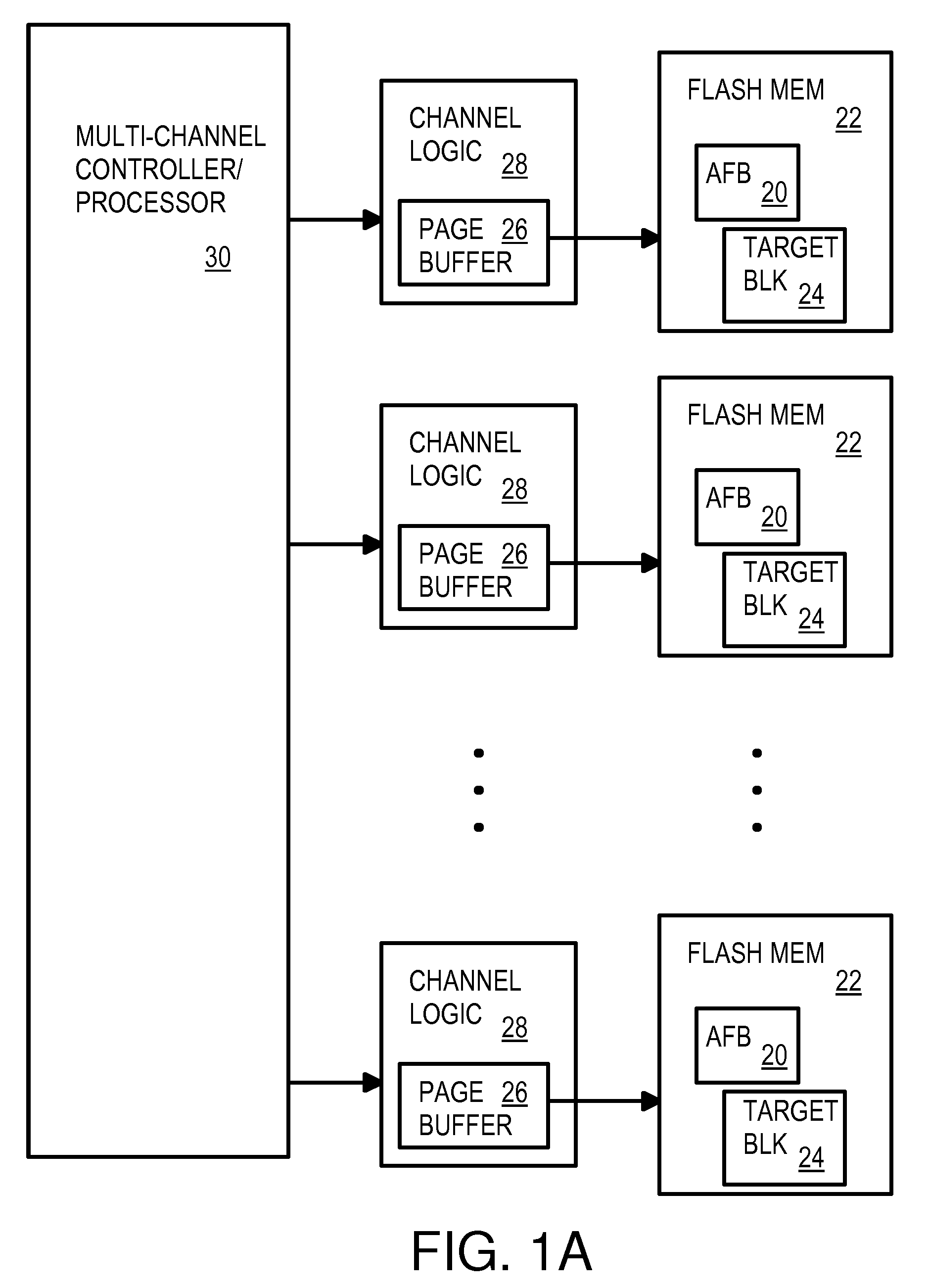

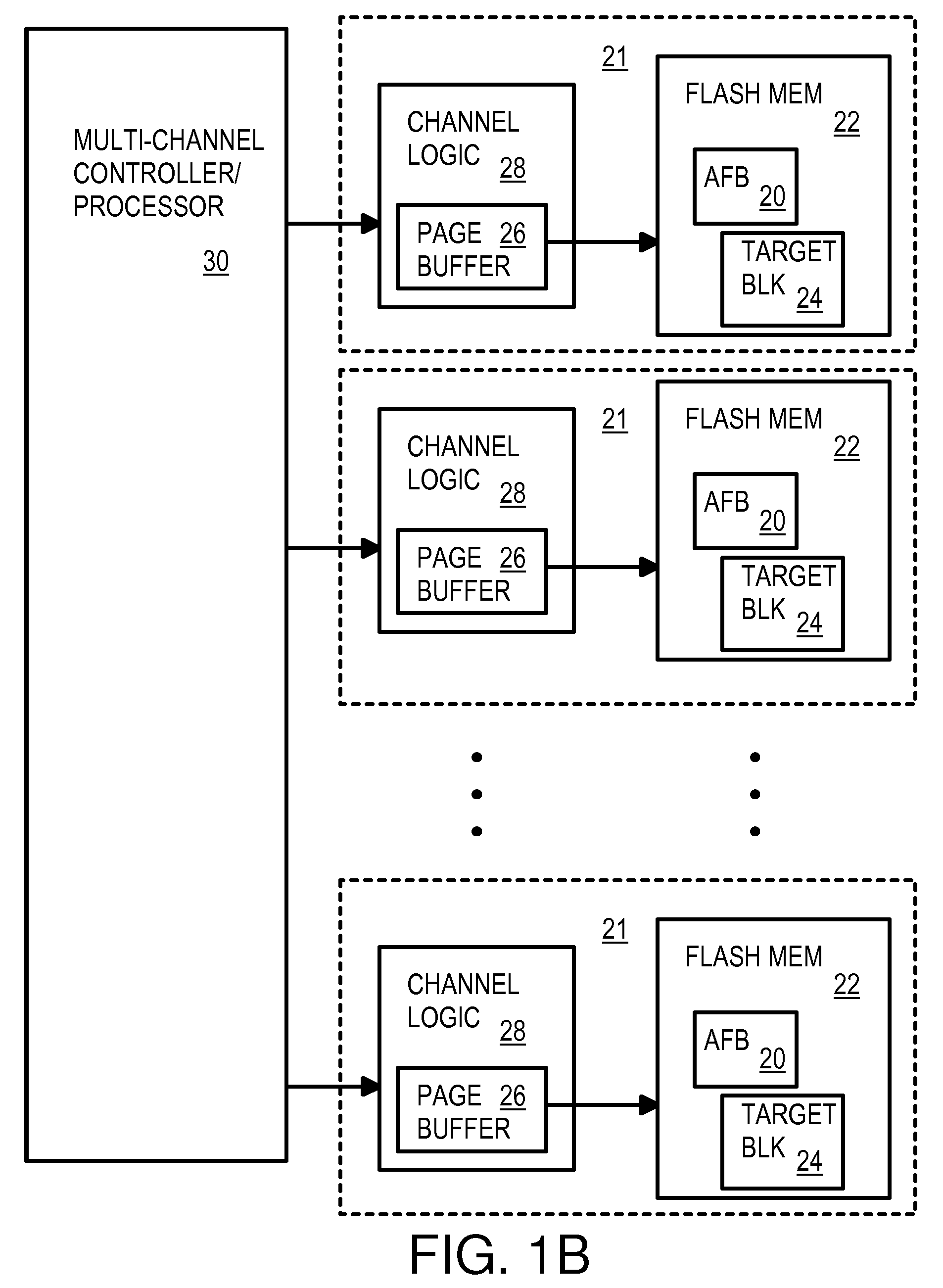

Multi-Operation Write Aggregator Using a Page Buffer and a Scratch Flash Block in Each of Multiple Channels of a Large Array of Flash Memory to Reduce Block Wear

InactiveUS20080250195A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSmall fragmentPage buffers

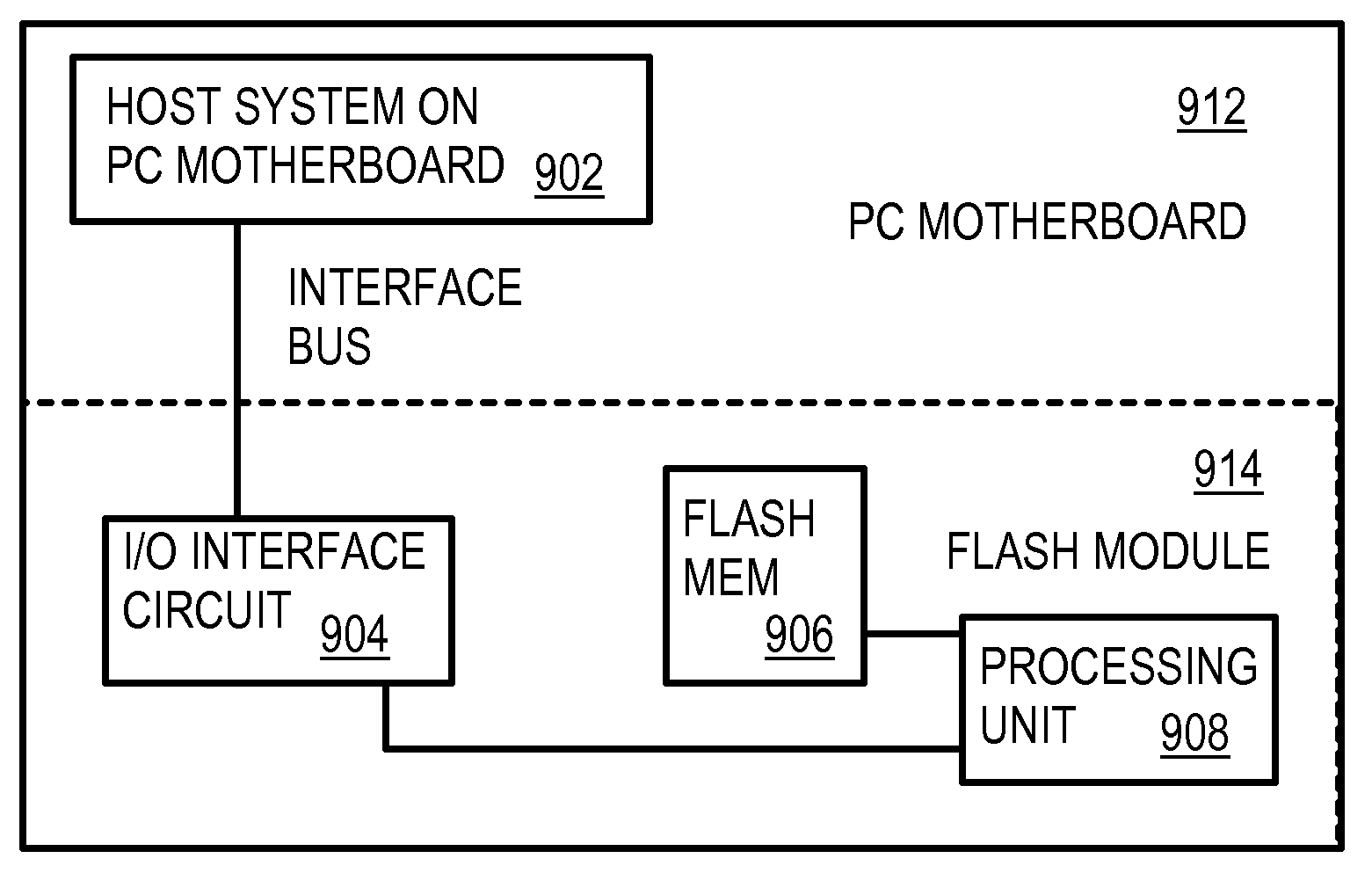

A flash system has multiple channels of flash memory chips that can be accessed in parallel. Host data is assigned to one of the channels by a multi-channel controller processor and accumulated in a multi-channel page buffer. When a page boundary in the page buffer is reached, the page buffer is written to a target physical block if full, or combined with old data fragments in an Aggregating Flash Block (AFB) when the logical-sector addresses (LSA's) match. Thus small fragments are aggregated using the AFB, reducing erases and wear of flash blocks. The page buffer is copied to the AFB when a STOP command occurs. Each channel has one or more AFB's, which are tracked by an AFB tracking table.

Owner:SUPER TALENT TECH CORP

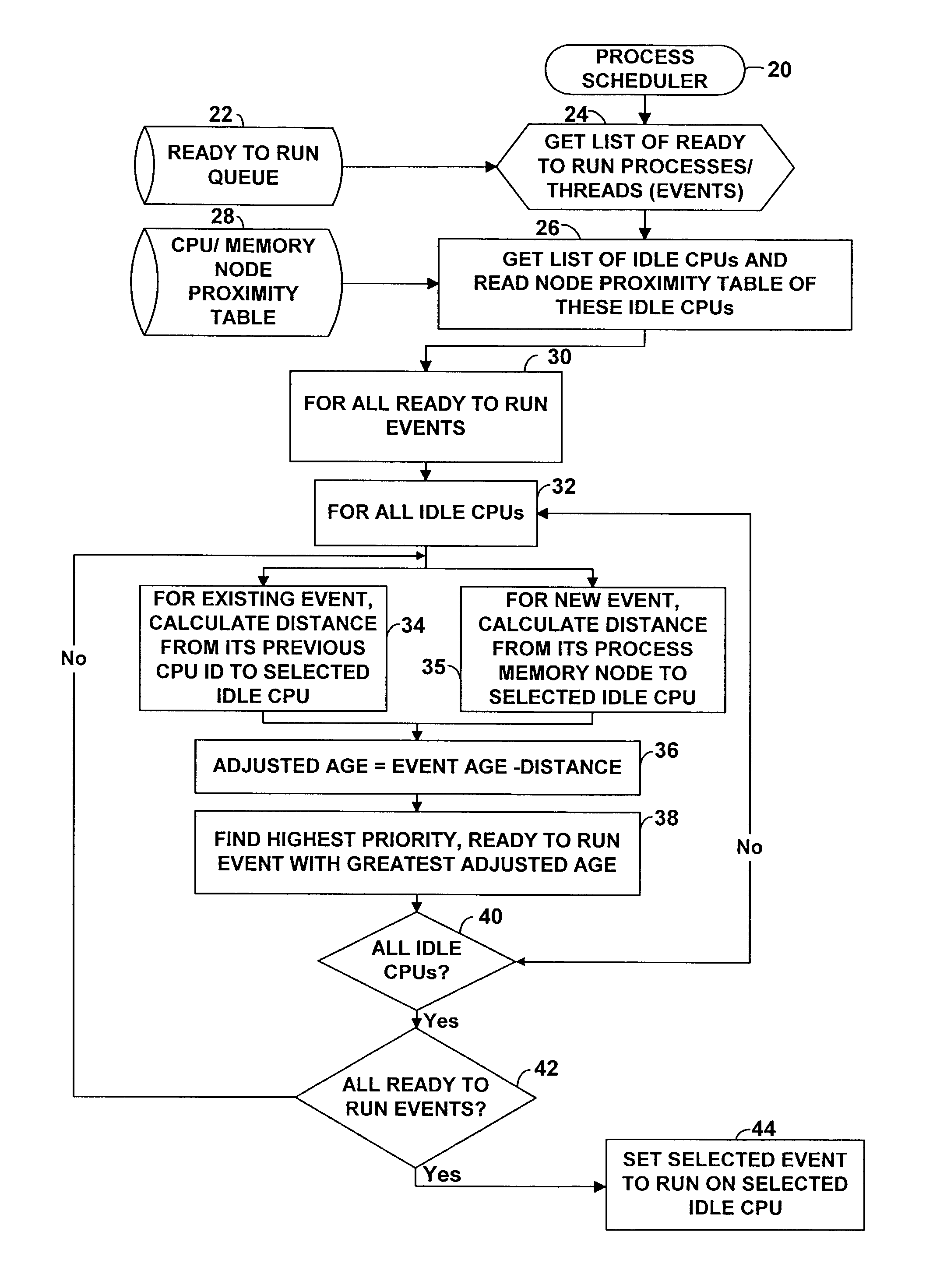

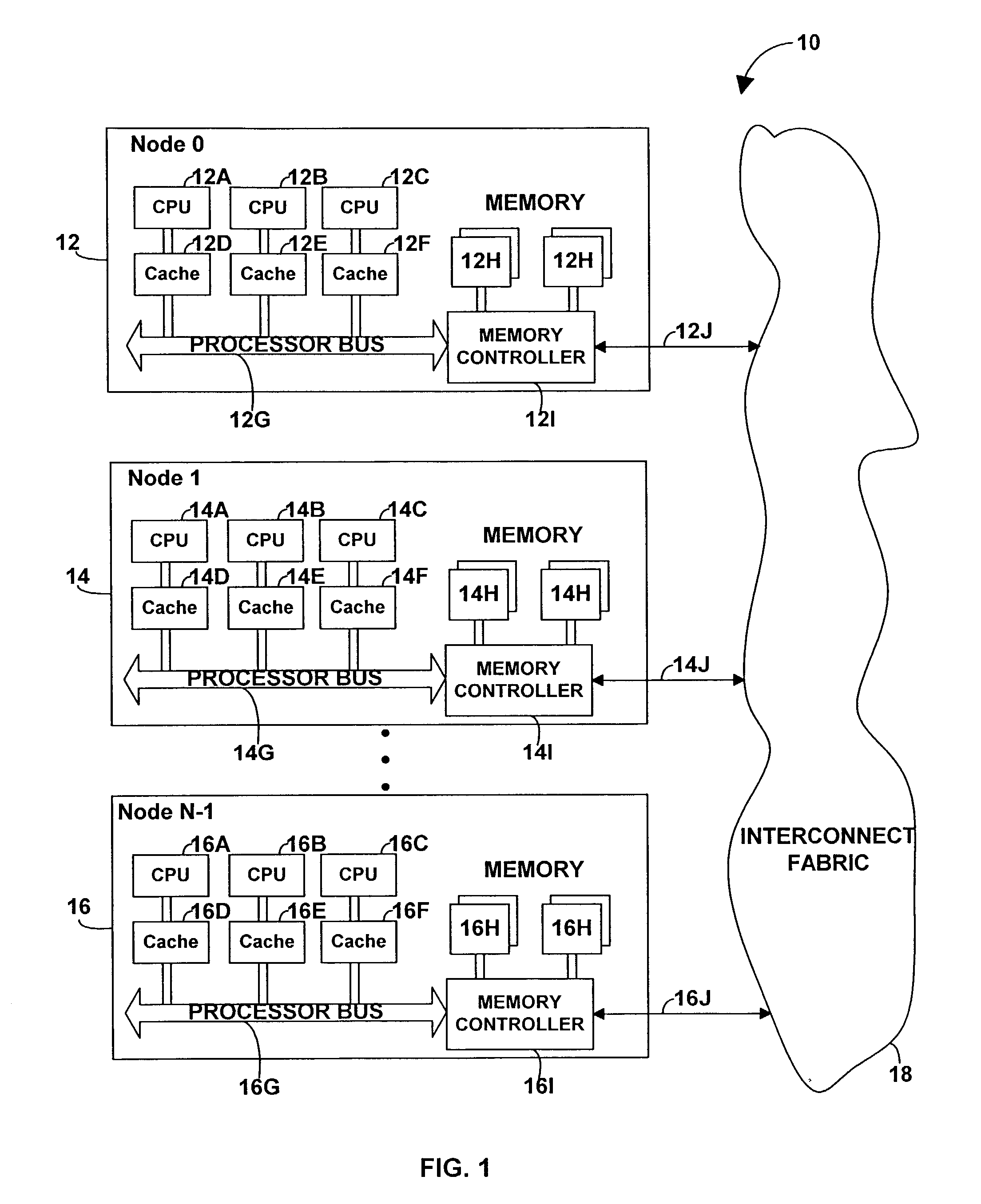

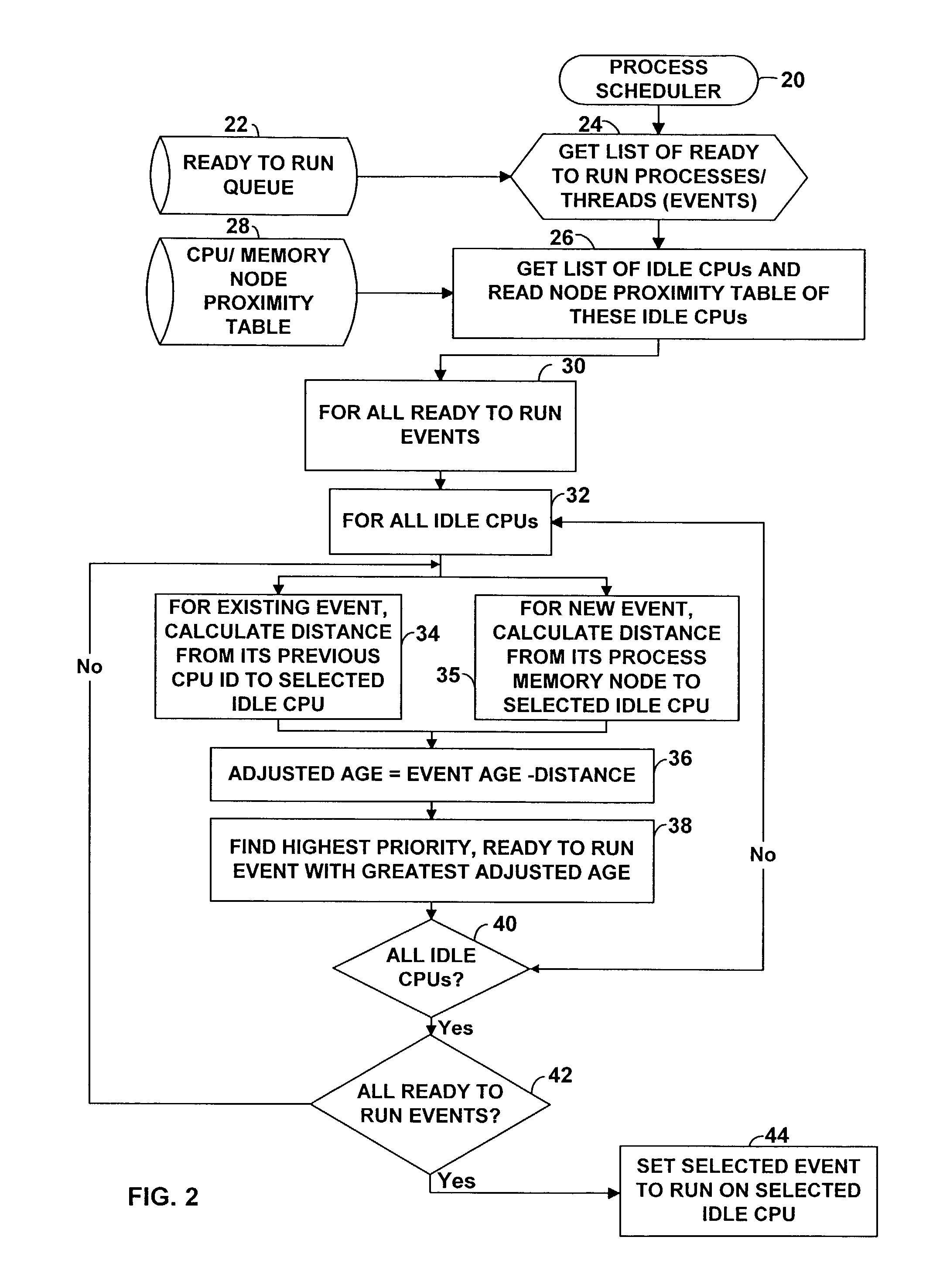

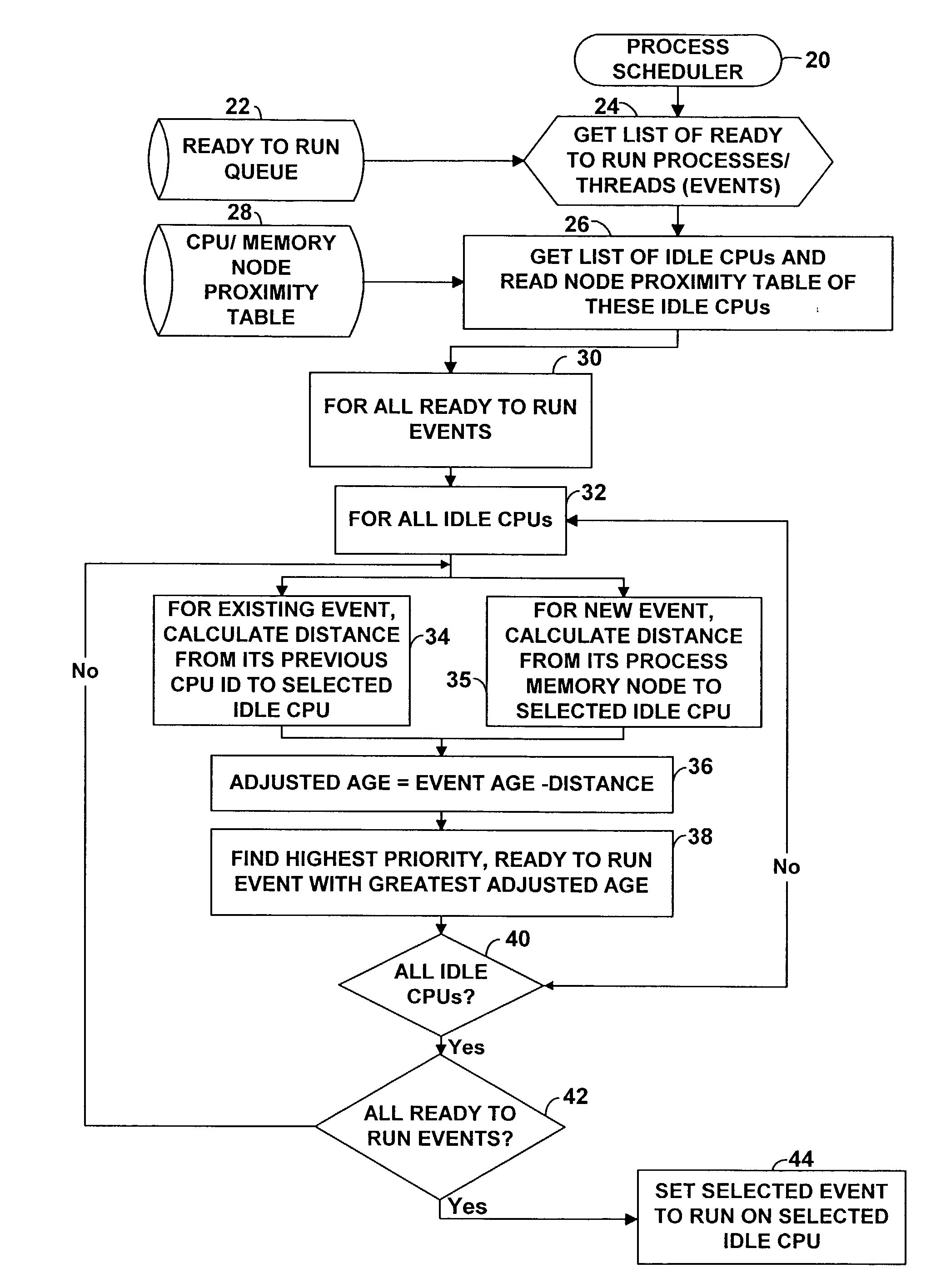

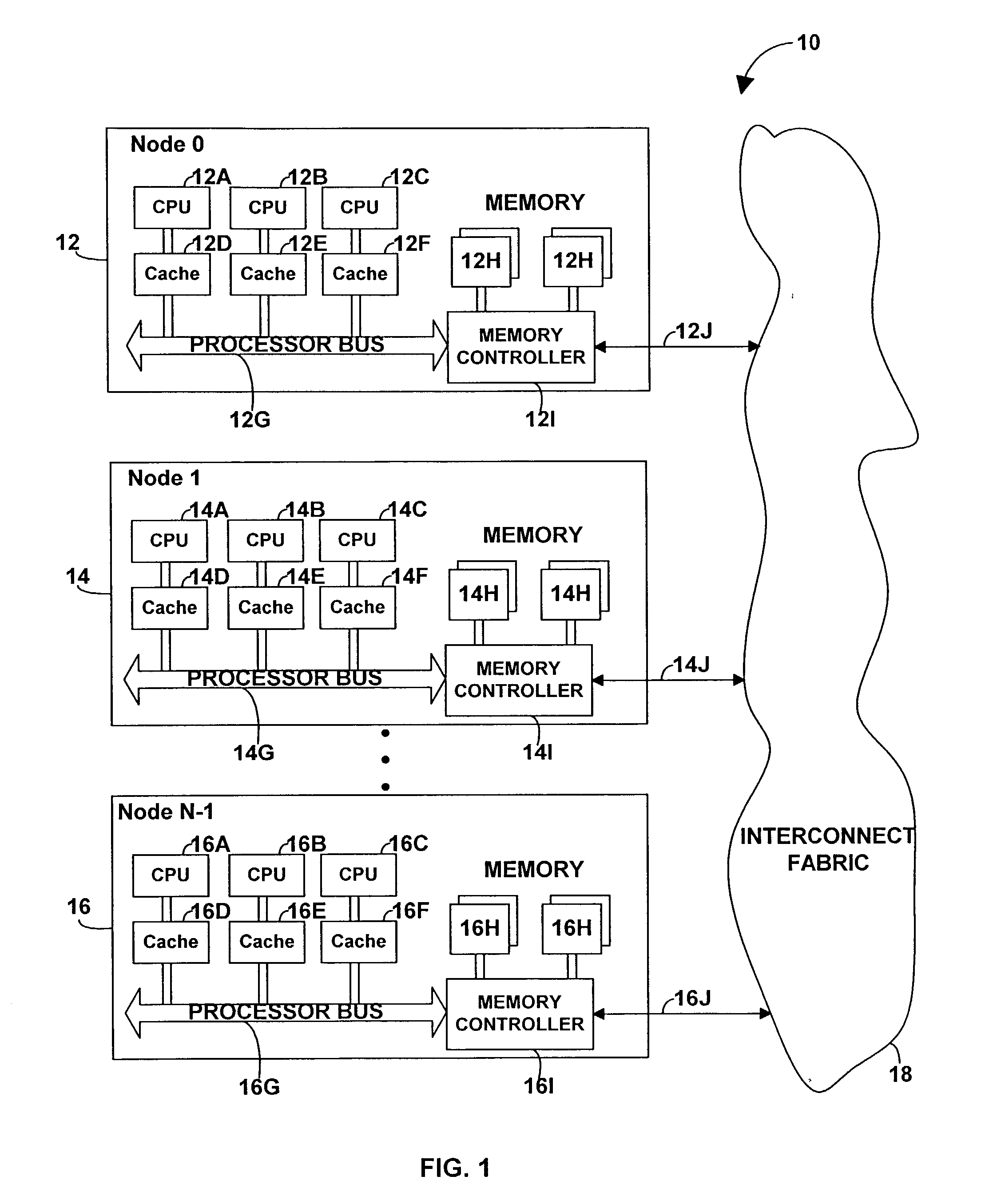

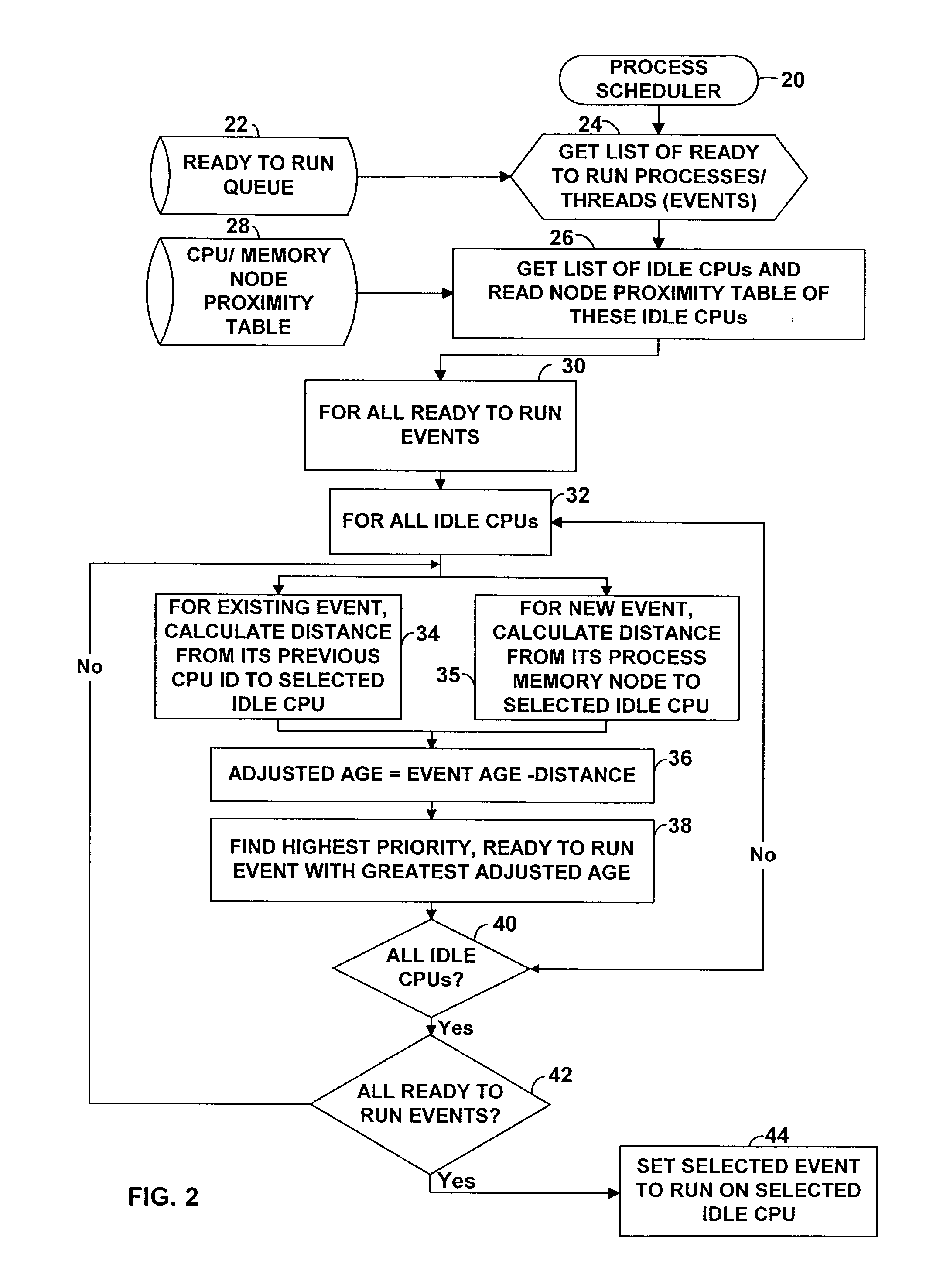

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS7143412B2Interprogram communicationDigital computer detailsError processingThread scheduling

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

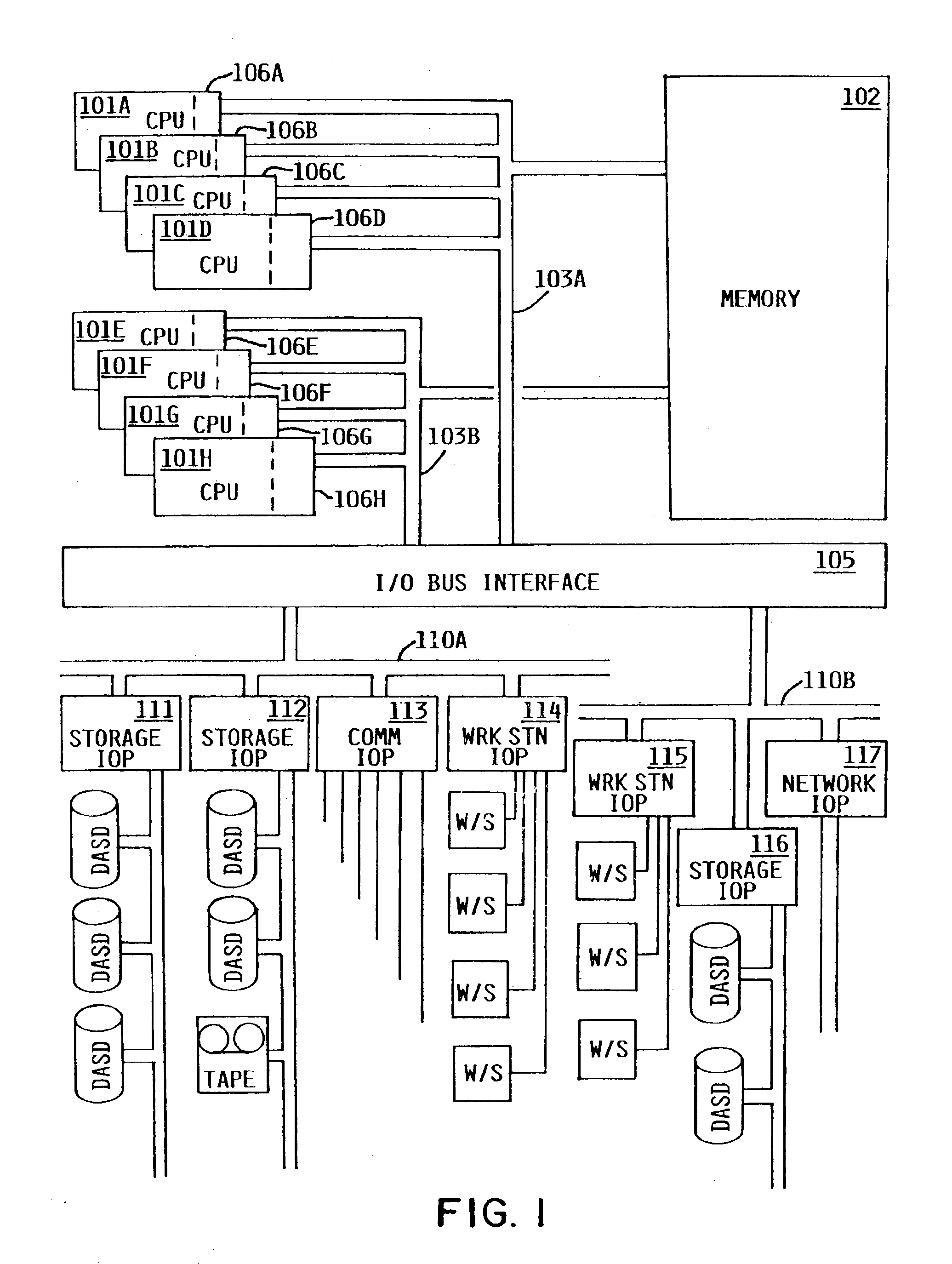

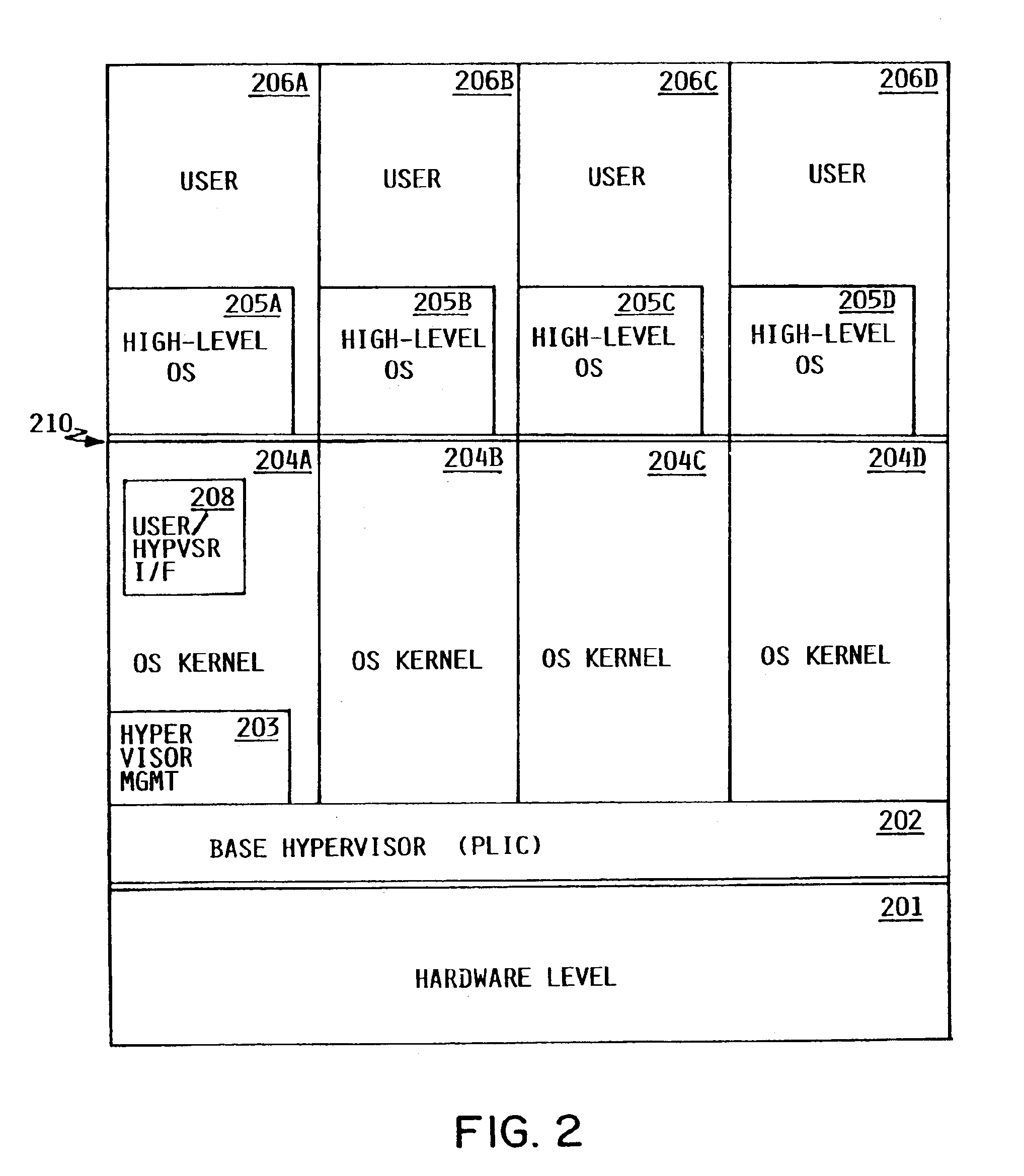

Method and apparatus for allocating processor resources in a logically partitioned computer system

InactiveUS6957435B2Efficient interfaceResource allocationGeneral purpose stored program computerComputer architectureComputerized system

A processor allocation mechanism for a logically partitionable computer system allows an administrator to specify processing capability allocable to each partition as an equivalent number of processors, where the processing capability may be specified as a non-integer value. This processing capability value is unaffected by changes to the processing capability values of other partitions. The administrator may designate multiple sets of processors, assigning each physical processor of the system to a respective processor set. Each logical partition is constrained to execute in an assigned processor set, which may be shared by more than one partition. Preferably, the administrator may designate a logical partition as either capped, meaning that a partition can not use excess idle capacity of the processors, or uncapped, meaning that it can.

Owner:IBM CORP

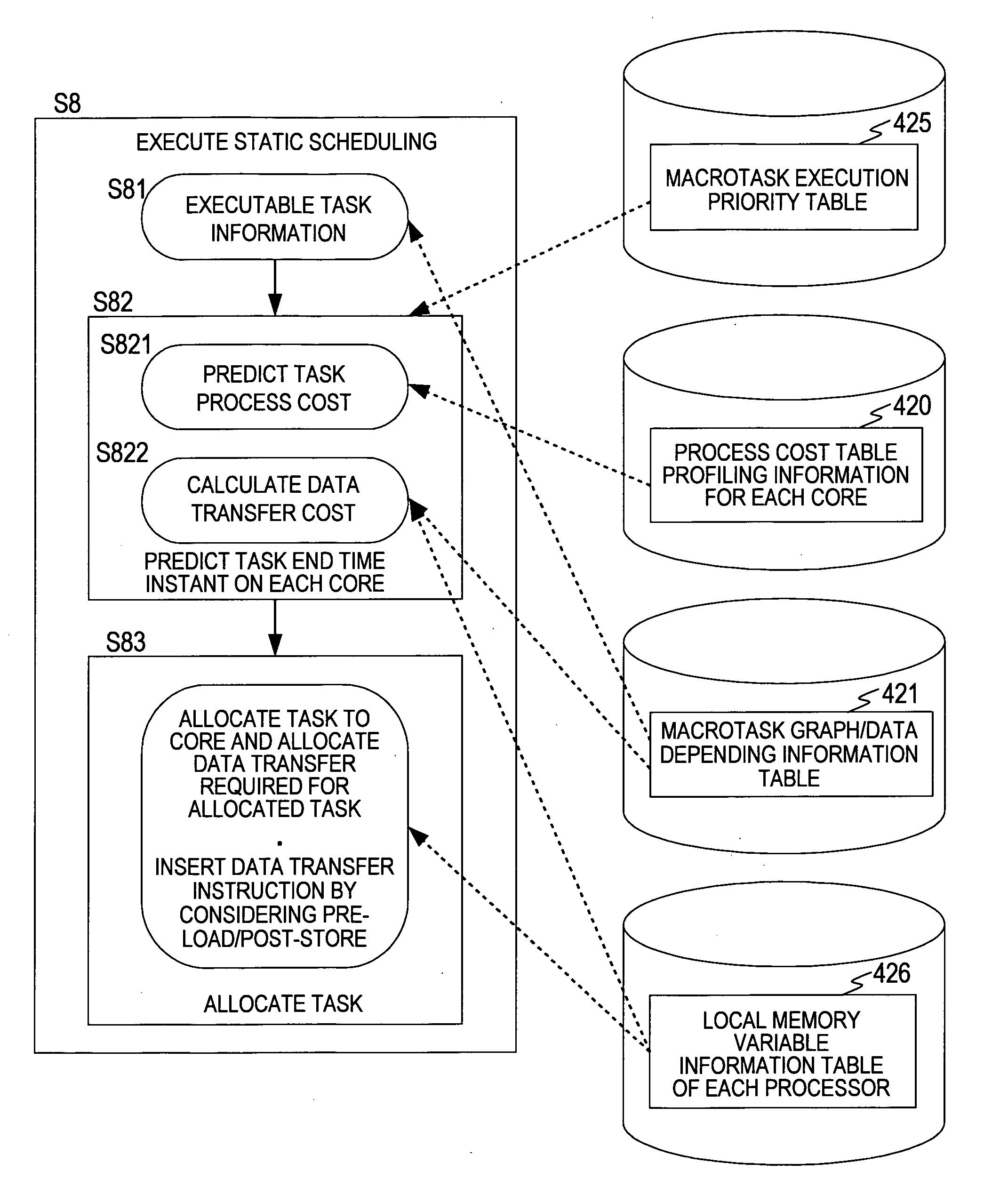

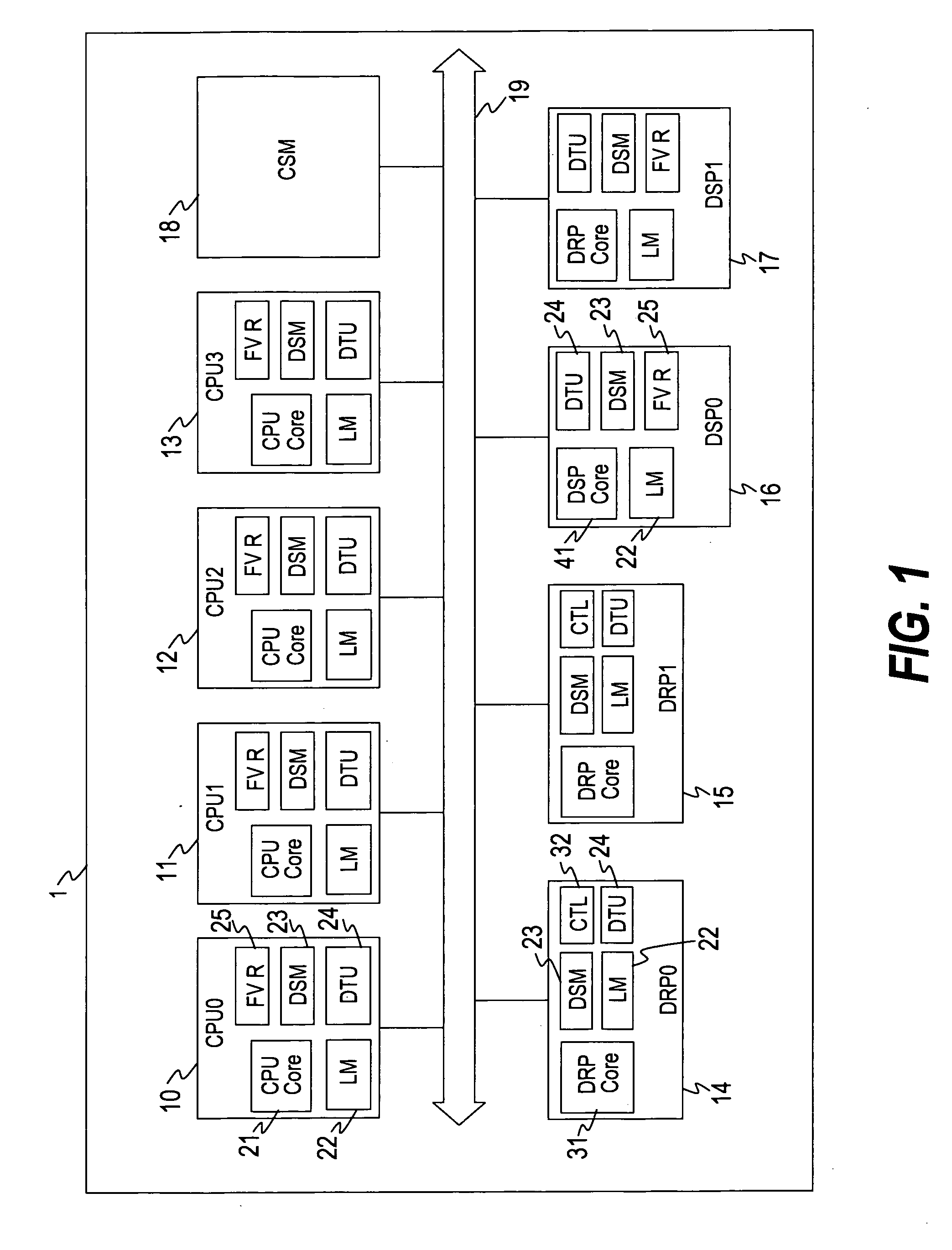

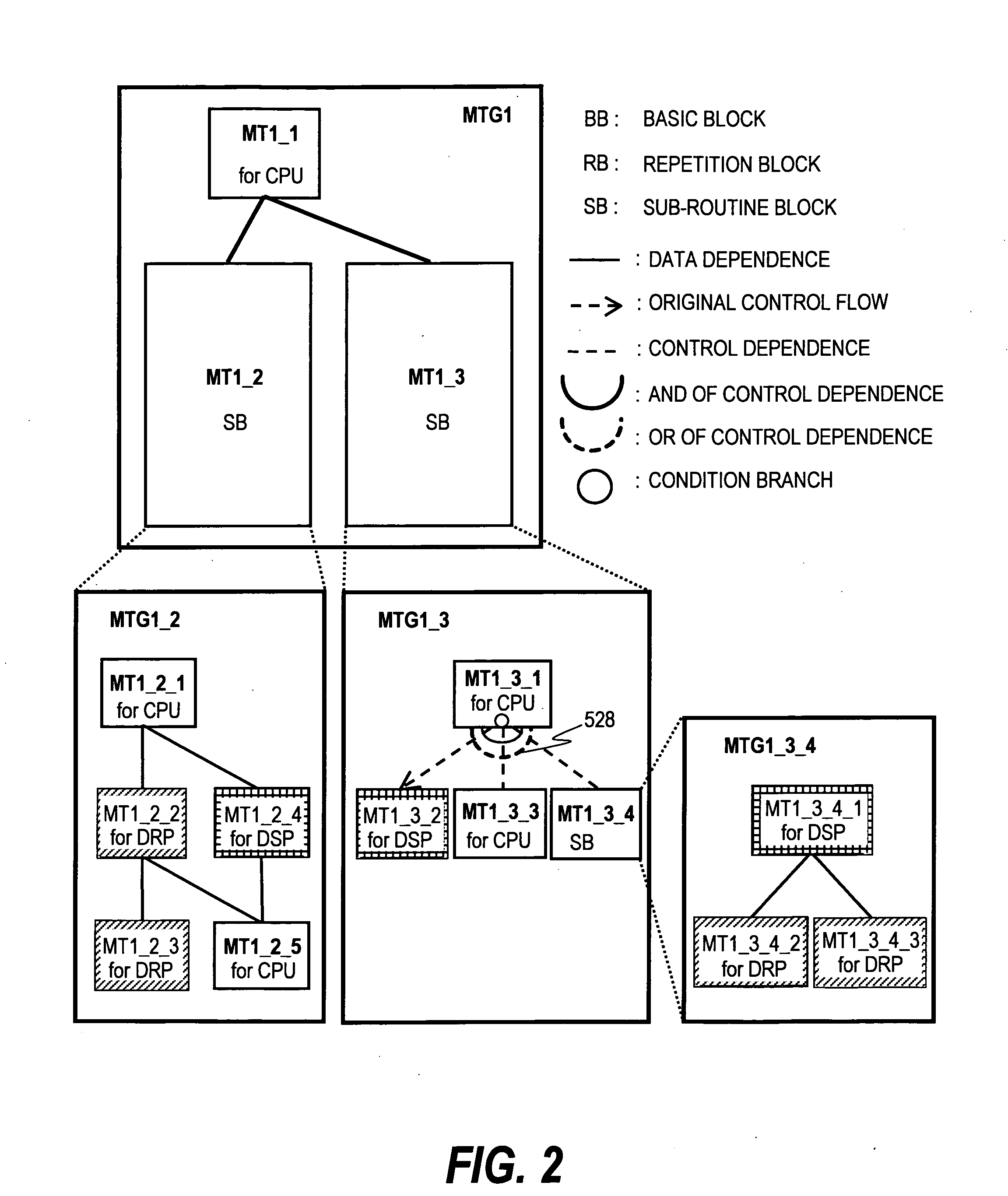

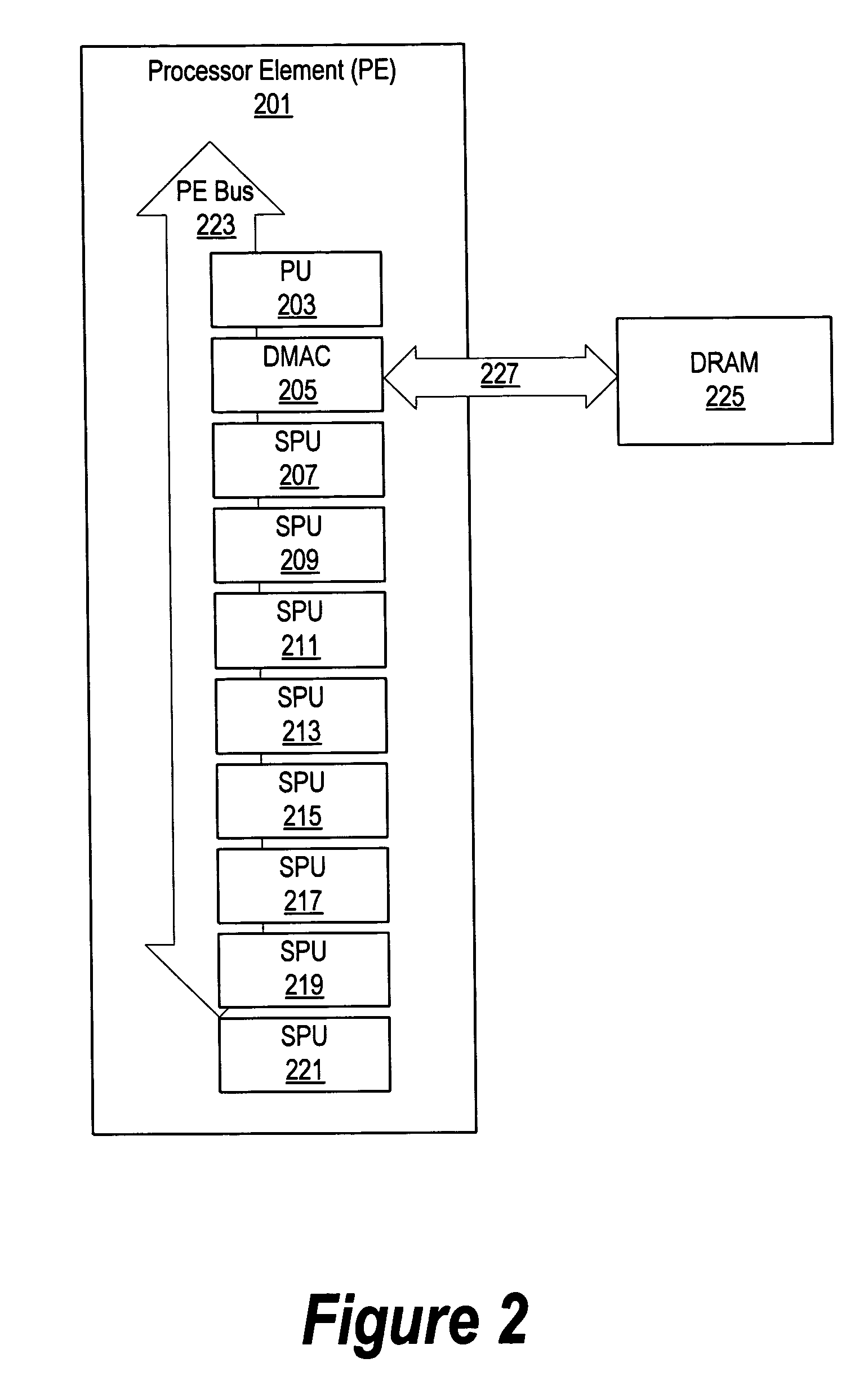

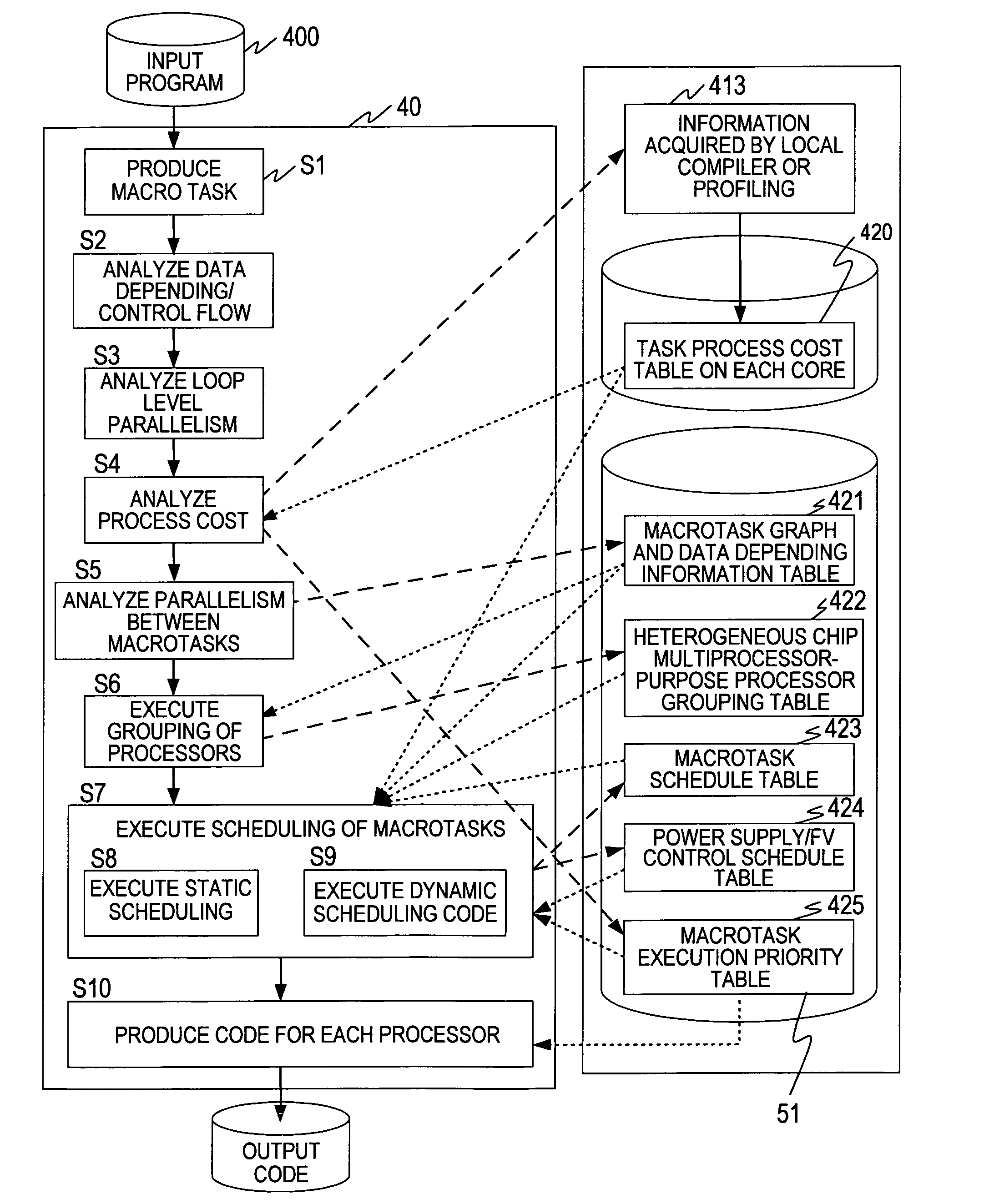

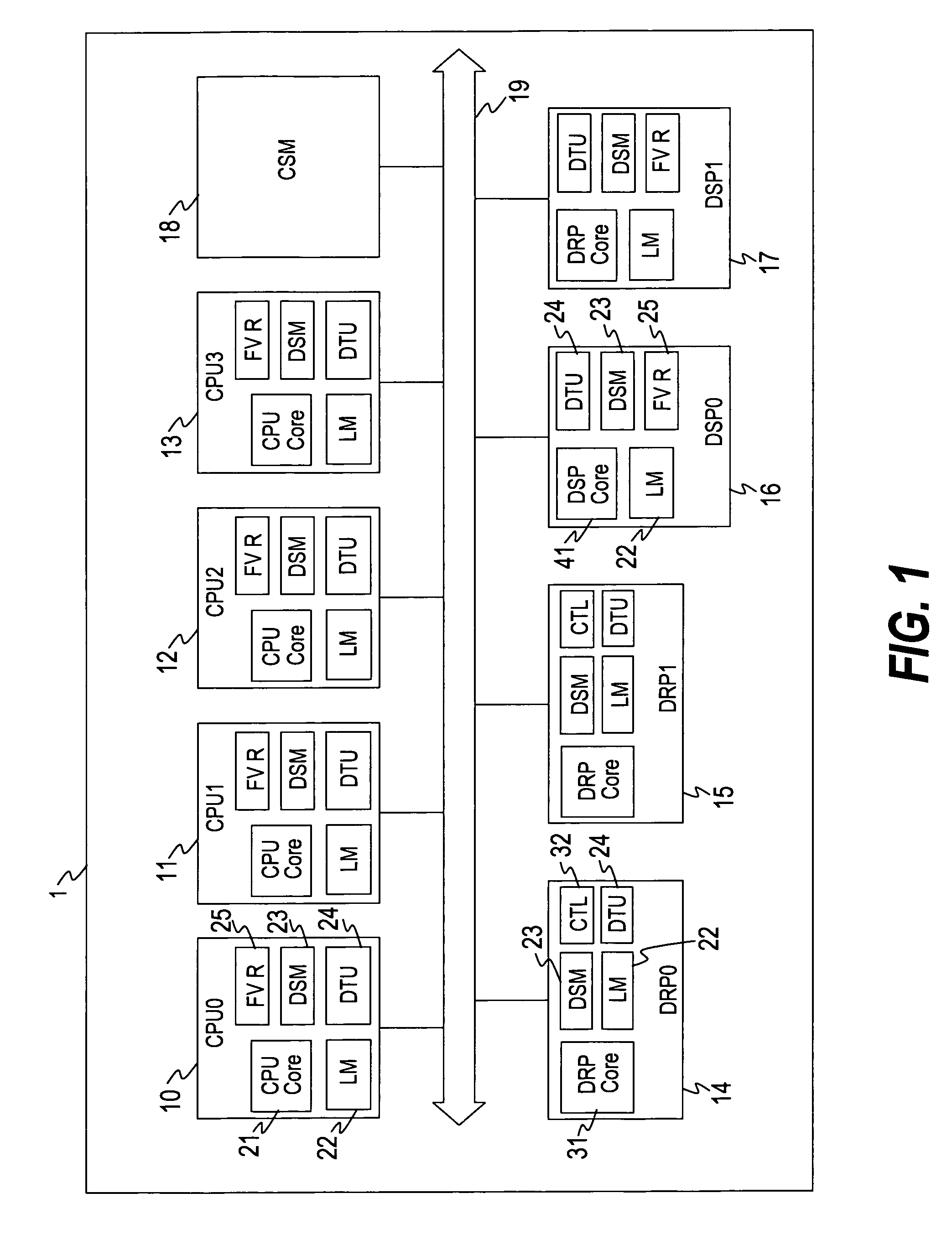

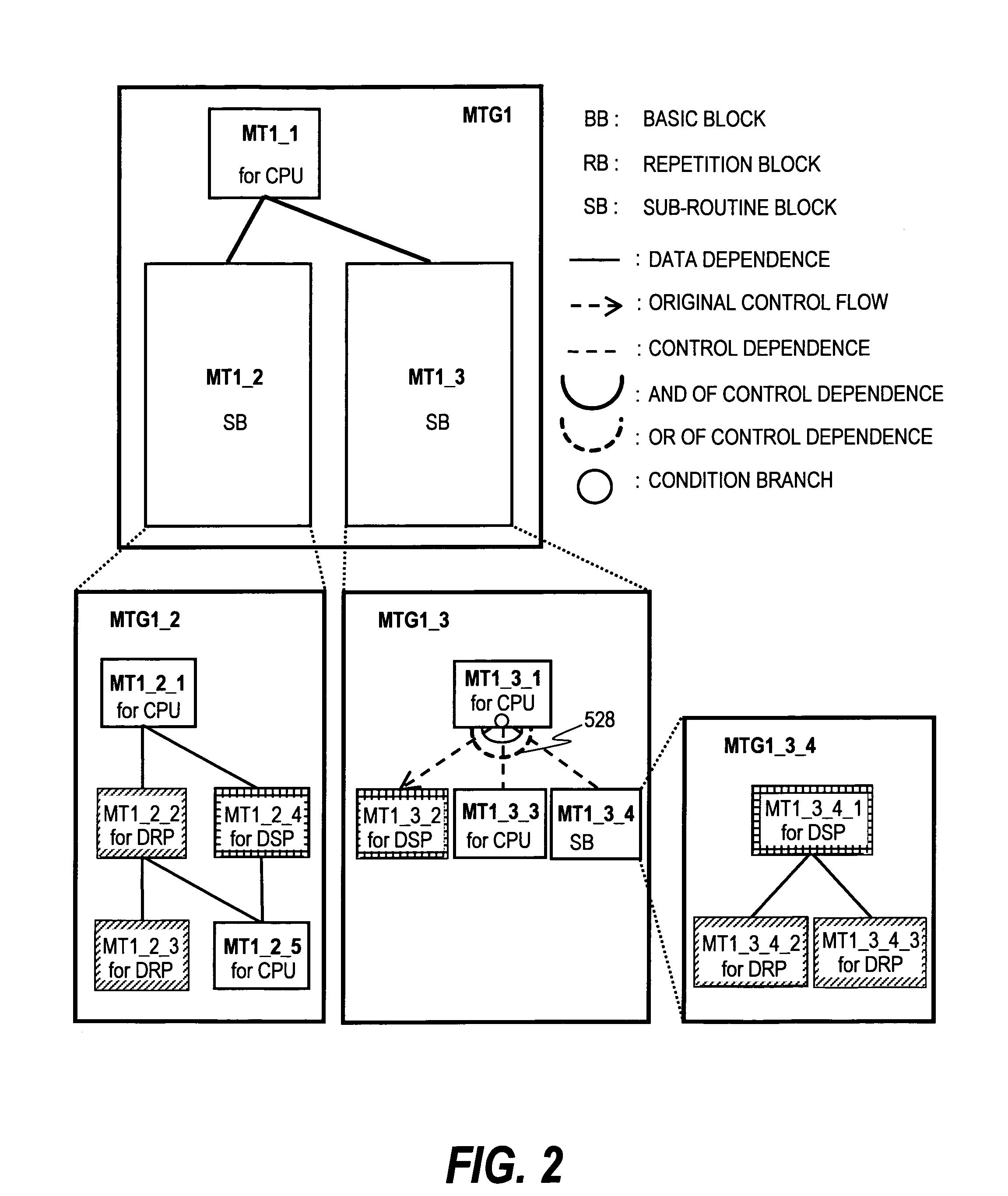

Method for controlling heterogeneous multiprocessor and multigrain parallelizing compiler

ActiveUS20070283358A1Improve efficiencyOverhead required can be suppressedEnergy efficient ICTResource allocationGeneral purposeCost comparison

A heterogeneous multiprocessor system including a plurality of processor elements having mutually different instruction sets and structures avoids a specific processor element from being short of resources to improve throughput. An executable task is extracted based on a preset depending relationship between a plurality of tasks, and the plurality of first processors are allocated to a general-purpose processor group based on a depending relationship among the extracted tasks. A second processor is allocated to an accelerator group, a task to be allocated is determined from the extracted tasks based on a priority value for each of tasks, and an execution cost of executing the determined task by the first processor is compared with an execution cost of executing the task by the second processor. The task is allocated to one of the general-purpose processor group and the accelerator group that is judged to be lower as a result of the cost comparison.

Owner:WASEDA UNIV

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS20040019891A1Interprogram communicationDigital computer detailsError processingThread scheduling

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

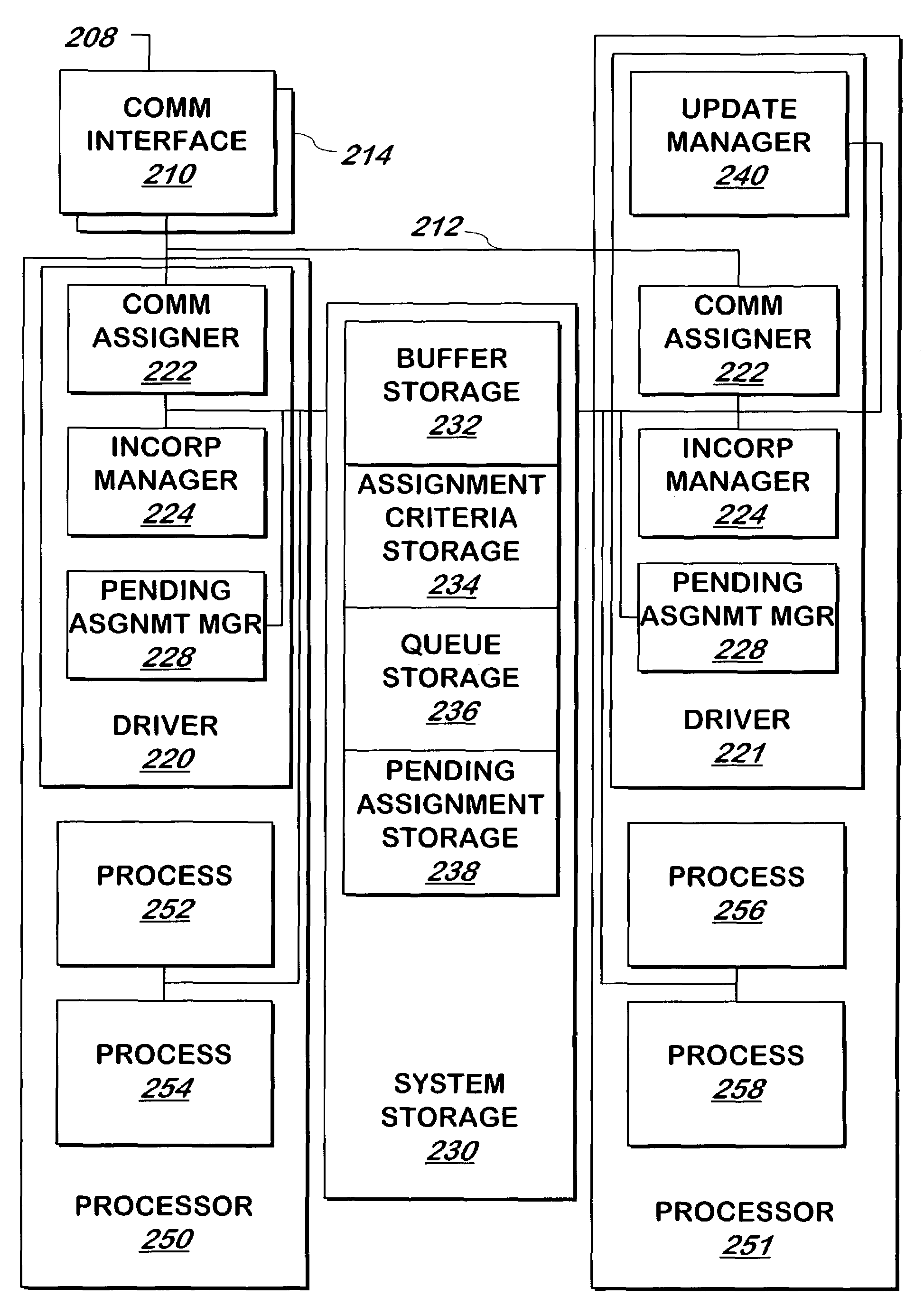

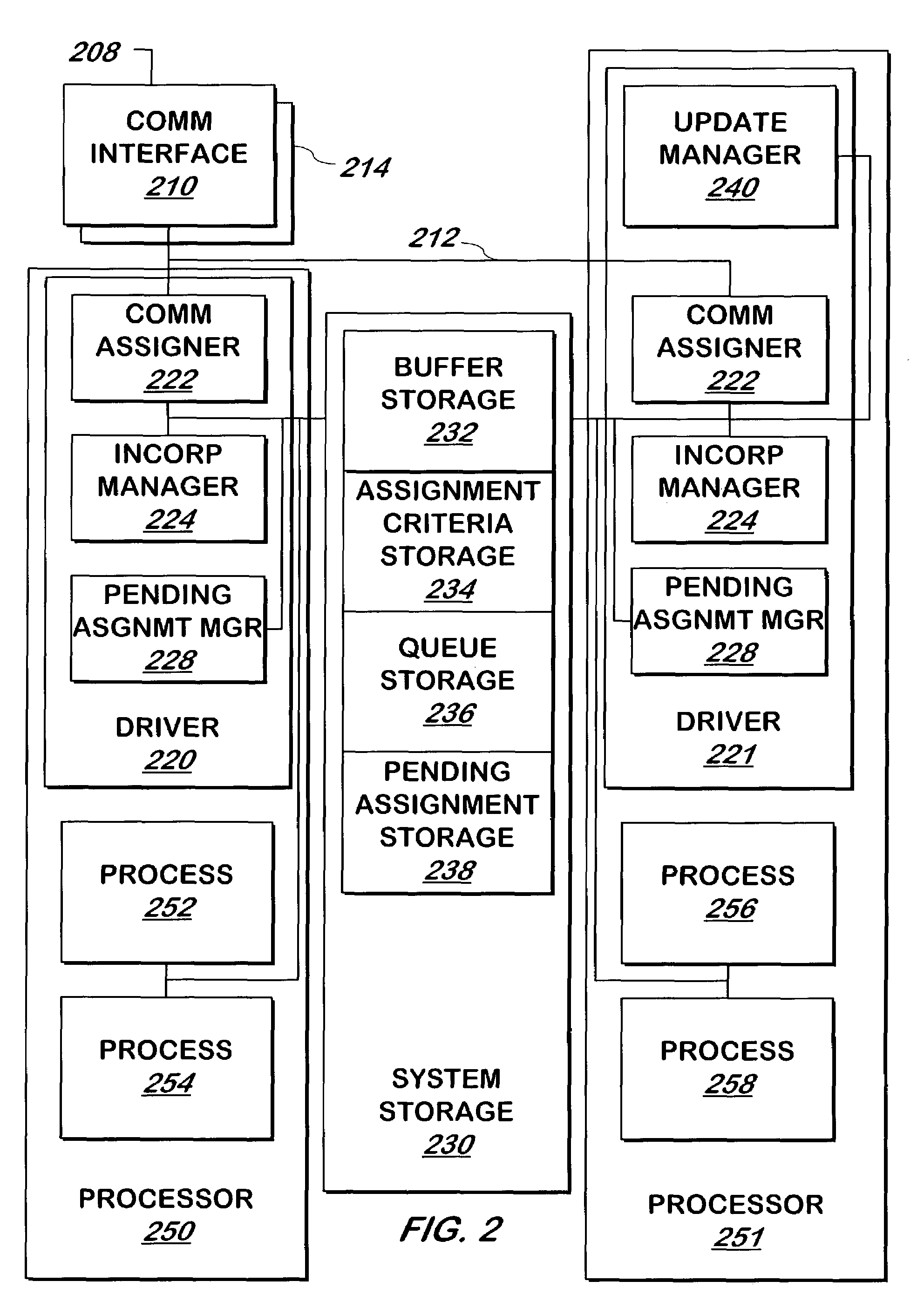

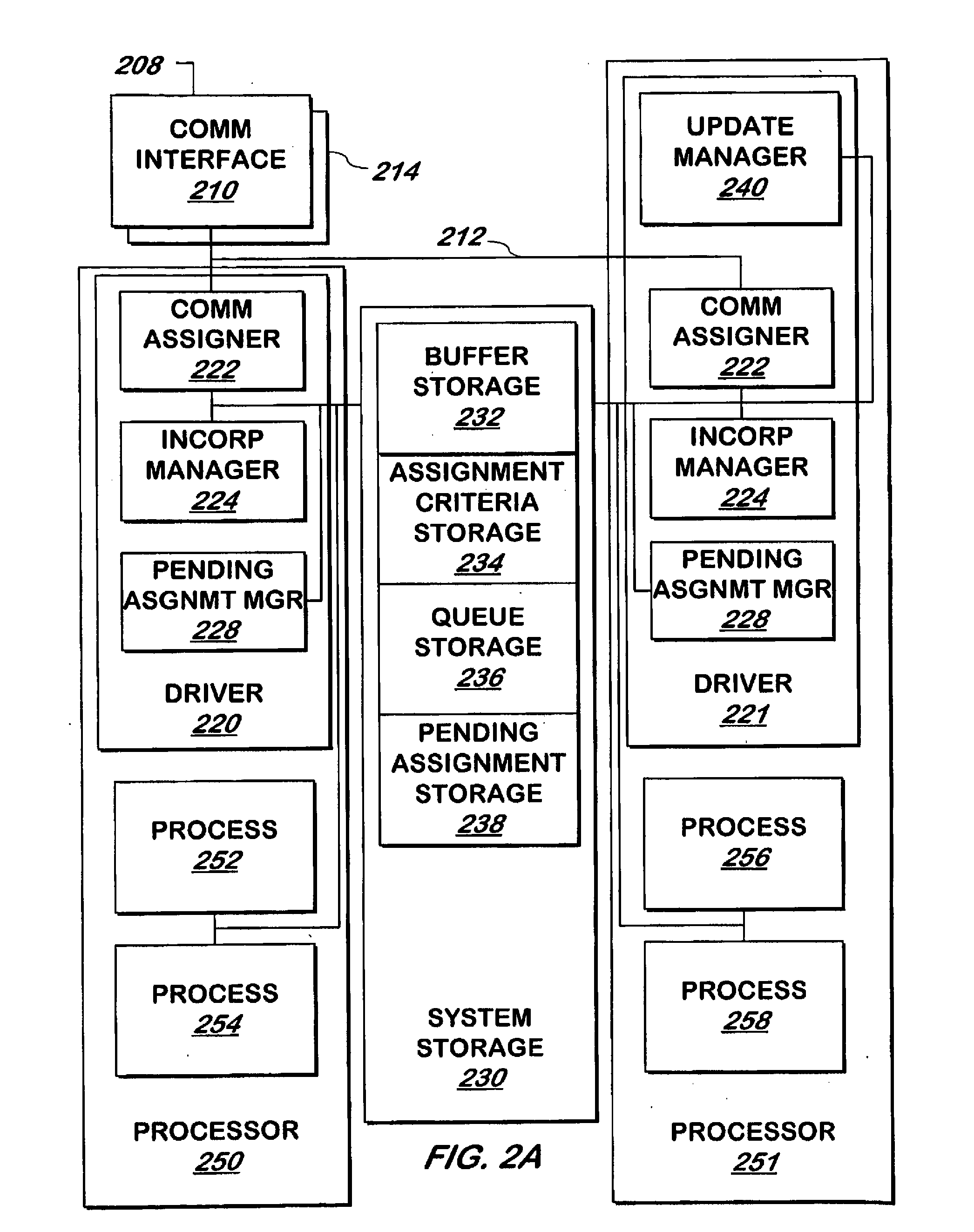

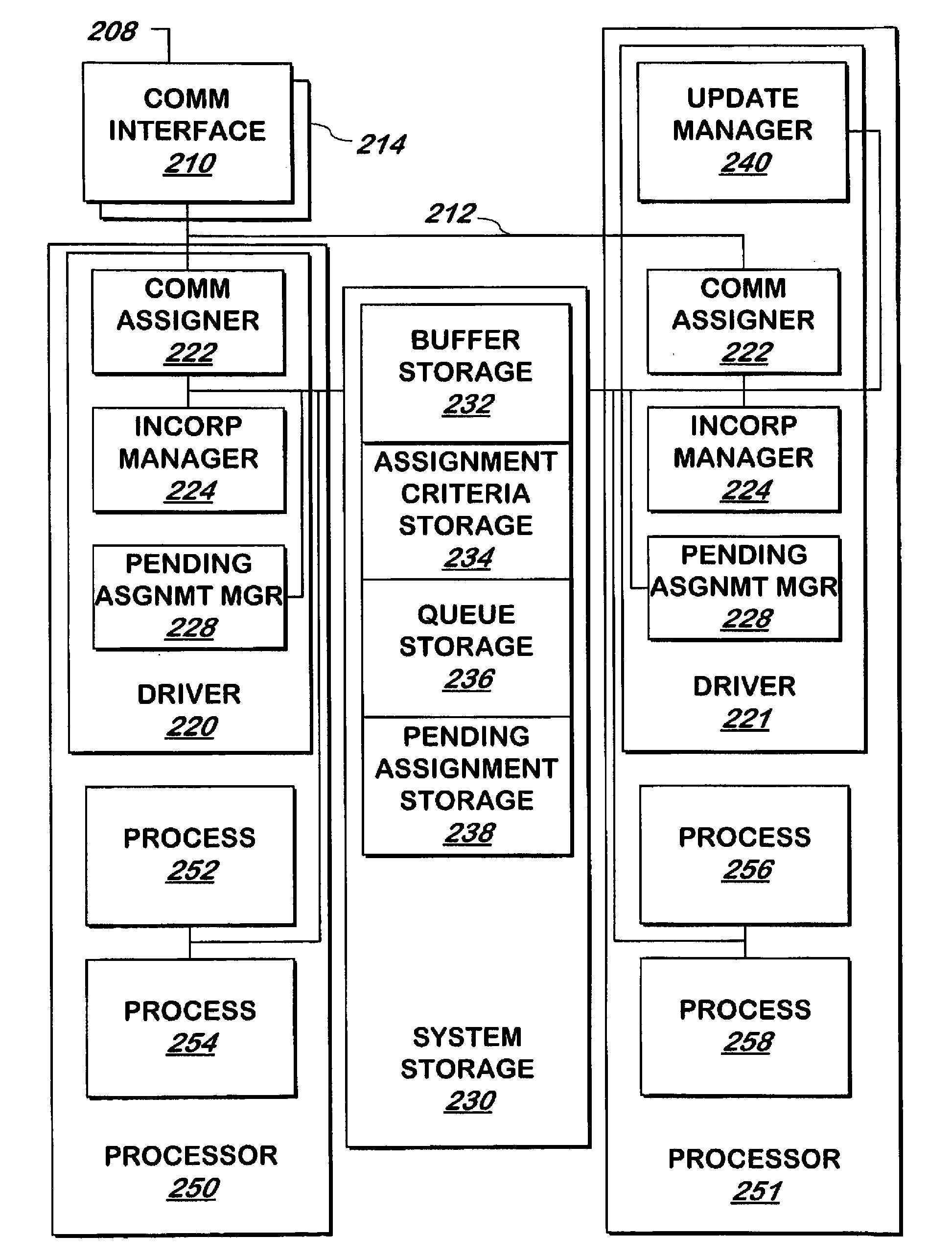

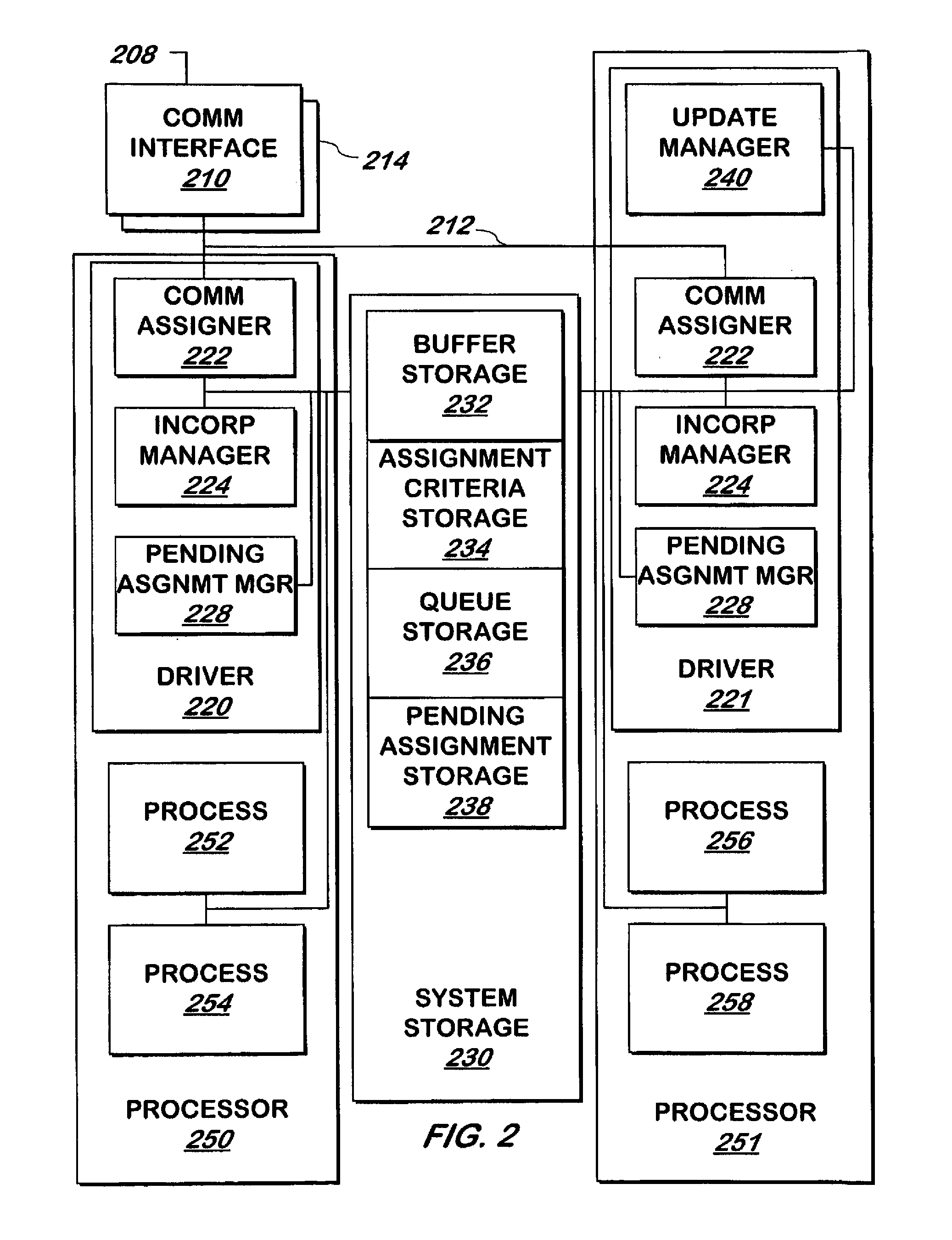

System and method for allocating communications to processors in a multiprocessor system

InactiveUS7386619B1Easy to handleGeneral purpose stored program computerMultiple digital computer combinationsLocking mechanismMulti processor

In a multiprocessor-system, a system and method assigns communications to processors, processes, or subsets of types of communications to be processed by a specific processor without using a locking mechanism specific to the resources required for assignment.

Owner:SLT LOGIC

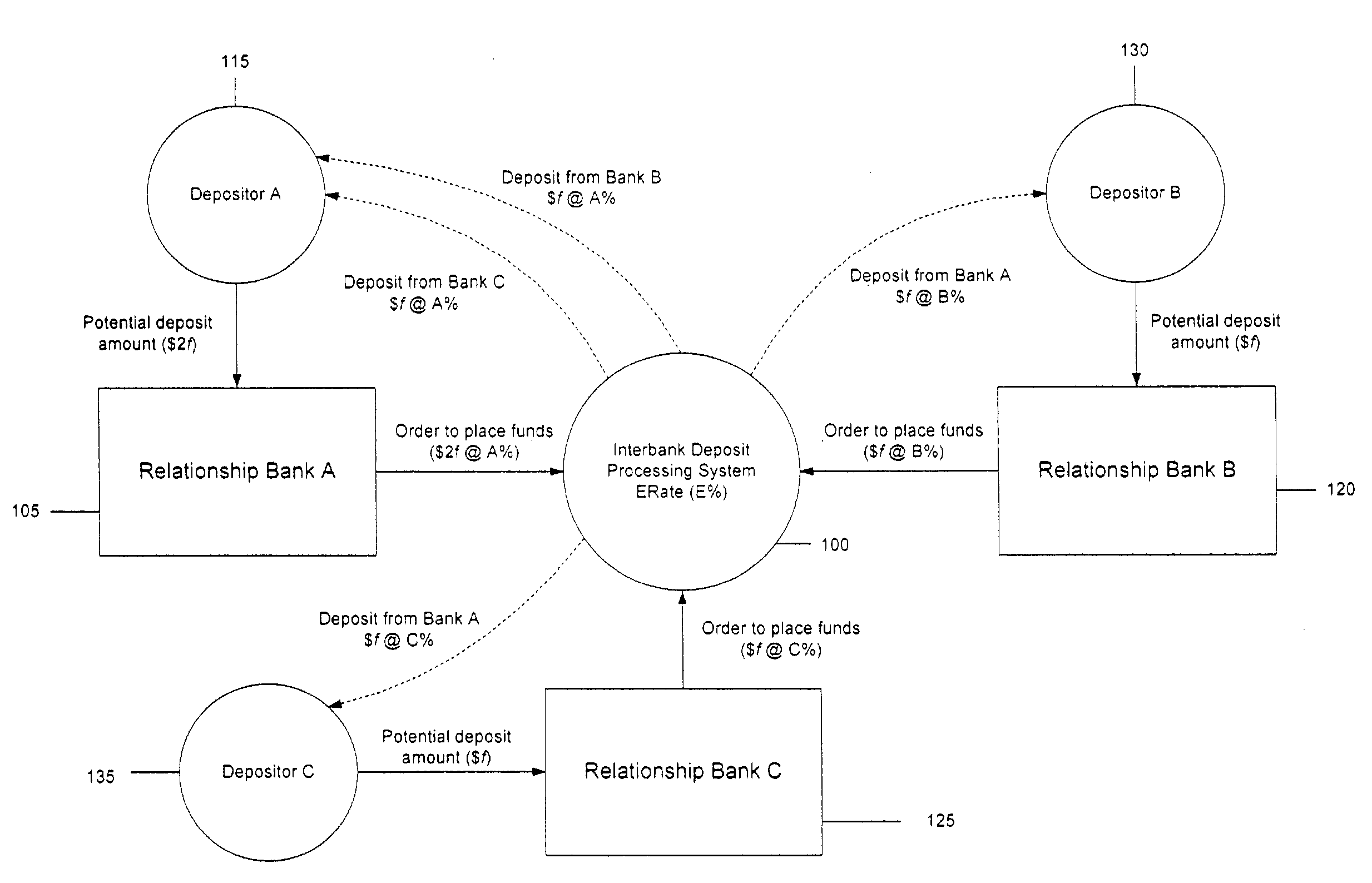

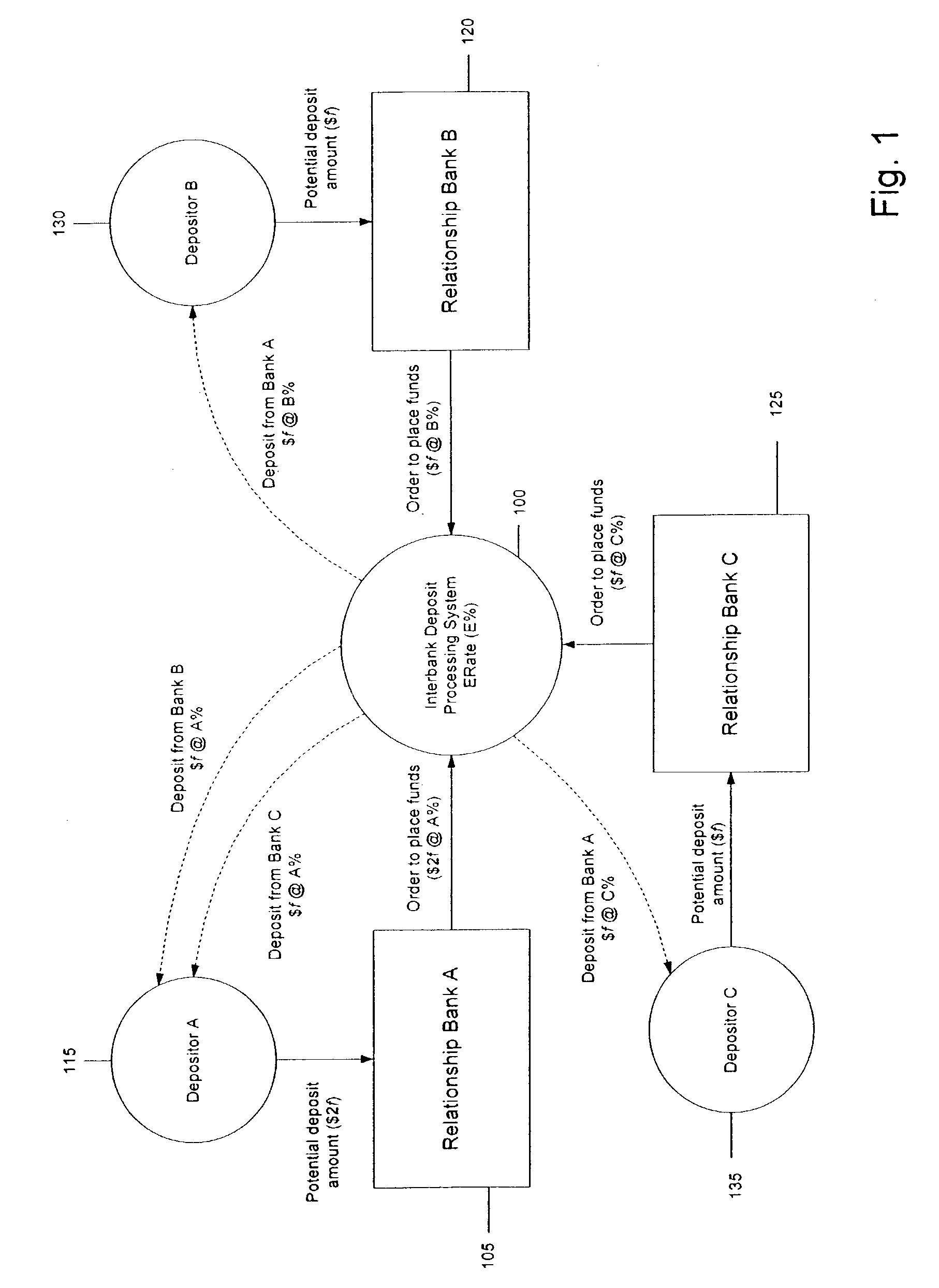

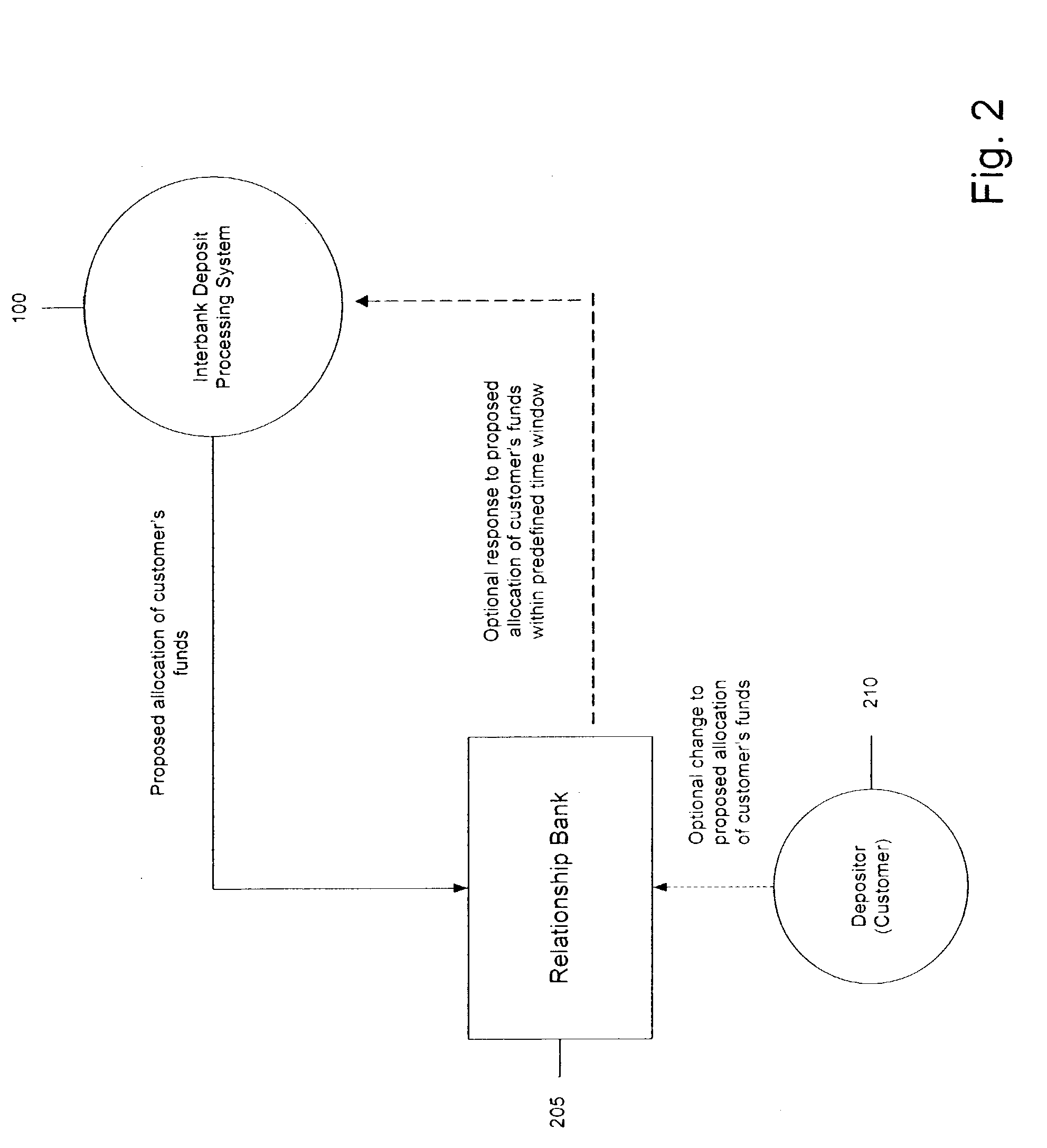

Method and apparatus for fully insuring large bank deposits

An Interbank Deposit Placement System (IDPS) that allows banks participating in the service to offer their customers multiple deposits so that potential deposit (fund) amounts exceeding an applicable Federal deposit insurance limit (e.g., $100,000) are fully insured. The IDPS partitions each of the potential deposit amounts into a plurality of deposit portions that do not exceed the Federal deposit insurance limit. In one embodiment, a proposed list of banks to which the deposit portions are allocated is presented to a recipient (e.g., bank representative, depositor) who is offered the option of modifying the proposed list during an established time window. After the time window expires, a deposit is established on behalf of each bank on the list to which the specific deposit portion was allocated by the processor.

Owner:INTRAFI NETWORK LLC

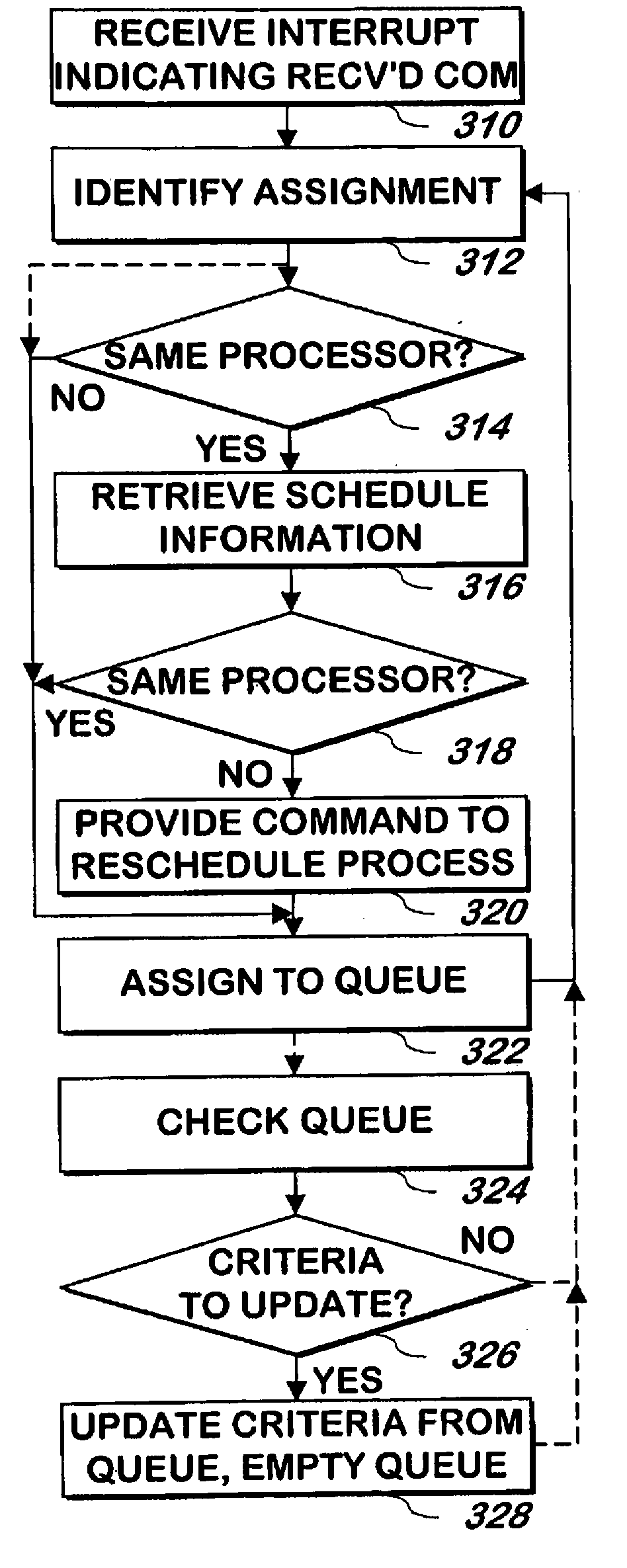

System and method for allocating communications to processors and rescheduling processes in a multiprocessor system

InactiveUS20090165003A1Easy to handleInterprogram communicationMemory systemsMulti processorLocking mechanism

In a multiprocessor system, a system and method assigns communications to processors, processes, or subsets of types of communications to be processed by a specific processor without using a locking mechanism specific to the resources required for assignment. The system and method can reschedule processes to run on the processor on which the assignment is made.

Owner:JACOBSON VAN +3

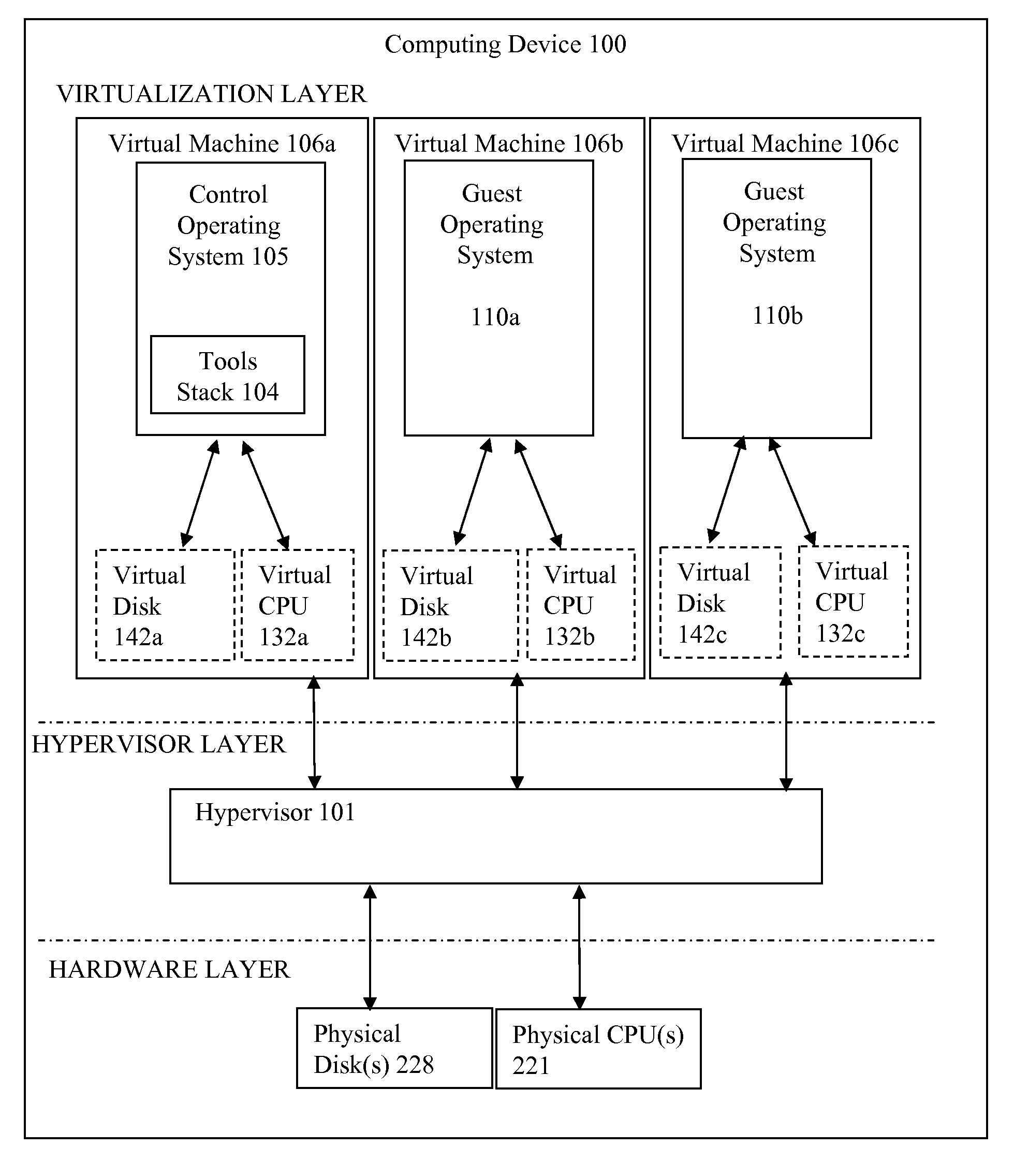

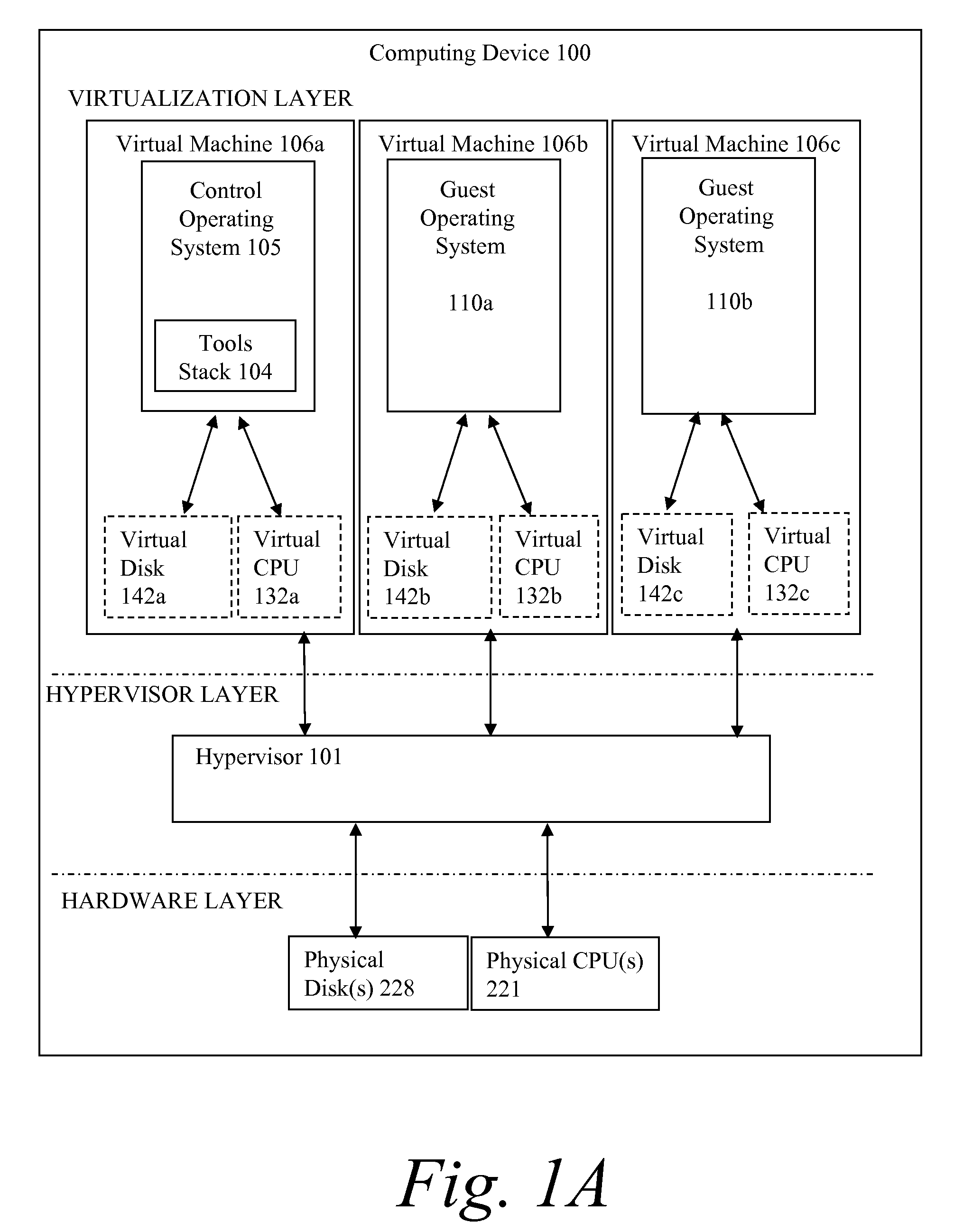

Systems and Methods for Facilitating Virtualization of a Heterogeneous Processor Pool

ActiveUS20100138828A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationPhysics processing unitFunctional type

A system for facilitating virtualization of a heterogeneous processor pool includes a processor allocation component and a hypervisor, each executing on a host computer. The processor allocation component identifies a plurality of physical processors available for computing and determines a set of flags, each of the set of flags identifying a type of functionality provided by each of a subset of the plurality of physical processors. The hypervisor, in communication with the processor allocation component, allocates, to at least one virtual machine, access to one of the subset of the plurality of physical processors.

Owner:CITRIX SYST INC

System and method for allocating communications to processors in a multiprocessor system

InactiveUS20080301406A1Easy to handleProgram control using wired connectionsGeneral purpose stored program computerLocking mechanismMulti processor

In a multiprocessor-system, a system and method assigns communications to processors, processes, or subsets of types of communications to be processed by a specific 5 processor without using a locking mechanism specific to the resources required for assignment.

Owner:JACOBSON VAN +3

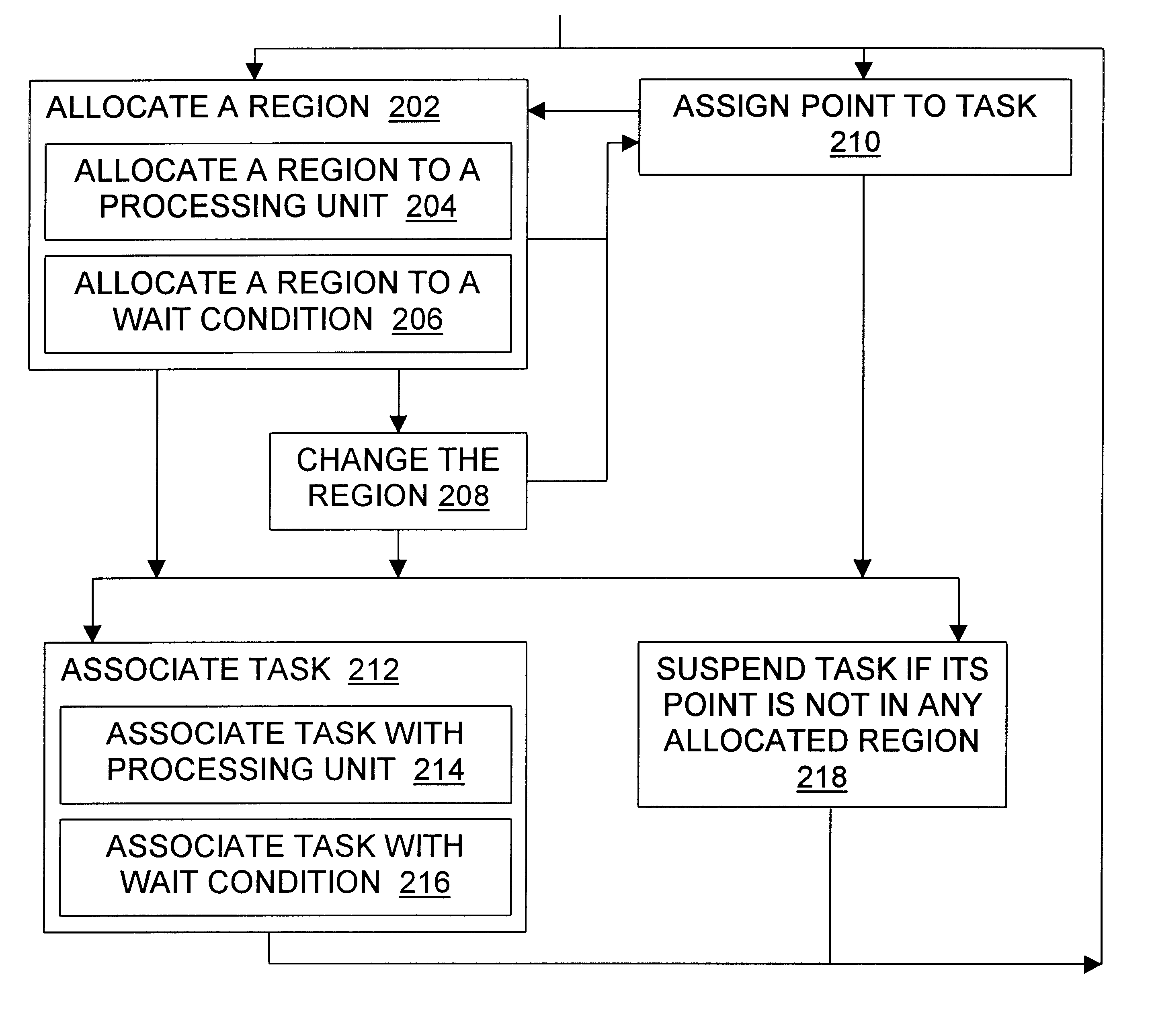

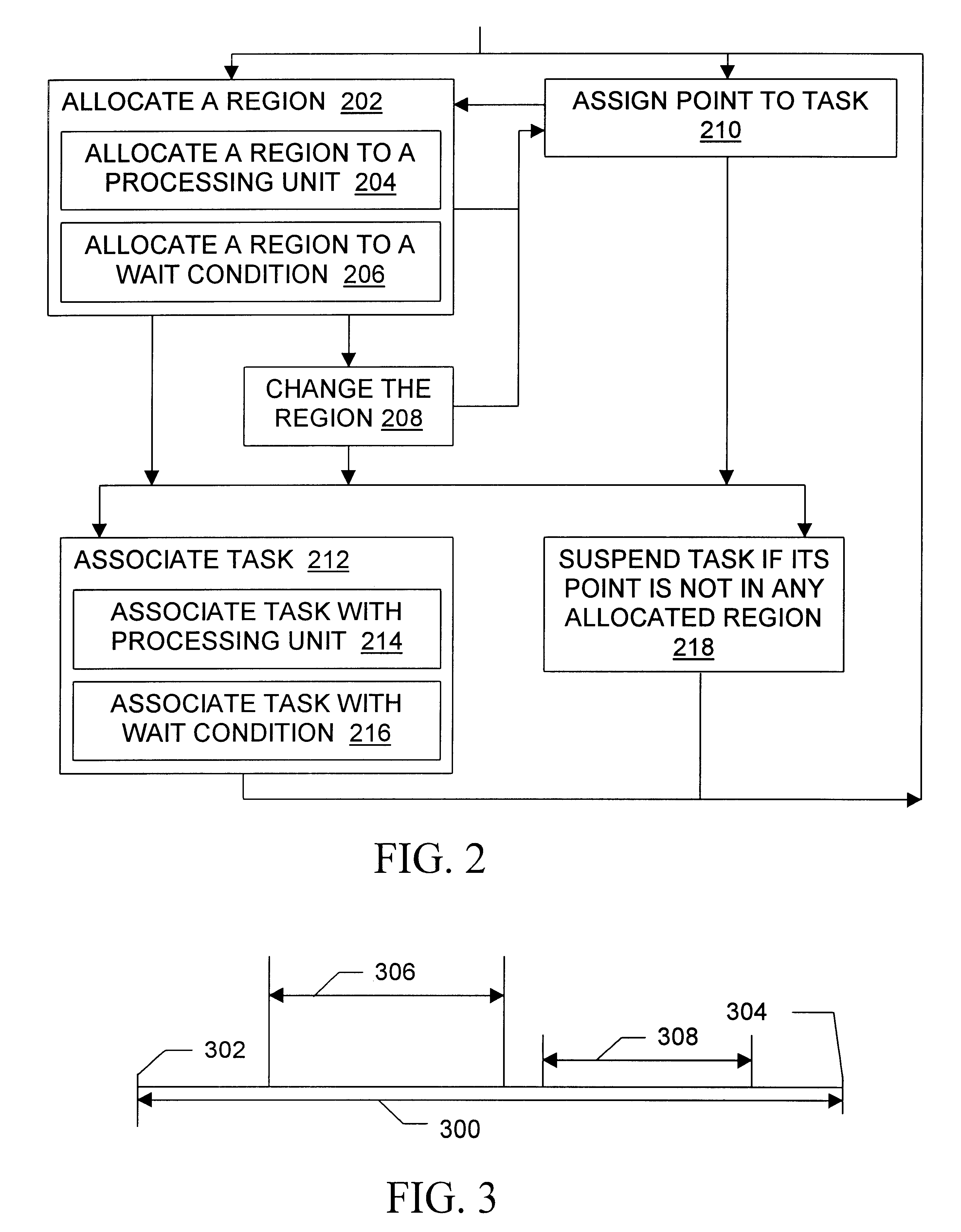

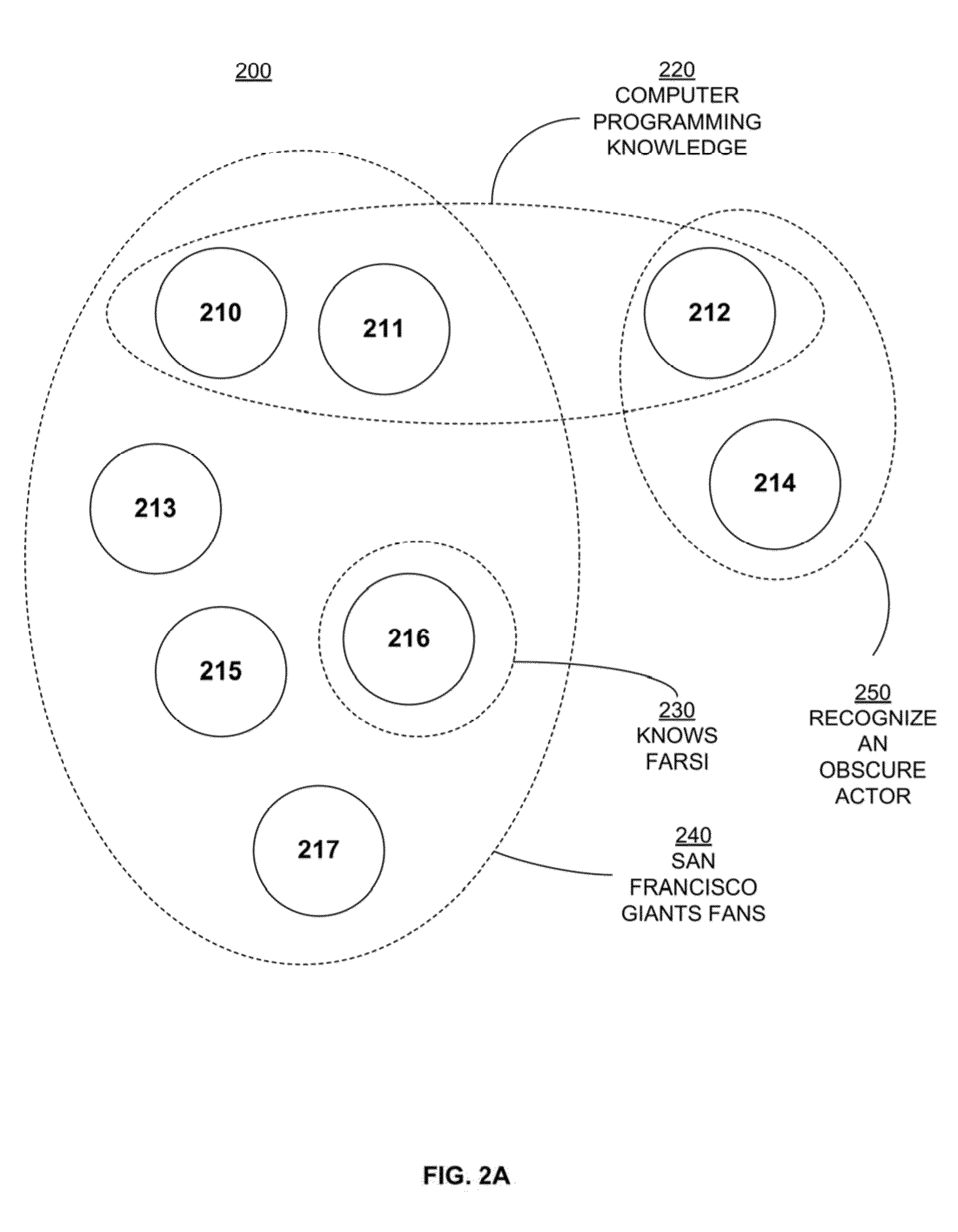

Task distribution

InactiveUS6647408B1Resource allocationGeneral purpose stored program computerDistribution methodOperating system

Methods, signals, devices, and systems are provided for matching tasks with processing units. A region within a multi-faceted task space is allocated to a processing unit. A point in the multi-faceted task space is assigned to a task. The task is then associated with the processing unit if the region allocated to the processing unit is close to the point assigned to the task. The region allocated to a processing unit may be changed. If no assigned point for a task is sufficiently close to any allocated processing unit region, the task is suspended. Overlapping regions may be assigned to different processing units. In some implementations, the union of the allocated regions covers the task space, while in others it does not. Regions may also be allocated to wait conditions and one or more dimensions of a region may be allocated to conventional processor allocators.

Owner:MICRO FOCUS SOFTWARE INC

Multi-operation write aggregator using a page buffer and a scratch flash block in each of multiple channels of a large array of flash memory to reduce block wear

InactiveUS8108590B2Memory architecture accessing/allocationMemory adressing/allocation/relocationSmall fragmentPage buffers

A flash system has multiple channels of flash memory chips that can be accessed in parallel. Host data is assigned to one of the channels by a multi-channel controller processor and accumulated in a multi-channel page buffer. When a page boundary in the page buffer is reached, the page buffer is written to a target physical block if full, or combined with old data fragments in an Aggregating Flash Block (AFB) when the logical-sector addresses (LSA's) match. Thus small fragments are aggregated using the AFB, reducing erases and wear of flash blocks. The page buffer is copied to the AFB when a STOP command occurs. Each channel has one or more AFB's, which are tracked by an AFB tracking table.

Owner:SUPER TALENT TECH CORP

System and method for dynamically partitioning processing across plurality of heterogeneous processors

InactiveUS20050081181A1Faster processorBig amount of dataResource allocationMultiple digital computer combinationsCurrent loadRunning time

A program is into at least two object files: one object file for each of the supported processor environments. During compilation, code characteristics, such as data locality, computational intensity, and data parallelism, are analyzed and recorded in the object file. During run time, the code characteristics are combined with runtime considerations, such as the current load on the processors and the size of the data being processed, to arrive at an overall value. The overall value is then used to determine which of the processors will be assigned the task. The values are assigned based on the characteristics of the various processors. For example, if one processor is better at handling intensive computations against large streams of data, programs that are highly computationally intensive and process large quantities of data are weighted in favor of that processor. The corresponding object is then loaded and executed on the assigned processor.

Owner:IBM CORP

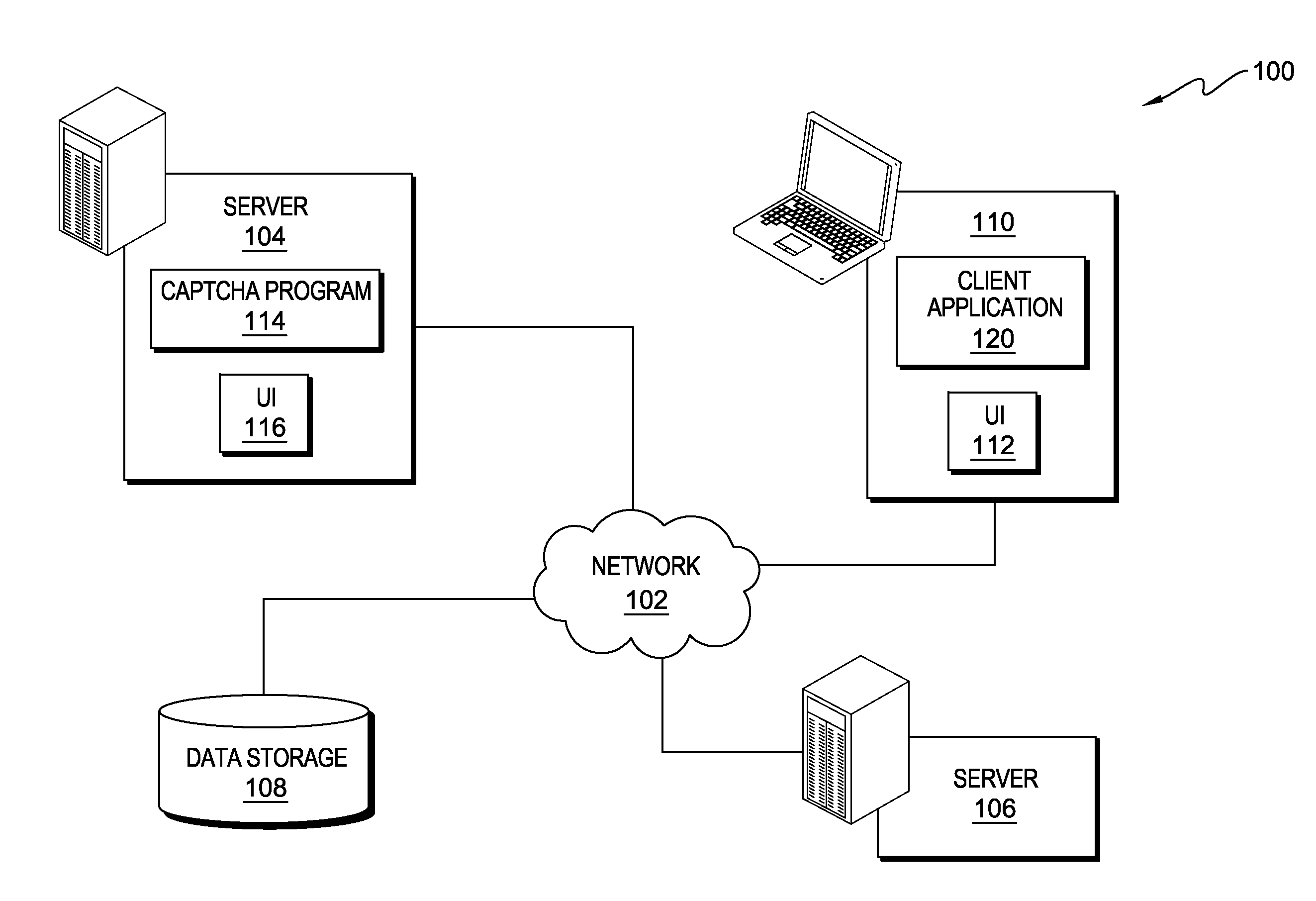

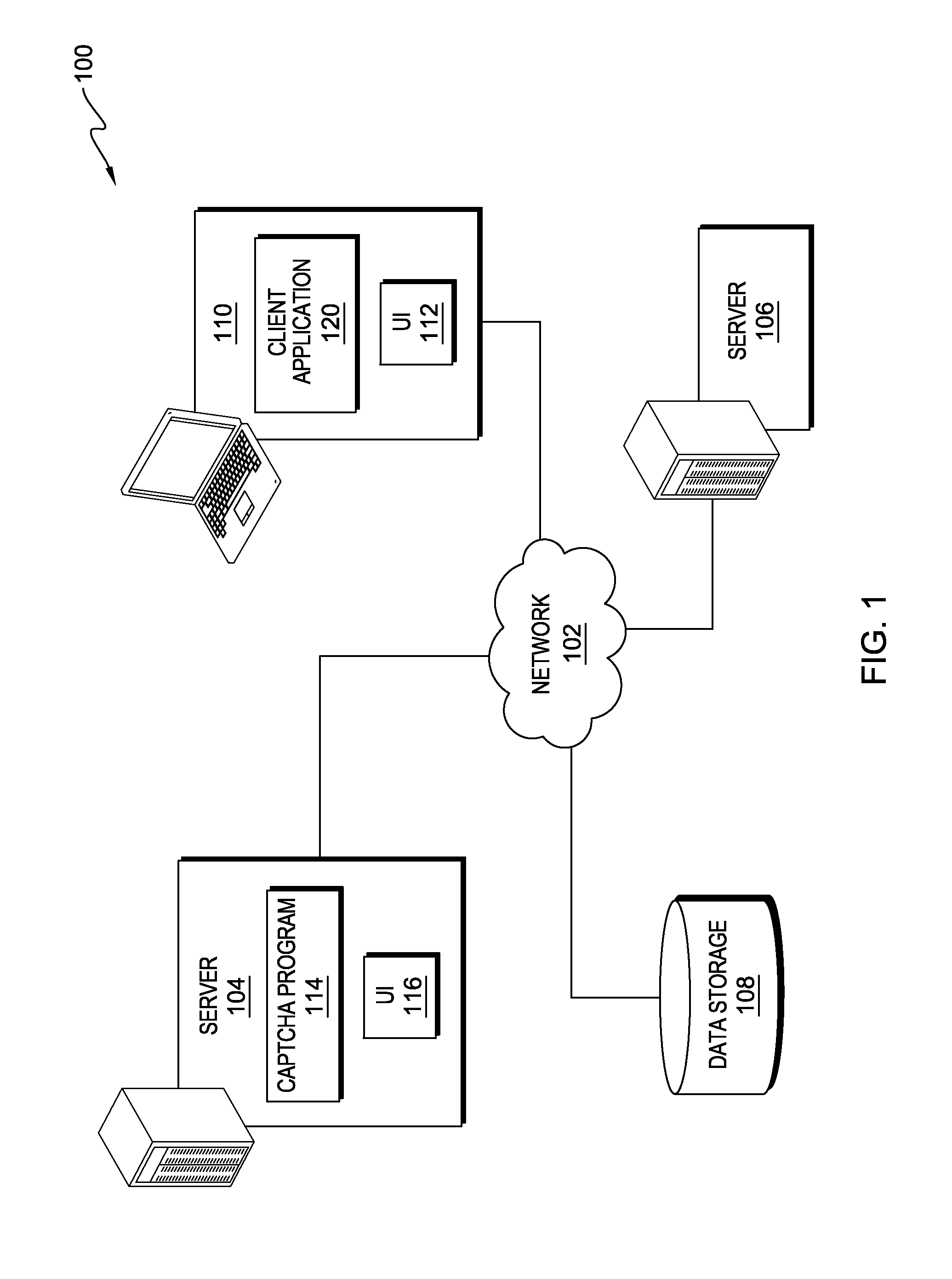

Captcha challenge incorporating obfuscated characters

InactiveUS20150365401A1Digital data processing detailsMultiple digital computer combinationsAlgorithmSoftware engineering

A method for determining if a user of a computer system is a human. A processor receives an indication that a computer security program is needed and acquires at least one image depicting a first string of characters including at least a first and second set of one or more characters. A processor assigns a substitute character to be used as input for each of the second set of one or more characters. A processor presents the at least one image and an indication of the substitute character and when to use the substitute character to the user. A processor receives a second string of characters from the user. A processor determines whether the second string of characters substantially matches the first string of characters based on the substitute character assigned to each of the second set of one or more characters and determines whether the user is a human.

Owner:KYNDRYL INC

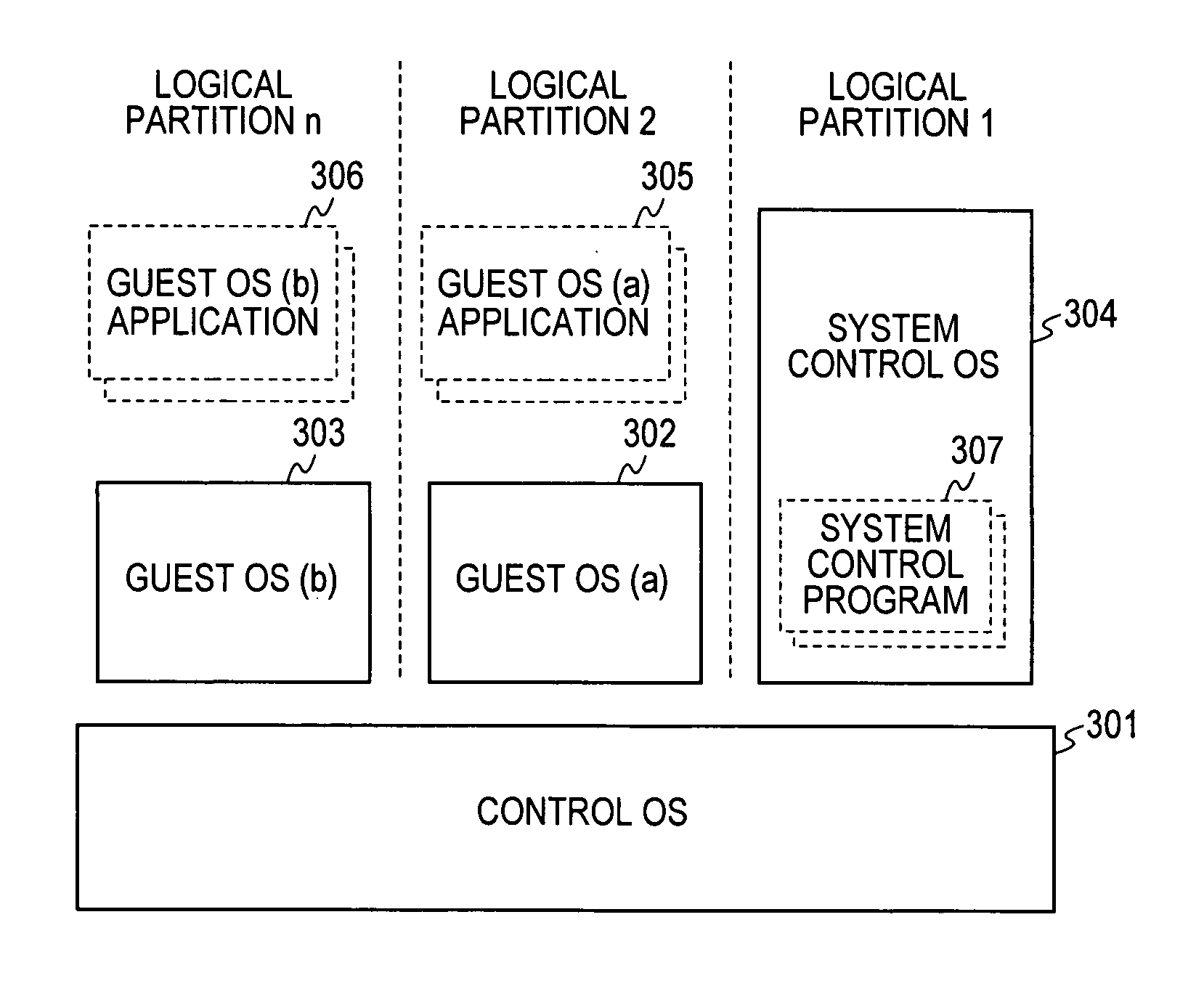

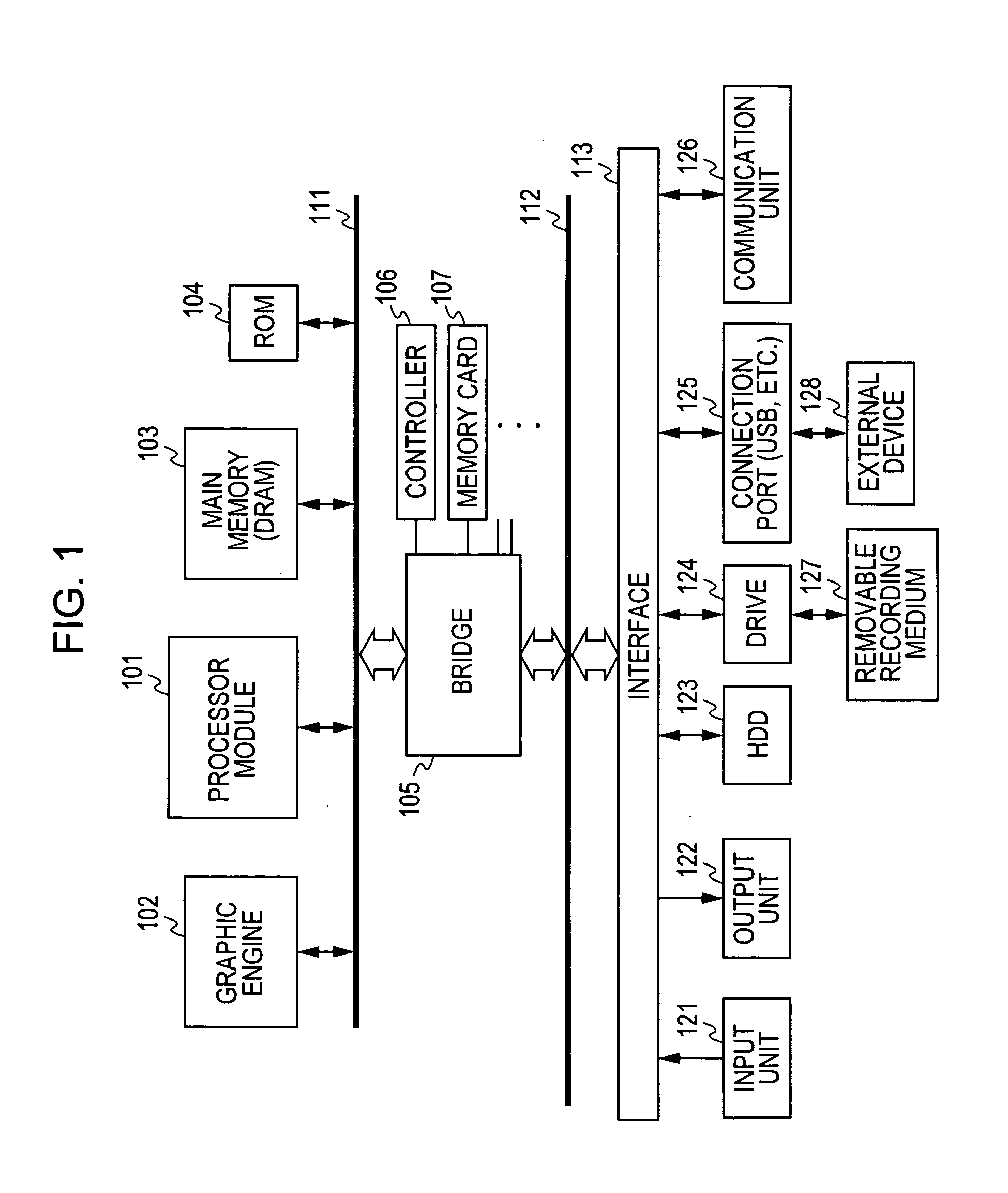

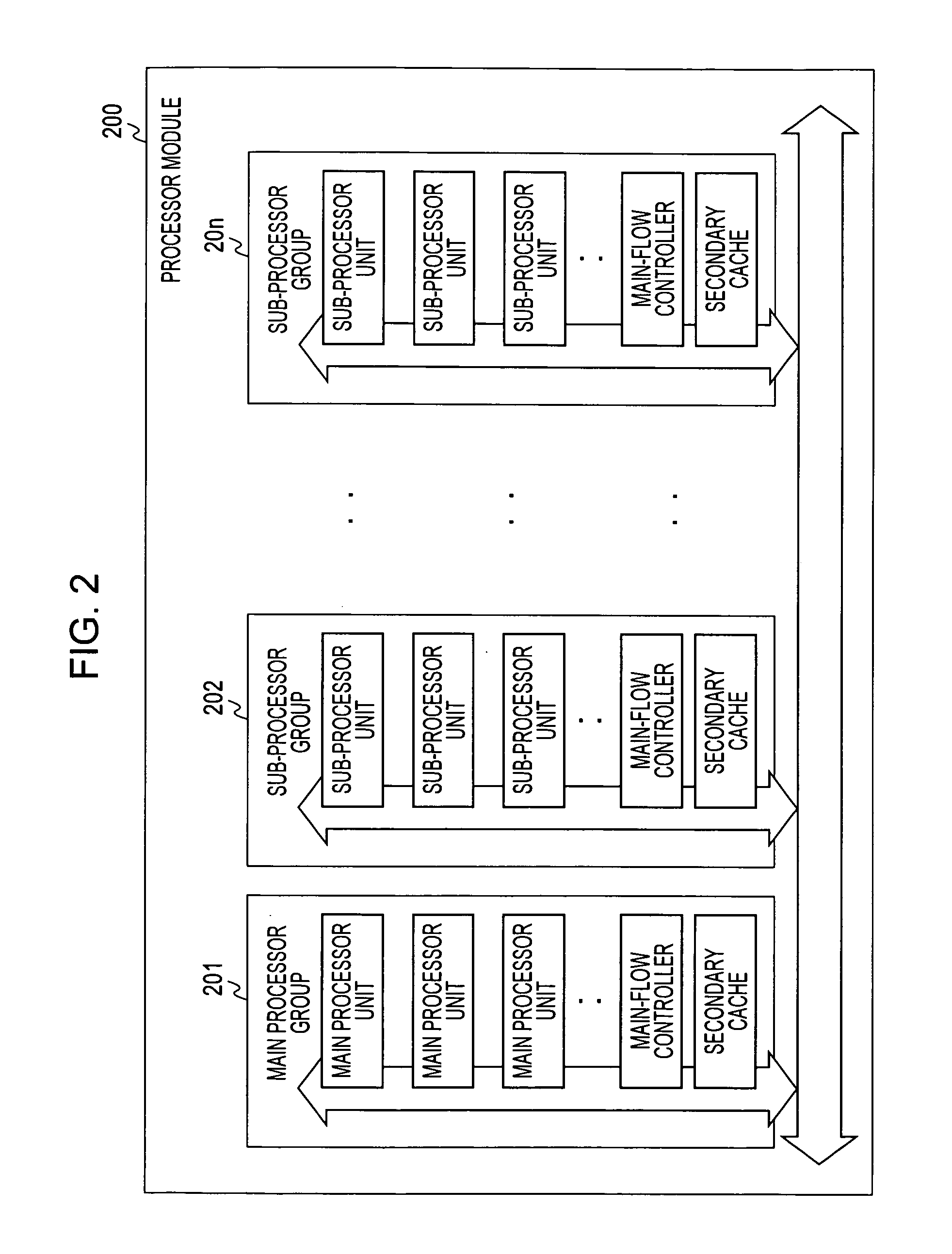

Information processing apparatus, process control method, and computer program

InactiveUS20060075207A1Efficient data processingHigh access frequencyMemory adressing/allocation/relocationMultiprogramming arrangementsInformation processingOperational system

An information processing apparatus includes a control operating system executing a process for allocating a plurality of logical processors to a physical processor in a time division manner, and a guest operating system for which a logical partition as an application entity of the logical processor is set. The control operating system sets and updates, as address conversion tables for determining an allocation relationship between the logical processor and the physical processor, two address conversion tables of a first conversion table that sets an allocation relationship between a logical partition address space and a physical address space and a second conversion table that sets an allocation relationship between a virtual address space in the guest operating system and the physical address space.

Owner:SONY CORP

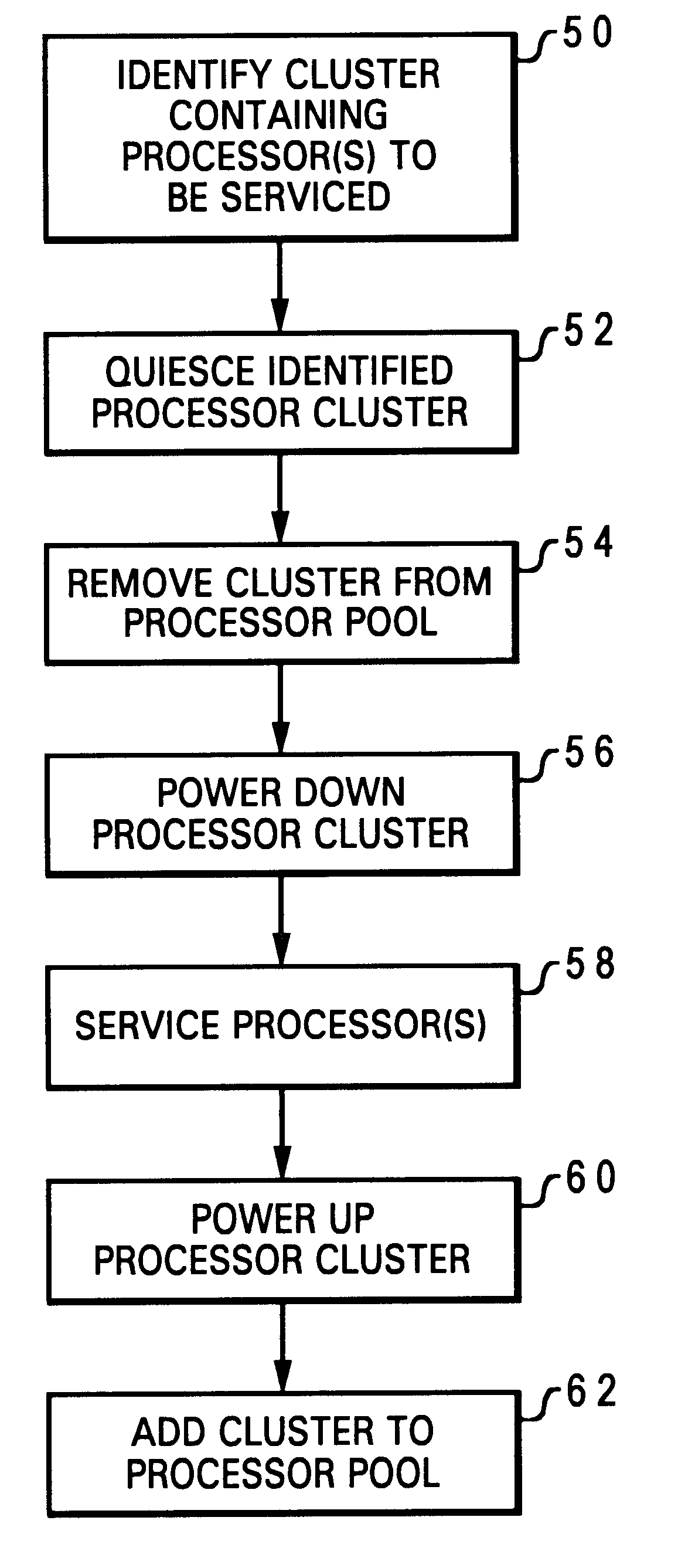

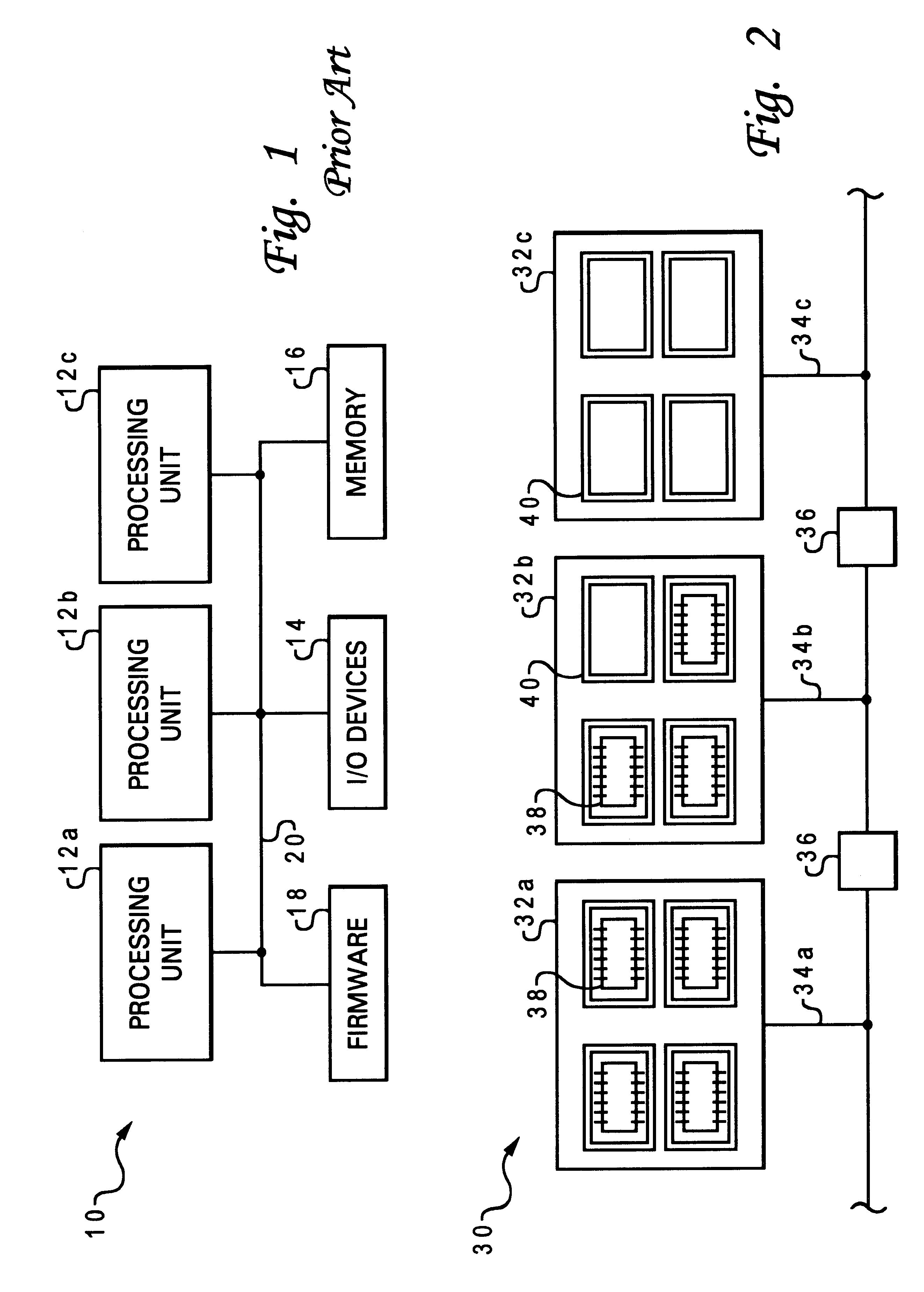

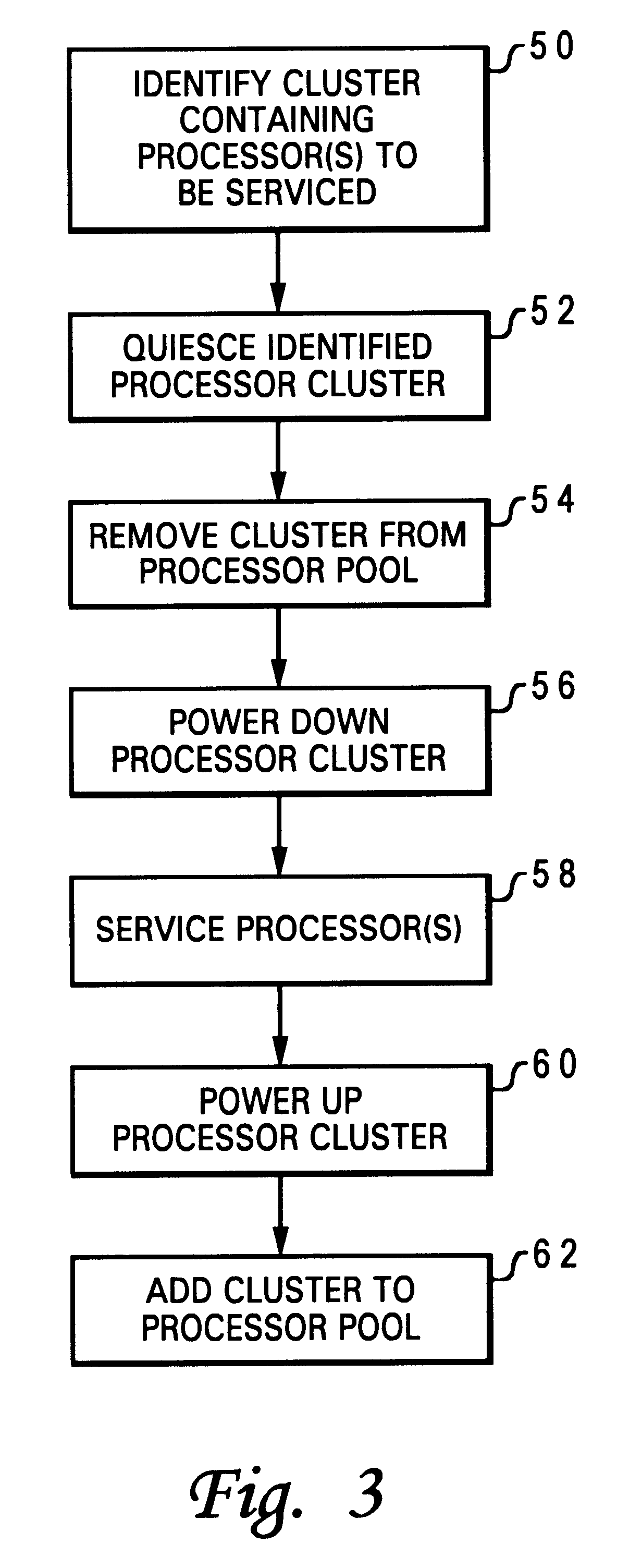

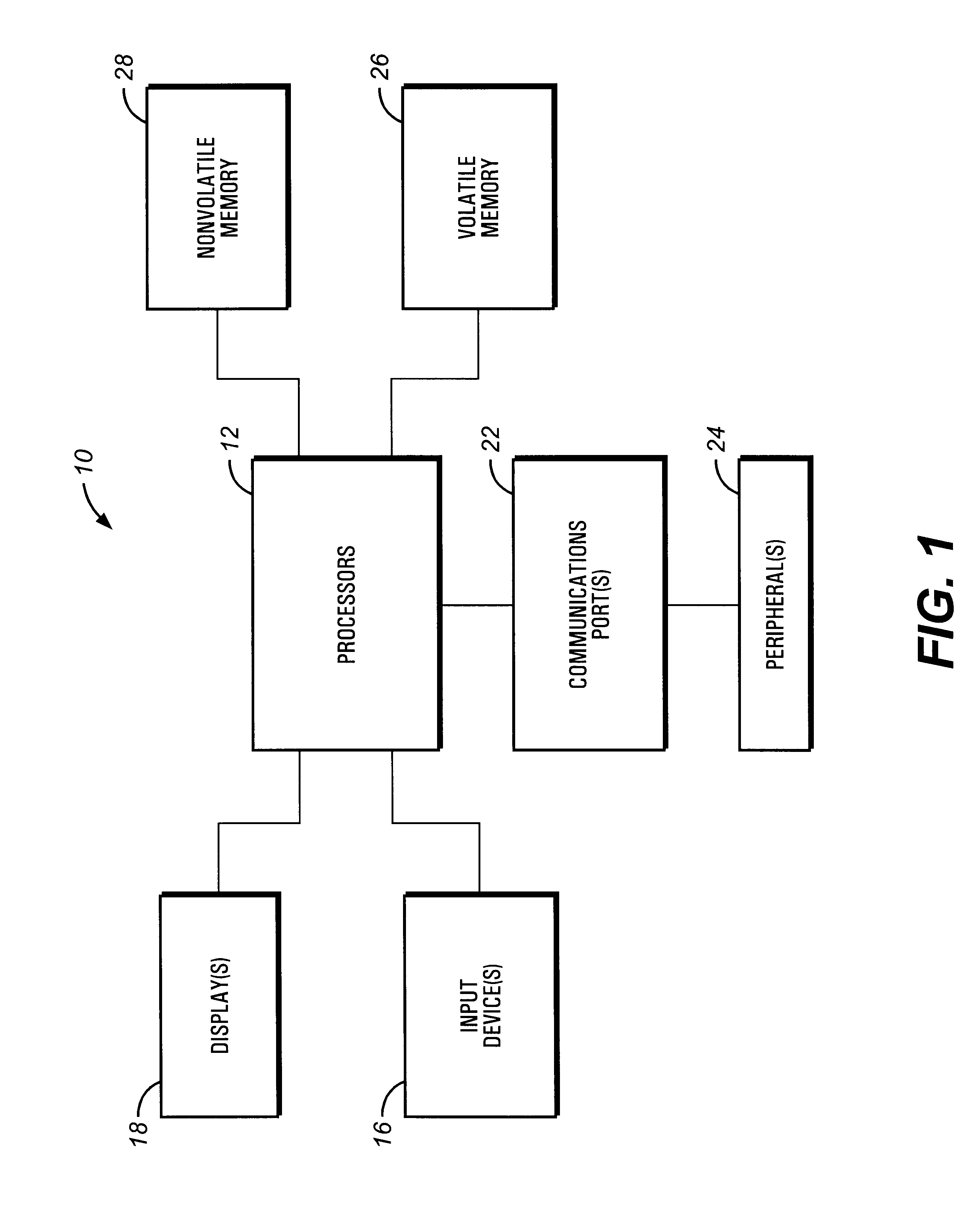

System upgrade and processor service

InactiveUS6378027B1Volume/mass flow measurementMultiple digital computer combinationsComputer architectureEngineering

A method of servicing a processor array of a computer system by quiescing a processor selected for maintenance and removing the selected processor from a processor pool used by the computer's operating system. The selected processor is then powered down while maintaining power to and operation of other processors in the processor array. The selected processor may be identified as being defective, or may have been selected for upgrading. The processor array may include several processor clusters, such that the quiescing, removing and powering down steps apply to all processors in one of the processing clusters. The operating system assigns one of the processors in the processor array to be a service processor, and if the service processor is the processor selected for maintenance, the OS re-assigns the service processor functions to another processor in the processor array.

Owner:LENOVO PC INT

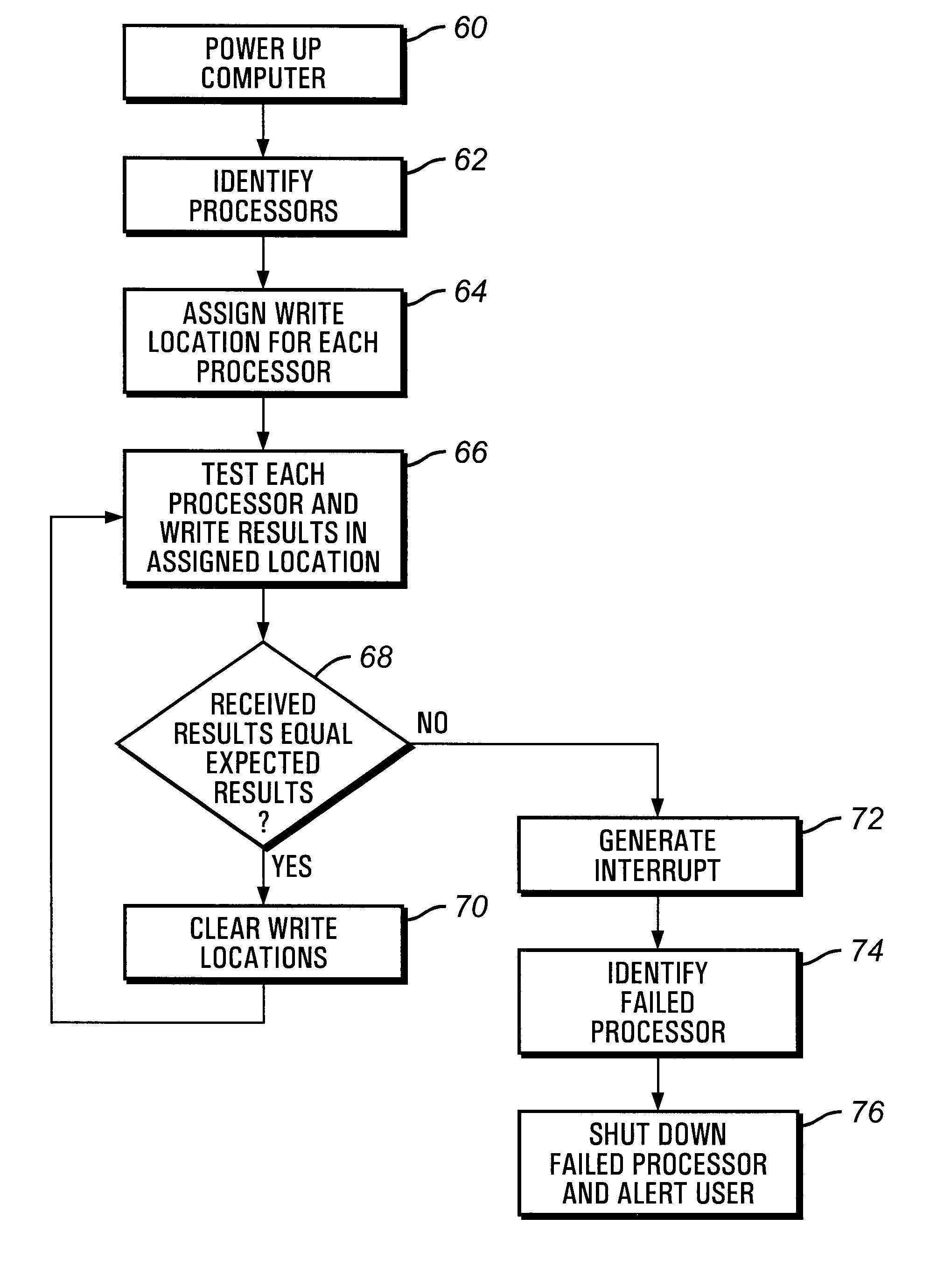

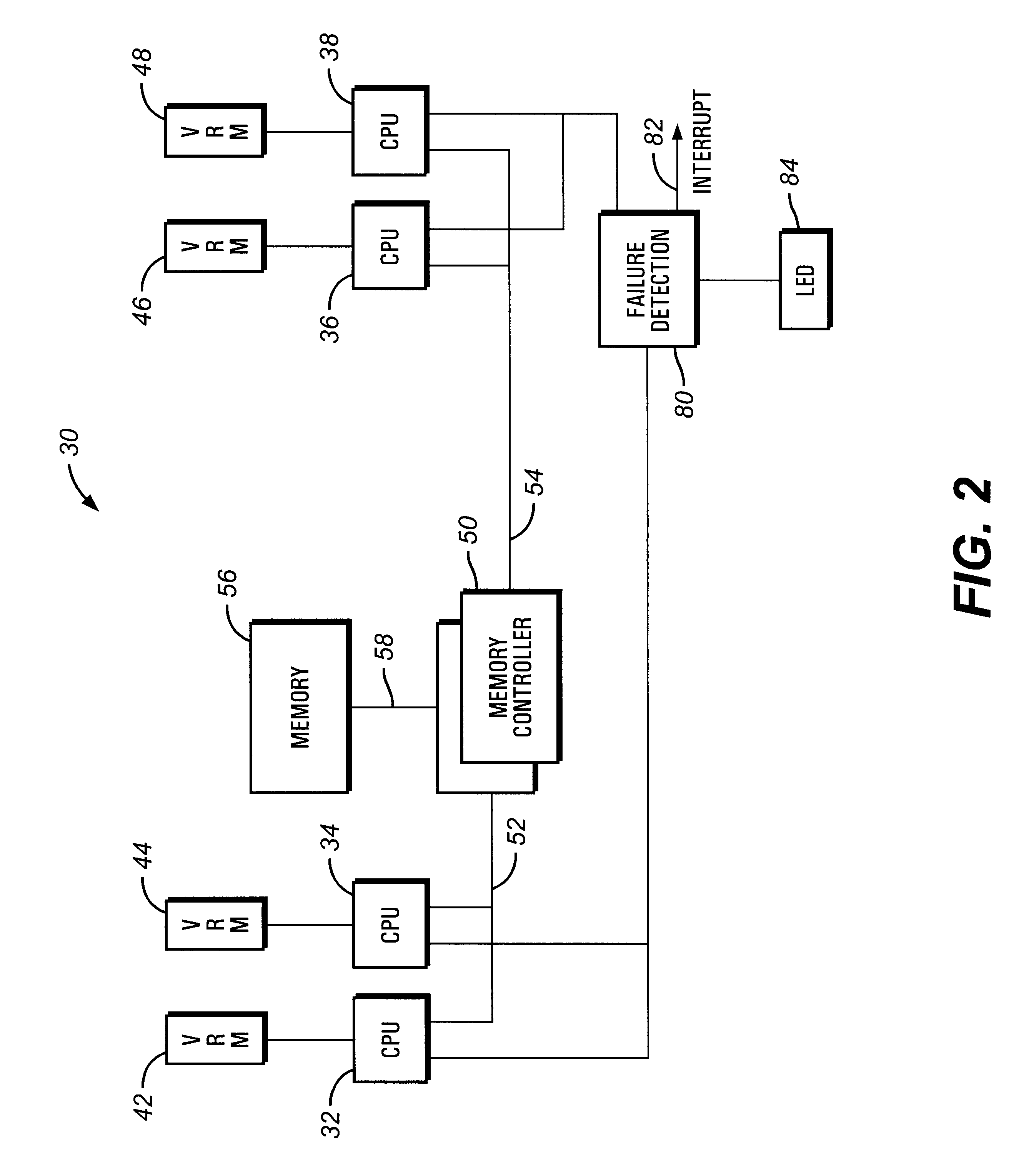

Method and apparatus for determining a processor failure in a multiprocessor computer

A multiprocessor computer includes a fault detection scheme which detects and identifies the failure of one of the processors. Each processor is assigned a write location, which may be a unique register. During normal computer operation, each processor intermittently performs a test and stores the results of the test in the assigned write location. The stored results are compared to expected results, and an error signal is generated if the stored results differ from the expected results to indicate that one of the processors has failed.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Communication Resource Allocation Strategy

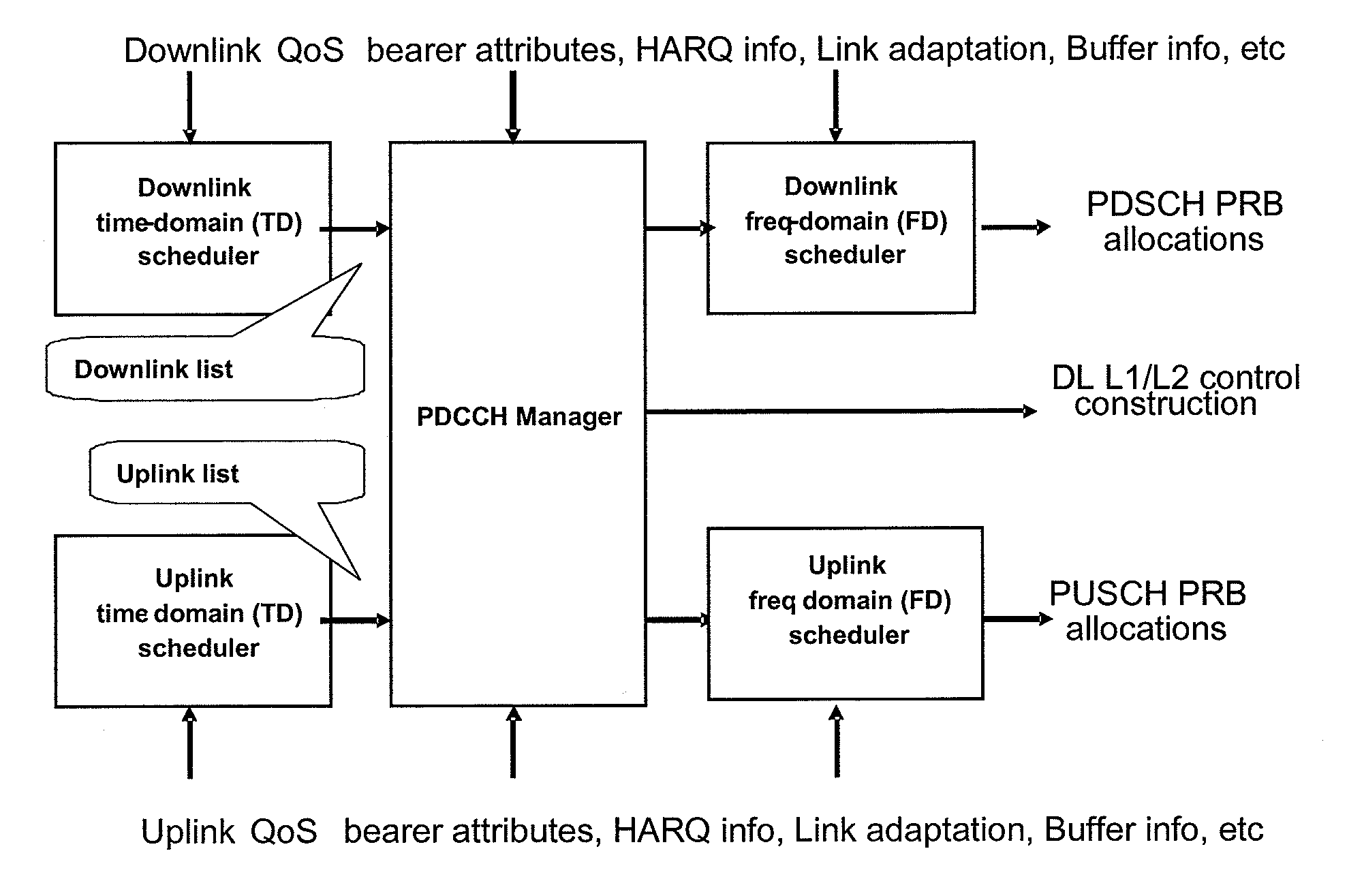

A scheduling processor allocates a time slot of a communication protocol to a user equipment for data transmission based on received control data of the same or another user equipment in a current time slot and received user data of the same or another user equipment in a preceding time slot, while ignoring user data of the same or any other user equipment received in the current time slot. The scheduling processor also allocates a frequency resource to the user equipment. A control channel managing processor allocates signaling resources on a control channel for the submission of control information to the user equipment, which informs of the time slot allocated by the time domain scheduling processor as well as of the frequency resource allocated by the frequency domain scheduling processor.

Owner:NOKIA SOLUTIONS & NETWORKS OY

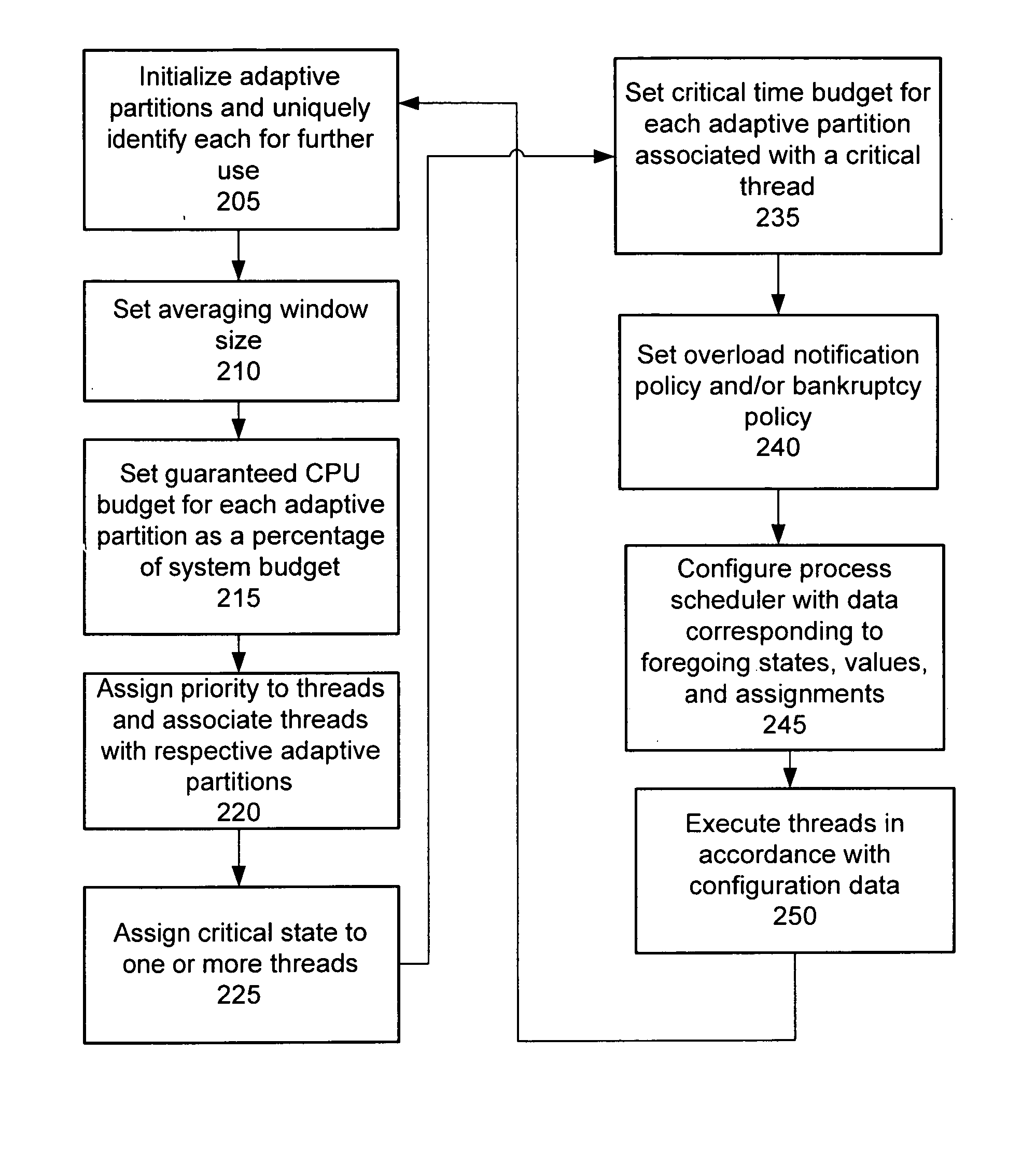

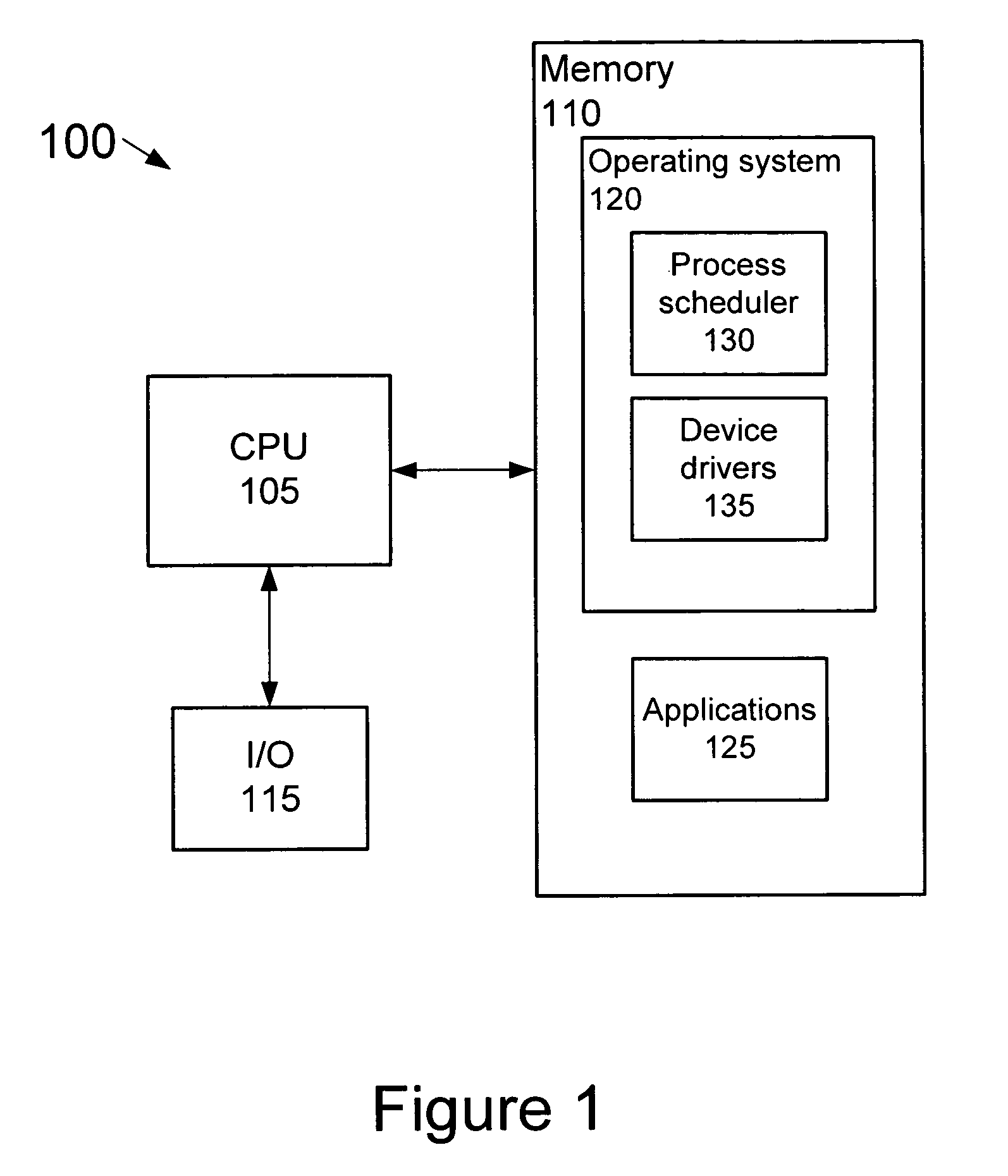

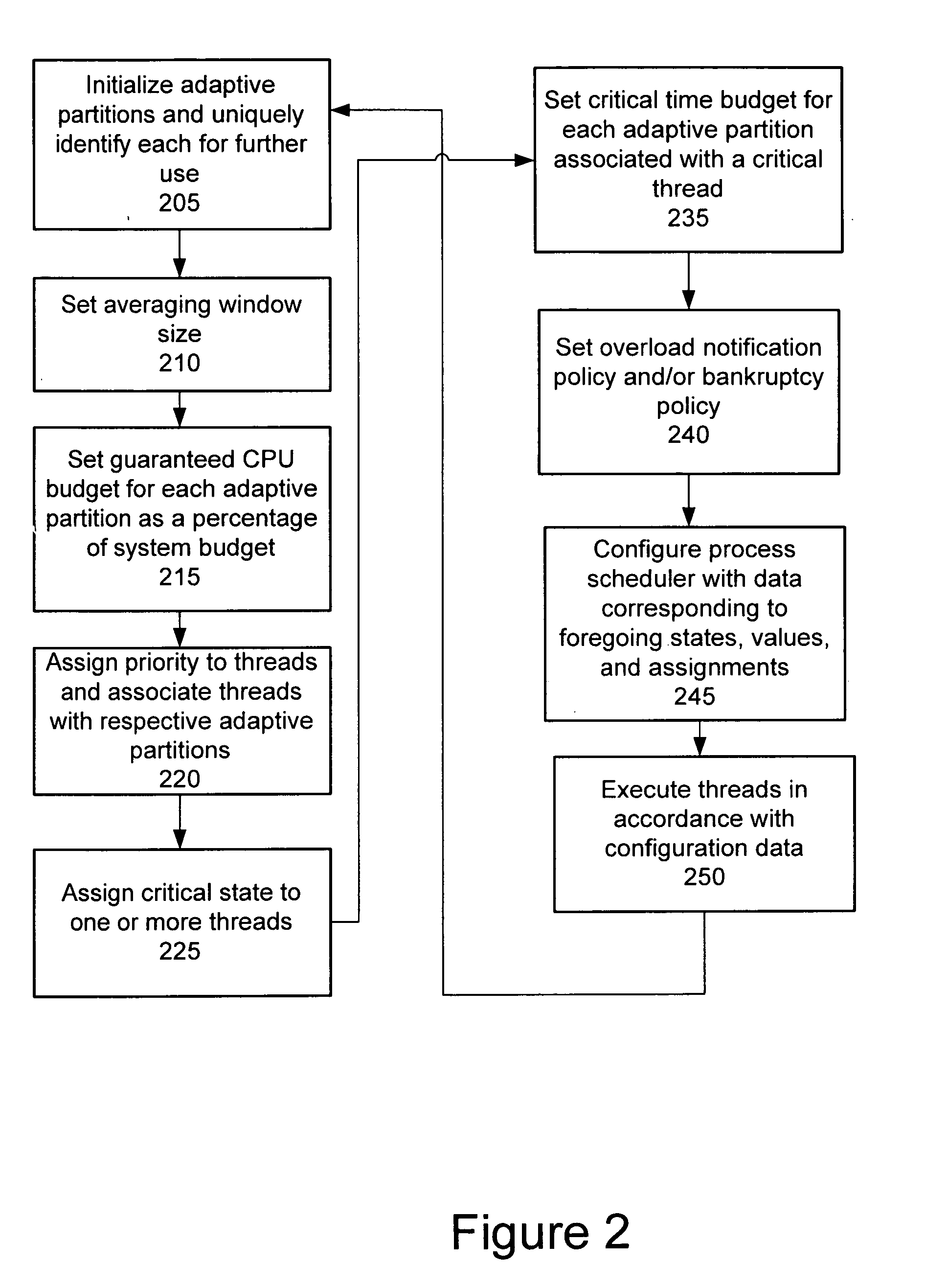

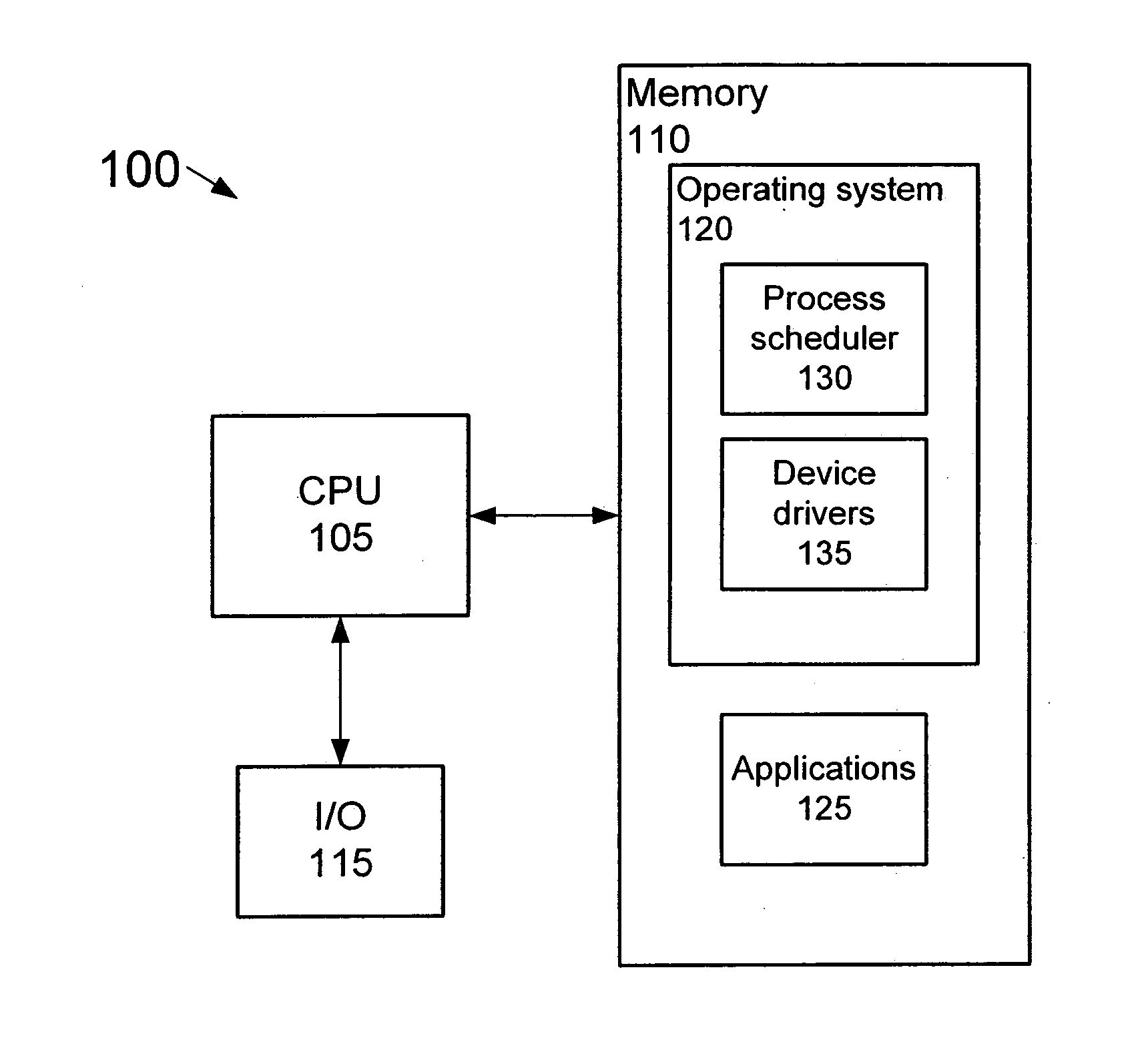

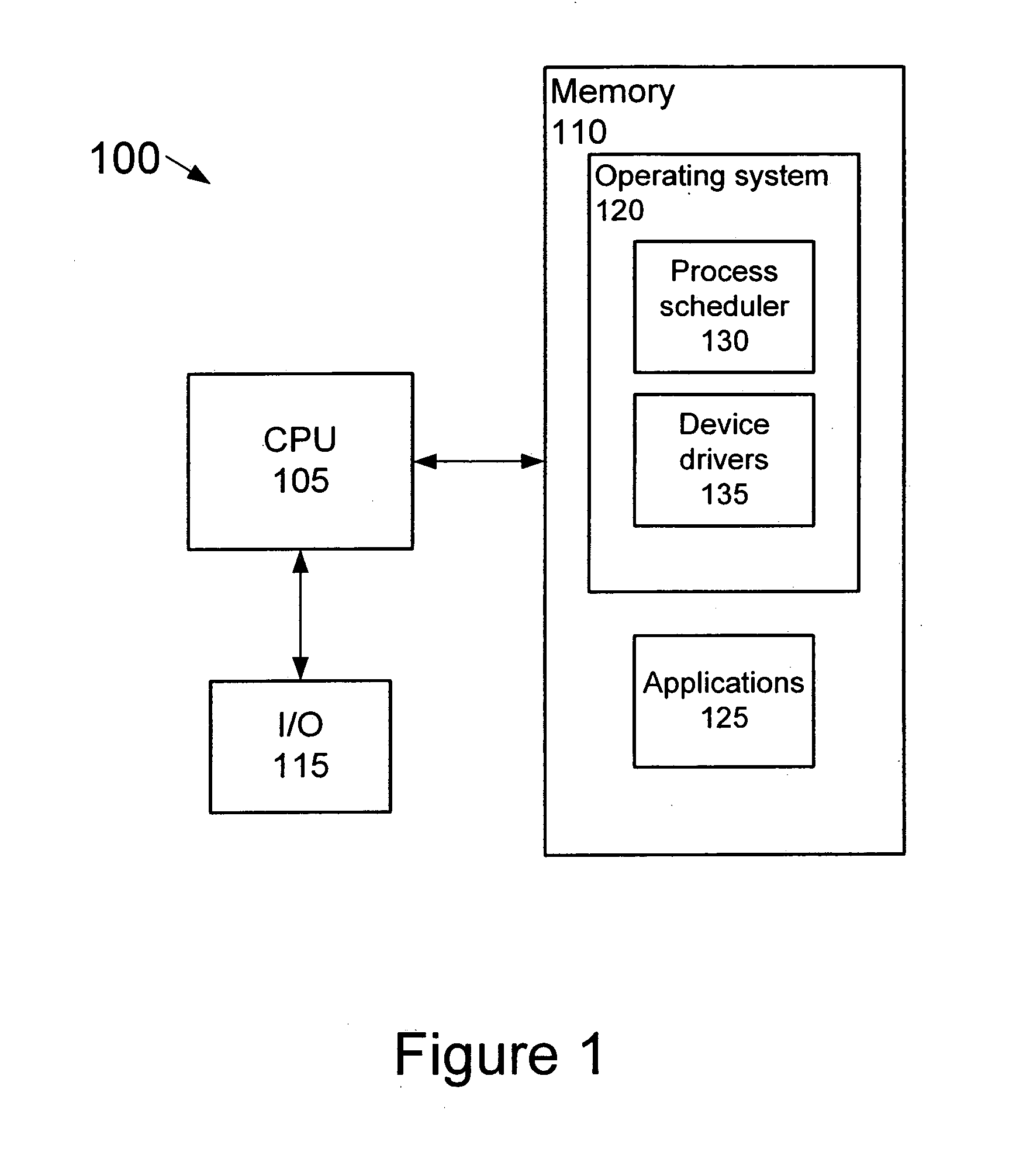

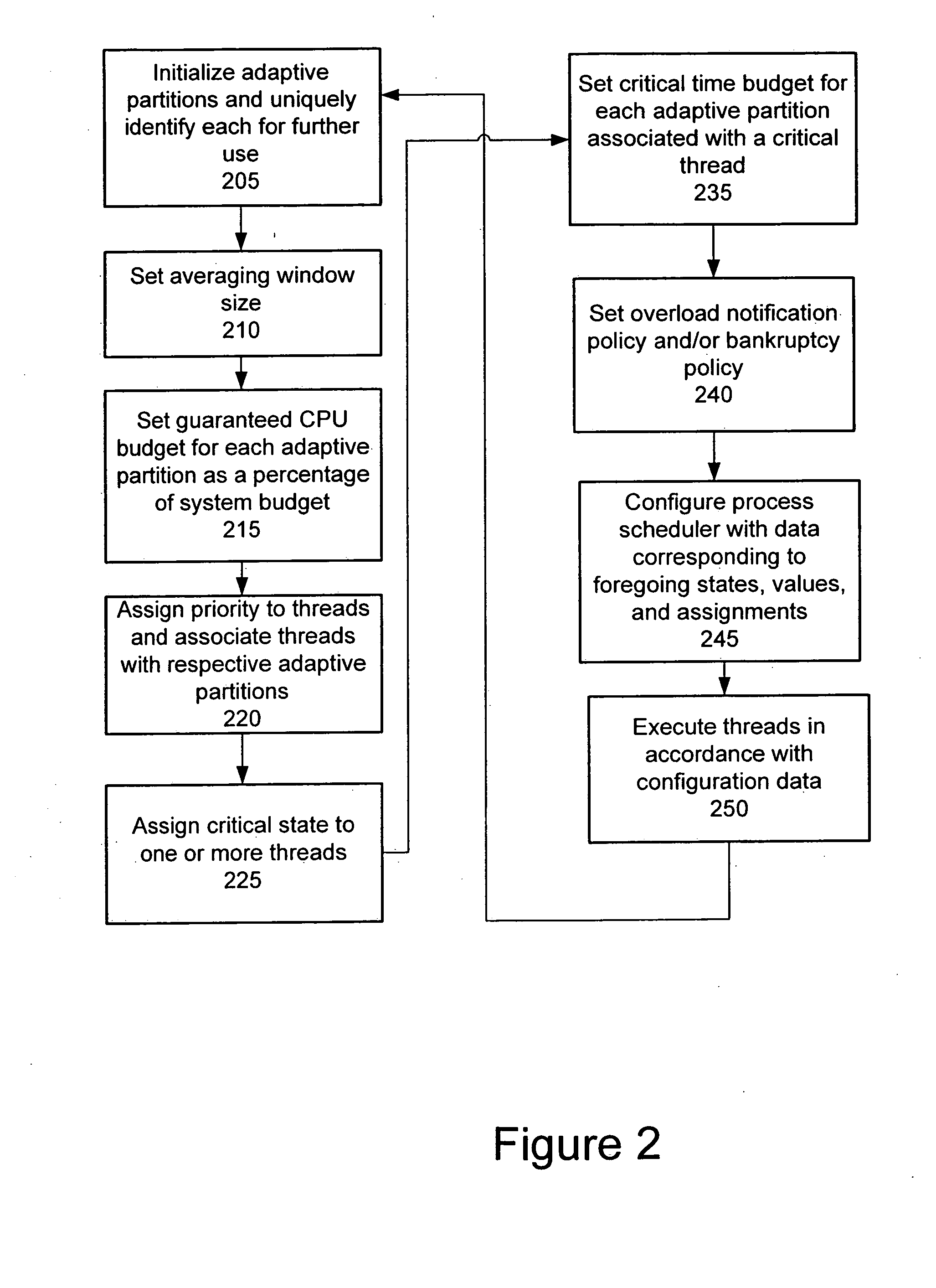

Process scheduler employing adaptive partitioning of process threads

ActiveUS20070226739A1Digital computer detailsMultiprogramming arrangementsParallel computingSymmetric multiprocessing

Owner:MALIKIE INNOVATIONS LTD

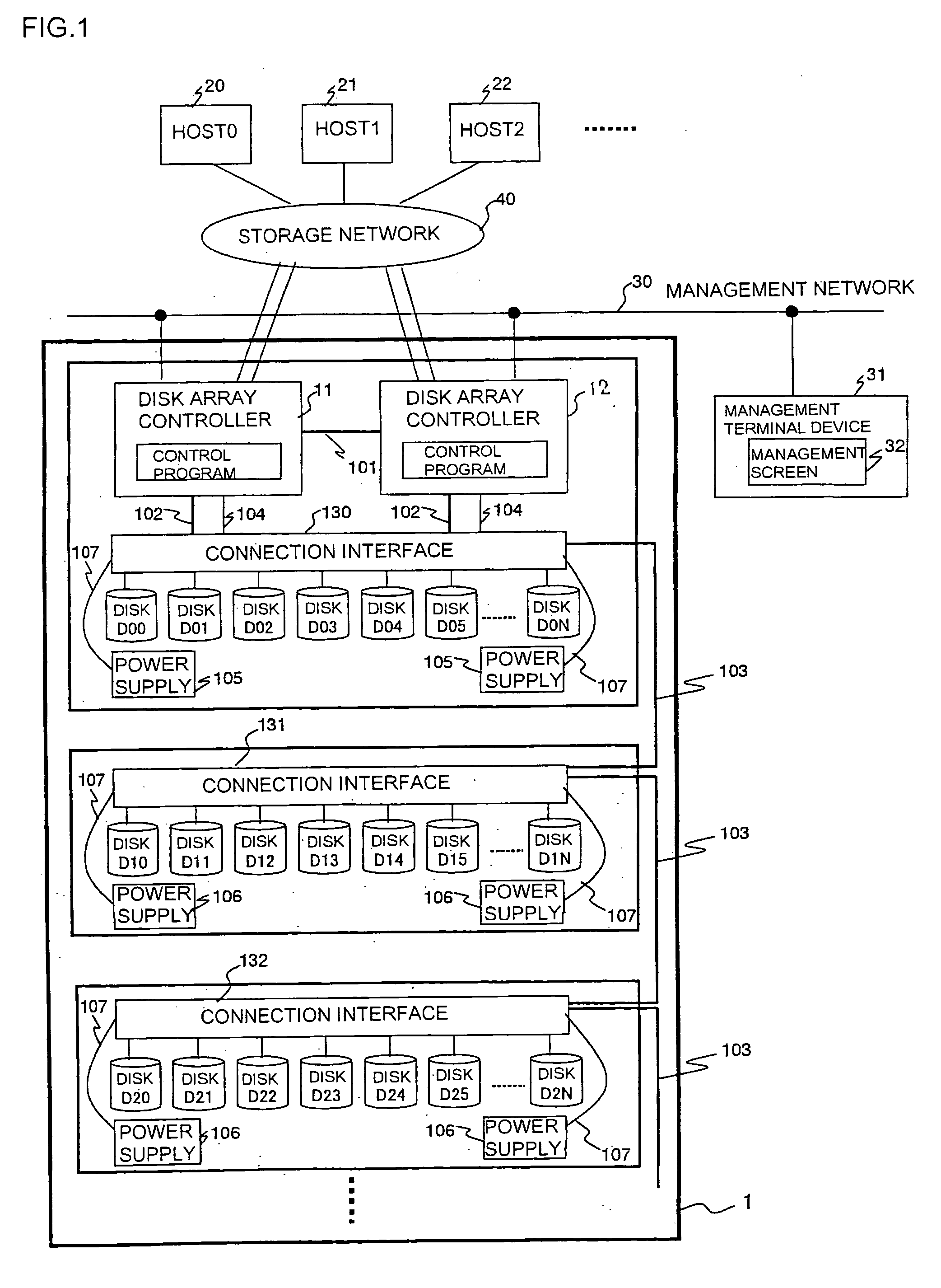

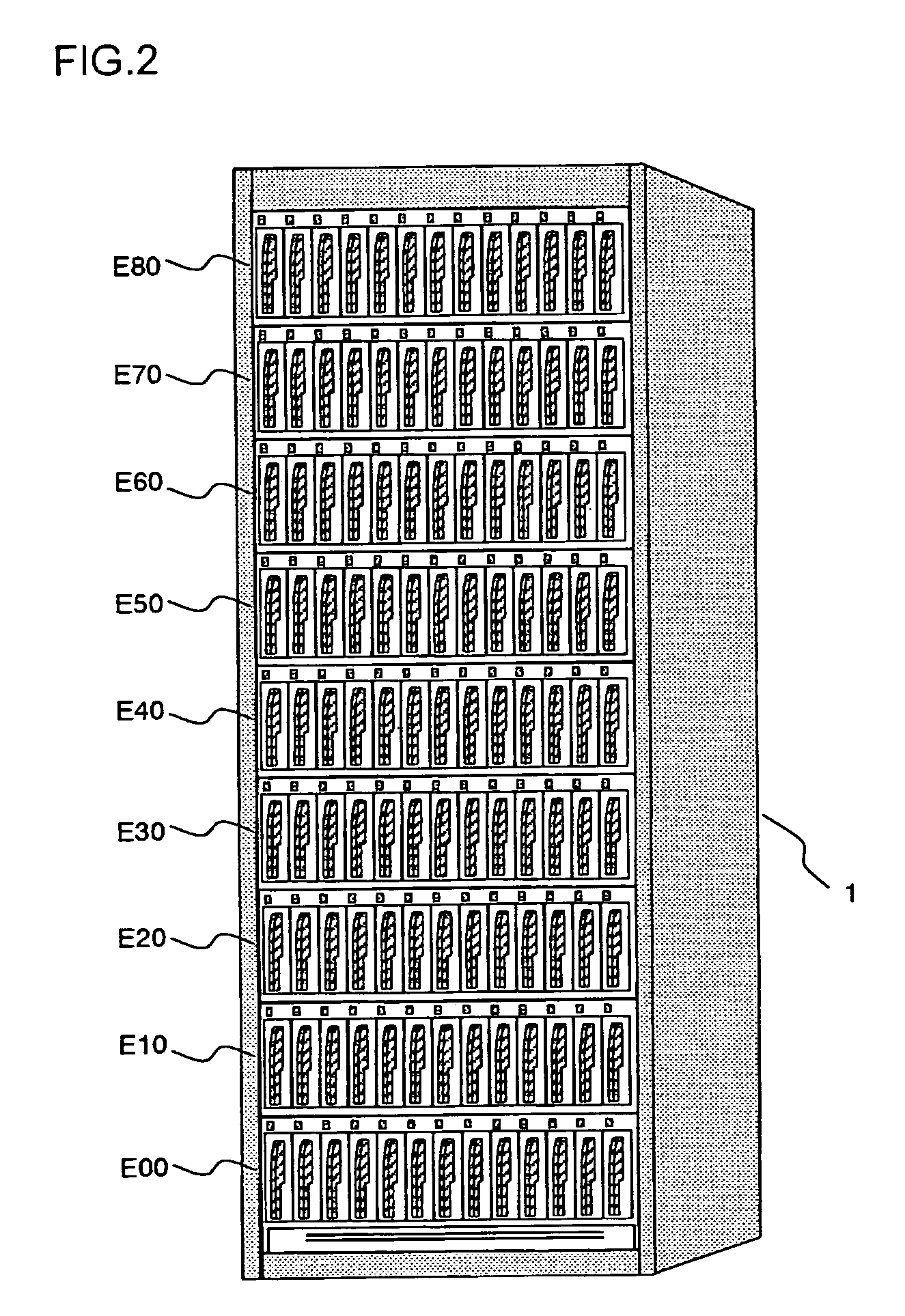

Disk array apparatus and method of controlling the same

InactiveUS20060224826A1Low costEasy to assembleMemory loss protectionError detection/correctionManagement unitParallel computing

To efficiently manage performance resources while preventing a failure of a control processing from affecting another control processing in a disk array apparatus. A disk array apparatus 1 has a disk array controller 11, the disk array controller 11 has a CPU incorporating a plurality of processor cores 1110 that cannot be physically separated from each other, each processor core serves as an unit processor, one unit processor manages the unit processors separately, allocates a self-contained control program to each unit processor in such a manner that the operation of the unit processor can be terminated appropriately or in such a manner that the unit processor can operate until the operation of the whole CPU is terminated, and manages the processing load or processing status of the allocated control program on a unit-processor basis.

Owner:HITACHI LTD

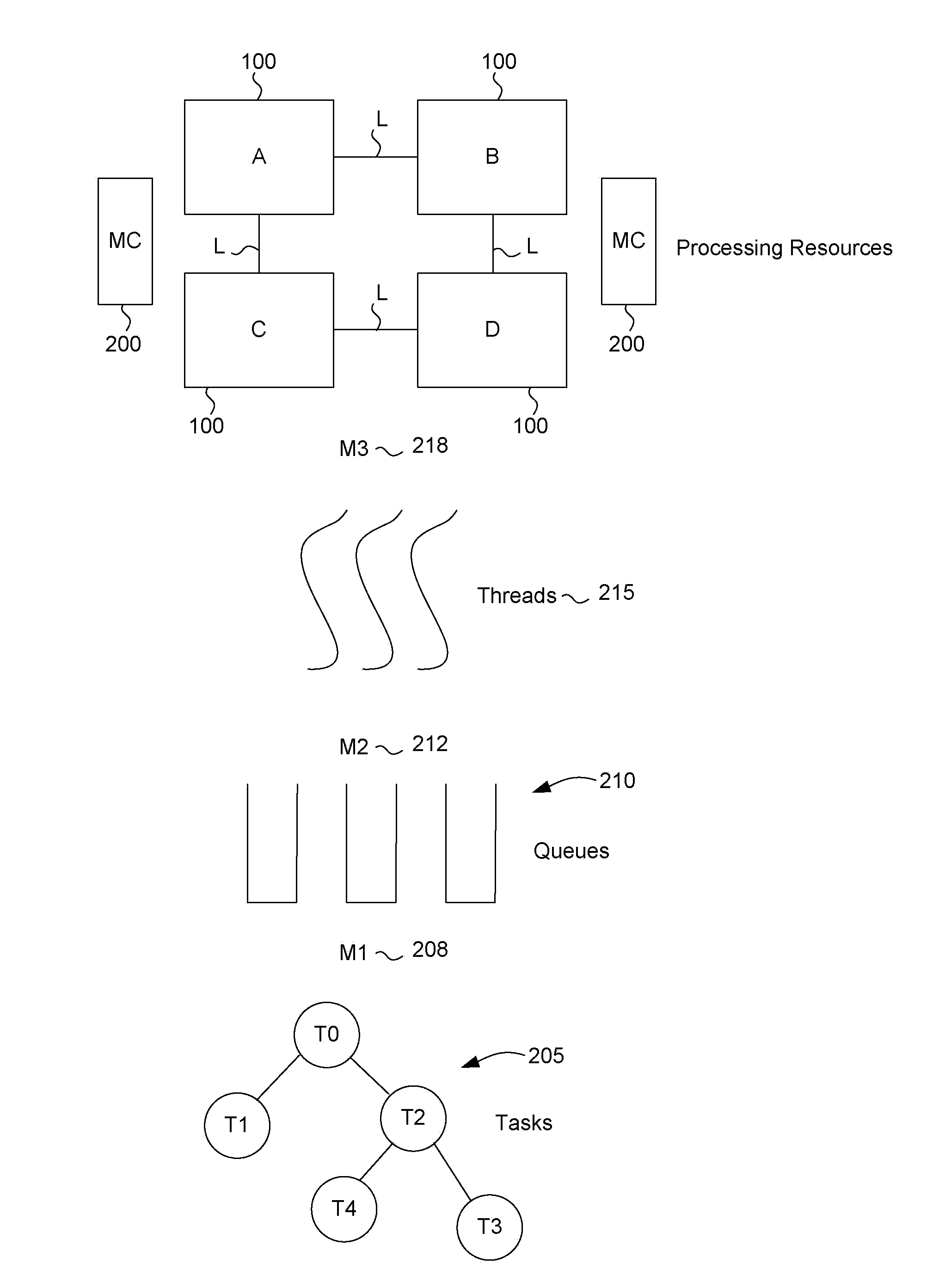

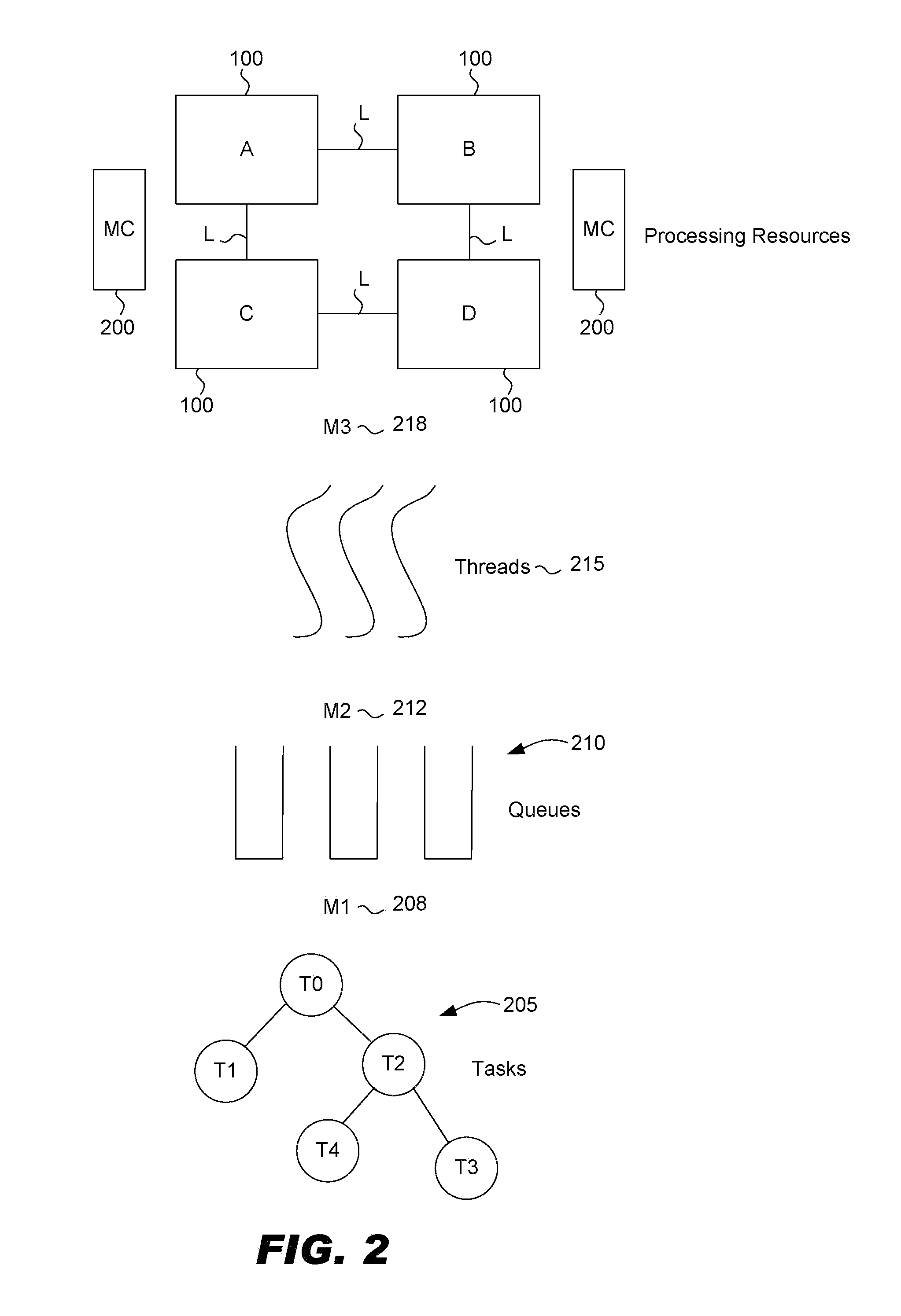

Numa aware system task management

ActiveUS20120102500A1Reduces memory access costMinimal costResource allocationMemory systemsMemory controllerMajorization minimization

Task management in a Non-Uniform Memory Access (NUMA) architecture having multiple processor cores is aware of the NUMA topology in task management. As a result memory access penalties are reduced. Each processor is assigned to a zone allocated to a memory controller. The zone assignment is based on a cost function. In a default mode a thread of execution attempts to perform work in a queue of the same zone as the processor to minimize memory access penalties. Additional work stealing rules may be invoked if there is no work for a thread to perform from its default zone queue.

Owner:SAMSUNG ELECTRONICS CO LTD

Process scheduler employing ordering function to schedule threads running in multiple adaptive partitions

ActiveUS20070061788A1Multiprogramming arrangementsMultiple digital computer combinationsParallel computingStorage cell

A system is set forth that includes a processor, one or more memory storage units, and software code stored in the one or more memory storage units. The software code is executable by the processor to generate a plurality of adaptive partitions that are each associated with one or more process threads. Each of the plurality of adaptive partitions has one or more corresponding scheduling attributes that are assigned to it. The software code further includes a scheduling system that is executable by the processor for selectively allocating the processor to run the process threads based on a comparison between ordering function values for each adaptive partition. The ordering function value for each adaptive partition is calculated using one or more of the scheduling attributes of the corresponding adaptive partition. The scheduling attributes that may be used to calculate the ordering function value include, for example, 1) the process budget, such as a guaranteed time budget, of the adaptive partition, 2) the critical budget, if any, of the adaptive partition, 3) the rate at which the process threads of an adaptive partition consume processor time, or the like. For each adaptive partition that is associated with a critical thread, a critical ordering function value also may be calculated. The scheduling system may compare the ordering function value with the critical ordering function value of the adaptive partition to determine the proper manner of billing the adaptive partition for the processor allocation used to run its associated critical threads. Methods of implementing various aspects of such a system are also set forth.

Owner:MALIKIE INNOVATIONS LTD

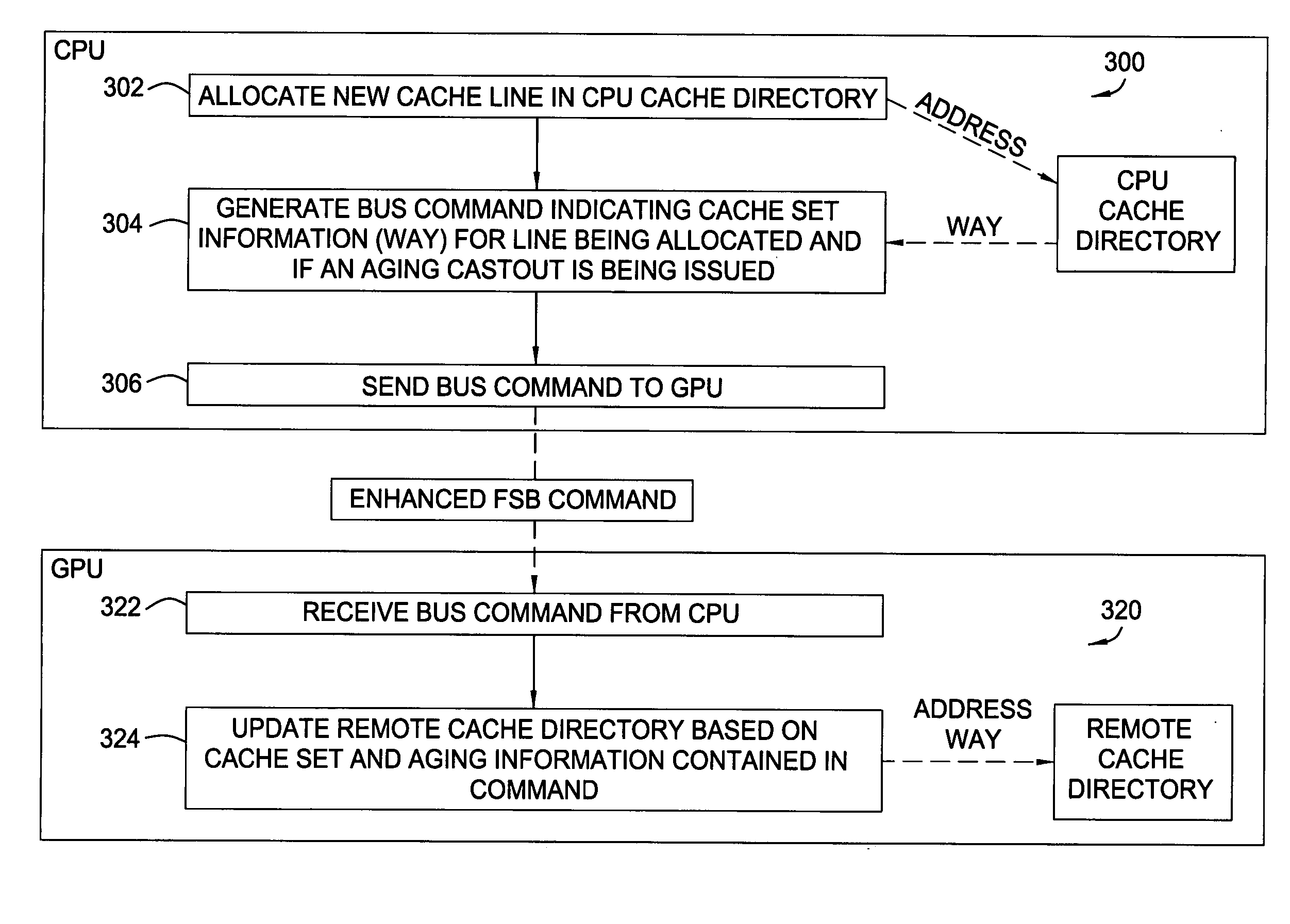

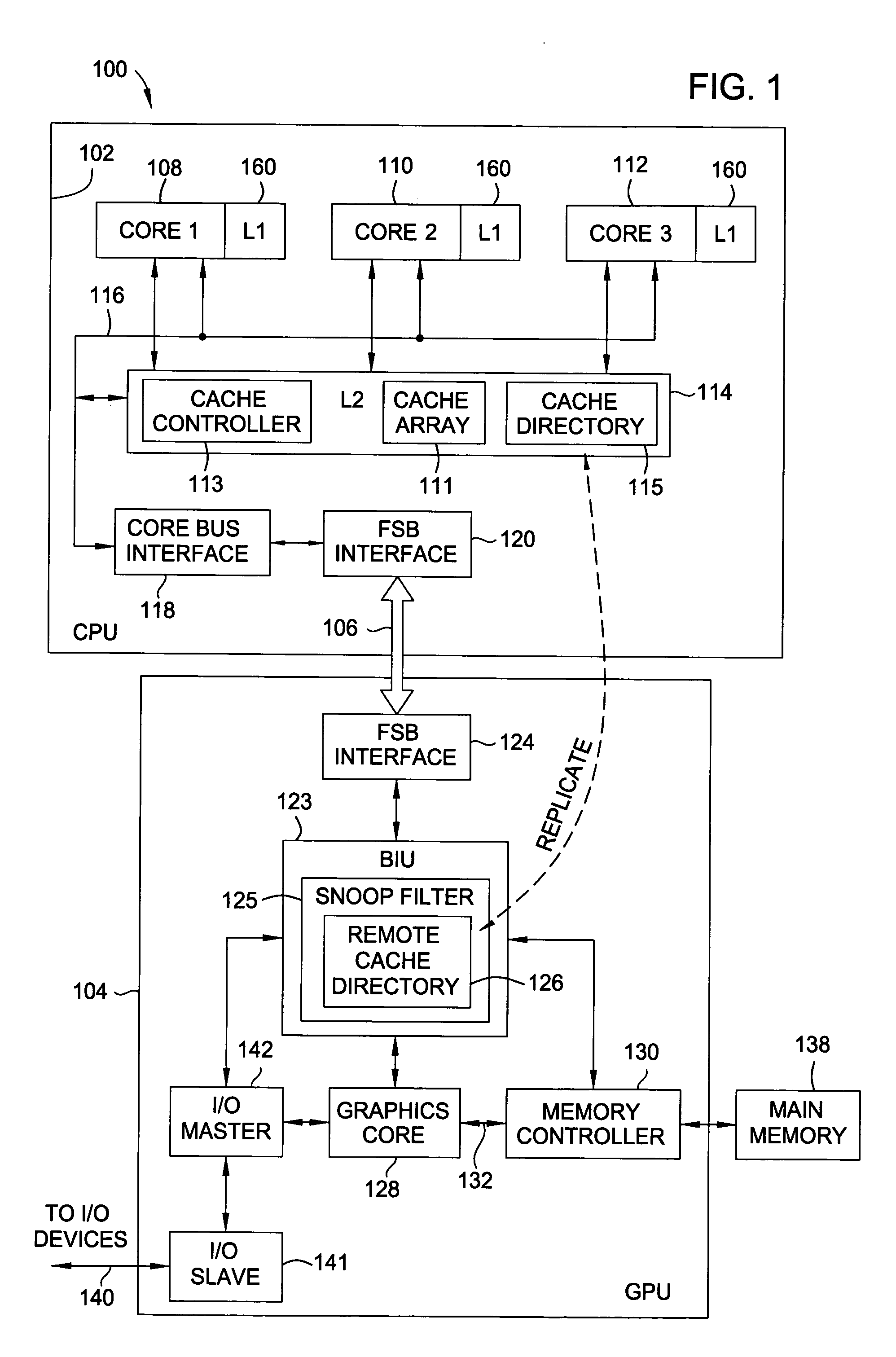

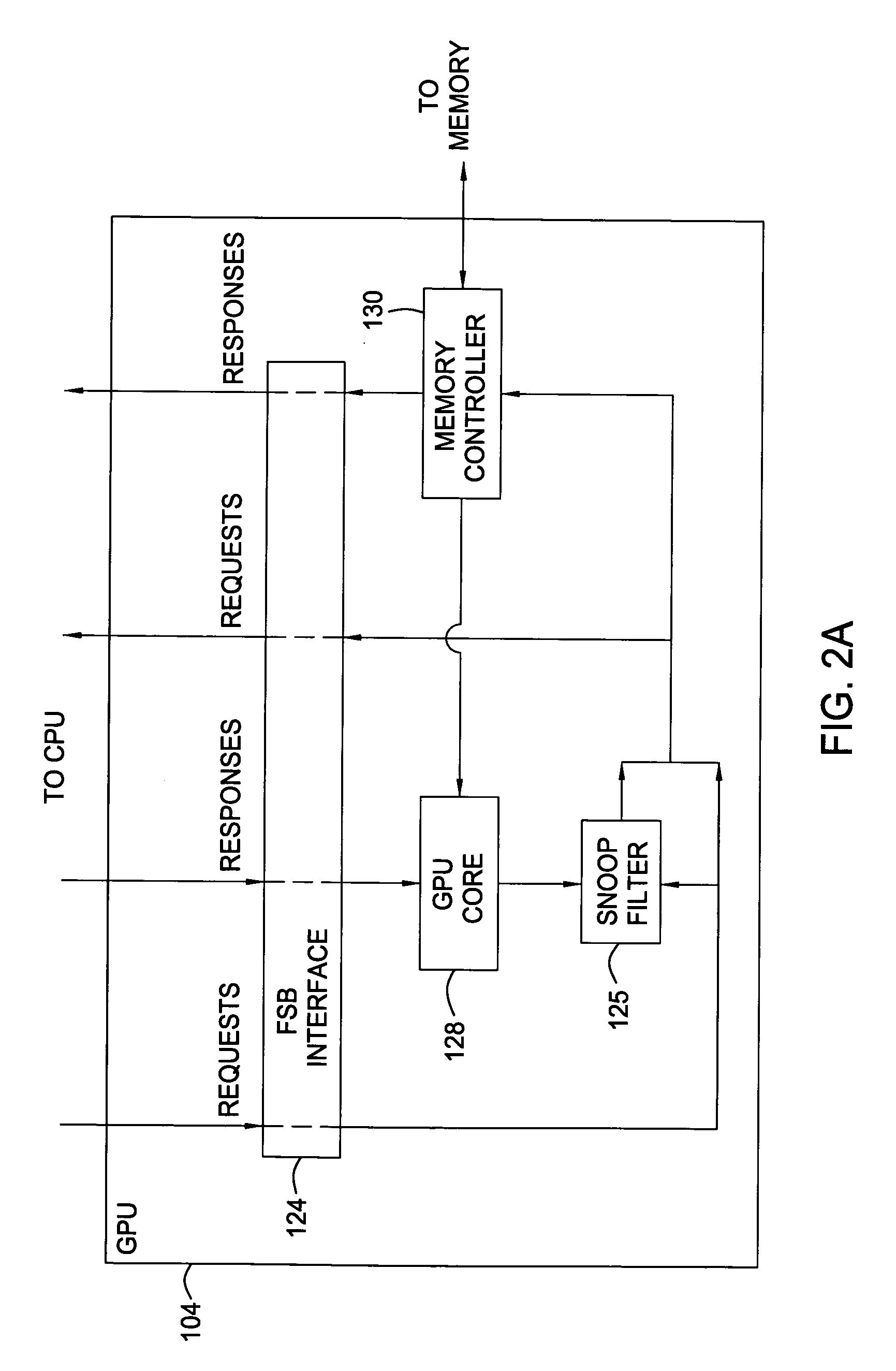

Enhanced bus transactions for efficient support of a remote cache directory copy

Methods and apparatus are provided that may be utilized to maintain a copy of a processor cache directory on a remote device that may access data residing in a cache of the processor. Enhanced bus transactions containing cache coherency information used to maintain the remote cache directory may be automatically generated when the processor allocates or de-allocates cache lines. Rather than query the processor cache directory prior to each memory access to determine if the processor cache contains an updated copy of requested data, the remote device may query its remote copy.

Owner:IBM CORP

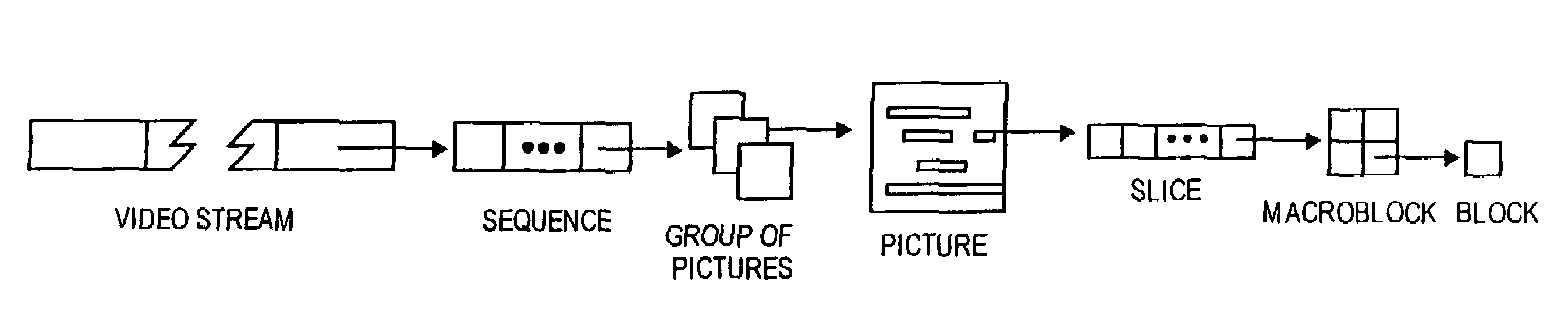

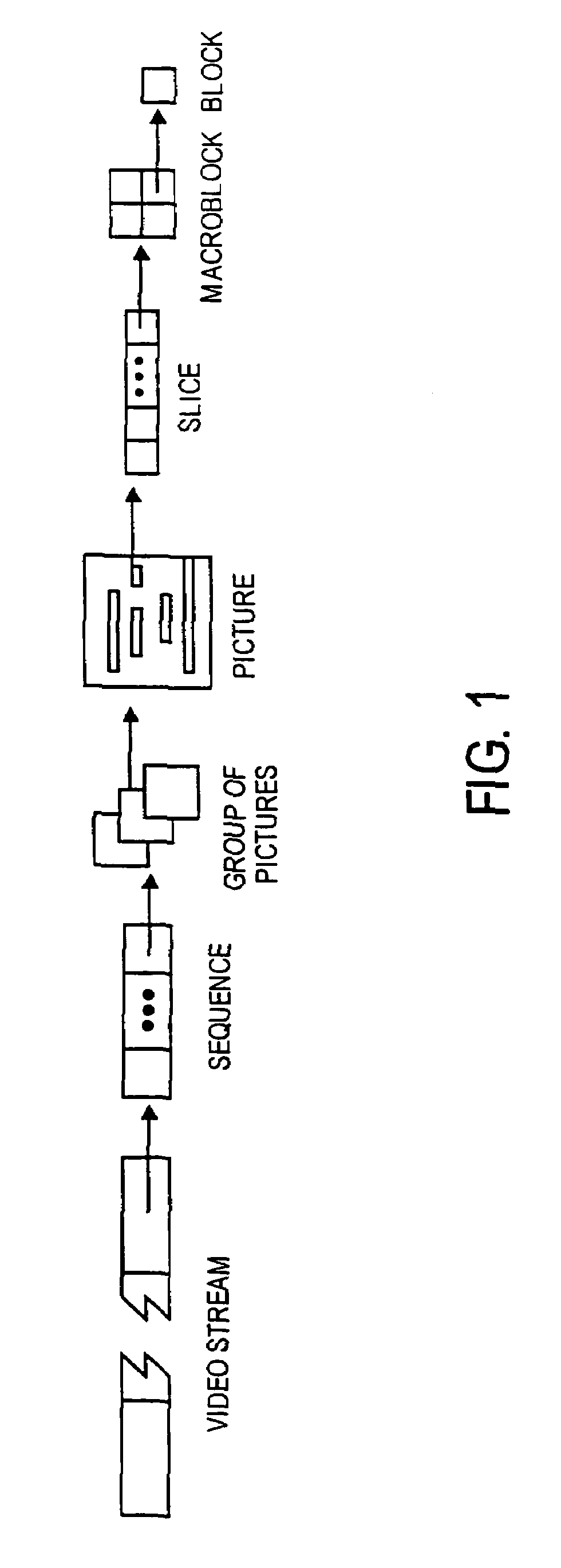

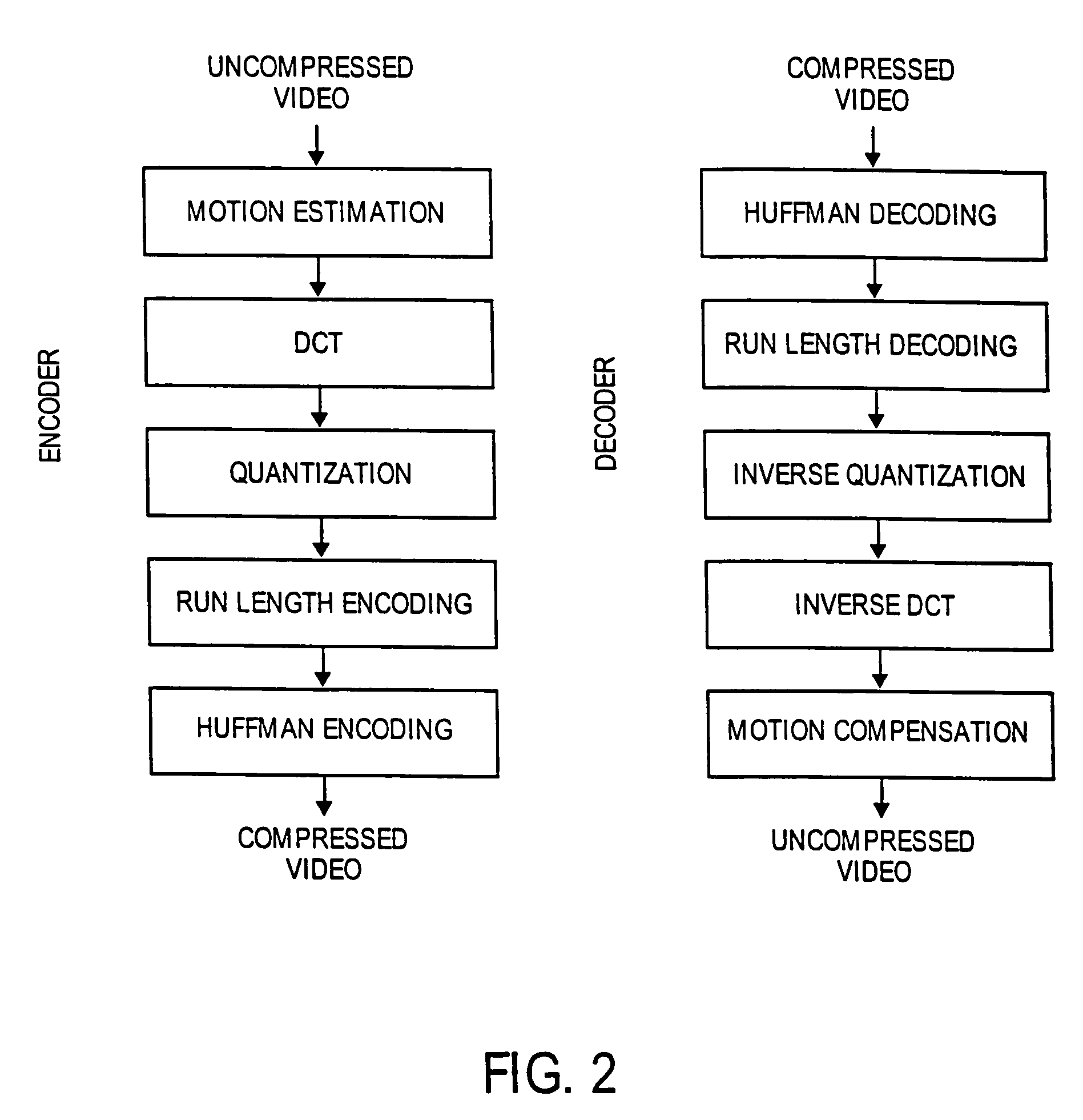

Method and apparatus for video decoding on a multiprocessor system

InactiveUS7227589B1Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningIndependent elementComputer architecture

A method and apparatus for decoding compressed video. The method includes reading a stream of compressed video into a memory. The video includes multiple pictures, with each picture having one or more independent elements. Thereafter, assigning, via a first processor of a group of processors sharing the memory, at least one independent element per processor to be decoded by the processors in parallel; and decoding the independent elements of the video stream in parallel.

Owner:INTEL CORP

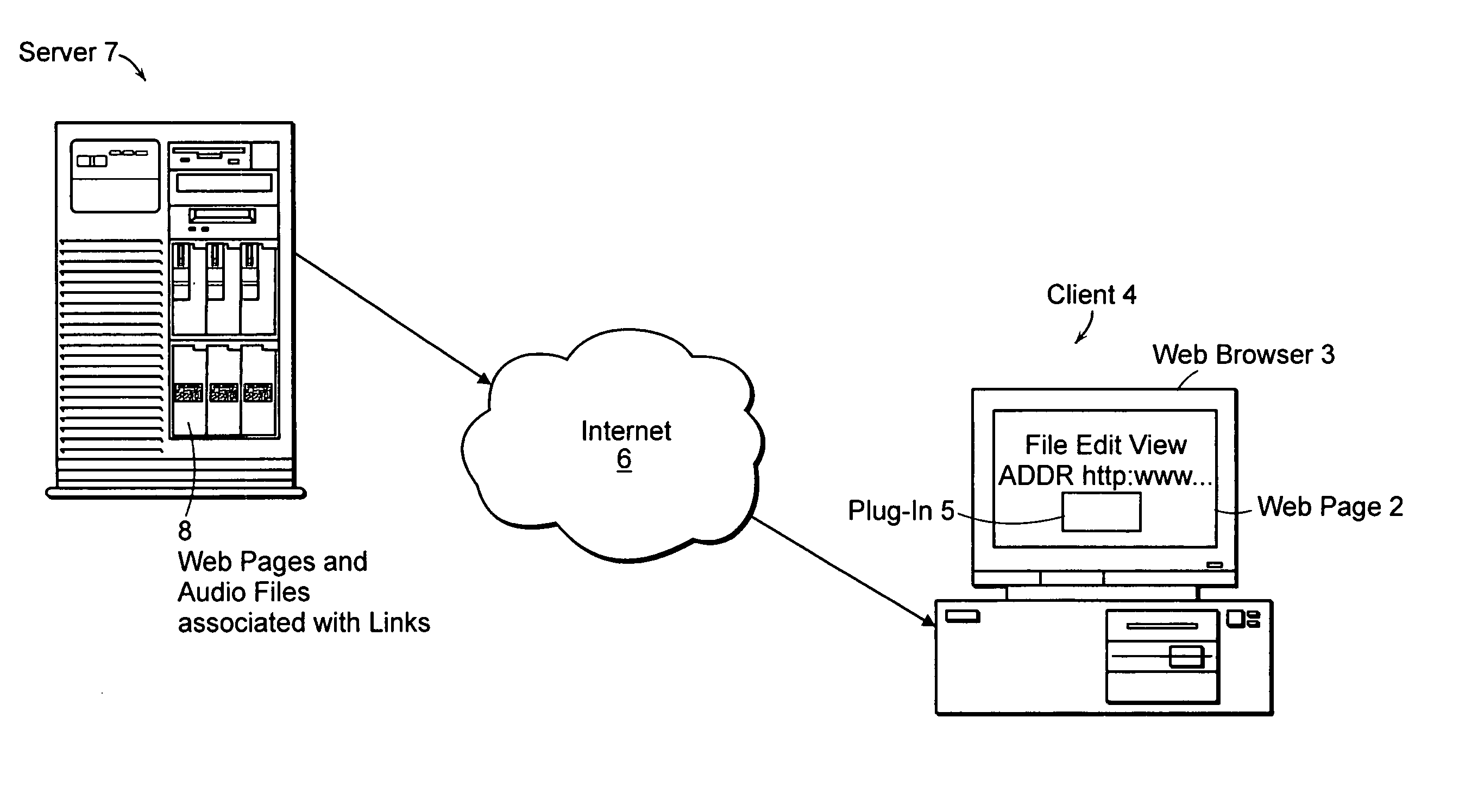

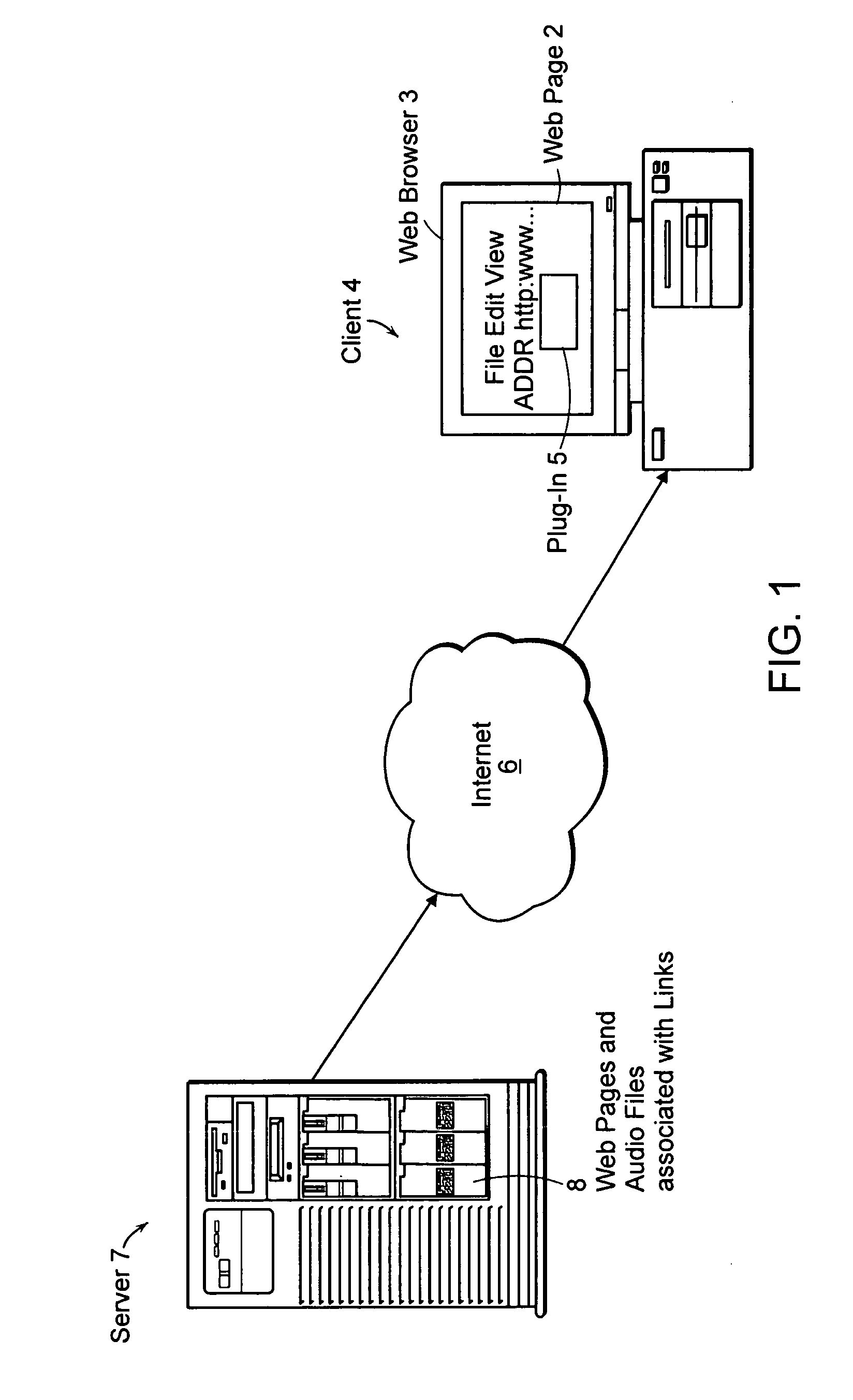

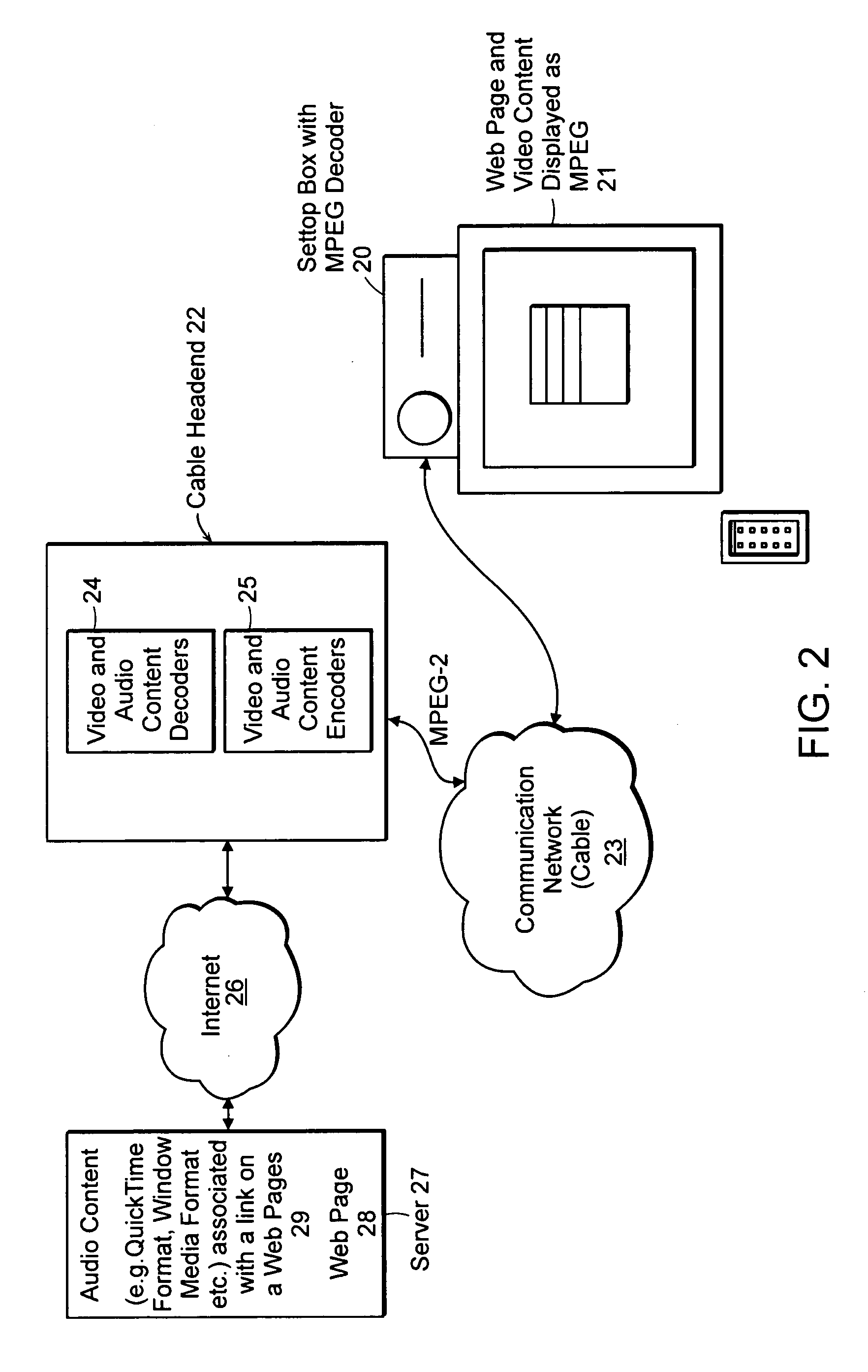

System and method for providing pre-encoded audio content to a television in a communications network

InactiveUS20070028278A1Digital computer detailsAnalogue secracy/subscription systemsMultiplexingContent distribution

A system and method for providing encoded audio content associated with visual source material in a communication network to a communication device associated with a television is disclosed. An interactive session is first established between the communication device and a content distribution platform in the communication network. A processor at the content distribution platform is assigned to the interactive session. The user may then request interactive content wherein the communication device sends a request for content to the content distribution platform and the content distribution platform retrieves the content. The visual source material may be a web page or other visual content. In order to display the web page on the television, the web page is encoded in a format that a decoder associated with the television can decode. For example, the web page may be encoded as an MPEG video stream wherein the decoder can decode an MPEG stream. The content distribution platform, which can be a cable headend, then receives a request for encoded audio content associated with a link in the visual source material wherein the request originates through use of the communication device associated with the television. The content distribution platform retrieves the encoded audio content and determines that the encoded audio content is in a format that can be decoded by the decoder. The content distribution platform then multiplexes the encoded audio content and at least a portion of the visual source material to form a multiplexed stream. The multiplexed stream is in an encoded format that can be decoded by the communication device associated with the television.

Owner:ACTIVE VIDEO NETWORKS INC

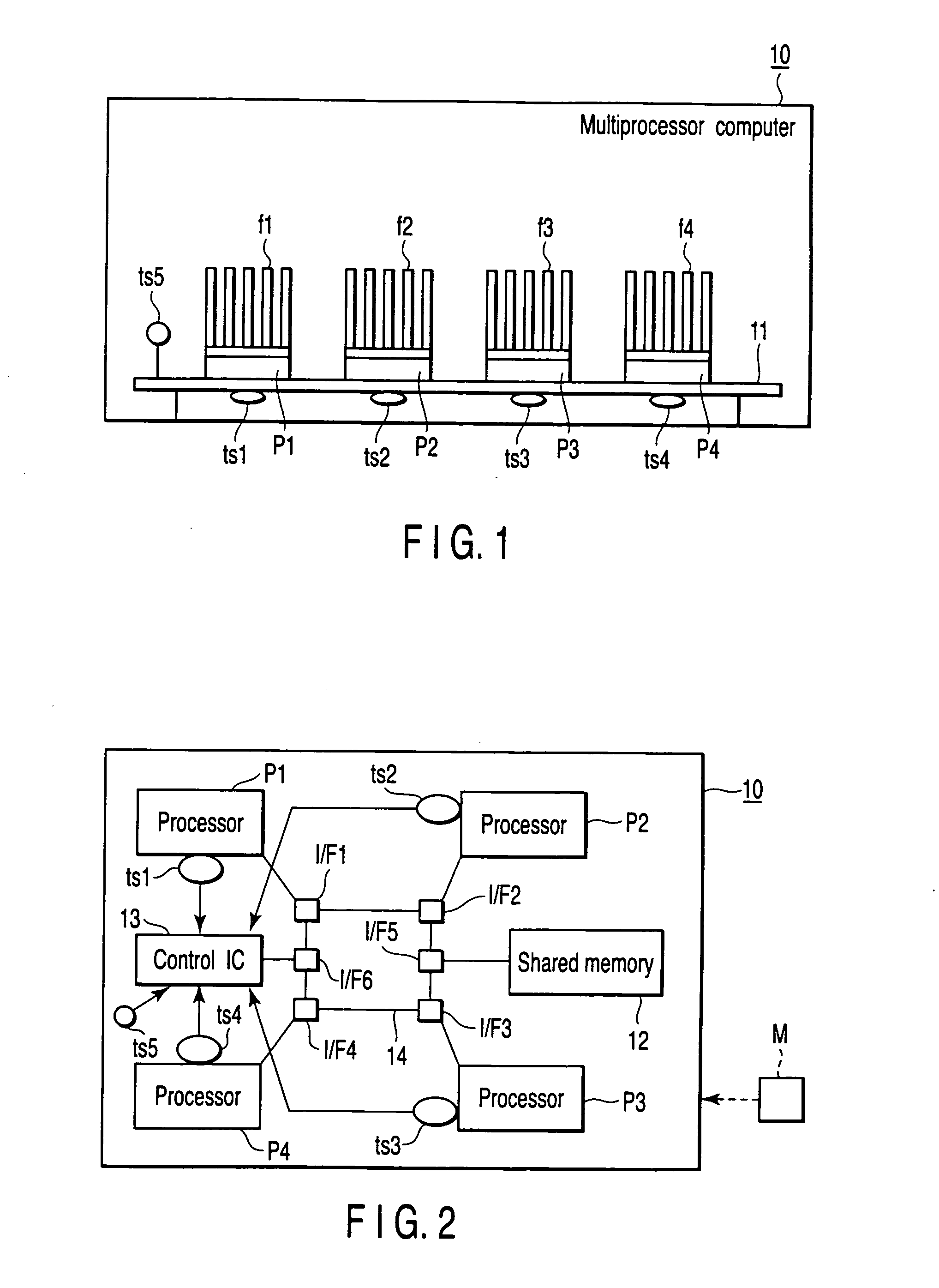

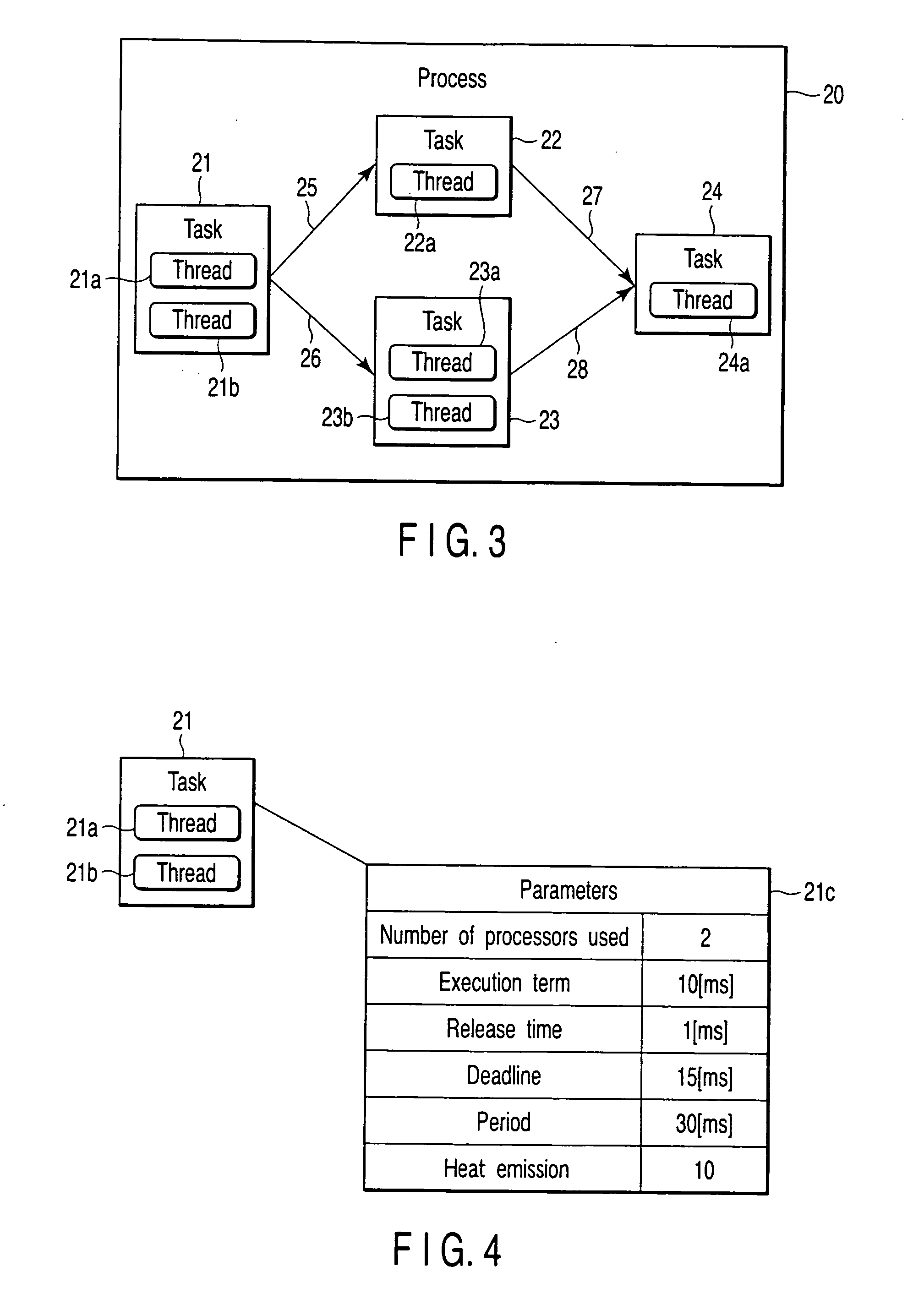

Multiprocessor computer and program

InactiveUS20060070074A1InhibitionLevel temperatureEnergy efficient ICTDigital data processing detailsTemperature controlMulti processor

According to an aspect of the present invention, the processor temperatures can be leveled among processors, thereby suppressing the occurrence of stop of processing due to overheating. For example, on the basis of the temperatures of the processors sensed by temperature sensors, the control IC assigns the processor whose temperature is the lowest to the task whose heat emission is the highest. This makes it possible to level the processor temperatures among processors and suppress occurrence of stop of processing due to overheating.

Owner:KK TOSHIBA

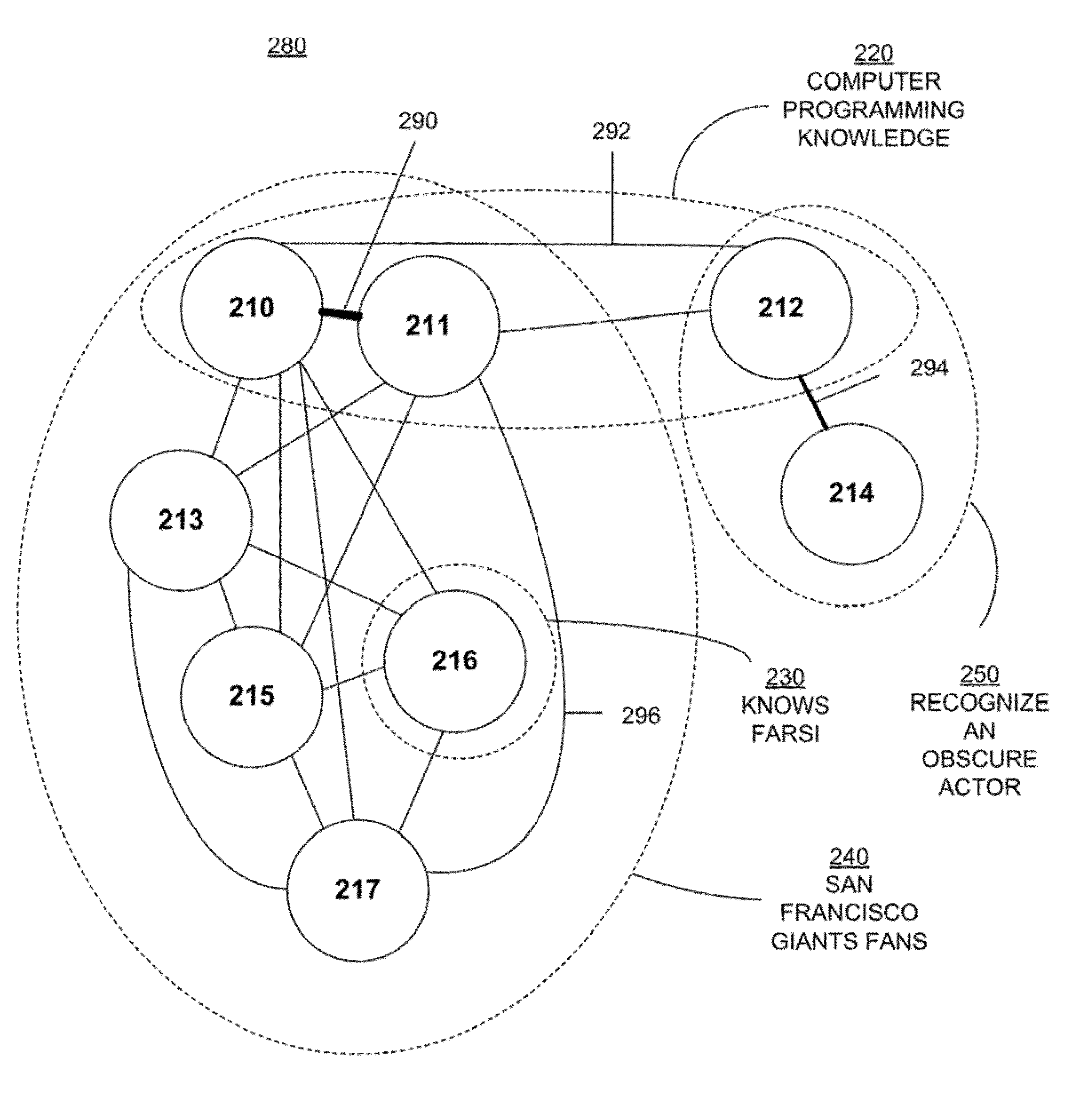

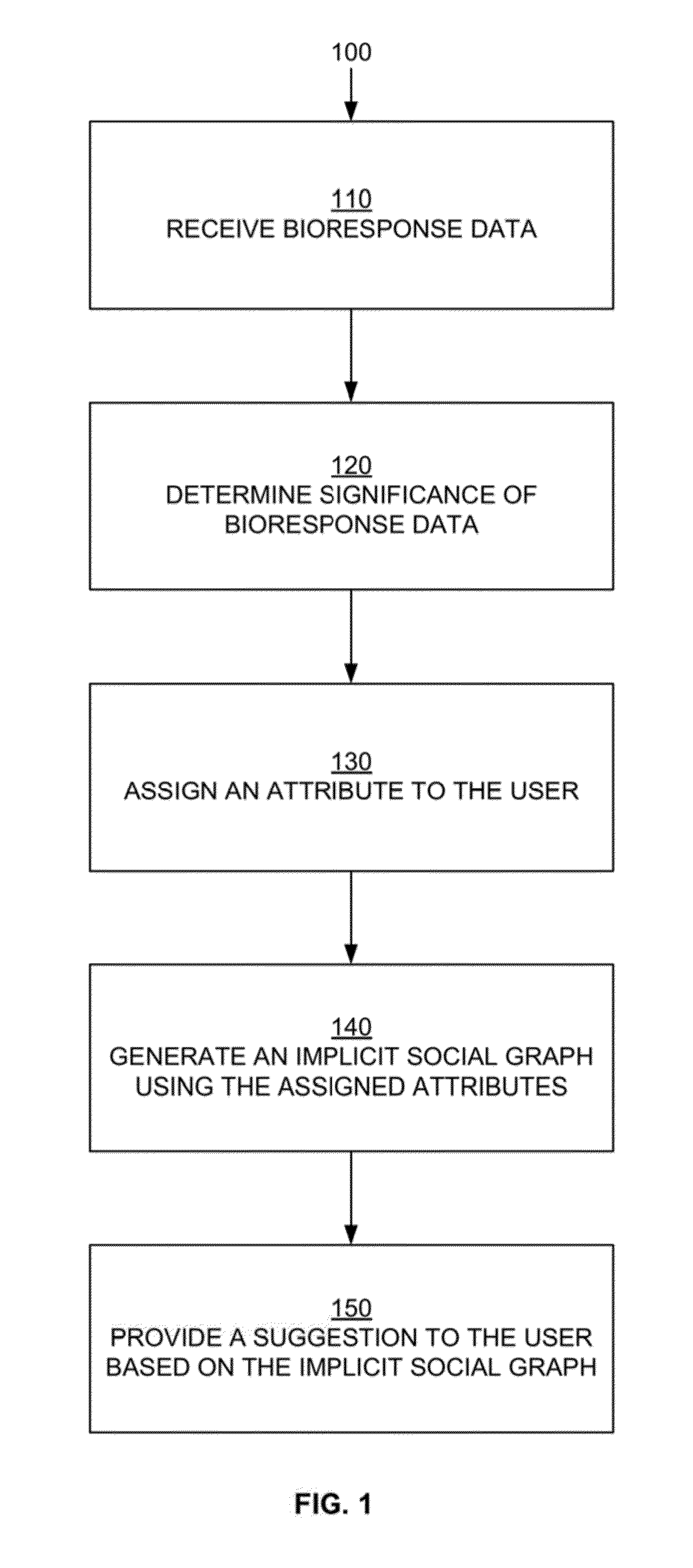

Method and system of generating an implicit social graph from bioresponse data

InactiveUS20150046496A1Input/output for user-computer interactionData processing applicationsUser deviceSocial graph

In one exemplary embodiment, a computer-implemented method of generating an implicit social graph includes receiving an eye-tracking data associated with a word. The eye-tracking data is received from a user device. The word is a portion of a digital document. The eye-tracking data comprises at least one fixation period of substantially seven-hundred and fifty milliseconds and at least one regression from another portion of the digital document to the word. A comprehension difficulty of the word is determined based on the eye-tracking data. One or more attributes to a user of the user device is assigned, by one or more processors based on the comprehension difficulty, wherein the one or more attributes are determined based on a meaning of the word. An implicit social graph is generated based on the one or more attributes.

Owner:KARMARKAR AMIT V +1

Method for controlling heterogeneous multiprocessor and multigrain parallelizing compiler

ActiveUS8250548B2Reduce executionReduce processEnergy efficient ICTMultiprogramming arrangementsGeneral purposeCost comparison

A heterogeneous multiprocessor system including a plurality of processor elements having mutually different instruction sets and structures avoids a specific processor element from being short of resources to improve throughput. An executable task is extracted based on a preset depending relationship between a plurality of tasks, and the plurality of first processors are allocated to a general-purpose processor group based on a depending relationship among the extracted tasks. A second processor is allocated to an accelerator group, a task to be allocated is determined from the extracted tasks based on a priority value for each of tasks, and an execution cost of executing the determined task by the first processor is compared with an execution cost of executing the task by the second processor. The task is allocated to one of the general-purpose processor group and the accelerator group that is judged to be lower as a result of the cost comparison.

Owner:WASEDA UNIV

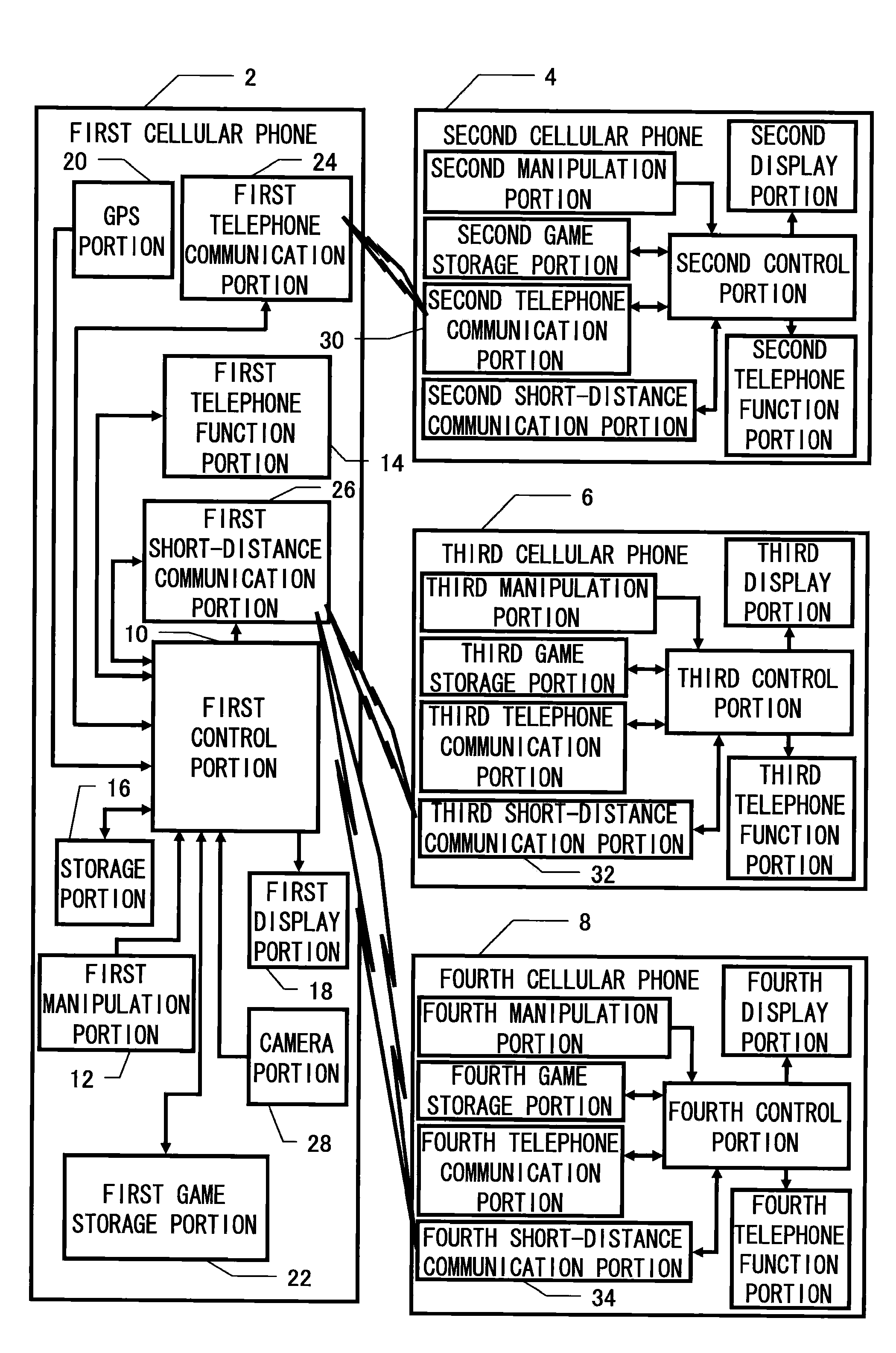

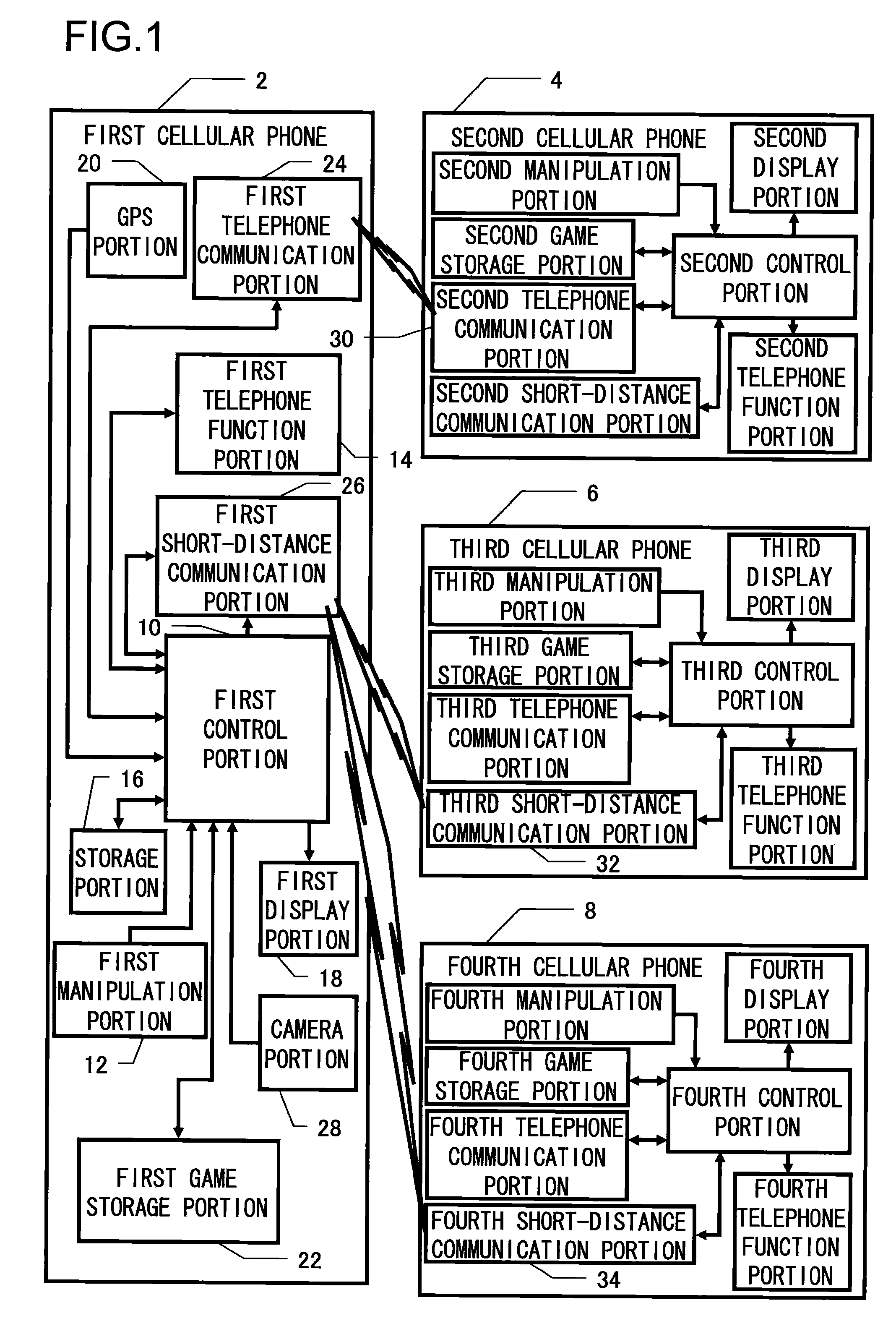

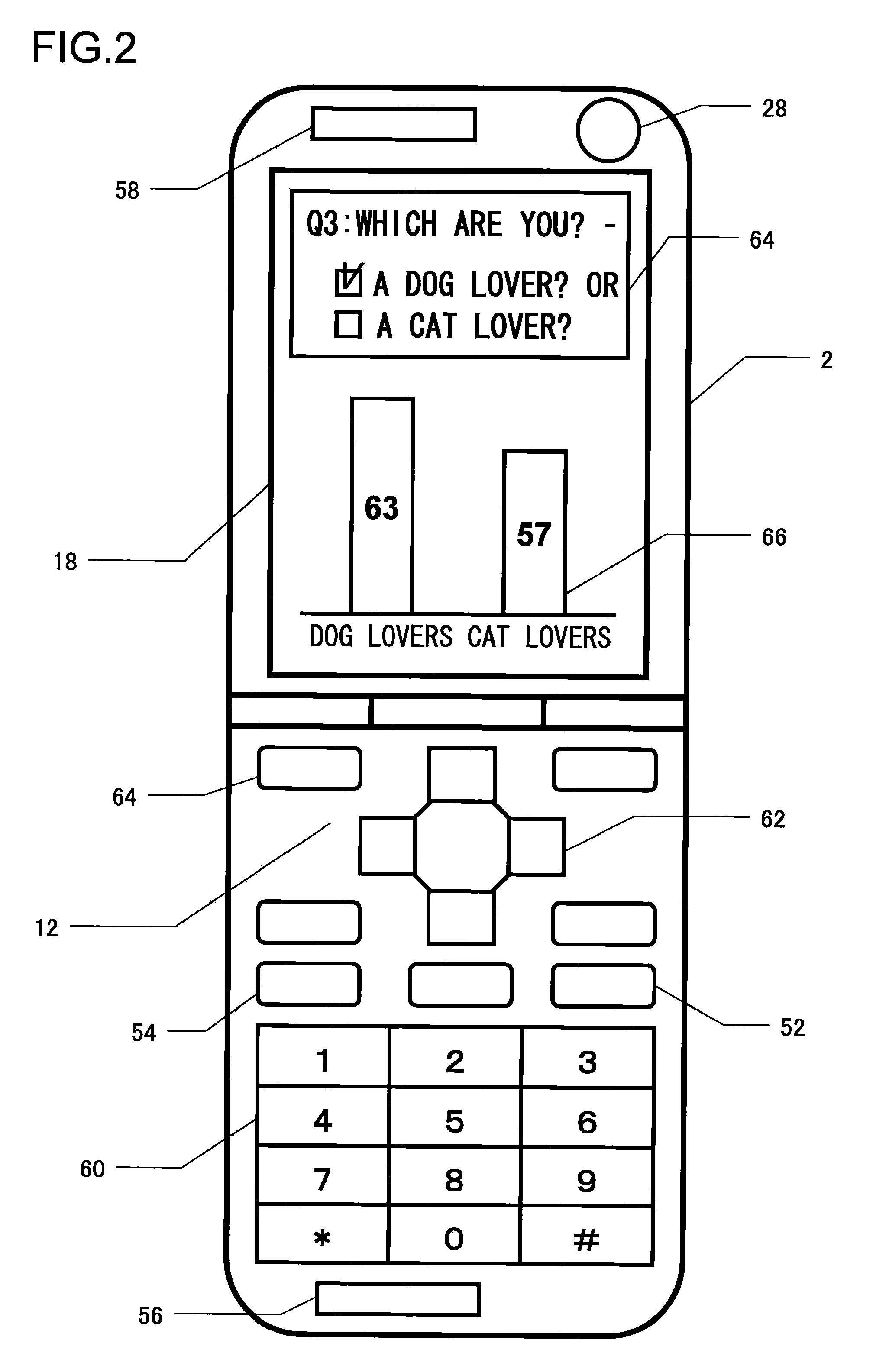

Information exchanging apparatus

ActiveUS20080268904A1Promote exchangePermits easy coordinationCommmunication supplementary servicesSubstation equipmentDistributorTelephone communication

An information exchanging apparatus capable of exchanging information with a plurality of outside apparatuses has: a first wireless communicator including a telephone transmitter and telephone receiver for wireless telephone communication with one of the outside apparatuses; a second wireless communicator other than the first wireless communicator; a transmitter arranged to transmit original information to the plurality of outside apparatuses through the second wireless communicator; a processor arranged to process response information from the plurality of outside apparatuses to be received through the second wireless communicator in response to the original information; and a distributor arranged to distribute result information from the processor to the plurality of outside apparatuses through the second wireless communicator.

Owner:ROHM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com