Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51 results about "PCI configuration space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

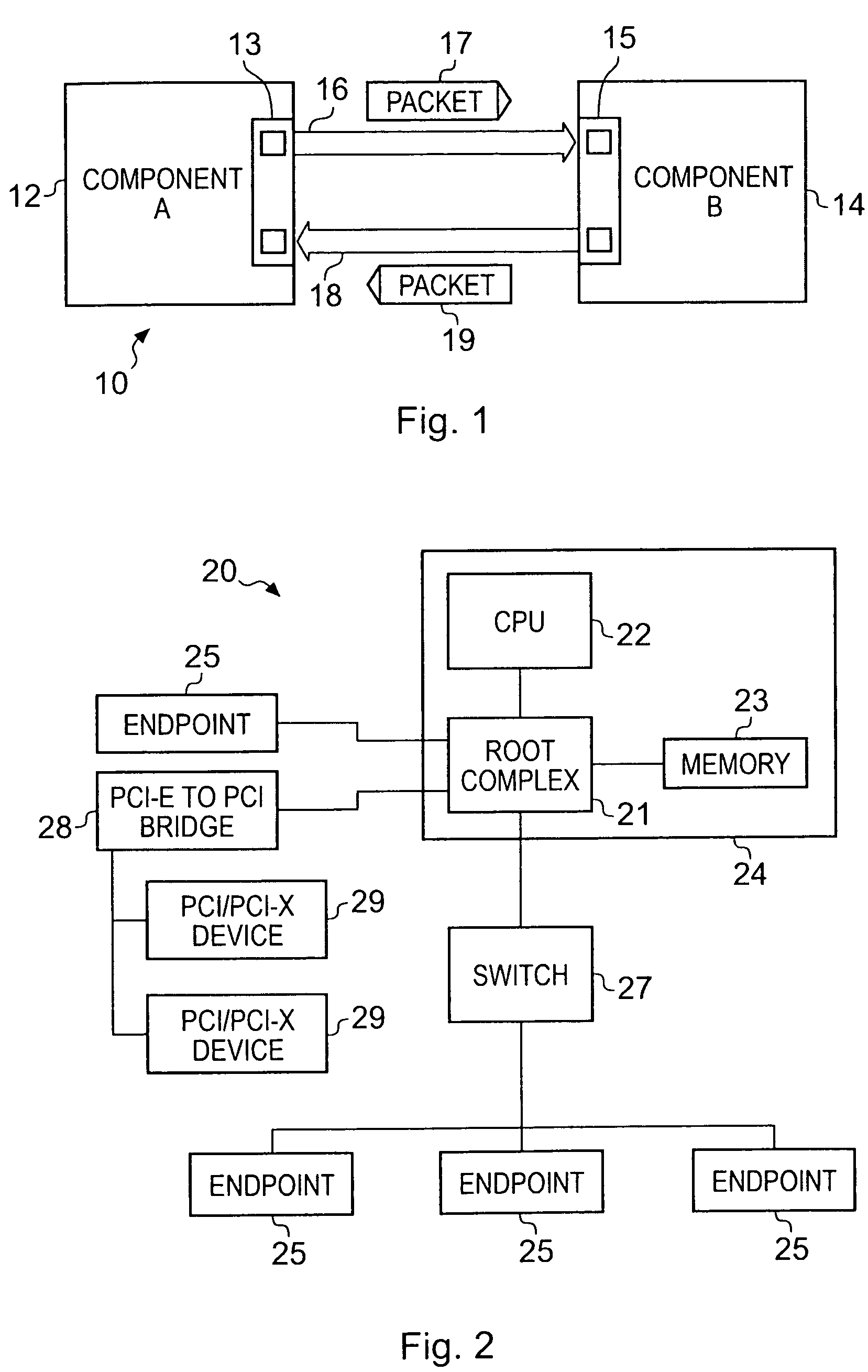

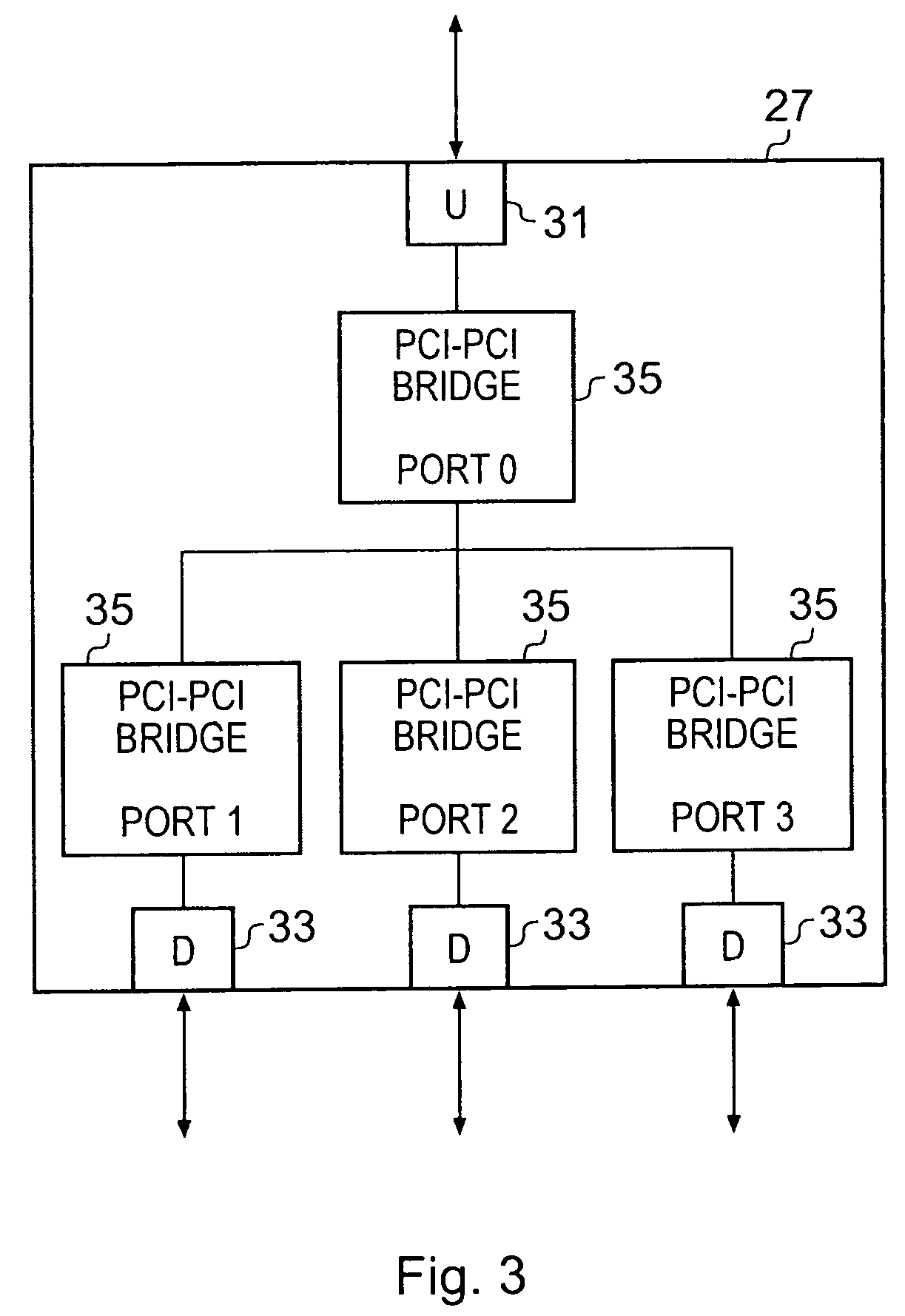

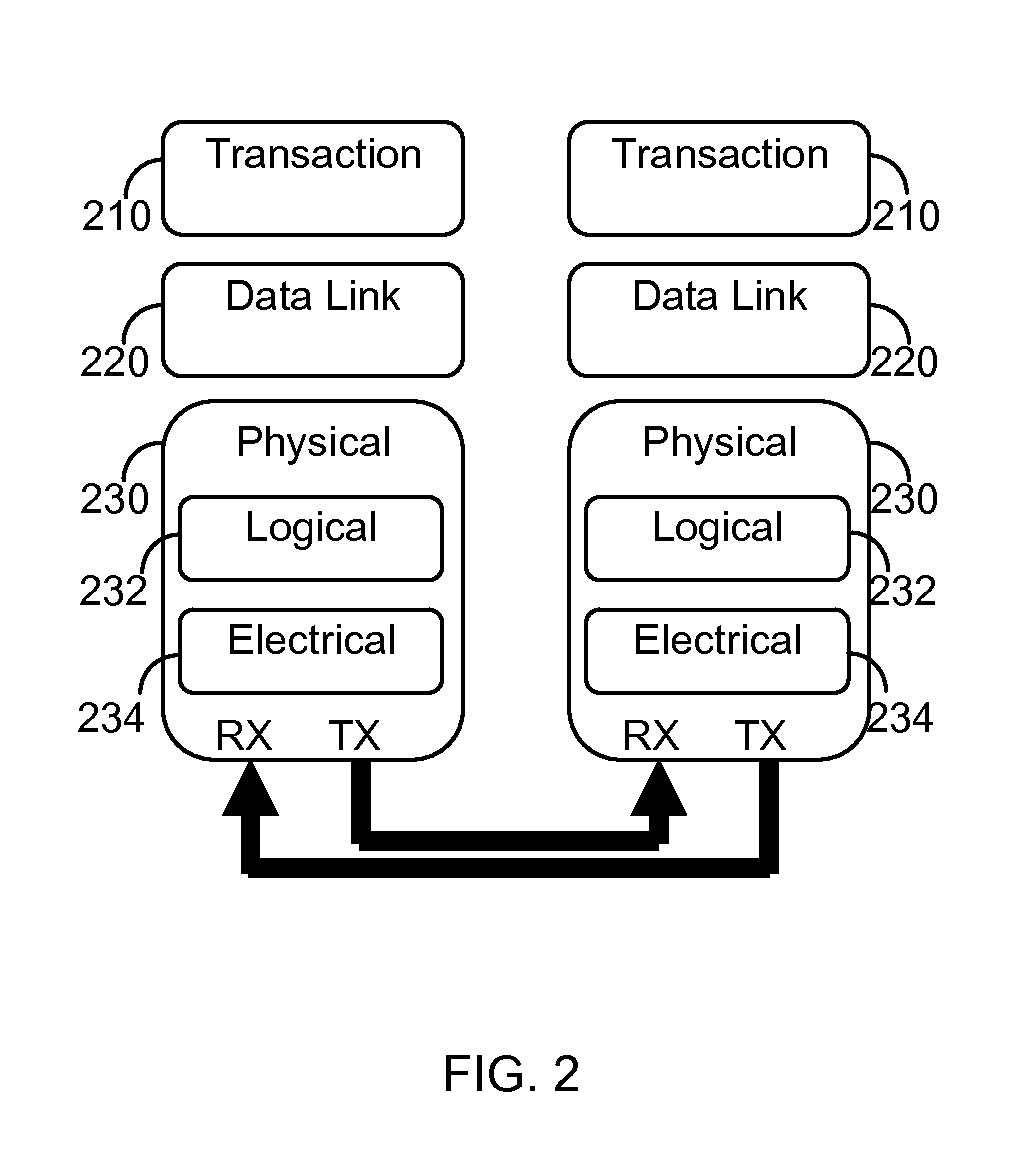

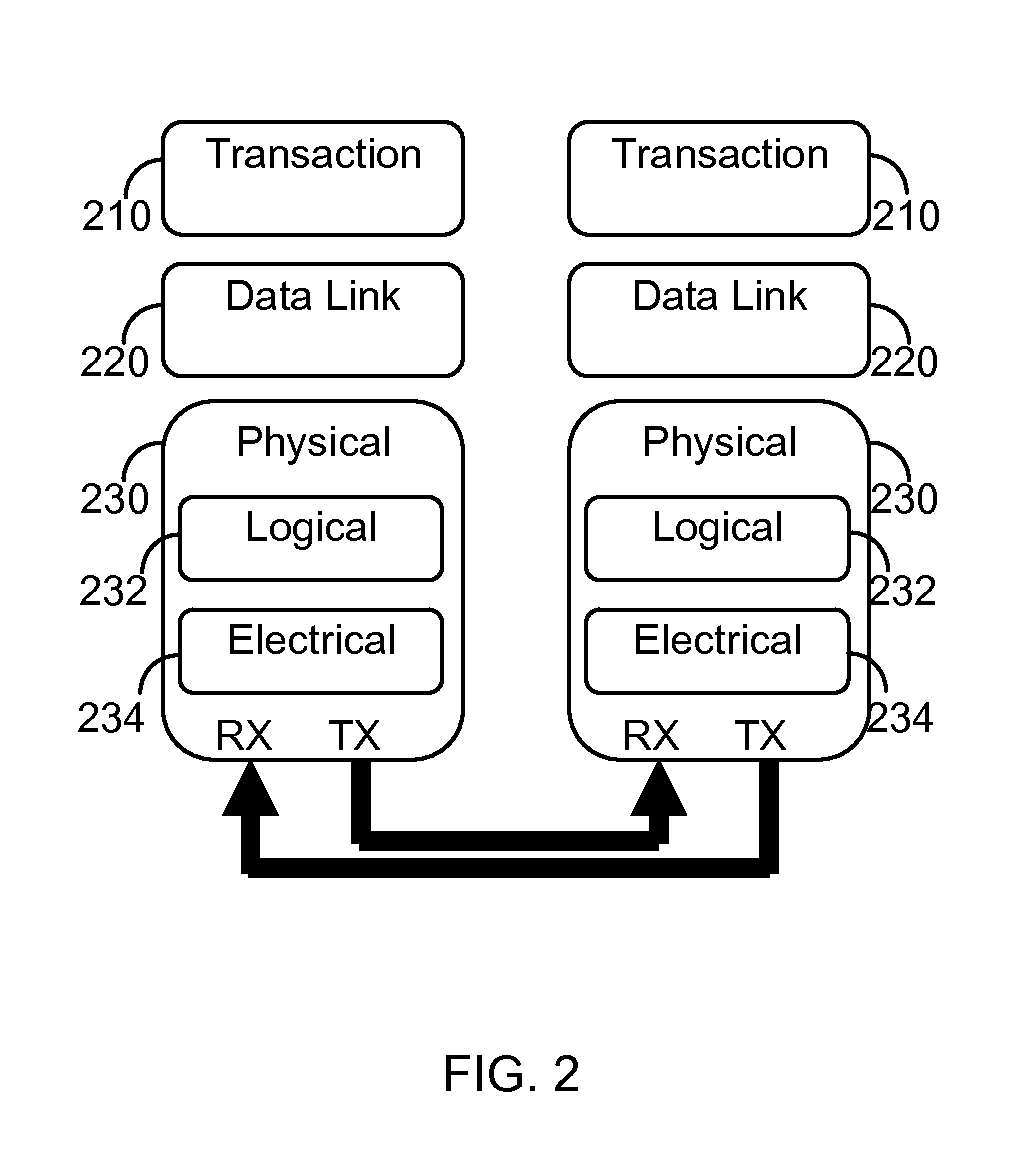

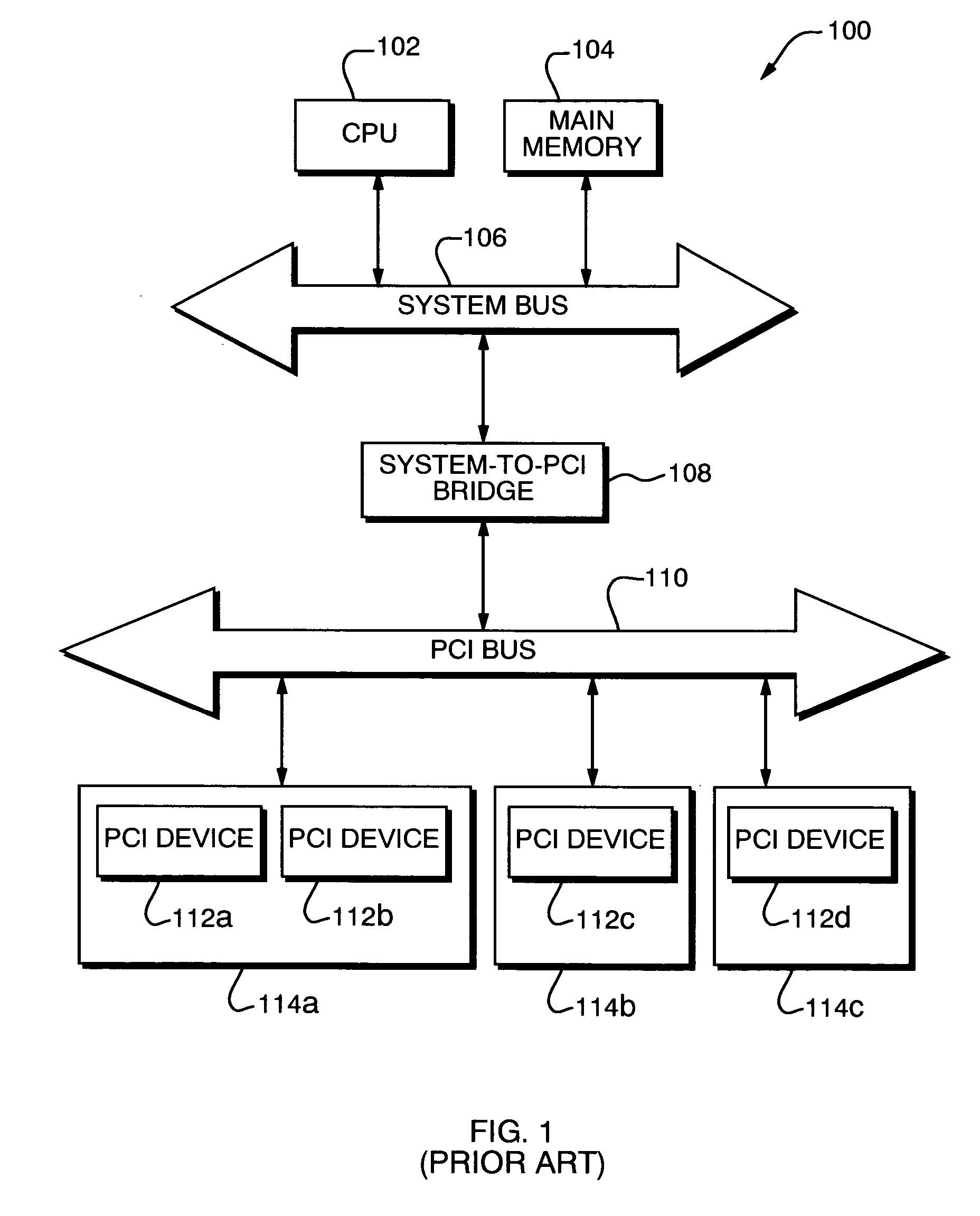

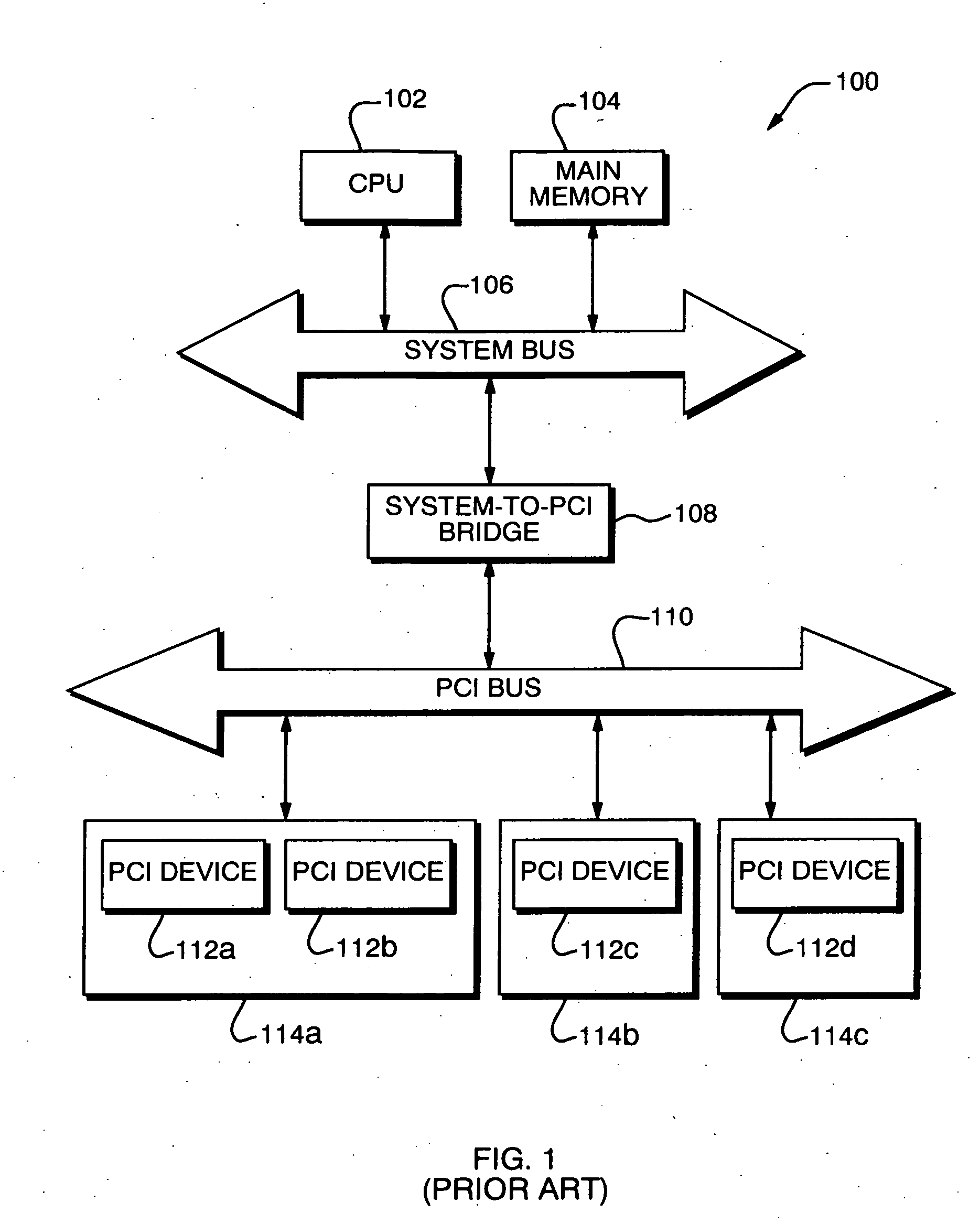

PCI configuration space is the underlying way that the Conventional PCI, PCI-X and PCI Express perform auto configuration of the cards inserted into their bus.

Flexible configuration space

A configuration space operation packet is received from a link. The configuration space operation packet is detected using a hardware mechanism. The configuration space operation packet is forwarded to a software-controlled entity for processing. A received packet can be detected as a configuration space operation packet from an address range of an address in a header of the received packet. The software-controlled entity can provide configuration space virtualisation.

Owner:ORACLE INT CORP

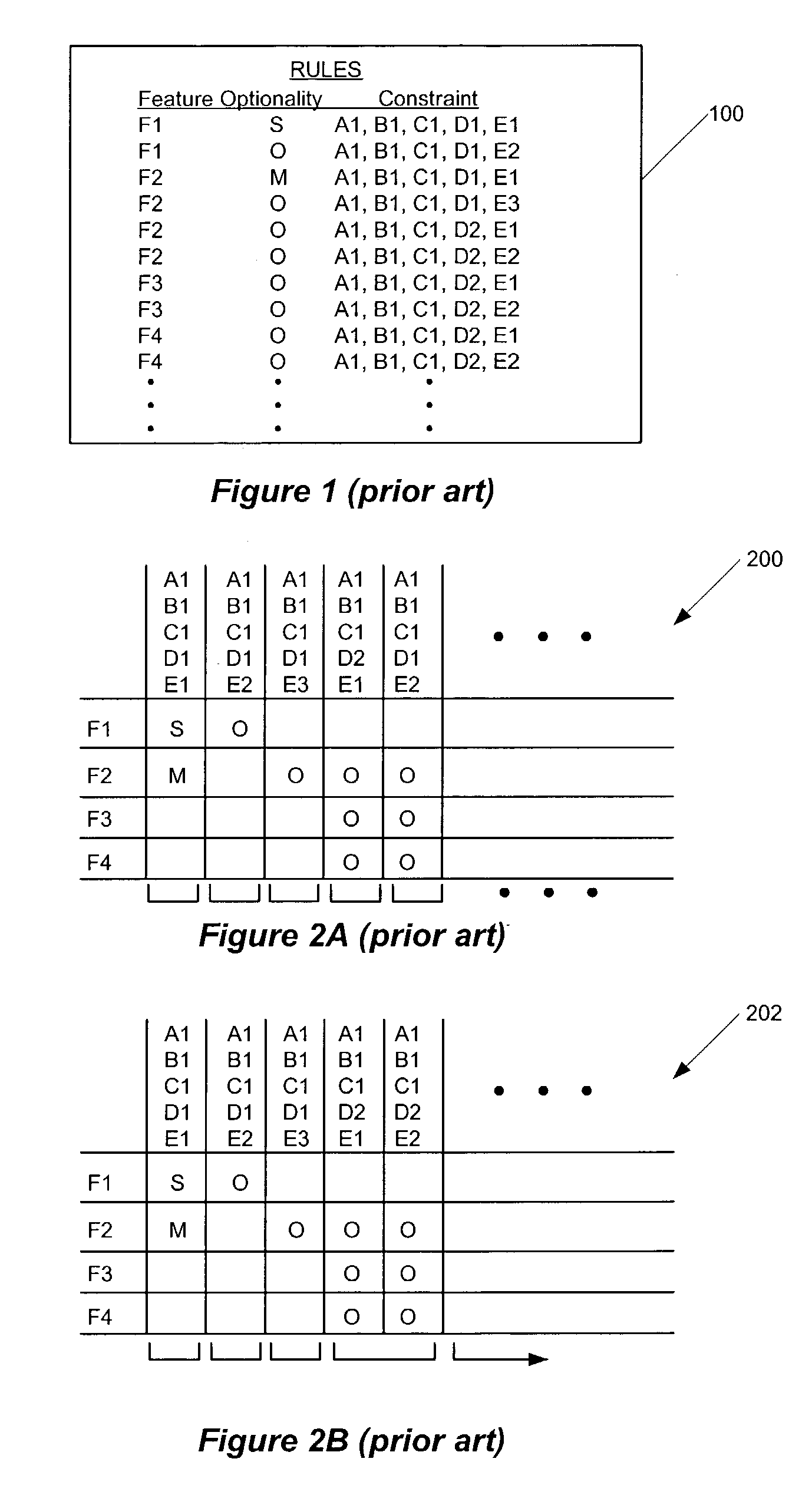

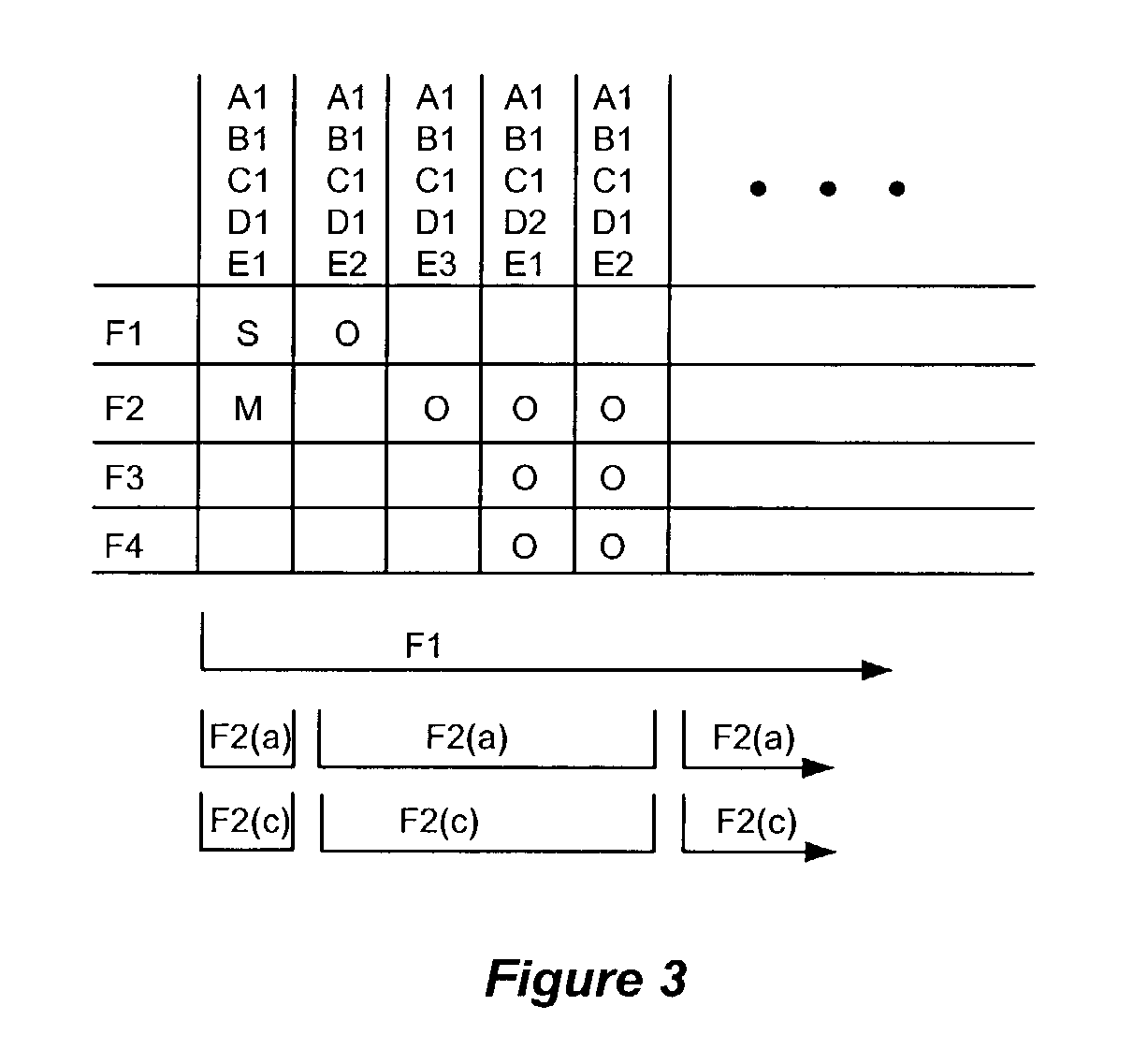

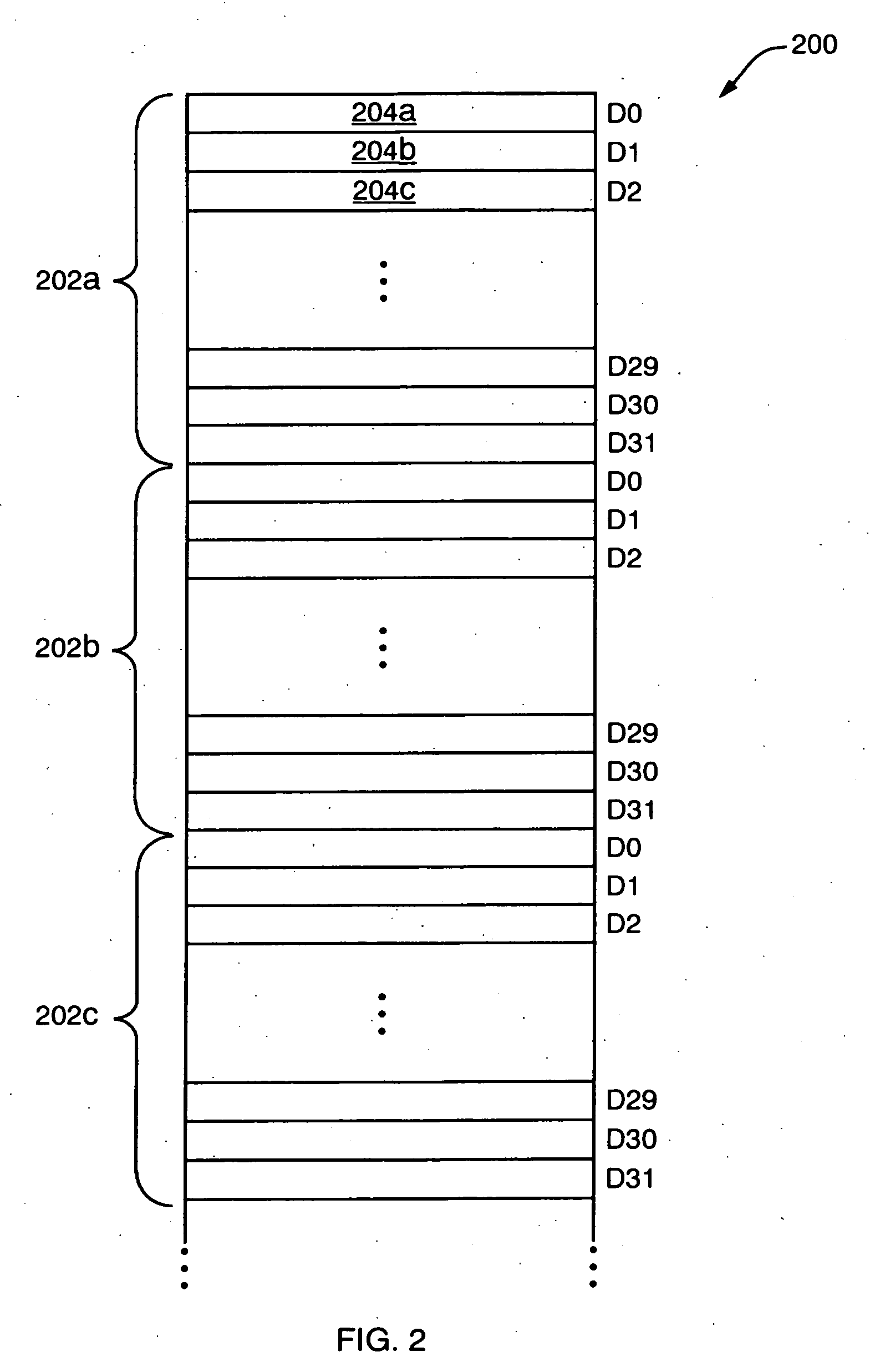

Configuration model consistency checking using flexible rule space subsets

ActiveUS7200582B1Constraint-based CADKnowledge representationTheoretical computer scienceSystems approaches

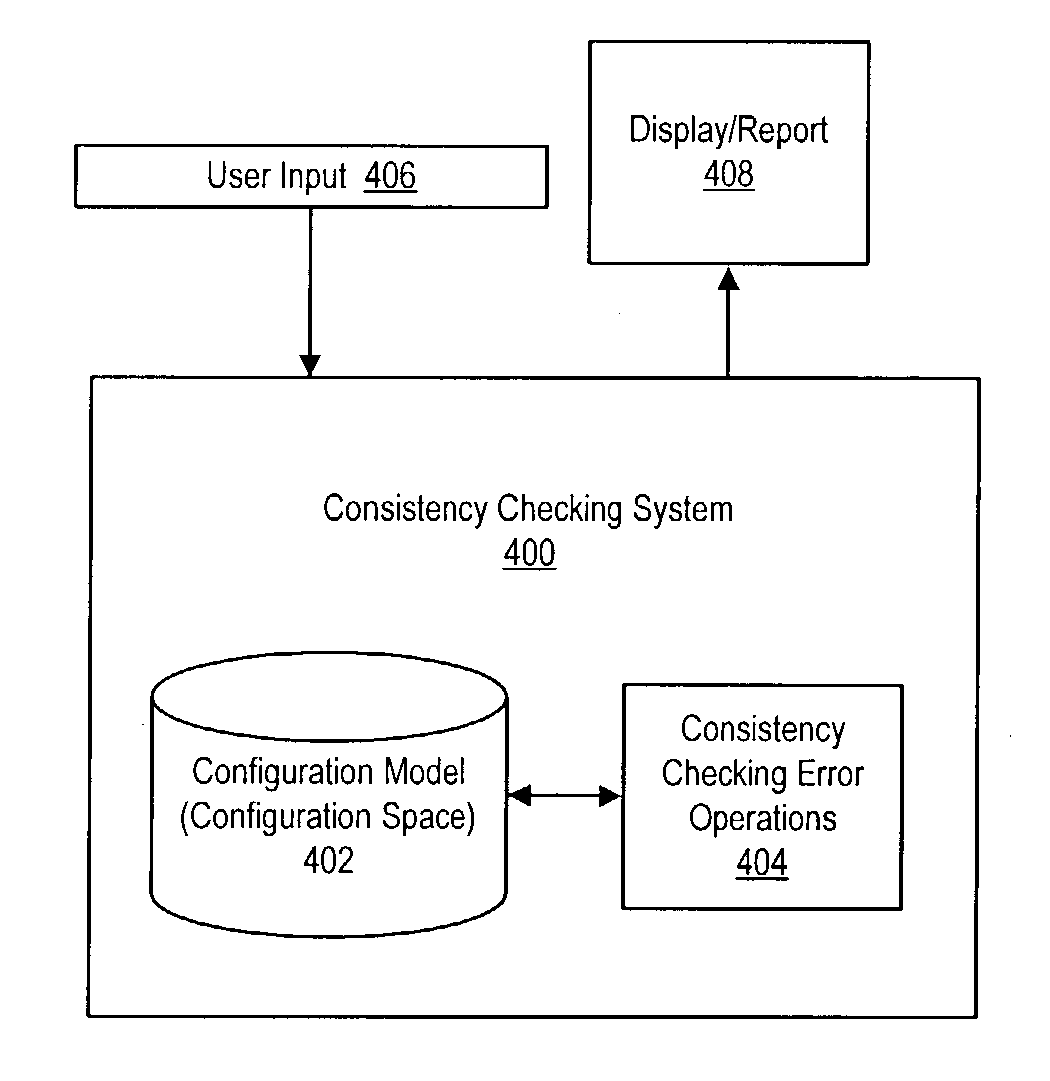

Inconsistencies between configuration rules represent a significant concern when modeling a product using configuration rules. The consistency checking system approaches a configuration model from the perspective of a sets of features and families. The configuration space of a model represents the entire set of all combinations of selections within a configuration model. The consistency checking system operates on subsets of the configuration space by consolidating data within the configuration space into minimized subsets that represent a portion of the configuration space where a particular consistency error can occur. Thus, the contents of each subset vary depending upon which consistency error is being checked, and consistency checking is performed on reduced subsets determined on an error by error basis rather than on the configuration space as a whole.

Owner:VERSATA DEV GROUP

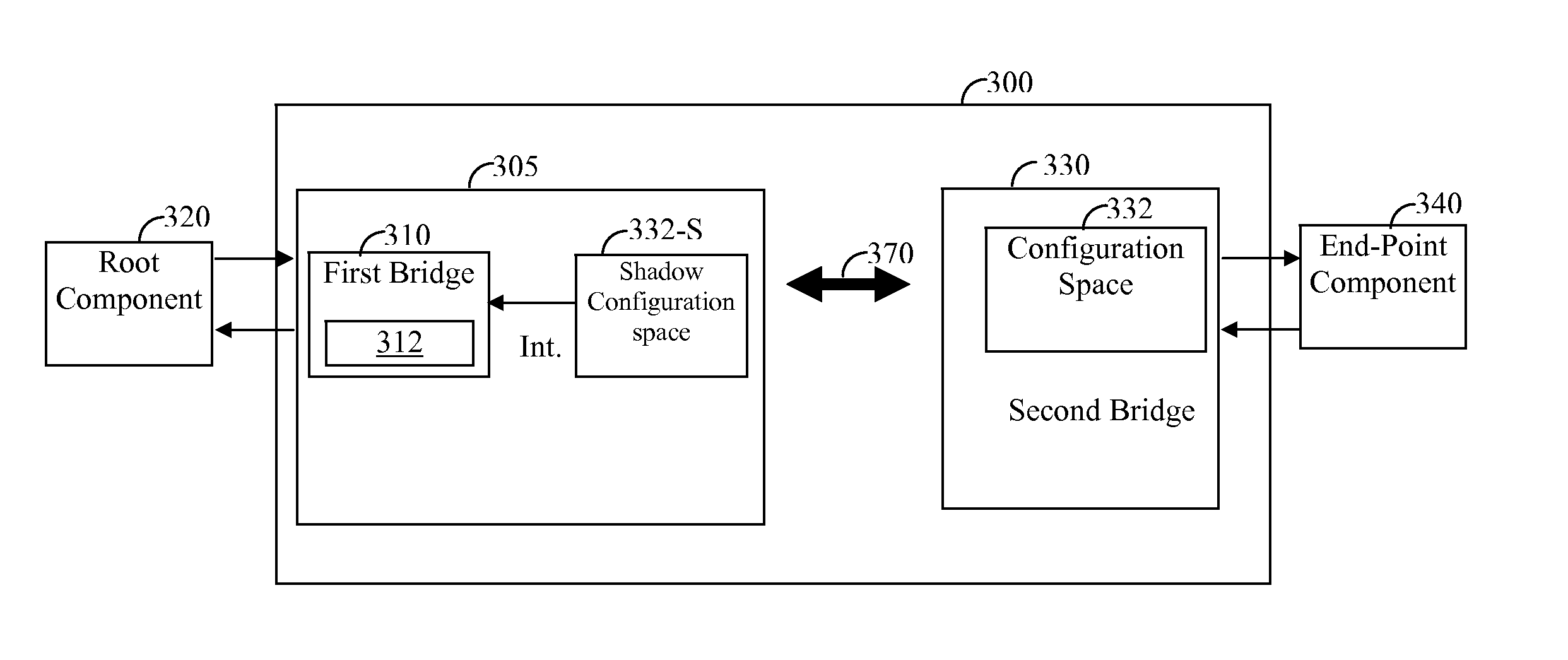

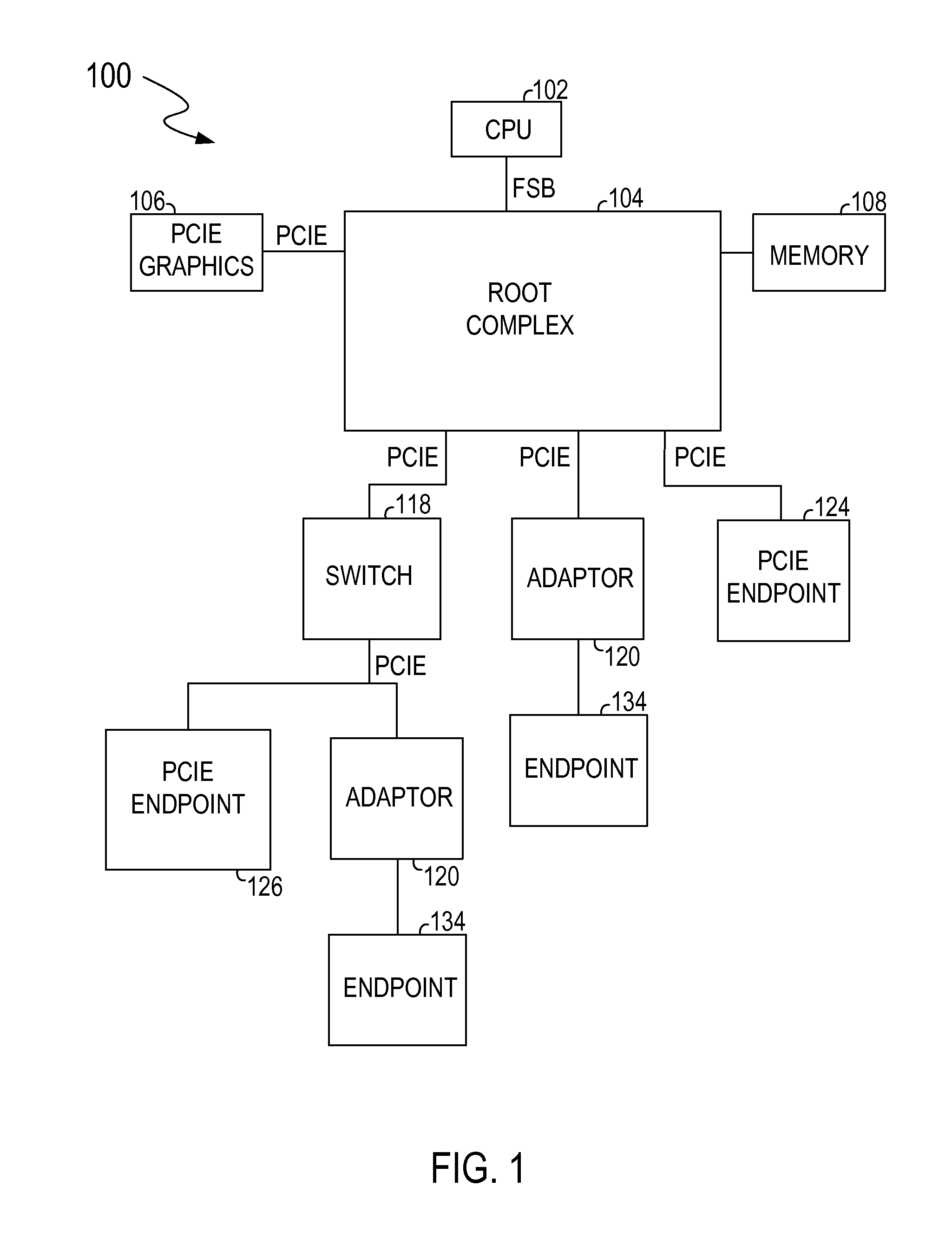

Hot Plug Process in a Distributed Interconnect Bus

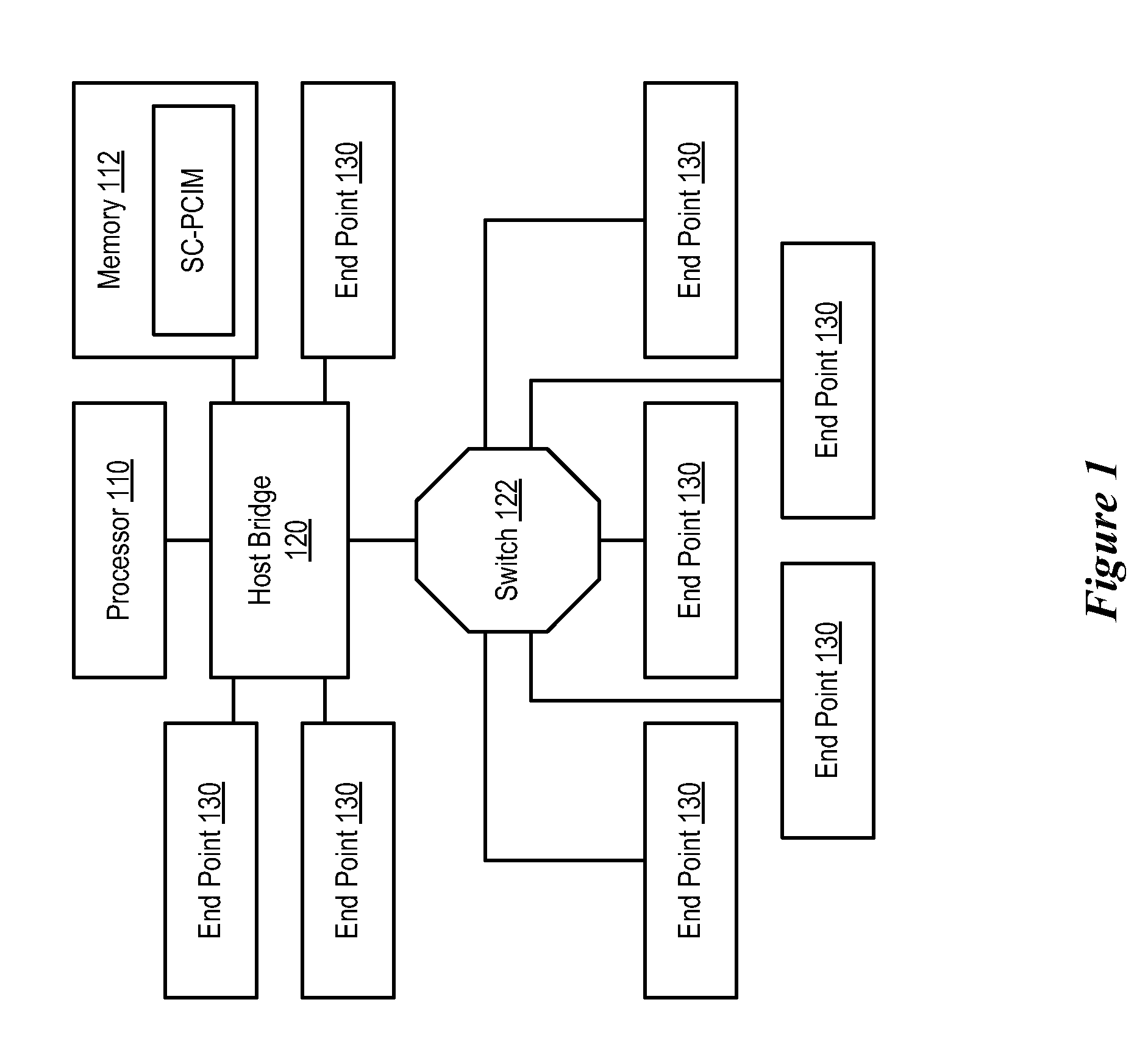

ActiveUS20120072633A1Component plug-in assemblagesElectric digital data processingProcessor registerPCI configuration space

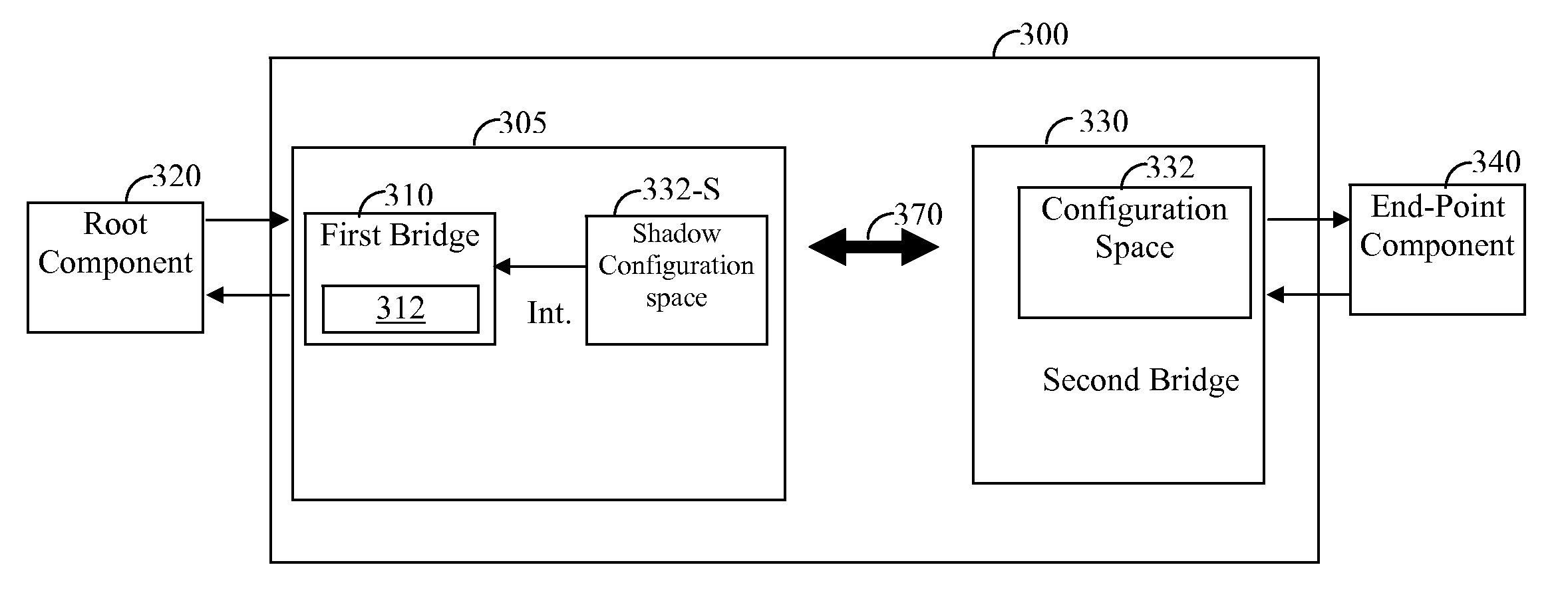

A distributed PCIe adapted to support a hot-plug process triggered by any change in a status of a distributed link, comprises an upstream bus unit including a first bridge connected to a root component and adapted to maintain a first configuration space and a copy of a second configuration space, the first configuration space bridge includes at least hot-plug registers specifying at least capabilities and status of a slot of the first bridge; and a second bridge connected to an endpoint component and adapted to maintain the second configuration space, the second configuration space includes at least hot-plug registers specifying at least capabilities and status of a slot of the second bridge.

Owner:QUALCOMM INC

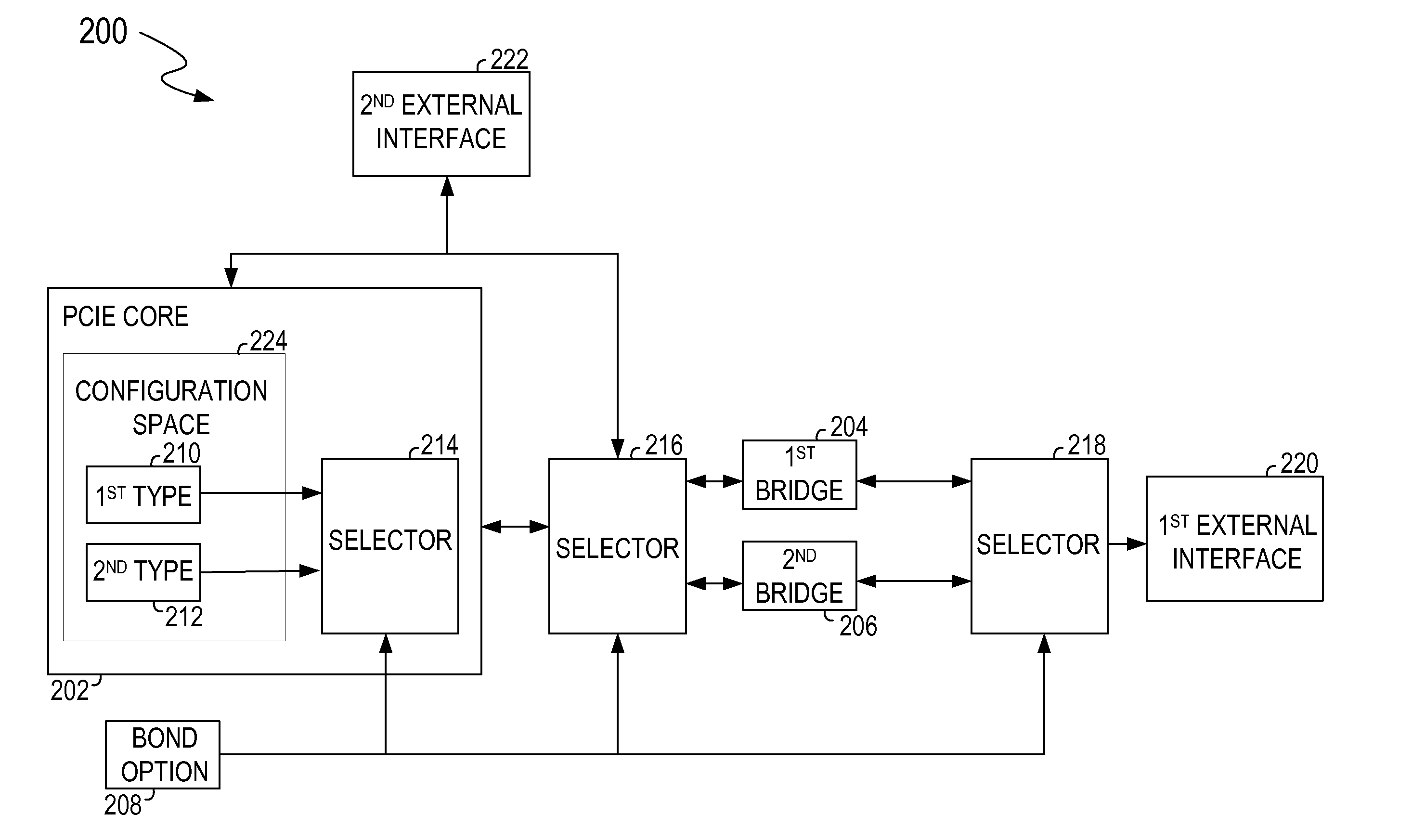

Use of bond option to alternate between PCI configuration space

InactiveUS20090292854A1Low costImprove efficiencyElectric digital data processingPCI configuration spaceEmbedded system

An adaptor for adapting one of a first device complying with a first bus, and a second device complying with a second bus to a Peripheral Component Interconnect Express (PCIe) interface. The adaptor comprises a first bridge for interconnecting the first bus with the PCIe bus, a second bridge for interconnecting the second bus with the PCIe bus, and a PCIe core coupled to the two bridges. A bond option signal is coupled to the two bridges and the PCIe core for enabling one of the two bridges, and one of the two bridges is configured by the PCIe core.

Owner:O2 MICRO INC

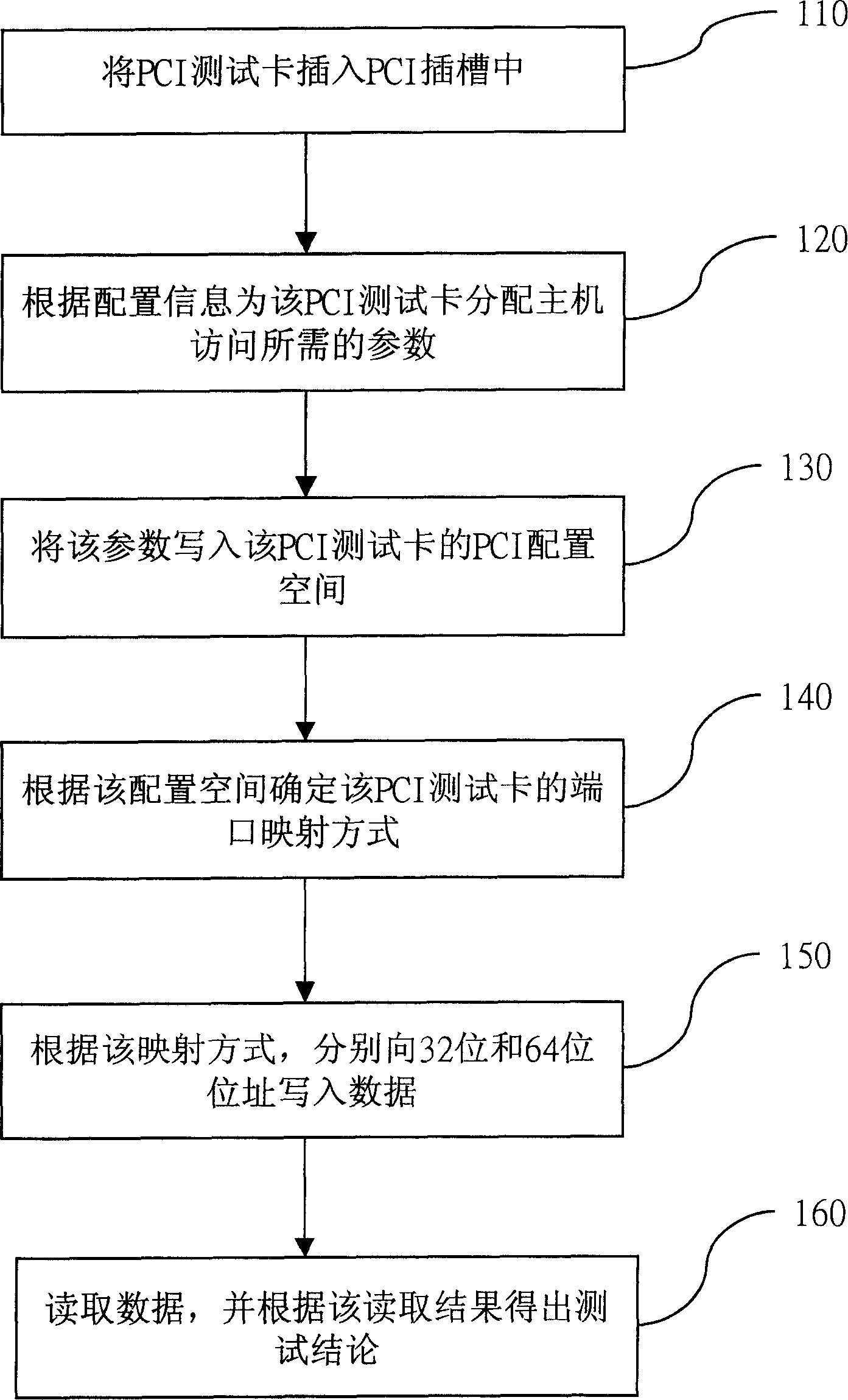

Method for testing interconnected bus of external components

InactiveCN1516014ALarge memory spaceVerify performanceDetecting faulty computer hardwareInternal memoryTest card

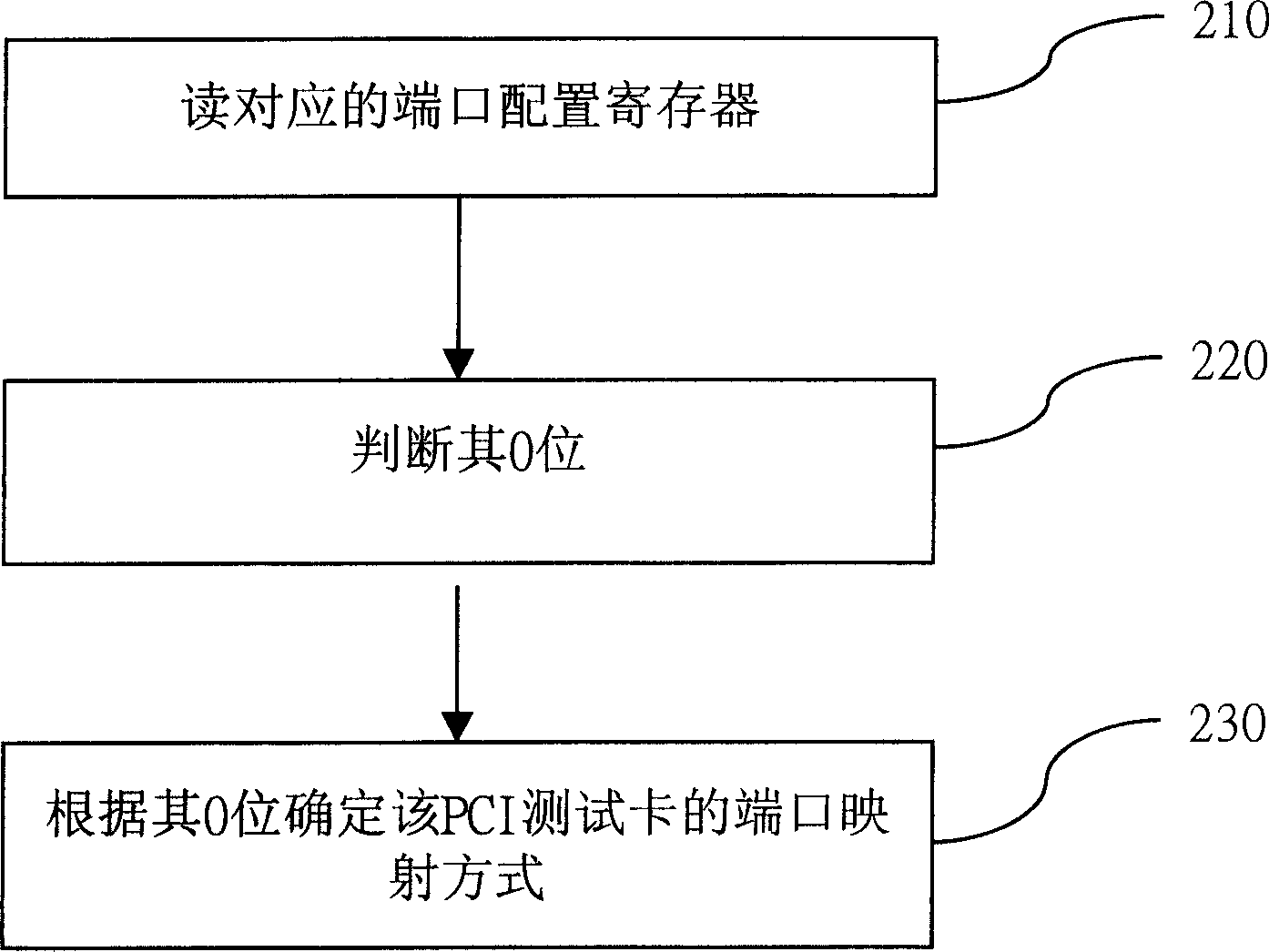

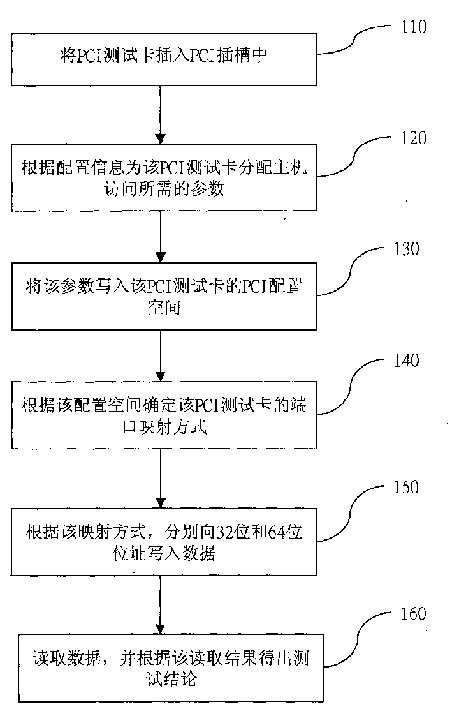

The present invention relates to a testing method of interconnection buss for peripheral components. It utilizes PCI test card to directly operate I / O and internal memory space of PCI bus map, firstly, the PCI test card is inserted into PCI slot, then according to the configuration information the parameters required for host access can be distributed for said PCI test card, then the parameters can be written into the PCI configuration space of PCI test card, according to said configuration space the port mapping mode of said PCI test card can be defined, the data can be written into 32-bit and 64-bit address respectively, finally, according to fetch result the test conclusion can be obtained.

Owner:INVENTEC CORP

Humanoid robot stable waling control method

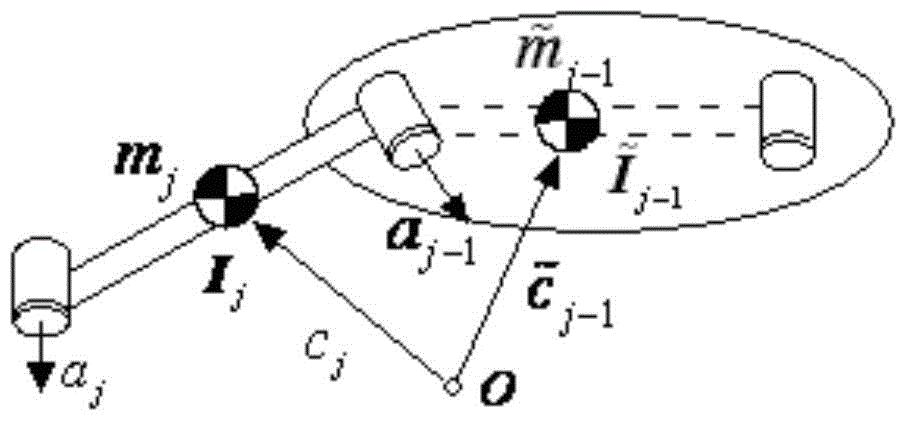

ActiveCN104407611ASuppress unknown perturbationsReasonable methodPosition/course control in two dimensionsRobotic systemsMomentum

The invention relates to a humanoid robot stable waling control method comprising the steps that step S1: momentum and angular momentum generated for compensation of a ZMP tracking error by a robot system are acquired; step S2: mapping from a robot configuration space to the momentum and the angular momentum is acquired by utilizing a momentum jacobian matrix based on the mode of differential kinematics; step S3: damping pseudo inverse calculation is performed on the momentum jacobian matrix so that inverse mapping of mapping in the step S2 is obtained, and thus a robot configuration space command is acquired and is corresponding to momentum compensation control task in walking; and step S4: the momentum compensation control task is allocated by adopting a dynamic priority switching mode, and movement commands of all joints are generated. Compared with methods in the prior art, parsing momentum control is applied to humanoid robot balance control via a ZMP calculation formula, and the control problem is integrated into a task space control system so that unknown disturbance can be suppressed by the humanoid robot by utilizing compensation momentum generated by local movement.

Owner:TONGJI UNIV

Configuration representation and modeling using configuration spaces

ActiveUS7953779B1Facilitate useful presentationOther databases browsing/visualisationCommerceGraphicsAutomatic transmission

Configuration spaces facilitate the useful presentation of data, particularly configuration data used for representing configured products. Products include features and common features can be grouped by families. For example, an automobile can include a transmission family. The transmission family could include features such as automatic transmission and 4-speed manual transmission. Configuration spaces can be achieved by consolidating selected data without loosing useful information. The degree of consolidation achieved can be significant enough to permit display of data using conventional display technology. Configuration spaces break down the “universe” of possible configurations into constituent spaces defined by groups of rules for a selected feature. Common dependencies between the selected feature and related features can be consolidated to produce a more minimal form of the data used for representing the selected features and related features. Configuration spaces can provide a useful graphical view of the breakdown of all rules written for a single feature or multiple features. The data present in this view can be analyzed to, for example, study the dependency paths of an existing configuration and better understand the impact of revising configuration relationships. Thus, configuration spaces aid in the creation and modification of configuration models.

Owner:VERSATA DEV GROUP

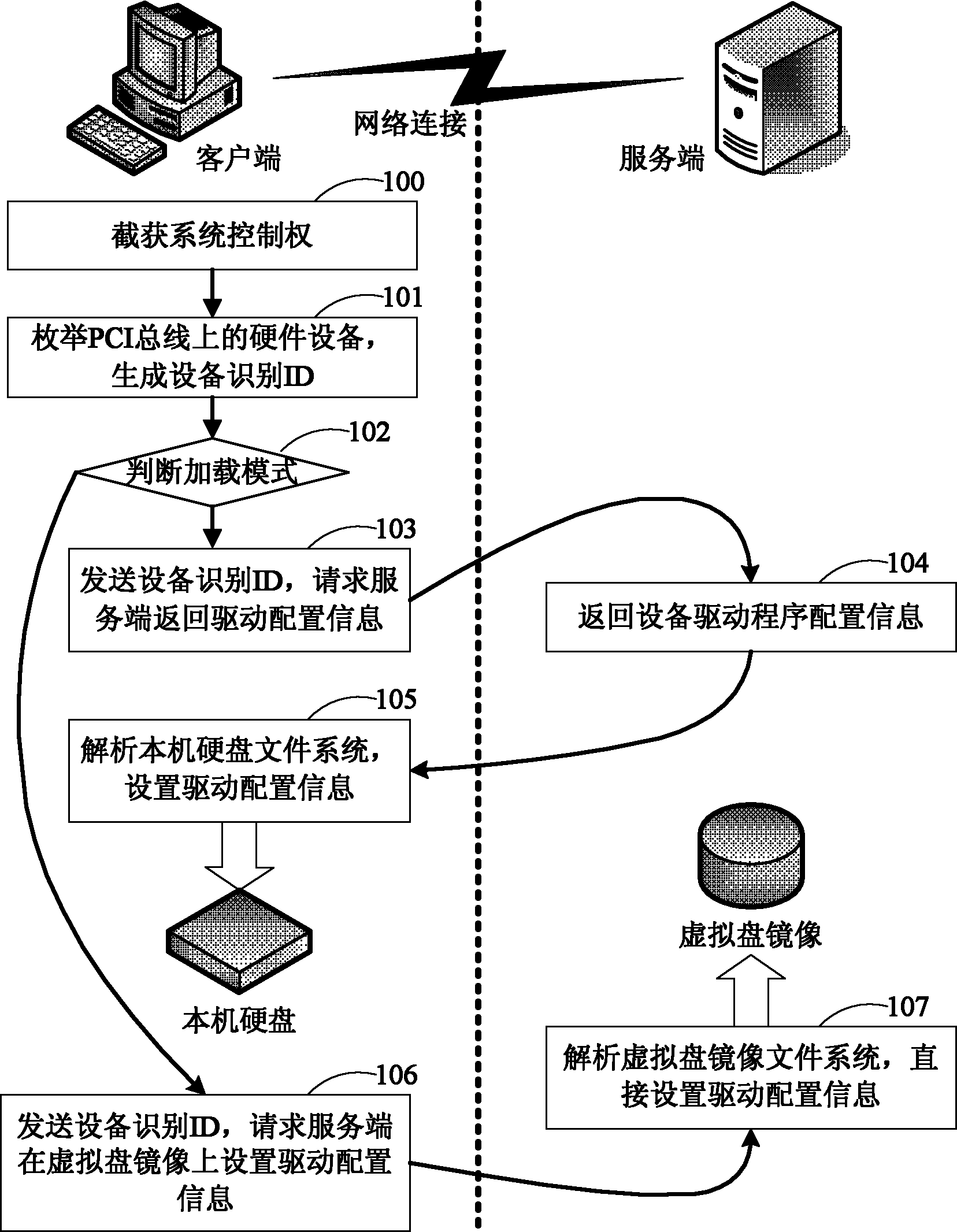

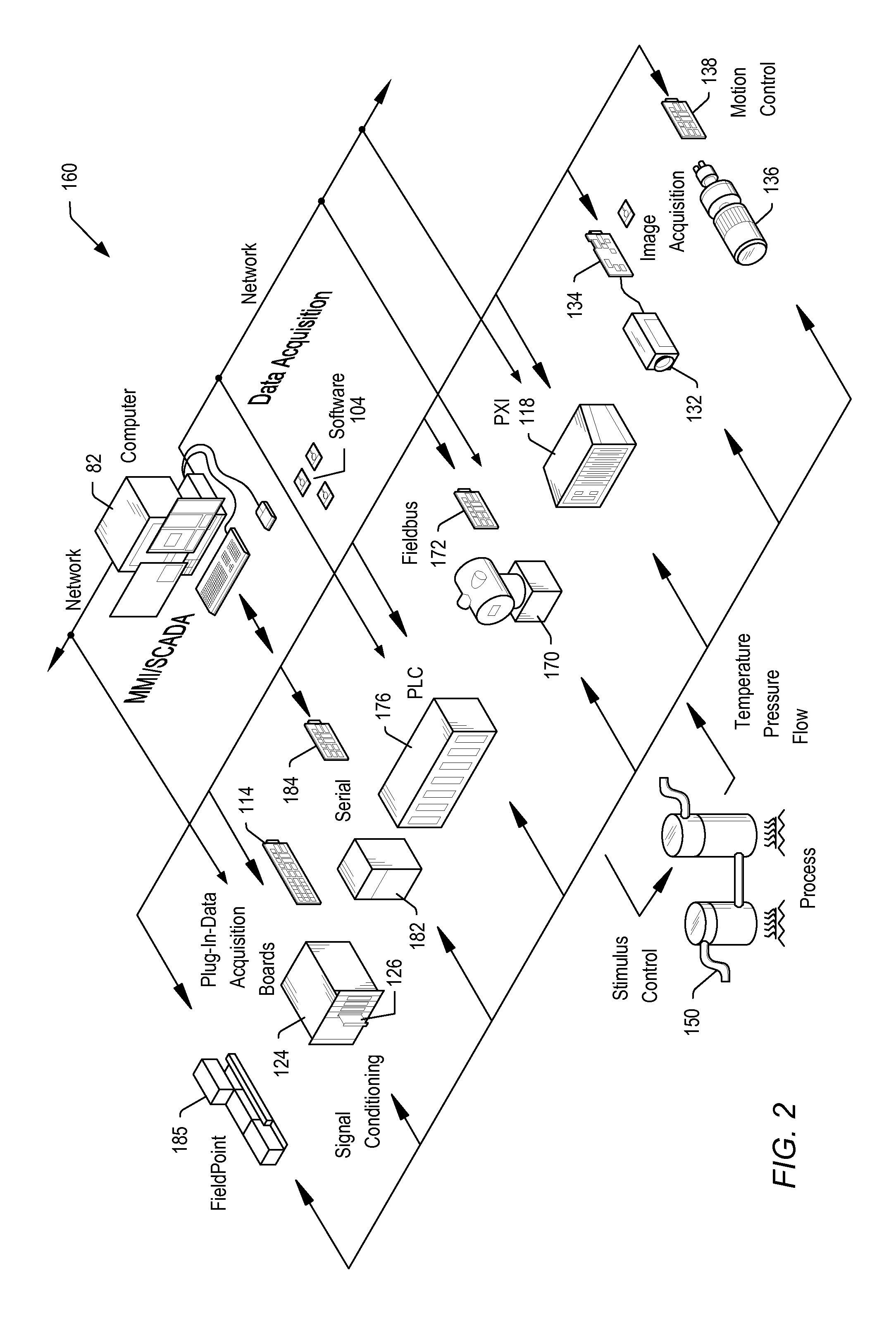

Device driving program configuration method based on network

ActiveCN102662884AAvoid the inconvenience of construction one by oneAvailable all over the placeTransmissionElectric digital data processingOperational systemManagement efficiency

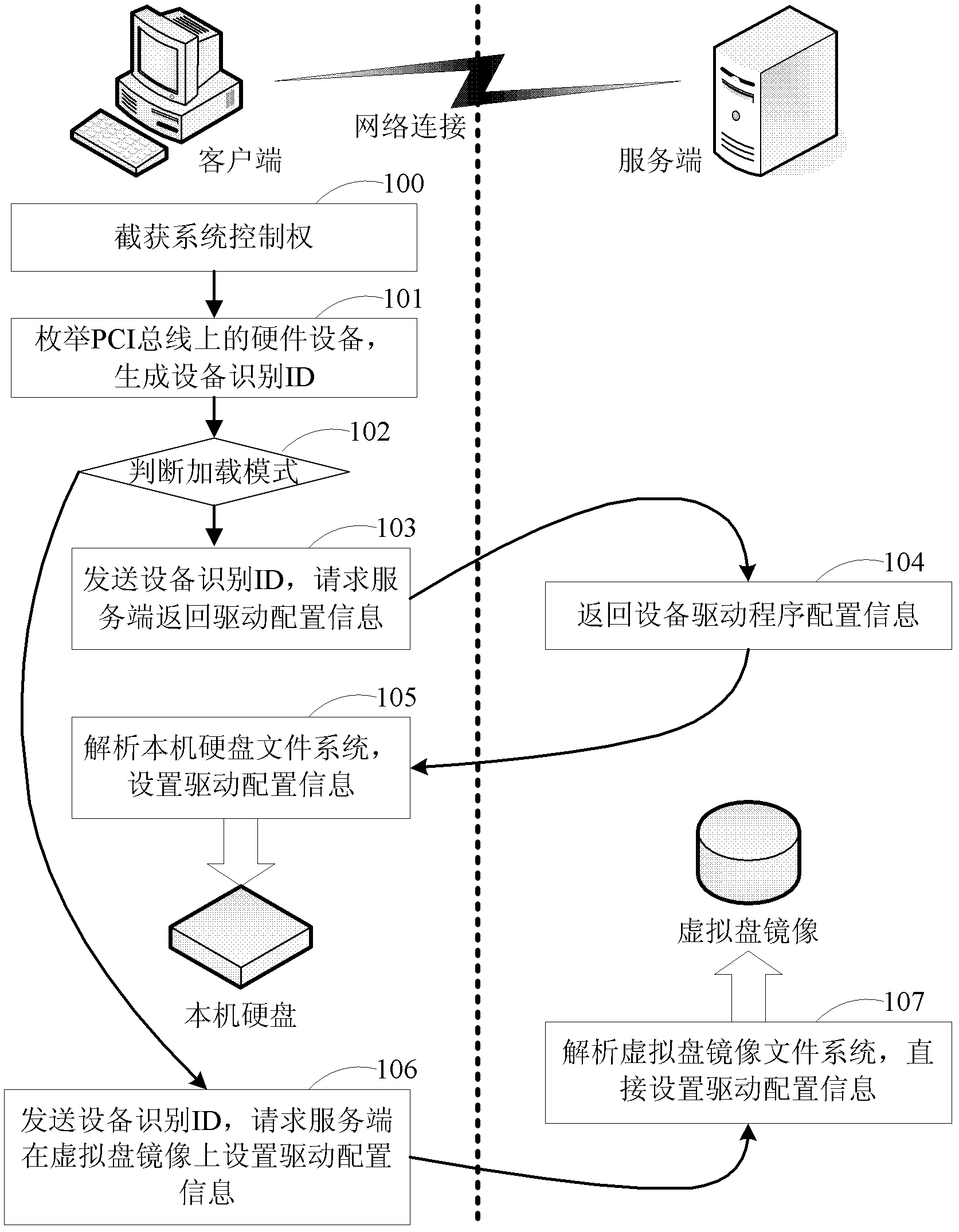

The invention discloses a device driving program configuration method based on a network. When a client operation system is not loaded yet or not loaded completely yet, the method can obtain peripheral component interconnect (PCI) configuration space information of corresponding devices by enumerating a hardware device on a client PCI bus and generates a device identity (ID) for a server to retrieve on the basis of device parameters in the information. A client sends the device ID to the server according to a loading mode of the client operation system, if the loading mode is a local hard disk mode, the server returns to corresponding device driving program configuration information, and the client stores the configuration information to a local hard disk; and if the loading mode is a virtual disk mode, the server sets corresponding device driving program configuration information on a virtual disk mirror image directly. By means of the device driving program configuration method, device driving program configuration of the client can be maintained in centralized mode, and management efficiency is improved.

Owner:HUBEI CENTURY NETWORK TECHNOLOGY CO LTD

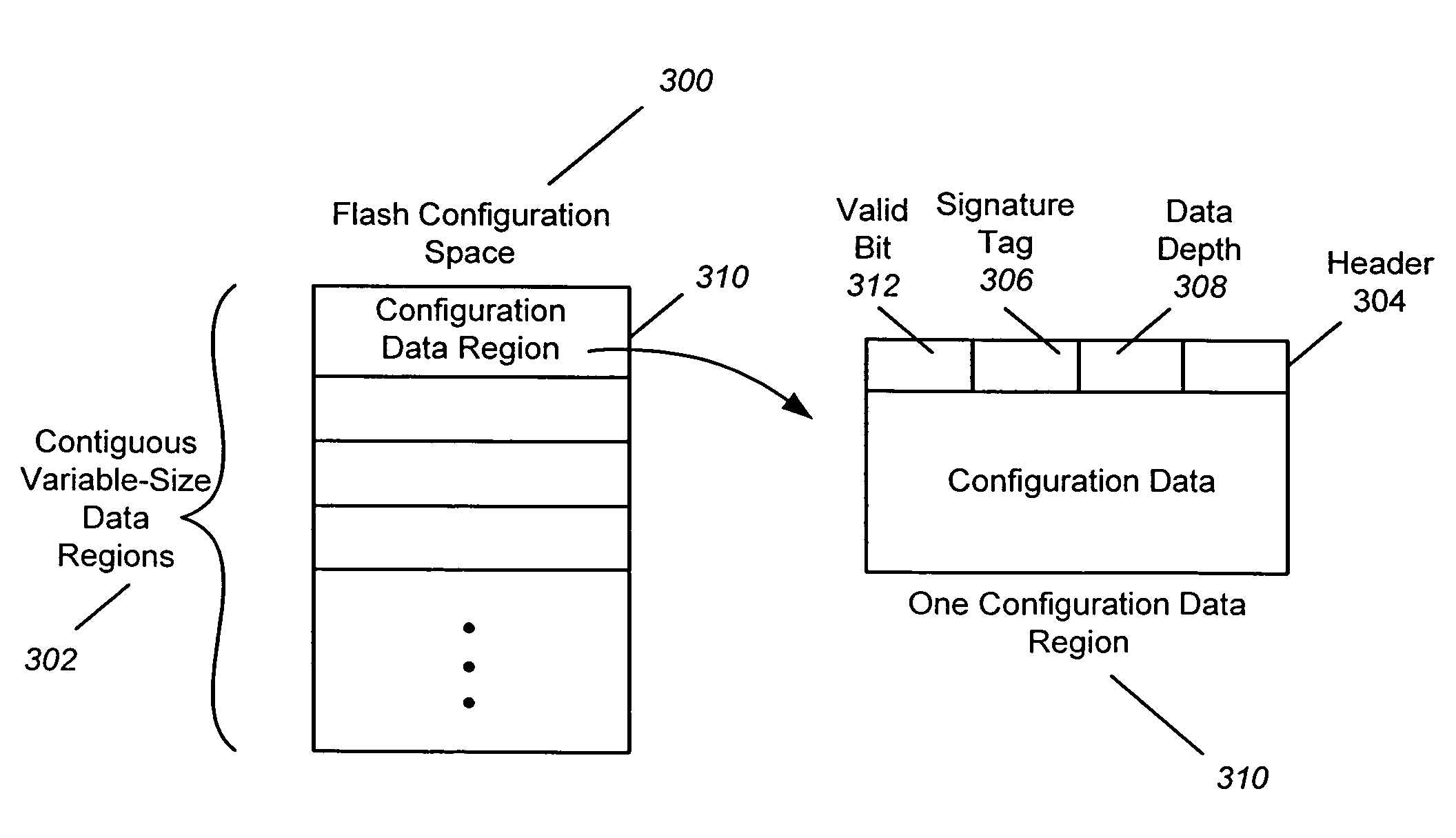

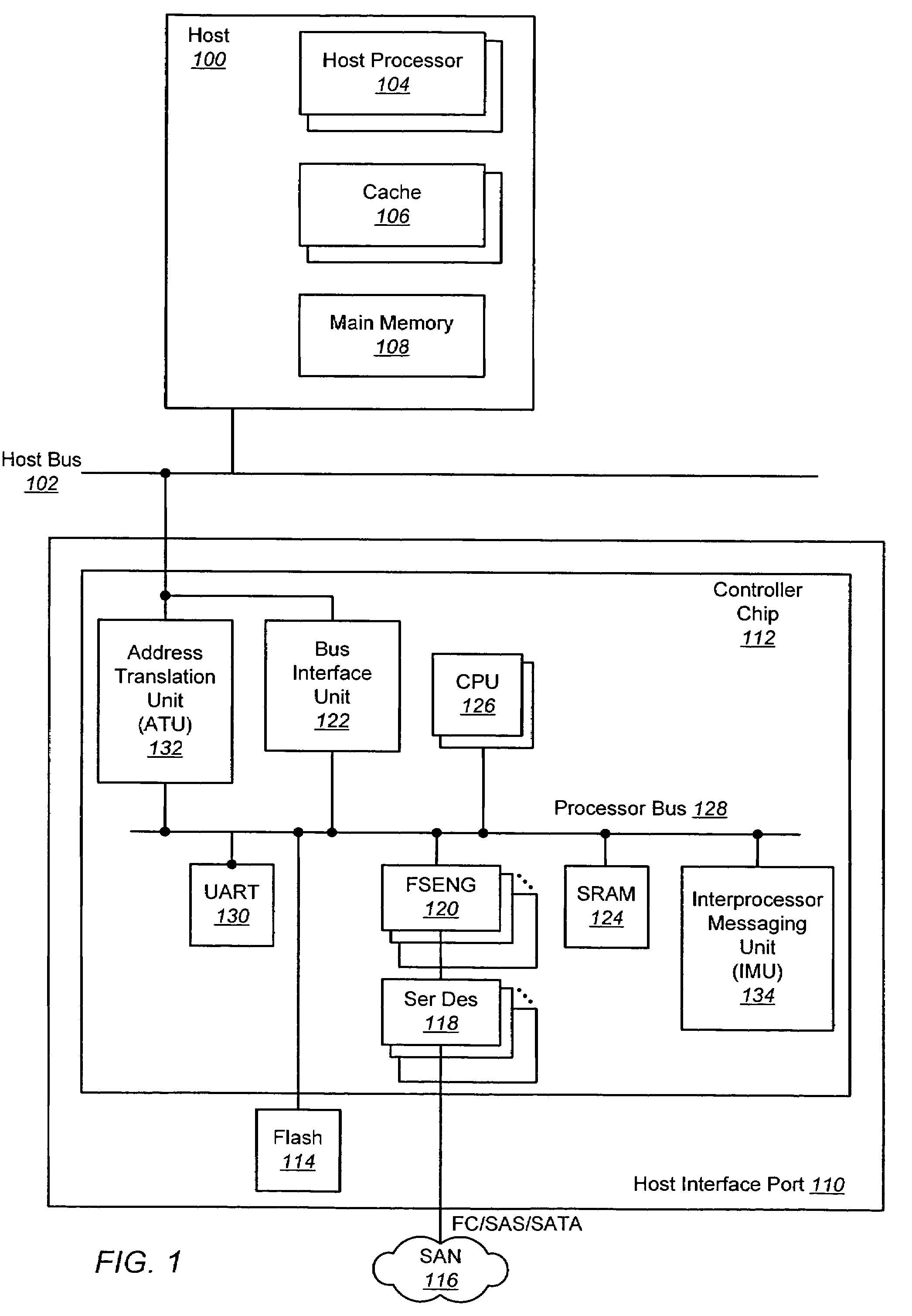

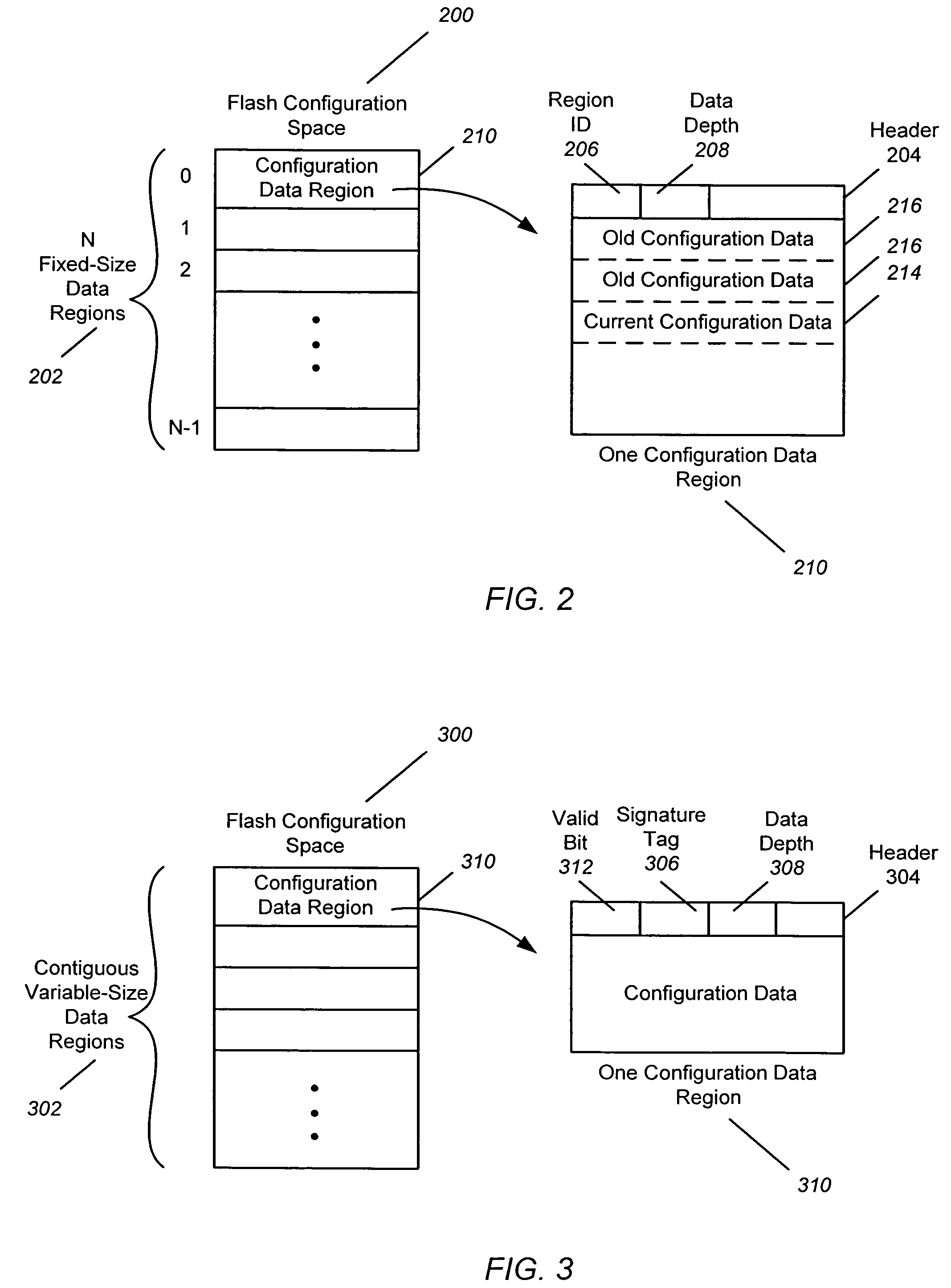

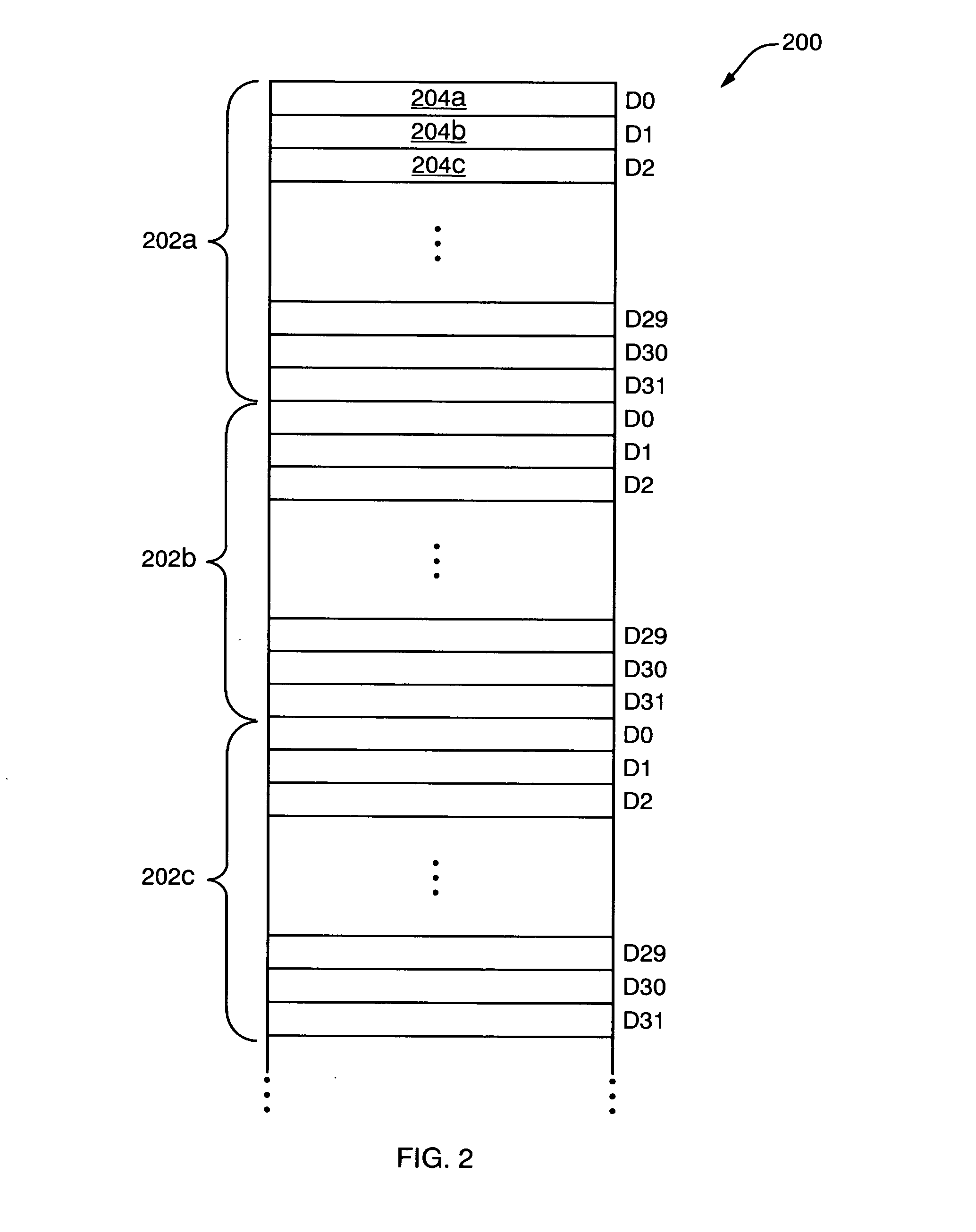

Managing configuration data in a flash configuration space in flash memory within a host interface port

A flash configuration space is disclosed for storing configuration data regions. Each configuration data region includes configuration data and a signature tag that identifies the configuration data with various levels of specificity. During a configuration data update, a header in each configuration data region is scanned to see if a valid matching configuration data region already exists. If no valid matching configuration data region exists, the signature tag and configuration data are written into the next available area in the flash configuration space. If a valid matching configuration data region is located, the header and configuration data are written into the next available area in the flash configuration space and the located configuration data region is invalidated. When the flash configuration space is full, all valid configuration data regions are saved, the flash configuration space is erased, and only current configuration data is written back into the flash configuration space in a priority order.

Owner:AVAGO TECH INT SALES PTE LTD

Hot plug process in a distributed interconnect bus

ActiveUS8443126B2Component plug-in assemblagesElectric digital data processingProcessor registerPCI configuration space

A distributed PCIe adapted to support a hot-plug process triggered by any change in a status of a distributed link, comprises an upstream bus unit including a first bridge connected to a root component and adapted to maintain a first configuration space and a copy of a second configuration space, the first configuration space bridge includes at least hot-plug registers specifying at least capabilities and status of a slot of the first bridge; and a second bridge connected to an endpoint component and adapted to maintain the second configuration space, the second configuration space includes at least hot-plug registers specifying at least capabilities and status of a slot of the second bridge.

Owner:QUALCOMM INC

Double CPU communication systems based on PCI shared memory

InactiveCN1564147AEnsure communication efficiencyGuaranteed reliabilityDigital computer detailsElectric digital data processingMemory addressCommunications system

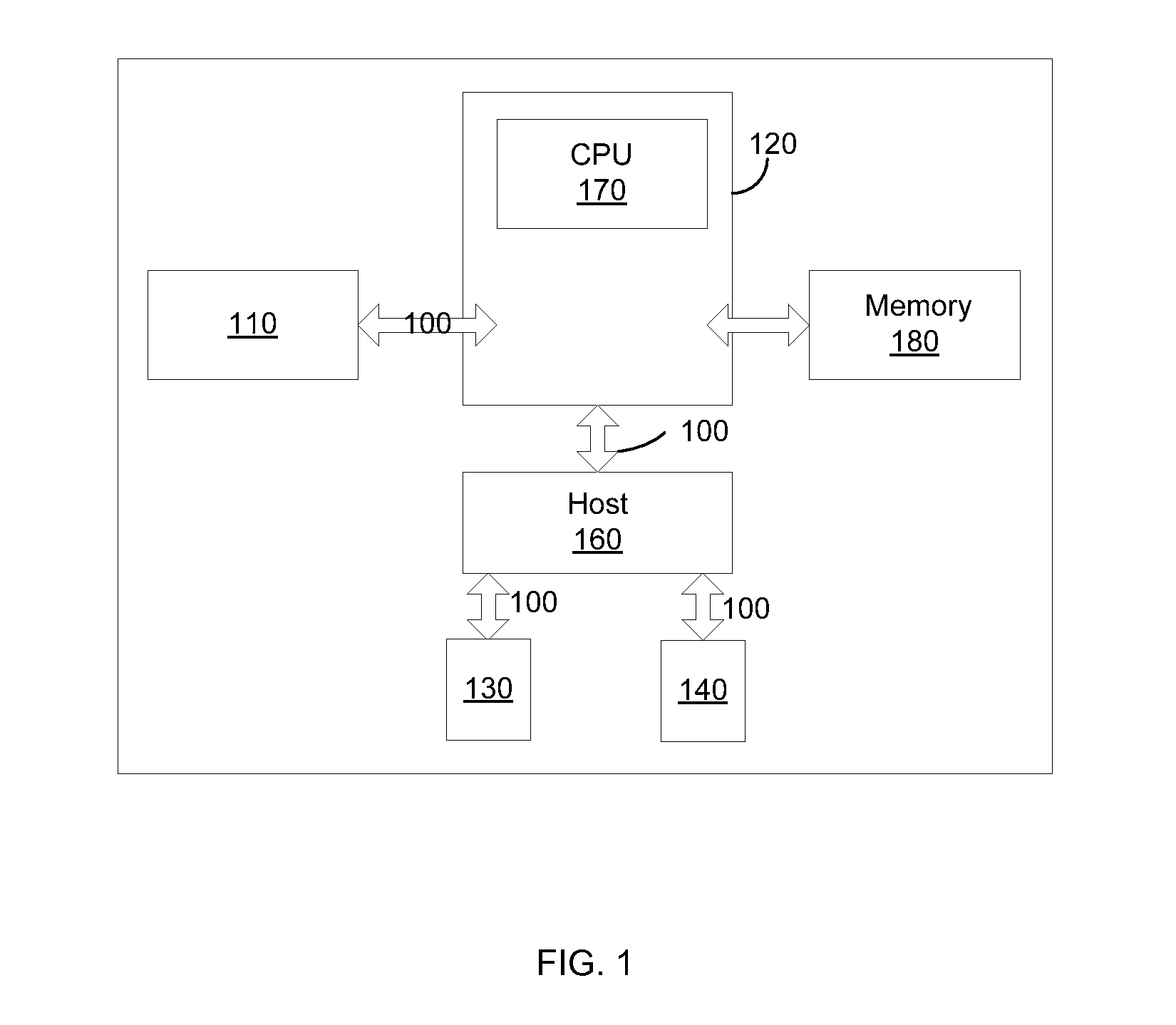

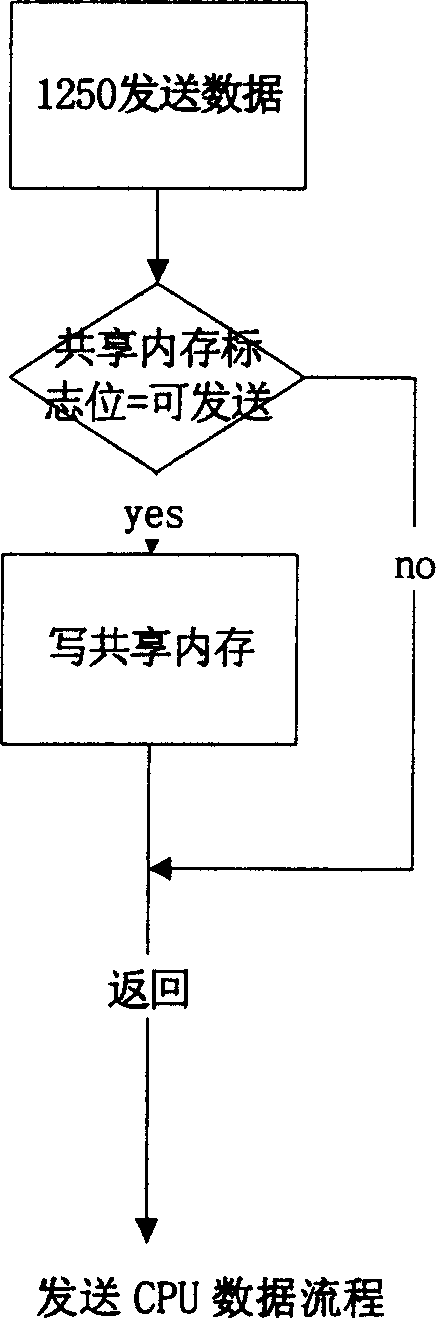

The system includes following arrangements: BCM1250 microprocessor assigns a physical memory as shared memory; setting up address mapping register in PCI configuration space; preserving a segment of memory address space for PPC8245 microprocessor; setting up BAR0 register in PCI configuration space, whose shared memory is divided into two communication channels: first channel is from PPC8245 to BCM1250, and second channel is from BCM1250 to PPC8245. Thus, communication between two CPU is realized through the said two channels. The invention realize first channel operated in reliable synchronous transmitting mode, and second channel operated in not reliable synchronous transmitting mode so as to guarantee both communication efficiency, reliability and stability of system.

Owner:HUAWEI TECH CO LTD

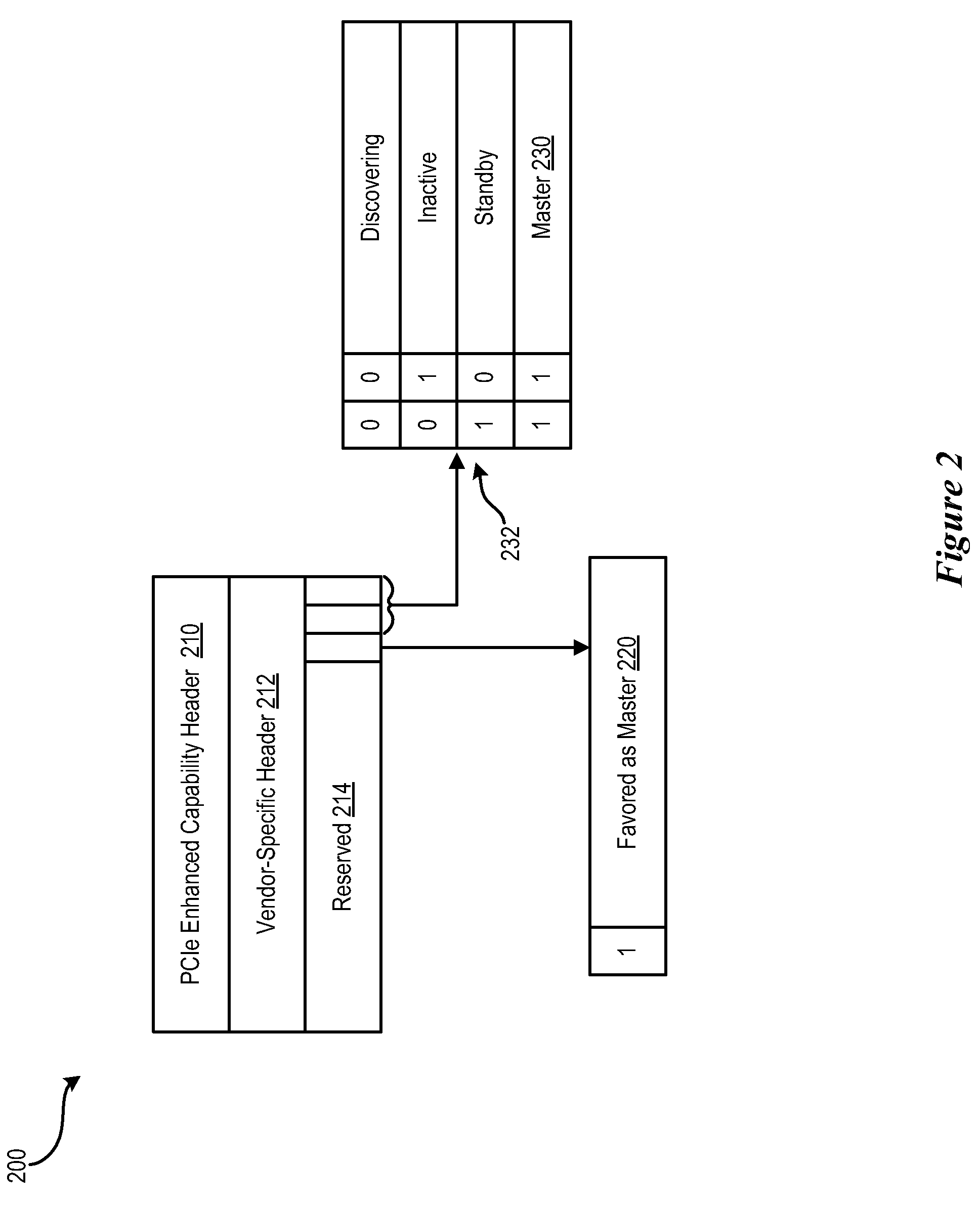

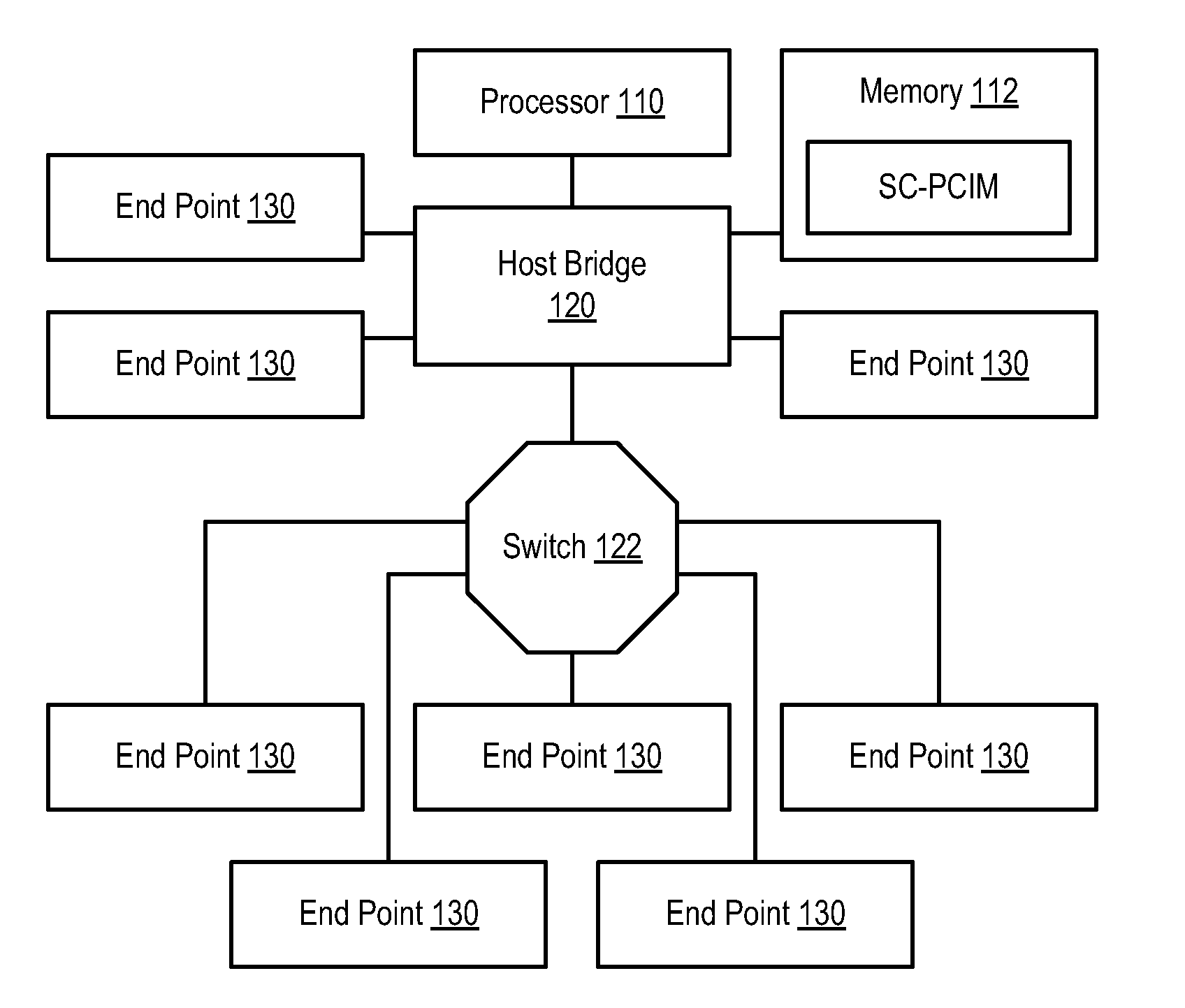

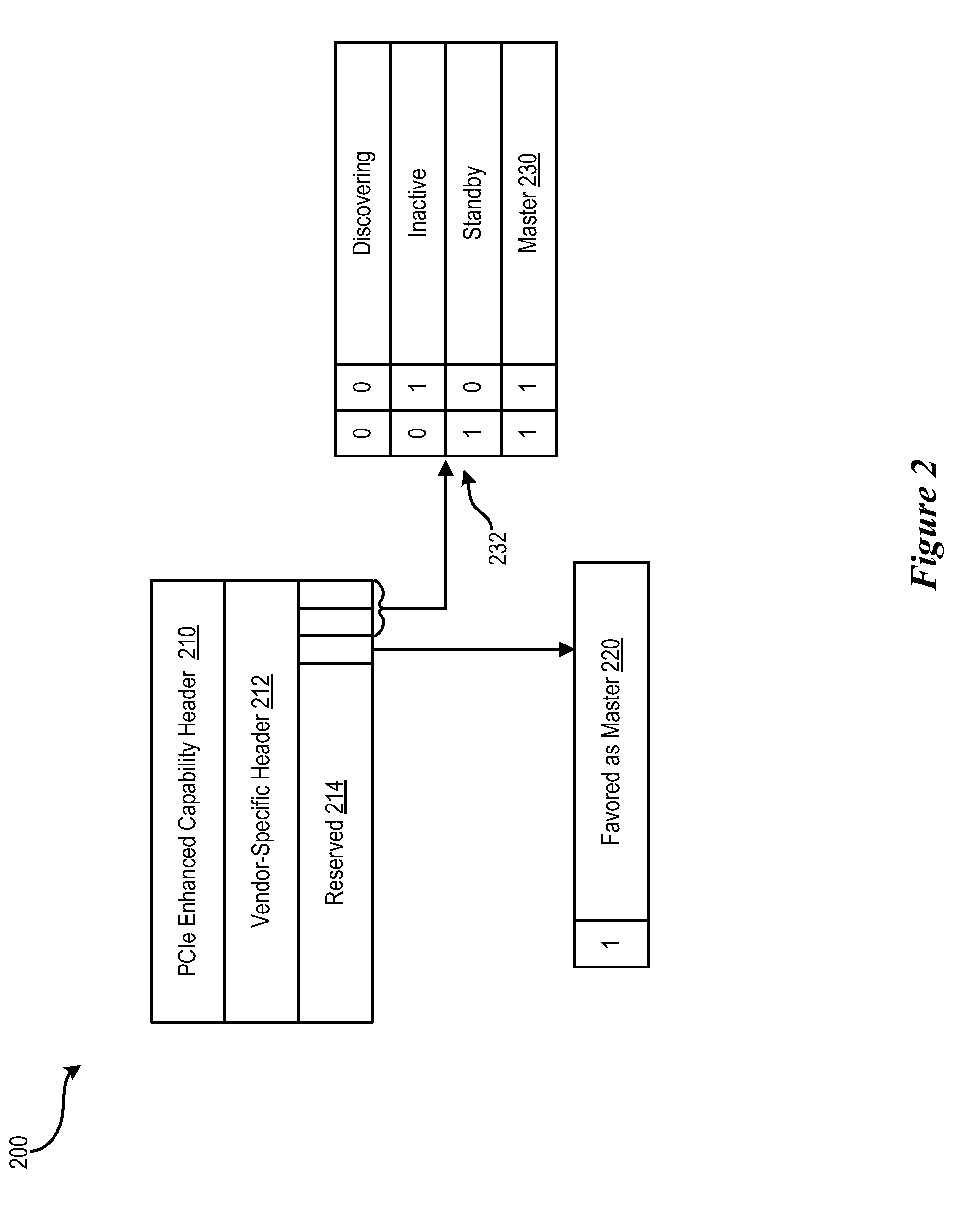

System and method for allowing coexistence of multiple PCI managers in a PCI express system

ActiveUS7603500B2Digital computer detailsInput/output processes for data processingPCI ExpressPCI configuration space

Owner:DELL PROD LP

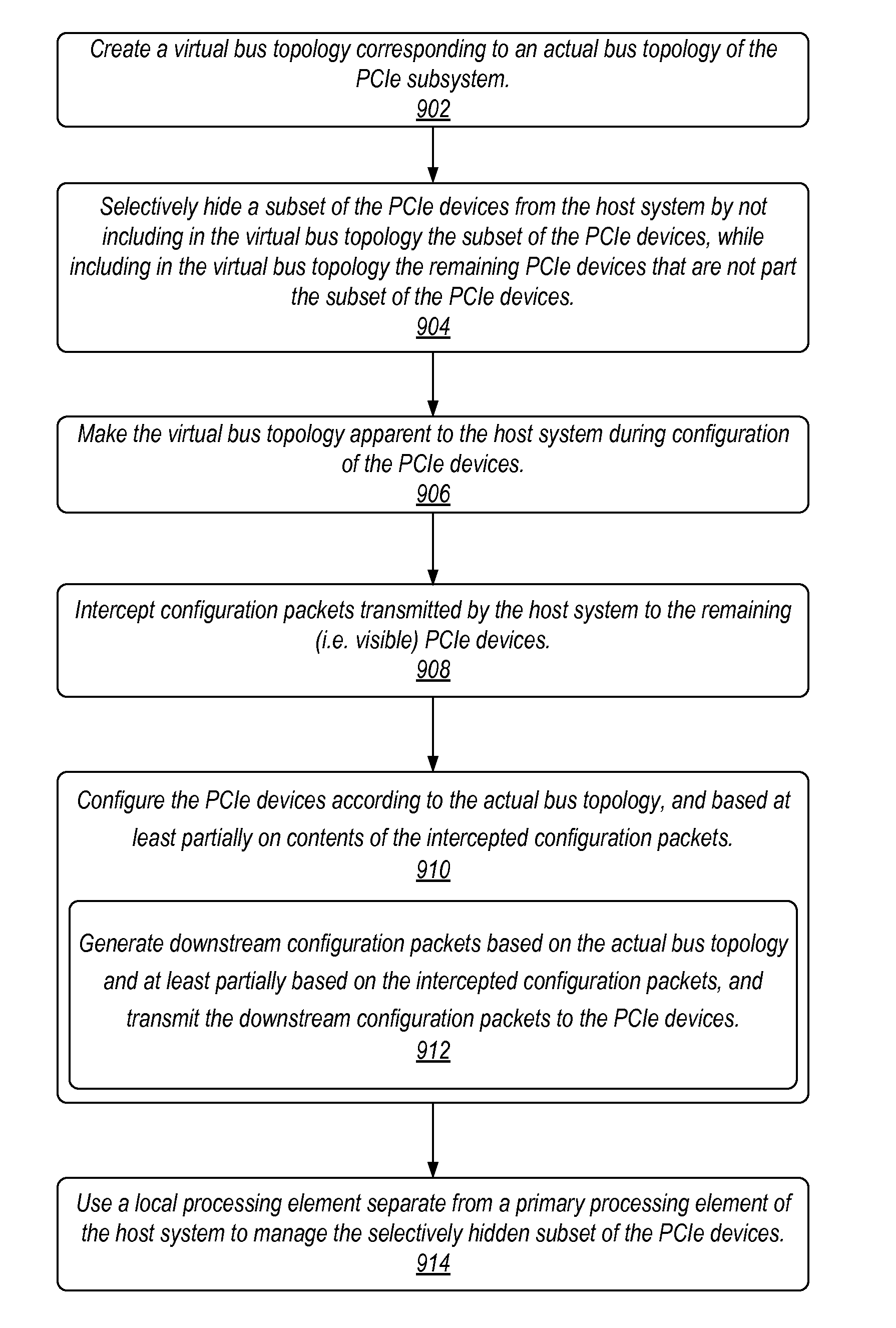

Selectively transparent bridge for peripheral component interconnect express bus systems

ActiveUS9244874B2Improve discontinuityReduce stepsResource allocationNetwork packetTechnical standard

A selectively transparent bridge facilitates a PCI device presenting itself to the host as a PCI-to-PCI bridge but selectively hiding and isolating hardware from the host bus. PCI configuration may be achieved through the standard PCI Express configuration mechanisms, but instead of configuring devices directly, a configuration processor in the selectively transparent bridge may intercept the configuration packets from the host, and create a virtual configuration to alter how the bus topology appears to the host. Devices are selectively hidden and managed by the configuration processor, resulting in simplified complexity and bus depth. Since the selectively transparent bridge appears to the host as a transparent bridge, no special drivers or resource preallocations are required, although the selectively transparent bridge fully supports special drivers and / or resource preallocations. Devices located / connected downstream of the bridge may therefore function with unmodified drivers.

Owner:NATIONAL INSTRUMENTS

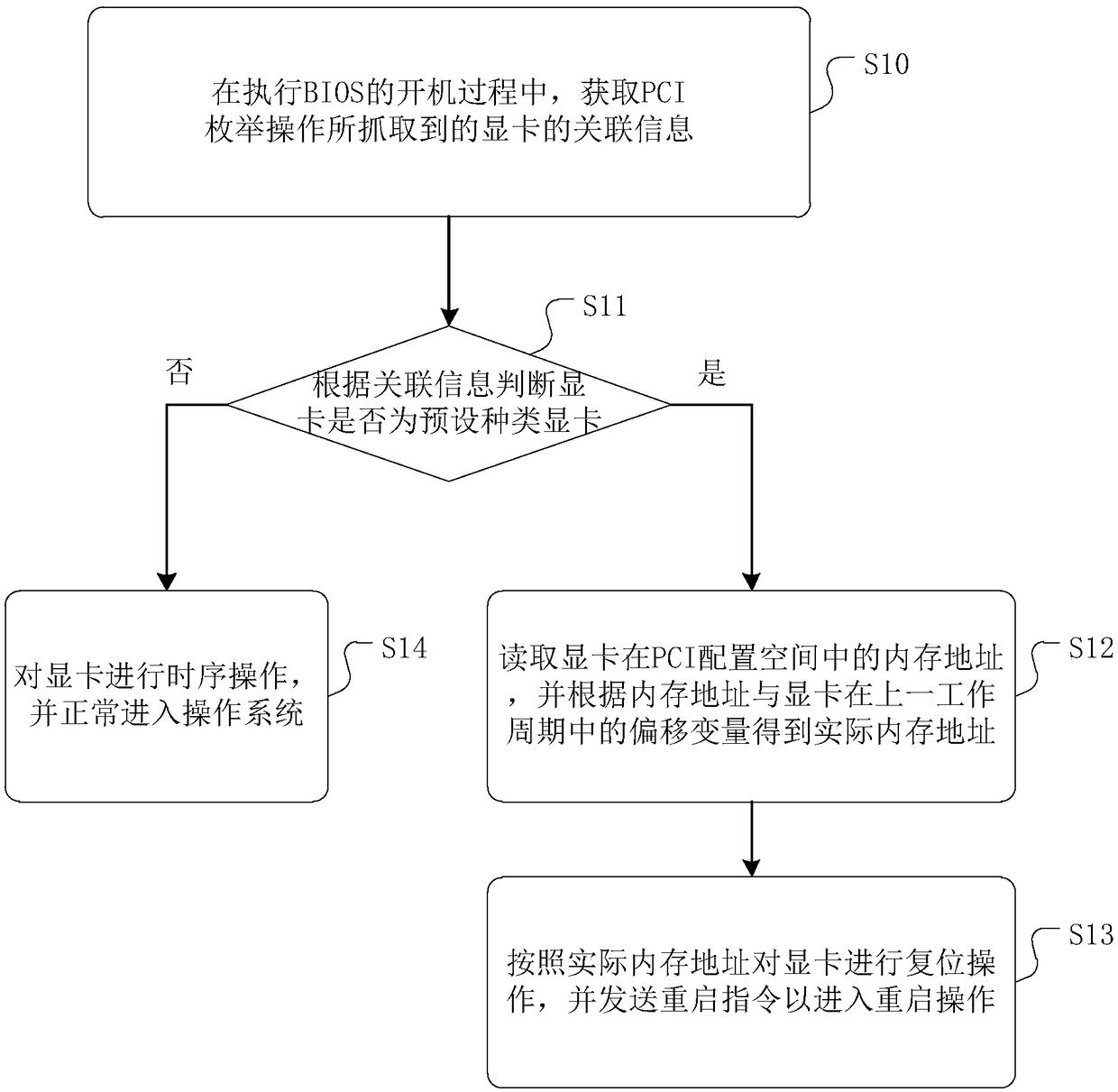

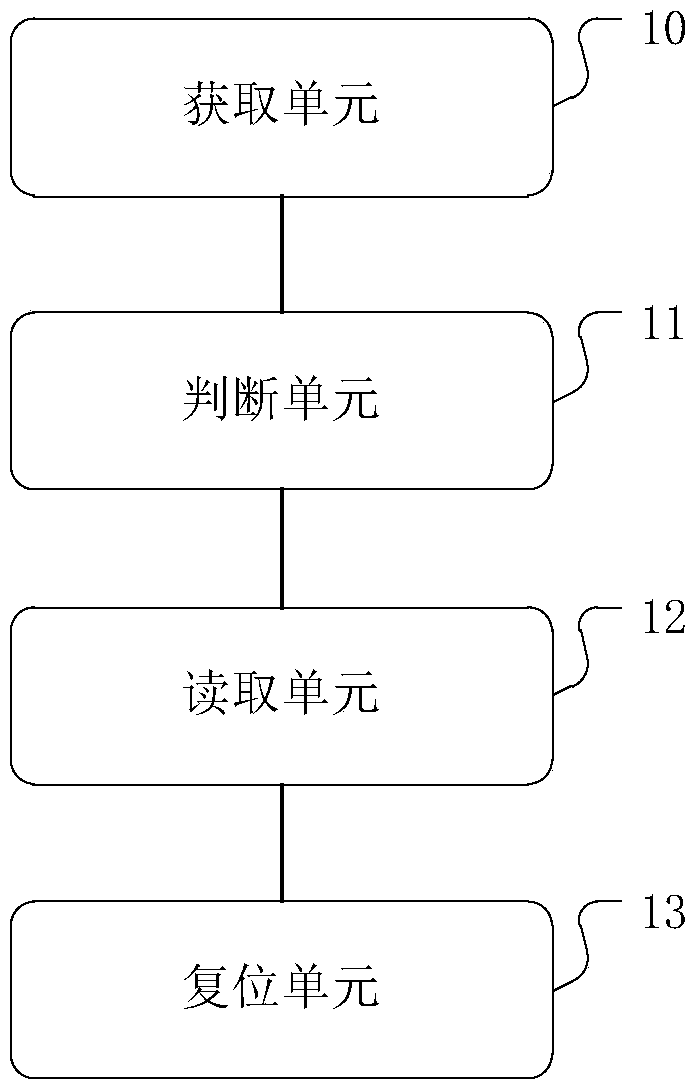

Method, device and apparatus for recognizing video cards of GPU servers and medium

ActiveCN108776595AReduce dependenceReduce procurement costsResource allocationBootstrappingMemory addressGraphic card

The invention discloses a method, device and apparatus for recognizing video cards of GPU servers and a medium. The method comprises the following steps of: in a startup process of a BIOS, obtaining associated information of a video card captured via a PCI enumeration operation; judging whether the video card is a preset type of video card or not; if the judging result is positive, reading a memory address of the video card in a PCI configuration space, and obtaining a practical memory address according to the memory address and an offset variable; and resetting the video card according to thepractical memory address and sending a restart instruction to enter a restart operation. Visibly, the practical memory address of the video card is obtained through the memory address in the PCI configuration space and the offset variable, so that the video card is reset according to the memory address. After the resetting, the video card is not located in the working state, and after being restarted, the video card is released, so that the video card can be recognized to enter normal using. Compared with the prior art, the method is capable of adopting video cards with relatively low cost and reducing the purchasing cost.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

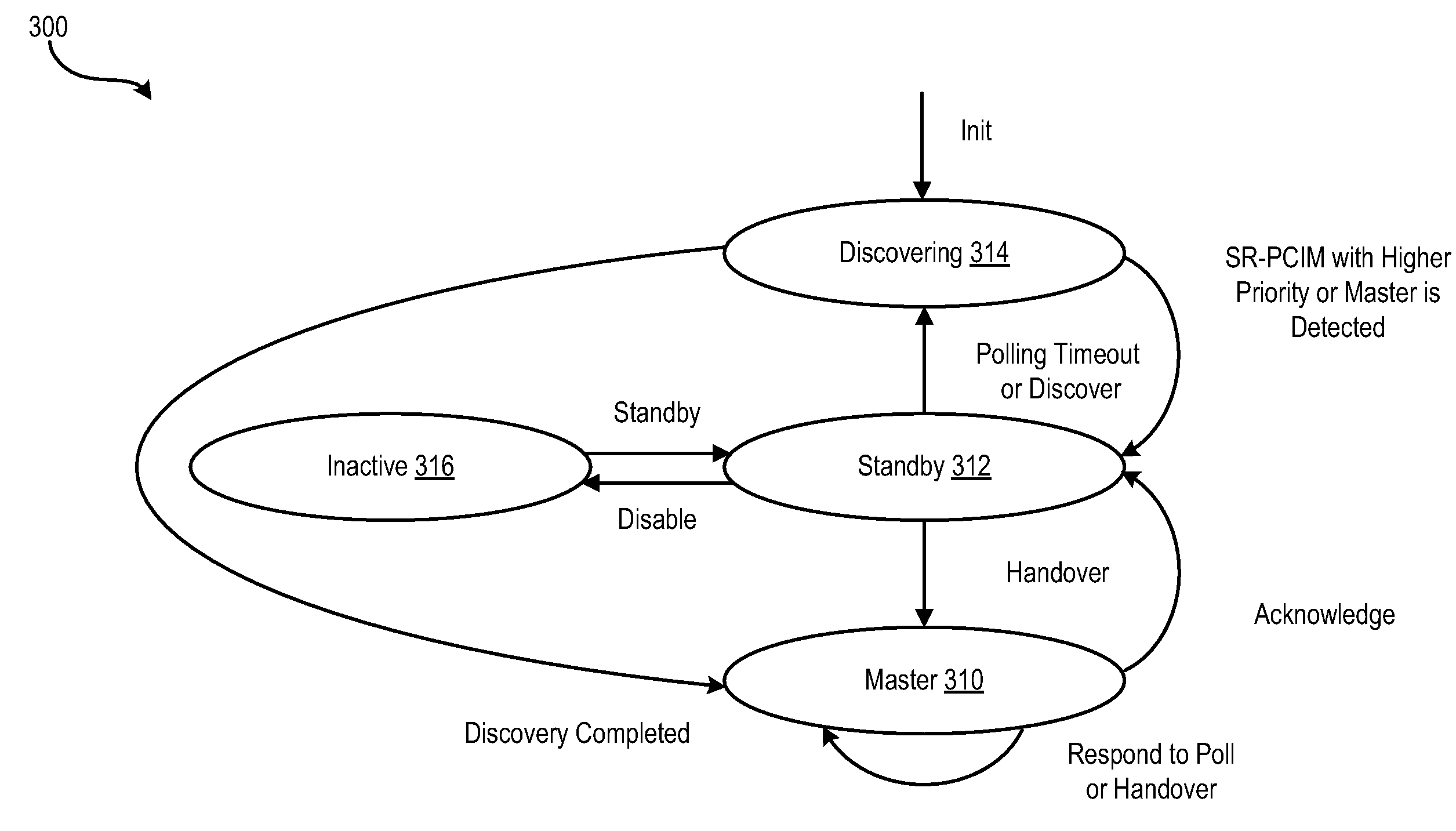

System and method for allowing coexistence of multiple PCI managers in a PCI express system

ActiveUS20090043941A1Digital computer detailsInput/output processes for data processingPCI ExpressPCI configuration space

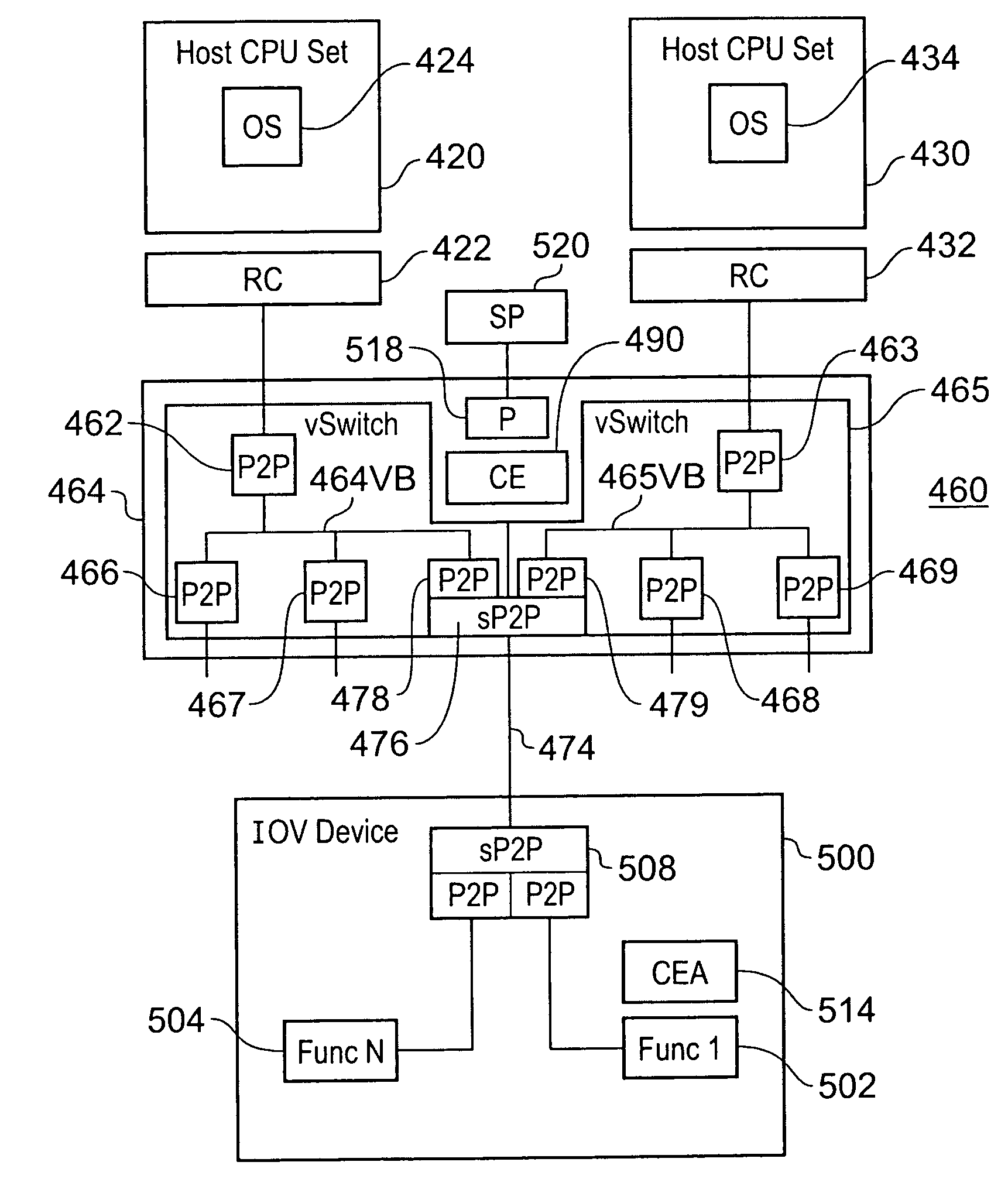

A system and method that allows a plurality of SR-PCIMs to operate within a PCIe fabric. The system and method describe a master SR-PCIM election process and transfer of mastership from a master SR-PCIM to a standby SR-PCIM under certain conditions. The system and method leverage the PCI configuration space and PCI messages so that SR-PCIMs from multiple vendors can potentially interoperate.

Owner:DELL PROD LP

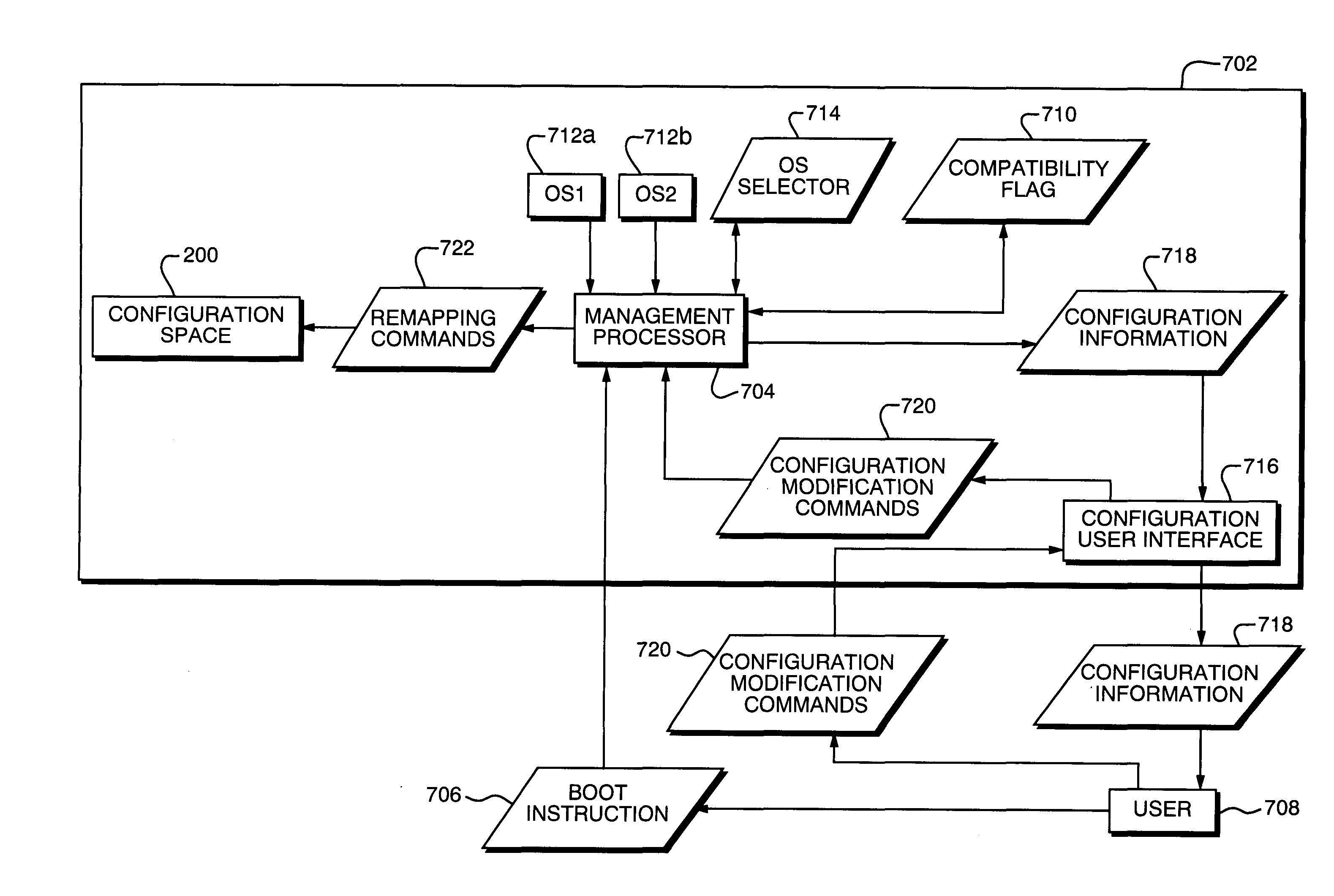

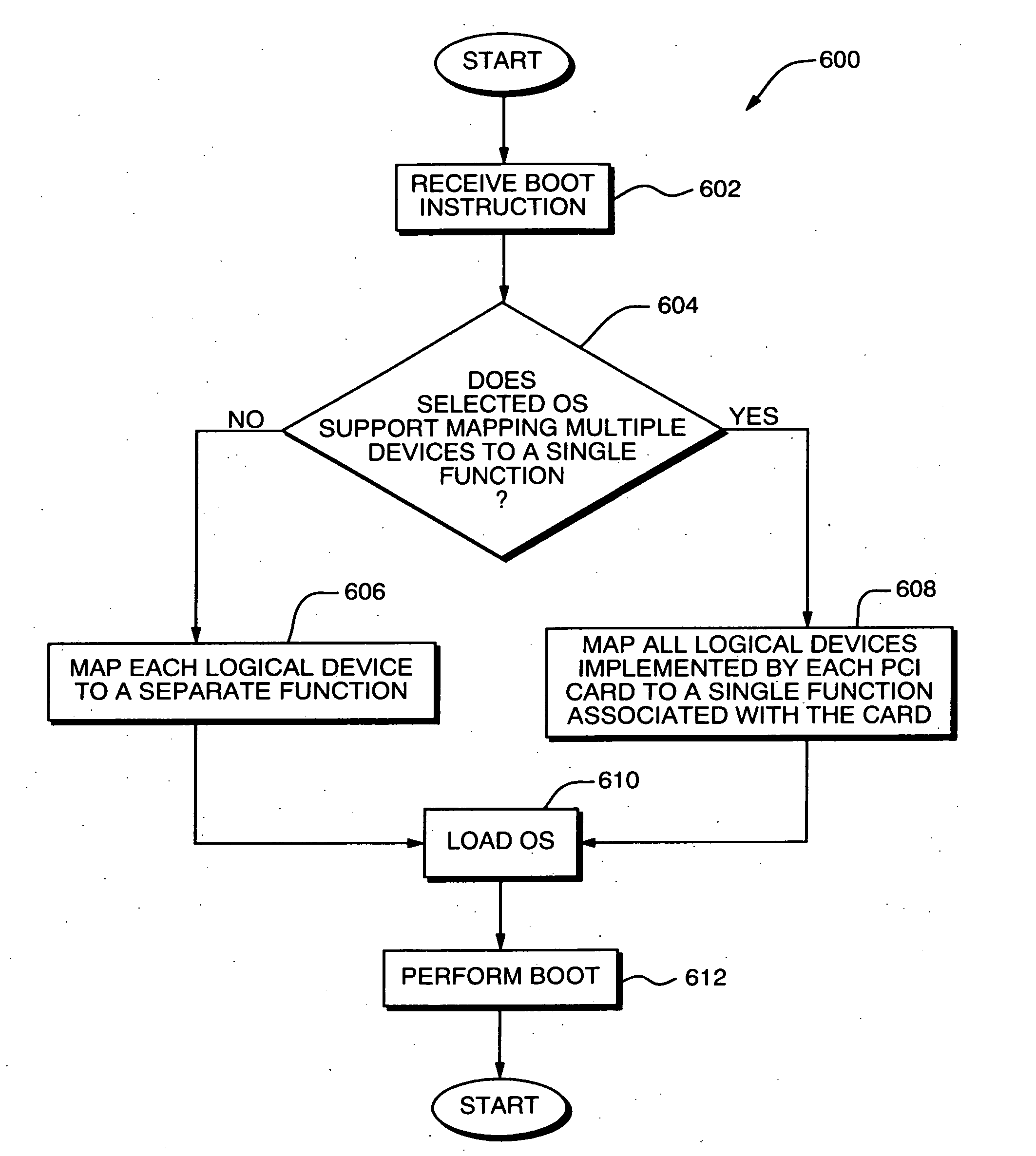

Configurable mapping of devices to bus functions

ActiveUS20050044277A1BootstrappingProgram loading/initiatingOperational systemPCI configuration space

Techniques are disclosed for enabling a single computer system to execute both operating systems that permit multiple devices to be mapped to a single PCI function and operating systems that do not permit such mapping. Prior to loading and executing an operating system (e.g., during system reset), the computer system determines whether the operating system supports mapping of multiple devices to a single function. If such mapping is supported, the computer system maps multiple devices on a single PCI card to a single function in the PCI configuration space for the card. If such mapping is not supported, the computer system maps each device to a separate PCI function. The computer system then loads and executes the operating system. The operating system is thereby enabled to access all devices on the bus according to the particular device-function mapping scheme supported by the operating system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

Selectively Transparent Bridge for Peripheral Component Interconnect Express Bus Systems

A selectively transparent bridge facilitates a PCI device presenting itself to the host as a PCI-to-PCI bridge but selectively hiding and isolating hardware from the host bus. PCI configuration may be achieved through the standard PCI Express configuration mechanisms, but instead of configuring devices directly, a configuration processor in the selectively transparent bridge may intercept the configuration packets from the host, and create a virtual configuration to alter how the bus topology appears to the host. Devices are selectively hidden and managed by the configuration processor, resulting in simplified complexity and bus depth. Since the selectively transparent bridge appears to the host as a transparent bridge, no special drivers or resource preallocations are required, although the selectively transparent bridge fully supports special drivers and / or resource preallocations. Devices located / connected downstream of the bridge may therefore function with unmodified drivers.

Owner:NATIONAL INSTRUMENTS

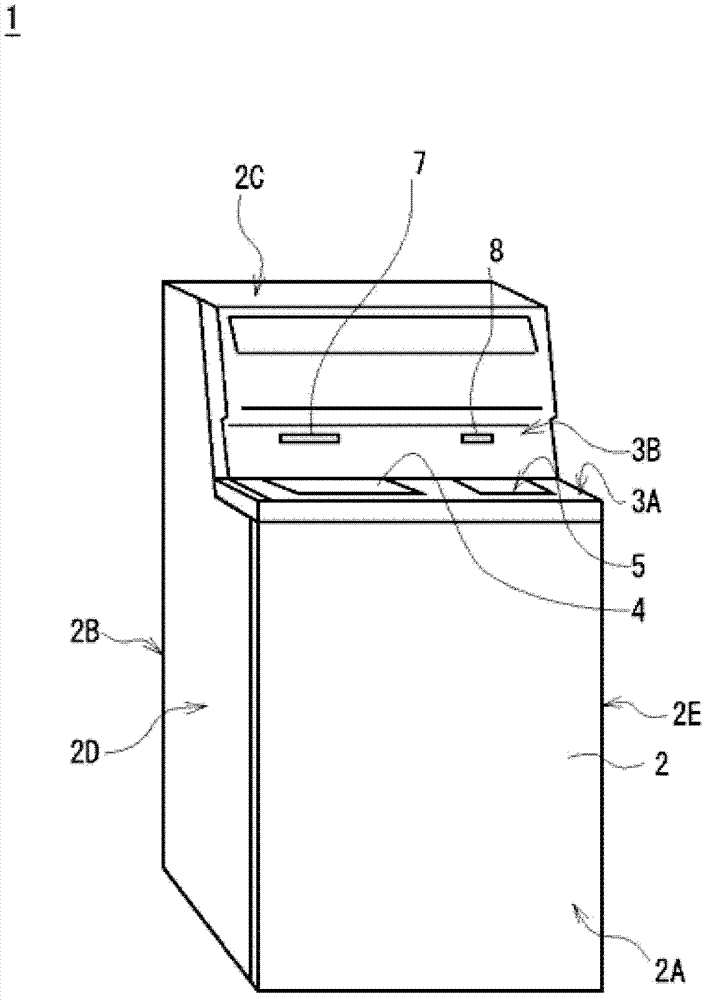

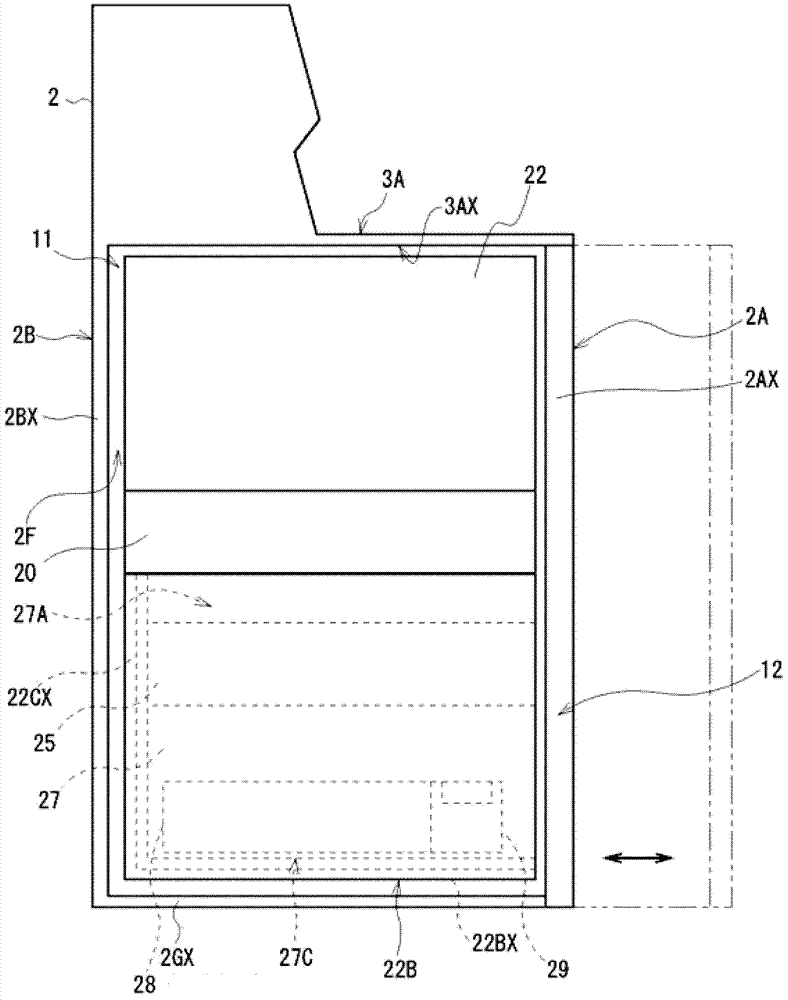

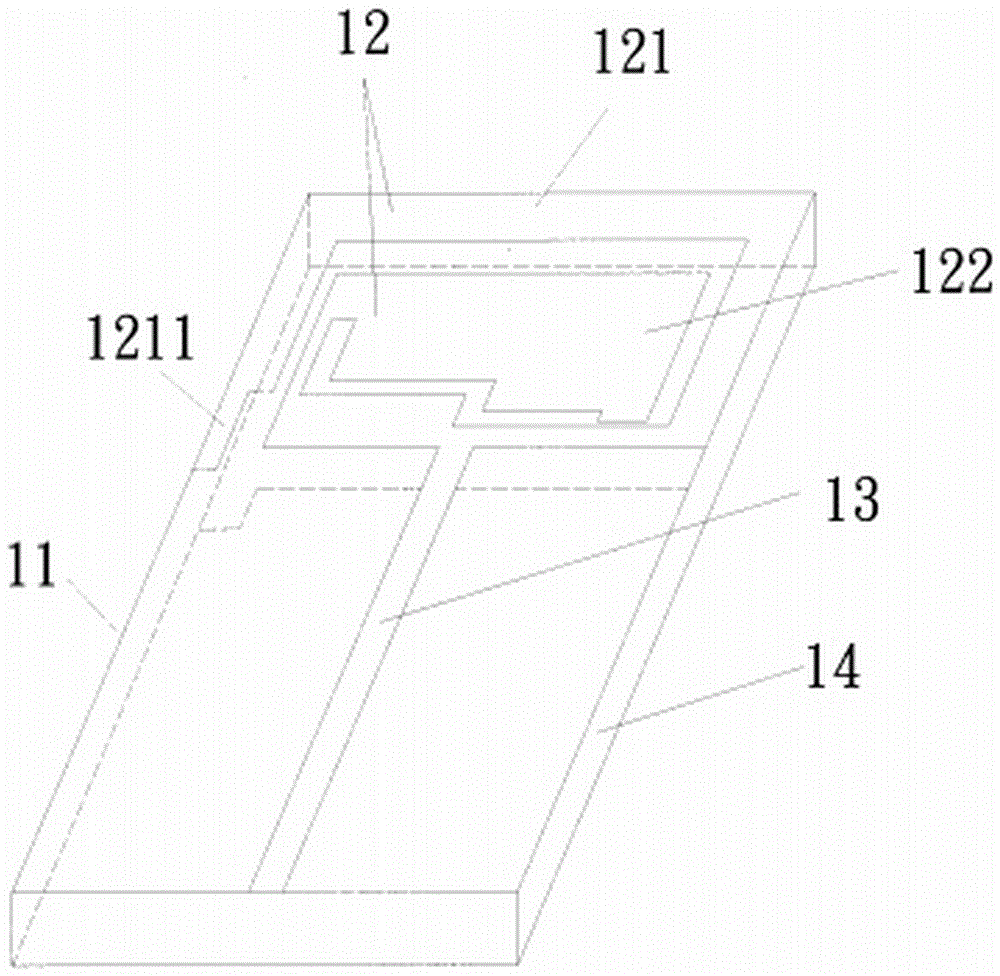

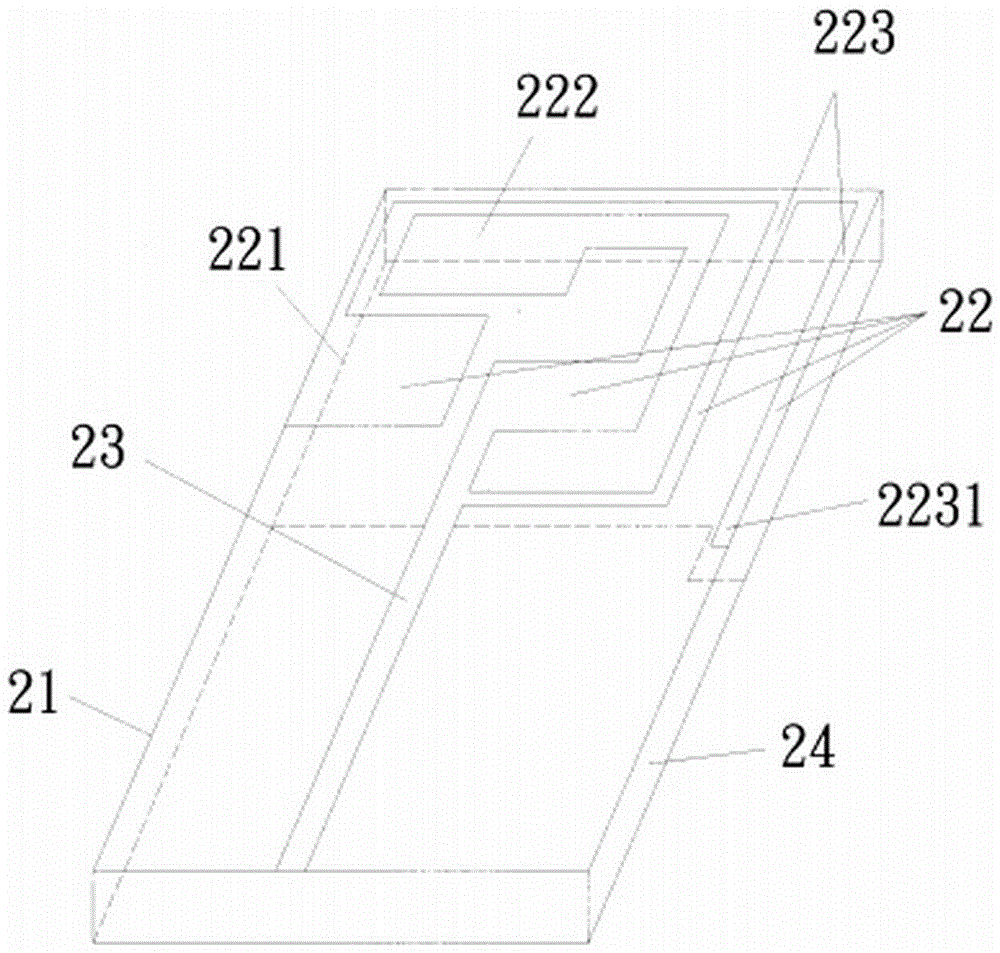

Locking device and automatic cash transaction device

InactiveCN103021075AConvenient rotation operationEasy to plug and unplugCoin/currency accepting devicesEngineeringPCI configuration space

The invention provides a locking device and an automatic cash transaction device. Even if the configuration space of a lock is reduced and the operationality of a key is greatly improved. The invention is provided with a lock, which has a key hole for key insertion; and a lock holding part mounted in a predetermined lock configuration surface and used for holding the key switchable between a parallel position and a cross posture, wherein the parallel posture is posture that the key is made to be in parallel with the lock configuration surface relative to the key insertion direction of the key hole, the cross posture is the posture that the key insertion direction is cross with the lock configuration surface, thus when the key is not subjected to rotation operation, the lock is set to be the parallel posture so as to reduce the protrusion amount from the lock configuration surface, thereby reducing the lock configuration space, and when the key is subjected to rotation operation, even though the lock configuration space is reduced, the operationality of the key is also greatly improved.

Owner:OKI ELECTRIC IND CO LTD

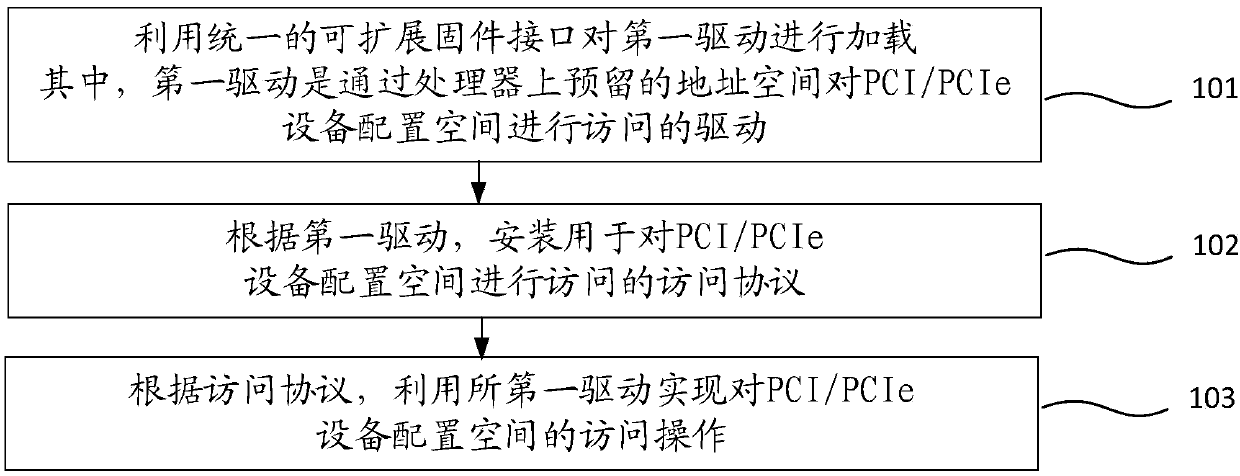

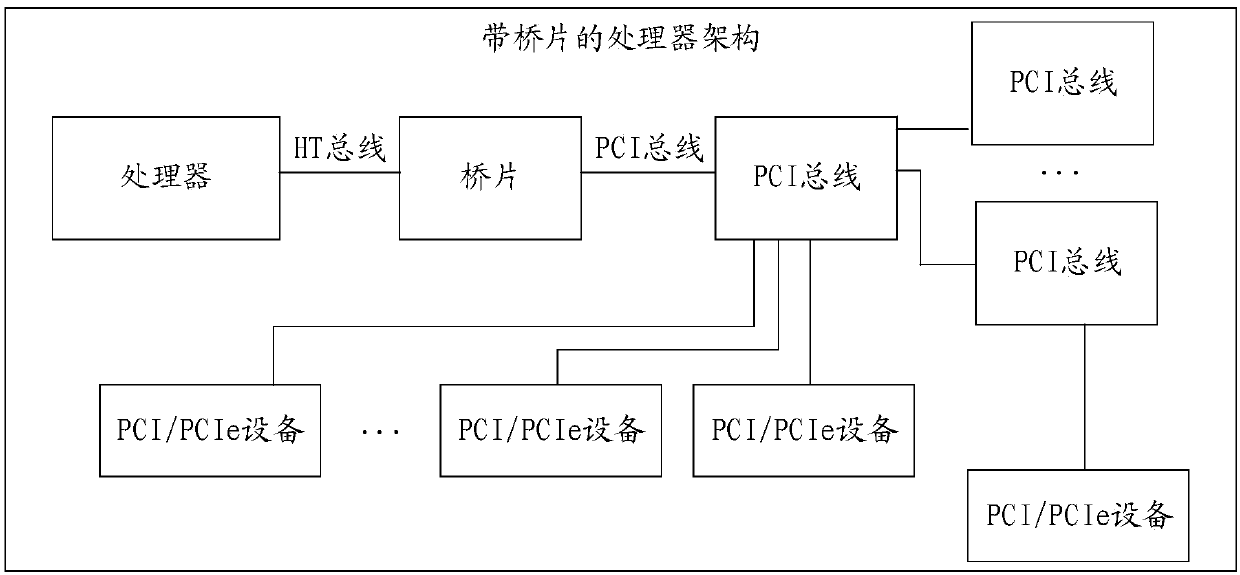

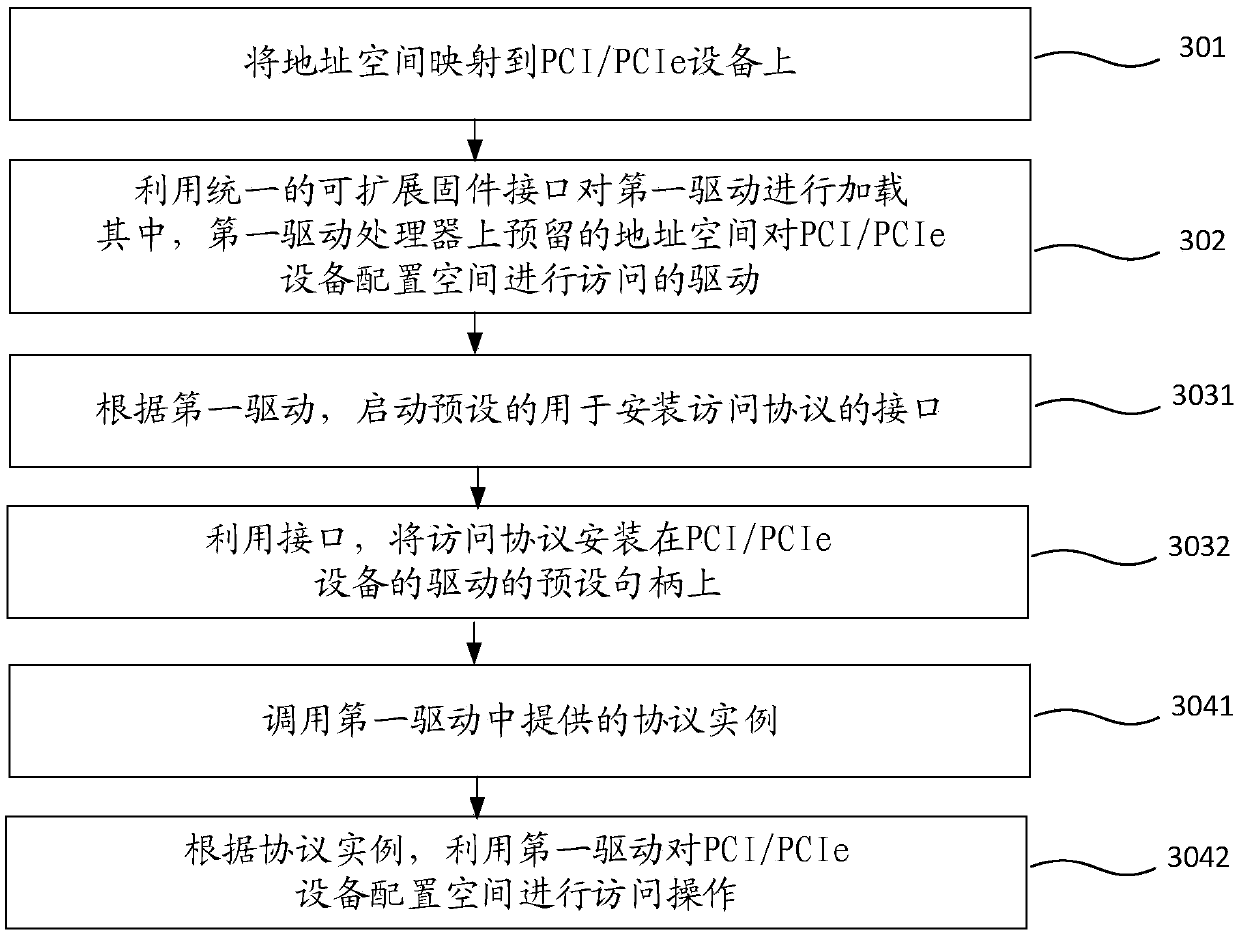

Configuration space access method and device, architecture and storage medium

The embodiment of the invention provides a configuration space access method and device, architecture and a storage medium. The processor architecture with the bridge chip comprises a processor and the bridge chip, the processor is connected with the bridge chip through an HT bus; an address space corresponding to the PCI / PCIe equipment configuration space is reserved in an address window in the HT interface of the processor; The method comprises the following steps: loading a first driver by using a unified extensible firmware interface, wherein the first driver is a driver for accessing a PCI / PCIe equipment configuration space through an address space reserved on a processor; According to the first driver, installing an access protocol for accessing the PCI / PCIe equipment configuration space; And according to the access protocol, realizing an access operation on the PCI / PCIe equipment configuration space by utilizing the first driver. Therefore, the access of the CPU to the PCI / PCIeequipment configuration space can be realized through the address space by utilizing the first driver, so that the realization mode of the access to the PCI / PCIe equipment configuration space is expanded, and the use of the bridge chip is ensured.

Owner:LOONGSON TECH CORP

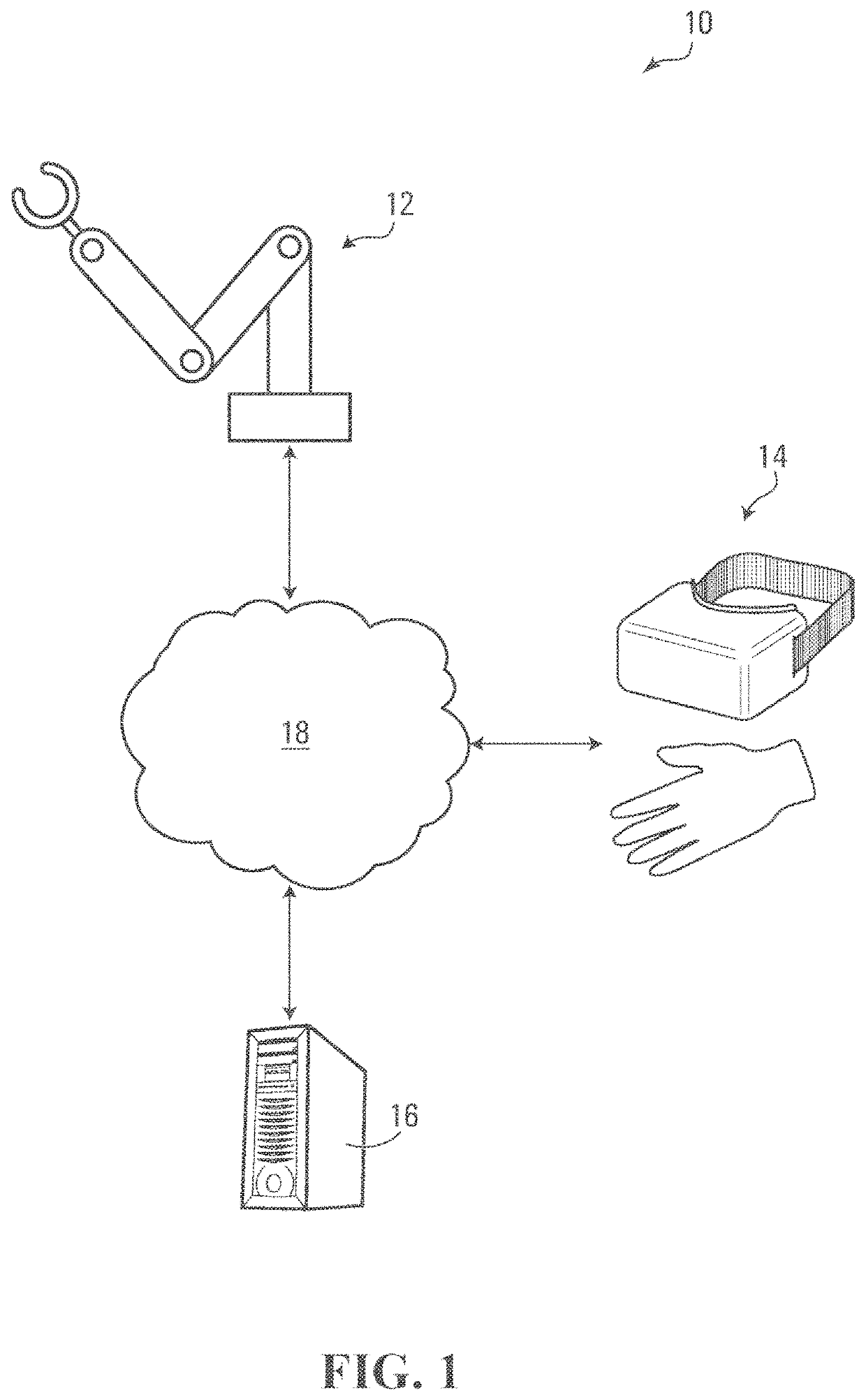

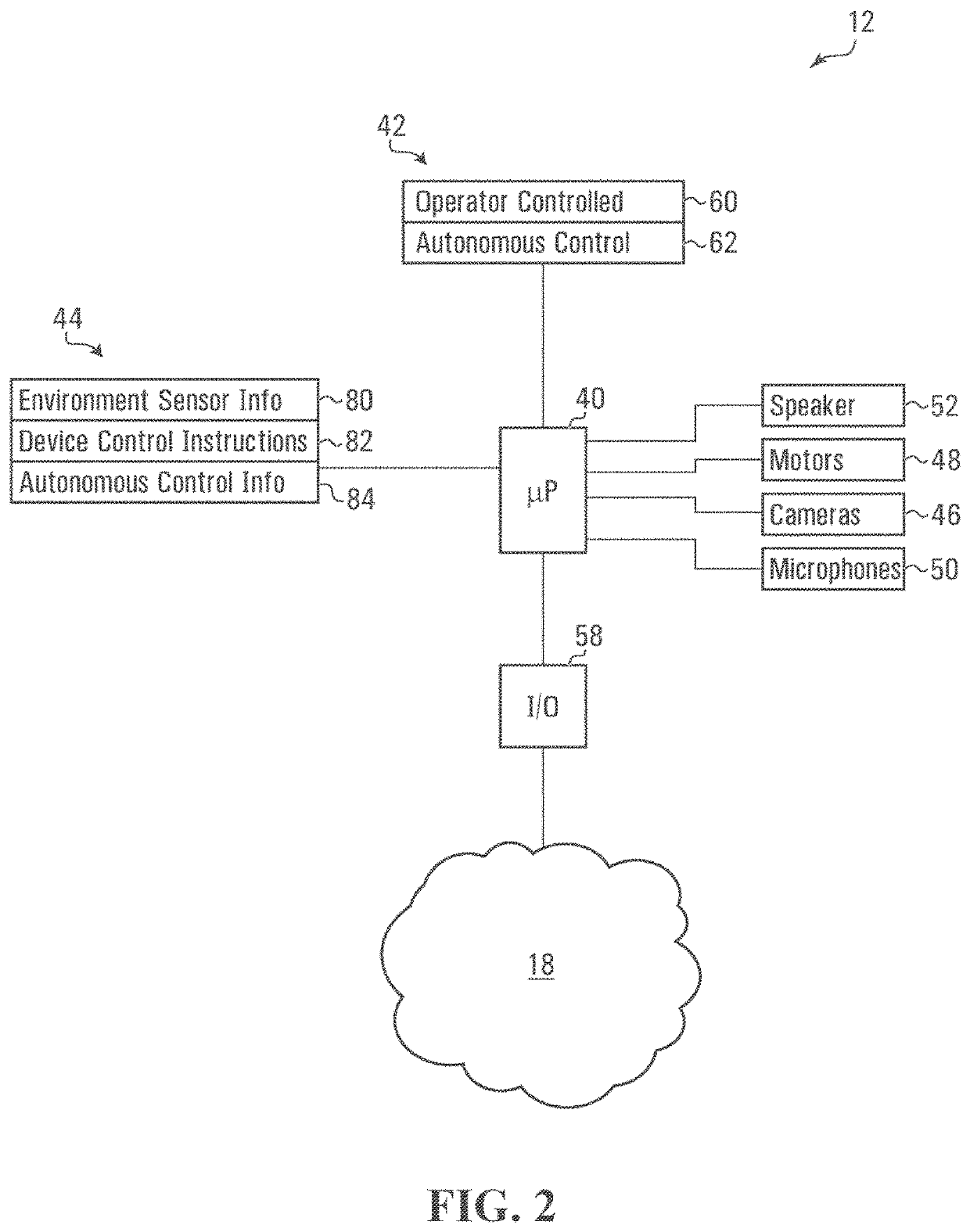

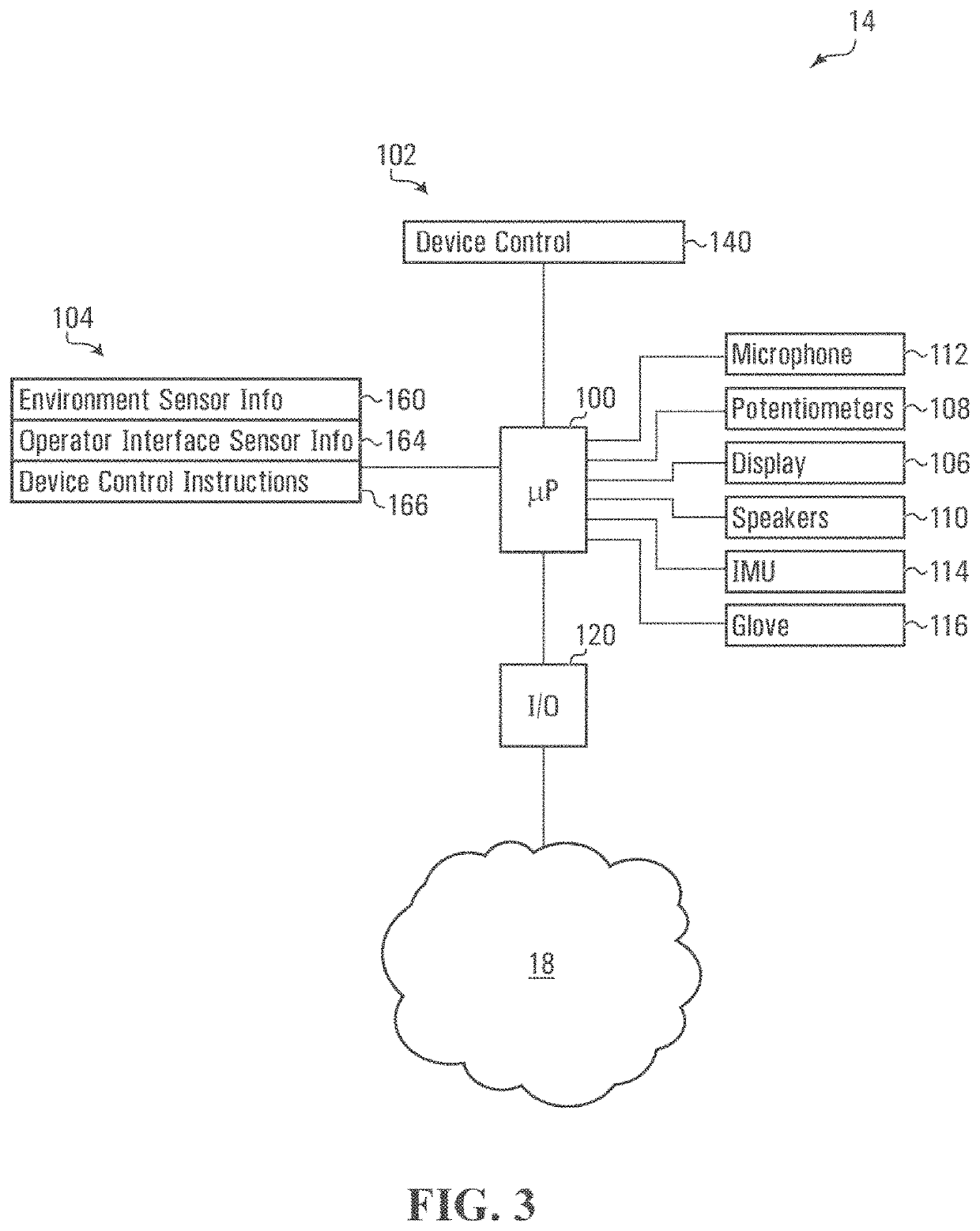

Facilitating device control

Systems, devices, articles, and methods are illustrated and described herein. A method of operation in a robotic system including a processor, a first device, and a second device involves receiving, by the processor, a training set including a first plurality of positions in a first configuration space that represents physical configurations of the first device, a second plurality of positions in a second configuration space that represents physical configurations of the second device, and information that represents pairs of positions. A representative pair includes a first representative position in the first configuration space and a second representative position in the second configuration space. The method involves creating, by the processor, from the training set, information that represents a map between a first run-time position in the first configuration space, and a second run-time position in the second configuration space, and returning, by the processor, the information that represents the map.

Owner:OCADO INNOVATION

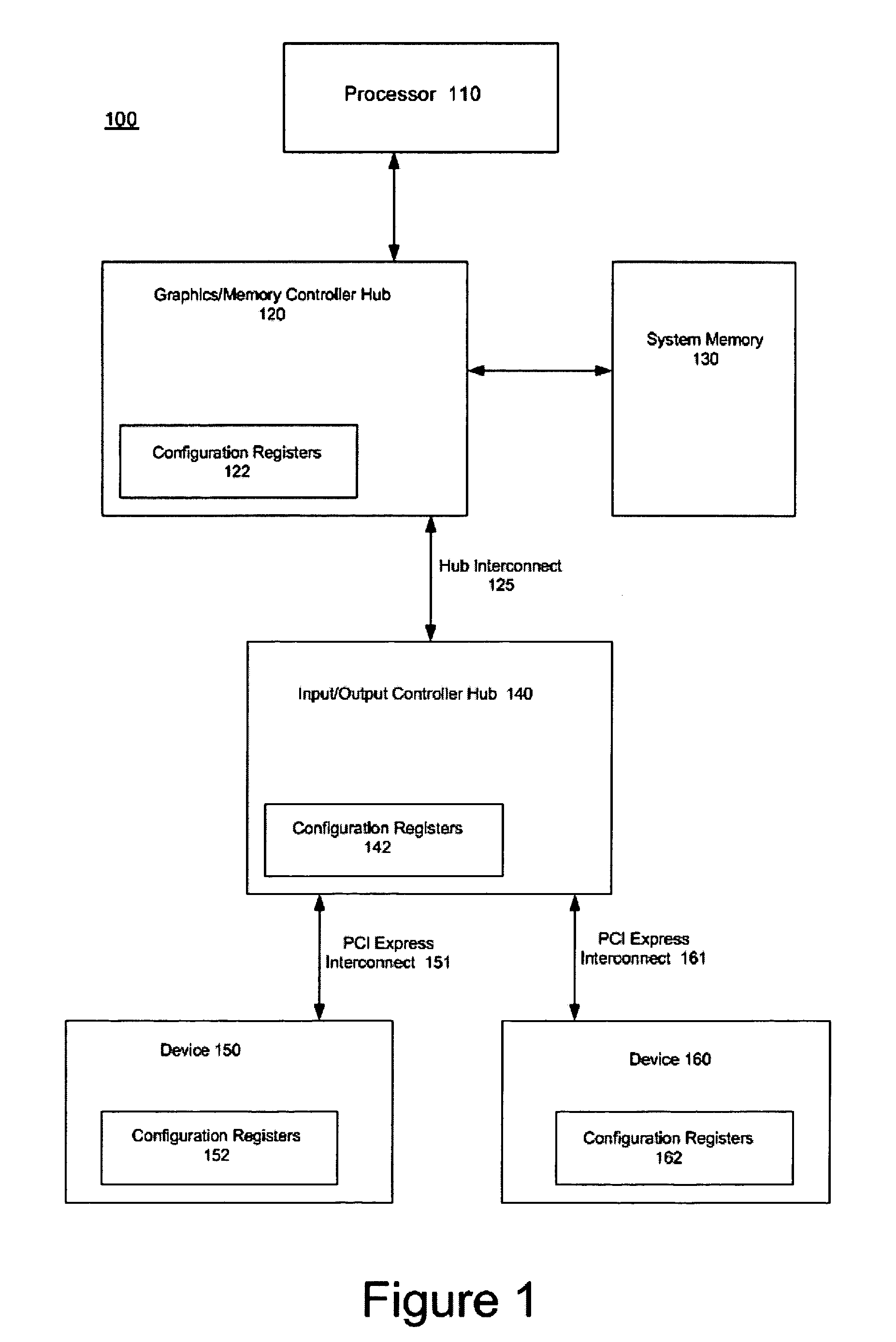

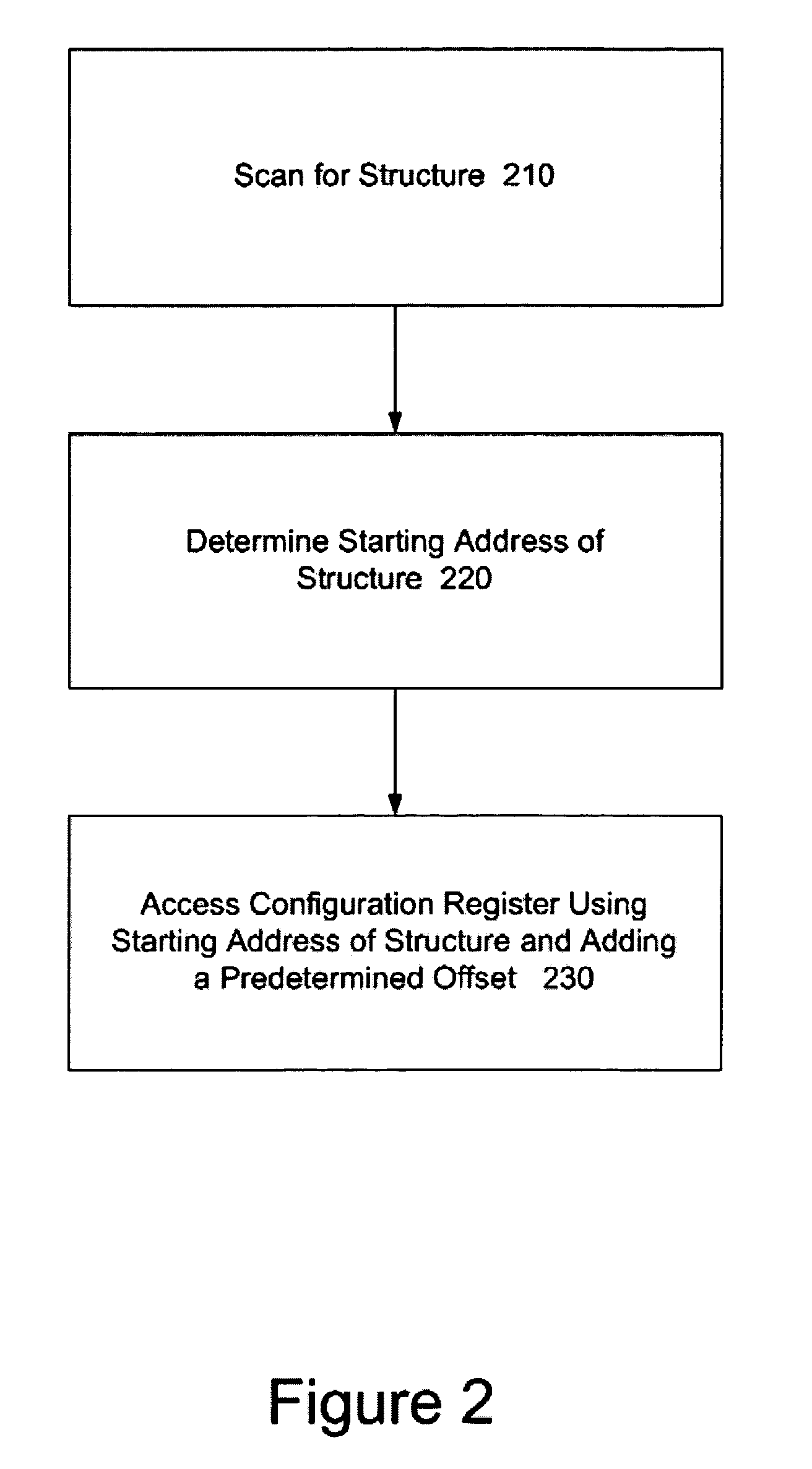

Method for addressing configuration registers by scanning for a structure in configuration space and adding a known offset

InactiveUS7366872B2Memory systemsInput/output processes for data processingProcessor registerPCI configuration space

A configuration memory space is scanned to locate an identification register whose value matches a predetermined value. The identification register identifies the location of a structure within the configuration space. The location of the beginning of the structure is used along with a predetermined (known) offset to determine the address of a desired configuration register.

Owner:INTEL CORP

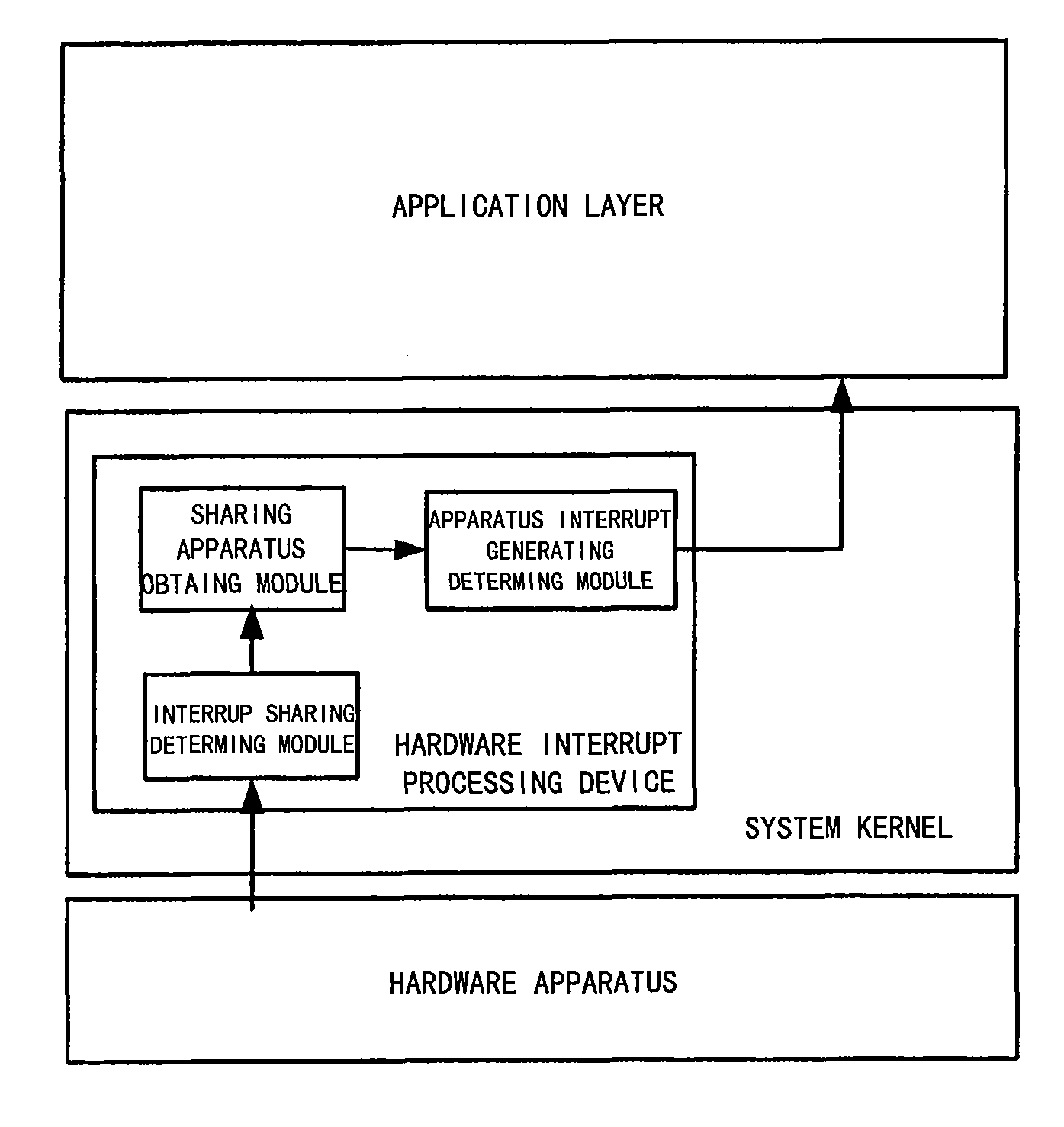

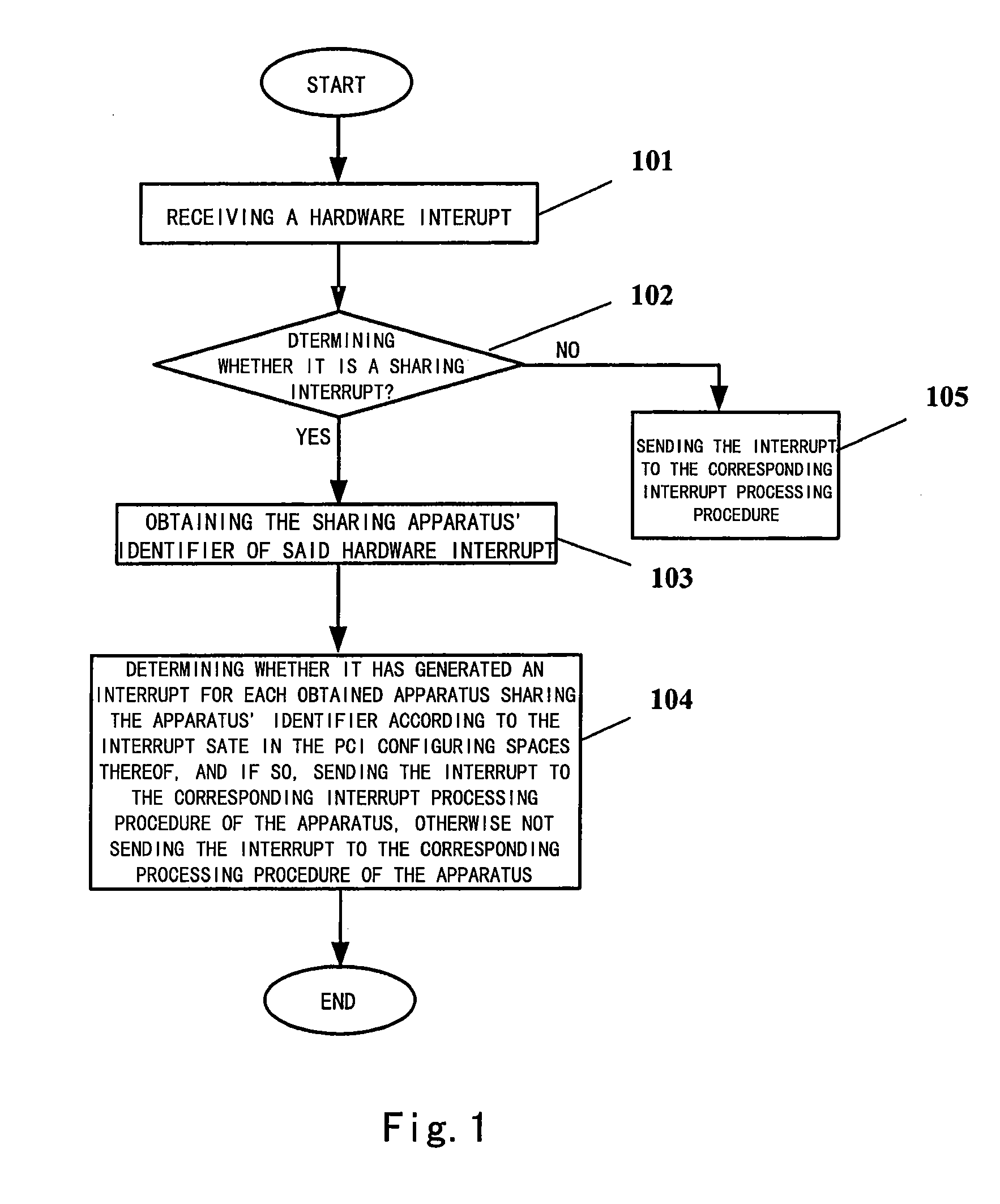

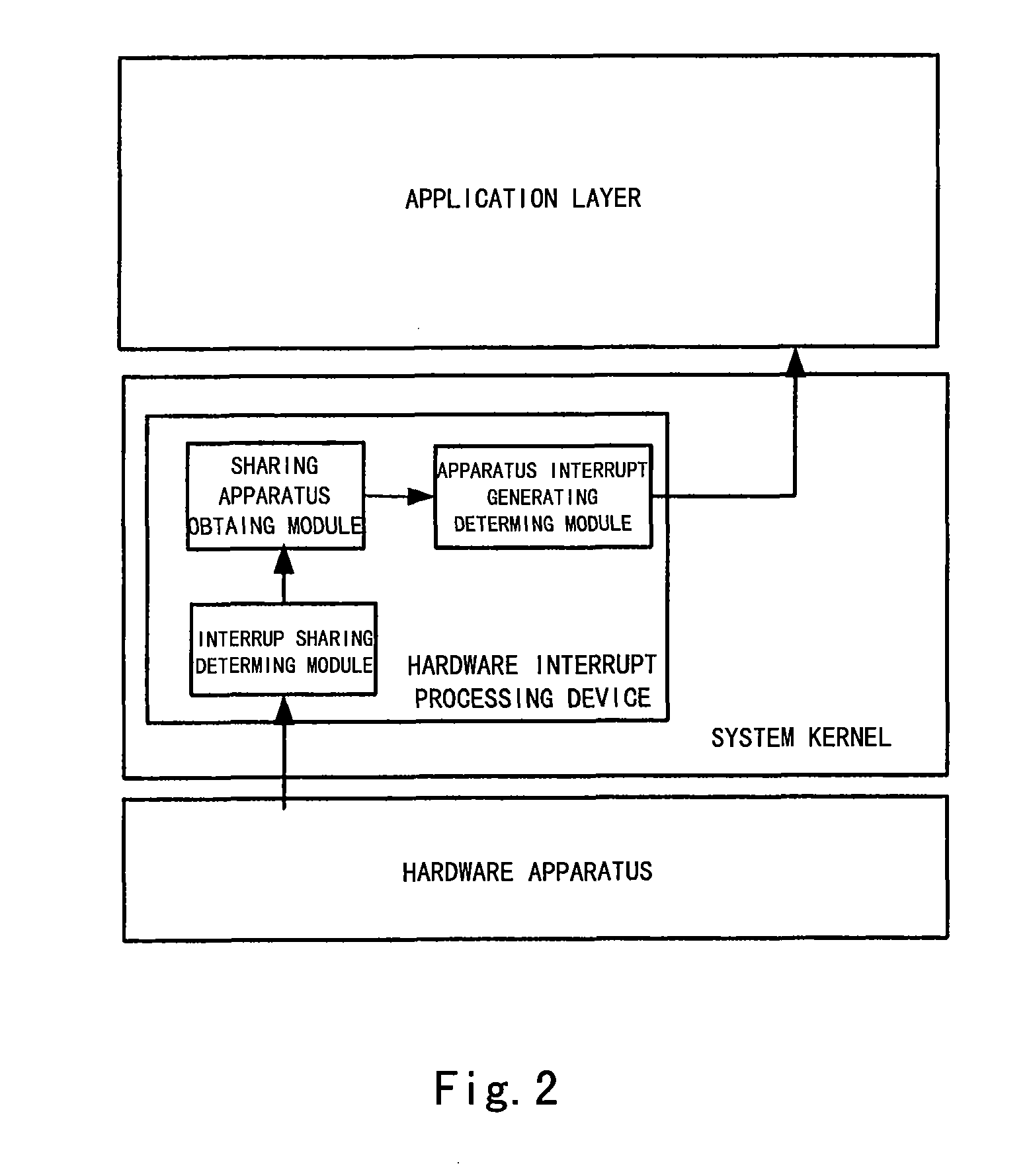

Processing method and processing device for a hardware interrupt

InactiveUS20080162764A1Avoid problemsPrecise processingProgram controlInterrupt handlerPCI configuration space

The present invention discloses a processing device and a processing method for a hardware interrupt, for processing the sharing interrupt. The processing method for the hardware interrupt comprises steps of: after receiving a hardware interrupt, determining whether the hardware interrupt is a sharing interrupt, and if not, sending the interrupt to a corresponding interrupt processing procedure, otherwise continuing; obtaining a sharing apparatus identifier of the hardware interrupt; for the device corresponding to each obtained sharing apparatus identifier, determining whether it has generated an interrupt according to the interrupt status in a status register of it's PCI configuration space, respectively, and if so, sending the interrupt to the corresponding interrupt processing procedure of the device, otherwise not sending the interrupt to he corresponding interrupt processing procedure. By way of the method of the present invention, the problem in which the interrupt processing doesn't match with the hardware device generating the hardware interrupt may be avoided.

Owner:LEGEND HOLDINGS +1

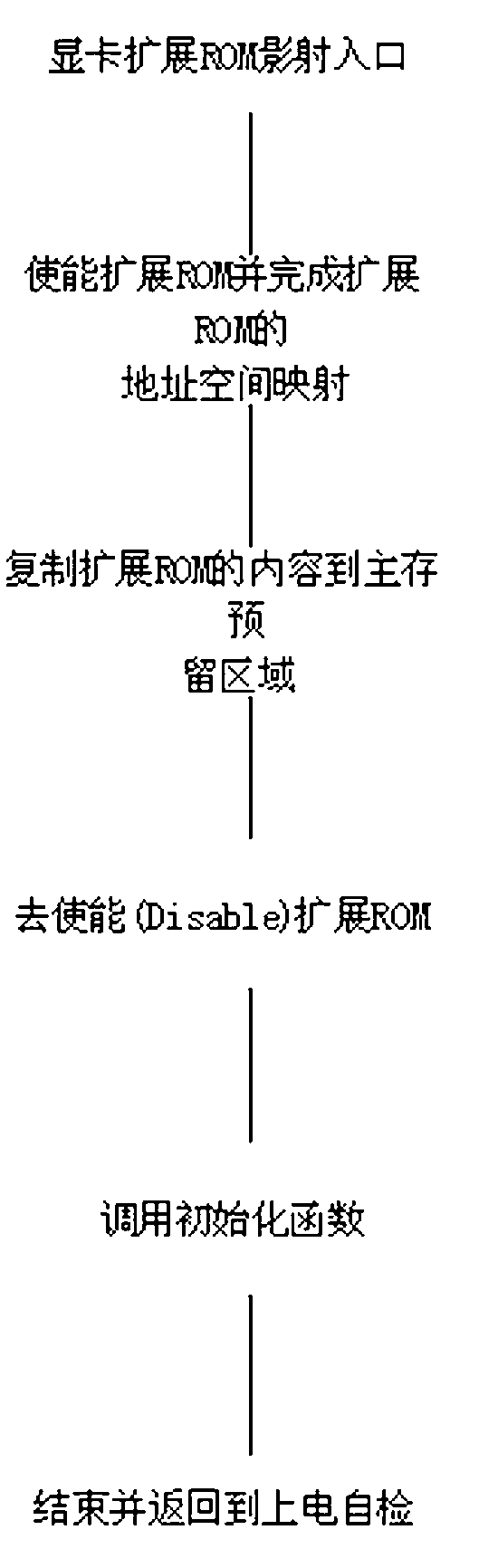

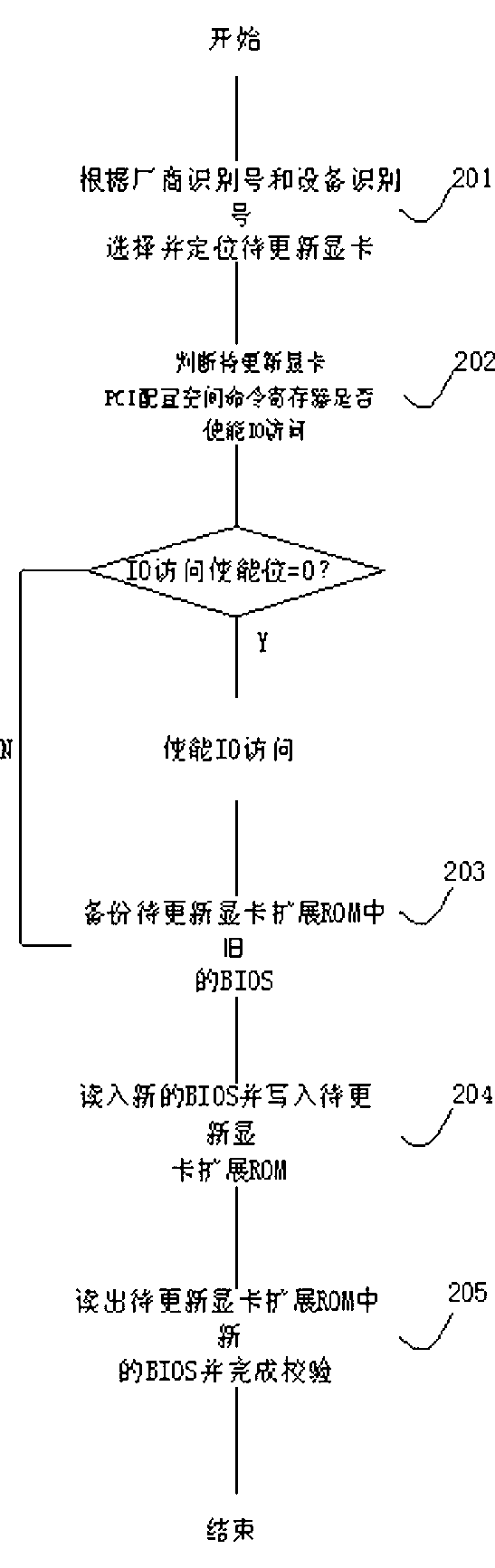

Display card basic input output system (BIOS) updating method based on input/output (IO) access mode

Provided is a display card basic input output system (BIOS) updating method based on an input / output (IO) access mode. The display card BIOS updating method based on the IO access mode comprises the following steps: starting a Microsoft Windows operating system and executing an updating program; selecting and positioning a to-be-updated display card according to a vendor identification number and a device identification number; judging whether a command register of peripheral component interconnect (PCI) configuration space of the to-be-updated display card enables IO access or not, reading an old BIOS in an expanded read only memory (ROM) of the to-be-updated display card through the IO access mode; writing a new BIOS into the expanded ROM of the to-be-updated display card through the IO access mode; reading the new BIOS in the expanded ROM of the to-be-updated display card through the access mode and completing calibration; and exiting the updating program and restarting the Microsoft Windows operating system. The display card BIOS updating method based on the IO access mode is capable of completing update of the display card BIOS conveniently, rapidly and reliably.

Owner:NO 709 RES INST OF CHINA SHIPBUILDING IND CORP

Configurable mapping of devices to bus functions

InactiveUS20060161692A1BootstrappingProgram loading/initiatingOperational systemPCI configuration space

Techniques are disclosed for enabling a single computer system to execute both operating systems that permit multiple devices to be mapped to a single PCI function and operating systems that do not permit such mapping. Prior to loading and executing an operating system (e.g., during system reset), the computer system determines whether the operating system supports mapping of multiple devices to a single function. If such mapping is supported, the computer system maps multiple devices on a single PCI card to a single function in the PCI configuration space for the card. If such mapping is not supported, the computer system maps each device to a separate PCI function. The computer system then loads and executes the operating system. The operating system is thereby enabled to access all devices on the bus according to the particular device-function mapping scheme supported by the operating system.

Owner:HEWLETT PACKARD DEV CO LP

Nearby service locating device

InactiveCN106211324AEfficient use ofLower antenna heightWireless communicationDirectional antennaOmni directional

The invention belongs to locating search technologies, and specifically discloses a nearby service locating device comprising a beacon node network, a mobile locating terminal and a server sub-unit, wherein the beacon node network is composed of a plurality of Bluetooth beacon node networks and a WiFi beacon node network, the WiFi beacon node network is composed of a plurality of omni-directional ceiling antennas, reasonable and compact radio frequency antennas are arranged at a configuration space on the mobile locating terminal, and thus the manufacturing cost is saved to a certain extent.

Owner:CHONGQING WEIRUI TECH CO LTD

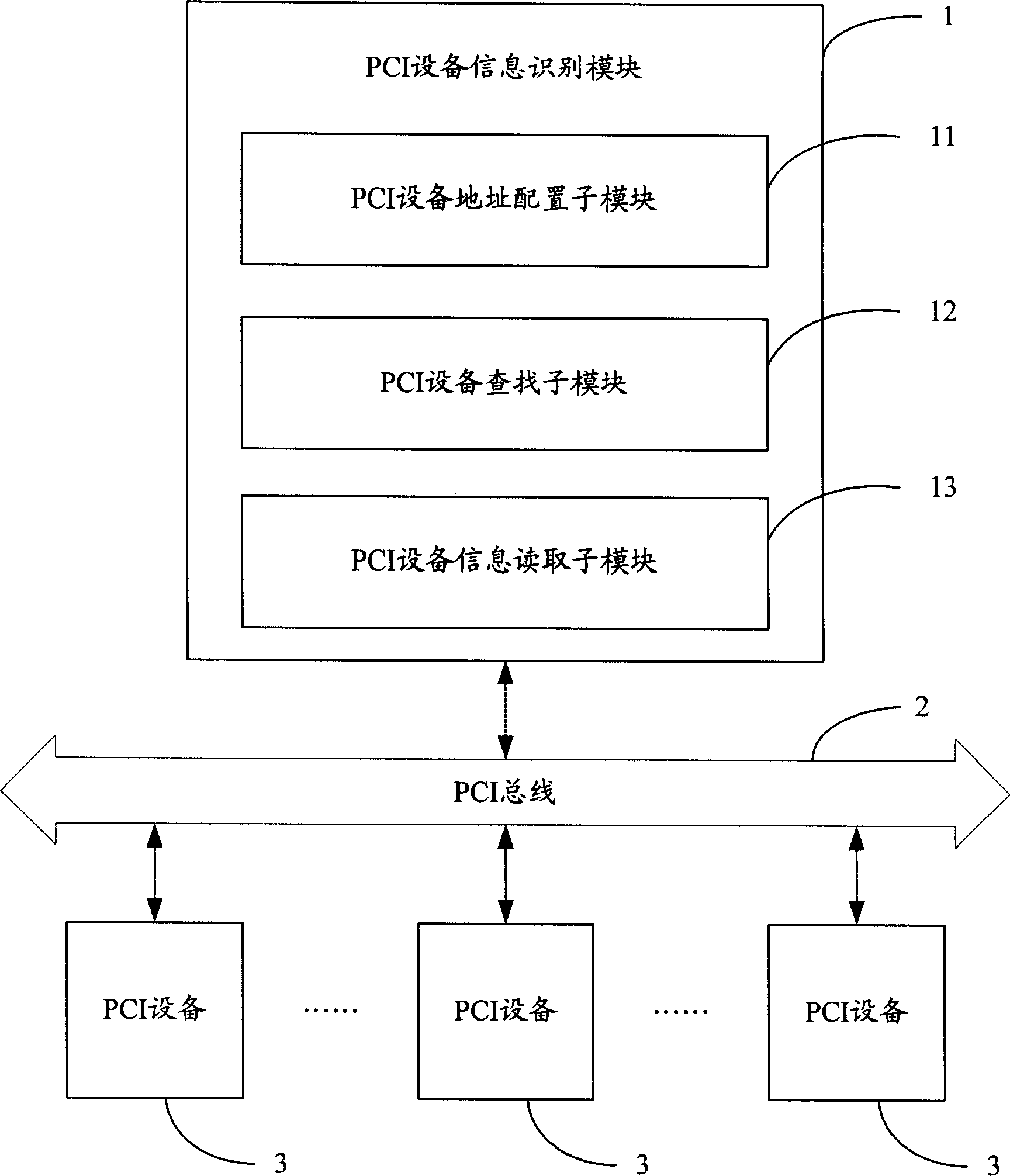

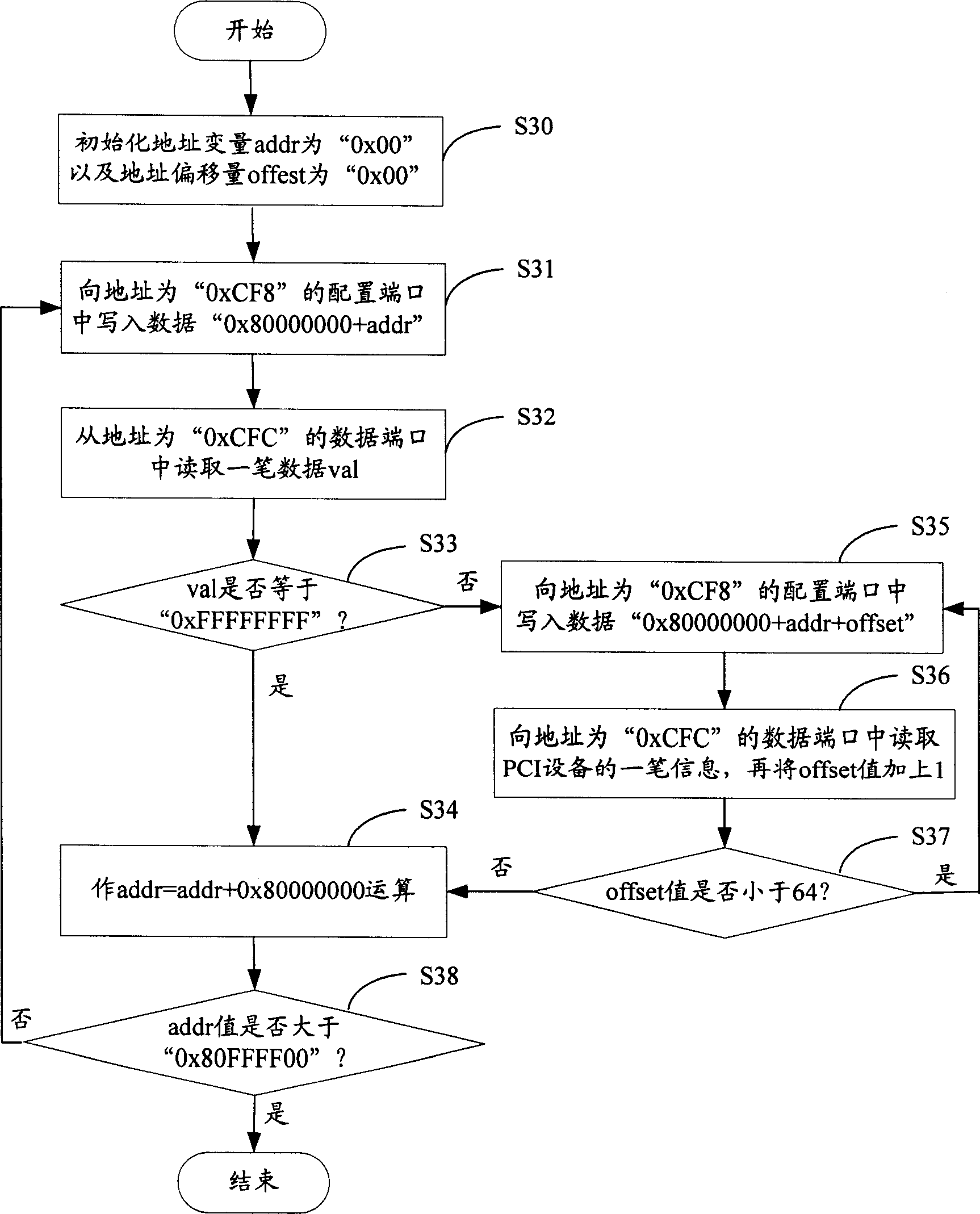

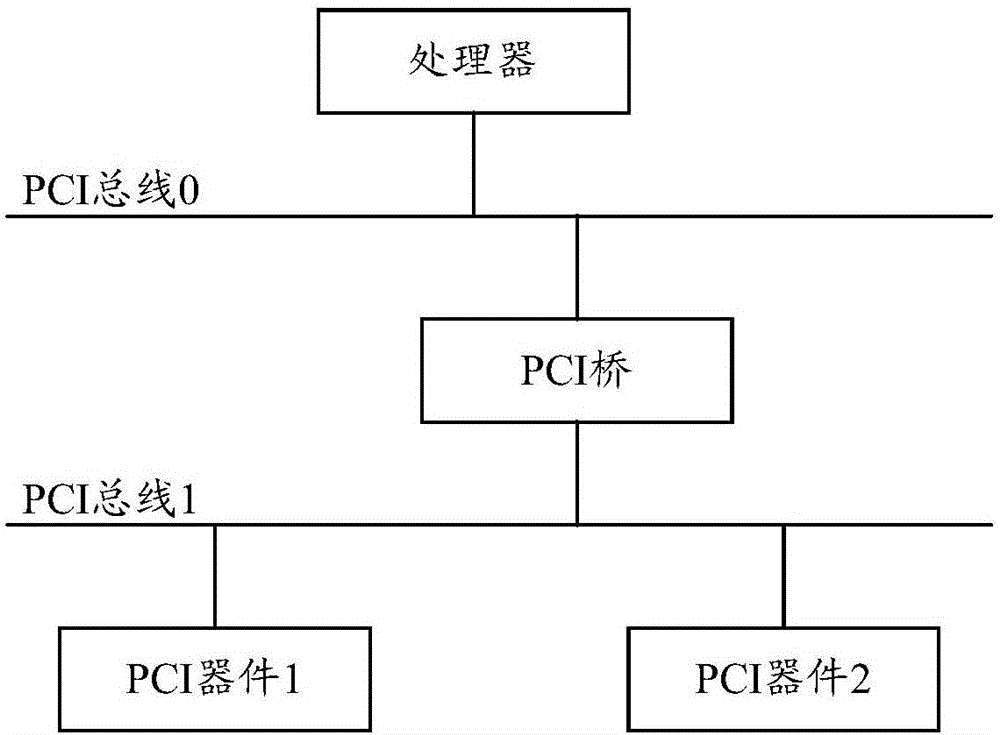

Information identifying system and method for peripheric component interconnect equipment

The invention provides a system and a method for identifying information of peripheral component interface devices. The method comprises steps of: initializing an address argument and an address shift value; writing a first address to a configuration port; reading data from a data port; judging on the PCI bus whether has corresponding PCI devices according to the data; writing a second address value to the configuration port if the corresponding device exists; reading PCI device information from the data port; adding 1 to the address shift value; judging whether the address shift value is less than 64; reading all information of the PCI device if the address shift value is less than 64; judging whether all PCI devices have been identified; reading and displaying all PCI device information if all PCI devices have been identified.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

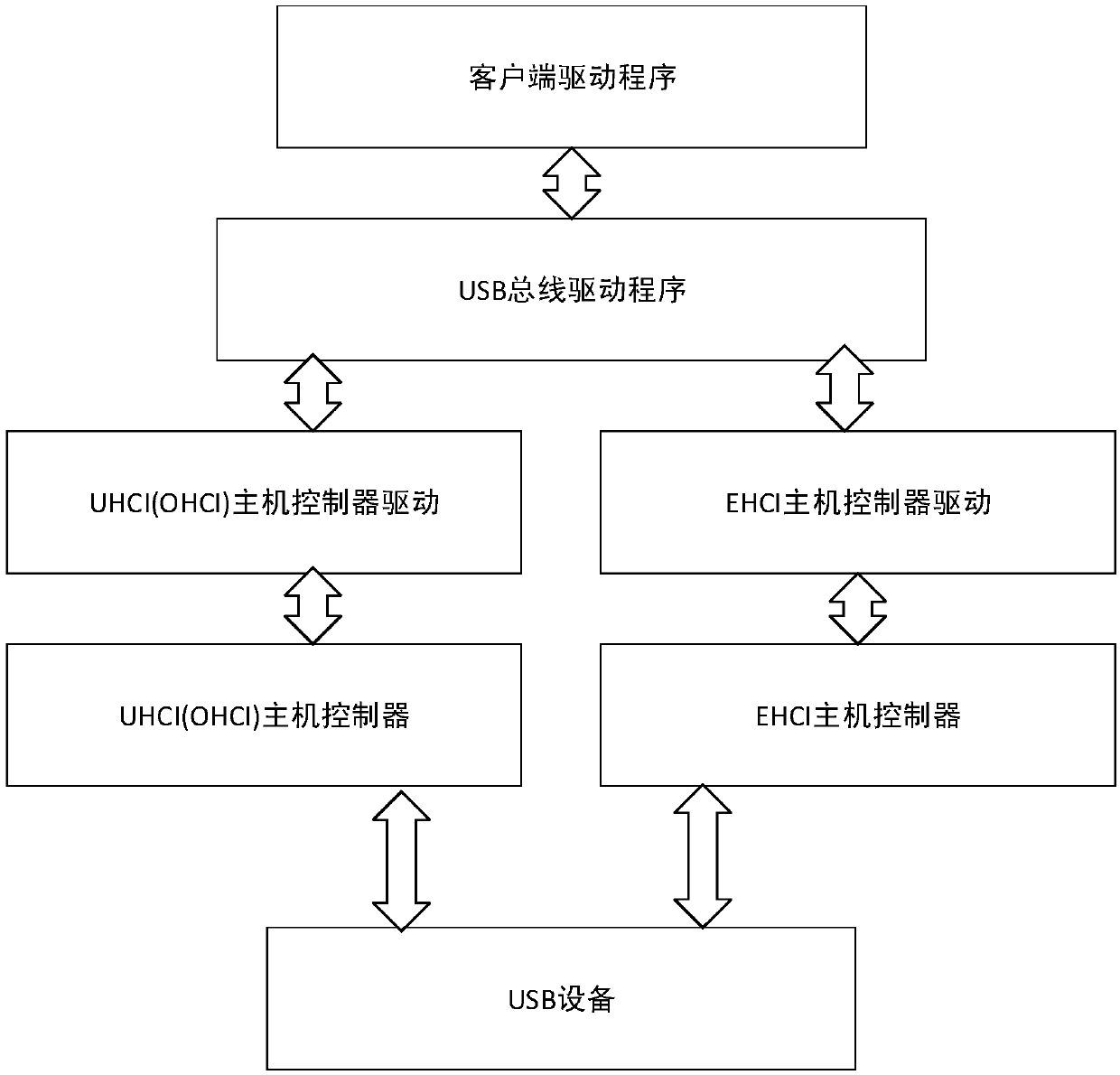

host controller driving implementation method of high-capacity storage equipment in a VxWorks system

ActiveCN109522056AAchieve direct accessSolve the problem of slow transfer rateBootstrappingMass storageLow speed

The invention relates to a host controller drive implementation method of high-capacity storage equipment in a VxWorks system, and belongs to the technical field of embedded communication. The methodcomprises the following steps: firstly, replacing a PCI (Peripheral Component Interconnect) configuration space by utilizing a BSP (Basic Service Provider) under a VxWorks system, and cutting off a related function for calling a PCI bus in the system to realize direct access to a host controller; Secondly, mapping the CPU address into a PCI address, obtaining a register base address for initializing a host controller by utilizing a conversion function from a physical address to a virtual address, and modifying an interrupt function of the host controller; And finally, different types of HCDs are hung on the USBD by utilizing host controller port routing control logic, so that the support for three transmission rates, namely low speed, full speed and high speed, is realized. According to the method, the problem that the transmission rate of the PCI-based host controller is low can be solved, meanwhile, a good solution is provided for achieving drive development of the non-PCI host controller under VxWorks, and the read-write speed of the high-capacity storage device is increased.

Owner:TIANJIN JINHANG COMP TECH RES INST

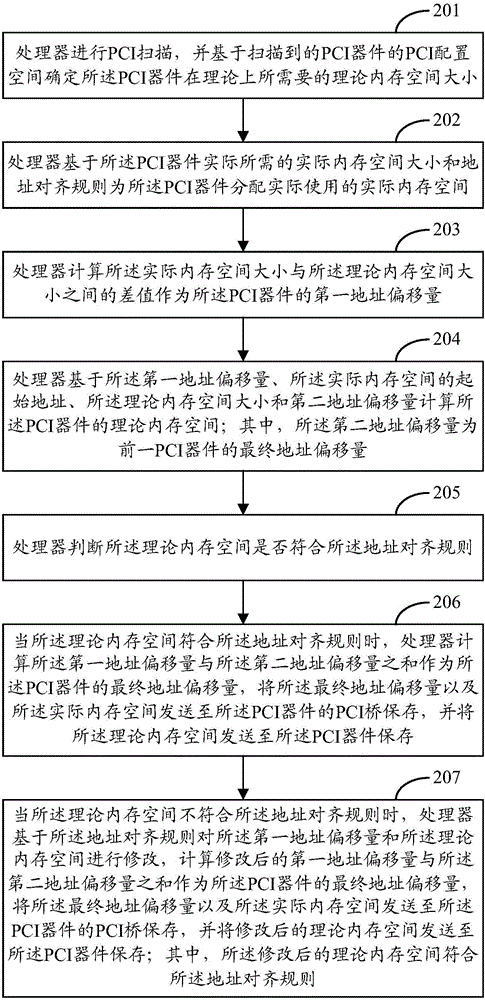

Peripheral component interconnect (PCI) memory space optimization method and device

ActiveCN106649133AReduce wasteSave memory spaceResource allocationMemory adressing/allocation/relocationParallel computingPCI configuration space

The present invention provides a peripheral component interconnect (PCI) memory space optimization method and device. The method comprises the steps that a processor determines, based on a scanned PCI configuration space of a PCI device, a theoretical memory space of the PCI device, allocates an actual memory space for the PCI device according to an actual memory space required by the PCI device actually and an address alignment rule, and determines the theoretical memory space of the PCI device according to a start address of the actual memory space, the actual memory space, the theoretical memory space, and a previous final address offset and an address alignment rule of the PCI device; and the processor sends the final address offset of the PCI device to a PCI bridge of the PCI device to store, and sends the theoretical memory space to the PCI device to store. Through adoption of the PCI memory space optimization method and device, the system memory space is saved, and limited system memory space is fully used.

Owner:HANGZHOU DPTECH TECH

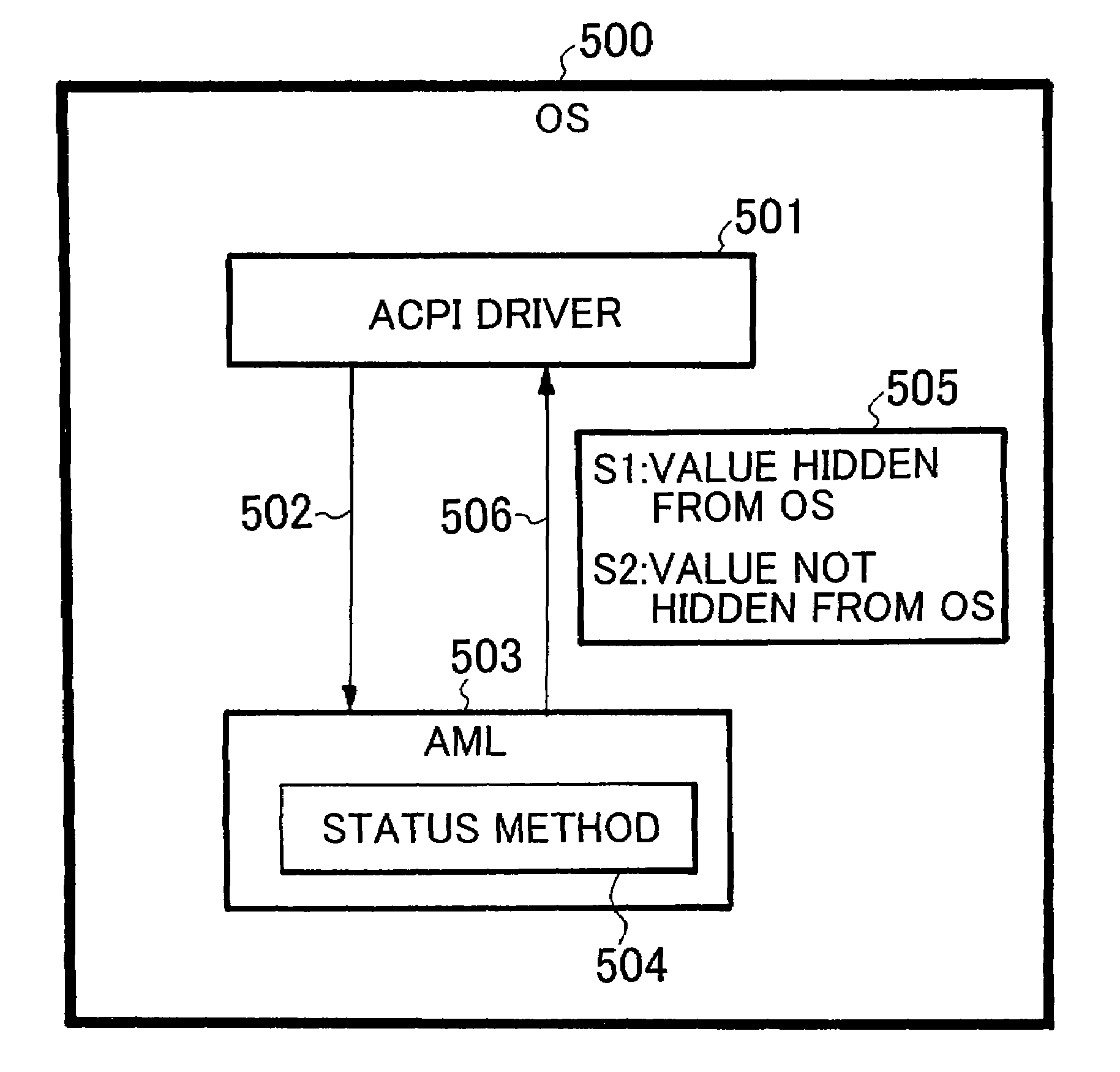

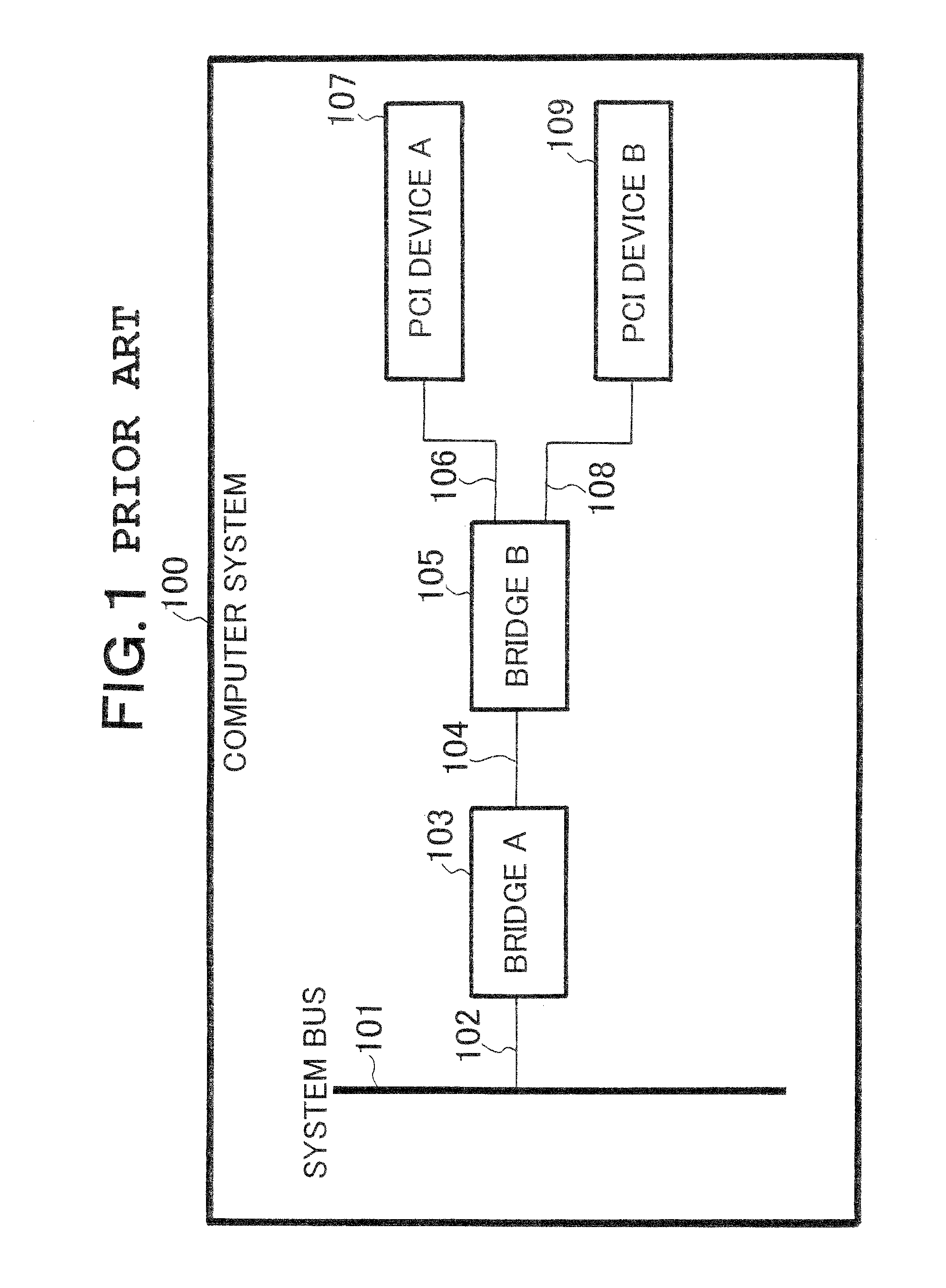

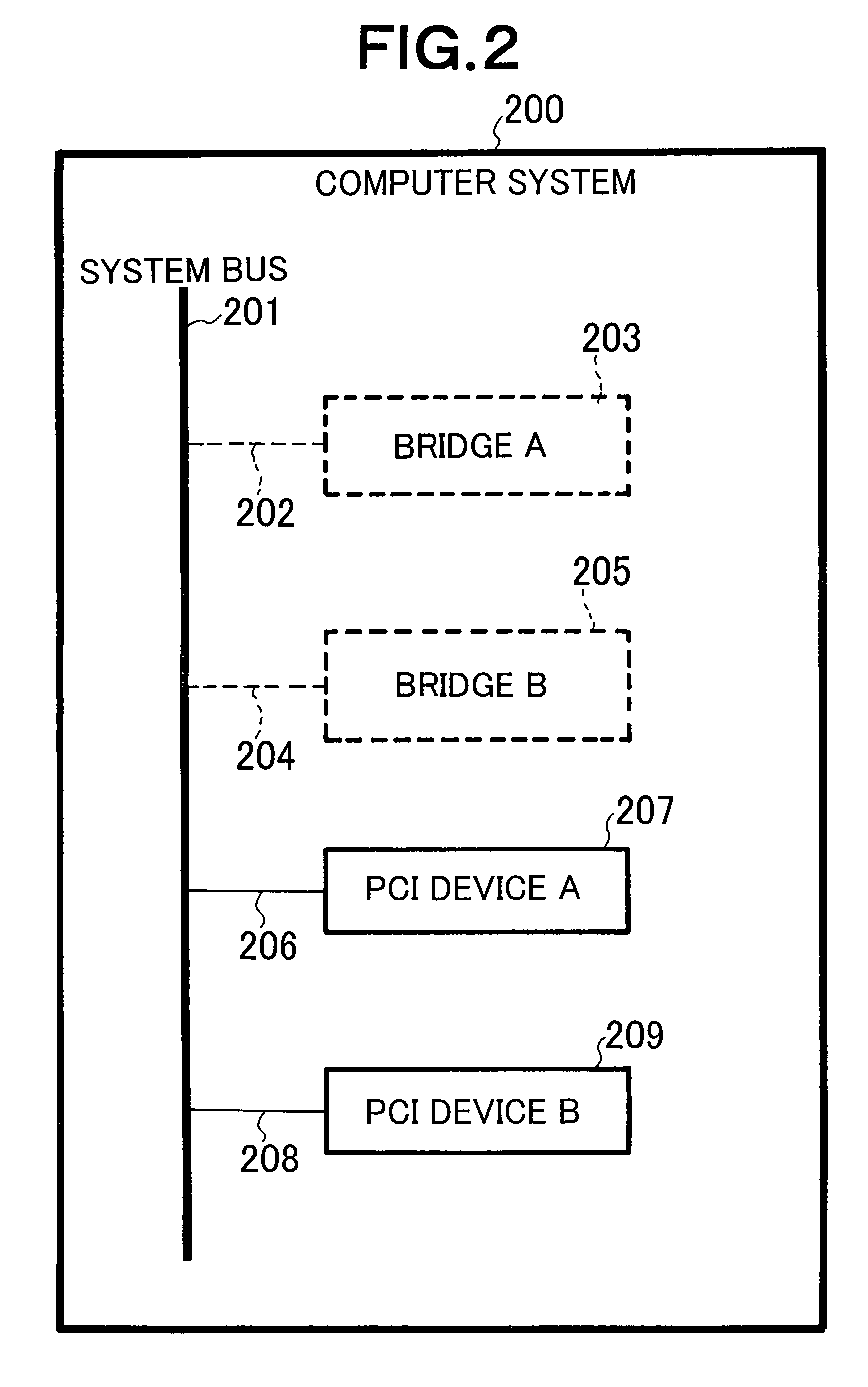

Method and apparatus for describing ACPI machine language in computer having multibridge PCI structure, and program thereof

There is provided a method for describing an ACPI machine language table used in a computer system having a multibridge PCI structure, which enables an OS to support hot plugs for PCI devices subordinate to a PCI multibridge. Upon receiving a call requesting a resource information method for a PCI device from an ACPI driver on an OS, a PCI configuration access is made to a subordinate bridge in a PCI device side, so that the ACPI machine language table supplied from a BIOS returns resource information of the PCI device. A PCI configuration access is made to a superordinate bridge in a PCI system bus side, to obtain resource information of the subordinate bridge. The resource information of the subordinate bridge is obtained from the superordinate bridge, and secondary resource information is obtained from a PCI configuration space of the subordinate bridge.

Owner:NEC CORP

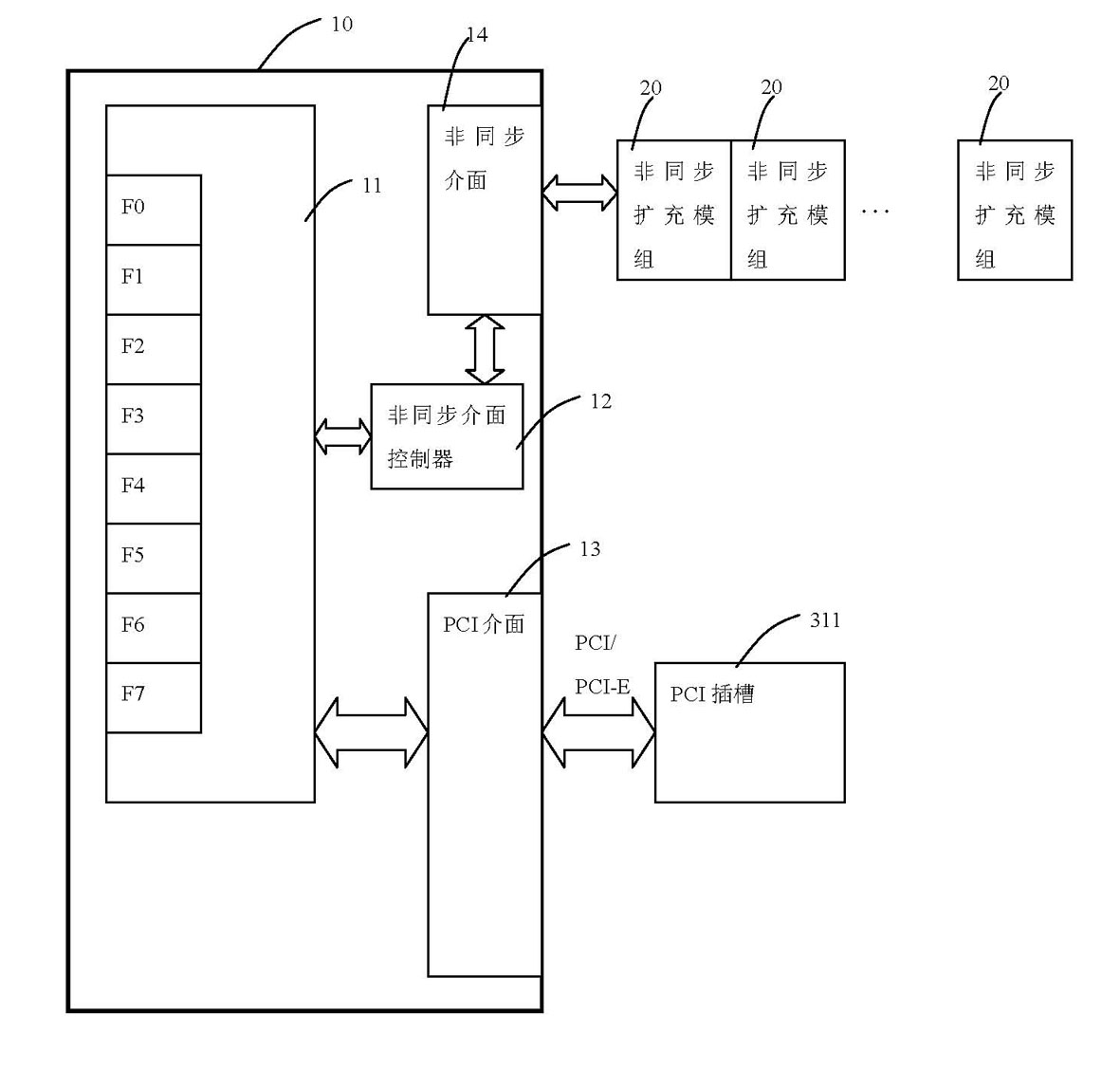

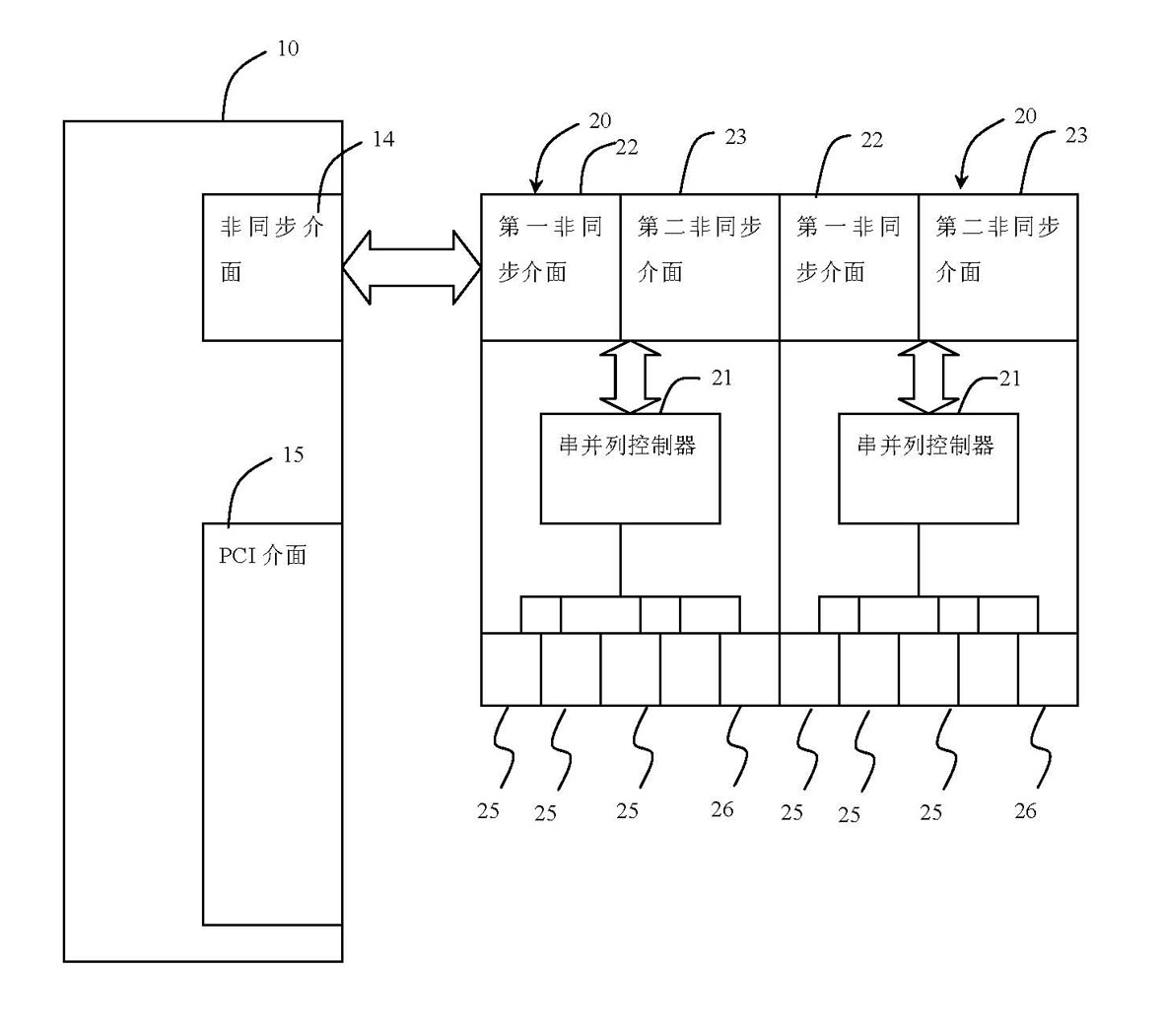

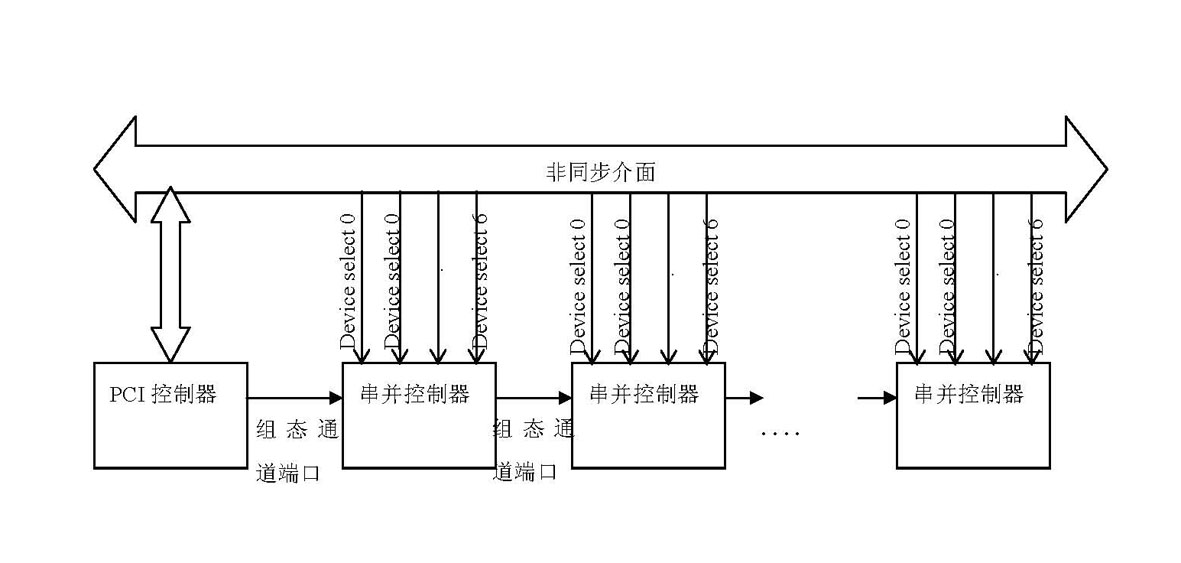

Asynchronous expansion system compatible with PCI (Programmable Communications Interface) interface

The invention discloses an asynchronous expansion system compatible with a PCI interface, which is characterized in that the asynchronous expansion system comprises a PCI riser card and a plurality of asynchronous expansion modules; the PCI riser card comprises a PCI controller set into a multi-function device, an asynchronous interface controller and an asynchronous interface; the asynchronous expansion modules respectively comprises a first asynchronous interface and a second asynchronous interface which are electrically connected to the asynchronous interface of the PCI riser card through the first asynchronous interface after mutually connecting in series; the PCI controller is used to set the numbers of each asynchronous expansion module; the resource setting of each asynchronous expansion module is obtained through the asynchronous interface controller; and the corresponding address resources are set and allocated according to the resources of each asynchronous expansion module so that the corresponding PCI configuration space is allocated to the corresponding asynchronous expansion module and the PCI controller successfully carries out a signal conversion program when an operation system carries out a scanning program.

Owner:KUNSHAN SHANGNISI ELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com