Method for testing interconnected bus of external components

A technology of peripheral component interconnection and testing method, which is applied in the direction of detecting faulty computer hardware, instruments, electrical digital data processing, etc., can solve problems such as insufficient coverage, limited system resources, and inability to test PCI bus performance, etc., to improve High test efficiency and resource coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

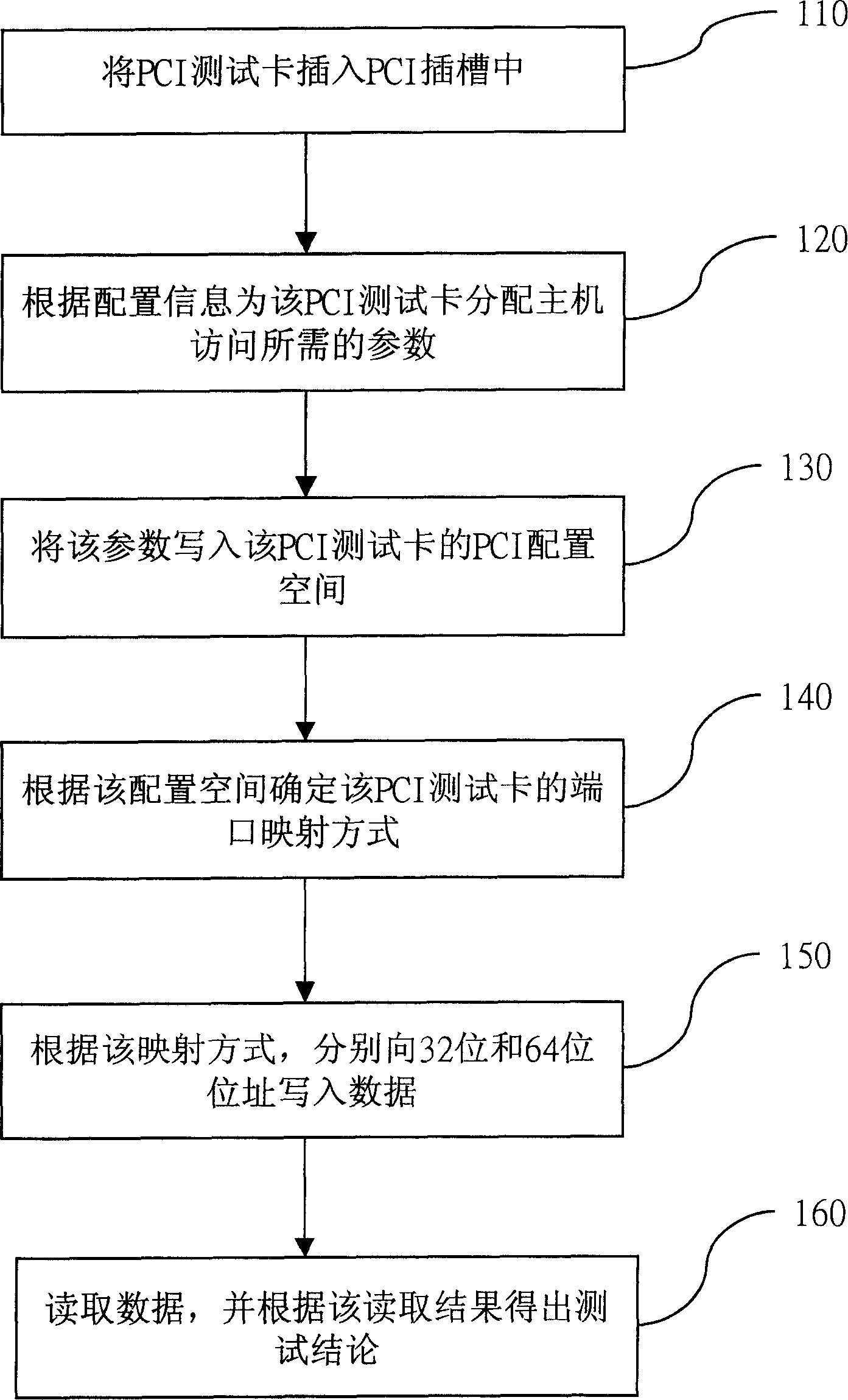

[0033] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0034] The PCI bus is a processor-independent local bus designed to meet high-speed data transmission. It has two multiplexed address data paths, 32-bit and 64-bit. One side is connected to the processor and memory bus interface, and the other side is Peripheral expansion provides high-speed channels. In terms of structure, the PCI bus is a first-level bus inserted between the CPU and the original system bus. A bridge circuit is used to manage this layer and realize data transmission between the upper and lower interfaces. In the bridge circuit manager Provide signal buffering, so that the PCI bus can support up to 10 external devices, and the PCI bus also supports bus master technology, which allows smart devices to obtain bus control rights to speed up data transmission when needed.

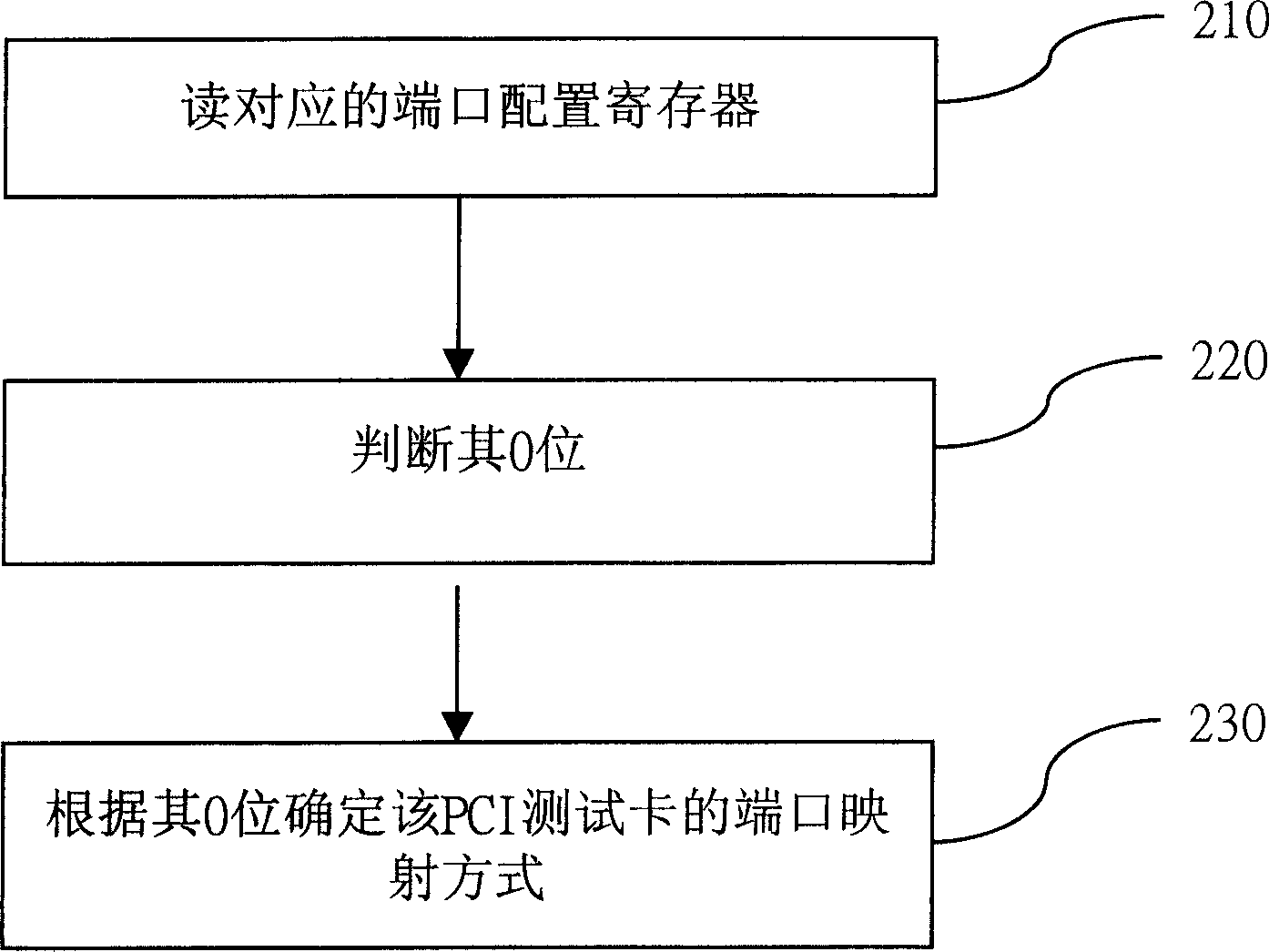

[0035] For a test method for the peripheral component interconnect bus, see fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com