Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

50 results about "Parasitic extraction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronic design automation, parasitic extraction is calculation of the parasitic effects in both the designed devices and the required wiring interconnects of an electronic circuit: parasitic capacitances, parasitic resistances and parasitic inductances, commonly called parasitic devices, parasitic components, or simply parasitics.

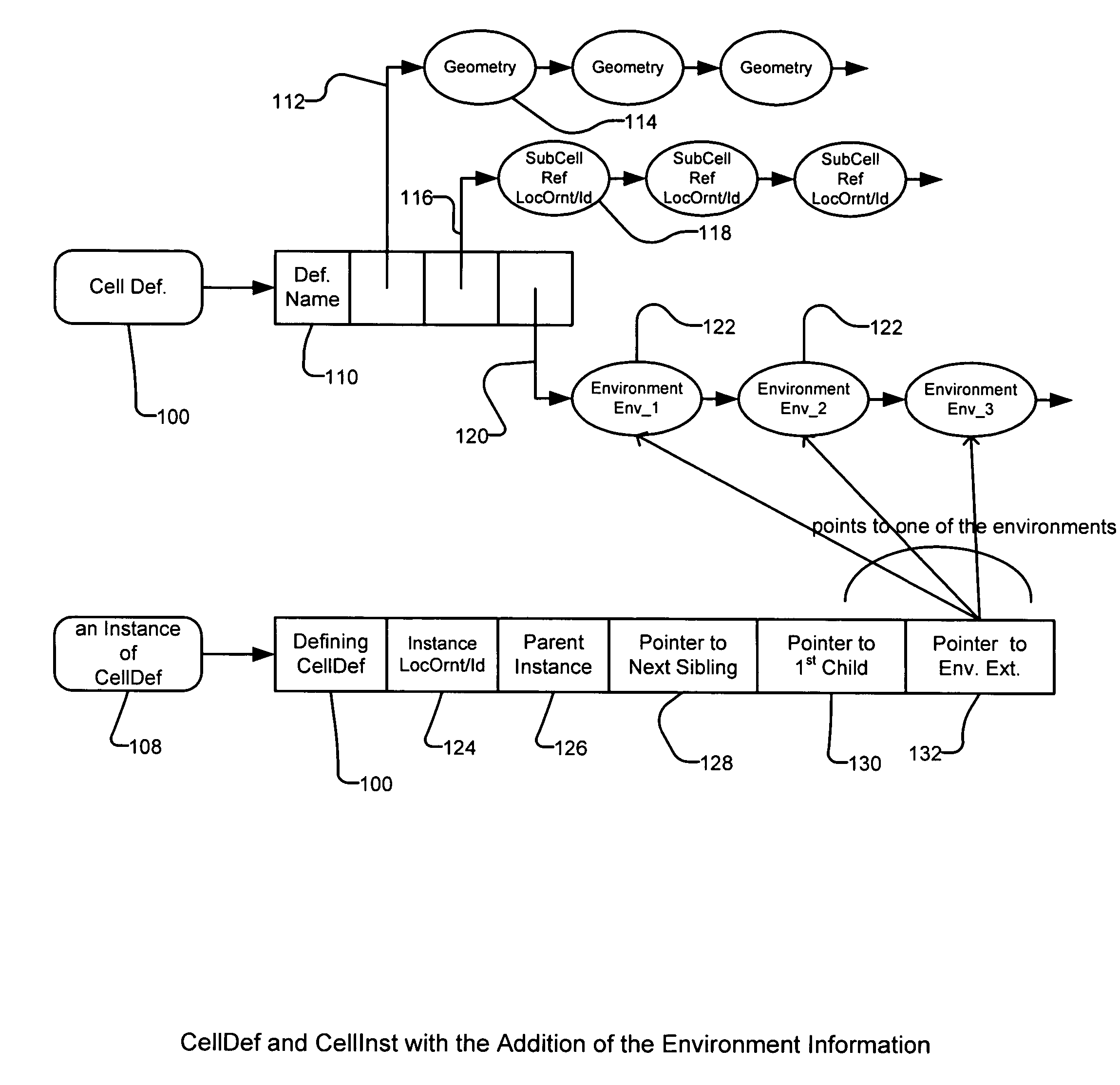

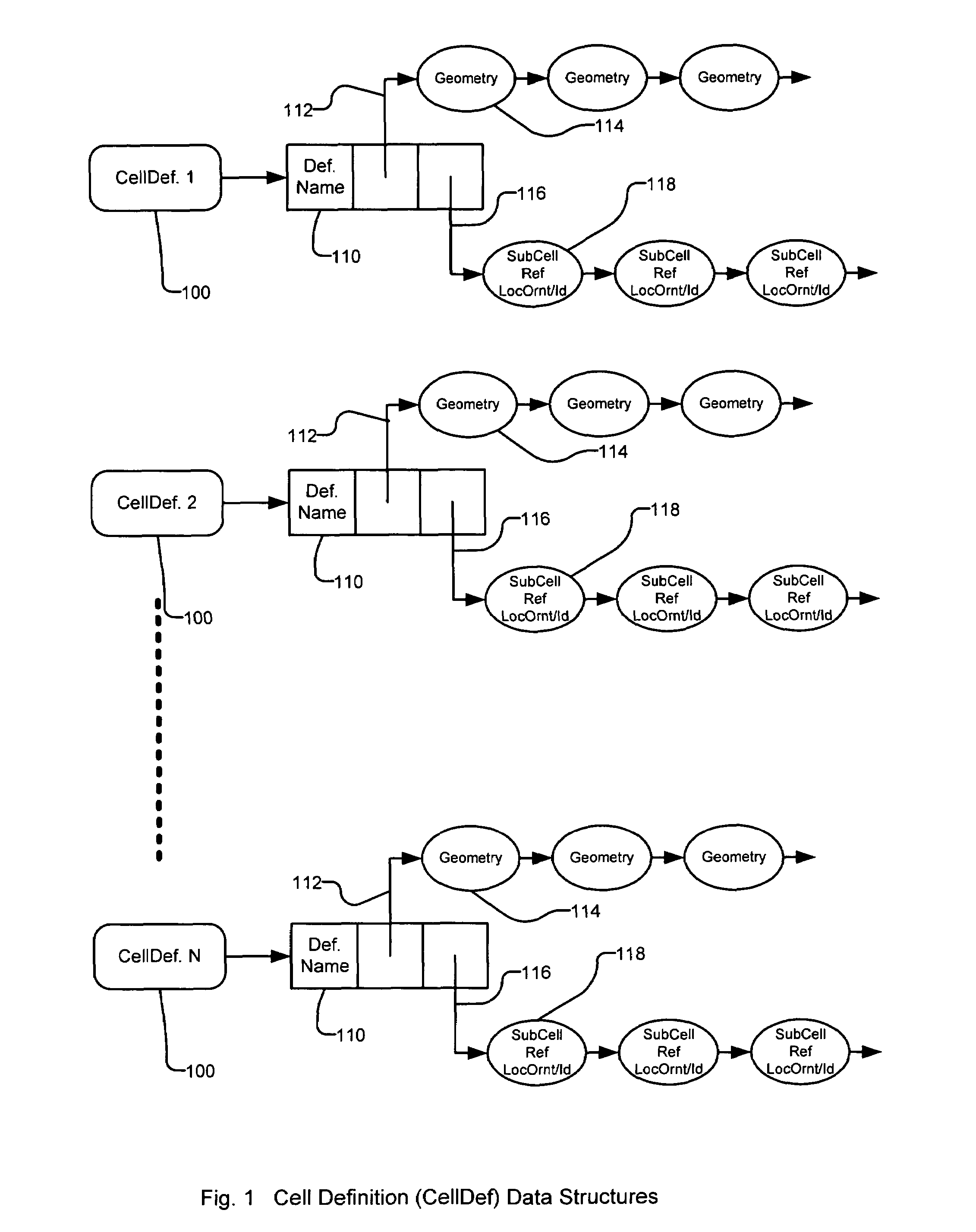

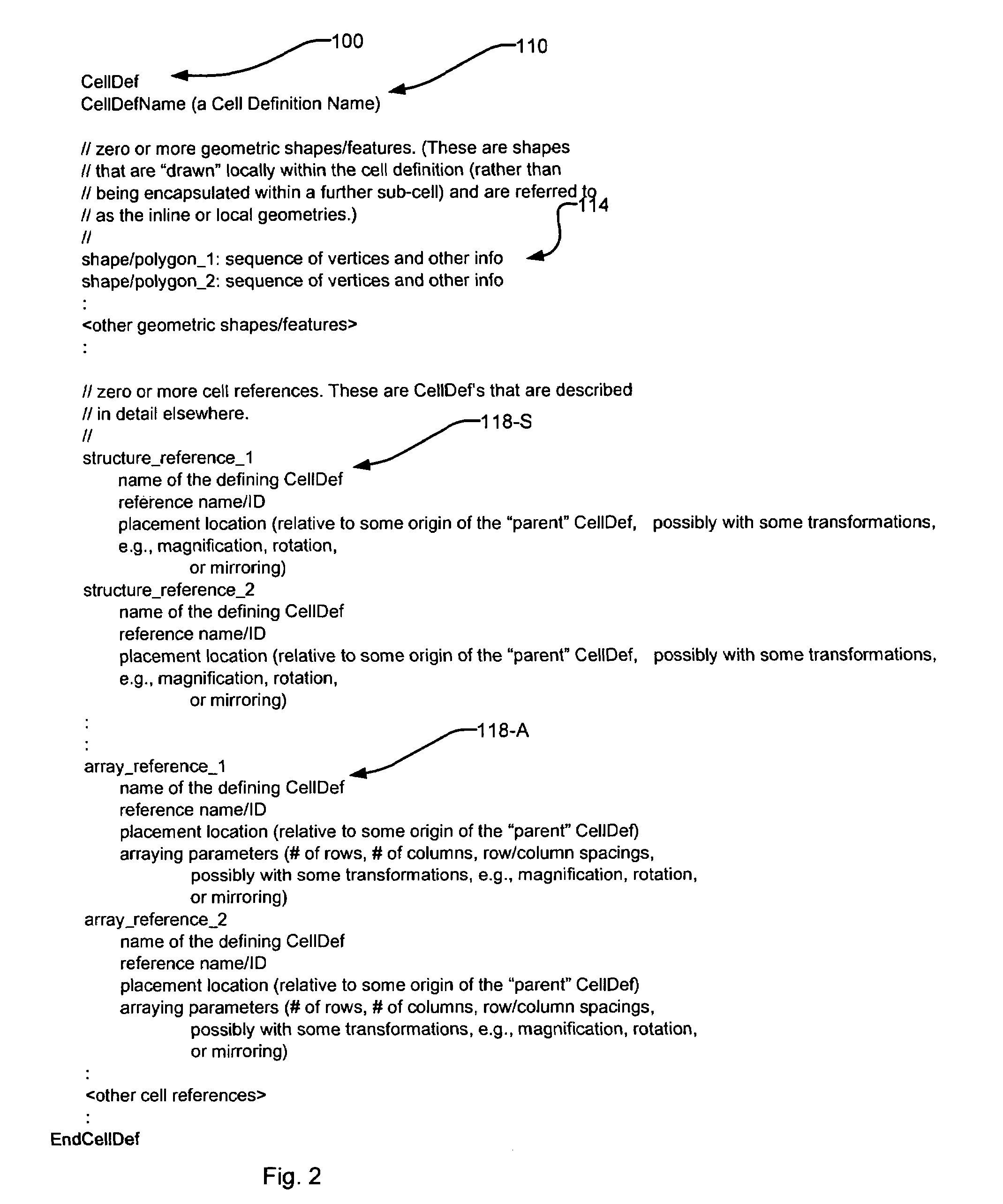

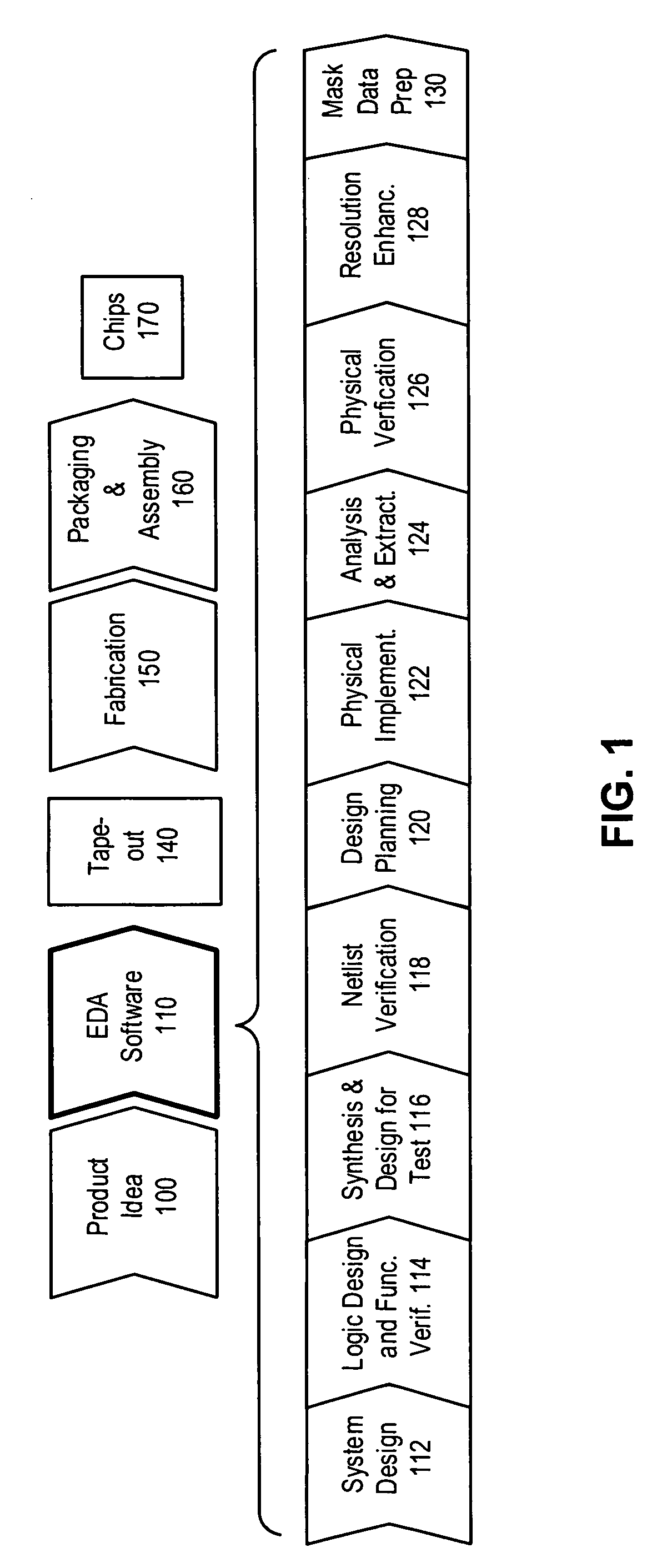

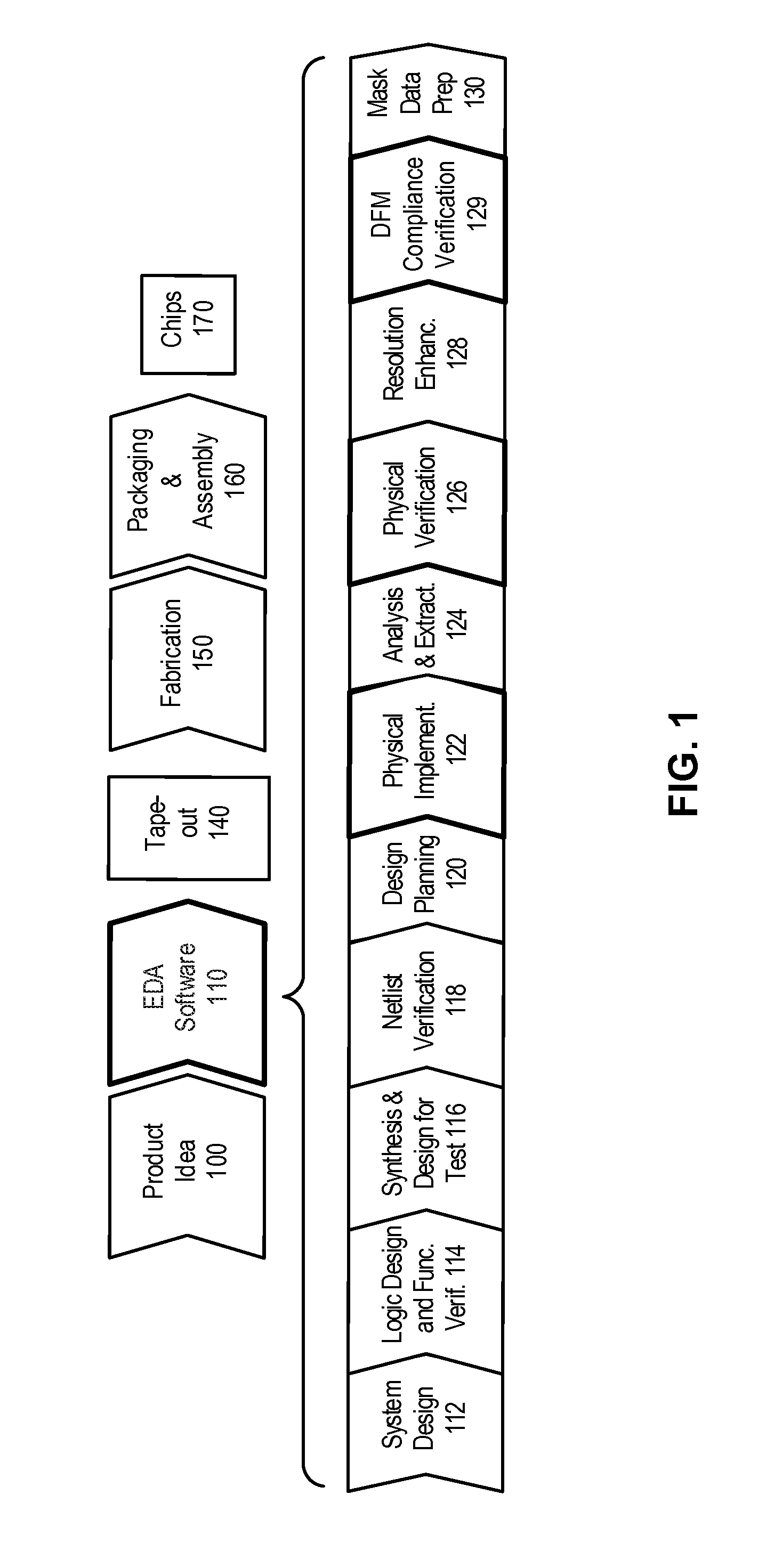

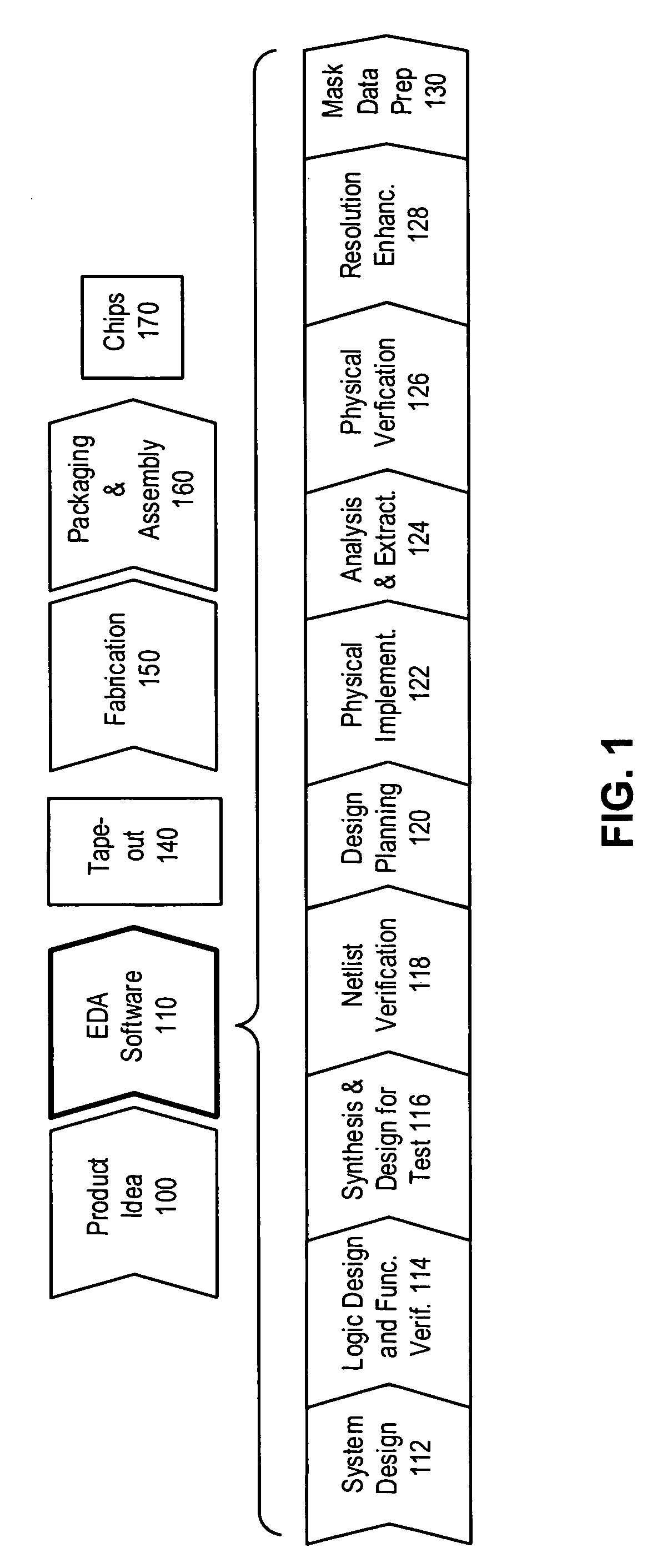

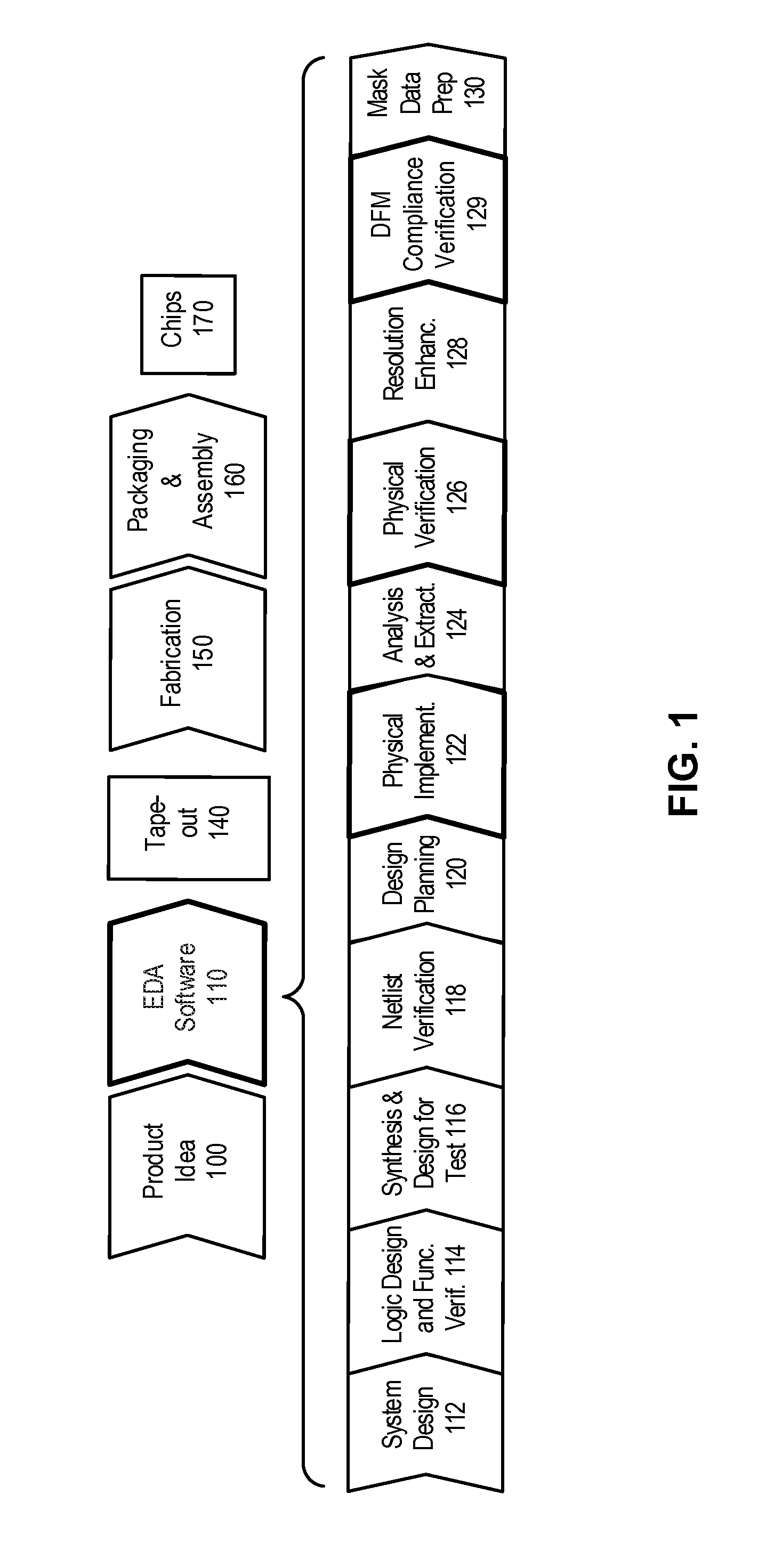

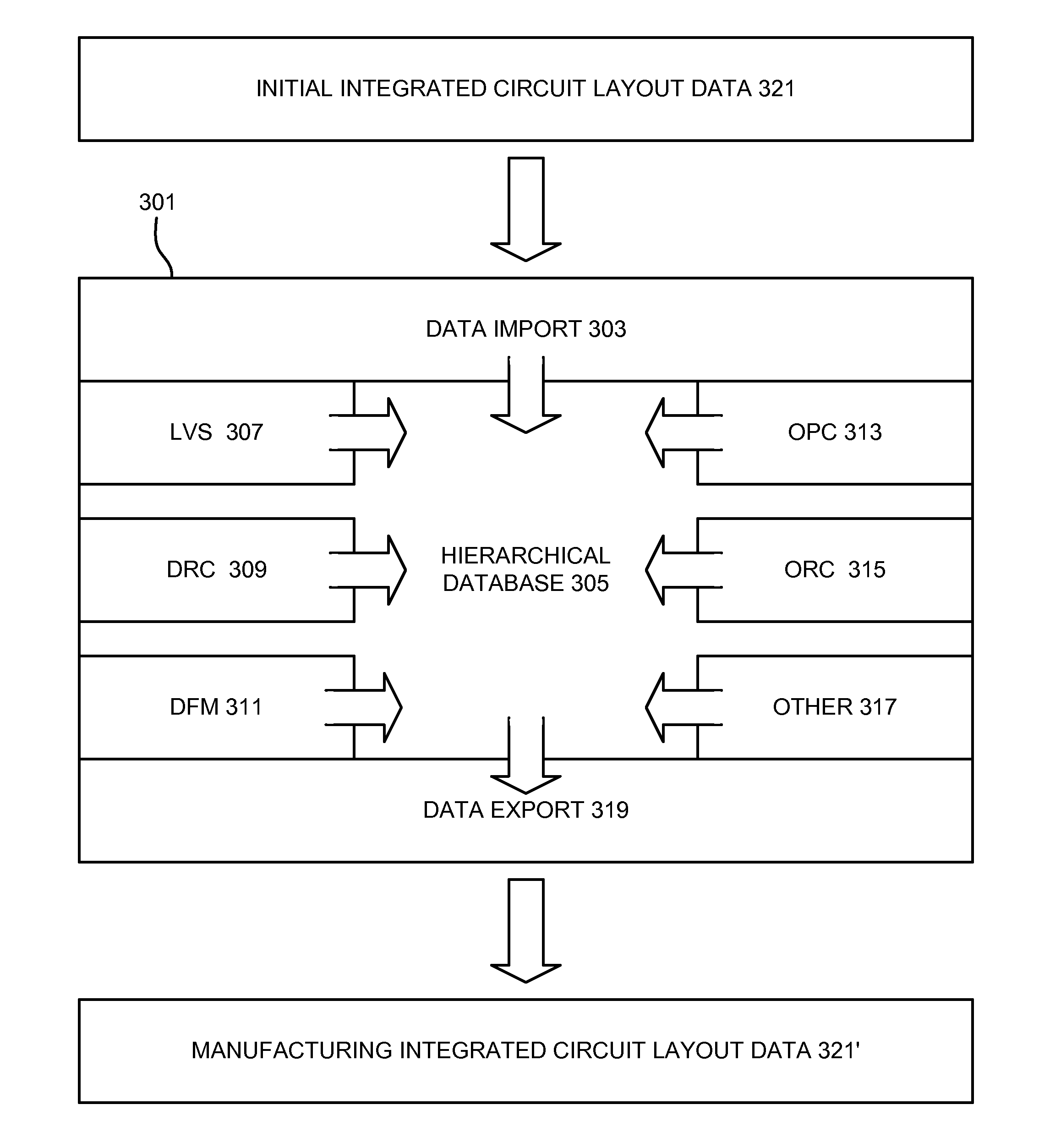

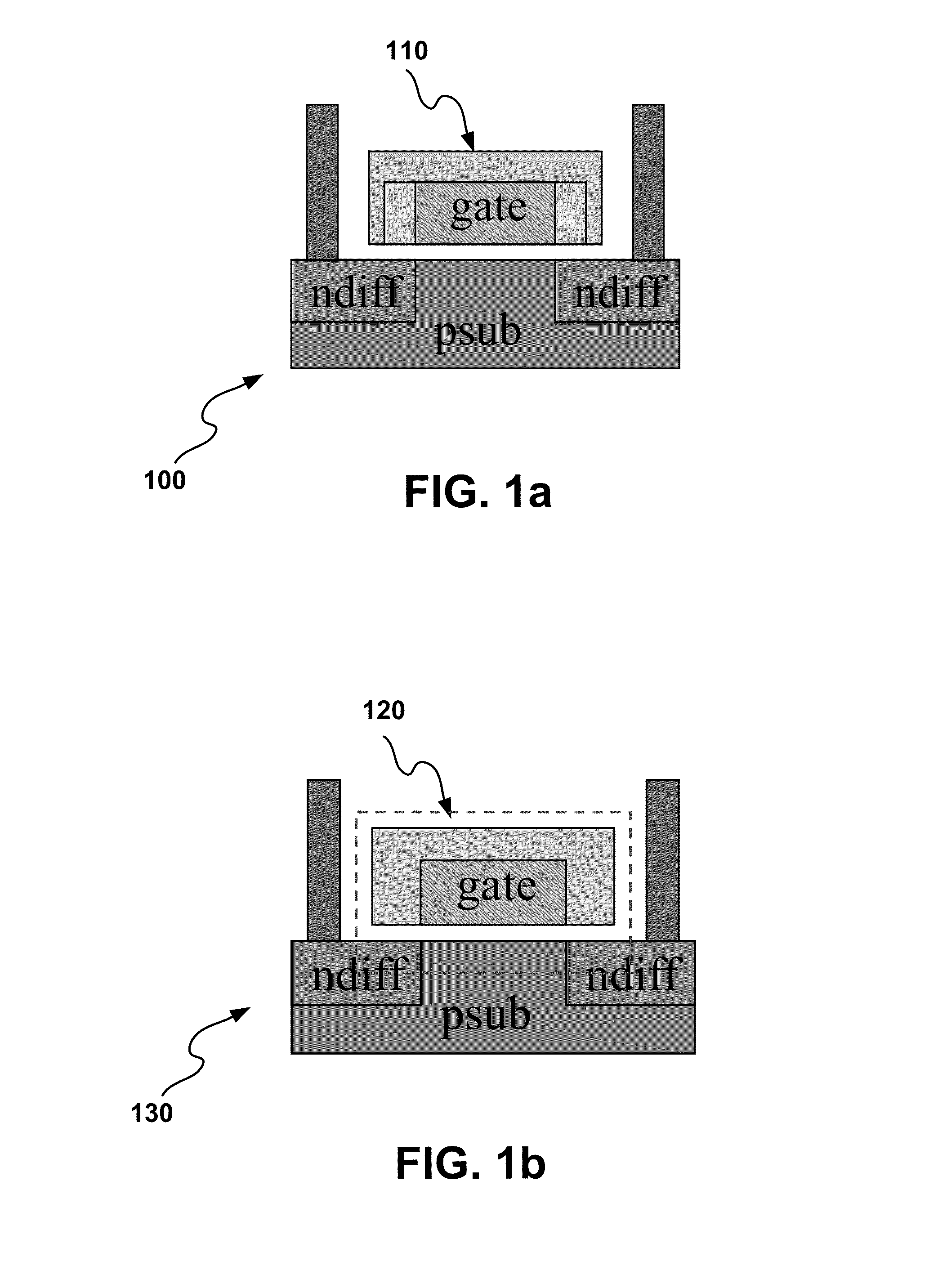

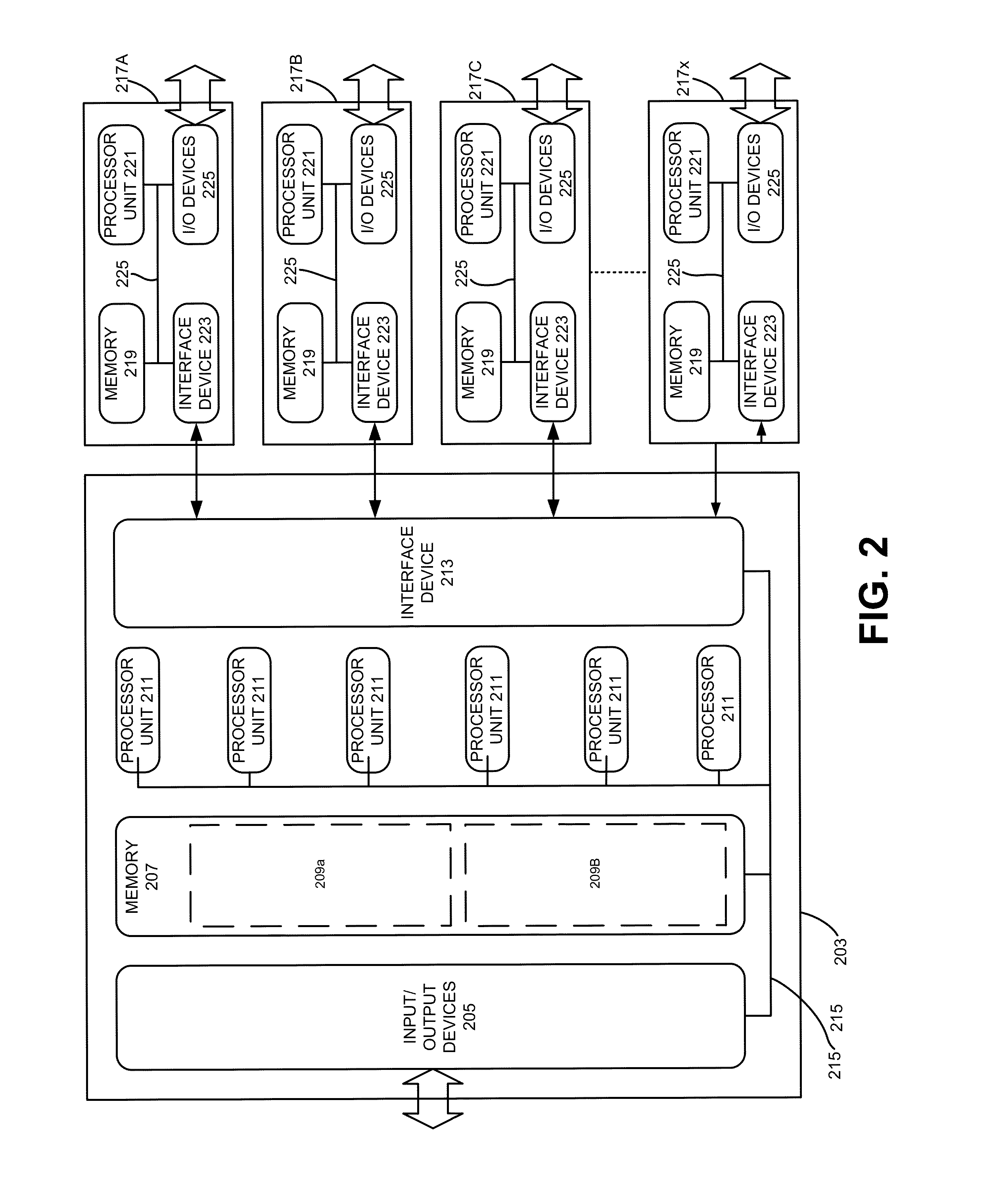

Method and system for reticle-wide hierarchy management for representational and computational reuse in integrated circuit layout design

ActiveUS20060143589A1Maximize reuseSaving in representational data volumeElectric discharge tubesOriginals for photomechanical treatmentComputation reuseComputer architecture

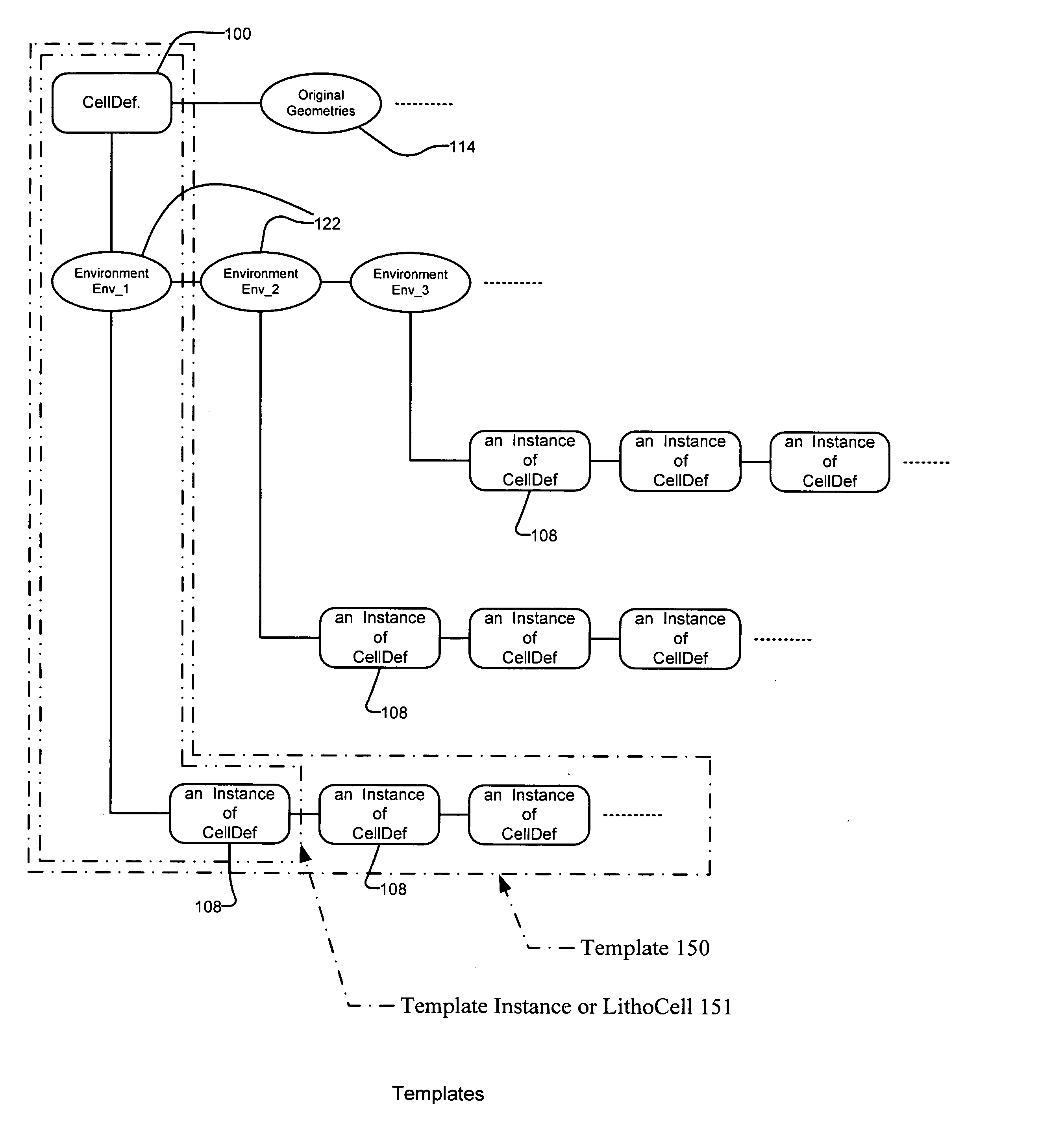

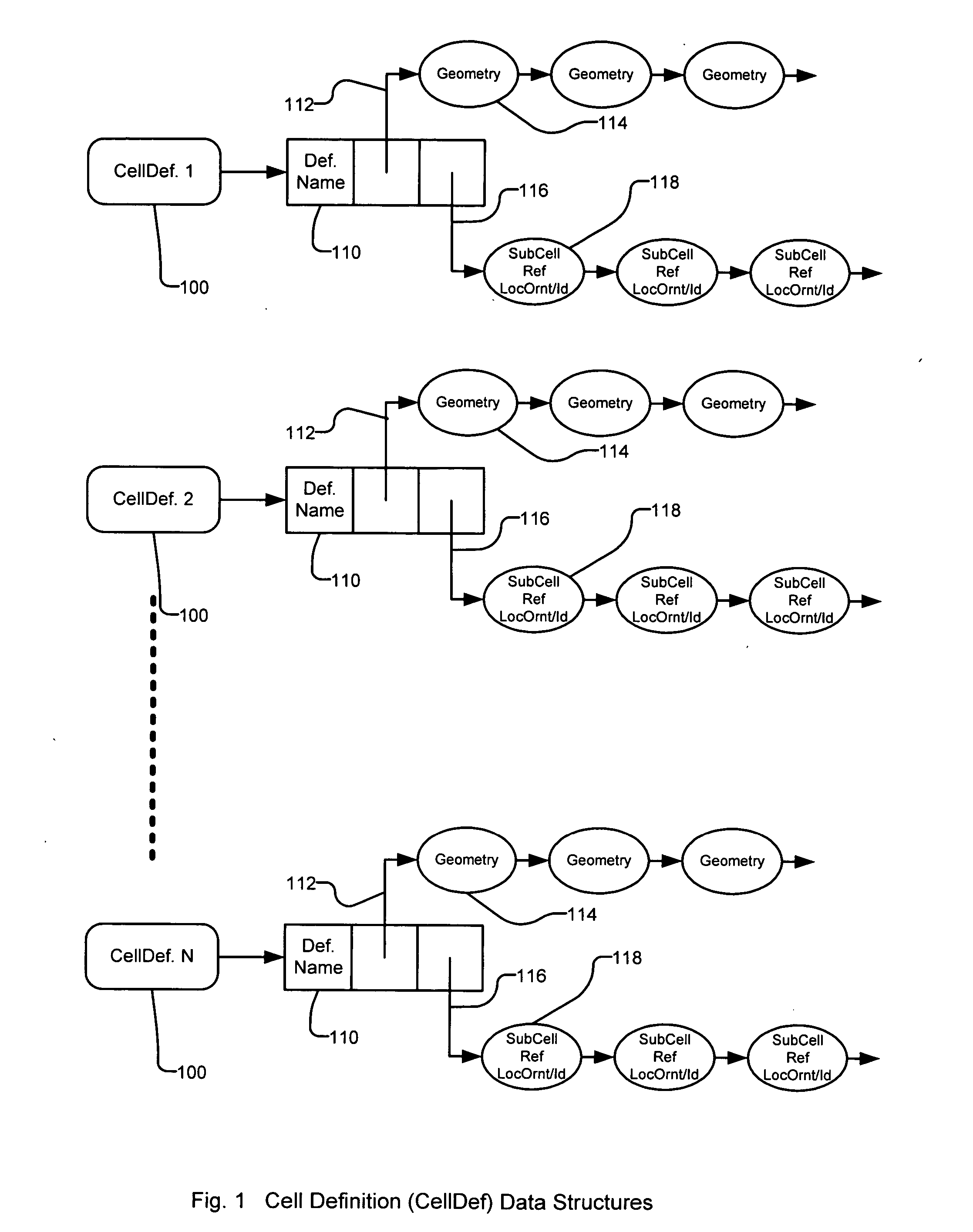

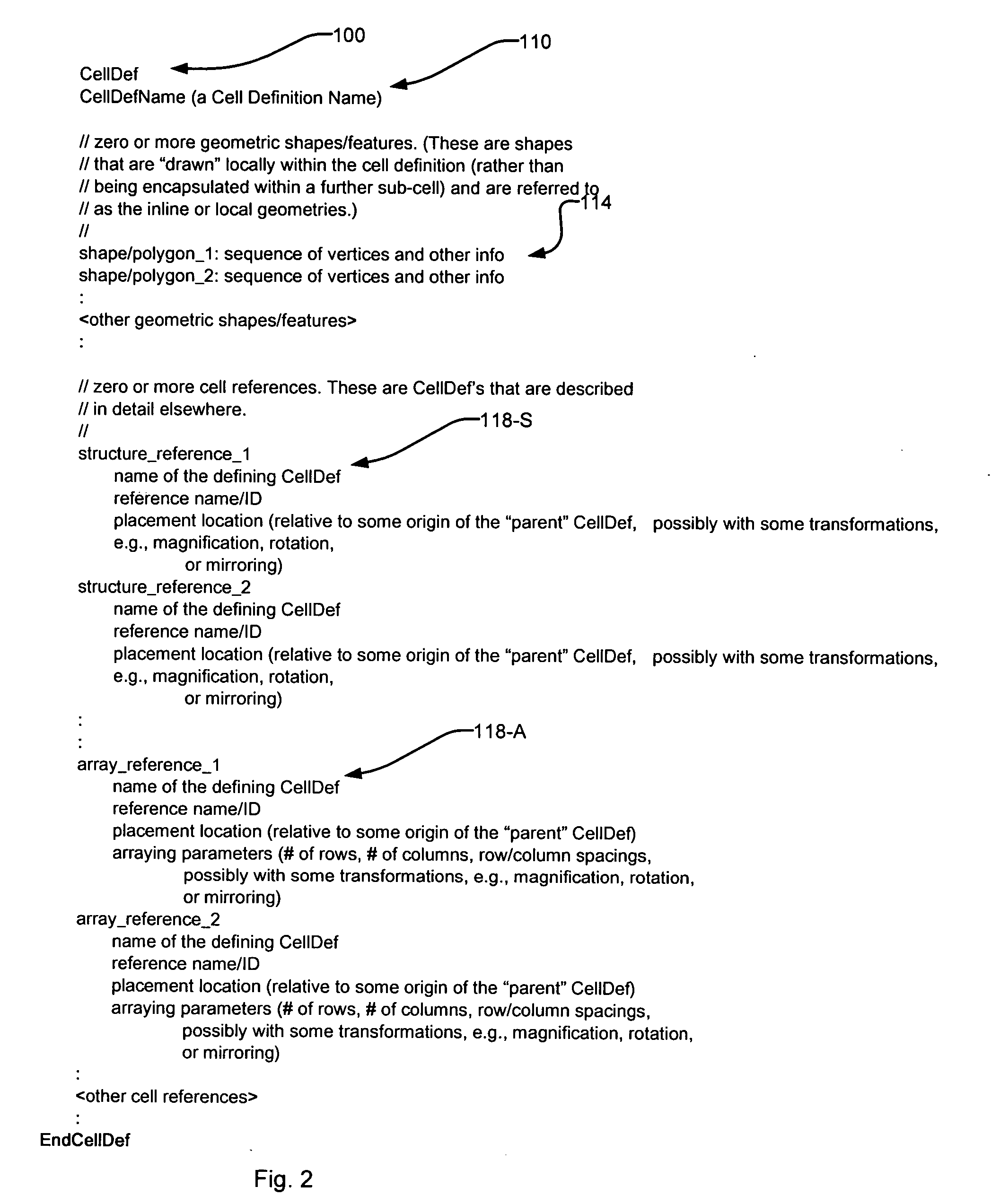

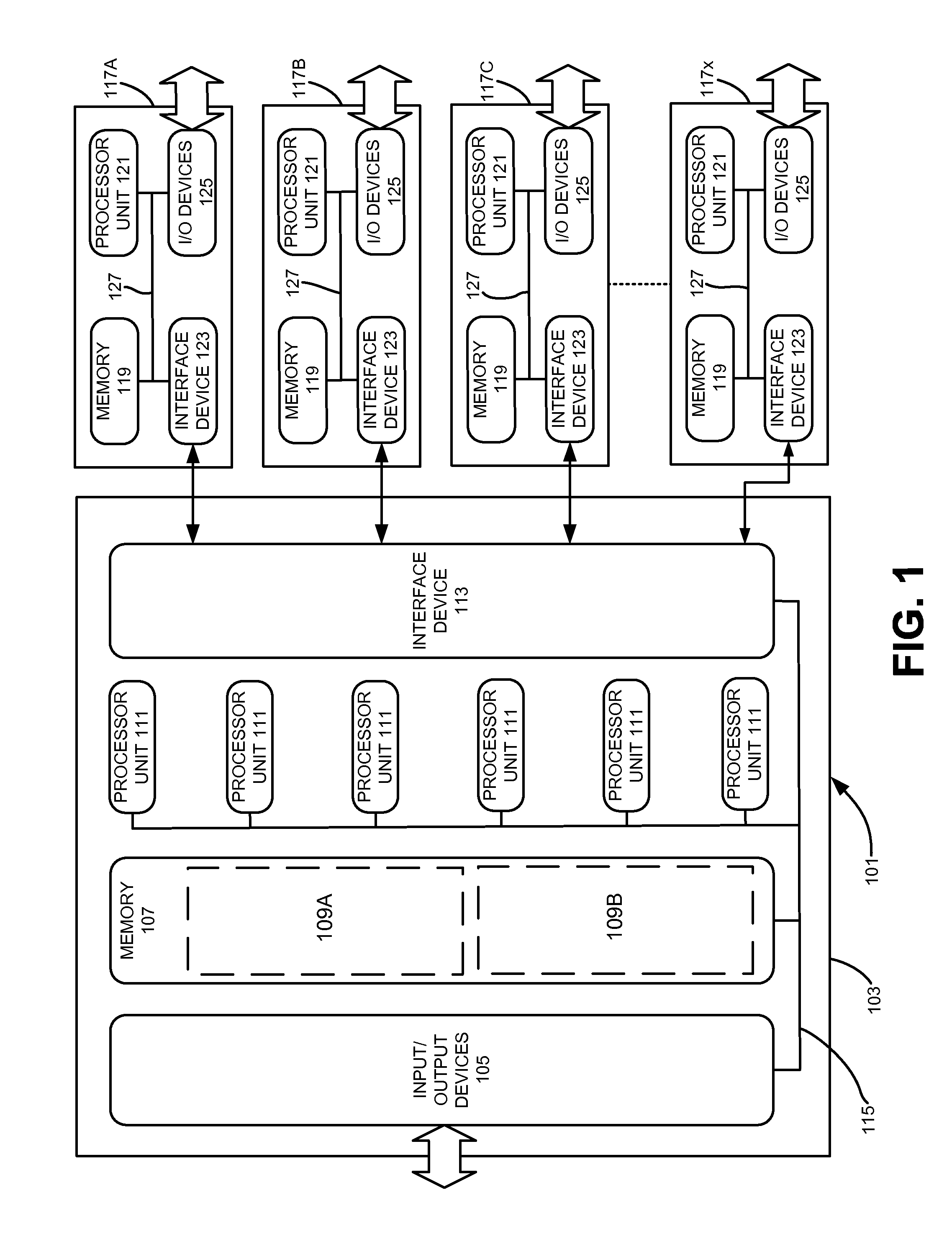

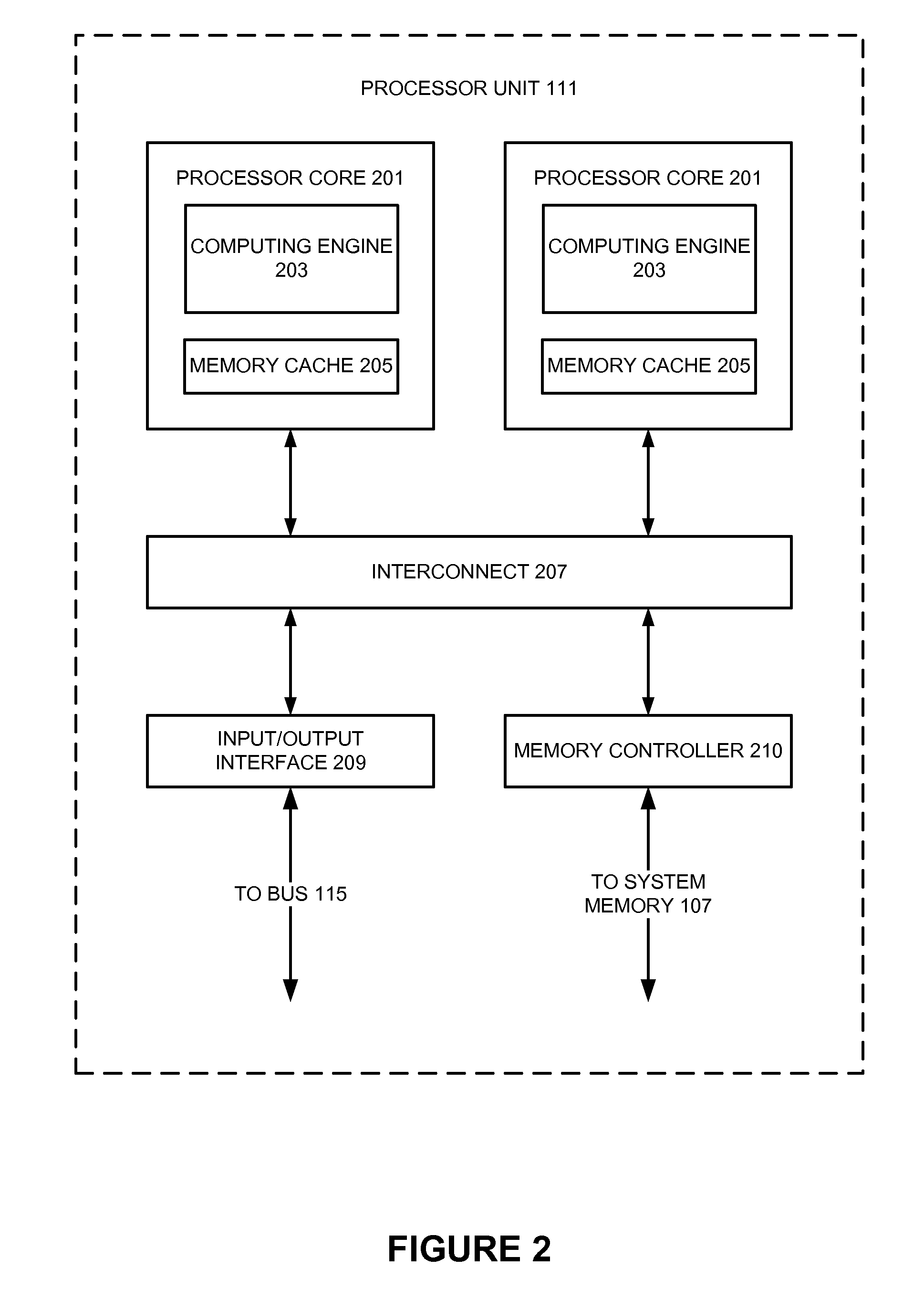

A hierarchical representation encapsulates the detailed internal composition of a sub-circuit using the notion of a cell definition (a CellDef). The CellDef serves as a natural unit for operational reuse. If the computation required for the analysis or manipulation (e.g. parasitic extraction, RET, design rule confirmation (DRC), or OPC) based on a CellDef or one cell instance can be applied, with no or minimal additional effort, to all or a significant subset of other instances of the cell, very substantial reduction in computational effort may be realized. Furthermore, a hierarchical representation also allows for the partitioning of the overall analysis / manipulation task into a collection of subtasks, e.g. one per CellDef. Multiple jobs may then be distributed across a large number of computational nodes on a network for concurrent execution. While this may not reduce the aggregate computational time, a major reduction in the overall turnaround time (TAT) is in itself extremely beneficial.

Owner:CADENCE DESIGN SYST INC

Capacitance measurements for an integrated circuit

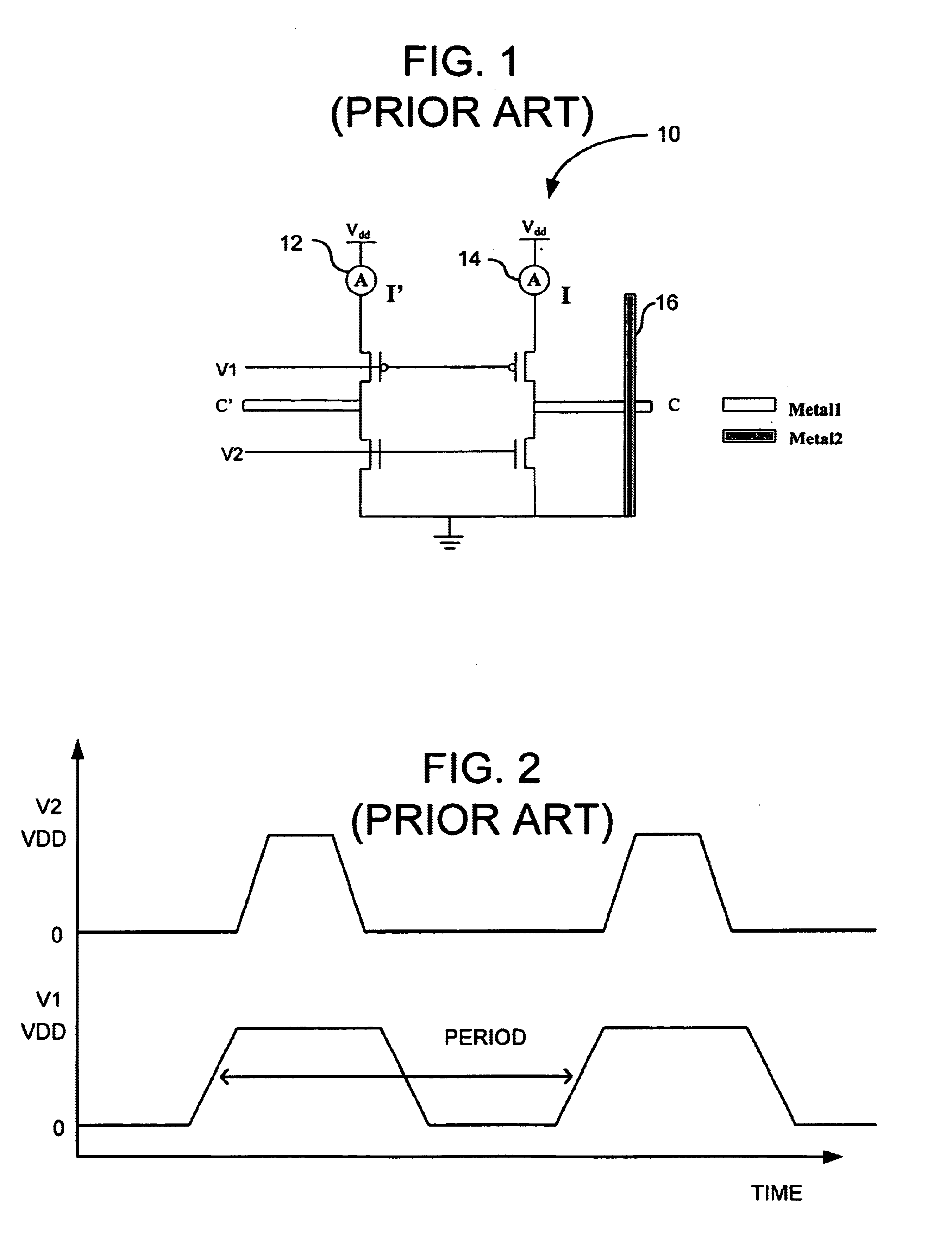

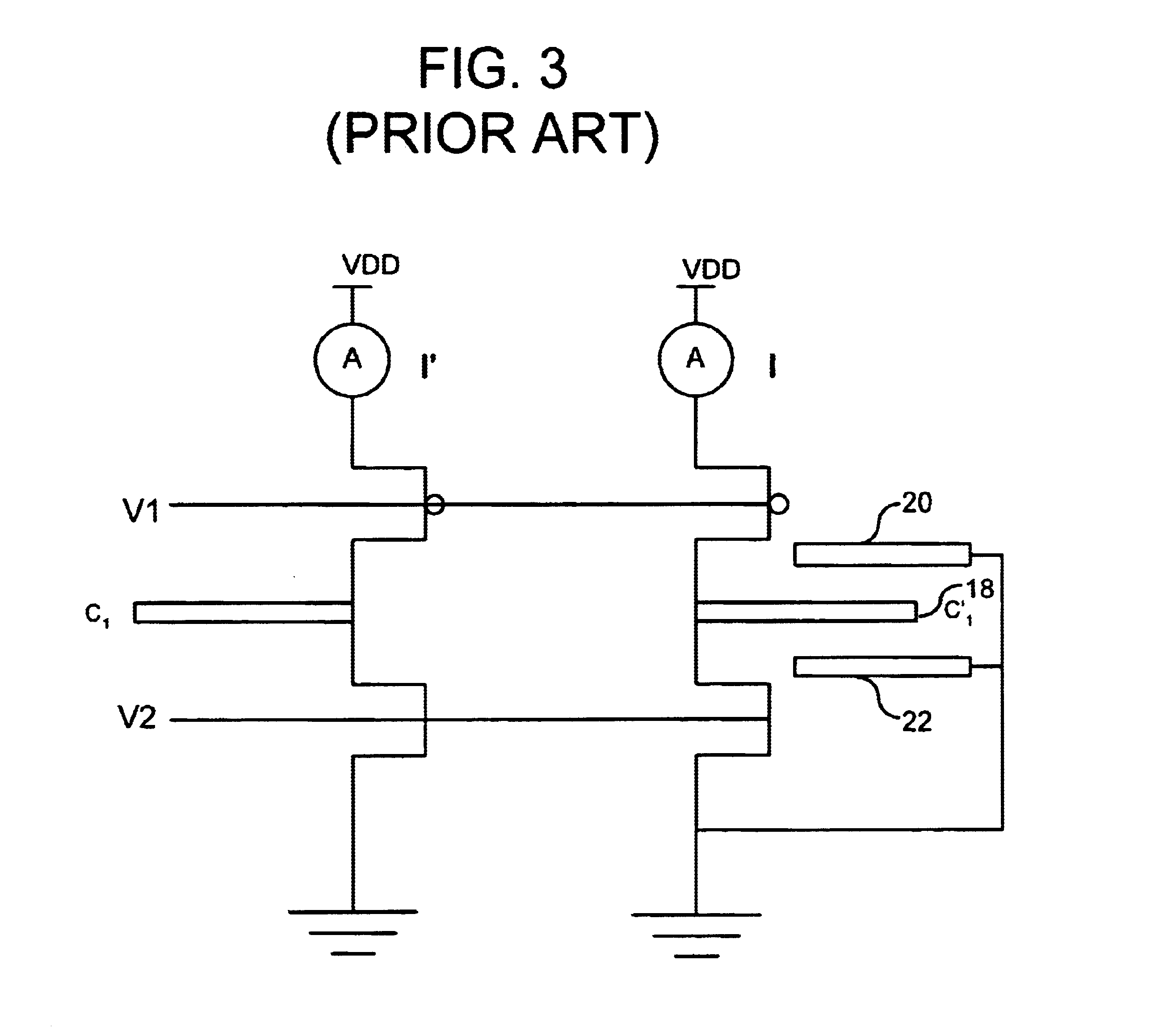

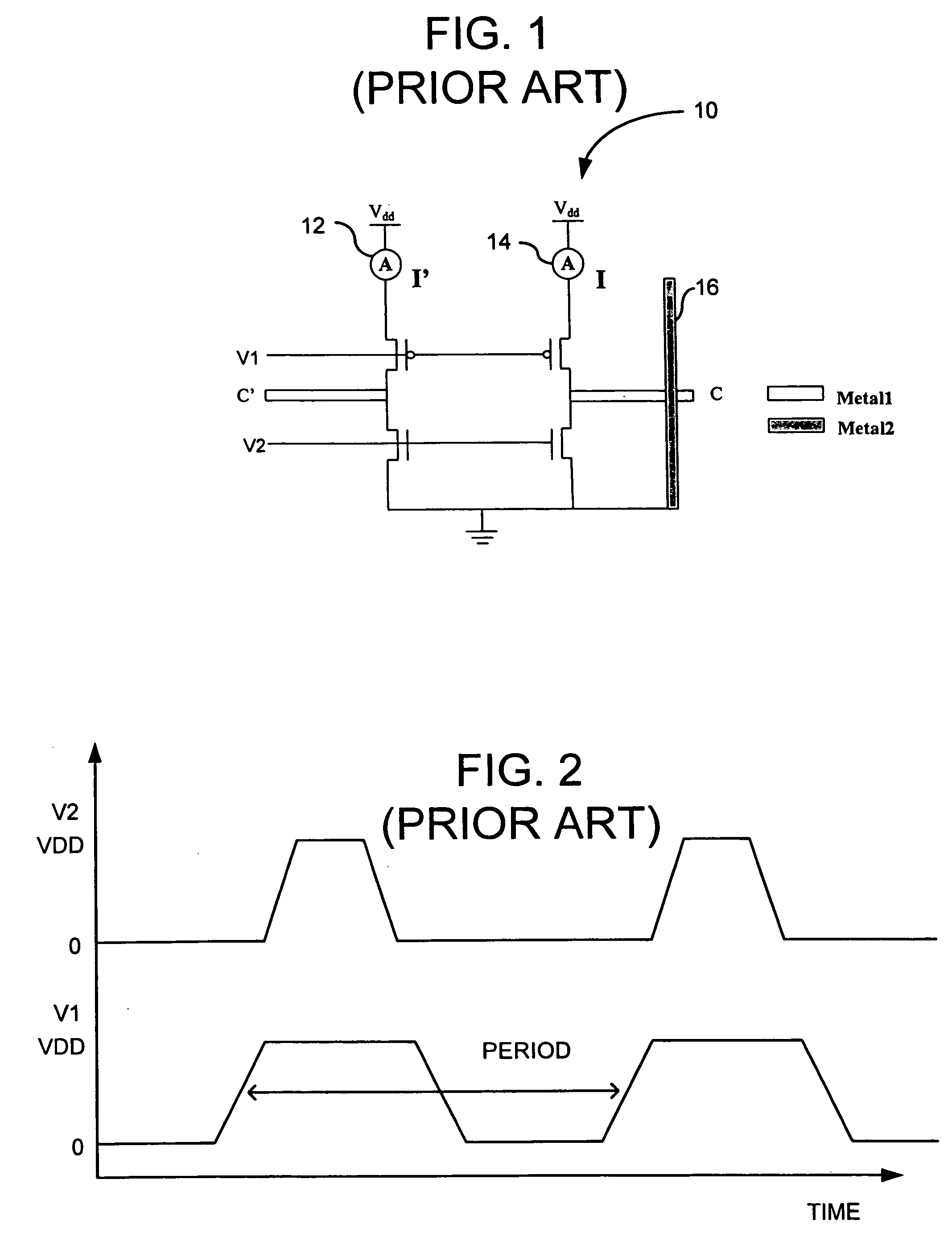

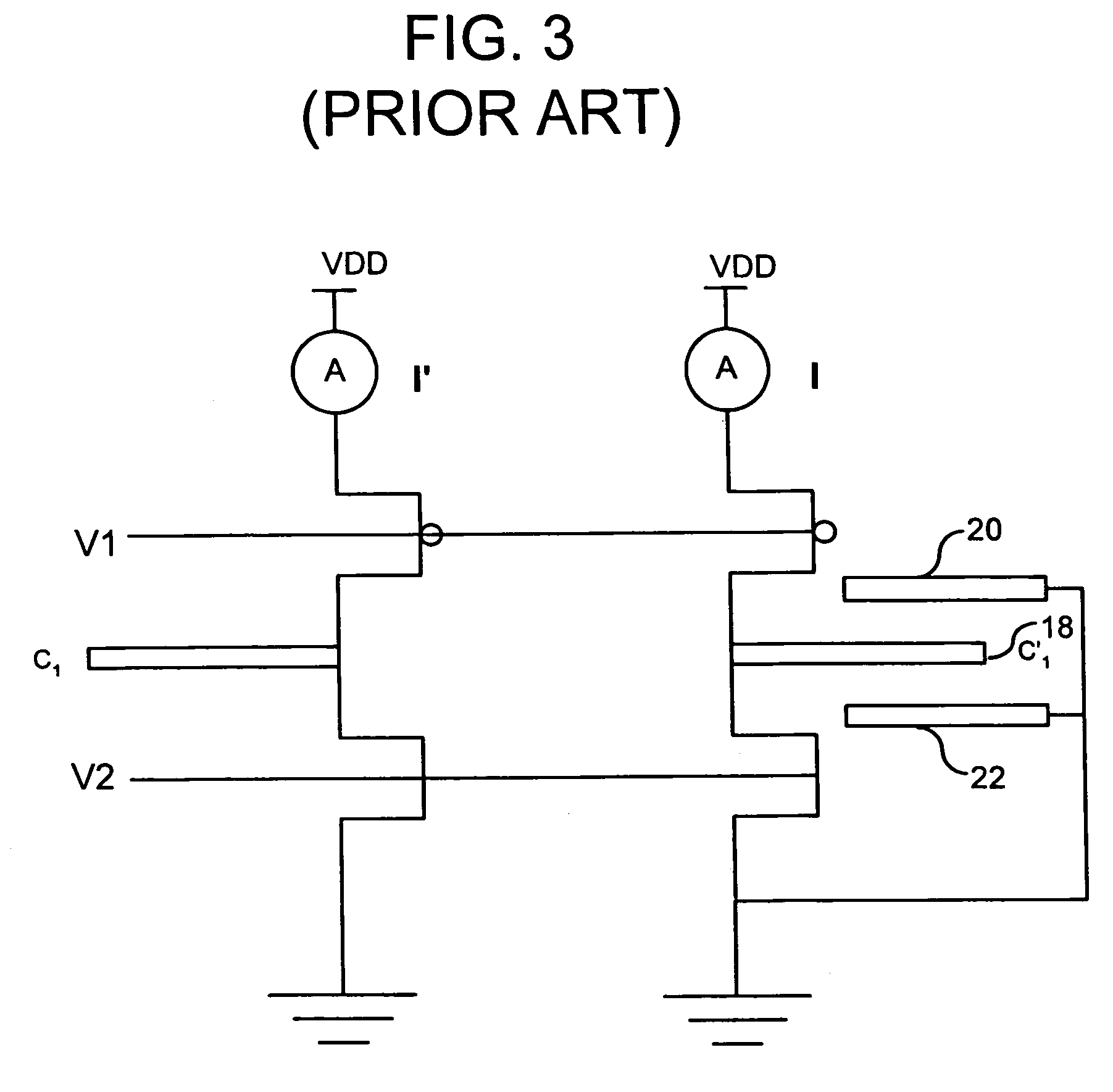

InactiveUS6934669B1Capacitance measurementsComputation using non-denominational number representationCouplingEngineering

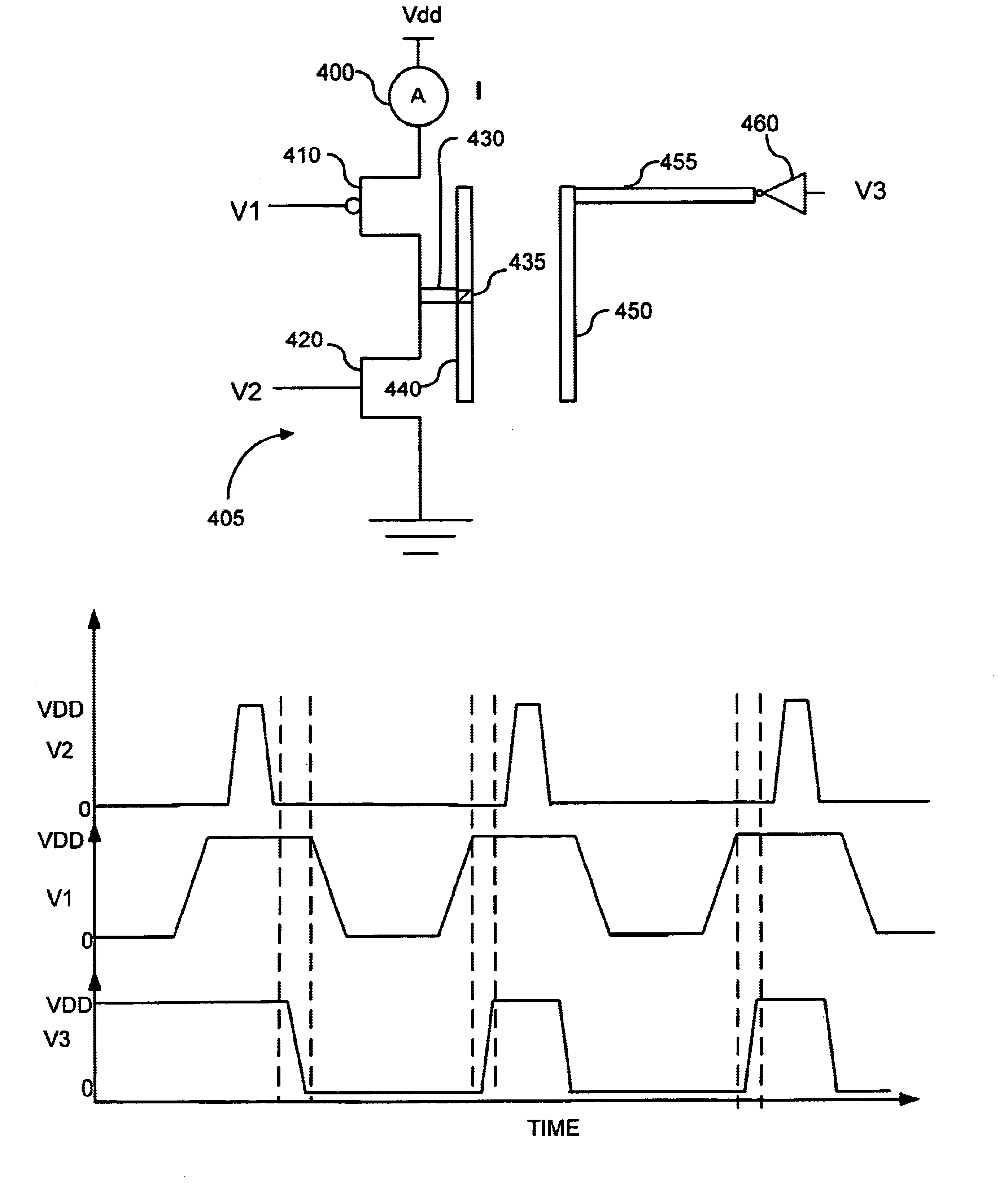

A method and apparatus for determining capacitance of wires in an integrated circuit is described. The capacitance information derived according to the invention can be used, for example, to calibrate a parasitic extraction engine or to calibrate an integrated circuit fabrication process. The capacitance information can also be used for timing and noise circuit simulations, particularly for deep sub-Micron circuit design simulations. Briefly, the invention allows measurement of both total capacitance of a line and cross coupling capacitance between two lines by applying predetermined voltage signals to specific circuit elements. The resulting current allows simple computation of total capacitance and cross coupling capacitance. Multiple cross coupling capacitance can be measured with a single device, thus improving the art of library generation, and the overall method is free of uncertainties related to transistor capacitance couplings. The capacitance values obtained can then be used to calibrate procedures, processes, devices, etc.

Owner:MENTOR GRAPHICS CORP

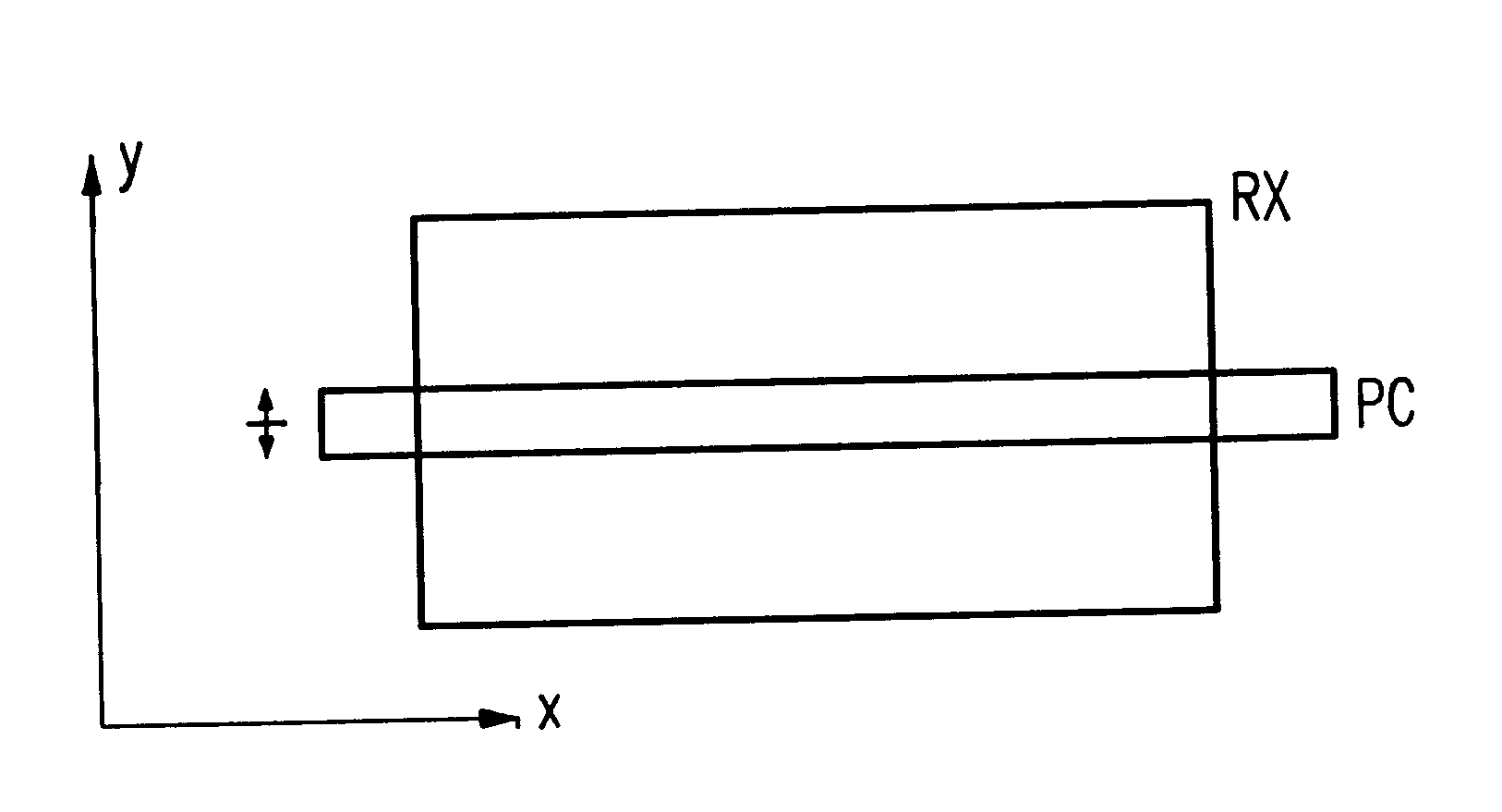

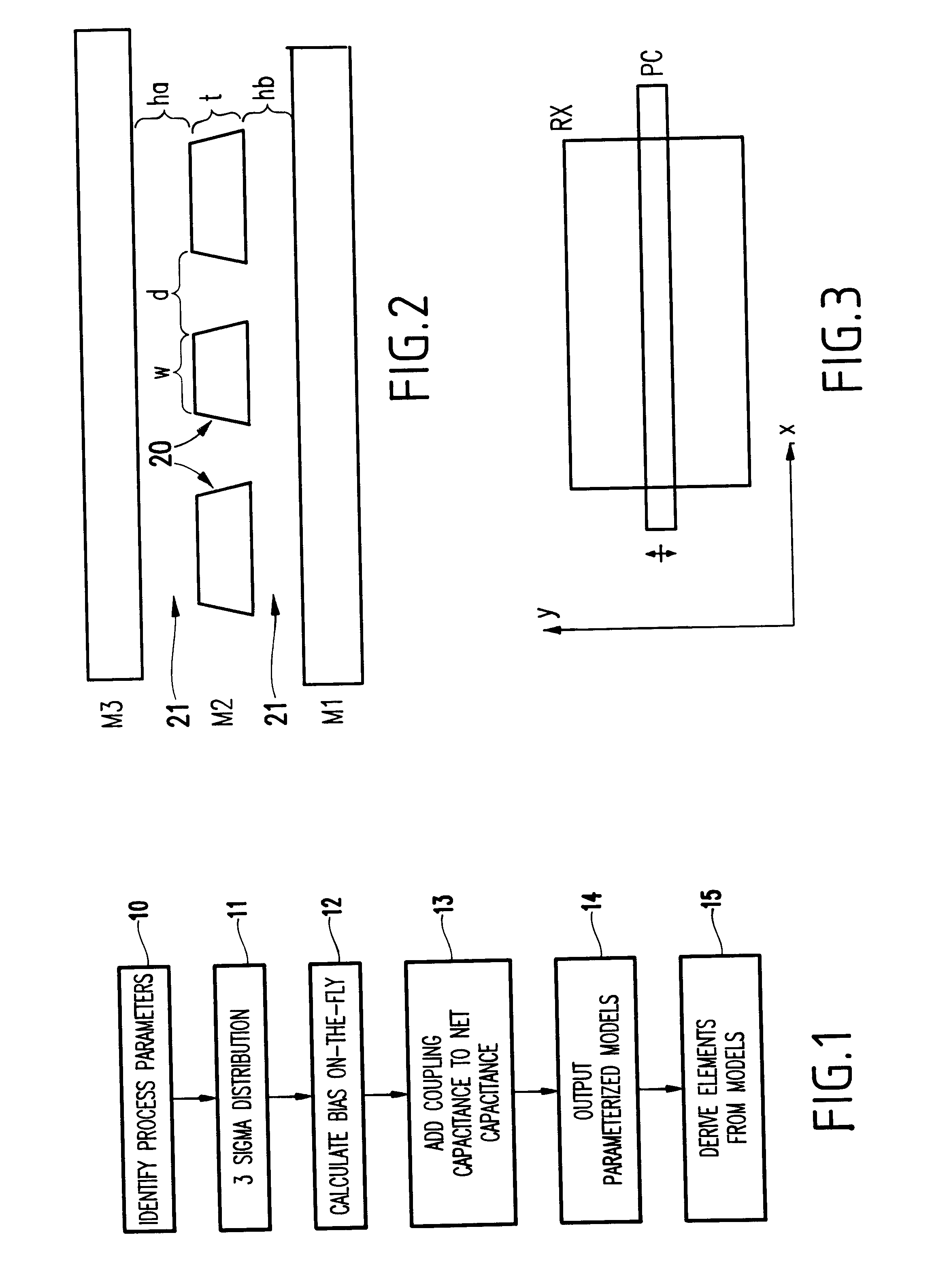

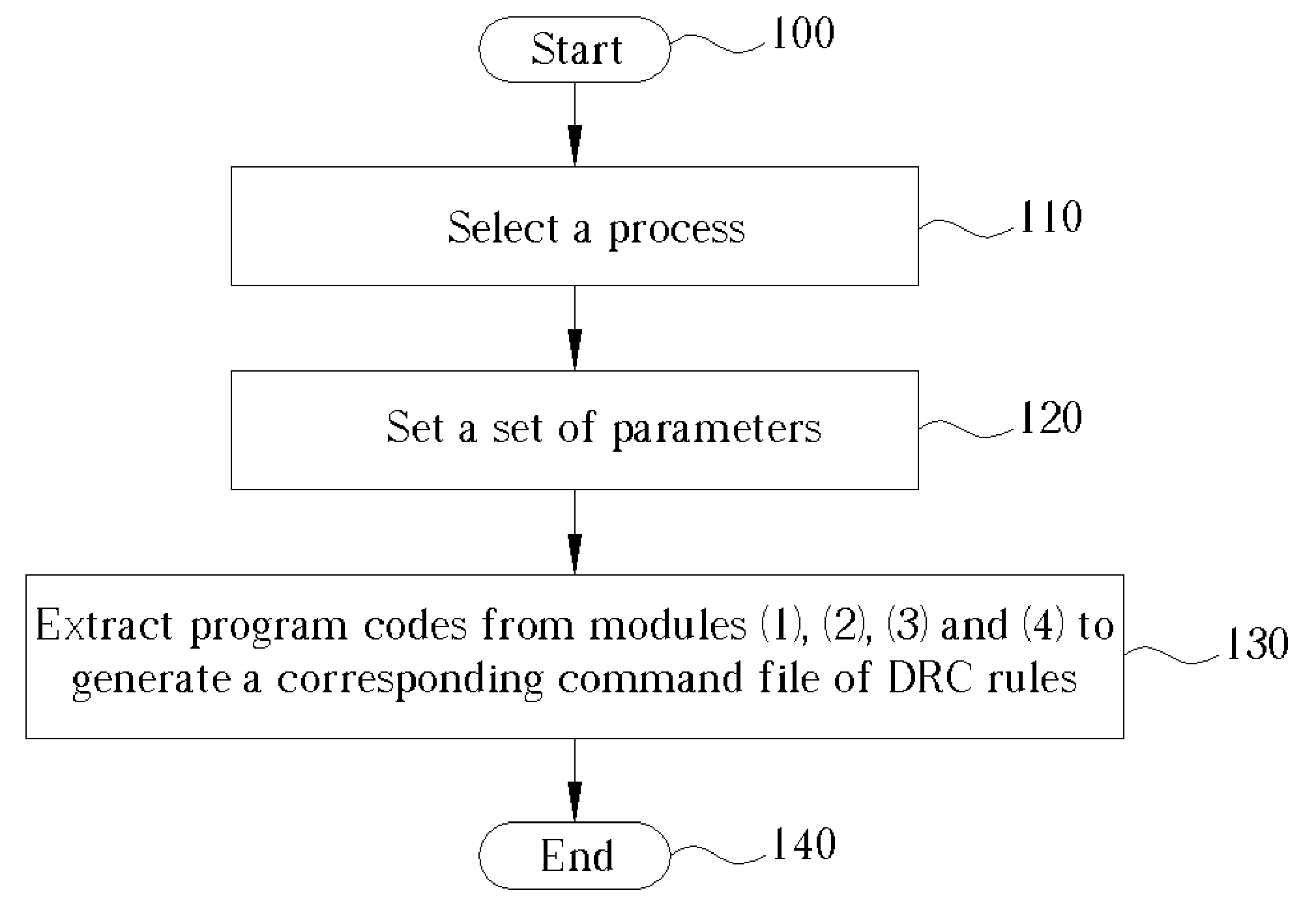

Process and system for maintaining 3 sigma process tolerance for parasitic extraction with on-the-fly biasing

InactiveUS6430729B1Big advantageComputer aided designSpecial data processing applicationsParasitic extractionIntegrated circuit

A method and structure for a method of determining characteristics of parasitic elements in an integrated circuit comprising, identifying manufacturing process parameters of devices in the integrated circuit, calculating a parasitic performance distribution for each of the devices based on the manufacturing process parameters, combining the parasitic performance distribution for each of the devices into a net parasitic value, and forming a parameterized model based on the net parasitic values.

Owner:IBM CORP

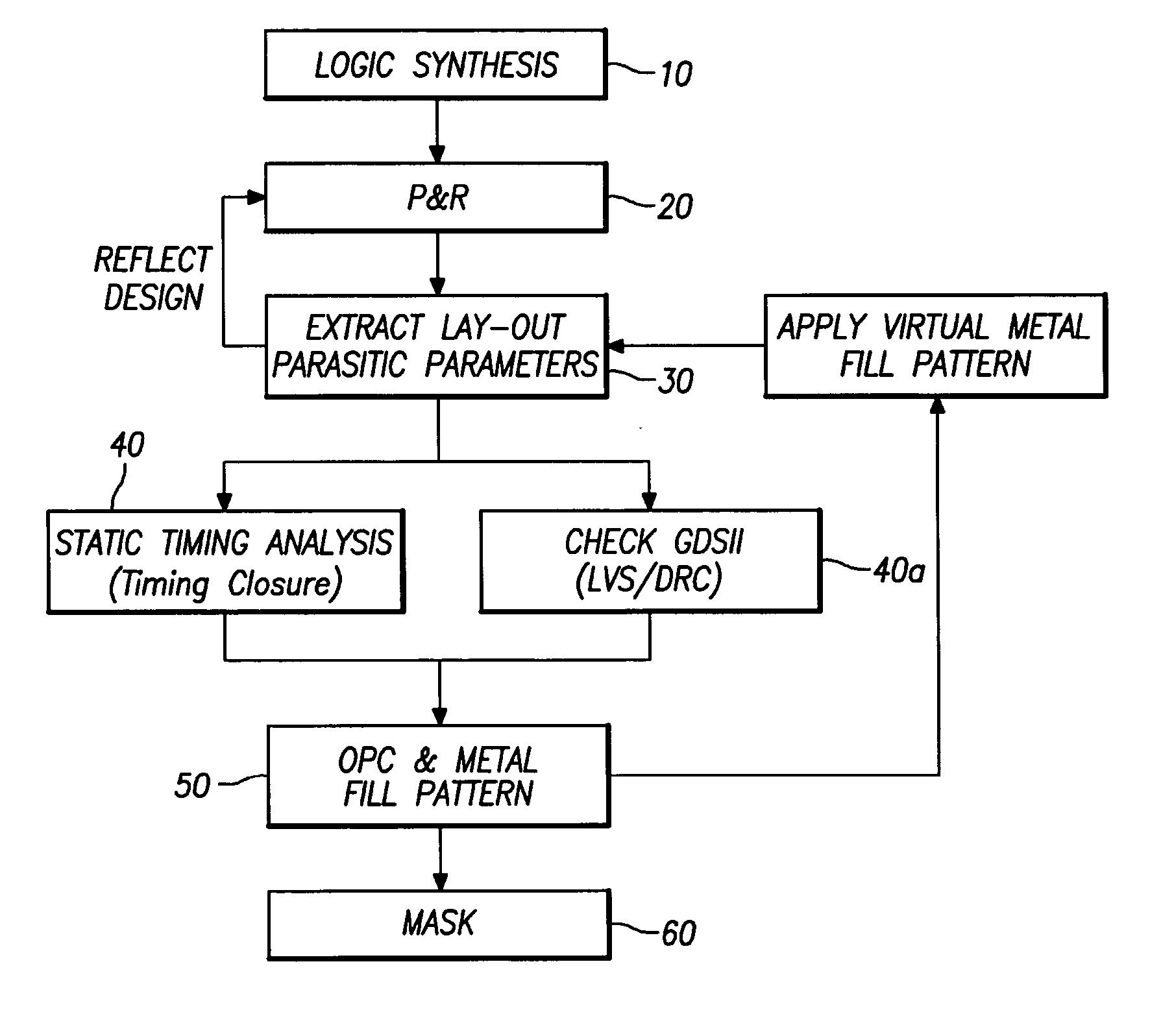

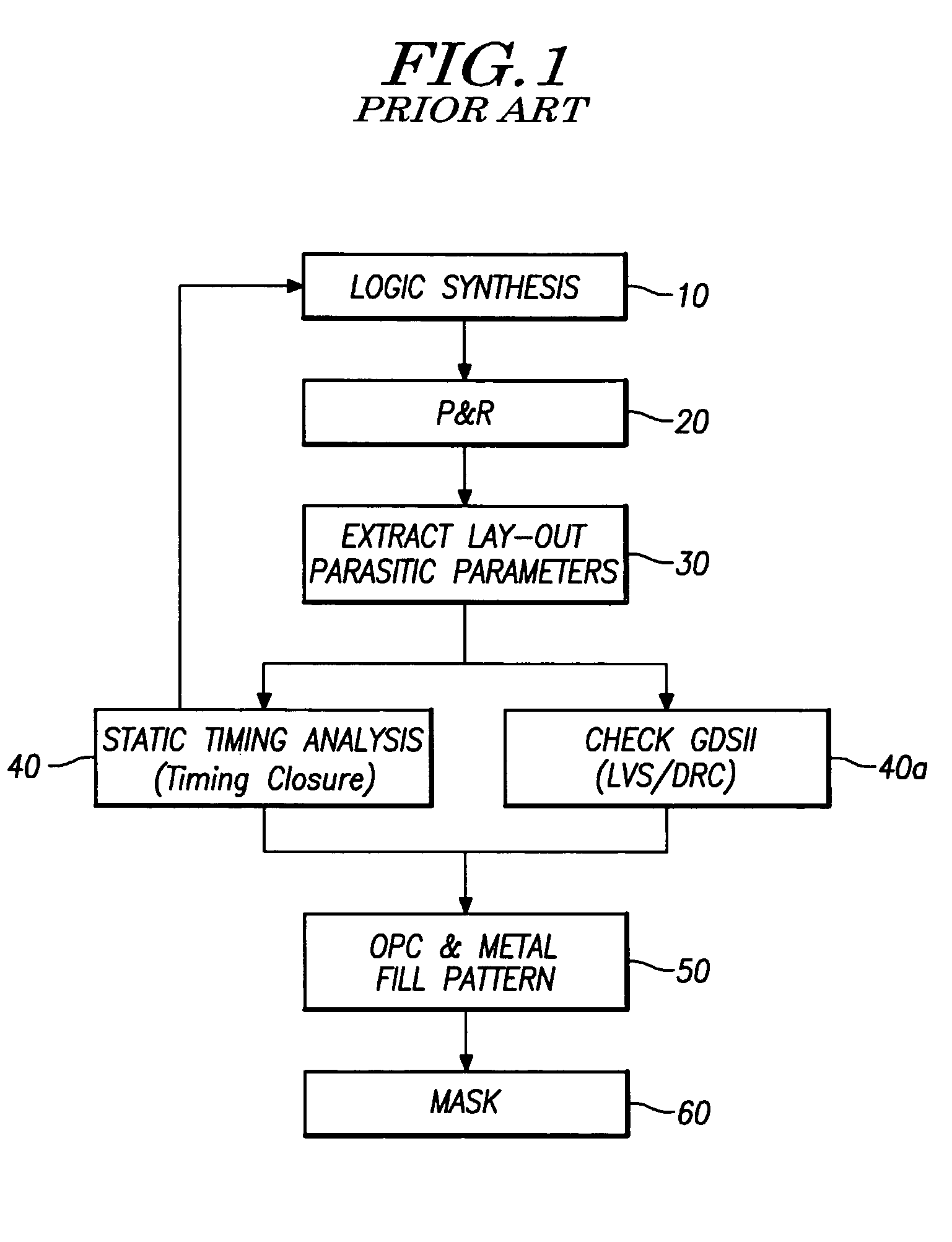

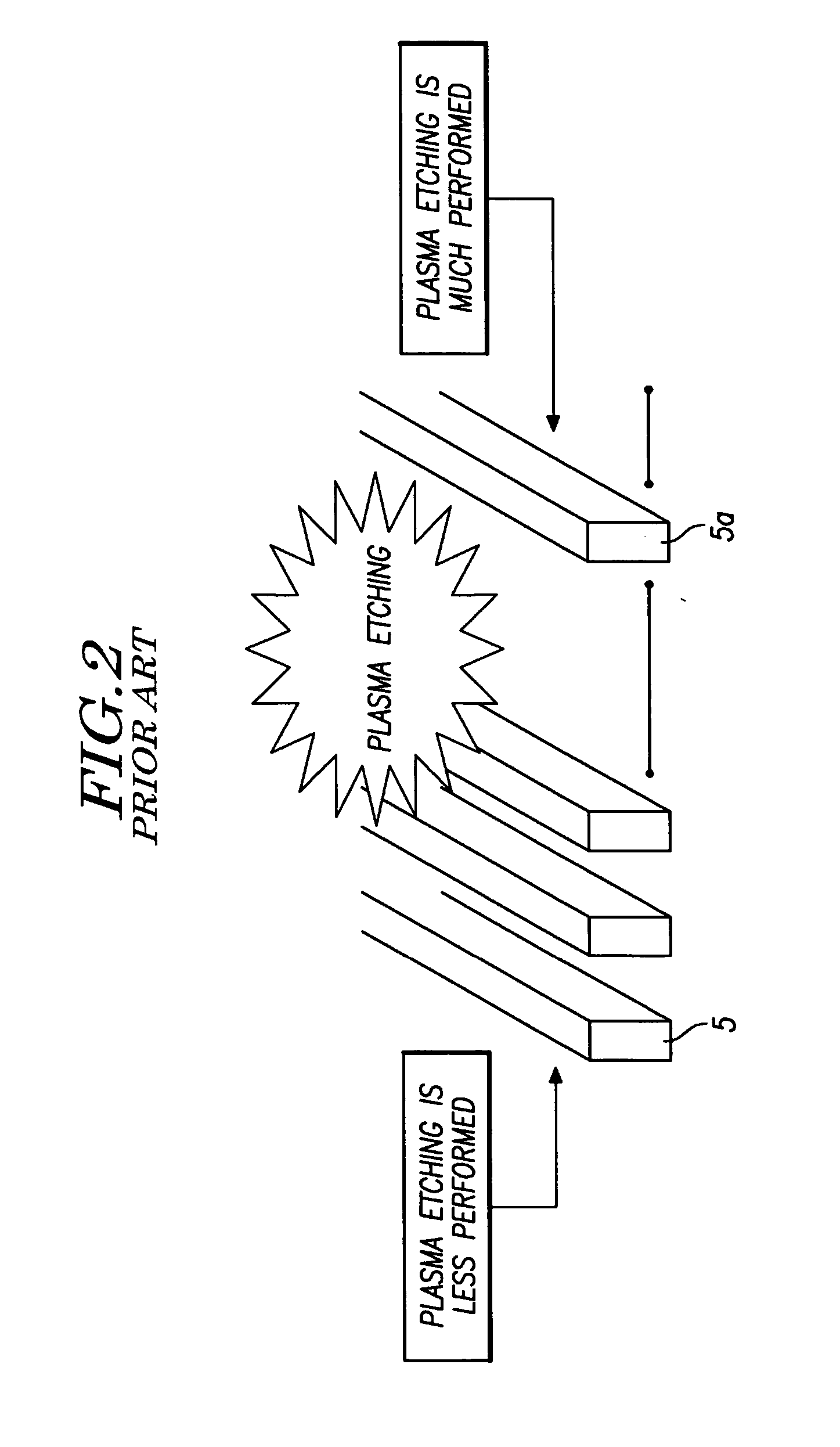

Method for designing a semiconductor device capable of reflecting a time delay effect for dummy metal fill

InactiveUS20070148794A1Reflecting delay effectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCapacitanceTime delays

Disclosed is a method for designing a semiconductor device. In an existing semiconductor design, a time delay effect caused by a dummy metal interconnection cannot be reflected. In order to address this disadvantage, a real metal fill pattern and a virtual metal fill pattern are employed for a layout parasitic extract step such that a time delay effect caused by the dummy metal pattern in semiconductor design is reflected. Accordingly, a semiconductor device can be designed by effectively reflecting a time delay effect. According to the method, since a real metal fill pattern and a virtual metal fill pattern are employed for a layout parasitic extract step so that resistor capacitance values of interconnections (including dummy interconnections) between logic elements are extracted, it is possible to more exactly design a semiconductor device by tacking a time delay effect into account.

Owner:DONGBU ELECTRONICS CO LTD

Capacitance measurements for an integrated circuit

A method and apparatus for determining capacitance of wires in an integrated circuit is described. The capacitance information derived according to the invention can be used, for example, to calibrate a parasitic extraction engine or to calibrate an integrated circuit fabrication process. The capacitance information can also be used for timing and noise circuit simulations, particularly for deep sub-micron circuit design simulations. Briefly, the invention allows measurement of both total capacitance of a line and cross coupling capacitance between two lines by applying predetermined voltage signals to specific circuit elements. The resulting current allows simple computation of total capacitance and cross coupling capacitance. Multiple cross coupling capacitance can be measured with a single device, thus improving the art of library generation, and the overall method is free of uncertainties related to transistor capacitance couplings. The capacitance values obtained can then be used to calibrate procedures, processes, devices, etc.

Owner:MENTOR GRAPHICS CORP

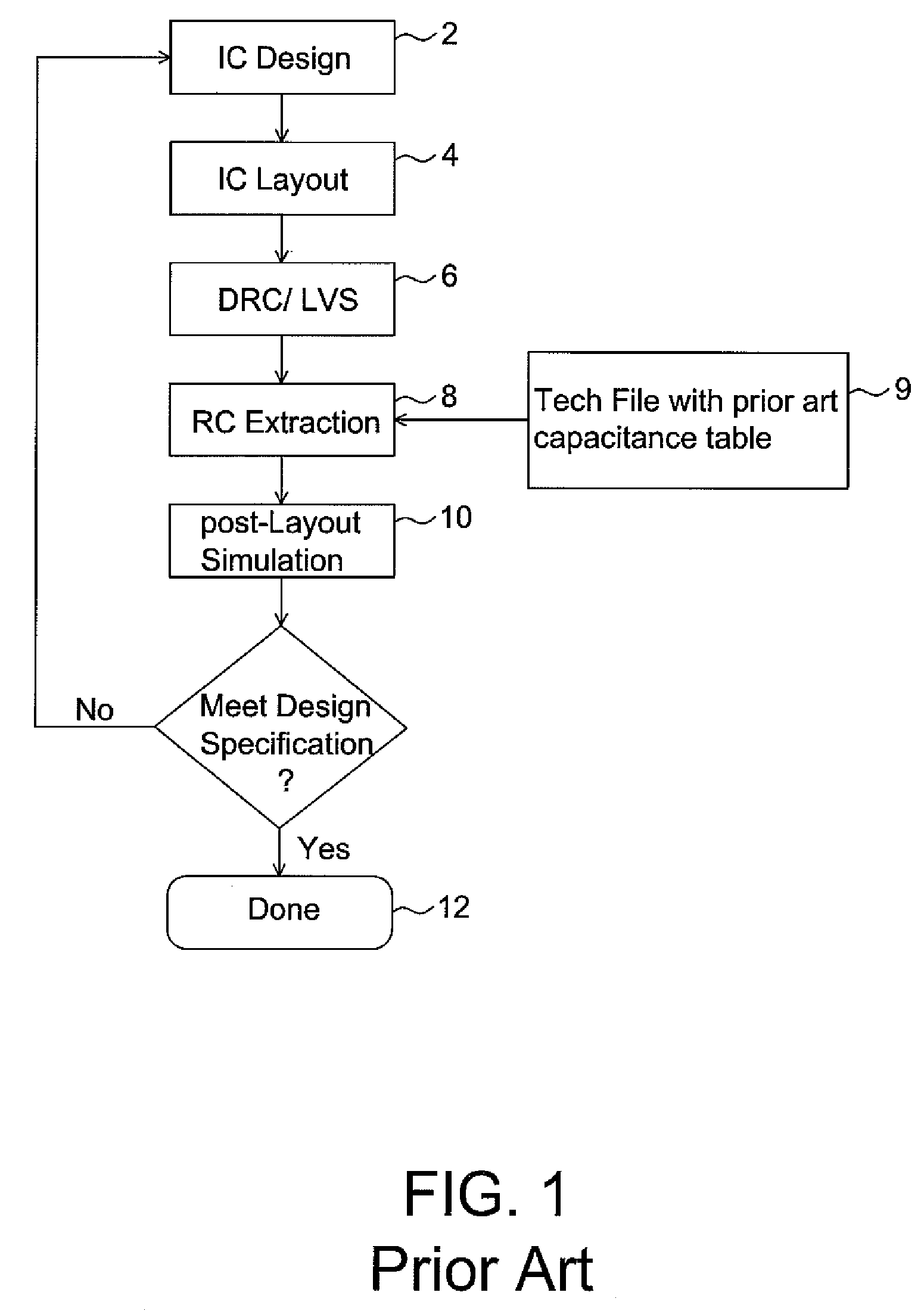

Accurate Parasitic Capacitance Extraction for Ultra Large Scale Integrated Circuits

InactiveUS20090007035A1Improve accuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVery large scale integrated circuitsParasitic capacitance

A system and method for extracting the parasitic contact / via capacitance in an integrated circuit are provided. Parasitic extraction using this system can lead to an improved accuracy on contact / via parasitic capacitance extraction by taking into account of the actual contact / via shape and size variation. The common feature of the various embodiments includes the step of generating a technology file, in which the contact / via capacitance in the capacitance table is derived from an effective contact / via width table. Each element of the effective contact / via width table is calibrated to have a parasitic capacitance matching to that of an actual contact / via configuration occurring in an IC.

Owner:TAIWAN SEMICON MFG CO LTD

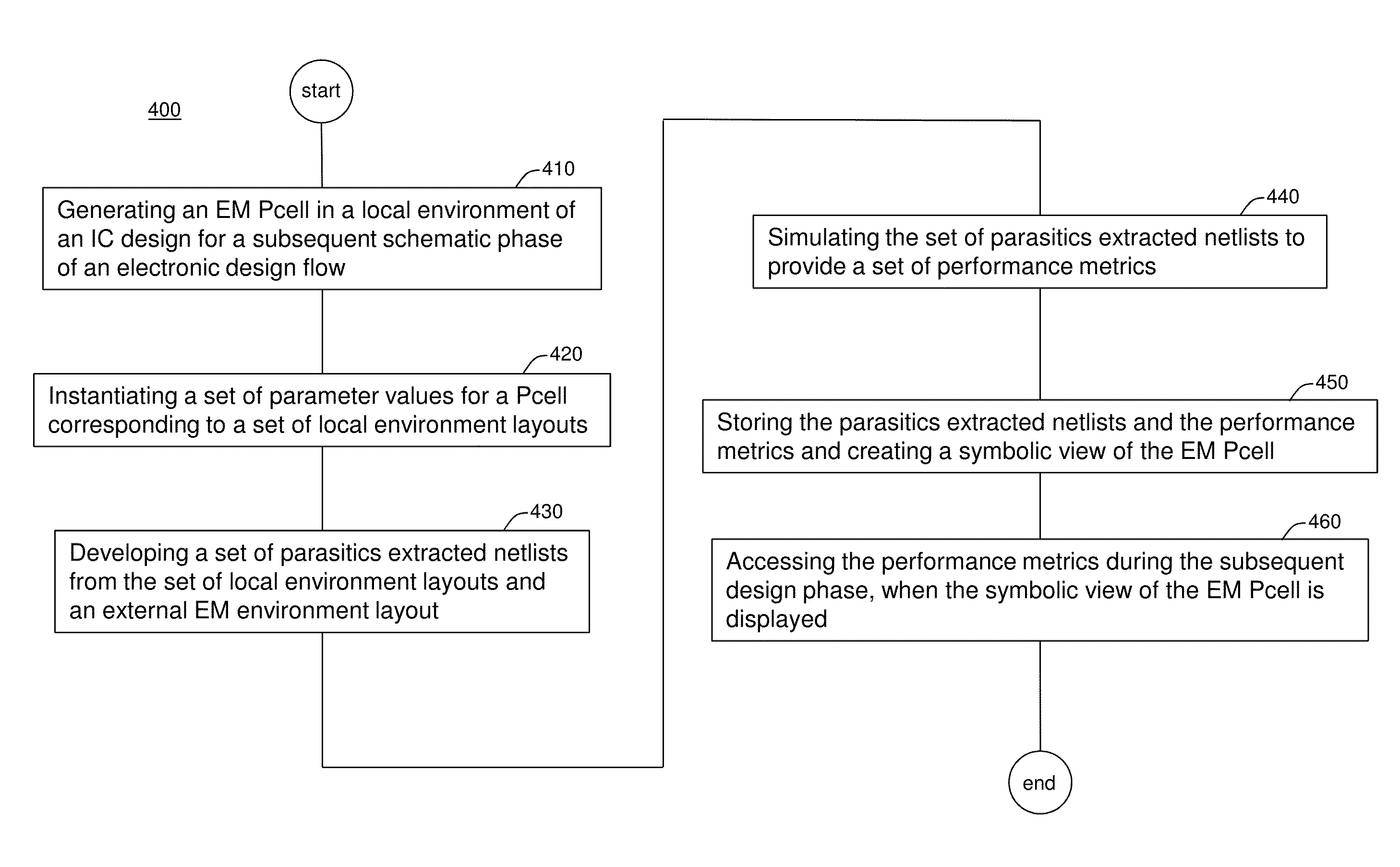

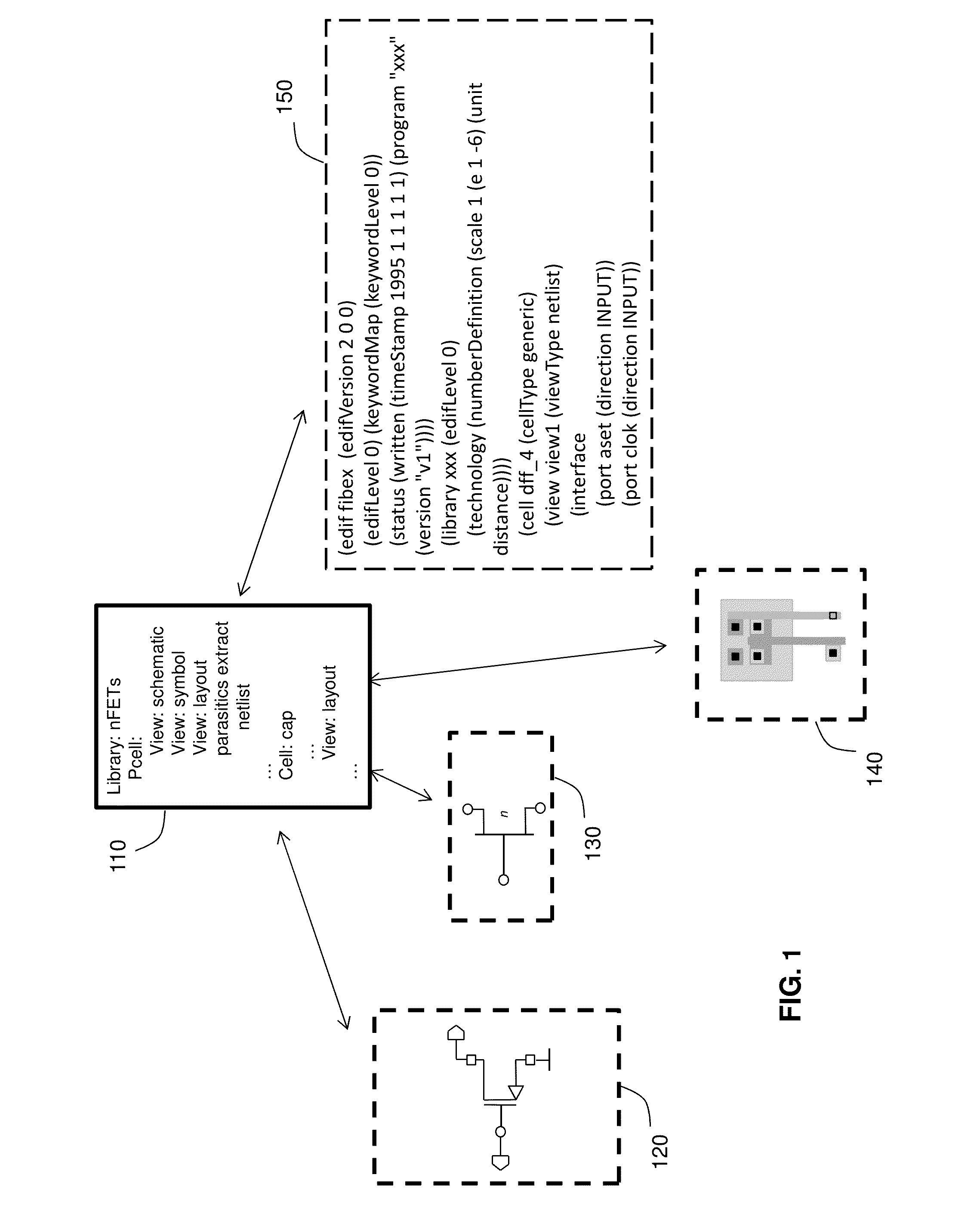

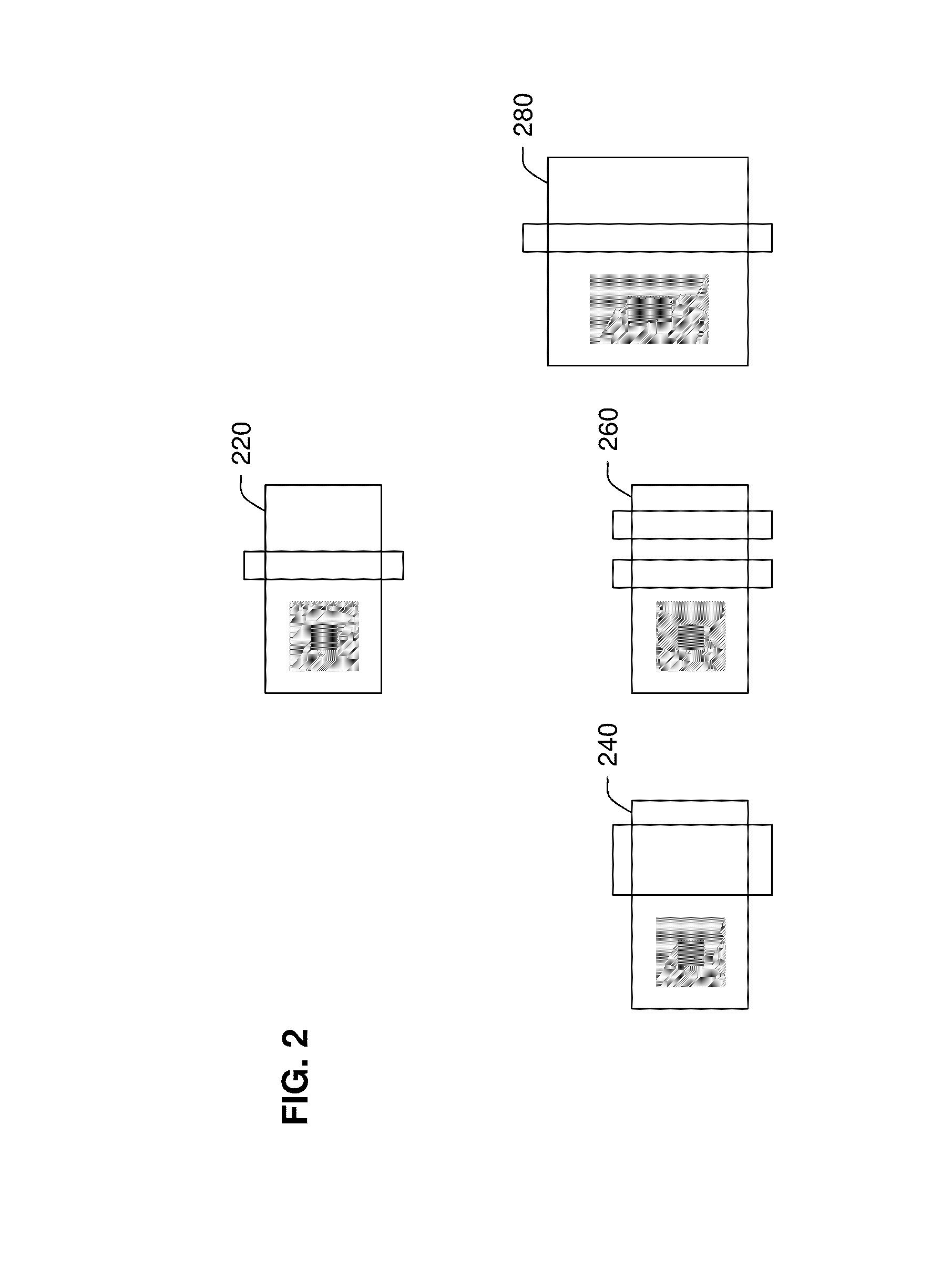

Generating an electromagnetic parameterized cell for an integrated circuit design

InactiveUS20160125115A1Improve accuracyImprove computing efficiencyDesign optimisation/simulationCAD circuit designParasitic extractionElectronic design

An electromagnetic parameterized cell (EM Pcell) is generated for a local environment of an integrated circuit (IC) design for an electronic design flow. A set of parasitics extracted netlists is developed from a set of Pcell layouts and an external EM environment. The parasitics extracted netlists are simulated to provide a set of performance metrics. When a symbolic view of the EM Pcell is displayed to a designer during a subsequent schematic phase of the design flow, the performance metrics are accessed from a design library, to increase accuracy of parameter value selection for the EM Pcell without a parasitics extraction of the physical layout and generation of a parasitics extracted netlist.

Owner:GLOBALFOUNDRIES INC

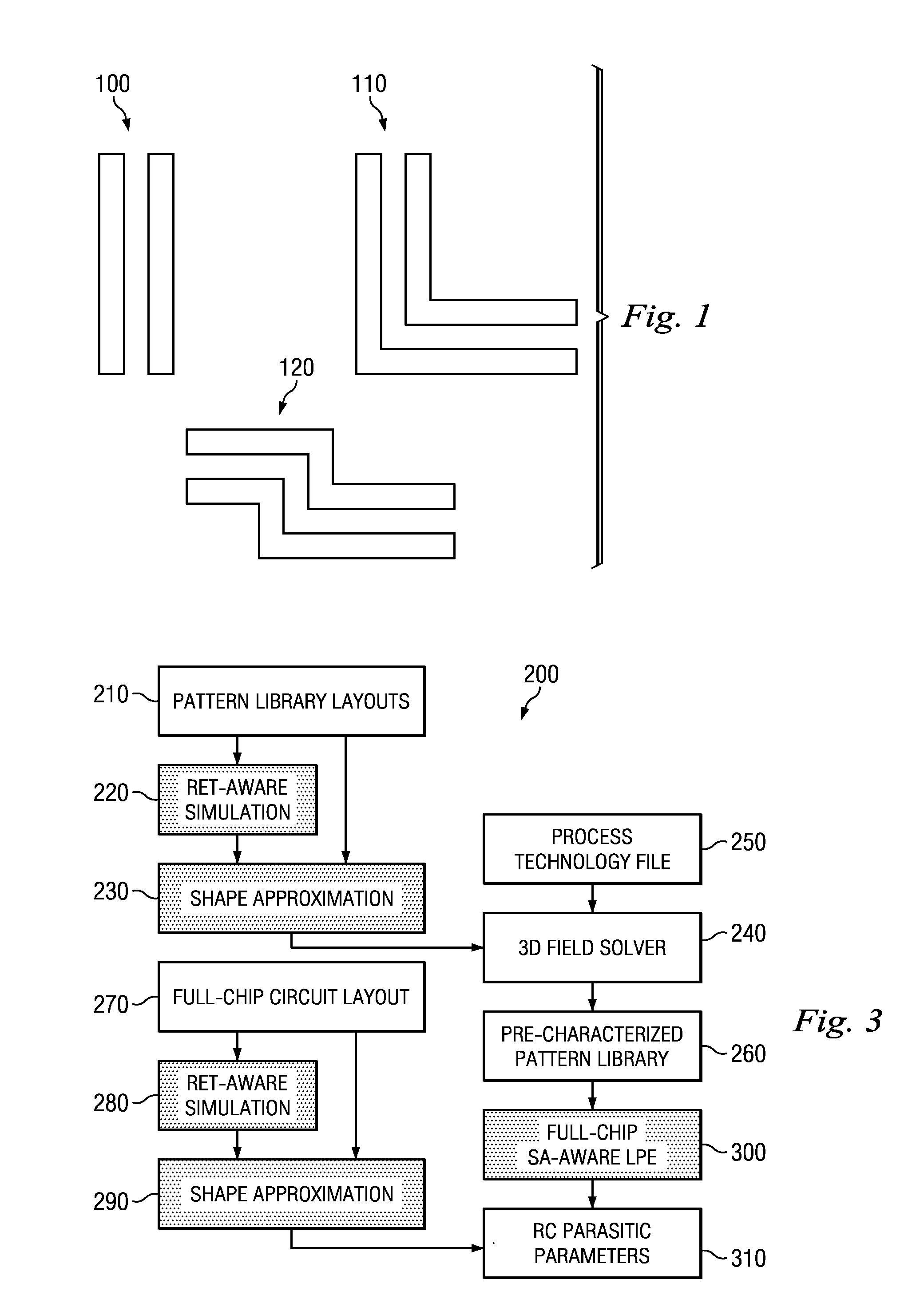

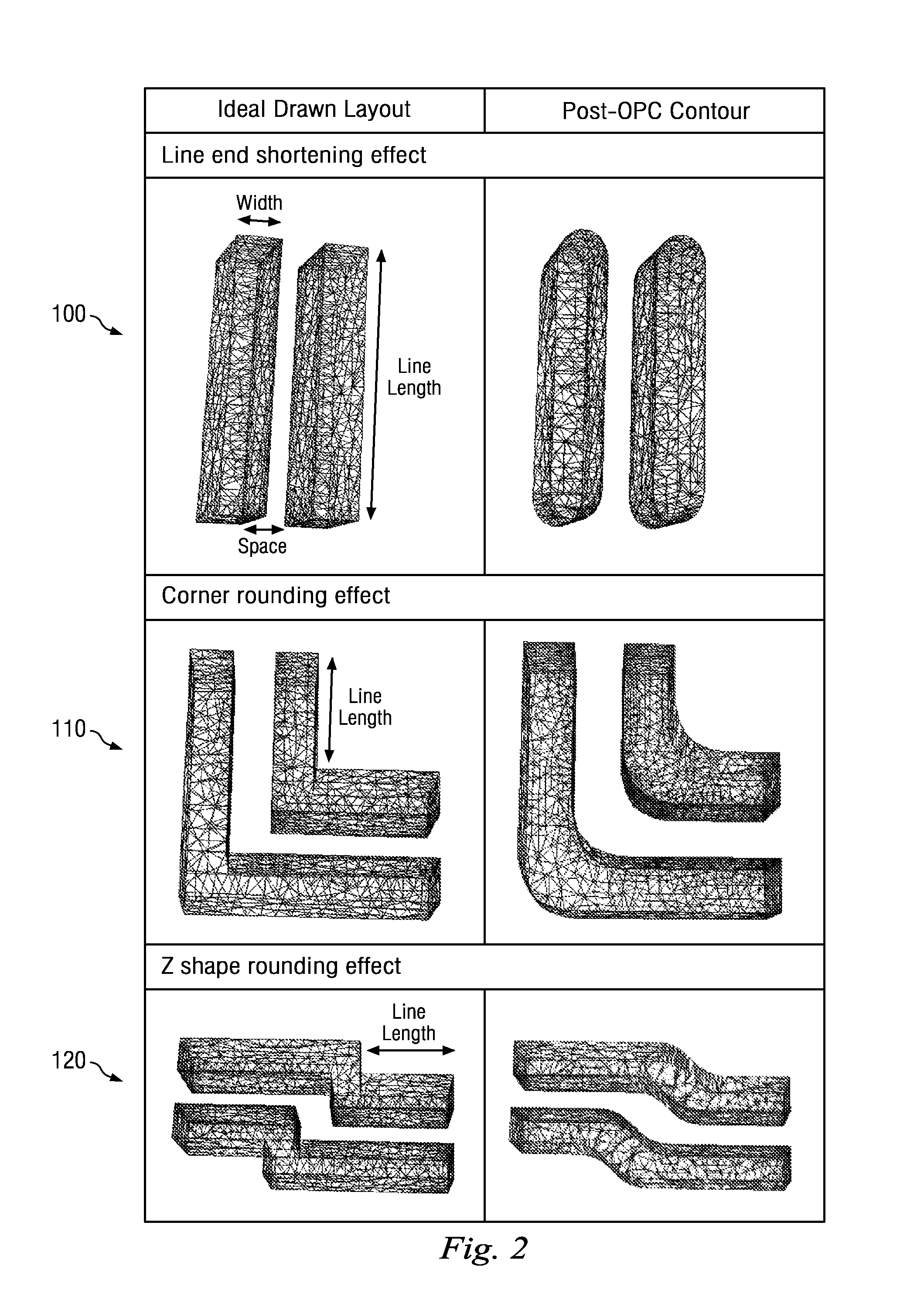

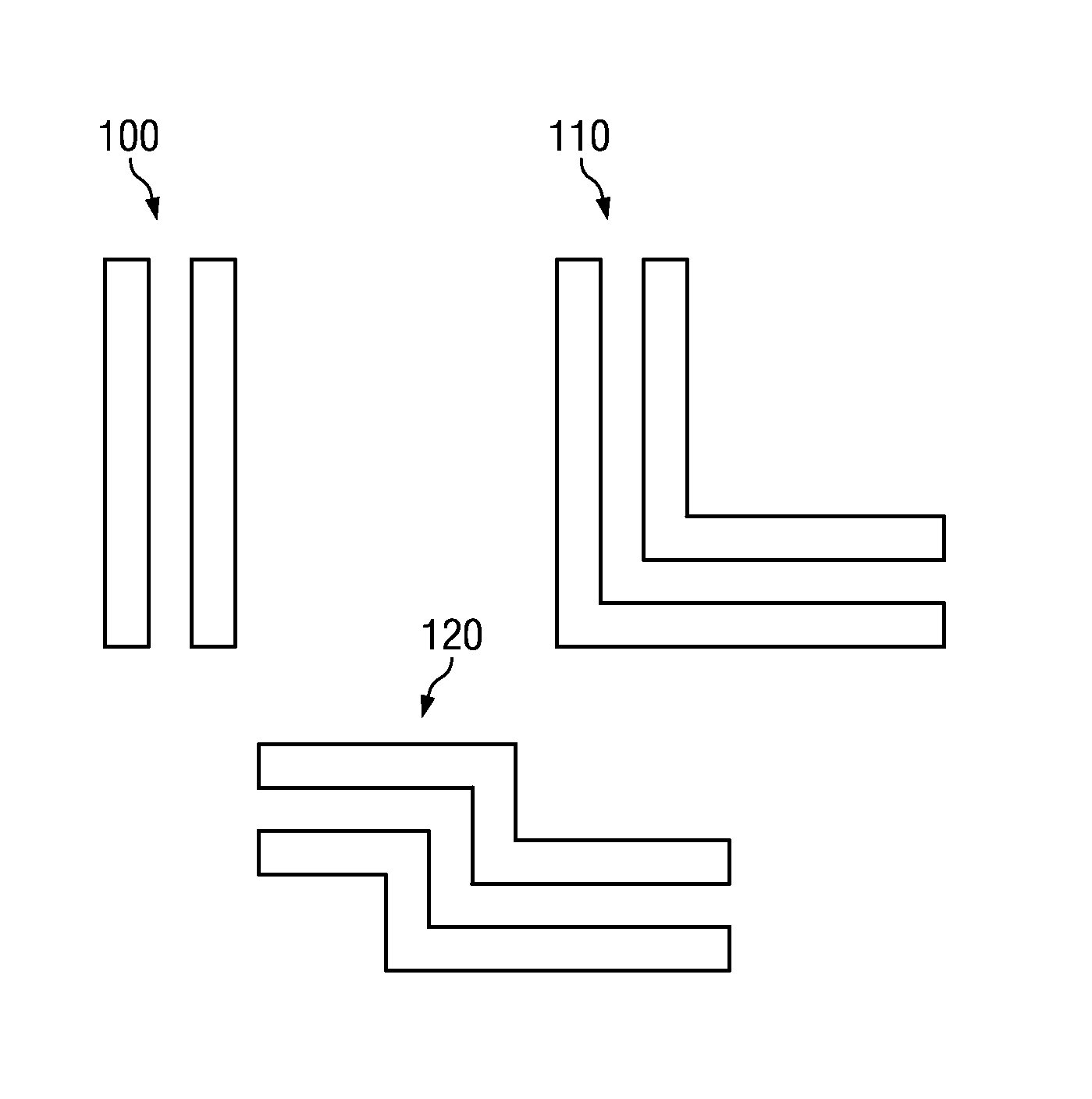

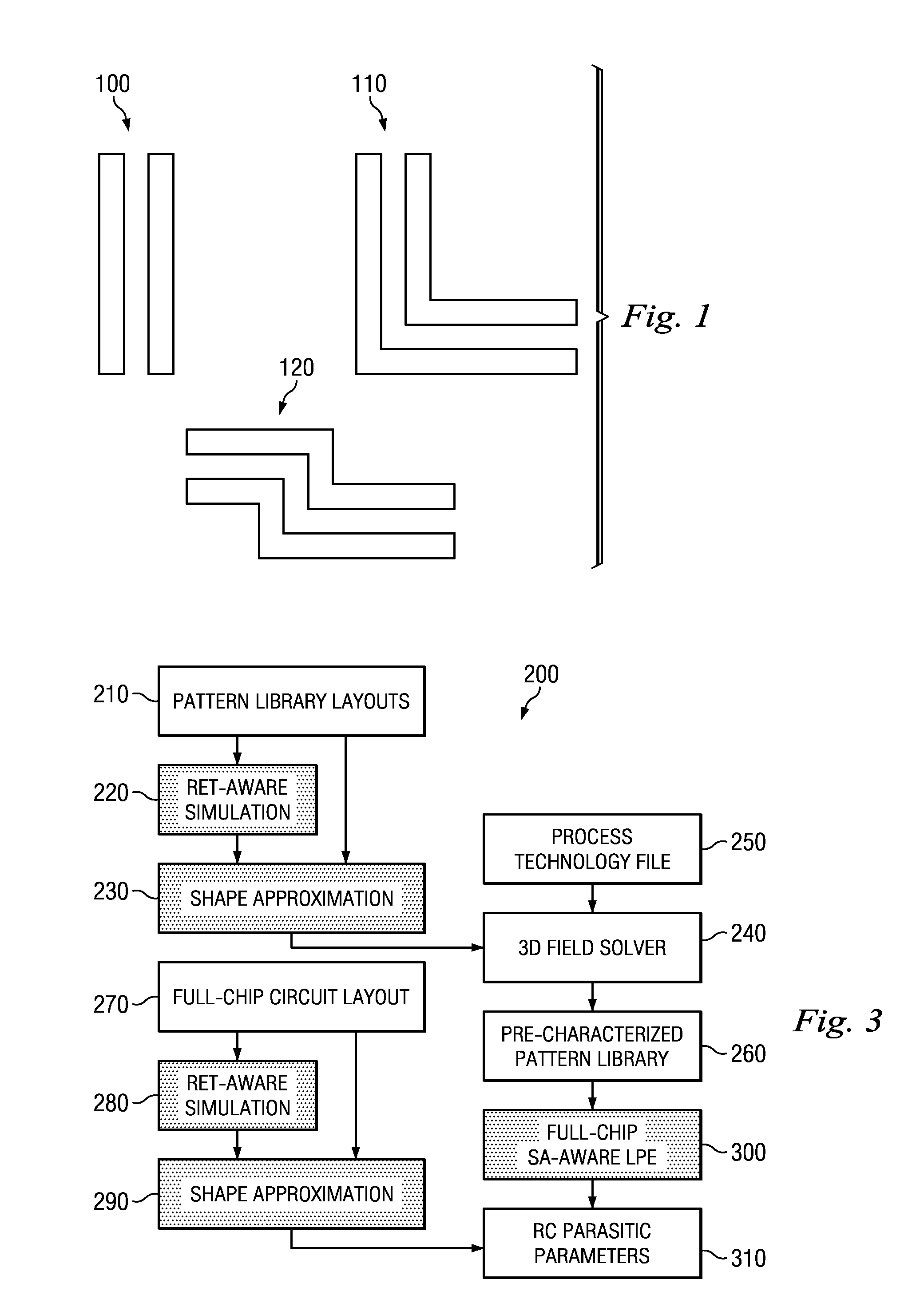

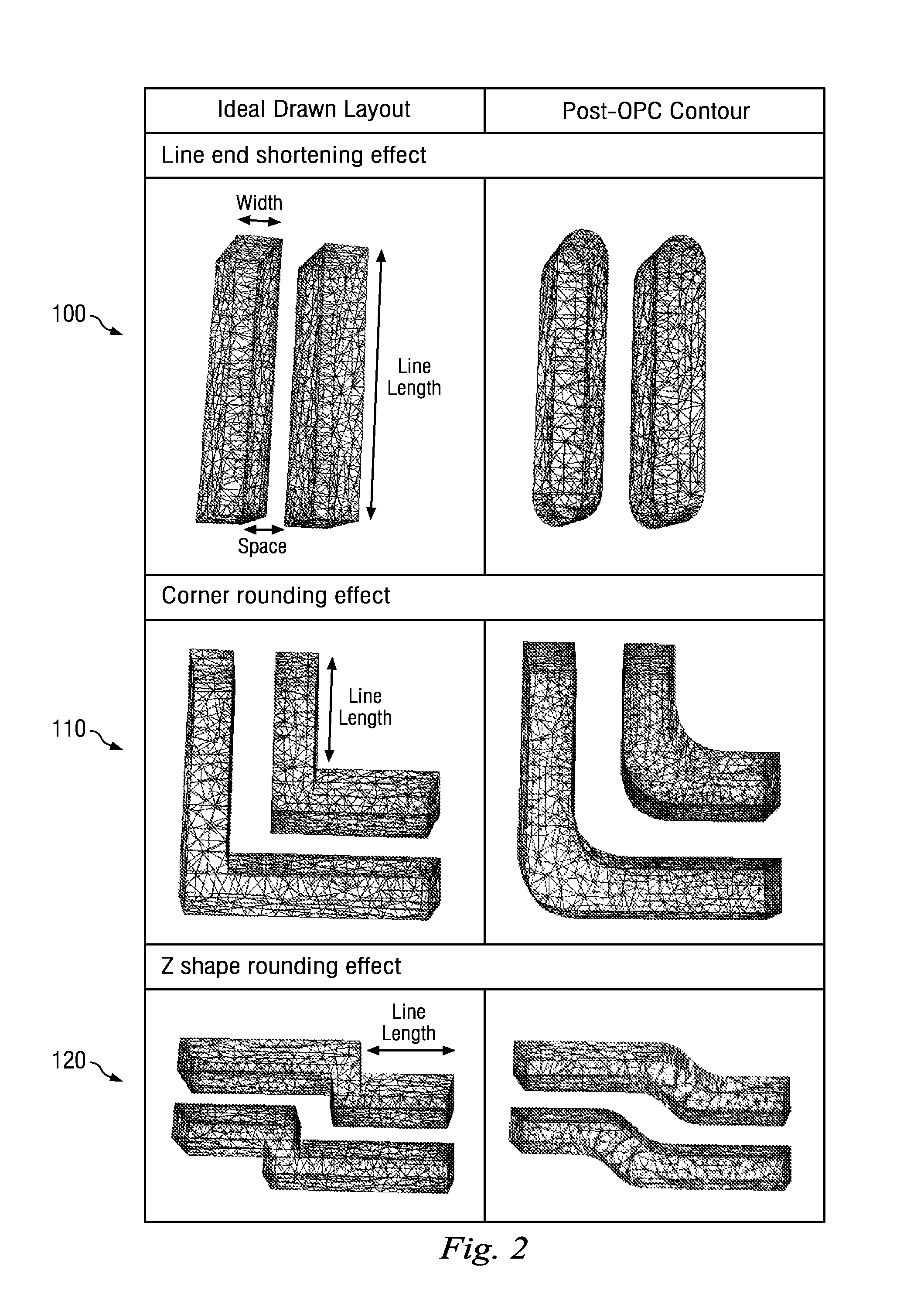

Method for improving accuracy of parasitics extraction considering sub-wavelength lithography effects

ActiveUS20120185807A1Computer aided designSoftware simulation/interpretation/emulationElectricityLithographic artist

The present disclosure involves a method. The method includes decomposing a layout of a circuit into a plurality of patterns. The method includes generating a plurality of contours to represent the plurality of patterns after the patterns have been subjected to a manufacturing process. The method includes generating a plurality of polygons that approximate geometries of the contours, respectively. The method includes associating each of the polygons with a respective one of a plurality of pattern elements in a pattern library, wherein the pattern elements each include a shape that resembles the associated polygon and electrical parameters extracted from the shape. The method includes calculating electrical performance of the circuit based on the pattern elements associated with the polygons.

Owner:TAIWAN SEMICON MFG CO LTD +1

Method and system for reticle-wide hierarchy management for representational and computational reuse in integrated circuit layout design

ActiveUS7401319B2Maximize reuseImprove executionElectric discharge tubesOriginals for photomechanical treatmentComputation reuseParallel computing

A hierarchical representation encapsulates the detailed internal composition of a sub-circuit using the notion of a cell definition (a CellDef). The CellDef serves as a natural unit for operational reuse. If the computation required for the analysis or manipulation (e.g. parasitic extraction, RET, design rule confirmation (DRC), or OPC) based on a CellDef or one cell instance can be applied, with no or minimal additional effort, to all or a significant subset of other instances of the cell, very substantial reduction in computational effort may be realized. Furthermore, a hierarchical representation also allows for the partitioning of the overall analysis / manipulation task into a collection of subtasks, e.g. one per CellDef. Multiple jobs may then be distributed across a large number of computational nodes on a network for concurrent execution. While this may not reduce the aggregate computational time, a major reduction in the overall turnaround time (TAT) is in itself extremely beneficial.

Owner:CADENCE DESIGN SYST INC

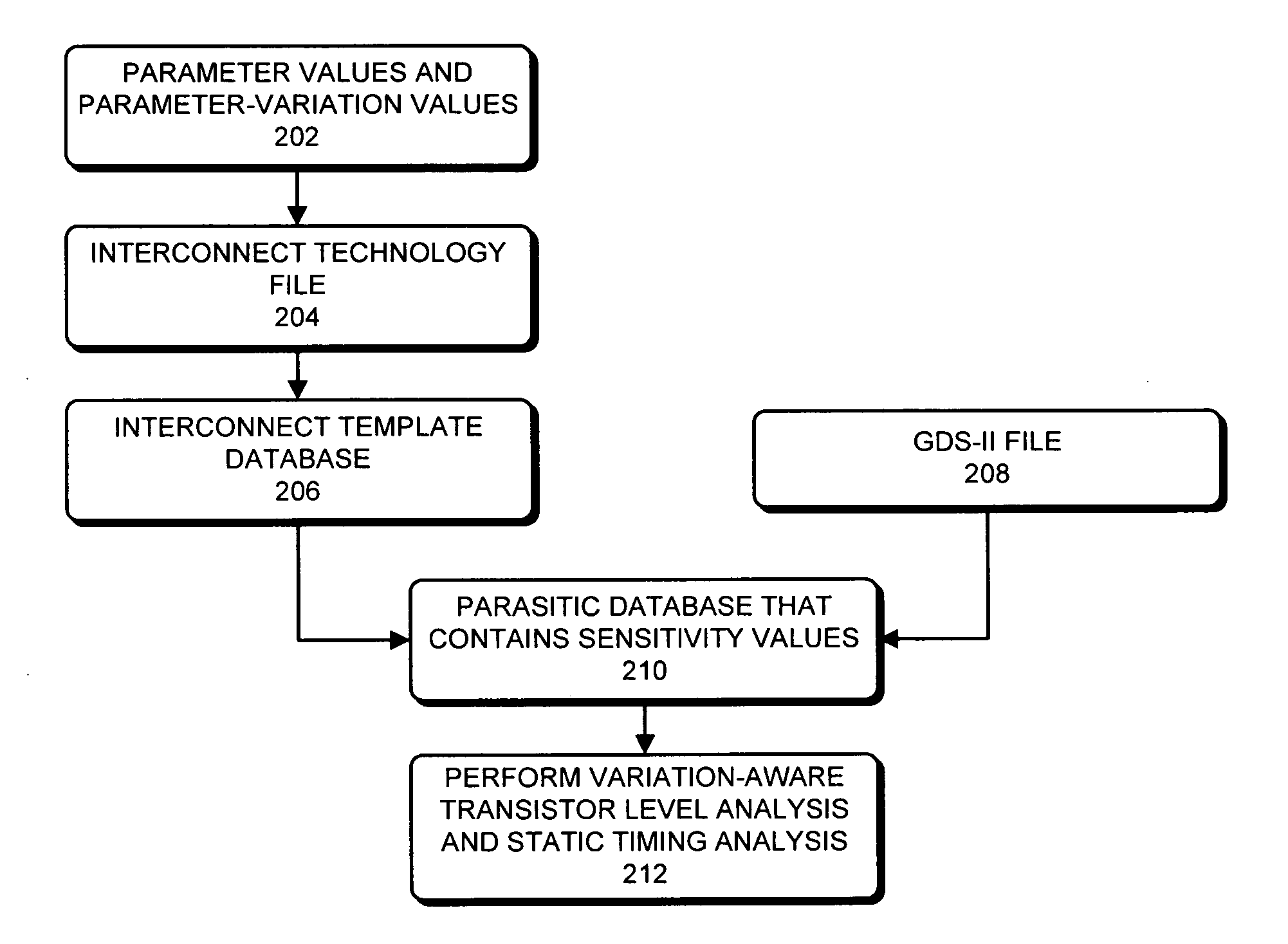

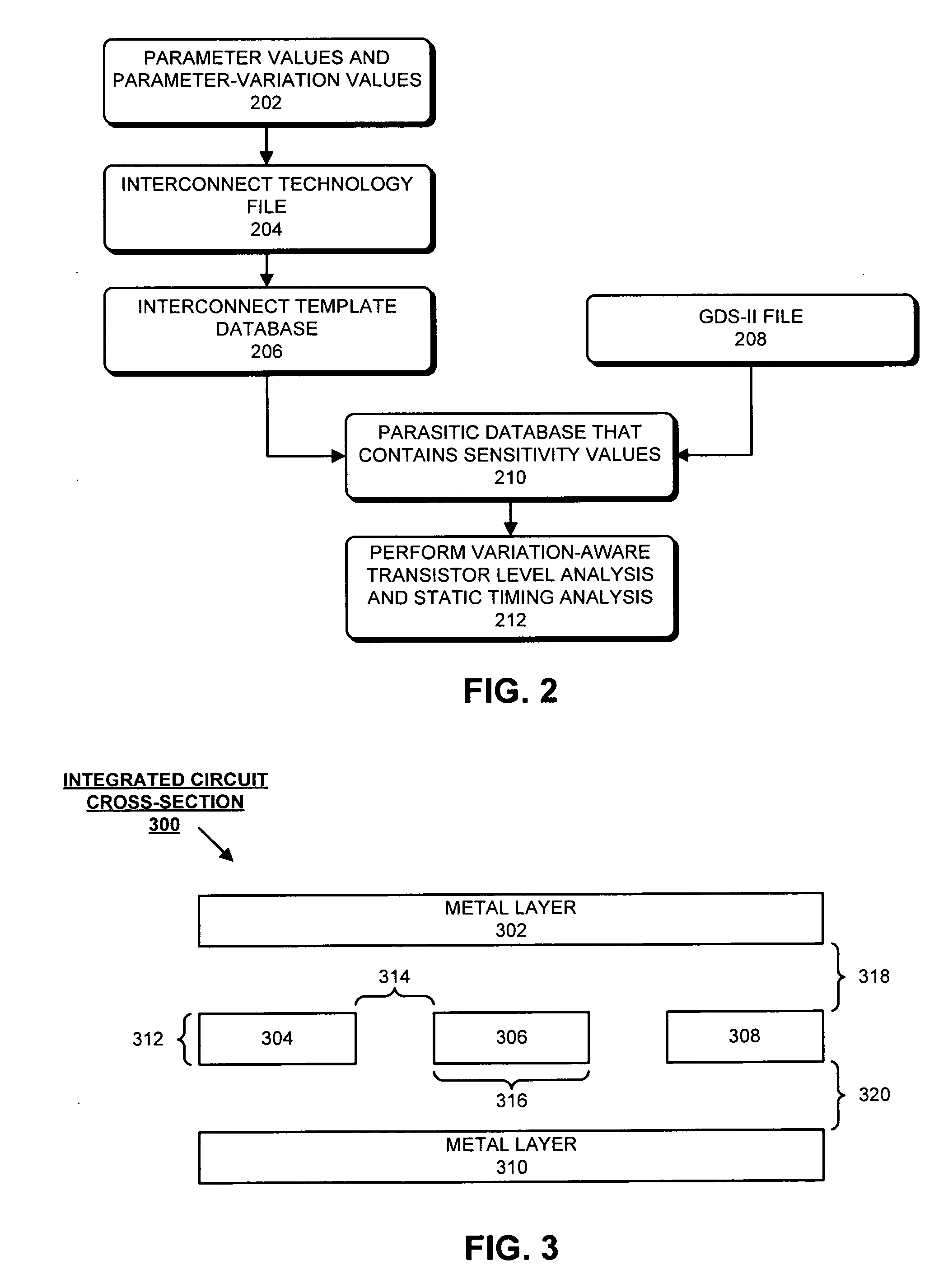

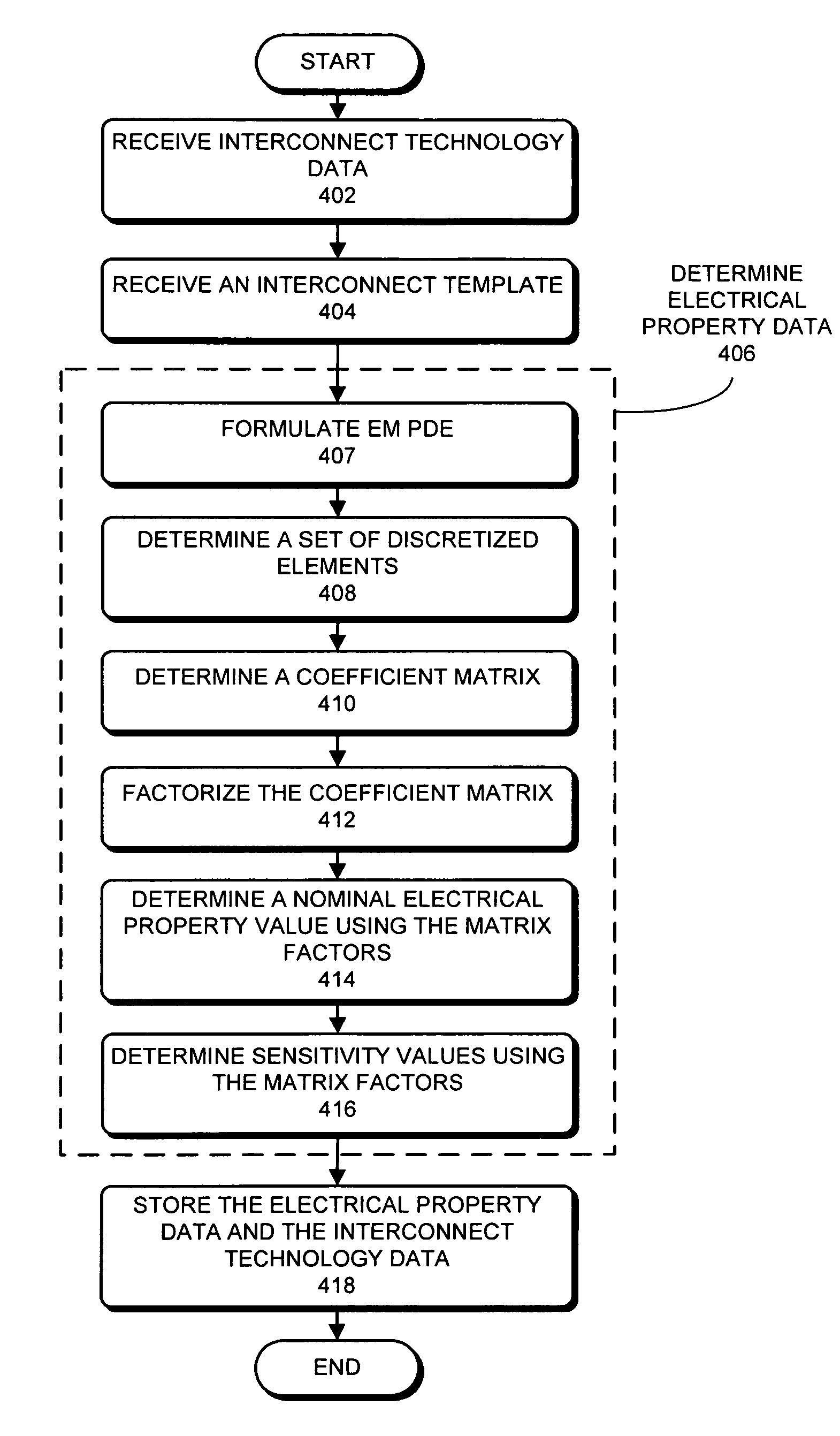

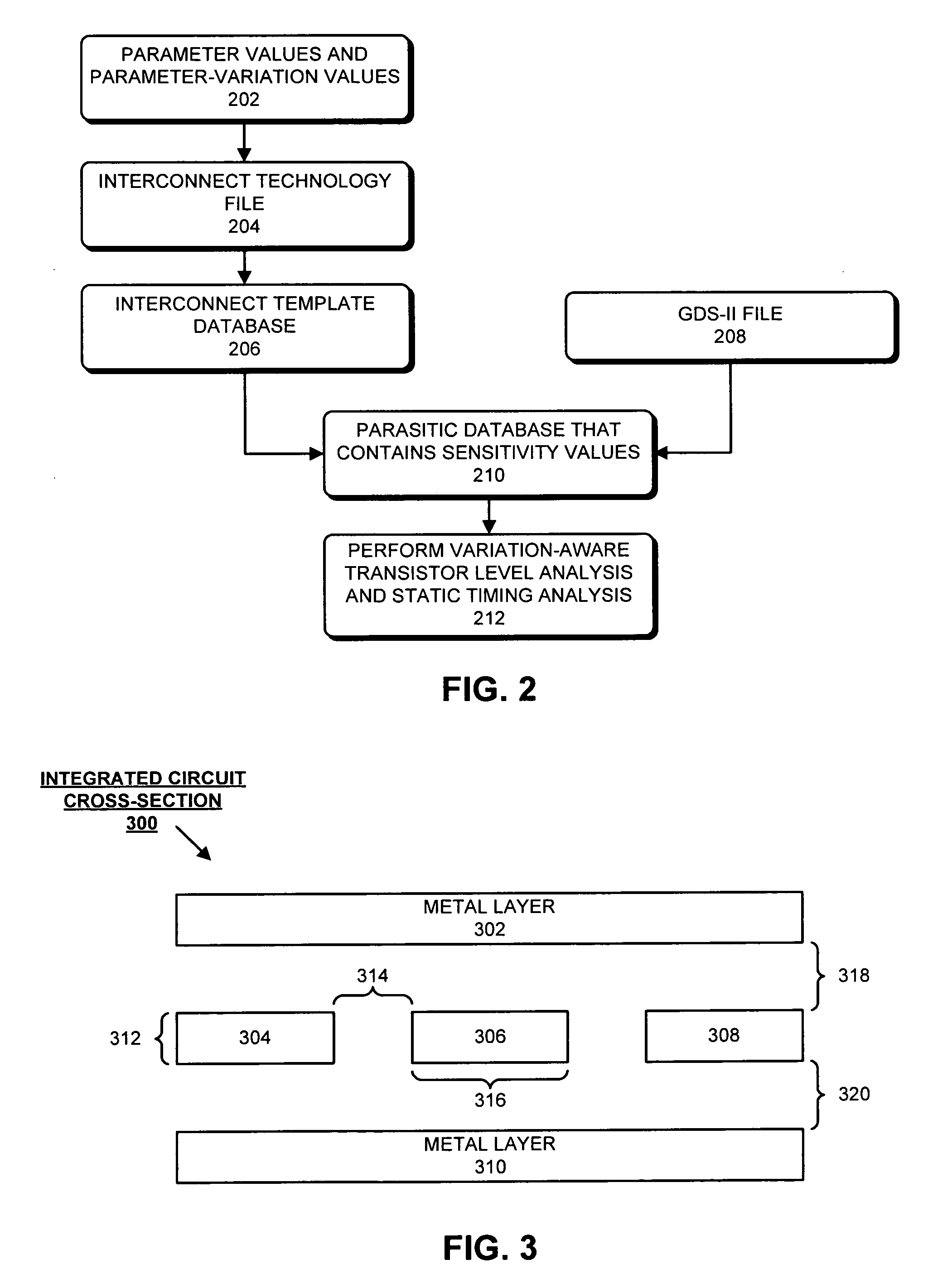

Method and apparatus for facilitating variation-aware parasitic extraction

ActiveUS20070124707A1Generate accuratelyDetecting faulty computer hardwareDesign optimisation/simulationElectricityProperty value

One embodiment of the present invention provides a system for determining an electrical property for an interconnect layer. During operation, the system receives interconnect technology data which includes nominal parameter values for a first interconnect layer, and parameter-variation values which represent variations in the nominal parameter values due to random process variations. Next, the system receives an interconnect template which describes the geometry of a portion of a second interconnect layer. The system then determines electrical property data for the interconnect template using the interconnect technology data. The electrical property data can include a nominal electrical property value, and sensitivity values which represent the sensitivities of the nominal electrical property value to variations in the nominal parameter values. Next, the system stores the electrical property data and the interconnect technology data in a storage.

Owner:SYNOPSYS INC

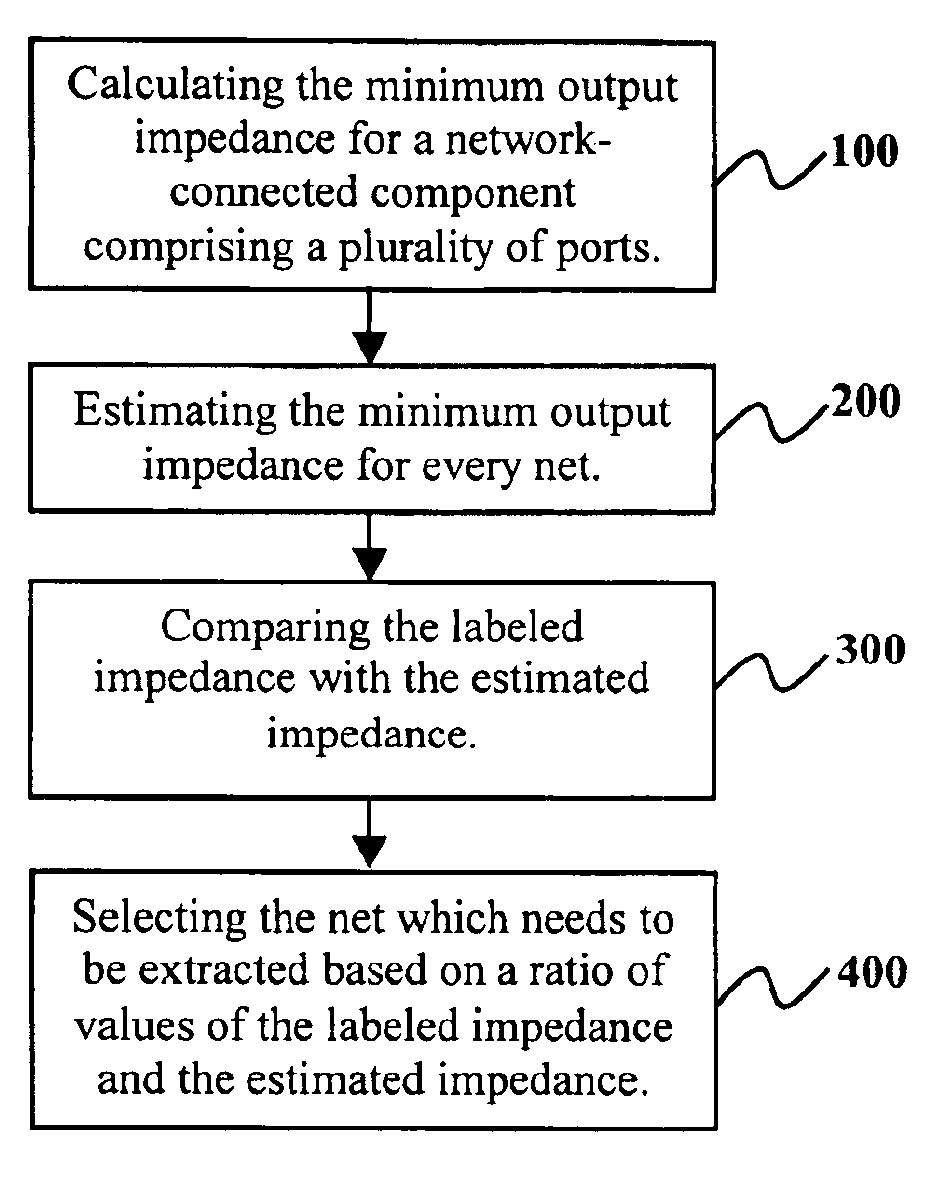

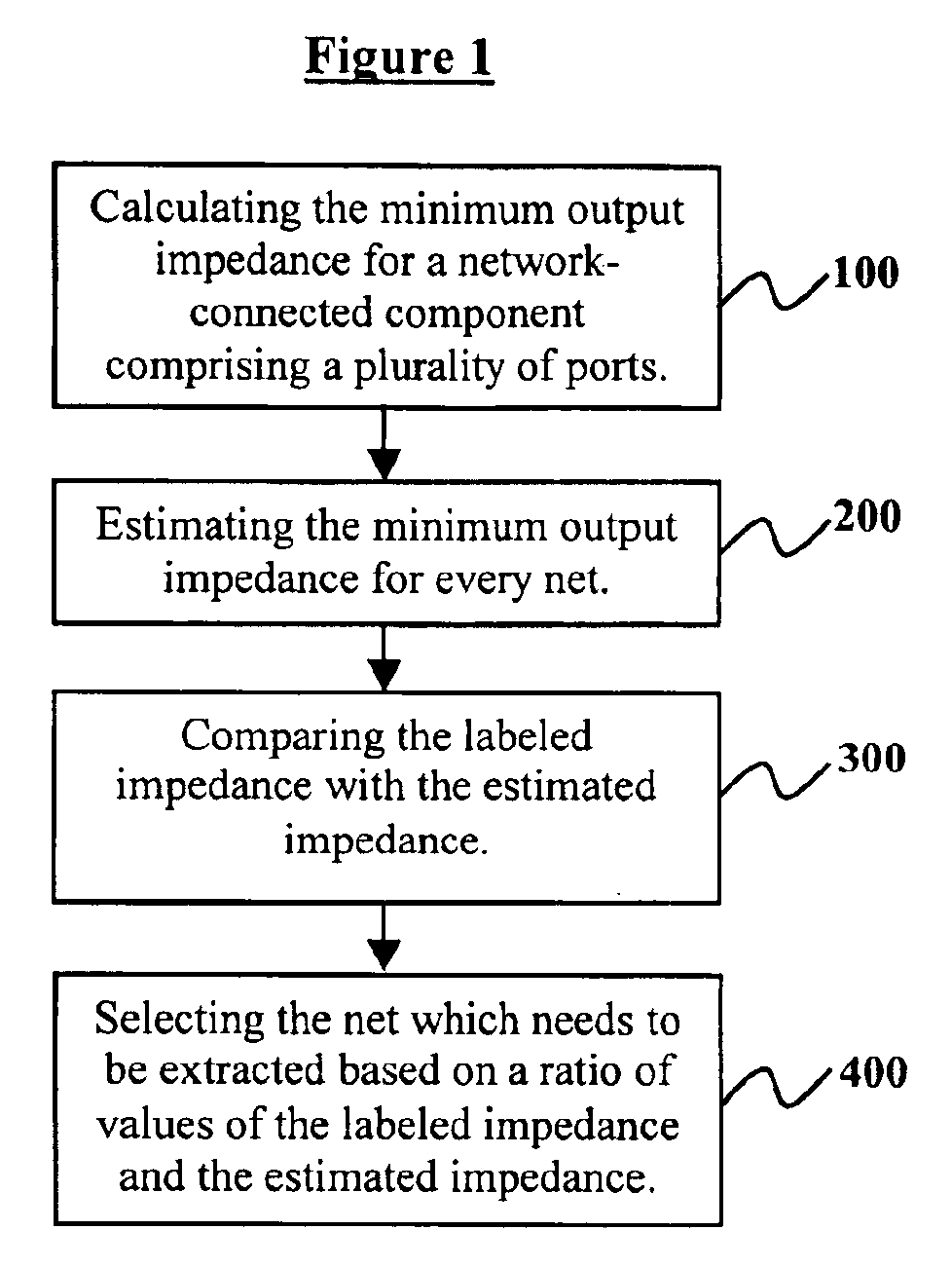

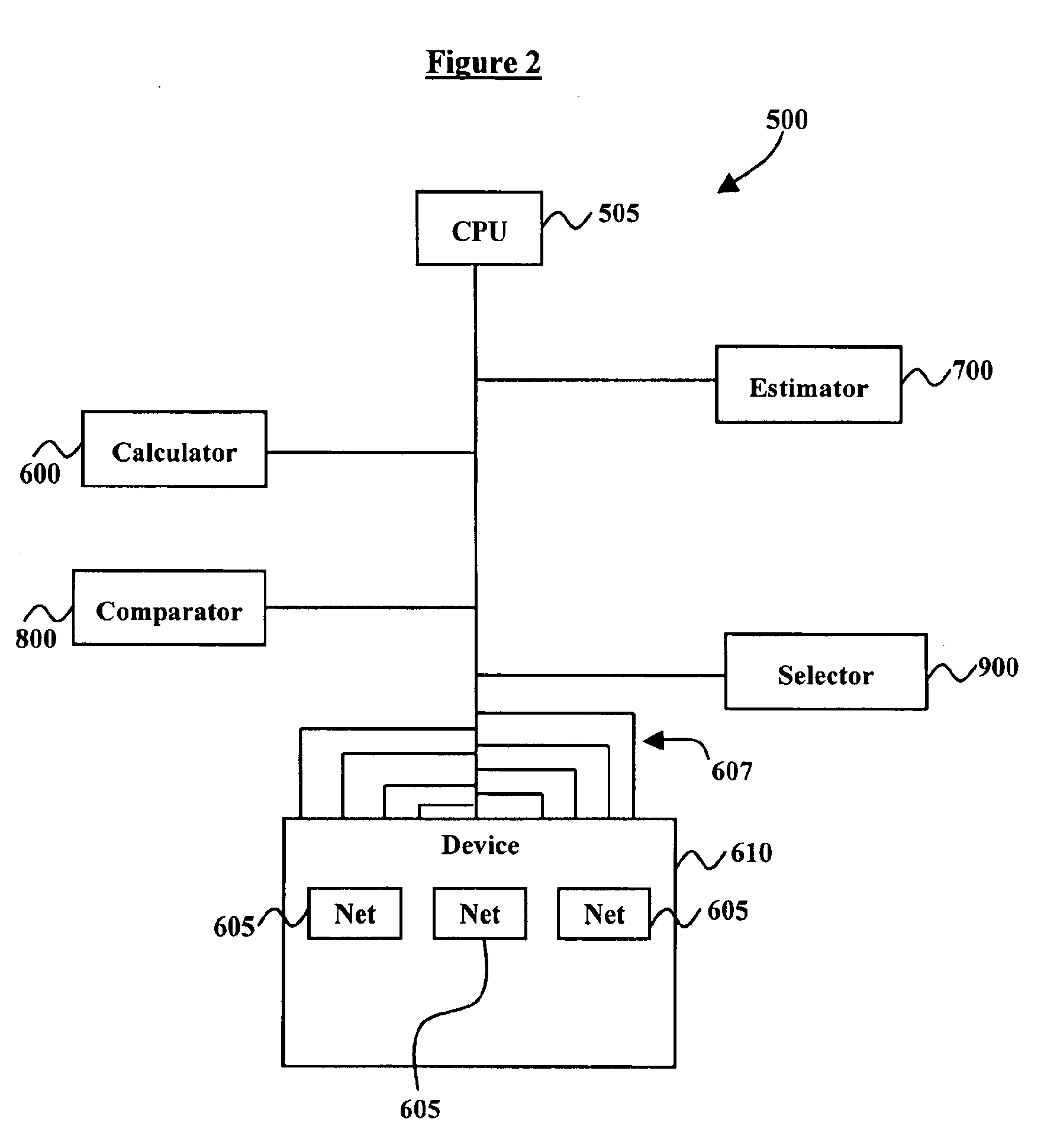

Balanced accuracy for extraction

InactiveUS20040003356A1Large positive impact on the efficiency of the extraction program andSize andComputer aided designSpecial data processing applicationsElectrical resistance and conductanceCapacitance

A method and system for performing parasitic extraction, wherein the method comprises calculating the minimum output impedance for a network-connected component comprising a plurality of ports thereby producing a labeled impedance, estimating the minimum output impedance for every net, comparing the labeled impedance with the estimated impedance, and selecting the net which needs to be extracted based on a ratio of values of the labeled impedance and the estimated impedance. The step of calculating comprises labeling every port with a minimum size of port impedance, a resistance from a port to power, and a minimum capacitance of a port-net inside the network connected component. The step of estimating comprises using a geometry of segments of the net comprising a summation of area and perimeter values of all the segments of the net, or calculating a resistance over a length of a total net versus an average width of the net.

Owner:IBM CORP

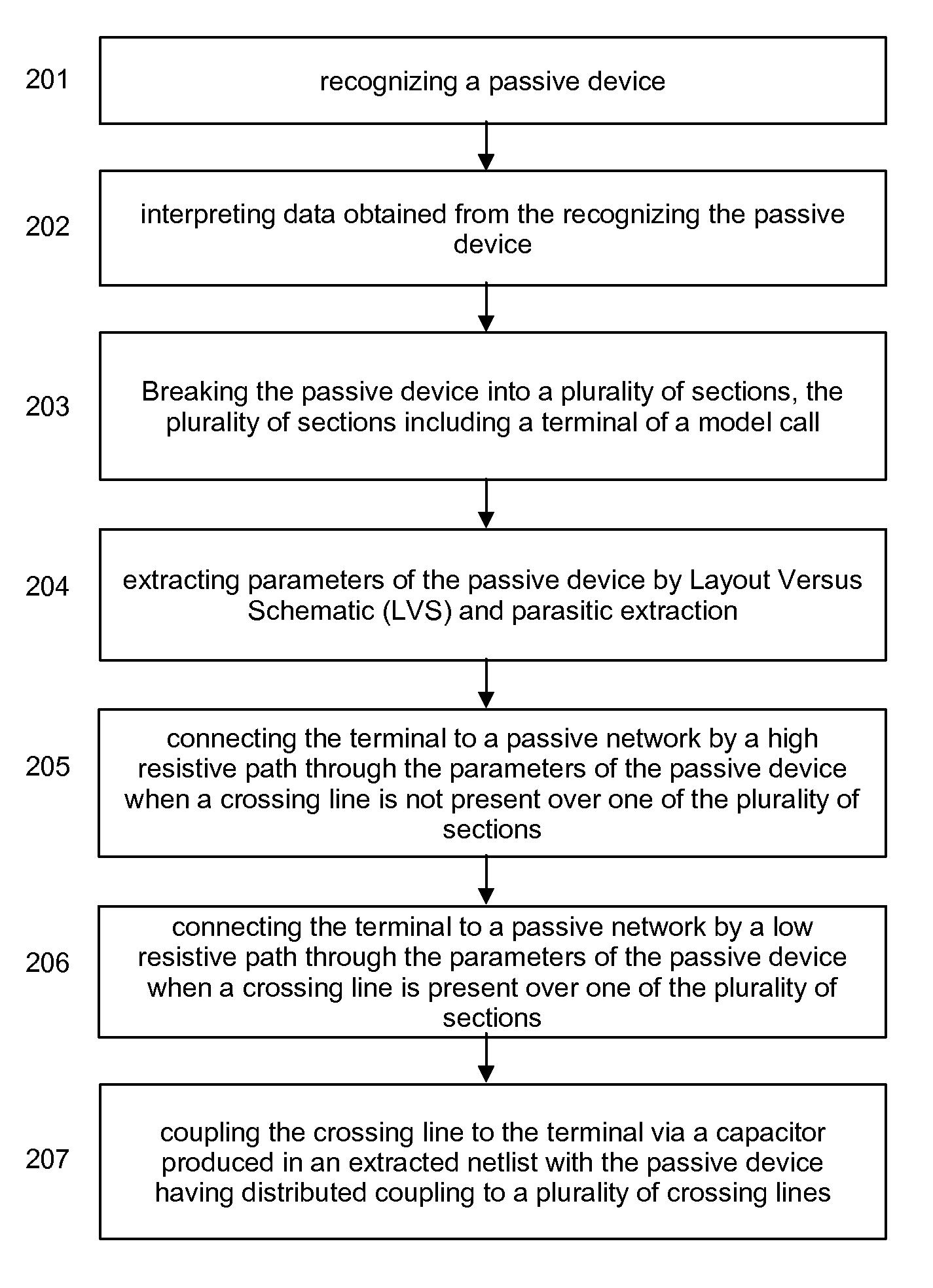

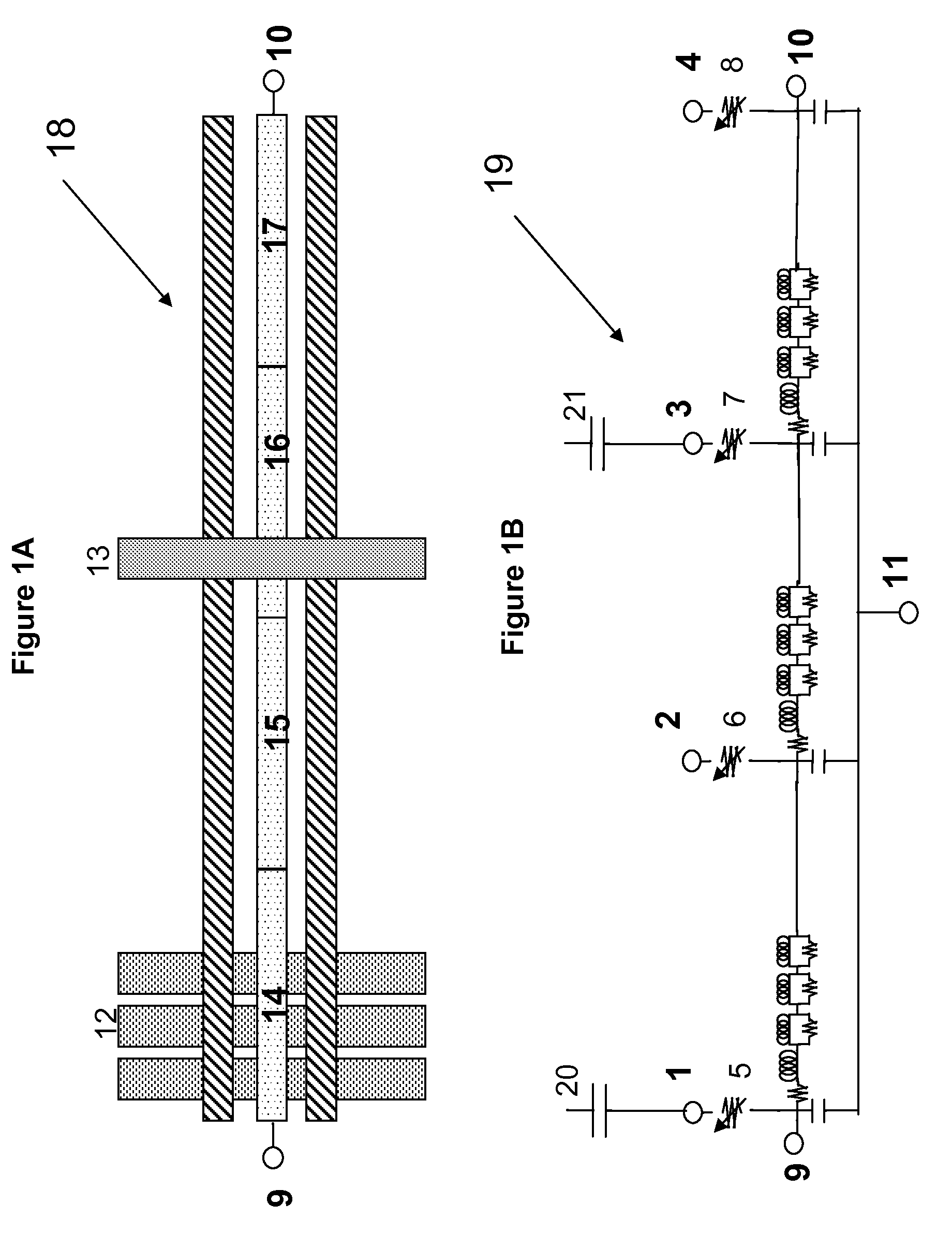

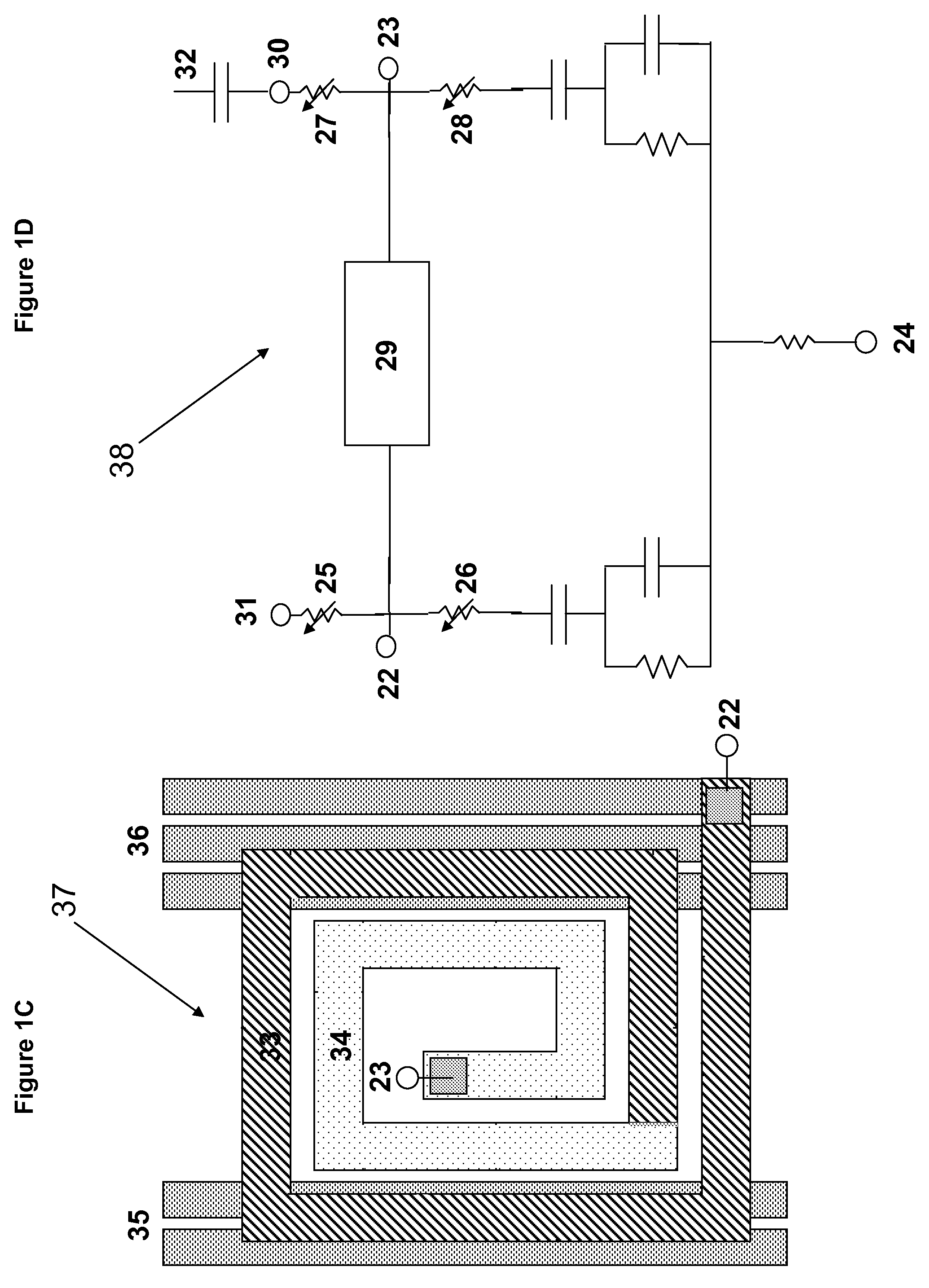

Method and system of linking on-chip parasitic coupling capacitance into distributed pre-layout passive models

InactiveUS8141013B2Accurately include post-layout parasiticsAccurate predictionDetecting faulty computer hardwareComputer aided designCapacitanceElectrical resistance and conductance

A method of linking on-chip parasitic coupling capacitance into distributed pre-layout passive models such as distributed transmission line models and on-chip spiral inductor models includes recognizing a passive device such as a distributed transmission line device and an on-chip spiral inductor device, interpreting data obtained from the recognizing the passive device, breaking the passive device into a plurality of sections, the plurality of sections including a terminal of a model call, extracting parameters of the passive device by Layout Versus Schematic (LVS) and parasitic extraction, connecting the terminal to a pre-layout passive network by selectively low and high resistive paths set by the parameters of the passive device depending on whether crossing lines are present or not present in one of the plurality of sections, connecting the terminal to a distributed passive model, and coupling the crossing lines to the terminal via capacitors produced in an extracted netlist with the passive device having distributed coupling to a plurality of crossing lines.

Owner:GLOBALFOUNDRIES INC

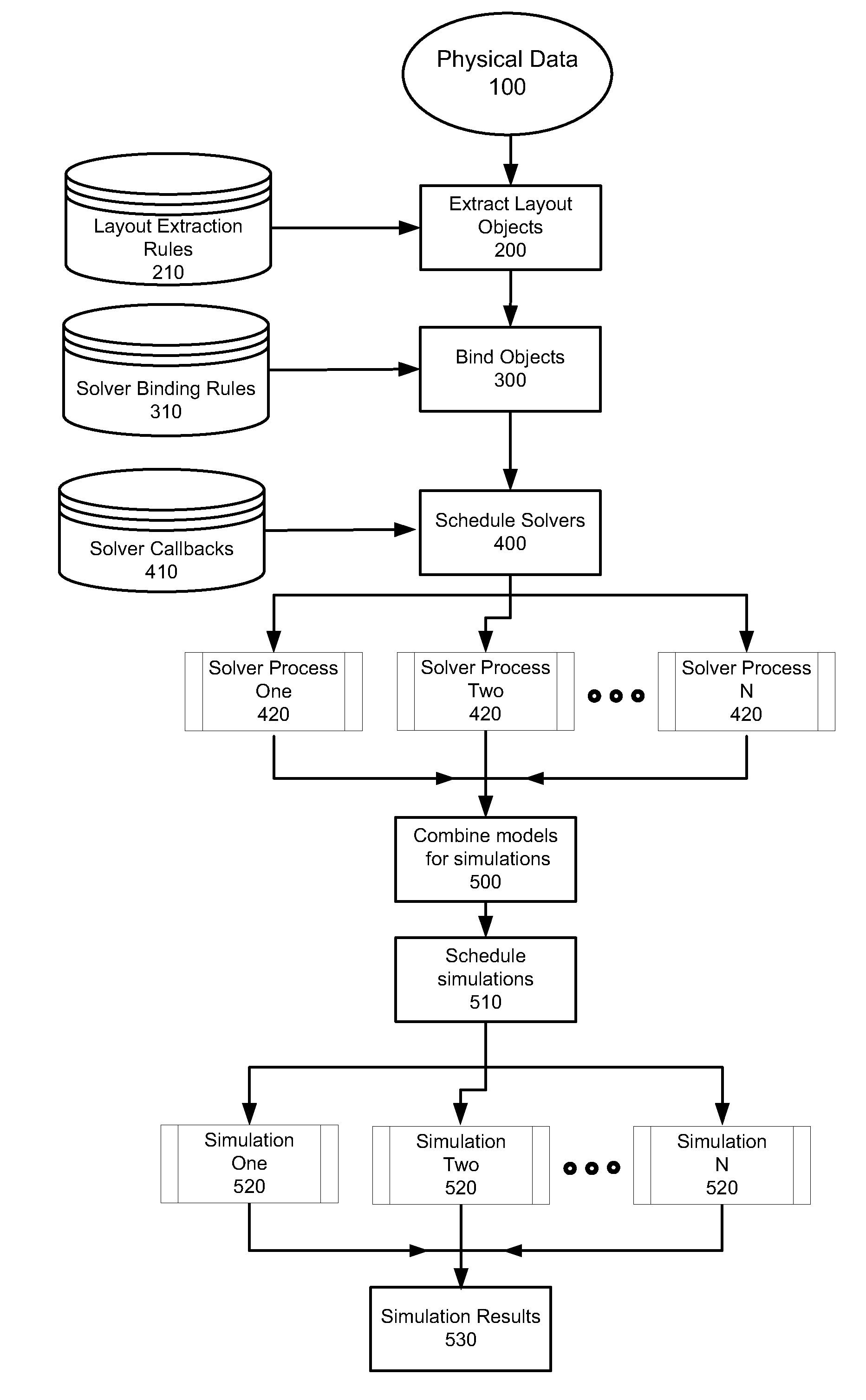

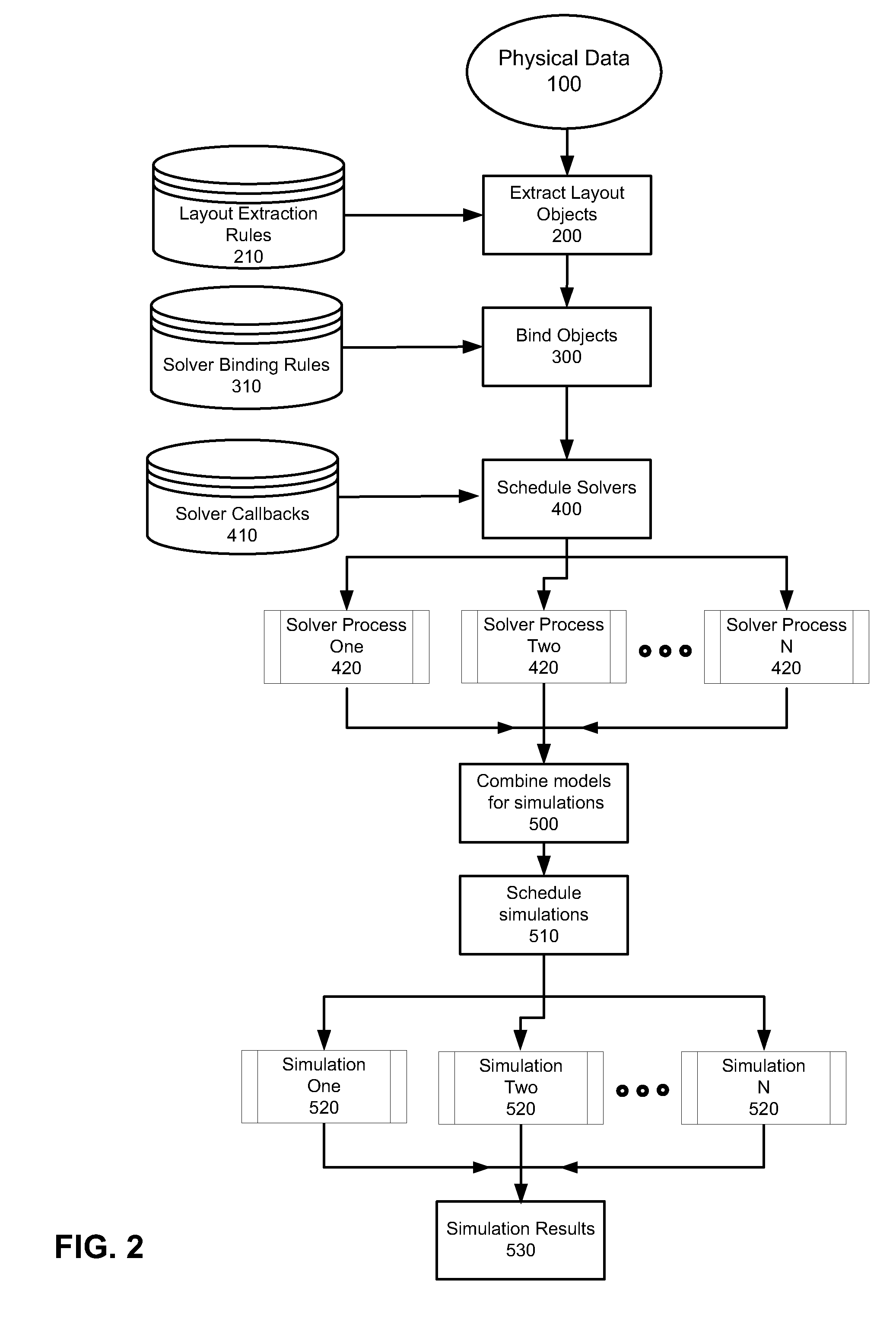

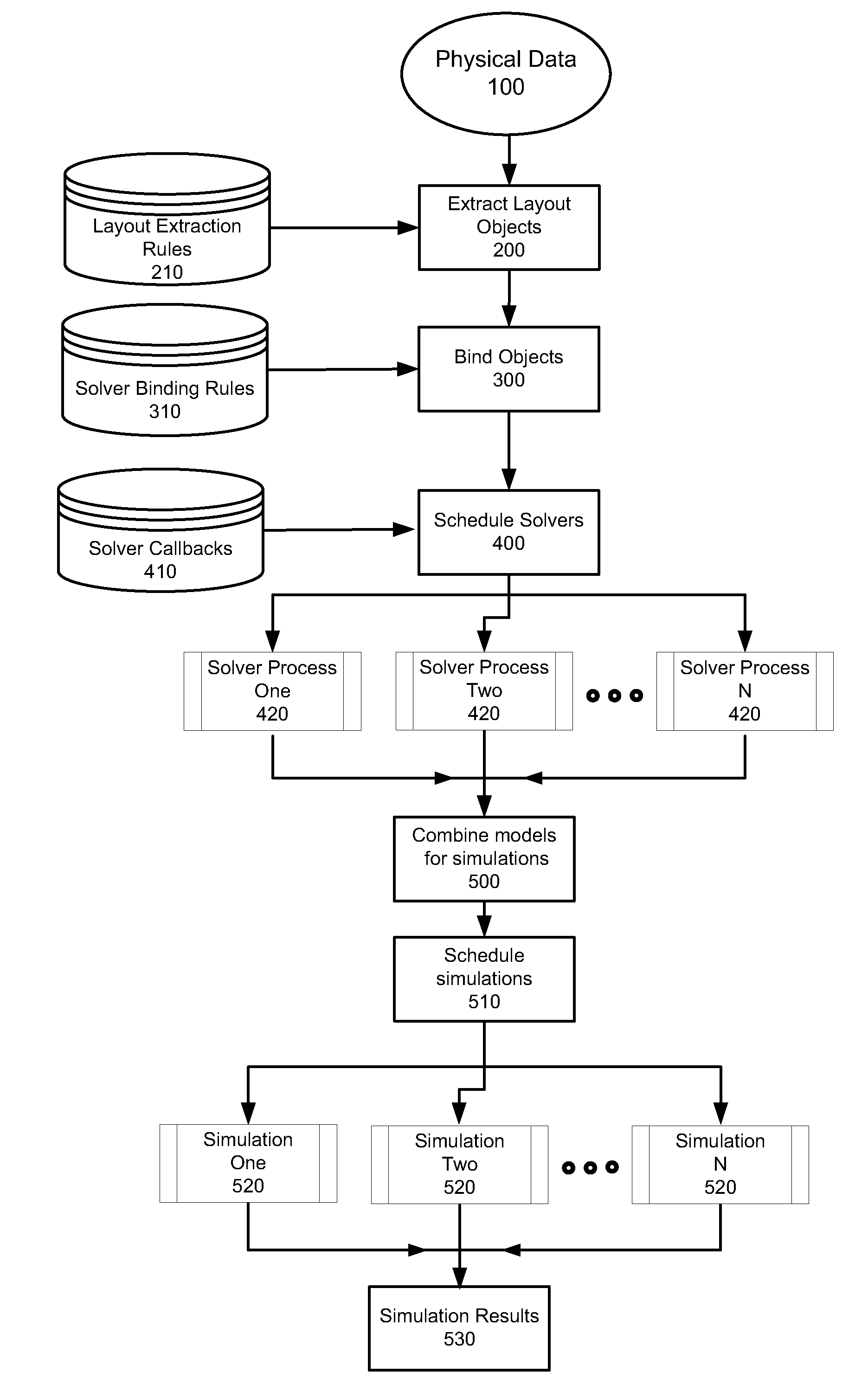

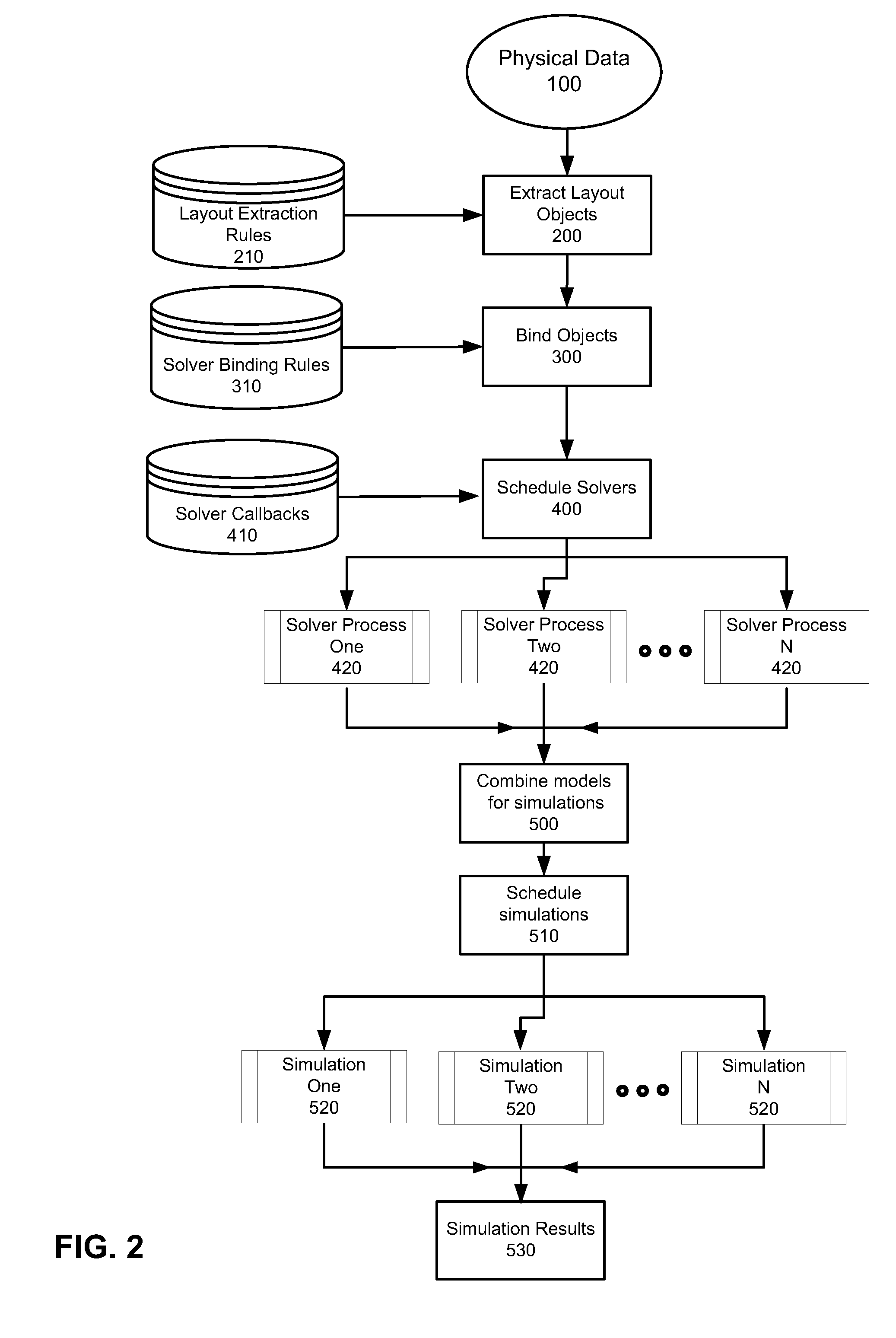

Method and apparatus for rule-based automatic layout parasitic extraction in a multi-technology environment

InactiveUS20110173582A1Knowledge representationComputer aided designParasitic extractionLayout extraction

A system for extracting a layout from an object in a fabric includes means for providing fabric data to a rule-based layout extraction engine; means for maintaining a layout extraction rule to select a layout object from the fabric data; means for maintaining a binding rule to bind the layout object to a solver; means for maintaining a boundary rule to specify a boundary condition for a solver; and means for executing the solver on the layout object to generate a model of the object.

Owner:CADENCE DESIGN SYST INC

Balanced accuracy for extraction

InactiveUS6854099B2Large positive impact on the efficiency of the extraction program andSize andComputer aided designSpecial data processing applicationsElectrical resistance and conductanceCapacitance

Owner:INT BUSINESS MASCH CORP

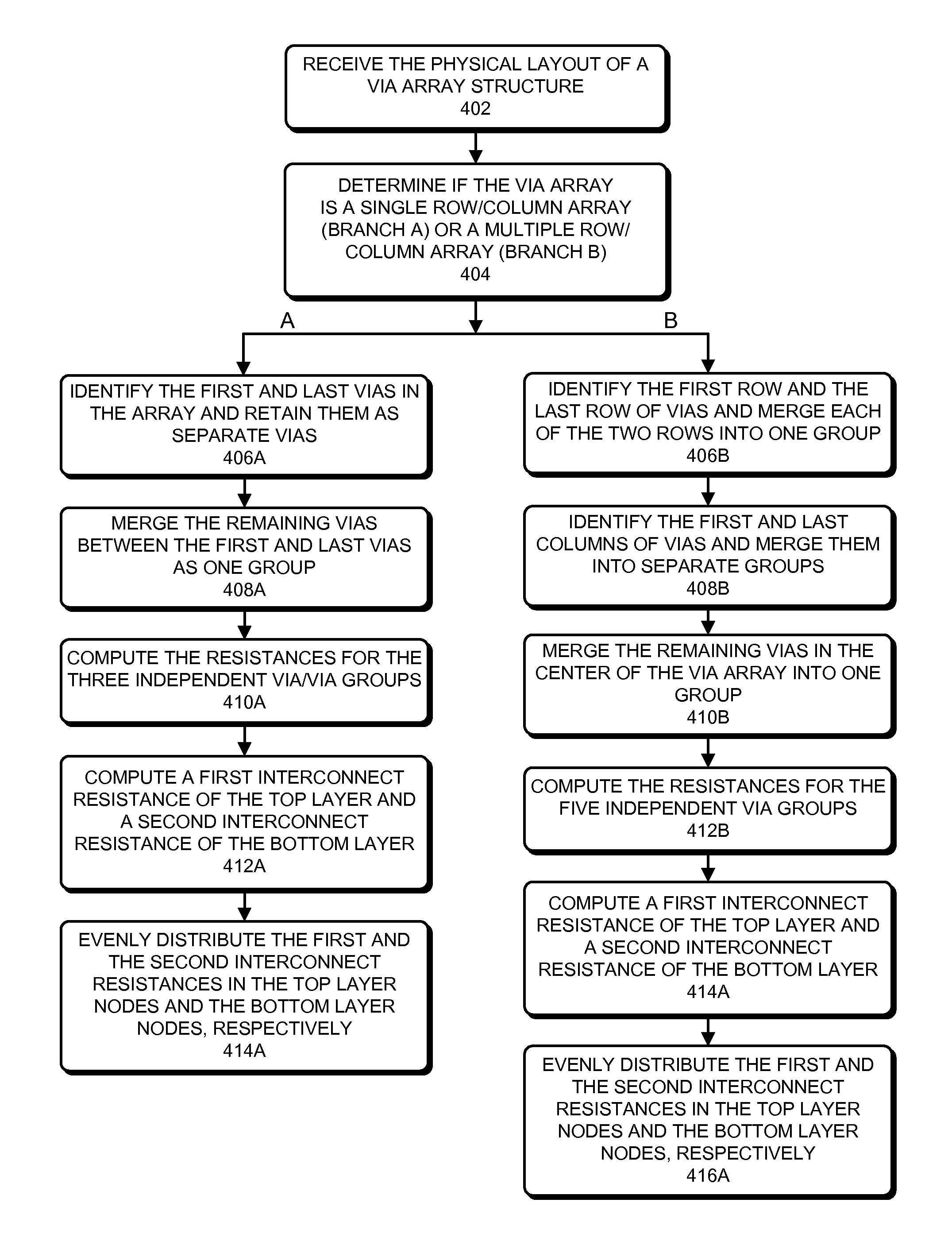

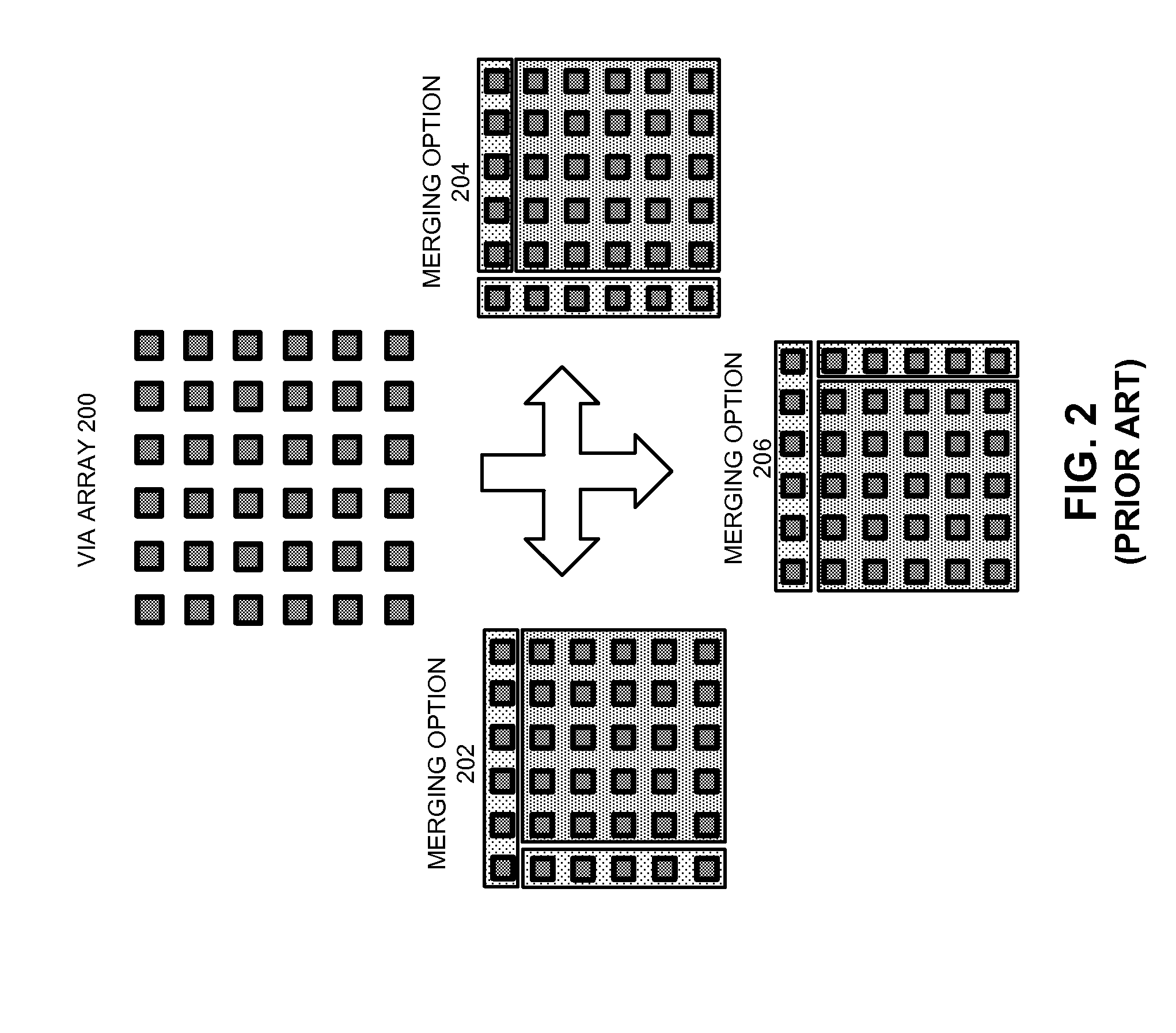

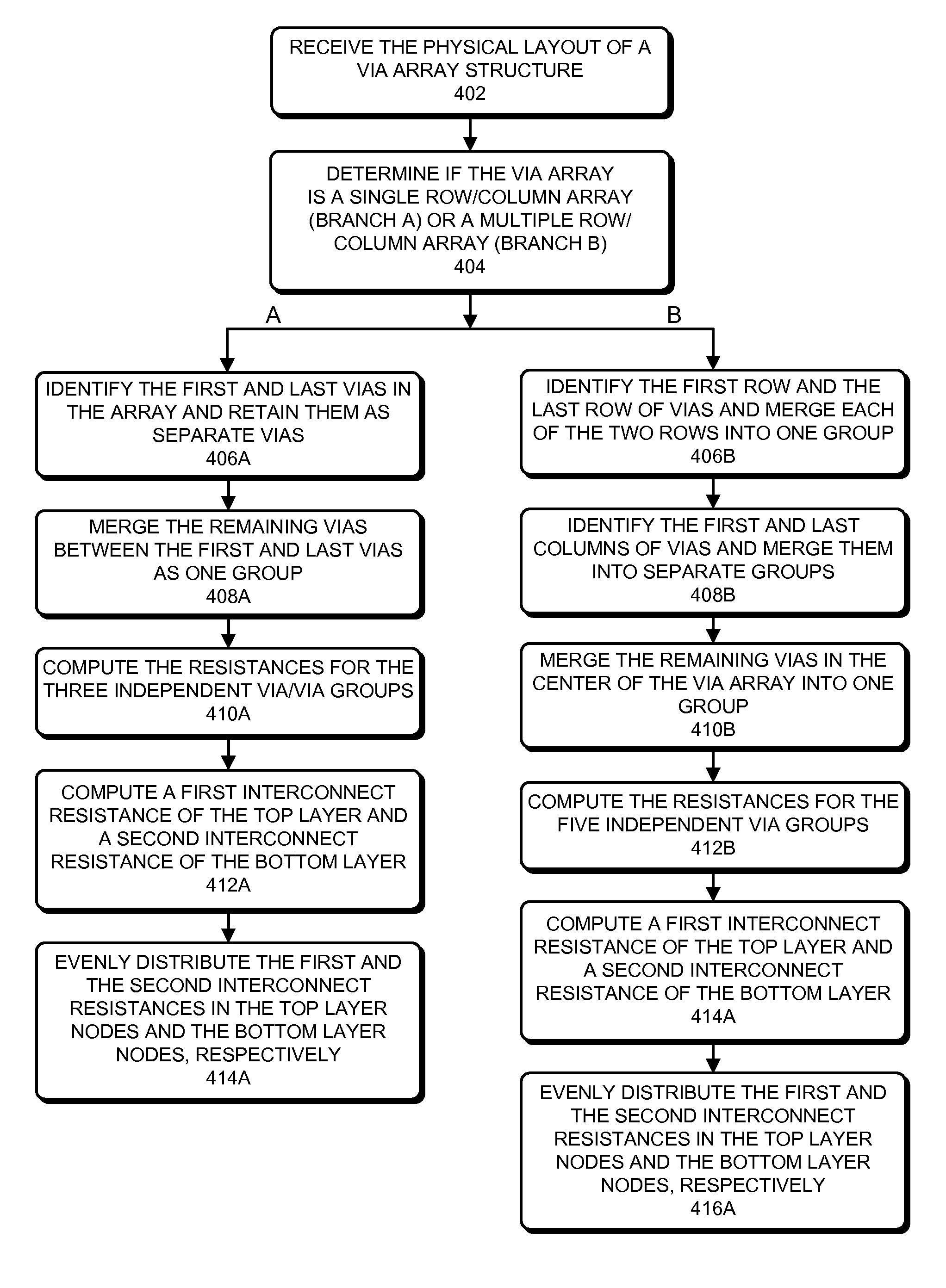

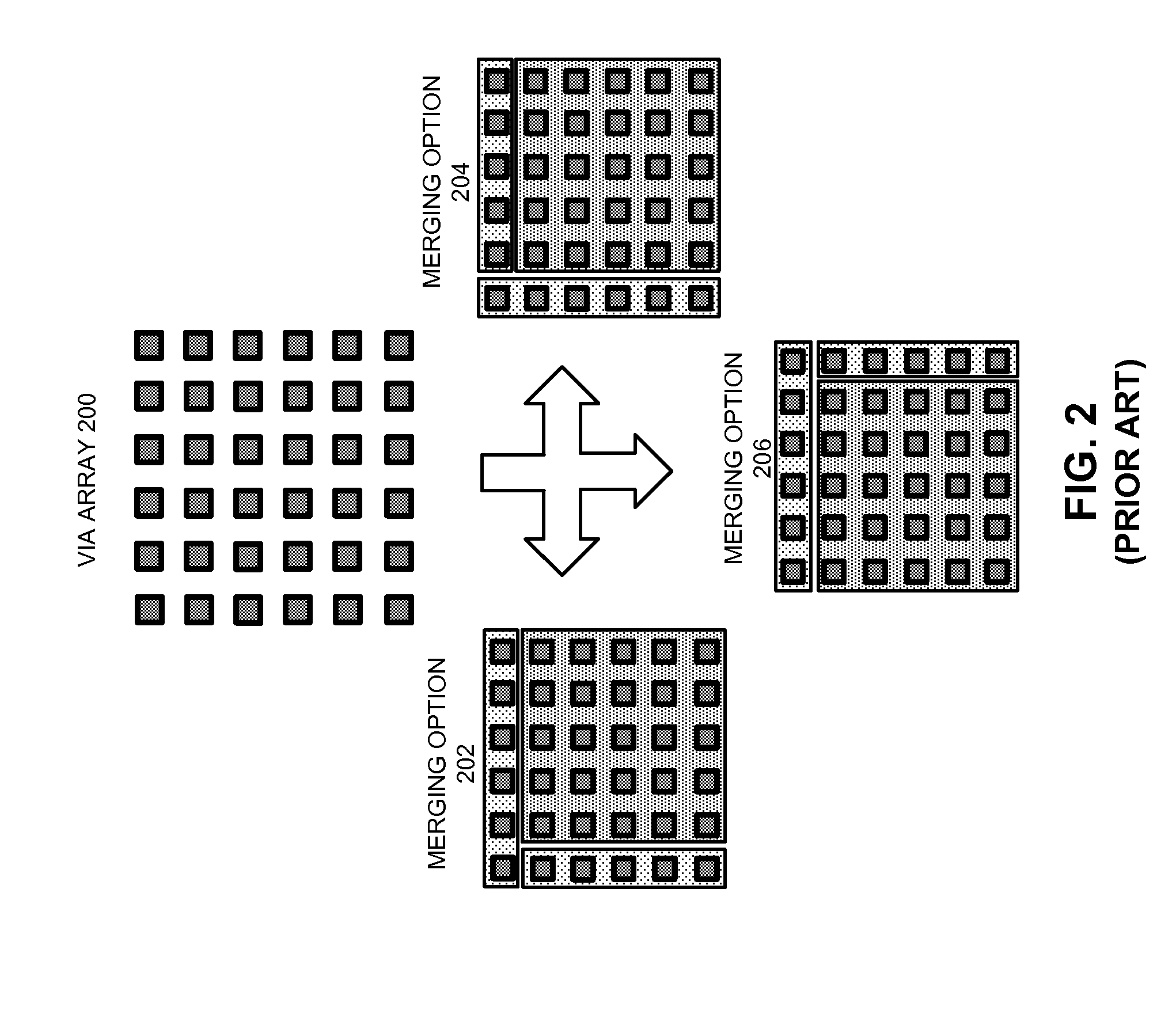

Method and apparatus for performing via array merging and parasitic extraction

ActiveUS20120317531A1CAD circuit designSoftware simulation/interpretation/emulationArray data structureParallel computing

Systems and techniques for performing parasitic extraction on a via array are described. If the via array is a single row or column via array, the system identifies a first via and a last via in the via array, and merges a set of vias between the first via and the last via into a center via. If the via array is a M×N (M≧2, N≧2) via array, the system merges the vias as follows: the first row and the last row of vias in the via array into a first row via and a last row via, respectively; the first column and the last column of vias in the via array into a first column via and a last column via, respectively; and a set of vias between the first and last rows and the first and last columns into a center via.

Owner:SYNOPSYS INC

Method and apparatus for facilitating variation-aware parasitic extraction

ActiveUS7587691B2Generate accuratelyDetecting faulty computer hardwareDesign optimisation/simulationElectricityProperty value

One embodiment of the present invention provides a system for determining an electrical property for an interconnect layer. During operation, the system receives interconnect technology data which includes nominal parameter values for a first interconnect layer, and parameter-variation values which represent variations in the nominal parameter values due to random process variations. Next, the system receives an interconnect template which describes the geometry of a portion of a second interconnect layer. The system then determines electrical property data for the interconnect template using the interconnect technology data. The electrical property data can include a nominal electrical property value, and sensitivity values which represent the sensitivities of the nominal electrical property value to variations in the nominal parameter values. Next, the system stores the electrical property data and the interconnect technology data in a storage.

Owner:SYNOPSYS INC

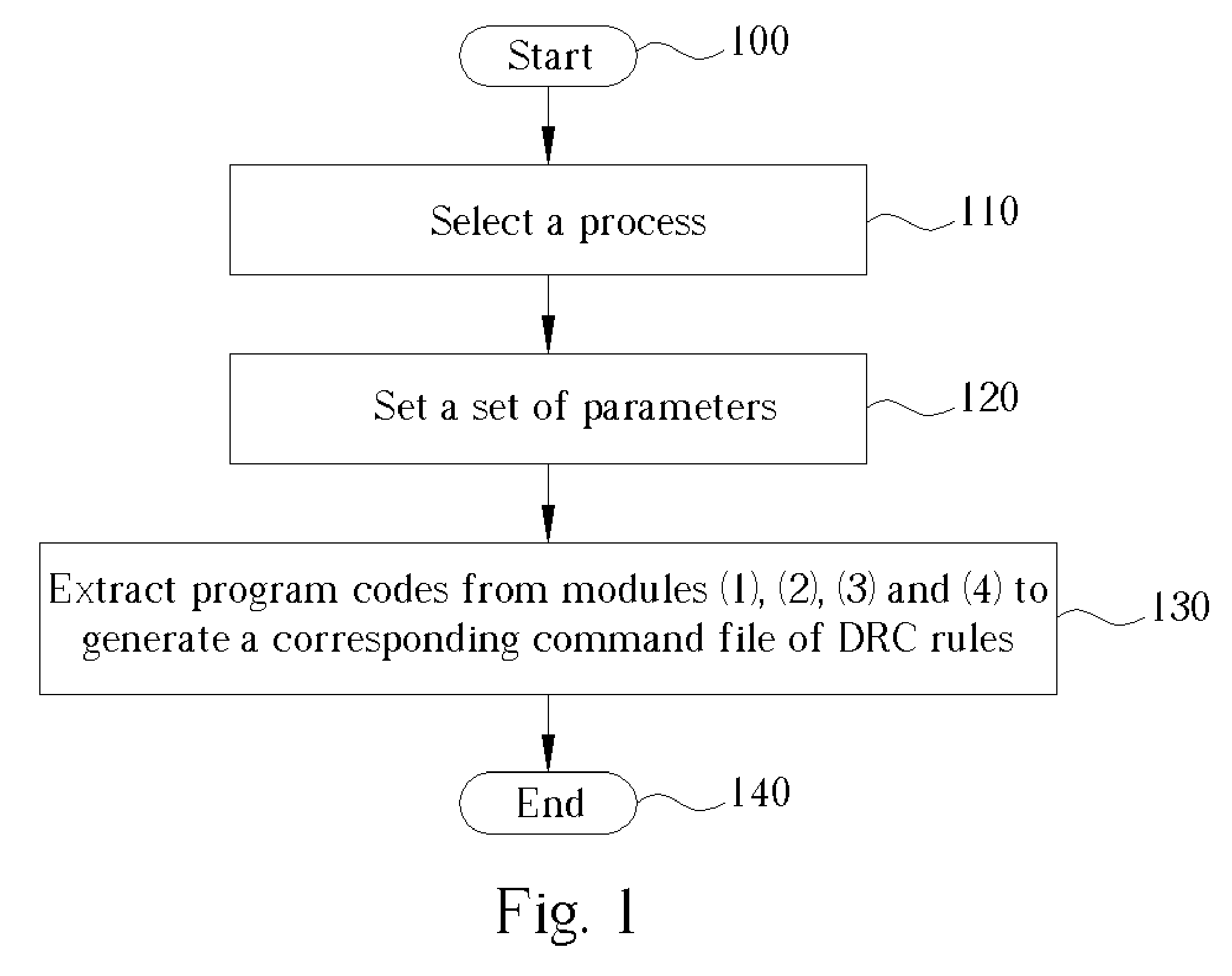

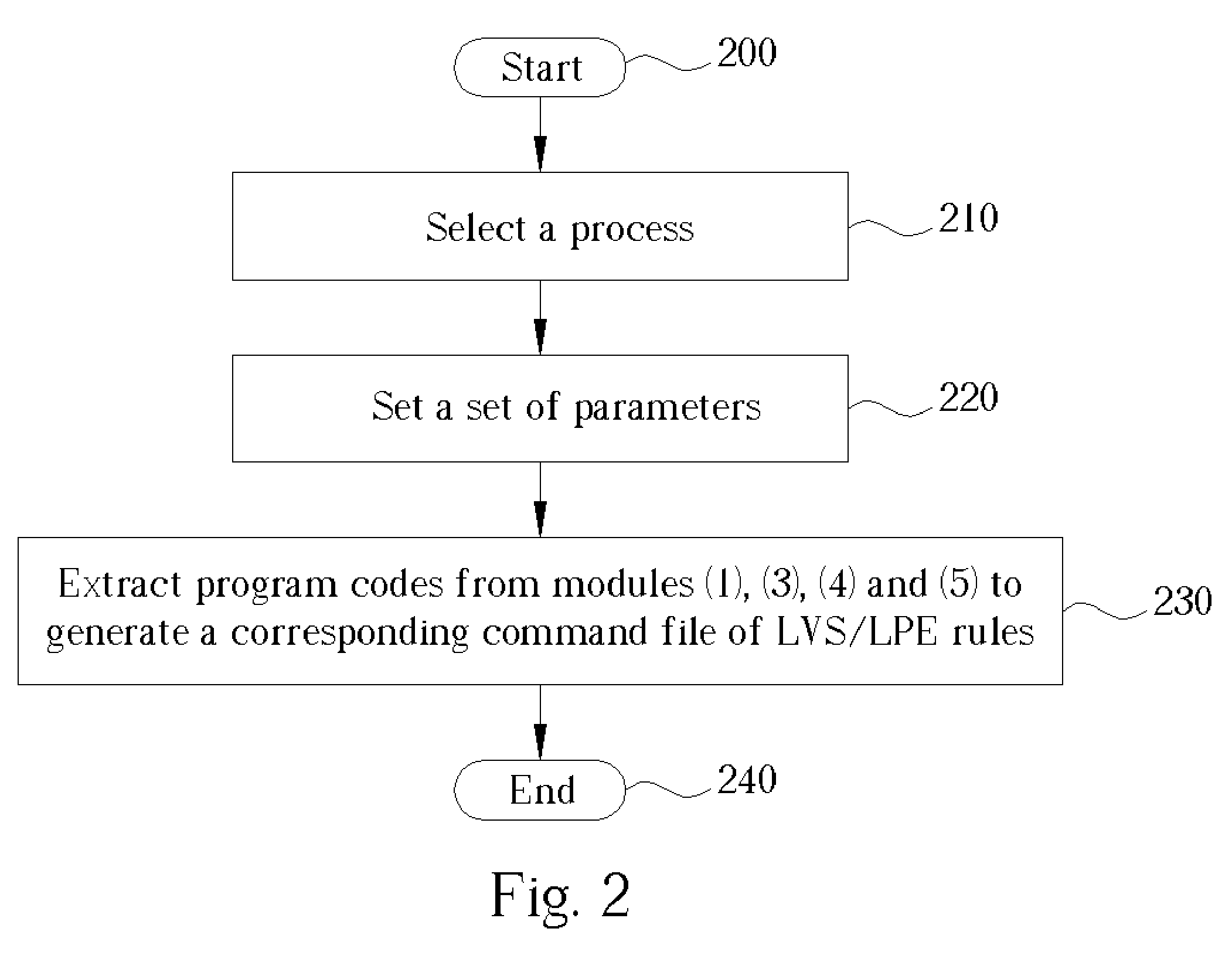

Method for generating a command file of a group of DRC rules and/or a command file of a group of LVS/LPE rules

InactiveUS7096441B2Efficient updateComputer aided designSpecial data processing applicationsLayout Versus SchematicParasitic extraction

Owner:FARADAY TECH CORP

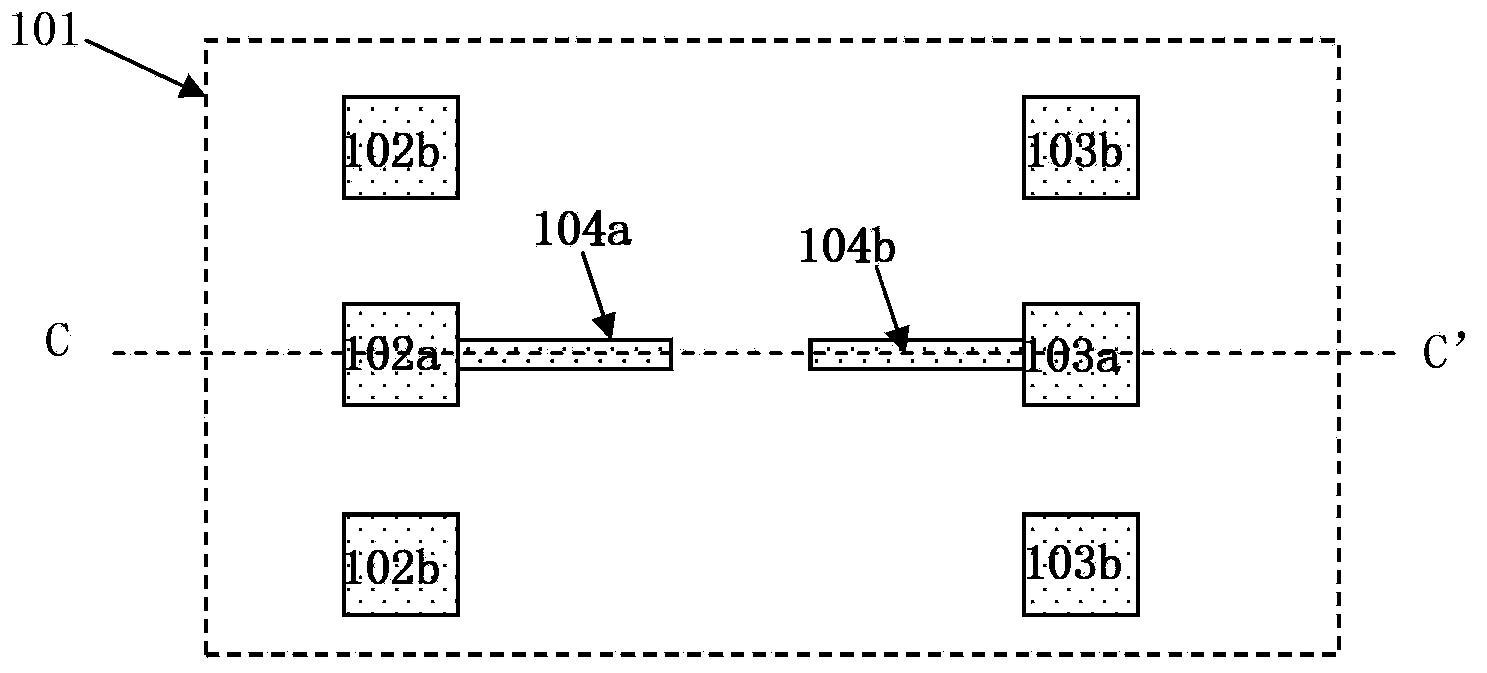

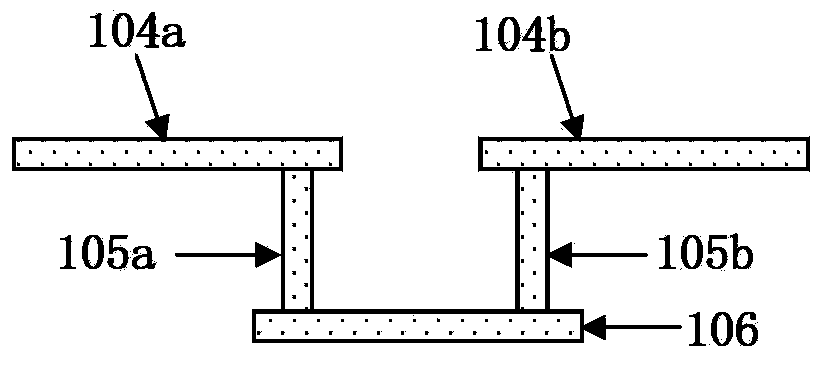

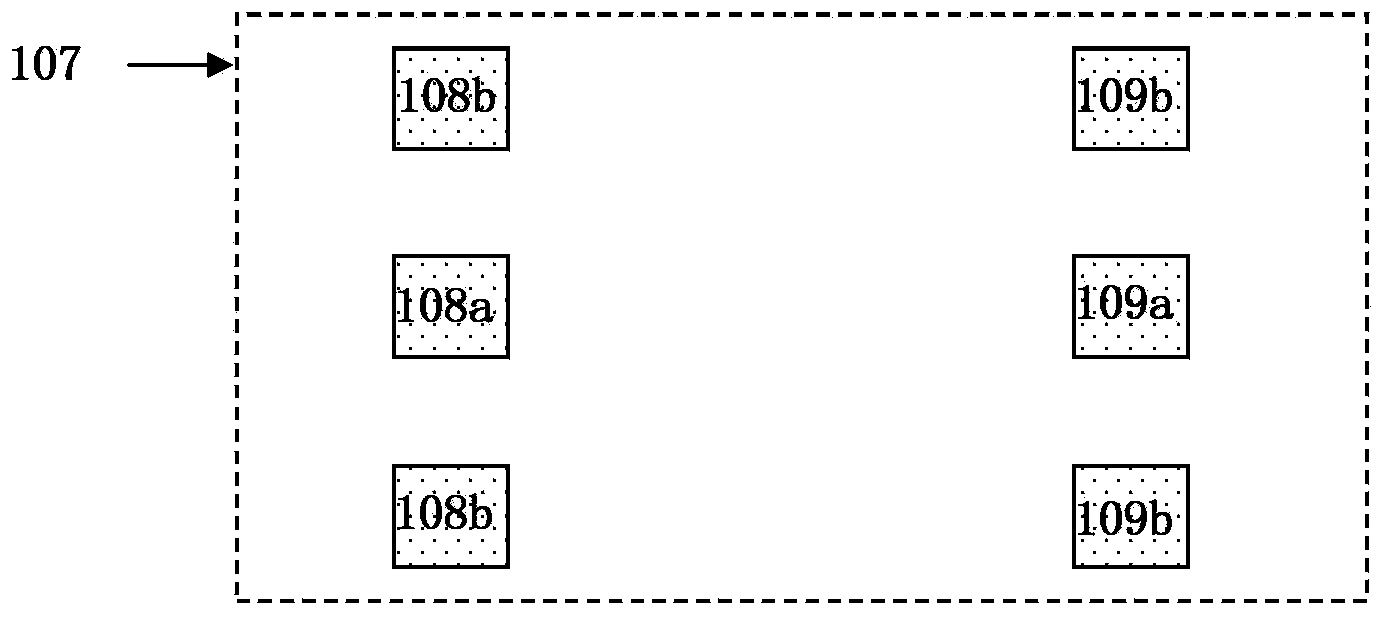

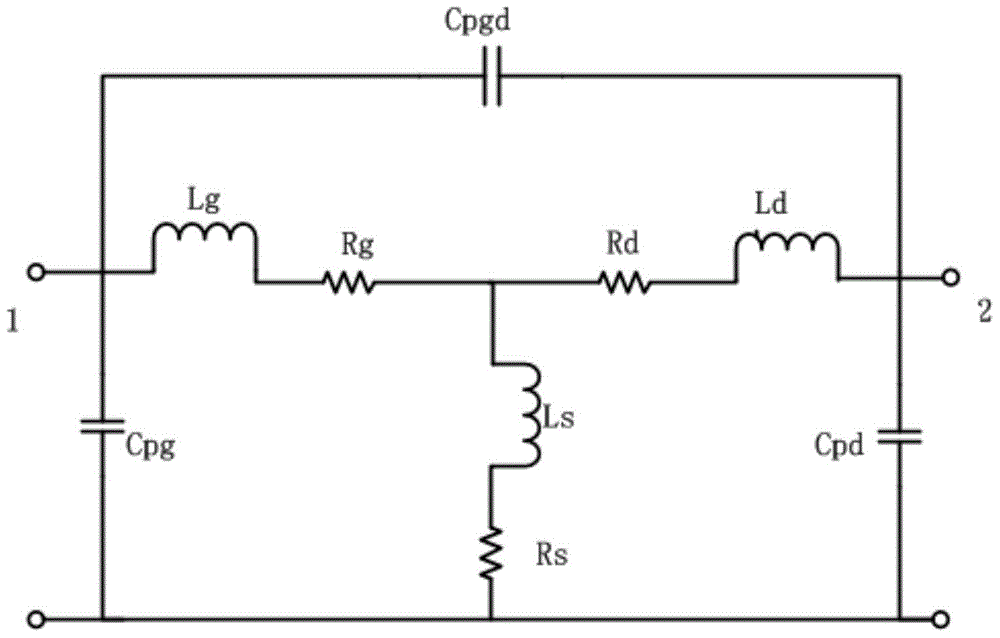

Through si via radio frequency test structure and parasitic extracting method thereof

ActiveCN103839921AReduce areaEliminate errorsSemiconductor/solid-state device detailsSolid-state devicesParasitic extractionRadio frequency

The invention discloses a through si via radio frequency test structure which is formed by a first test structure and a second open circuit de-embedding structure. The first test structure comprises a first port and a second port of a GSG bonding pad structure; signal ends of the first port and the second port are connected in a short circuit manner by a first top metal; a tested through si via is arranged between signal ends of the first port and the second port; the top of the tested through si via is connected with the first top metal; the bottom of tested through si via is connected with a second back metal; and grounding terminals of the first port and the second port are respectively connected with the second back metal through a grounding through si via array. The second open circuit de-embedding structure and the first test structure, after the first top metal and tested through si via are removed, are the same in structure. The invention also discloses a parasitic extracting method of the through si via radio frequency test structure. According to the invention, the accuracy of testing the parasitic resistance and inductance of the through si via can be improved, and the test structure area and the process cost can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Performing via array merging and parasitic extraction

ActiveUS8484599B2CAD circuit designSoftware simulation/interpretation/emulationArray data structureParasitic extraction

Systems and techniques for performing parasitic extraction on a via array are described. If the via array is a single row or column via array, the system identifies a first via and a last via in the via array, and merges a set of vias between the first via and the last via into a center via. If the via array is a M×N (M≧2, N≧2) via array, the system merges the vias as follows: the first row and the last row of vias in the via array into a first row via and a last row via, respectively; the first column and the last column of vias in the via array into a first column via and a last column via, respectively; and a set of vias between the first and last rows and the first and last columns into a center via.

Owner:SYNOPSYS INC

Method for improving accuracy of parasitics extraction considering sub-wavelength lithography effects

ActiveUS8438505B2Computer aided designTotal factory controlElectrical performanceParasitic extraction

The present disclosure involves a method. The method includes decomposing a layout of a circuit into a plurality of patterns. The method includes generating a plurality of contours to represent the plurality of patterns after the patterns have been subjected to a manufacturing process. The method includes generating a plurality of polygons that approximate geometries of the contours, respectively. The method includes associating each of the polygons with a respective one of a plurality of pattern elements in a pattern library, wherein the pattern elements each include a shape that resembles the associated polygon and electrical parameters extracted from the shape. The method includes calculating electrical performance of the circuit based on the pattern elements associated with the polygons.

Owner:TAIWAN SEMICON MFG CO LTD +1

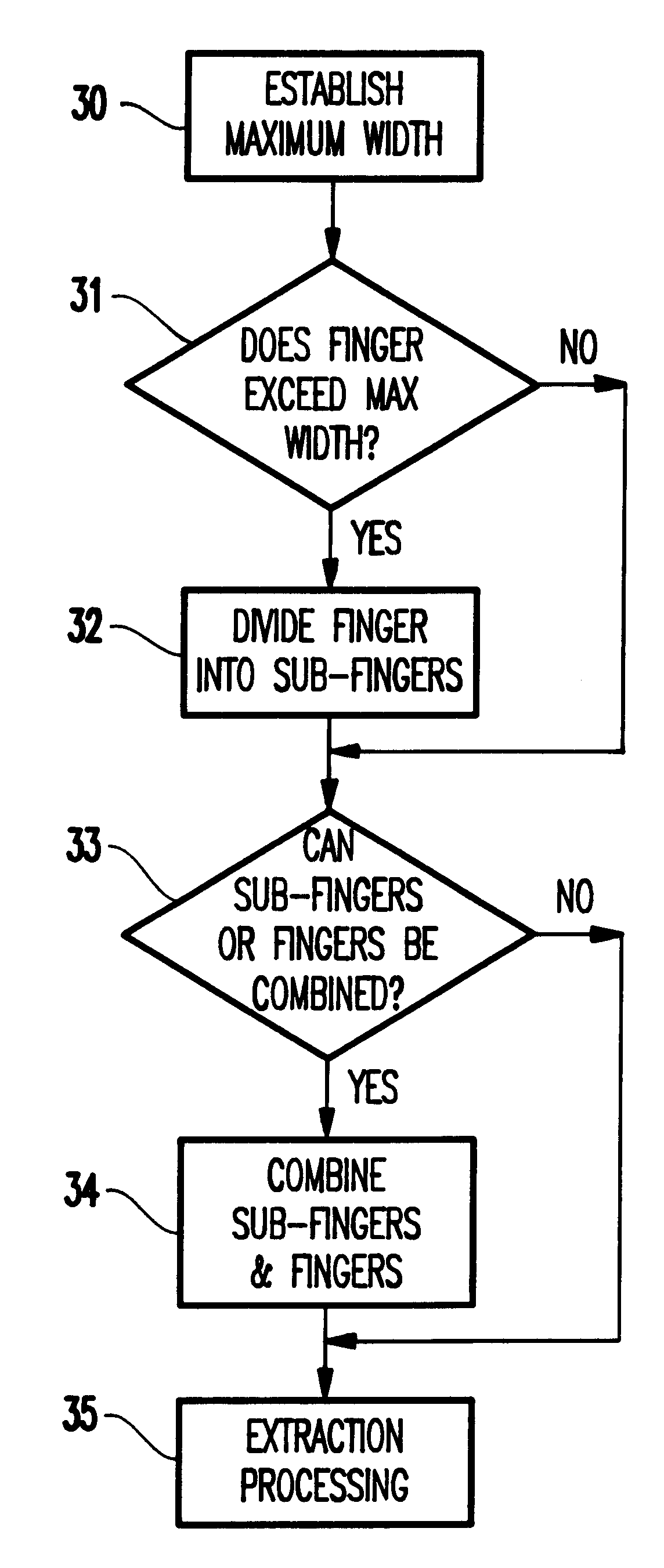

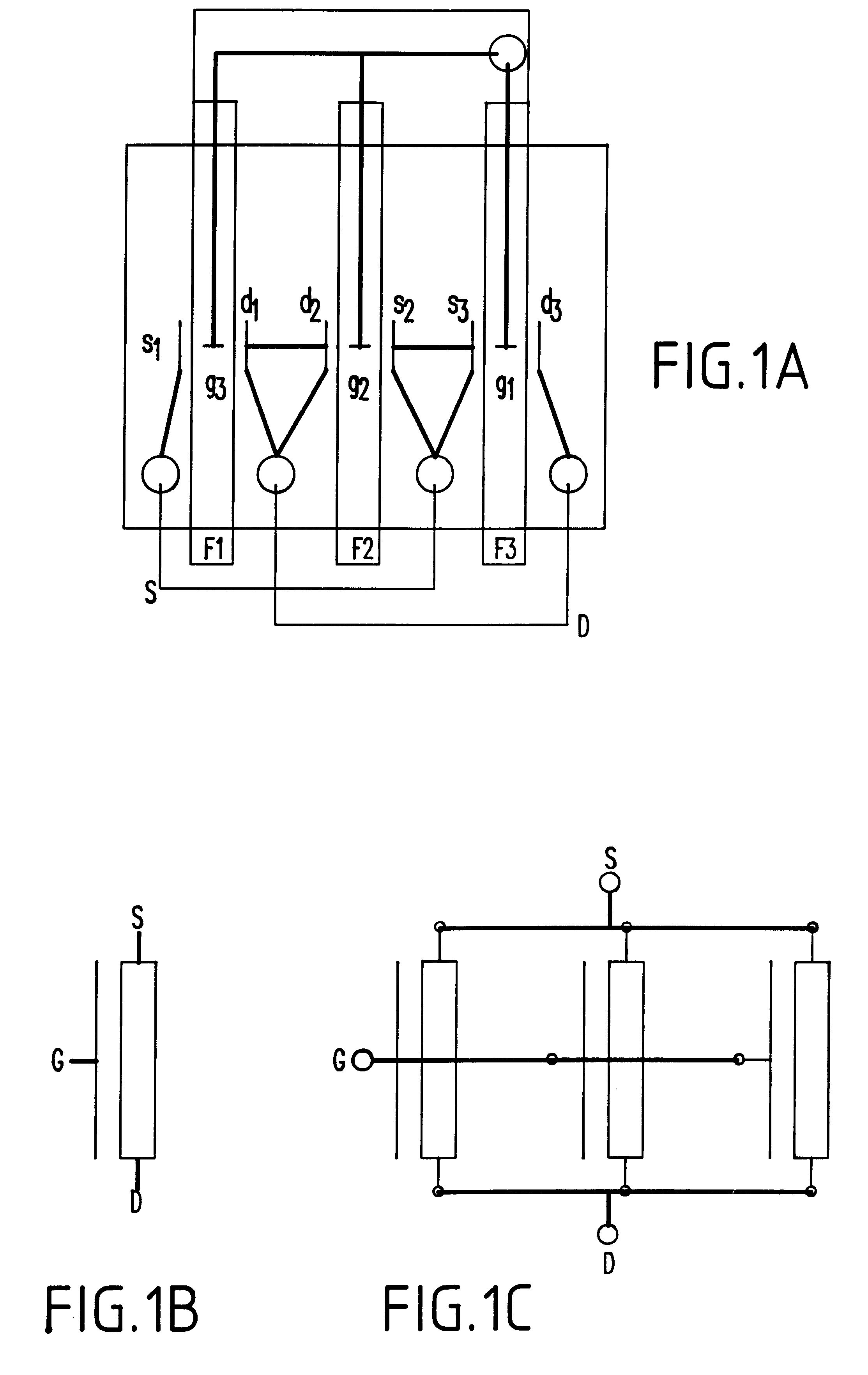

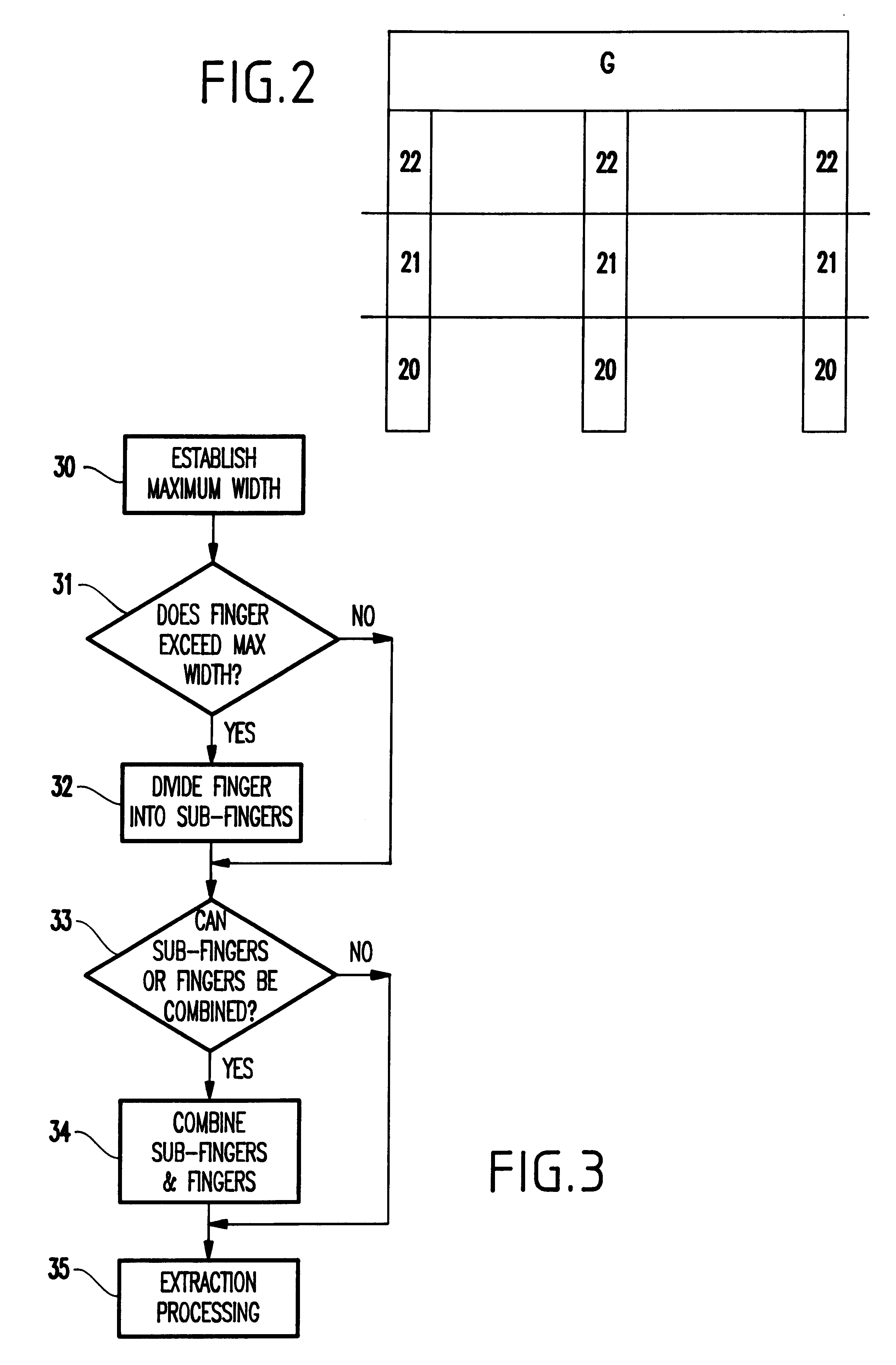

Method of performing parasitic extraction for a multi-fingered transistor

InactiveUS6519752B1Computer aided designSpecial data processing applicationsEngineeringParasitic extraction

A method and structure for performing parasitic extraction for a multi-fingered device comprising of establishing a maximum processing width of a finger of the device, dividing fingers of the device that exceed the maximum width into sub-fingers, determining whether ones of the fingers and the sub-fingers have similar characteristics, combining ones of the fingers and the sub-fingers that have similar characteristics into combined fingers, and extracting parasitic values from the fingers, the sub-fingers and the combined fingers.

Owner:IBM CORP

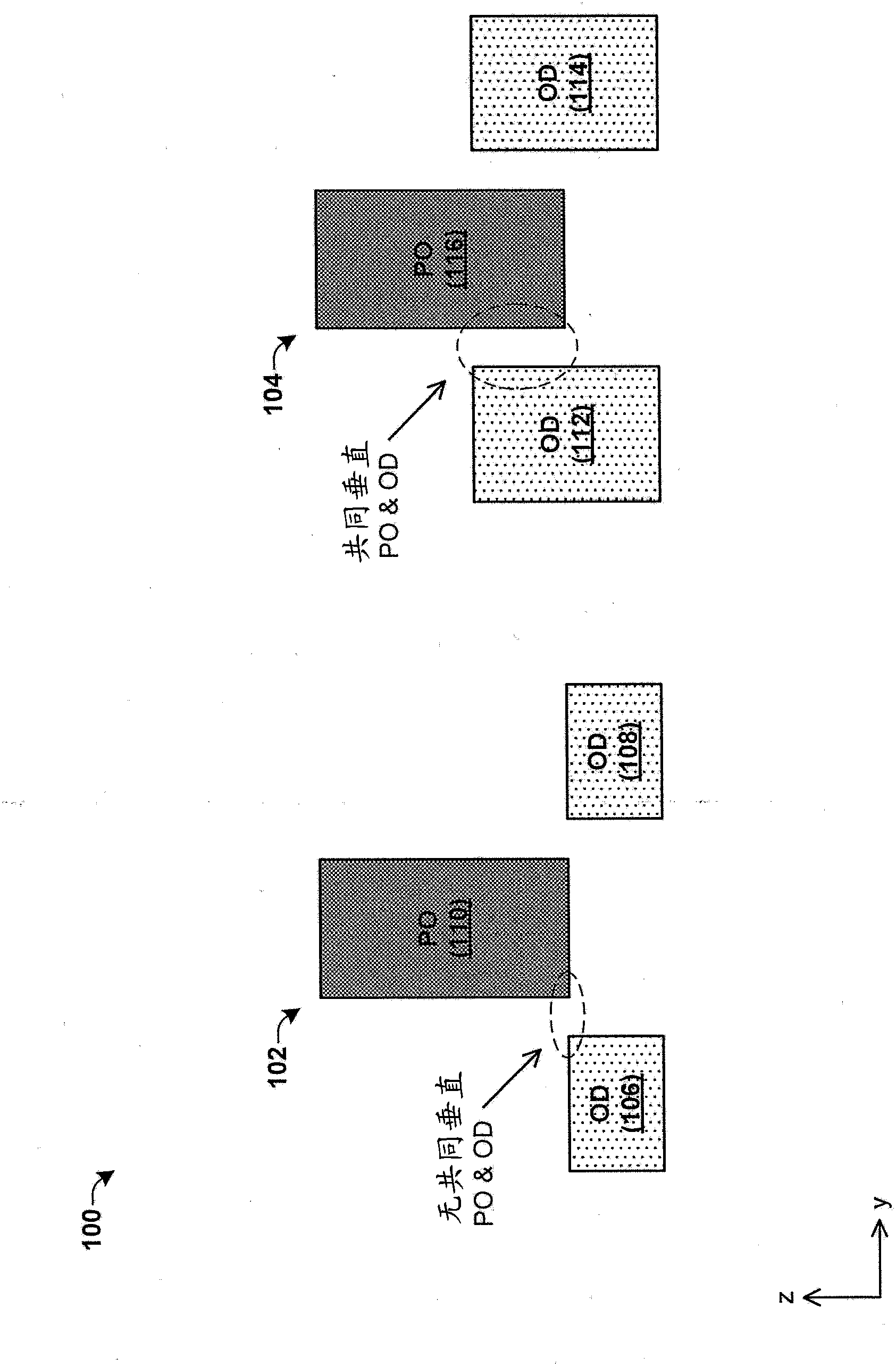

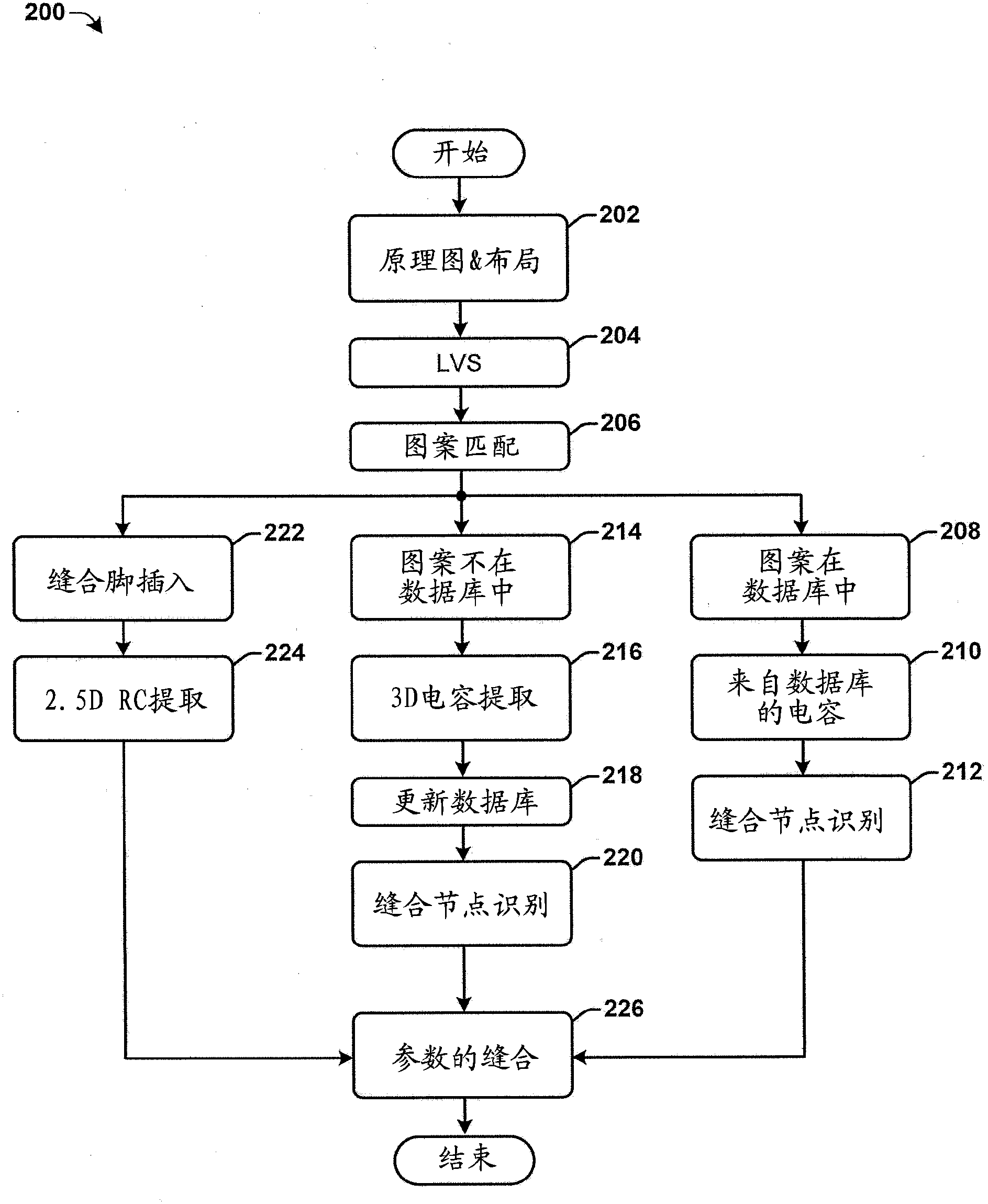

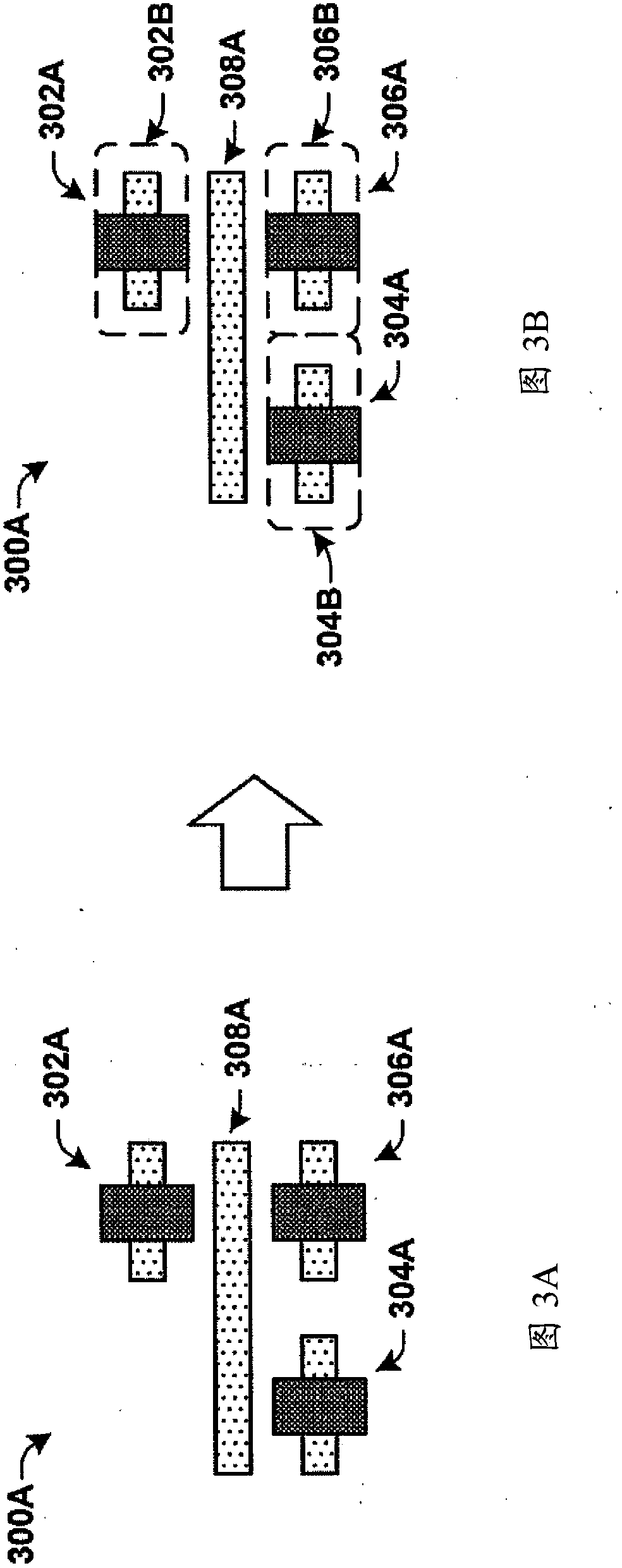

Pattern Matching Based Parasitic Extraction With Pattern Reuse

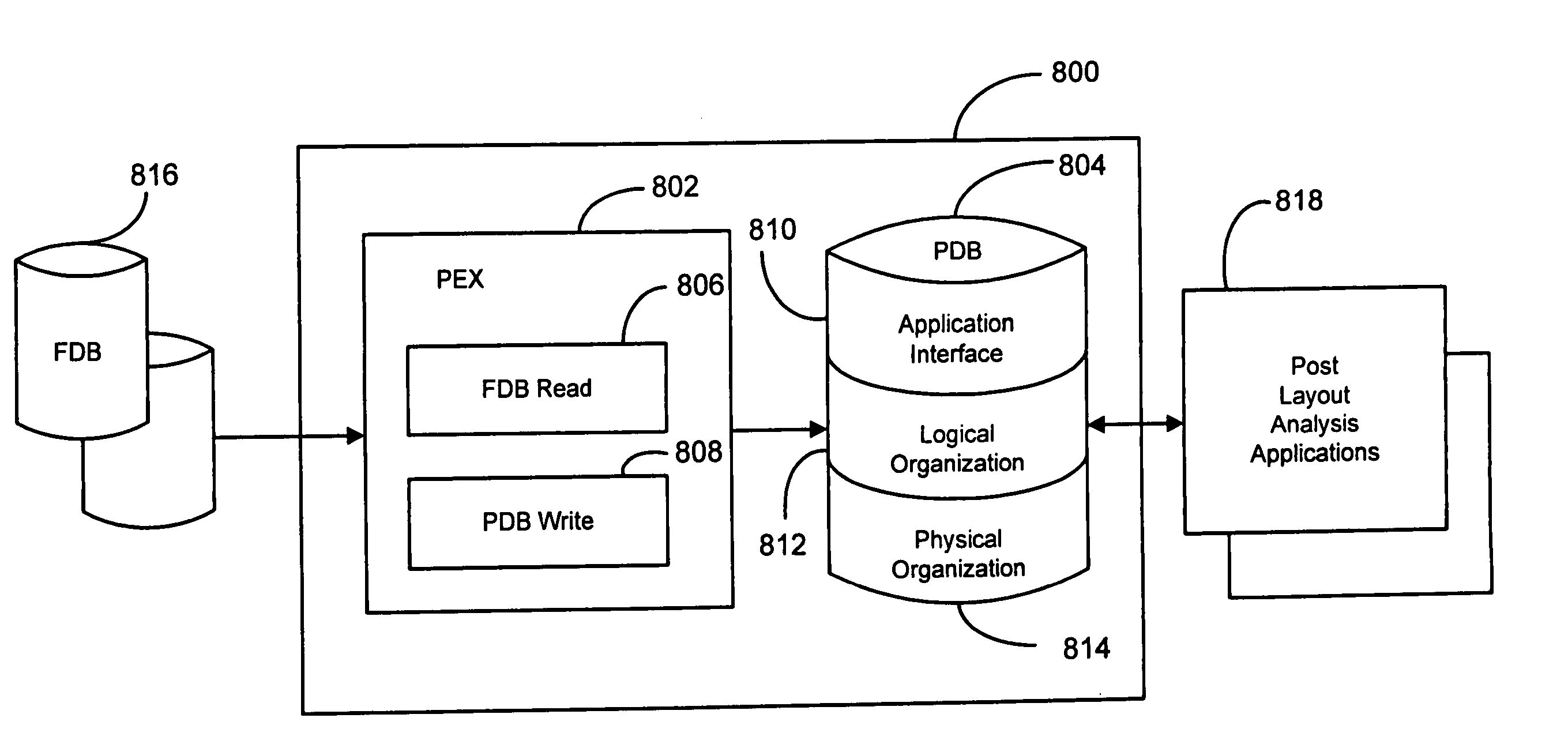

The present disclosure relates to a method and apparatus for accurate RC extraction. A pattern database is configured to store layout patterns and their associated 3D extraction parameters. A pattern-matching tool is configured to partition a design into a plurality of patterns, and to search the pattern database for a respective pattern and associated 3D extraction parameters. If the respective pattern is already stored in the pattern database, then the associated 3D extraction parameters stored in the database are assigned to the respective pattern without the need to extract the respective pattern. If the respective pattern is not stored in the pattern database, then the extraction tool extracts the pattern and stores its associated 3D extraction parameters in the pattern database for future use. In this manner a respective pattern is extracted only once for a given design or plurality of designs. Moreover, the extraction result may be applied multiple times for a given design simultaneously, speeding up computation time. The extraction result may also be applied to a plurality of designs simultaneously.

Owner:TAIWAN SEMICON MFG CO LTD

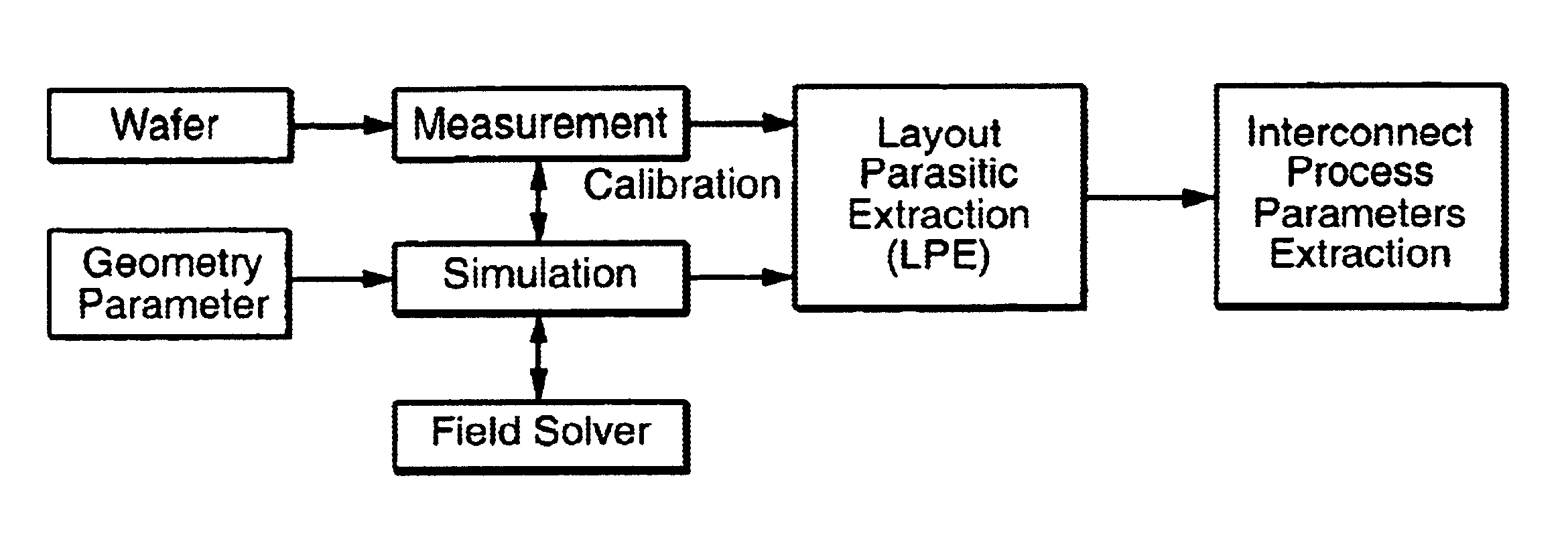

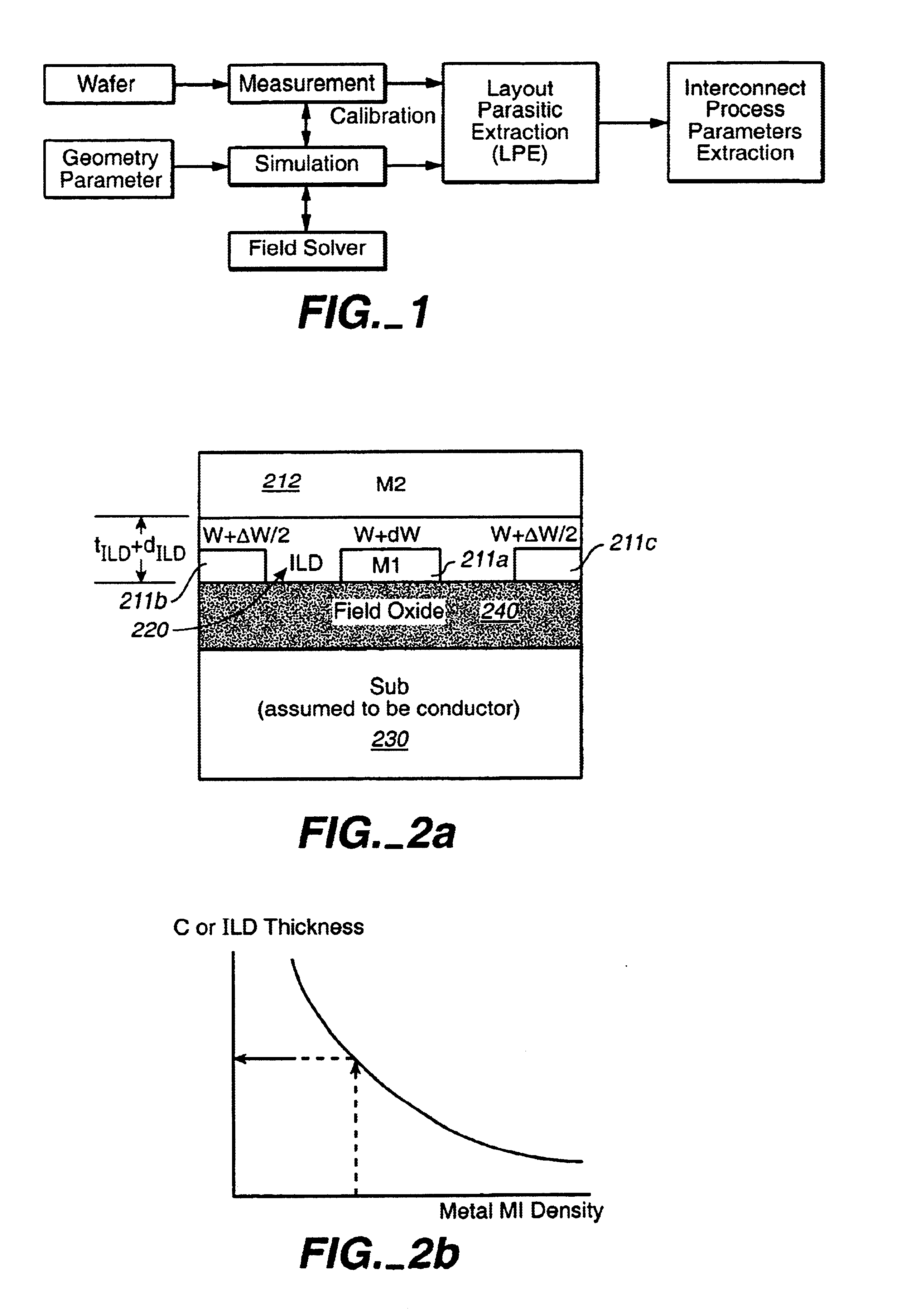

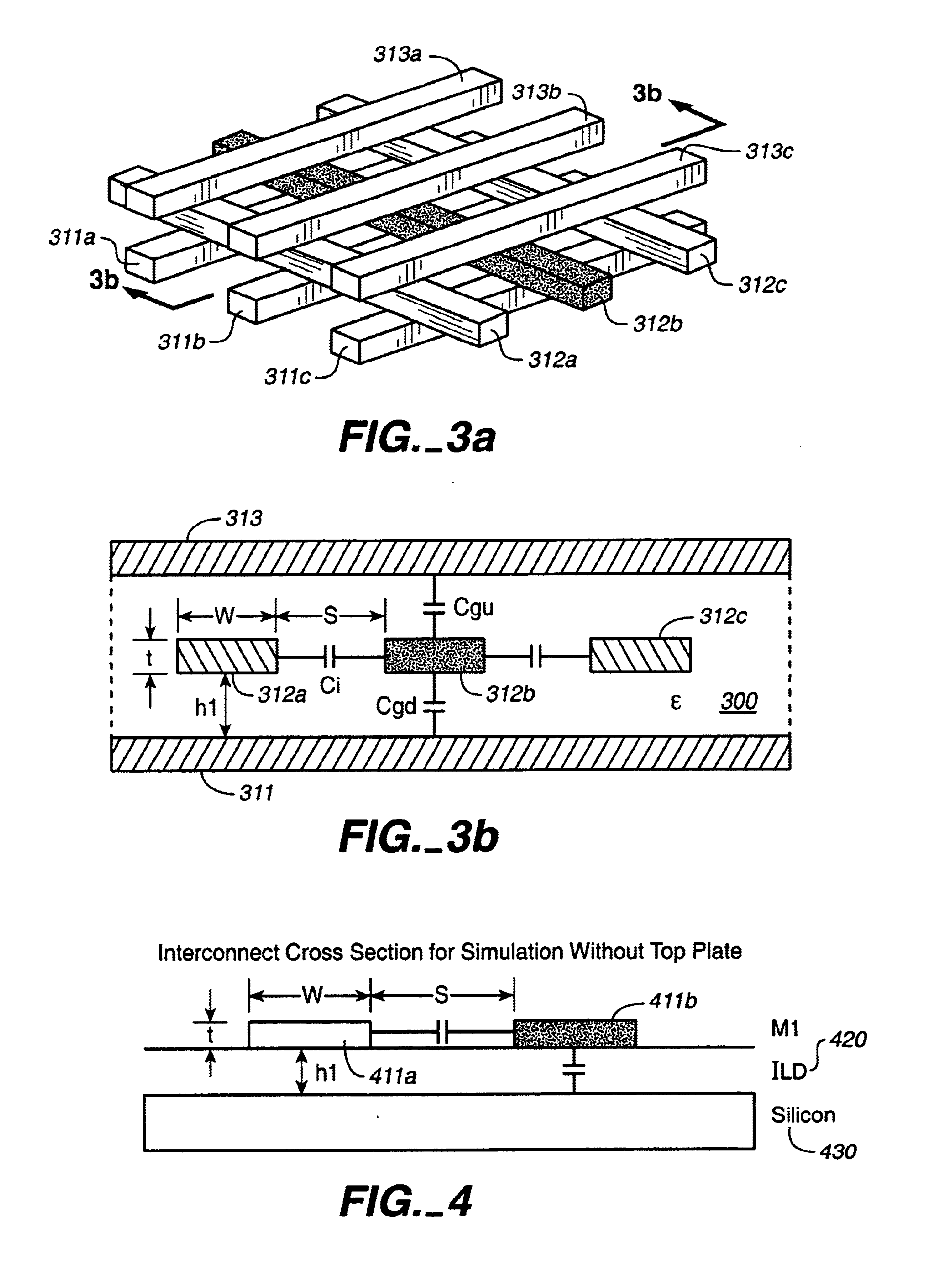

Optimization methods for on-chip interconnect geometries suitable for ultra deep sub-micron processes

InactiveUS6887791B2Semiconductor/solid-state device detailsSolid-state devicesPhysical verificationParasitic extraction

The present invention presents optimization methods for interconnect geometries that readily extend to the UDSM region for determining on-chip interconnect process parameters more realistically and accurately than in the prior art. A method for reconstruction flow that re-assembles each of a number of optimized structures into one optimized interconnect process file, such as a process technology file for extractors. This optimized process technology file can use not only extracted interconnect process parameters but also the input of LPE (Layout Parasitic Extraction) tools in physical verification stage.

Owner:CADENCE DESIGN SYST INC

Electrostatic Damage Protection Circuitry Verification

InactiveUS20100185995A1EliminatedEfficient analysisComputer aided designSoftware simulation/interpretation/emulationParasitic extraction

Techniques for efficiently determining whether an interconnect line has an impedance component value below a maximum specified value. A specified maximum impedance component value is used to limit the number of interconnect lines that are analyzed by a parasitic extraction analysis process. An analysis window is created based upon the characteristics of the interconnect lines and the specified maximum impedance component value. The size of the window corresponds to the minimum length of the interconnect line that would have the specified maximum impedance component value. Once the analysis window has been created, the interconnect lines are examined to determine if any of them reaches to (or beyond) the analysis window, whereby interconnect lines that exceed the specified maximum impedance component value can be identified. If there are any remaining interconnect lines that have not been determined to exceed the specified maximum impedance component value through the use of the analysis window, then the impedance component values of these remaining interconnect lines can be specifically determined using a parasitic extraction process.

Owner:PIKUS FEDOR G +2

Method and apparatus for rule-based automatic layout parasitic extraction in a multi-technology environment

InactiveUS8650518B2Knowledge representationComputer aided designParasitic extractionLayout extraction

A system for extracting a layout from an object in a fabric includes means for providing fabric data to a rule-based layout extraction engine; means for maintaining a layout extraction rule to select a layout object from the fabric data; means for maintaining a binding rule to bind the layout object to a solver; means for maintaining a boundary rule to specify a boundary condition for a solver; and means for executing the solver on the layout object to generate a model of the object.

Owner:CADENCE DESIGN SYST INC

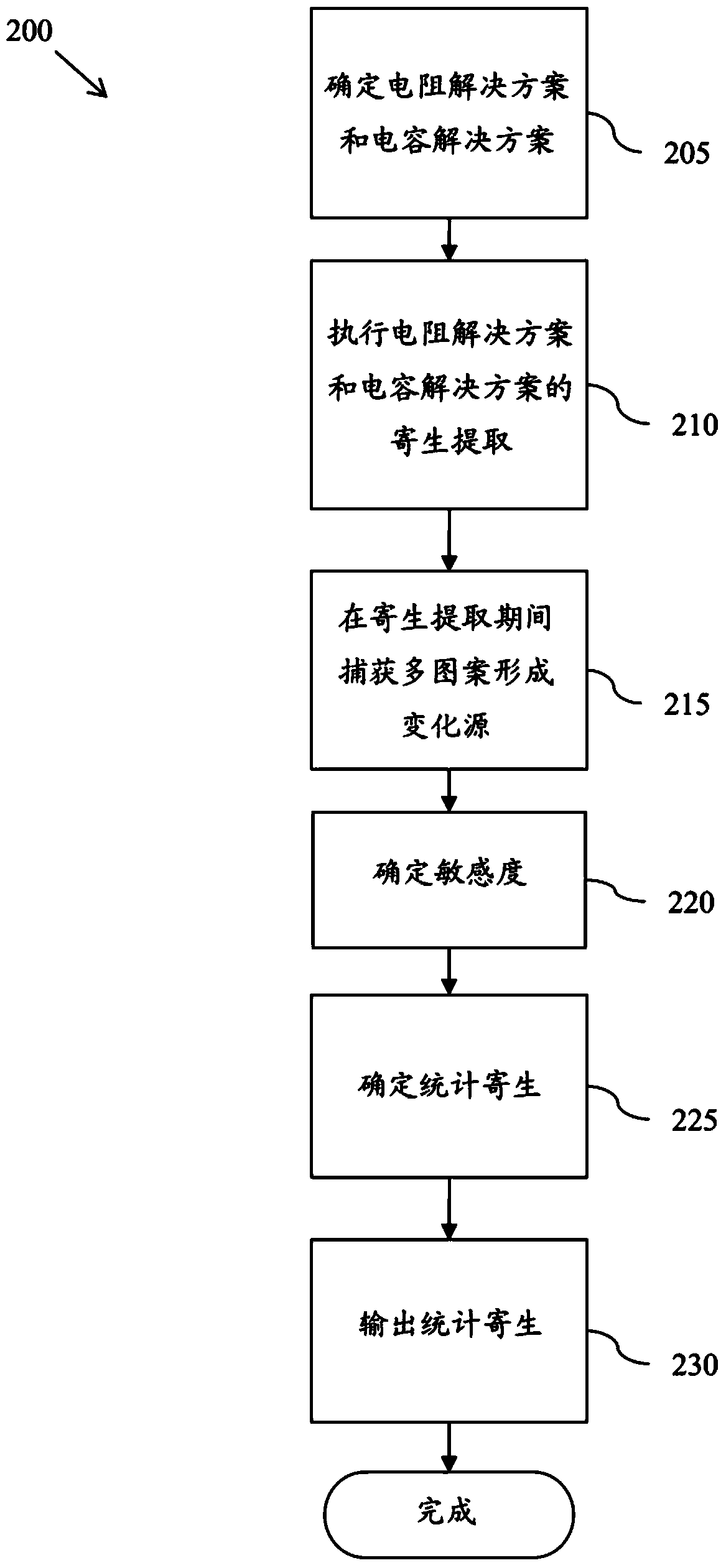

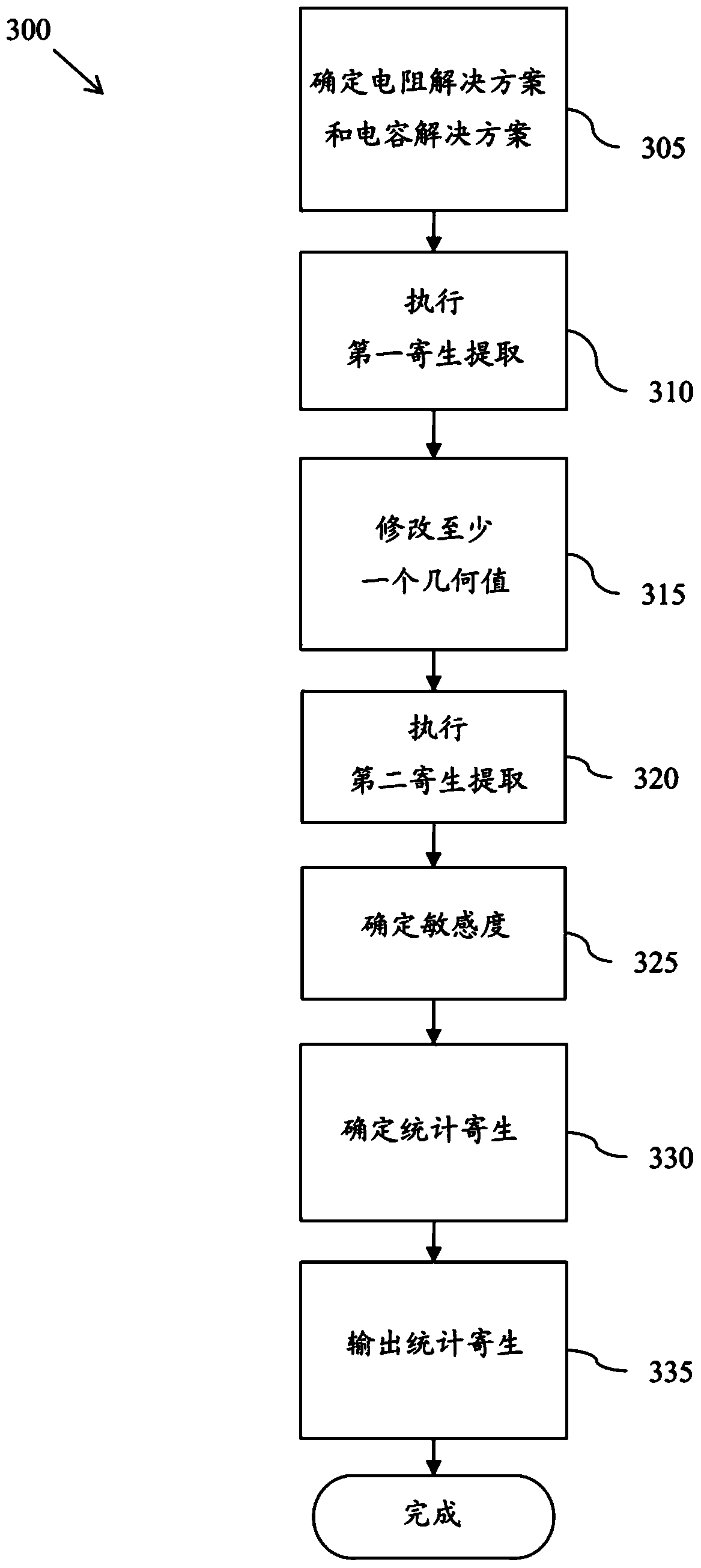

Parasitic extraction in an integrated circuit with multi-patterning requirements

InactiveCN103793548AComputer aided designSpecial data processing applicationsCapacitanceElectrical resistance and conductance

Systems and methods are provided for extracting parasitics in a design of an integrated circuit with multi-patterning requirements. The method includes determining resistance solutions and capacitance solutions. The method further includes performing parasitic extraction of the resistance solutions and the capacitance solutions to generate mean values for the resistance solutions and the capacitance solutions. The method further includes capturing a multi-patterning source of variation for each of the resistance solutions and the capacitance solutions during the parasitic extraction. The method further includes determining a sensitivity for each captured source of variation to a respective vector of parameters. The method further includes determining statistical parasitics by multiplying each of the resistance solutions and the capacitance solutions by the determined sensitivity for each respective captured source of variation. The method further includes generating as output the statistical parasitics in at least one of a vector form and a collapsed reduced vector form.

Owner:GLOBALFOUNDRIES INC

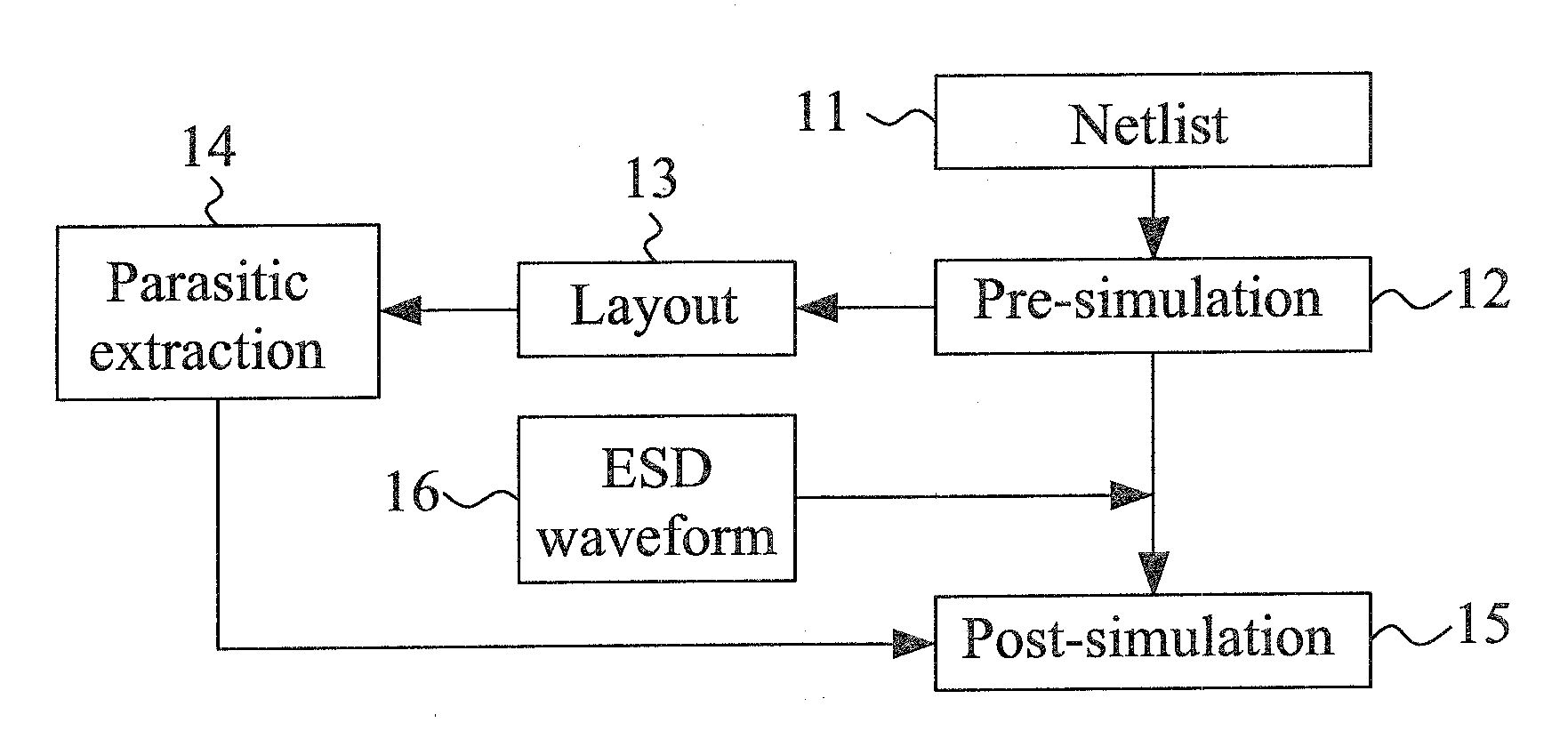

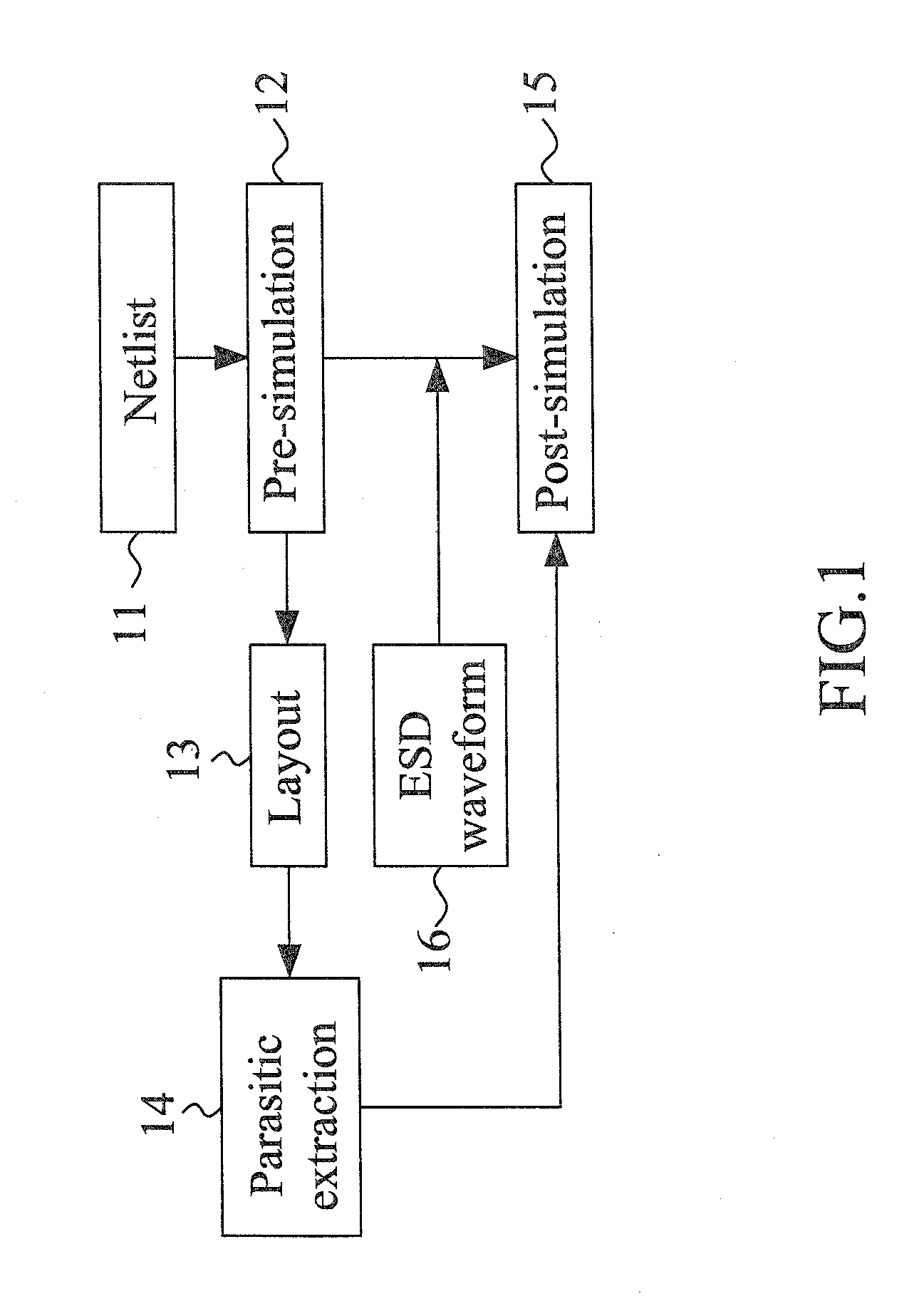

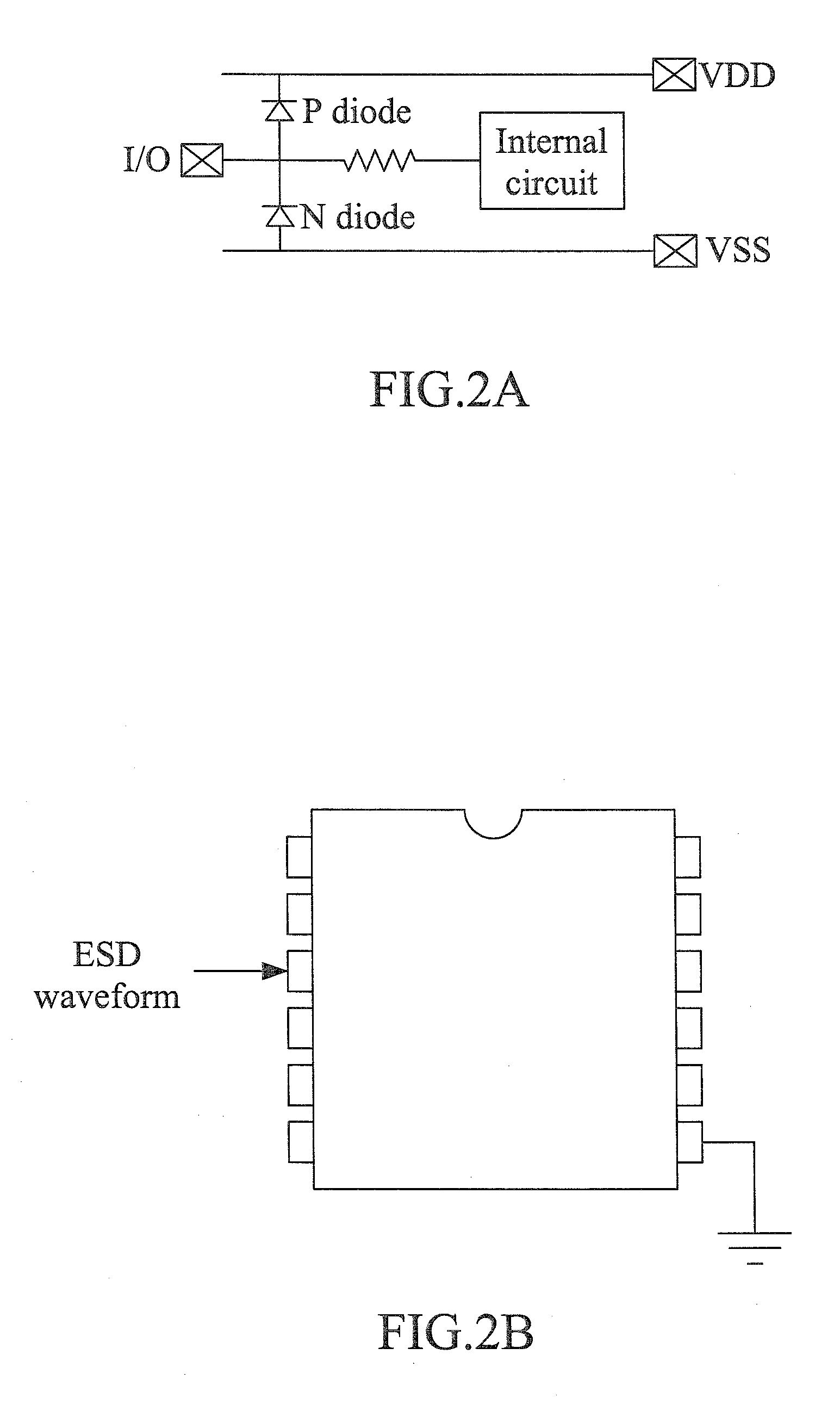

Method of simulating an ESD circuit layout

InactiveUS20130042218A1Easy to identifyAvoid faultDetecting faulty computer hardwareCAD circuit designParasitic extractionEngineering

A method of simulating an electrostatic discharge (ESD) circuit layout is disclosed. A netlist of an electronic circuit is pre-simulated. A circuit layout, including an ESD circuit layout, is accordingly generated. Parasitic is extracted according to the generated circuit layout. The ESD circuit layout is post-simulated according to an ESD waveform and a result of the parasitic extraction.

Owner:HIMAX TECH LTD

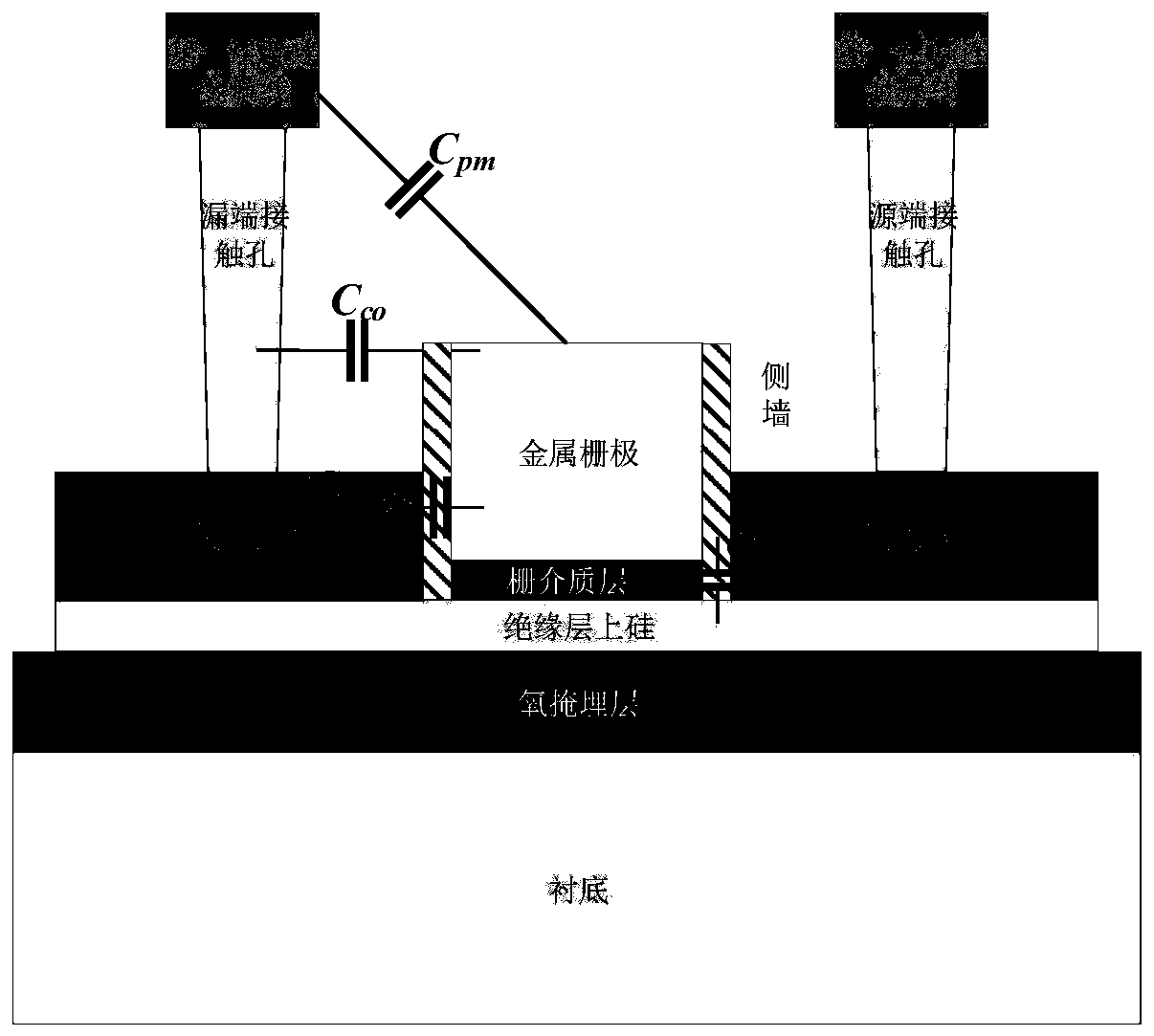

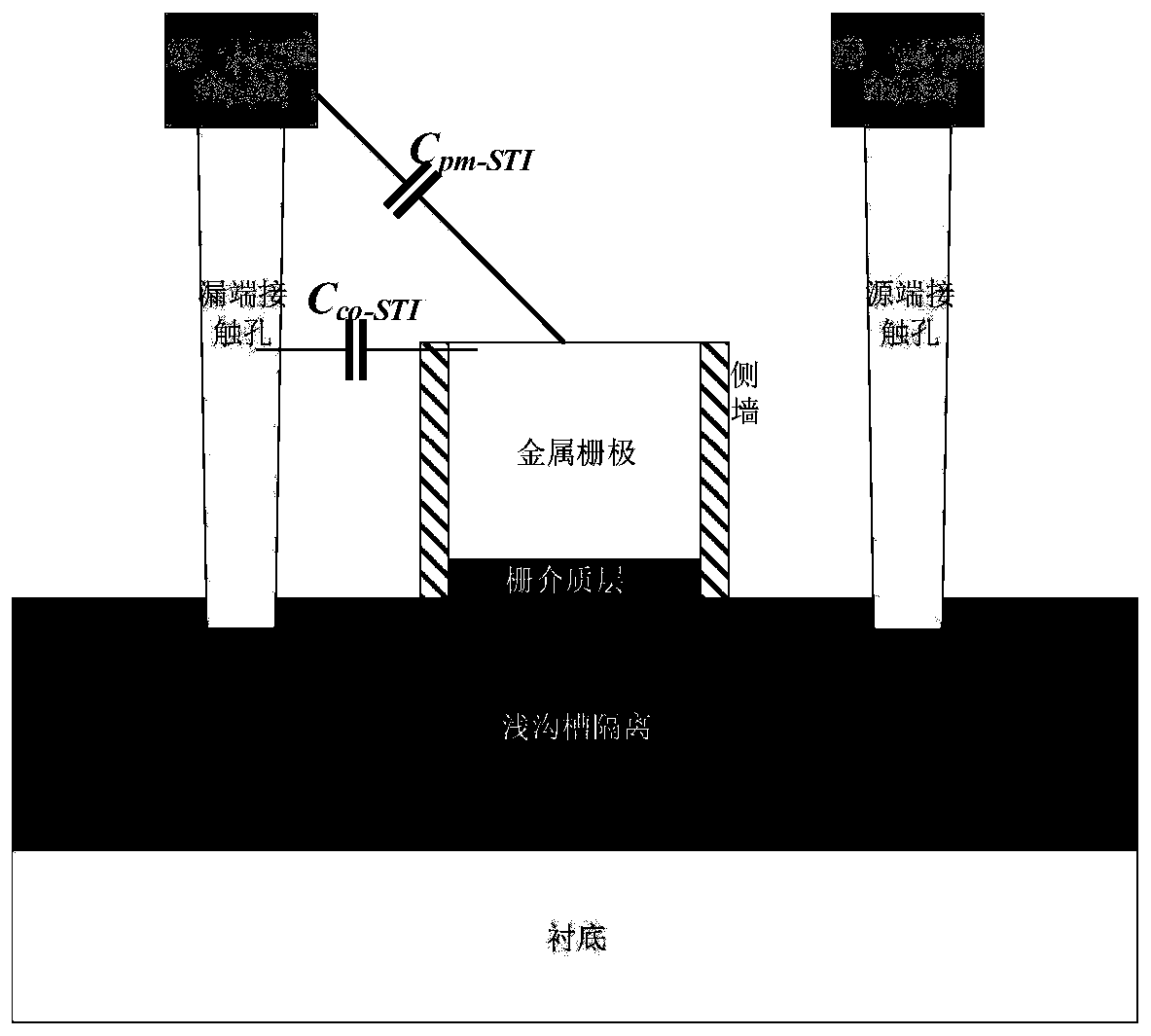

Gate-around parasitic interconnection capacitance extraction method for source-drain raised FDSOI device

ActiveCN110416104AAvoid simulation inaccuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsParasitic capacitanceInterconnection

The invention discloses a gate-around parasitic interconnection capacitance extraction method for a source-drain raised FDSOI device. According to the method, the de-embedding structure of the source-drain contact hole in the shallow trench isolation region (CT-on-STI for short) can be utilized to remove the influence of active region capacitance Cf and gate and source-drain raised region parasitic capacitance Cp-RSD on the extraction of gate-around parasitic interconnection capacitance and source-drain contact hole parasitic capacitance Cco and the parasitic capacitance Cpm of the first layermetal on the gate and source-drain contact hole, and the values of the gate-around parasitic interconnection capacitance Cco and Cpm of the source-drain raised FDSOI device are accurately obtained with the help of a three-dimensional finite element simulation tool through the structure of the source-drain contact hole in the raised source-drain region (CT-on-RSD for short) so that the model of the gate-around parasitic interconnection capacitance is accurately established in a map parasitic extraction tool and the phenomenon of repeated extraction of the interconnection capacitance Cco and the Cpm in the process of extracting the gate-around parasitic capacitance can be avoided.

Owner:EAST CHINA NORMAL UNIV +1

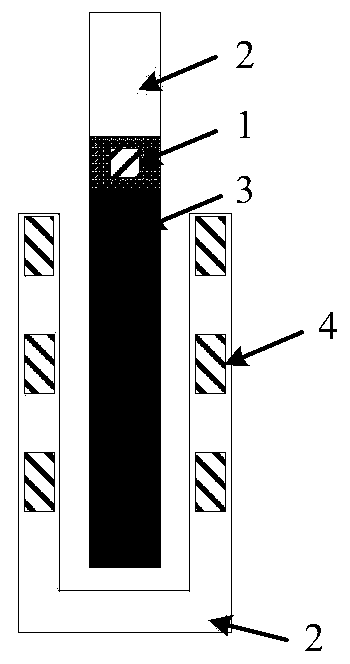

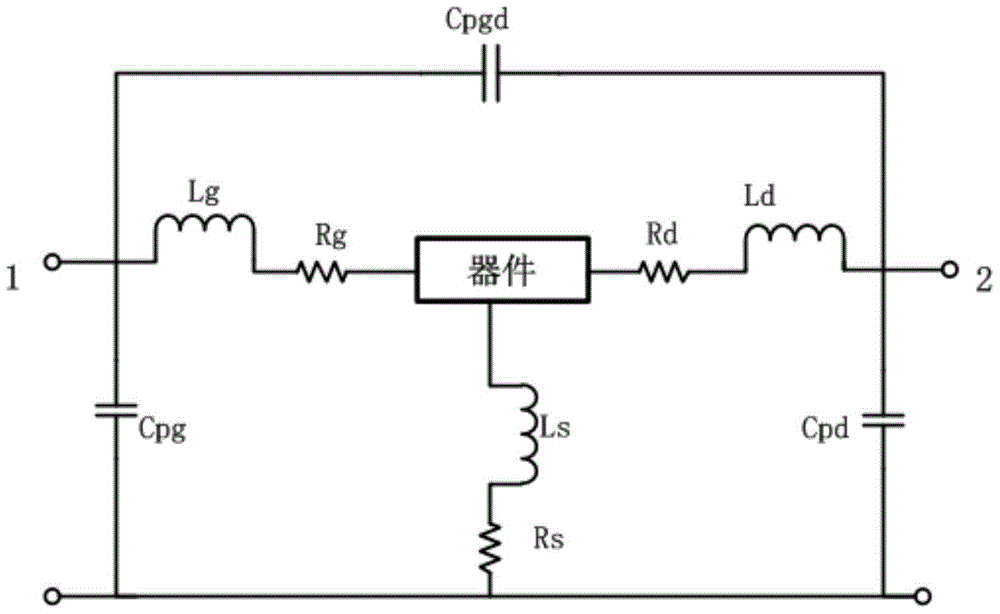

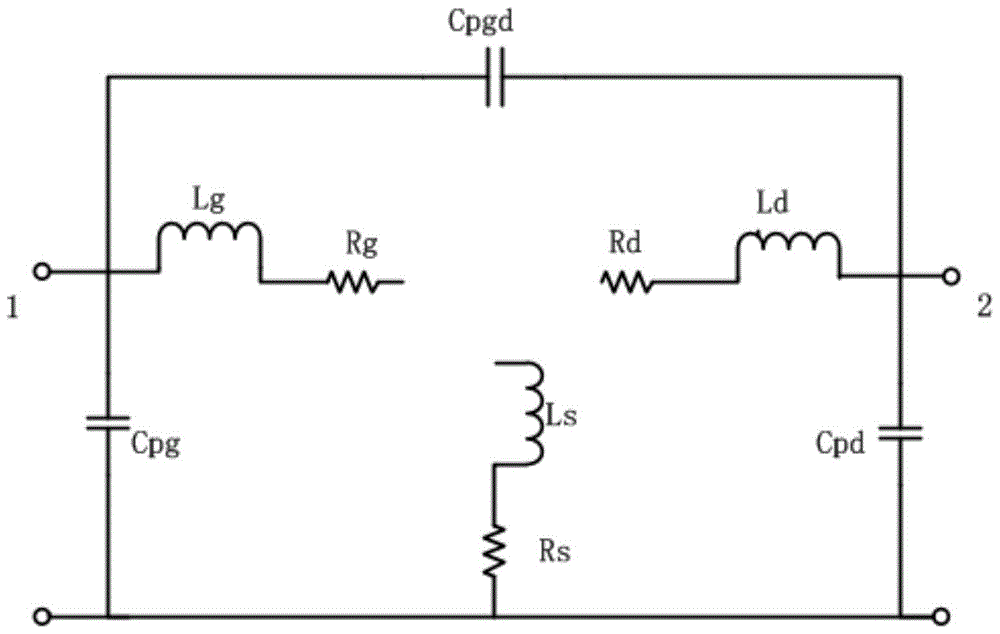

Method for extracting device equivalent circuit model parameters and pad parasitic parameters extraction method

ActiveCN104298837BHigh precisionHigh speedSpecial data processing applicationsElectrical resistance and conductanceParasitic capacitance

The invention discloses a method for extracting parameters of an equivalent circuit model of a device, which mainly solves the problems of complicated extraction process and inaccurate extraction results in the prior art. The parasitic parameter extraction method is to divide the short-circuit pad equivalent circuit stripped of parasitic capacitance into independent networks for further analysis, and simultaneously extract parasitic resistance and parasitic inductance parameters. The invention also discloses a method for extracting parasitic parameters of pads, which uses the above-mentioned equivalent circuit parameter extraction method. The simulation results show that the results of the parasitic parameters extracted by the present invention are more consistent with the scattered parameters of the actual device test results, and the extracted parameters are more accurate and fast.

Owner:SOUTHEAST UNIV

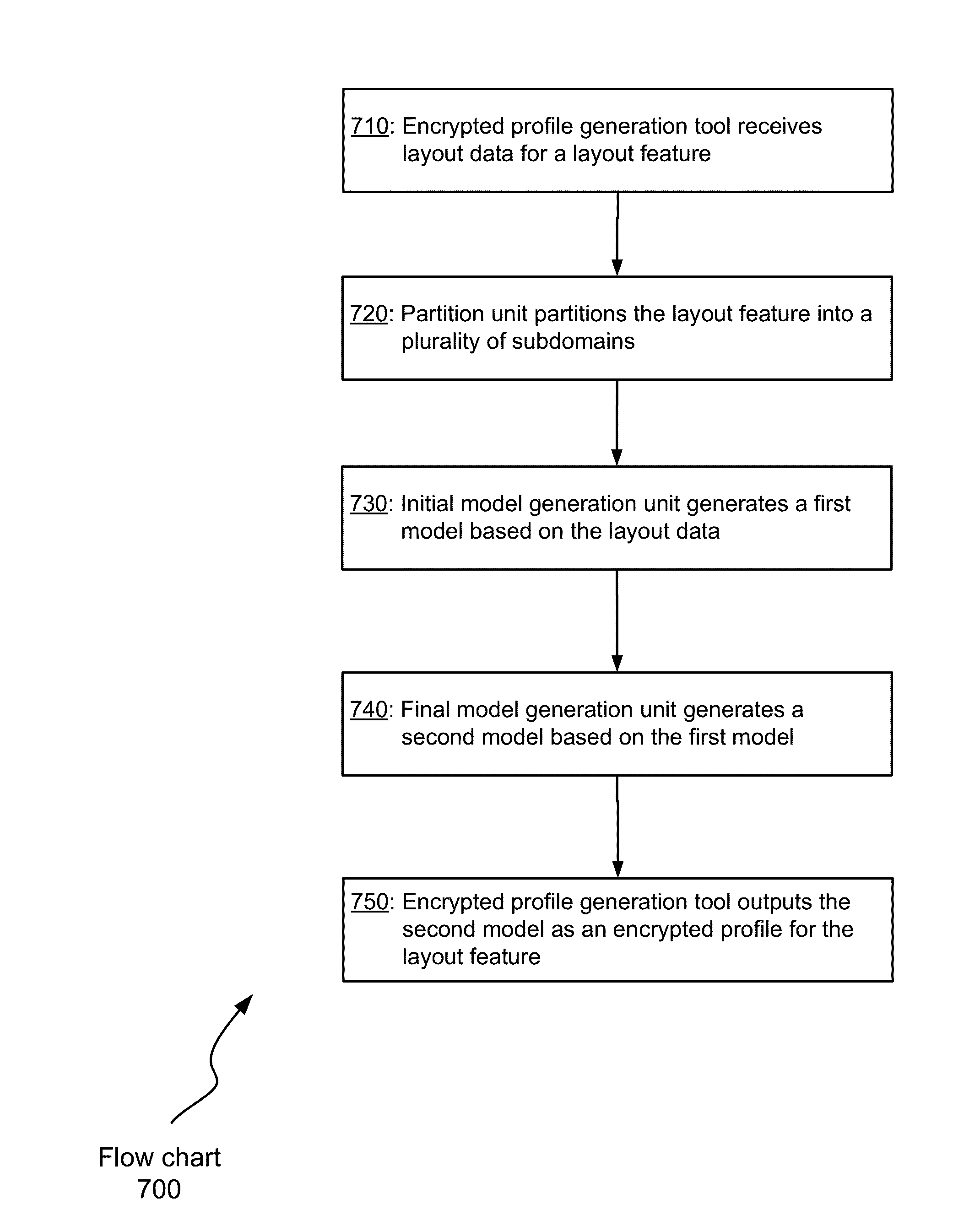

Encrypted profiles for parasitic extraction

Aspects of the invention relate to techniques for generating encrypted profiles for layout features. According to various implementations of the invention, a layout feature is partitioned into subdomains. The subdomains are associated with boundary nodes and internal nodes. Based on layout design and process profile data for the layout feature, a first electric parameter relationship is determined for the boundary nodes and the internal nodes. An encrypted profile for the layout feature is then generated by converting the first electric parameter relationship into a second electric parameter relationship involving the boundary nodes. The encrypted profile may be used for extracting parasitic parameters associated with the layout feature.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com