Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

155 results about "Hardware reset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A hardware reset or hard reset of a computer system is a hardware operation that re-initializes the core hardware components of the system, thus ending all current software operations in the system. This is typically, but not always, followed by booting of the system into firmware that re-initializes the rest of the system, and restarts the operating system.

Methods, systems and computer program products for secure firmware updates

ActiveUS7069452B1Avoid accessReduce stepsDigital computer detailsUnauthorized memory use protectionData storeControl equipment

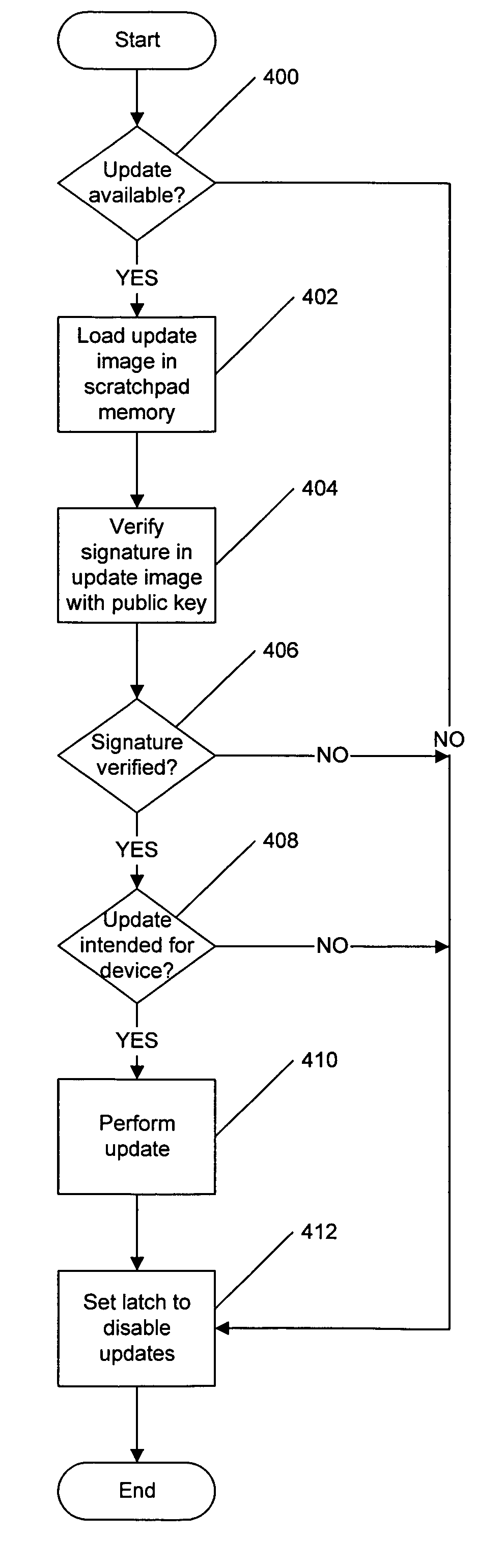

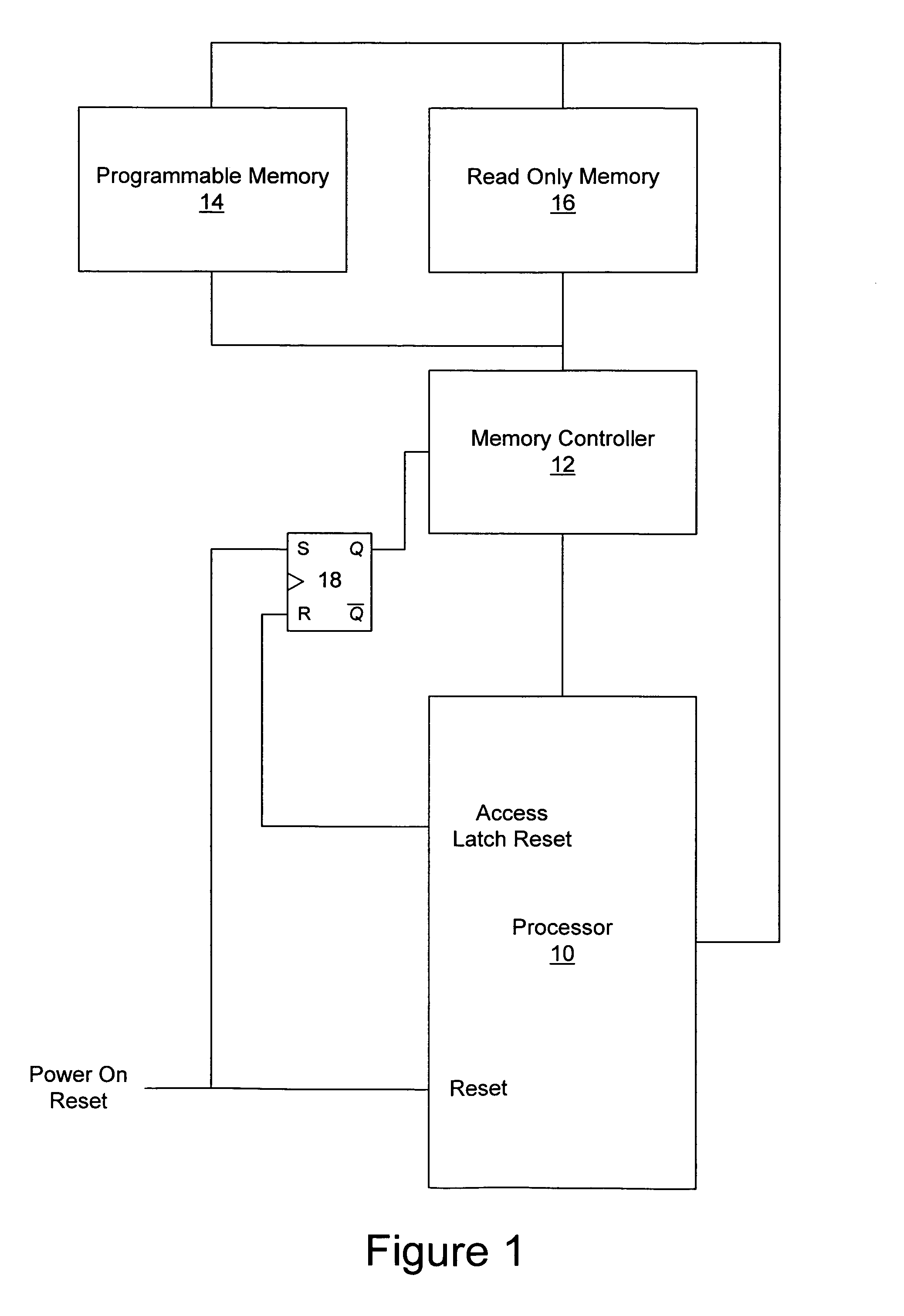

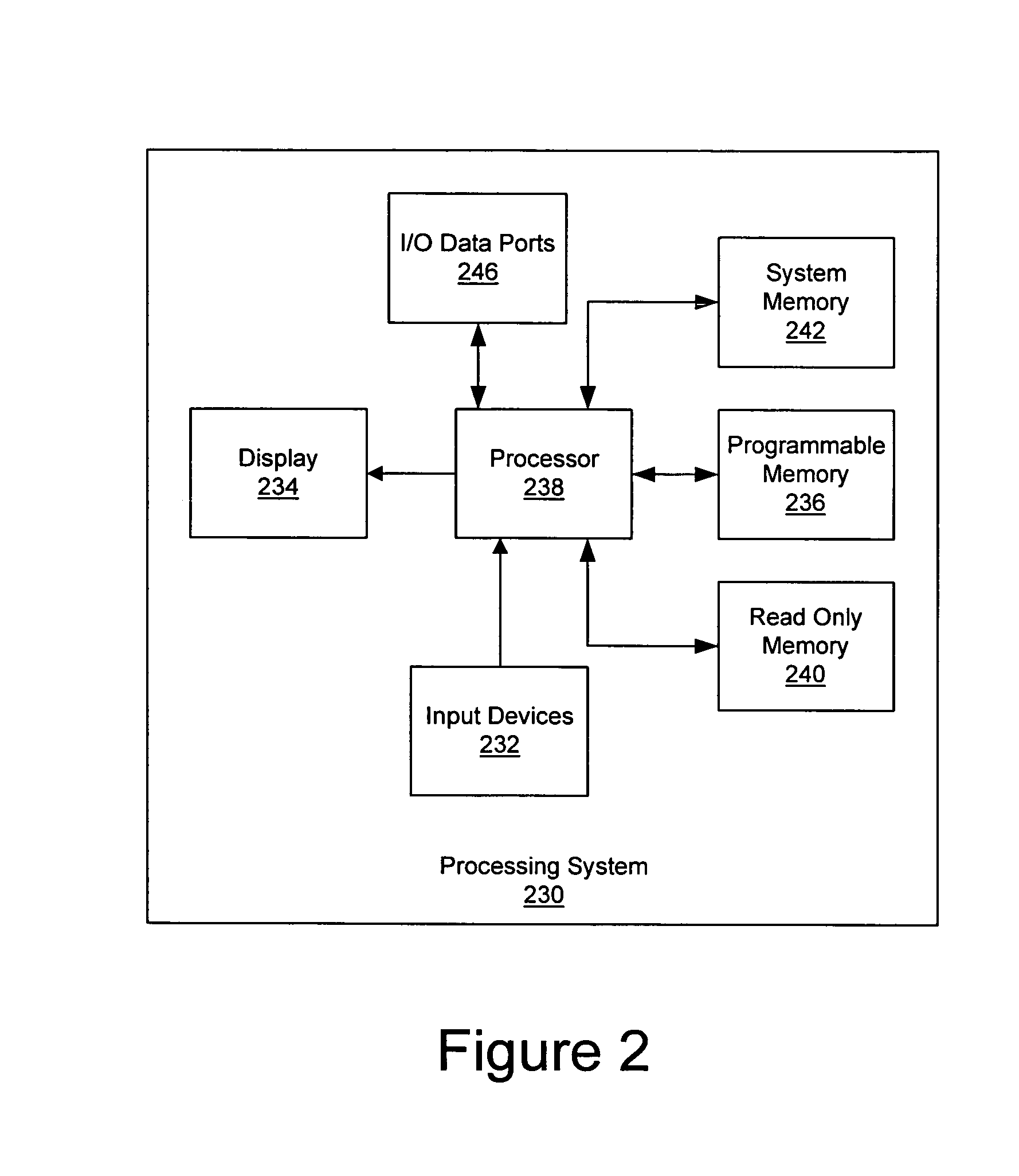

Methods, systems and computer program products which provide secure updates of firmware (i.e. data stored in a programmable memory device of a processing system) are disclosed. Updates of a programmable memory of a device may be controlled by providing an update window of finite duration during which the programmable memory may be updated. Access to the programmable memory may be based on the state of an access latch. The access latch may be set to allow access after a hardware reset of the device. An update control program may be executed to control access to the programmable memory and the latch reset to prevent access upon completion of the update control program. Verification of the update may be provided through encryption techniques and rules incorporated in certificates for application of updates to provide for selectively updating devices. Also disclosed are methods of securely providing differing functionality to generic devices.

Owner:IBM CORP

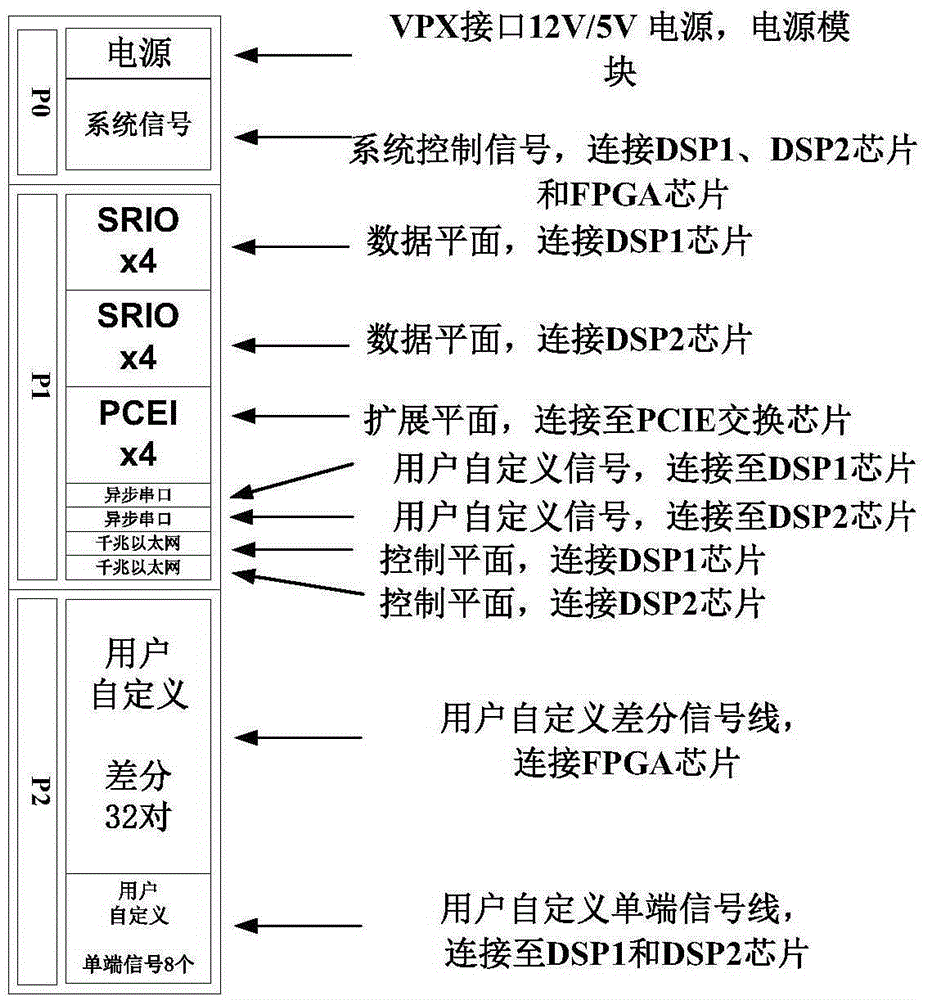

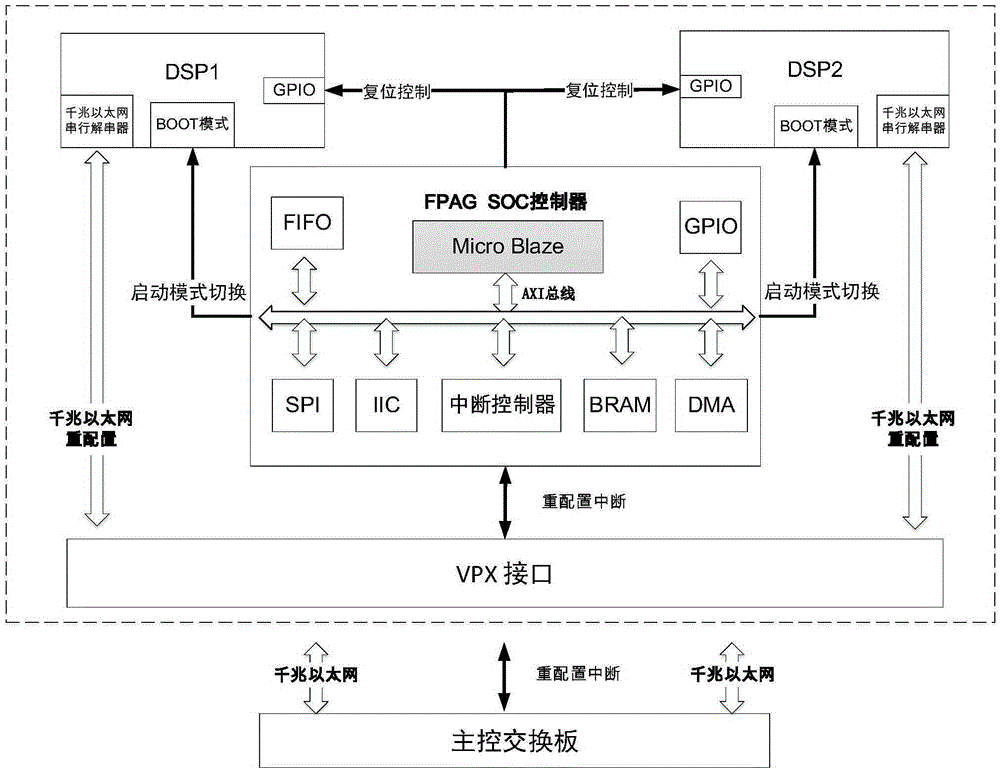

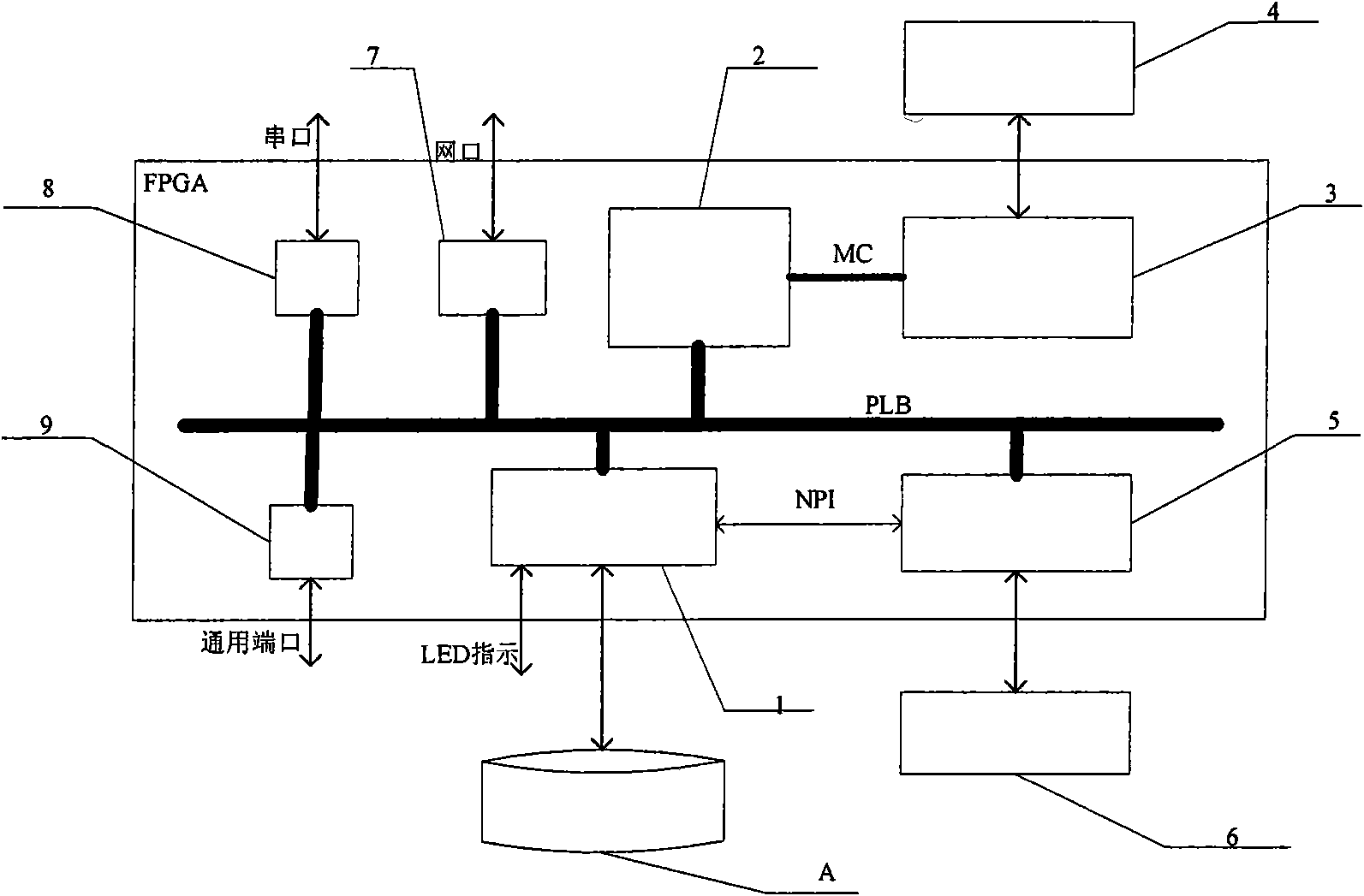

VPX parallel DSP signal processing board card based on SoC online reconstruction

InactiveCN105279133AIncrease flexibilityImprove real-time performanceDigital computer detailsElectric digital data processingDigital signal processingData signal

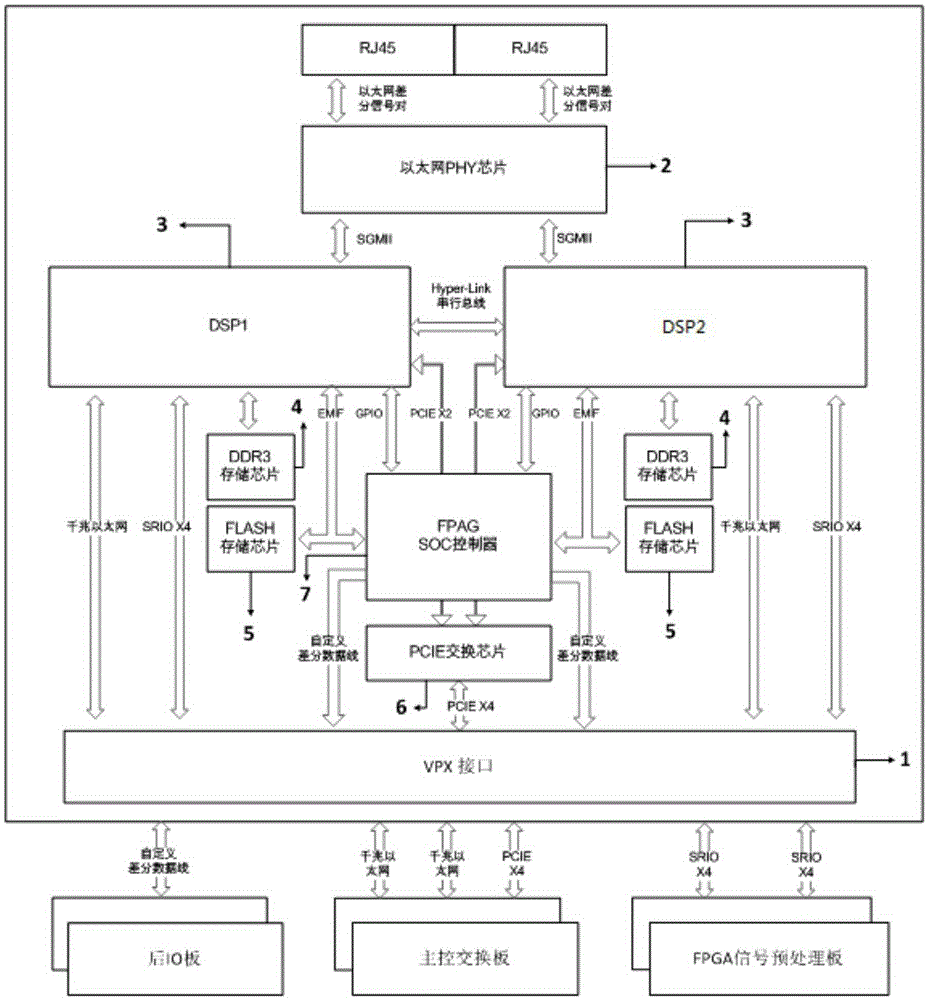

The invention discloses a VPX parallel DSP (Digital Signal Processing) board card based on SoC (System on a Chip) online reconstruction. An FPGA (Field Programmable Gate Array) chip is used as a board stage SoC controller; and two DSP chips are used as core operation chips of a DSP board card. During the practical configuration of the DSP chips, the FPGA chip used as the SoC controller can complete the dynamic re-configuration of work code by GE (Gigabit Ethernet) through the hardware resetting on the DSP and the switching on the starting mode; and the flexibility and the real-time performance during the DSP are greatly improved. The DSP chips receive two kinds of high-speed serial bus signals of SRIO (Serial Rapid Input Output) X4 and the GE transmitted through a VPX interface, repacking the transferred PCIE (Peripheral Component Interface Express) X2 high-speed serial bus signal through a PCIE exchange chip, and receives a data signal to be processed and a control instruction; or the DSP chips receive the GE protocol signal of a peripheral component through an RJ45 net port.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

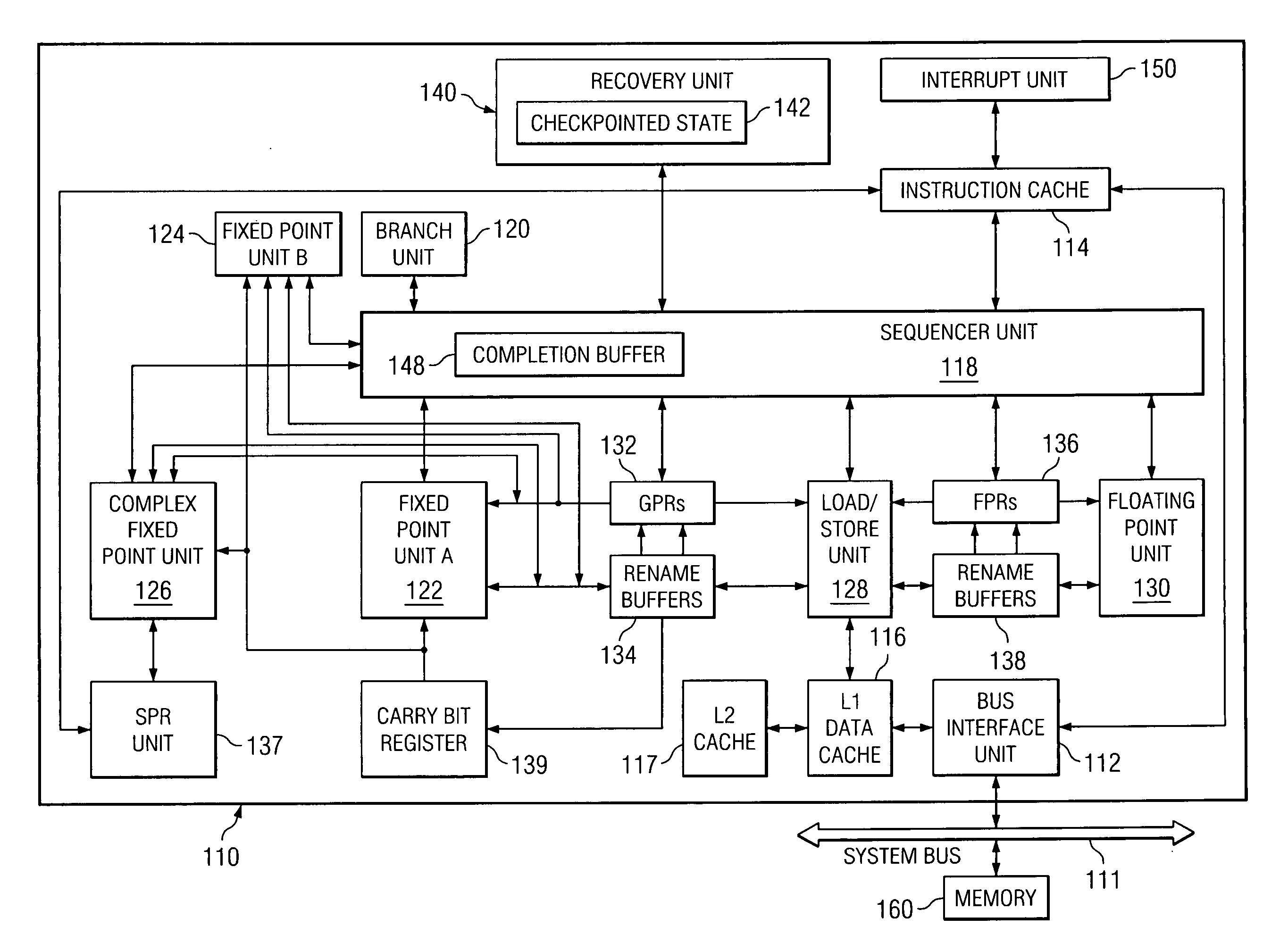

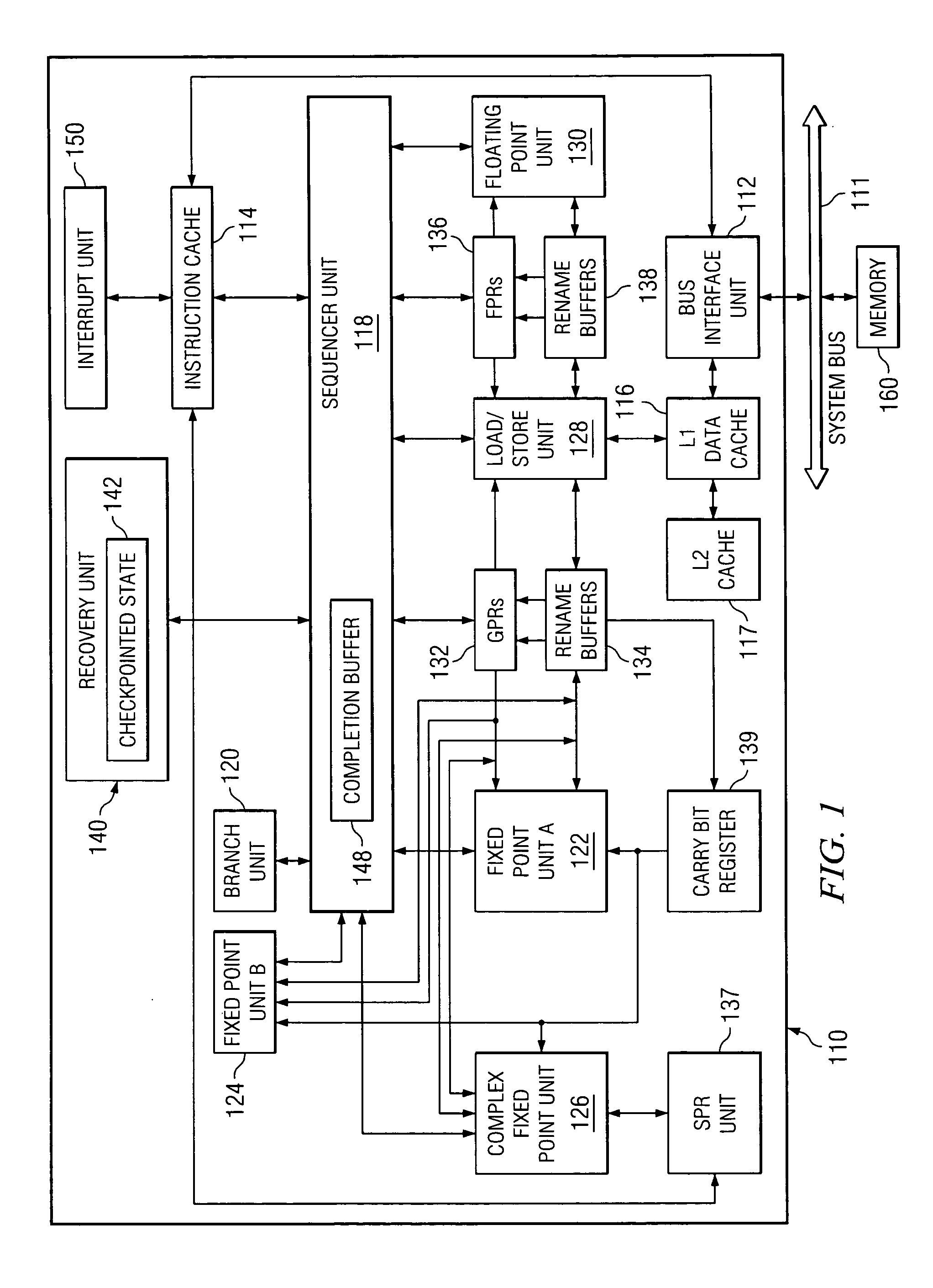

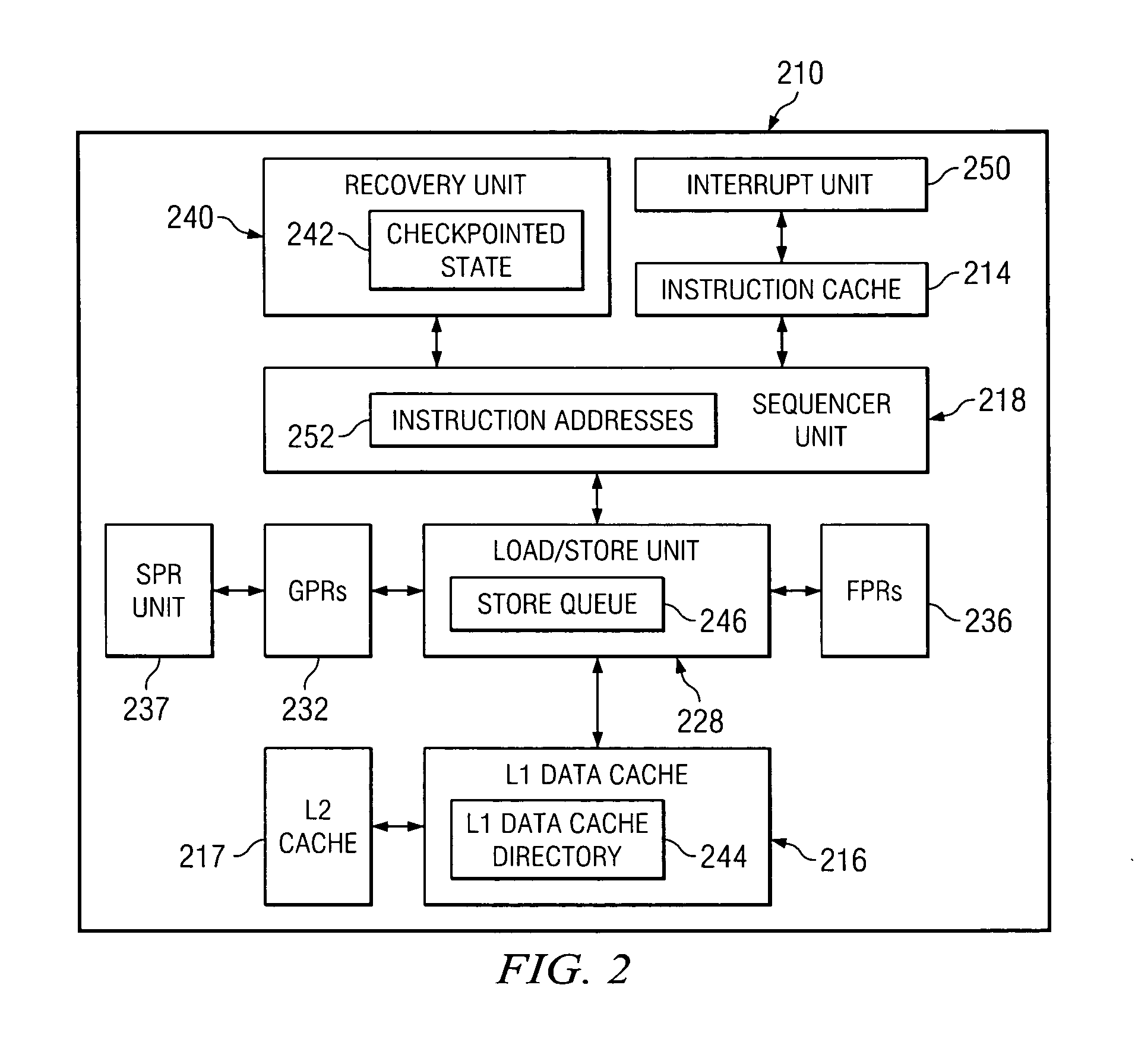

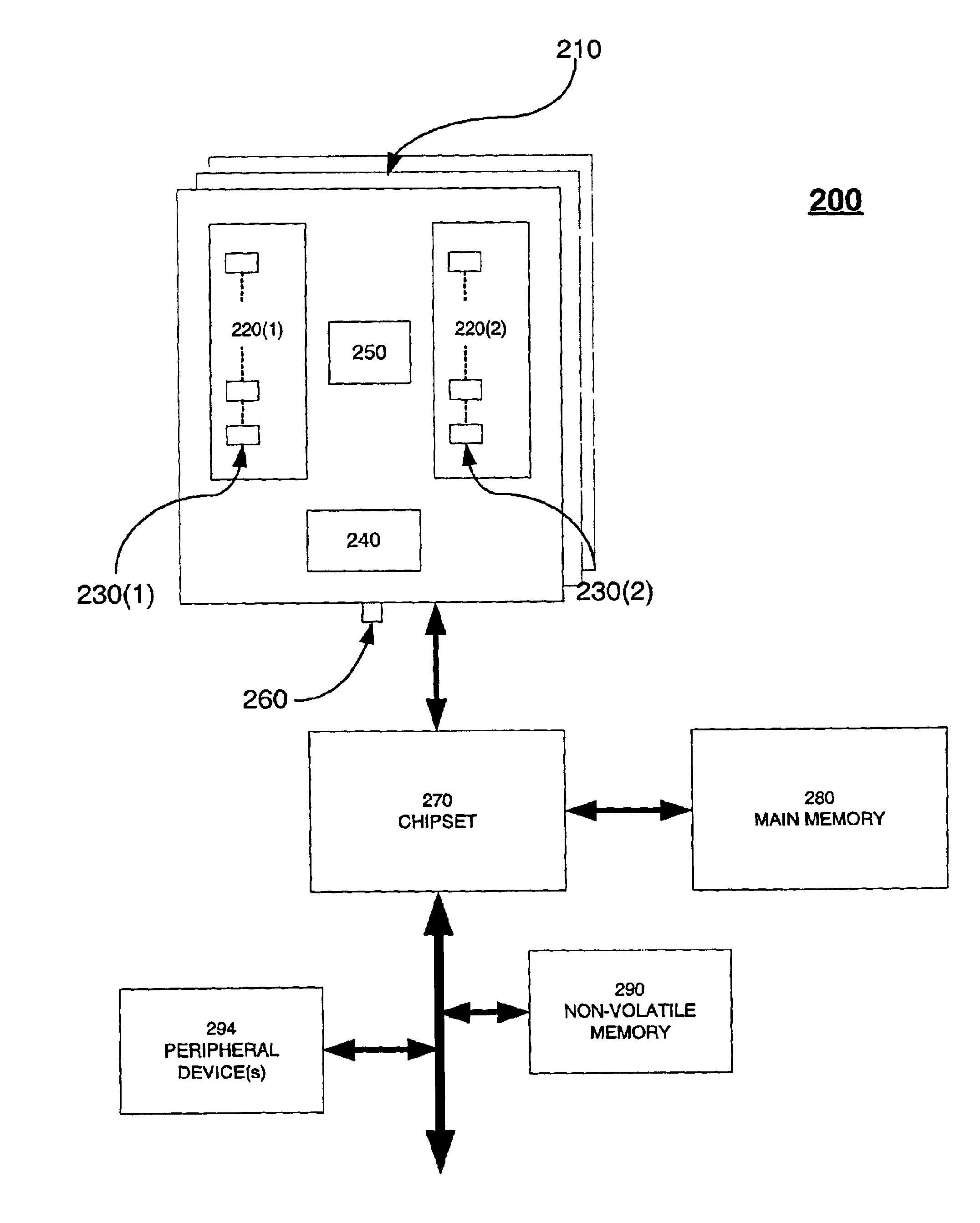

Mini-refresh processor recovery as bug workaround method using existing recovery hardware

InactiveUS20060184771A1Plurality of obstructionOptimize performance impactDigital computer detailsMemory systemsData processing systemData treatment

A method in a data processing system for avoiding a microprocessor's design defects and recovering a microprocessor from failing due to design defects, the method comprised of the following steps: The method detects and reports of events which warn of an error. Then the method locks a current checkpointed state and prevents instructions not checkpointed from checkpointing. After that, the method releases checkpointed state stores to a L2 cache, and drops stores not checkpointed. Next, the method blocks interrupts until recovery is completed. Then the method disables the power savings states throughout the processor. After that, the method disables an instruction fetch and an instruction dispatch. Next, the method sends a hardware reset signal. Then the method restores selected registers from the current checkpointed state. Next, the method fetches instructions from restored instruction addresses. Then the method resumes a normal execution after a programmable number of instructions.

Owner:IBM CORP

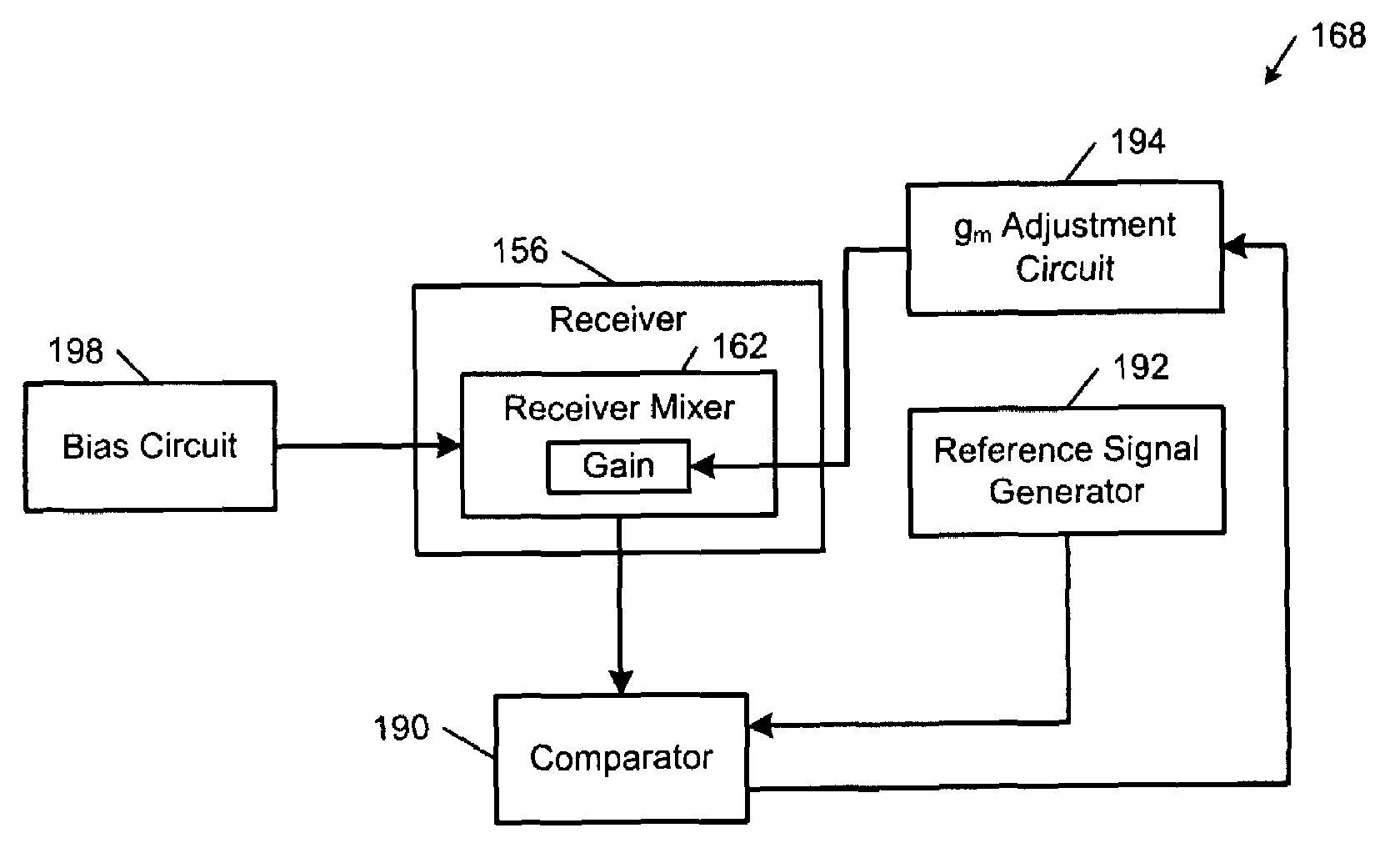

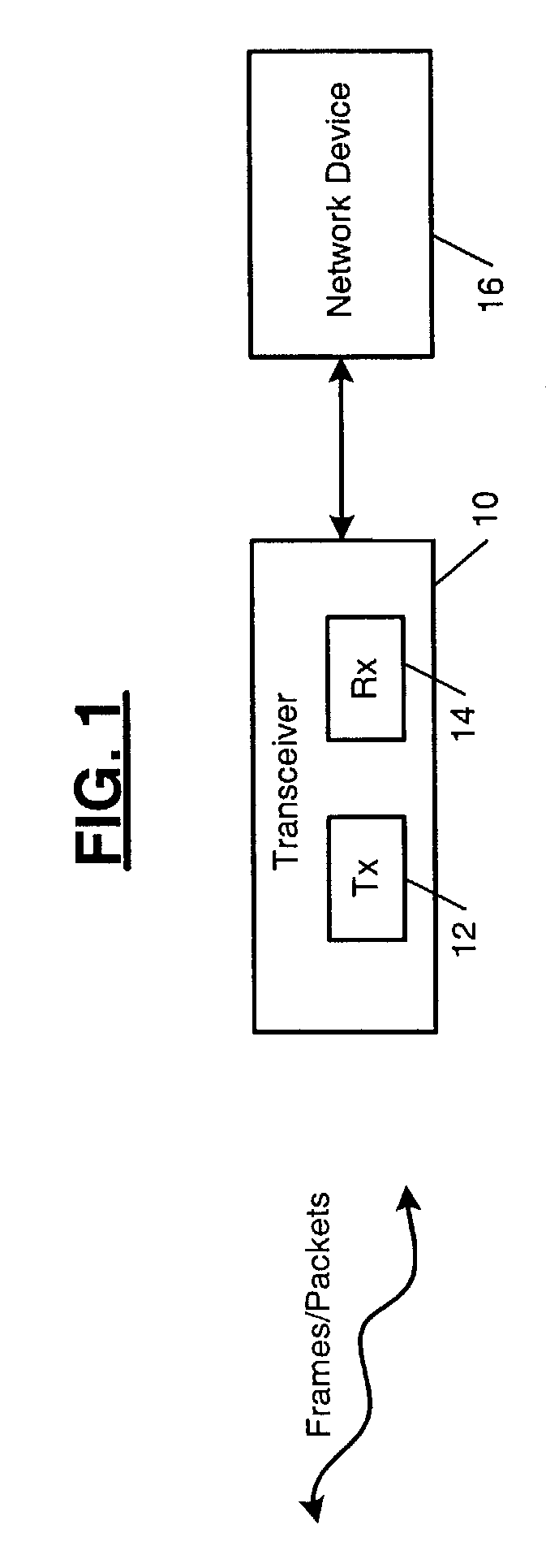

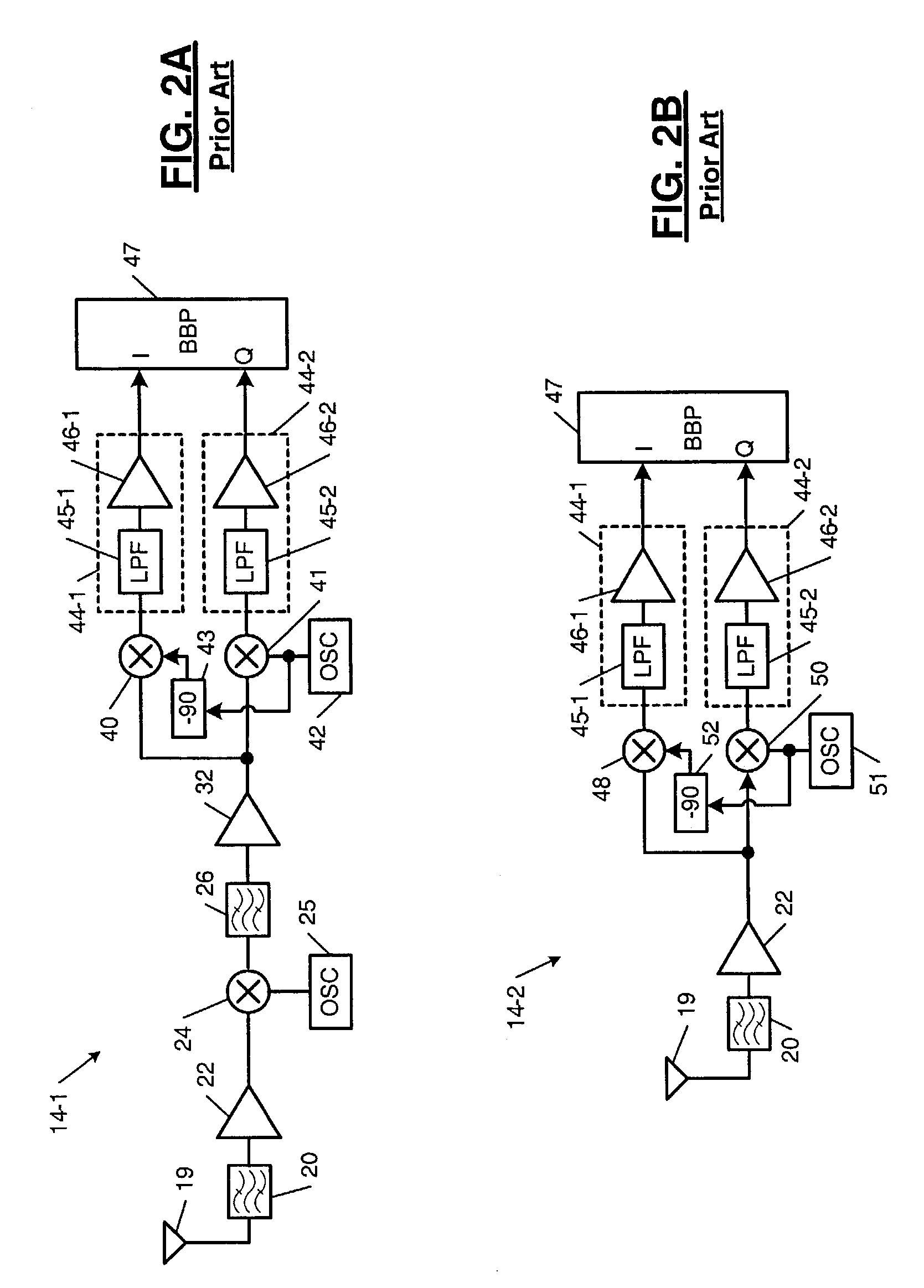

Mixer gain calibration method and apparatus

A gain calibration circuit for a radio frequency mixer in a wireless transceiver includes a reference signal generator that generates a reference signal. A comparator receives the reference signal and a second signal that is proportional to current flowing through the transmitter mixer and generates a difference signal. An adjustment circuit adjusts a transconductance gain of the mixer based on the difference signal. The adjustment circuit includes a plurality of binary weighted transconductance cells. The transconductance gain is calibrated during idle time between data packets or after power on, hardware reset, or software reset.

Owner:MARVELL INT LTD

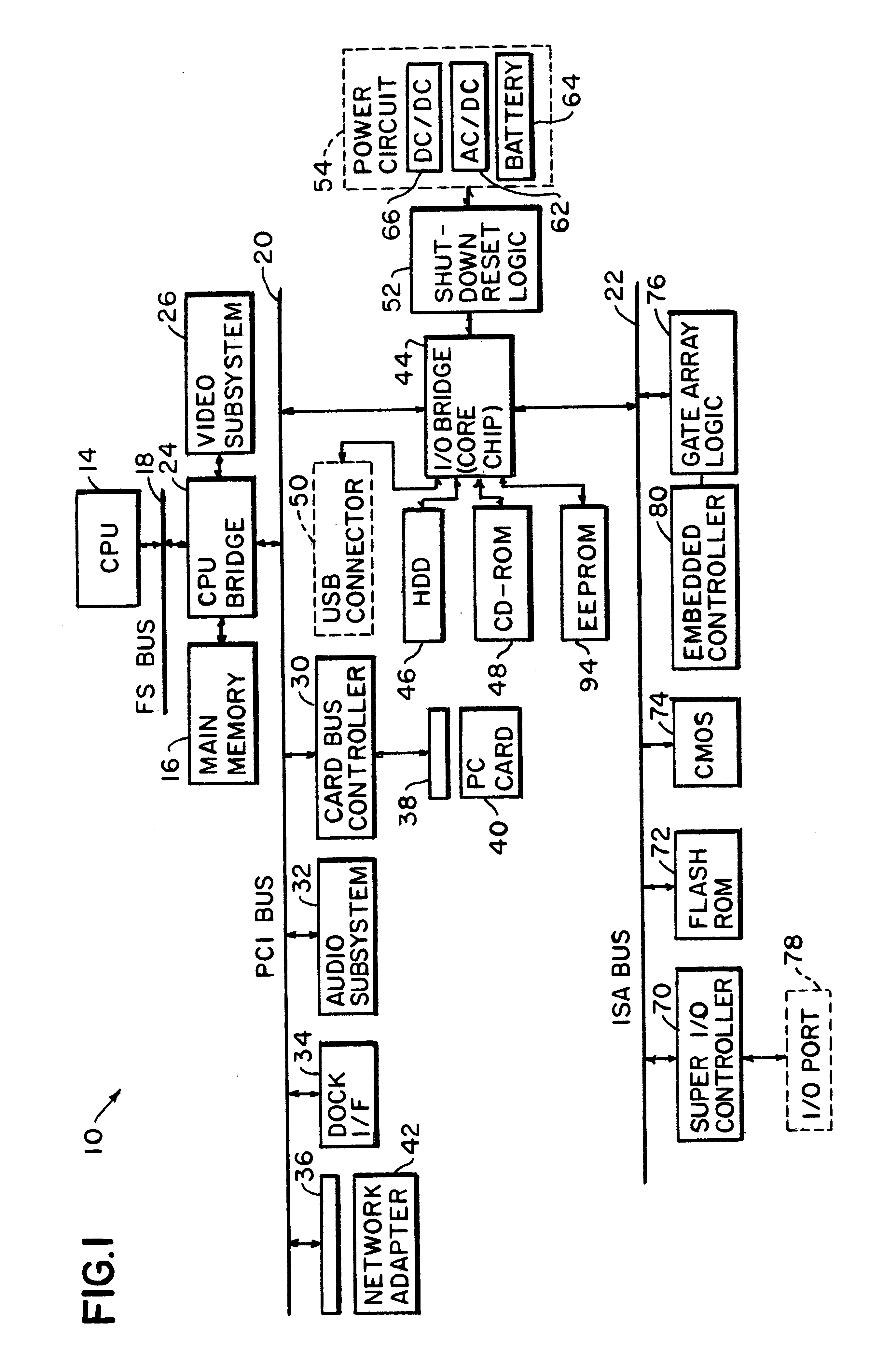

Computer and power control method for executing predetermined process in said computer prior to turning off its power

InactiveUS6895515B1Easy constructionSure easyVolume/mass flow measurementDigital computer detailsPower Management UnitEngineering

The invention realizes the execution of a predetermined process just before the turn-off of the power of a computer, without incurring increase in the load.A shutdown reset logic 52 is provided between a power management unit 68 on a core chip and a power circuit 54. The logic 52 is enabled just before the system is shut down, and it interrupts the inputting of a power-off signal −SUSC output from the power management unit 68 to the power circuit 54, inputs a signal LAST#PWG#PIIX4 representing a faulty power state to the power management unit 68 to cause a hardware reset, and inputs a signal −PERSW#PIIX4 representing the turn-on of a power switch 92. This causes the POST to be started, and the POST turns off the power of the system after enabling the WOL function of the network adapter.

Owner:IBM CORP

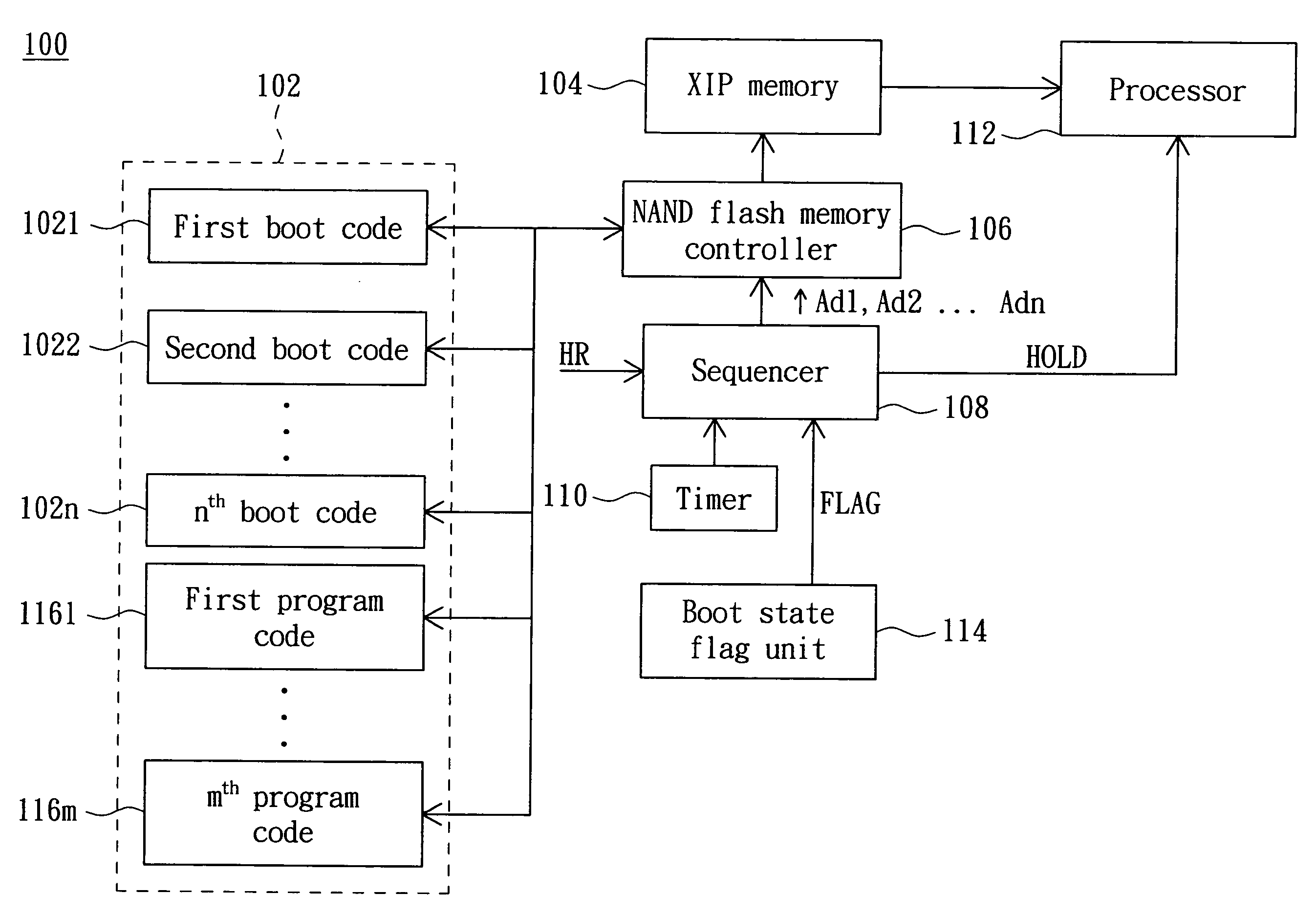

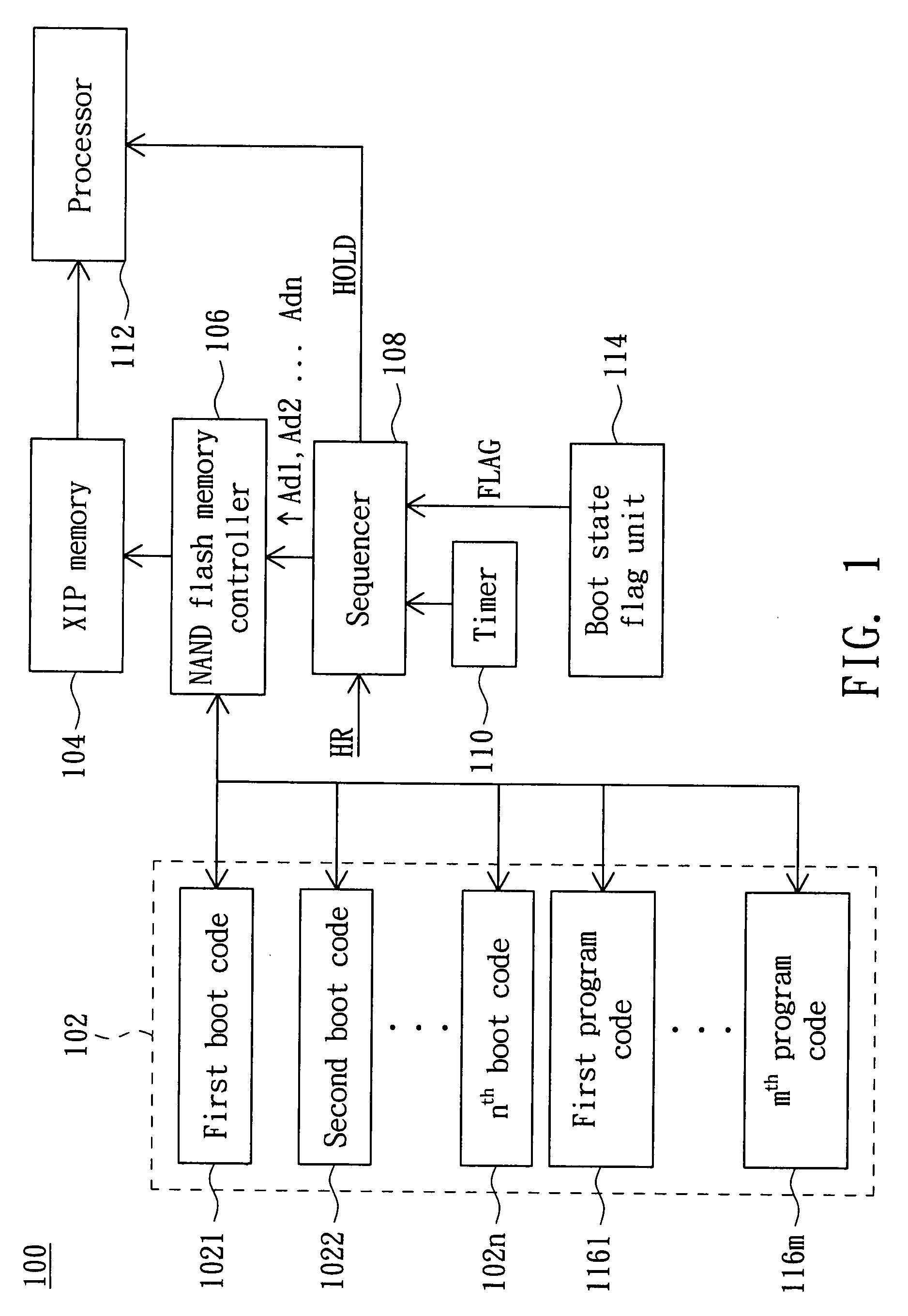

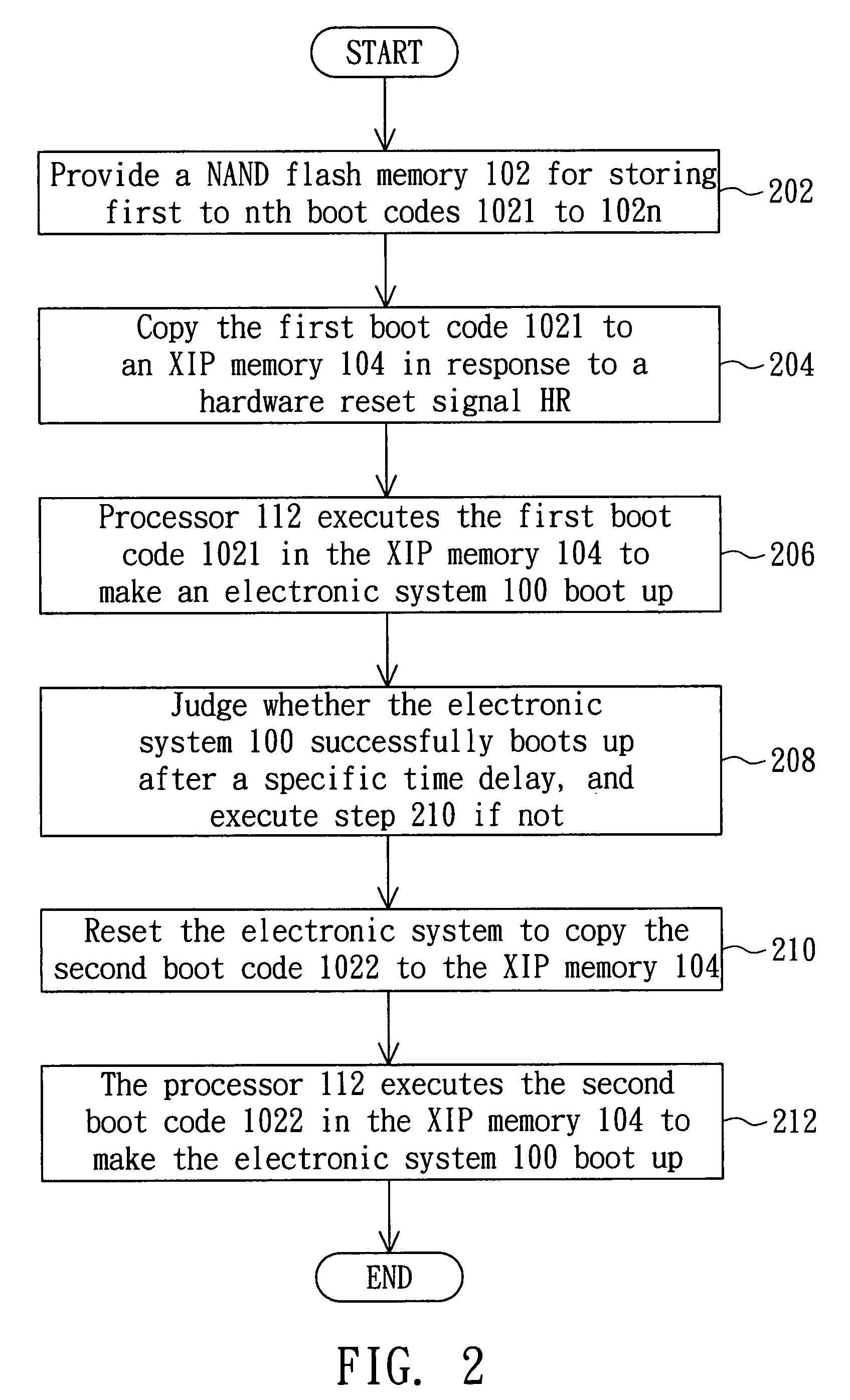

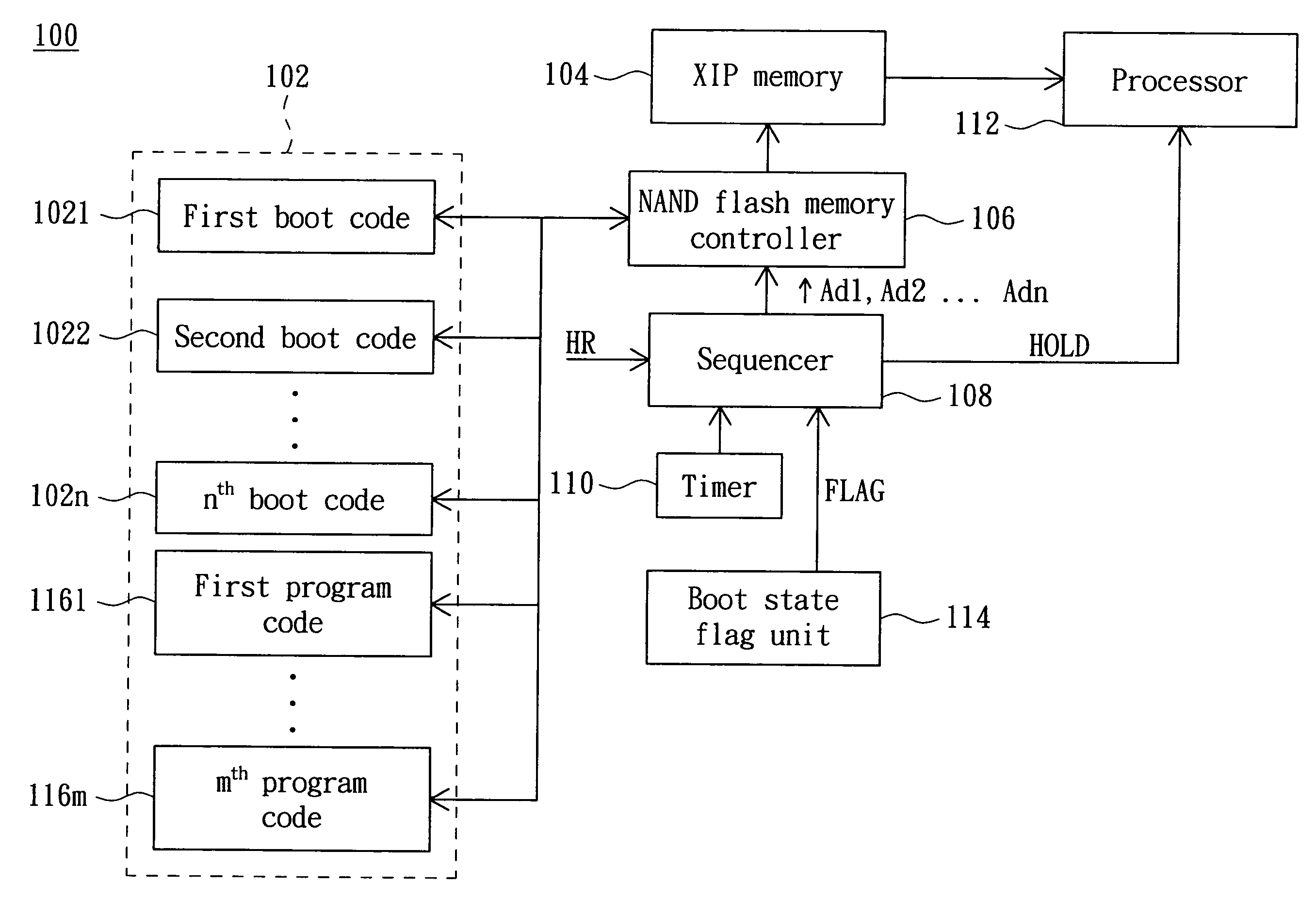

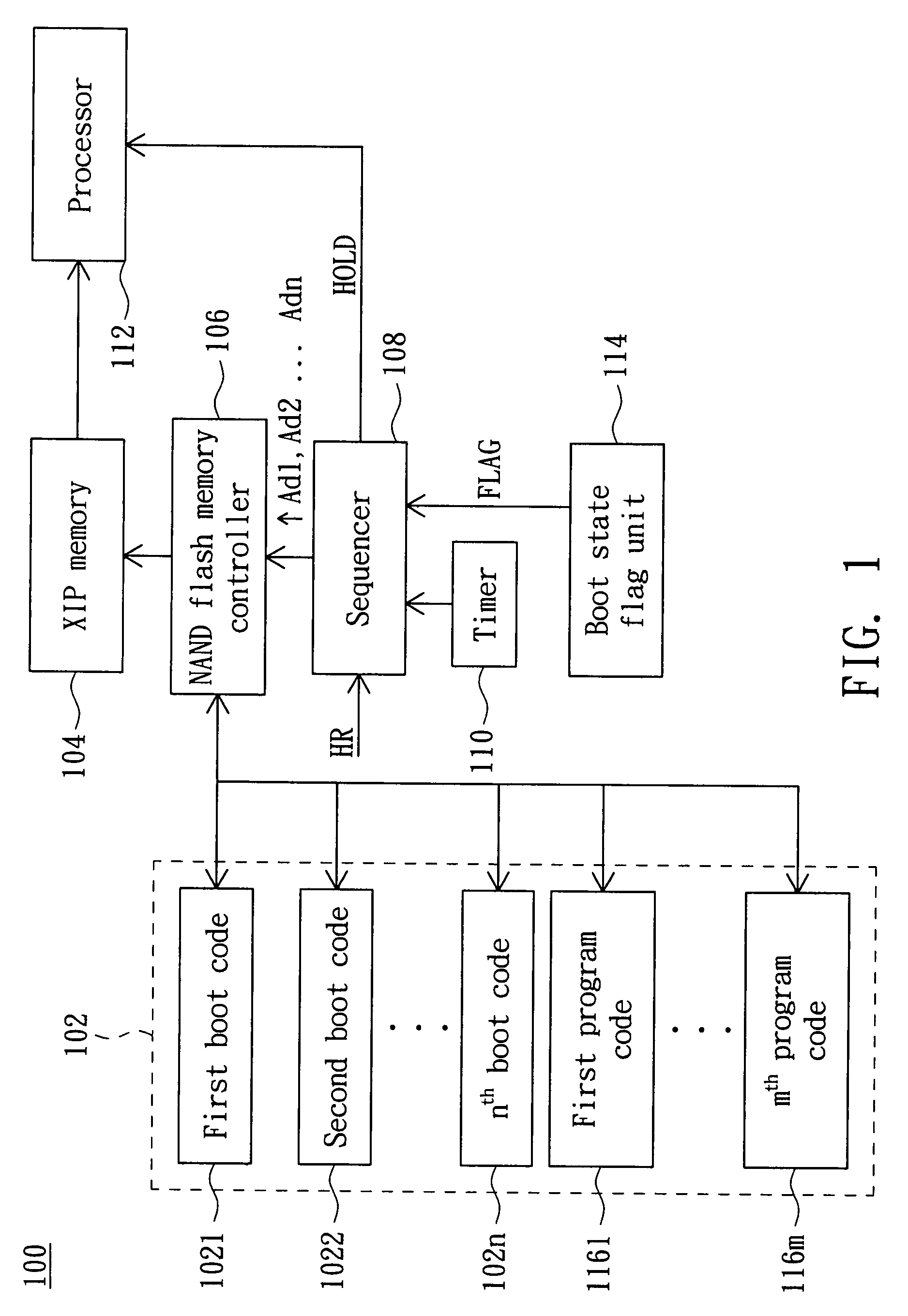

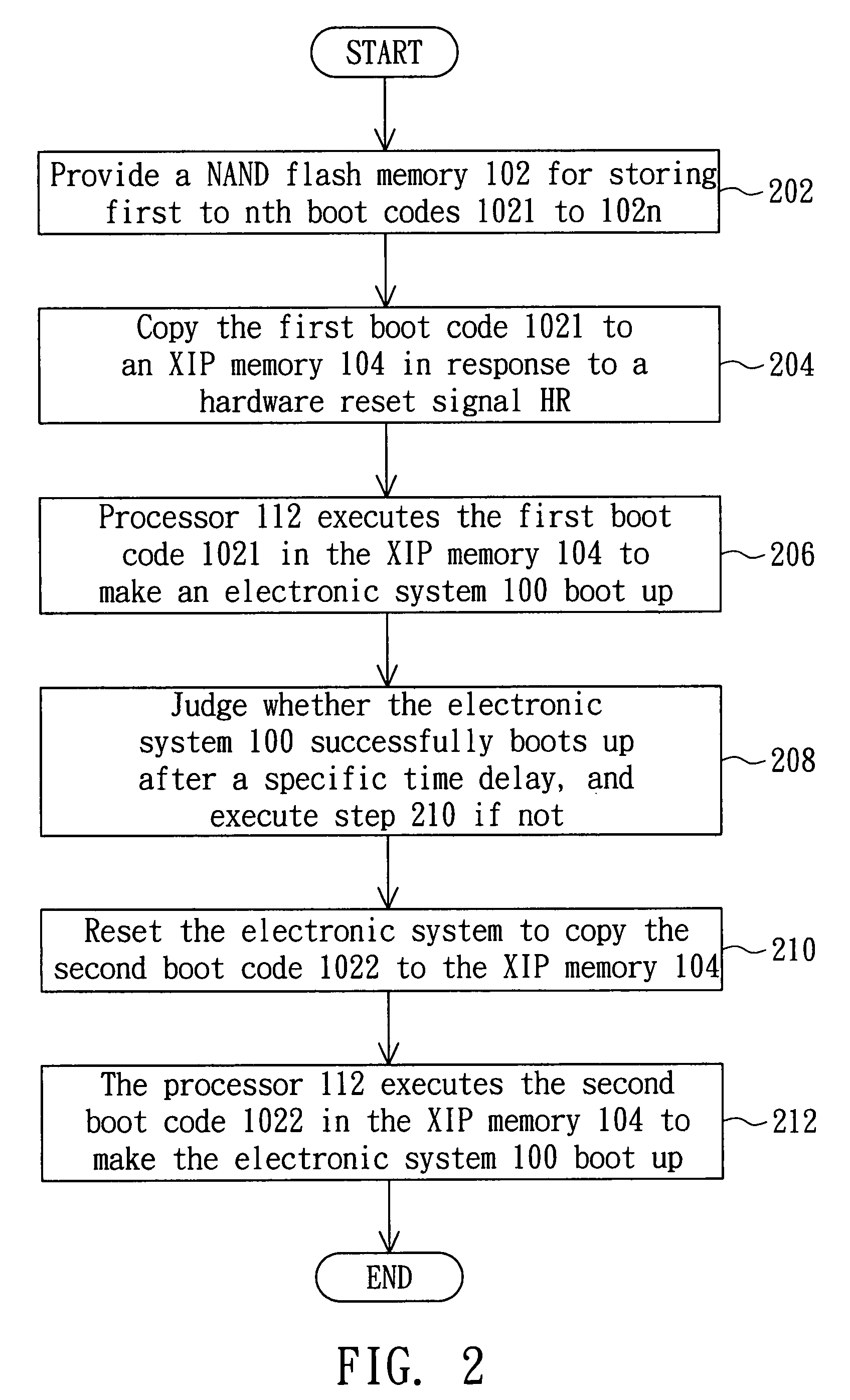

Electronic system with nand flash memory storing boot code and highly reliable boot up method

InactiveUS20080082814A1Additional drawbackIncrease success rateError preventionTransmission systemsElectronic systemsTime delays

A boot up method makes an electronic system boot up by a processor according to a boot code in a NAND flash memory and includes the following steps. First, the flash memory storing a boot code or boot codes is provided. Next, a first boot code is copied to an XIP memory in response to a hardware reset signal. Then, the processor executes the first boot code in the XIP memory and thus makes the system boot up. Next, whether the system boots up successfully is judged after a time delay. When the system fails to boot up, the system is reset and a second boot code is copied to the XIP memory. Thereafter, the processor executes the second boot code in the XIP memory and thus boots up the system. If the system still fails to boot up, the above-mentioned steps are repeated until the system boots up successfully.

Owner:MAGIC PIXEL

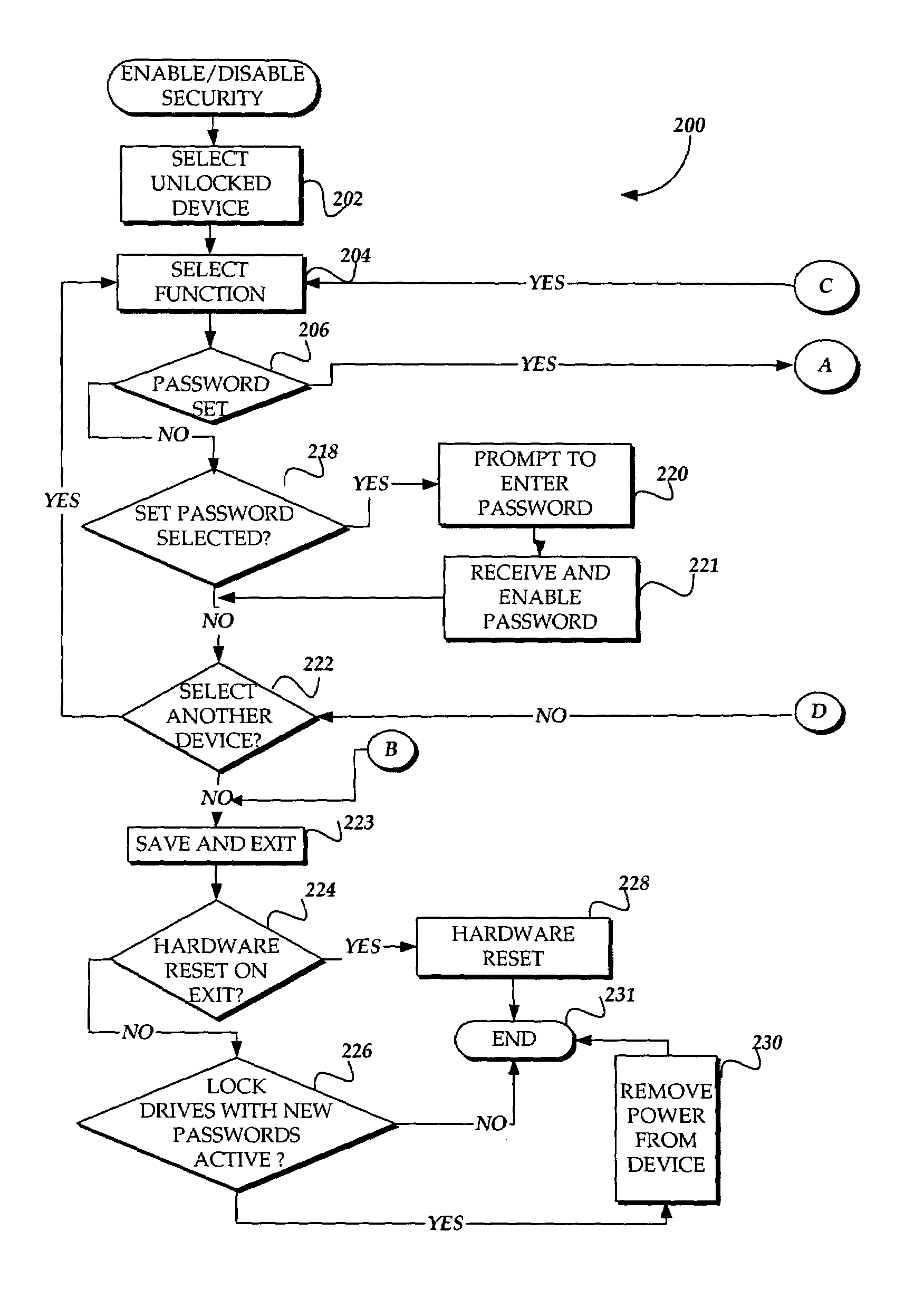

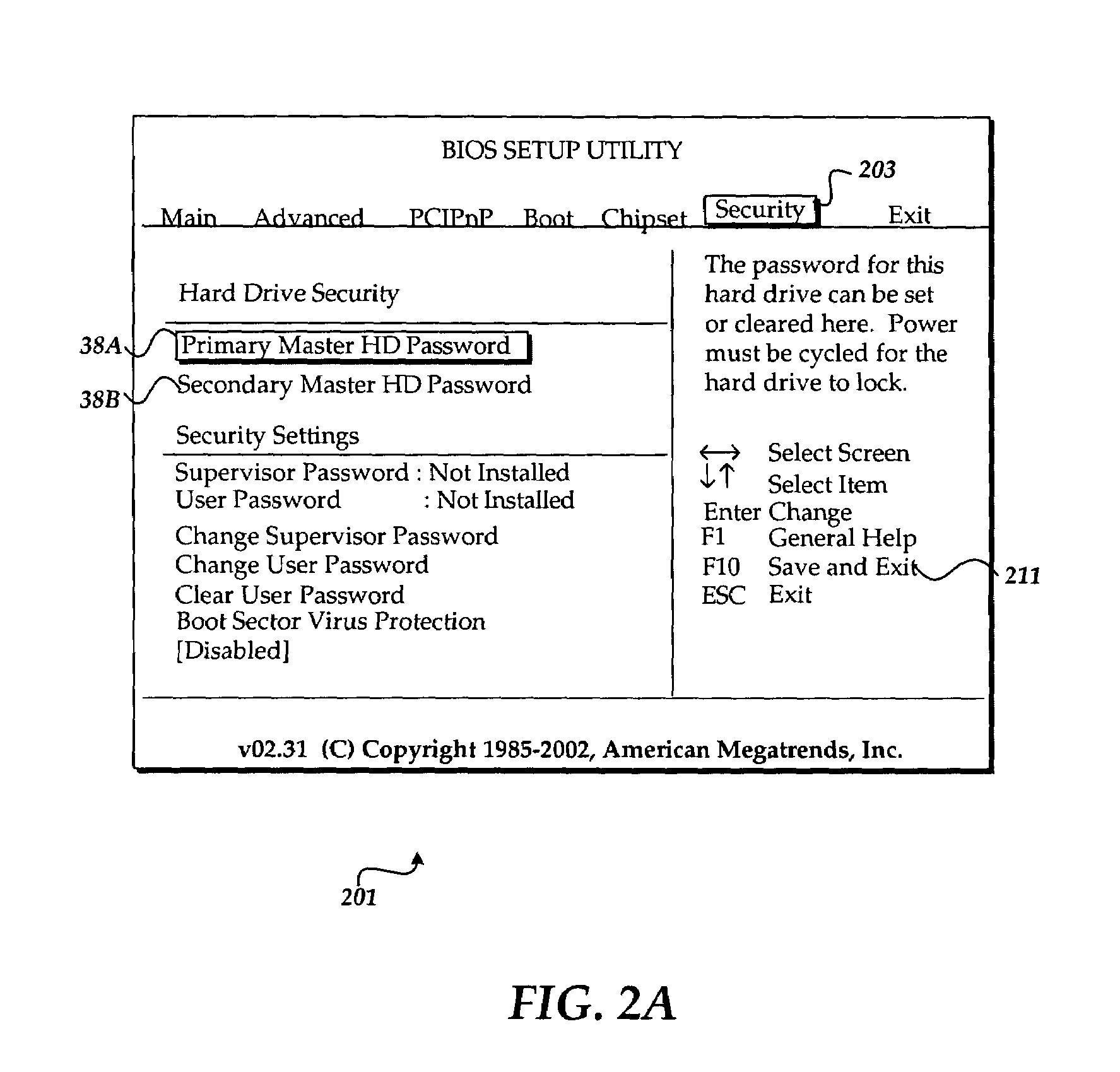

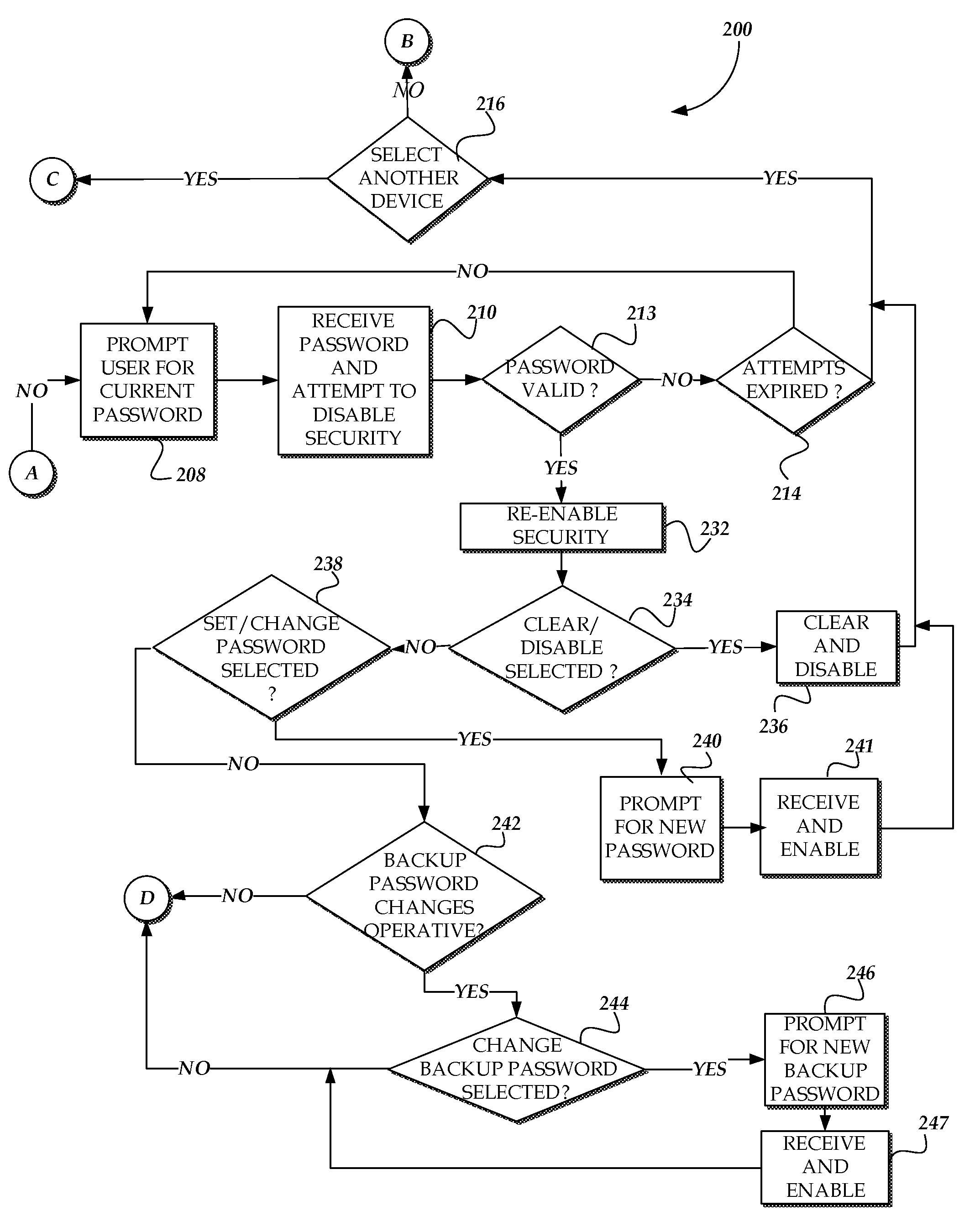

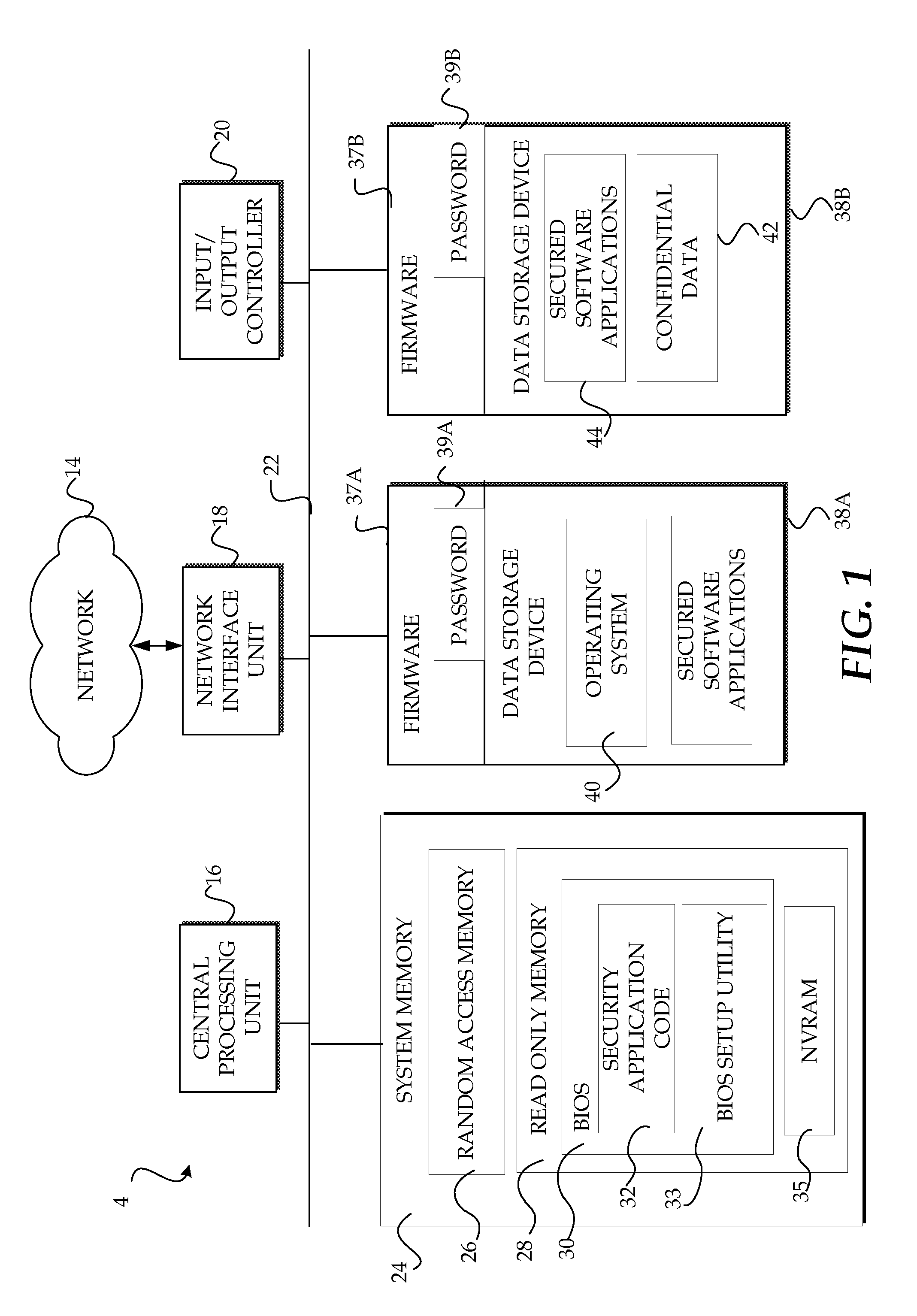

Securing the contents of data storage devices within a computer

InactiveUS7743241B1Avoid changeRemoval of powerDigital data processing detailsDigital computer detailsSleep stateOperational system

Each data storage device that supports the standard security features and is enabled with a security password may be locked when power is removed from the device. When power is returned, a determination is made as to whether the data storage device is locked and returning from a powered off state or a hardware reset. If locked, a password may be received from a user. After the security password is received, the data storage device is unlocked, allowing access to the data on the device. A setup utility is provided for manipulating the security and backup passwords for each device. Other features include: presenting locked devices to the operating system, the use of a backup password to unlock a device in lieu of the security password, requiring or not requiring password entry from a user to unlock a device when returning from a sleep state, setting maximum or high security, an automatic hardware reset upon exiting the setup utility, and disabling change password capabilities for devices without an enabled security password.

Owner:AMERICAN MEGATRENDS

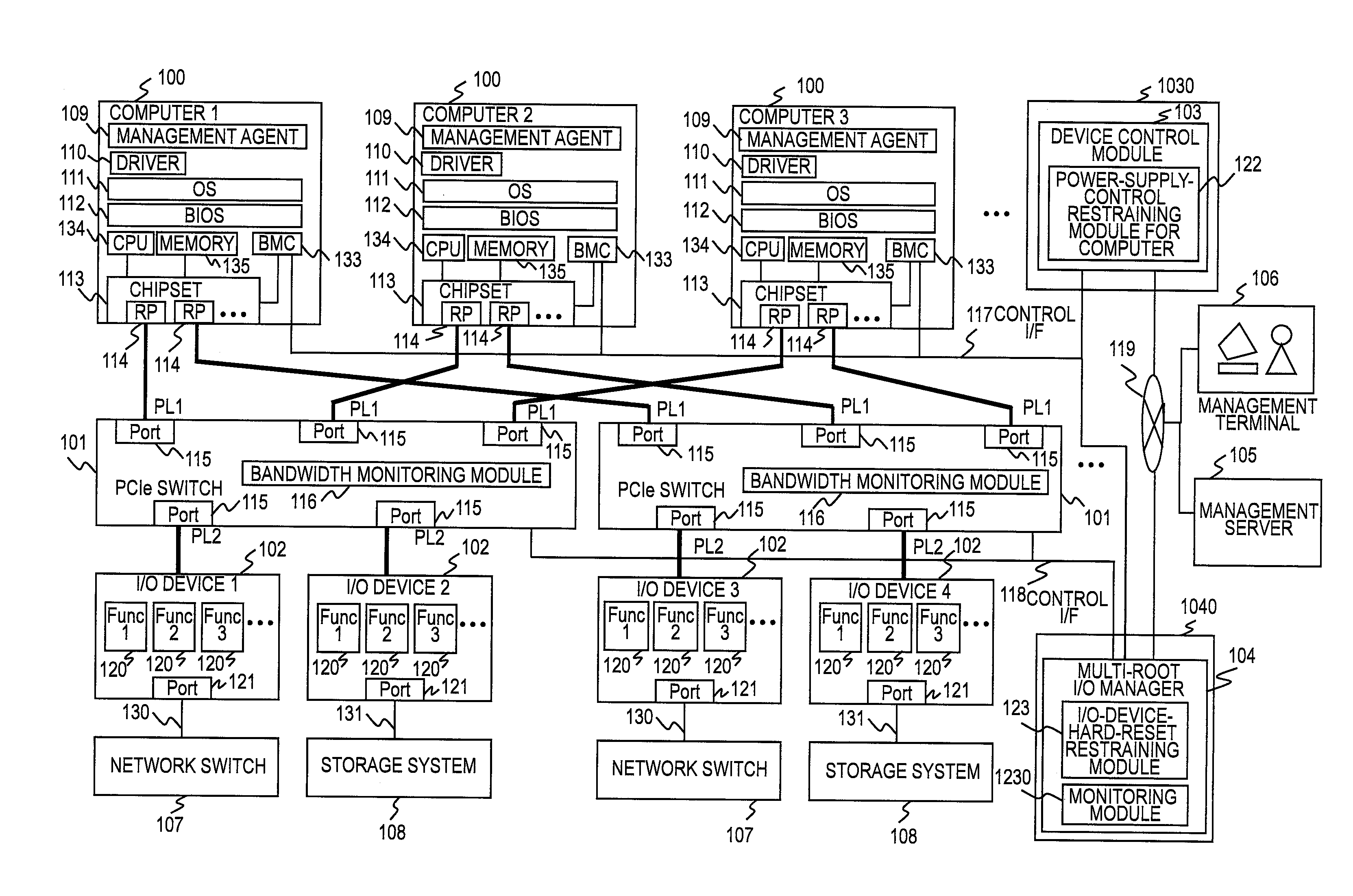

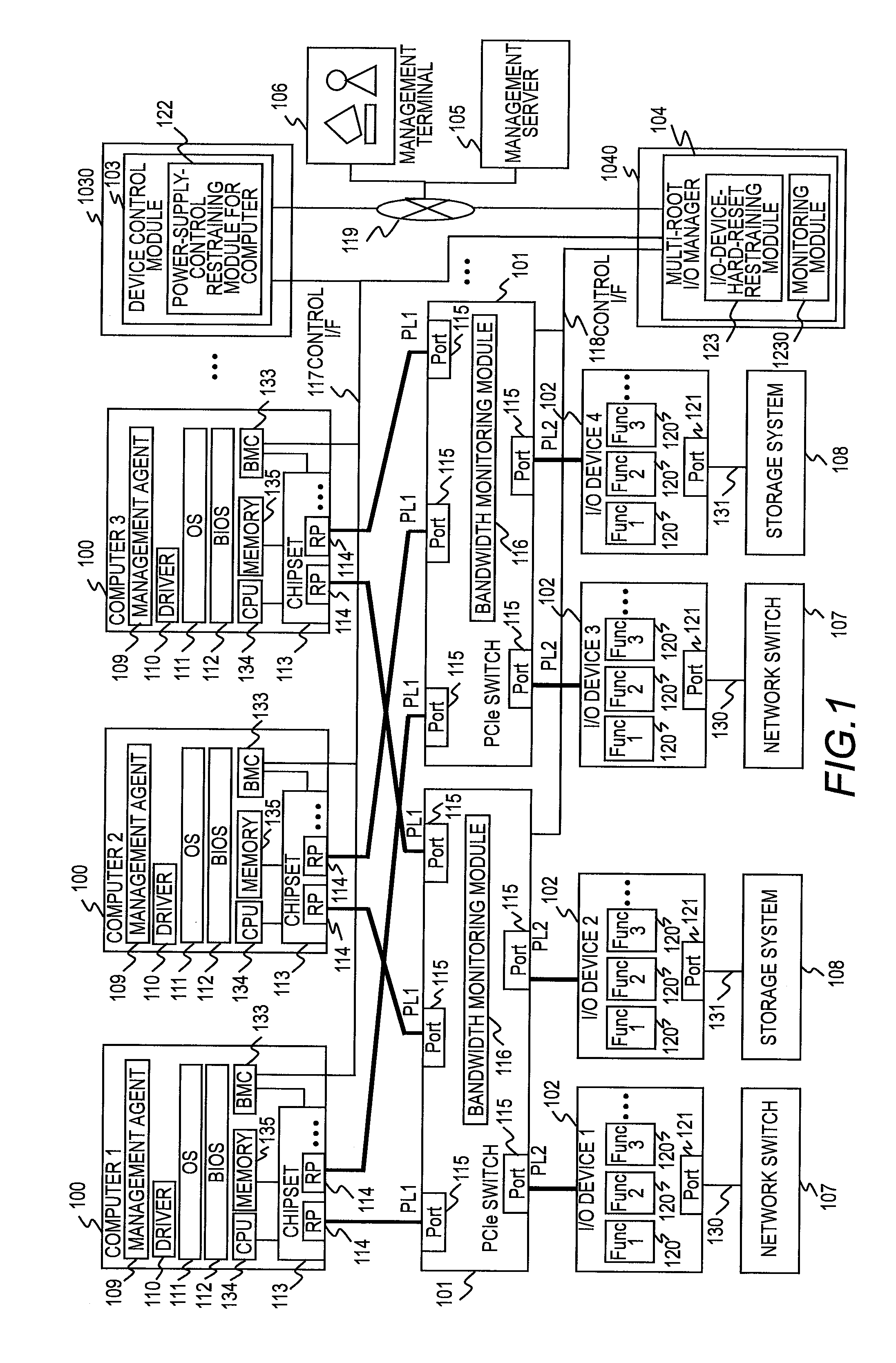

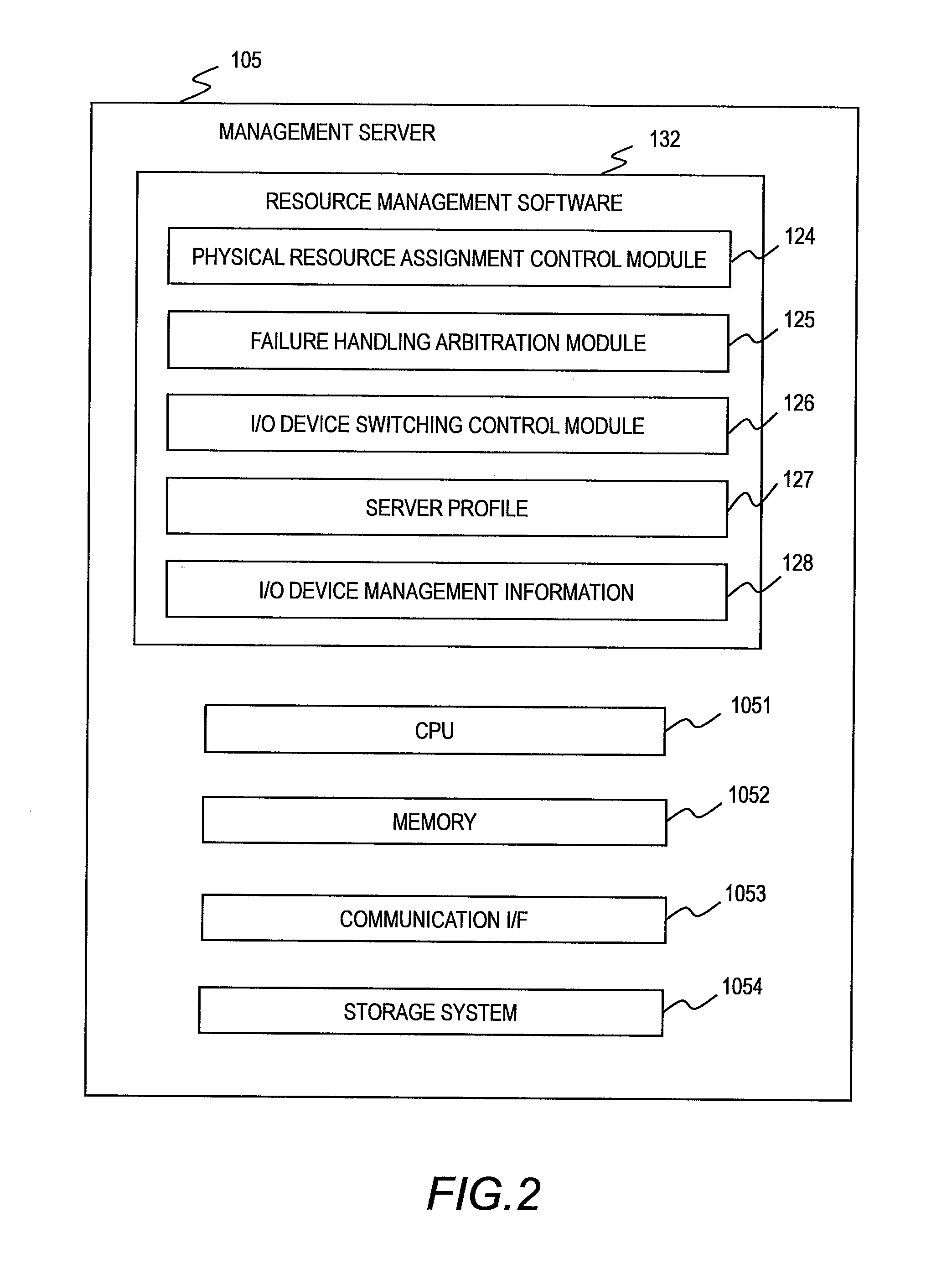

Compound computer system and method for sharing PCI devices thereof

InactiveUS20100153615A1Easy to set upElectric digital data processingResource managementComputer science

A resource management module of a management server for controlling a multi-root I / O manager connected to a PCI switch for connecting a plurality of I / O devices and a plurality of computers with each other includes: failure handling content information indicating, for each computer sharing a multi-root I / O device, a content of a failure handling at an occurrence of a failure in the multi-root I / O device; and failure handling availability status information indicating whether a hardware reset of the multi-root I / O device is possible and updates, upon reception of a notification of the occurrence of the failure in the multi-root I / O device, the failure handling availability status information, and instructs, based on the failure handling availability status information, the multi-root I / O manager to restrain or cancel the hardware reset of the multi-root I / O device.

Owner:HITACHI LTD

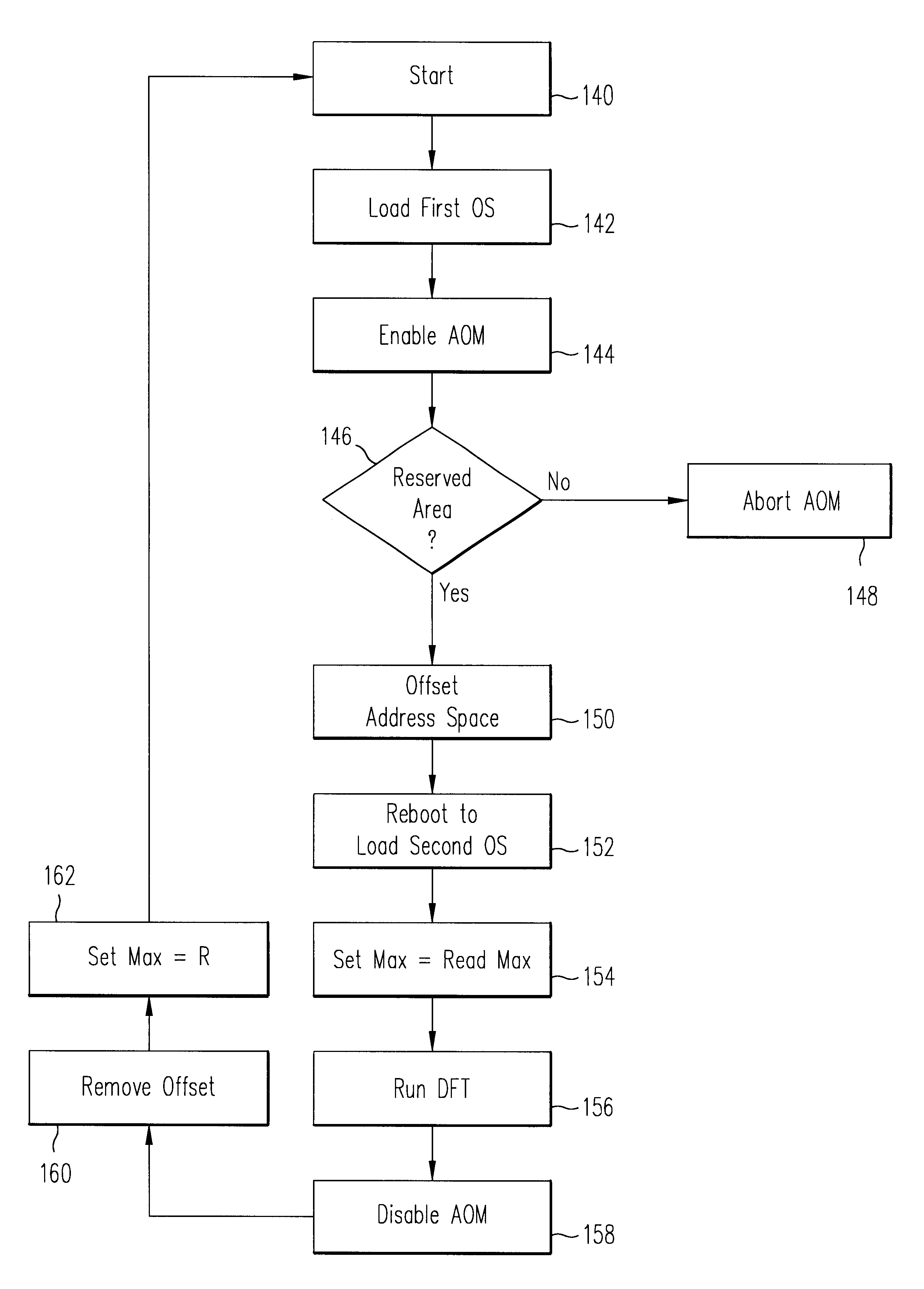

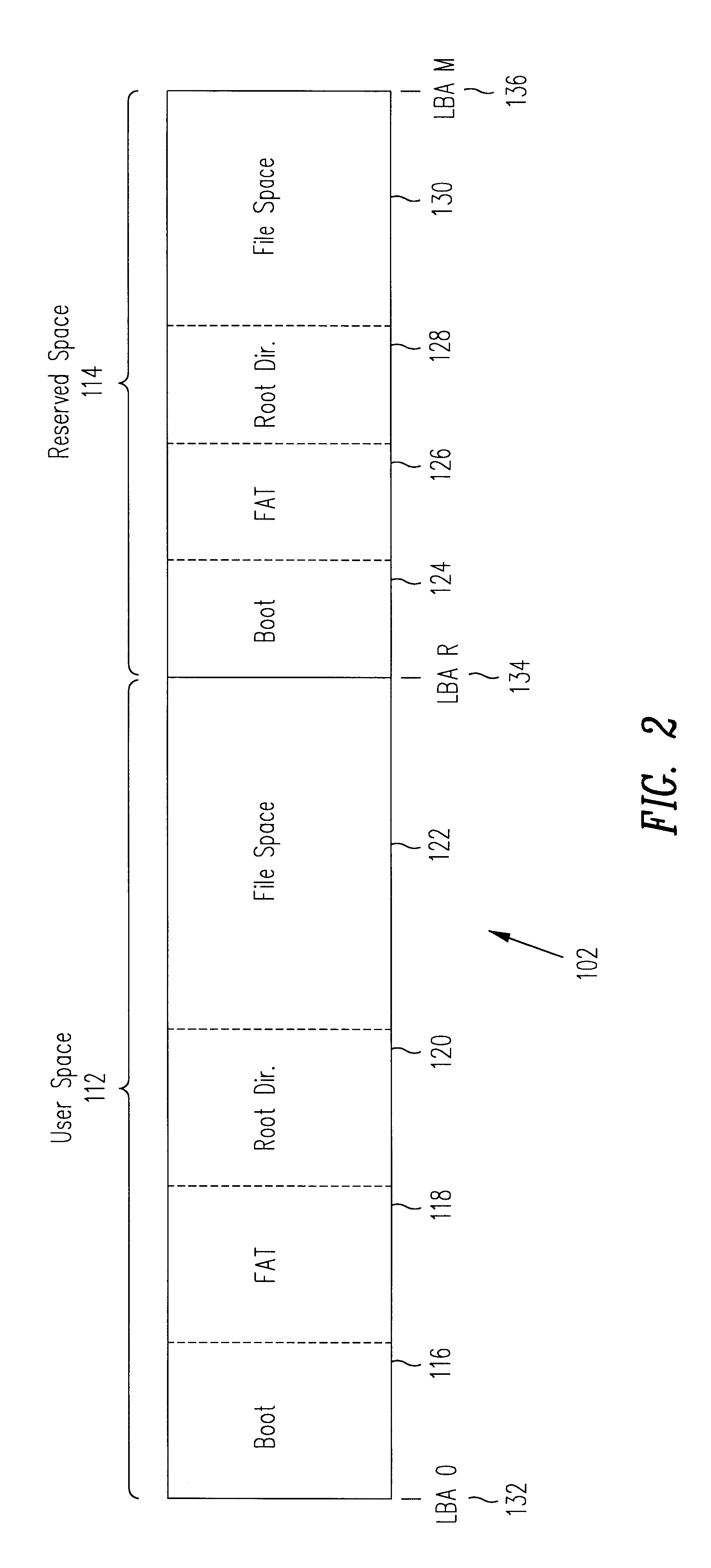

Address offset feature for a hard disk drive

InactiveUS6415383B1Program control using stored programsDigital computer detailsPower-on resetHard disc drive

A method of changing the operating system in a computer system by using an address offset mode (AOM) feature for the address space of a hard disk drive connected to the computer system. Initialization of the computer loads the first operating system (OS) from a user area in the disk drive address space. An enable AOM command offsets the disk drive address space and reinitializes the computer to load a second OS from a reserve space in the disk drive address space. A command setting the maximum size of the address space of the hard disk drive provides a wrap around feature allowing the entire address space of the disk drive to be addressable for diagnostics or updating purposes. The computer is returned to operation with the first OS by a disable AOM command, or alternatively, by a power on reset, a software reset or a hardware reset. The method of changing operating systems is coded in the hard disk drive and does not require additions or modifications to the memory or the BIOS ROM of the computer system.

Owner:IBM CORP

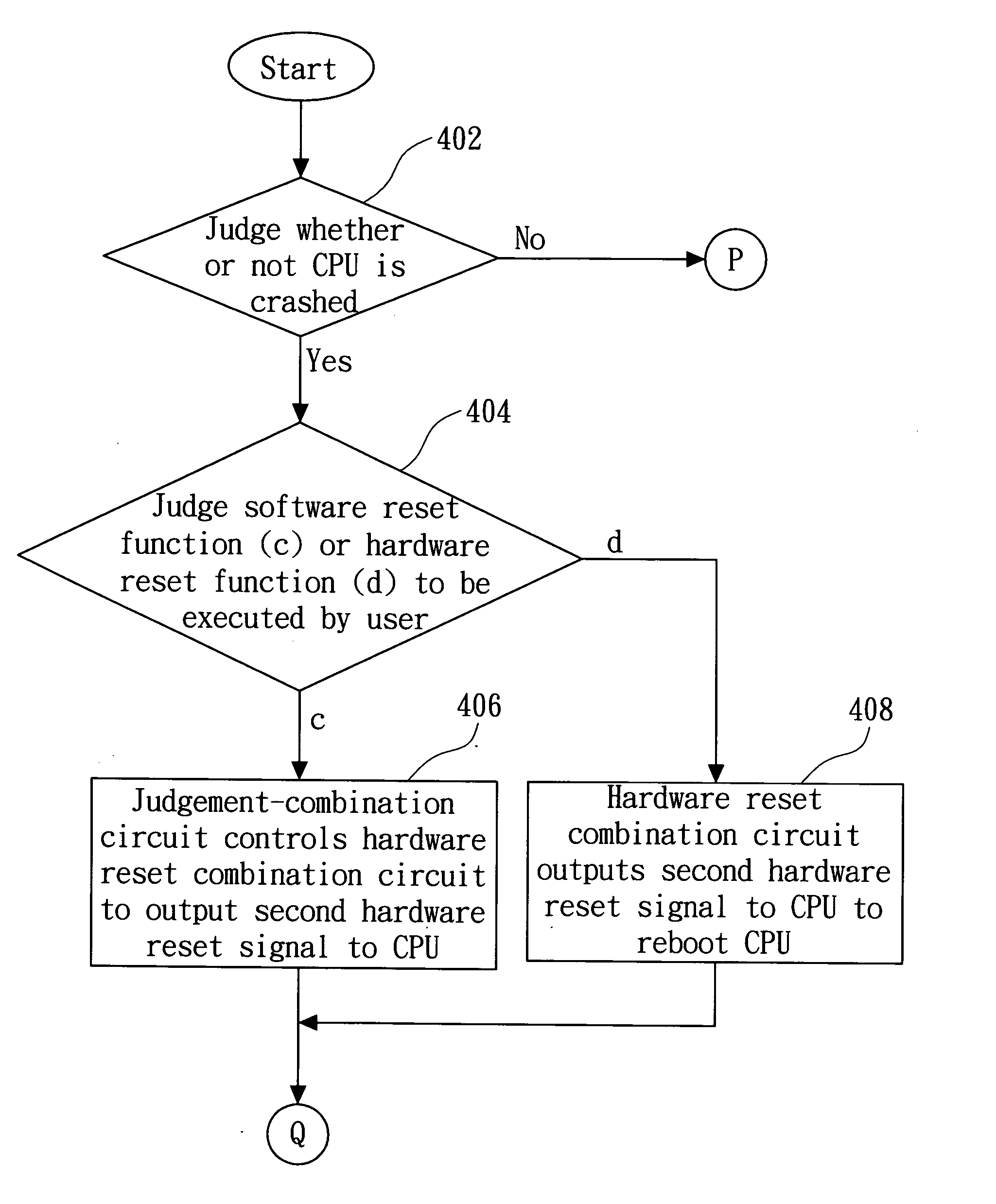

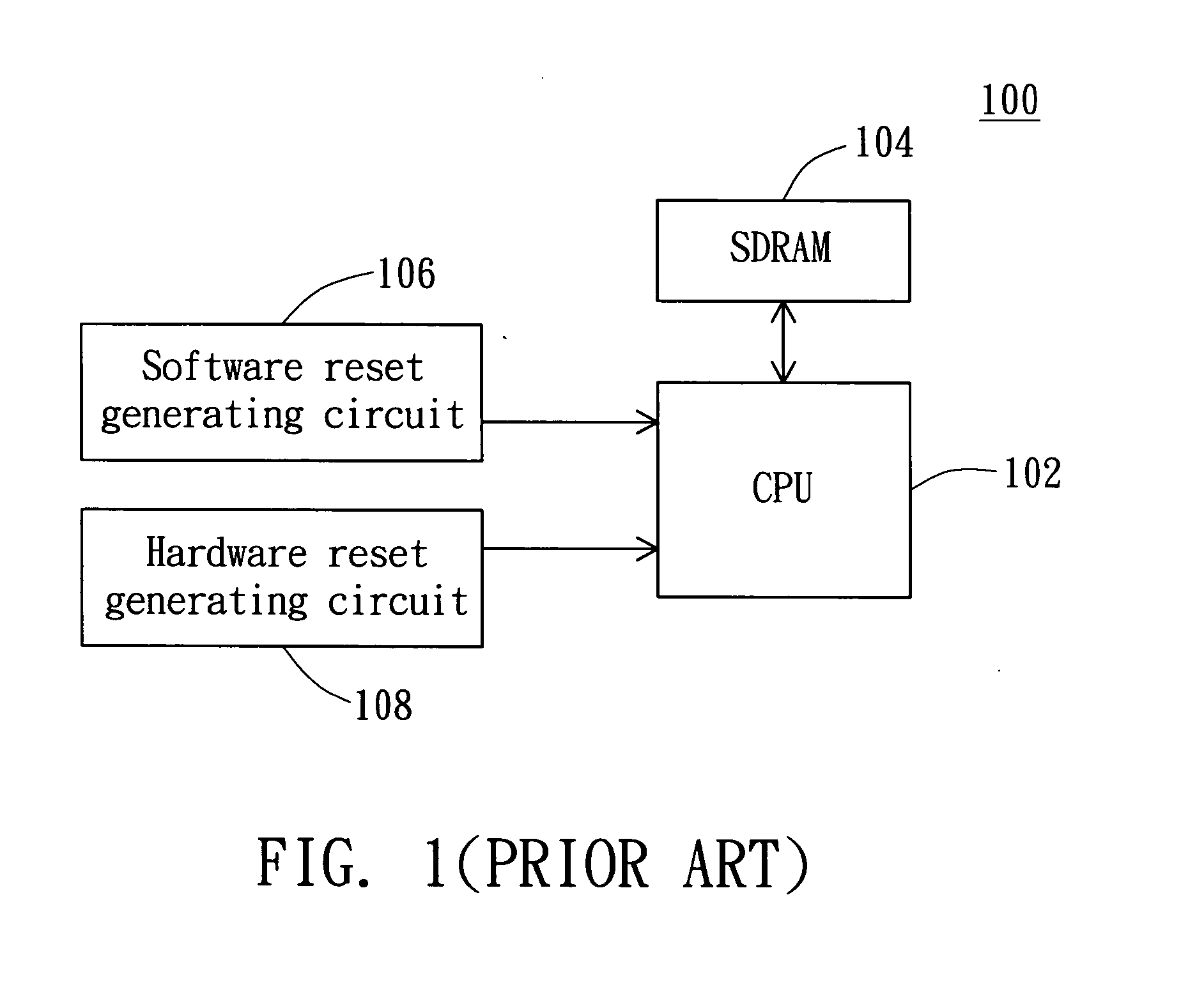

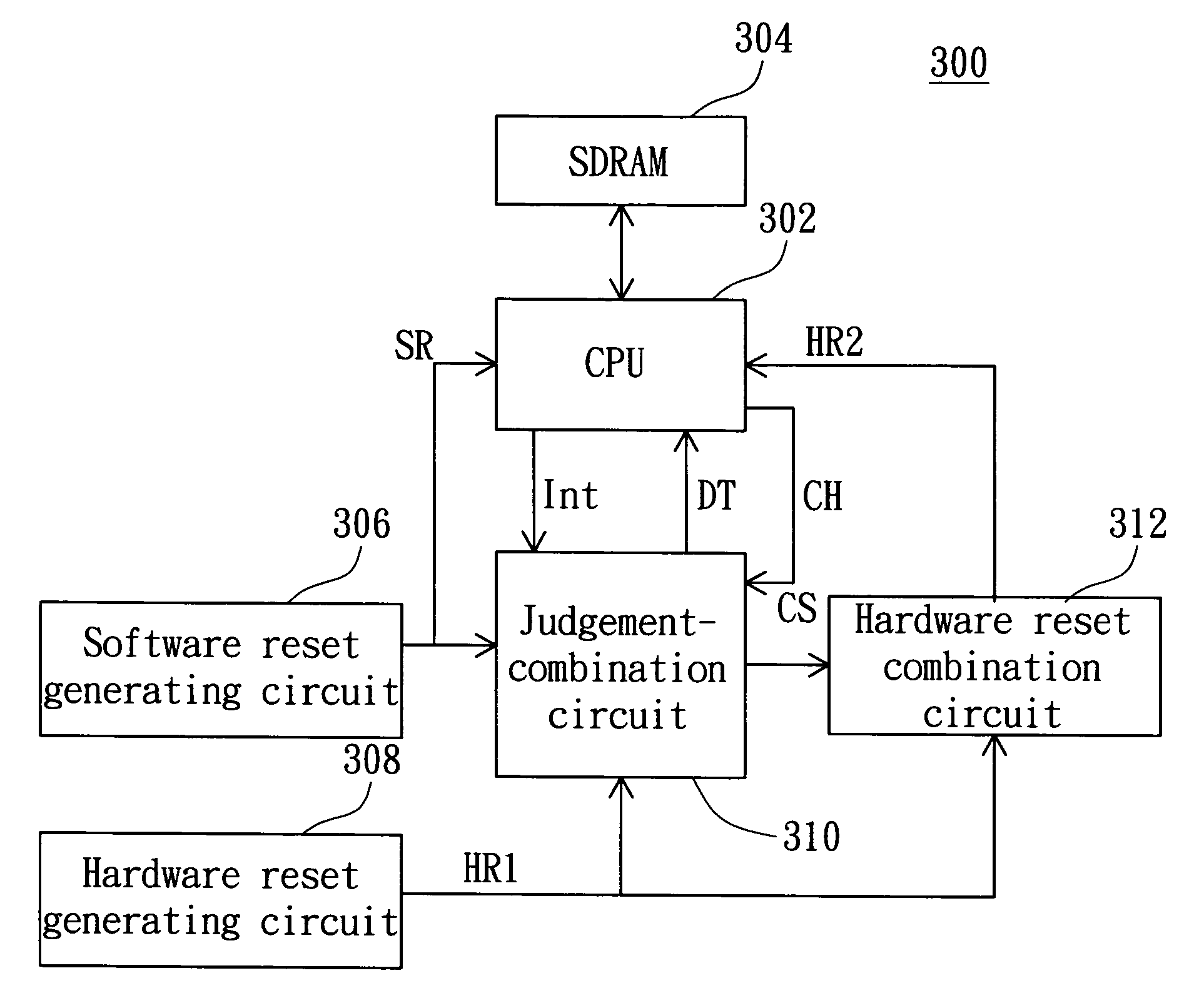

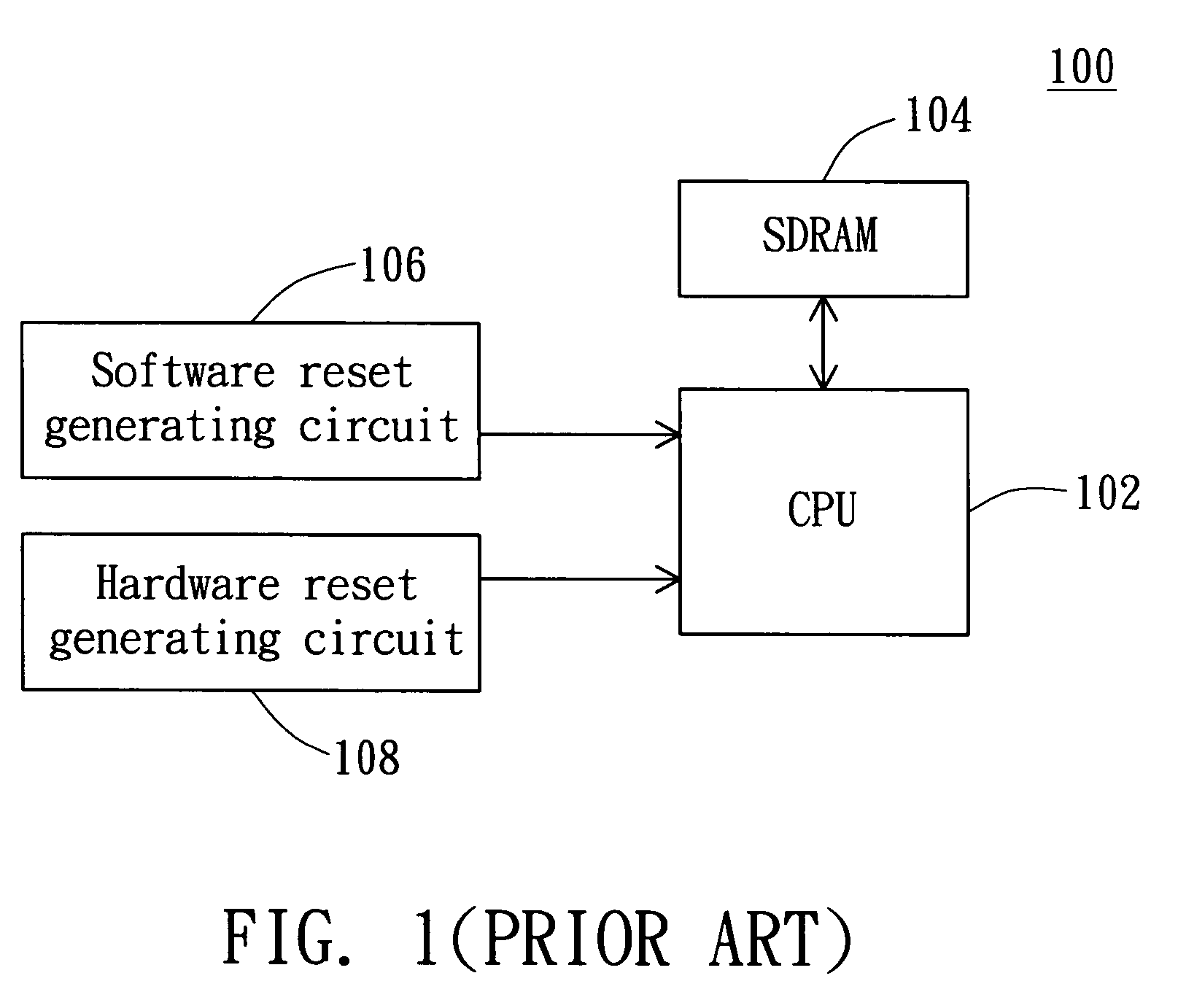

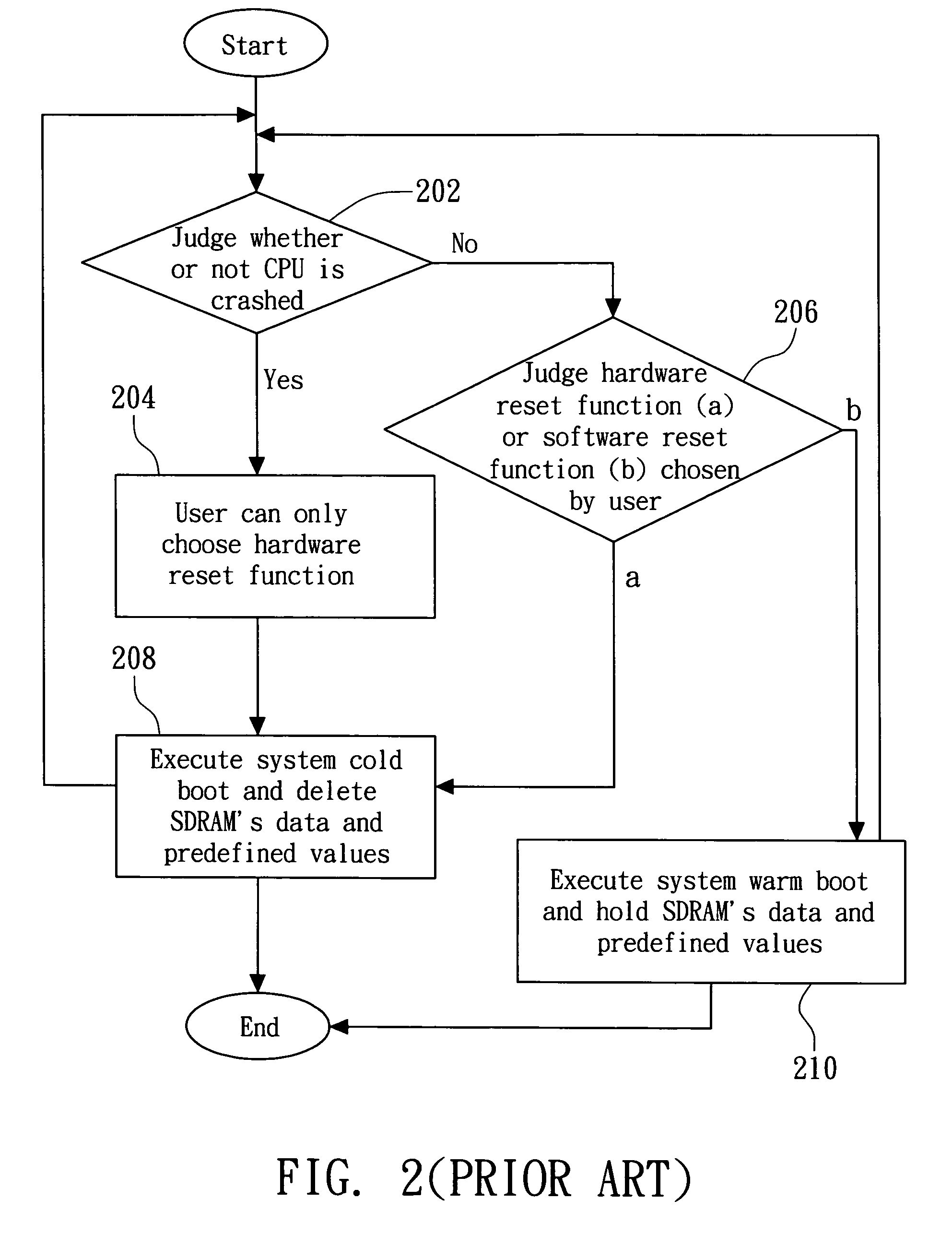

Booting method capable of executing a warm boot or a cold boot when a CPU crash occurs and computer system therefor

ActiveUS20050055598A1Eliminate timeData can be lostDigital computer detailsData resettingSystem recoveryBooting

A booting method capable of executing a warm boot or a cold boot when a CPU crash occurs in a computer system having a CPU and a memory. First, when the CPU is in a crash state, it is detected that a user wants to execute a hardware reset function or a software reset function. Next, a hardware reset operation is executed to reboot the CPU. Then, when the user chooses to execute the hardware reset function, data and predefined values of the memory are deleted to make the computer system return to a default state. Thereafter, when the user chooses to execute the software reset function, the hardware reset operation is regarded as an operation to replace a software reset operation, and the computer system holds the data and predefined values to make the computer system return to a setting state before the computer system is crashed.

Owner:HTC CORP

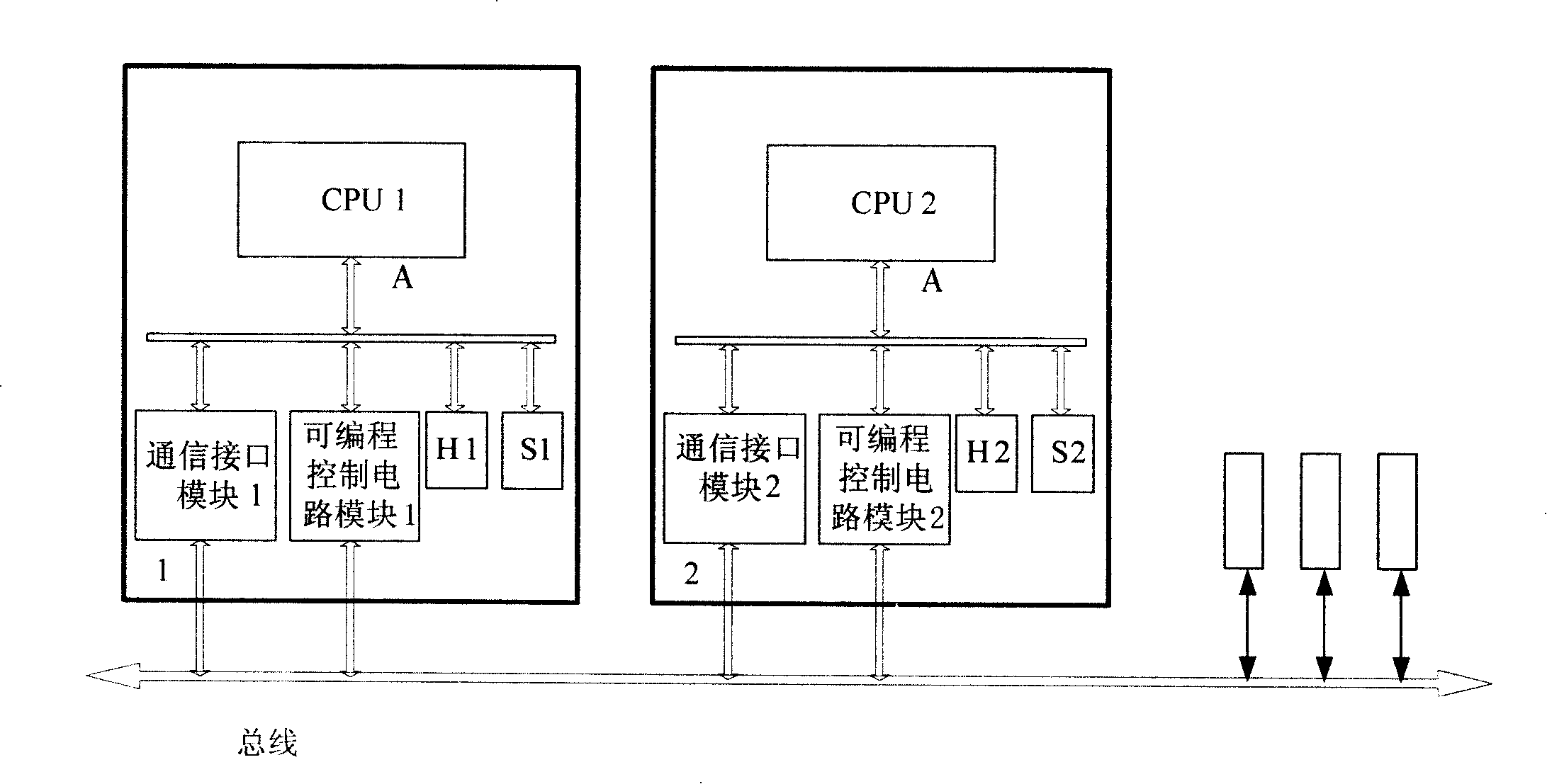

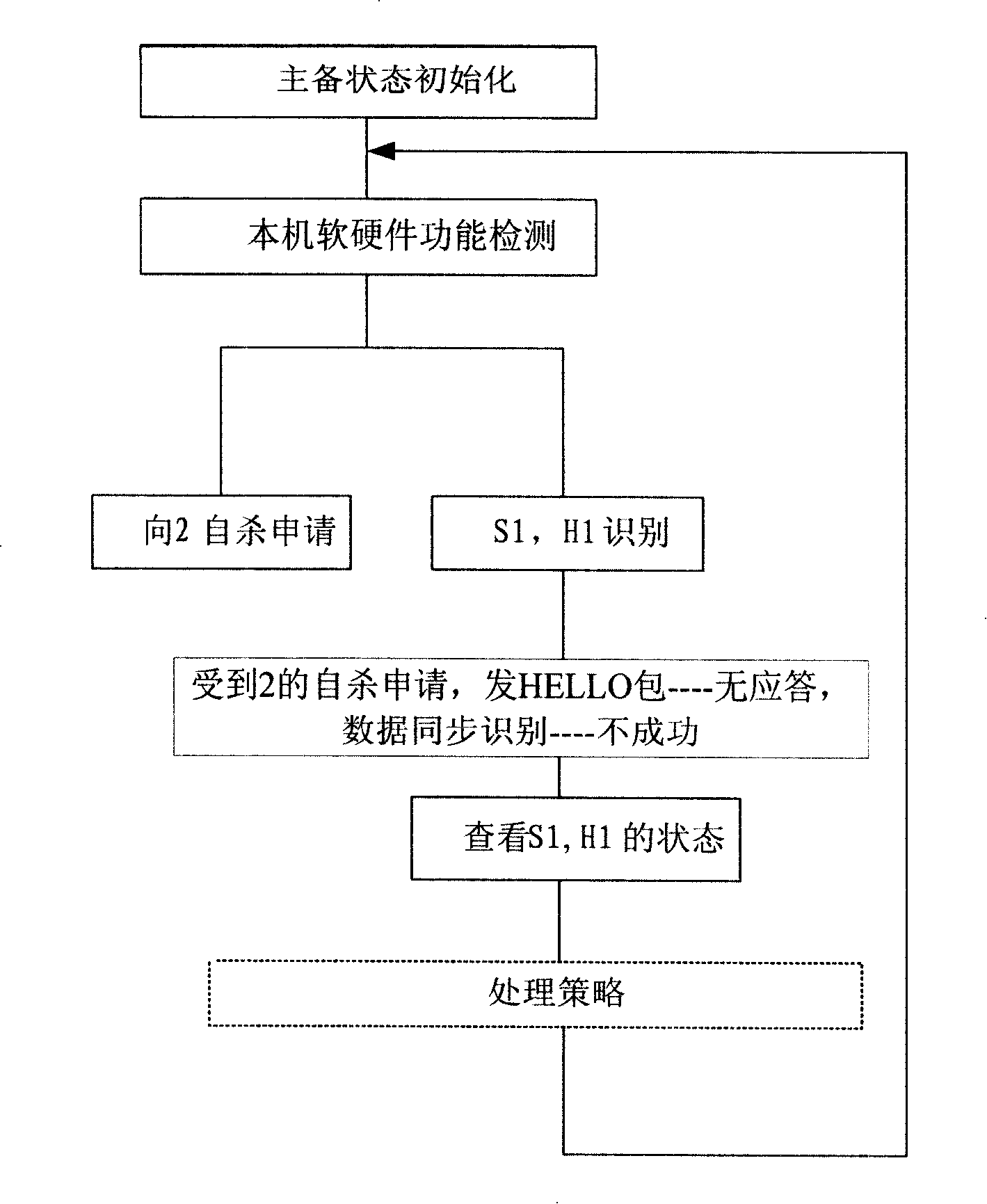

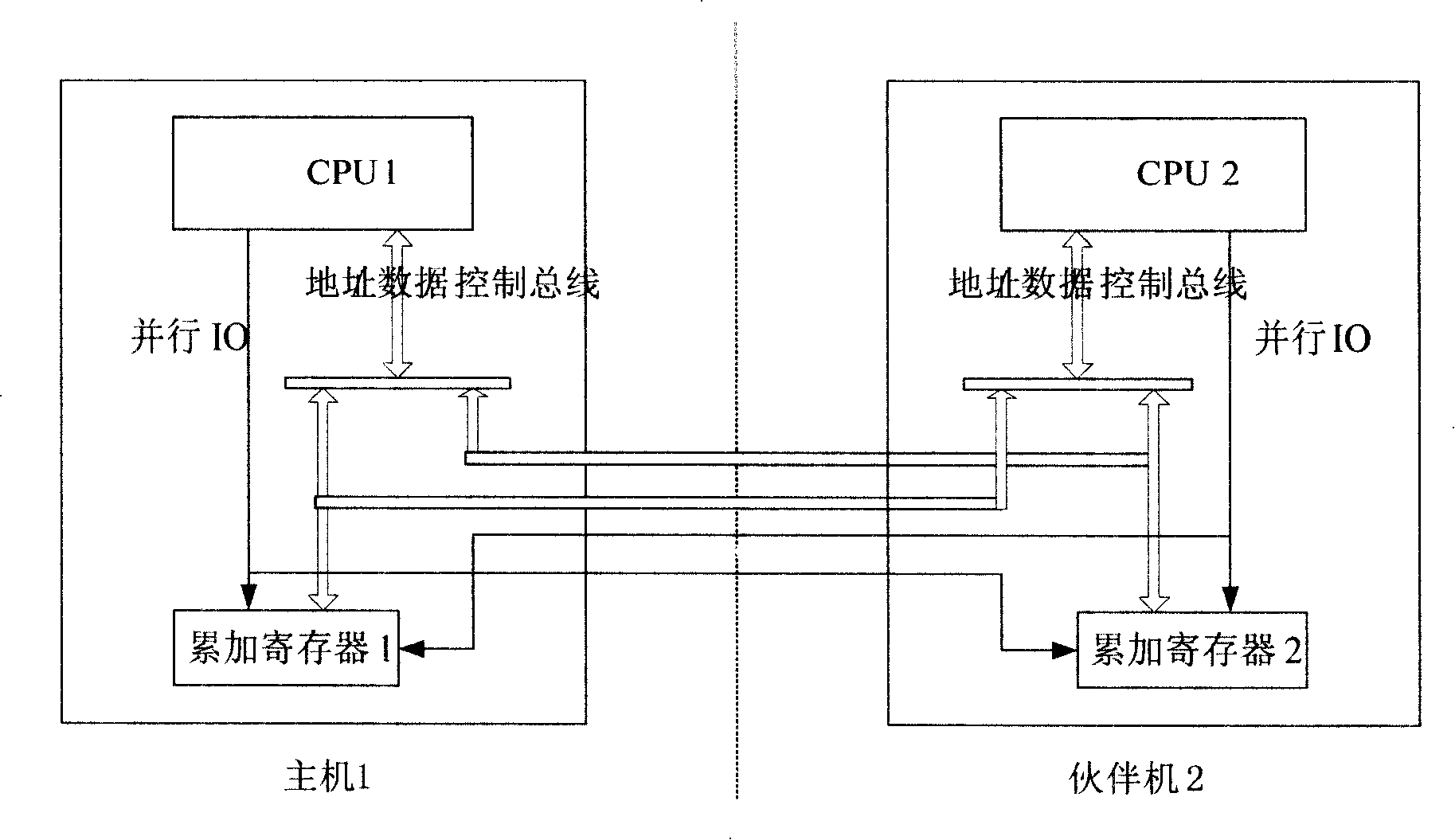

Apparatus and method of synthesis fault detection for main-spare taking turns

ActiveCN101207408AFlexible upgradeImplement hot backupError preventionData switching networksData synchronizationCommunication interface

The invention discloses a comprehensive fault detecting device and a method for shifting a main computer and a standby computer, and relates to the application communication field. The invention aims at providing comprehensive detection in main-standby shifting condition. The main computer and the partner computer of a main-standby shifting comprehensive fault detecting device are symmetric in structures. Each of the main computer and the partner computer respectively includes a CPU, a programmable control circuit module which is connected with the CPU through a CPU address / data / control bus, a communication interface module, a hardware reset register, and a software reset register; the programmable control circuit module contains a summation meter inside. A main-standby shifting comprehensive fault detecting method includes the steps of initializing a programmable control circuit and the application software; conducting state detection and data synchronization on the main computer and the partner computer periodically, and determining whether a mark in the hardware reset register and the software reset register is read according to the detection result. The invention is applicable for an important working unit which needs the communication and control bus distribution system with main-standby shifting function.

Owner:ZTE CORP

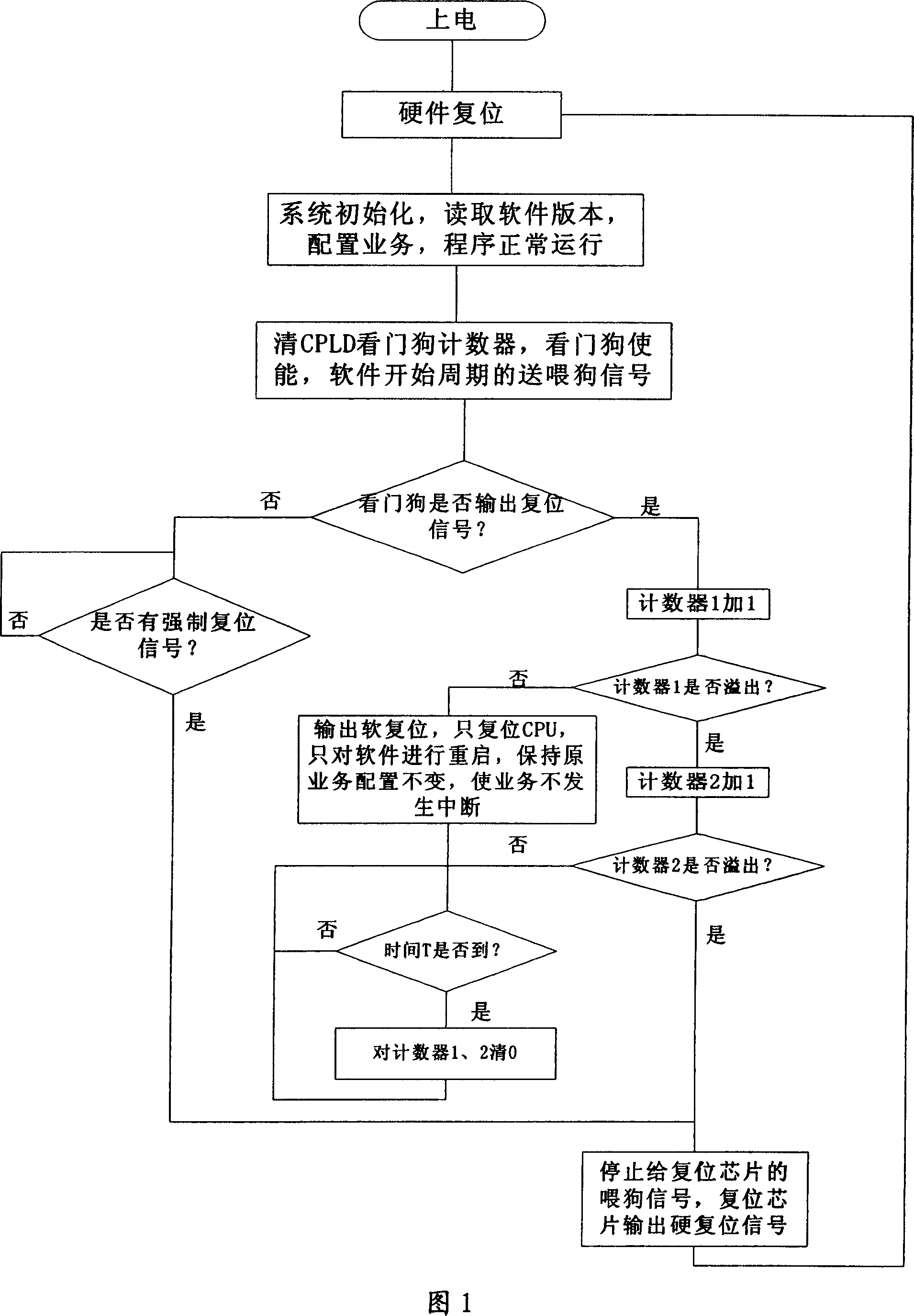

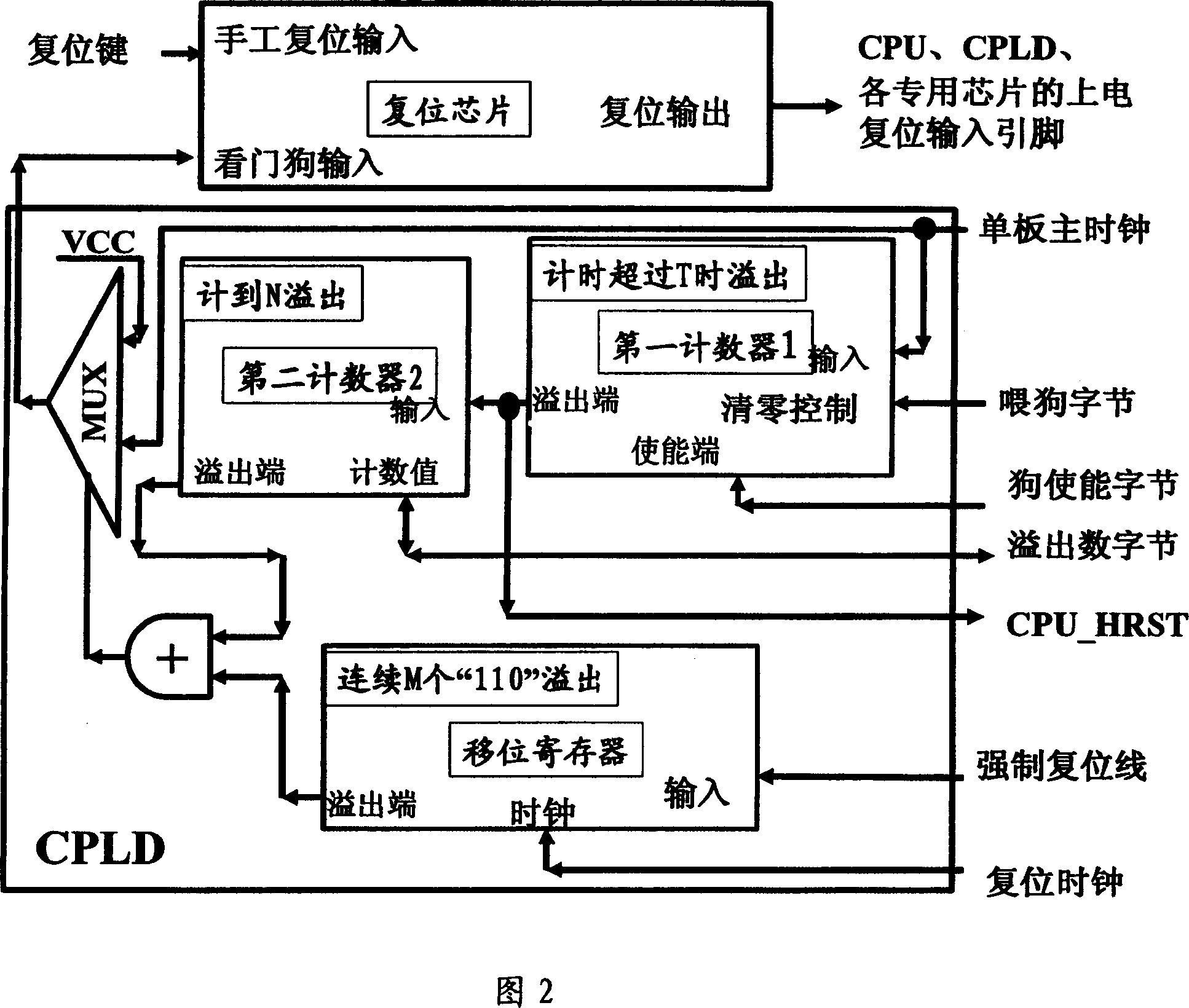

Resetting method for preventing system from dead to stop operation by associating software and hardware

ActiveCN1979381AImprove stabilityIncrease flexibilityError detection/correctionData resettingComputer hardwareSignal on

The invention discloses a reset method for preventing system from halting and interrupting services by software and hardware cooperation, comprising the steps of: selecting software reset or hardware reset on the condition that system is abnormal; for the software reset caused by software, the system only resets the CPU and does not process the service so as to assure the service is not interrupted as software reset; if the system exceeds the preset number of software resets in the preset time, making hardware reset. And the invention largely improves system stability and intelligently processes reset signals on different conditions, improving system reset flexibility and reducing possibility of service interrupt caused by abnormal reset.

Owner:BEIJING ZHIGU TECH SERVICE

Deterministic hardware reset for FRC machine

InactiveUS6954886B2Guaranteed uptimeElectronic circuit testingError detection/correctionScan lineLogic state

A processor includes one or more execution cores, each execution core having an associated scan chain to provide data to a set of voltage nodes of the core. A reset module drives a data pattern onto the scan line, responsive to a reset event. The data pattern places the set of voltage nodes of each execution core into specified logic states. For a processor including multiple execution cores configured to operate in an FRC mode, identical data patterns are driven onto the scan chains to reduce indeterminacy in the reset machine state of the processor.

Owner:INTEL CORP

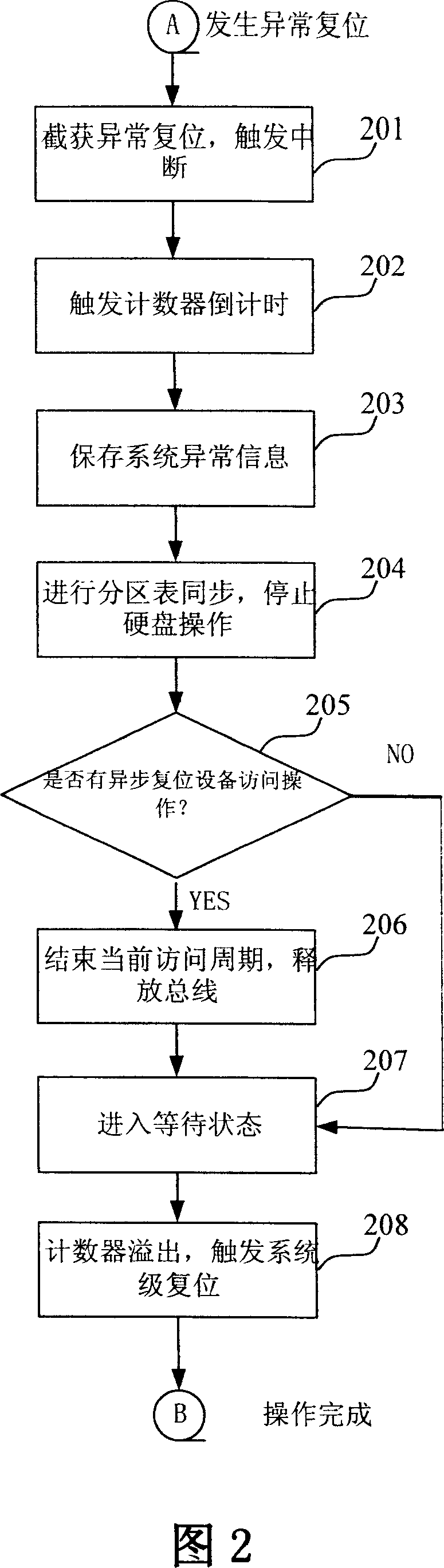

Abnormal reset system protection method and reset protection system

InactiveCN101025700AValid recordAvoid illegal occupationError detection/correctionData resettingSystem protectionProtection system

The invention relates to a system protecting method for abnormal reset and a reset protecting system, and the method comprises the steps of: 1. when system abnormal reset occurs, automatically capturing system hardware reset by the reset protecting system and not distributing the reset to a processor; 2. the reset protecting system utilizes the hardware reset to trigger to make system protection operations; 3. when all system protection operations end, the reset protecting system releases the captured hardware reset and triggers the processor to reset. And the invention avoids harddisk damage caused by abnormal reset and assures the system bus is not occupied by asynchronous reset as reset. Besides, it can store abnormal information, convenient to collect data about reset problem difficult to reproduce as debugging a device and quickly locate repeated restart failure.

Owner:ZTE CORP

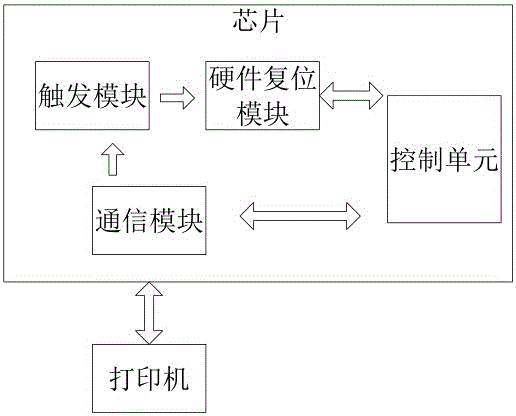

Software reset consumable chip and system, and use method thereof

The invention relates to the field of printing, and specifically relates to a software reset consumable chip and system, and a use method thereof. The invention is implemented by the following technical scheme: the software reset consumable chip comprises a control unit comprising a communication module for receiving a reset signal, wherein the communication module is connected with the control unit; the software reset consumable chip further comprises a hardware reset module; the communication module sends the reset signal to a trigger module or the control unit, and the trigger module or the control unit can trigger a reset mark to the hardware reset module; and the hardware reset module starts program reset according to the reset mark. The invention aims at providing the software reset consumable chip and system, and the use method thereof. The reset signal is responded depending on the hardware reset module arranged in the chip to perform software reset on the chip without adding additional trigger space of pins or affecting the function continuity of the chip.

Owner:HANGZHOU CHIPJET TECH

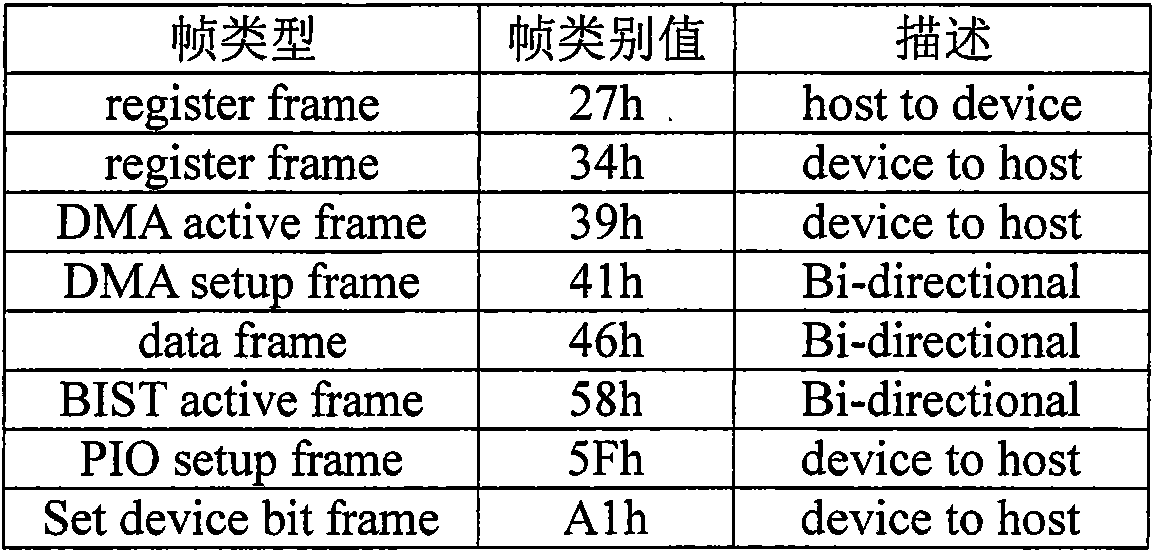

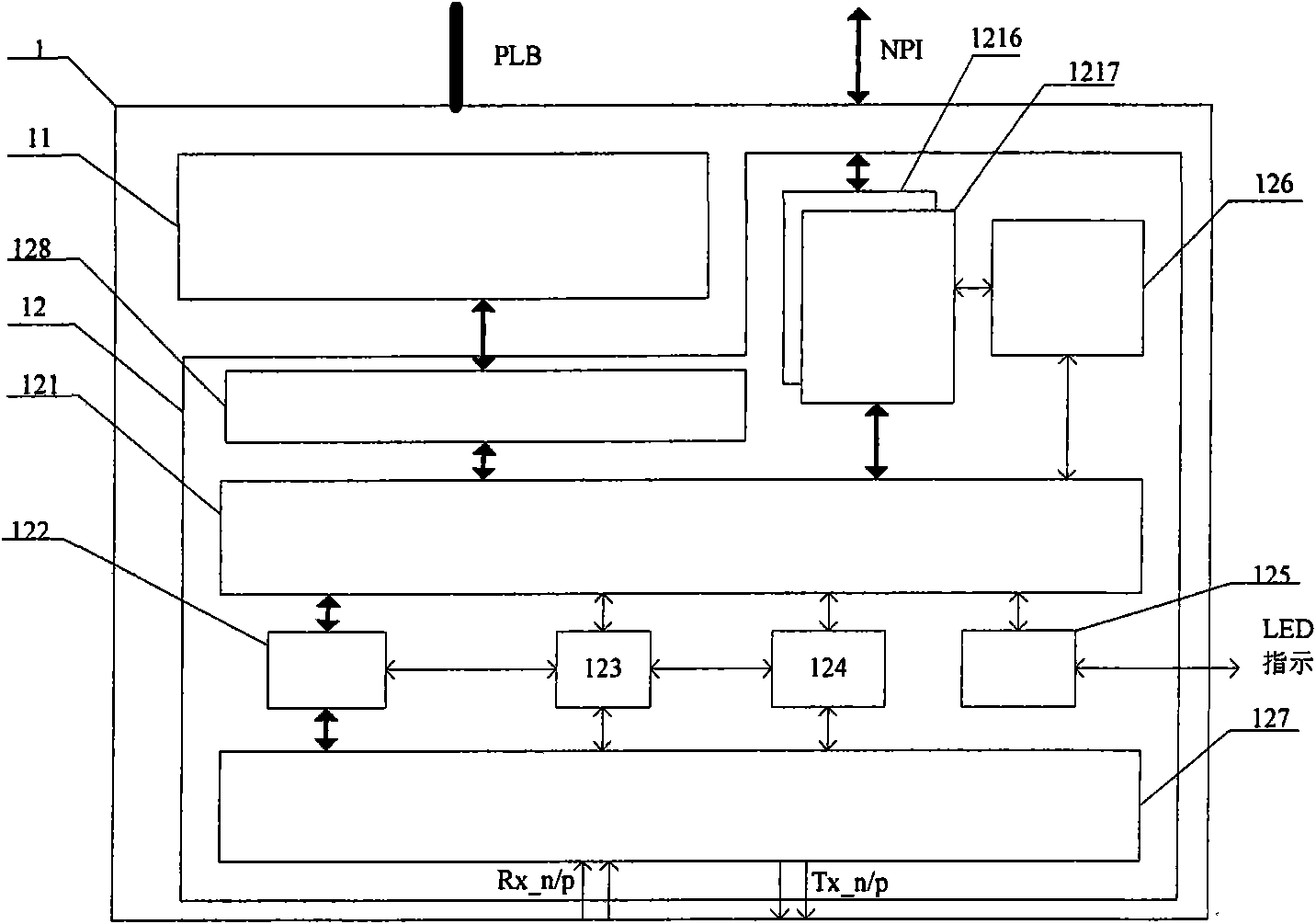

SATA controller based on FPGA

InactiveCN101599004AReduce areaImprove reliabilityInput/output to record carriersElectricityCode module

A SATA controller based on FPGA comprises a cyclic redundancy check module for executing cyclic redundancy check calculation on data, a scrambling / descrambling code module for executing scrambling / descrambling code calculation on data, a frame generating module for finishing the packaging of frame, a frame sending module for controlling the sending, pausing and ending of frame, a frame receiving module for finishing the analysis of frame, a register group for storing the control and state information of the controller, a subscriber interface module for realizing the information and data switching between a processor and the controller, and between a memory and the controller through PLB and NPI interfaces, an out-of-band-signal control module for controlling the electricity and hardware resetting process on a rigid disk and founding the communication link between the controller and the rigid disk, an interface transfer rate select module for automatically selecting the interface transfer rate of the rigid disk, a reset module for generating the reset signal of each submodule, a gigabit-grade transceiver mainly for finishing 8B / 10B coder and decoder, deserializing,clock amending and the like and an LED indication modular for indicating the working condition of the rigid disk.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

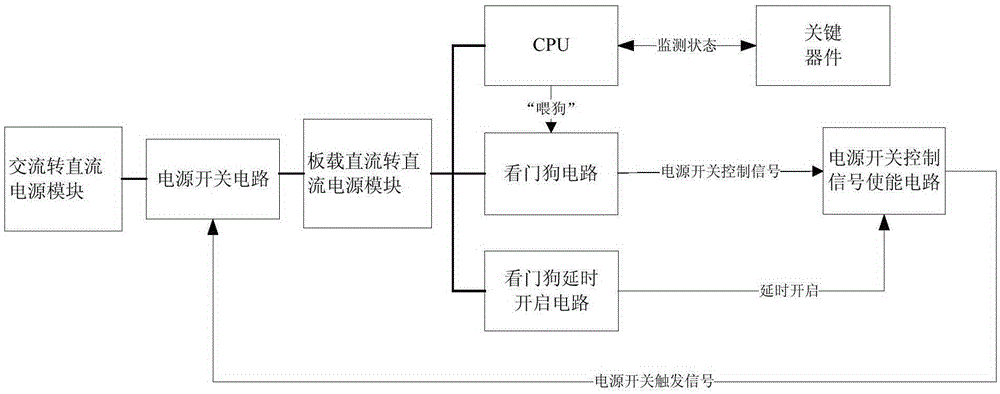

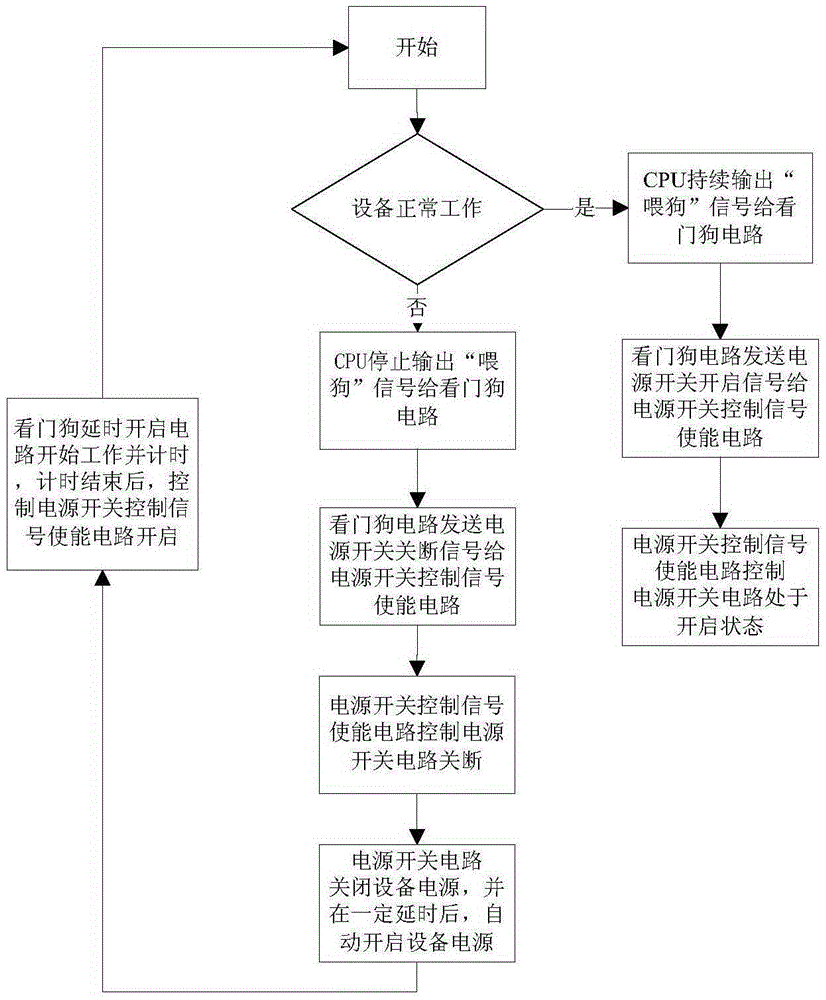

Circuit with automatic power-off restarting function in equipment failure

InactiveCN105302263ASolve unsolvable problemsA state that prevents repeated restartsFault responseData resettingPower switchingControl signal

The invention provides a circuit with an automatic power-off restarting function in equipment failure. A CPU of the equipment is connected with a key device of the equipment and the CPU is capable of monitoring the working state of the key device; when the equipment has hardware damage-free failure, the CPU stops outputting a feeding-dog signal, a watchdog circuit does not trigger the system hardware reset any more, and outputs a power switch control signal; a power switch circuit turns off the direct-current power supply of the equipment after being triggered; and after certain time delay, the power switch circuit automatically starts the direct-current power supply of the equipment to ensure that the equipment is restarted to restore the normal work. According to the circuit provided by the invention, the failure problems of all the hardware damage-free units can be solved; no matter whether the units with failures have hardware reset functions or not, the adopted power-off restarting manner is more thorough than the traditionally adopted hardware reset manner.

Owner:中电科网络安全科技股份有限公司

Electronic system with NAND flash memory storing boot code and highly reliable boot up method

InactiveUS7870378B2Additional drawbackIncrease success rateError preventionTransmission systemsElectronic systemsTime delays

A boot up method makes an electronic system boot up by a processor according to a boot code in a NAND flash memory and includes the following steps. First, the flash memory storing a boot code or boot codes is provided. Next, a first boot code is copied to an XIP memory in response to a hardware reset signal. Then, the processor executes the first boot code in the XIP memory and thus makes the system boot up. Next, whether the system boots up successfully is judged after a time delay. When the system fails to boot up, the system is reset and a second boot code is copied to the XIP memory. Thereafter, the processor executes the second boot code in the XIP memory and thus boots up the system. If the system still fails to boot up, the above-mentioned steps are repeated until the system boots up successfully.

Owner:MAGIC PIXEL

Securing the contents of data storage devices within a computer

ActiveUS8245026B1Avoid changeRemoval of powerDigital data processing detailsDigital computer detailsComputer hardwareOperational system

Owner:AMERICAN MEGATRENDS

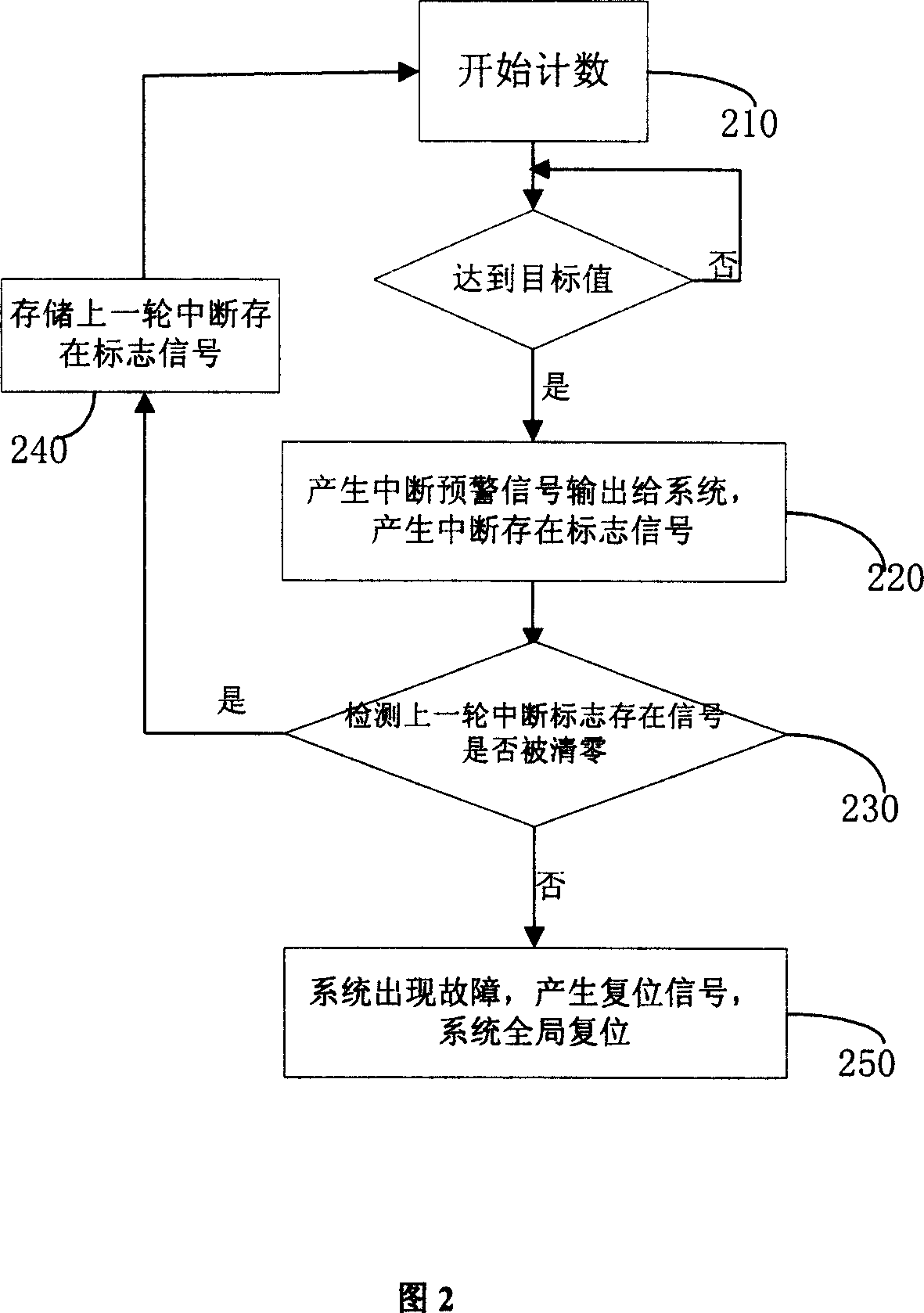

Safeguard device and safeguard interruption prewarm method

The invention relates to a door dog device with alarm function, wherein said device comprises latch, counter, and controller; when the counter reaches the target value preset in latch, it can alarm to the system via interruption alarm signal, and send out interruption mark signal to the controller, therefore, the system can based on alarm signal store and copy the system data, to avoid data loss and error caused by system reset without alarm function; in addition, the zero of door dog can be processed by several methods as hardware reset, software reset and automatic reset, without additional timer in system to periodically reset the door dog, to save system resource and reduce cost.

Owner:南通江涌投资开发有限公司

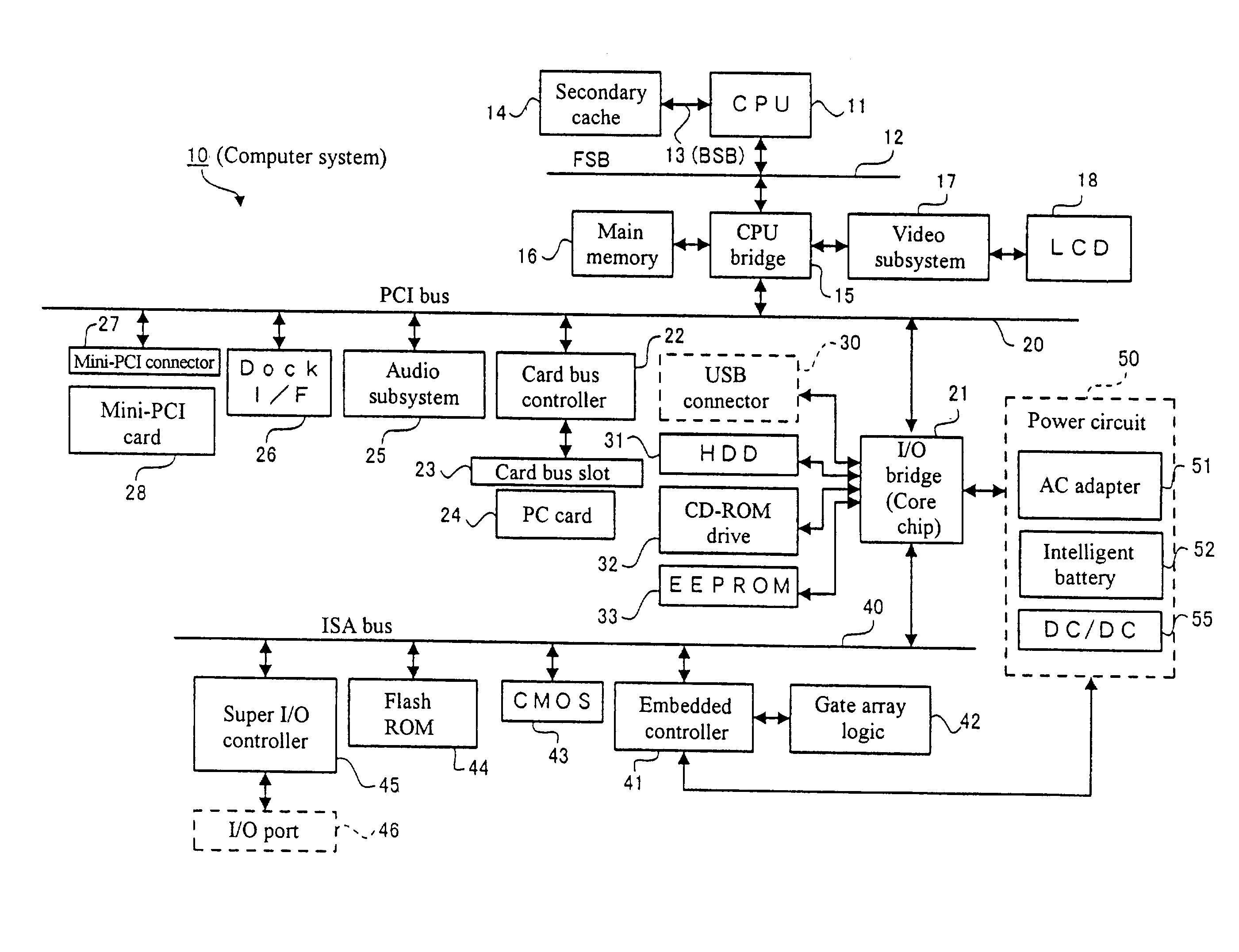

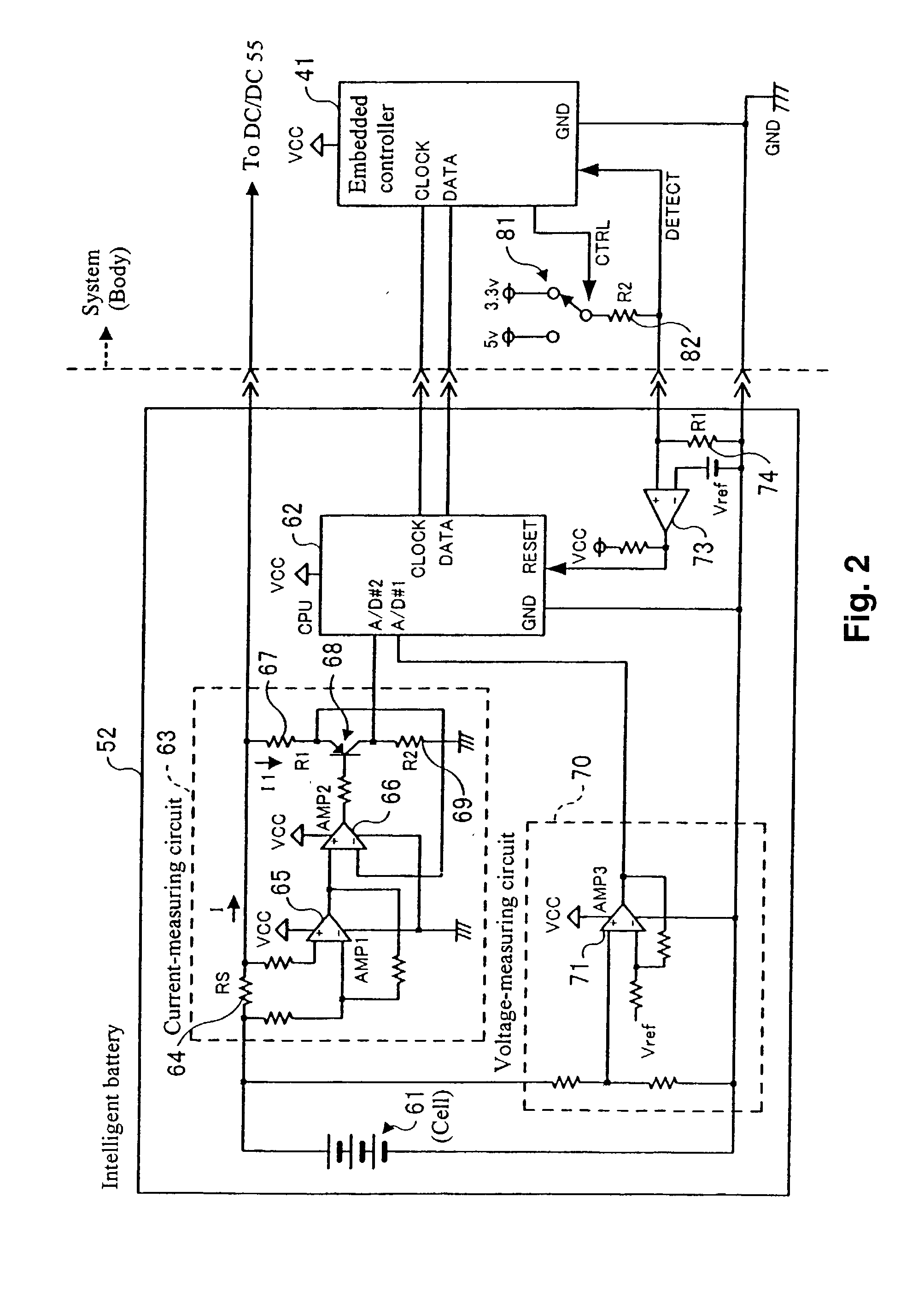

Electrical apparatus, computer equipment, intelligent battery, and control method for battery

InactiveUS20030115001A1Batteries circuit arrangementsElectrical testingHardware resetElectrical battery

The apparatus of this invention has a resetting function for software- or hardware-resetting a battery when a CPU in the battery hangs up and becomes inoperable or inoperative to make it possible to recover the CPU of the battery from a hang-up state. An electrical apparatus having a body for consuming power and constituted so as to be able to connect with a battery for supplying power to the body by discharging after being charged, has trouble recognition means for recognizing a trouble of the battery and resetting means for resetting the battery in accordance with the recognition by the trouble recognition means.

Owner:IBM CORP

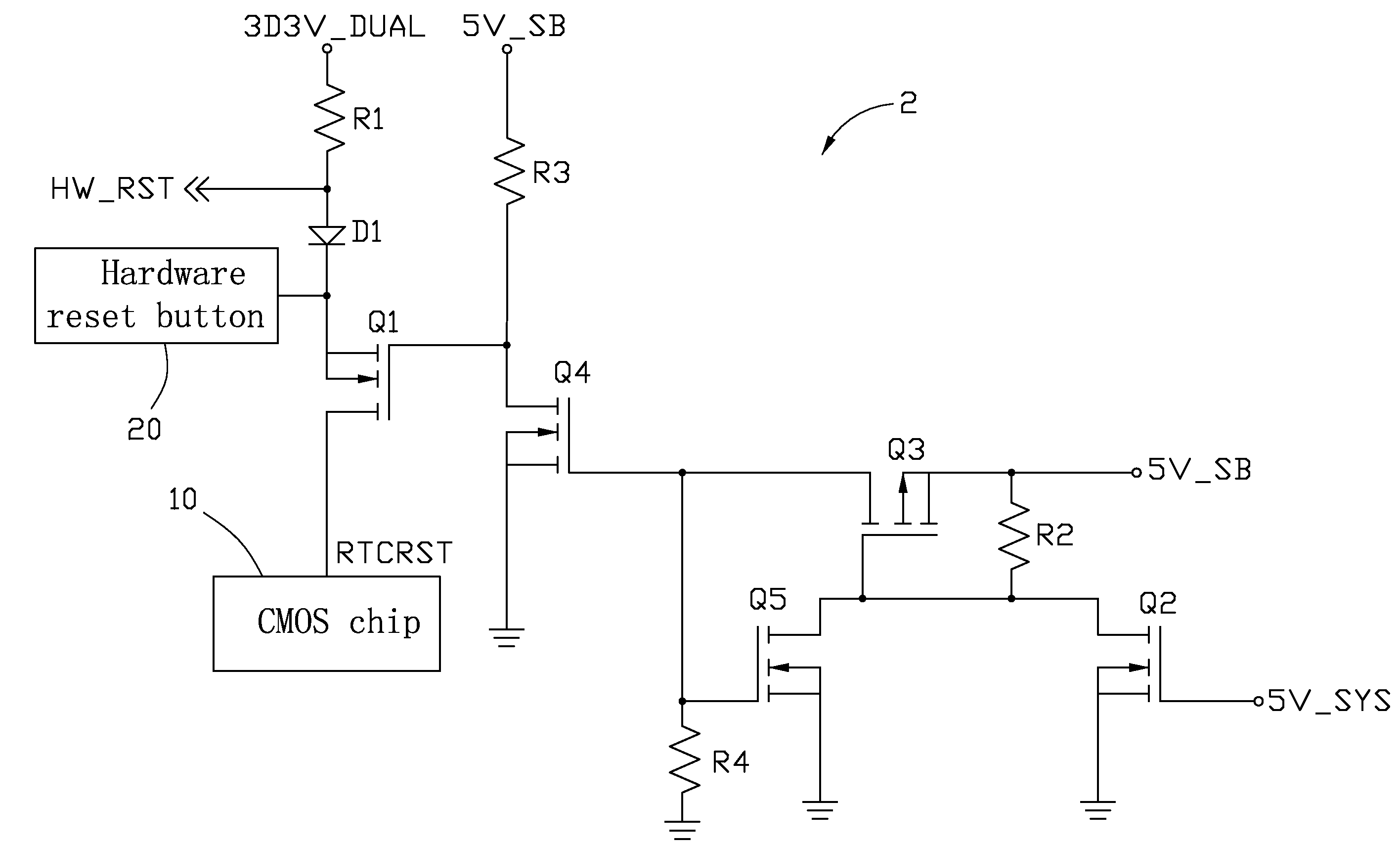

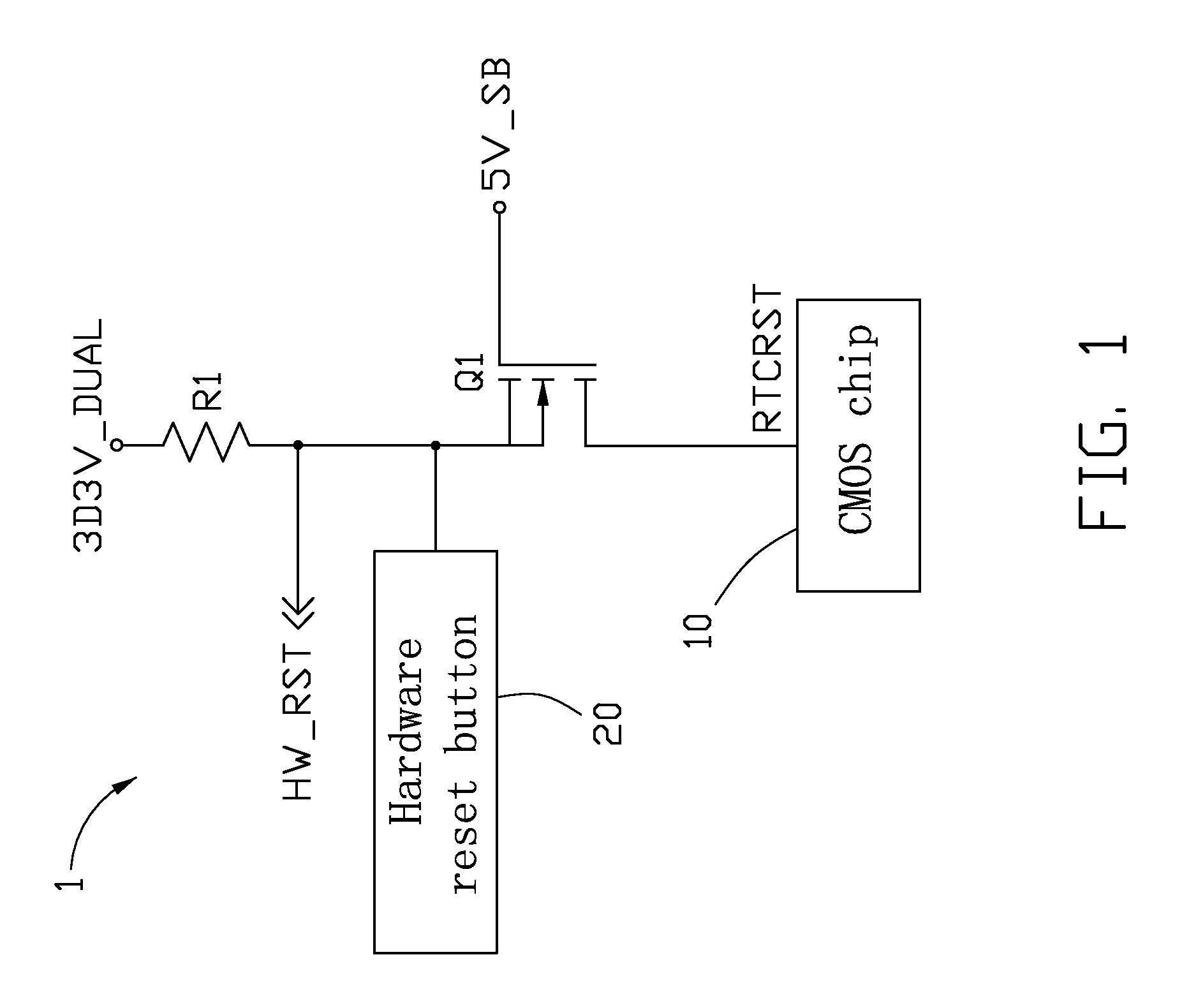

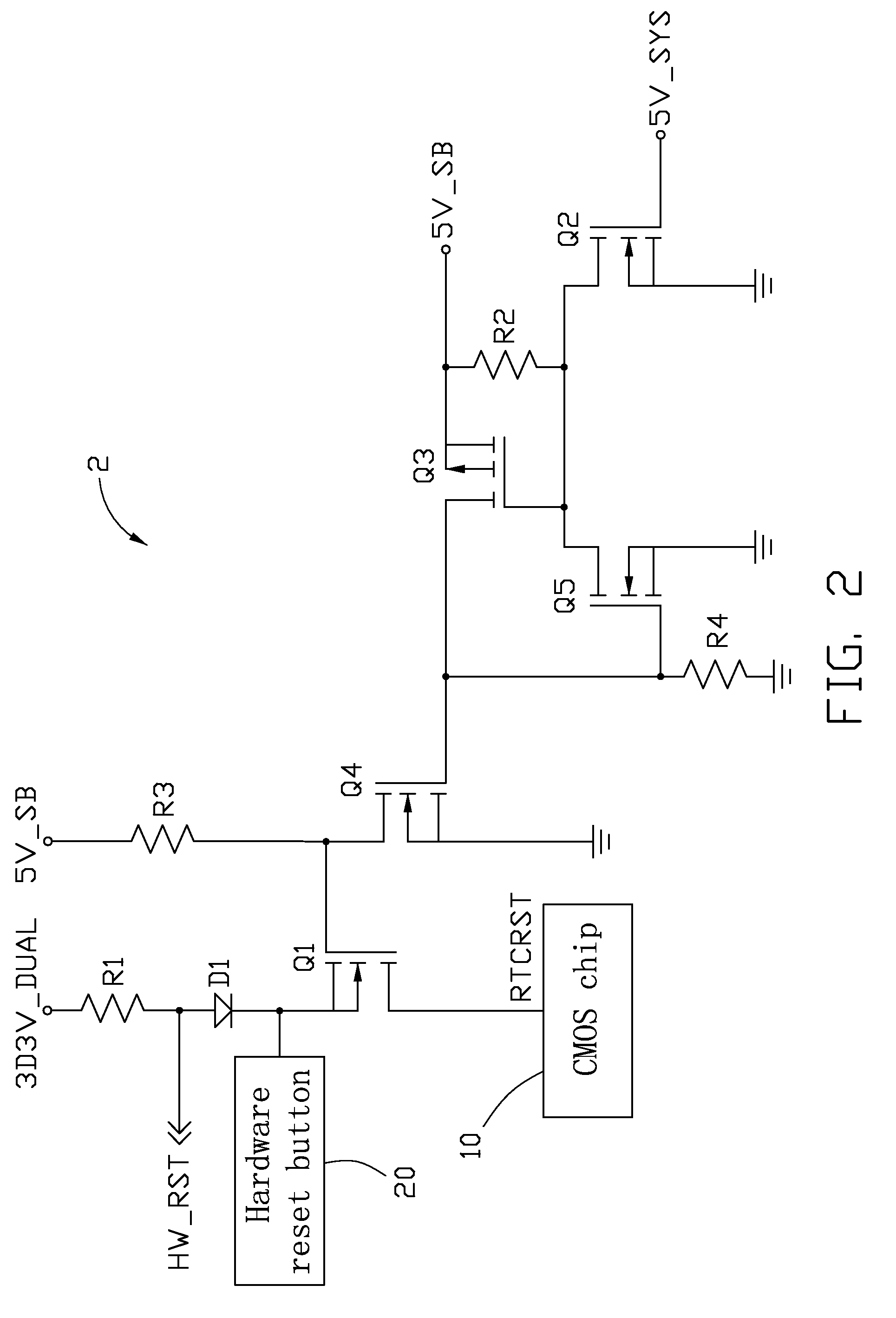

Circuit for clearing CMOS information

A circuit for clearing complementary metal oxide semiconductor (CMOS) information of a CMOS chip of a computer includes a resistor and an electronic switch. The electronic switch includes a first terminal, a second terminal, and a third terminal. The first terminal is connected to a standby power supply of the computer. The second terminal is connected to a software reset pin of the CMOS chip. The third terminal is connected to a dual power supply of the computer via the resistor, and is connected to a hardware reset pin of the computer. The standby power supply is provided, and the first electronic switch is turned on before the computer is booted up. The software reset pin may be triggered to clear CMOS information of the CMOS chip upon the condition that the hardware reset pin is triggered.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

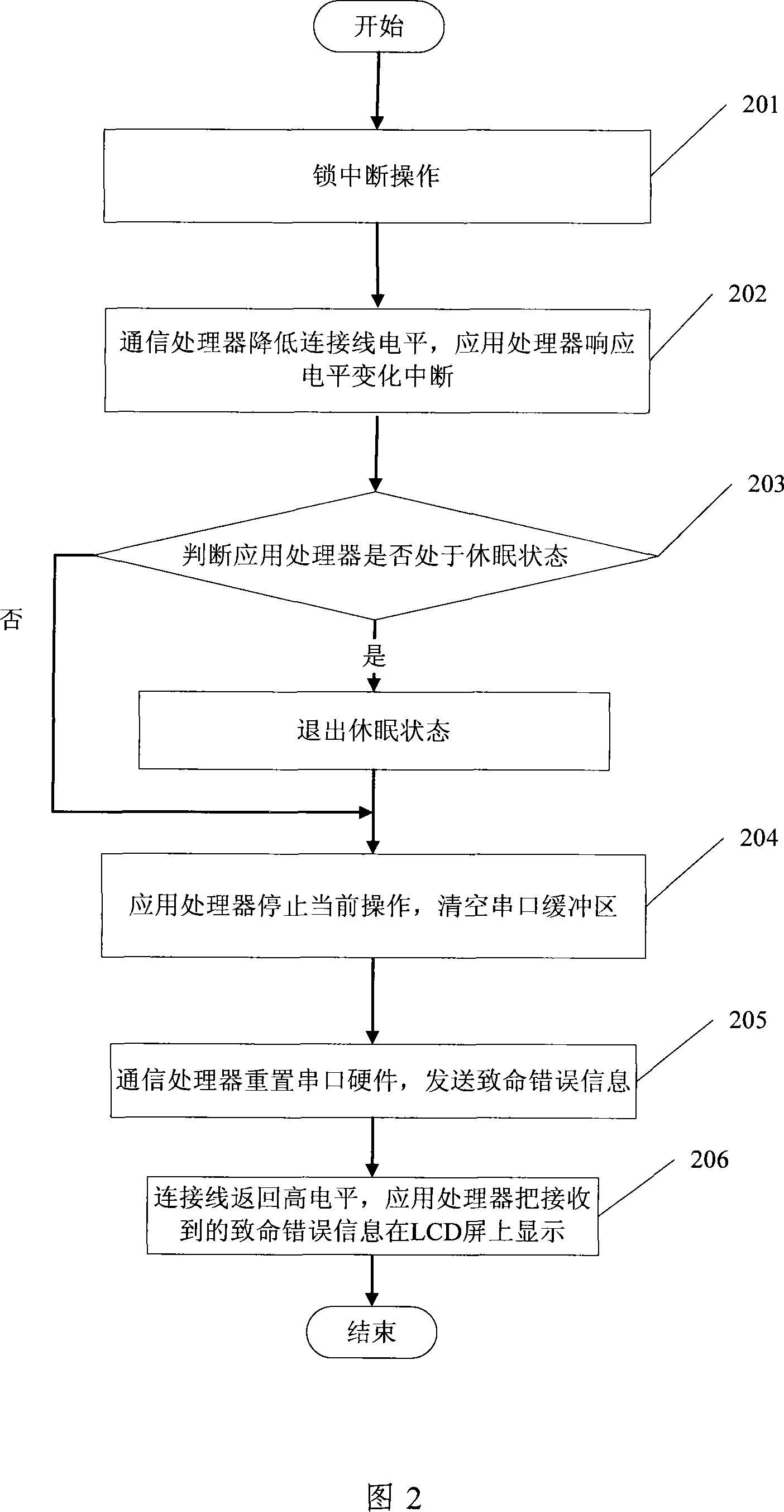

Mobile phones communication processor causing death error information instantaneously displaying method

InactiveCN101178680AOvercoming crashesFind the cause of the crashError detection/correctionRadio/inductive link selection arrangementsMobile phoneApplication processor

The invention discloses a method for instantly displaying fatal error information of a communication processor of a mobile phone. When a fatal error occurs in the program operation of the communication processor, it jumps to the crash processing step; firstly, the lock interrupt operation is performed on other hardware devices; By changing the level of a connection line with the application processor, a notification of fatal error information is issued; the application processor responds to the level change interrupt and stops all current operations, including the interactive operation between the application processor and the communication processor , and clear the serial port buffer, ready to receive fatal error information; the communication processor resets the serial port hardware, and sends the fatal error information to the application processor through the serial port; finally, after the application processor receives the fatal error information, it displays the information on the mobile phone screen It can quickly and effectively find and solve the fatal error information of the mobile phone communication processor.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

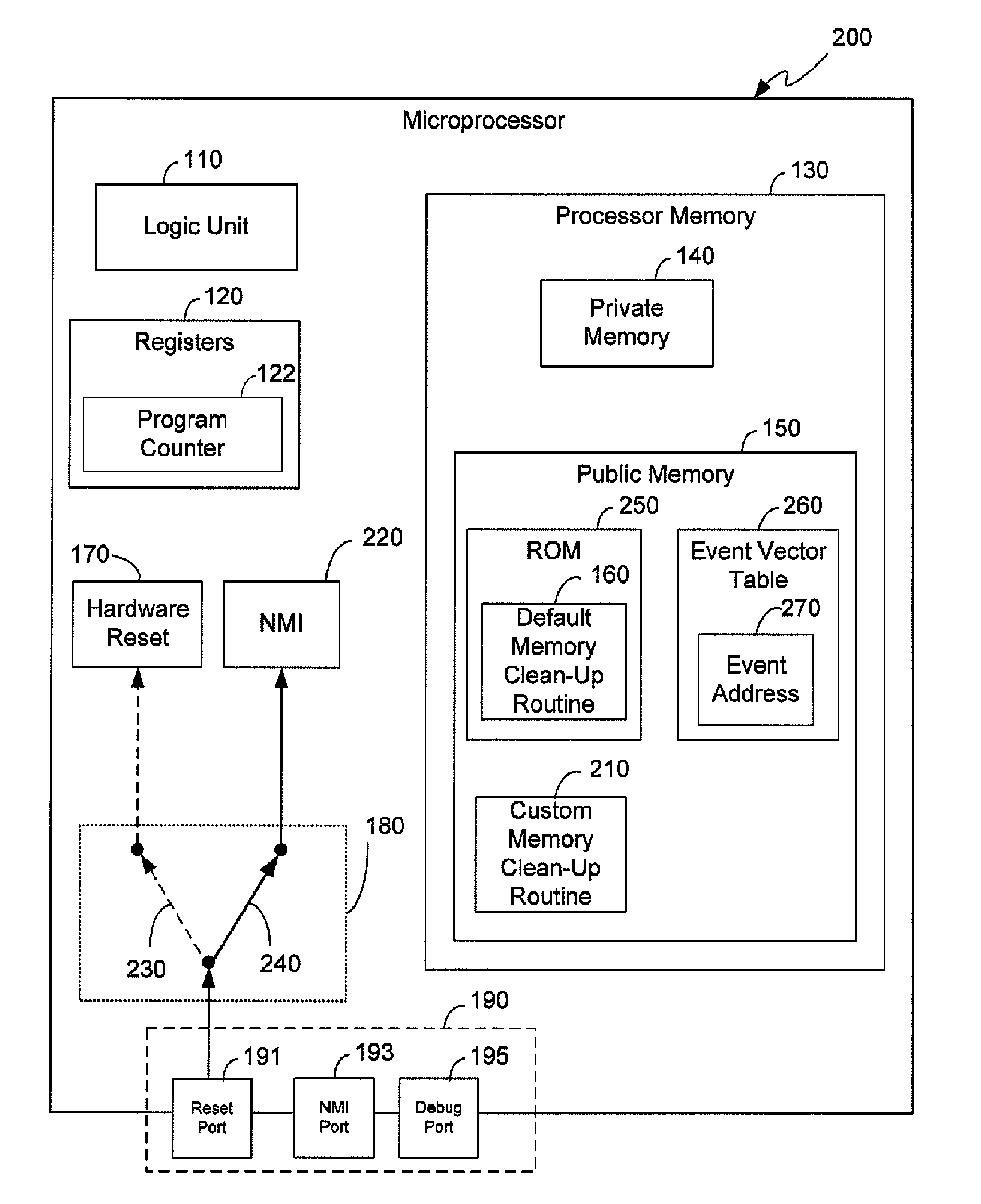

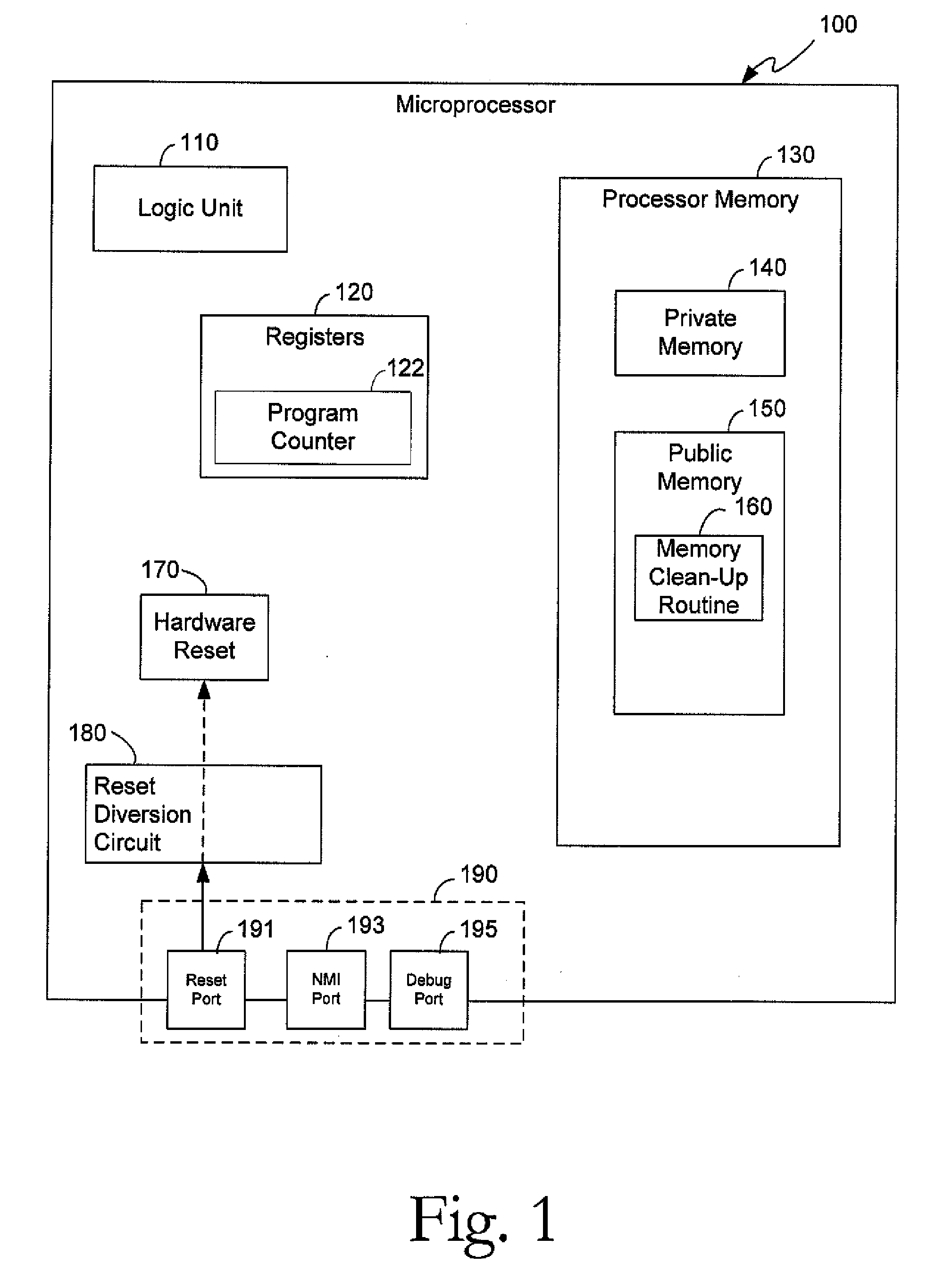

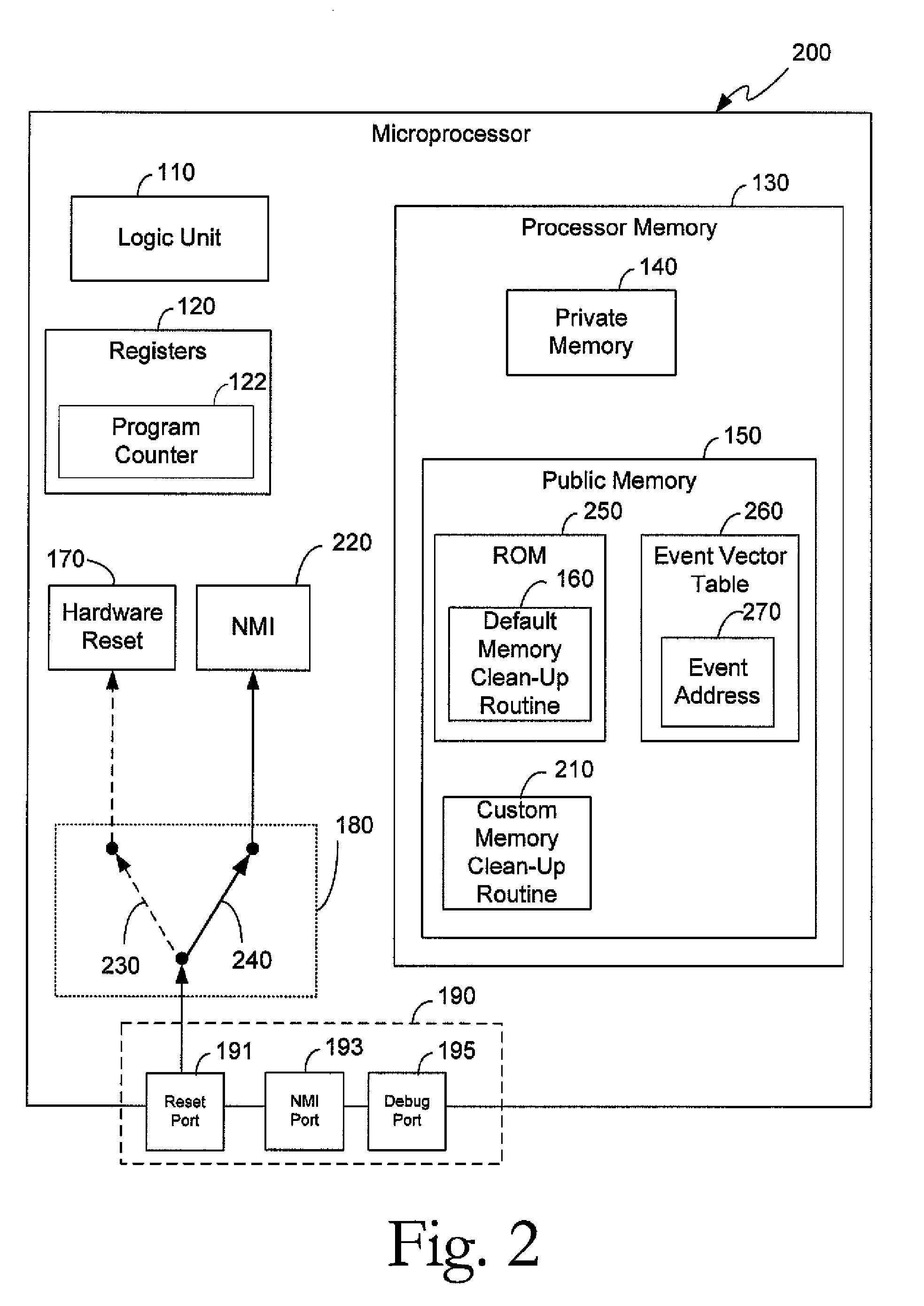

Method and apparatus for hardware reset protection

A method and apparatus for protecting access to sensitive information stored in vulnerable storage areas (e.g., public memory, registers, cache) of a microprocessor. A microprocessor having a reset port to receive external reset commands may have a reset diversion circuit that may be selectively enabled. The microprocessor may operate in an open mode or a secure mode, indicating the absence or the potential presence, respectively, of sensitive information in the vulnerable storage areas. In open mode, the reset diversion circuit may be disabled such that external reset requests triggers a hardware reset. In secure mode, sensitive information may be recorded on vulnerable storage areas. The reset diversion circuit may be enabled to divert external reset requests to an interrupt which may trigger execution of a software code. The software code, when executed, may perform a secured system clean-up routine to erase the vulnerable storage areas prior to reset.

Owner:ANALOG DEVICES INC

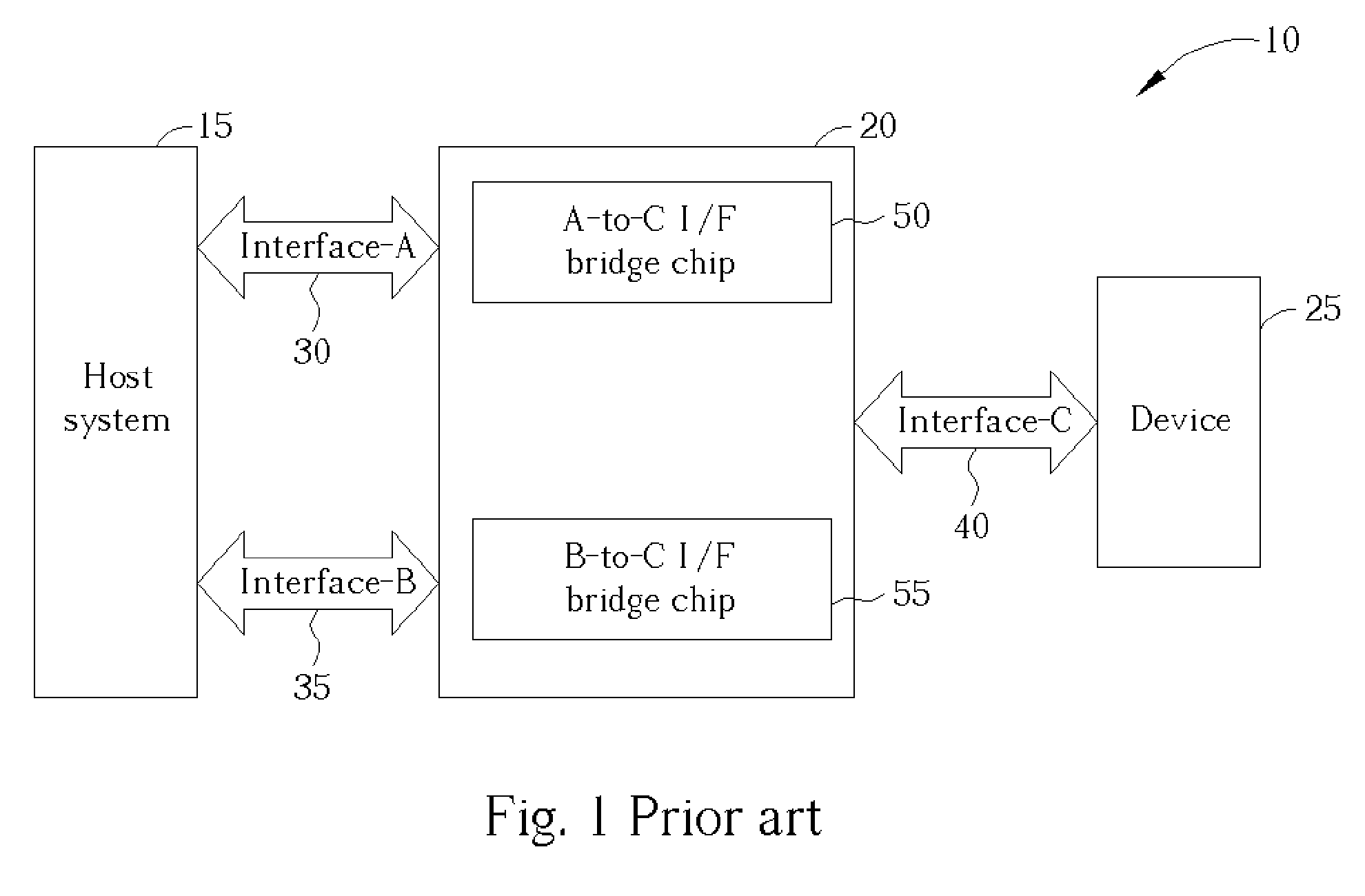

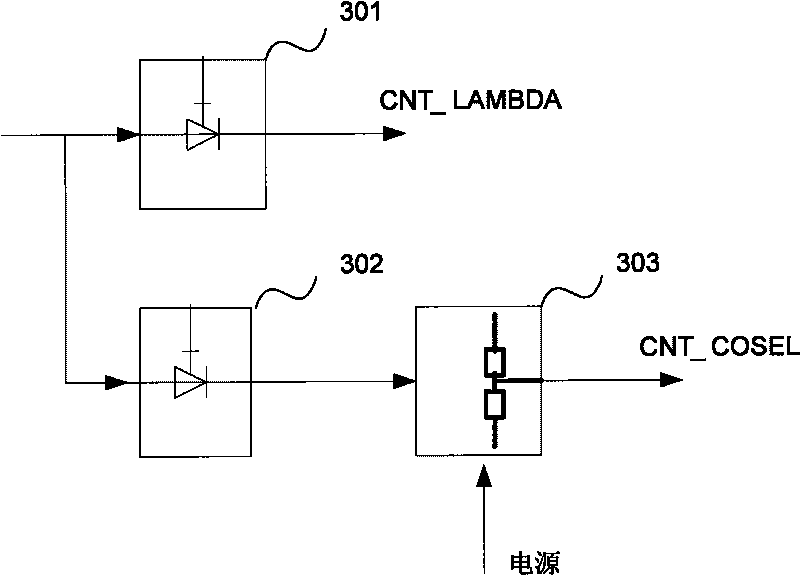

Method of function activation on a bridge system

Owner:MEDIATEK INC

Reset method and monitor

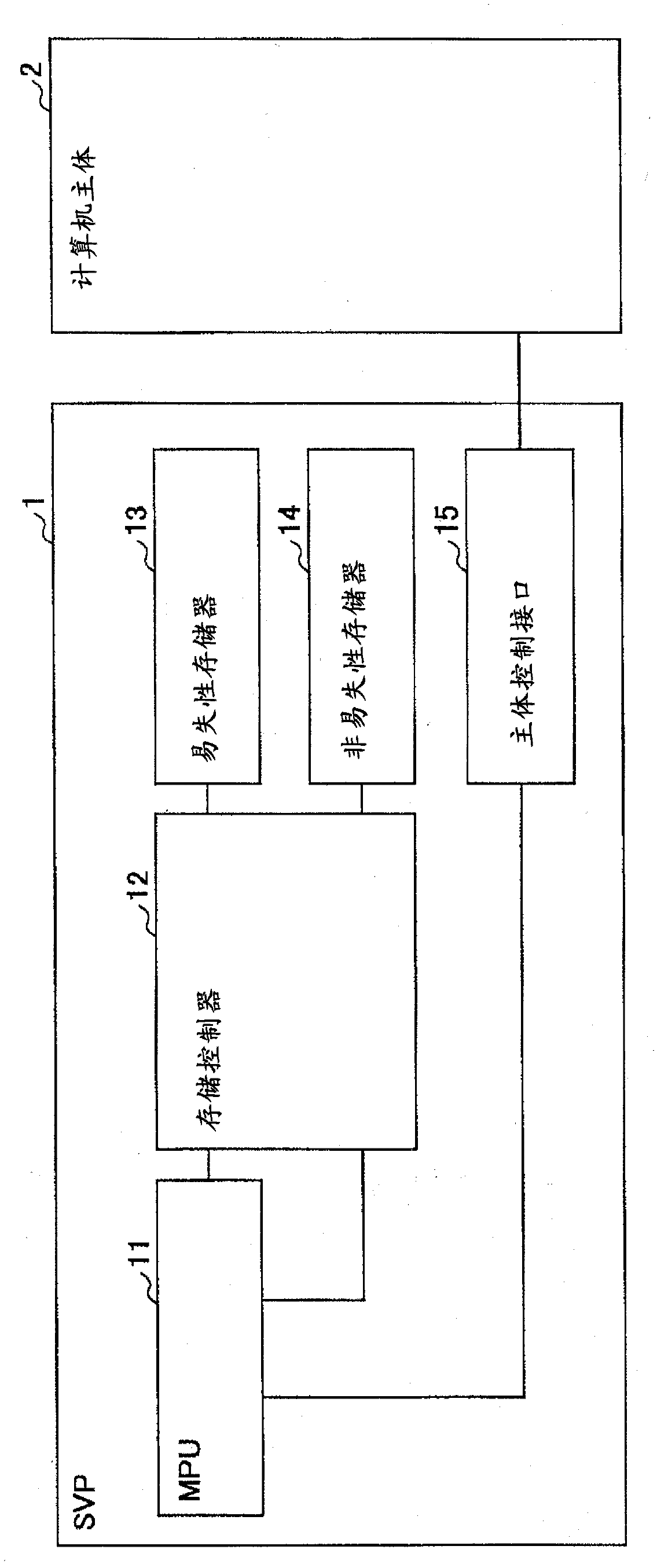

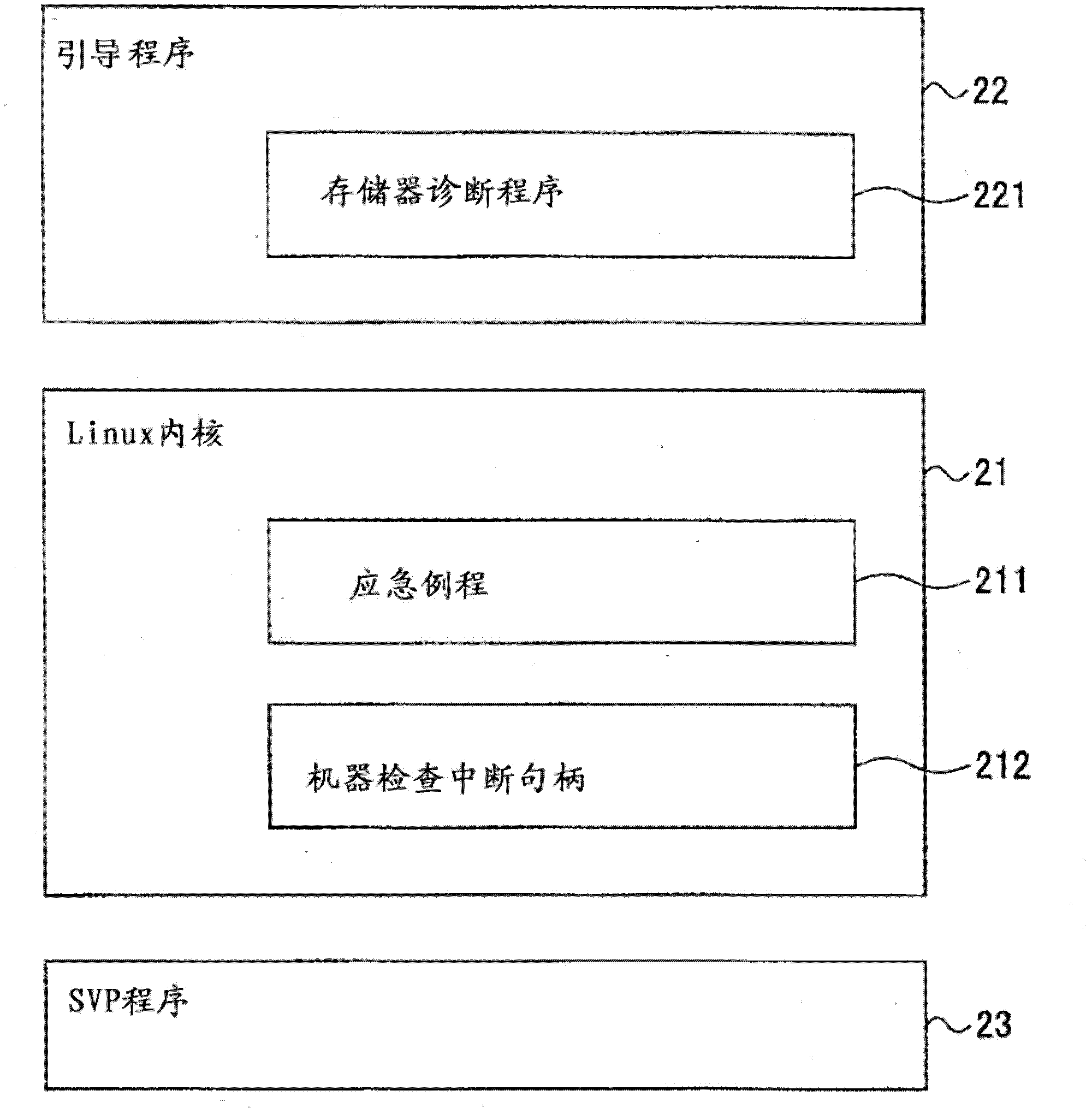

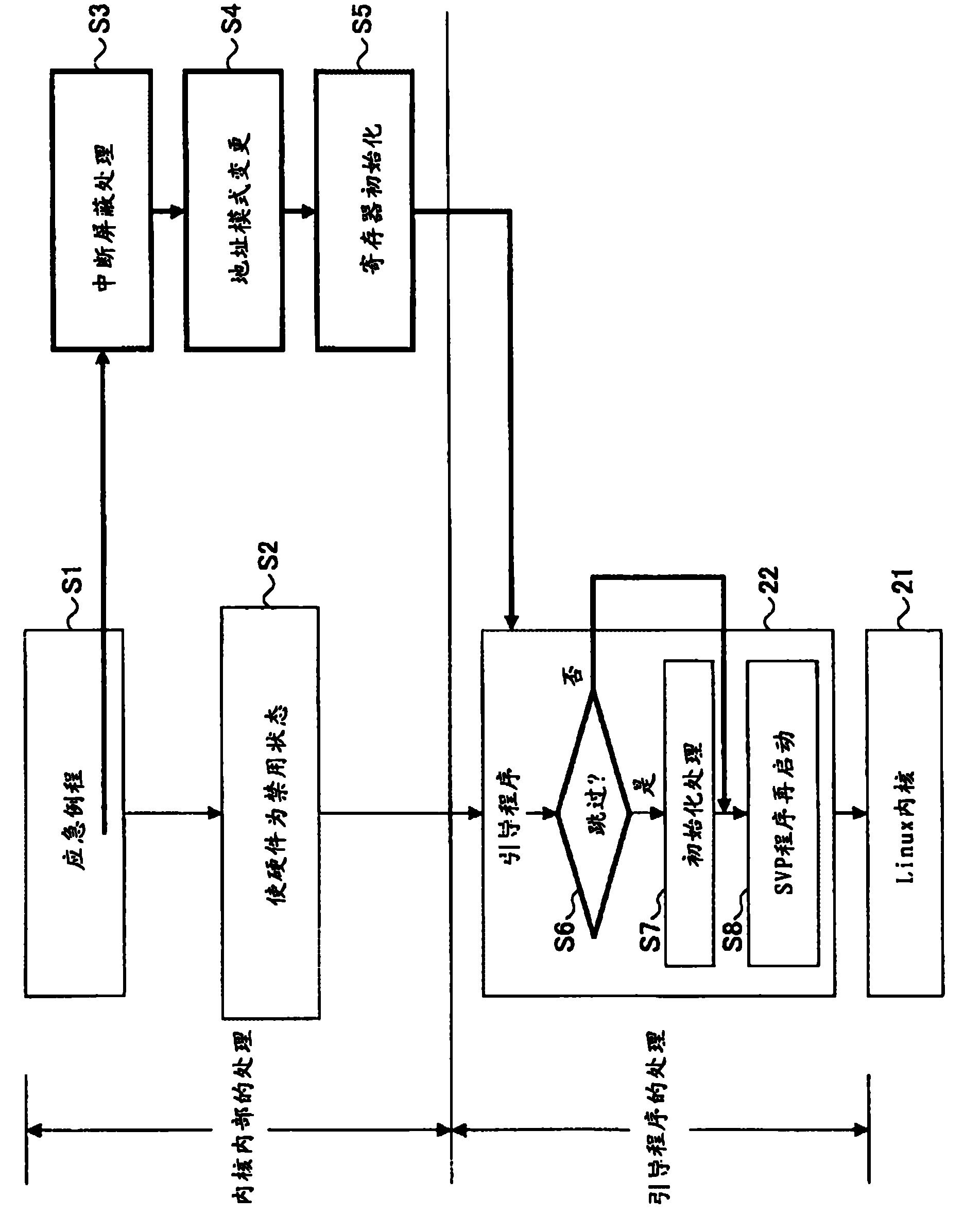

A reset method performs a software reset in a state in which data stored in a volatile memory is retained, when an abnormality is generated in a monitoring apparatus. Depending on hardware of the monitoring apparatus, the hardware may include a function to perform a hardware reset in a state in which the data stored in the volatile memory is retained, but the software reset is performed with respect to the hardware that does not include such a hardware reset function. The volatile memory may store control information for controlling a host computer that is monitored by the monitoring apparatus, in addition to data including fault check materials to be retained when the fault is generated. The monitoring apparatus may read the fault information from the hardware of the monitoring apparatus for every predetermined time, in order to perform a process to judge whether an abnormal value is reached.

Owner:FUJITSU LTD

Booting method capable of executing a warm boot or a cold boot when a CPU crash occurs and computer system therefor

ActiveUS7159107B2Eliminate timeData can be lostDigital computer detailsData resettingComputerized systemBooting

Owner:HTC CORP

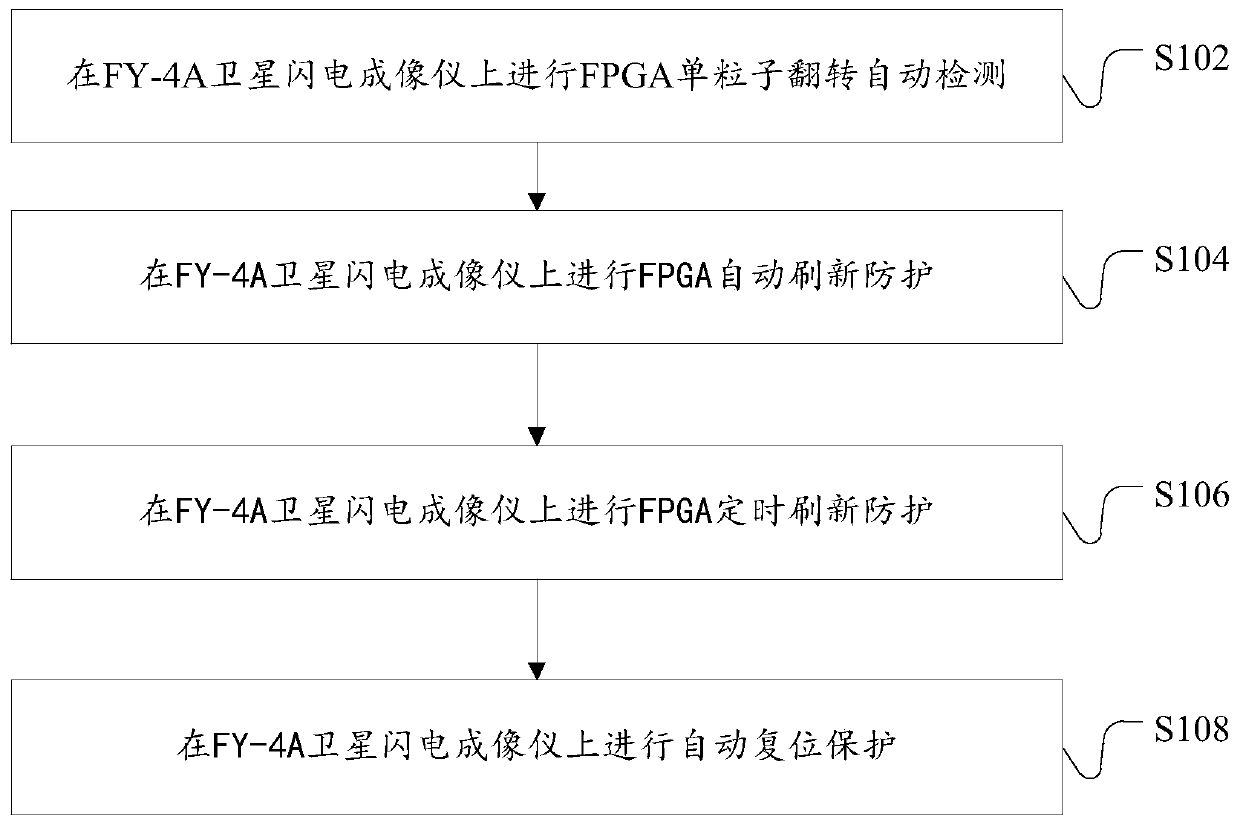

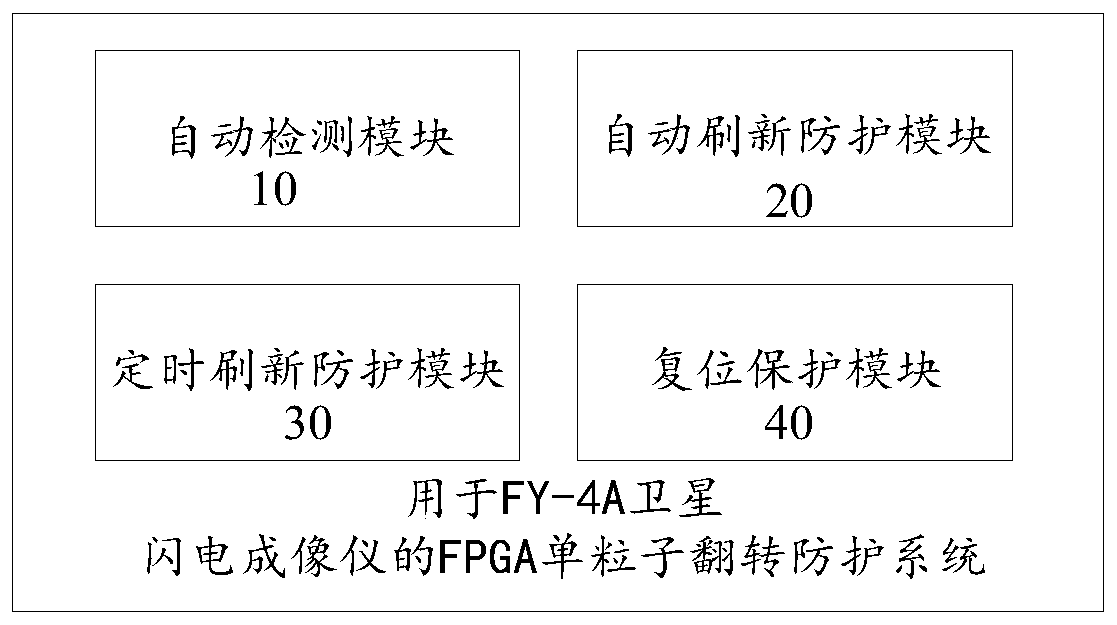

FPGA single event upset protection method and system for FY-4A satellite lightning imager

PendingCN109976962AReduce the impactRealize the technical effect of flipping automatic recoveryMarginal checkingElectromagentic field characteristicsSingle event upsetLightning detection

The invention discloses an FPGA single event upset protection method and system for an FY-4A satellite lightning imager. The method comprises: the automatic detection of FPGA single-event flipping onthe FY-4A satellite lightning imager; the FPGA automatic refresh protection on the FY-4A satellite lightning imager; and the FPGA timing refresh protection on the FY-4A satellite lightning imager; automatic reset protection on the FY-4A satellite lightning imager. The method solves the technical problem of lacking single-event flip protection measures for the single-event effect study of the FY-4Asatellite lightning imager FPGA. According to the characteristics of lightning observation missions and the timeliness of lightning detection products recovery, the method adopts multiple measures ofsingle-event flip protection such as automatic discrimination and automatic command, dynamic refresh and timing refresh, software reset and hardware reset to realize FPGA single particle. Flip automatic recovery. Through the above work, the current FY-4A satellite lightning imager has effectively reduced the impact of single-event flipping effects on lightning detection products.

Owner:NAT SATELLITE METEOROLOGICAL CENT

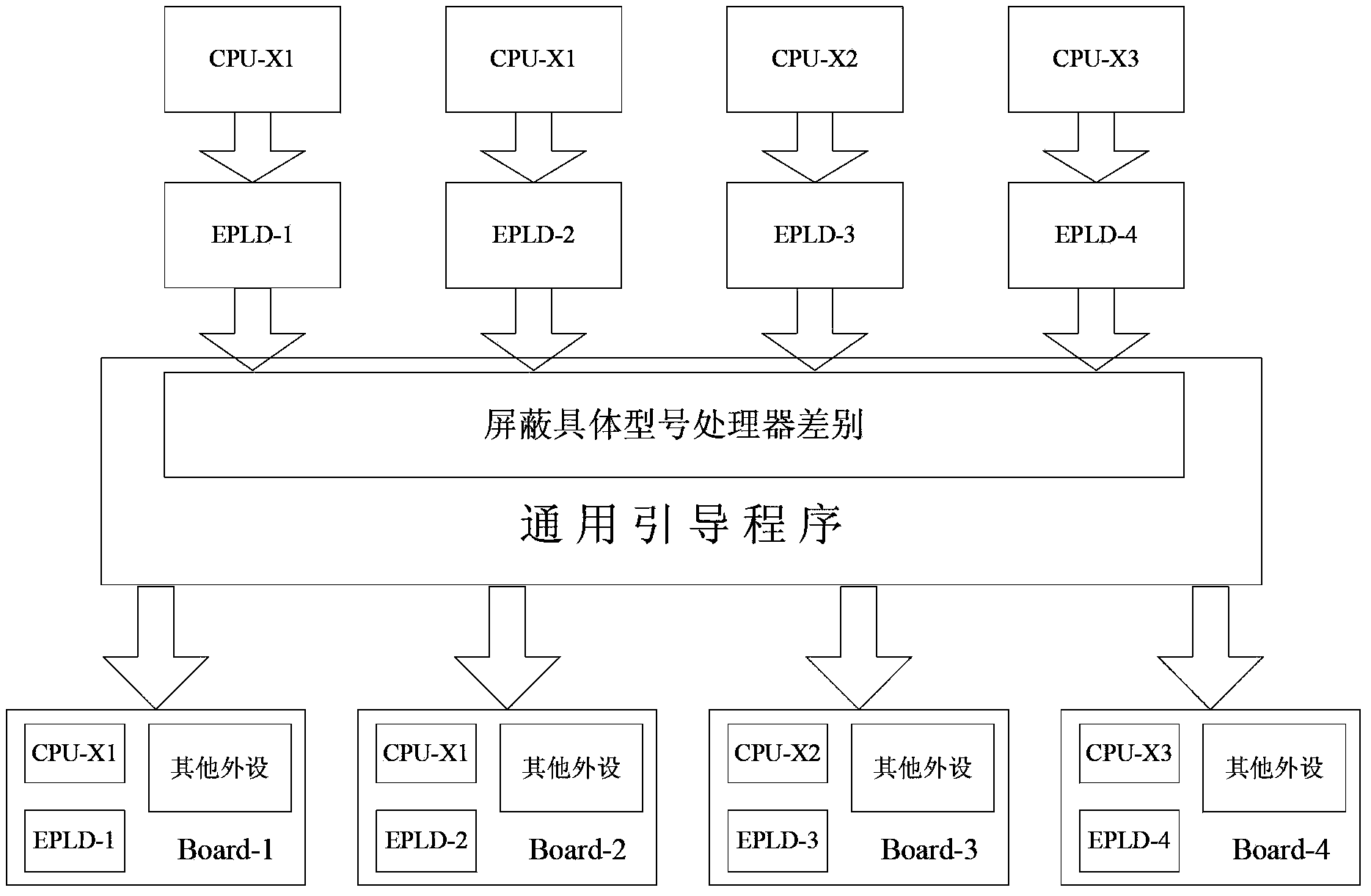

Processor initialization method and device

InactiveCN103514001AIncrease flexibilityEasy maintenanceProgram loading/initiatingComputer scienceBooting

The invention discloses a processor initialization method and device. The method includes the steps that processors in the same framework are configured during the hardware resetting period, wherein the processors belong to a same series and are same in kernel; the processors and off-chip resources of the processors are initialized. According to the processor initialization method and device, the processors in the same framework are configured and initialized through a same bootstrap program, and bootstrap programs of like products are compiled into a same file, and therefore flexibility of the bootstrap programs is improved, the editions of the bootstrap programs are convenient to maintain and manage, different types of hardware equipment, namely the off-chip resources, are initialized, and hardware difference is further masked for underlying software.

Owner:ZTE INTELLIGENT IOT TECH

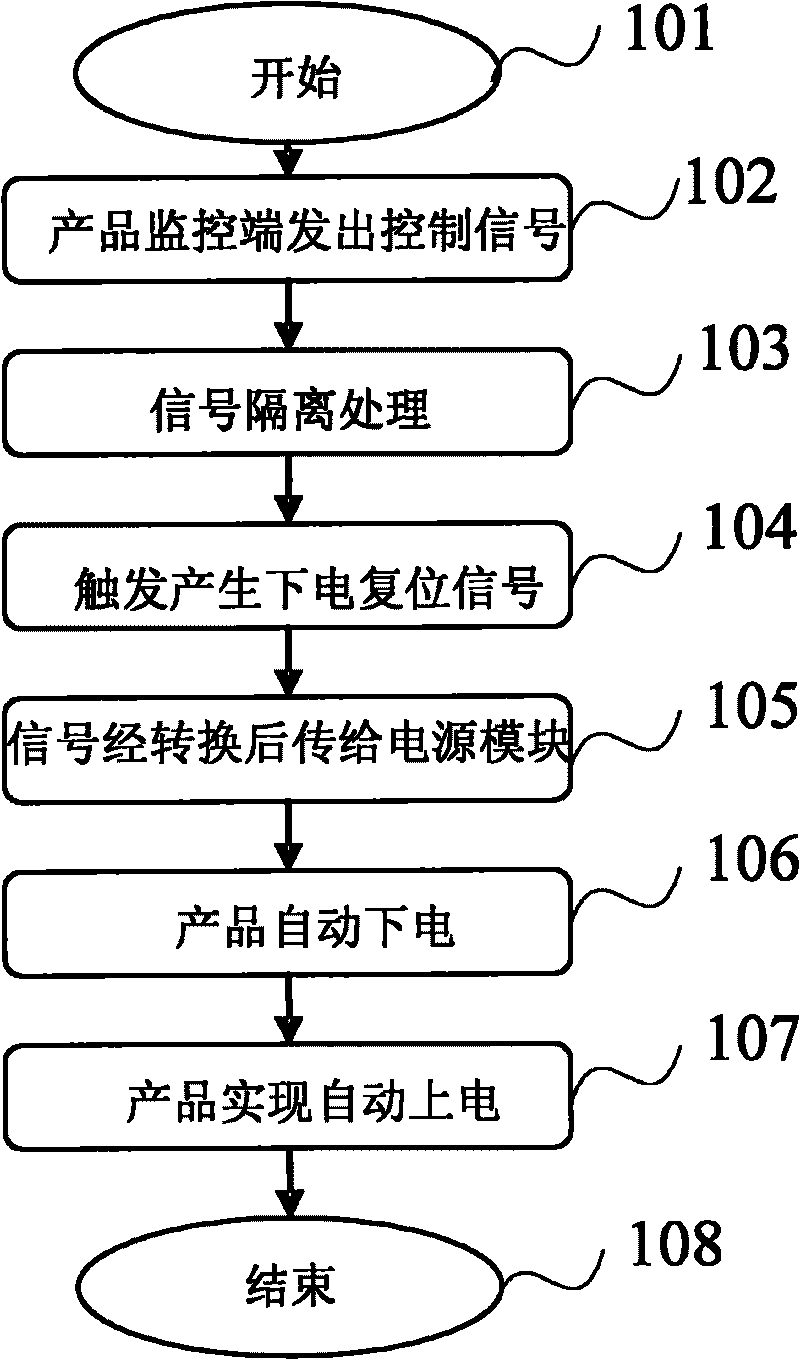

Method, device and system for realizing reset control

InactiveCN101751098AAvoid participationRealize power-off resetData resettingElectricityControl manner

The invention discloses a method and a device for power down reset control. The device for the power down reset control comprises a power supply circuit, an interference isolating circuit, a reset signal generation circuit and a control signal output circuit, wherein the power supply circuit is used for supplying a power supply to the device; the interference isolating circuit is used for realizing the interference isolation between a control circuit and the reset signal generation circuit; the reset signal generation circuit is used for generating a reset signal; and the control signal output circuit is used for outputting a reset control signal of the power supply of a product. The method for the power down reset control comprises the following steps of: inputting a monitoring end control signal; performing interference isolation on the monitoring end control signal and triggering the monitoring end control signal to generate a power down reset signal; and converting the power down reset signal, and outputting the reset control signal of the power supply of the product to realize automatic power down reset of the product. The method and the device realize pure hardware reset and self repair of the product in a control mode, and realize the automation of the operating process.

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com