Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Suppression of drop in withstand voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

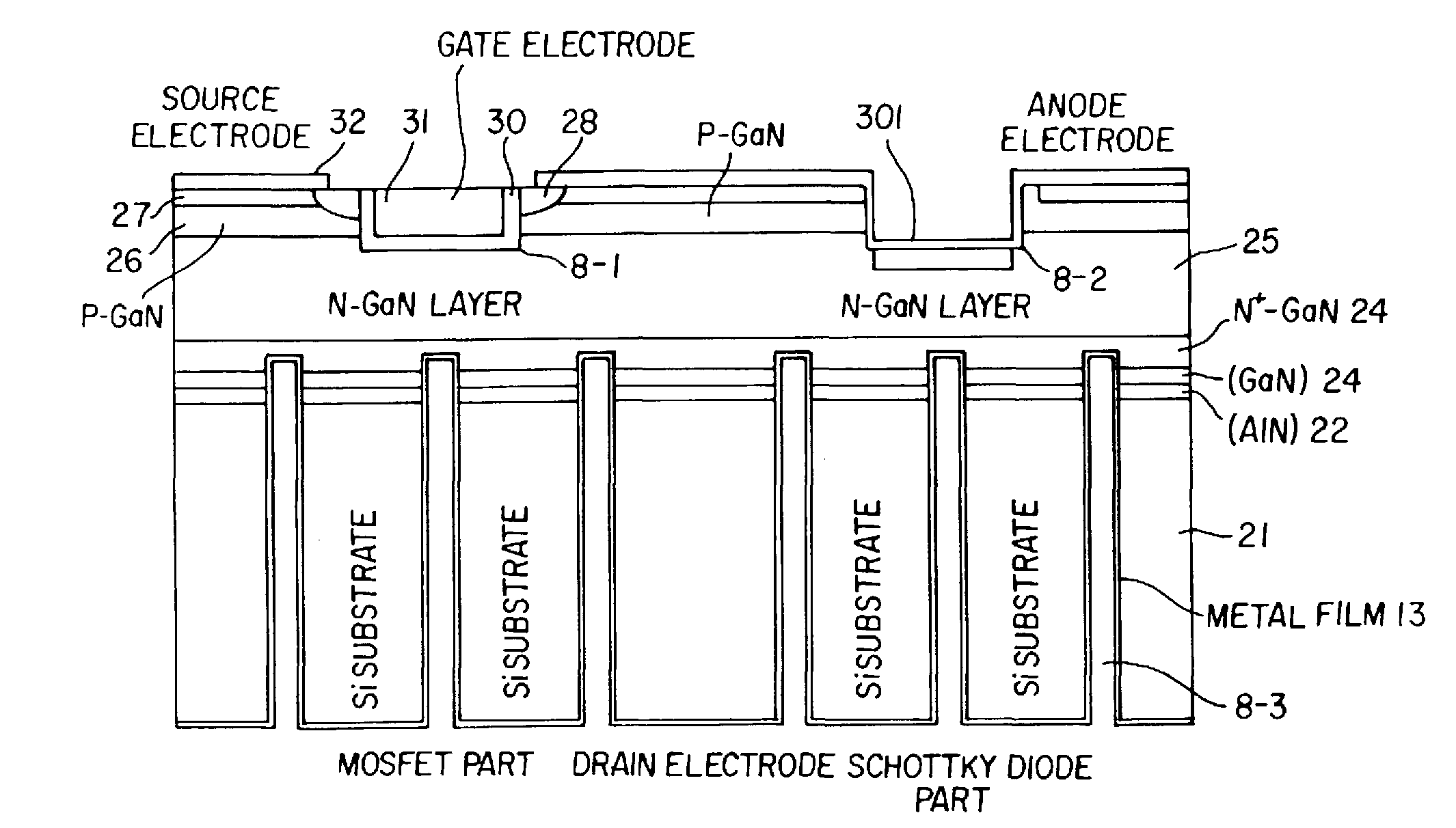

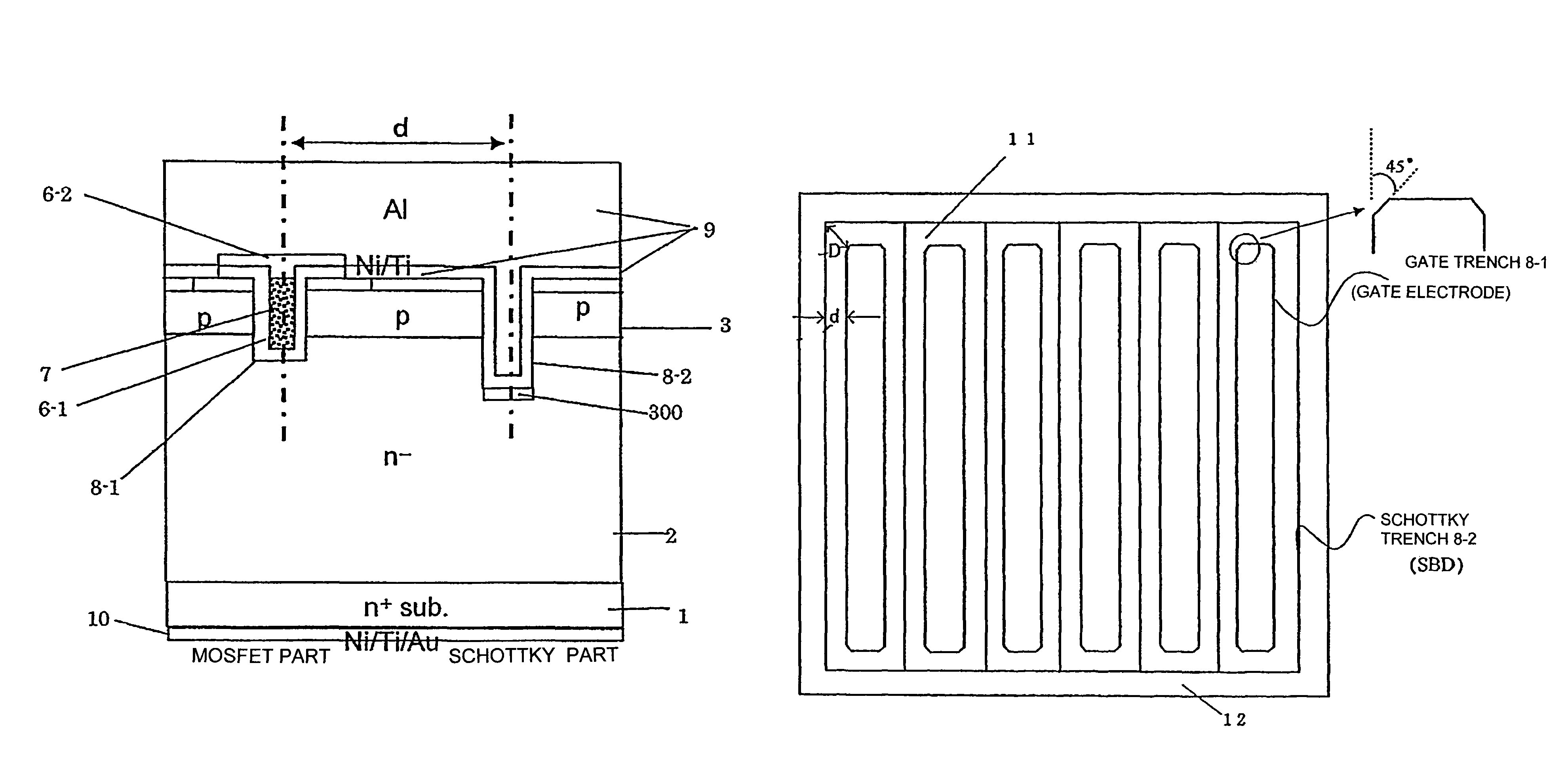

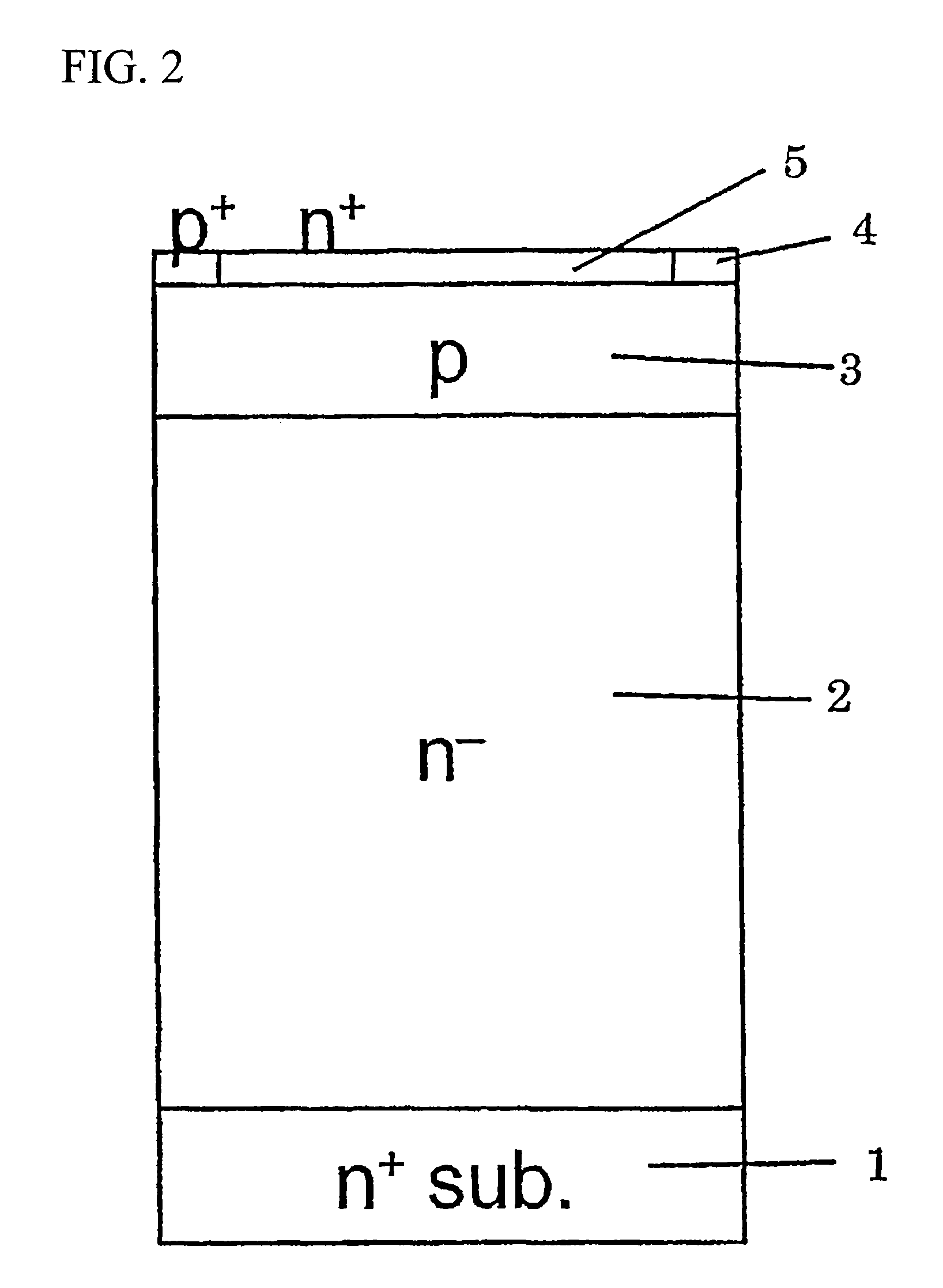

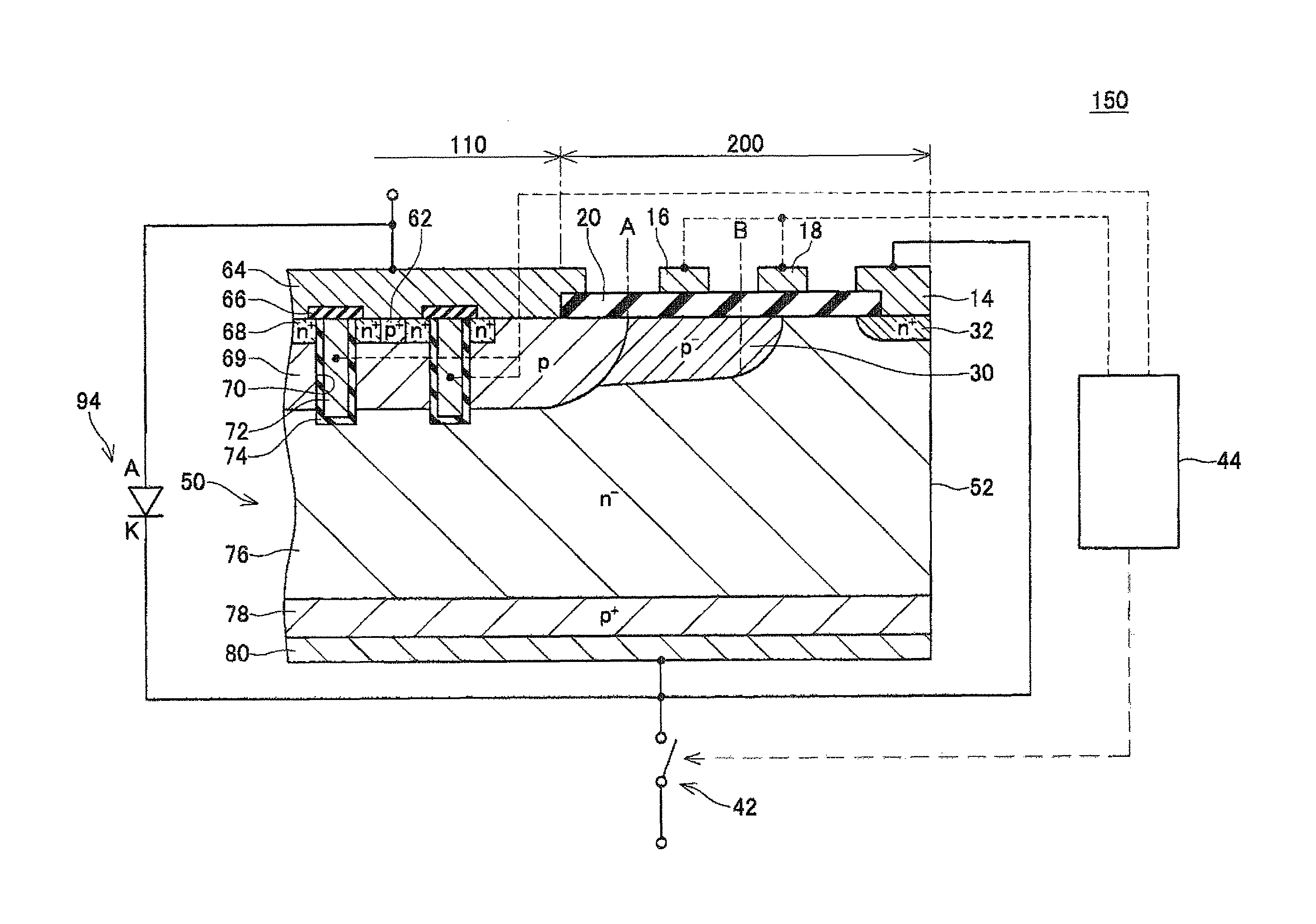

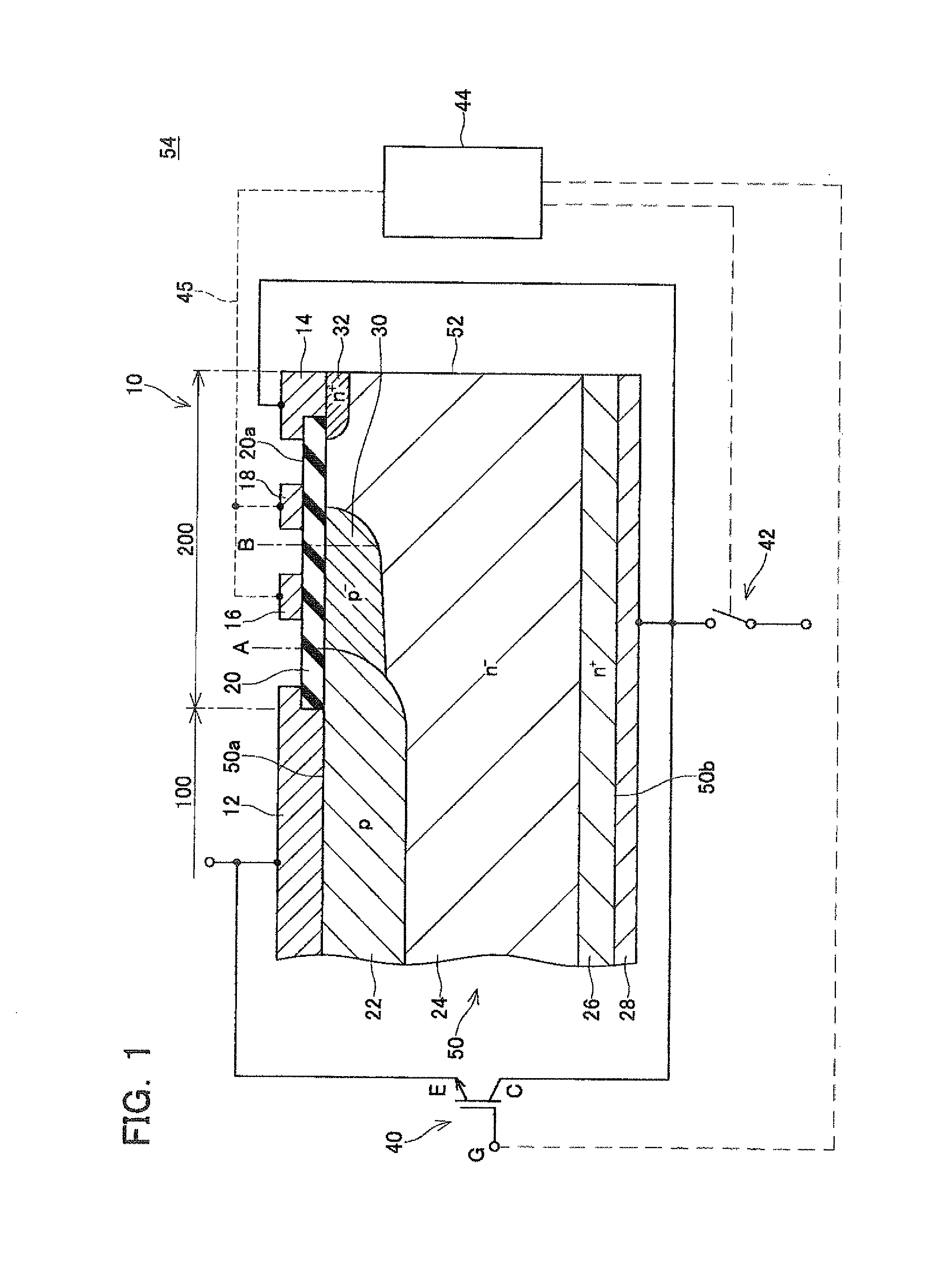

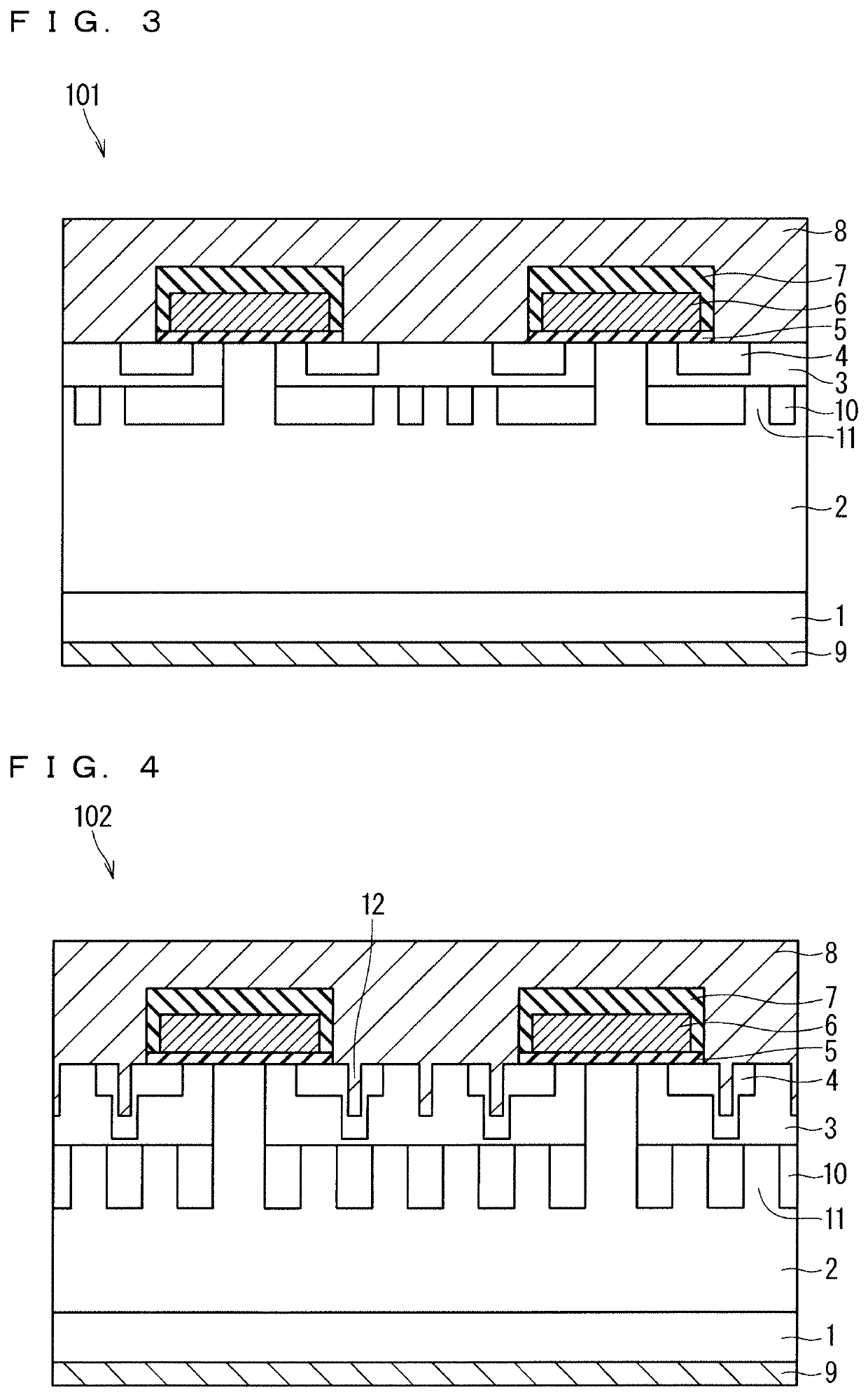

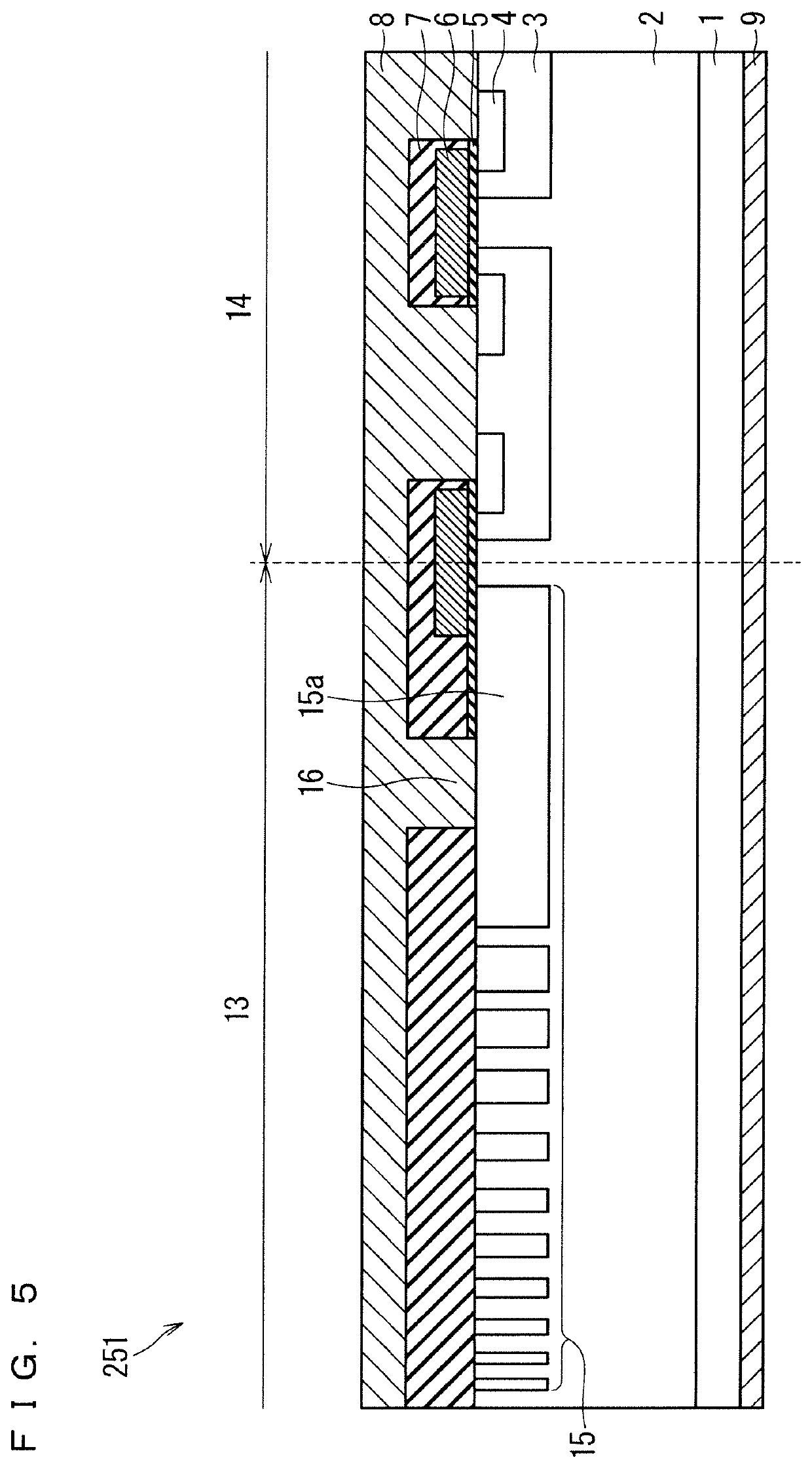

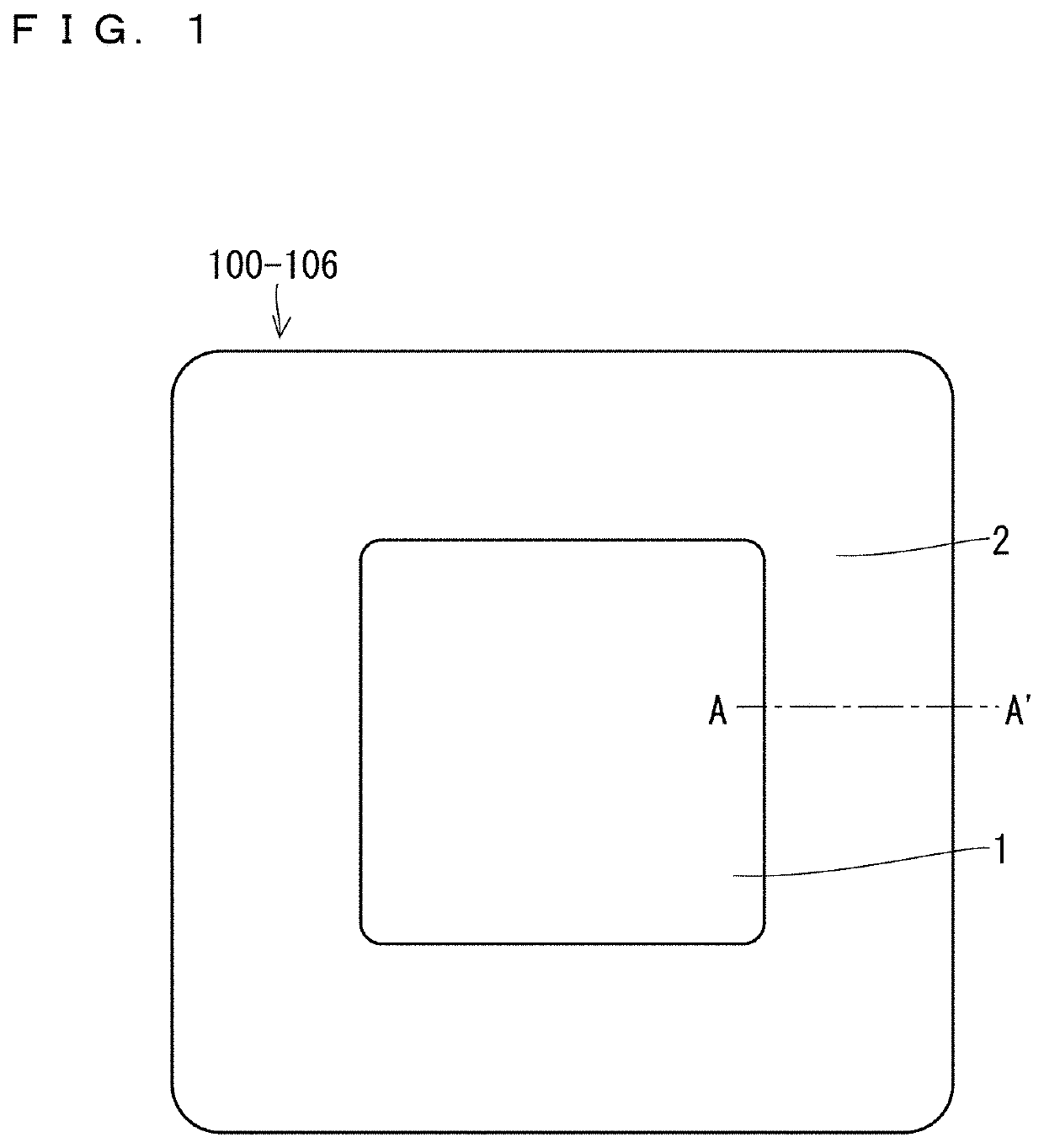

Wide band gap semiconductor device and method for producing the same

ActiveUS20090283776A1Lower on-resistanceShort reverse recovery timeSemiconductor/solid-state device manufacturingDiodeBroadbandWide band

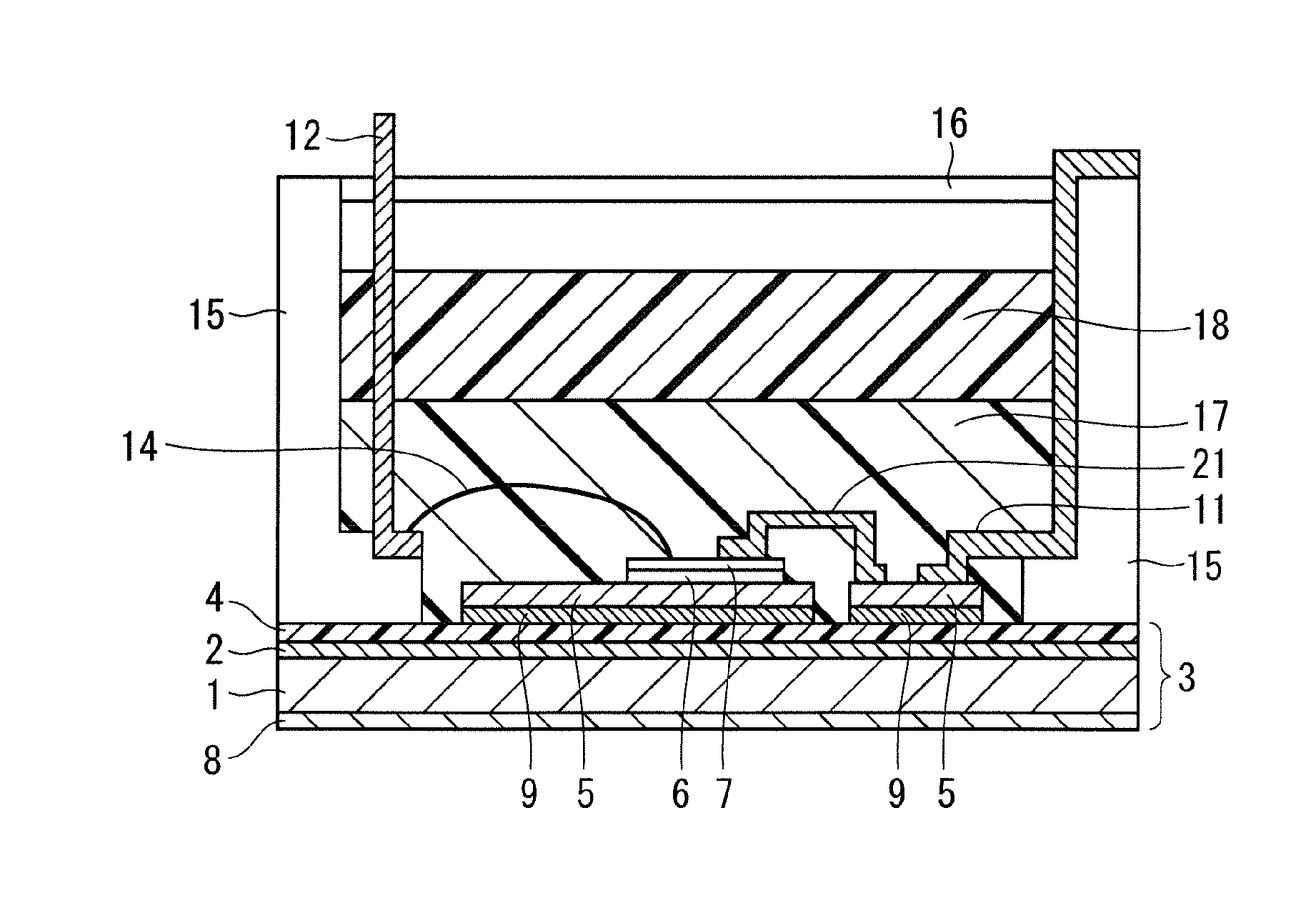

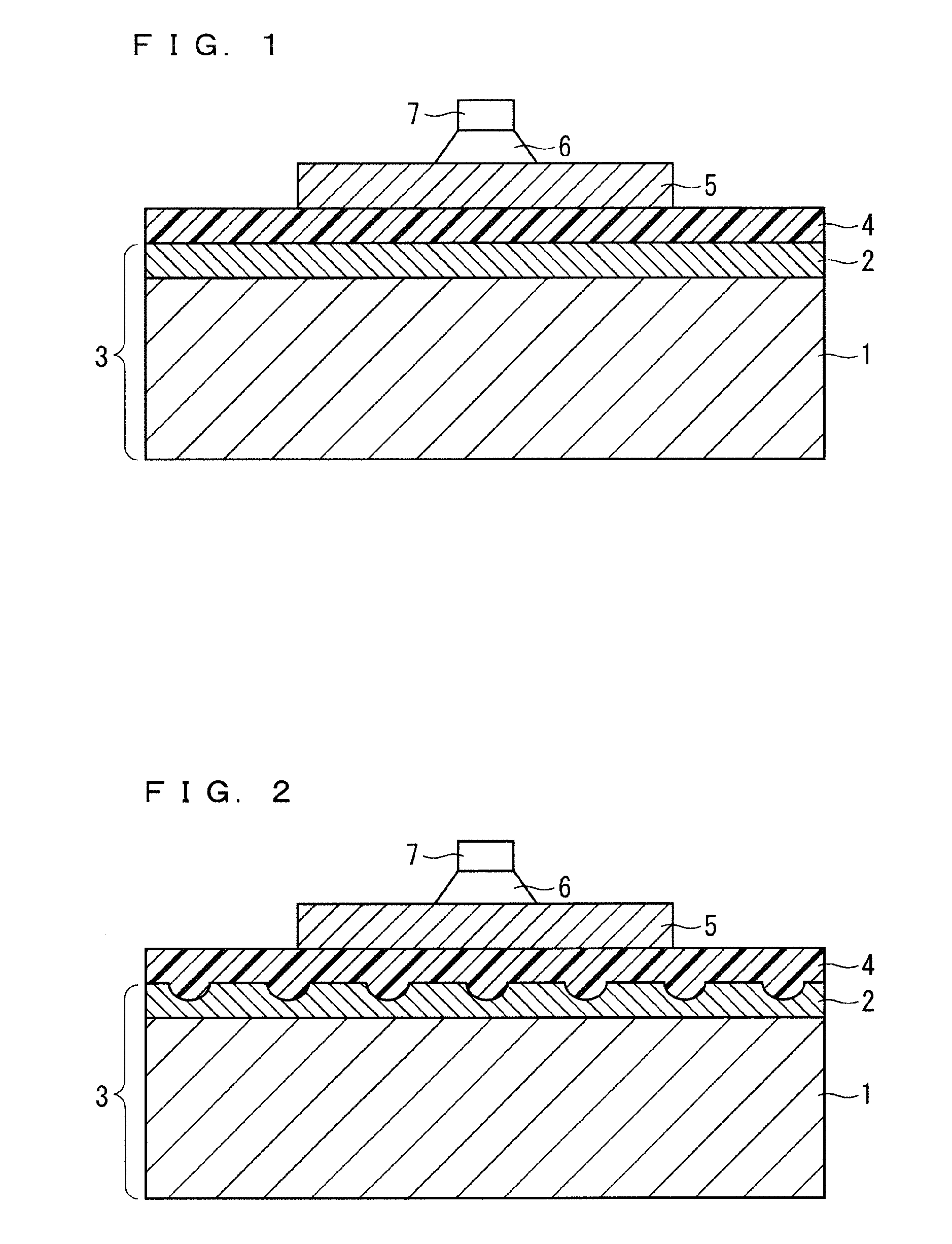

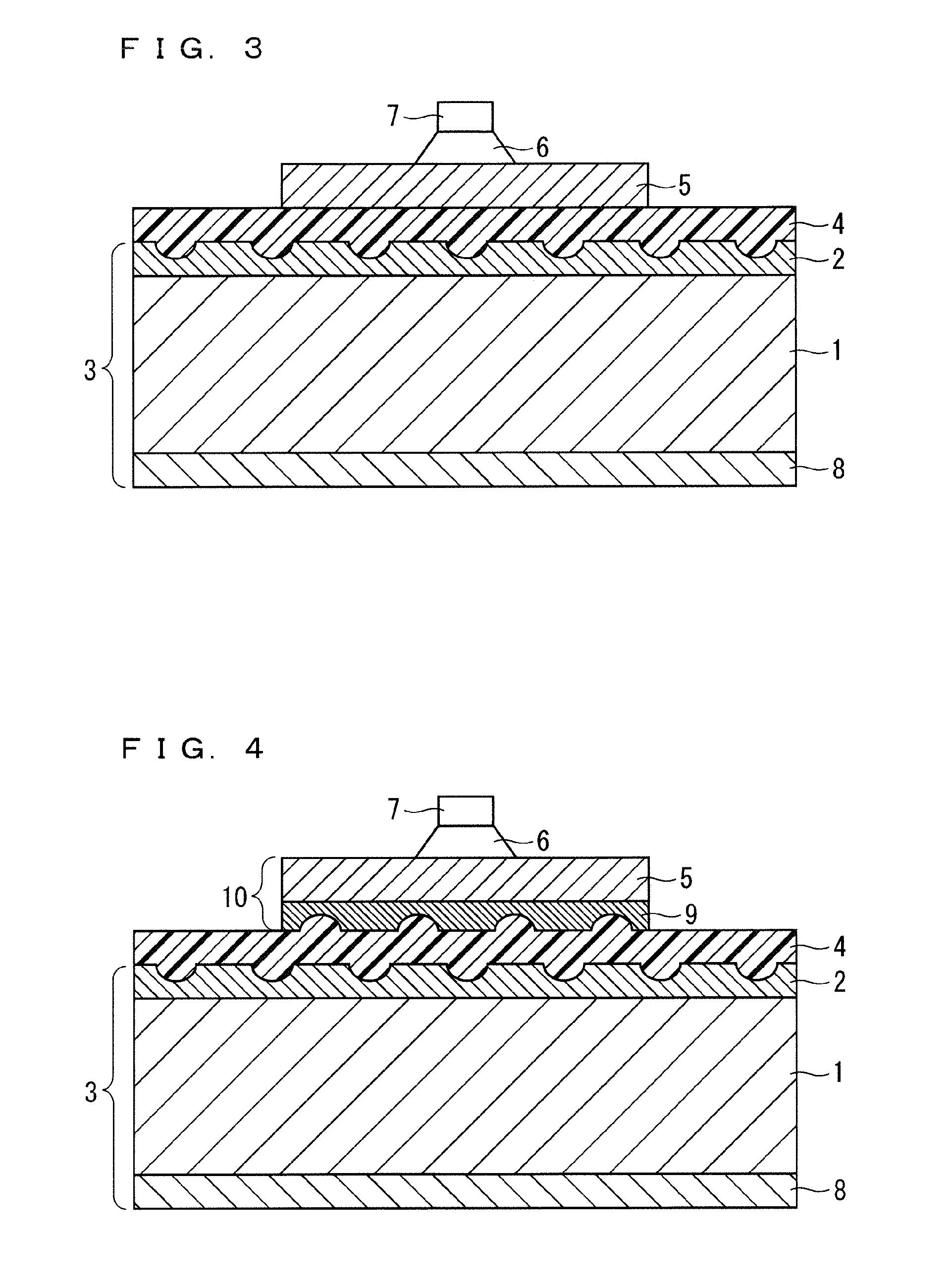

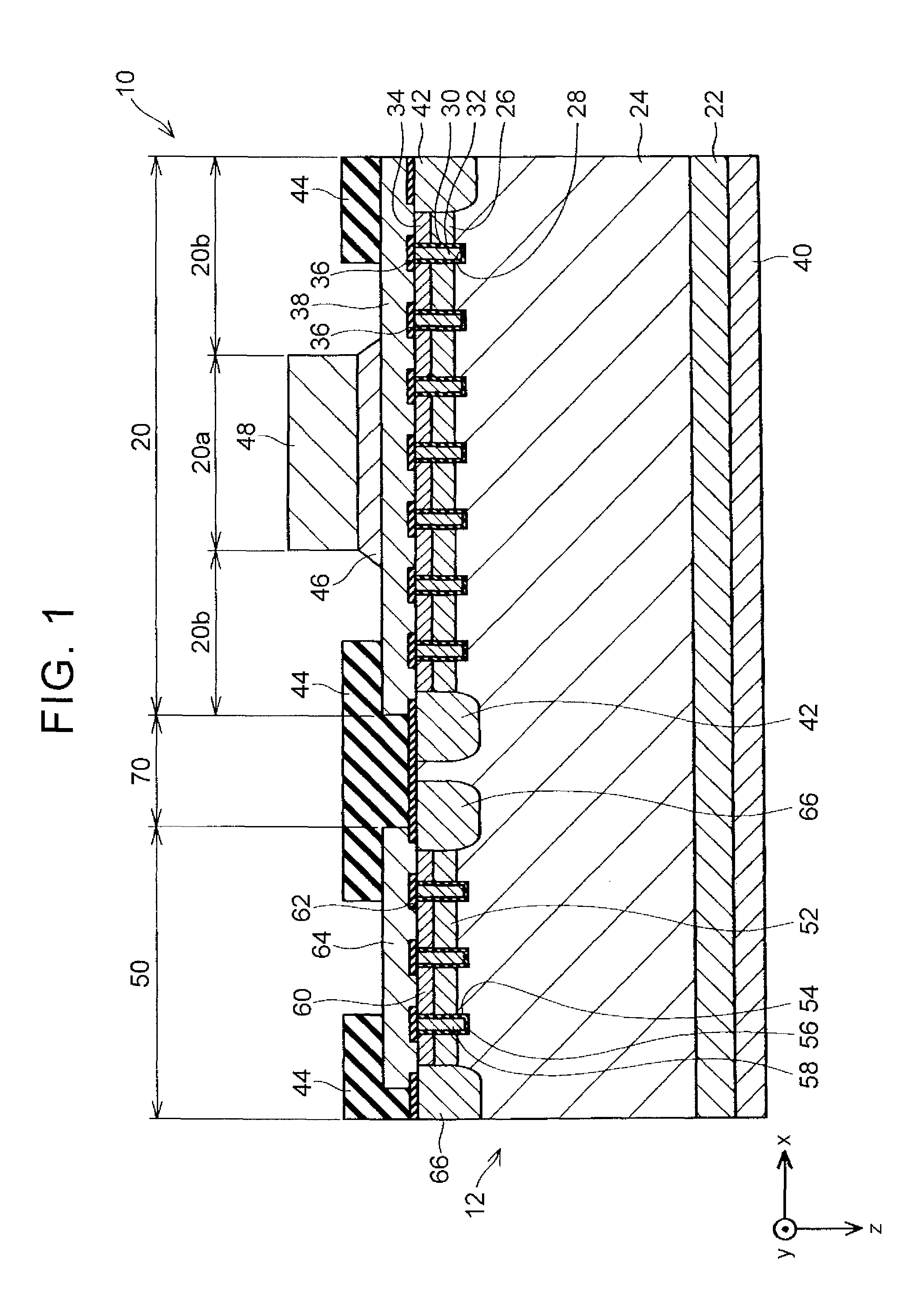

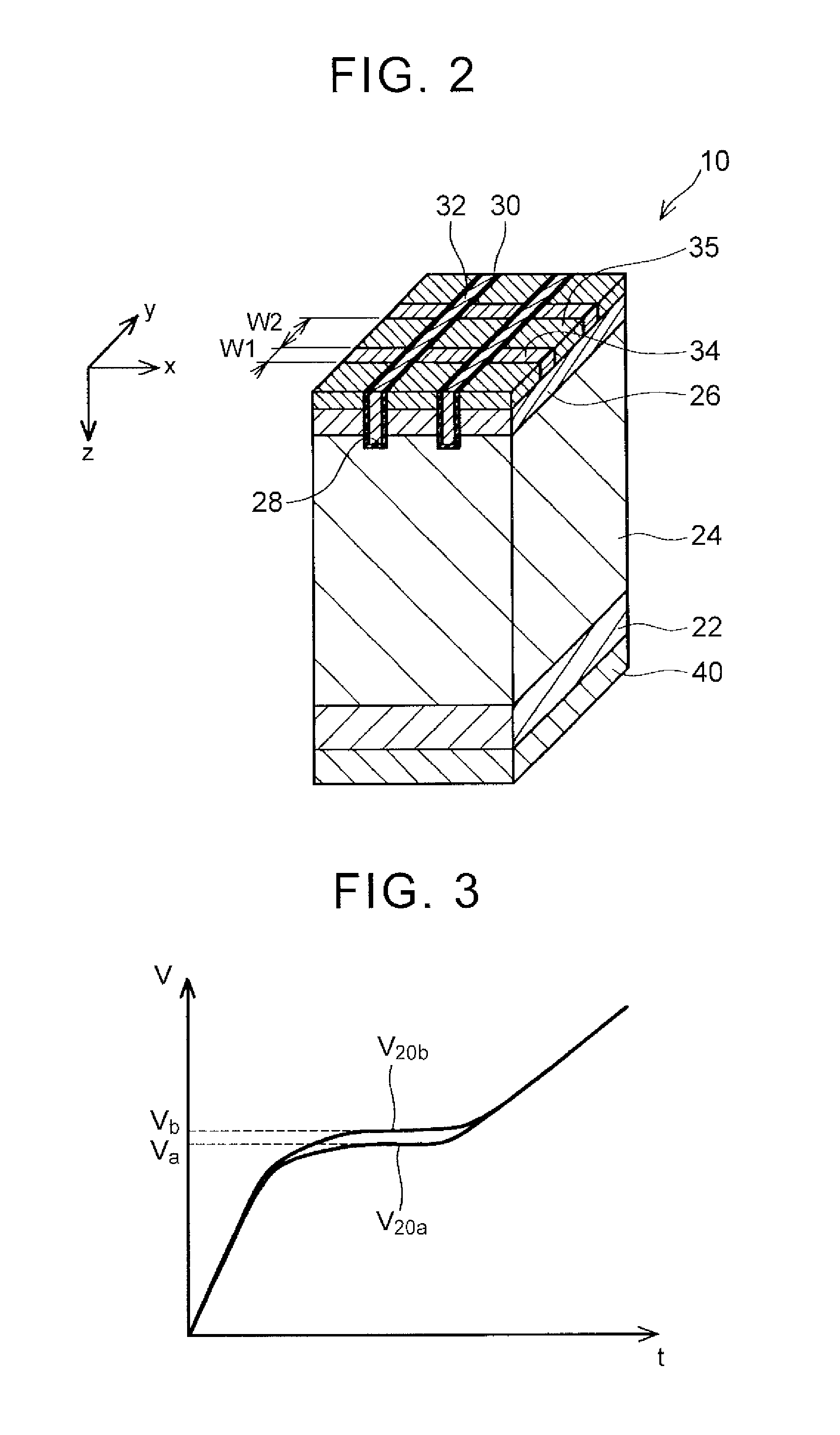

A wide band gap semiconductor device is disclosed. A first trench in a gate electrode part and a second trench in a source electrode part (Schottky diode part) are disposed so that the first and second trenches are close to each other while and the second trench is deeper than the first trench. A metal electrode is formed in the second trench to form a Schottky junction on a surface of an n-type drift layer in the bottom of the second trench. Further, a p+-type region is provided in part of the built-in Schottky diode part being in contact with the surface of the n-type drift layer, preferably in the bottom of the second trench. The result is a wide band gap semiconductor device which is small in size and low in on-resistance and loss, and in which electric field concentration applied on a gate insulating film is relaxed to suppress lowering of withstand voltage to thereby increase avalanche breakdown tolerance at turning-off time.

Owner:FUJI ELECTRIC CO LTD

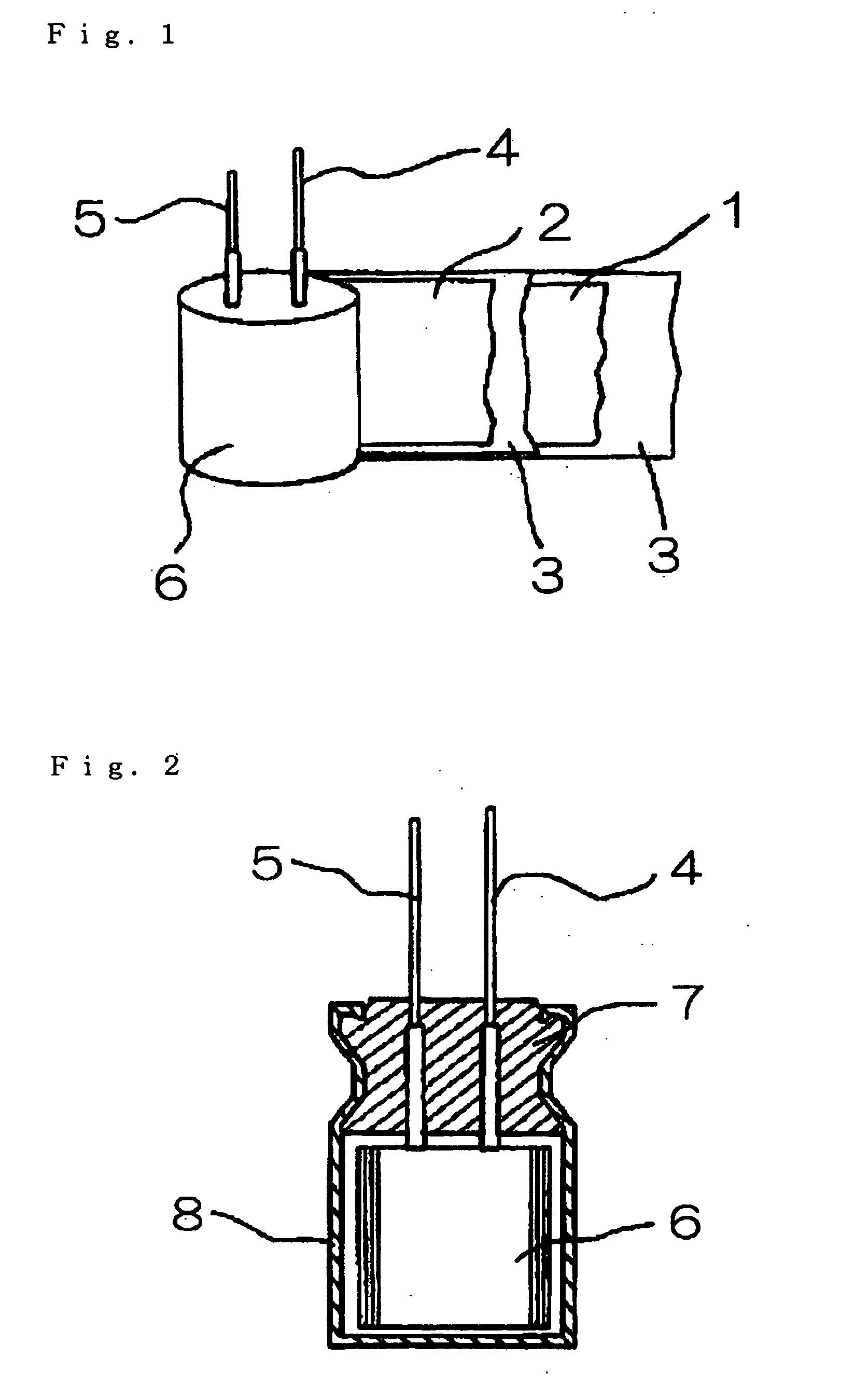

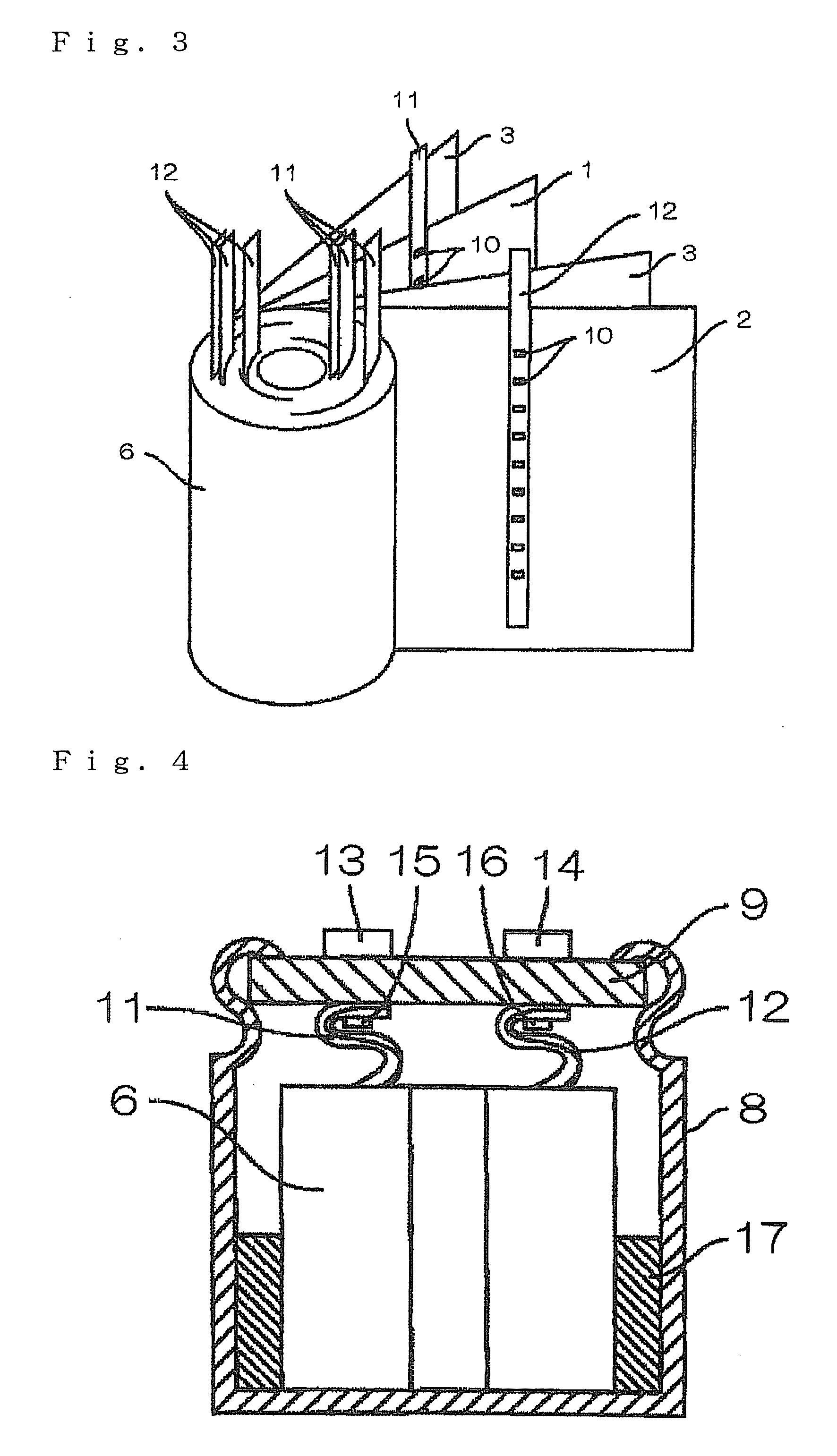

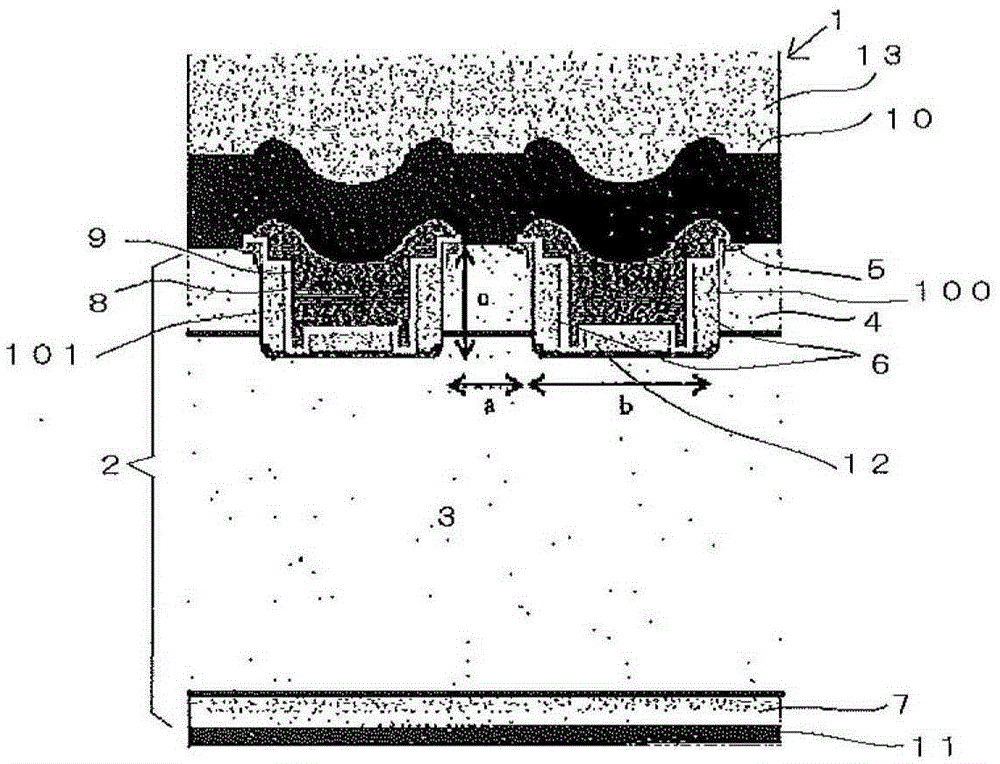

Electrolytic capacitor

ActiveUS20100053847A1Reduce resistanceSuppression of drop in withstand voltageHybrid capacitor electrolytesClosuresElectrolysisEngineering

Provide is an aluminum electrolytic capacitor exhibiting low specific resistance and low impedance property and realizing high reliability. An electrolytic capacitor has a structure in which: a capacitor element which is formed by rolling an anode foil and a cathode foil each connected with an electrode extraction lead through a separator and which is impregnated with a drive electrolytic solution is included in a cylindrical outer case having a closed-end; and an open end of the outer case is sealed with an elastic sealing body, in which: the drive electrolytic solution contains a tricyanomethide salt represented by the below-indicated chemical formula (1); and the drive electrolytic solution has a water content of 3.0 wt % or less:where, R represents a cation pairing with a tricyanomethide ion in formation of a tricyanomethide salt.

Owner:NICHICON CORP

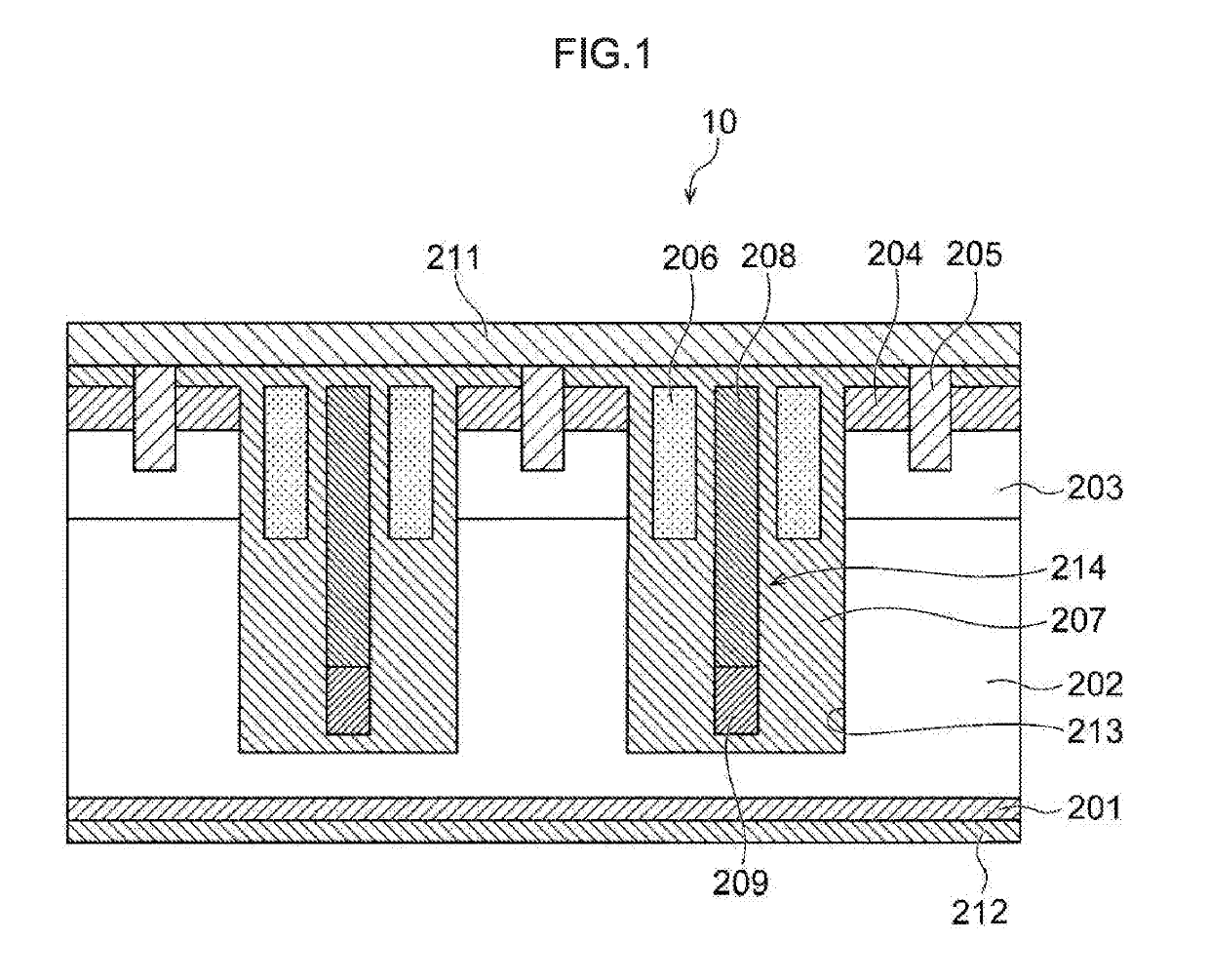

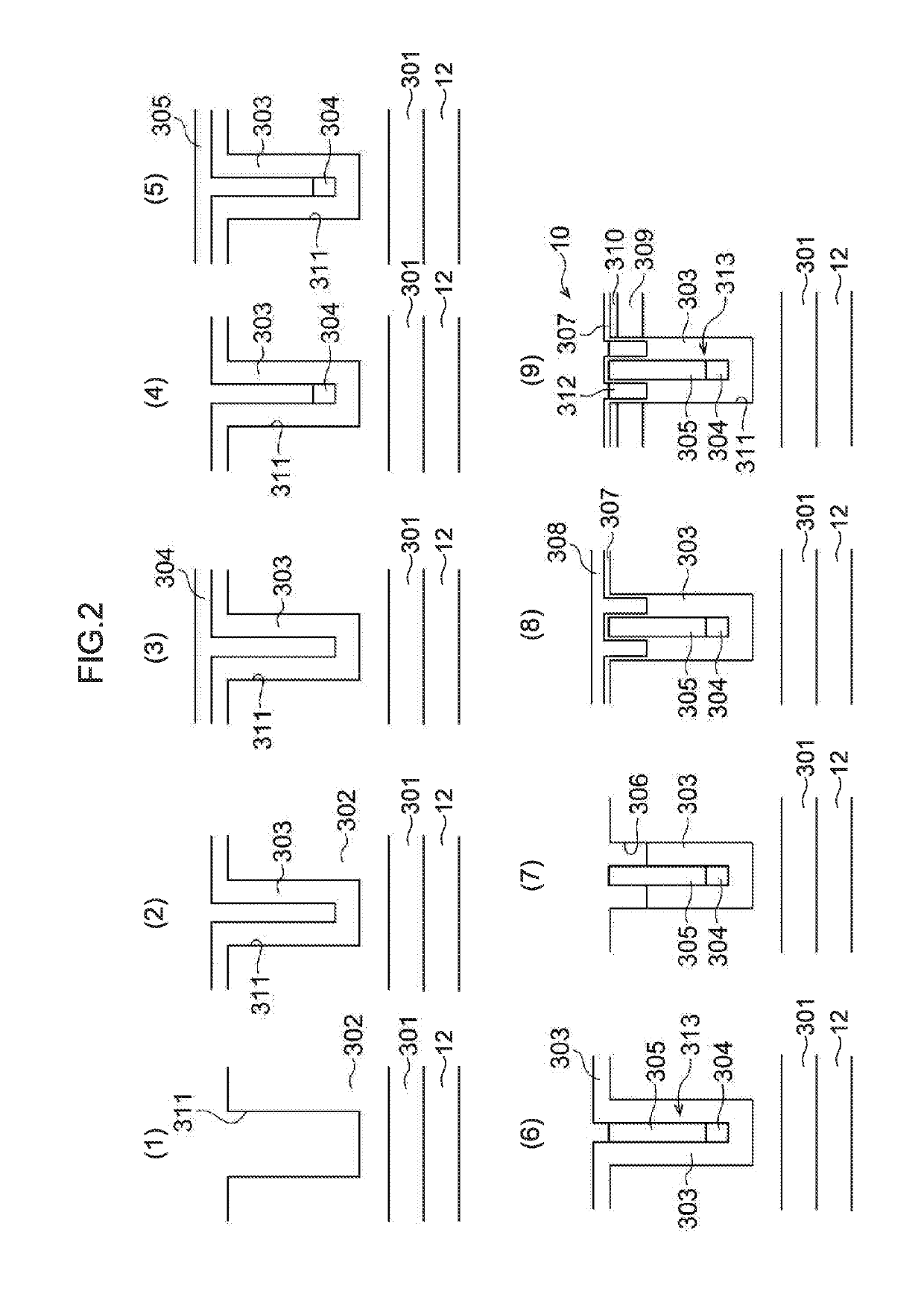

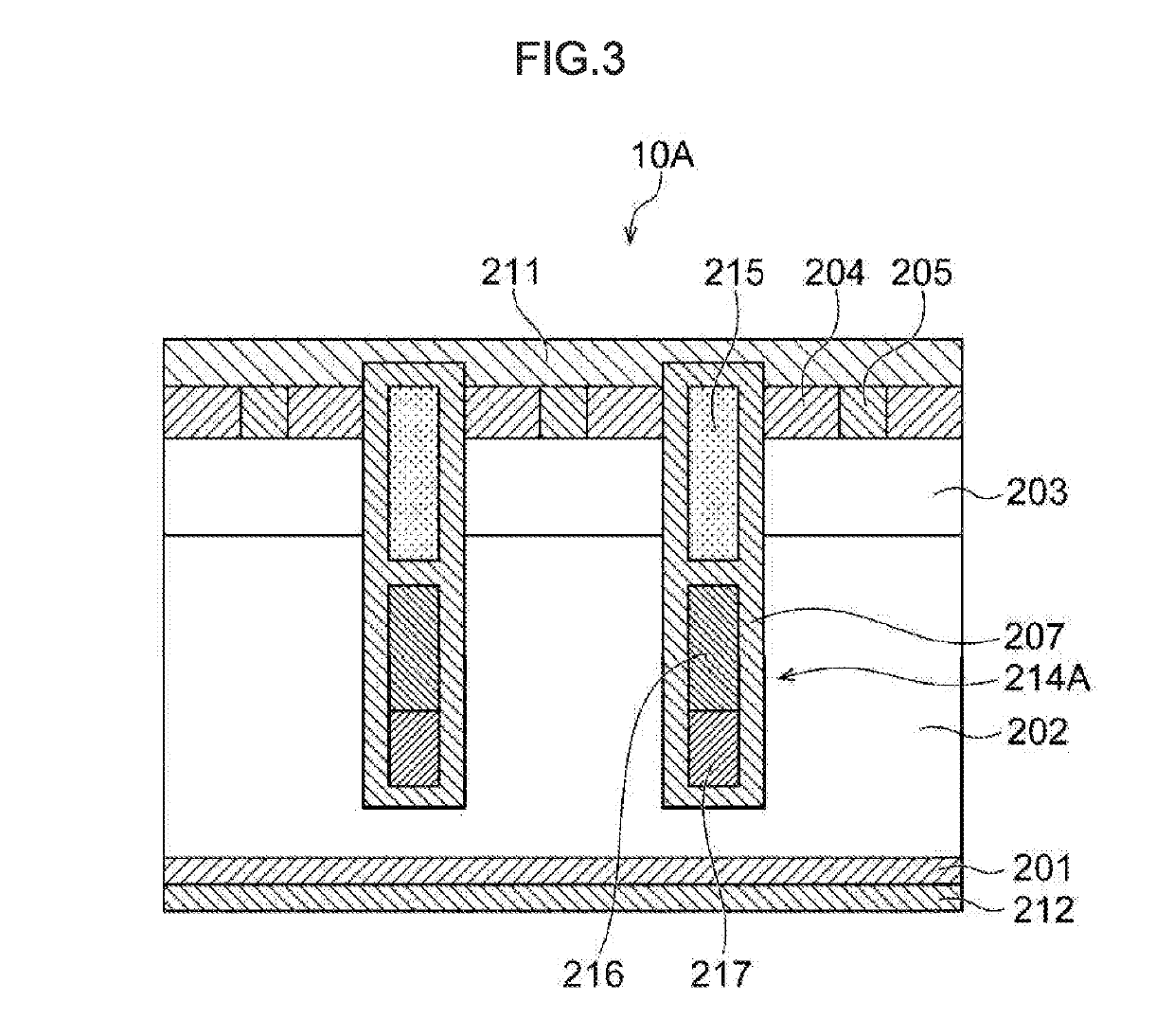

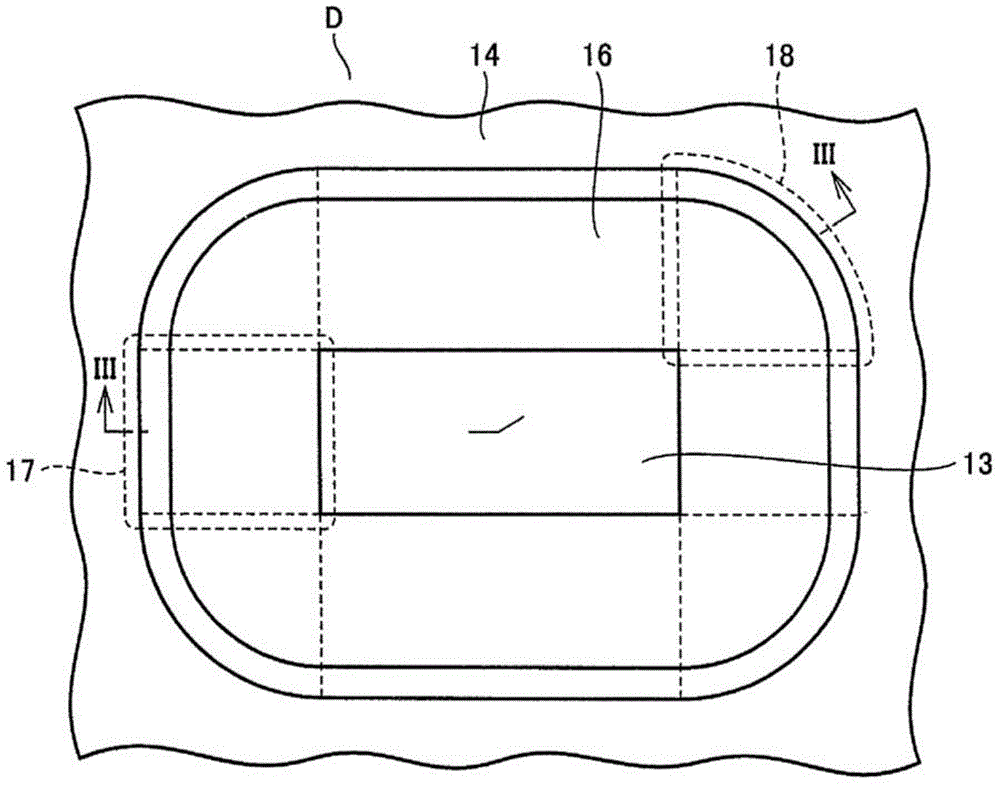

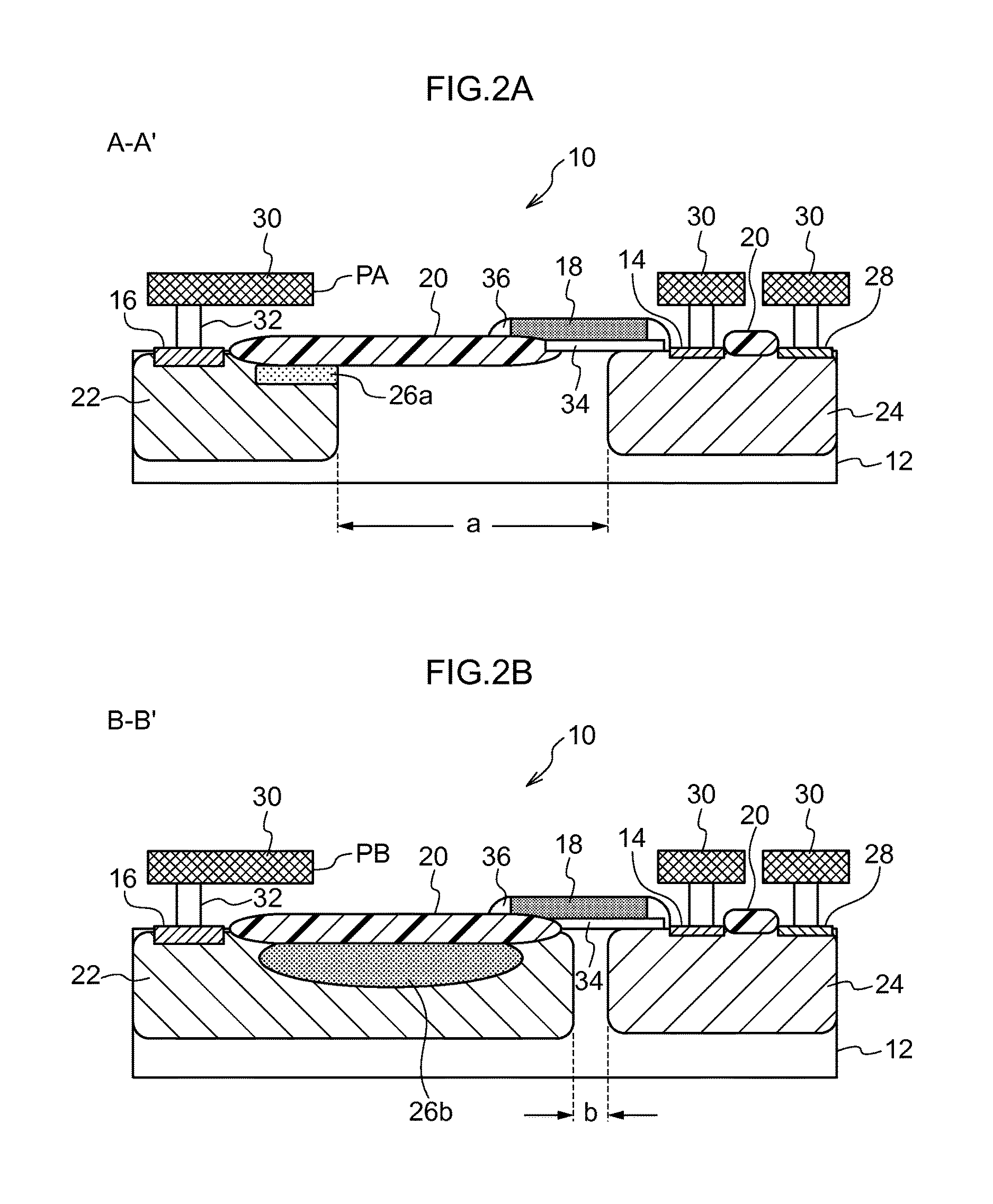

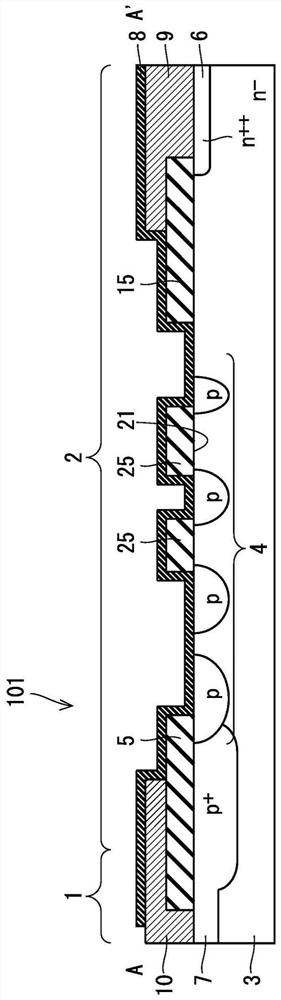

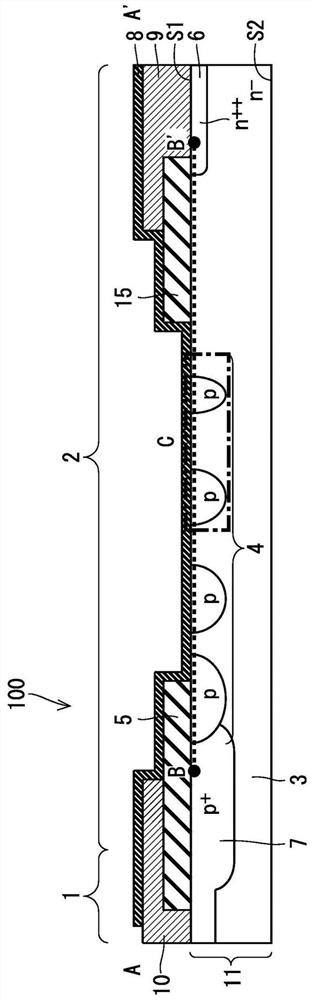

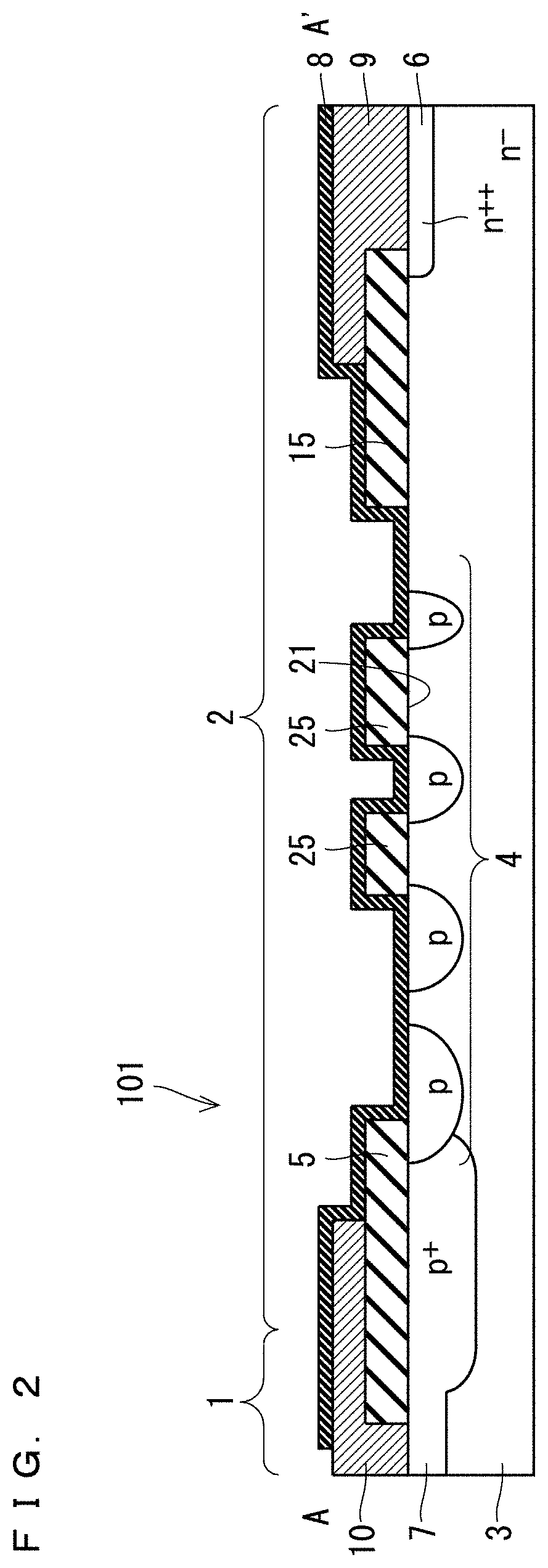

Semiconductor device and semiconductor device manufacturing method

ActiveUS20190259873A1Improve pressure resistanceReduce voltageSemiconductor/solid-state device manufacturingDiodeElectrical conductorDevice material

A semiconductor device including: a first semiconductor layer having a first conductive type; a second semiconductor layer provided on the first semiconductor layer, the second semiconductor layer having a second conductive type that is a conductive type different from the first conductive type; an impurity region of the first conductive type formed at a surface of the second semiconductor layer; first electrodes contacting the impurity region, the second semiconductor layer, and the first semiconductor layer via a first insulating film; and second electrodes contacting the first electrodes via a second insulating film, and contacting the first semiconductor layer via a third insulating film, the second electrodes including PN junctions at borders between upper portions that contact the first semiconductor layer via the third insulating film and lower portions that contact the first semiconductor layer via the third insulating film.

Owner:LAPIS SEMICON CO LTD

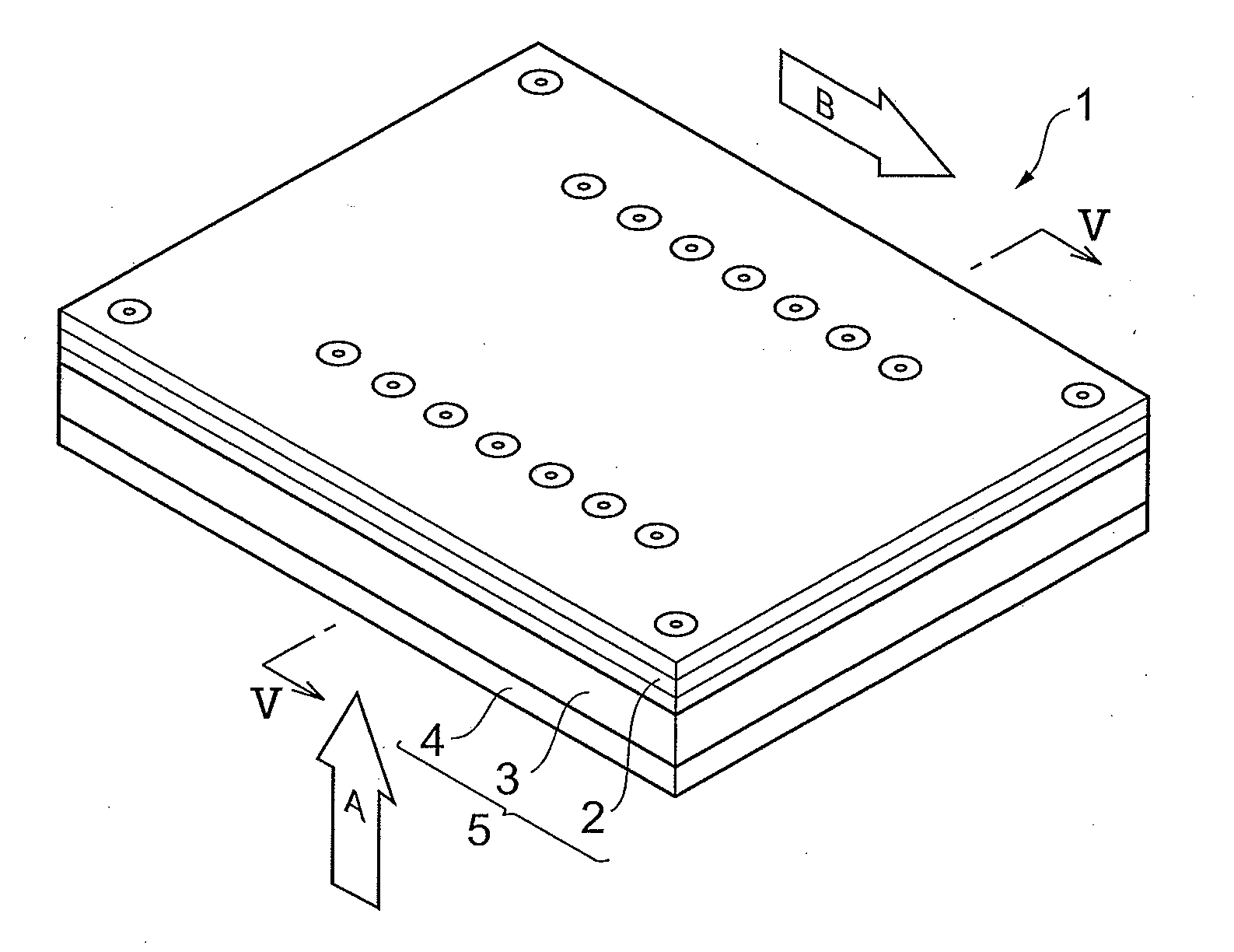

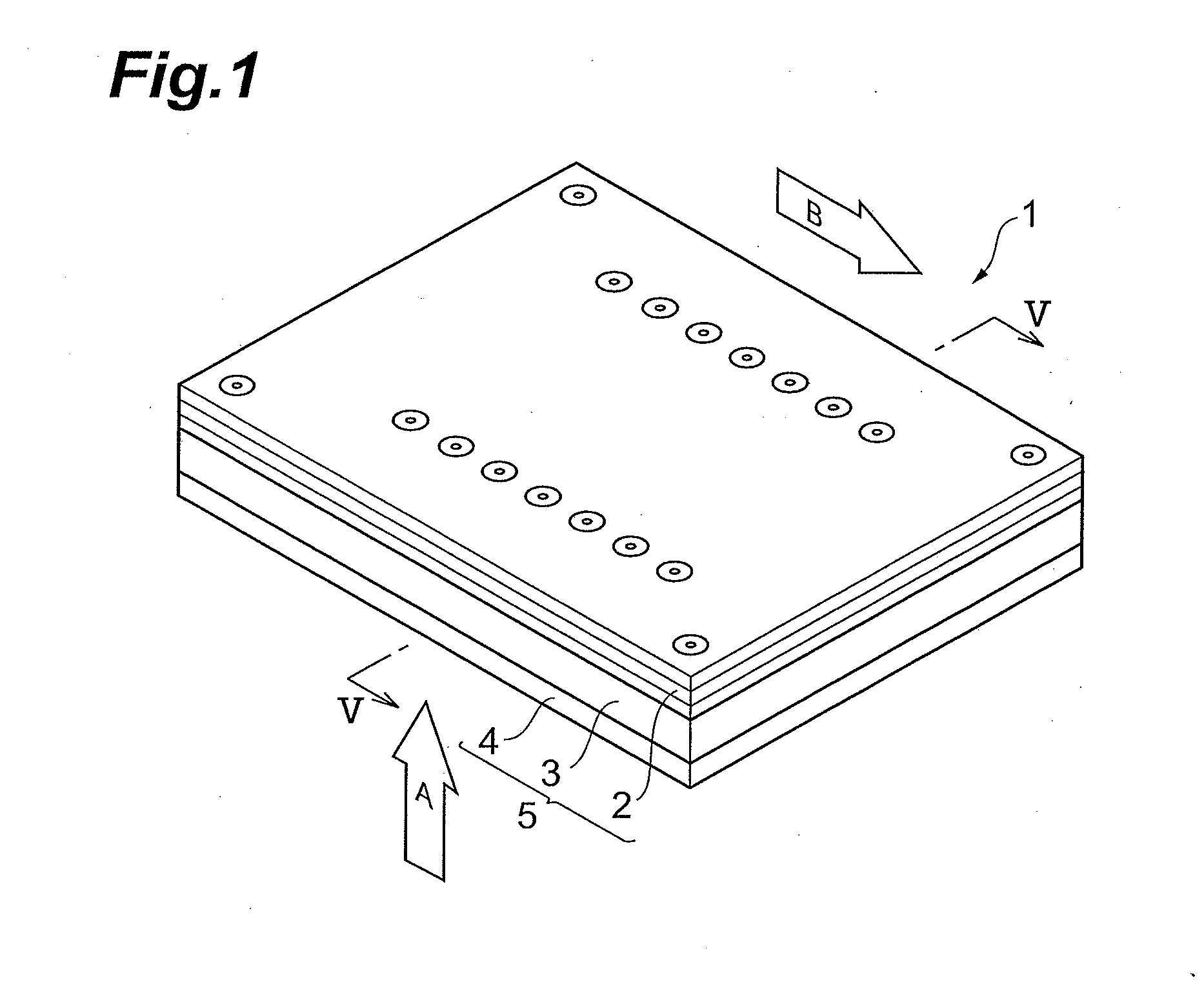

Metal base substrate, power module, and method for manufacturing metal base substrate

ActiveUS20150332982A1Improve pressure resistanceEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesCopperMetal

A metal base substrate of the present invention includes a copper plate made of copper, a metal layer that is formed on the copper plate and is made of a metal different from the copper, an insulating resin sheet that is formed by bonding a sheet made of an insulating resin onto the metal layer, and a circuit pattern formed on the insulating resin sheet.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device

ActiveUS20130069694A1Reduce withstand voltageAvoid changeElectronic switchingElectric pulse generatorCell regionDevice material

A semiconductor device may be provided with a semiconductor substrate, an insulating film disposed on a surface of the semiconductor substrate, at least one electrode disposed on a surface of the insulating film, and a voltage applying circuit configured to apply a first voltage to the at least one electrode. The semiconductor substrate may be provided with a cell region and a non-cell region adjacent to the cell region. The cell region is provided with a semiconductor element, and the non-cell region is provided with a withstand voltage structure. The insulating film may be disposed on a surface of the non-cell region. The at least one electrode may be electrically insulated from the semiconductor substrate. The voltage applying circuit may apply the first voltage to the electrode during at least a part of a first period in which a second voltage is not applied to the semiconductor element.

Owner:DENSO CORP

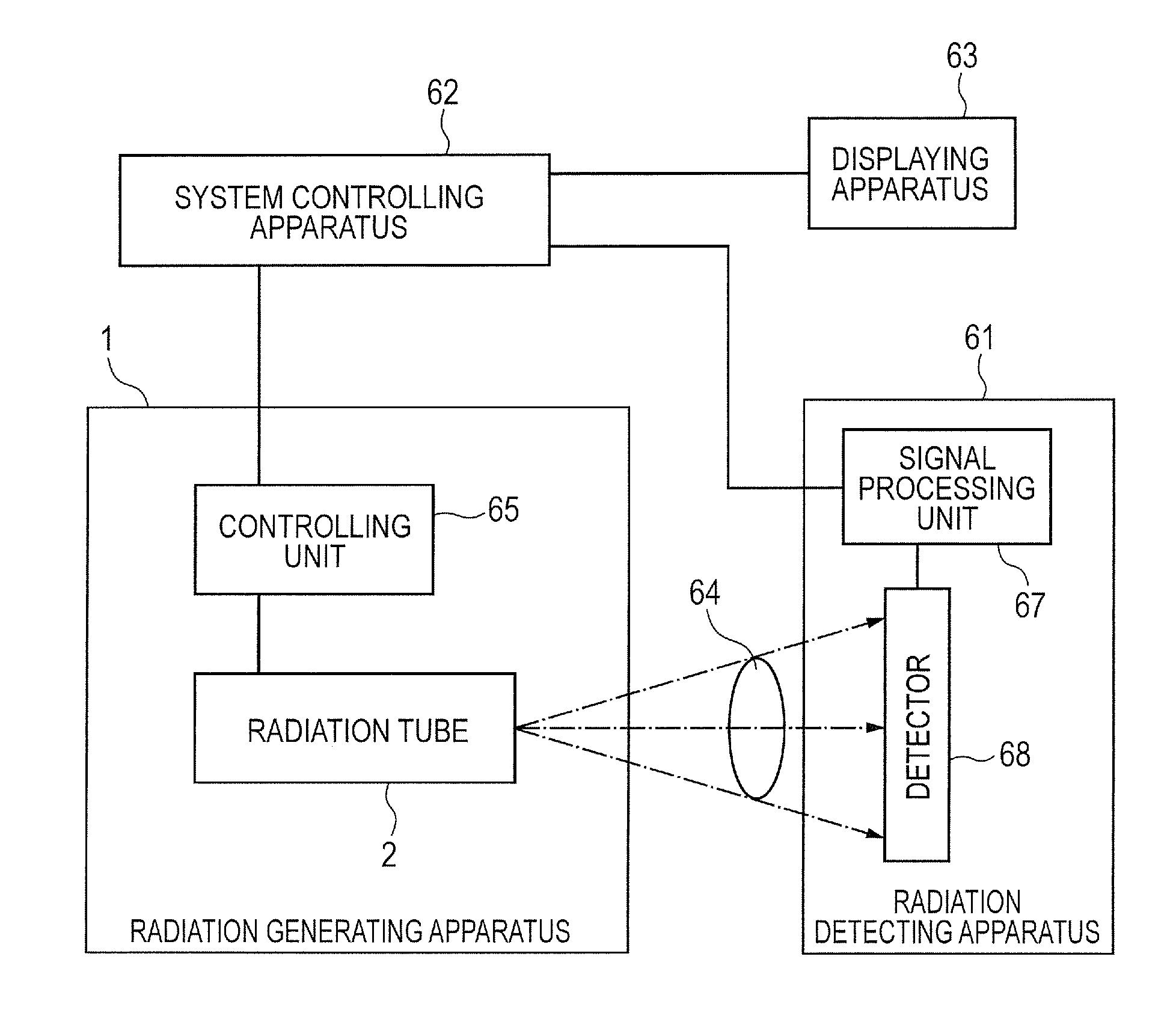

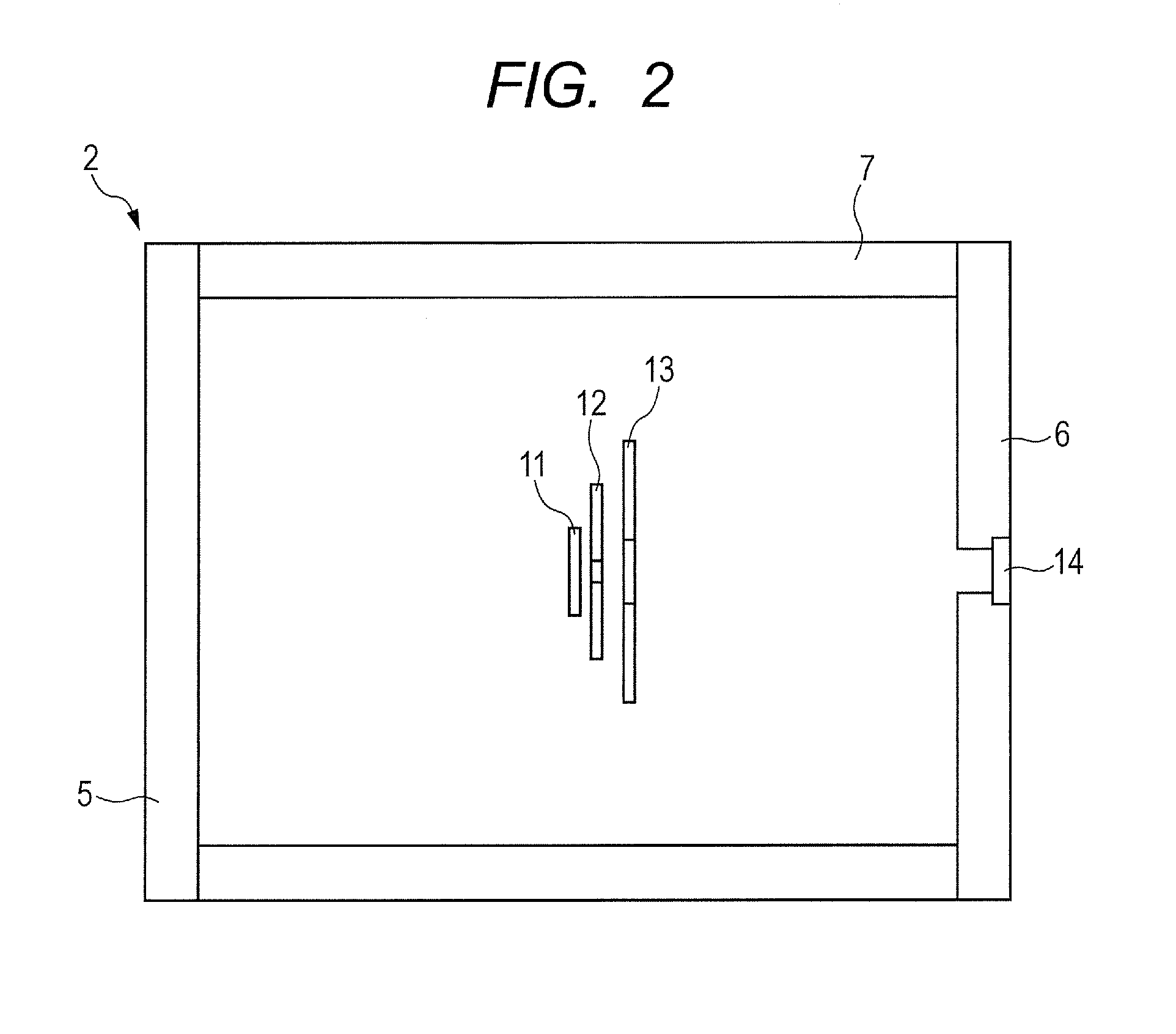

Radiation generating apparatus

InactiveUS20130148781A1Rapid coolingImprove pressure resistanceX-ray tube electrodesX-ray tube vessels/containerEngineeringVoltage

In a radiation generating apparatus of the present invention, a radiation tube in which a tubular side wall is arranged between a cathode and an anode is enclosed in an envelope filled with an insulating liquid. A thermally-conductive fin projecting to a side of a barrel portion of the radiation tube is provided on at least a part of an inner surface of the envelope, and the fin is provided on an area except for an area facing a position of the barrel portion at which potential of the barrel portion is higher than potential of the fin. Since a proper-shape cooling structure is provided on a proper position in the envelope, it is possible to secure withstand voltage and also made the entire apparatus compact in size.

Owner:CANON KK

Electrolytic capacitor

ActiveUS8116069B2Reduce resistanceSuppression of drop in withstand voltageHybrid capacitor electrolytesClosuresCapacitanceElectrolysis

Provide is an aluminum electrolytic capacitor exhibiting low specific resistance and low impedance property and realizing high reliability. An electrolytic capacitor has a structure in which: a capacitor element which is formed by rolling an anode foil and a cathode foil each connected with an electrode extraction lead through a separator and which is impregnated with a drive electrolytic solution is included in a cylindrical outer case having a closed-end; and an open end of the outer case is sealed with an elastic sealing body, in which: the drive electrolytic solution contains a tricyanomethide salt represented by the below-indicated chemical formula (1); and the drive electrolytic solution has a water content of 3.0 wt % or less:where, R represents a cation pairing with a tricyanomethide ion in formation of a tricyanomethide salt.

Owner:NICHICON CORP

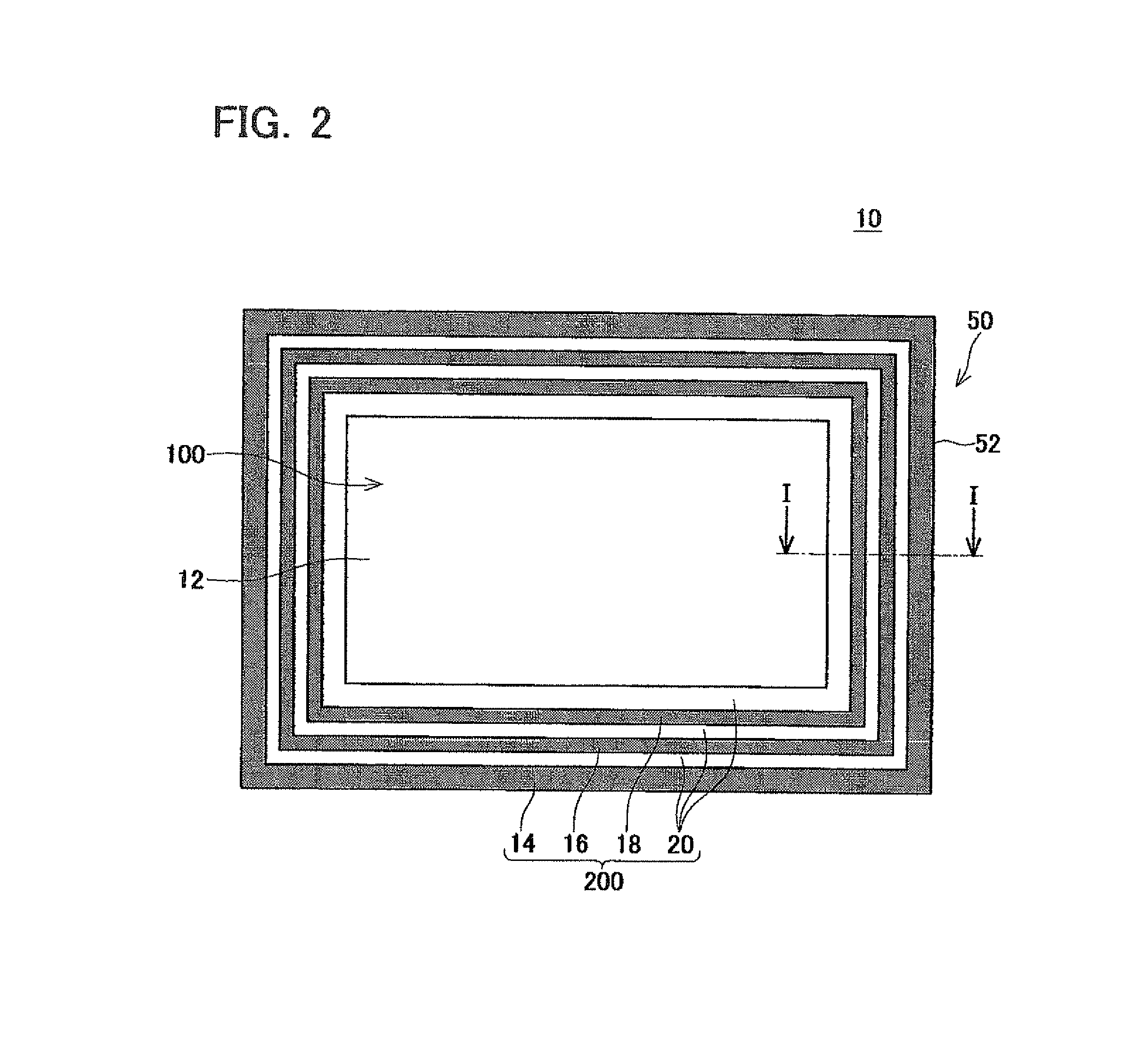

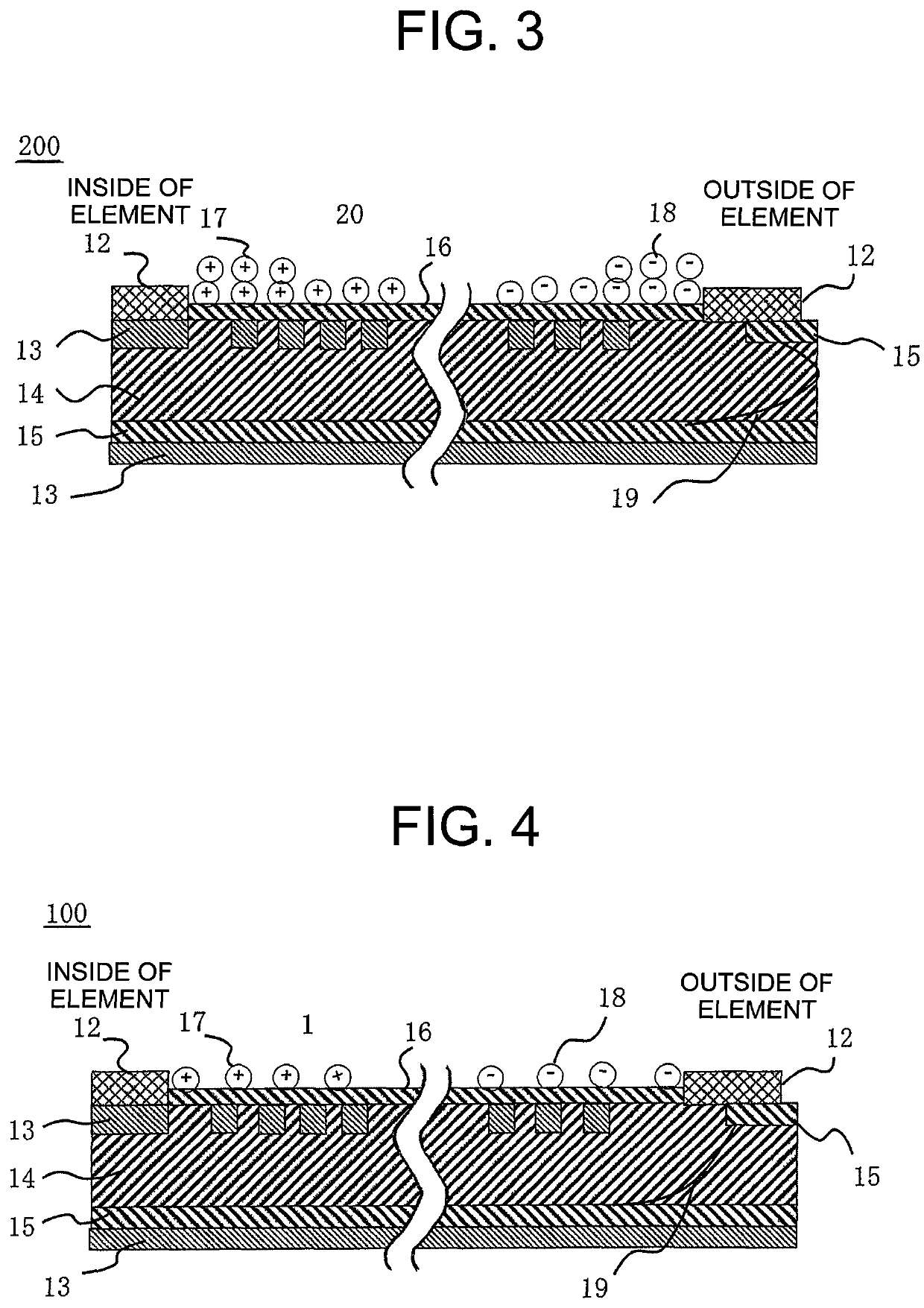

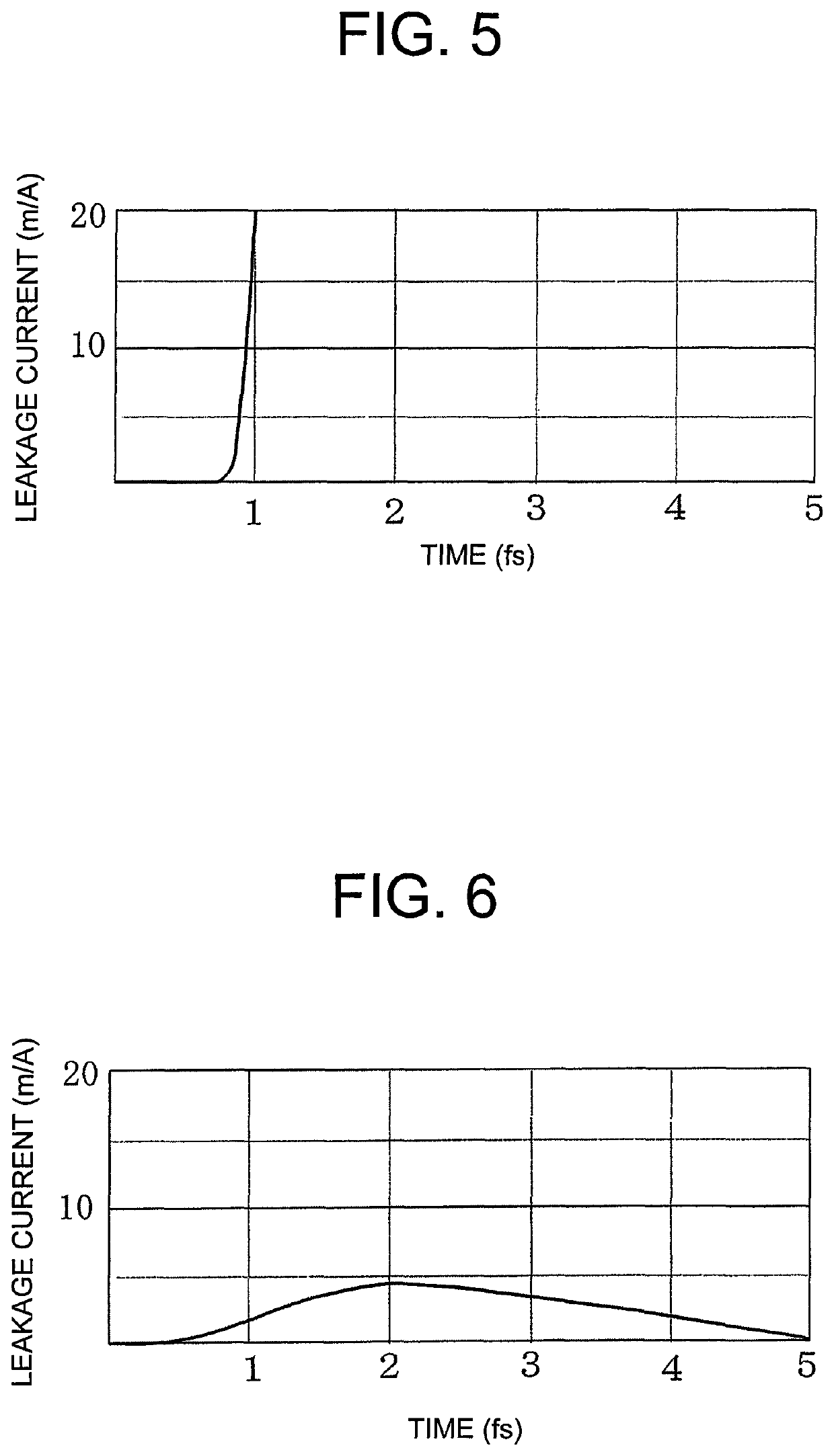

Low on-resistance wide band gap semiconductor device and method for producing the same

ActiveUS8564028B2Small sizeLower on-resistanceSemiconductor/solid-state device manufacturingDiodeBroadbandWide band

Owner:FUJI ELECTRIC CO LTD

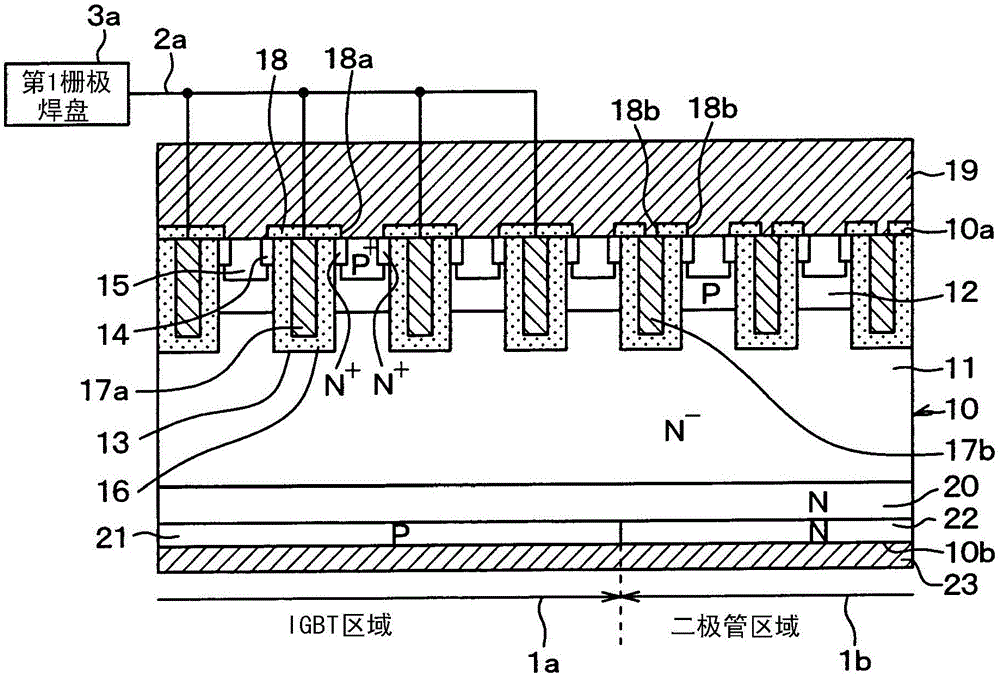

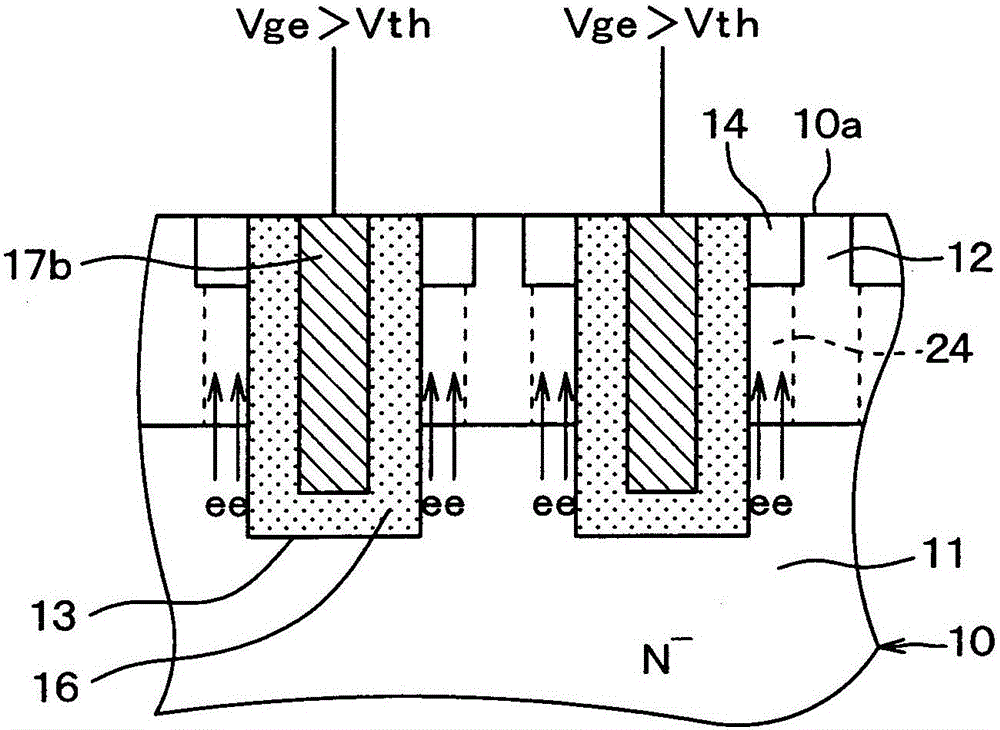

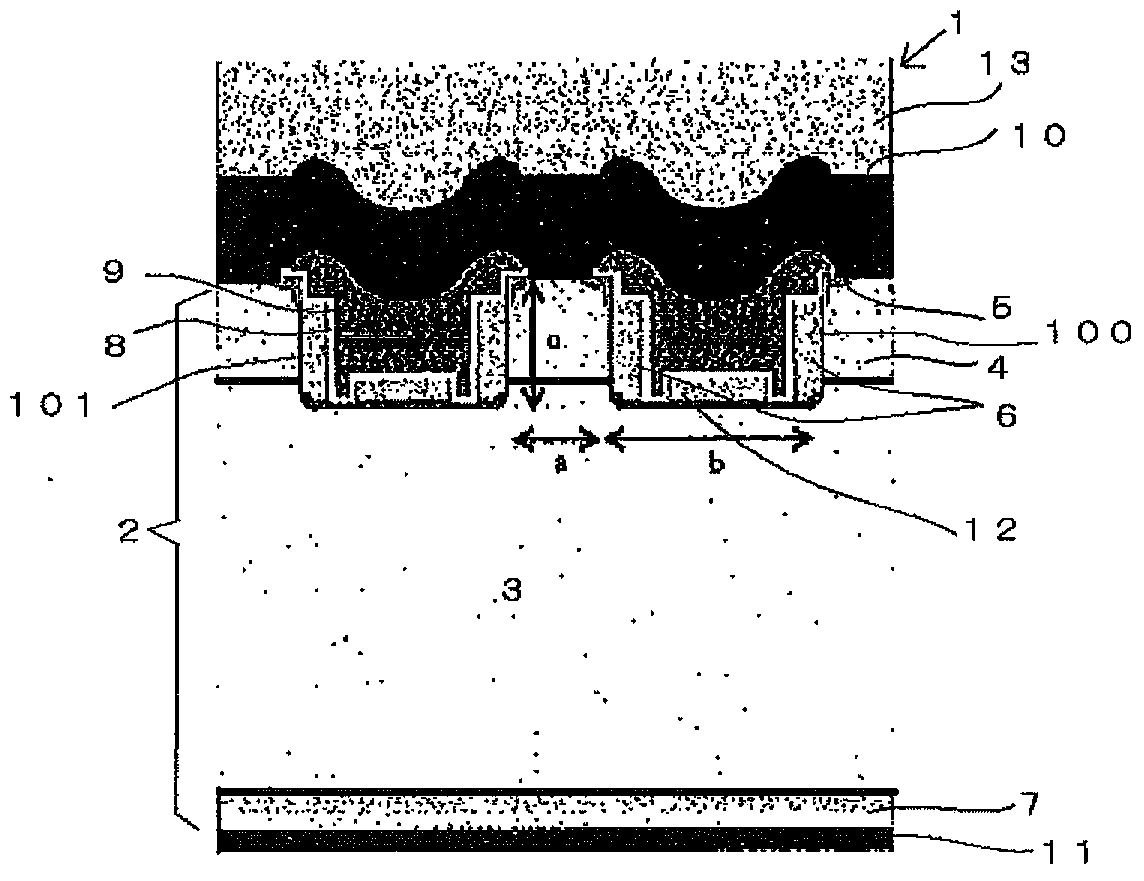

Semiconductor device

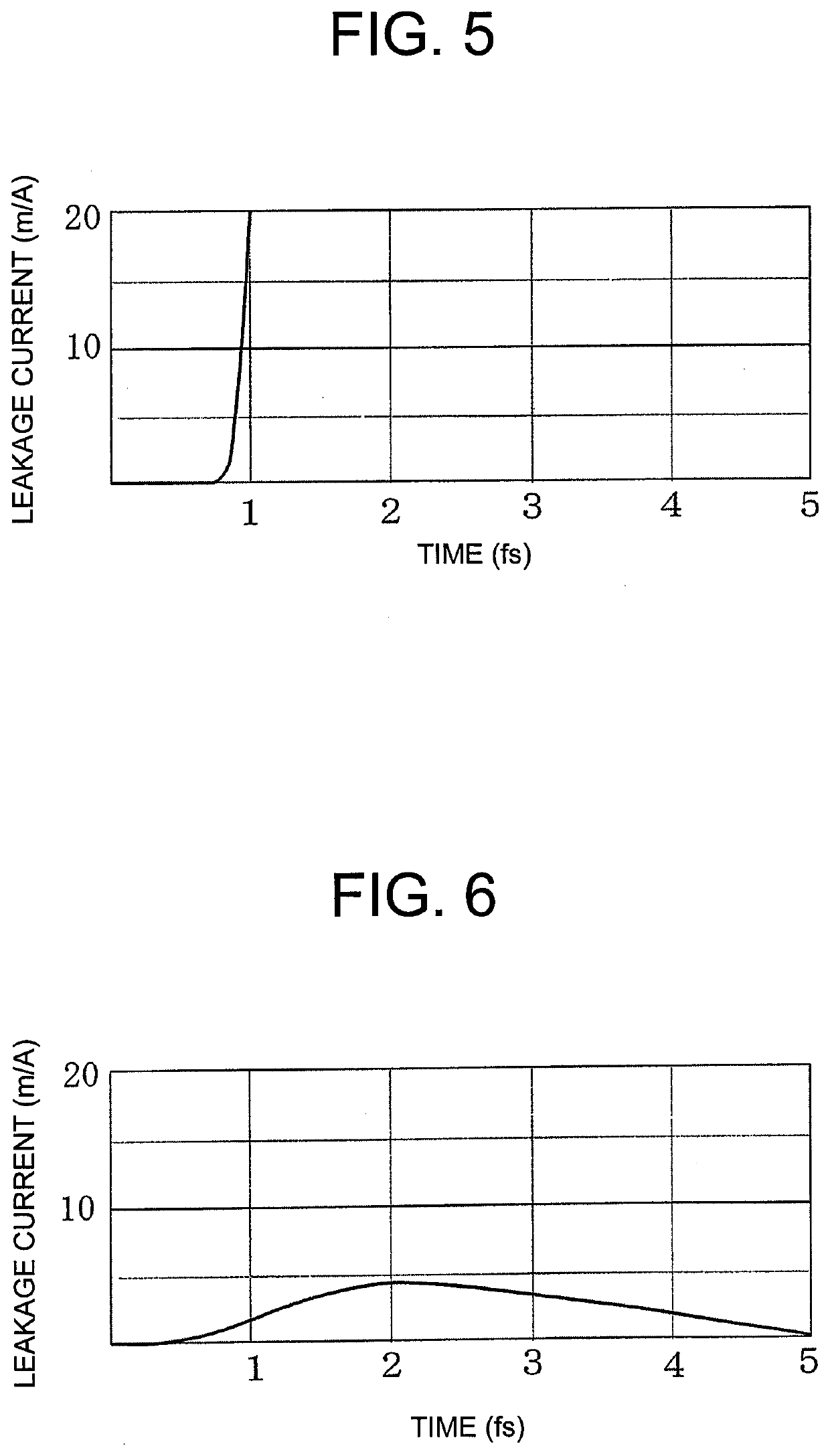

ActiveCN106537598AReduce conduction lossSuppression of drop in withstand voltageTransistorSolid-state devicesPower semiconductor deviceCathode ray

This semiconductor device includes a drift layer (11), a base layer (12) formed on the drift layer, a collector layer (21) and a cathode layer (22) disposed opposing the base layer, a plurality of trenches (13) penetrating the base layer, gate electrodes (17a, 17b) formed in the respective trenches, an emitter region (14) formed in a surface part of the base layer in such a manner as to contact each trench, a first electrode (19) connected to the base layer and the emitter region, and a second electrode (23) connected to the collector layer and the cathode layer. The gate electrode (17b) in a diode region of the semiconductor substrate can be controlled in a different way from that of the gate electrode (17a) in an IGBT region, and a voltage is applied to the gate electrode (17b) so as not to form an inversion layer (24) in the base layer.

Owner:DENSO CORP

Semiconductor device and method of manufacturing the same

ActiveUS6974996B2Withstand voltage can be suppressedIncrease ratingsTransistorSolid-state devicesSilicon oxideTrench gate

In a semiconductor device having a trench-gate structure in which polysilicon doped with boron is embedded in a trench, insulating film formed on the inner wall of the trench comprises ONO film, and silicon nitride film constituting the ONO film is formed to such film thickness and film quality that boron can be suppressed from passing through the silicon nitride film. Silicon oxide film is formed so that a top oxide film is thin and a bottom oxide film is thick.

Owner:DENSO CORP

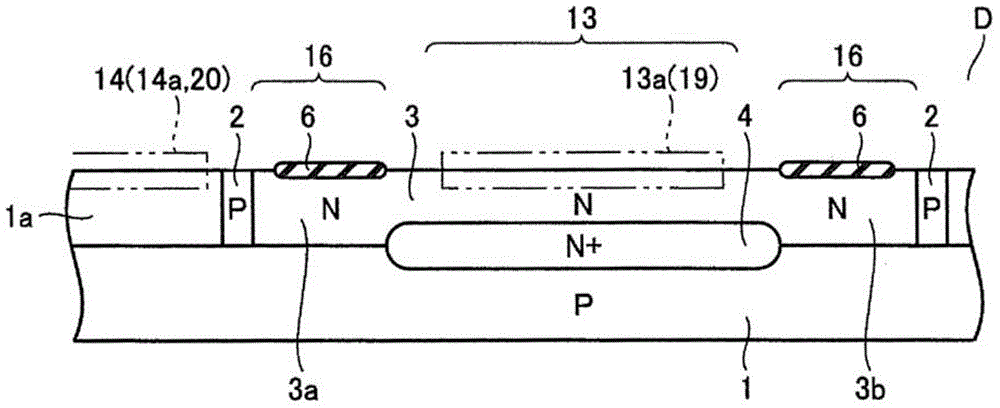

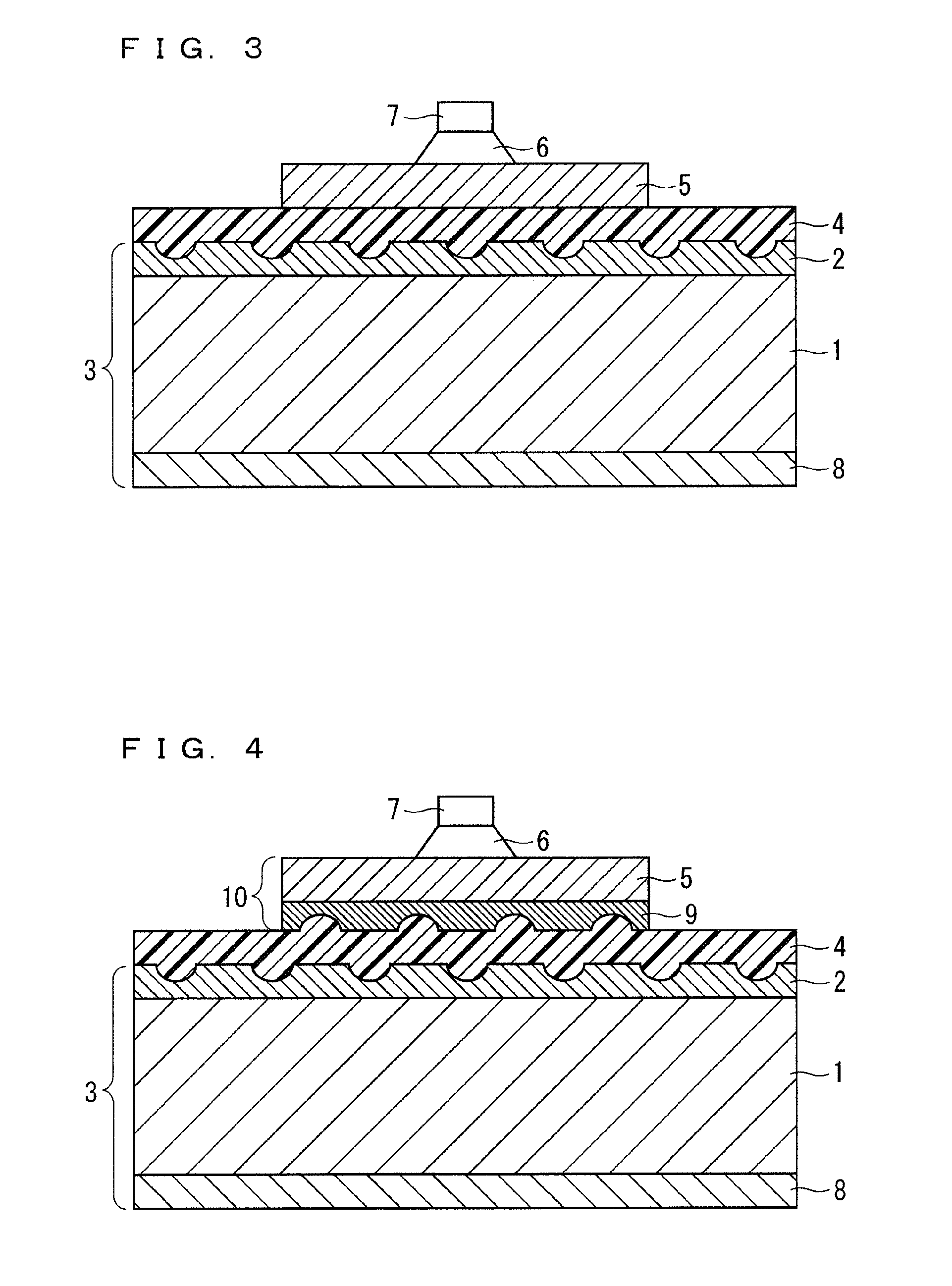

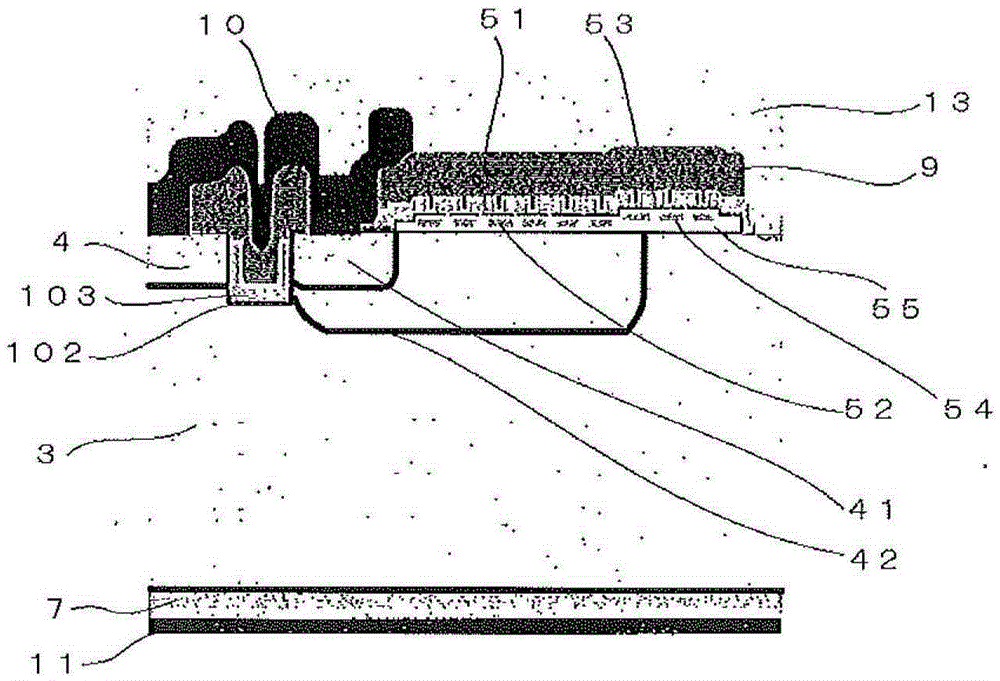

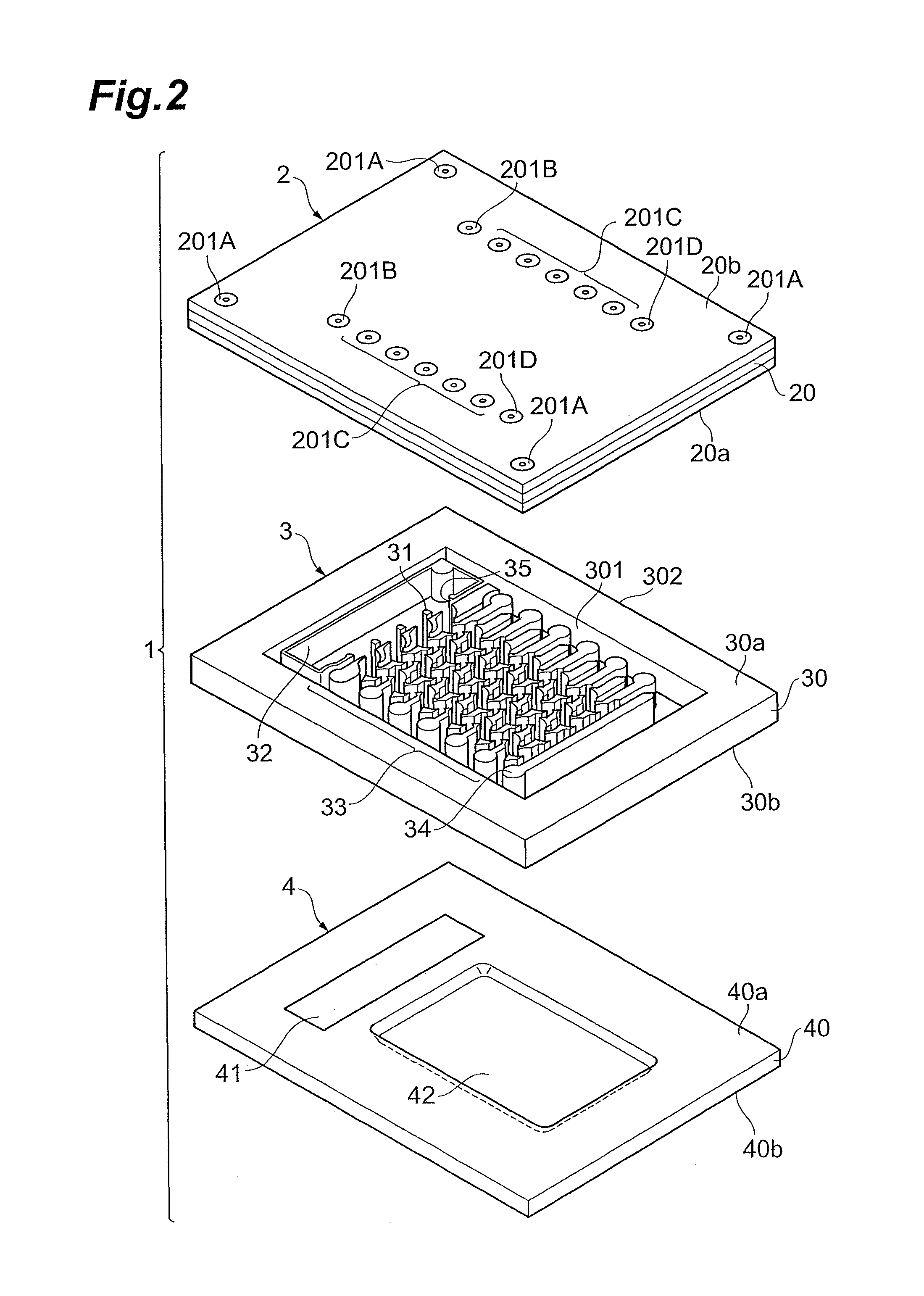

Photomultiplier tube

ActiveUS20120091890A1Improve pressure resistanceHigh strengthMutiple dynode arrangementsPhotomultiplierElectron

The photomultiplier tube 1 is provided with a casing 5 made of an upper frame 2 and a lower frame 4, an electron multiplying part 33 having dynodes 33a to 33l arrayed on the lower frame 4, a photocathode 41, and an anode part 34. Conductive layers 202 are installed on an opposing surface 20a of the upper frame 2. The electron multiplying part 33 is provided with base parts 52a to 52d of the respective dynodes 33a to 33d installed on the side of the lower frame 4, and power supplying parts 53a to 53d connected to the conductive layers 202 at one end parts of the respective base parts 52a to 52d in a direction along the opposing surface 40a. The base parts 52a to 52d are constituted in such a manner that the both end parts are joined to the opposing surface 40a, the central part is spaced away from the opposing surface 40a, and a cross sectional area at the one end part on the side of each of the power supplying parts 53a to 53d is made greater than a cross sectional area at another end part.

Owner:HAMAMATSU PHOTONICS KK

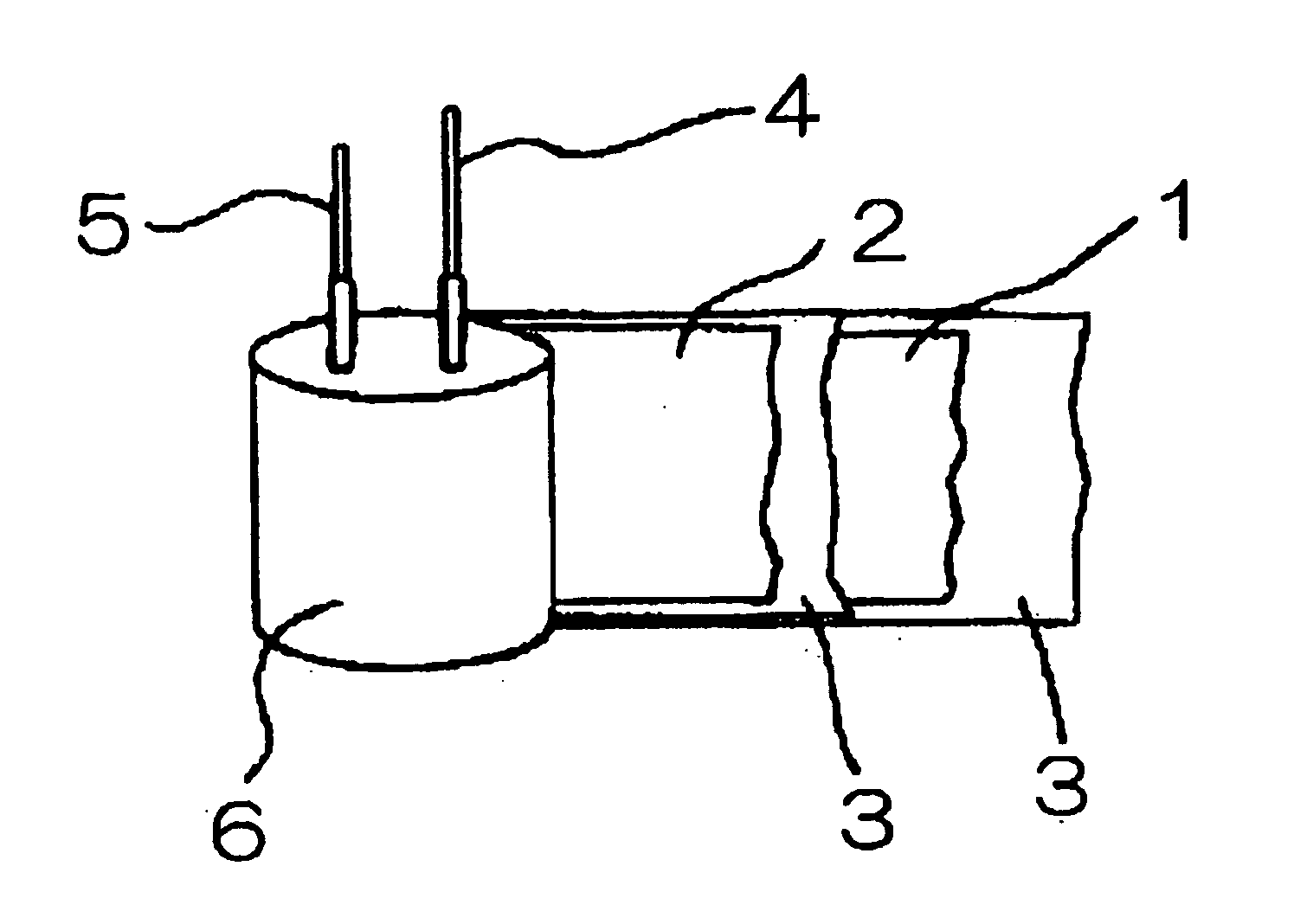

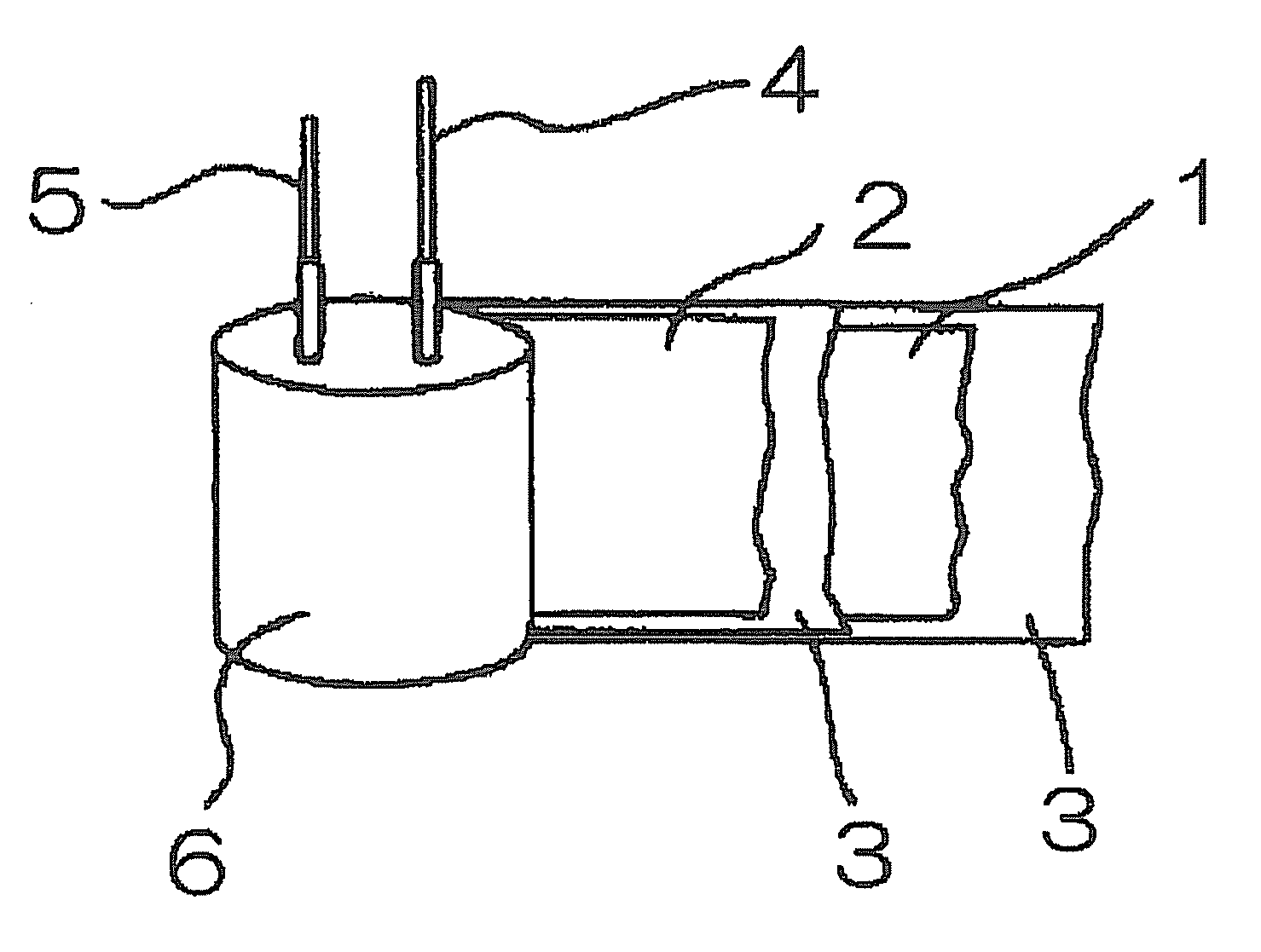

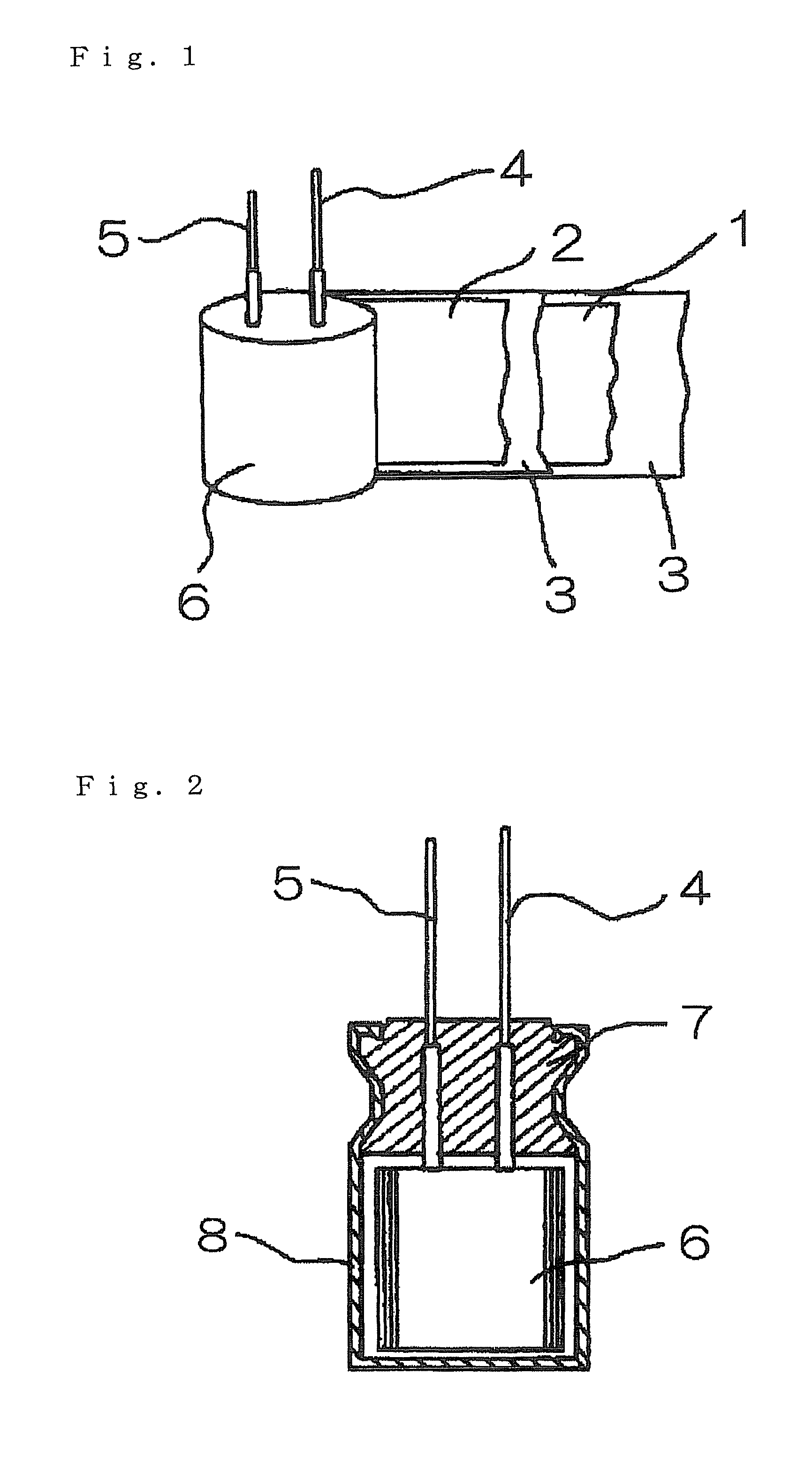

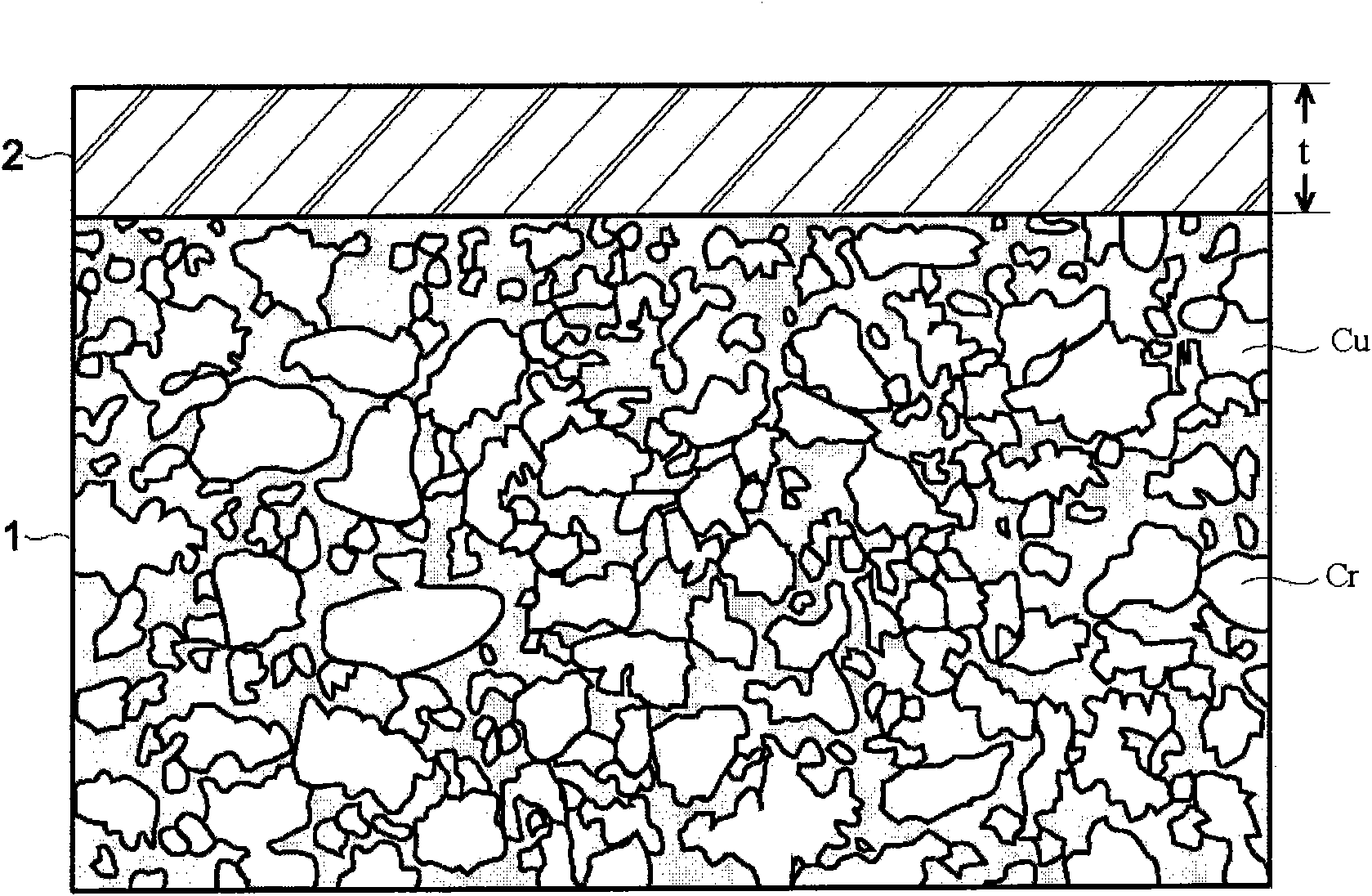

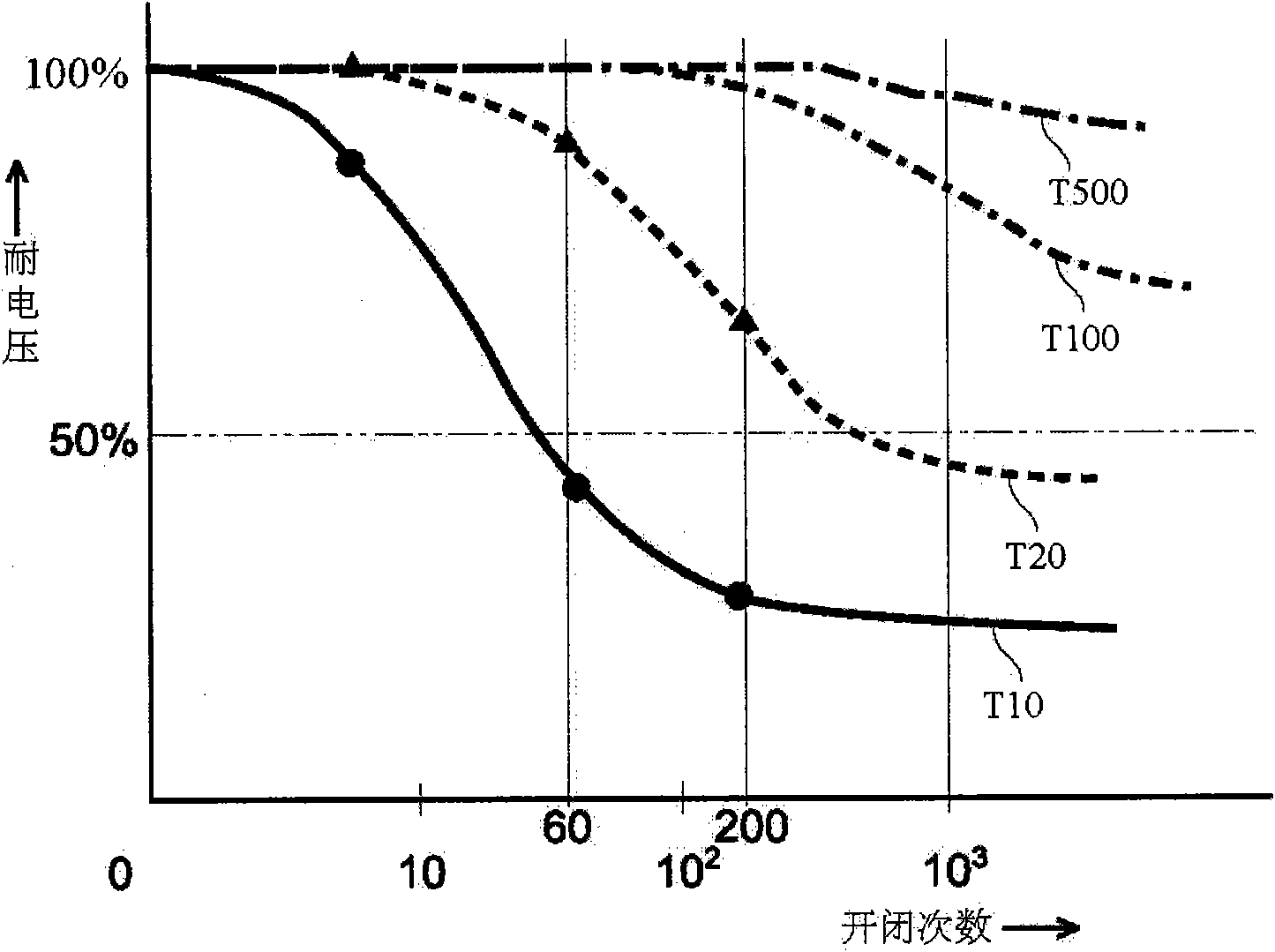

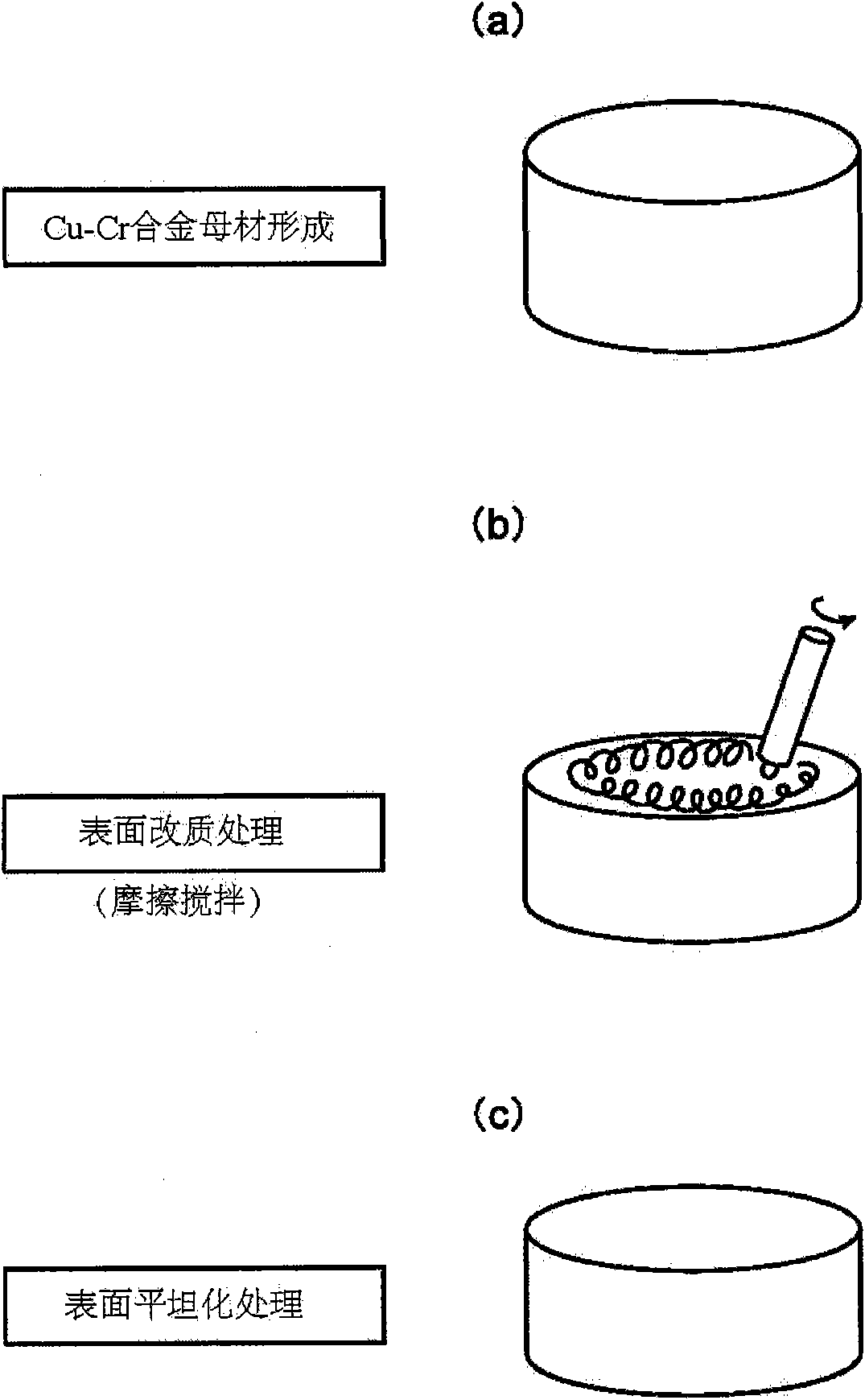

Electrode contact member of vacuum circuit breaker and process for production of the same

InactiveCN101911236AImprove breaking performanceImprove conductivityContact materialsSolid state diffusion coatingElectrode ContactFriction stir processing

The invention provides an electrode contact member of vacuum circuit breaker which is obtained by forming a thick Cr fine dispersion layer on the surface of a Cu-Cr alloy base metal and which brings about improved dielectric strength and interrupting performance and a process for easy production of the member though easy formation of a Cr fine dispersion layer. The electrode contact member comprises a Cu-Cr alloy base metal (1) comprising 40 to 80wt% of Cu and 20 to 60wt% of Cr and a Cr fine dispersion layer (2) of 500mu m to 3mm in thickness formed on the surface of the base metal (1) through surface treatment by friction stir processing. The Cr fine dispersion layer (2) is subjected to surface flattening treatment prior to use.

Owner:JAPAN AE POWER SYST

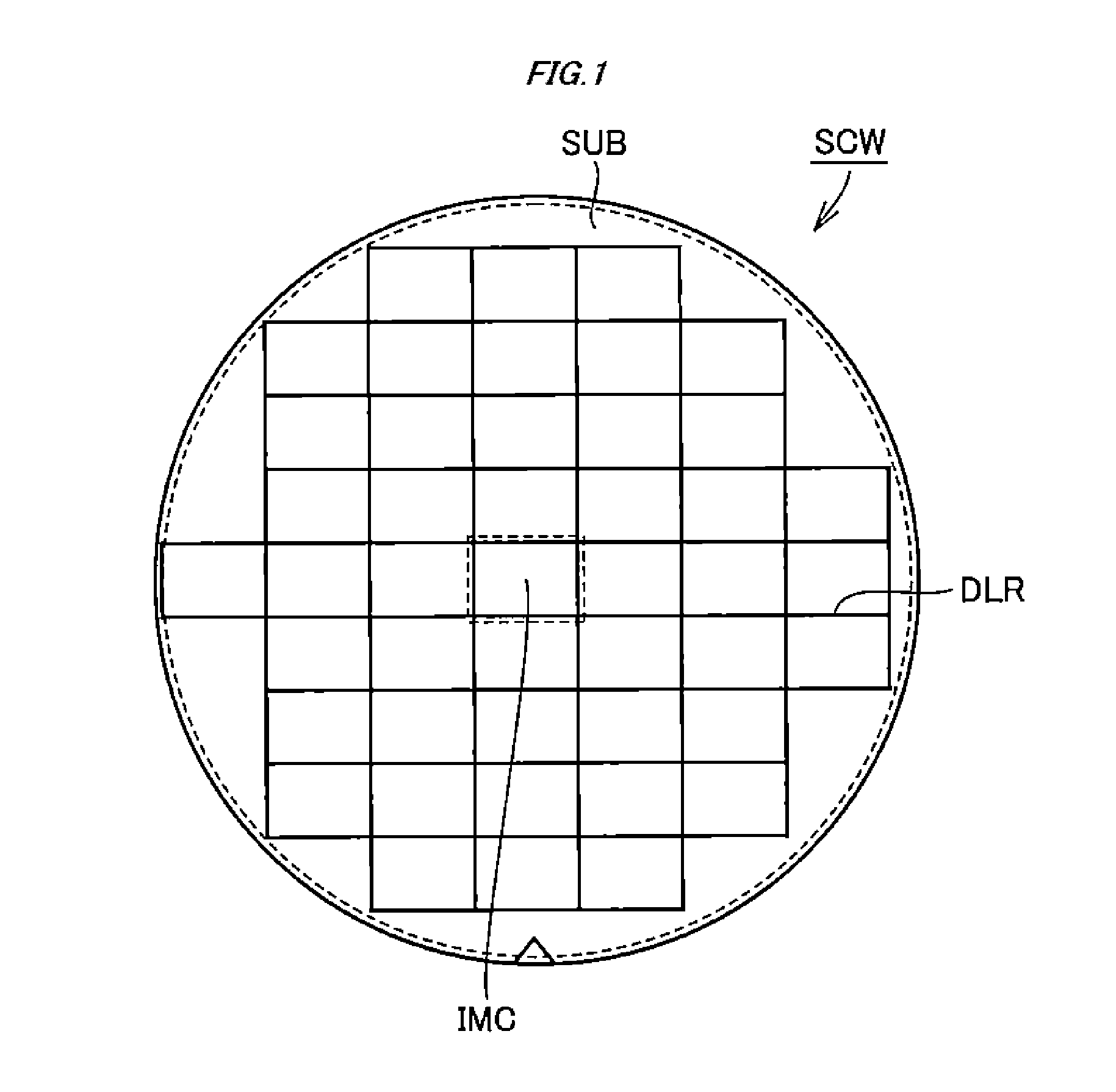

Semiconductor device and method of manufacturing the same

ActiveUS20160049470A1Improve accuracyReduce withstand voltageTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A semiconductor device including a well resistance element of high accuracy and high withstand voltage and a method of manufacturing the semiconductor device are provided.The semiconductor device includes a semiconductor substrate, a well region, an input terminal, an output terminal, a separation insulating film, and an active region. The input terminal and the output terminal are electrically coupled to the well region. The separation insulating film is arranged to be in contact with the upper surface of the well region in an intermediate region between the input terminal and the output terminal. The active region is arranged to be in contact with the upper surface of the well region. The separation insulating film and the active region in the intermediate region have an elongated shape in plan view. In the intermediate region, a plurality of separation insulating films and a plurality of active regions are alternately and repeatedly arranged.

Owner:RENESAS ELECTRONICS CORP

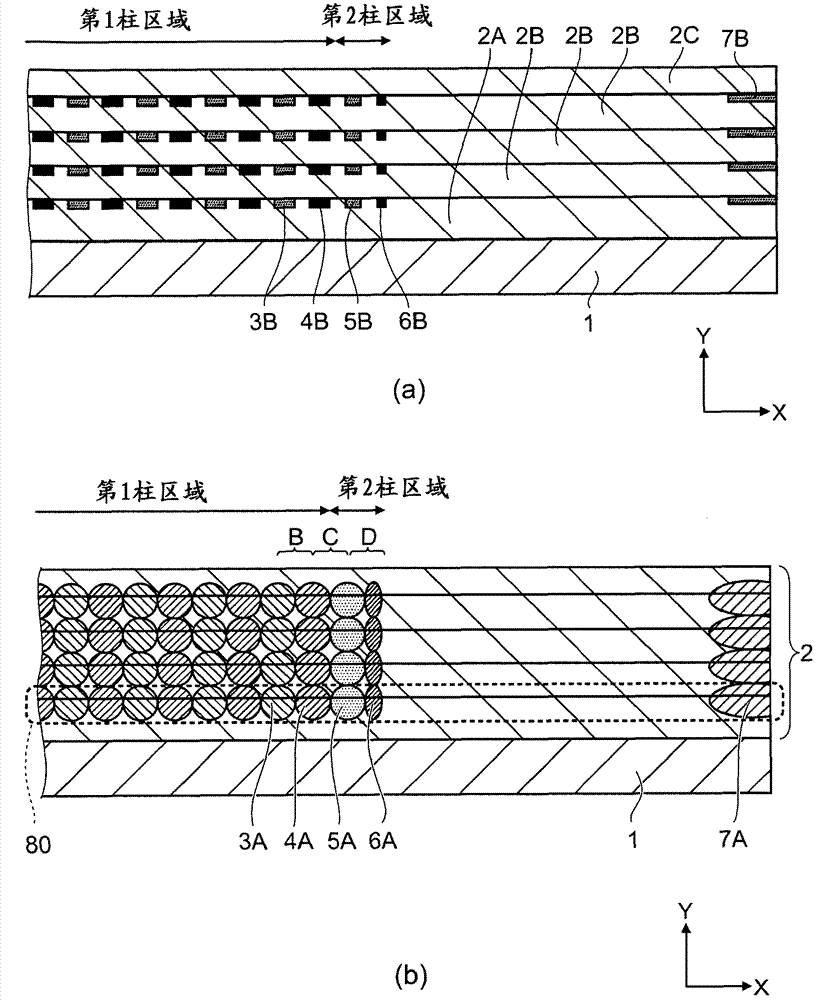

Power semiconductor device

InactiveCN103022127AReduce withstand voltageSuppression of drop in withstand voltageSemiconductor devicesPower semiconductor deviceHigh resistance

A power semiconductor device in an embodiment of the invention includes a high resistance epitaxial layer having a first pillar region and a second pillar region as a drift layer. The first pillar region includes a plurality of first pillars of the first conductivity type and a plurality of second pillars of the second conductivity type disposed alternately along a first direction. The second pillar region is adjacent to the first pillar region along the first direction. The second pillar region includes a third pillar and a fourth pillar of a conductivity type opposite to a conductivity type of the third pillar. A net quantity of impurities in the third pillar is less than a net quantity of impurities in each of the plurality of first pillars. A net quantity of impurities in the fourth pillar is less than the net quantity of impurities in the third pillar.

Owner:KK TOSHIBA

Semiconductor device

ActiveUS9100000B2Suppression of drop in withstand voltageReduce voltageElectronic switchingElectric pulse generatorPower semiconductor deviceCell region

Owner:DENSO CORP

Semiconductor device and method for manufacturing the same

ActiveCN104659078ASuppress voltage dropSuppression of drop in withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor

An N type diffusion layer in which a high-side circuit region is disposed is formed from a surface of a P type epitaxial layer covering a surface of a P type semiconductor substrate to reach the surface of the semiconductor substrate. An N type high breakdown voltage isolation region is formed with a prescribed width to surround high-side circuit region. High breakdown voltage isolation region includes a corner portion located along a corner pattern of rectangular high-side circuit region, and a linear portion located along a linear pattern thereof. The concentration of an impurity in an N type diffusion layer of corner portion is set to be higher than the concentration of an impurity in an N type diffusion layer of linear portion.

Owner:MITSUBISHI ELECTRIC CORP

Metal base substrate, power module, and method for manufacturing metal base substrate

ActiveUS9578754B2Suppression of drop in withstand voltageEasy to manufactureInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsComputer moduleCopper

A metal base substrate of the present invention includes a copper plate made of copper, a metal layer that is formed on the copper plate and is made of a metal different from the copper, an insulating resin sheet that is formed by bonding a sheet made of an insulating resin onto the metal layer, and a circuit pattern formed on the insulating resin sheet.

Owner:MITSUBISHI ELECTRIC CORP

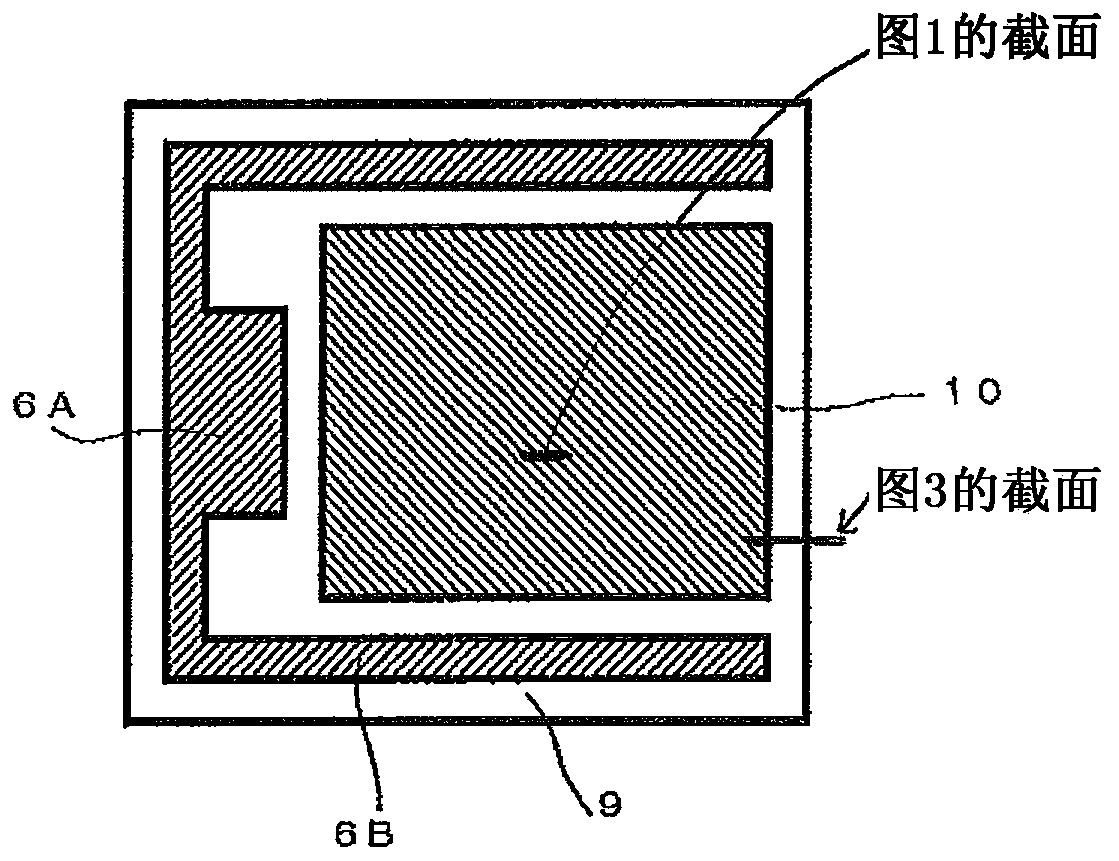

Semiconductor device

ActiveCN106549044AInhibition reachSuppression of drop in withstand voltageSemiconductor devicesElectrical conductorDevice material

In one embodiment, a semiconductor device may include a controller that may be configured to receive an information signal from a detachable device wherein the information signal may be selectively representative of an output signal of the controller according to codes of the detachable device and to receive a sense input that may be representative of the output signal and to determine a code received from the detachable device according to a value of the sense signal and the information signal.the distance between the conductive layer at the upper portion of the semiconductor substrate and the upper surface of the semiconductor substrate is larger than the distance between the conductive layer at the upper portion of the semiconductor substrate and the upper surface of the semiconductor area.

Owner:SANKEN ELECTRIC CO LTD

Semiconductor device

InactiveUS20140346561A1Decrease short-circuit energy densityAvoid temperature riseSemiconductor/solid-state device detailsSolid-state devicesTrench gateSemiconductor

In a semiconductor substrate of a semiconductor device, a drift layer, a body layer, an emitter layer, and a trench gate electrode are formed. When the semiconductor substrate is viewed in a plane manner, the semiconductor substrate is divided into a first region covered with a heat dissipation member, and a second region not covered with the heat dissipation member. A density of trench gate electrodes in the first region is equal to a density of trench gate electrodes in the second region. A value obtained by dividing an effective carrier amount of channel parts formed in the first region by an area of the first region is larger than a value obtained by dividing an effective carrier amount of channel parts formed in the second region by an area of the second region.

Owner:DENSO CORP

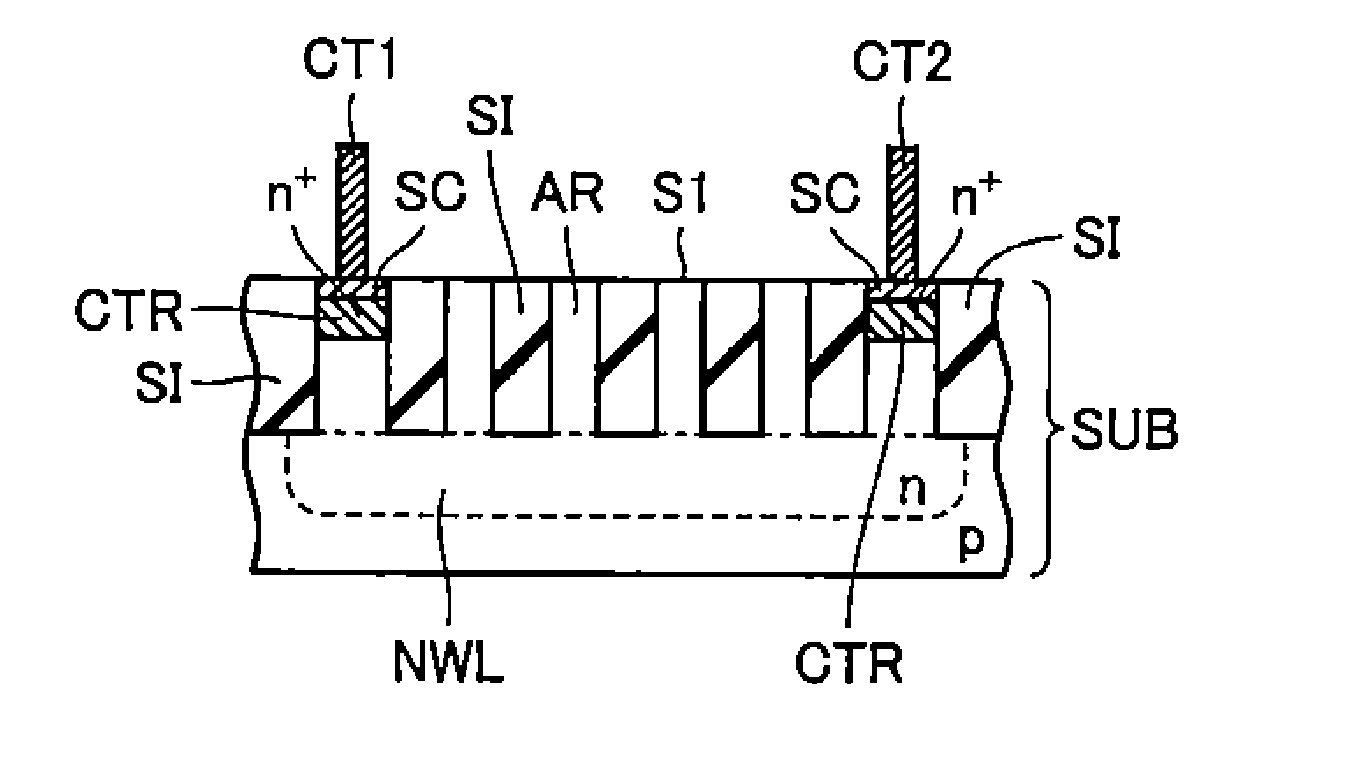

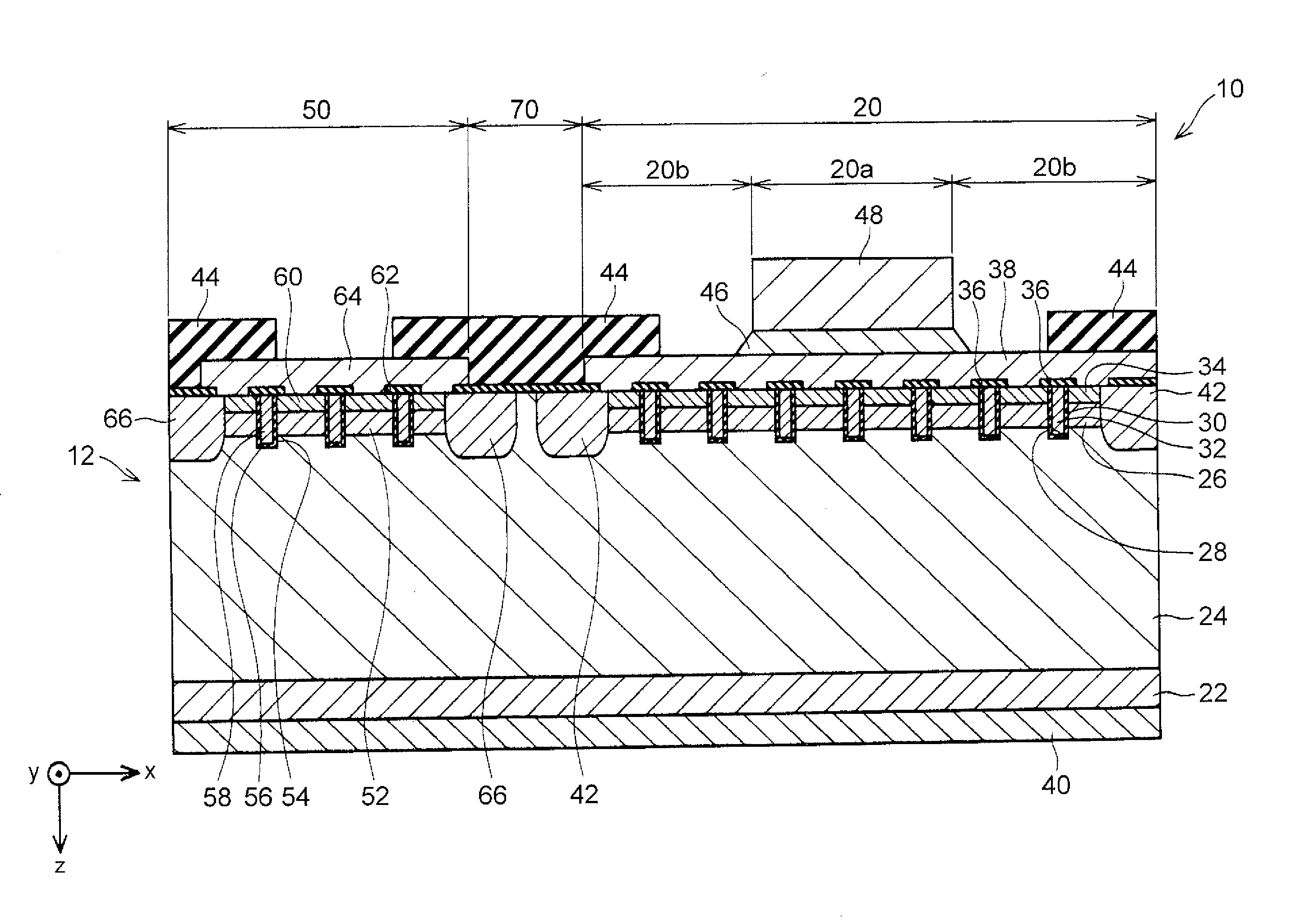

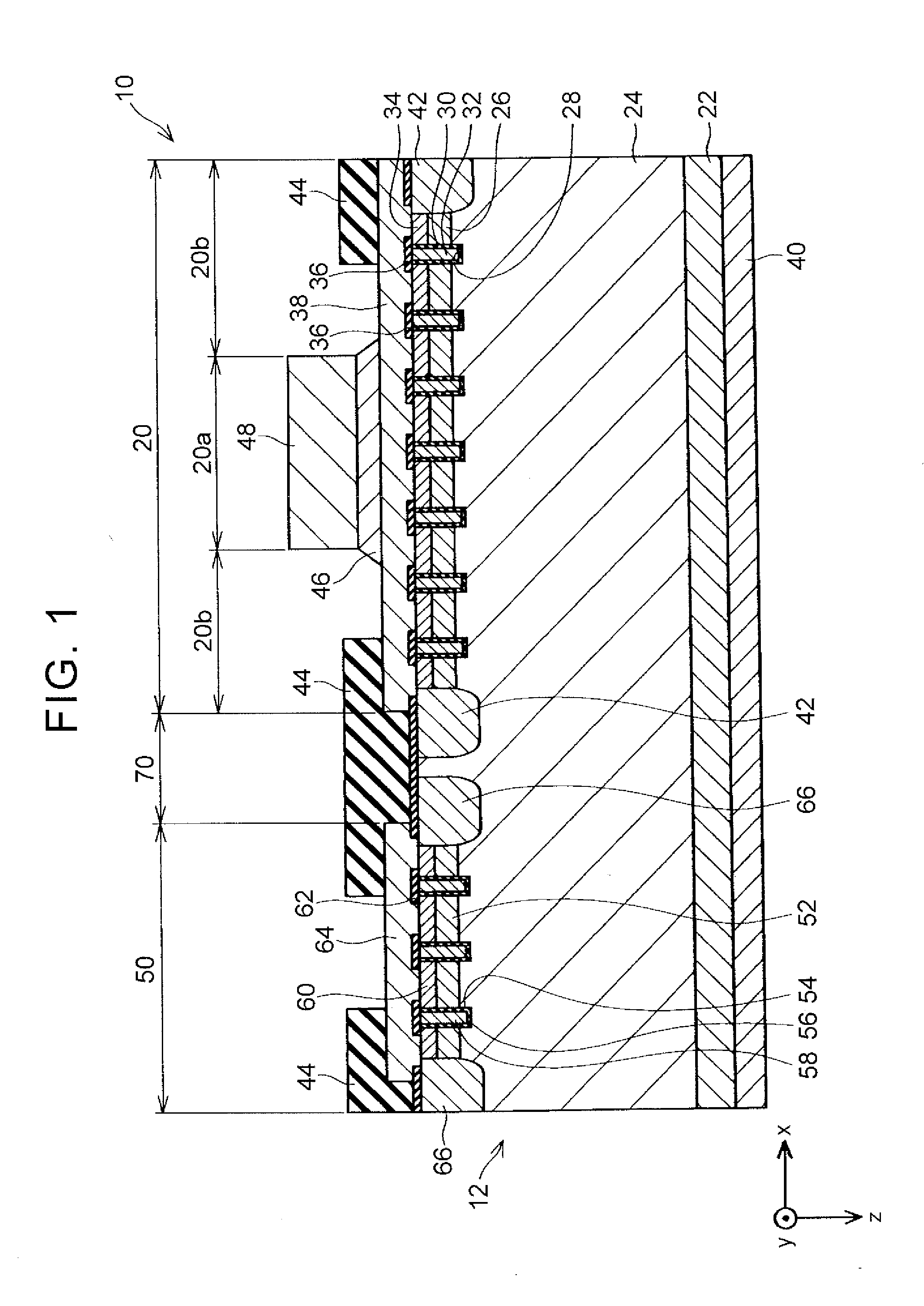

Semiconductor device and semiconductor device manufacturing method

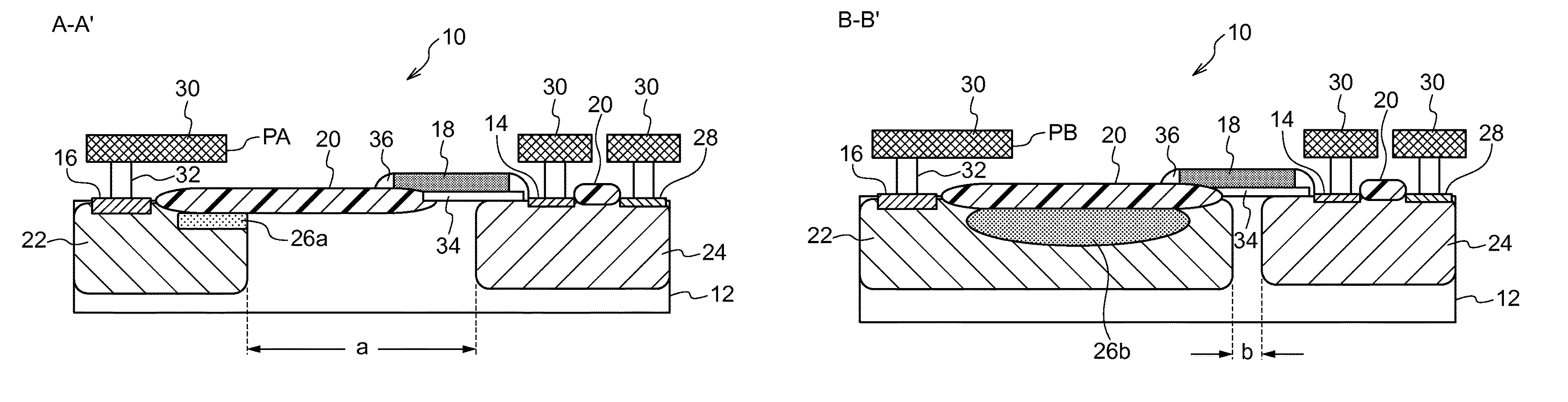

ActiveUS20160056237A1Suppression of drop in withstand voltageReduce withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice material

There is provided a semiconductor device including: a semiconductor substrate; a first semiconductor region that includes an extension portion extending in a specific direction at a specific width as viewed along a direction orthogonal to the main surface; a second semiconductor region that is shaped to include a portion running along the extension portion of the first semiconductor region as viewed along the direction orthogonal to the main surface; a field relaxation layer that relaxes a field generated between the first semiconductor region and the second semiconductor region, that is formed on the second semiconductor region side of the main surface, and that is formed by a semiconductor layer; and a conductor that is connected to the second semiconductor region, and that has an end portion on the first conductor region side positioned within the range of the field relaxation layer.

Owner:LAPIS SEMICON CO LTD

Semiconductor device

InactiveUS9006839B2Suppression of drop in withstand voltageIncrease capacitySemiconductor/solid-state device detailsSolid-state devicesTrench gateSemiconductor

In a semiconductor substrate of a semiconductor device, a drift layer, a body layer, an emitter layer, and a trench gate electrode are formed. When the semiconductor substrate is viewed in a plane manner, the semiconductor substrate is divided into a first region covered with a heat dissipation member, and a second region not covered with the heat dissipation member. A density of trench gate electrodes in the first region is equal to a density of trench gate electrodes in the second region. A value obtained by dividing an effective carrier amount of channel parts formed in the first region by an area of the first region is larger than a value obtained by dividing an effective carrier amount of channel parts formed in the second region by an area of the second region.

Owner:DENSO CORP

Semiconductor device and semiconductor device manufacturing method

ActiveUS9553144B2Suppression of drop in withstand voltageReduce withstand voltageSemiconductor devicesPower semiconductor deviceElectrical conductor

A semiconductor device includes a semiconductor substrate; a first semiconductor region that includes an extension portion extending in a specific direction at a specific width as viewed along a direction orthogonal to the main surface; a second semiconductor region that is shaped to include a portion running along the extension portion of the first semiconductor region as viewed along the direction orthogonal to the main surface; a field relaxation layer that relaxes a field generated between the first semiconductor region and the second semiconductor region, that is formed on the second semiconductor region side of the main surface, and that is formed by a semiconductor layer; and a conductor that is connected to the second semiconductor region, and that has an end portion on the first conductor region side positioned within the range of the field relaxation layer.

Owner:LAPIS SEMICON CO LTD

Photomultiplier tube

ActiveUS8587196B2Reduce withstand voltageSuppression of drop in withstand voltageMutiple dynode arrangementsMultiplier dynodesPhotocathodeDynode

The photomultiplier tube 1 is provided with a casing 5 made of an upper frame 2 and a lower frame 4, an electron multiplying part 33 having dynodes 33a to 331 arrayed on the lower frame 4, a photocathode41, and an anode part 34. Conductive layers 202 are installed on an opposing surface 20a of the upper frame 2. The electron multiplying part 33 is provided with base parts 52a to 52d of the respective dynodes 33a to 33d installed on the side of the lower frame 4, and power supplying parts 53a to 53d connected to the conductive layers 202 at one end parts of the respective base parts 52a to 52d in a direction along the opposing surface 40a. The base parts 52a to 52d are constituted in such a manner that the both end parts are joined to the opposing surface 40a, the central part is spaced away from the opposing surface 40a, and a cross sectional area at the one end part on the side of each of the power supplying parts 53a to 53d is made greater than a cross sectional area at another end part.

Owner:HAMAMATSU PHOTONICS KK

Semiconductor device

ActiveCN106549044BInhibition reachSuppression of drop in withstand voltageSemiconductor devicesElectrical conductorDevice material

A semiconductor device. It aims to solve the following problems: the potential division effect of the capacitive FP is strong, and the depletion layer can easily reach the end of the n-region. It is characterized in that the edge region has: a semiconductor base; a semiconductor region of a second conductivity type opposite to the first conductivity type, which is arranged in the semiconductor base in a pn-bonded manner; and a conductor layer above and on the semiconductor region. A plurality of the conductor layers are arranged side by side above the region outside the semiconductor region, the conductor layer is insulated from the semiconductor region and the region outside the semiconductor region, and the conductor layer above the region outside the semiconductor region is separated from the upper surface of the region outside the semiconductor region The distance between them is greater than the distance between the conductor layer above the semiconductor region and the upper surface of the conductor region. The distance between the conductor layer above the semiconductor base and the upper surface of the semiconductor base is greater than the distance between the conductor layer above the semiconductor region and the upper surface of the semiconductor region.

Owner:SANKEN ELECTRIC CO LTD

SiC-MOSFET

An object of the present disclosure is to suppress decrease in withstand voltage and increase in ON voltage and to increase body diode current. An SiC-MOSFET includes: a source region formed on a surface layer of a base region; a gate electrode facing a channel region which is a region of the base region sandwiched between a drift layer and the source region via a gate insulating film; a source electrode having electrically contact with the source region; and a plurality of first embedded regions of a second conductivity type formed adjacent to a lower surface of the base region. The plurality of first embedded regions are formed immediately below at least both end portions of the base region, and three or more first embedded regions are formed to be separated from each other.

Owner:MITSUBISHI ELECTRIC CORP

Power semiconductor device

PendingCN114388611ASuppression of drop in withstand voltageSemiconductor devicesPower semiconductor deviceEngineering physics

Owner:MITSUBISHI ELECTRIC CORP

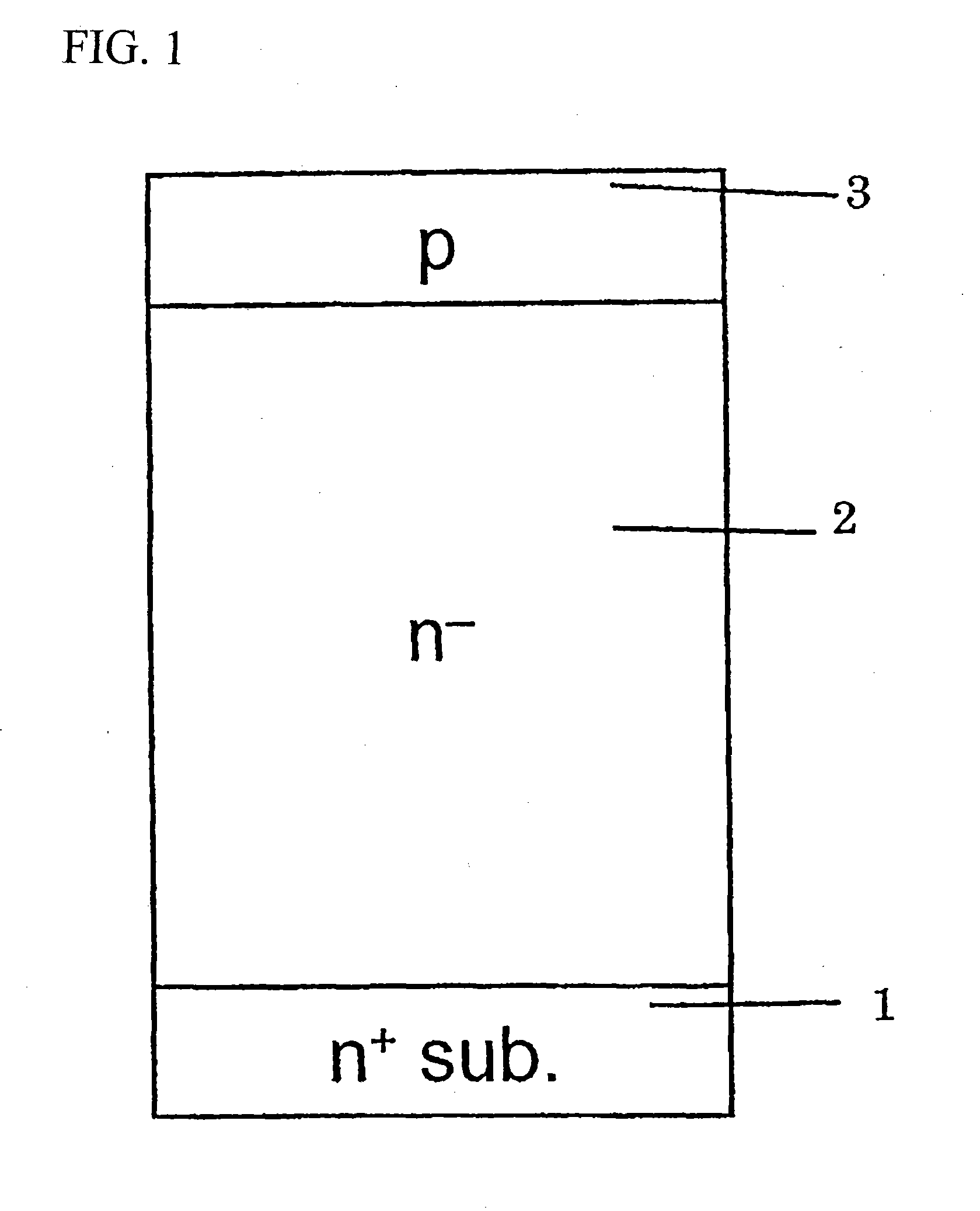

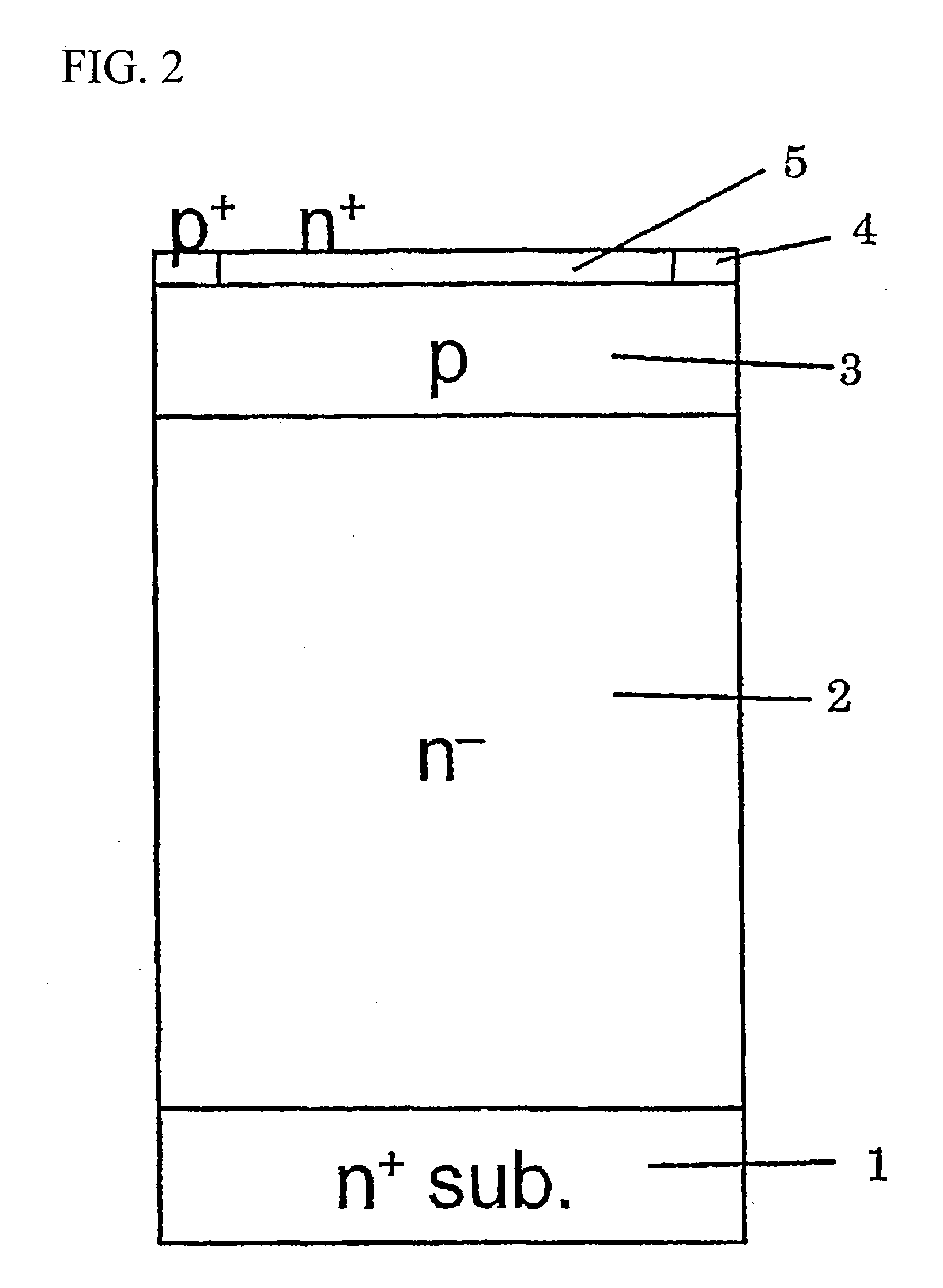

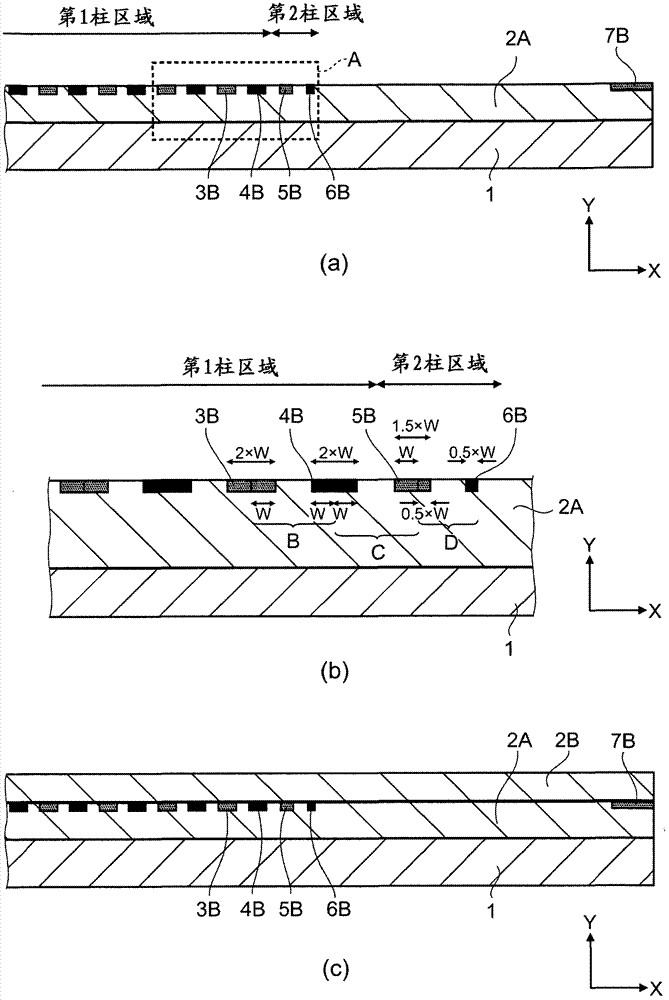

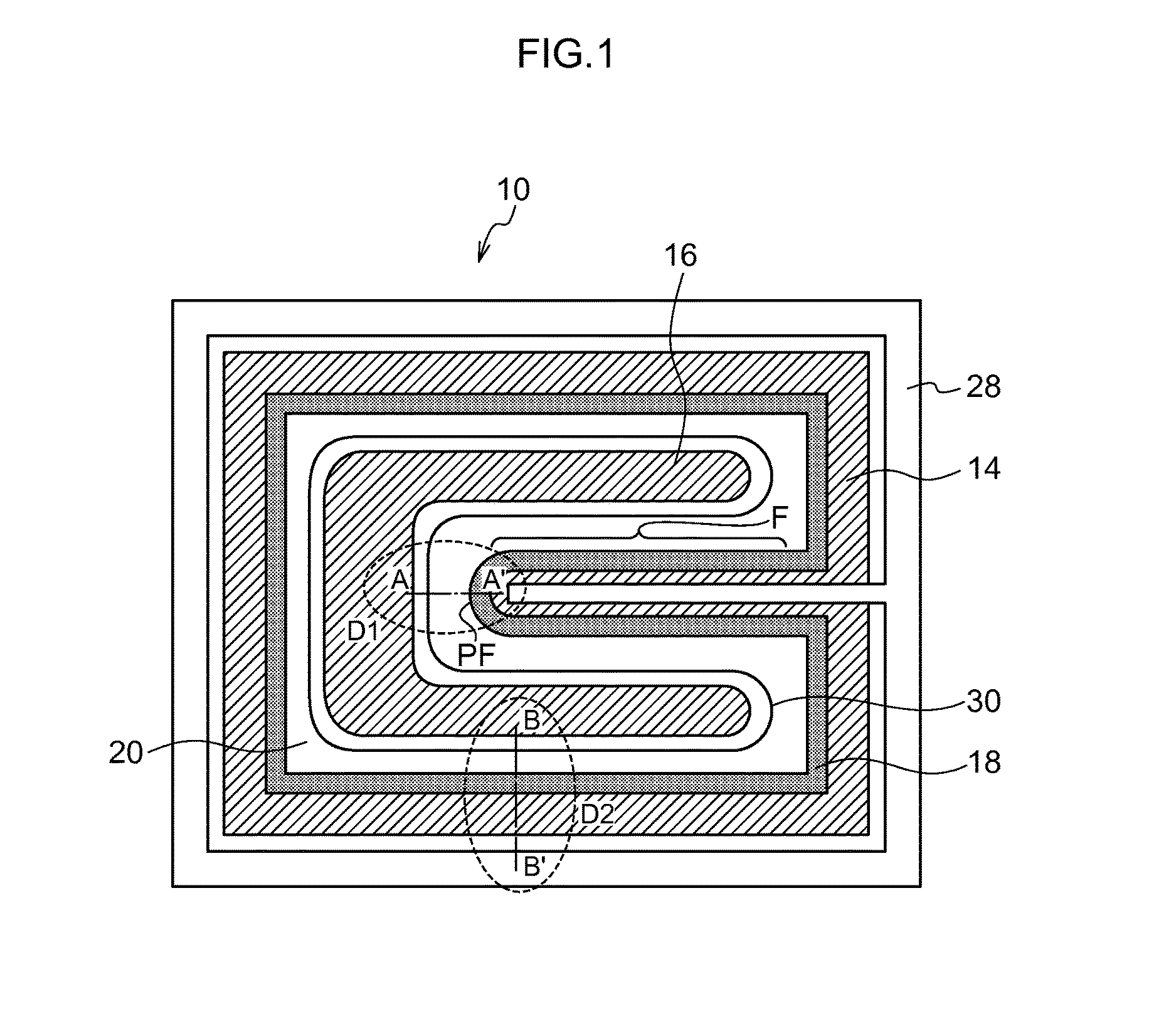

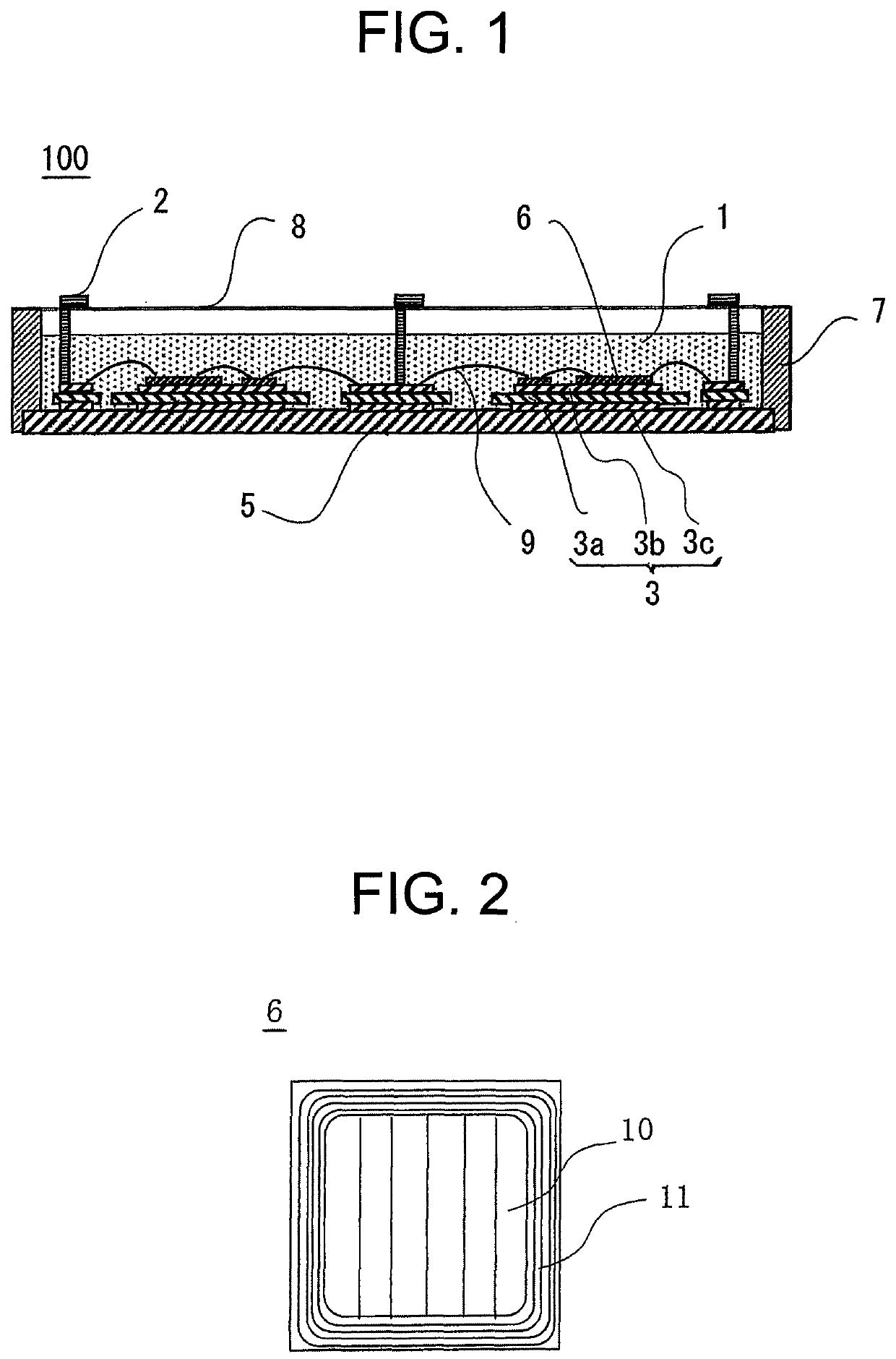

Superjunction semiconductor device and method of manufacturing superjunction semiconductor device

PendingCN111816694ASuppression of drop in withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrically conductiveEngineering

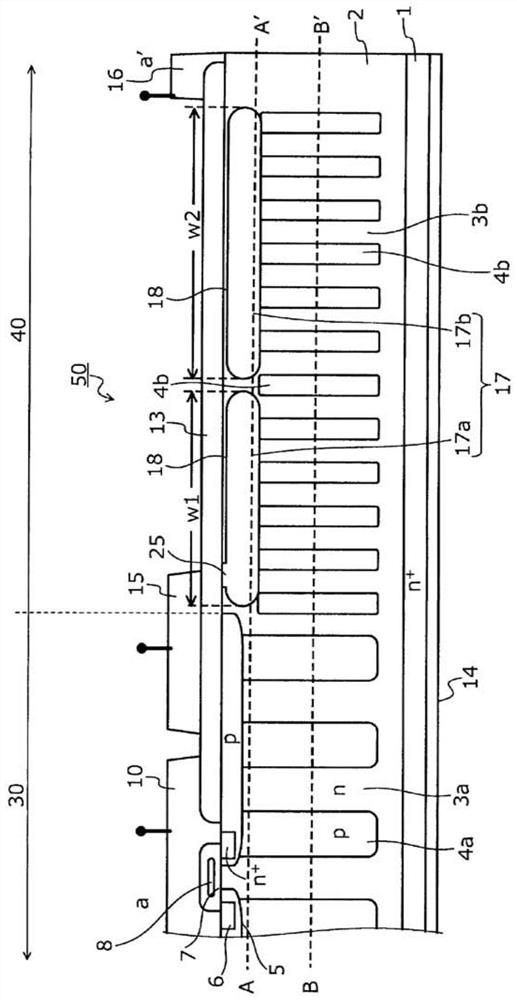

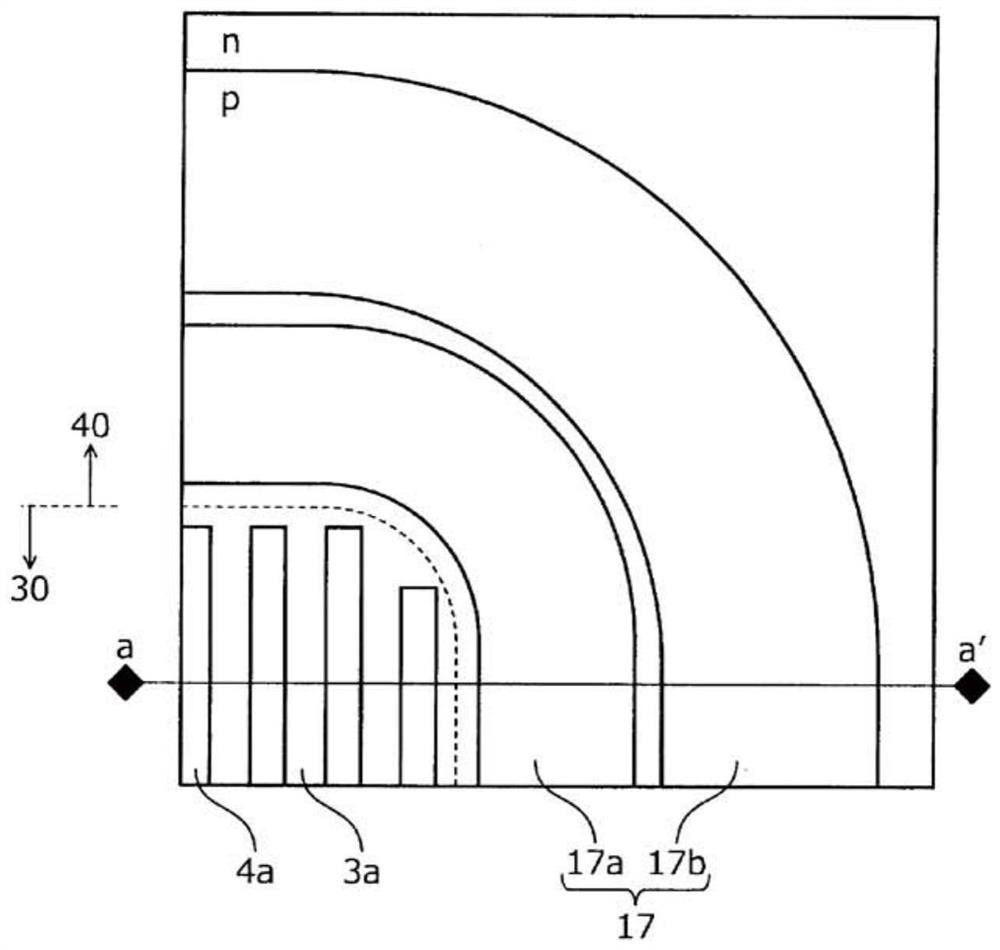

The invention provides a superjunction semiconductor device and a method of manufacturing the superjunction semiconductor device, which can restrain voltage resistance reduction caused by manufacturing deviation. The semiconductor device has an active region (30) through which current flows and a termination structure region (40). On a front surface of a semiconductor substrate (1) of a first conductivity type, a first semiconductor layer (2) of the first conductivity type is provided. On a surface of the first semiconductor layer (2) in the active region (30), a first parallel pn structure isprovided including first columns (3a) of the first conductivity type and second columns (4a) of a second conductivity type disposed repeatedly alternating one another in a plane parallel to the frontsurface. In the termination structure region (40), a second parallel pn structure is provided including third columns (3b) of the first conductivity type and fourth columns (4b) of the second conductivity type disposed repeatedly alternating one another. On a surface of the second parallel pn structure, a first semiconductor region (17) of the second conductivity type is provided including pluralregions apart from one another.

Owner:FUJI ELECTRIC CO LTD

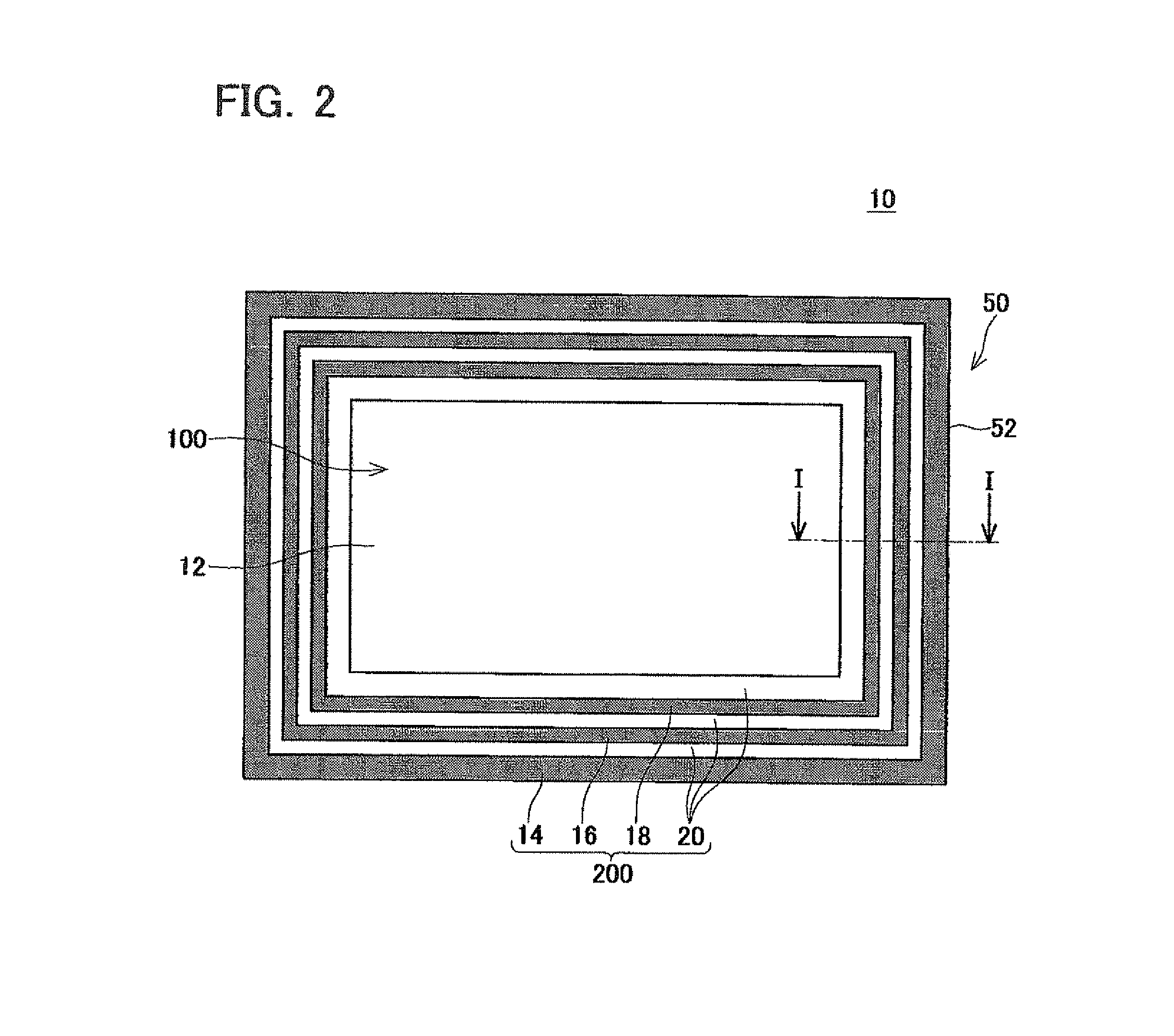

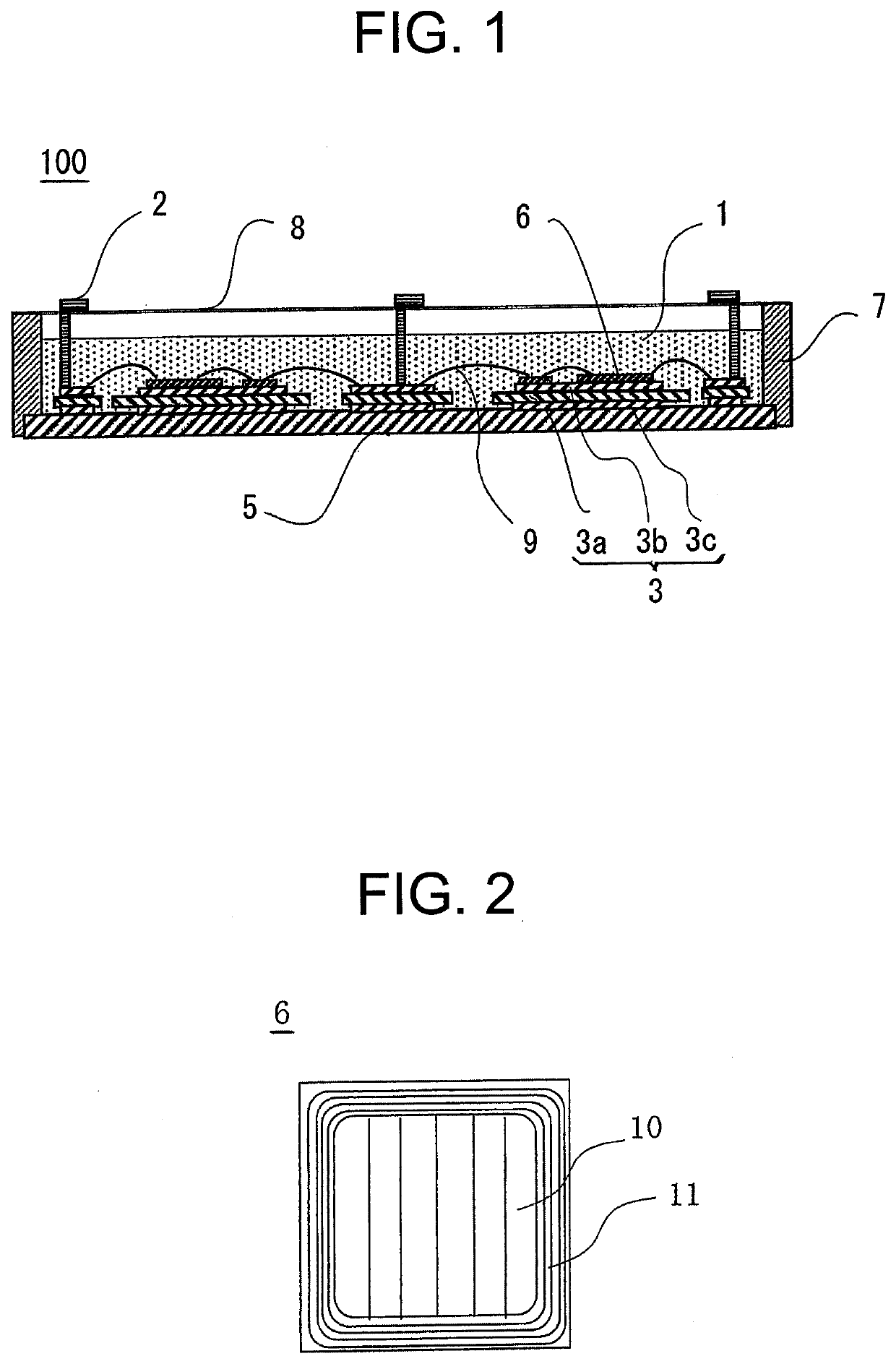

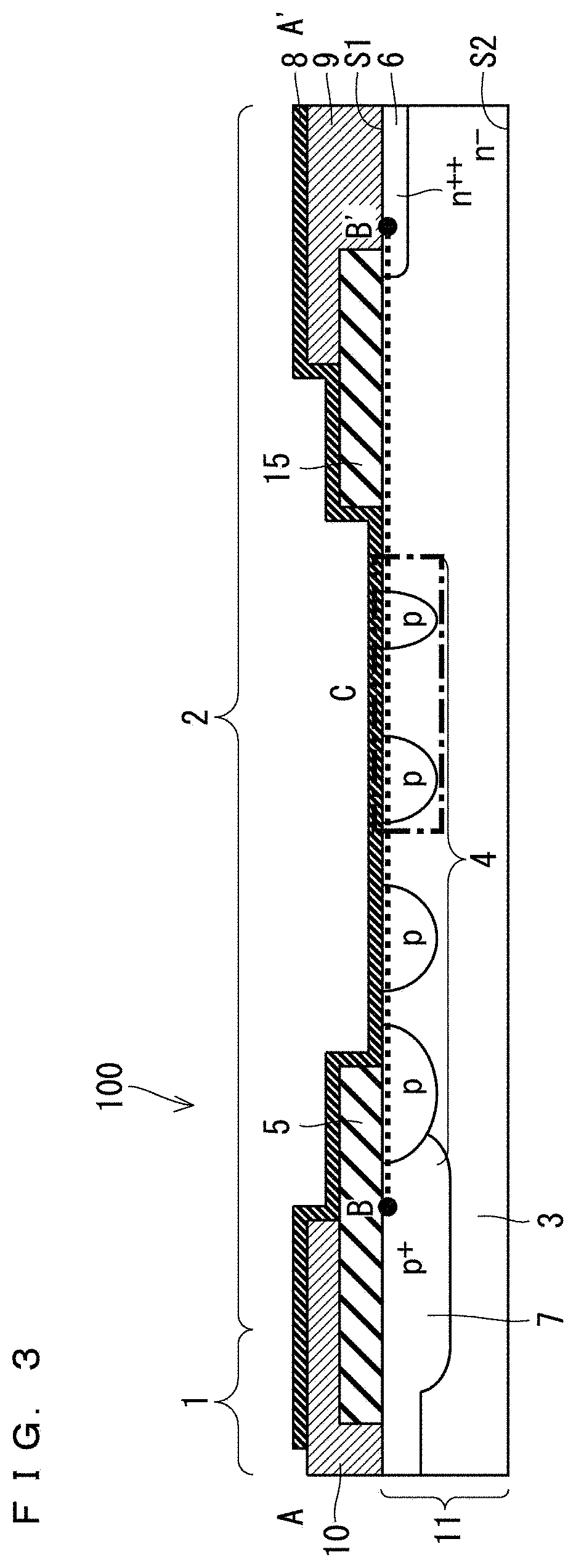

Power semiconductor module

ActiveUS20200091024A1Maintain abilitySuppression of drop in withstand voltageSemiconductor/solid-state device detailsSolid-state devicesSilicone GelsEngineering physics

Provided is a power semiconductor module including: a metal base plate; an insulating substrate arranged on the metal base plate and provided with an electrode; a semiconductor element arranged on the insulating substrate; a case arranged on the metal base plate so as to surround the insulating substrate and the semiconductor element; and a potting material filled into a space defined by the metal base plate and the case so as to encapsulate the insulating substrate and the semiconductor element. The potting material includes: a silicone gel; and a conductivity-imparting agent that is added to the gel and contains a silicon atom and an ionic group.

Owner:MITSUBISHI ELECTRIC CORP

Power semiconductor device

PendingUS20220130951A1Suppress reduction in withstand voltageReduce withstand voltageSemiconductor devicesSemi insulatingPower semiconductor device

An object of a technique of the present disclosure is to suppress reduction in withstand voltage in a power semiconductor device. A semiconductor base includes an n− type semiconductor substrate and at least one p type diffusion layer formed separately from each other on a surface layer on a side of a first main surface of the semiconductor substrate in a terminal region. A power semiconductor device includes at least one insulating film formed on a first main surface of the semiconductor base between an insulating film and the insulating film. A semi-insulating film has contact with the insulating film on the insulating film, and has contact with the first main surface in at least two regions where the insulating film is not formed between the insulating films and.

Owner:MITSUBISHI ELECTRIC CORP

Power semiconductor module

ActiveUS10892203B2Maintain abilitySuppression of drop in withstand voltageSemiconductor/solid-state device detailsSolid-state devicesSilicone GelsEngineering physics

Provided is a power semiconductor module including: a metal base plate; an insulating substrate arranged on the metal base plate and provided with an electrode; a semiconductor element arranged on the insulating substrate; a case arranged on the metal base plate so as to surround the insulating substrate and the semiconductor element; and a potting material filled into a space defined by the metal base plate and the case so as to encapsulate the insulating substrate and the semiconductor element. The potting material includes: a silicone gel; and a conductivity-imparting agent that is added to the gel and contains a silicon atom and an ionic group.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com