Superjunction semiconductor device and method of manufacturing superjunction semiconductor device

A technology of superjunction semiconductor and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reduced withstand voltage, increased n-type drift layer, shortened depletion layer expansion distance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

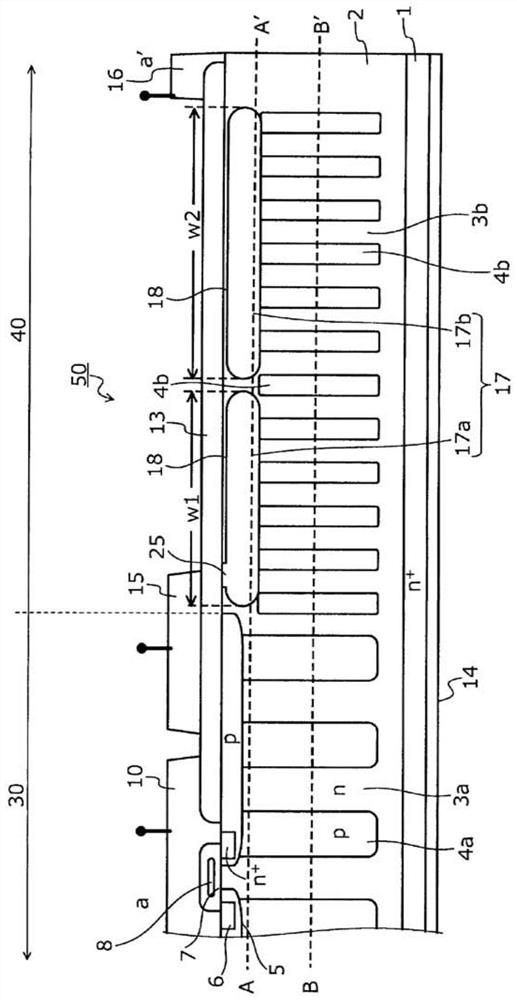

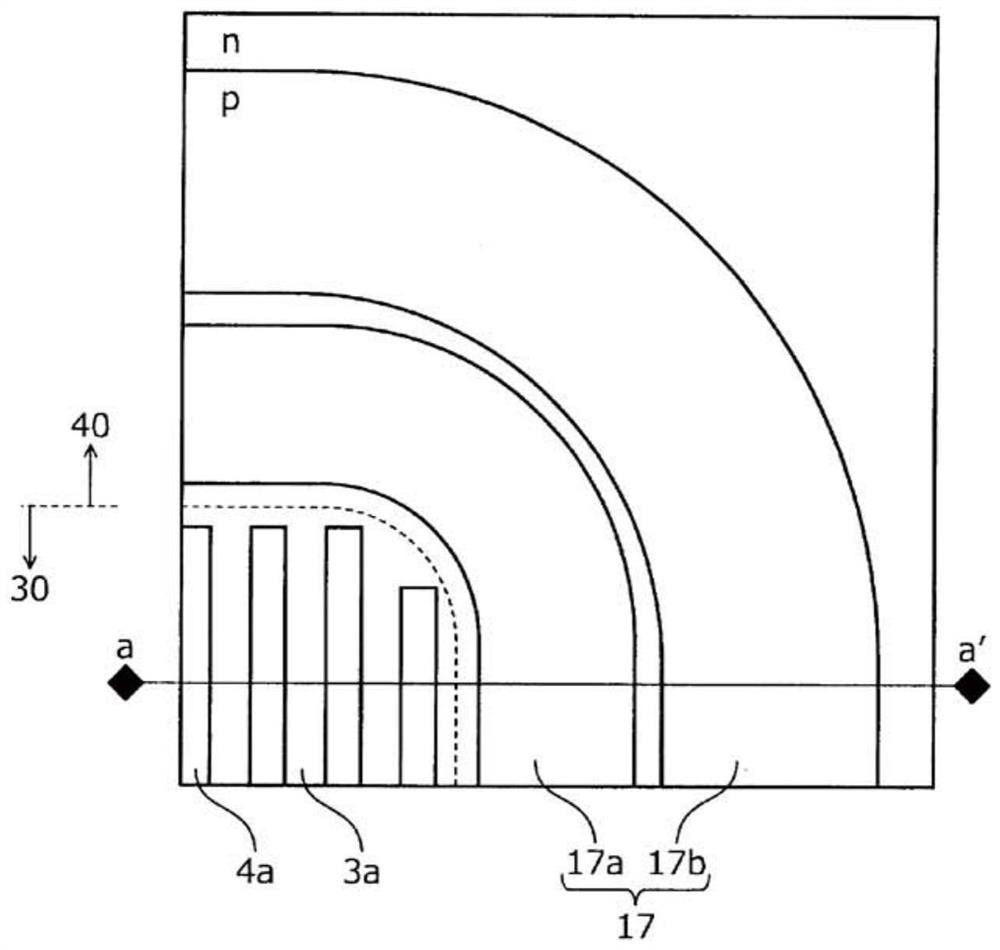

[0111] The super junction semiconductor device of the present invention will be described by taking the SJ-MOSFET as an example. figure 1 It is a cross-sectional view showing the structure of the SJ-MOSFET of the first embodiment. figure 2 shows the structure of the SJ-MOSFET of Embodiment 1 figure 1 A top view of part A-A' of . in addition, image 3 shows the structure of the SJ-MOSFET of Embodiment 1 figure 1 Top view of part B-B' of . in addition, Figure 4 shows the structure of the SJ-MOSFET of Embodiment 1 figure 1 Another top view of part B-B' of . figure 1 Yes Figure 2 ~ Figure 4 A cross-sectional view of part a-a' of .

[0112] figure 1 The shown SJ-MOSFET 50 is equipped with a MOS (Metal Oxide Semiconductor: Metal Oxide Semiconductor) on the front side (the surface on the side of the p-type base region 5 described later) of a semiconductor substrate (silicon substrate: semiconductor chip) including silicon (Si). ) gate of the SJ-MOSFET50. This SJ-M...

Embodiment approach 2

[0127] Figure 5 is a cross-sectional view showing the structure of the SJ-MOSFET of the second embodiment. Figure 5 The A-A' part is the same as that showing the structure of the SJ-MOSFET of the first embodiment figure 2 The same part of the top view. In addition, the structure of the SJ-MOSFET of Embodiment 2 is shown Figure 5 The B-B' part is the same as that showing the structure of the SJ-MOSFET of the first embodiment image 3 The same part of the top view. In addition, the structure of the SJ-MOSFET of Embodiment 2 is shown Figure 5 Other top view of the B-B' section with Figure 4 same top view.

[0128] Embodiment 2 is different in that no p-type P-type device not connected to the first Resurf region 17a and the second Resurf region 17b is arranged between the first Resurf region 17a and the second Resurf region 17b. Column area 4b.

[0129] Embodiment 2 Even if the p-type column region 4b not connected to the first resurf region 17a and the second resurf...

Embodiment approach 3

[0161] Figure 14 It is a cross-sectional view showing the structure of the SJ-MOSFET of the third embodiment. Embodiment 3 differs from Embodiments 1 and 2 in that the RESURF region 17 is divided into a first RESURF region 17a, a second RESURF region 17b, a third RESURF region 17c, and a second RESURF region 17a. The four RESURF regions 17d are the four.

[0162] In Embodiment Mode 3, the width w1 of the first resurf region 17a, the width w2 of the second resurf region 17b, the width w3 of the third resurf region 17c, and the width w4 of the fourth resurf region 17d are preferably There is a relationship of w1≤w2≤w3≤w4. exist Figure 14 Among them, the end 25 of the first resurf region 17a is a part of the p-type base region 5 , and the first resurf region 17a can be connected to the field plate electrode 15a through the p-type base region 5 . Similarly, the second RESURF region 17b, the third RESURF region 17c, and the fourth RESURF region 17d can also be connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com