Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

175results about How to "Reduce standby power" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

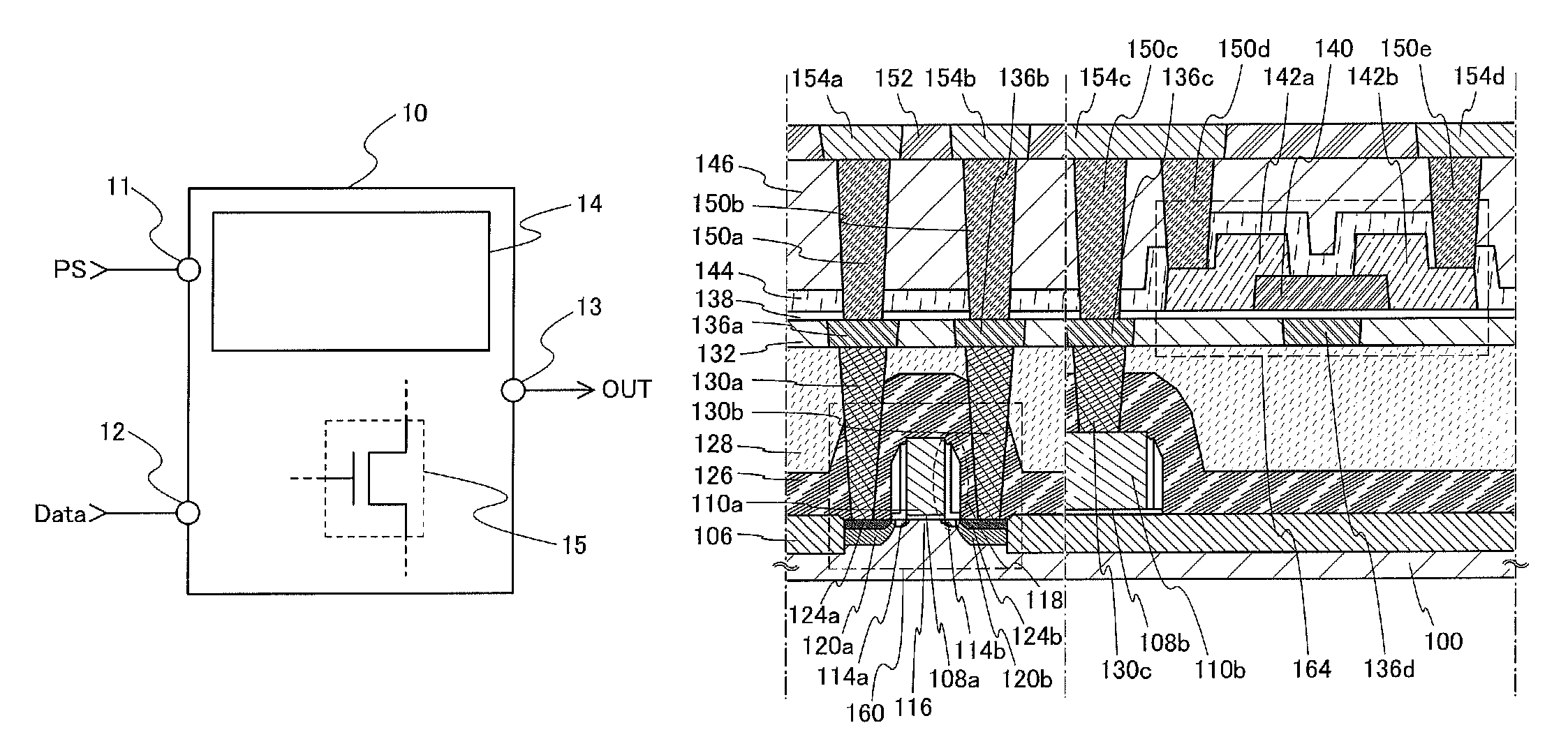

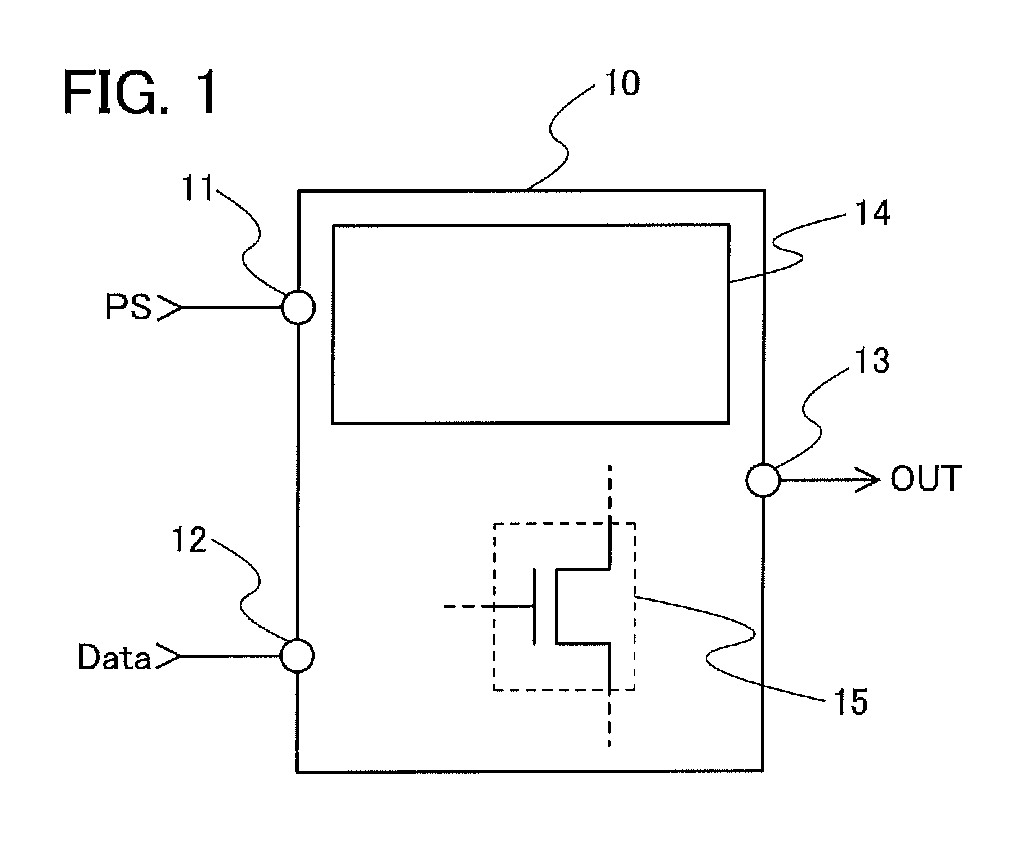

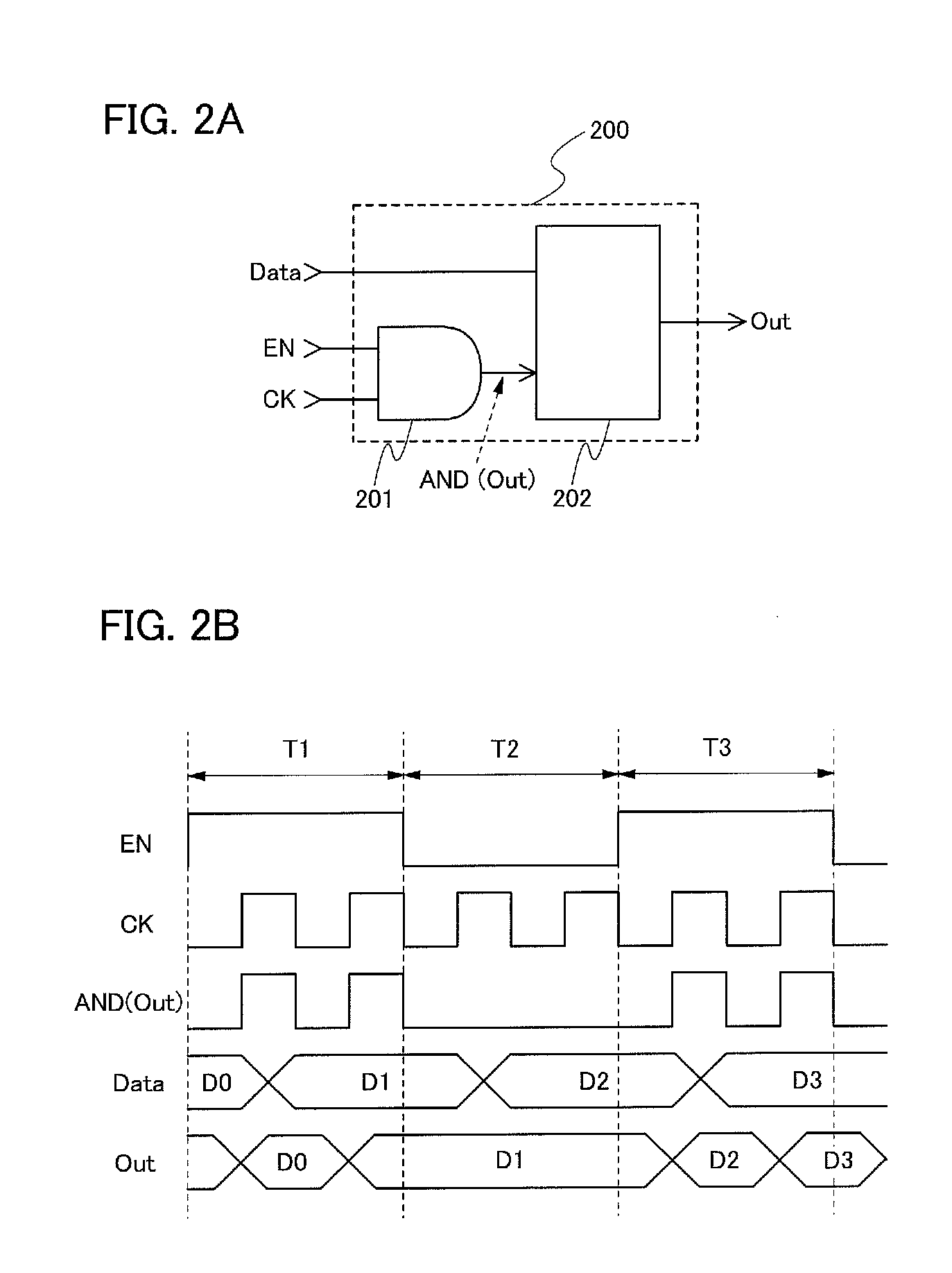

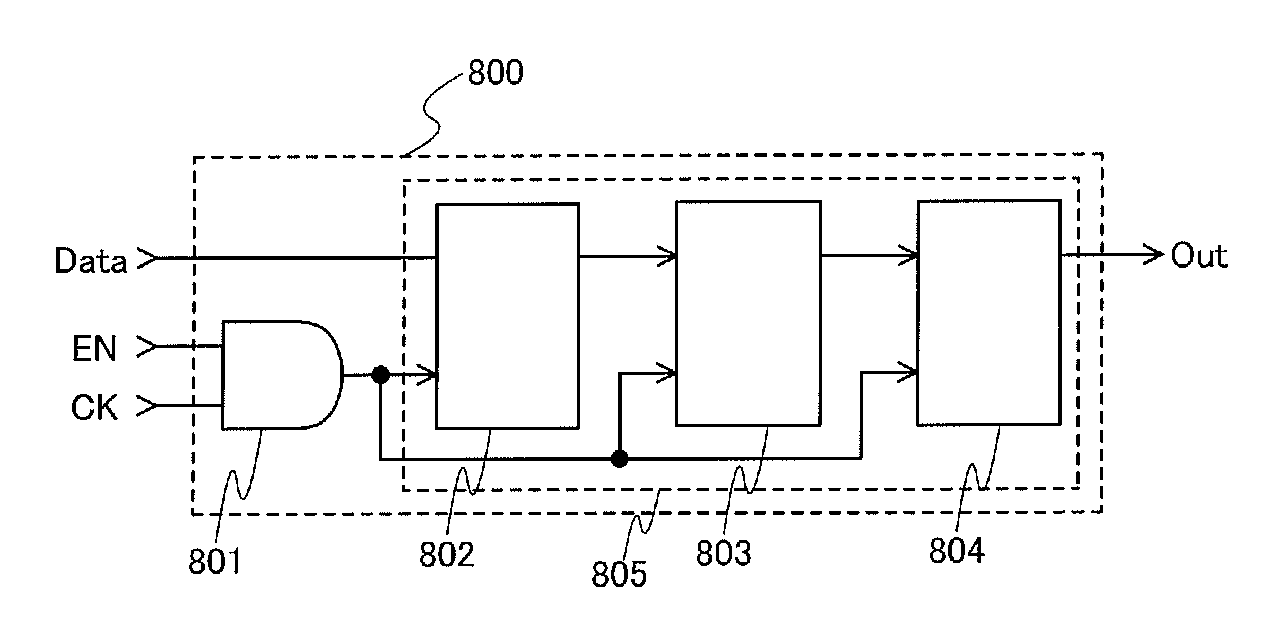

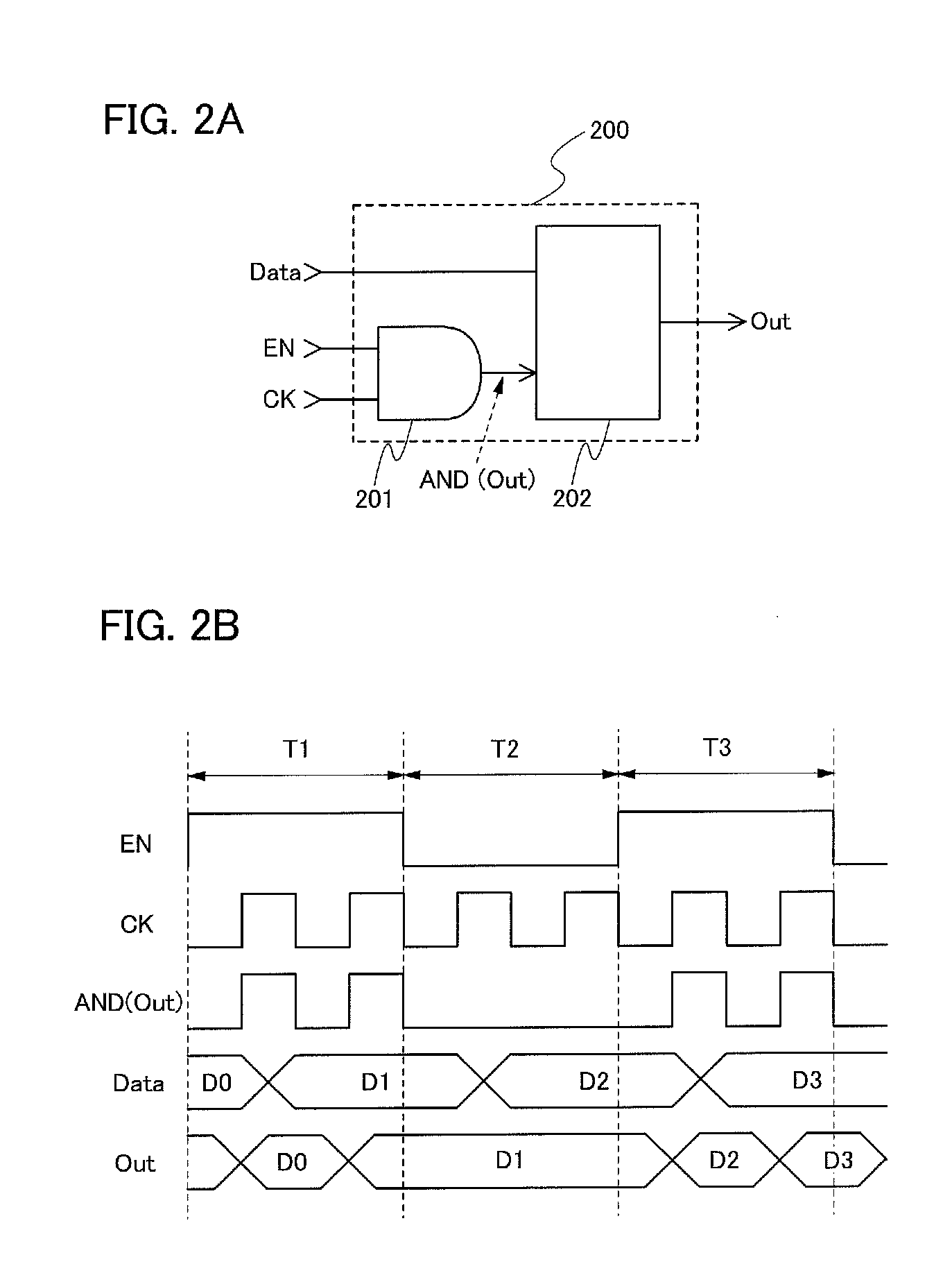

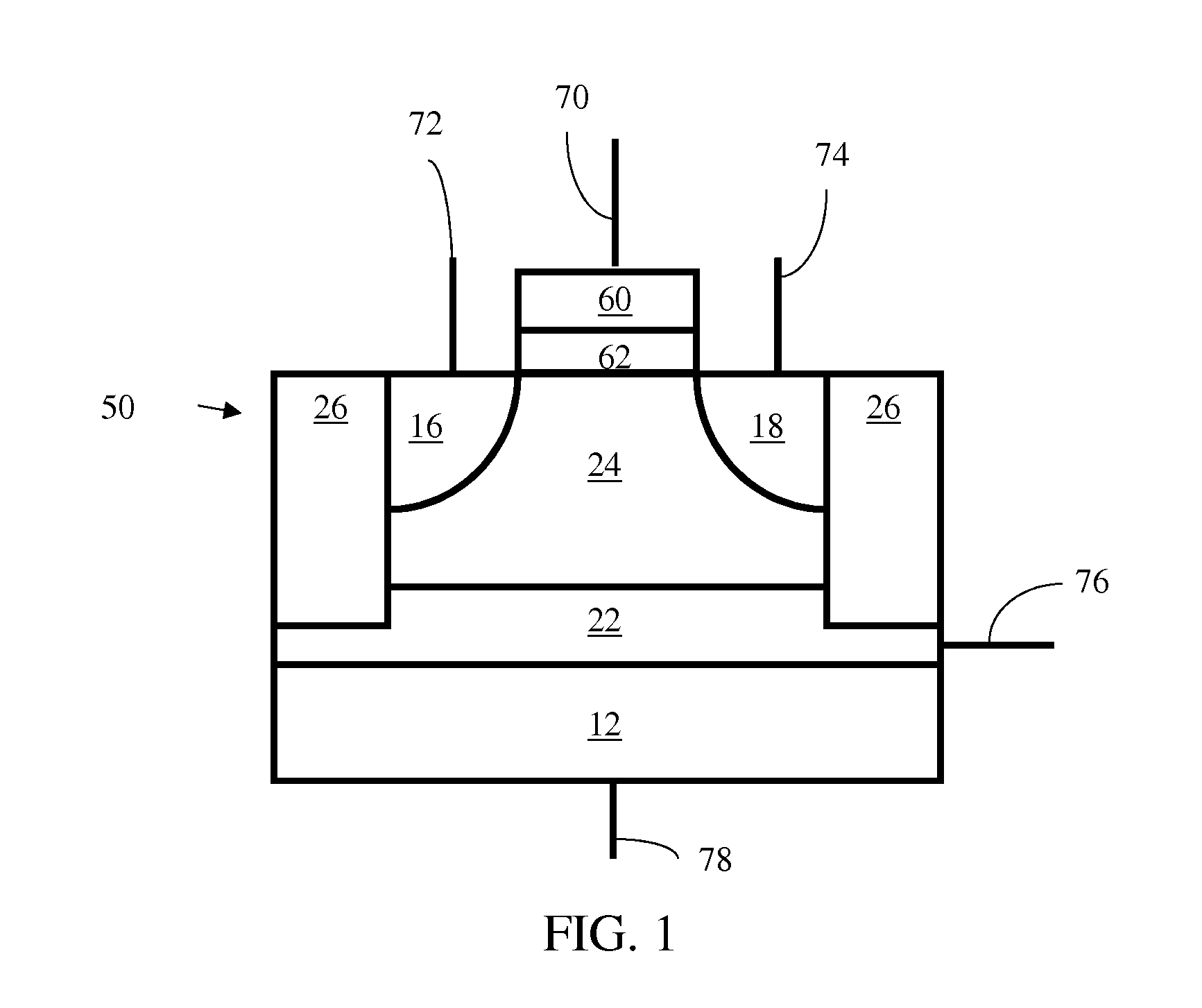

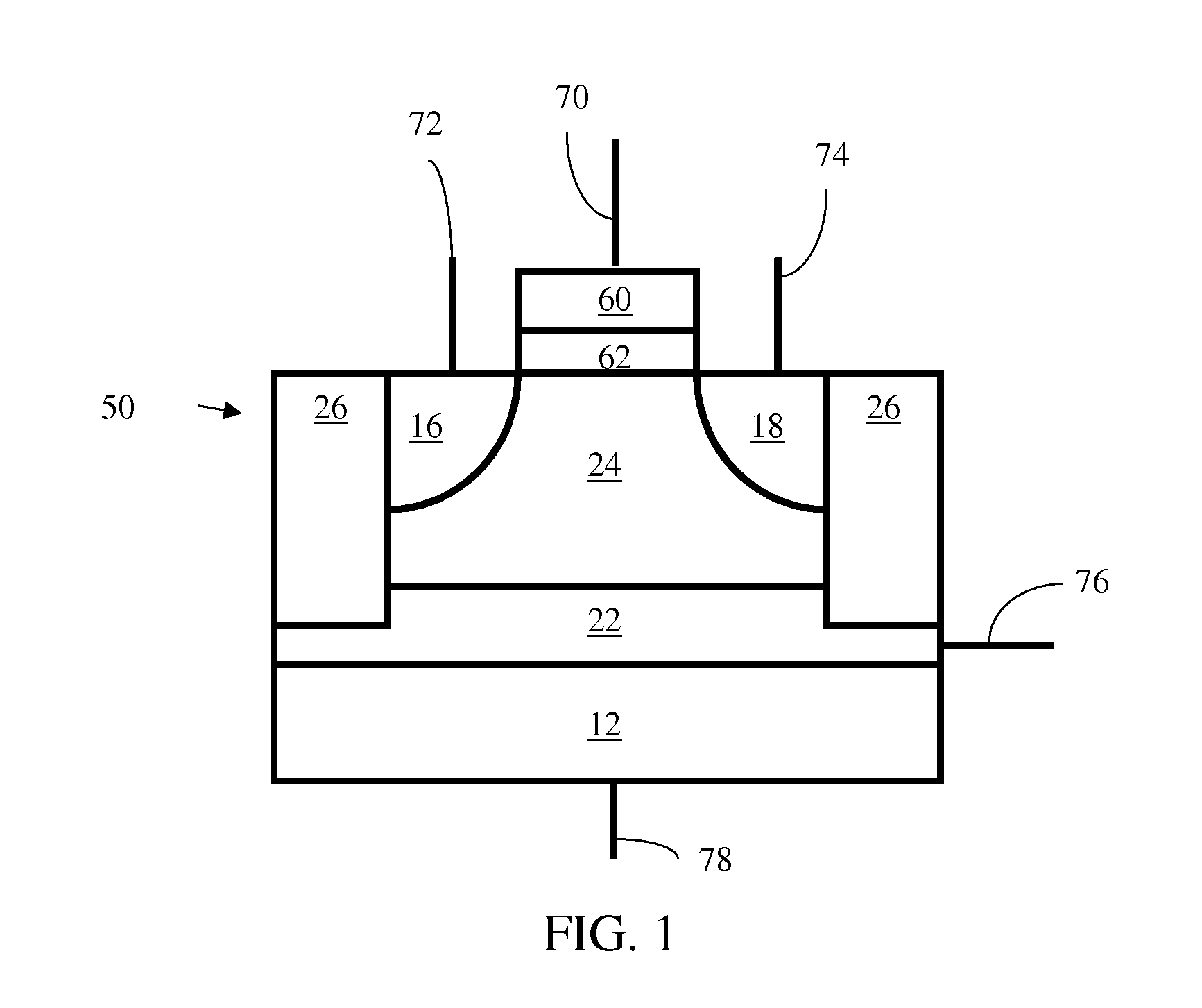

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

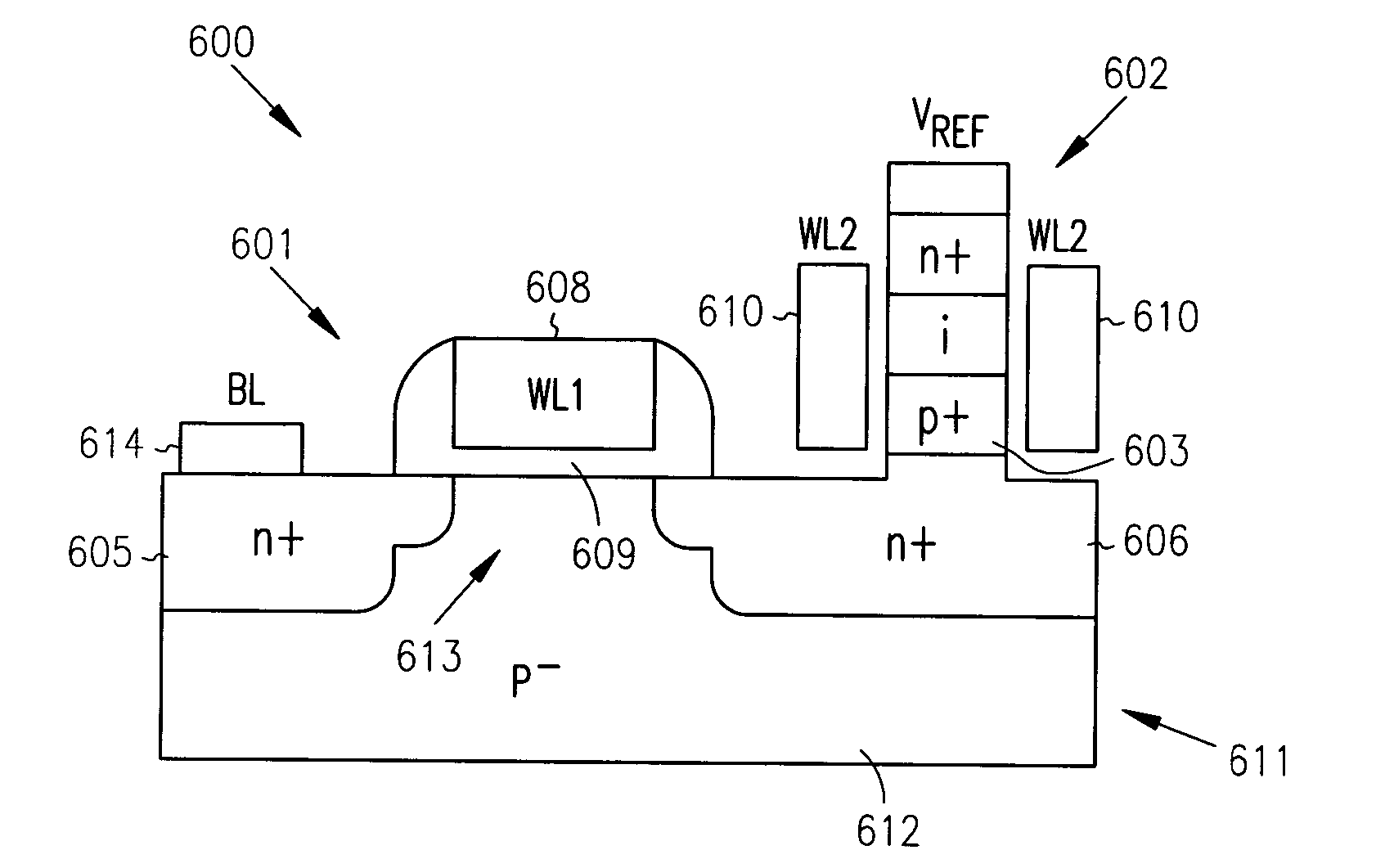

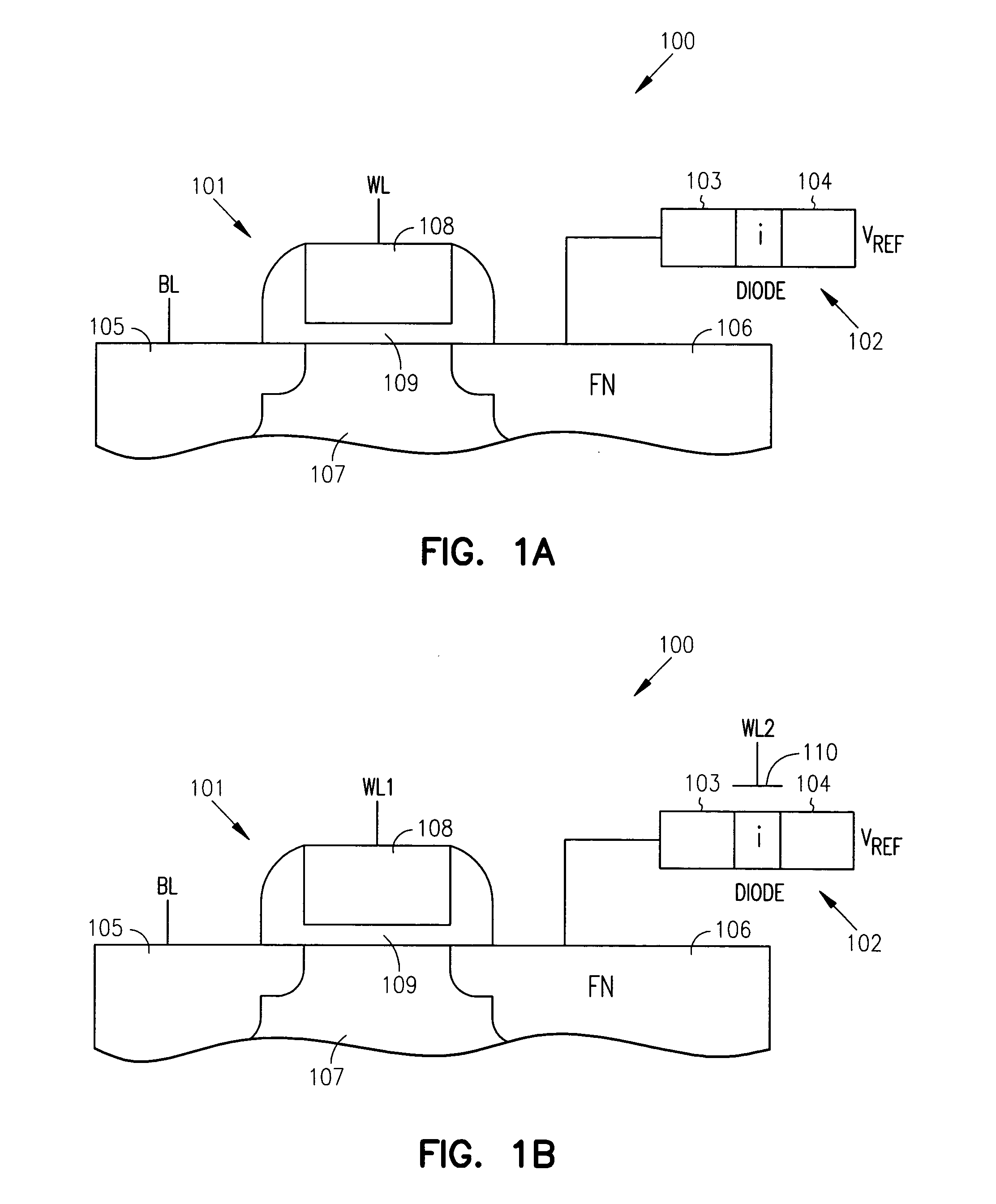

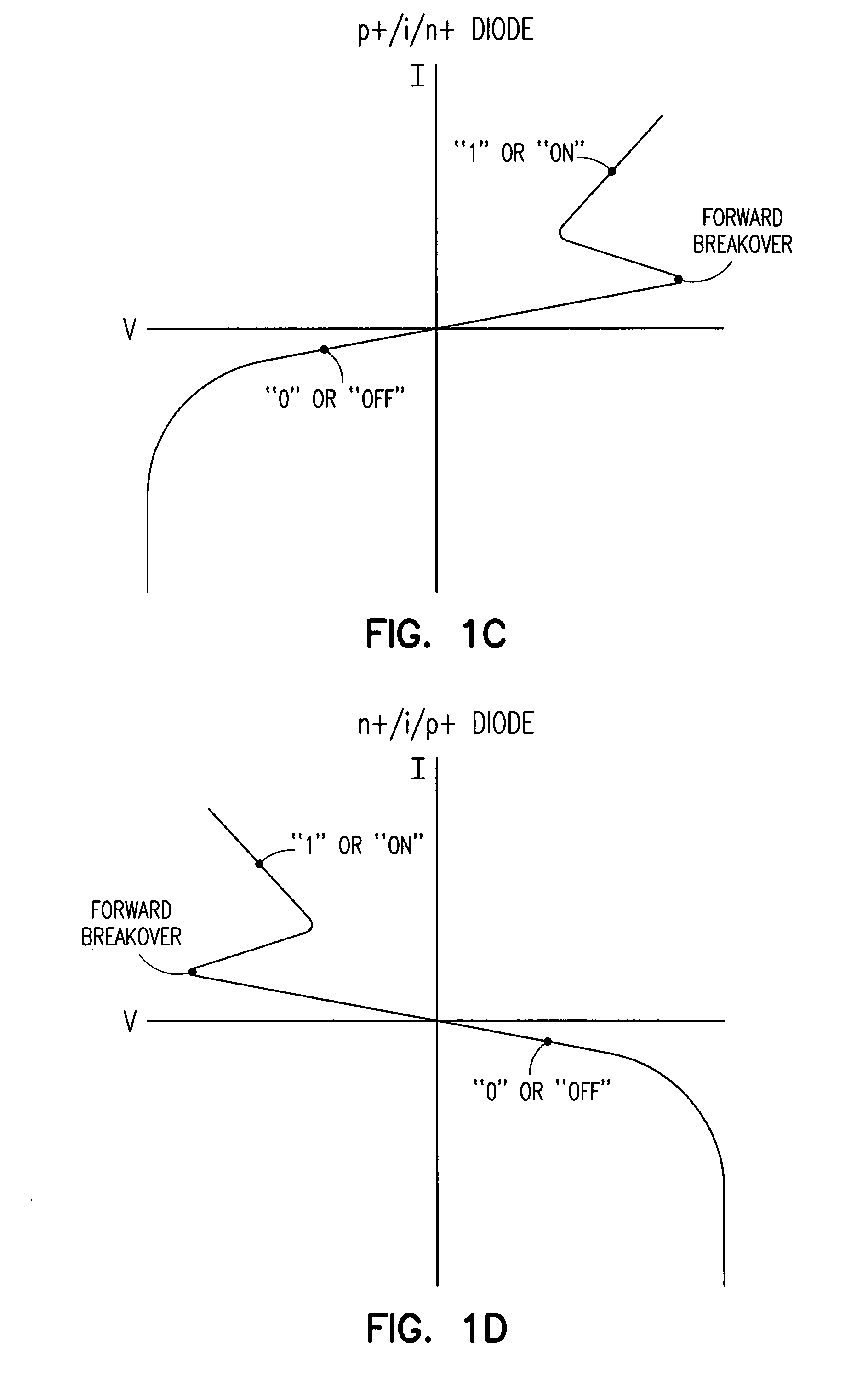

High-performance one-transistor memory cell

ActiveUS20050001232A1Reduce standby powerAddressing slow performanceTransistorThyristorCharge retentionSemiconductor

One aspect of this disclosure relates to a memory cell. In various embodiments, the memory cell includes an access transistor having a floating node, and a diode connected between the floating node and a diode reference potential line. The diode includes an anode, a cathode, and an intrinsic region between the anode and the cathode. A charge representative of a memory state of the memory cell is held across the intrinsic region of the diode. In various embodiments, the memory cell is implemented in bulk semiconductor technology. In various embodiments, the memory cell is implemented in semiconductor-on-insulator technology. In various embodiments, the diode is gate-controlled. In various embodiments, the diode is charge enhanced by an intentionally generated charge in a floating body of an SOI access transistor. Various embodiments include laterally-oriented diodes (stacked and planar configurations), and various embodiments include vertically-oriented diodes. Other aspects and embodiments are provided herein.

Owner:MICRON TECH INC

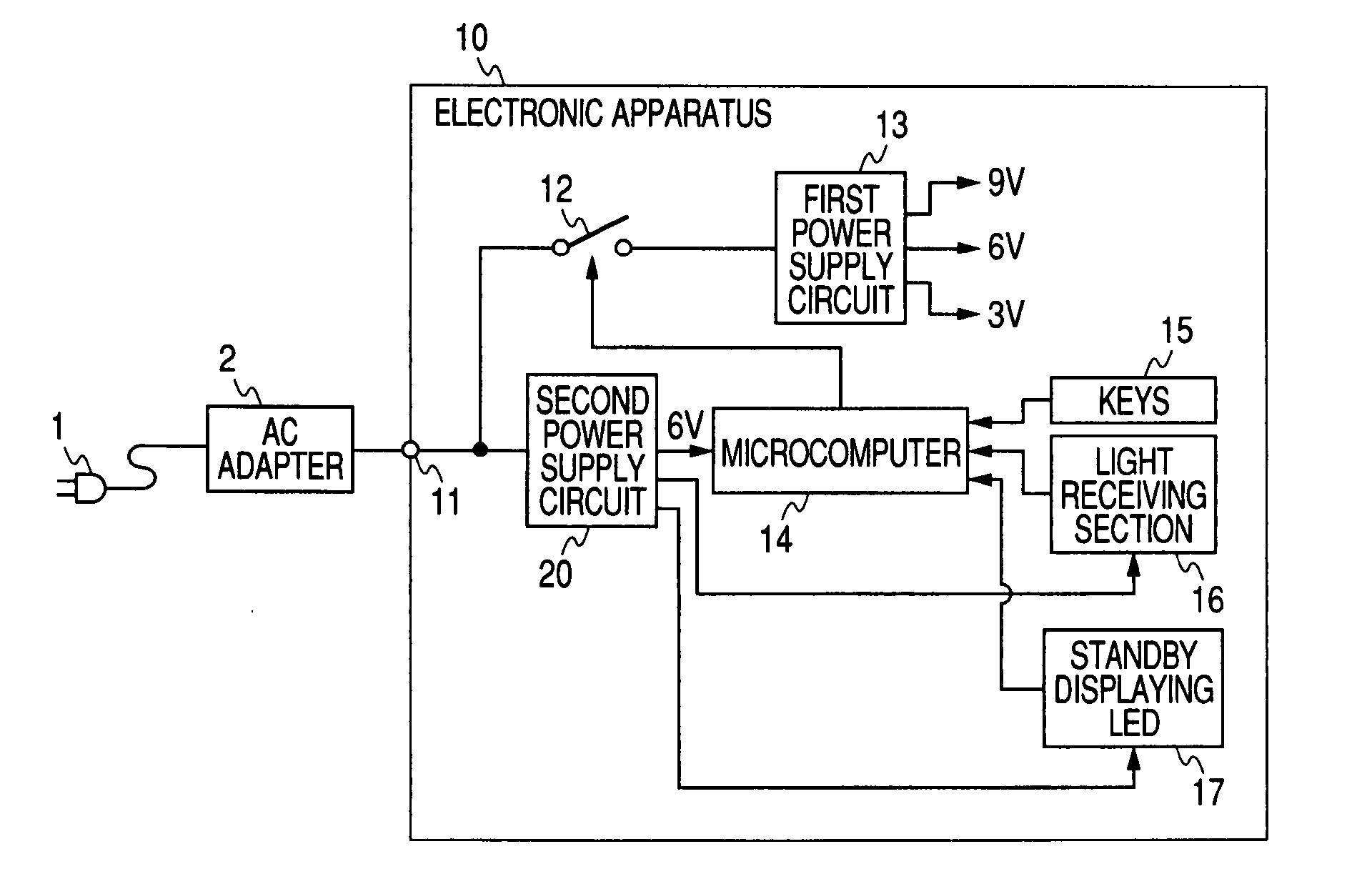

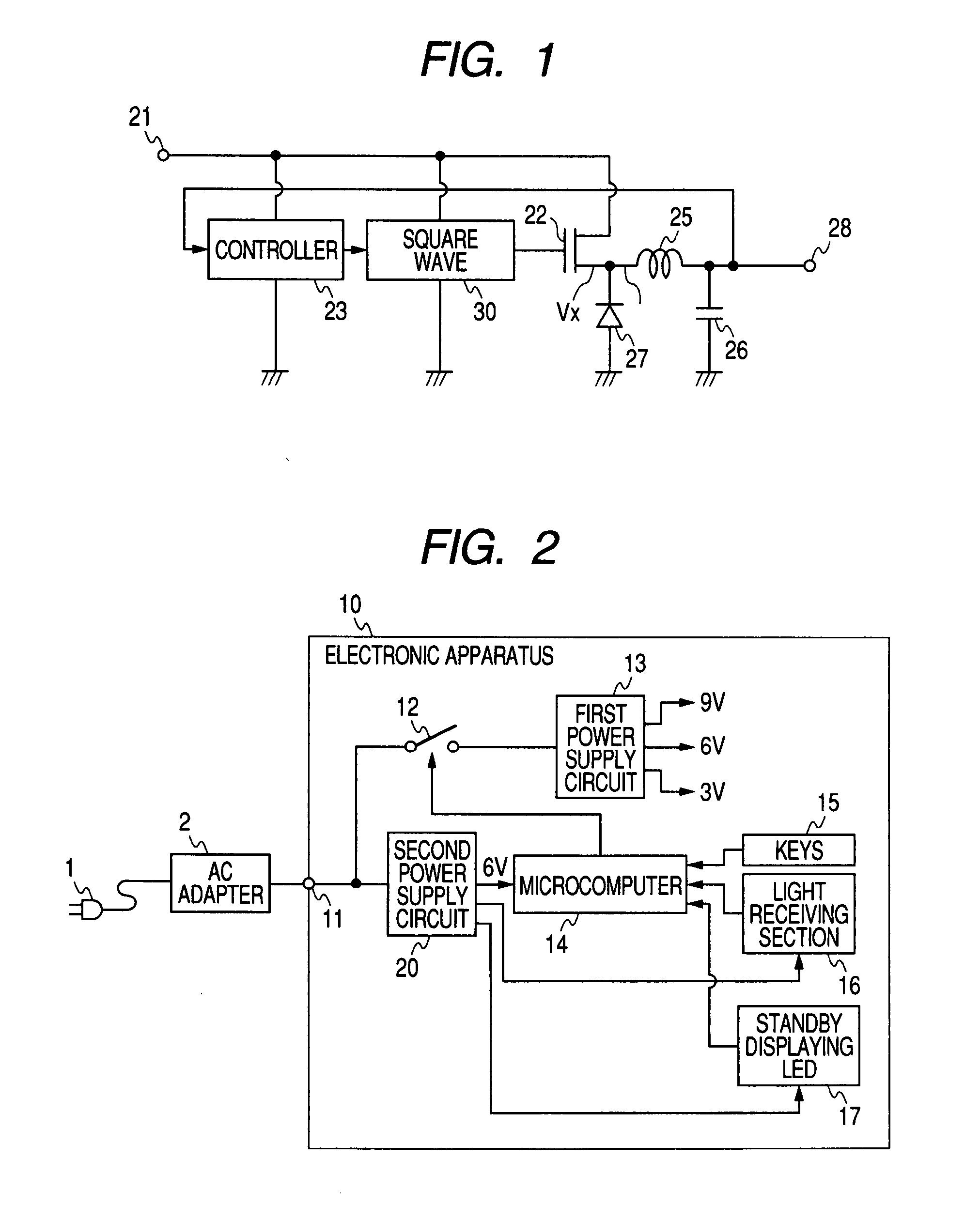

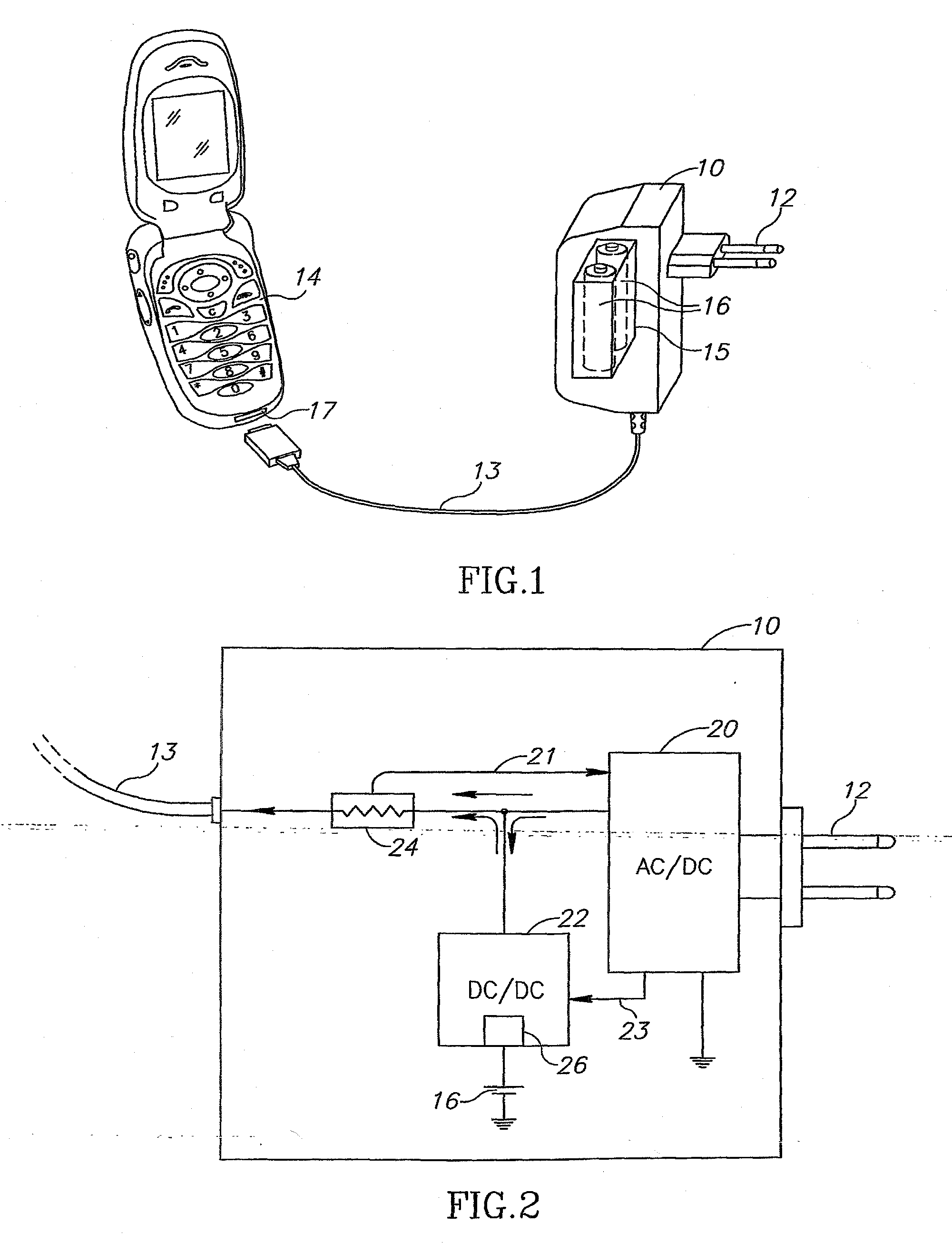

Switching power supply, electronic apparatus, and method of controlling switching power supply circuit

InactiveUS20080007237A1Reduce standby powerReduce power consumptionAc-dc conversionDc-dc conversionEngineeringControl switch

A switching power supply device may include a switching element for switching an input direct-current power, a smoothing section for smoothing and then outputting the direct-current power switched by the switching element, a square wave generating section for generating a square wave with a constant duty cycle to control switching by the switching element, and a control section for watching an output voltage of the smoothing section to control a period of generating the square wave generated by the square wave generating section so that the output voltage may be organized within a certain range.

Owner:SONY CORP

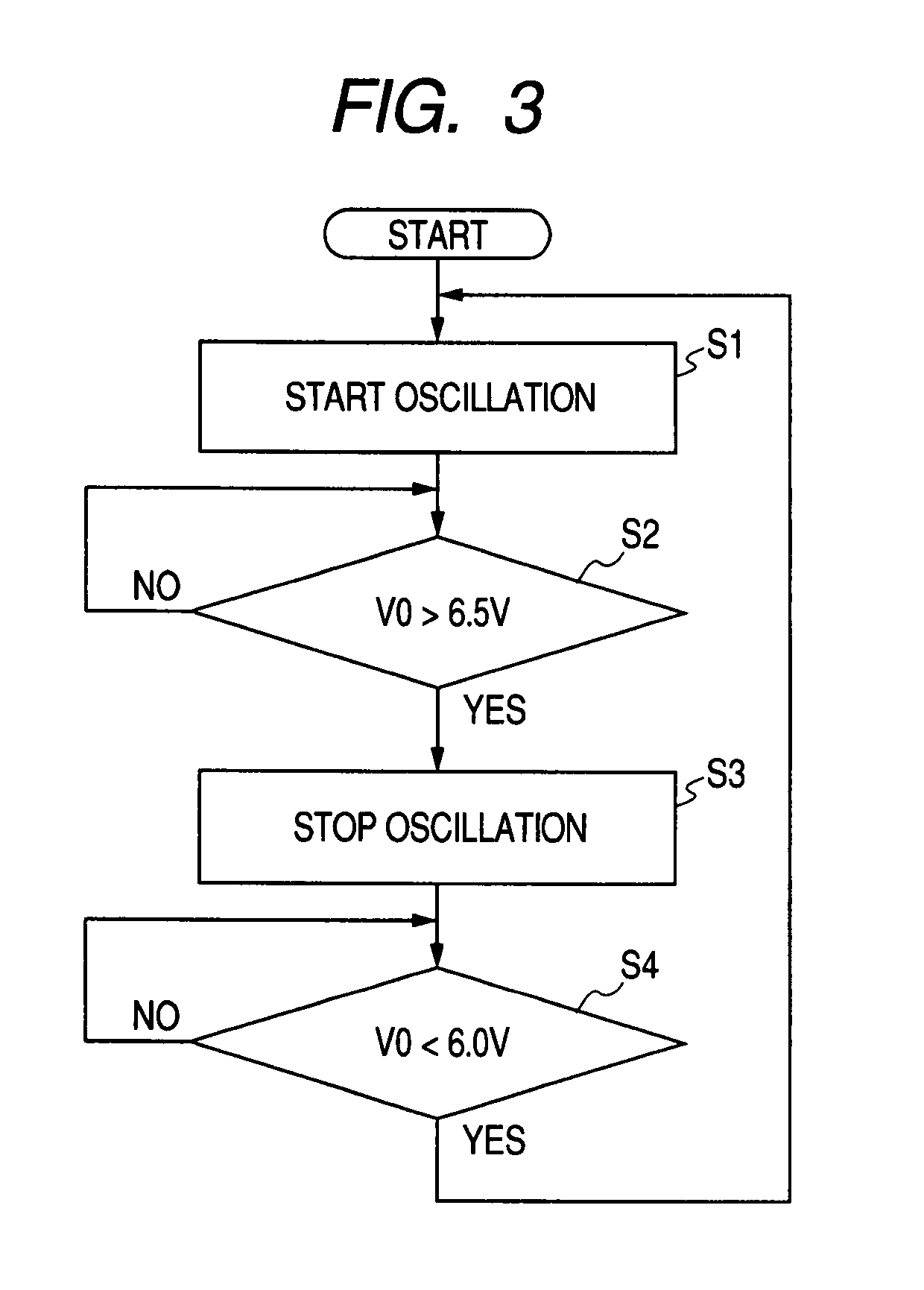

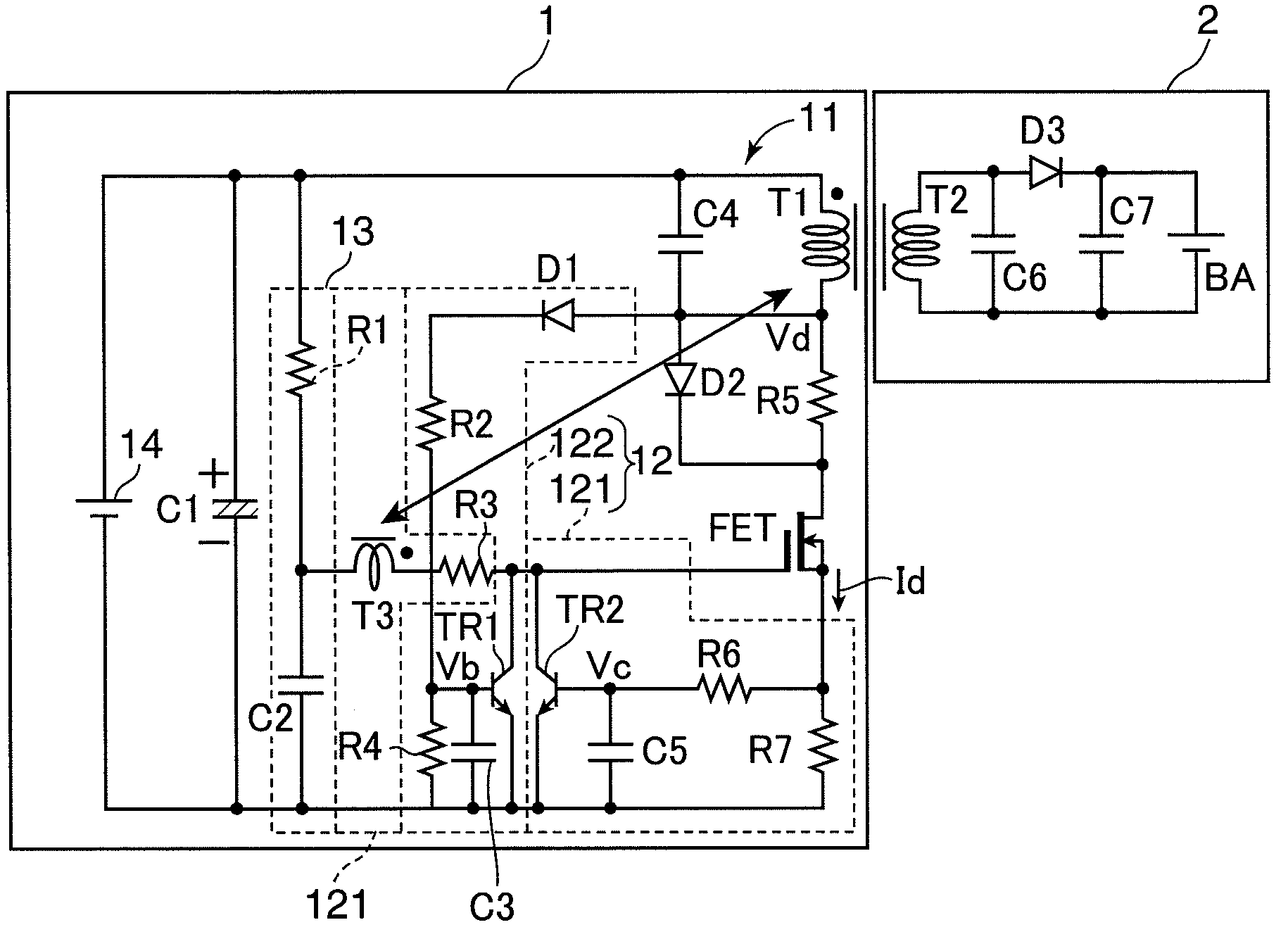

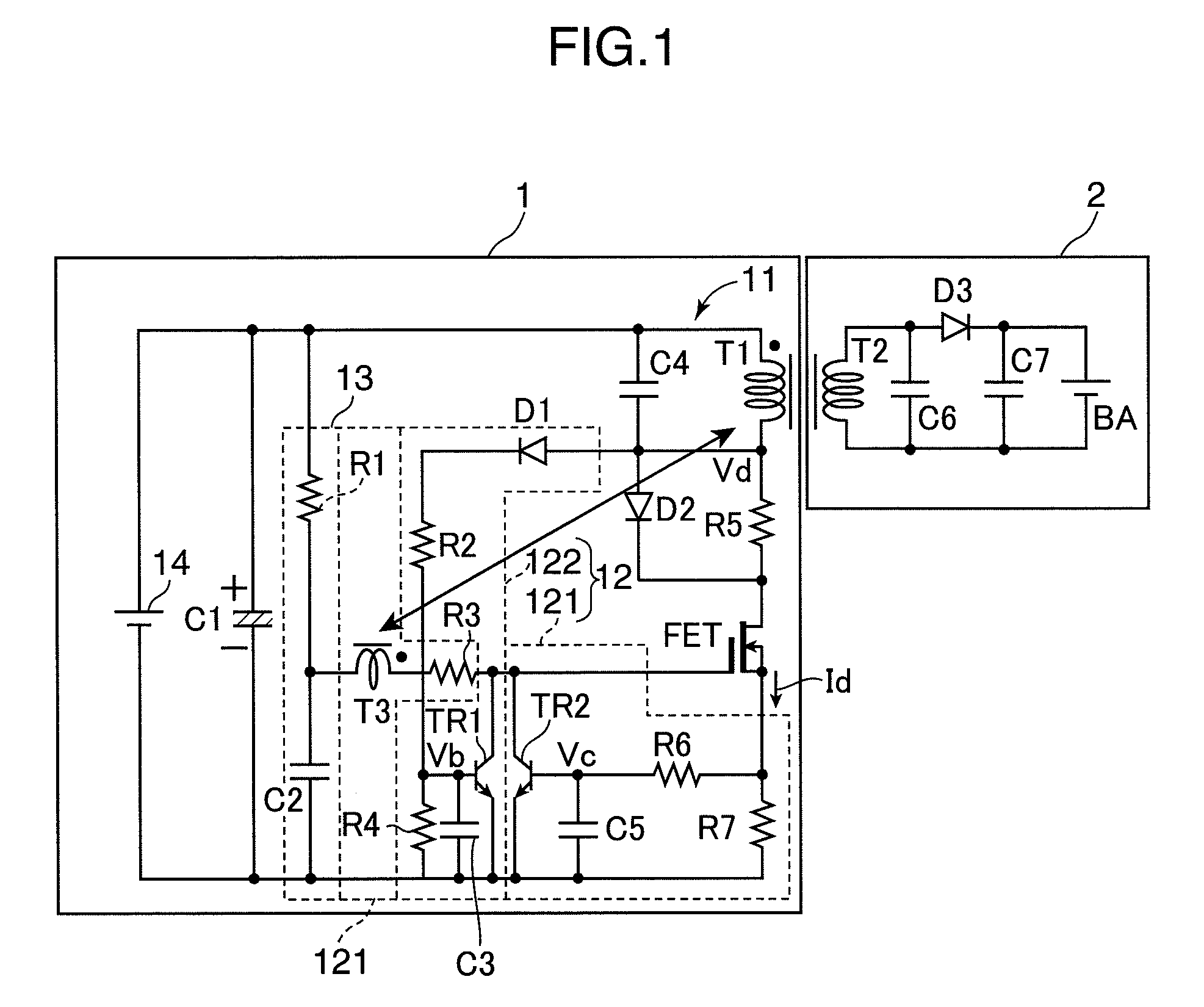

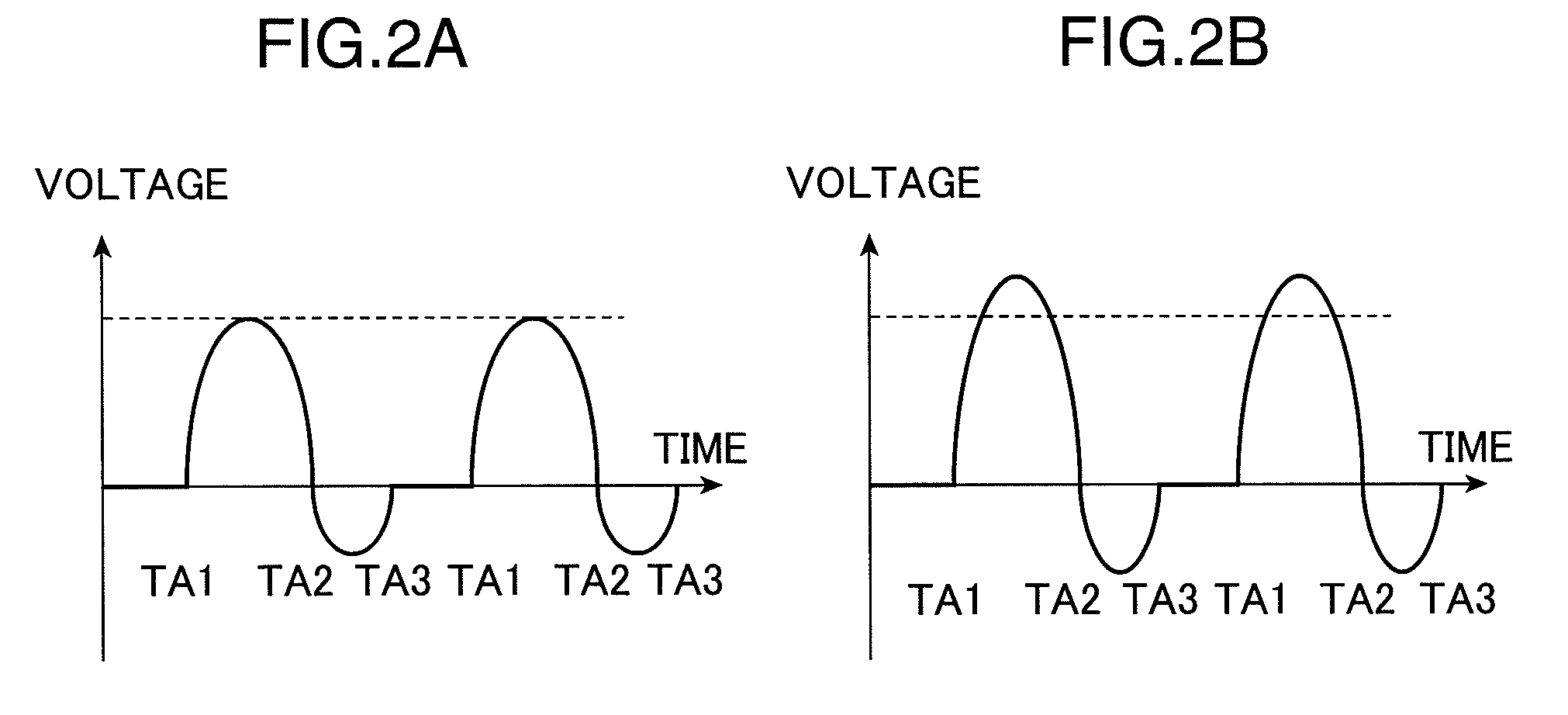

Contactless power transmission circuit

ActiveUS20100171367A1Reduce standby powerElectric signal transmission systemsBatteries circuit arrangementsElectric power transmissionElectric power

A driving circuit drives a switching element such that an ON-period of the switching element is shorter when a power receiving device is detected not to be placed than when the power receiving device is placed.

Owner:PANASONIC CORP

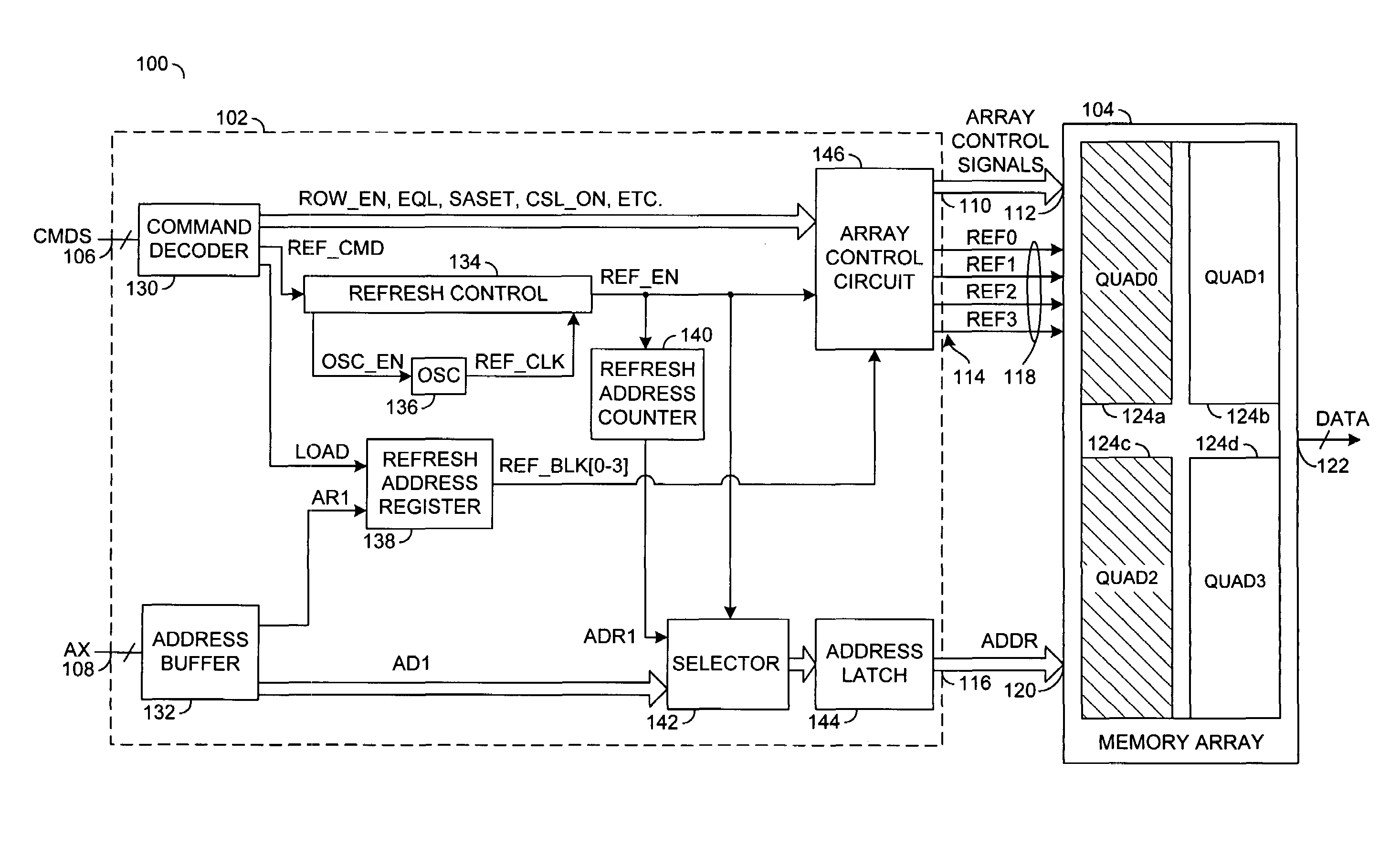

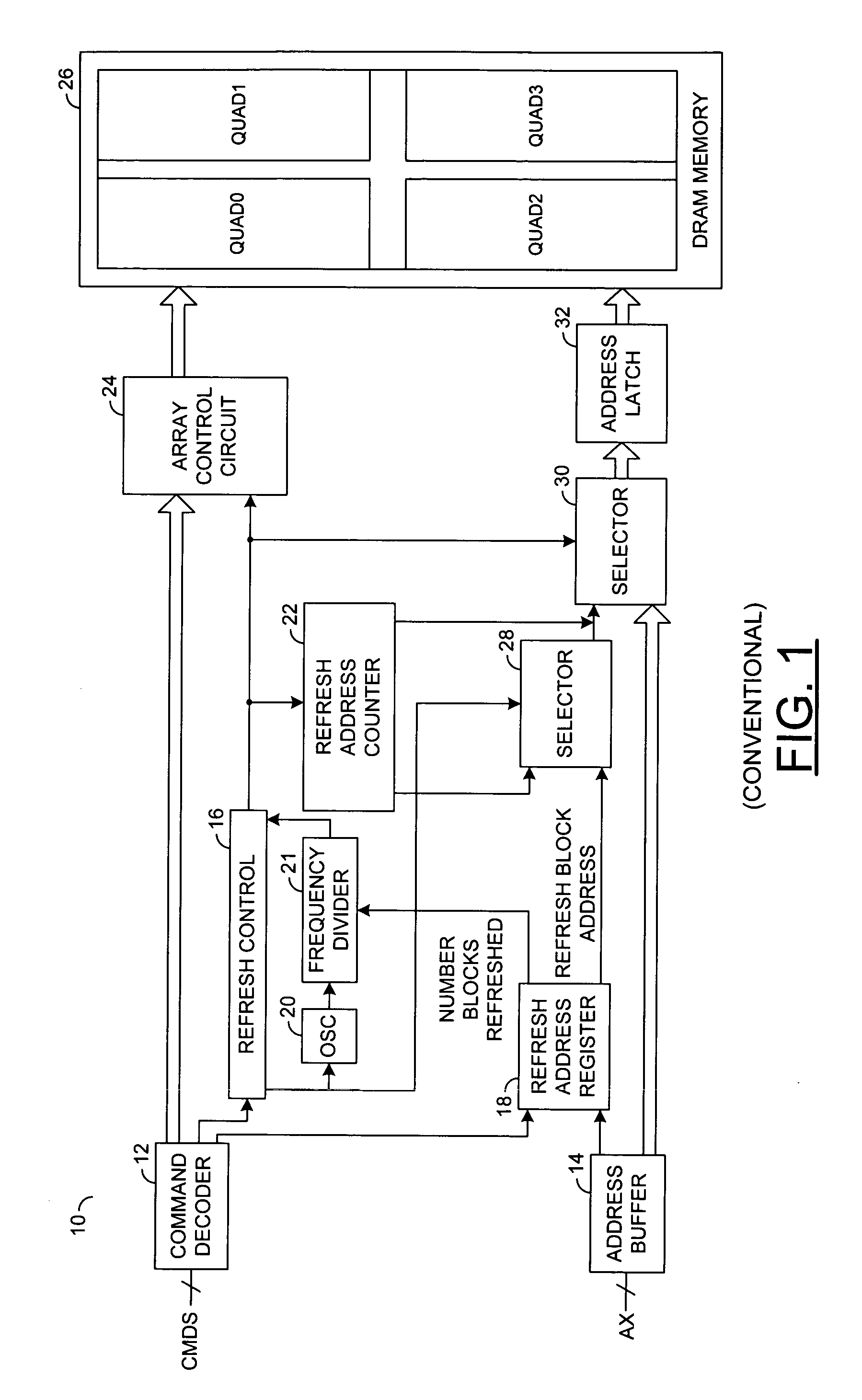

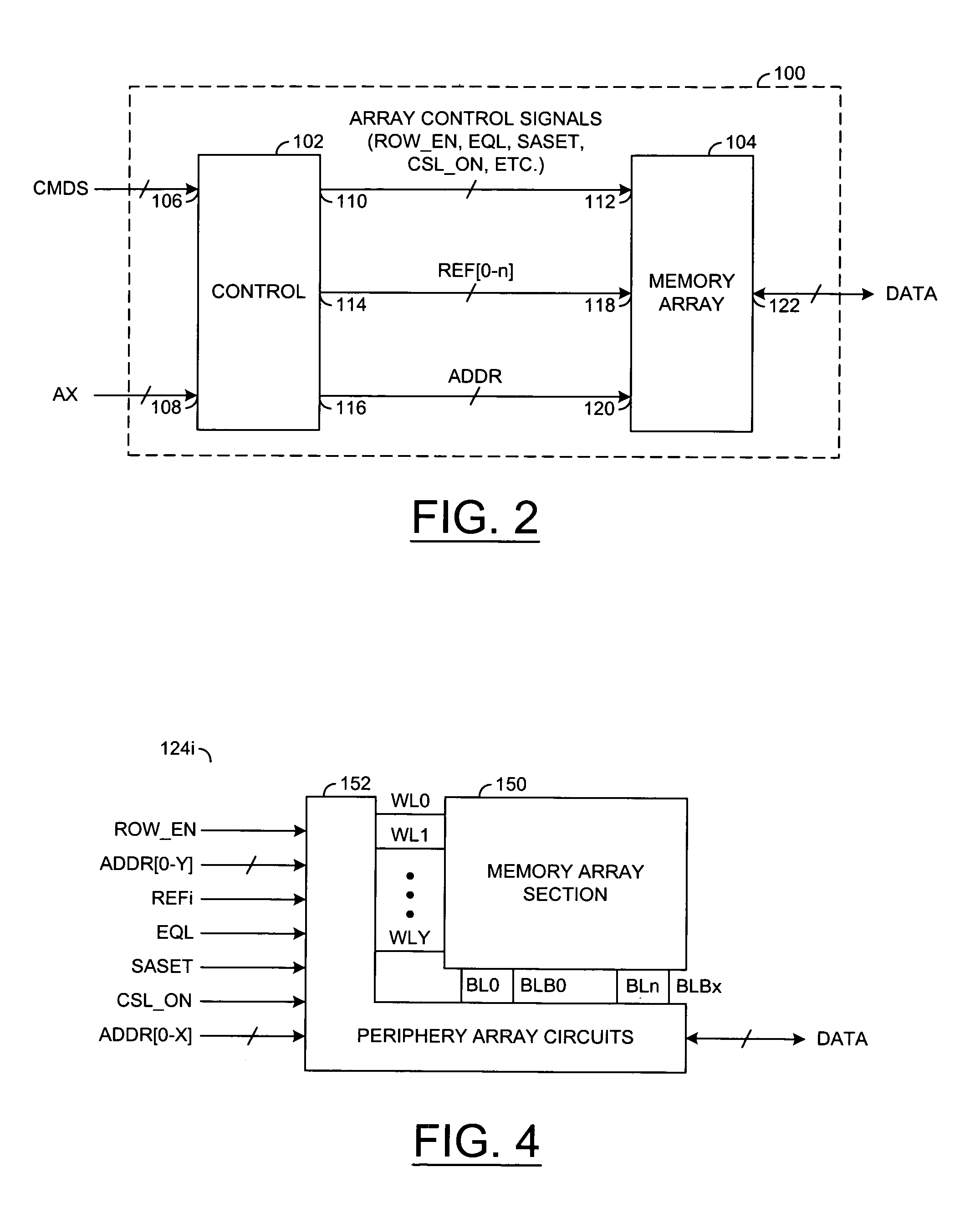

Method and architecture for reducing the power consumption for memory devices in refresh operations

InactiveUS7057960B1Reduced Power RequirementsReduce power consumptionDigital storageControl signalComputer science

A method for reducing power consumption during background operations in a memory array with a plurality of sections comprising the steps of (i) controlling the background operations in one or more sections of the memory array in response to one or more control signals and (ii) presenting the one or more control signals and one or more decoded address signals to one or more periphery array circuits of the one or more sections.

Owner:INNOMEMORY LLC

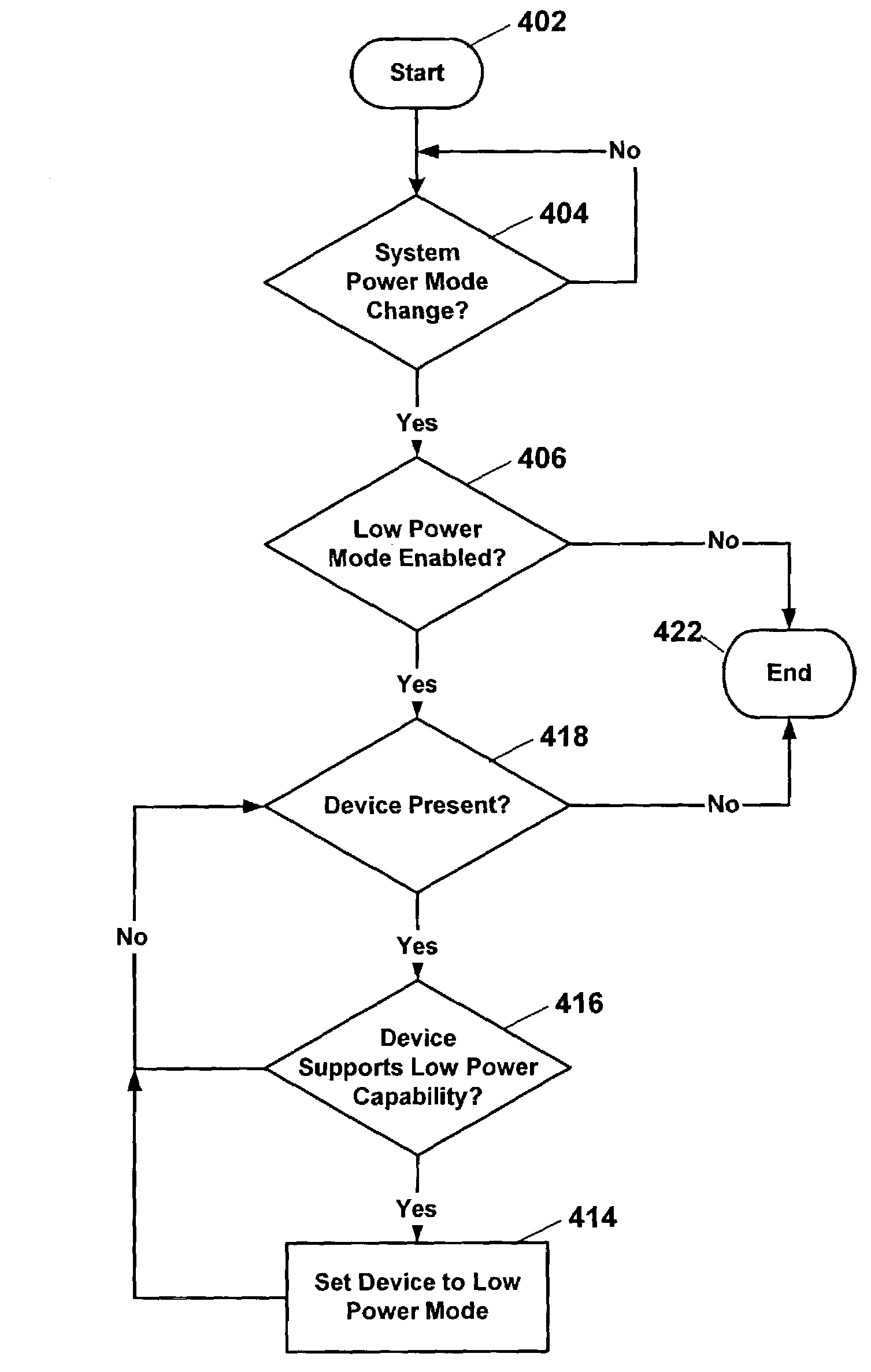

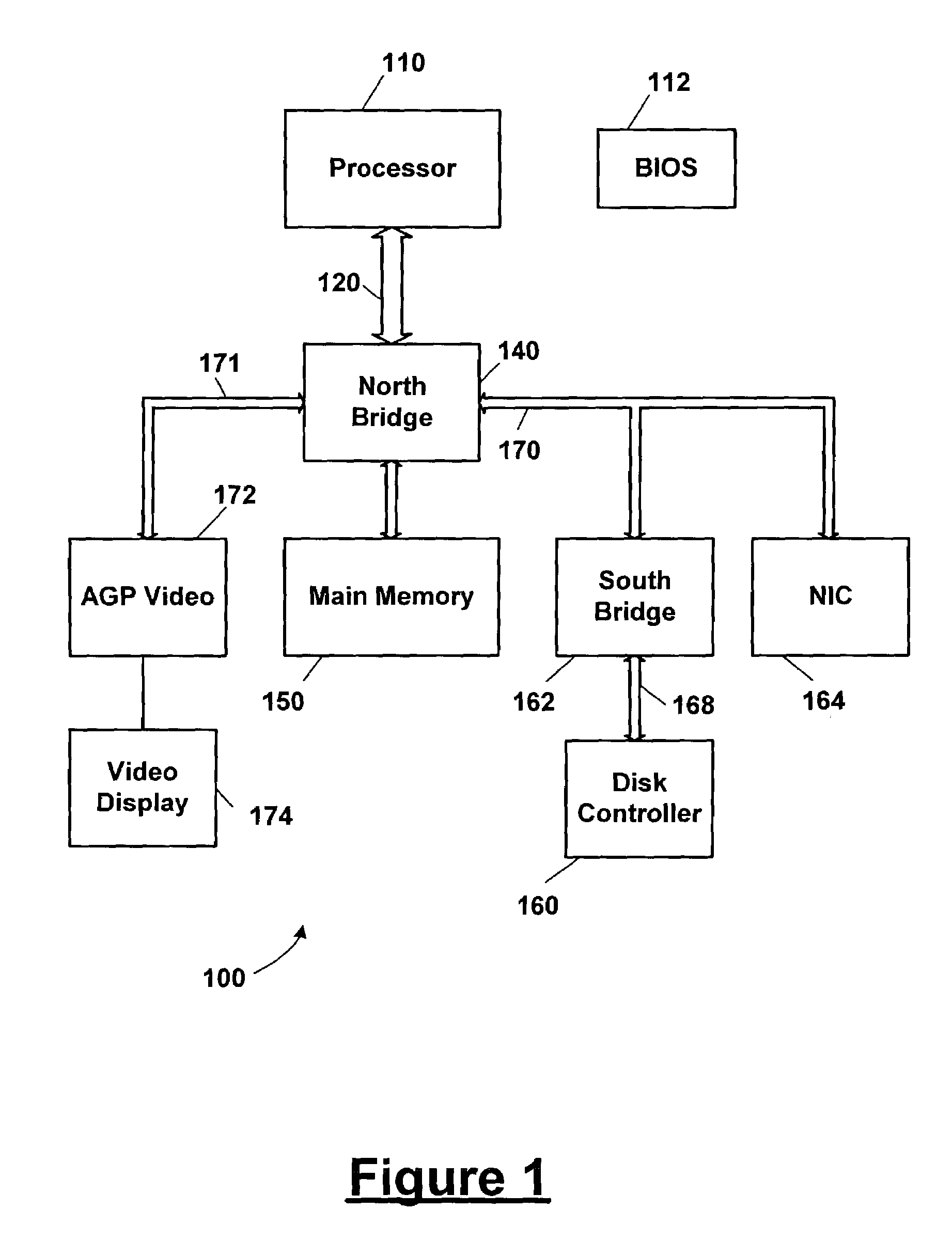

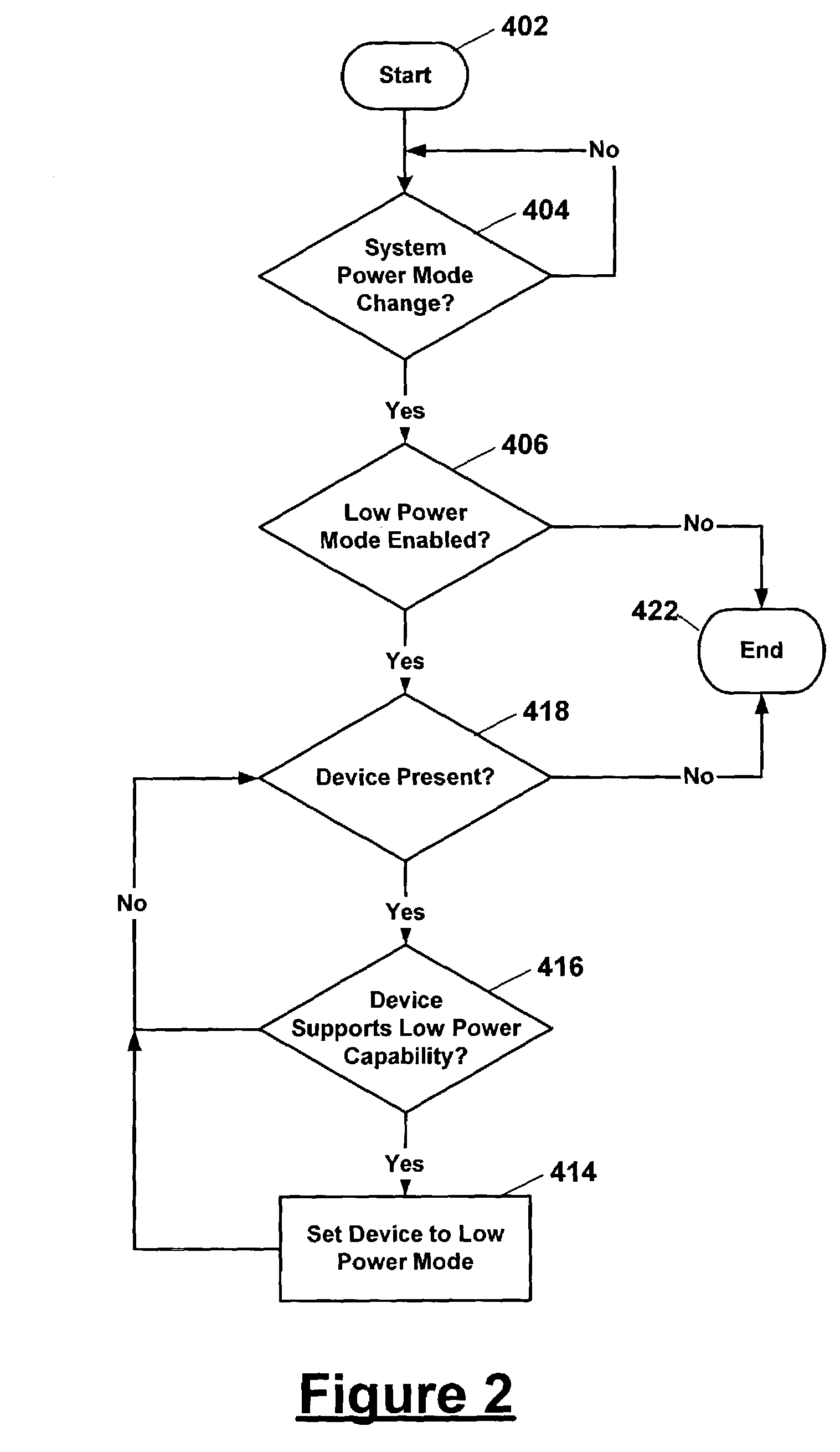

Low power mode for device power management

ActiveUS7437575B2Reduce standby powerVolume/mass flow measurementPower supply for data processingPower modeHandling system

Owner:DELL PROD LP

Logic circuit and semiconductor device

ActiveUS20110102018A1Reduce hydrogen concentrationTotal current dropTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5x1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

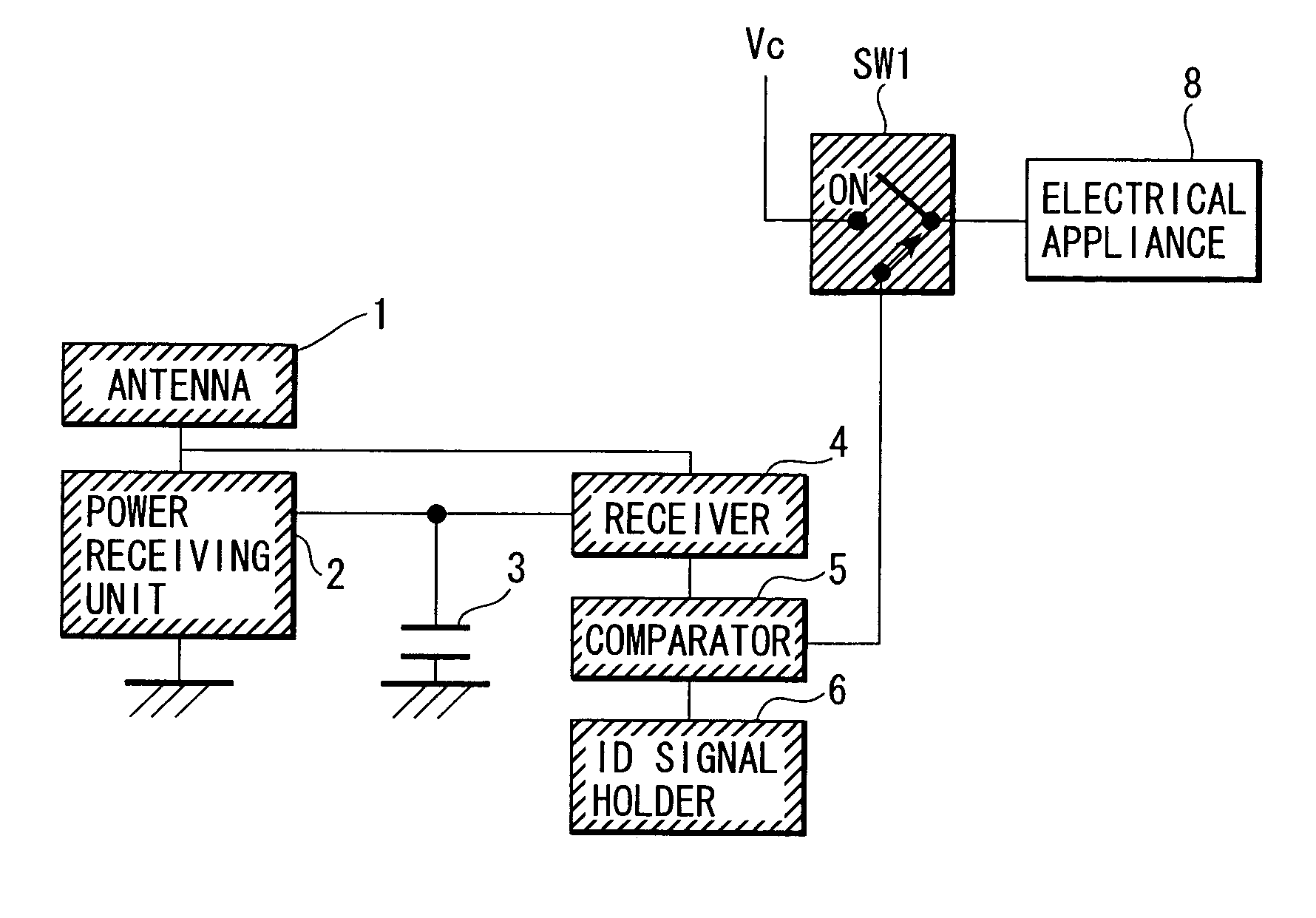

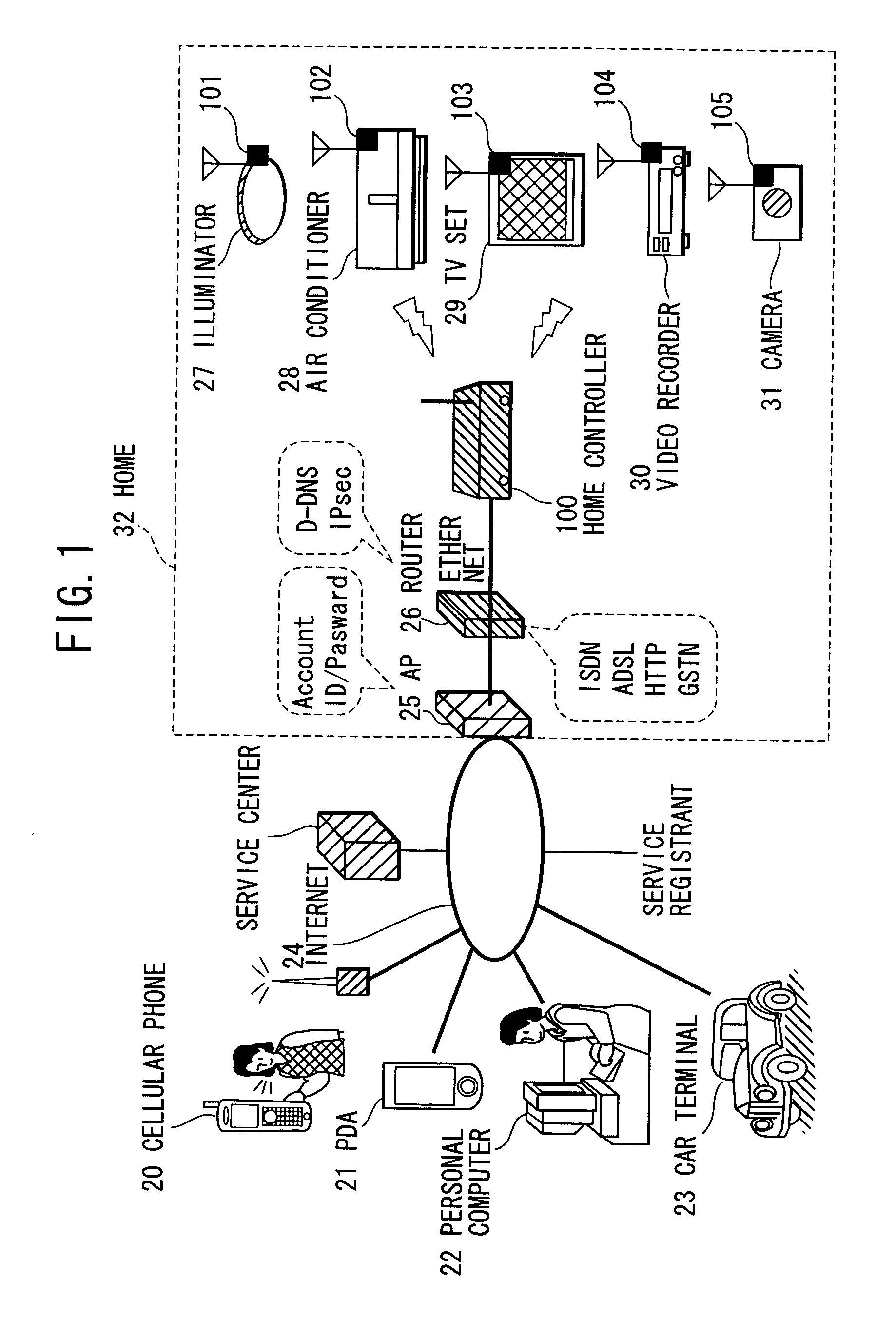

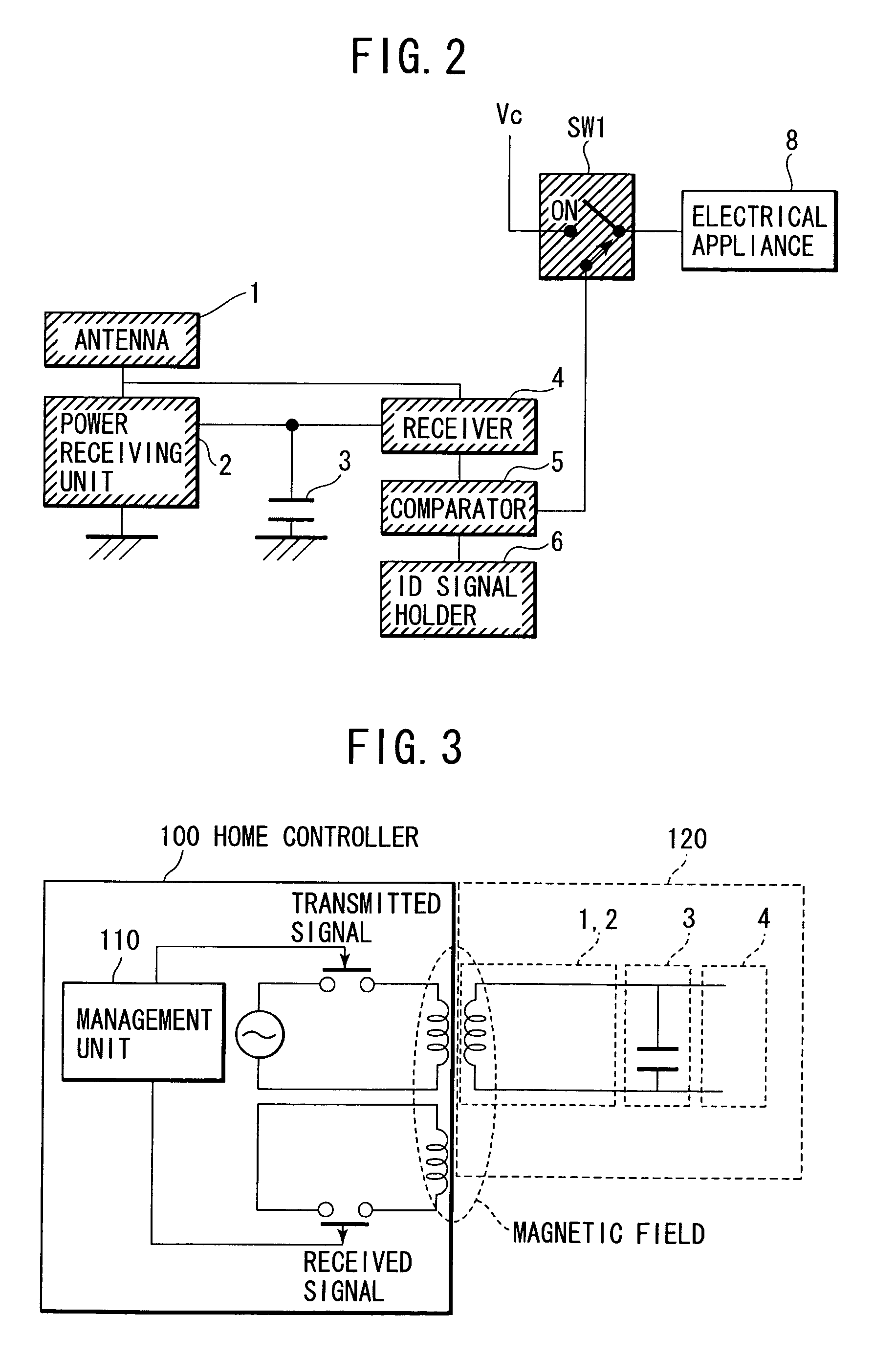

Appliance control apparatus and electrical appliance

InactiveUS20060012489A1Reduce standby power consumptionSave energyProgramme controlElectric signal transmission systemsThe InternetStandby power

Power is taken out from radio waves through an antenna and a power receiving unit. A signal receiver, a comparator, and an ID signal holder are operated with the taken-out power to compare an ID contained in a received signal with an ID read out from the ID signal holder. When both the ID's are matched with each other, a switch for a main power source is turned on. In trying to remotely operate household electrical appliances by utilizing the Internet that has become increasingly popular, standby power is consumed if the electrical appliances are kept in a standby state at all times. Since power is taken out from radio waves, the invention is able to cut the standby power in an environment where the radio waves are transferred via radio communication that is expected to be more and more prevalent in future.

Owner:HITACHI LTD

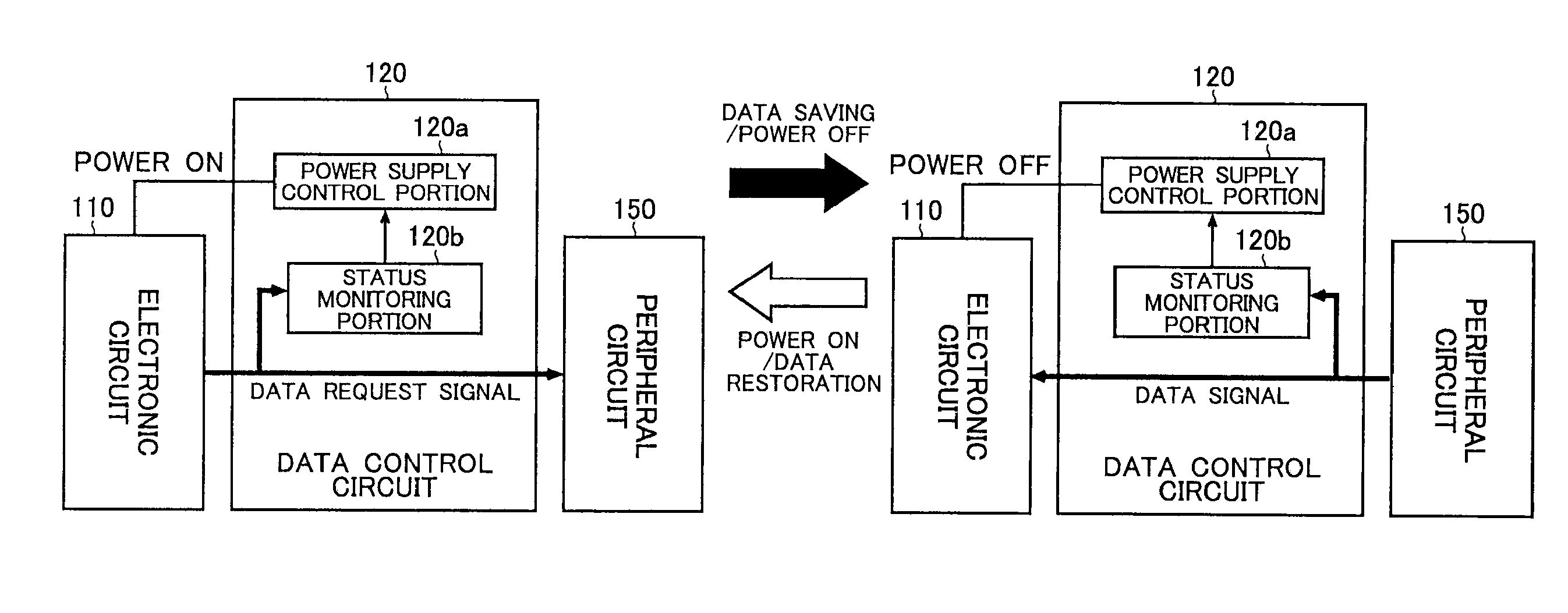

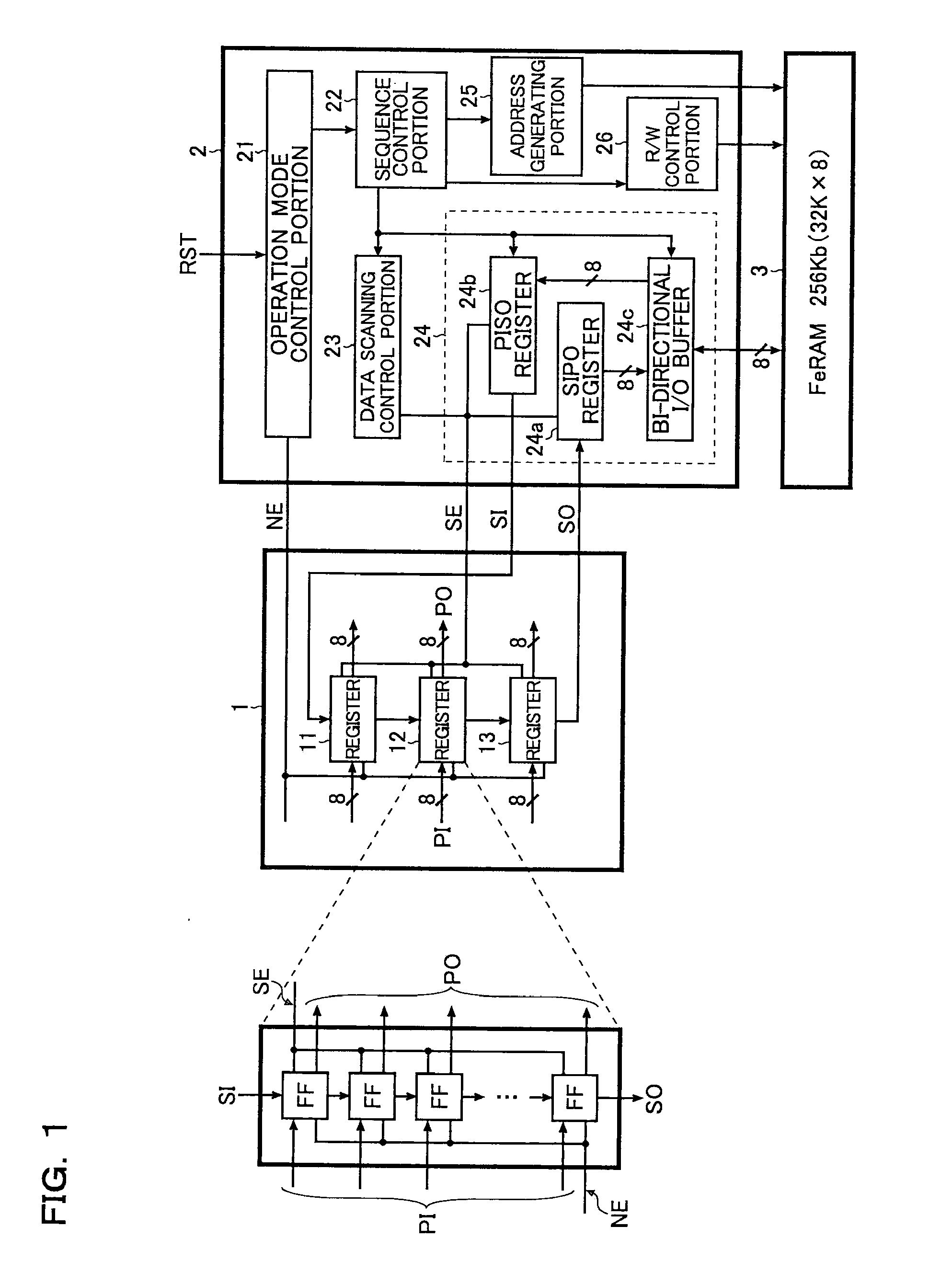

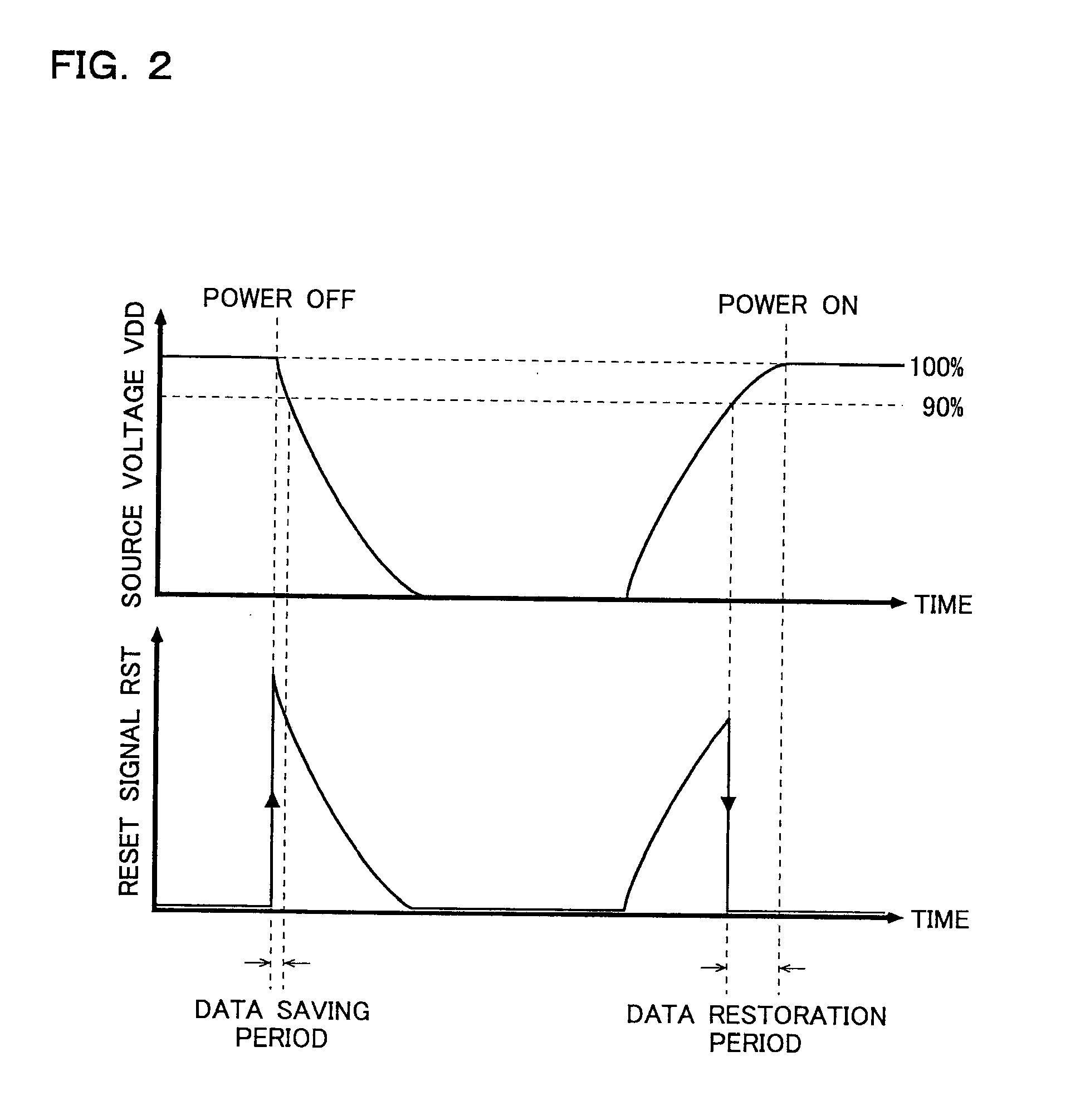

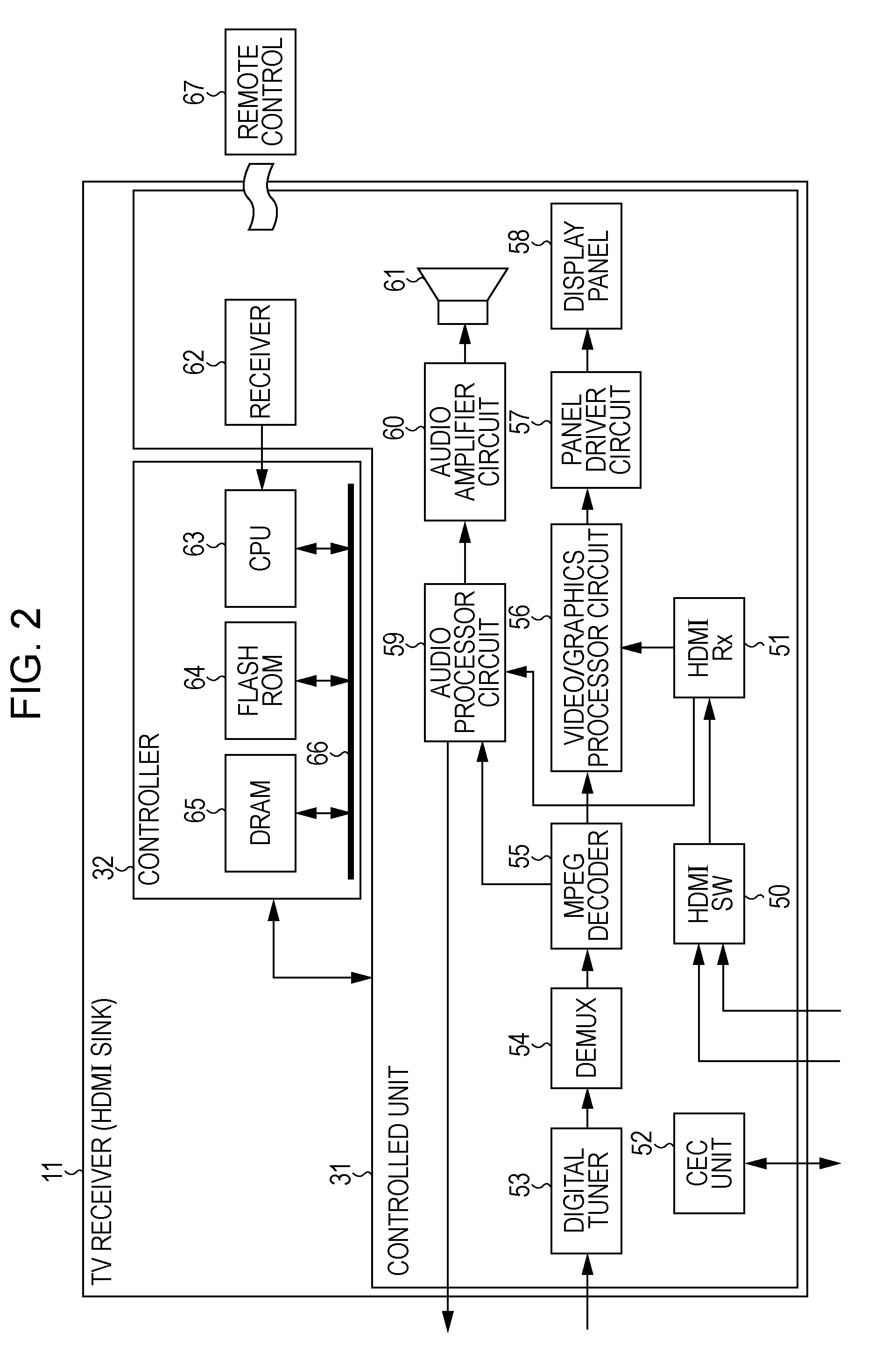

Data Processing Apparatus And Data Control Circuit For Use Therein

ActiveUS20080071972A1Improve usabilityReduce standby powerMemory loss protectionDigital data processing detailsLower limitData control

A data processing apparatus has a data saving control portion. At shutdown, within the period after a fall in the source voltage is detected until the source voltage falls down to the lower limit at which the apparatus is guaranteed to operate, the data saving control portion saves to a non-volatile memory all the data needed to restore the state of an electronic circuit portion.

Owner:ROHM CO LTD

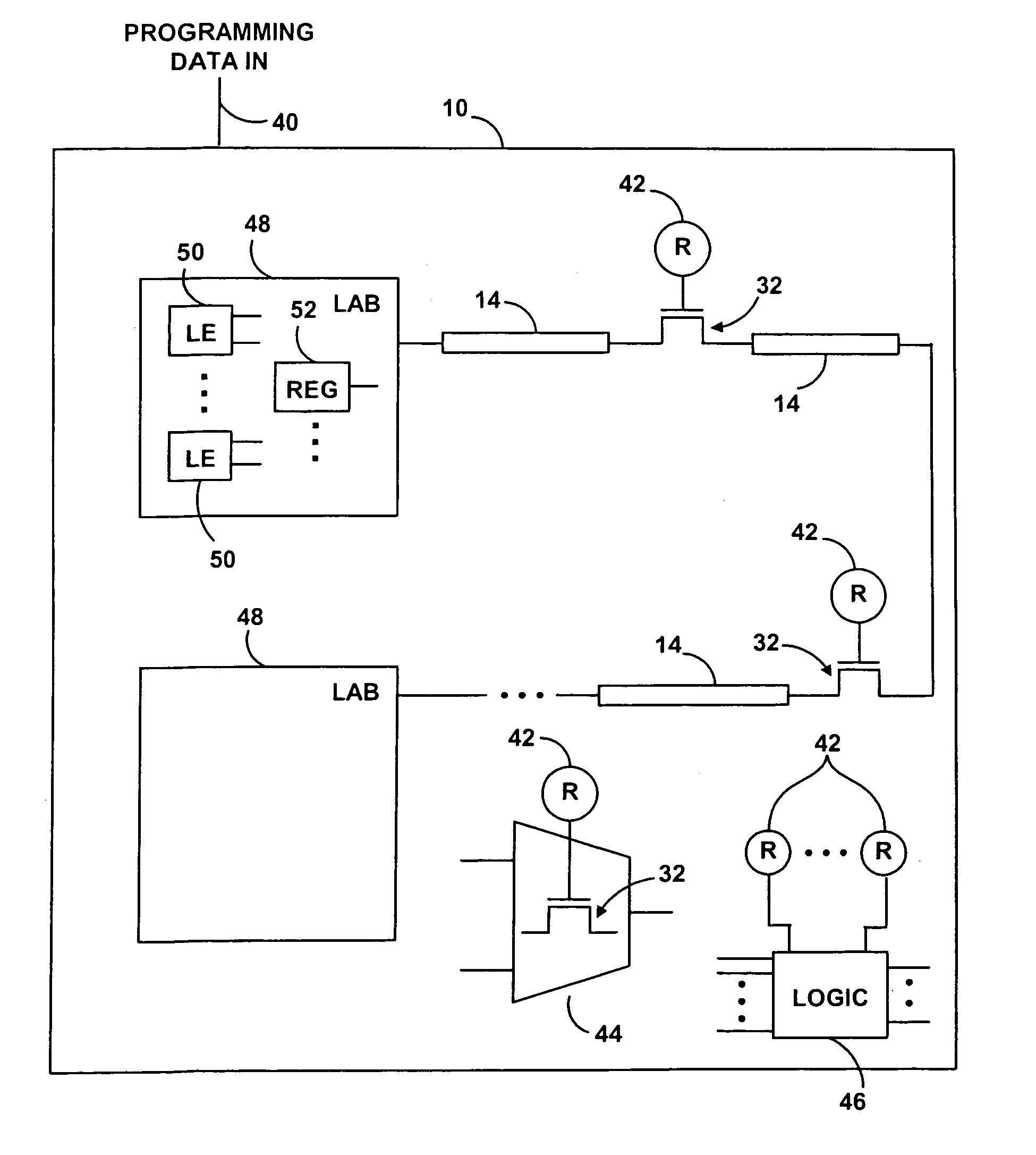

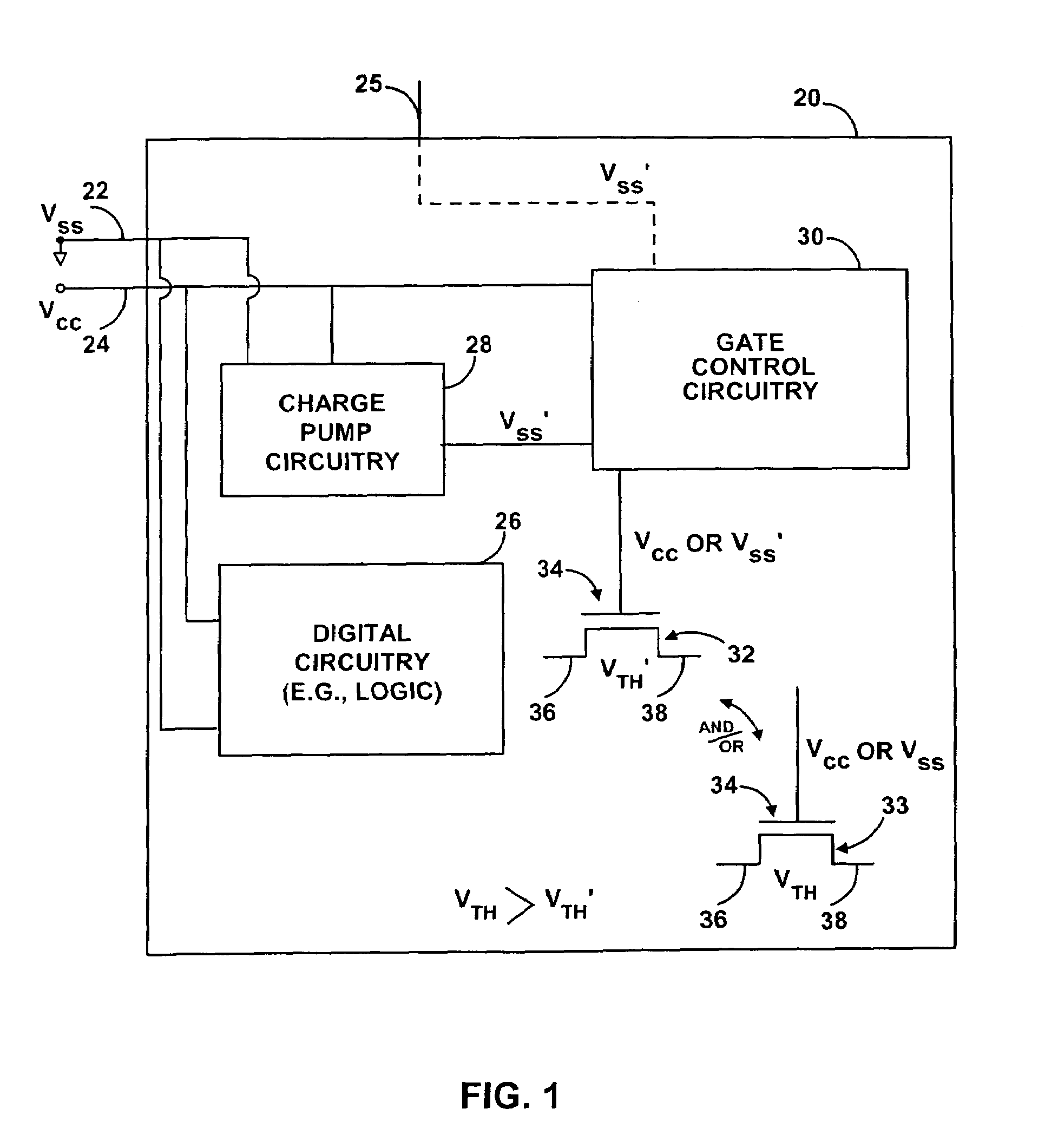

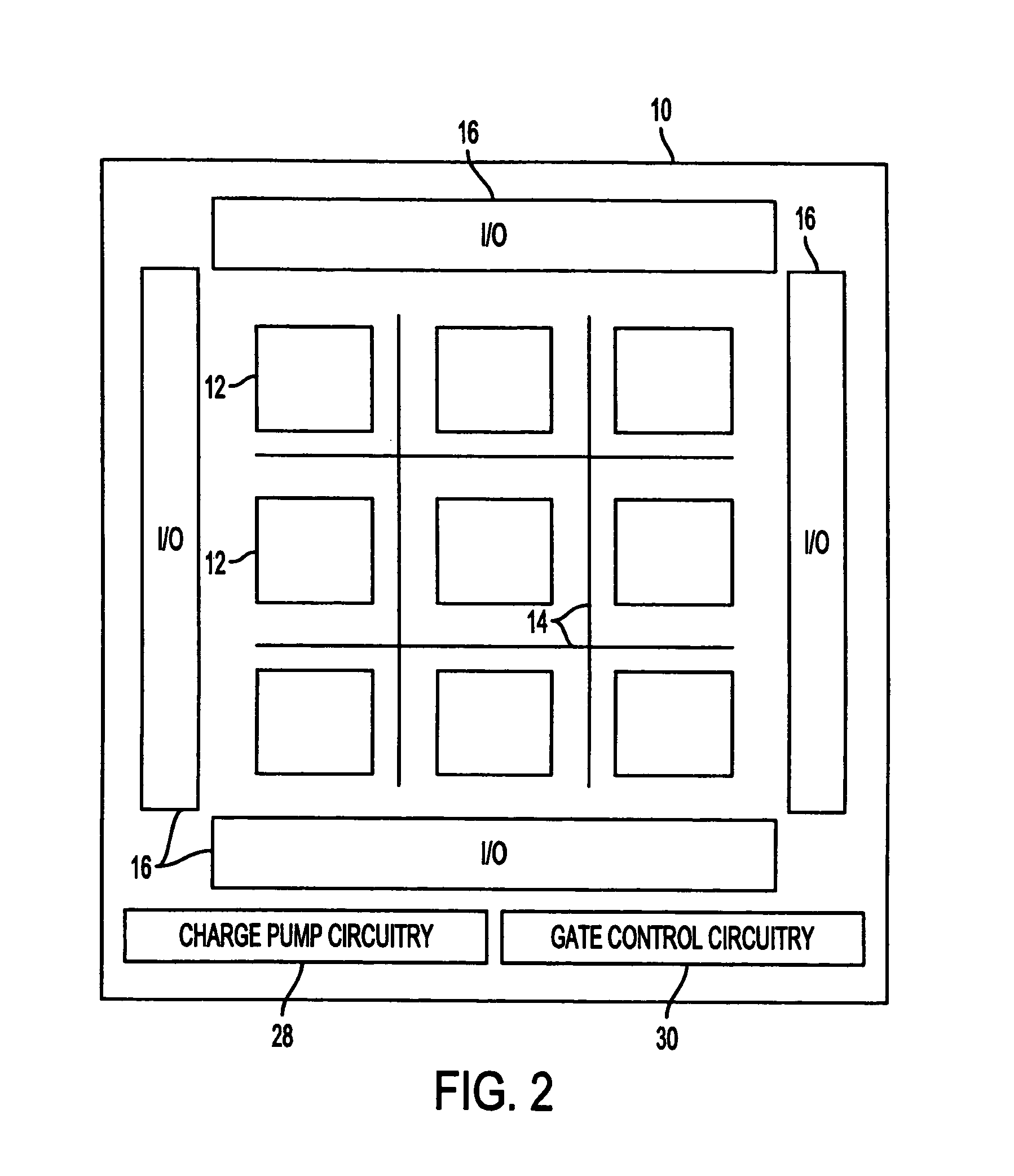

Integrated circuits with reduced standby power consumption

ActiveUS6940307B1Improved standby power consumption propertyReduce power consumptionPower reduction by control/clock signalLogic circuits characterised by logic functionProgrammable logic deviceStandby power

Integrated circuit standby power consumption may be reduced using a reverse-bias transistor control arrangement that reduces transistor leakage current. Integrated circuit transistors may be turned off using a reverse bias voltage rather than a ground voltage. A charge pump circuit on the integrated circuit may be used to generate the reverse bias voltage. The reverse bias voltage may also be provided from an external source. The integrated circuit may be a programmable logic device in which logic is configured by providing programming data to configuration cells. The configuration cells may be used to apply either a positive power supply voltage to a given transistor to turn that transistor on or to provide the reverse bias voltage to that transistor to turn that transistor off.

Owner:ALTERA CORP

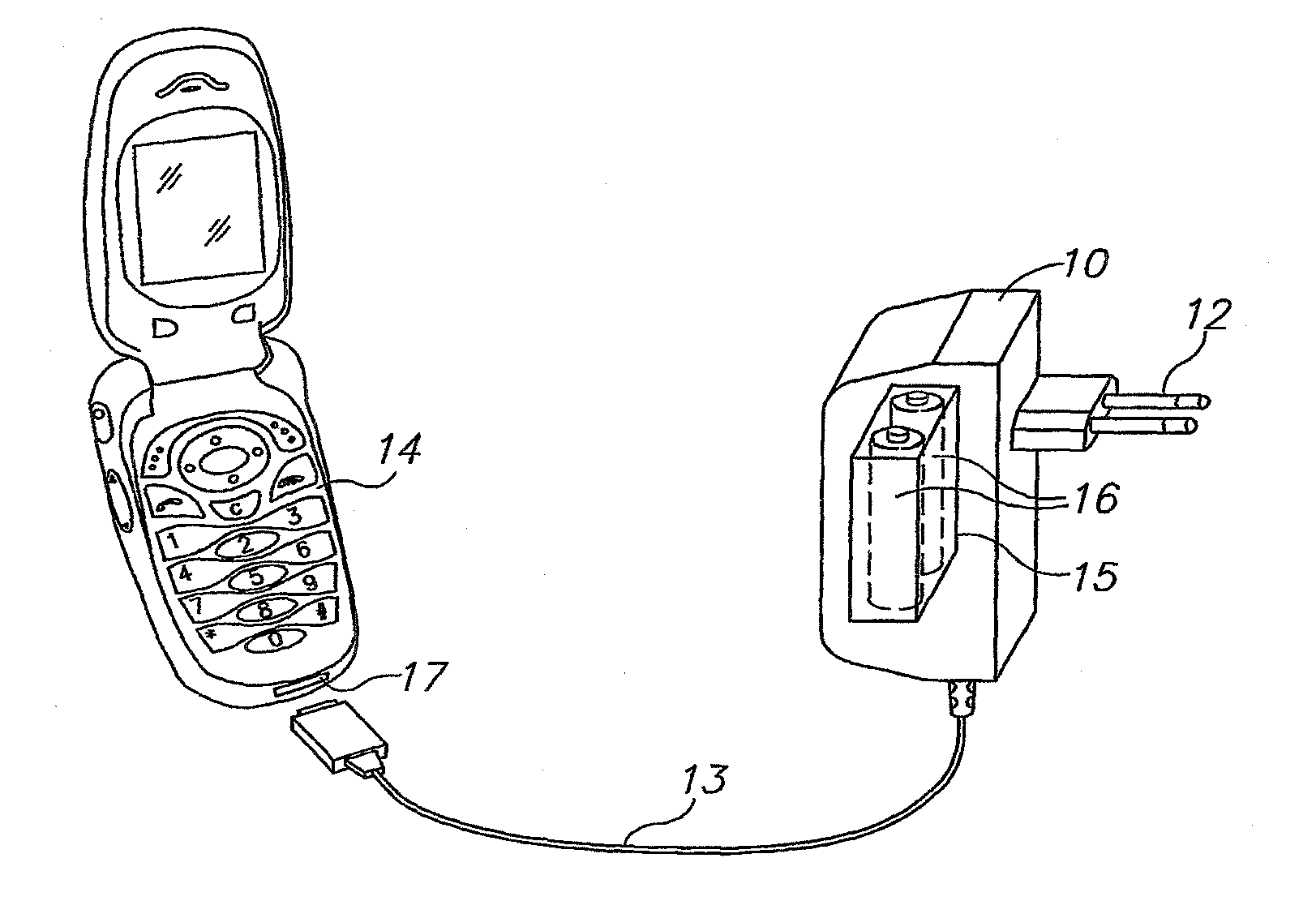

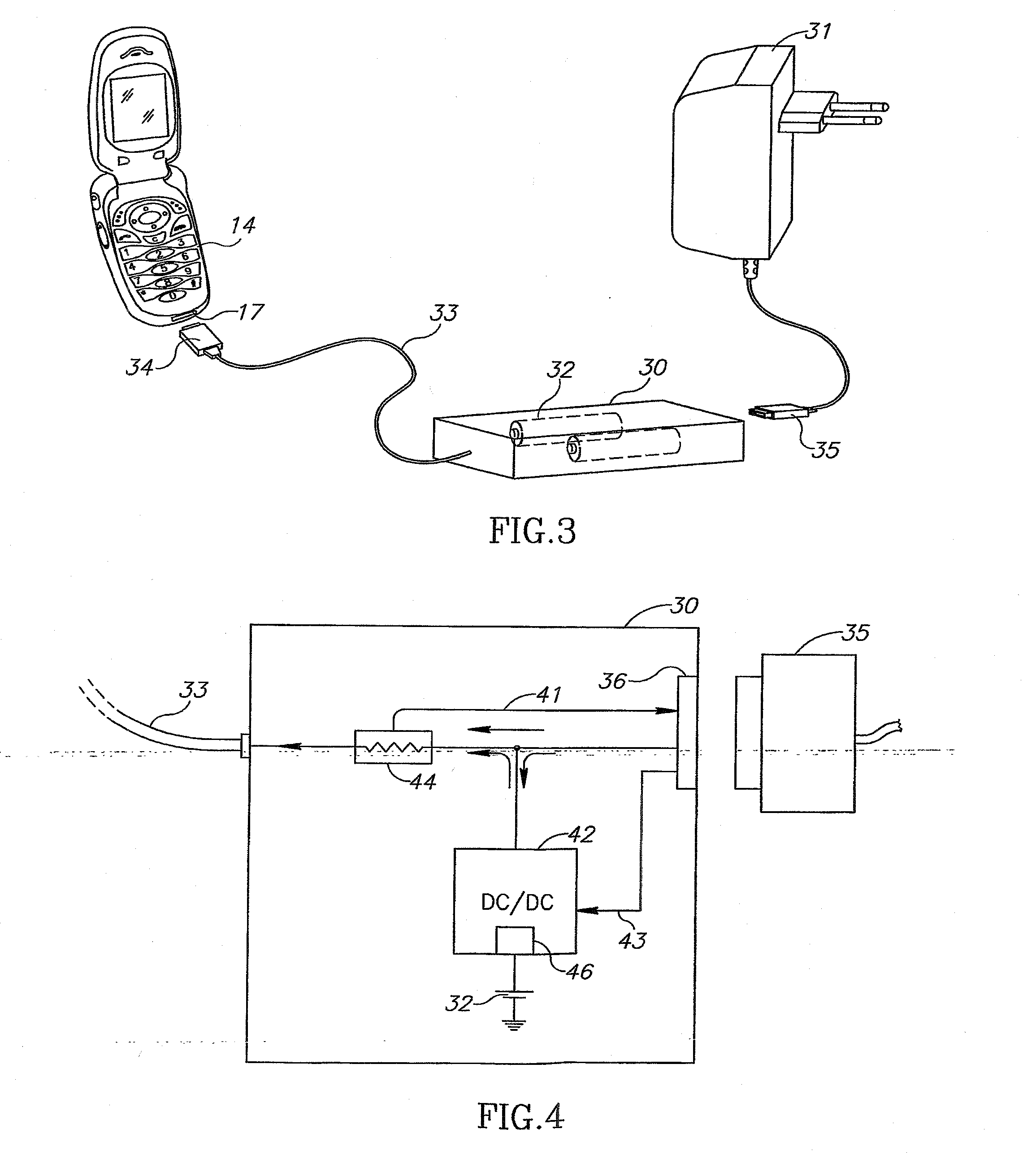

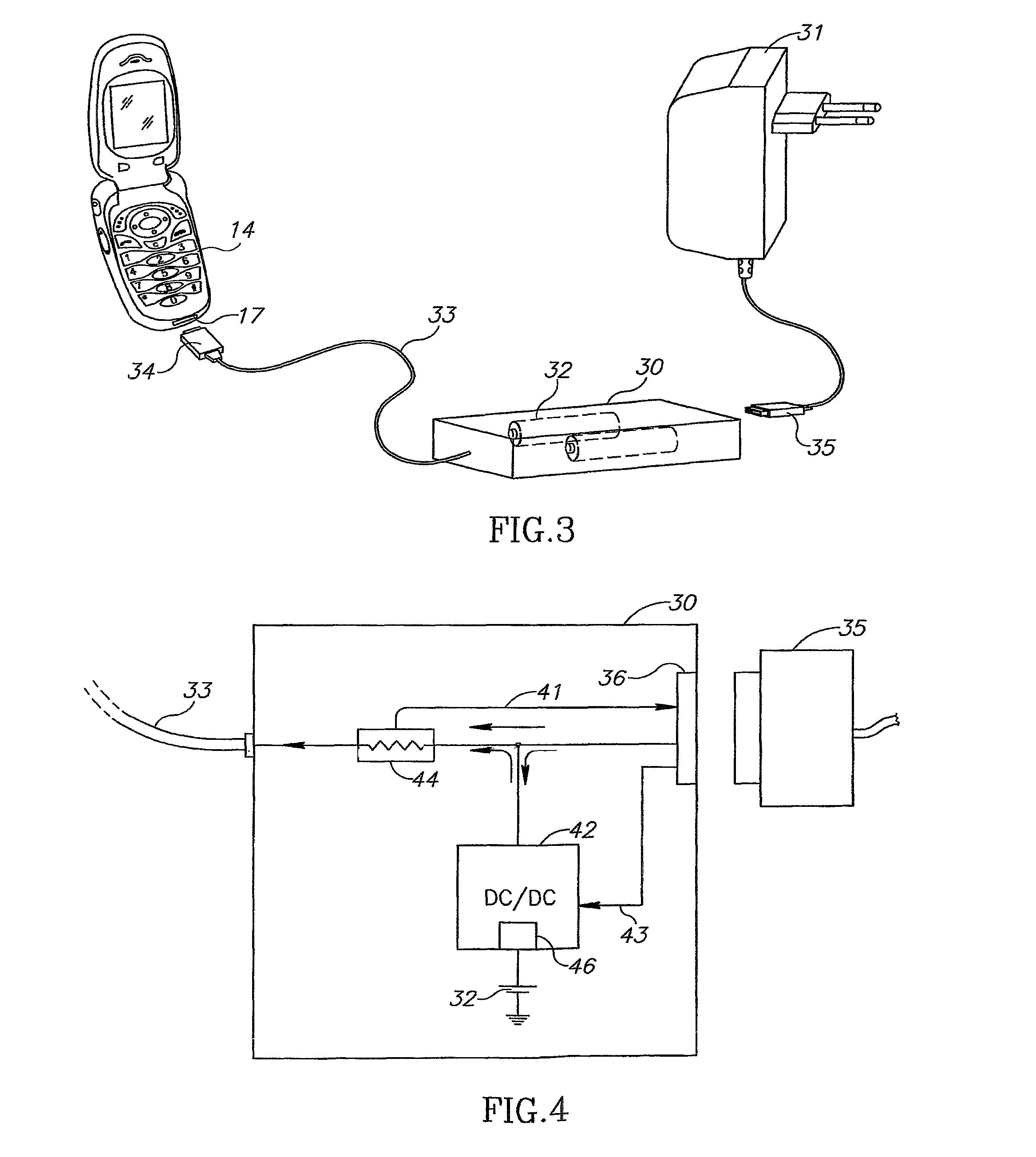

Battery Powered Charger

ActiveUS20110148344A1Eliminate currentEasy complianceElectric powerBattery load switchingEngineeringAC power

A charger for recharging the batteries of a portable electronic device even when no external power source is available. A battery or cell is installed within the charger, and when no access is available to a fixed power source into which the charger can be plugged, the internal battery or cell can be used to recharge the electronic device. The internal battery can be a primary battery or a secondary battery. In the latter case, the internal battery can be maintained in a charged state by means of circuitry which, when the charger is plugged into the external power source, charges the internal battery as well as the battery of the electronic device. The external power source can be either an AC power wall socket, in which case the charger includes AC / DC voltage conversion circuits, or a car lighter socket, or the DC output of a conventional wall charger.

Owner:TOWER SEMICONDUCTOR

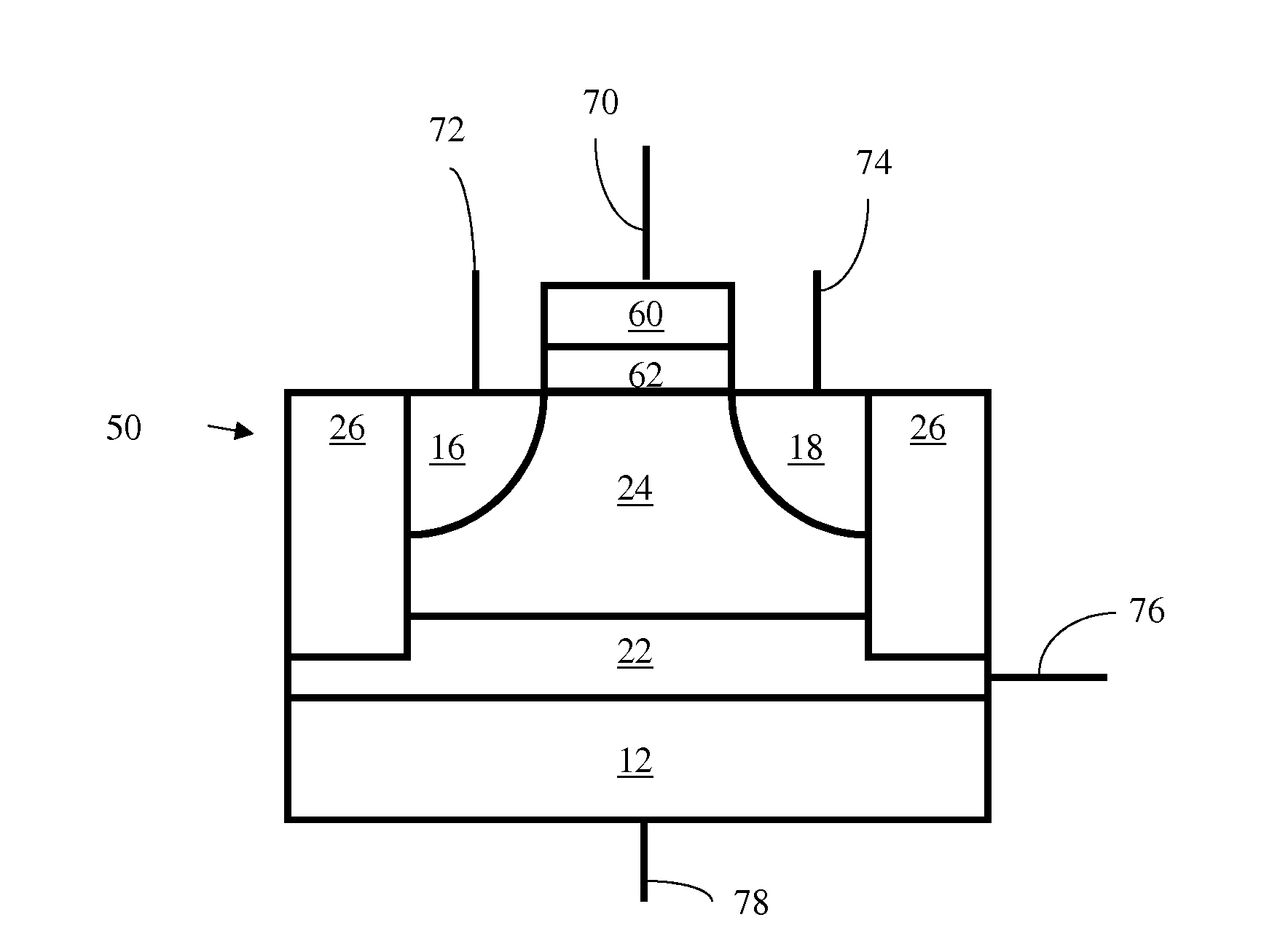

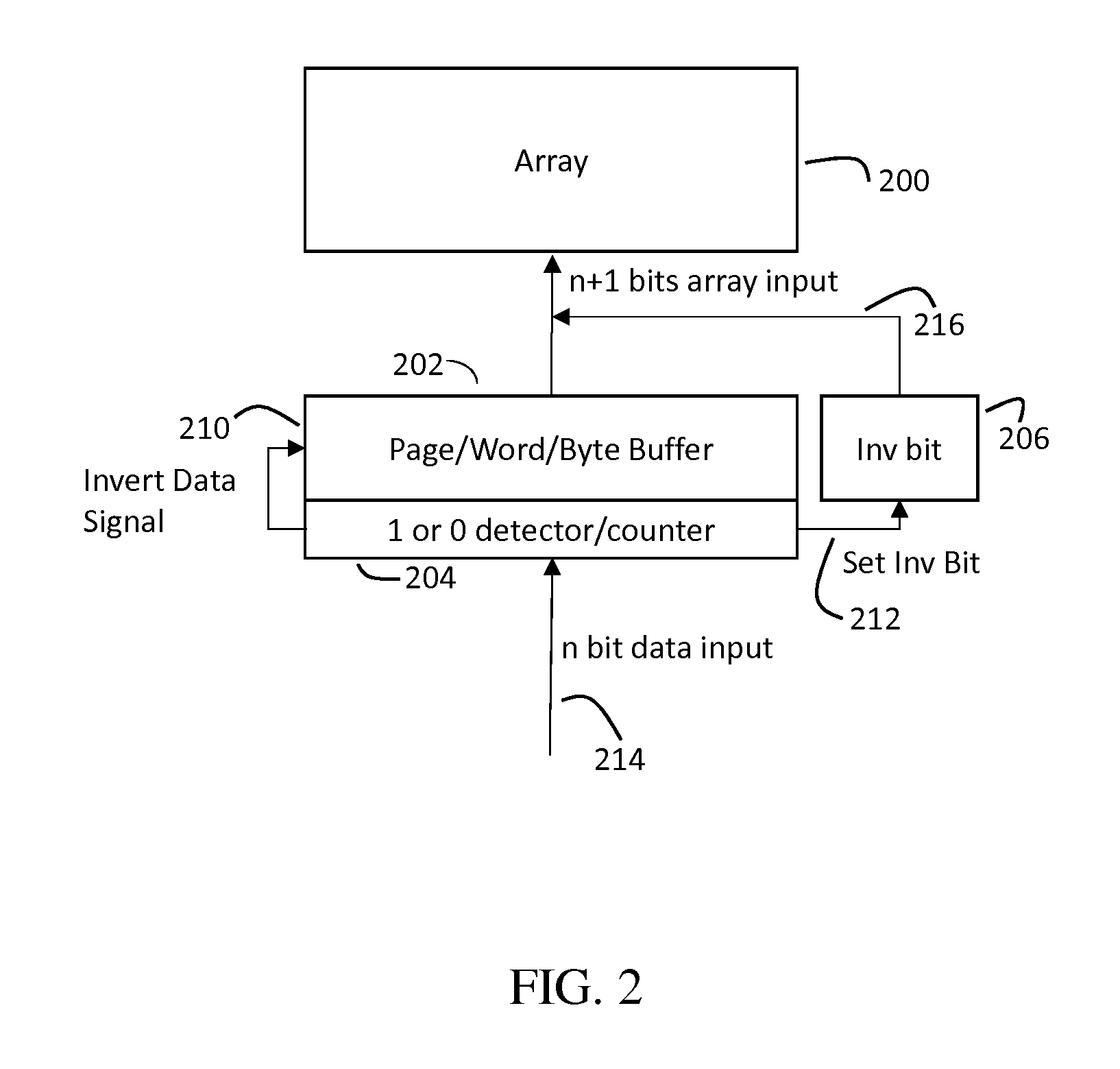

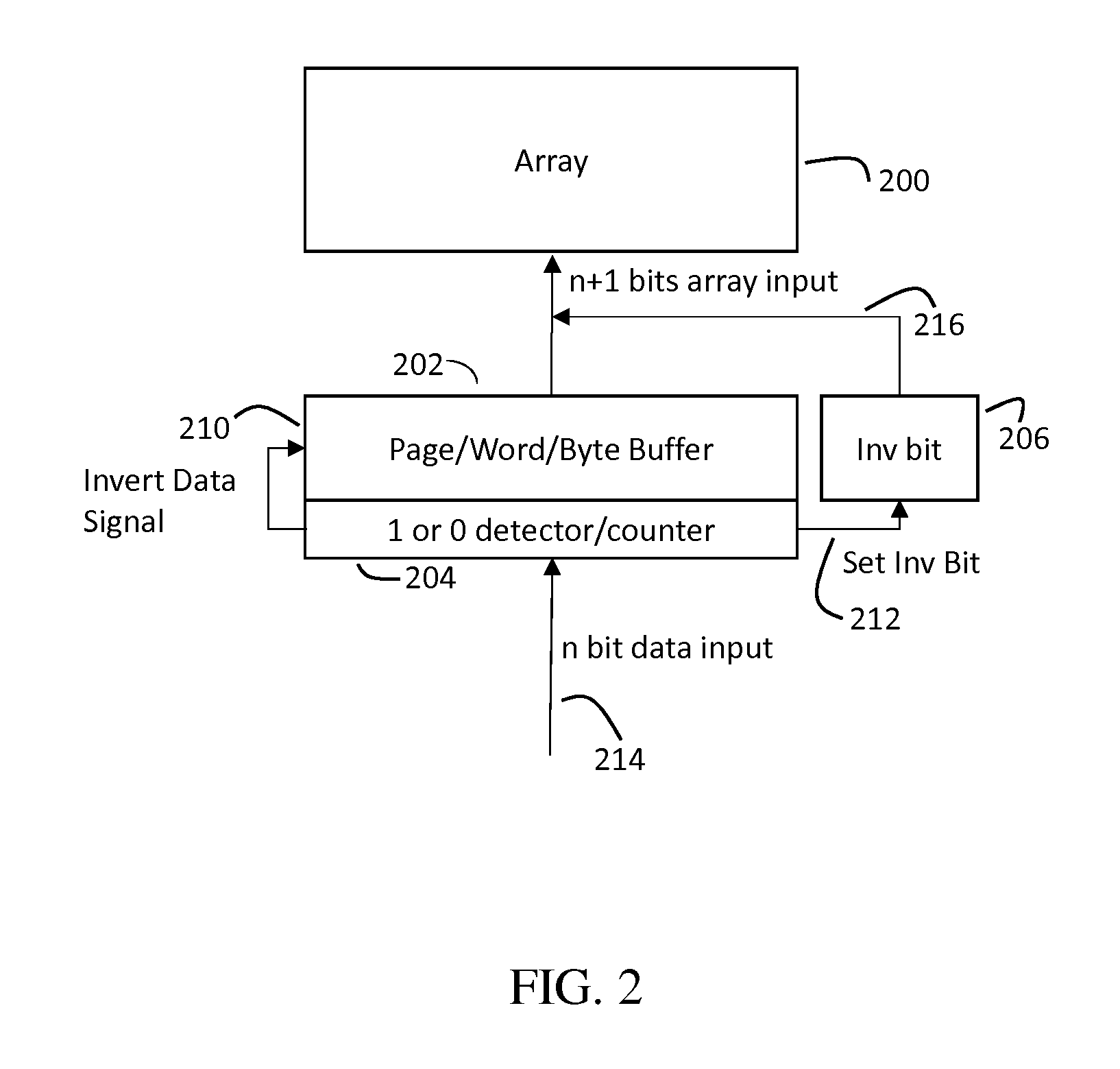

Systems and Methods for Reducing Standby Power in Floating Body Memory Devices

Methods, devices, arrays and systems for reducing standby power for a floating body memory array. One method includes counting bits of data before data enters the array, wherein the counting includes counting at least one of: a total number of bits at state 1 and a total number of all bits; a total number of bits at state 0 and the total number of all bits; or the total number of bits at state 1 and the total number of bits at state 0. This method further includes detecting whether the total number of bits at state 1 is greater than the total number of bits at state 0; setting an inversion bit when the total number of bits at state 1 is greater than the total number of bits at state 0; and inverting contents of all the bits of data before writing the bits of data to the memory array when the inversion bit has been set.

Owner:ZENO SEMICON

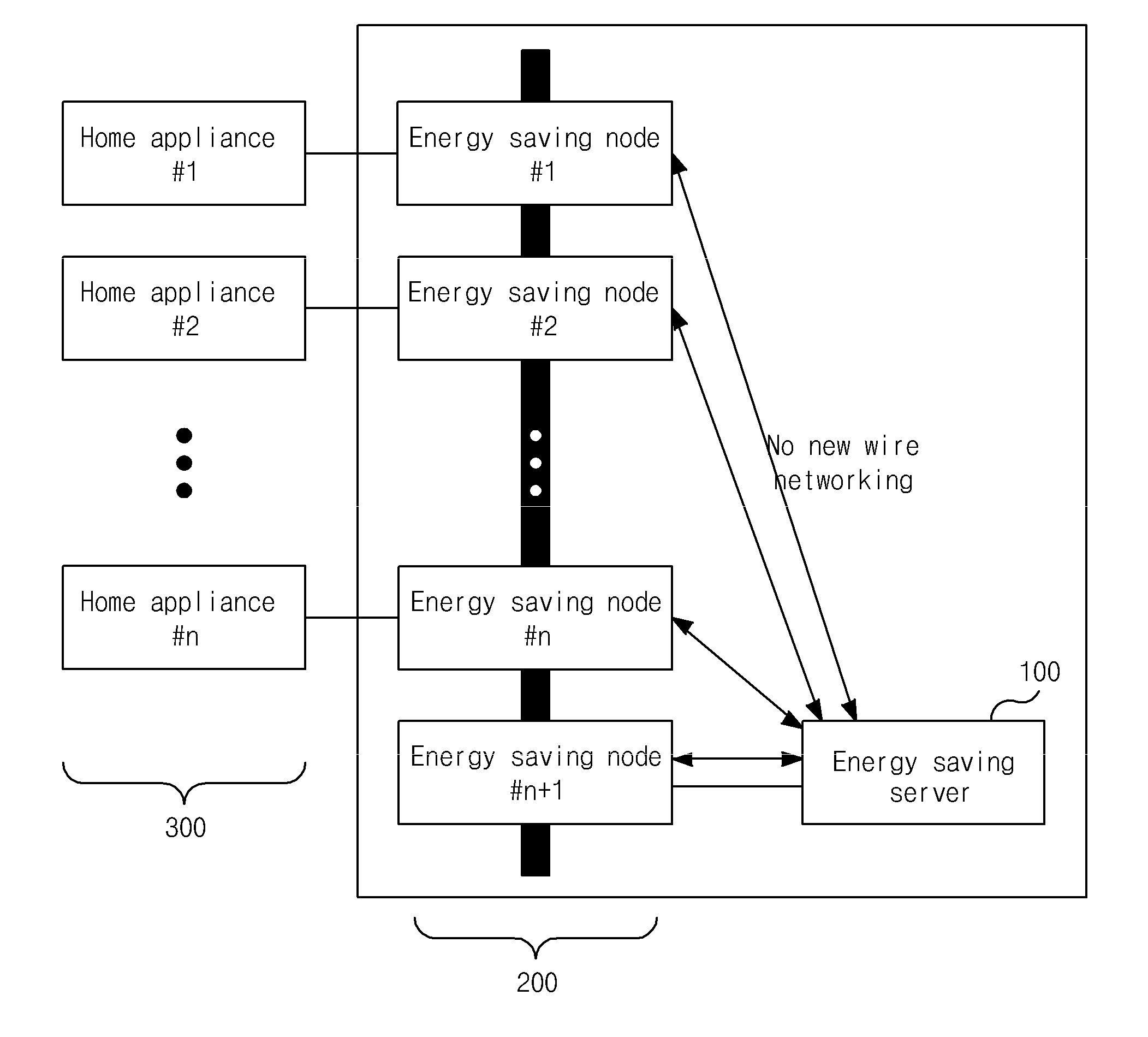

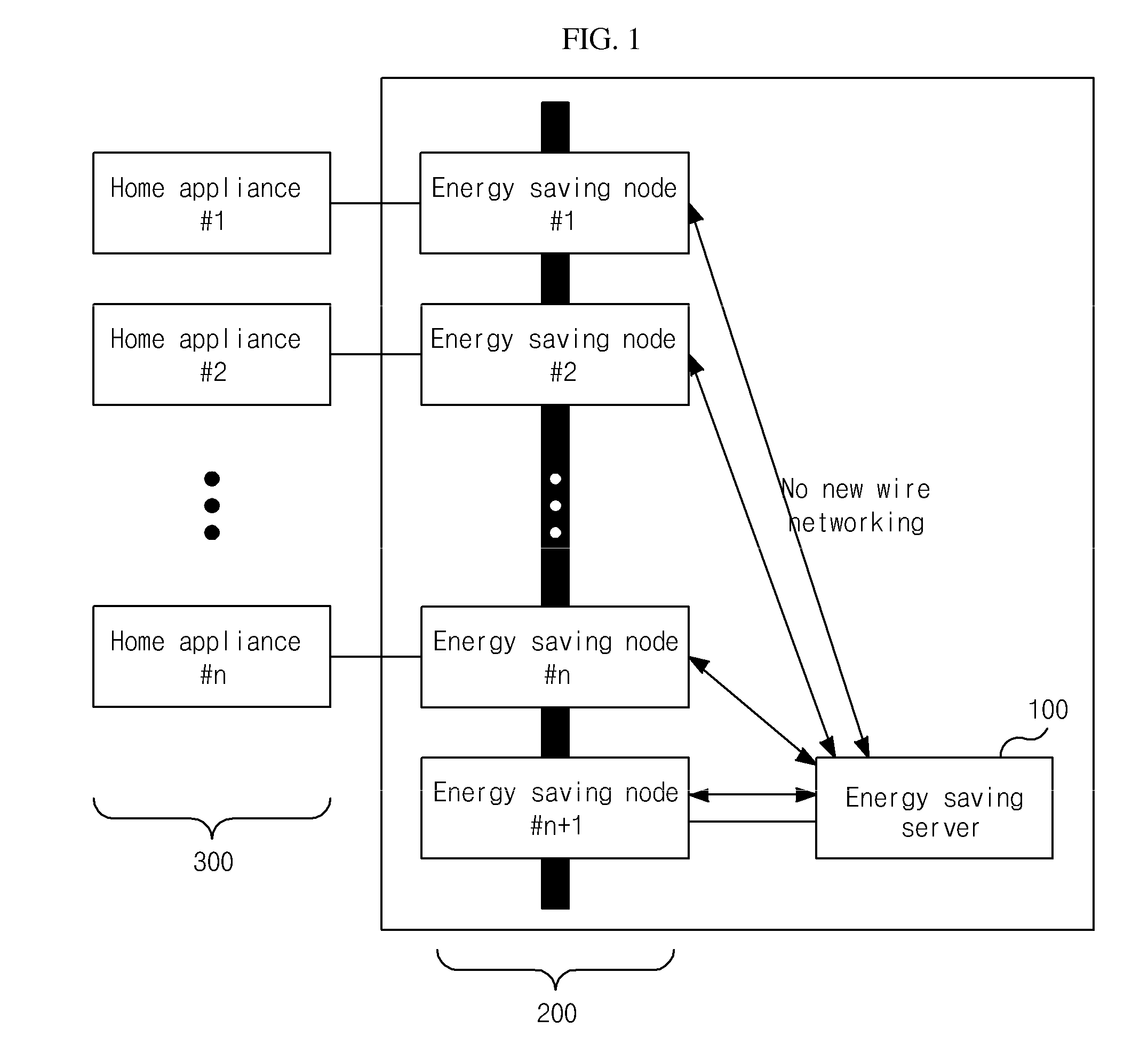

System and methods for monitoring energy consumption and reducing standby power

ActiveUS20100156666A1Reduce standby powerEnergy efficient ICTElectric signal transmission systemsStandby powerHome appliance

A power saving system and method for the home appliances and home network devices is provided. The system provides an energy consumption monitoring and standby power saving system that is connected to home appliances and that may detect the amount of power consumed by corresponding home appliances. The system includes one or more energy saving nodes which approve application or shut-off power to a corresponding home appliances, and an energy saving server that is connected to each of the energy saving nodes and collects status information of the corresponding home appliances including said amount of power consumption from said nodes.

Owner:KOREA ELECTRONICS TECH INST

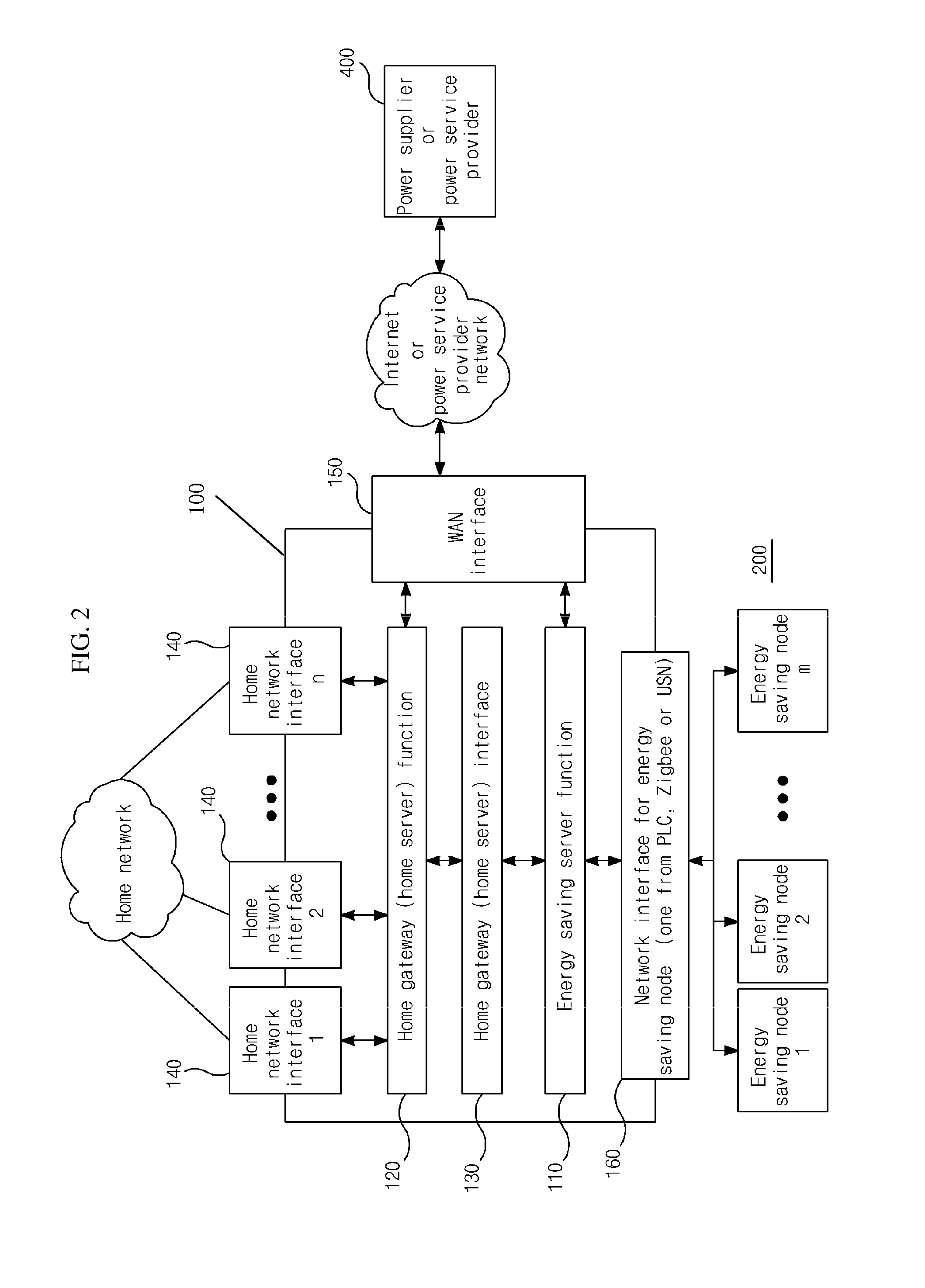

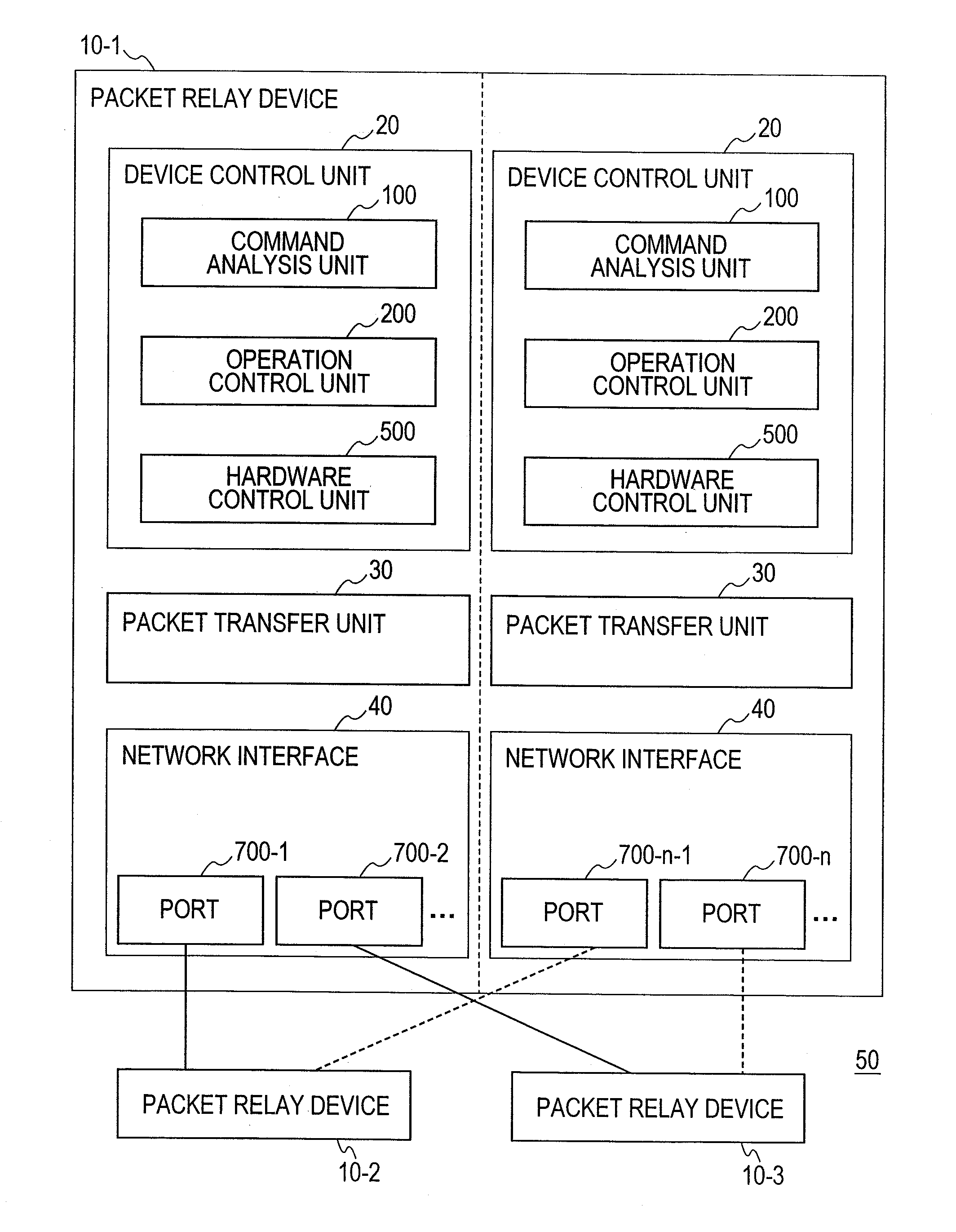

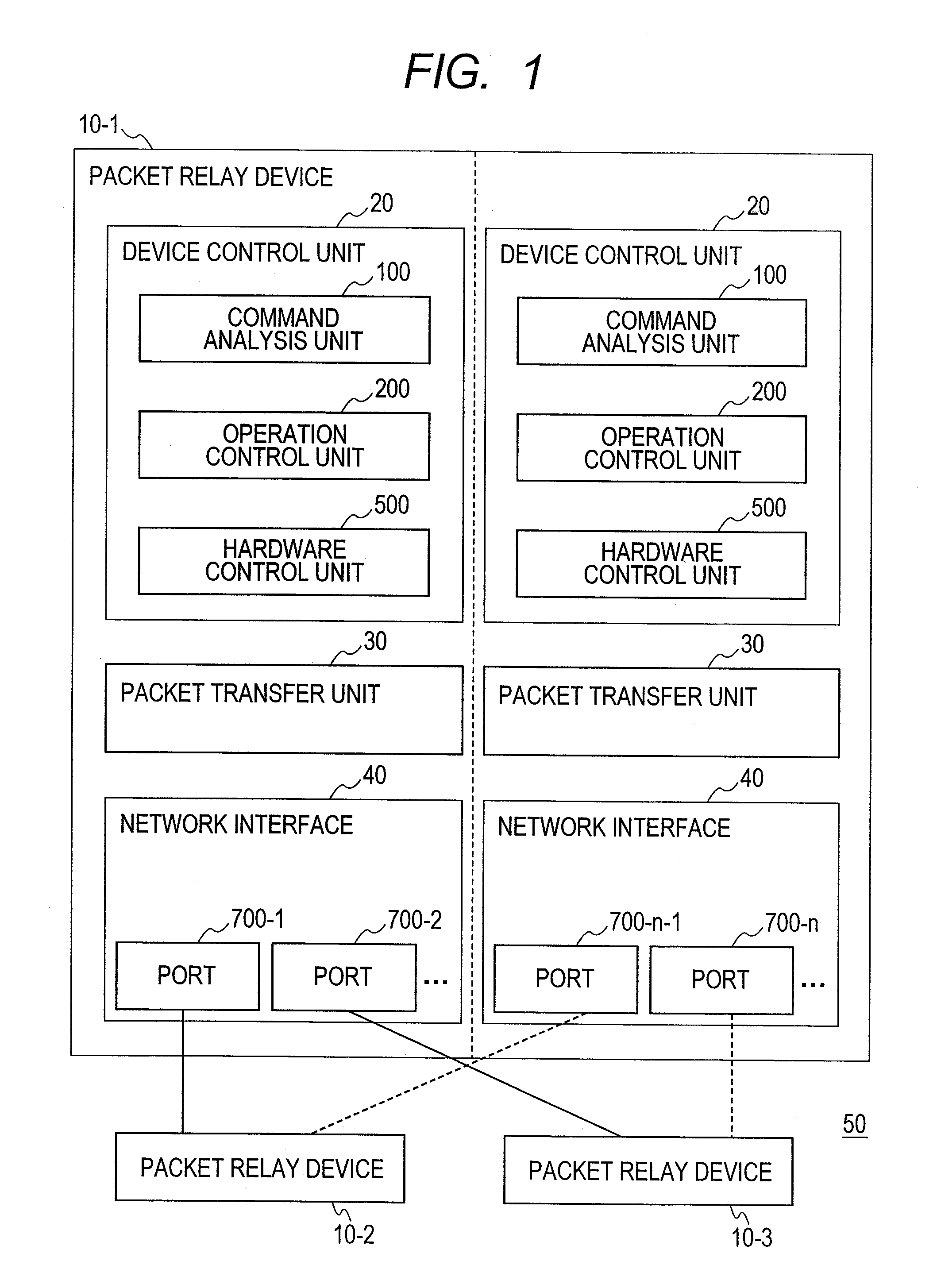

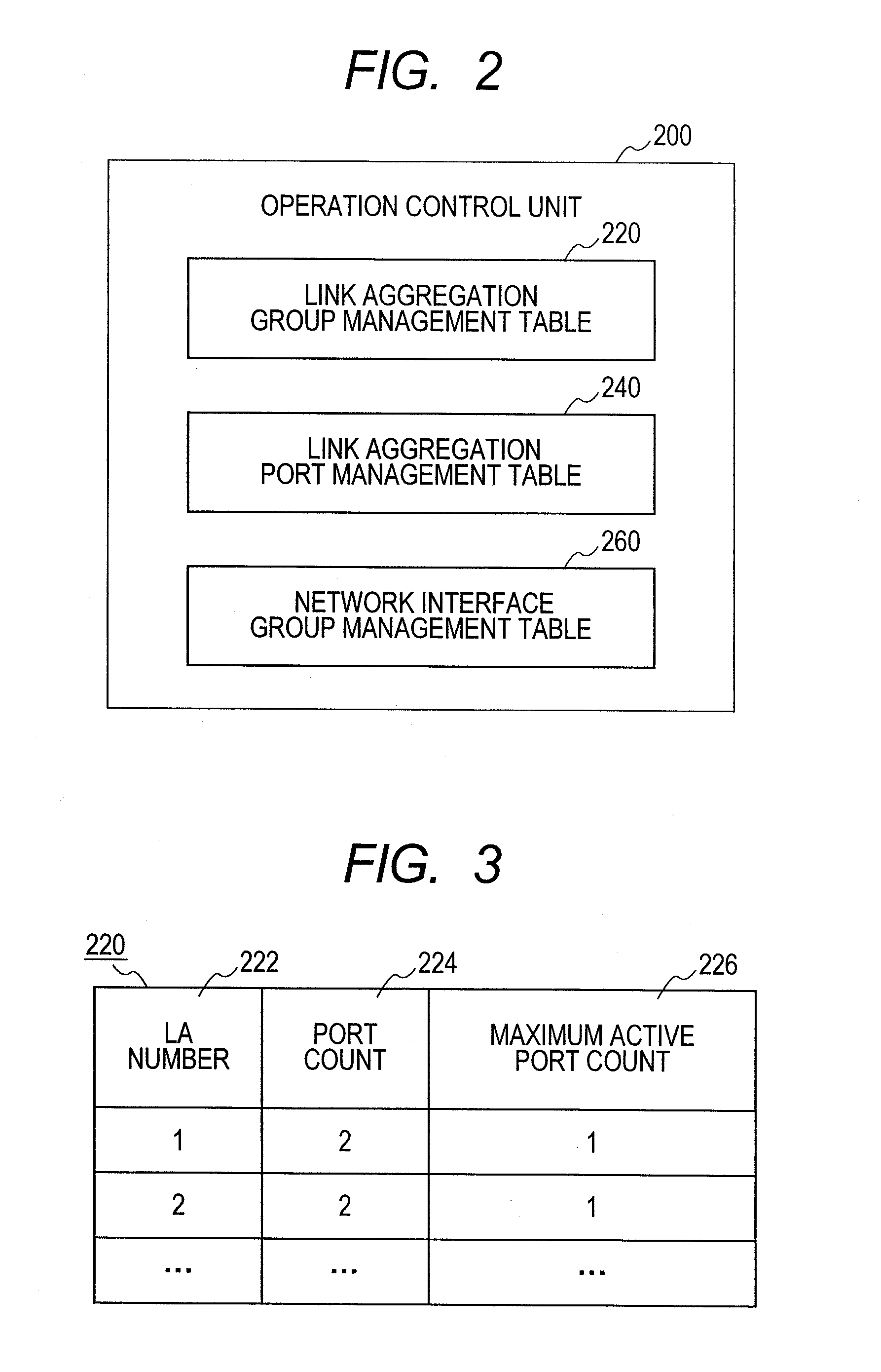

Packet relay device

ActiveUS20110211585A1Reduce standby power consumptionContinue communicationEnergy efficient ICTData switching by path configurationDevice MonitorLink aggregation

A packet relay device determines a port to be placed on standby in a link aggregation, determines whether there is an active port among ports belonging to redundant network interfaces, and, if a network interface has no active port, places the network interface on standby. The packet relay device monitors whether a failure has occurred in an active network interface and, if a failure is detected, activates a standby network interface and places the failed network interface on standby.

Owner:ALAXALA NETWORKS

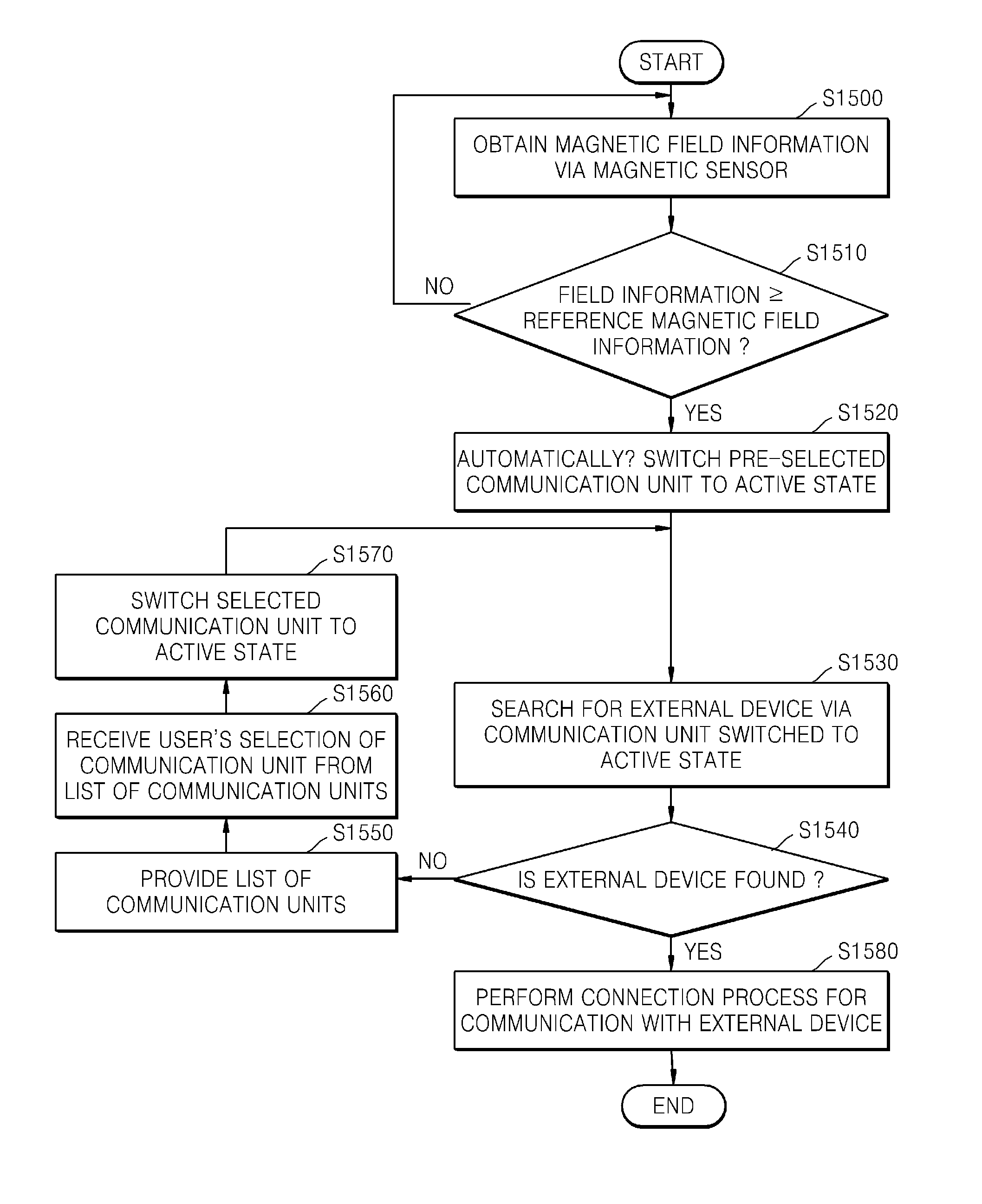

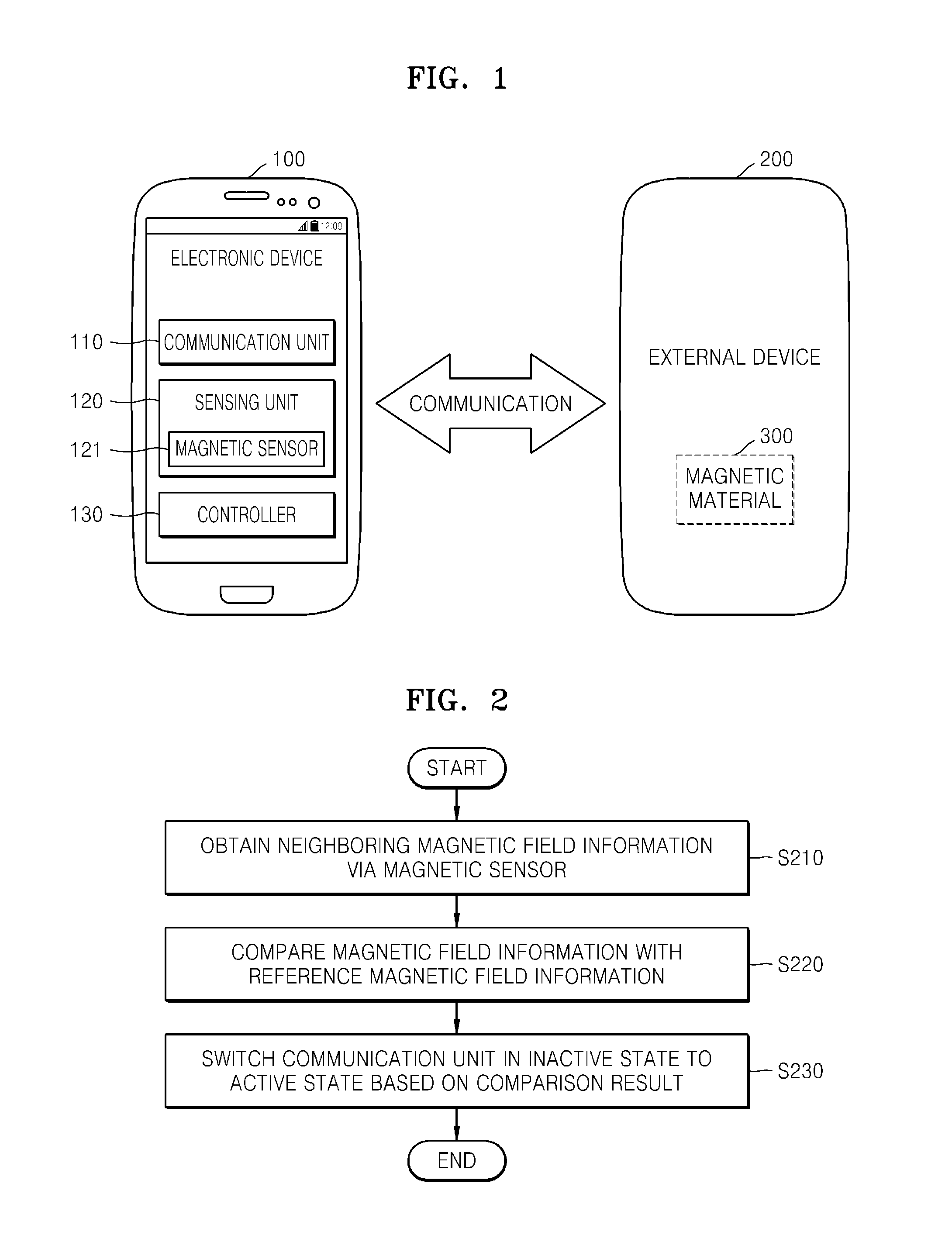

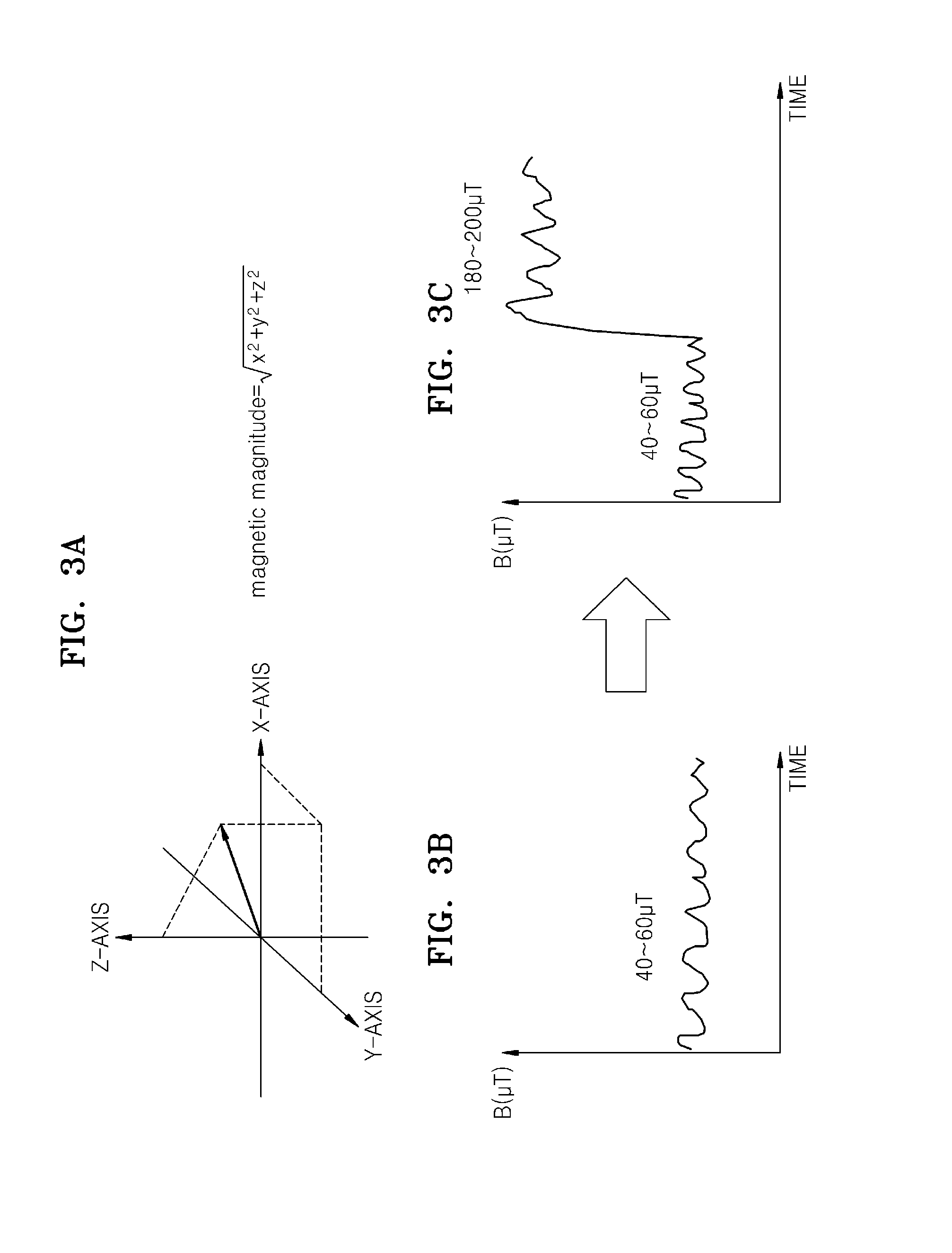

Method of controlling communication unit via magnetic sensor and electronic device using the method

InactiveUS20140342671A1Firmly connectedReduce standby powerPower managementRadio transmissionCommunication unitControl communications

A method of controlling a communication unit of an electronic device is provided. The method includes: obtaining magnetic field information via a magnetic sensor; comparing the obtained magnetic field information with reference magnetic field information; and switching the communication unit in an inactive state to an active state based on a result of the comparing, wherein the communication unit is capable of communicating with an external device in the active state.

Owner:SAMSUNG ELECTRONICS CO LTD

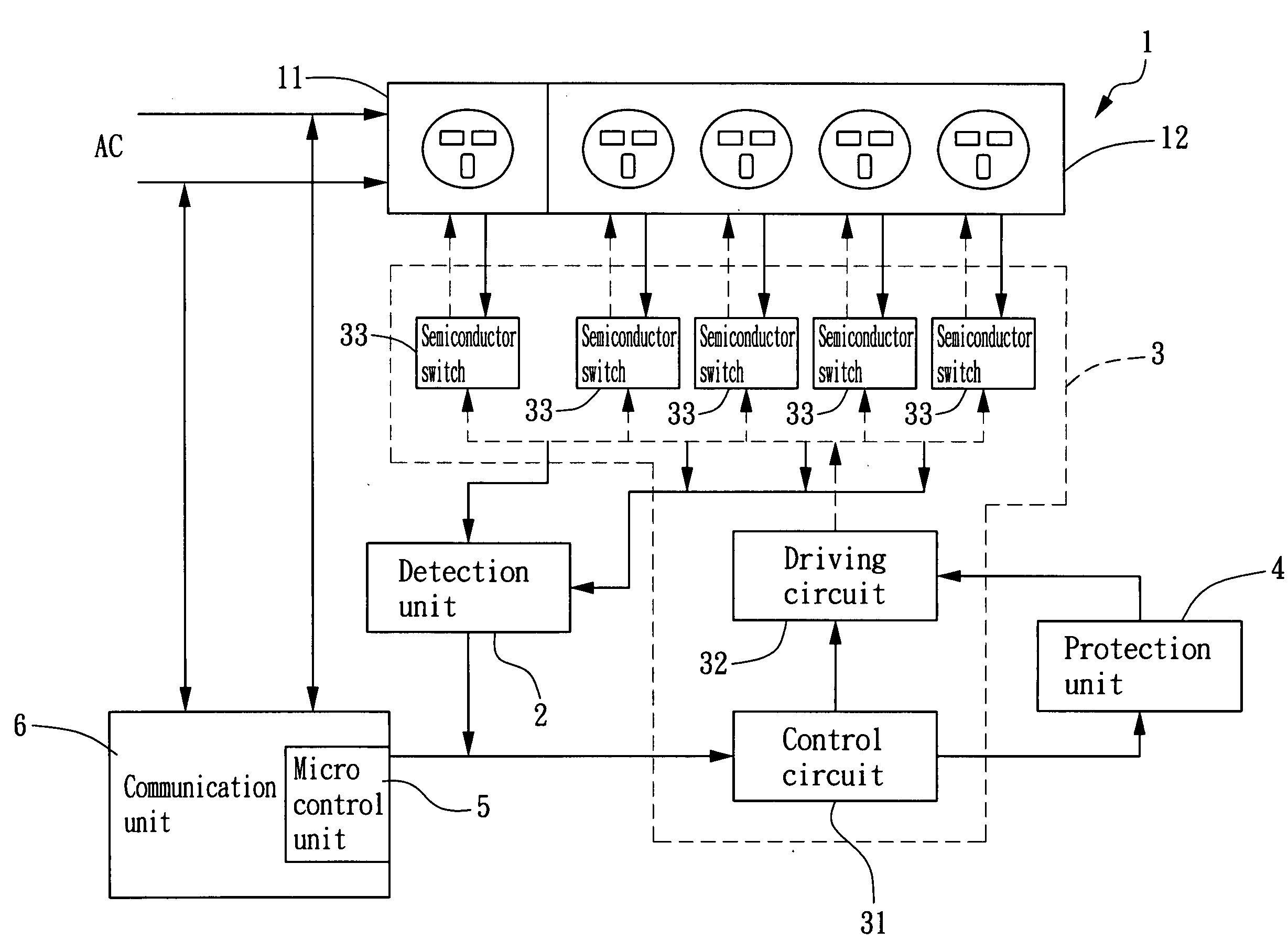

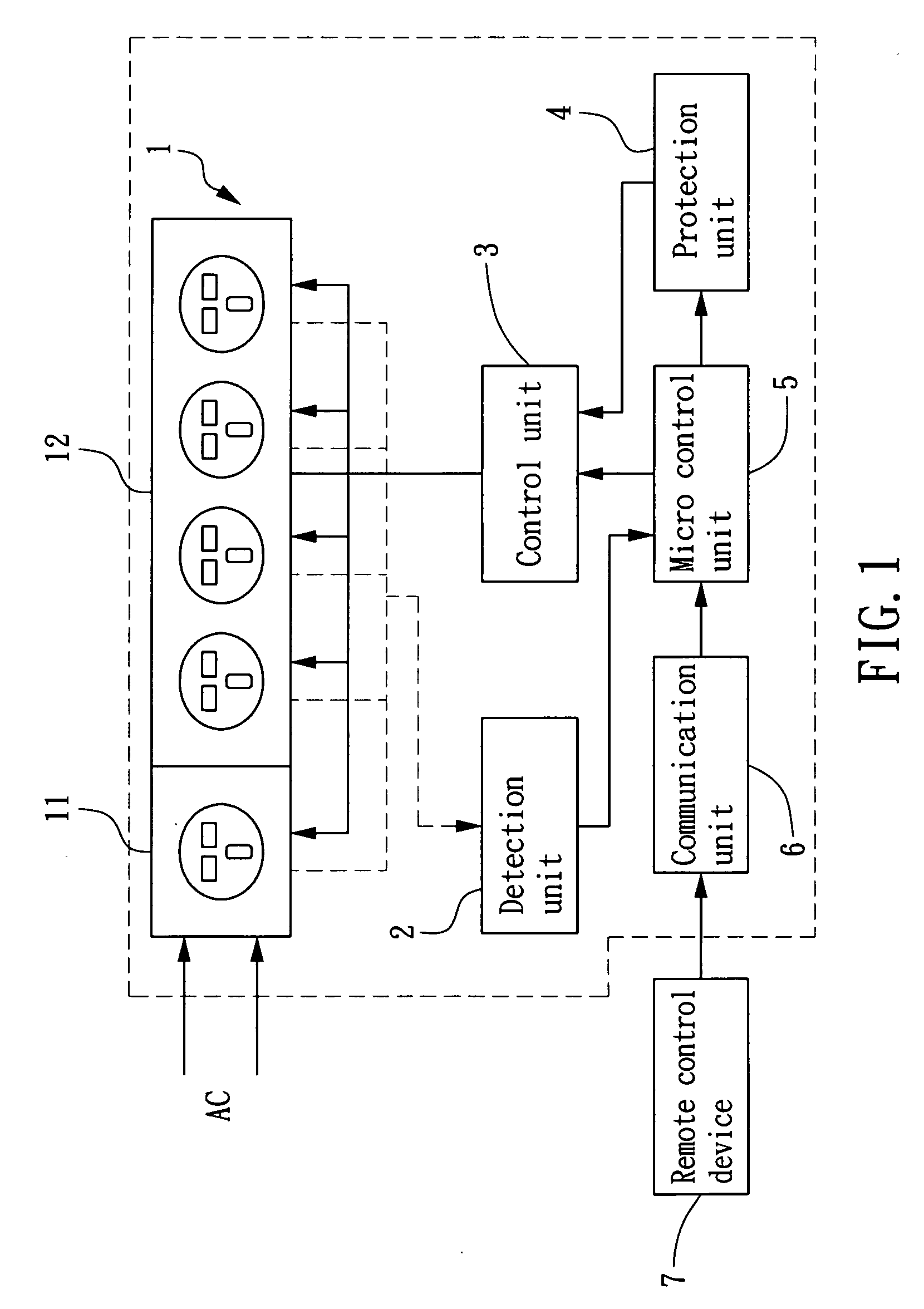

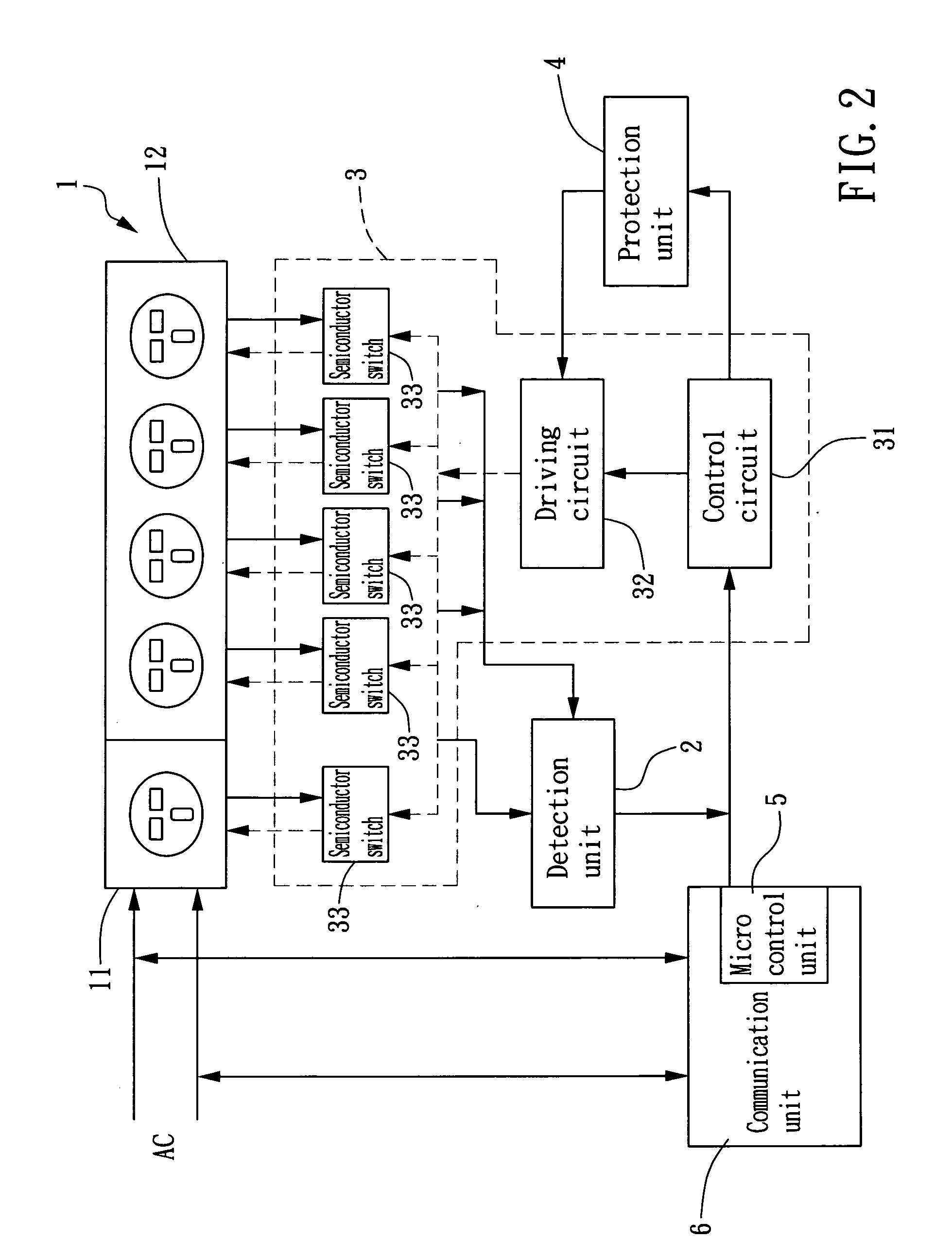

Smart client-server socket

ActiveUS20090150509A1Reduce standby powerReduce power consumptionVolume/mass flow measurementMultiple digital computer combinationsCommunication unitClient-side

A smart client-server socket is disclosed, which comprises: a micro process unit, for signal and operation control; a communication unit, capable of receiving commands from a user for enabling the user to direct electric products connected to a server jack or / and client jacks of the smart client-server socket to enter / exit a stand-by mode; a detection unit, capable of detecting the power consumption of electric product connected to the server jack while informing the micro process unit to perform a stand-by process as soon as the detected power consumption is lower than a specific rated value; and a control unit, for executing the activating / deactivating of the server jack and client jacks according to signals received from the micro process unit.

Owner:IND TECH RES INST

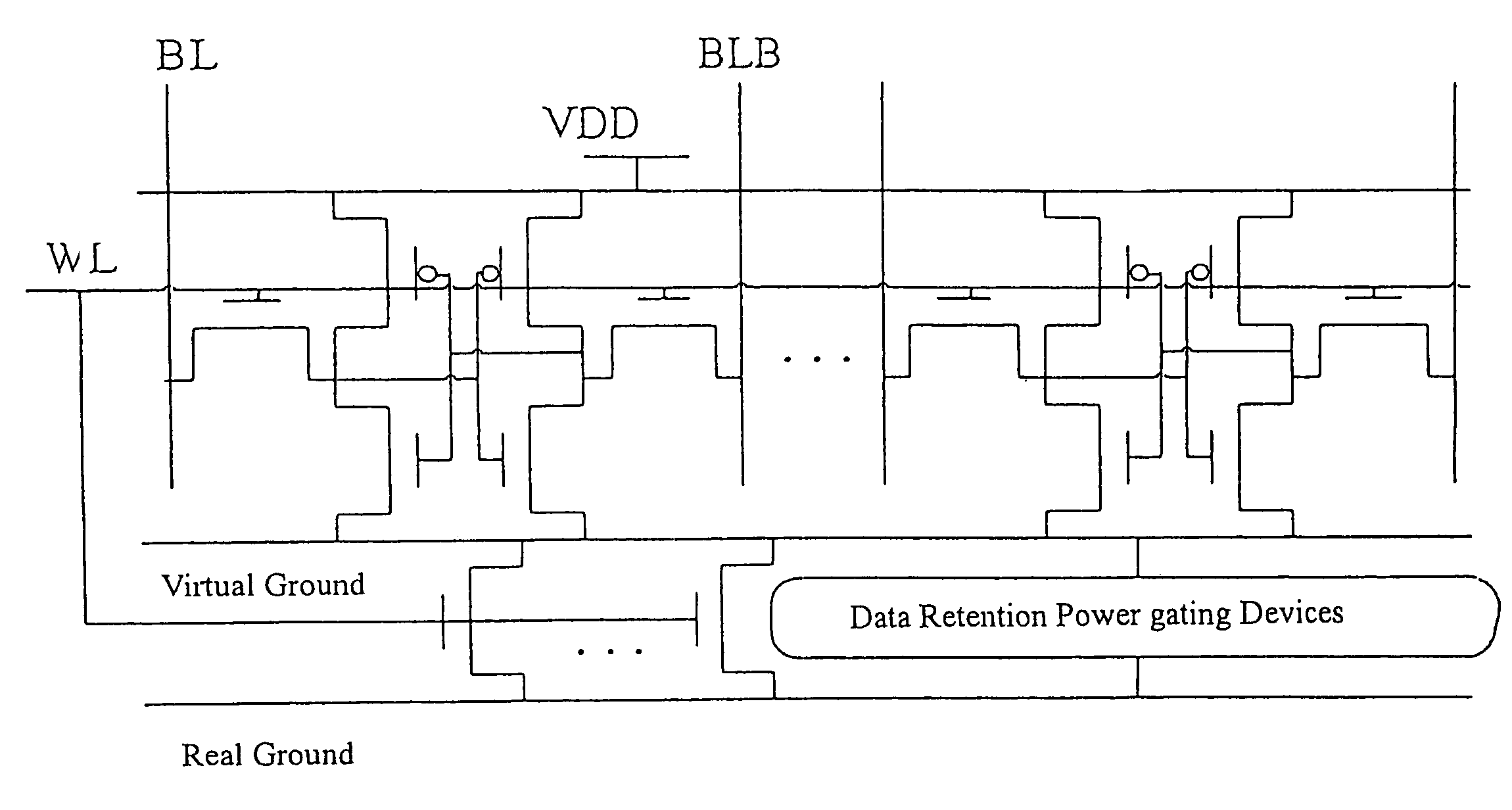

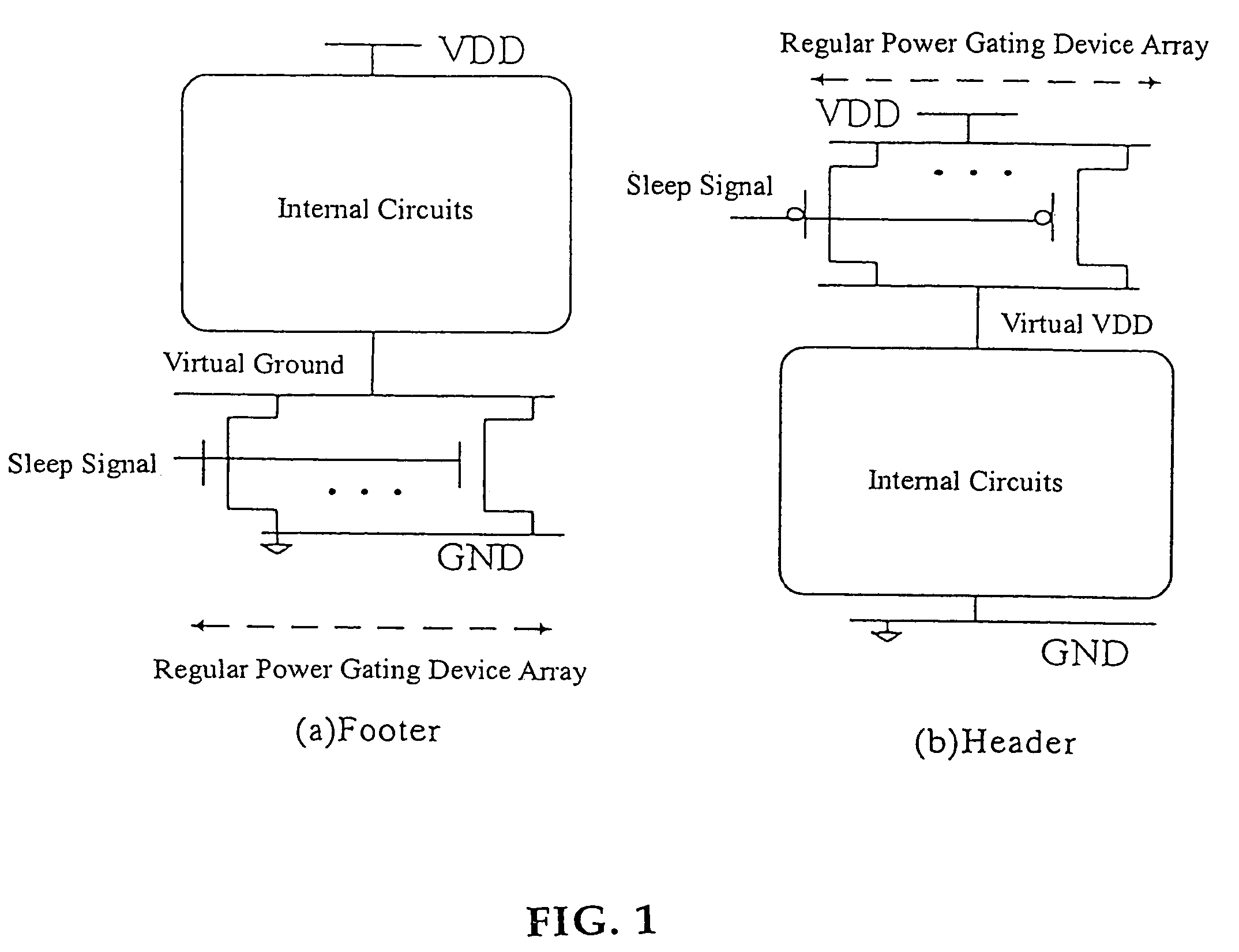

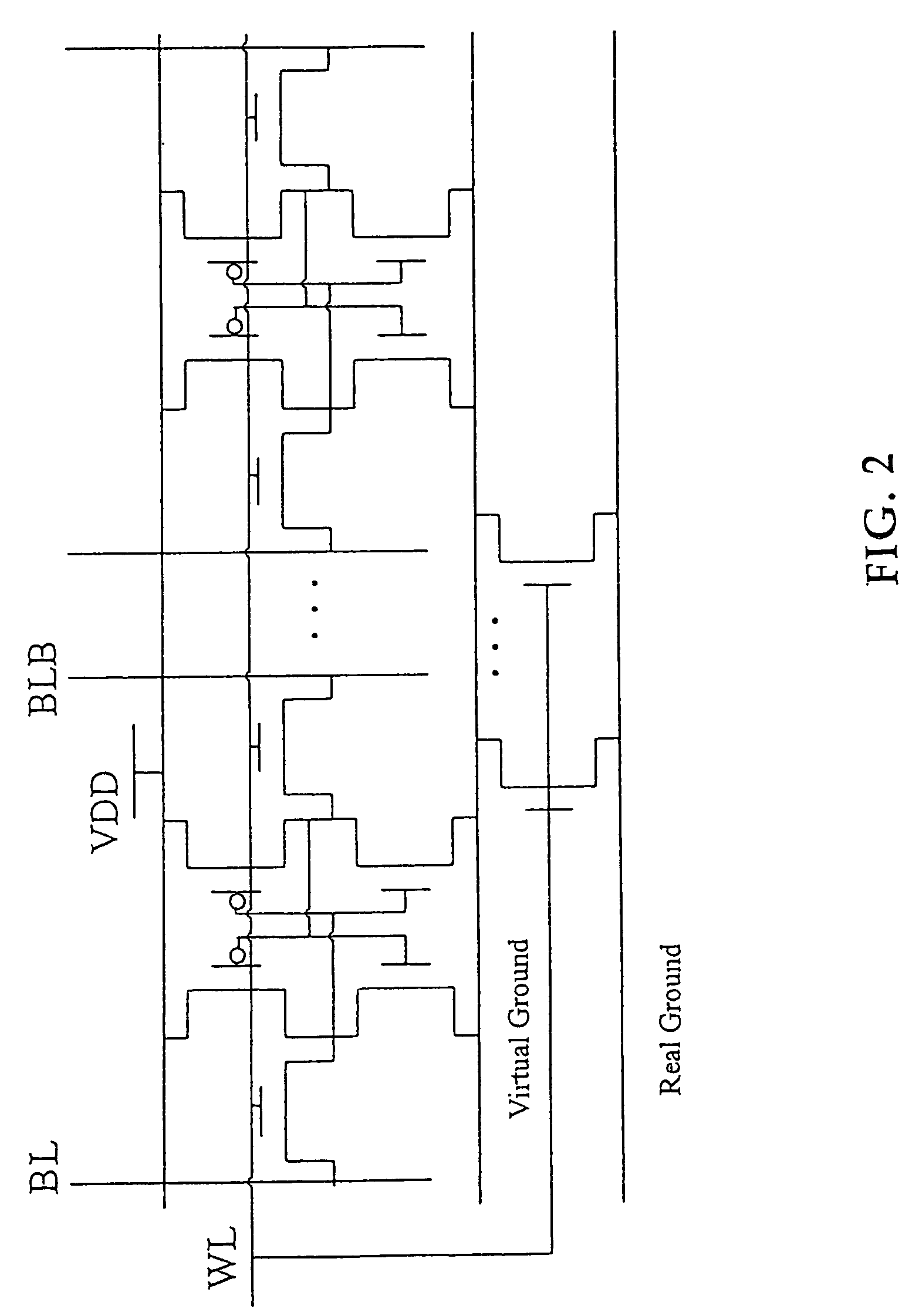

Power gating structure having data retention and intermediate modes

InactiveUS7190187B2Maintain efficiencyActive powerReliability increasing modificationsPower reduction by control/clock signalEngineeringOperation mode

The present invention provides a power gating structure having data retention and intermediate modes and able to operate under multiple modes. A conventional power gating structure has only turn-on and turn-off functions, and is used to suppress a leakage current problem which has become more and more serious in advance manufacture processes, under a turn-off mode. However, in a memory circuit, such as latch, register and SRAM, when the power gate is turned off, a new power gating structure is required for data retention. The power gating structure of the present invention can be set into one of 4 different operational modes: a data retention mode for maintaining the static noise margin of the memory, an intermediate mode for reducing the interference on ground and power levels, an active mode used when the circuit operates in normal condition, and a standby mode used when the circuit does not operate.

Owner:NAT CHIAO TUNG UNIV

Systems and methods for reducing standby power in floating body memory devices

Methods, devices, arrays and systems for reducing standby power for a floating body memory array. One method includes counting bits of data before data enters the array, wherein the counting includes counting at least one of: a total number of bits at state 1 and a total number of all bits; a total number of bits at state 0 and the total number of all bits; or the total number of bits at state 1 and the total number of bits at state 0. This method further includes detecting whether the total number of bits at state 1 is greater than the total number of bits at state 0; setting an inversion bit when the total number of bits at state 1 is greater than the total number of bits at state 0; and inverting contents of all the bits of data before writing the bits of data to the memory array when the inversion bit has been set.

Owner:ZENO SEMICON

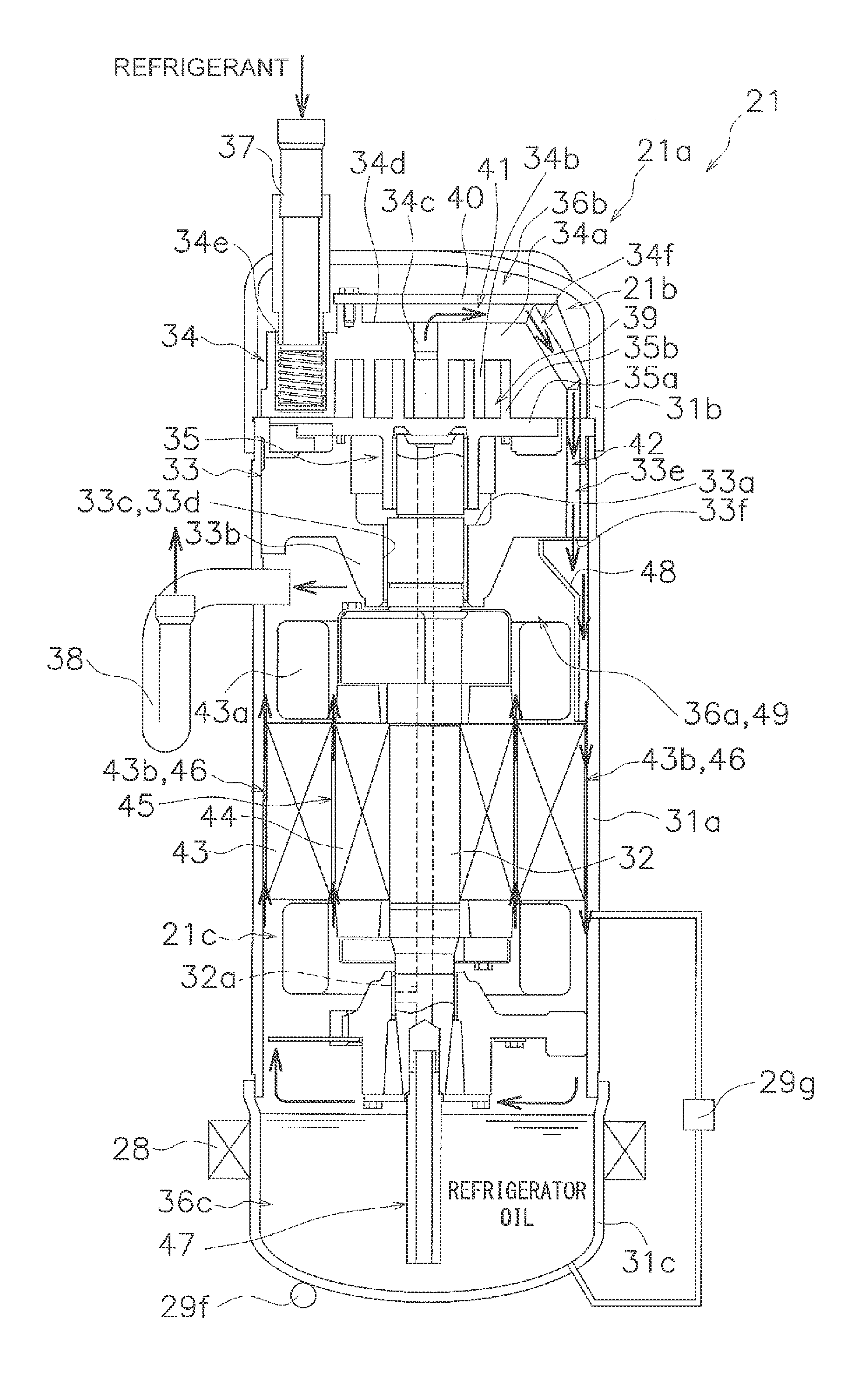

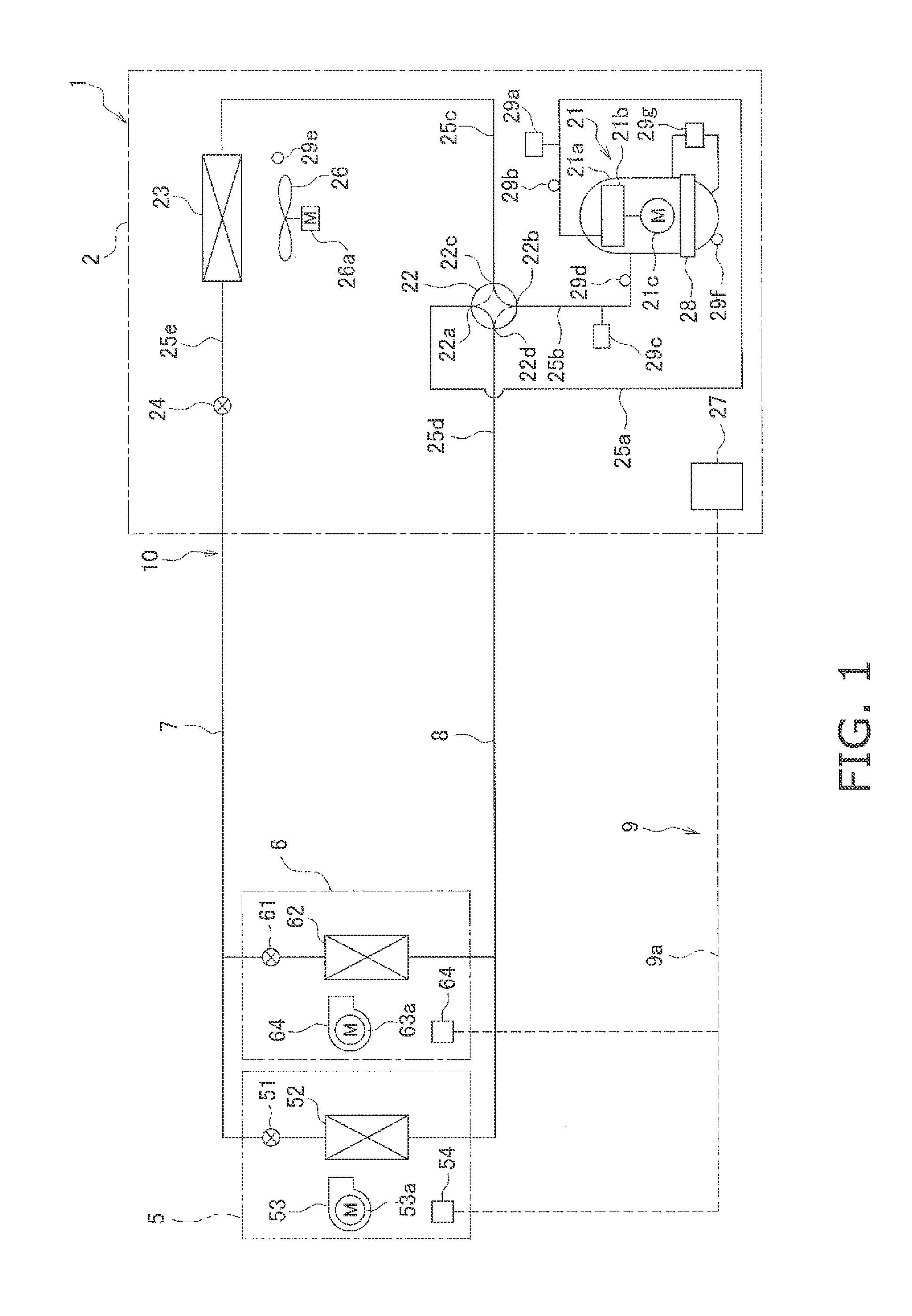

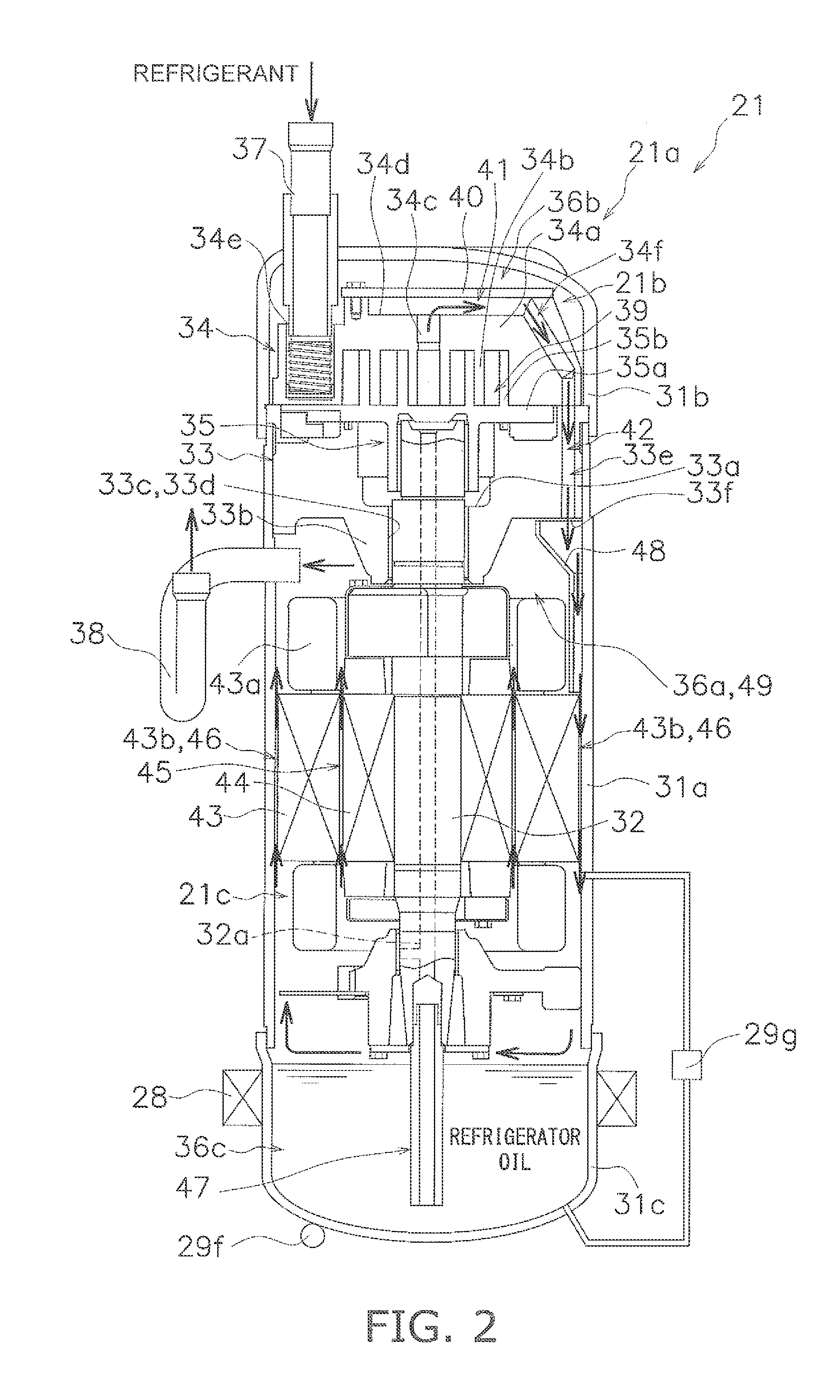

Refrigeration apparatus

ActiveUS20160018148A1Reduce standby powerImprove reliabilityRotary/oscillating piston combinations for elastic fluidsCompressorInterior spaceEngineering

A refrigeration apparatus includes a compressor and a controller. The compressor has a casing and a compression element. Compressed refrigerant is sent out of the casing after being discharged into an internal space of the casing. An oil sump formed in the casing collects refrigerator oil. A heater heats the refrigerator oil collected. The controller controls the heater while the refrigeration apparatus is stopped so that a temperature of the refrigerator oil collected in the oil sump reaches a first oil temperature target value. The first oil temperature target value is set in order to keep a refrigerant condensation amount of the refrigerant equal to or less than an allowable condensation amount at which the concentration or viscosity of the refrigerator oil needed to lubricate the compressor can be maintained. The refrigerant condensation amount is caused by in-dome condensation at the start of operation of the refrigeration apparatus.

Owner:DAIKIN IND LTD

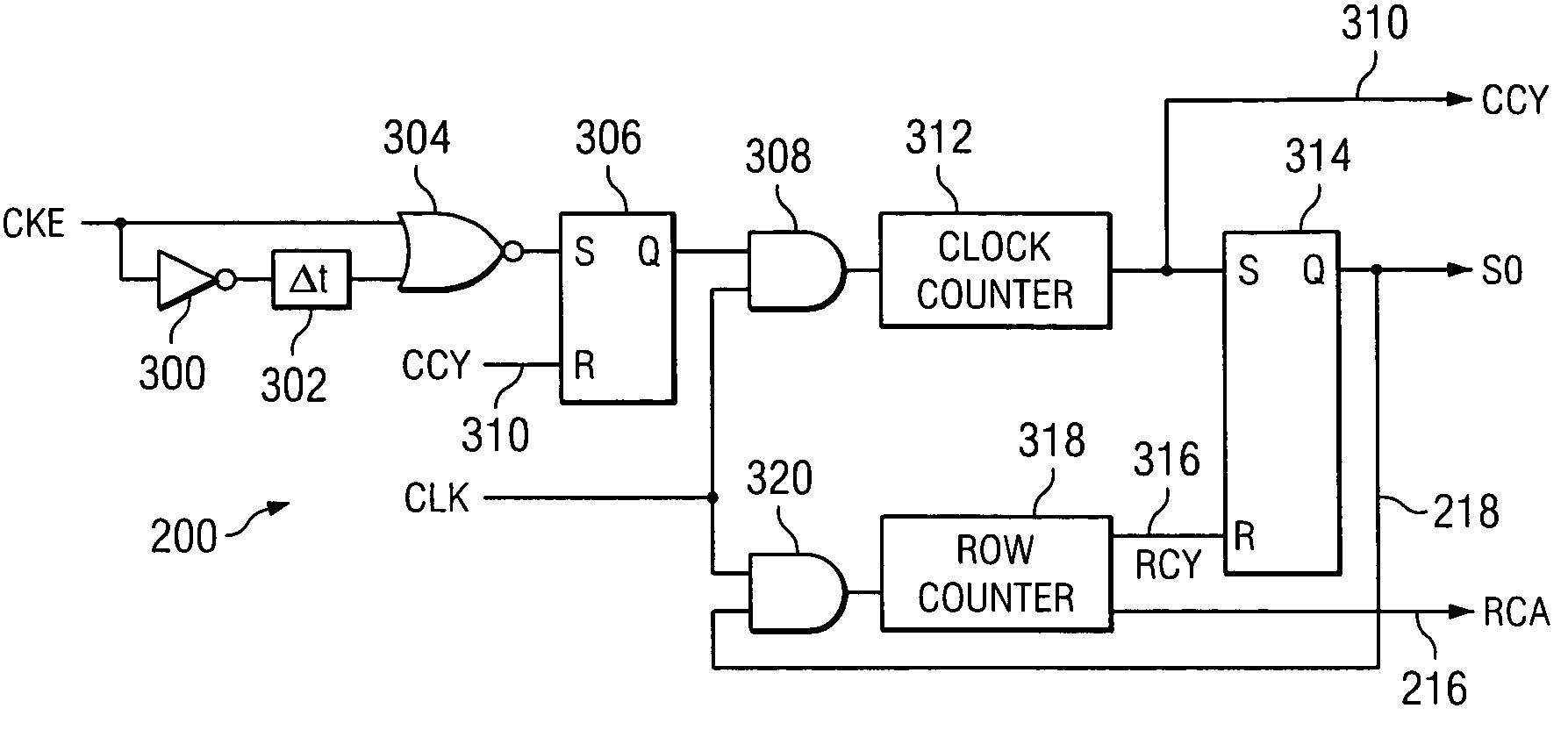

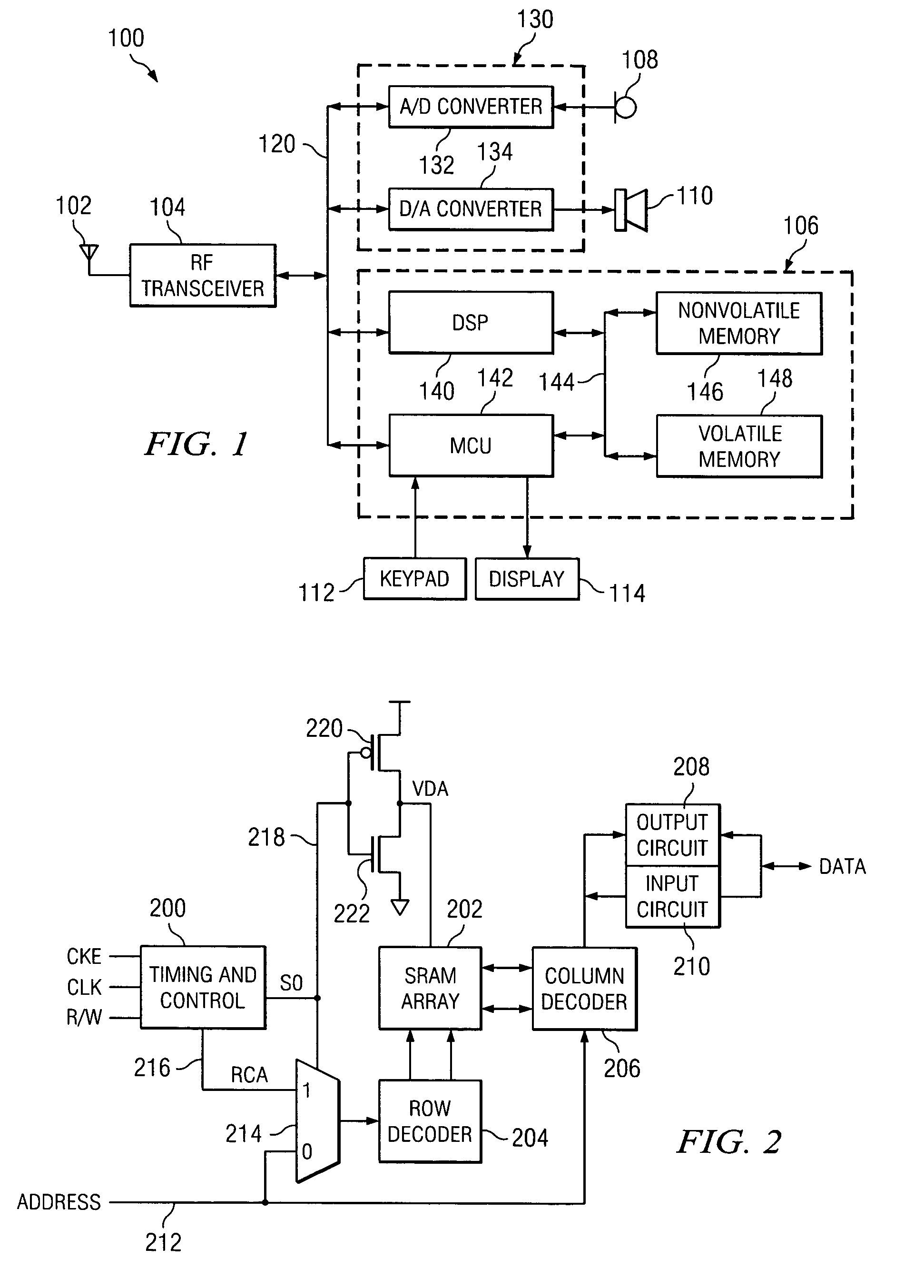

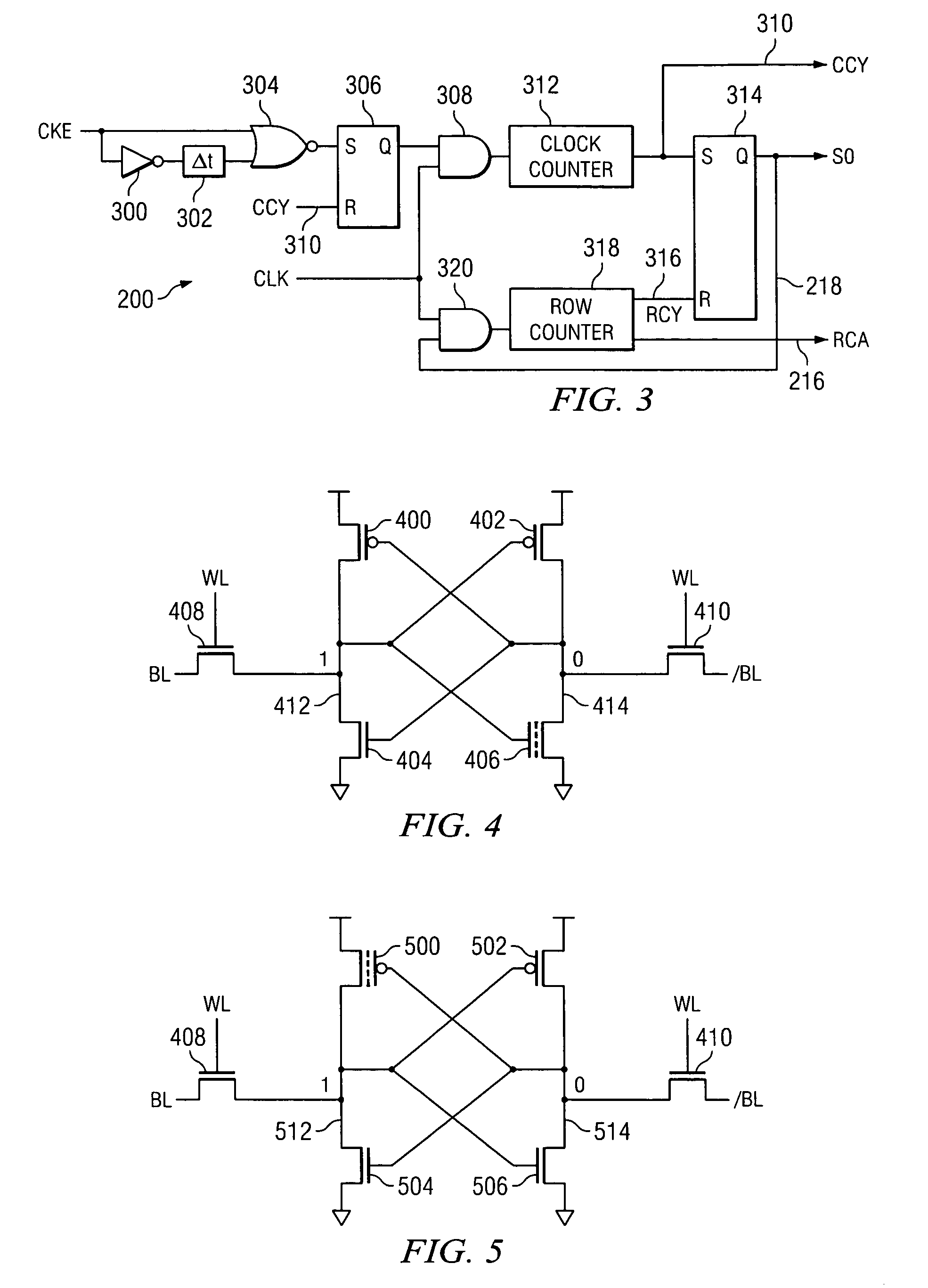

Circuit and method for reducing SRAM standby power

A method of operating a memory circuit to reduce standby current is disclosed. The method includes applying a first voltage (Vdd) to a power terminal (224) of a memory cell having a first (612) and a second (614) data terminal. A data bit is stored in a memory cell (600,602,604,606). A second voltage (VDA) different from the first voltage is applied to the power terminal. A third voltage (Ground) is applied to the first and second data terminals. The first voltage is applied to the power terminal.

Owner:TEXAS INSTR INC

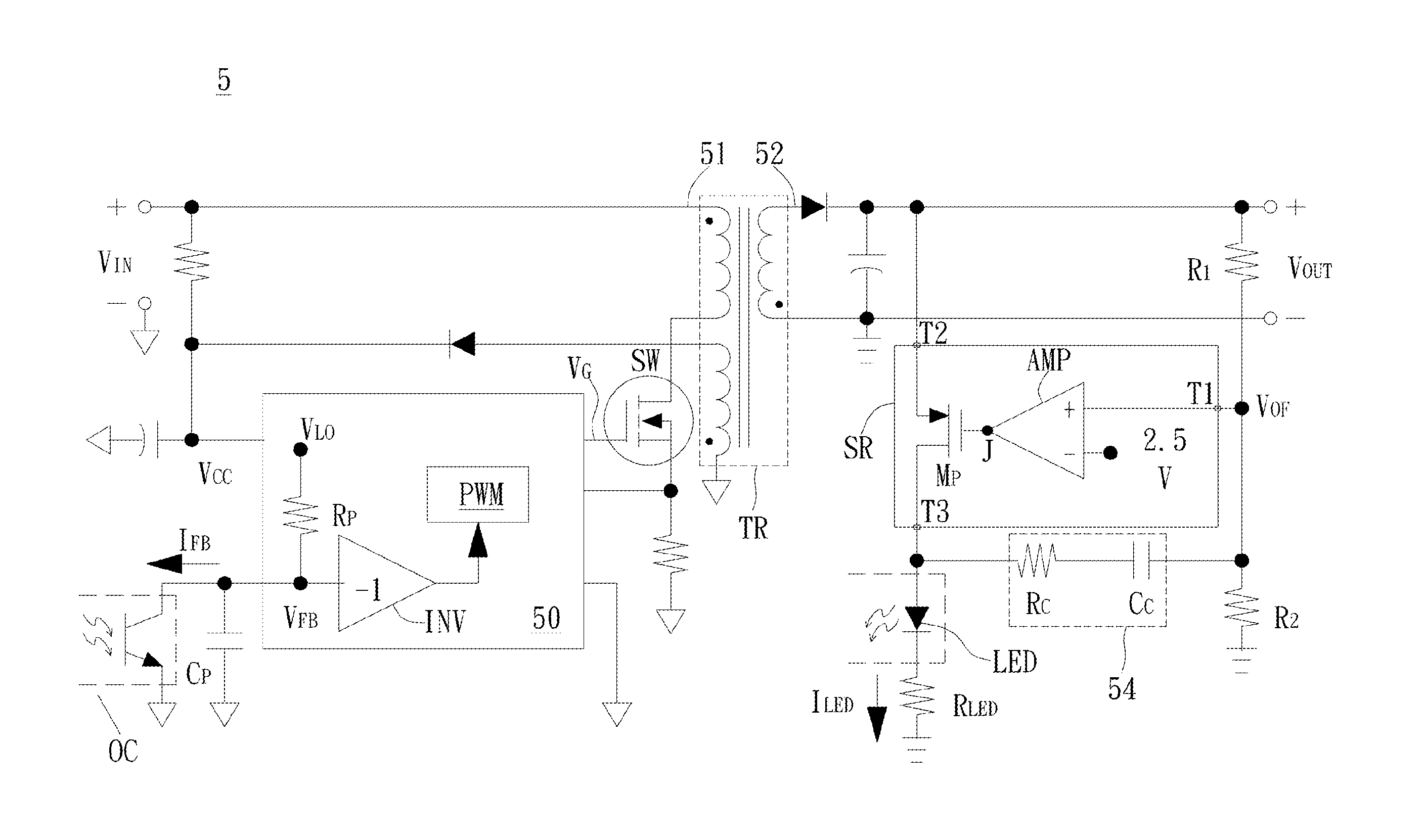

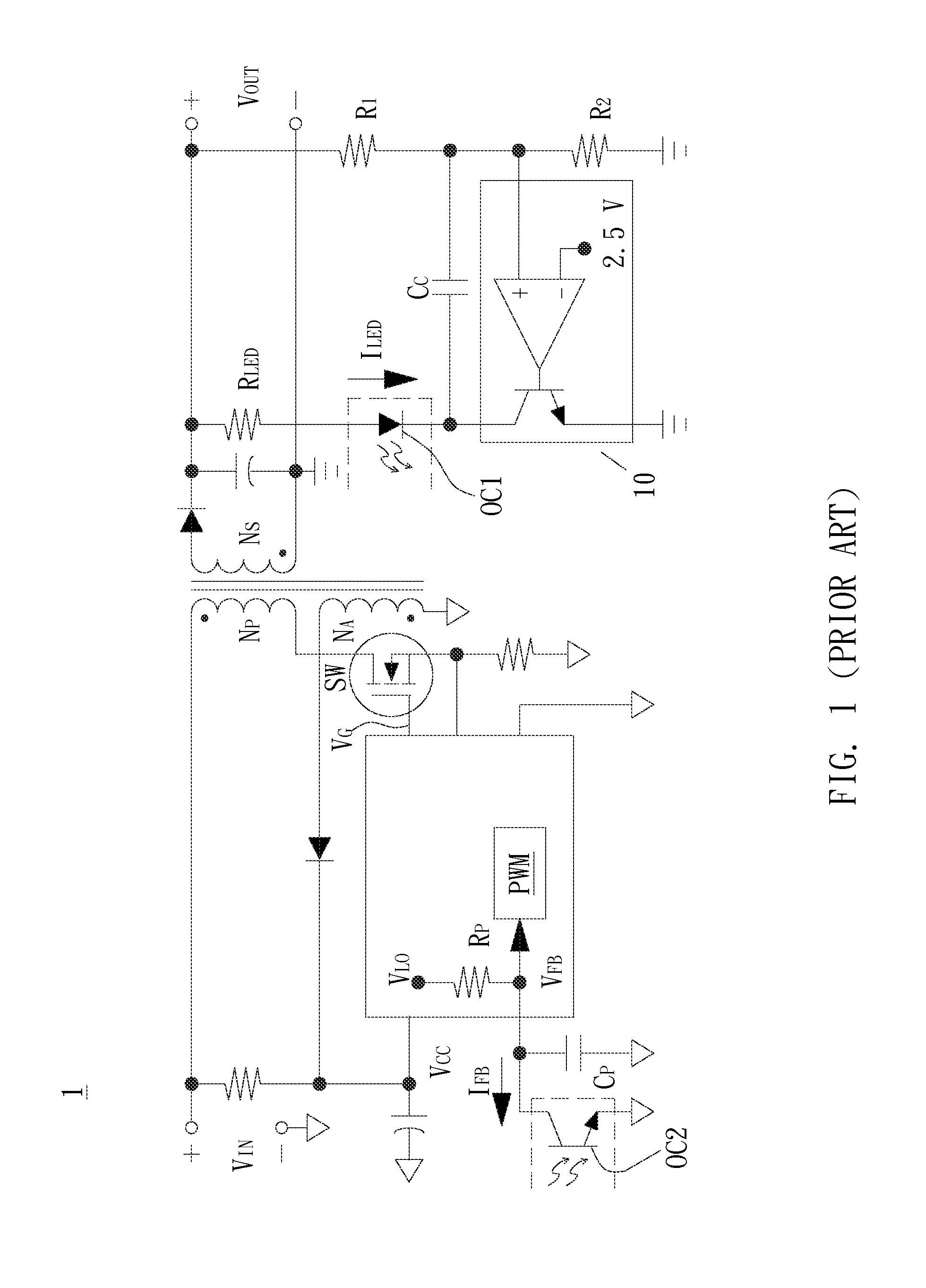

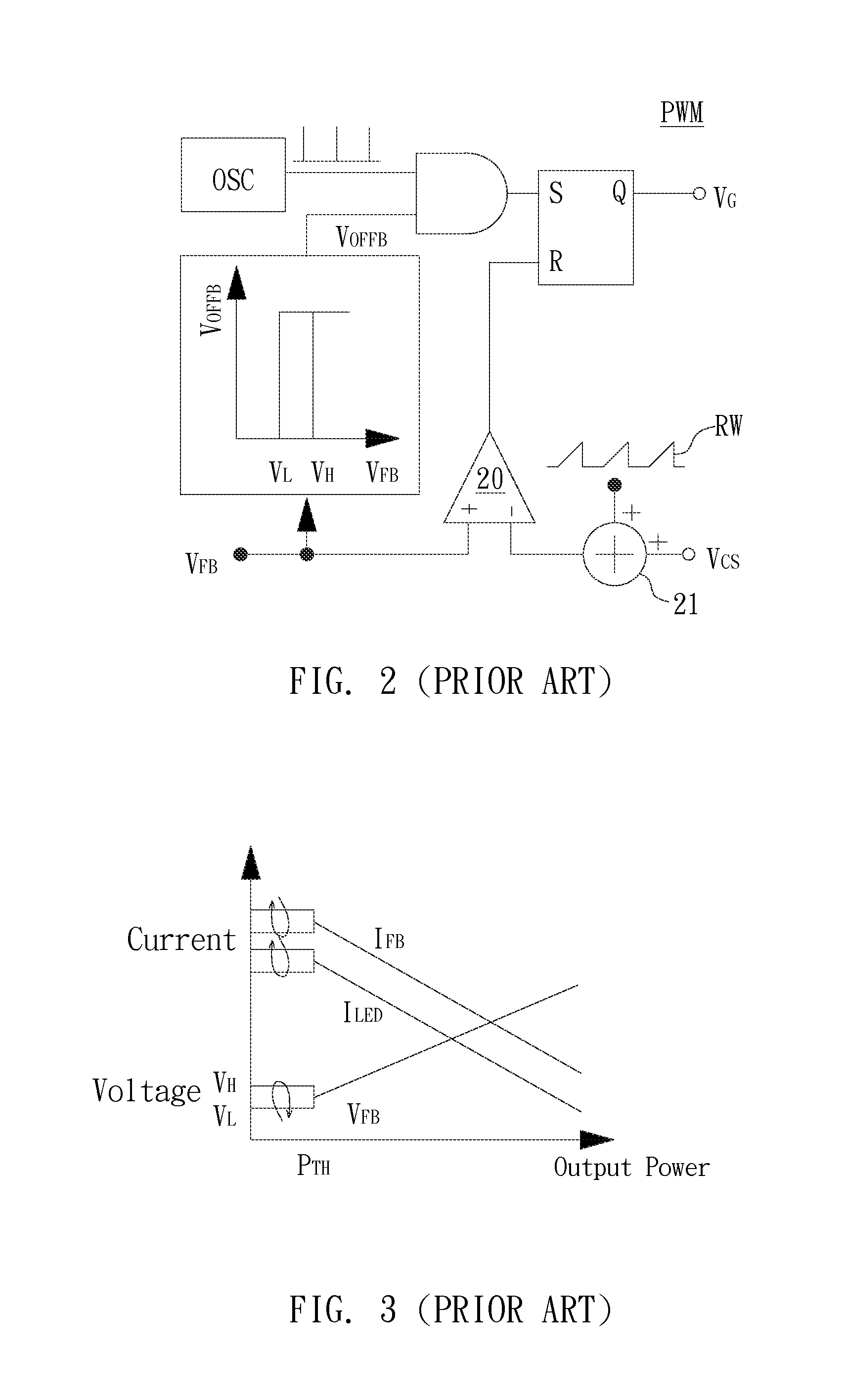

Isolated power converter, inverting type shunt regulator, and operating method thereof

InactiveUS20140140107A1Decreasing opto-coupling currentEnhanced feedback voltageEfficient power electronics conversionDc-dc conversionMOSFETPower flow

An isolated power converter, an inverting type shunt regulator, and an operating method thereof are disclosed. The isolated power converter includes a transformer, an inverting type shunt regulator, a controller, and an optocoupler. The inverting type shunt regulator is located on the secondary side of the transformer. The inverting type shunt regulator includes an error amplifier and a MOSFET. The controller is located on the primary side of the transformer. The controller includes an inverting unit cooperated with the MOSFET. The controller receives a feedback voltage. The optocoupler is coupled to the inverting type shunt regulator and the controller to provide an opto-coupling current to the controller.

Owner:NOVELTEK SEMICON CORP

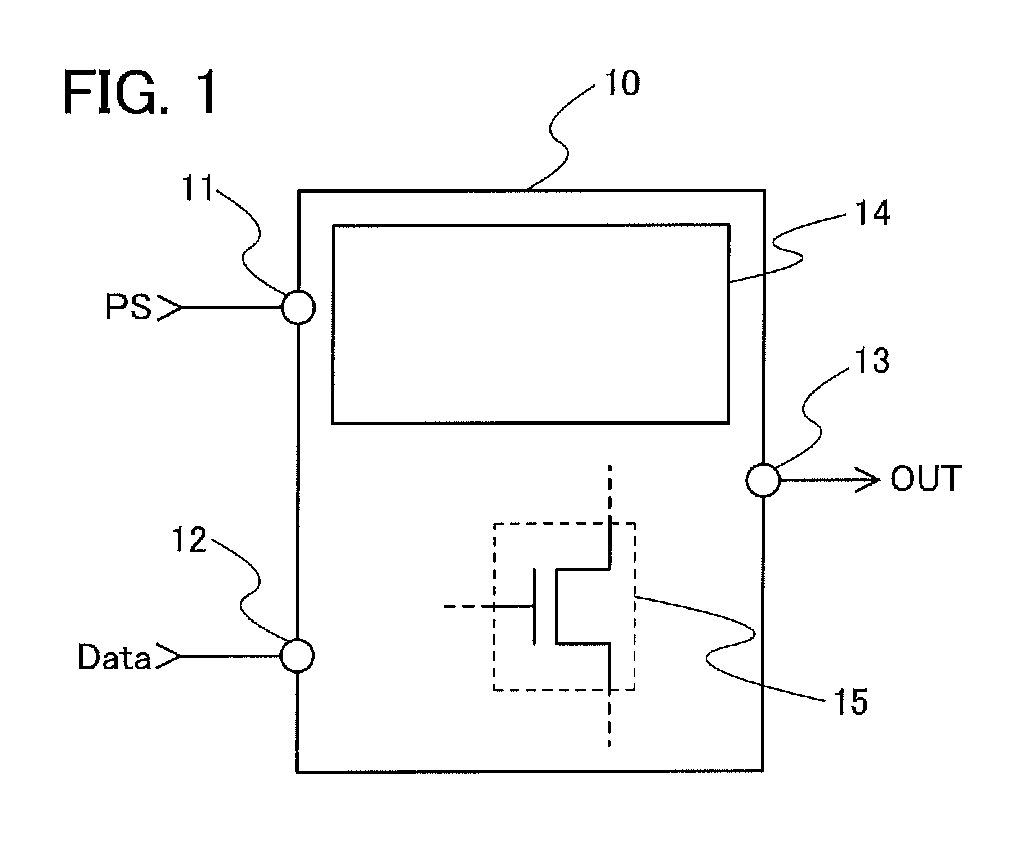

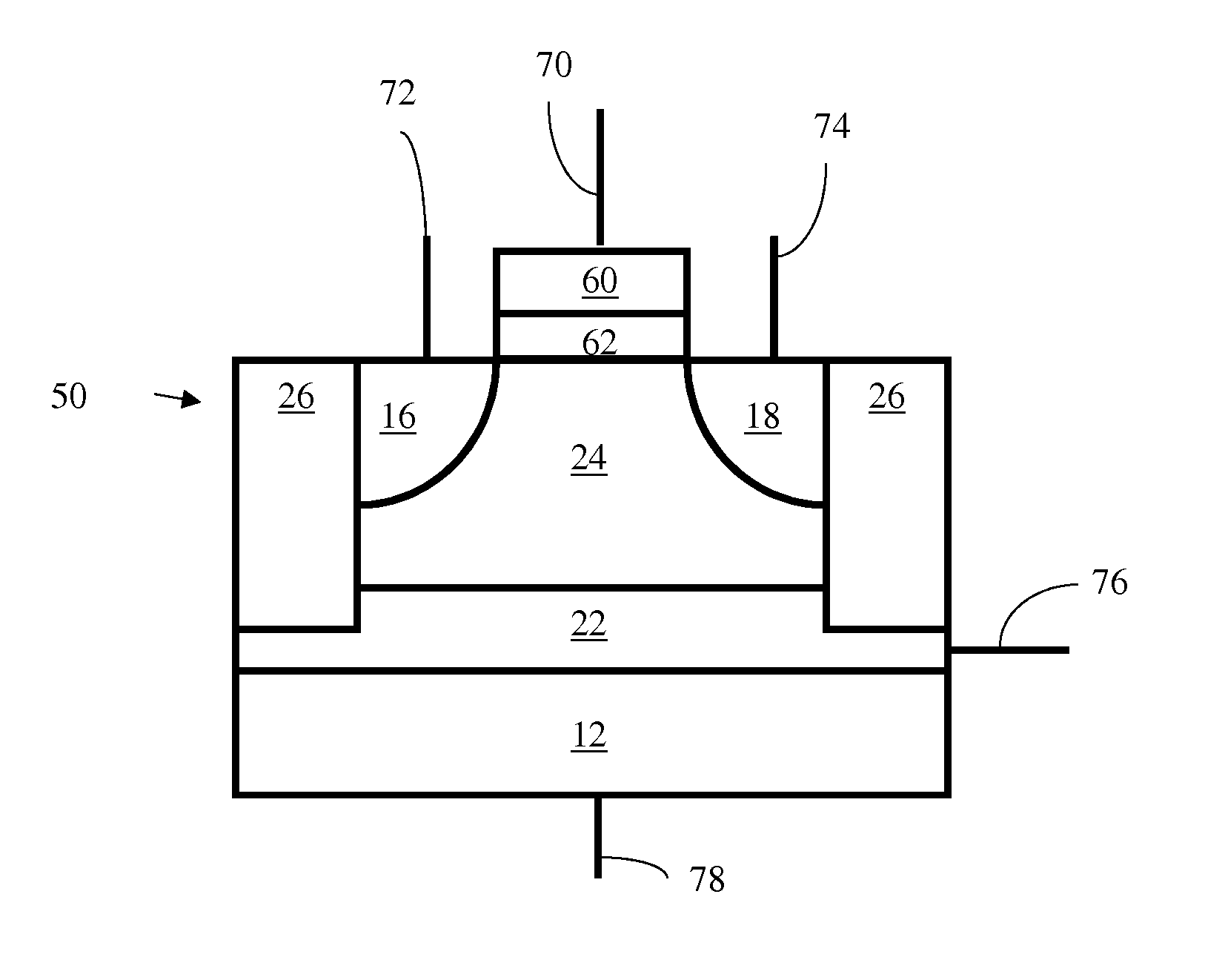

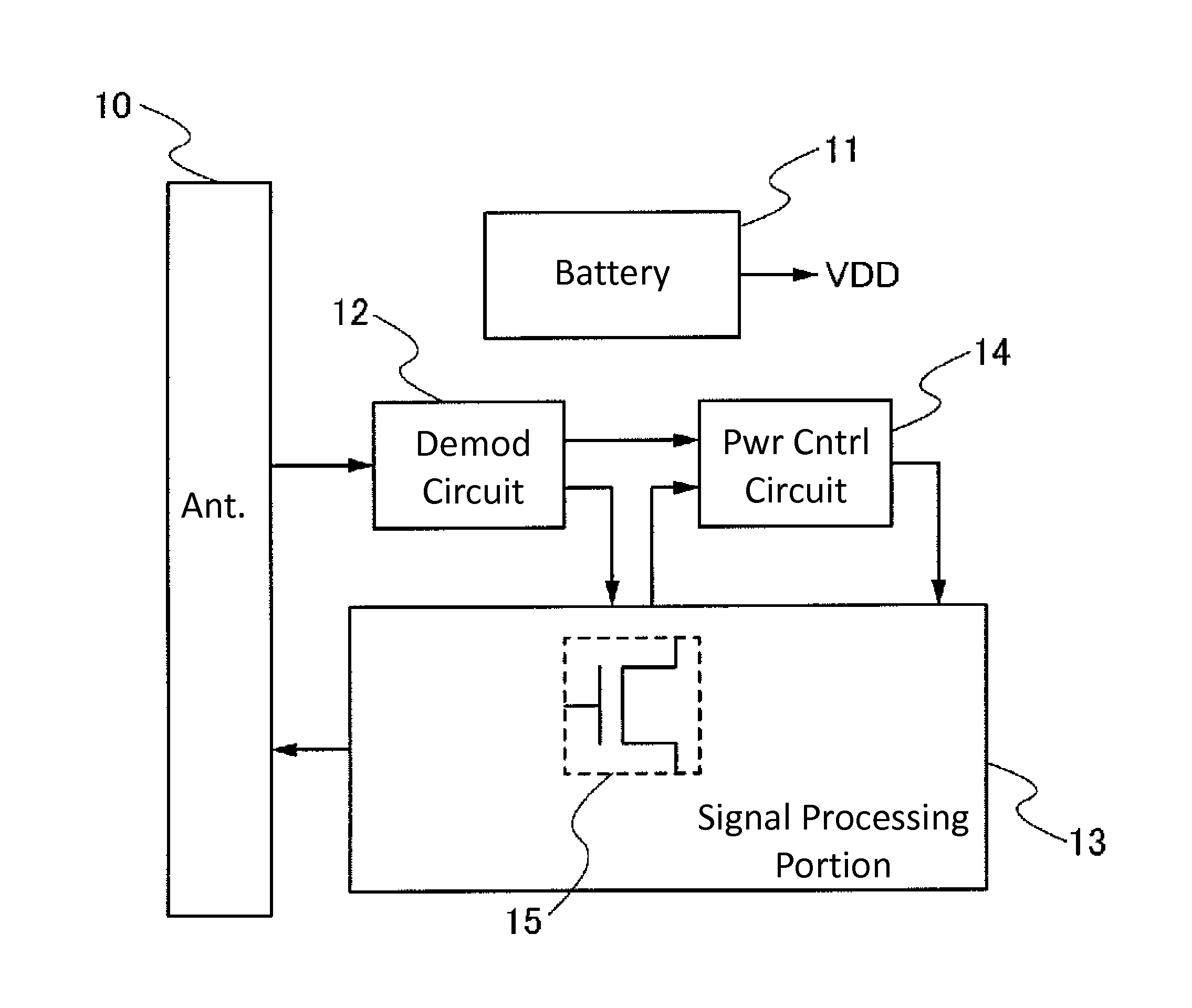

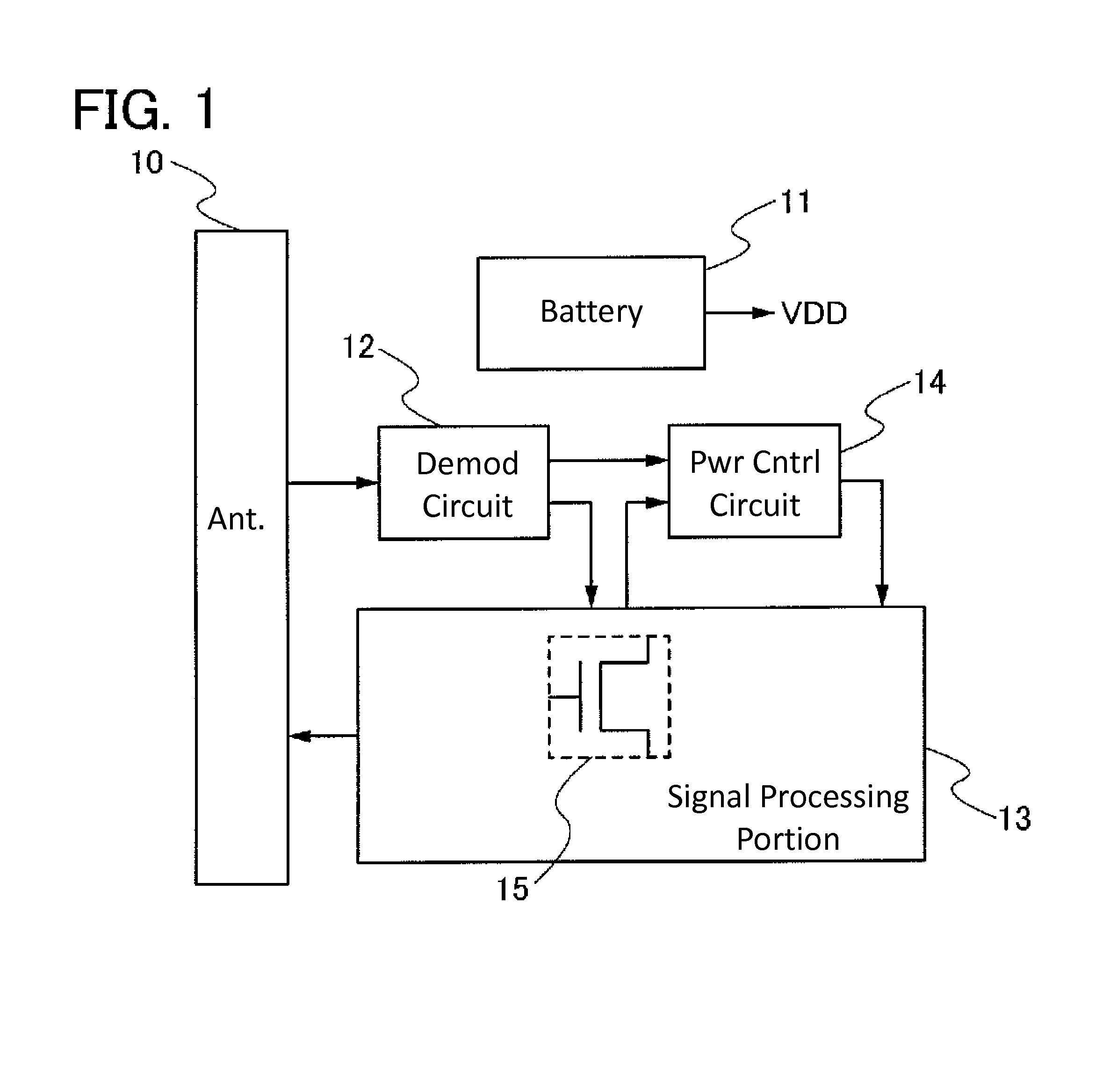

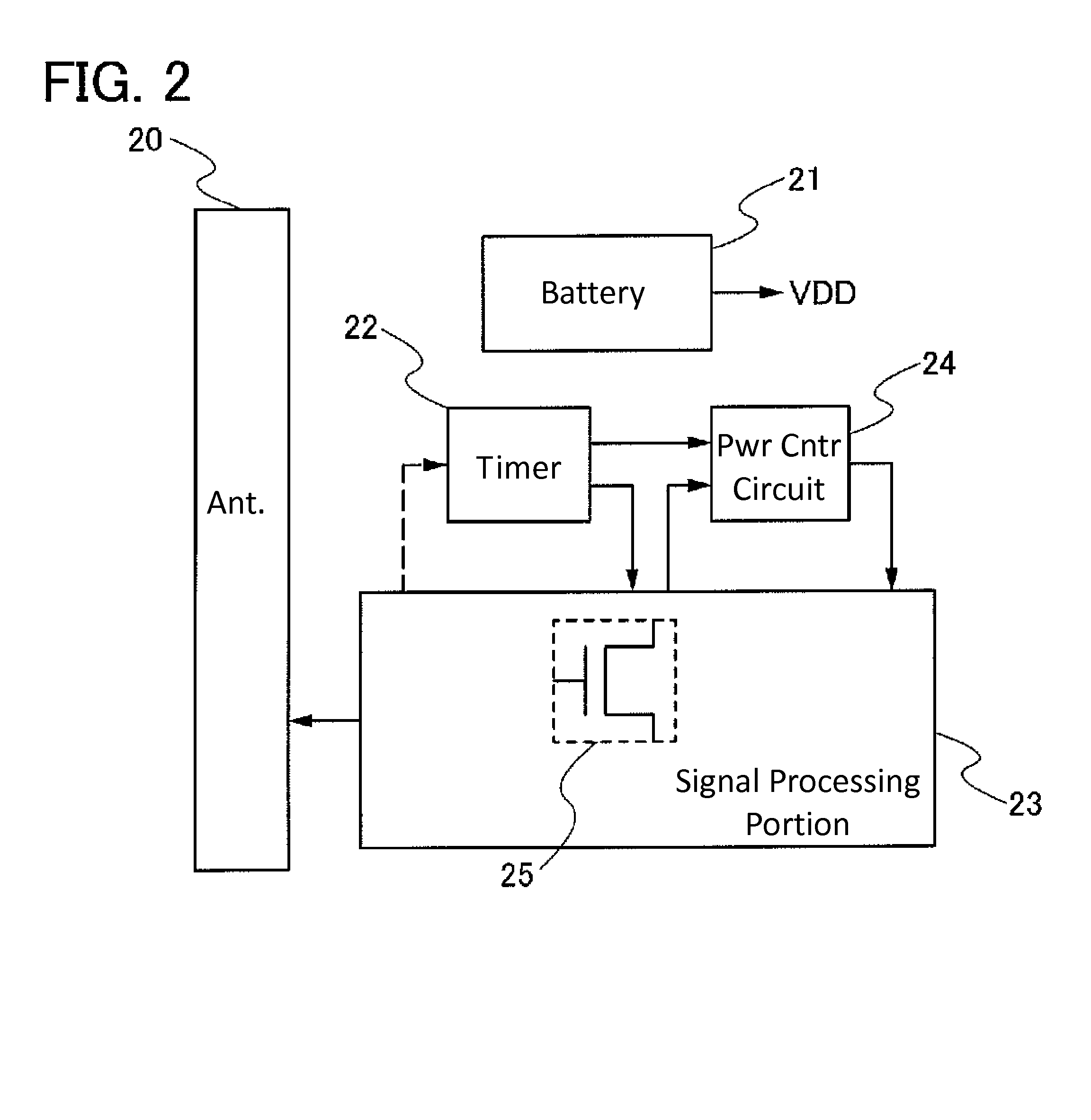

Semiconductor device

InactiveUS8467825B2High percentage in total power consumptionReduce power consumptionTransistorEnergy efficient ICTPower semiconductor deviceHydrogen concentration

An object is to achieve low power consumption and a long lifetime of a semiconductor device having a wireless communication function. The object can be achieved in such a manner that a battery serving as a power supply source and a specific circuit are electrically connected to each other through a transistor in which a channel formation region is formed using an oxide semiconductor. The hydrogen concentration of the oxide semiconductor is lower than or equal to 5×1019 (atoms / cm3). Therefore, leakage current of the transistor can be reduced. As a result, power consumption of the semiconductor device in a standby state can be reduced. Further, the semiconductor device can have a long lifetime.

Owner:SEMICON ENERGY LAB CO LTD

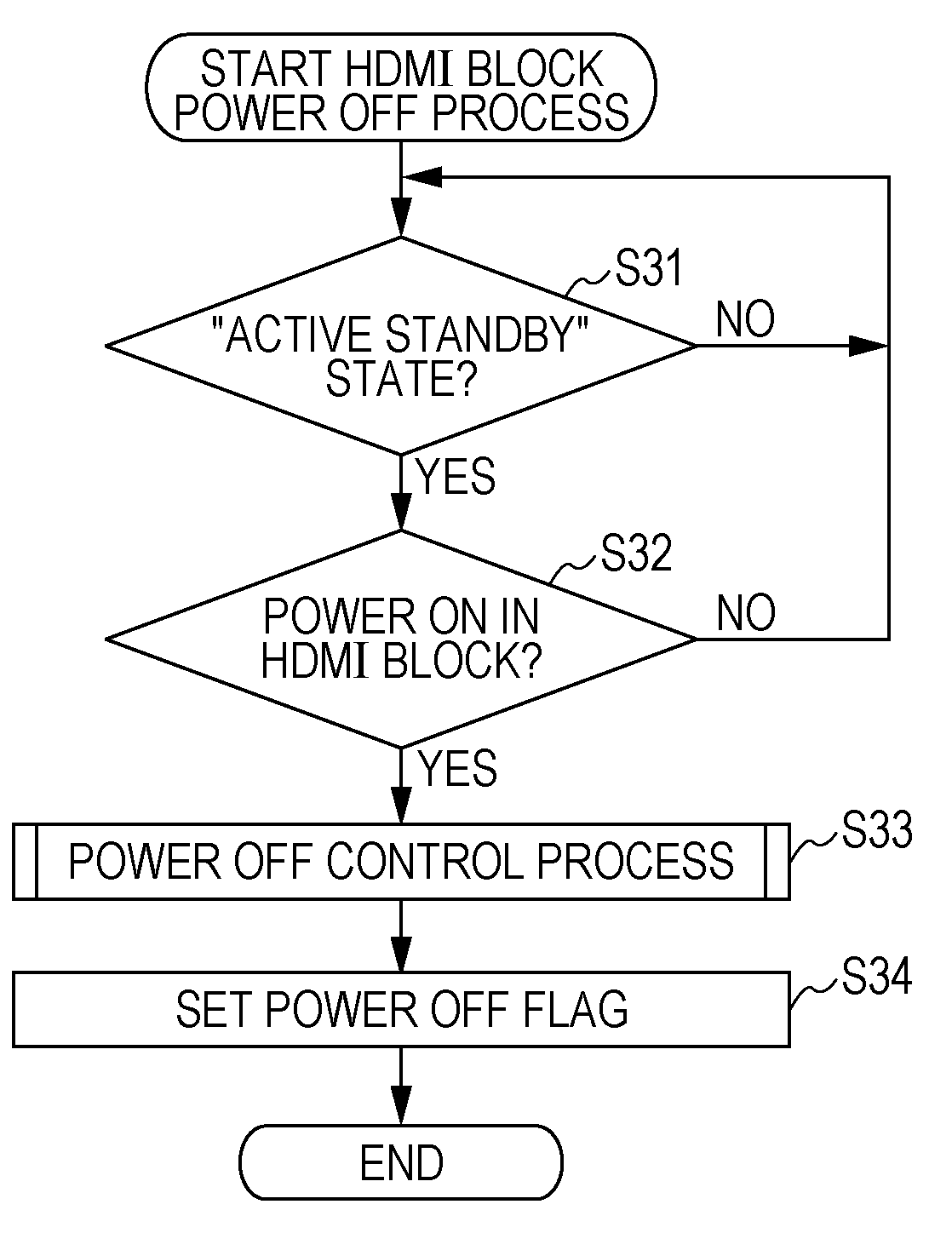

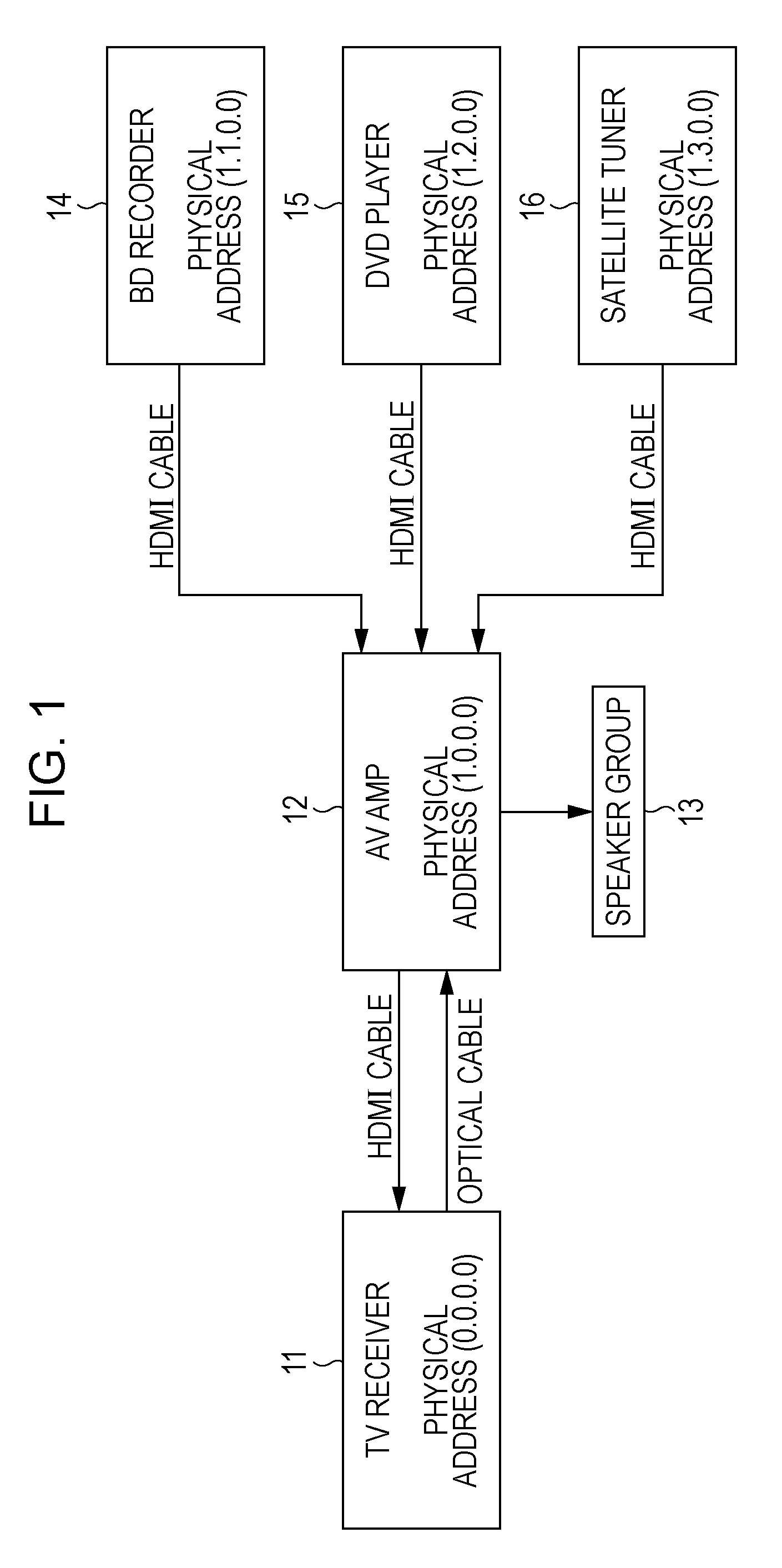

Information processing apparatus, method, and program

InactiveUS20100131782A1Reduce standby power of SMPSReduce standby powerTelevision system detailsVolume/mass flow measurementStandby powerControl channel

An information processing apparatus including a baseband signal manager, a determining unit, and a power supply controller is connected to one or more apparatus via an interface. The interface includes a signal channel for transmitting baseband signals and a control channel for bidirectionally transmitting control signals. The baseband signal manager transmits a baseband signal sent from a first apparatus to a second apparatus as-is when the information processing apparatus is in a standby power state. The determining unit determines the power state of the second apparatus on the basis of a control signal sent from the second apparatus. When it is determined by the determining unit that the second apparatus is not powered on, the power supply controller suspends power supply to the baseband signal manager.

Owner:SONY CORP

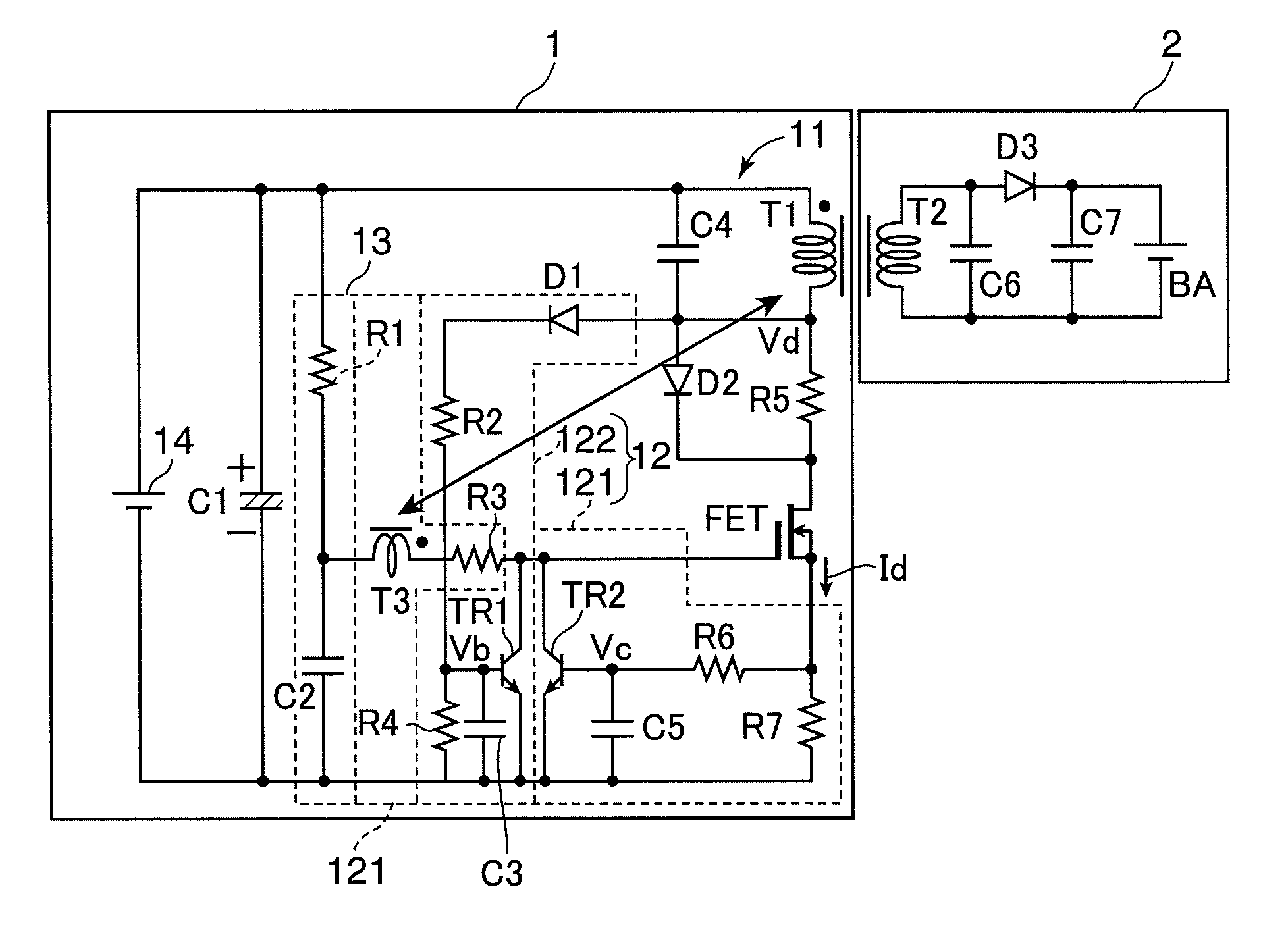

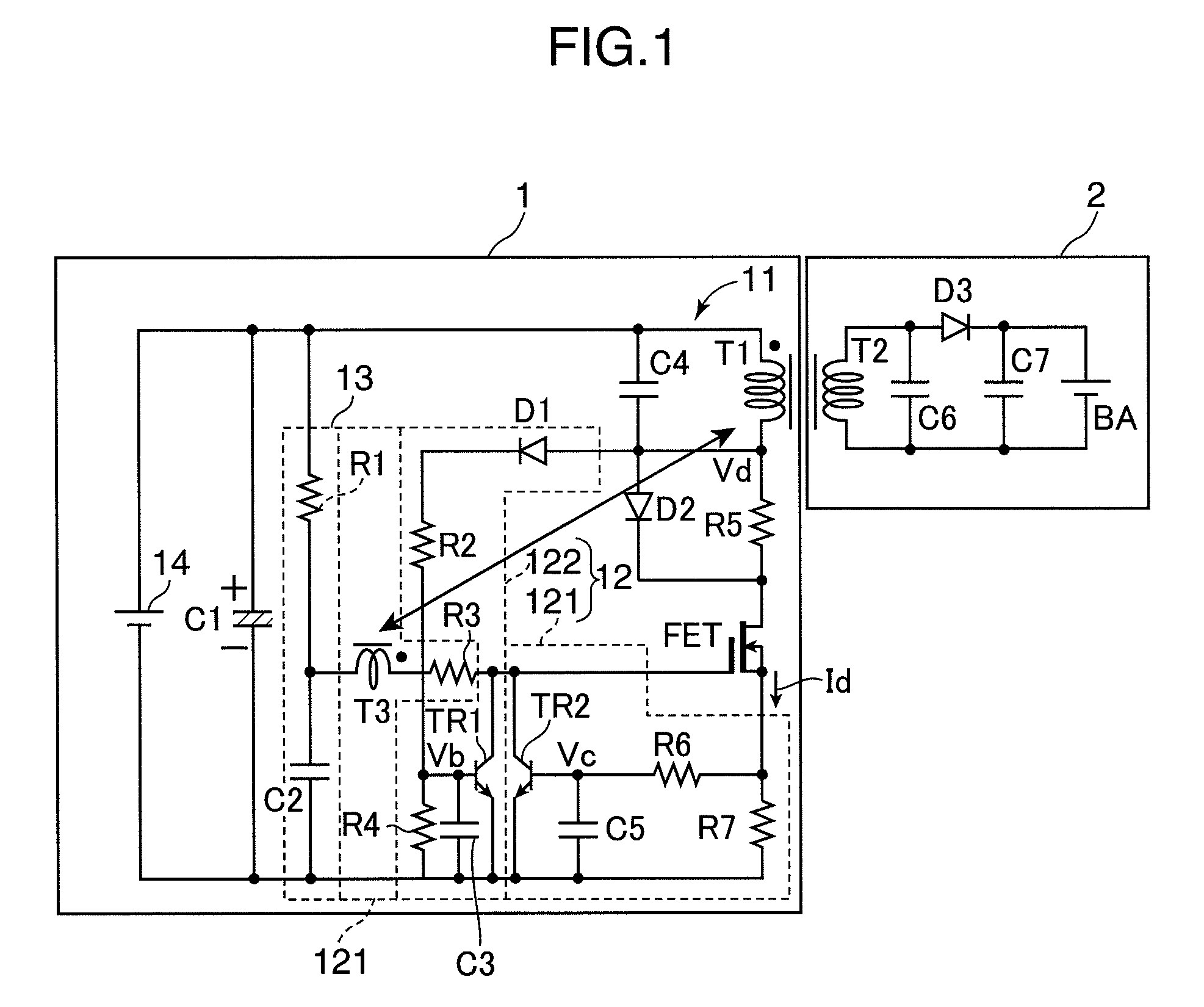

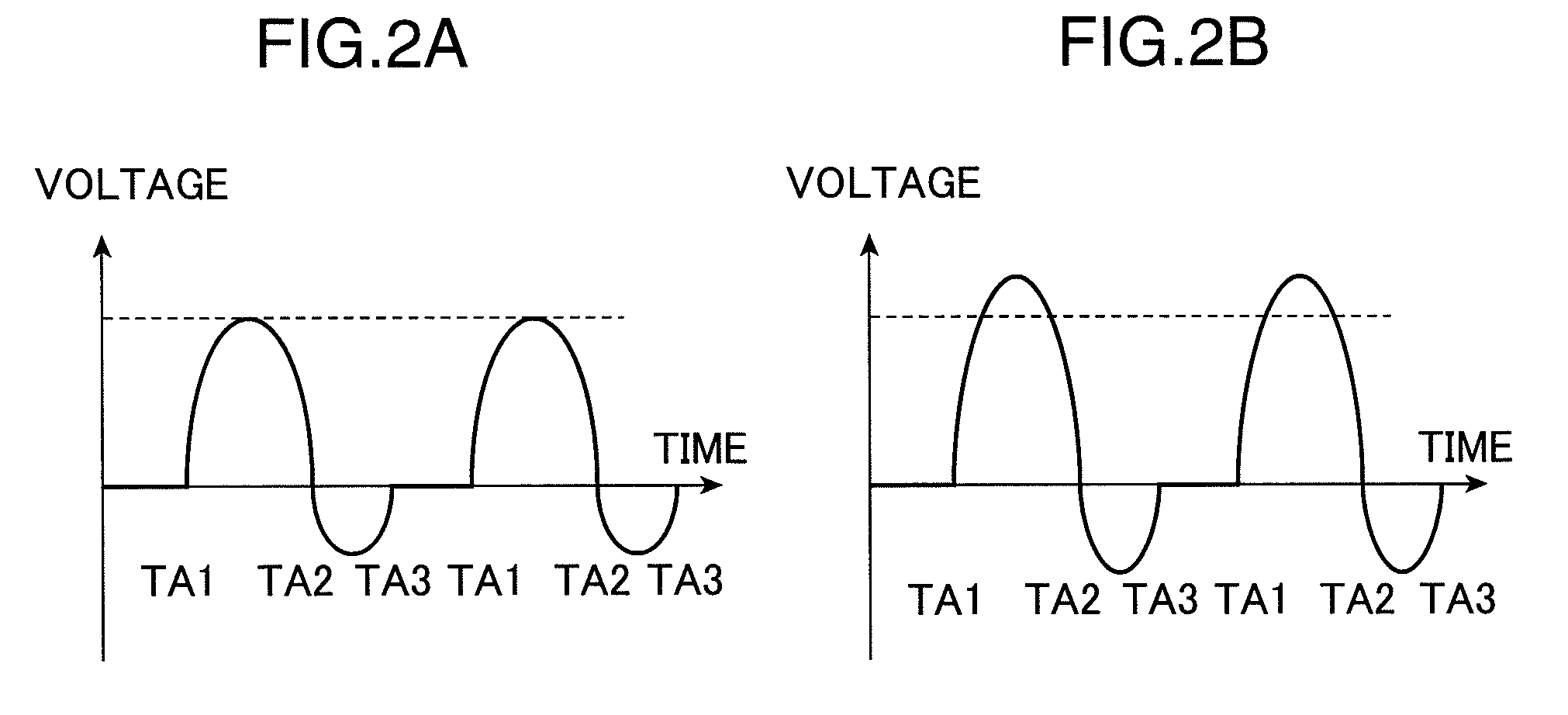

Contactless power transmission circuit

ActiveUS8319376B2Reduce standby powerElectric signal transmission systemsBatteries circuit arrangementsElectric forceElectric power transmission

A driving circuit drives a switching element such that an ON-period of the switching element is shorter when a power receiving device is detected not to be placed than when the power receiving device is placed.

Owner:PANASONIC CORP

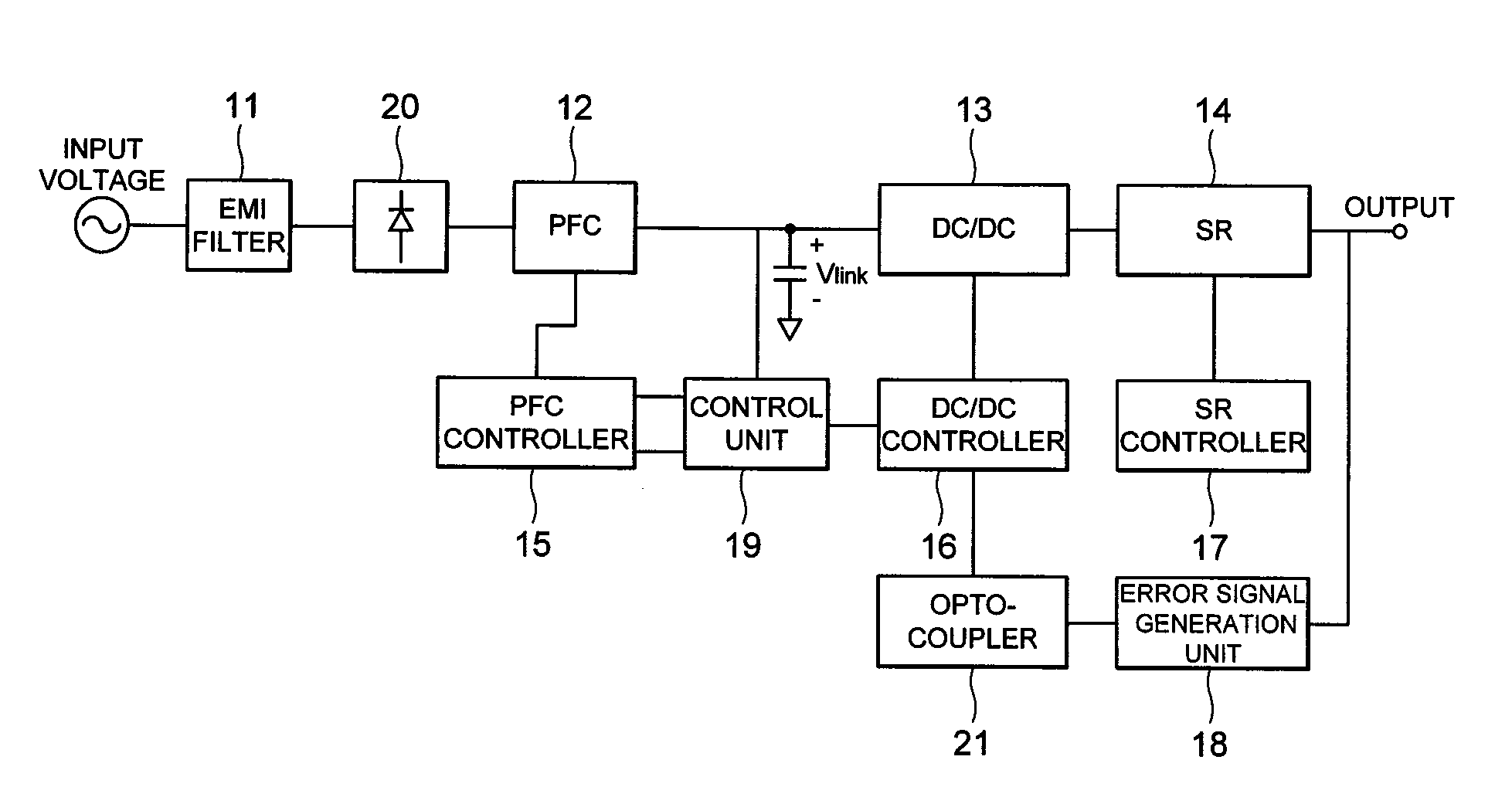

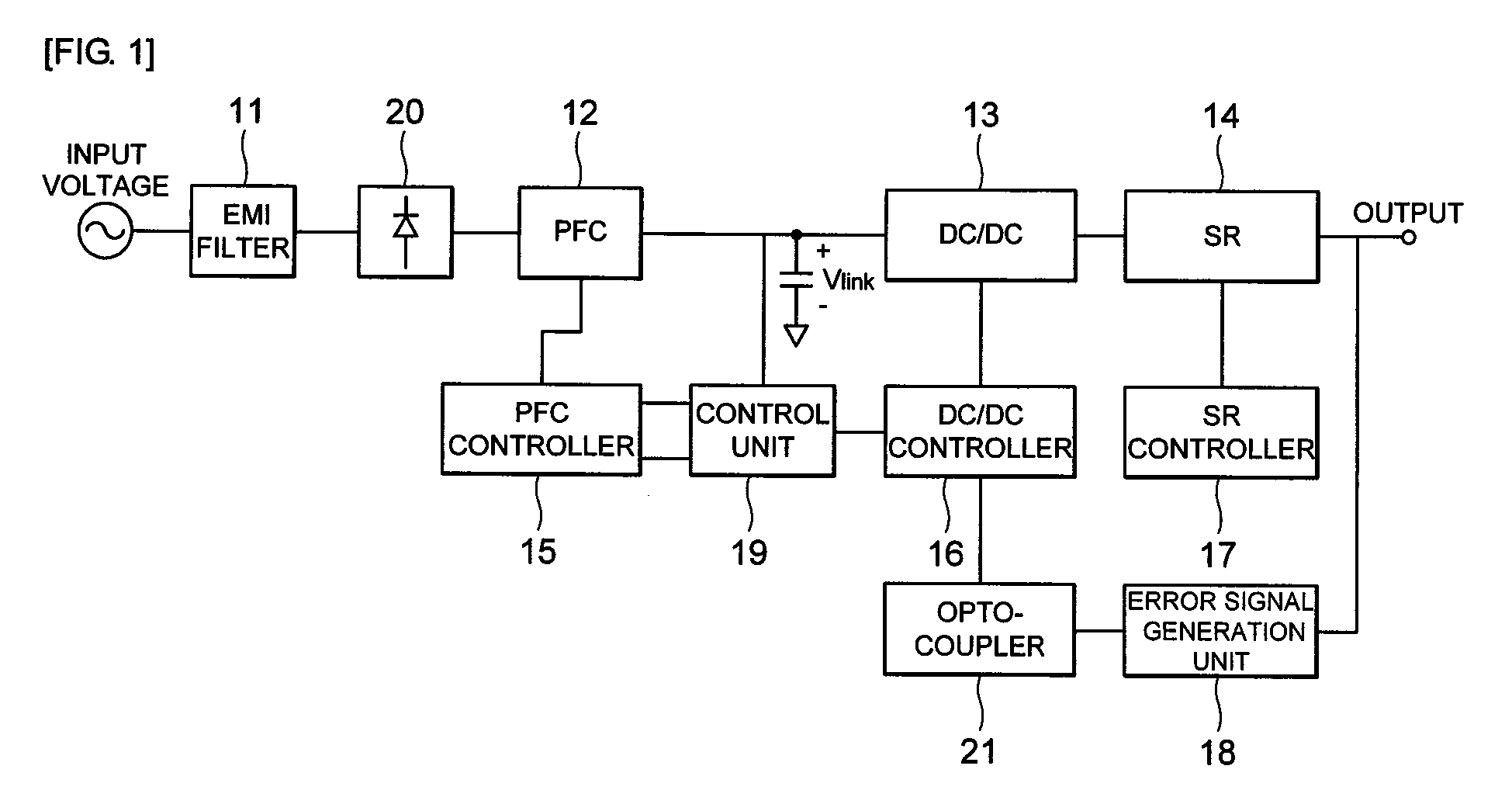

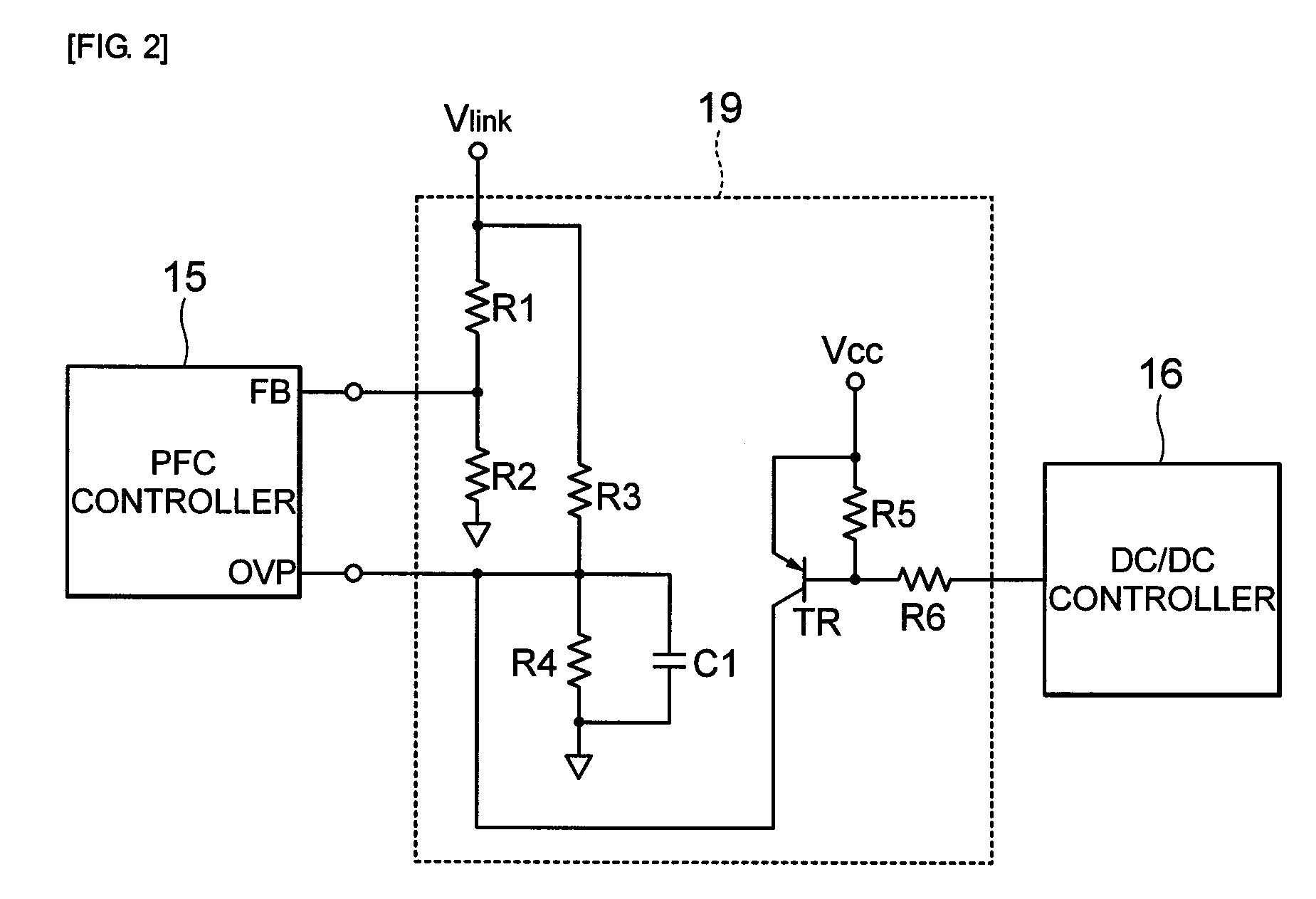

Switching mode power supply for reducing standby power

InactiveUS8194419B2Reduce standby powerMinimize power consumptionEfficient power electronics conversionAc-dc conversionOvervoltageStandby power

A switching mode power supply includes an EMI filter unit, a PFC unit, a DC / DC unit, a PFC controller including a feedback stage to which a link voltage at an output side of the PFC unit is fed back and an overvoltage protection stage, a DC / DC controller generating a burst mode operation signal in a light-load or no-load condition, an error signal generation unit for sensing an output voltage of the power supply to generate an error signal, and a control unit for enabling the PFC unit to operate in a burst mode by connecting the overvoltage protection stage and the feedback stage. When the error signal is smaller than a predetermined value, the DC / DC controller generates the burst mode operation signal. When the link voltage fed back to the feedback stage exceeds a threshold voltage of the overvoltage protection stage, the PFC controller deactivates the PFC unit.

Owner:SOLUM CO LTD +1

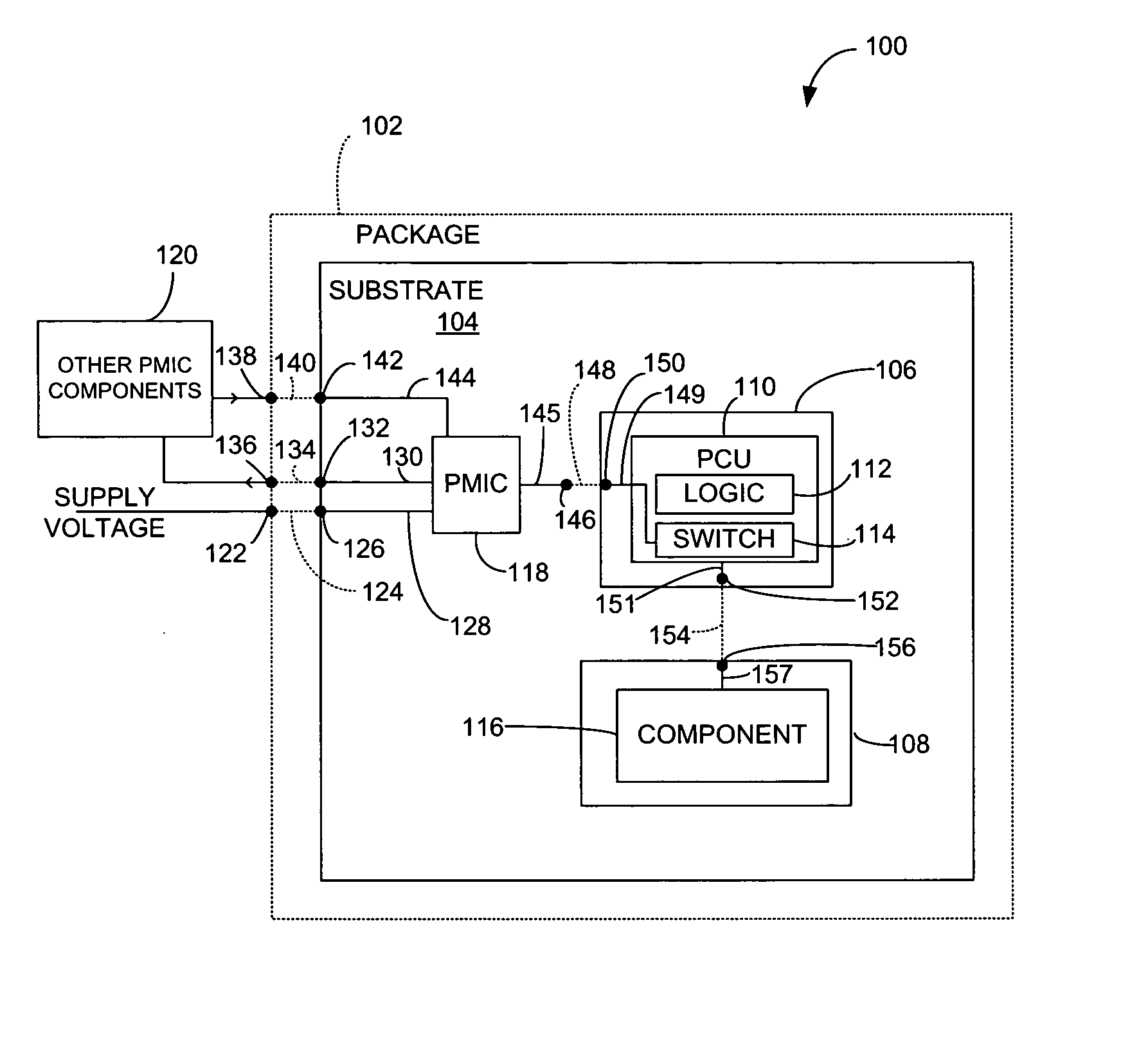

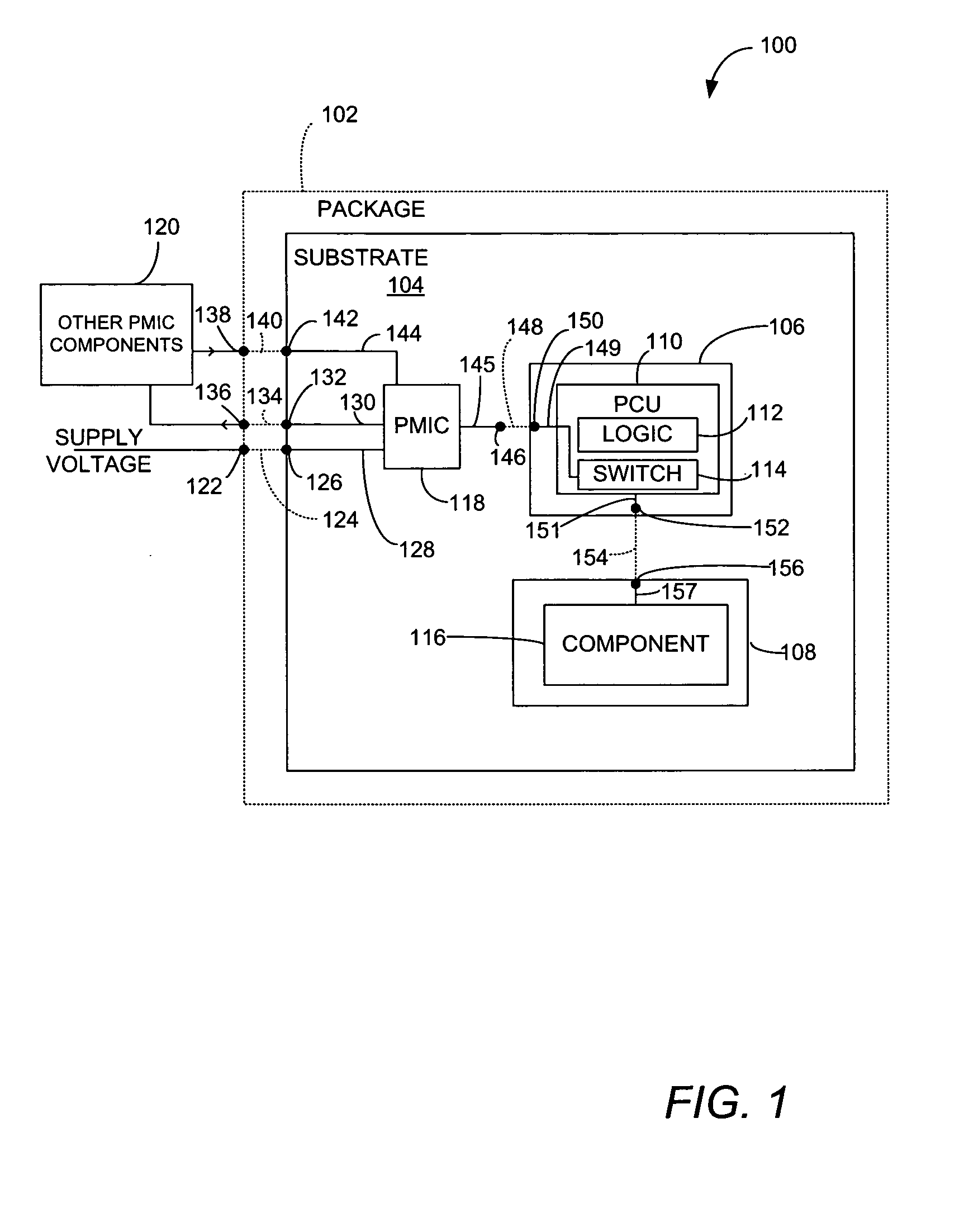

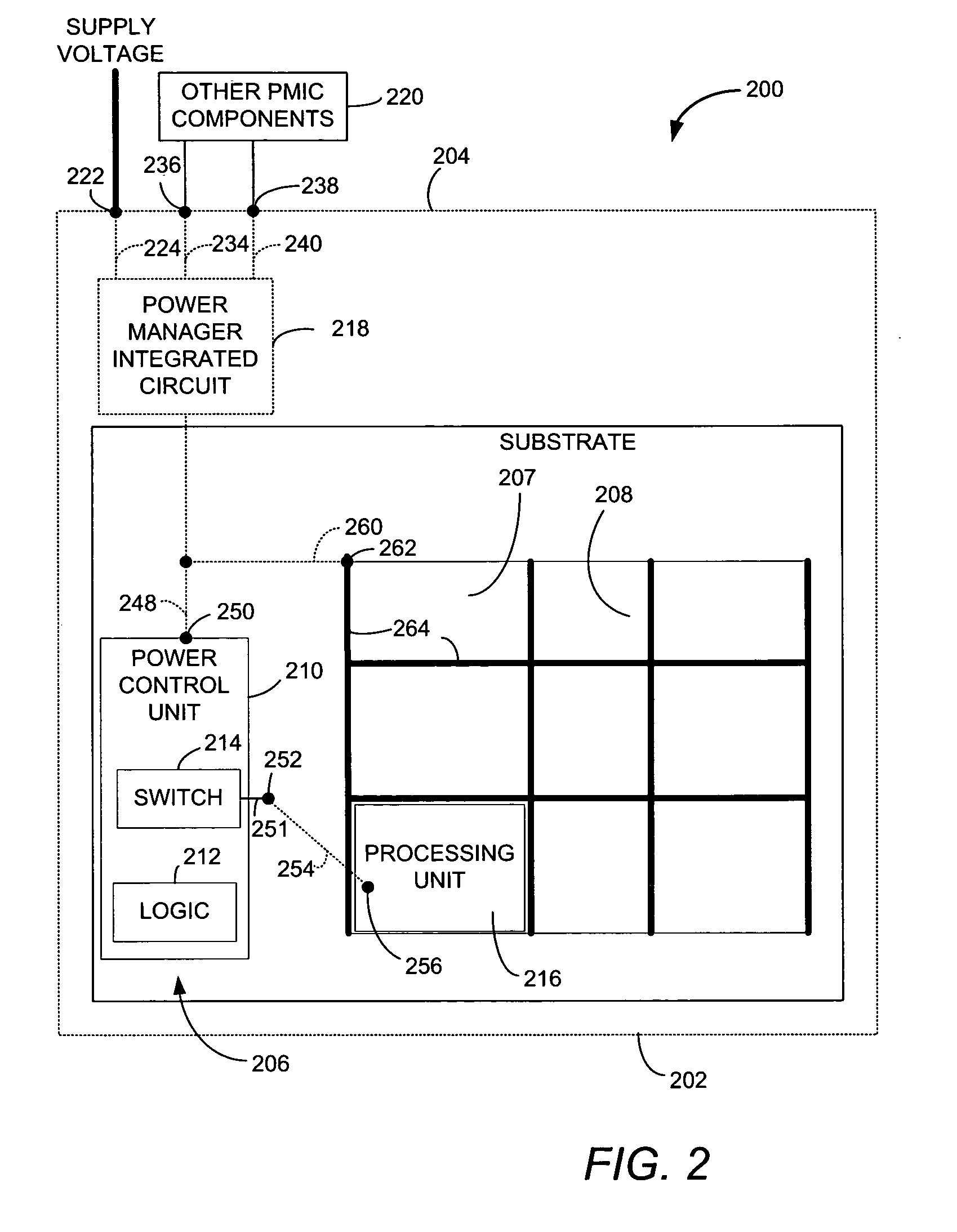

System and method of silicon switched power delivery using a package

ActiveUS20070262438A1Easy to placeCurrent leakageSemiconductor/solid-state device detailsSolid-state devicesEngineeringDistributed power

In one particular embodiment, an integrated circuit includes a package and a substrate electrically and physically coupled to the package. The package includes a first pin, a second pin, and metallization coupling the first pin to the second pin. The substrate is coupled to the package via the first pin and the second pin. The substrate includes a plurality of power domains and a power control unit. The second pin of the package is coupled to a particular power domain of the plurality of power domains. The power control unit includes logic and a switch, where the switch includes a first terminal coupled to a voltage supply terminal, a control terminal coupled to the logic, and a second terminal coupled to the first pin of the package. The logic selectively activates the switch to distribute power to the particular power domain via the metallization of the package.

Owner:QUALCOMM INC

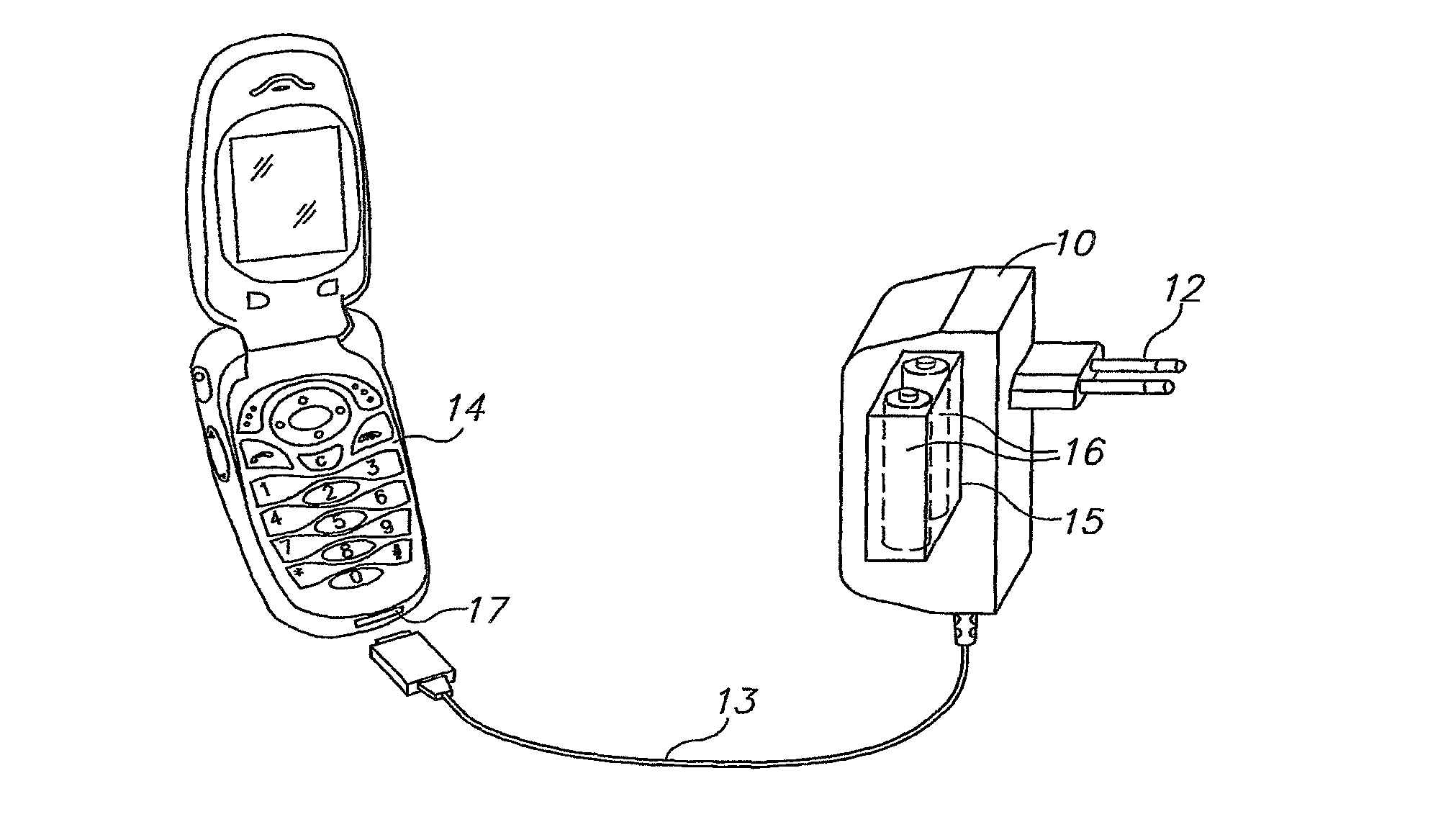

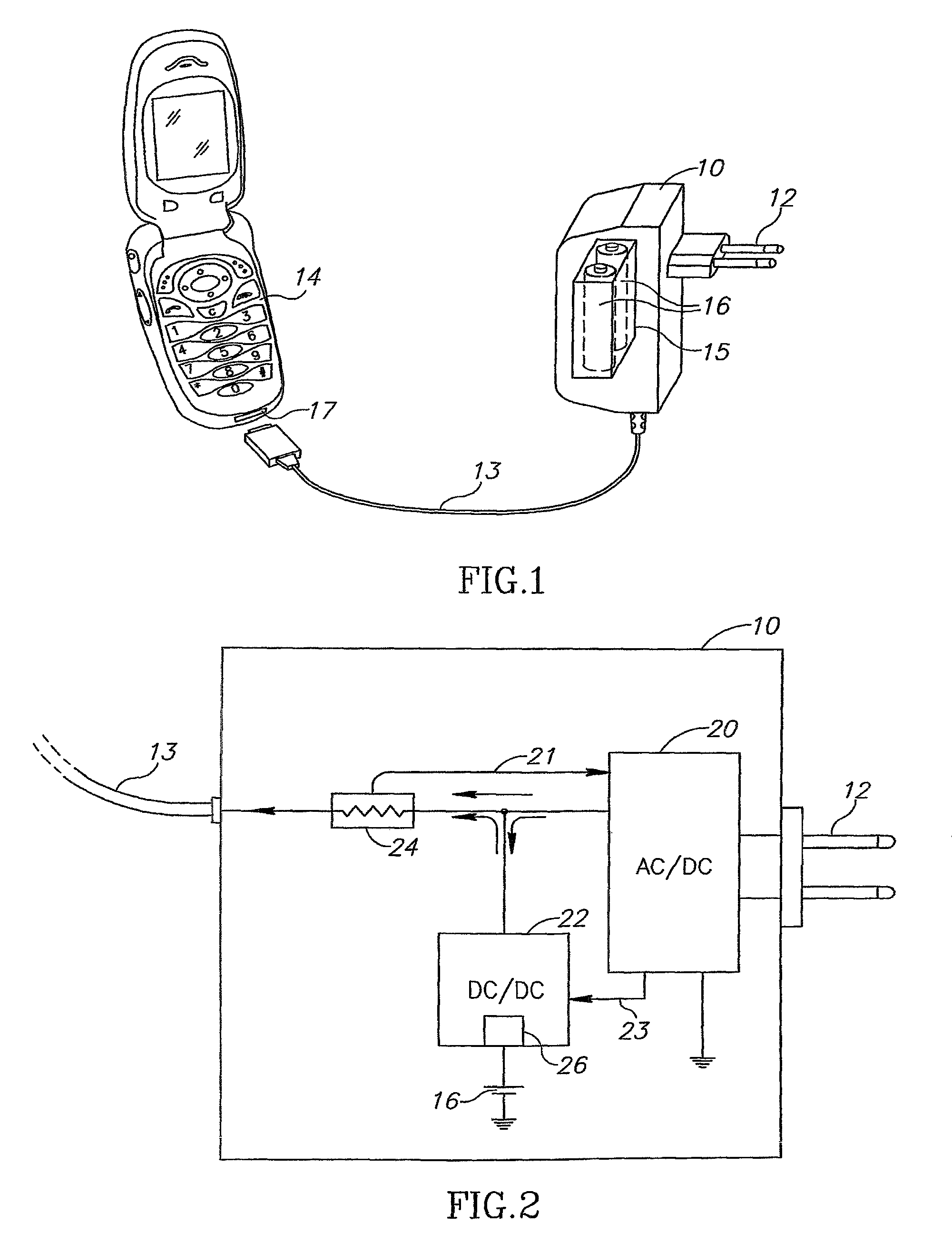

Battery powered charger

ActiveUS8253373B2Easy complianceReduce standby powerElectric powerBattery load switchingElectrical batteryEngineering

A charger for recharging the batteries of a portable electronic device even when no external power source is available. A battery or cell is installed within the charger, and when no access is available to a fixed power source into which the charger can be plugged, the internal battery or cell can be used to recharge the electronic device. The internal battery can be a primary battery or a secondary battery. In the latter case, the internal battery can be maintained in a charged state by means of circuitry which, when the charger is plugged into the external power source, charges the internal battery as well as the battery of the electronic device. The external power source can be either an AC power wall socket, in which case the charger includes AC / DC voltage conversion circuits, or a car lighter socket, or the DC output of a conventional wall charger.

Owner:TOWER SEMICONDUCTOR

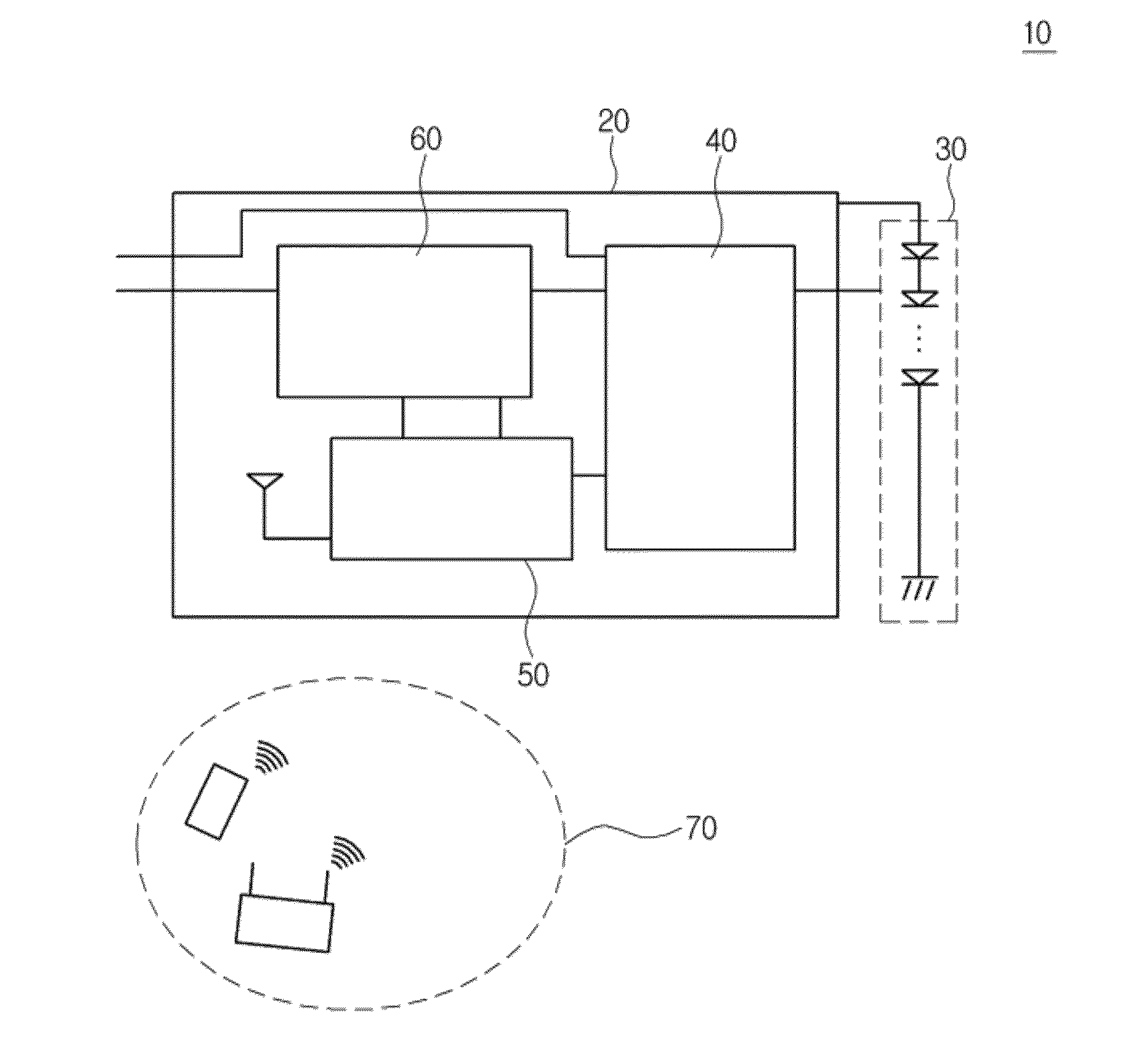

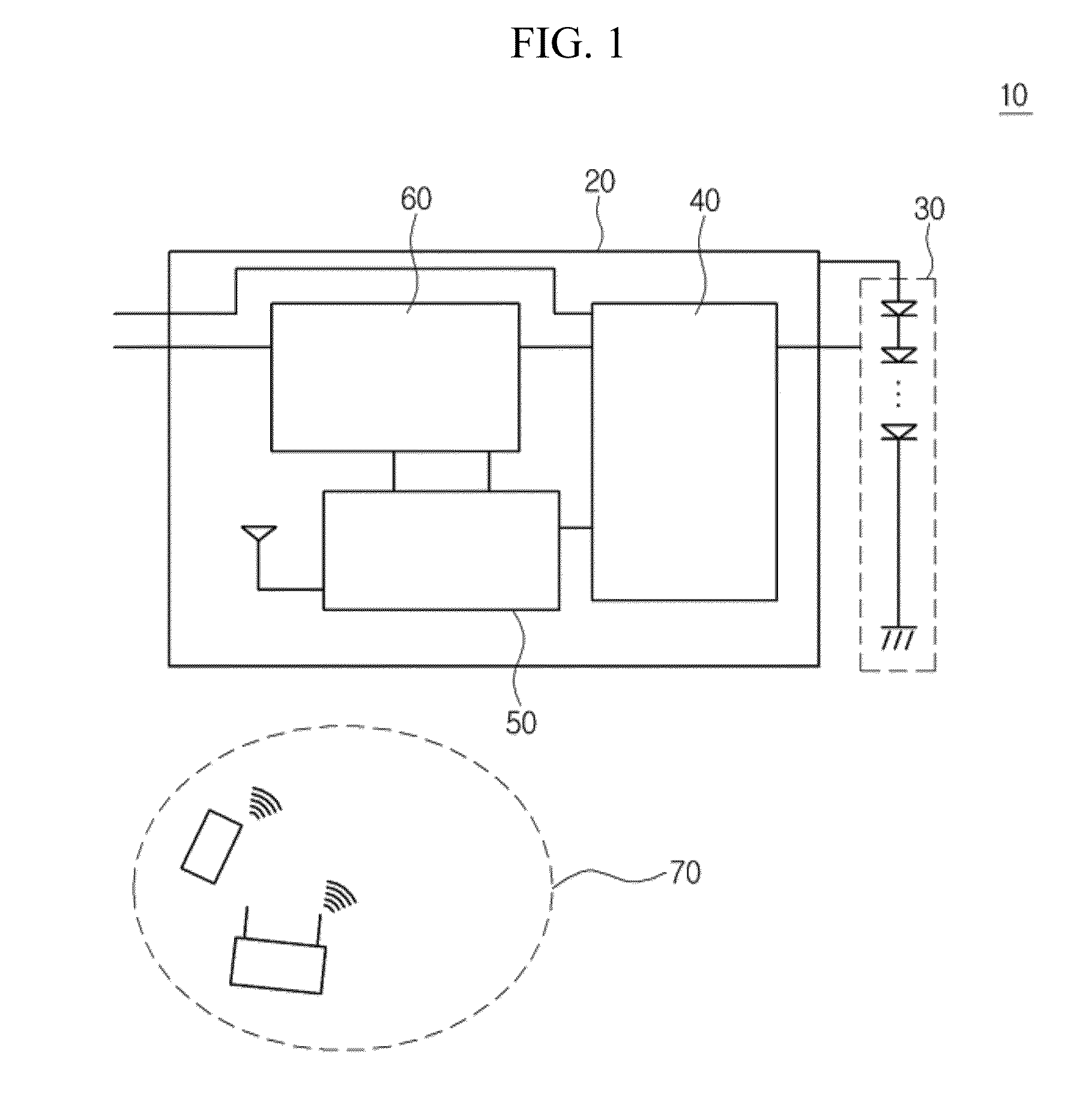

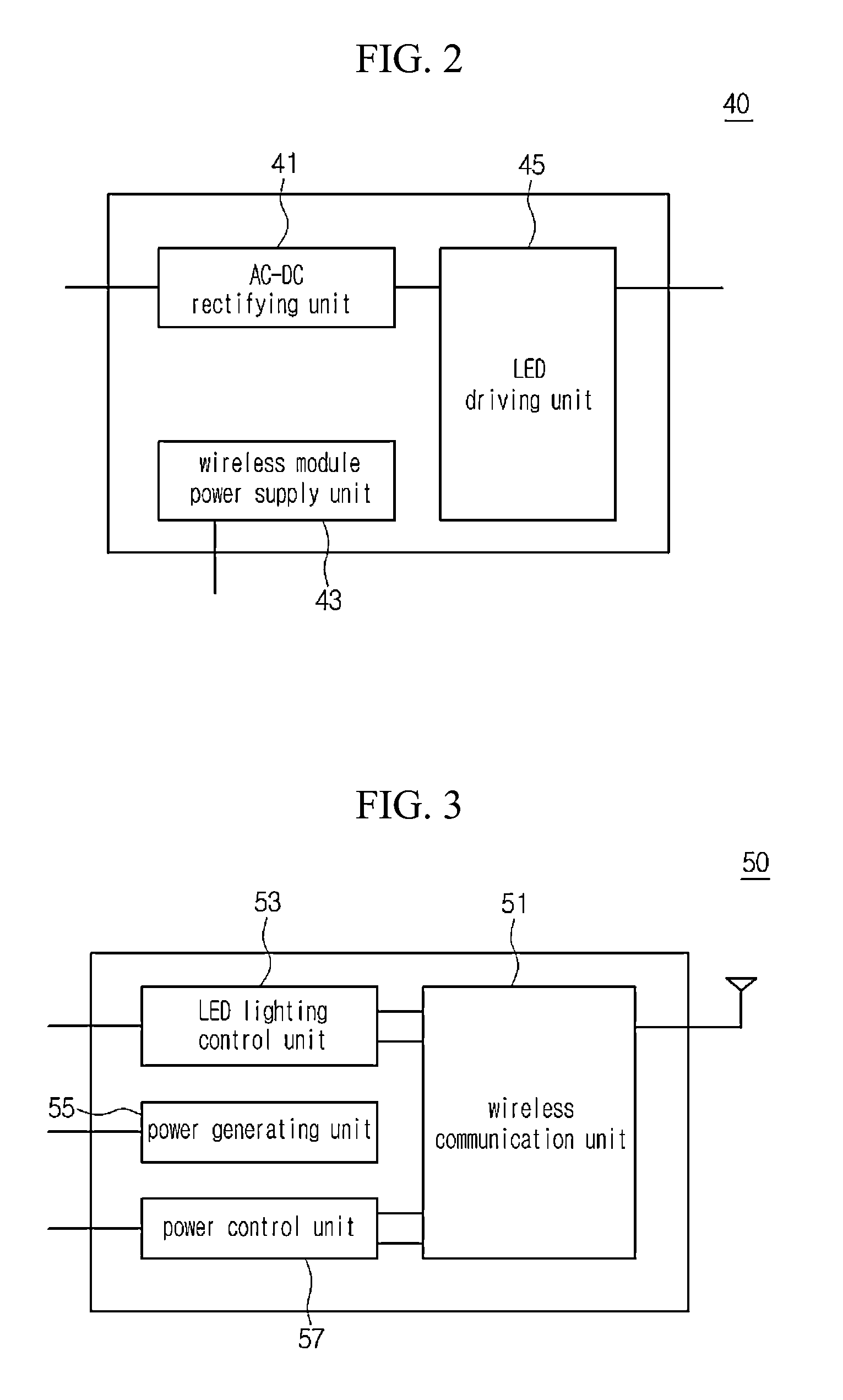

Power supply device for LED and light emitting device having the same

ActiveUS20140062332A1Reduce power consumptionGuaranteed uptimeElectrical apparatusElectroluminescent light sourcesControl signalStandby power

Disclosed is a power supply device including a wired controller receiving AC power to generate a driving voltage, and outputting a lighting driving signal, a wireless controller wirelessly receiving a lighting control signal and outputting the lighting control signal to the wired controller, and a standby power supply unit receiving a reference standby voltage based on the driving voltage, storing the reference standby voltage, and supplying the reference standby voltage to the wireless controller as standby power. In the lighting control device based on wired / wireless communication, the power is always obtained from the super capacitor to turn on the wireless controller, so that the turn-on state of the power generator of the wired controller is not always required. The power consumption is reduced by reducing the standby power.

Owner:LG INNOTEK CO LTD

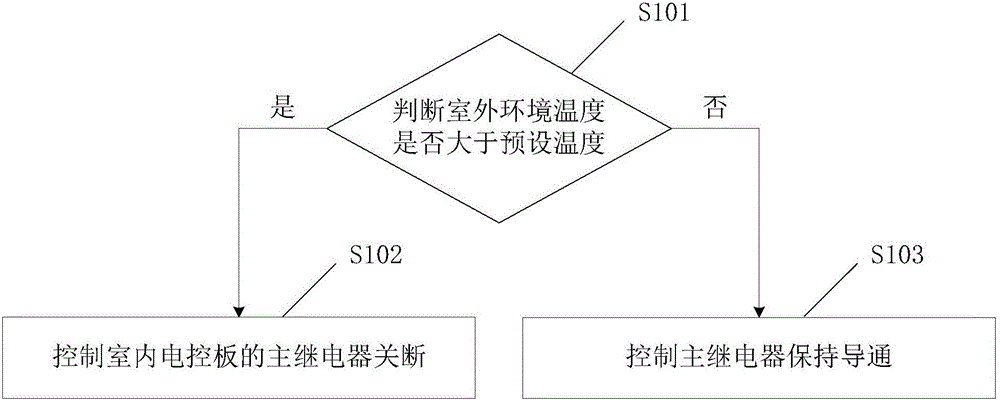

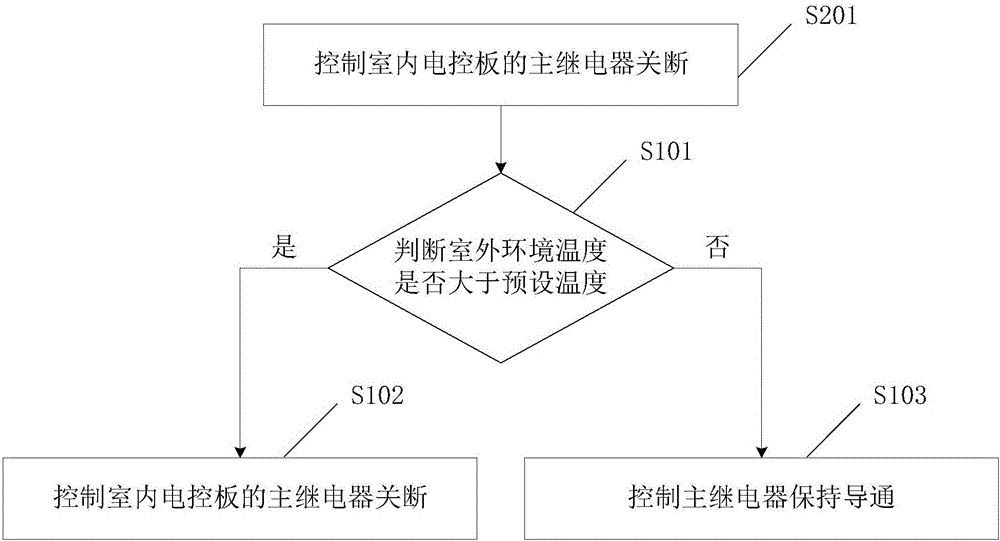

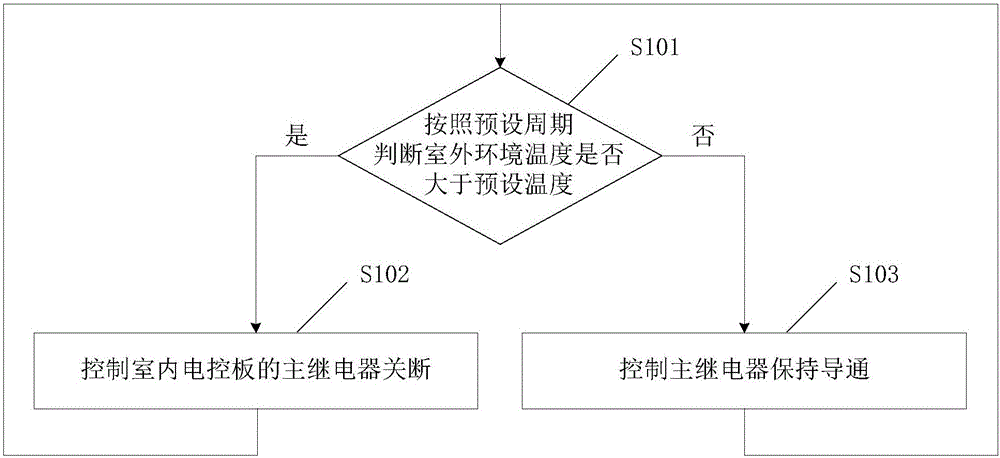

Air conditioner and standby control method thereof

InactiveCN105757881AReduce standby powerGuaranteed normal warm-upSpace heating and ventilation safety systemsLighting and heating apparatusFrostStandby power

The invention provides an air conditioner and a standby control method thereof. An indoor controller of the air conditioner can judge whether the outdoor environment temperature is more than a preset temperature; when the outdoor environment temperature is less than or equal to the preset temperature, a main relay of an indoor electric control plate is controlled to be switched on so as to supply power to an outdoor unit of the air conditioner, so that the normal preheating of a compressor and the normal frost melting at the bottom of a condenser can be ensured; if the outdoor environment temperature is more than the preset temperature, the main relay is controlled to be switched off and the power supply to the outdoor unit is switched off, so that the air conditioner enters a low-power-consumption standby mode; through the segmental standby treatment for the outdoor environment temperature, when the outdoor environment temperature is more than the preset temperature, the power supply to the outdoor unit is stopped and the standby power of the air conditioner is reduced.

Owner:GUANGDONG CHIGO AIR CONDITIONING

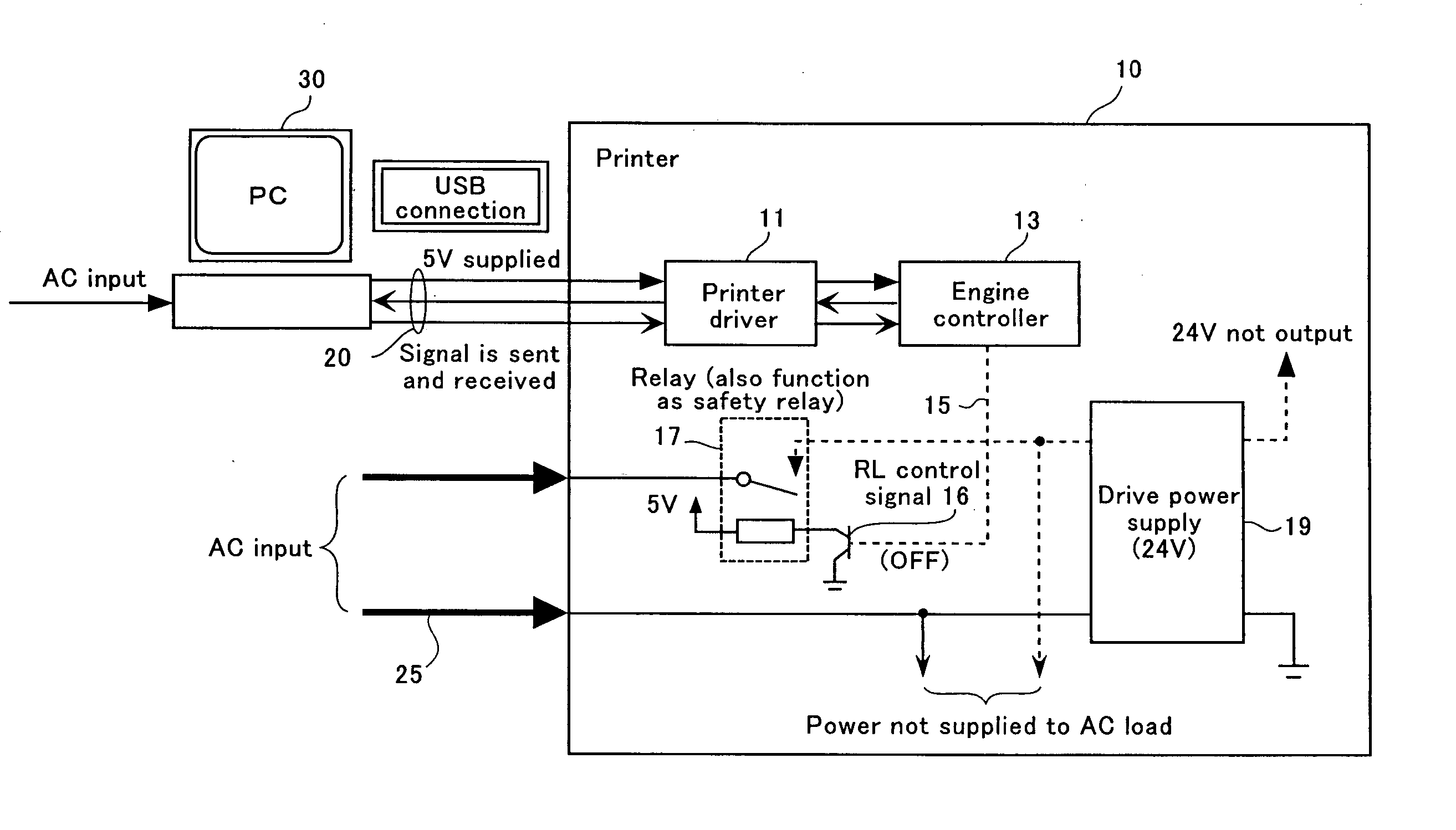

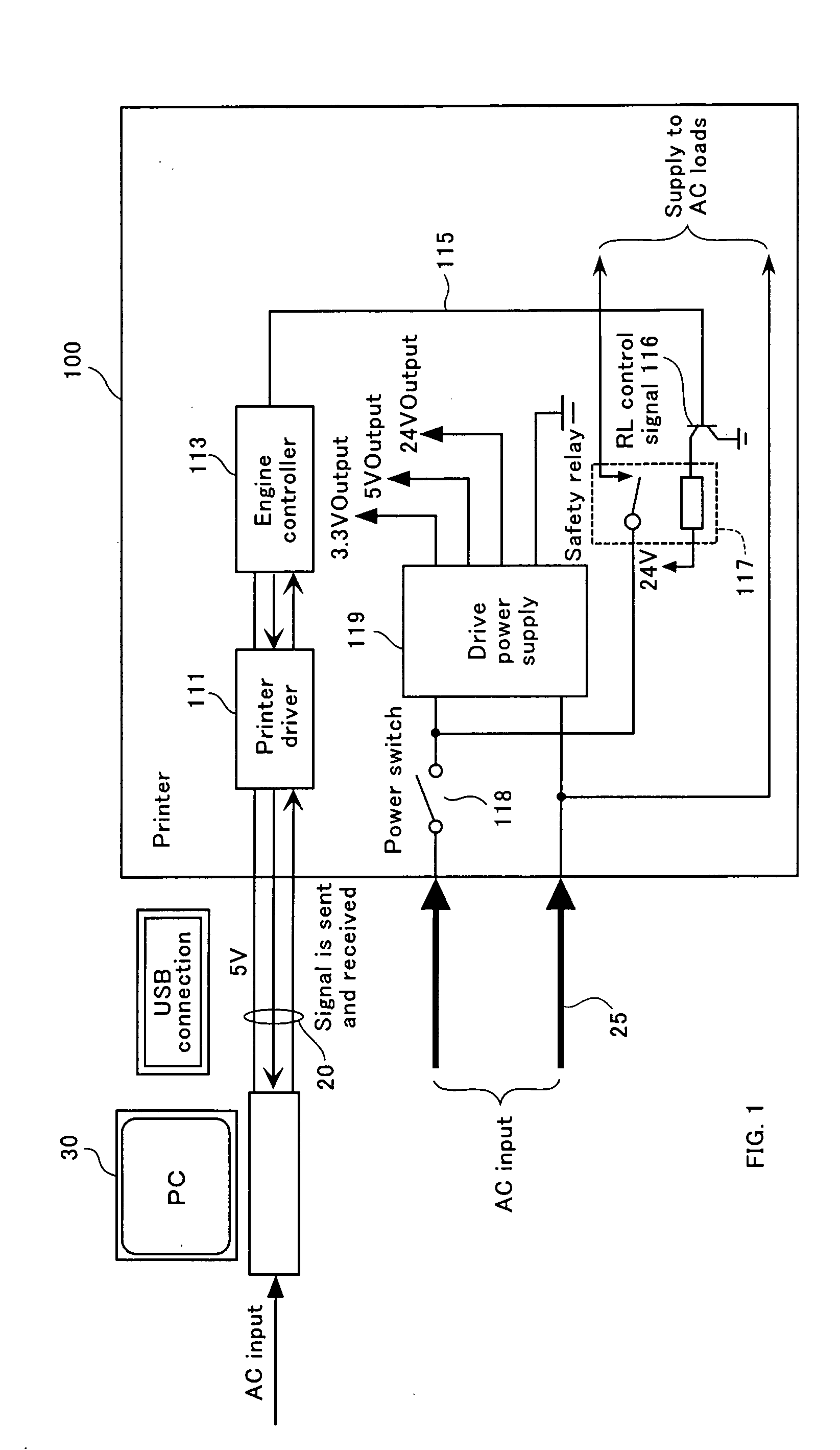

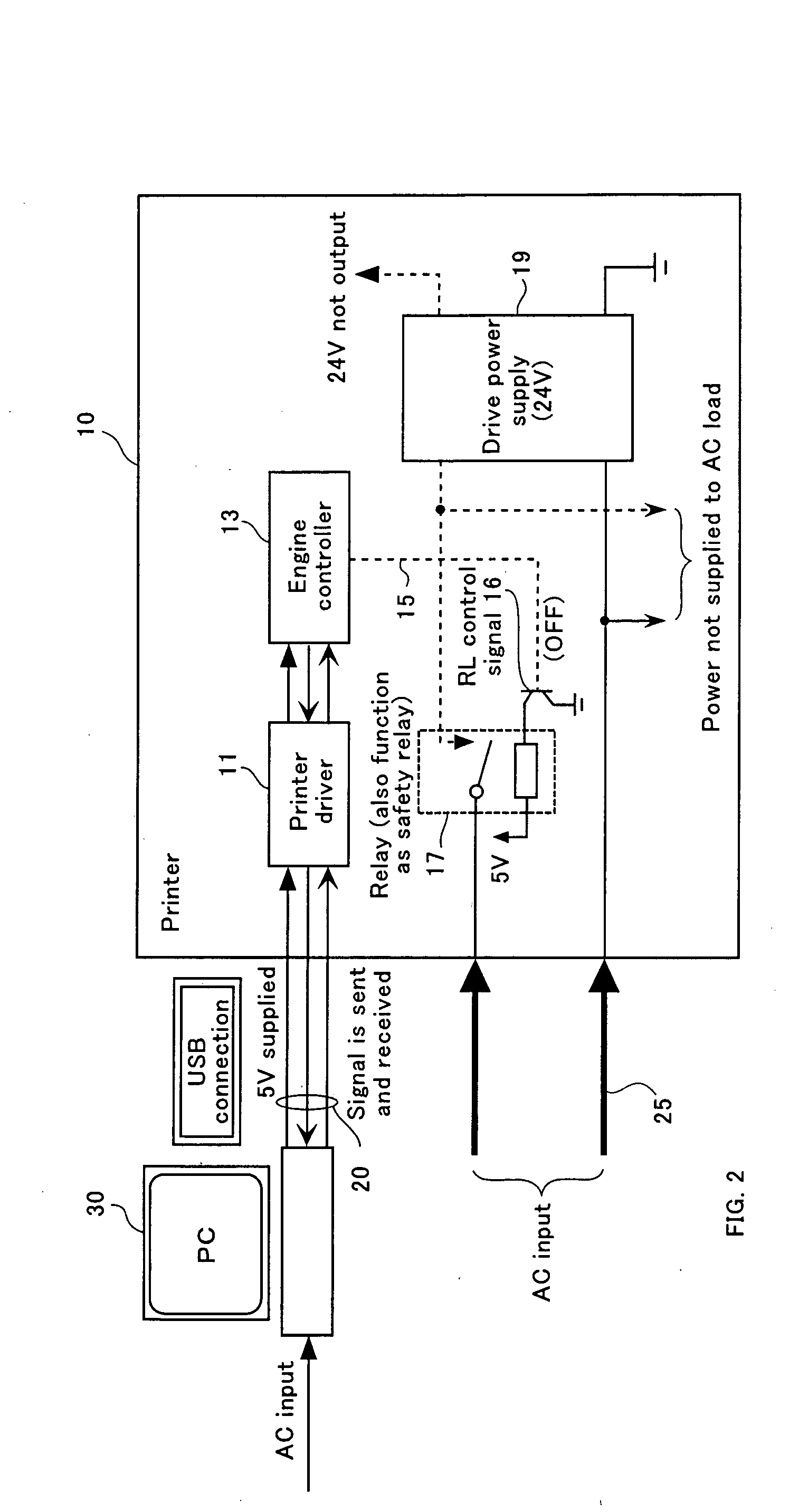

Image forming device

InactiveUS20050063725A1Eliminate needReduce standby powerElectrographic process apparatusOther printing apparatusComputer printingEngineering

A printer (image forming device) (10), which includes AC loads driven by an AC power, is connected to an external device (30) via a single power line for a logic operation and a signal line. More specifically, a printer driver (11) and an engine controller (13) operate on a 5V power supply voltage obtained via a USB cable (20). When a standby state is entered, a relay (17) is turned off, an AC power supply to a drive power supply (19) is disconnected, and a power supply to the AC loads is disconnected. When the standby state is released by a signal received from the PC (30), an ON signal is generated for the relay (17) to supply the AC power. In this way, the standby power is reduced to improve energy saving.

Owner:COPYER

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com