Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

50results about "Networks with variable switch closing time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

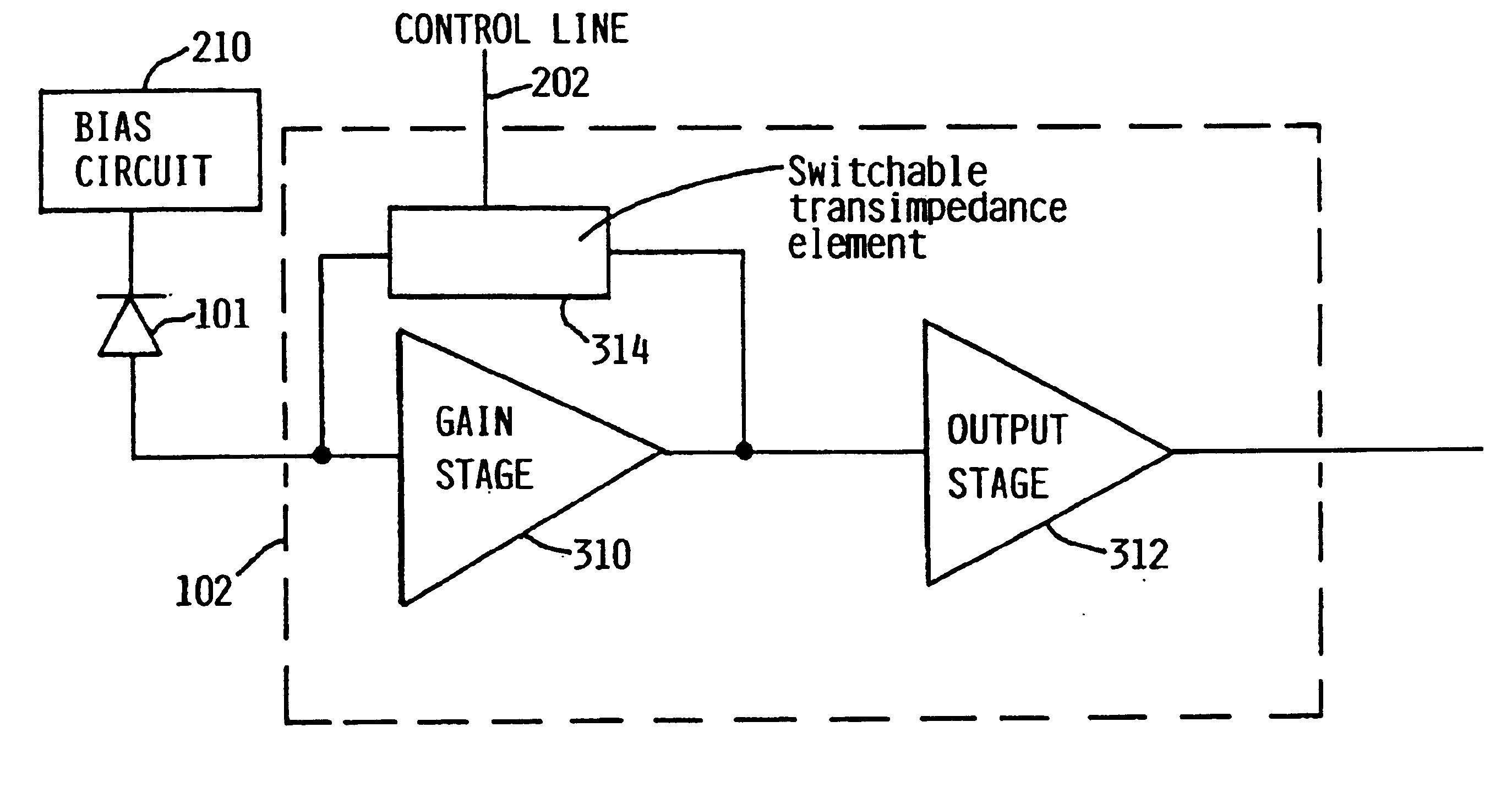

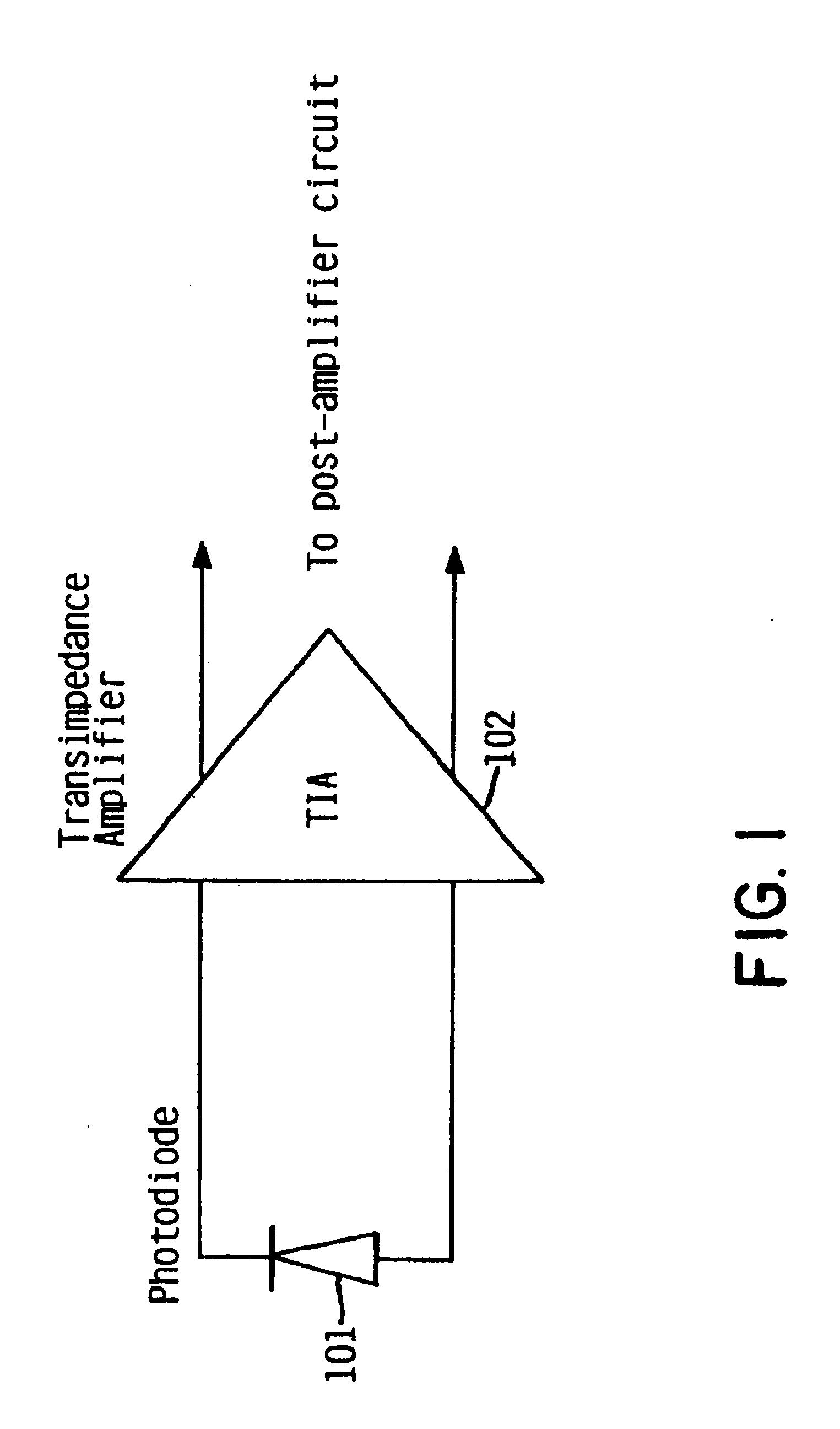

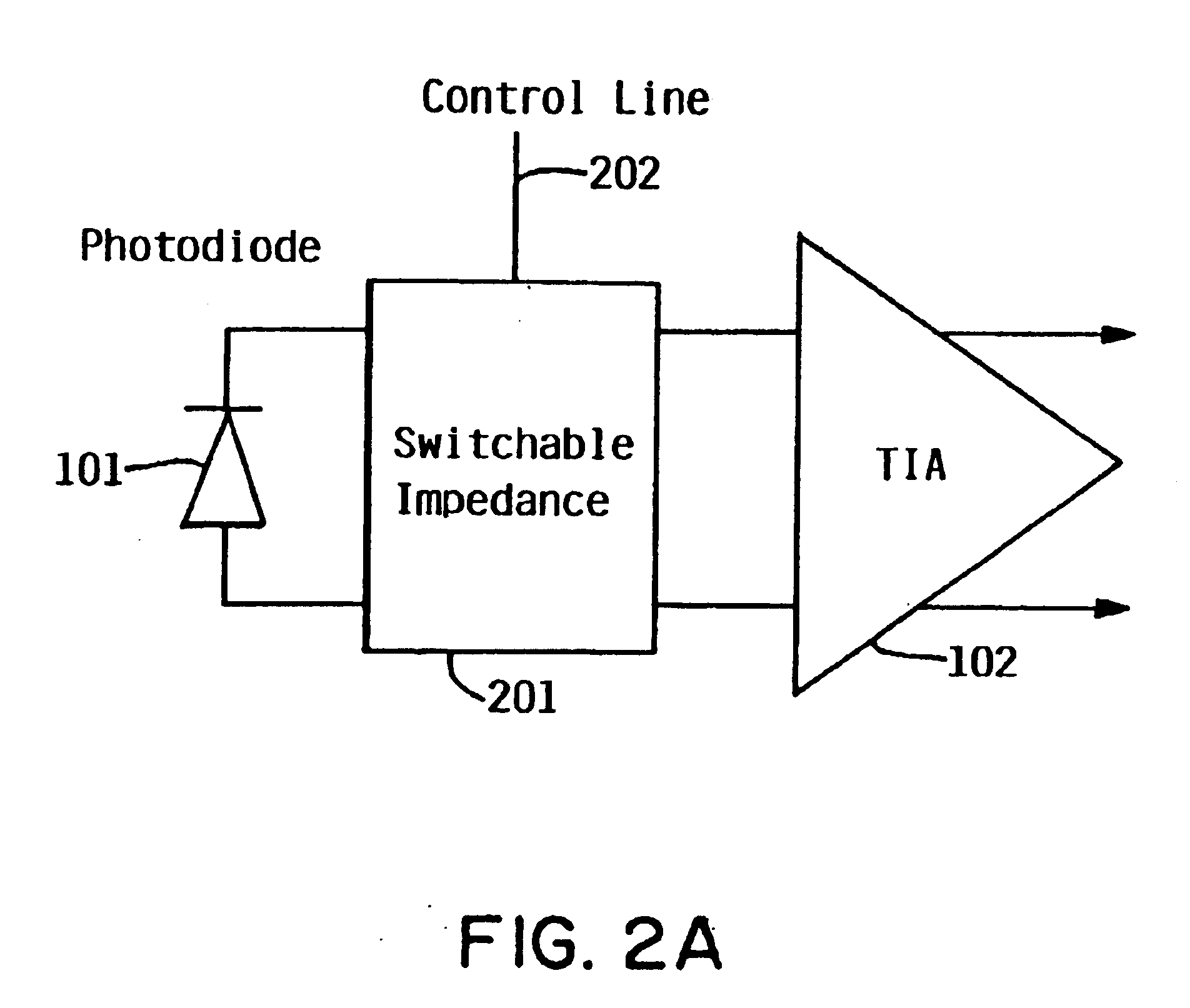

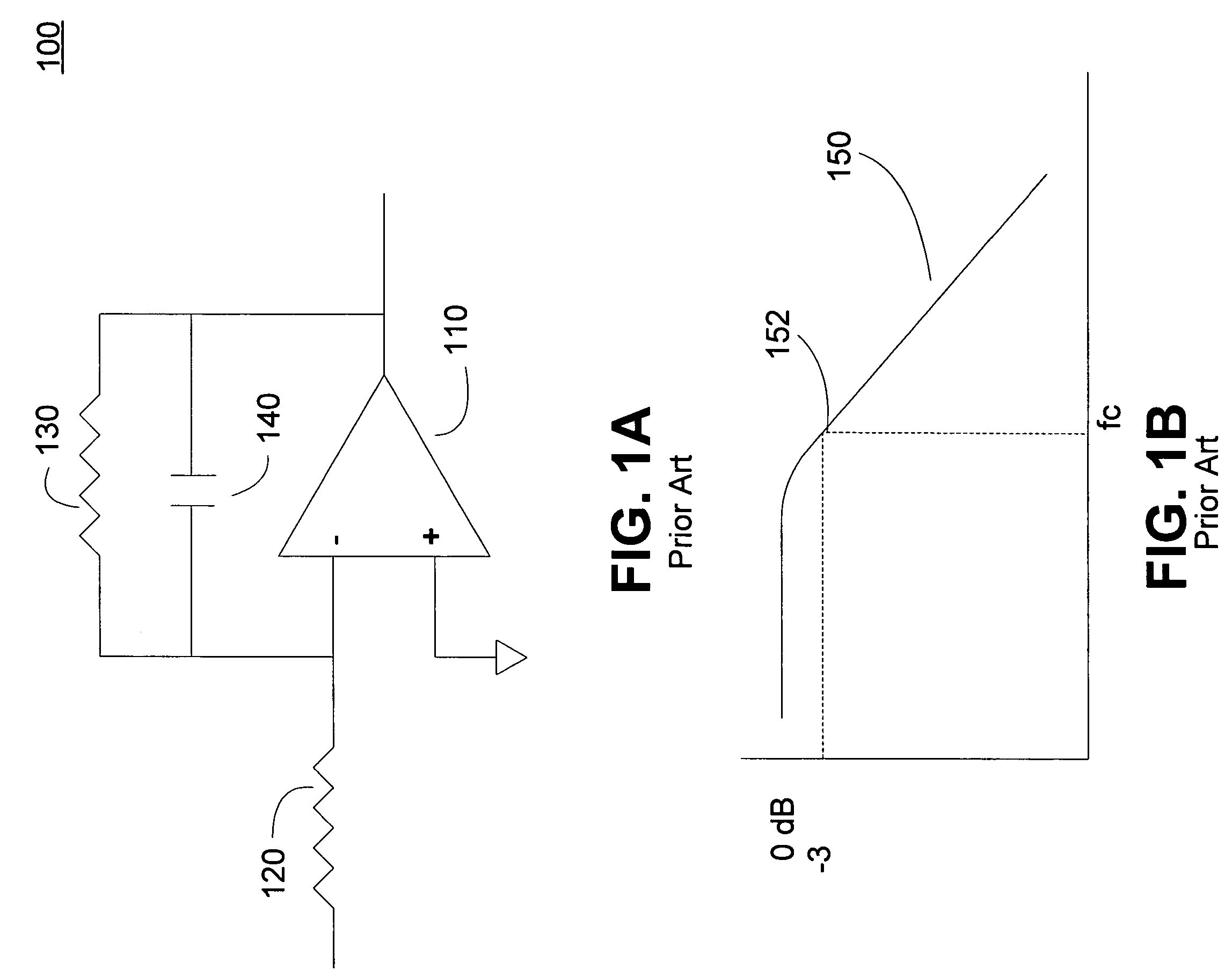

Switchable-bandwidth optical receiver

InactiveUS6862322B1Improve performanceModulated-carrier systemsGain controlAudio power amplifierEngineering

A switchable bandwidth optical receiver is implemented in a front-end of the receiver in at least one of three ways. A switchable impedance may be provided at the input to a preamplifier of the front end, the preamplifier of the front-end may have a switchable impedance therein, and / or a switchable filter may be provided at an output of the preamplifier.

Owner:IBM CORP

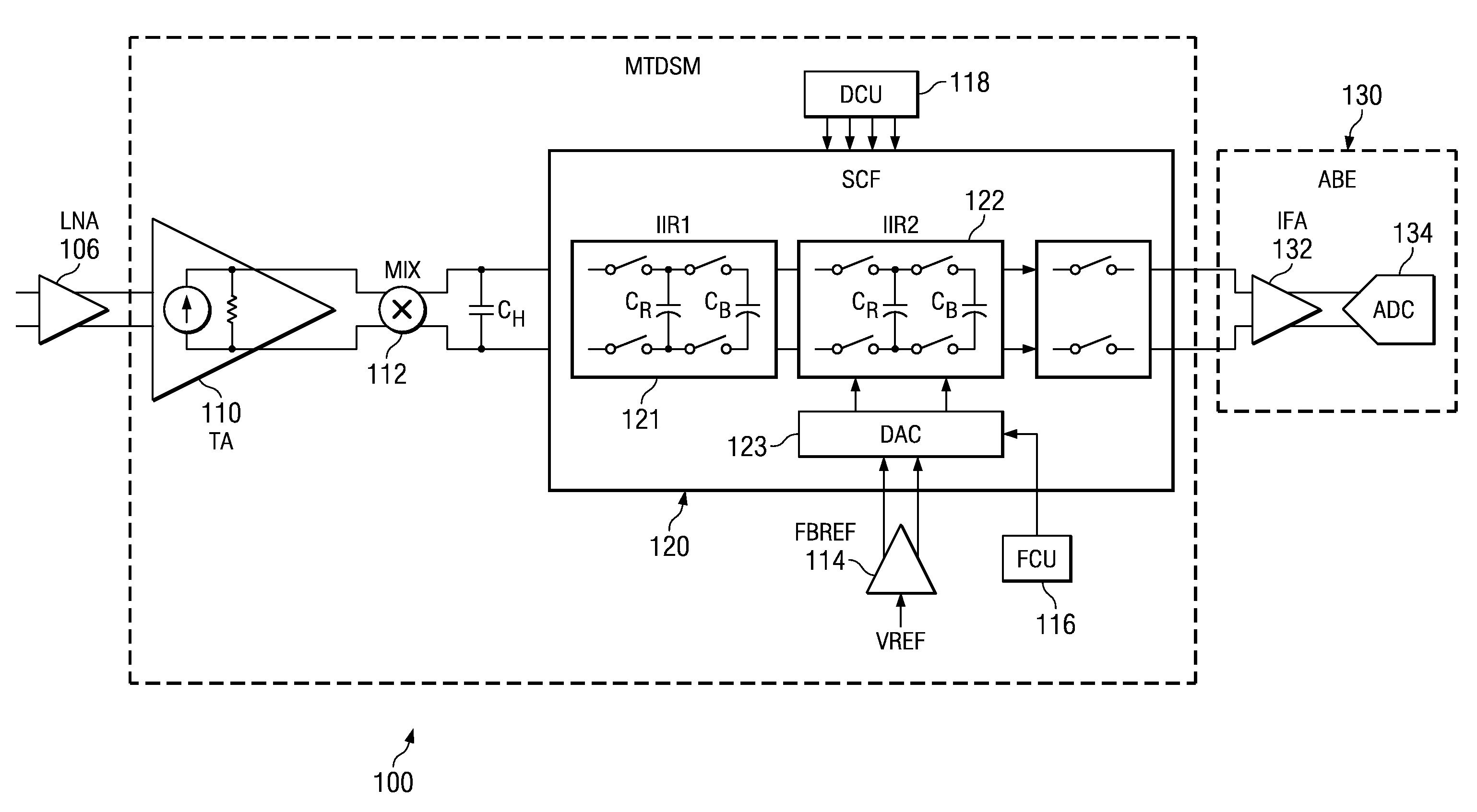

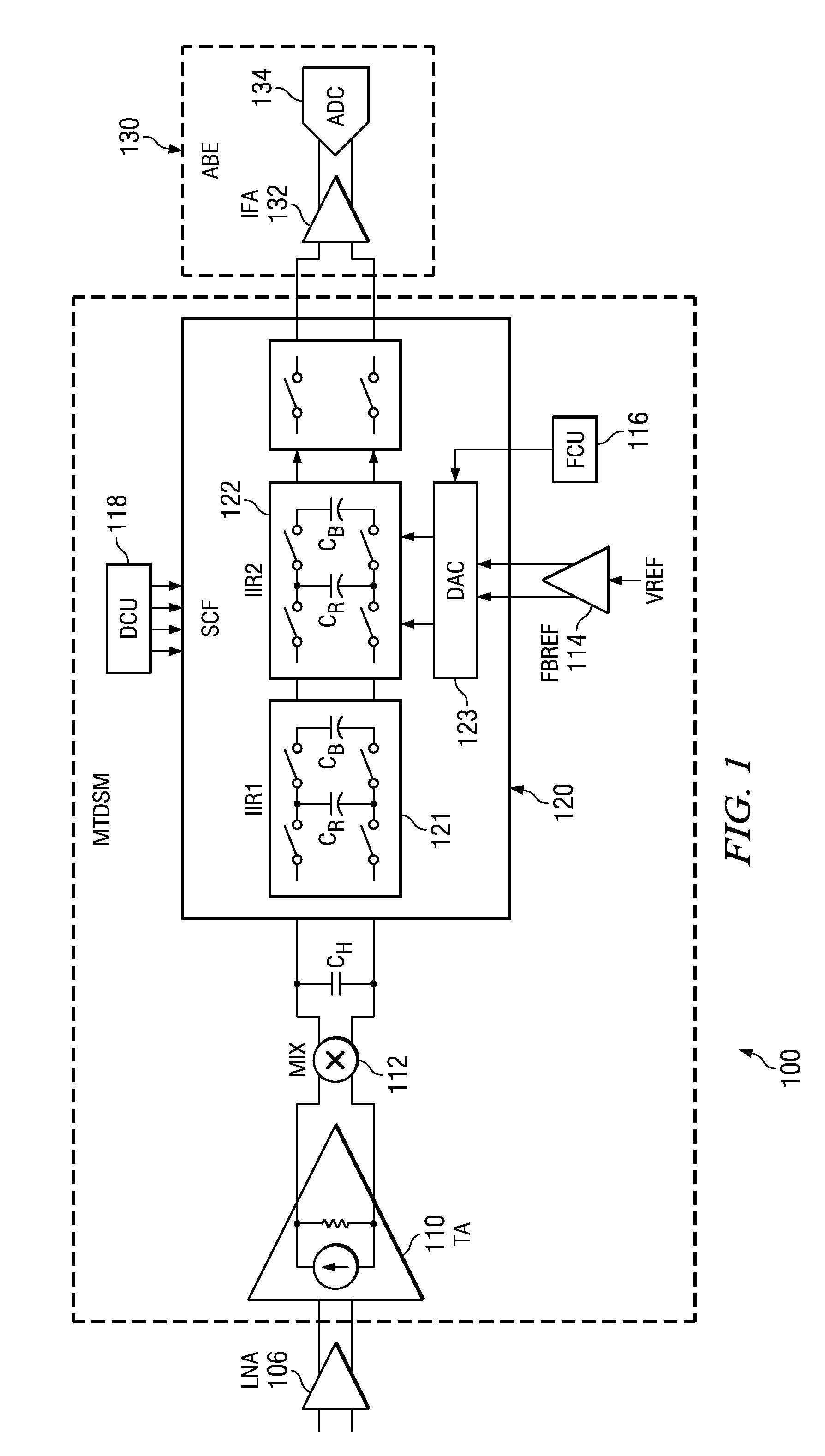

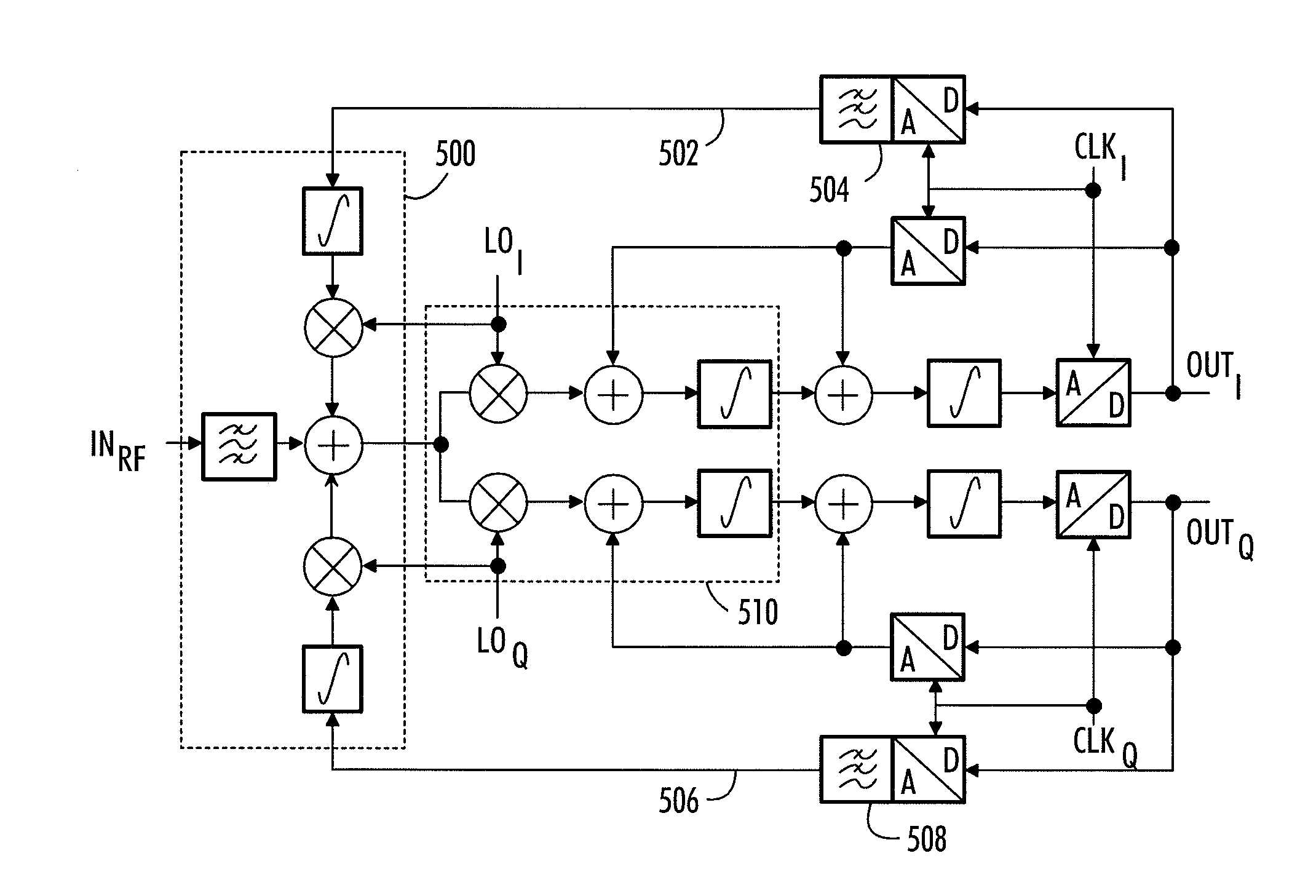

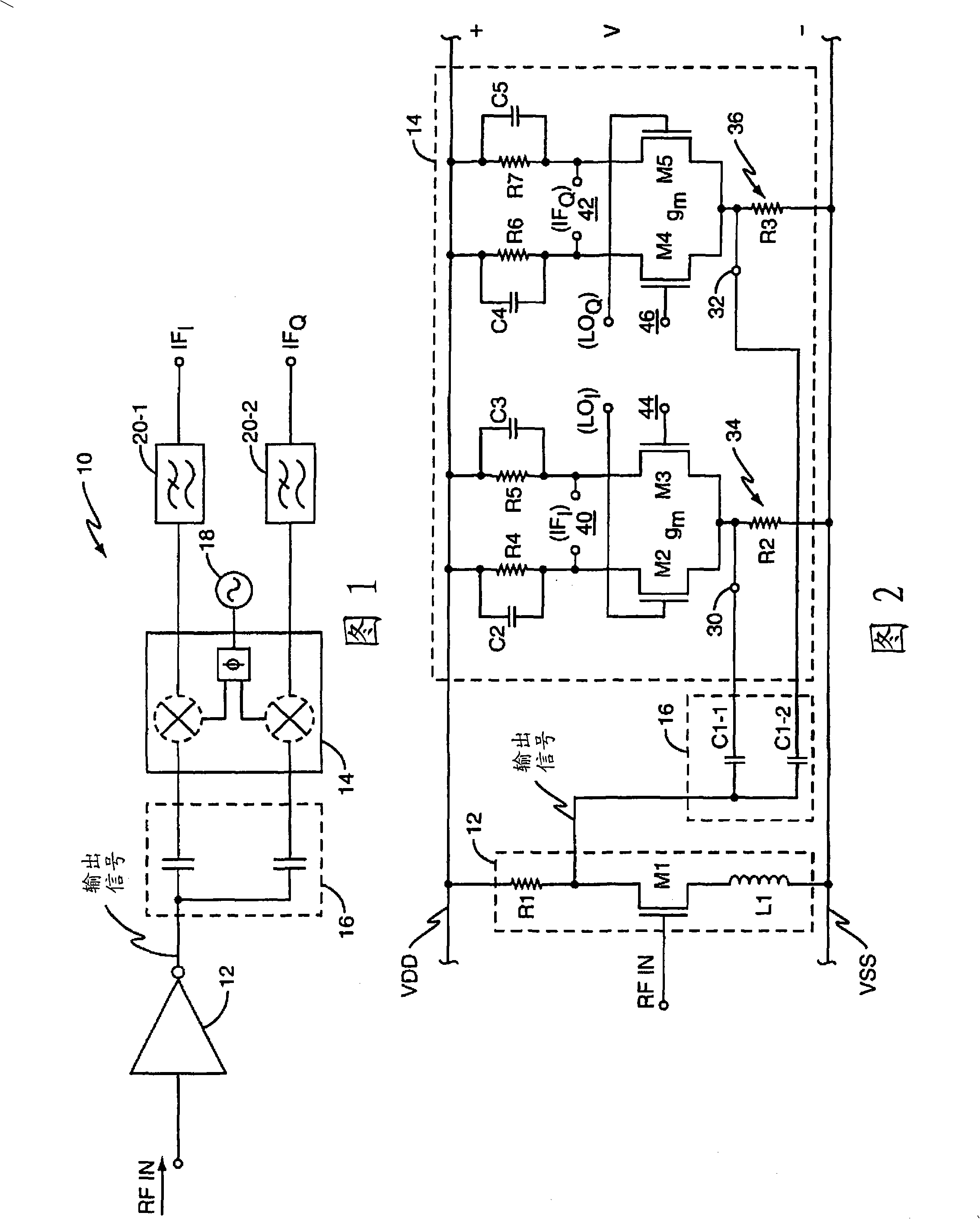

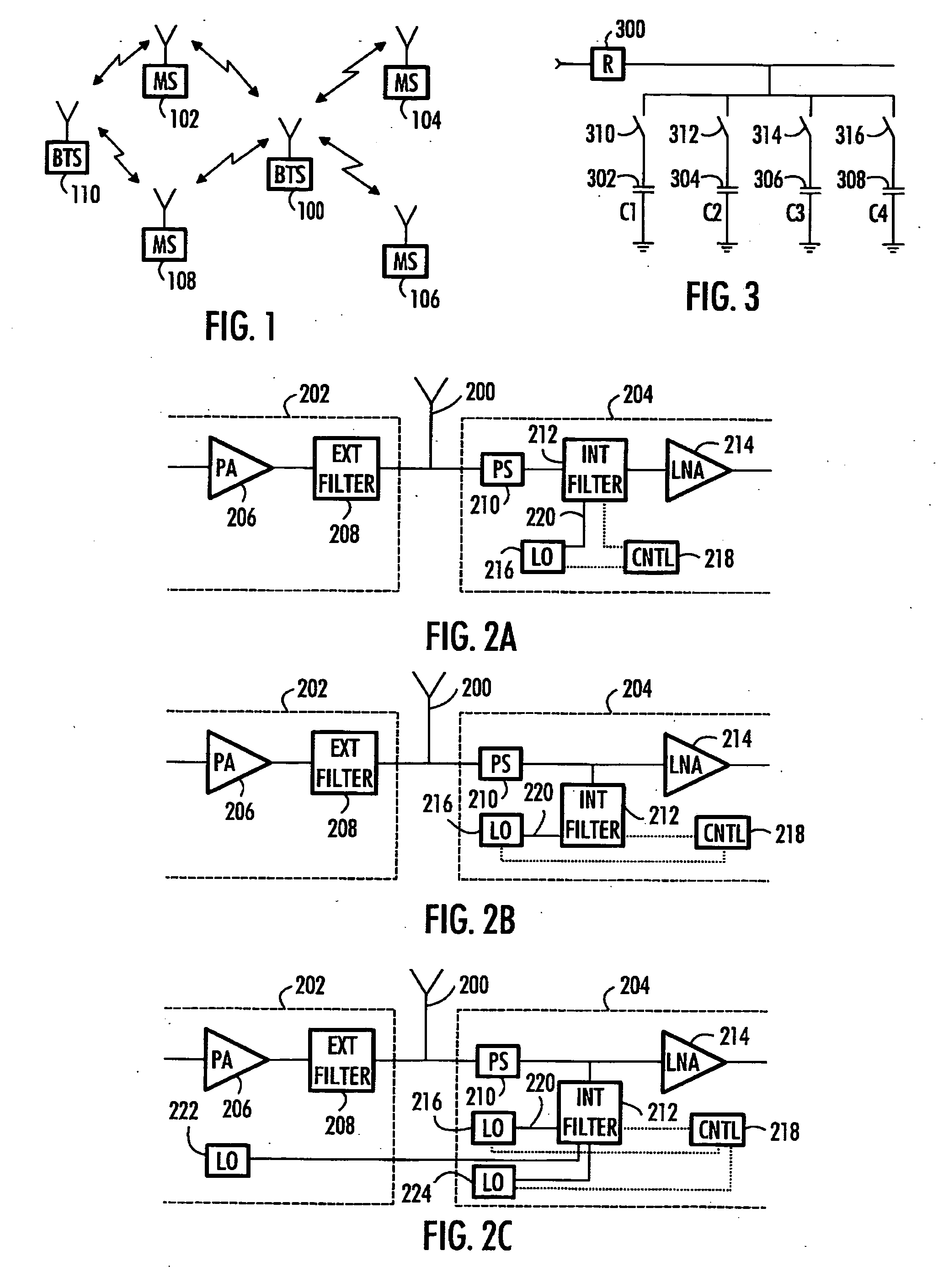

Multi-Tap Direct Sub-sampling Mixing System for Wireless Receivers

ActiveUS20090002066A1Transversal filtersSwitched capacitor networksHybrid systemAudio power amplifier

A multi-tap direct sub-sampling mixing system for wireless receivers is provided with a dynamically configurable passive switched capacitor filter. A front end amplifier is connected to receive a signal. The passive switched capacitor filter is connected to receive the amplified signal and has an output for providing a filtered signal. The switched capacitor filter has at least two sections that are each operable as a pole, wherein a first section of the at least two sections has sets of at least two stacked capacitors interconnected with a set of switches operable to amplify in input voltage provided to an input of the first section in response to operation of the set of switches; and a back end section connected to the output of the switched capacitor filter to receive the filtered signal.

Owner:TEXAS INSTR INC

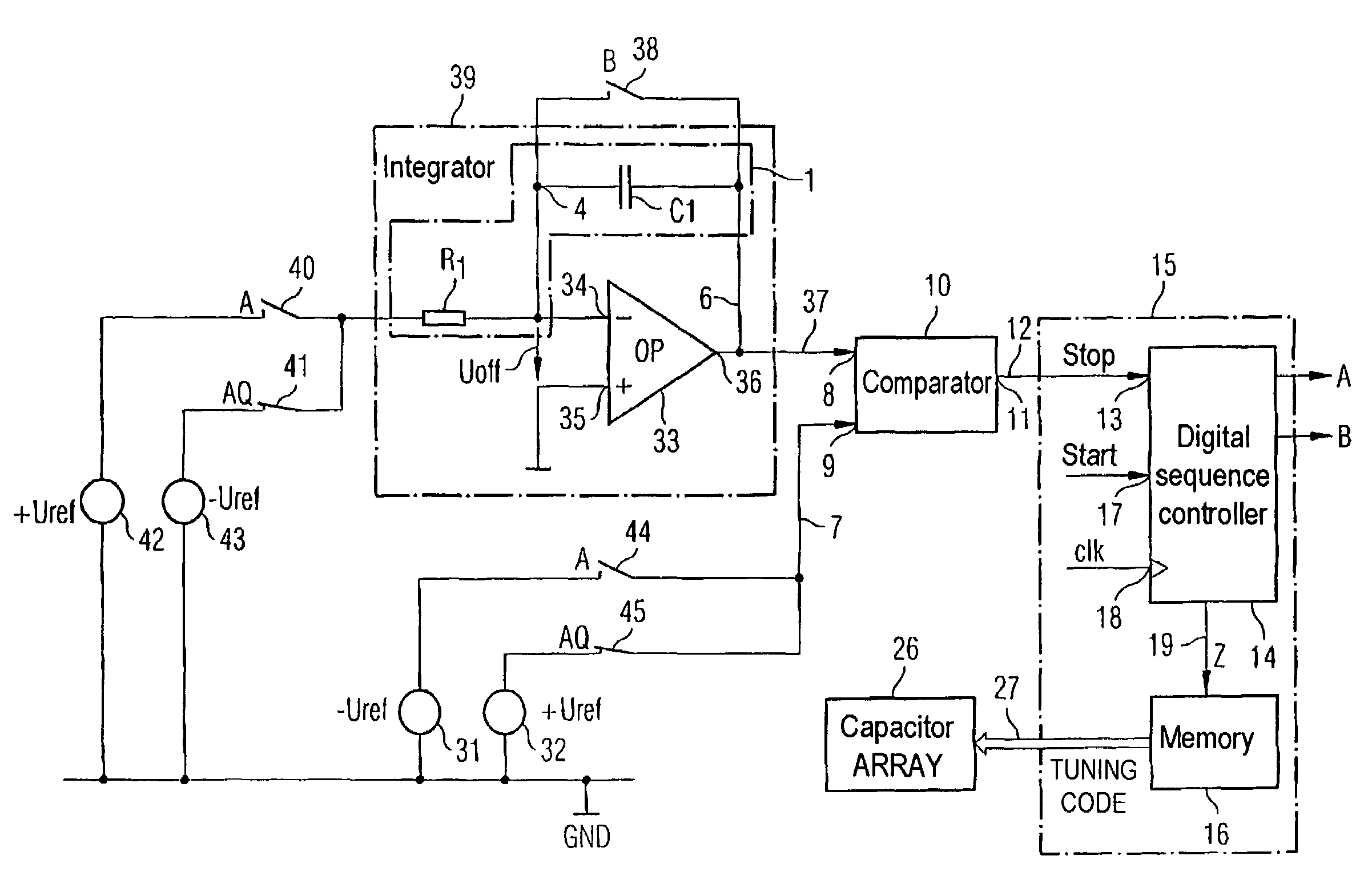

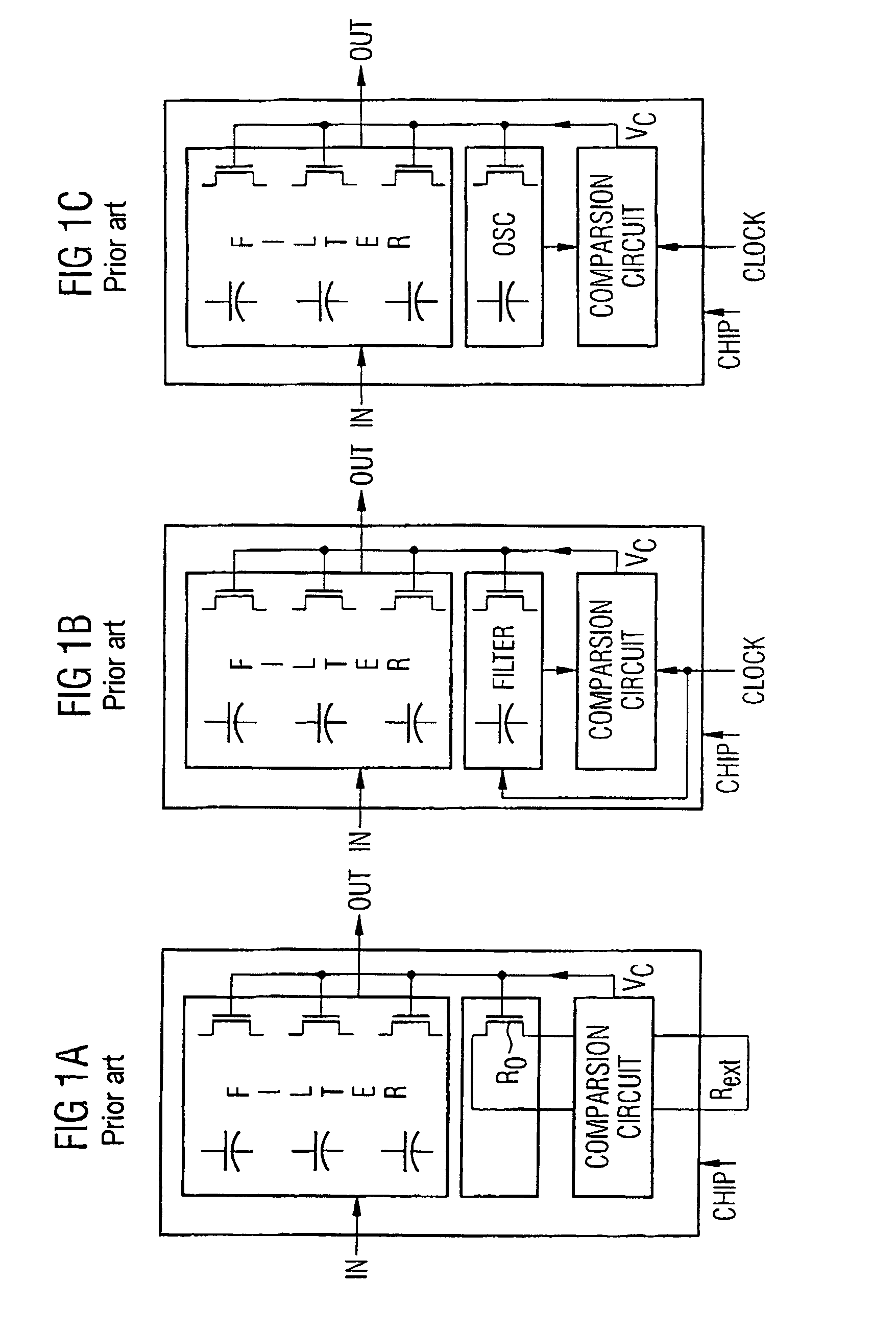

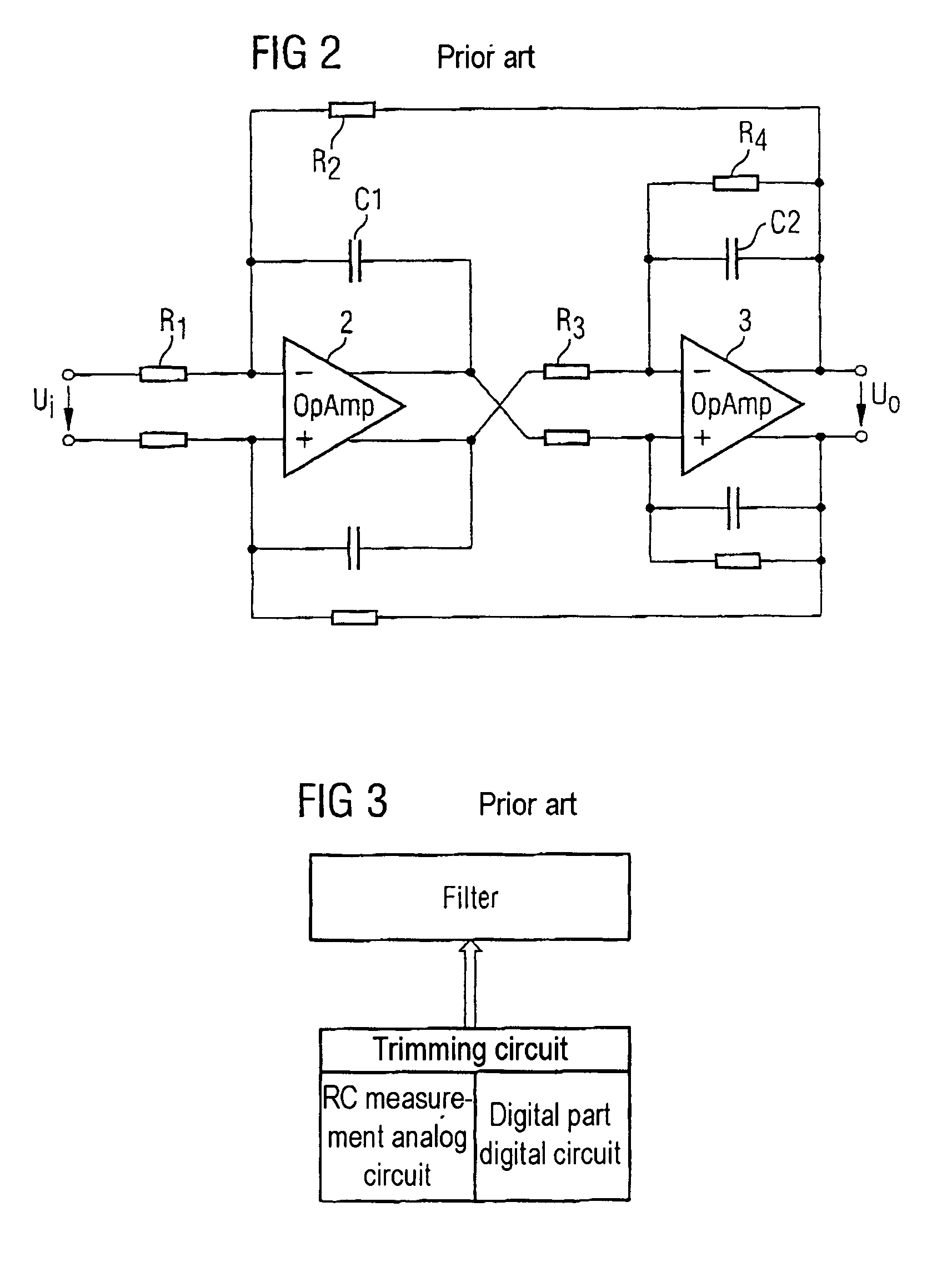

Tuning circuit for a filter

ActiveUS7002404B2Space minimizationImprove accuracyMultiple-port networksTransmission control/equlisationCapacitanceRC time constant

The invention relates to a tuning circuit for tuning a filter stage, which has an RC element (1) with an RC time constant (τ), with the RC time constant (τ) being the product of the resistance of a resistor (R1) in the RC element (1) and the capacitance of a capacitor (C1), which is connected in series with the resistor (R1), in the RC element (1), having a comparator (10) for comparison of the voltage which is produced at the potential node (4) between the resistor (R1) and the capacitor (C1), with a reference ground voltage; and having a controller (15) which varies the charge on the capacitor (C1) in the RC element (1) until the comparator (10) indicates that the voltage which is produced at the potential node (4) is equal to the reference ground voltage, with the controller (15) switching a capacitor array (26) as a function of the charge variation time, which capacitor array (26) is connected in parallel with the capacitor (C1) in the RC element (1), in order to compensate for any discrepancy between the RC time constant (τ) of the RC element (1) and a nominal value.

Owner:MAXLINEAR INC

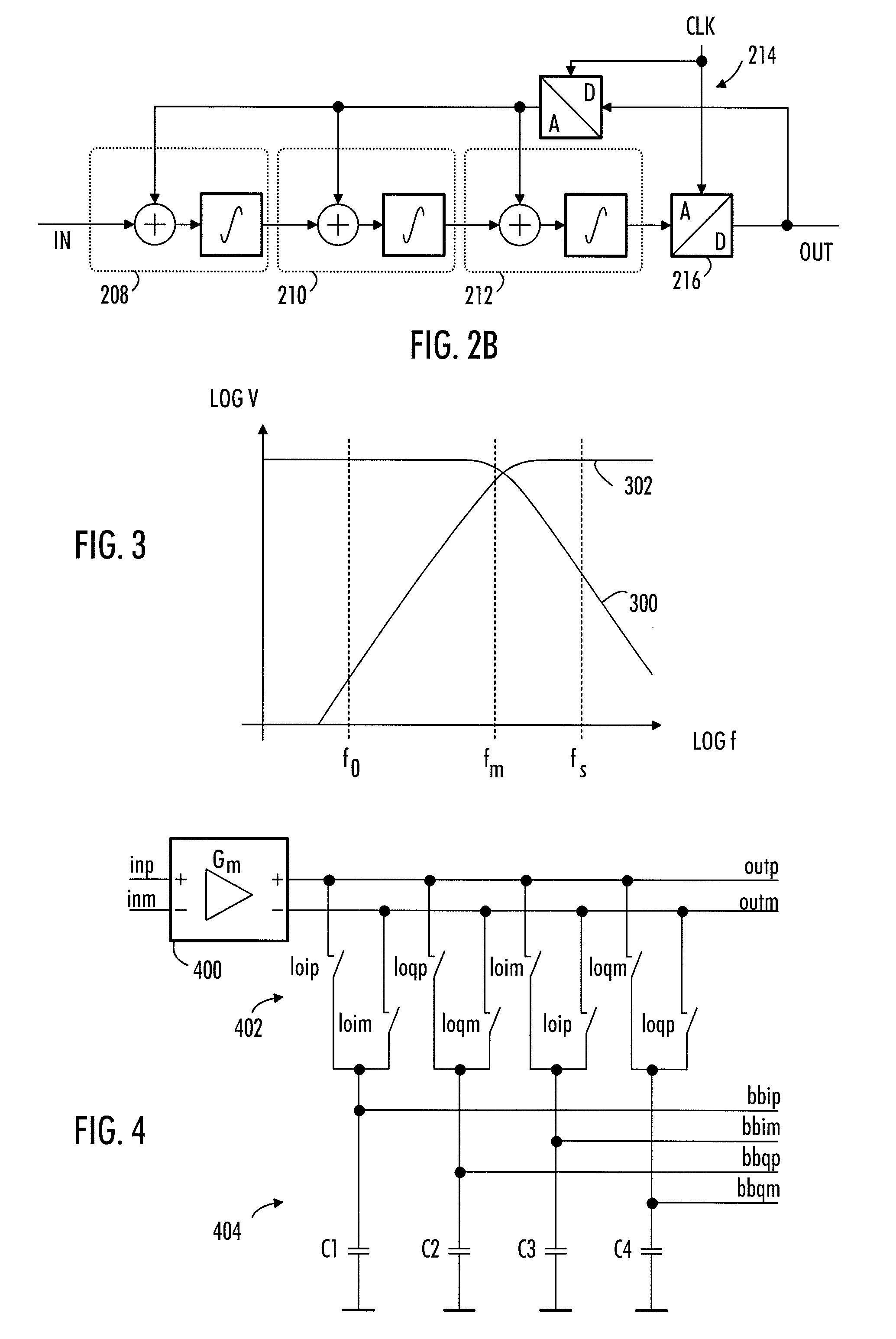

Reconfigurable baseband filter

ActiveUS20040209591A1Reduce switching noiseSimultaneous amplitude and angle demodulationActive element networkCommunications systemEngineering

A reconfigurable baseband filter for use in a multimode communication system is disclosed. One or more filter elements can each be configured as a plurality of sub-elements. The value of each of the filter elements can be varied by switching between at least two of the plurality of sub-elements. Switching noise within a desired passband can be reduced by switching at a rate that is greater than the desired passband. The switching noise in the passband can be further reduced by pseudo-randomly switching between the sub-elements. The filter can use a delta-sigma modulator to generate a pseudo-random switching signal.

Owner:SPREADTRUM

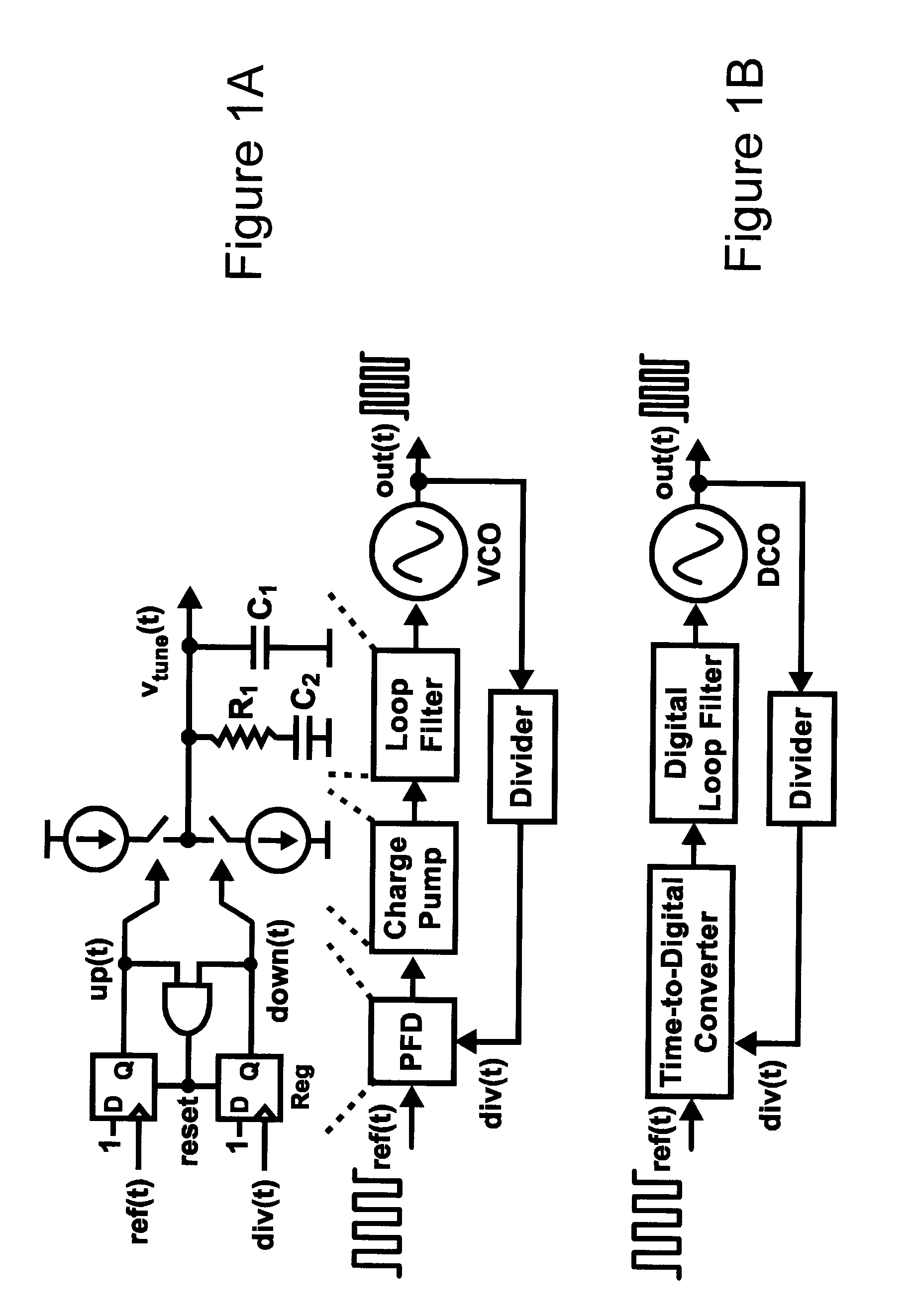

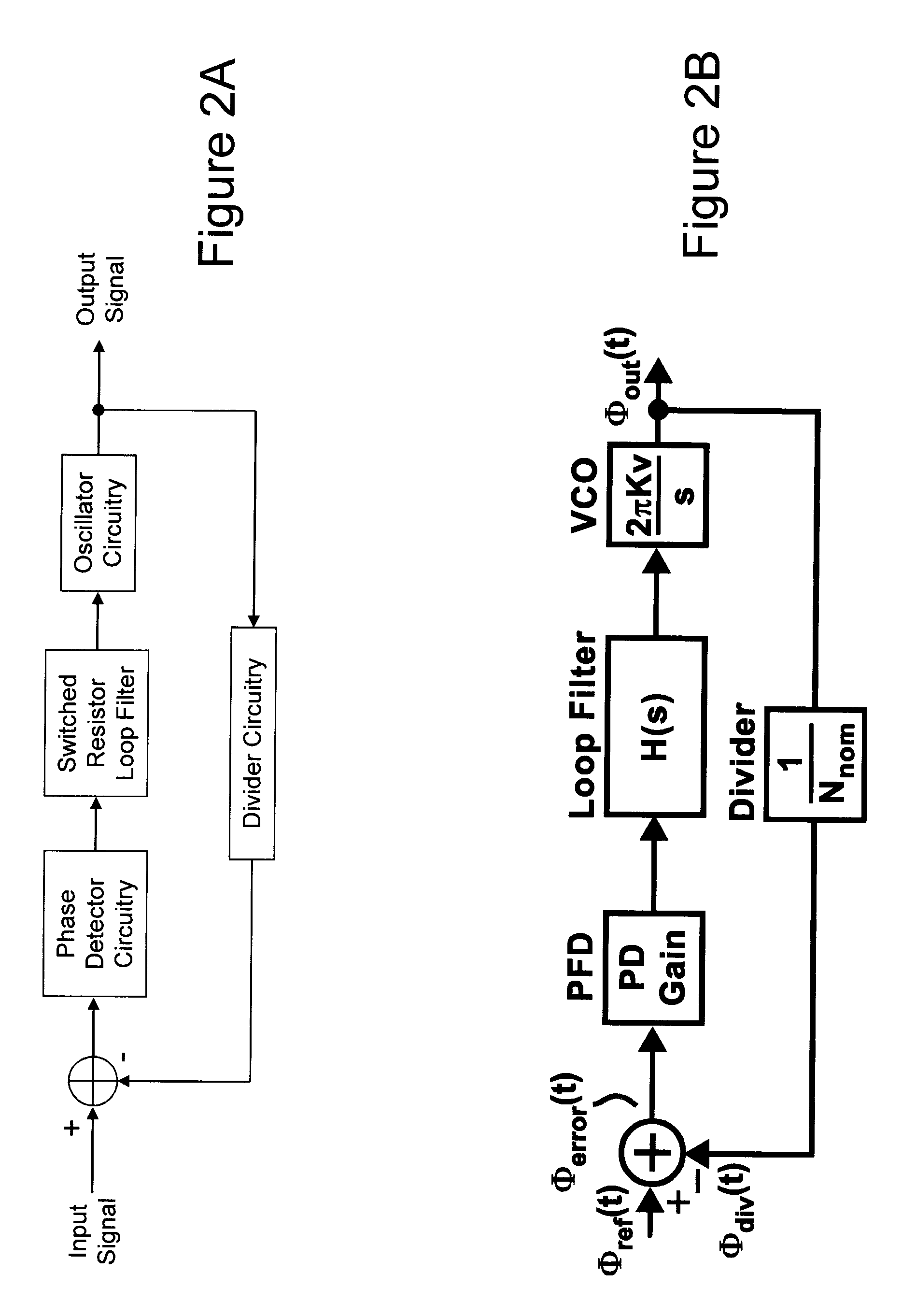

Phase Locked Loop Circuitry Having Switched Resistor Loop Filter Circuitry, and Methods of Operating Same

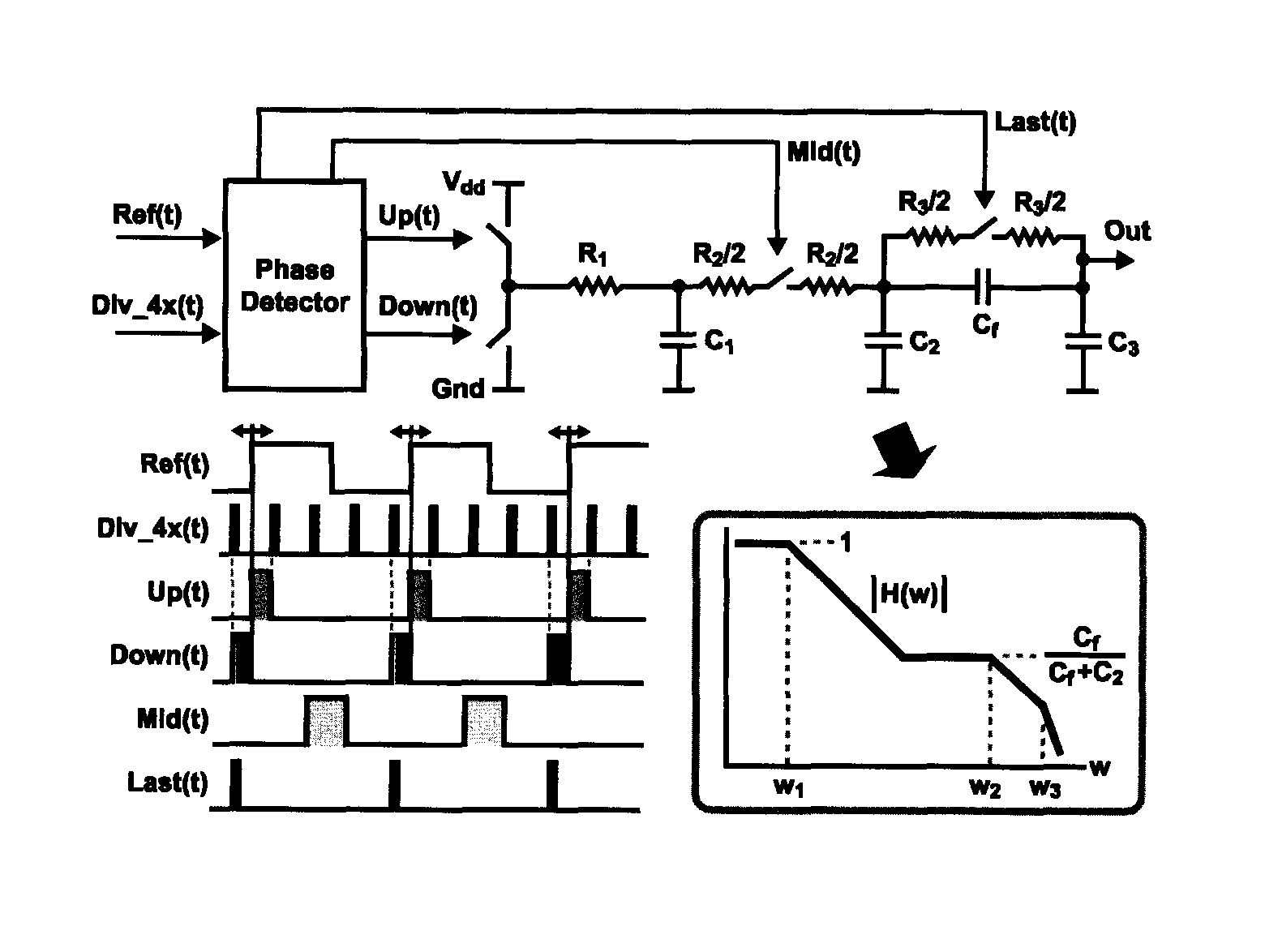

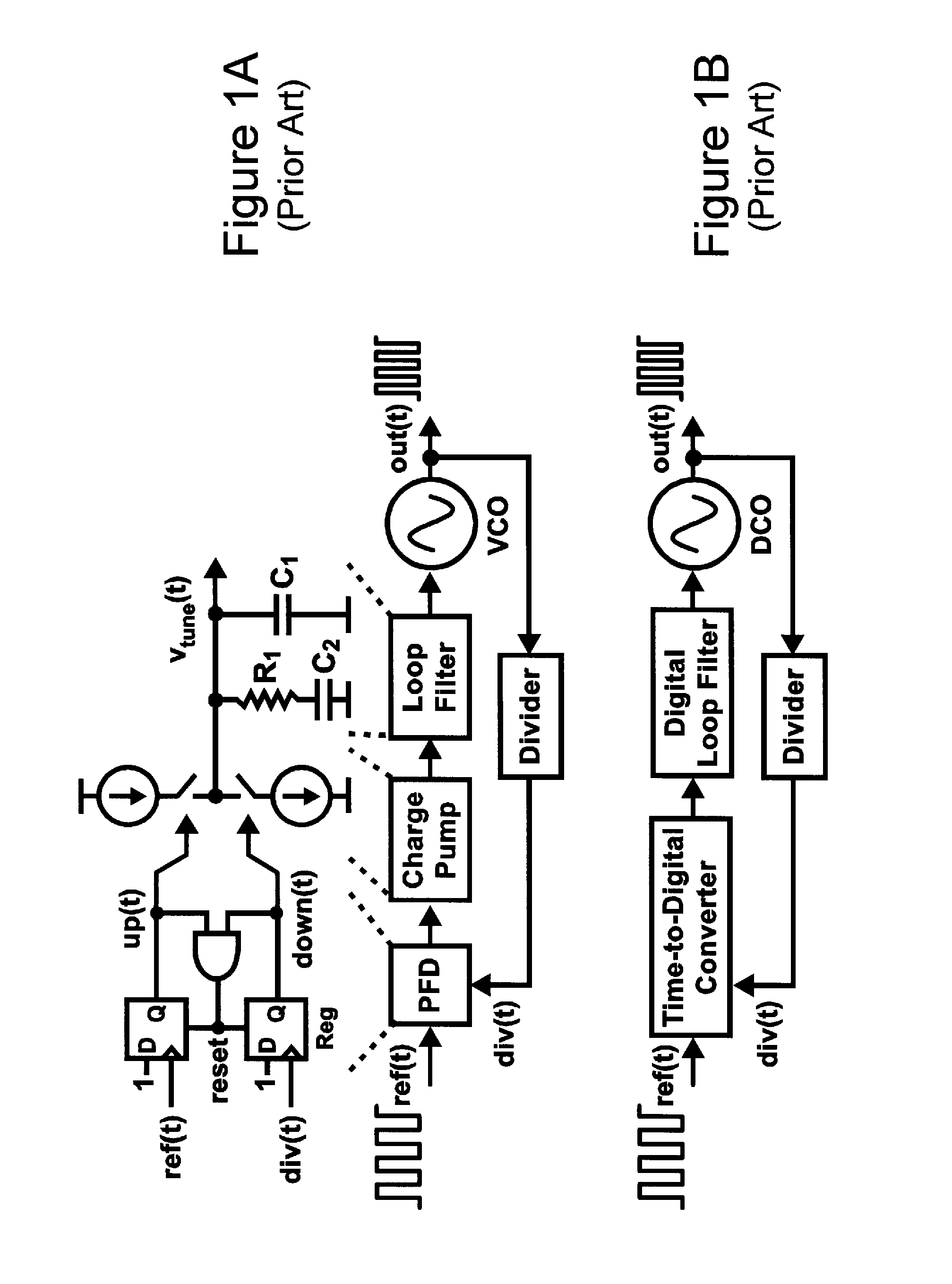

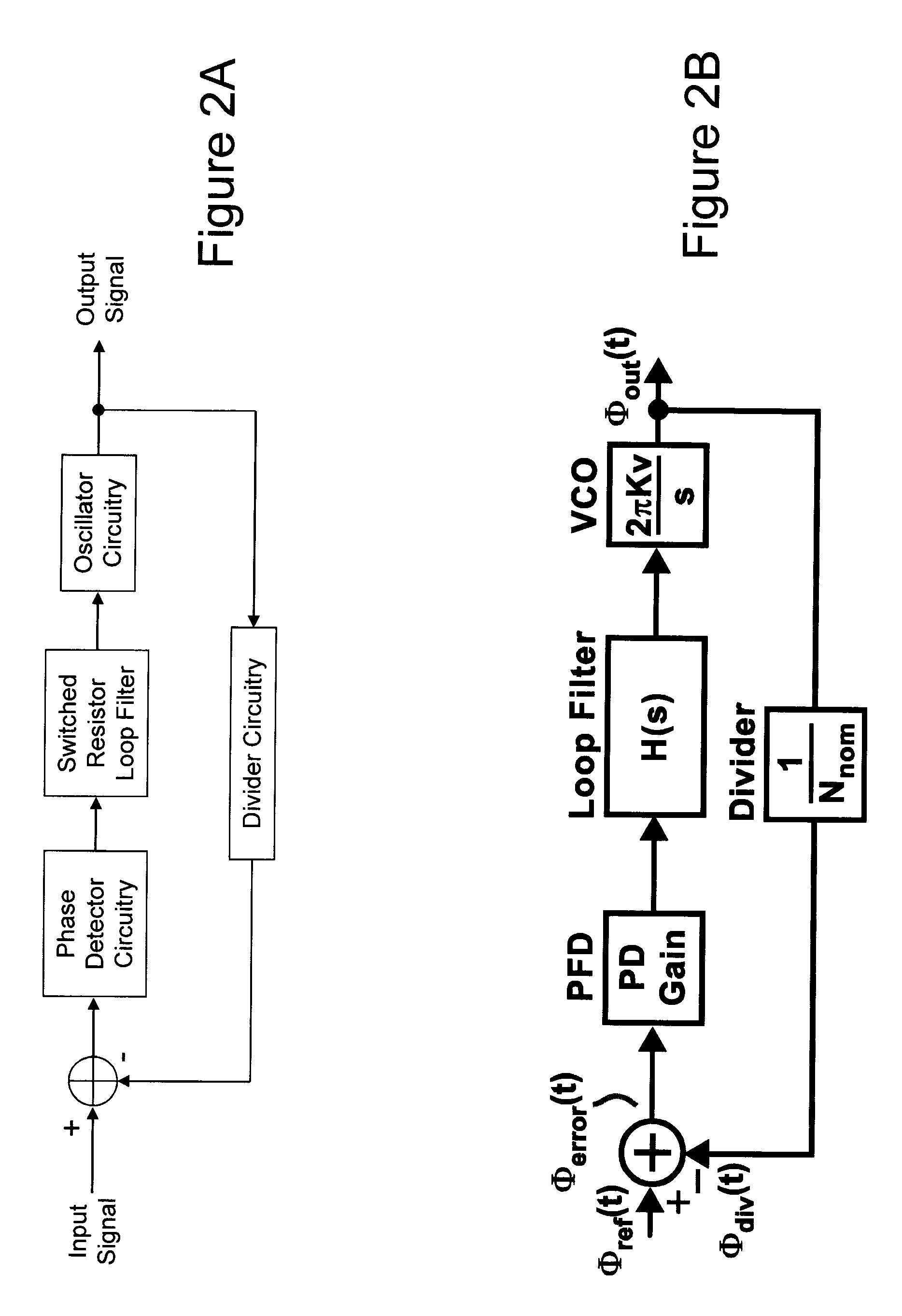

ActiveUS20110050301A1Reduce areaOptimizationPulse automatic controlNetworks with variable switch closing timeCapacitanceLoop filter

Owner:SITIME

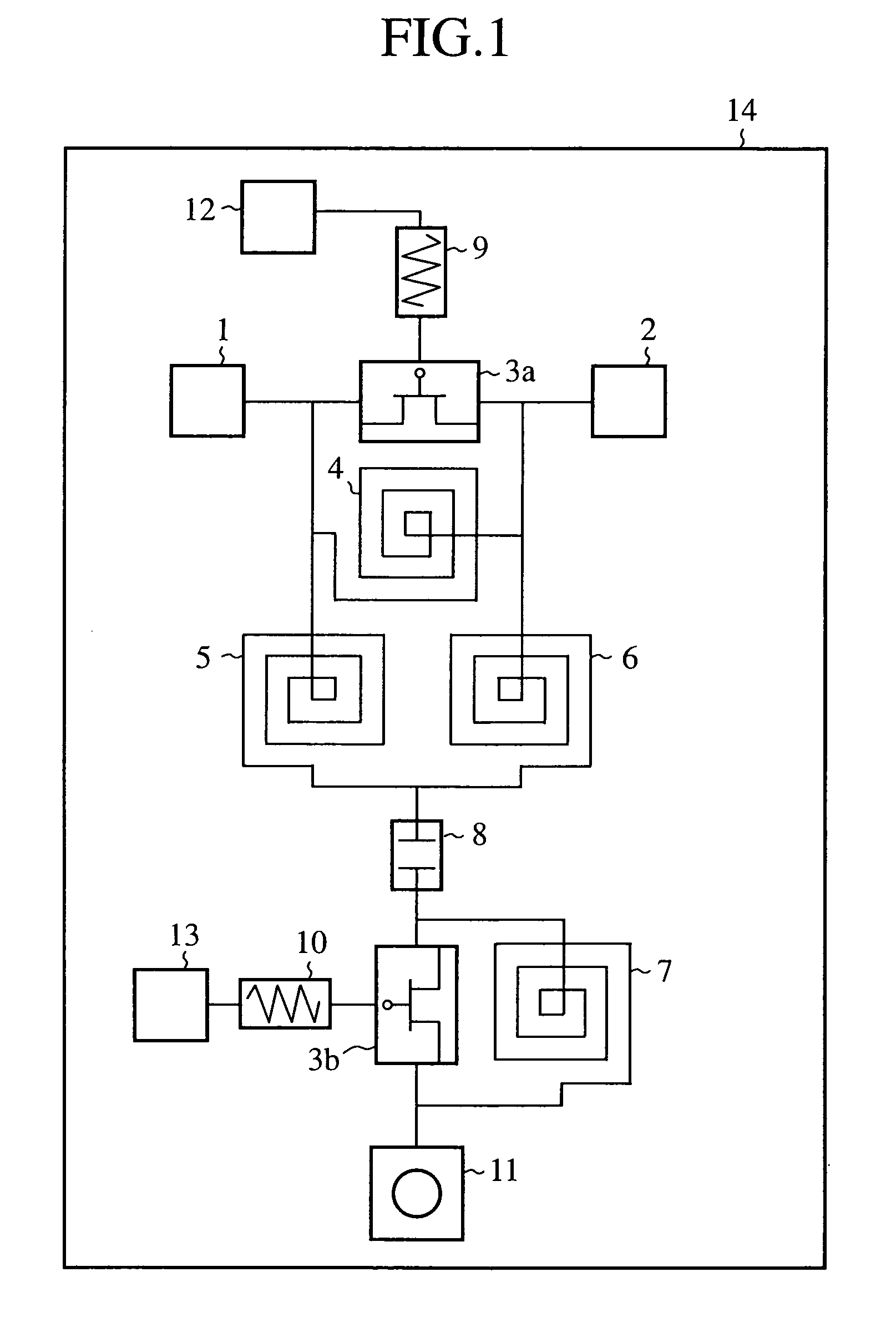

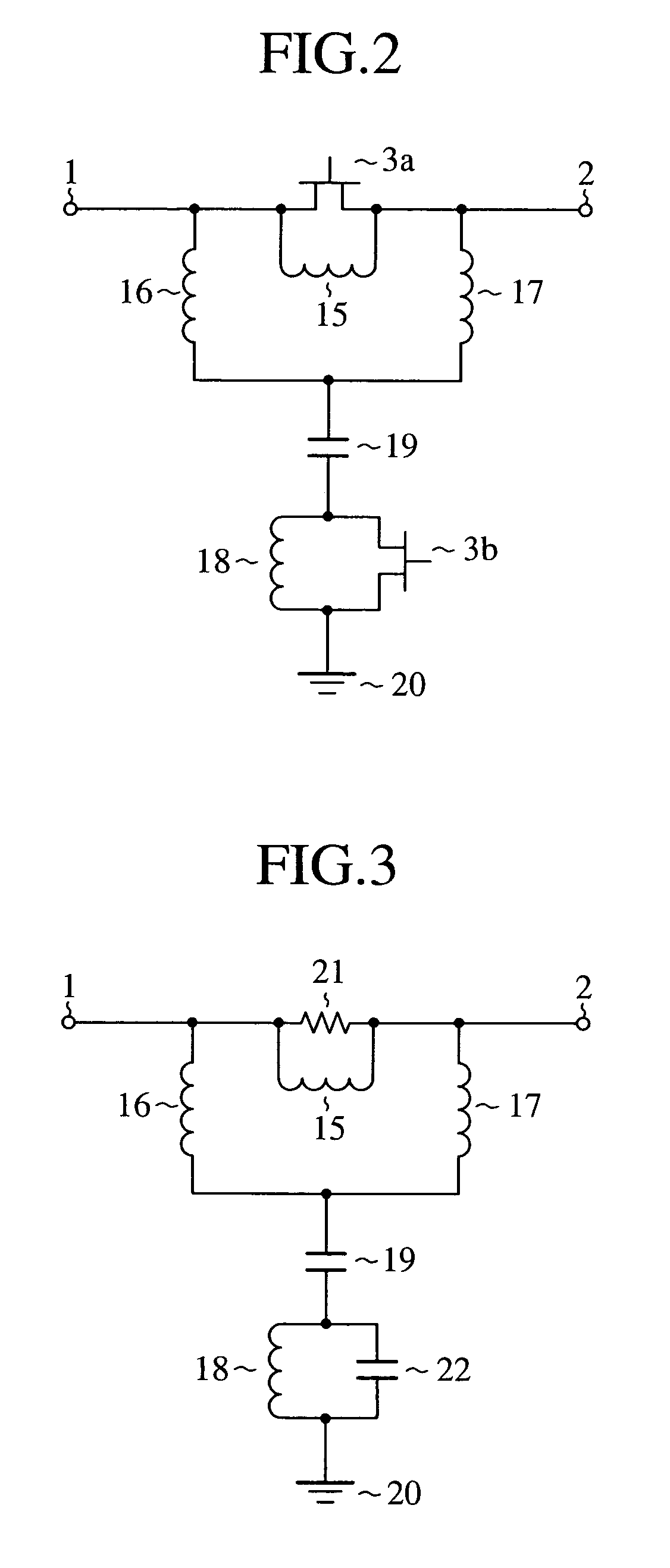

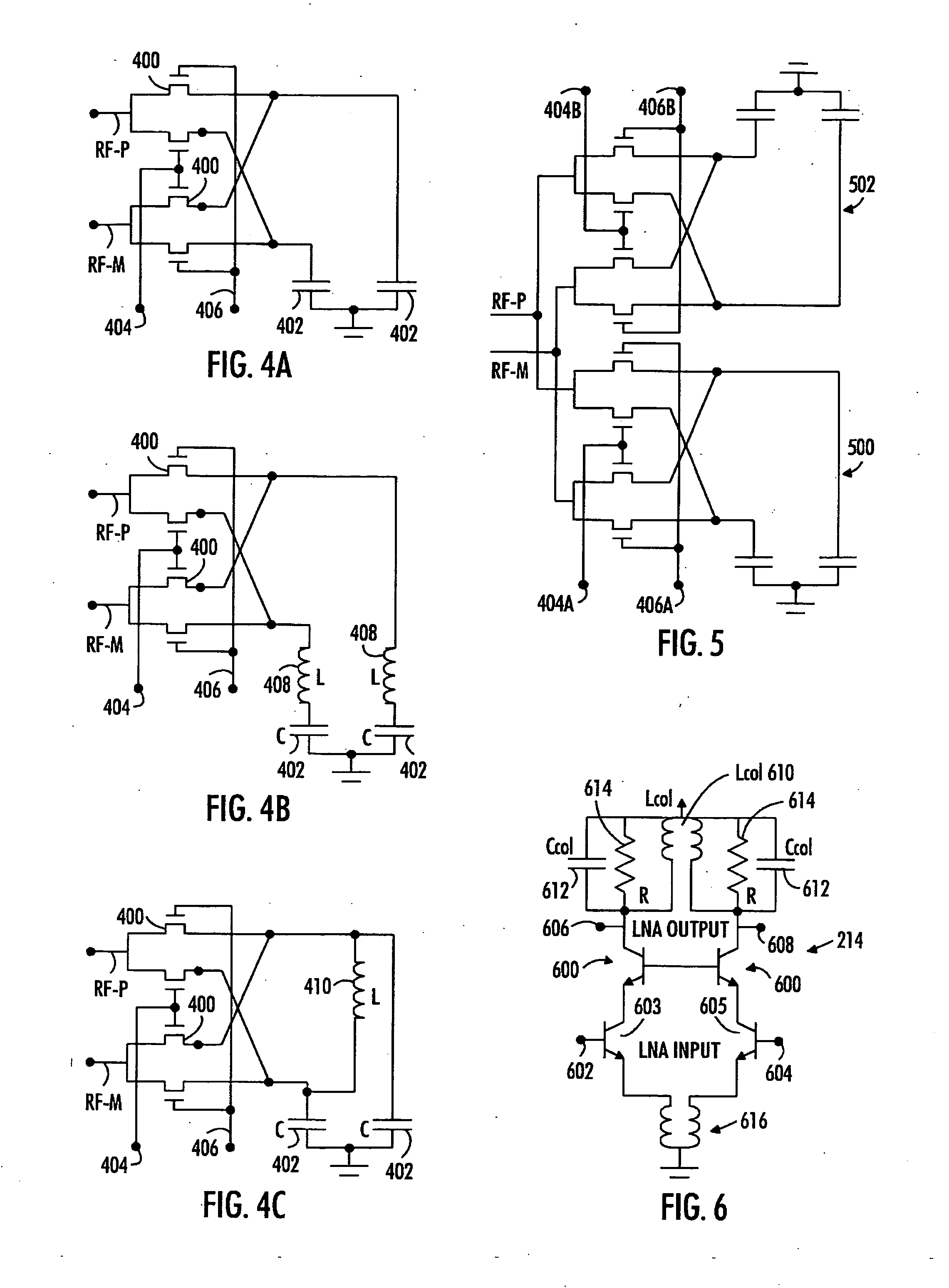

Transceiver including a weaved connection

A transceiver includes a local oscillation module, a transmitter section, and a receiver section. The local oscillation module is operable to generate a transmit local oscillation and a receive oscillation. The transmitter section includes a transmit mixing module and a transmit weaved connection that is operable to high frequency filter the transmit location oscillation. The transmit mixing module mixes the filtered transmit location oscillation with a transmit signal to produce an up-converted signal. The receiver section includes a receive mixing module and a receive weaved connection that is operable to high frequency filter the receive location oscillation. The receive mixing module mixes the filtered receive location oscillation with an RF received signal to produce a down-converted signal.

Owner:AVAGO TECH INT SALES PTE LTD

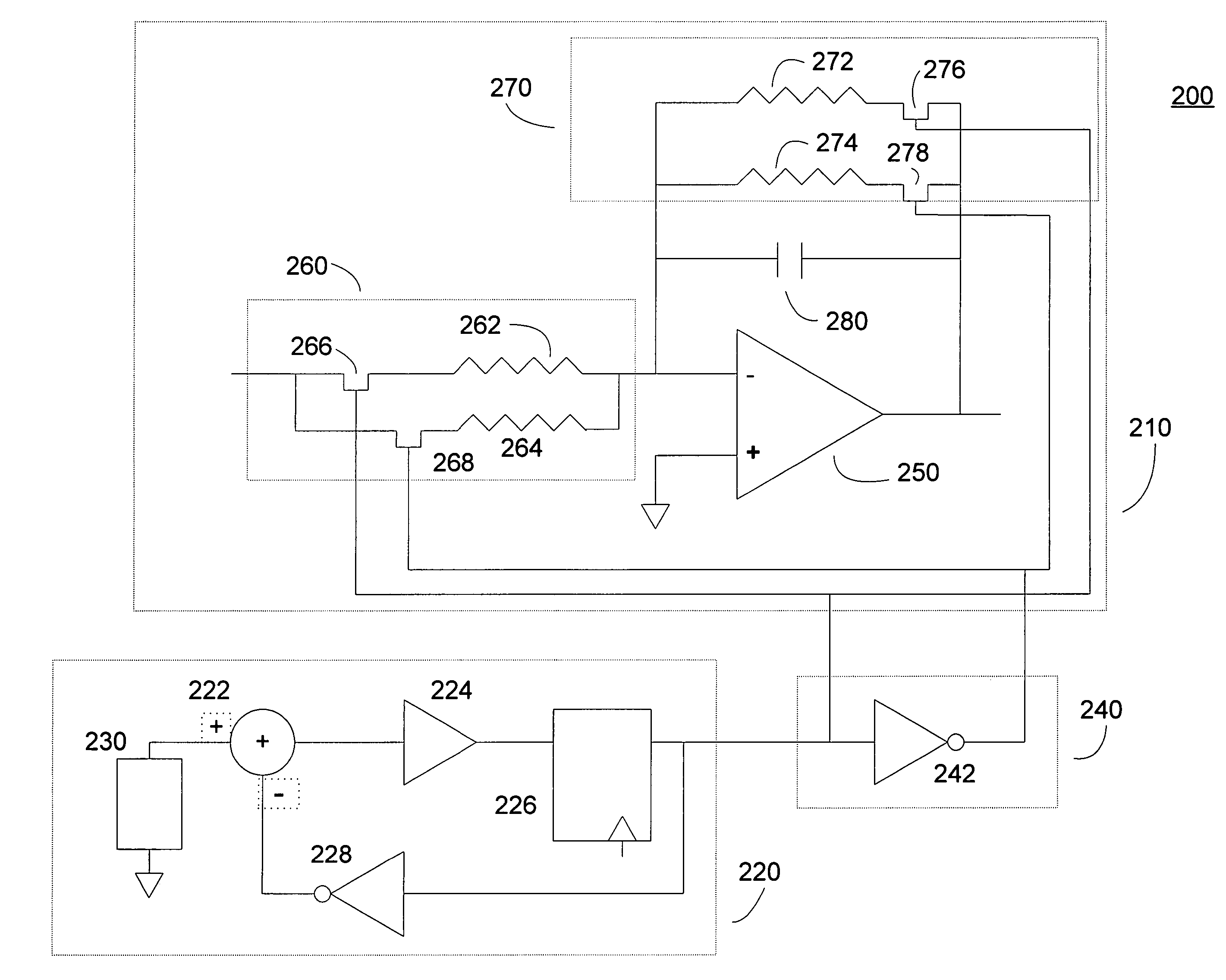

Phase locked loop circuitry having switched resistor loop filter circuitry, and methods of operating same

ActiveUS8299826B2Reduce areaOptimizationPulse automatic controlNetworks with variable switch closing timeCapacitancePhase detector

Phase-locked loop circuitry to generate an output signal, the phase-locked loop circuitry comprising oscillator circuitry, switched resistor loop filter, coupled to the input of the oscillator circuitry (which, in one embodiment, includes a voltage-controlled oscillator), including a switched resistor network including at least one resistor and at least one capacitor, wherein an effective resistance of the switched resistor network is responsive to and increases as a function of one or more pulsing properties of a control signal (wherein pulse width and frequency (or period) are pulsing properties of the control signal), phase detector circuitry, having an output which is coupled to the switched resistor loop filter, to generate the control signal (which may be periodic or non-periodic). The phase-locked loop circuitry may also include frequency detection circuitry to provide a lock condition of the phase-locked loop circuitry. The frequency detection circuitry includes (i) circuitry to generate a signal which is representative of the frequency of the output signal of the phase-locked loop circuitry, (ii) comparison circuitry to compare the signal which is representative of the frequency of the output signal of the phase-locked loop circuitry to a reference input to the phase-locked loop circuitry, and (iii) a switched capacitor network including at least one capacitor.

Owner:SITIME

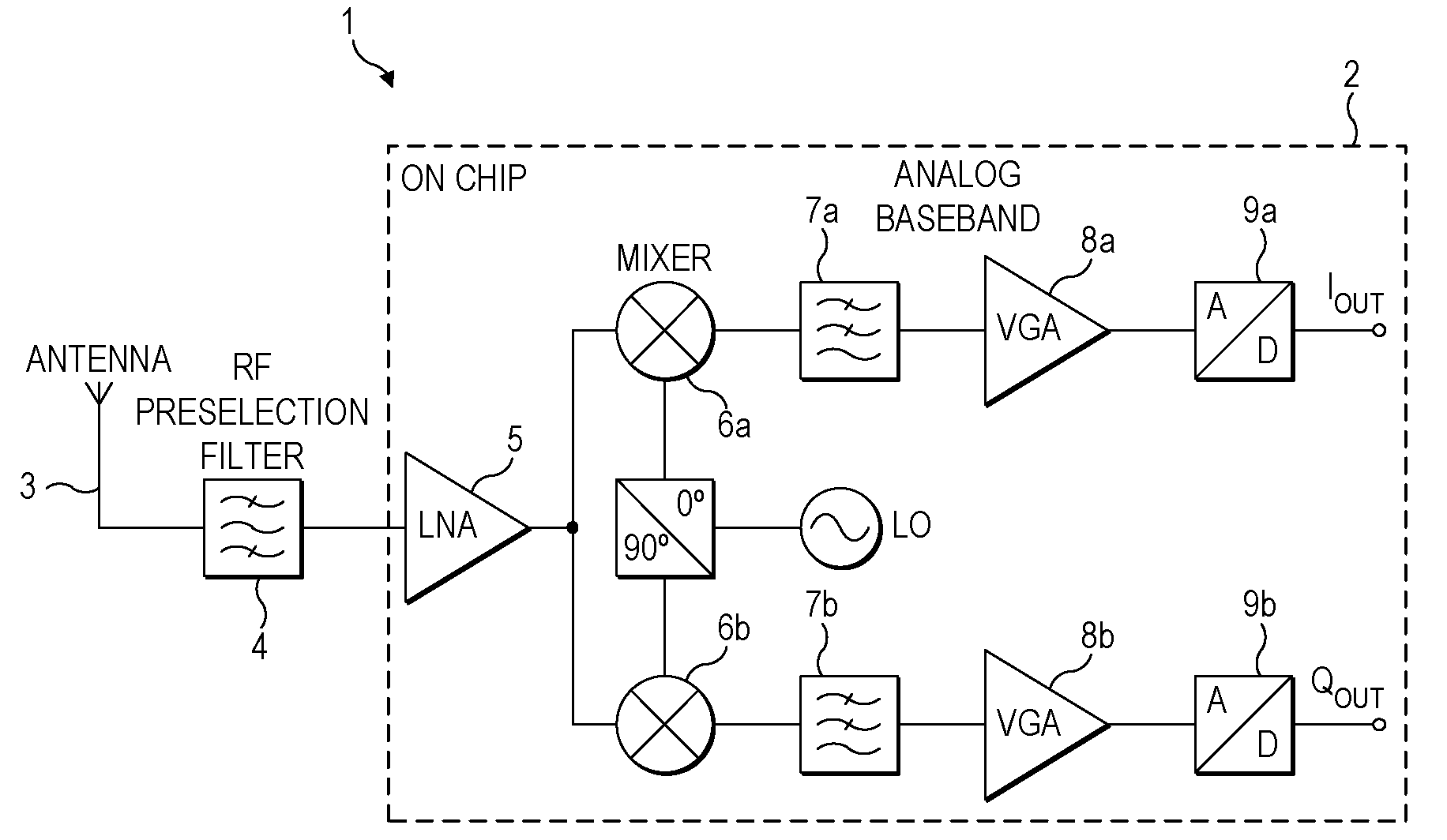

Apparatus comprising frequency selective circuit and method

ActiveUS20100097258A1Improve frequency selectivityImprove Noise PerformanceElectric signal transmission systemsTransversal filtersBandpass filteringAnalog signal

An apparatus, having as an input an analog signal, is provided. The apparatus comprises a first circuit comprising an impedance transferring circuit configured to band pass filter the input signal, obtaining a filtered signal; the impedance transferring circuit comprising: a transconductance amplifier (1102), and a switching arrangement (1106, 1108) and an impedance circuit (404) connected in series, the switching arrangement being configured to switch the impedance of the impedance circuit of the impedance transferring circuit from base band to the frequency of the input signal. The apparatus further comprises a second circuit (1112) configured to perform down mixing to the filtered signal obtaining a base band signal and a feedback loop connecting the base band signal to the switching arrangement (1114, 1116) and the impedance circuit, the signal of the feedback loop configured to control the properties of the first circuit.

Owner:WSOU INVESTMENTS LLC

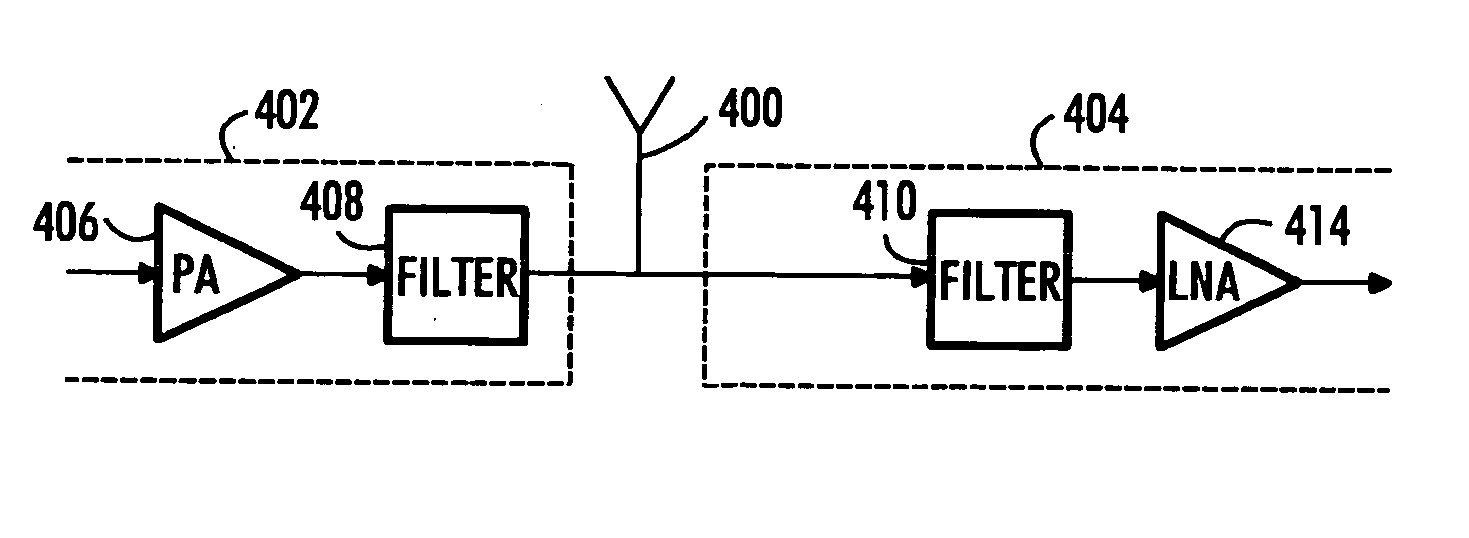

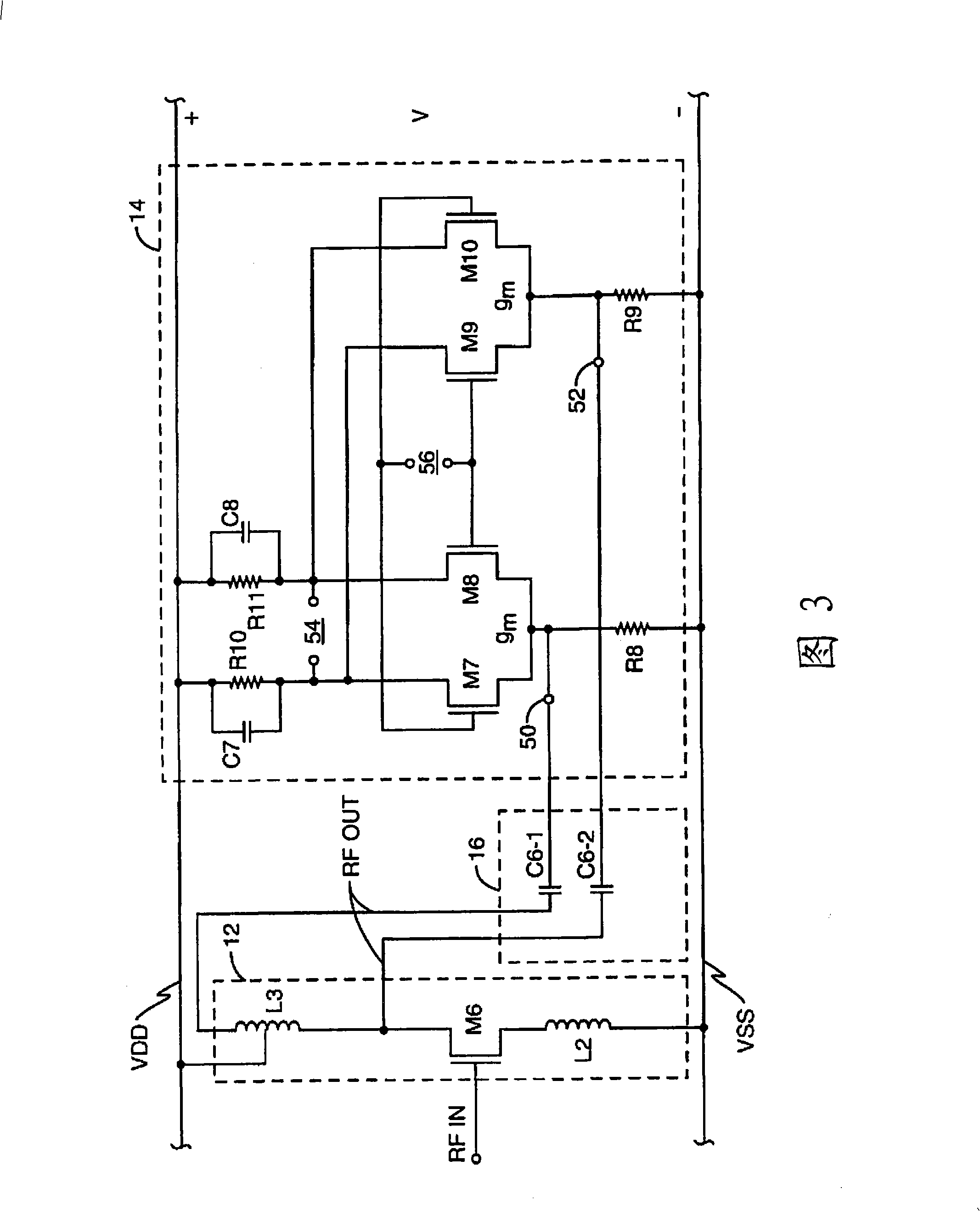

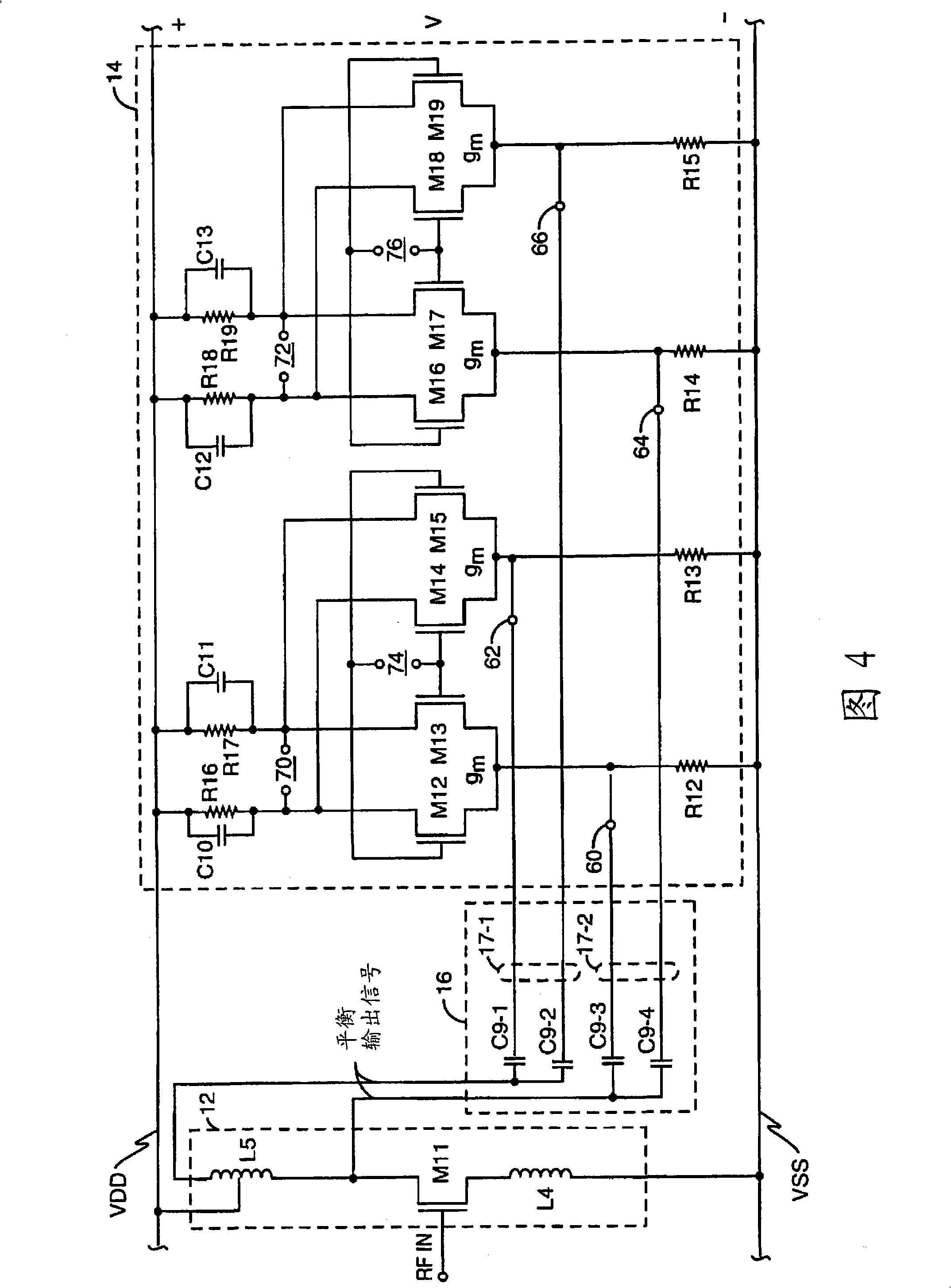

Transmitter, power amplifier and filtering method

ActiveUS20070218844A1Increases total transmitter chain efficiencyImprove power amplifier efficiencyResonant long antennasModulation with suppressed carrierAudio power amplifierTransceiver

A filtering method, a transceiver and a transmitter are provided. The transmitter comprises a power amplifier amplifying an RF signal and having multiple stages, and a local oscillator, the power amplifier comprising between at least two stages of the power amplifier an impedance circuitry for forming an impedance at a frequency related to the frequency of the local oscillator, and a switch for switching the impedance of the impedance circuitry means to RF frequency.

Owner:NOKIA TECHNOLOGLES OY

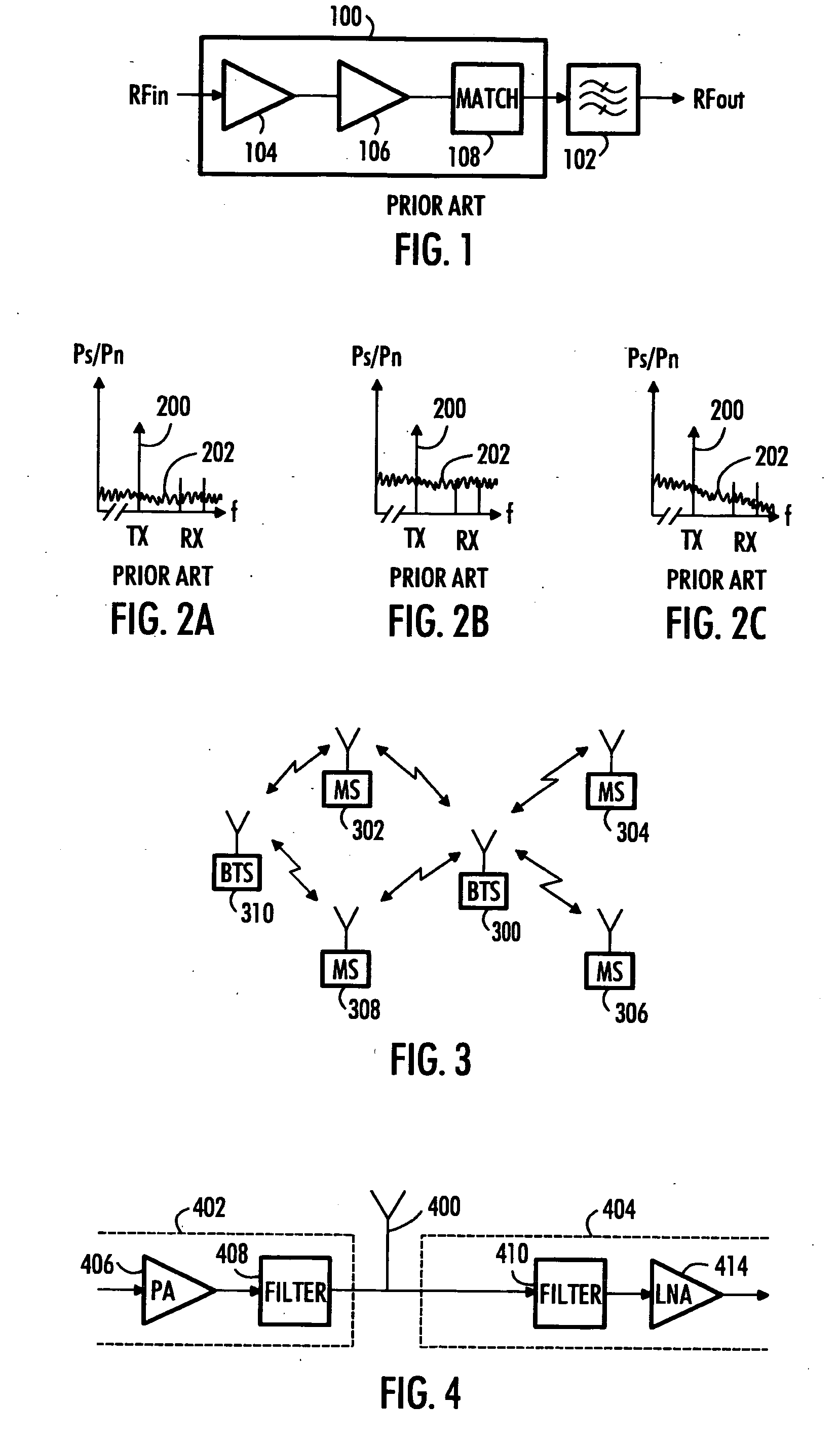

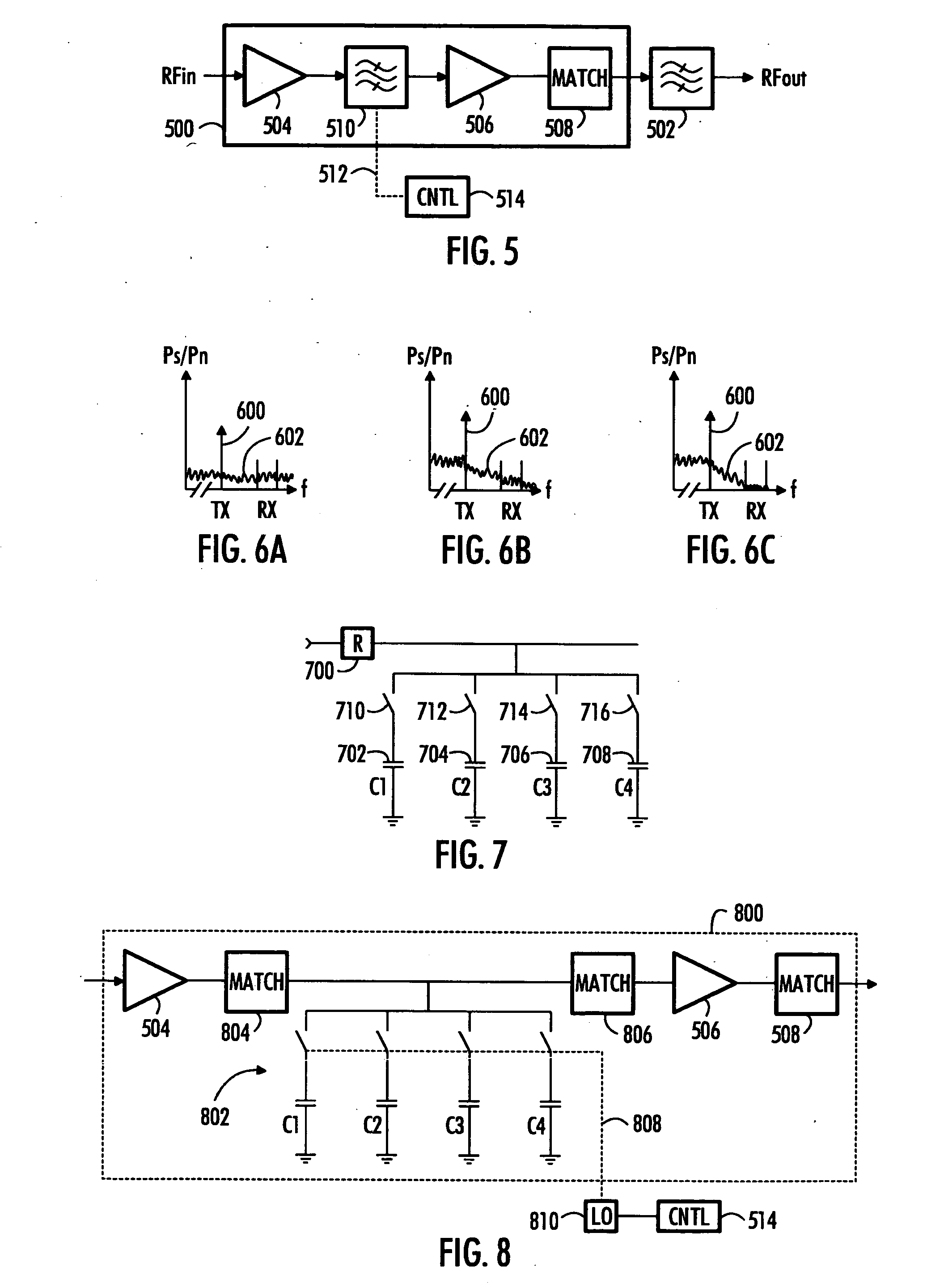

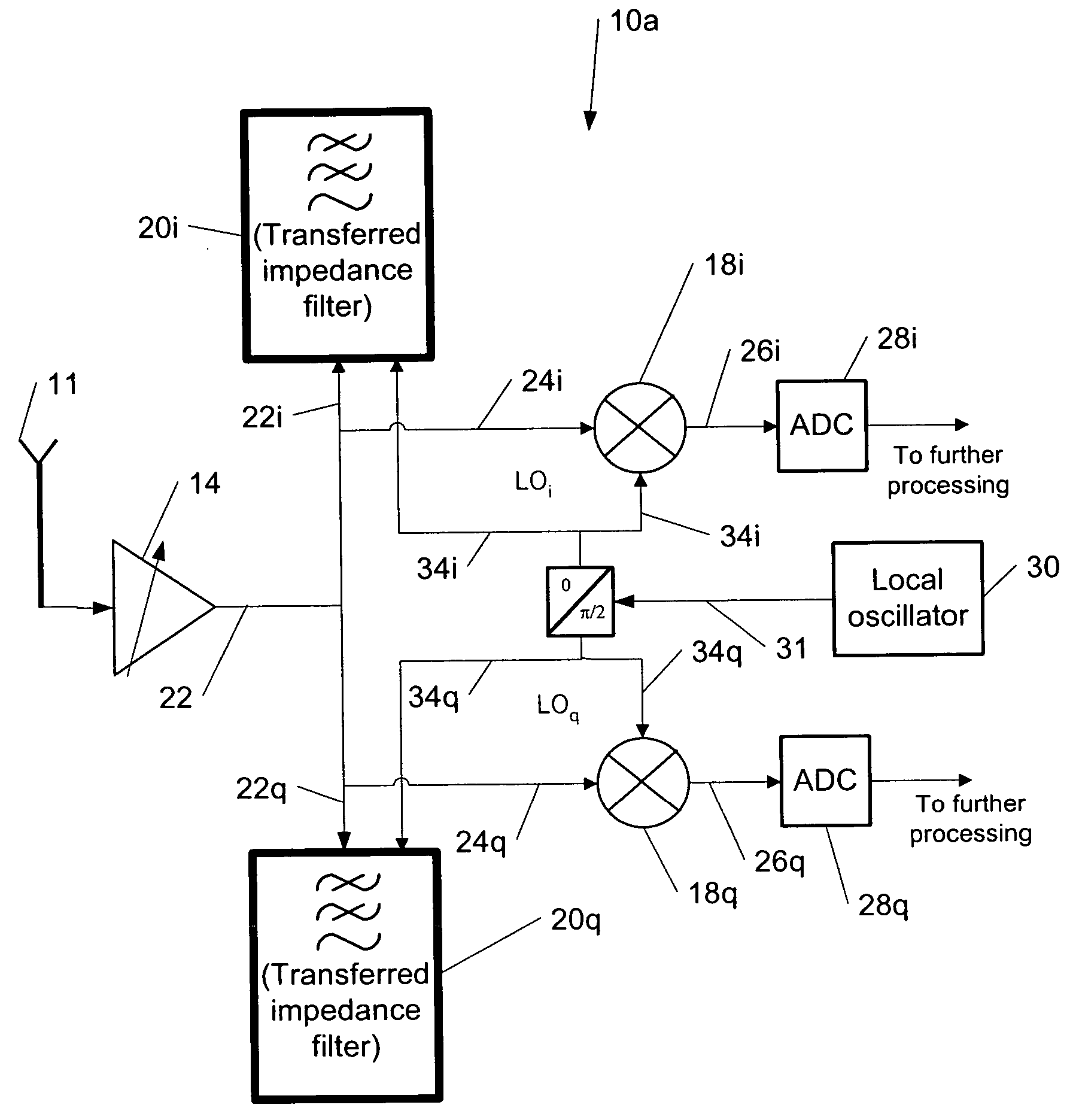

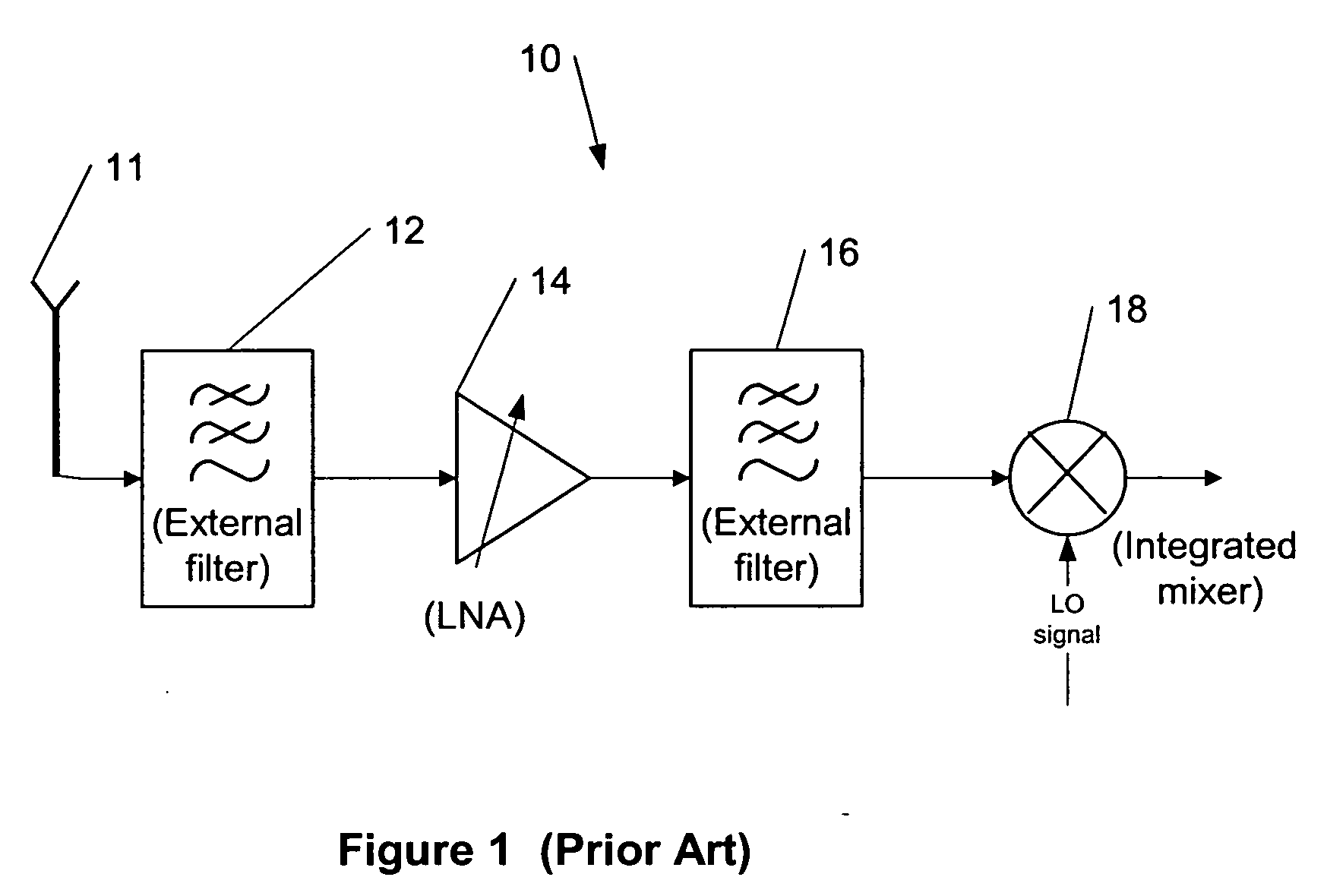

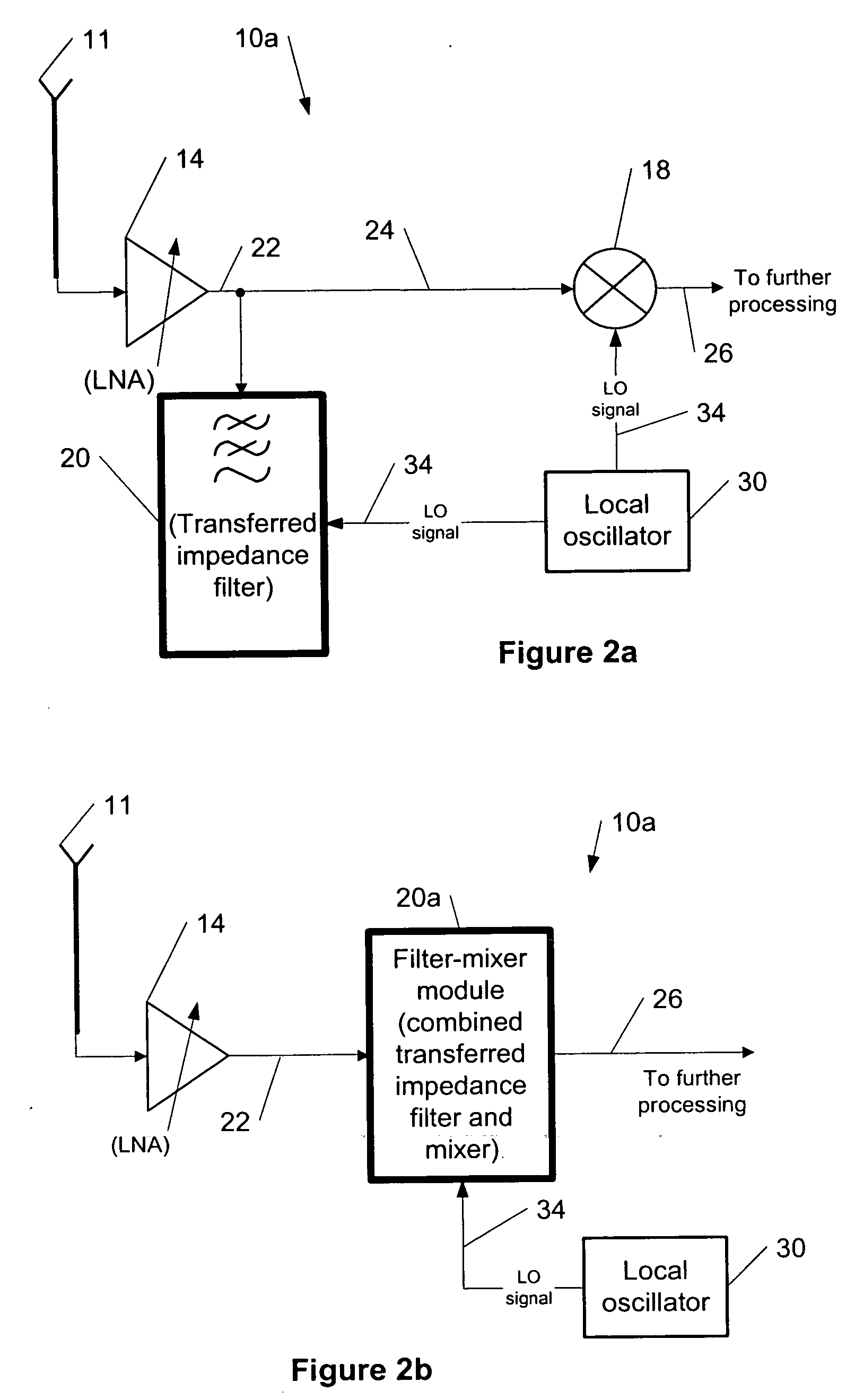

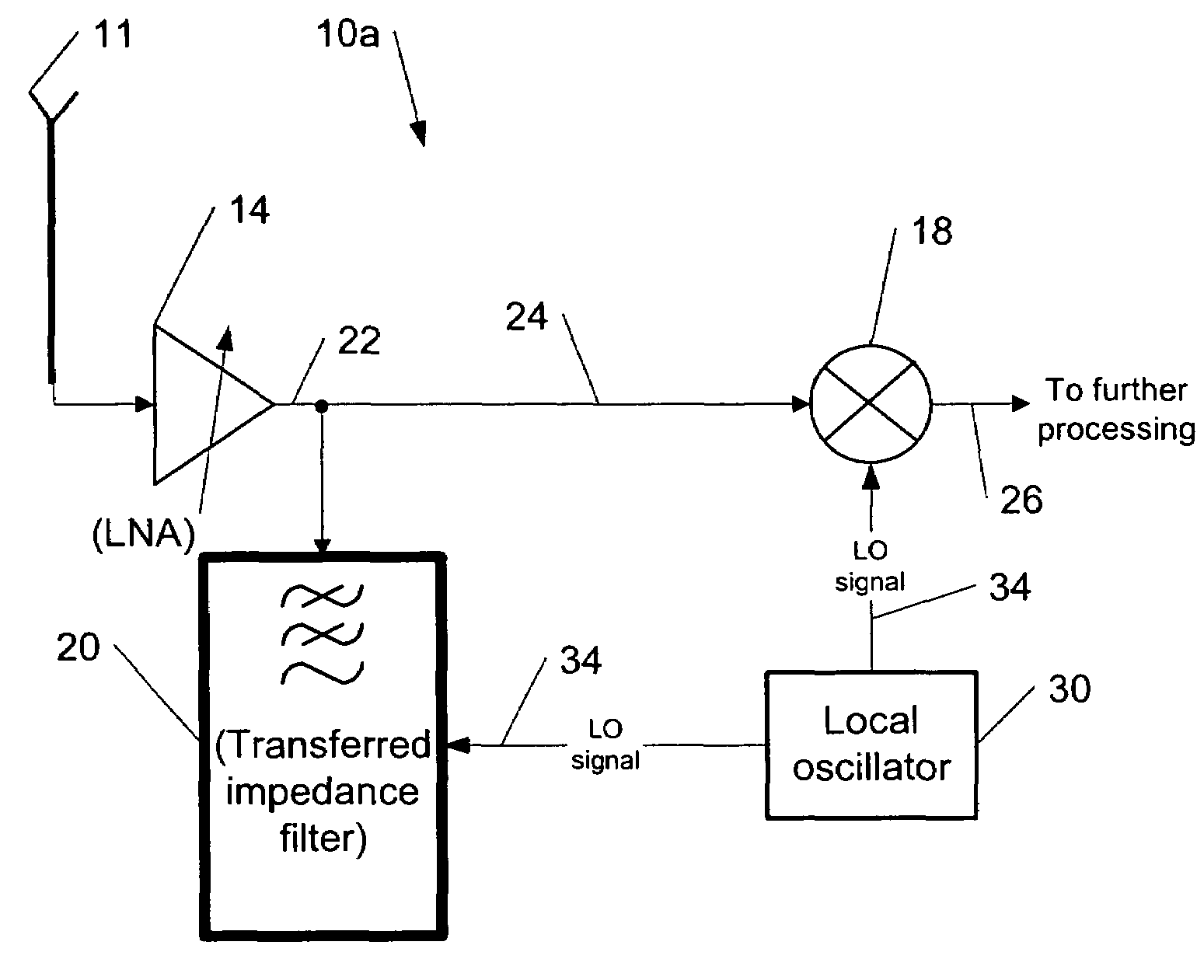

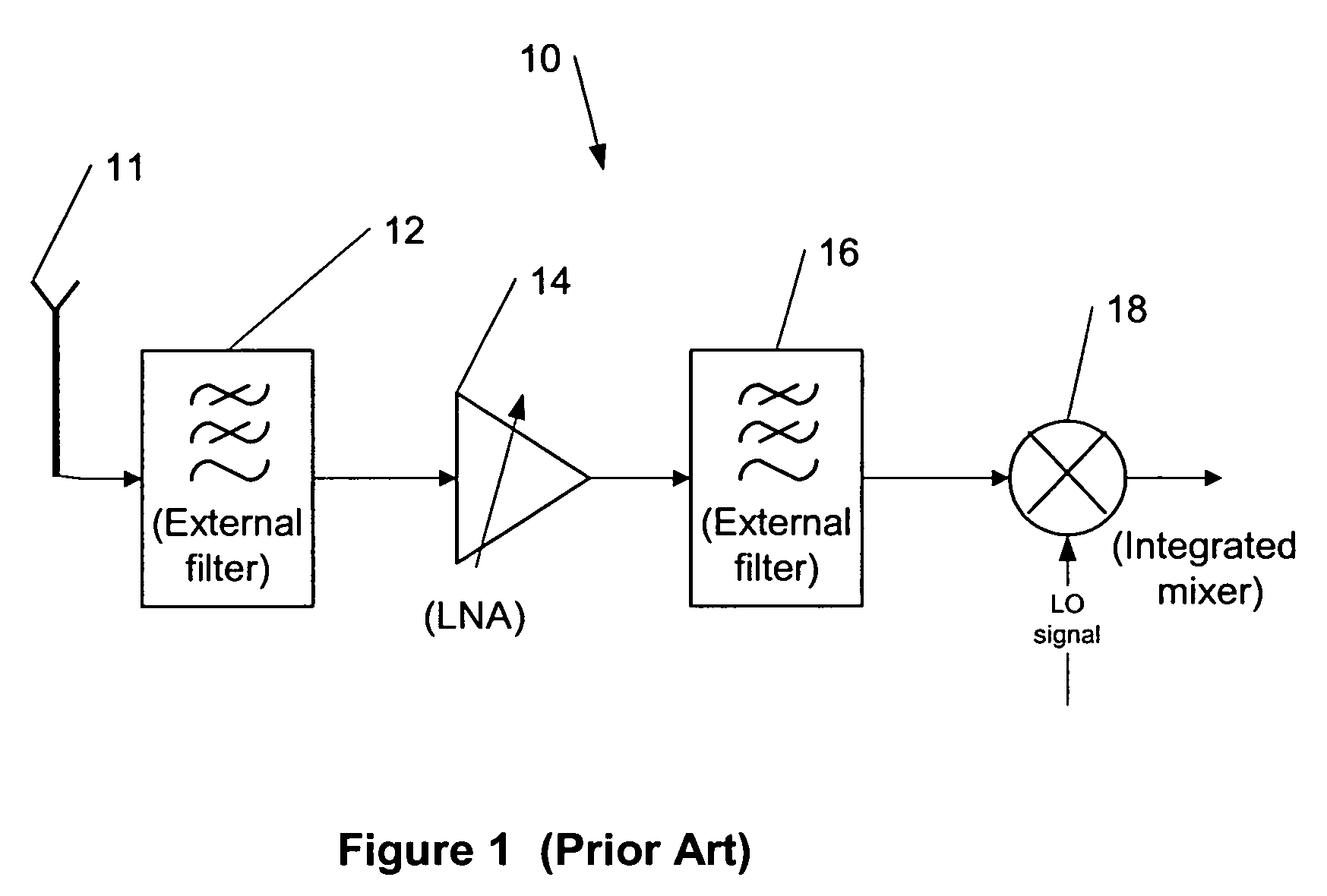

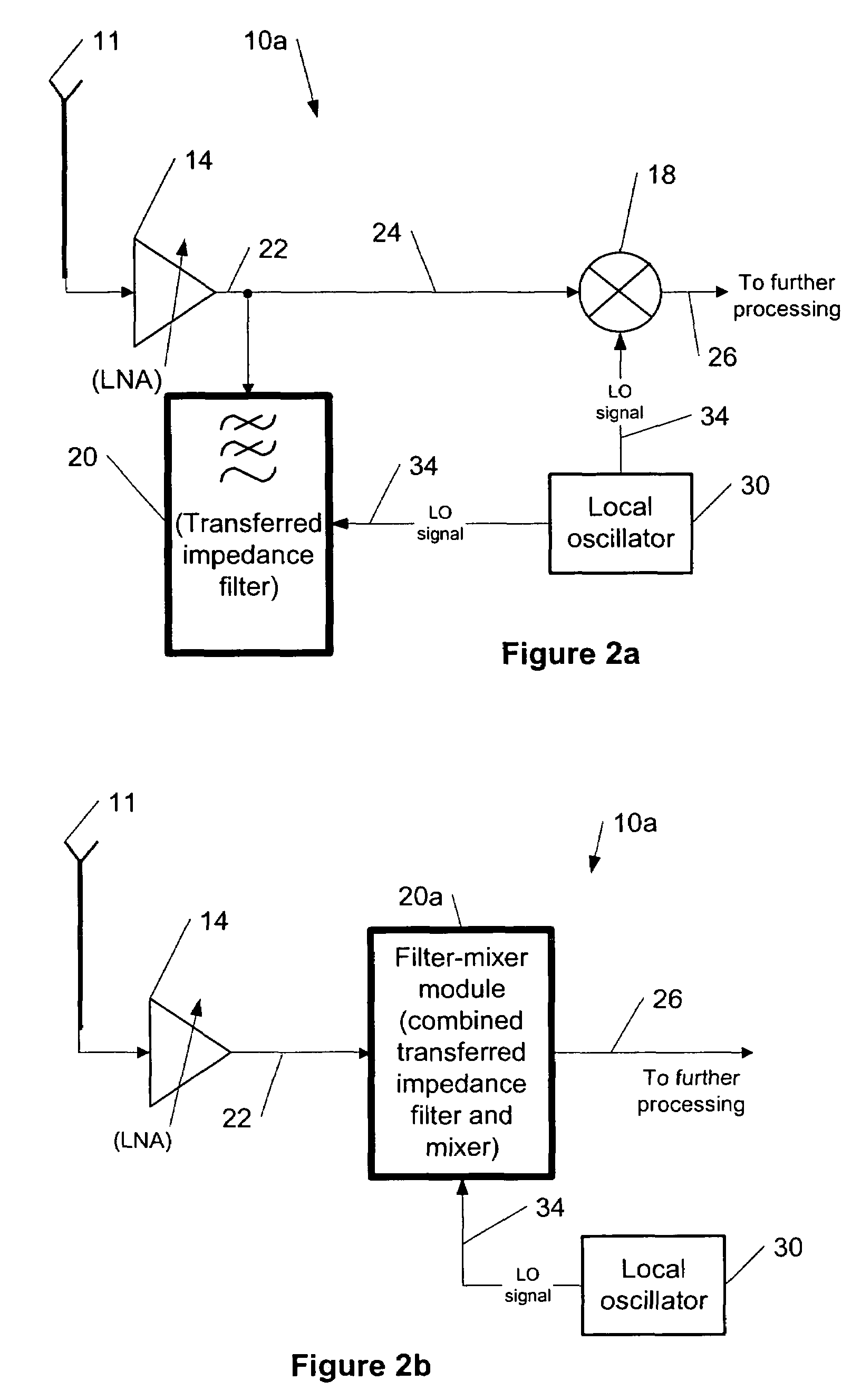

Transferred-impedance filtering in RF receivers

ActiveUS20060208791A1Easy accessNetworks with variable switch closing timeOscillations generatorsRFICFrequency filtering

The present invention provides a method for using transferred-impedance filtering in RF (radio frequency) receivers (e.g., inside of a mobile communication device), wherein said filtering can be done with MOS-switches transferring impedance of a regular RC or RCL circuit to RF frequency filtering inside an RFIC (radio frequency integrated circuit).

Owner:NOKIA TECHNOLOGLES OY

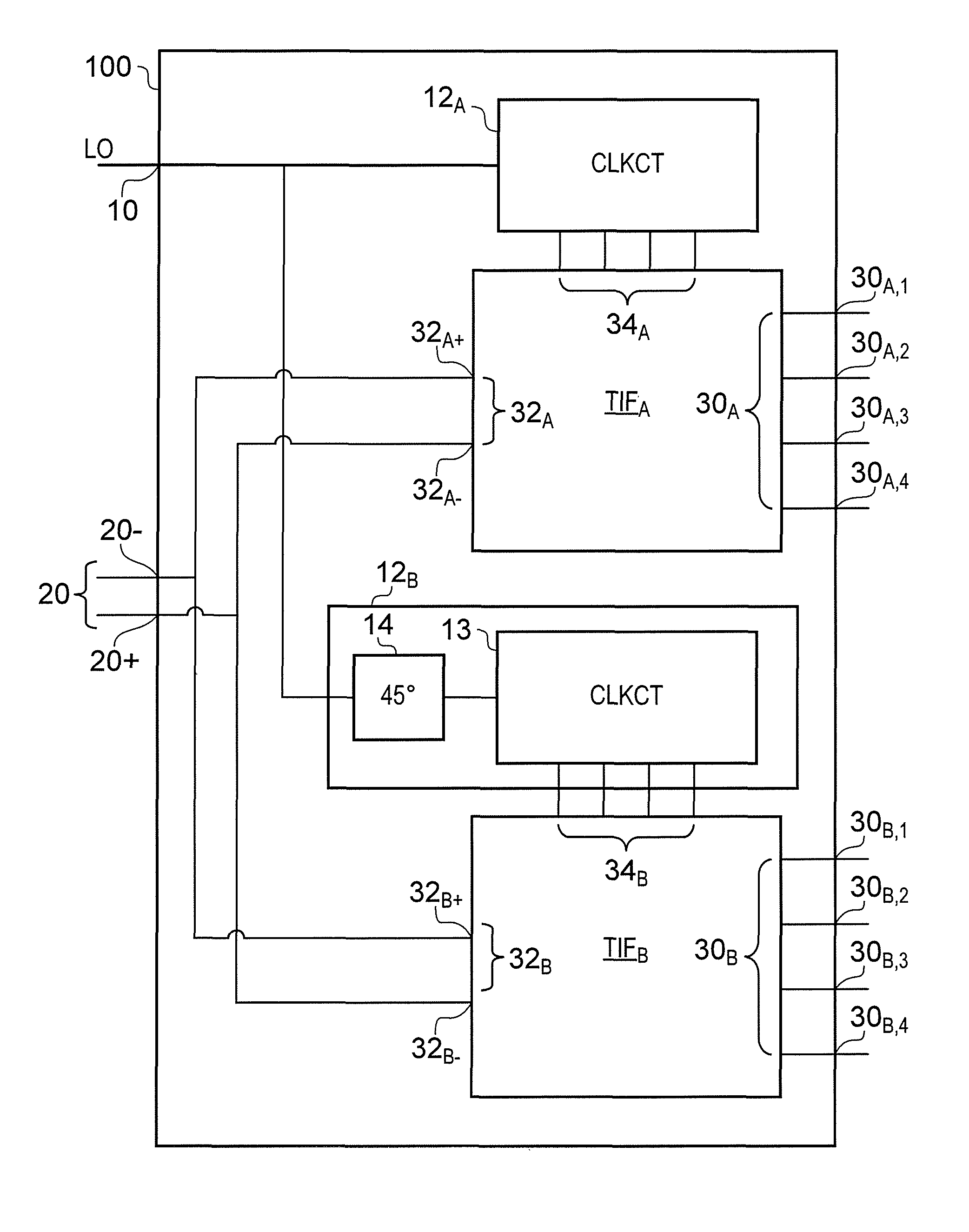

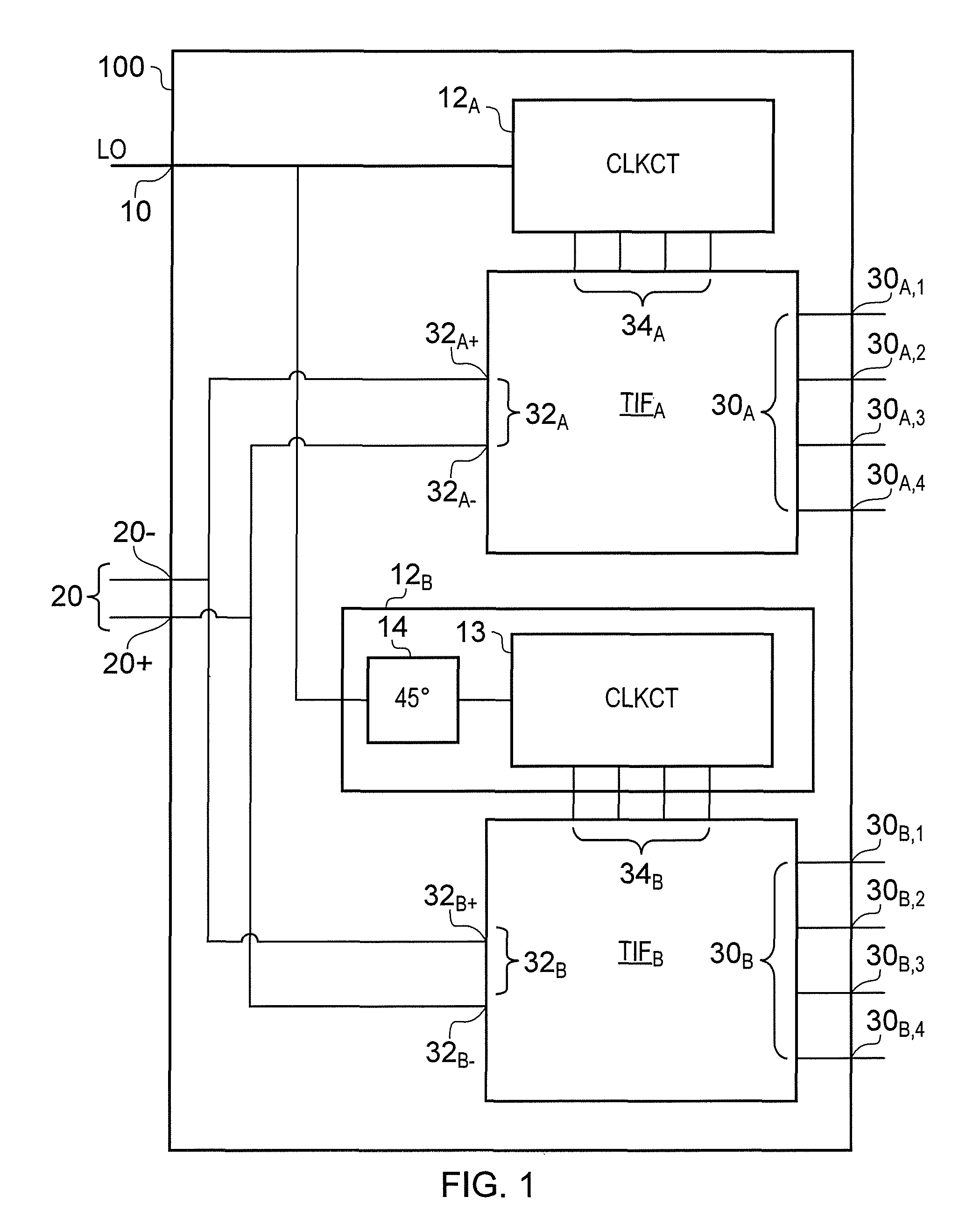

Multiple-phase frequency translated filter

A frequency translation filter includes a baseband filter circuit, a clock generator, and a switching circuit. The baseband filter circuit is operable to provide a baseband filter response. The clock generator is operable to generate multiple-phase clock signals at a desired frequency. The switching circuit is operable to frequency translate the baseband filter response of the baseband filter circuit to a high frequency filter response in accordance with the multiple-phase clock signals.

Owner:AVAGO TECH INT SALES PTE LTD

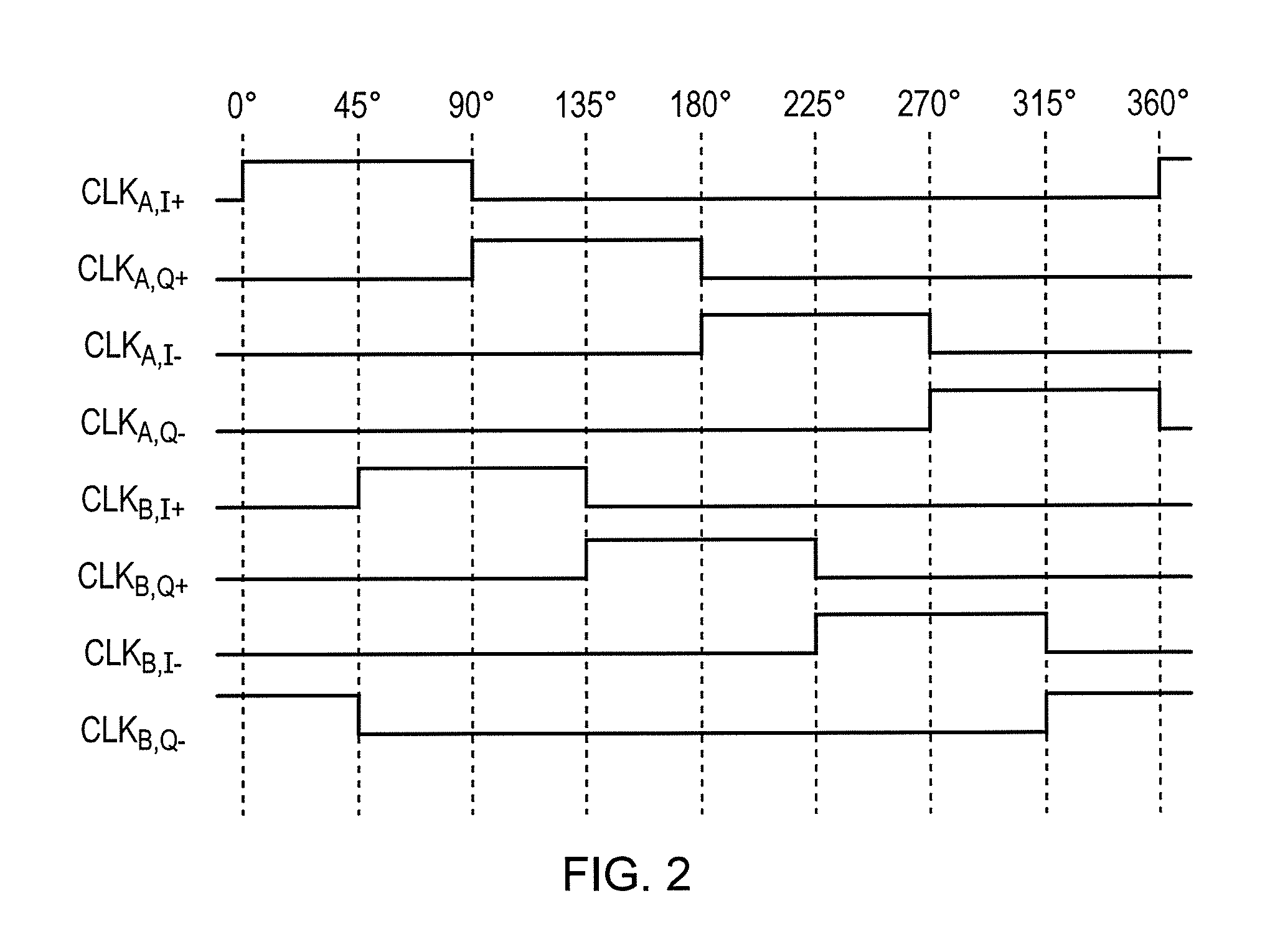

Signal filtering

ActiveUS9191127B2Reduced harmonic foldingSpeed up the descentNetwork topologiesNetworks with variable switch closing timeEngineeringClock generator

A signal filter (100) comprises a first transferred impedance filter, TIF, (TIFA) having four differential signal paths (PA,1, PA,2, PA,3, PA,4) and a second TIF (TIFB) having four differential signal paths (PB,1, PB,2, PB,3, PB,4)- A first differential signal port of the first TIF (32A) is coupled to a first differential signal port of the second TIF (32B). A first clock generator (12A) is arranged to provide first-TIF clock signals (CLKA,I+, CLKA,Q+, CLKA,I−, CLKA,Q−) having four non-overlapping phases for selecting the respective first-TIF differential signal paths (PA,1, PA,2, PA,3, PA,4), and a second clock generator (12B) is arranged to provide second-TIF clock signals (CLKB,I+, CLKB,Q+, CLKB,J−, CLKB,Q−) having four non-overlapping phases for selecting the respective second-TIF differential signal paths (PB,1, PB,2, PB,3, PB,4). The phases of the second-TIF clock signals (CLKB,I+, CLKB,Q+, CLKB,I−, CLKB,Q−) are equal to the phases of the first-TIF clock signals (CLKA,I+, CLKA,Q+, CLKA,I−, CLKA,Q−) delayed by 45 degrees. The first-TIF first, second, third and fourth clock signals (CLKA,I+, CLKA,Q+, CLKA,I−, CLKAQ−) and the second-TIF first, second, third and fourth clock signals (CLKB,I+, CLKB,Q+, CLKB,I−, CLKB,Q−) have a duty cycle in the range 16.75% to 25%.

Owner:TELEFON AB LM ERICSSON (PUBL)

Transferred-impedance filtering in RF receivers

ActiveUS7187230B2Networks with variable switch closing timeOscillations generatorsRFICFrequency filtering

Owner:NOKIA TECH OY

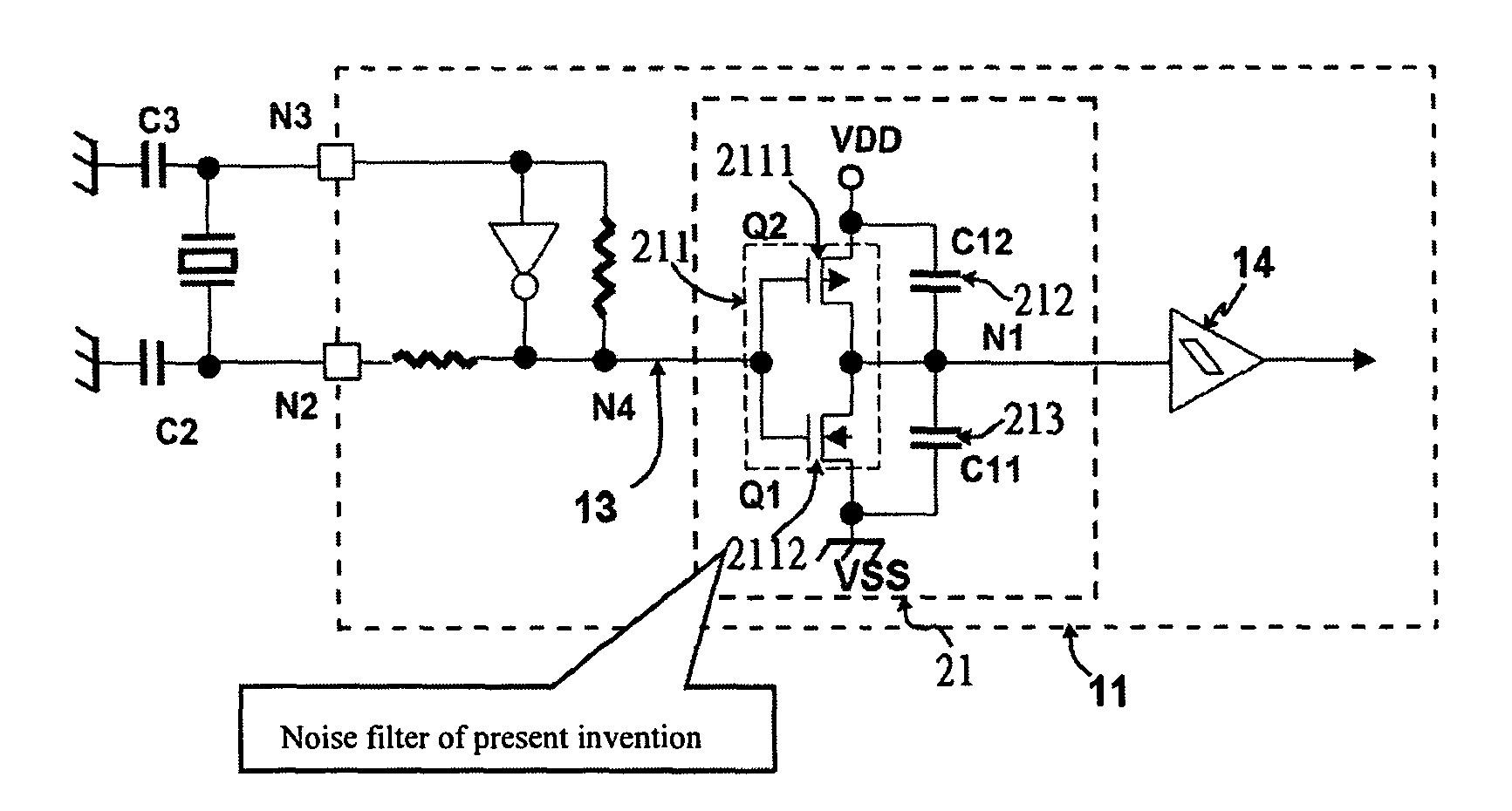

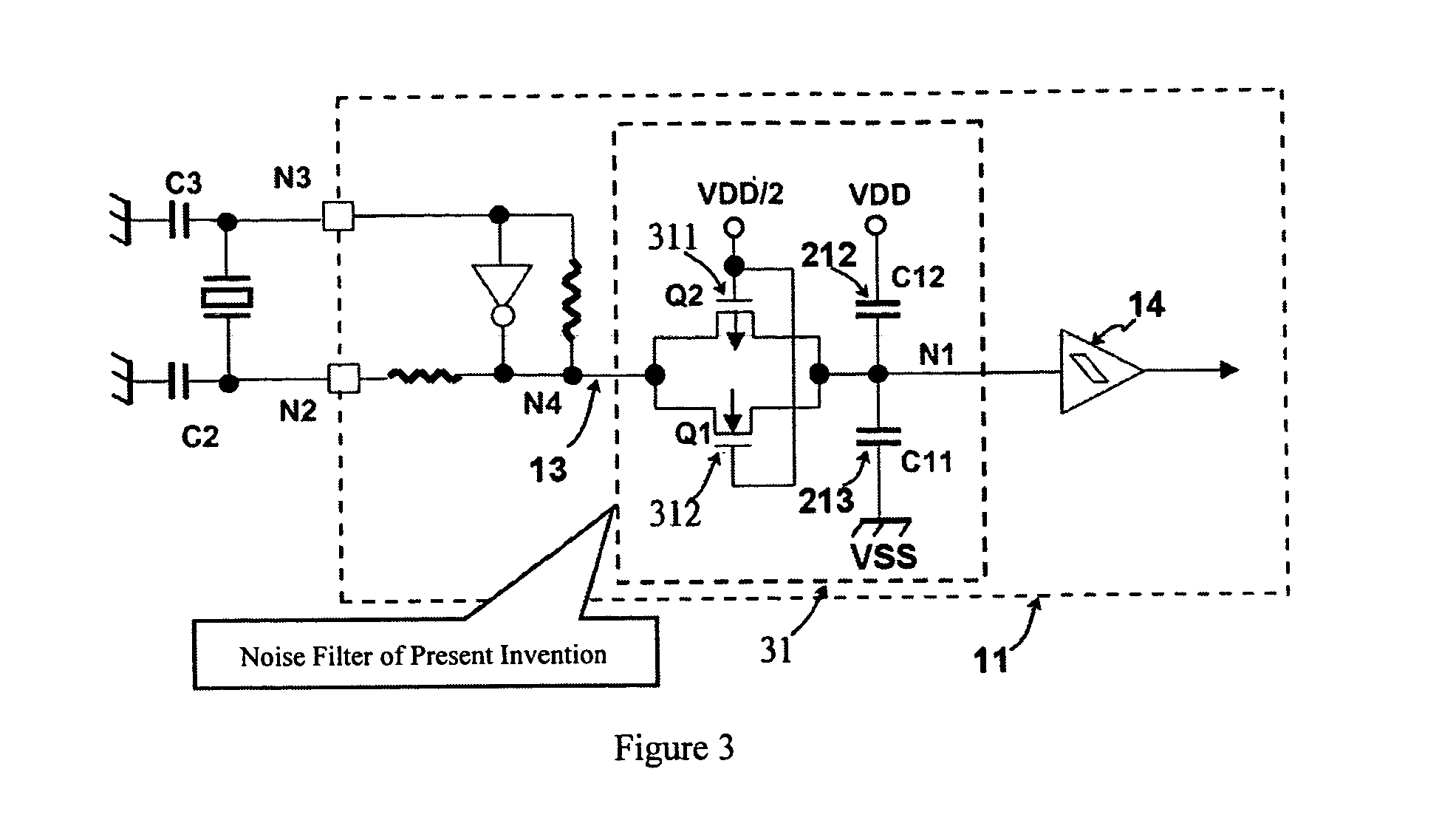

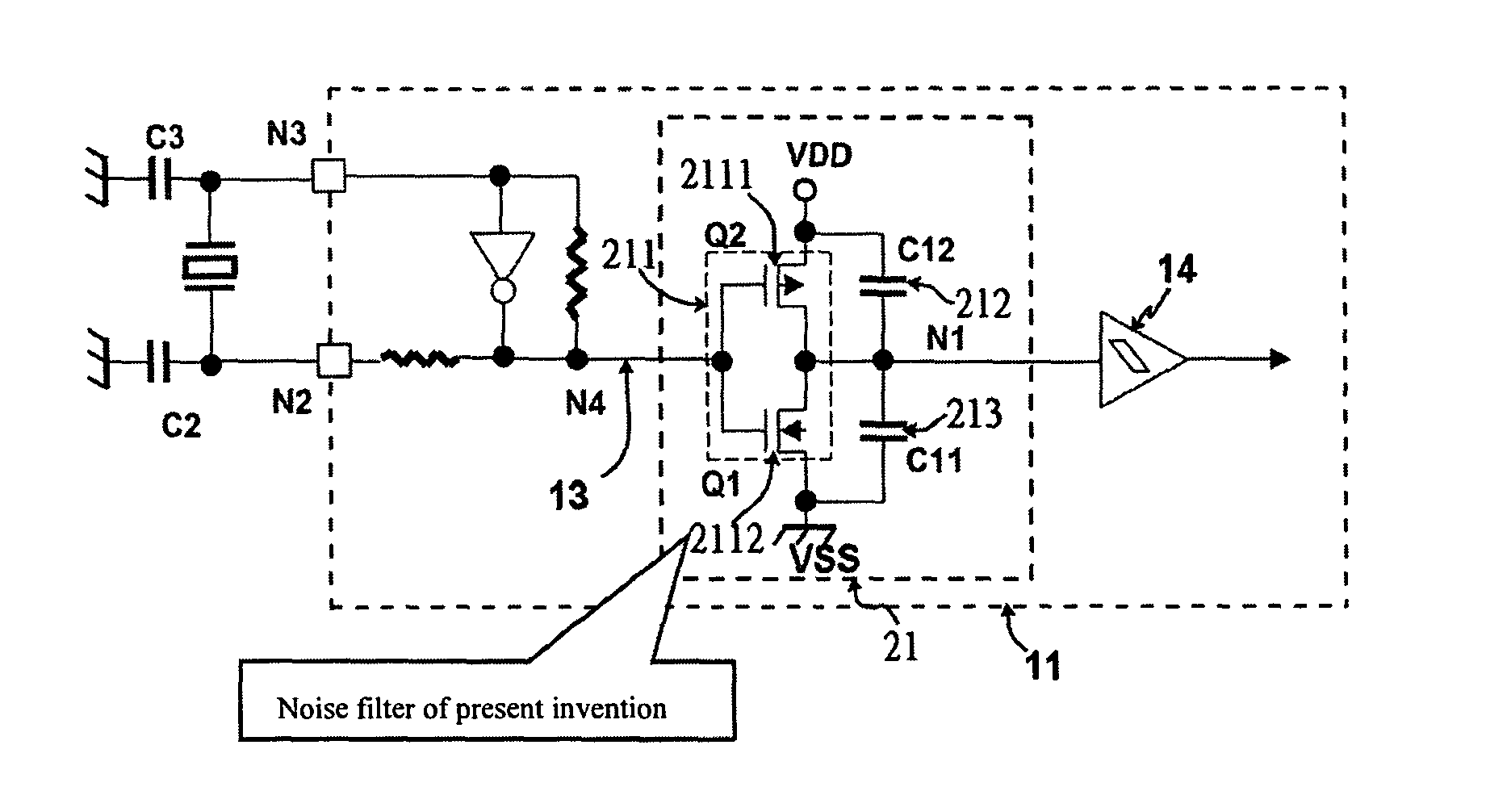

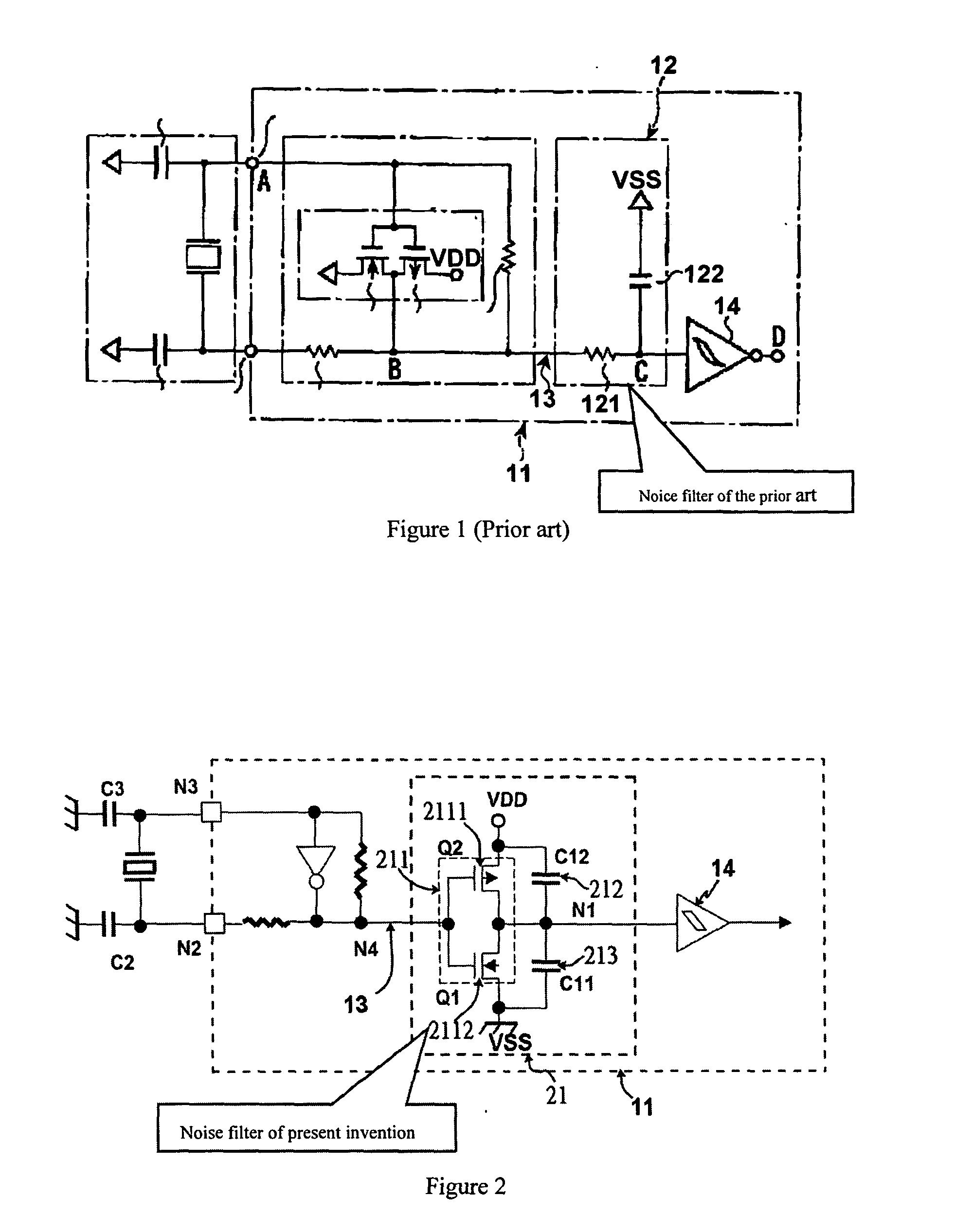

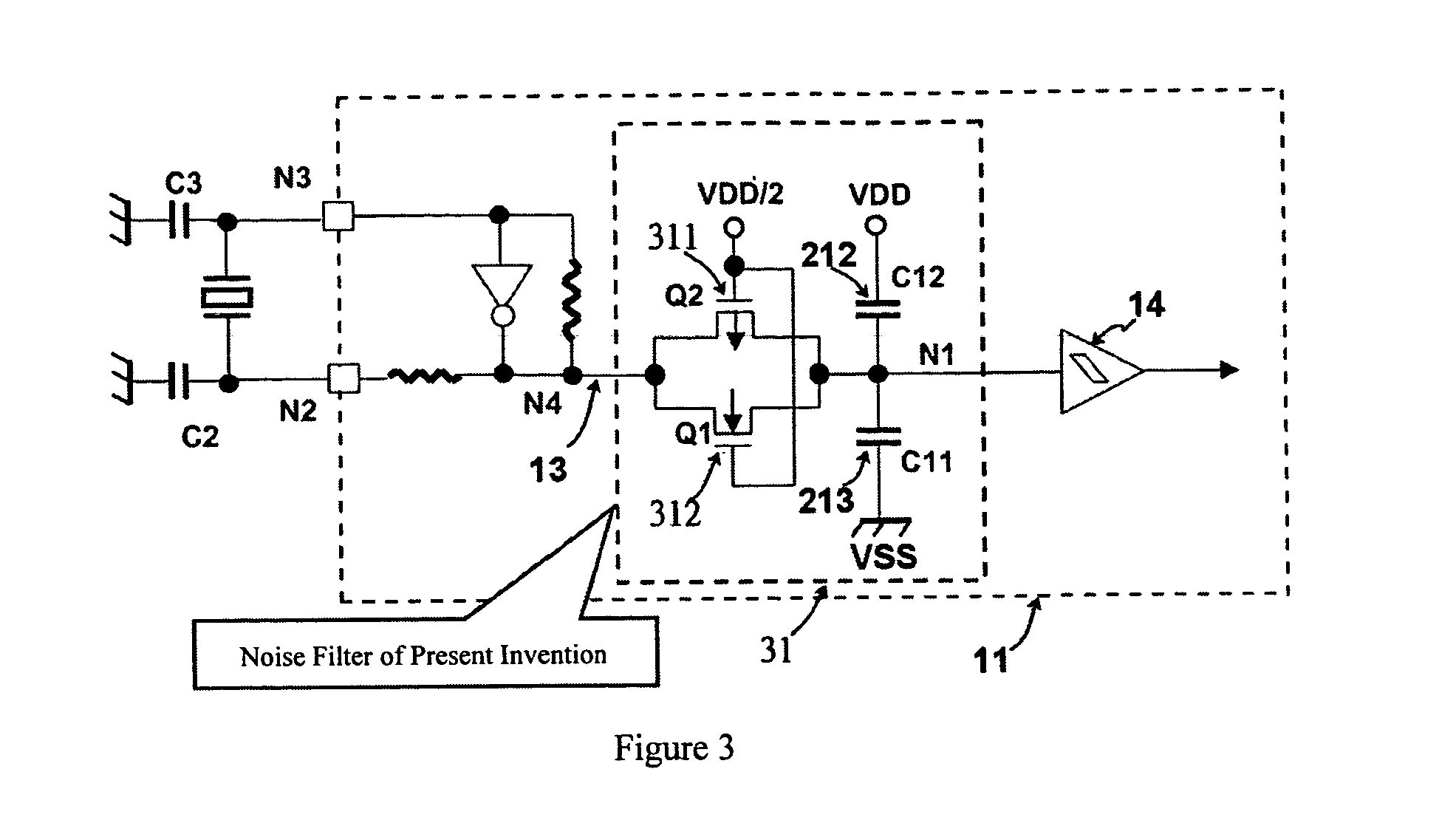

Noise filter for an integrated circuit

InactiveUS7057450B2Avoid misuseHigh frequencyPulse automatic controlNetworks with variable switch closing timeCMOSEngineering

A noise filter for an integrated circuit is proposed. The noise filter comprises a CMOS inverter and two capacitors. The input of the CMOS inverter is coupled with an input pad of the integrated circuit and the output of the CMOS inverter is coupled with an input buffer. The first capacitor is inserted between the output of the CMOS inverter and a first voltage source and the second capacitor is inserted between the output of the CMOS inverter and a second voltage source. A transfer gate may be in stead of the CMOS inverter.

Owner:WINBOND ELECTRONICS CORP

Mixer circuit and method

ActiveCN101331679AModulation transference balanced arrangementsNetworks with variable switch closing timeCapacitanceFrequency mixer

Owner:TELEFON AB LM ERICSSON (PUBL)

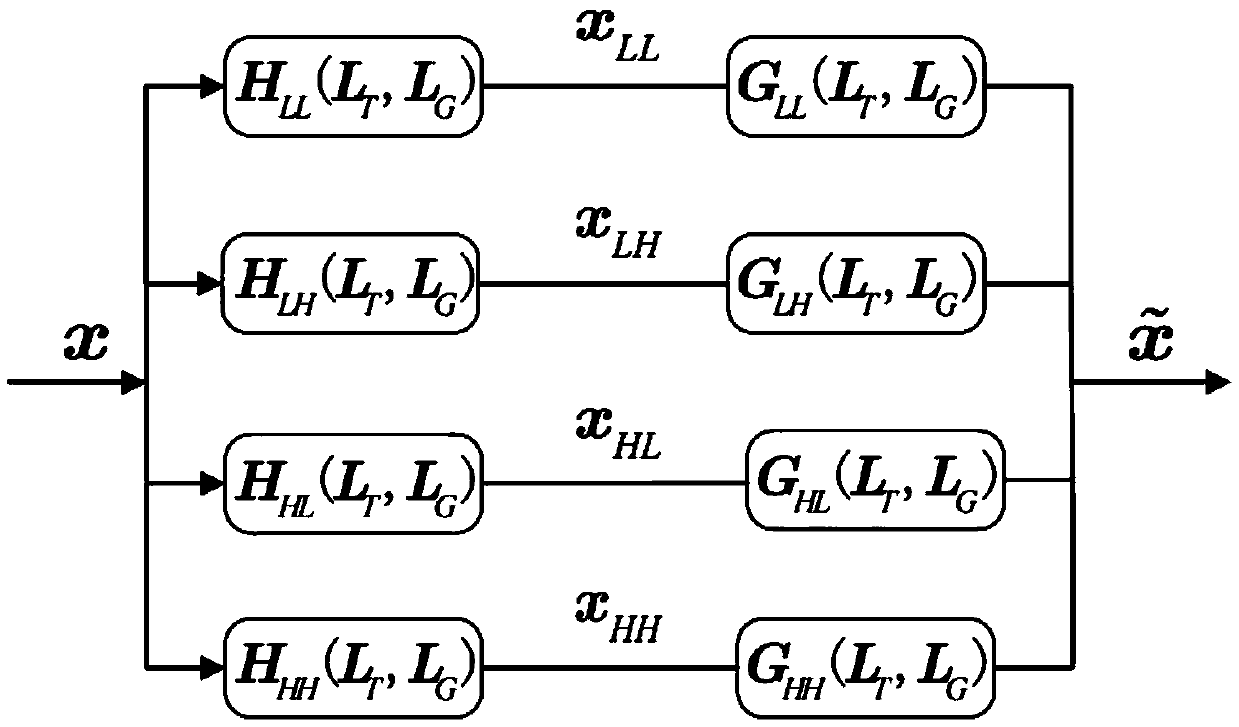

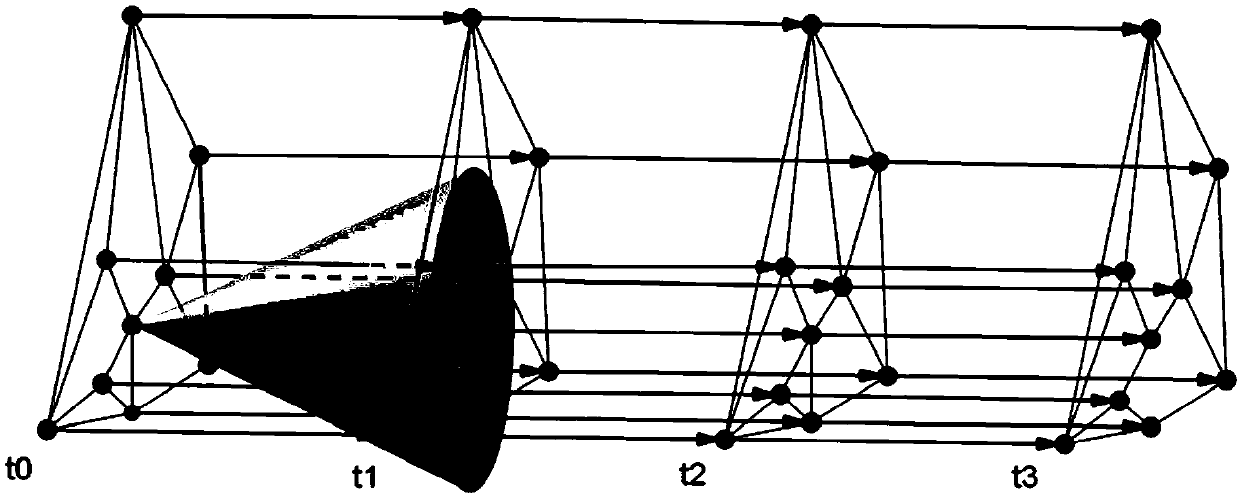

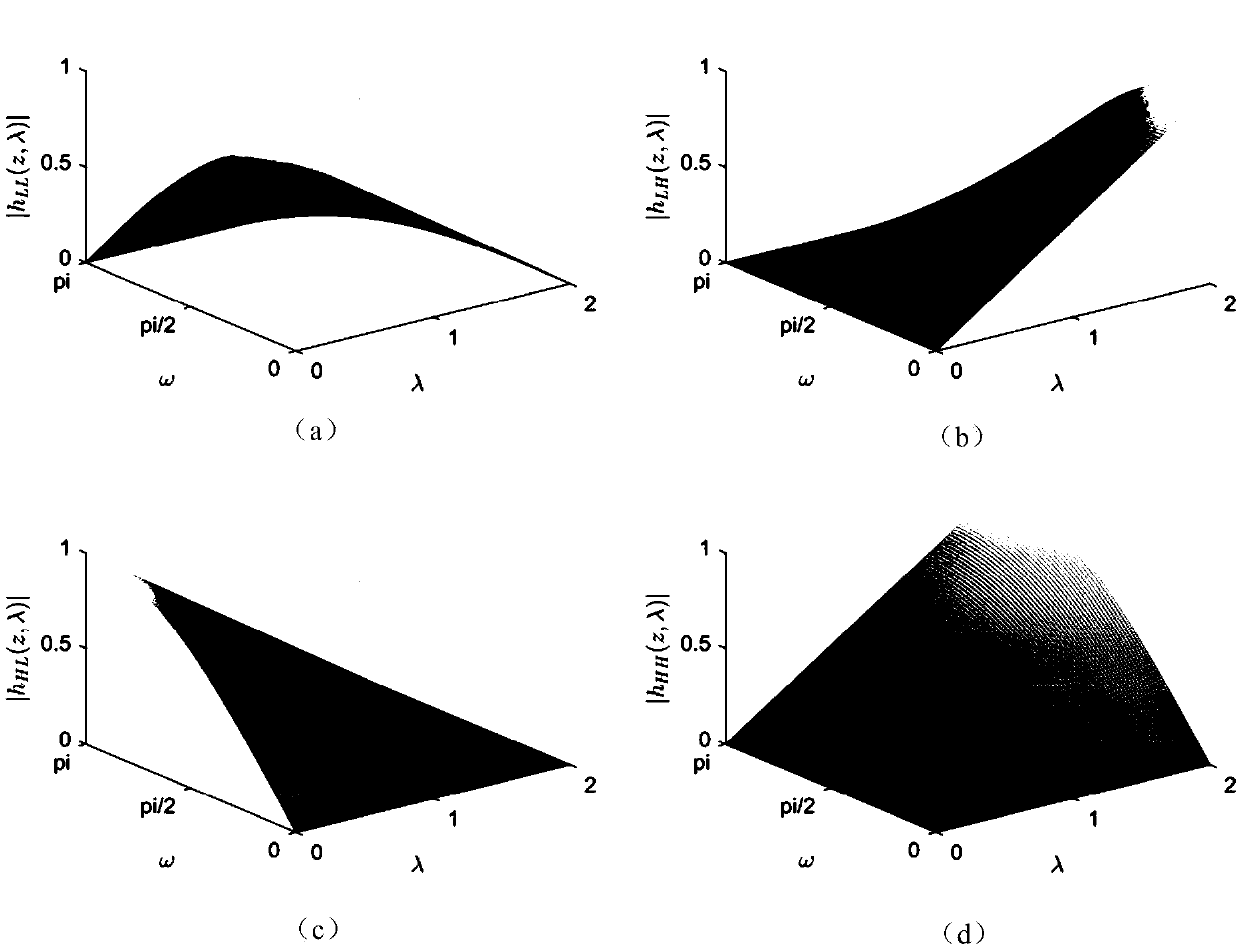

Design method of time-varying separable non-downsampled filter bank based on iterative calculation

ActiveCN109586688AWith frequency responseFully refactorableNetworks with variable switch closing timeN-path filtersSeparable filterReconstruction problem

The invention discloses a design method of a time-varying separable non-downsampled filter bank based on iterative calculation. The method comprises the steps of: firstly, based on the properties of atwo-dimensional separable filter, designing an analysis filter bank with a frequency response; and finally, converting the reconstruction problem of the output signal of an integrated filter bank toa global least squares problem, converting the global least squares problem into a local least squares problem, and performing solution through an iteration mode. The iteration calculation method is low in iteration times, the designed time-varying separable non-downsampled filter bank has the complete reconstruction feature and the better denoising performance, and the analysis filter has frequency response.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Reconfigurable baseband filter

ActiveUS7676211B2Simultaneous amplitude and angle demodulationActive element networkCommunications systemEngineering

A reconfigurable baseband filter for use in a multimode communication system is disclosed. One or more filter elements can each be configured as a plurality of sub-elements. The value of each of the filter elements can be varied by switching between at least two of the plurality of sub-elements. Switching noise within a desired passband can be reduced by switching at a rate that is greater than the desired passband. The switching noise in the passband can be further reduced by pseudo-randomly switching between the sub-elements. The filter can use a delta-sigma modulator to generate a pseudo-random switching signal.

Owner:SPREADTRUM

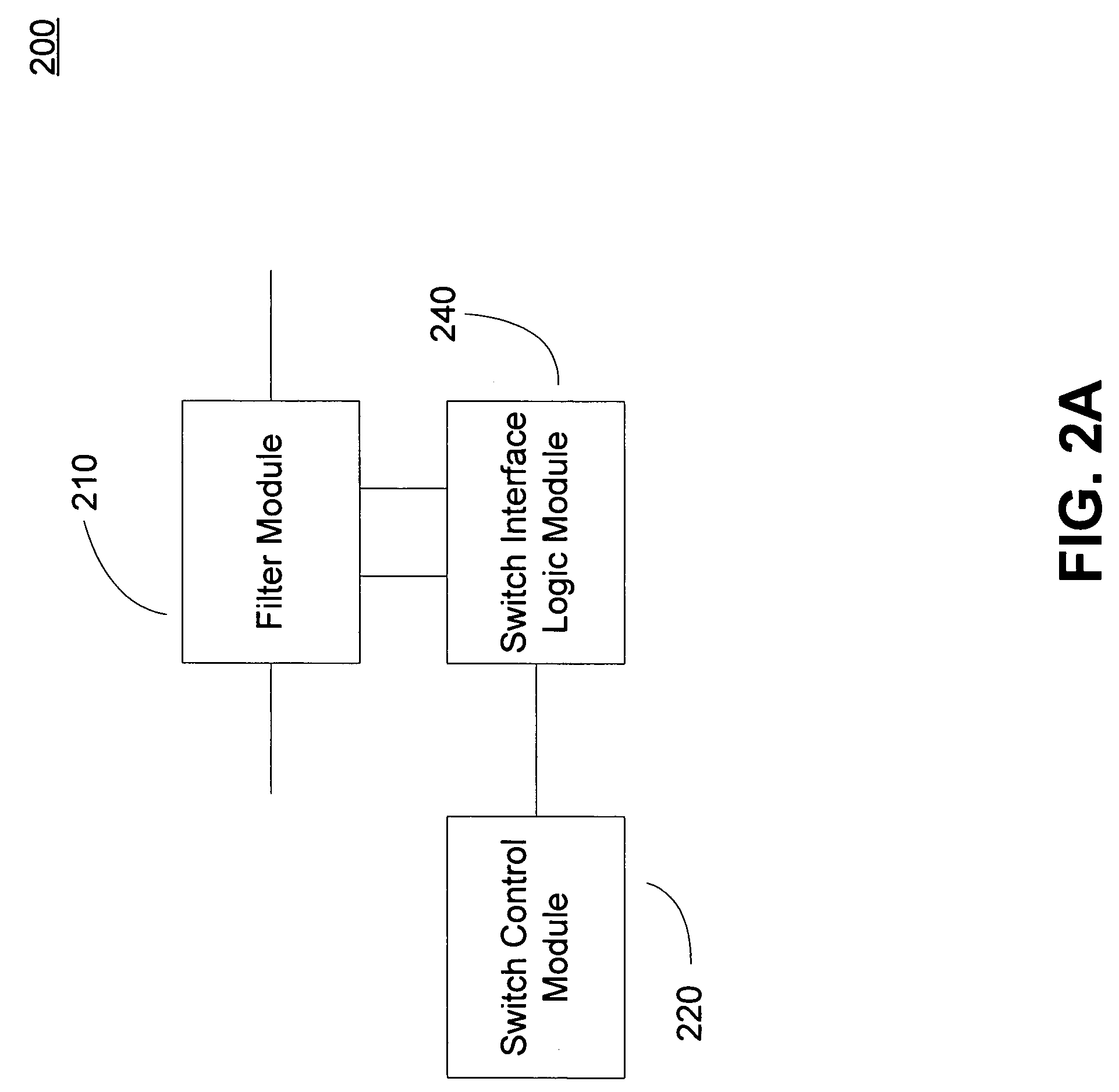

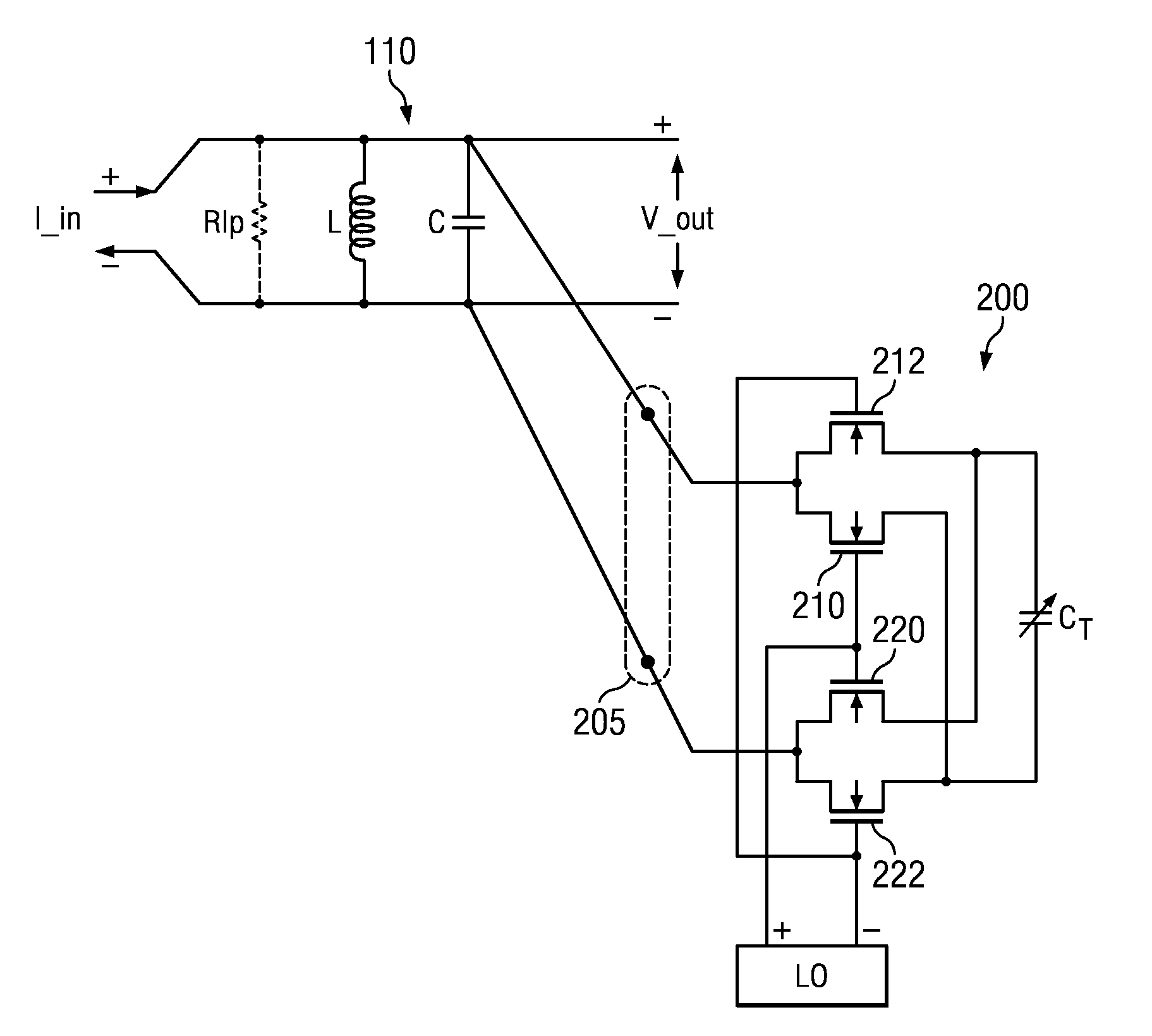

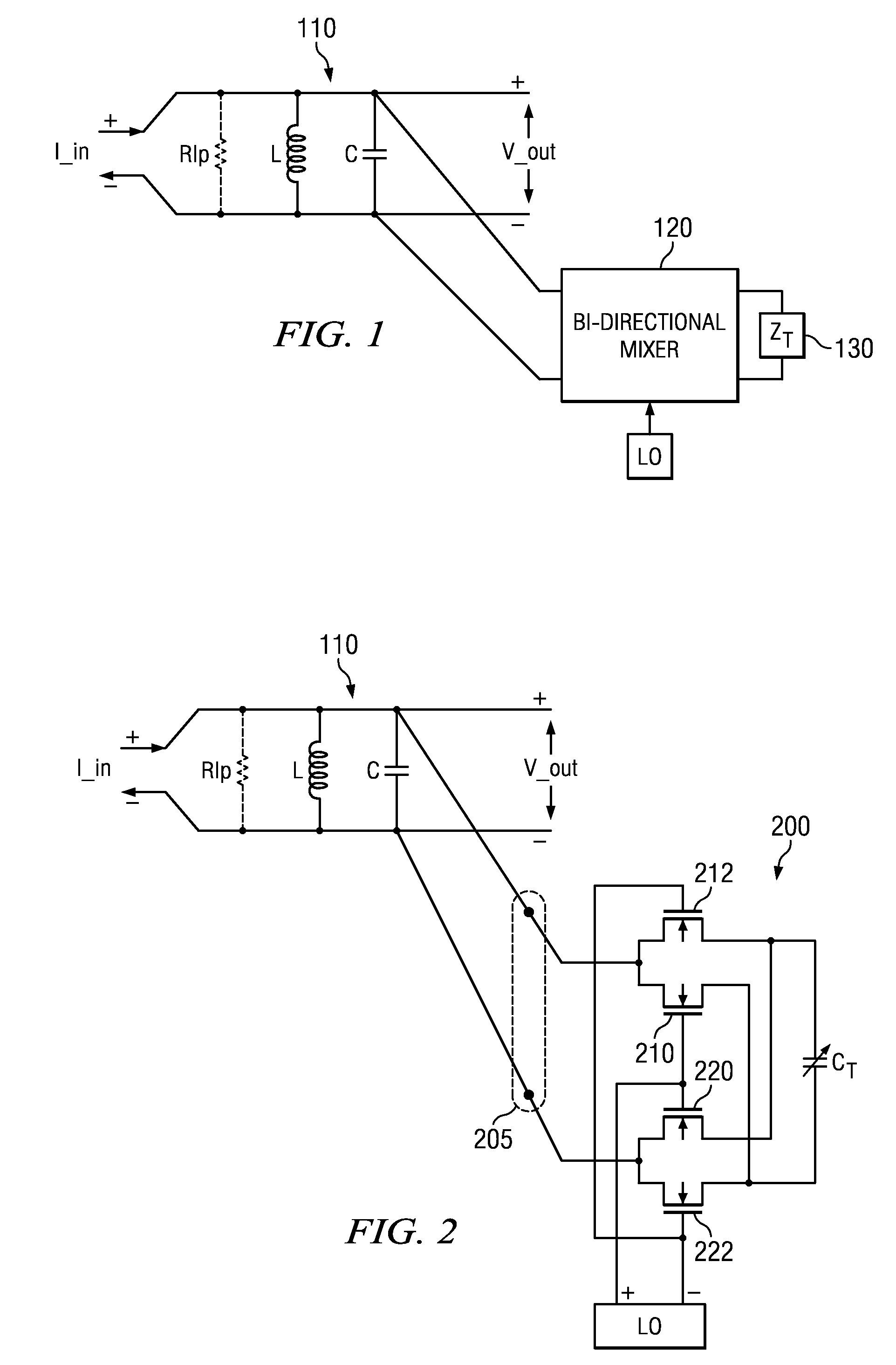

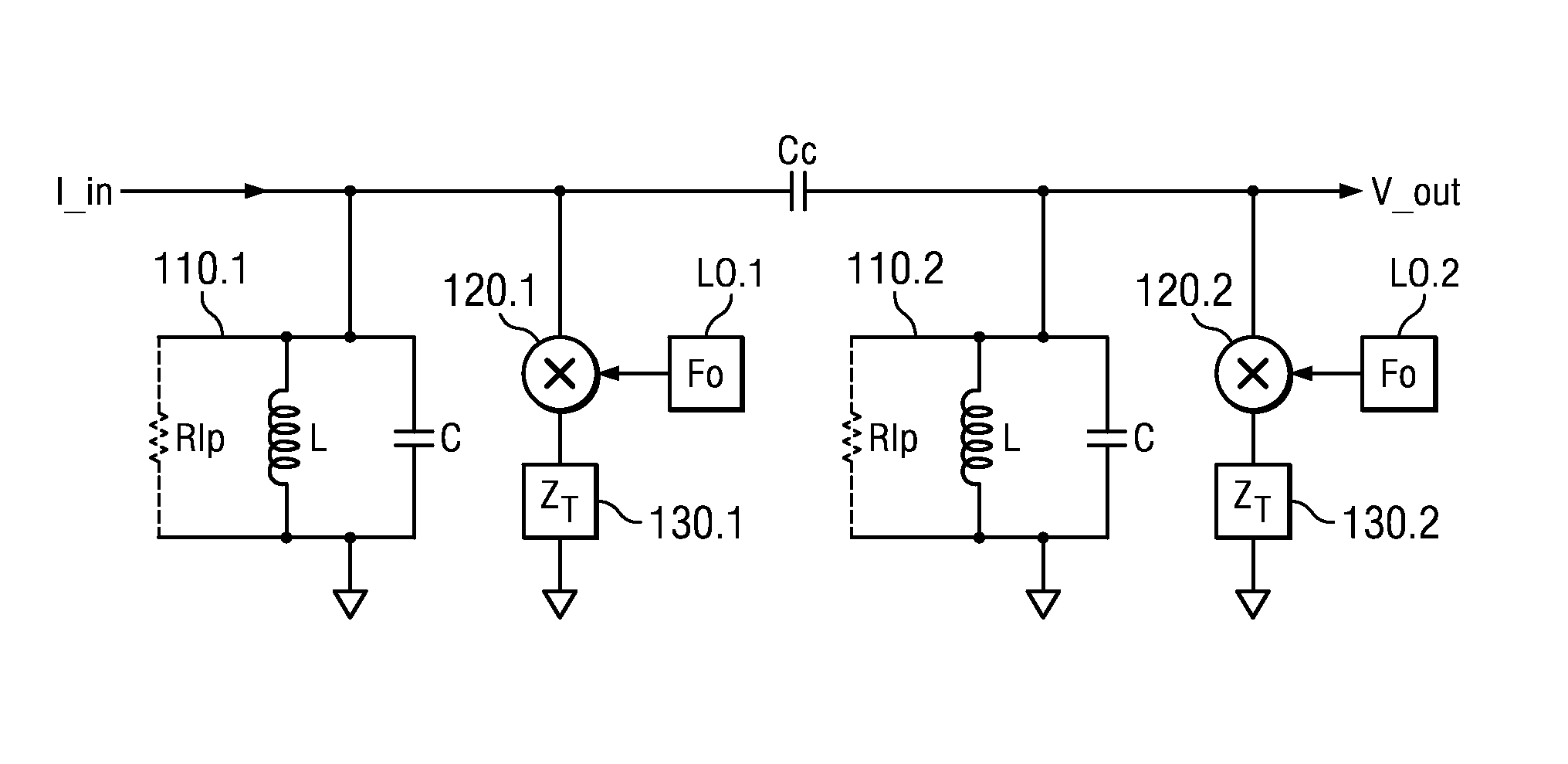

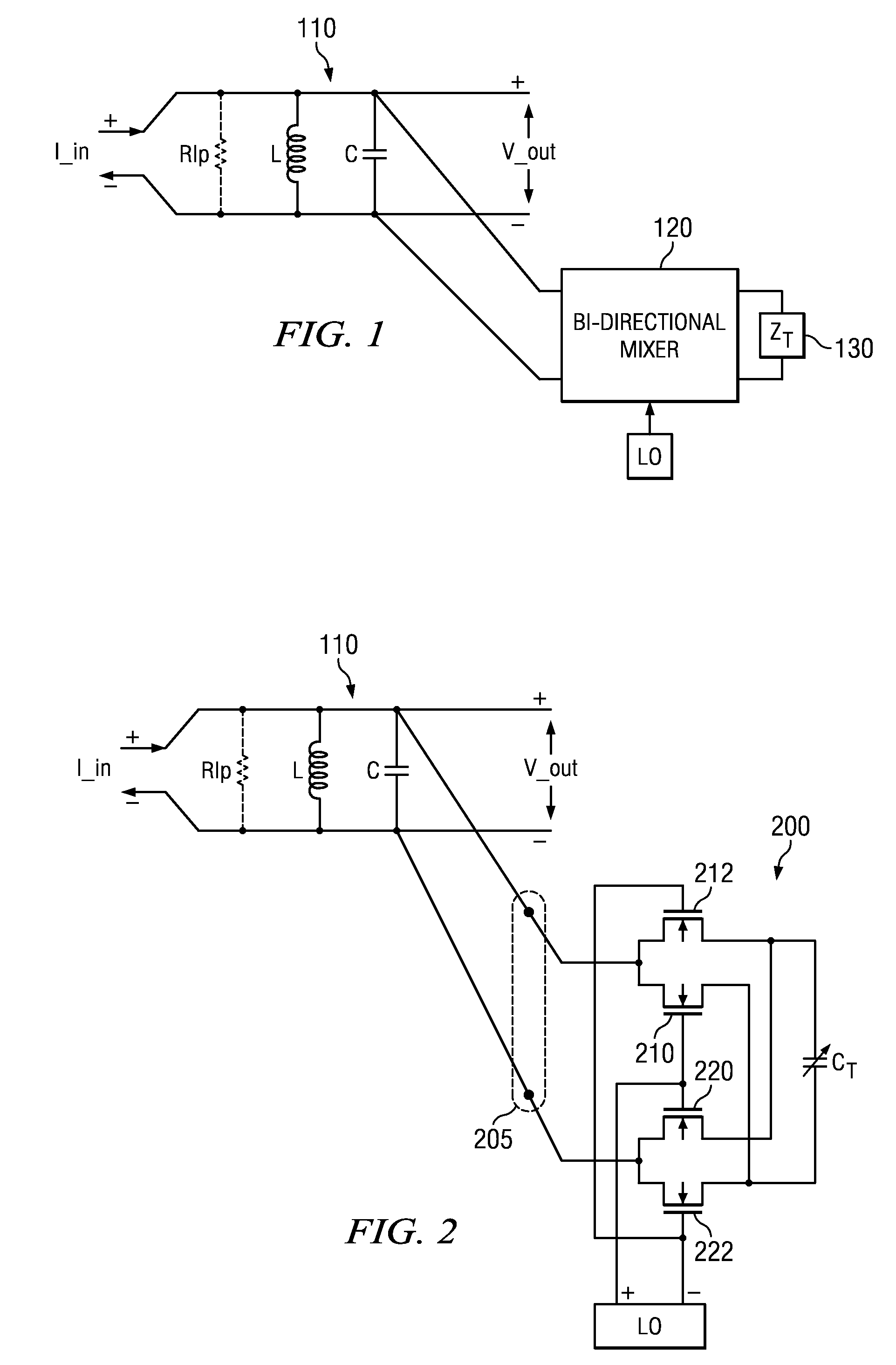

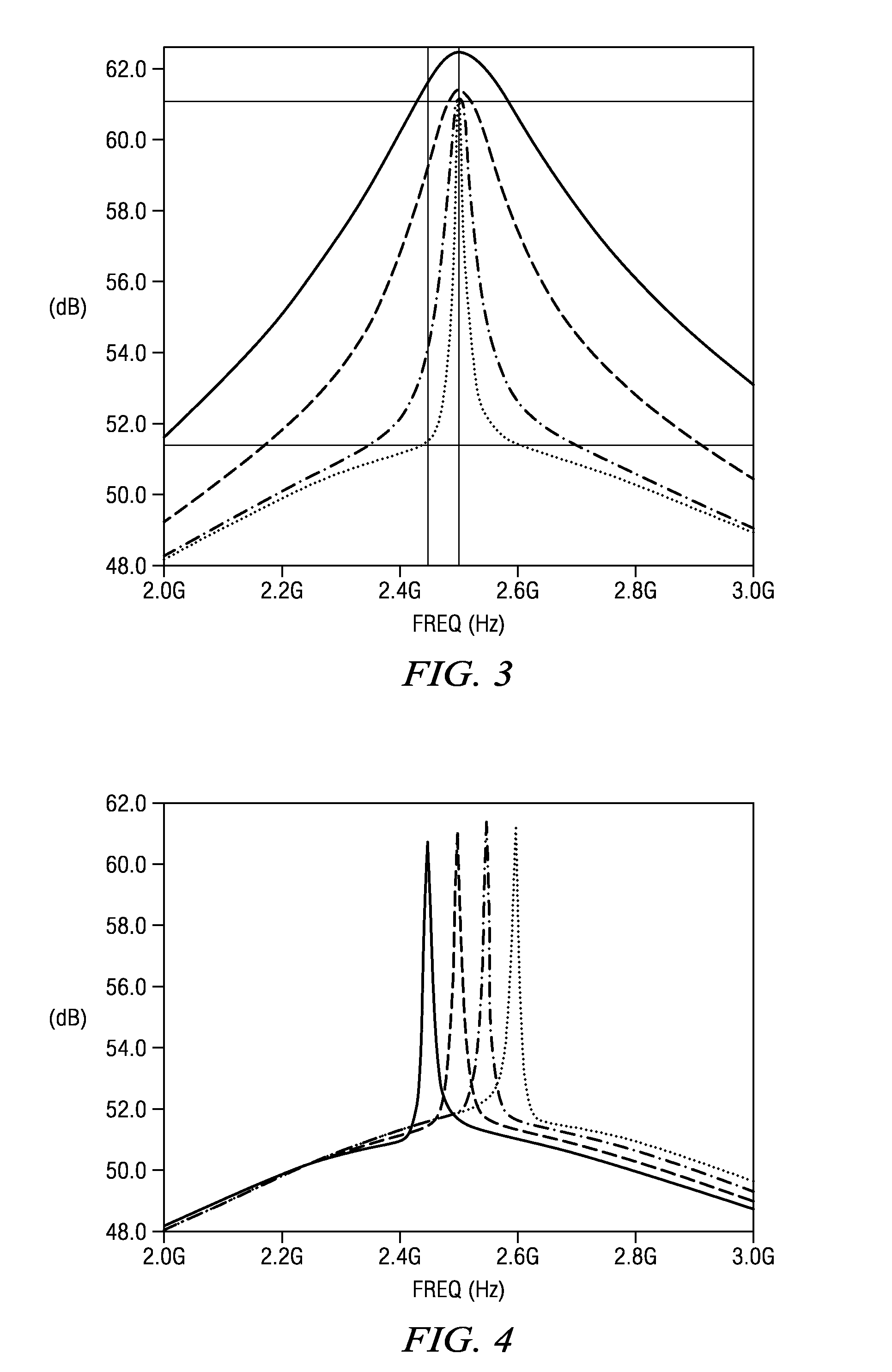

Narrow band RF filter circuits, devices and processes using impedance translation

An active filter circuit includes an inductance-capacitance (LC) circuit (110) for wireless frequency input, a bi-directional mixer (120) and a filter impedance (130) series-coupled across at least part of the LC circuit (110), and another mixer (420) coupled to at least some portion of the LC circuit. Other circuits, processes, receivers, transmitters and transceivers are disclosed.

Owner:TEXAS INSTR INC

Phase-shifting circuit and multibit phase shifter

ActiveUS20070273456A1Small sizeReduce lossMultiple-port networksNetwork simulating reactancesCapacitancePhase shifted

A phase-shifting circuit includes: a first parallel circuit which is connected across input and output terminals of a high frequency signal, composed of a first inductor and a first switching element that exhibits a through state in an ON state and a capacitive property in an OFF state, and produces parallel resonance at a prescribed frequency when the first switching element is in the OFF state; a series circuit composed of a second inductor and a third inductor and connected in parallel with the first parallel circuit; a capacitor having its first terminal connected to a point of connection of the second and third inductors; and a second parallel circuit which is connected across a second terminal of the capacitor and a ground, composed of a fourth inductor and a second switching element that exhibits a through state in an ON state and a capacitive property in an OFF state, and produces parallel resonance at a prescribed frequency when the second switching element is in the OFF state. The phase-shifting circuit establishes by switching an operation mode of setting the first switching element at the ON state and the second switching element at the OFF state, or an operation mode of setting the first switching element at the OFF state and the second switching element at the ON state.

Owner:MITSUBISHI ELECTRIC CORP

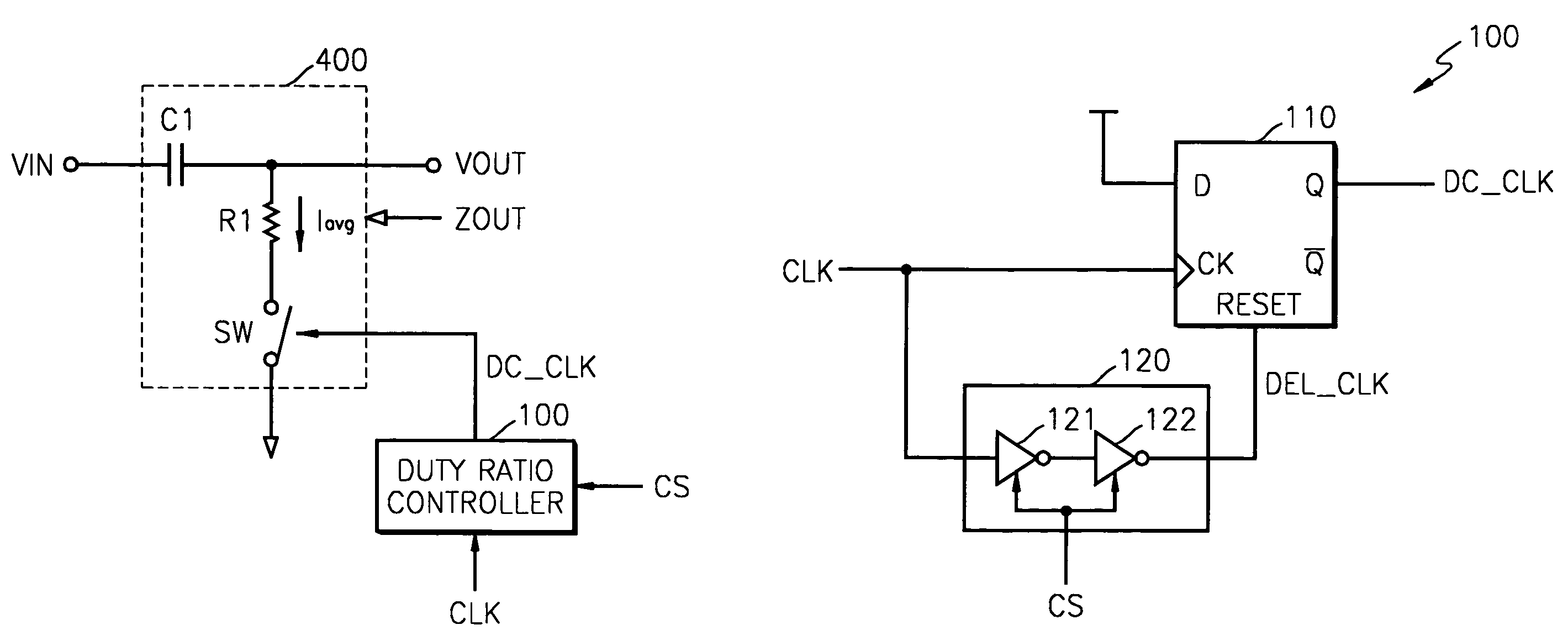

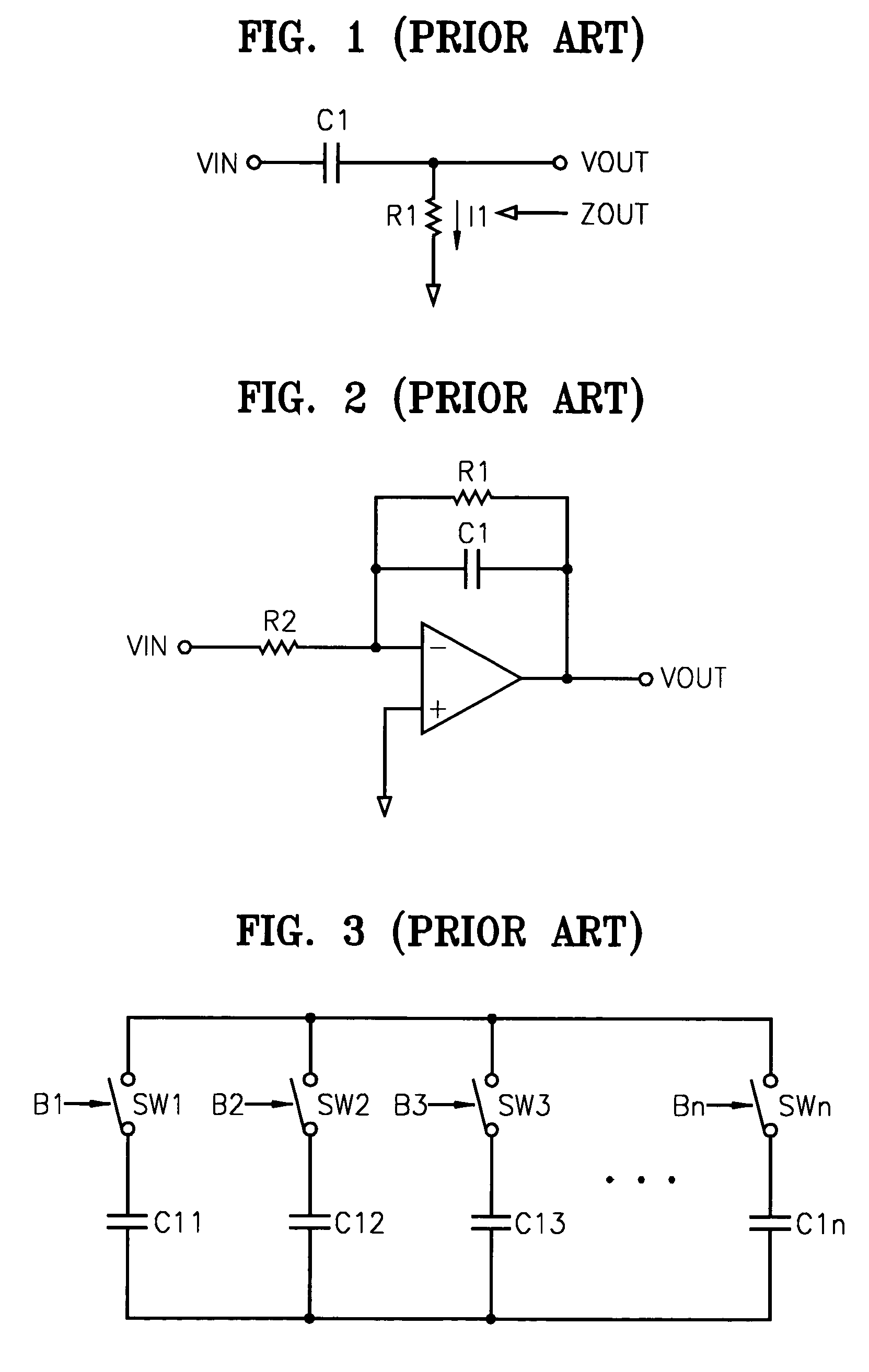

Device for controlling a frequency response by scaling an impedance

ActiveUS20040169532A1Pulse automatic controlNetworks with variable switch closing timeControl signalEngineering

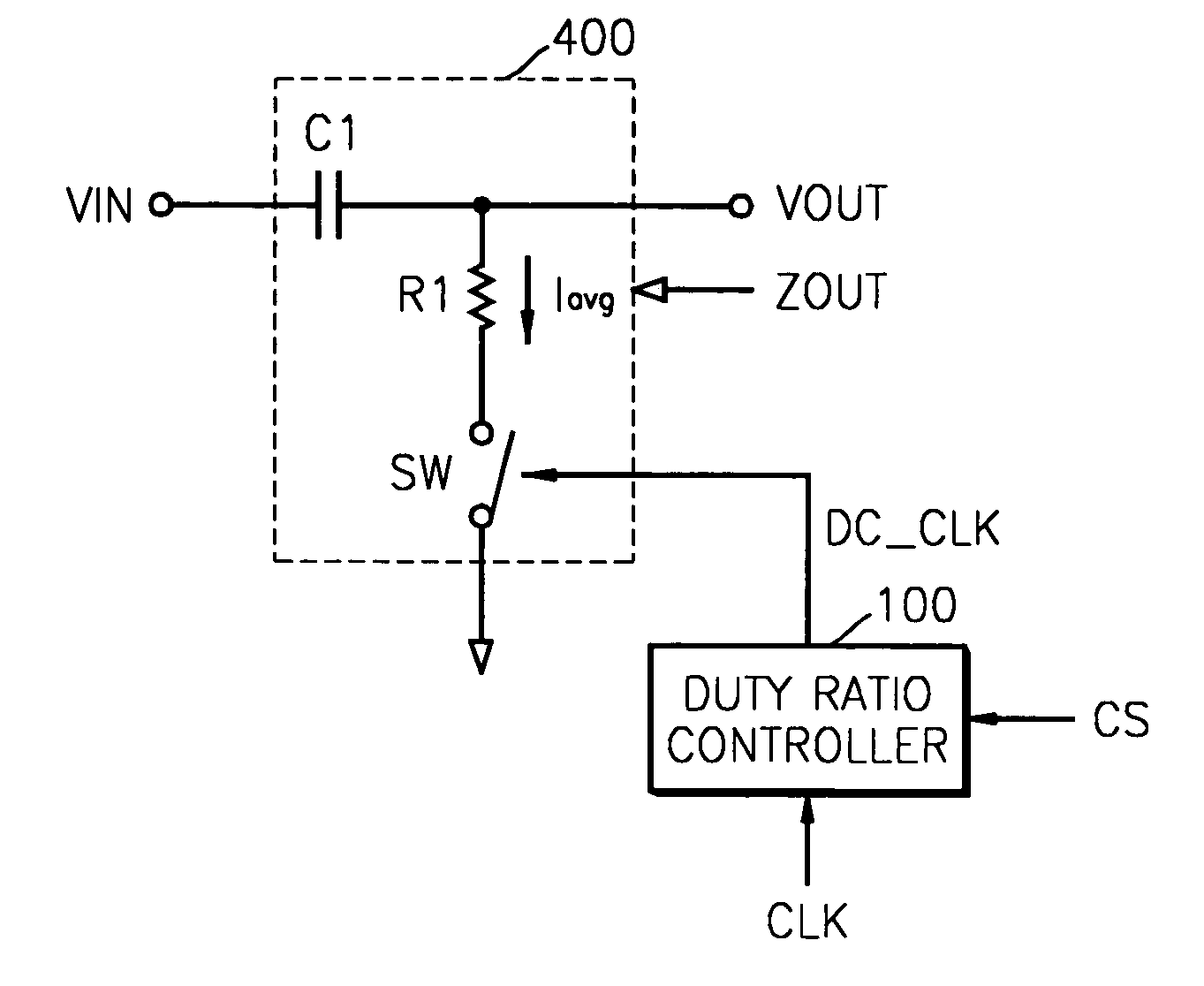

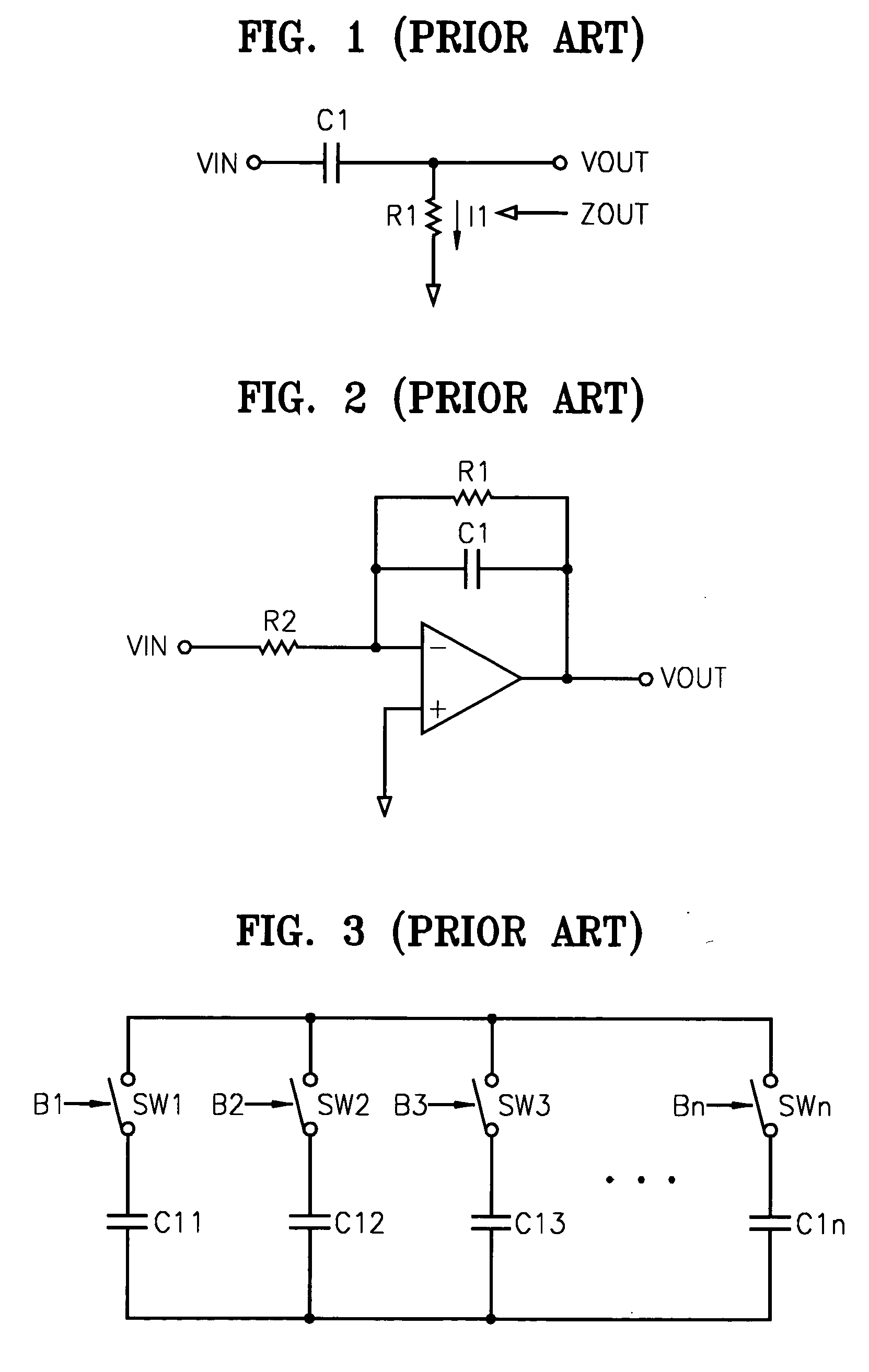

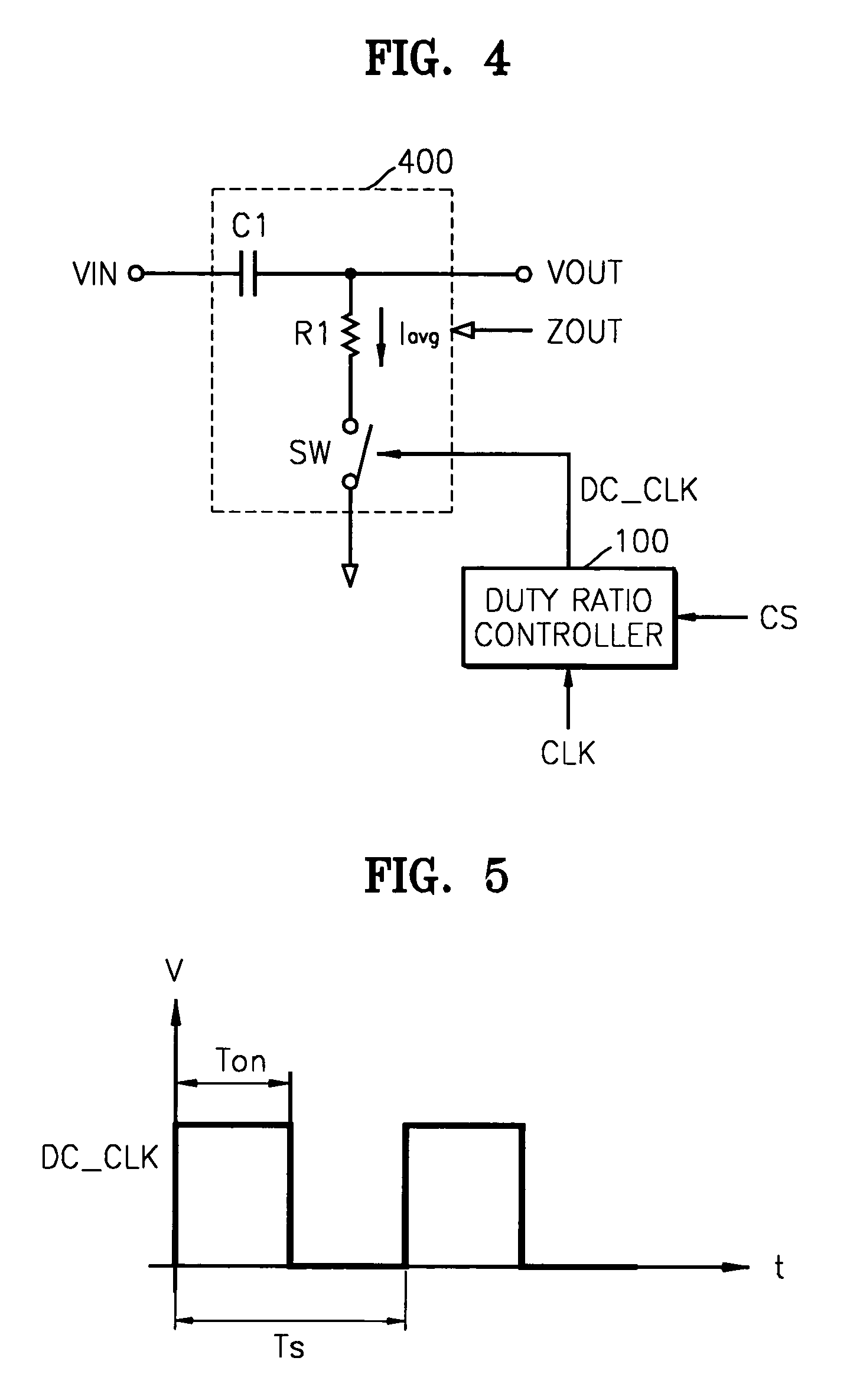

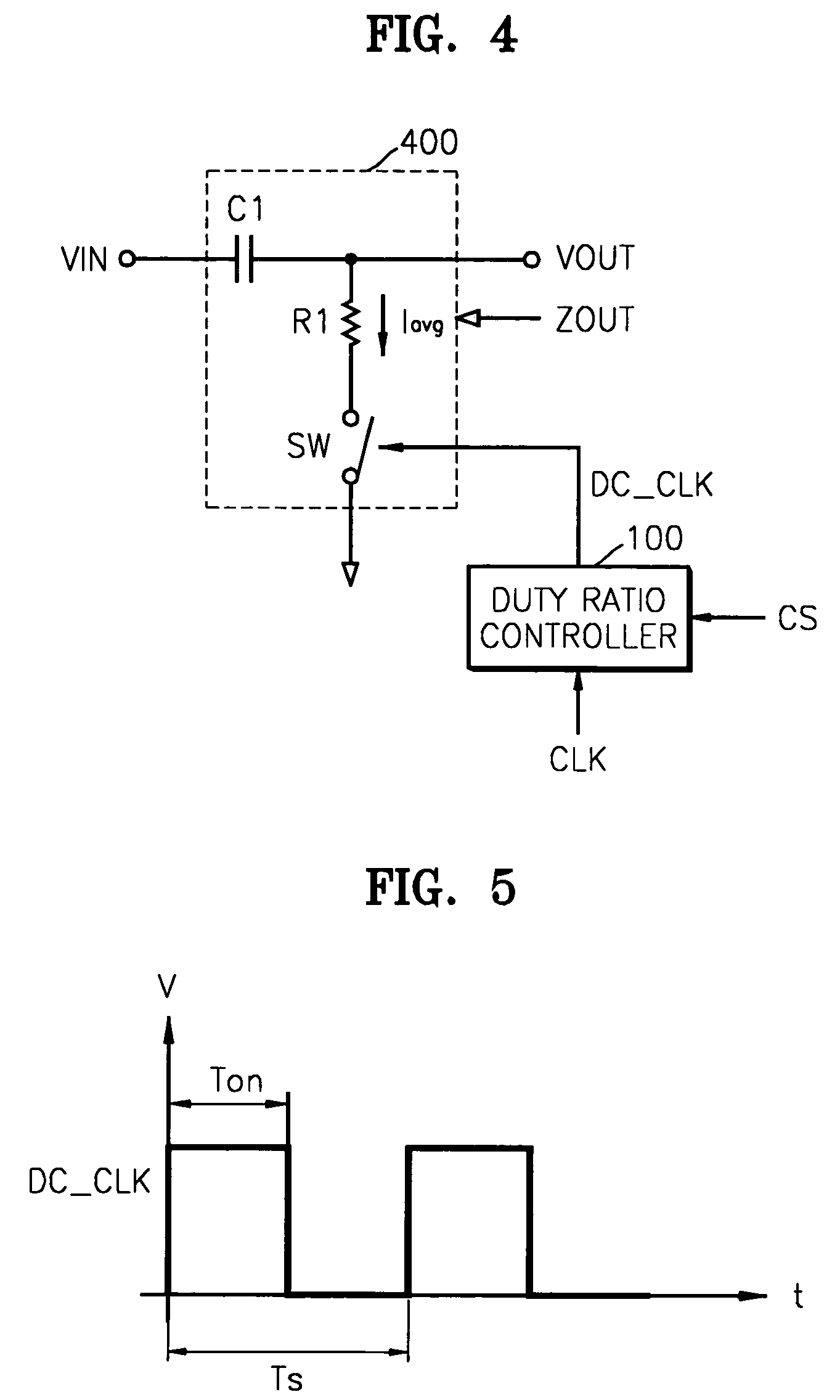

Provided is a device for controlling a frequency response by scaling an impedance. The device includes a filter and a duty ratio controller. The filter generates an output signal after removing a frequency from an input signal, and comprises a first impedance component and a switch. The switch, which is serially connected to the first impedance component, is switched on or off in response to a duty-controlled clock signal. The duty ratio controller receives a clock signal, controls a duty ratio of the clock signal, and generates the duty-controlled clock signal. The duty ratio controller comprises a flip-flop, which has a clock terminal that receives the clock signal, and a reset terminal, which receives a delayed signal obtained after delaying the clock signal by a time delay. The duty ratio controller further comprises a delay component that receives the clock signal, generates the delayed signal, and controls the time delay in response to a duty control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Phase-shifting circuit and multibit phase shifter

ActiveUS7541894B2Small sizeReduce lossMultiple-port networksNetwork simulating reactancesPhase shiftedEngineering

A phase-shifting circuit includes: a first parallel circuit which is connected across input and output terminals of a high frequency signal, composed of a first inductor and a first switching element that exhibits a through state in an ON state and a capacitive property in an OFF state, and produces parallel resonance at a prescribed frequency when the first switching element is in the OFF state; a series circuit composed of a second inductor and a third inductor and connected in parallel with the first parallel circuit; a capacitor having its first terminal connected to a point of connection of the second and third inductors; and a second parallel circuit which is connected across a second terminal of the capacitor and a ground, composed of a fourth inductor and a second switching element that exhibits a through state in an ON state and a capacitive property in an OFF state, and produces parallel resonance at a prescribed frequency when the second switching element is in the OFF state. The phase-shifting circuit establishes by switching an operation mode of setting the first switching element at the ON state and the second switching element at the OFF state, or an operation mode of setting the first switching element at the OFF state and the second switching element at the ON state.

Owner:MITSUBISHI ELECTRIC CORP

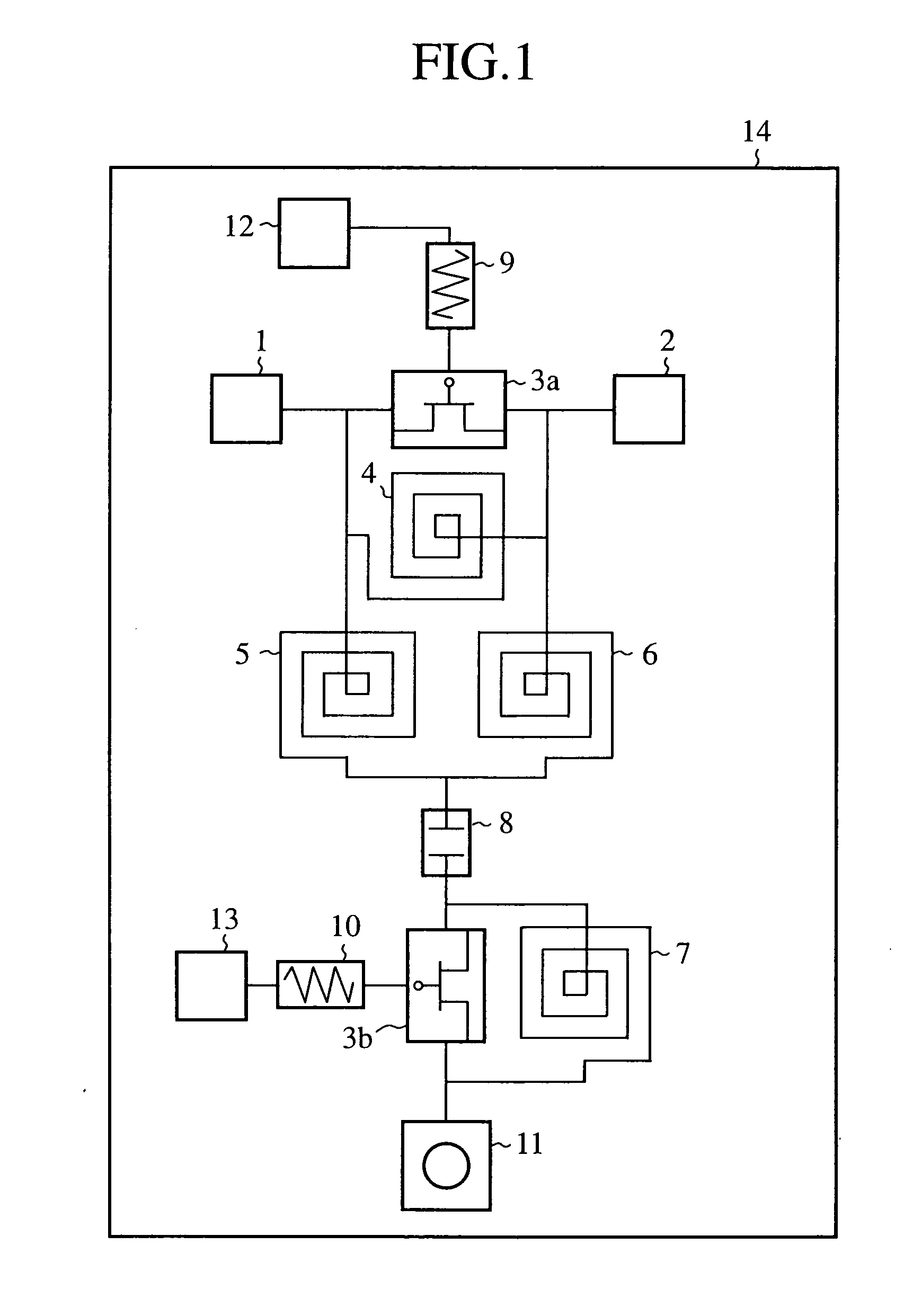

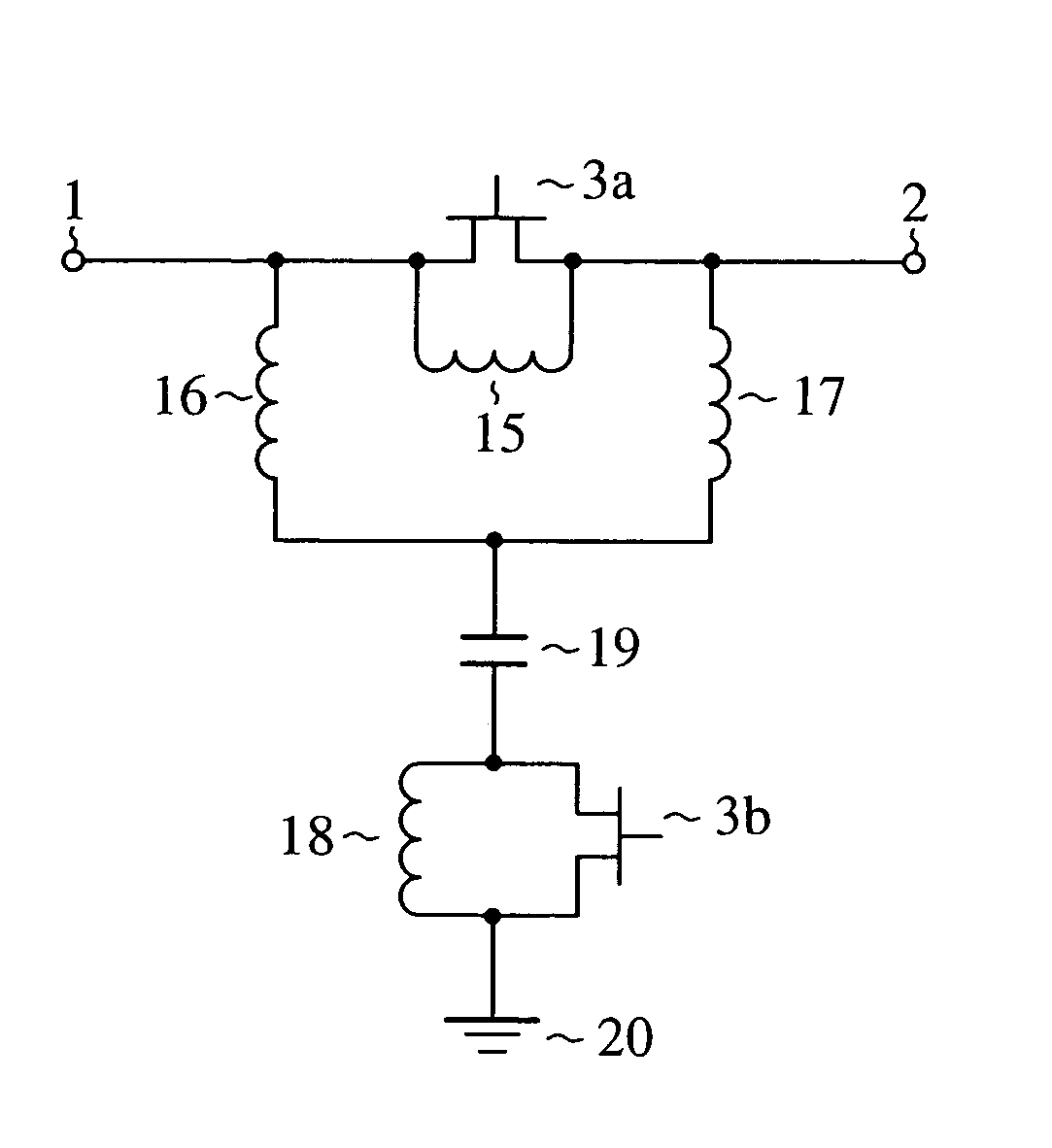

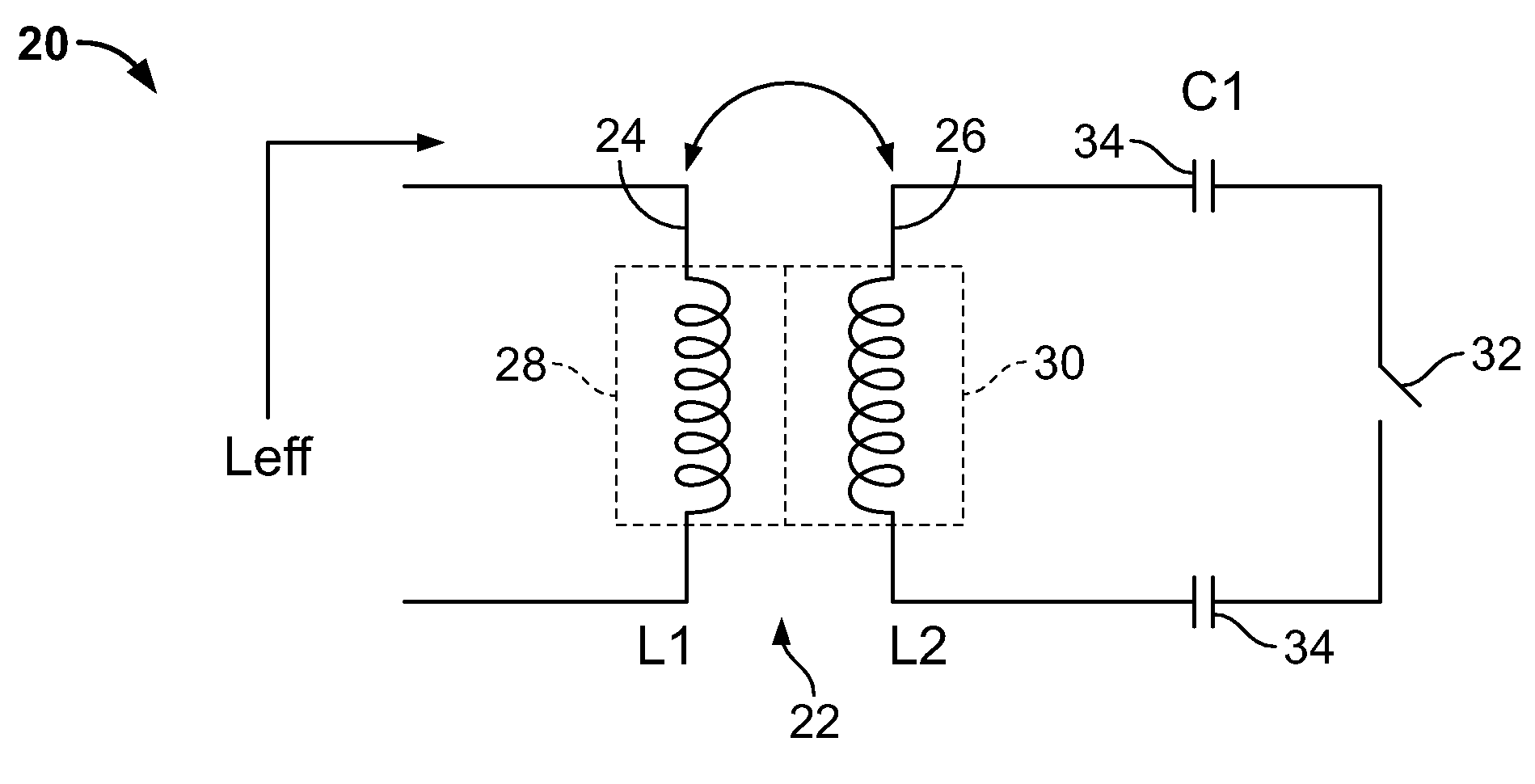

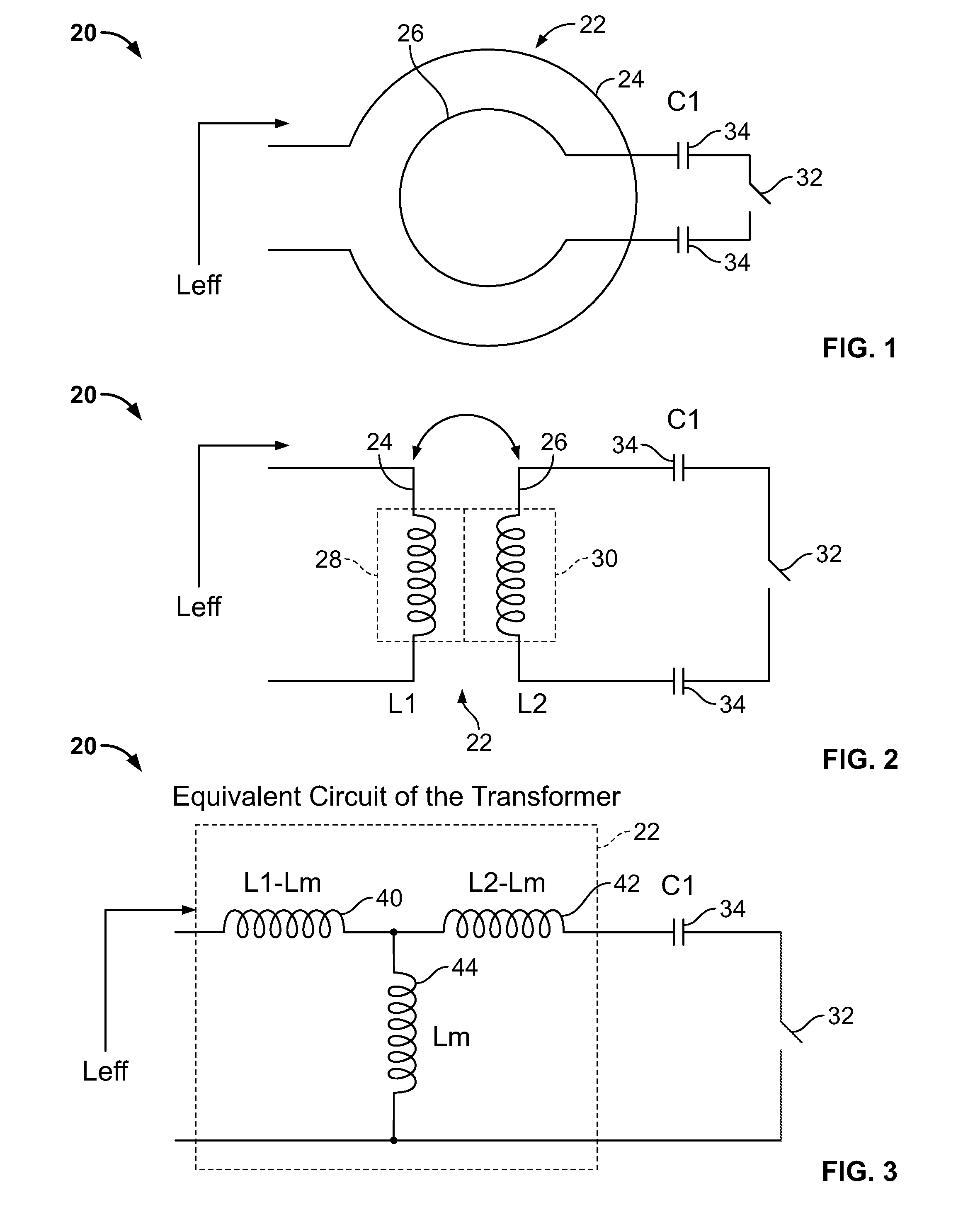

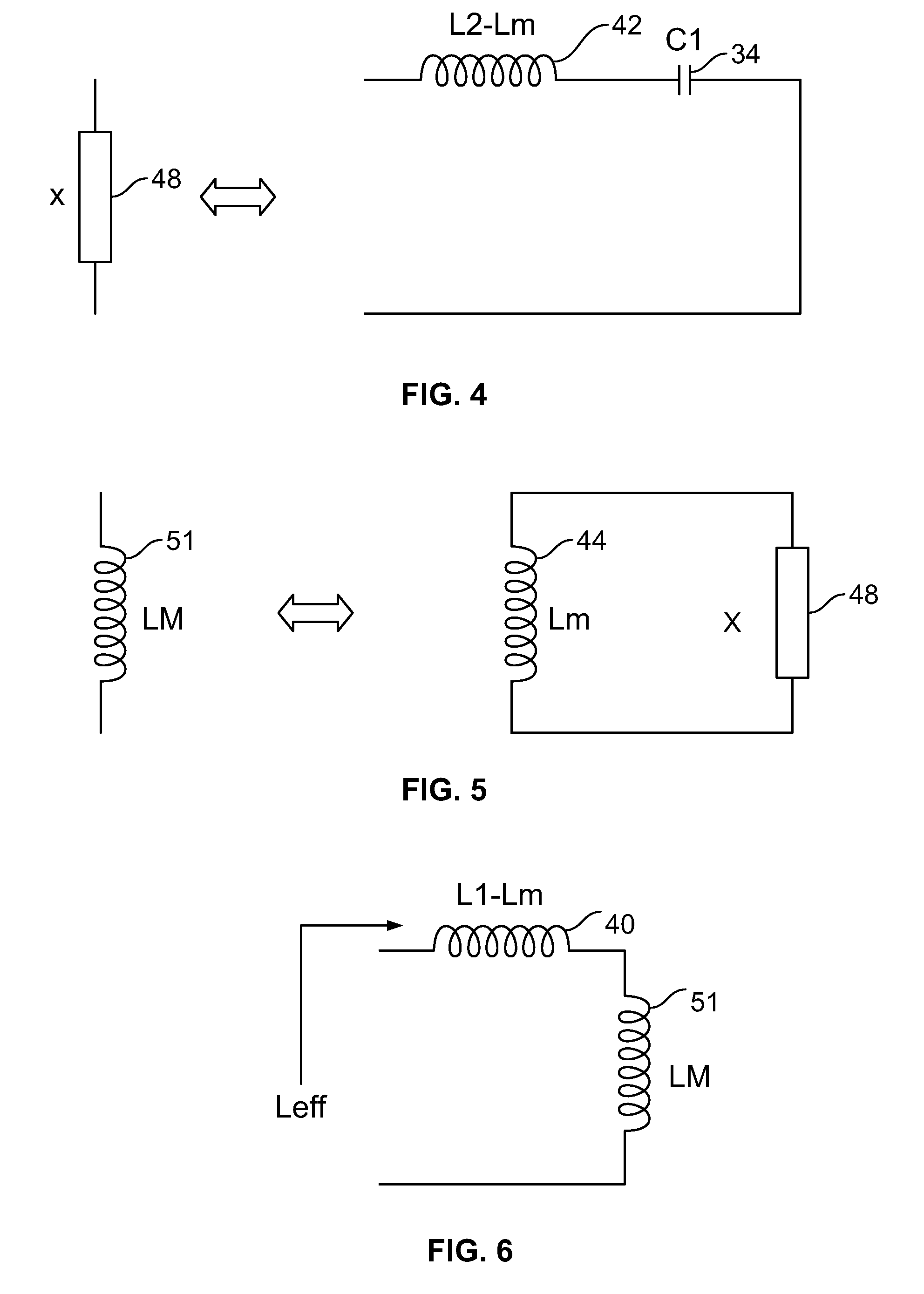

Tunable capacitively loaded transformer providing switched inductance for rf/microwave integrated circuits

InactiveUS20100123536A1Networks with variable switch closing timeInductance without magnetic coreMicrowaveTransformer

A tunable transformer providing switched inductance includes a primary winding and a secondary winding. A switch is connected to the secondary winding of the transformer. At least one capacitor is also connected to the secondary winding of the transformer with the switch.

Owner:AUTOLIV ASP INC

Narrow band RF filter circuits, devices and processes using impedance translation

An active filter circuit includes an inductance-capacitance (LC) circuit (110) for wireless frequency input, a bi-directional mixer (120) and a filter impedance (130) series-coupled across at least part of the LC circuit (110), and another mixer (420) coupled to at least some portion of the LC circuit. Other circuits, processes, receivers, transmitters and transceivers are disclosed.

Owner:TEXAS INSTR INC

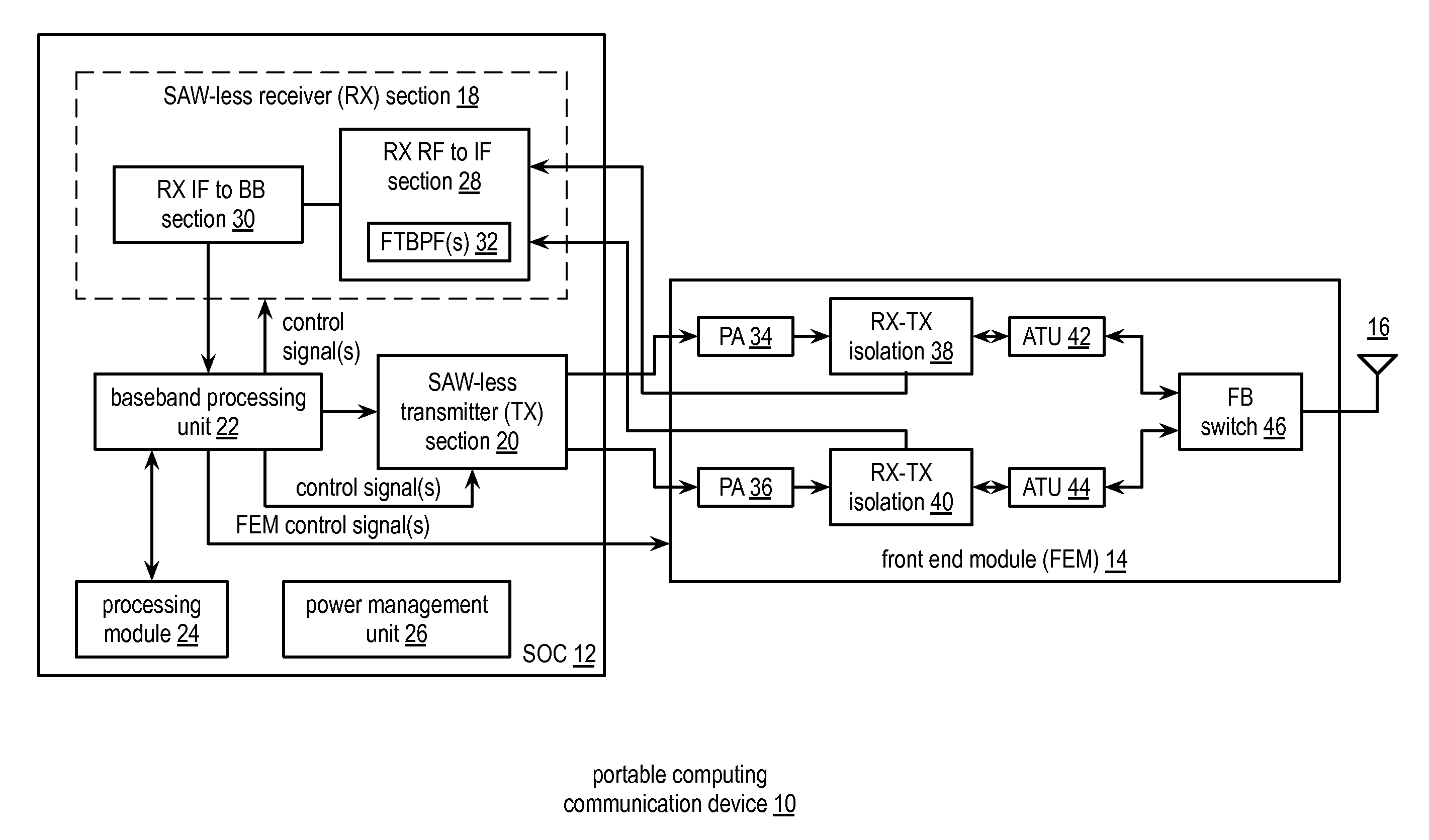

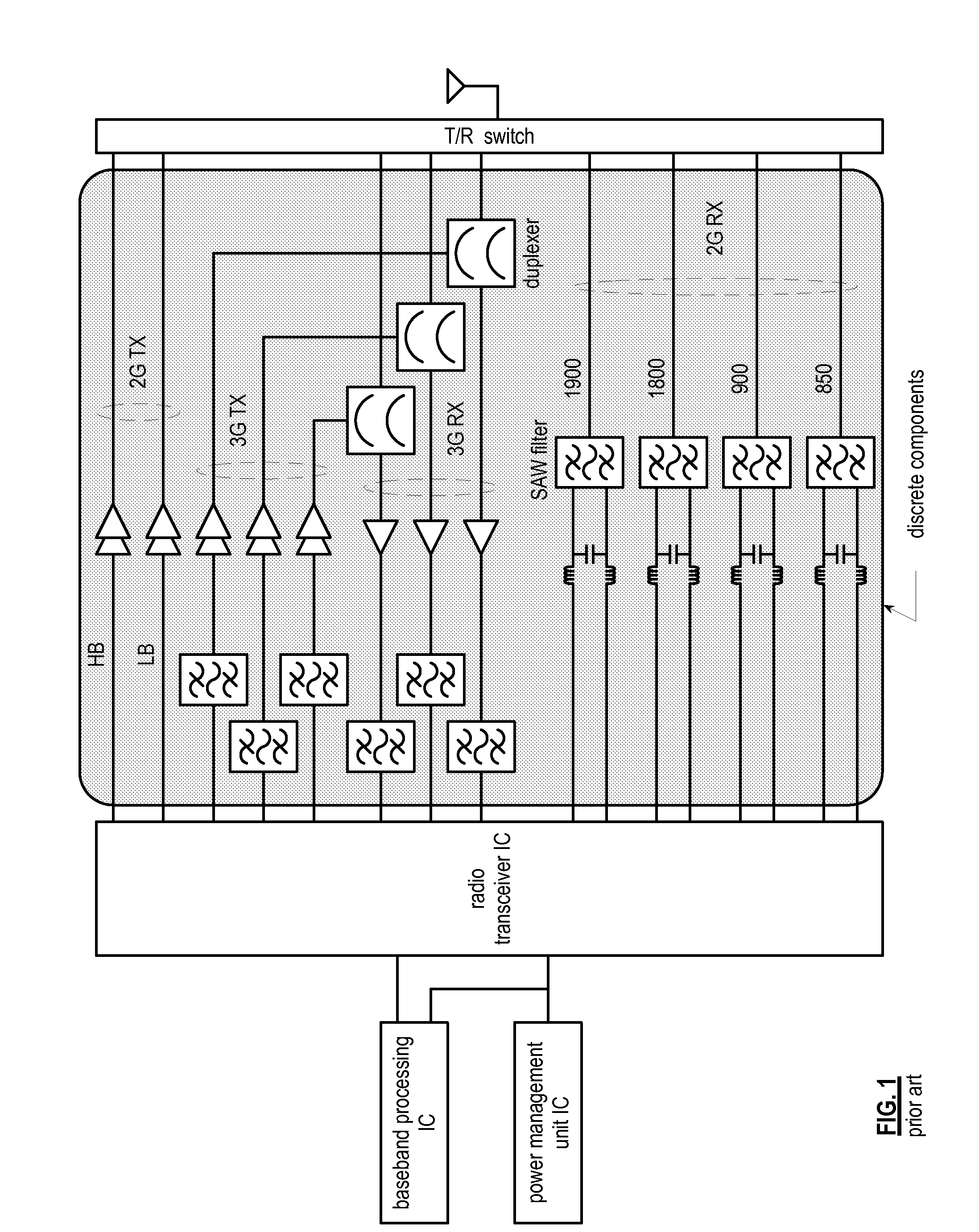

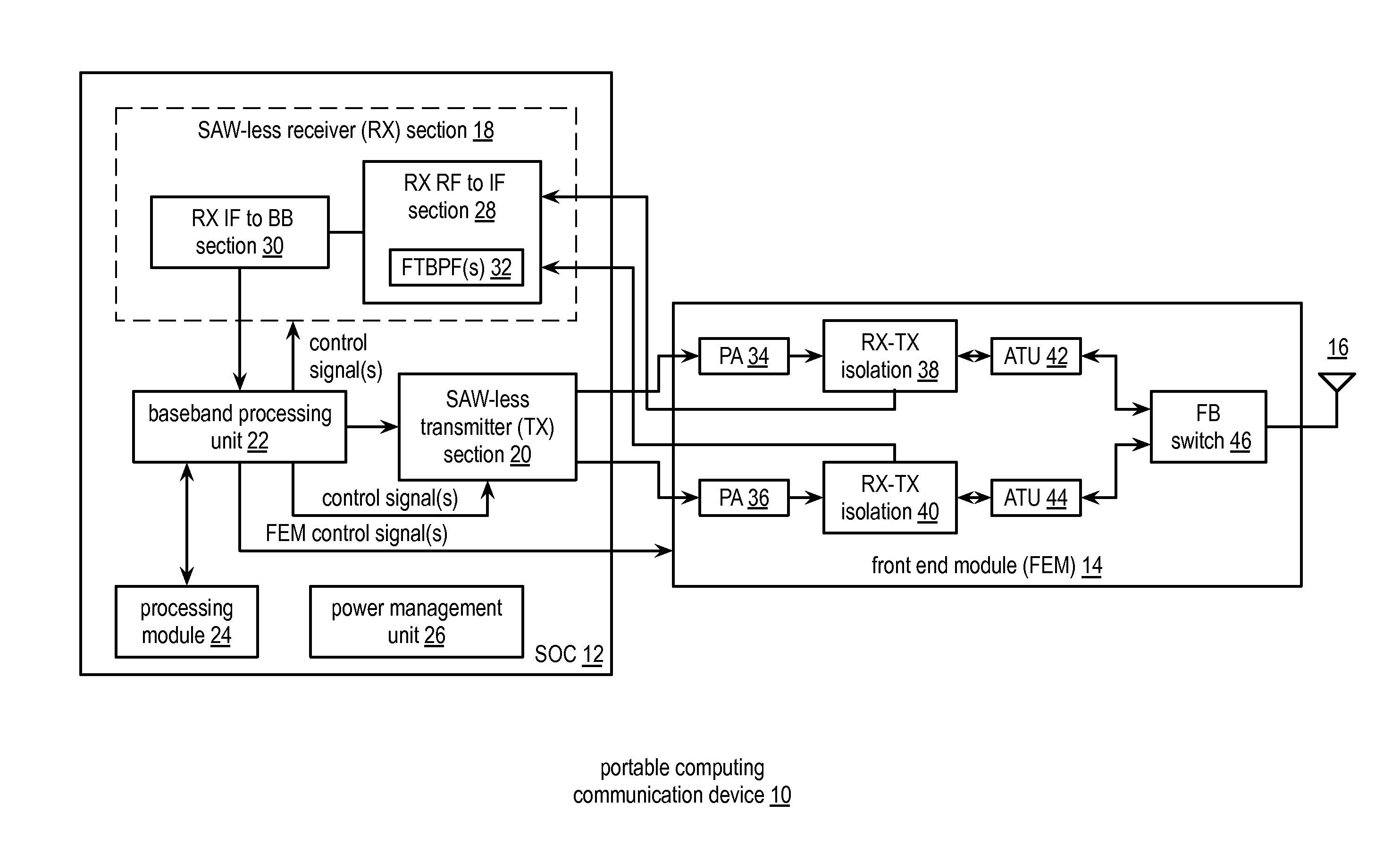

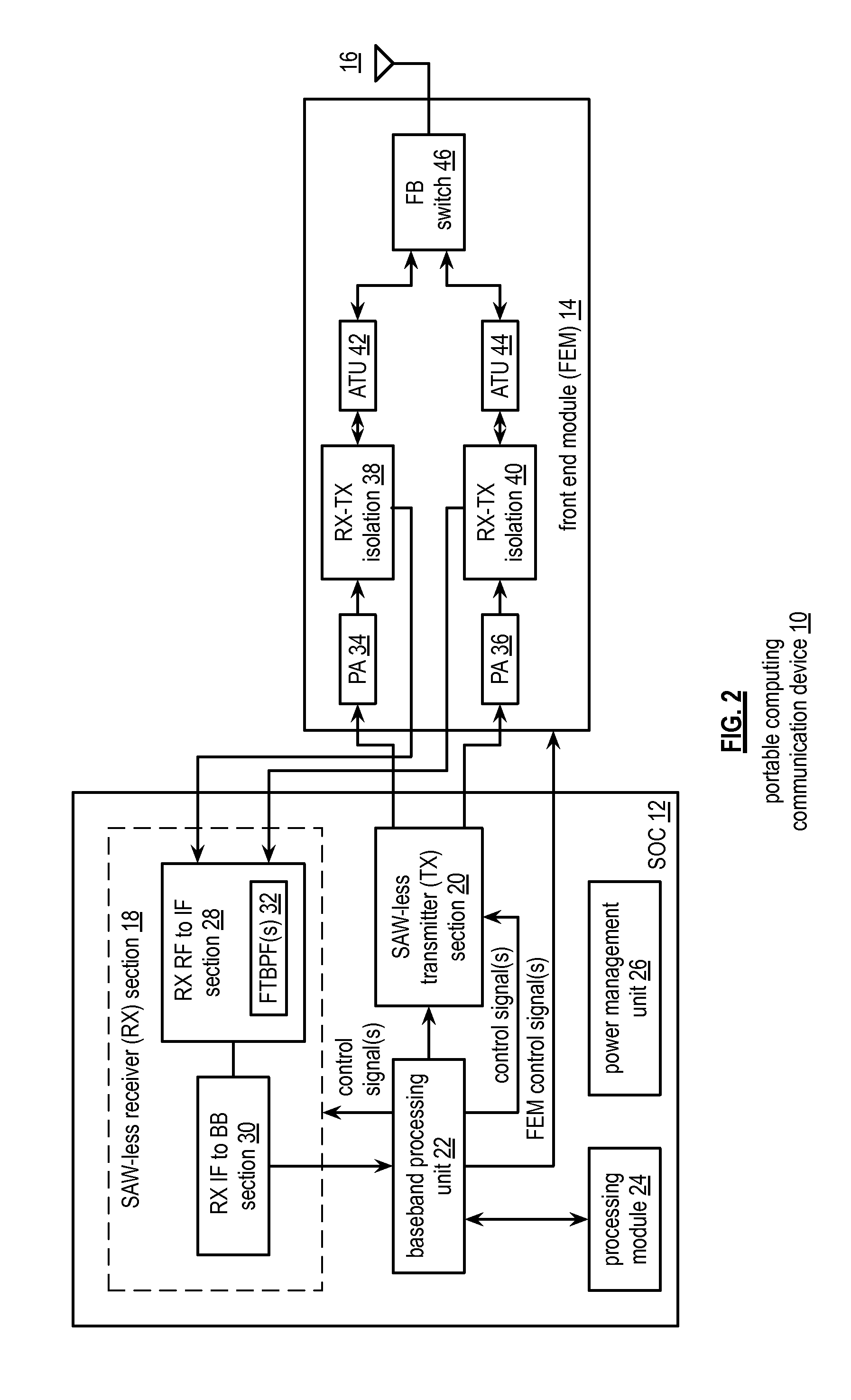

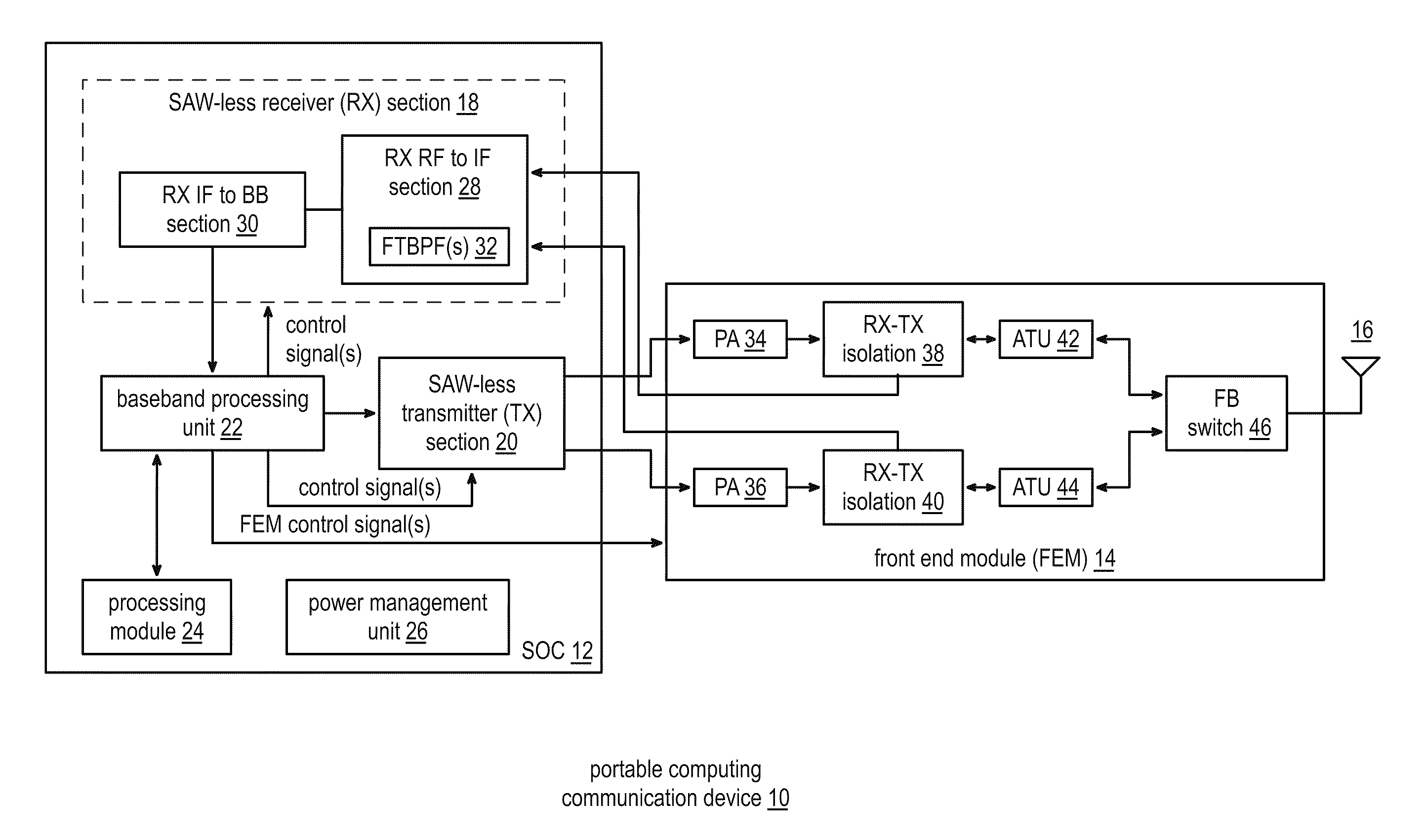

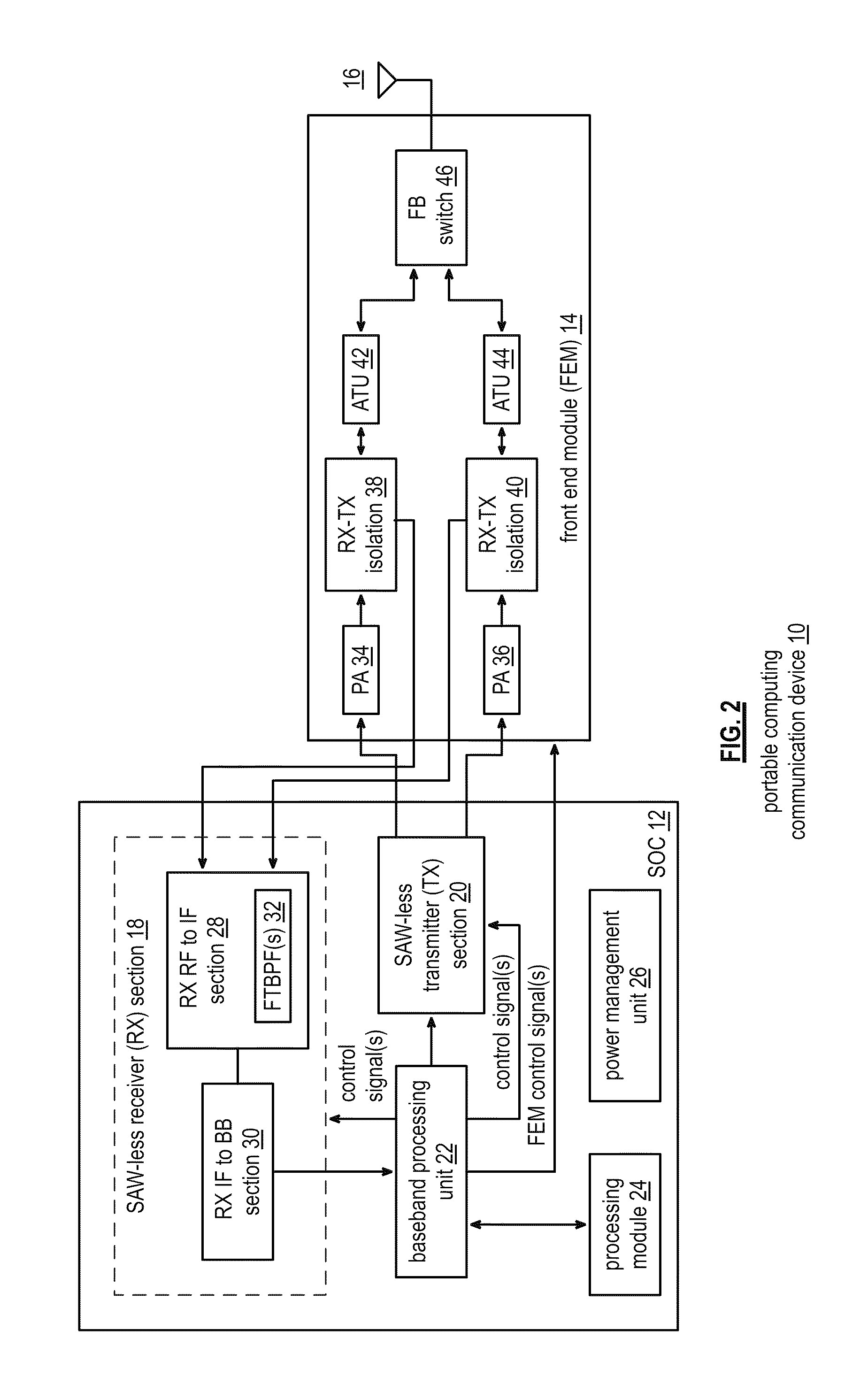

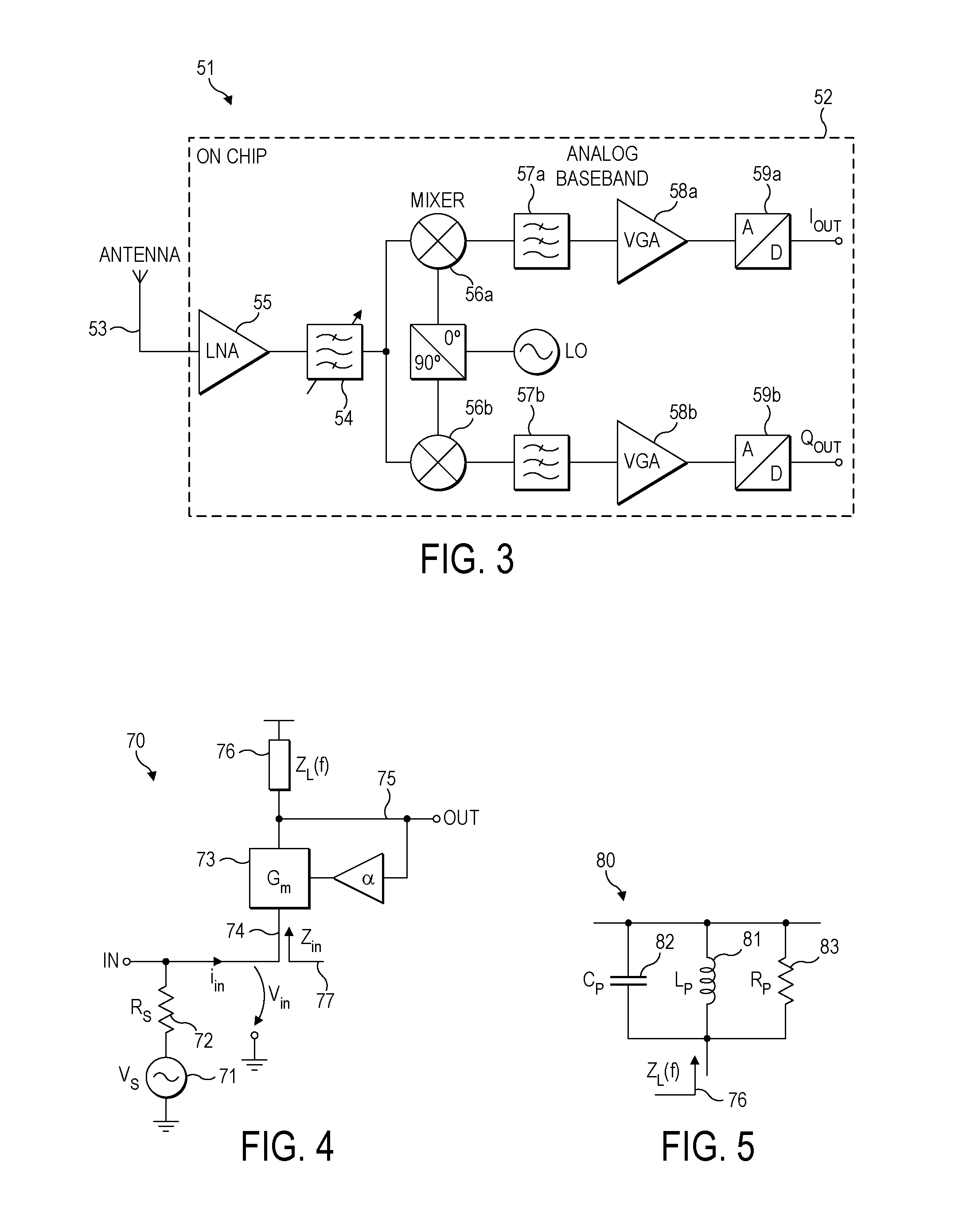

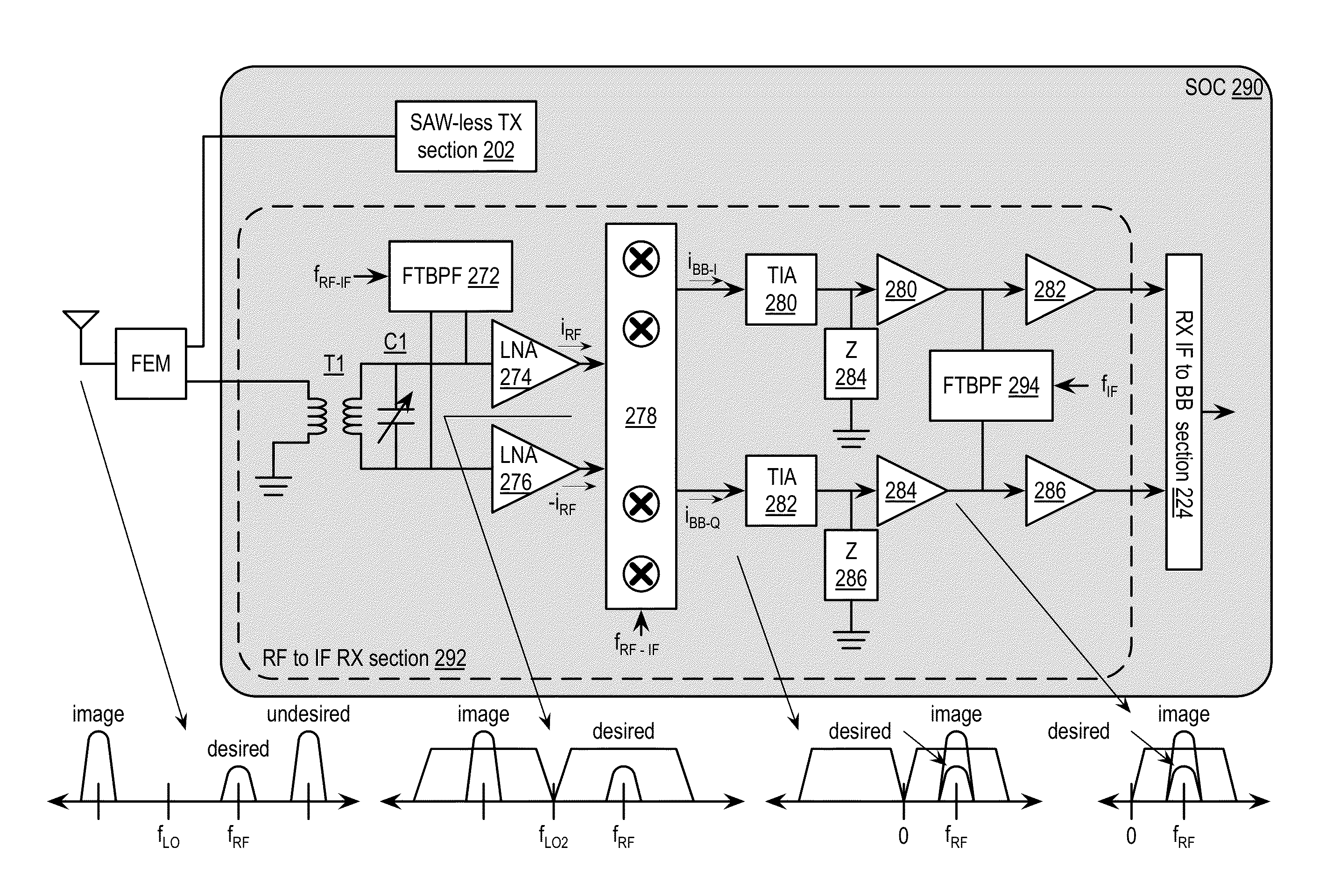

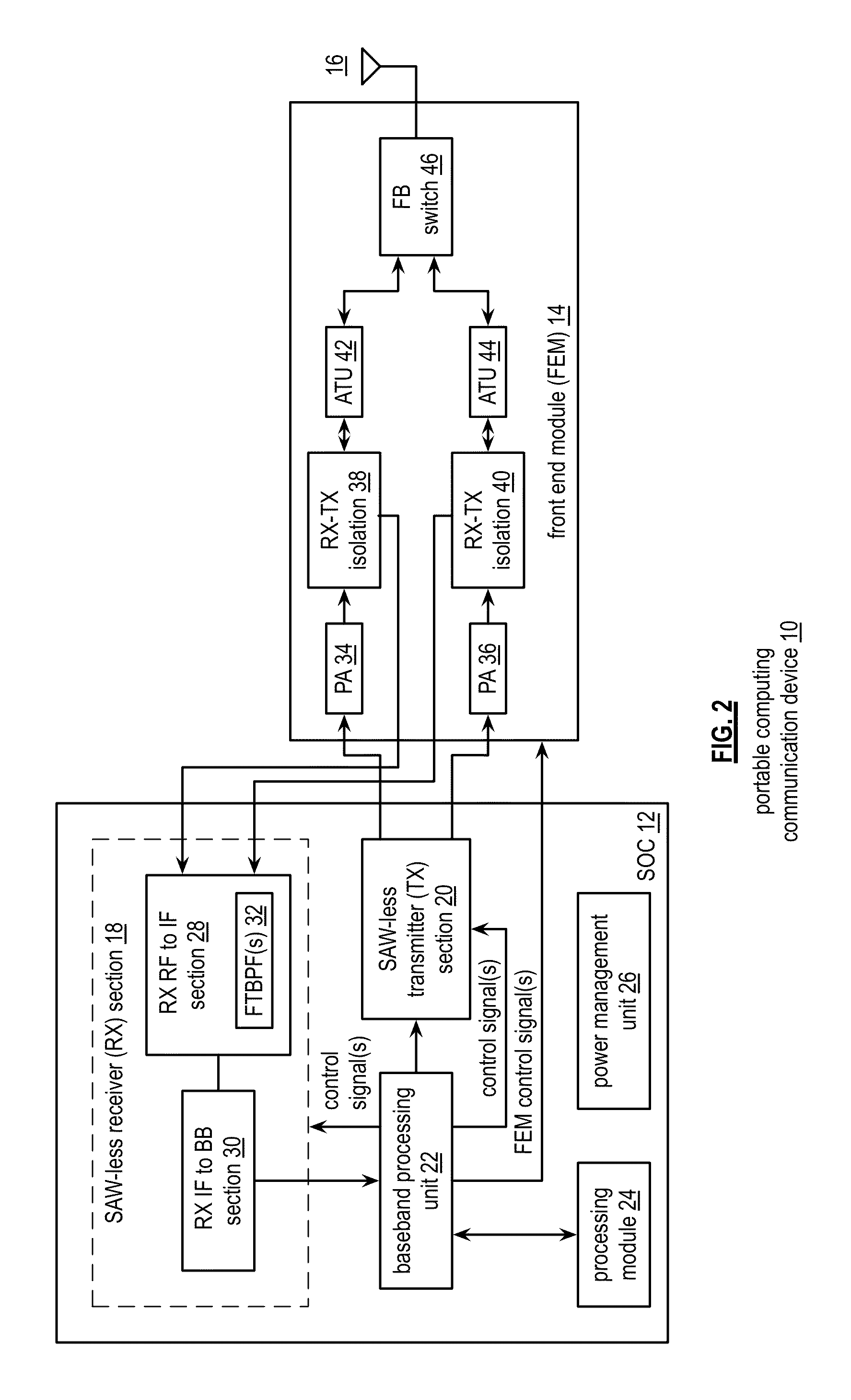

Saw-less receiver with a frequency translated BPF having a negative resistance

A SAW-less receiver includes an FEM interface module, an RF to IF receiver section, and a receiver IF to baseband section. The RF to IF receiver section includes an RF frequency translated bandpass filter (FTBPF), an LNA, and a mixing section. The RF FTBPF frequency translates a baseband filter response to an RF filter response and filters an inbound RF signal in accordance with the RF filter response, wherein the inbound RF signal includes a loss error due to switching loss and / or inductor loss. The RF FTBPF also compensates the loss error based on a negative resistance. The LNA amplifies the compensated inbound RF signal and the mixing section mixes the amplified inbound RF signal with a local oscillation to produce an inbound IF signal. The receiver IF to baseband section converts the inbound IF signal into one or more inbound symbol streams.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

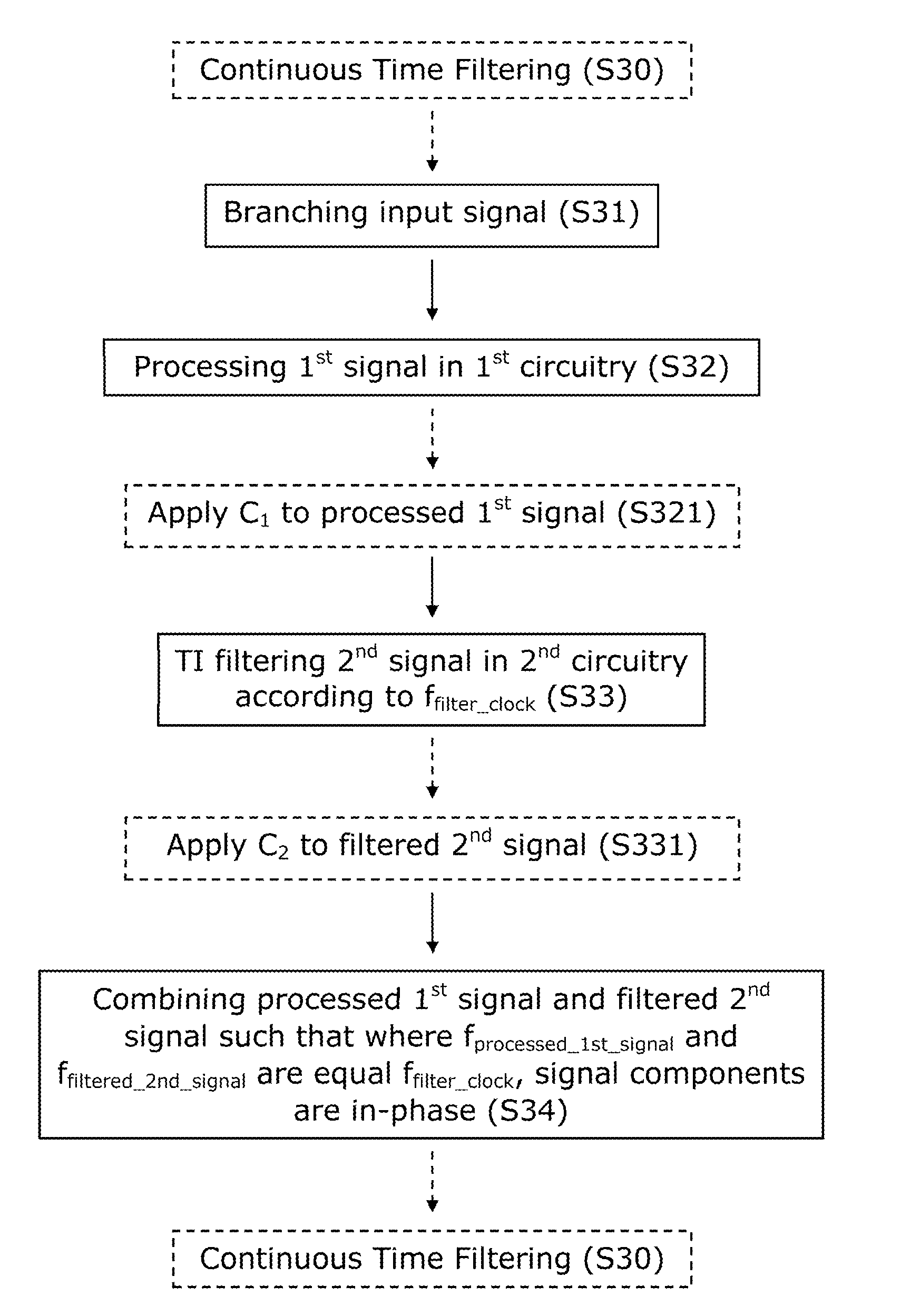

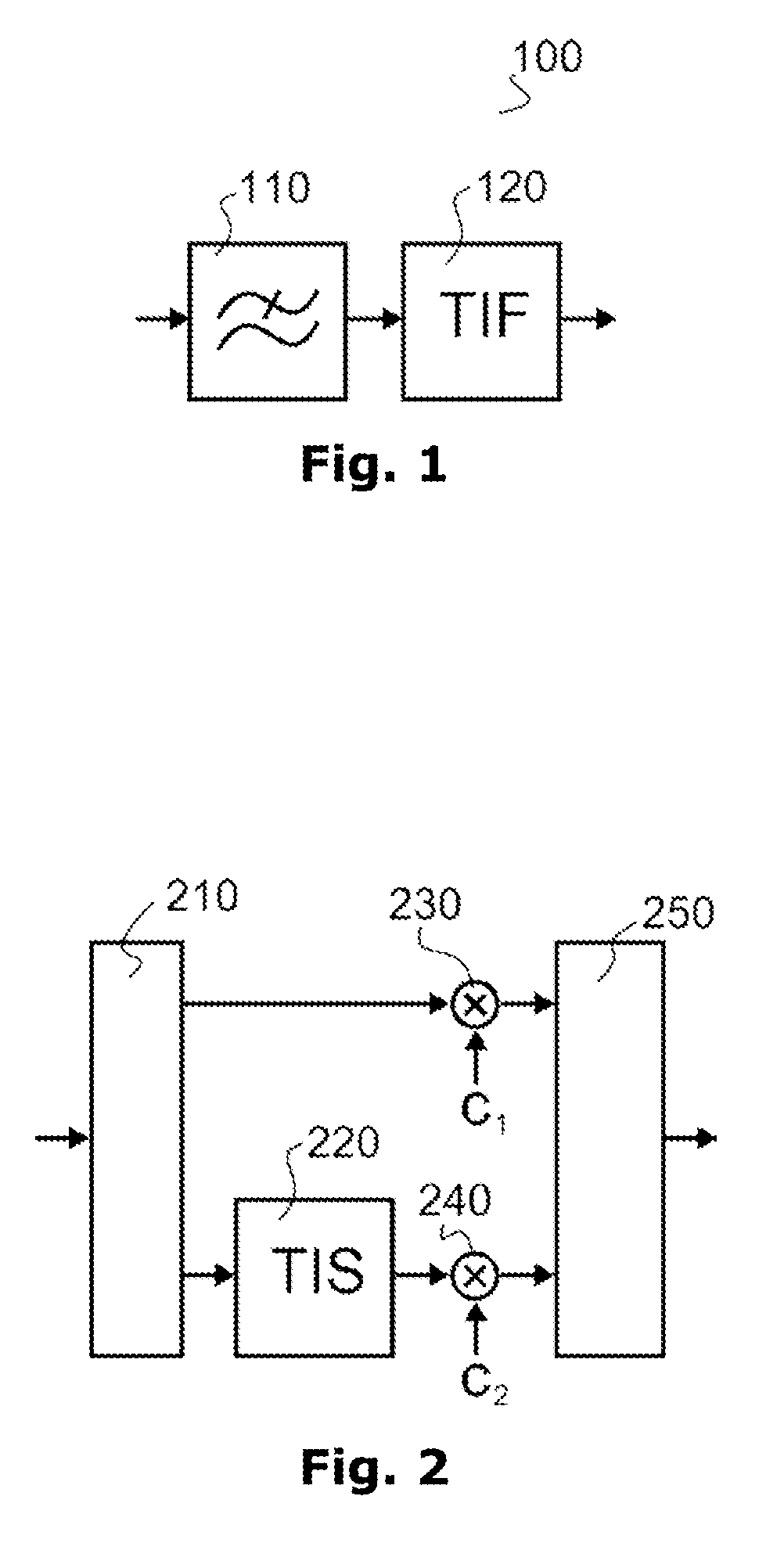

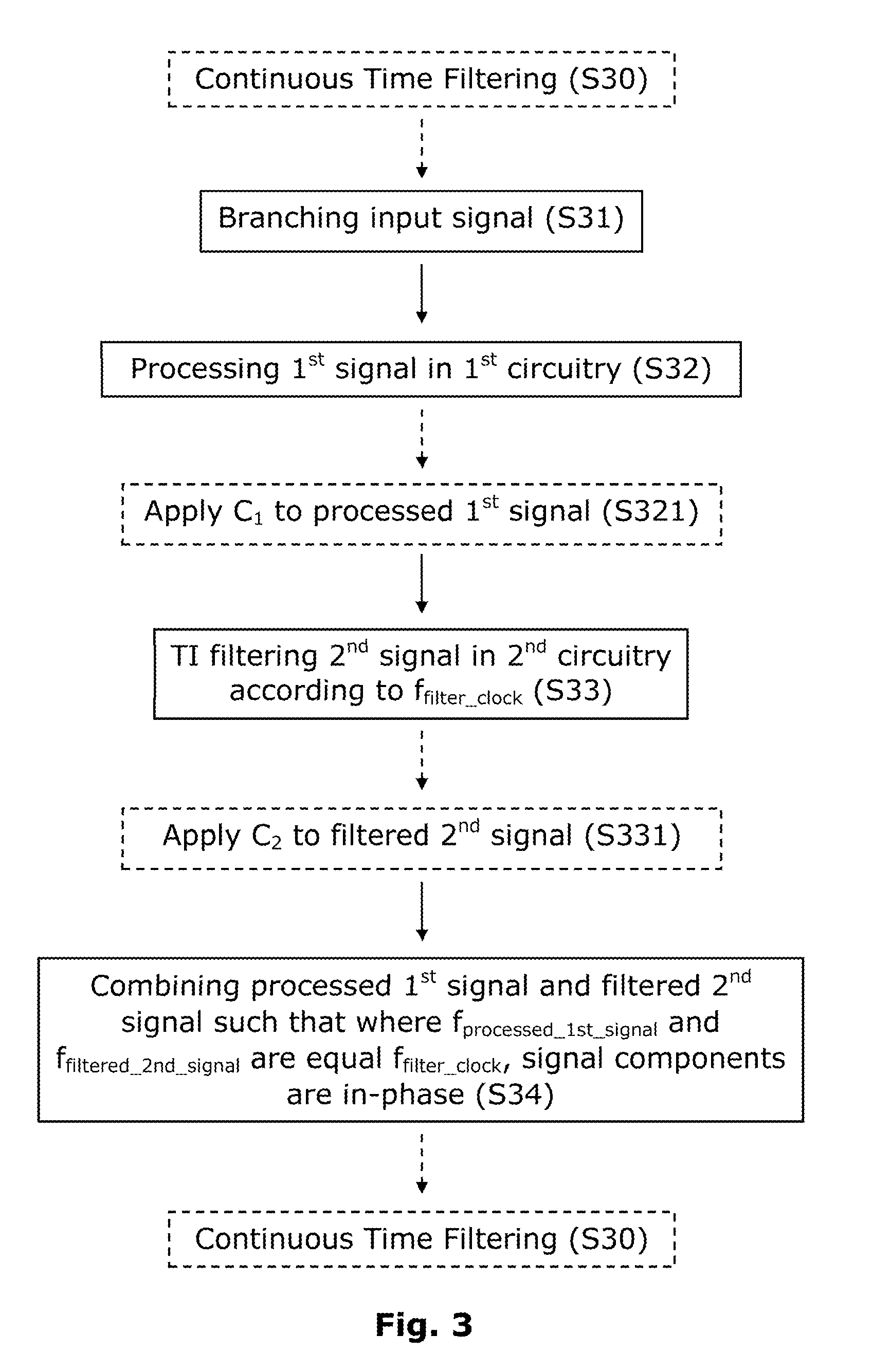

Filter

InactiveUS20130235959A1Suppressing signal component in signalUniform gainNetworks with variable switch closing timeN-path filtersEngineeringTransfer impedance

An apparatus and method suppress unwanted signal components in receiving signals during wireless communication. A first circuitry is arranged to process a first signal, a second circuitry is arranged to apply transferred impedance filtering on a second signal according to a filter clock frequency, a signal branching circuitry is arranged to branch an input signal into the first circuitry and the second circuitry, and a signal combining circuitry is arranged to combine the processed first signal and the filtered second signal such that signal components of the first signal processed in the first circuitry and the filtered second signal are in-phase for signal frequencies equal to the filter clock frequency.

Owner:AVAGO TECH INT SALES PTE LTD

Device for controlling a frequency response by scaling an impedance

InactiveUS7015747B2Pulse automatic controlNetworks with variable switch closing timeControl signalEngineering

Provided is a device for controlling a frequency response by scaling an impedance. The device includes a filter and a duty ratio controller. The filter generates an output signal after removing a frequency from an input signal, and comprises a first impedance component and a switch. The switch, which is serially connected to the first impedance component, is switched on or off in response to a duty-controlled clock signal. The duty ratio controller receives a clock signal, controls a duty ratio of the clock signal, and generates the duty-controlled clock signal. The duty ratio controller comprises a flip-flop, which has a clock terminal that receives the clock signal, and a reset terminal, which receives a delayed signal obtained after delaying the clock signal by a time delay. The duty ratio controller further comprises a delay component that receives the clock signal, generates the delayed signal, and controls the time delay in response to a duty control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

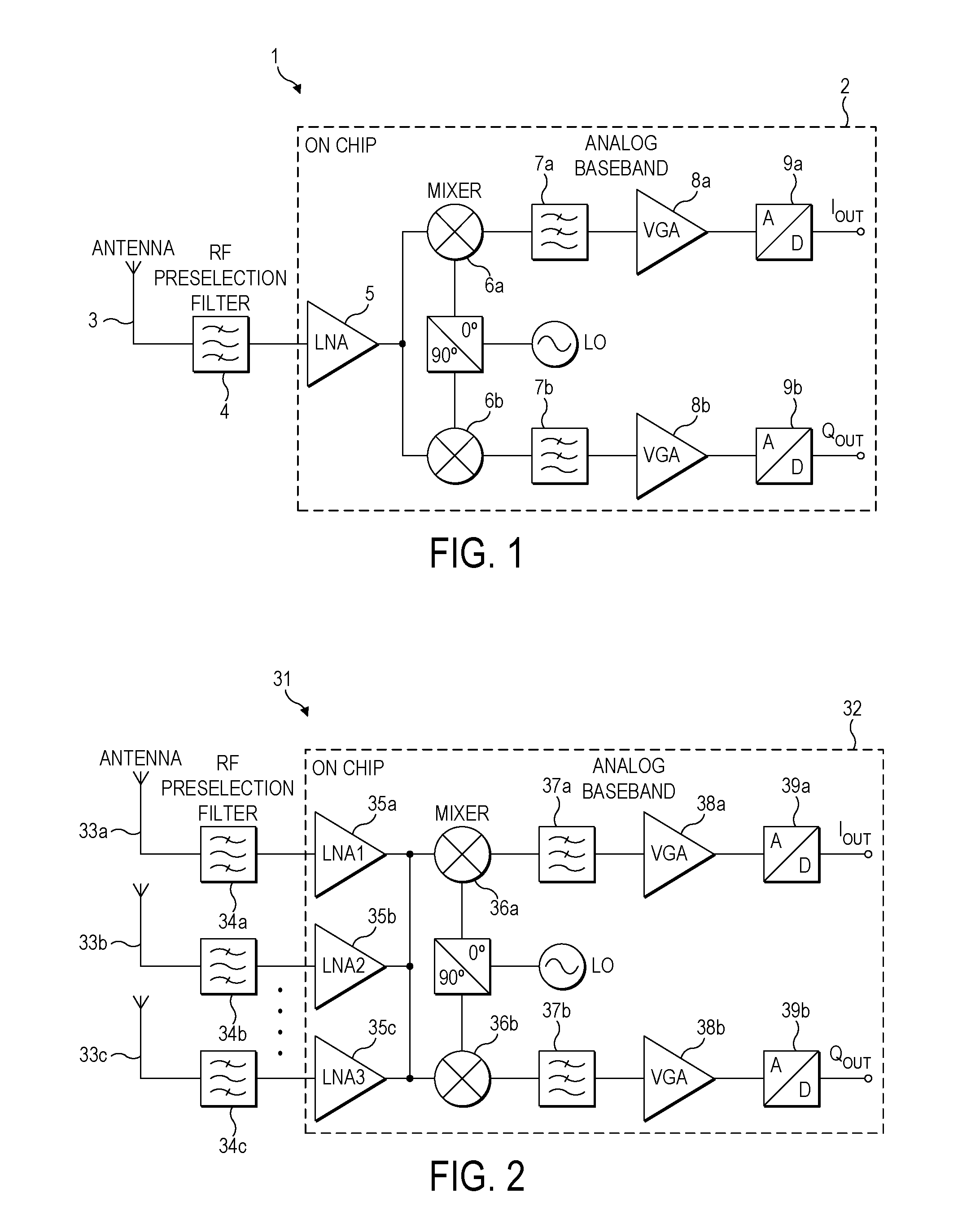

Amplifier with On-Chip Filter

ActiveUS20120171980A1Networks with variable switch closing timeTransmissionUltrasound attenuationAntenna impedance

An integrated circuit for a radio receiver comprising a radio-frequency amplifier and a radio-frequency filter is described. The amplifier receives radio-frequency signals from an antenna, the filter is connected to the amplifier output, and the output of the filter is provided to a processing stage of the receiver. The amplifier comprises an amplifying stage controlled by a radio-frequency input signal and a signal fed back from the filter. The amplifier input impedance is substantially matched to the antenna impedance at a frequency band of interest. The signal fed back from the filter providing attenuation of signals outside the frequency band of interest at the amplifier input. The filter comprises one or more filter components. A filter component comprises a first input and a second input for receiving the amplifier output, a first switch arranged to selectively connect the first input to a first impedance, a second switch arranged to selectively connect the first input to a second impedance, a third switch arranged to selectively connect the second input to the first impedance, and a fourth switch arranged to selectively connect the second input to the second impedance. The first and fourth switches are controlled by a first oscillator signal and the second and third switches are controlled by a second oscillator signal that is 180° out of phase with the first oscillator signal.

Owner:TELEFON AB LM ERICSSON (PUBL)

Noise filter for an integrated circuit

ActiveUS20050024130A1Avoid misuseHigh frequencyPulse automatic controlNetworks with variable switch closing timeCMOSSnubber

A noise filter for an integrated circuit is proposed. The noise filter comprises a CMOS inverter and two capacitors. The input of the CMOS inverter is coupled with an input pad of the integrated circuit and the output of the CMOS inverter is coupled with an input buffer. The first capacitor is inserted between the output of the CMOS inverter and a first voltage source and the second capacitor is inserted between the output of the CMOS inverter and a second voltage source. A transfer gate may be in stead of the CMOS inverter.

Owner:WINBOND ELECTRONICS CORP

Receiver, transceiver and receiving method

InactiveUS20070218856A1High selectivityReduce filter costNetworks with variable switch closing timeTransmissionAudio power amplifierTransceiver

A receiving method, a transceiver and a receiver are provided. The receiver comprises an antenna for receiving a radio frequency signal, a local oscillator, an amplifier for amplifying the received signal, a phase shifter connected between the antenna and the amplifier, the phase shifter converting a high impedance at one end of the phase shifter to a low impedance at the other end, and vice versa. The receiver further comprises a filter, the frequency response of the filter being determined on a frequency related to the frequency of the local oscillator, the filter comprising a switching arrangement which converts the frequency response to radio frequency.

Owner:NOKIA CORP

Multiple-phase frequency translated filter

A frequency translation filter includes a baseband filter circuit, a clock generator, and a switching circuit. The baseband filter circuit is operable to provide a baseband filter response. The clock generator is operable to generate multiple-phase clock signals at a desired frequency. The switching circuit is operable to frequency translate the baseband filter response of the baseband filter circuit to a high frequency filter response in accordance with the multiple-phase clock signals.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com