Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

66 results about "Z-buffering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer graphics, z-buffering, also known as depth buffering, is the management of image depth coordinates in 3D graphics, usually done in hardware, sometimes in software. It is one solution to the visibility problem, which is the problem of deciding which elements of a rendered scene are visible, and which are hidden. Z-buffering was first described in 1974 by Wolfgang Straßer in Chapter 6 (page 6-1) of his PhD thesis. The painter's algorithm is another common solution which, though less efficient, can also handle non-opaque scene elements. The z-buffer uses the Image space method for hidden surface detection. A z-buffer can refer to a data structure or to the method used to perform operations on that structure.

Rendering pipeline

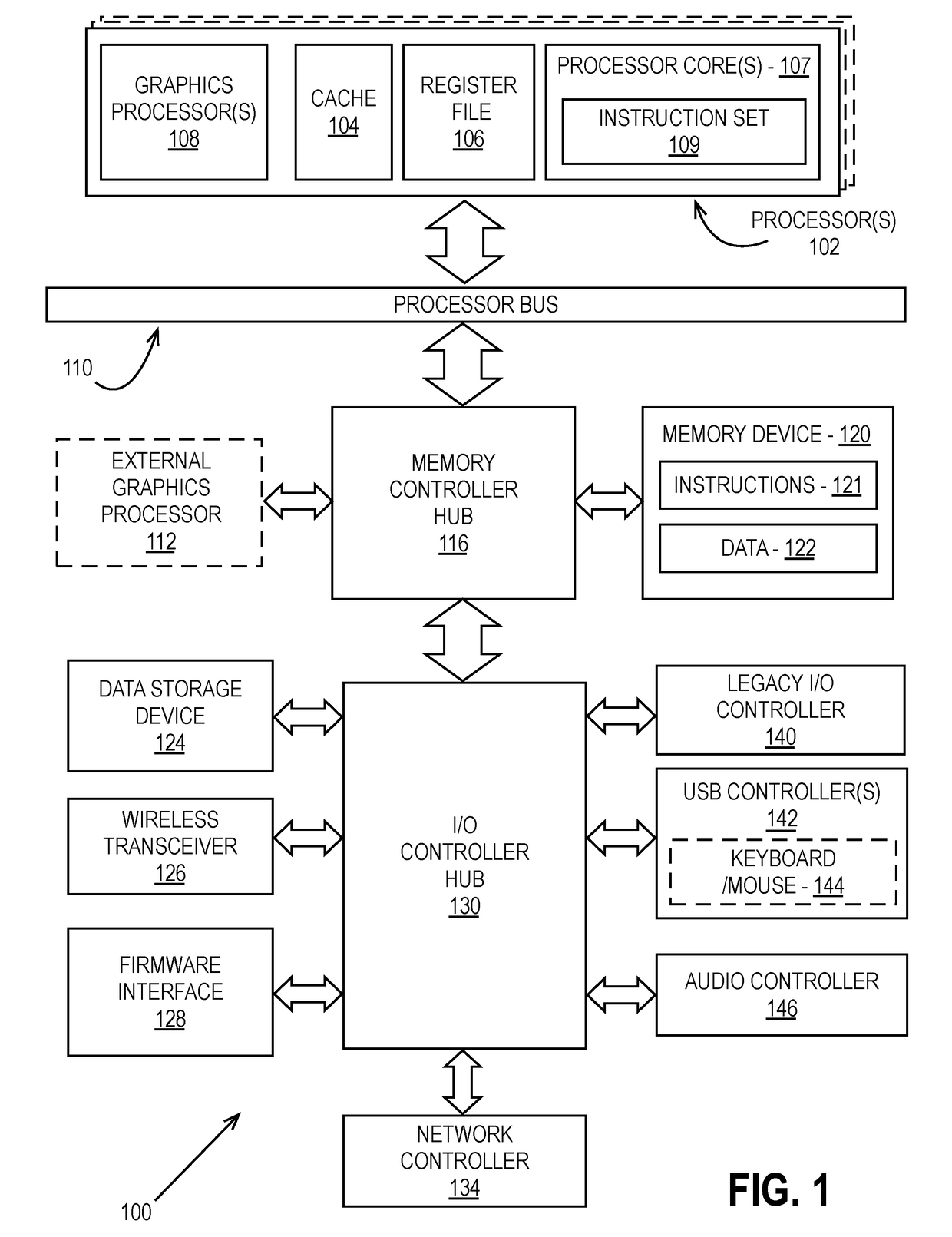

InactiveUS7170515B1EfficientlyReduce memory bandwidth3D-image rendering3D modellingComputational scienceVisibility

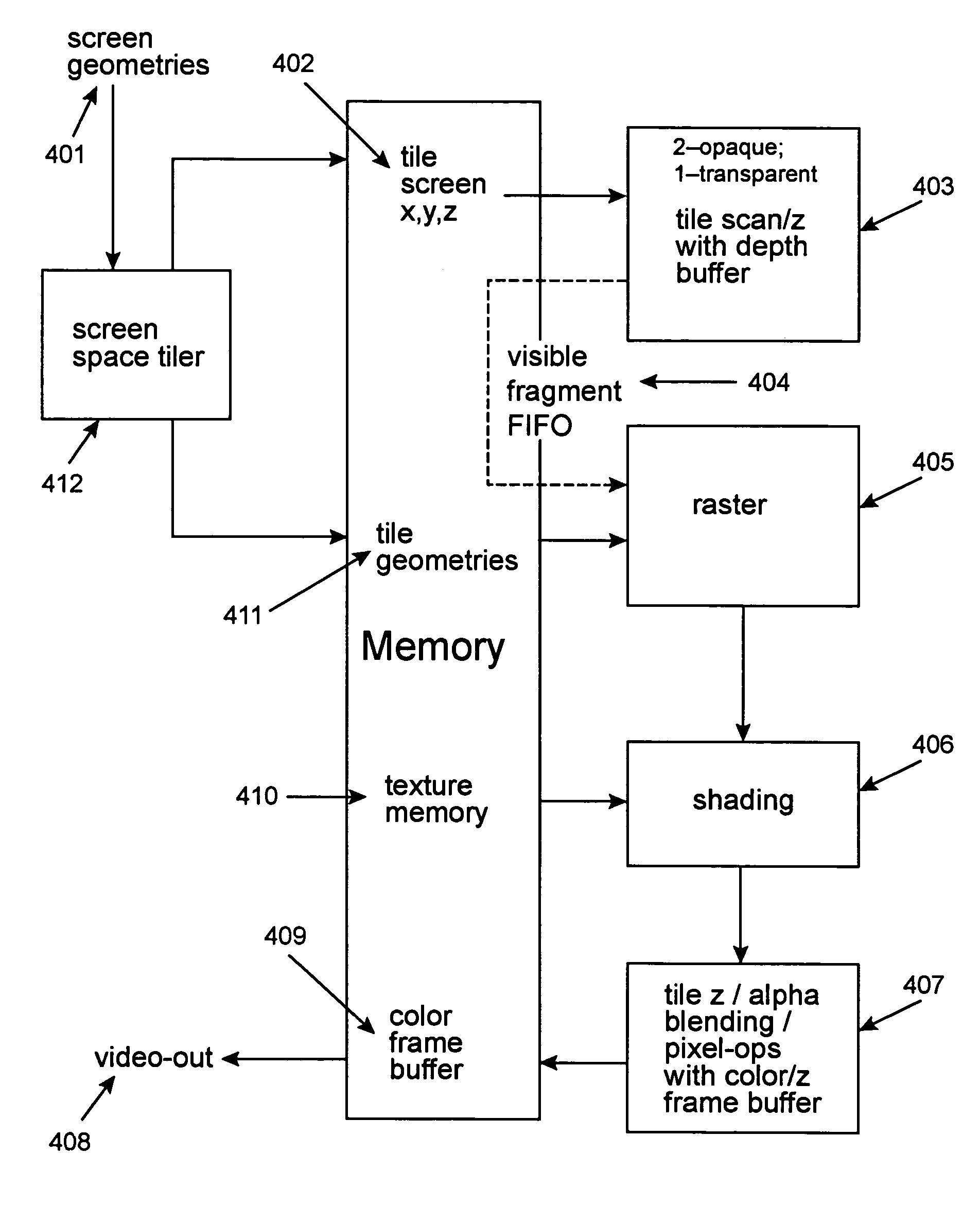

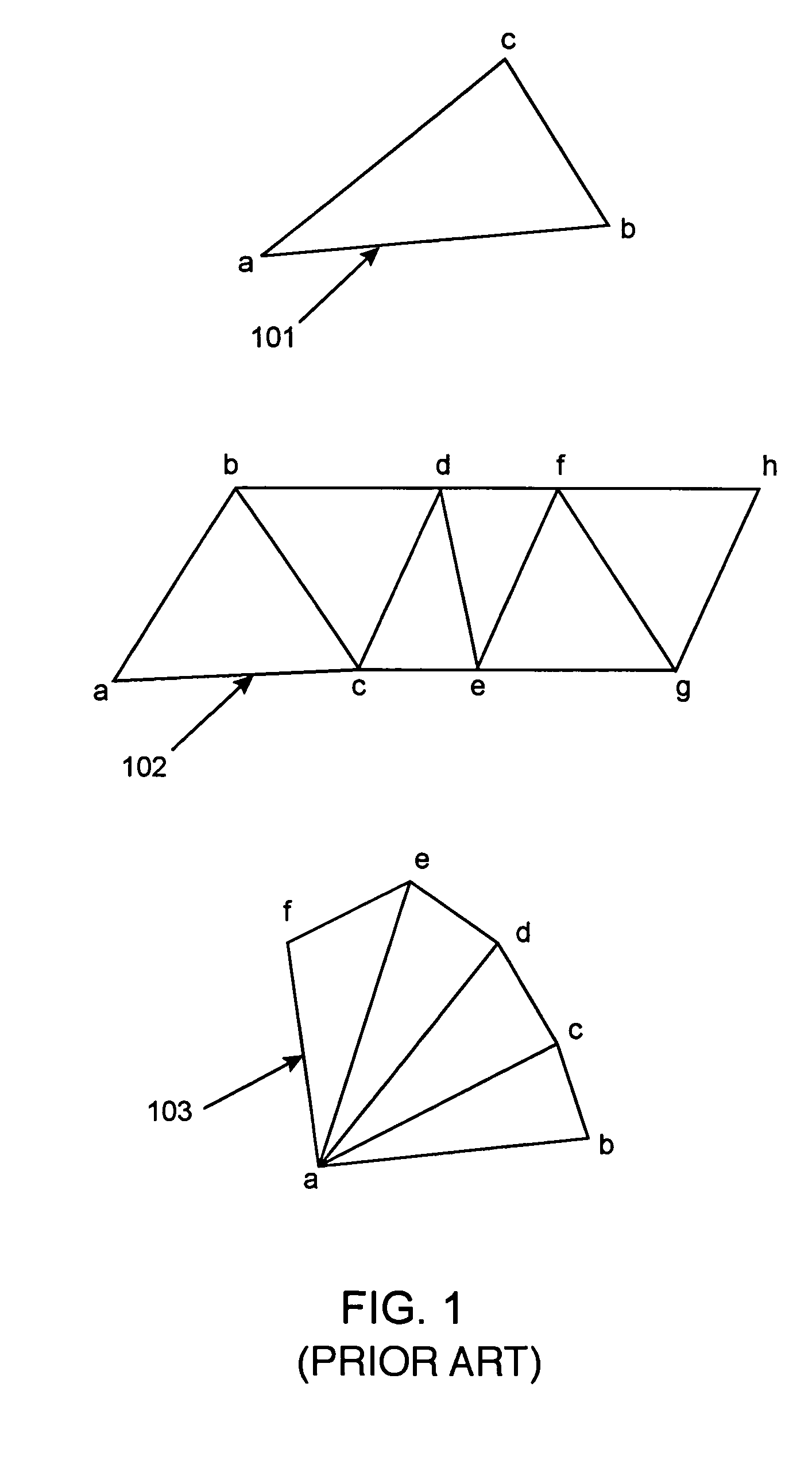

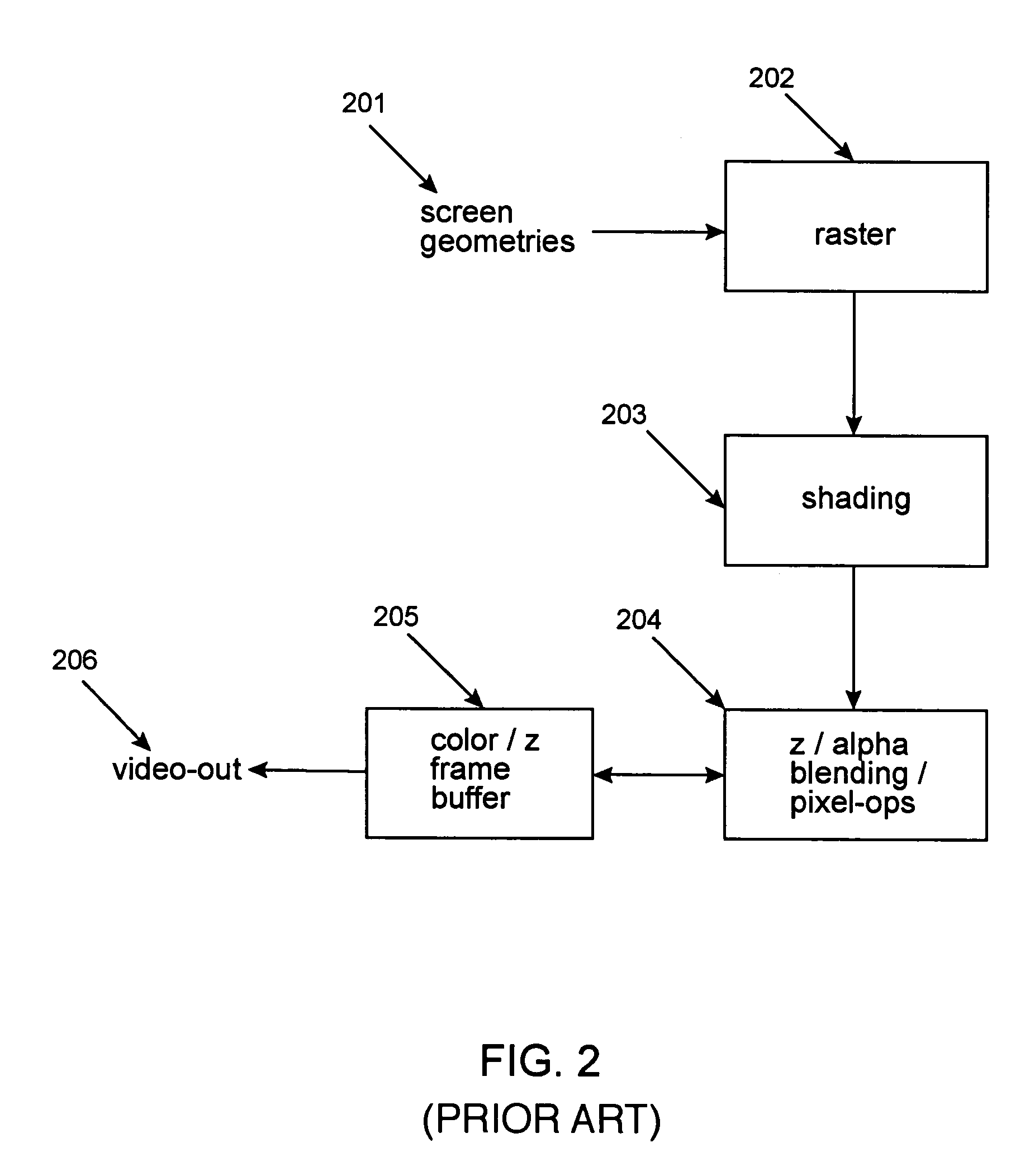

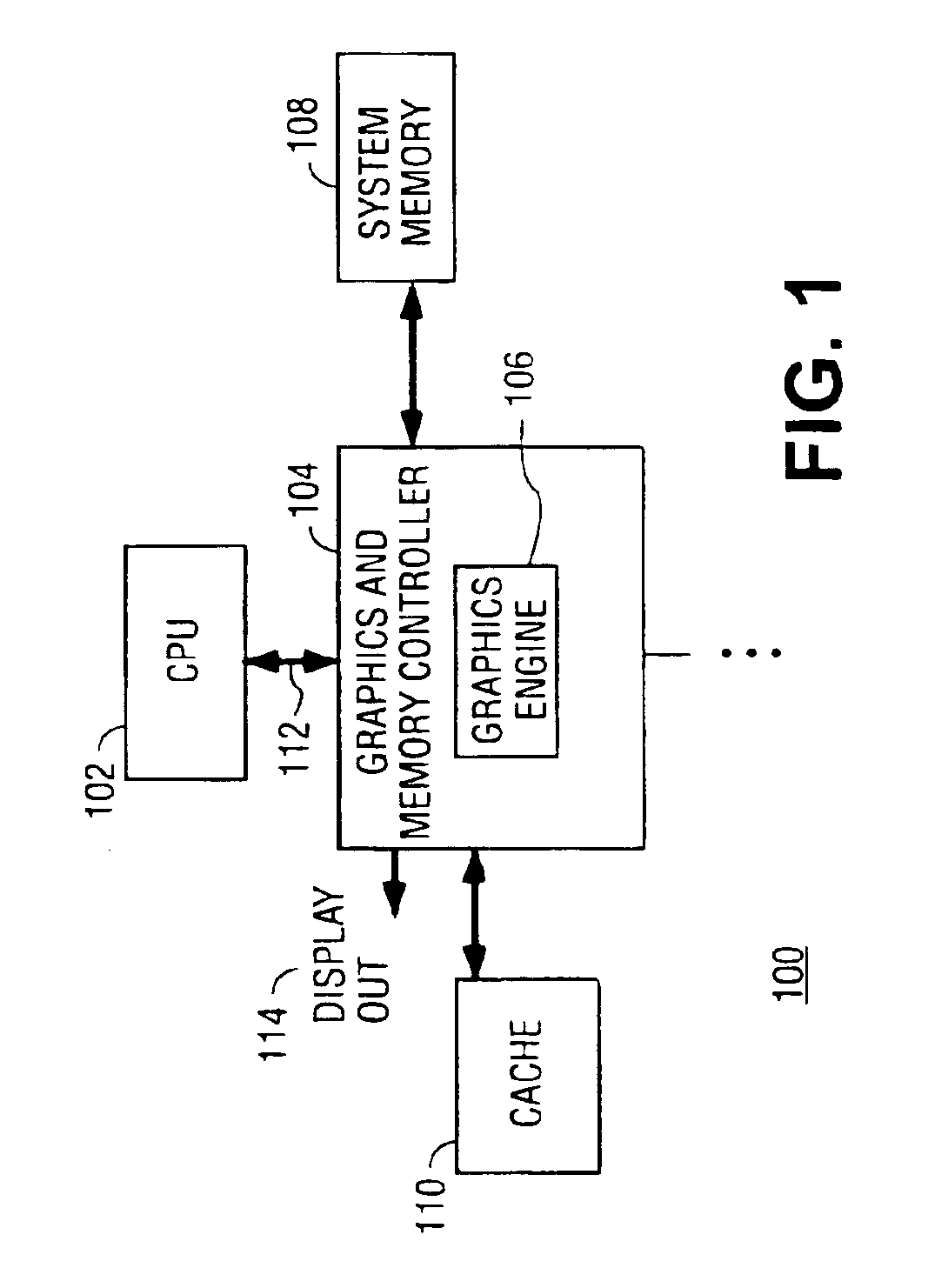

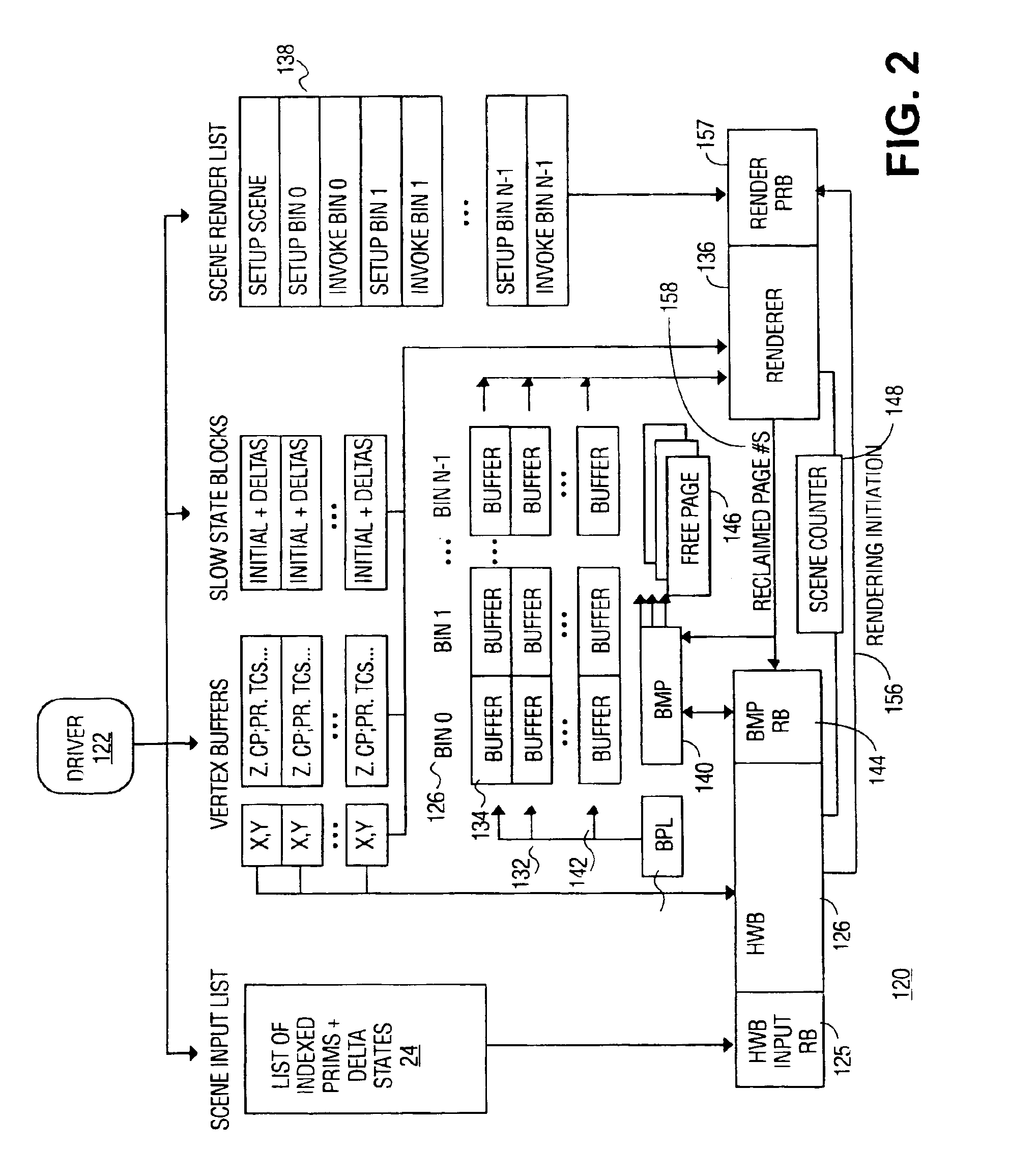

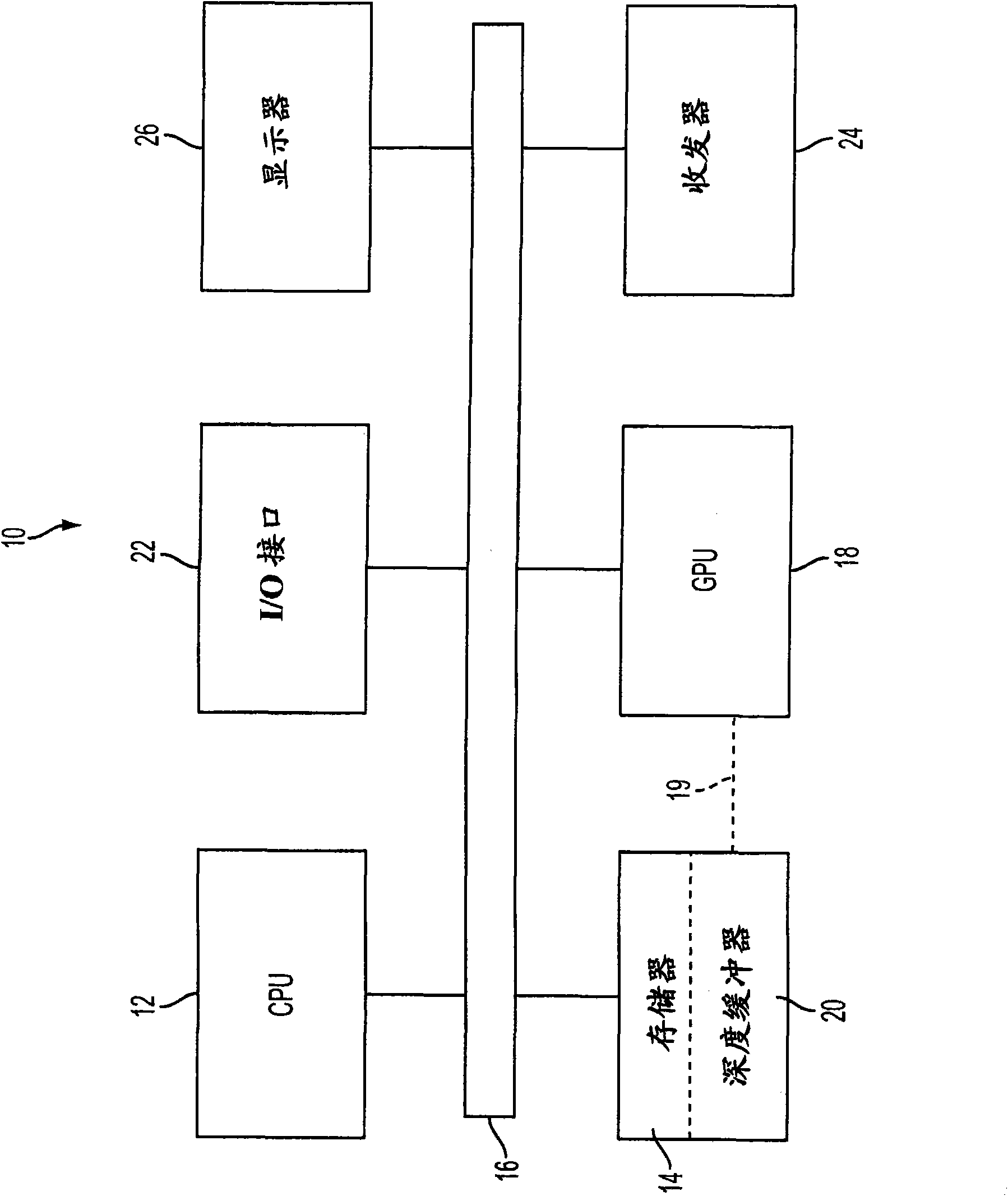

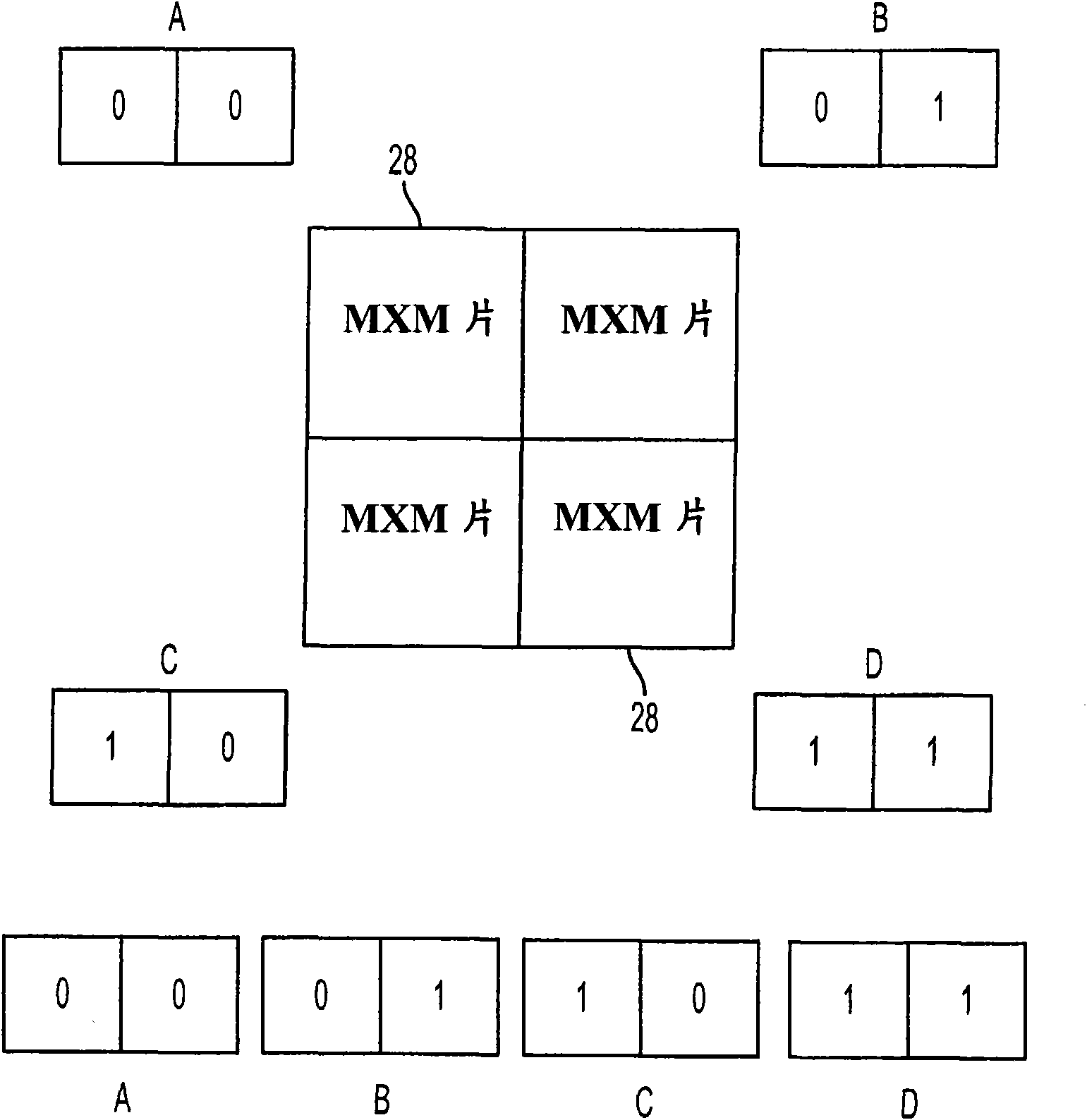

A rendering pipeline system for a computer environment uses screen space tiling (SST) to eliminate the memory bandwidth bottleneck due to frame buffer access and performs screen space tiling efficiently, while avoiding the breaking up of primitives. The system also reduces the buffering size required by SST. High quality, full-scene anti-aliasing is easily achieved because only the on-chip multi-sample memory corresponding to a single tile of the screen is needed. The invention uses a double-z scheme that decouples the scan conversion / depth-buffer processing from the more general rasterization and shading processing through a scan / z engine. The scan / z engine externally appears as a fragment generator but internally resolves visibility and allows the rest of the rendering pipeline to perform setup for only visible primitives and shade only visible fragments. The resulting reduced raster / shading requirements can lead to reduced hardware costs because one can process all parameters with generic parameter computing units instead of with dedicated parameter computing units. The invention processes both opaque and transparent geometries.

Owner:NVIDIA CORP

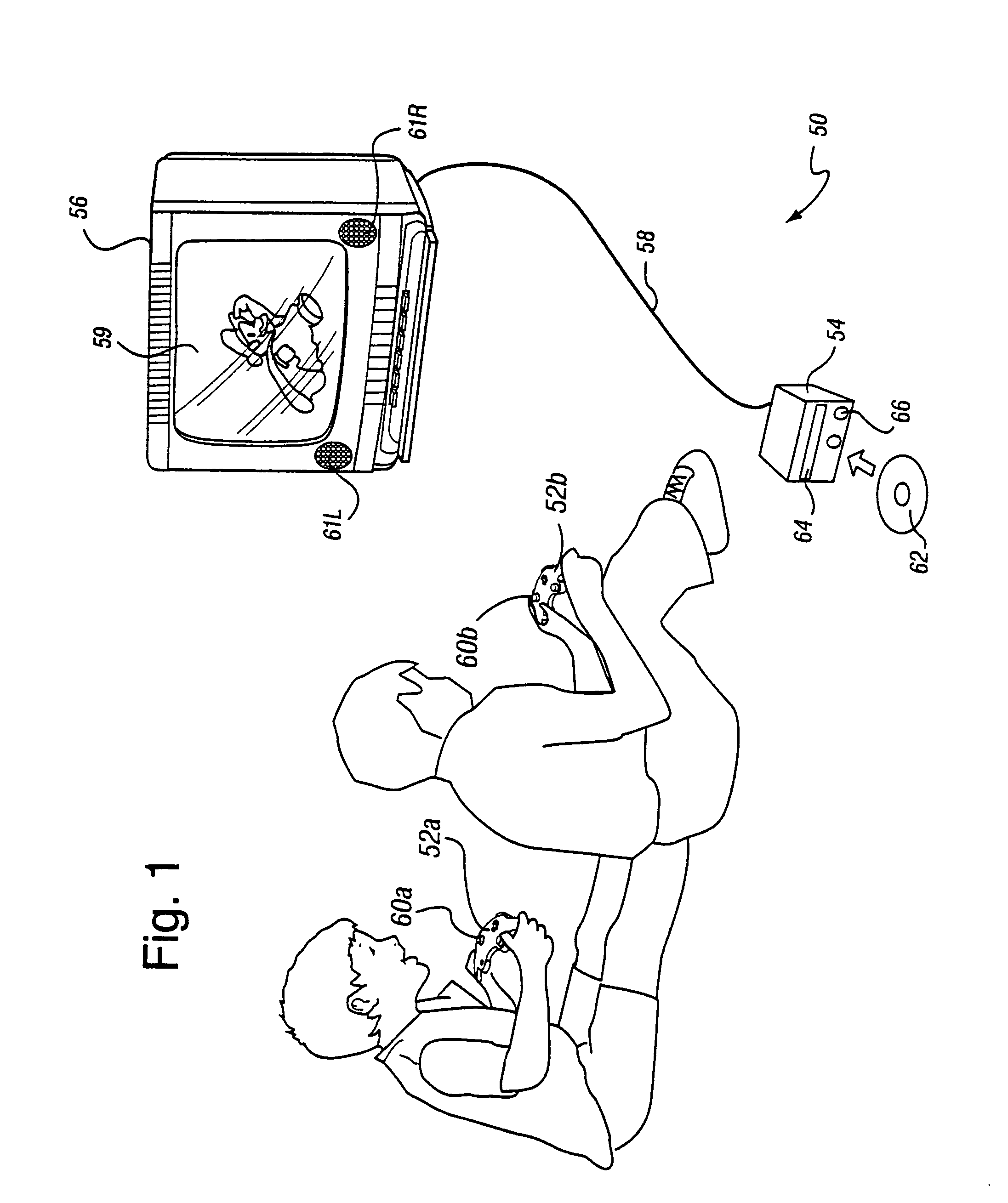

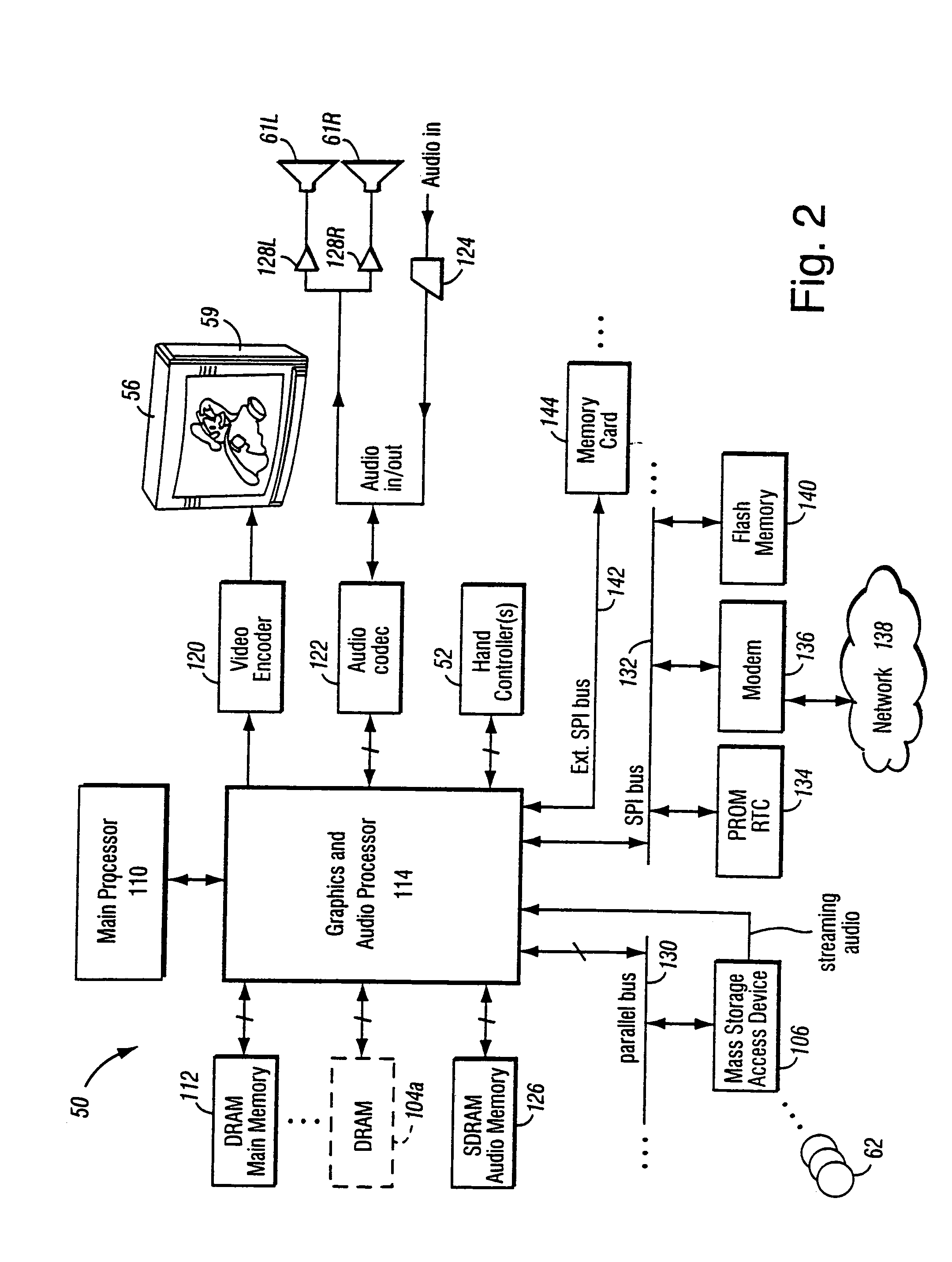

Method and apparatus for anti-aliasing in a graphics system

InactiveUS6999100B1Low costHigh cost-effectiveImage enhancementCathode-ray tube indicatorsInterlaced videoAnti-aliasing

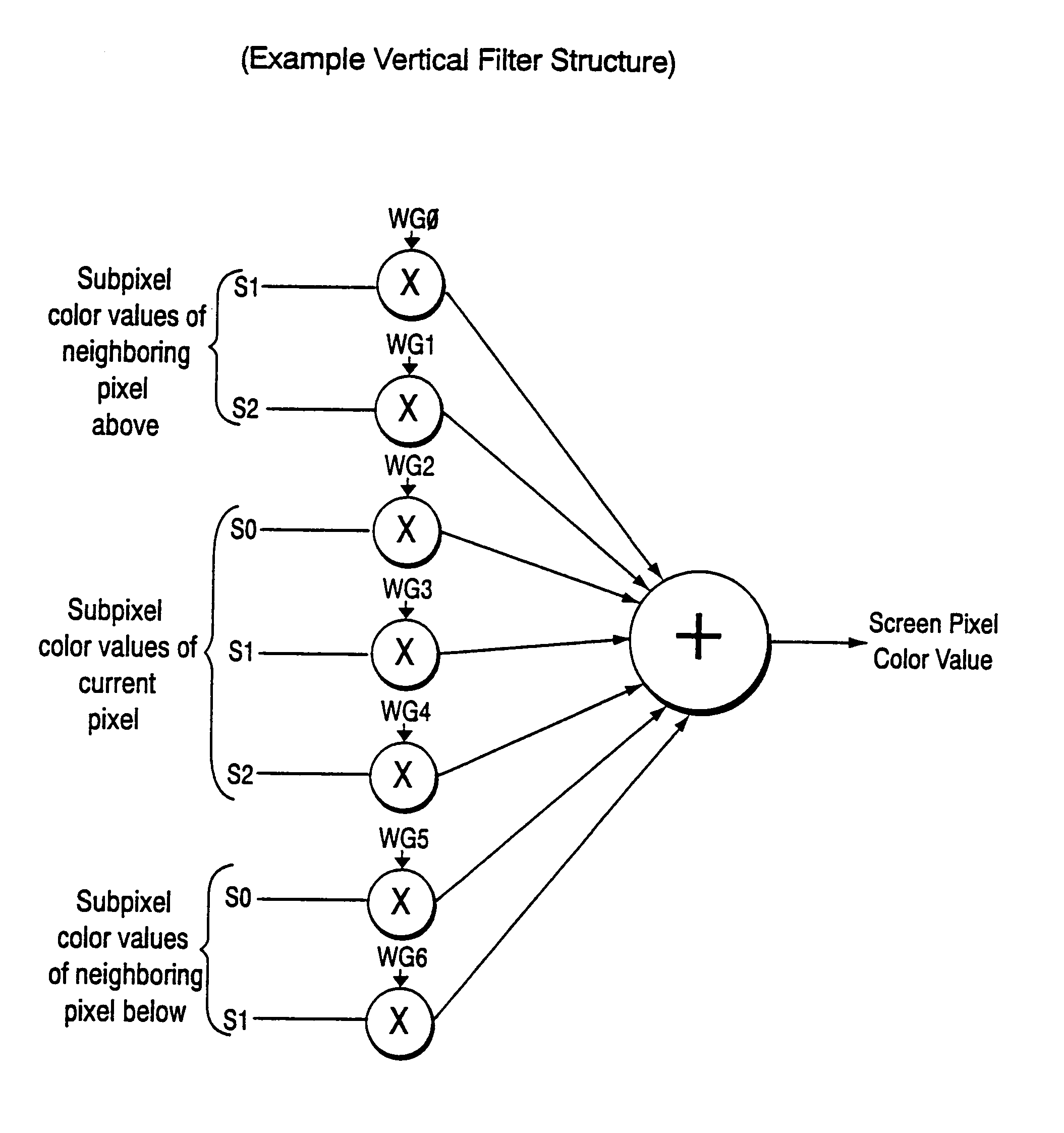

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The system achieves highly efficient full-scene anti-aliasing by implementing a programmable-location super-sampling arrangement and using a selectable-weight vertical-pixel support area blending filter. For a 2×2 pixel group (quad), the locations of three samples within each super-sampled pixel are individually selectable. A twelve-bit multi-sample coverage mask is used to determine which of twelve samples within a pixel quad are enabled based on the portions of each pixel occupied by a primitive fragment and any pre-computed z-buffering. Each super-sampled pixel is filtered during a copy-out operation from a local memory to an external frame buffer using a pixel blending filter arrangement that combines seven samples from three vertically arranged pixels. Three samples are taken from the current pixel, two samples are taken from a pixel immediately above the current pixel and two samples are taken from a pixel immediately below the current pixel. A weighted average is then computed based on the enabled samples to determine the final color for the pixel. The weight coefficients used in the blending filter are also individually programmable. De-flickering of thin one-pixel tall horizontal lines for interlaced video displays is also accomplished by using the pixel blending filter to blend color samples from pixels in alternate scan lines.

Owner:NINTENDO CO LTD

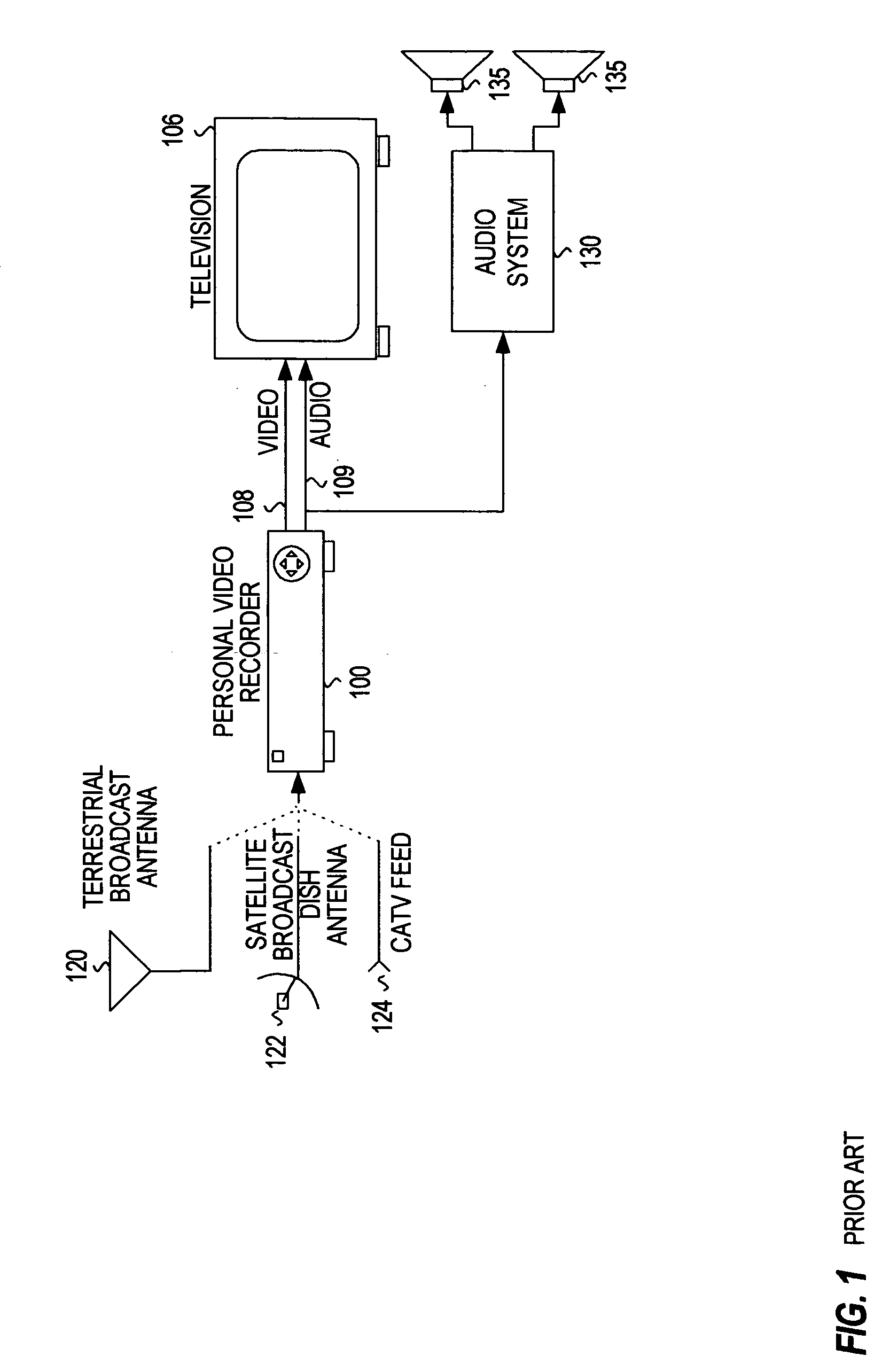

Personal video recorders with automated buffering

InactiveUS20050138659A1Television system detailsAnalogue secracy/subscription systemsVideocassette recorderComputer science

Owner:TIME WARNER

Method and apparatus for implementing efficient floating point Z-buffering

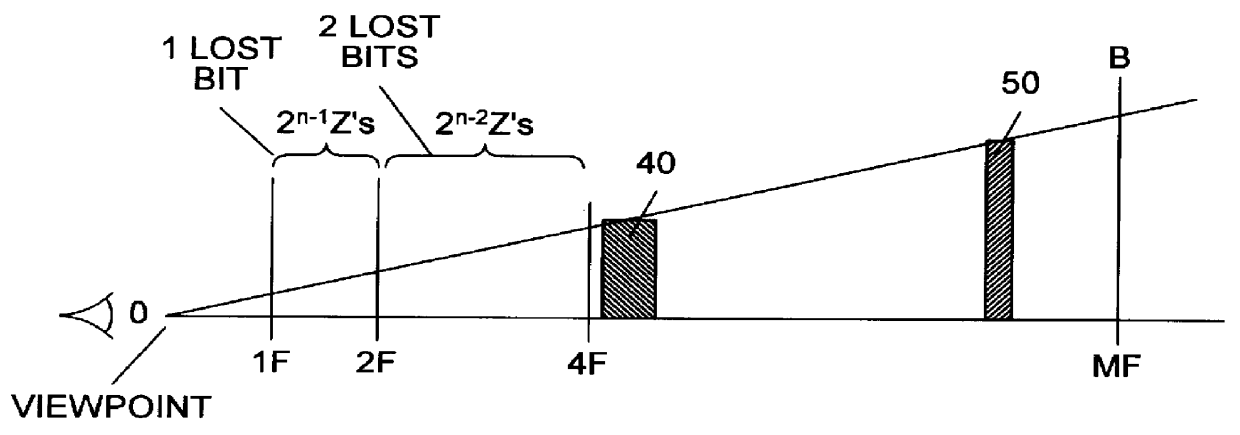

A method for handling Z-values in accordance with the present invention. The Z-values correspond to vertices of a given primitive being processed within a graphics pipeline. The Z-values received by the pipeline are represented in a first floating point format (such as IEEE floating point format) which includes a mantissa portion and an exponent portion. The method comprises determining which of the Z-values for the given primitive has the largest value of the exponent portion. In one embodiment, this includes comparing current exponent values to a current greatest exponent value until all Z-values are tested. The method subsequently comprises generating a common Z exponent value in response to determining the largest exponent value for the given primitive. In one embodiment, the common Z exponent value is generated by subtracting a constant value from the largest exponent value. The method next comprises converting the Z-values of the given primitive to a fixed point format in which the mantissa portion is scaled to the common Z exponent value. The converted values are then forwarded with the primitive as graphics processing continues with a first set of operations which utilize the Z-values (represented in the fixed point format) and the common Z exponent value. Since it is likely the Z exponents for the given primitive are closely related, the Z-values may be represented with a single exponent value. After this first set of operations, the Z-values are converted back to a second floating point format. A second set of graphics operations (namely, hidden surface removal) is then performed using this second floating point format. By using the common Z exponent and the intermediate fixed point format for representation, Z-values of the given primitive are more efficiently handled throughout the rendering pipeline.

Owner:ORACLE INT CORP

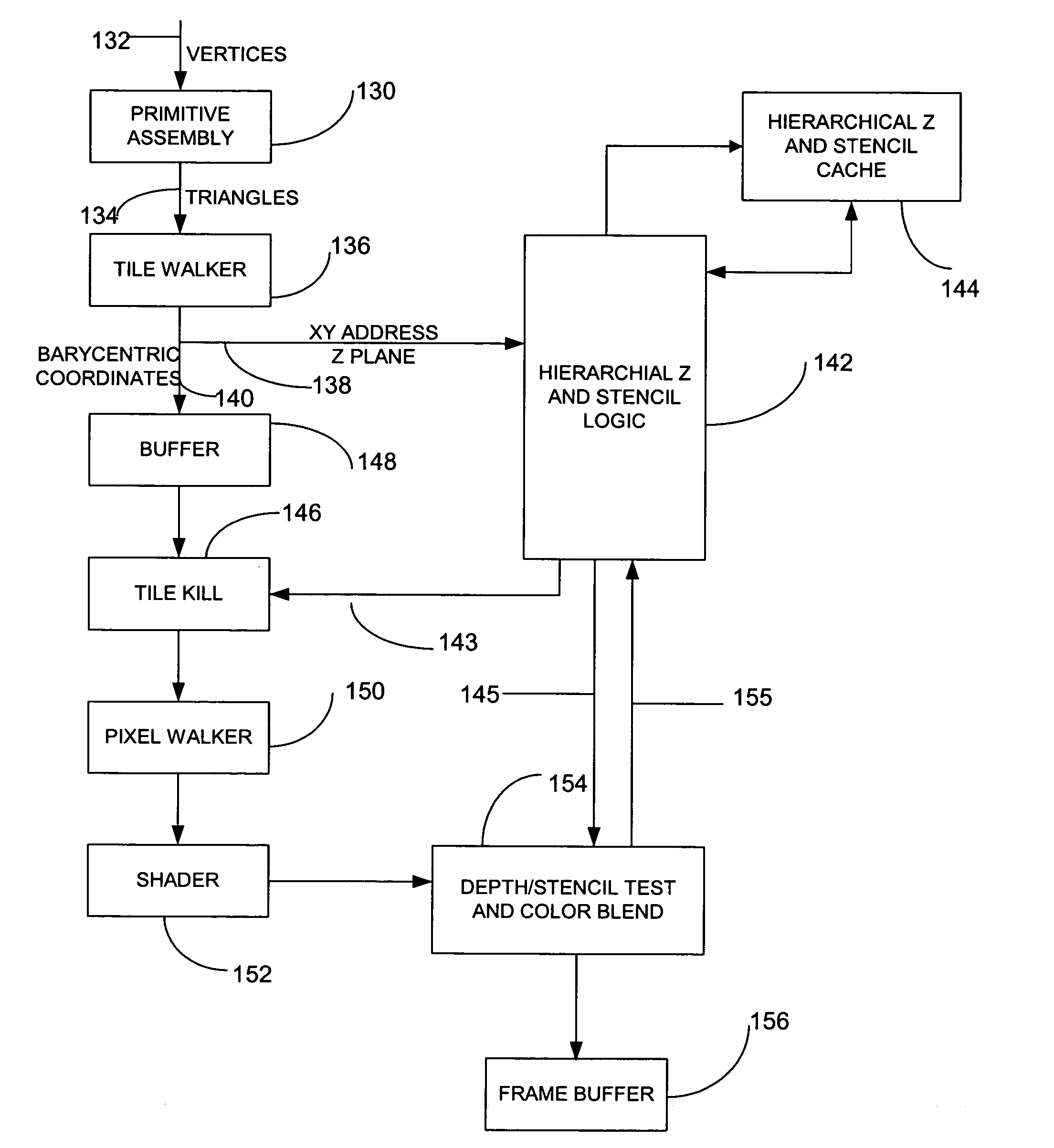

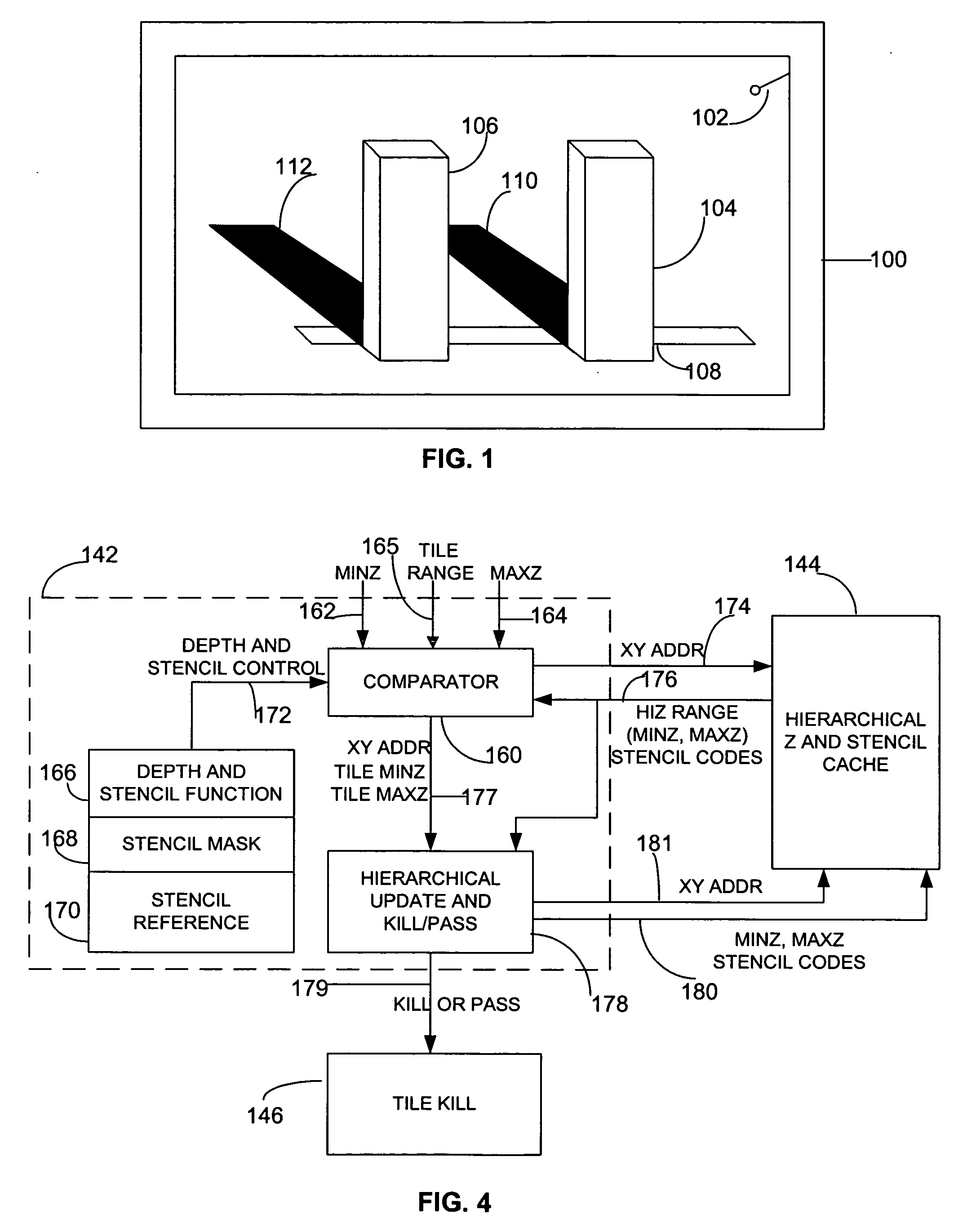

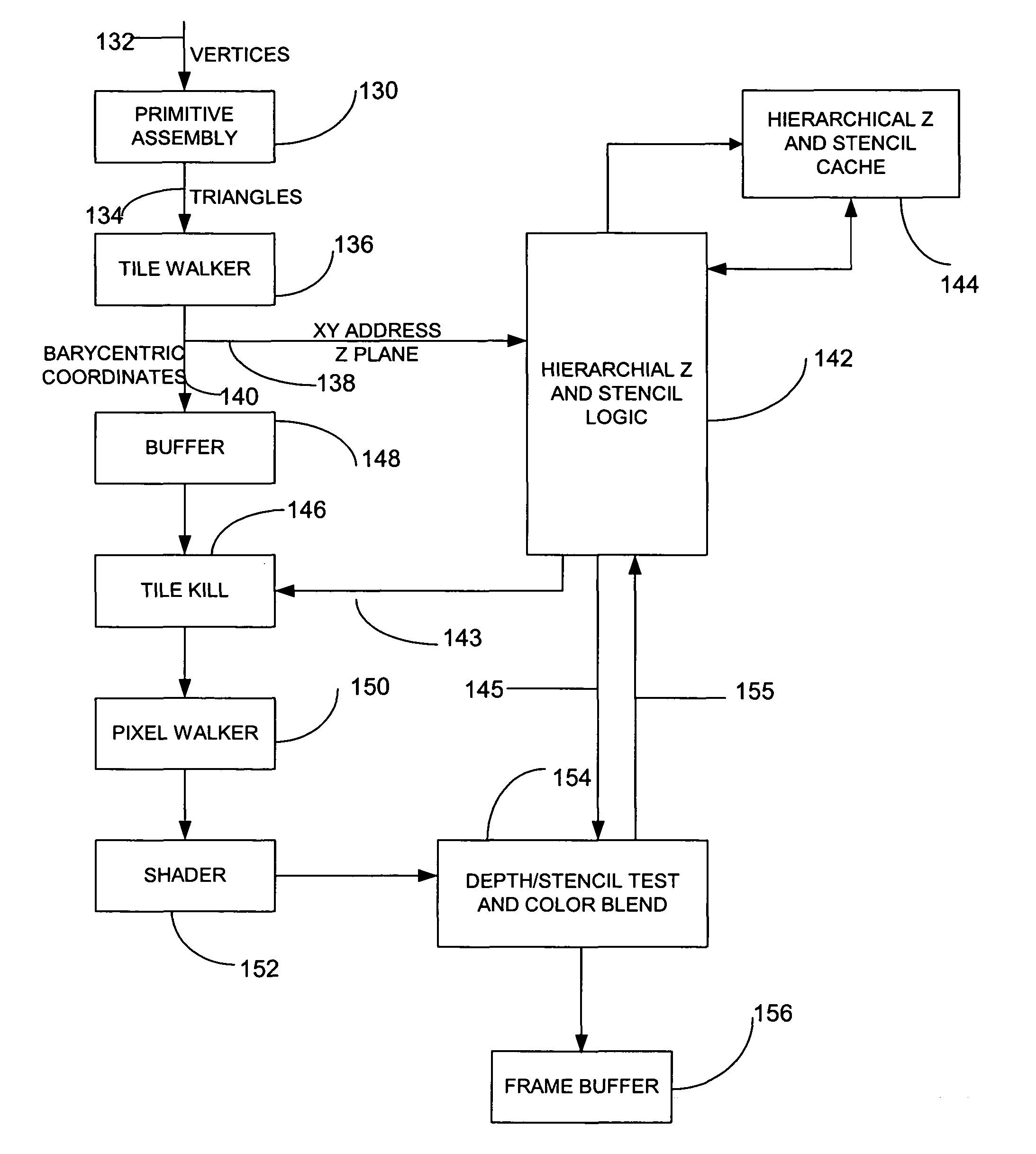

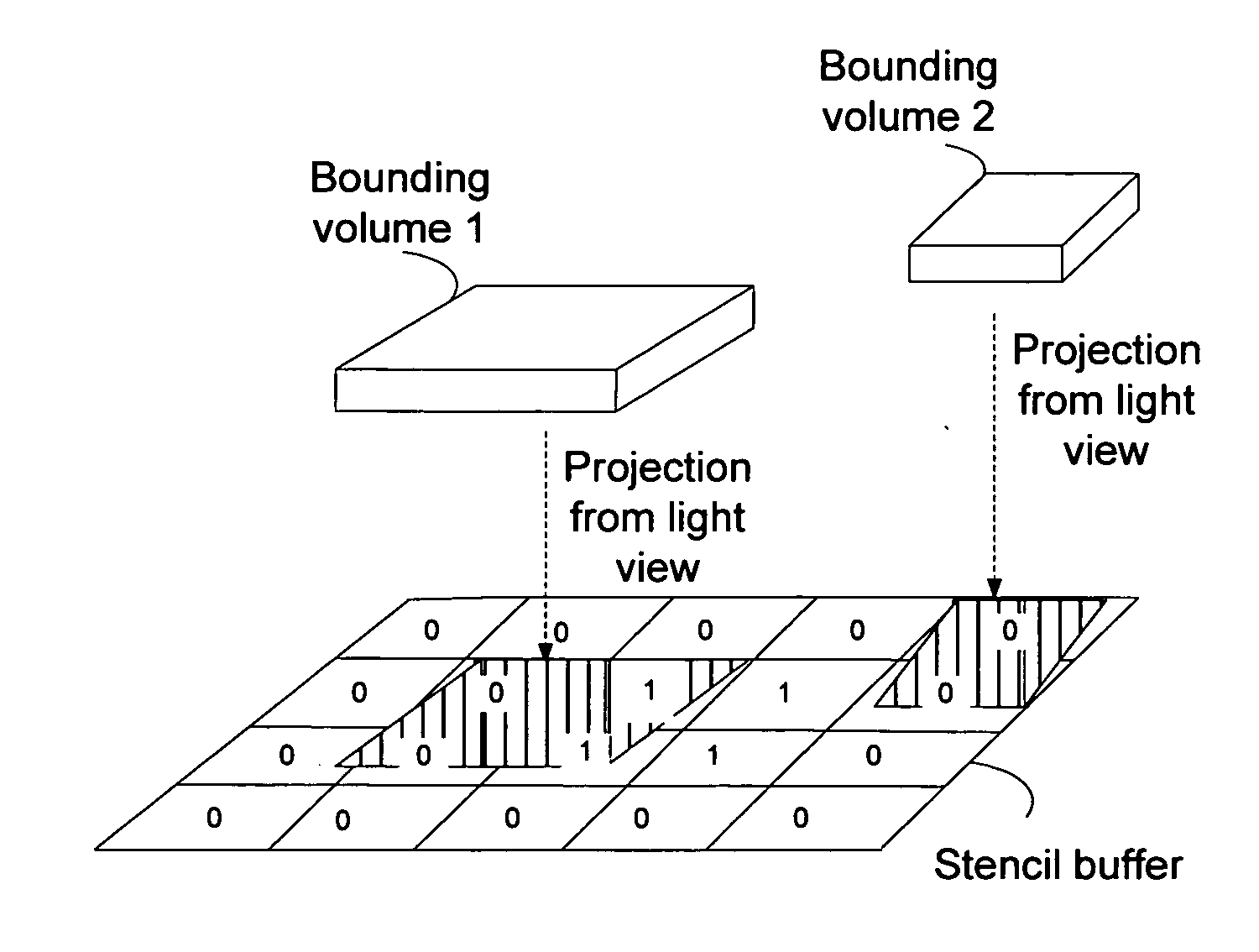

Method and apparatus for hierarchical Z buffering and stenciling

ActiveUS20050195187A1Digital computer detailsCathode-ray tube indicatorsComputational scienceGraphics

A method and apparatus for hierarchical Z buffering stenciling includes comparing an input tile Z value range with a hierarchical Z value range and a stencil code. The method and apparatus also updates the hierarchical Z value range and stencil code in response the comparison and determines whether to render a plurality of pixels within the input tile based on the comparison of the input tile Z value range with the hierarchical Z value range and stencil code. In determining whether to render the tile, a stencil test and a hierarchical Z value test is performed. If one of the test fails, the tile is killed as it is determined that the pixels are not visible in the graphical output. If the stencil test passes and the hierarchical Z test passes, the pixels within the tile are rendered, as it is determined that the pixels may be visible.

Owner:ATI TECH INC

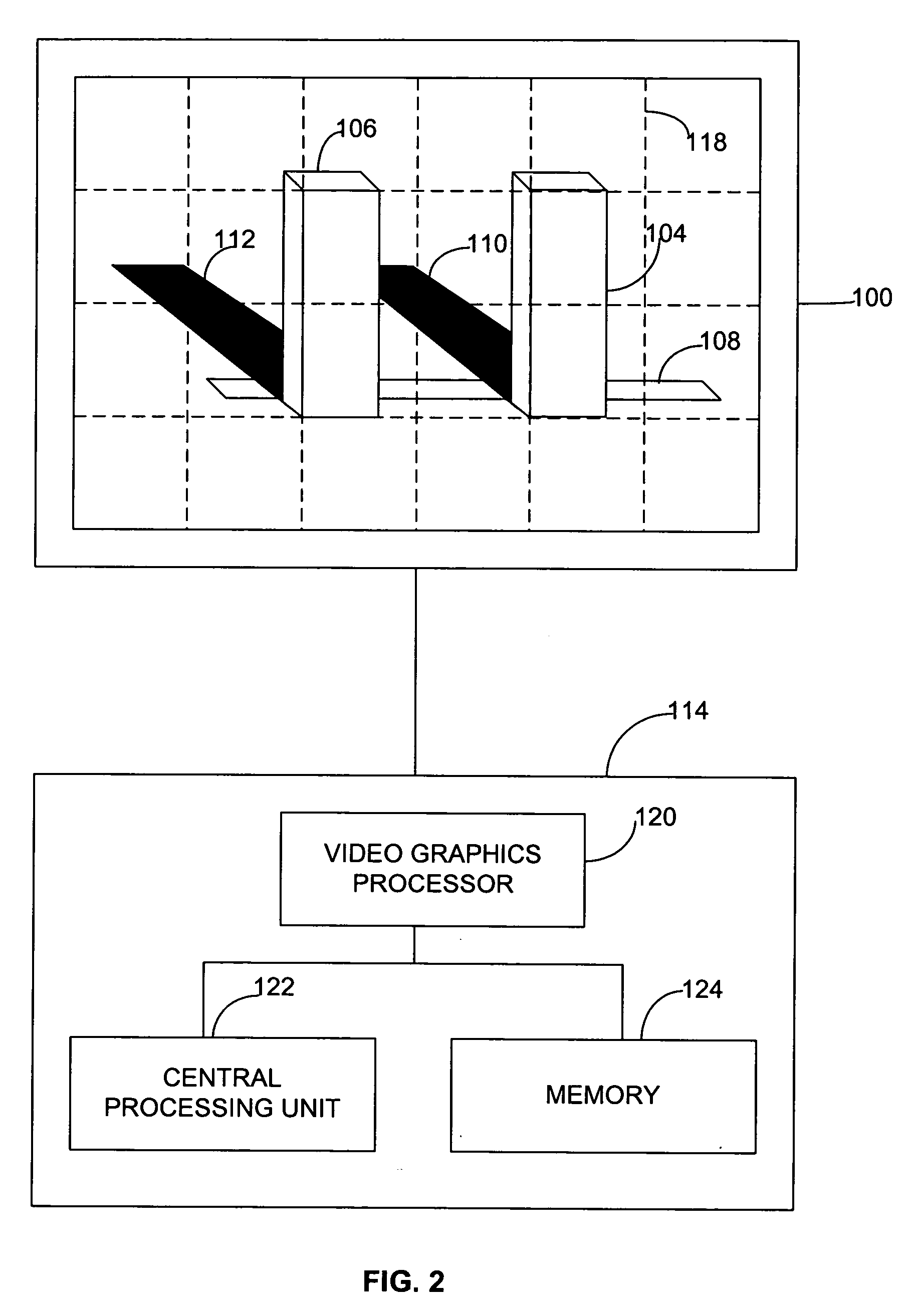

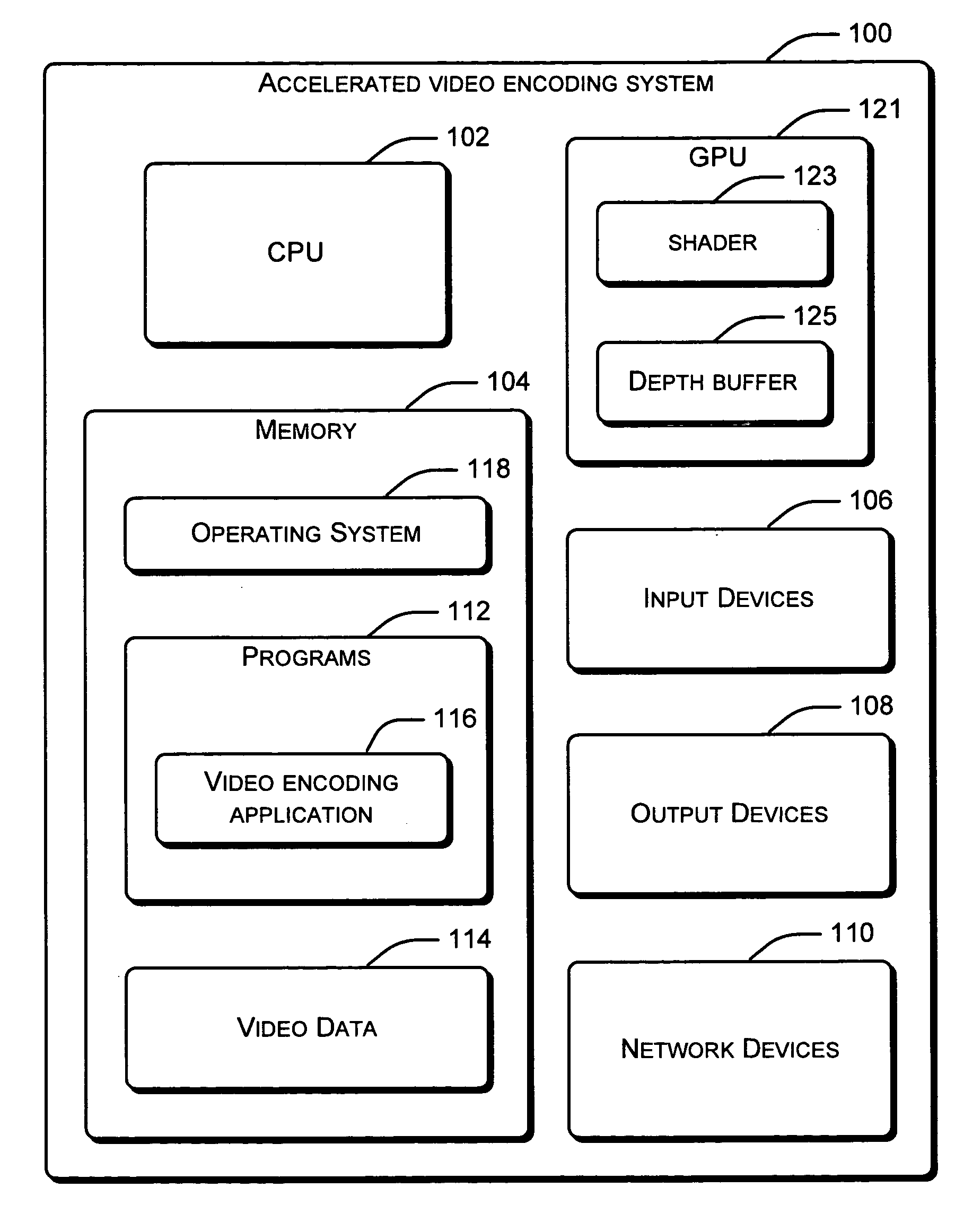

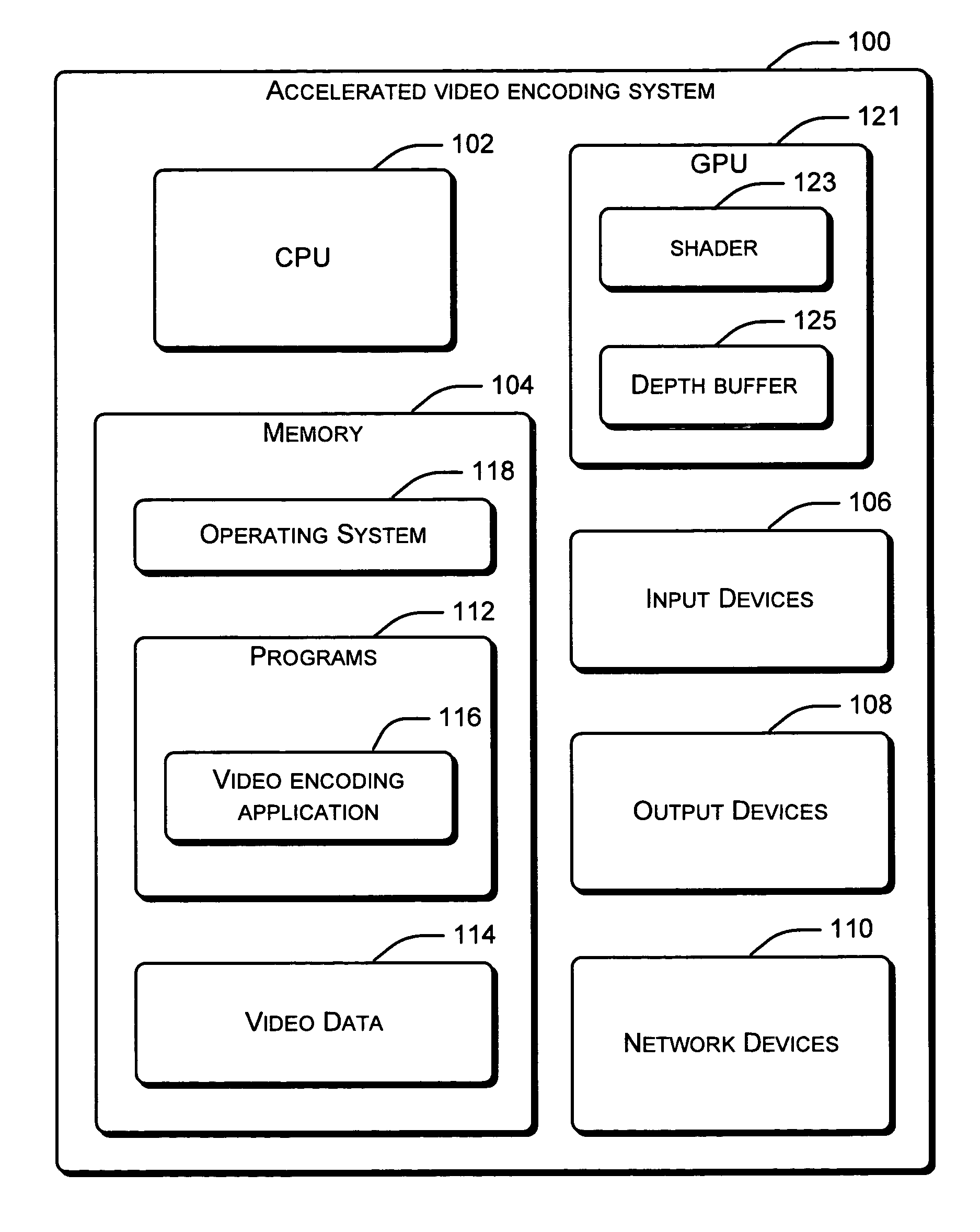

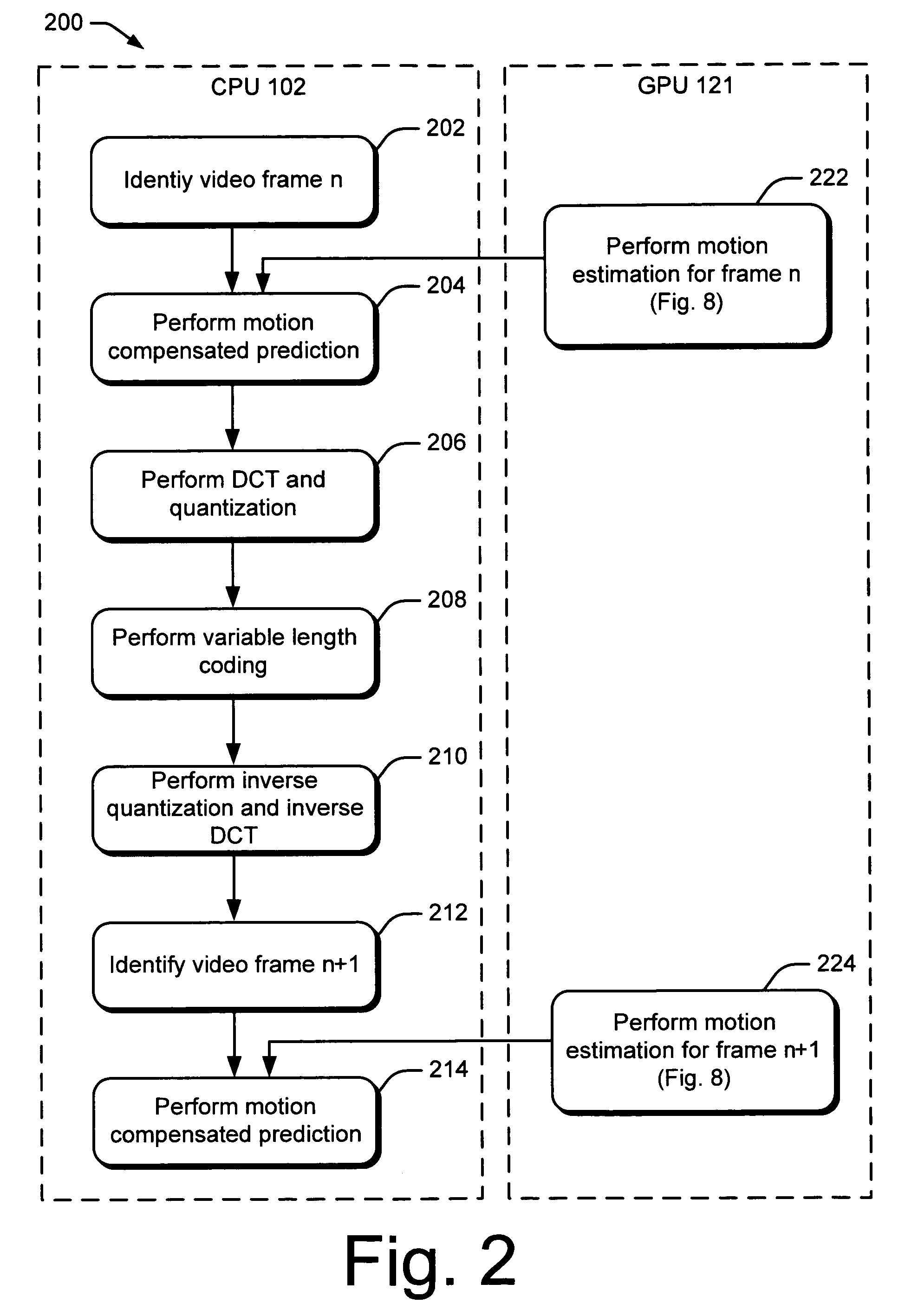

Accelerated video encoding using a graphics processing unit

ActiveUS20060056708A1Improve video performanceImprove performanceDigitally marking record carriersImage analysisGraphicsCollocation

The systems and methods described herein are directed at accelerating video encoding using a graphics processing unit. In one aspect, a video encoding system uses both a central processing unit (CPU) and a graphics processing unit (GPU) to perform video encoding. The system implements a technique that enables the GPU to perform motion estimation for video encoding. The technique allows the GPU to perform a motion estimation process in parallel with the video encoding process performed by the CPU. The performance of video encoding using such a system is greatly accelerated as compared to encoding using just the CPU. In another aspect, data related to motion estimation is arranged and provided to the GPU in a way that utilizes the capabilities of the GPU. Data about video frames may be collocated to enable multiple channels of the GPU to process tasks in parallel. The depth buffer of the GPU may be used to consolidate repeated calculations and searching tasks during the motion estimation process. The use of frame collocation and depth buffer enables the GPU to be better utilized and to further accelerate video encoding.

Owner:MICROSOFT TECH LICENSING LLC

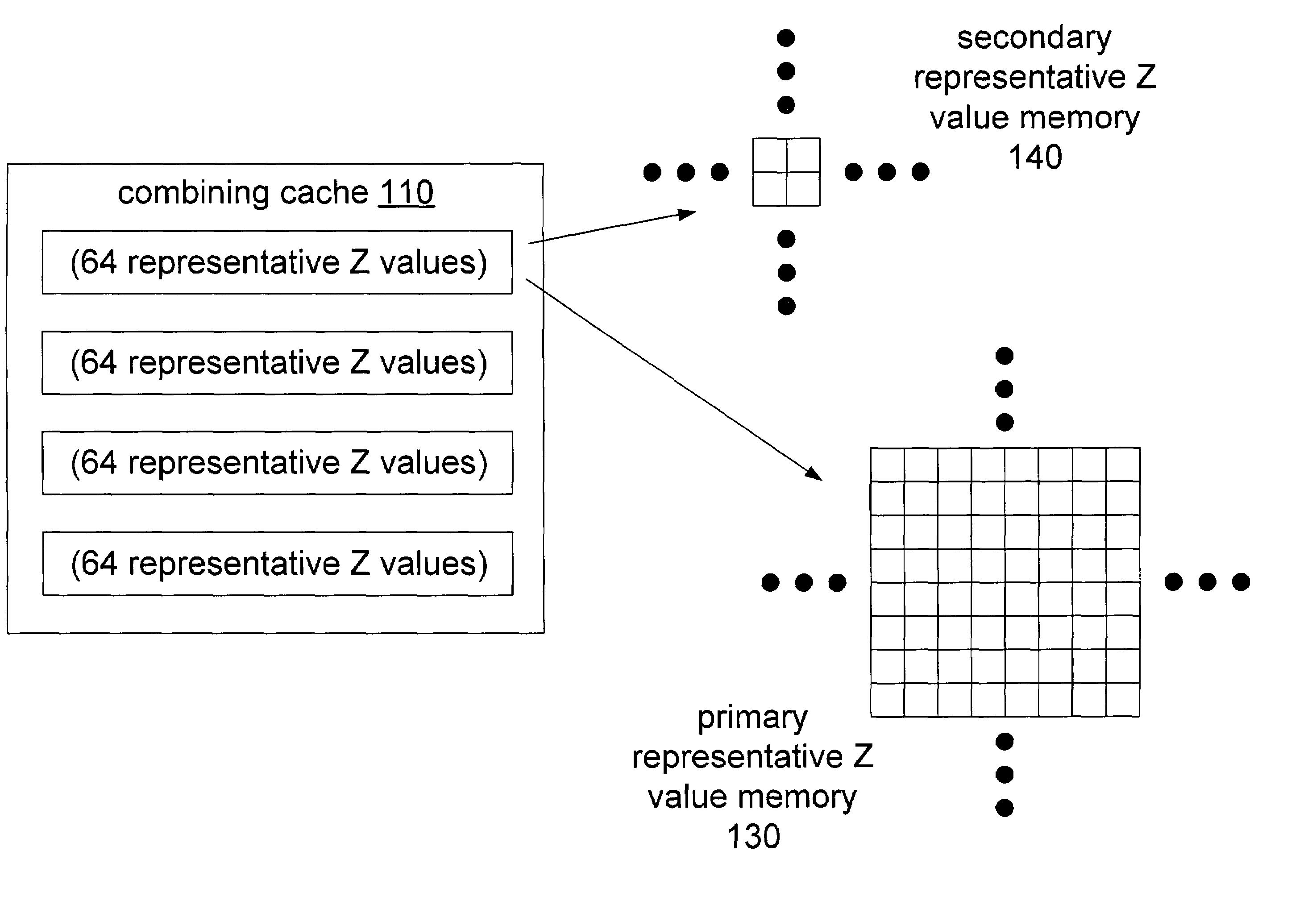

System, method, and apparatus for multi-level hierarchical Z buffering

Owner:QUALCOMM INC

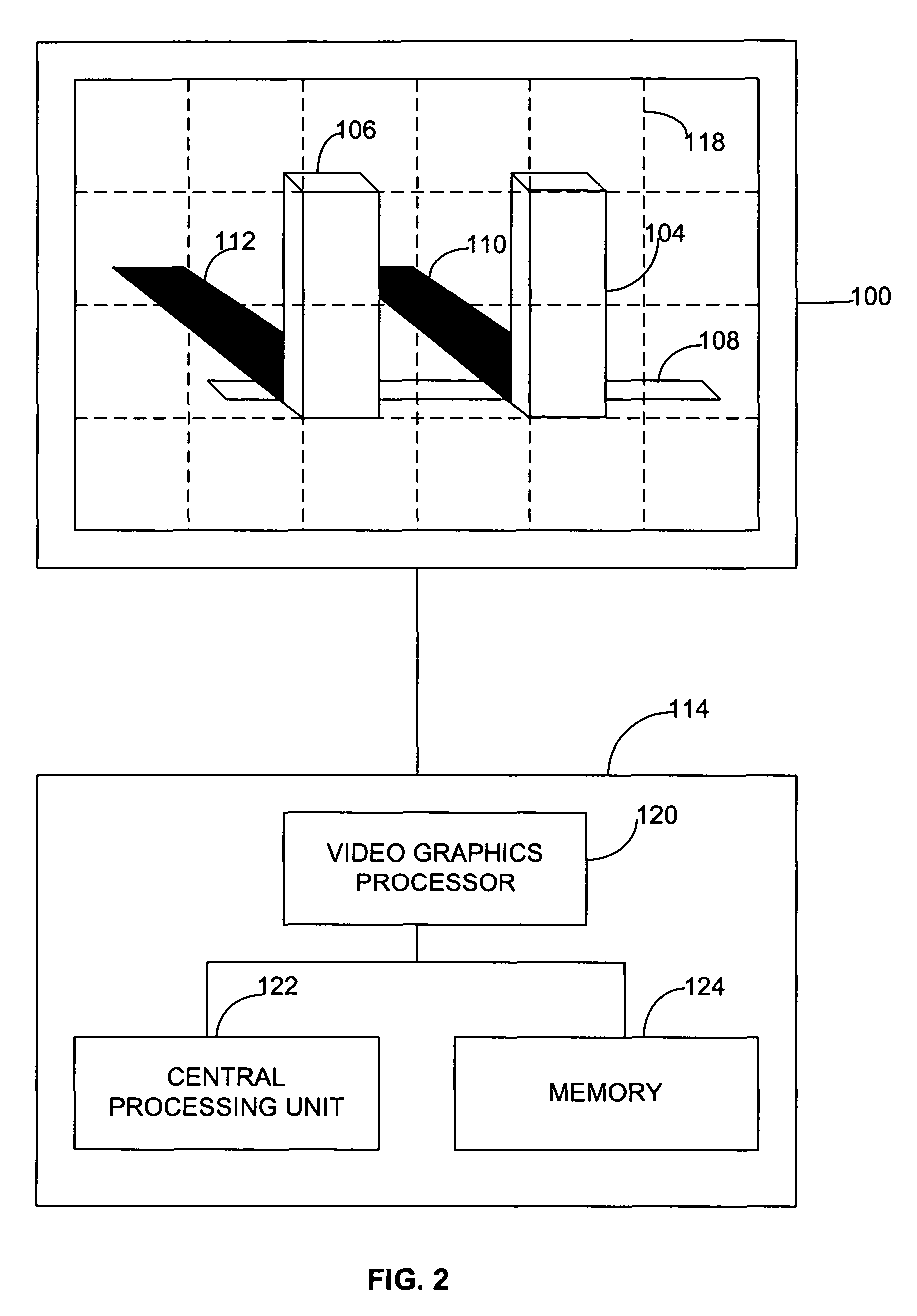

System and method for reducing the rendering load for high depth complexity scenes on a computer graphics display

InactiveUS6362818B1Reduce pixel rendering loadCost-effective3D-image rendering3D modellingGraphicsDisplay device

This invention relates generally to the field of computer graphics display, and more particularly to reducing the amount of time needed to render complex virtual scenes on a computer graphics display. This invention combines the advantages of the prior art methods of list priority and depth buffering (e.g. Z-buffering) with new simplified and enhanced full buffer processes. In one embodiment, a simplified full buffer arrangement enables the elimination of rendering primitives prior to pixel shading for regions of the screen which have previously been covered by closer primitives. Another embodiment provides for an enhanced full buffer that combines the coverage of a previously rendered primitive in a partial buffer and associates it with a current primitive to cover pixel arrays. This enhanced full buffer technique enables the use of higher order model primitives such as strips, fans and meshes, to increase the effectiveness of the full buffer by allowing more than one primitive to combine to fill a scanned pixel region on the screen.

Owner:ROCKWELL COLLINS SIMULATION & TRAINING SOLUTIONS

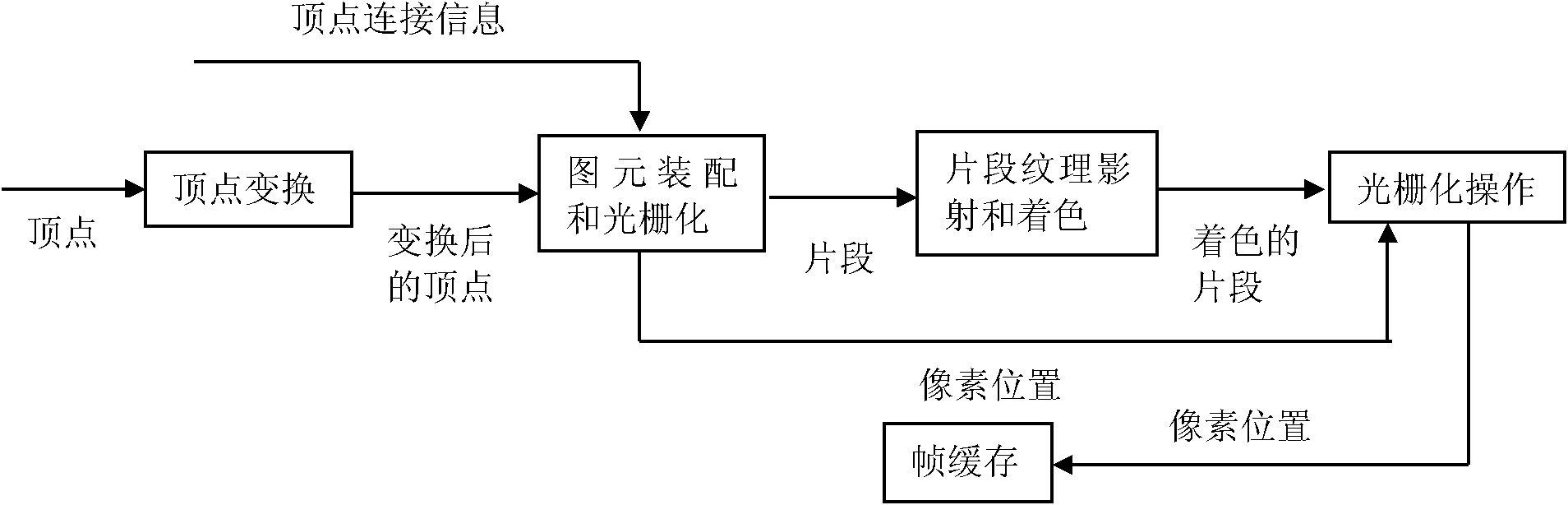

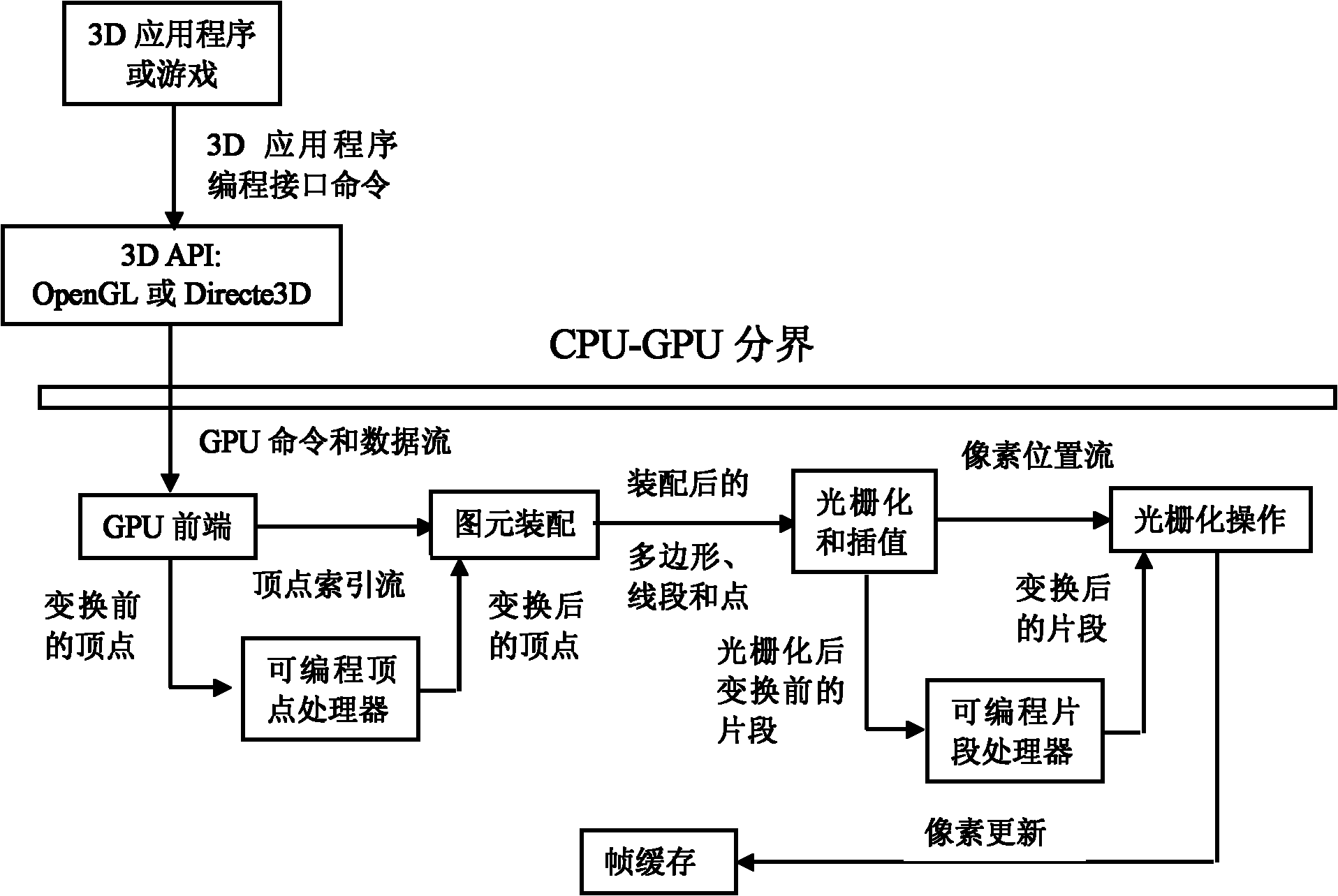

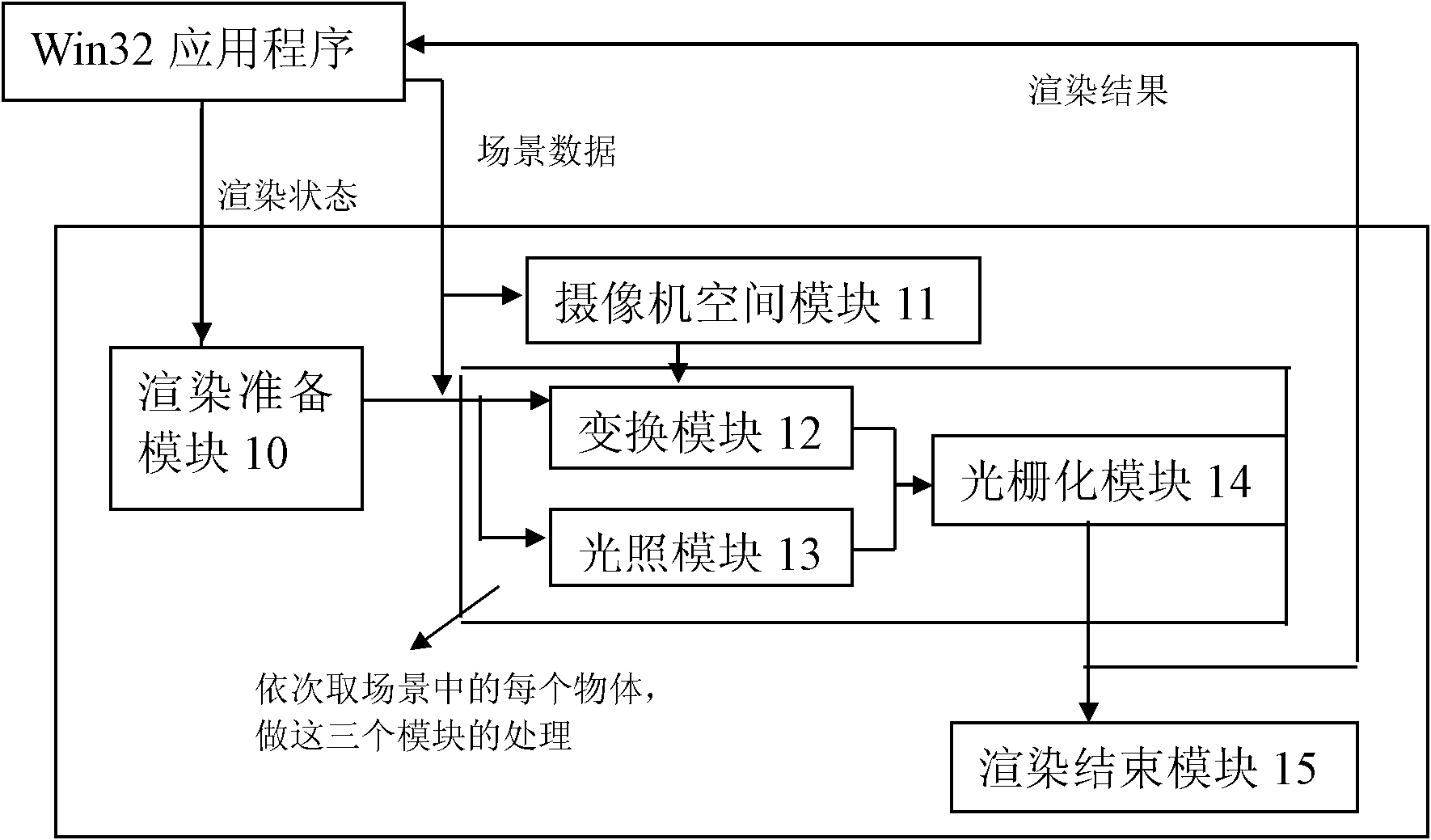

CPU-based graphic rendering engine and realization method

InactiveCN102722861AImprove portabilityMultiple controllabilityProcessor architectures/configuration3D-image renderingZ-bufferingTransformation matrix

The invention discloses a CPU-based graphic rendering engine and a realization method. The CPU-based graphic rendering engine consists of a rending preparation module, a camera space module, a conversion module, an illumination module, a rasterization module, a rendering ending module. The realization method for graphic rendering comprises the following steps that: an application program sets a rendering state and sends the rendering state to the rendering preparation module and meanwhile, the rendering preparation module initializes a color buffer region and a depth buffer region; the camera space module establishes a view conversion matrix and a projection conversion matrix according to camera data in a scene; objects in the scene are taken successively and the conversion module, the illumination module and the rasterization module carry out processing on the objects to complete rendering on all the subjects; after all the objects in the scene are rendered, a rendering result is posted back to the application program and is then output; and the rendering ending module empties the color buffer region and the depth buffer region that are prepared during the rendering preparation stage. According to the invention, it can be realized that graphic rendering is carried out directly based on a CPU without relying on a display card, thereby realizing good portability and realizing controllability on an effect of a subtitle system.

Owner:CHINA DIGITAL VIDEO BEIJING

Accelerated video encoding using a graphics processing unit

ActiveUS7558428B2Improve video performanceEasy to codeDigitally marking record carriersImage analysisGraphicsCollocation

The systems and methods described herein are directed at accelerating video encoding using a graphics processing unit. In one aspect, a video encoding system uses both a central processing unit (CPU) and a graphics processing unit (GPU) to perform video encoding. The system implements a technique that enables the GPU to perform motion estimation for video encoding. The technique allows the GPU to perform a motion estimation process in parallel with the video encoding process performed by the CPU. The performance of video encoding using such a system is greatly accelerated as compared to encoding using just the CPU.In another aspect, data related to motion estimation is arranged and provided to the GPU in a way that utilizes the capabilities of the GPU. Data about video frames may be collocated to enable multiple channels of the GPU to process tasks in parallel. The depth buffer of the GPU may be used to consolidate repeated calculations and searching tasks during the motion estimation process. The use of frame collocation and depth buffer enables the GPU to be better utilized and to further accelerate video encoding.

Owner:MICROSOFT TECH LICENSING LLC

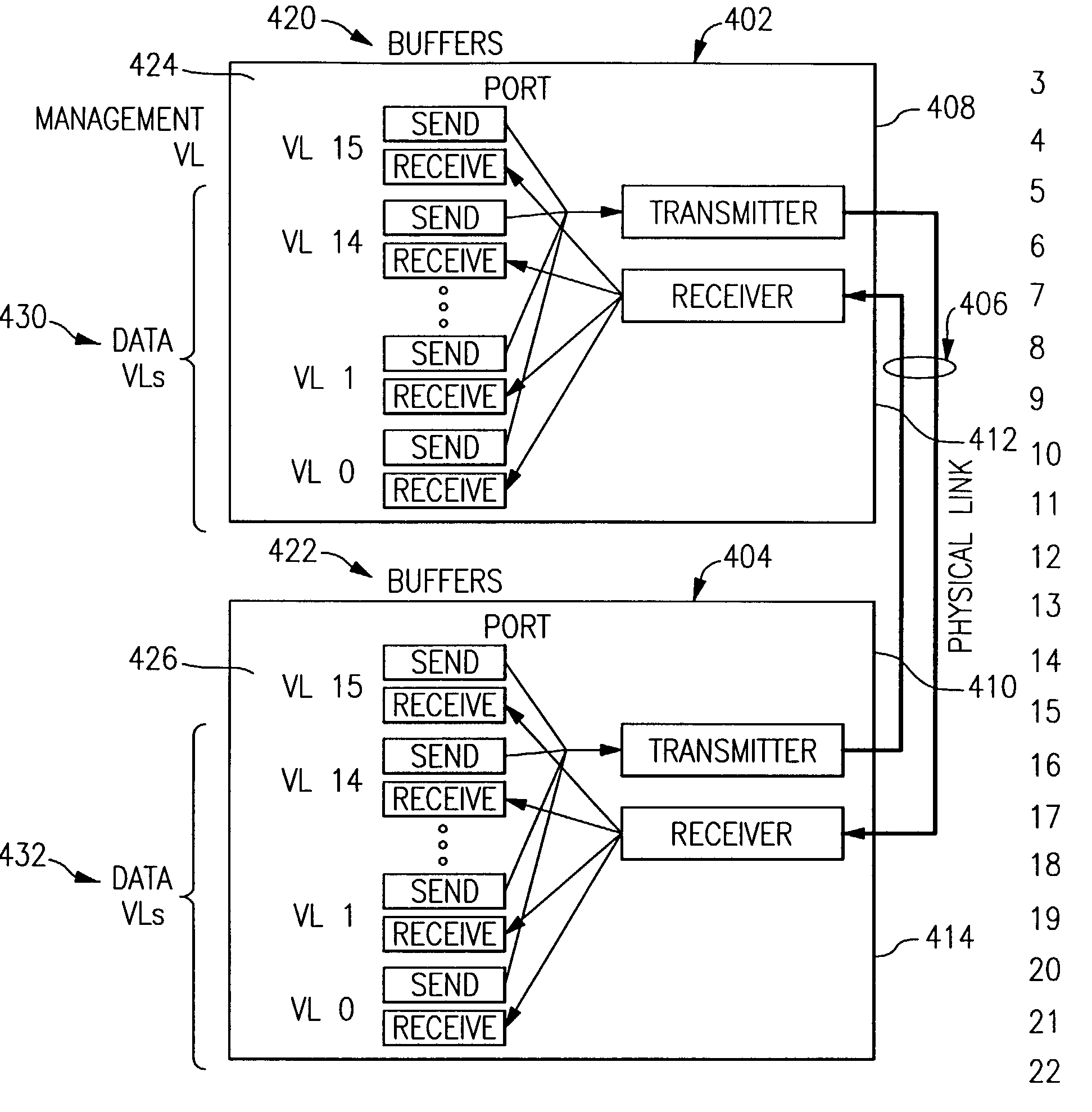

Long distance repeater for digital information

InactiveUS7233570B2Extended operating distanceError preventionTransmission systemsDigital dataData transmission

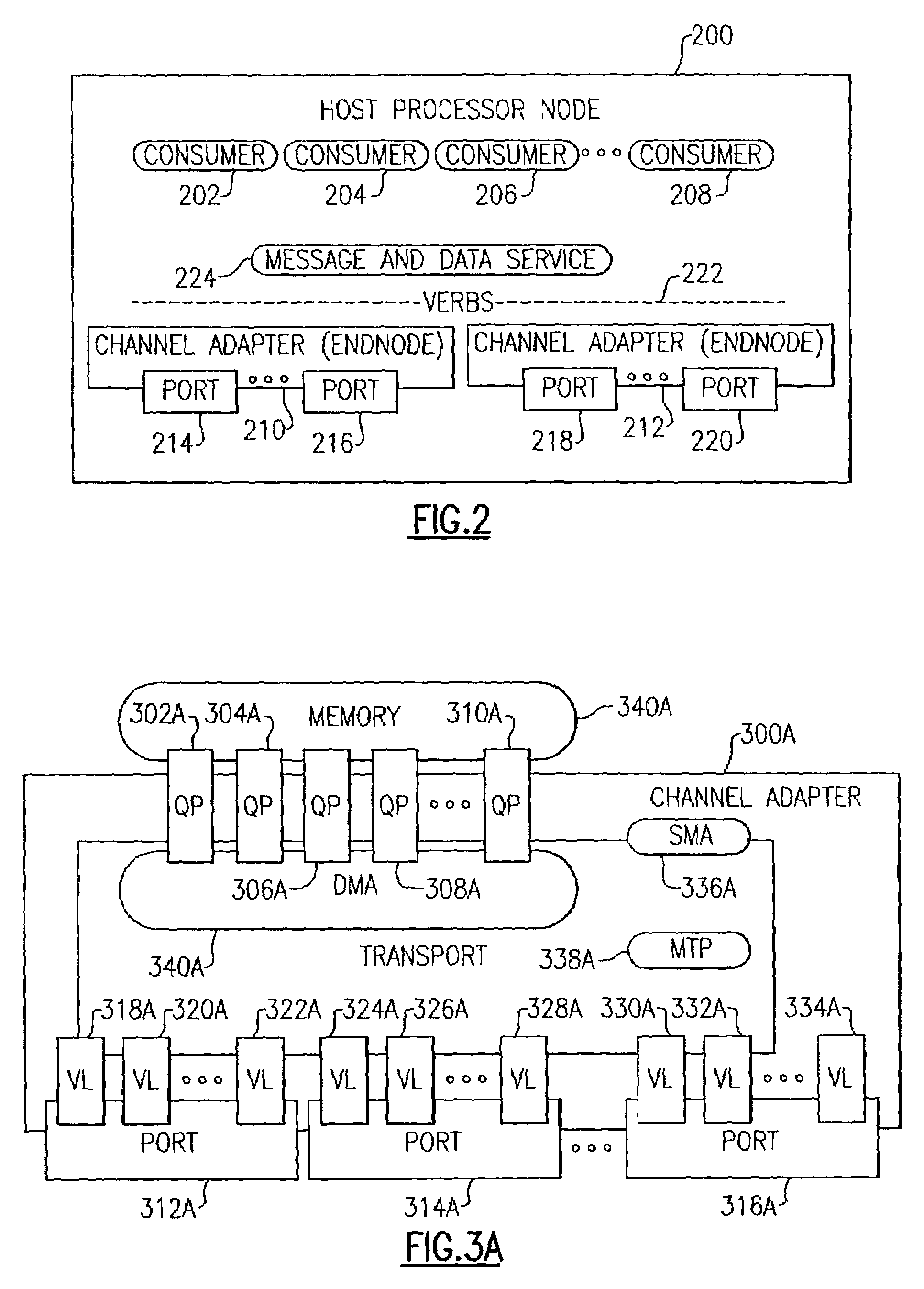

An apparatus and method for extending digital data transmission link distances provide a mechanism in which data is transmitted over relatively long distances using a repeater to provide data buffering and handle the flow control. The repeater function incorporates large virtual lane receiver buffers in its long distance ports. Enough virtual lanes are implemented so that service level to virtual lane mapping is not required, allowing the repeaters to be made invisible to Subnet Management.

Owner:IBM CORP

System, method and computer program product for geometrically transforming geometric objects

Owner:NVIDIA CORP

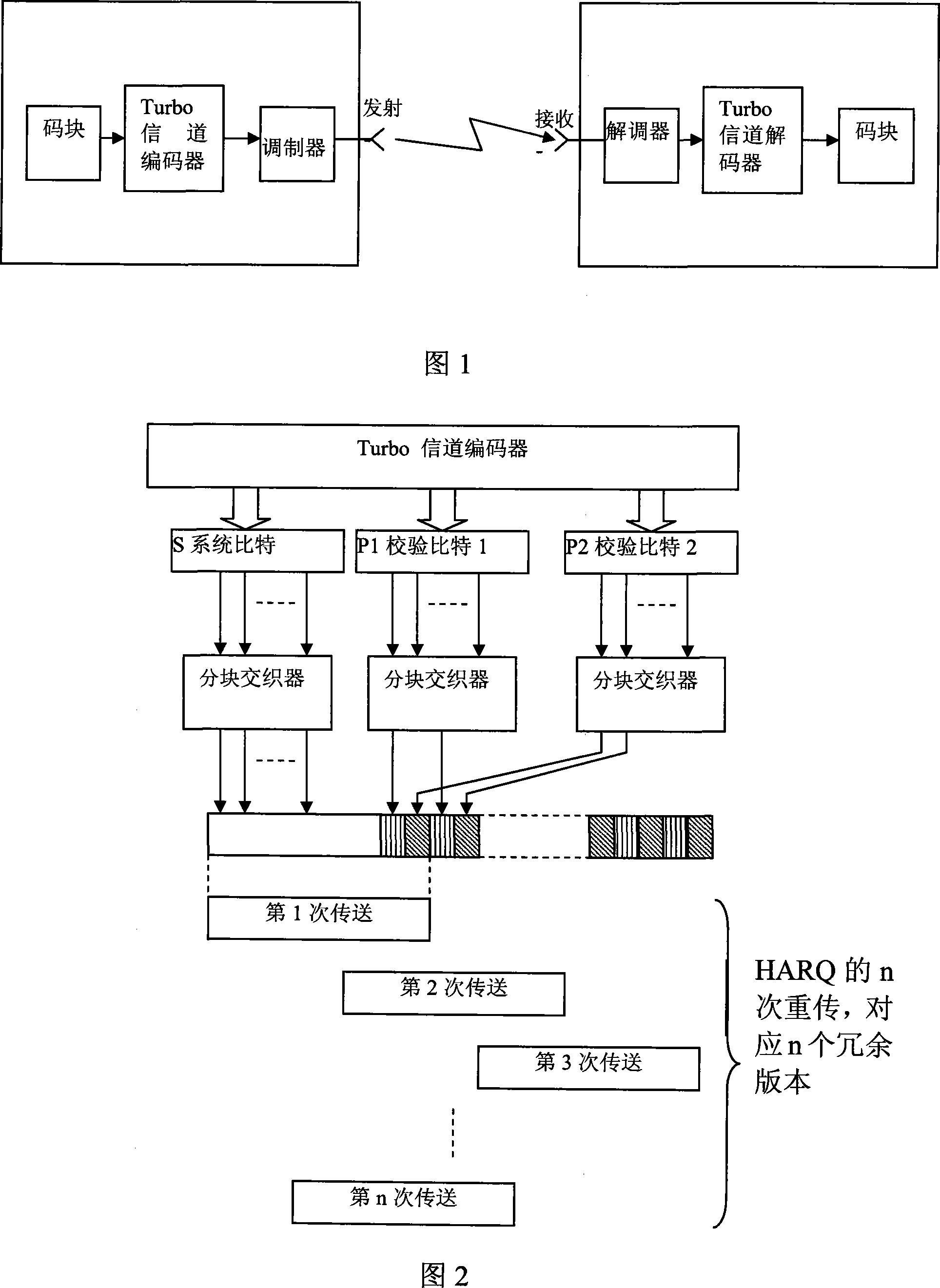

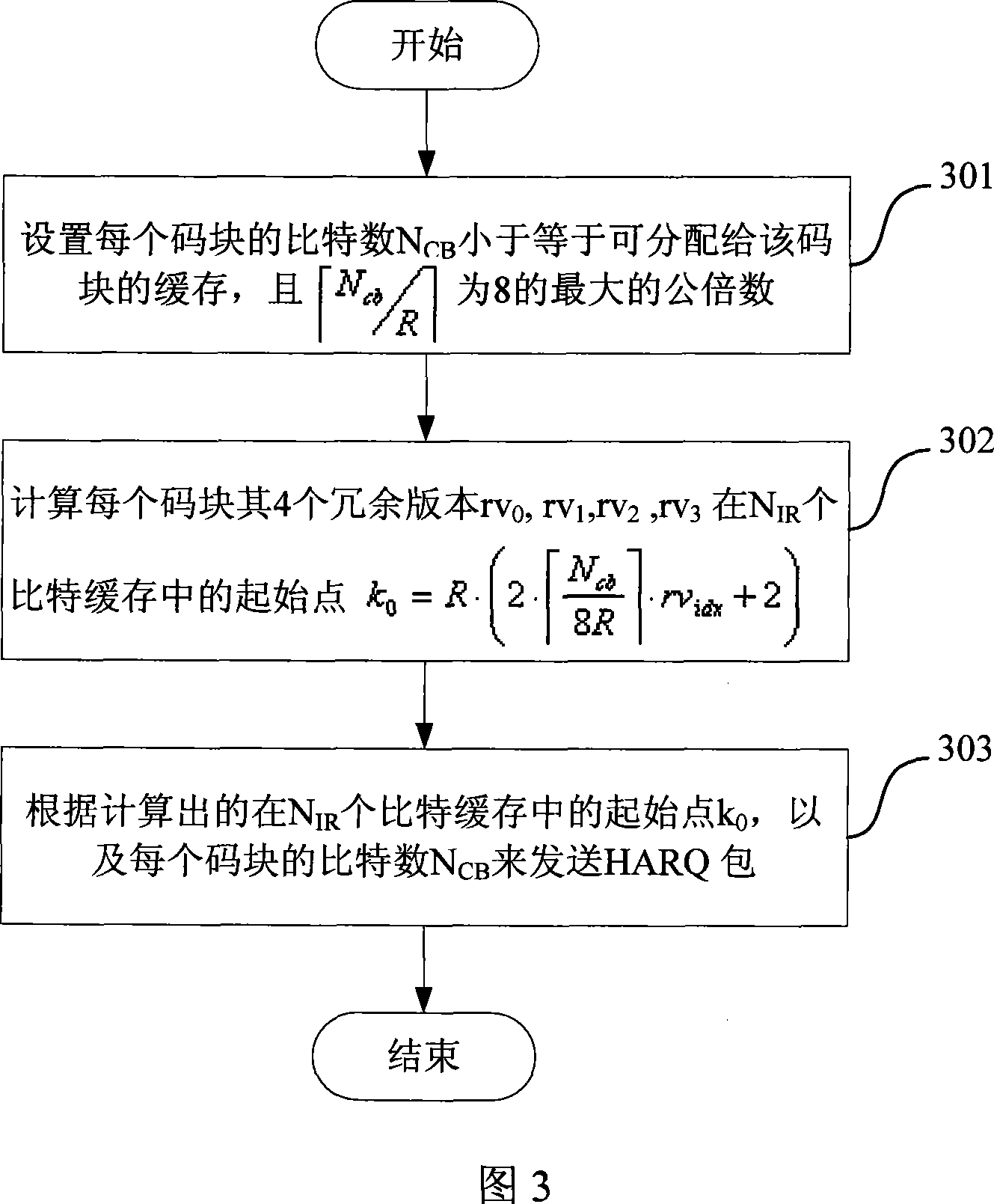

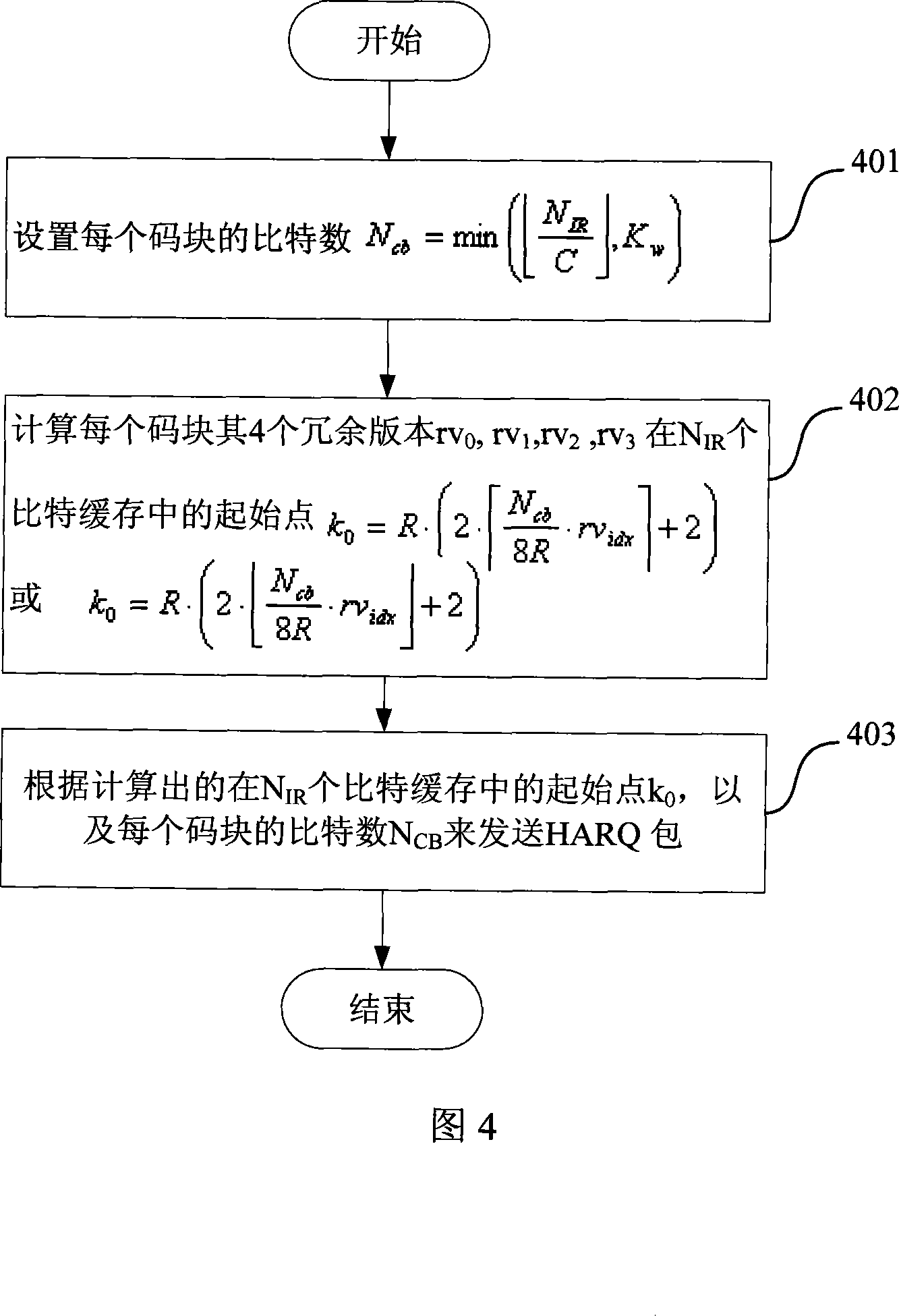

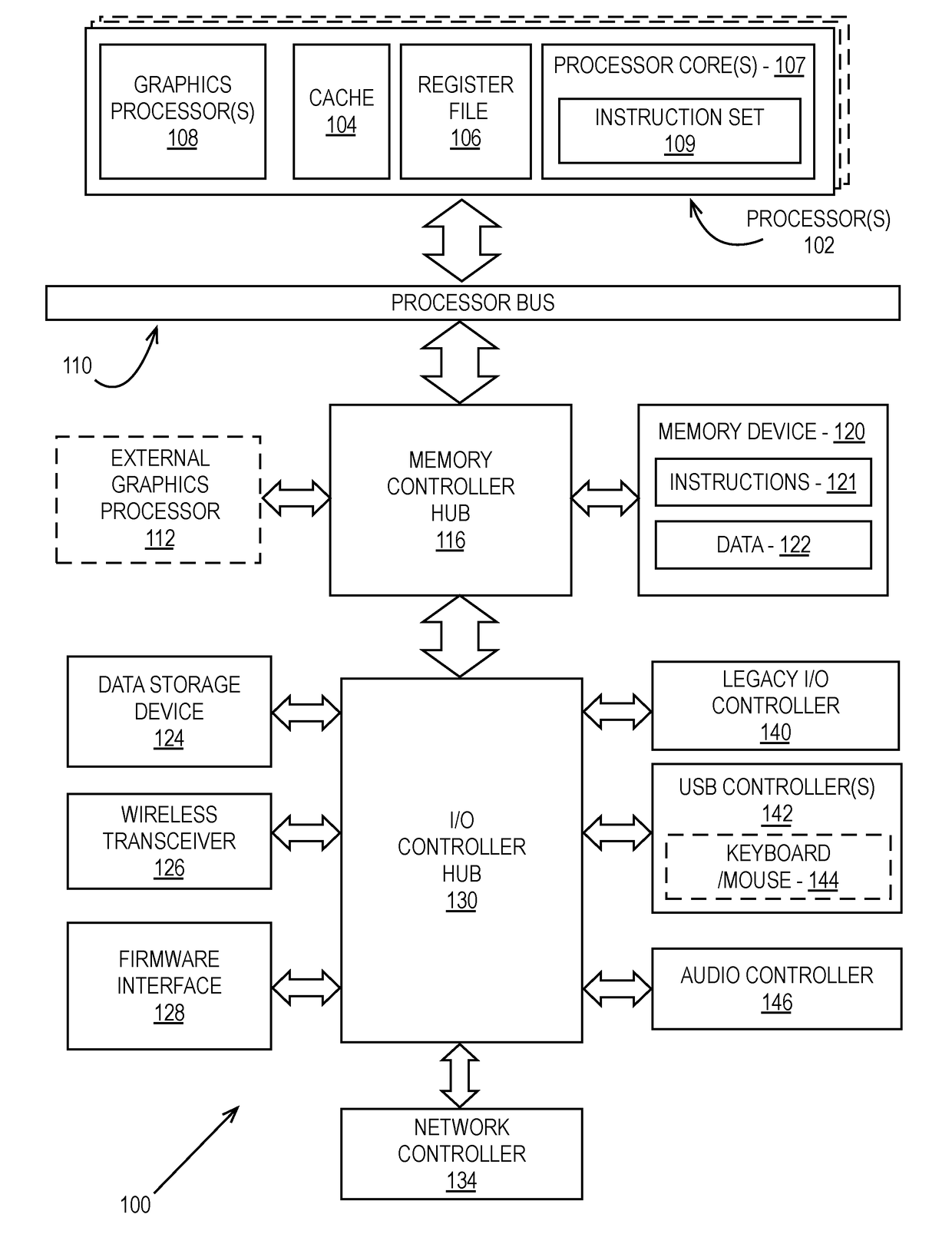

A buffering setting method of phase rate matching

InactiveCN101217352AImprove performanceEvenly spacedError prevention/detection by using return channelCoding blockCommunications system

The invention discloses a buffer-setting method matching with a stage speed which is applied to a sending terminal of a digital communication system. The invention comprises the following procedures: the bit number Ncb of each code block is selected in buffering, the Ncb is set to be no larger than the buffering which can be assigned to the code block, the formula (I) is the largest common multiple of 8 and R is the number of rows of the specified area of the sending terminal; the initial point formula (II) of the four redundancy versions rv0, rv1, rv2, rv3 in bit buffering of each code block is calculated, wherein, the value of the rvidx is the number of the four redundancy versions: 0, 1, 2, 3; a hybrid automatic retransmission request packet is sent according to the calculated result of the initial point with the number being NIR in bit buffering and the bit number Ncb of each code block. The invention can lead the positions of RV to be evenly distributed, thus improving the performance of the hybrid automatic retransmission request.

Owner:ZTE CORP

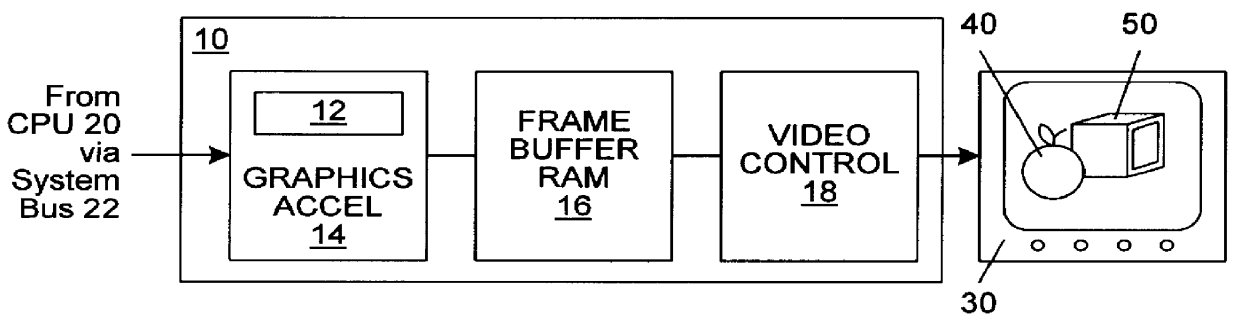

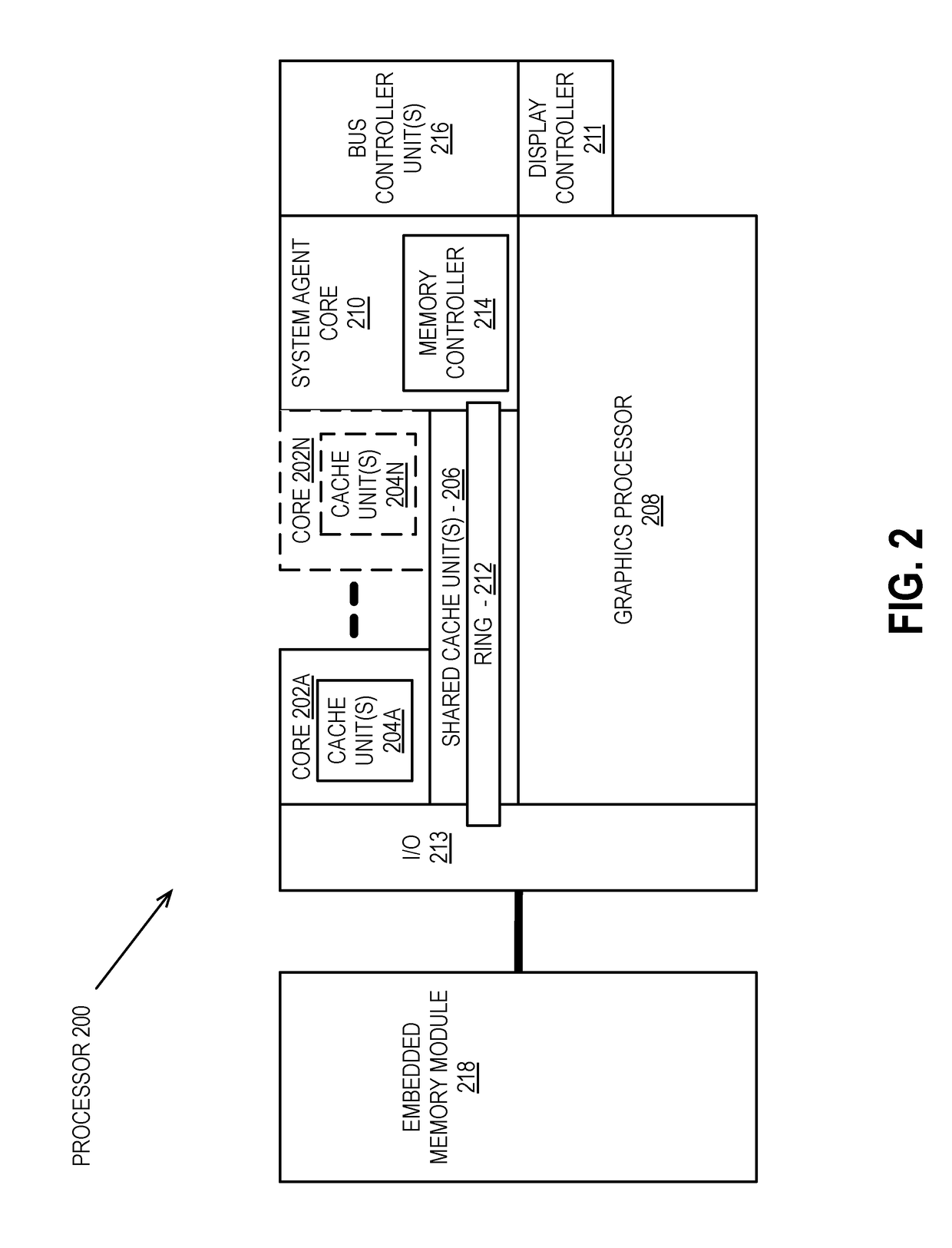

Apparatus and method for an efficient 3D graphics pipeline

A graphics processing apparatus and method are described. For example, one embodiment of a graphics processing apparatus comprises: an input assembler of a graphics pipeline to determine a first set of triangles to be drawn based on application-provided parameters; a depth buffer to store depth data related to the first set of triangles; a vertex shader to perform position-only vertex shading operations on the first set of triangles in response to an indication that the graphics pipeline is to initially operate in a depth-only mode; a culling and clipping module to read depth values from the depth buffer to identify those triangles in the first set of triangles which are fully occluded by other objects in a current frame and to generate culling data usable to cull occluded triangles, the culling and clipping module to associate the culling data with a replay token to be used to identify a subsequent rendering pass through the graphics pipeline; the input assembler, upon detecting the replay token in the subsequent rendering pass, to access the culling data associated therewith to remove culled triangles from the first set of triangles to generate a second set of triangles; the vertex shader to perform full vertex shading operations on the second set of triangles during the subsequent rendering pass, the replay token to be destroyed during or following the subsequent rendering pass.

Owner:INTEL CORP

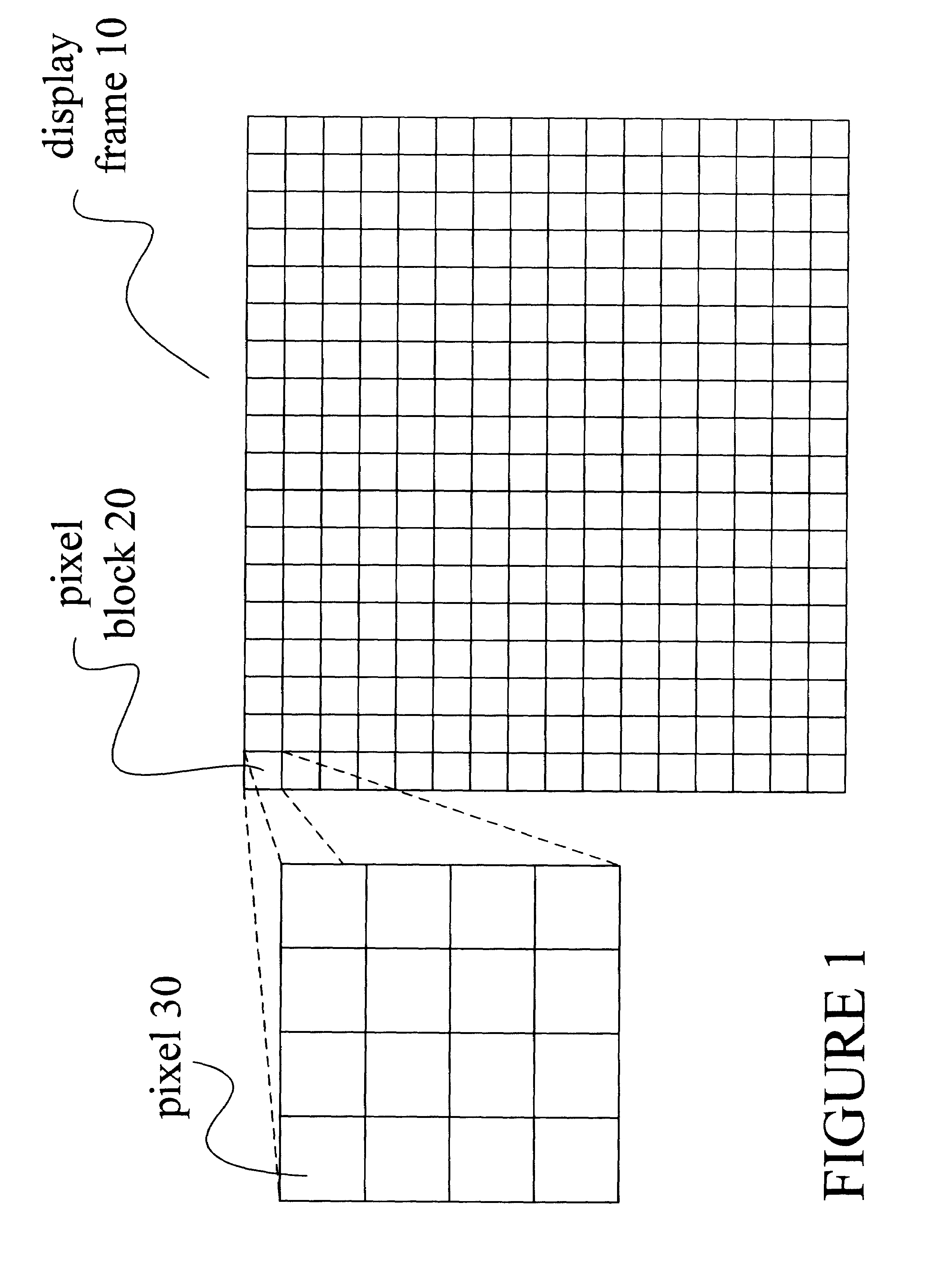

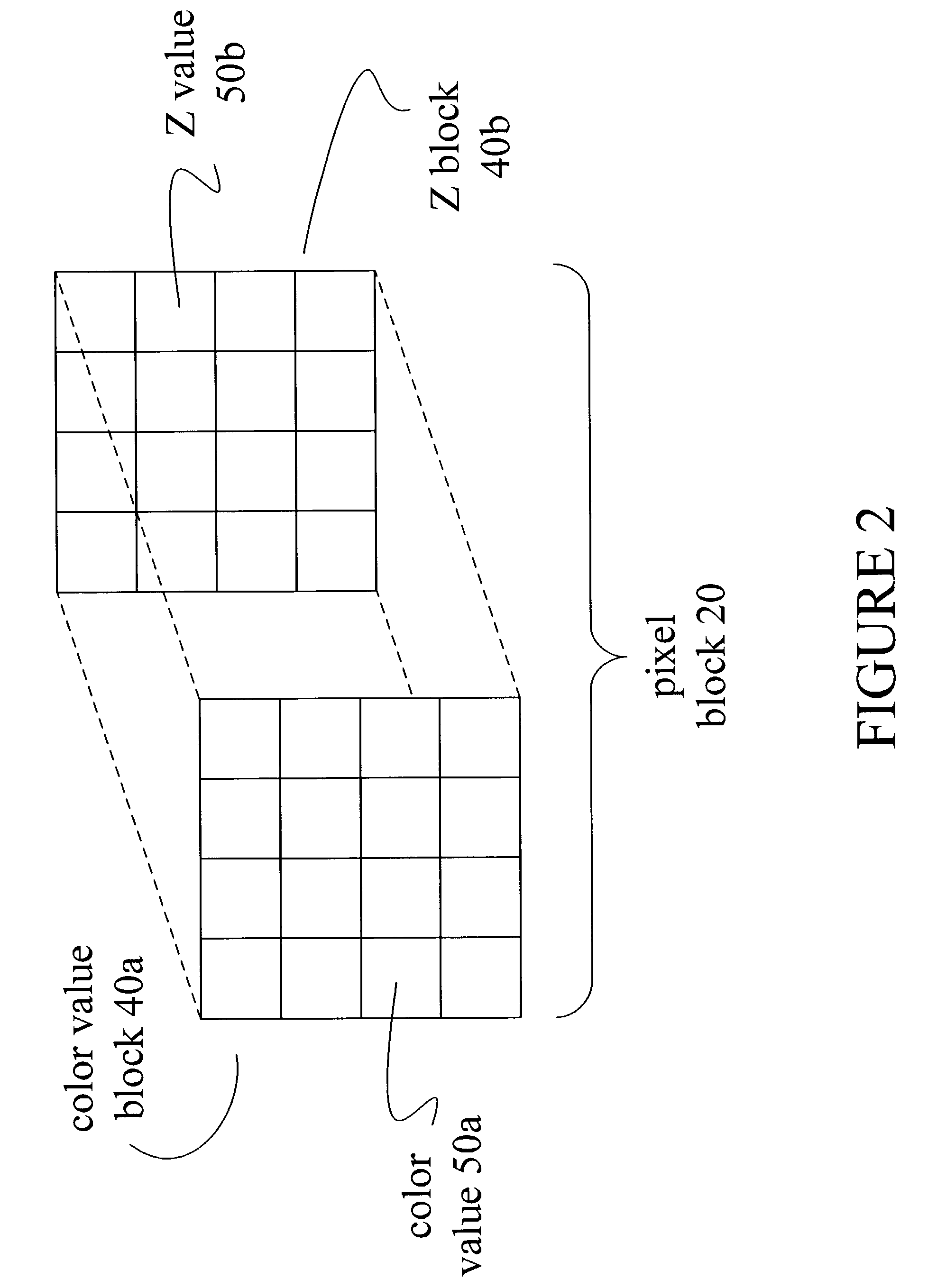

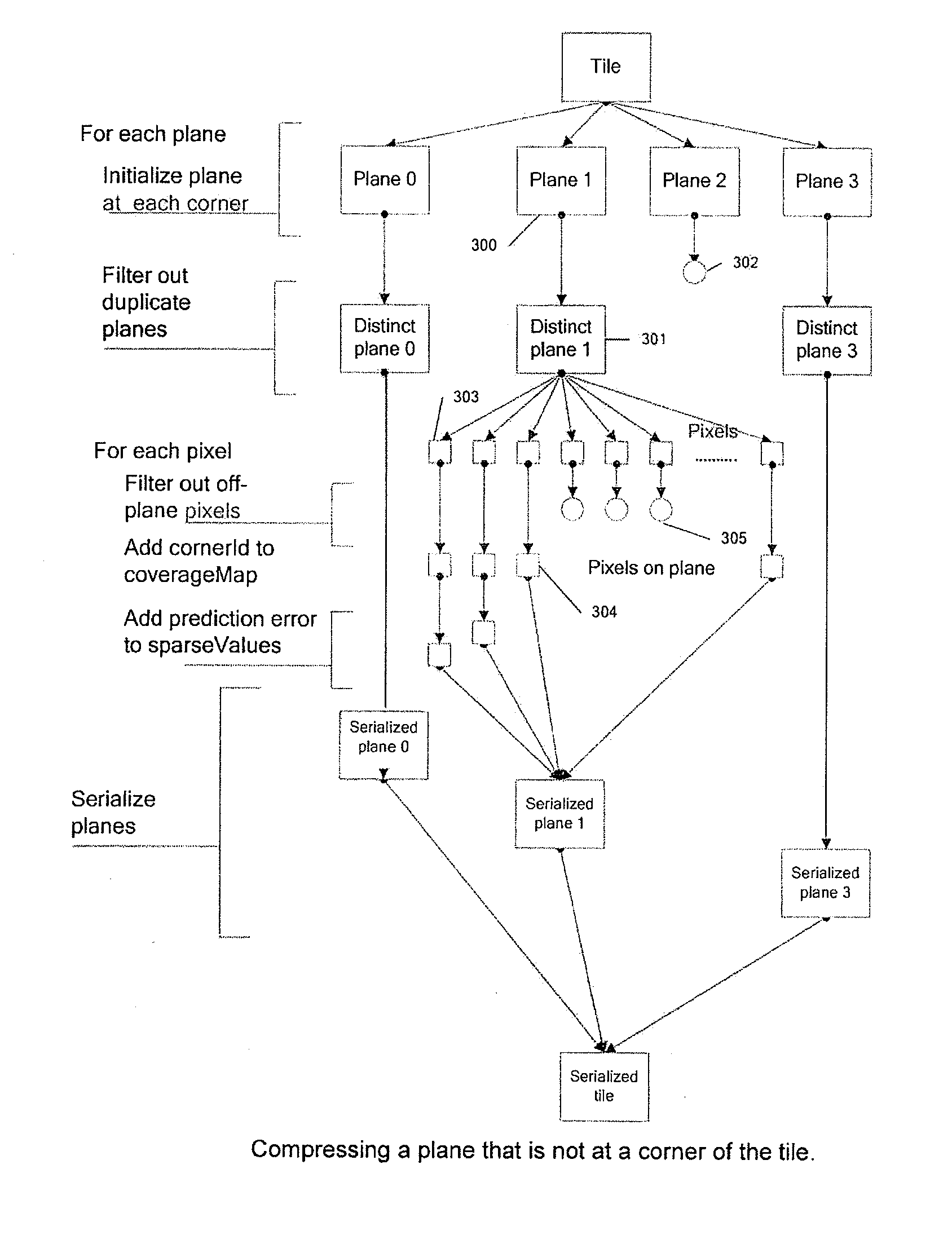

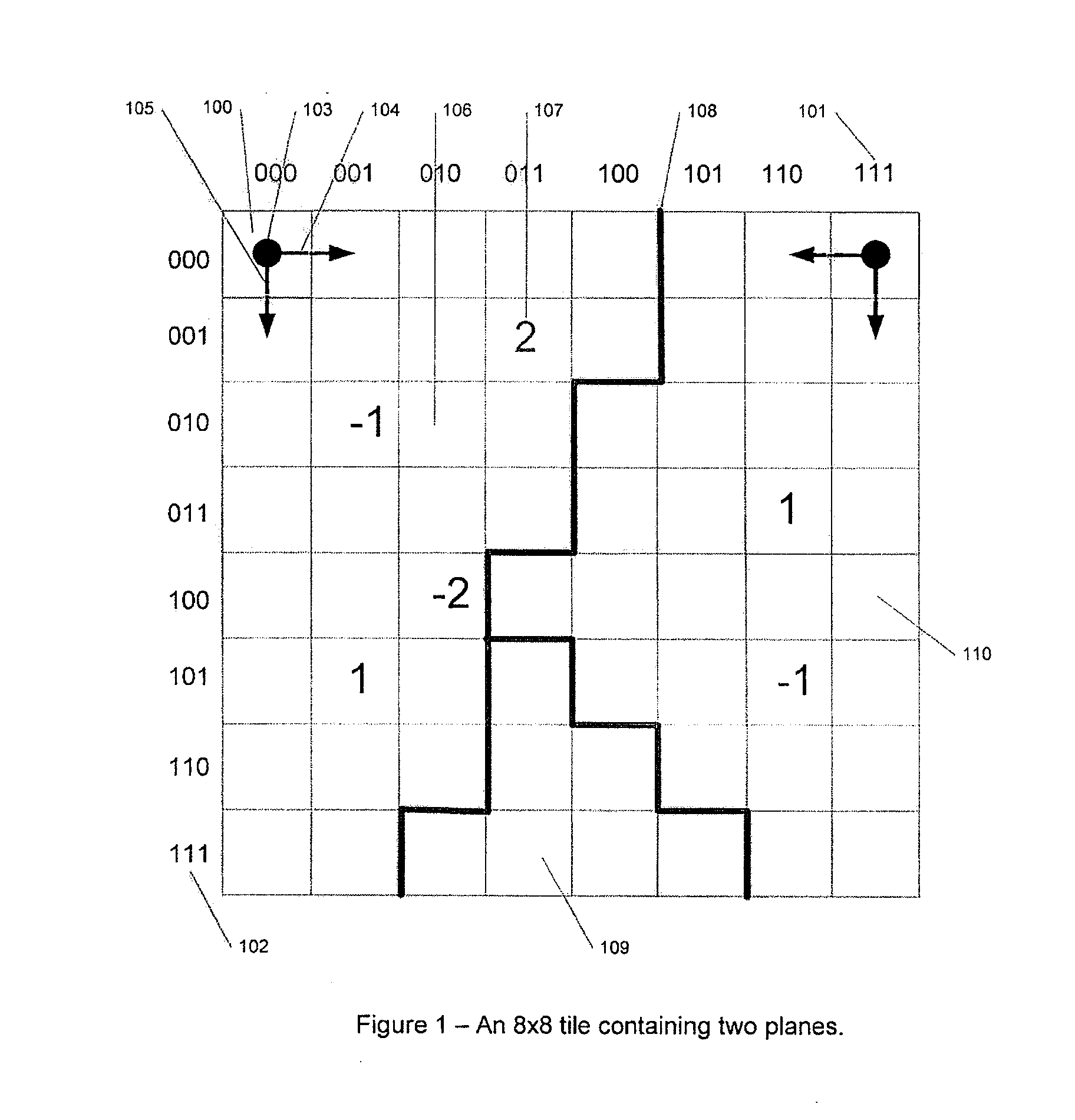

Method and apparatus for tile based depth buffer compression

ActiveUS20120212489A1Image codingDetails involving image processing hardware3D computer graphicsZ-buffering

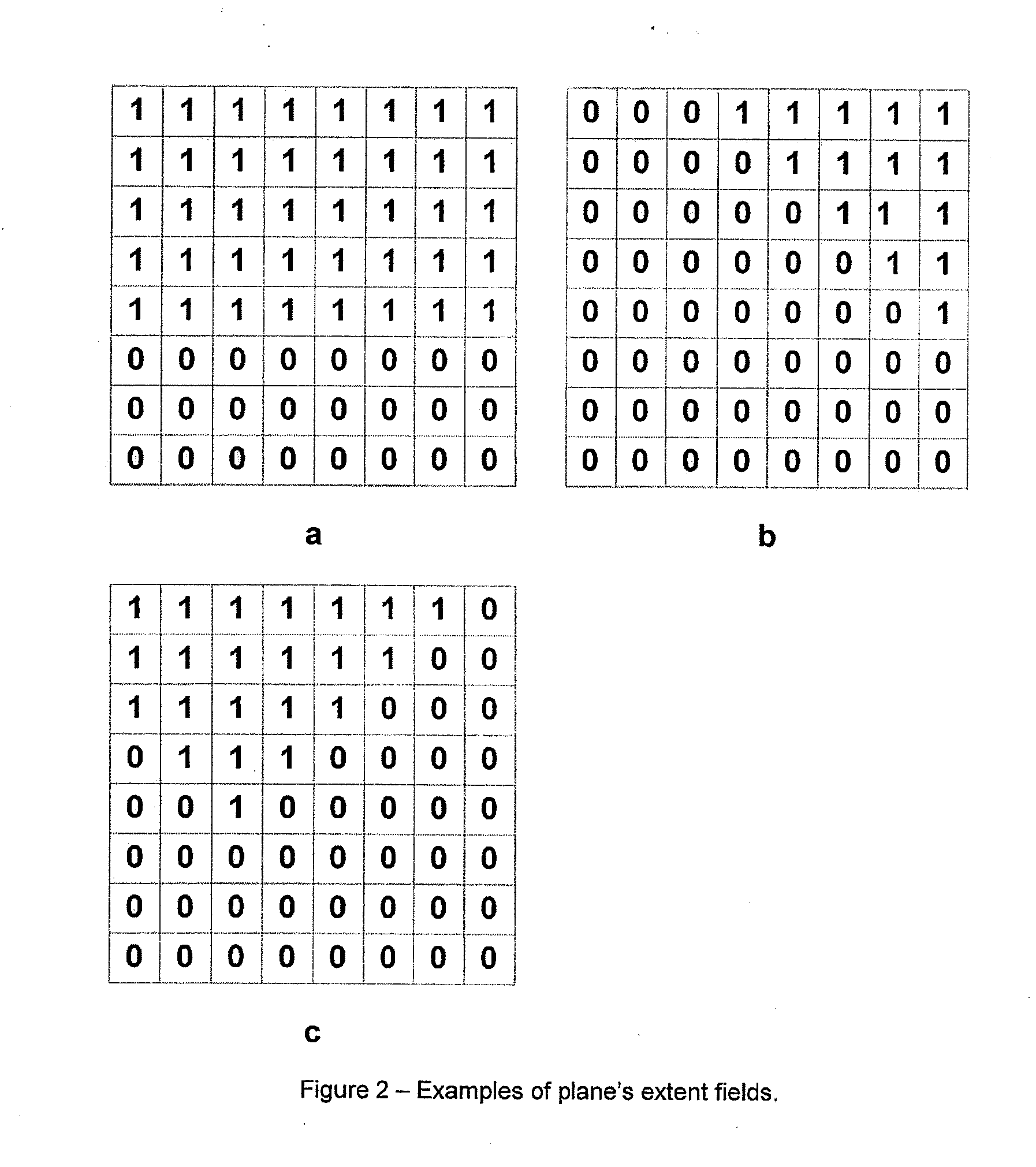

A method and apparatus are provided for compressing depth buffer data in a three dimensional computer graphics system. The depth buffer data is divided into a plurality of rectangular tiles corresponding to rectangular areas in an associated image. The number of starting point locations in a tile are identified and a difference in depth value determined between each starting point and depth values of each of at least two further locations. Using this information depth values are predicted at a plurality of other locations in the tile and where these predicated values substantially match an actual depth value at location is assigned to a plane associated with respective starting point. Starting point location depth value difference data and plane assignment data for each tile and locations in the tile not assigned to a plane, then stored.

Owner:IMAGINATION TECH LTD

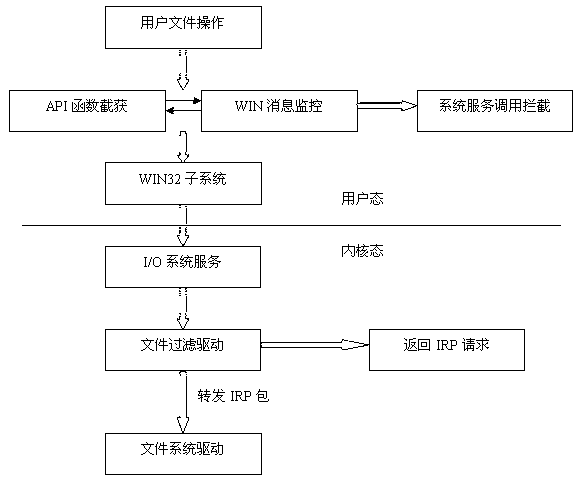

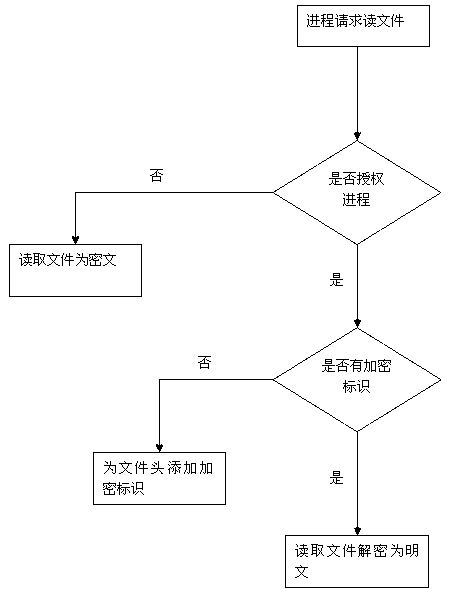

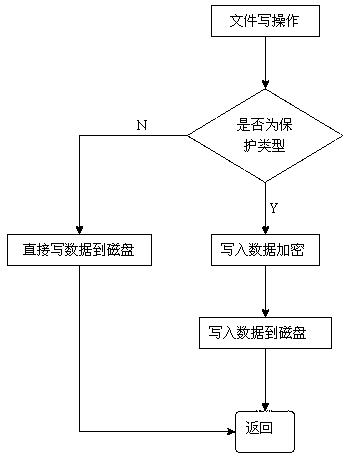

Host file security monitoring method

InactiveCN103218575AChange behaviorChange performanceInternal/peripheral component protectionSoftware systemScreening method

The invention relates to the technical field of information security, in particular to a host file security monitoring and protecting method. The method is a file transparent encryption method based on a driver layer and is completely transparent to users; the users cannot sense file encryption and decryption in a use process; an application layer encryption method with higher security and quicker speed is used for assisting; and a file transparent encryption scheme based on a conventional file screening method is provided for more complicated software systems. According to the method, the process and files of a local computer are identified, and security files are automatically encrypted and decrypted, so that problems of memory mapping, file buffering and the like are solved, and the safety is increased.

Owner:WUHAN YOUNG TECH CO LTD

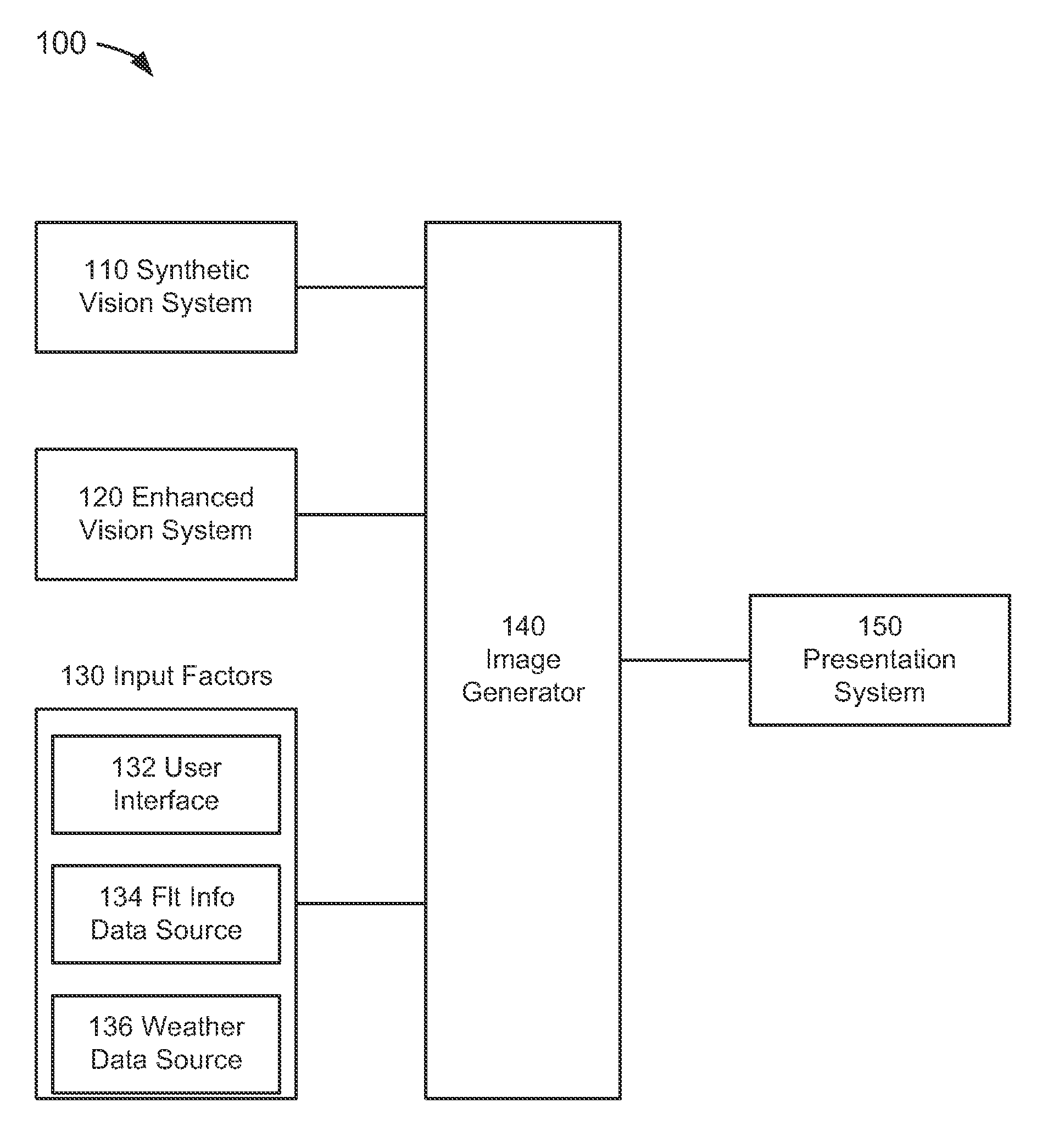

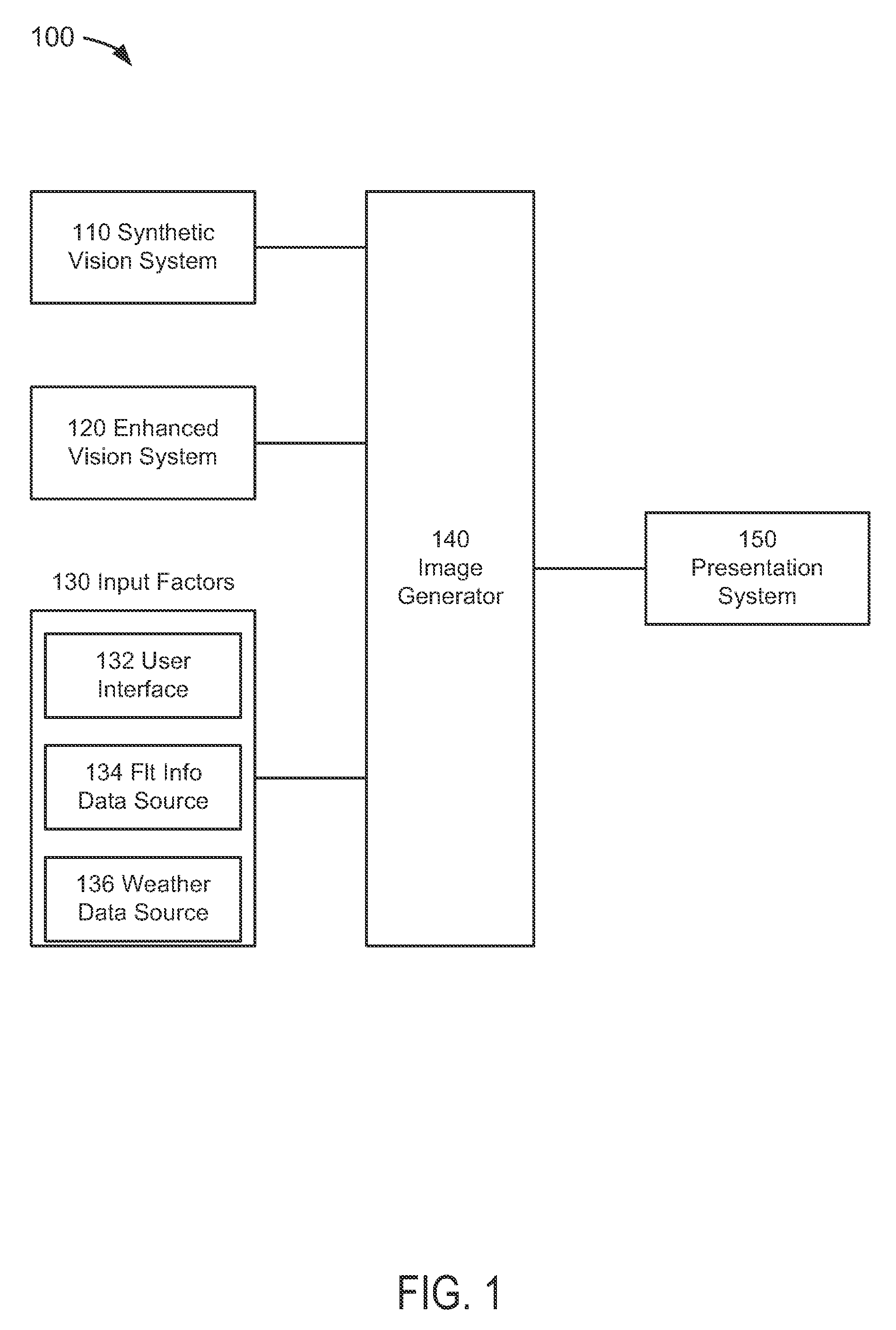

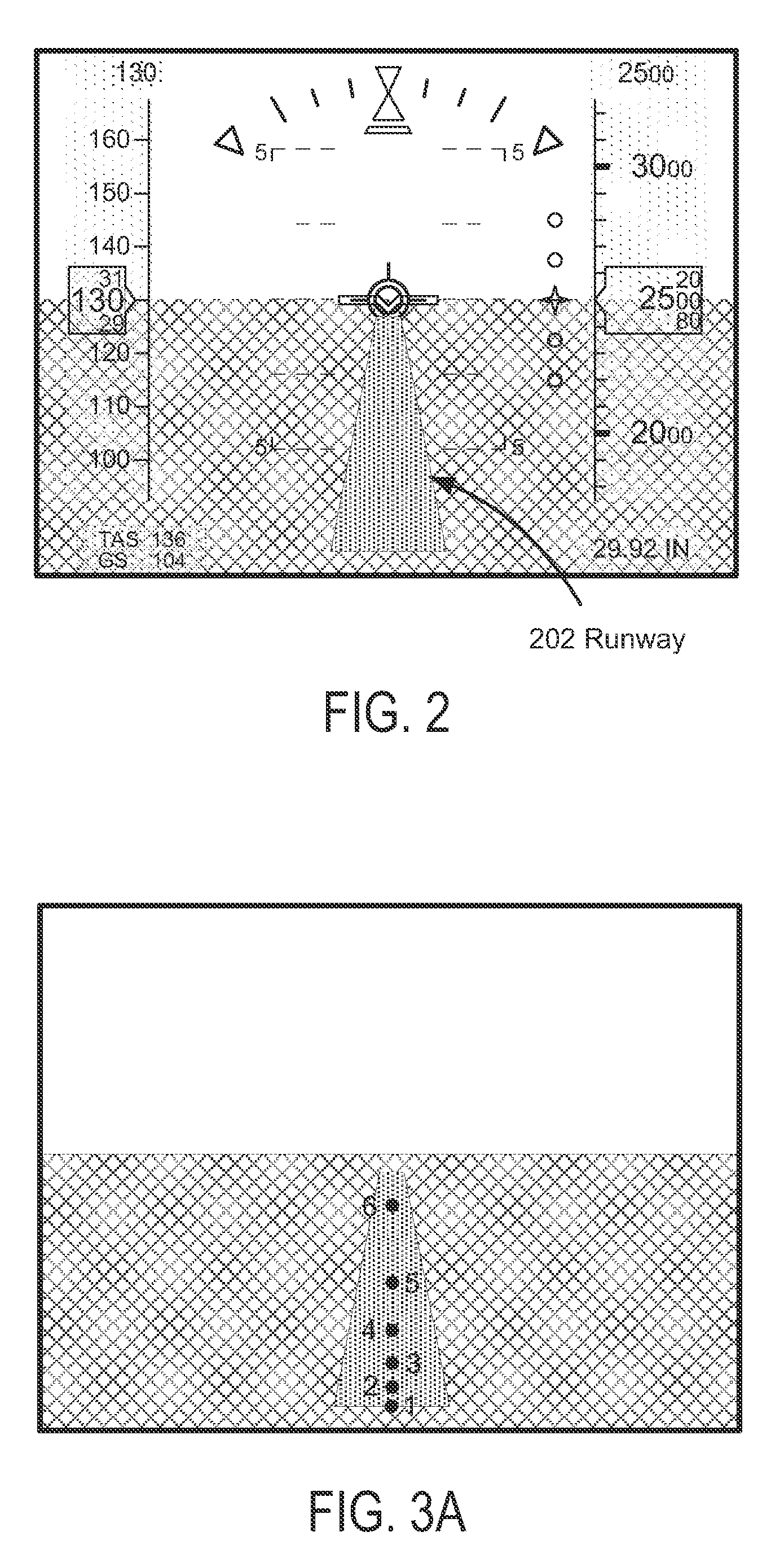

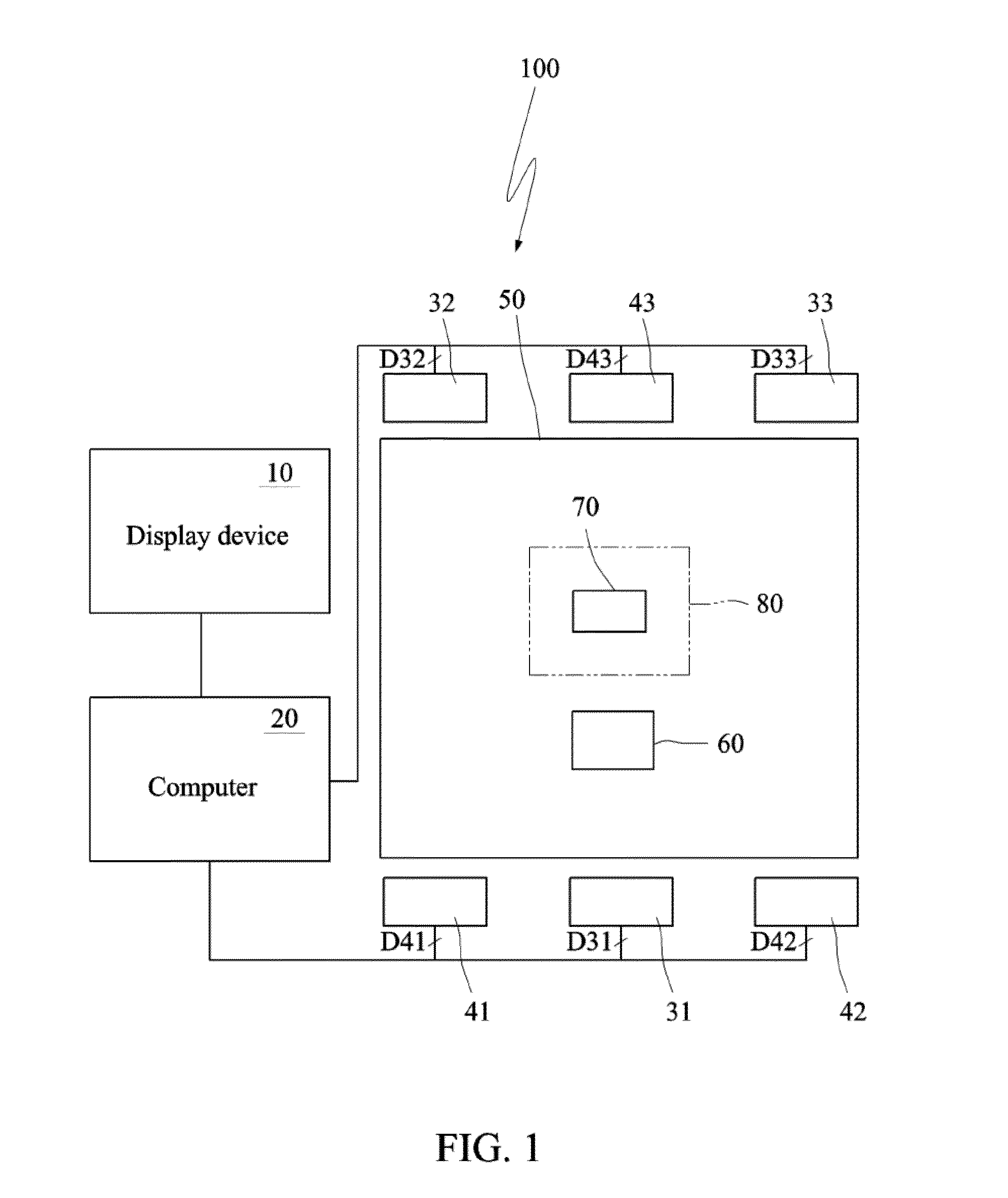

Image combining system, device, and method of multiple vision sources

Present novel and non-trivial system, device, and method for combining image data received from two or more vision systems are disclosed. A system may be comprised of a first vision source, a second vision source, and an image generator (“IG”). The first vision source may be could configured to generate a first image data set and a depth buffer data set, and the second vision data source could configured to generate a second image data set. The IG could be configured to receive both the first and second image data sets; the depth buffer data set; and generate a third image data set as a function of both image data sets, the depth buffer data set, and a pixel cutoff distance that may be fixed or variable. In addition, the pixel cutoff distance may be determined as a function of input variable data.

Owner:ROCKWELL COLLINS INC

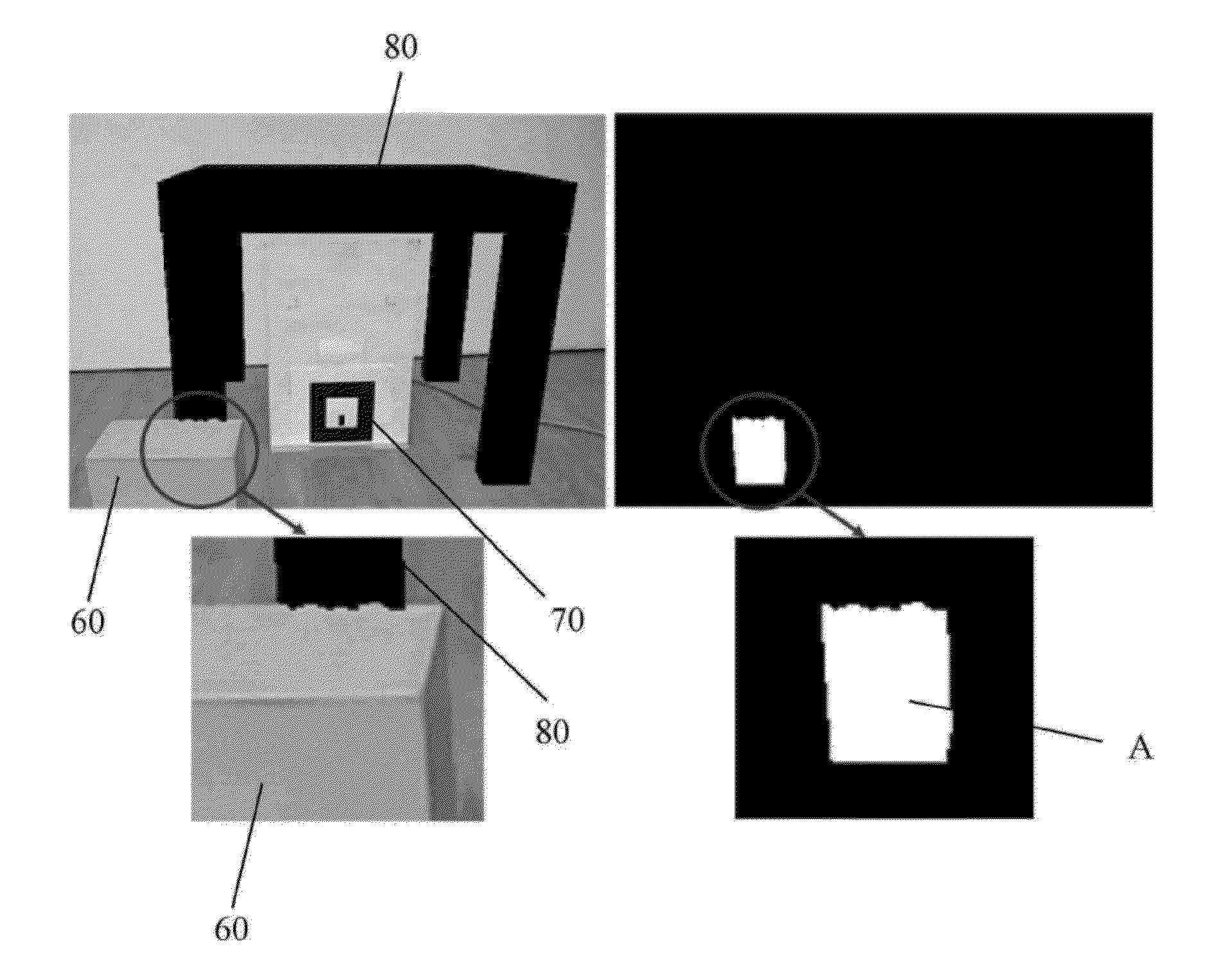

Method for Optimizing Occlusion in Augmented Reality Based On Depth Camera

ActiveUS20160210787A1Facilitate shadingImprove visualization resultAnimationImage renderingVirtual modelImaging data

A method for optimizing occlusion occurring in an augmented reality system comprising a depth camera and a two-dimensional camera comprises the steps of: capturing, by a depth camera, a scene and an object in the scene to obtain initial depth data, and capturing, by the two-dimensional camera, the scene and the object to obtain two-dimensional image data; in-painting the initial depth data to obtain in-painted depth data; performing a depth buffer calculation according to the in-painted depth data and a virtual model to obtain an occlusion relationship between the object and the virtual model, and generating an occluded partial image according to the two-dimensional image data and the virtual model; estimating partially approximated polygon according to the occluded partial image; and generating an occluded result according to the partially approximated polygon, the two-dimensional image data and the virtual model.

Owner:NATIONAL TSING HUA UNIVERSITY

Method and apparatus for hierarchical Z buffering and stenciling

A method and apparatus for hierarchical Z buffering stenciling includes comparing an input tile Z value range with a hierarchical Z value range and a stencil code. The method and apparatus also updates the hierarchical Z value range and stencil code in response the comparison and determines whether to render a plurality of pixels within the input tile based on the comparison of the input tile Z value range with the hierarchical Z value range and stencil code. In determining whether to render the tile, a stencil test and a hierarchical Z value test is performed. If one of the test fails, the tile is killed as it is determined that the pixels are not visible in the graphical output. If the stencil test passes and the hierarchical Z test passes, the pixels within the tile are rendered, as it is determined that the pixels may be visible.

Owner:ATI TECH INC

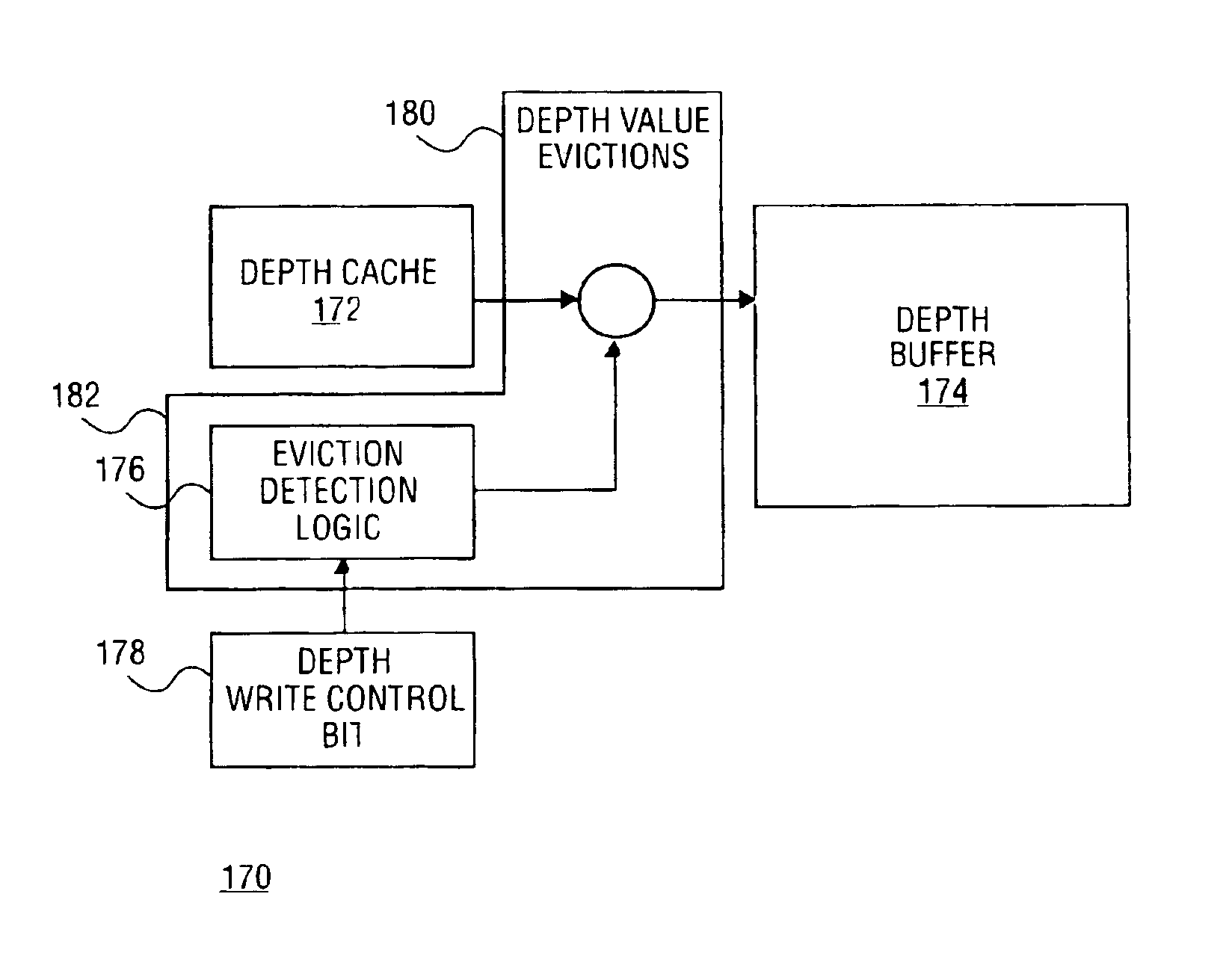

Depth write disable for rendering

InactiveUS6954208B2Reduce bandwidth requirementsImprove performanceImage memory managementElectric digital data processingComputer graphics (images)Intermediate depth

A depth write disable apparatus and method for controlling evictions, such as depth values, from a depth cache to a corresponding depth buffer in a zone rendering system. When the depth write disable circuitry is enabled, evictions from the depth cache (as which typically occur during the rendering of the next zone) to the depth buffer are prevented. In particular, once the depth buffer is initialized (i.e. cleared) to a constant value at the beginning of a scene, the depth buffer does not need to be read. The depth cache handles intermediate depth reads and writes within each zone. Since the memory resident depth buffer is not required after a scene is rendered, it never needs to be written. The final depth values for a zone can thus be discarded (i.e., rather than written to the depth buffer) after each zone is rendering.

Owner:INTEL CORP

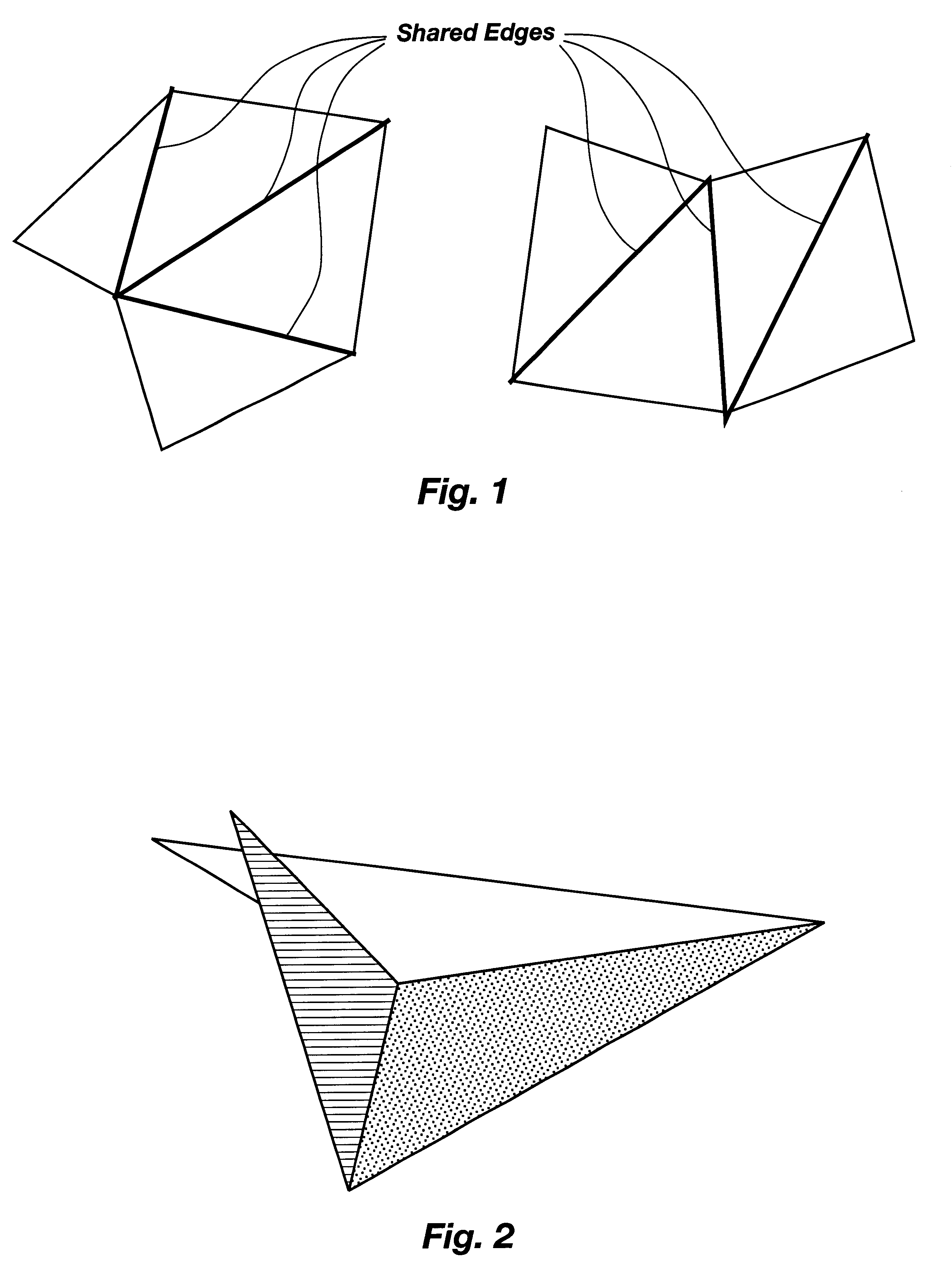

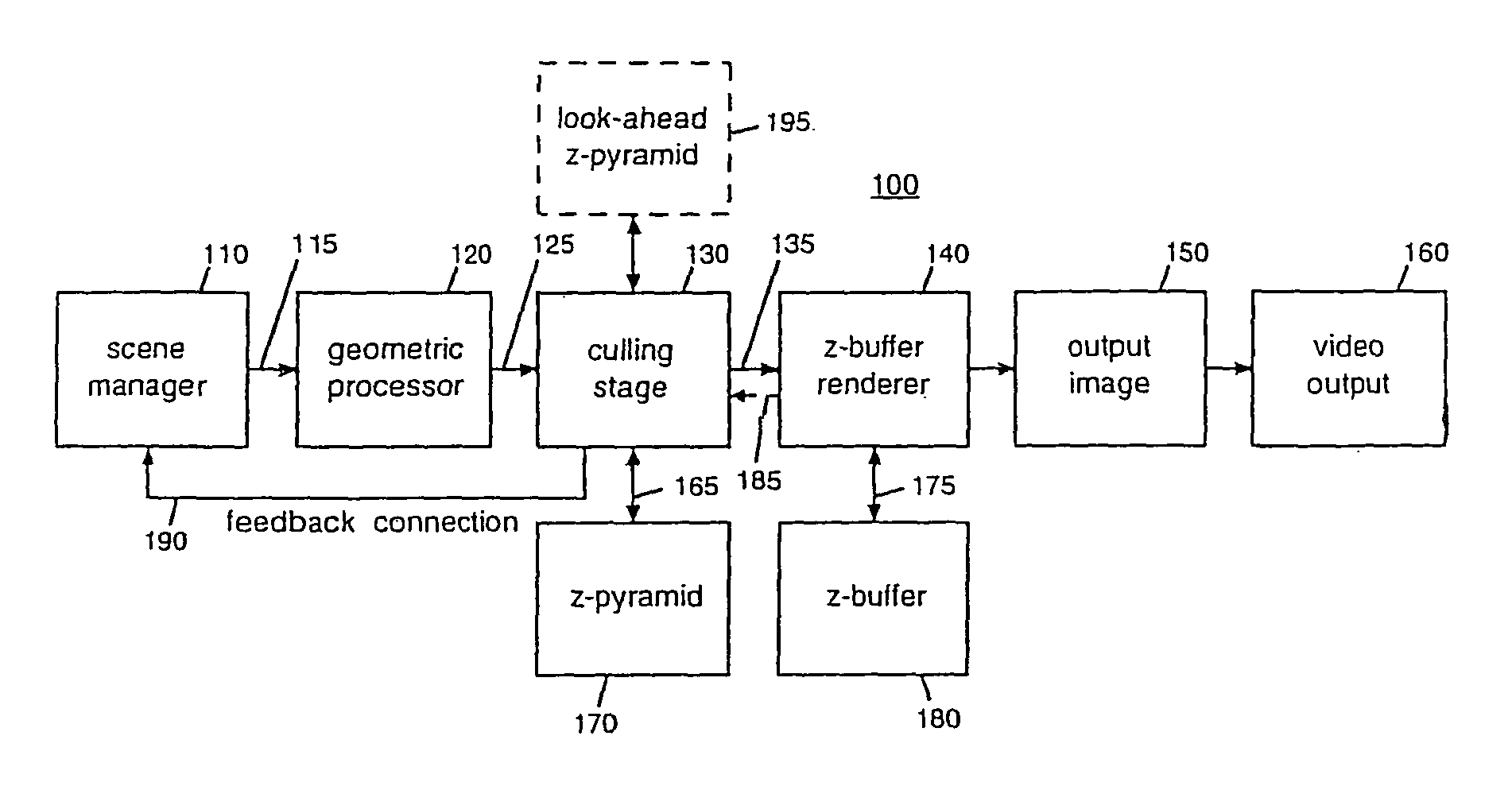

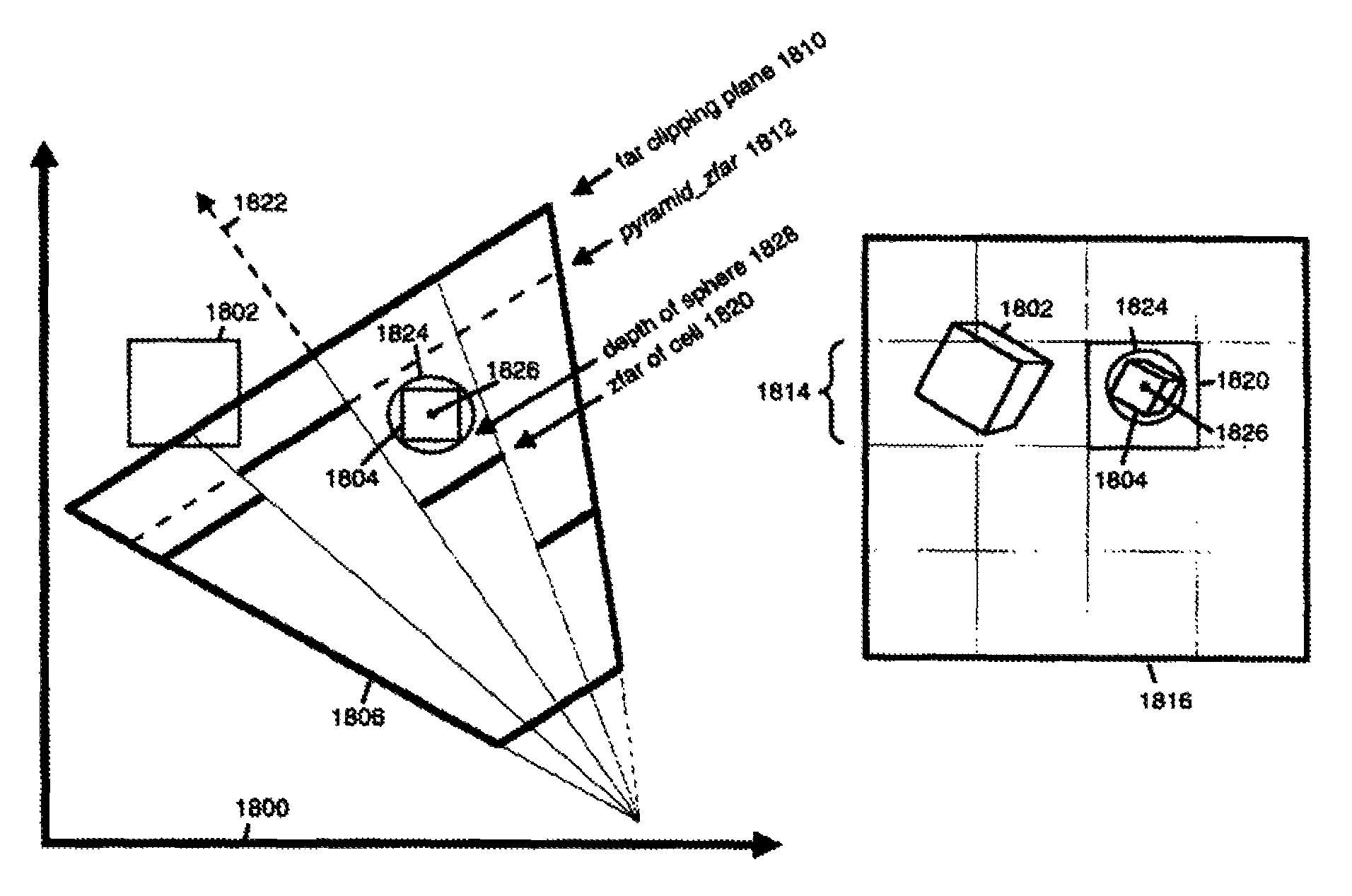

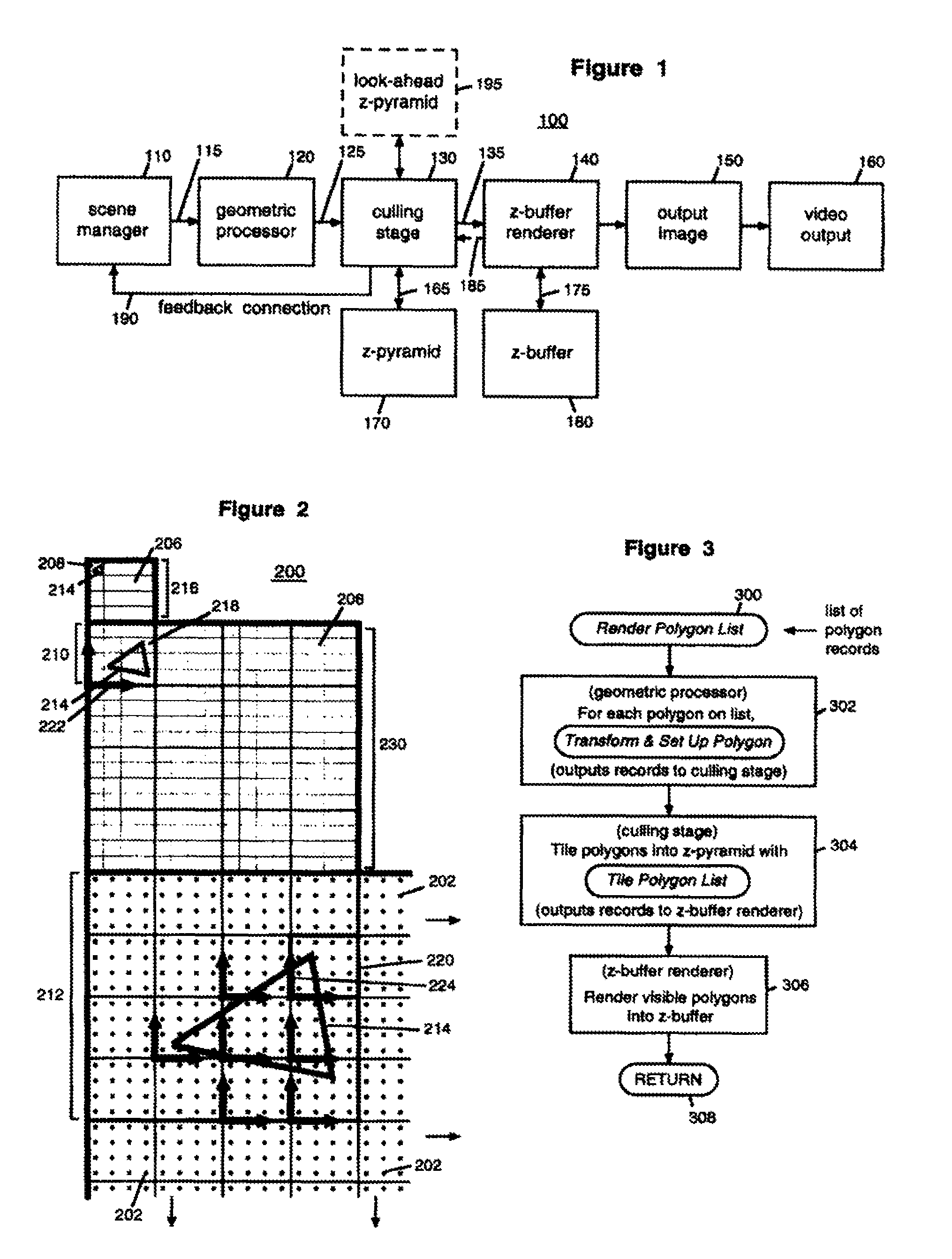

System, method and computer program product for updating a far clipping plane in association with a hierarchical depth buffer

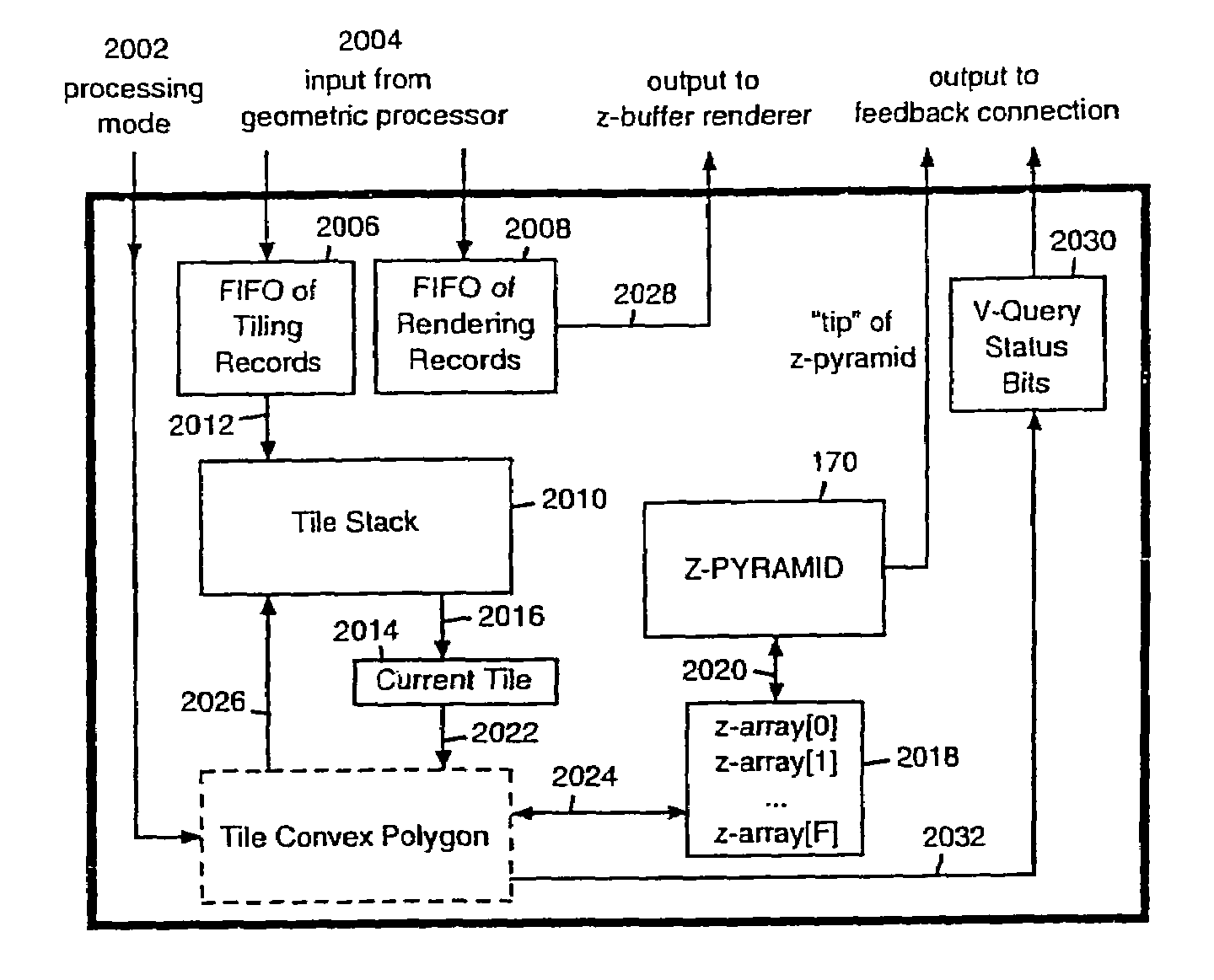

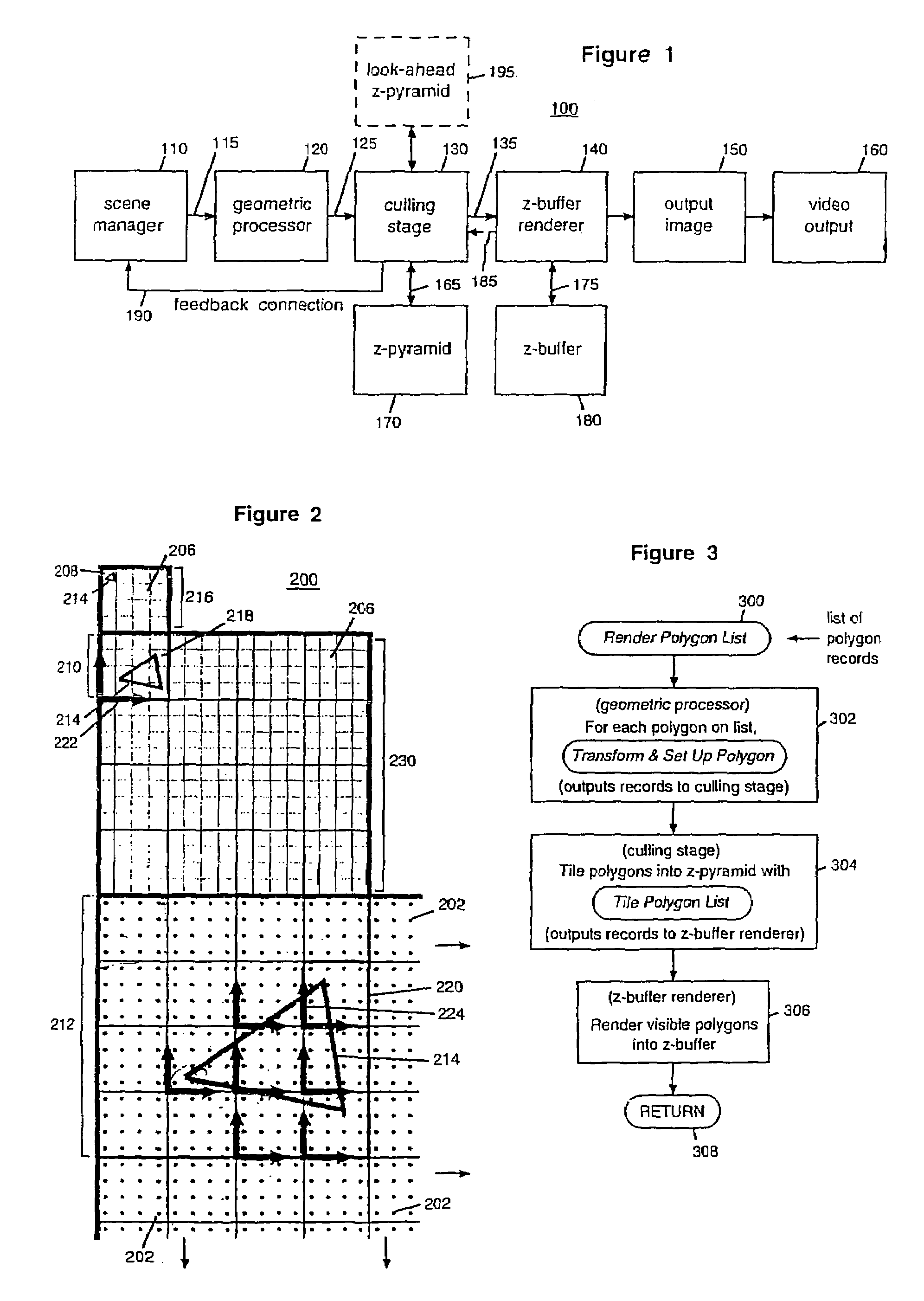

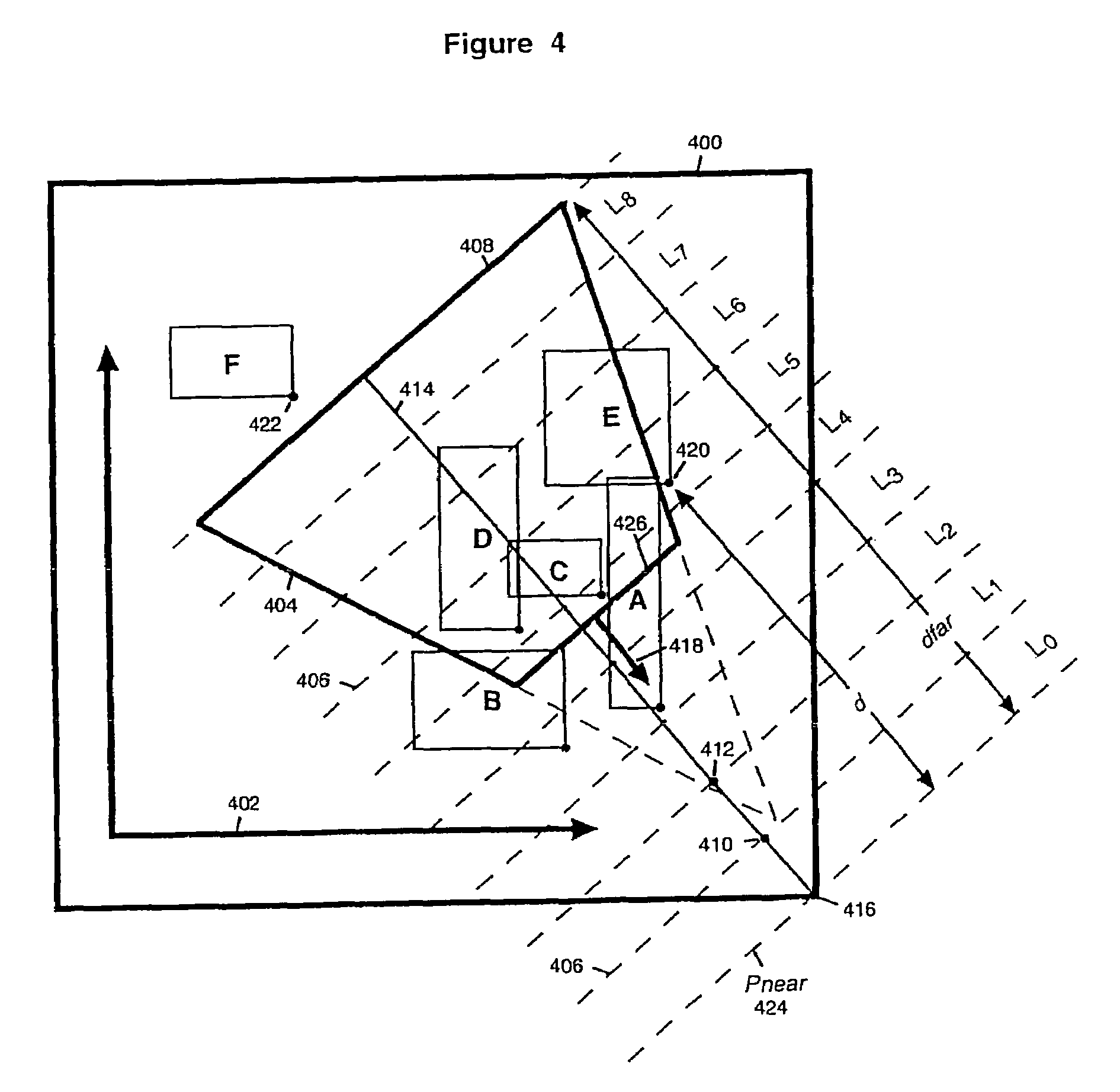

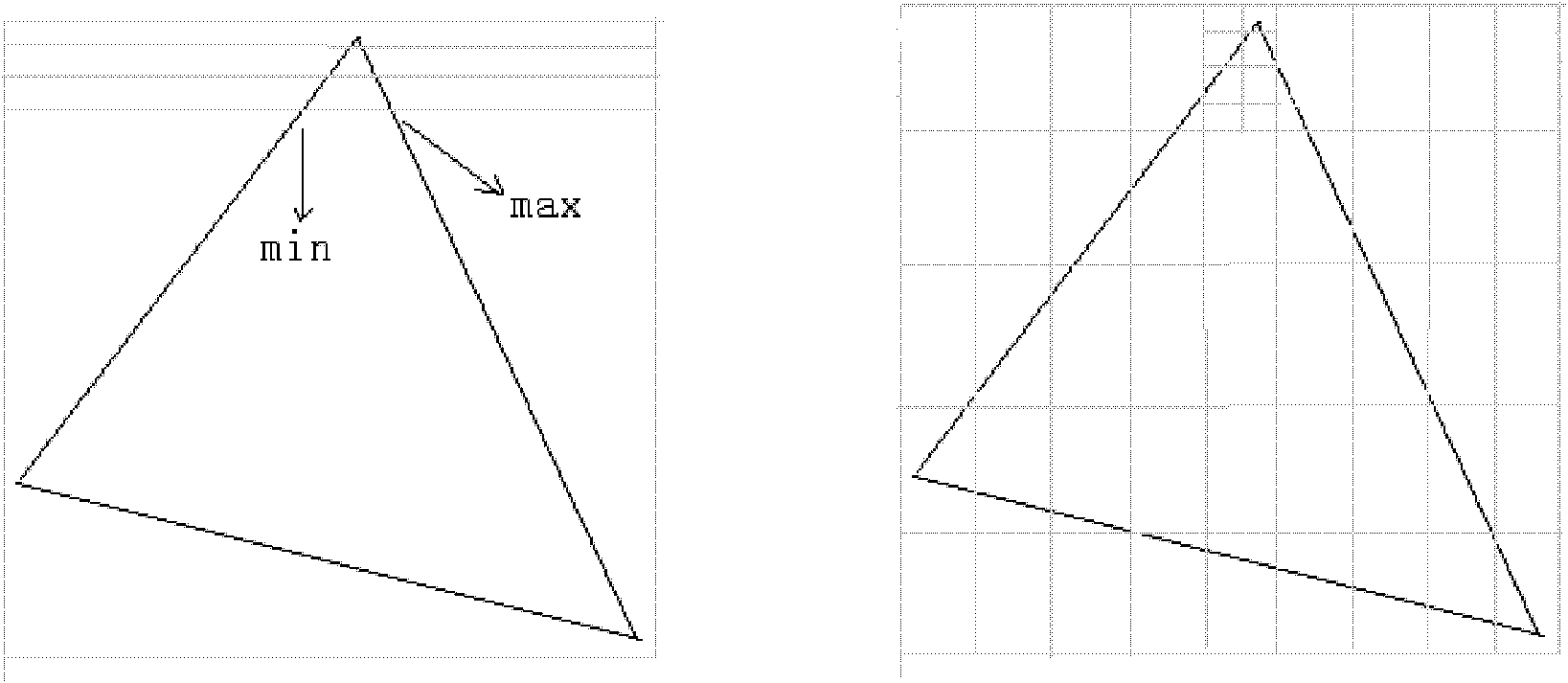

Z-buffer rendering of three-dimensional scenes is made more efficient through a method for occlusion culling by which occluded geometry is removed prior to rasterization. The method uses hierarchical z-buffering to reduce the quantity of image and depth information that needs to be accessed. A separate culling stage in the graphics pipeline culls occluded geometry and passes visible geometry on to a rendering stage. The culling stage maintains its own z-pyramid in which z-values are stored at low precision (e.g., in 8 bits). The efficiency of hierarchical z-buffering is improved through hierarchical evaluation of line and plane equations.

Owner:NVIDIA CORP

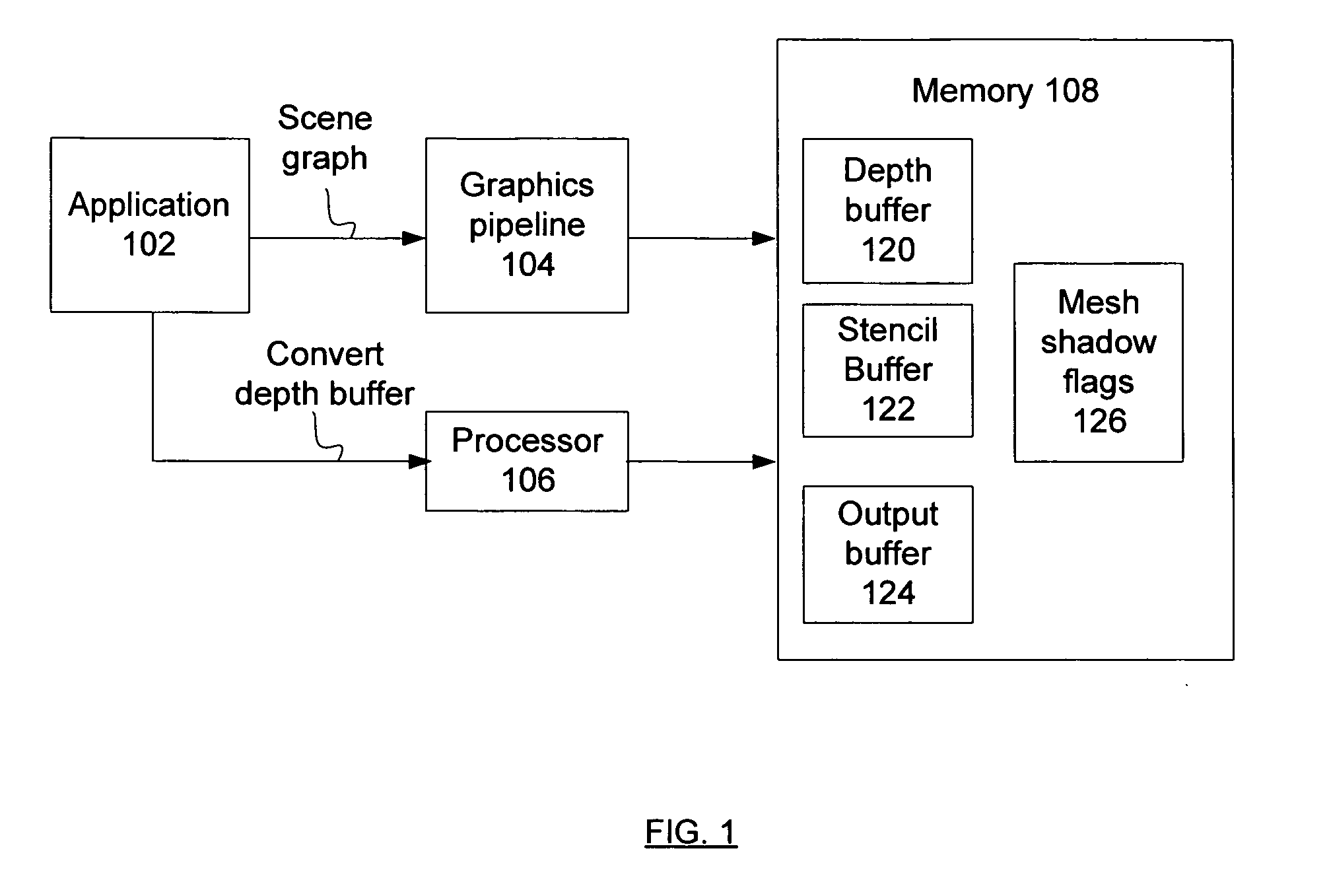

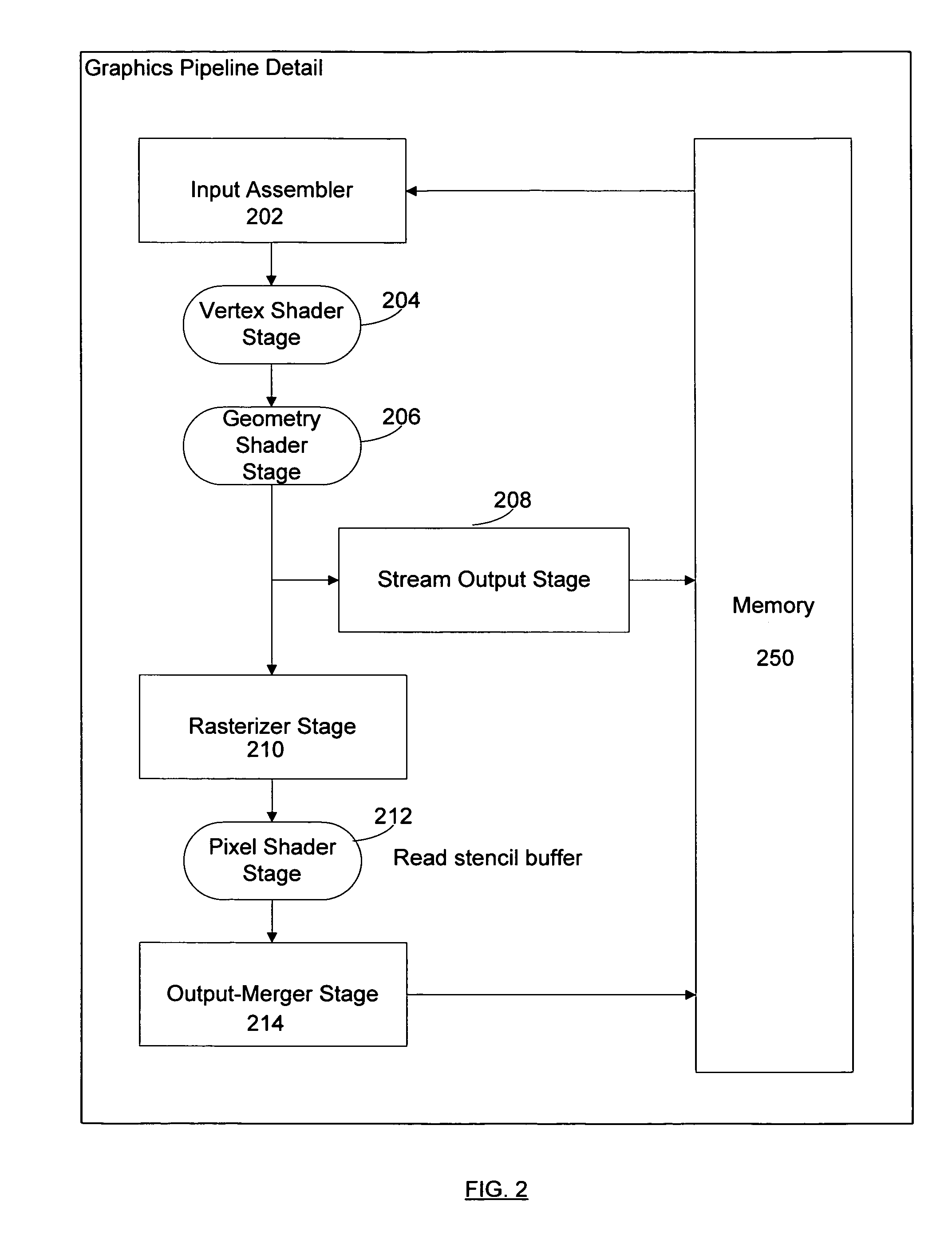

Image processing techniques

InactiveUS20110141112A1Cathode-ray tube indicators3D-image renderingComputer graphics (images)Z-buffering

Hierarchical culling can be used during shadow generation by using a stencil buffer generated from a light view of the eye-view depth buffer. The stencil buffer indicates which regions visible from an eye-view are also visible from a light view. A pixel shader can determine if any object could cast a shadow by comparing a proxy geometry for the object with visible regions in the stencil buffer. If the proxy geometry does not cast any shadow on a visible region in the stencil buffer, then the object corresponding to the proxy geometry is excluded from a list of objects for which shadows are to be rendered.

Owner:INTEL CORP

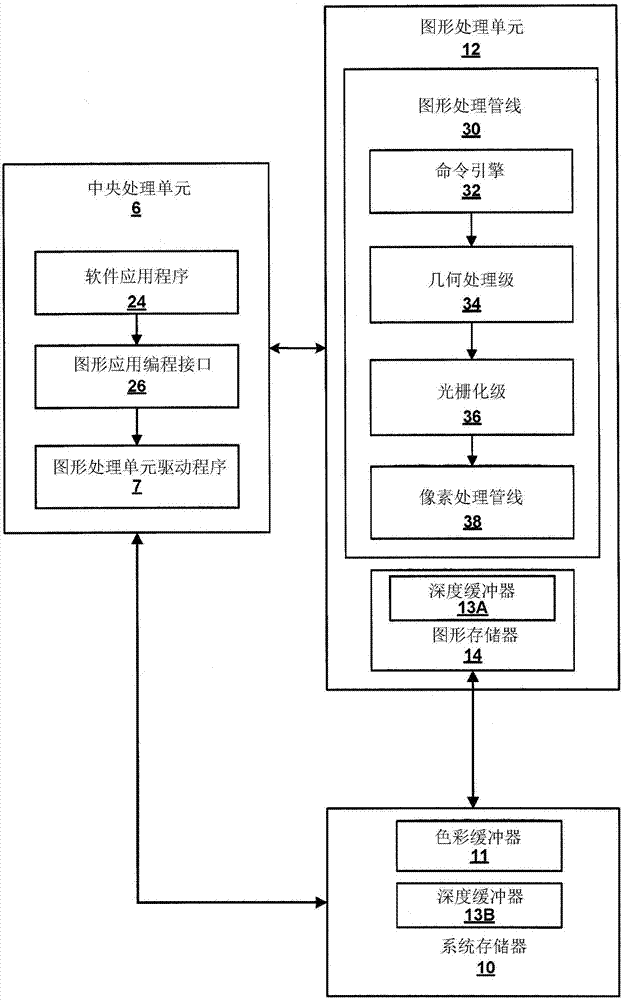

Hybrid rendering in graphics processing

ActiveCN107209923AImage memory managementProcessor architectures/configurationGraphicsMain processing unit

This disclosure presents techniques and structures for graphics processing. In one example, a method of graphics processing may include rendering, with a graphics processing unit (GPU), one or more portions of a frame using one or more graphics operations, and writing, with the GPU, color data directly to a color buffer in a system memory in accordance with the one or more graphics operations. The method may further include writing, with the GPU, depth data to a depth buffer in a graphics memory in accordance with the one or more graphics operations, and resolving, with the GPU, the depth buffer in the graphics memory to the system memory when the rendering of the one or more portions of the frame is complete.

Owner:QUALCOMM INC

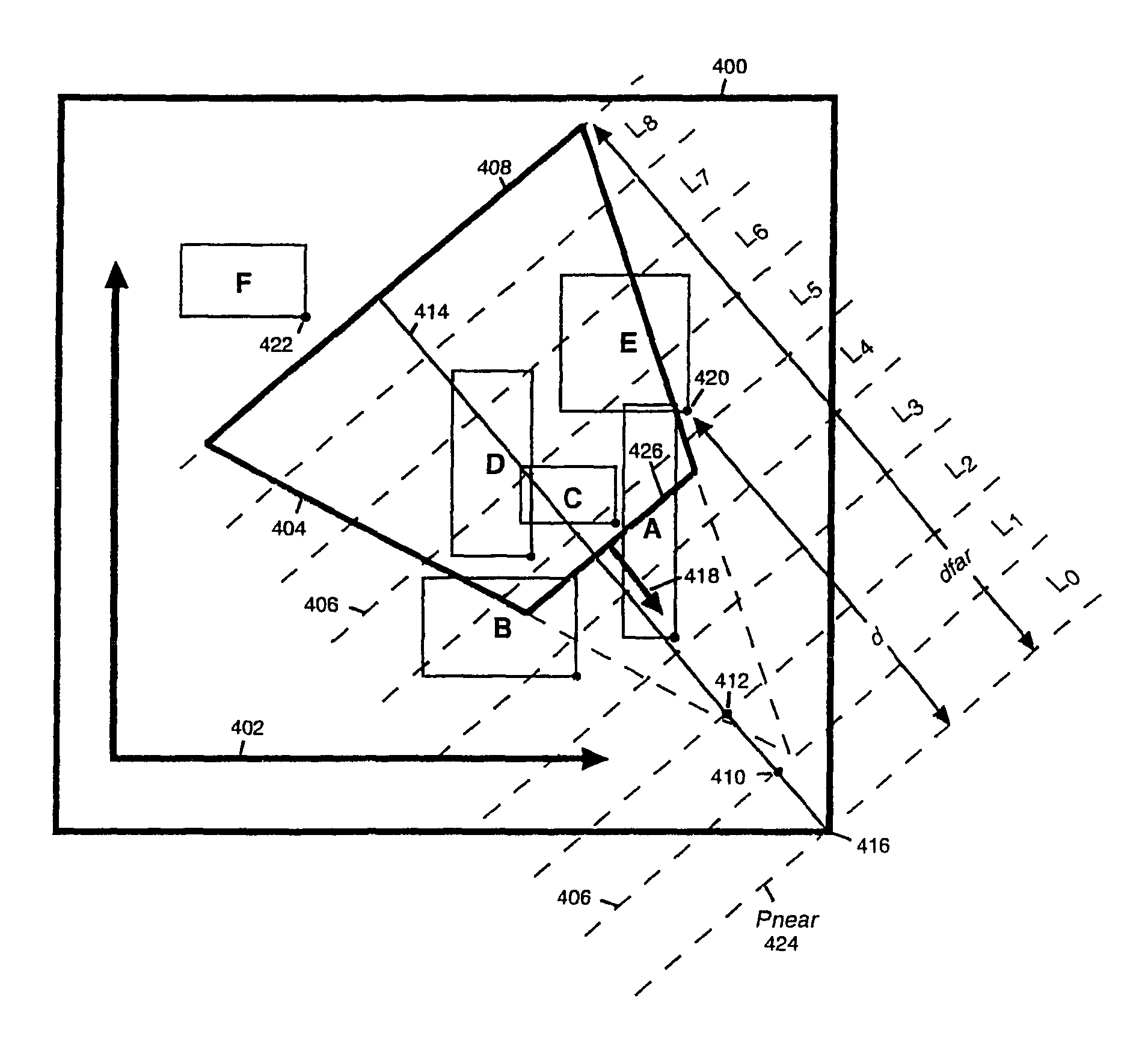

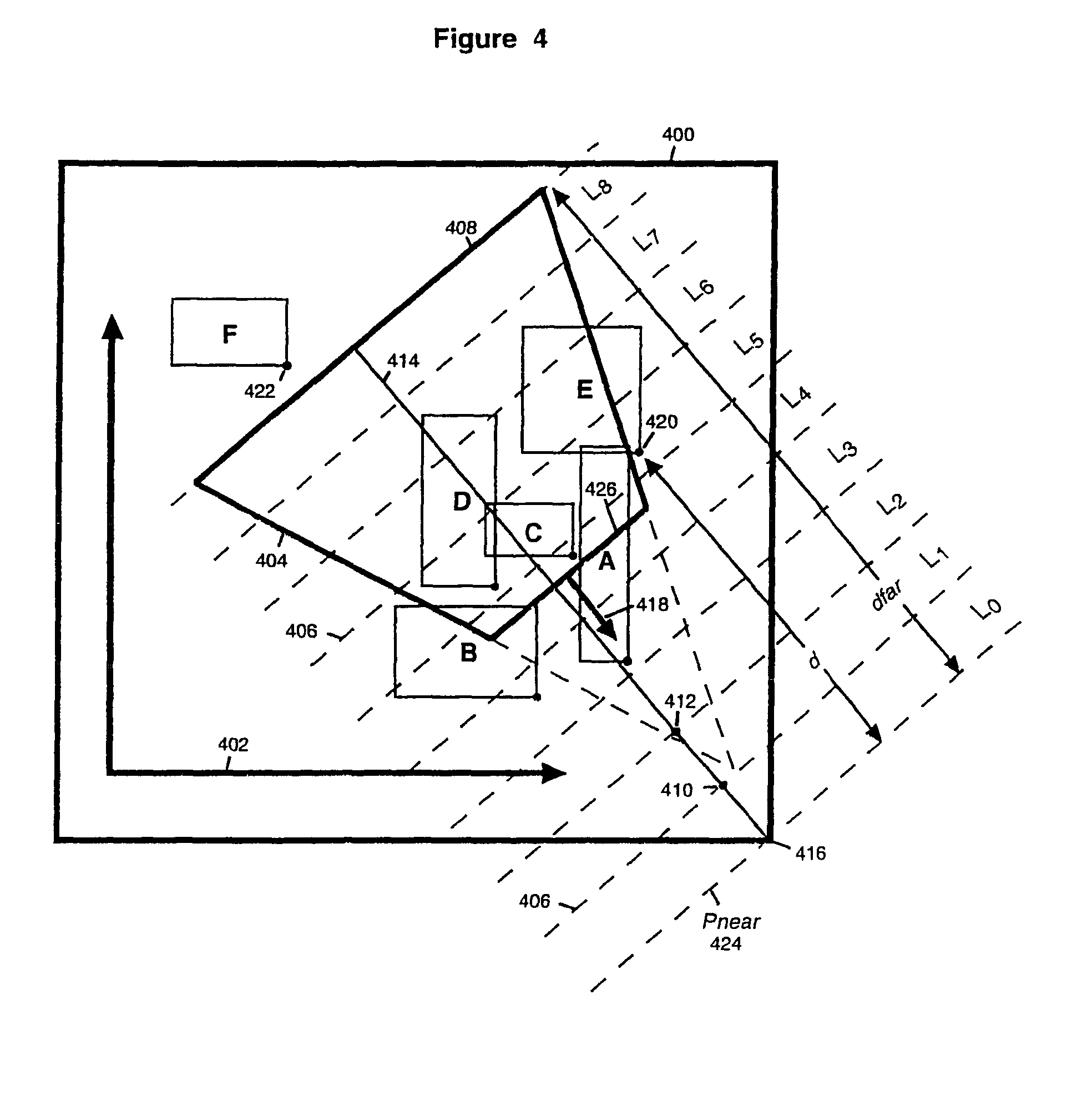

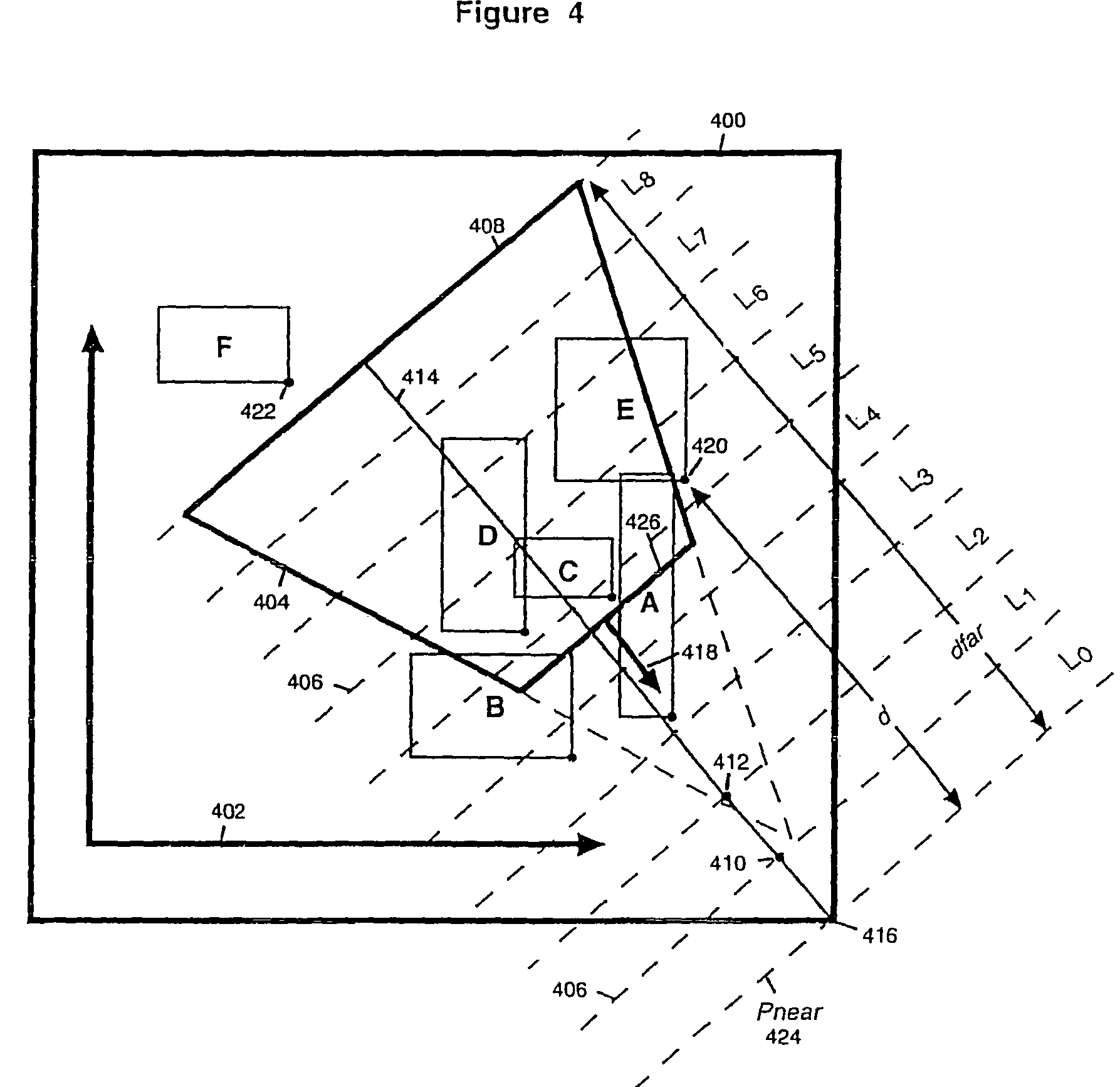

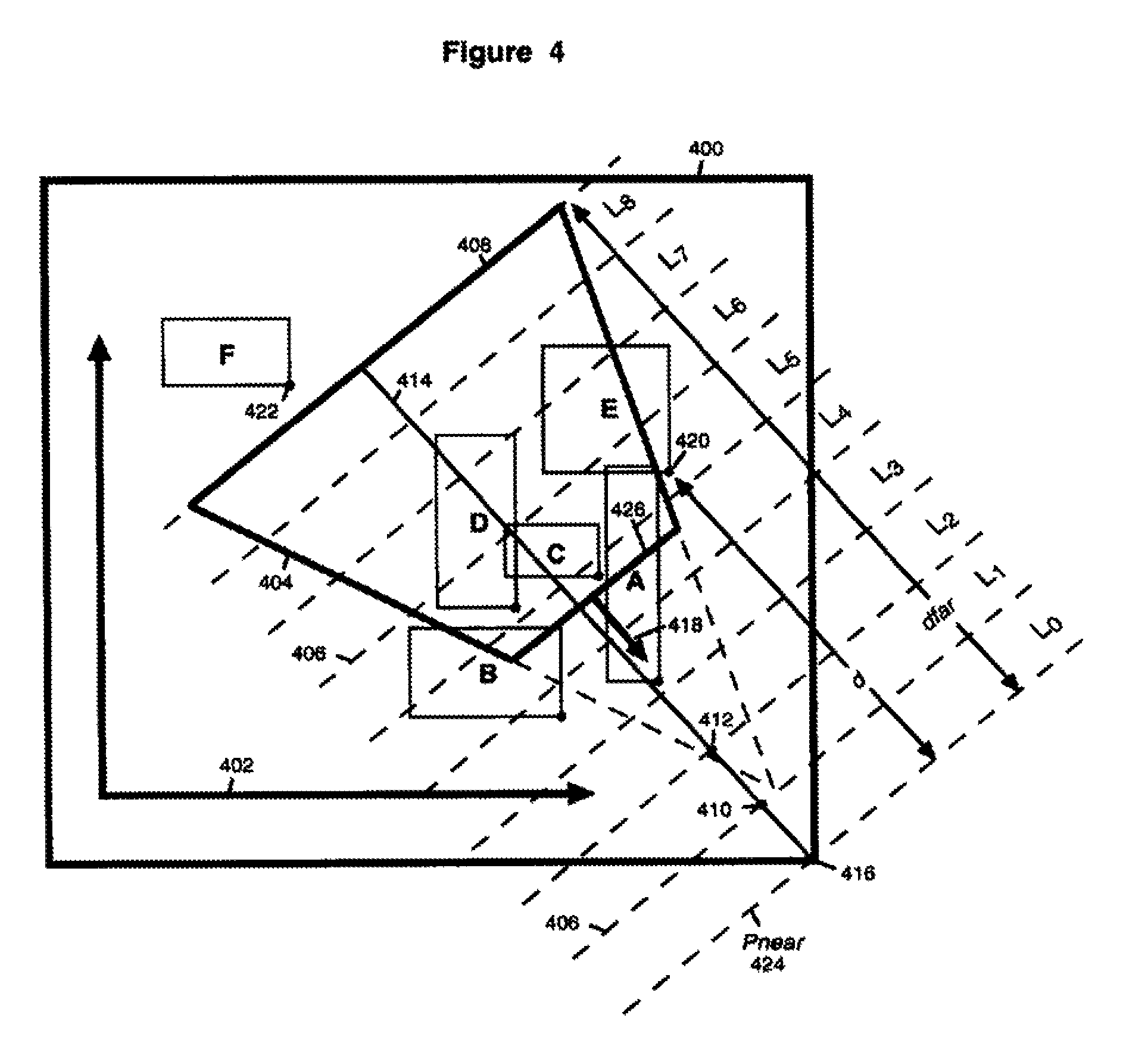

System, method and computer program product for transforming a polynomial equation from a coordinate frame of one tile to a coordinate frame of another tile at a finer level of a hierarchy

InactiveUS7969436B1Reduce amountReducing bus trafficCharacter and pattern recognitionCathode-ray tube indicatorsGraphicsCulling

Z-buffer rendering of three-dimensional scenes is made more efficient through a method for occlusion culling by which occluded geometry is removed prior to rasterization. The method uses hierarchical z-buffering to reduce the quantity of image and depth information that needs to be accessed. A separate culling stage in the graphics pipeline culls occluded geometry and passes visible geometry on to a rendering stage. The culling stage maintains its own z-pyramid in which z-values are stored at low precision (e.g., in 8 bits). The efficiency of hierarchical z-buffering is improved through hierarchical evaluation of line and plane equations.

Owner:NVIDIA CORP

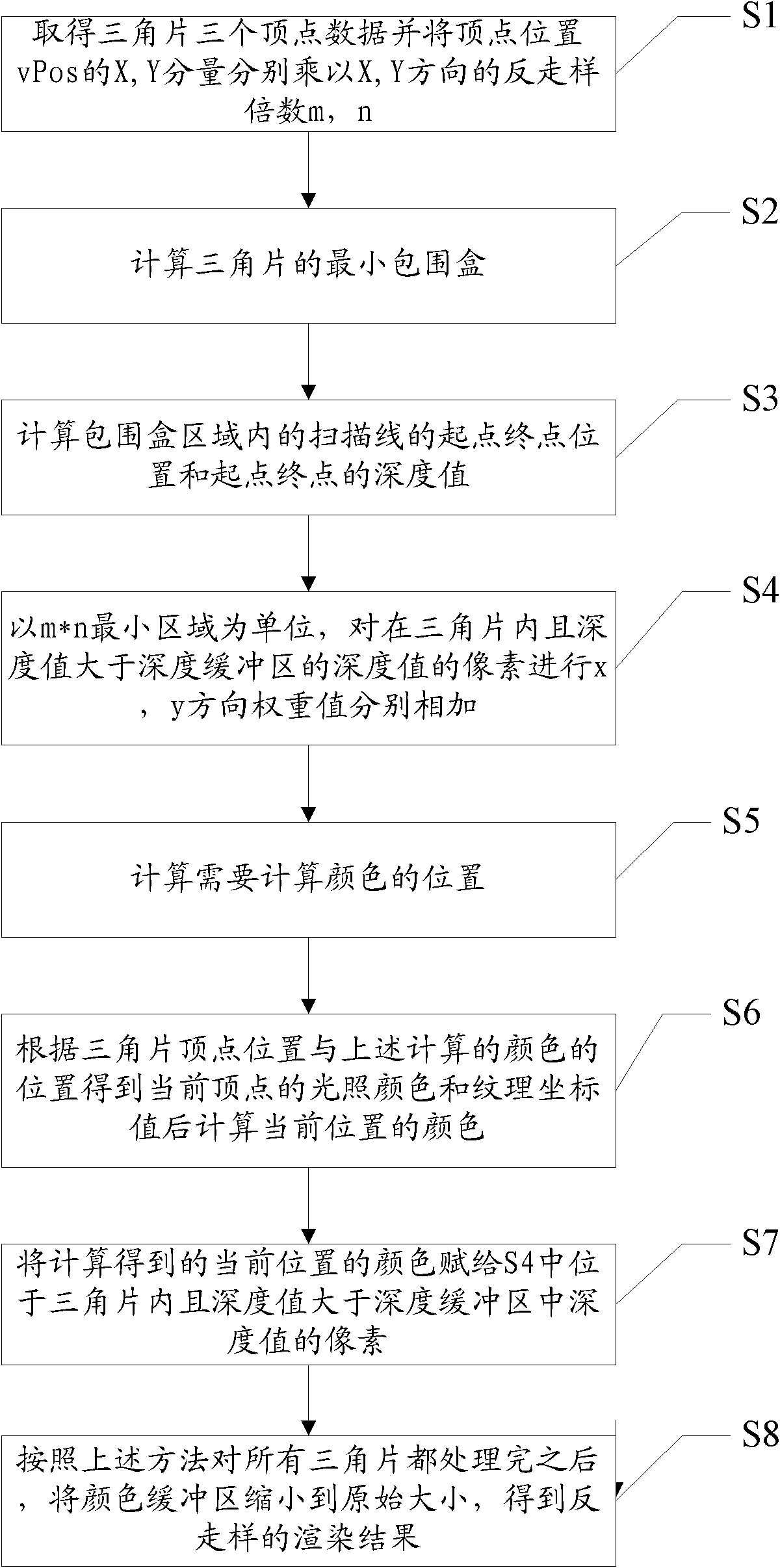

Method for anti-aliasing improvement at rasterization phase in graphic rendering pipeline

InactiveCN102722902AAchieve anti-aliasing effectImprove computing efficiencyTelevision system detailsColor television detailsGraphicsAnti-aliasing

The invention discloses a method for anti-aliasing improvement at a rasterization phase in a graphic rendering pipeline. The method comprises the following steps that: before a rasterization phase, according to an anti-aliasing level, an amplified color buffer region and a depth buffer region are prepared and initialization is carried out; rasterization processing is successively carried out on triangular plates forming an object; and after processing on all the triangular plates is completed, the size of the amplified color buffer region is shrunk to an original one, thereby obtaining an anti-aliasing rendering result. According to the embodiment of the invention, calculation efficiency can be effectively improved on the condition that there is a texture.

Owner:CHINA DIGITAL VIDEO BEIJING

Depth buffer compression

InactiveCN101802872AImage codingDigital video signal modificationParallel computingCompression device

Owner:TELEFON AB LM ERICSSON (PUBL)

System, method and computer program product for geometrically transforming geometric objects

InactiveUS7952579B1Reduce amountReduce trafficCathode-ray tube indicators3D-image renderingGraphicsPlane equation

Owner:NVIDIA CORP

System and method of capturing and rendering a stereoscopic panorama using a depth buffer

ActiveUS10346950B2Reduce distortion problemsGeometric image transformationSteroscopic systemsHuman anatomyComputer graphics (images)

A system and method of capturing and rendering stereoscopic panoramic content is provided. The system may capture information from a virtual scene to generate a stereoscopic panorama in the form of a stereoscopic cube map. Using the pre-captured cube map, the system may render stereoscopic images during gameplay, image viewing, and / or playback of a three dimensional video. The system may capture camera distance information during capture for use in distortion reduction during image rendering and playback. The system may implement additional distortion reduction measures. Further, the system may use the capture camera distance information to write to depth buffers corresponding to rendered images for use when introducing dynamic gameplay elements into the scene. Additionally, the system may use realistic camera models to simulate human anatomy and reduce distortions associated with simplistic camera models.

Owner:HIDDEN PATH ENTERTAINMENT INC

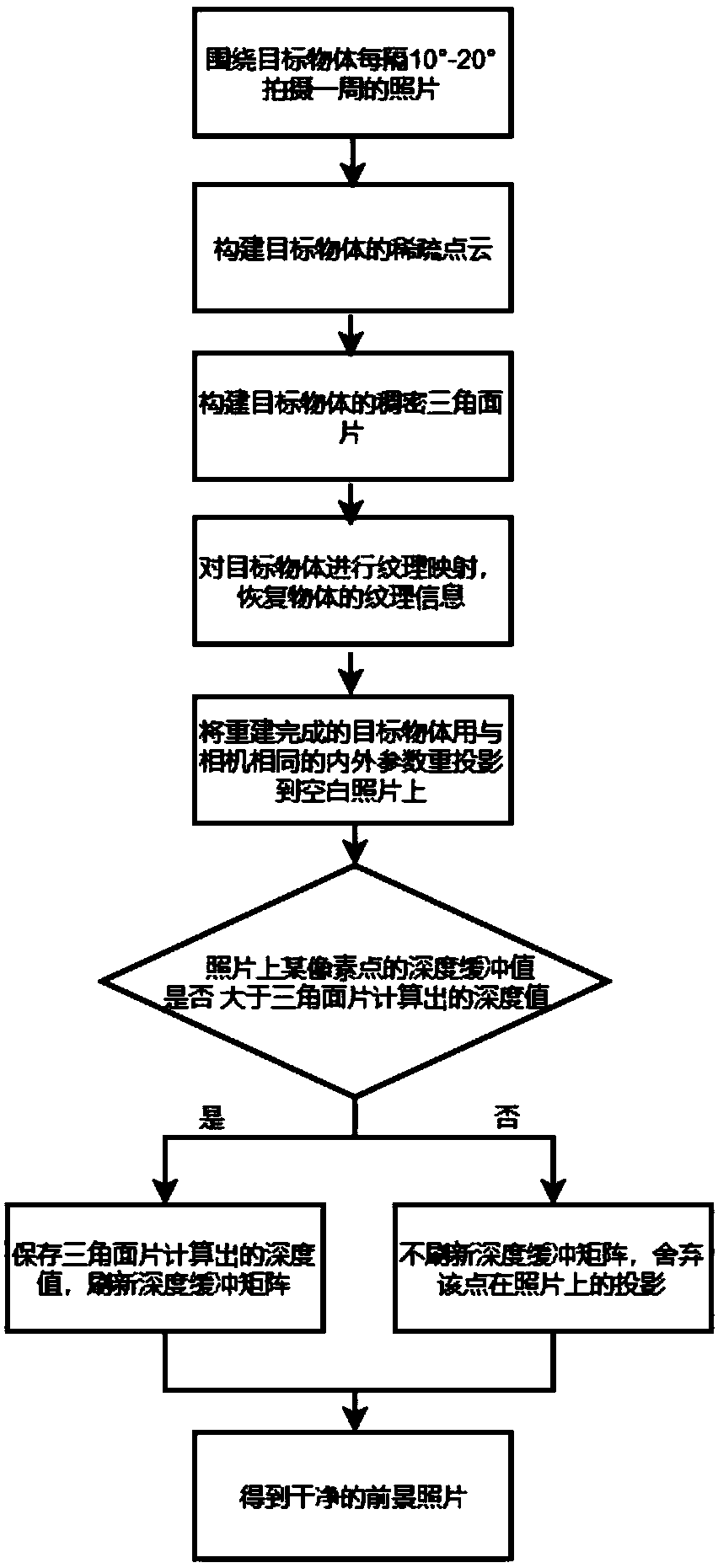

A pre-background separation method based on three-dimensional reconstruction results

The invention discloses a pre-background separation method based on three-dimensional reconstruction results. A target object is taken by a photo every 10-20 angles with a camera. The camera's motiontrajectory is a circle. The two-dimensional limited Delaunay triangulation algorithm is used to construct the initial spatial triangle mesh. The mesh is diffuse and encrypted and then reconstructed using three-dimensional reconstruction. The algorithm (PMVS) performs patch optimization and filtering to obtain a dense point cloud, and then constructs a dense triangular mesh; the pixels surrounded by the triangular patches of the target object are assigned according to the texture, and the surface shape information of the target object is obtained through the bump mapping; The weight of the target object is projected onto the blank photo, and the depth buffer matrix of the photo is set. By comparing the depth buffer value of the pixel with the triangle patch depth value on the target object,the depth information is retained or discarded, and finally a clean foreground photo is obtained. The present invention can separate stationary foreground objects in a natural background.

Owner:SOUTHEAST UNIV

Low-power processing in depth read-only operating regimes

ActiveUS20140104267A1More internal bandwidthReduce power consumptionDetails involving image processing hardware3D-image renderingGraphicsOperational system

Techniques are disclosed for suppressing access to a depth processing unit associated with a graphics processing pipeline. The method includes receiving a graphics primitive from a first pipeline stage associated with the graphics processing pipeline. The method further includes determining that the graphics primitive is visible over one or more graphics primitives previously rendered to a frame buffer, and determining that the depth buffer is in a read-only mode. The method further includes suppressing an operation to transmit the graphics primitive to the depth processing unit. One advantage of the disclosed technique is that power consumption is reduced within the GPU by avoiding unnecessary accesses to the depth processing unit.

Owner:NVIDIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com