Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45 results about "Partial-response maximum-likelihood" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

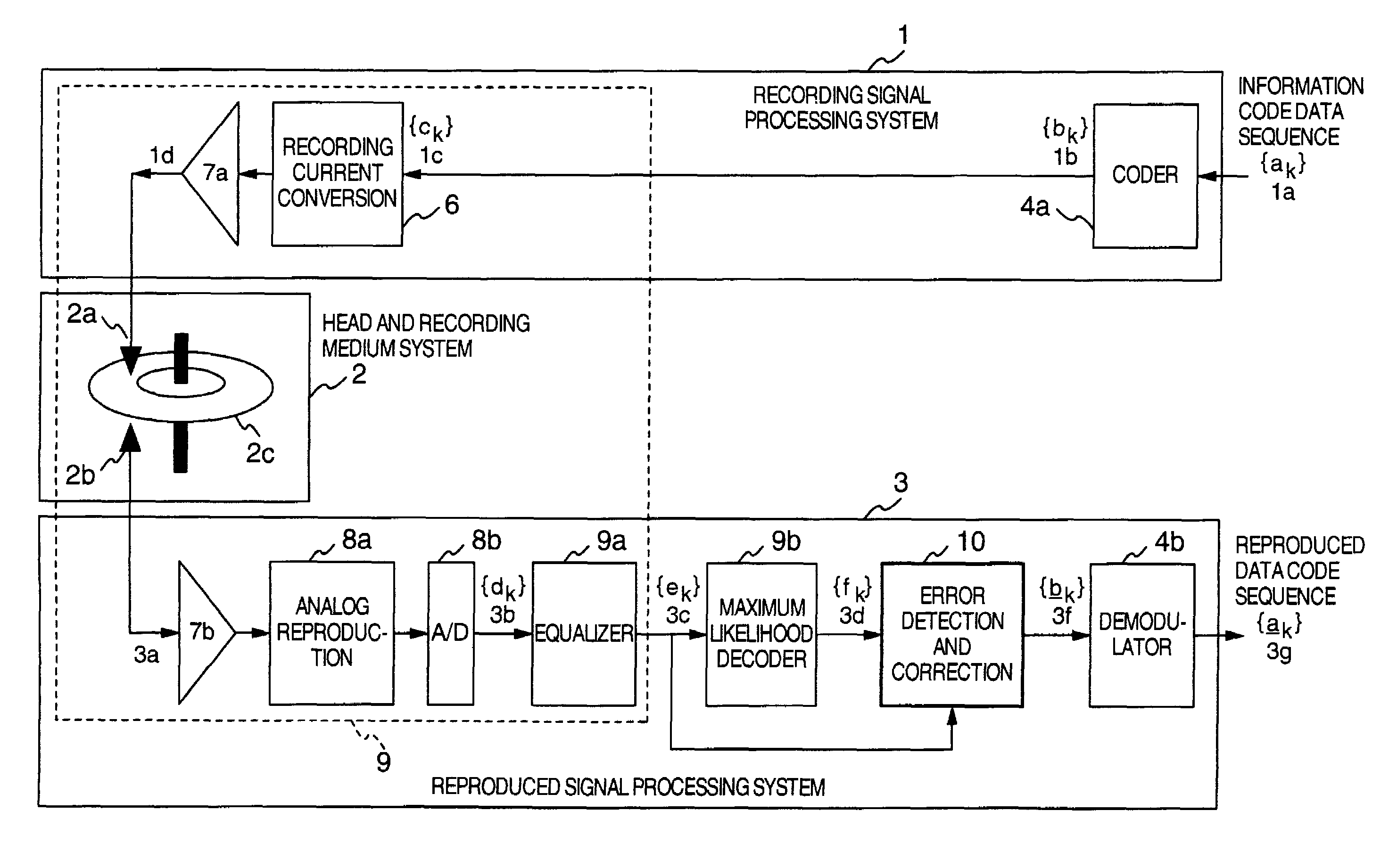

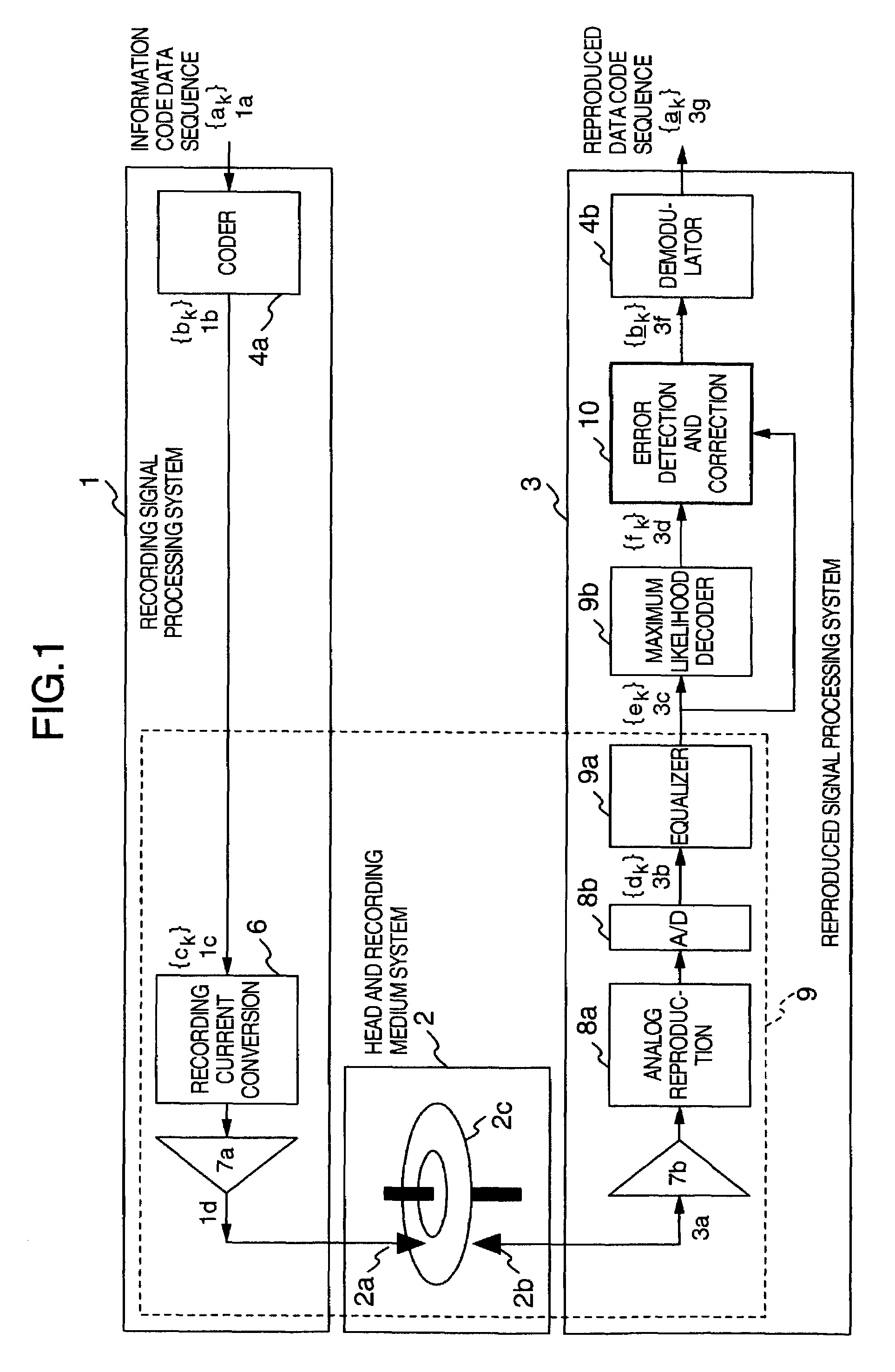

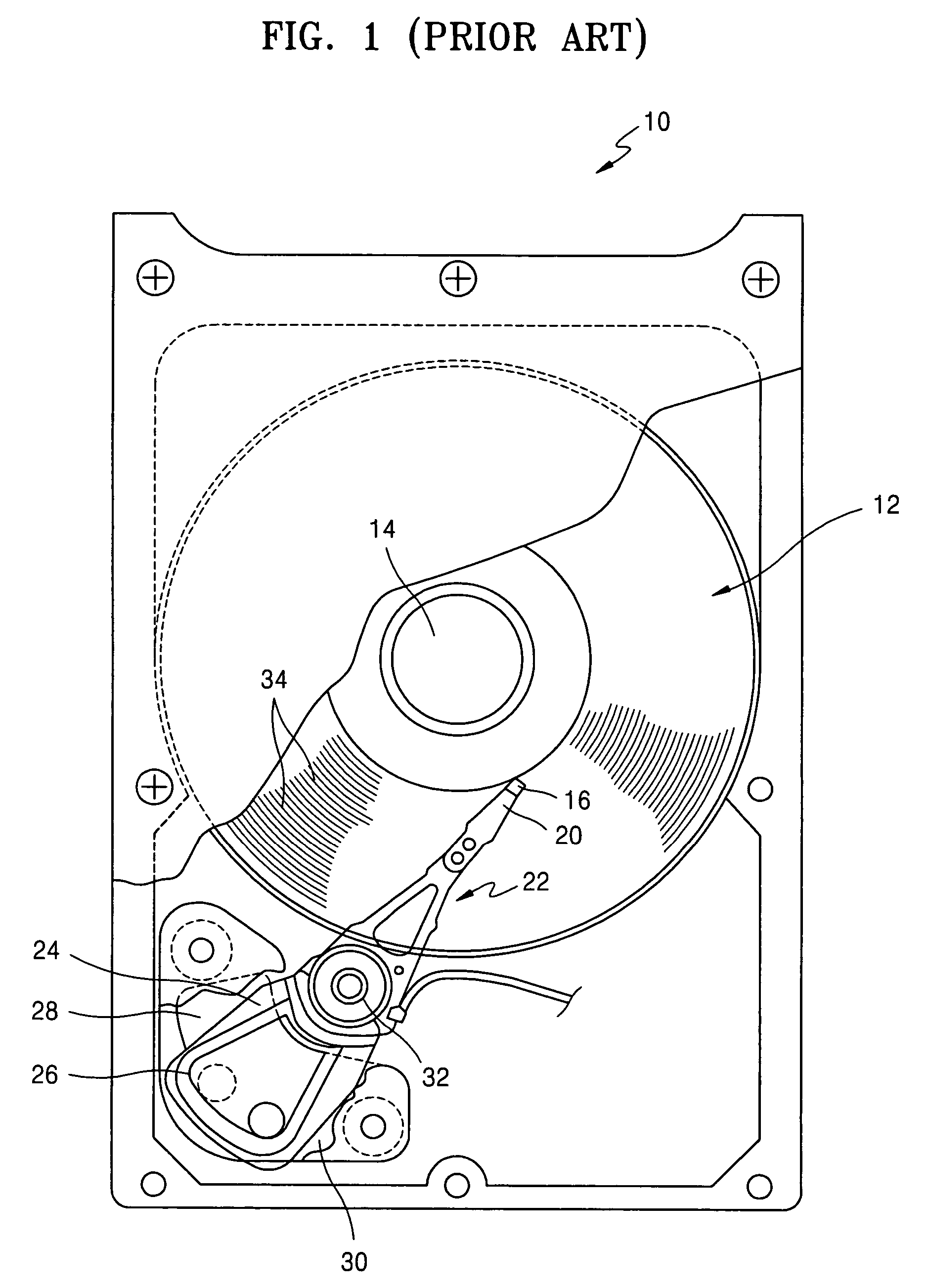

In computer data storage, partial-response maximum-likelihood (PRML) is a method for recovering the digital data from the weak analog read-back signal picked up by the head of a magnetic disk drive or tape drive. PRML was introduced to recover data more reliably or at a greater areal-density than earlier simpler schemes such as peak-detection. These advances are important because most of the digital data in the world is stored using magnetic recording on Hard Disk Drives (HDD) or a digital tape recorders.

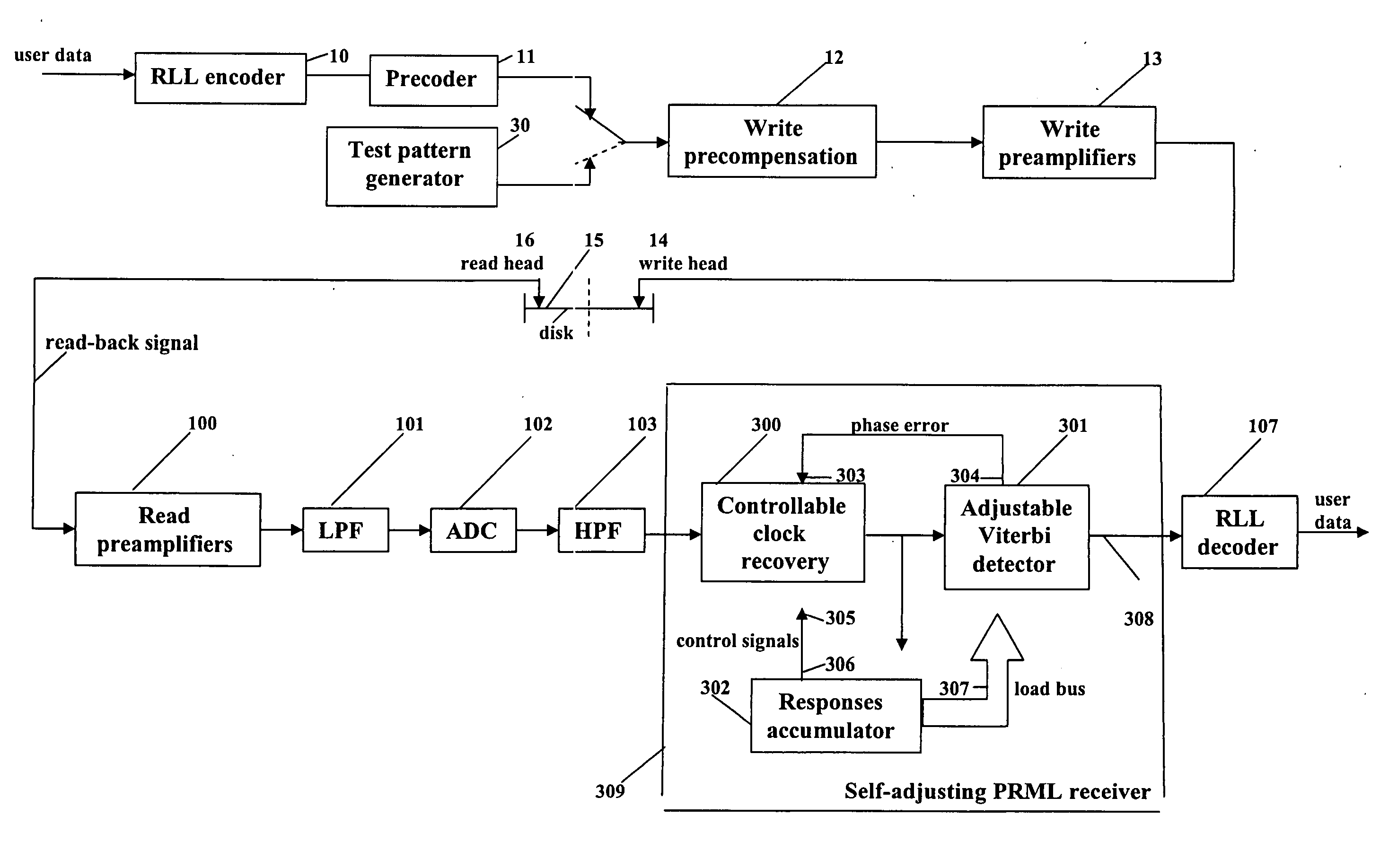

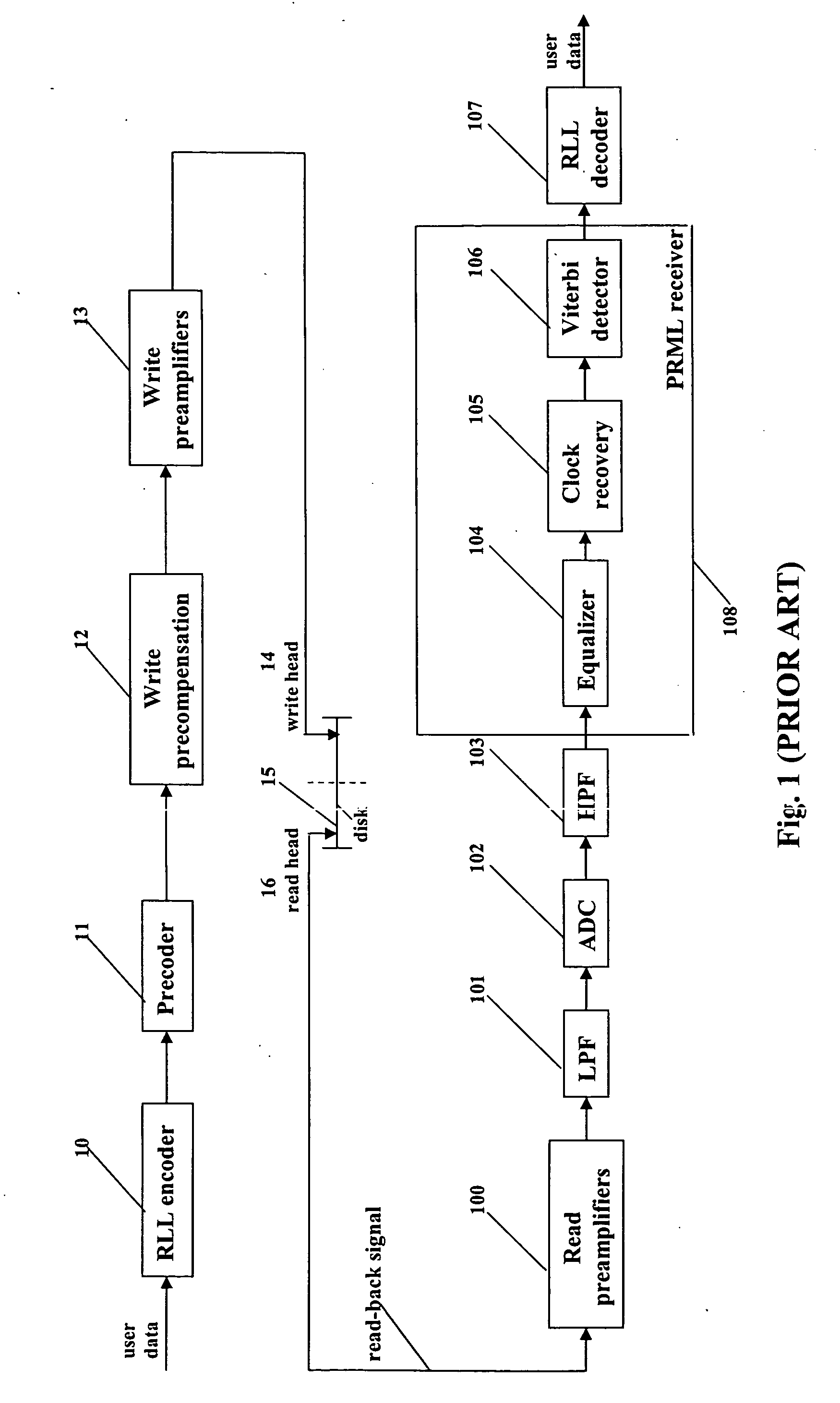

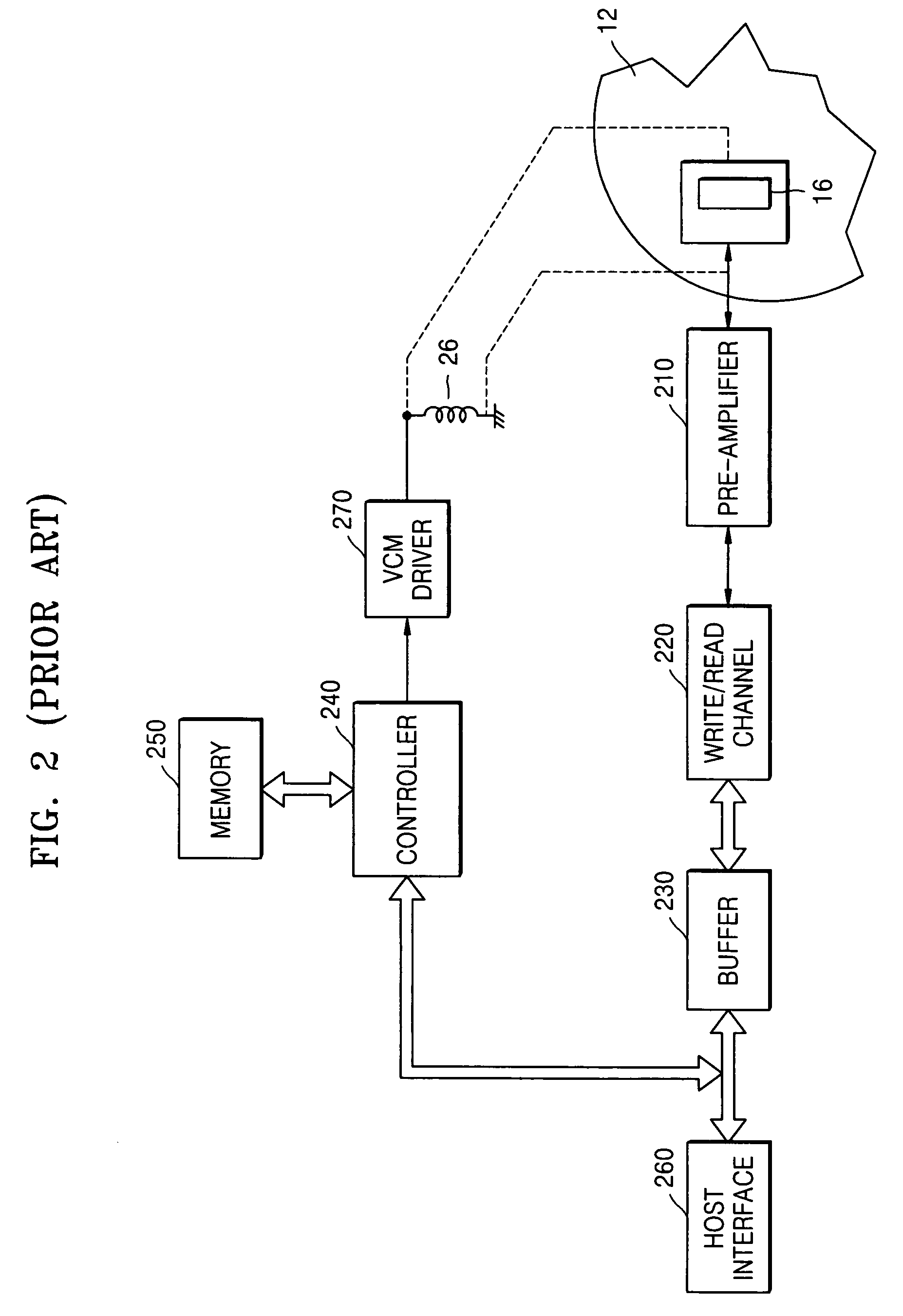

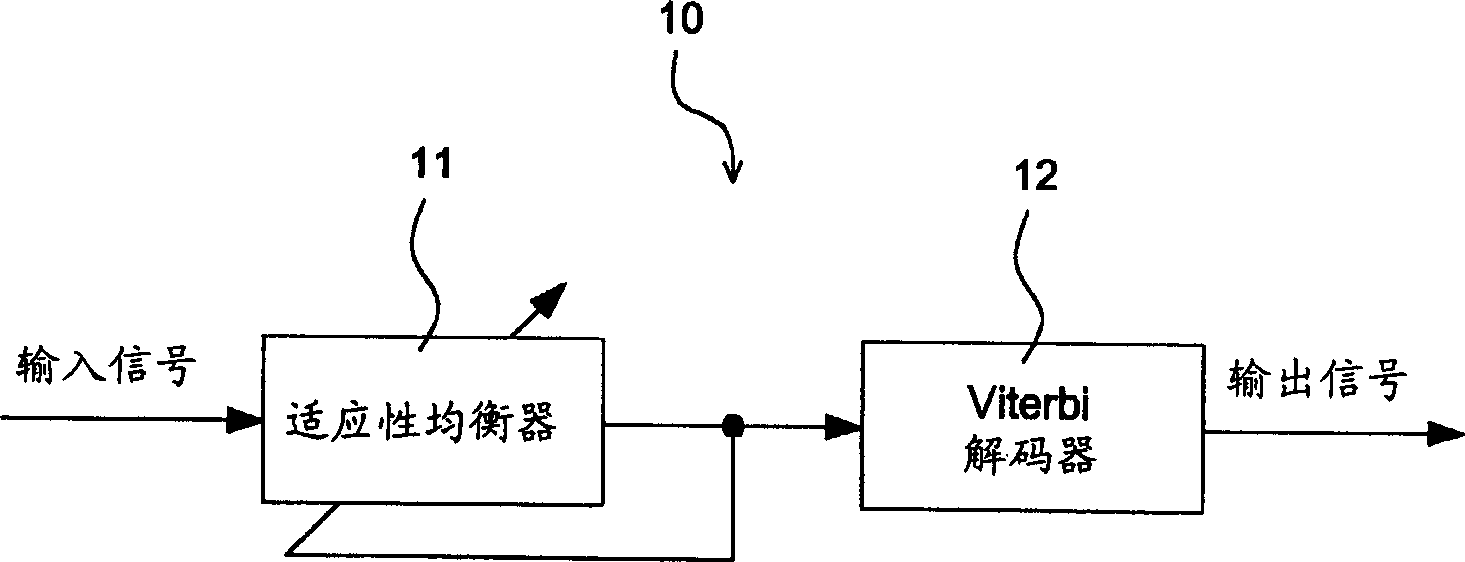

Self-adjusting PRML receiver

Owner:GUZIK TECHN ENTERPRISES

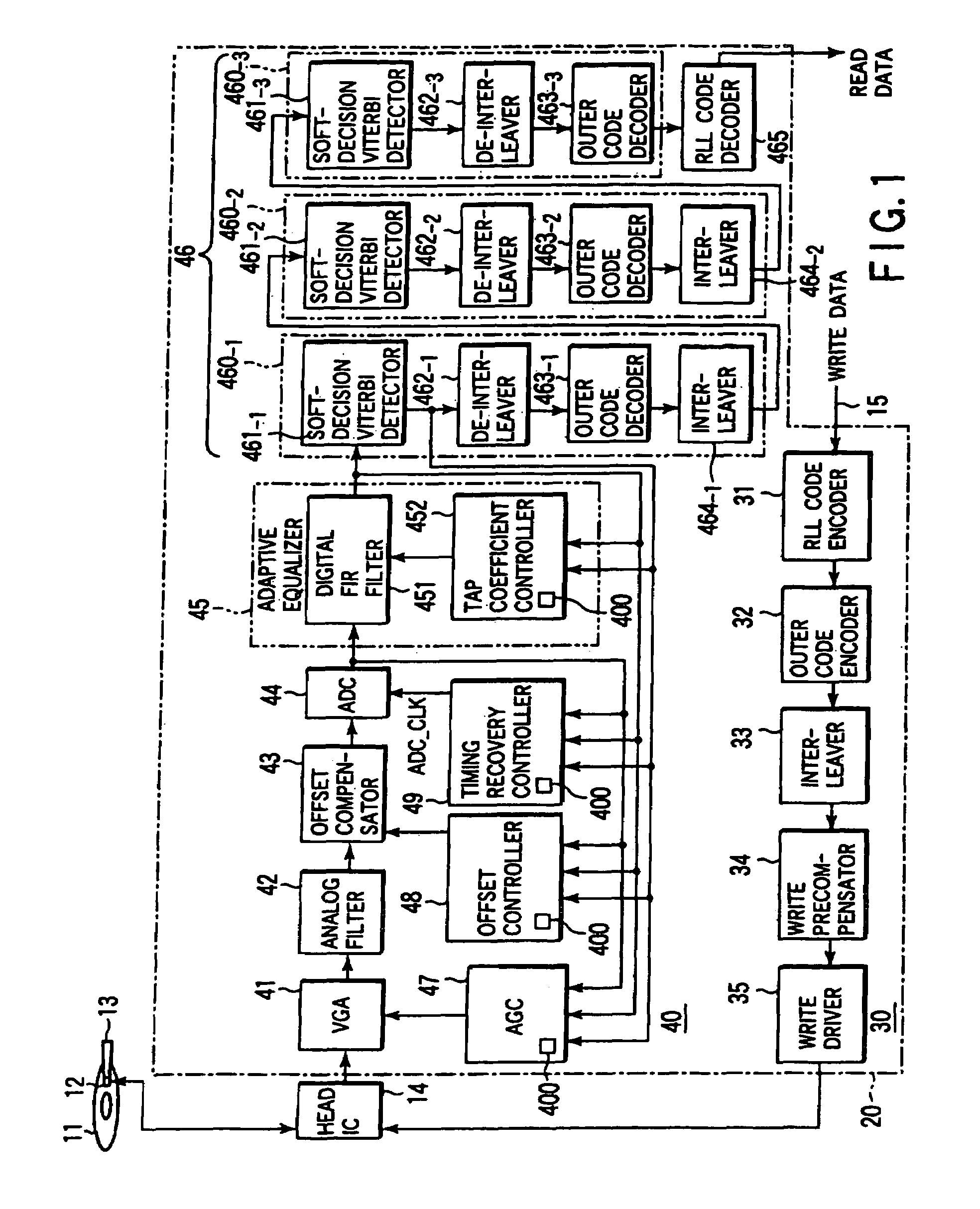

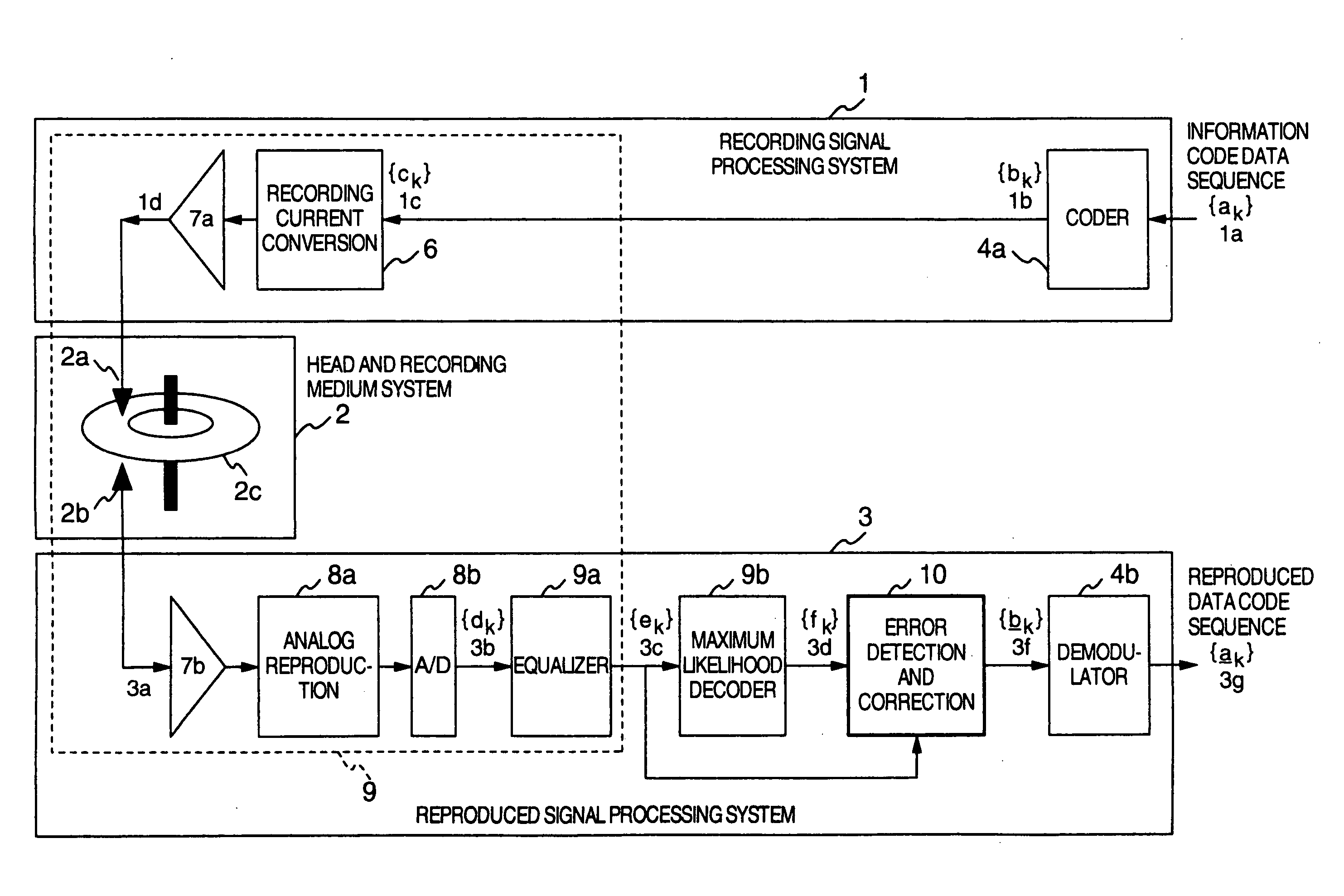

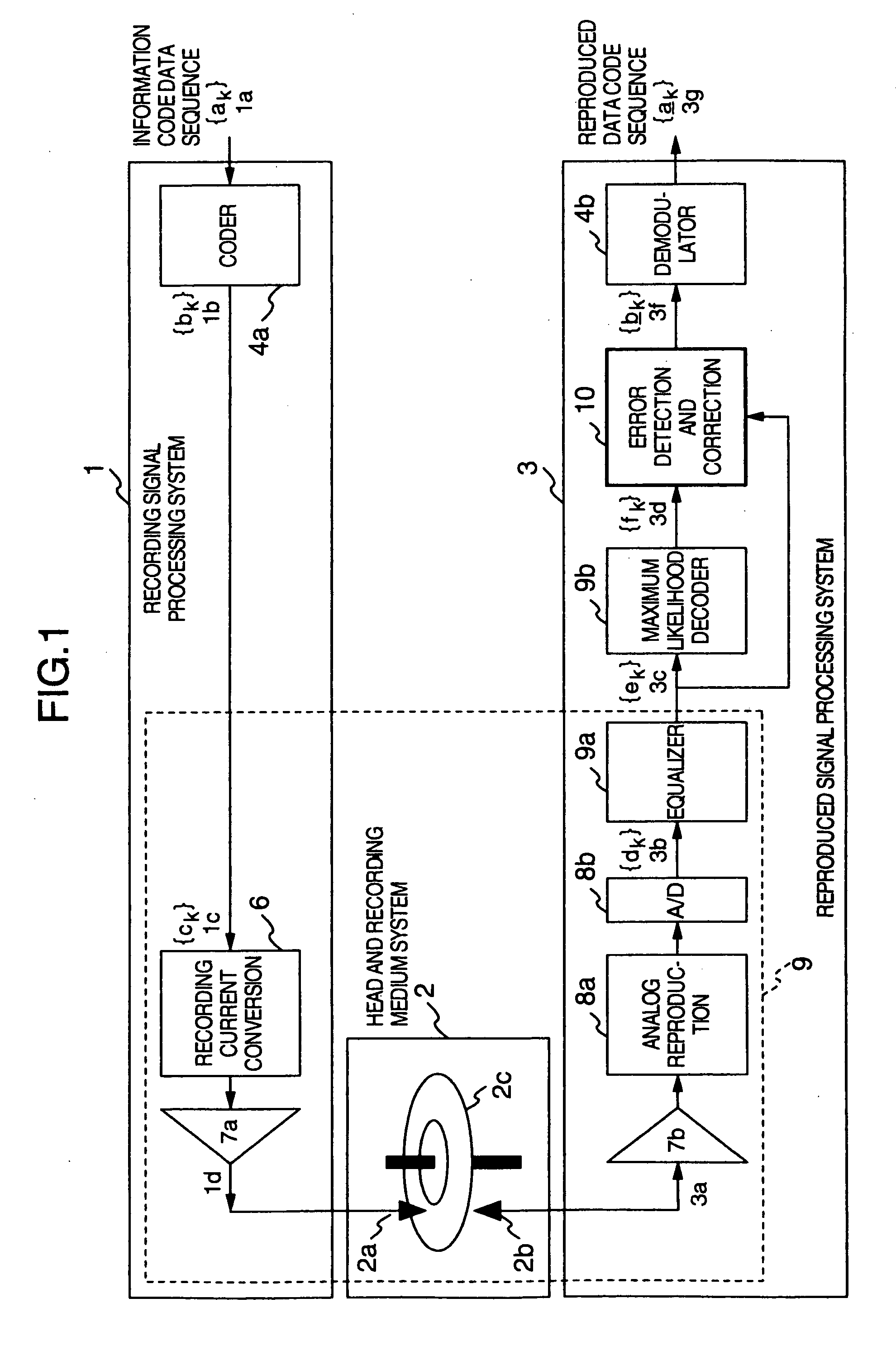

Signal processing device utilizing partial response maximum likelihood detection

InactiveUS7257172B2Other decoding techniquesRecord information storageControl objectiveViterbi detector

A partial response (PR) waveform generator generates a digital value sequence of an expected PR waveform based on the output of a soft-decision Viterbi detector included in, for example, a first-stage decoder unit incorporated in an iterative decoder. The generator also generates flag information indicative of whether reliability of the digital value sequence is low or high, in parallel with the generation of the digital value sequence. An error detector detects error values in a PR equalized sample value sequence, needed for feedback control of a control target, using the digital value sequence of the expected PR waveform as a digital value sequence of a reference waveform. An error output controller controls the output of the error values detected by the error detector in accordance with the state of the flag information generated by the generator.

Owner:KK TOSHIBA

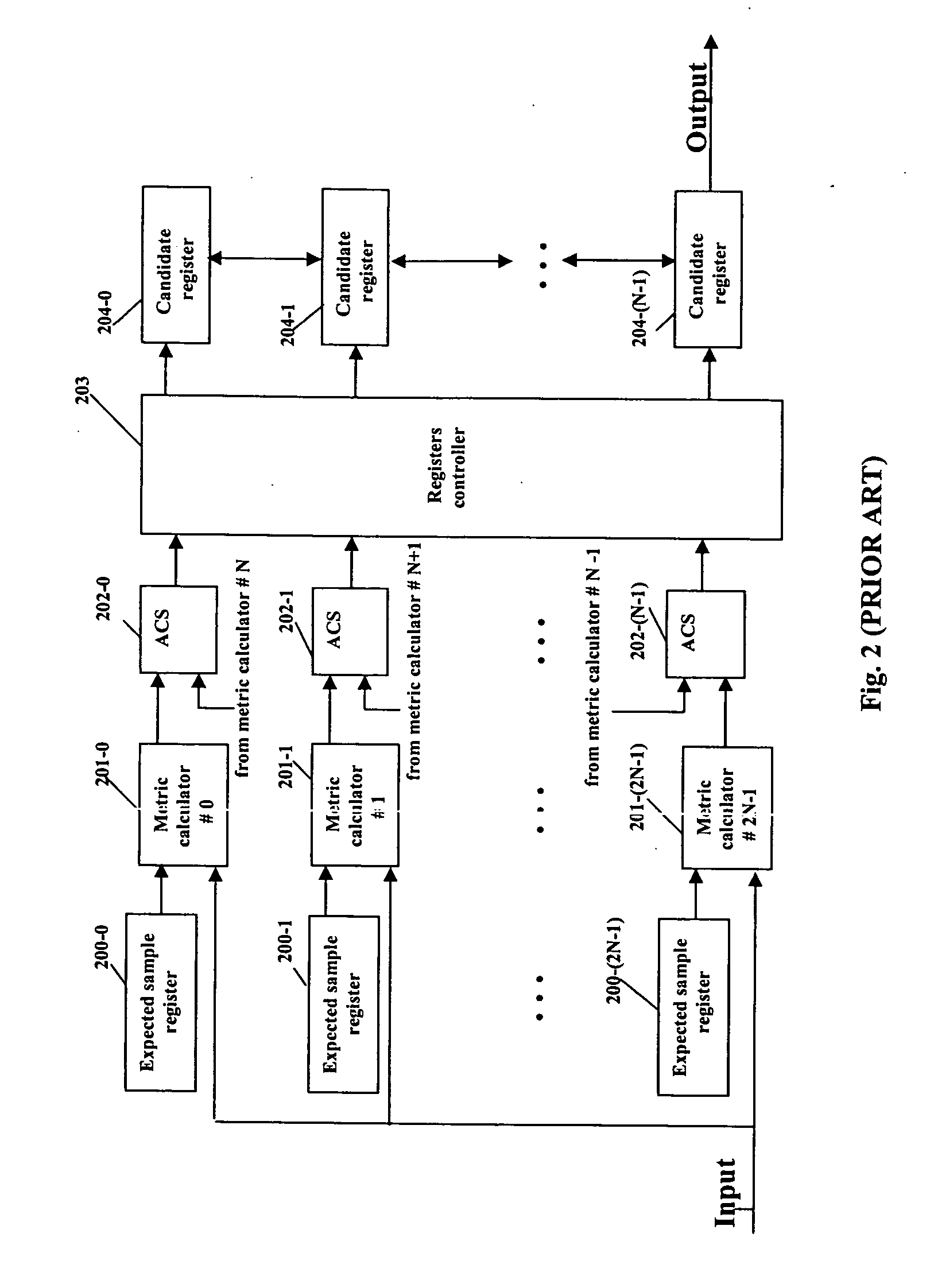

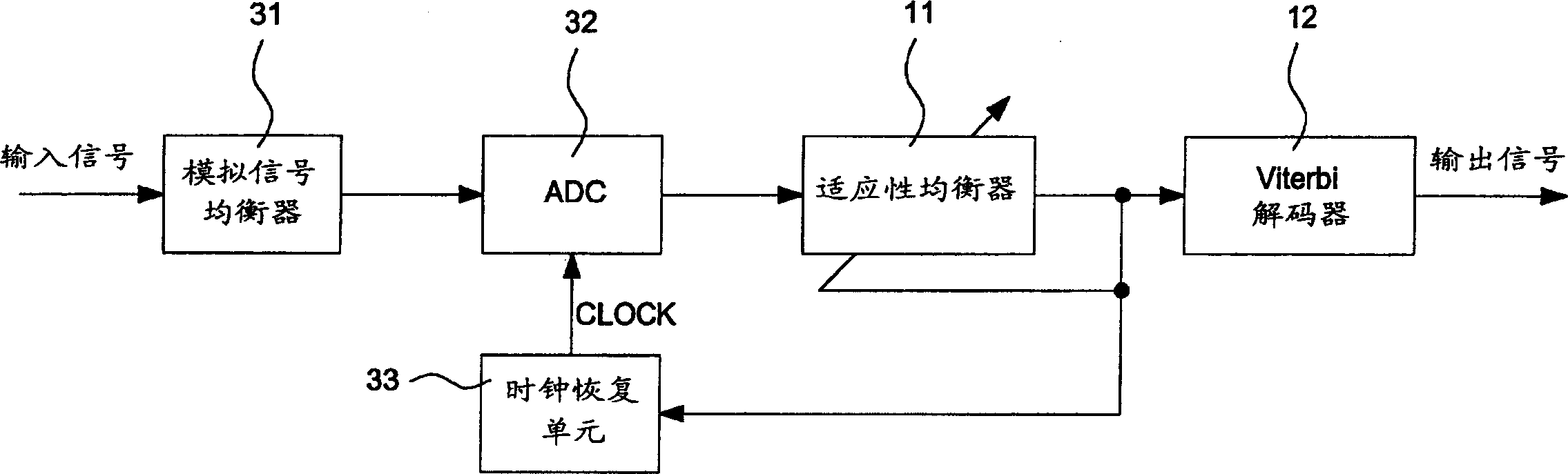

Self-adjusting PRML receiver

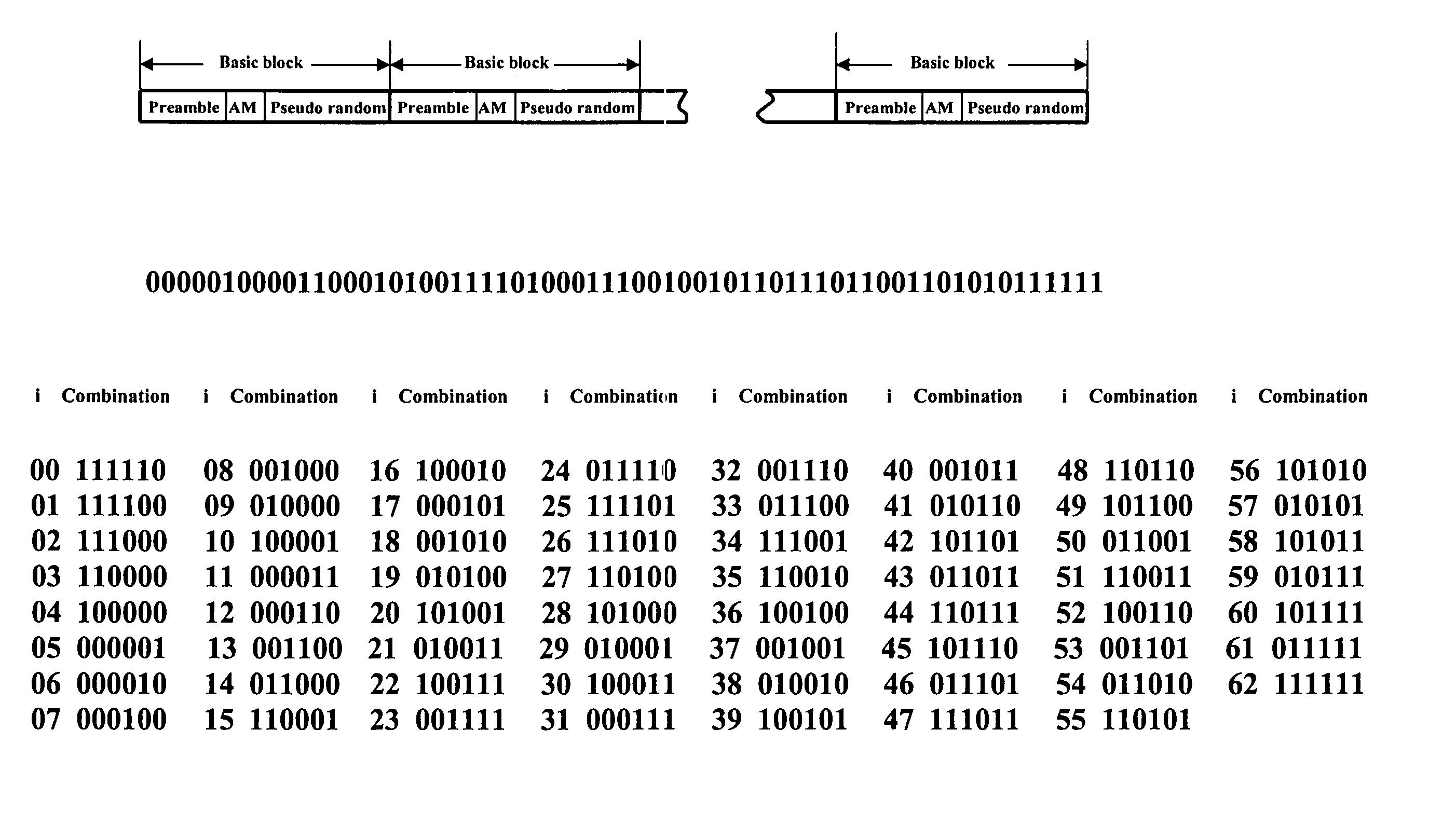

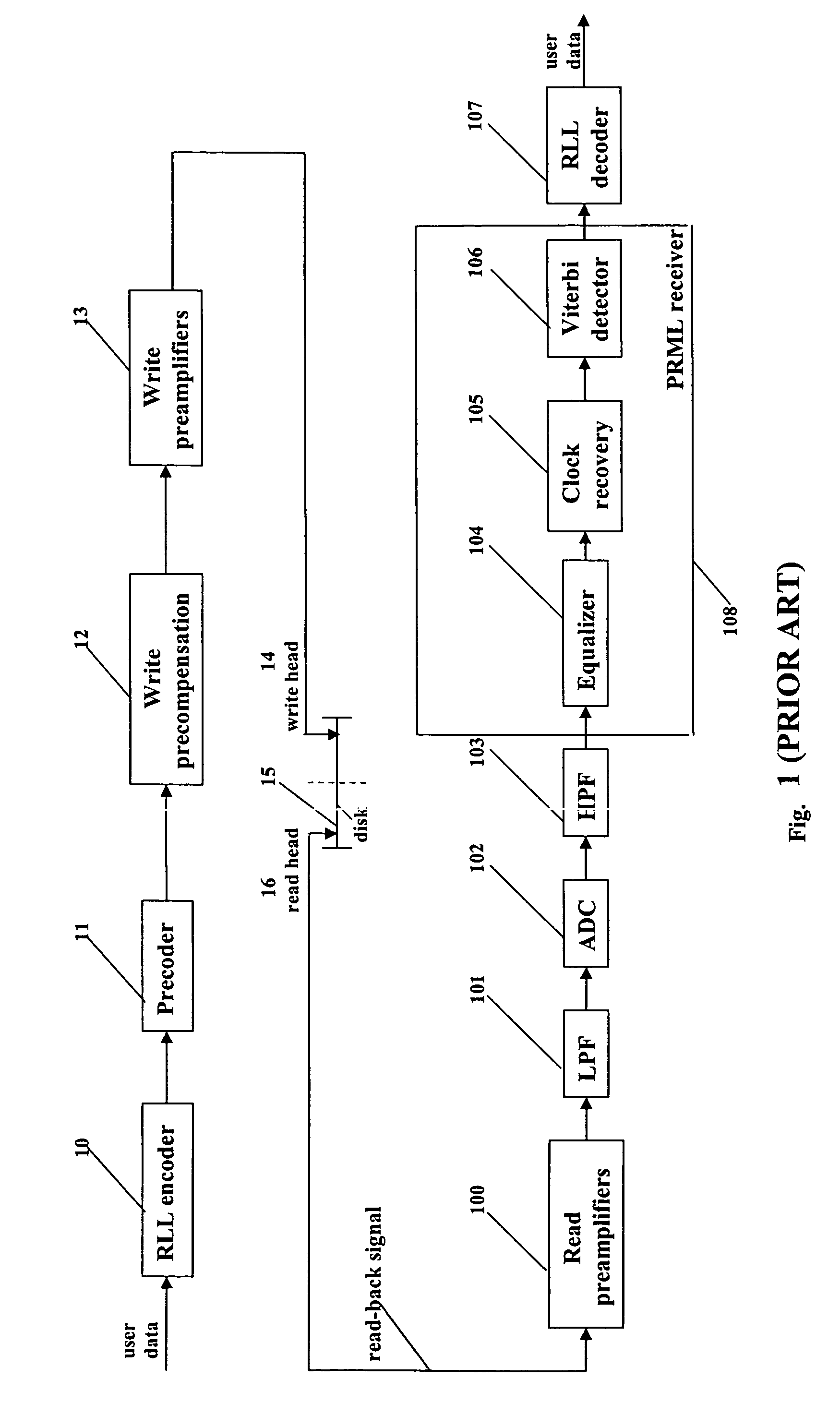

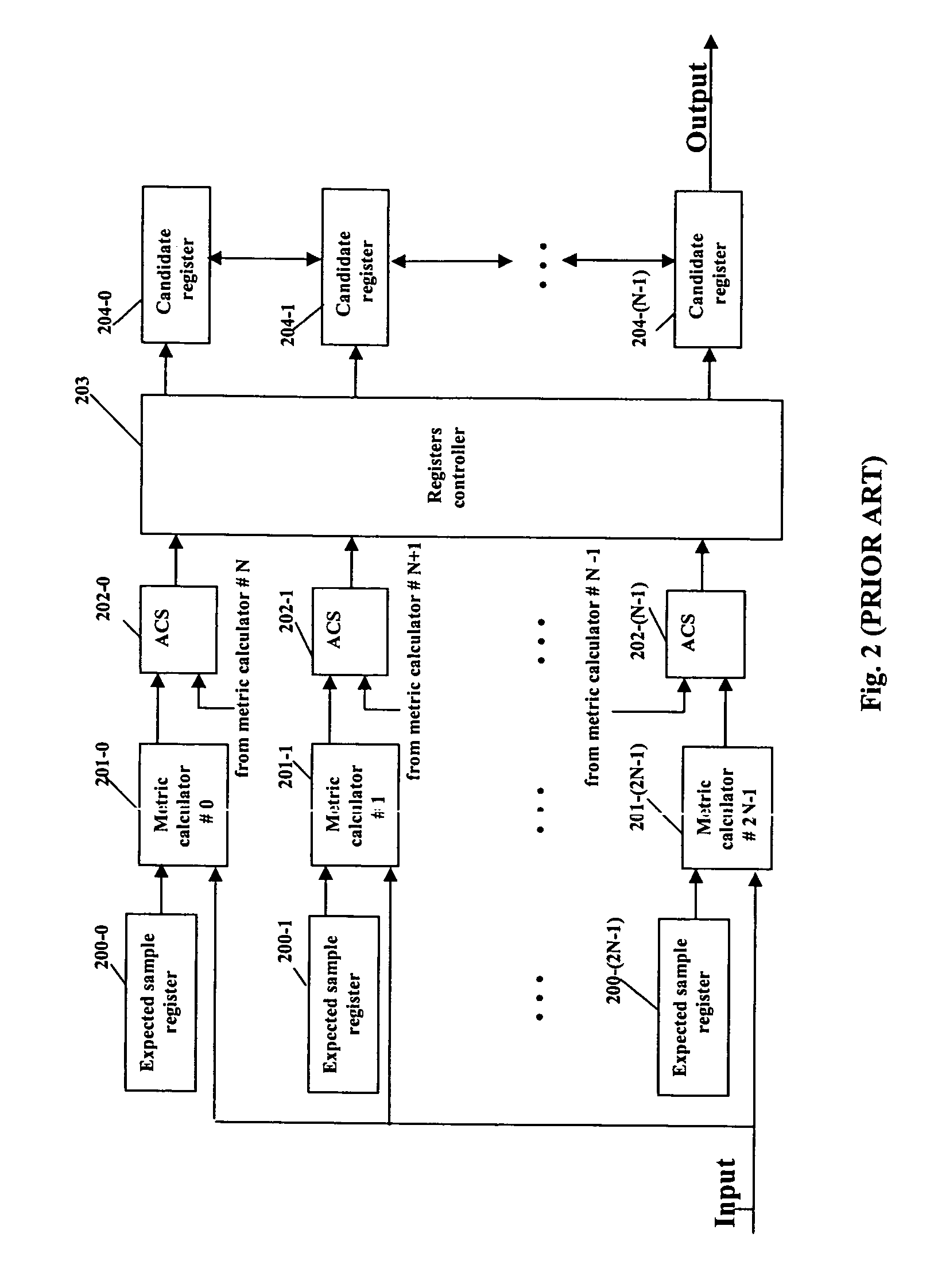

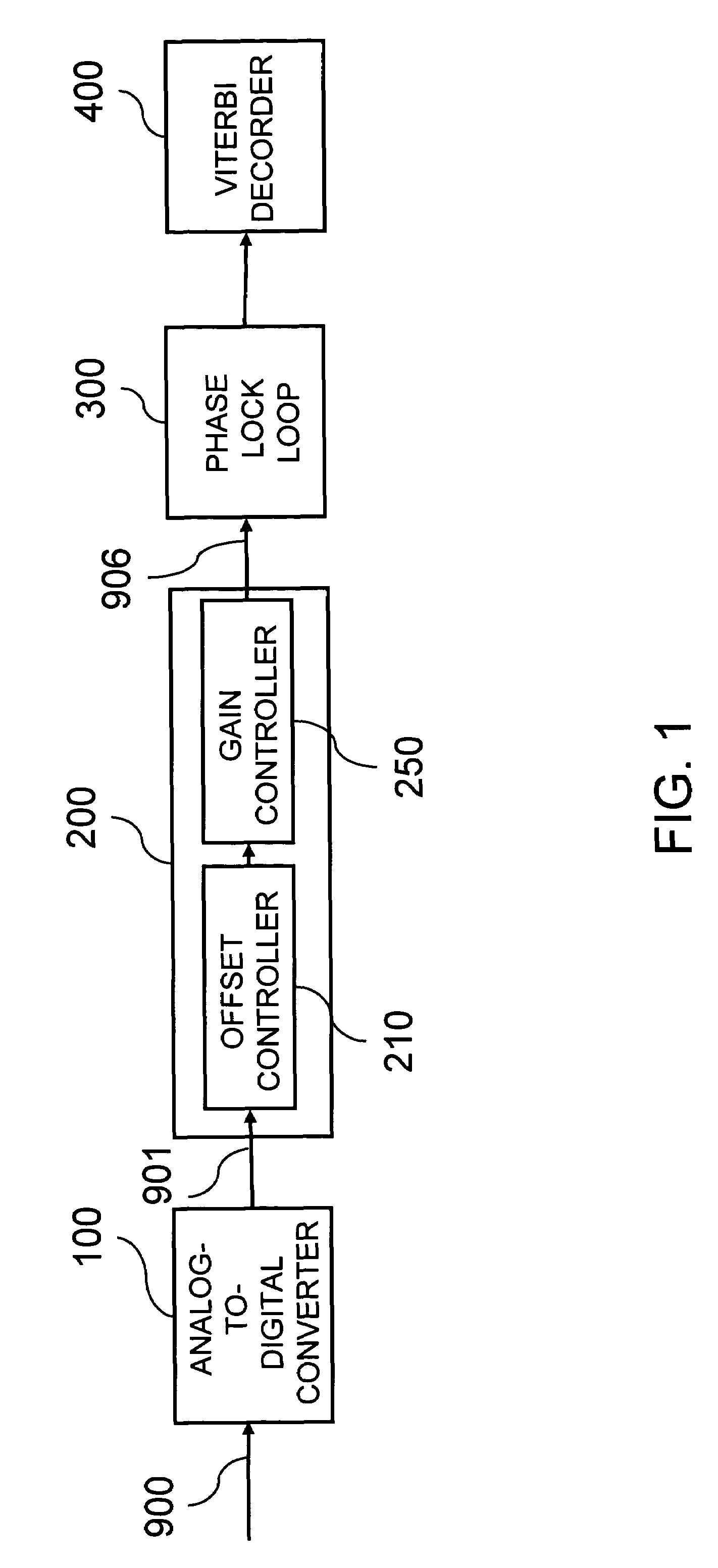

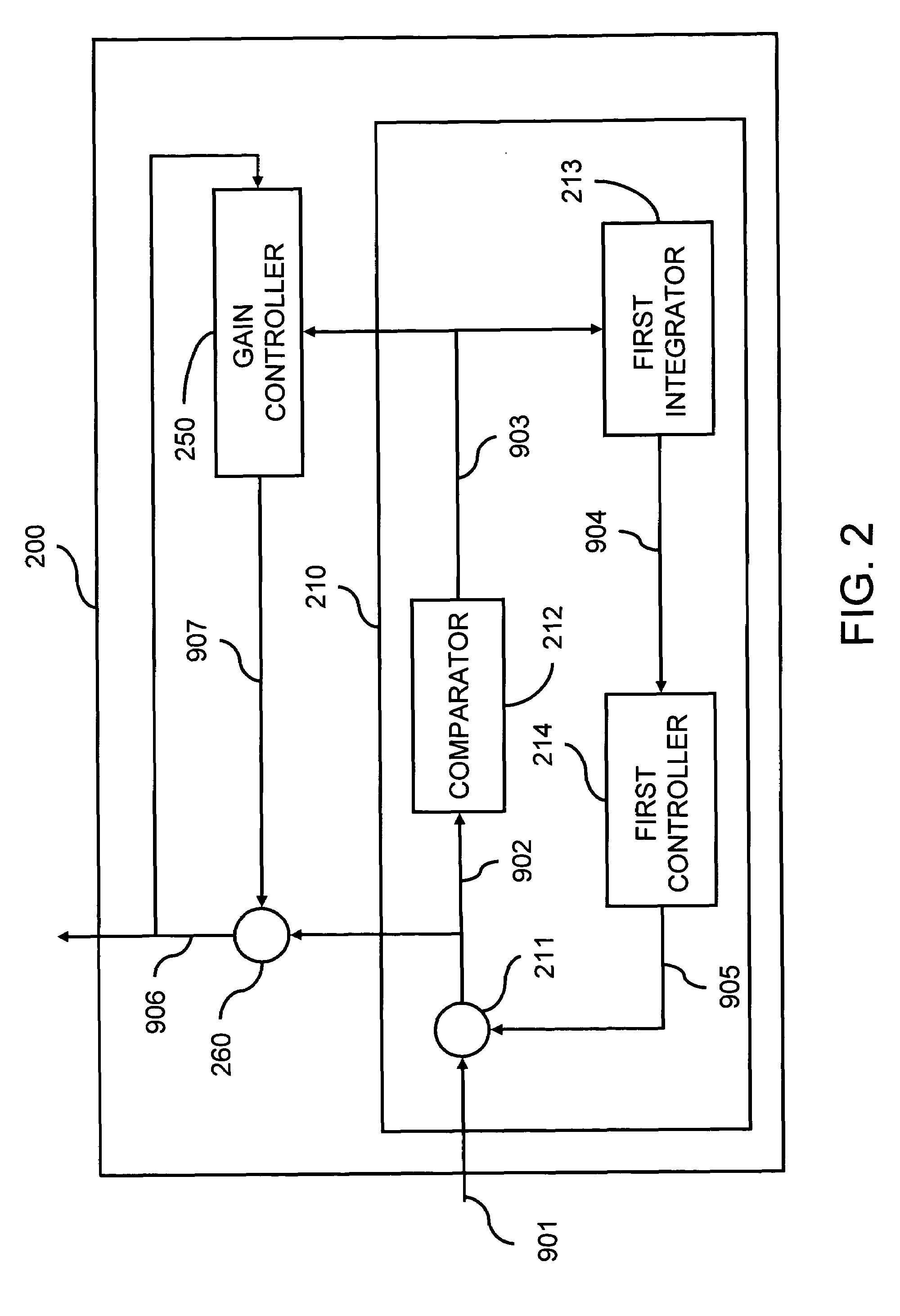

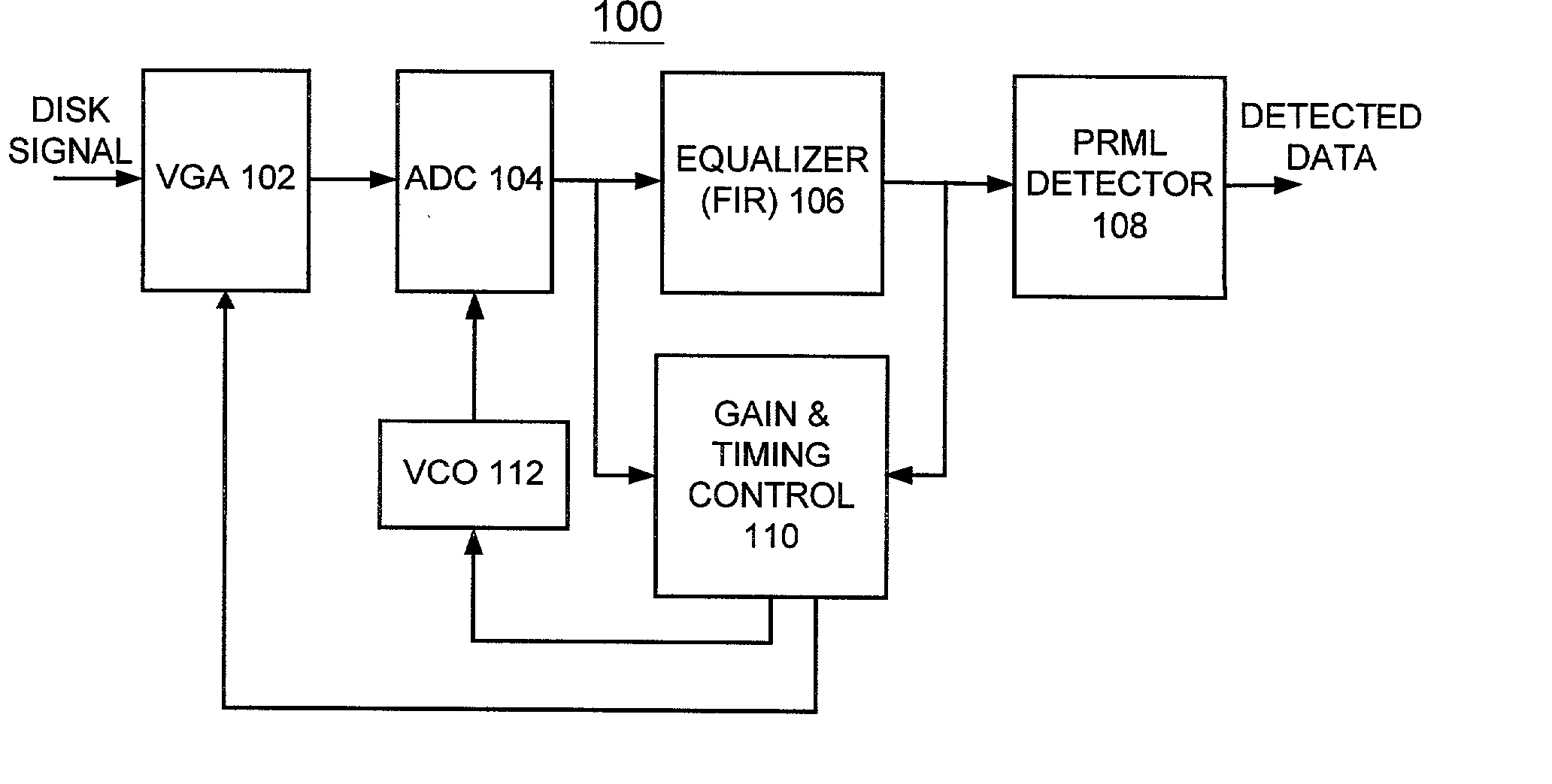

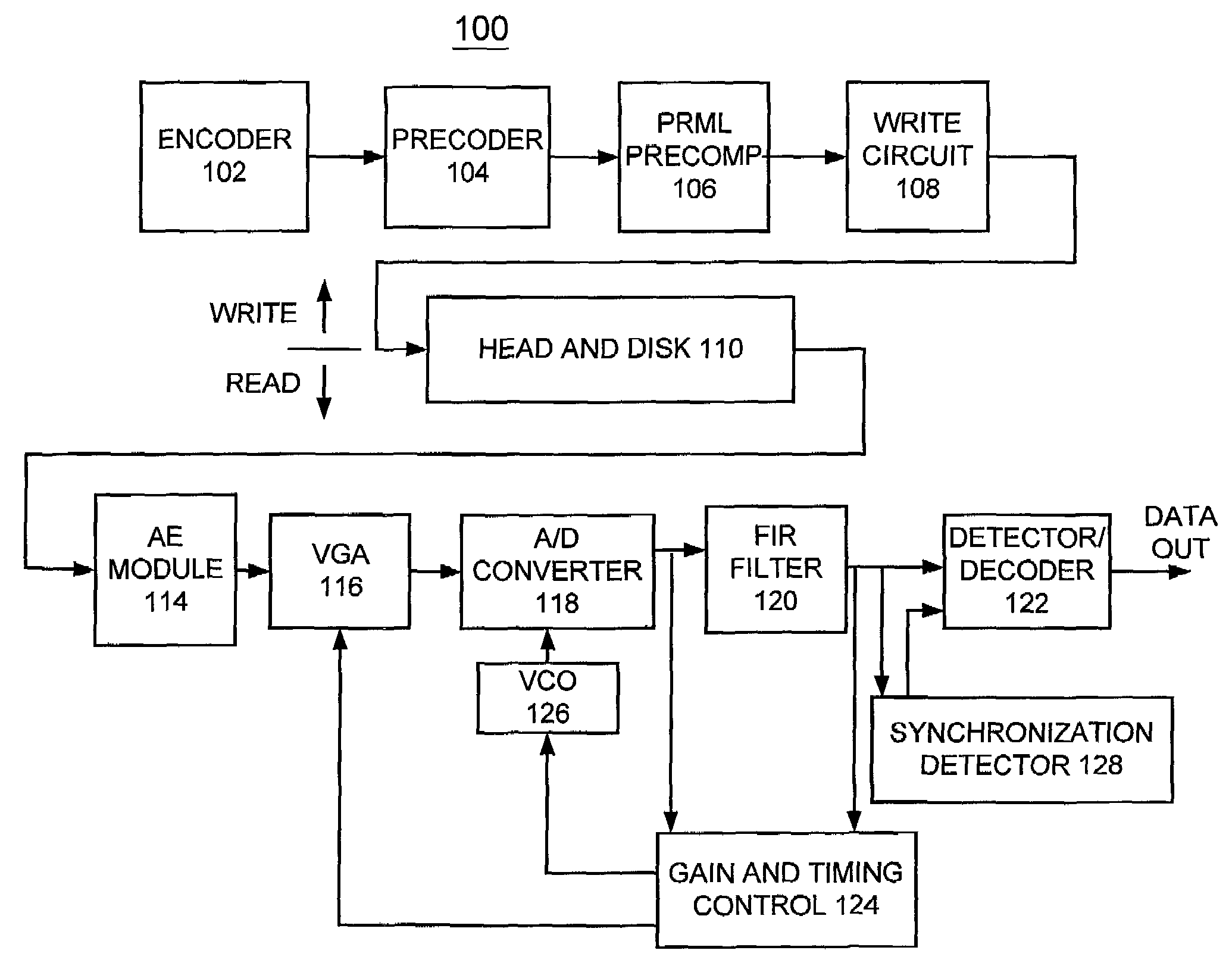

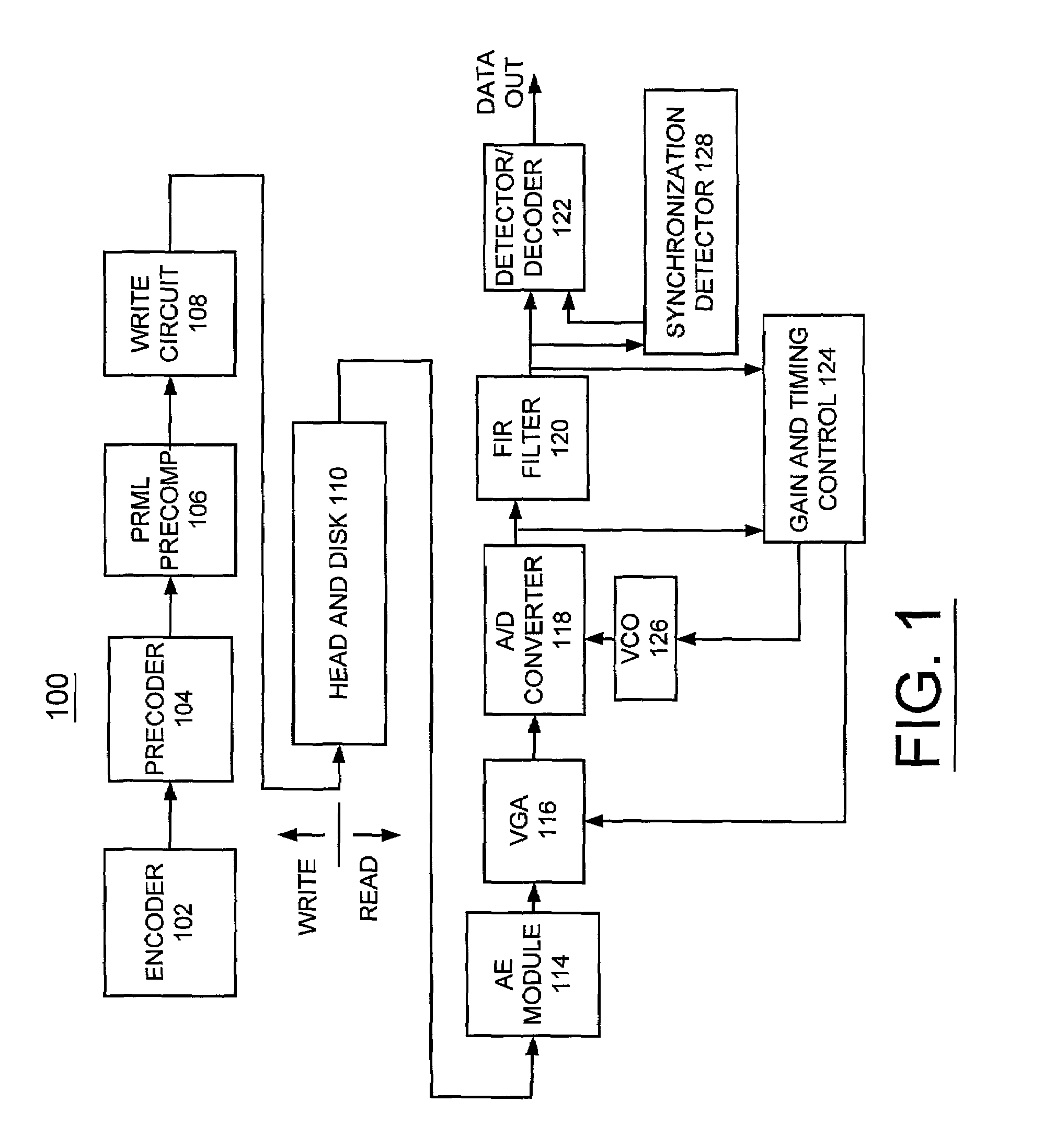

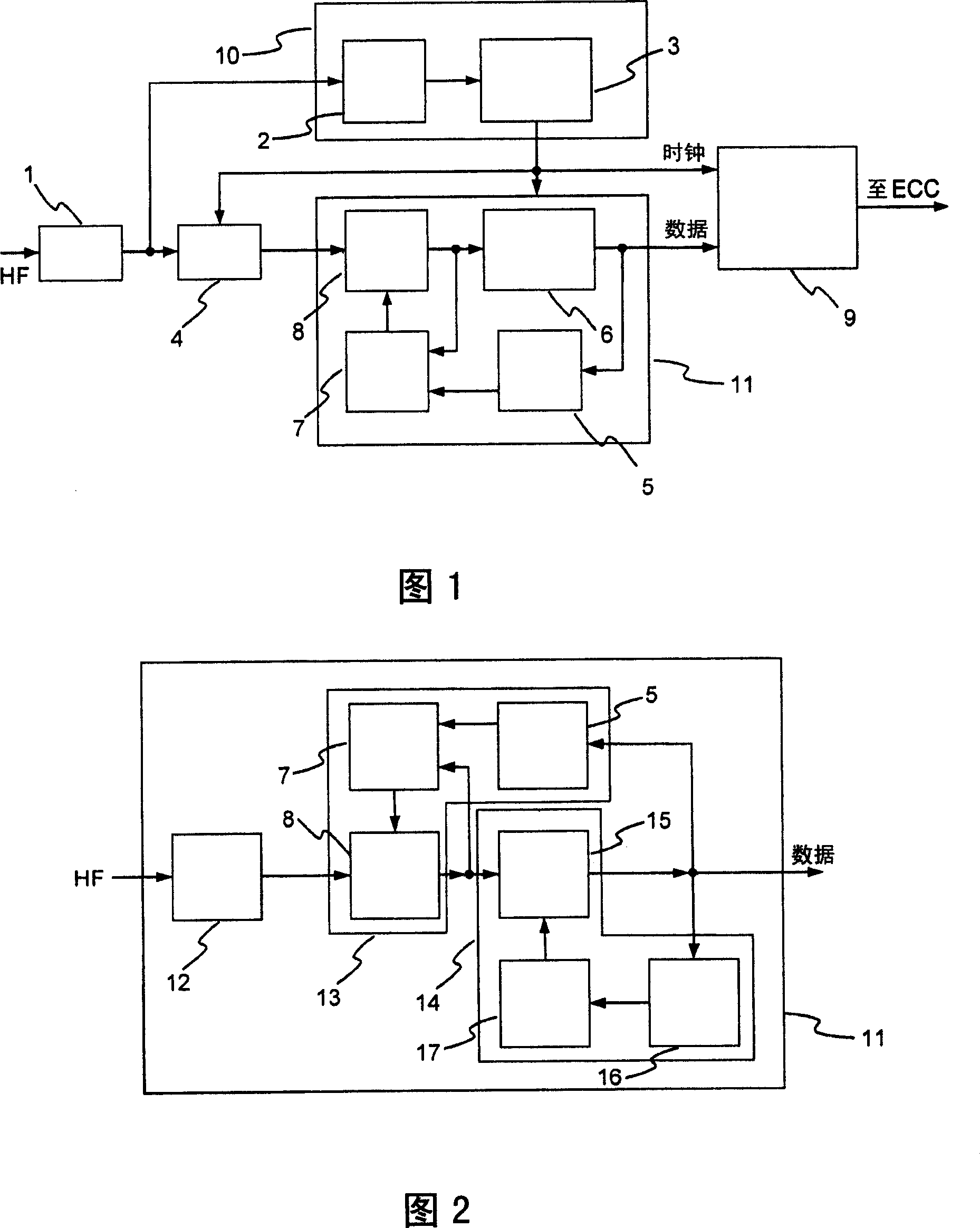

InactiveUS20060061496A1Modification of read/write signalsCode conversionViterbi detectorClock recovery

A partial response maximum likelihood (PRML) data detecting in a magnetic recording storage device is carried out with a preliminary measuring of write-read channel responses to all nonzero binary combinations of a given length. Decoding of the user data is performed according to a Viterbi algorithm, where the previously measured responses are used as expected samples for branch metric calculations. The measurement of the write-read channel responses and the decoding of the user data are fulfilled by a self-adjusting PRML receiver that contains a controllable clock recovery, a responses accumulator and an adjustable Viterbi detector. The controllable clock recovery produces a set of read-back signal samples containing exactly one sample per bit with or without phase error correction. The responses accumulator calculates averaged responses of the write-read channel. The adjustable Viterbi detector reconstructs the user data that were written to the disk.

Owner:GUZIK TECHN ENTERPRISES

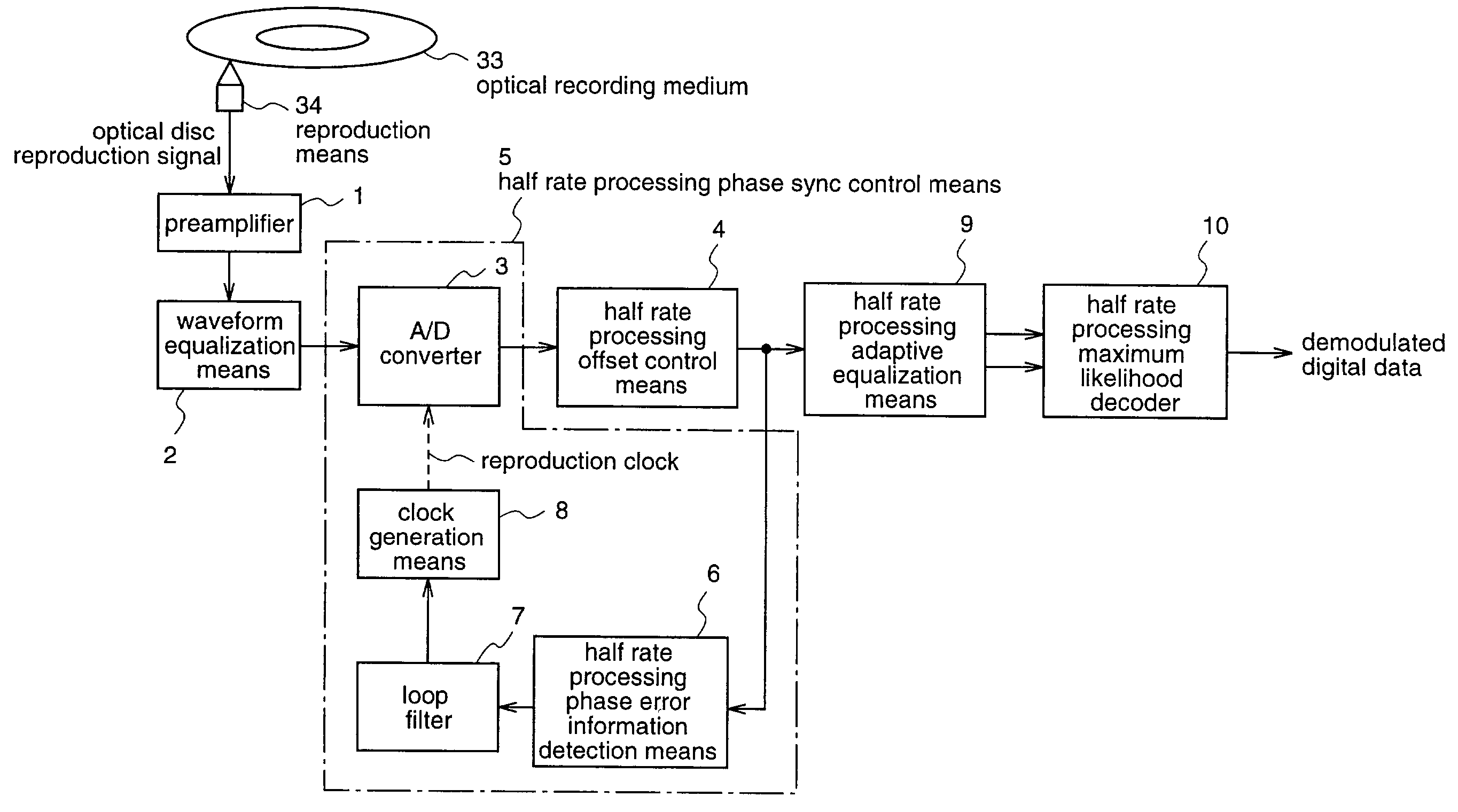

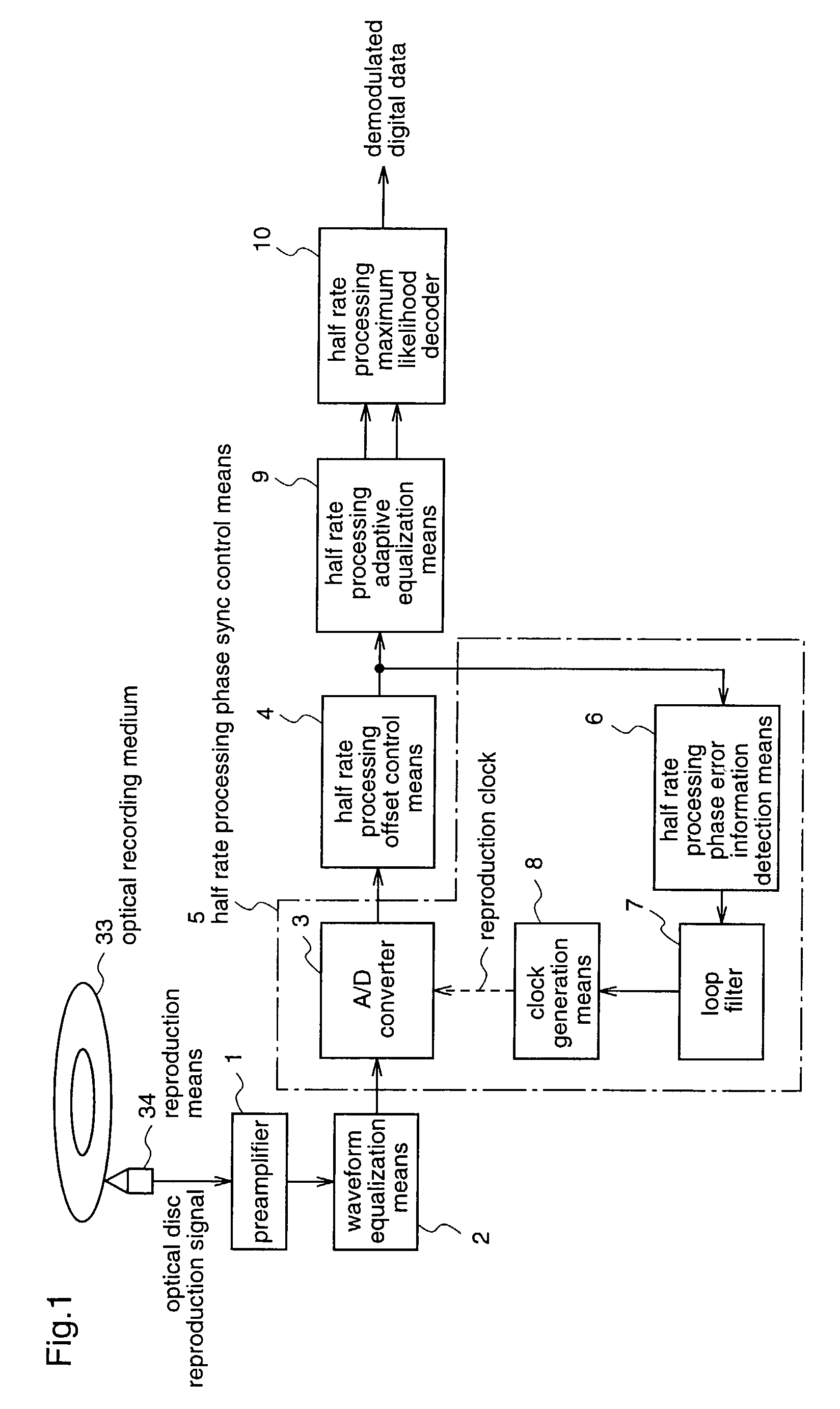

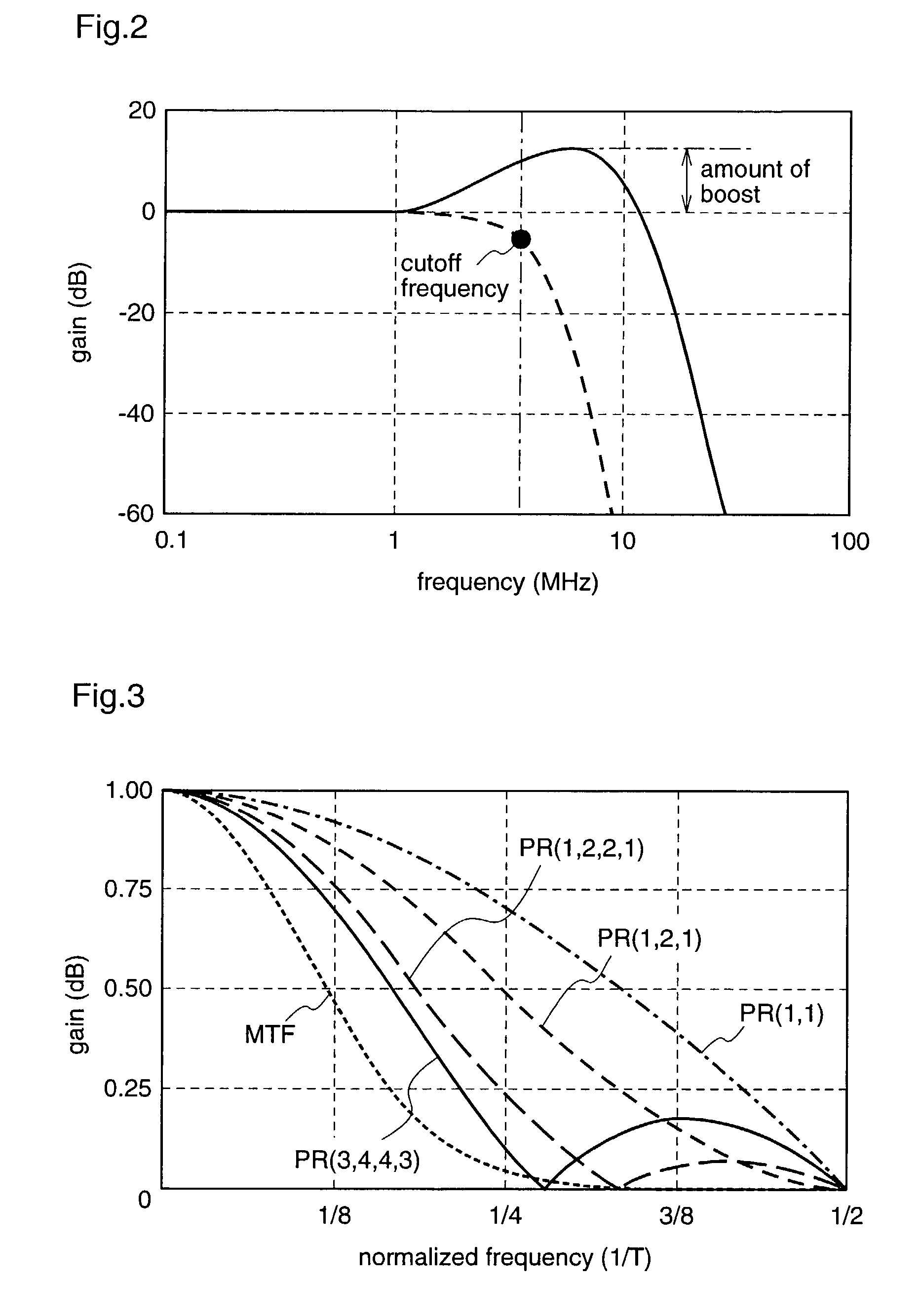

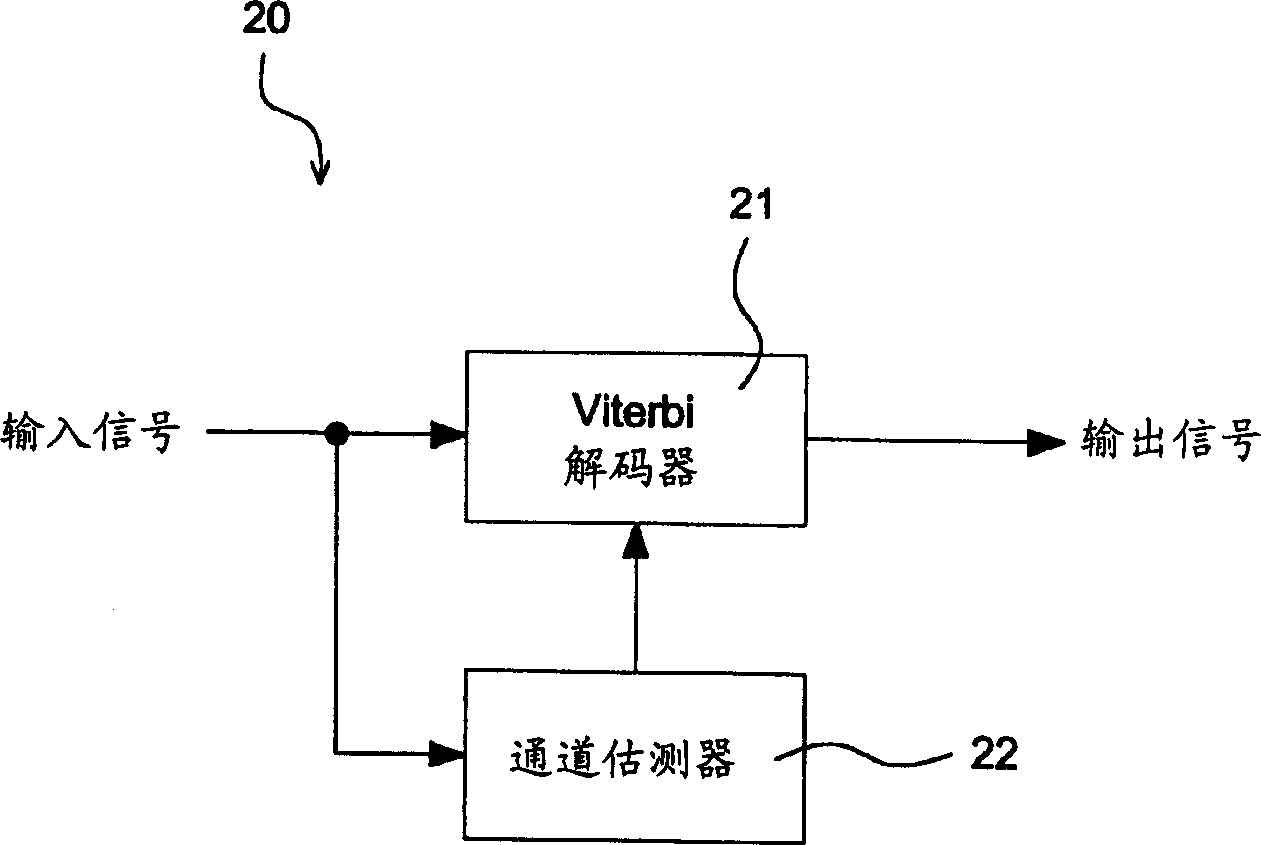

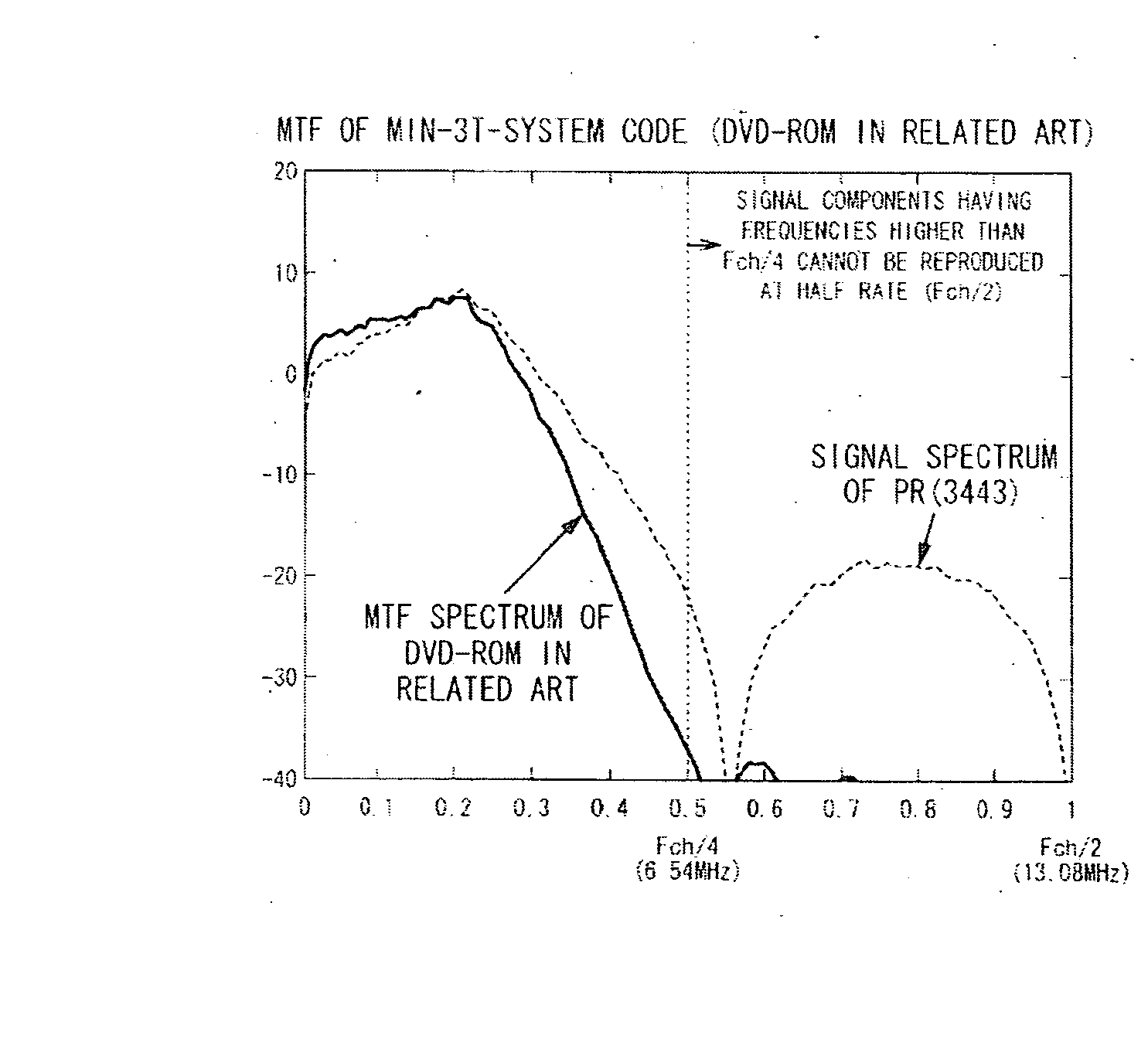

Digital data reproduction apparatus

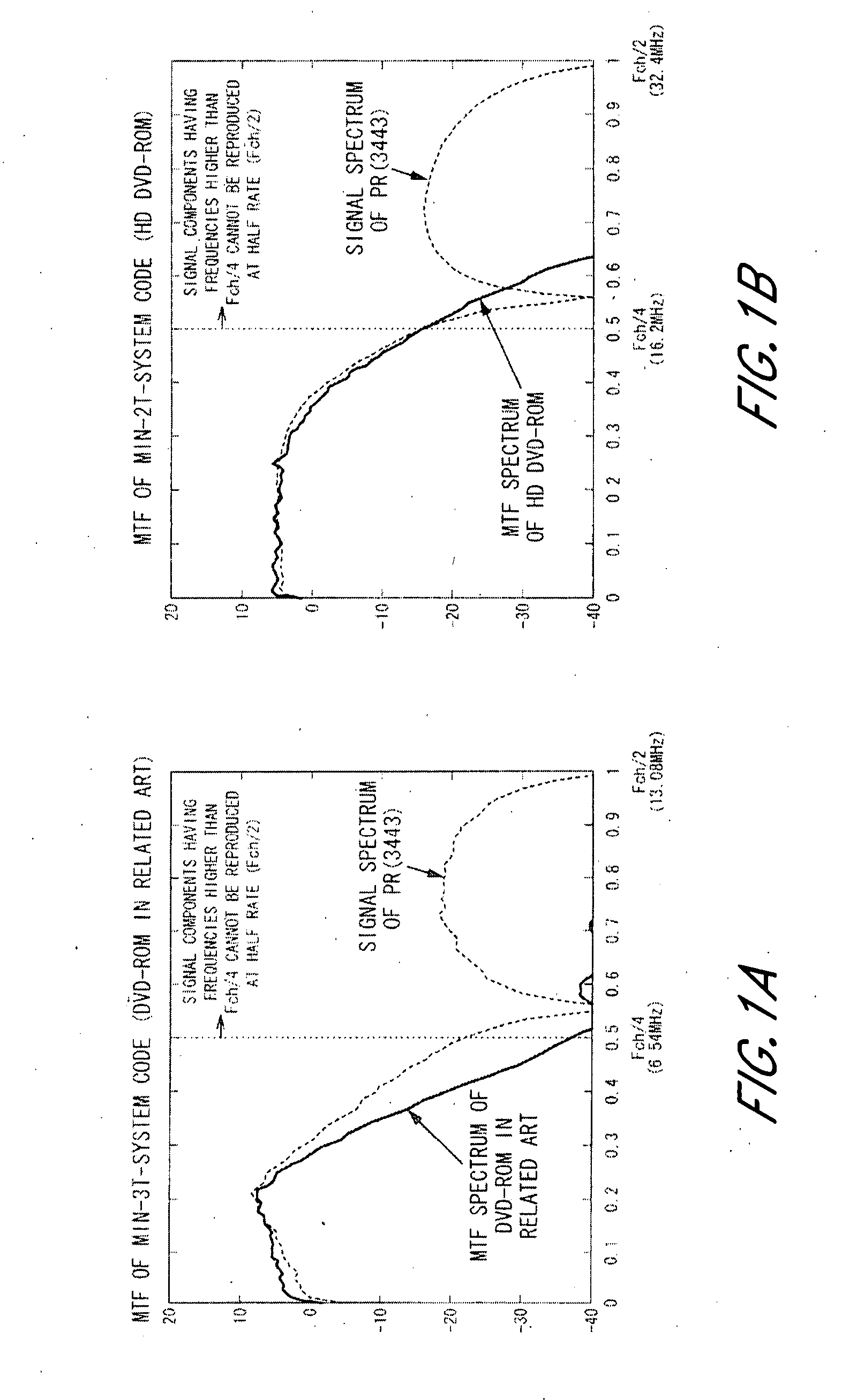

InactiveUS6963528B2Reliable controlImprove reliabilityTelevision system detailsModification of read/write signalsDigital dataHigh density

In a digital data reproduction apparatus for demodulating digital data from an optical recording medium, PRML (Partial Response Maximum Likelihood) signal processing effective to high-density recording / reproduction is carried out by using a half rate processing offset control means which performs data demodulation using half of the channel bit frequency, a half rate processing phase sync control means, a half rate processing adaptive equalization means, and a half rate processing maximum likelihood decoder, and the digital data recorded on the optical recording medium are reproduced while restoring signal components which are missing in the time direction, by linear interpolation or Nyquist interpolation. Therefore, digital data reproduction performance is improved, and power consumption is reduced.

Owner:PANASONIC CORP

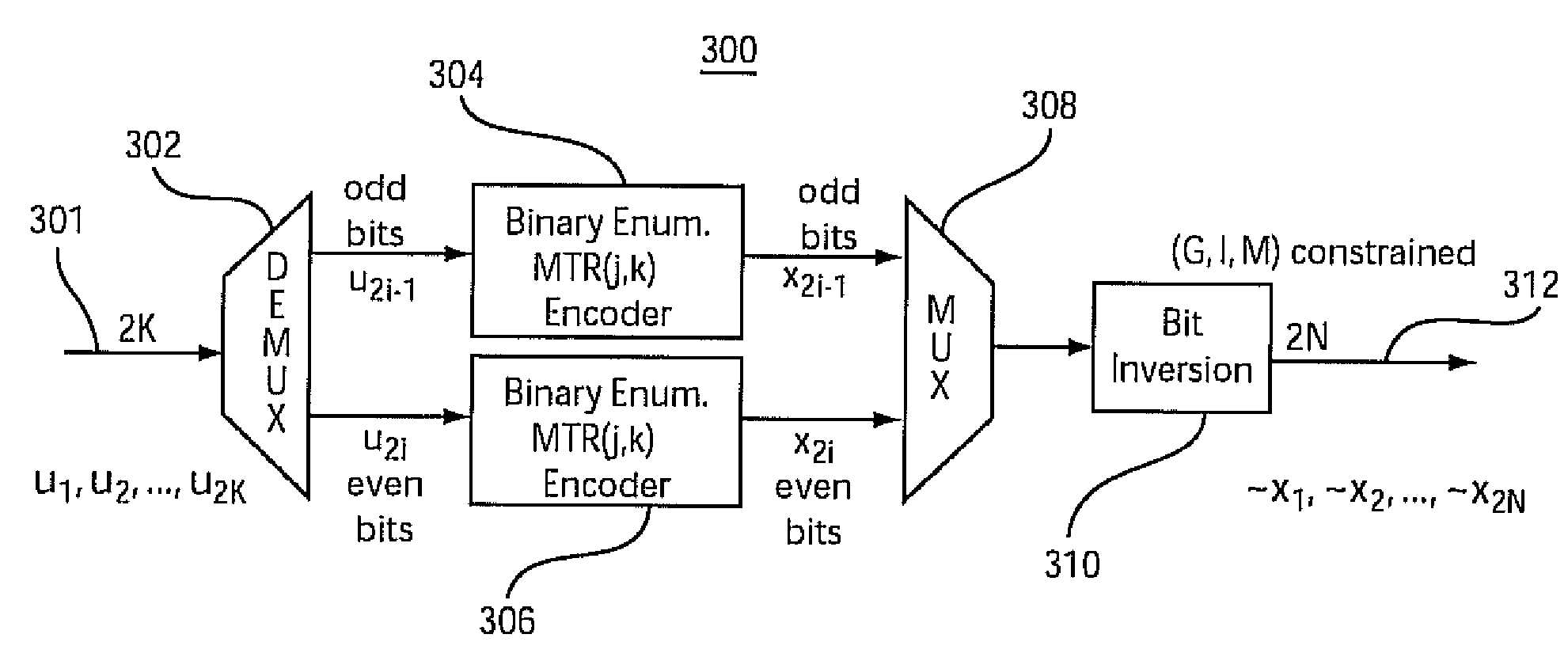

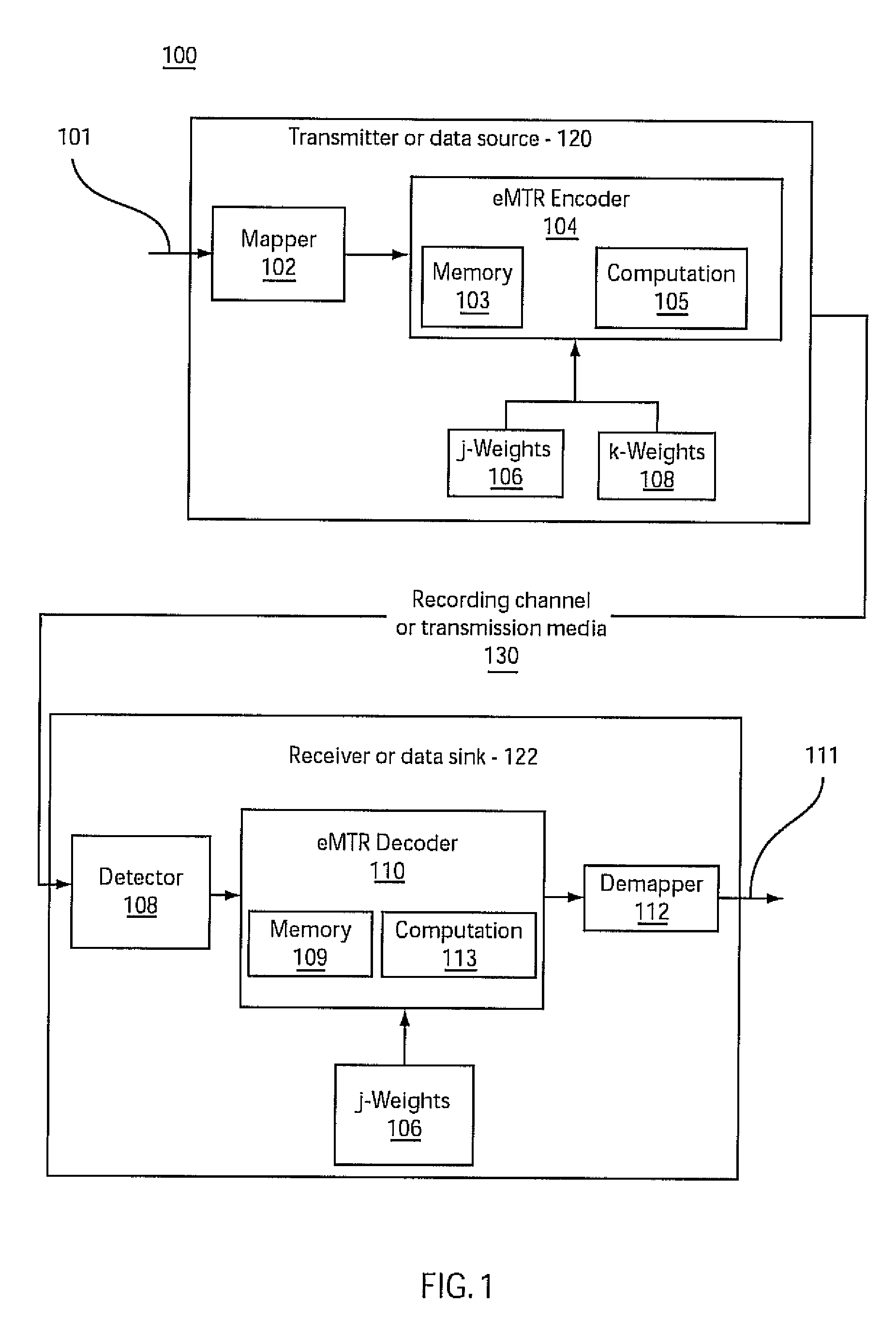

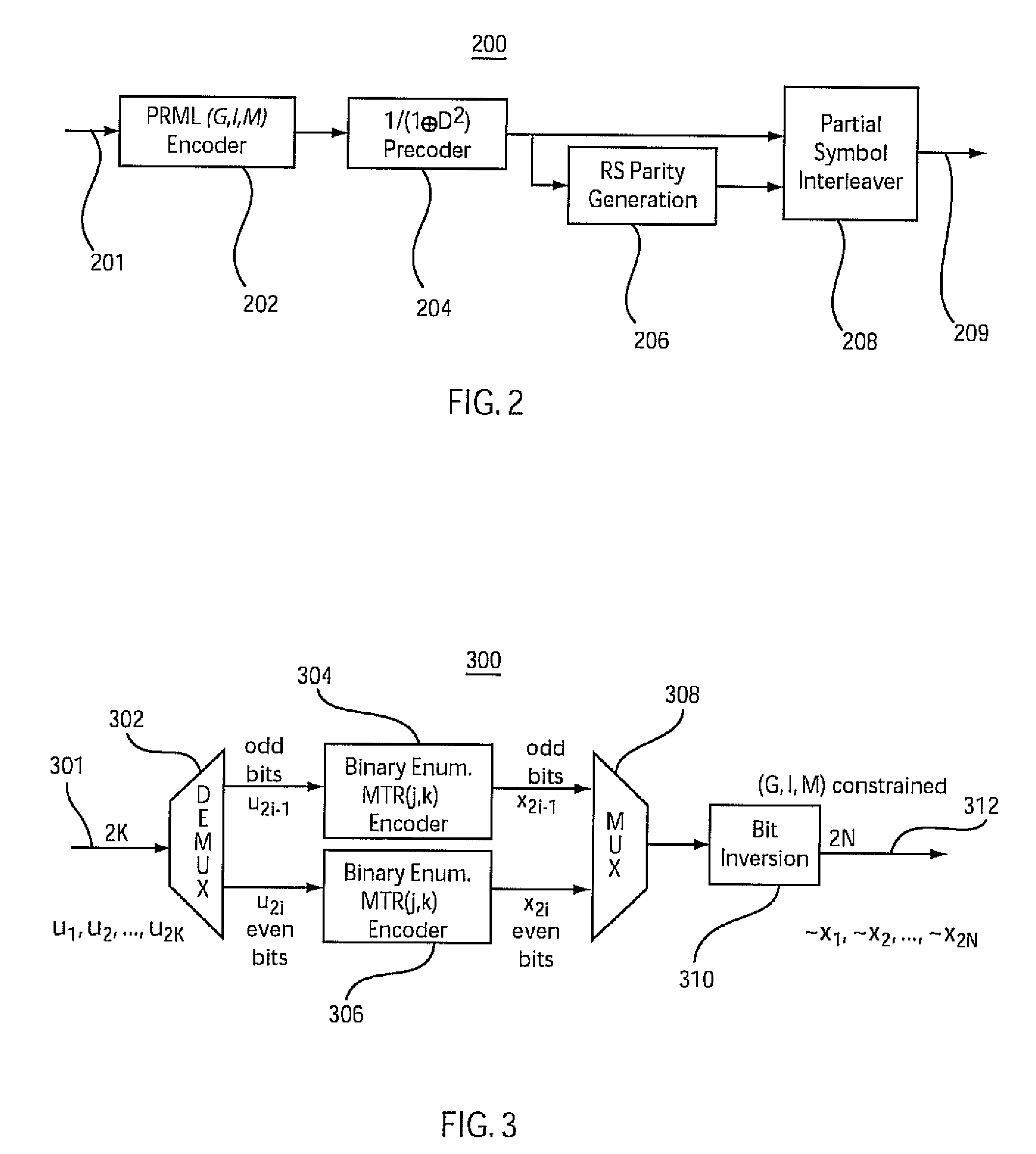

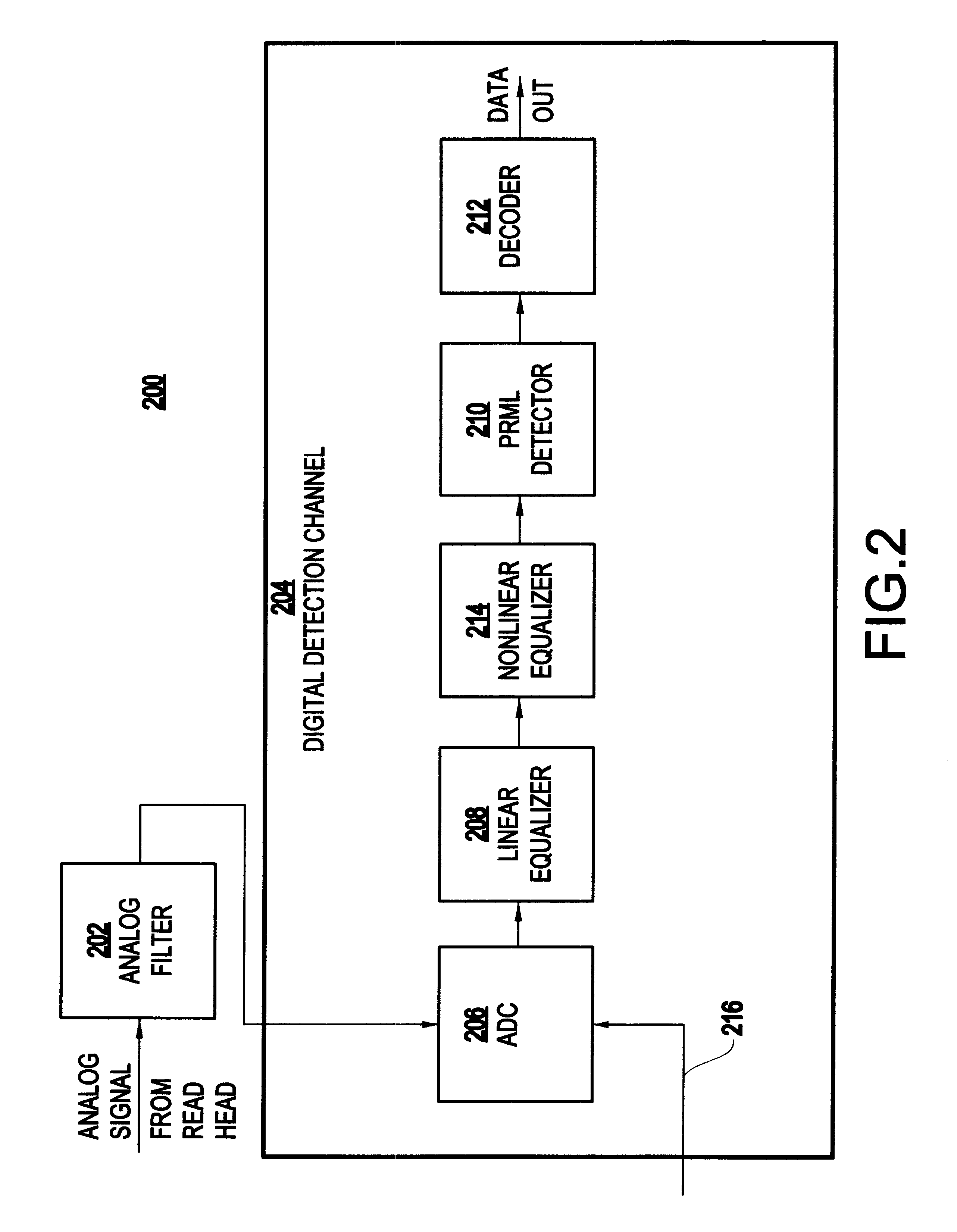

Systems and methods for enumerative encoding and decoding of maximum-transition-run codes and PRML (G,I,M) codes

InactiveUS7616134B1Television system detailsError detection/correctionSequence transformationDatapath

Systems and methods for encoding / decoding are provided. The systems and methods include encoding a stream of K-bit input sequences into a stream of (G, I, M)-constrained 2N-bit output sequences by transforming each K-bit input bit sequence into two separate data paths including even and odd bits. Enumerative maximum-transition-run (eMTR) encoding of the even bits generates constrained even bits, and enumerative maximum-transition-run (MTR) encoding of the odd bits generates constrained odd bits. The constrained even and constrained odd bits are interleaved to form a stream of (G, I, M)-constrained 2N-bit output sequences where G is a global constraint, I is an interleave constraint, and M is a variable frequency oscillator constraint of a partial-response maximum-likelihood (PRML) codeword. Decoding systems and methods are also provided.

Owner:GLOBALFOUNDRIES INC

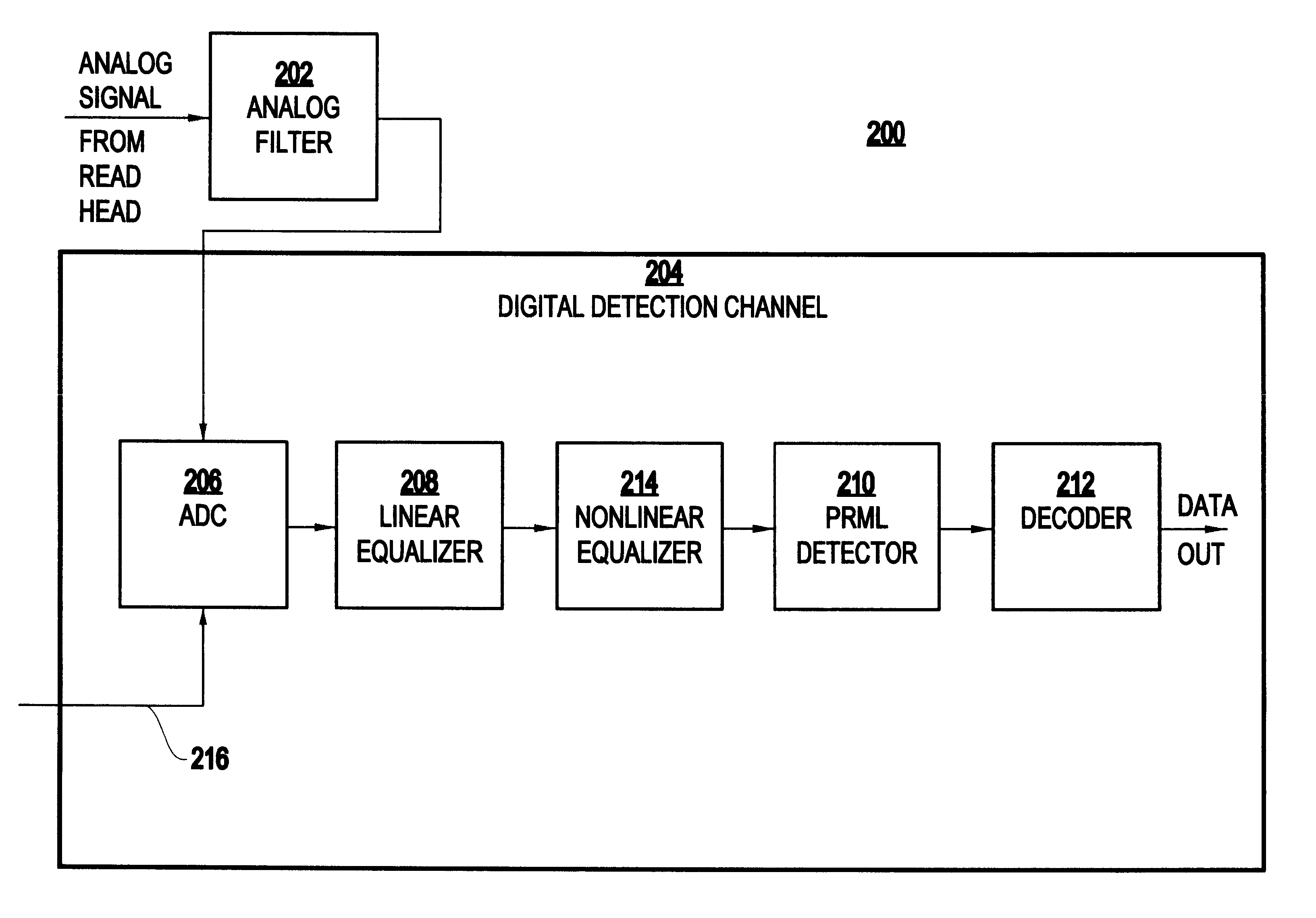

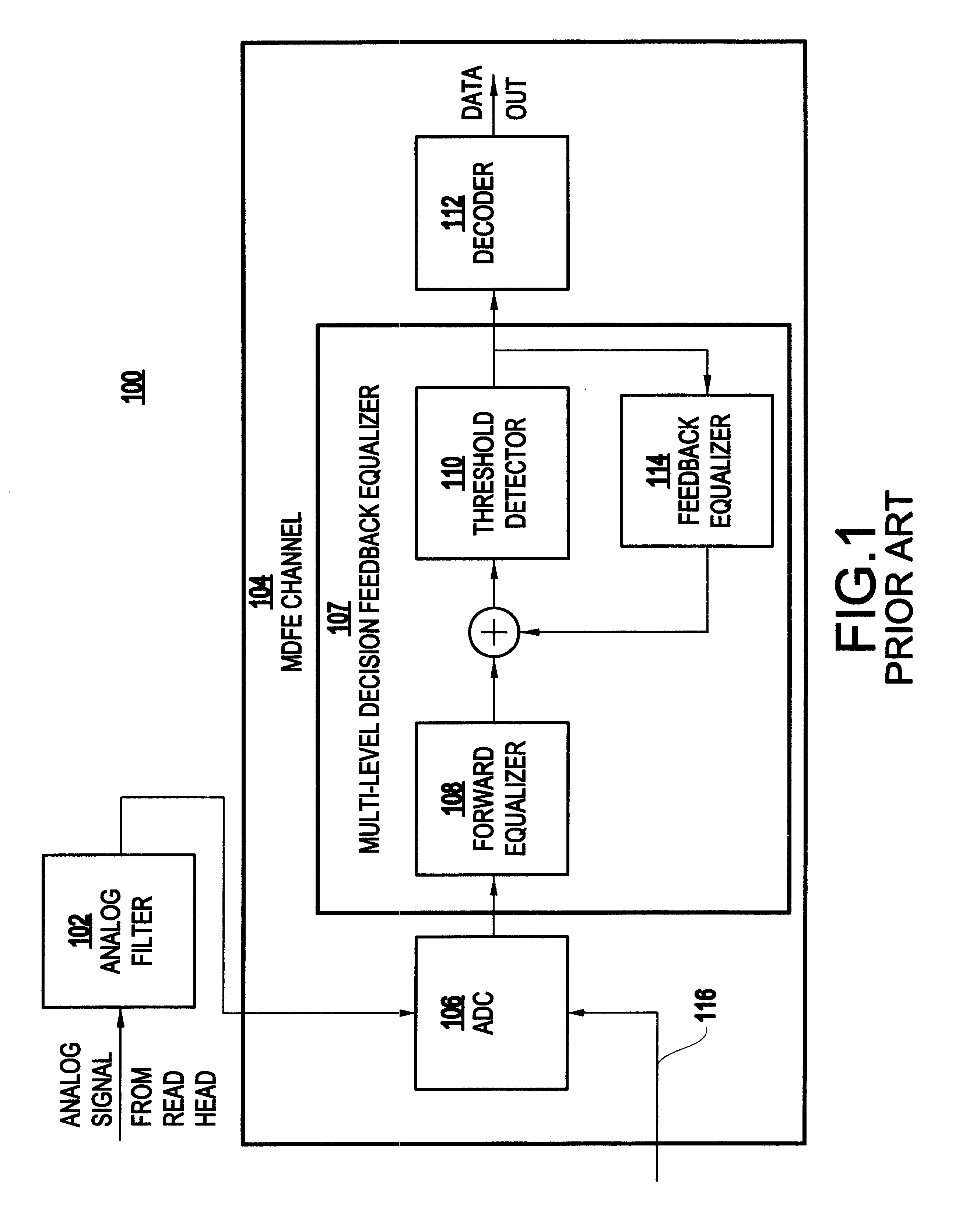

Nonlinear equalizer and decoding circuit and method using same

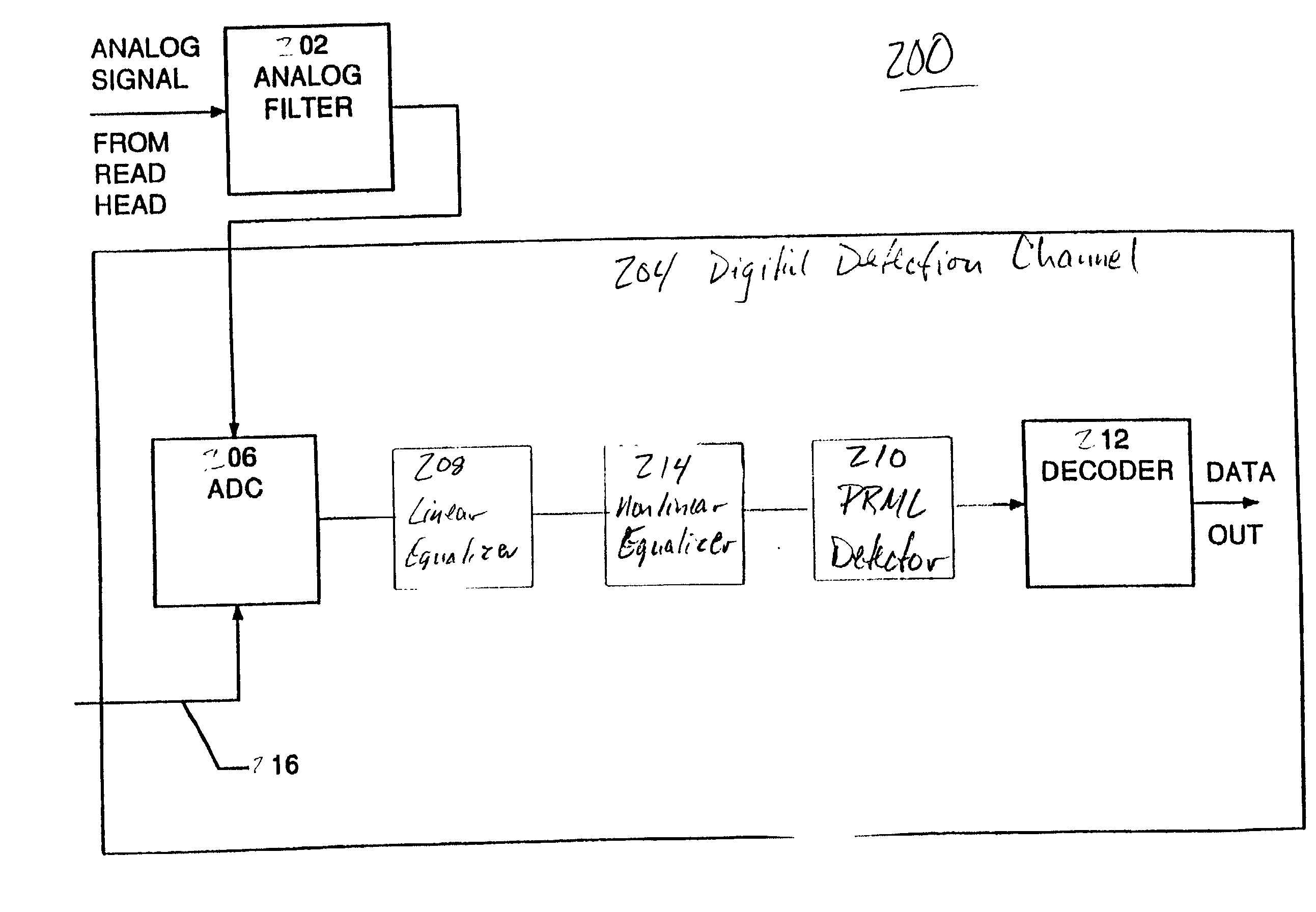

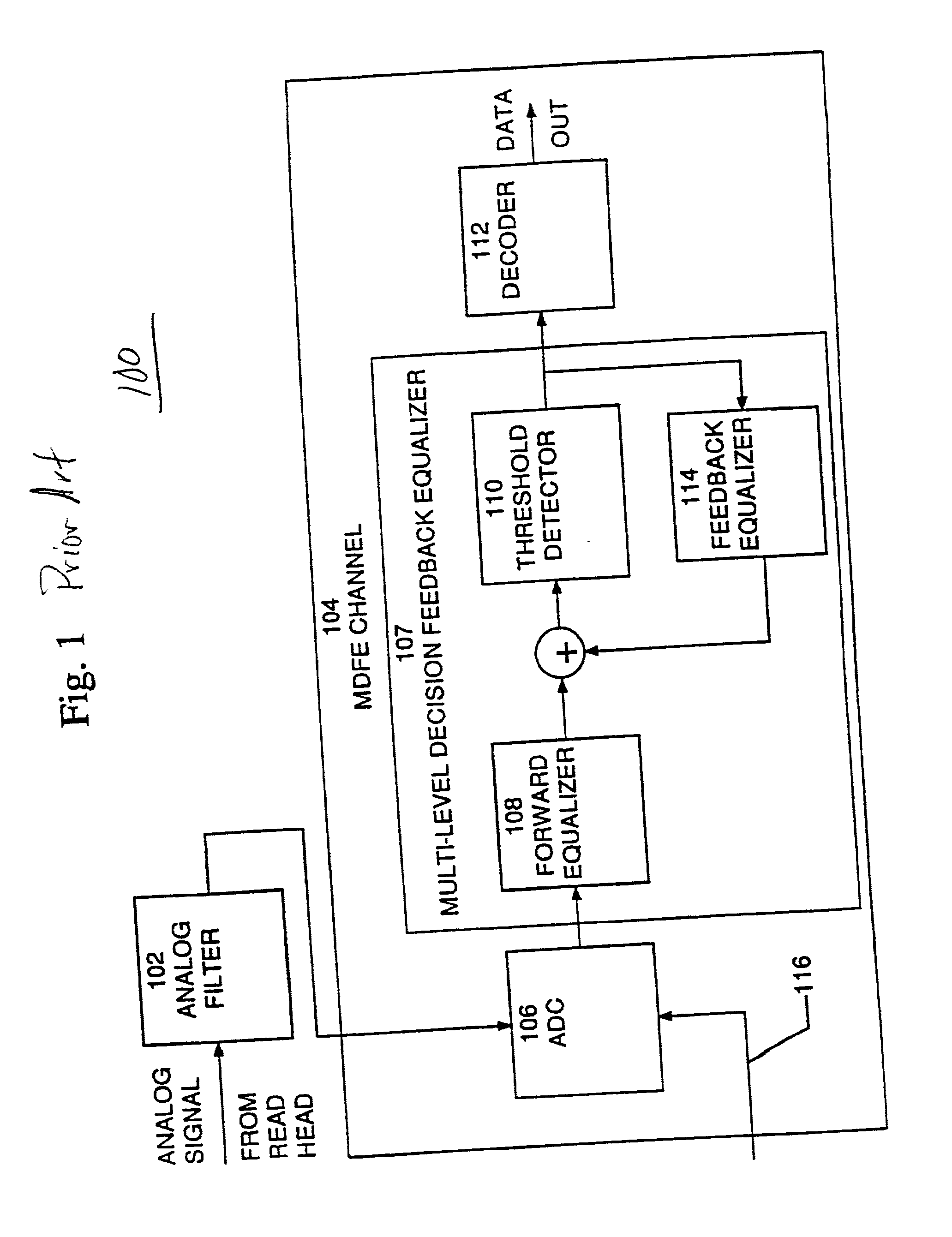

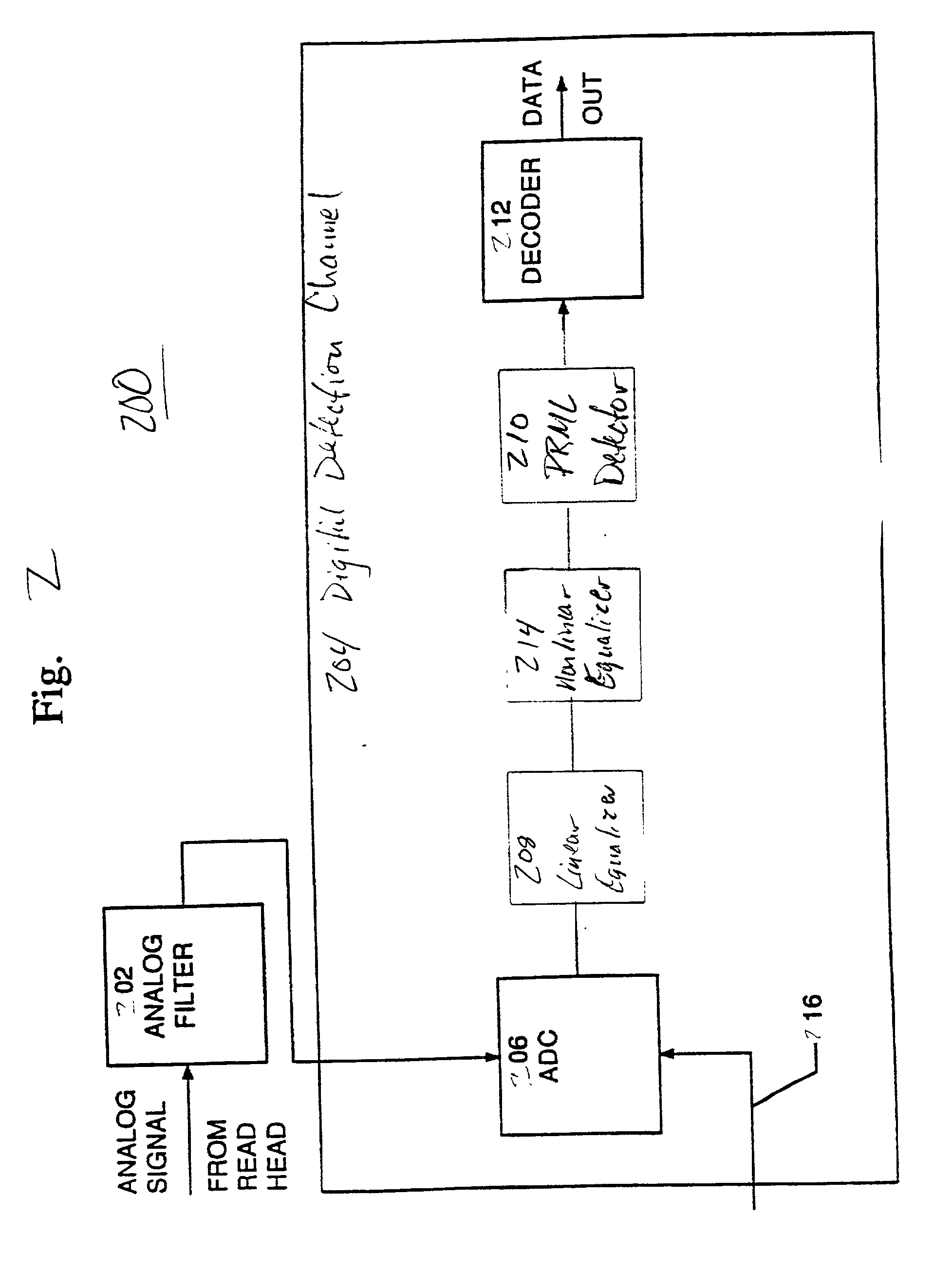

InactiveUS6678105B2Eliminate interferenceLess memoryMultiple-port networksModification of read/write signalsSignal conditioningAnalog signal

A decoding circuit has a nonlinear equalizer which employs a signal conditioning algorithm for conditioning a partial response sampled signal to eliminate intersymbol interference. The inventive decoding circuit has an analog-to-digital converter for sampling an analog signal, a linear equalizer for adjusting the amplitude and phase relations of the sampled signal, a nonlinear equalizer for conditioning the sampled signal and outputting a partial response sampled signal having two nonzero samples, and a partial response maximum likelihood detector, for detecting the partial response sampled signal having two nonzero samples.

Owner:IBM CORP

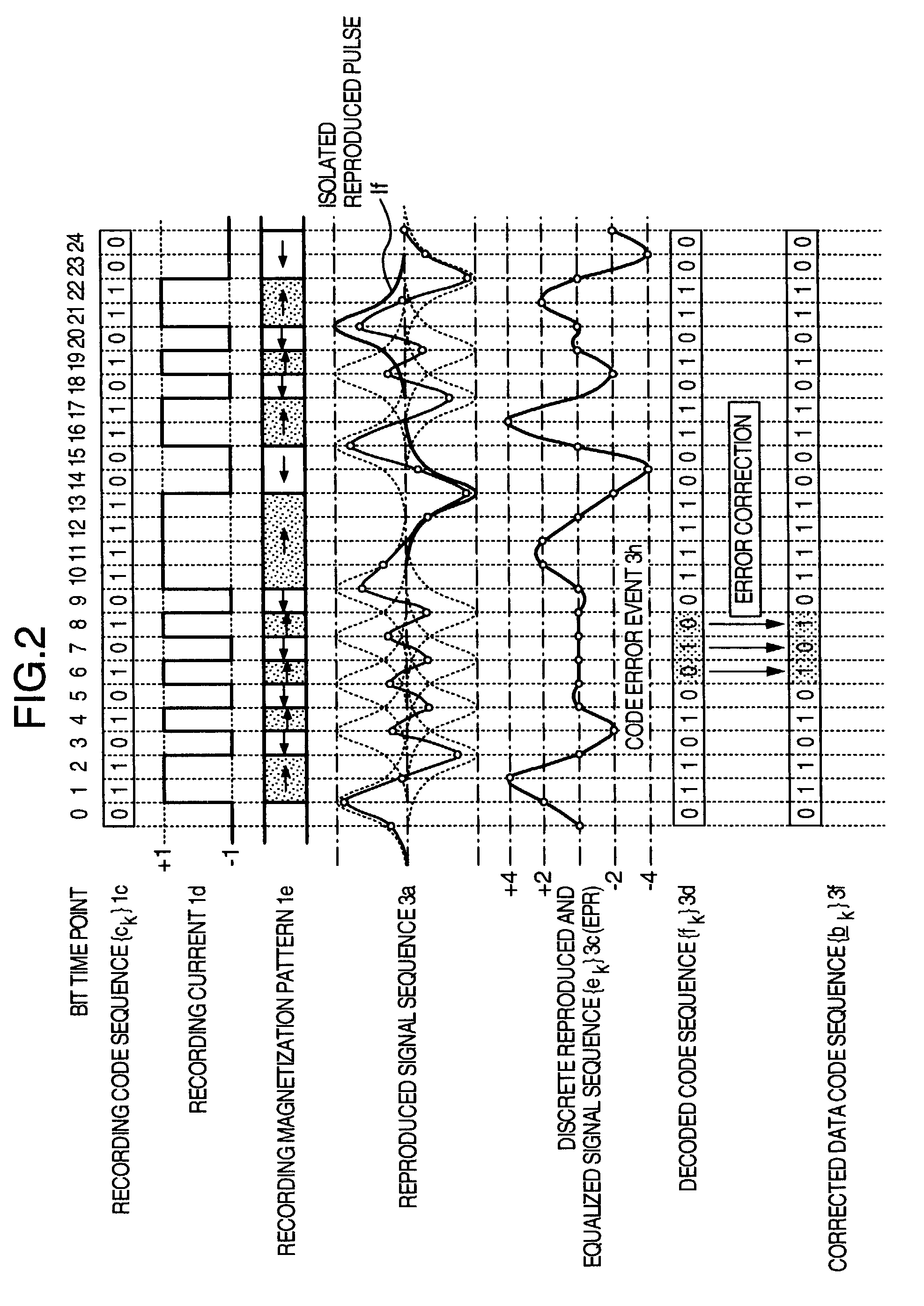

Data decoding method and circuit and information recording and reproducing apparatus using the same

InactiveUS7024617B2Raise the possibilityData representation error detection/correctionOther decoding techniquesDecoding methodsMaximum likelihood detection

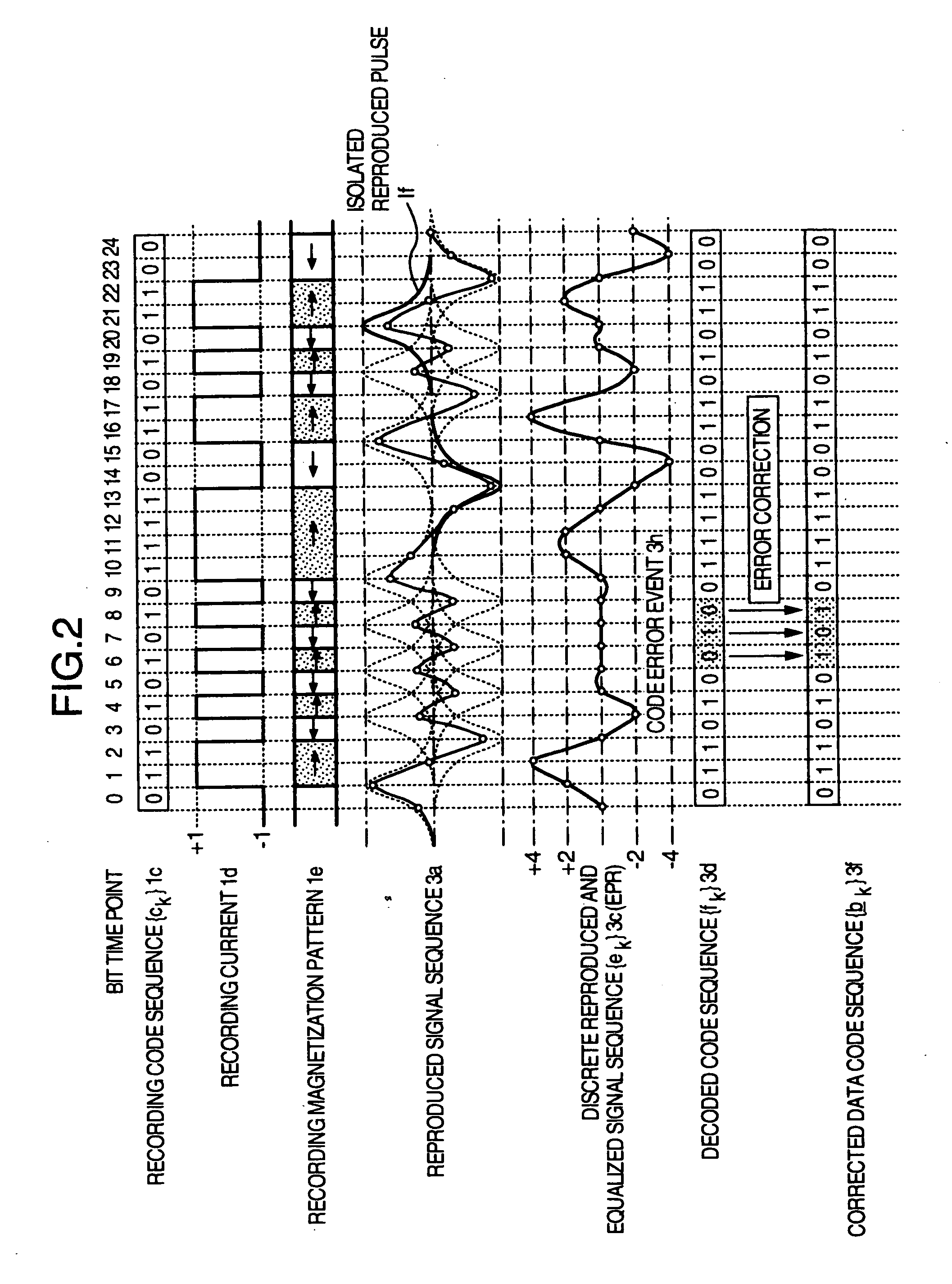

In a partial-response maximum-likelihood (PRML) signal detection and processing technique, reduction of data detection error events caused due to medium noise is achieved. For a PRML detection data result obtained after PRML data demodulation, a code error event that depends on a signal distance, and which has a high frequency of occurrences, is noticed and its occurrence probability is estimated. A locally-existing medium noise quantity is estimated from preceding and subsequent code patterns of the PRML detection data result. Based on this, the occurrence probability of the error event is compensated to improve the detection precision. As a result, data modulation with reliability higher than conventional maximum likelihood detection can be realized with a simple circuit structure.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD +1

Asymmetry compensator for partial response maximum likelihood (PRML) decoder

InactiveUS7724636B2Improve stabilityImprove signal qualityModification of read/write signalsRecord information storageEngineeringOptical recording

Owner:IND TECH RES INST

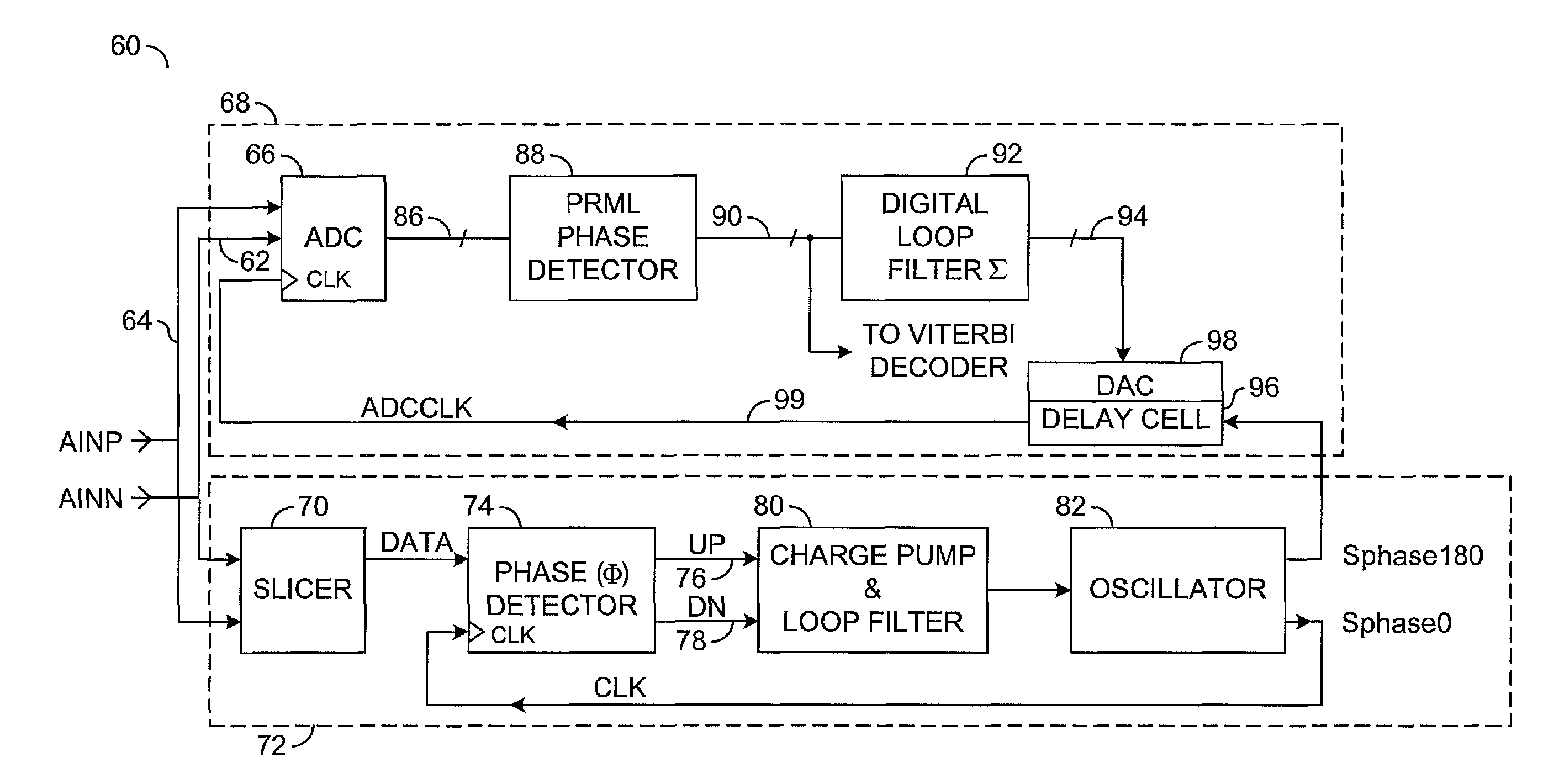

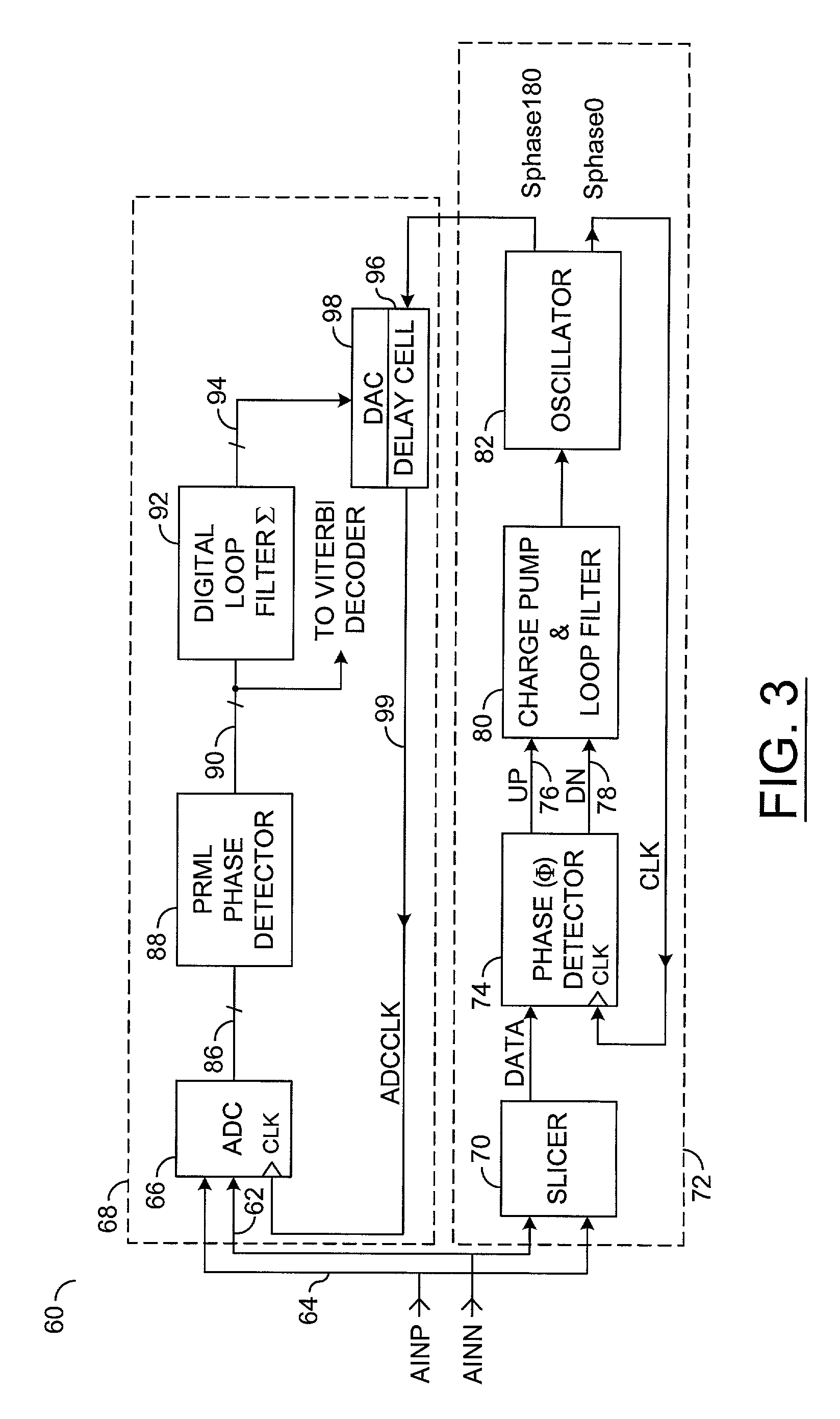

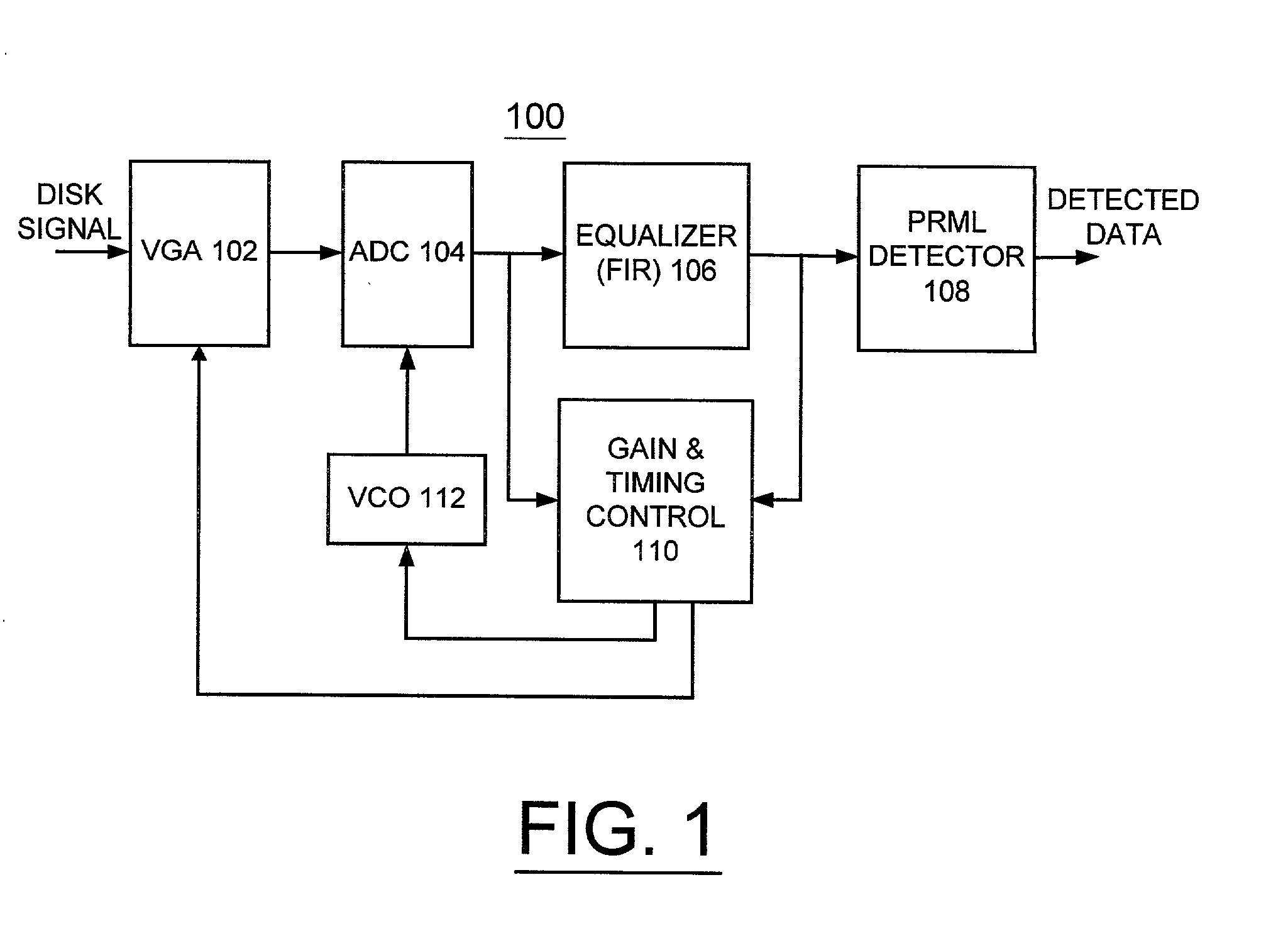

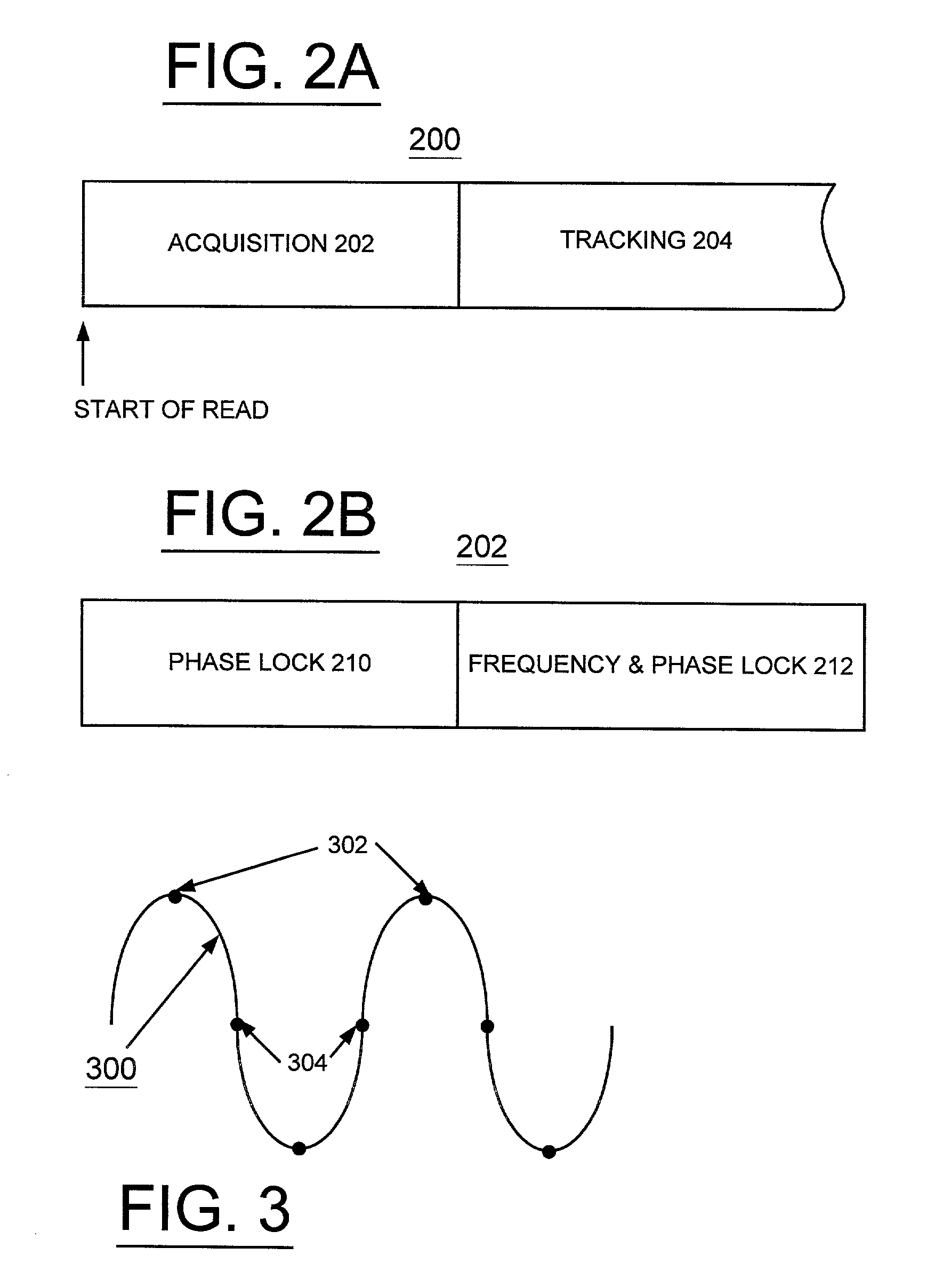

Apparatus and method for acquiring phase lock timing recovery in a partial response maximum likelihood (PRML) channel

InactiveUS6990163B2Lower latencyRecovery timePulse automatic controlRecord information storageDigital feedbackData signal

The present invention is a method of acquiring phase lock to a data signal in a digital channel having a digital feedback loop. The method generally comprises: (A) applying the data signal to an analog phase lock loop configured to have (i) at least two poles and (ii) presend intermediate output signal frequency locked to the data signal; (B) applying the data signal and the intermediate output signal to the digital channel; and (C) adjusting a delay constant for the digital feedback loop to (i) compensate for variations in phase between the data signal and the intermediate output signal and (ii) acquire phase lock by using a single pole in the digital channel.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Variable parameter self-adaptive PRML (Partial Response Maximum Likelihood) data sink and data processing method thereof

ActiveCN102243880AProcessing speedMeet the requirements of high-speed data transmissionDisposition/mounting of headsCode moduleTarget Response

The invention relates to a variable parameter self-adaptive PRML (Partial Response Maximum Likelihood) data sink for a high density optical disk storage system on the basis of freedom clock sampling and a data processing method thereof. The data sink comprises a free clock sampling module, a variable parameter self-adaptive signal conditioning module, a clock recovering module, a self-adaptive maximum likelihood coding module and a target response selecting module; according to the invention, by adopting a variable parameter self-adaptive signal conditioning technology, a digital interpolating clock recovering technology and a PRML (Partial Response Maximum Likelihood) principle-based maximum likelihood coding technology, high speed data transmission requirements when high-density storage data is read out can be met, meanwhile the intersymbol interference can be well eliminated, and the error rate is reduced.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

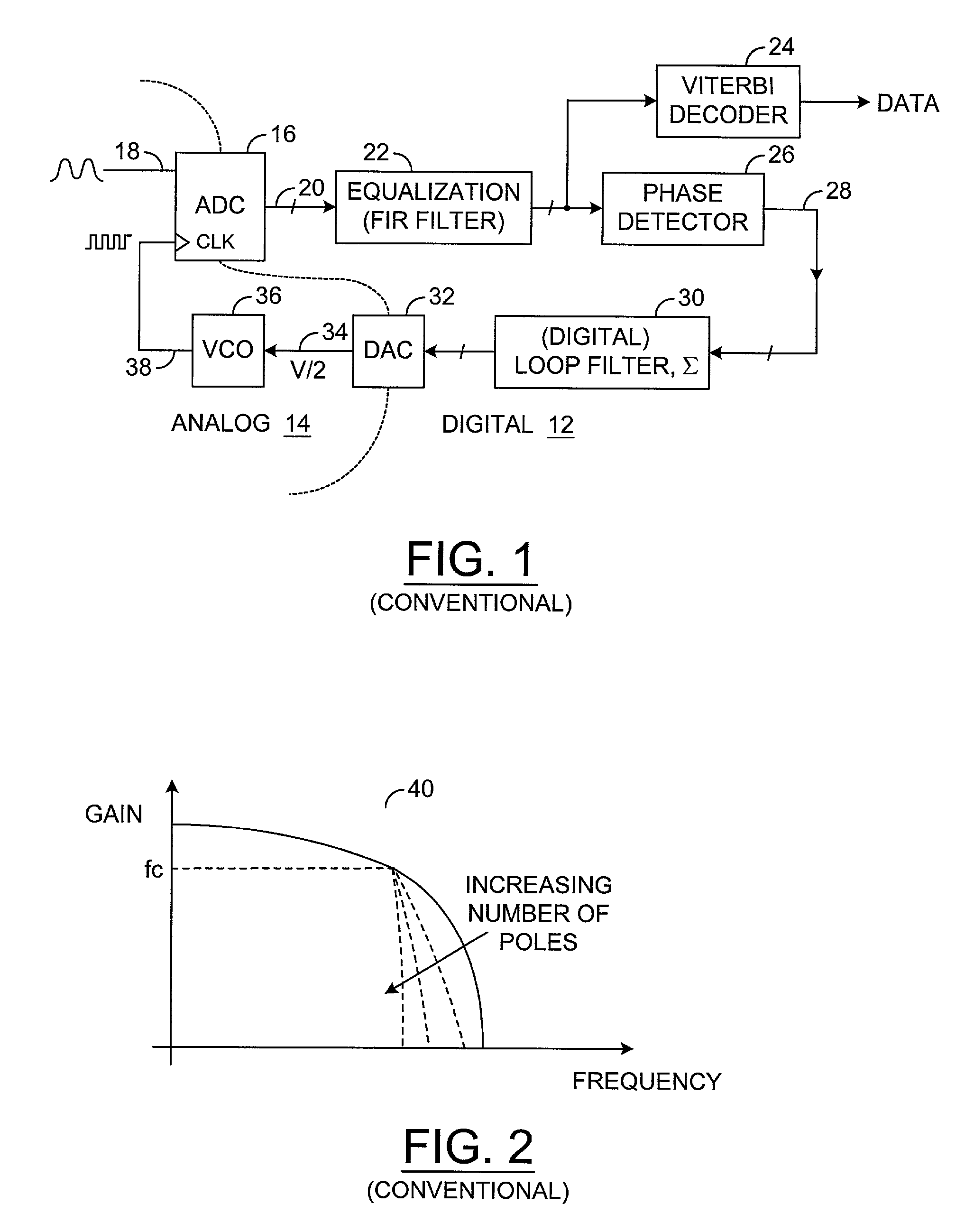

Method and apparatus for enhanced timing loop for a PRML data channel

InactiveUS20020126749A1Increase heightExtension of timeMultiple-port networksModification of read/write signalsChannel dataDirect-access storage device

Methods and apparatus for enhanced timing loop are provided for a partial-response maximum-likelihood (PRML) data channel in a direct access storage device (DASD). An acquisition timing circuit for generating an acquisition timing signal includes a plurality of compare functions for receiving and comparing consecutive input signal samples on an interleave with a threshold value. The acquisition timing circuit includes a majority rule voting function coupled to the plurality of compare functions for selecting a timing interleave. Tracking timing circuitry for generating a timing error signal during a read operation includes a channel data detector. The channel data detector receives disk signal input samples and includes a multiple-state path memory. The tracking timing circuit includes a low latency detector receiving disk signal input samples. A selector function is coupled to an output of the low latency detector and is coupled to the multiple-state path memory for selecting a state. The selector function utilizes the low latency detector output and selects the state of the path memory. The selector function provides a low latency output corresponding to the selected state. The low latency output is used for generating the timing error signal during a read operation.

Owner:WESTERN DIGITAL TECH INC

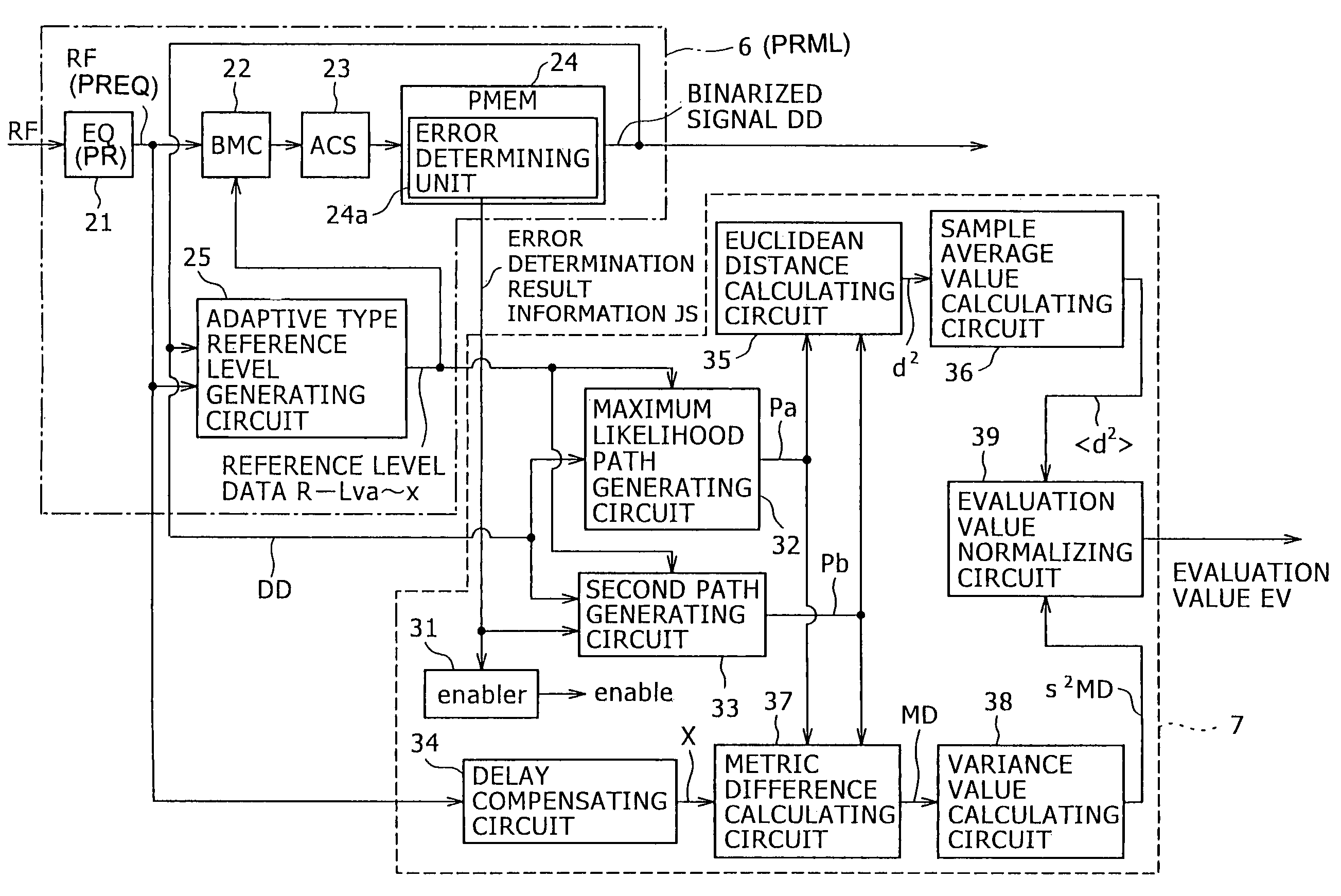

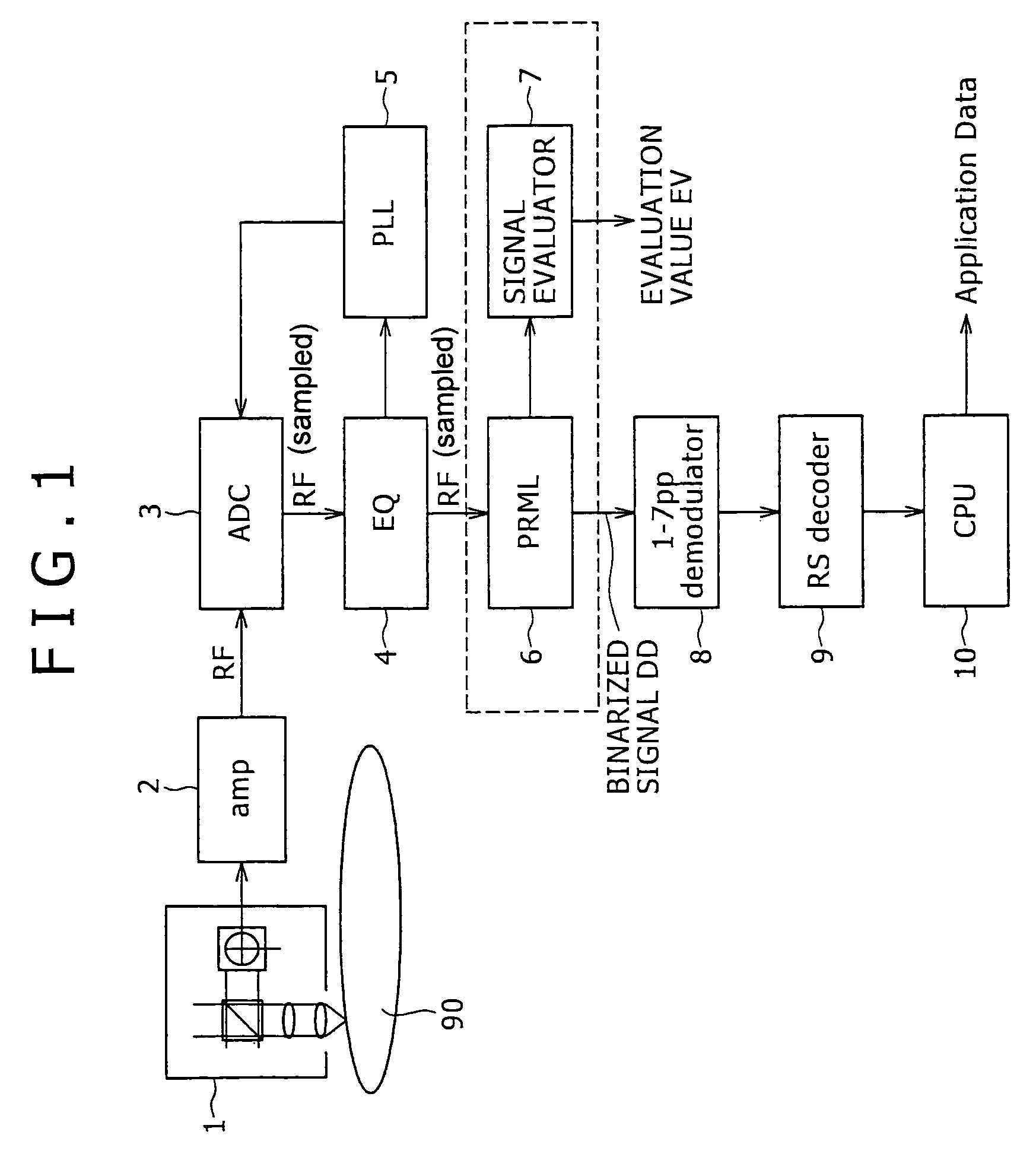

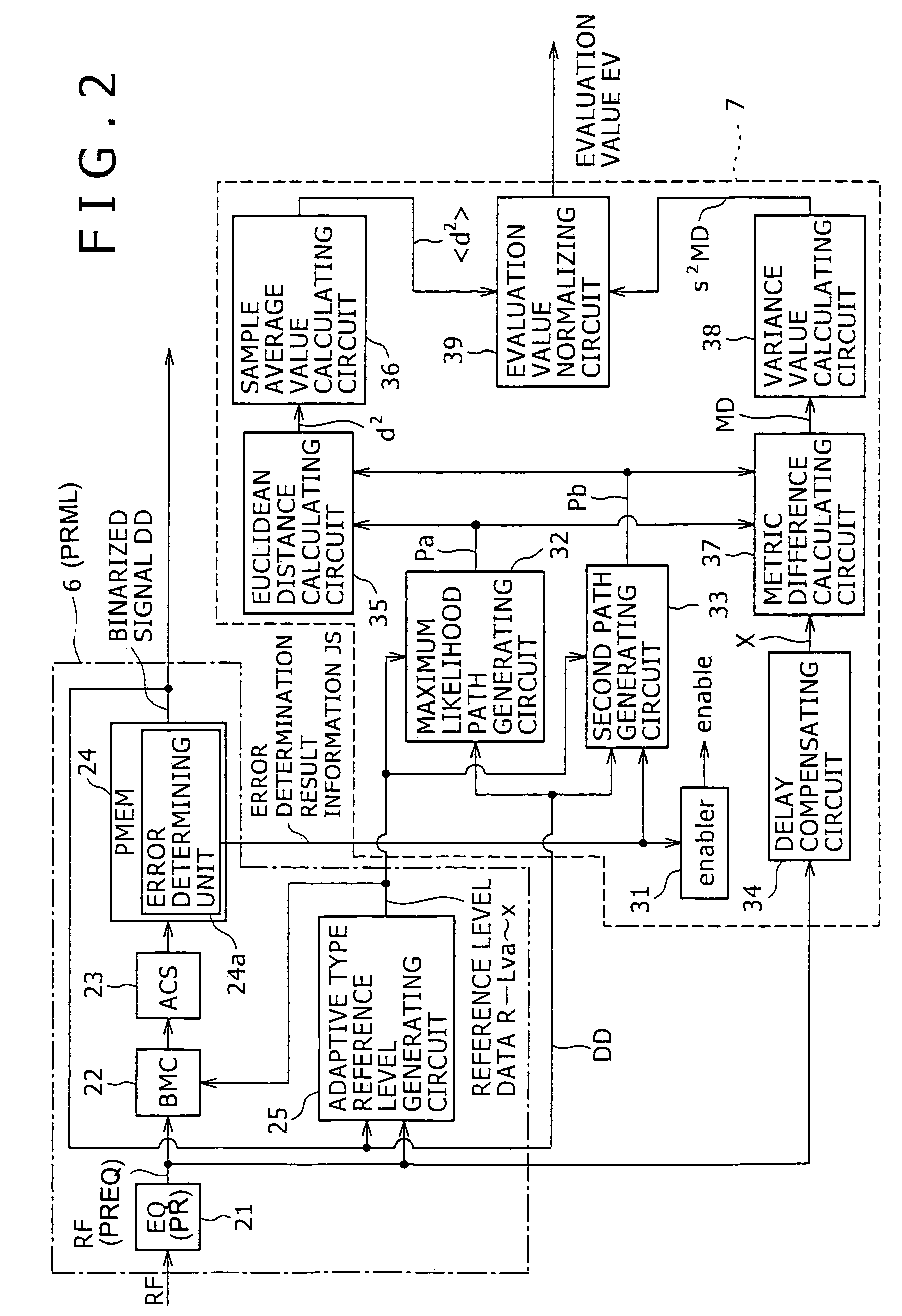

Maximum likelihood decoding device, signal evaluating method, and reproducing apparatus

InactiveUS7603611B2Suppress errorConvenient and accurateModification of read/write signalsData representation error detection/correctionViterbi detectorData signal

The invention relates to a maximum likelihood decoding device that performs Partial Response Maximum Likelihood decoding on a reproduced data signal from a recording media or another source. The device includes a Viterbi detector that performs bit detection from the reproduced signal. The Viterbi device can have variable setting for branch metric calculations based on the reference levels in the reproduced signal. The device measures and attempts to reduce the Euclidean distance between a maximum likelihood path selected by the Viterbi detector and a second path.

Owner:SONY CORP

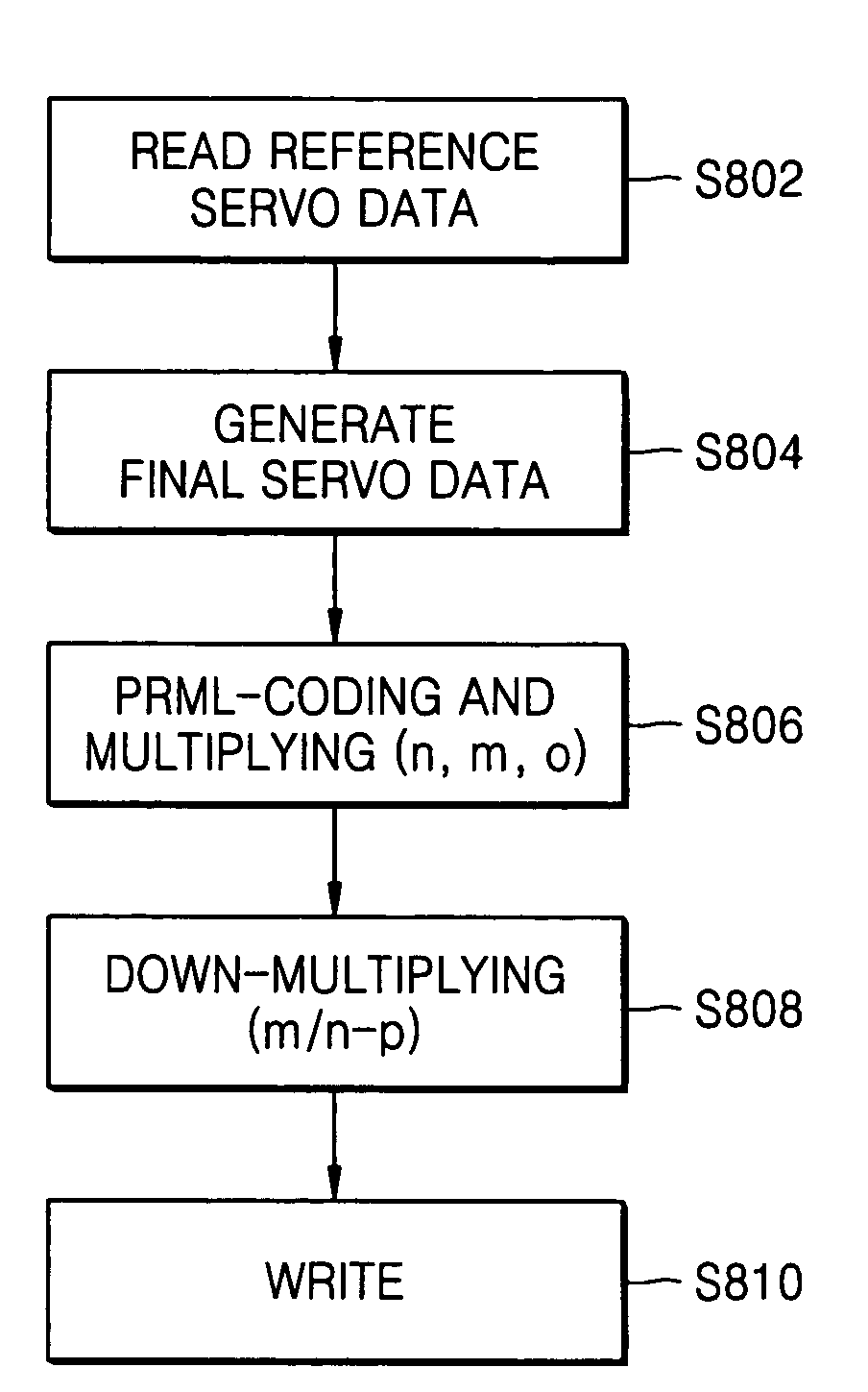

Method of forming servo data of HDD and self servo write method using the same

InactiveUS7663830B2Reduce the cushioning forceModification of read/write signalsDriving/moving recording headsComputer sciencePartial-response maximum-likelihood

Owner:SAMSUNG ELECTRONICS CO LTD

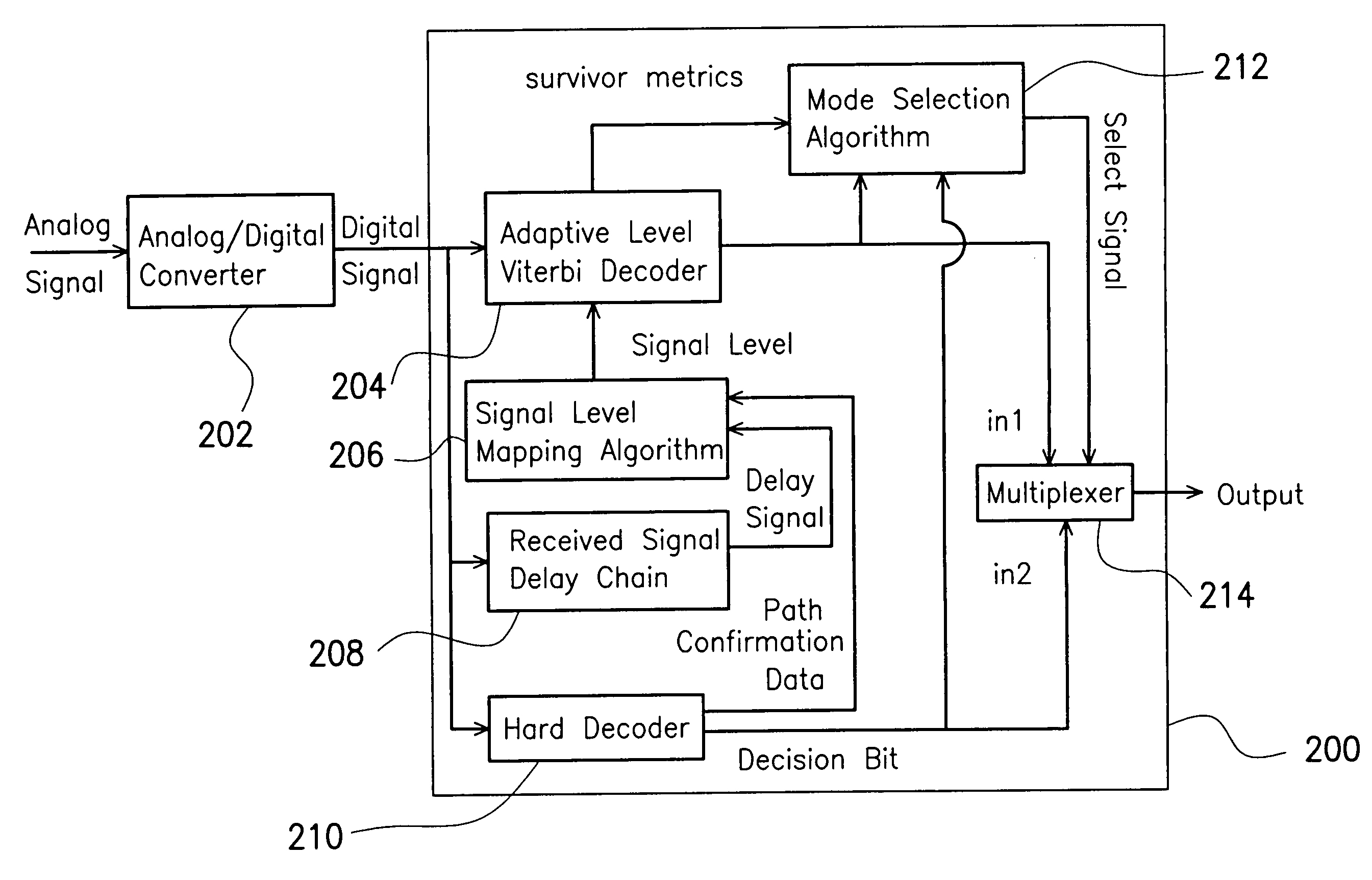

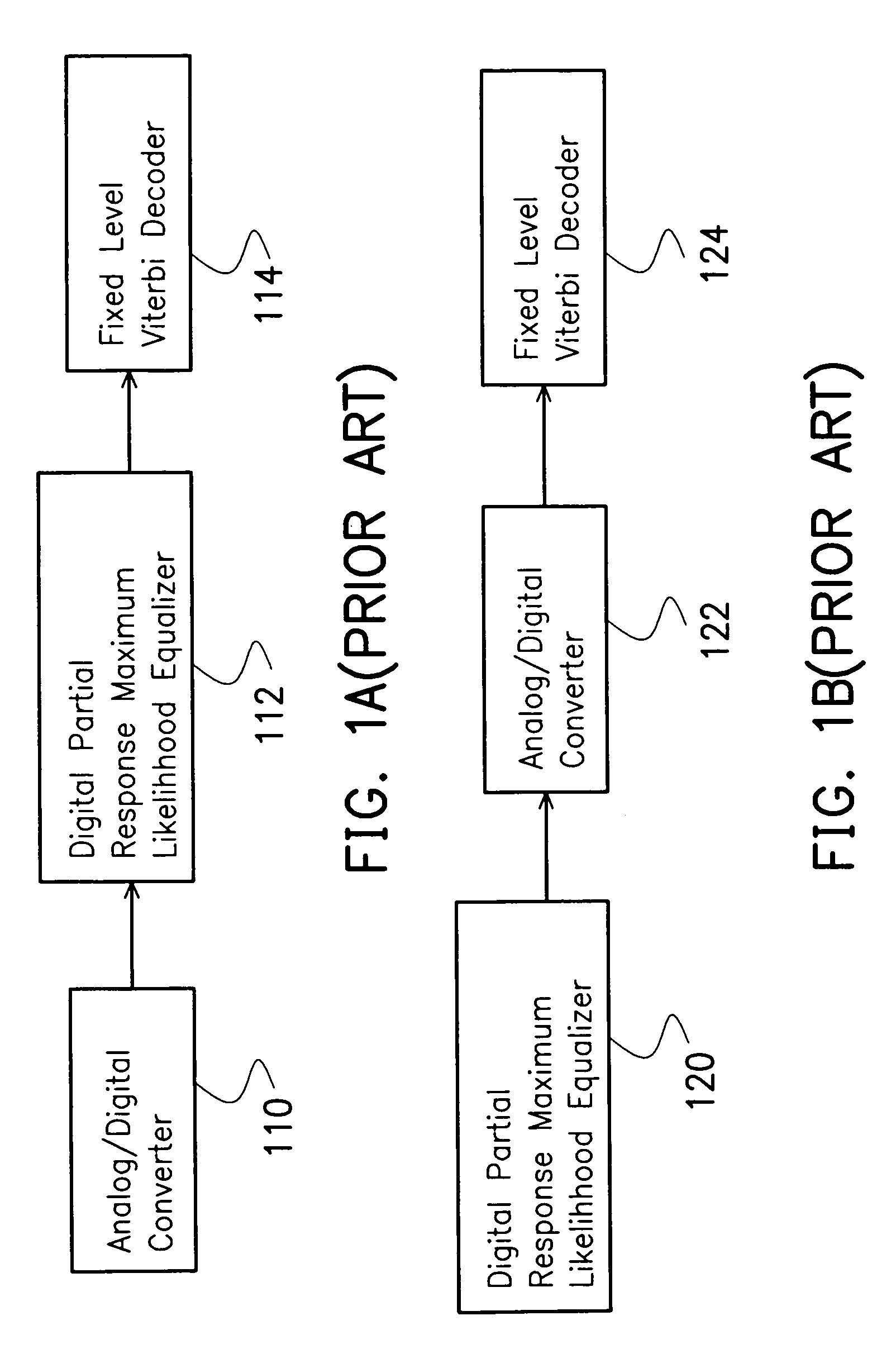

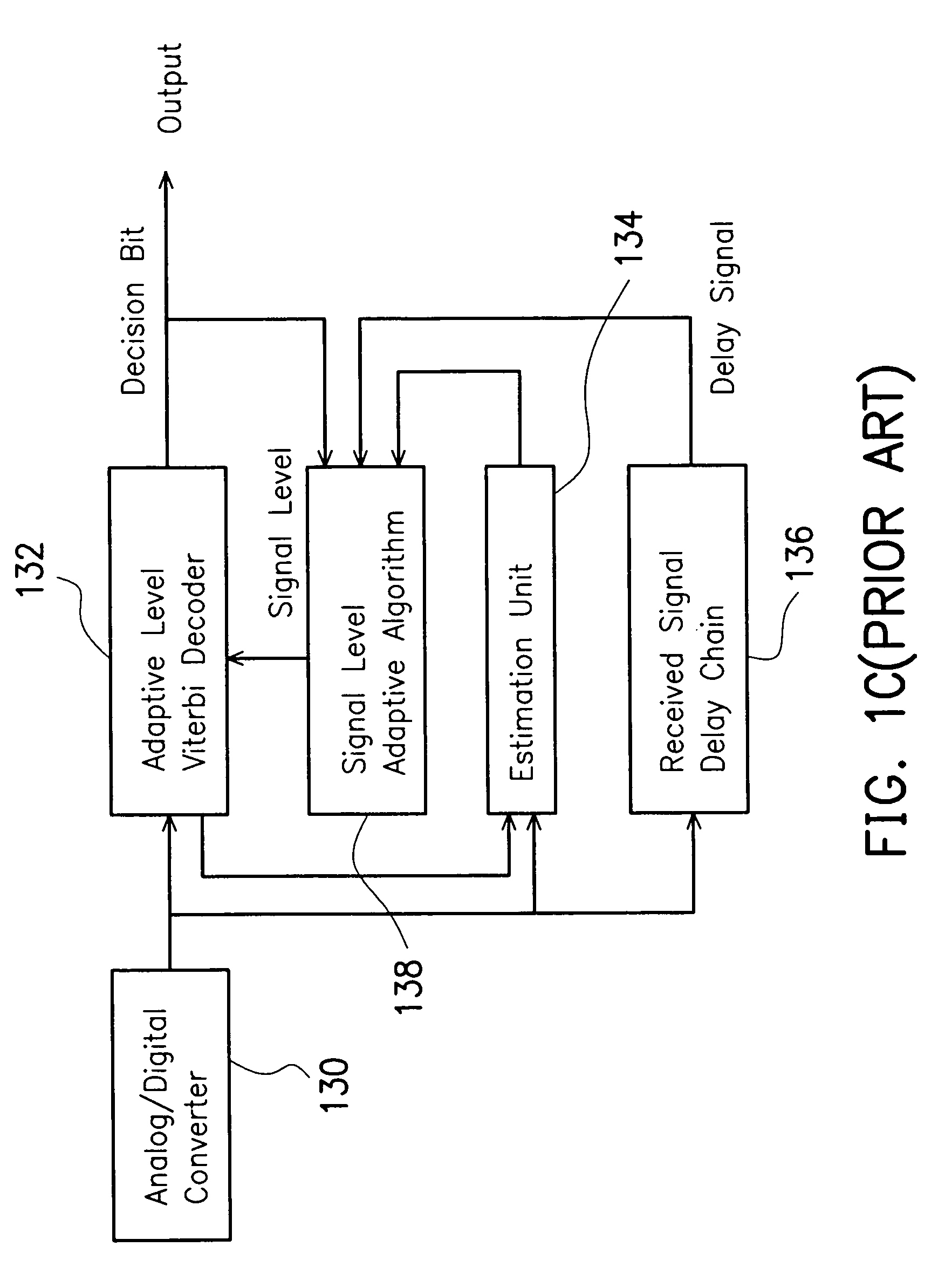

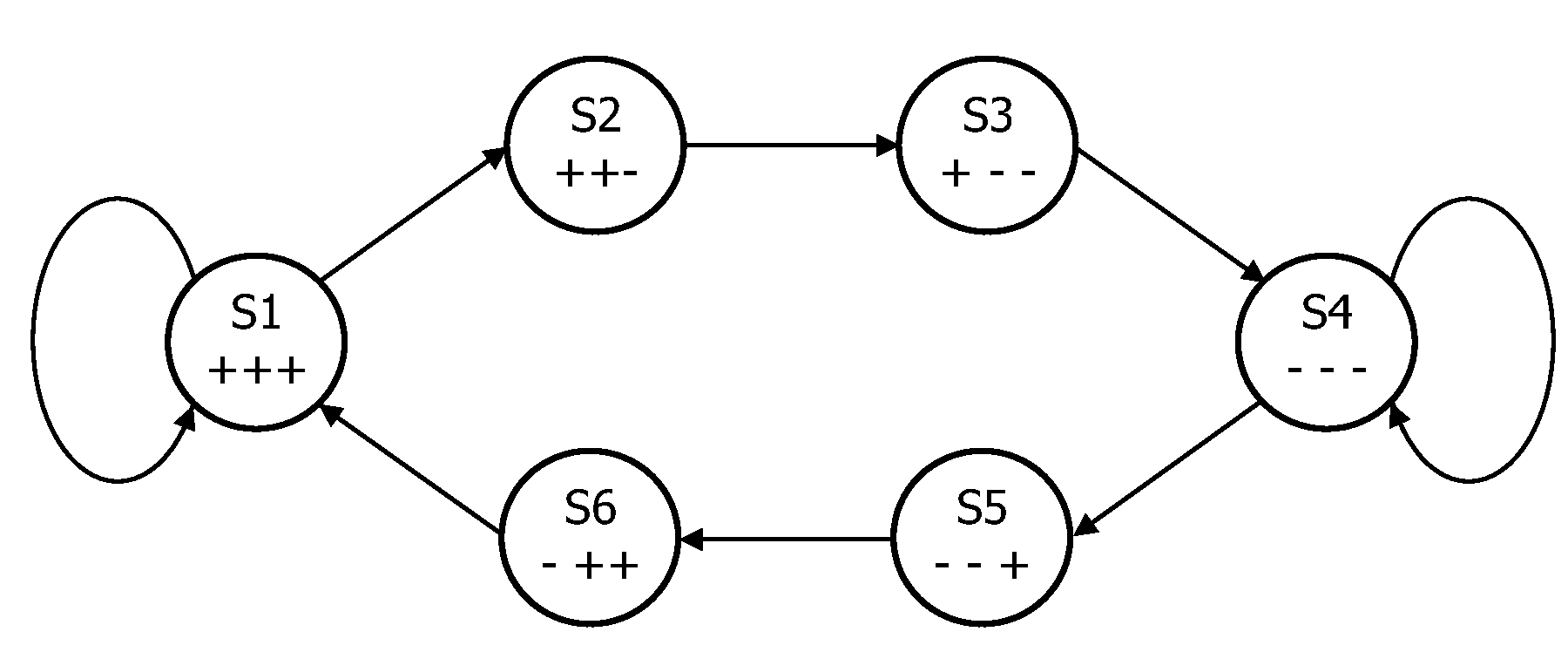

Viterbi decoder of partial response maximum likelihood channel

InactiveUS7145968B2Reduce errorsKeep for a long timeData representation error detection/correctionOther decoding techniquesDigital converterPartial-response maximum-likelihood

A Viterbi decoder of a partial response maximum likelihood channel. In an optical disc drive, a system of partial response maximum likelihood has an analog / digital converter. This analog / digital converter receives an analog signal and outputs a digital signal to a Viterbi decoder. The Viterbi decoder has an adaptive level Viterbi decoder, a signal level mapping algorithm, a received signal delay chain, a hard decoder, and a multiplexer. The adaptive level Viterbi decoder and the hard decoder receive a digital signal output from the analog / digital converter to decode simultaneously. Whether the output of the multiplexer is the decision bit of the adaptive level Viterbi decoder or the hard decoder is determined by the mode selection algorithm.

Owner:MEDIATEK INC

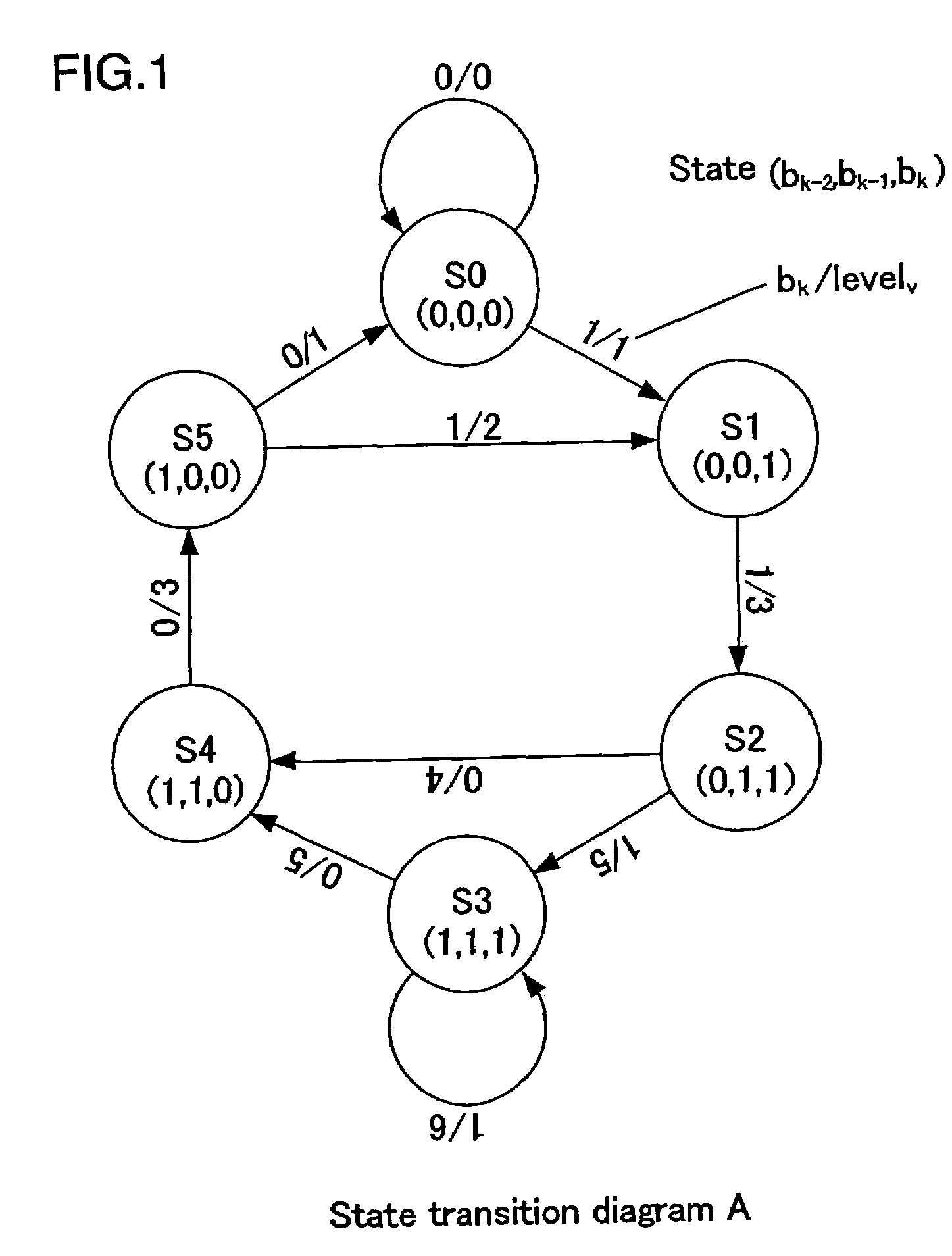

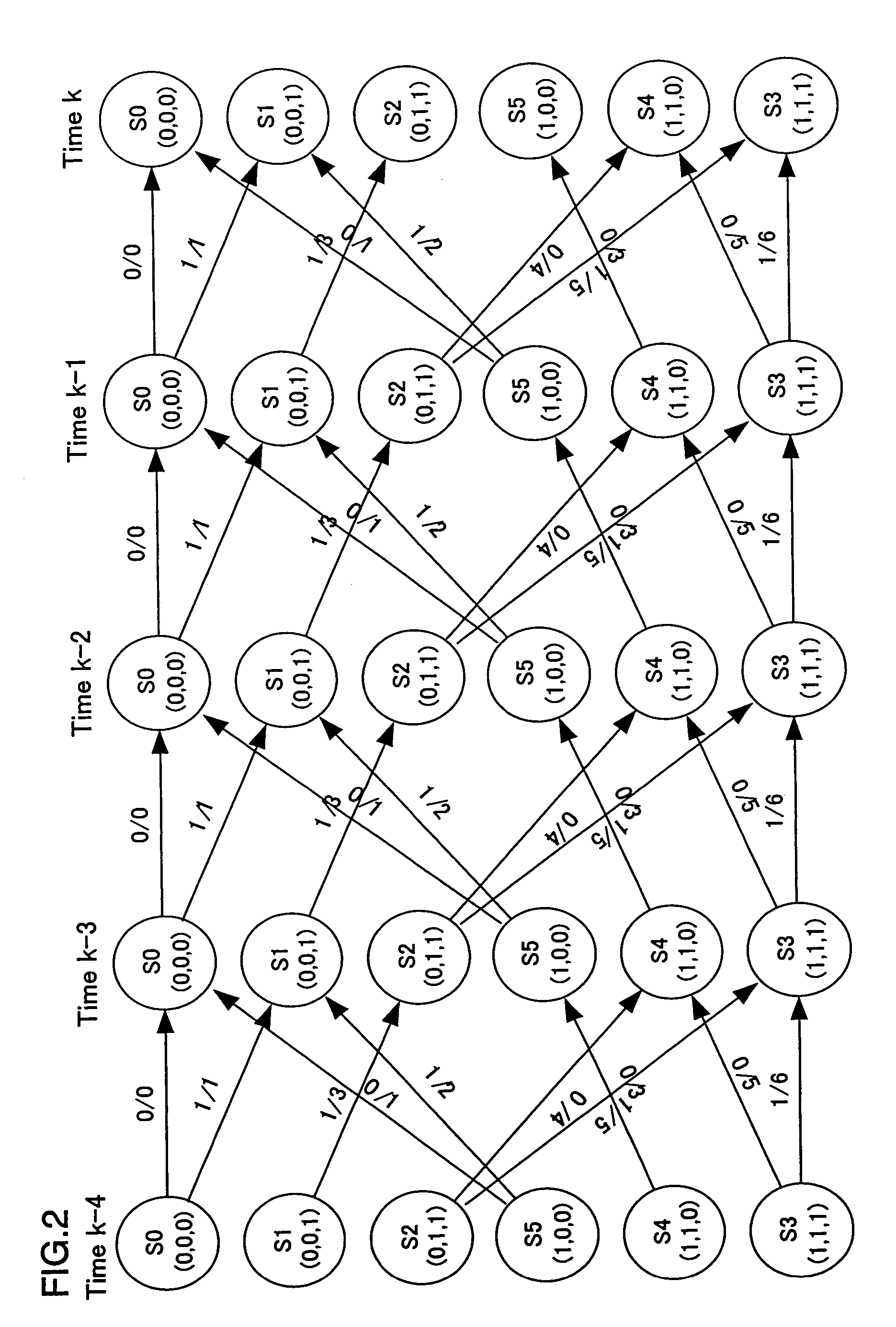

Partial response maximum likelihood system possessing branch estimating equipment

InactiveCN1485847AError correction/detection using convolutional codesSignal processing using self-clocking codesAnalog-to-digital converterPartial-response maximum-likelihood

The invention provides a part response maximum likelihood (PRML) system having a branch estimating device which comprises, an analog-to-digital converter for receiving an analog input signal, and transforming the analog input signal into digital signal sequence according to the triggering of the sampling clock, a branch estimating device for receiving the digital signal sequence and estimating each of the branch characteristic value, and a Viterbi code converter for receiving the digital signal sequence and the branch characteristic value and decoding the output signal. The PRML system by theinvention can reduce the circuit and raise the speed.

Owner:MEDIATEK INC

Apparatus for reproducing data on recording medium and method for reproducing data on the medium

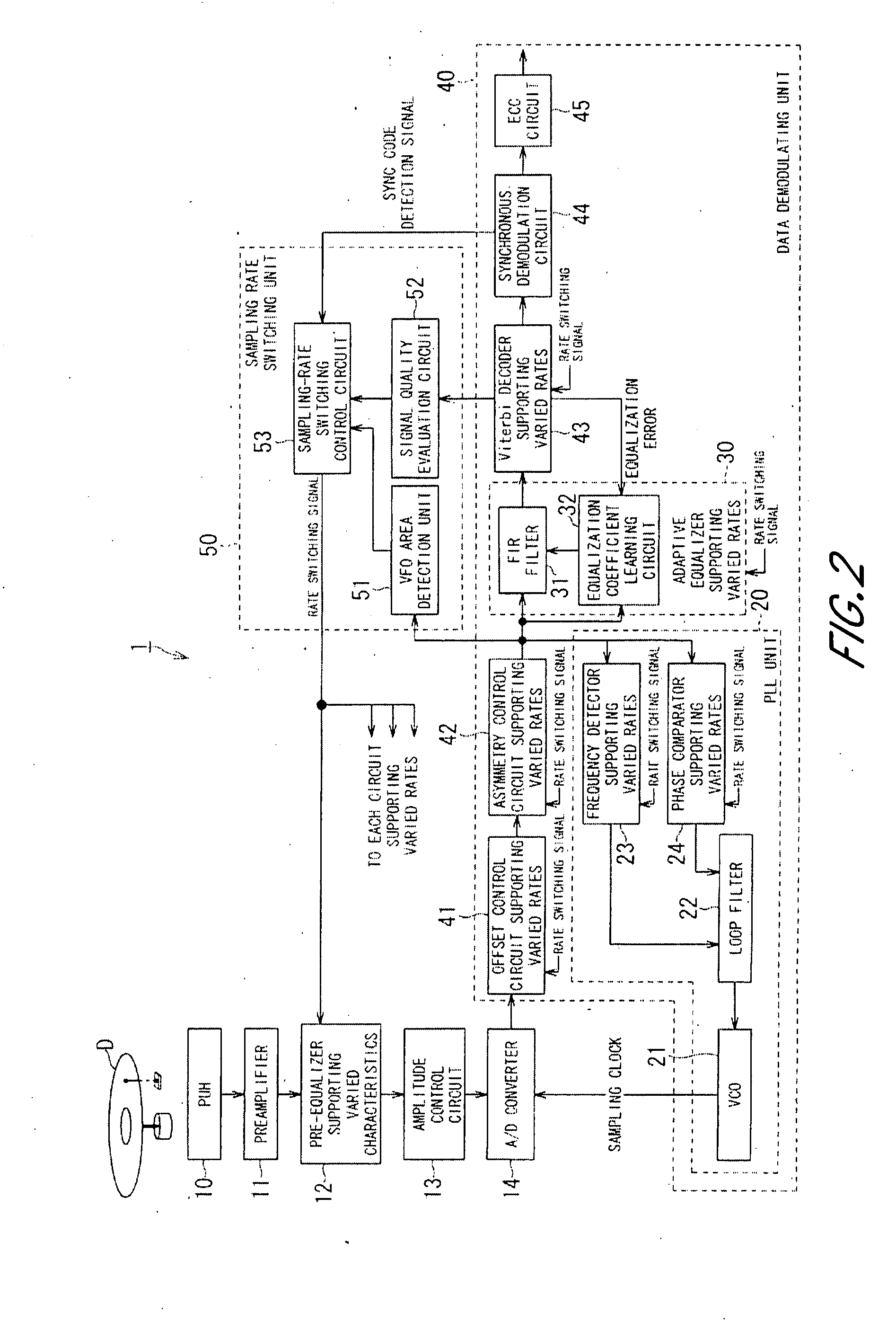

InactiveUS20080019249A1Reduce power consumptionGuaranteed uptimeTelevision system detailsModification of read/write signalsDigital dataHigh rate

An apparatus for reproducing digital data recorded on a recording medium by a Partial Response Maximum Likelihood method, the digital data being recorded in a code pattern in which the same code continuously appears at least two times, includes an analog-to-digital converting unit that samples an analog reproduction signal recorded on the recording medium and converts the sampled analog reproduction signal into a digital signal; a sampling rate switching unit that adaptively switches the sampling rate in the analog-to-digital converting unit from a higher rate to a lower rate; and a data demodulating unit that reproduces and demodulates the digital signal subjected to the analog-to-digital conversion in the analog-to-digital converting unit by the Partial Response Maximum Likelihood method in accordance with the switching between the higher rate and the lower rate.

Owner:KK TOSHIBA

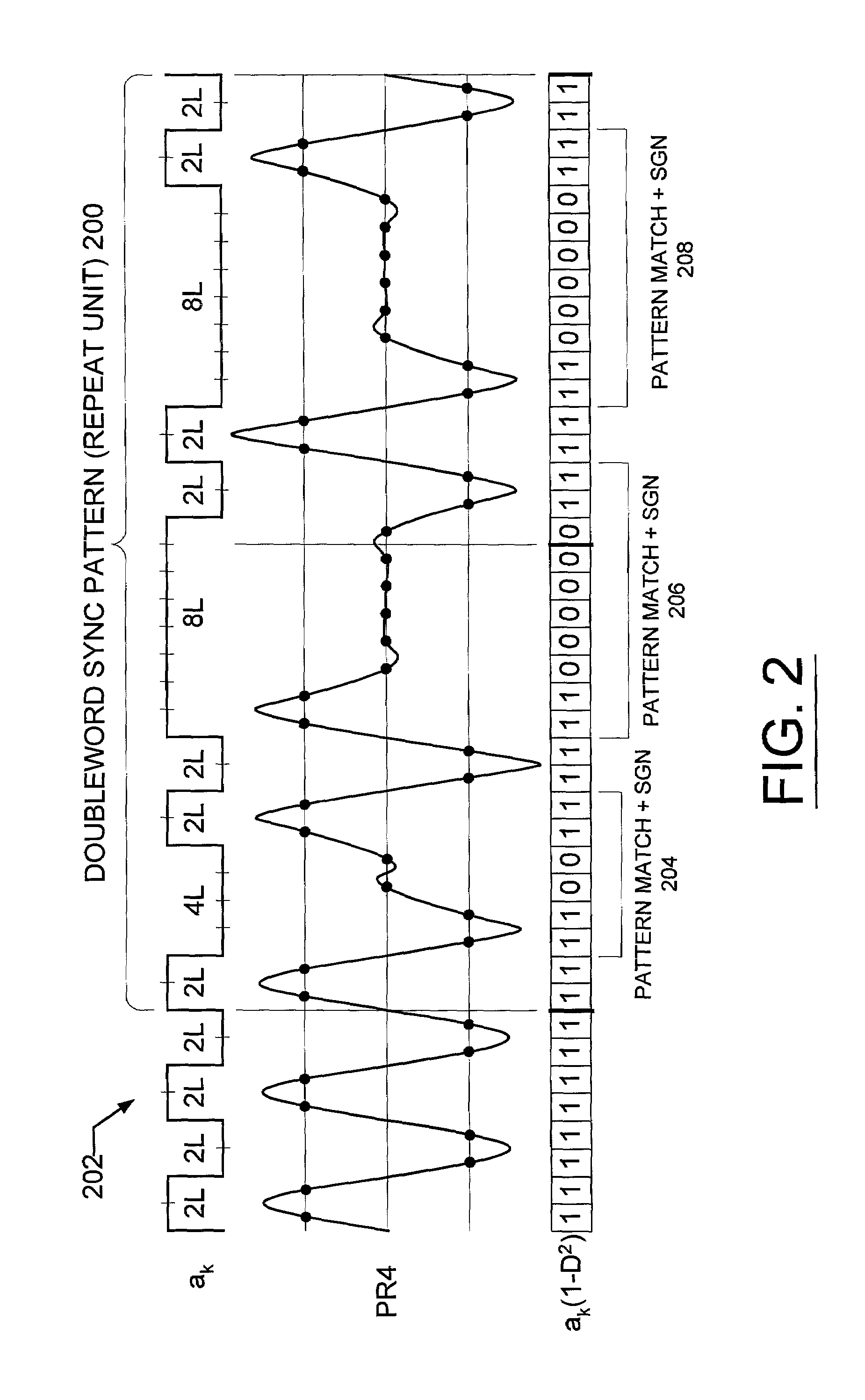

Method and apparatus for word synchronization with large coding distance and fault tolerance for PRML systems

InactiveUS7010065B2Improve performanceIncrease distanceModification of read/write signalsData representation error detection/correctionData synchronizationFault tolerance

A method and apparatus are provided for word synchronization with large coding distance and fault tolerance for a partial-response maximum-likelihood (PRML) data channel in a direct access storage device (DASD). A Viterbi detector receives equalized PR4 samples including a predefined word synchronization pattern. The Viterbi detector is a dedicated detector optimized for detecting the predefined word synchronization pattern. The Viterbi detector includes a two-state Viterbi trellis and a word synchronization detector for the two-state Viterbi trellis. The predefined word synchronization pattern includes only even length magnets. The predefined word synchronization pattern is a repetition code including pairs of ones and pairs of zeros and includes multiple pattern match sequences. The Viterbi detector is optimized with branches removed from the Viterbi trellis, thus increasing coding distance. The two-state Viterbi trellis and word synchronization detector of the Viterbi detector operate on a 2T basis, where 1 / T is the sample rate.

Owner:WESTERN DIGITAL TECH INC

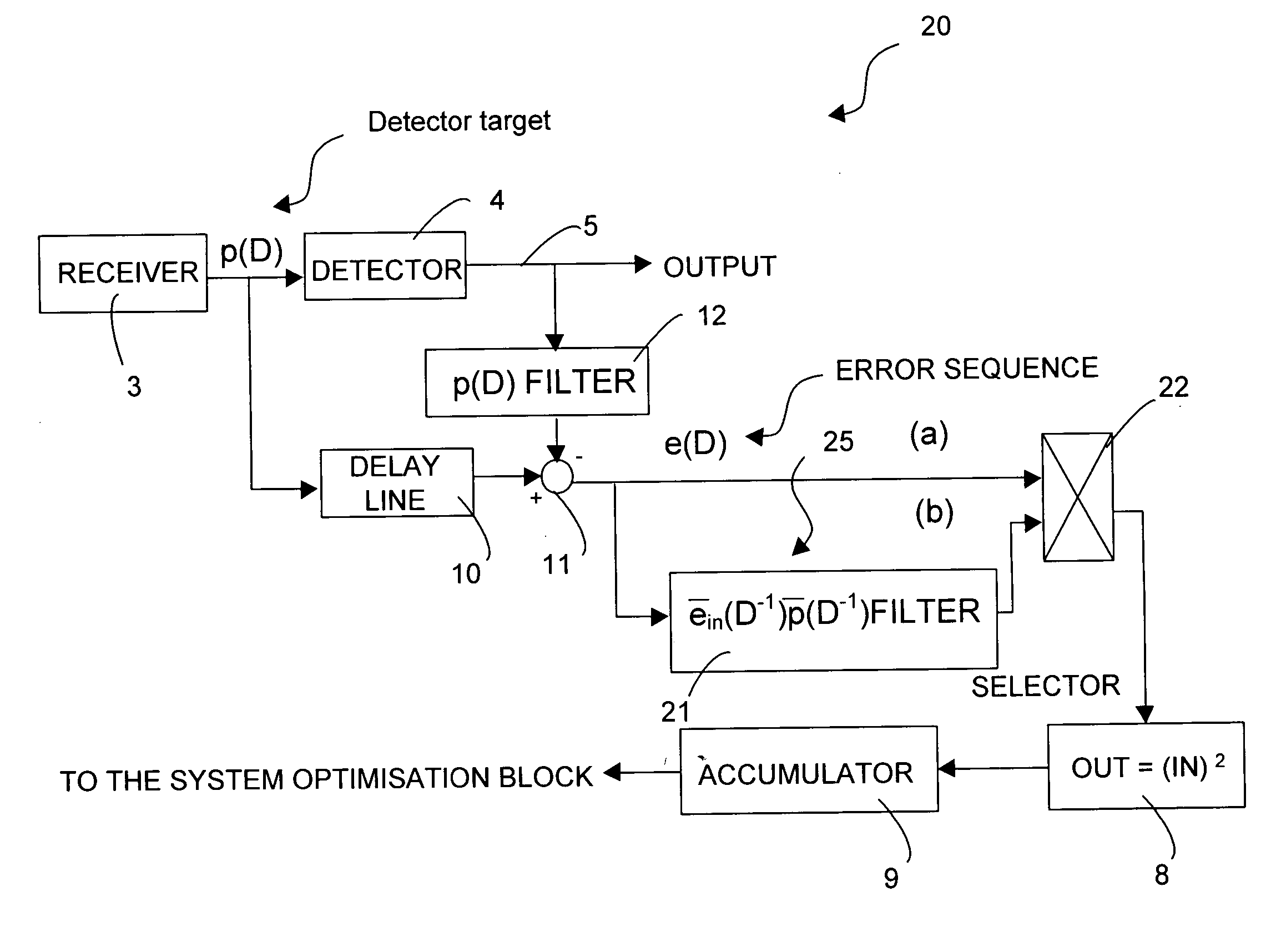

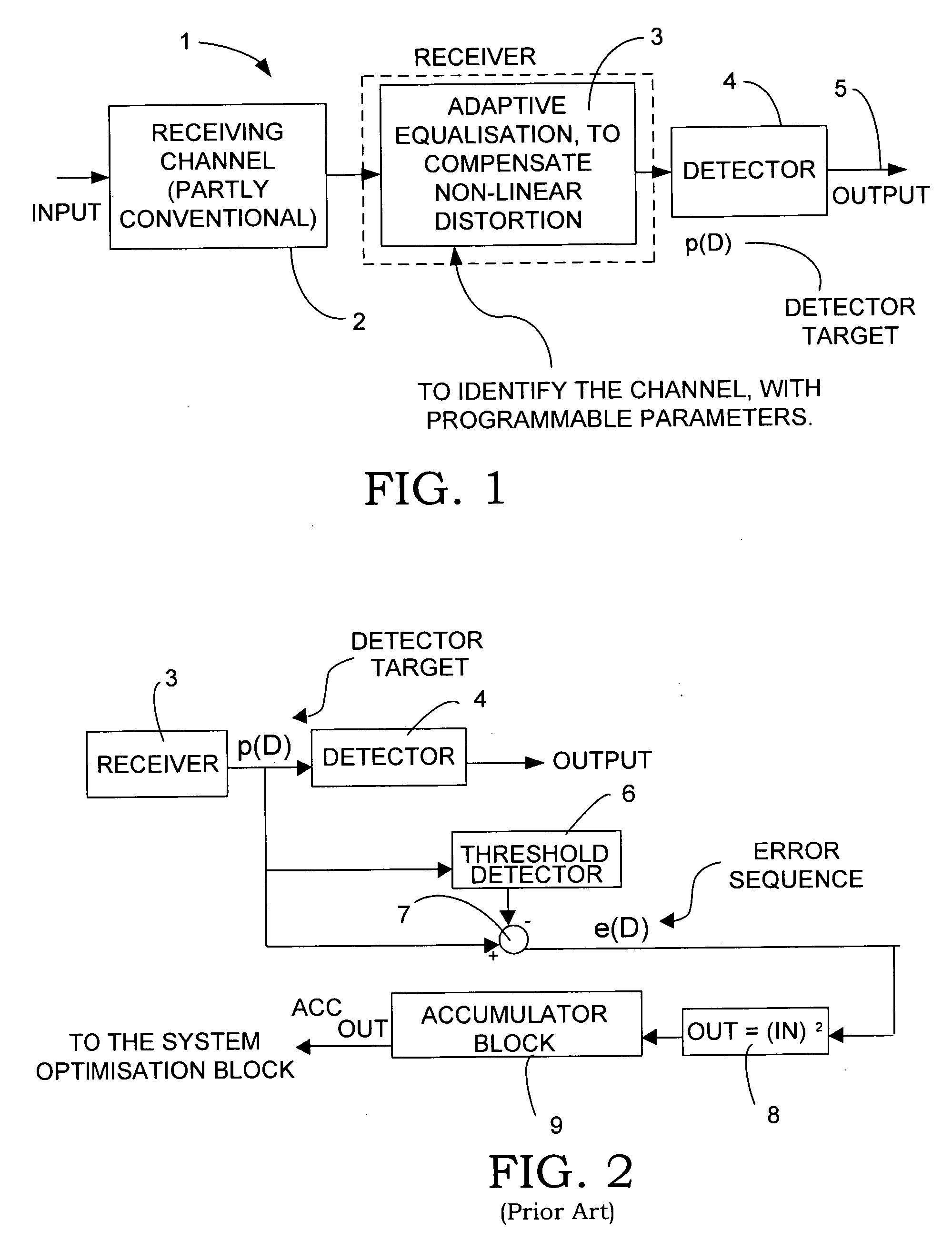

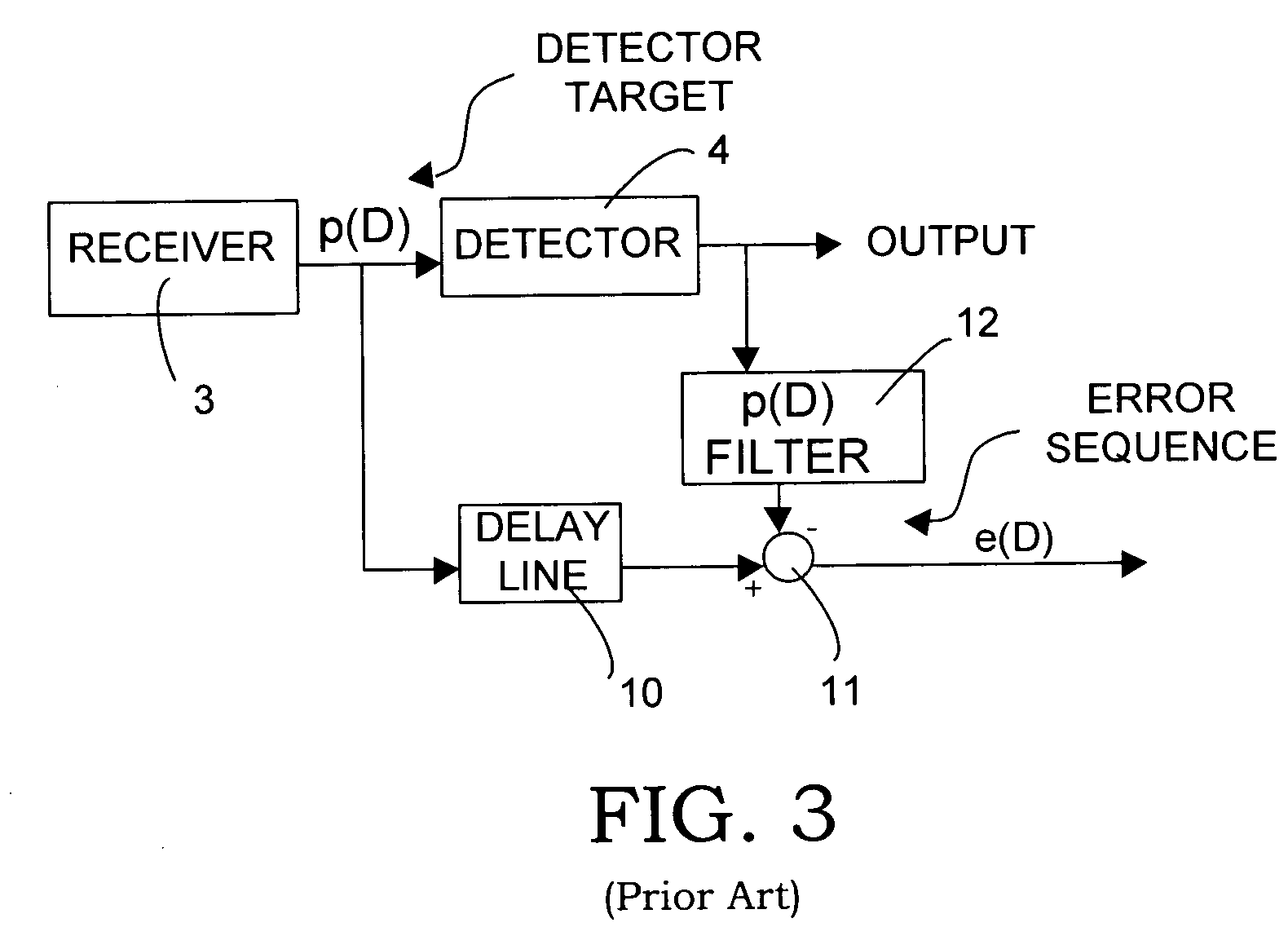

Method and apparatus for optimizing a PRML data-receiving channel for data-storage systems

InactiveUS20060171049A1Modification of read/write signalsRecord information storageMass storageEngineering

A method is provided for optimizing a PRML (Partial Response Maximum Likelihood) receiving channel for mass memory data receiving systems comprising an input receiving channel, a receiver placed downstream of the channel, a detector connected in cascade to the receiver, and a summing node being input both the receiver output through a delay line, and the output from the detector through an impulsive filter. The method includes performing an indirect estimate of the noise strength by filtering out the error sequence, i.e. the output signal from the summing node, through a filter, and selecting either the output from the summing node or the output from the filter to obtain an optimization parameter for feedback to the receiving system.

Owner:STMICROELECTRONICS SRL

Arrangment for adaptive bit recovery

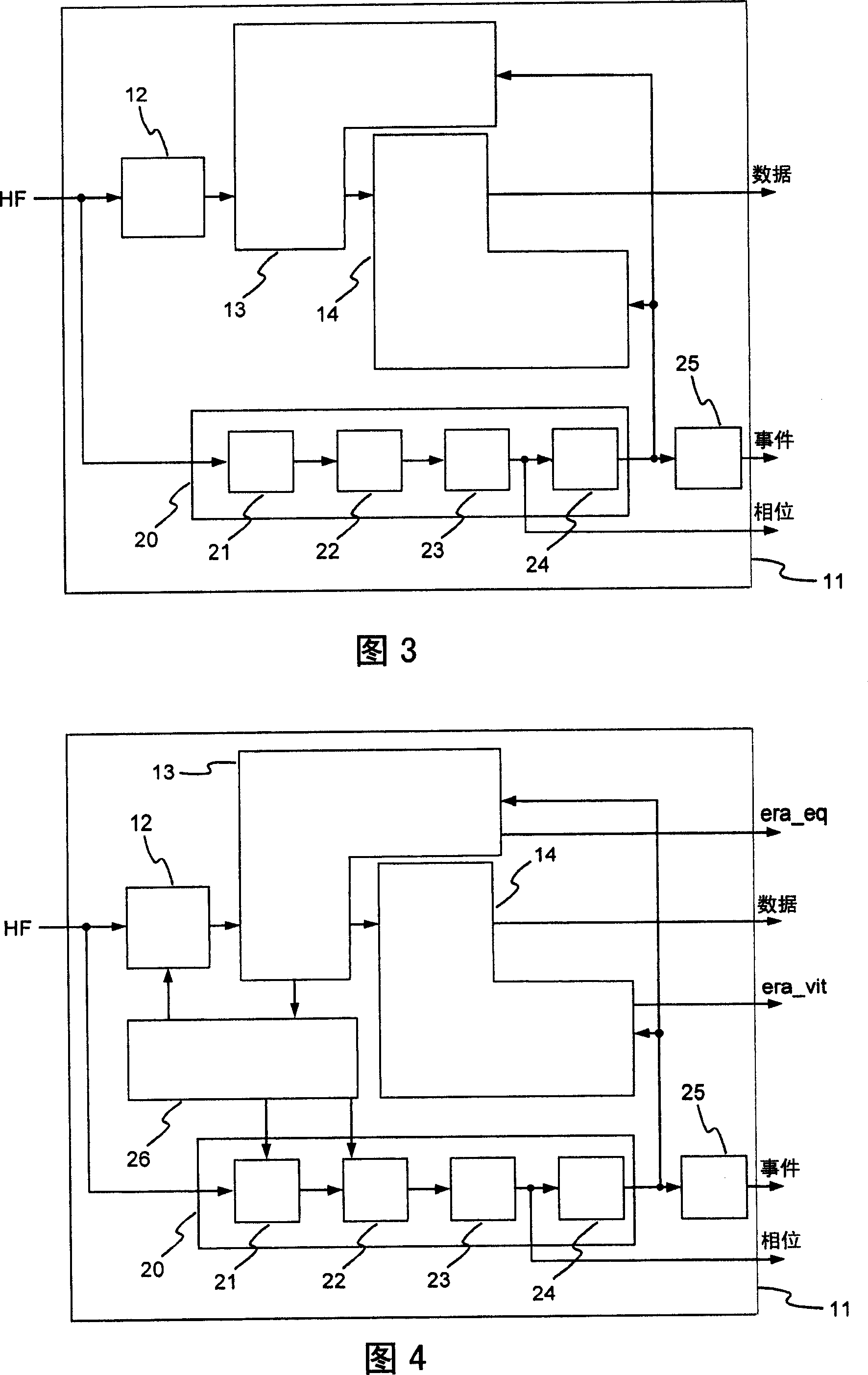

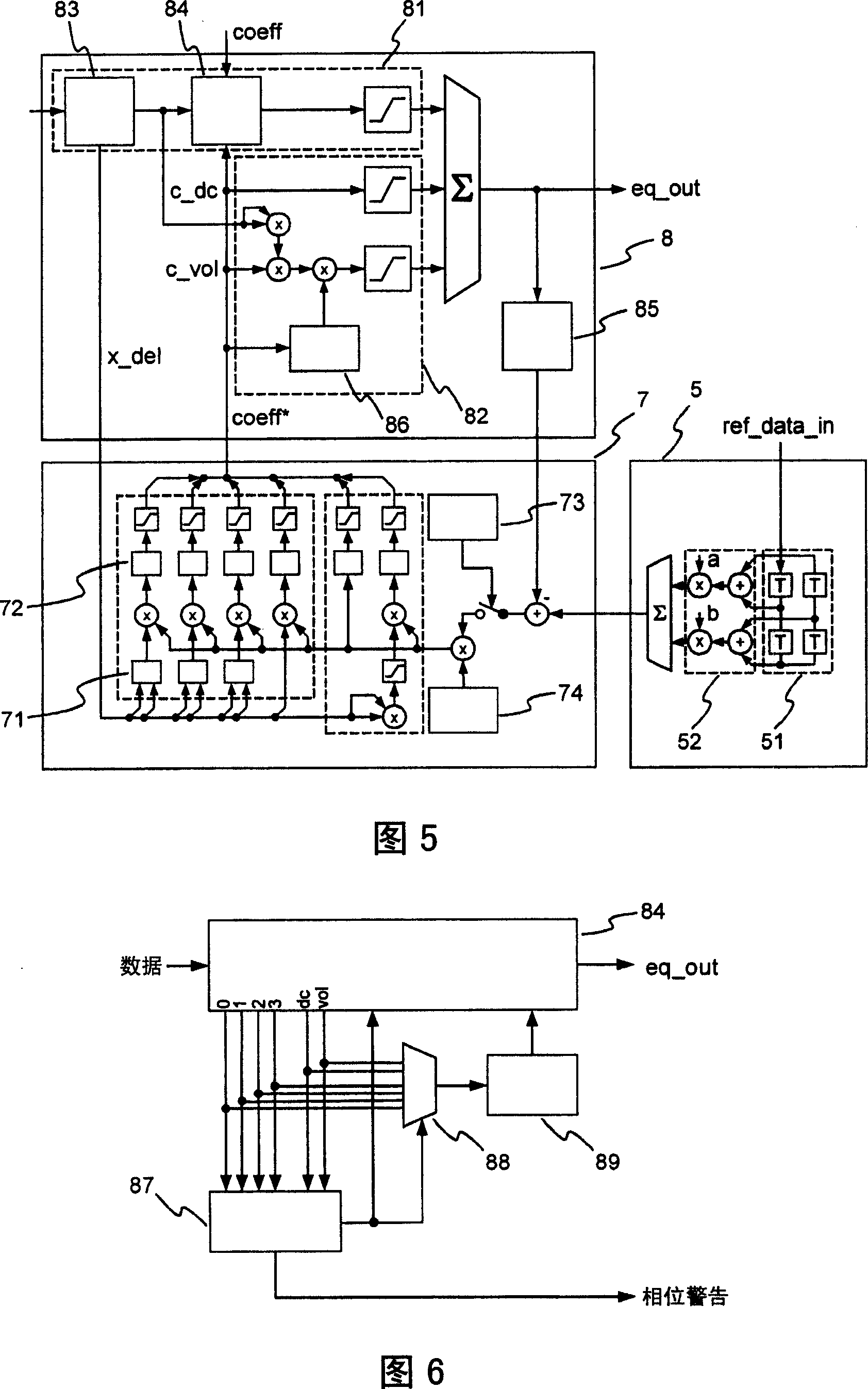

InactiveCN101099295AModification of read/write signalsOther decoding techniquesComputer hardwareSelf adaptive

The present invention relates to an arrangement for adaptive bit recovery, and to an apparatus for reading from and / or writing to recording media using such arrangement. According to the invention, an arrangement for adaptive bit recovery including an adaptive equalizer (13) and an adaptive partial response maximum likelihood detector (14) further includes an overflow control block (86) for the adaptive equalizer (13) for monitoring one or more of the adaptation coefficients and / or a state violation checker (162) for monitoring the allowed states and indicating state violations as well as and a noise detector (155) for detecting larger deviations of the target values.

Owner:THOMSON LICENSING SA

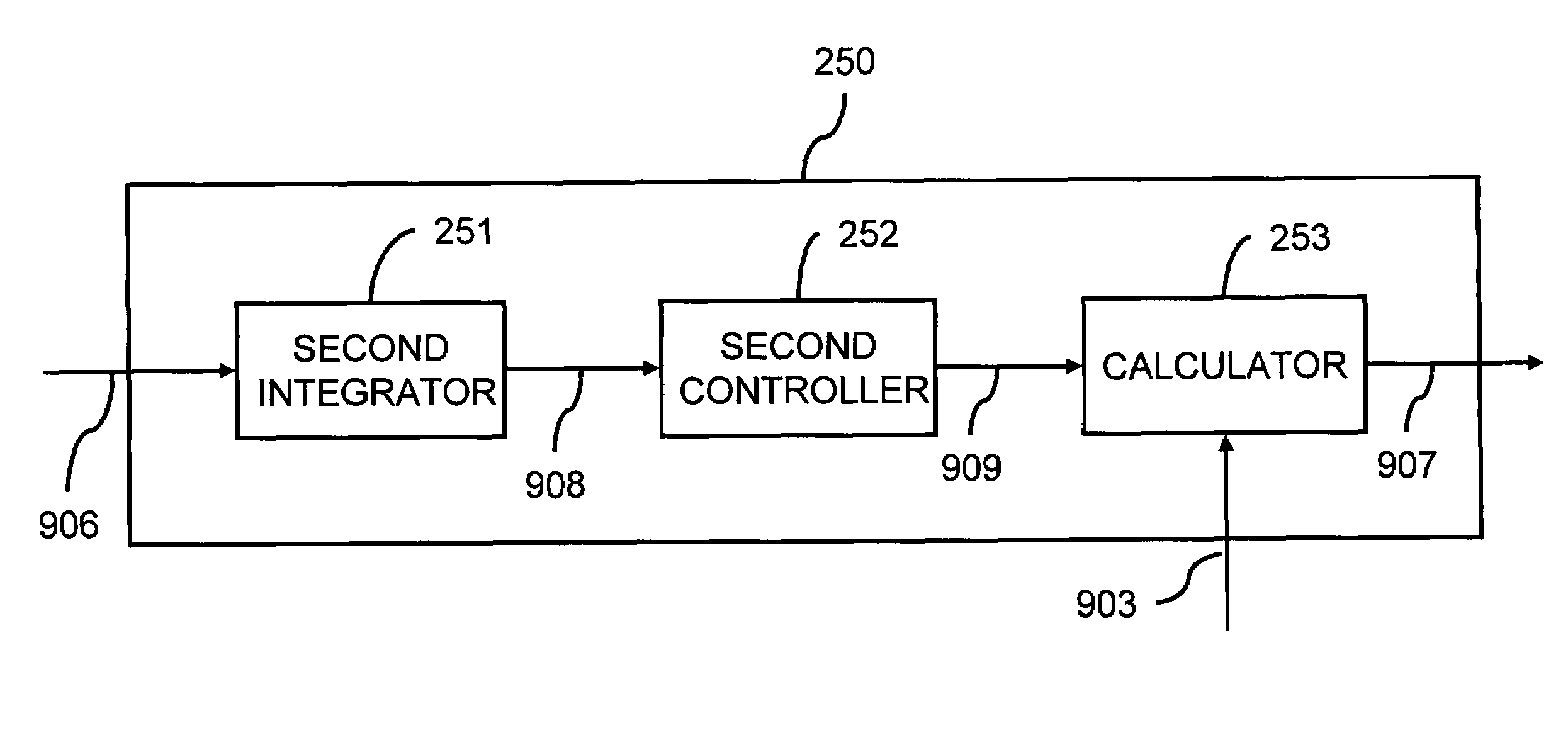

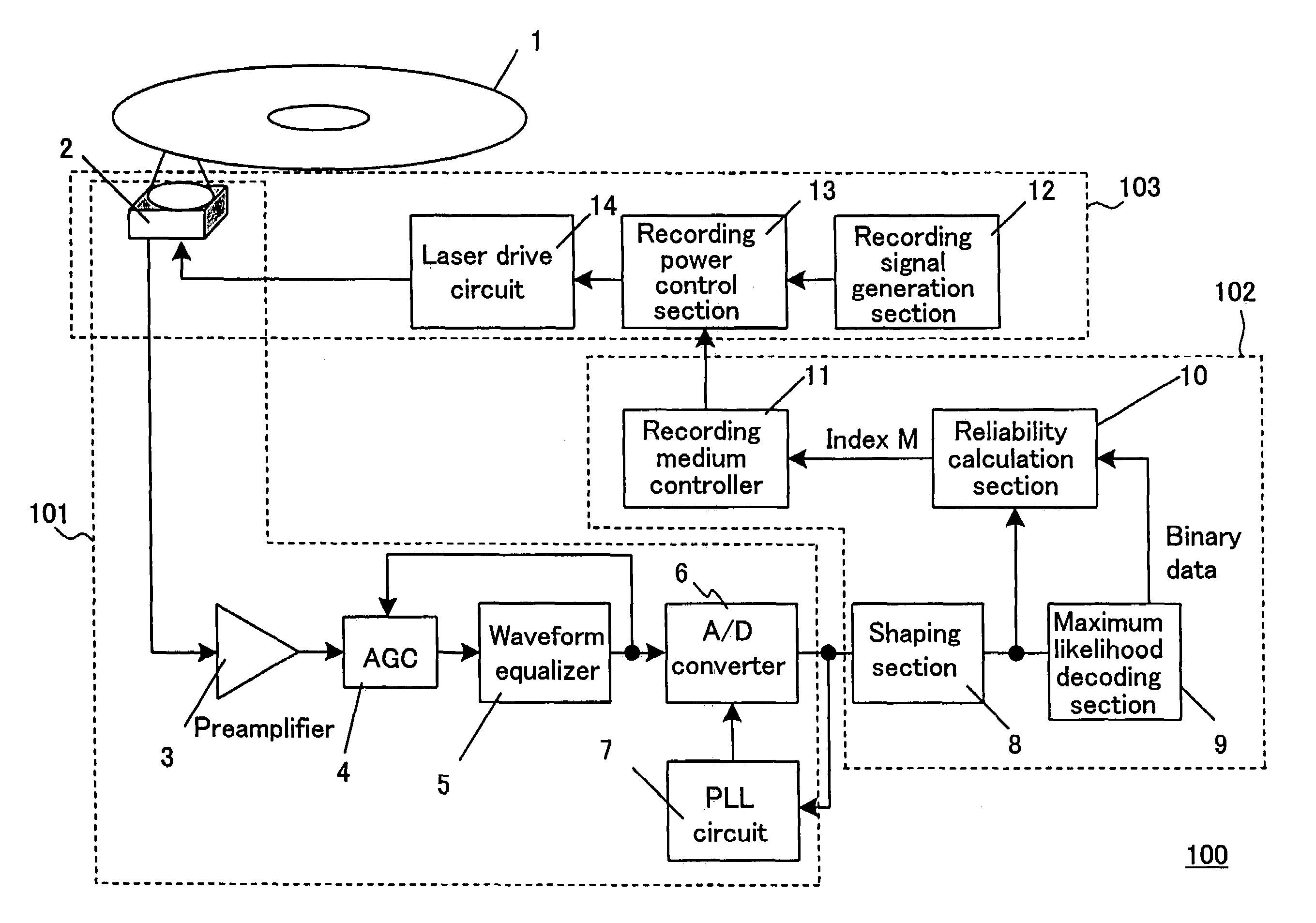

Recording/reproduction apparatus which adjusts recording power based on a partial response maximum likelihood (PRML) technique

ActiveUS7646686B2High sensitivityTelevision system detailsFilamentary/web record carriersPartial-response maximum-likelihoodComputer science

A recording / reproduction apparatus, comprising a first recording section for recording test information onto a medium using at least one recording power, a reproduction section for reproducing at least one test signal indicating the test information from the medium, and a second recording section for recording information onto the medium using one of the at least one recording power. The reproduction section comprises a decoding section for performing maximum likelihood decoding of the at least one test signal and generating at least one binary signal indicating a result of the maximum likelihood decoding, a calculation section for calculating a reliability of the result of the maximum likelihood decoding based on the at least one test signal and the at least one binary signal, and an adjustment section for adjusting a recording power for recording the information onto the medium to the one recording power based on the reliability.

Owner:PANASONIC CORP

Data decoding method and circuit and information recording and reproducing apparatus using the same

InactiveUS20060156208A1Raise the possibilityData representation error detection/correctionOther decoding techniquesDecoding methodsMaximum likelihood detection

In a partial-response maximum-likelihood (PRML) signal detection and processing technique, reduction of data detection error events caused due to medium noise is achieved. For a PRML detection data result obtained after PRML data demodulation, a code error event that depends on a signal distance, and which has a high frequency of occurrence, is noticed and its occurrence probability is estimated. A locally-existing medium noise quantity is estimated from preceding and subsequent code patterns of the PRML detection data result. Based on this, the occurrence probability of the error event is compensated to improve the detection precision. As a result, data modulation with reliability higher than conventional maximum likelihood detection can be realized with a simple circuit structure.

Owner:WESTERN DIGITAL TECH INC

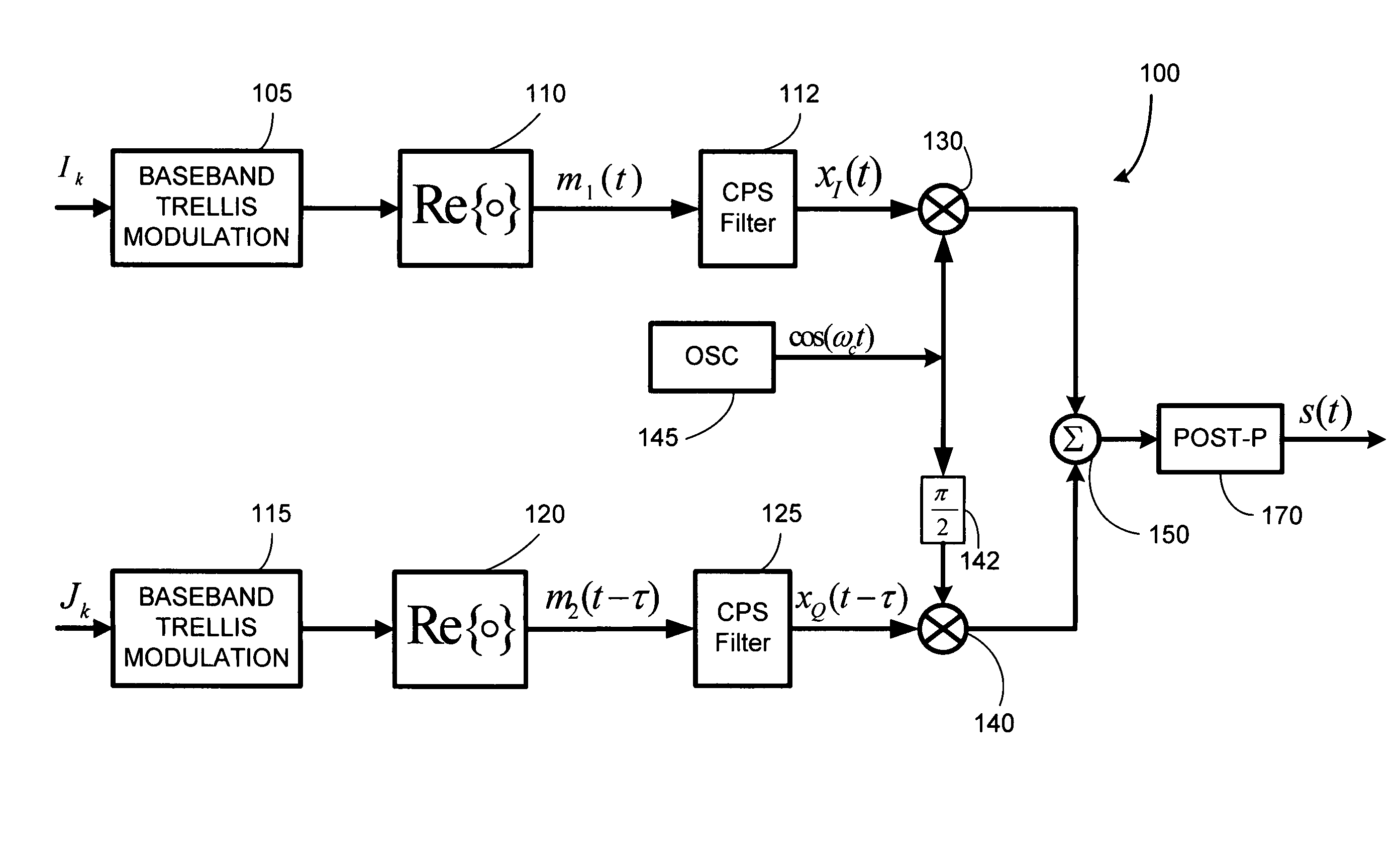

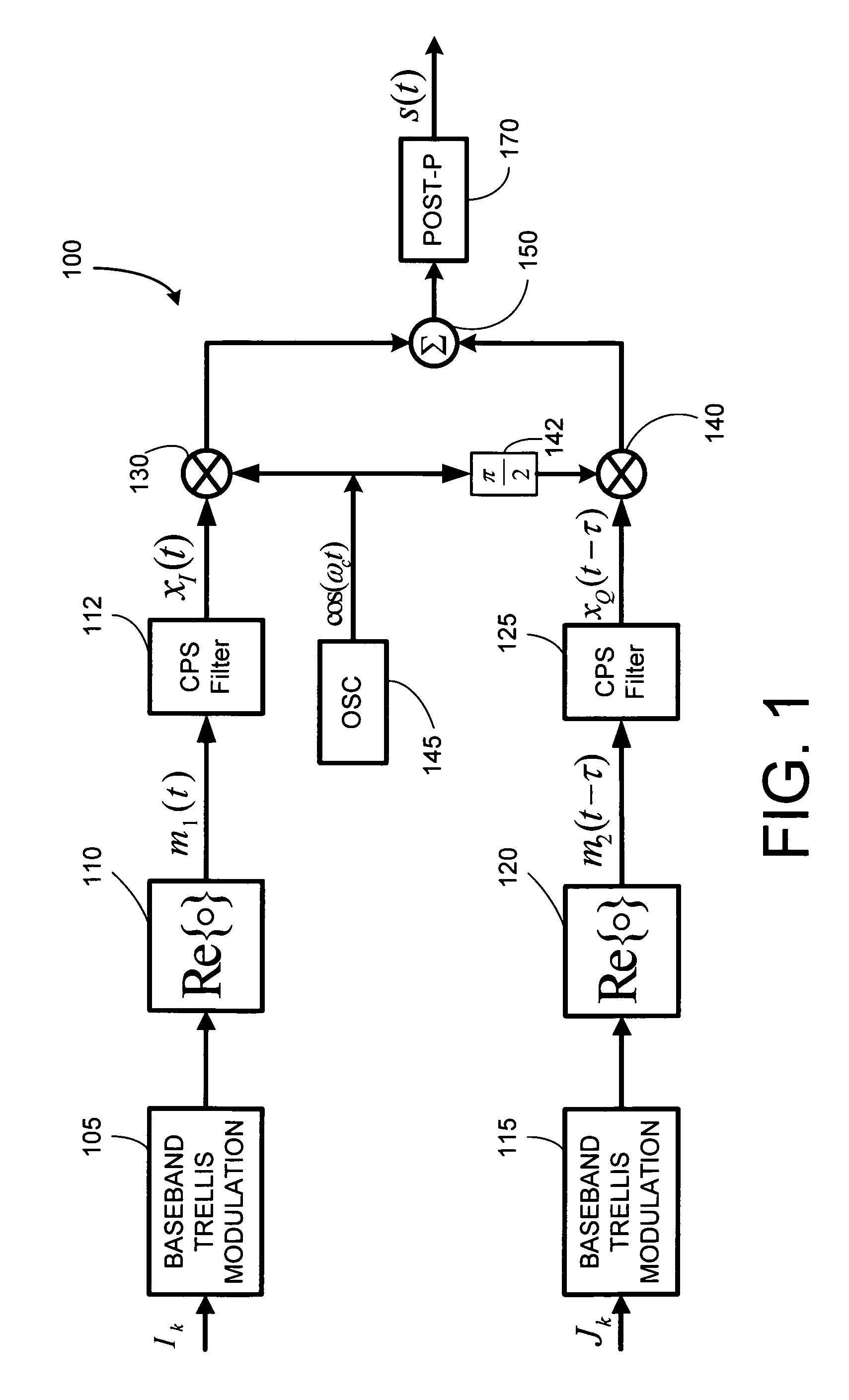

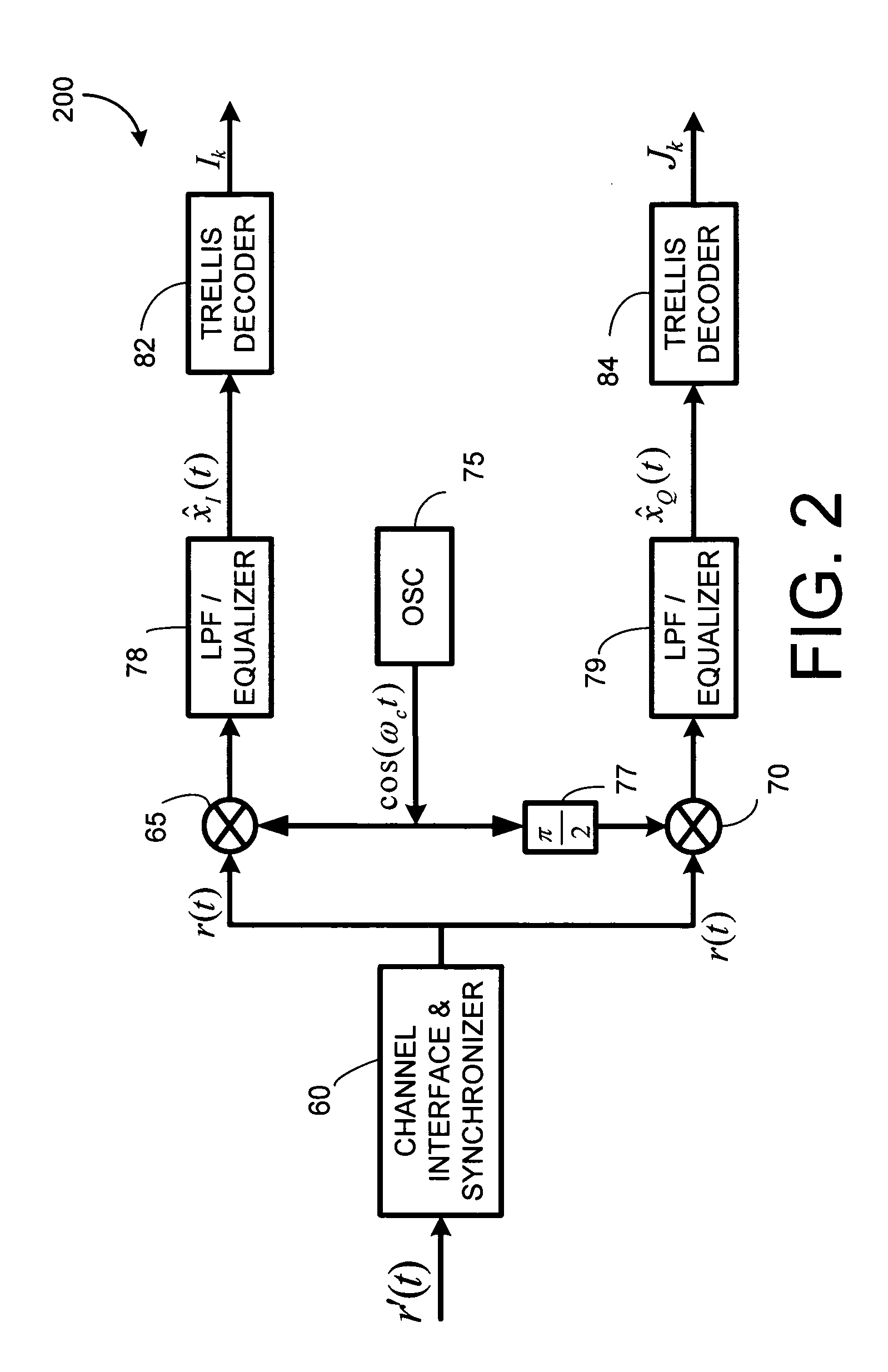

Compact pulse shaping for QM-MSK and PAM/QAM transmission

InactiveUS20110188603A1Modulation with suppressed carrierAmplitude-modulated carrier systemsHigh bandwidthPulse shaping

Compact pulse shape partial response (CPS PR) signaling is developed for trellis based signals like QM-MSK, and for PAM / QAM type signals to improve the performance to bandwidth tradeoff. Compact pulse shaped signals are partial response signals that employ a very short pulse shaping filter and use Viterbi decoding to optimally detect the CPS signal in presence of its inherent inter-symbol interference. The CPS filters considered herein have much shorter impulse response than the well-known raised cosine (RC) filter. There is no need to equalize the received signal to eliminate ISI or to allow a fixed amount of ISI between received signal samples as sampled at the symbol rate as is common in partial response maximum likelihood (PRML) systems. Numerical results indicate that CPS QM-MSK and CPS QAM provides between several dB of gain, depending on constellation size, over PR-CPM and RC QAM, when compared at a given value of bandwidth, i.e., B99Tb.

Owner:TRELLIS PHASE COMM LP

Nonlinear equalizer and decoding circuit and method using same

InactiveUS20020171961A1Eliminate interferenceLess memoryMultiple-port networksModification of read/write signalsSignal conditioningEngineering

A decoding circuit has a nonlinear equalizer which employs a signal conditioning algorithm for conditioning a partial response sampled signal to eliminate intersymbol interference. The inventive decoding circuit has an analog-to-digital converter for sampling an analog signal, a linear equalizer for adjusting the amplitude and phase relations of the sampled signal, a nonlinear equalizer for conditioning the sampled signal and outputting a partial response sampled signal having two nonzero samples, and a partial response maximum likelihood detector, for detecting the partial response sampled signal having two nonzero samples.

Owner:IBM CORP

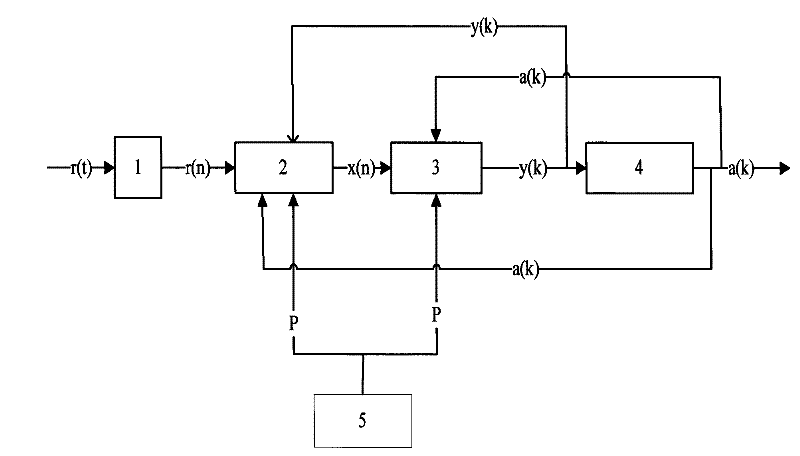

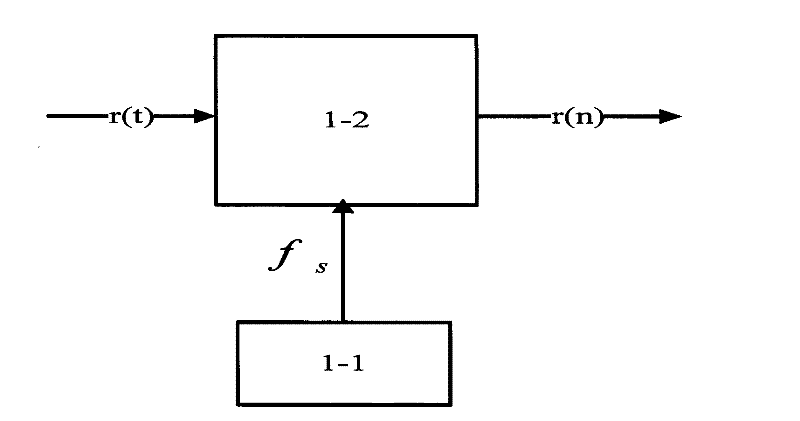

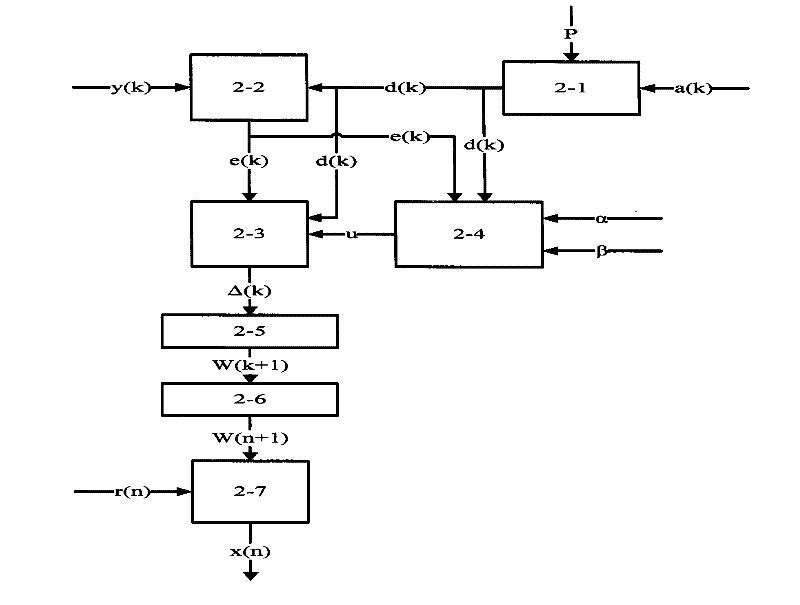

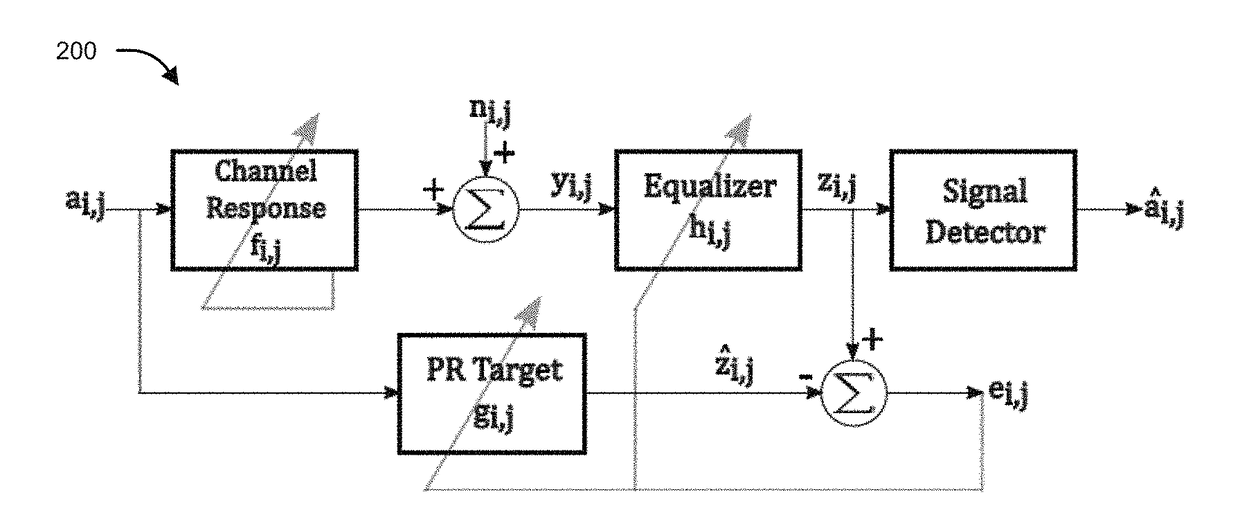

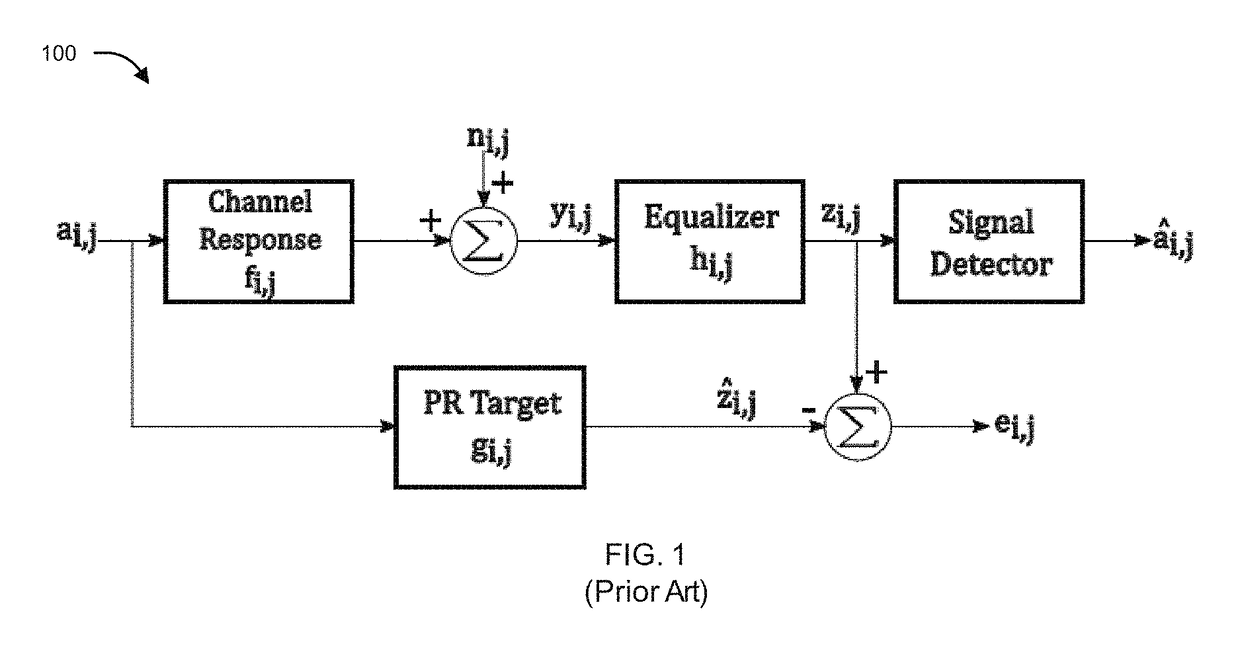

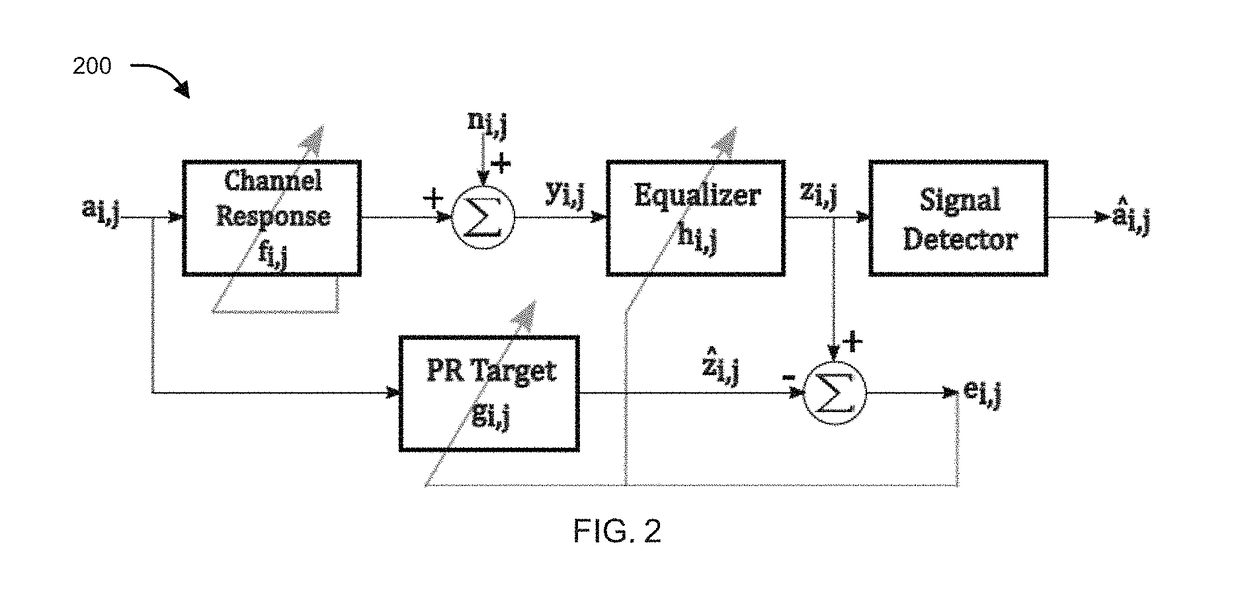

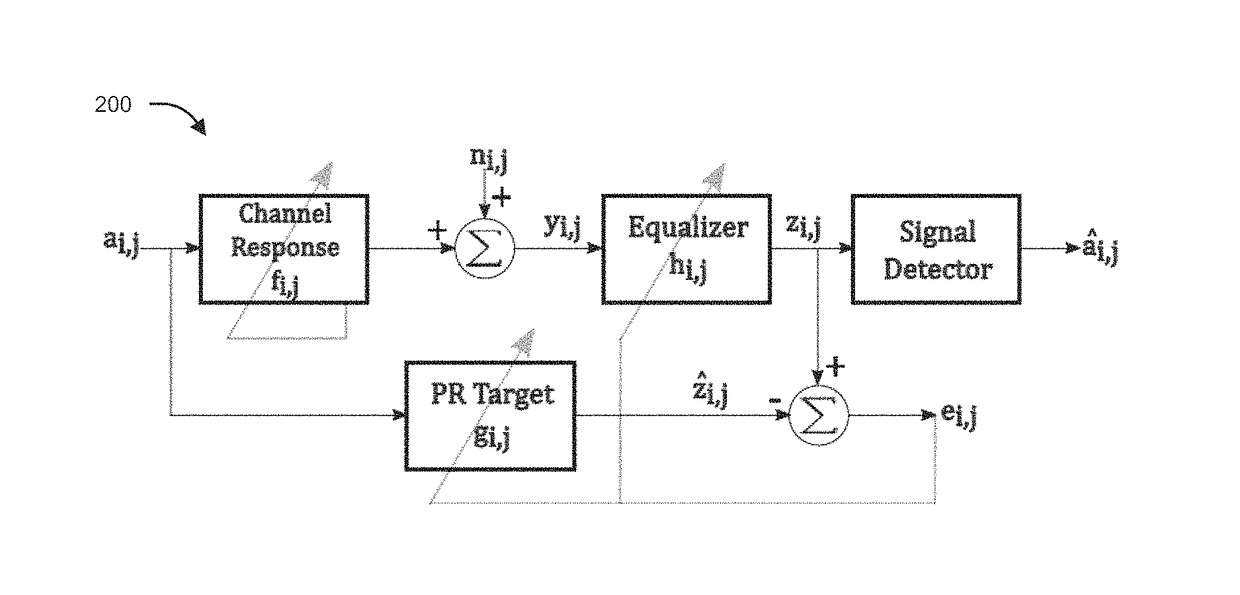

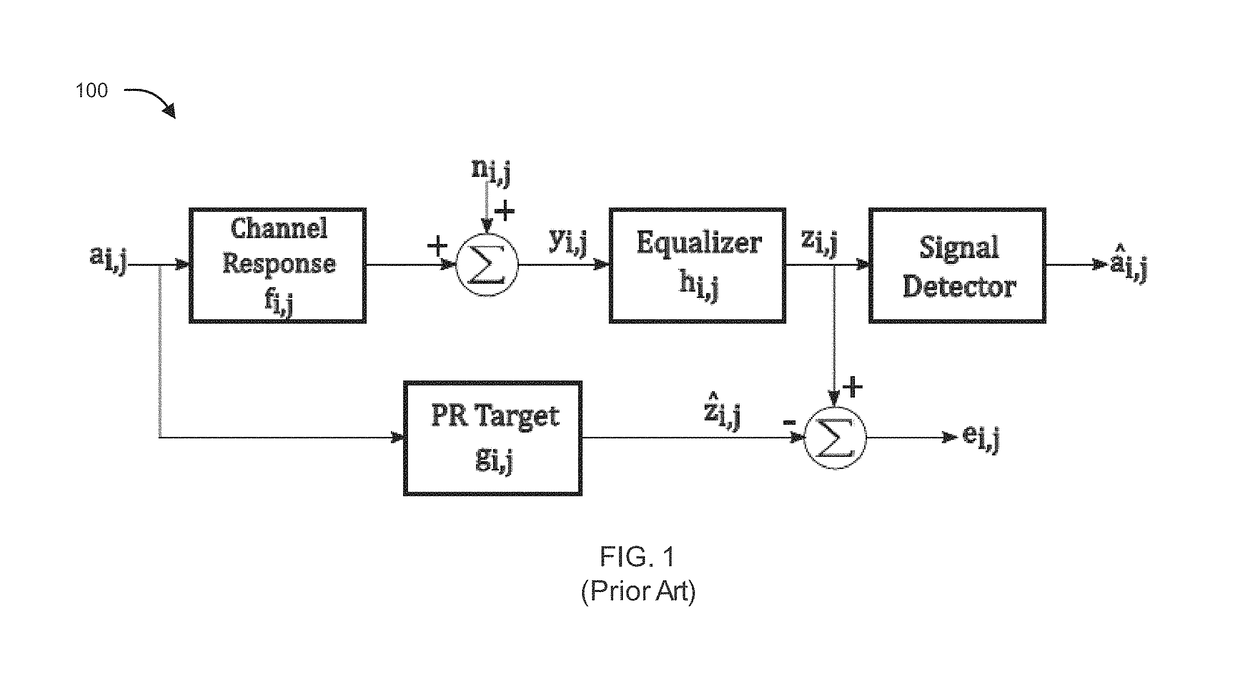

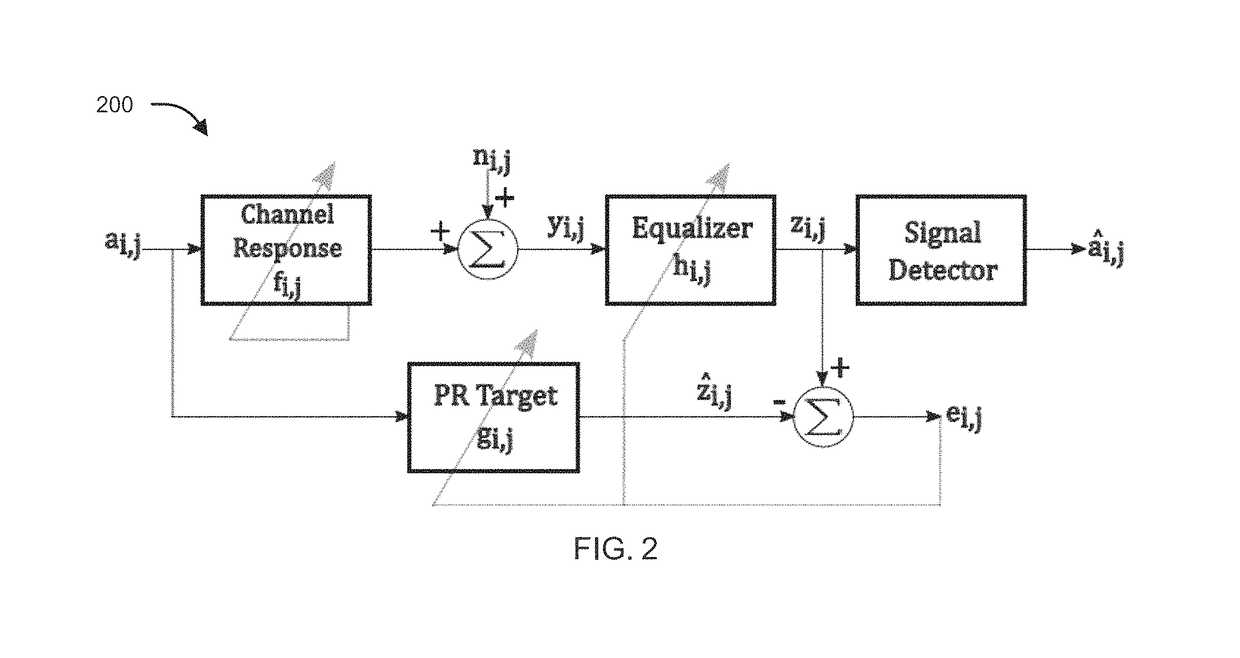

Method and apparatus for joint adaptation of two-/multi- dimensional equalizer and partial response target

ActiveUS20180018997A1Increase bit densitySimple designModification of read/write signalsRecord information storageAlgorithmData recording

The present disclosure relates to a method and apparatus for processing of multi-dimensional readback signal from magnetic recording or optical, physical data recording so as to reduce / control Inter Symbol Interference (ISI) and noise within acceptable limits. The method is based on Partial Response Maximum Likelihood (PRML) detection and takes care of time varying channel conditions. In an embodiment, the filter coefficients of both the equalizer and the partial response (PR) target are jointly adapted to account for the channel condition for both separable and non-separable targets thus reducing signal detection complexity. In an aspect, the disclosure provides an apparatus that incorporates an adaptation engine along with the equalizer and the PR target that updates filter coefficients of both the equalizer and the PR target following the formulated mathematical equations.

Owner:INDIAN INSTITUTE OF SCIENCE

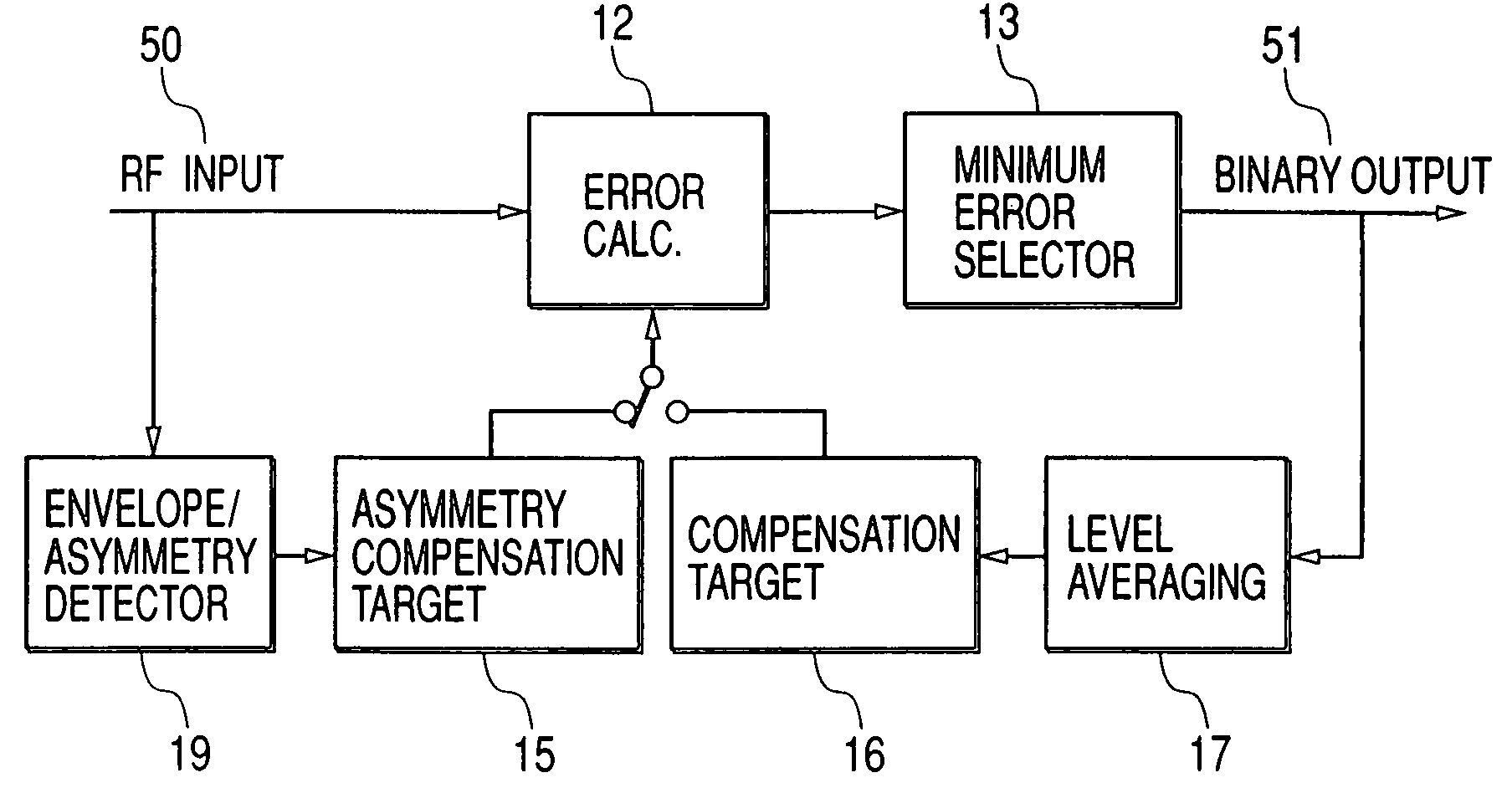

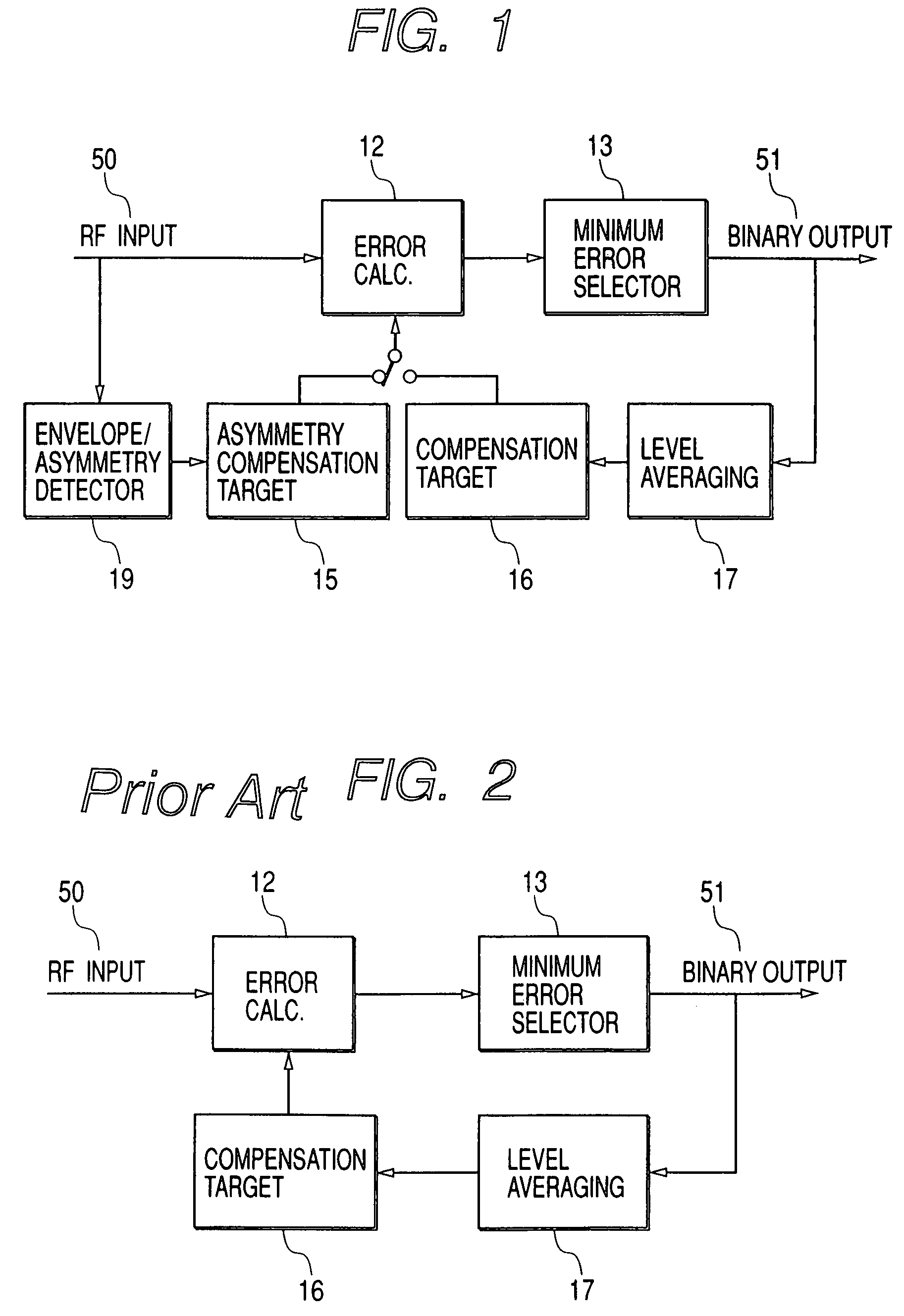

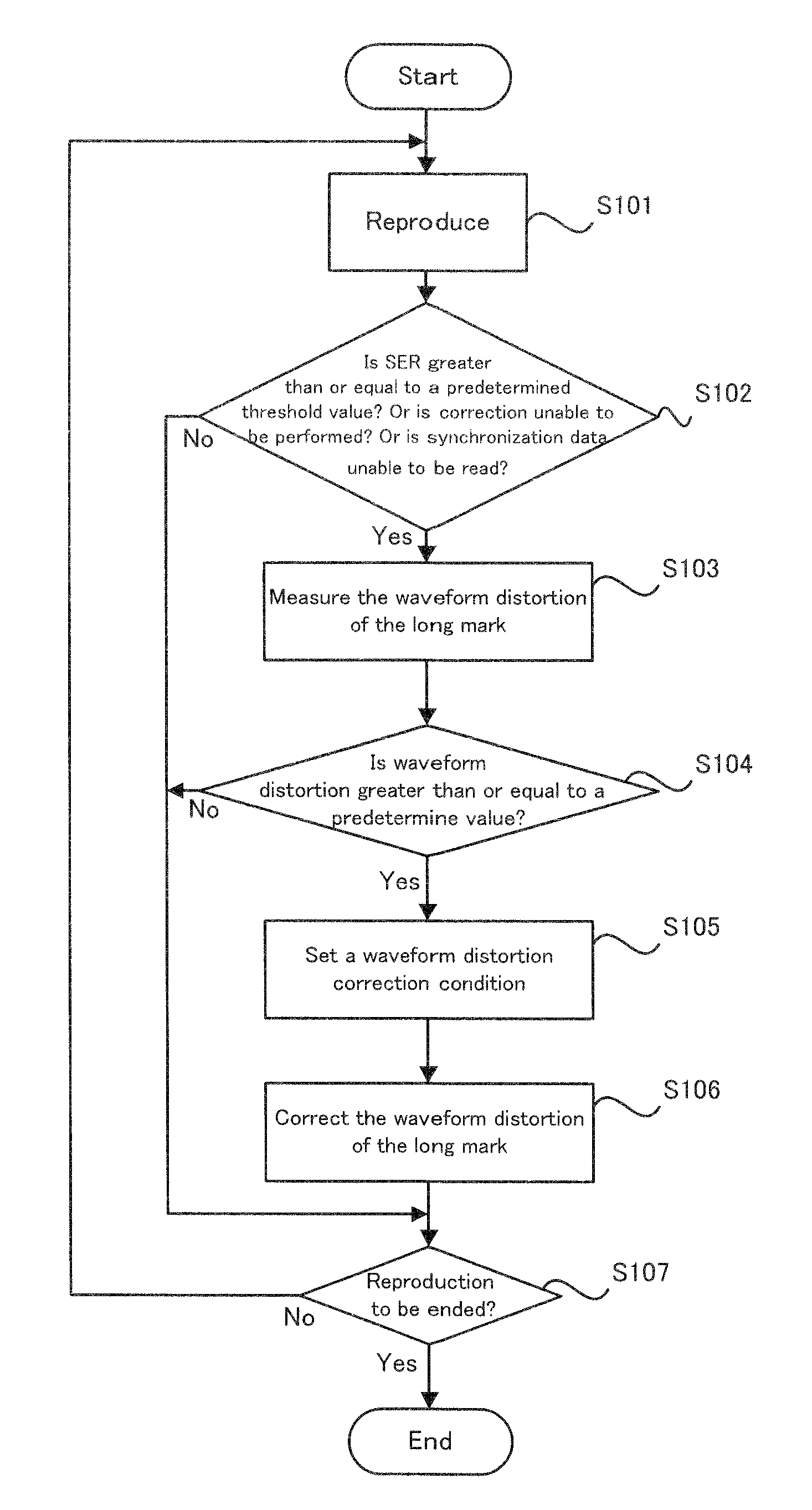

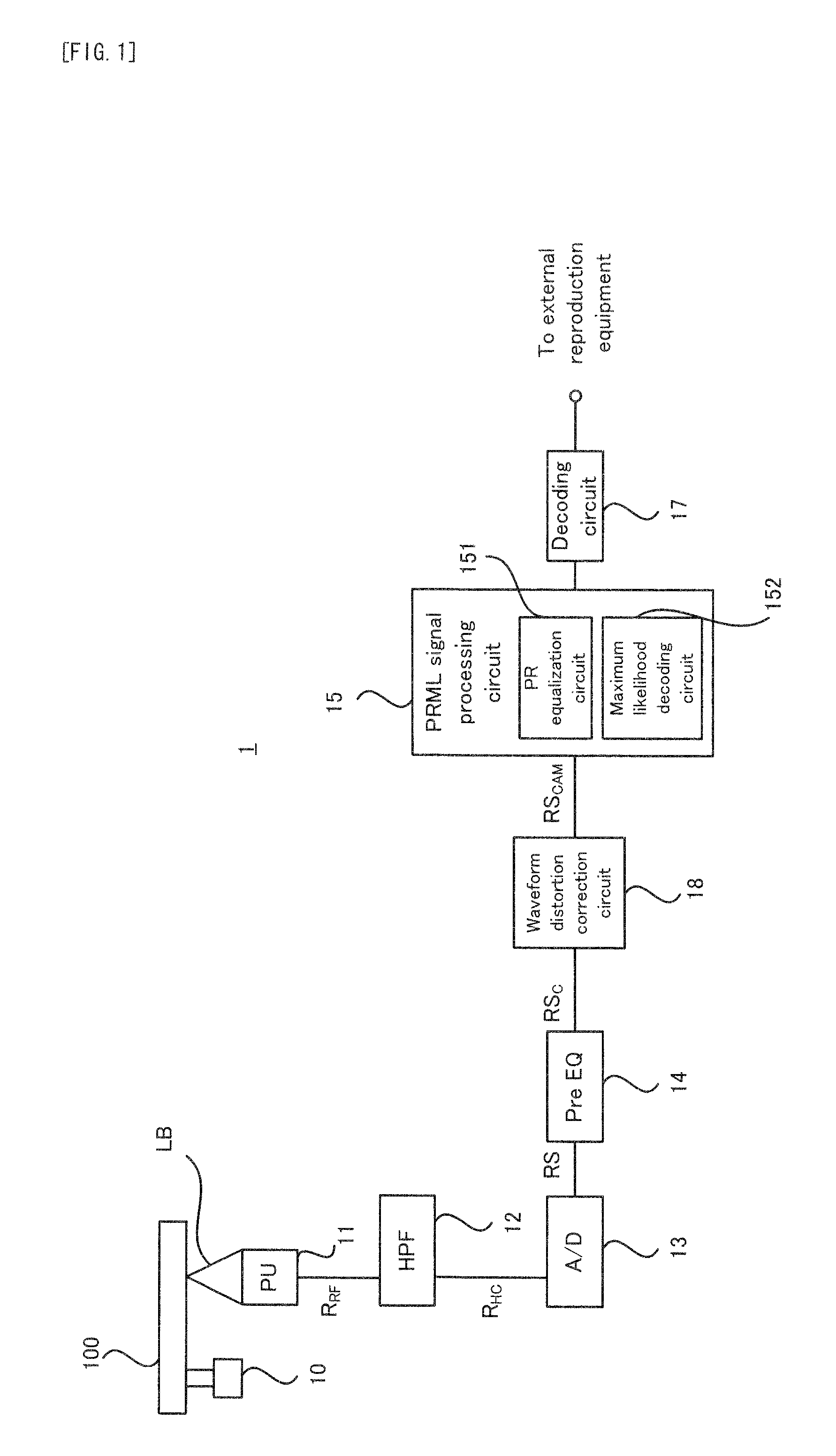

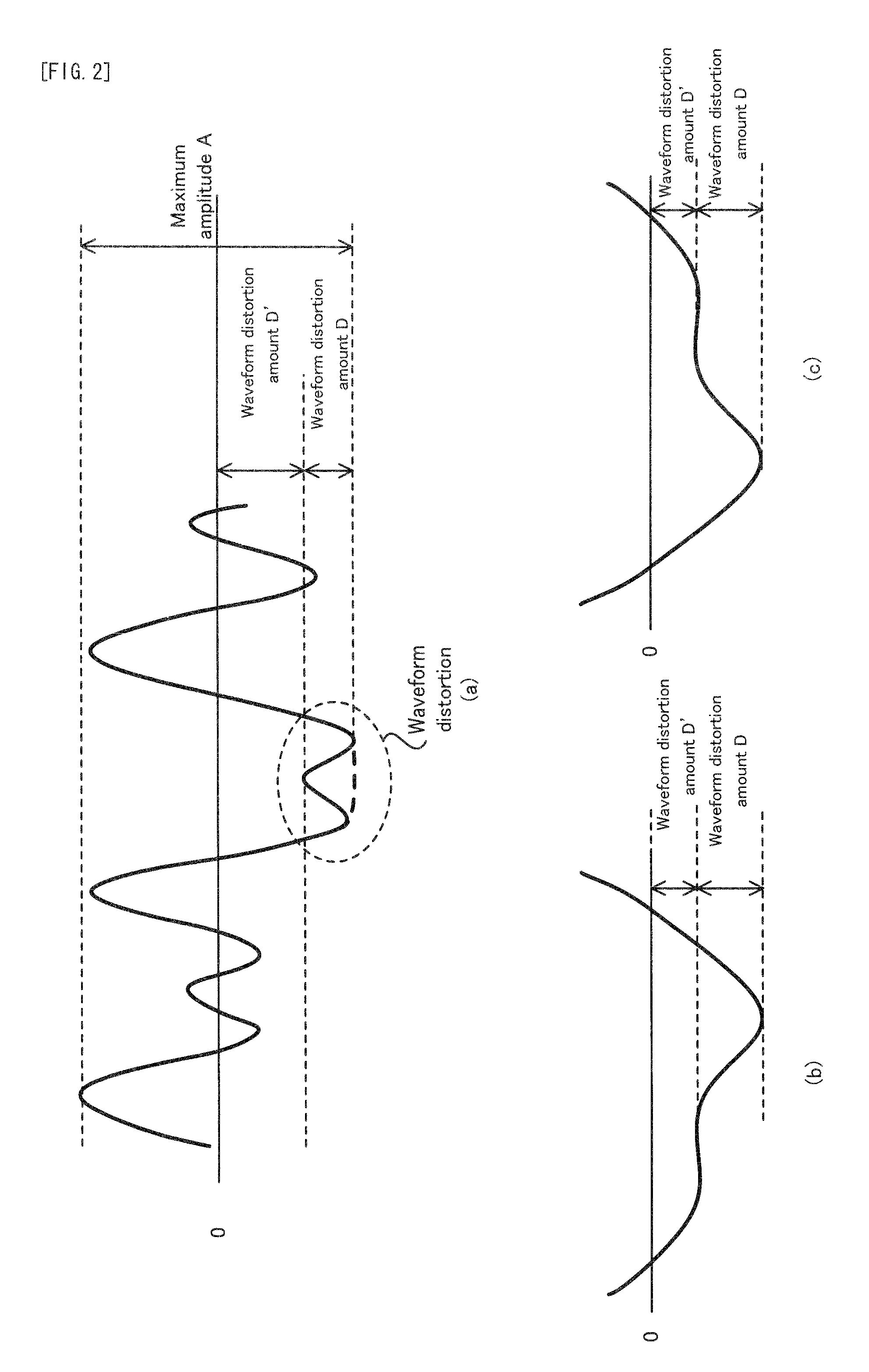

PRML (partial response maximum likelihood) information reproducing method and information reproducing apparatus for implementing the same

InactiveUS7440379B2Excellent readout performance without any deterioration in media interchangeabilityInterchangeability is assuredTelevision system detailsBathsPartial-response maximum-likelihoodComputer science

An information reproducing method using PRML technology which provides asymmetry compensation and also assures media interchangeability. To compensate for asymmetry, target levels are basically adapted to readout signals and either restriction type (1) (time reversal and level reversal symmetry) or restriction type (2) (time reversal symmetry) is imposed between target levels. As a consequence, asymmetry compensation is made regardless of a readout signal distortion such as mark shift which might deteriorate media interchangeability.

Owner:HITACHI-LG DATA STORAGE +1

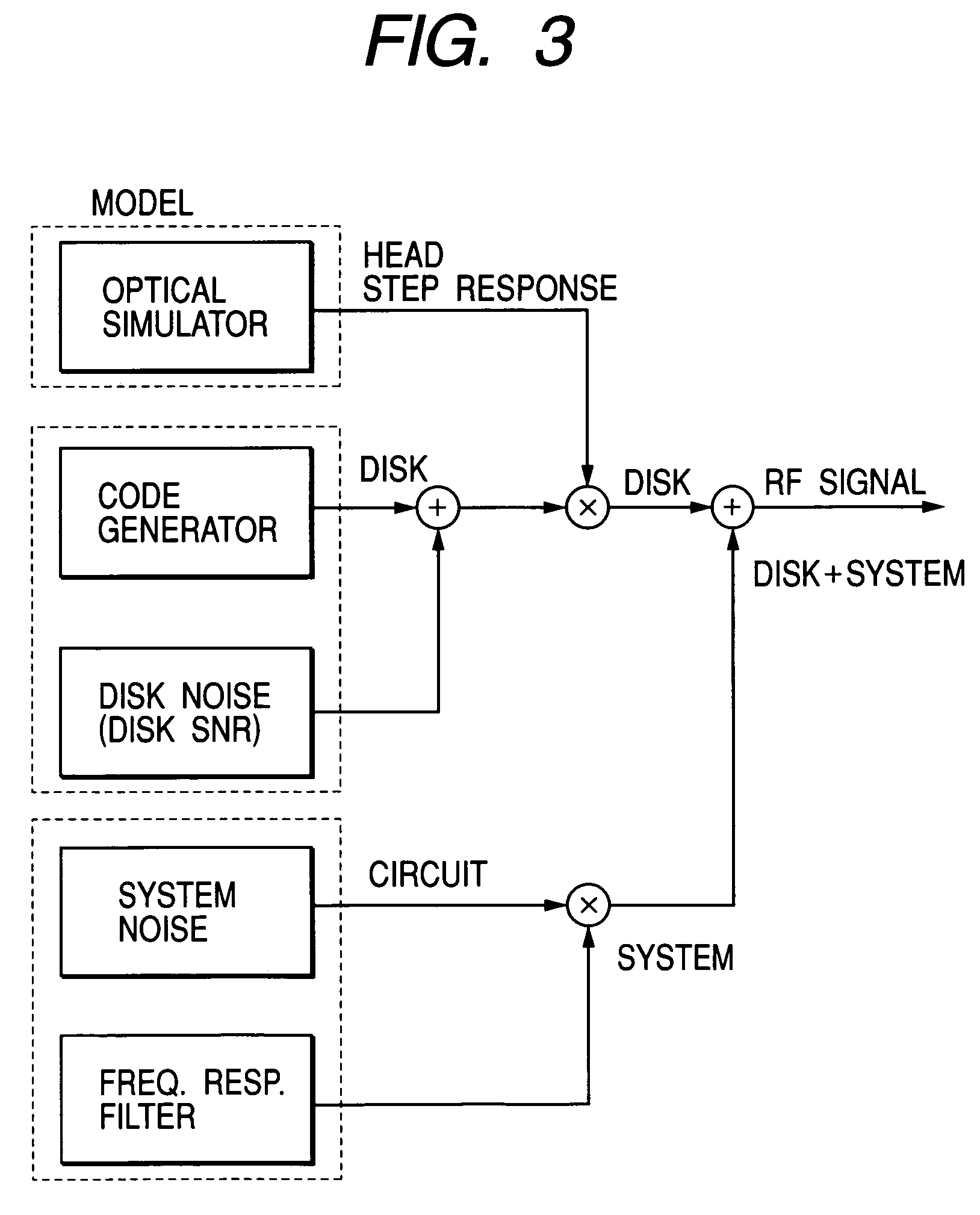

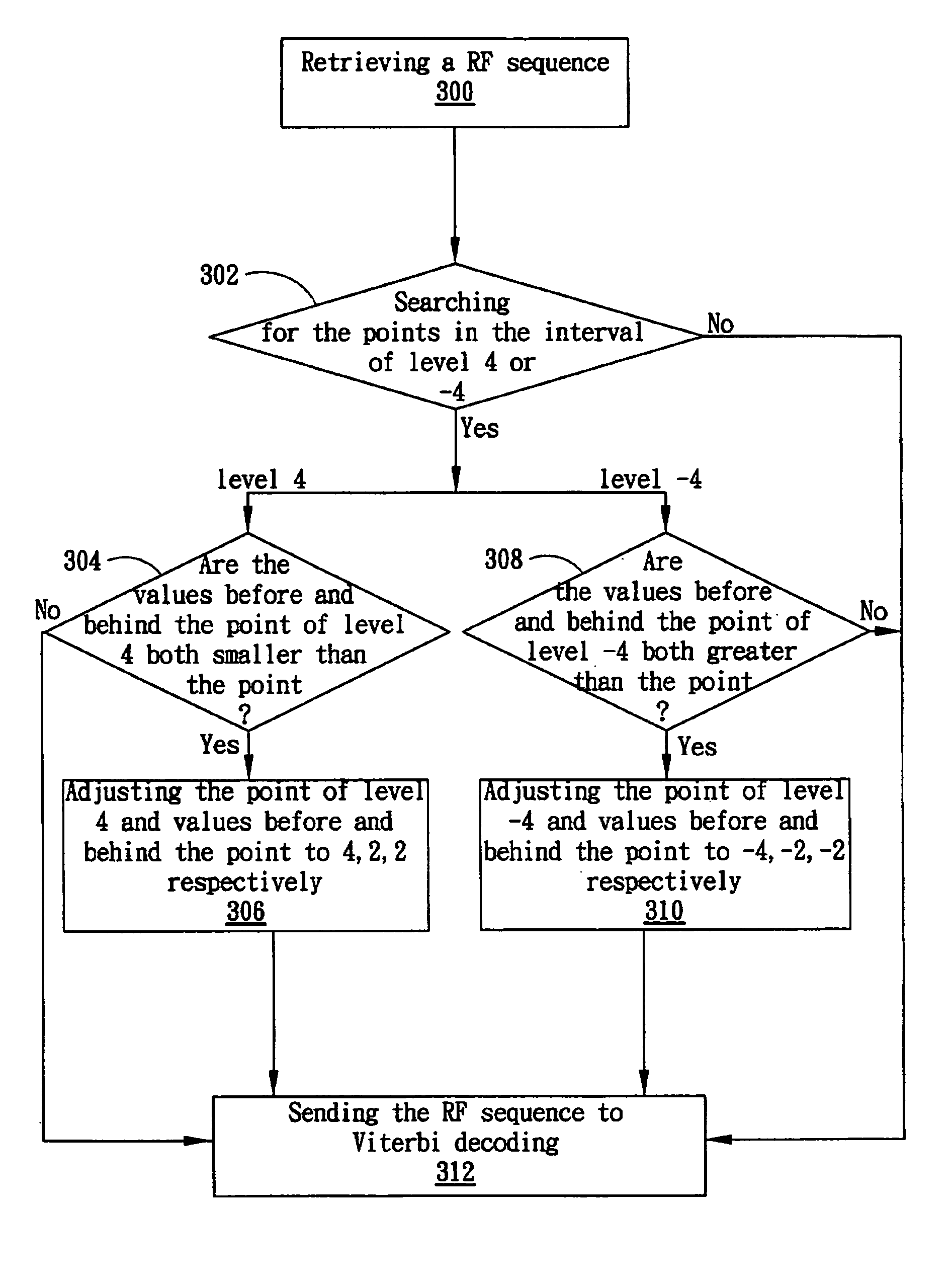

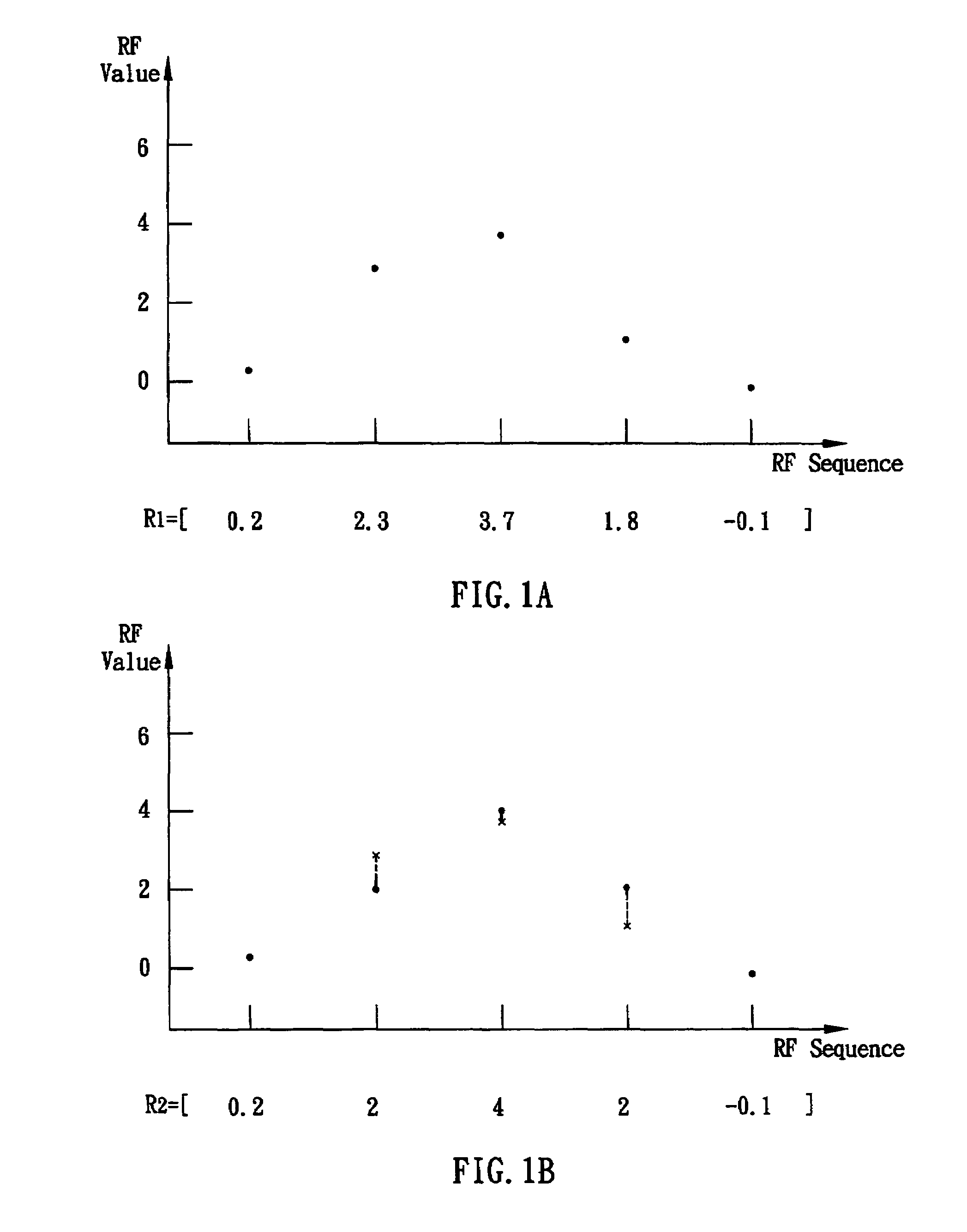

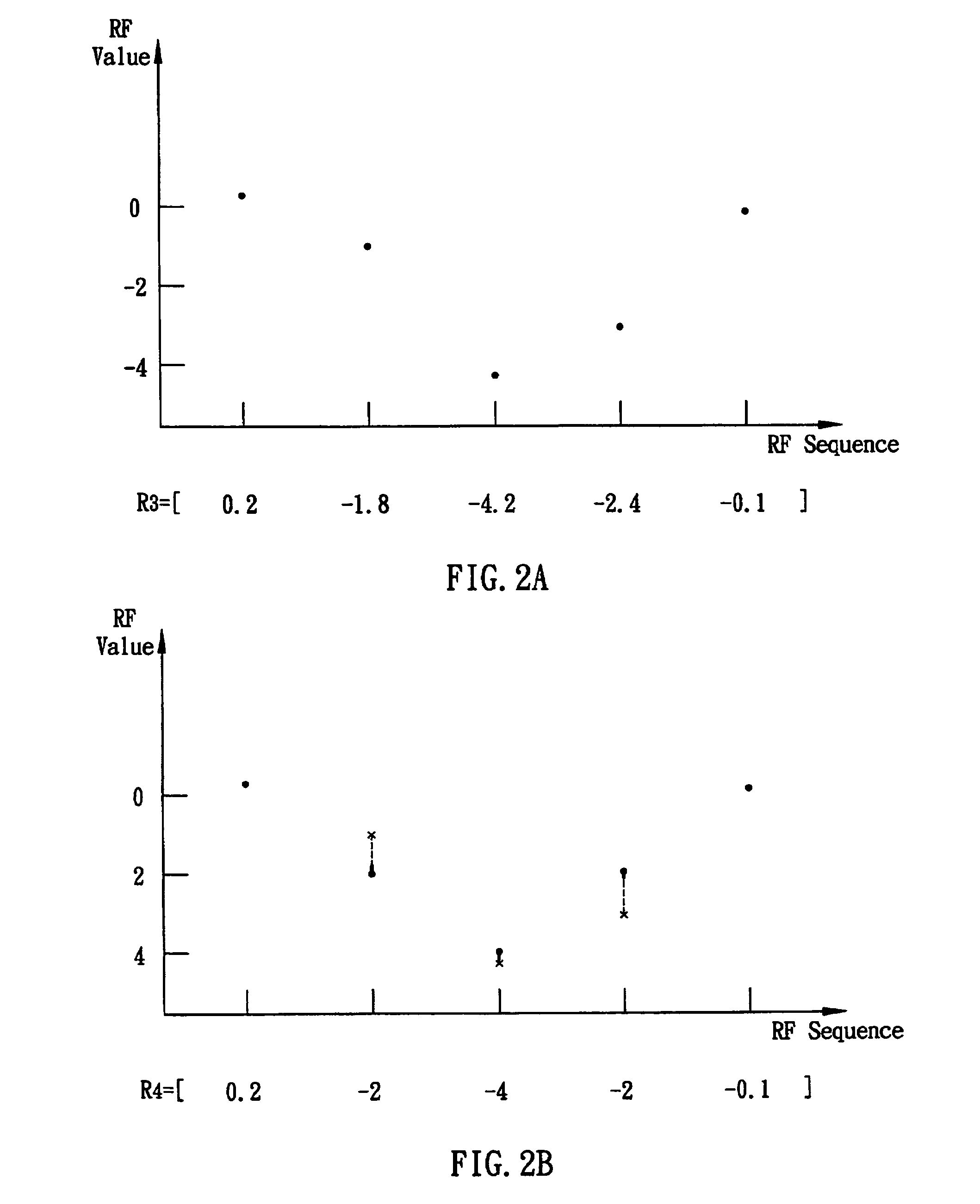

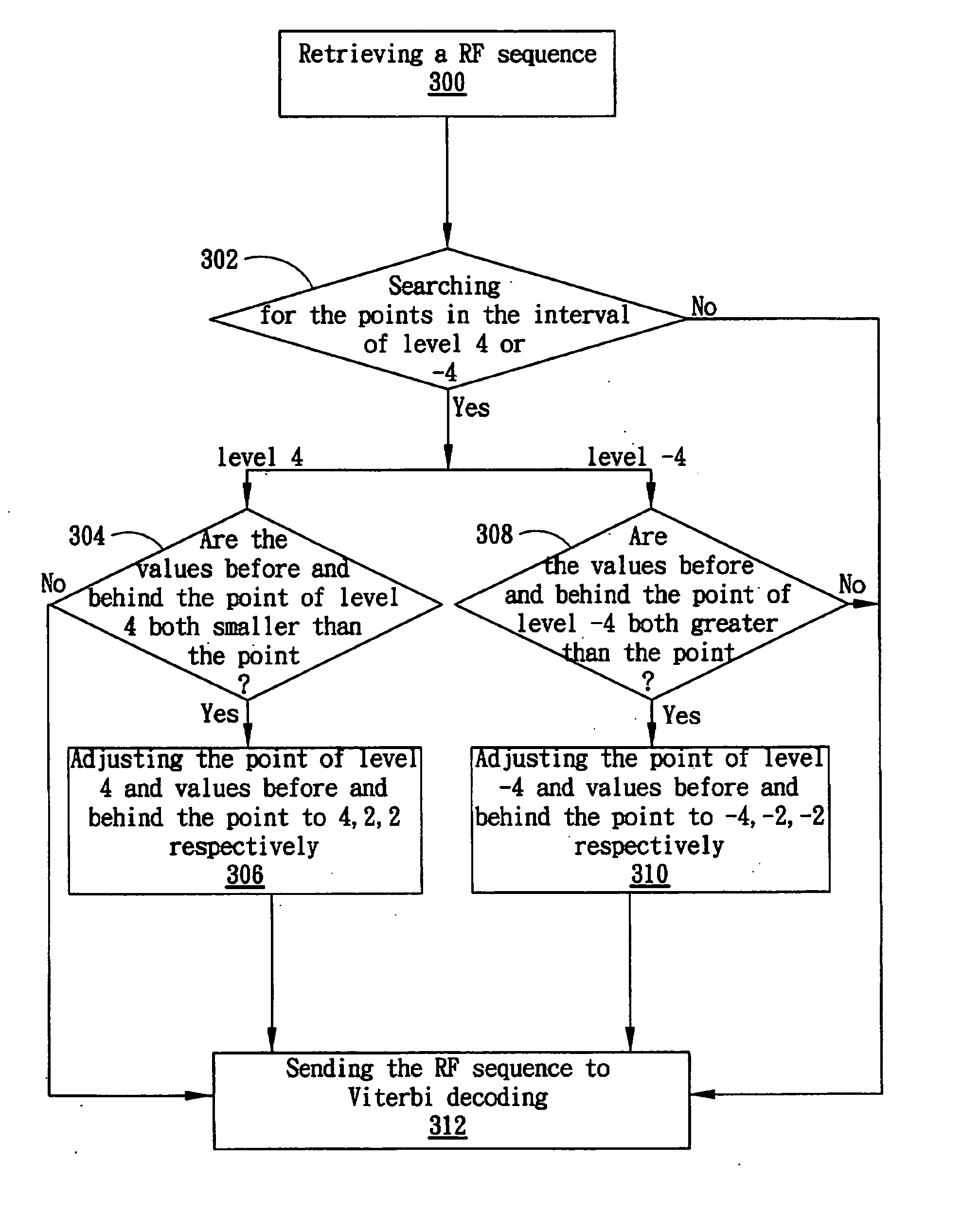

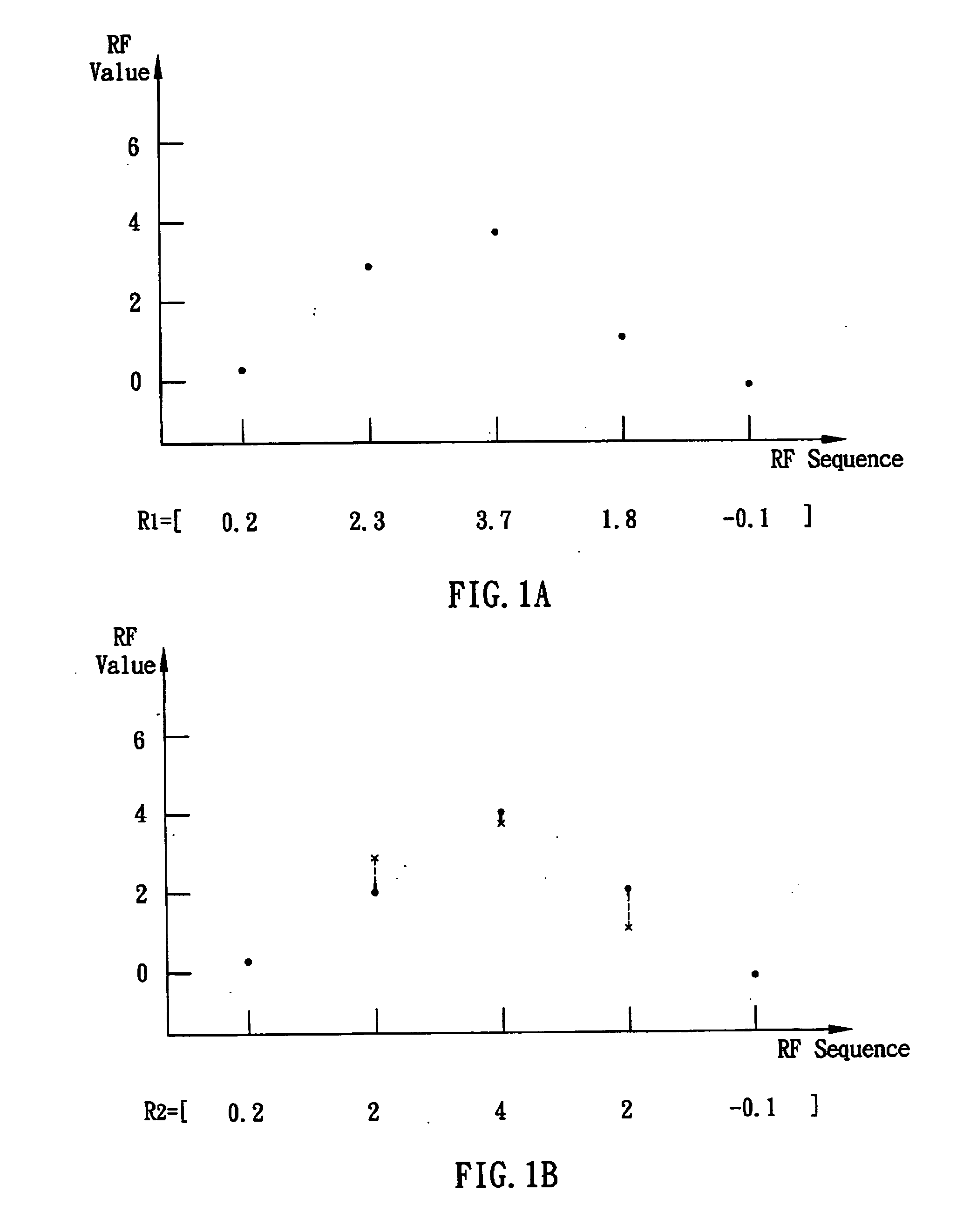

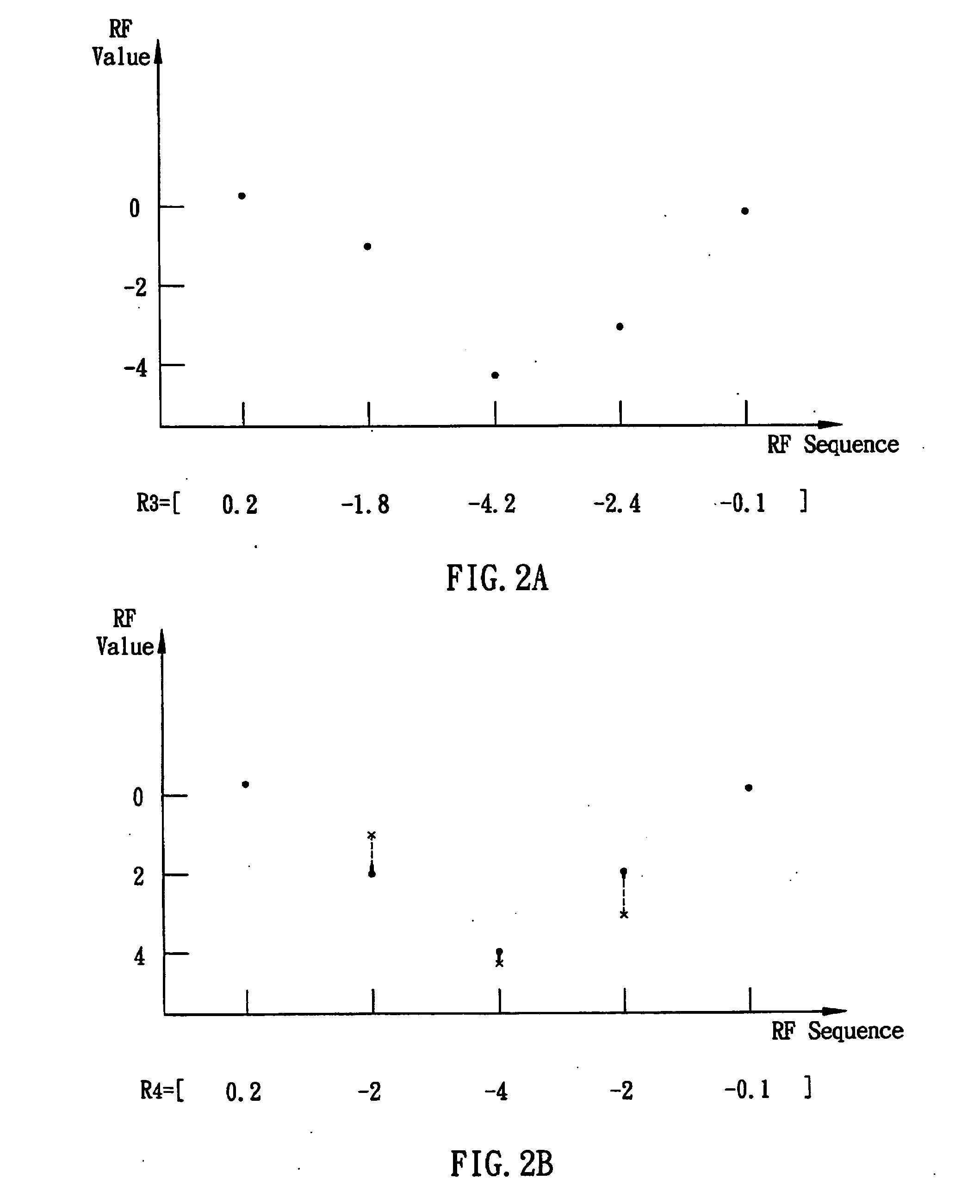

Optical storage device decoding method

InactiveUS7324023B2Improve reliabilityReduce error rateModification of read/write signalsRecord information storageDecoding methodsPresent method

A decoding method for optical storage device, which decodes channel bits upon a disc by partial response maximum likelihood (PRML) detection, is proposed. Unlike the conventional skills, the present method does not decode the detected RF signals directly, but adjusts values of parts of detected RF signals to their original ideal values before channel decoding instead, thereby reducing the decoding error rate of channel bits. The decoding method includes the step of: retrieving a first sequence of RF signals; identifying if the first sequence of RF signals contains a signal combination which satisfies a particular condition; adjusting a plurality of RF signals in the first sequence of RF signals to some pre-determined RF signals' value and then forming a second sequence of RF signals; and decoding the second sequence of RF signals. In a preferred embodiment of the invention, the method is applied to an optical storage system of PR (1,2,2,2,1) channel.

Owner:LITE ON IT

Optical storage device decoding method

InactiveUS20070057823A1Improve reliabilityReduce error rateModification of read/write signalsRecord information storageDecoding methodsPresent method

A decoding method for optical storage device, which decodes channel bits upon a disc by partial response maximum likelihood (PRML) detection, is proposed. Unlike the conventional skills, the present method does not decode the detected RF signals directly, but adjusts values of parts of detected RF signals to their original ideal values before channel decoding instead, thereby reducing the decoding error rate of channel bits. The decoding method includes the step of: retrieving a first sequence of RF signals; identifying if the first sequence of RF signals contains a signal combination which satisfies a particular condition; adjusting a plurality of RF signals in the first sequence of RF signals to some pre-determined RF signals' value and then forming a second sequence of RF signals; and decoding the second sequence of RF signals. In a preferred embodiment of the invention, the method is applied to an optical storage system of PR (1,2,2,2,1) channel.

Owner:LITE ON IT

Partial Response Maximum Likelihood Decoding

InactiveUS20080259758A1Reduce partLow hardware requirementsTelevision system detailsData representation error detection/correctionViterbi decoderSymbol of a differential operator

A partial response maximum likelihood decoder, such as a Viterbi decoder, implements a set of combined states where each combined state can represent at least two states from a plurality of complementary sets of states. For each data symbol and each combined state, a Viterbi processor (703) determines a path metric and a substate indication for each path to the combined state. A path selection processor (709) of the Viterbi processor (703) selects a selected path and a selected sub state indication for the path which corresponds to a highest likelihood path metric. The substate indication is an indication of which of the complementary set of states the combined state represents for the data symbol. The invention allows a substantial complexity reduction and / or reduced computational burden as the Viterbi algorithm can be applied to a reduced number of combined states.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Method and apparatus for joint adaptation of two-/multi-dimensional equalizer and partial response target

ActiveUS10026441B2Increase bit densitySimple designModification of read/write signalsRecord information storageAlgorithmData recording

The present disclosure relates to a method and apparatus for processing of multi-dimensional readback signal from magnetic recording or optical, physical data recording so as to reduce / control Inter Symbol Interference (ISI) and noise within acceptable limits. The method is based on Partial Response Maximum Likelihood (PRML) detection and takes care of time varying channel conditions. In an embodiment, the filter coefficients of both the equalizer and the partial response (PR) target are jointly adapted to account for the channel condition for both separable and non-separable targets thus reducing signal detection complexity. In an aspect, the disclosure provides an apparatus that incorporates an adaptation engine along with the equalizer and the PR target that updates filter coefficients of both the equalizer and the PR target following the formulated mathematical equations.

Owner:INDIAN INSTITUTE OF SCIENCE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com