Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

46 results about "Multiplication of vectors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

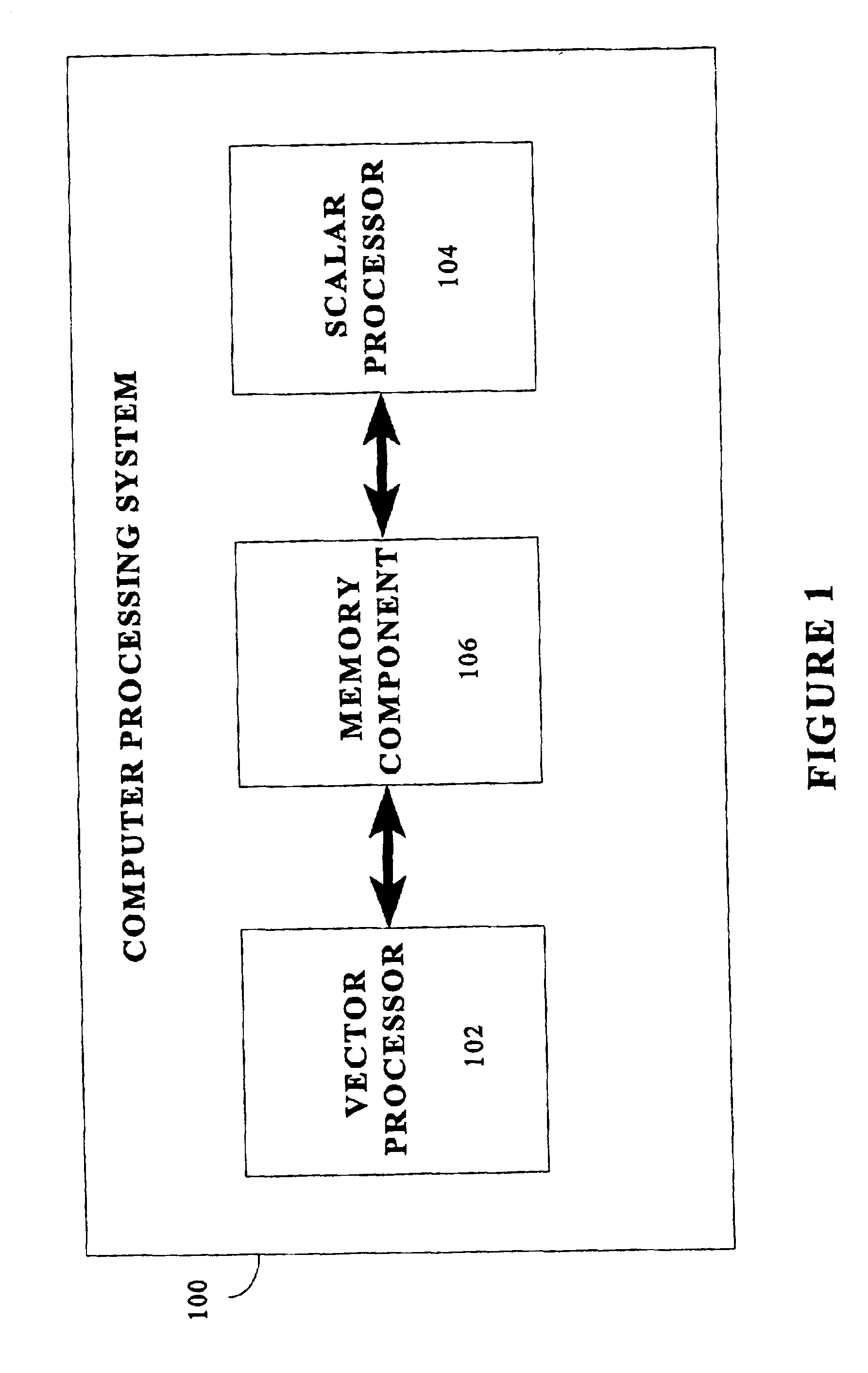

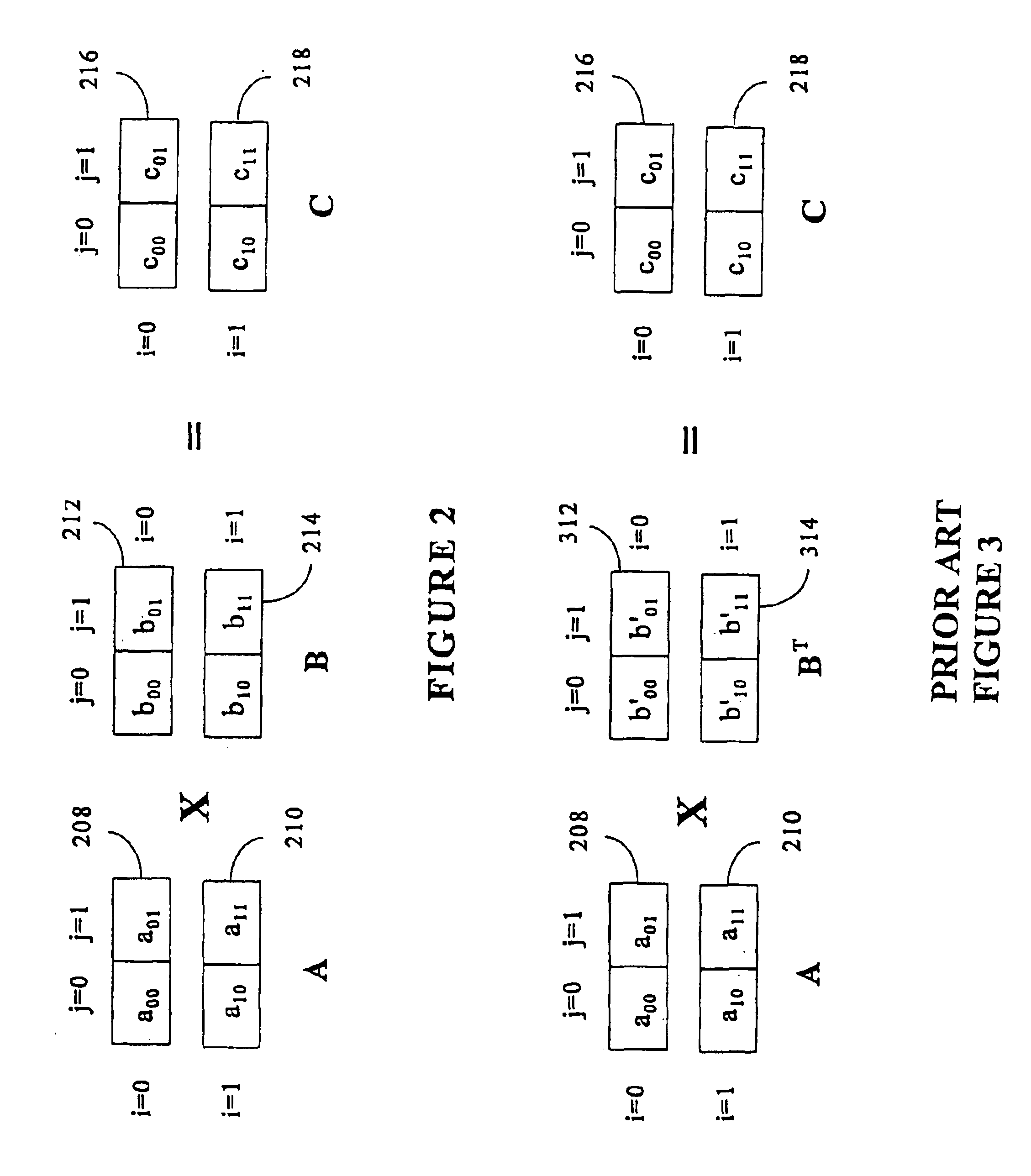

Matrix multiplication in a vector processing system

InactiveUS20050193050A1Efficient and rapid matrix multiplicationEfficient executionComputation using non-contact making devicesProgram controlAlgorithmProcessor register

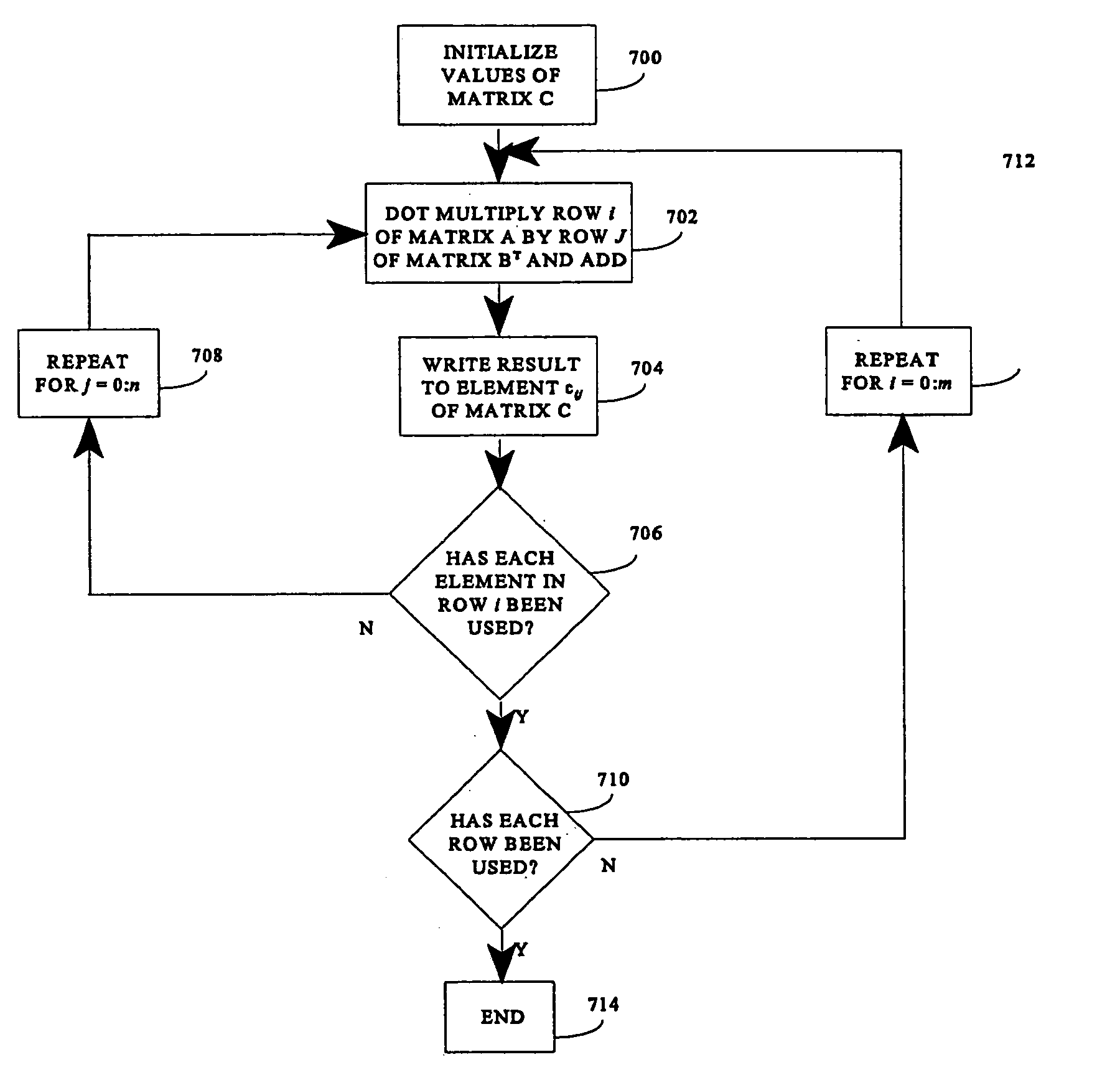

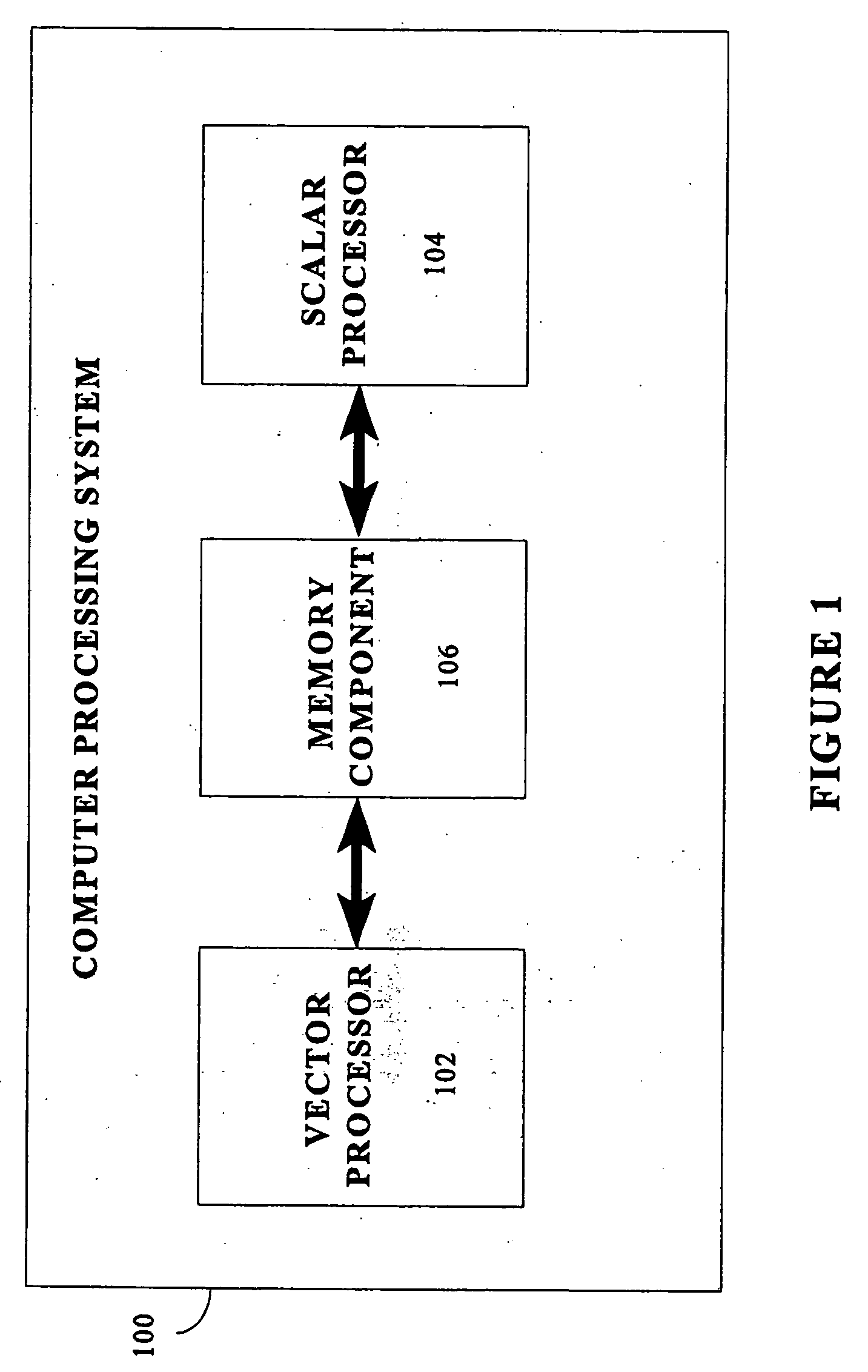

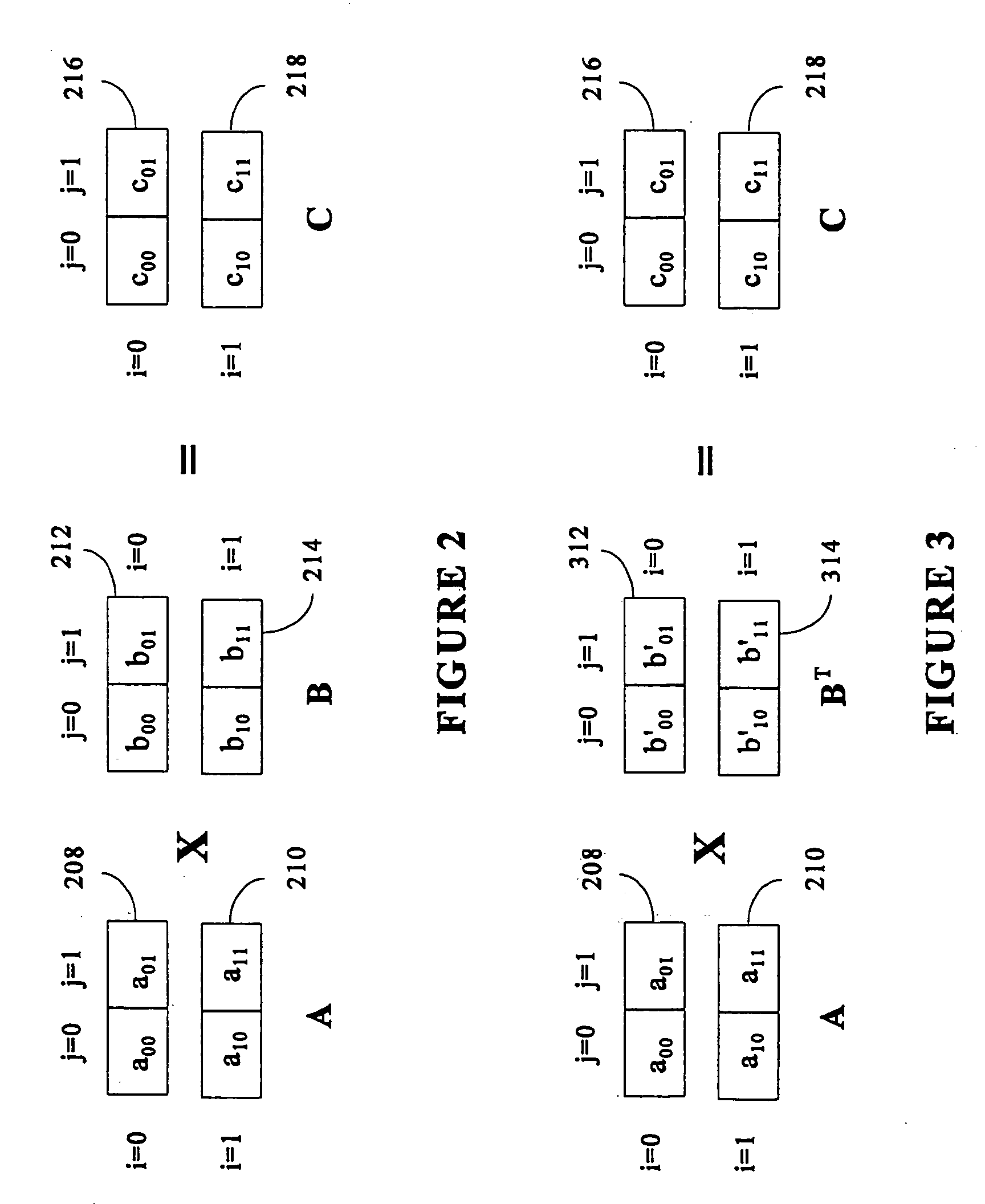

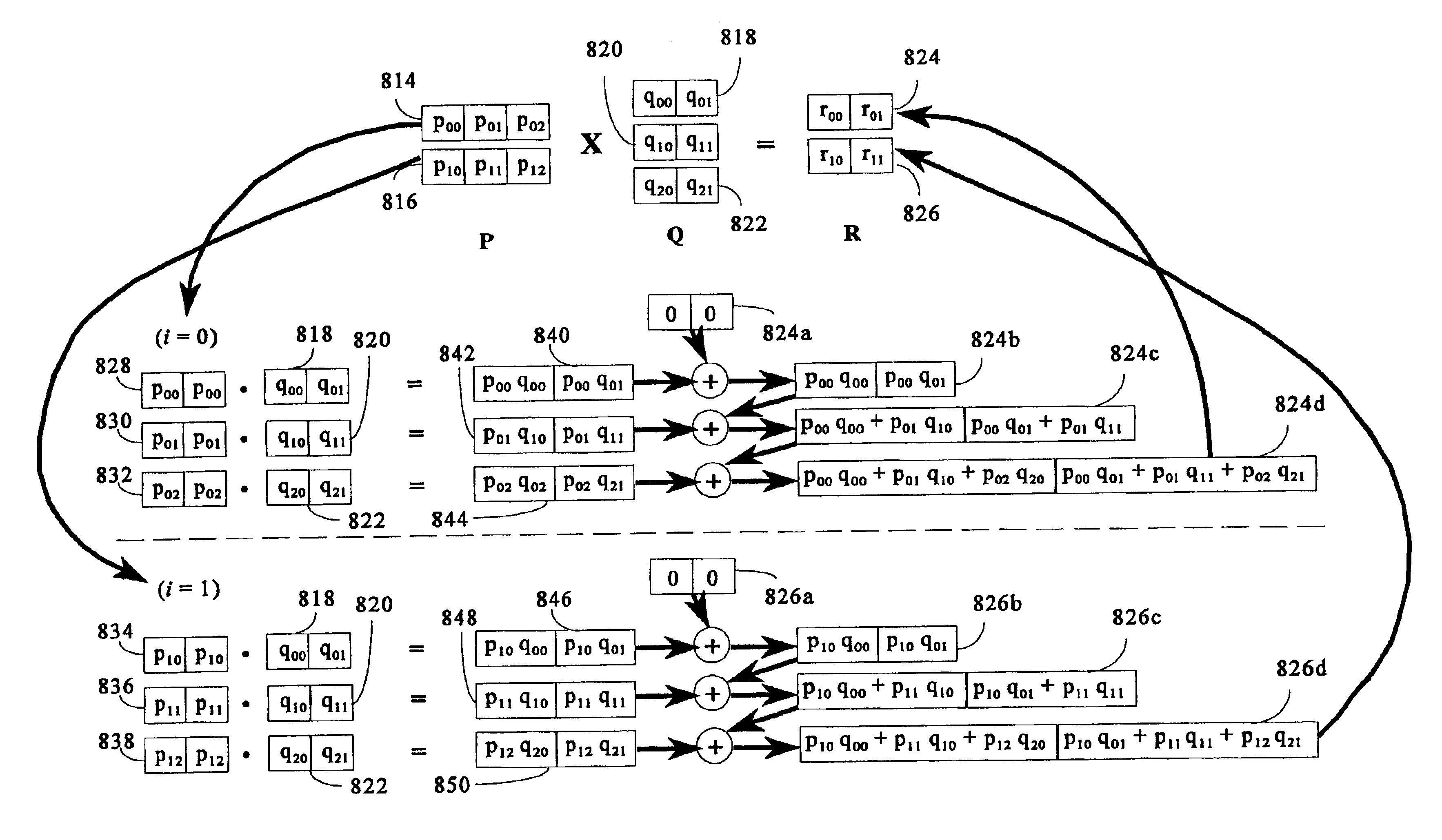

To perform multiplication of matrices in a vector processing system, partial products are obtained by dot multiplication of vector registers containing multiple copies of elements of a first matrix and vector registers containing values from rows of a second matrix. The dot products obtained from this dot multiplication are subsequently added to vector registers which form a product matrix. Each matrix can be divided into submatrices to facilitate the rapid and efficient multiplication of large matrices, which is done in parts by computing partial products of each submatrix. The matrix multiplication avoids rounding errors as it is bit-by-bit compatible with conventional matrix multiplication methods.

Owner:APPLE INC

Matrix multiplication in a vector processing system

InactiveUS6901422B1Increase speedMaintaining bit-by-bit compatabilityComputation using non-contact making devicesProgram controlMultiplication of vectorsProcessor register

The present invention is directed to a system and method for multiplication of matrices in a vector processing system. Partial products are obtained by dot multiplication of vector registers containing multiple copies of elements of a first matrix and vector registers containing values from rows of a second matrix. The dot products obtained from this dot multiplication are subsequently added to vector registers which make up a product matrix. In an embodiment of the present invention, each matrix may be divided into submatrices to facilitate the rapid and efficient multiplication of large matrices, which is done in parts by computing partial products of each submatrix. The matrix multiplication performed by the present invention avoids rounding errors as it is bit-by-bit compatible with conventional matrix multiplication methods.

Owner:APPLE INC

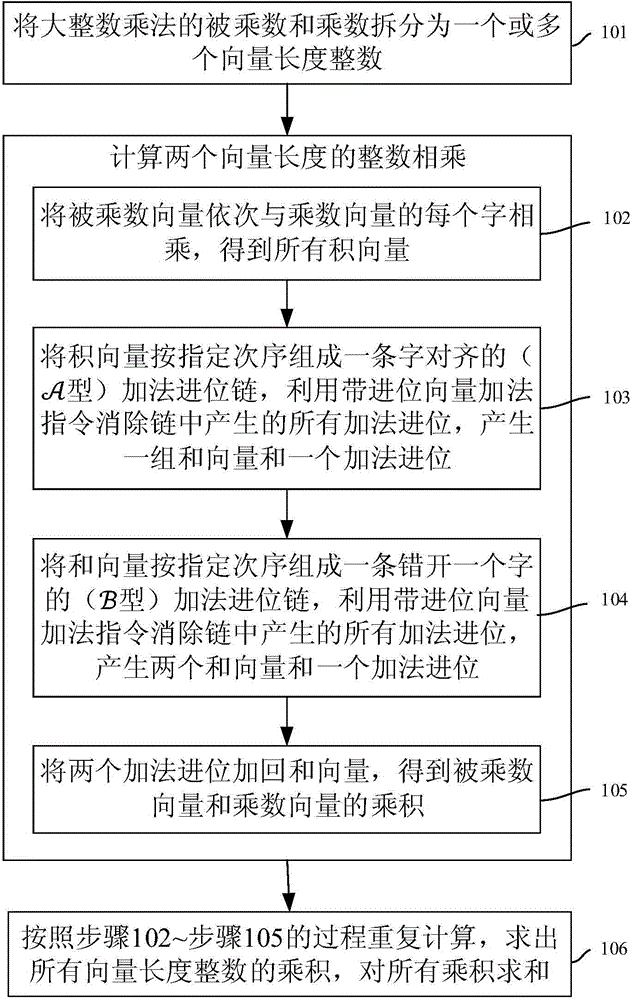

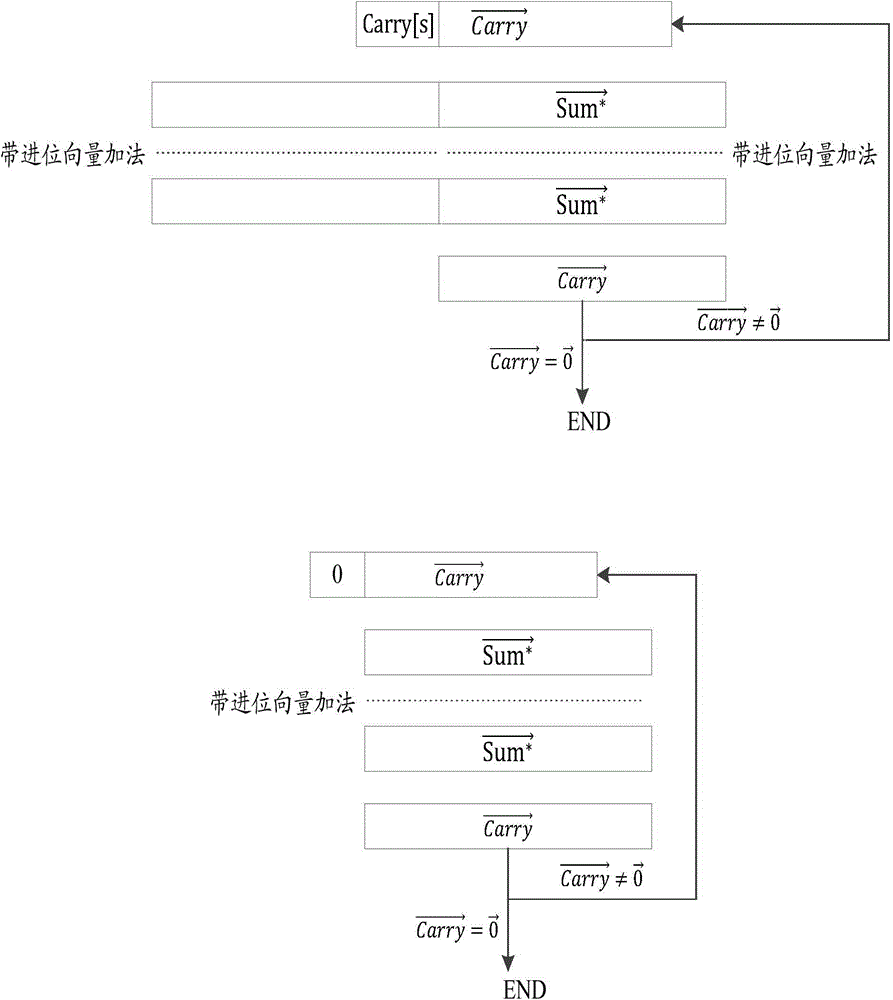

Large integer multiplication realizing method and device based on vector instructions

ActiveCN104461449AReduce the number of instructionsImprove computing throughputDigital data processing detailsXeon PhiTwo-vector

The invention provides a large integer multiplication realizing method and device based on vector instructions. The multiplicand and the multiplier of the large integer multiplication are each split into one or more vector length integers, the integers are multiplied, and all products are summed; when the integers with two vector lengths are multiplied, product vectors generated by all the vector multiplication instructions form two addition carry chains according to the appointed sequence, the vector addition instructions with carries are utilized for making carries generated by vector addition each time serve as input of the next vector addition instruction, all the addition carries in the chains are eliminated, and only two addition carries are generated and added back to obtain the product of the integers with the two vector lengths. Specifically, if the length of the multiplicand and the length of the multiplier are smaller than 1 / n of the vector length, multiplication of n groups of integers is combined into the one-time multiplication of vector length integers, and the calculation handling capacity is promoted by n times. Based on the large integer multiplication method, the invention further discloses a high-speed large integer multiplication device based on an Intel Xeon Phi co-processor. According to the method, instruction numbers needed by the large integer multiplication method are reduced, calculation delay is reduced, and the calculation handling capacity is improved.

Owner:DATA ASSURANCE & COMM SECURITY CENT CHINESE ACADEMY OF SCI

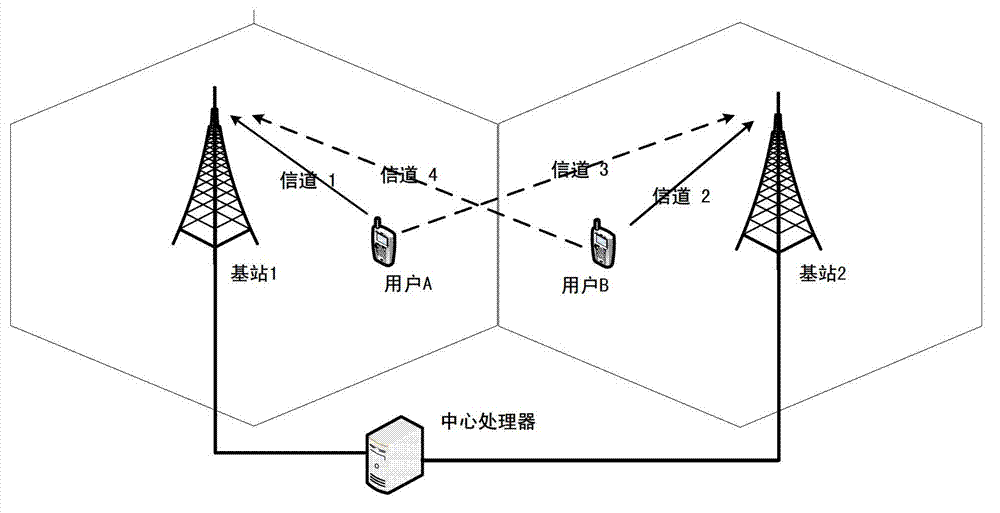

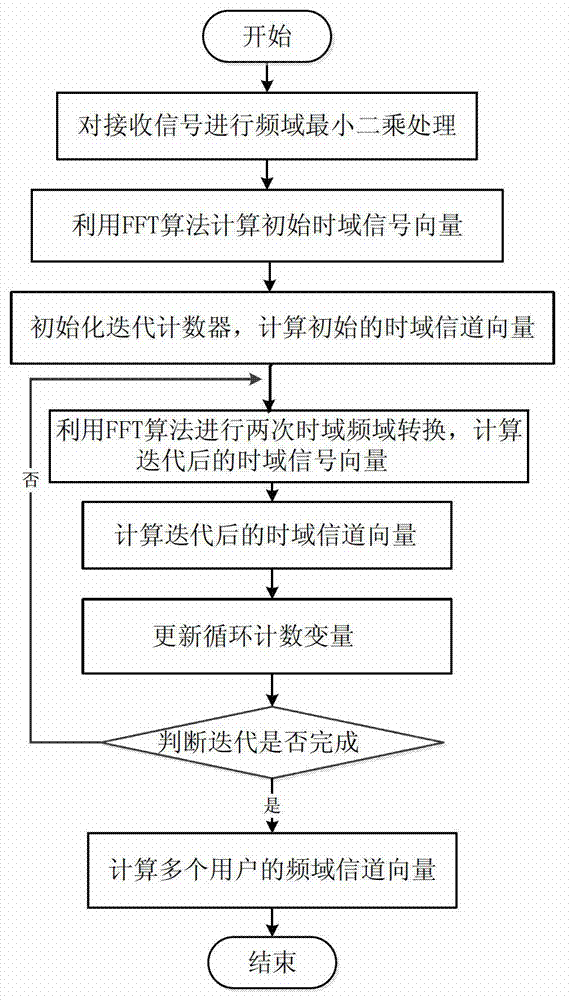

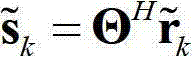

Estimation method for low-complexity channel in time division duplex (TDD) multi-base station cooperative system

InactiveCN102891815ASolve non-perfectly orthogonal problemsSuppress interferenceBaseband system detailsMulti-frequency code systemsMultiplication of vectorsSeries expansion

The invention discloses an estimation method for low-complexity channel in a time division duplex (TDD) multi-base station cooperative system, belonging to the field of wireless communication technology. The estimation method comprises the steps of: acquiring a frequency domain signal and a primary time domain signal vector, setting a primary iteration counting variable m to be equal to 0, acquiring a primary time domain channel vector, acquiring a time domain signal vector vm+1 after being subjected to m+1 iterations, acquiring the time domain channel vector after being subjected to m+1 iterations, updating a circulating counting variable m, and if m is greater than P, continuously acquiring a time domain signal vector, otherwise, obtaining frequency domain channels of K users. According to a channel estimation algorithm provided by the invention, matrix inversion in a minimum mean square error algorithm is converted to matrix power series by utilizing a series expansion manner, multiplication of matrix and vector can be realized by means of fast fourier transform and inverse fast fourier transform, the estimation method has the advantages of low complexity and excellent property, and can be realized without small-scale statistics information of the channel.

Owner:BEIHANG UNIV +1

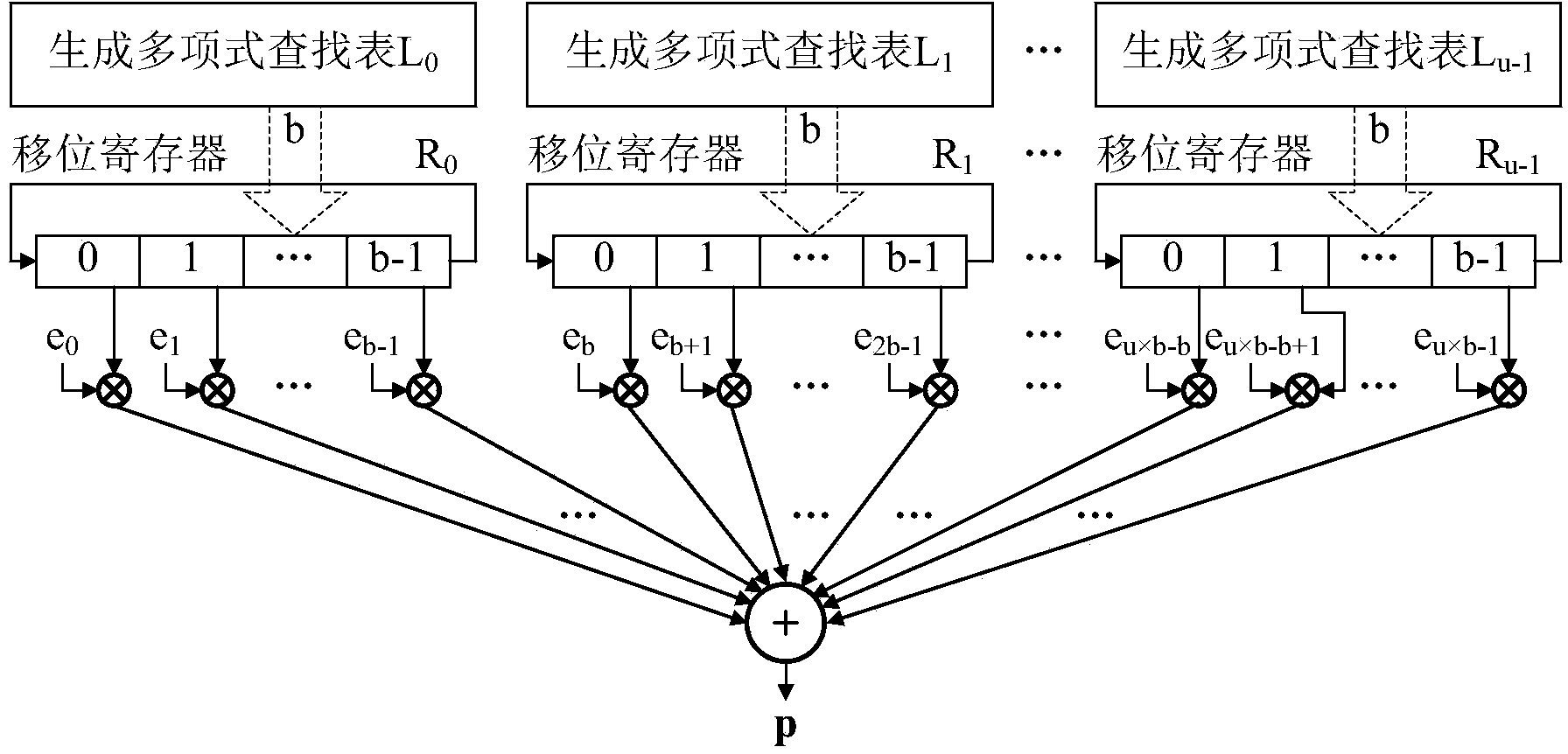

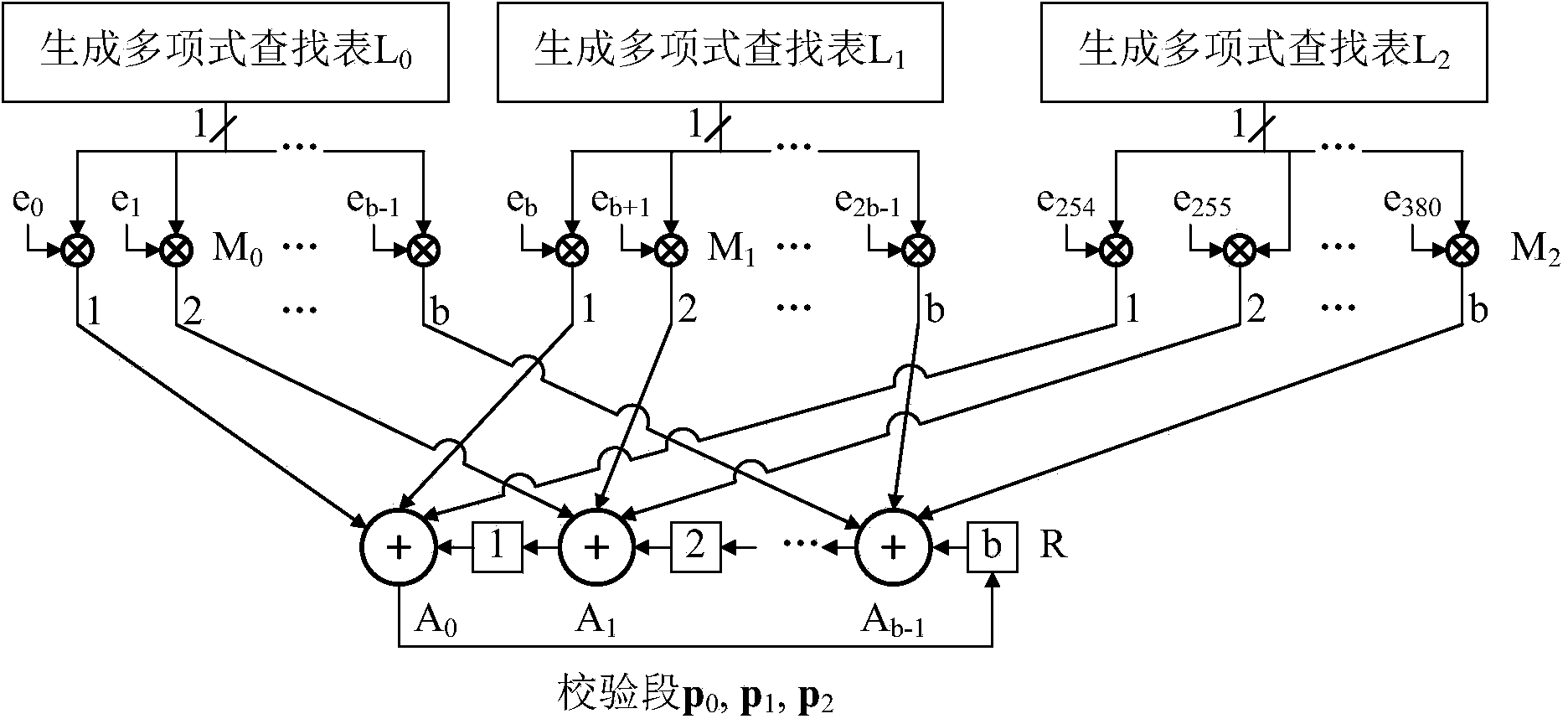

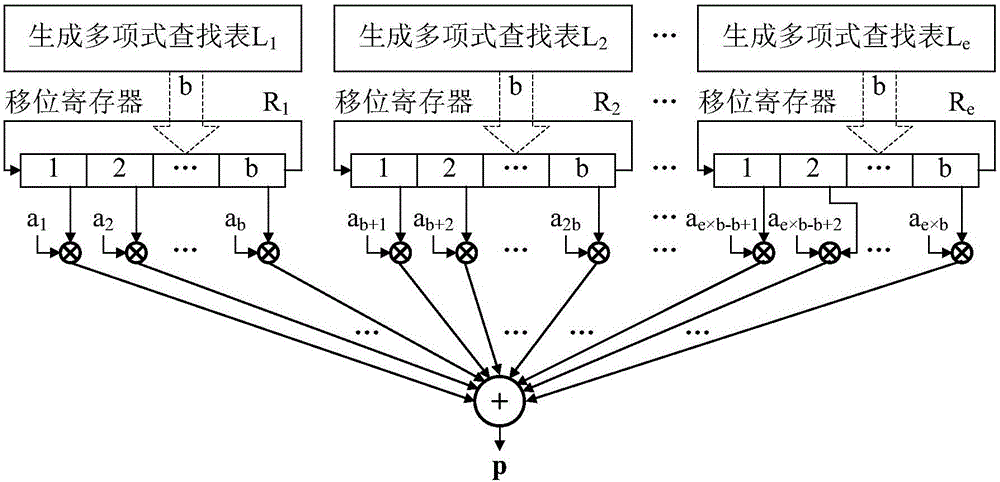

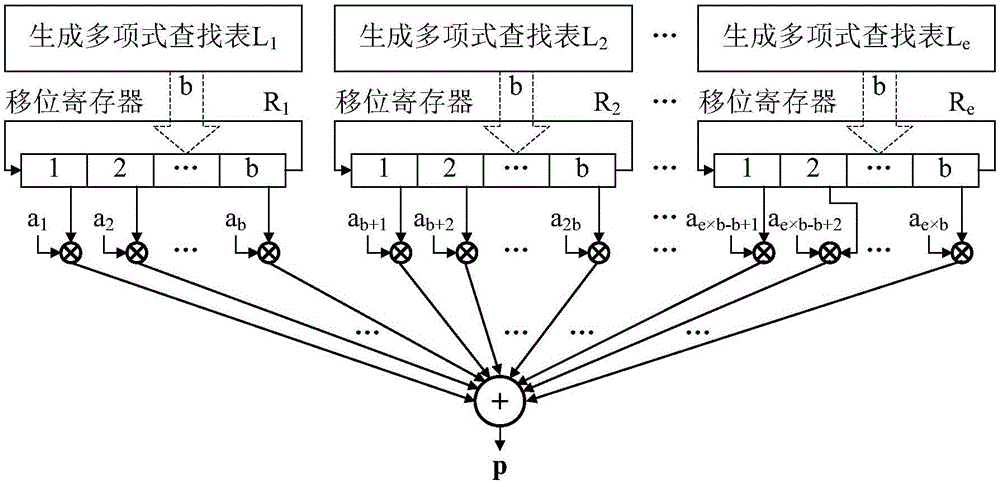

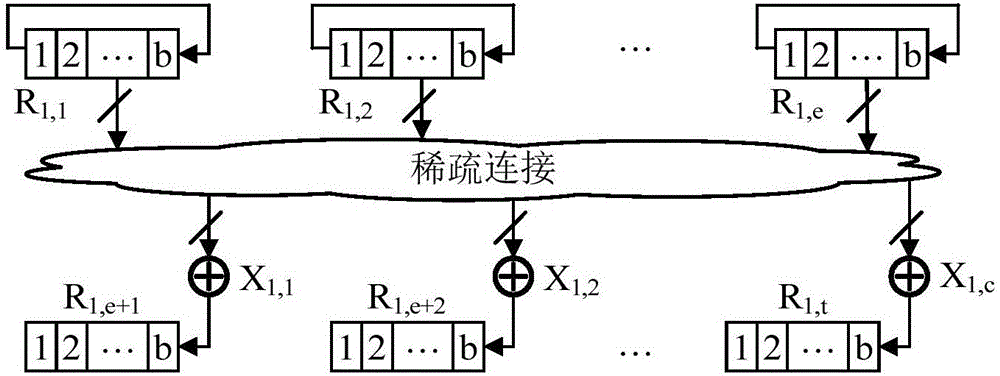

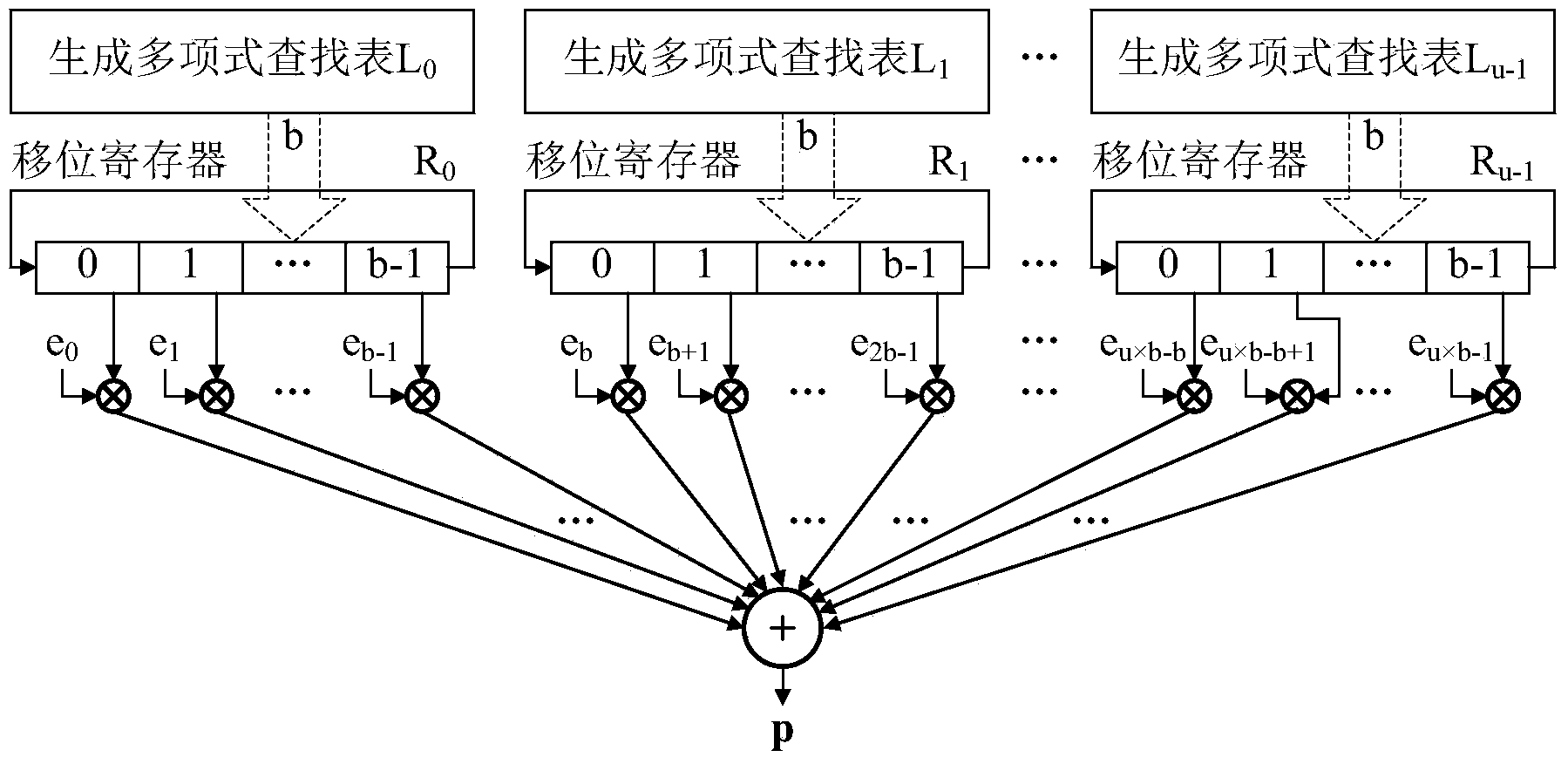

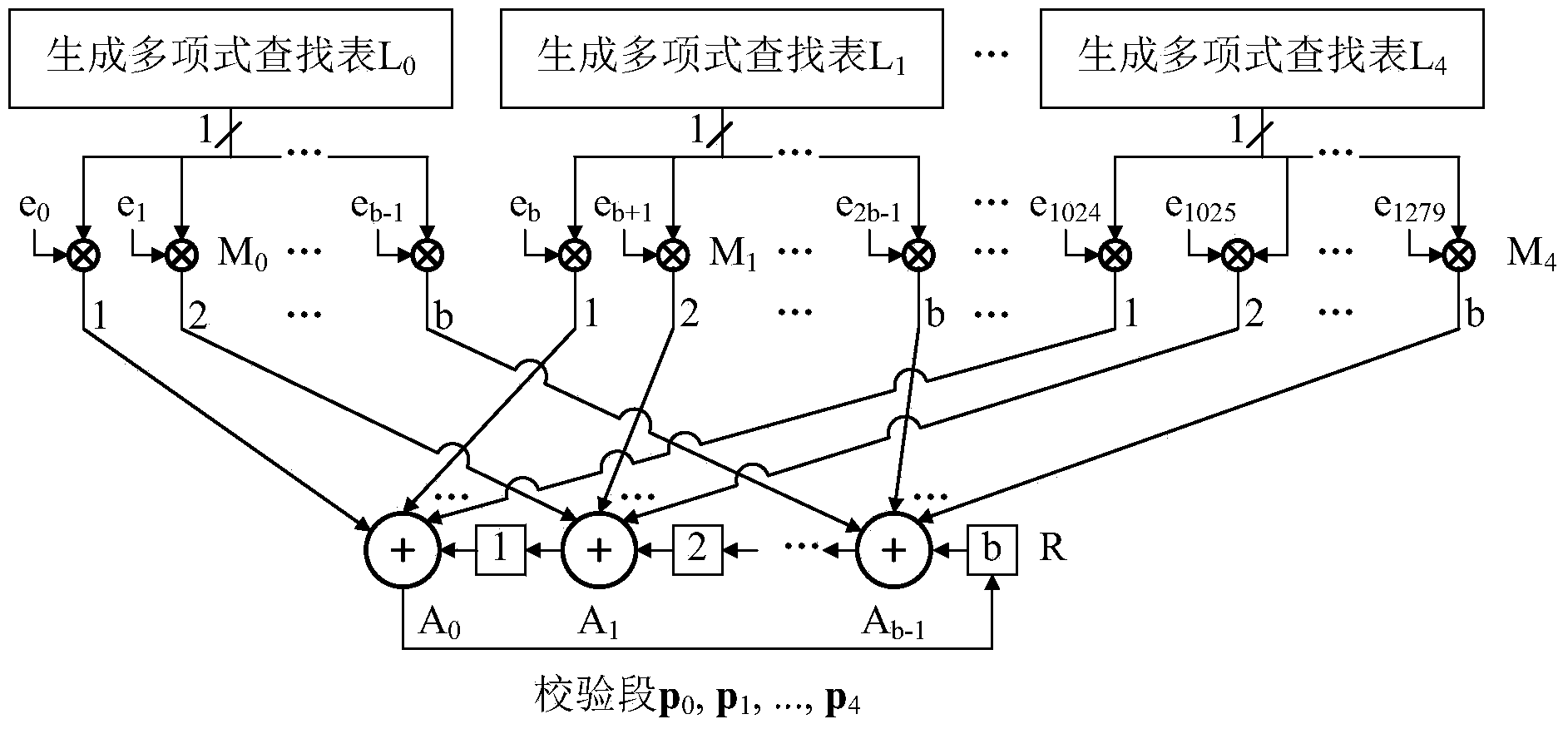

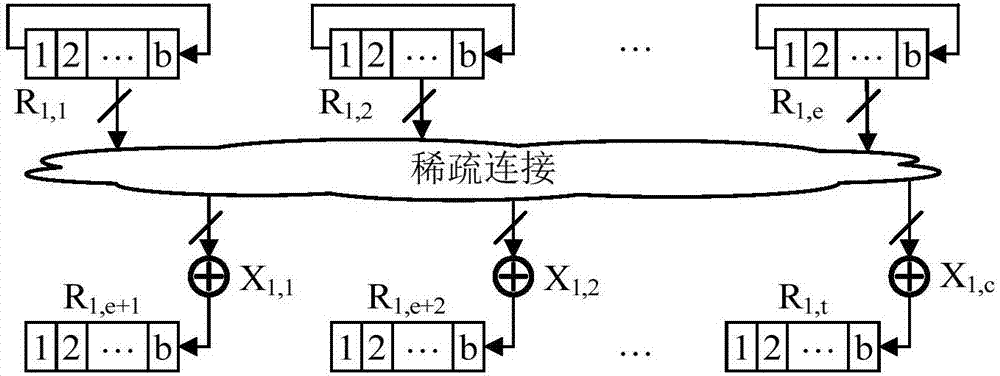

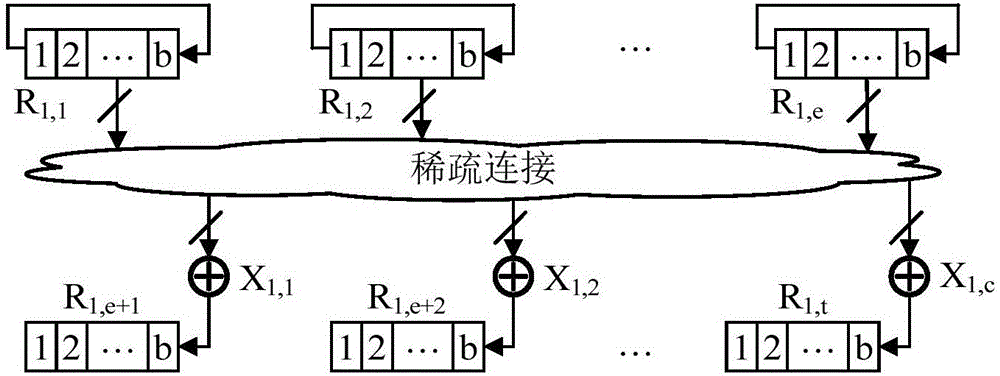

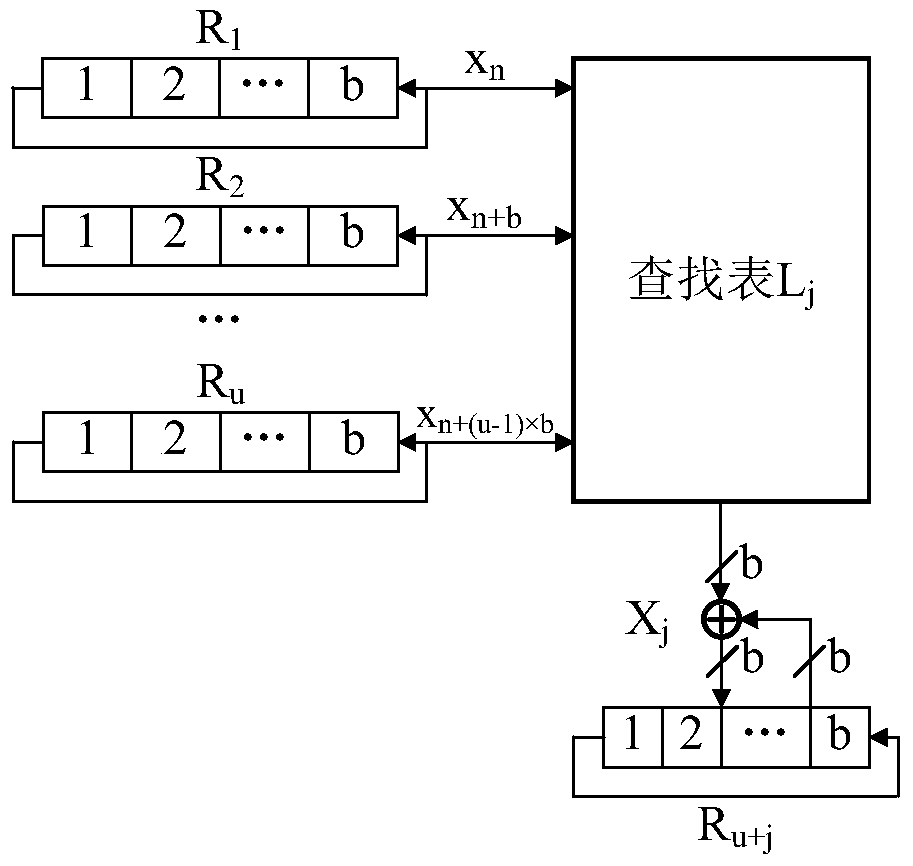

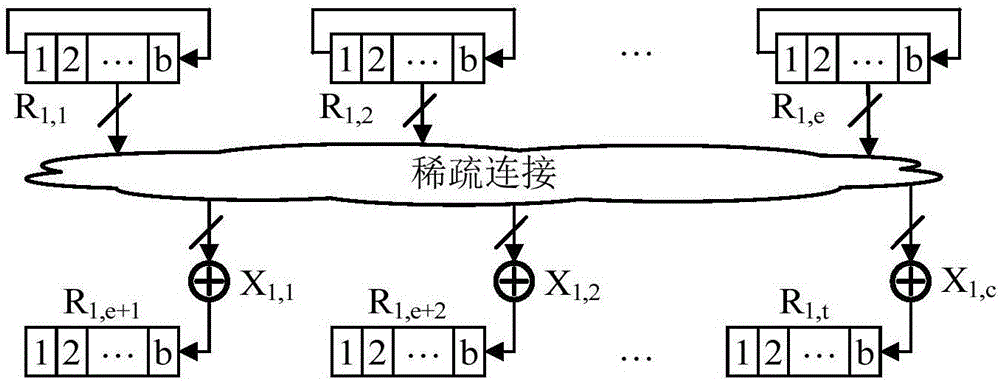

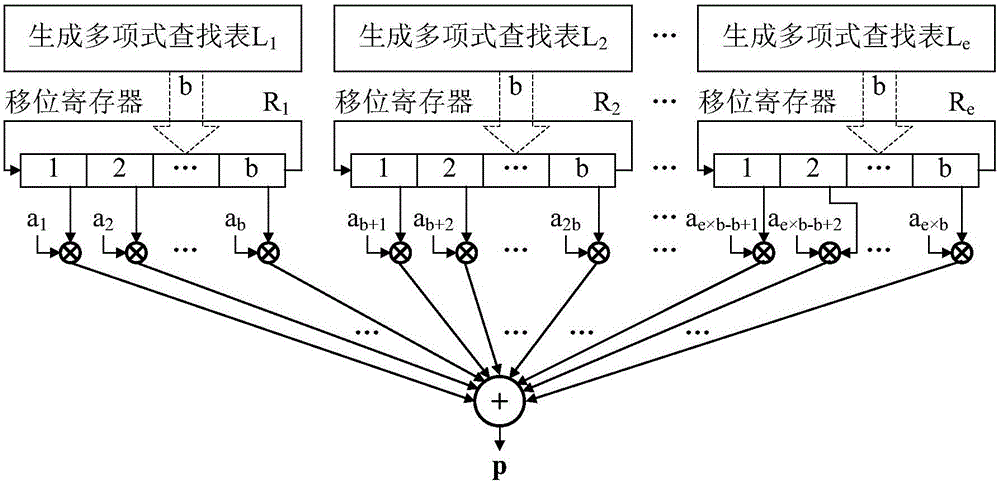

Full parallel input quasi-cyclic matrix multiplier based on ring shift left in DTMB

InactiveCN103929199ASimple structureReduce registerError correction/detection using multiple parity bitsShift registerBinary multiplier

The invention provides a full parallel input quasi-cyclic matrix multiplier based on ring shift left in a DTMB, wherein the multiplier is used for achieving multiplication of vectors m and quasi-cyclic matrixes F in DTMB standard multiple rate QC-LDPC approximate lower triangular codes. The multiplier comprises three generator polynomial lookup tables for prestoring all circulant matrix generator polynomials in the matrixes F, three 127-bit binary multipliers for carrying out scalar multiplying on vector fields of the m and generator polynomial bits, 127 4-bit binary adders for carrying out modulor-2 addition on products and shifting register content, and a 127-bit shifting register for storing the sum of results obtained after 1-bit ring shift left is carried out. The full parallel input multiplier is compatible with all code rates and has the advantages that the number of the registers is small, power consumption is little, cost is low, work frequency is high and the handling capacity is large.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

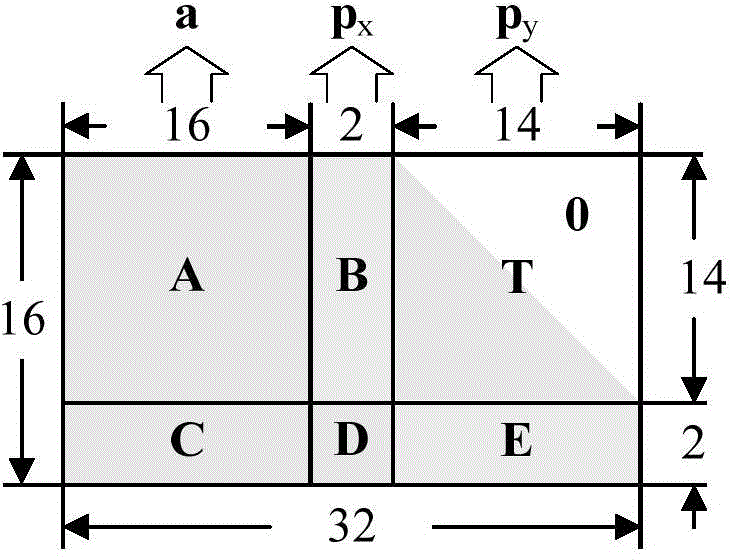

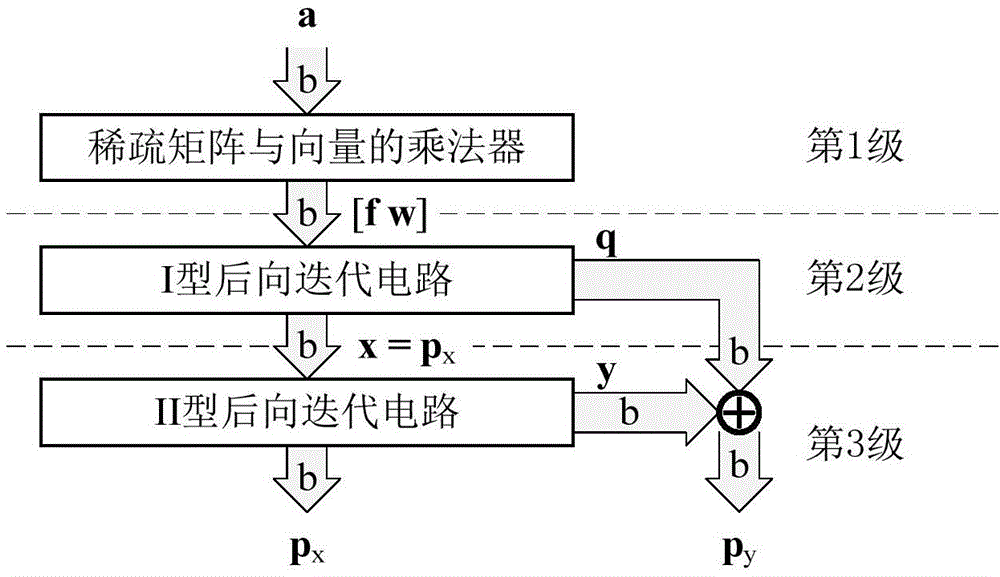

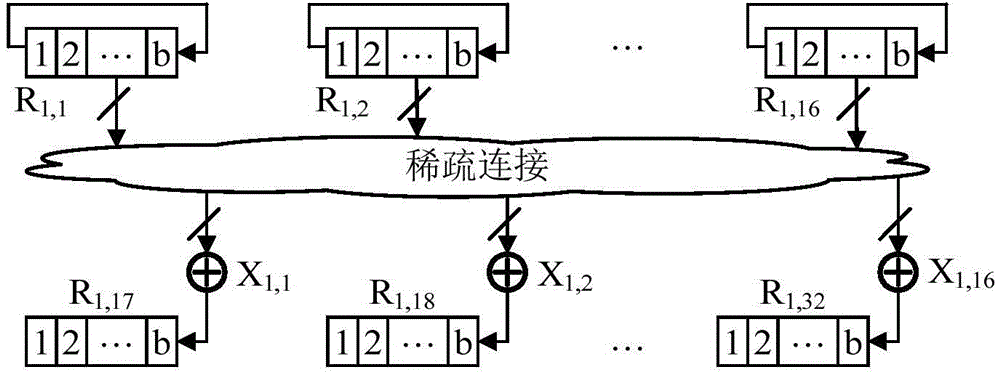

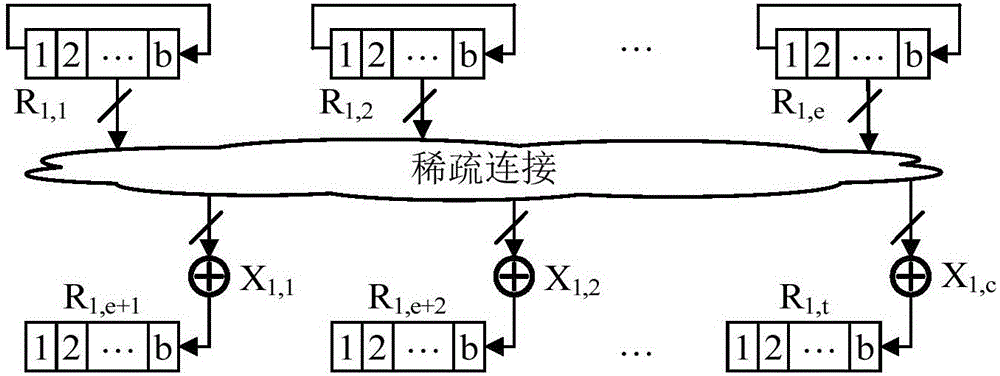

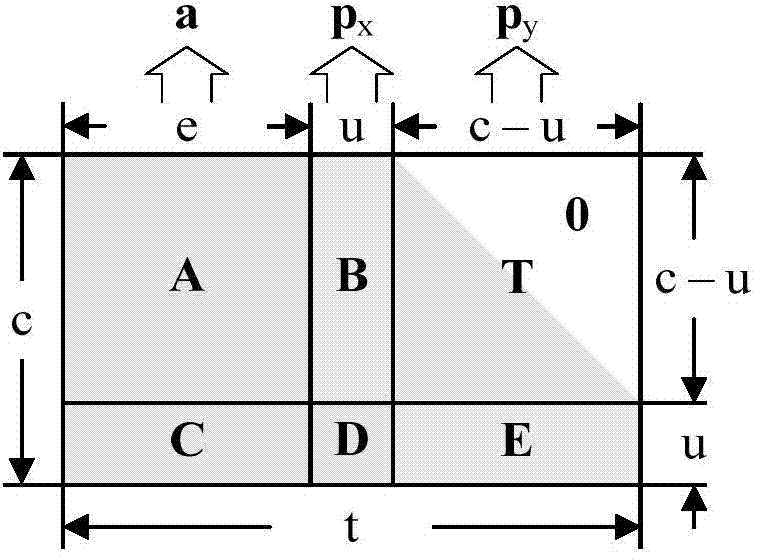

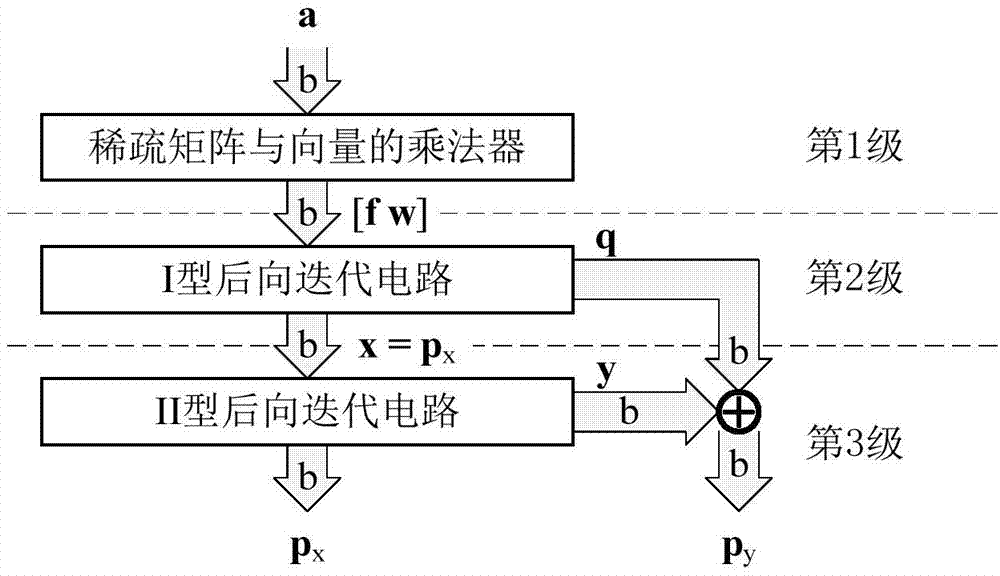

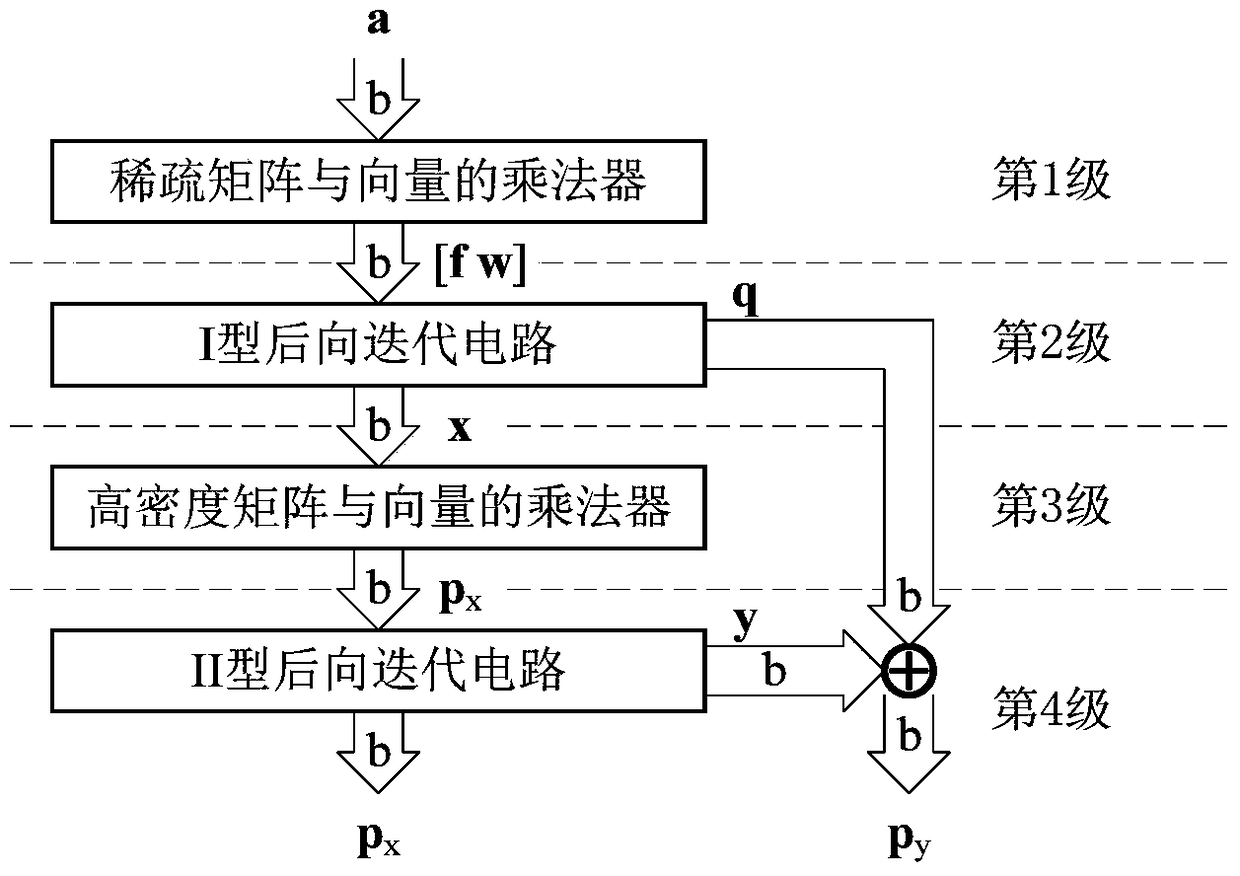

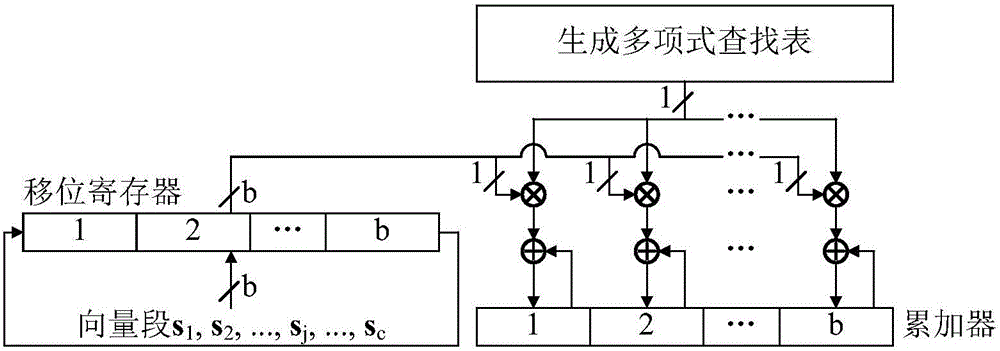

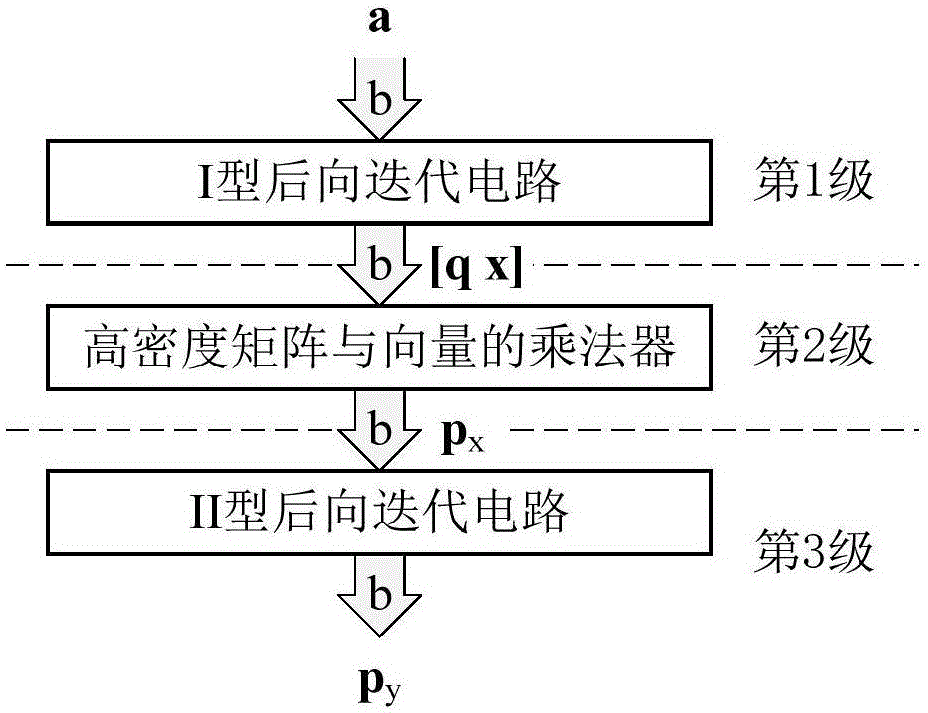

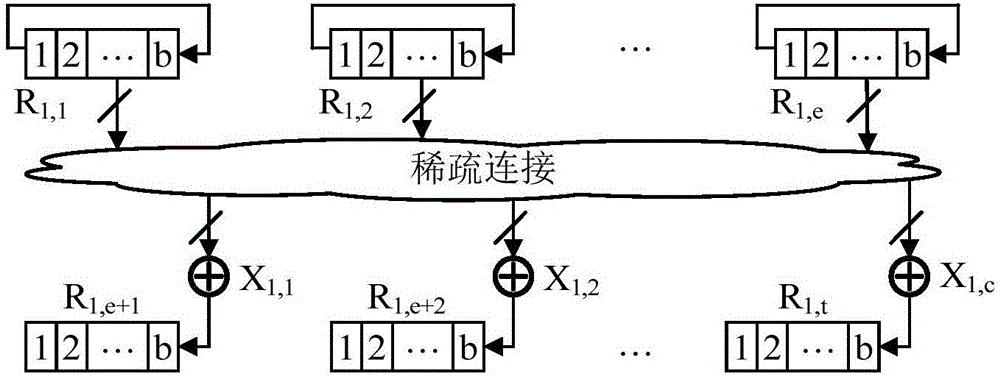

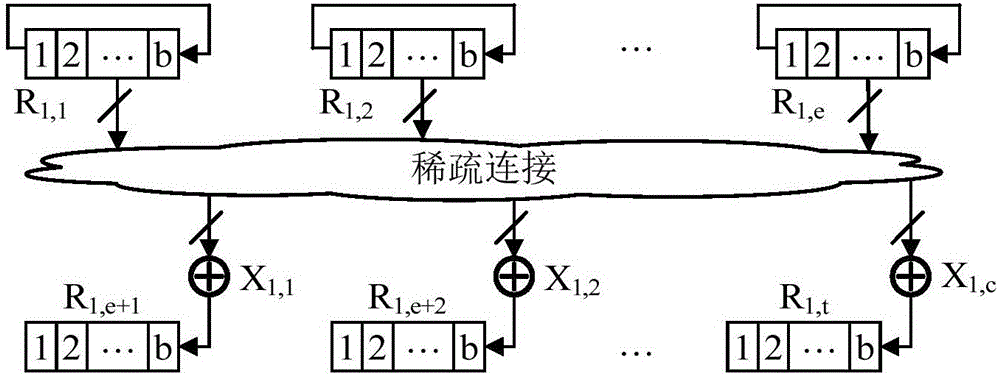

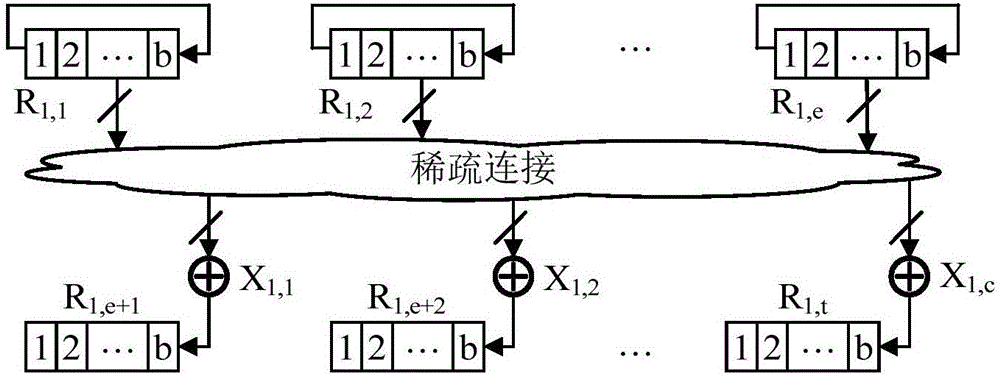

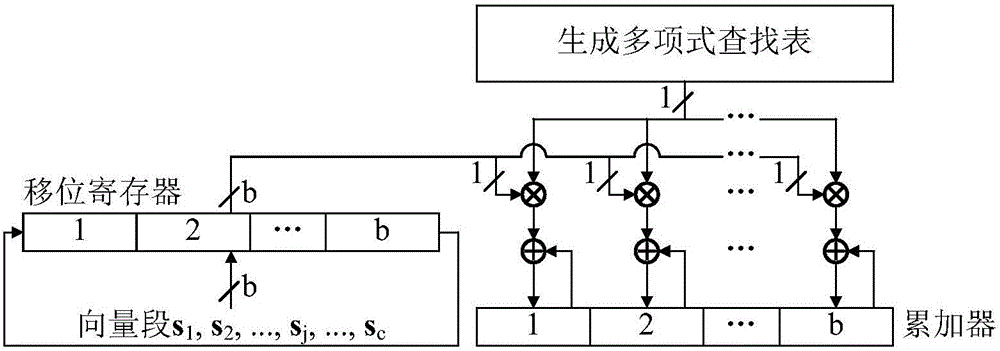

High-speed QC (quasi-cyclic)-LDPC (low-density parity-check) encoder on basis of three levels of flow lines in WPAN (wireless personal area network)

InactiveCN104579366ASimple structureImprove encoding speedError correction/detection using multiple parity bitsThree levelMultiplication of vectors

The invention provides a high-speed QC (quasi-cyclic)-LDPC (low-density parity-check) encoder on the basis of three-level assembly lines in a WPAN (wireless personal area network). The high-speed QC-LDPC encoder comprises a sparse matrix and vector multiplier, a type-I backward iterative circuit and a type-II backward iterative circuit. Sparse matrix and vector multiply operation can be implemented by the aid of the sparse matrix and vector multiplier, and backward iterative operation can be implemented by the aid of the type-I backward iterative circuit and the type-II backward iterative circuit. Each integral encoding procedure is divided into the three levels of flow lines. The high-speed QC-LDPC encoder with the 1 / 2 code rate in a WPAN system has the advantages of simple structure, low cost, high throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

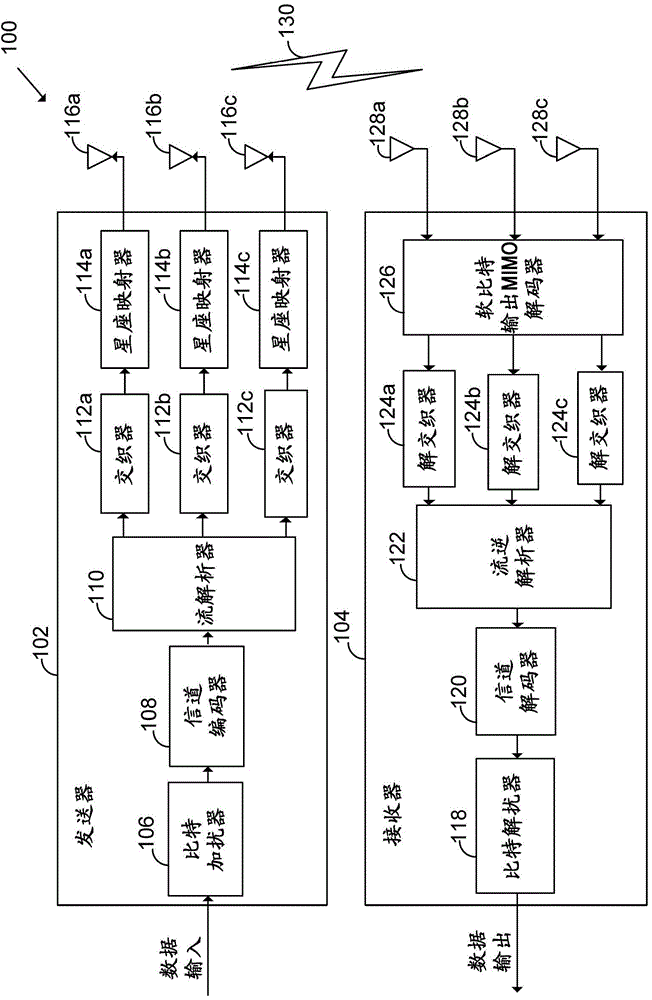

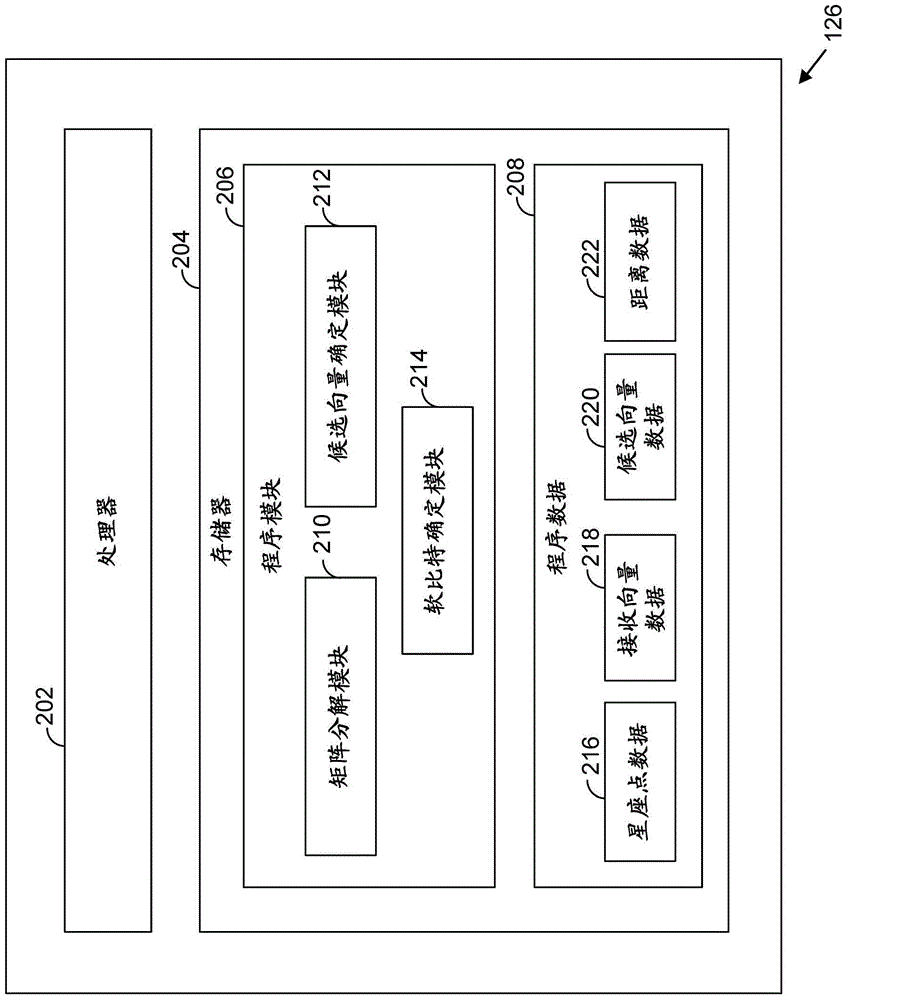

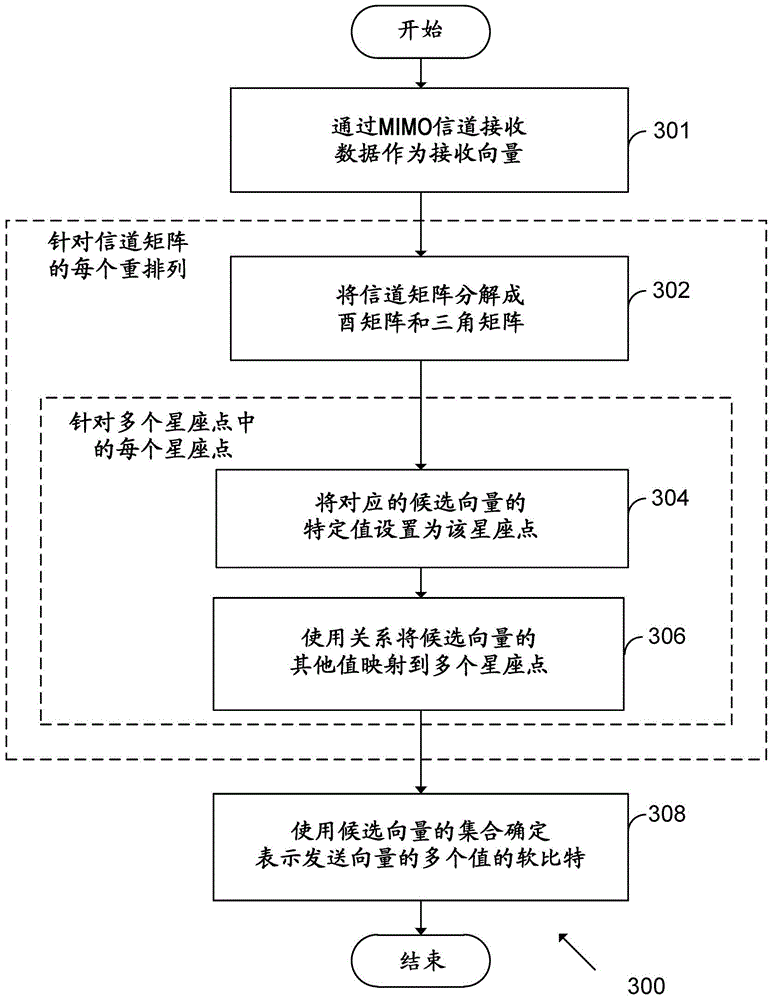

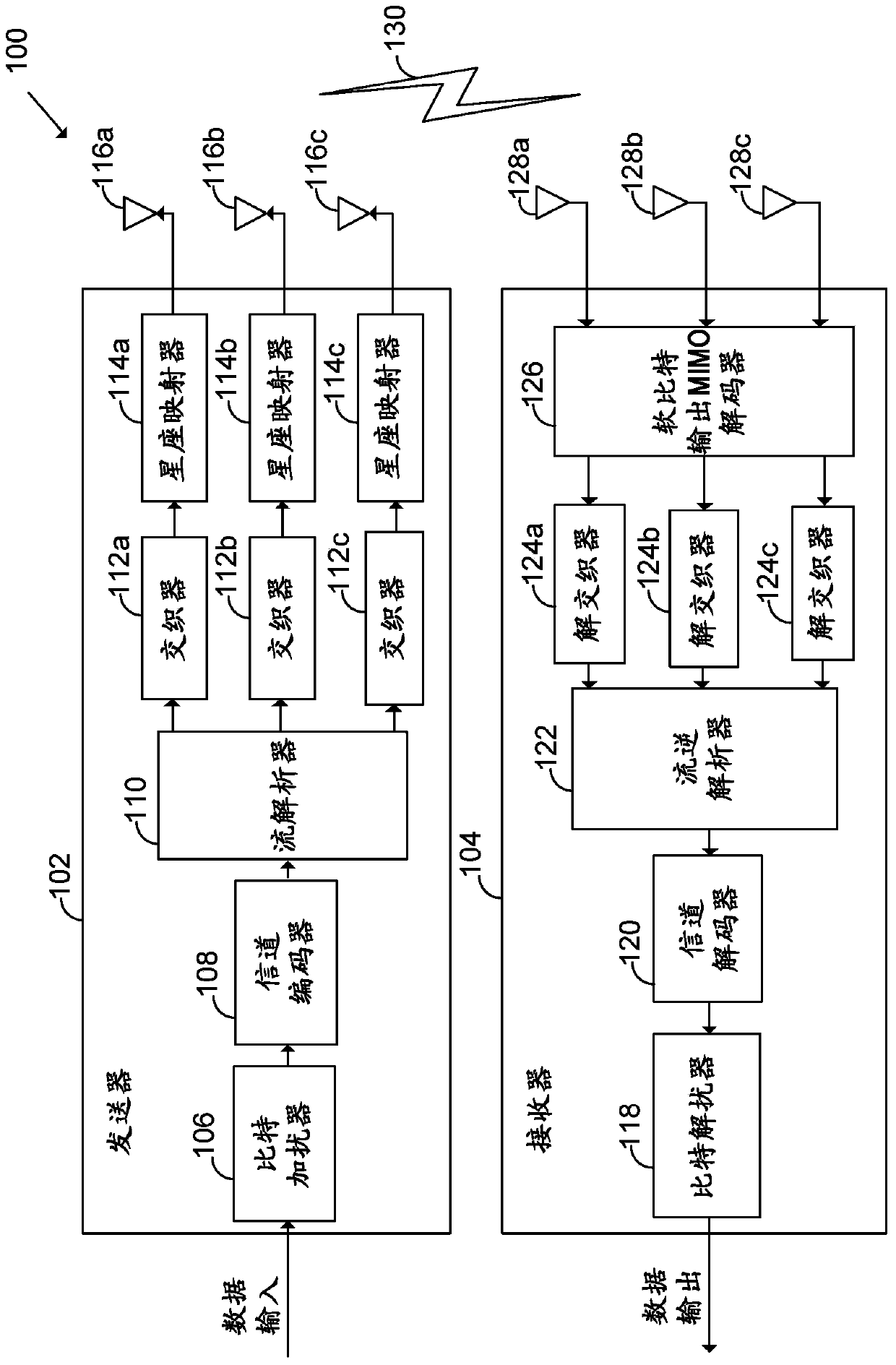

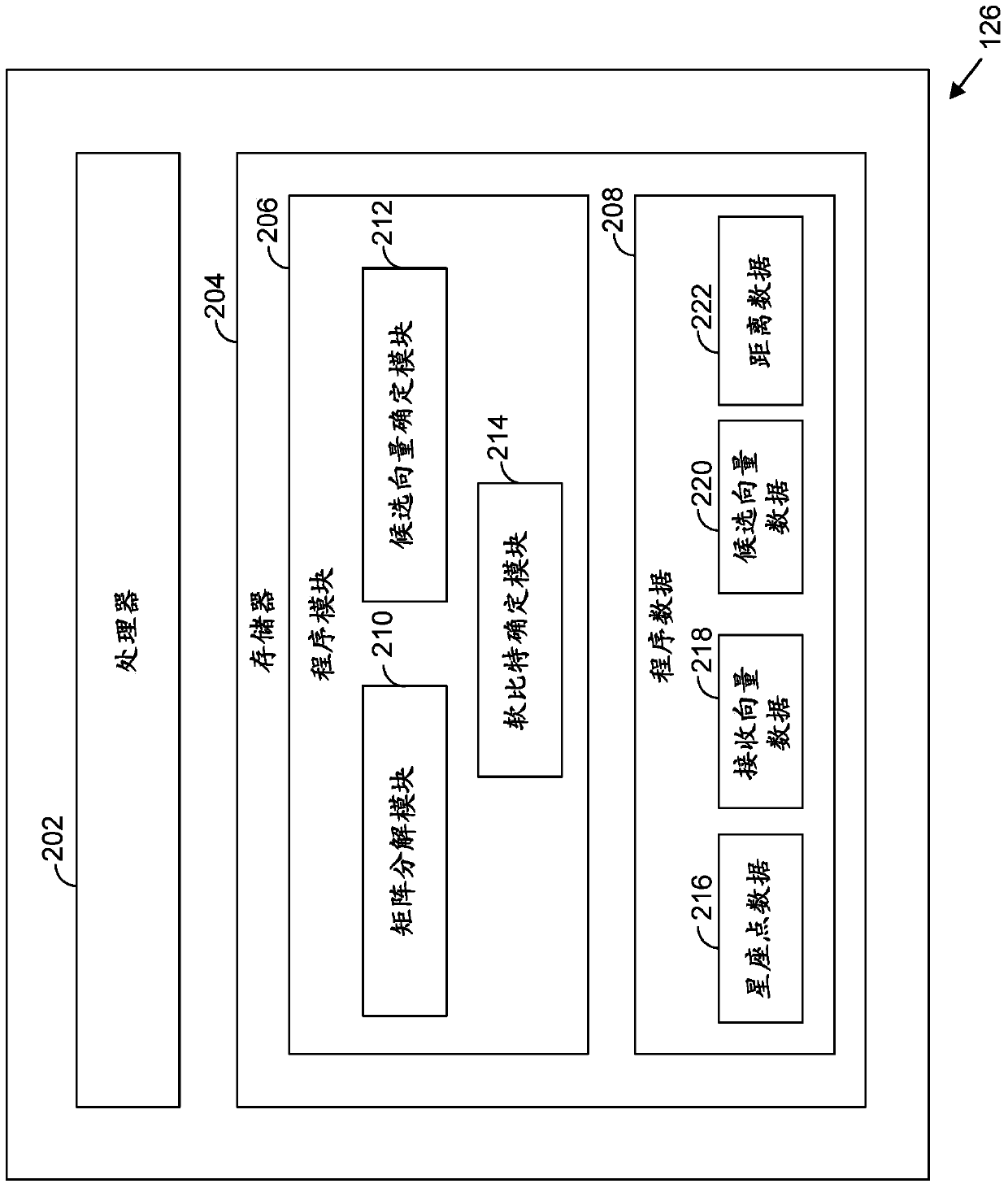

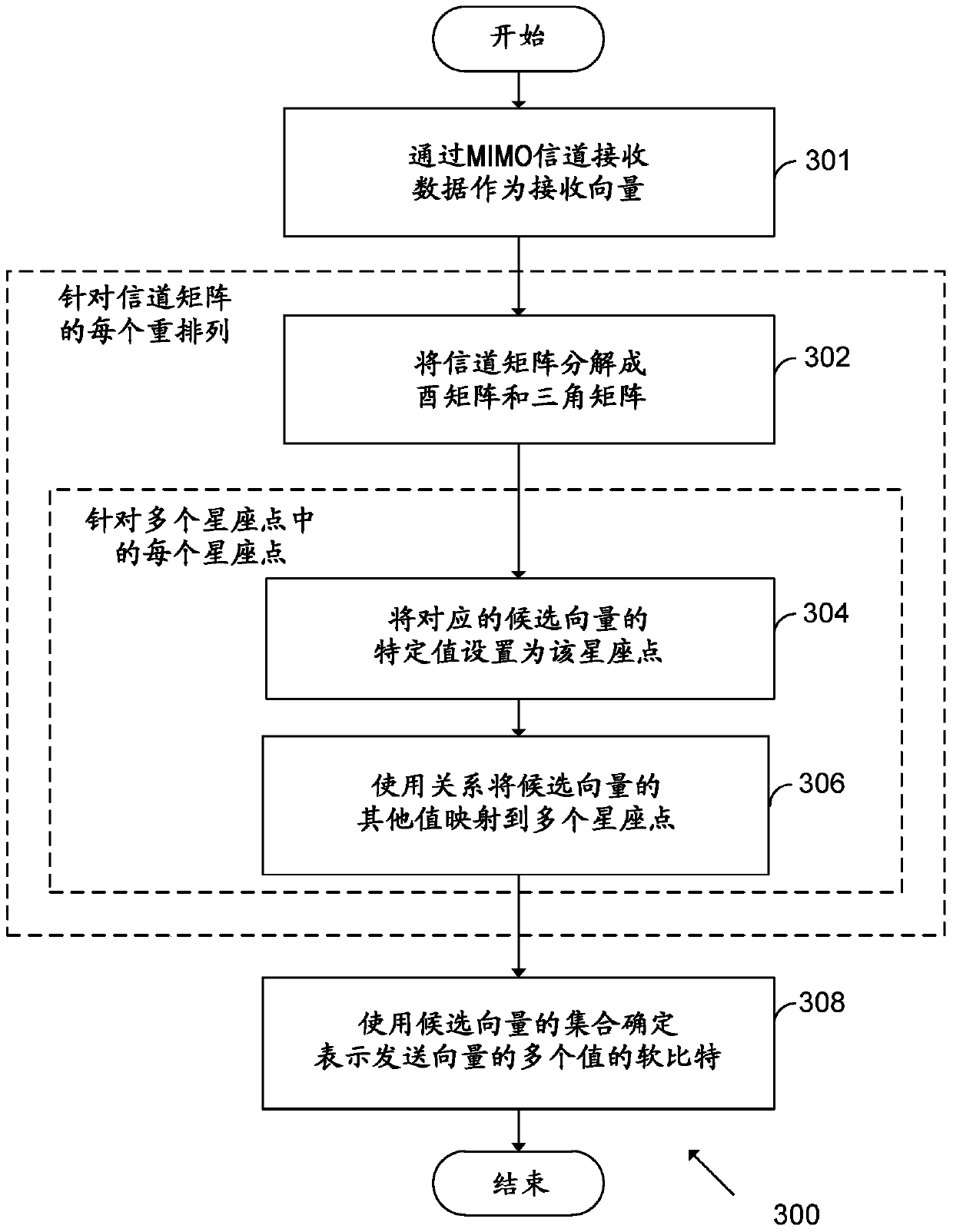

Low complexity soft output MIMO decoder

A method and processing block for receiving data transmitted in a MIMO system is provided. Data is transmitted as a transmit vector of values from multiple transmitting antennas and received as a receive vector of values at multiple receiving antennas. Candidate vectors are determined based on each of a plurality of constellation points of the constellation configuration used in the transmission scheme. A channel matrix is decomposed into a unitary matrix and a triangular matrix, such that a relationship links: (i) a function of the unitary matrix and the receive vector, and (ii) a multiplication of the triangular matrix and the transmit vector. A best candidate vector from the set of candidate vectors is utilized for the computation of soft bits representing the values of the transmit vector.

Owner:NORDIC SEMICONDUCTOR

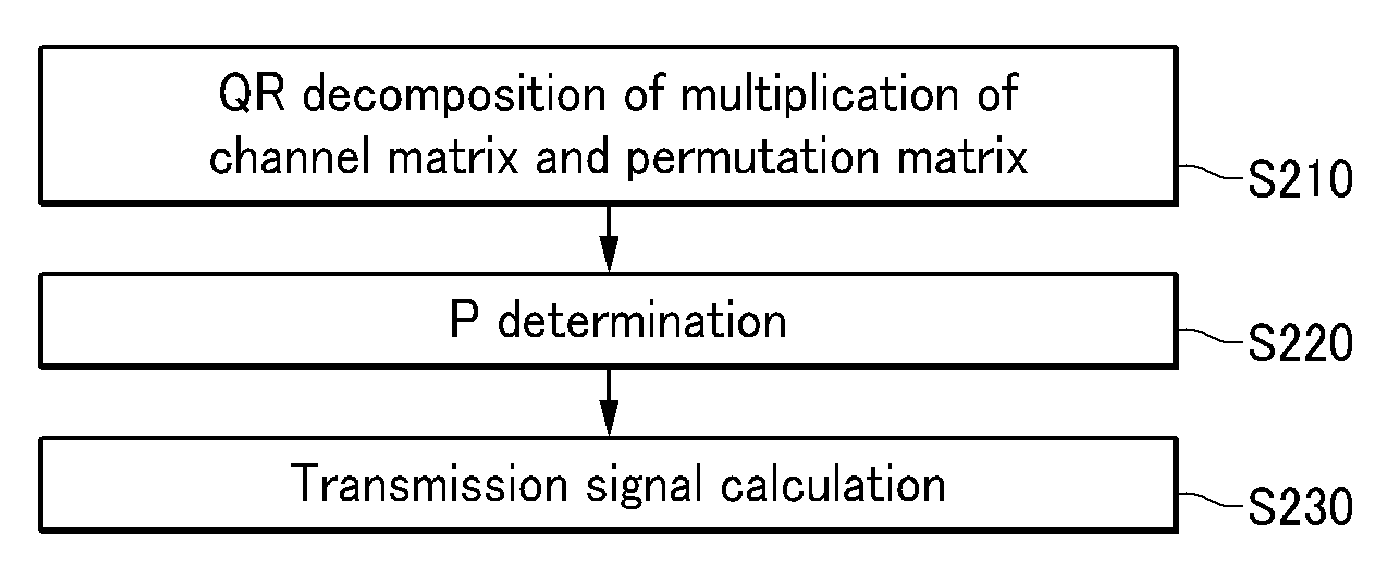

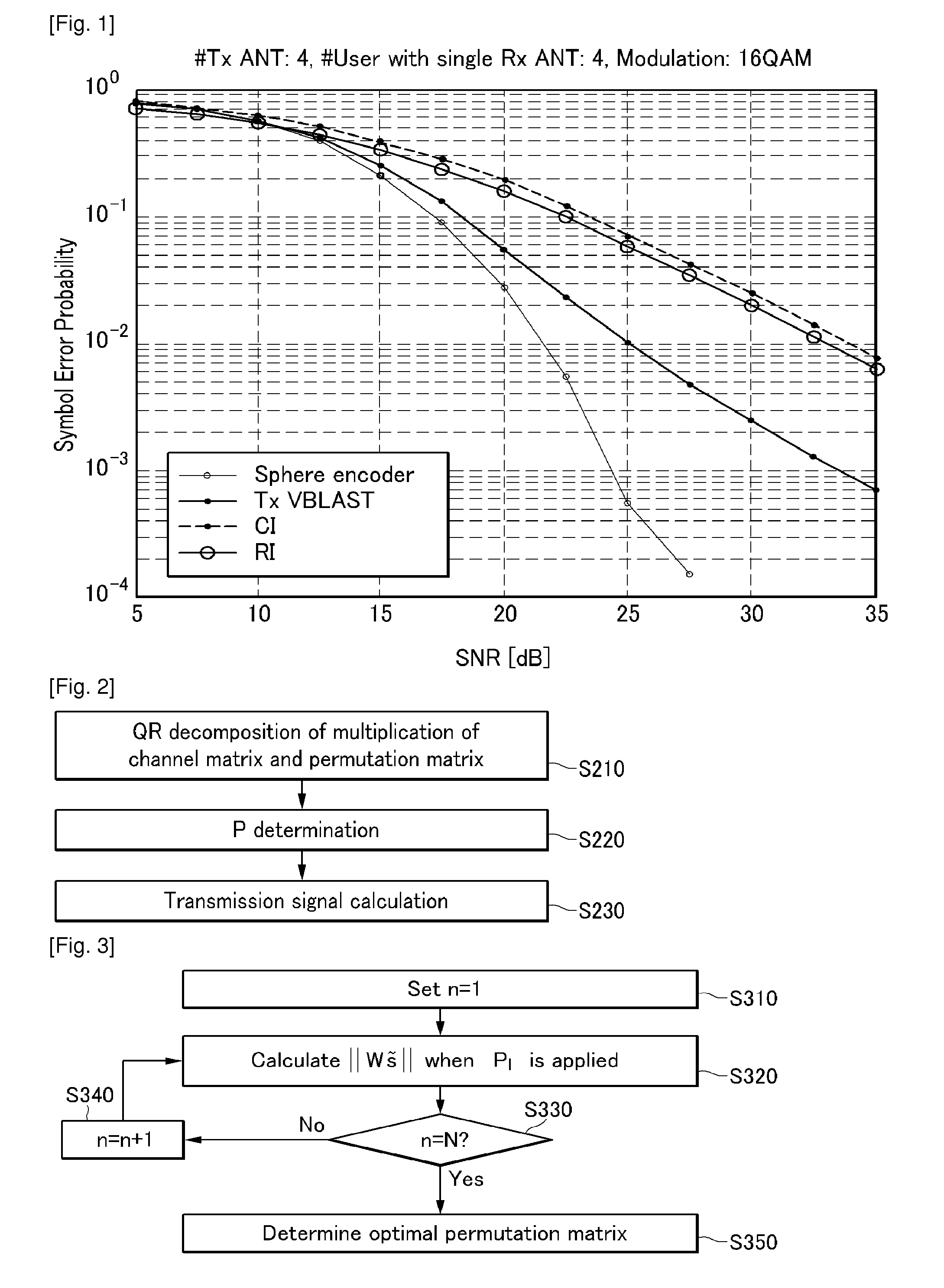

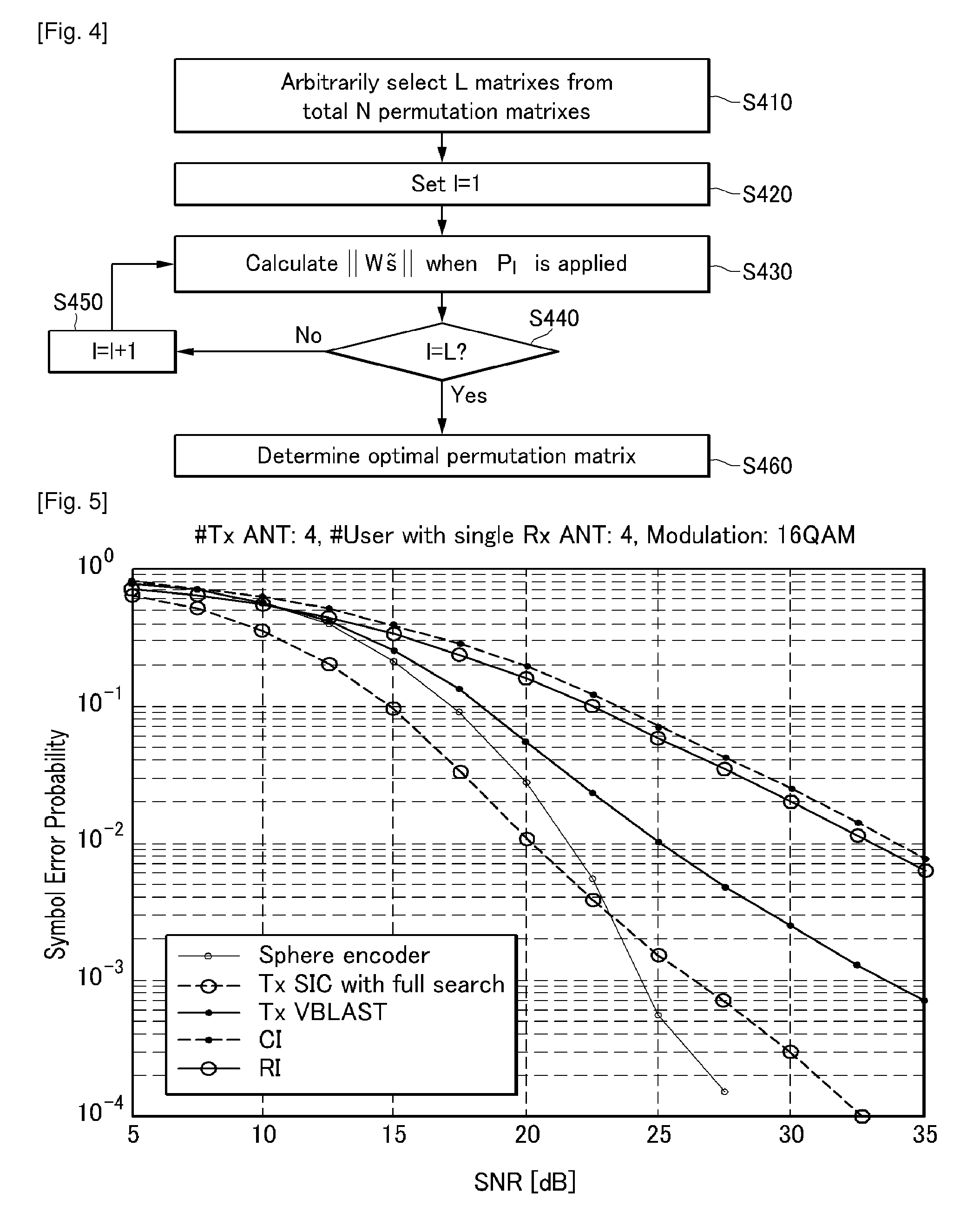

Method for transmission interferance cancellation for mu-mimo

ActiveUS20100255797A1Reduce complexityImprove performancePower managementSpatial transmit diversityPrecodingMultiuser system

The present invention relates to a transmission interference cancellation method for a multiuser MIMO system. The method includes decomposing a channel matrix to represent formulae of permutation matrixes including a first matrix and a second matrix; determining an optimal permutation matrix among a plurality of available permutation matrixes using a norm of multiplication of the second matrix and a transmitting data vector; and determining the second matrix using the determined optimal permutation matrix and calculating a transmitting precoding vector using the determined second matrix and the transmitting data vector.

Owner:SAMSUNG ELECTRONICS CO LTD +1

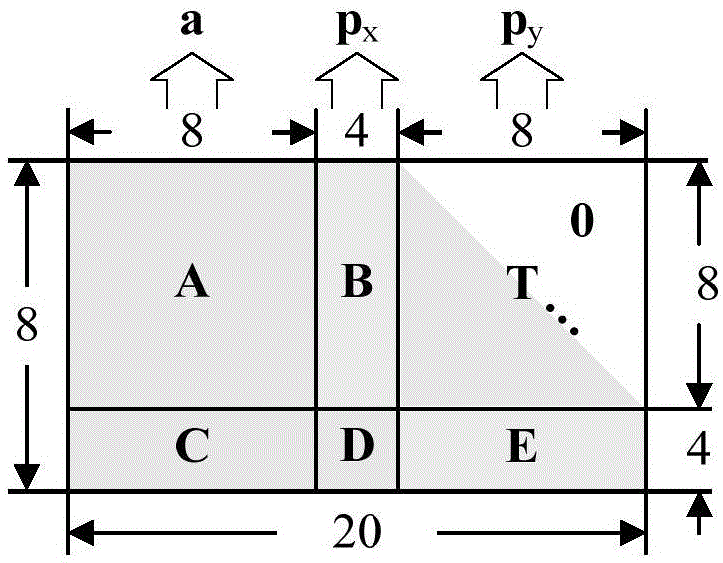

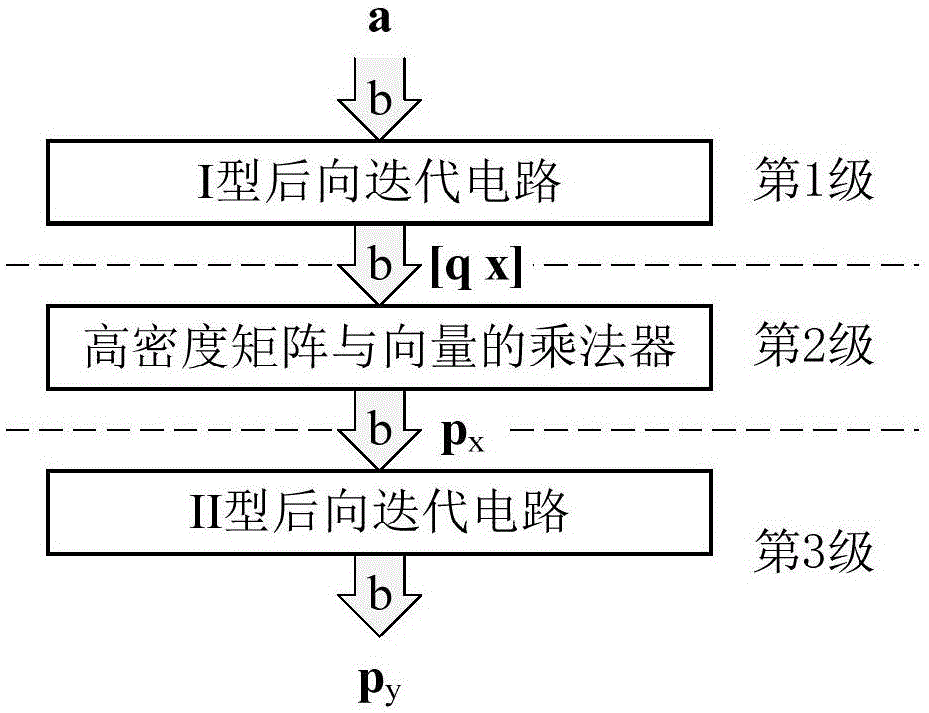

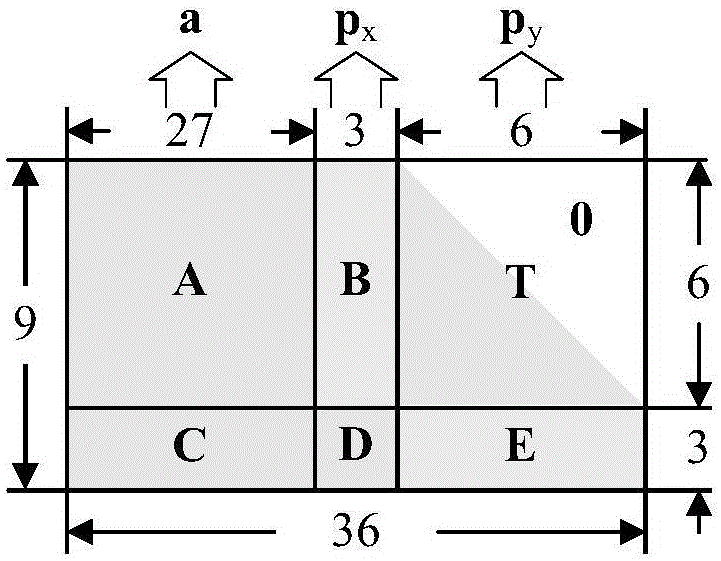

High-speed QC-LDPC encoder based on three-stage pipeline in deep space communication

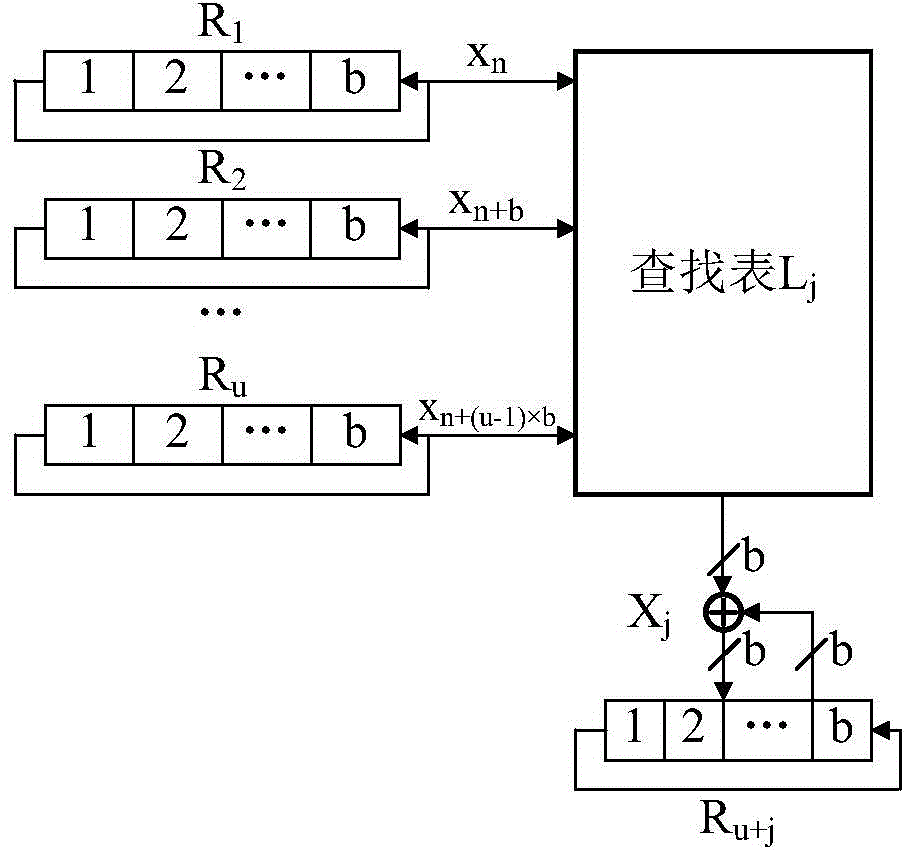

InactiveCN105141319ASimple structureImprove encoding speedError correction/detection using multiple parity bitsCommunications systemHigh density

The invention provides a high-speed QC-LDPC encoder based on a three-stage pipeline in deep space communication. The encoder comprises a type-I backward iteration circuit, a high-density matrix and vector multiplier and a type-II backward iteration circuit. The high-density matrix and vector multiplier realizes high-density matrix and vector multiplication operation, and the type-I backward iteration circuit and the type-II backward iteration circuit both realize backward iteration operation. The whole encoding process is divided into three pipeline stages. The provided 1 / 2 code-rate high-speed QC-LDPC encoder in deep space communication has the advantages of simple structure, low cost and large throughput capacity and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

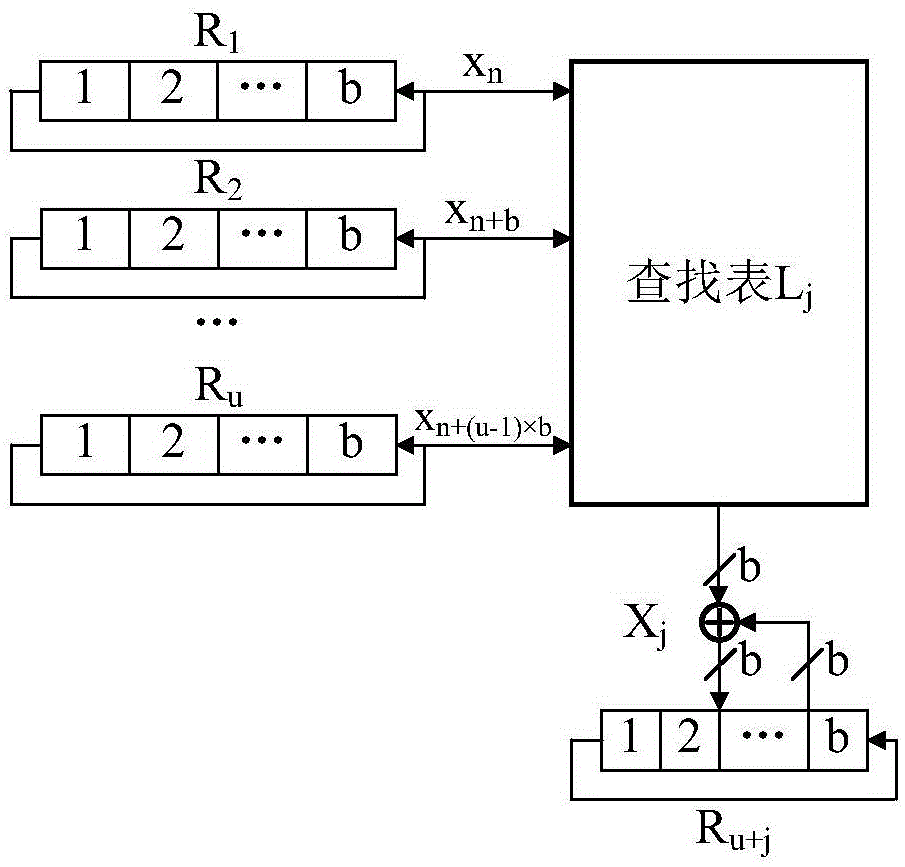

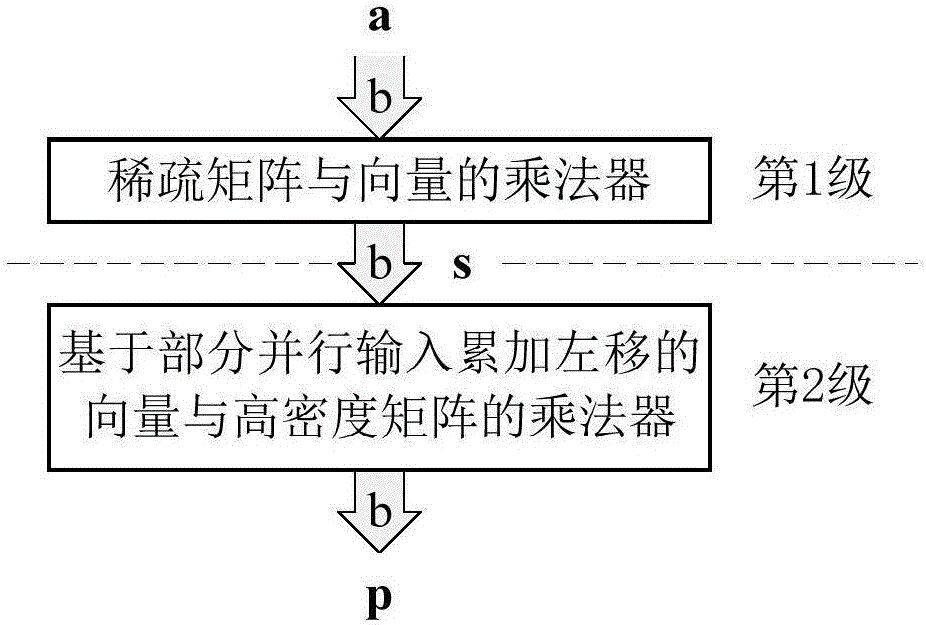

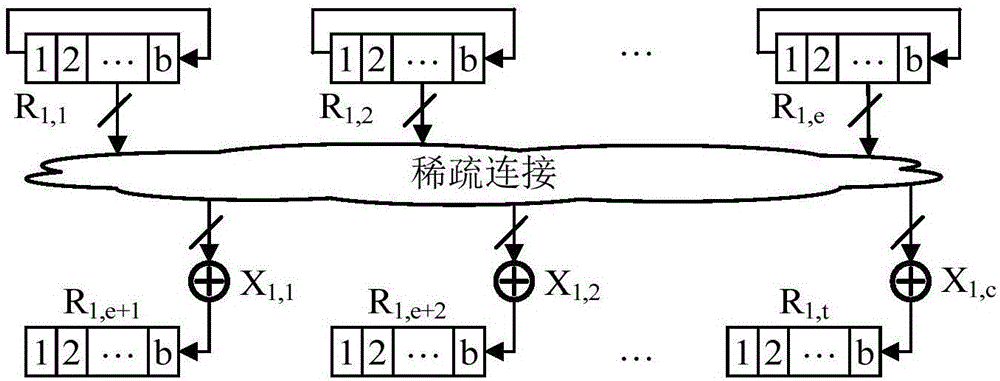

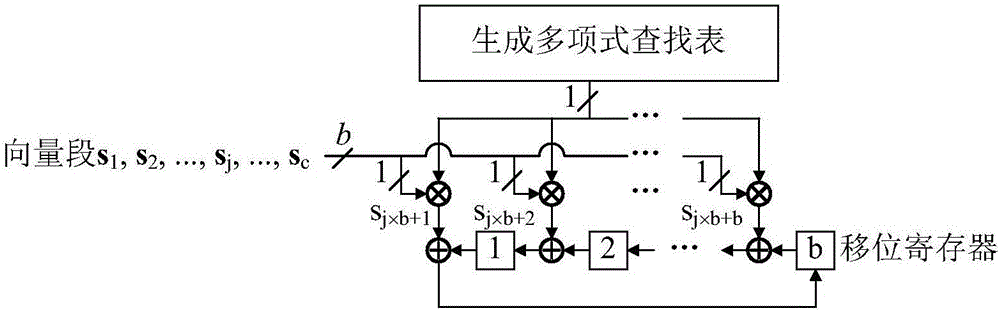

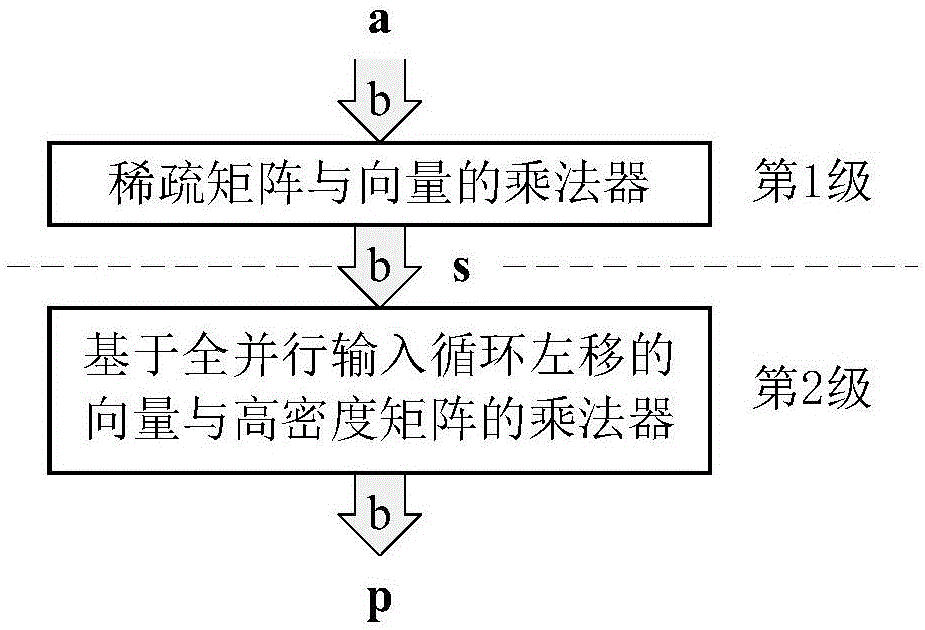

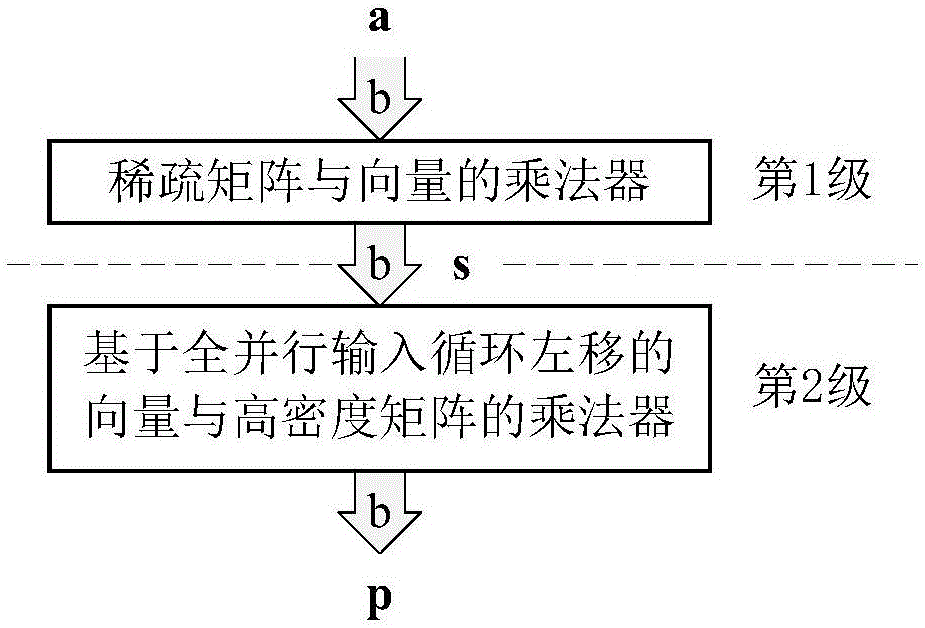

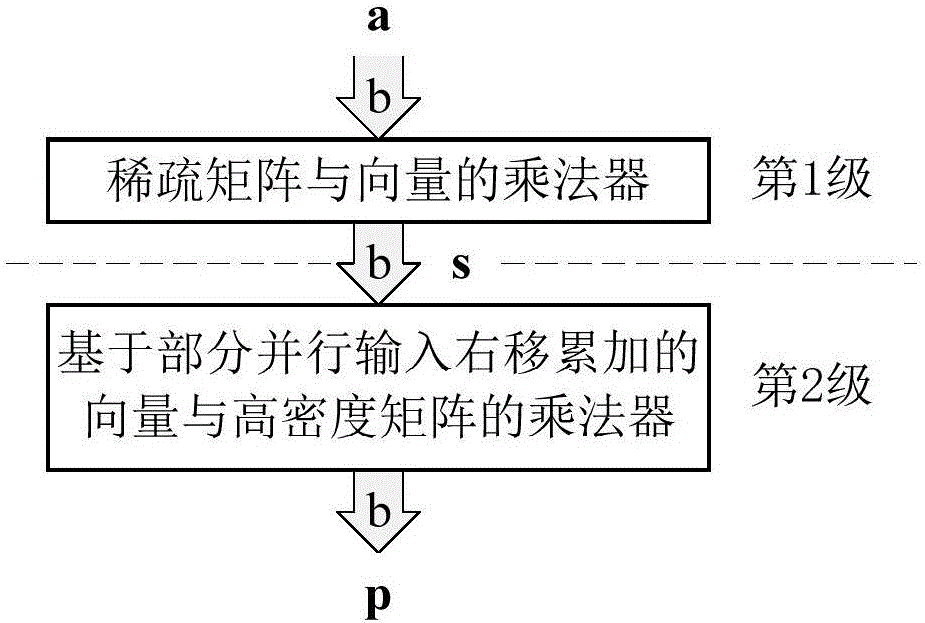

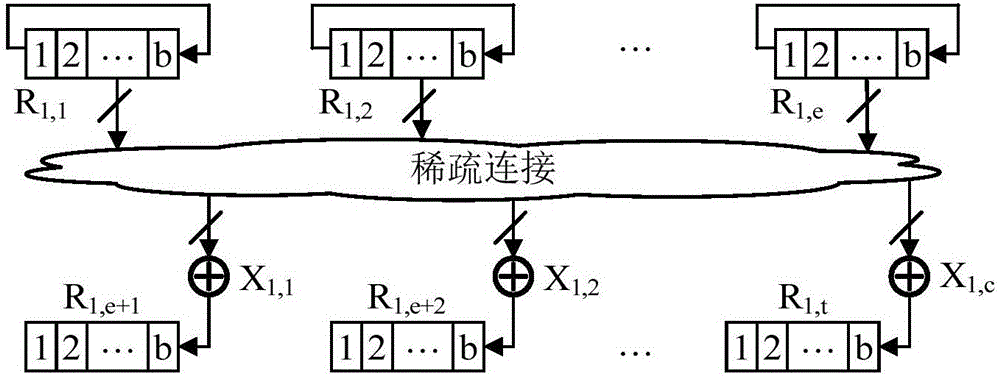

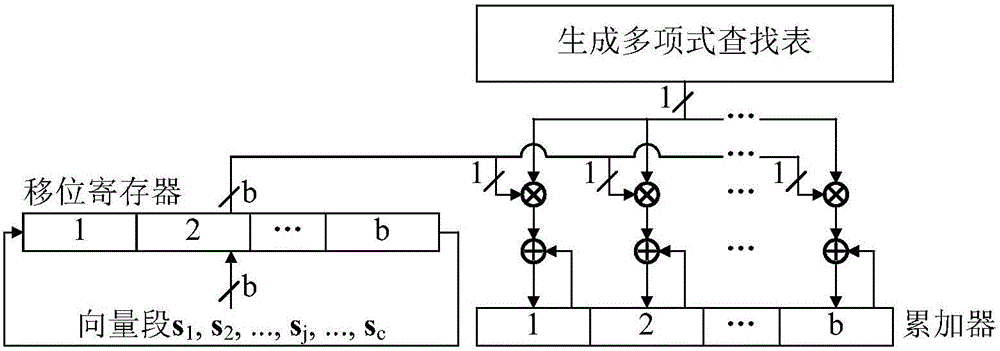

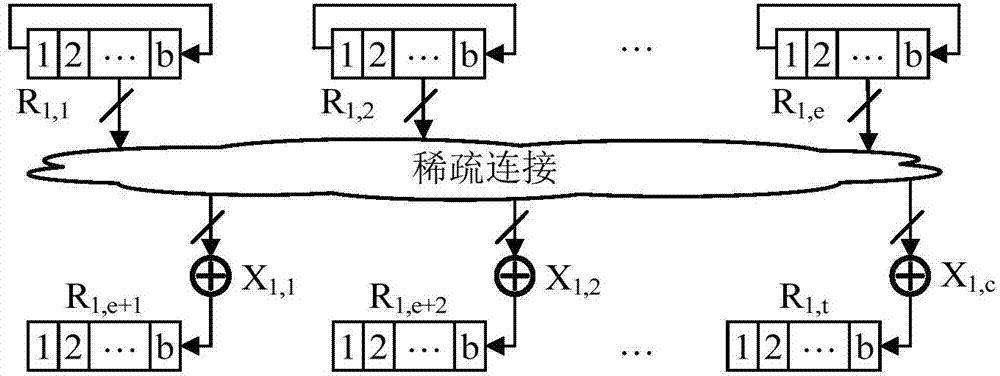

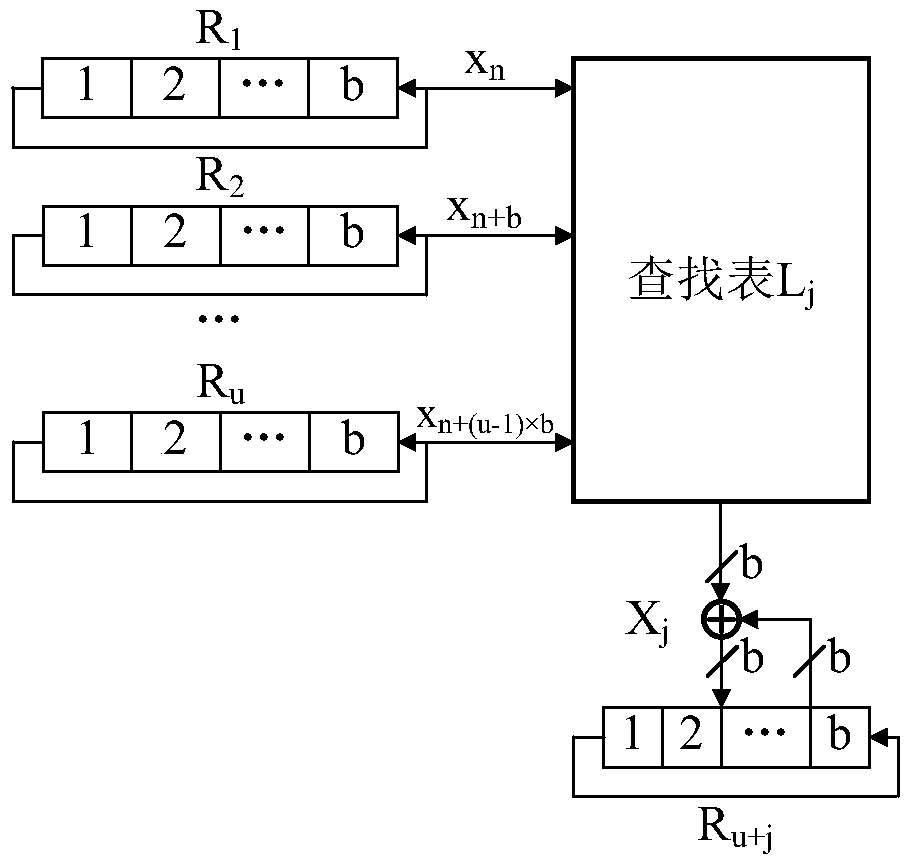

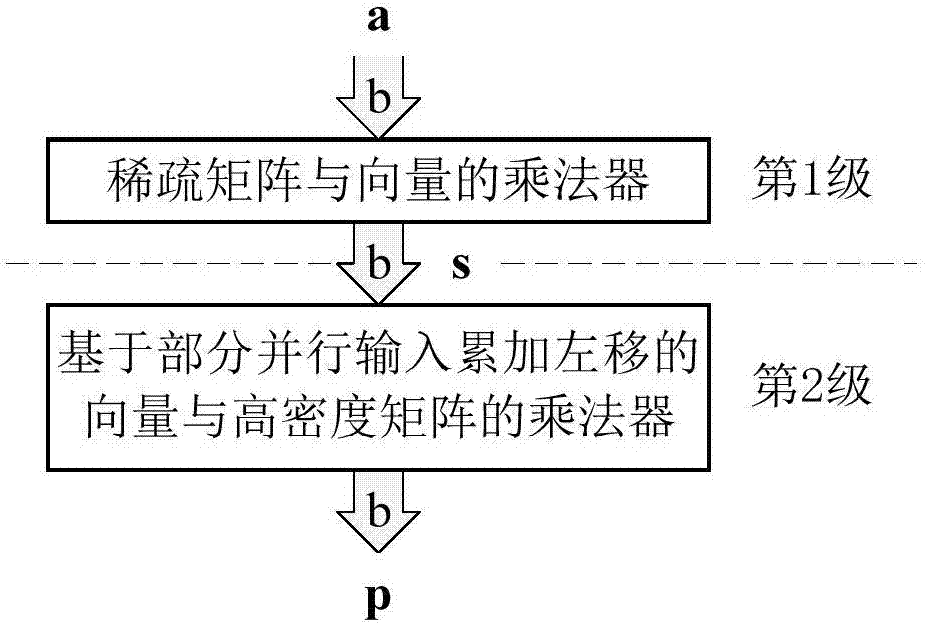

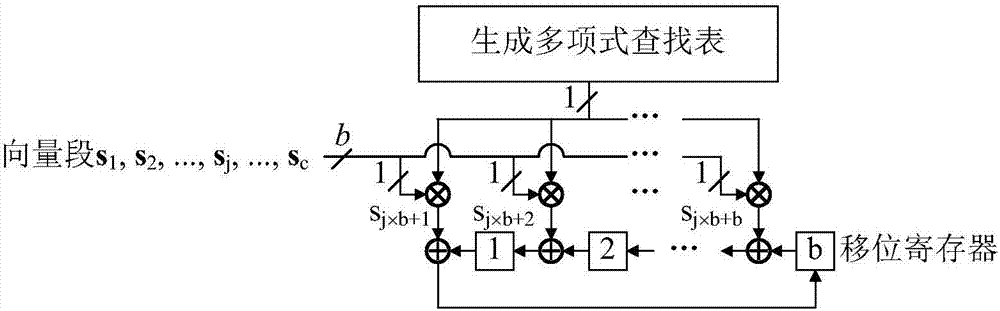

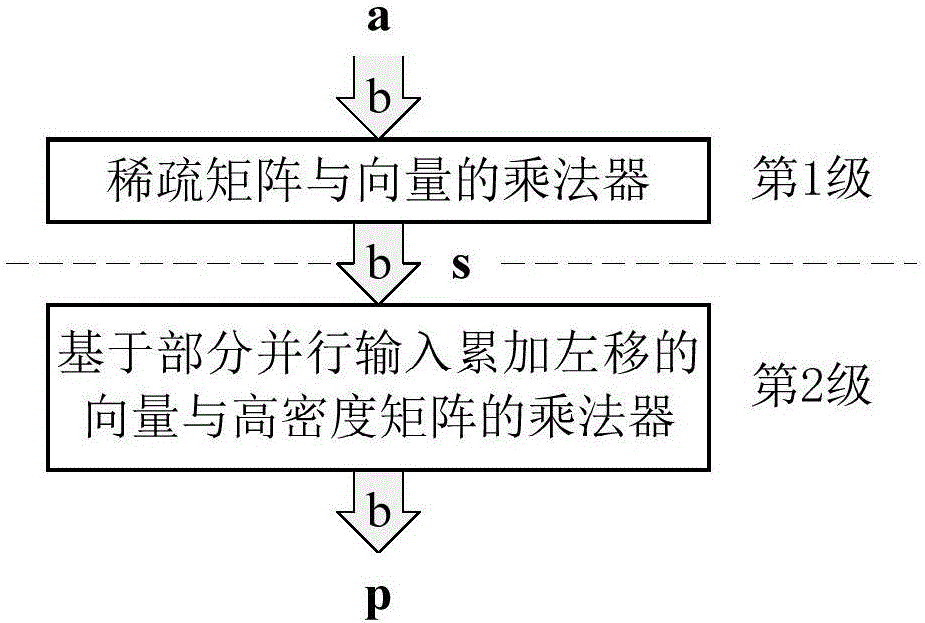

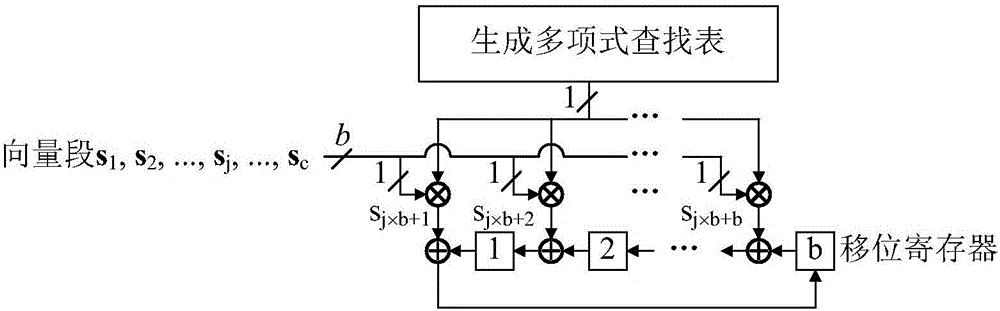

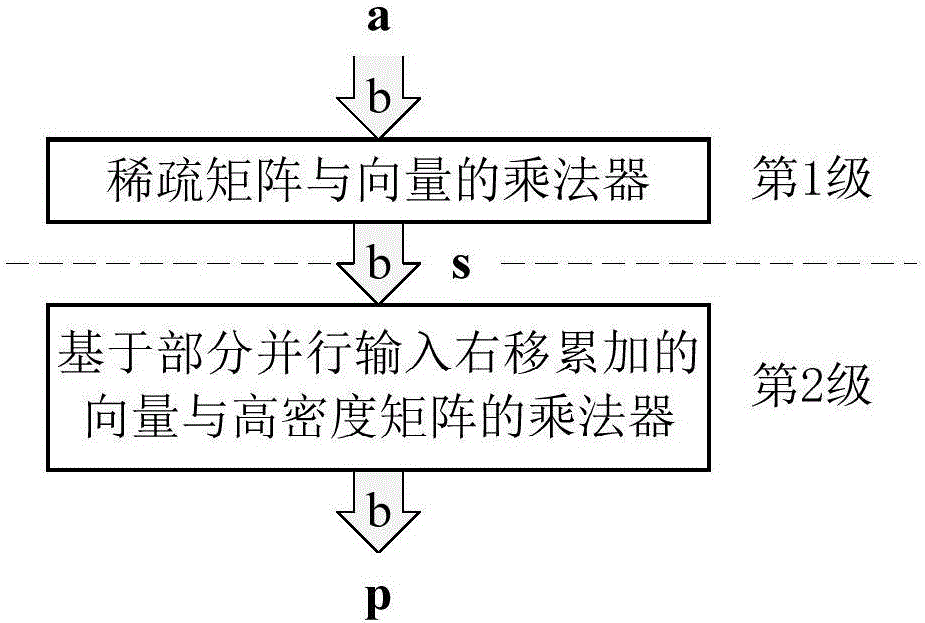

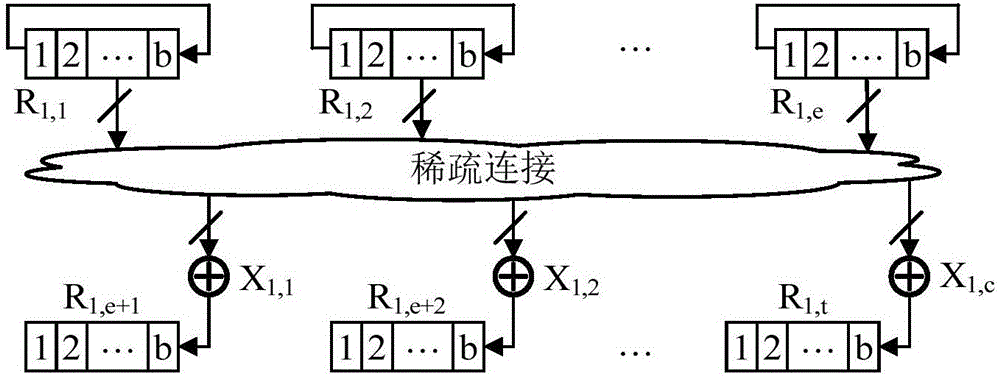

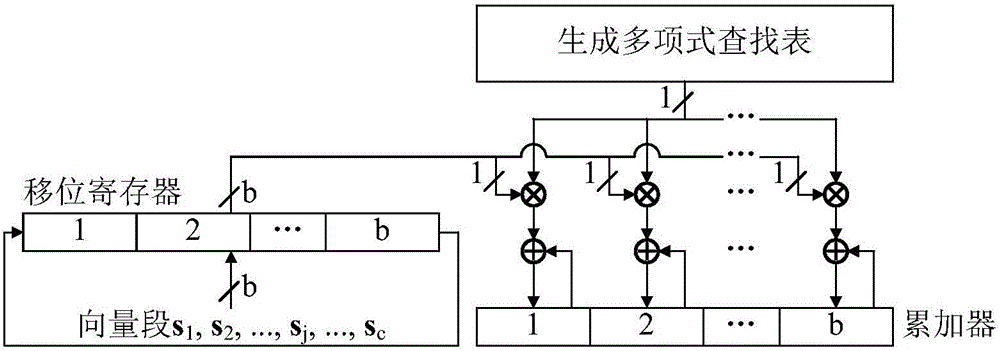

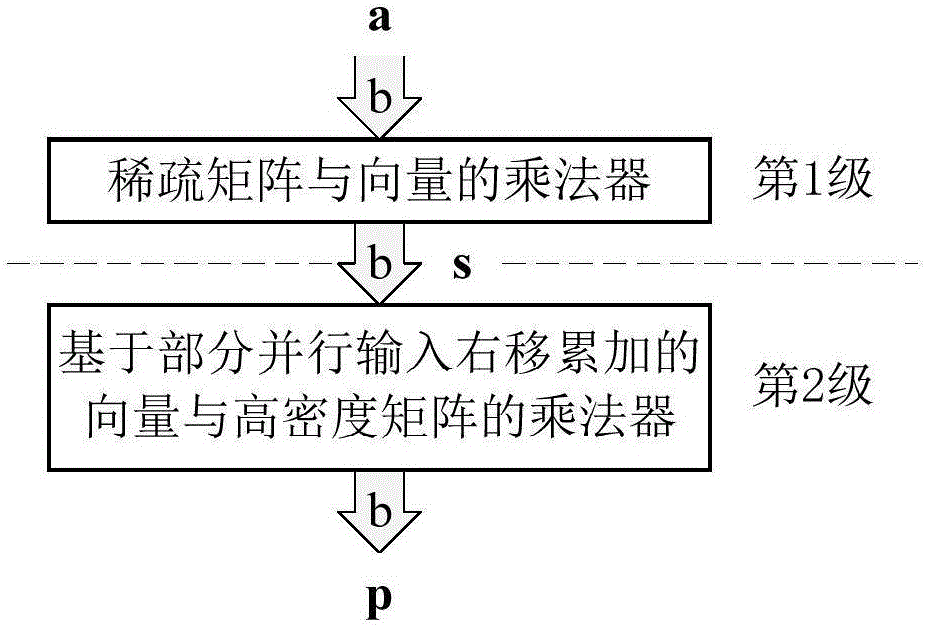

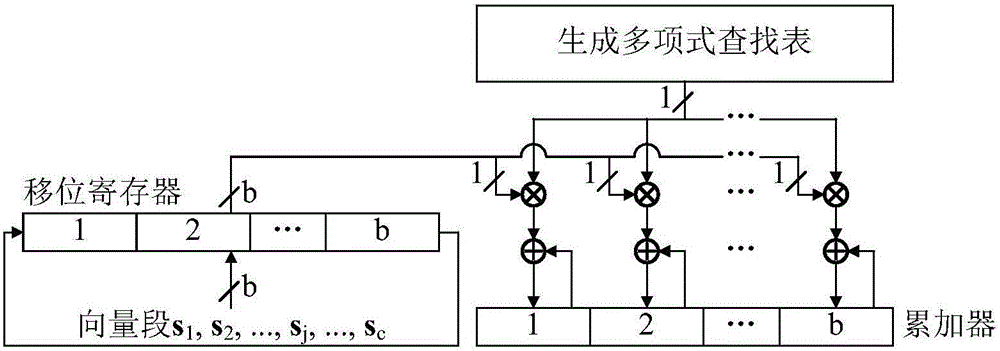

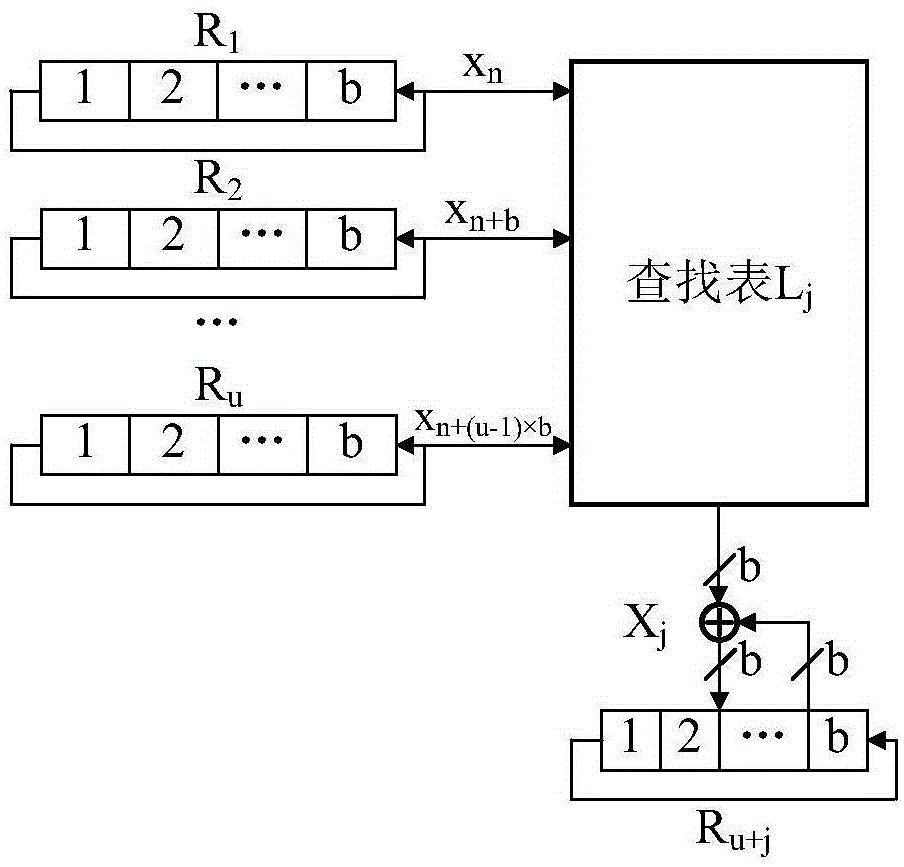

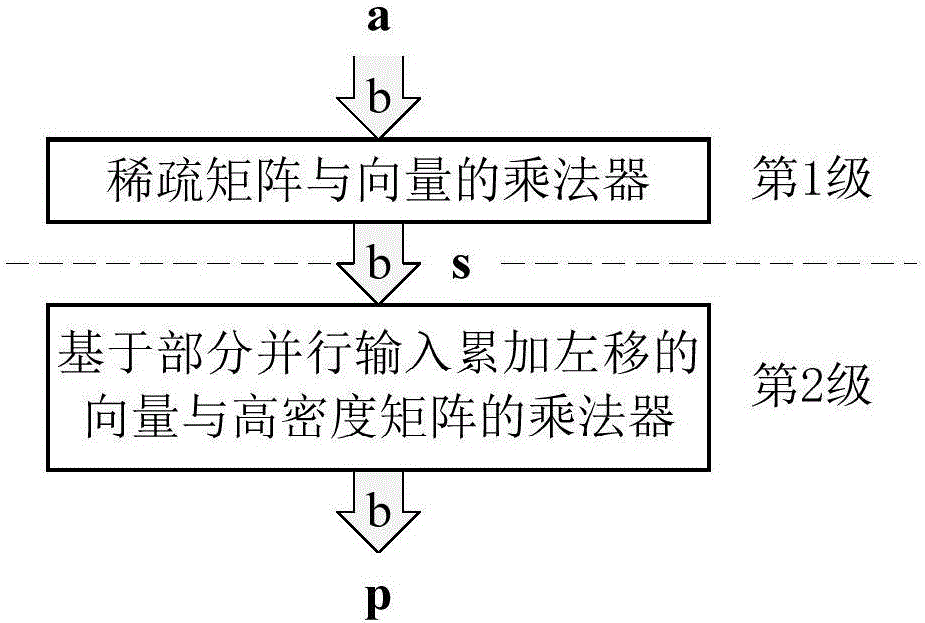

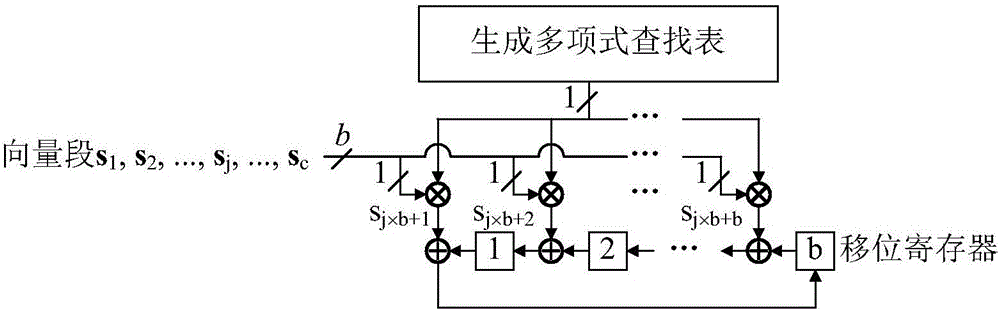

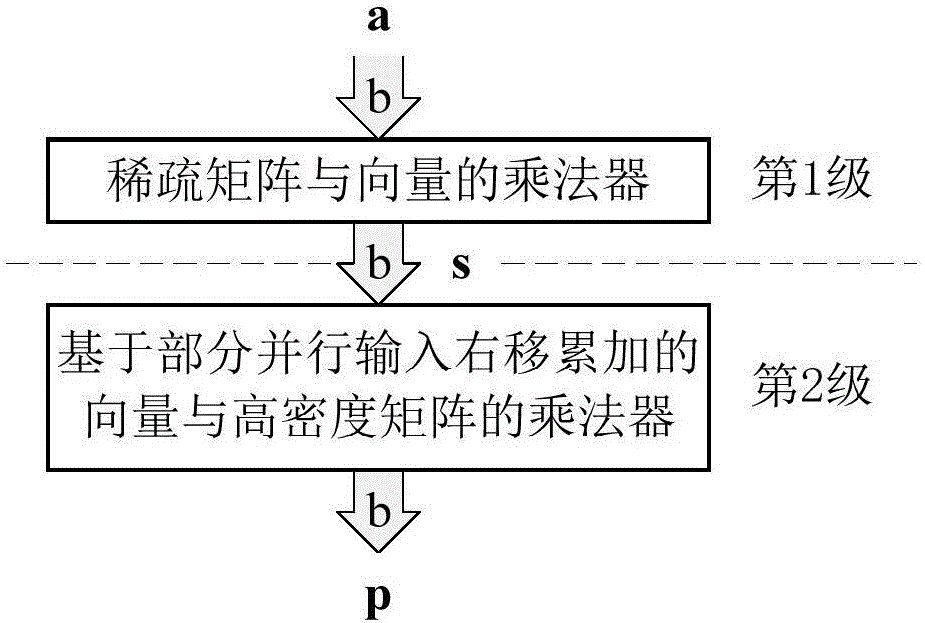

Two-level partial parallel inputting, accumulating and left-shifting LDPC encoder

InactiveCN106385264AError correction/detection using multiple parity bitsCode conversionBinary multiplierHigh density

The invention provides a two-level streamline-based QC-LDPC encoder. The encoder comprises one sparse matrix and vector multiplier and one vector and high-density matrix multiplier, wherein the sparse matrix and vector multiplier realizes multiplication operation of sparse matrixes and vectors, the vector and high-density matrix multiplier employs a partial parallel inputting, accumulating and left-shifting mechanism to realize multiplication operation of vectors and high-density matrixes. The entire encoding process is divided into two-level streamlines. The QC-LDPC encoder has the advantages of low cost and large throughput.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

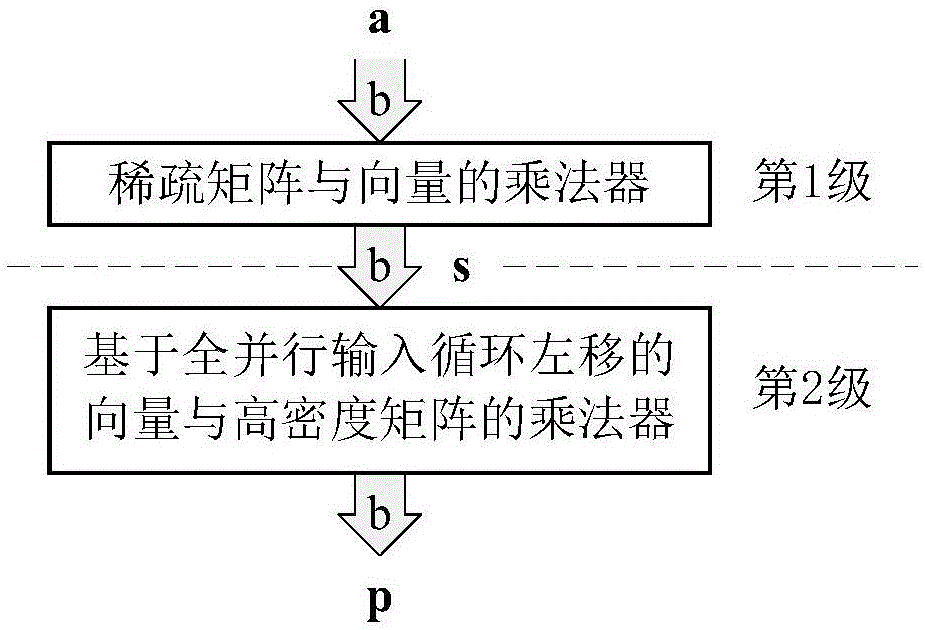

Two-level all-parallel input ring shift left LDPC coder

InactiveCN106452459AError correction/detection using multiple parity bitsCode conversionMultiplication of vectorsSparse matrix

The invention provides a QC-LDPC (Quasi Cyclic-Low Density Parity Check) coder based on a two-level pipeline. The QC-LDPC coder includes 1 multiplier of sparse matrix and vector and 1 multiplier of vector and high density matrix. The multiplier of sparse matrix and vector can realize multiplication of sparse matrix and vector. The multiplier of vector and high density matrix uses an all-parallel input ring shift left mechanism to realize multiplication of vector and high density matrix. The whole coding process is divided into two-level pipelines. The QC-LDPC coder has the advantages of being high in the work efficiency and being high in the throughput.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

LDPC encoder for secondary level full parallel input ring shift left in deep space communication

InactiveCN106571830AError correction/detection using multiple parity bitsCode conversionCommunications systemBinary multiplier

The invention provides a QC-LDPC encoder based on a secondary pipeline in deep space communication. The encoder comprises a sparse matrix and vector multiplier and a vector and high-density matrix multiplier. The sparse matrix and vector multiplier realizes sparse matrix and vector multiplication. The vector and high-density matrix multiplier uses a full parallel input ring shift left mechanism to realize vector and high-density matrix multiplication. The whole coding process is divided into two levels of pipeline. According to the invention, the 8 / 11 bit rate QC-LDPC encoder in a deep space communication system has the advantages of high operating frequency, high throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

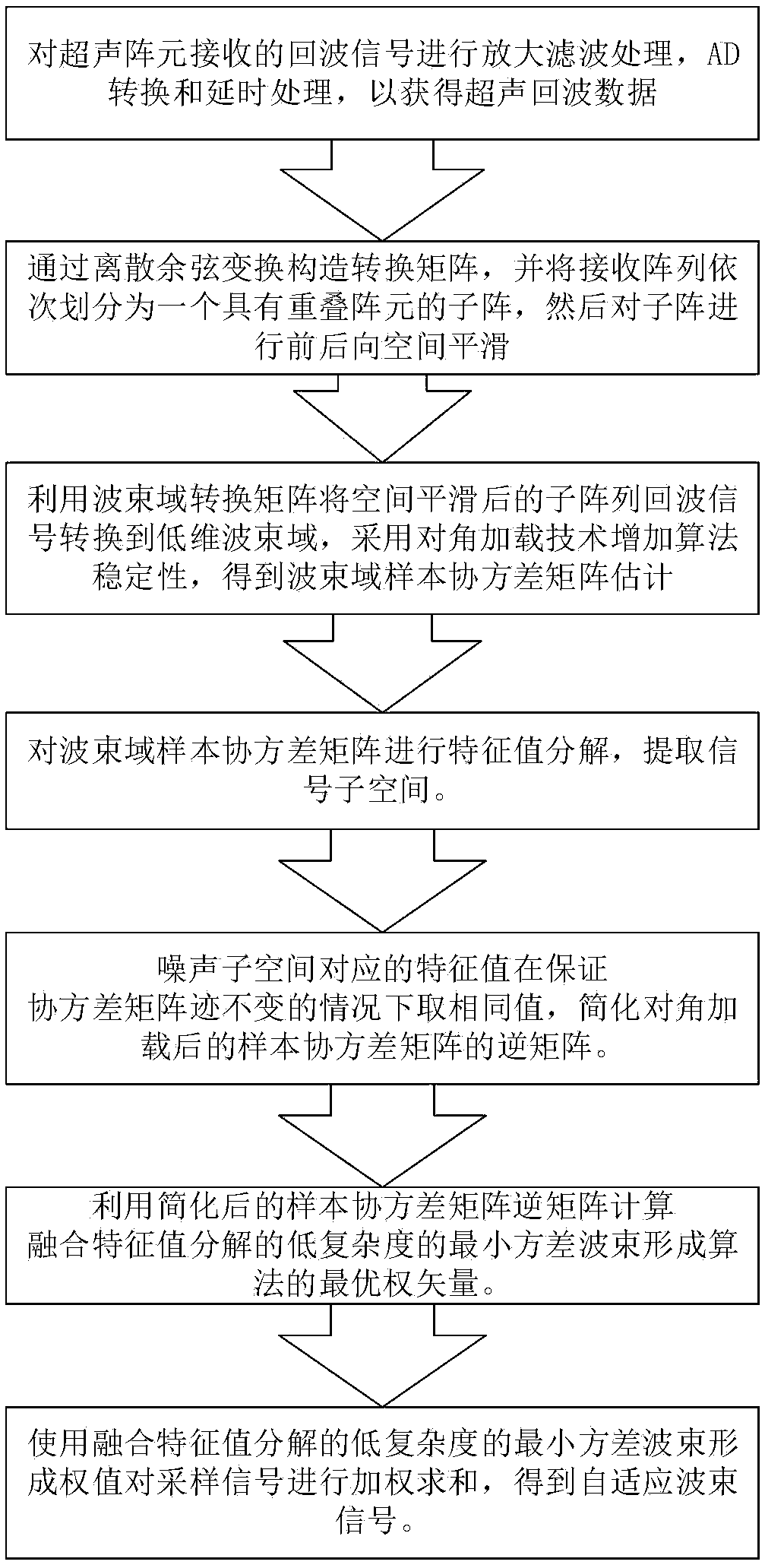

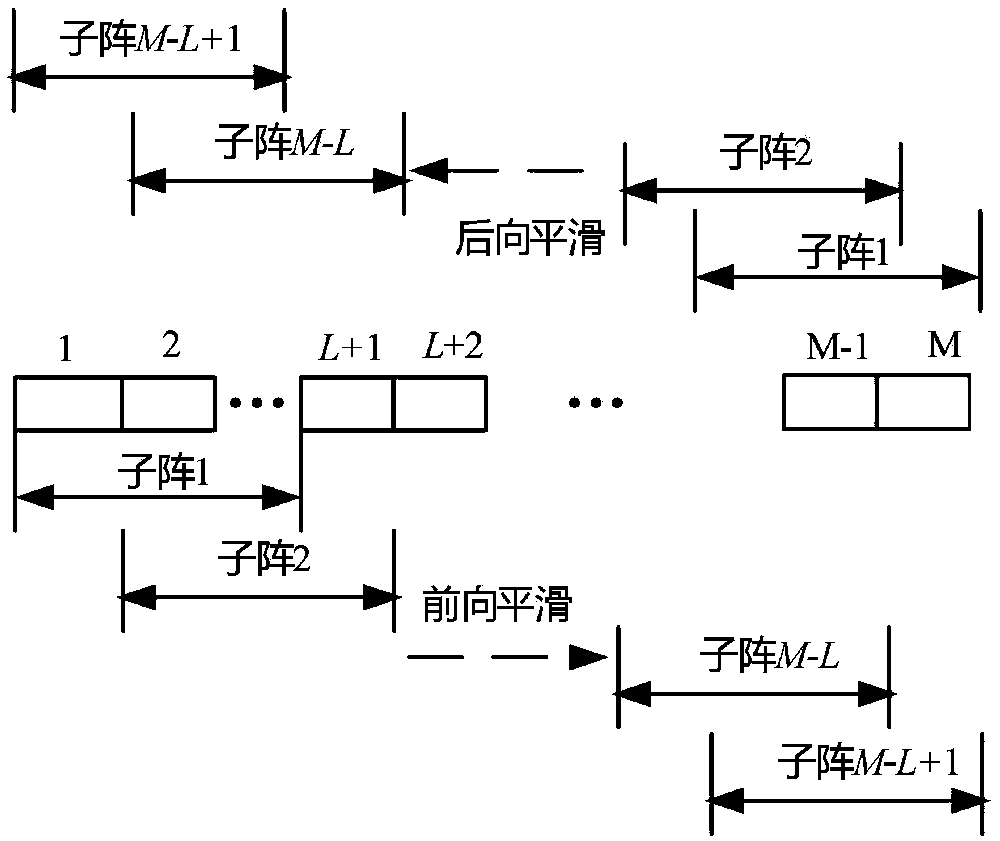

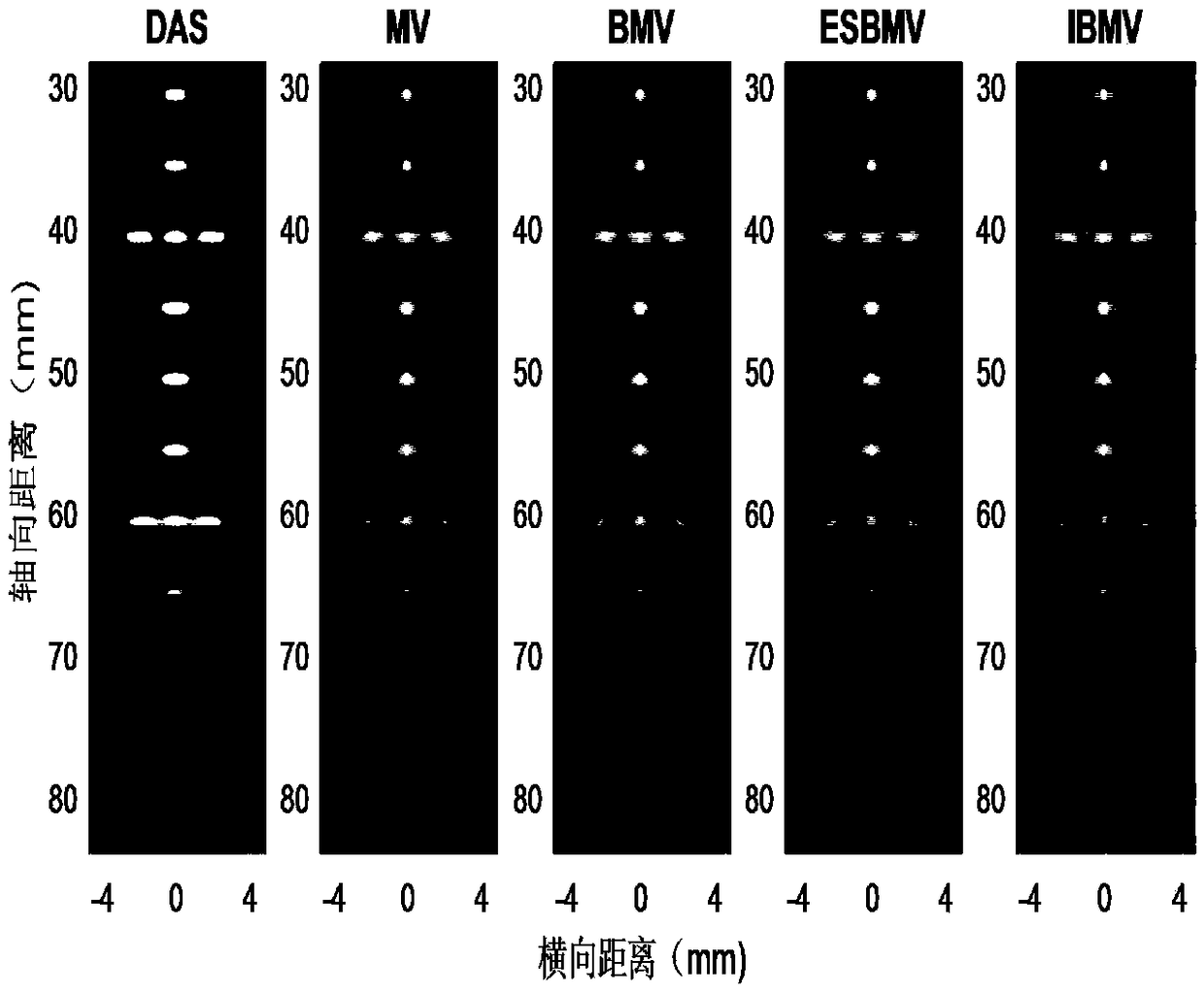

Eigenvalue decomposition-fused low-complexity minimum variance ultrasound imaging method

ActiveCN109187771AReduce complexityHigh-resolutionProcessing detected response signalSonificationDecomposition

The invention relates to an eigenvalue decomposition-fused low-complexity minimum variance ultrasound imaging method, and belongs to the field of ultrasound imaging. Firstly, echo data is converted toa beam domain with fewer dimensions by means of discrete cosine transform; and then a sample covariance matrix is subjected to eigenvalue decomposition to extract signal subspaces, a maximum eigenvalue and an eigenvector corresponding to the maximum eigenvalue are selected, remaining eigenvalues are the same value on the condition that it is guaranteed that a trace of the sample covariance matrixis invariable, and inversion of the matrix is simplified into multiplication of a vector. According to the algorithm, the operation time can be obviously shorter than that of an eigenvalue decomposition-based minimum variance algorithm, the good robustness is achieved on noise, and the imaging effect is obviously better than that of a traditional delay and sum algorithm, minimum variance algorithm and beam domain minimum variance algorithm.

Owner:STATE GRID EAST INNER MONGOLIA ELECTRIC POWER CO LTD MAINTENANCE BRANCH +1

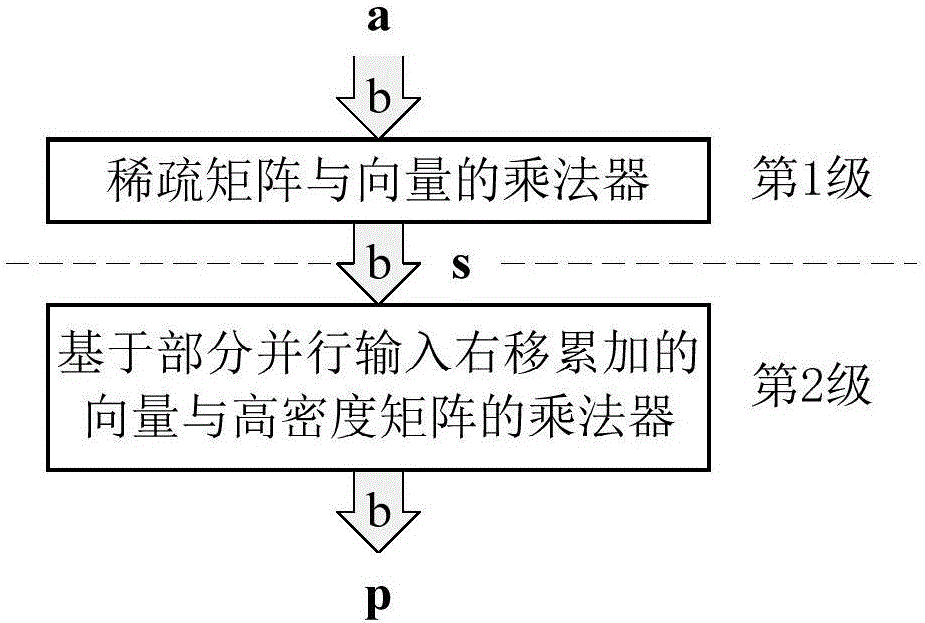

LDPC encoder with secondary part parallel input rightward movement accumulation in CMMB

InactiveCN106385262AError correction/detection using multiple parity bitsCode conversionBinary multiplierHigh density

The invention provides a QC-LDPC encoder based on a secondary streamline in CMMB. The encoder comprises one multiplexer for a sparse matrix and a vector, and a multiplexer for the vector and a high-density matrix. The multiplexer for the sparse matrix and the vector realizes multiplication operation between the sparse matrix and the vector. A partial parallel input rightward movement accumulation mechanism is utilized in the multiplexer for the vector and the high-density matrix, thereby realizing multiplication operation between the vector and the high-density matrix. A whole coding process is divided into two stages of streamlines. The 3 / 4-code-rate QC-LDPC encoder in the CMMB system according to the invention has advantages of low cost, high throughput amount, etc.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

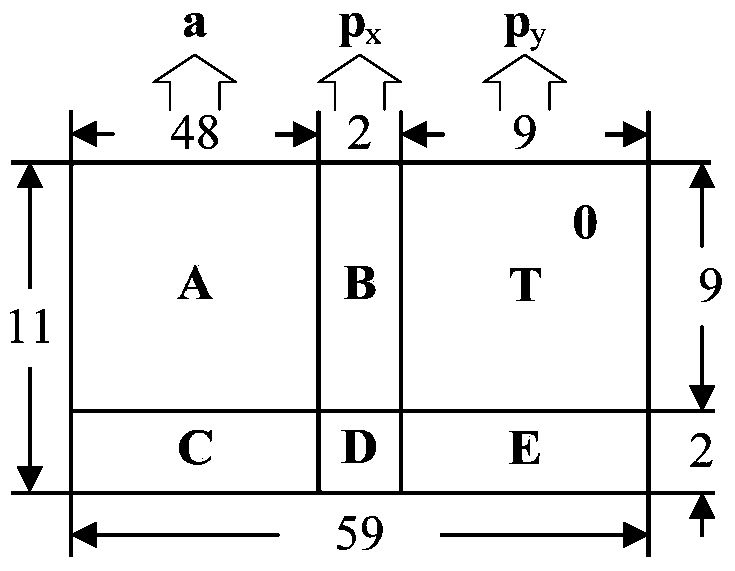

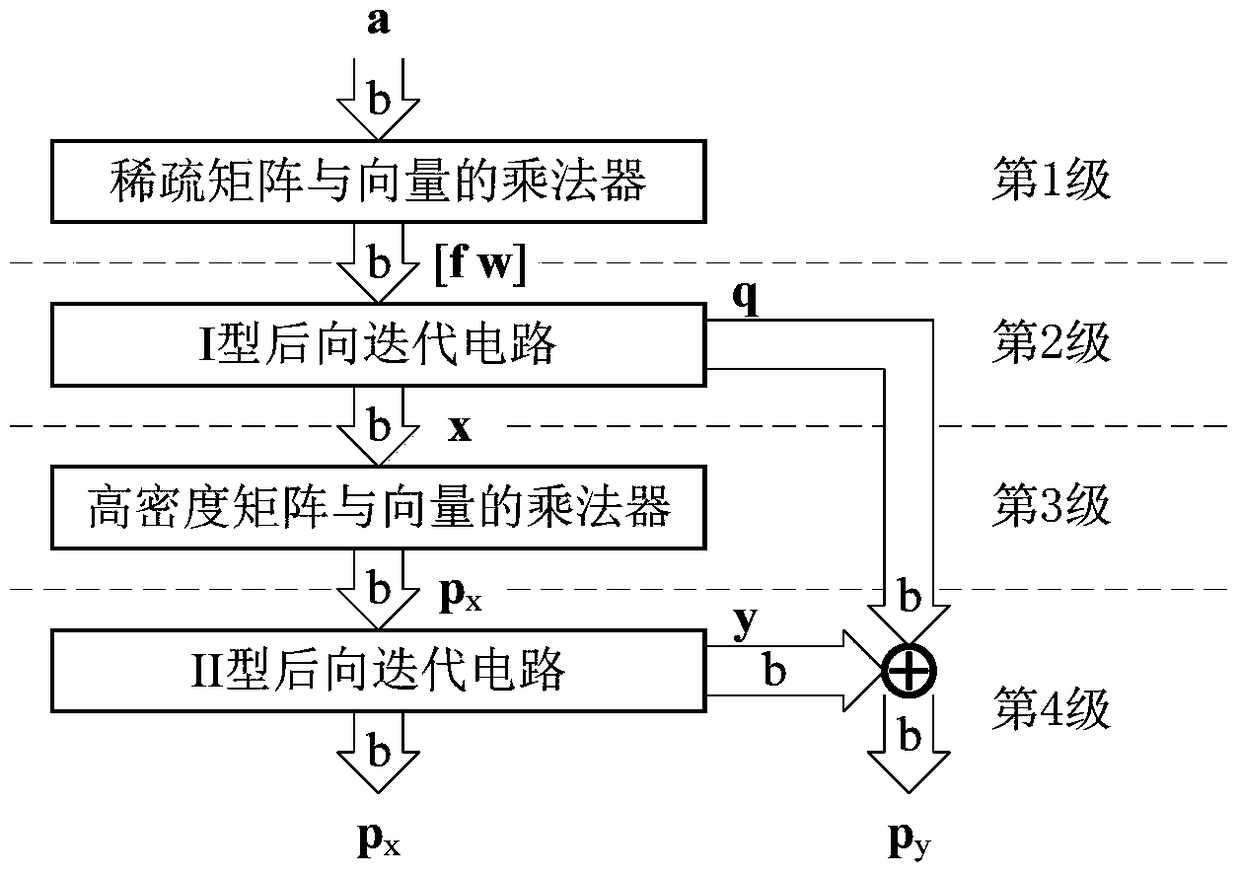

High-speed QC-LDPC (quasi-cyclic low-density parity-check) encoder based on four-level assembly lines

InactiveCN104579365ASimple structureImprove encoding speedError correction/detection using multiple parity bitsBinary multiplierHigh density

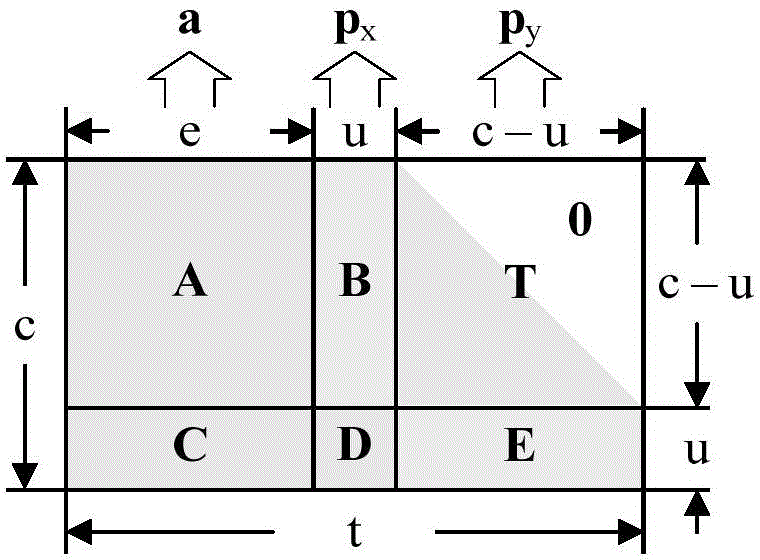

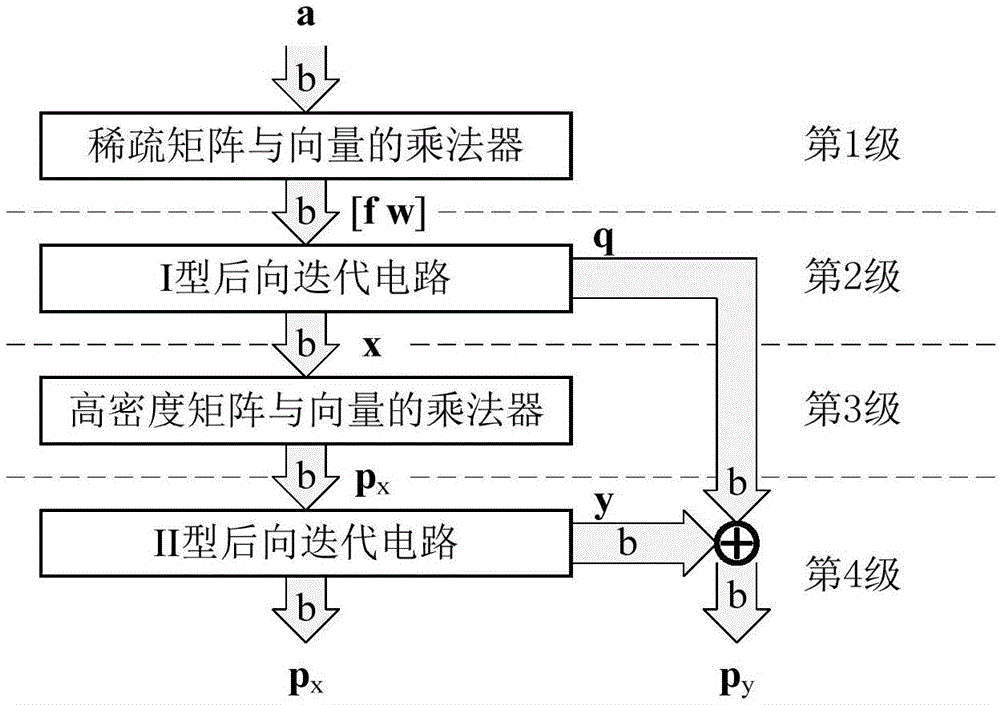

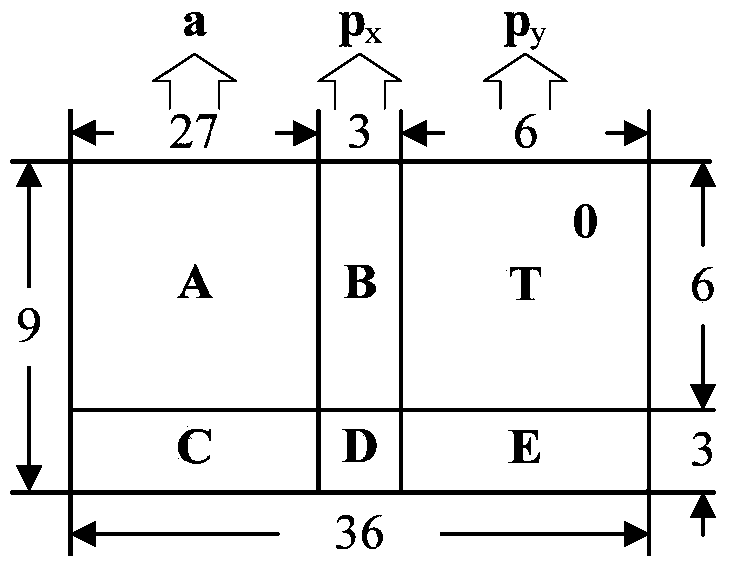

The invention provides a high-speed QC-LDPC (quasi-cyclic low-density parity-check) encoder based on four-level assembly lines. The encoder comprises a multiplier for sparse matrixes and vectors, an I-type backward iterative circuit, a multiplier for high-density matrixes and vectors and an II-type backward iterative circuit. The multiplier for the sparse matrixes and vectors is used for multiplication of the sparse matrixes and vectors, the multiplier for the high-density matrixes and vectors is used for multiplication of the high-density matrixes and vectors, and each of the I-type backward iterative circuit and the II-type backward iterative circuit is used for backward iterative operation. The whole encoding process is divided into the four-level assembly lines. The high-speed QC-LDPC encoder has the advantages of simple structure, low cost, high throughput capacity and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Full parallel input quasi-cyclic matrix multiplier based on ring shift left in CMMB

InactiveCN103929198ASimple structureReduce registerError correction/detection using multiple parity bitsShift registerMultiplication of vectors

The invention provides a full parallel input quasi-cyclic matrix multiplier based on ring shift left in a CMMB, wherein the multiplier is used for achieving multiplication of vectors m and quasi-cyclic matrixes F in CMMB standard multiple rate QC-LDPC approximate lower triangular codes. The multiplier comprises five generator polynomial lookup tables for prestoring all circulant matrix generator polynomials in matrixes F, five 256-bit binary multipliers for carrying out scalar multiplying on vector fields of the m and generator polynomial bits, 256 6-bit binary adders for carrying out modulor-2 addition on products and shifting register content, and a 256-bit shifting register for storing the sum of results obtained after 1-bit ring shift left is carried out. The full parallel input multiplier is compatible with all code rates and has the advantages that the number of the registers is small, power consumption is little, cost is low, work frequency is high and the handling capacity is large.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

High-speed QC-LDPC encoder based on three-stage assembly line

InactiveCN104518804ASimple structureImprove encoding speedError correction/detection using multiple parity bitsMultiplication of vectorsThree stage

The invention provides a high-speed QC-LDPC (quasi-cyclic low-density parity-check) encoder based on a three-stage assembly line. The encoder comprises a sparse matrix and vector multiplier, a type-I backward iterative circuit and a type-II backward iterative circuit, wherein the sparse matrix and vector multiplier is used for sparse matrix and vector multiply operation; the type-I backward iterative circuit and the type-II backward iterative circuit are used for backward iterative operation; the whole encoding process is divided into three assembly line stages. The high-speed QC-LDPC encoder provided by the invention has the advantages of simple structure, low cost, high throughput capacity and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

High-speed qc-ldpc encoder based on four-stage pipeline in cmmb

InactiveCN104518803BSimple structureImprove encoding speedError correction/detection using multiple parity bitsBinary multiplierHigh density

The invention provides a high-speed QC-LDPC (Quasi-cyclic Low-density Parity-check) encoder based on a four-stage flow line in CMMB (China Mobile Multimedia Broadcasting). The encoder comprises a sparse matrix and vector multiplier, a I-type backward iteration circuit, a high-density matrix and vector multiplier and a II-type backward iteration circuit. The sparse matrix and vector multiplier realizes sparse matrix and vector multiplication, the high-density matrix and vector multiplier realizes high-density matrix and vector multiplication, and the I-type backward iteration circuit and the II-type backward iteration circuit realize backward iteration operation. The whole encoding process is divided into four stages of flow lines. 3 / 4 code rate high-speed QC-LDPC encoder in a CMMB system has the advantages of simple structure, low cost, great throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

LDPC encoder based on second-level partial parallel input accumulative left shift in CDR

InactiveCN107196663AError correction/detection using multiple parity bitsCode conversionBinary multiplierHigh density

The invention provides a QC-LDPC encoder based on a two-stage pipeline in CDR, which includes a multiplier for a sparse matrix and a vector and a multiplier for a vector and a high-density matrix. The multiplier of sparse matrix and vector realizes the multiplication operation of sparse matrix and vector, and the multiplier of vector and high-density matrix adopts the mechanism of partial parallel input accumulation left shift to realize the multiplication operation of vector and high-density matrix. The entire encoding process is divided into two stages of pipeline. The 3 / 4 code rate QC-LDPC encoder in the CDR system provided by the present invention has the advantages of low cost, high throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Low complexity soft output mimo decoder

A method and processing block for receiving data transmitted in a MIMO system are provided. Data is transmitted from the multiple transmit antennas as transmit vectors having multiple values and received at the multiple receive antennas as receive vectors having multiple values. Candidate vectors are determined based on each of a plurality of constellation points of the constellation configuration used in the transmission scheme. The channel matrix is decomposed into unitary and triangular matrices such that a relationship relates (i) the function of the unitary matrix and the receive vector, and (ii) the multiplication of the triangular matrix and the transmit vector. The best candidate vector from the set of candidate vectors is used to compute the soft bits representing the value of the transmitted vector.

Owner:NORDIC SEMICONDUCTOR

LDPC encoder with two-stage partial parallel inputting accumulation left shift in DTMB

InactiveCN106788457AError correction/detection using multiple parity bitsCode conversionHigh densityMultiplication of vectors

The invention provides a QC-LDPC encoder based on two-stage assembly line in DTMB. The encoder comprises a sparse-matrix-and-vector multiplier and a vector-and-high-density-matrix multiplier. The sparse-matrix-and-vector multiplier is used for realizing multiplication of a sparse matrix and a vector; and the vector-and-high-density-matrix multiplier employs a partial parallel inputting accumulation left shift mechanism to realize multiplication of a vector and a high-density matrix. The whole encoding process is divided into two stages of assembly lines. The QC-LDPC encoder with the four-fifth code rate has advantages of low cost and high handling capacity.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Secondary part parallel input right shift accumulation LDPC encoder in deep space communication

InactiveCN106374938AError correction/detection using multiple parity bitsCode conversionCommunications systemHigh density

The invention provides a QC-LDPC encoder based on a secondary assembly line in deep space communication. The encoder comprises a multiplier of a sparse matrix and a vector and a multiplier of a vector and a high density matrix. The multiplier of the sparse matrix and the vector realizes multiplication of the sparse matrix and the vector. The multiplier of the vector and the high density matrix uses a part parallel input right shift accumulation mechanism to realize multiplication of the vector and the high density matrix. The whole coding process is divided into two levels of assembly line. The QC-LDPC encoder with 8 / 11 bit rate in a deep space communication system has the advantages of low cost, high throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

High-speed qc-ldpc encoder based on four-stage pipeline in dtmb

InactiveCN104539297BSimple structureImprove encoding speedError correction/detection using multiple parity bitsBinary multiplierHigh density

The invention provides a high-speed QC-LDPC encoder based on a four-stage pipeline in DTMB, the encoder includes a multiplier of a sparse matrix and a vector, an I-type backward iterative circuit, and a high-density matrix and vector multipliers and a Type II backward iteration circuit. The sparse matrix-vector multiplier realizes the sparse matrix-vector multiplication operation, the high-density matrix-vector multiplier realizes the high-density matrix-vector multiplication operation, and both Type I and Type II backward iteration circuits implement backward iteration operations. The whole encoding process is divided into 4 pipelines. The 4 / 5 code rate high-speed QC-LDPC encoder in the DTMB system provided by the invention has the advantages of simple structure, low cost, large throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

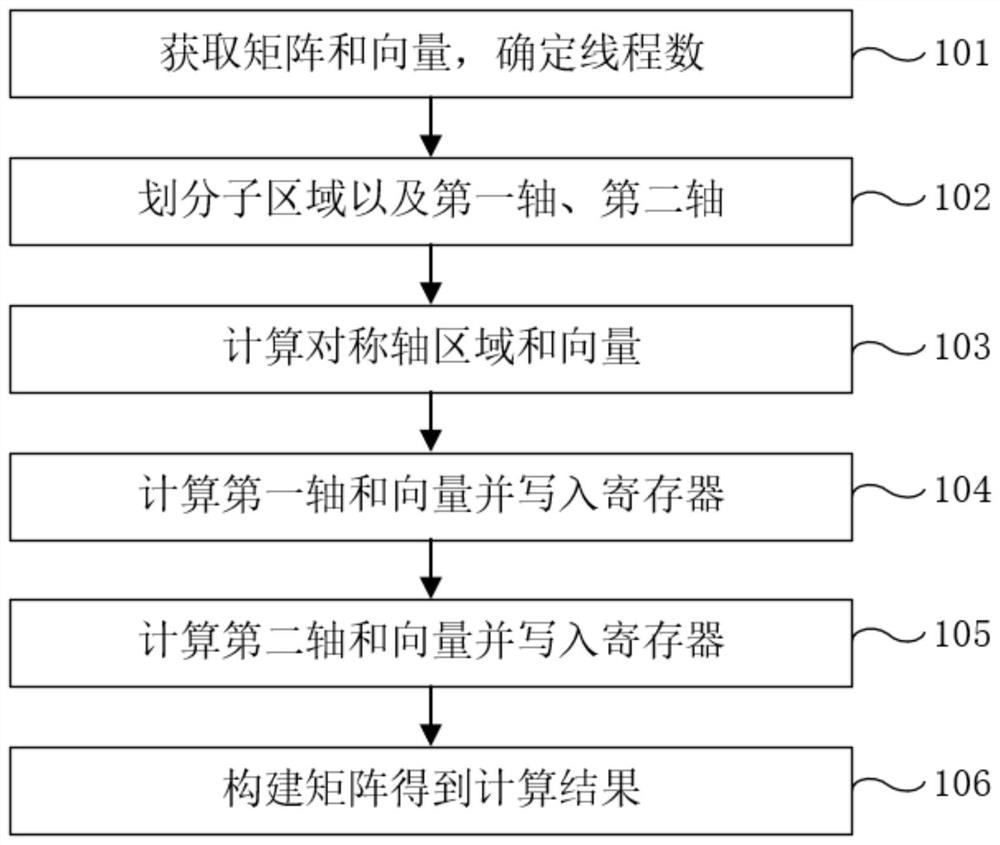

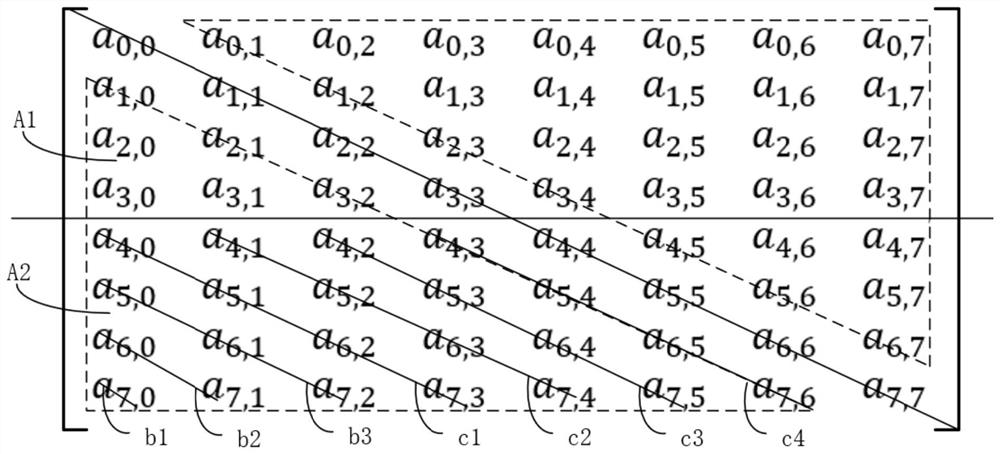

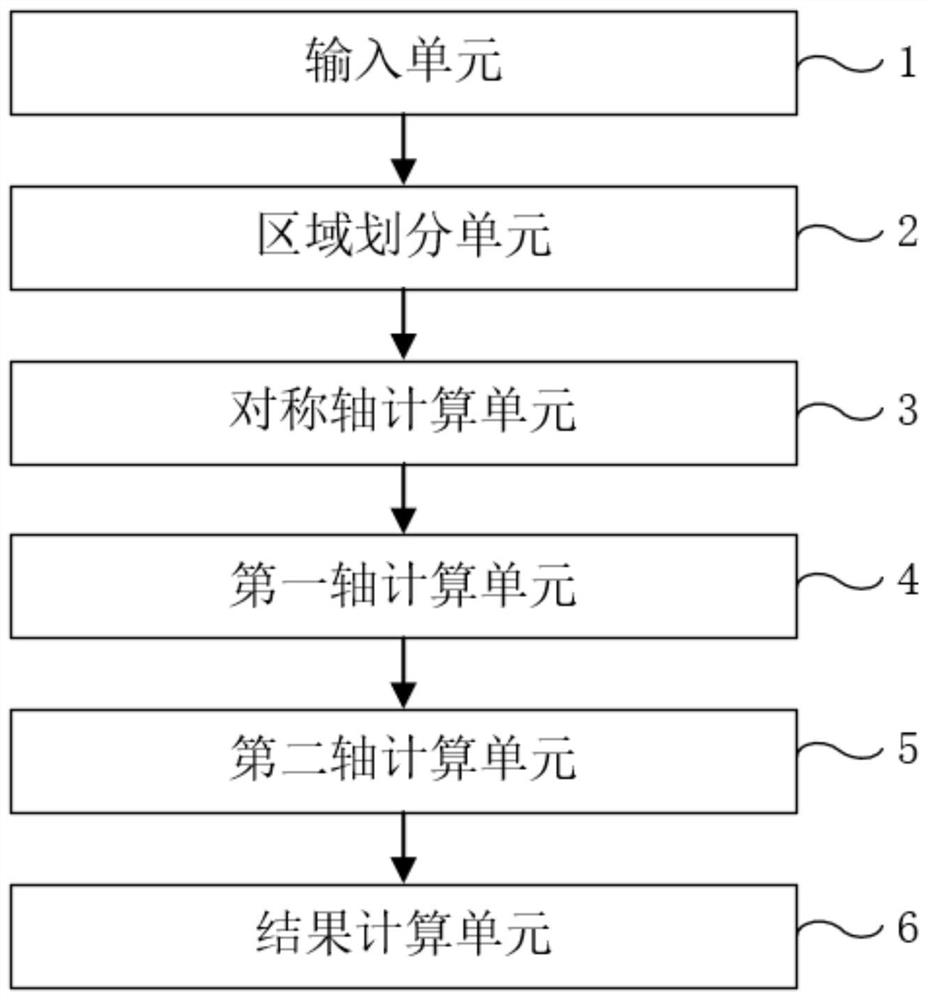

Symmetric matrix and vector multiplication parallel computing method and system

PendingCN114780913AFast implementation of multiplication calculationsRealize the multiplication calculationResource allocationComplex mathematical operationsComputational scienceConcurrent computation

The invention provides a symmetric matrix and vector multiplication parallel computing method and system, and the method comprises the steps: obtaining a symmetric matrix and a vector, and determining a thread count; dividing sub-regions; in each sub-region, defining a first axis and / or a second axis parallel to the symmetry axis; calculating a symmetry axis region and a vector, and writing into a register; performing two times of different first multiplication calculation on the first axis to obtain two groups of different data, and respectively writing the two groups of different data into a register; and performing two different second multiplication calculation on the second axis to obtain two or four groups of different data, and respectively writing the data into the register to obtain a calculation result of multiplication of the symmetric matrix and the vector. According to the scheme, multiplication calculation of the symmetric matrix and the vector can be accurately and rapidly achieved, the processing sequence of the elements in the matrix is reasonably planned, resources are reasonably allocated to all the threads, write-in conflicts can be effectively avoided, multi-thread parallel calculation is achieved, the calculation efficiency is high, loads of all the threads are balanced, and thread resources are reasonably distributed.

Owner:SHANGHAI LINCTEX DIGITAL TECH CO LTD

Secondary part parallel input right shift accumulation LDPC encoder

InactiveCN106374939AError correction/detection using multiple parity bitsCode conversionHigh densityBinary multiplier

The invention provides a QC-LDPC encoder based on a secondary assembly line. The encoder comprises a multiplier of a sparse matrix and a vector and a multiplier of a vector and a high density matrix. The multiplier of the sparse matrix and the vector realizes multiplication of the sparse matrix and the vector. The multiplier of the vector and the high density matrix uses a part parallel input right shift accumulation mechanism to realize multiplication of the vector and the high density matrix. The whole coding process is divided into two levels of assembly line. The QC-LDPC encoder provided by the invention has the advantages of low cost, high throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Second-level part parallel input right shift accumulated LDPC (Low-Density Parity-Check) encoder in CDR

InactiveCN106452458AError correction/detection using multiple parity bitsCode conversionHigh densityBinary multiplier

The invention provides a QC-LDPC (Low-Density Parity-Check) encoder based on a second-level pipeline in CDR. The encoder comprises a sparse matrix and vector multiplier and a vector and high-density matrix multiplier. The sparse matrix and vector multiplier is used for realizing multiplication of a sparse matrix and a vector. A partial parallel input right shift accumulation mechanism is employed in the vector and high-density matrix multiplier. The vector and high-density matrix multiplier is used for realizing multiplication of a vector and a high-density matrix. A whole encoding process is divided into two-level pipelines. The 3 / 4 code rate QC-LDPC encoder in the CDR system provided by the invention has the advantages of low cost and high throughput.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

High-speed QC-LDPC (quasi-cyclic low-density parity-check) encoder based on three-stage assembly line in CMMB (China mobile multimedia broadcasting)

InactiveCN105119608ASimple structureImprove encoding speedError correction/detection using multiple parity bitsBinary multiplierHigh density

The invention provides a high-speed QC-LDPC (quasi-cyclic low-density parity-check) encoder based on a three-stage assembly line in CMMB (China mobile multimedia broadcasting). The encoder comprises an I-type backward iteration circuit, a high-density matrix and vector multiplier and an II-type backward iteration circuit. The high-density matrix and vector multiplier is used for implementing the multiply operation of a high-density matrix and a vector, and the I-type and the II-type backward iteration circuits are used for implementing the backward iteration operation. An entire encoding process is divided into three stages of assembly lines. The 3 / 4 code-rate high-speed QC-LDPC encoder in a CMMB system has the advantages of simple structure, low cost, large throughput and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Two-level partial parallel inputting, accumulating and left-shifting LDPC encoder in CMMB

InactiveCN106385263AError correction/detection using multiple parity bitsCode conversionBinary multiplierHigh density

The invention provides a two-level streamline-based QC-LDPC encoder in CMMB. The encoder comprises one sparse matrix and vector multiplier and one vector and high-density matrix multiplier, wherein the sparse matrix and vector multiplier realizes multiplication operation of sparse matrixes and vectors, and the vector and high-density matrix multiplier employs a partial parallel inputting, accumulating and left-shifting mechanism to realize multiplication operation of vectors and high-density matrixes. The entire encoding process is divided into two-level streamlines. The 3 / 4 code rate QC-LDPC encoder in a CMMB system has the advantages of low cost and large throughput.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

LDPC encoder of secondary full parallel input cycle left shift in DTMB

InactiveCN106411326AError correction/detection using multiple parity bitsCode conversionBinary multiplierHigh density

The present invention provides a LDPC encoder of secondary full parallel input cycle left shift in a DTMB. The encoder comprises a multiplier of a sparse matrix and a vector and a multiplier of a vector and a high-density matrix. The multiplier of the sparse matrix and the vector realizes the multiplication of the sparse matrix and the vector, and the multiplier of the vector and the high-density matrix employs full parallel input cycle left shift mechanism so as to realize the multiplication of the vector and the high-density matrix. The whole encoding process is divided into 2-level streamlines. The 4 / 5 code rate QC-LDPC (Quasi-Cyclic LDPC) encoder in the DTMB system is high in work efficiency and large in throughput, etc.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

LDPC coder for two-level part parallel input, right shift and accumulation in DTMB

InactiveCN106487390AError correction/detection using multiple parity bitsCode conversionHigh densityBinary multiplier

The invention provides a QC-LDPC coder based on two-level pipelines in DTMB. The coder comprises a sparse matrix and vector multiplier and a vector and high-density matrix multiplier; the sparse matrix and vector multiplier is used for realizing multiplication of a sparse matrix and a vector; and the vector and high-density matrix multiplier is used for realizing multiplication of a vector and a high-density matrix by adopting a part parallel input, right shift and accumulation mechanism. The whole coding process is divided into two-level pipelines; and the QC-LDPC coder having the 4 / 5 code rate in the DTMB system provided by the invention has the advantages of being low in cost, high in throughput capacity and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com