Full parallel input quasi-cyclic matrix multiplier based on ring shift left in CMMB

A quasi-circular matrix and cyclic left-shift technology, applied in the field of channel coding, can solve the problems of high circuit power consumption, low throughput, and high cost, so as to improve the operating frequency and throughput, reduce registers and delays, and reduce power consumption. and cost effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

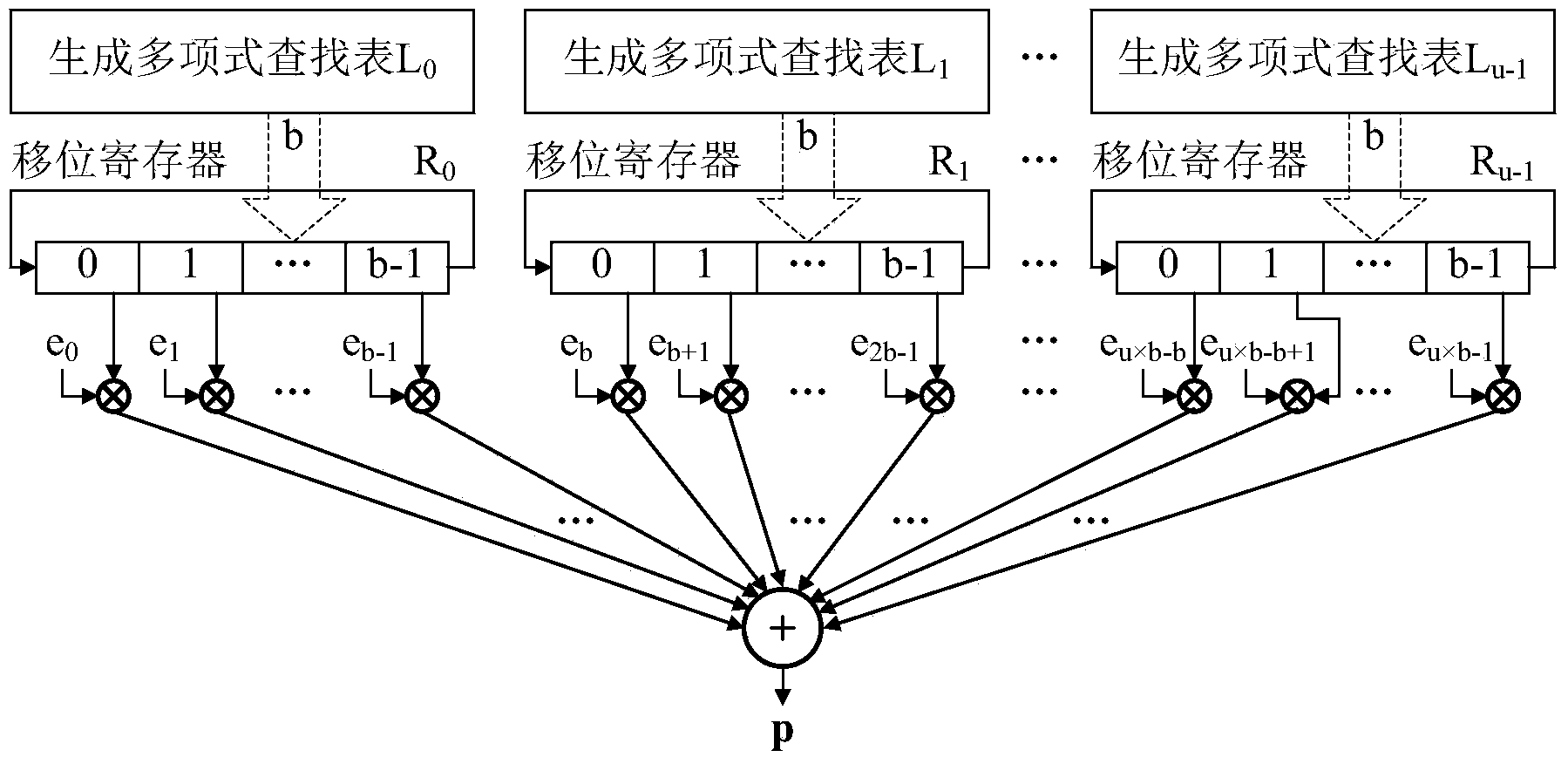

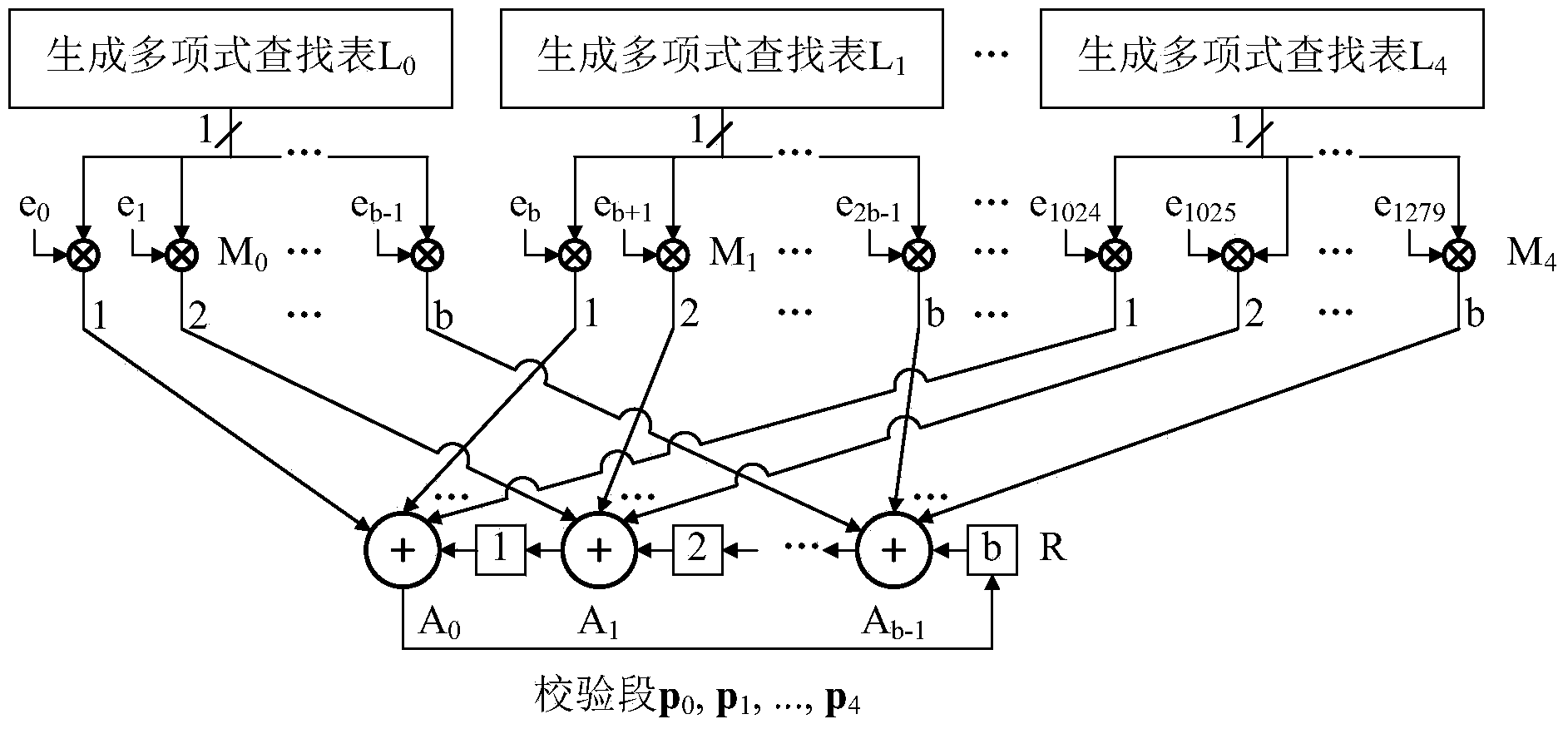

[0030] make and are the generating polynomials f i,j The result of a rotate right by n bits and a rotate left by n bits, where 0≤n≤b. Then, the i-th item on the right side of the equation (7) can be expanded as

[0031] m i F i , j = e i × b f i , j r ( 0 ) + ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com