Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

58 results about "Order of operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In mathematics and computer programming, the order of operations (or operator precedence) is a collection of rules that reflect conventions about which procedures to perform first in order to evaluate a given mathematical expression.

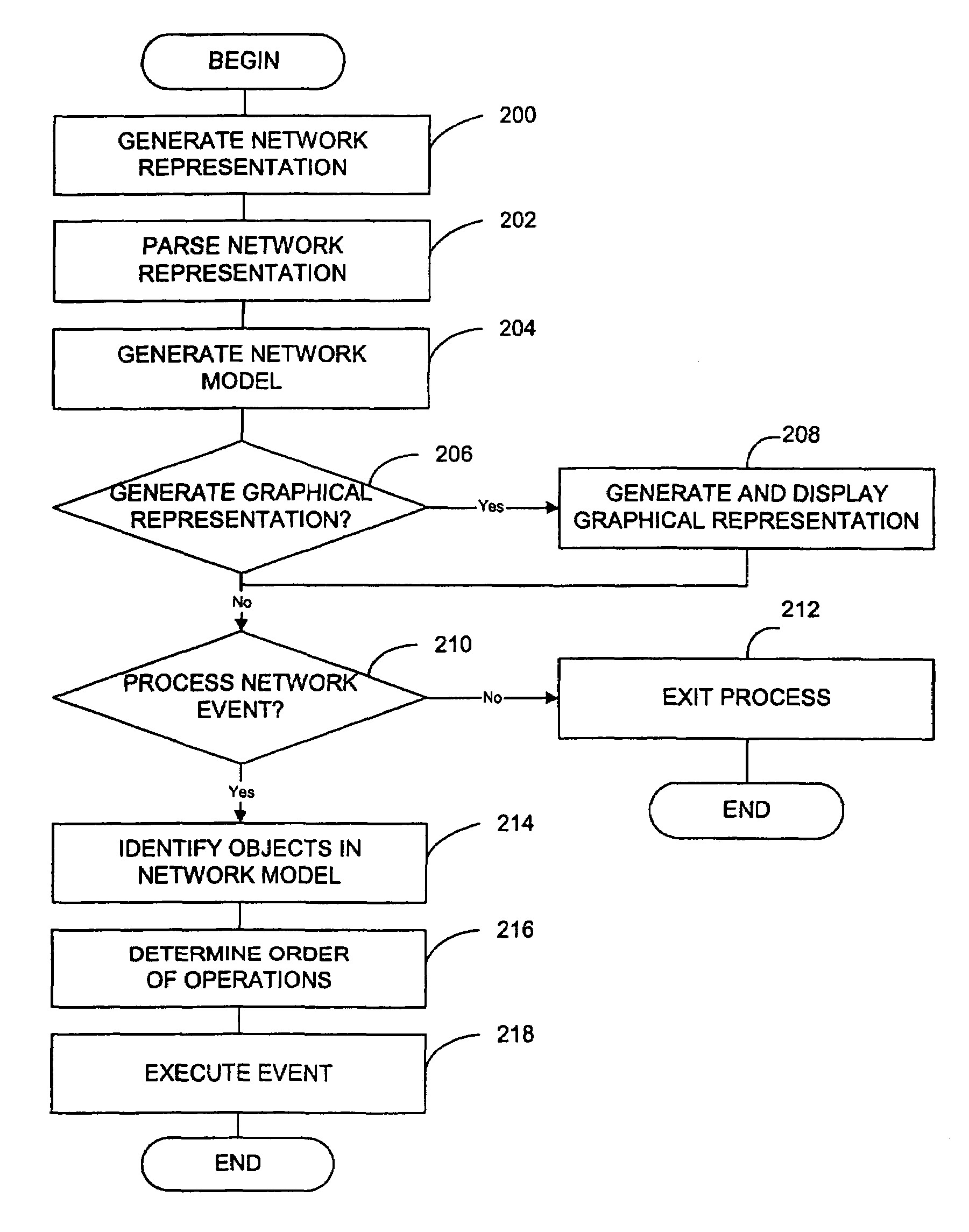

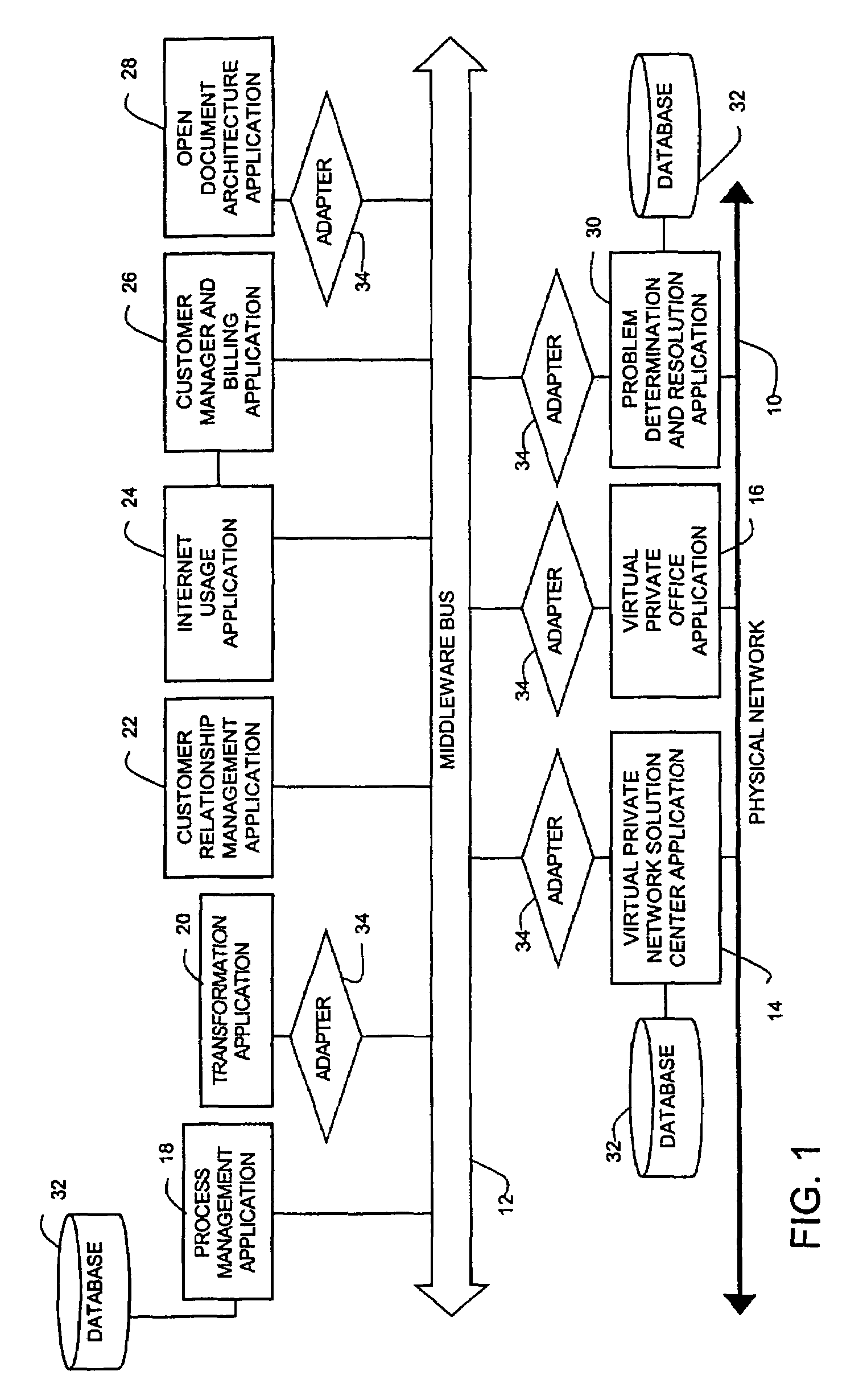

Method and system for modelling a communications network

ActiveUS7392300B2Analogue computers for electric apparatusDigital computer detailsOrder of operationsNetwork model

A system and method of modelling a communications network using a computer system is disclosed, the method including generating a network representation using computer-readable code that represents structured information; parsing the network representation; generating a network model using the parsed network representation, the network model including a plurality of network objects and relationships between the plurality of network objects; and storing the network model in memory. Any type of network may be modeled. The computer-readable code may be any suitable language or instructions for representing structured information such as, for example, extensible mark-up language (XML). A network inventory adapter receives the network representation from the network. The network inventory adapter is a software component that may be used to connect applications to the network. The network inventory adapter receives the network representation from the network and reads and parses the network representation to determine which network objects are to be operated on and the order of operation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

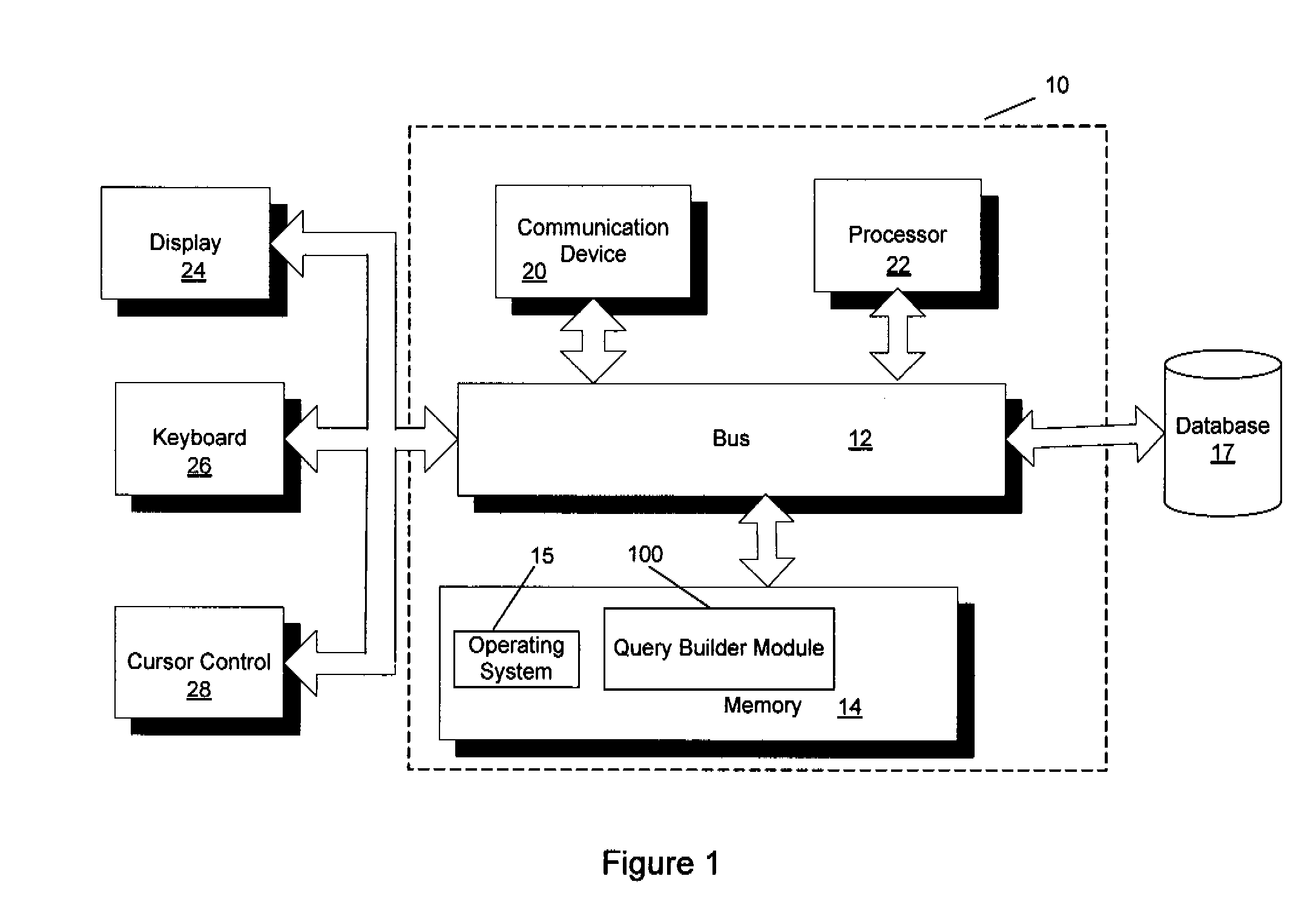

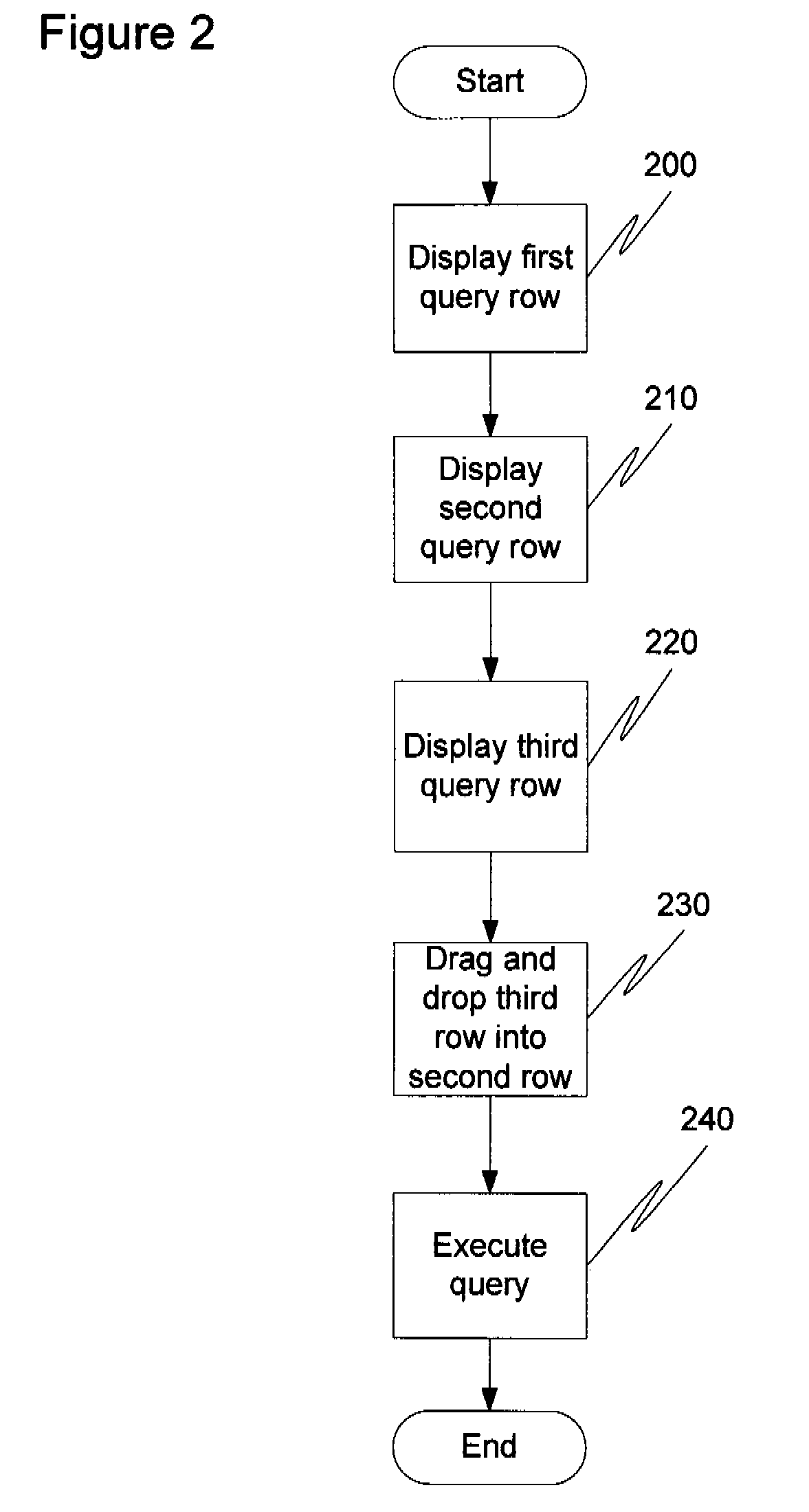

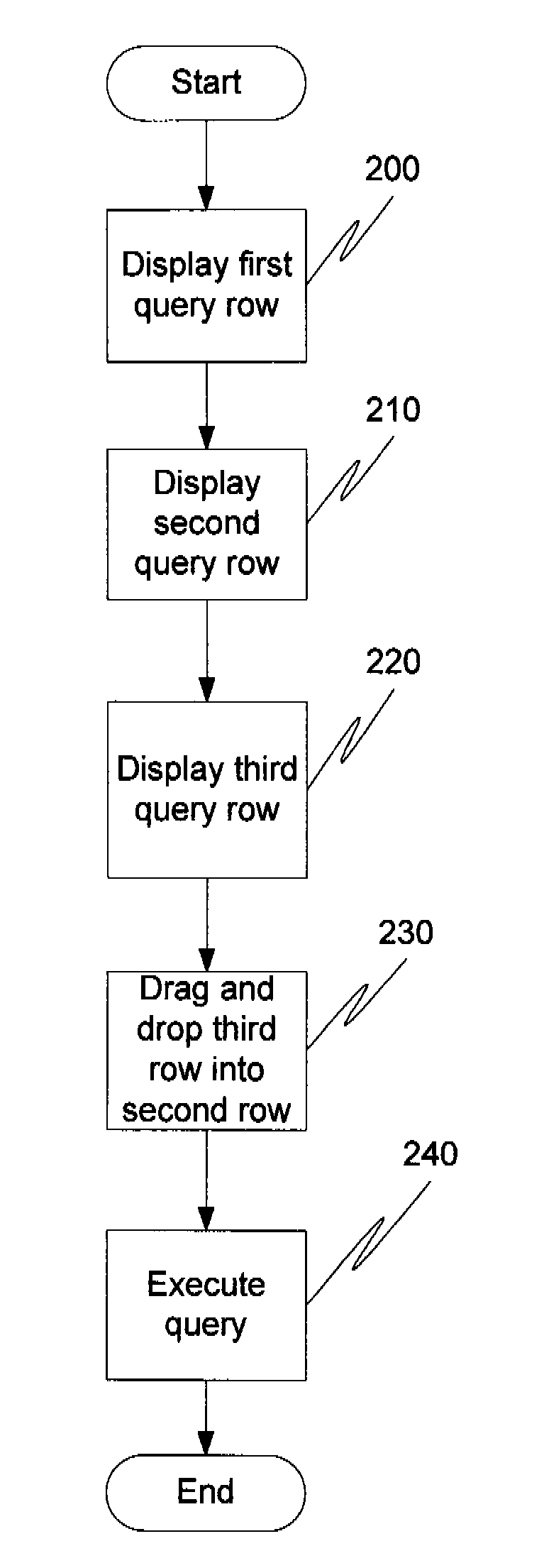

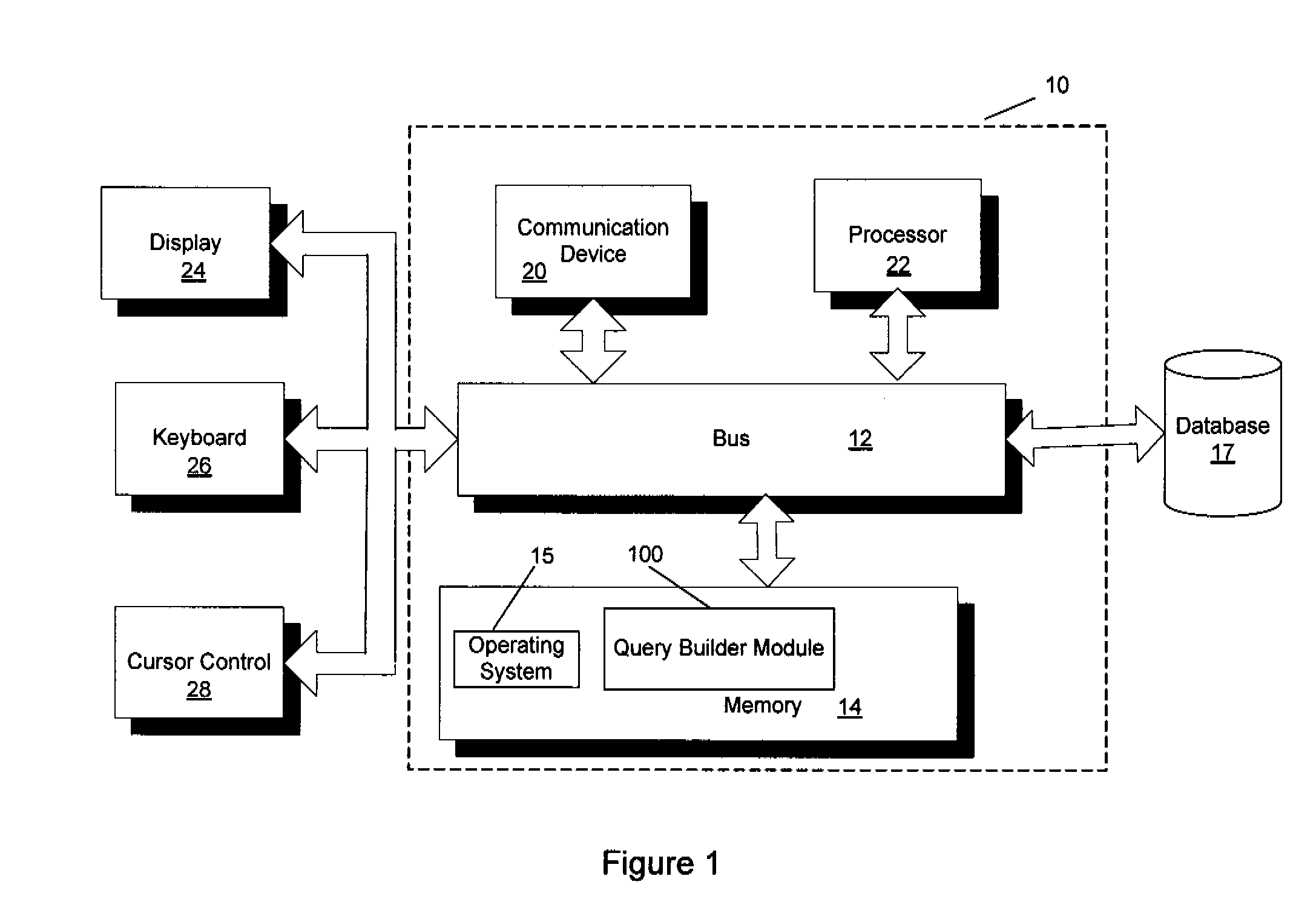

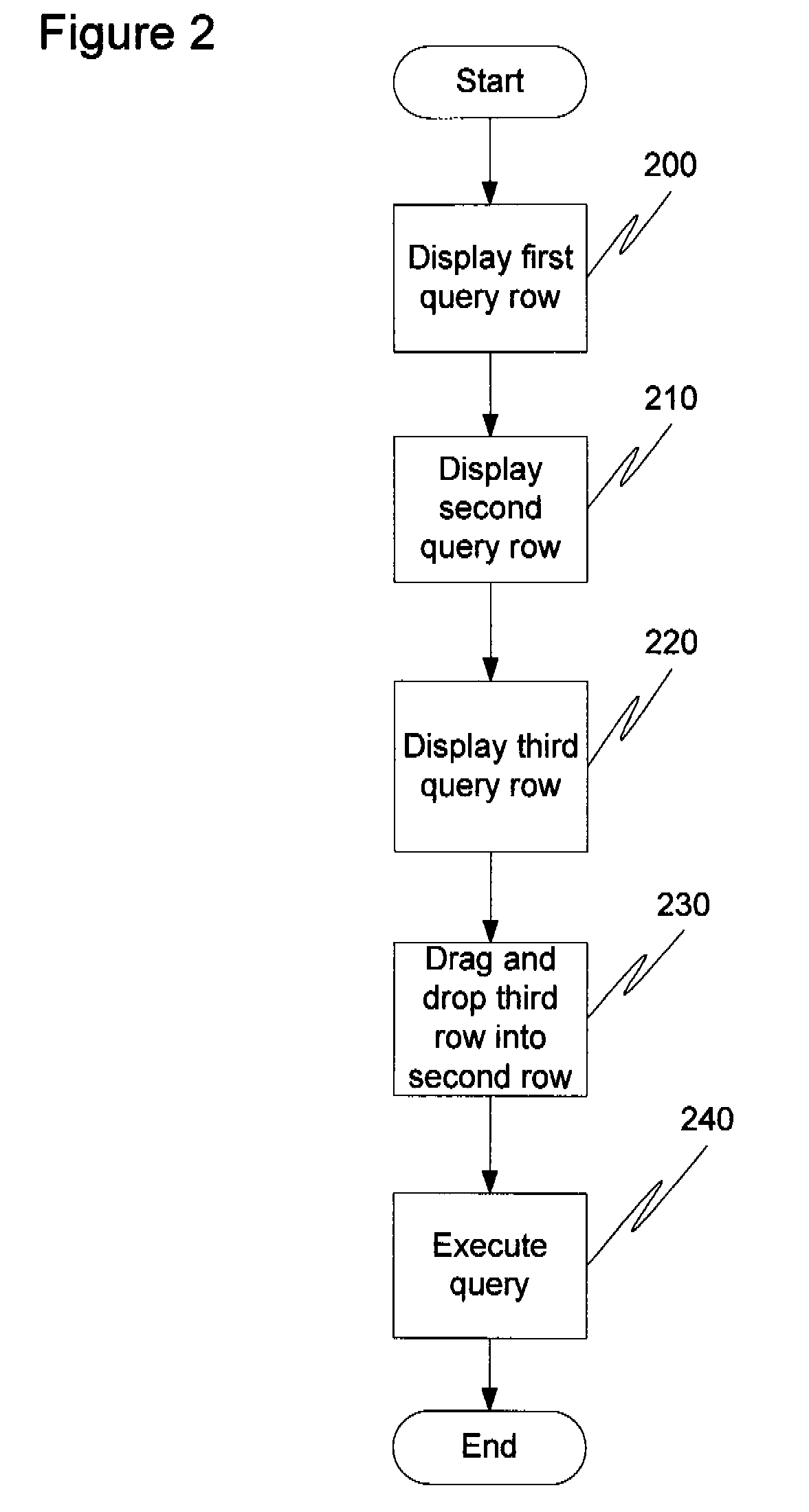

Criteria builder for query builder

ActiveUS20100161646A1Digital data information retrievalDigital data processing detailsDrag and dropOrder of operations

Systems and methods are provided that programmatically provide a user interface for forming a query, comprising. A query builder displays a first row of query criteria, a second row of query criteria, the second row being logically connected to the first row by a first Boolean connector, and a third row of query criteria, the third row being logically connected to the second row by a second Boolean connector. In response to a user drag-and-drop operation, the query builder nests the third row of query criteria in the second row of query criteria. Thus, a drag-and-drop operation obviates the need for cumbersome groups of parentheses when defining the order of operation of the query.

Owner:ORACLE INT CORP

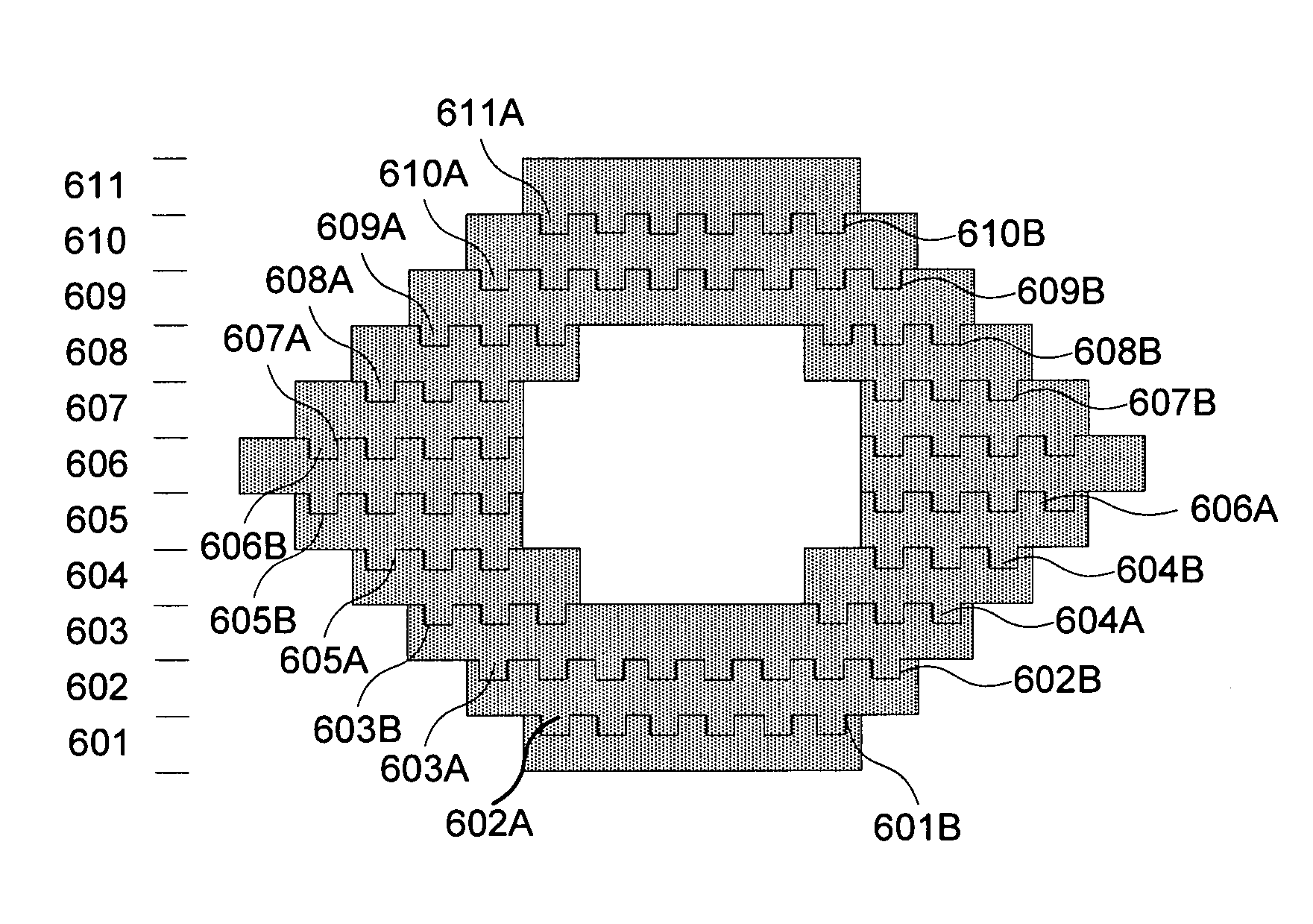

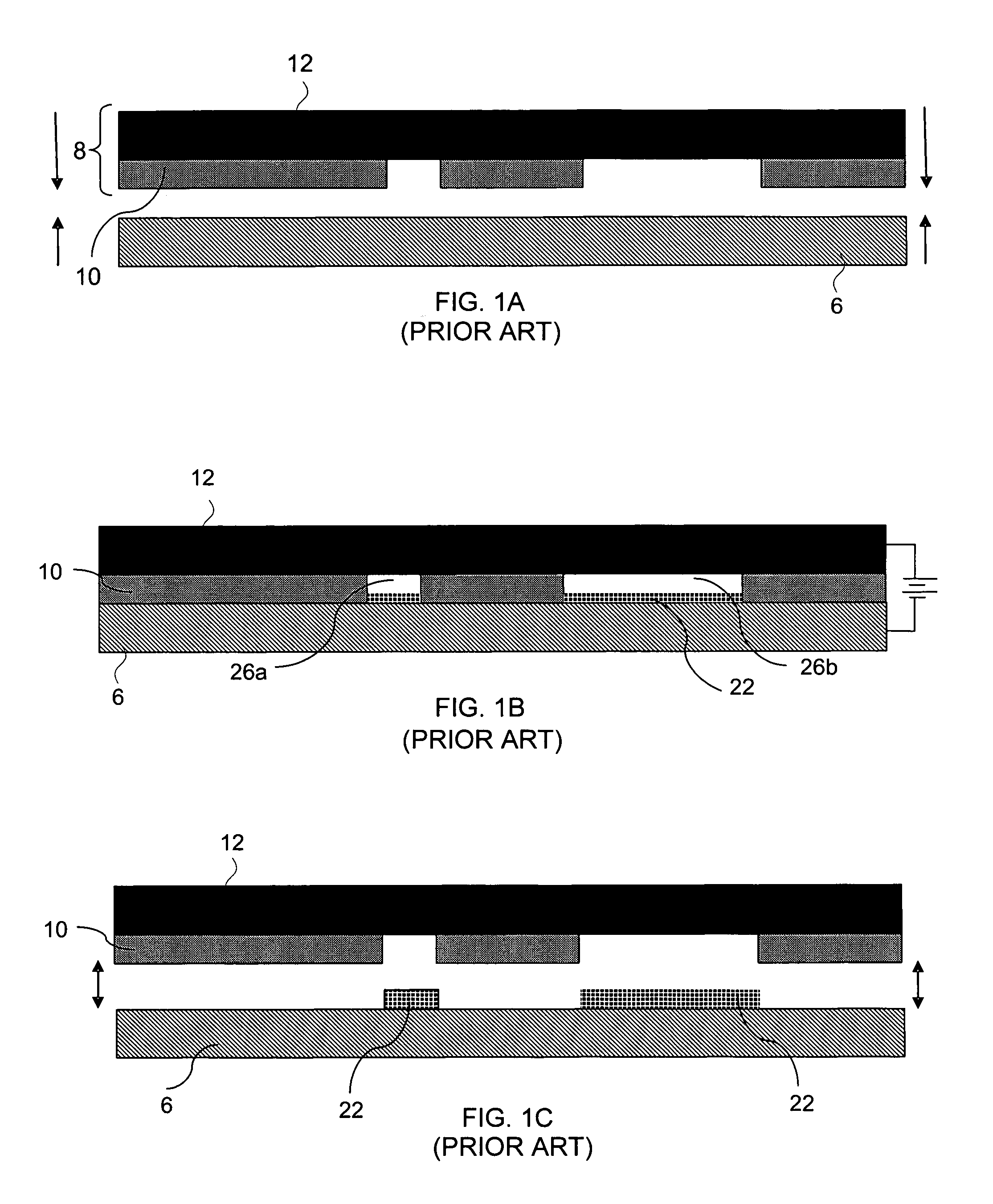

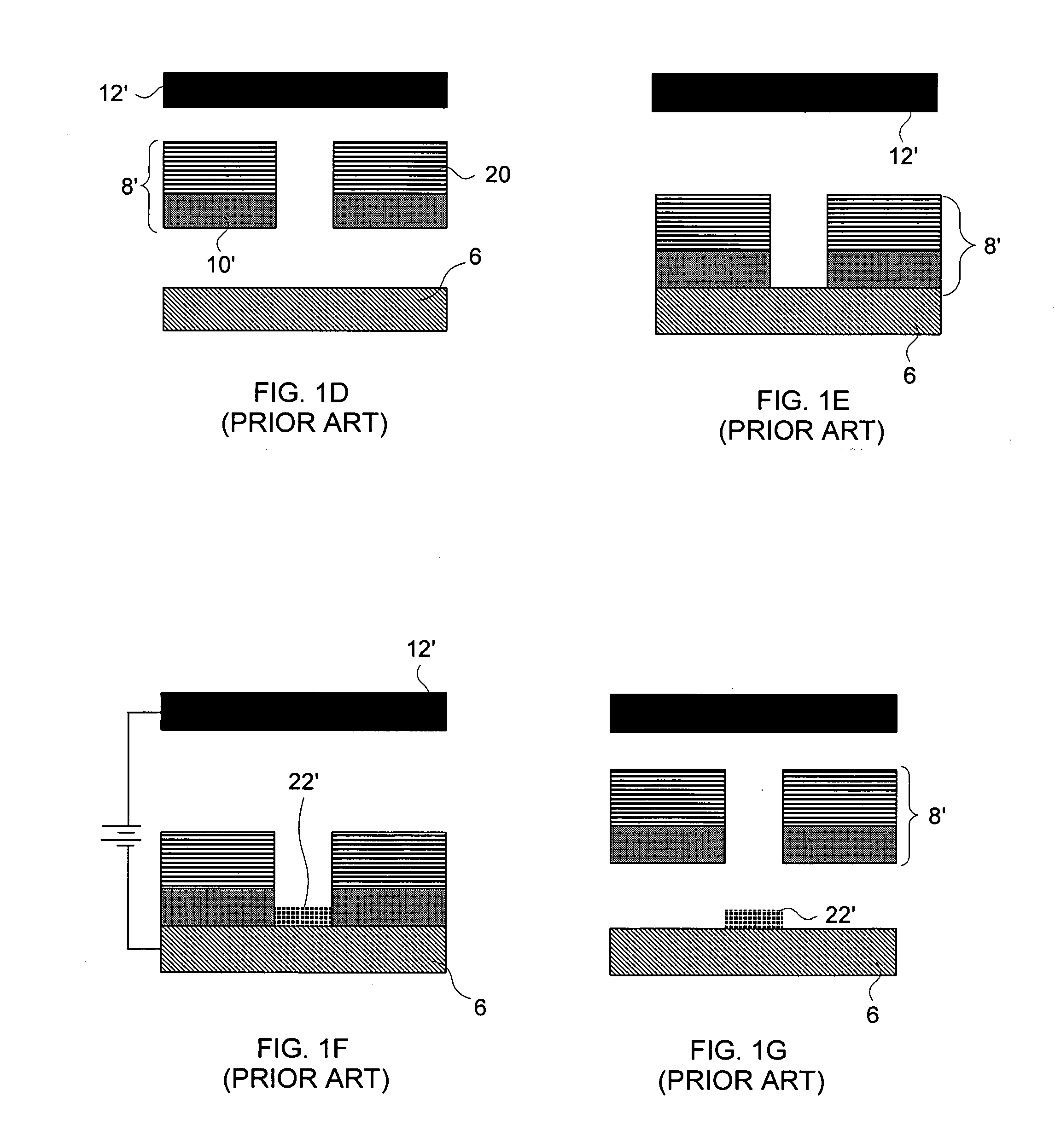

Methods of and apparatus for electrochemically fabricating structures via interlaced layers or via selective etching and filling of voids

ActiveUS7252861B2Advanced manufacturing technologyImprove propertiesAcceleration measurement using interia forcesPretreated surfacesOrder of operationsEngineering

Multi-layer structures are electrochemically fabricated by depositing a first material, selectively etching the first material (e.g. via a mask), depositing a second material to fill in the voids created by the etching, and then planarizing the depositions so as to bound the layer being created and thereafter adding additional layers to previously formed layers. The first and second depositions may be of the blanket or selective type. The repetition of the formation process for forming successive layers may be repeated with or without variations (e.g. variations in: patterns; numbers or existence of or parameters associated with depositions, etchings, and or planarization operations; the order of operations, or the materials deposited). Other embodiments form multi-layer structures using operations that interlace material deposited in association with some layers with material deposited in association with other layers.

Owner:MICROFAB

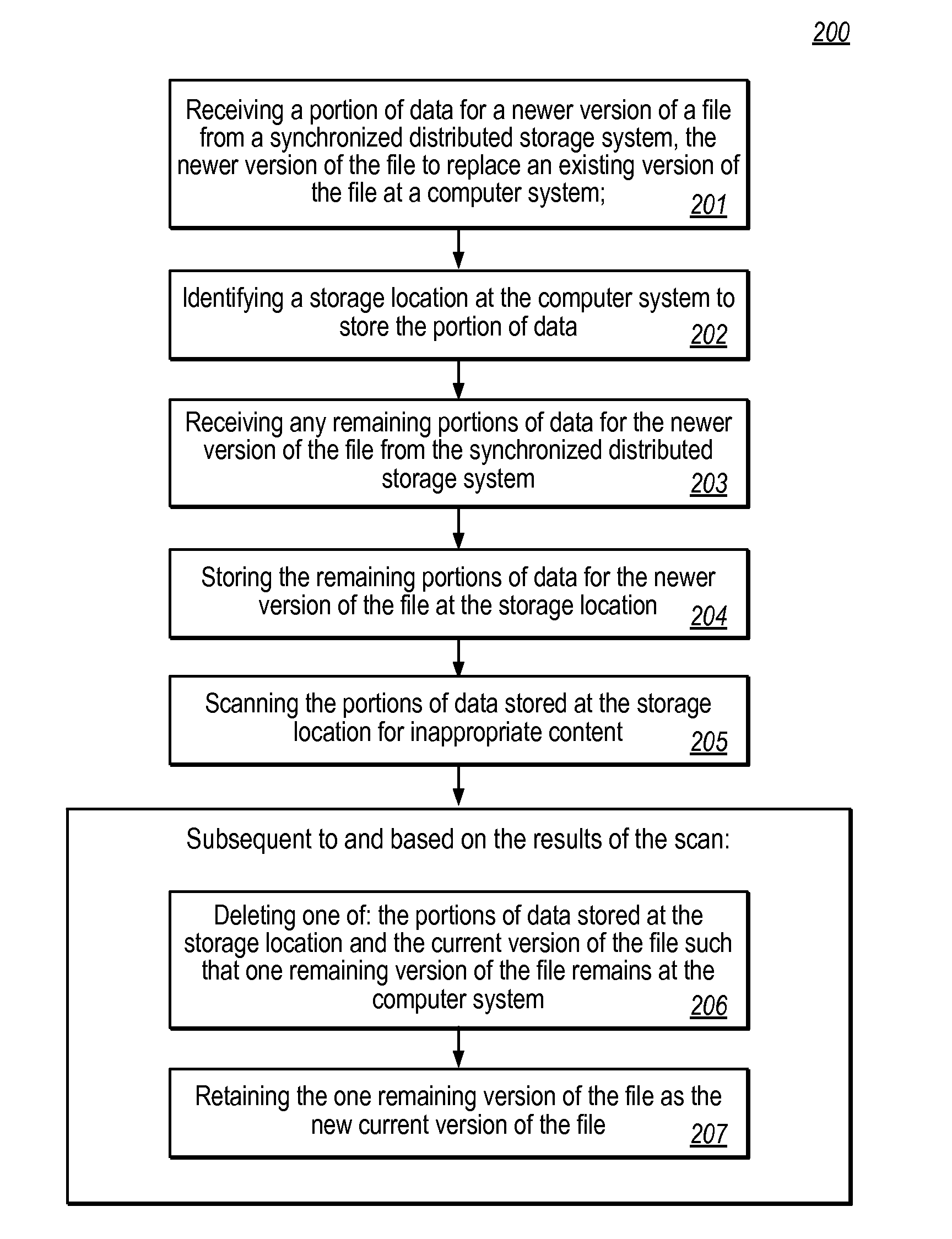

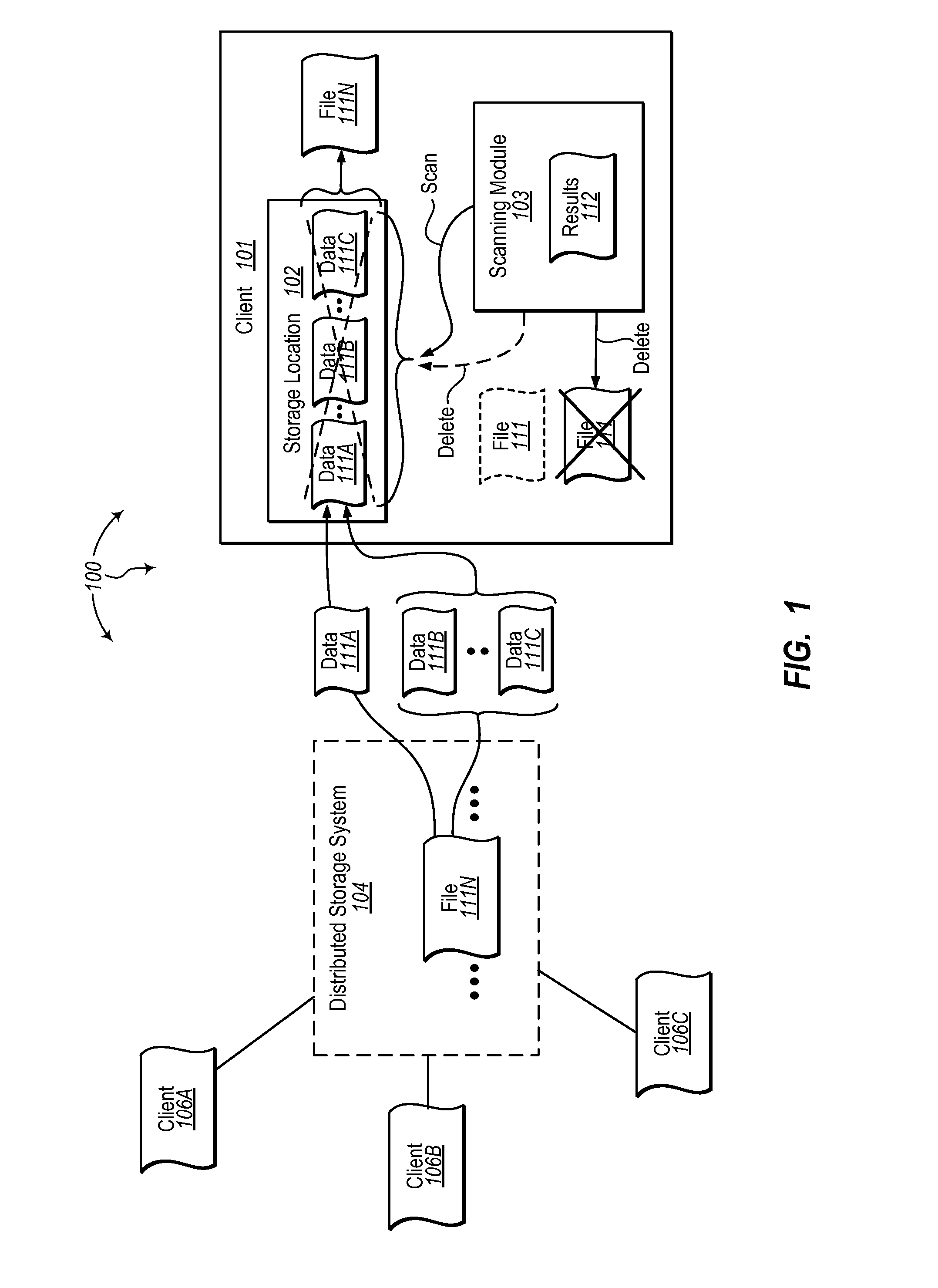

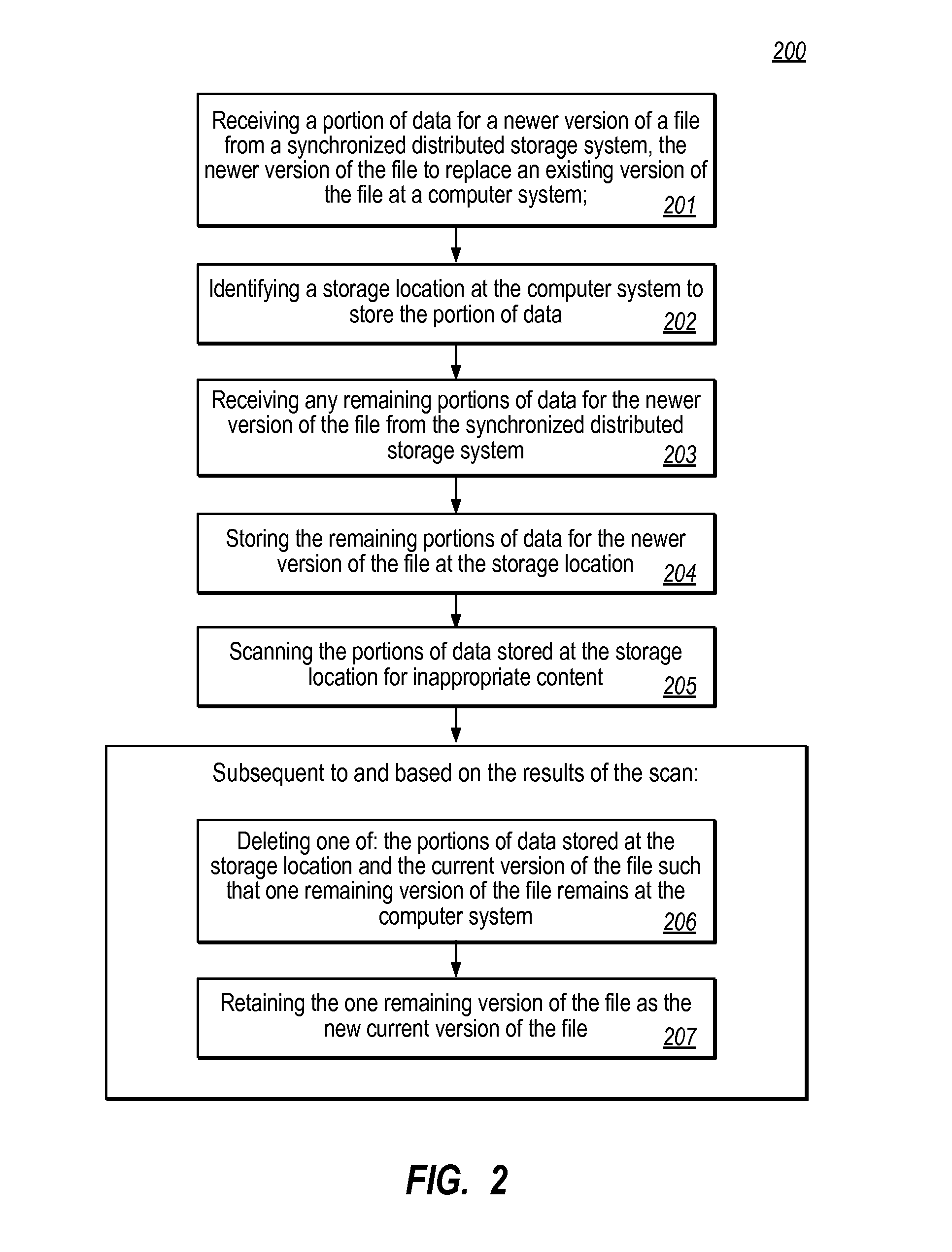

Scanning files for inappropriate content during synchronization

ActiveUS20140373147A1Memory loss protectionError detection/correctionData synchronizationFile synchronization

The present invention extends to methods, systems, and computer program products for scanning files for inappropriate content during file synchronization. Embodiments of the invention are mindful of the order of operations when scanning files for inappropriate content and in subsequent file processing. In some embodiments, during synchronization, an intermediary server scans a file for inappropriate content. The file is not permitted to be fully downloaded to a client device until the scan determines that the file does not contain inappropriate content. In other embodiments, during synchronization, a client device scans a newer version of a file for inappropriate content. An older version of the file is not deleted until the scan determines that the newer version of the file does not contain inappropriate content. In further embodiments, server side scanning and client side scanning are both used to enhance capabilities for detecting inappropriate content.

Owner:MICROSOFT TECH LICENSING LLC

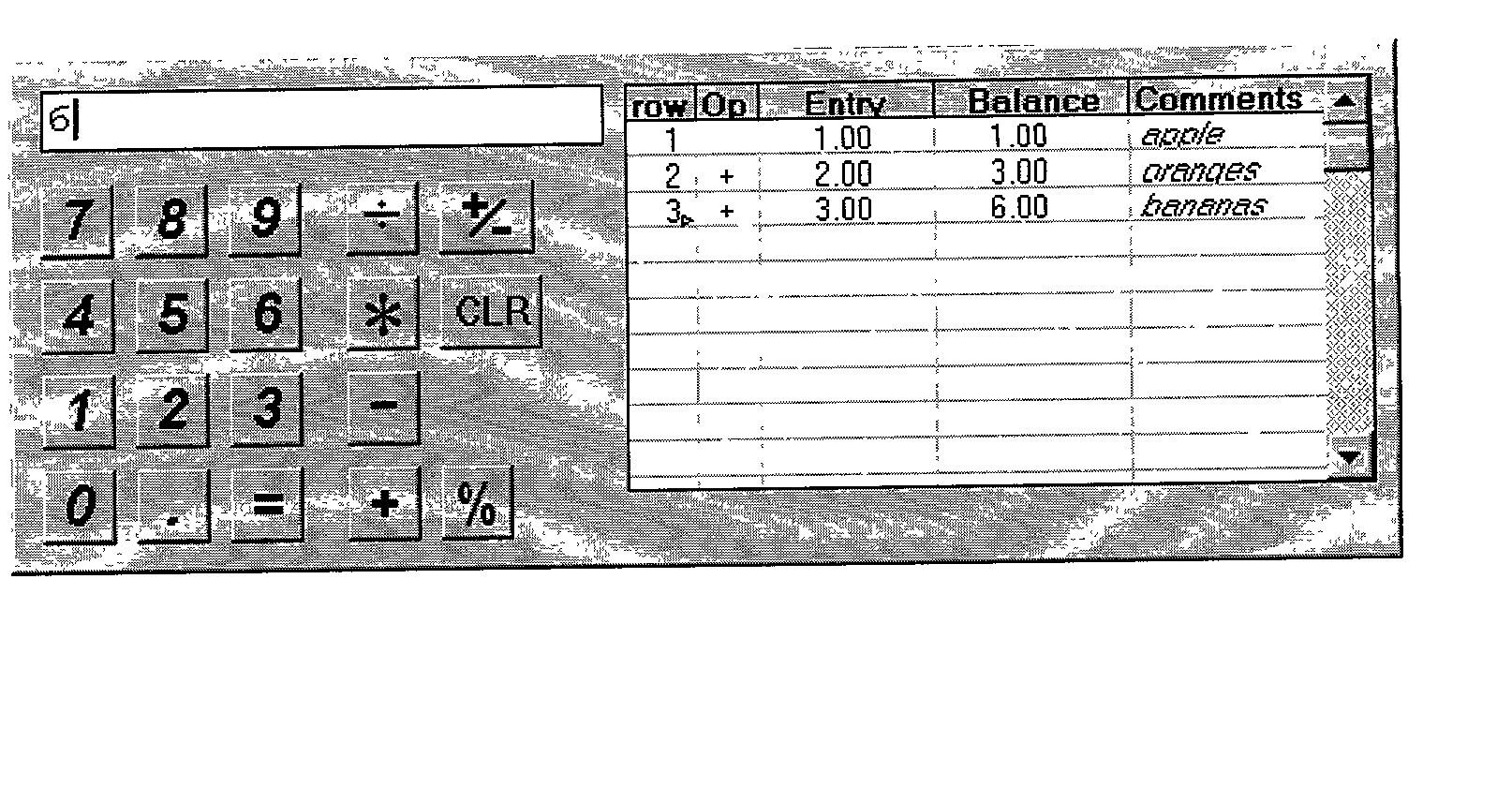

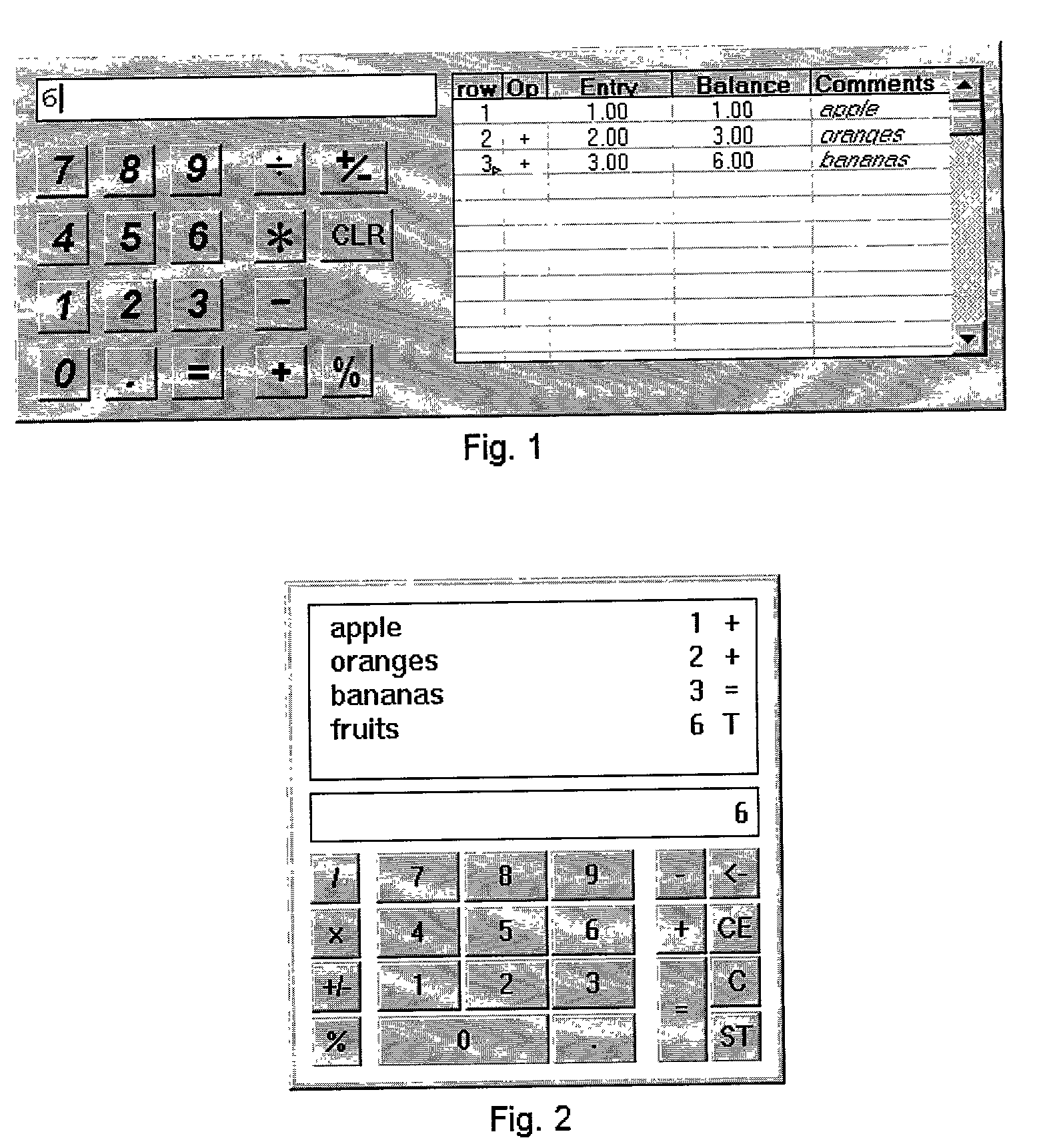

System and method for calculation using formulas in number fields

Owner:BENNETT PAUL W

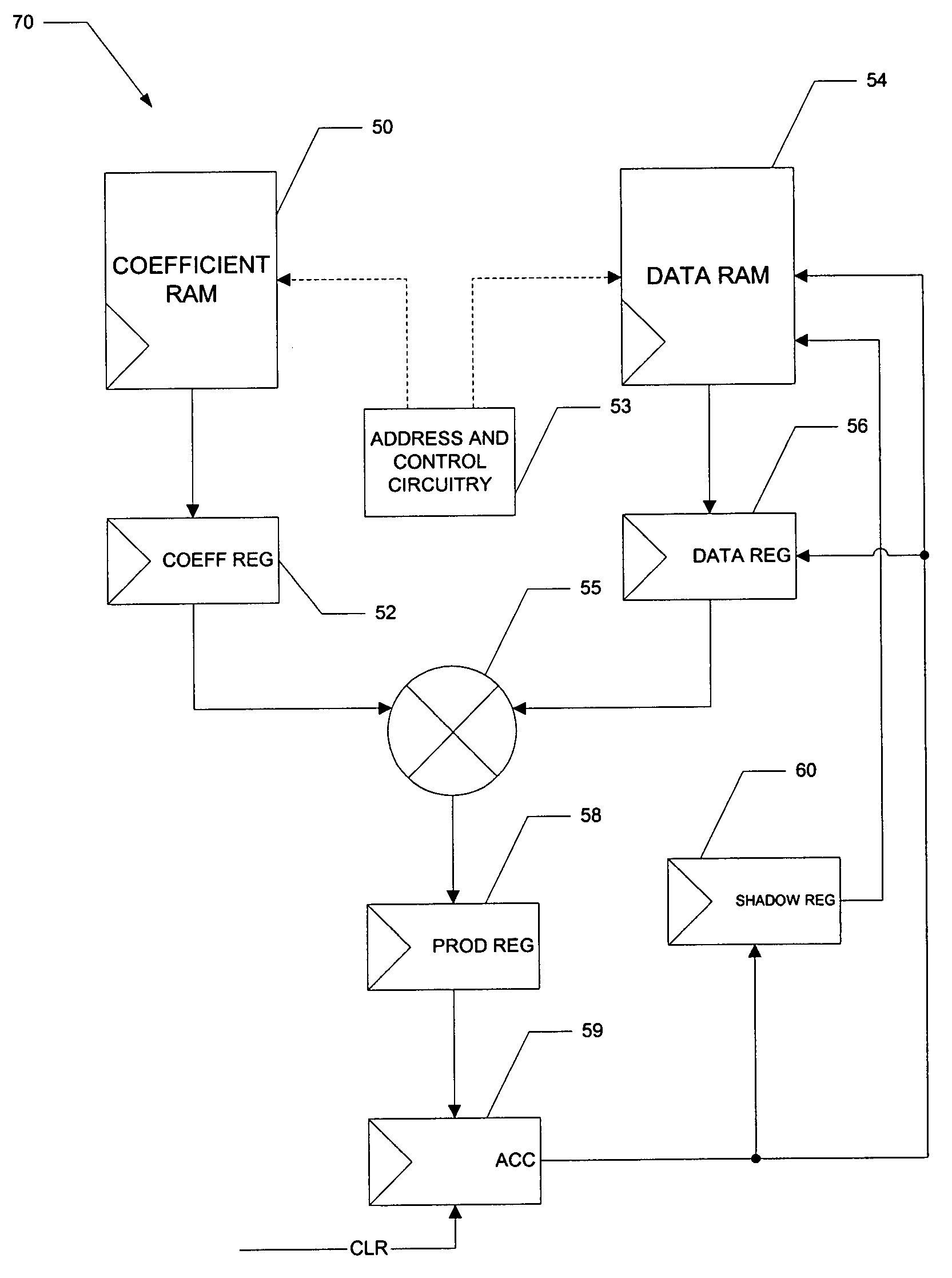

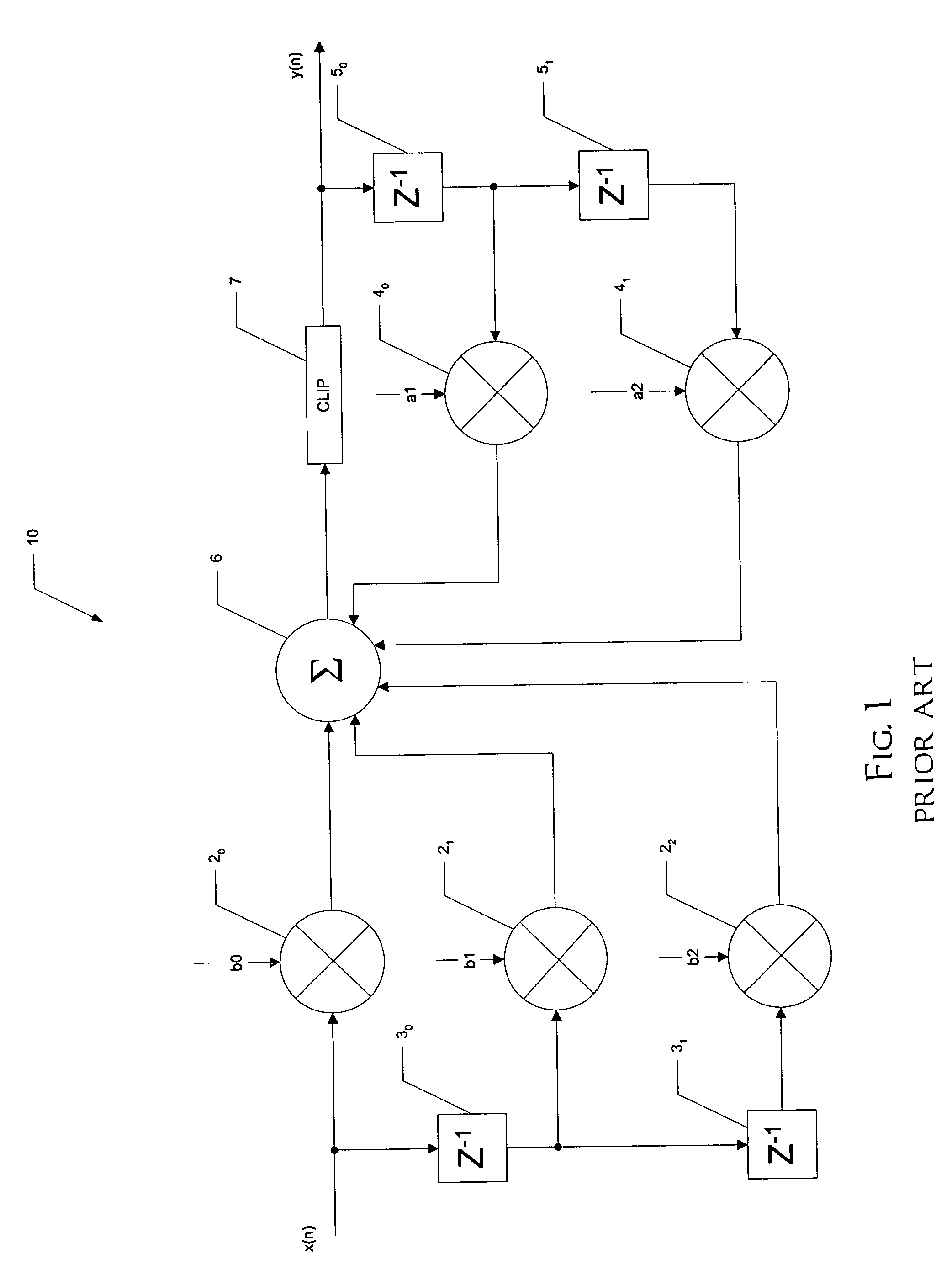

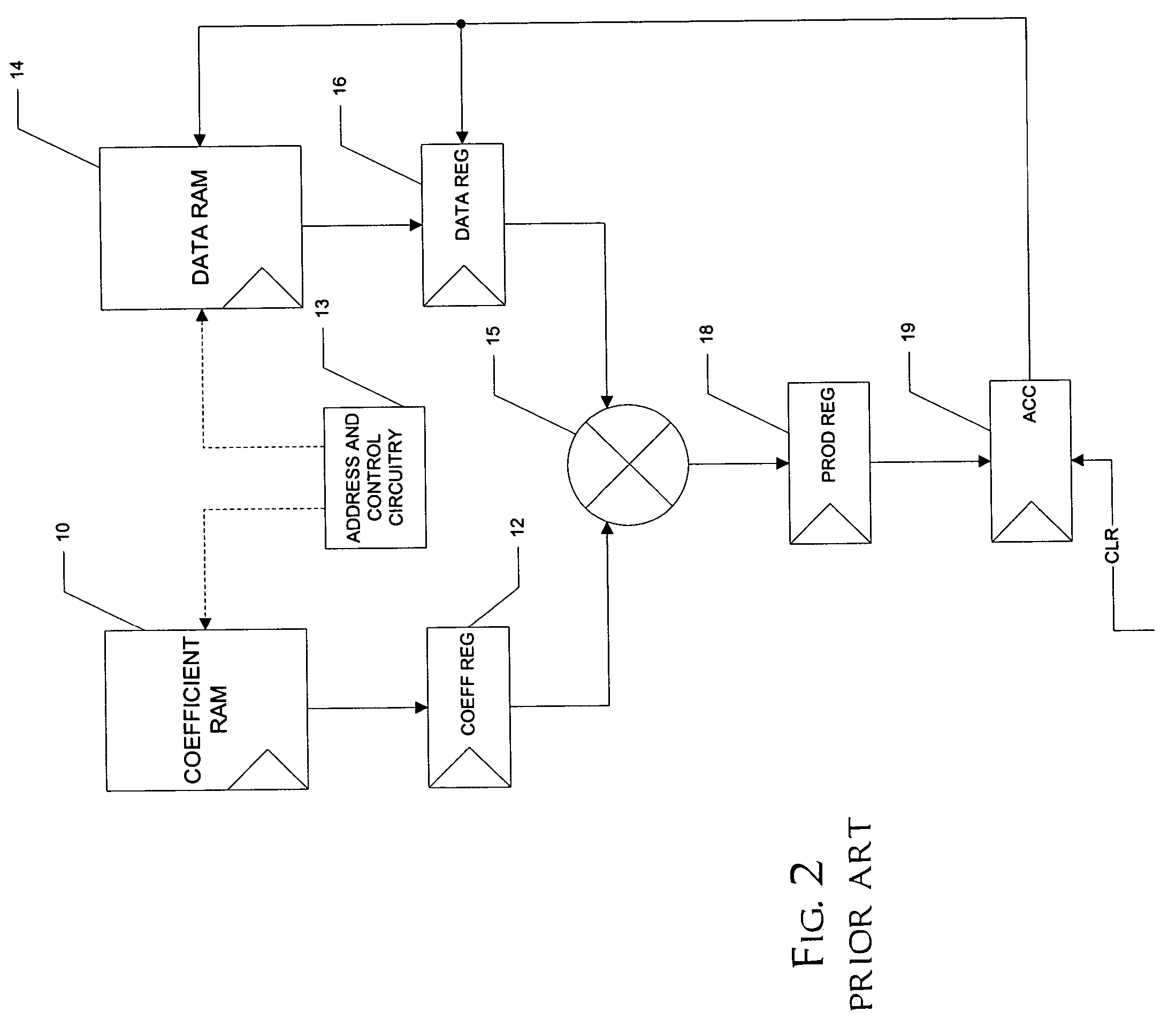

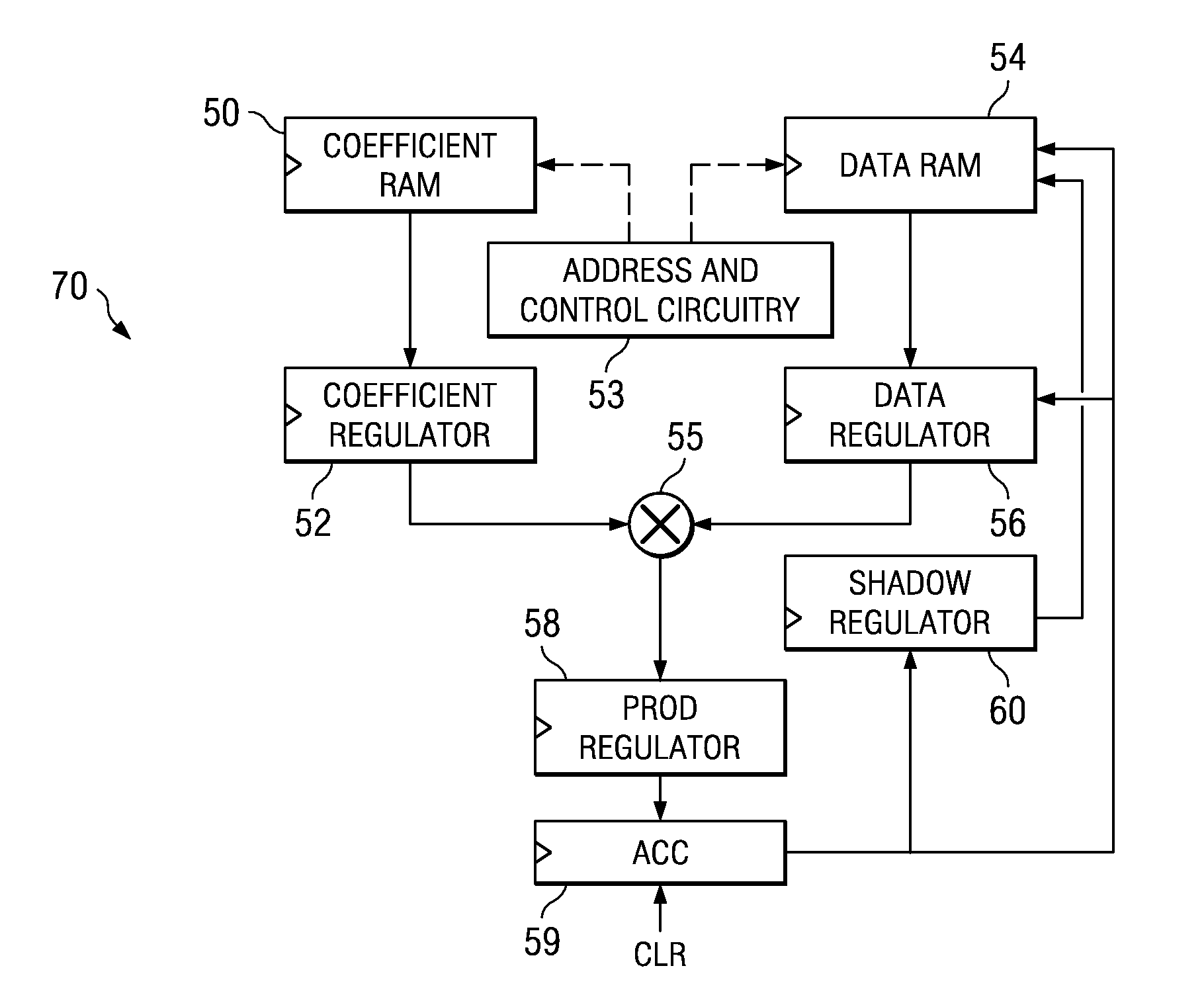

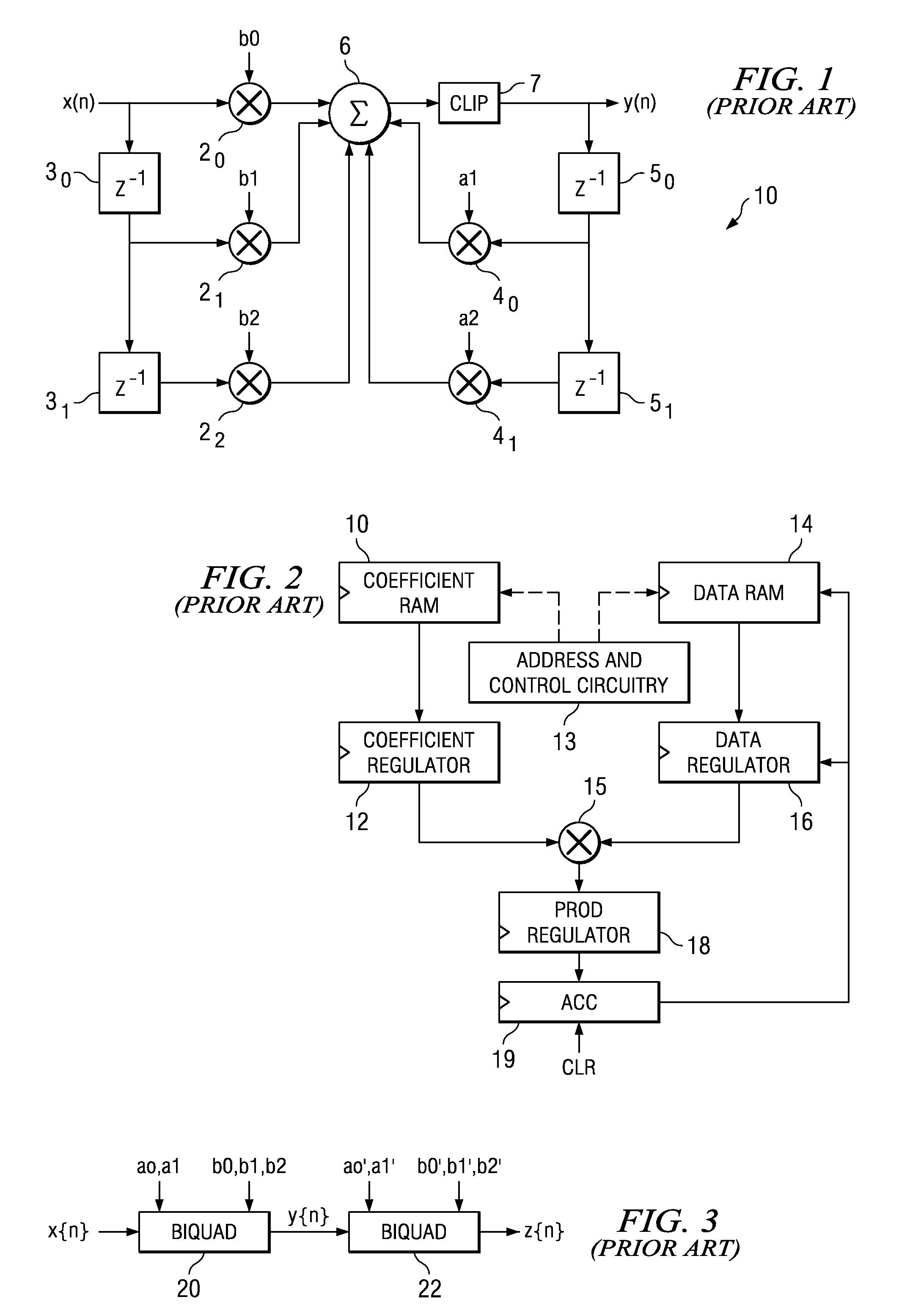

Biquad digital filter operating at maximum efficiency

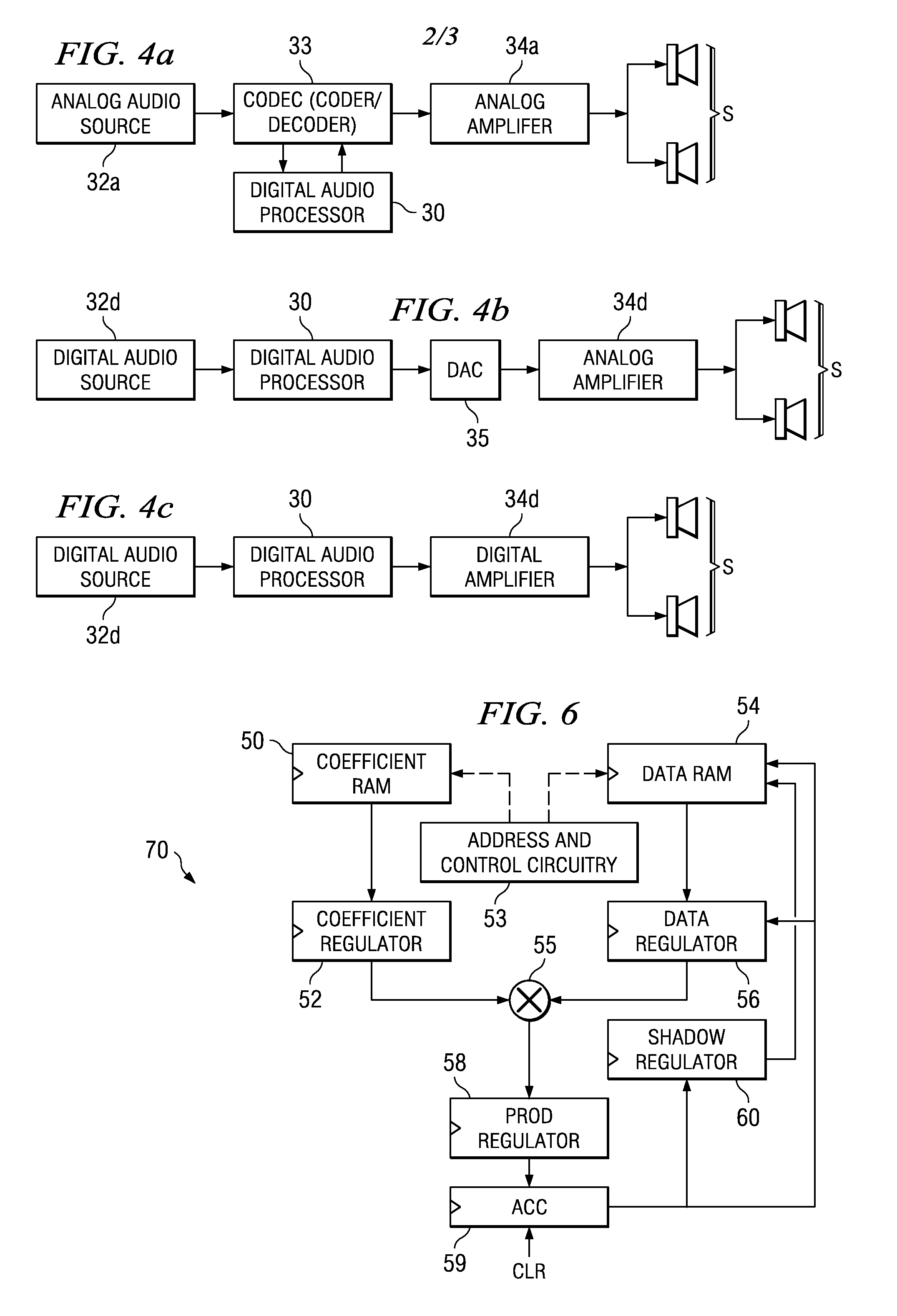

ActiveUS20050076073A1Increase initiativeEasily incorporated into audio processing circuitryDigital technique networkDigital data processing detailsIir filteringOrder of operations

An architecture for a biquad (70), second-order infinite impulse response (IIR) digital filter, that is capable of operating at maximum efficiency, is disclosed. The biquad (70) includes coefficient memory (50) and data memory (52), along with control circuitry (53) that loads values from these memories (50, 52) into a coefficient register (52) and a data register (54), respectively. A multiplier (55) multiplies the values in the coefficient register (52) and data register (54), with the resulting product being stored in a product register (58). An accumulator (59) adds successive product results to derive a new output value in each instance of the IIR filter. A shadow register (60) temporarily stores the output of the accumulator (59) from a previous instance, permitting this output to be stored in the data memory (52) at a later time in the sequence. This permits the order of operations in the second and successive biquads to be altered so that each successive biquad instance can start well before the previous result is derived; as a result, the multiplier (55) is fed with values each cycle, enabling maximum efficiency operation.

Owner:TEXAS INSTR INC

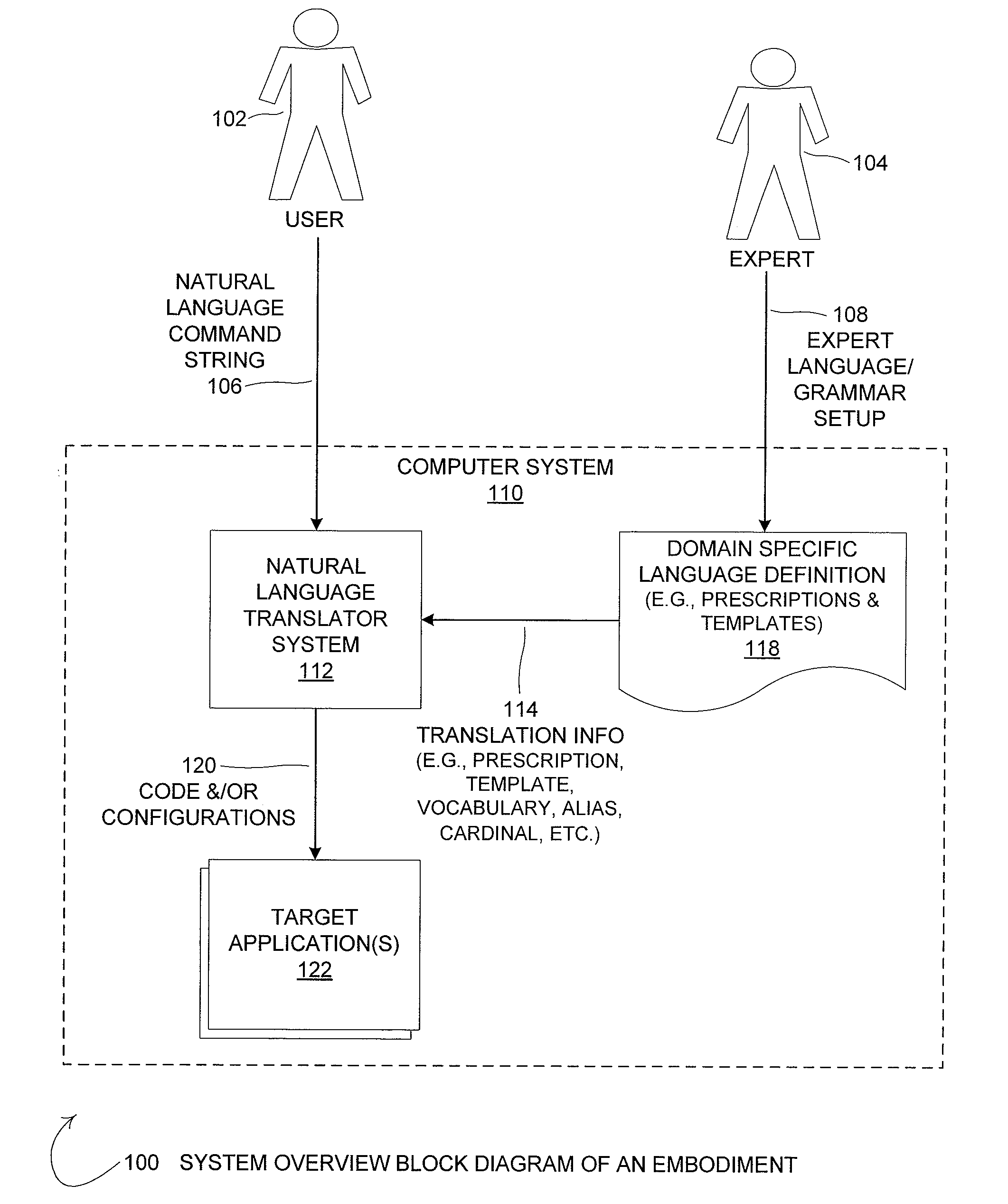

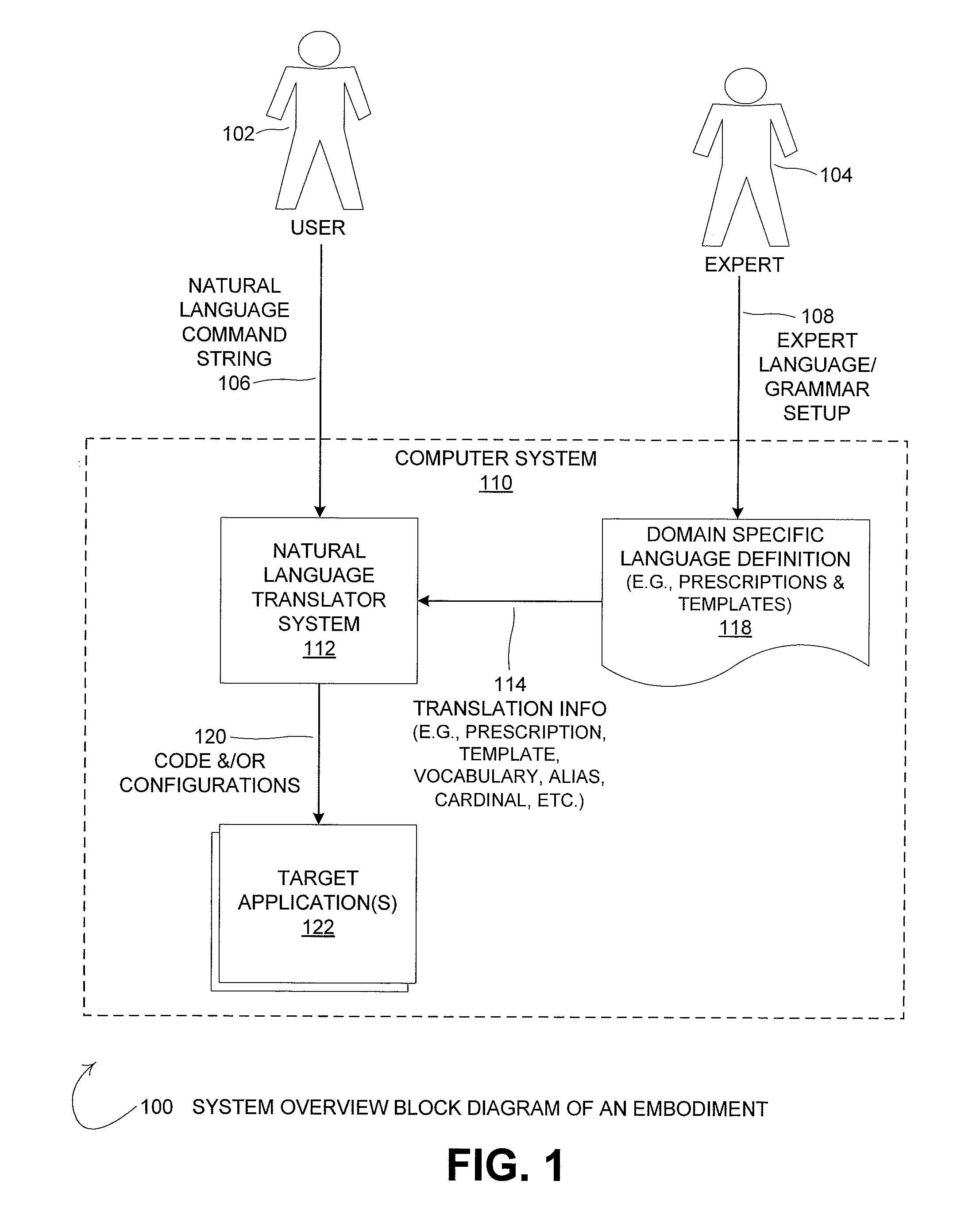

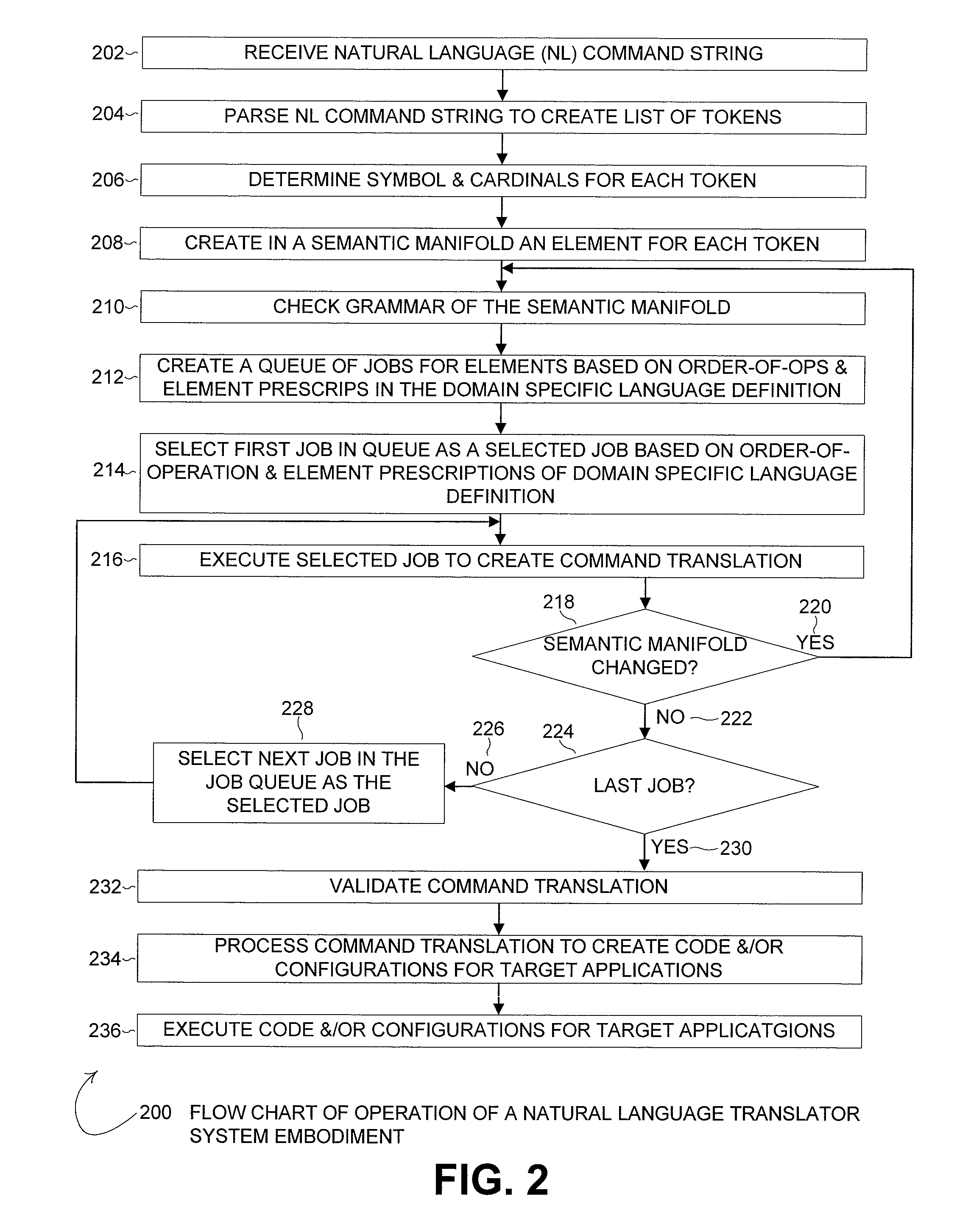

Method and system for controlling target applications based upon a natural language command string

Disclosed is a method and system for controlling applications based upon a natural language command string. Embodiments may utilize skills of expert users of one or more target applications to create a domain specific language definition. An embodiment may then permit a less sophisticated user to control target applications using natural language command strings. An embodiment may process the natural language command string to obtain the complex code and / or configurations necessary to control the target applications. During the processing, each word (i.e., token / element) of the natural language command string is processed and compared with the domain specific language definition, which provides cardinal, order-of-operation, and other applicable data for each token / element, as well as translation procedures (i.e., jobs) that when run for each token / element provide the translation for the natural language command string. An embodiment may also permit a job to create new grammar to be evaluated recursively with additional jobs.

Owner:MAXWELL WORTHINGTON

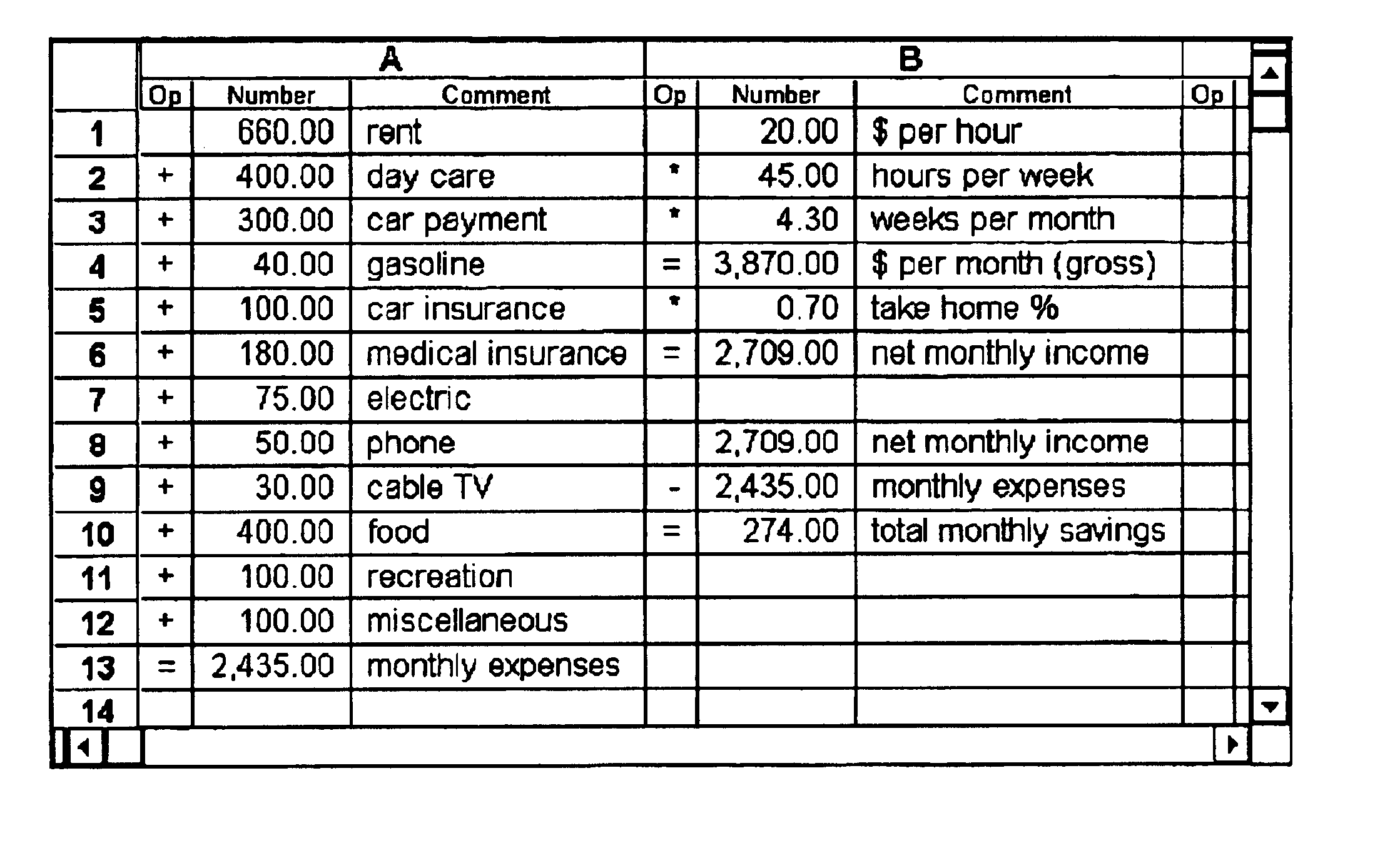

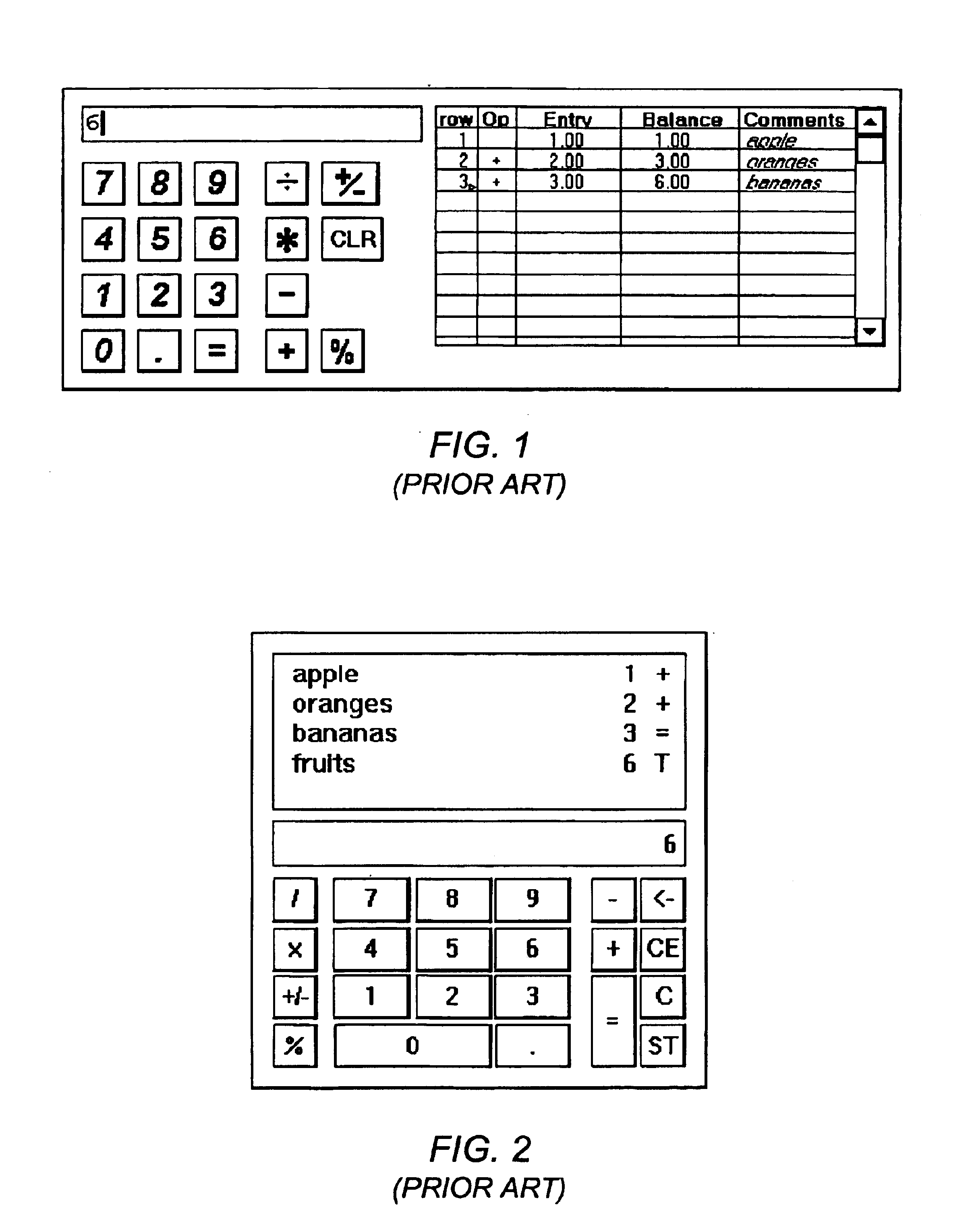

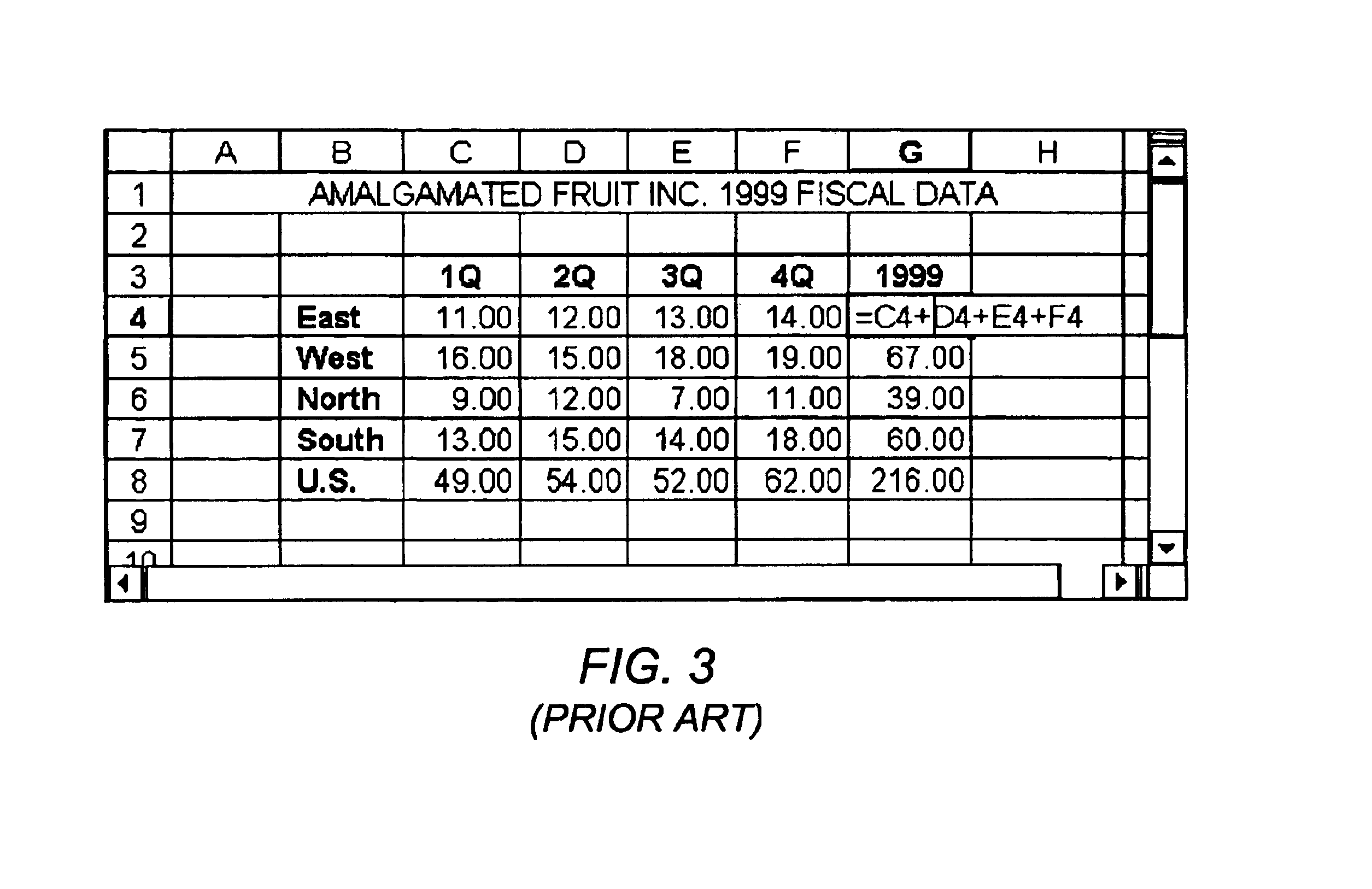

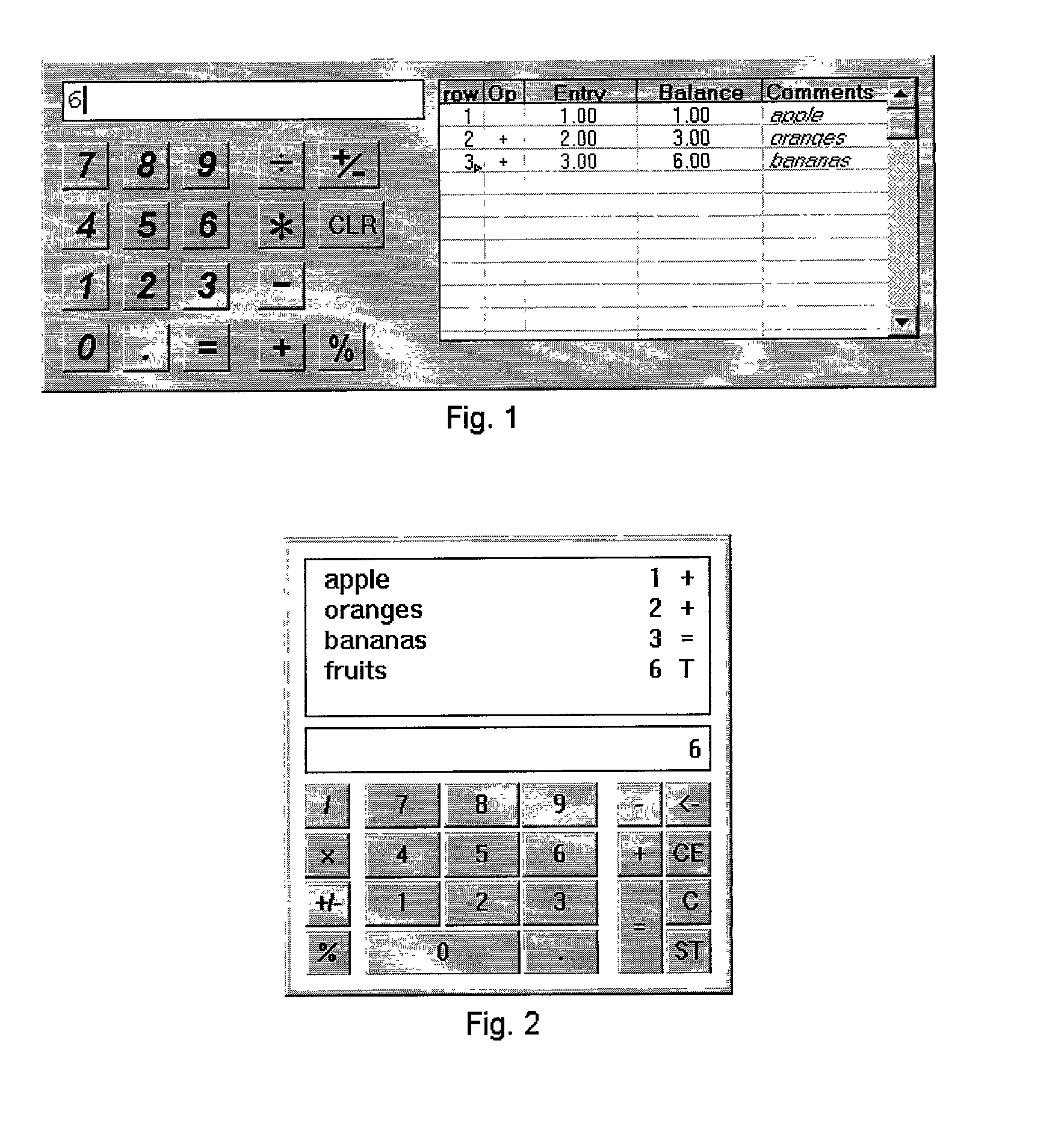

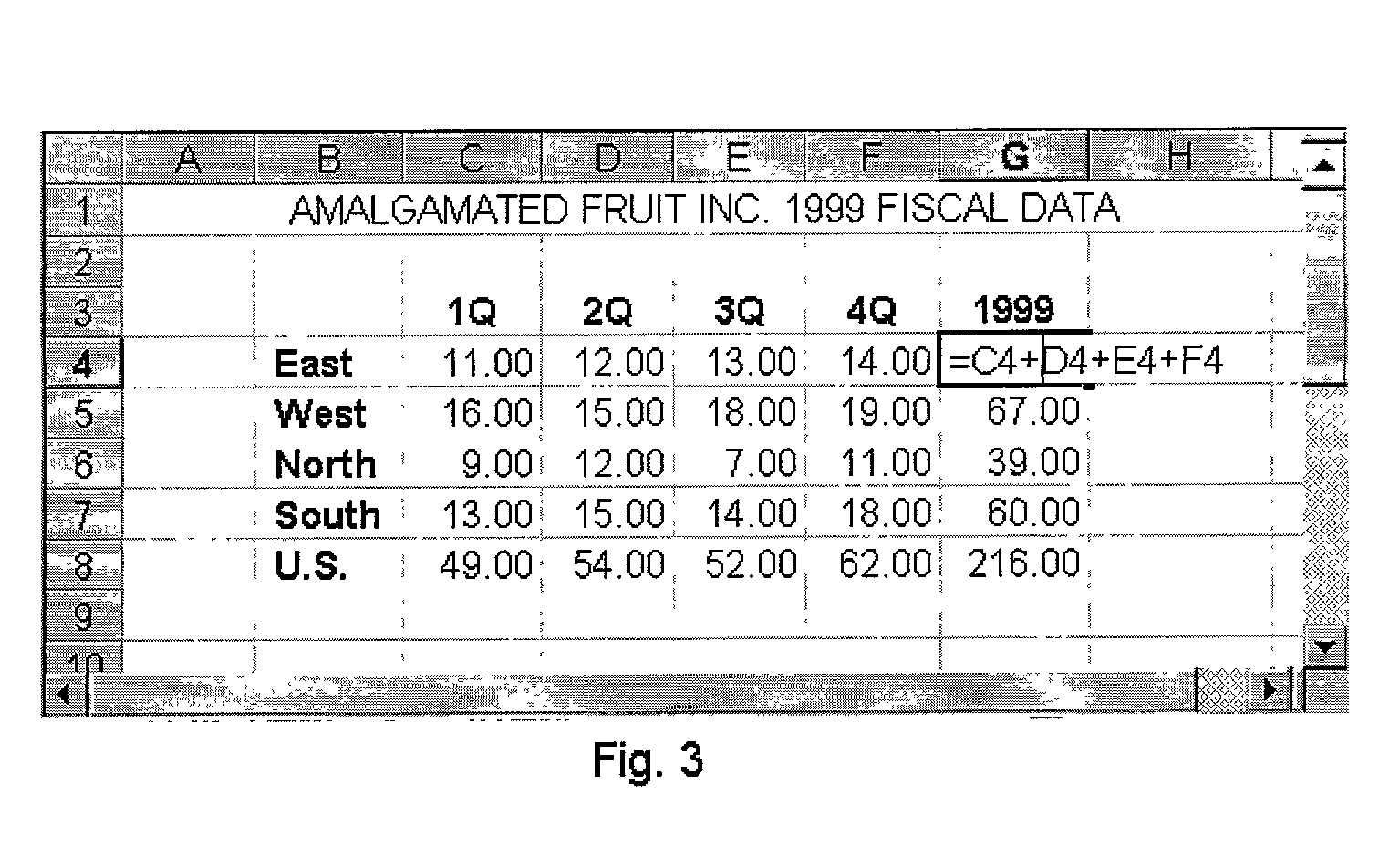

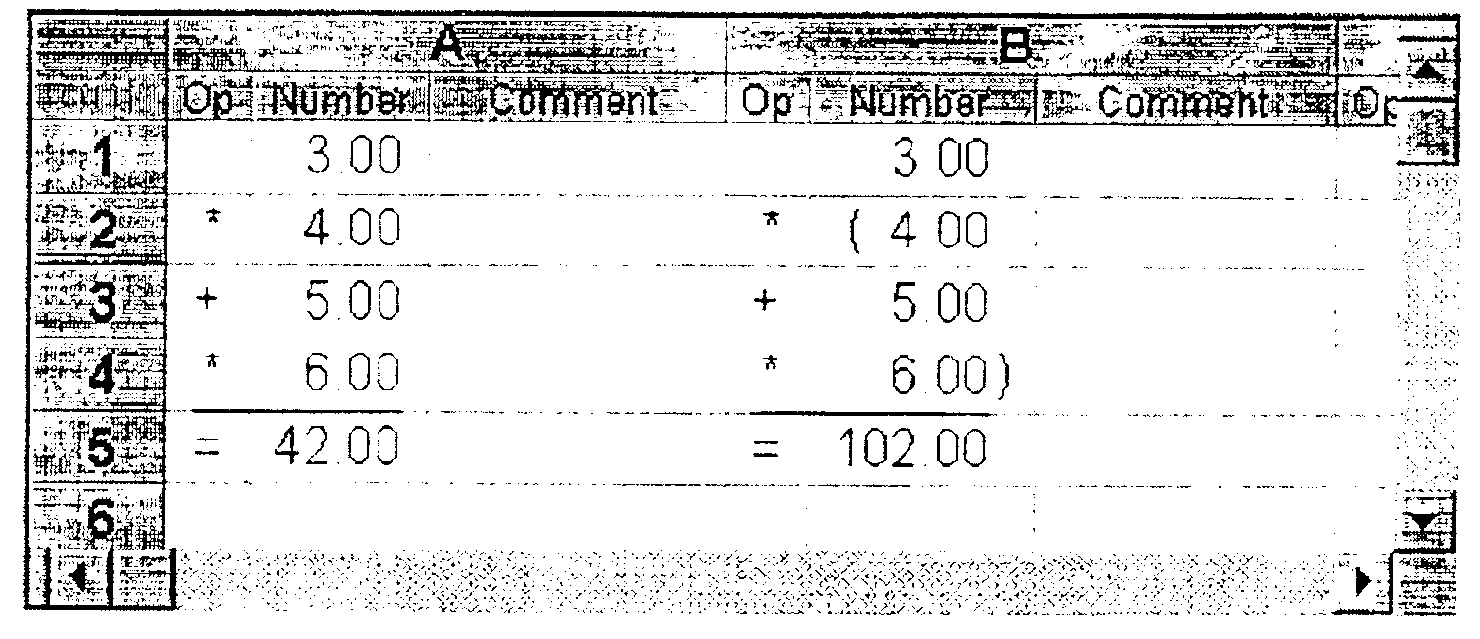

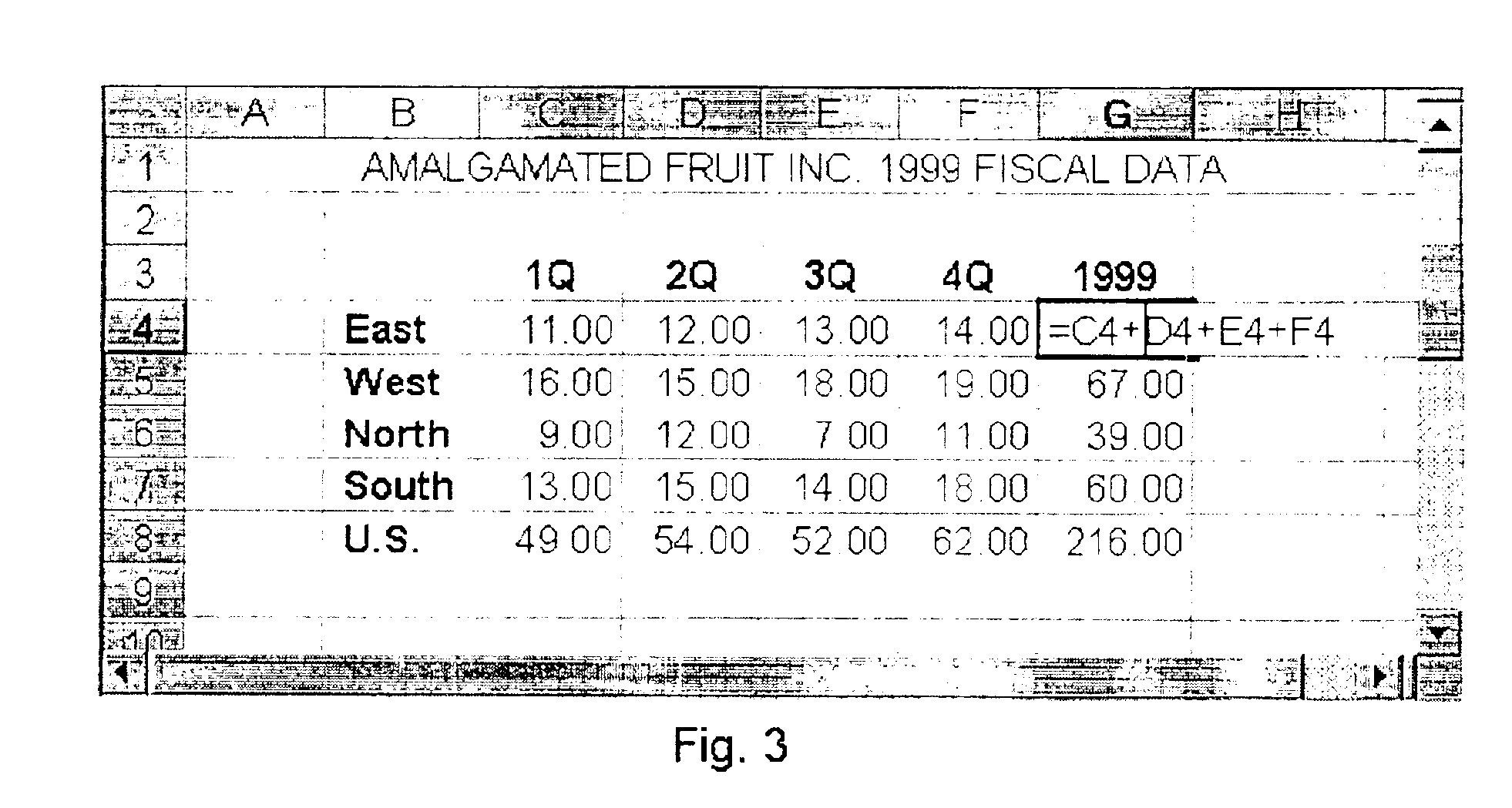

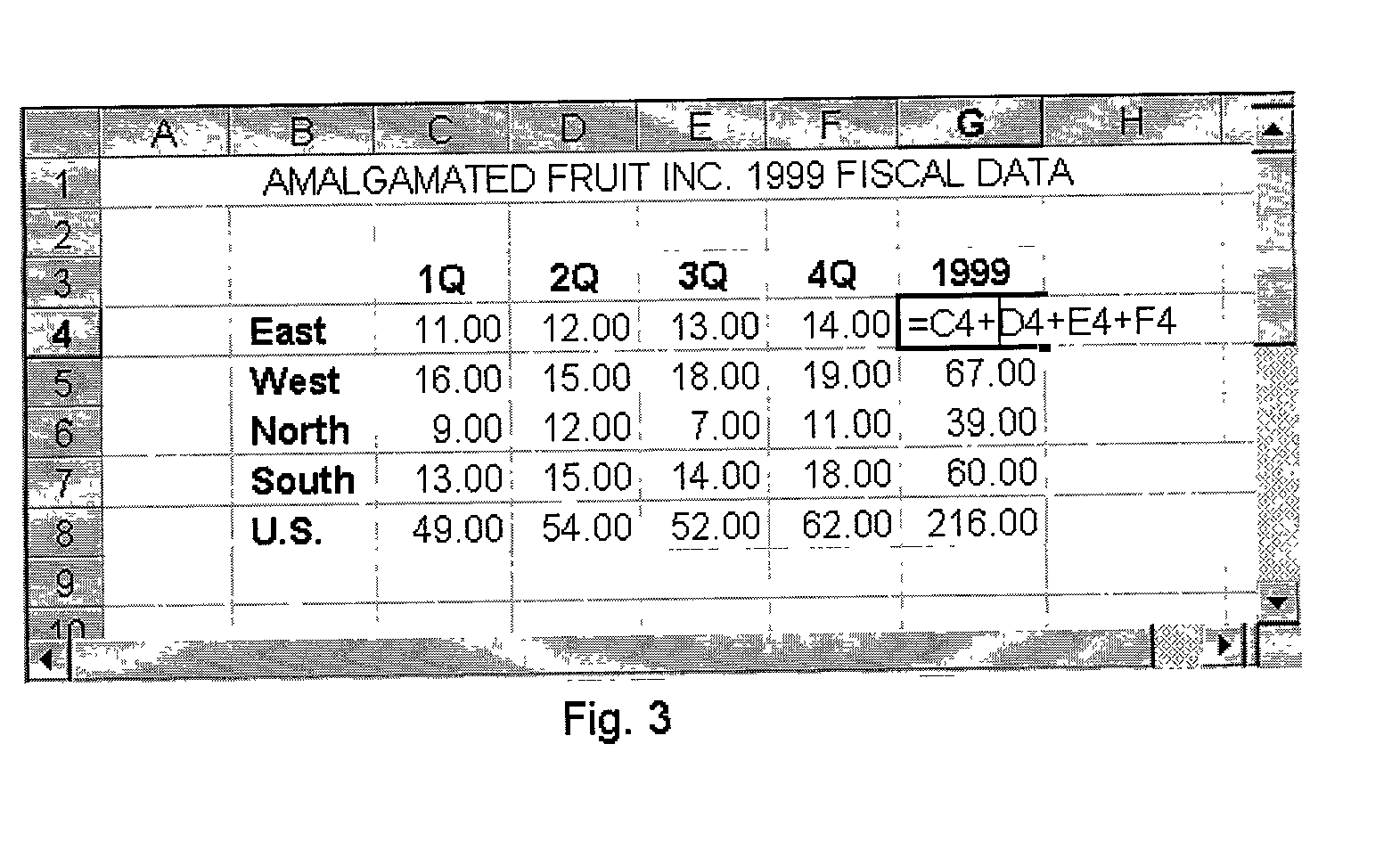

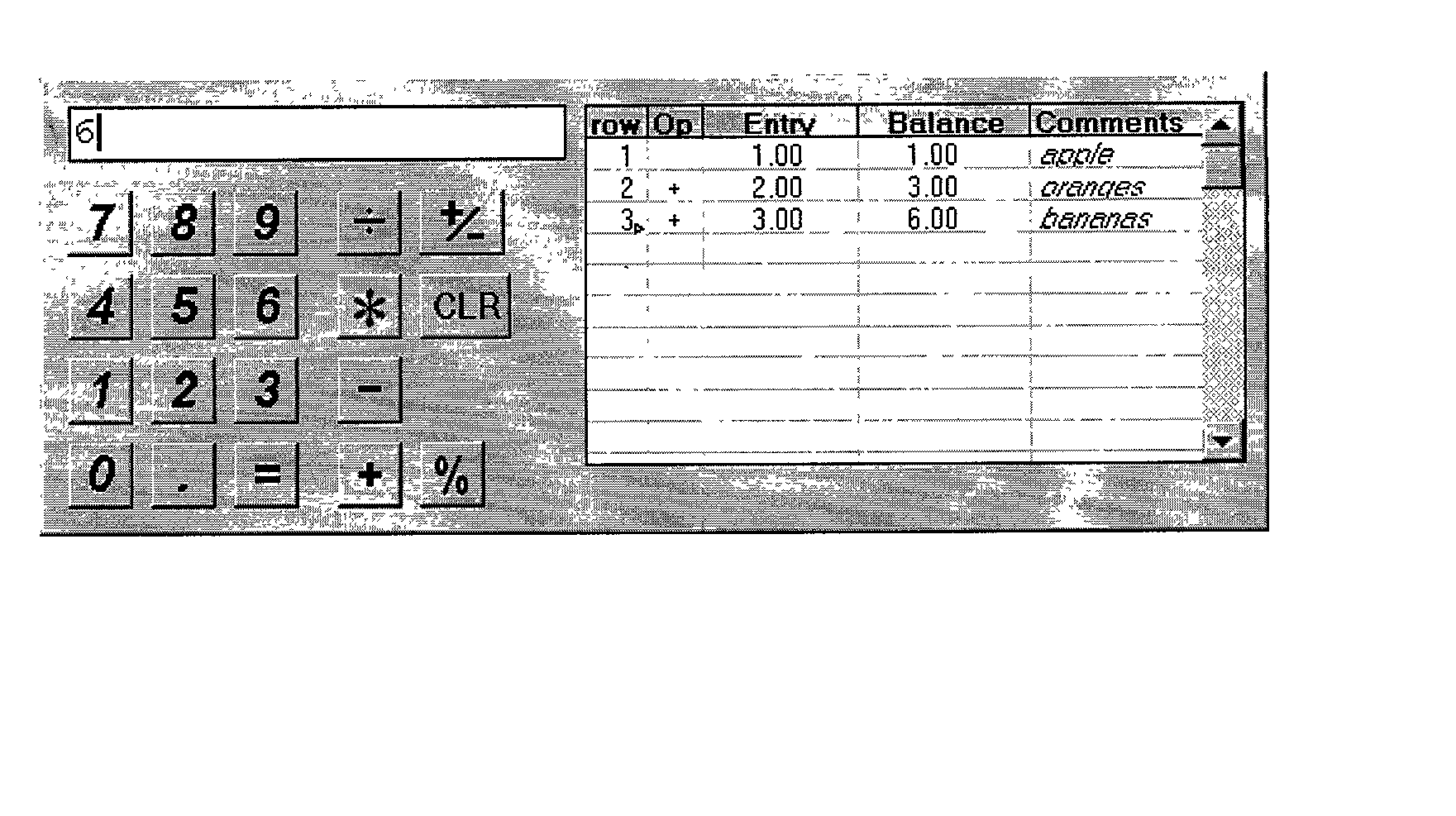

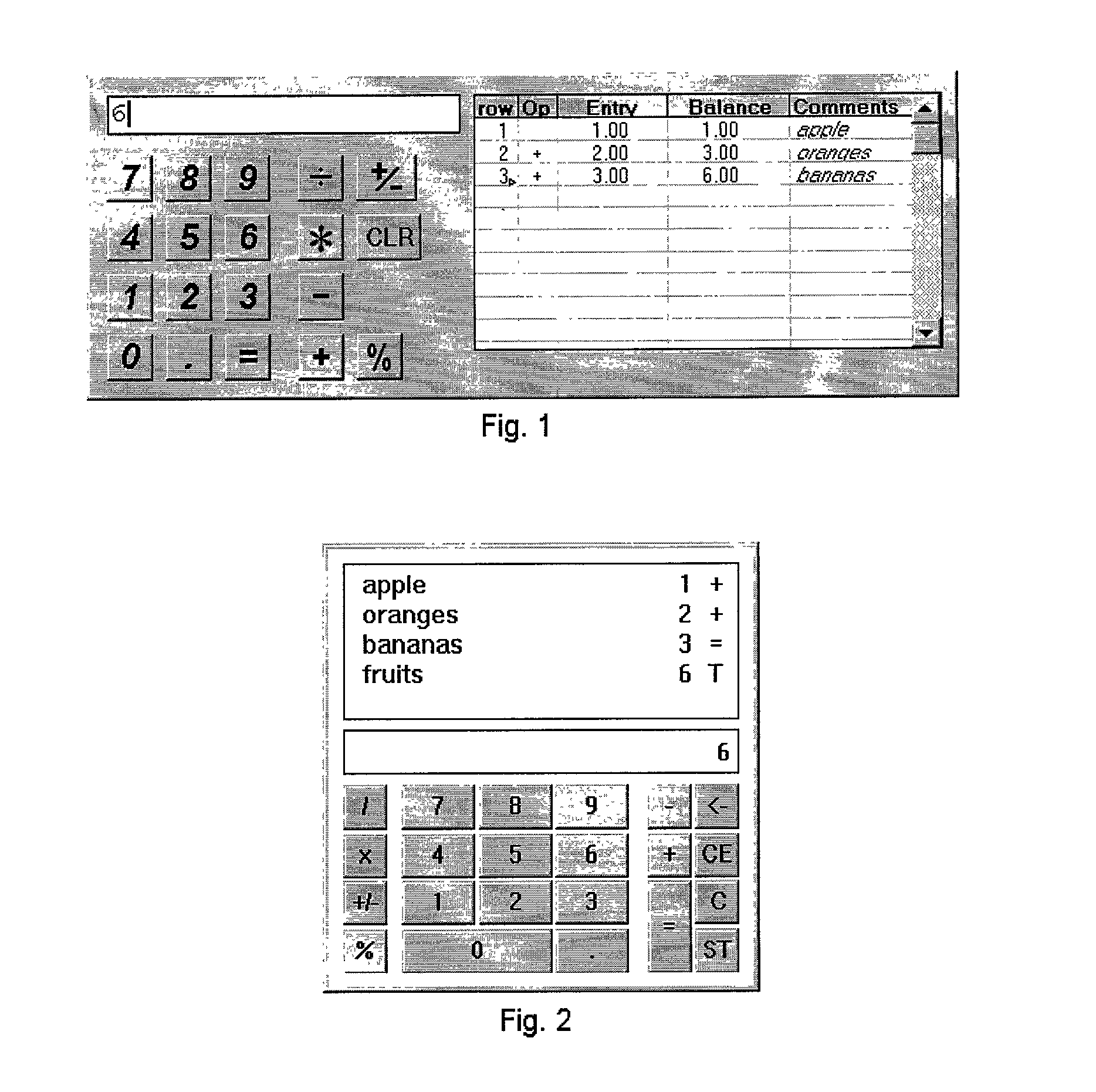

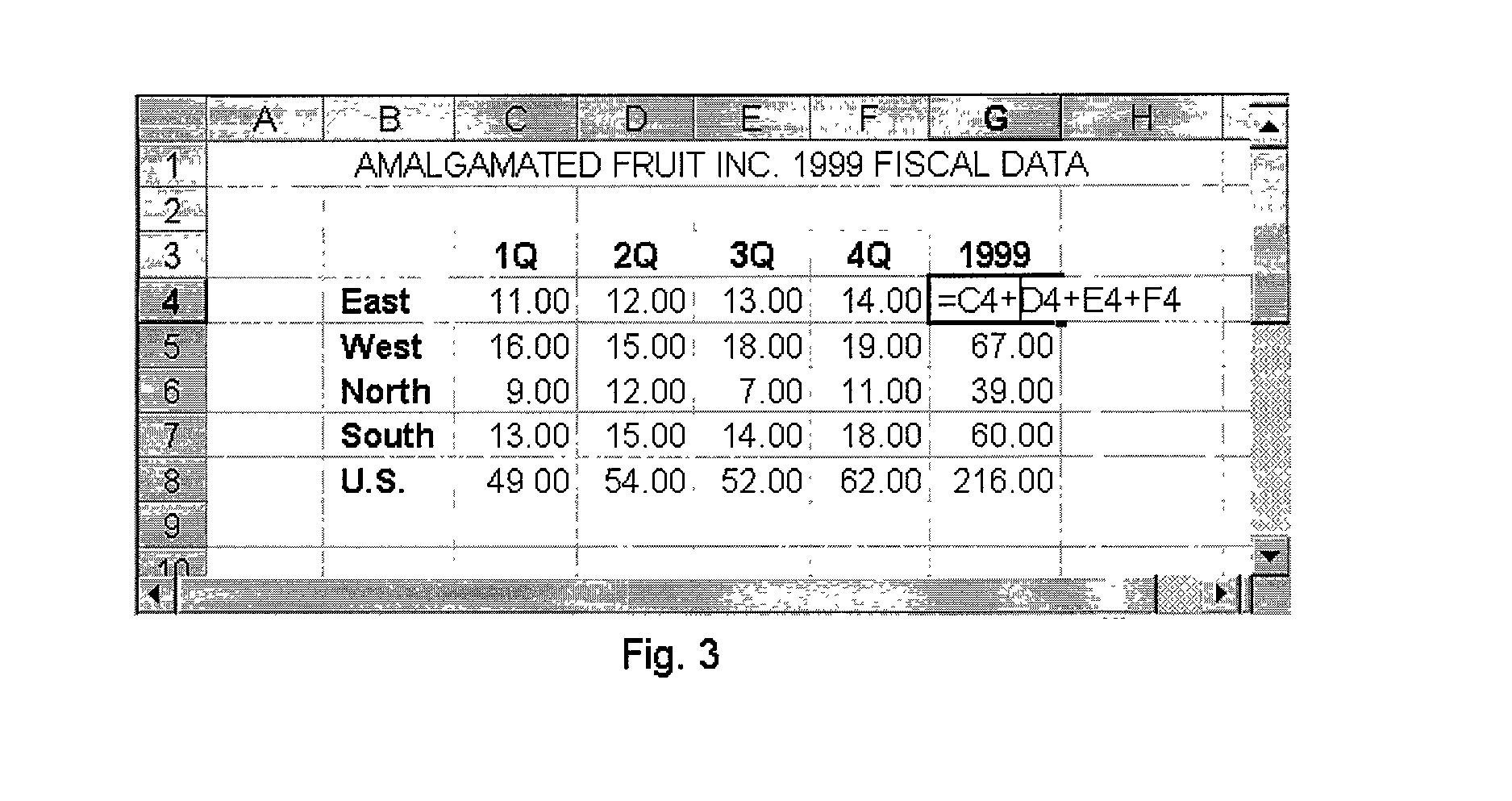

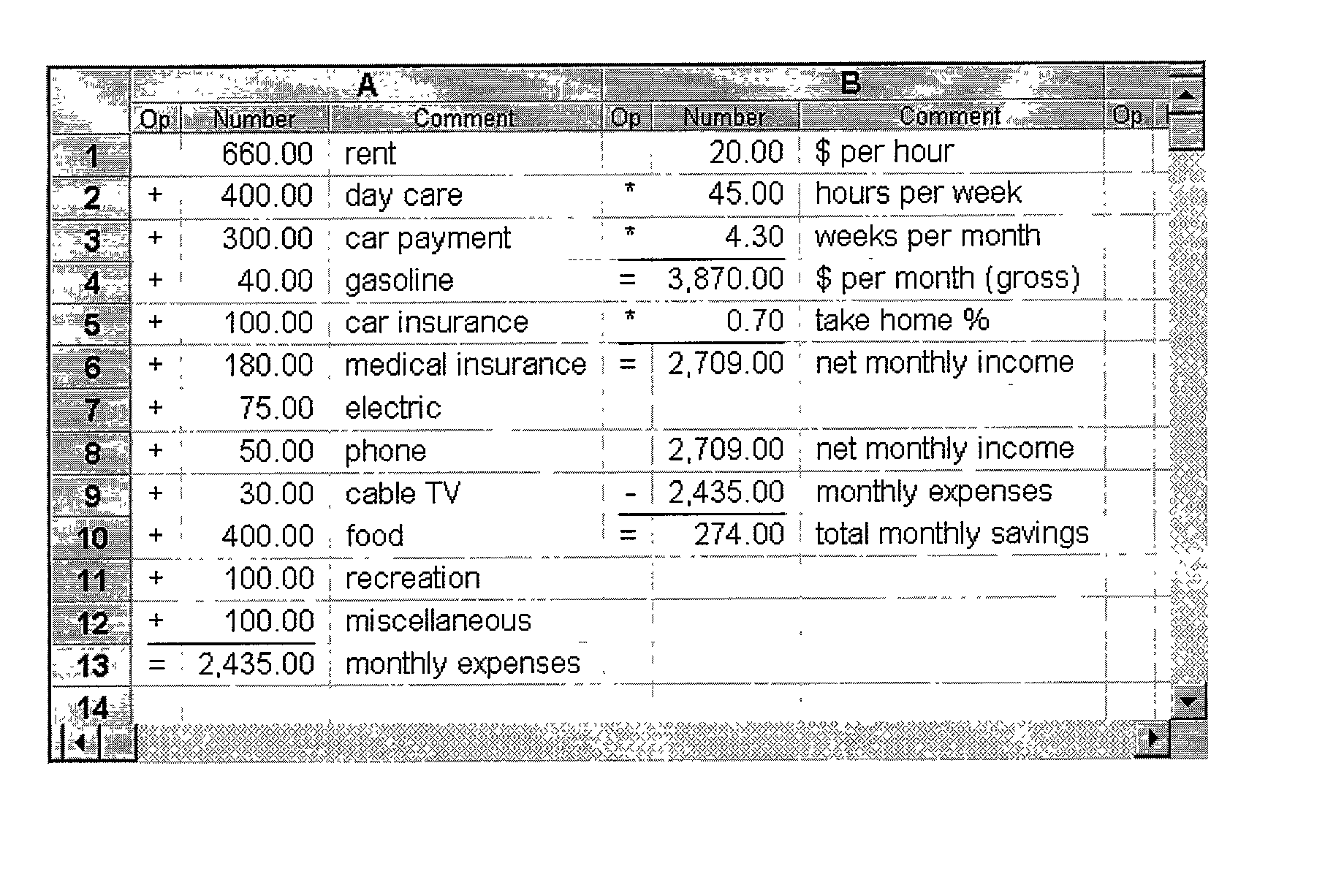

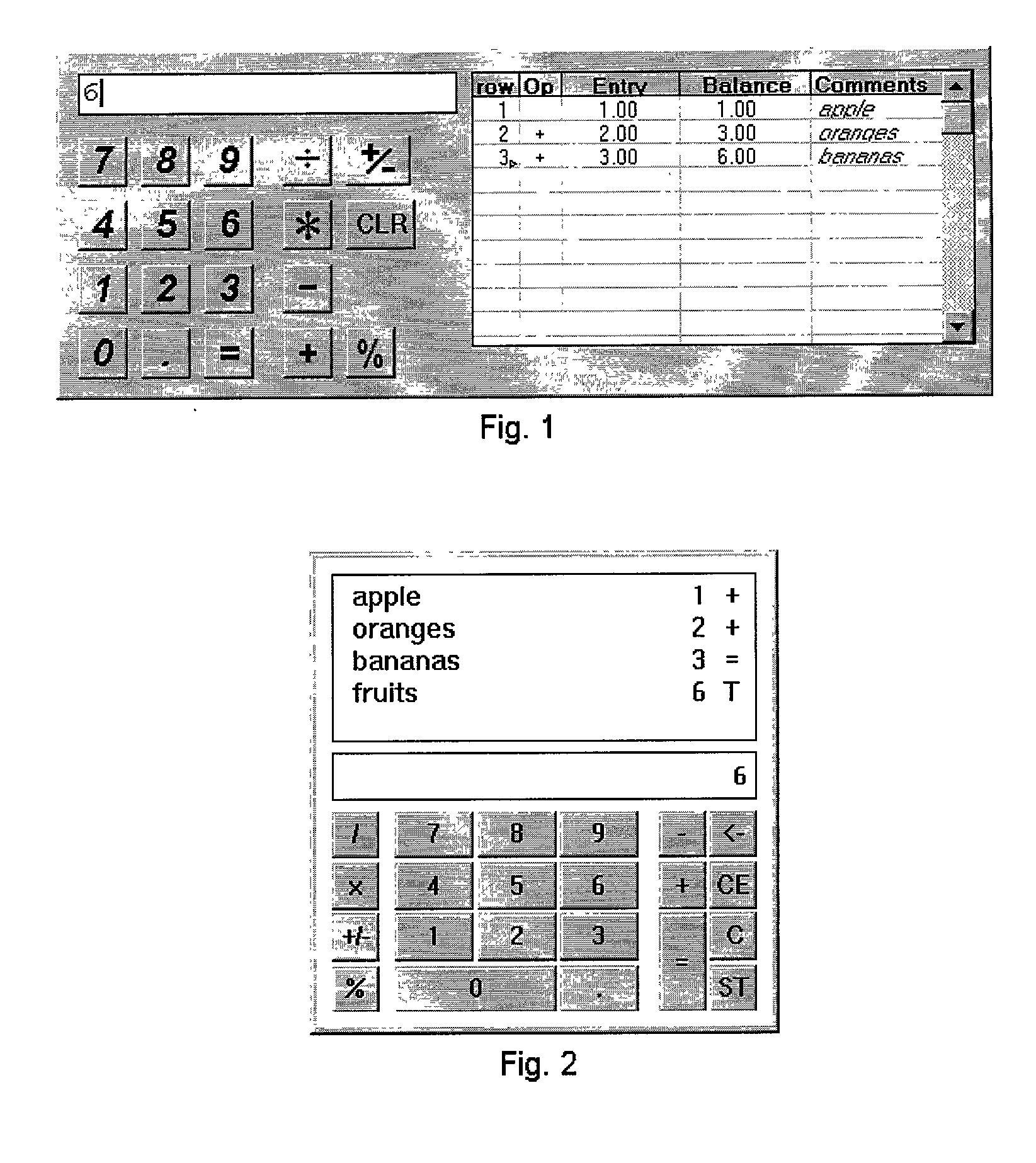

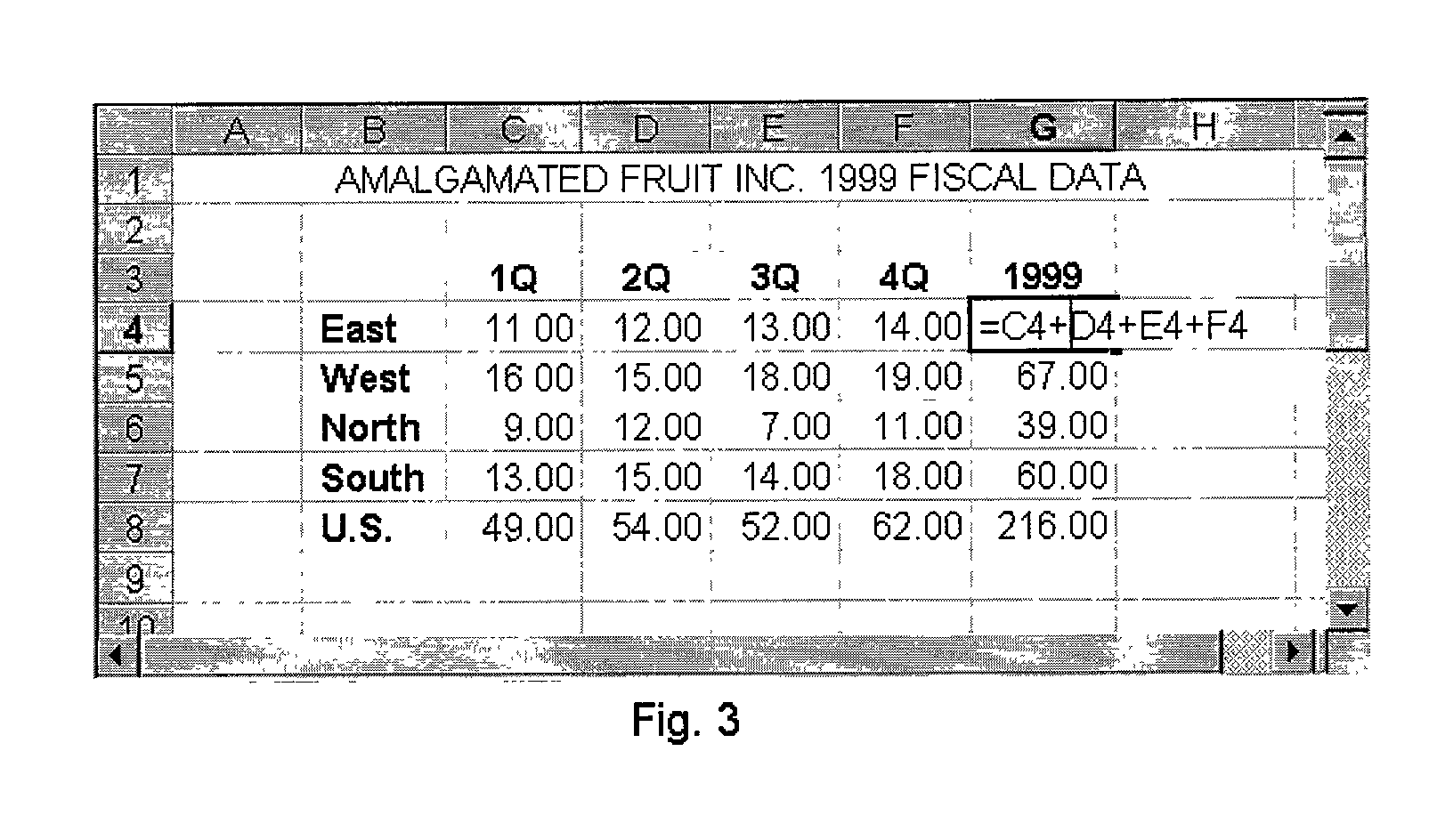

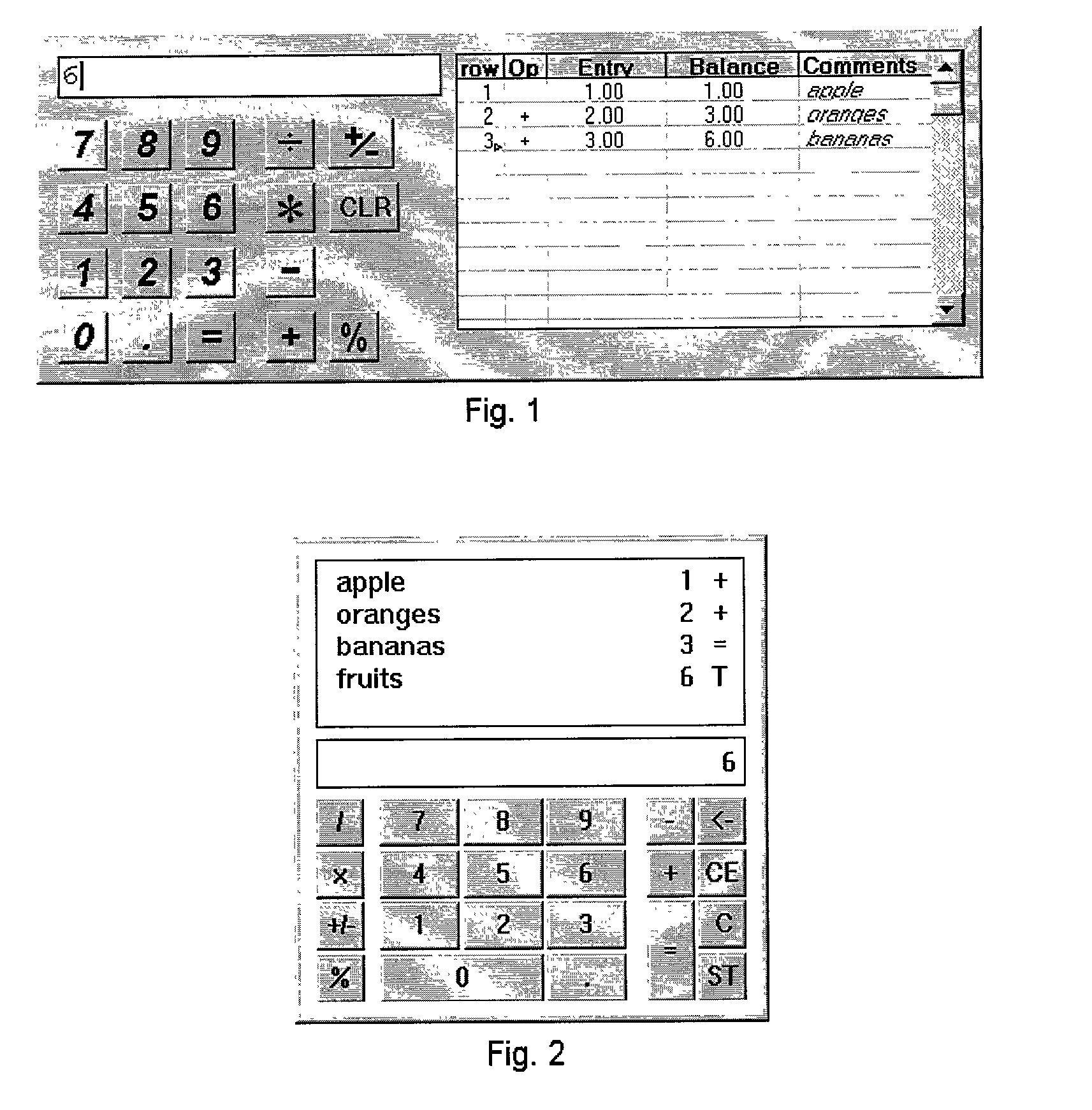

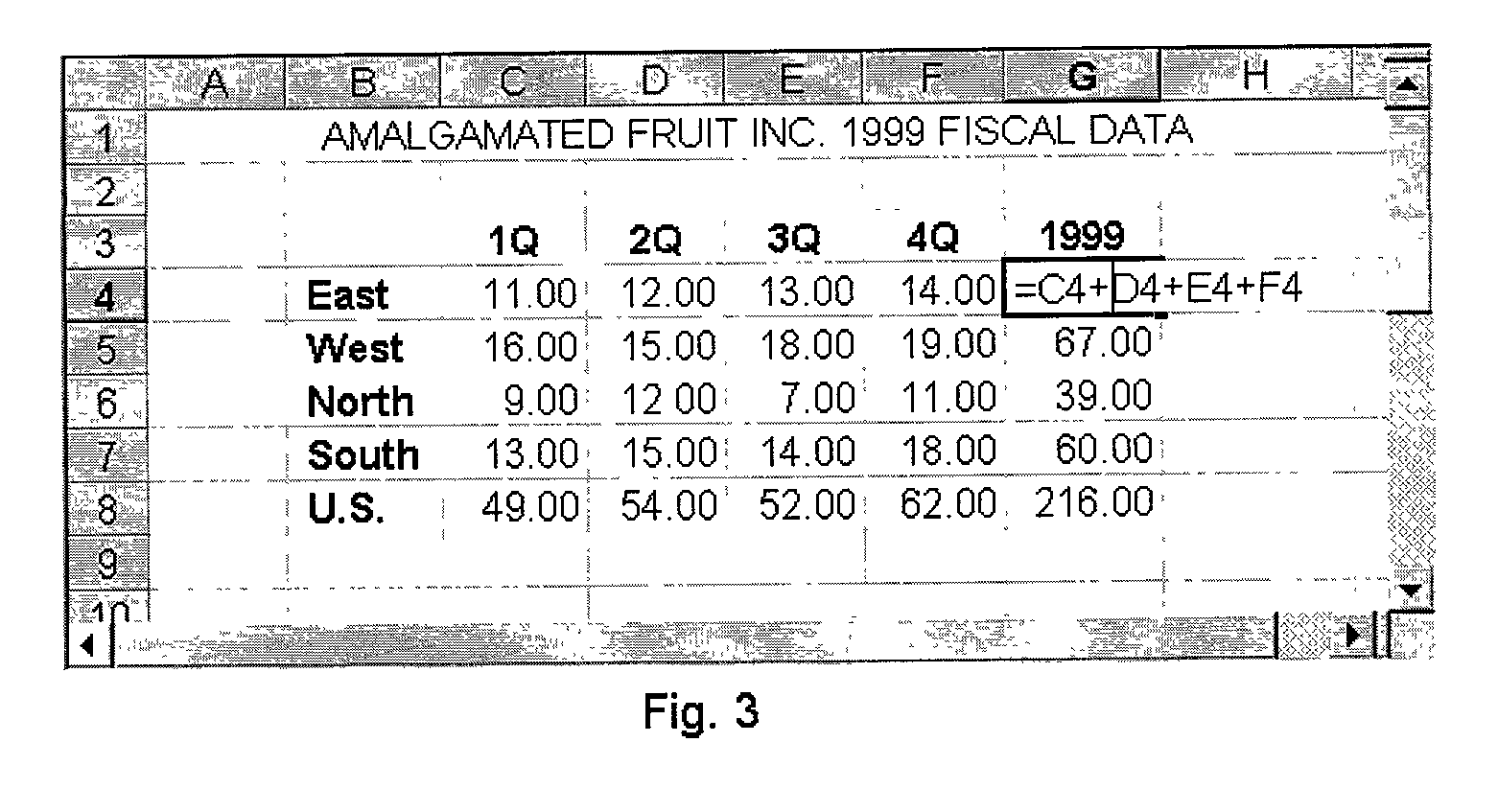

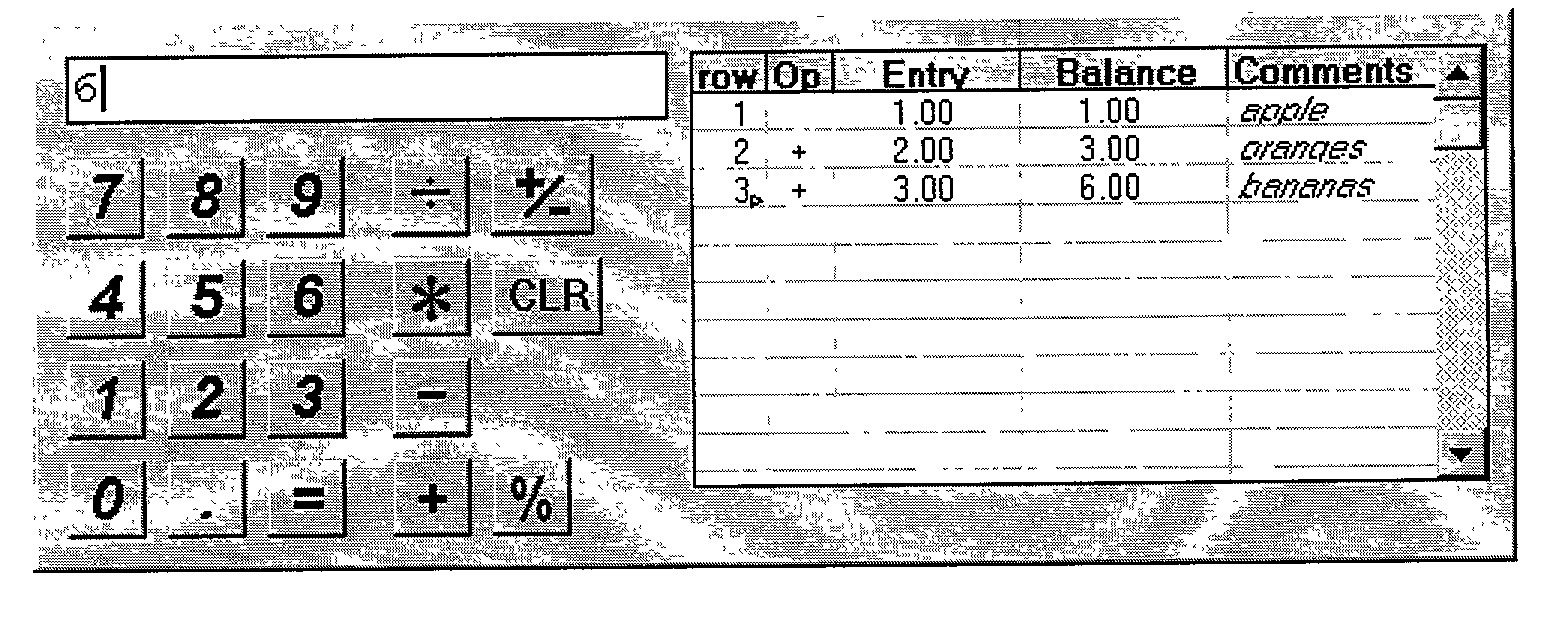

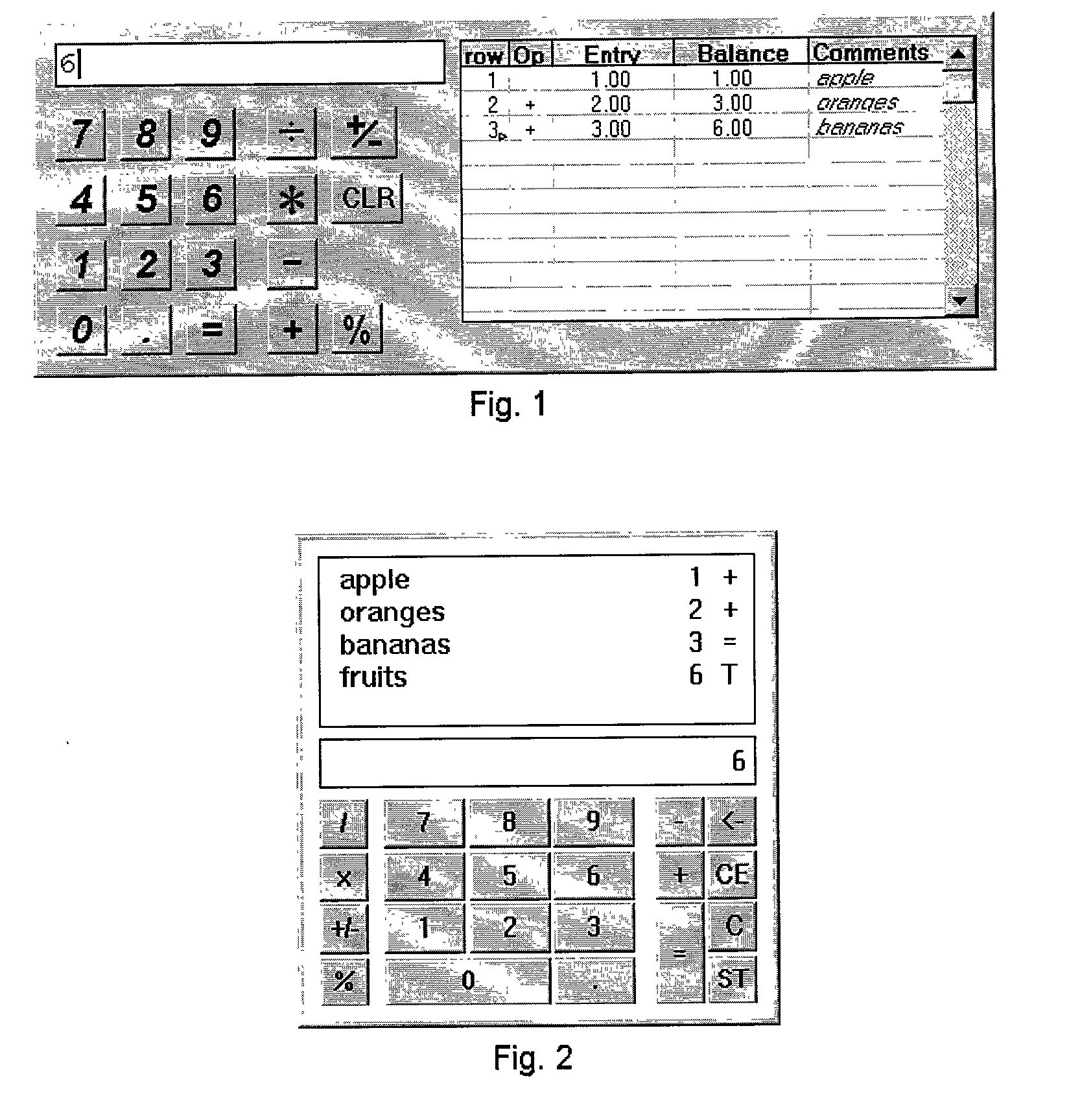

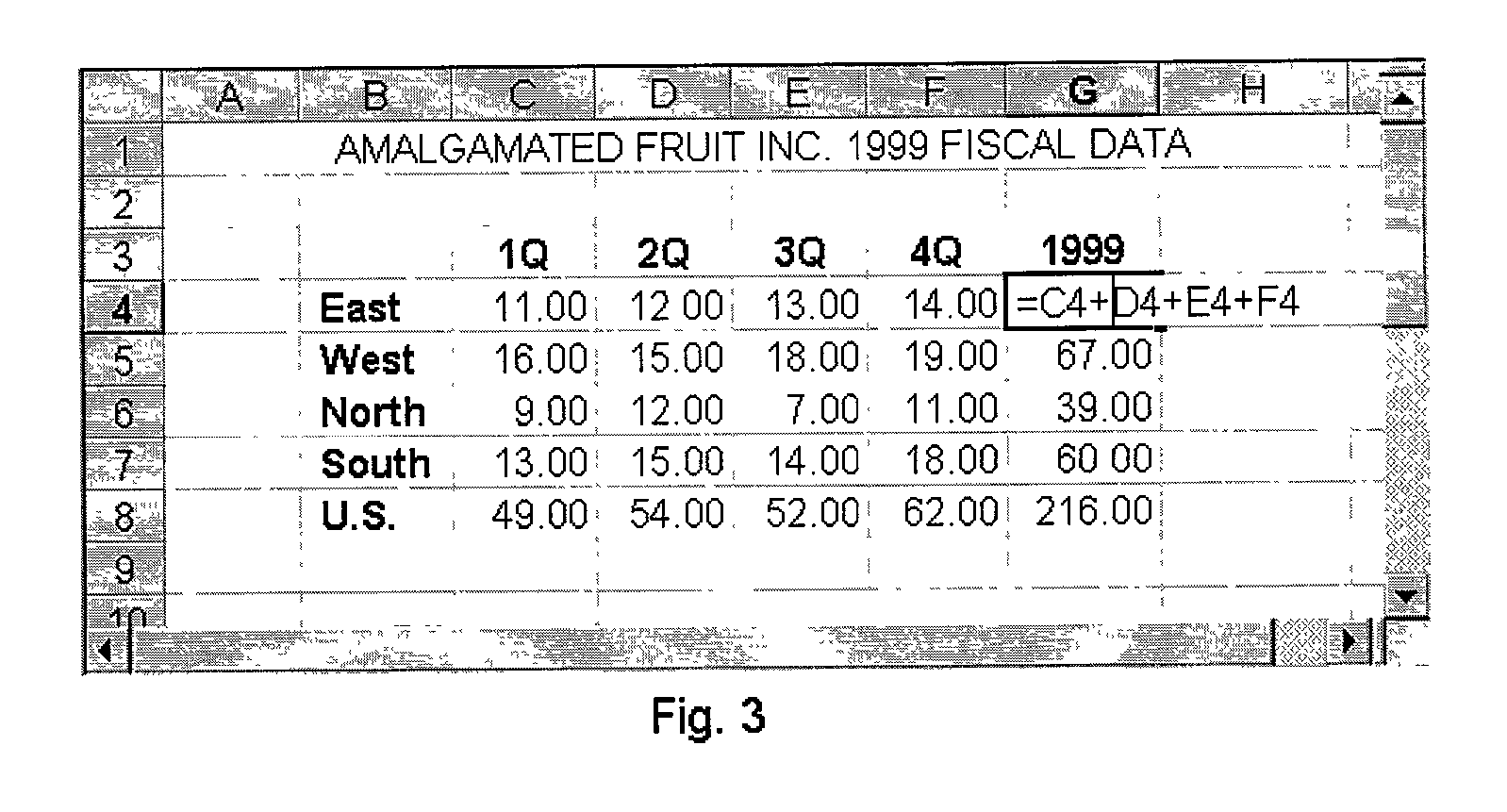

System and method for calculation using spreadsheet lines and vertical calculations in a single document

InactiveUS20020143831A1Text processingSpecial data processing applicationsElectronic formOrder of operations

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

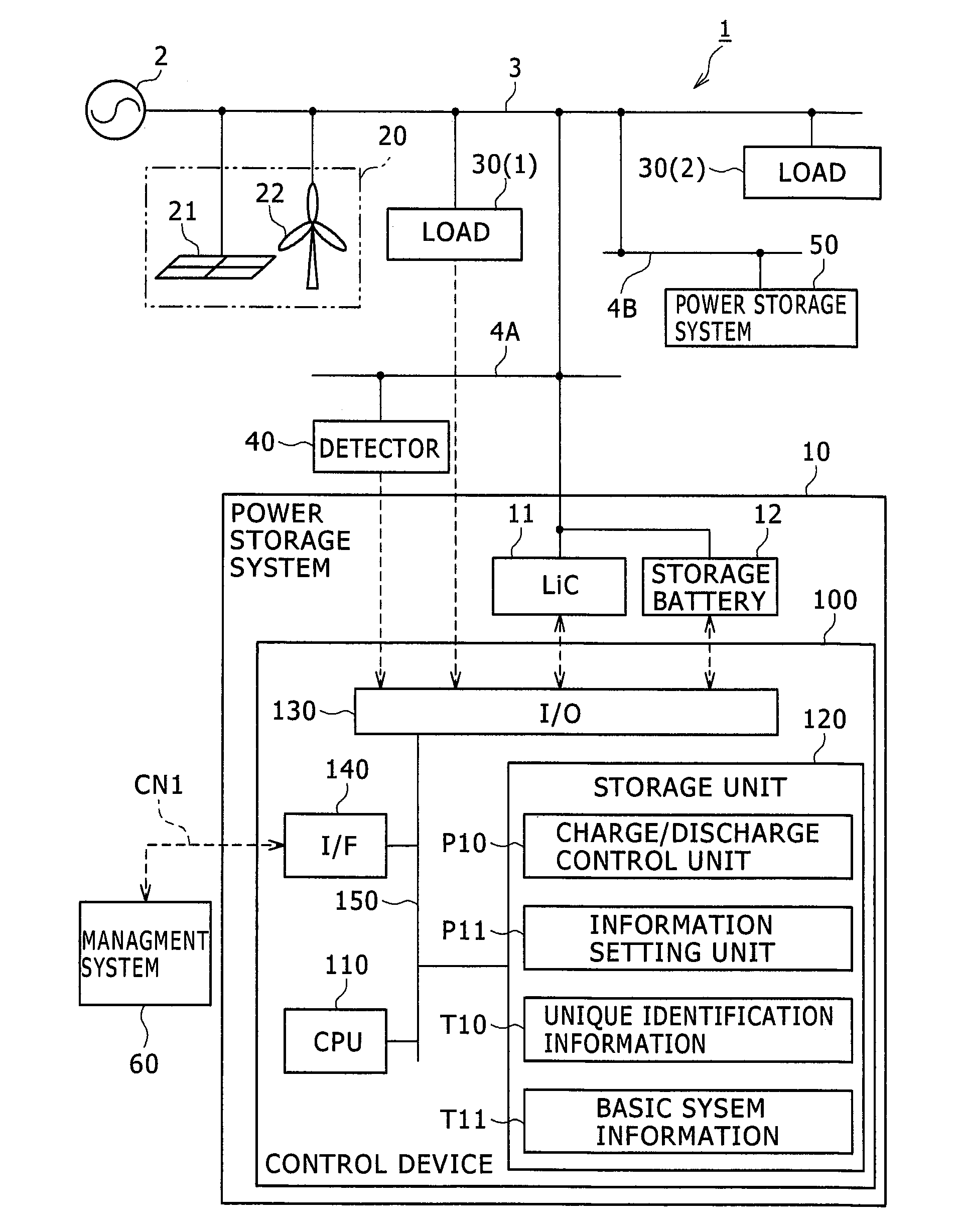

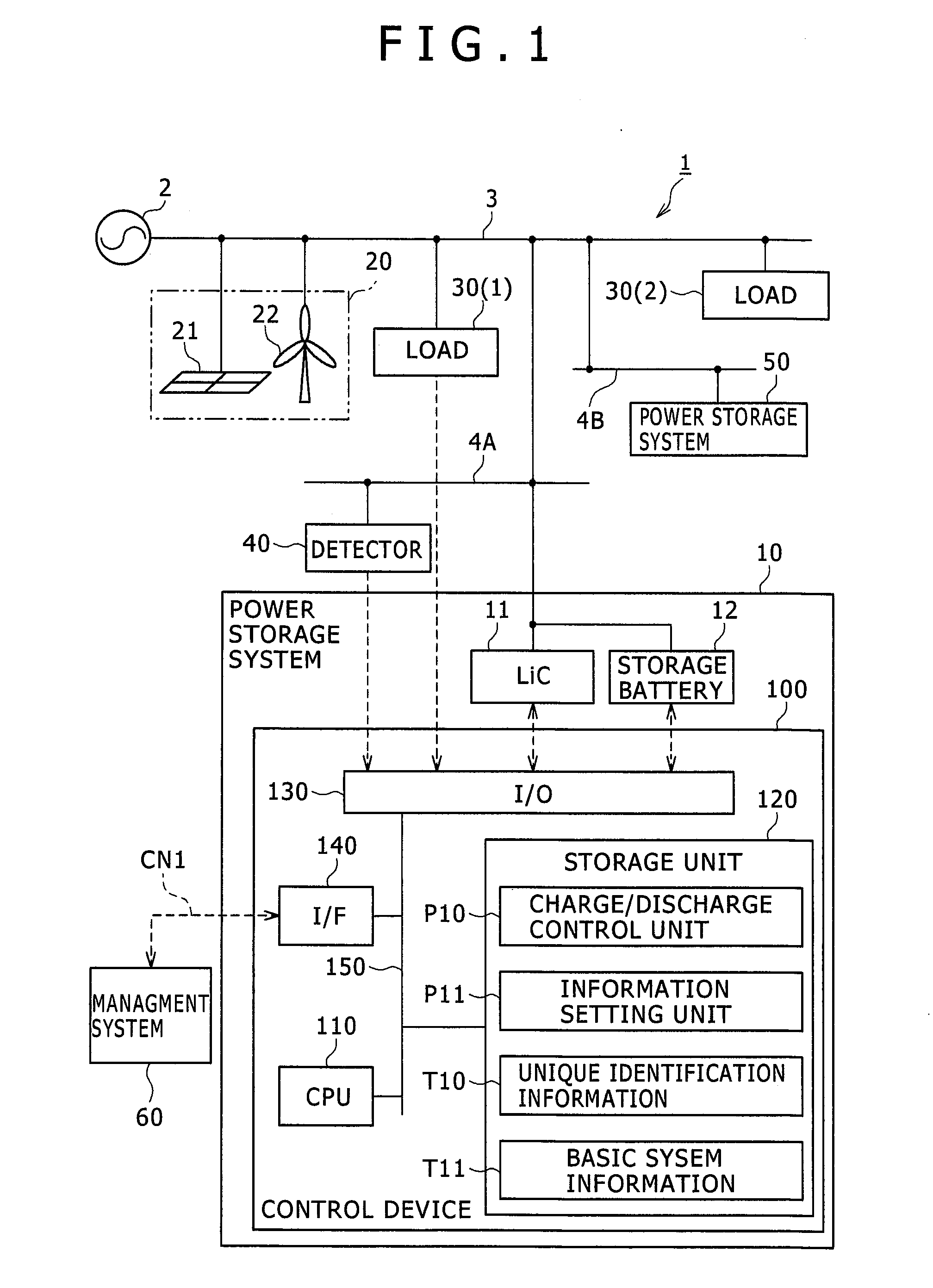

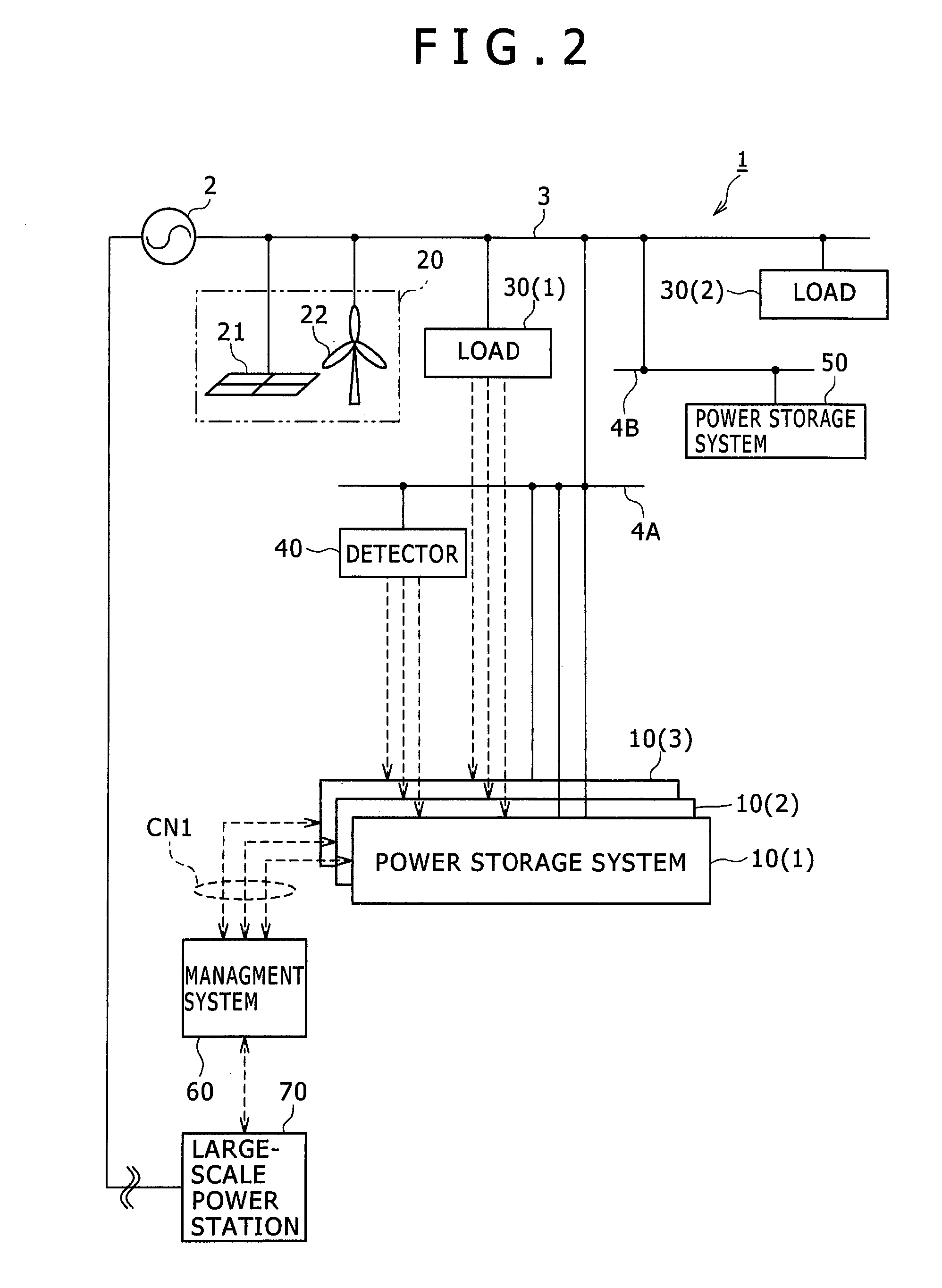

Power grid stabilization system and power grid stabilization method

ActiveUS20140365027A1Suppress interferenceMechanical power/torque controlLevel controlElectric power systemOrder of operations

Plural distributed power storage systems are used to stabilize a power system. Plural power storage systems 10 are provided in a power system. The power storage systems 10 are connected to a management system 60 via a communication network CN1. The power storage systems each include a power storage device 11, 12, and a control device 100 for controlling the power storage device. The control device stores performance information about the power storage system including the control device, location information indicating a location in the power system of the power storage system including the control device, and order information indicating an order of operation allocated to the power storage system including the control device. When a disturbance occurs in the power system, the control device performs a predetermined compensation operation based on the location information and the order information, and then returns to a preset stand-by state.

Owner:HITACHI LTD

System and method for calculation using vertical parentheses

InactiveUS6961898B2Easy to useEasy accessText processingDigital computer detailsElectronic formOrder of operations

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

System and method for calculation using formulas in number fields

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

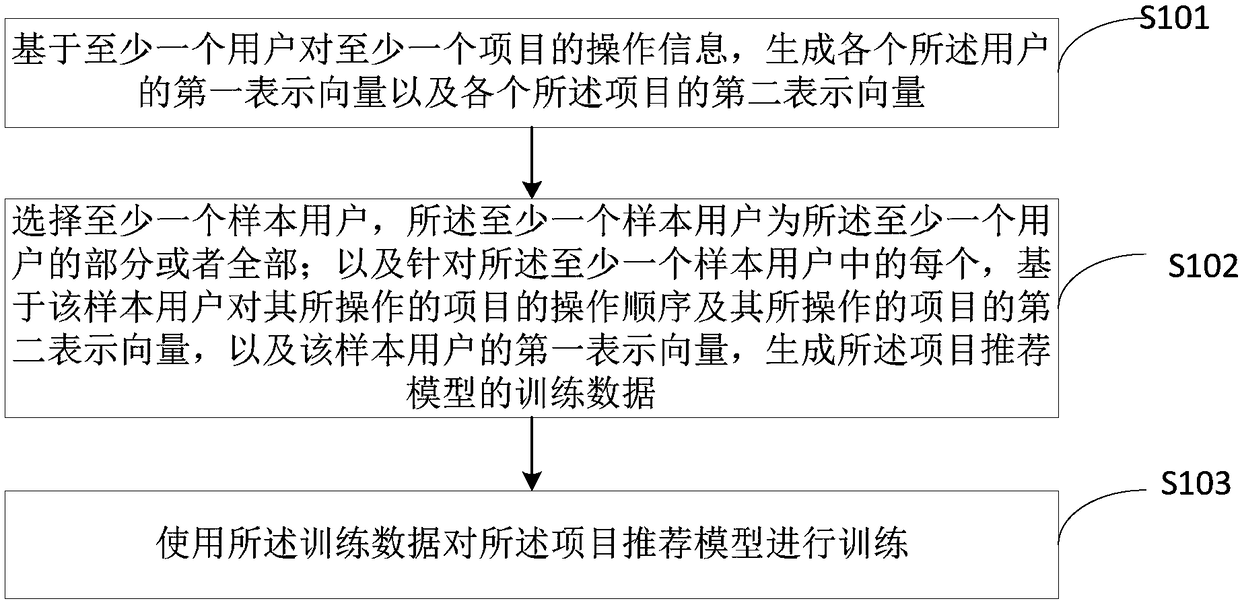

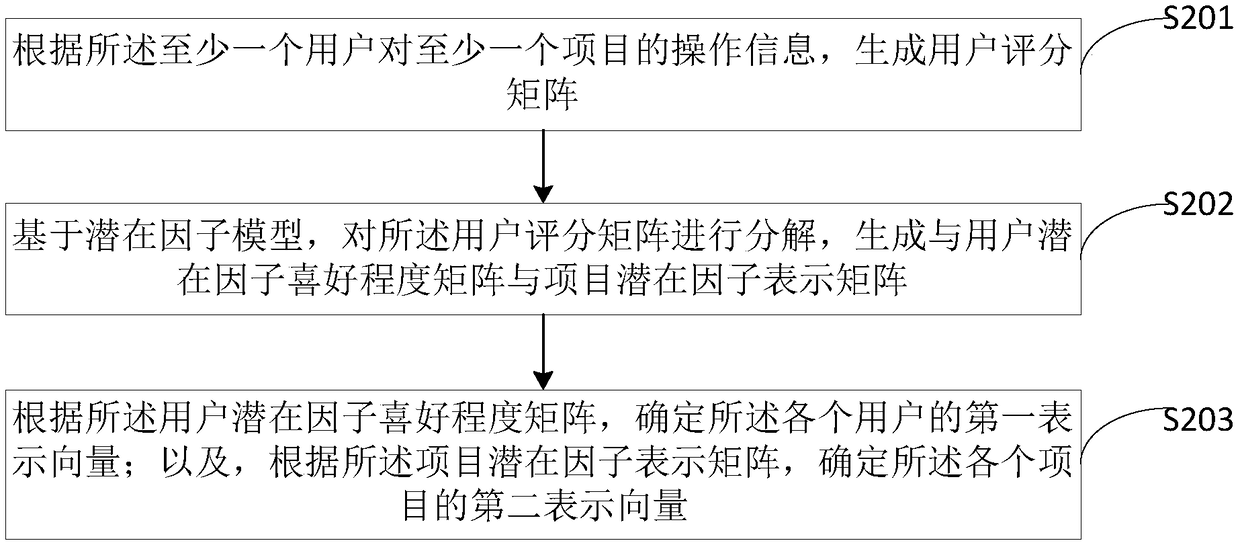

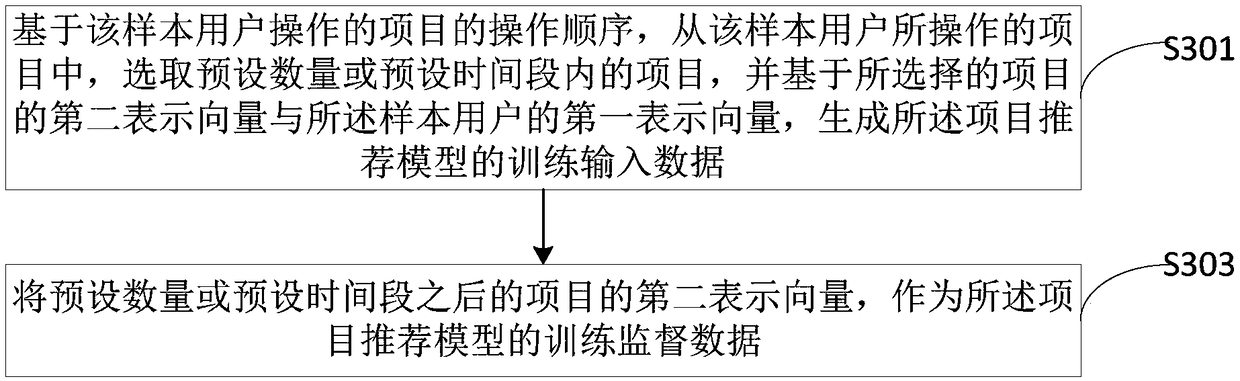

Item recommendation model training method, item recommendation method and device

ActiveCN109389168AImprove effectivenessDescribe interestsCharacter and pattern recognitionOffice automationRecommendation modelOrder of operations

The invention discloses an item recommendation model training method, an item recommendation method and device. The item recommendation model training method of the invention comprises the following steps: generating a first representation vector of each user and a second representation vector of each item based on at least one user's operation information of at least one item; selecting at leastone sample user, the at least one sample user being part or all of the at least one user; and generating, for each of the at least one sample user, training data of the item recommendation model basedon an order of operation of the item operated by the sample user and a second representation vector of the item operated by the sample user, and a first representation vector of the sample user; training the item recommendation model by using the training data. The present application can better describe the user's interest preference, improve the effectiveness of the model, and improve the accuracy of project recommendation using the model.

Owner:GUOXIN YOUE DATA CO LTD

Biquad digital filter operating at maximum efficiency

ActiveUS7159002B2Easily incorporated into audio processing circuitryDigital technique networkDigital data processing detailsIir filteringOrder of operations

An architecture for a biquad (70), second-order infinite impulse response (IIR) digital filter, that is capable of operating at maximum efficiency, is disclosed. The biquad (70) includes coefficient memory (50) and data memory (52), along with control circuitry (53) that loads values from these memories (50, 52) into a coefficient register (52) and a data register (54), respectively. A multiplier (55) multiplies the values in the coefficient register (52) and data register (54), with the resulting product being stored in a product register (58). An accumulator (59) adds successive product results to derive a new output value in each instance of the IIR filter. A shadow register (60) temporarily stores the output of the accumulator (59) from a previous instance, permitting this output to be stored in the data memory (52) at a later time in the sequence. This permits the order of operations in the second and successive biquads to be altered so that each successive biquad instance can start well before the previous result is derived; as a result, the multiplier (55) is fed with values each cycle, enabling maximum efficiency operation.

Owner:TEXAS INSTR INC

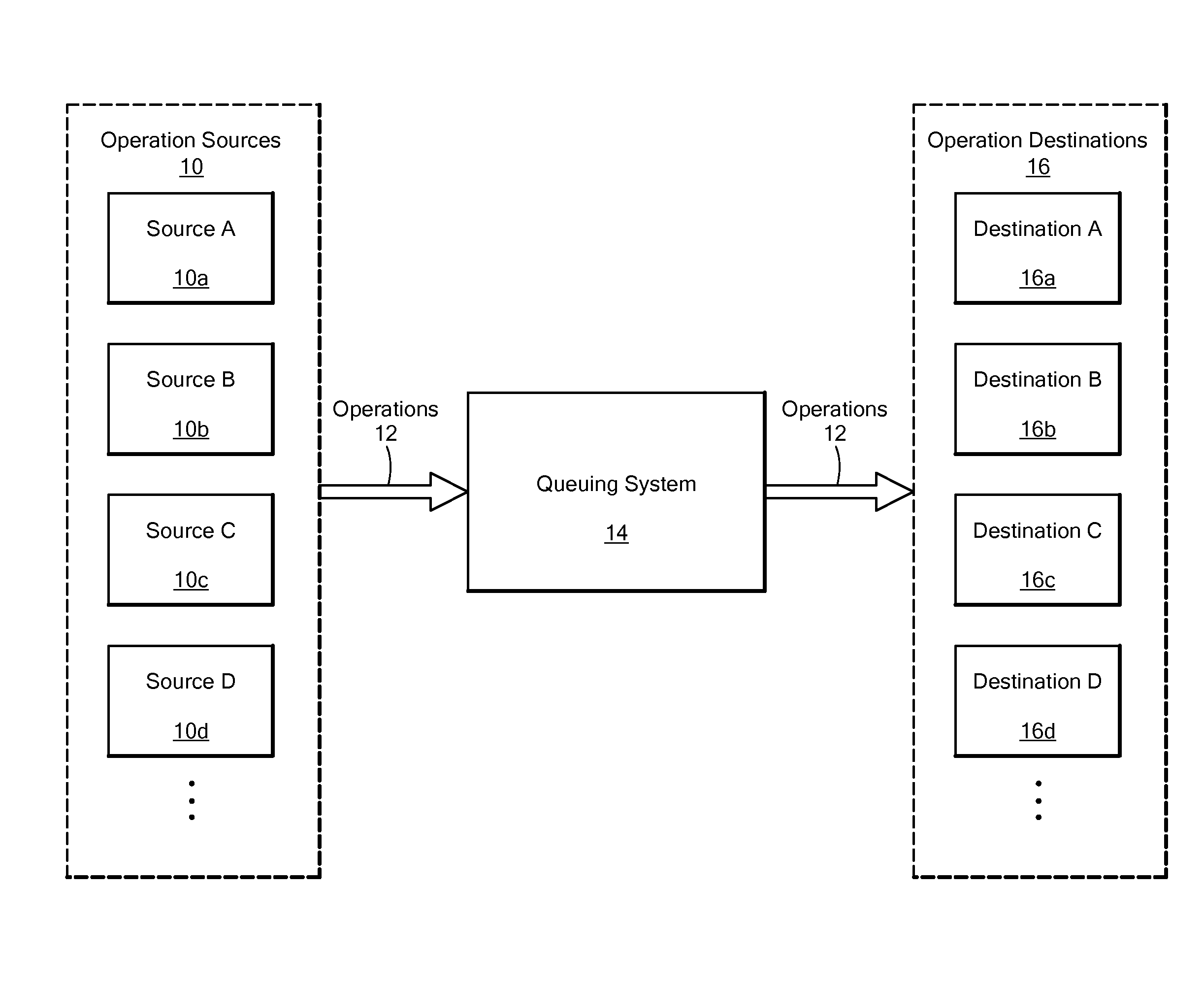

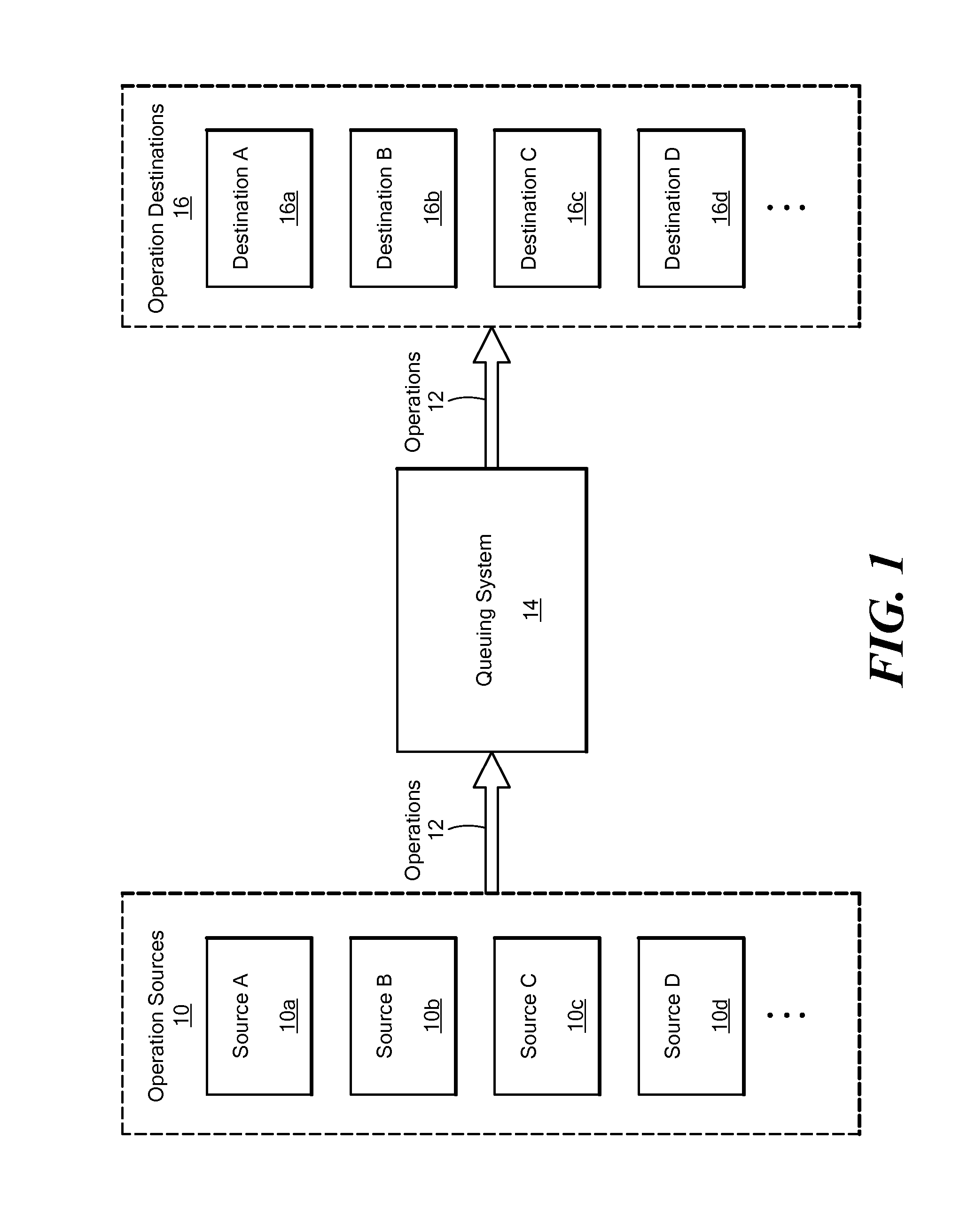

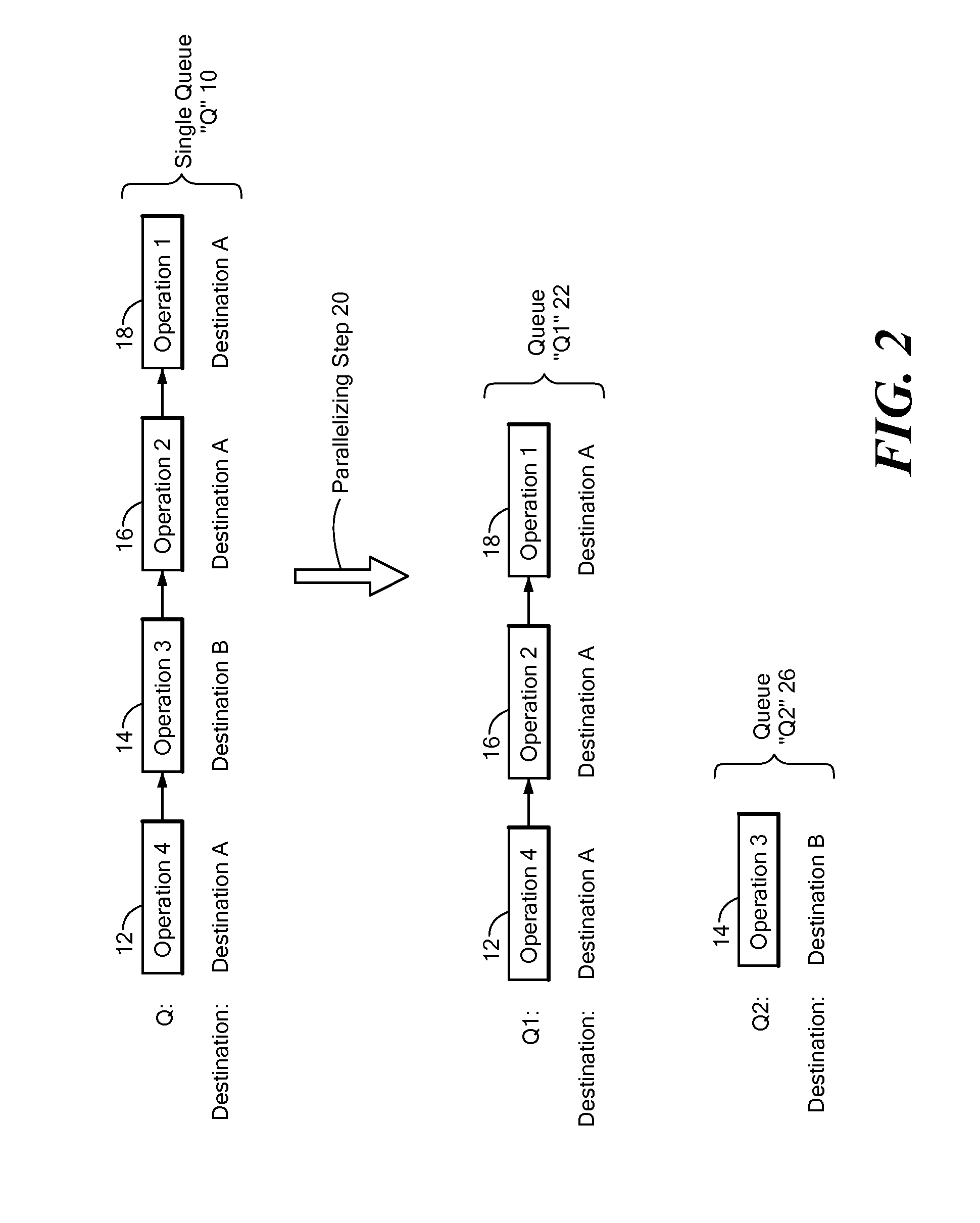

Method and system for dynamic queue splitting for maximizing throughput of queue based operations while maintaining per-destination order of operations

InactiveUS20080123671A1Reduce continuityImprove parallelismData switching by path configurationOrder of operationsBelow threshold level

A system for providing dynamic queue splitting to maximize throughput of queue entry processing while maintaining the order of queued operations on a per-destination basis. Multiple queues are dynamically created by splitting heavily loaded queues in two. As queues become dormant, they are re-combined. Queue splitting is initiated in response to a trigger condition, such as a queue exceeding a threshold length. When multiple queues are used, the queue in which to place a given operation is determined based on the destination for that operation. Each queue in the queue tree created by the disclosed system can store entries containing operations for multiple destinations, but the operations for a given destination are all always stored within the same queue. The queue into which an operation is to be stored may be determined as a function of the name of the operation destination. Just as a single queue may be split into two queues, if one of the two queues starts backing up, the disclosed system may further split that queue into two. Thus each queue in the queue tree may be split into two new queues if its performance falls below a threshold level. Successively more bits from a function applied to destination names for operations may be used to determine specific queues into which operations should be placed as the depth of the queue tree increases.

Owner:IBM CORP

System and method for calculation using vertical parentheses

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

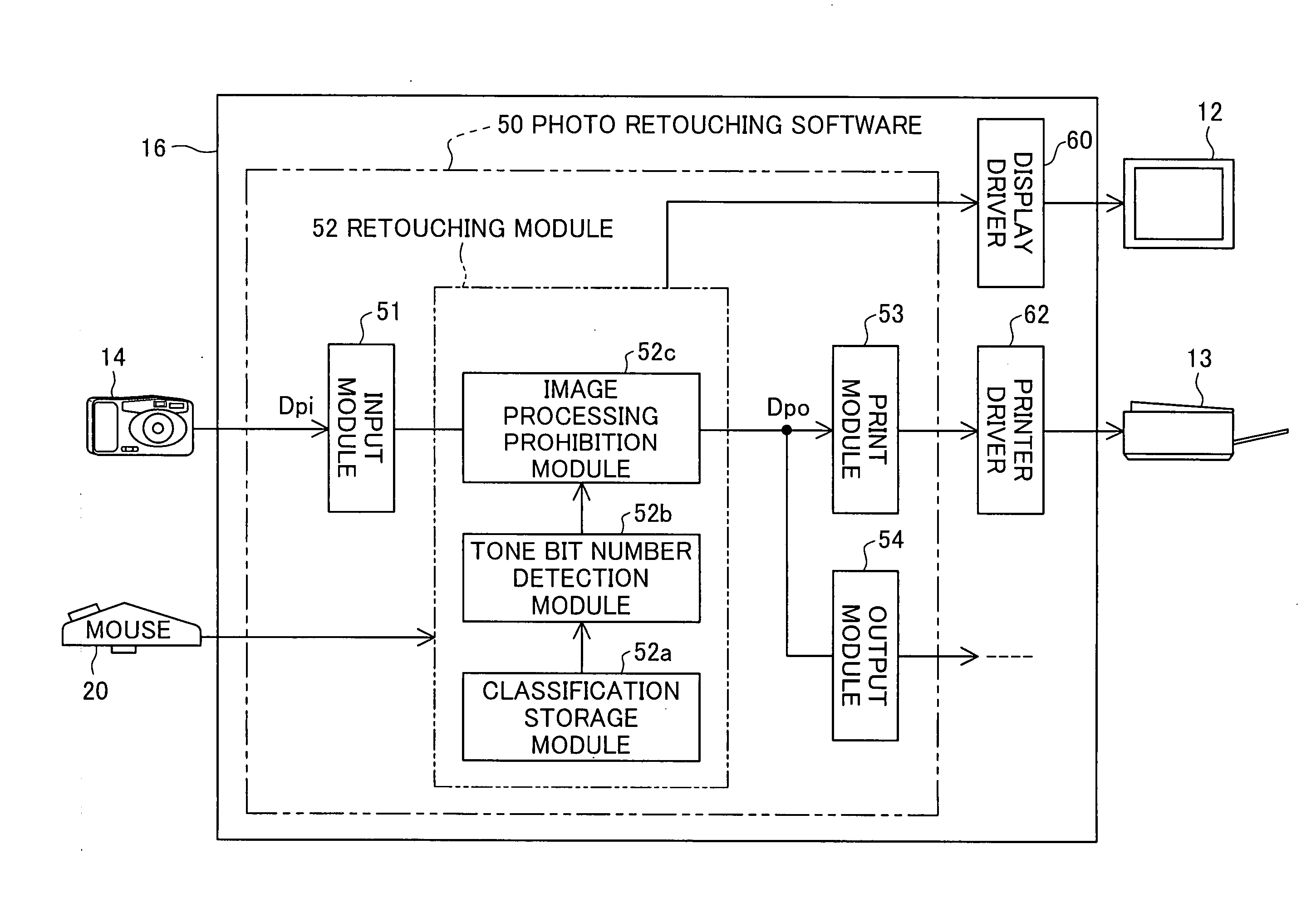

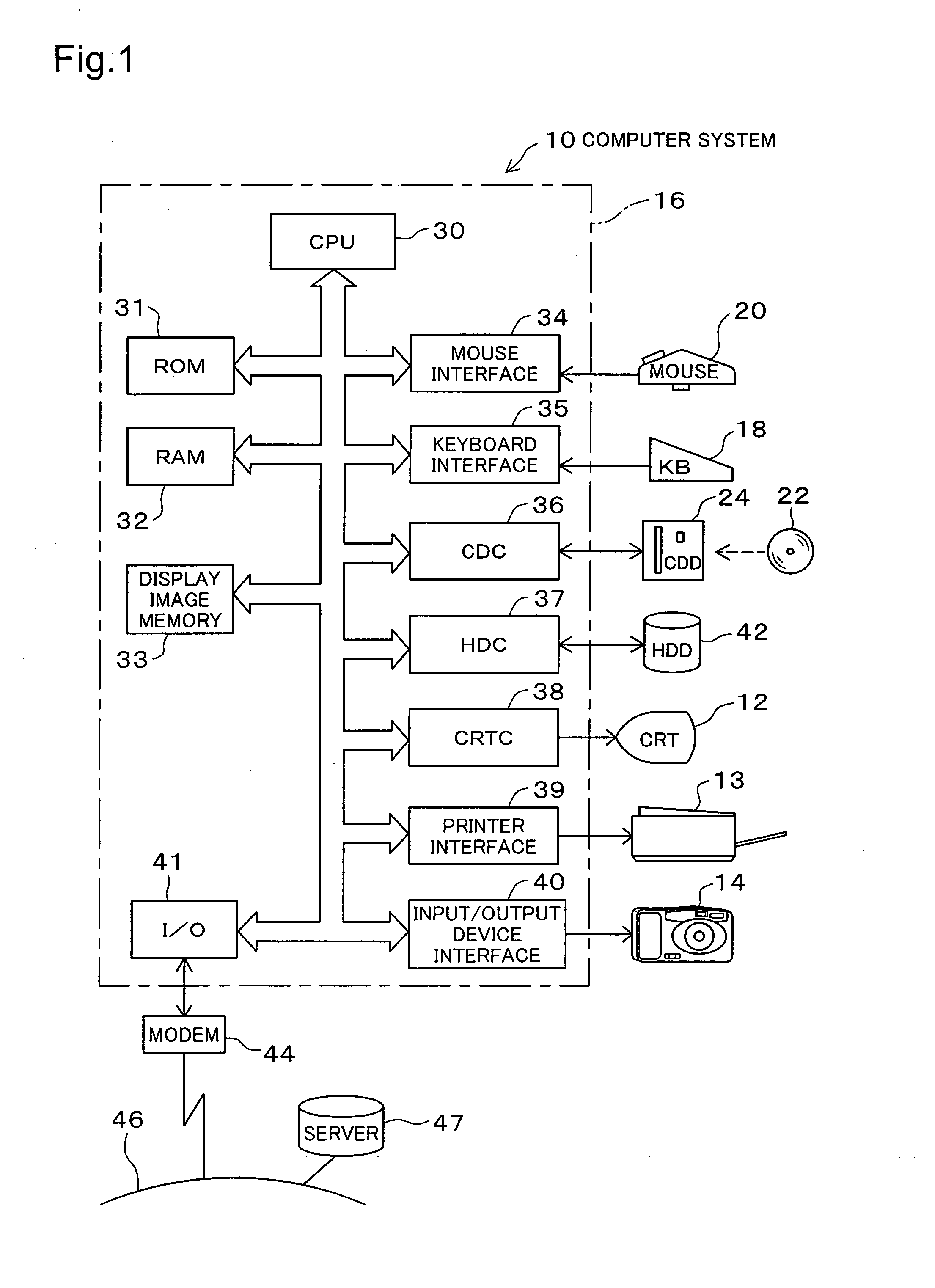

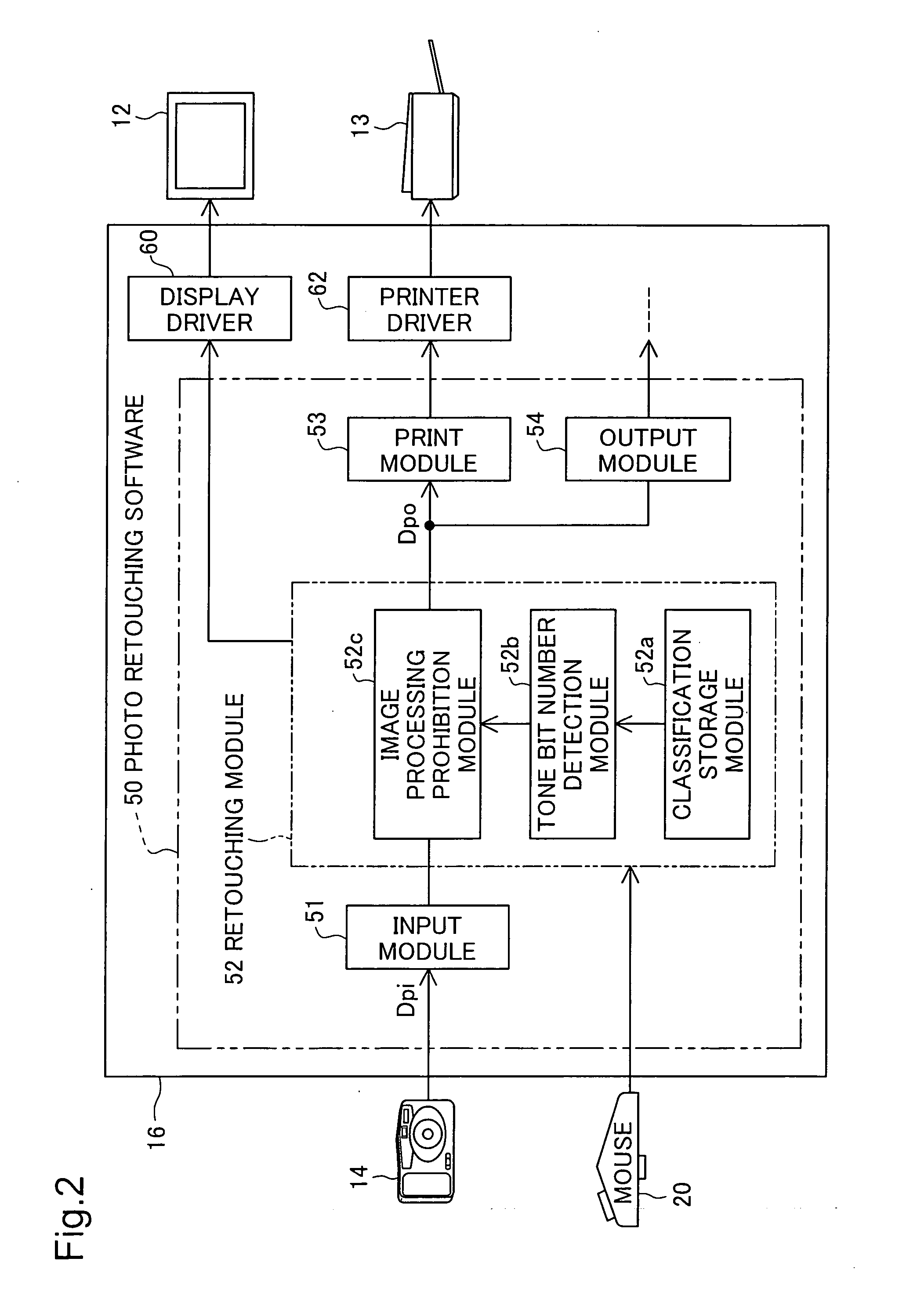

Image processing apparatus, image processing method, and computer program product

InactiveUS20050219578A1Prevent potential deterioration of picture qualityDigitally marking record carriersDigital computer details8-bit colorLight irradiation

In a computer system of the invention, a menu button BT2 ‘Retouching Pre-Process’ clicked to activate a retouching pre-process and a menu button BT3 ‘Retouching Post-Process’ clicked to activate a retouching post-process are vertically downward aligned in a processing menu window MN corresponding to an order of operation procedure. The retouching pre-process includes 16-bit color support image processing options, for example, ‘brightness adjustment’ and ‘contrast adjustment’. The retouching post-process includes 8-bit color support image processing options, for example, ‘unsharp mask’ and ‘light irradiation’. When the operator clicks the menu button BT2 ‘Retouching Pre-process’ to execute any image processing option included in the retouching pre-process after execution of any image processing option included in the retouching post-process with regard to input image data, the computer system opens a message box to notify the operator of prohibition of a return to the retouching pre-process. The computer system thus effectively prevents execution of any image processing option included in the retouching pre-process after execution of any image processing option included in the retouching post-process. This arrangement desirably prevents potential deterioration of the picture quality in a retouching process that includes both the 16-bit color support image processing and the 8-bit color support image processing.

Owner:SEIKO EPSON CORP

Criteria builder for query builder

ActiveUS8312038B2Digital data information retrievalDigital data processing detailsDrag and dropOrder of operations

Systems and methods are provided that programmatically provide a user interface for forming a query, comprising. A query builder displays a first row of query criteria, a second row of query criteria, the second row being logically connected to the first row by a first Boolean connector, and a third row of query criteria, the third row being logically connected to the second row by a second Boolean connector. In response to a user drag-and-drop operation, the query builder nests the third row of query criteria in the second row of query criteria. Thus, a drag-and-drop operation obviates the need for cumbersome groups of parentheses when defining the order of operation of the query.

Owner:ORACLE INT CORP

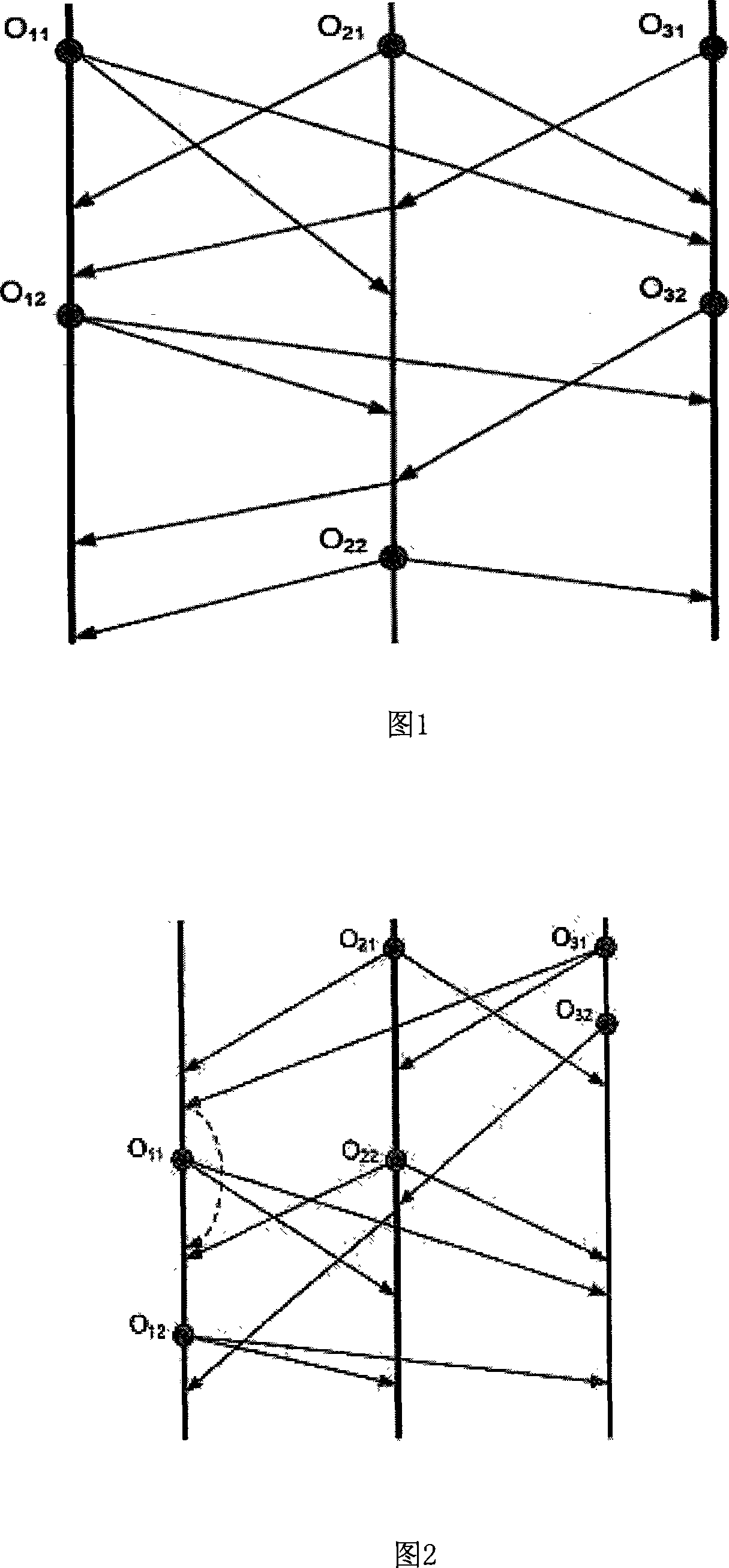

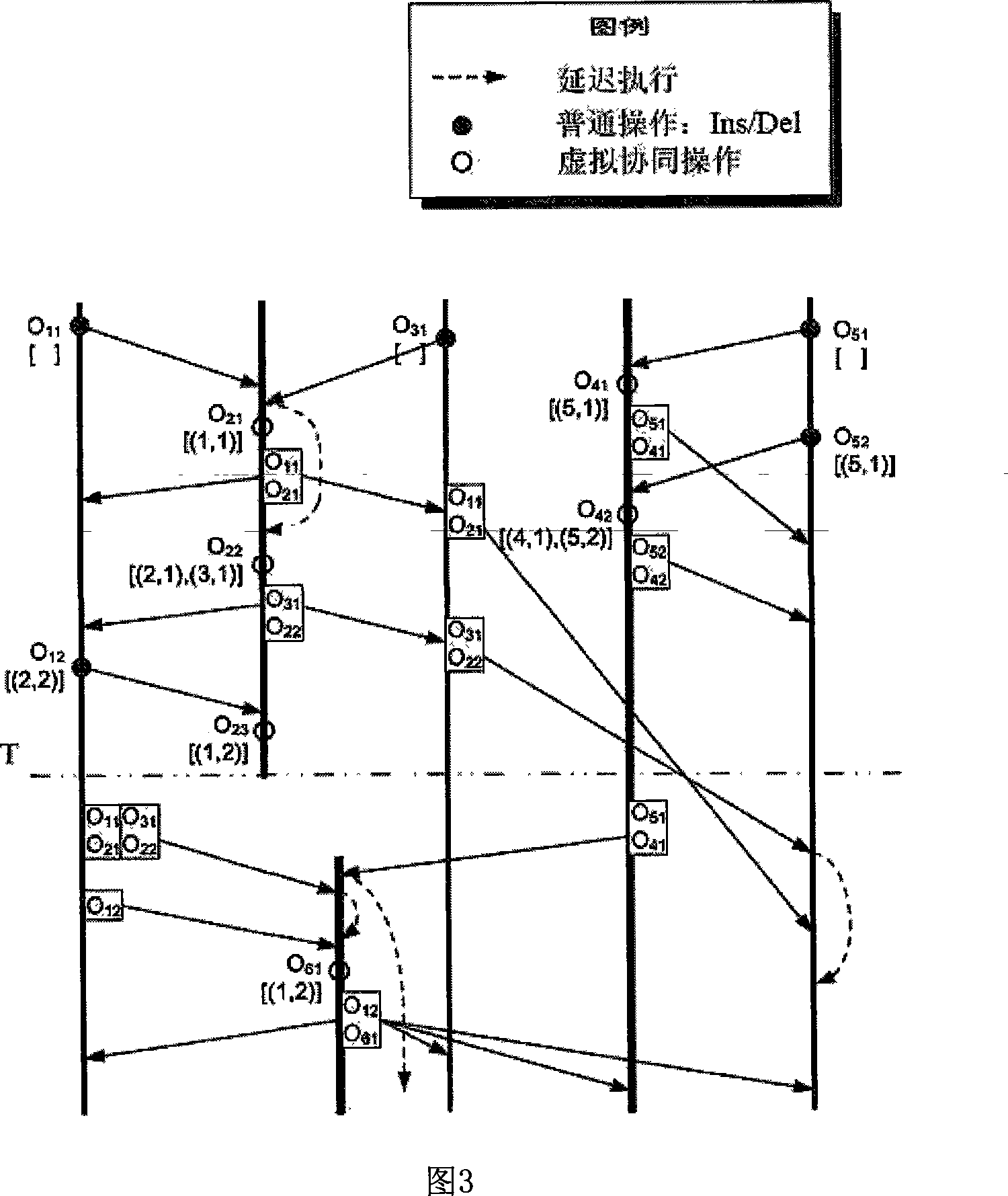

Cooperation interaction optimizing method under vast scale cooperative surroundings

InactiveCN101119365ATransmissionSpecial data processing applicationsOrder of operationsTeleoperation

The invention belongs to the technical field of teamwork supported by computers; more specifically discloses a teamwork exchanging and optimizing method under large scaled teamwork environments. The method adopts a preferential method of Leader station to set up a real time group editing teamwork exchanging module, and comprises the strategies adjustment at the teamwork exchanging mode between consumers and the Leader preferential teamwork exchanging module; through limiting the simultaneous order of the long distance operation at all teamwork stations to effectively control the length of the arrow time stamp of the direct cause and result orders of operation under high concurrent large scaled teamwork environments. The method also comprises that, through reasonably zoning on the real time group editing dialogues according to the network statuses between teamwork stations and suitably introducing some simulated teamwork stations to work with the exchanging module, the invention can further maintain relatively high teamwork sensing performance in consumers. The invention is beneficial for solving the cause and result concurrent inspecting problem of the real time editing activities under high concurrent large scaled teamwork situations, and greatly improving the performance of group editing activities.

Owner:FUDAN UNIV

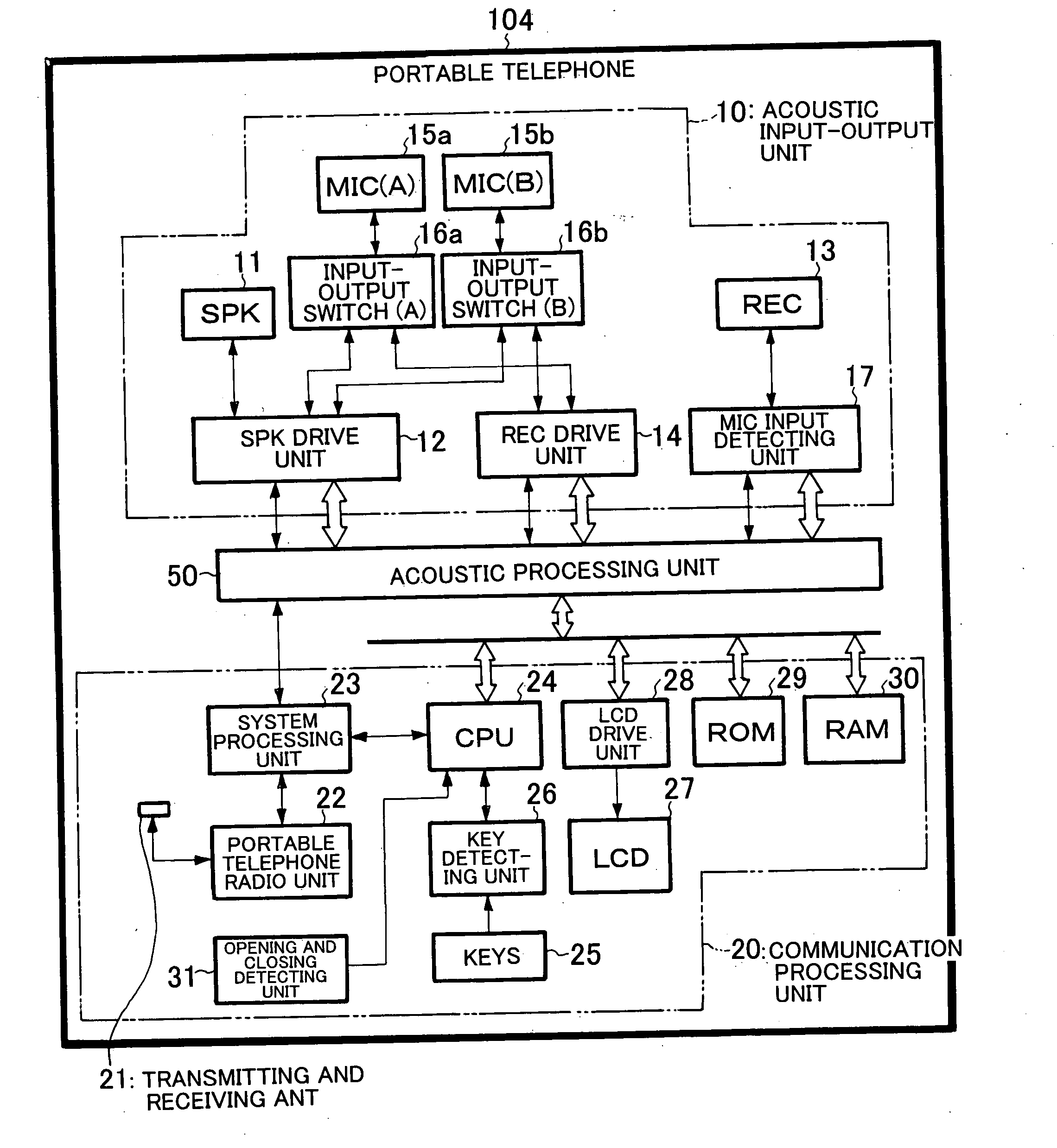

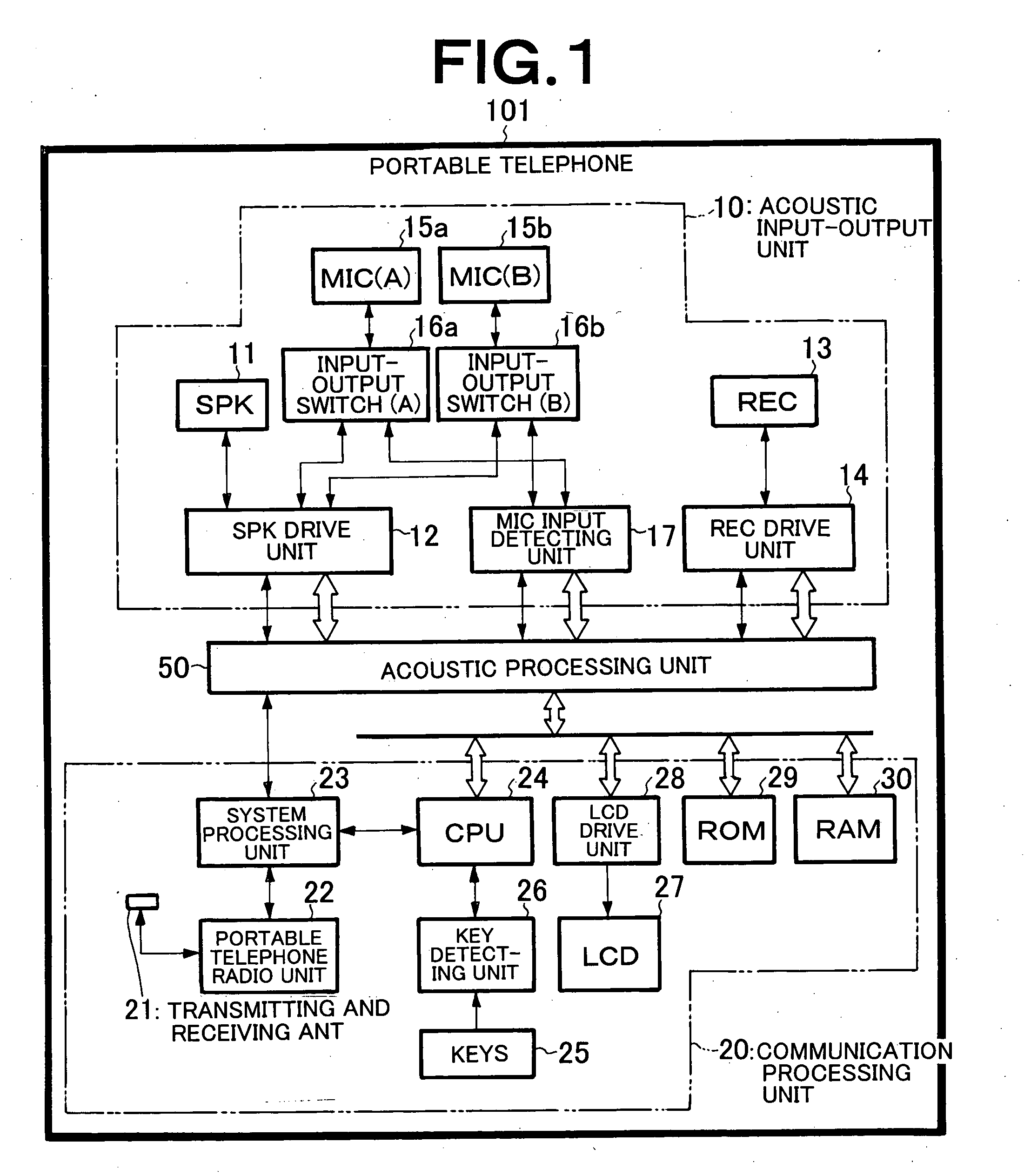

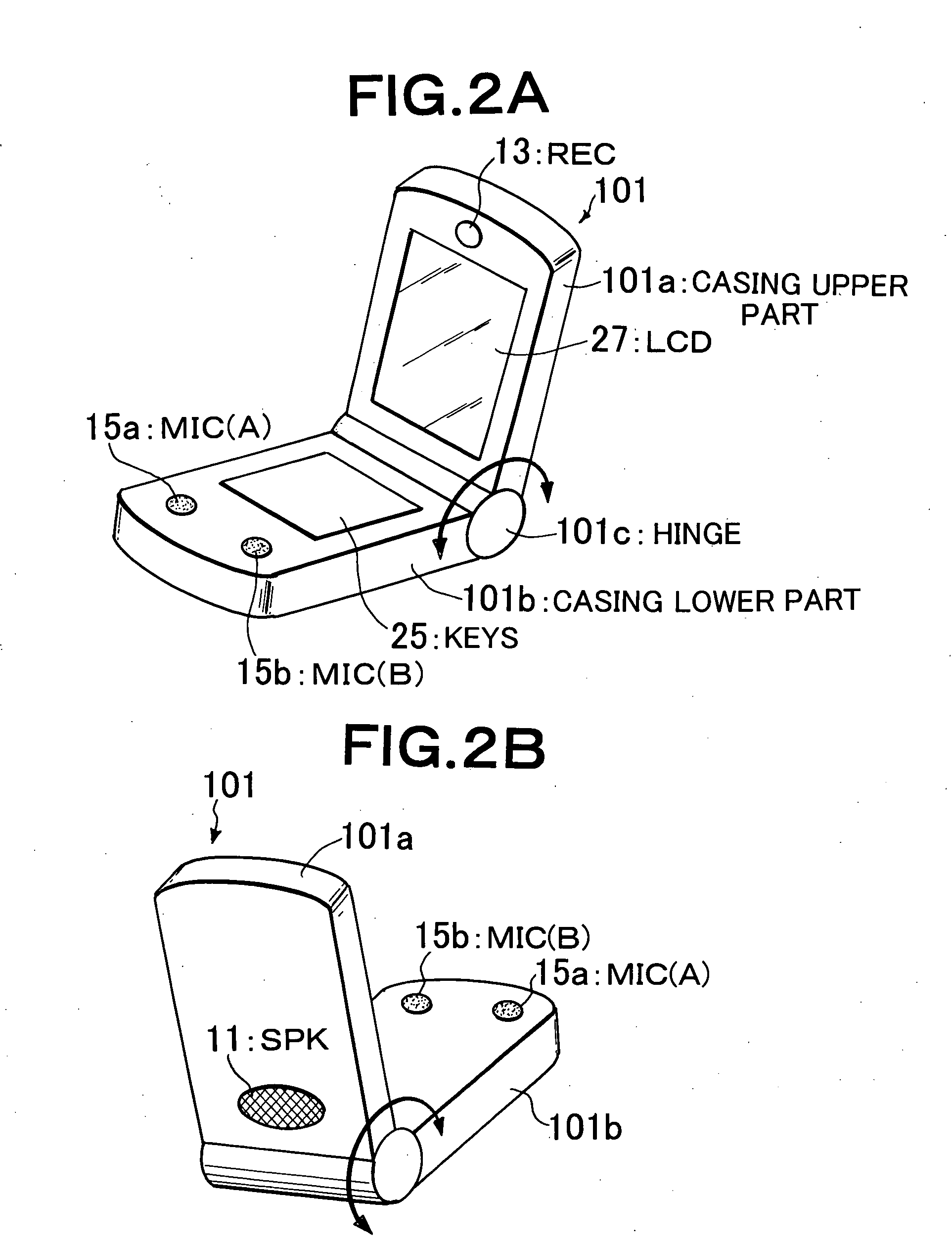

Portable communication terminal

InactiveUS20050181820A1Smoothly executing acoustic processingImpedence networksSubstation speech amplifiersOrder of operationsOutput device

Acoustic input and output devices are made to operate properly according to communication processing. A portable communication terminal includes an acoustic input-output unit including a plurality of acoustic input elements to conduct acoustic inputting and acoustic output elements to conduct acoustic outputting, a communication processing unit which selectively executes mutually different communication processes using at least one of the elements included in the acoustic input-output unit, and an acoustic processing unit which determines an order of operation of the acoustic input-output unit to be conducted by the elements according to a communication process executed by the communication processing unit and gives the determined operation order to the acoustic input-output unit.

Owner:NEC CORP

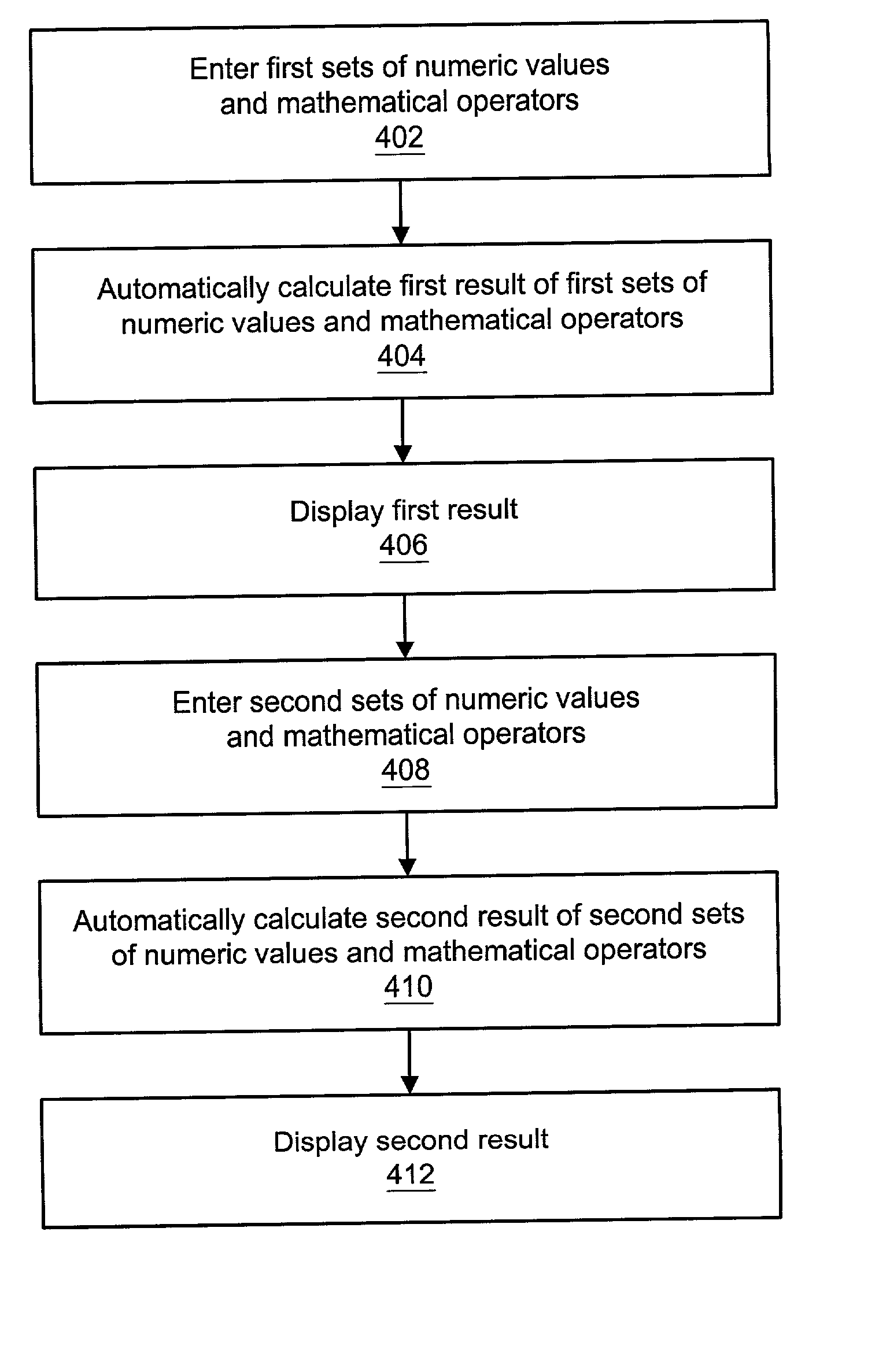

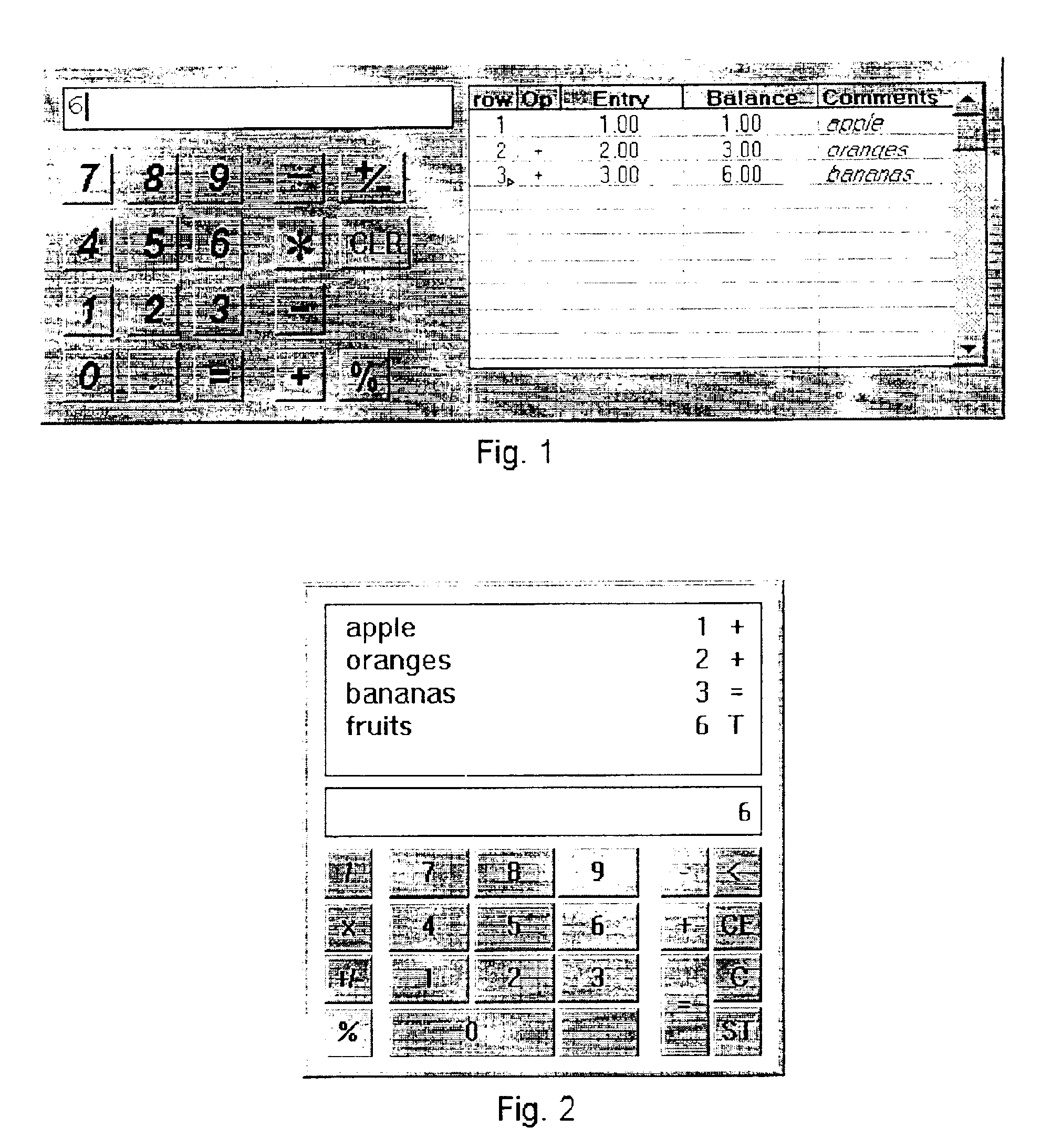

System and method for calculation using a subtotal function

InactiveUS20040205676A1Text processingSpecial data processing applicationsElectronic formOrder of operations

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:UMAX DATA SYST

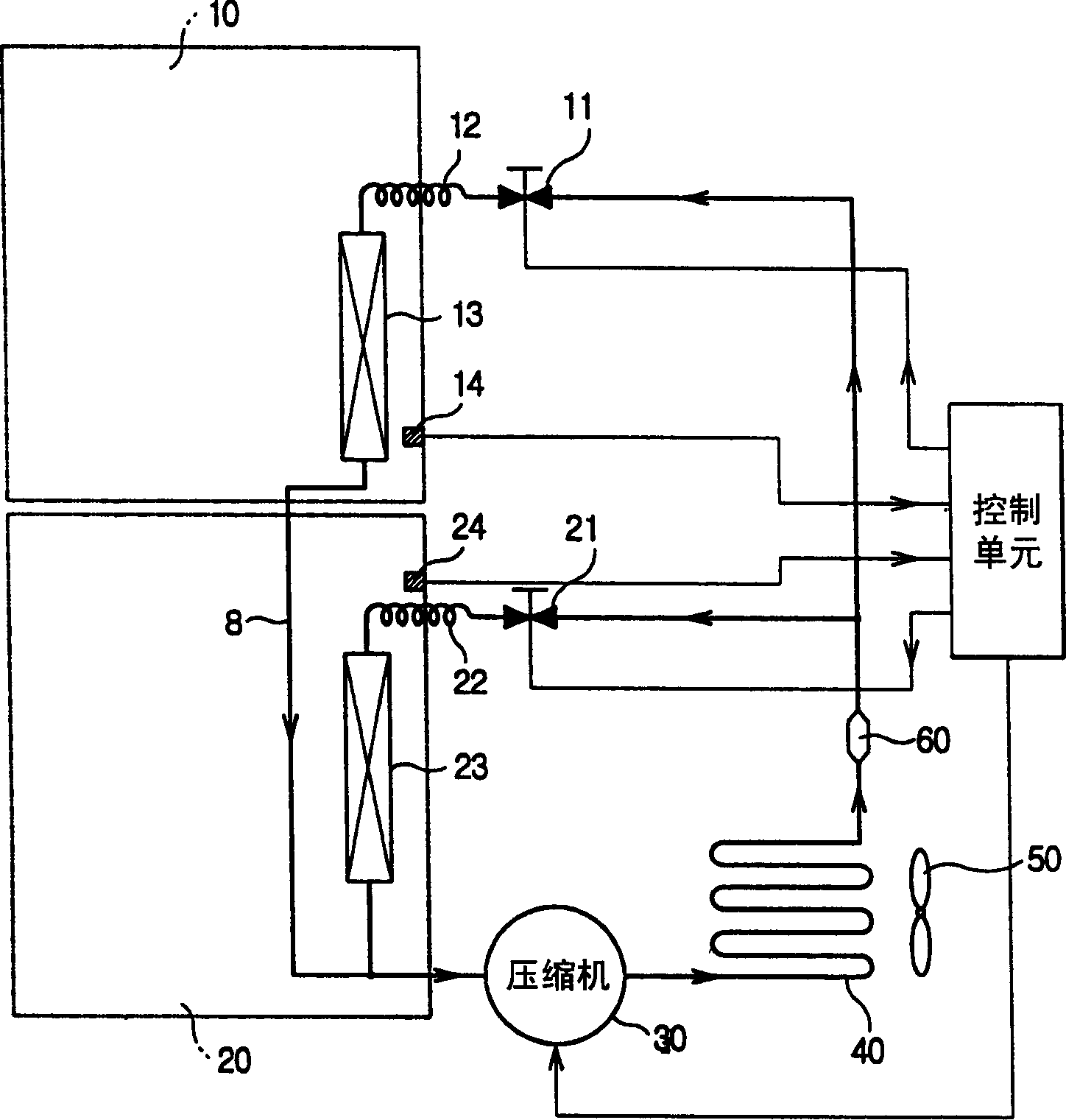

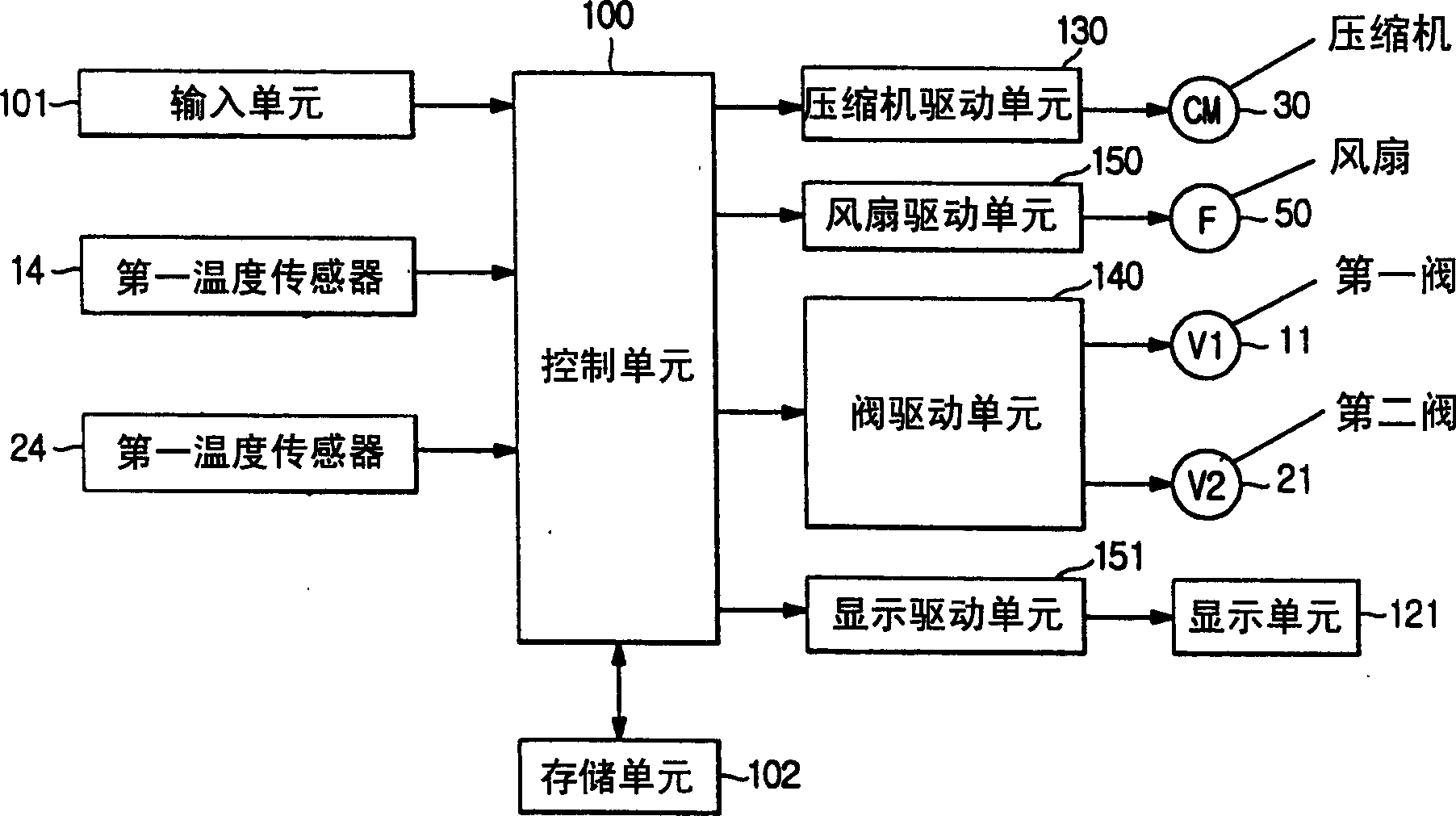

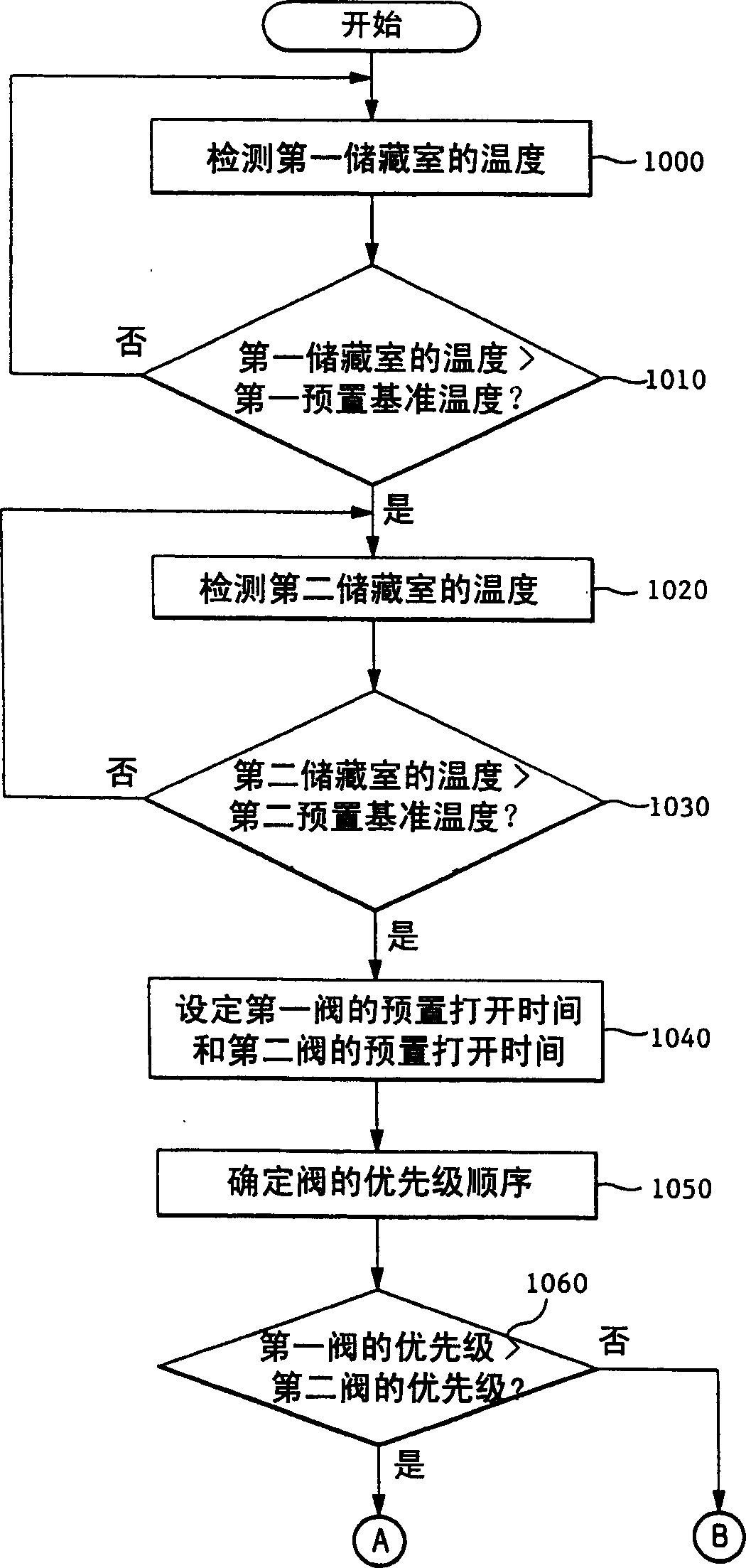

Control method for multi-chamber type kimchi refrigerator

A method of controlling a multi-compartment type kimchi refrigerator having a plurality of evaporators which are mounted in respective storage compartments to refrigerate the storage compartments, a compressor which supplies the evaporators with refrigerant, and valves which are mounted in inlet sides of the evaporators, respectively, to be selectively opened and closed on the basis of temperatures of the storage compartments. The method includes selectively opening or closing the valves in priority order of operations of the valves in response to a signal to supply the refrigerant to two or more of the evaporators.

Owner:SAMSUNG ELECTRONICS CO LTD

System and method for calculation using multi-field columns with modifiable field order

InactiveUS20020143830A1Text processingSpecial data processing applicationsOrder of operationsElectronic form

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

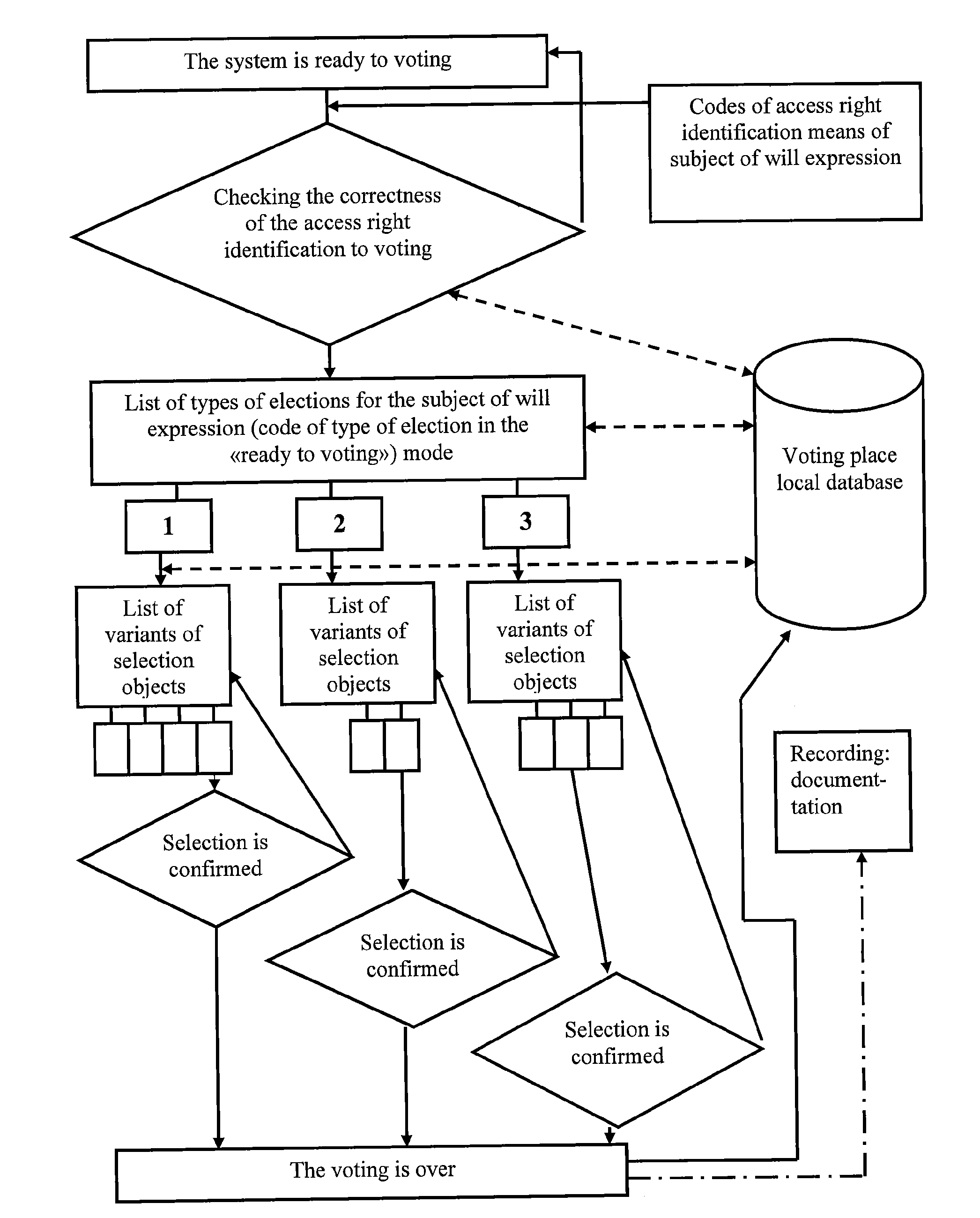

Method and system for preparation and implementation of electronic voting

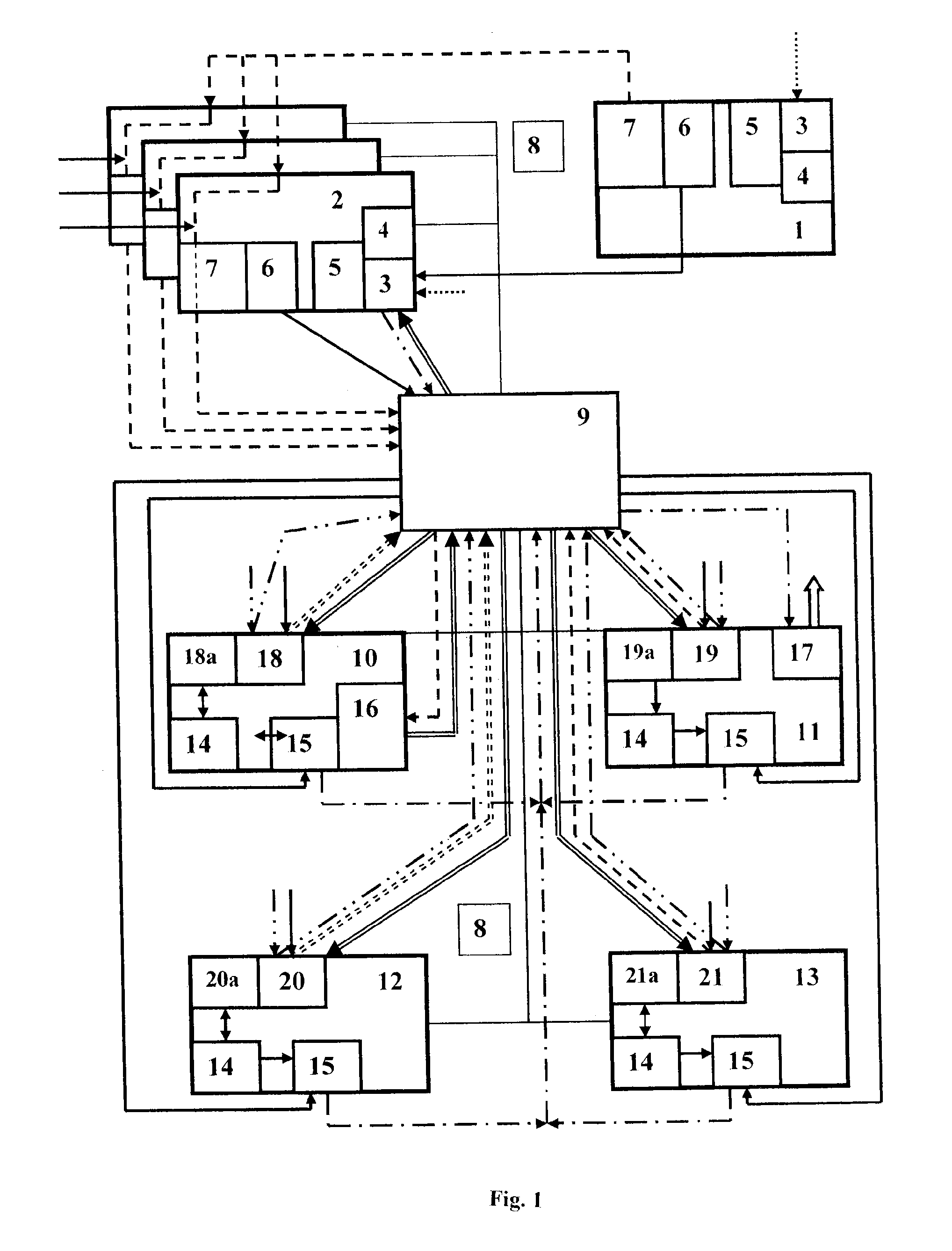

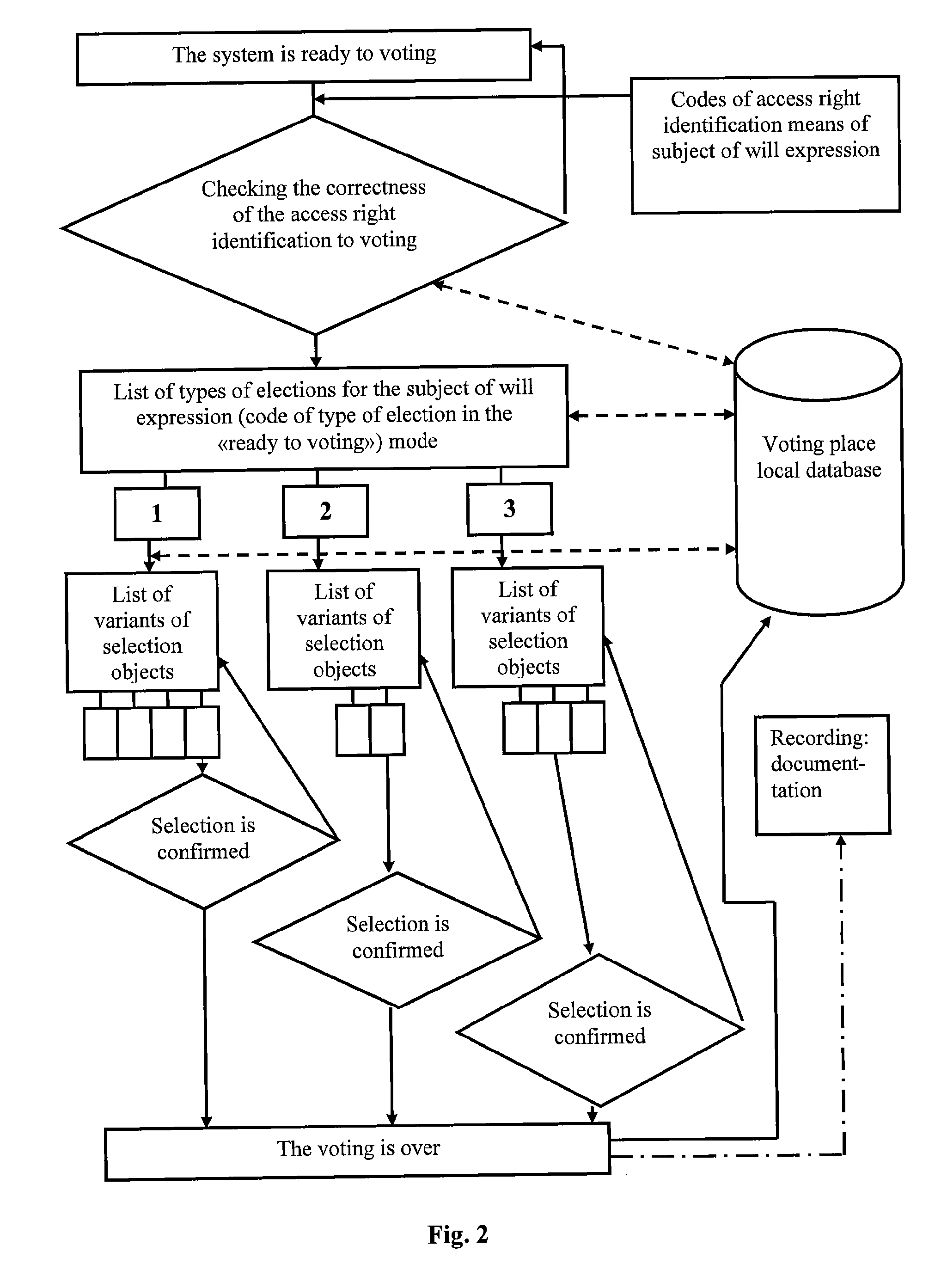

InactiveUS20090200375A1Simple processAutomatically performVoting apparatusCo-operative working arrangementsDocumentation procedureOrder of operations

The invention discloses a method for preparation and implementation of electronic voting by means of an automated system according to the invention comprising a control terminal, an official person workstation at a voting precinct and terminals of voting places used for input, saving, display and output of information, creation of local databases in a dynamic mode, said databases comprising voting data blocks, data blocks of modes of functioning of the built-in terminals and devices including a voting device, as well an condition for access to the voting device, display devices and to devices for documenting the persons whose access right is identified by comparing their access codes sent to the automated system terminals with the access codes stored in a local memory. The system automatically tracks the performance of the devices, switches them according to the installed order of operations, while providing an access according to the established rules of operations, provides automatic processing of the voting process and the voting results, and forms protocols on the voting summary by an approved form in an authorized access mode. The documentation of the voting results and protocols is carried out on the same non-volatile carrier.

Owner:FEDERALNY TSENTR INFORMATIZATSII PRI TSENTRALNOY IZBIRATELNOY KOMISSII ROSSIYSKOY FEDERATSII

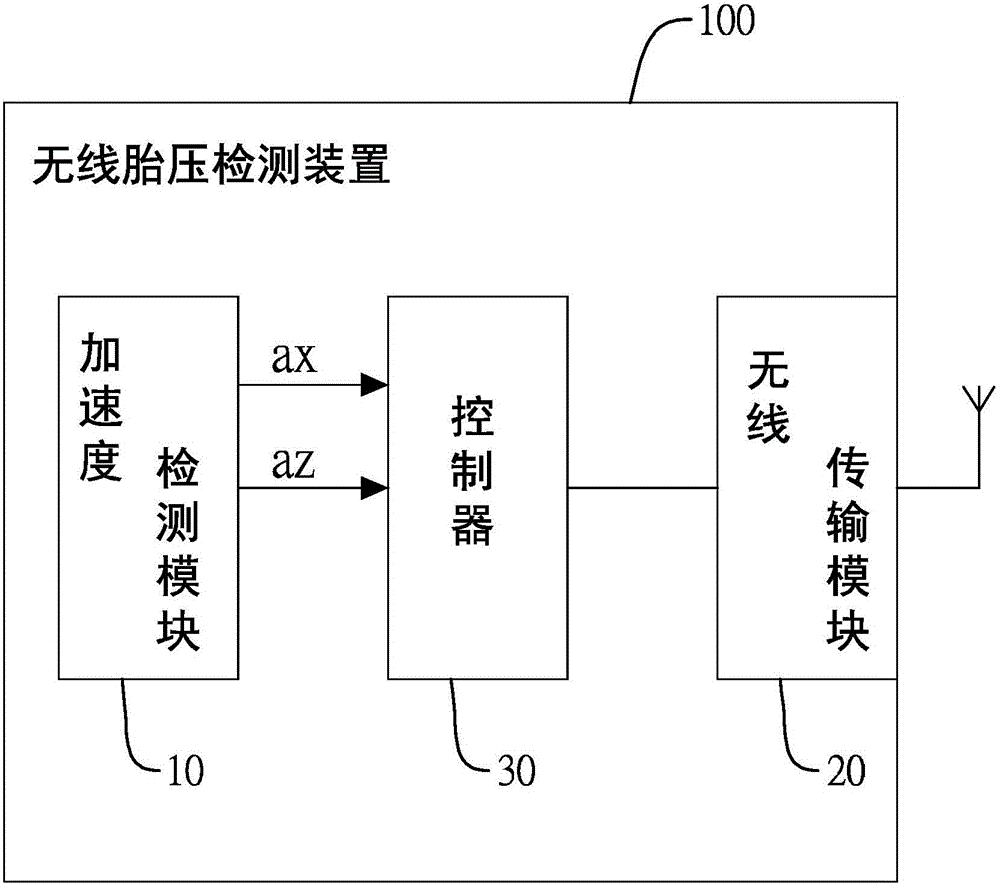

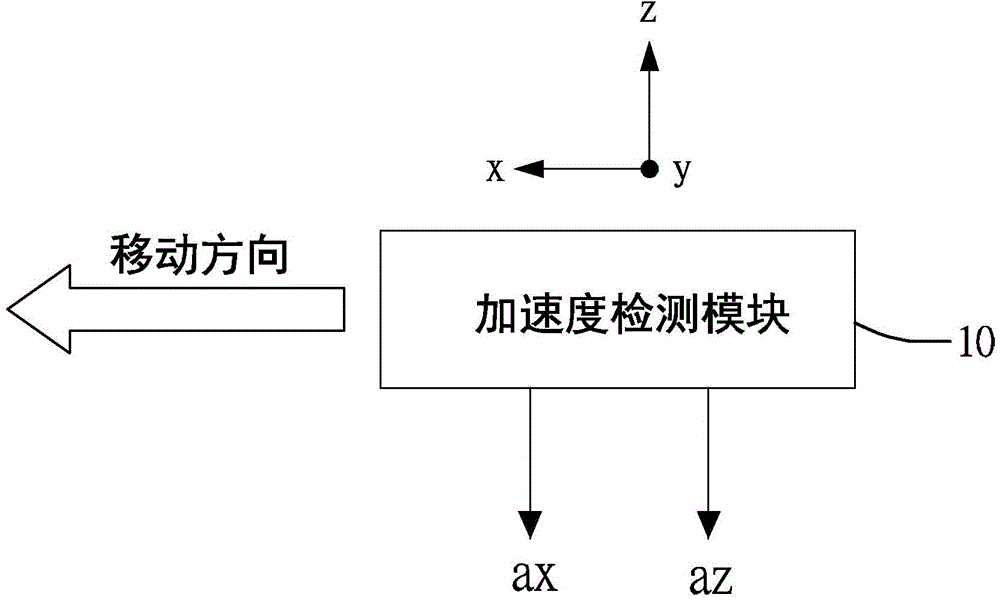

Localizable wireless tire pressure detection device, system and location method thereof

A detection-localizable wireless tire pressure detection device, a system and a location method thereof are disclosed. The method comprises the following steps: receiving a radial acceleration value and a tangential acceleration value of a tire; respectively carrying out calculations between the radial acceleration value and a gravitational acceleration value and between the tangential acceleration value and the gravitational acceleration value so as to respectively obtain a radial vector calculated value and a tangent vector calculated value; judging an operation status according to increases or decreases of the radial vector calculated value and the tangent vector calculated value; judging whether transition of the operation status occurs; and judging location information of the tire according to transition order of operation statuses when transition of the operation status to another operation status is judged.

Owner:ORANGE ELECTRONICS

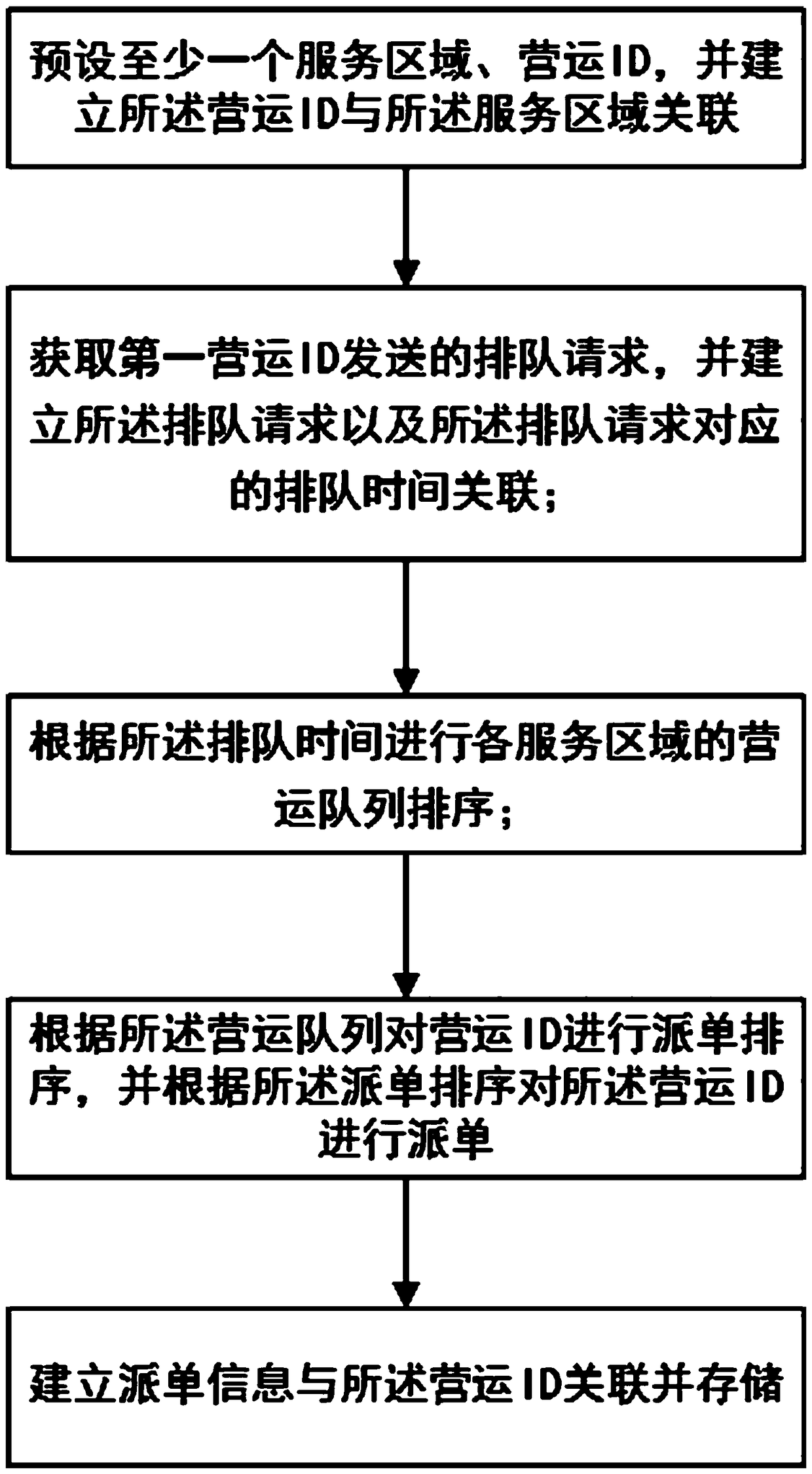

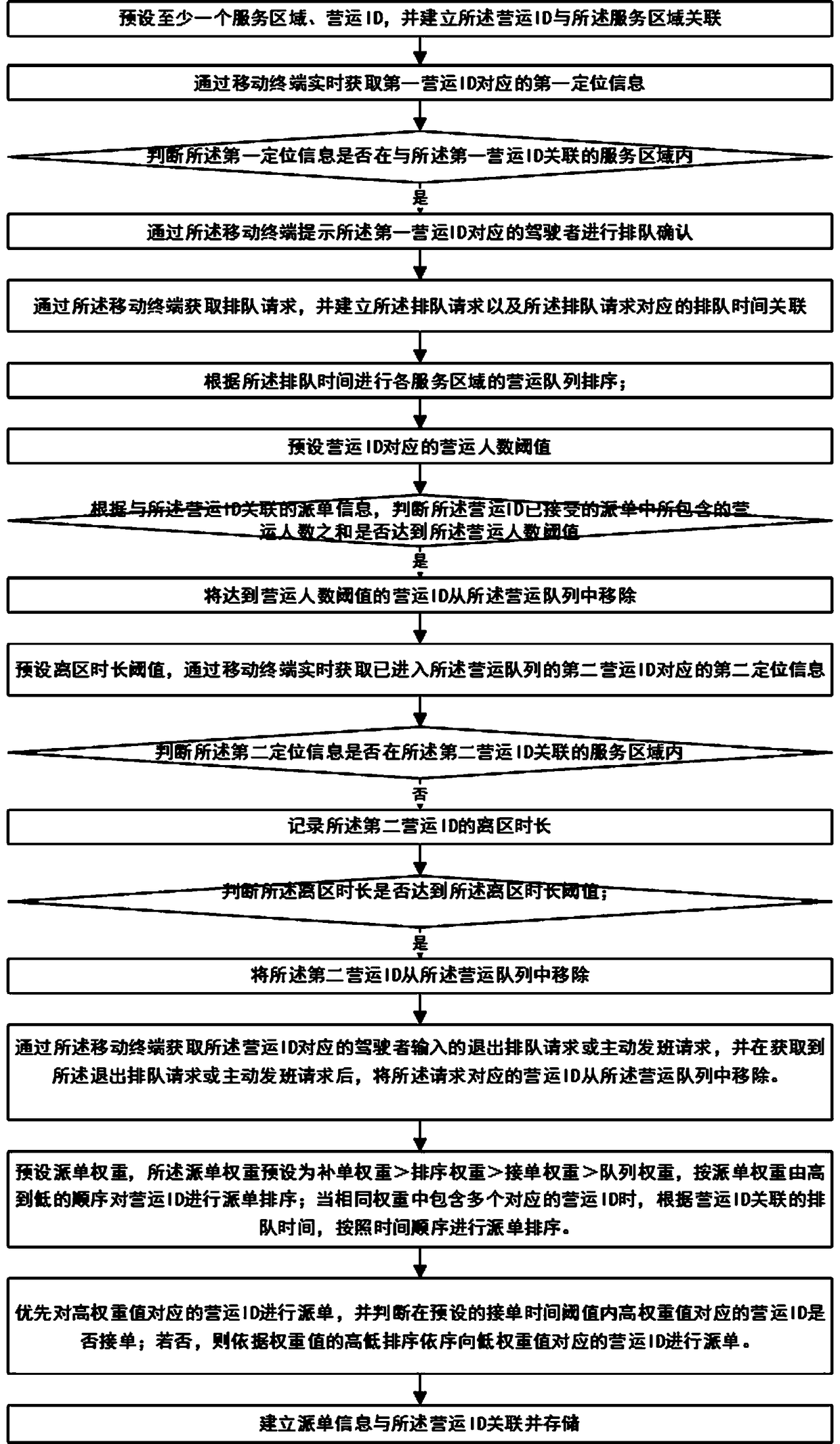

Intercity vehicle queuing dispatching method and medium

The invention discloses an intercity vehicle queuing dispatching method and medium; the method comprises the following steps: presetting at least one service area and operation IDs, and building association between the operation IDs and the service area; obtaining a queuing request sent by a first operation ID, and building association between the queuing request and a queuing time corresponding to the queuing request; ranking operation queues of each service area according to the queuing time; ranking dispatching orders of operation IDs according to the operation queues, dispatching the operation IDs according to the ranked dispatching orders, and building association between the dispatching information and the operation IDs and storing same. The method sets the service areas and operation IDs, manages the operation vehicle service areas so as to prevent packed operation of the operation vehicles, ranks dispatching orders via the operation queues, and reasonably dispatches operation IDs in sequence. The method can effectively manage intercity operation vehicles, and can reasonably distribute resources.

Owner:XIAMEN GNSS DEV & APPL CO LTD

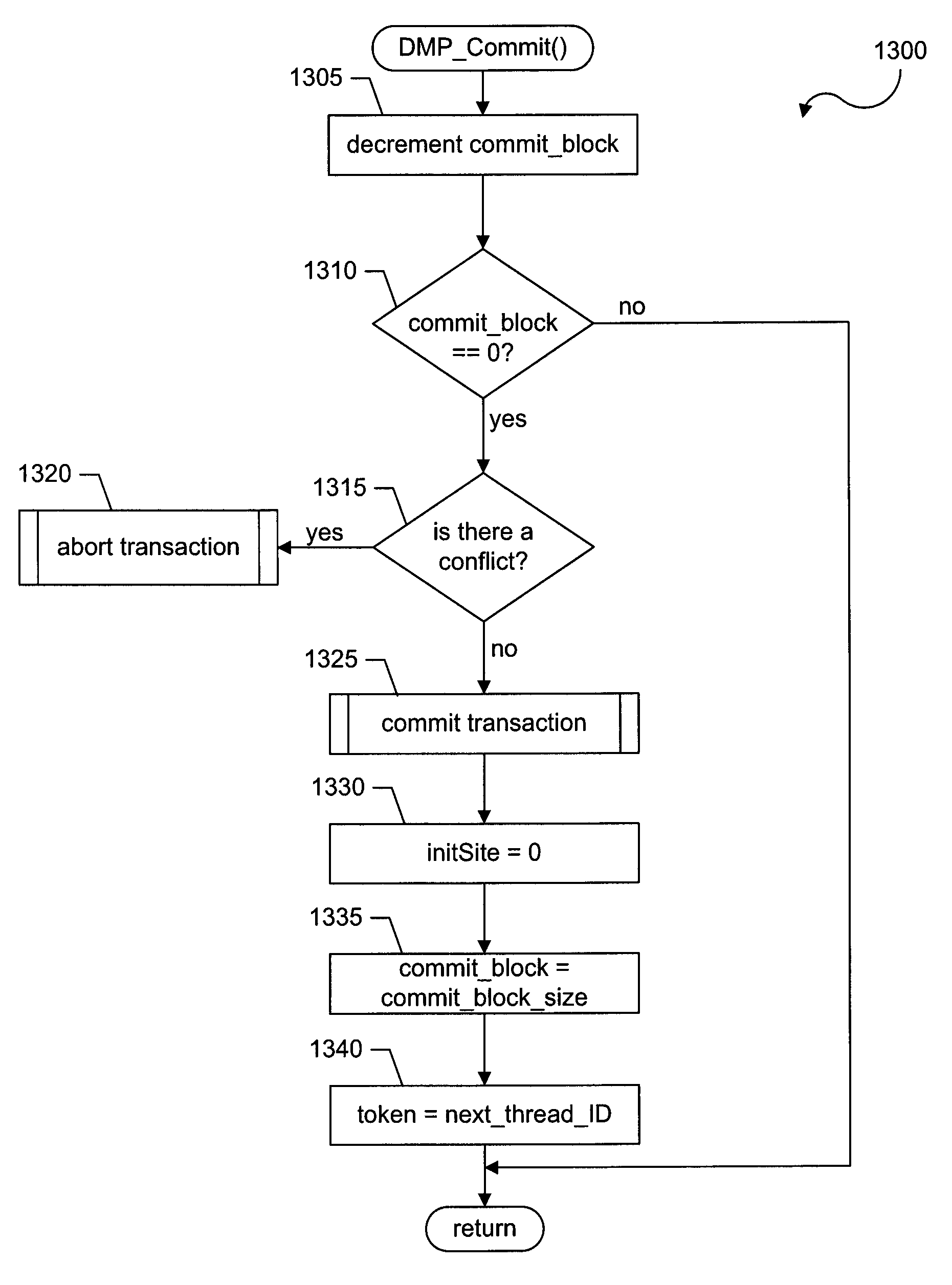

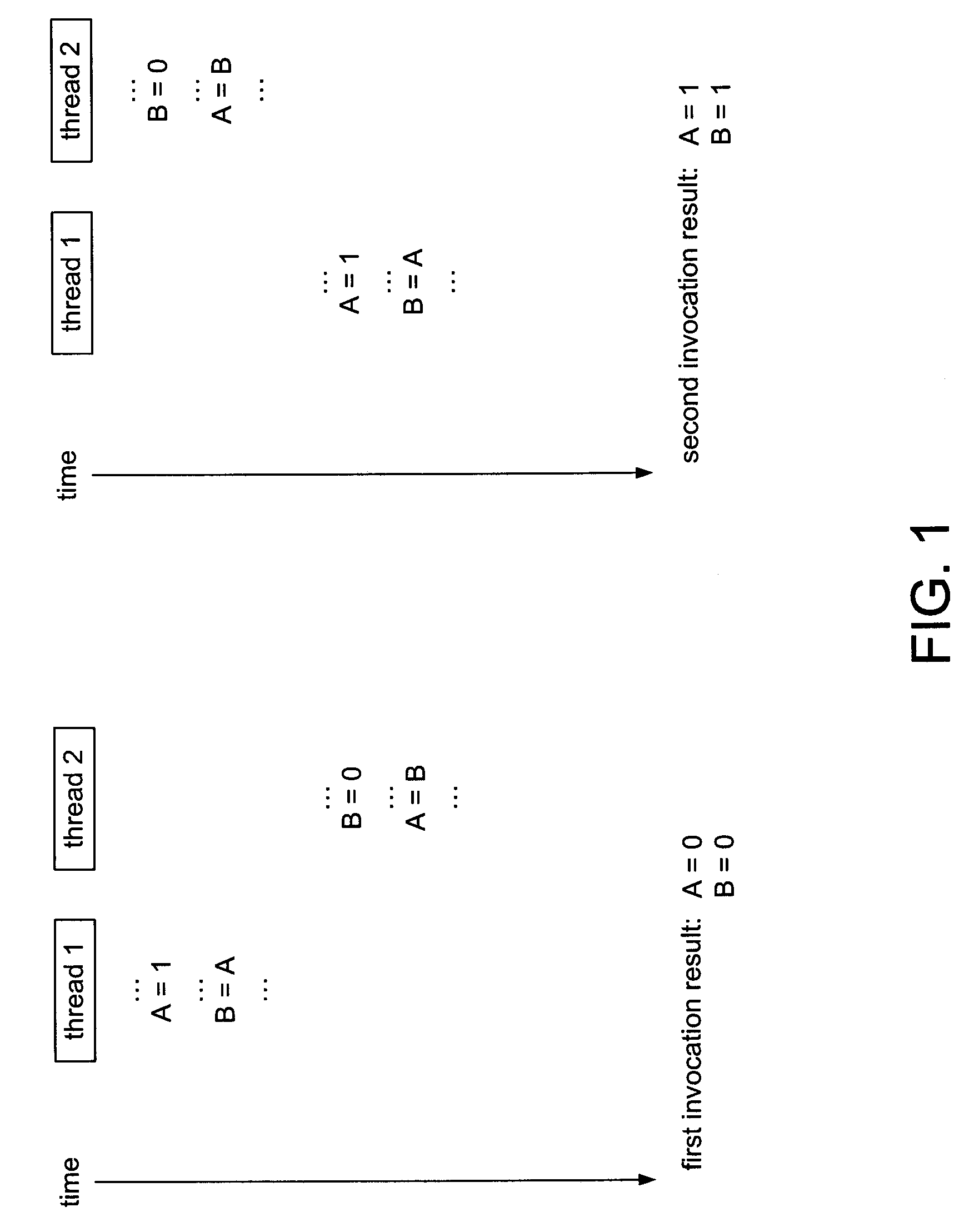

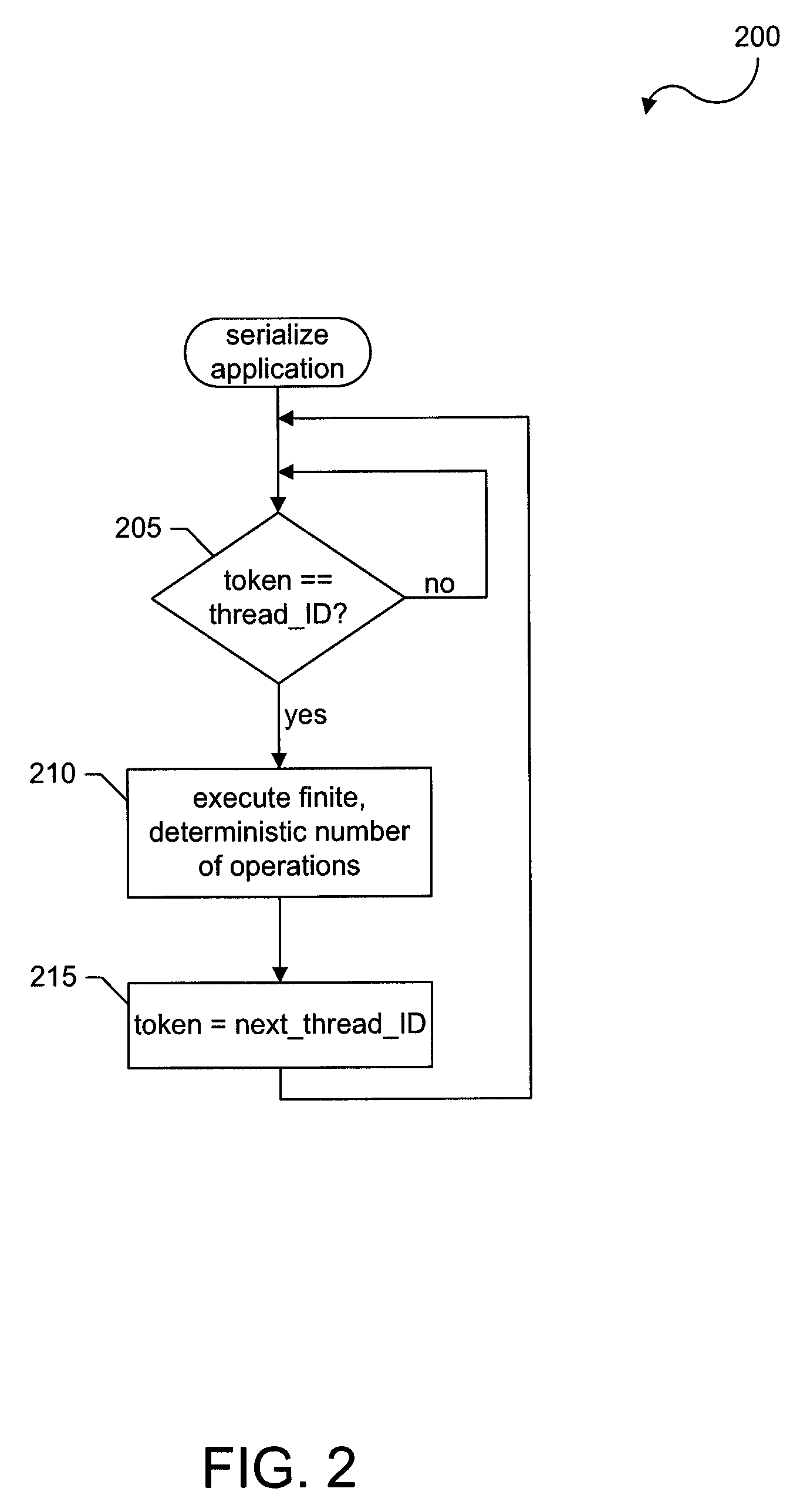

Critical path deterministic execution of multithreaded applications in a transactional memory system

InactiveUS8739163B2Program synchronisationError detection/correctionOrder of operationsCritical path method

A hardware and / or software facility for controlling the order of operations performed by threads of a multithreaded application on a multiprocessing system is provided. The facility may serialize or selectively-serialize execution of the multithreaded application such that, given the same input to the multithreaded application, the multiprocessing system deterministically interleaves operations, thereby producing the same output each time the multithreaded application is executed. The facility divides the execution of the multithreaded application code into two or more quantum specifying a deterministic number of operations, and the facility specifies a deterministic order in which the threads execute the two or more quantum. The deterministic number of operations may be adapted to follow the critical path of the multithreaded application. Specified memory operations may be executed regardless of the deterministic order, such as those accessing provably local data. The facility may provide dynamic bug avoidance and sharing of identified bug information.

Owner:UNIV OF WASHINGTON

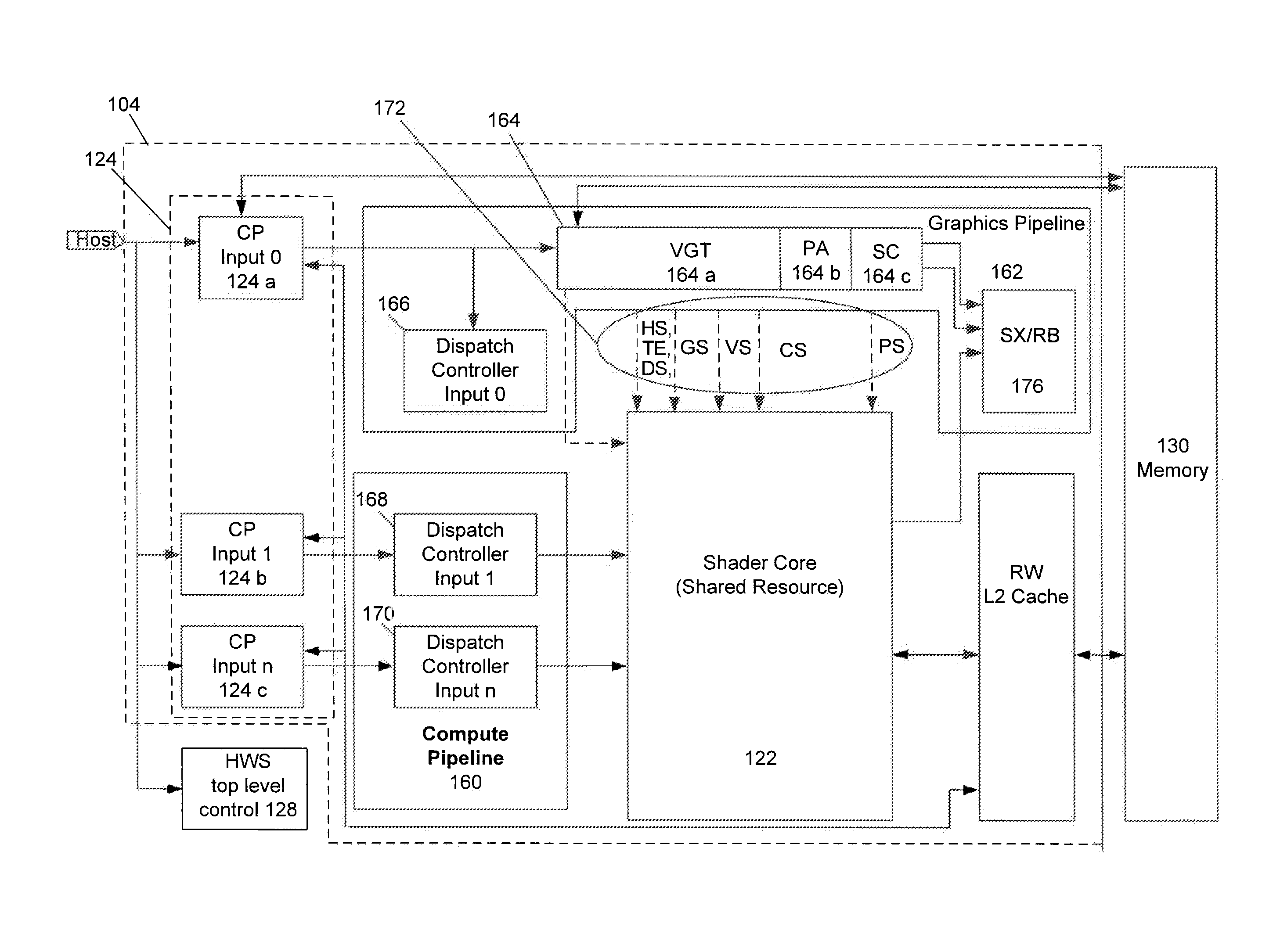

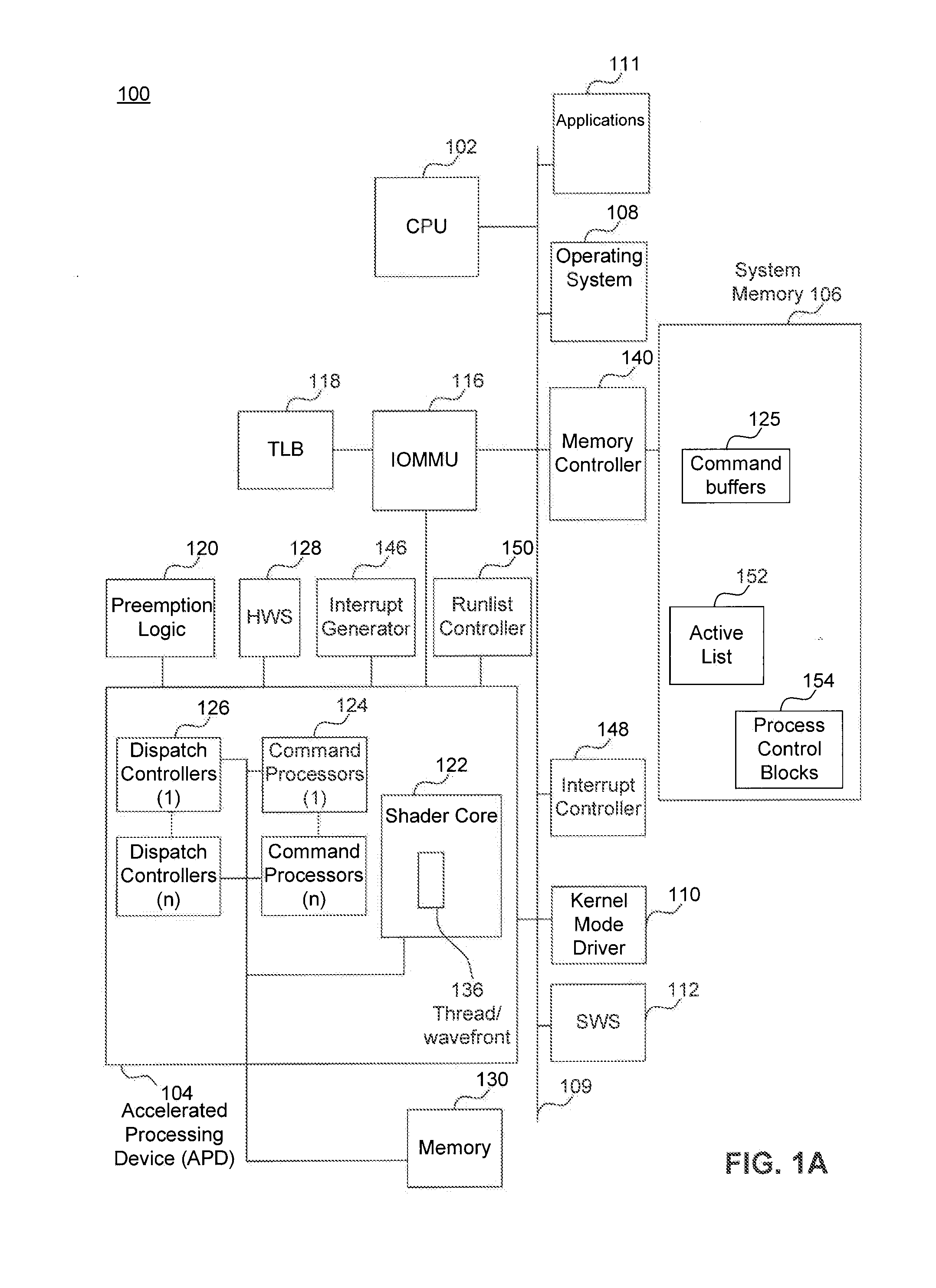

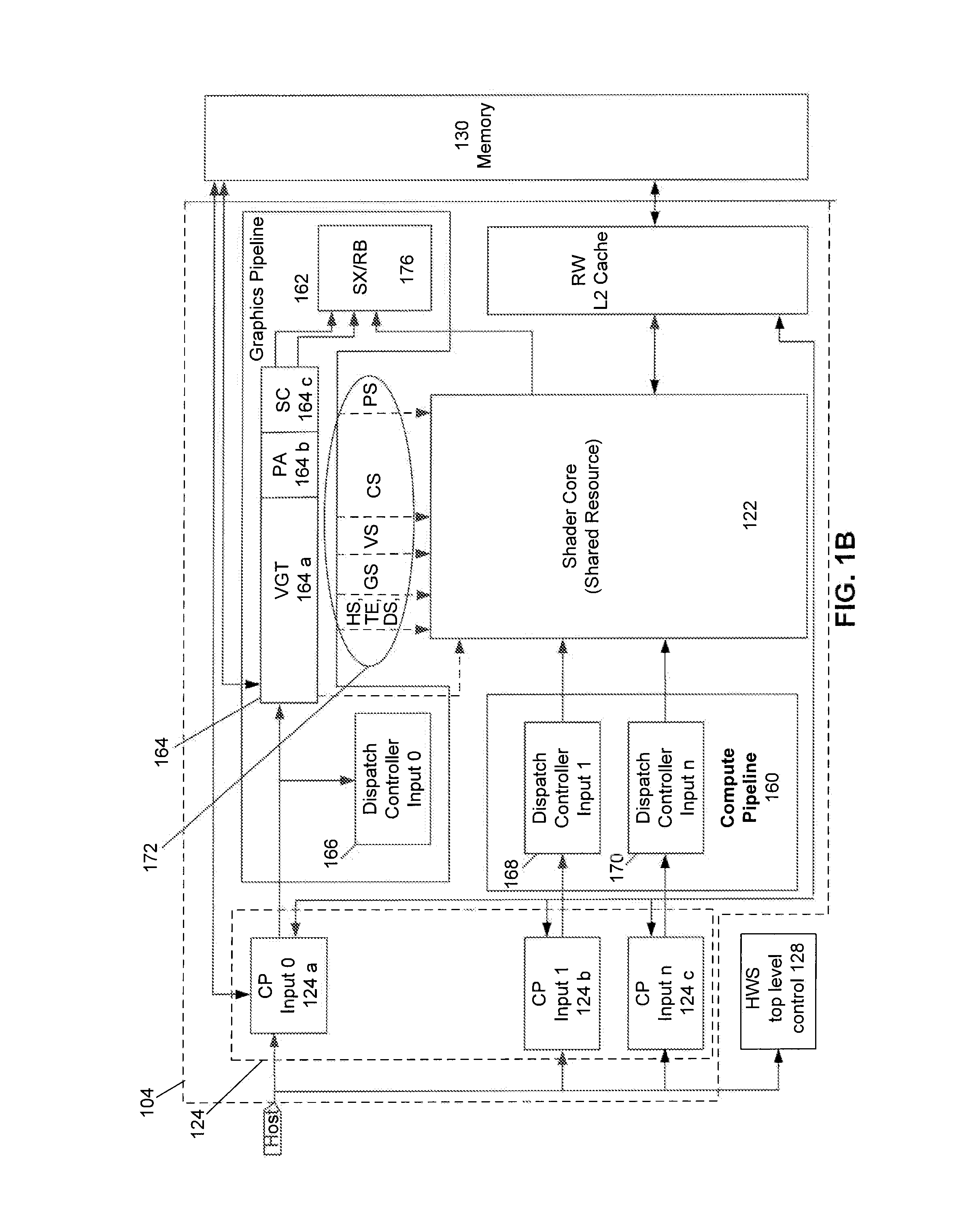

Visibility Ordering in a Memory Model for a Unified Computing System

Provided is a method of permitting the reordering of a visibility order of operations in a computer arrangement configured for permitting a first processor and a second processor threads to access a shared memory. The method includes receiving in a program order, a first and a second operation in a first thread and permitting the reordering of the visibility order for the operations in the shared memory based on the class of each operation. The visibility order determines the visibility in the shared memory, by a second thread, of stored results from the execution of the first and second operations.

Owner:ATI TECH INC +1

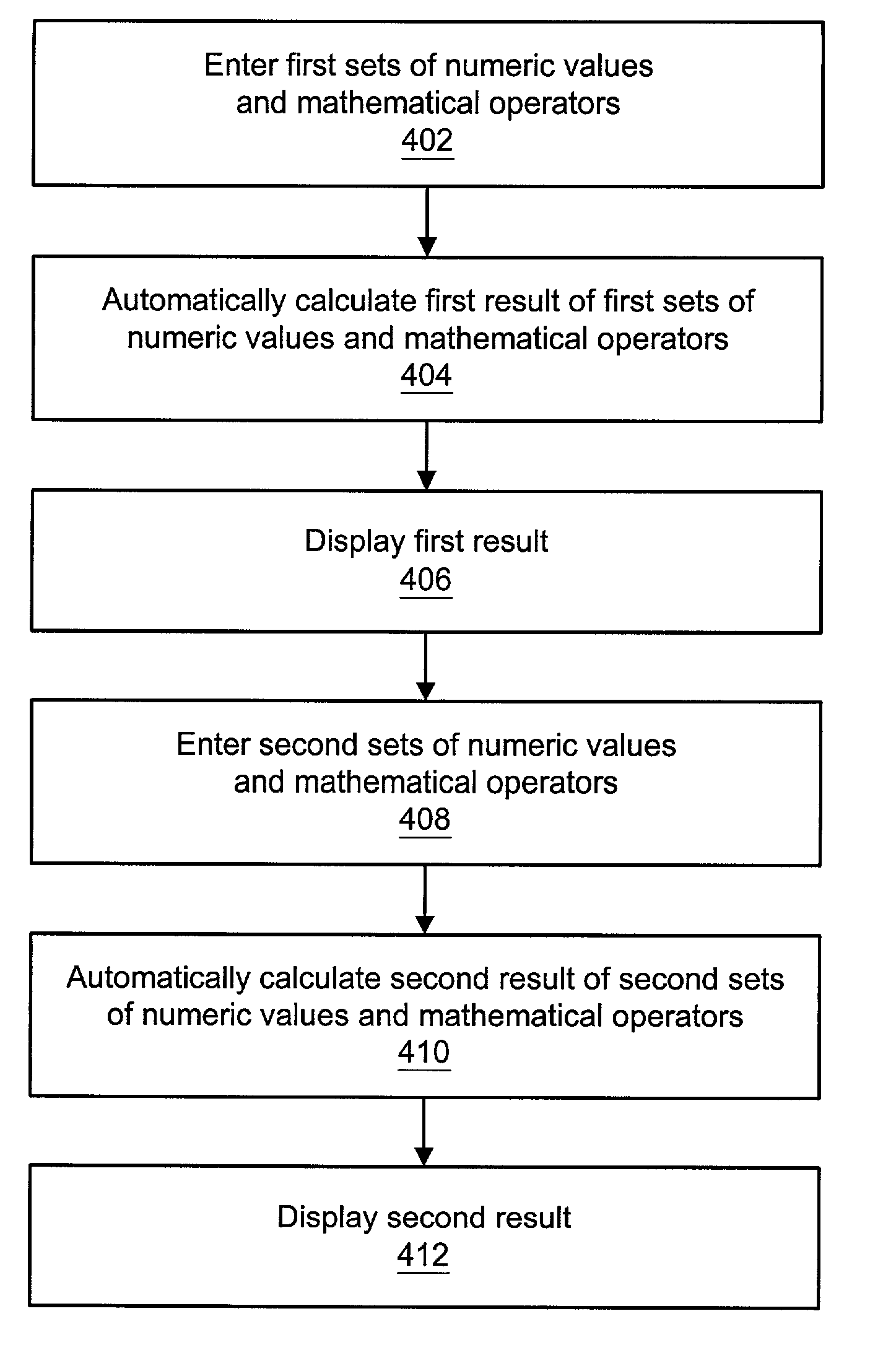

System and method for calculation using a calculator input mode

InactiveUS20020143730A1Digital data processing detailsText processingElectronic formOrder of operations

Systems and methods for computer-based numerical calculation using a calcsheet are provided. A calcsheet may provide one or more columns for vertical calculation, each column having a plurality of fields including operation fields, number fields, and optional comment fields. The calcsheet may include multiple columns of vertical calculations. A user may type in calculations in a manner similar to the entry of calculations on a hand held calculator, and the calculations may be displayed in a vertical format in substantially any column. Number fields in a calcsheet may include mathematical formulas or references to other fields. A set of fields (such as all operation fields in a column, for example) may be hidden. The display order of fields may be altered. Parentheses spanning multiple rows may be used to alter the order of operations. Spreadsheet lines and vertical calculations may be used in a single document or display screen. Mathematical formulas may include a subtotal function which calculates a subtotal of the numeric values from preceding number fields.

Owner:BENNETT PAUL W

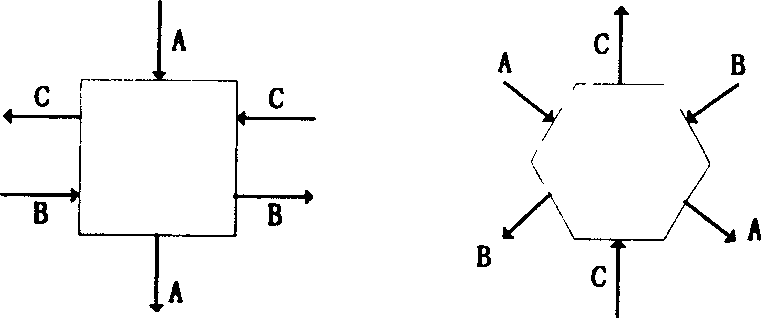

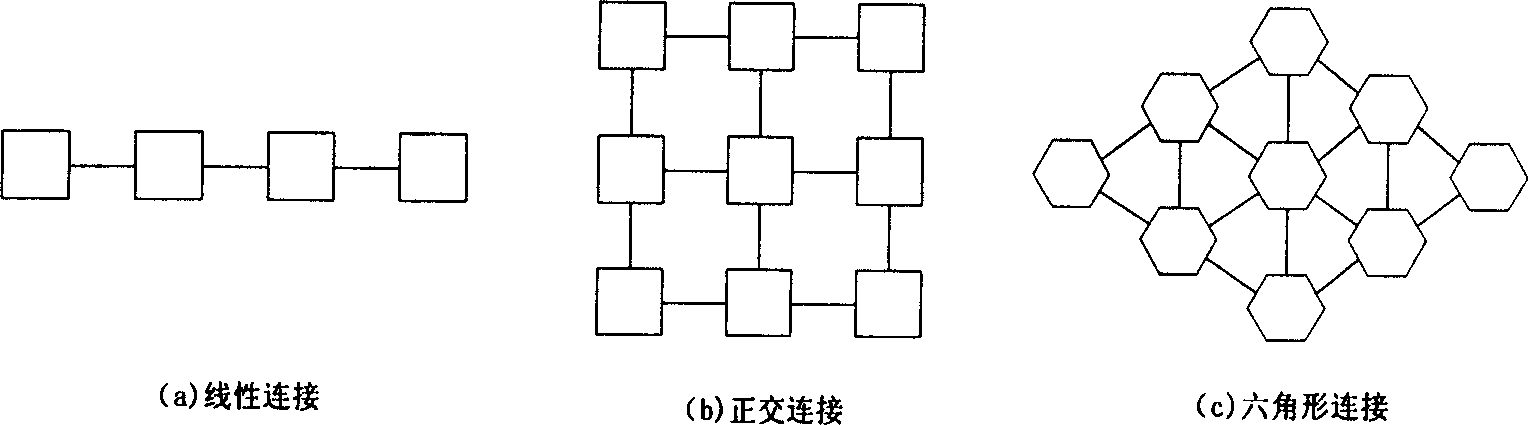

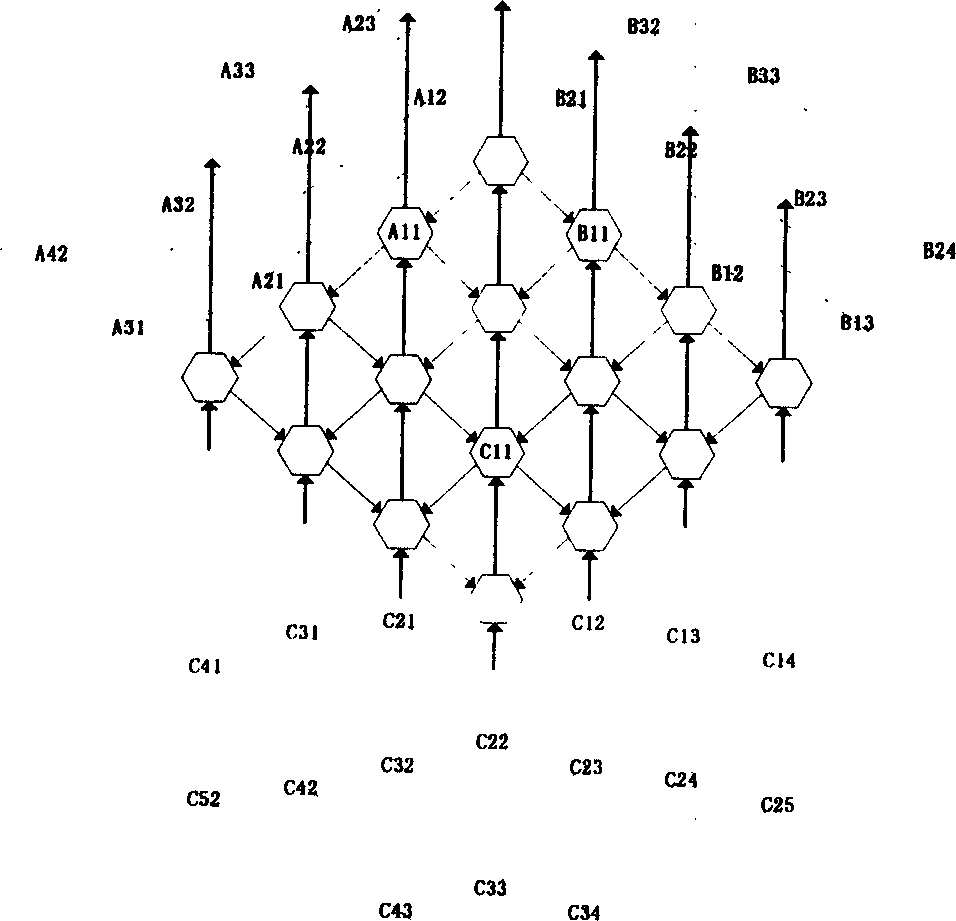

'One space skip' high-activity matrix multiplier

InactiveCN1560727AStable utilizationIncrease profitComputation using non-contact making devicesBinary multiplierOrder of operations

The invention is 'one interval jump' high efficient multiplier. It is based on basic Knng-Leiserson matrix multiplication, it compresses the intervals between each layer of data, then redesigns the connecting mode and data inputting of each multiplication unit, and changes the calculation order of the multiplier, thus the multiplication can be carried on in jump in the calculation unit with the same vertical direction, in order to realize the correct function of the multiplier, acquires matrix multiplier with higher efficiency. The multiplication unit using rate reach 100%, the calculating speed is faster than the Knng-Leiserson multiplier.

Owner:FUDAN UNIV

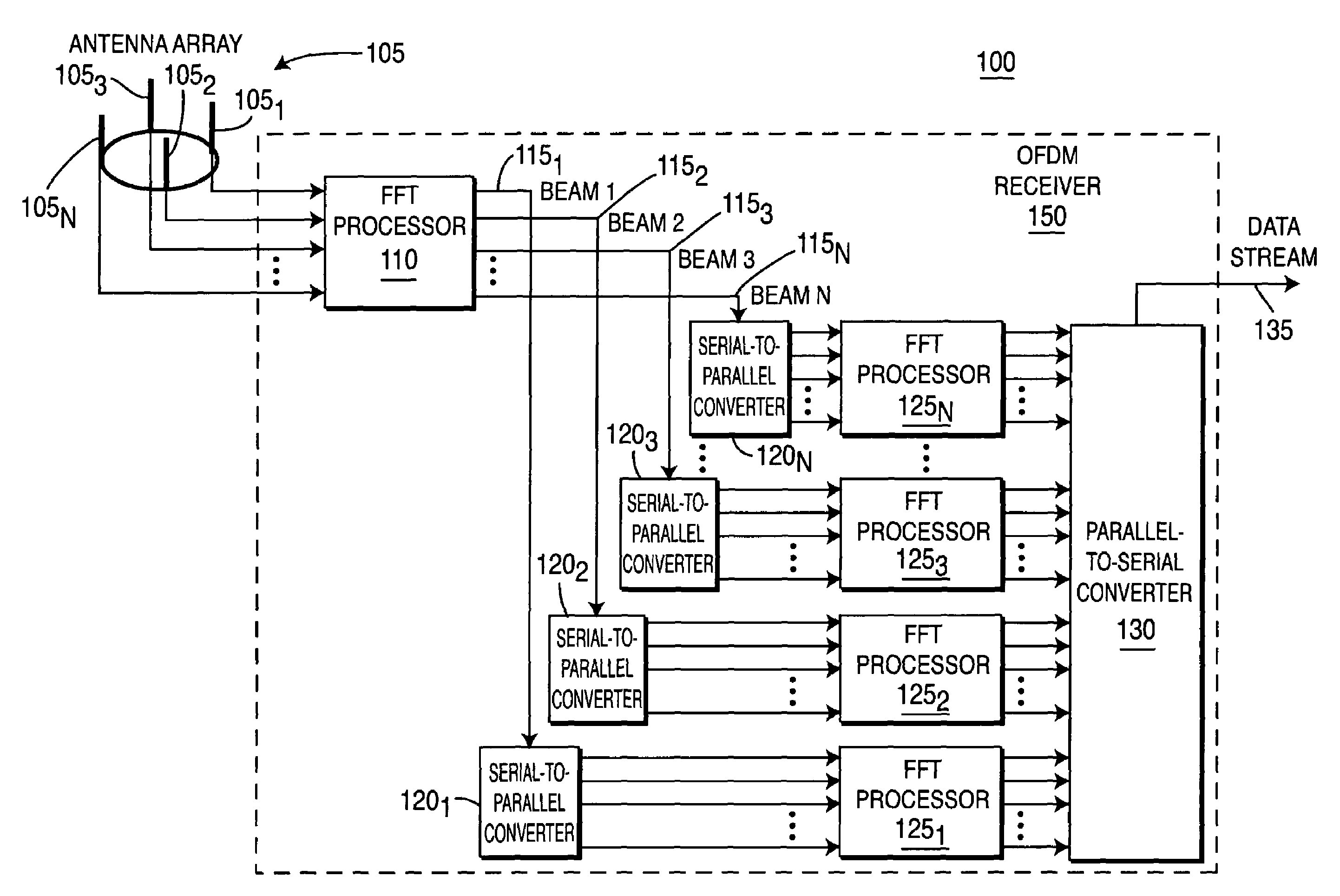

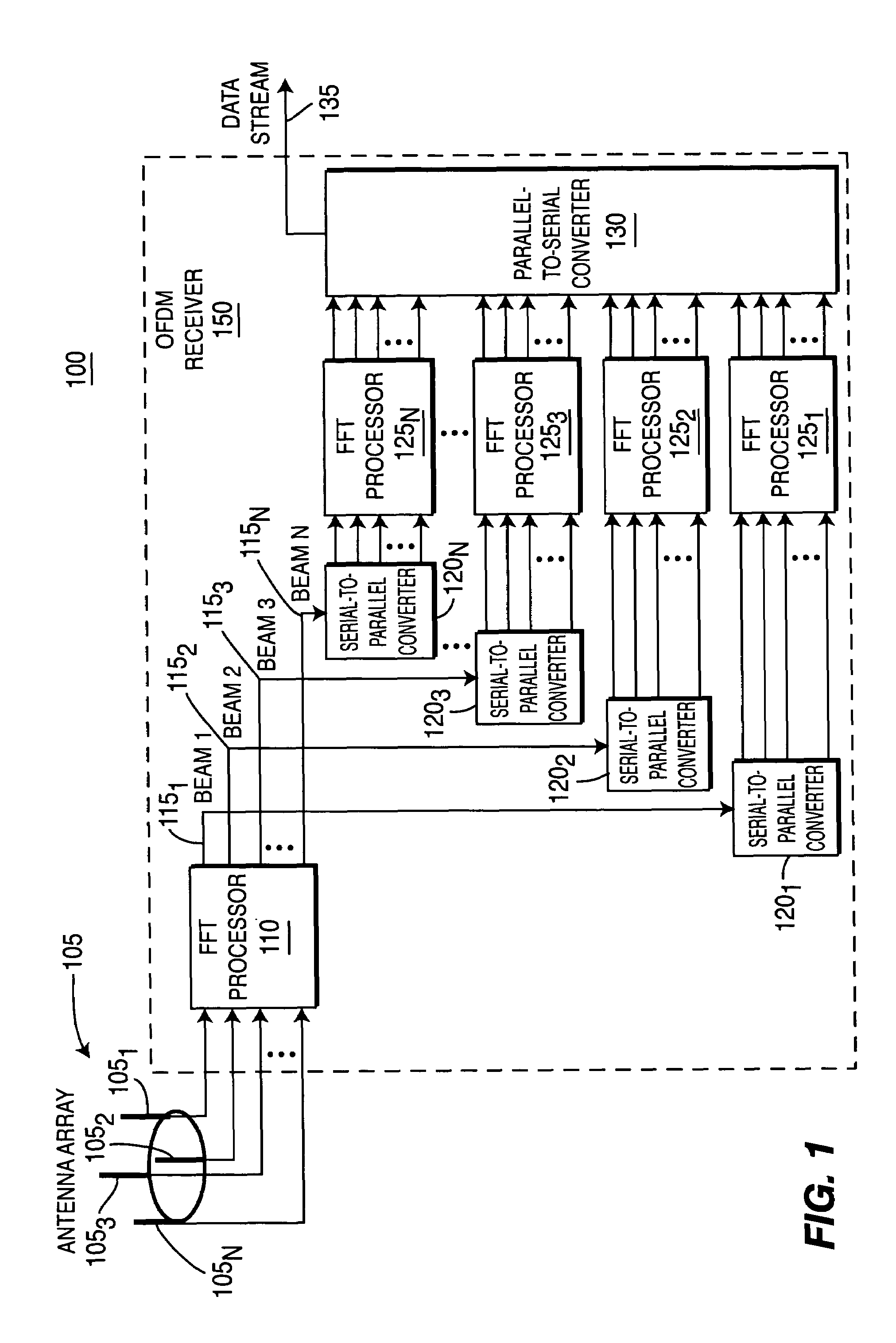

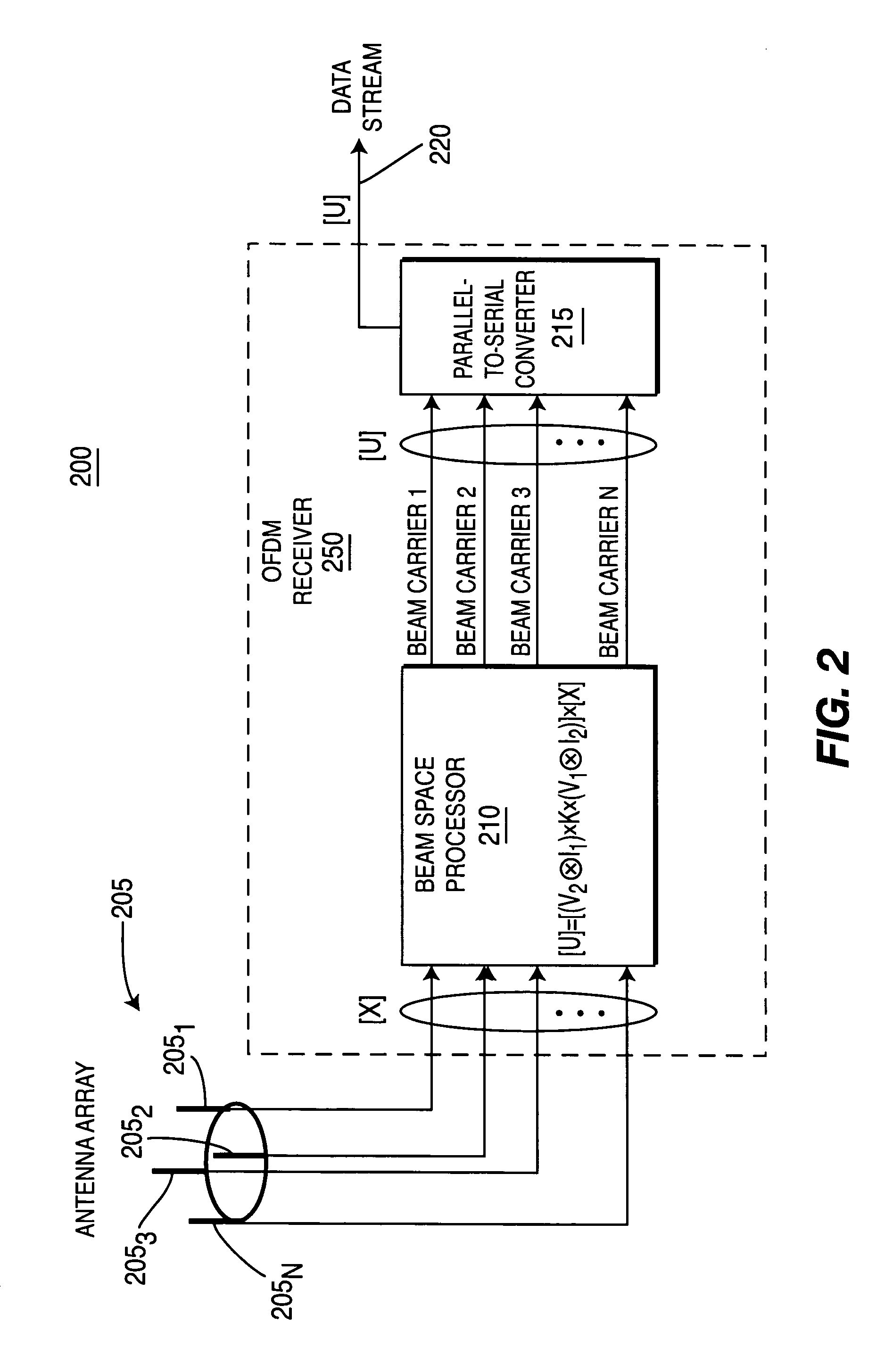

Wireless communication apparatus using fast fourier transforms to create, optimize and incorporate a beam space antenna array in an orthogonal frequency division multiplexing receiver

InactiveUS7453964B2Polarisation/directional diversitySecret communicationFast Fourier transformOrder of operations

A wireless communication apparatus which uses fast Fourier transforms (FFTs) in an orthogonal frequency division multiplexing (OFDM) receiver which incorporates a beam space antenna array. The beam space antenna array may be implemented with a Butler matrix array. The beam space antenna array may be a circular array, vertical array, or a combination of both circular and vertical arrays, for providing the desired angular antenna coverage. In one embodiment, the antenna array is optimized because the FFTs are linear invariant transform operators, whereby the order of operations in the OFDM receiver can be interchanged.

Owner:INTERDIGITAL TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com