Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

110 results about "High-Level Data Link Control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

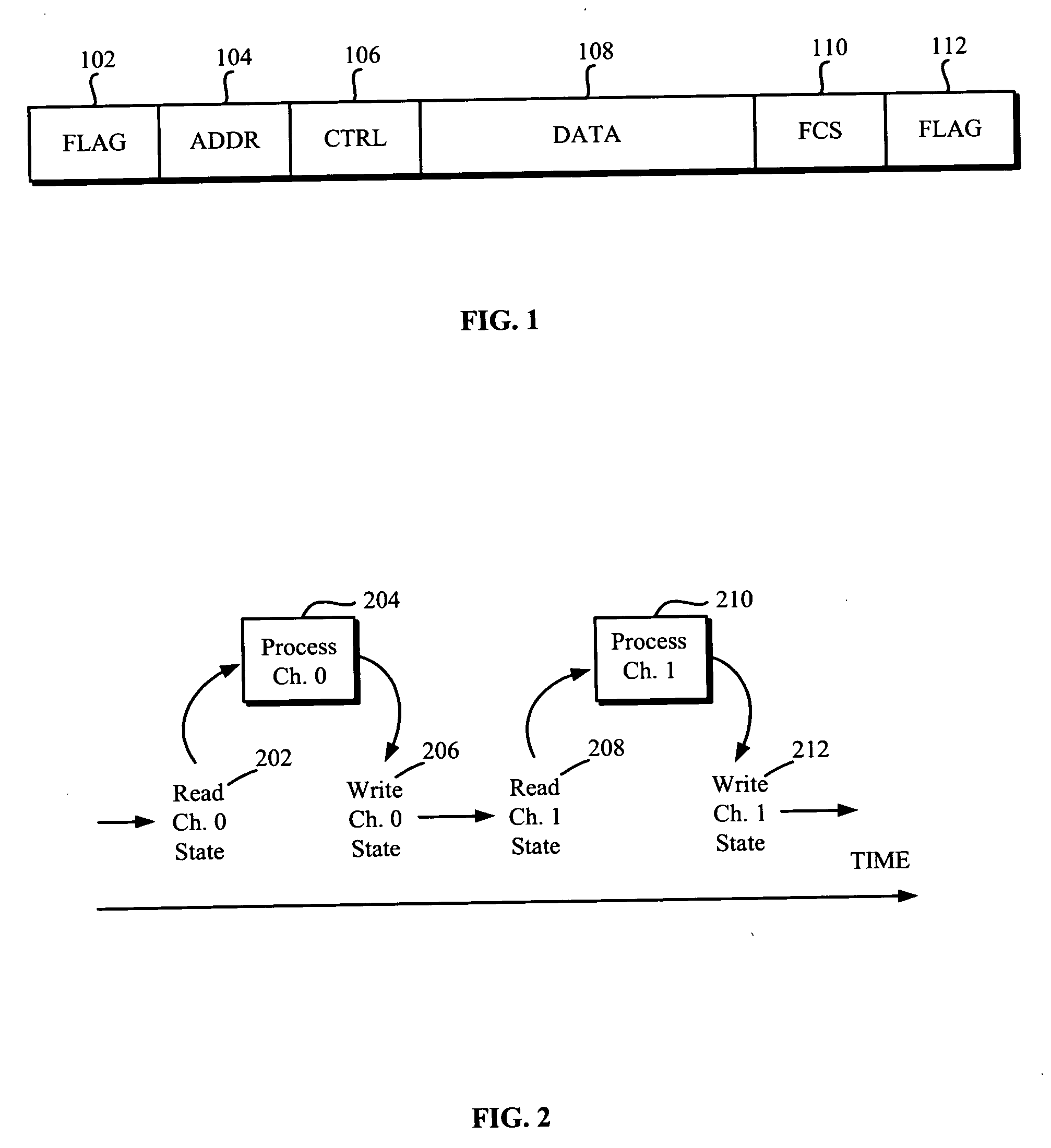

High-Level Data Link Control (HDLC) is a bit-oriented code-transparent synchronous data link layer protocol developed by the International Organization for Standardization (ISO). The standard for HDLC is ISO/IEC 13239:2002.

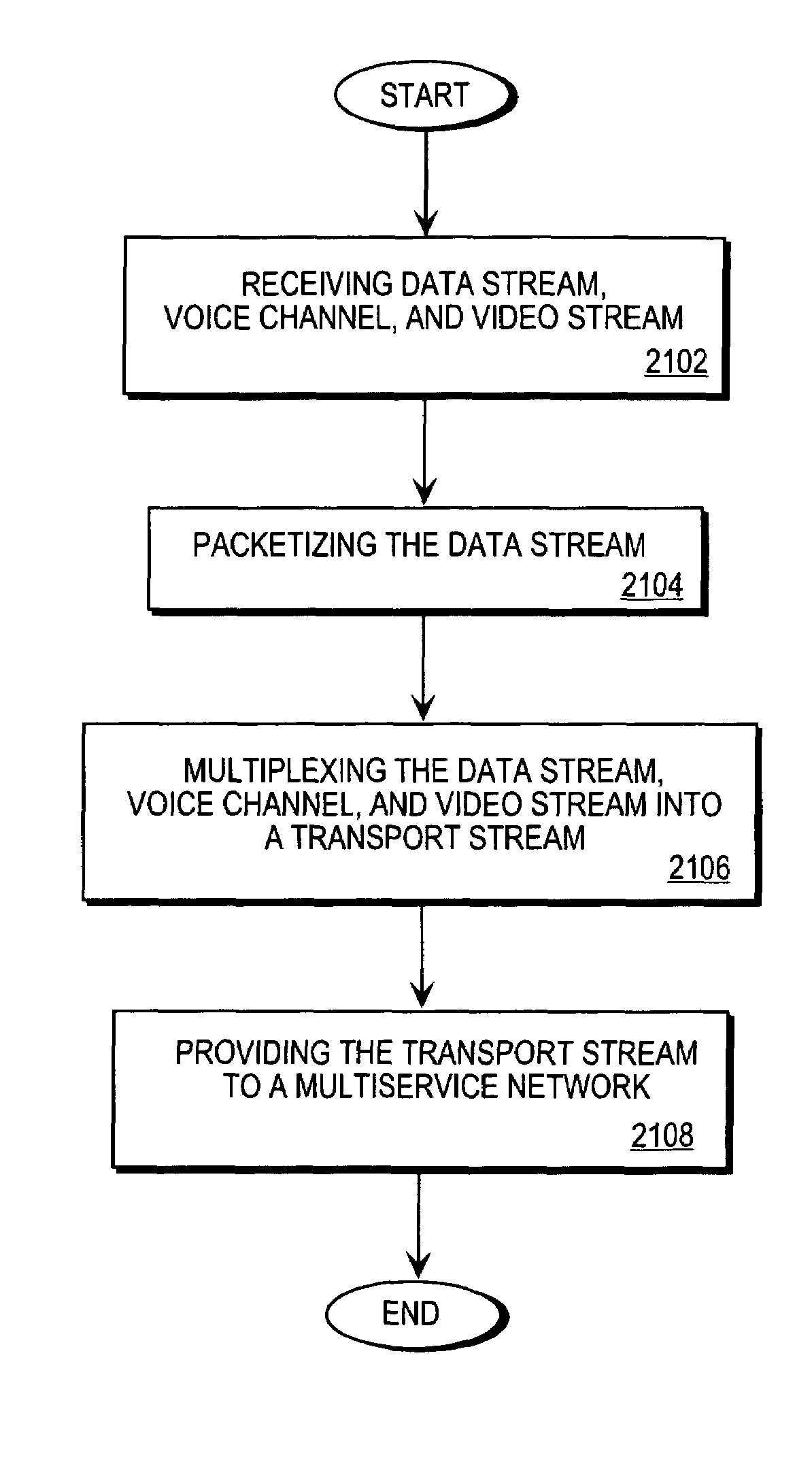

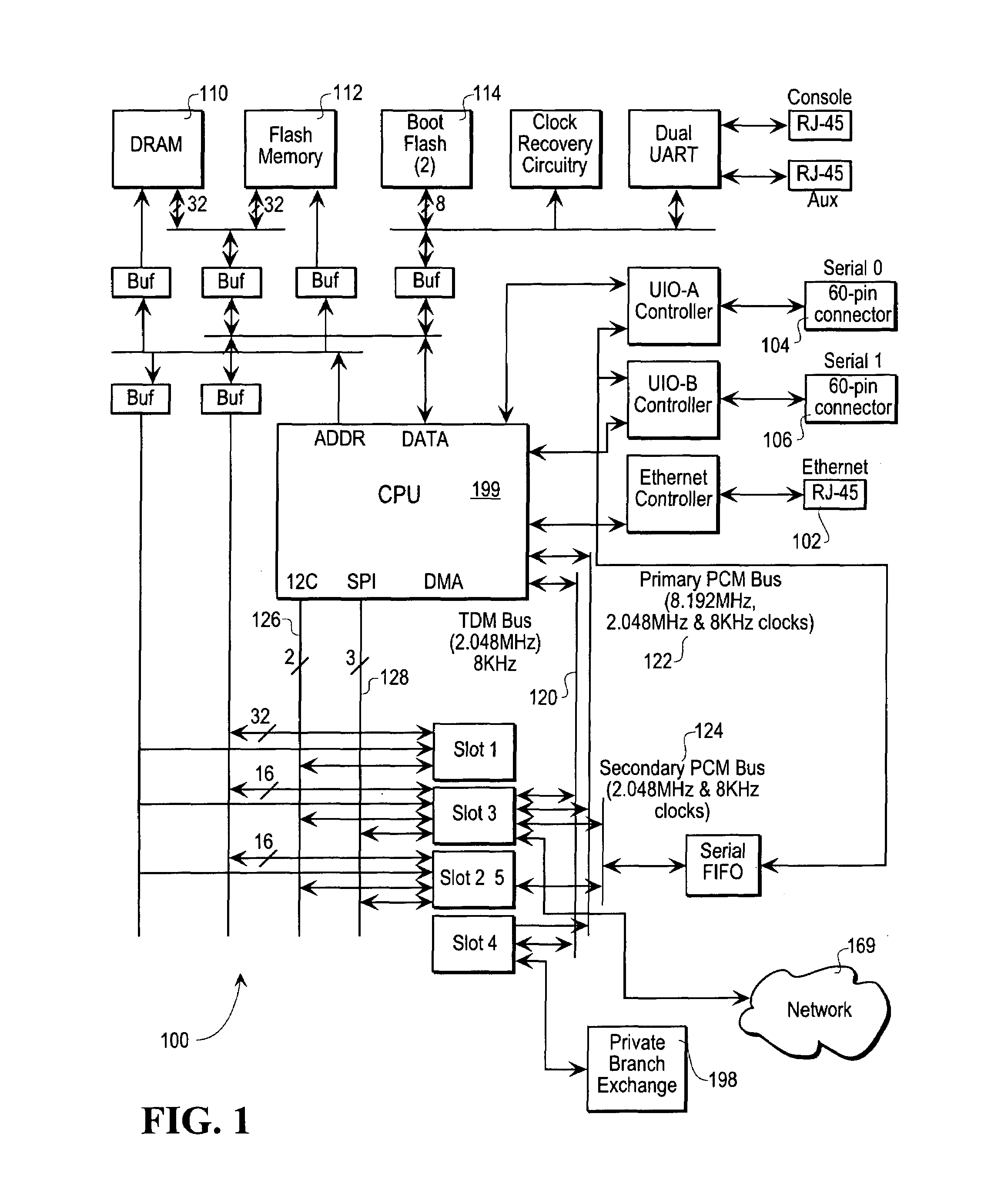

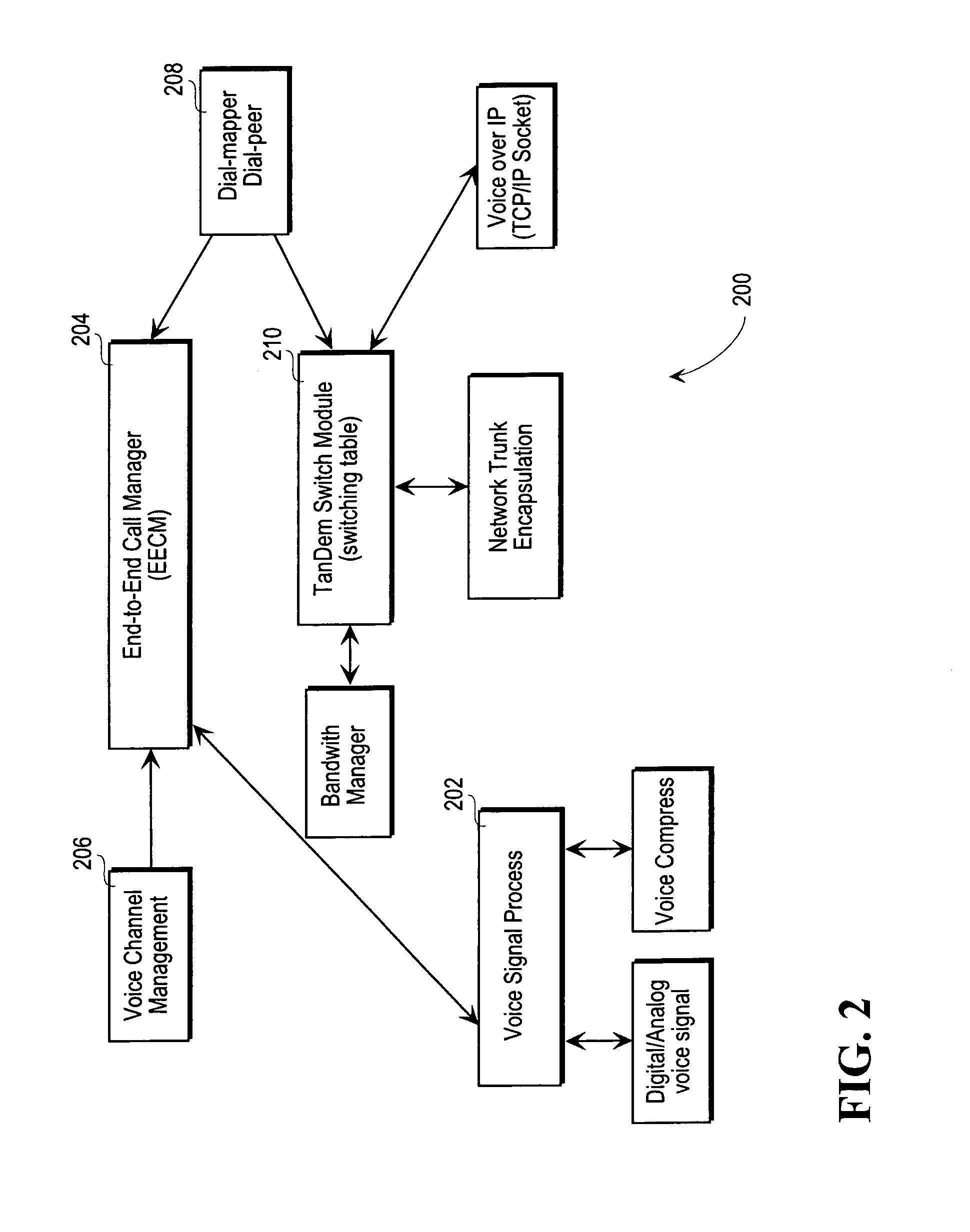

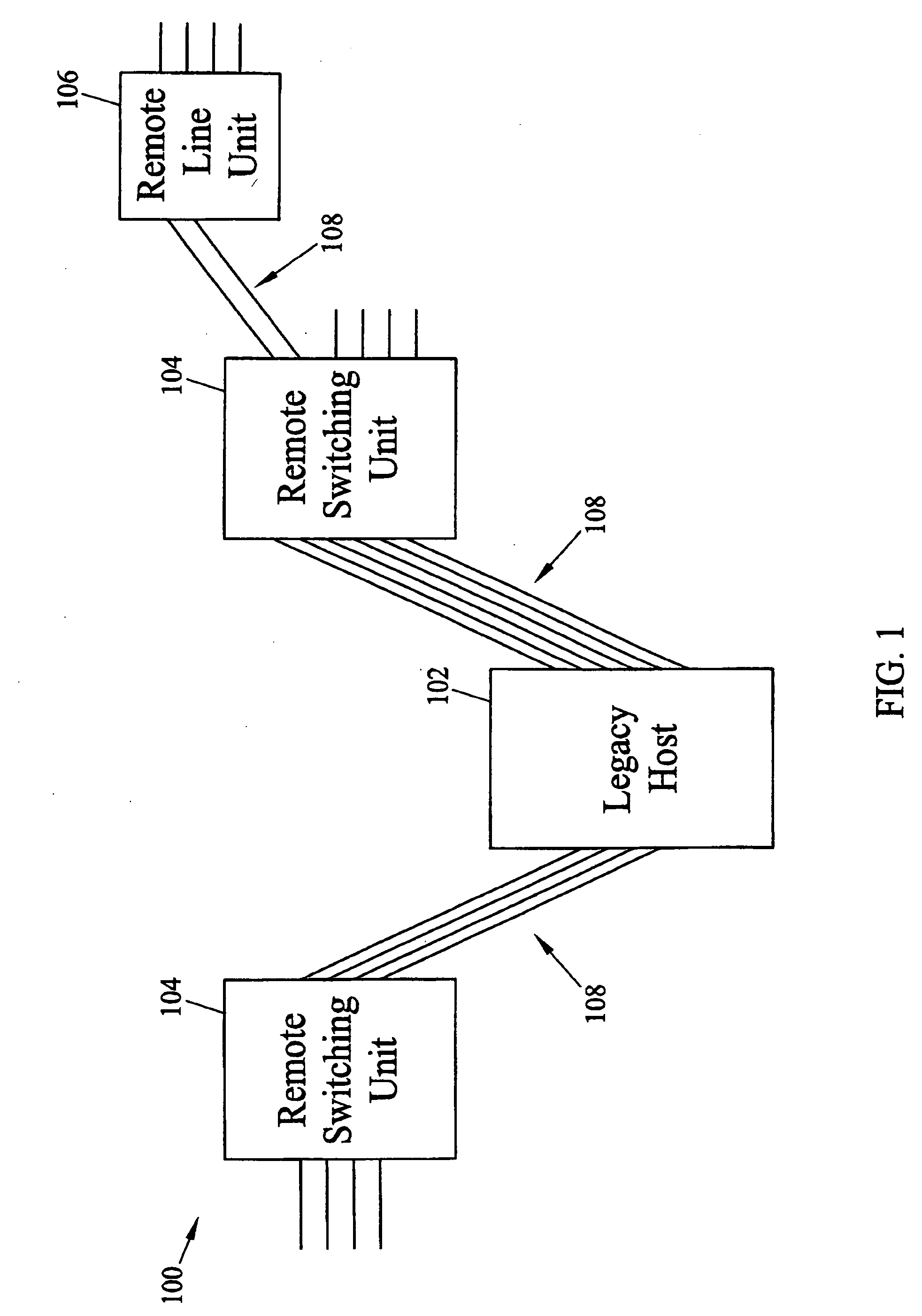

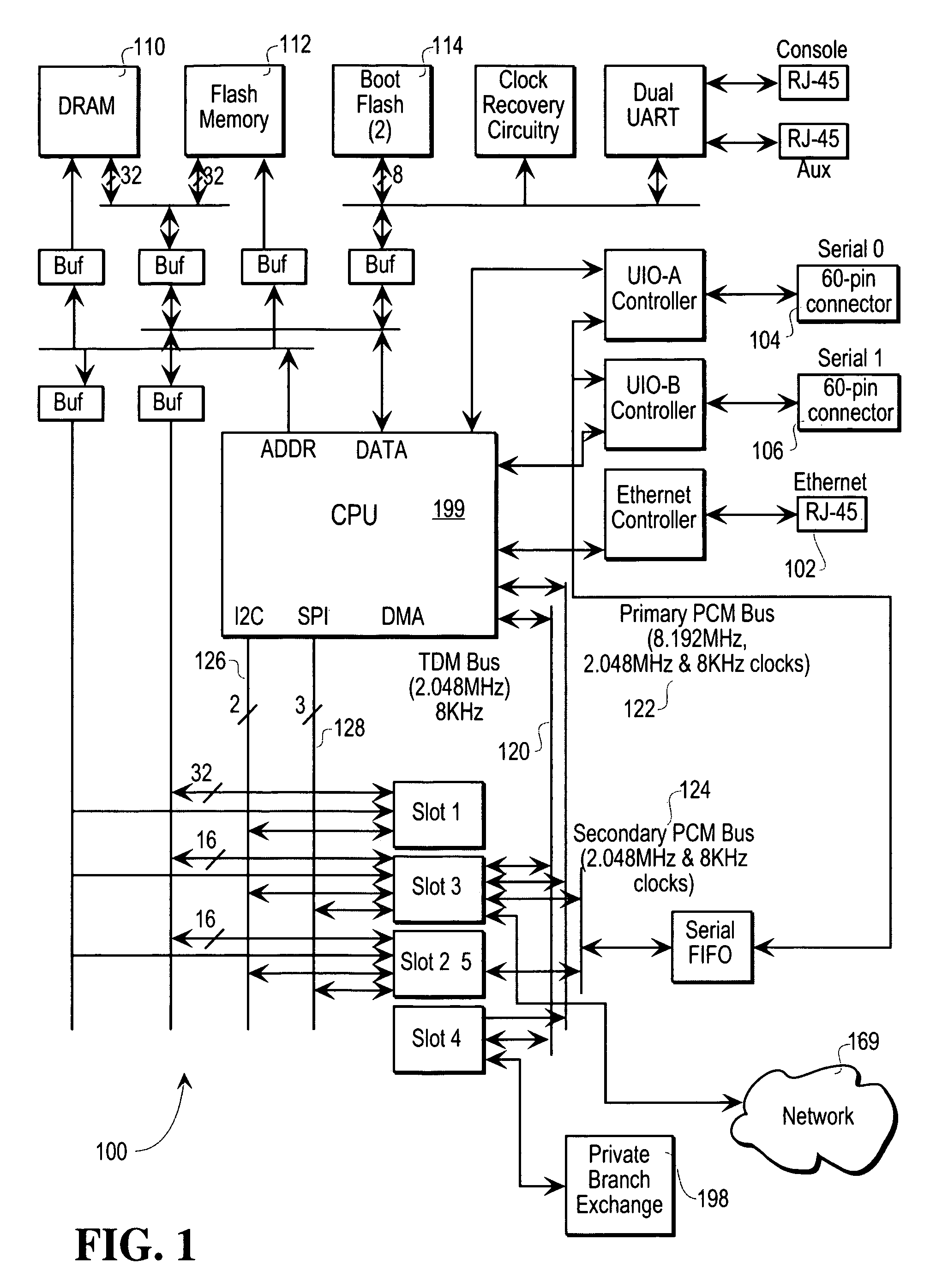

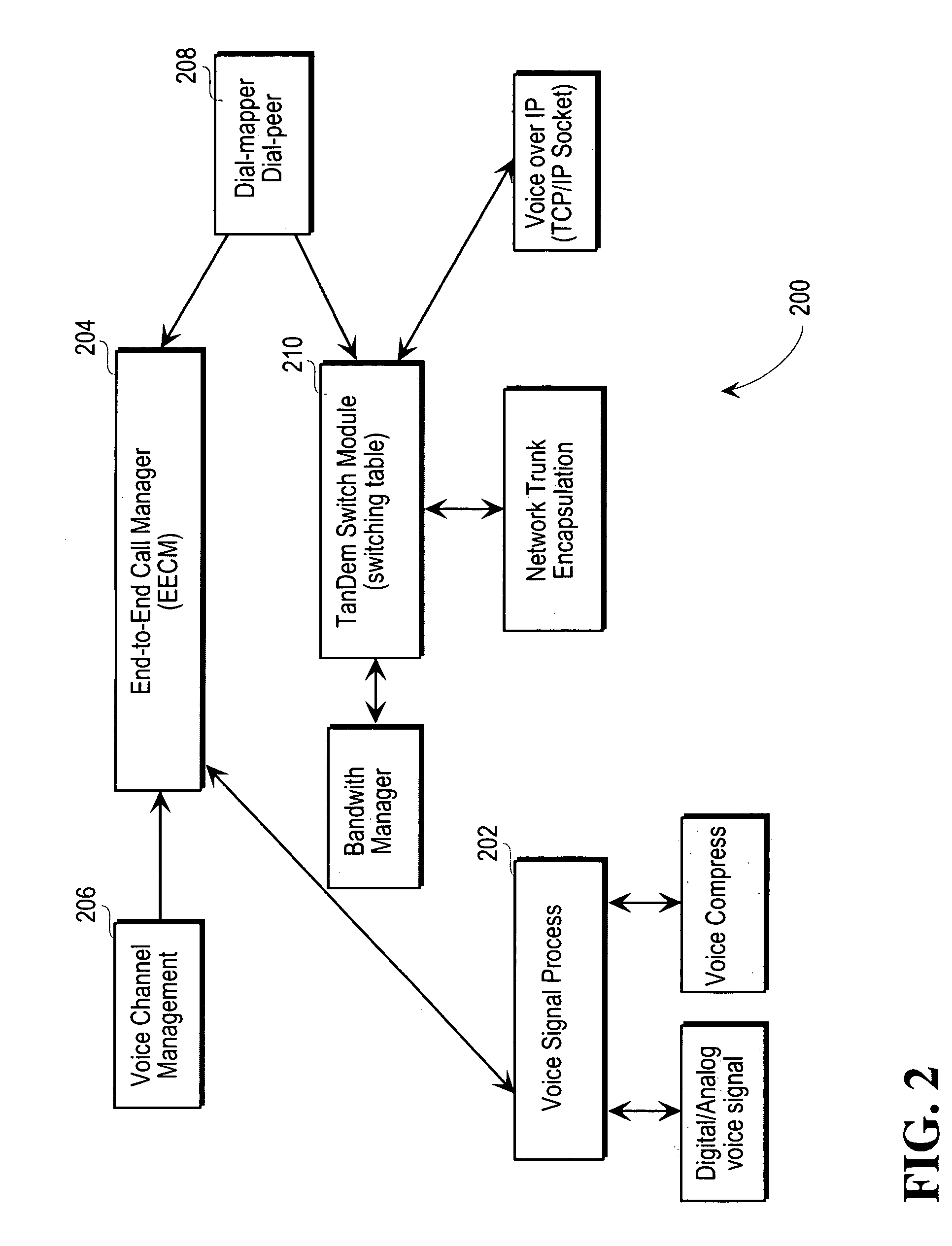

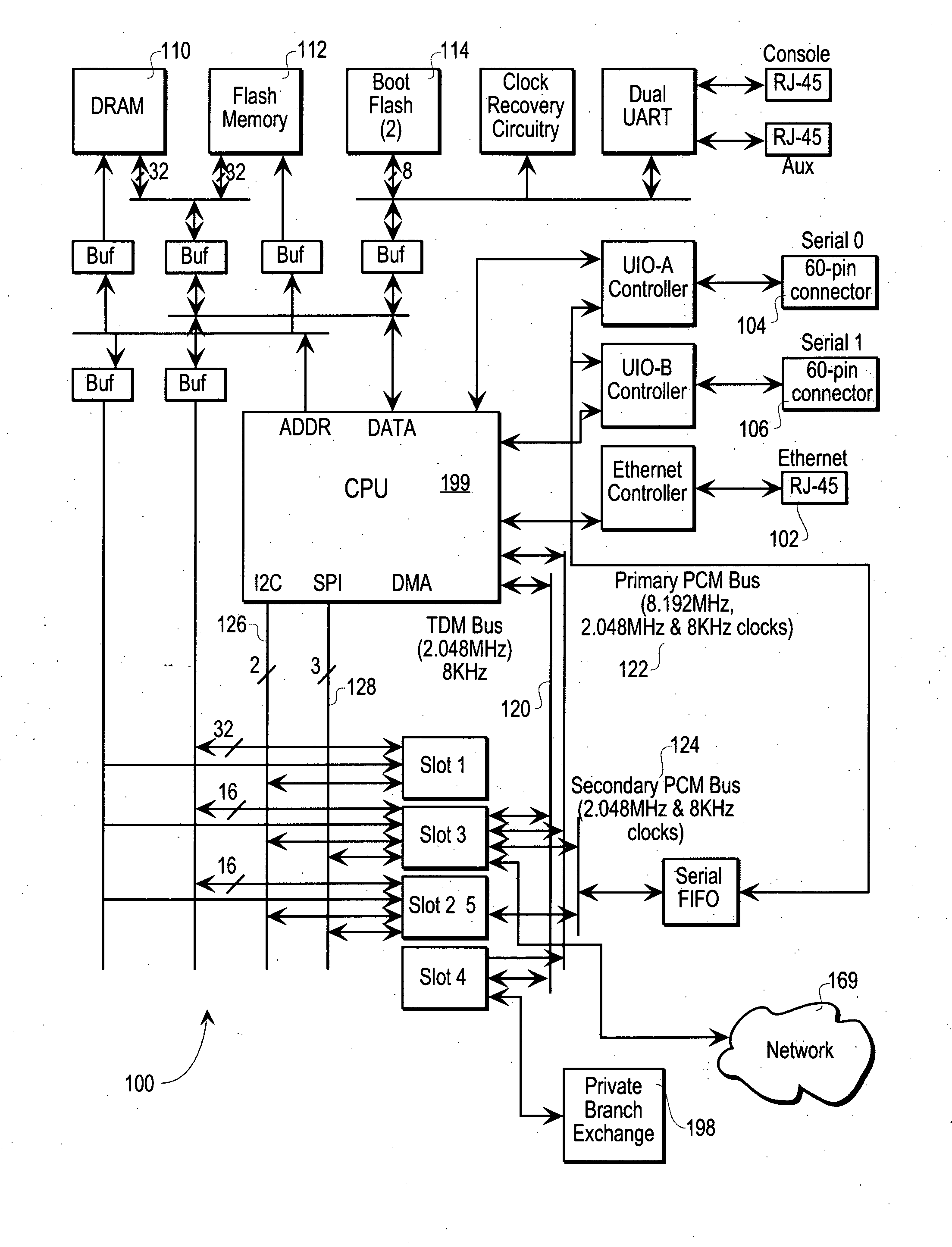

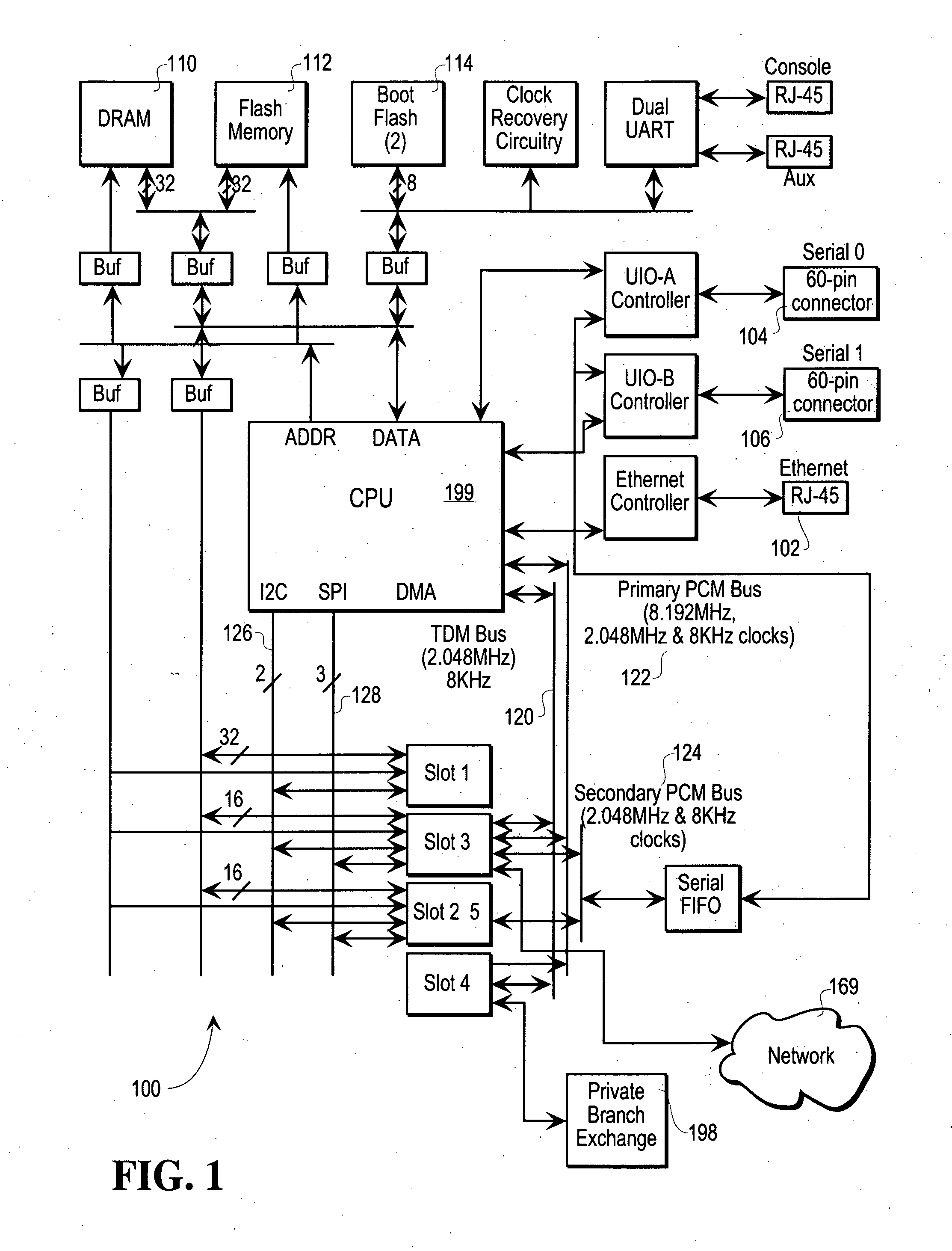

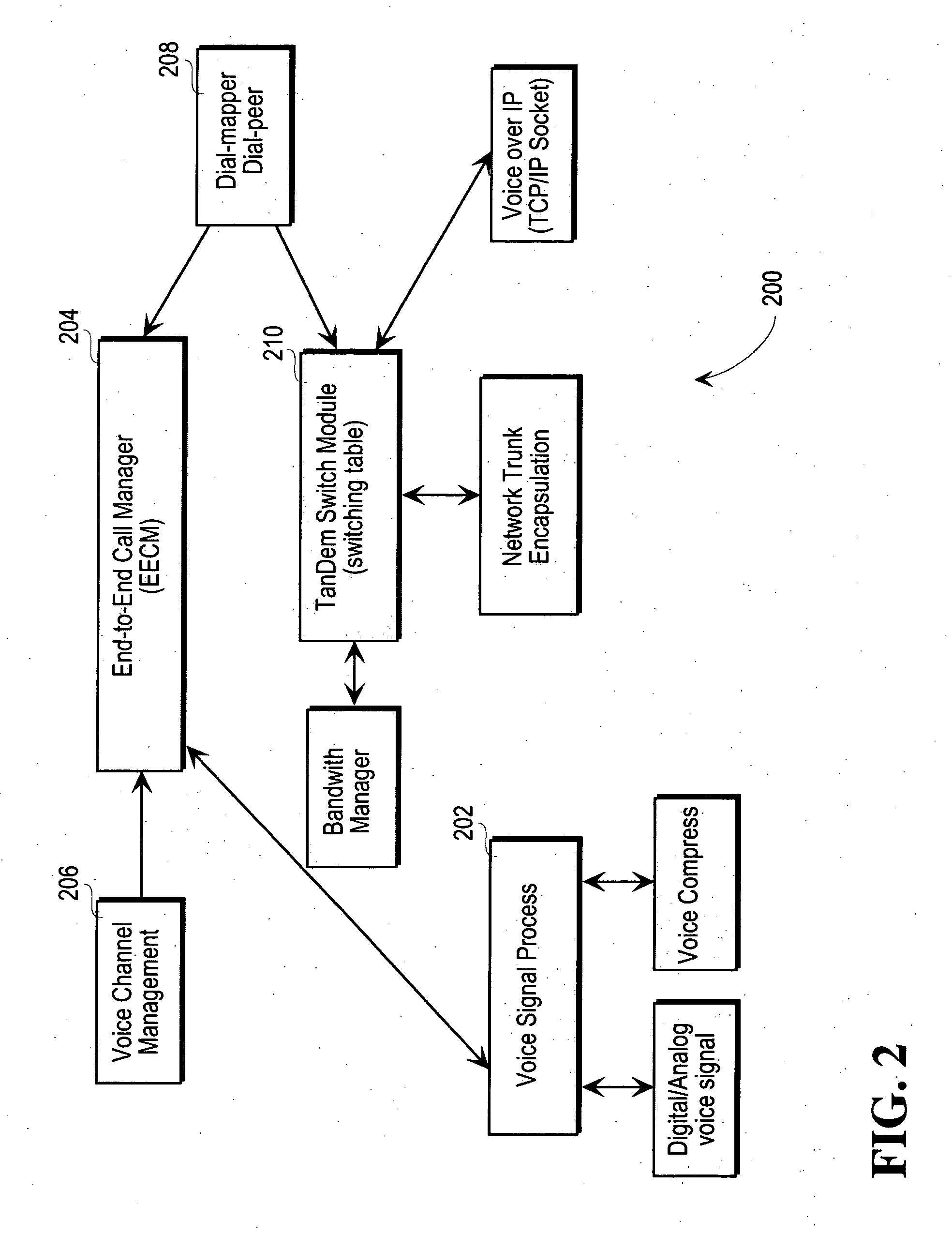

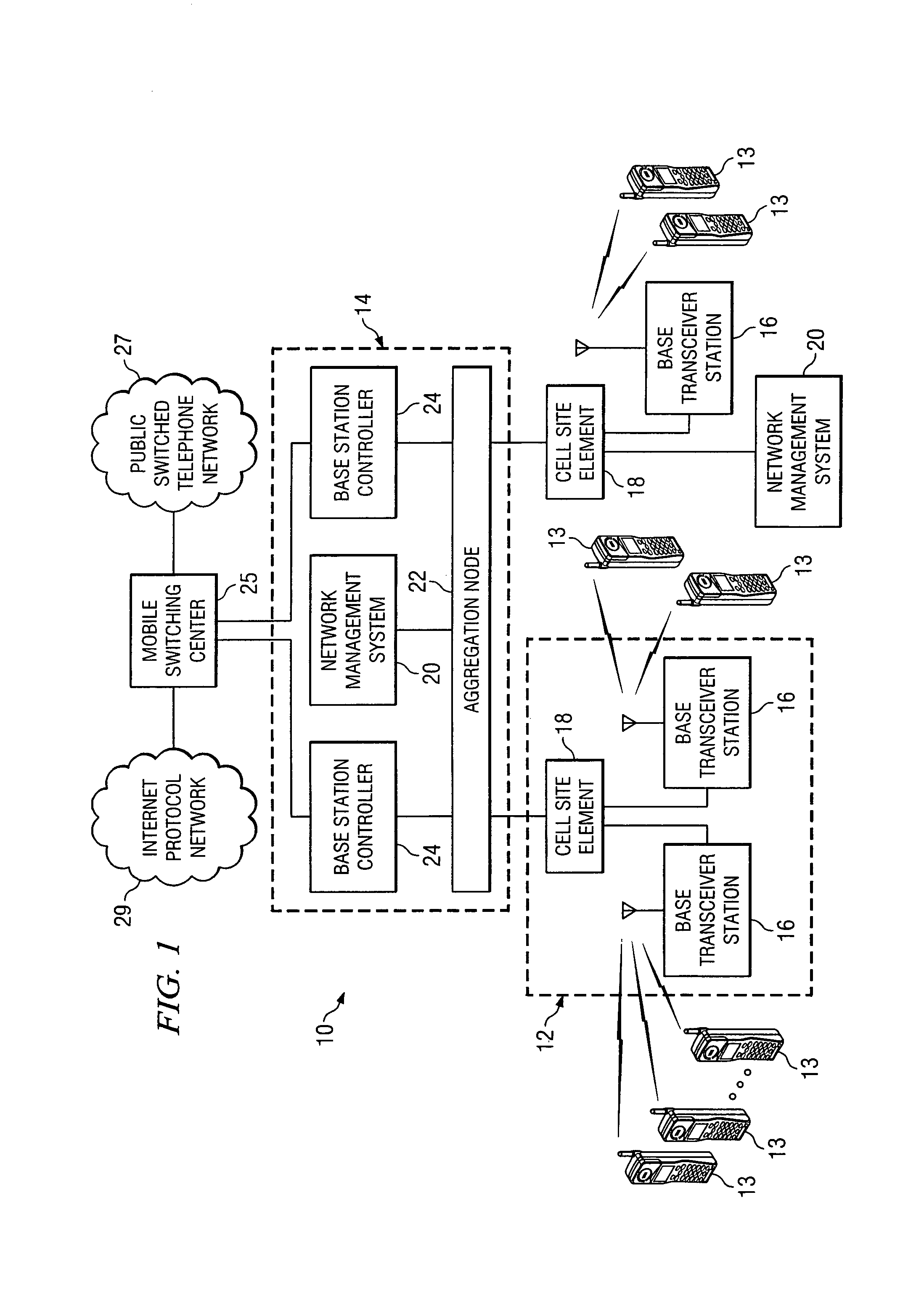

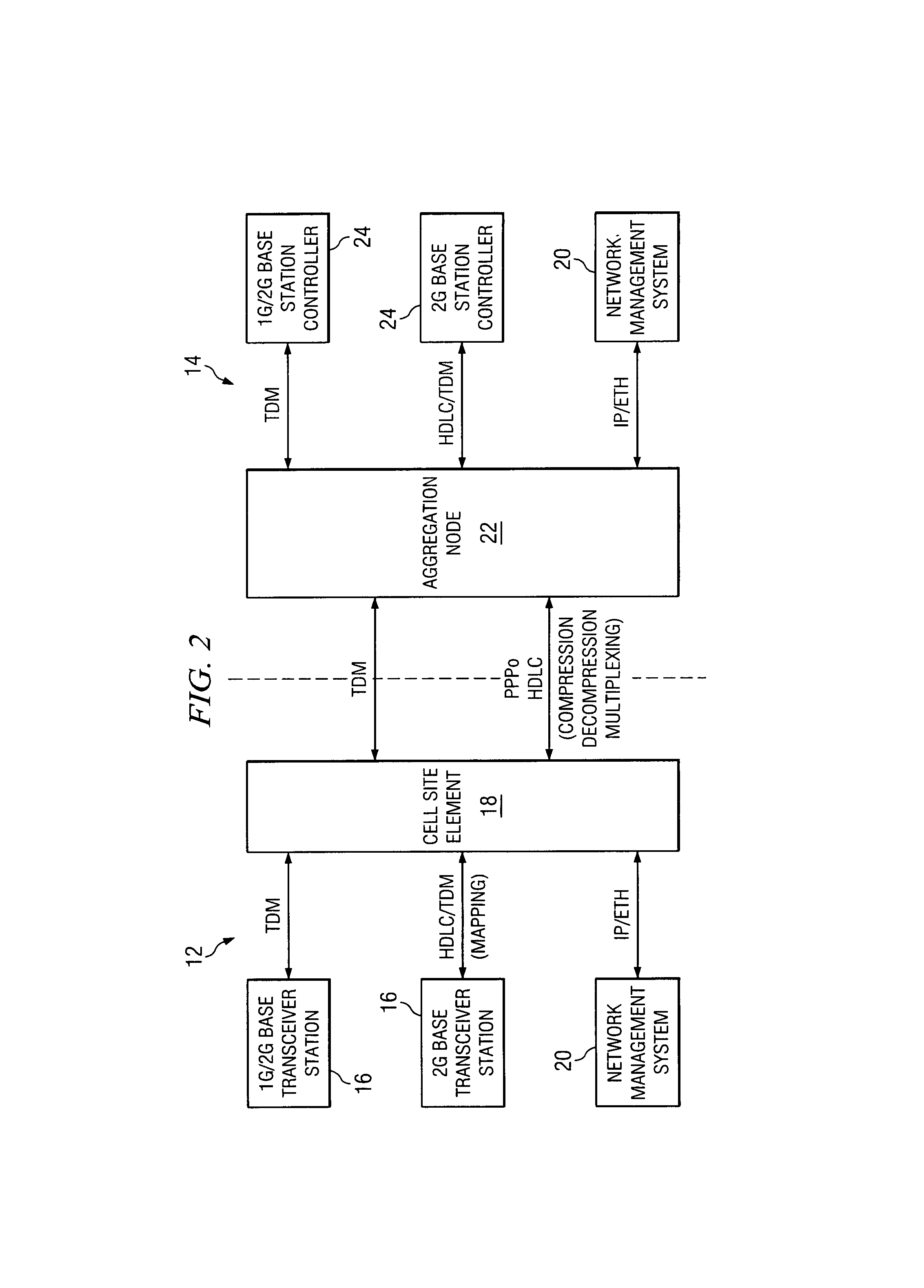

Method and apparatus for routing integrated data, voice, and video traffic

A Multiservice Access Concentrator (MAC) receives information comprising at least one data stream, at least one voice channel, at least one video stream, Local Area Network (LAN)-based traffic, and facsimile traffic. The received data stream is packetized, and the packetized data stream is multiplexed with the voice channel and the video stream to form an integrated transport stream. The voice channel comprises compressed and uncompressed voice information. The integrated transport stream is provided to at least one multi-service network using a software-configurable trunk. The multi-service network includes cell-based and packet-based networks comprising Asynchronous Transfer Mode (ATM), Frame Relay, High-level Data Link Control (HDLC), Internet Protocol (IP), and Time Division Multiplex (TDM) networks, as well as leased-line carrier services. The trunk is configured at a physical level and a protocol level using at least one trunk option.

Owner:CISCO TECH INC

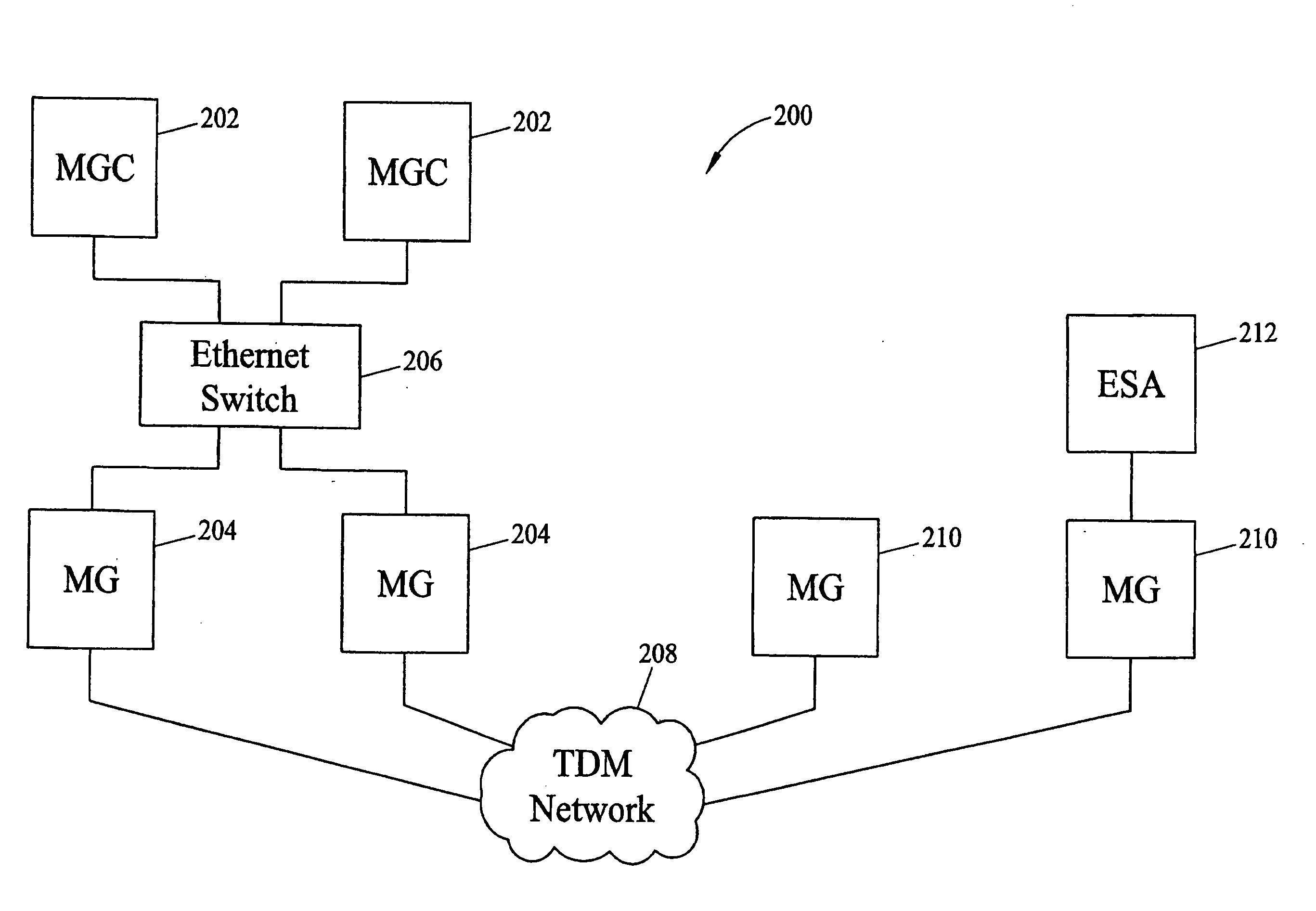

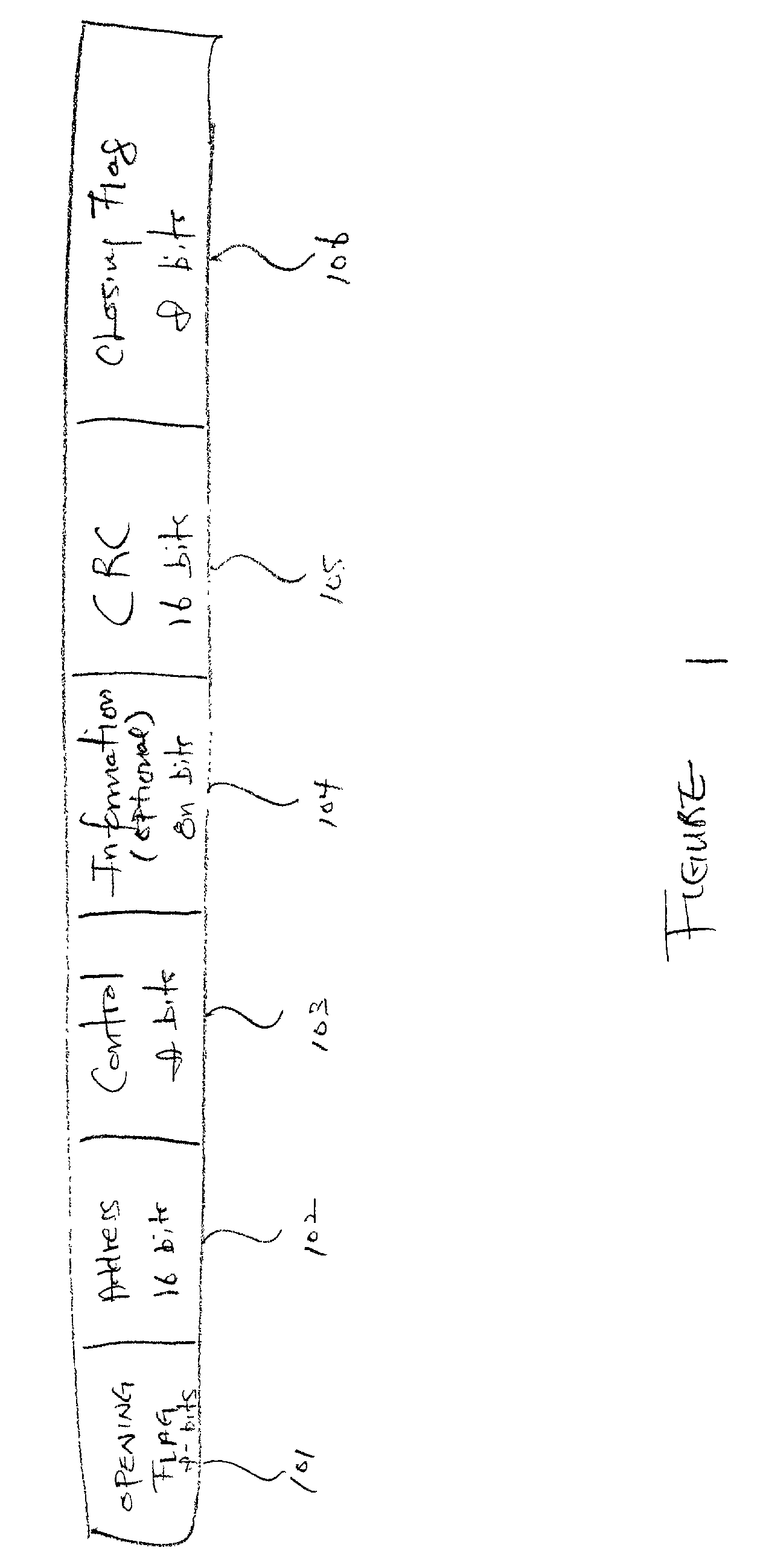

Methods and systems for providing transport of media gateway control commands using high-level datalink control (HDLC) protocol

InactiveUS20050105559A1Interconnection arrangementsTime-division multiplexTime-division multiplexingHigh-Level Data Link Control

A media gateway controller can manage a remote media gateway by sending standard media gateway control commands over an HDLC channel in a time division multiplexed link. The media gateway control commands are sent from the media gateway controller to a local media gateway, where the commands are encapsulated in a command packet and placed in the information field of an HDLC frame. The remote media gateway receives the HDLC frame, removes the media gateway control command, and takes the steps necessary to process the command. The command packet may include a packet header that identifies the type of command contained in the packet.

Owner:GENBAND

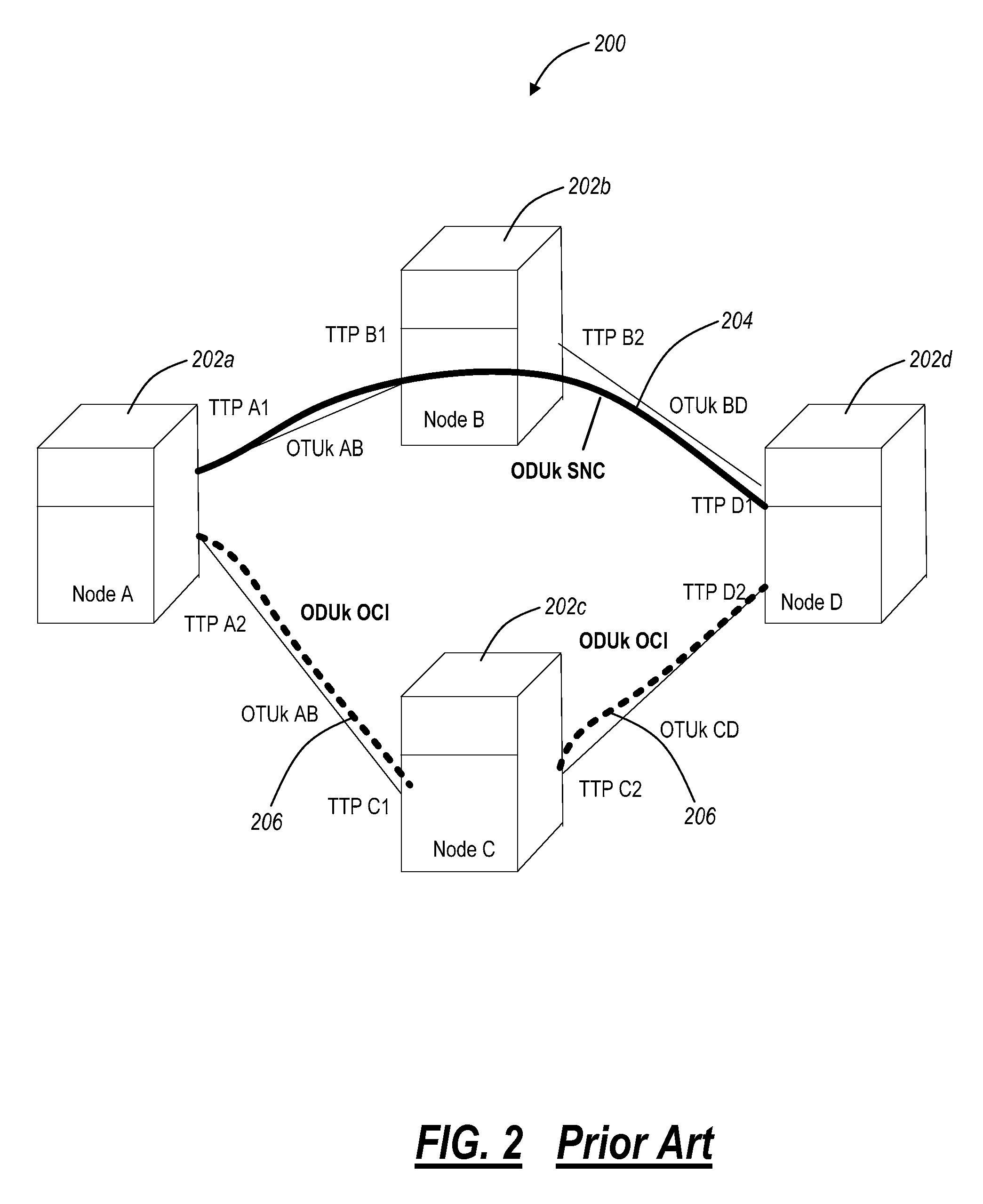

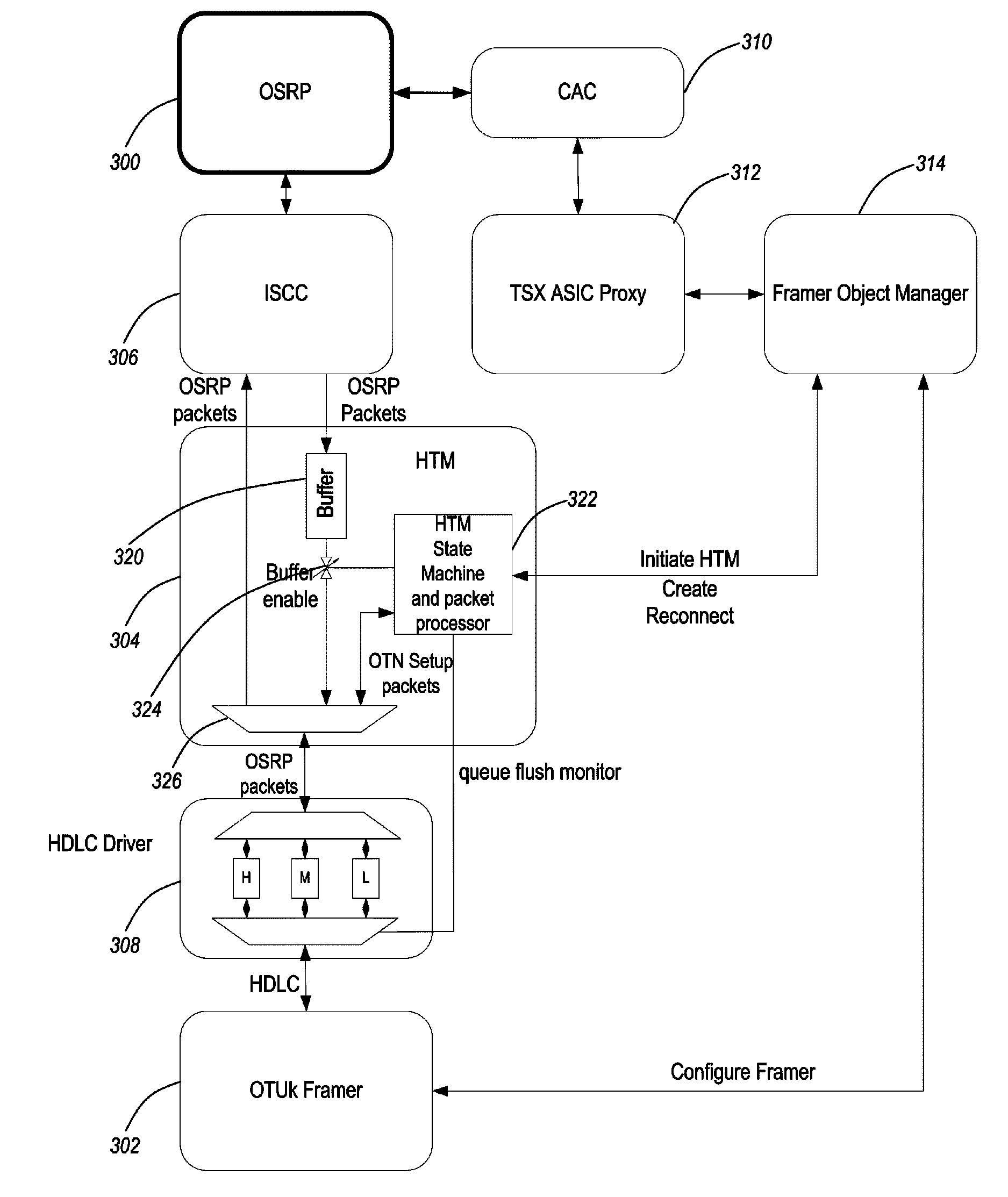

Systems and methods for rapid optical transport network circuit provisioning

ActiveUS20100272438A1Speeding up Optical Transport Network connection changeFast mesh restorationMultiplex system selection arrangementsLaser detailsOptical Transport NetworkHigh-Level Data Link Control

The present disclosure provides systems and methods for rapid circuit provisioning in Optical Transport Networks (OTN) using signaling and routing protocols thereby enabling fast mesh restoration. The present invention utilizes a shim layer between OTN messaging (e.g., GCC or High-Level Data Link Control (HDLC)) and the associated signaling and routing protocol (e.g., OSRP, GMPLS, etc.). If an ODUk Connection CTP or TTP needs to be created, the shim layer runs a fast “OTN Setup” protocol, while buffering out going OTN messages. Incoming messages are still processed and do not require additional buffering. The purpose of the OTN Setup protocol is to allow the OTUk to re-frame on its client ODUk, while buffering out-going messages. When re-framing completes, buffers are released and the OTN messaging resumes without dropping any of the signaling frames.

Owner:CIENA

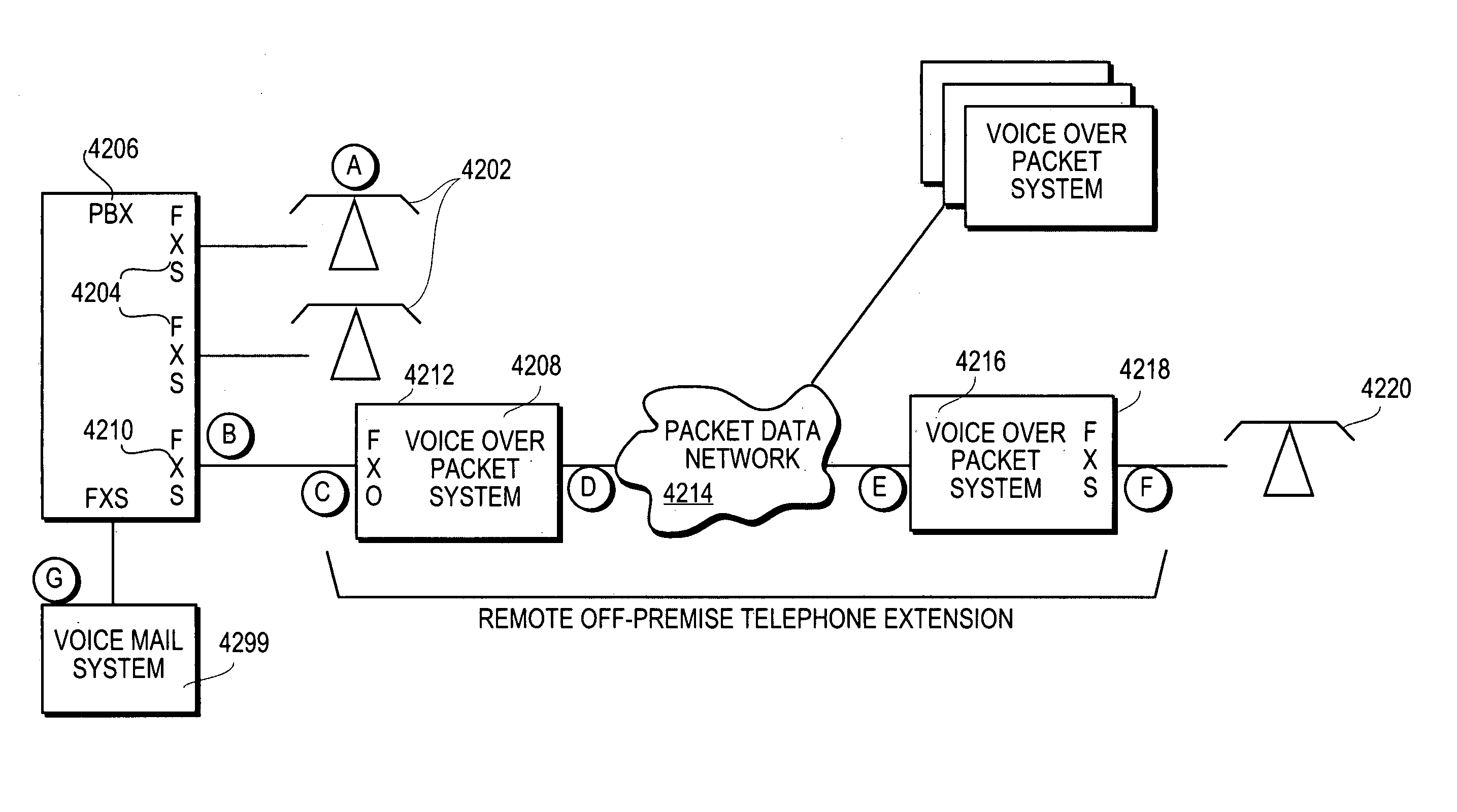

Method and apparatus for providing ringing timeout disconnect supervision in remote telephone extensions using voice over packet-data-network systems (VOPS)

InactiveUS7339924B1Current supply arrangementsData switching by path configurationFrame RelayNetworked system

A Multiservice Access Concentrator (MAC) provides a time limit for a first ringing voltage signal in response to an attempted call. The call is attempted via a voice over packet-data-network system (VOPS), wherein the VOPS comprises voice over Internet Protocol (IP), voice over Frame Relay, voice over Asynchronous Transfer Mode (ATM), and voice over High-level Data Link Control (HDLC) network systems. Generation of the first ringing voltage signal is terminated upon expiration of the time limit. A control message is transmitted to terminate the attempted call, wherein the control message is transmitted via the VOPS.

Owner:CISCO TECH INC

Method and apparatus for dynamically adjusting bandwidth of advanced data link control channel

InactiveCN101039333AIncrease profitNormal processing is not affectedStore-and-forward switching systemsManagement unitResponse side

The present invention discloses a method and device for bandwidth dynamic regulation for HDLC channel. A HDLC treating unit in the initiating side receives a HDLC frame according to the mapping arrangement information of the time interval channel in the receiving direction, and sends a regulation notice of the channel; a HDLC collocating management unit in the response side makes over the mapping arrangement information of the time interval channel in the receiving / sending direction of this terminal according to the obtained regulation notice of the channel, a HDLC treating unit in the response side receives and sends the HDLC frame with basis of the mapping arrangement information of the time interval channel in the receiving / sending direction, and sends a regulation response of the channel; a HDLC collocating management unit in the initiating side makes over the mapping arrangement information of the time interval channel in the receiving direction of this terminal according to the obtained regulation response of the channel, a HDLC treating unit in the initiating side sends the HDLC frame with basis of the mapping arrangement information of the time interval channel in the sending direction. The negotiation about HDLC channel bandwidth regulation between the two sides is accomplished by controlling frame alternation.

Owner:HUAWEI TECH CO LTD

Method and apparatus for providing multiple quality of service levels in a wireless packet data services connection

ActiveUS7096261B2Network traffic/resource managementInformation formatPoint-to-Point ProtocolGrade of service

The packets generated by each of multiple packet data applications are provided to a single Point-to-Point Protocol (PPP) stack and a single High-level Data Link Control (HDLC) framing layer to convert data packets into byte streams suitable for transmission through Radio Link Protocol (RLP) connections. Each of the resultant multiple byte streams is then provided to one of multiple RLP connections having different retransmission and delay properties. The RLP connection selected for sending data from each application is based on the grade of service most appropriate for the application. At the receiver, the data from the multiple RLP connections is provided to a single PPP stack.

Owner:QUALCOMM INC

Systems and methods for rapid optical transport network circuit provisioning

ActiveUS8259733B2Fast mesh restorationFast “OTN SetupMultiplex system selection arrangementsLaser detailsProtocol for Carrying Authentication for Network AccessOptical Transport Network

The present disclosure provides systems and methods for rapid circuit provisioning in Optical Transport Networks (OTN) using signaling and routing protocols thereby enabling fast mesh restoration. The present invention utilizes a shim layer between OTN messaging (e.g., GCC or High-Level Data Link Control (HDLC)) and the associated signaling and routing protocol (e.g., OSRP, GMPLS, etc.). If an ODUk Connection CTP or TTP needs to be created, the shim layer runs a fast “OTN Setup” protocol, while buffering out going OTN messages. Incoming messages are still processed and do not require additional buffering. The purpose of the OTN Setup protocol is to allow the OTUk to re-frame on its client ODUk, while buffering out-going messages. When re-framing completes, buffers are released and the OTN messaging resumes without dropping any of the signaling frames.

Owner:CIENA

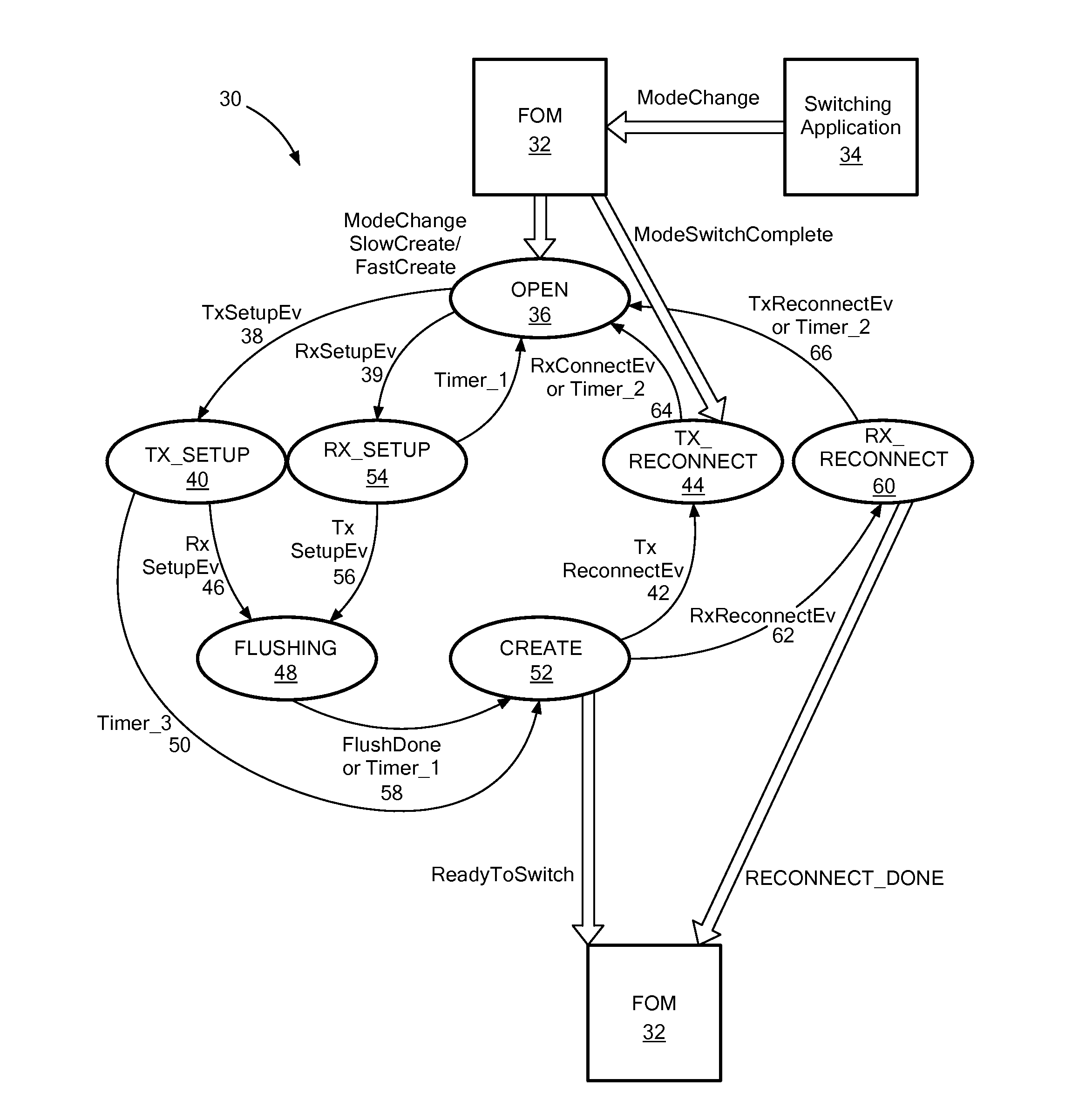

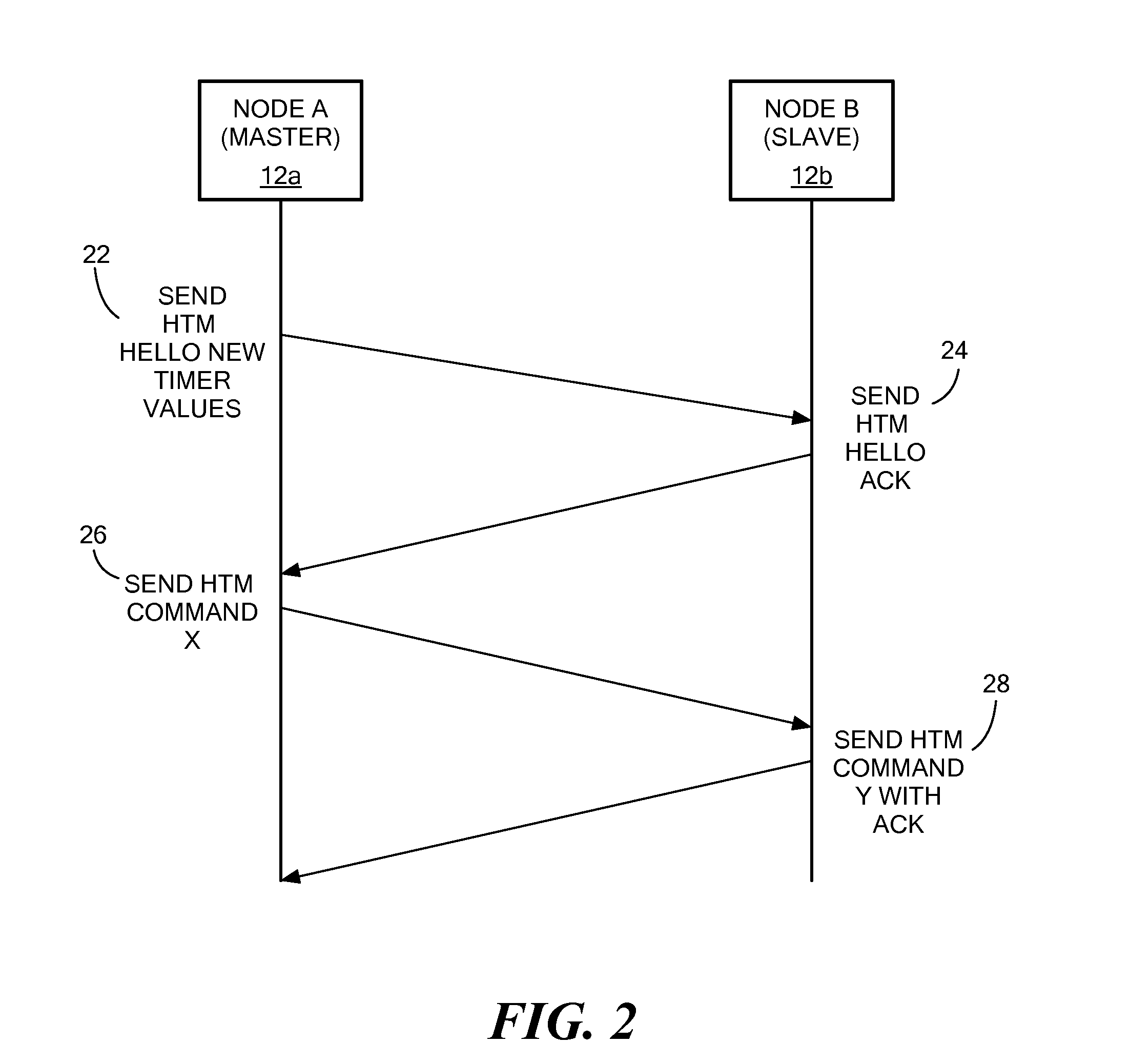

Method and system for optical network smart timer management via delay measurement between spans

A method and system for determining timers in an High Level Data Link Control (HDLC) Traffic Manager (HTM) state machine are disclosed. According to one aspect, the invention provides for determining a transit delay between two nodes by sending a first packet having a delay measurement byte to a second node that is on a link between the first node and the second node. The method also includes receiving a second packet with the delay measurement byte from the second node. The delay measurement byte sent by the second node is adjusted by the second node to indicate its receipt by the second node. A measured delay value is determined. The measured delay value is the delay between a time of sending the first packet to the second node and receiving the second packet from the second node. The measured delay value is determined by the hardware of the first node. Upon determining the measured delay value, timer values of the HTM state machine are set based on the measured delay value.

Owner:CIENA

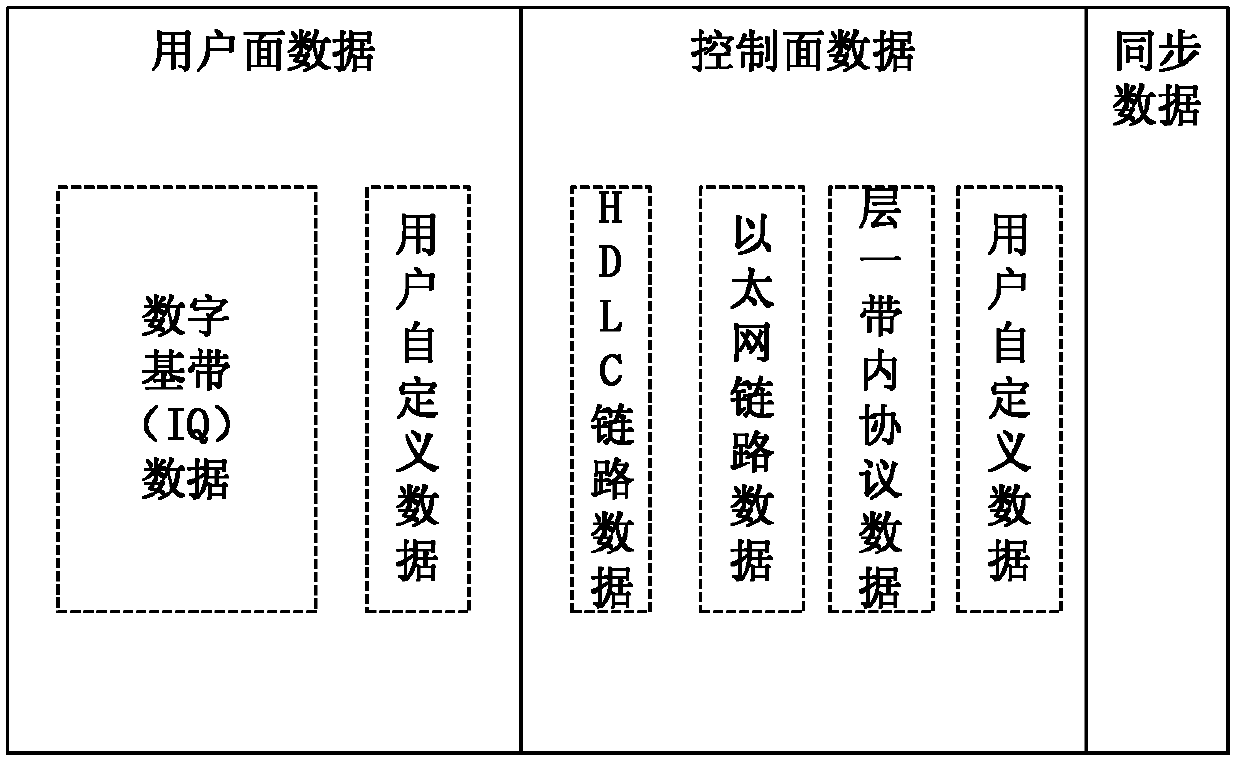

Processing method and processing device for DCC (Data Communication Channel) overhead of SDH (Synchronous Digital Hierarchy) service in packet transport network

ActiveCN102665151ASave RAM resourcesSave resourcesMultiplex system selection arrangementsData switching networksClock rateStructure of Management Information

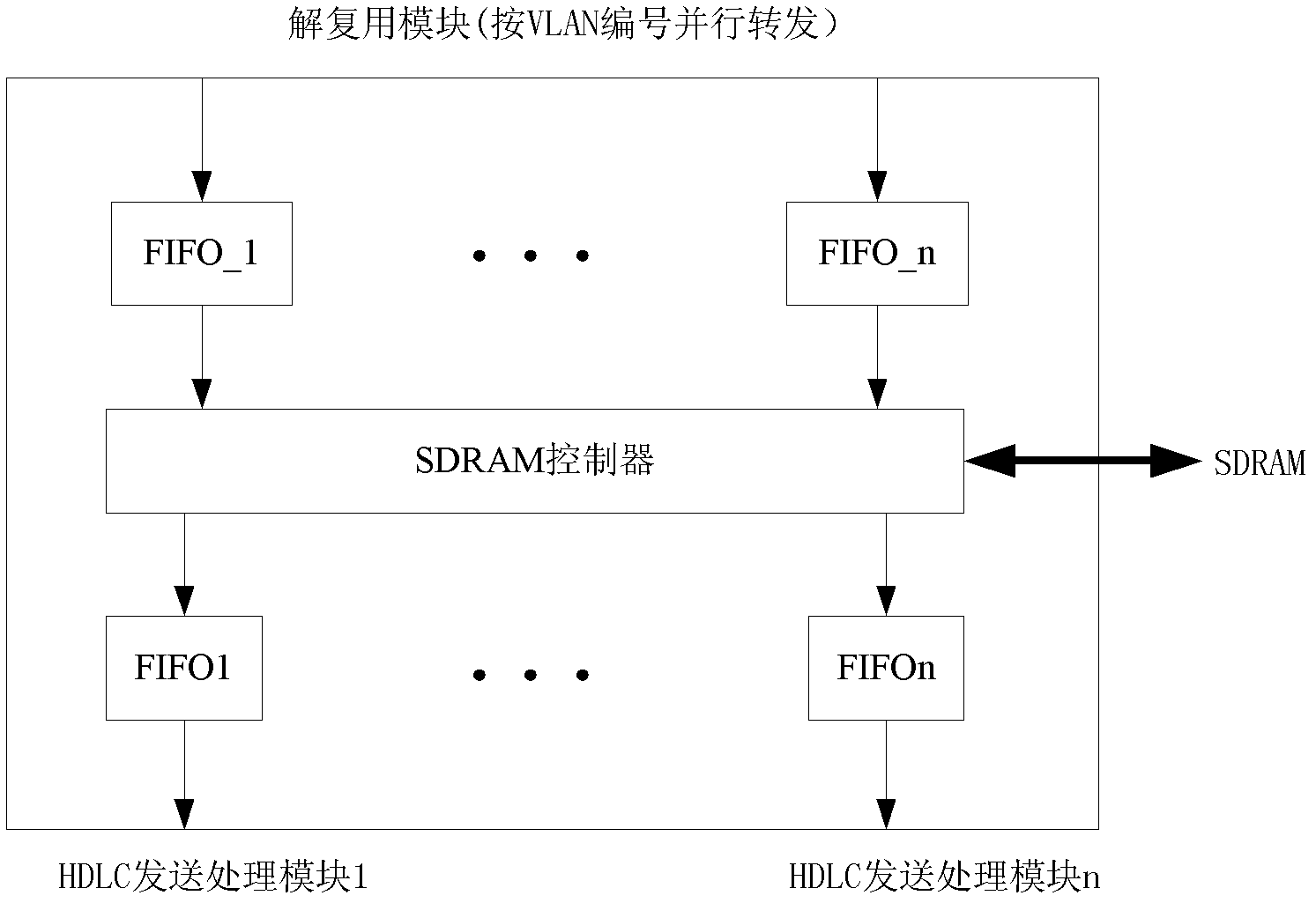

The invention relates to a processing method and a processing device for the DCC overhead of SDH service in a packet transport network. The system comprises an external SDRAM (synchronous dynamic random access memory), moreover, the system adopts an SDRAM-based trilevel cache structure, the first level of cache exists in an Ethernet-to-multichannel HDLC (High-level Data Link Control) demultiplexing module, the second level of cache is the SDRAM, the third level of cache exists in an HDLC transmission processing module, the first level of cache and the third level of cache assist the second level of cache to carry out a multichannel parallel DCC overhead data storage and forwarding function and adaptation function of a back panel side Ethernet clock rate and a line side overhead clock rate; and the space of the second level of cache as the SDRAM is uniformly allocated according to the number of DCC overhead channels to be processed. The processing method and the processing system disclosed by the invention utilize the external SDRAM to satisfy the demand of DCC overhead processing on RAM resource, and can carry out multichannel DCC overhead processing, and moreover, the designed SDRAM-based trilevel cache structure can effectively meet the requirement of multichannel DCC overhead data on parallel transmission.

Owner:FENGHUO COMM SCI & TECH CO LTD

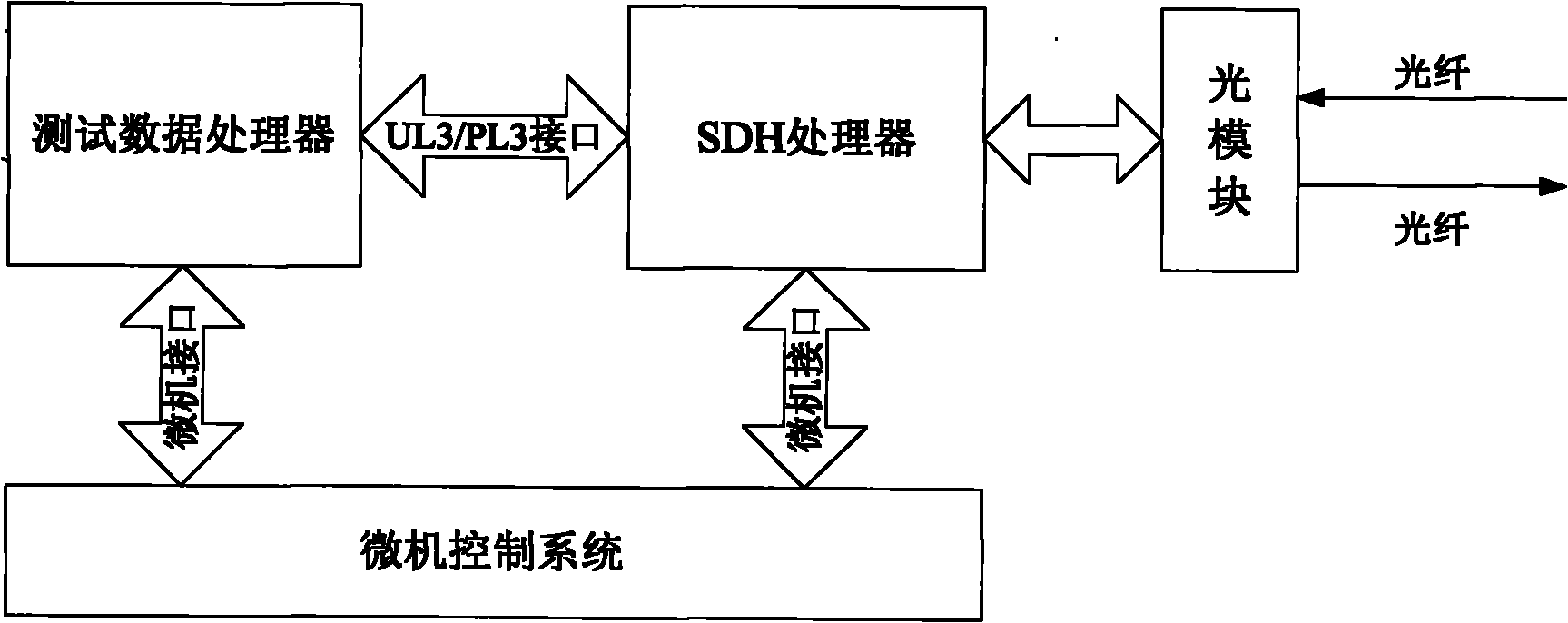

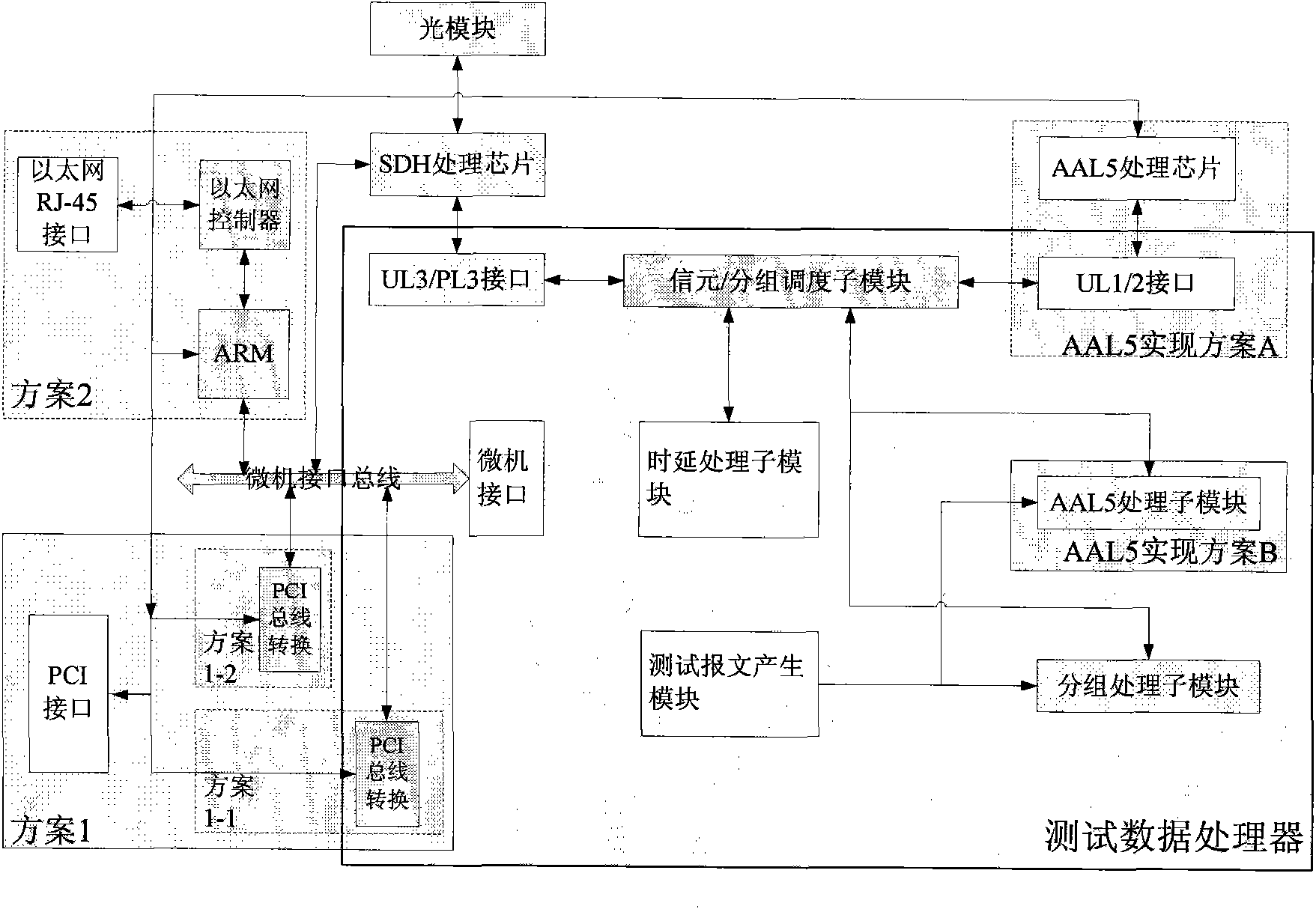

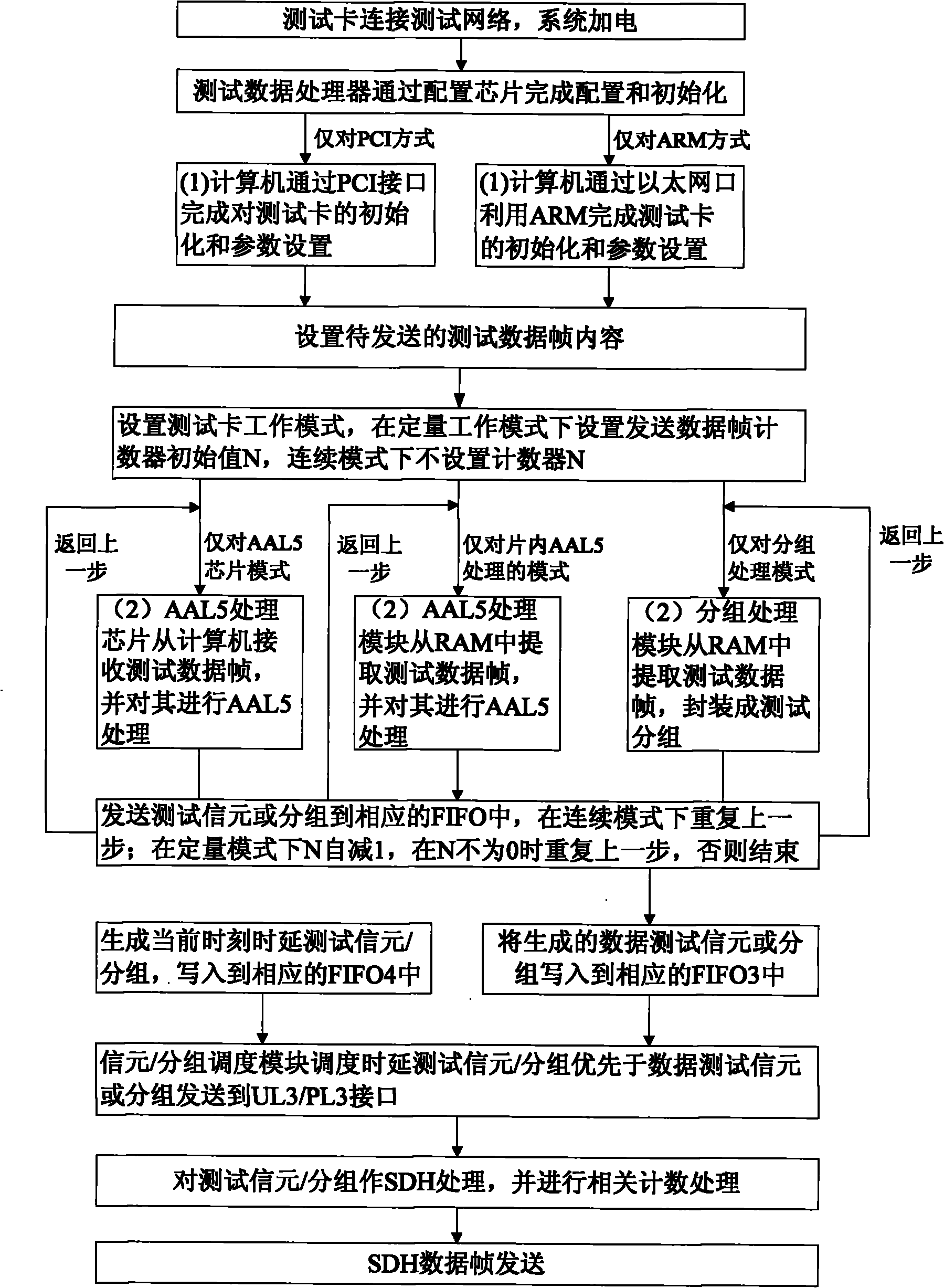

SDH (Synchronous Digital Hierarchy) multi-domain comprehensive test device and test method thereof

InactiveCN101834664AImprove test efficiencyReduce the difficulty of operationFibre transmissionTransmission monitoring/testing/fault-measurement systemsAsynchronous Transfer ModeLoopback

The invention discloses an SDH (Synchronous Digital Hierarchy) multi-domain comprehensive test device and a test method thereof, mainly solving the problem that single test equipment tests the network performance of an ATM (Asynchronous Transfer Mode) network transmitting in an SDH mode or an IP (Internet Protocol) packet network packed by adopting an HDLC (High level Data Link Control) protocol.The SDH multi-domain comprehensive test device mainly comprises a test data processor, an SDH processor and a microcomputer control system. The test method comprises the following steps of: (1) initializing the working mode of the SDH multi-domain comprehensive test device; (2) generating test information cells or packets of the corresponding working mode by the test data processor, mapping into an SDH frame and sending to a tested network element by the SDH processor; (3) extracting the test information cells or the packets from the loopback SDH frame by the SDH processor; (4) processing thereceived test information cells or packets by the test data processor; and (5) analyzing and displaying a test result by the microcomputer control system. The invention can not only test a single-mode or multi-mode multi-rate SDH network, but also realize that the single equipment tests the network performance of the ATM network and the packet network, and has easy and convenient operation and high cost performance.

Owner:XIDIAN UNIV

Method and apparatus for providing ringing timeout disconnect supervision in remote telephone extensions using voice over packet-data-network systems (VOPS)

InactiveUS20080175233A1Time-division multiplexCurrent supply arrangementsFrame RelayNetworked system

A Multiservice Access Concentrator (MAC) provides a time limit for a first ringing voltage signal in response to an attempted call. The call is attempted via a voice over packet-data-network system (VOPS), wherein the VOPS comprises voice over Internet Protocol (IP), voice over Frame Relay, voice over Asynchronous Transfer Mode (ATM), and voice over High-level Data Link Control (HDLC) network systems. Generation of the first ringing voltage signal is terminated upon expiration of the time limit. A control message is transmitted to terminate the attempted call, wherein the control message is transmitted via the VOPS.

Owner:CISCO TECH INC

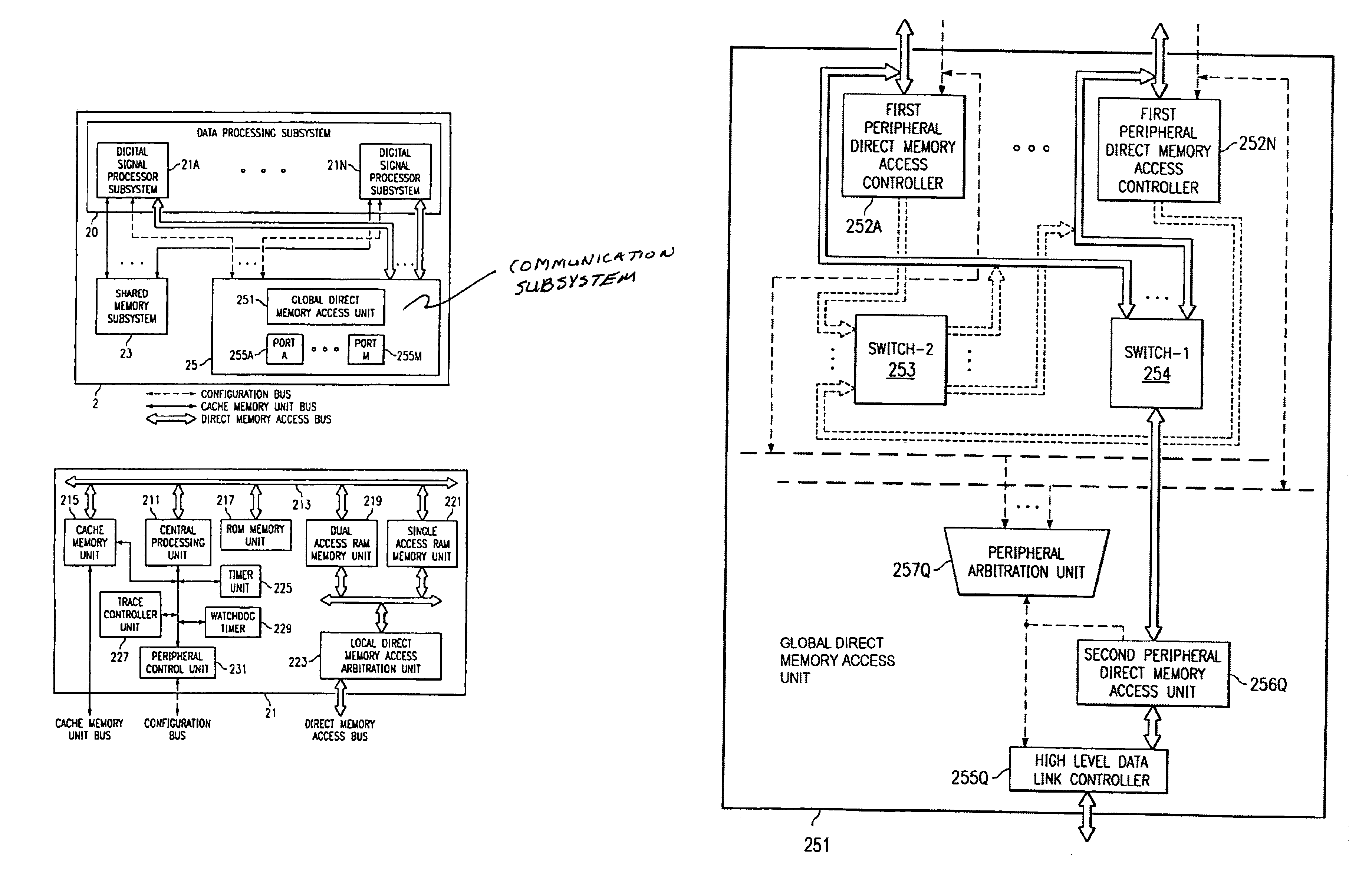

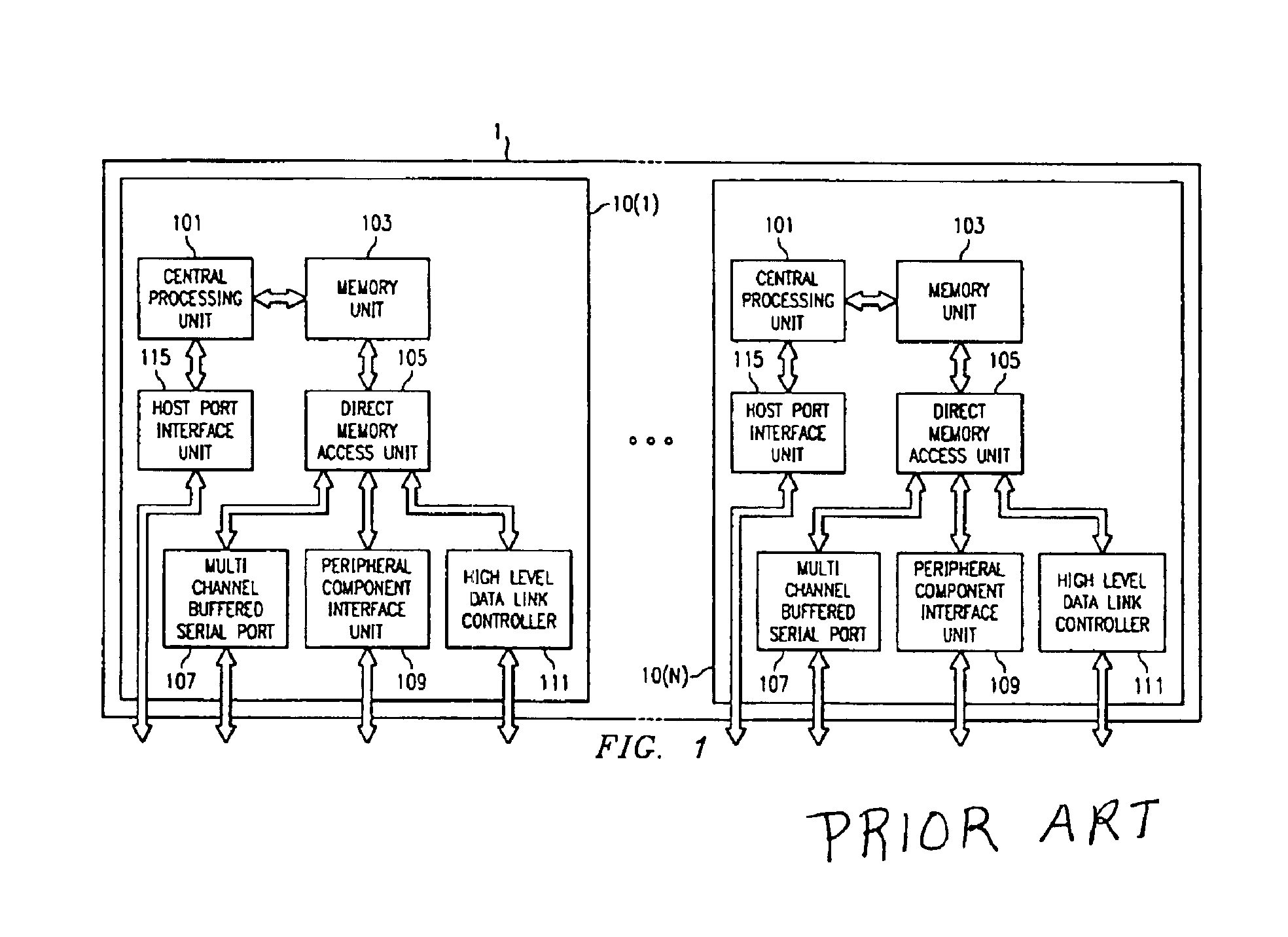

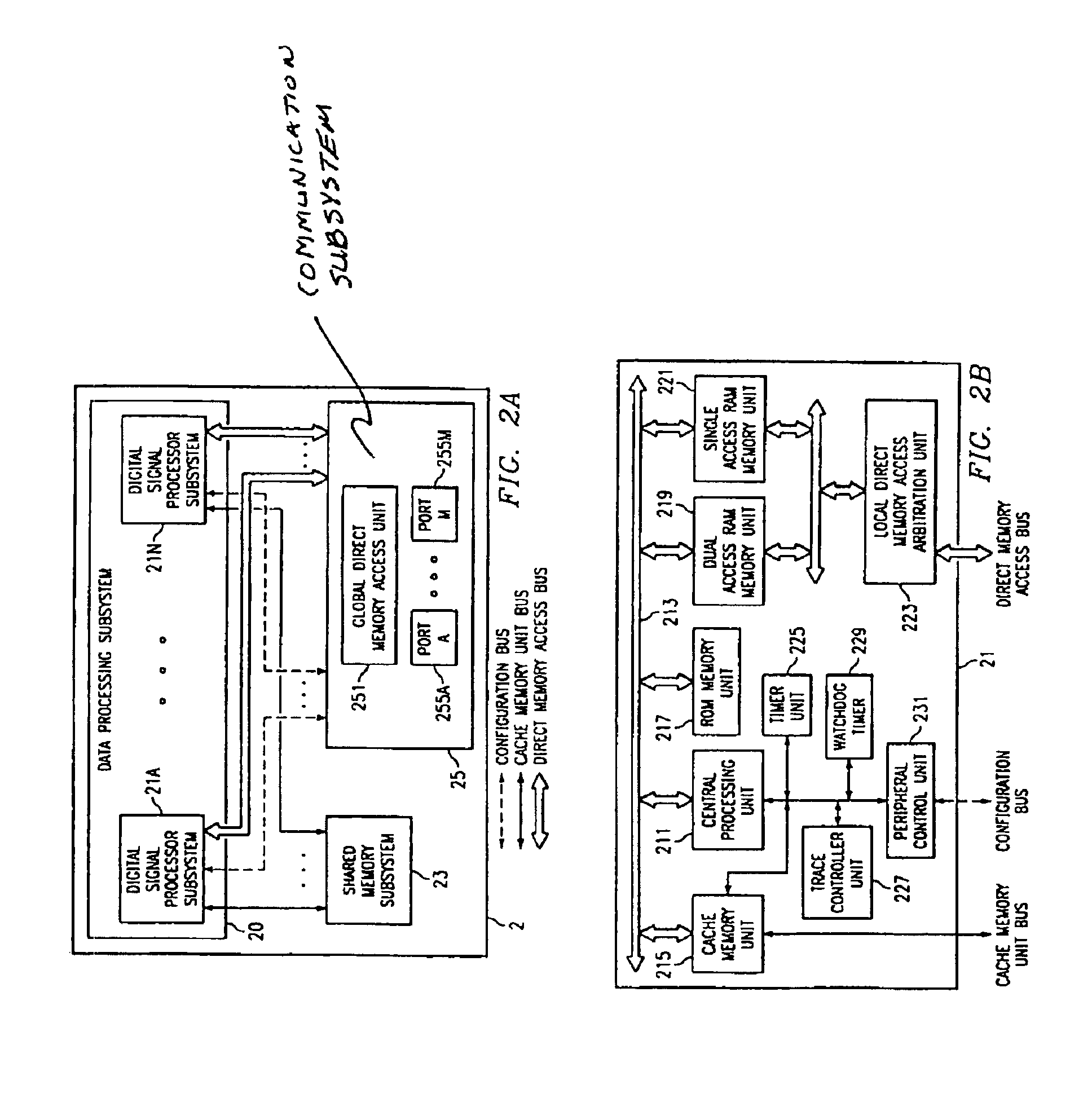

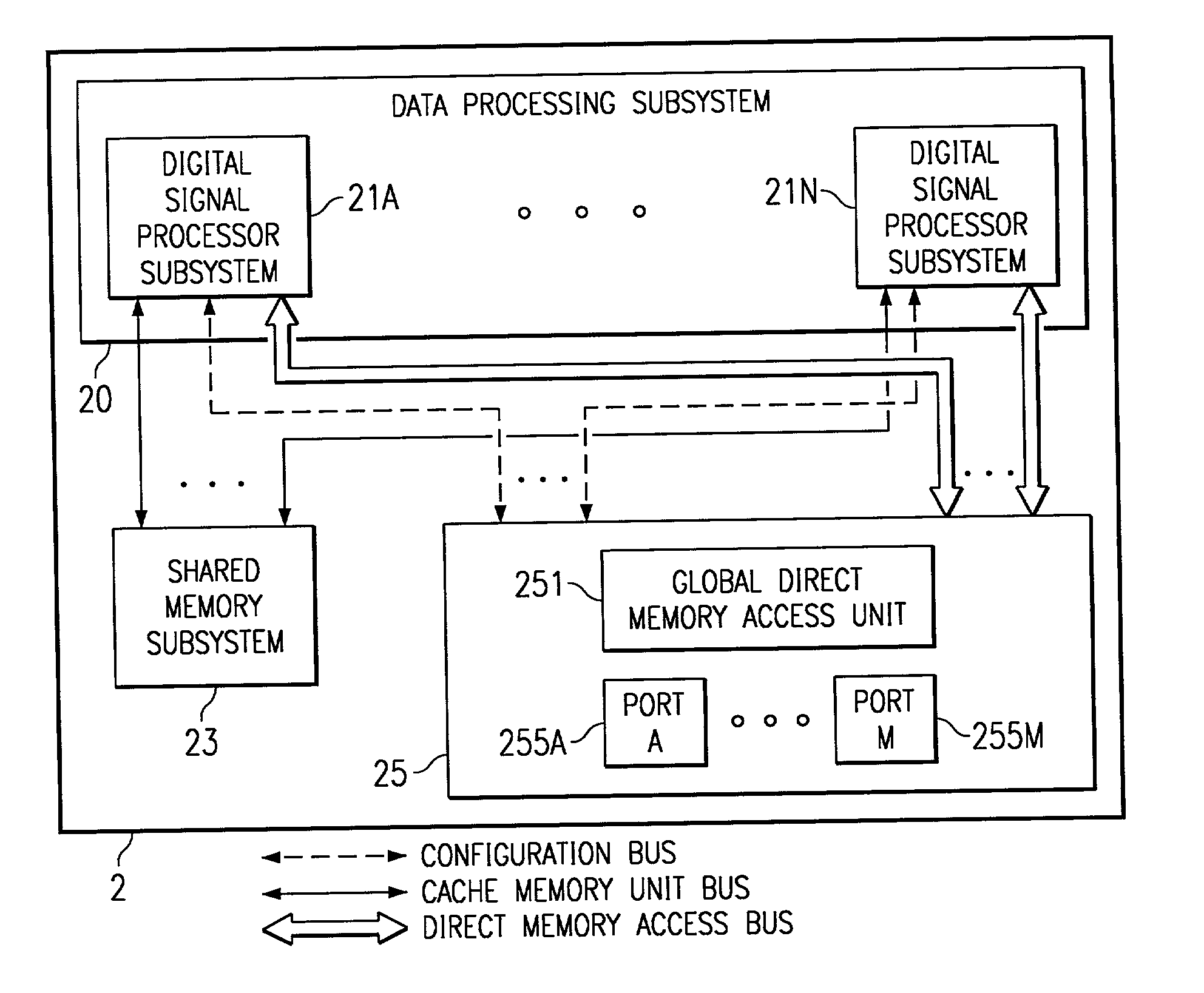

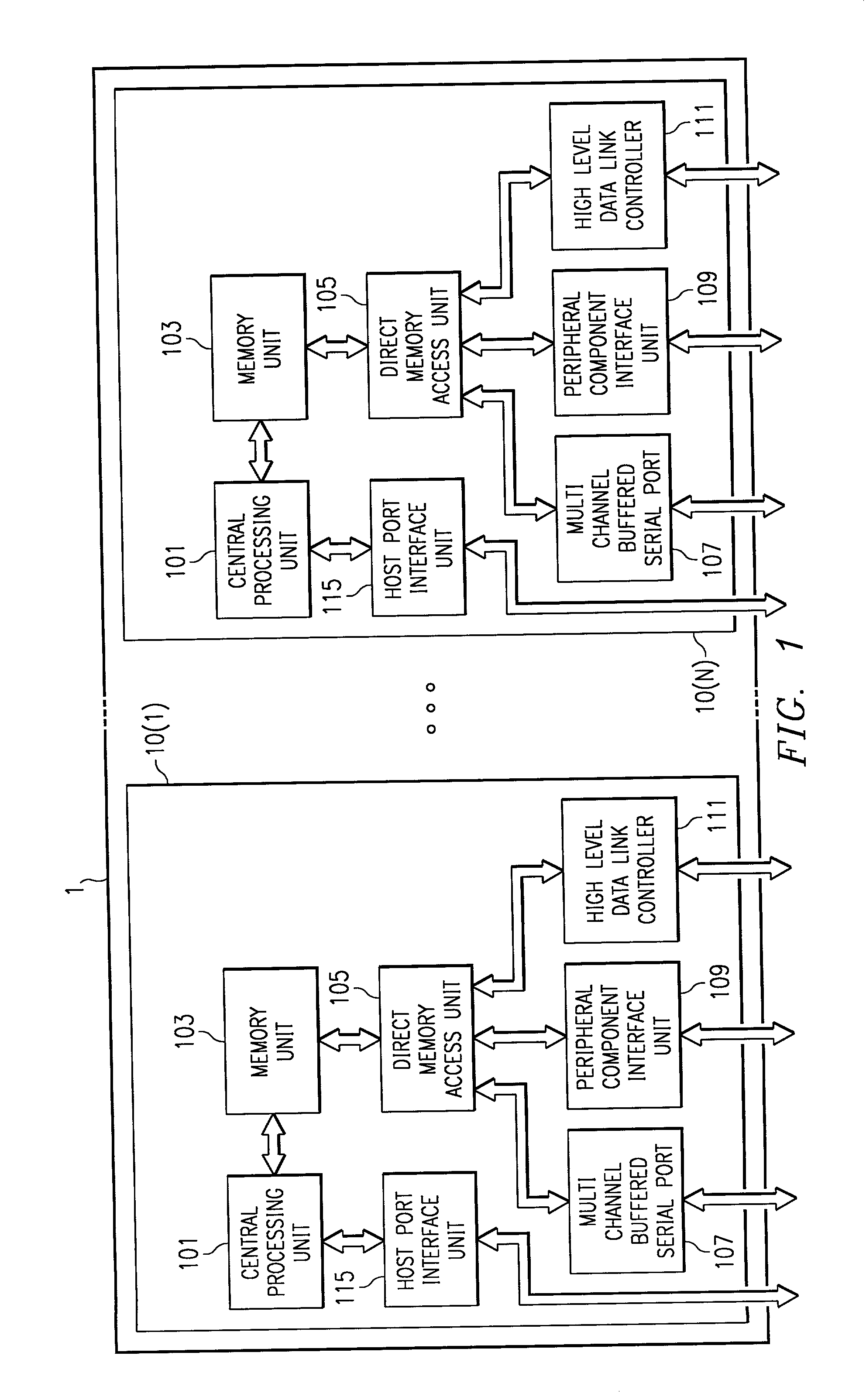

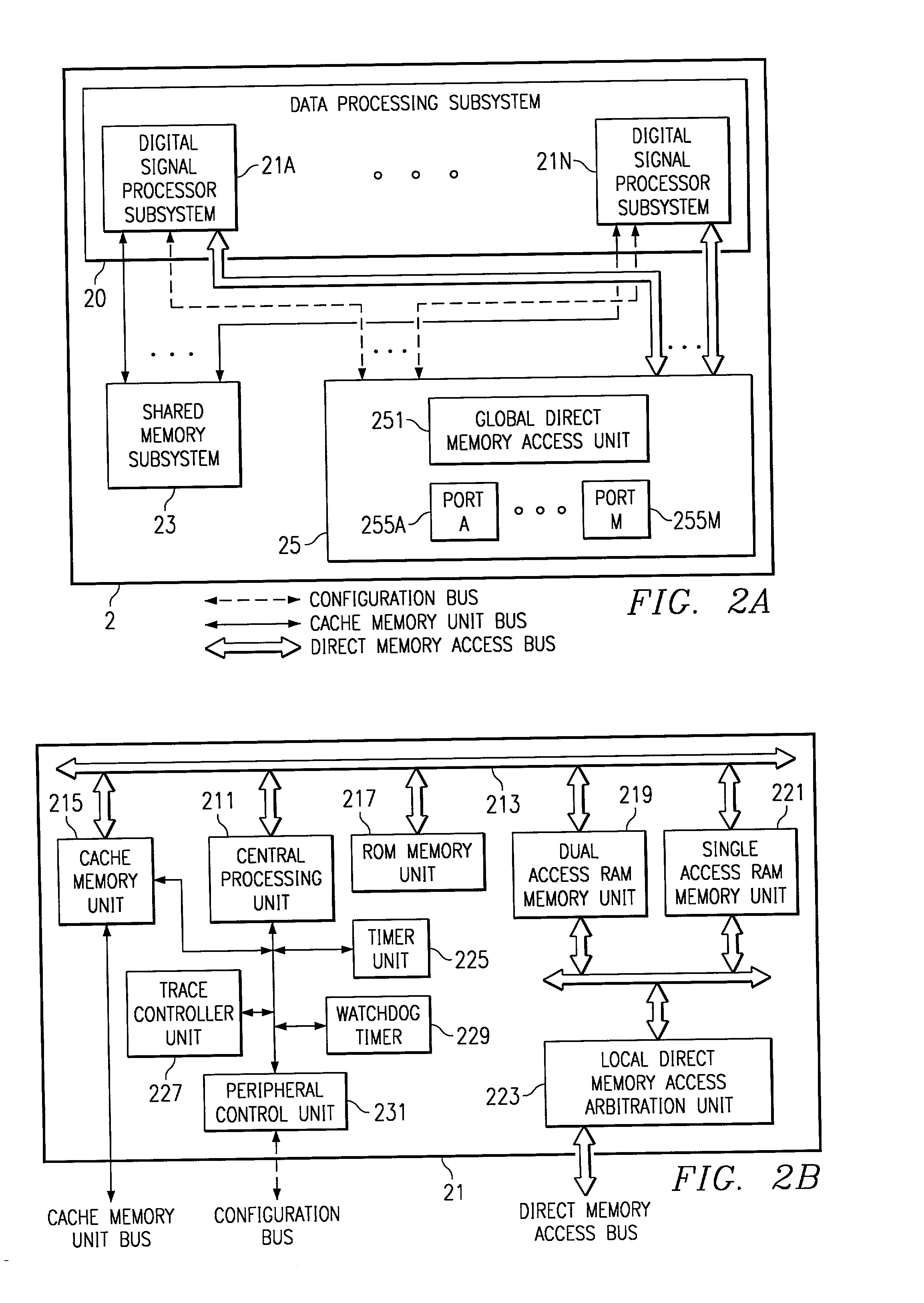

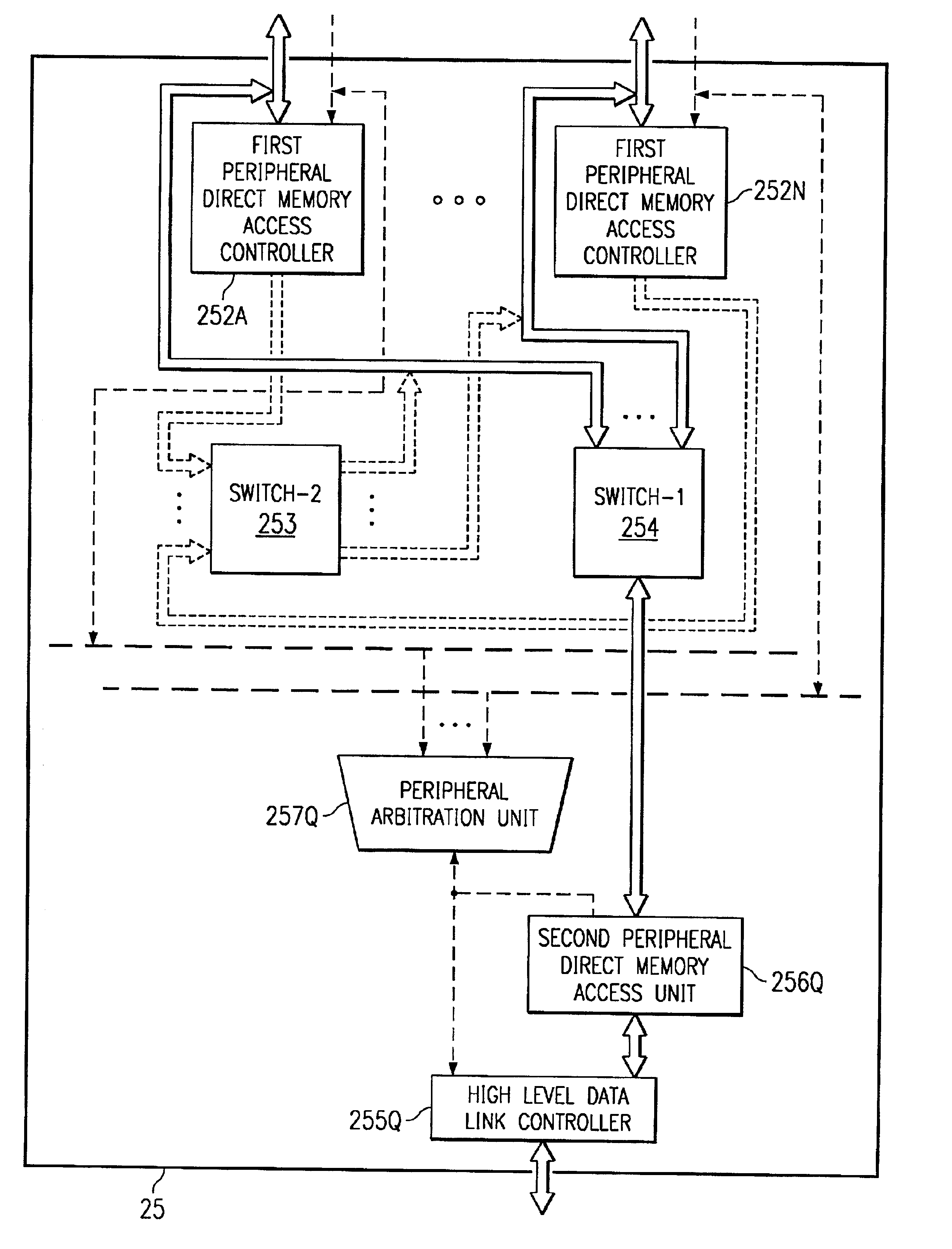

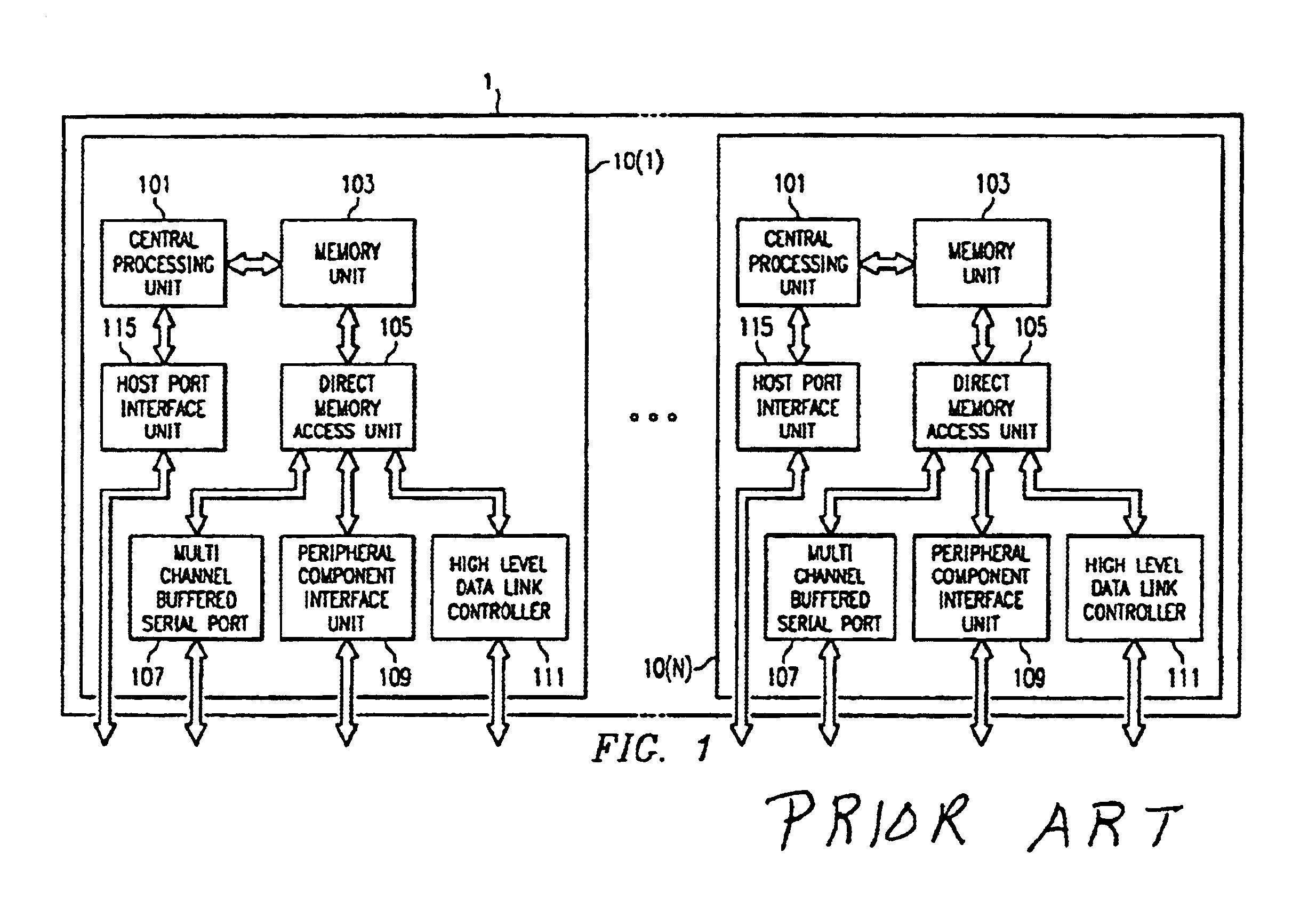

Apparatus and method for responding to a interruption of a packet flow to a high level data link controller in a signal processing system

InactiveUS7054958B2Digital computer detailsInput/output processes for data processingData processing systemDirect memory access

In a data processing system including a plurality of digital signal processor subsystems, selected peripheral components are shared by the digital signal processor subsystems. In particular, the high level data link controller is shared by the subsystems. Using a first interrupt signal after each transfer of signal groups from the peripheral direct memory access unit, the data can be efficiently transferred from a channel memory of the peripheral direct memory access unit to the high level data link controller. A second interrupt from the high level data link controller when a last word of a packet is transferred thereto causes a new channel memory to be accessed. An abort signal is generated when a signal group for a packet being processed by the high level data link controller is not available in a timely manner.

Owner:TEXAS INSTR INC

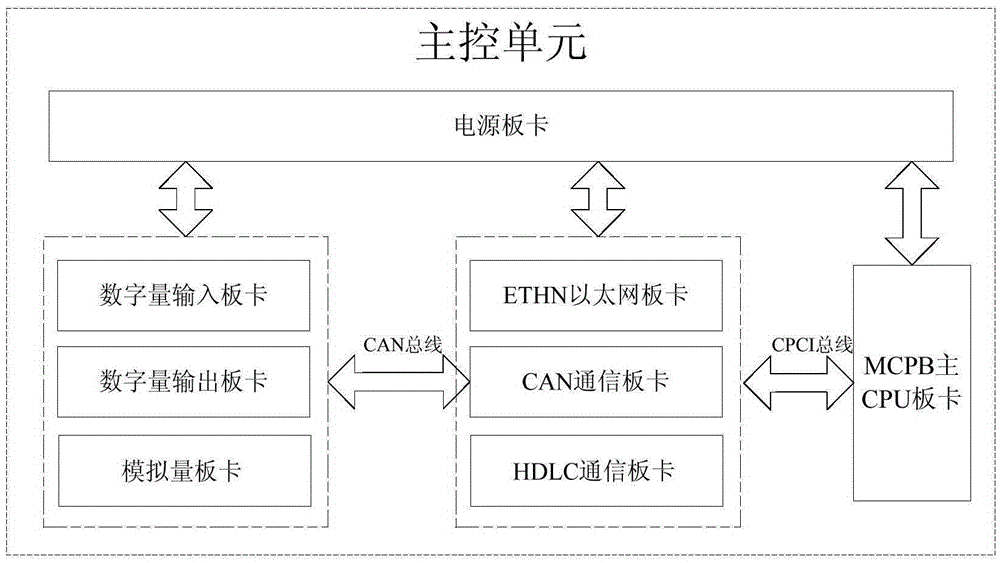

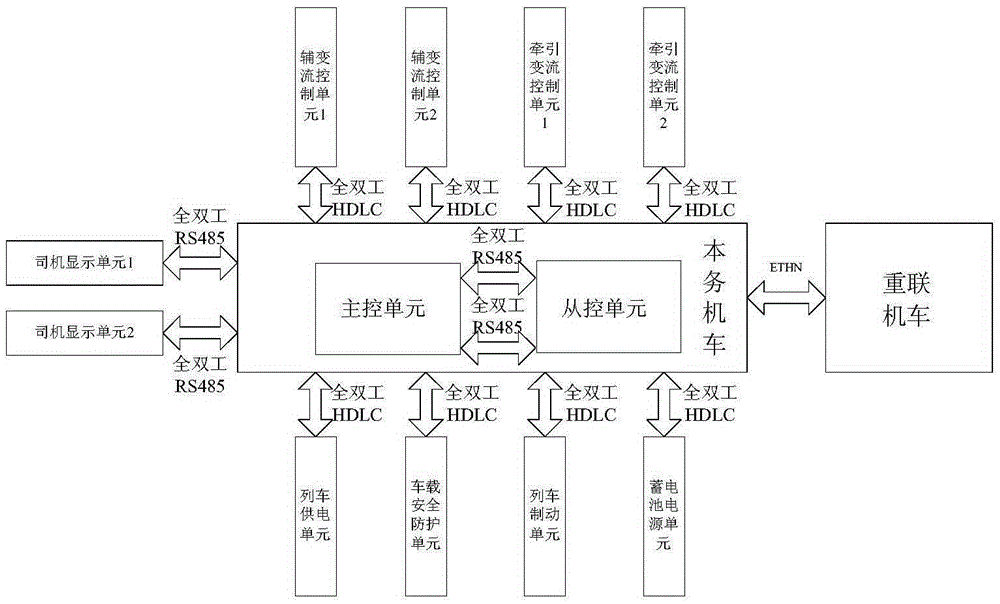

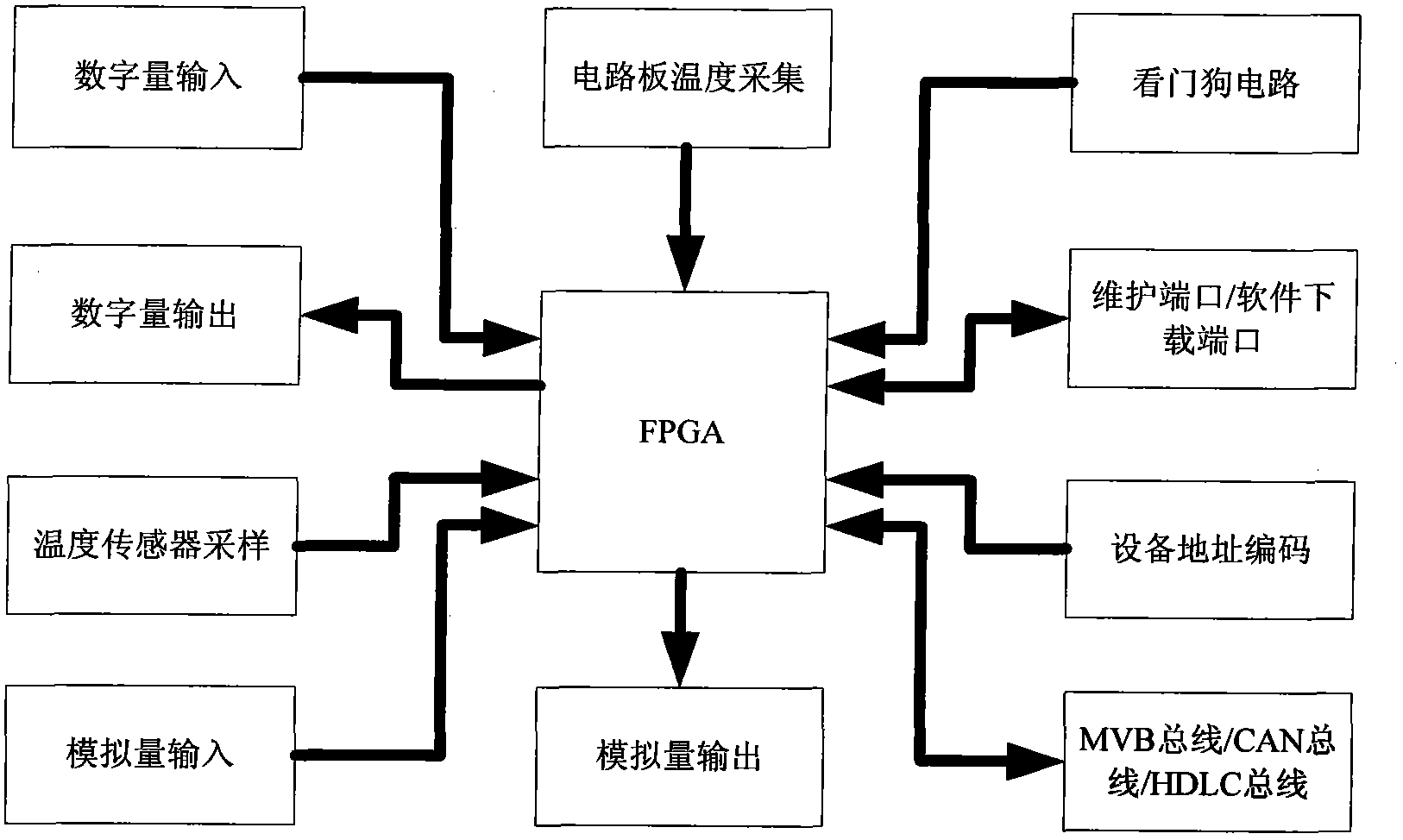

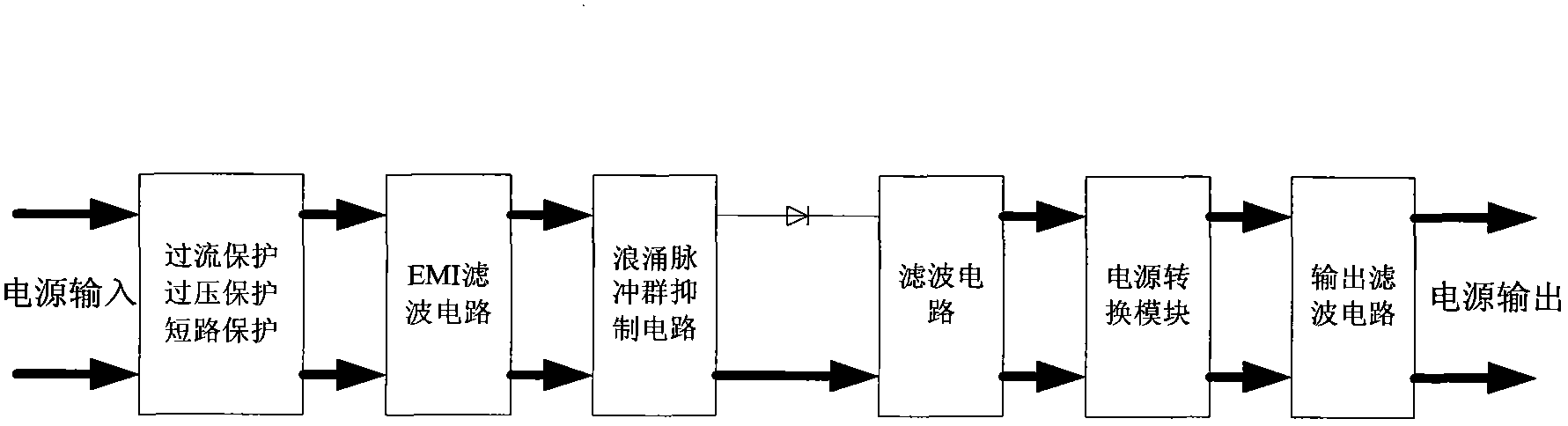

Main control unit of electric locomotive based on QNX (Quick Unix)

ActiveCN105425642AHighly integratedImprove reliabilityProgramme control in sequence/logic controllersHigh-Level Data Link ControlDigital input

The invention discloses a main control unit of an electric locomotive based on a QNX (Quick Unix). The electric locomotive comprises the main control unit and a slave control unit which have the same software and hardware configuration, constitute a hot standby redundancy system and communicate with each other through full duplex RS485, wherein the hardware structure of the main control unit comprises a power board card, an MCPB (Main CPU (Central Processing Unit) board) card, a CAN (Controller Area Network) communication board card, an HDLC (High-level Data Link Control) communication board card, an ETHN (Ethernet) board card, a digital input board card, a digital output board card and an analog board card; according to the specific requirements of a novel electric locomotive, acquisition and processing of state information of the locomotive and storage of key data of the locomotive are realized, and each device of the locomotive is controlled to run harmonically and normally. Various functions of the novel electric locomotive can be met, the integration degree is high, the size is small, the cost is reasonably reduced, the universality is strong, and the locomotive is easy to maintain, strong in instantaneity and high in reliability.

Owner:CRRC DALIAN INST CO LTD

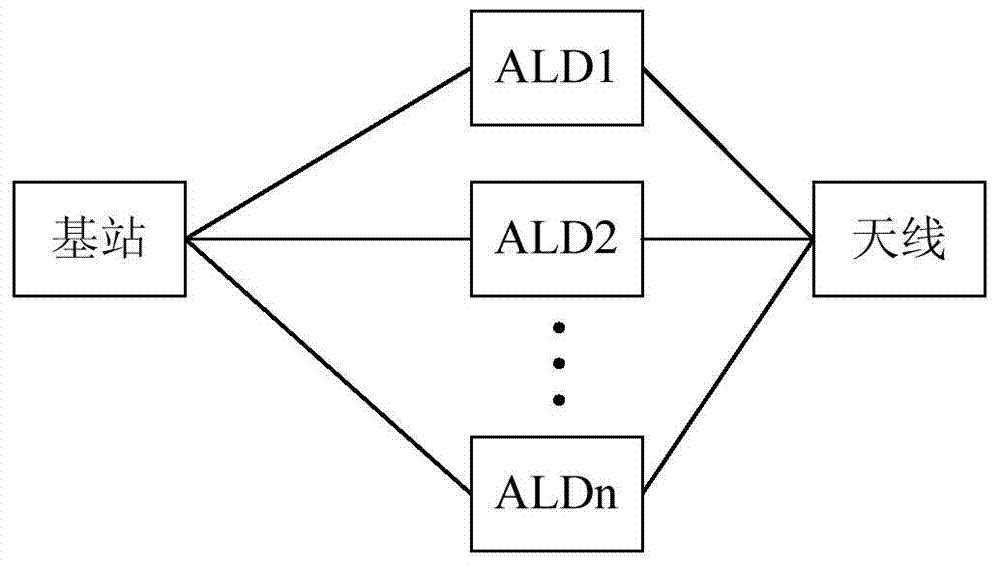

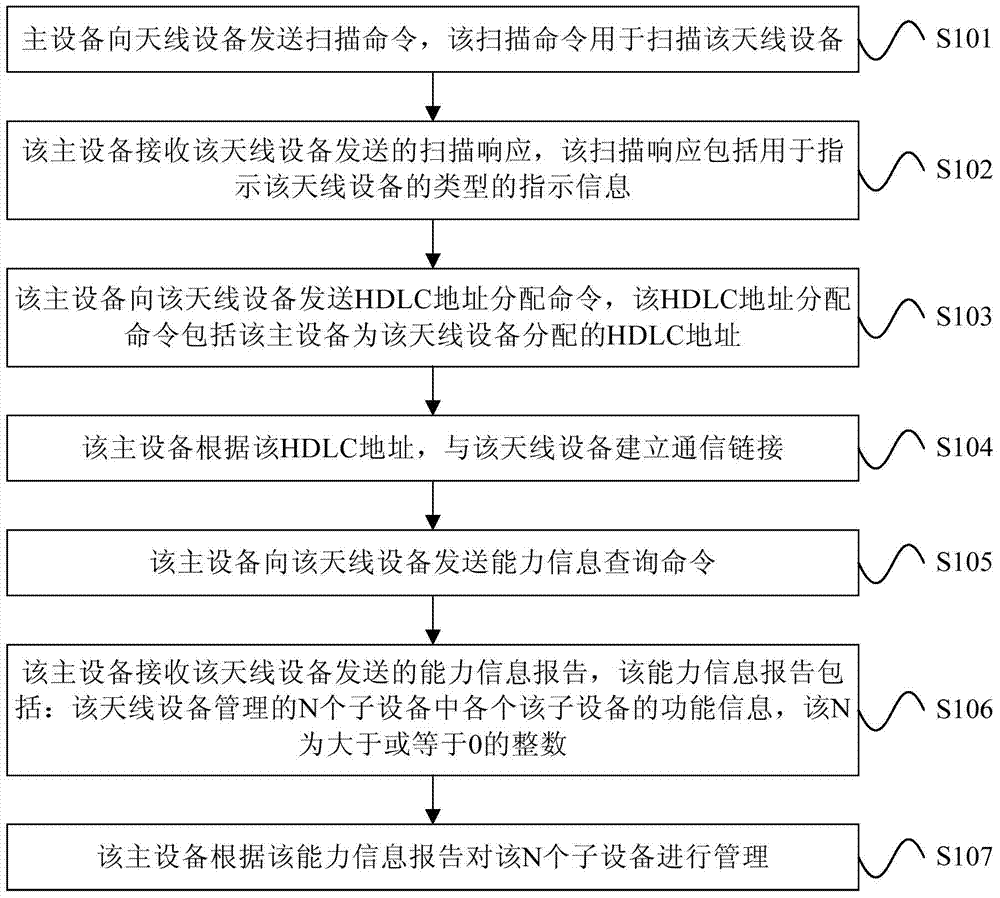

Antenna device management method and device

ActiveCN104507116AReduce complexityTransmissionWireless communicationCommunication linkComputer science

An embodiment of the invention provides an antenna device management method and device. The method includes the steps: transmitting a scanning command for scanning an antenna device to the antenna device by a main device; receiving scanning response transmitted by the antenna device; transmitting an HDLC (high-level data link control) address assignment command to the antenna device; building a communication link with the antenna device according to an HDLC address; transmitting a capability information inquiry command to the antenna device; receiving a capability information report transmitted by the antenna device. The scanning response comprises indicating information for indicating the type of the antenna device, the type of the antenna device is a container antenna device, the HDLC address assignment command comprises the HDLC address assigned by the main device for the antenna device, the capability information report comprises functional information of N sub-devices managed by the antenna device, and N is larger than or equal to zero. The complexity of the main device managing the antenna device is reduced.

Owner:HUAWEI TECH CO LTD

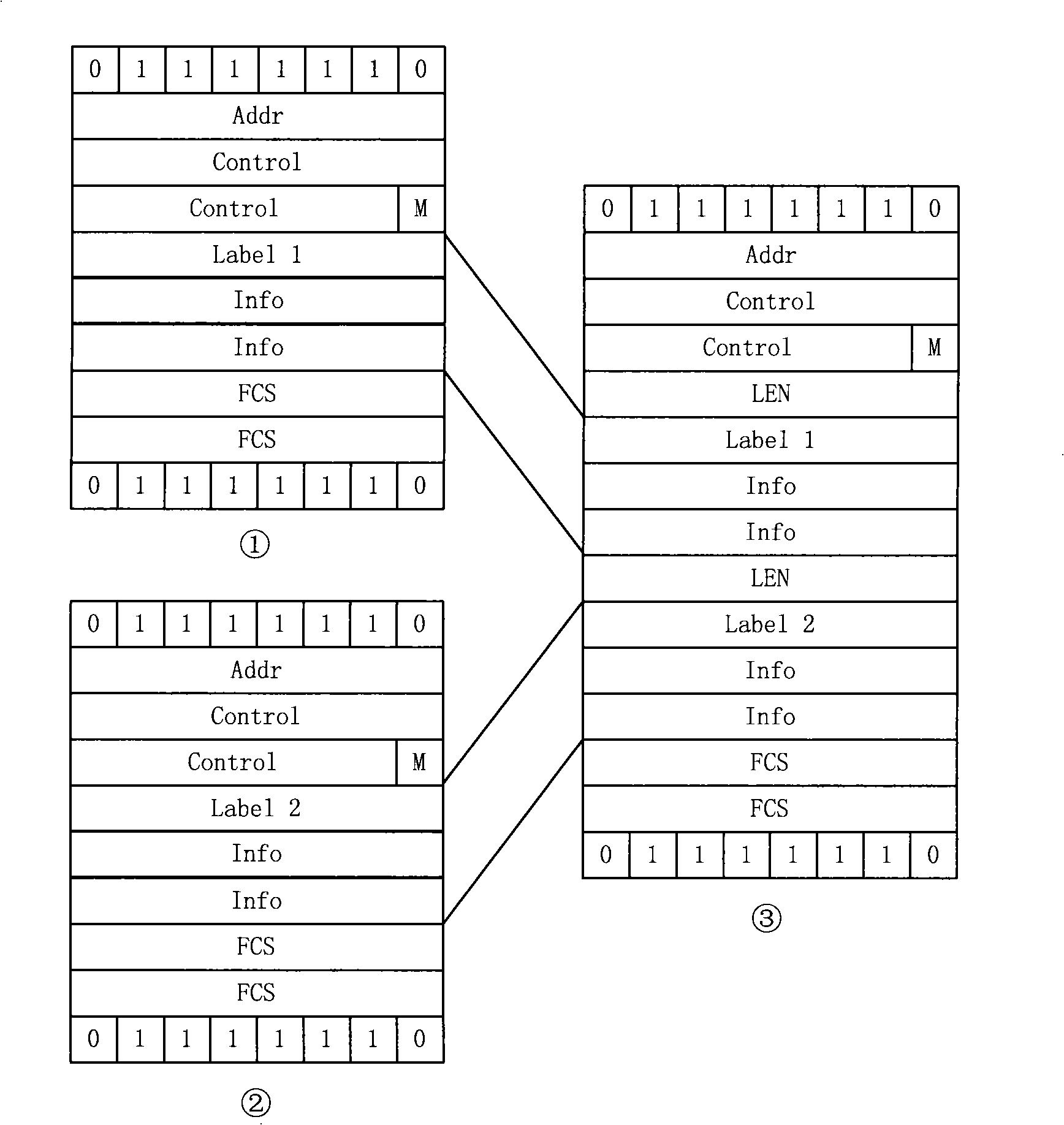

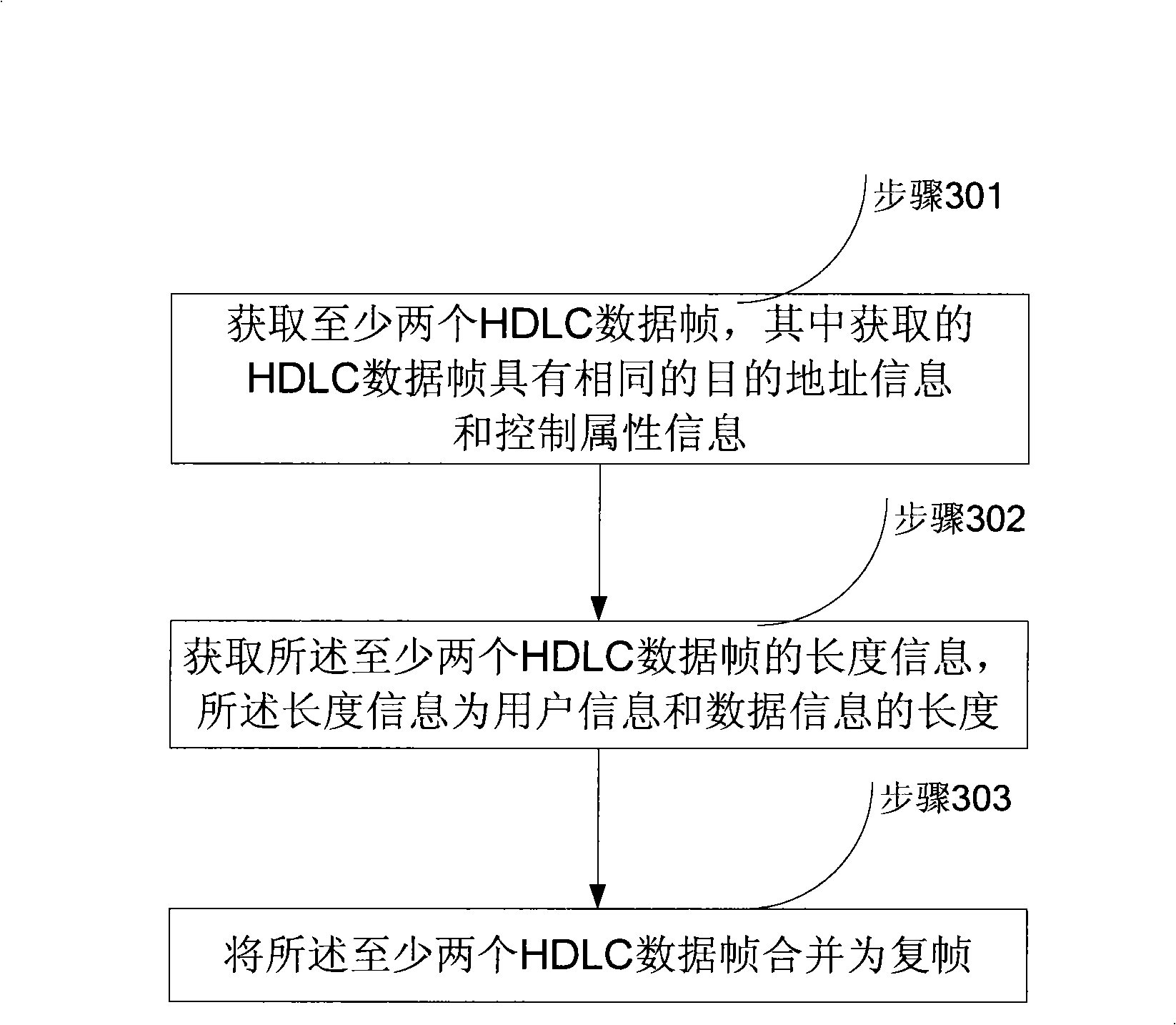

Multi-frame synthesizing and parsing method and apparatus, multi-frame processing system

The embodiment of the present invention discloses a method for multi-frame synthesizing, including: acquiring at least two high-level data link control HDLC data frames, wherein the acquired HDLC data frames have identical destination address information and control properties information; acquiring the length information of the at least two HDLC data frames, wherein, the length information is the length of user information and data information of each HDLC data frame; combining the at least two HDLC data frames into a multi-frame which includes the destination address information and control properties information, and user information, data information and length information of the at least two HDLC data frames. Also provided is a method for synthesizing multi-frame, a device for parsing multi-frame and a multi-frame processing system, accordingly realizing that the inventive multi-frame combination method is used to advance transmission efficiency, and advanced transmission efficiency will be more obvious if there is more synthetic single frame data.

Owner:XFUSION DIGITAL TECH CO LTD

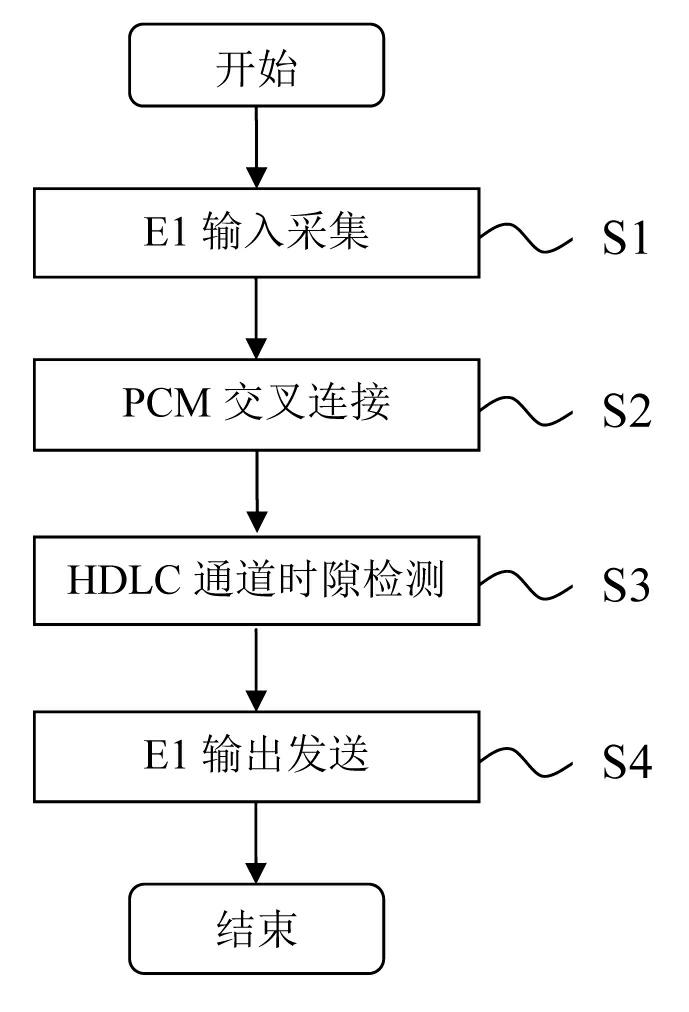

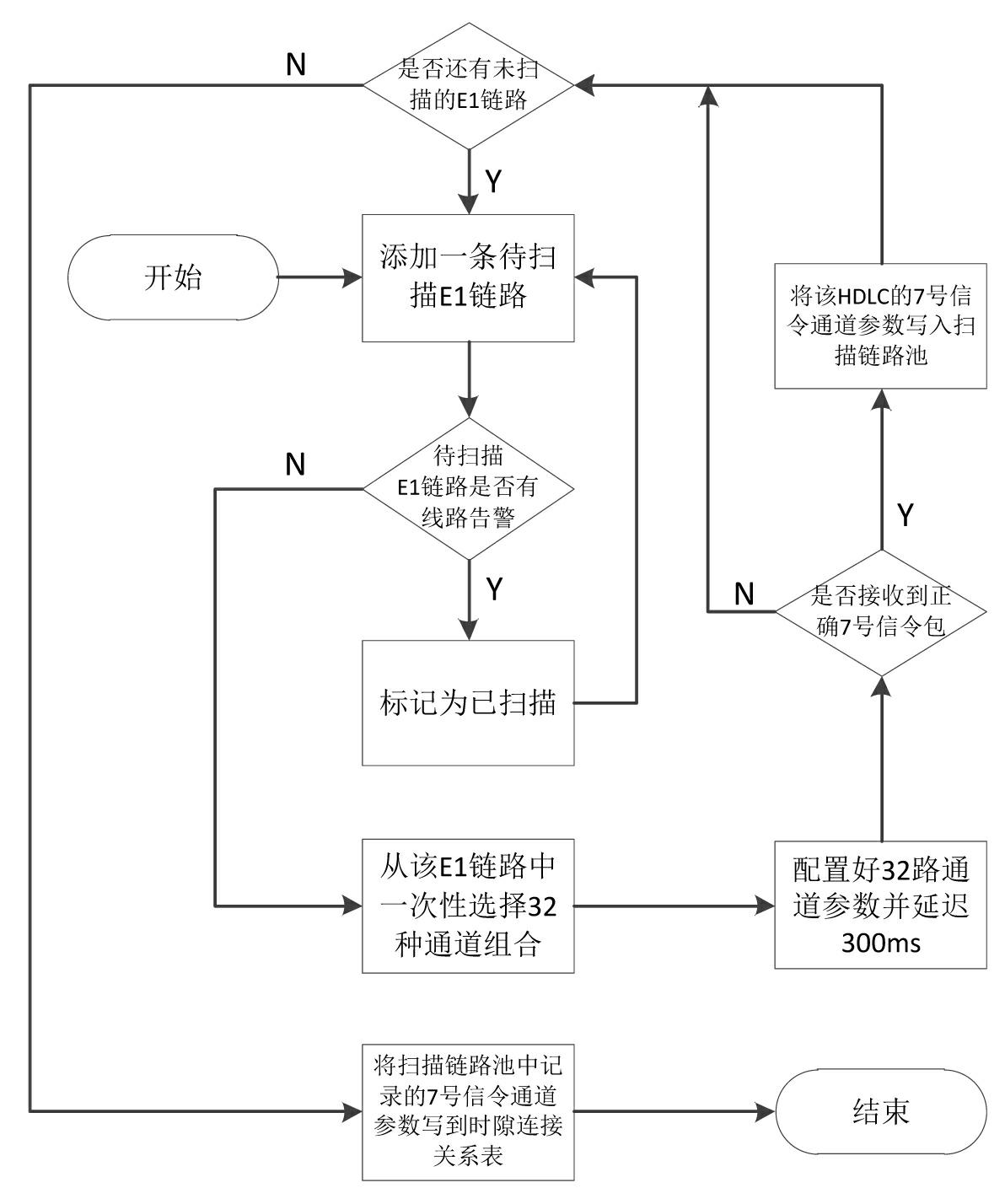

Method and device for detecting signalling No.7 channel based on E1

InactiveCN102202243AAvoid mistakesSimple and reasonable structureSelection arrangementsCross connectionChannel parameter

The invention discloses a method and a device for detecting a signalling No.7 channel based on E1, comprising the following steps: S1. an E1 inputting and collecting step: collecting multi-path E1 input signals with signalling No.7; S2. a step of connecting pulse code modulation (PCM) in crossing manner: carrying out timelot cross connection on the multi-path E1 input signals; S3. a high level data link control (HLDL) channel timeslot detection step: the timeslot channel detection of the crossed obtained signal; and S4. an E1 output sending step: converging the detected effective signalling No.7 channel timeslot to an output port. The invention also discloses a device for realizing the method. As the method and device finish the convergence of the signalling No.7 from input to output, thus the condition that the error possibly appear in HDLC channel parameters of manually configured collection equipment can be avoided, and the E1 interface resources of the collection equipment also can be saved. As the practical detection method and device, the method and the device in the invention can be widely applied to a signalling No.7 monitoring system.

Owner:珠海市佳讯实业有限公司

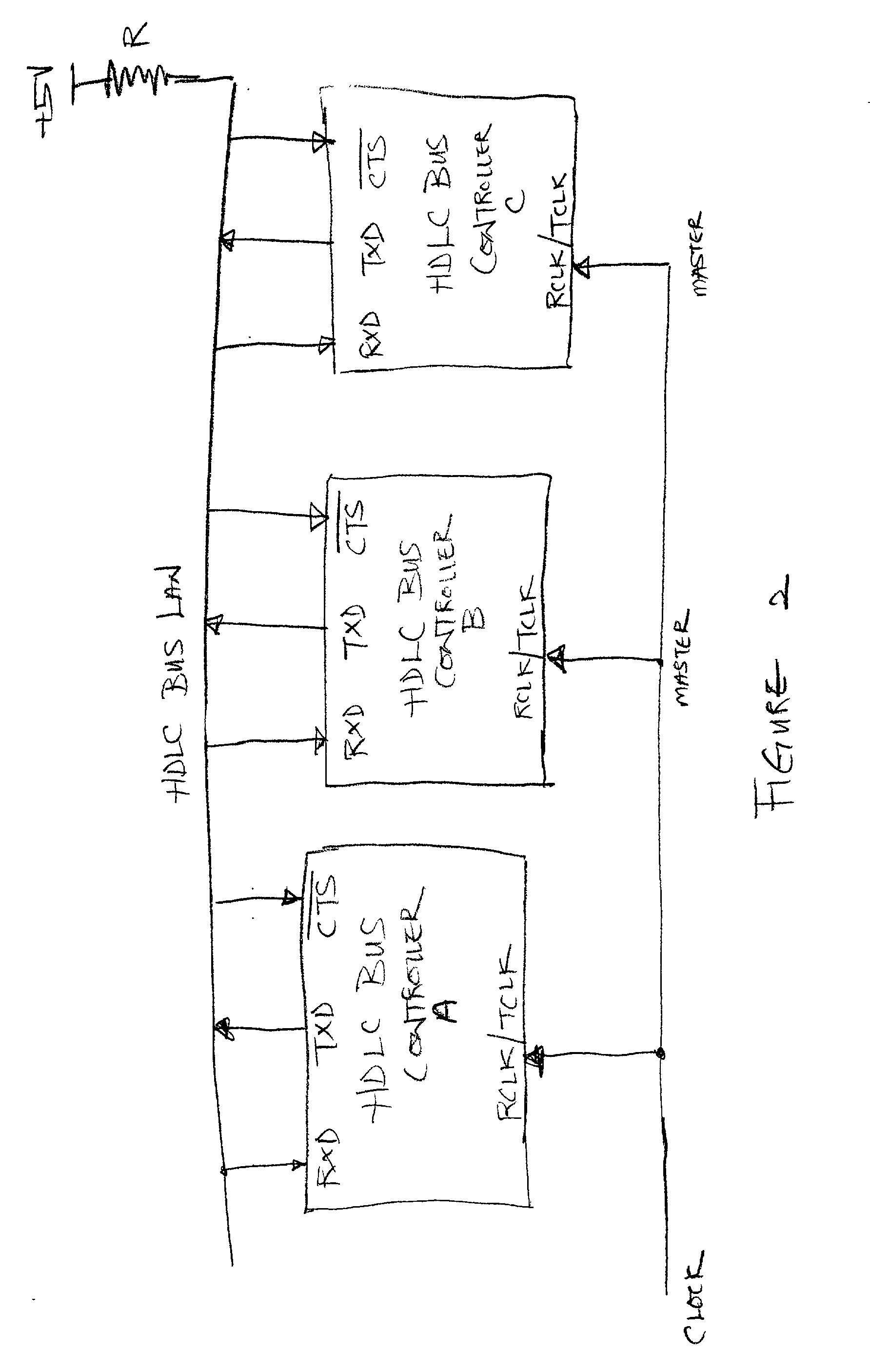

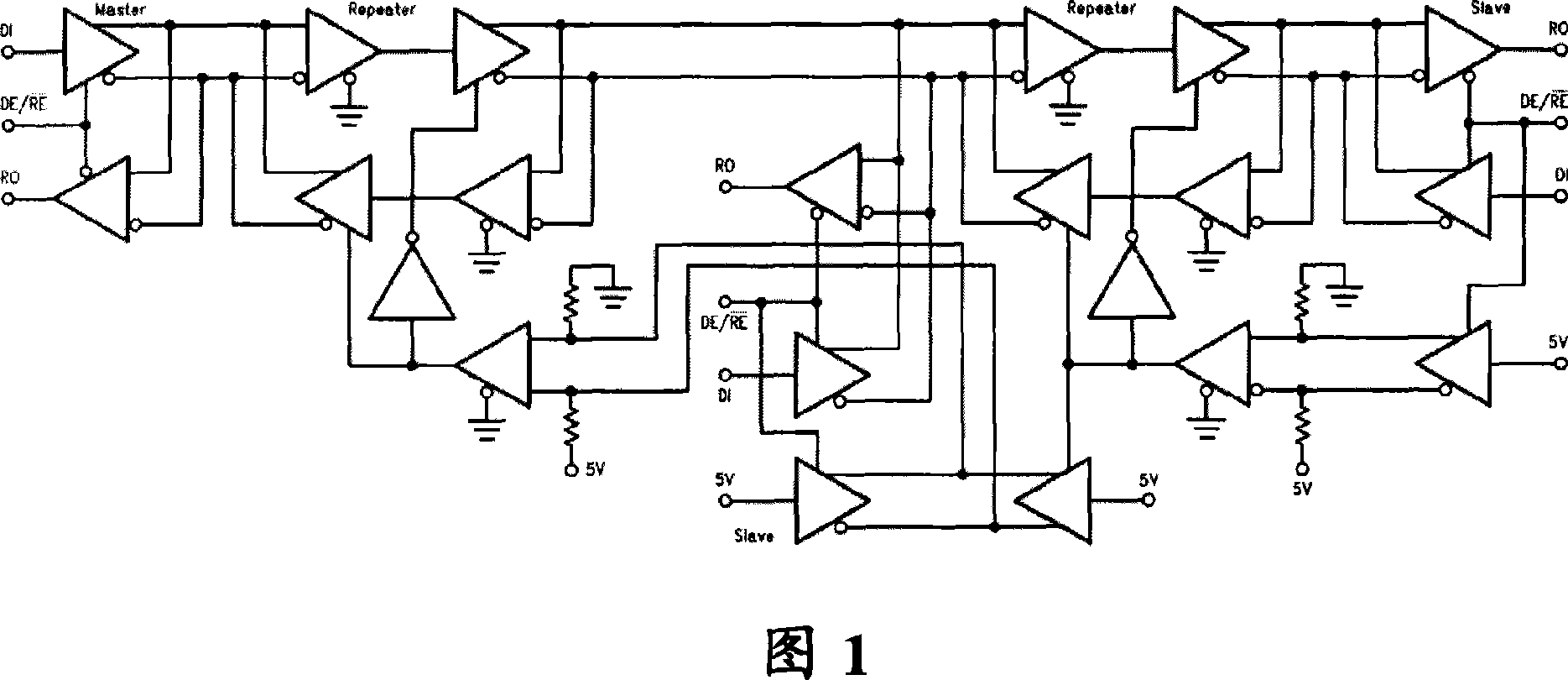

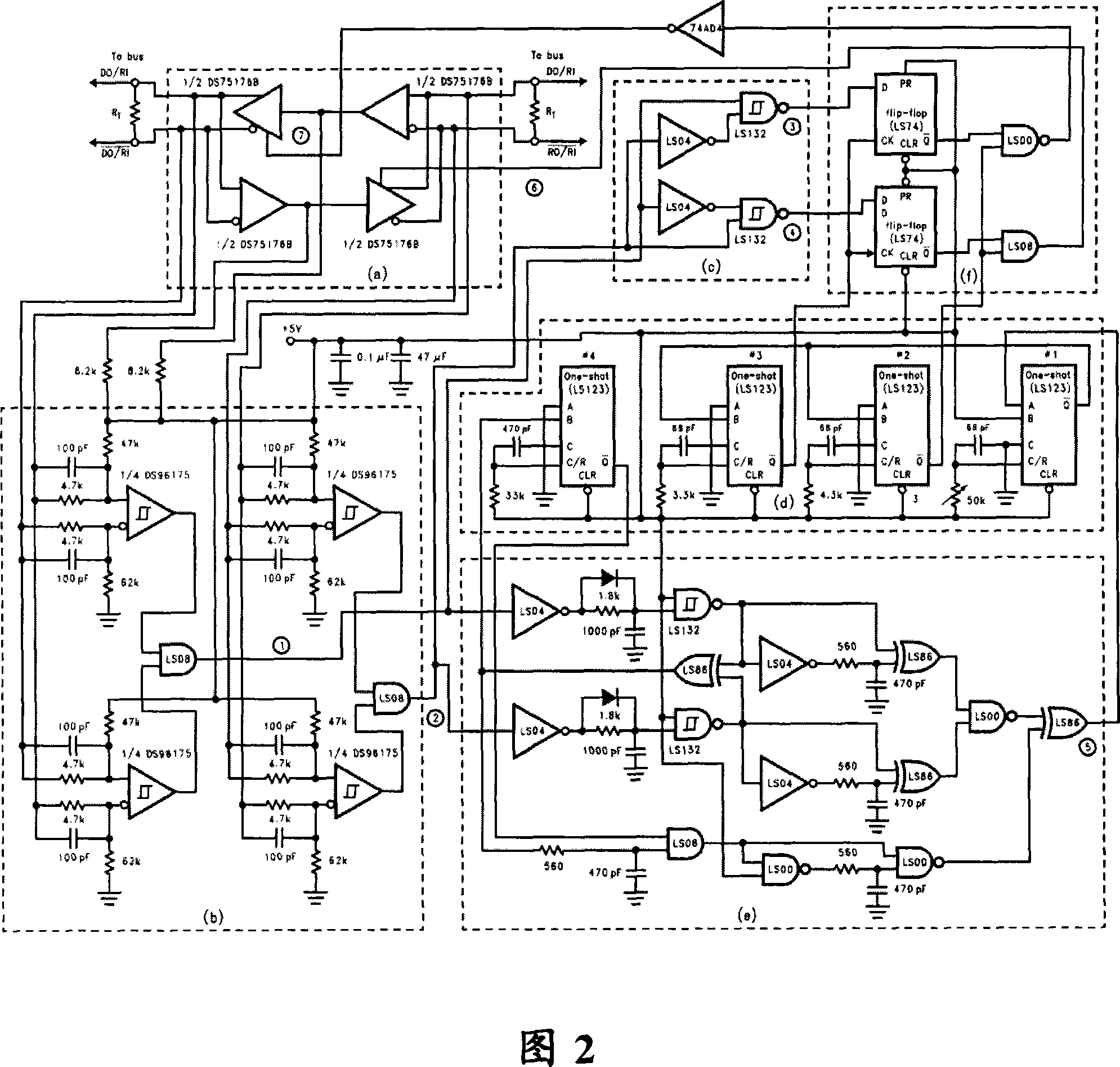

Method and apparatus for providing full duplex/half duplex radially distributed serial control bus architecture

A communication network includes peripheral cards in the backplane that are individually connected using separate interface cables to the system controller for individual isolation to provide full duplex / half duplex radially distributed serial control bus architecture with high level data link control (HDLC) bus interface which provides for collision detection, fault isolation and peripheral card communication fault recovery.

Owner:FORSTER ENERGY

System and method for compressing communication flows in a network environment

ActiveUS7460516B1Facilitate data exchangeEliminate and greatly reduce disadvantageNetwork traffic/resource managementTime-division multiplexHigh-Level Data Link ControlUser Datagram Protocol

A method for compressing data is provided that includes receiving a packet communicated by a mobile station and extracting a high-level data link control (HDLC) payload from the packet. A compression operation may then be performed on the HDLC payload in order to reduce a number of bytes associated with the packet. A key may be built that maps the HDLC payload associated with the packet to the key, the key being broken into segments that are positioned into a selected one or more of a source internet protocol (IP) address field, a user datagram protocol (UDP) source port field, and a UDP destination port field of a UDP packet. Remaining fields of the HDLC payload may be copied and positioned into a payload field of the UDP packet. The UDP packet may then be communicated to a routing functionality such that it may be directed to a next destination.

Owner:CISCO TECH INC

Apparatus and method for controlling block signal flow in a multi digital signal processor configuration from a shared peripheral direct memory controller to high level data link controller

InactiveUS20030093594A1Input/output processes for data processingData conversionData processing systemDirect memory access

In a data processing system including a plurality of digital signal processor subsystems, selected peripheral components are shared by the digital signal processor subsystems. In particular, the high level data link controller is shared by the subsystems. Using a first interrupt signal after each transfer of signal groups from the peripheral direct memory access unit, the data can be efficiently transferred from a channel memory of the peripheral direct memory access unit to the high level data link controller. A second interrupt from the high level data link controller when a last word of a packet is transferred thereto causes a new channel memory to be accessed.

Owner:TEXAS INSTR INC

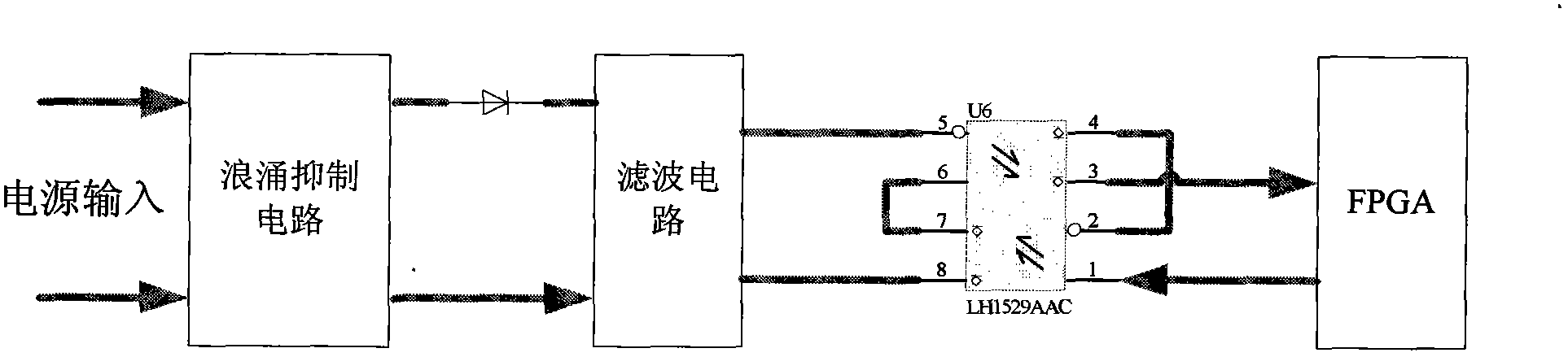

Compact-type expanded input-output (IO) device

ActiveCN102681463AAbundant resourcesRich interfaceProgramme controlComputer controlCommunication interfaceContact type

The invention relates to a compact-type expanded input-output (IO) device, and the expanded IO device comprises a shell, a circuit board which is arranged inside the shell and a power supply module, wherein the circuit board consists of a soleplate with a processor and a small plate with a communication interface, and the soleplate is connected with the small plate through a double-row connector. The compact-type expanded IO device has abundant hardware resources, diversity interfaces and wide application range; by adopting a compact-type structure, the size is small; the internal circuit adopts the modularized design, the circuit board consists of the soleplate with the processor and the small plate with the communication interface, the soleplate comprises a high-speed field programmable gate way (FPGA) microprocessor chip, the multi-threading simultaneous control can be realized, so that the contact-type expanded IO device can be used as a main device; and meanwhile, the communication interface on the small plate can be configured as a multifunction vehicle bus (MVB) interface and a high-level data link control (HDLC) bus interface, so that the compact-type expanded IO device can be connected with a main device through a network hard wire to be used as an auxiliary device, and the contact-type compacted IO device can be managed and controlled by the main device through a network protocol.

Owner:CRRC QINGDAO SIFANG ROLLING STOCK RES INST

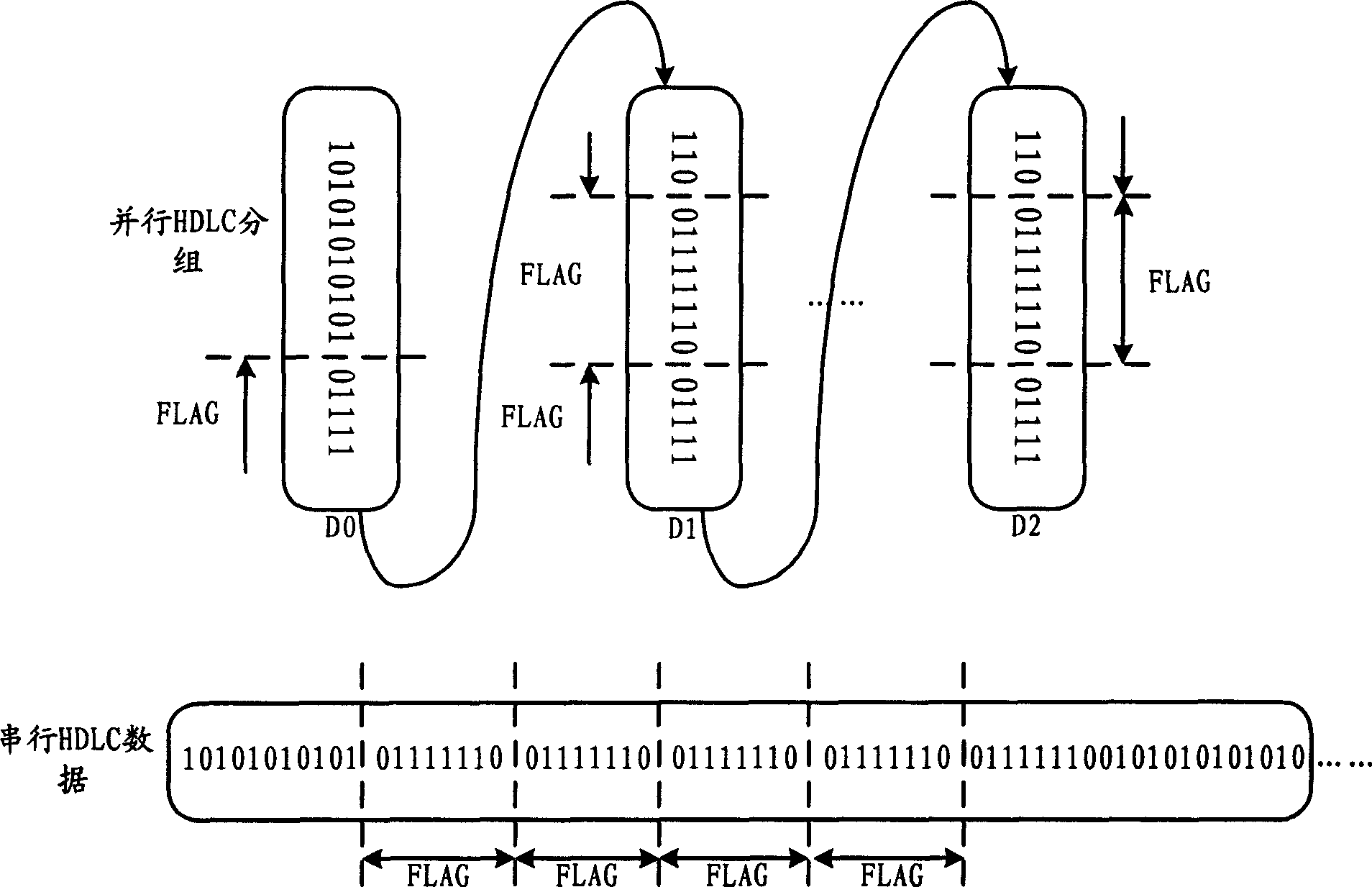

Method and system for parallel transmitting serial data according to high level data link control

ActiveCN1917519AAvoid it happening againReduce complexityData switching networksShift registerData stream

The invention can effectively reduces the occupation on redundancy bandwidth, avoid the generation of flag bit sequence of segments and lower the load of CPU. In the invention, reading the k bits of next group to the shift register from serial HDLC data stream; if the valid data only have C bits, C<K, then the front K-C bits in flag bit sequence are filled into the remaining space of shift register; sending the data in the shift register, and recording C; when needing to send next HDLC frame, the rear K-C+A bits in flag bit sequence are filled into the shift register, and then reading the valid data of the next HDLC frame from the serial HDLC data stream; wherein, A represents the bit numbers in flag bit sequence.

Owner:HUAWEI TECH CO LTD

Apparatus and method for distribution of signals from a high level data link controller to multiple digital signal processor cores

In a data processing system including a plurality of digital signal processor subsystems, selected peripheral components are shared by the digital signal processor subsystems. In particular, the high level data link controller is shared by the subsystems. When a packet is received by a shared high level data link controller, the data signal groups are processed and placed in a temporary storage unit. The address signal group of the received packet is applied to channel block unit where the digital signal processor subsystem, to which the packet is directed, is identified and an INTERRUPT signal corresponding to the identified digital signal processor subsystem is generated. The INTERRUPT signal is applied to a switch. The switch, which receives the signal groups from the temporary storage unit, directs the signal groups to a buffer memory in the channel associated with the identified signal processing subsystem. In response to a predetermined condition, the signal groups are forwarded to the identified digital signal processor subsystem. The channel block unit, in response to preselected signal groups, can direct the packet to a digital signal processor subsystem that is different from the digital signal processor subsystem identified by the address signal group.

Owner:TEXAS INSTR INC

Method and equipment for allocating high-level data link control link bandwidths

InactiveCN103379551AIncrease profitReduce wasteNetwork traffic/resource managementTraffic capacityRadio equipment

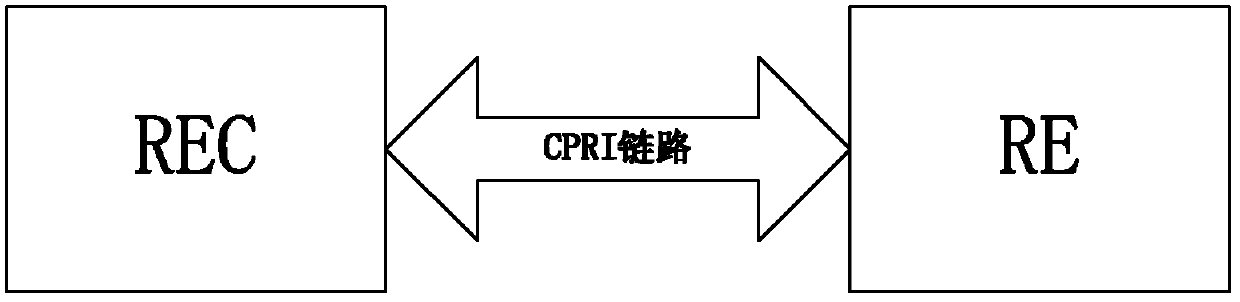

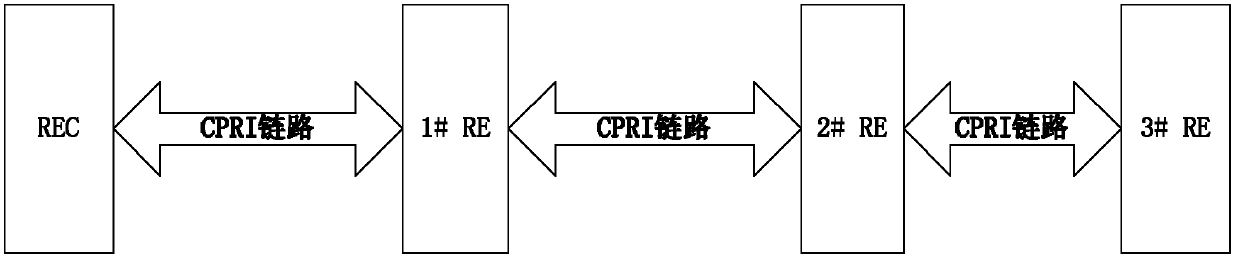

The present invention provides a method and device for allocating a bandwidth of a high-level data link control link. The method is applied to a common public radio interface CPRI link formed by a radio equipment controller REC and over two radio equipments REs through link networking and comprises: an RE making statistics on communication traffic from the RE to an uplink HDLC sub-link of the REC; the RE determining, according to the communication traffic obtained through statistics and a current link bandwidth of the uplink HDLC sub-link, whether it is needed to adjust a link bandwidth of the uplink HDLC sub-link; when the RE determines that the link bandwidth of the uplink HDLC sub-link needs to be adjusted, sending a bandwidth adjustment request message to the REC; and the RE, together with the REC, adjusting the link bandwidth of the uplink HDLC sub-link according to a bandwidth adjustment response message that is returned by the REC and carries bandwidth adjustment amount.

Owner:ZTE CORP

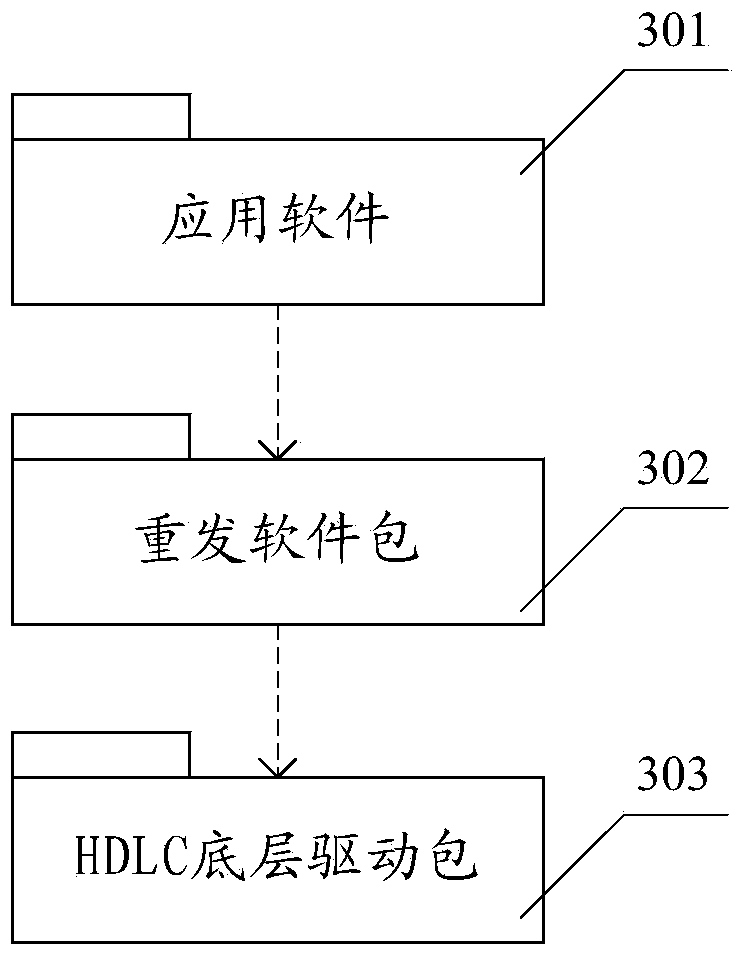

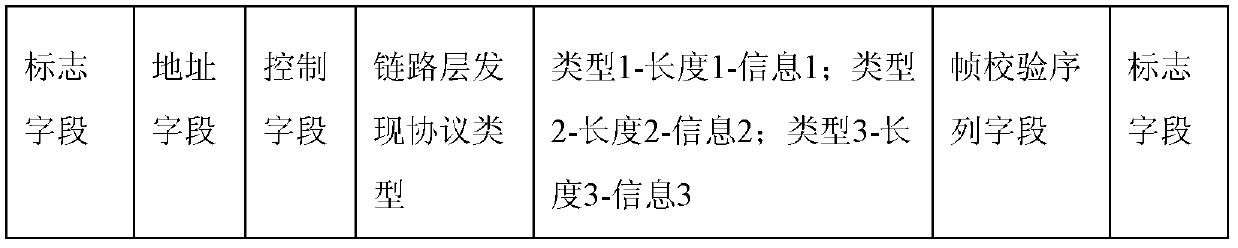

High-level data link control data sending method

InactiveCN104283650ALow costReduce time spentError prevention/detection by using return channelHigh level techniquesNetwork packetHigh-Level Data Link Control

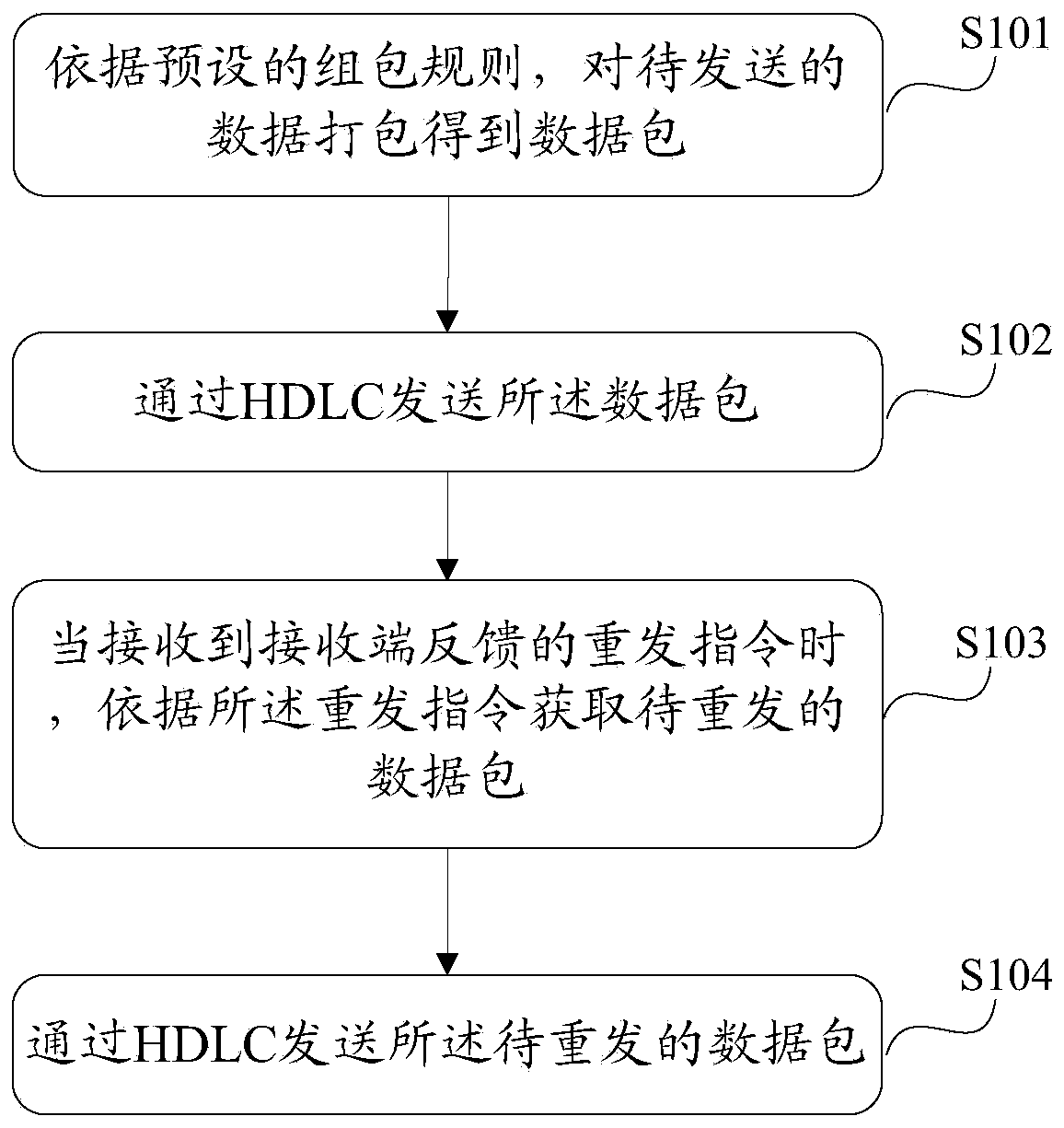

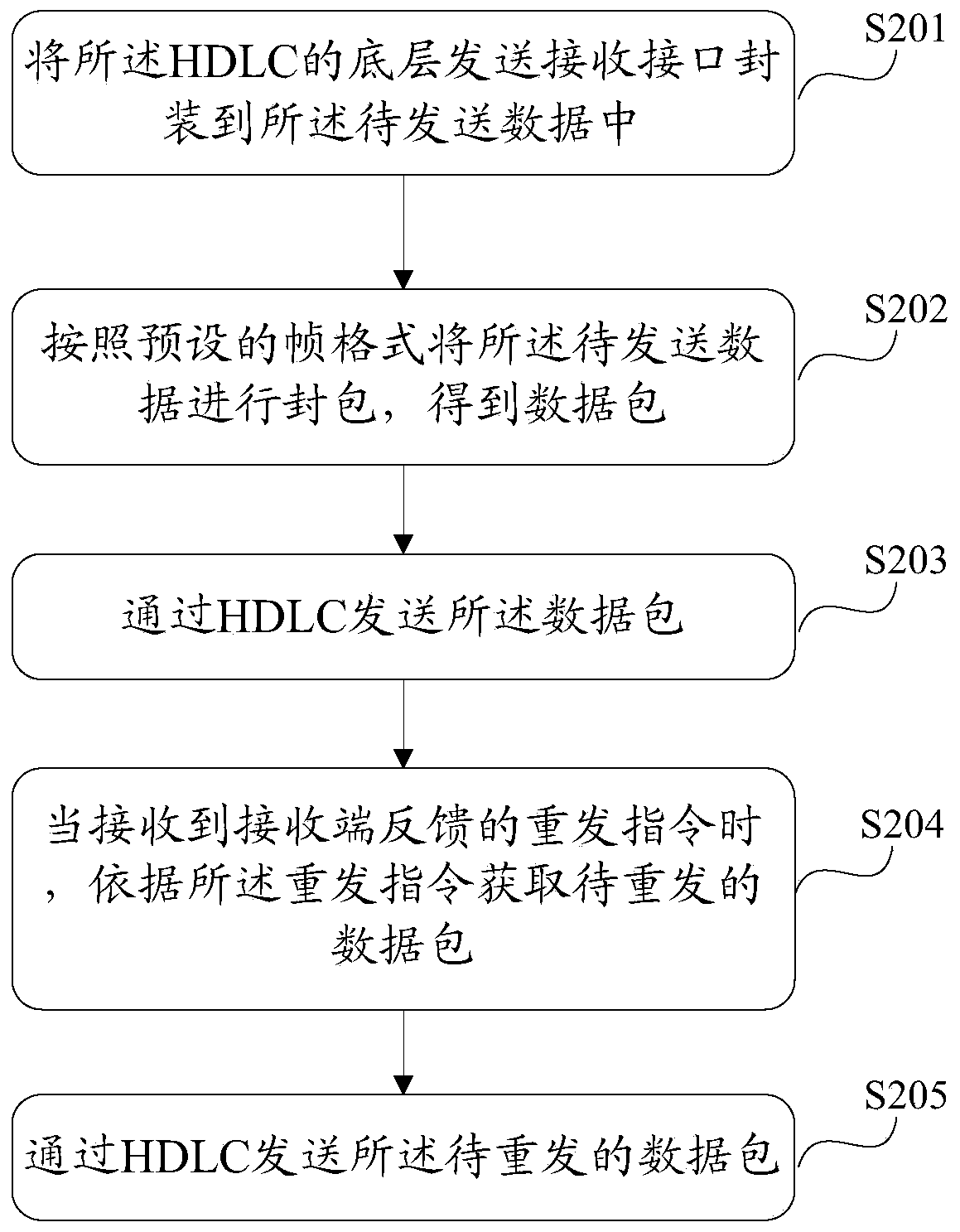

The invention provides an HDLC resending method. The HDLC resending method is applied to a sending terminal. According to the HDLC resending method provided by the invention, when the sending terminal is used for sending a data packet, an added header contains a packet sending sequence and a packet sending type and is used for sending the data packet by virtue of HDLC; when receiving a resending command, the sending terminal directly acquires a data packet to be resent according to the resending command and resends the data packet without judging whether the resending is needed or not, and thus occupied time of the resending process to the sending terminal is shortened, and the speed of sending data by the sending terminal is not influenced. In addition, with the adoption of the HDLC resending method, the packet sending sequence and the packet sending type are added in the data packet only without changing an HDLC chip, and thus the cost of the HDLC can not be increased.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Method, device and system for managing link status information of low-speed link

InactiveCN102437932AImplement storage managementNetworks interconnectionInformation repositoryManagement information base

The embodiment of the invention provides a method for managing link status information of a low-speed link. The method comprises the following steps that: a first notification message sent by a second network device through the low-speed link, is received by a first network device; the first notification message is an HDLC (High-level Data Link Control) protocol message or a PPP (Point-to-point Protocol) protocol message of the link status information of the low-speed link at the side of the second network device; the first notification message is analyzed by the first network device to obtain the link status information of the low-speed link at the side of the second network device; and the link status information of the low-speed link at the side of the second network device is stored into a management information base. In addition, the embodiment of the invention further provides a device and system for managing the link status information of the low-speed link. According to the invention, the transmission of the link status information of the low-speed link between the network devices is realized and the management of the link status information of the low-speed link is realized.

Owner:李金良

Bus relay device

InactiveCN101146121AImprove driving abilitySimplify complexityBus networksDependabilityData transmission

The invention provides a bus relay device, which includes a two-way drive unit, used to receive data on the bus, perform drive regeneration and generate signals with powerful drive capability; a bus status detection unit, used to perform the bus sampling on both sides of the two-way drive unit, judge the bilateral bus status according to a high level data link control protocol and determine the data transmission direction and detect whether any conflict occurs; a drive control unit, used to control the two-way drive unit according to the data transmission direction and a conflict making unit, used to generate conflict data and send the conflict data to the adjacent bus relay device, after the bus status detection unit detects the conflict. The invention greatly simplifies the complexity of the relay design, improves reliability and effectively improves the bus drive capability.

Owner:ZTE CORP

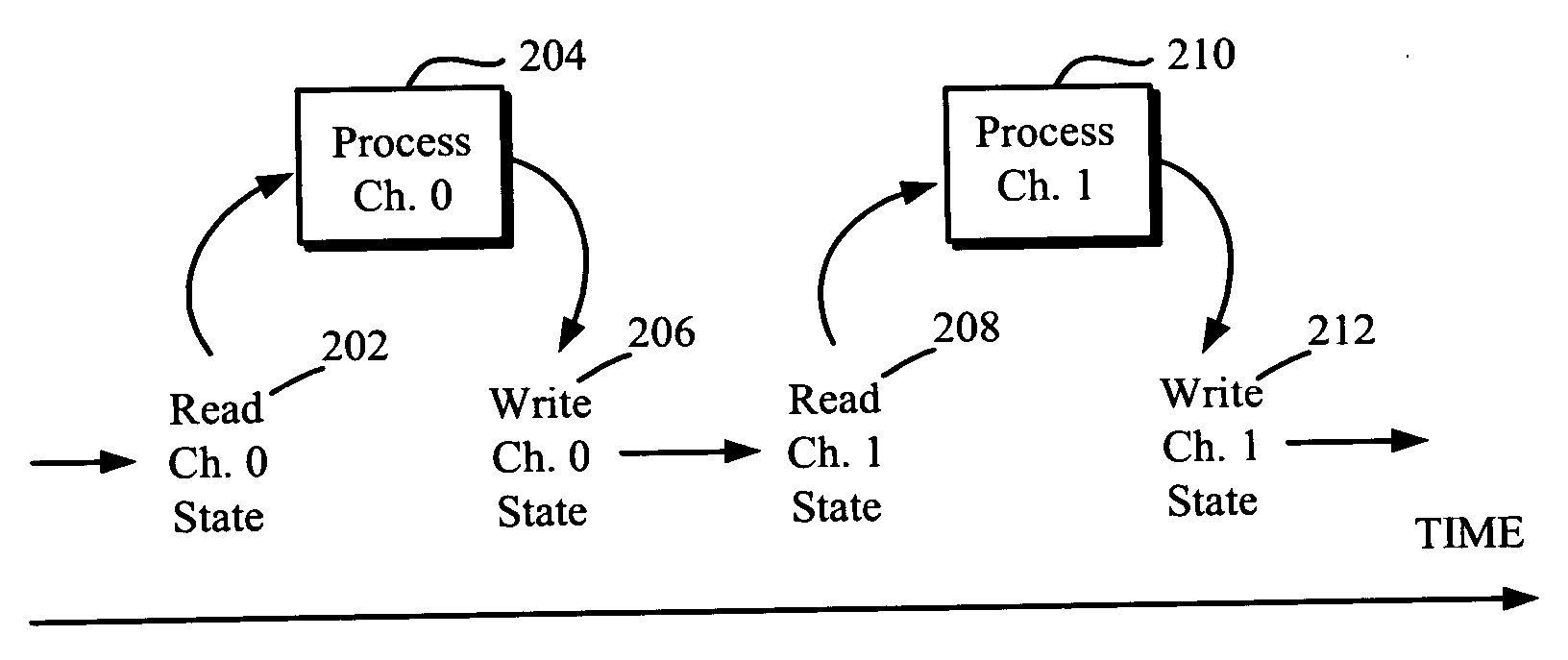

Systems and methods for using HDLC channel context to simultaneously process multiple HDLC channels

ActiveUS20050053083A1Time-division multiplexData switching by path configurationNetwork processingHigh-Level Data Link Control

Systems and methods are disclosed for using High-level Data Link Control (HDLC) channel context information to simultaneously process multiple HDLC channels. Preferred embodiments of the present invention enable a single network processing engine to process multiple HDLC channels. The current state of the HDLC channel can be evaluated, stored, and restored, which means that the processing of a channel can be halted, the channel state read and stored, and the state of a different channel written to the processing engine. This allows the engine to begin processing a new channel, and then, at a later stage, restore the state of the original channel and resume processing.

Owner:MICRON TECH INC

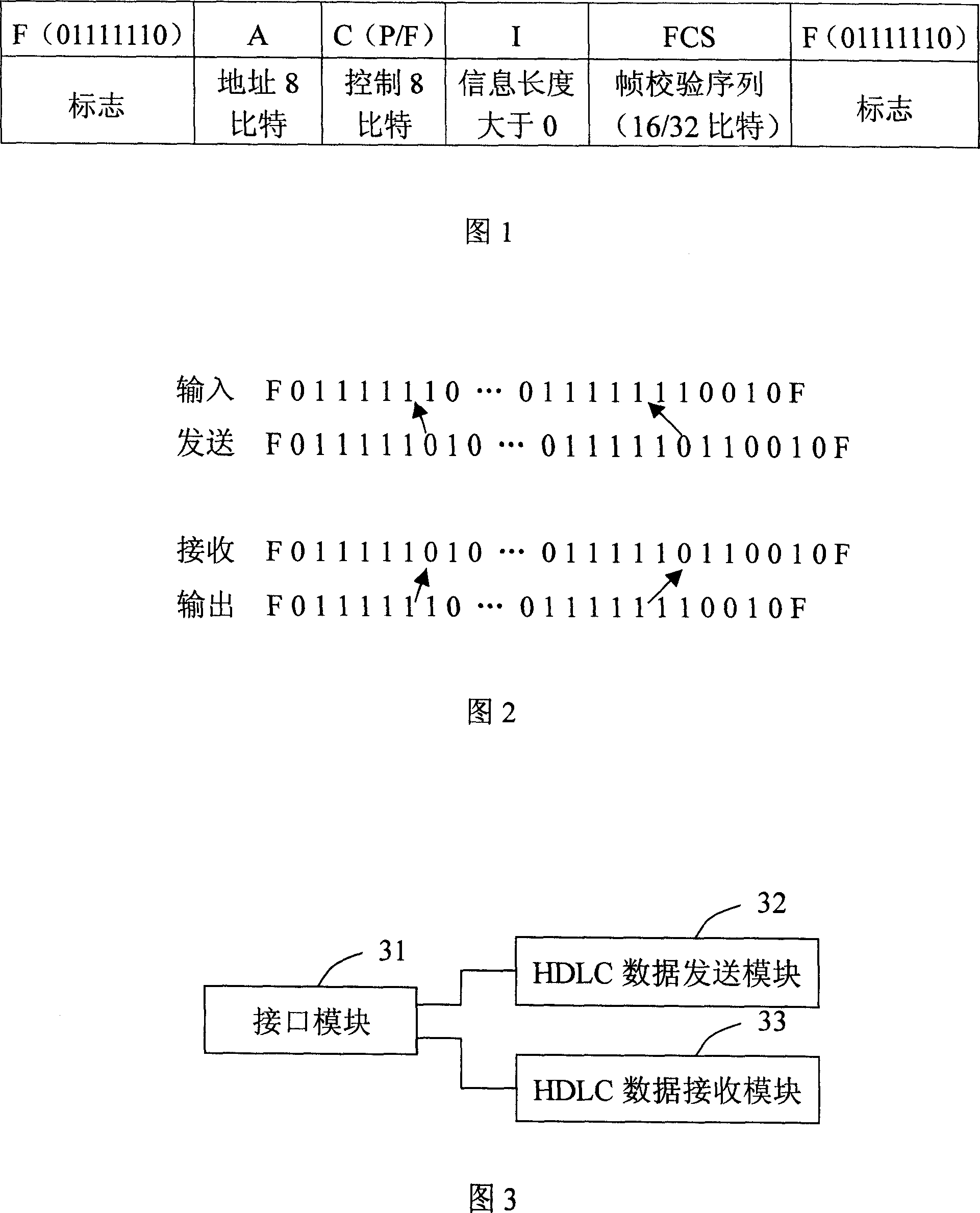

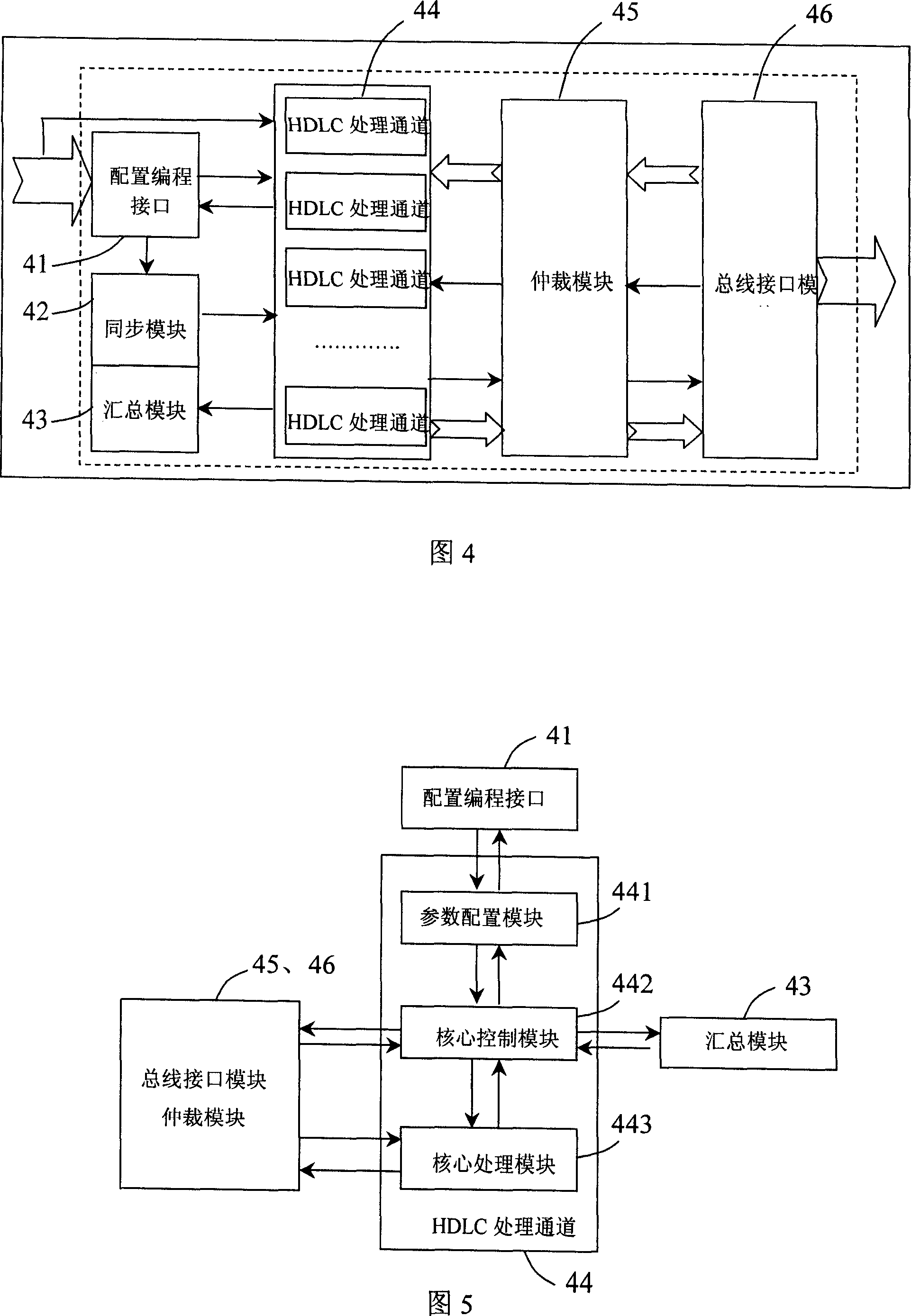

Device and method for controlling high-level data link

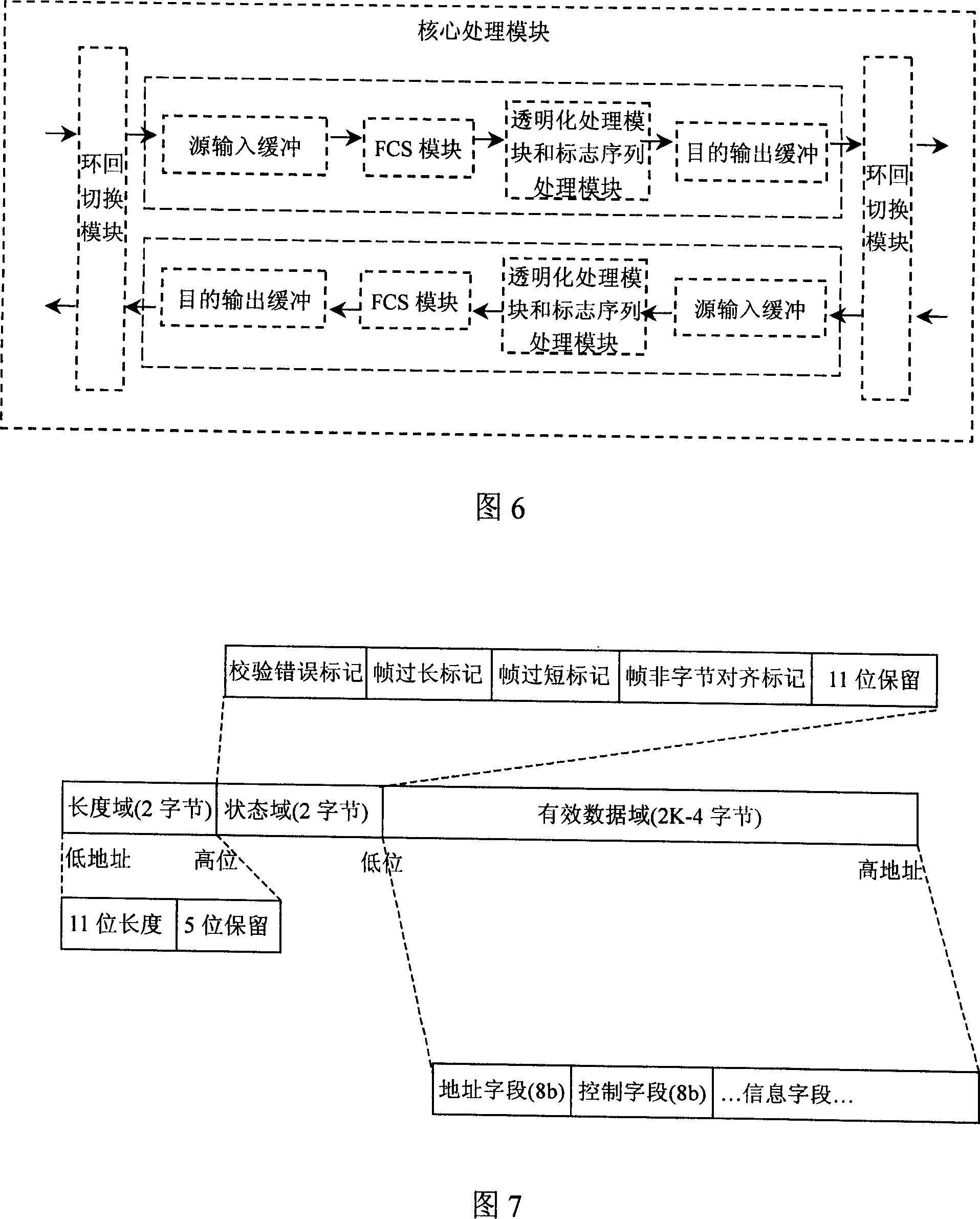

This invention relates to a kind of device of realizing high-level data link control. It includes: bus interface module that has outer interactive function through advanced high-performance bus, HDLC processing lane that connects with stated bus interface module. The stated HDLC processing lane includes core processing module and core control module, the stated core control module controls core processing module according to peripherals DMA request and reads data form peripherals to have HDLC processing through bus interface module. After the completion of core processing module handle, it informs related peripherals or CPU to read the completed data. This invention also provides a corresponding high-level data link control method. Through the providing DMA data movement function in the HDLC processing of this invention, it reduces CPU load and saves CPU processing resource.

Owner:HUAWEI TECH CO LTD

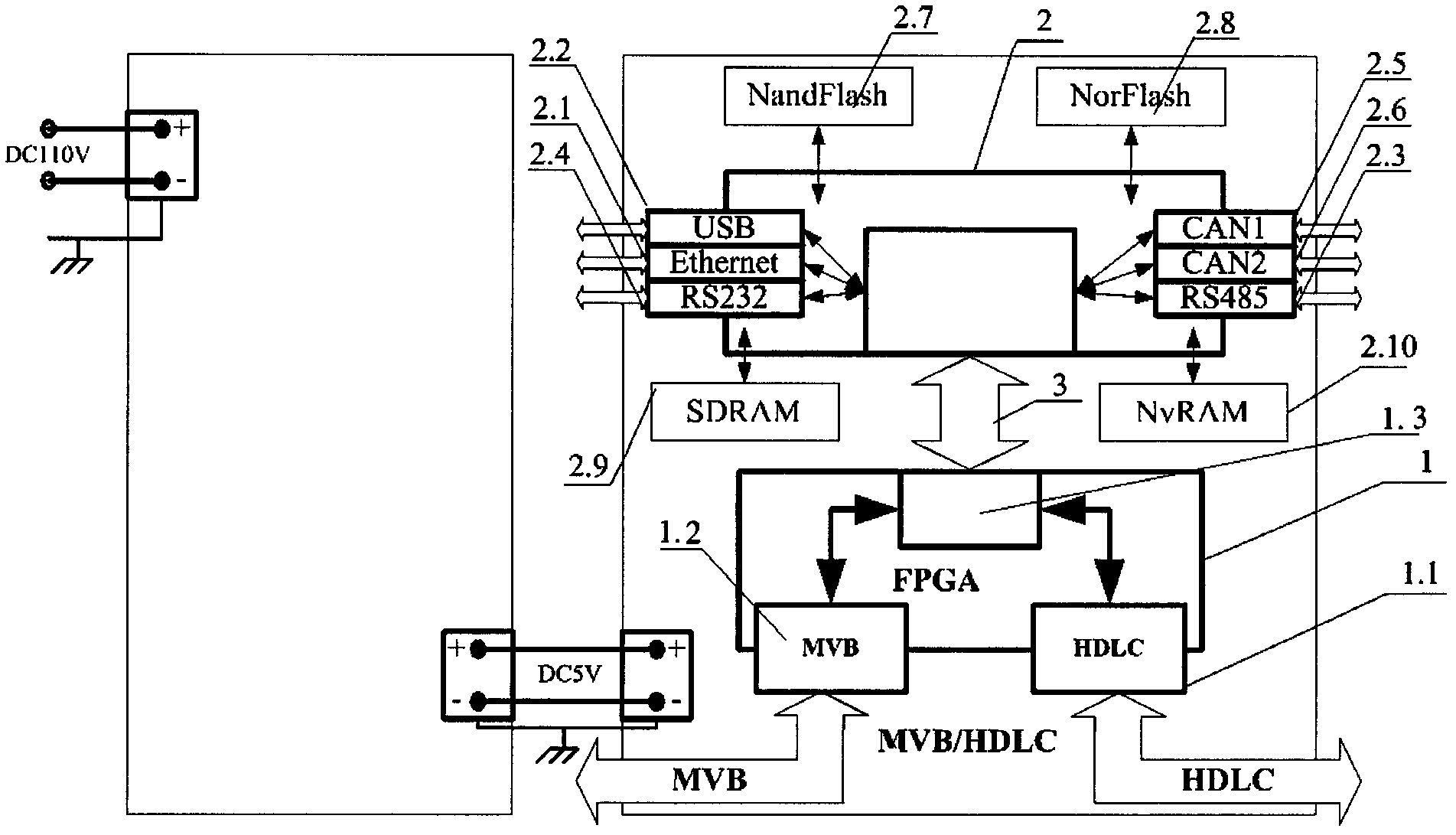

MVB (Multifunction Vehicle Bus)/HDLC (High-level Data Link Control) gateway device

InactiveCN102546480ASignificant technological progressAchieve conversionNetwork connectionsBus networksArea networkBus interface

The invention relates to a control system for a railway locomotive network, belongs to an HDLC (High-level Data Link Control) communication network technology, and particularly relates to an MVB (Multifunction Vehicle Bus) / HDLC gateway device. The MVB / HDLC gateway device comprises an MVB / HDLC converting board and a gateway power supply module for supplying voltage for the MVB / HDLC converting board. The MVB / HDLC converting board comprises an FPGA (Field Programmable Gate Array) module and a CPU (Central Processing Unit) module. An HDLC link control processing circuit and an MVB link control processing circuit are arranged in the FPGA module. A memory, an Ethernet communication interface circuit, a USB (Universal Serial Bus) interface circuit, an RS485 port circuit, an RS232 interface circuit, a first CAN (Controller Area Network) bus interface circuit and a second CAN bus interface circuit are arranged in the CPU module. The FPGA module and the CPU module are connected with each other through a parallel bus. According to the MVB / HDLC gateway device disclosed by the invention, functions of HDLC communication, Ethernet communication, various buses and MVB mutual communication are realized. The MVB / HDLC gateway device has the advantages of small volume, strong practical applicability and the like.

Owner:WUHAN ZHENGYUAN ELECTRIC

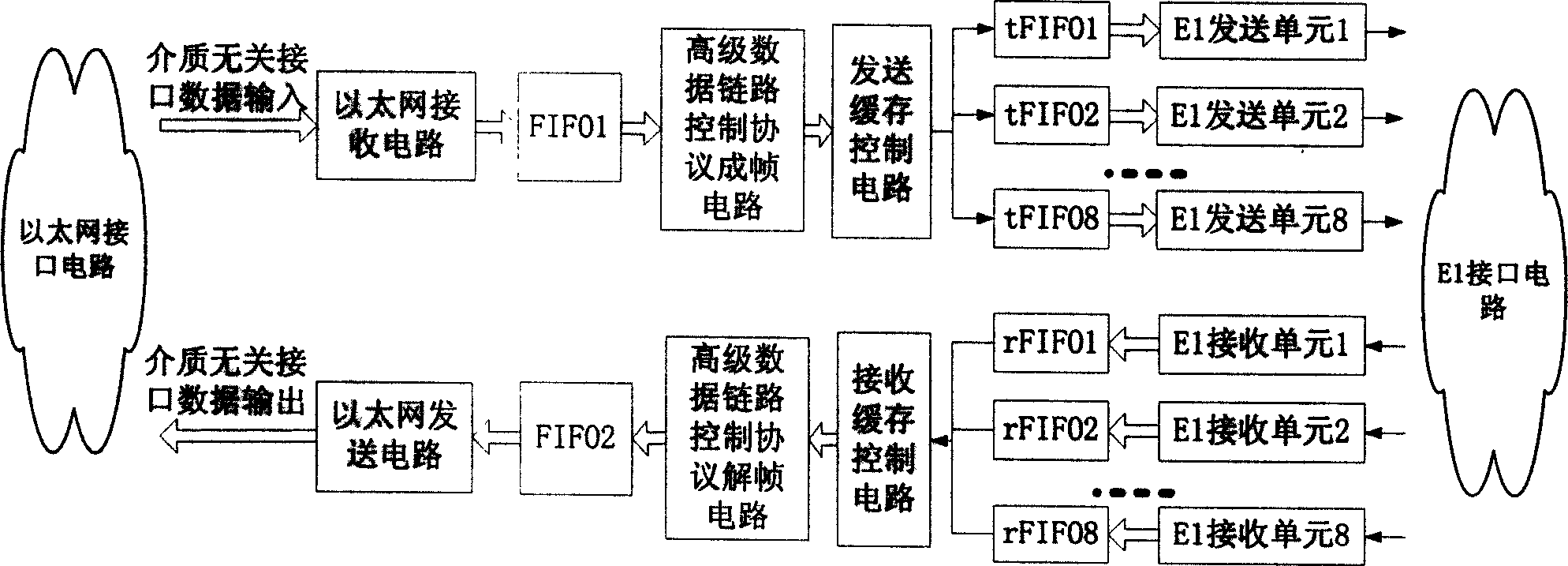

System for transmitting data frame of Etheent based on insertion between frames

In sending direction, medium independent interface data of LAN A are input to following cascaded parts: Ethernet receiving circuit, FIFO1ú¼framing circuit in protocol of high level data link control (HDLC), sending buffer control circuit, E1 sending buffer, E1 sending circuit, and interface circuit of E1 line. In receiving direction, input signal of interface circuit of E1 line passes through following cascaded parts: E1 receiving circuit, E1 receiving buffer, receiving buffer control circuit, de-framing circuit in protocol of HDLC, FIFO2, sending circuit of Ethernet, then through medium independent interface, data inputted to LAN B. in the system, after Ethernet data frame reaches, each E1 line is polled in sequence. One integrated data frame is transferred in sequence through free line pulled from each route. The invention can eliminate issue of different time delay when one split Ethernet data frame is transferred through multiple routes of E1 line together.

Owner:TSINGHUA UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com