Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83 results about "Digital filter design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System for digital filtering in a fixed number of clock cycles

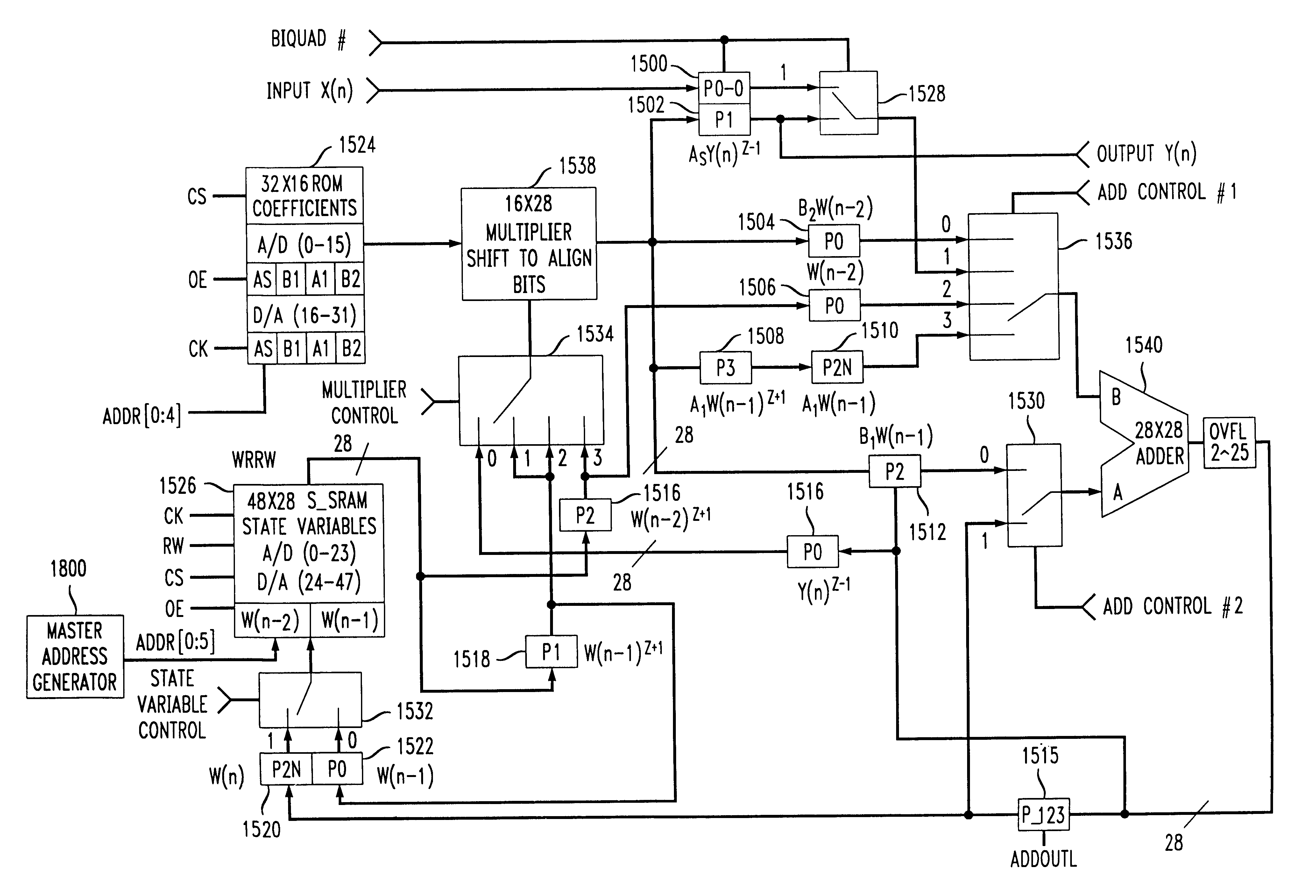

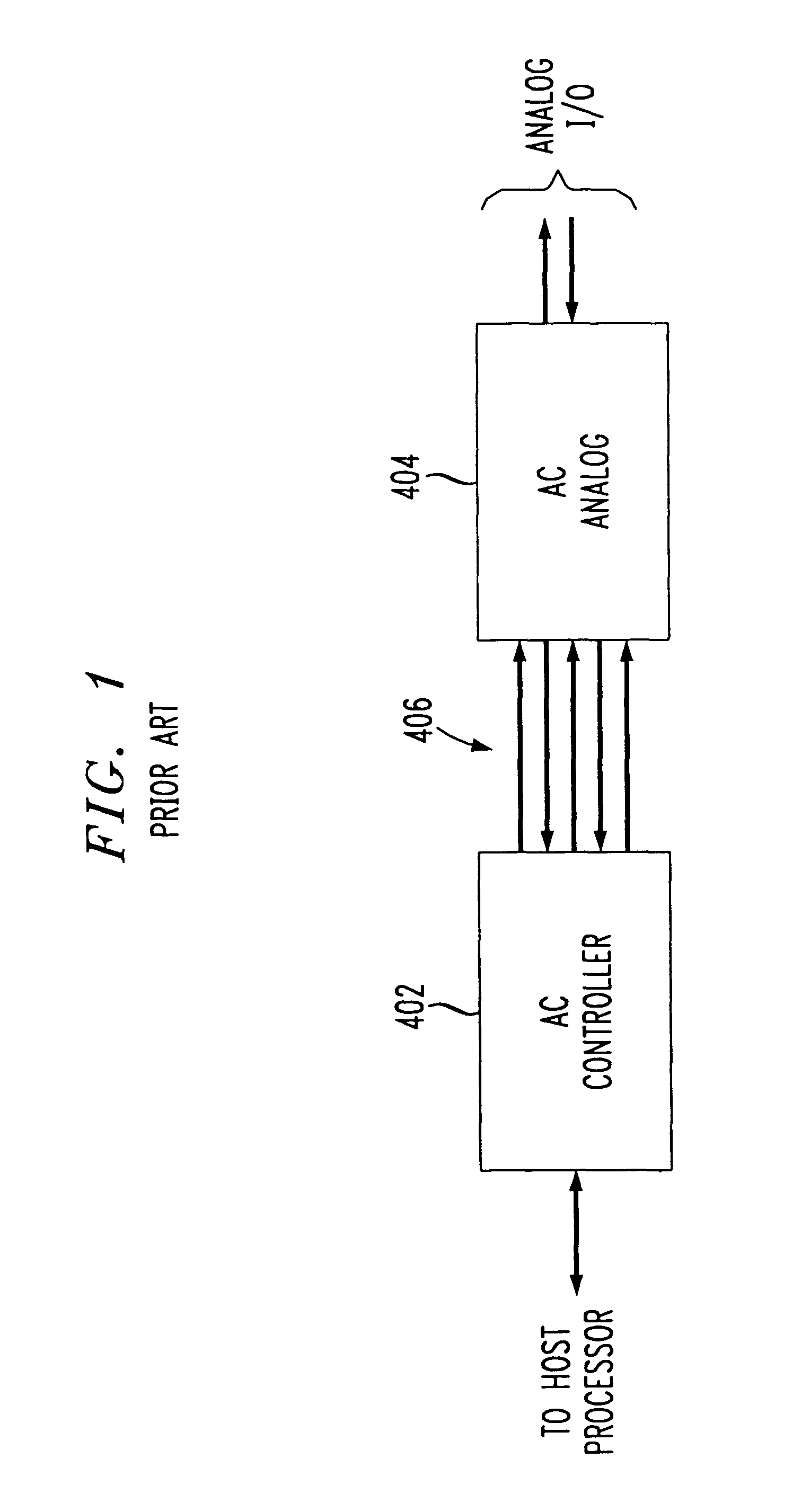

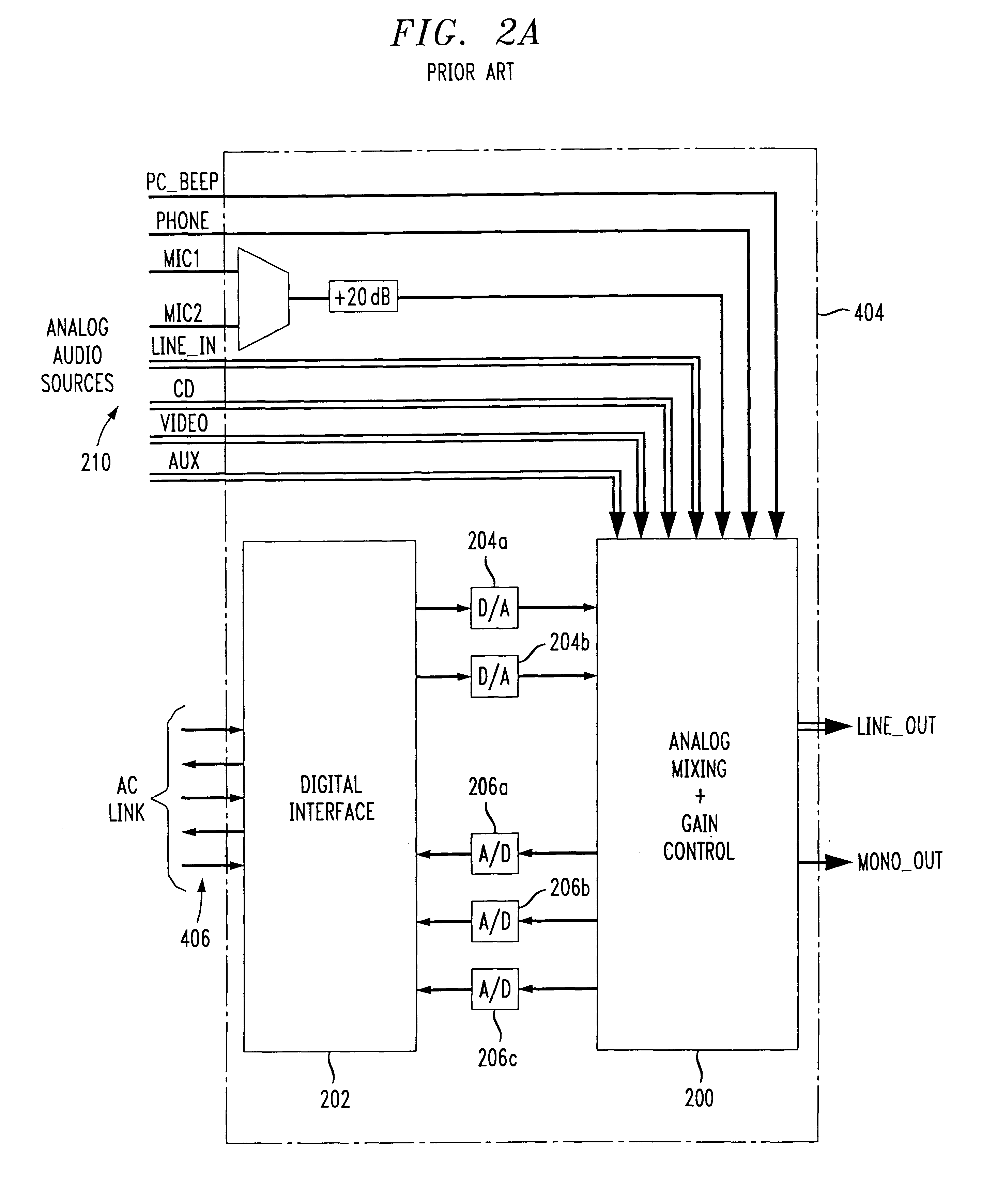

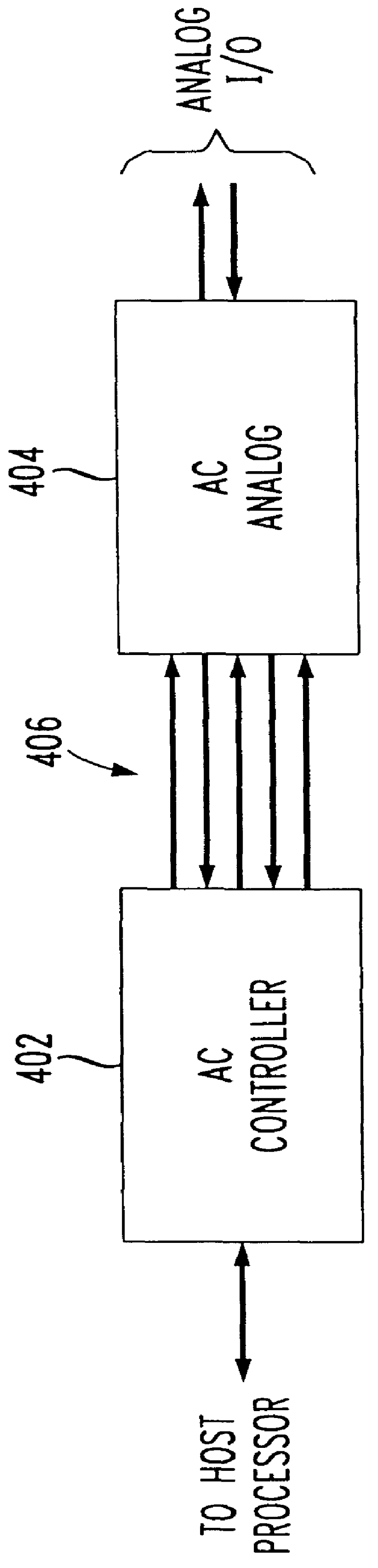

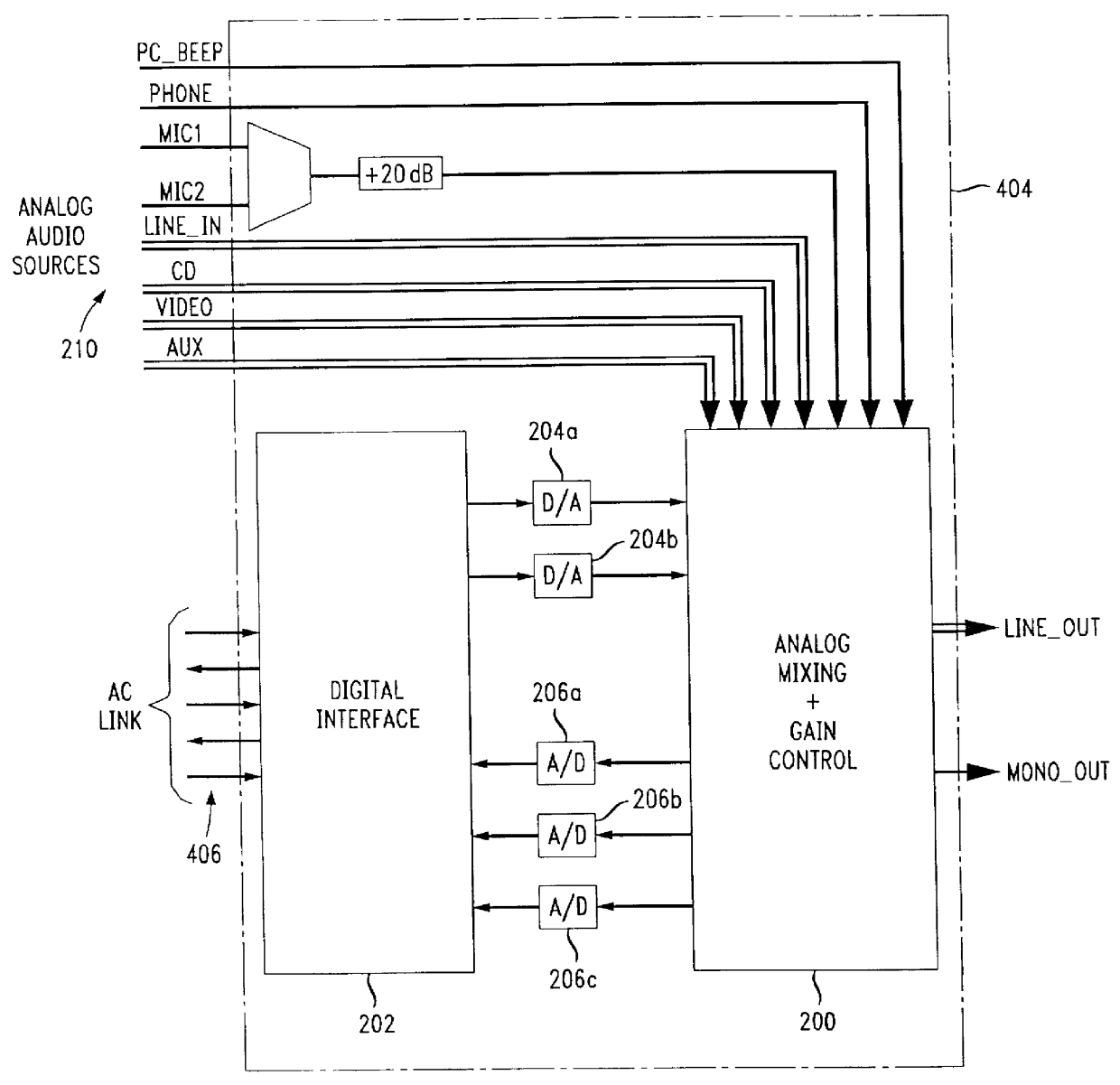

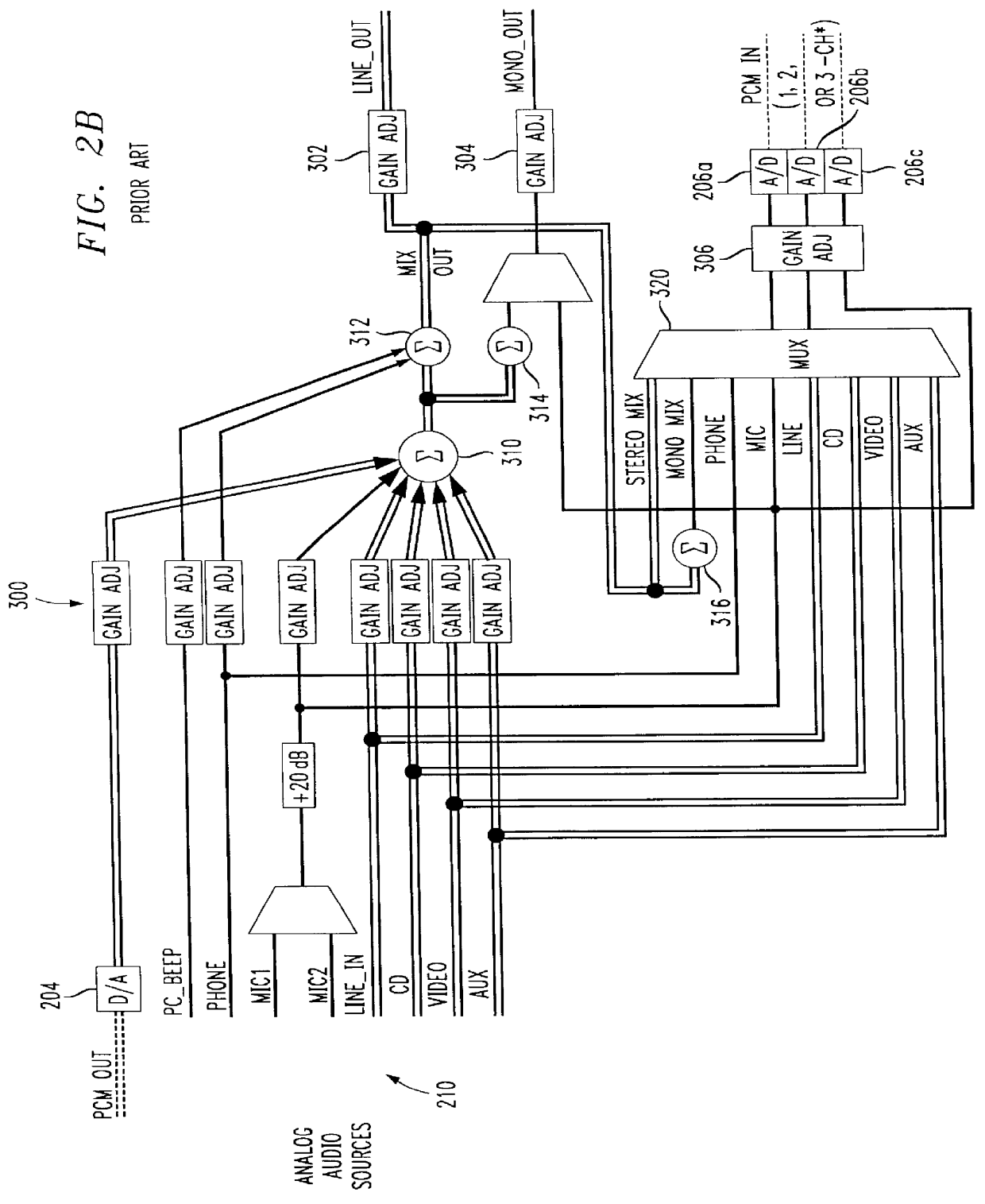

InactiveUS6175849B1Digital technique networkComplex mathematical operationsIir filteringState variable

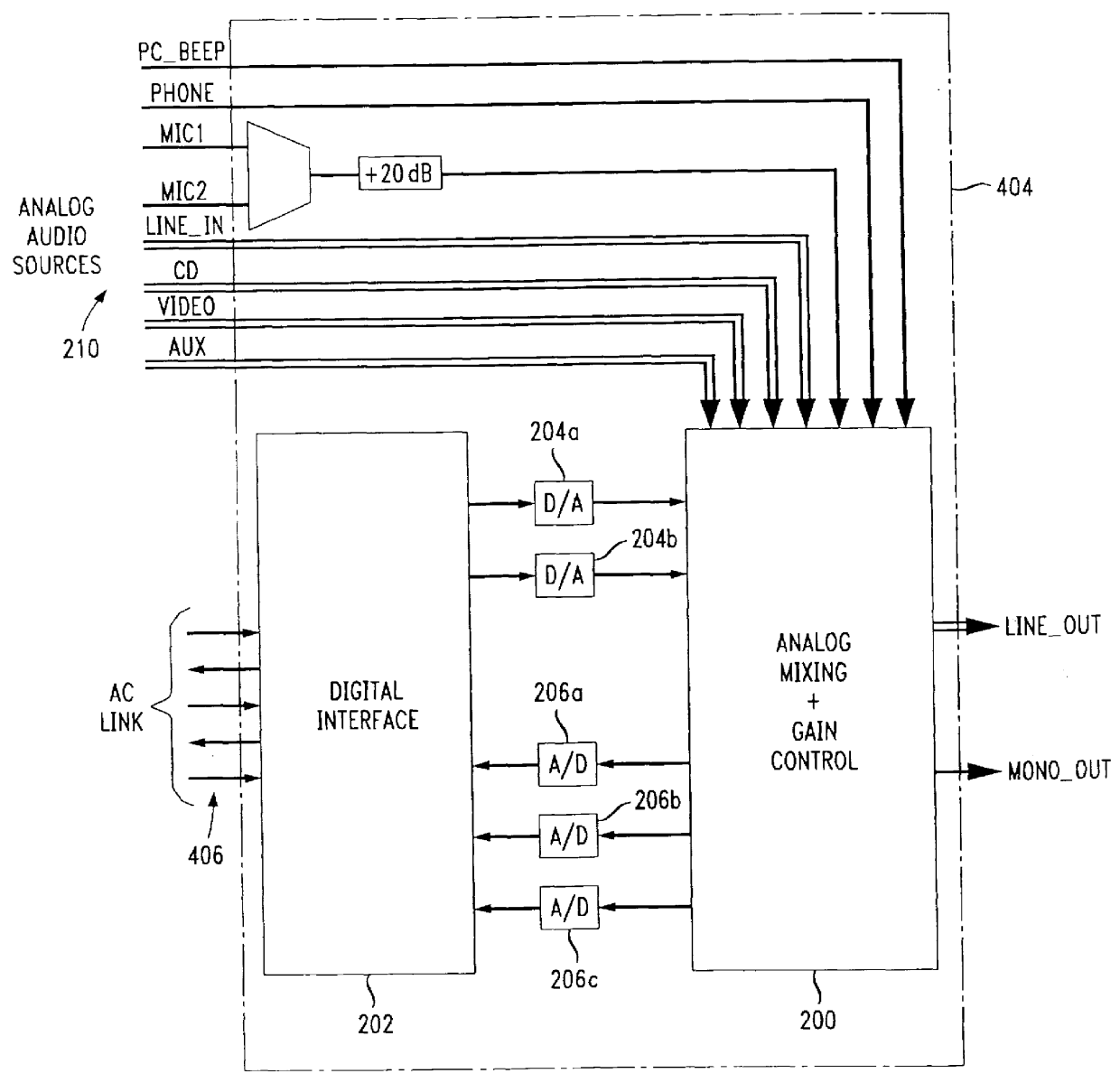

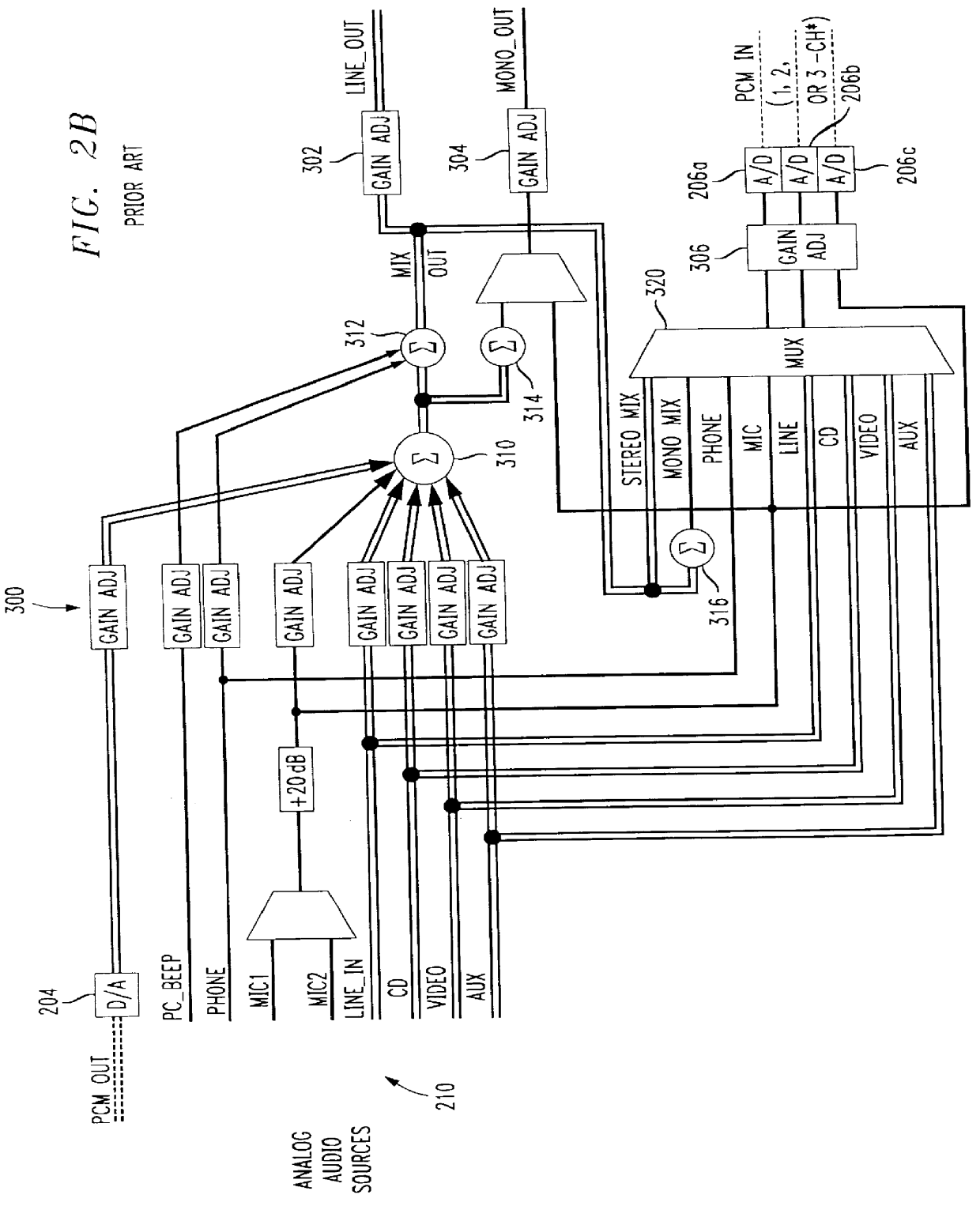

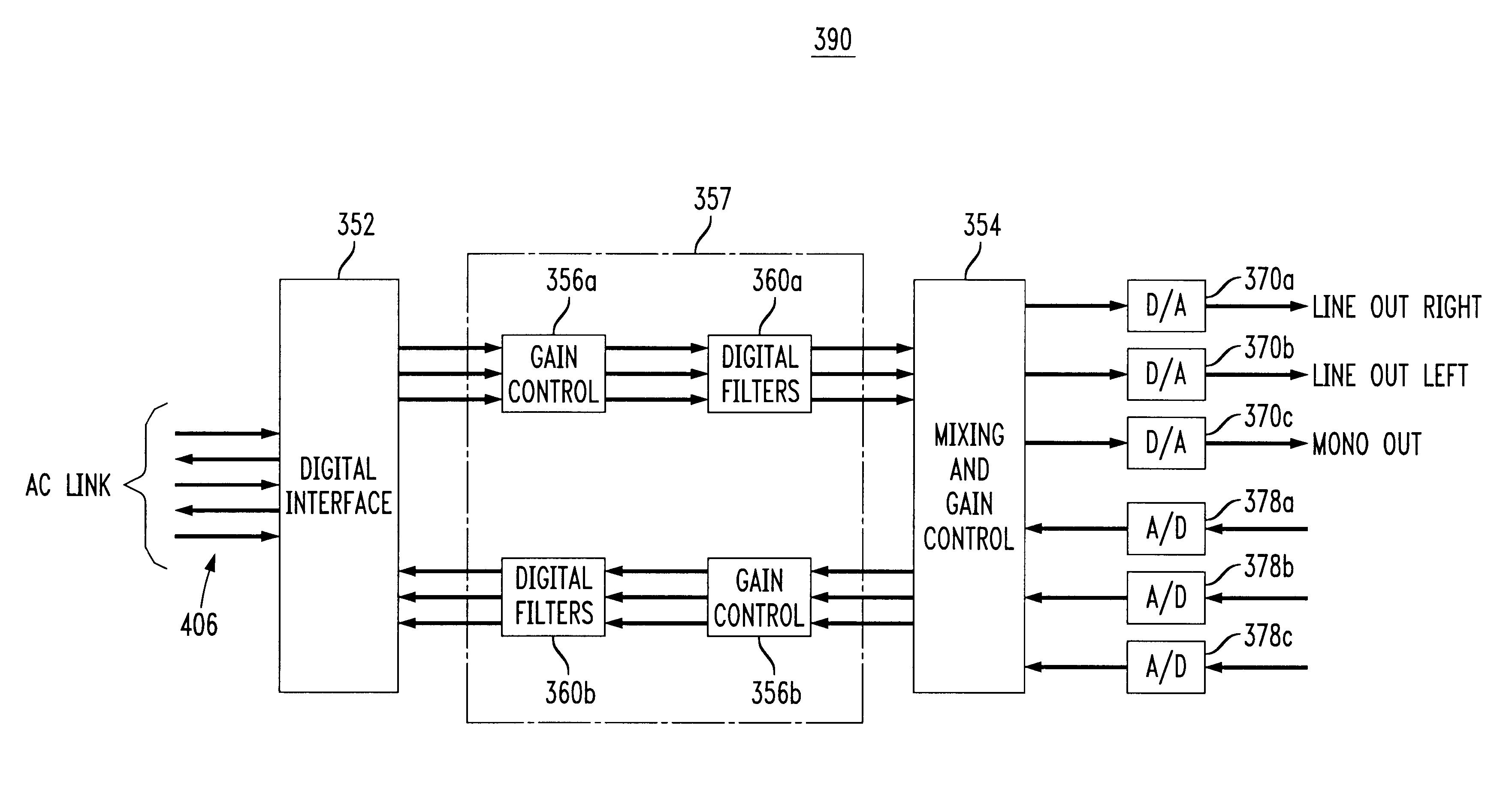

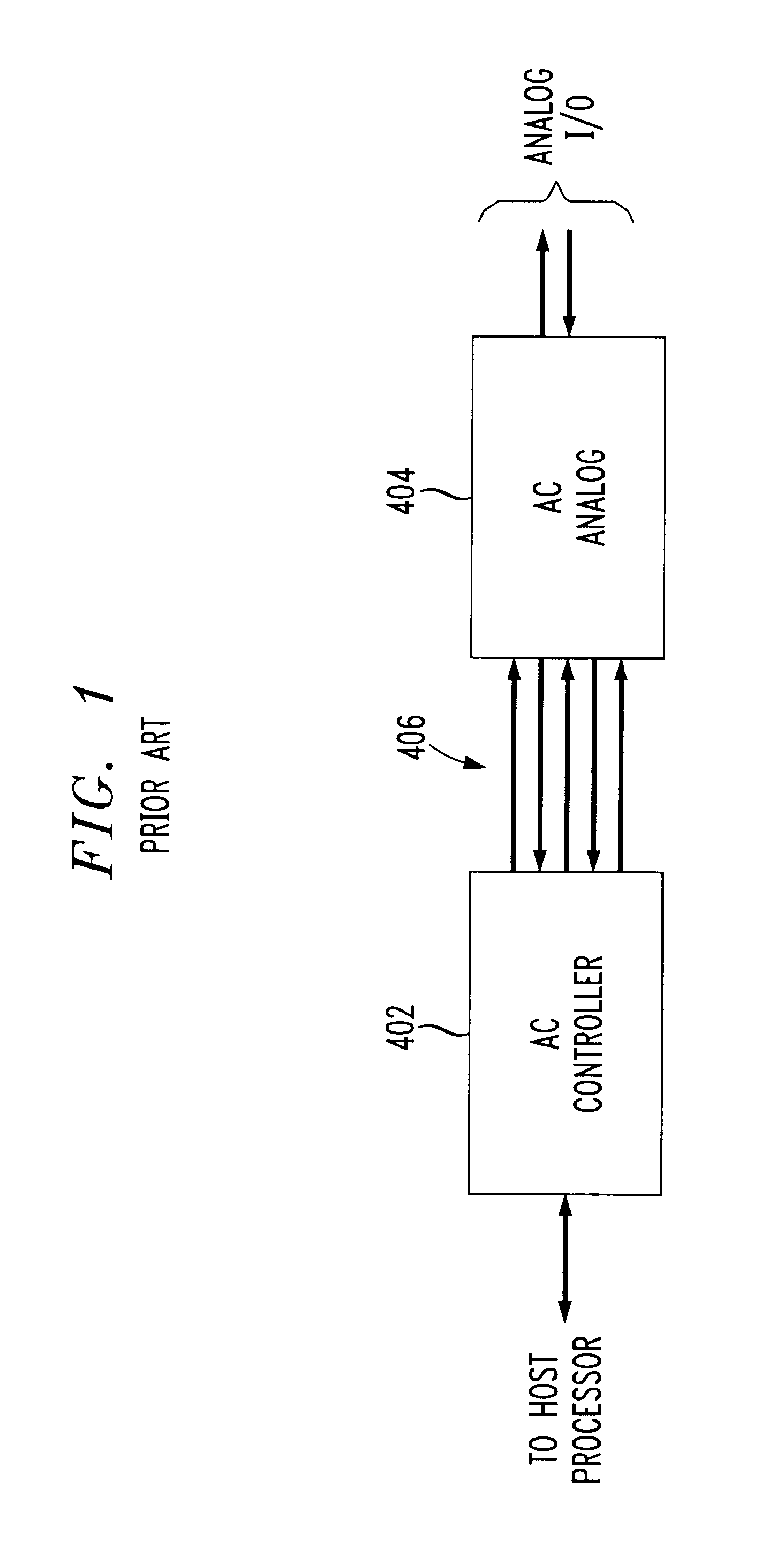

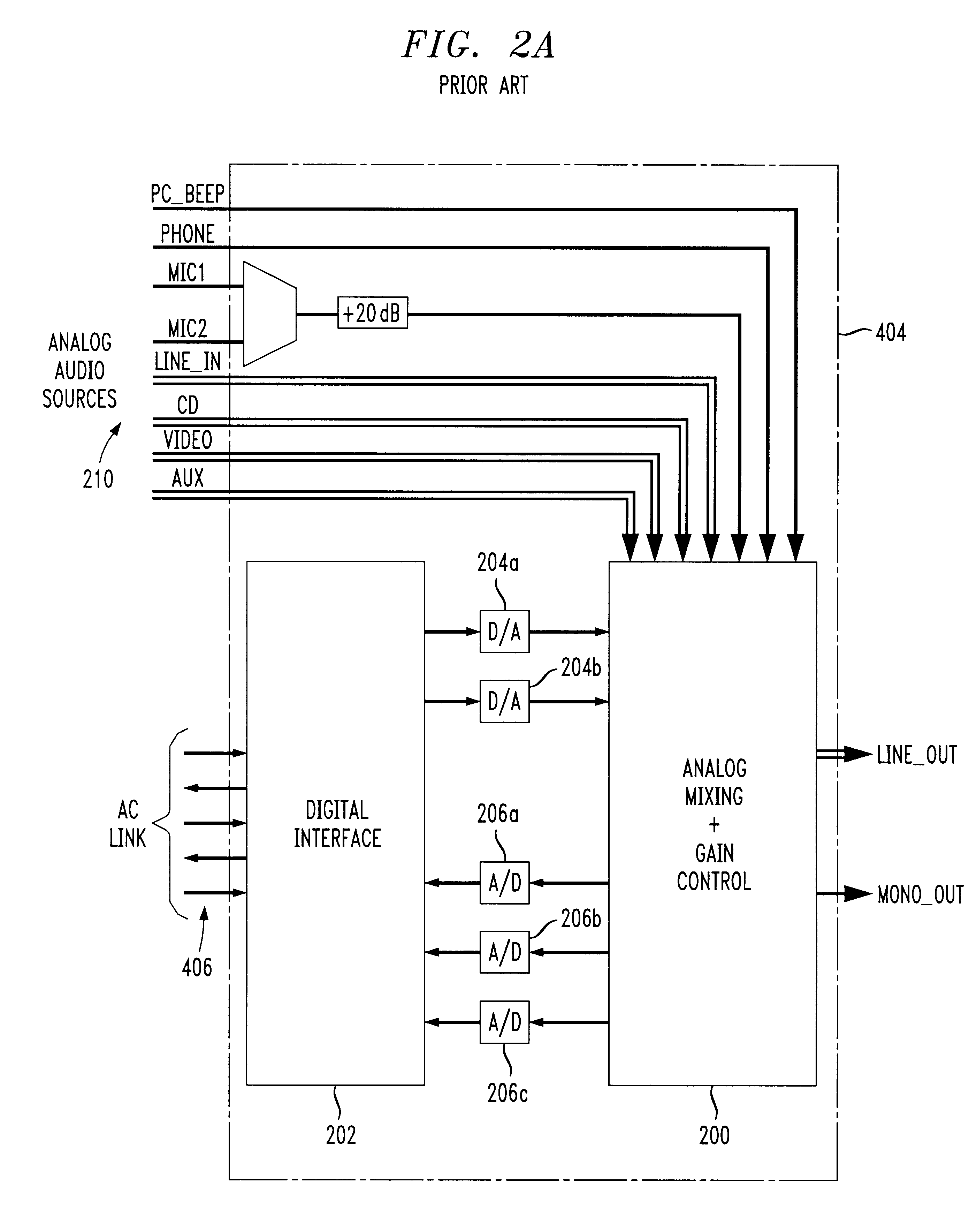

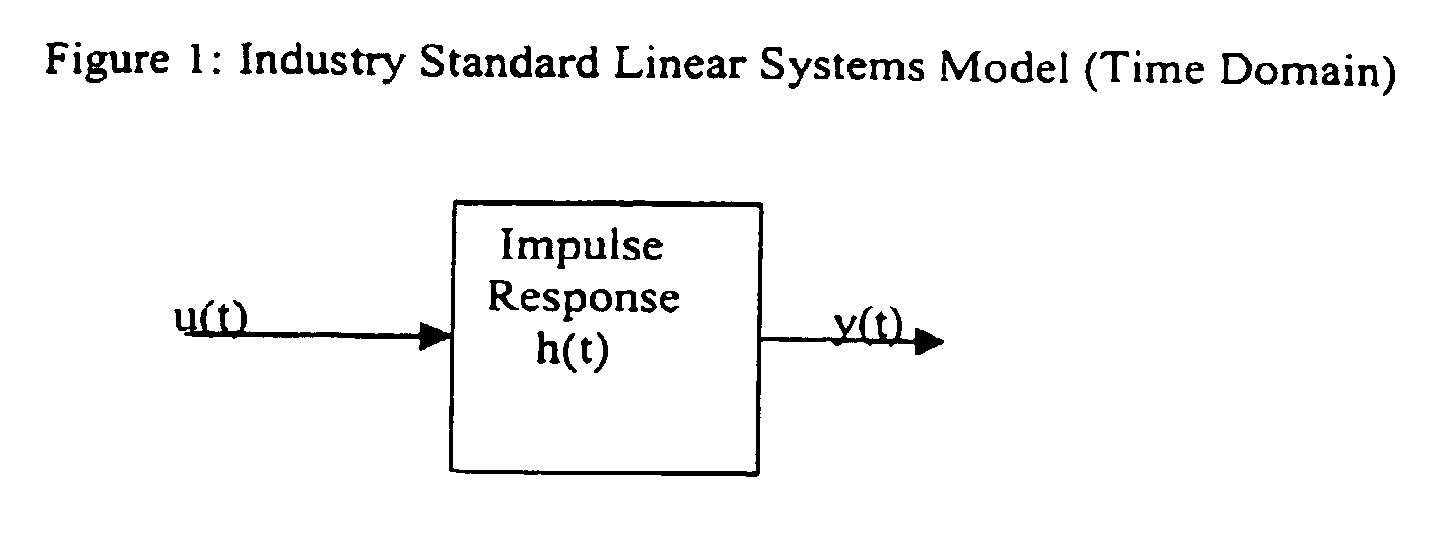

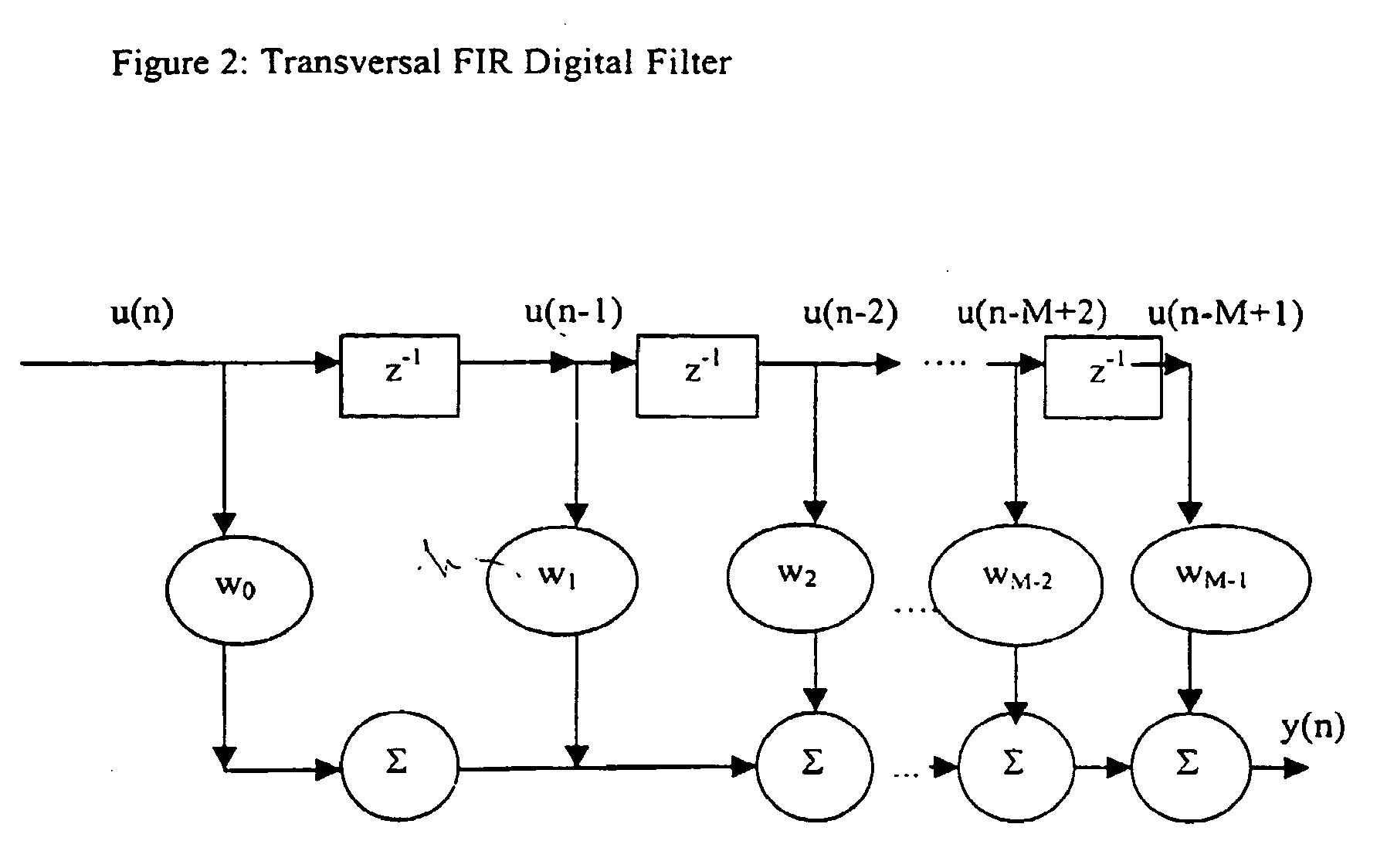

An integrated circuit, e.g. an AC '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a DC buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A RAM is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional modules of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional modules.

Owner:WSOU INVESTMENTS LLC +1

Recursive digital filter with reset

InactiveUS6167415ADigital technique networkComplex mathematical operationsIir filteringState variable

An integrated circuit, e.g. an Audio Codec (AC) '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a direct current (DC) buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A random access memory (RAM) is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional blocks of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional blocks.

Owner:LUCENT TECH INC +1

Distributed gain for audio codec

InactiveUS6215429B1Electric signal transmission systemsDigital technique networkIir filteringState variable

An integrated circuit, e.g. an AC '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a DC buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A RAM is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional blocks of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional blocks.

Owner:LUCENT TECH INC

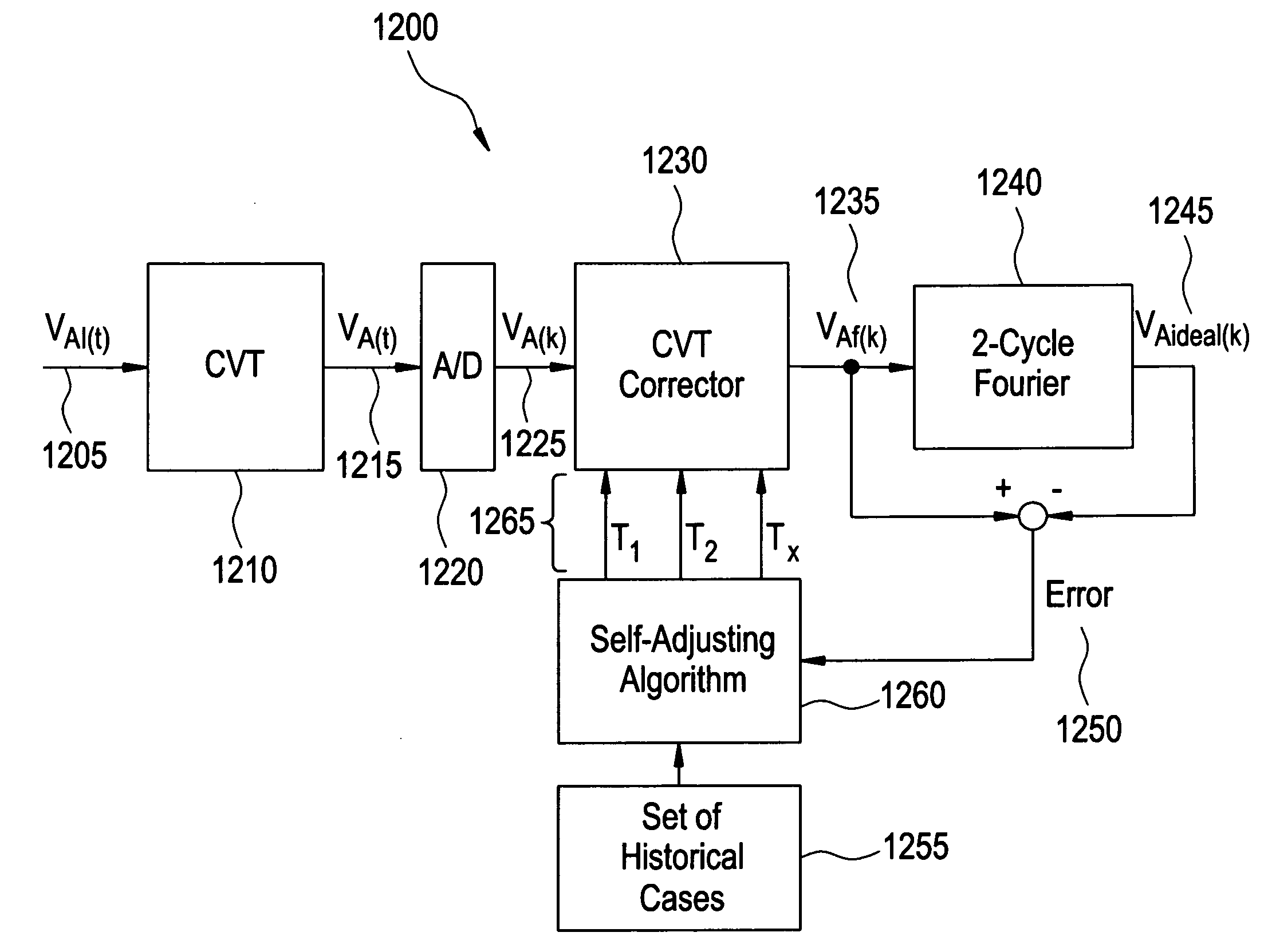

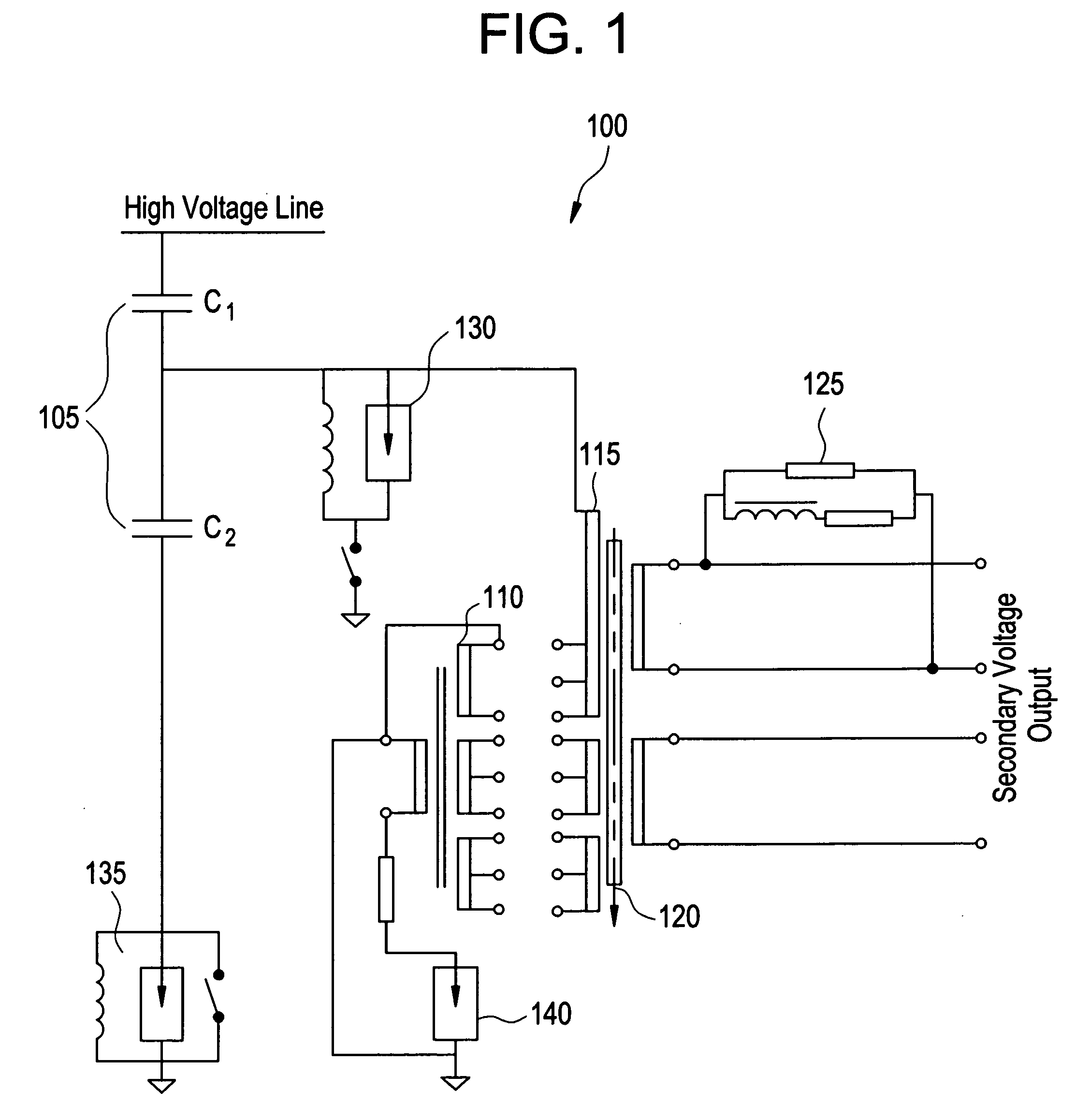

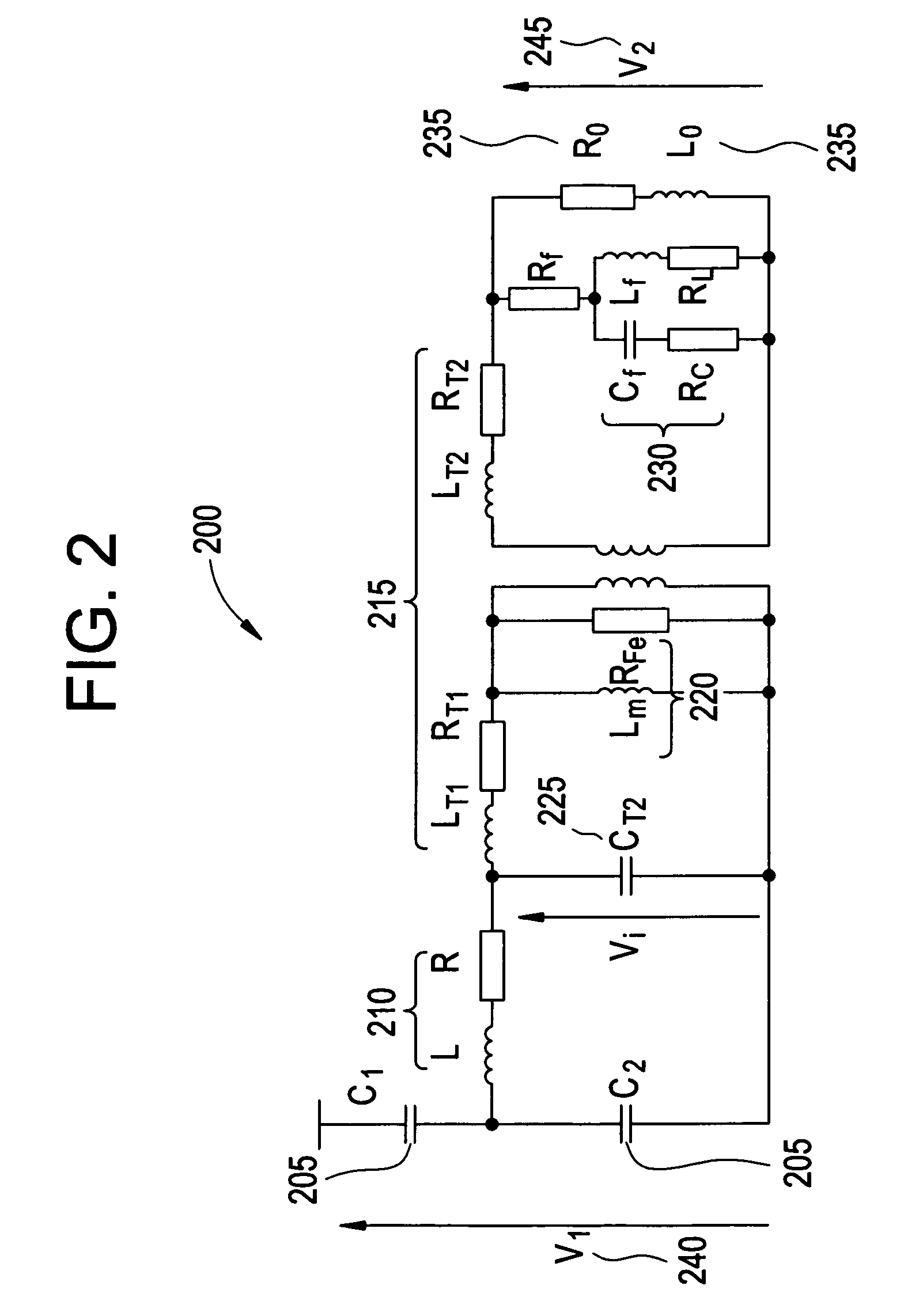

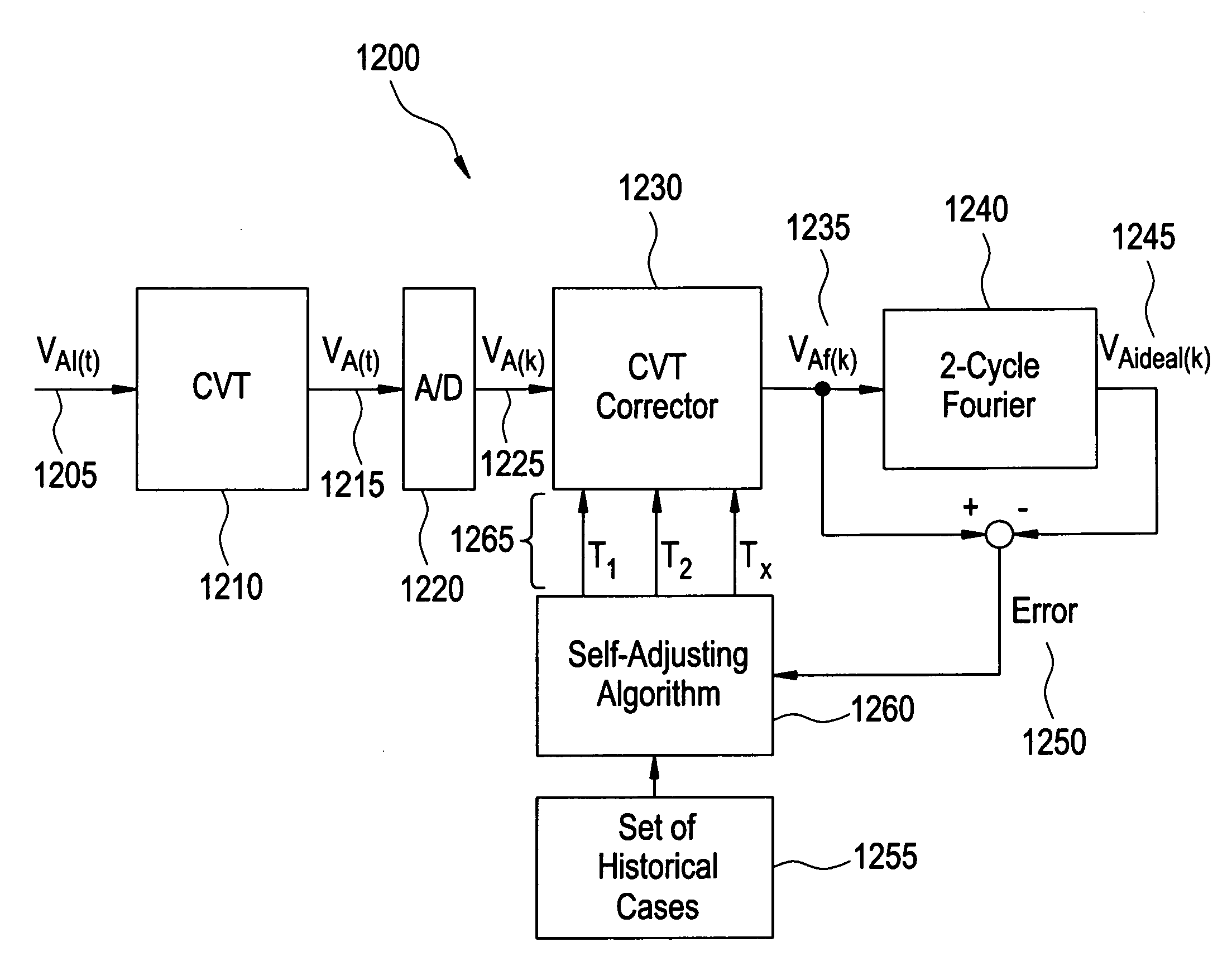

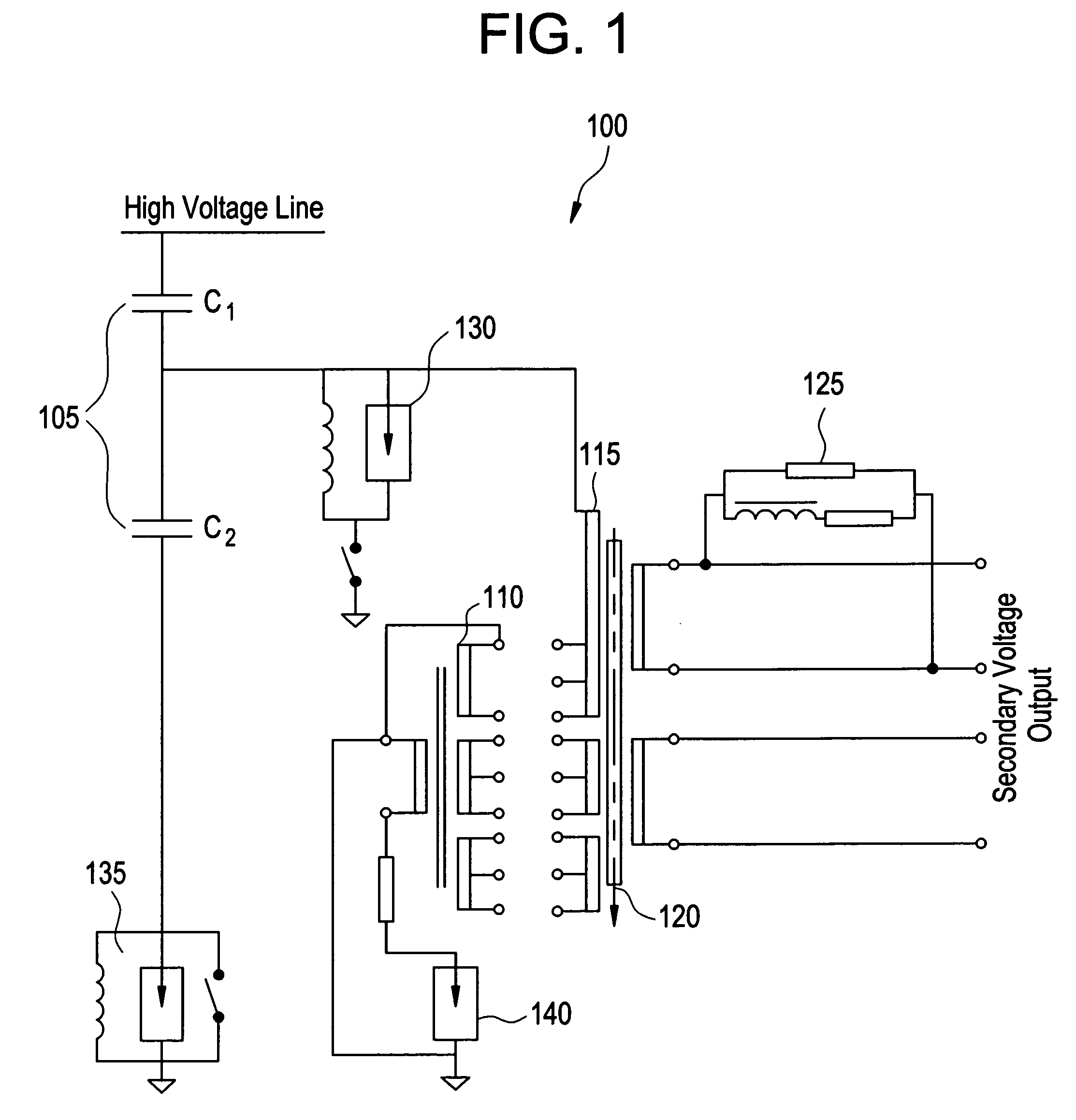

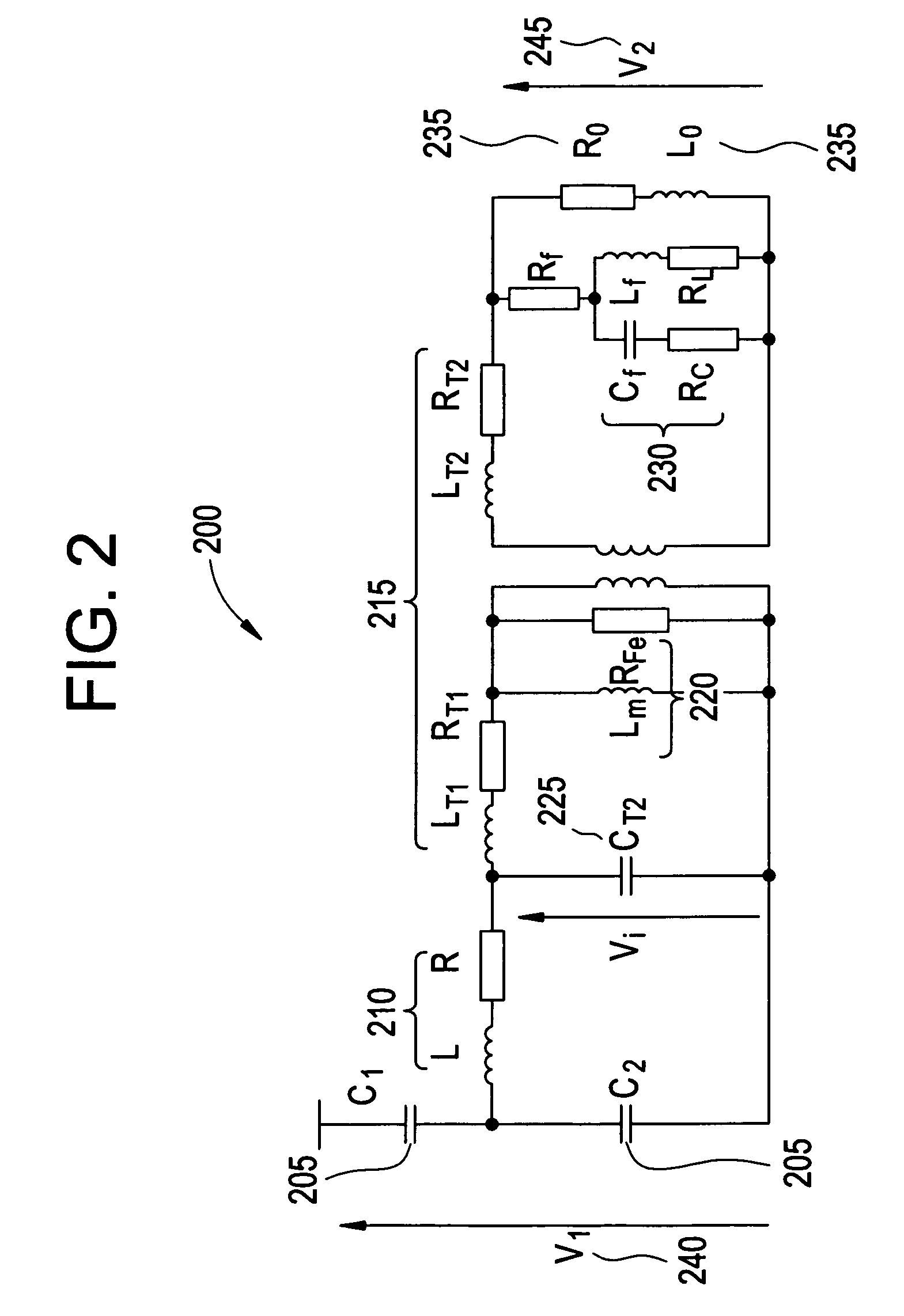

Self-adjusting voltage filtering technique compensating for dynamic errors of capacitive voltage transformers

ActiveUS20080243413A1Digital technique networkVoltage/current isolationNumerical stabilityTransformer

A method of digitally correcting the raw output voltage from a Capacitive Voltage Transformer (CVT) with the intent to remove transient components impacting on transient accuracy of protection function. A typical CVT is represented using three parameters in the linear CVT model. A digital filter designed based on the three parameters and incorporating a dedicated mechanism to ensure numerical stability of the former. A method of self-adjusting the said filter based on system events and performed after the method has been deployed in the field and supplied from a specific CVT.

Owner:GENERAL ELECTRIC CO

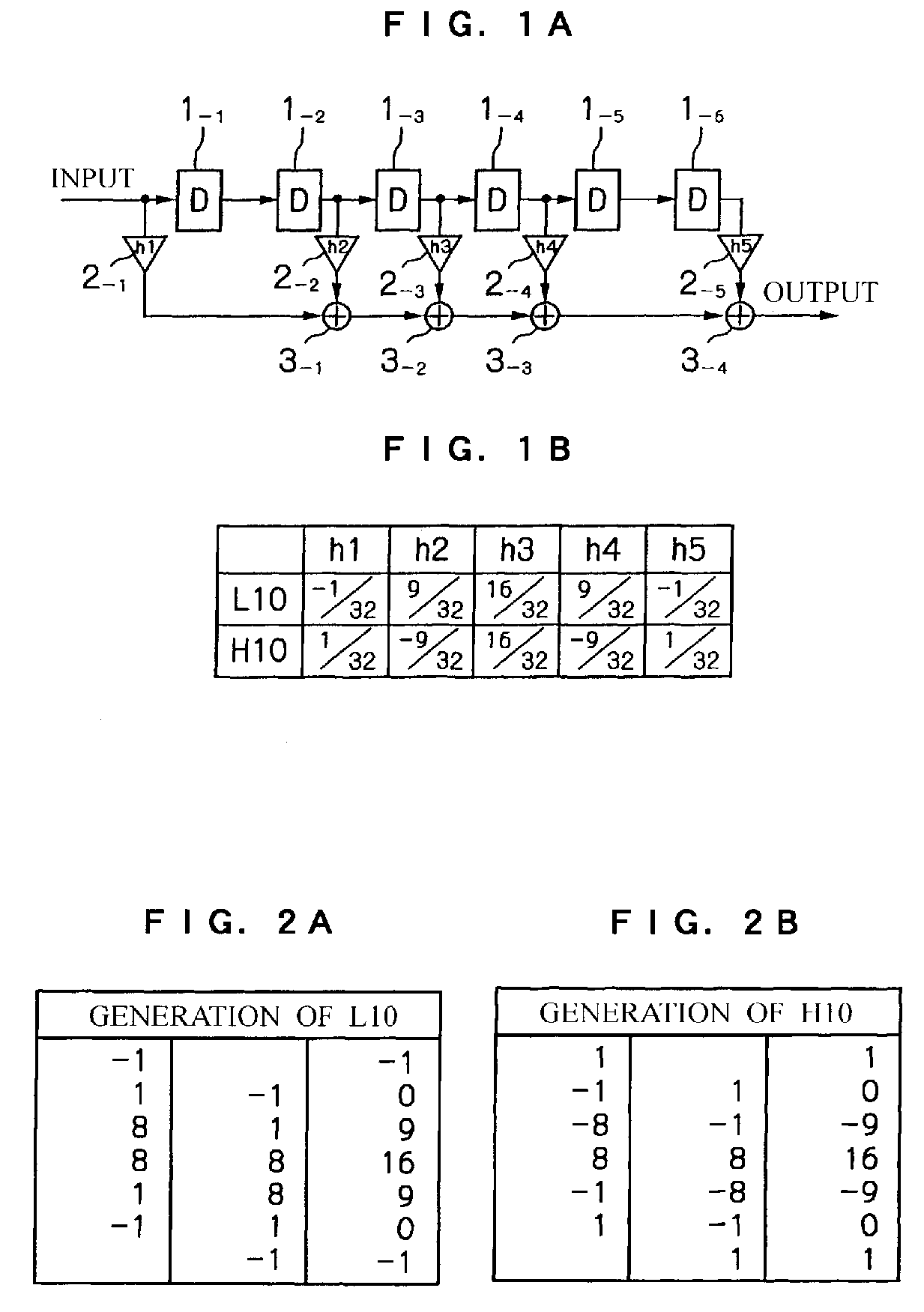

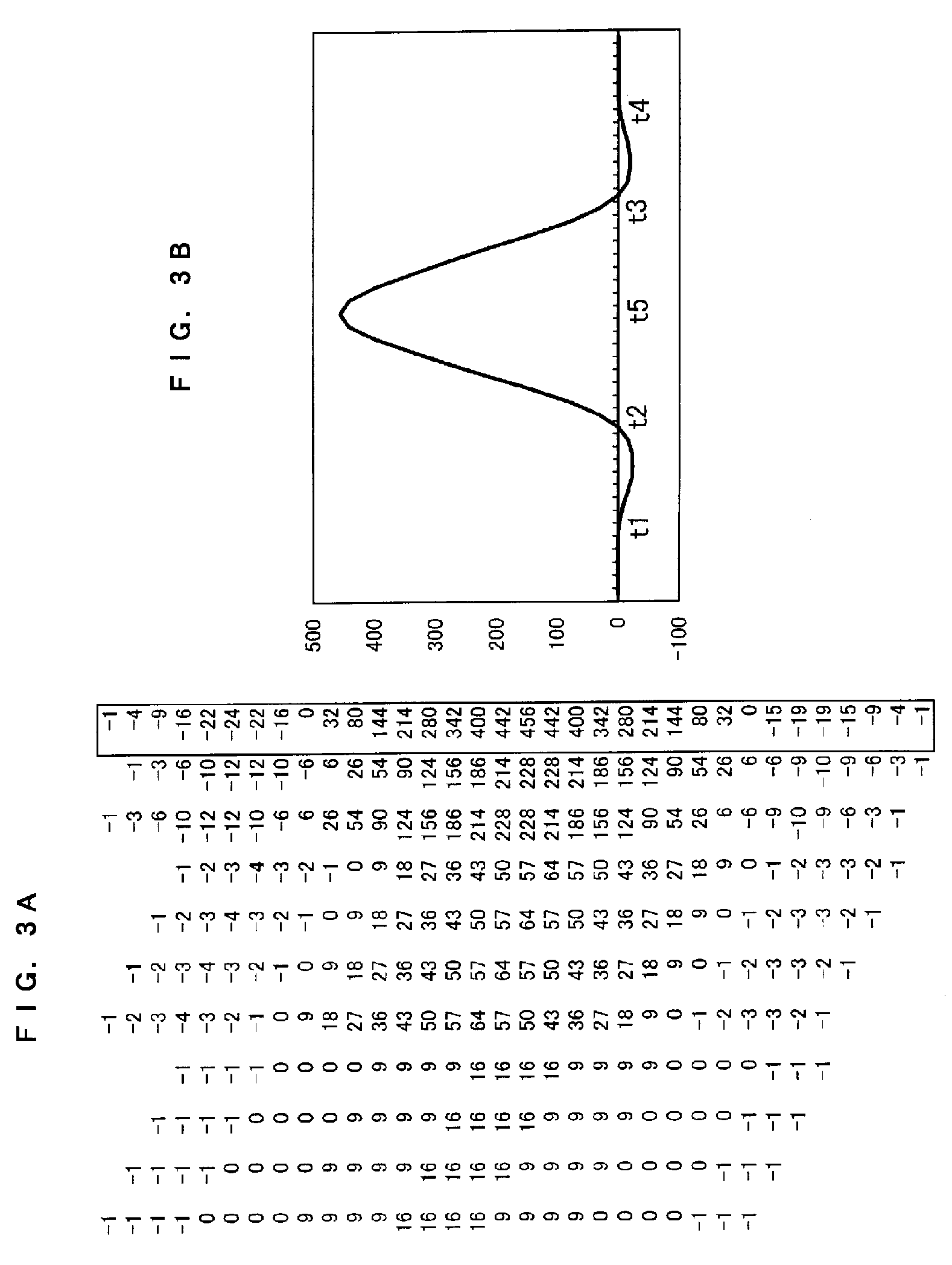

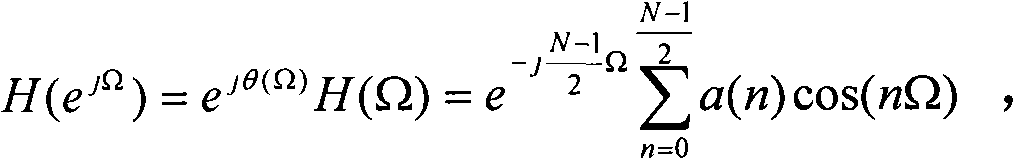

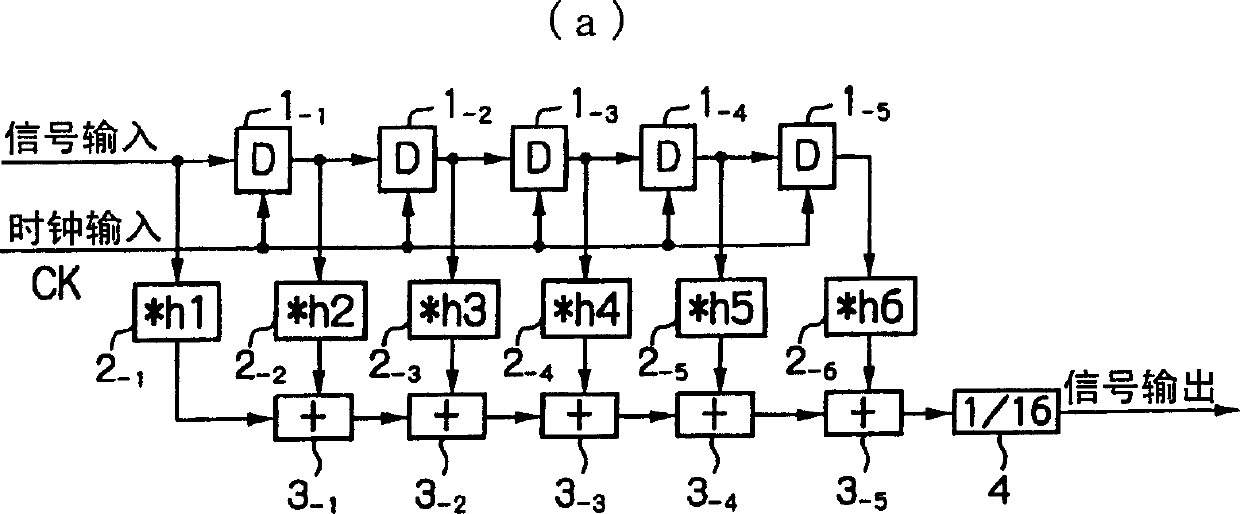

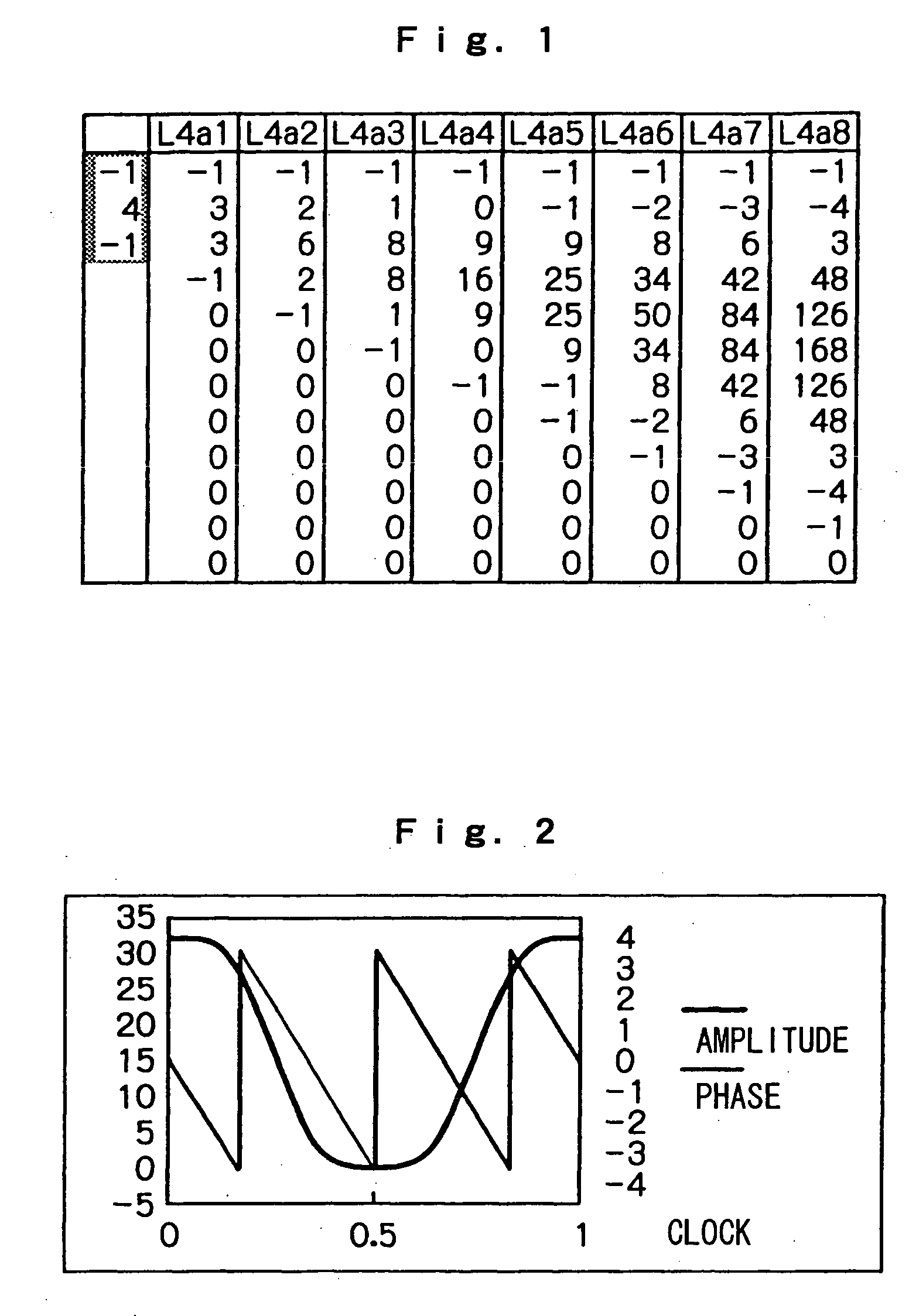

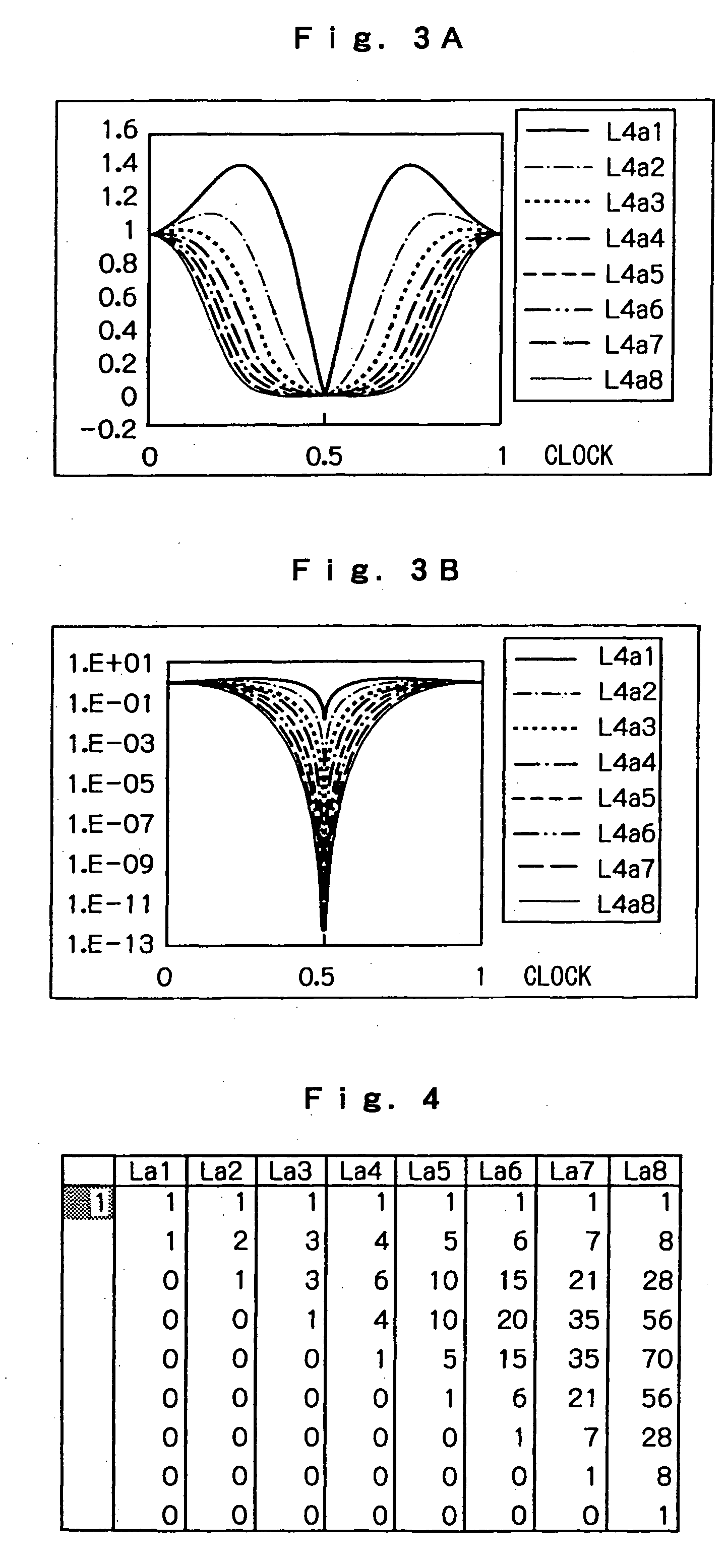

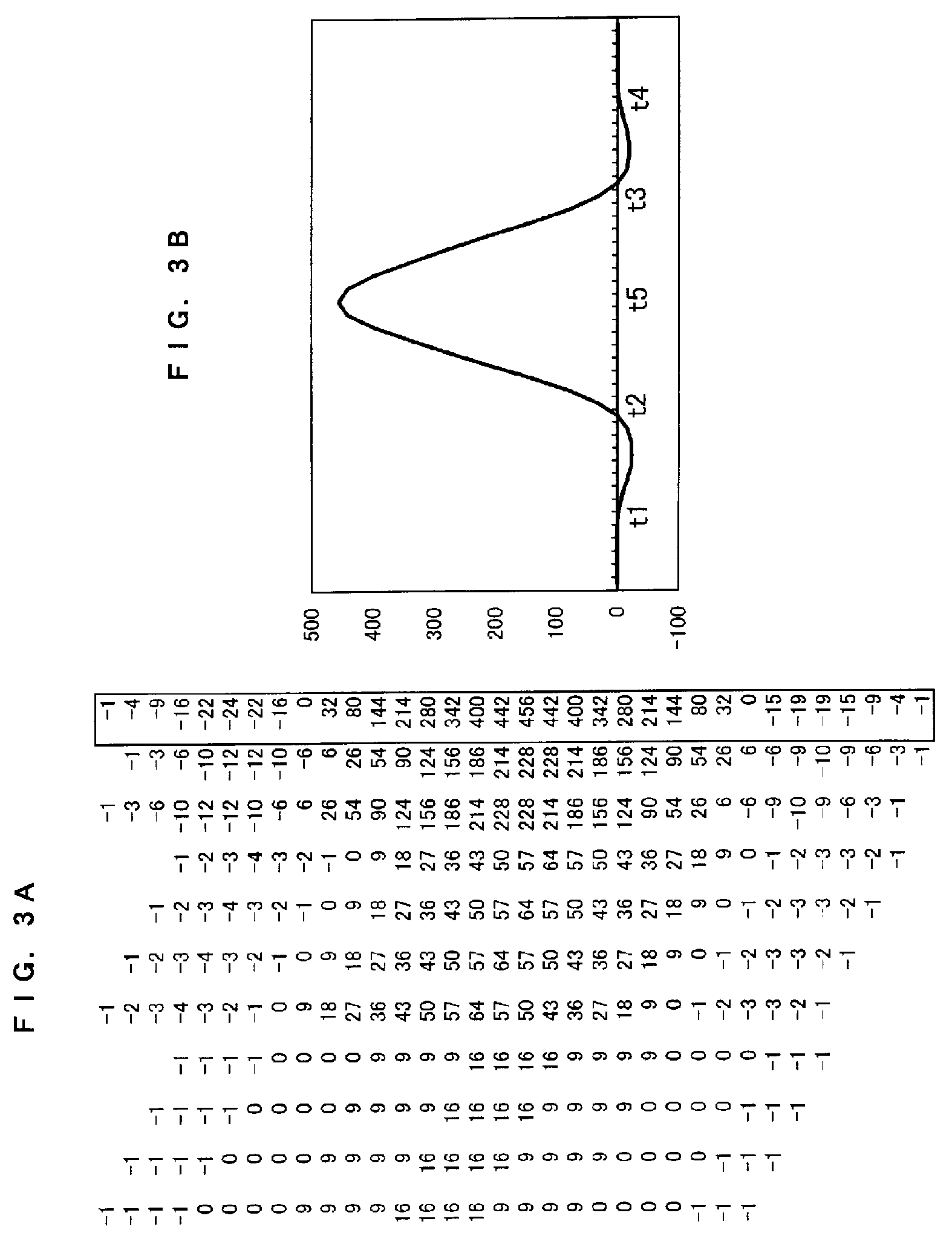

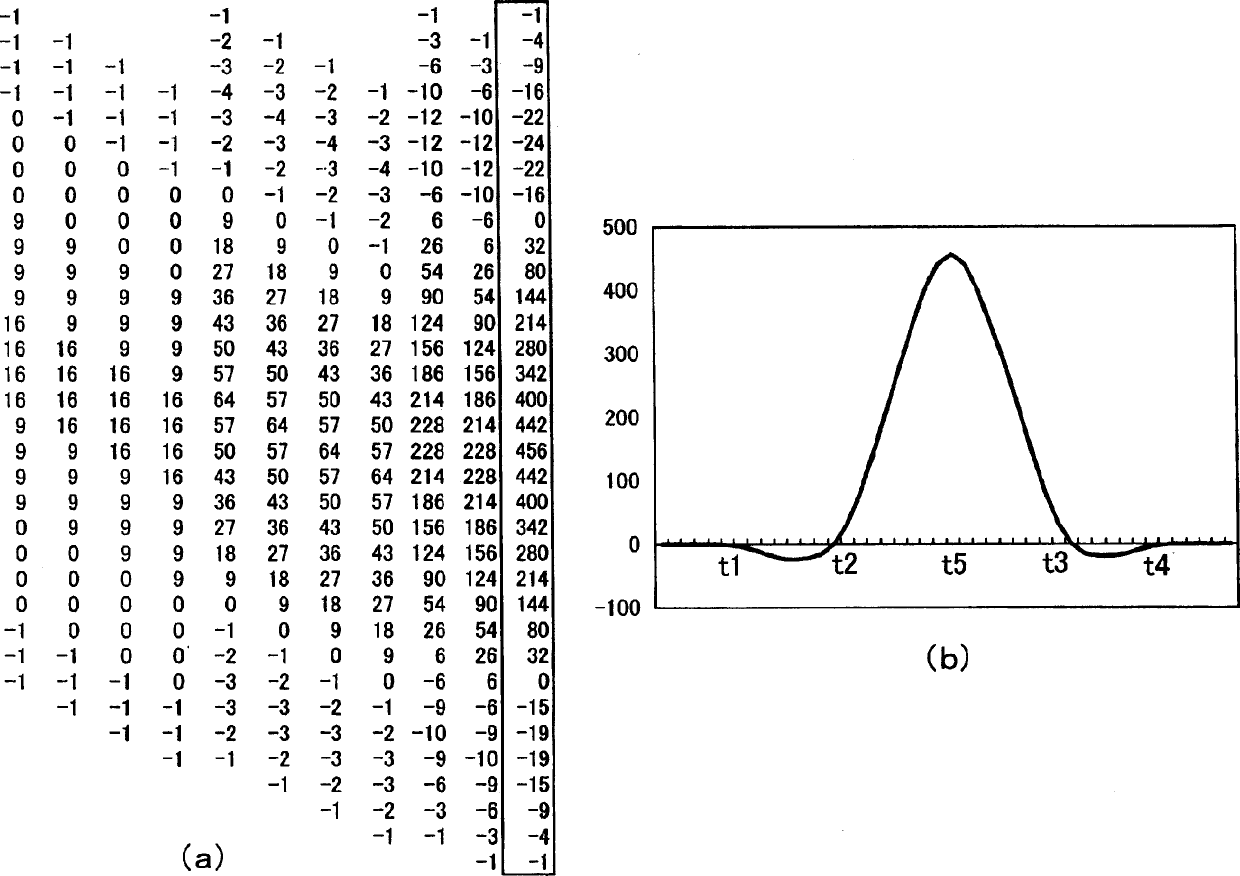

Digital filter design method and device, digital filter design program, and digital filter

InactiveUS20050171989A1Simple designEliminate useDigital technique networkComplex mathematical operationsNon symmetricEngineering

A digital filter is designed by combining unit filters (L10′, H10′) having a predetermined asymmetric numerical sequence as filter coefficients (H1 to H3). Thus, it is possible to automatically obtain a desired digital filter coefficient only by combining the unit filter. Moreover, a symmetric numerical sequence {−1, 0, 9, 16, 9, 0, −1} / 32 is divided at the center into two parts and one of them is used as the asymmetric filter coefficients (H1 to H3). This reduces the number of taps required for the digital filter designed, eliminates use of a window function, and prevents generation of a discretization error in the filter characteristic obtained.

Owner:NSC CO LTD

Design method of high-order limited impulse response digital filter

InactiveCN101295969AHigh precisionPassband fluctuation is smallDigital technique networkPhysical realisationDigital filter designNetwork method

The invention relates to a method for designing a high-order finite impulse response digital filter, which comprises the following steps that: a neural network method is utilized and the amplitude-frequency response error sum of squares of a filter to be designed and an ideal filter serves as the calculation energy function of a neural network; the gradient descent learning algorithm is adopted to train the weight of the neural network to minimize the amplitude-frequency response error sum of squares of the filter to be designed and the ideal filter; when the neural network is stabilized, each parameter of the finite impulse response digital filter can be obtained and then the design of the finite impulse response digital filter is completed. The high-order finite impulse response digital filter designed by the method of the invention is characterized by small pass band fluctuation, large stop-band attenuation, controllable boundary frequency and high precision, etc., especially by that no matrix inversion algorithm is required to be carried out in the design, thus having fast operation speed, and the filter has broad application prospect in the engineering fields such as data transmission, high-precision televisions, radar and sonar systems and voice and image processing, etc.

Owner:HUNAN UNIV

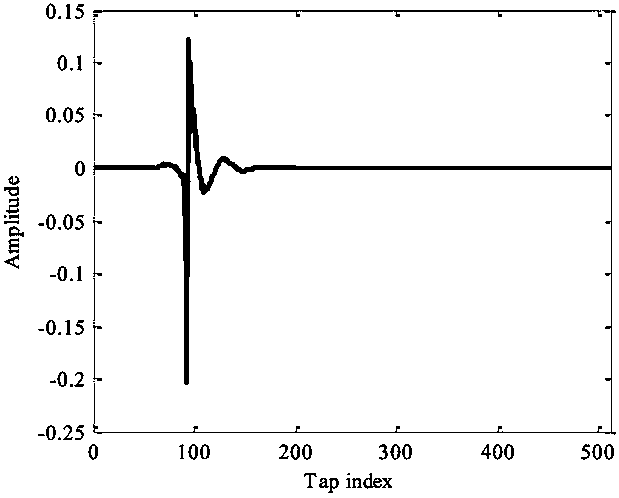

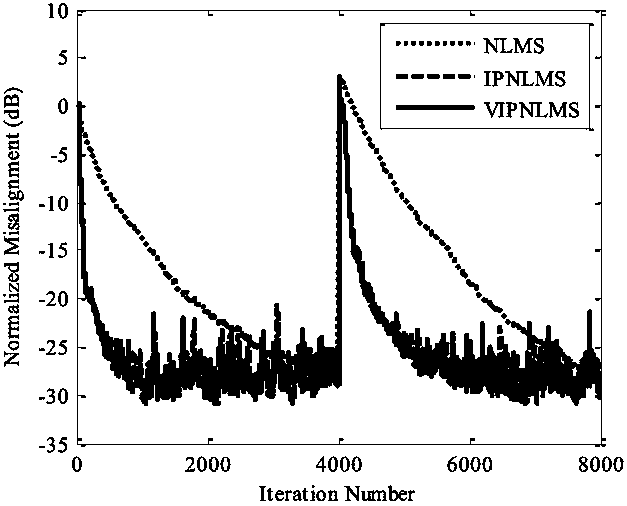

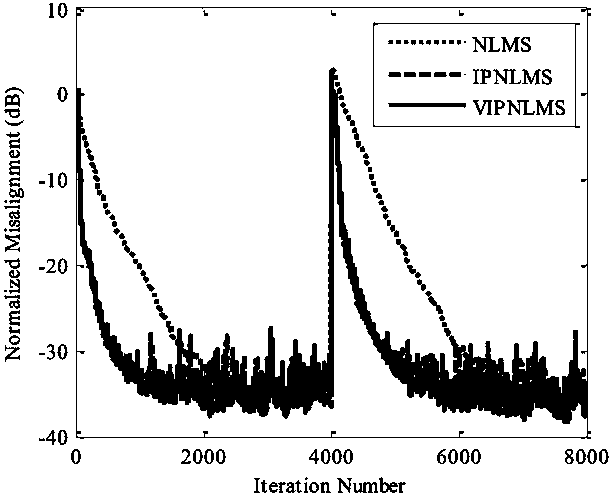

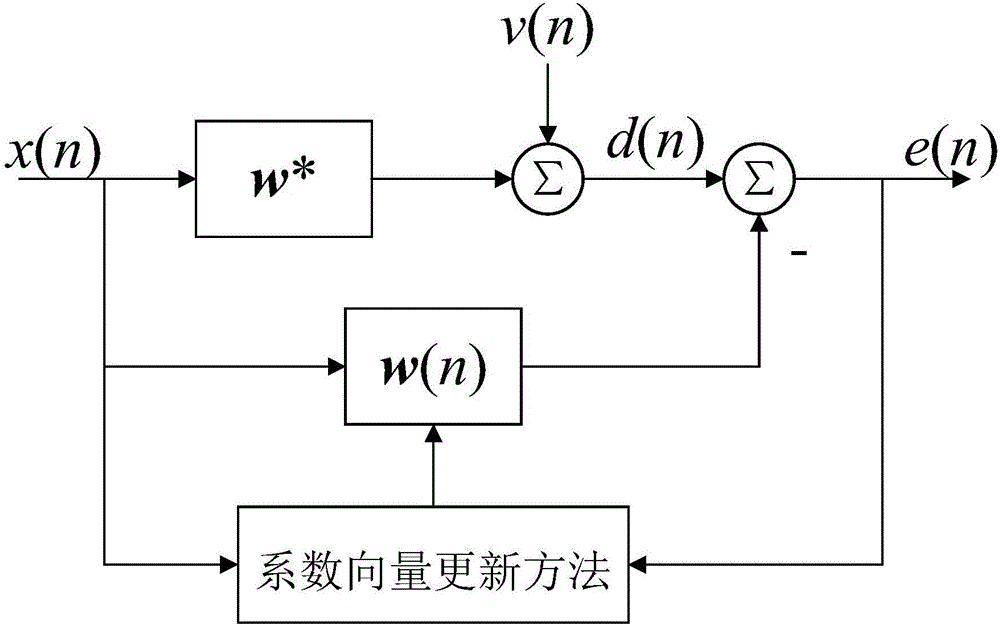

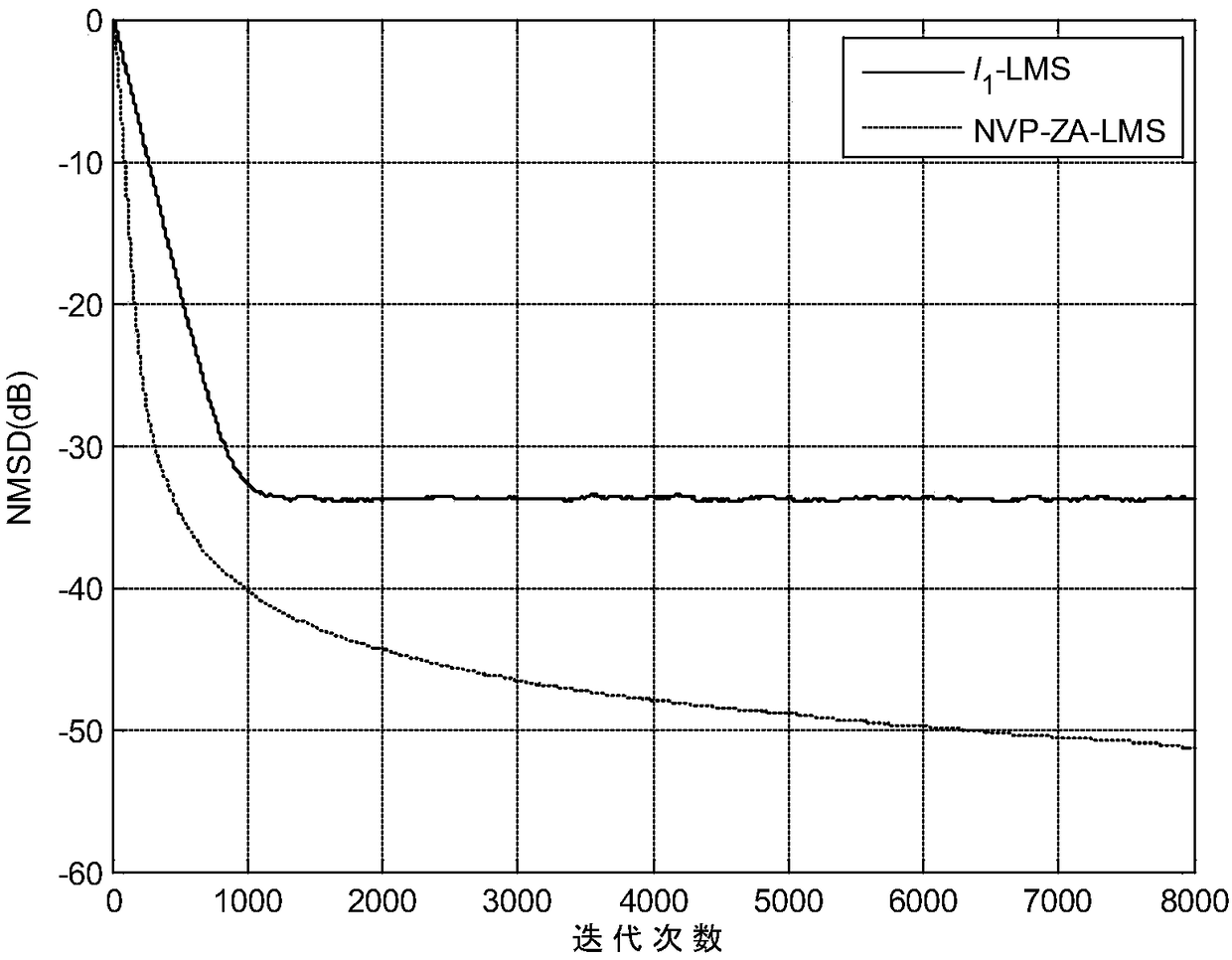

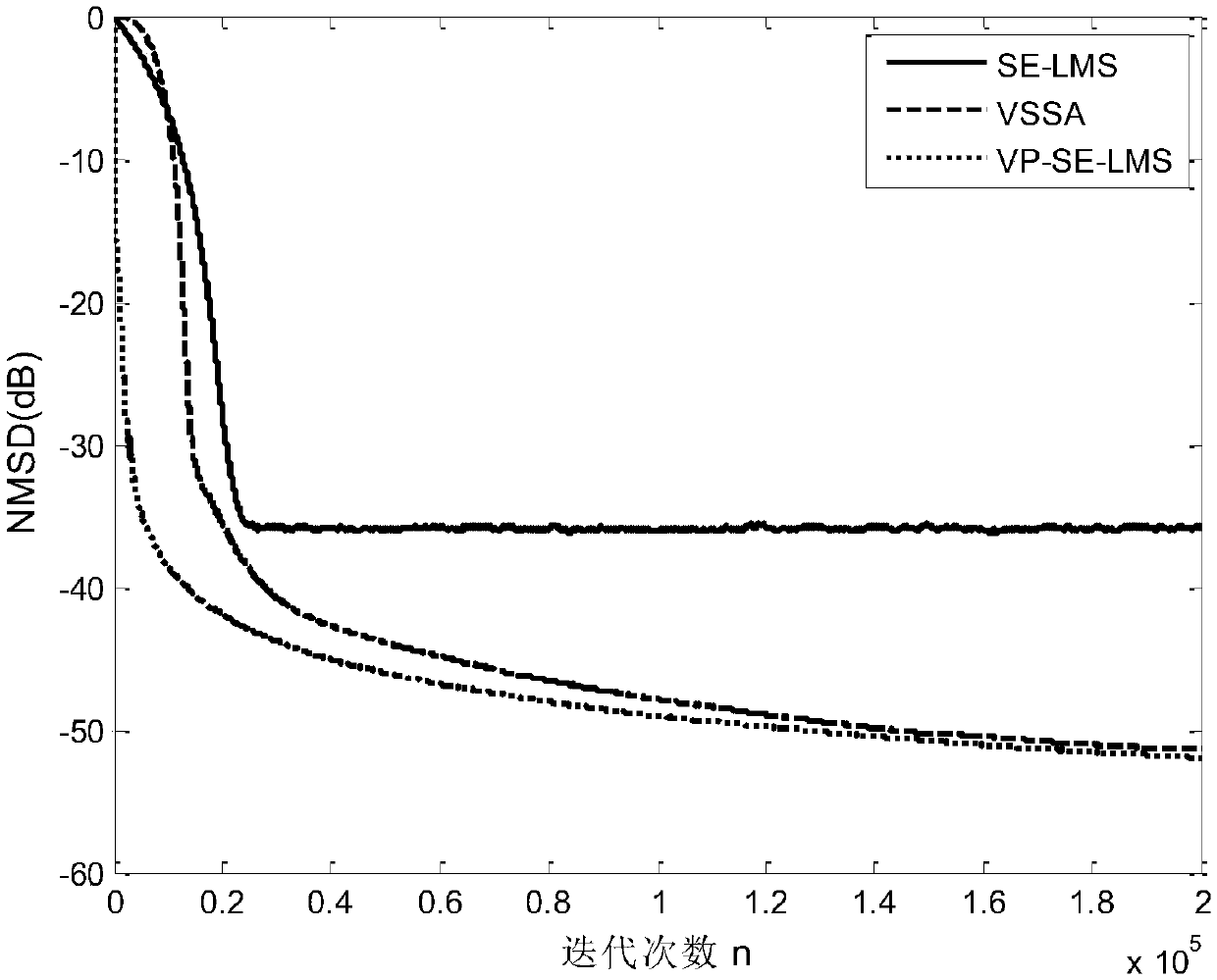

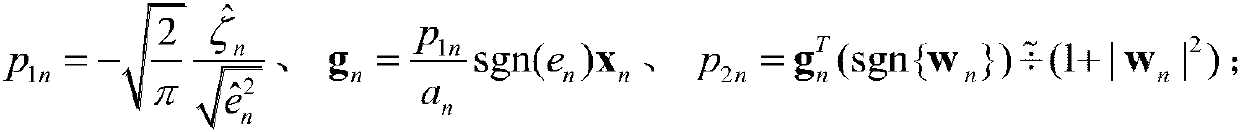

Variable parameter proportion self-adaptive filter

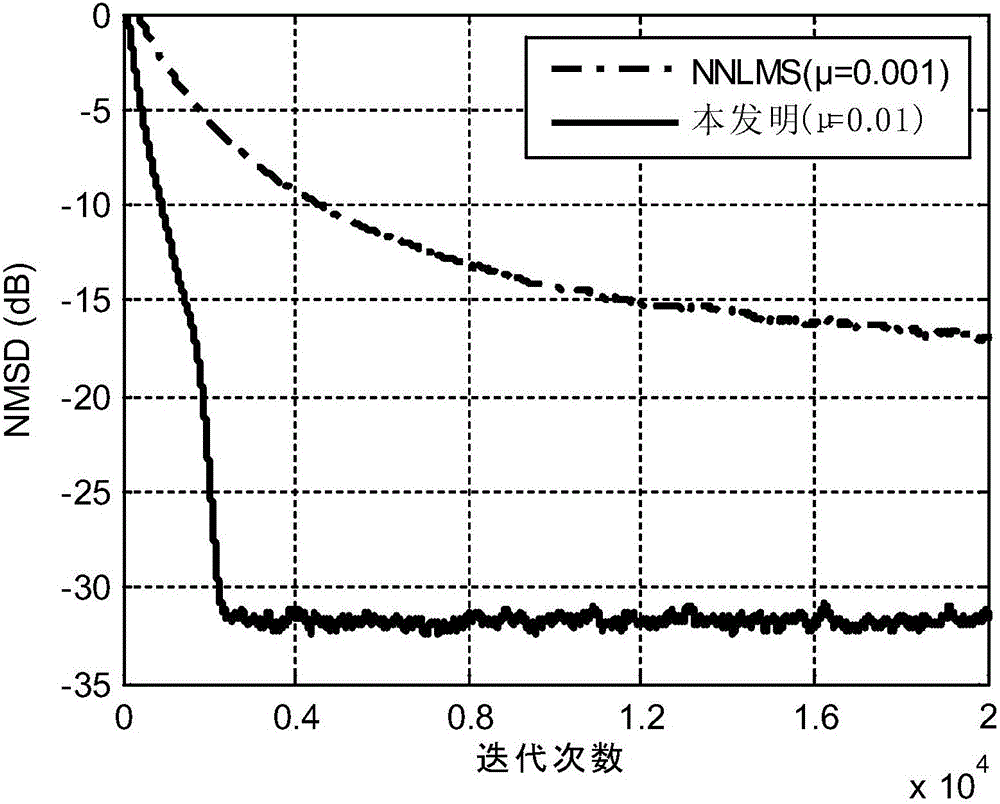

InactiveCN103716013AFast convergenceLow steady-state misalignment volatilityAdaptive networkSelf adaptiveDigital filter design

The invention discloses a variable parameter proportion self-adaptive filter and belongs to the field of design of digital filters. The variable parameter proportion self-adaptive filter adopts a time-varying parameter to adjust a coefficient gain value of the self-adaptive filter. The time-varying parameter can be a monotone increasing function representing the specific value of the error signal power to the system noise power. In an initial phase of the self-adaptive filter, the specific value of the error signal power to the system noise power is larger, so that a large coefficient of the self-adaptive filter has a large gain value. In a convergence phase of the self-adaptive filter, the specific value of the error signal power to the system noise power is small, so that the large coefficient of the self-adaptive filter has a small gain value. Therefore, by adopting the variable parameter method, the high convergence speed of the proportion self-adaptive filter can be kept, and low steady state imbalance fluctuation of the proportion self-adaptive filter can be also obtained.

Owner:SUZHOU UNIV

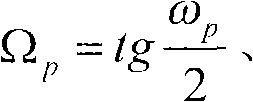

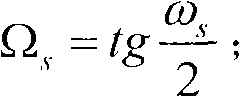

Method for designing digital filter applied in inertia device

InactiveCN102055434AImprove denoising effectSatisfactory filter performanceDigital technique networkBilinear transformUltrasound attenuation

The invention relates to a method for designing a digital filter applied in an inertia device. The method is characterized by comprising the following steps of: determining an amplitude attenuation allowable value according to the precision of the inertia device, determining a phase delay allowable value according to the performance index of a strap-down inertial navigation system, and determining certain technical parameters of the filter according to the actual signal power spectrum analysis of the inertia device; designing a reference analog filter, converting the reference analog filter into an infinite impulse response (IIR) digital filter by using a bilinear transform method, observing a bode diagram in the filter parameter adjusting process, and performing off-line simulation calculation according to the actually measured data; and performing judgment by using de-noising effect, common cutoff frequency, amplitude attenuation and phase delay as fuzzy variables and using fuzzy rules to optimize the integral performance index. The digital filter designed by using the method can effectively filter the noise in the inertia device, meanwhile, controls the amplitude attenuation and the phase delay in an allowable range, and ensures the precision of the signals.

Owner:北京华力创通科技股份有限公司

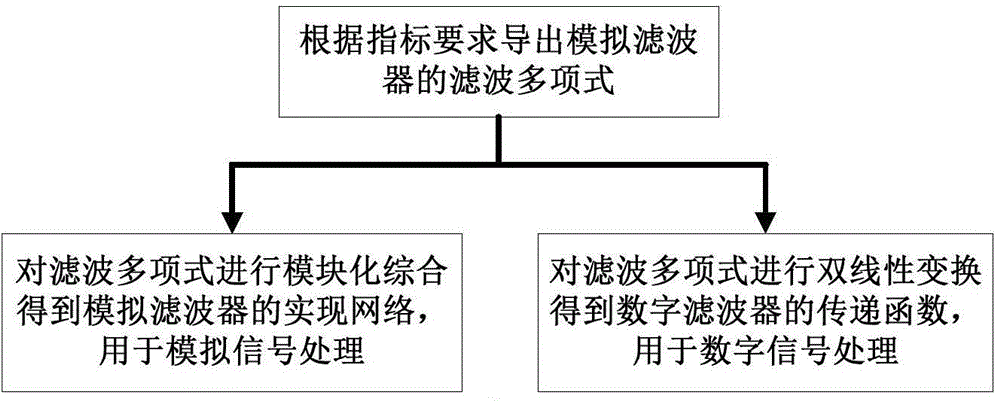

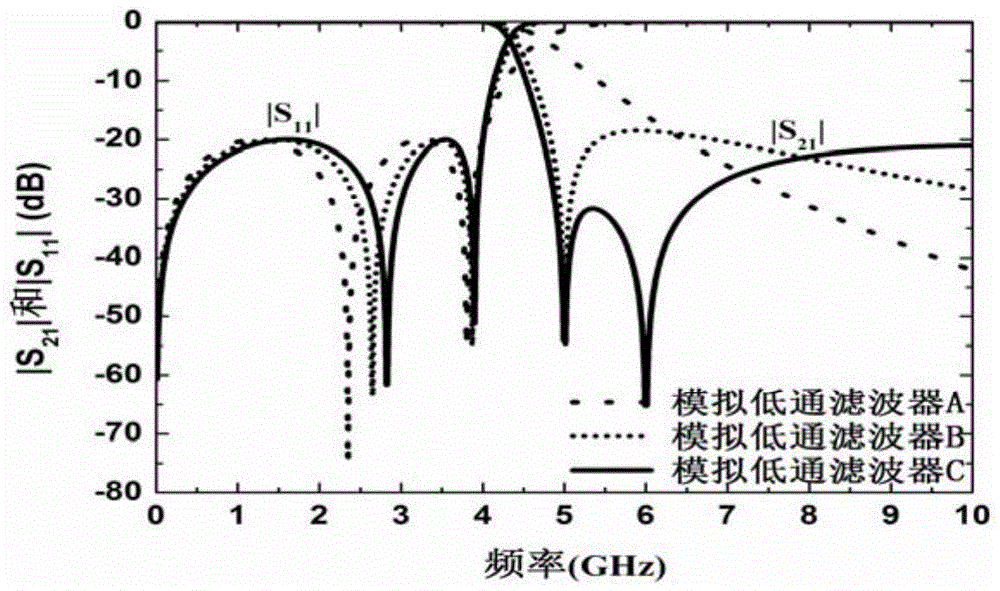

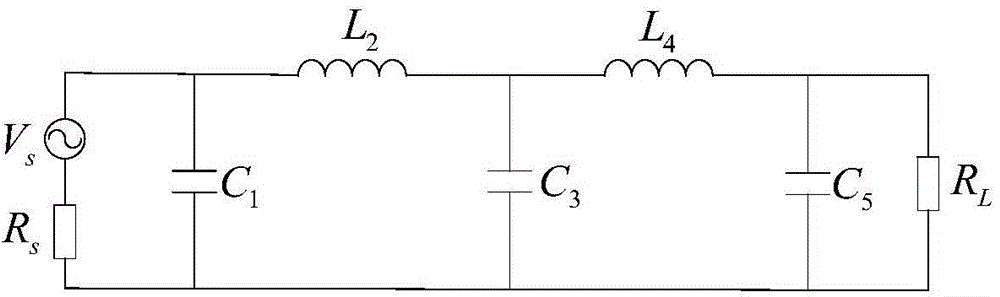

Filter direct synthetic method

InactiveCN104363004AIncrease flexibilityGood harmonic suppressionDigital technique networkTransmission zerosDigital filter design

The invention discloses a filter direct synthetic method. By means of the filter direct synthetic method, the transmission zero points of filters can be flexible arranged, a smoothing polynomial of the filters can be led out, and the smoothing polynomial includes all information of the filters and can be directly used for achieving the filters. Effective connection is conduced through some basic structures which can achieve one or more transmission zero points, an achieving network of the filters is finally obtained, and modularization synthesis can be achieved; the method can be used for designing digital filters through bilinear transformation; the types of the filters comprise the low-pass type, the high-pass type, the band-pass type, the band elimination type and the like. The filter direct synthetic method has the advantages of being simple, fast and accurate.

Owner:肖飞

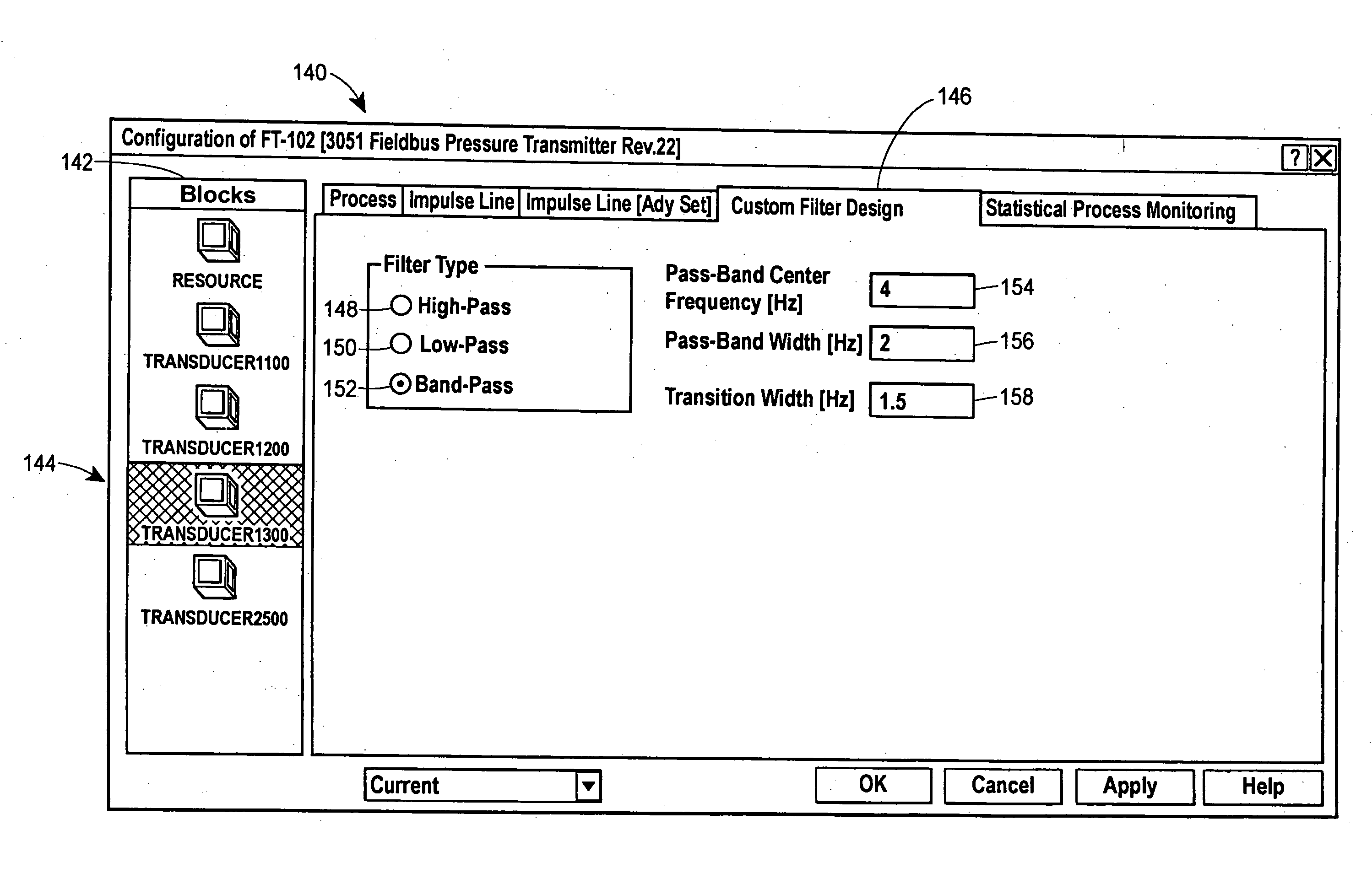

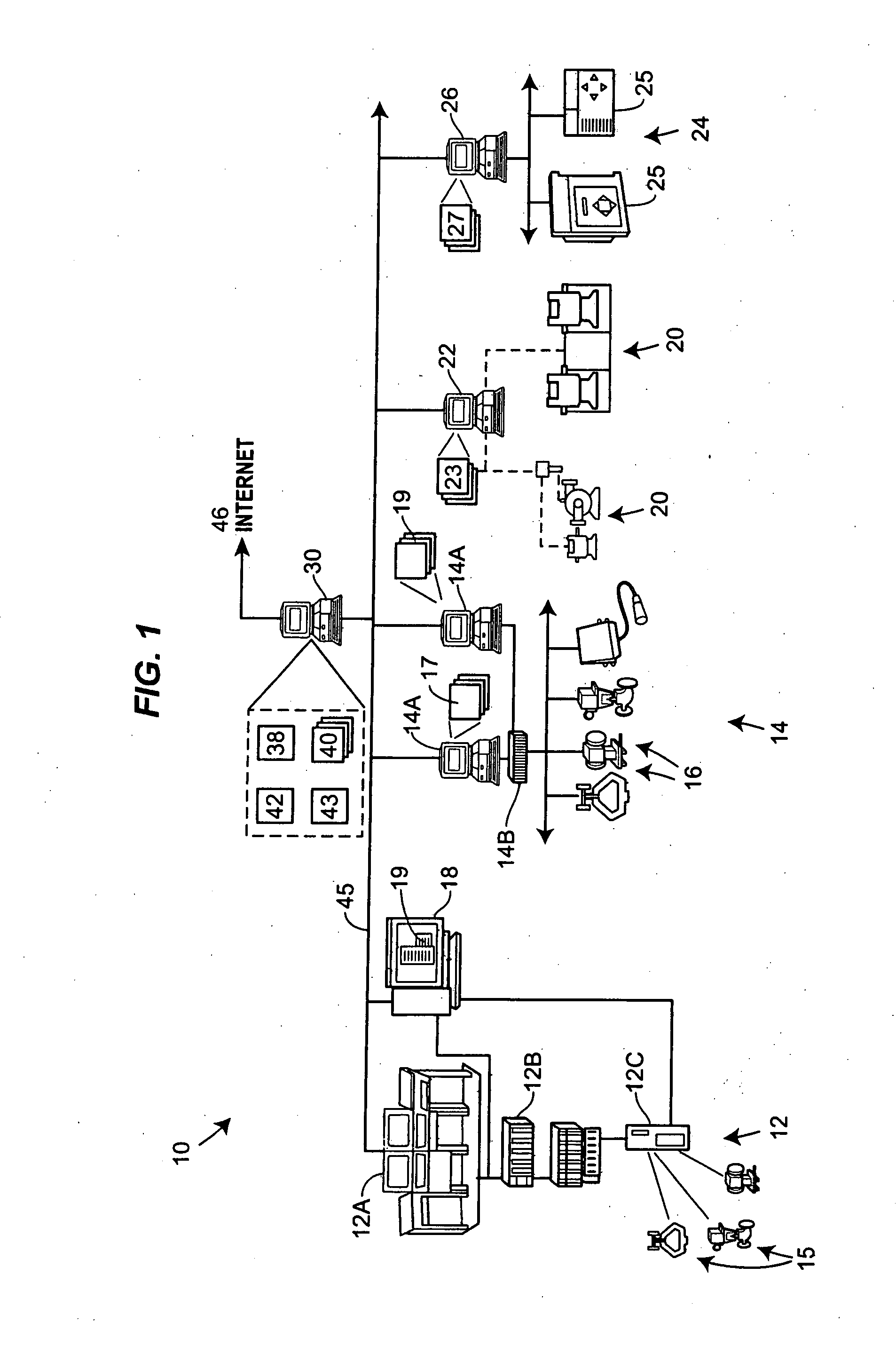

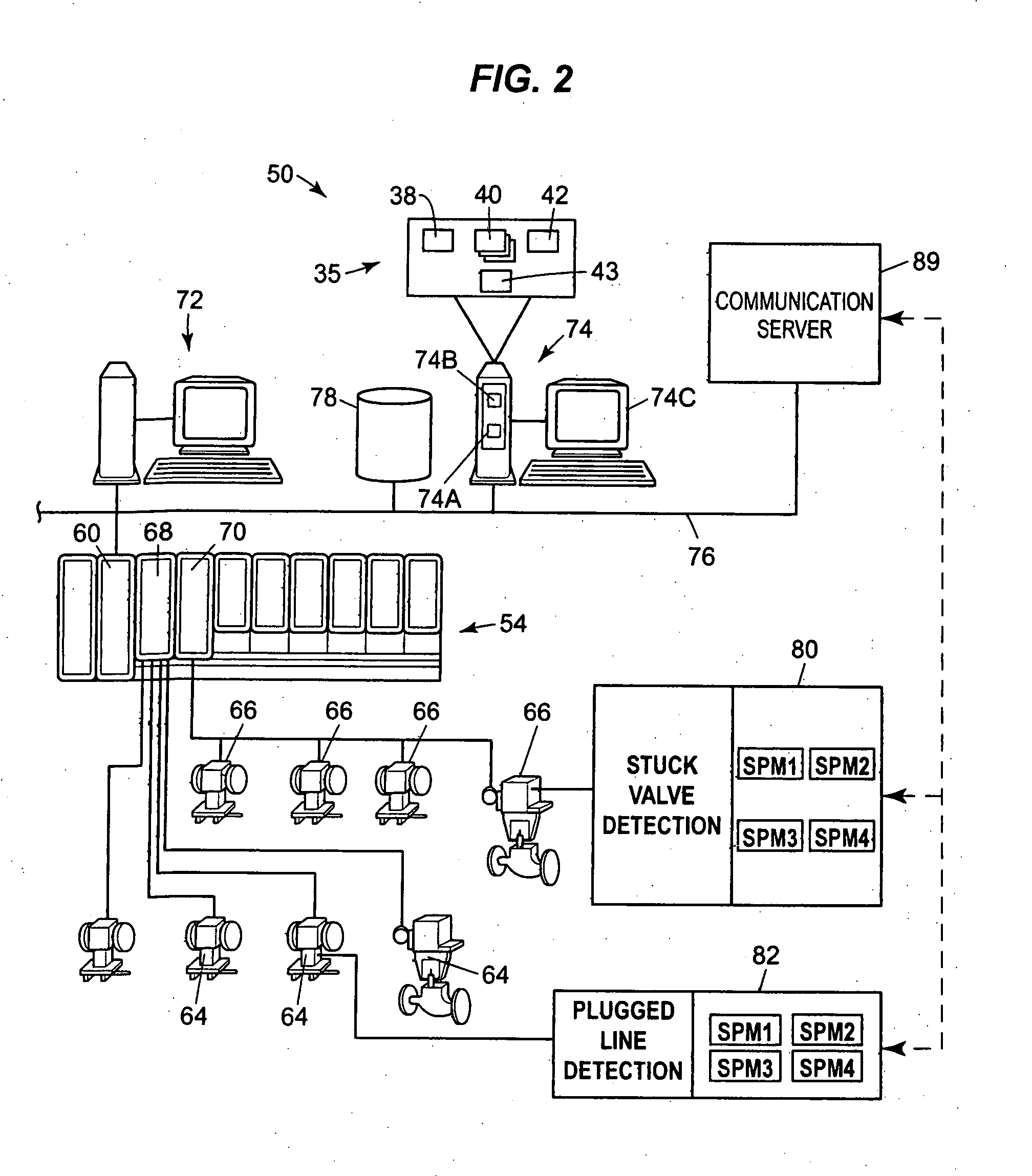

Field device with capability of calculating digital filter coefficients

A digital filter design algorithm is implemented directly within a process control field device or other process related equipment. Filter design parameters are exposed so that filter design parameter values may be provided to the digital filter design algorithm so that the digital filter design algorithm may calculate digital filter coefficients for a digital filter having desired frequency response characteristics. The digital filter design parameter values may be provided by a user, or may be provided as process variable data output from a process control field device or other process related equipment. Once the coefficients of the digital filter having the desired frequency response characteristics have been calculated, the digital filter may be applied to process variable data received by the process control field device or other process related equipment.

Owner:FISHER-ROSEMOUNT SYST INC

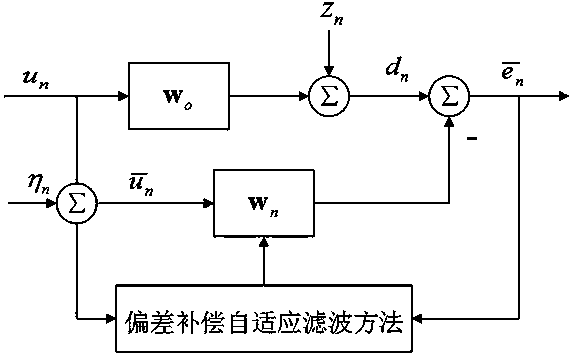

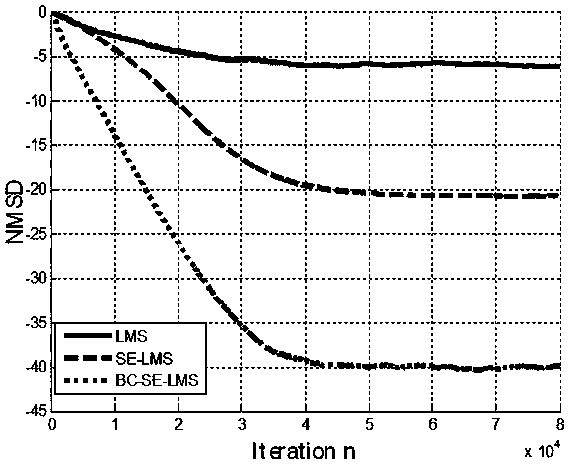

Robust deviation compensation self-adaptive filter and filtering method thereof

ActiveCN107592096AImprove performanceEliminate estimation biasAdaptive networkPhase noiseEngineering

The invention discloses a robust deviation compensation self-adaptive filter and a filtering method thereof, and belongs to the field of design of digital filters. The robustness of the self-adaptivefilter is kept under the influence of input noise and pulse noise by main utilization of a deviation compensation method and a symbolic operation method; the deviation compensation method can be utilized for inhibiting influence of the input noise on an unknown system; the symbolic operation method can be utilized for reducing influence of the pulse noise on the unknown system; and thus, the deviation compensation self-adaptive filter can be applied to electronic and communication equipment having input noise and interference pulse.

Owner:SUZHOU UNIV

Programmable overflow protection in digital processing

InactiveUS6112220AComputation using non-contact making devicesDigital signal processingIir filtering

An integrated circuit, e.g. an AC '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a DC buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A RAM is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional blocks of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional blocks.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

Nonnegative adaptive filter

ActiveCN106059531AFast convergenceImprove robustnessAdaptive networkCommunications systemError function

The invention discloses a nonnegative adaptive filter, and belongs to the field of digital filter design. The filter is obtained by a cost function composed of a 10-norm and a logarithm absolute error function which minimize a coefficient vector. Minimization of the 10-norm speeds up convergence of a nonnegative adaptive filter estimation unknown system, while minimization of the logarithm absolute error function improves the robustness of the nonnegative adaptive filter. The nonnegative adaptive filter can be applied to an occasion in which an electronic or communication system is interfered by high pulse noise.

Owner:SUZHOU UNIV

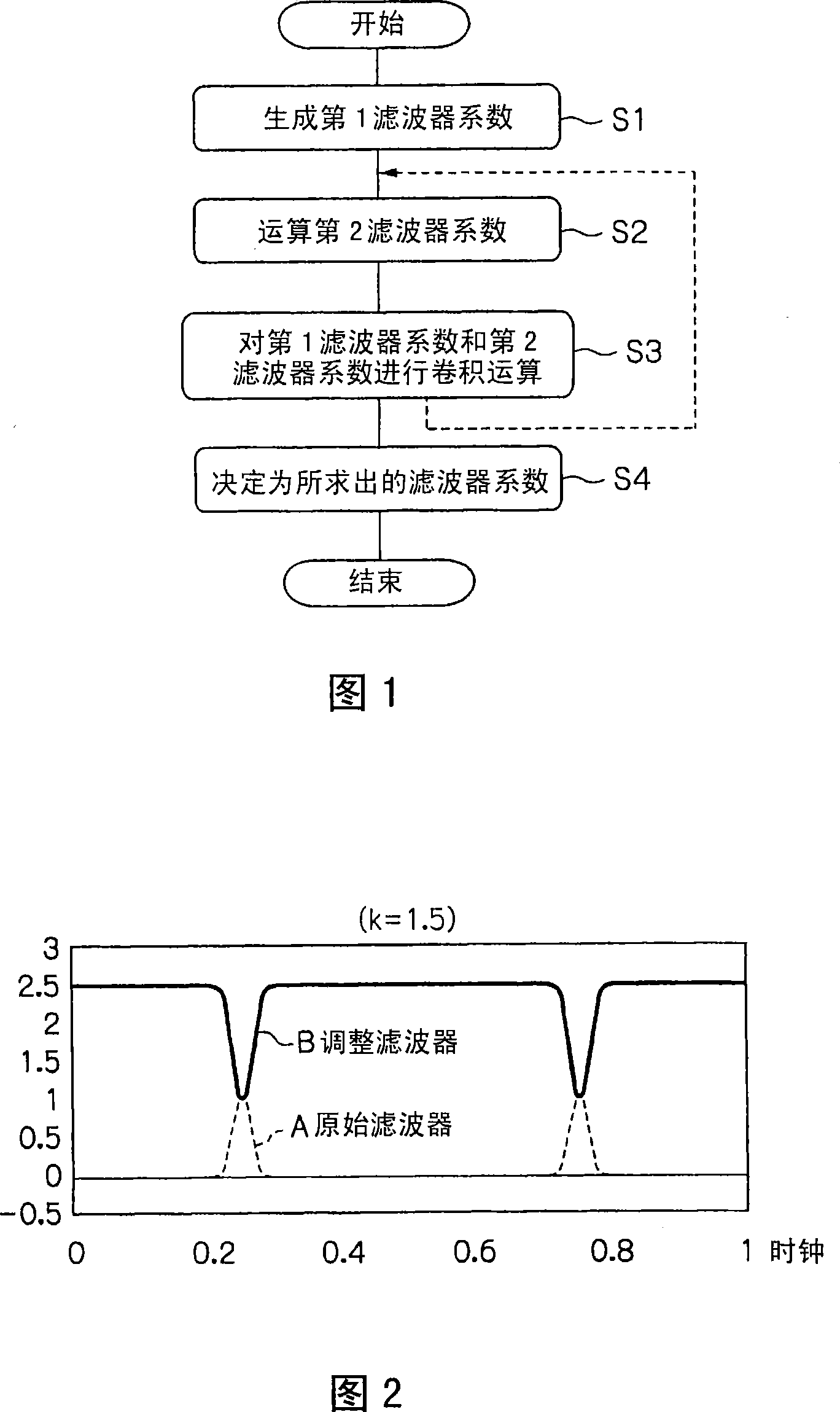

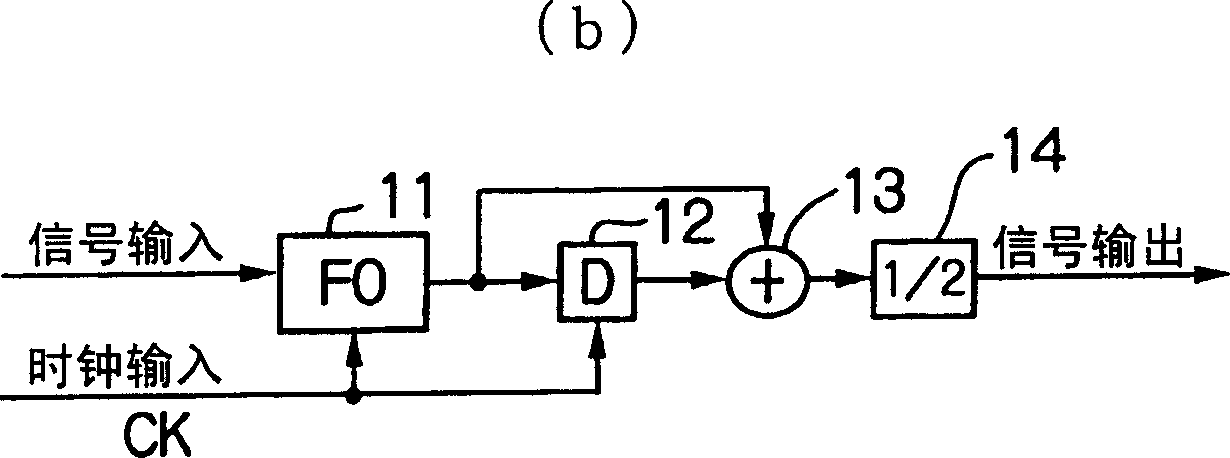

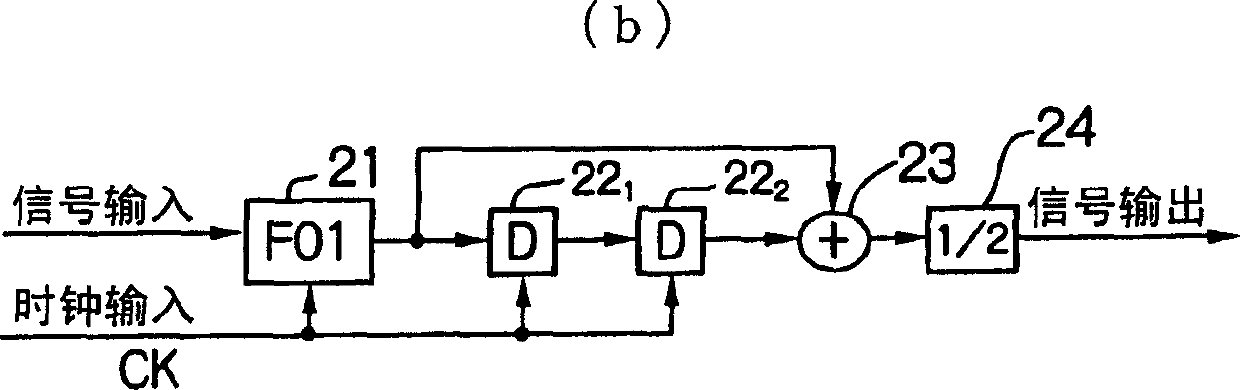

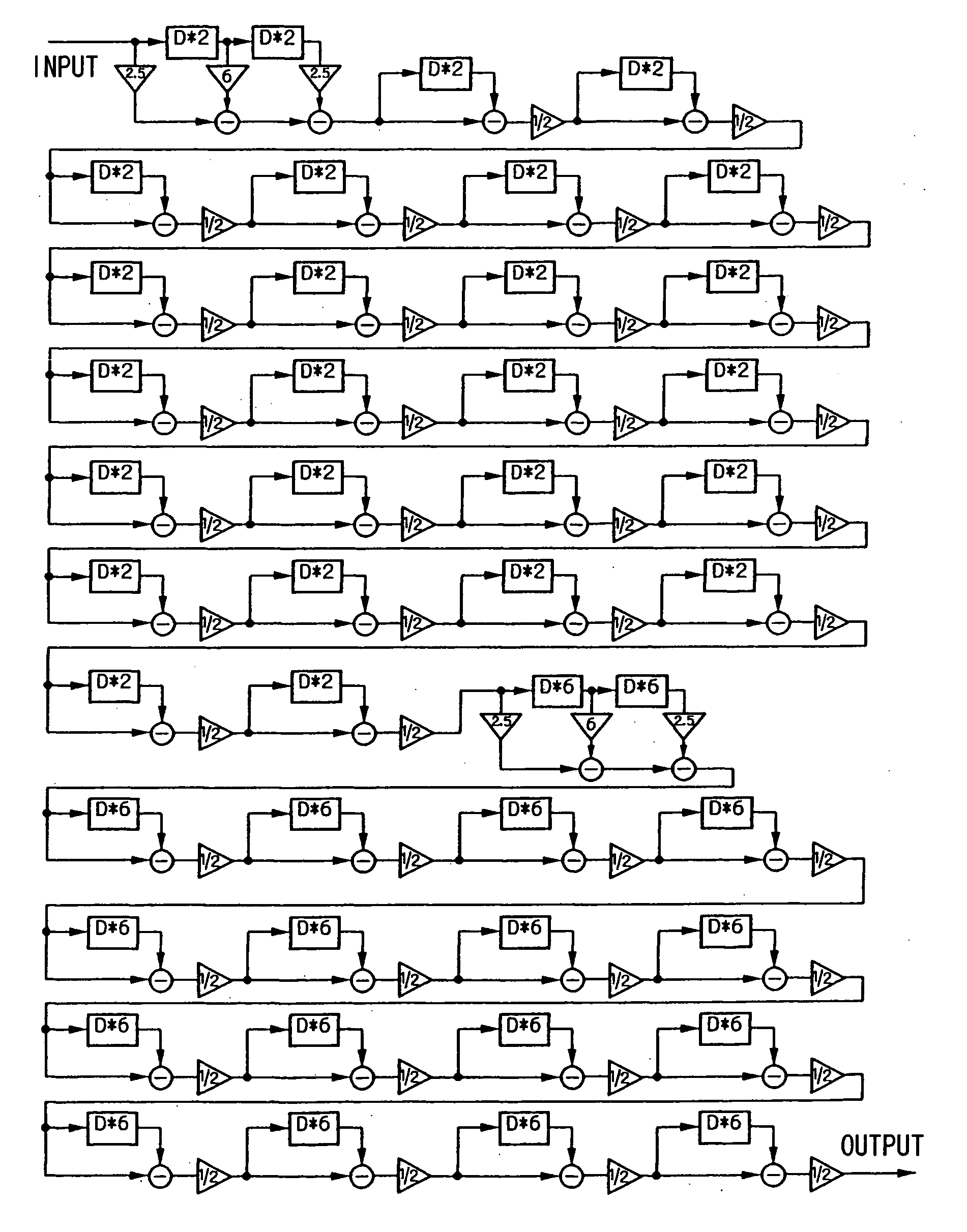

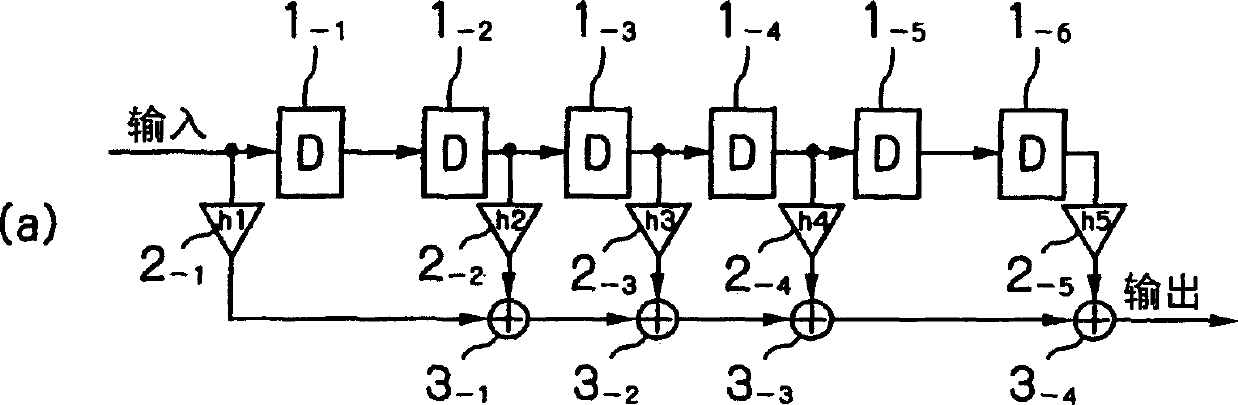

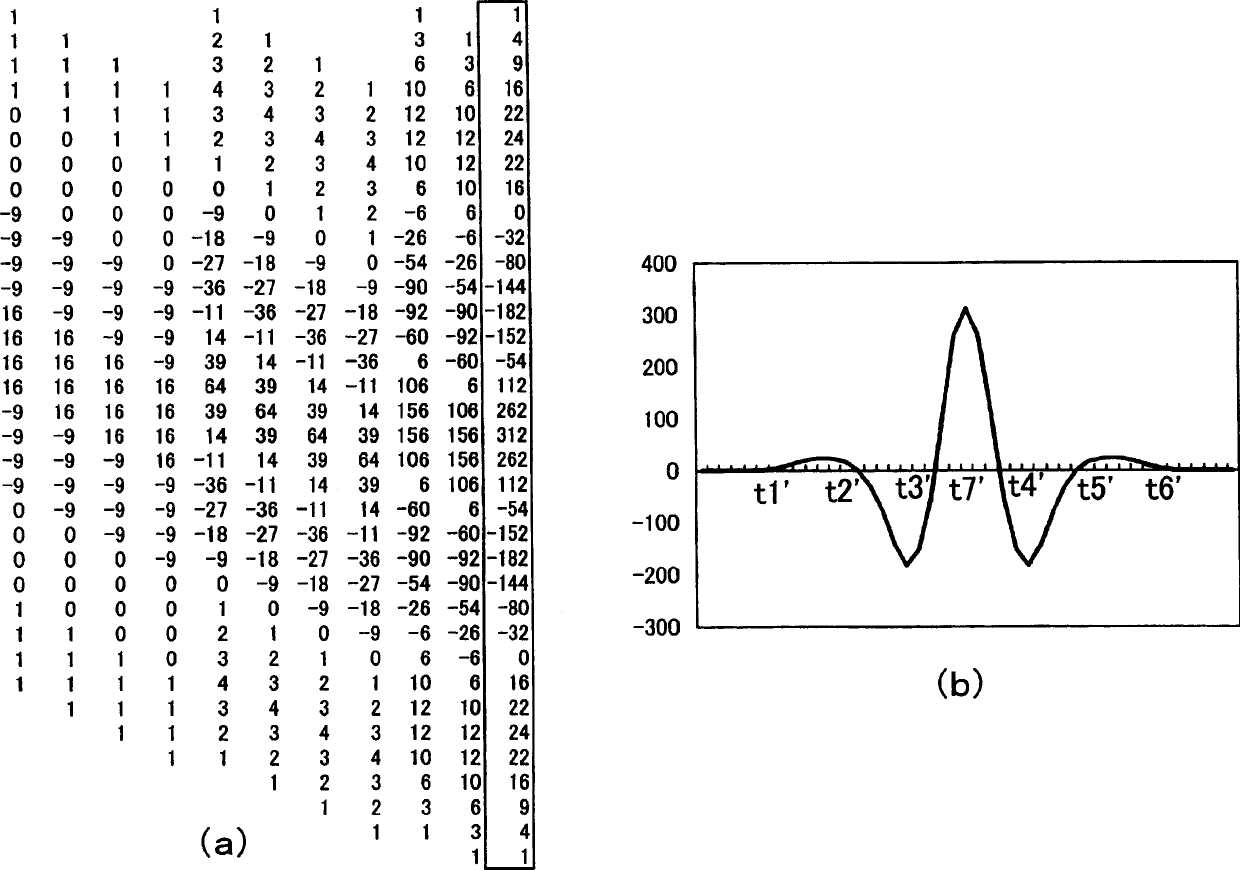

Digital filter and its designing method, designing apparatus, and program for designing digital filter

InactiveUS20070208793A1Simple design methodDigital technique networkComplex mathematical operationsDigital filter designDesign methods

Owner:NSC CO LTD

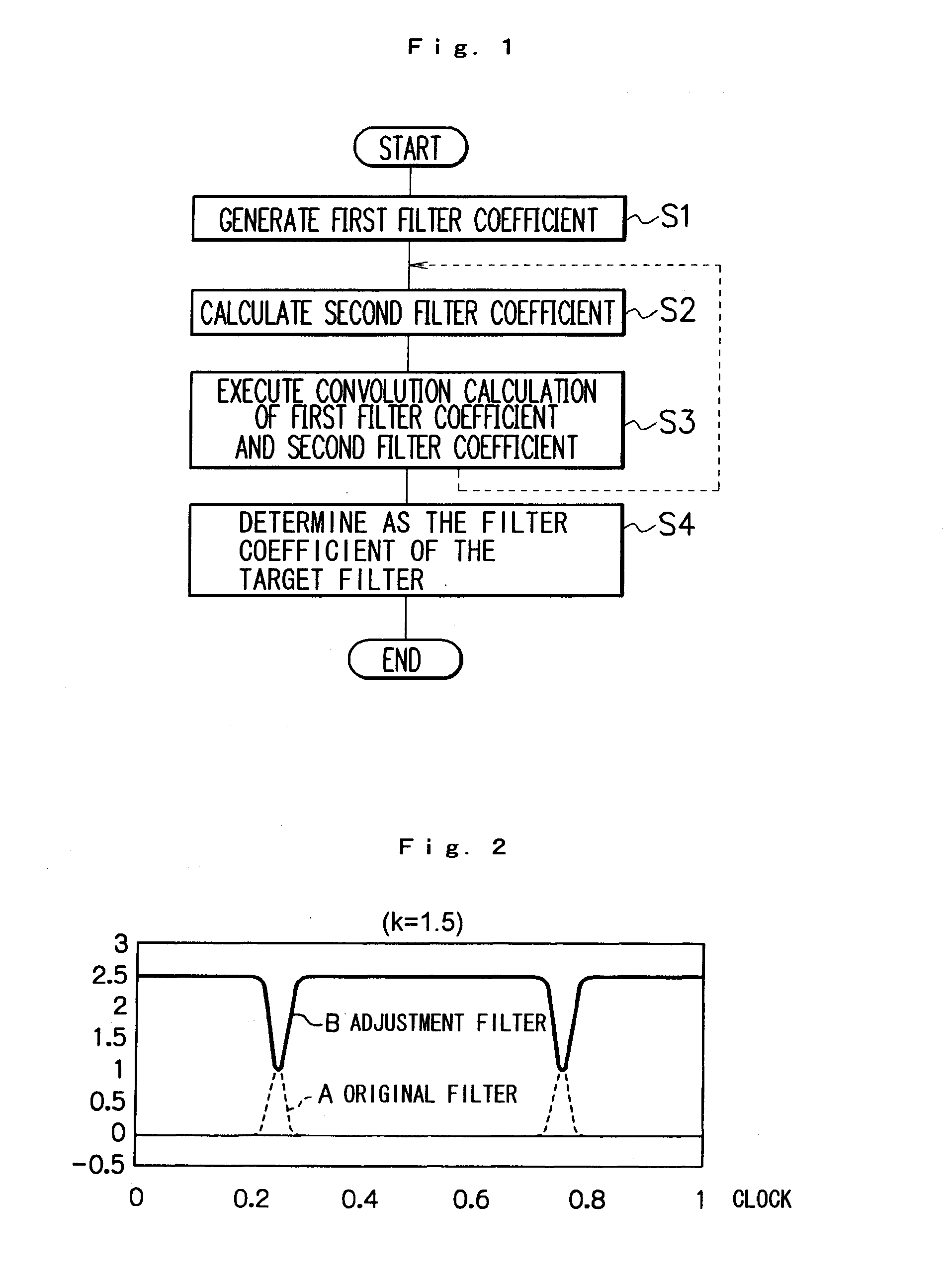

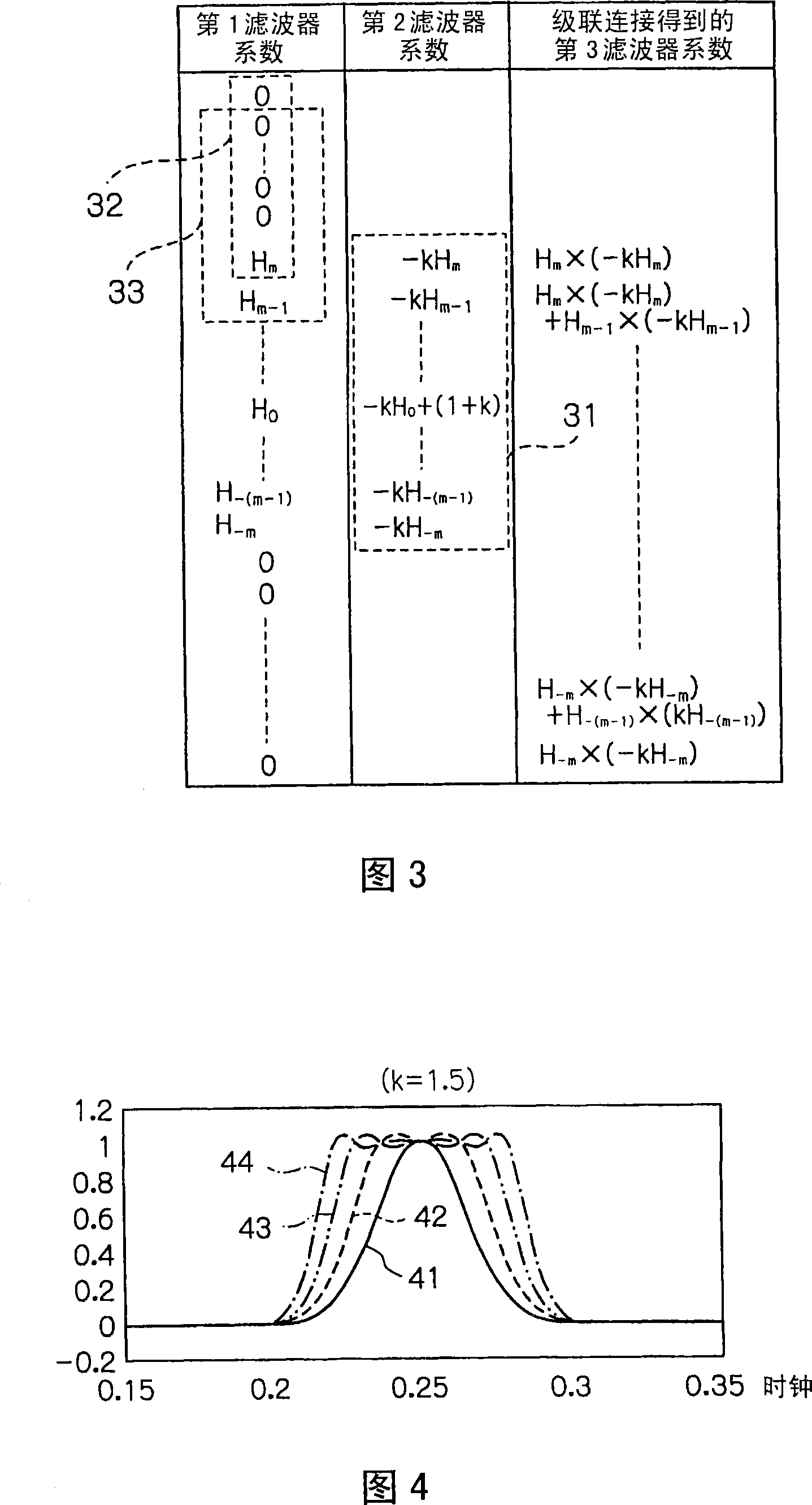

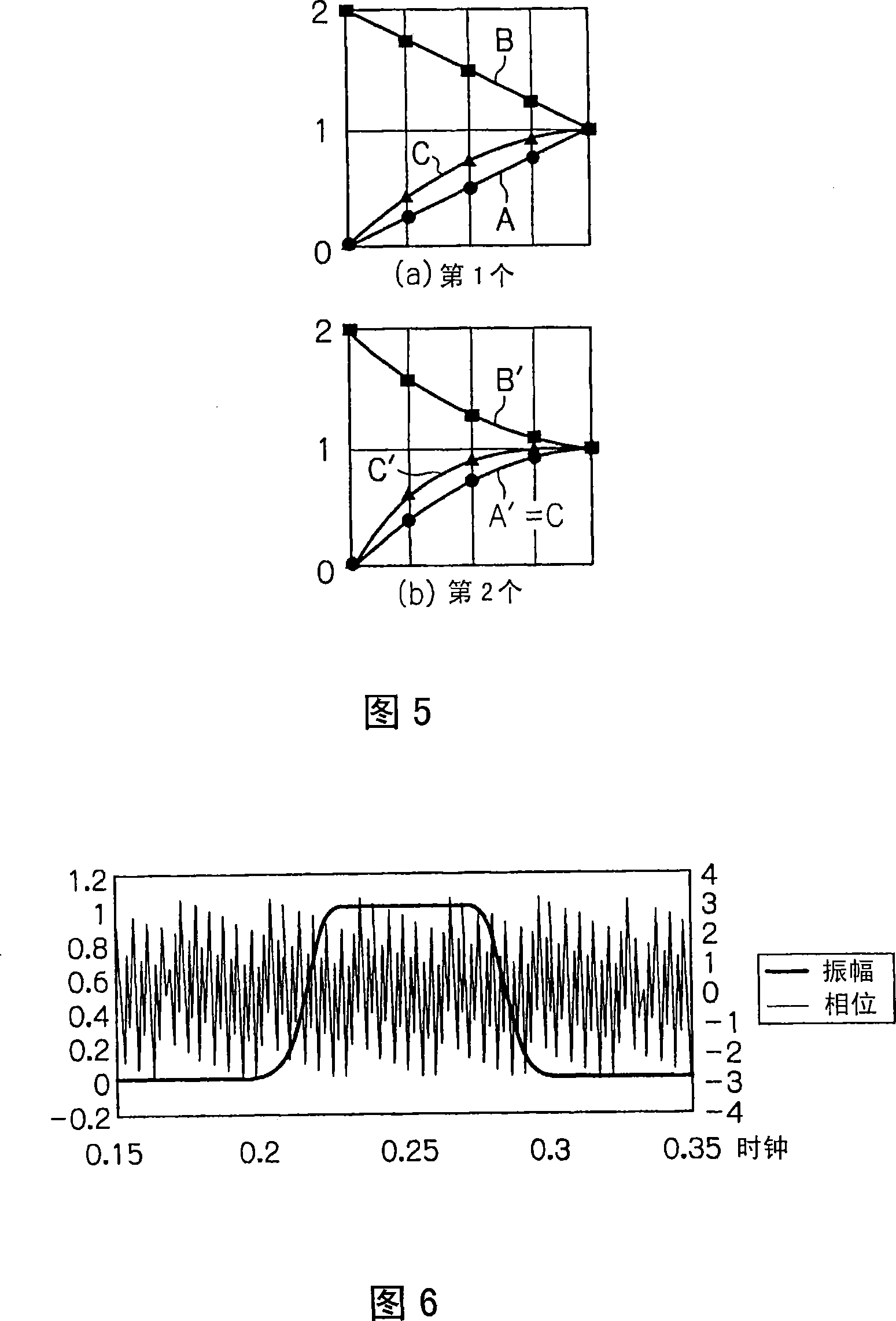

Digital filter and its designing method, desiging apparatus, and program for designing digital filter

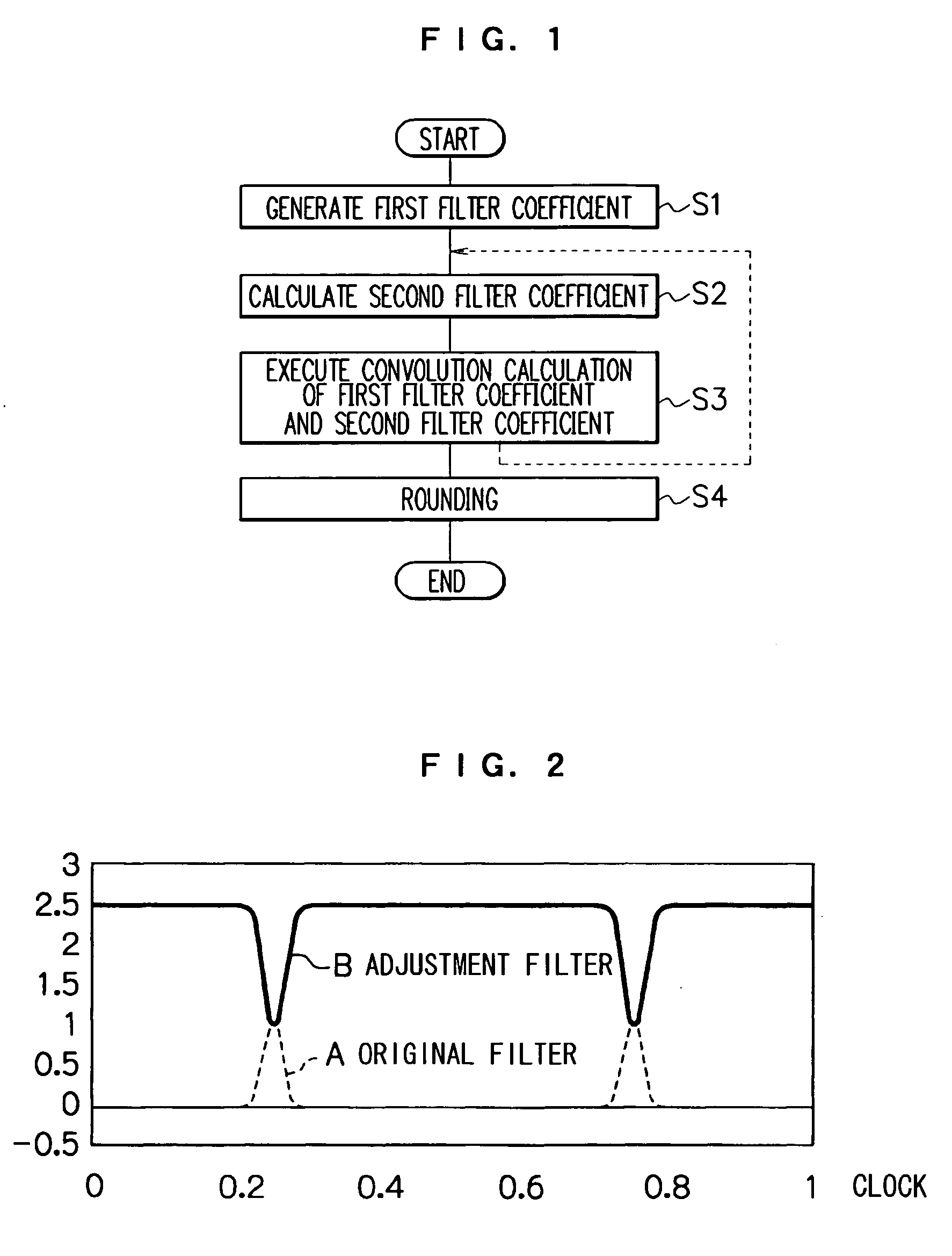

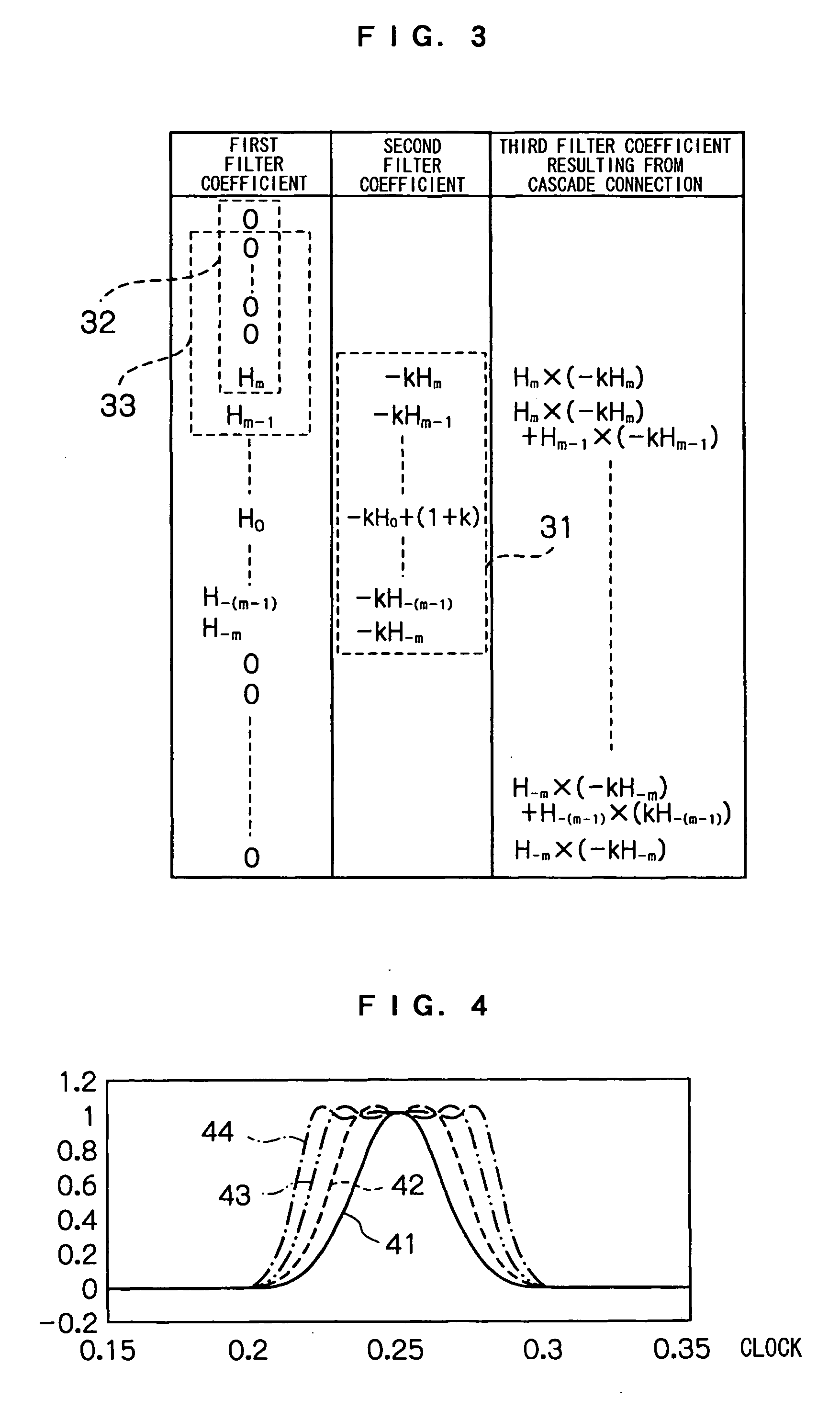

An original filter having first filter coefficients where the numeral sequence is symmetrical and a regulation filter having second filter coefficients realizing reverse direction frequency amplitude characteristics B in contact with the frequency amplitude characteristics A of the original filter at a maximum amplitude ''1'' are connected in the longitudinal way, and filter coefficients to be determined are designed by product-sum operation of the first and the second filter coefficients.

Owner:NEURO SOLUTION CORP

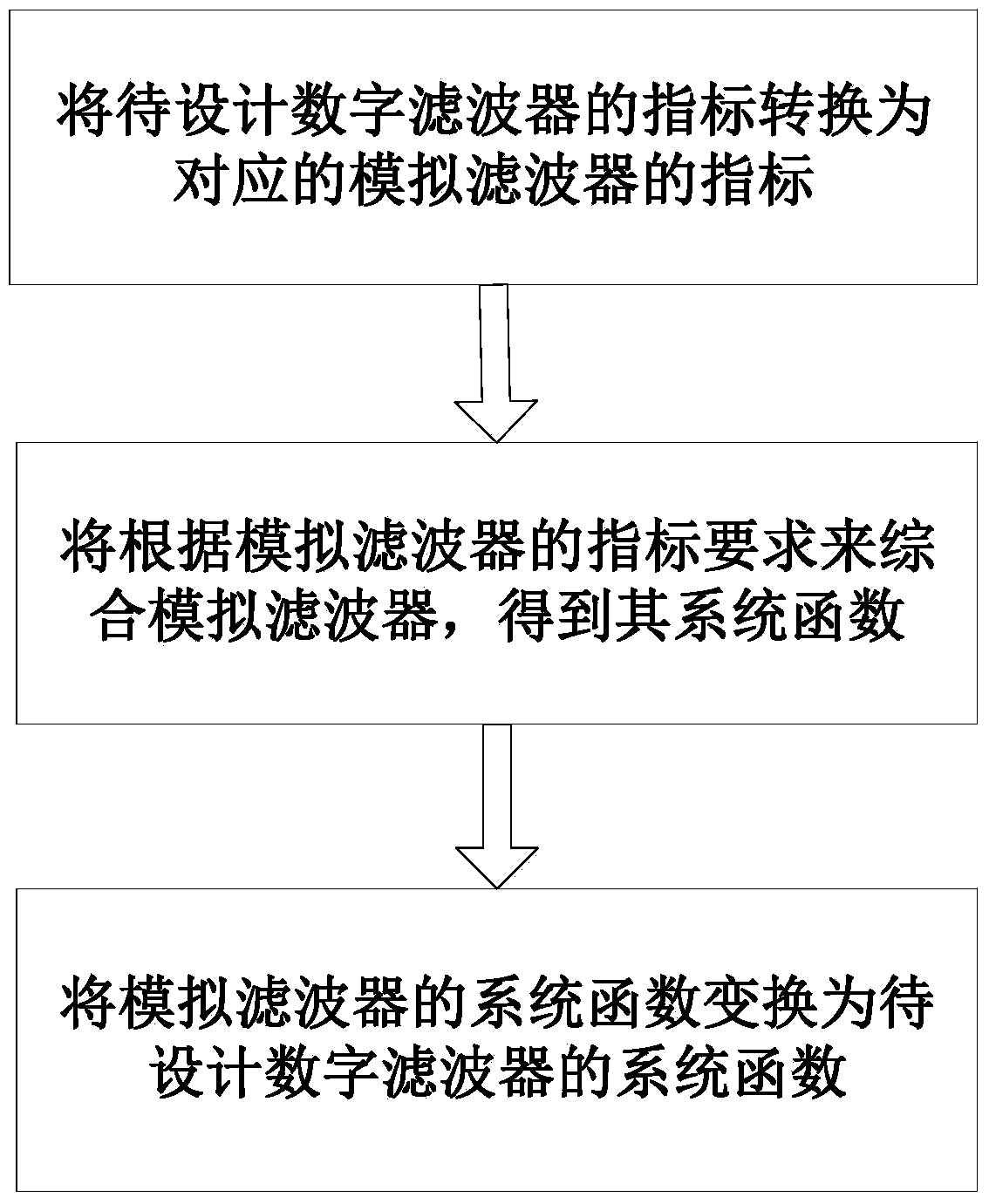

Method for designing digital filter

InactiveCN103956987AFrequency response flexible controlAccurate bandwidth controlDigital technique networkTransmission zerosDigital filter design

The invention discloses a method for designing a digital filter. The method specifically comprises the steps that the index of the digital filter to be designed is converted into the index of a corresponding analog filter; the analog filter is integrated directly in a corresponding frequency domain according to the index of the corresponding analog filter, so that a system function of the analog filter is obtained; the obtained system function of the analog filter is converted into the system function of the digital filter to be designed. By the aid of the method for designing the digital filter, asymmetrical frequency response of single-frequency bands or multi-frequency bands can be achieved, the order of the filter cannot be changed, the frequency response of the filter can be adjusted flexibly by changing the position of a transmission zero, and thus the filter can meet actual requirements. The bend width of each frequency band can be accurately controlled, and fluctuation in each band is constant.

Owner:唐萍

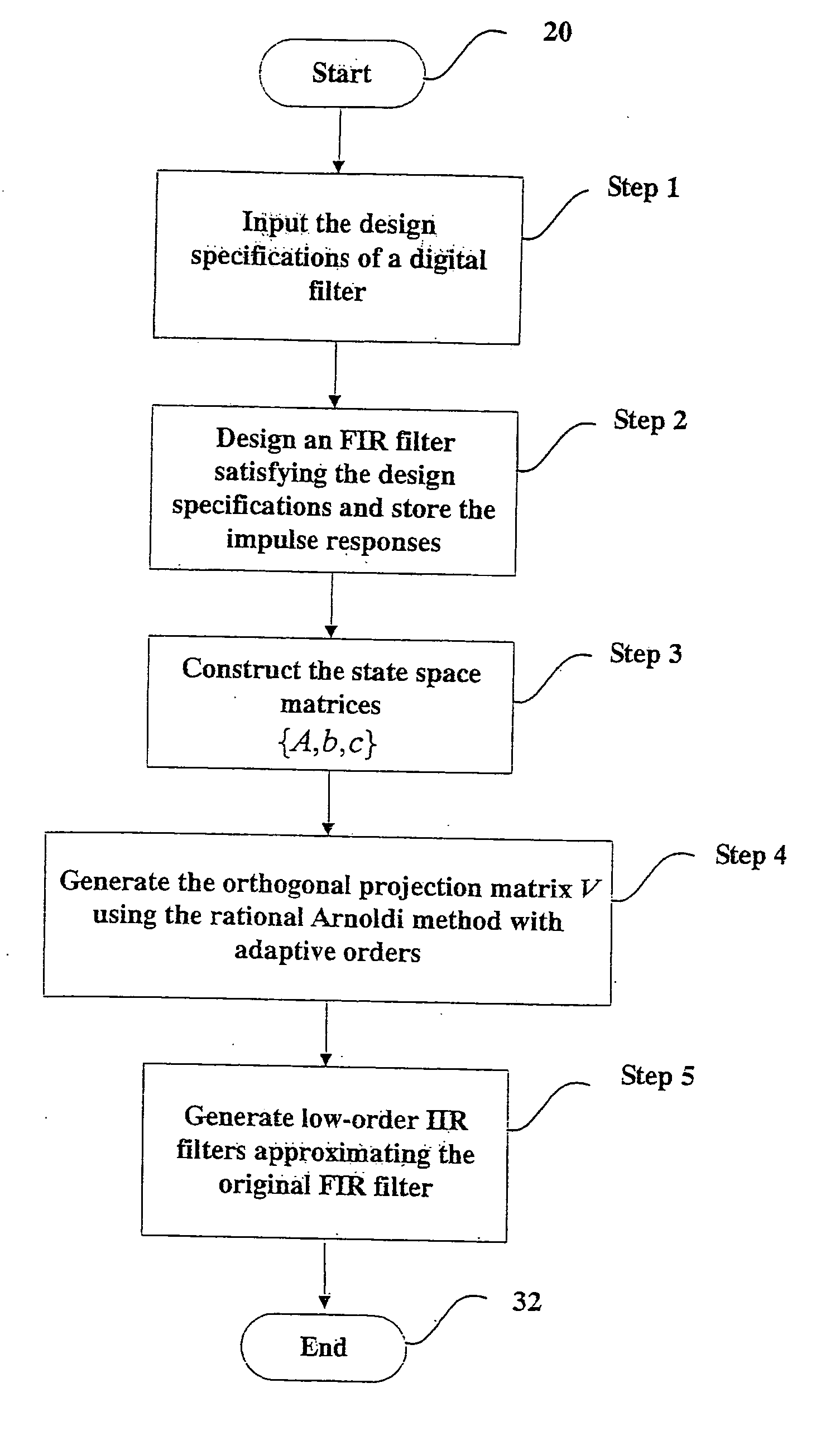

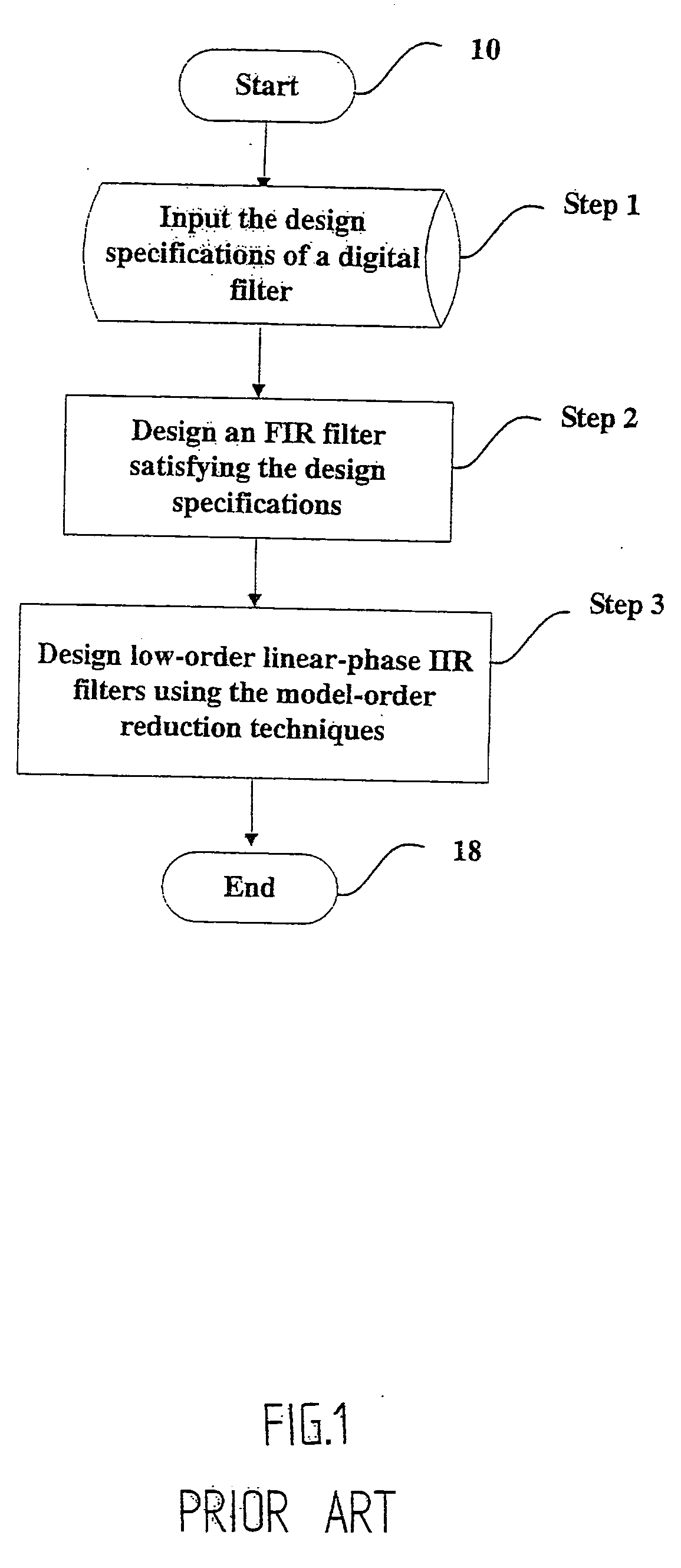

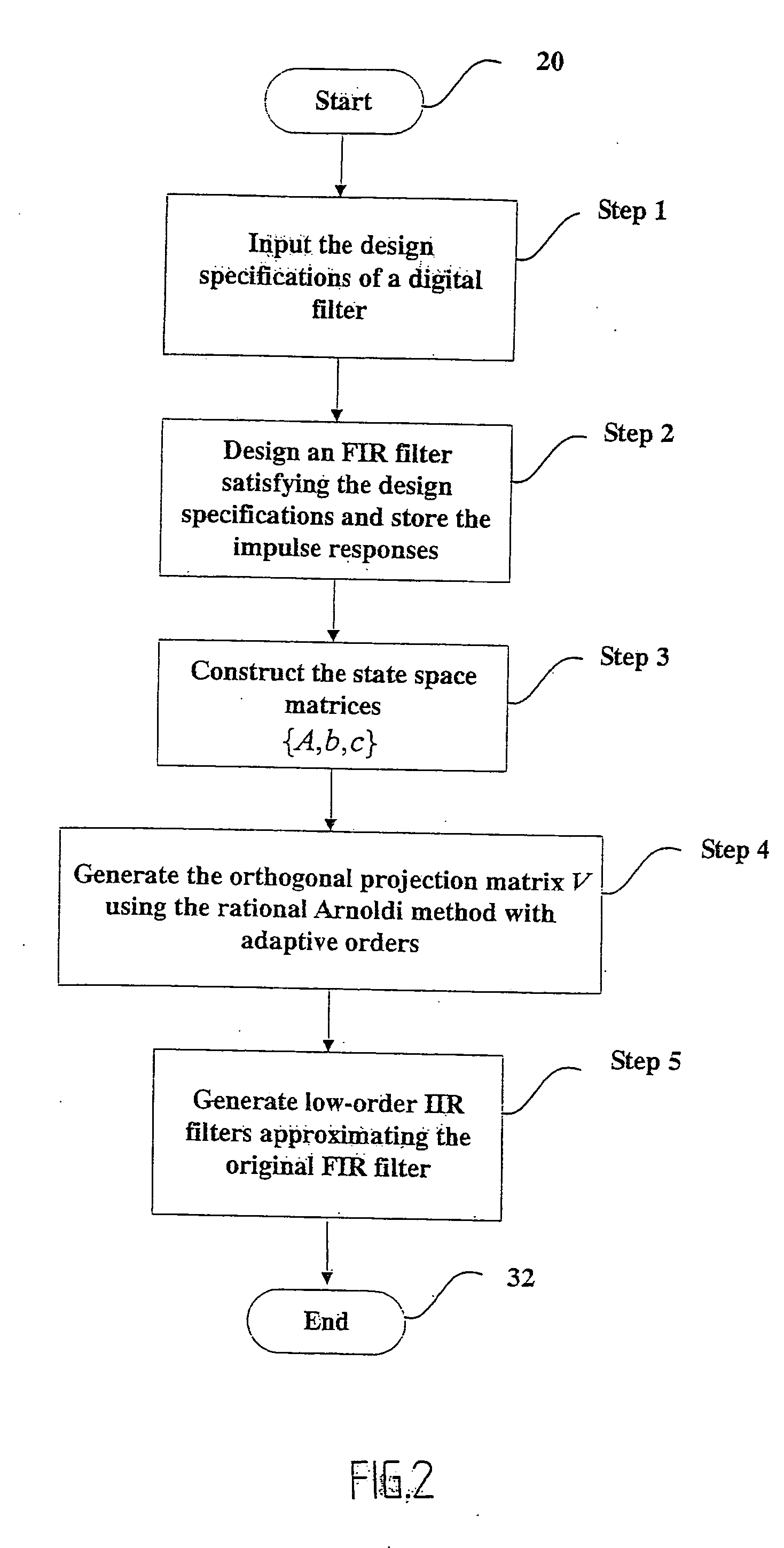

Efficient digital filter design tool for approximating an FIR filter with a low-order linear-phase IIR filter

InactiveUS20050235023A1Avoid failureEfficiently keeps water out of the pull chain switchDigital technique networkComplex mathematical operationsIir filteringComputation complexity

A method and apparatus for designing low-order linear-phase IIR filters is disclosed. Given an FIR filter, the method utilizes a new Krylov subspace projection method, called the rational Arnoldi method with adaptive orders, to synthesize an approximated IIR filter with small orders. The method is efficient in terms of computational complexity. The synthesized IIR filter can truly reflect essential dynamical features of the original FIR filter and indeed satisfies the design specifications. In particular, the linear-phase property is stilled remained in the passband.

Owner:CHANG GUNG UNIVERSITY

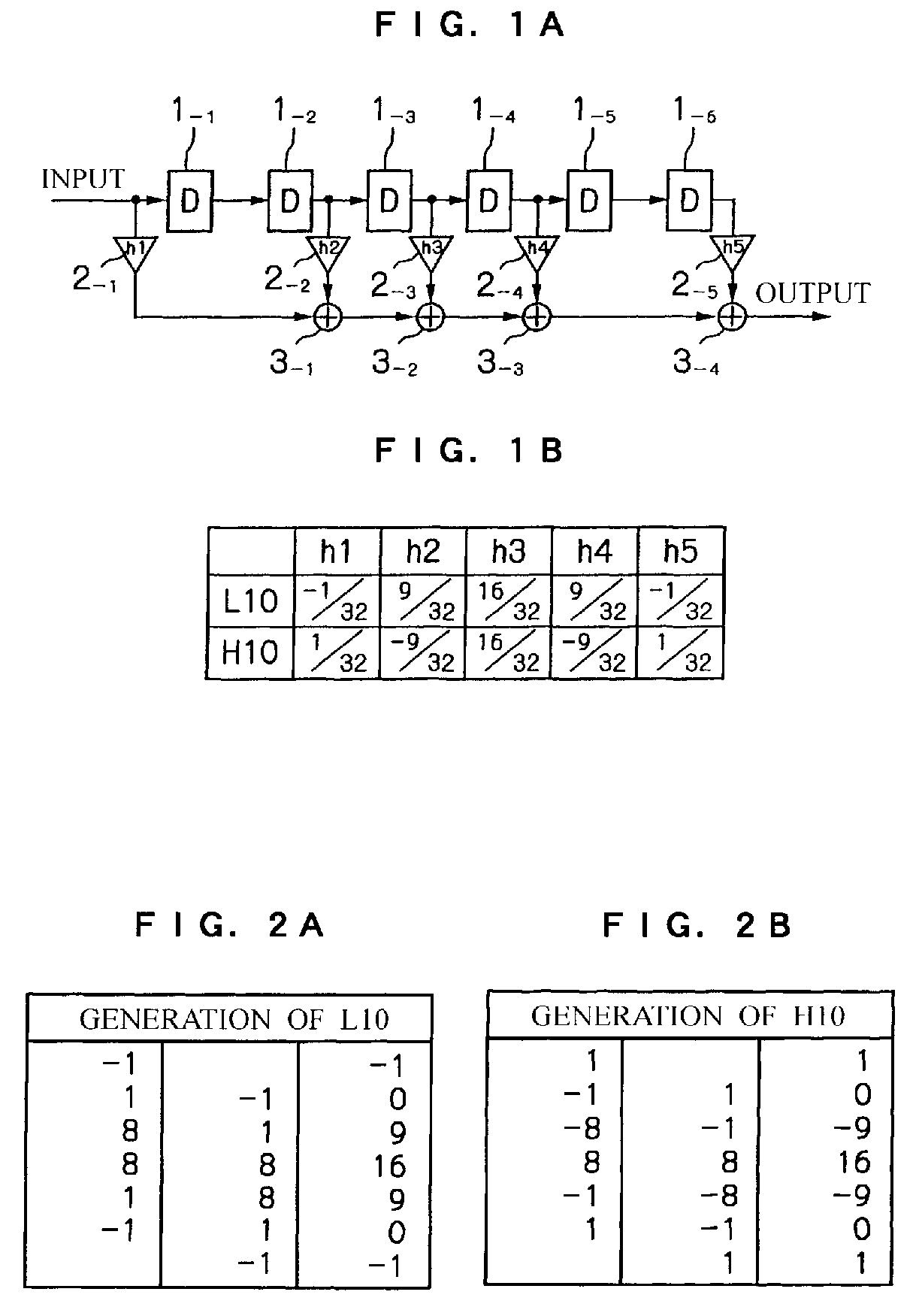

Digital filter designing method, digital filter designing program, digital filter

InactiveCN1669220ASimple designSimple structureDigital technique networkEngineeringDigital filter design

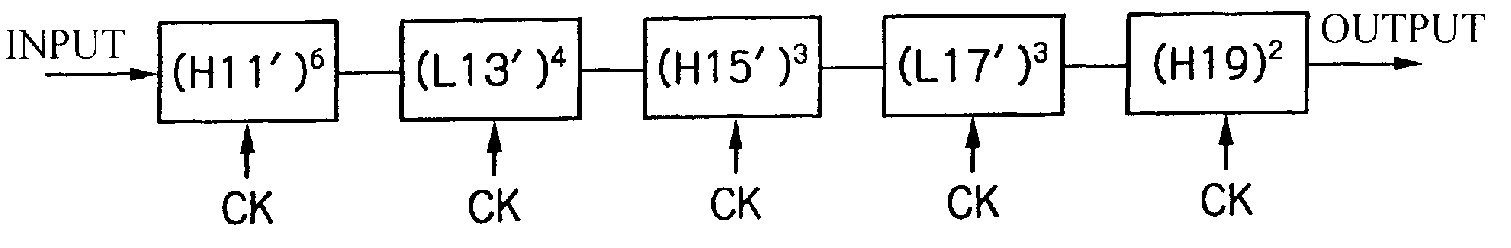

According to a basic unit filter having a predetermined basic numeric string as a filter coefficient, a high-pass unit filter (H15) and a low-pass unit filter (L13) having pass ranges having a common center frequency Fc are created. These are connected in the longitudinal way to design a band pass filter. Characteristic values obtained by combining a few types of unit filters are cancelled by each other. Thus, without pulling out a necessary frequency band and only by the longitudinal connection of the high-pass unit filter (H15) and the low-pass unit filter (L13), it is possible to extract a superimposed portion as a band pass filter pass range.

Owner:NEURO SOLUTION CORP

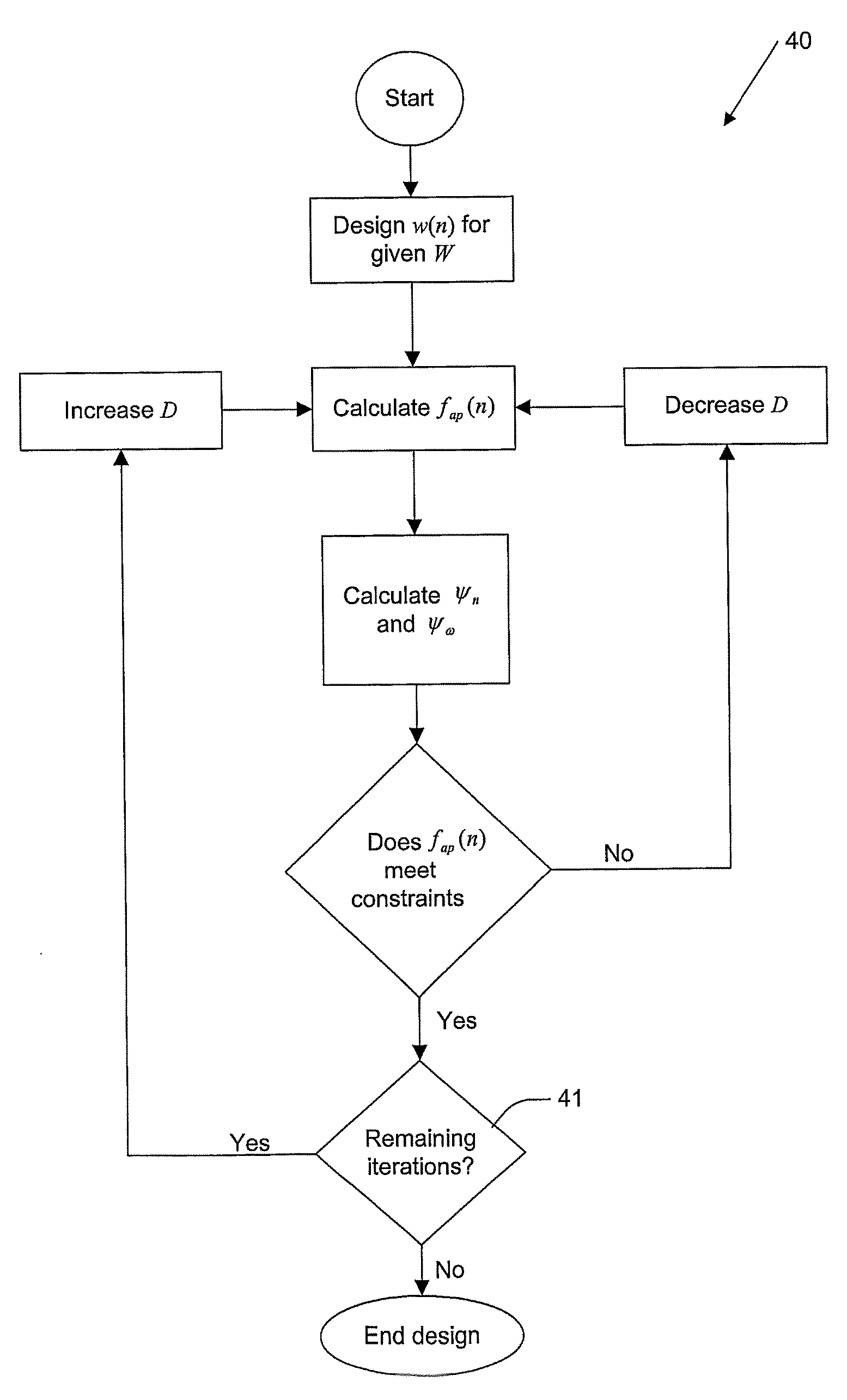

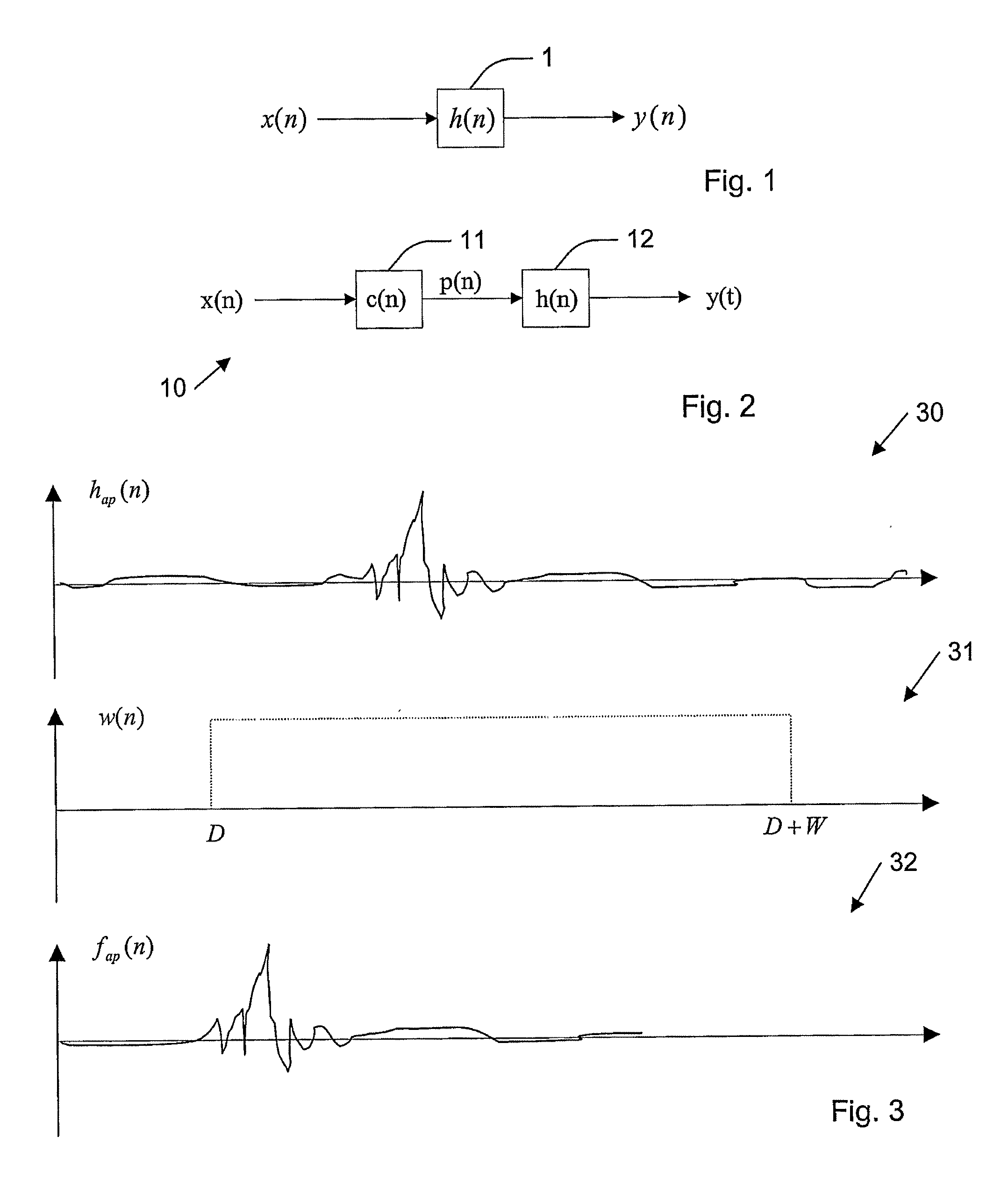

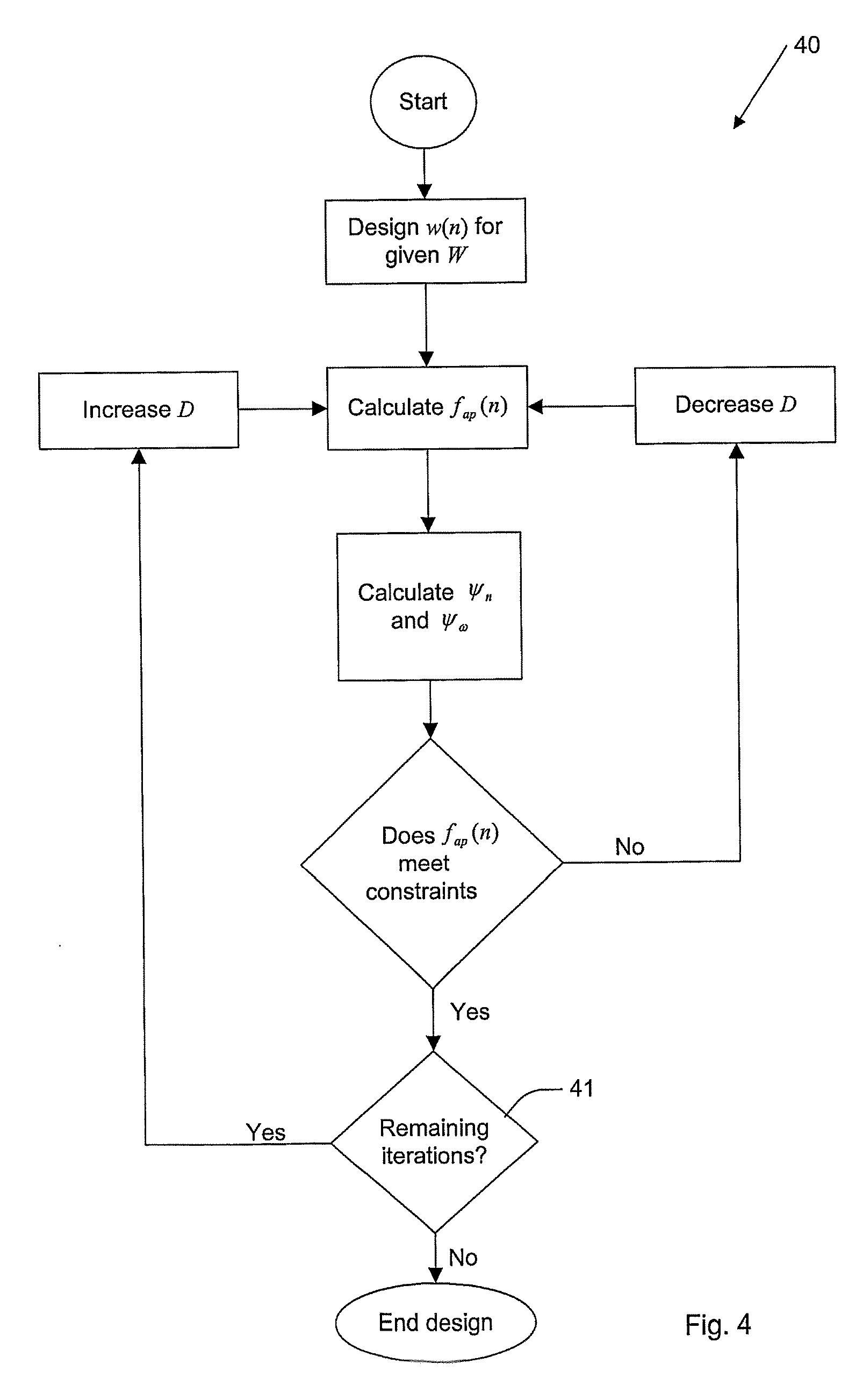

Digital Filter Design System And Method

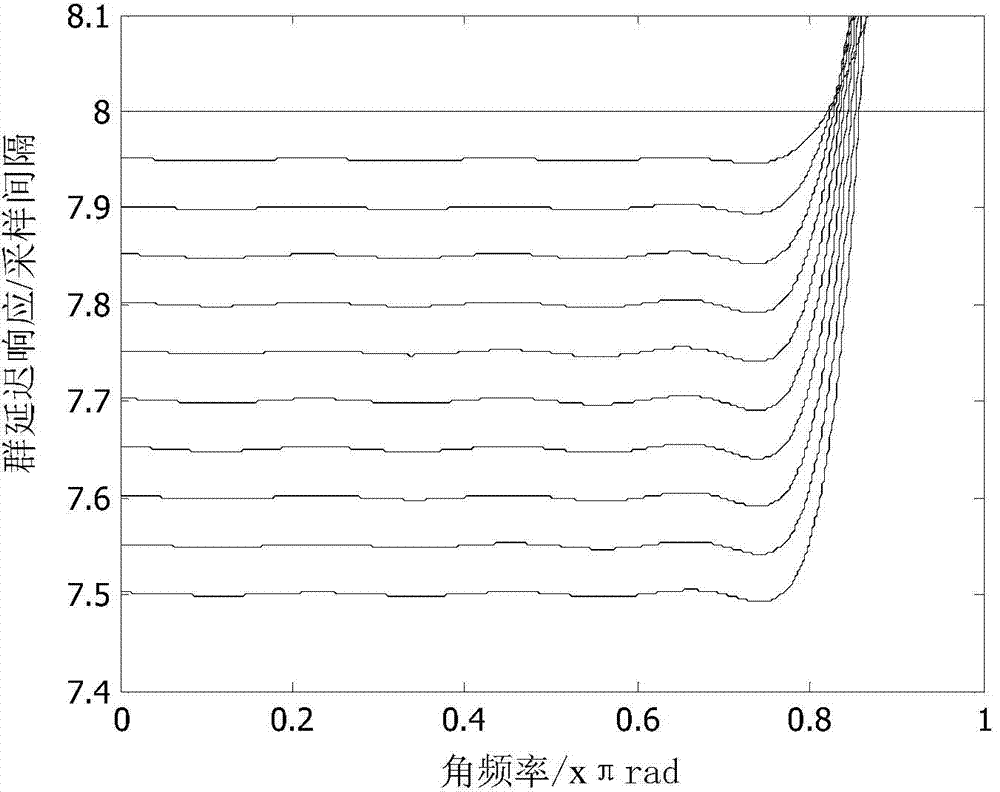

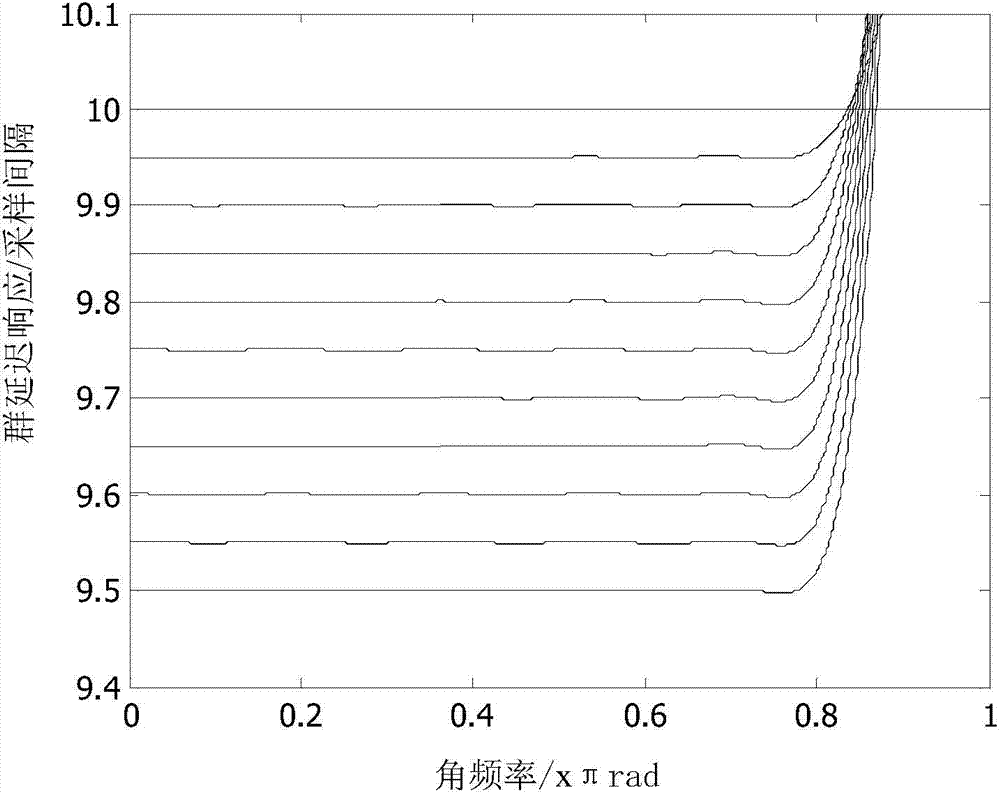

InactiveUS20070174376A1Simple designMaximizing group delayDigital technique networkComplex mathematical operationsSonarLoudspeaker

A new method of designing digital filters for specific magnitude and phase requirements that minimises the filter's group-delay given arbitrary error tolerances is presented in this patent application. The method is extended to include optimising the original filter design based on the group-delay minimisation routine. A particular example that describes the linearisation of a filter channel under these conditions and given these constraints is shown. Embodiments may be applied to any digital filter design technique implemented in software, hardware, or a combination of both for applications such as equalisation or any area where filters are useful. The method disclosed is broadly applicable in the field of signal processing and may be used to advantage, for example in: channel equalisation, speaker and audio correction, echo-cancellation, control applications, digital audio broadcast, sonar and ultrasonics.

Owner:CLARITY EQ

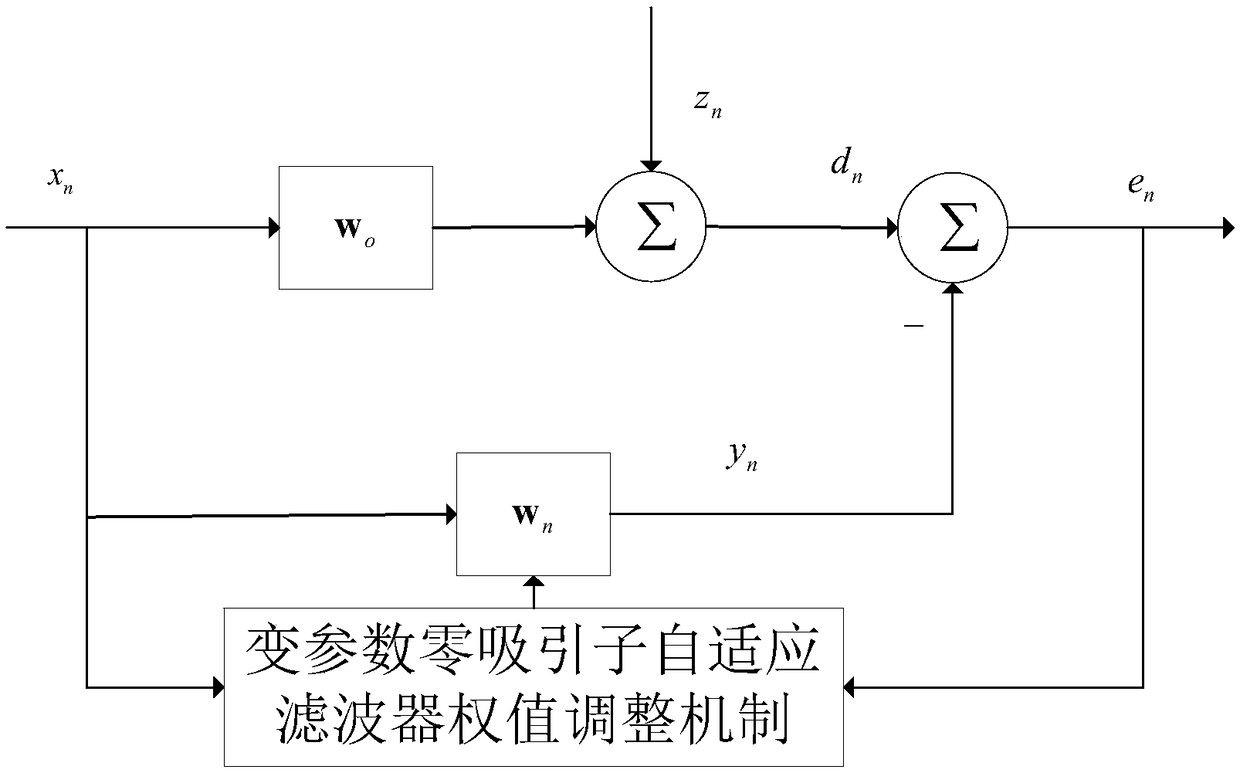

Adaptive filter with variable parameters and zero attractors

ActiveCN109347457AFast convergenceAdaptive networkDigital technique networkNoise controlDigital filter design

The invention discloses an adaptive filter with variable parameters and zero attractors, and belongs to the field of digital filter design. The filter mainly uses time-varying step parameters and regularization parameters that control the intensity of the zero attractors to speed up the convergence speed of the adaptive filter and reduce its steady-state offset. The adaptive filter with variable parameters and zero attractors disclosed by the invention has a great improvement in performance compared with the conventional filter when the input is white signal input. The adaptive filter with variable parameters and zero attractors disclosed by the invention can be applied to applications such as echo cancellation and active noise control.

Owner:SUZHOU UNIV

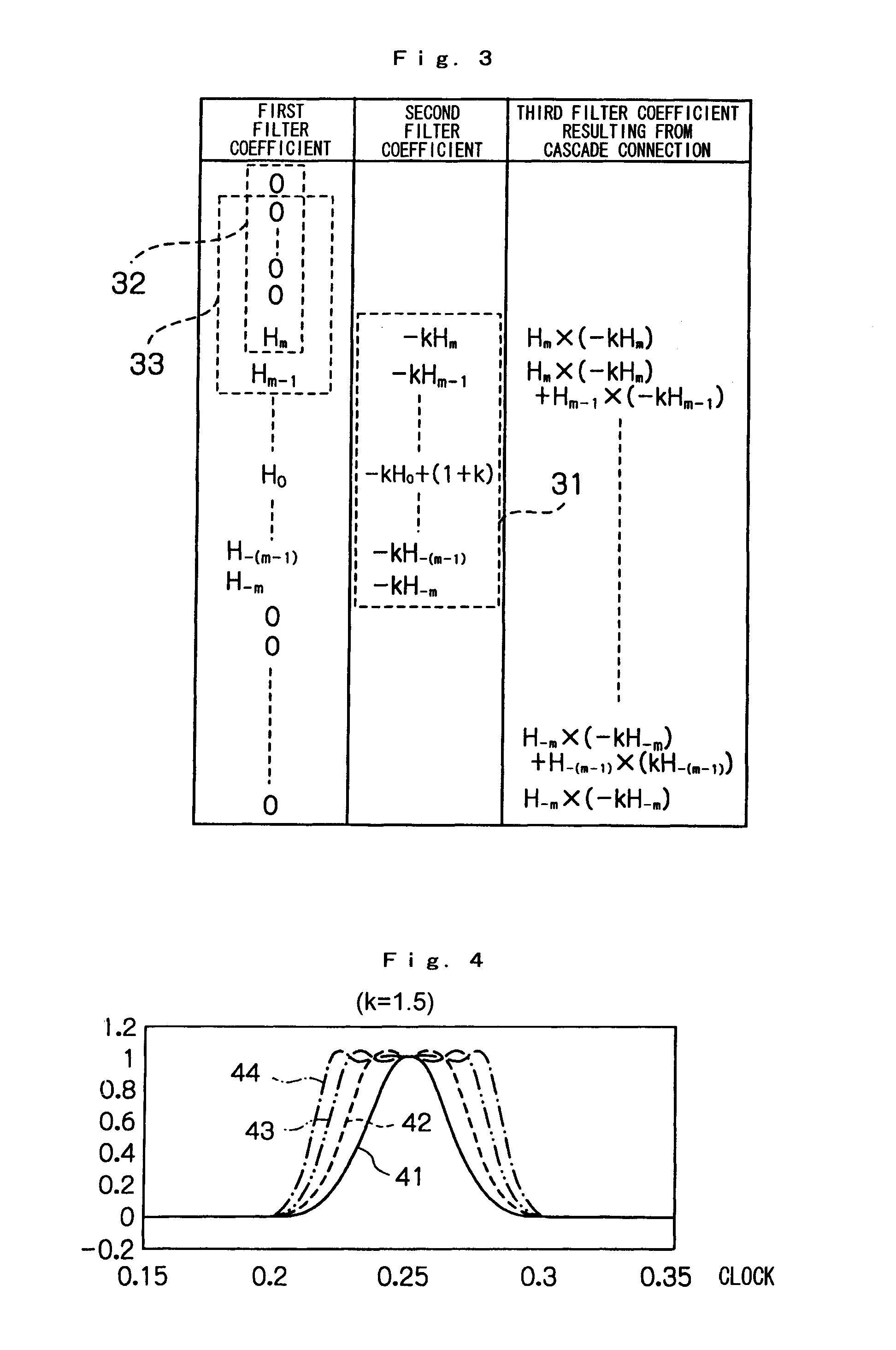

Digital filter design method and device, digital filter design program, digital filter

InactiveUS20050289206A1Reduce the number of tapsSimple structureDigital technique networkComplex mathematical operationsMoving averageUltrasound attenuation

A numerical string consisting of a ratio of “−1, m, −1” or “1, m, 1” is subjected to a predetermined moving average calculation n times. A numerical string thus obtained is used as filter coefficients of a basic filter and at least one basic filter is combined in an arbitrary way for cascade connection, thereby calculating the filter coefficients of the digital filter to be obtained. This significantly reduces the number of taps and the number of multipliers used as compared to the conventional FIR filter. Moreover, by using the numerical strings “−1, m, −1” and “1, m, 1” so that the filter impulse response becomes a finite-base function, it is possible to obtain a preferable frequency characteristic having no discretization error and having a great attenuation amount out of band.

Owner:NSC CO LTD

Interference canceling method based on improved all-pass fractional delay filter

InactiveCN104716927AGuaranteed convergenceGuaranteed numerical stabilityDigital technique networkNumerical stabilityMathematical model

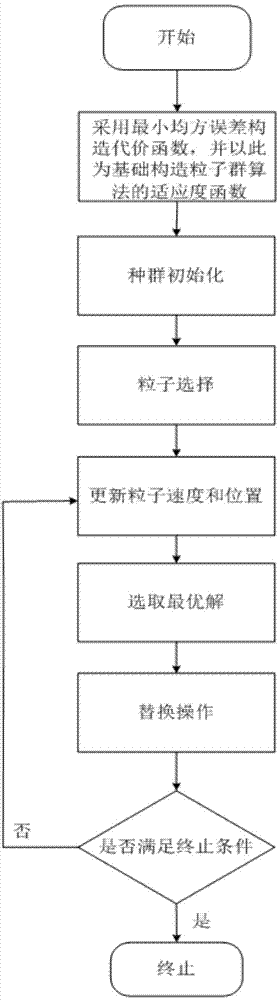

The invention belongs to the technical field of digital filter design and in particular relates to an interference canceling method based on an improved all-pass fractional delay filter. The interference canceling method comprises the specific steps of utilizing a minimum mean square error criterion to construct a mathematic model of the all-pass fractional delay filter, utilizing a particle swarm optimization method based on natural selection to solve the mathematic model of the all-pass fractional delay filter and further construct the all-pass fractional delay filter, obtaining reference signals, utilizing the constructed all-pass fractional delay filter to filter the reference signals and carrying out interference canceling process on the filtered signals and signals received by a radar. The interference canceling method uses a natural-selection particle swarm algorithm, guarantees the solving convergence of the filter, quickens the convergence speed, avoids complex numeric calculation, guarantees the solving numerical stability of the all-pass fractional delay filter and enables design of the variable fractional delay filter to be more flexible.

Owner:XIDIAN UNIV

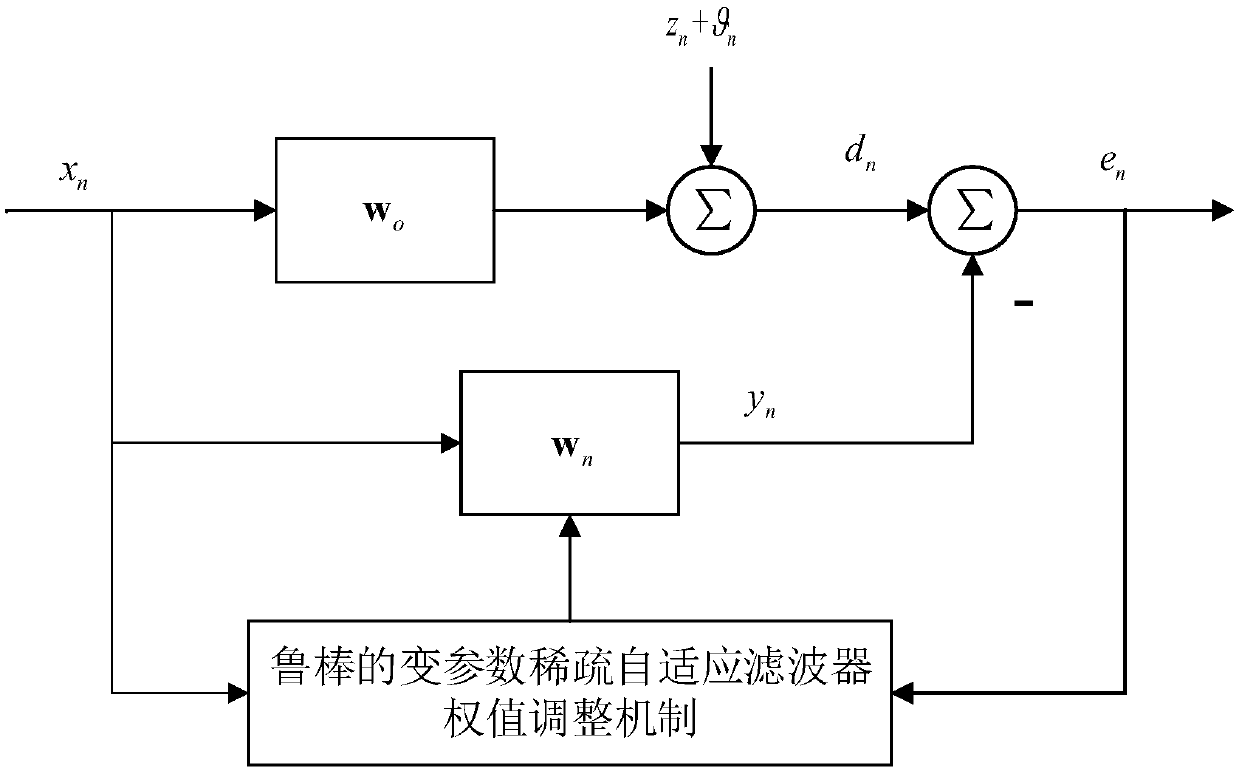

Robust variable-parameter sparse self-adaptive filter

ActiveCN109617538AImprove performanceSuppress interferenceAdaptive networkPattern recognitionDigital filter design

The invention discloses a robust variable-parameter sparse self-adaptive filter, and belongs to the field of digital filter designing. The filter mainly utilizes a time-varying step size parameter anda regularization parameter controlling zero attractor intensity to increase convergence speed of the self-adaptive filter and reduce steady-state misadjustment thereof. Compared with a traditional symbol filter, the robust variable-parameter sparse self-adaptive filter disclosed by the invention has better convergence performance when input is a white signal and influences of impulse noises exist. The robust variable-parameter sparse self-adaptive filter disclosed by the invention can be applied to the fields of electronics and communication equipment of echo cancellation, noise cancellers, signal enhancement and interference pulses and the like.

Owner:SUZHOU UNIV

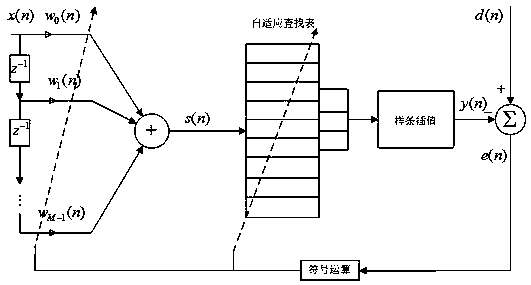

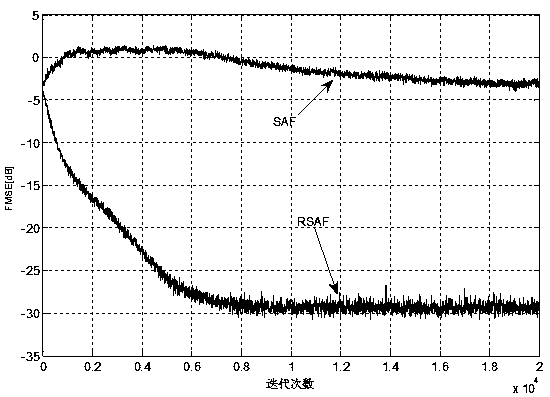

Robust spline adaptive filter

ActiveCN107800403AImprove robustnessImprove anti-pulse interference abilityDigital adaptive filtersNonlinear distortionCommunications system

The invention discloses a robust spline adaptive filter, and belongs to the field of digital filter design. According to the spline adaptive filter, an optimal nonlinear unknown system is approximatedby adopting a spline function, and the resistance to pulse interference is enhanced by adopting a method of performing symbolic operation on error signals. The spline adaptive filter can be used foroccasions where electronic, speech and communication systems are subjected to nonlinear distortion and pulse noise interference.

Owner:苏州容润通信技术有限公司

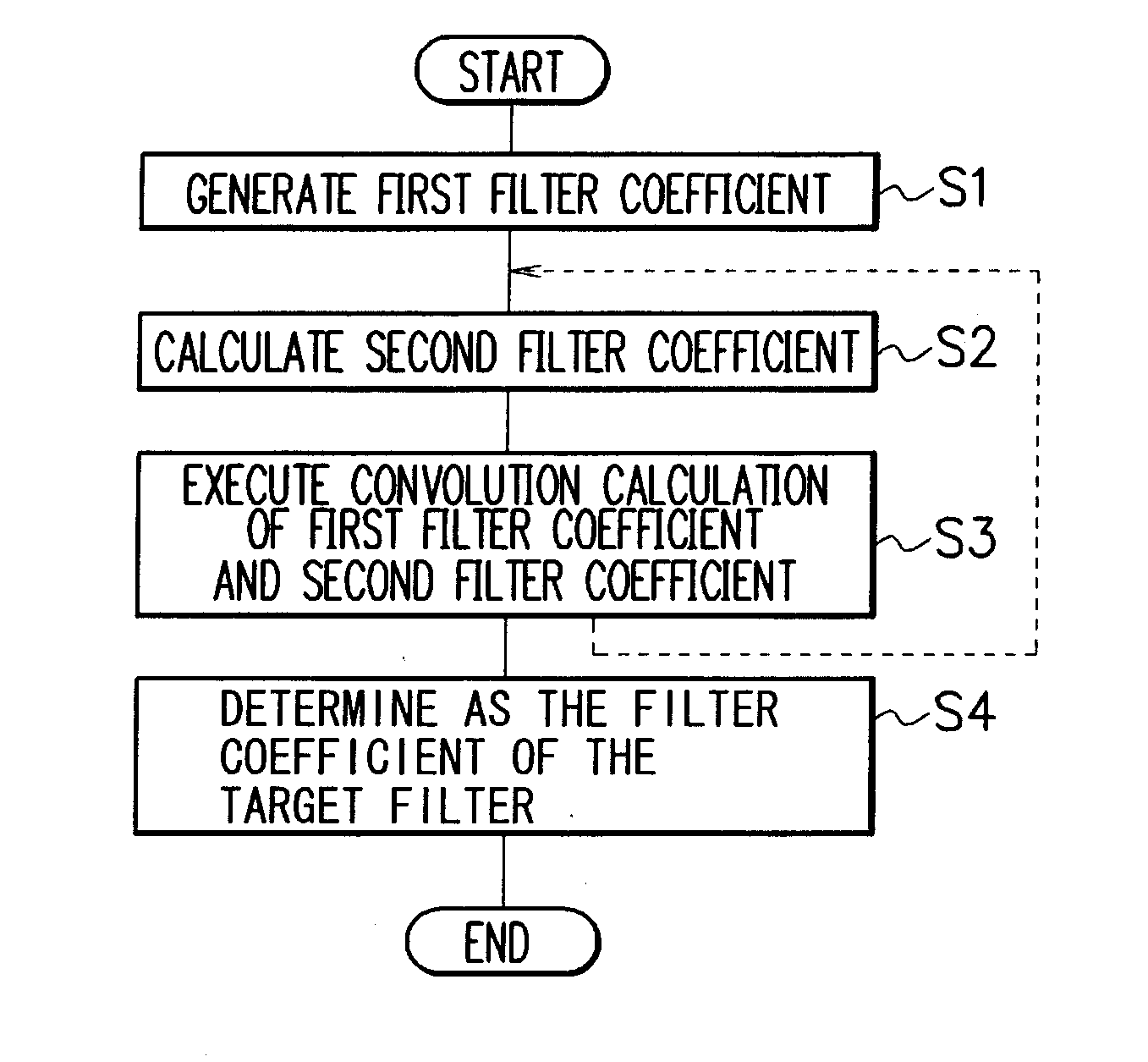

Digital filter, design method thereof, design device, and digital filter design program

InactiveUS20060208831A1Simple design methodMultiple-port networksTransmission control/equlisationDigital filter designComputer science

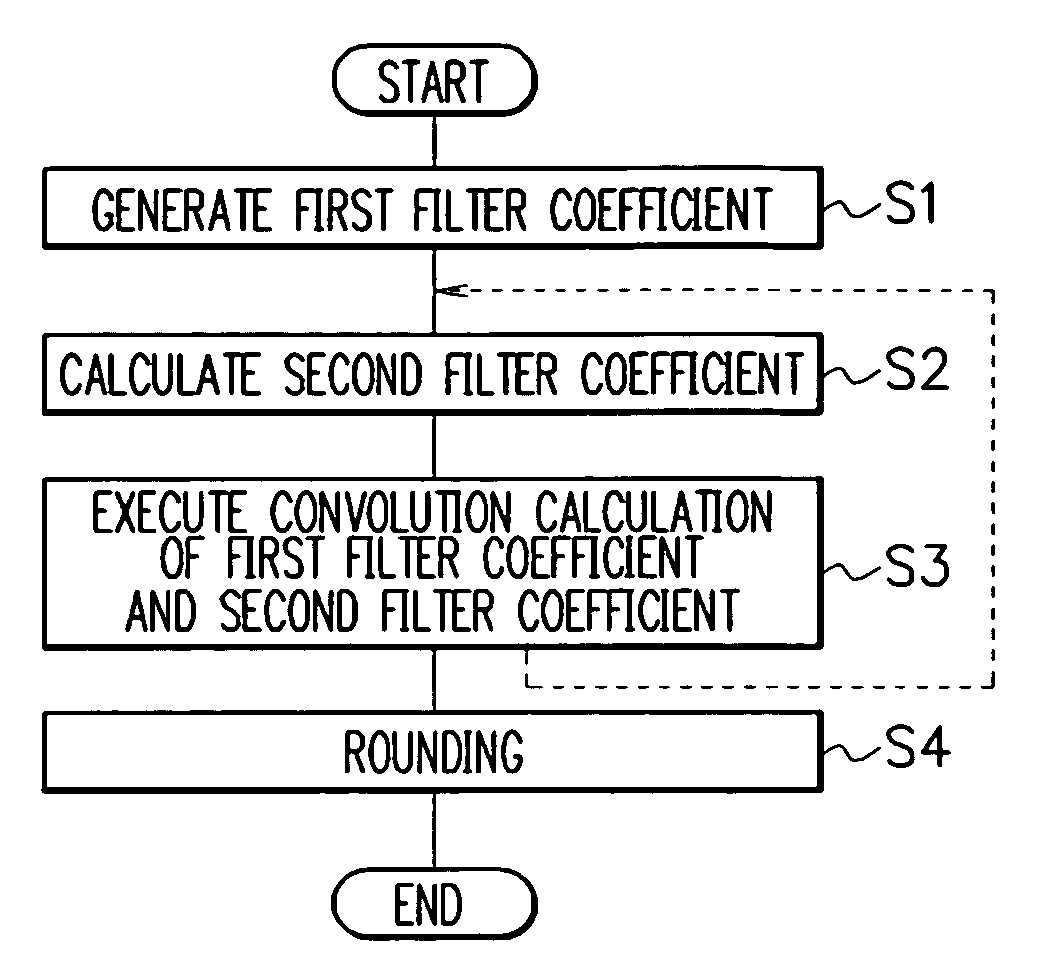

An original filter is connected to an adjustment filter in the longitudinal way. The original filter has a first filter coefficient of a symmetric numeric string. The adjustment filter has a contact point at a position where the maximum value is acquired in the original filter frequency amplitude characteristic A and has a symmetric second filter coefficient realizing the frequency amplitude characteristic B having the minimum value at the contact point. By executing a convolution calculation of the first filter coefficient and the second filter coefficient, it is possible to design a desired filter coefficient.

Owner:NSC CO LTD

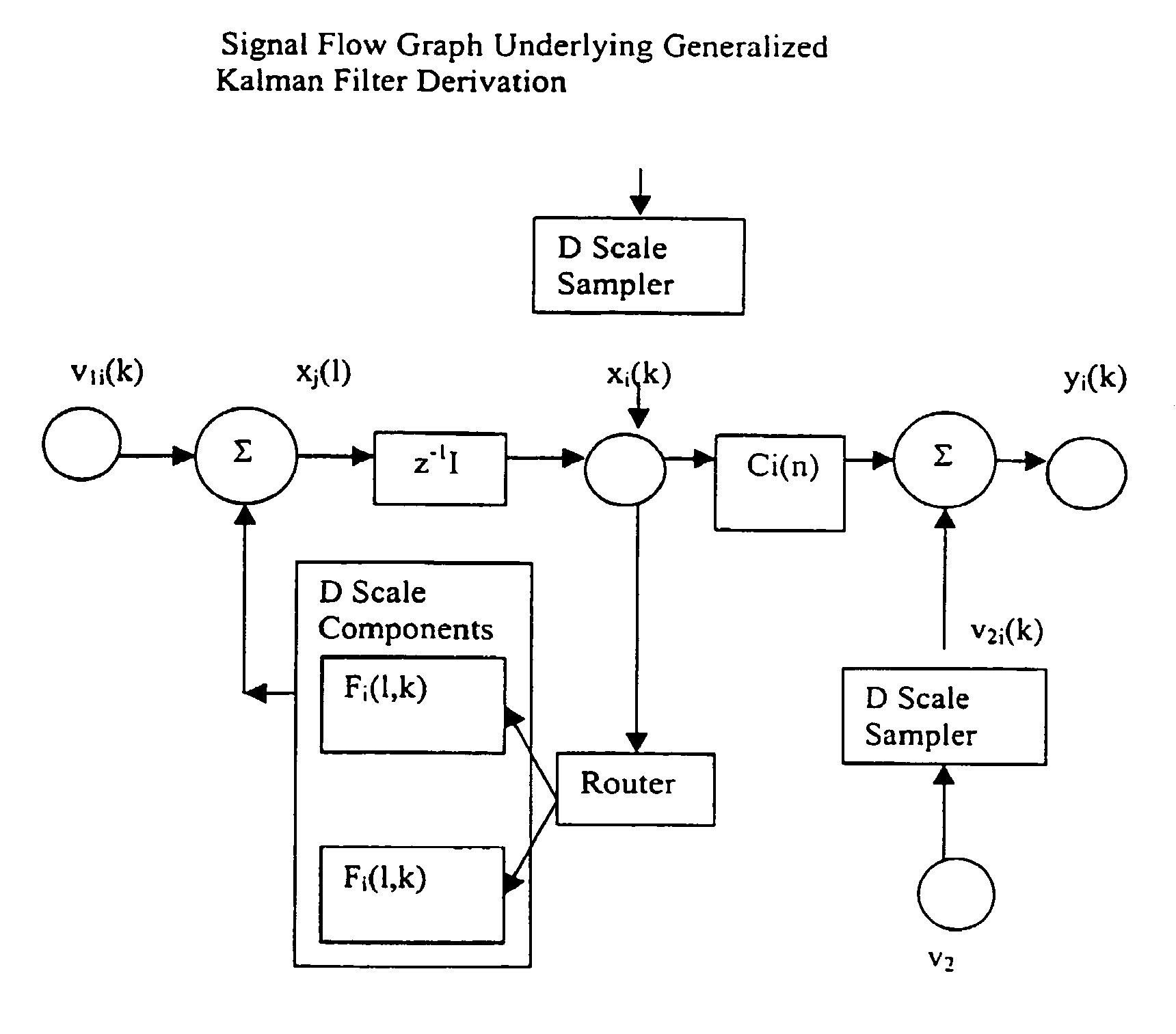

N dimensional non-linear, static, adaptive digital filter design using d scale non-uniform sampling

InactiveUS20090244395A1Improve effectivenessImprove performanceAdaptive networkColor signal processing circuitsDigital filter designFilter bank

The present invention is a filter design that extracts information from a signal by employing D scale nonuniform sampling. In one embodiment a D scale multiresolution sampler, filter bank router, filter bank sampler controller, phase shifter, and consolidator constitute a maximal arrangement for a D scale FIR / IIR filter design.

Owner:DRUCK PHILIP

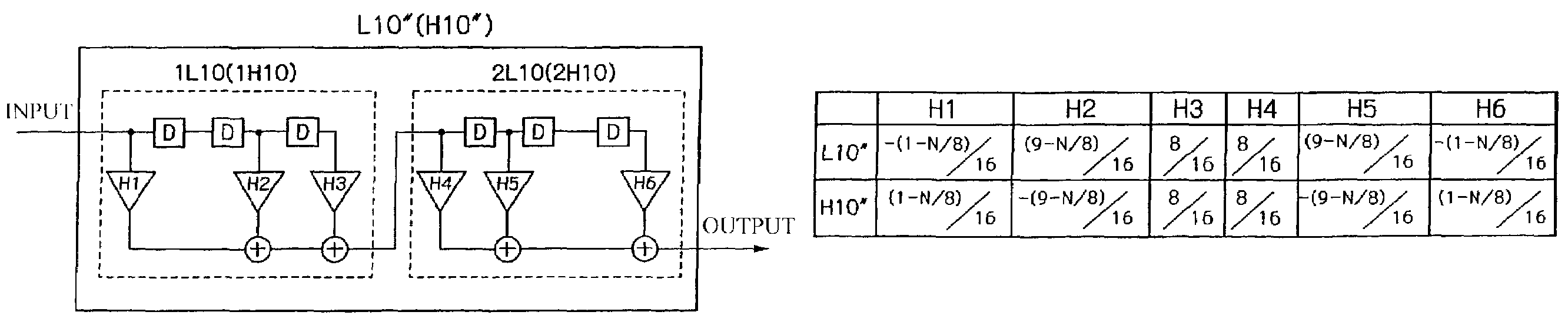

Digital filter design method and device, digital filter design program, and digital filter

InactiveUS7529788B2Simple designEliminate useDigital technique networkComplex mathematical operationsNon symmetricEngineering

A digital filter is designed by combining unit filters (L10′, H10′) having a predetermined asymmetric numerical sequence as filter coefficients (H1 to H3). Thus, it is possible to automatically obtain a desired digital filter coefficient only by combining the unit filter. Moreover, a symmetric numerical sequence {−1, 0, 9, 16, 9, 0, −1} / 32 is divided at the center into two parts and one of them is used as the asymmetric filter coefficients (H1 to H3). This reduces the number of taps required for the digital filter designed, eliminates use of a window function, and prevents generation of a discretization error in the filter characteristic obtained.

Owner:NSC CO LTD

Digital filter design method and device, digital filter design program, and digital filter

InactiveCN1706101ASimple designAchieve frequency characteristicsDigital technique networkDigital filter designWindow function

A symmetric unit filter (L10') is designed by combining in series two unit filters (1L10, 2L10) having asymmetric numerical sequences as filter coefficients (H1 to H3 and H4 to H6). Thus, by designing a filter by series connection, it is possible to automatically obtain a desired digital filter coefficient only by combining one type of unit filter (L10') in series. Moreover, a symmetric numerical sequence {-1, 0, 9, 16, 9, 0, -1} / 32 is divided at the center into two parts and one of them is used as the asymmetric filter coefficients (H1 to H3 and H4 to H6). This reduces the number of necessary taps, eliminates use of a window function, and prevents generation of a discretization error in the filter characteristic obtained.

Owner:NEURO SOLUTION CORP

Self-adjusting voltage filtering technique compensating for dynamic errors of capacitive voltage transformers

Owner:GENERAL ELECTRIC CO

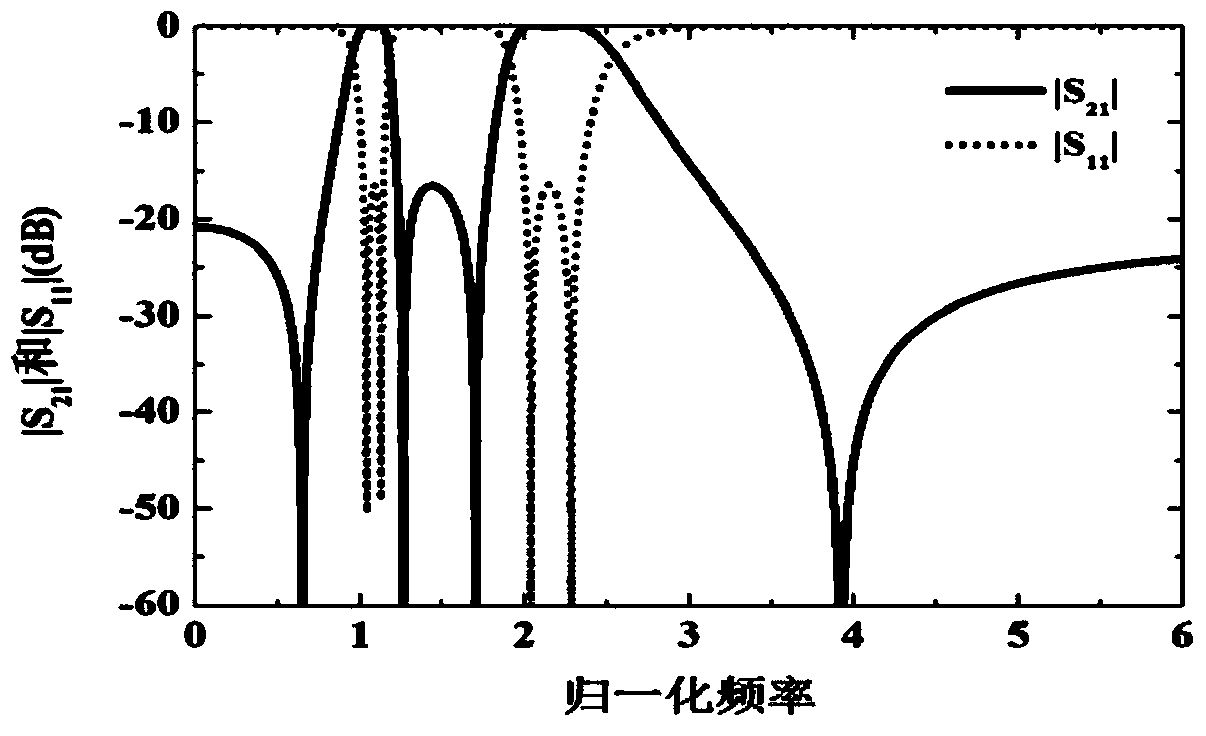

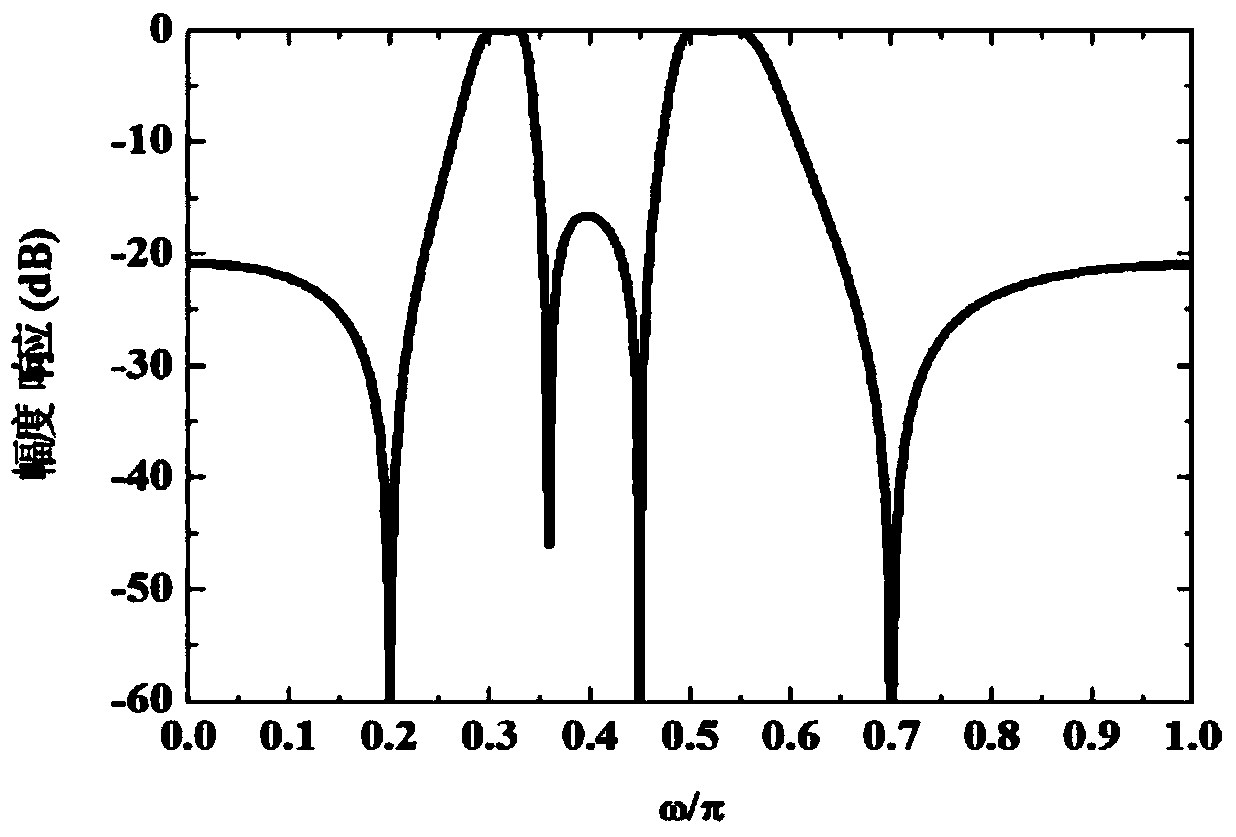

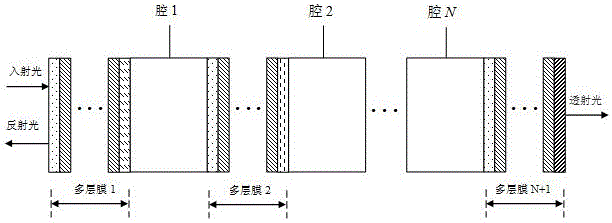

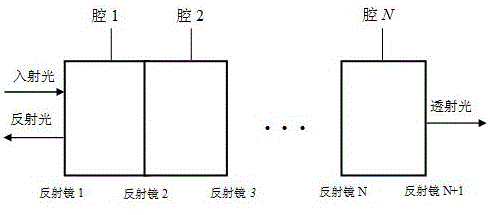

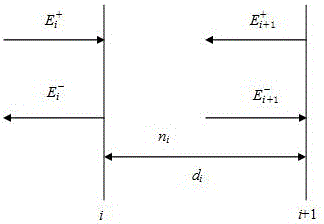

One-dimensional film-cavity type unequal bandwidth optical interleaver design method

ActiveCN106054318ASimple structureHigh flatnessOptical light guidesDielectricDigital signal processing

Owner:SHANGHAI UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com