Method for preparing backside-polished PERC battery

A backside polishing and battery technology, which is applied in the field of backside polishing PERC battery preparation, can solve problems such as unreachable reflectivity, pollution, and increased input costs, and achieve obvious electrical performance gains, elimination of micro-nano structures, and obvious efficiency gains. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

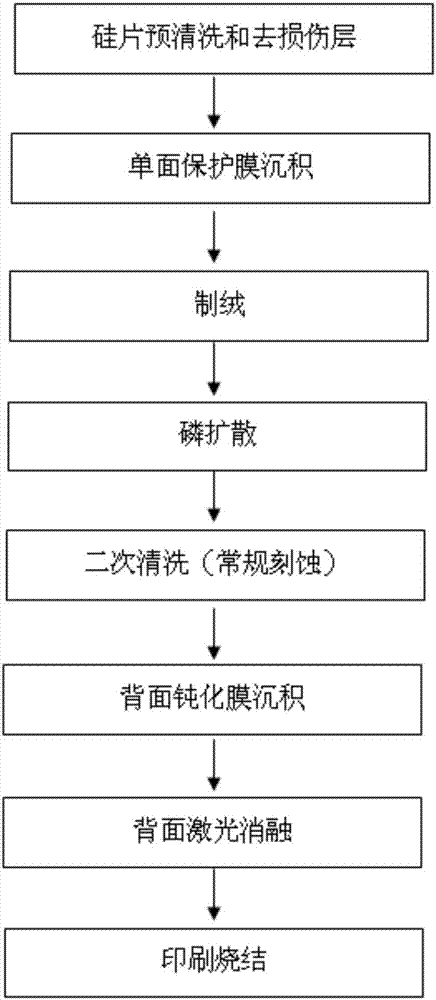

[0036] A preparation method of a backside polished PERC battery of the present invention, such as figure 1 shown, including the following steps:

[0037] (1) Carry out pre-cleaning and dedamage layer to silicon chip, silicon chip is diamond wire cut monocrystalline silicon chip (also can adopt diamond wire cut polysilicon silicon chip), pre-cleaning solution is potassium hydroxide and H 2 o 2 The mixed aqueous solution, the concentration of potassium hydroxide in the solution is 2wt%, and the H in the solution 2 o 2 The concentration is 1wt%, and the treatment time for removing the damaged layer is 5mins. After the treatment, the resulting silicon wafers were washed with deionized water and dried.

[0038] (2) deposit silicon nitride thin film on the silicon wafer back side that step (1) obtains as protective film, the thickness of silicon nitride thin film is 40nm, adopts plasma chemical vapor deposition method (PECVD method) to carry out backside deposition, the process ...

Embodiment 2

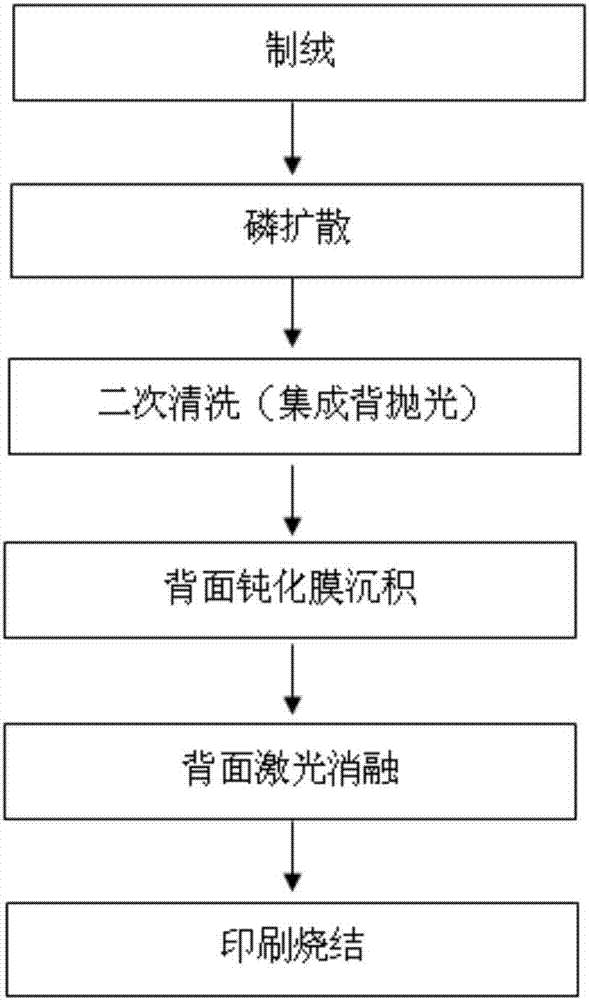

[0044] A preparation method of a backside polished PERC cell of the present invention, comprising the following steps:

[0045] (1) Deposit a silicon oxide film on the back of the silicon wafer as a protective film. The silicon wafer is a diamond wire cut single crystal silicon wafer (diamond wire cut polysilicon silicon wafers can also be used), the thickness of silicon oxide is 20nm, and the silicon oxide film deposition equipment is plasma chemistry. Vapor deposition equipment, the process parameters of the PECVD method used are deposition pressure of 0.15mbar, deposition temperature of 400°C, microwave power of 3000W, silane gas flow of 190sccm, ammonia gas flow of 570sccm, and deposition time of 5mins to obtain a single-sided protective film of silicon wafers.

[0046] (2) the silicon wafer coated with the single-sided protective film obtained in step (1) is carried out using a texture-making process, and the texture-making solution is potassium hydroxide aqueous solution...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com