Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Shorting of contact" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

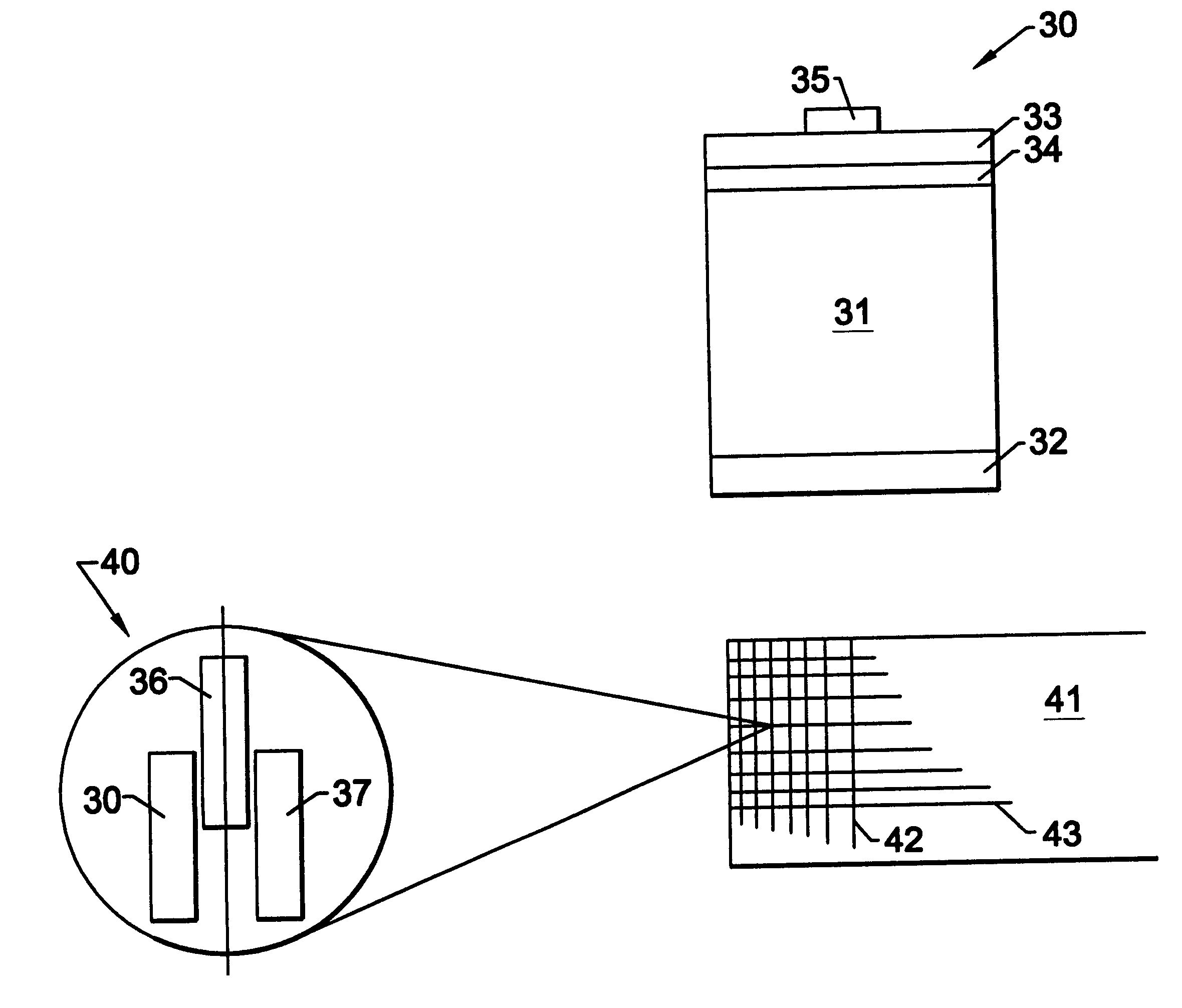

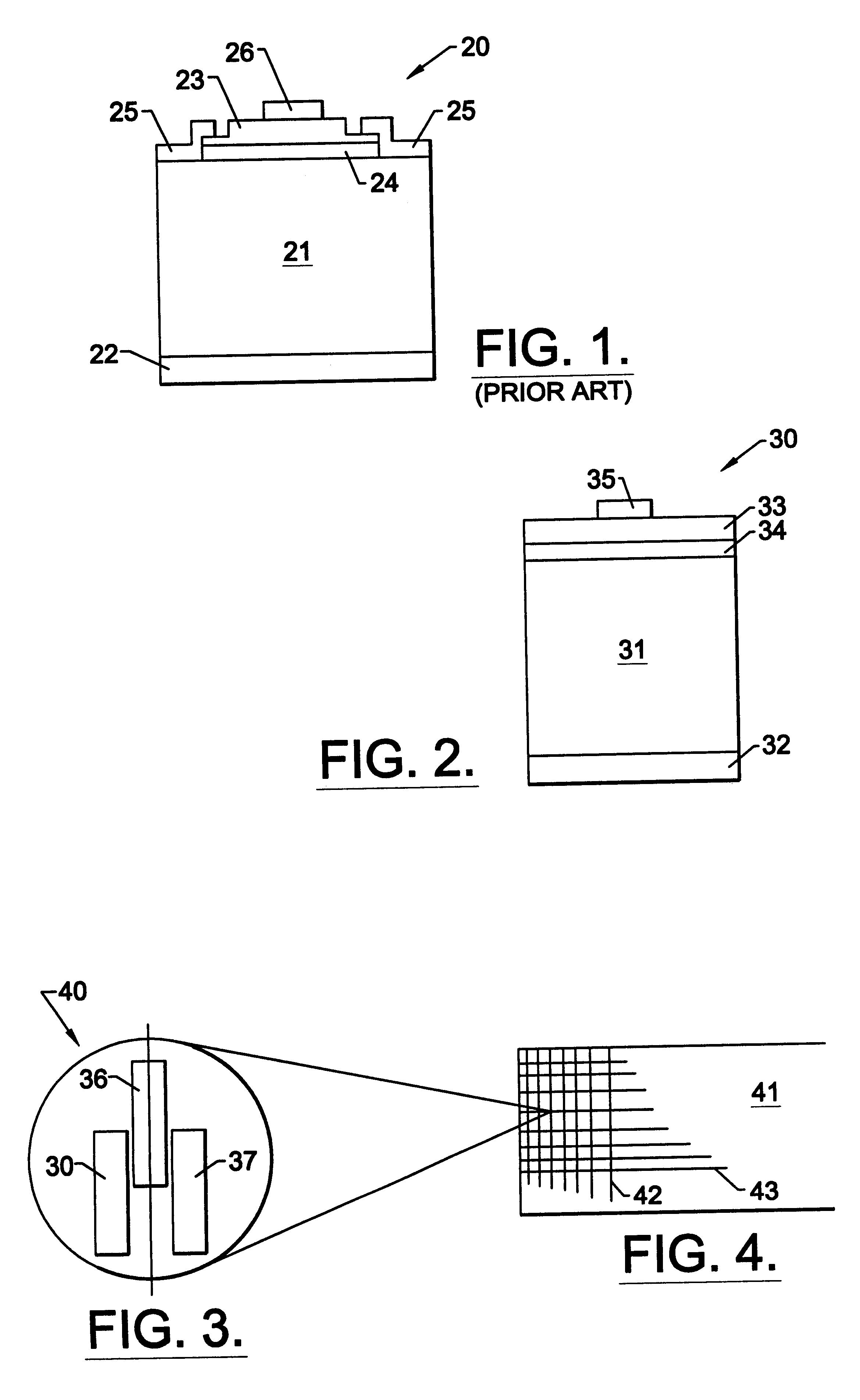

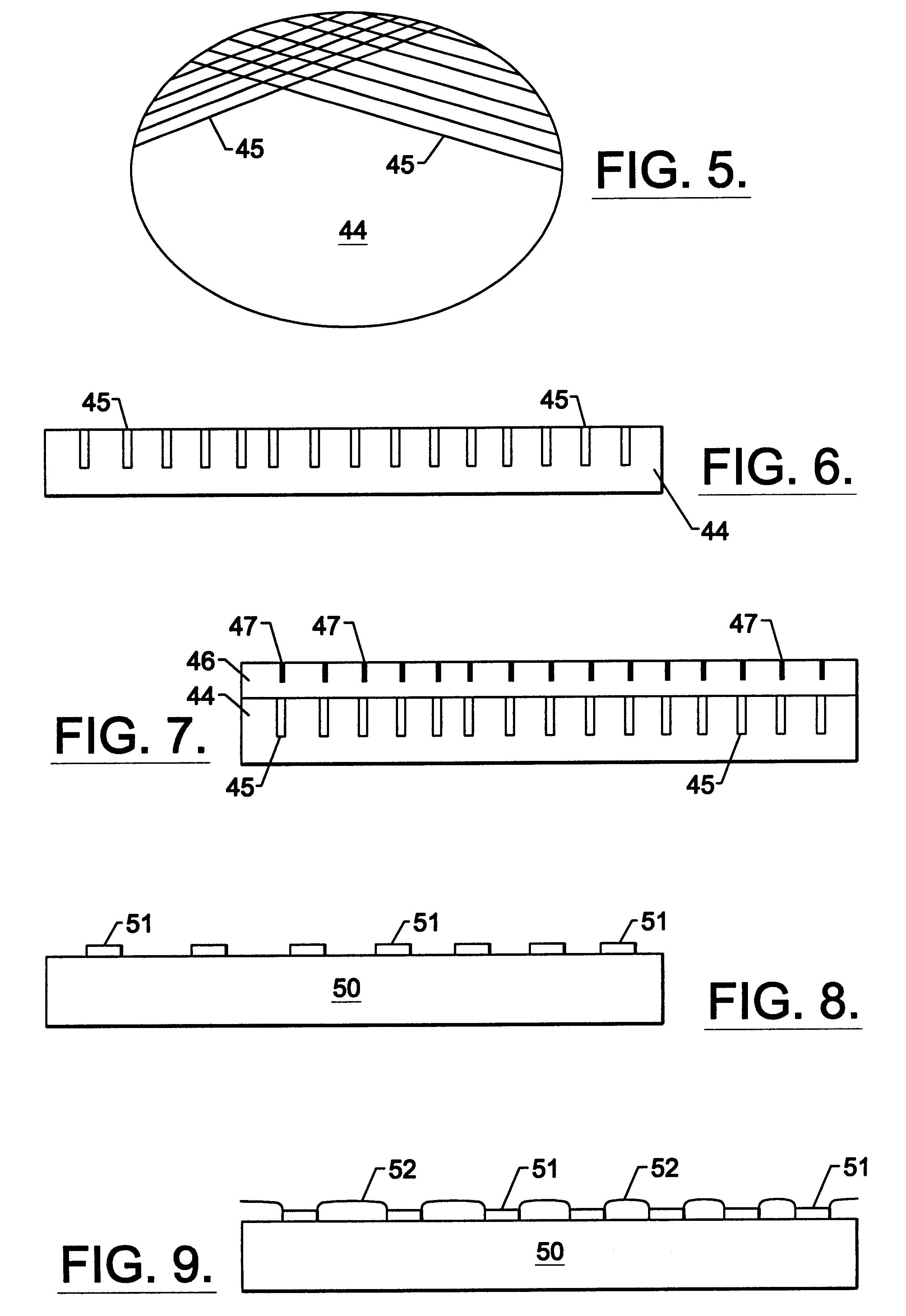

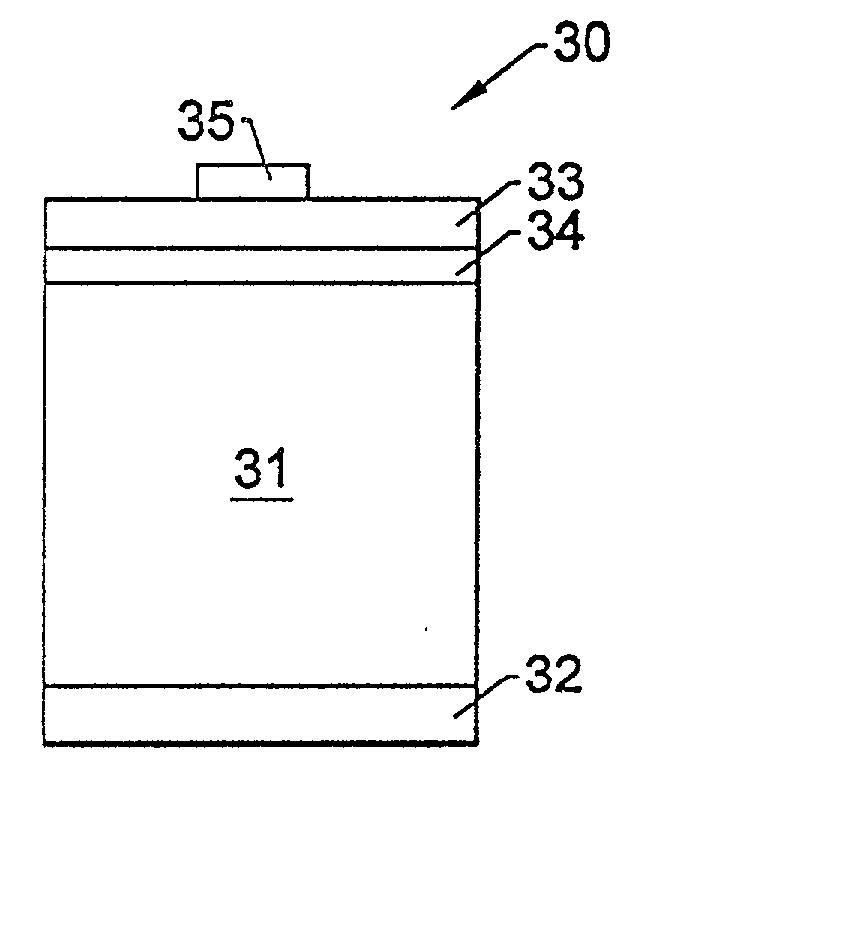

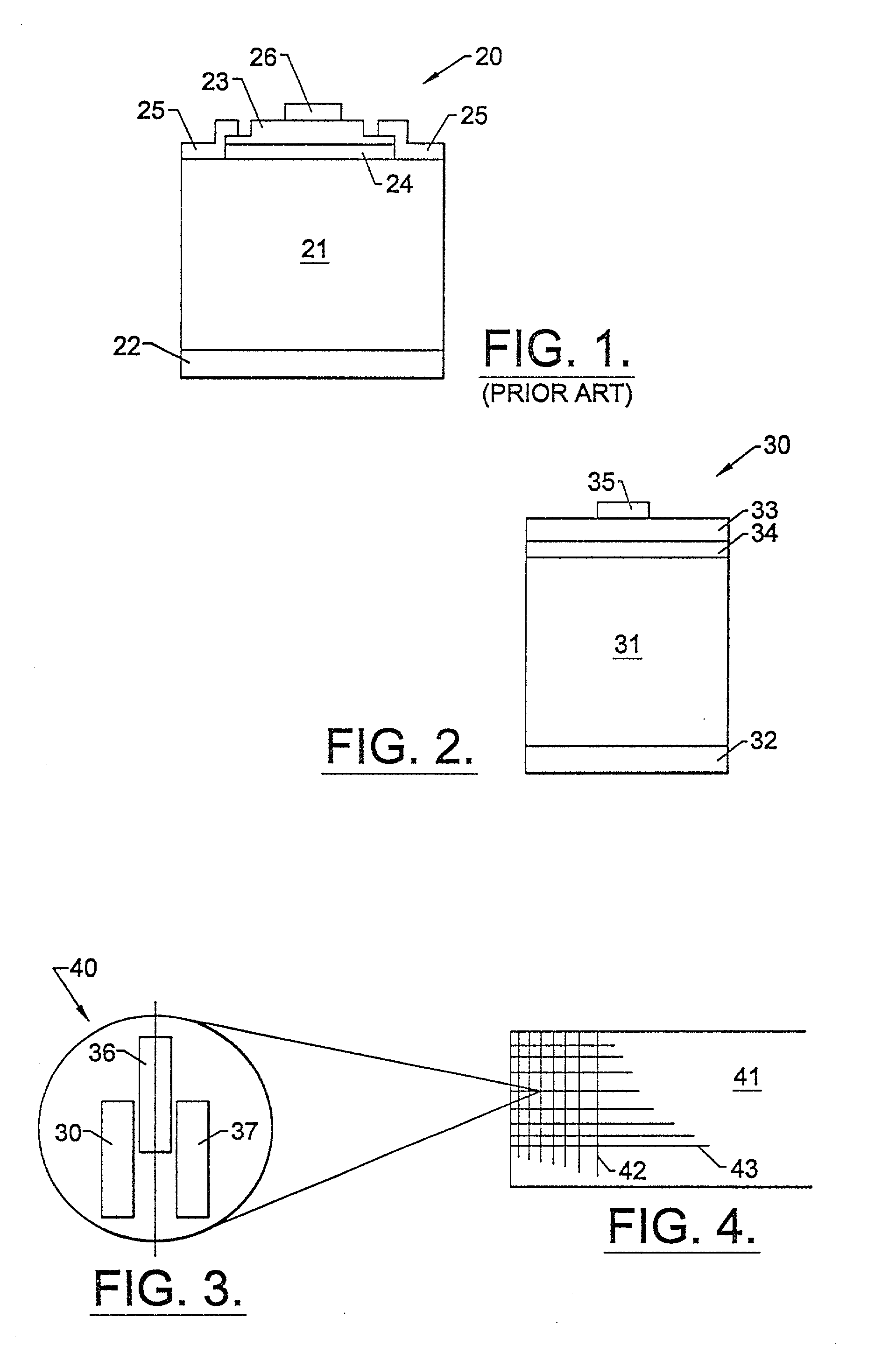

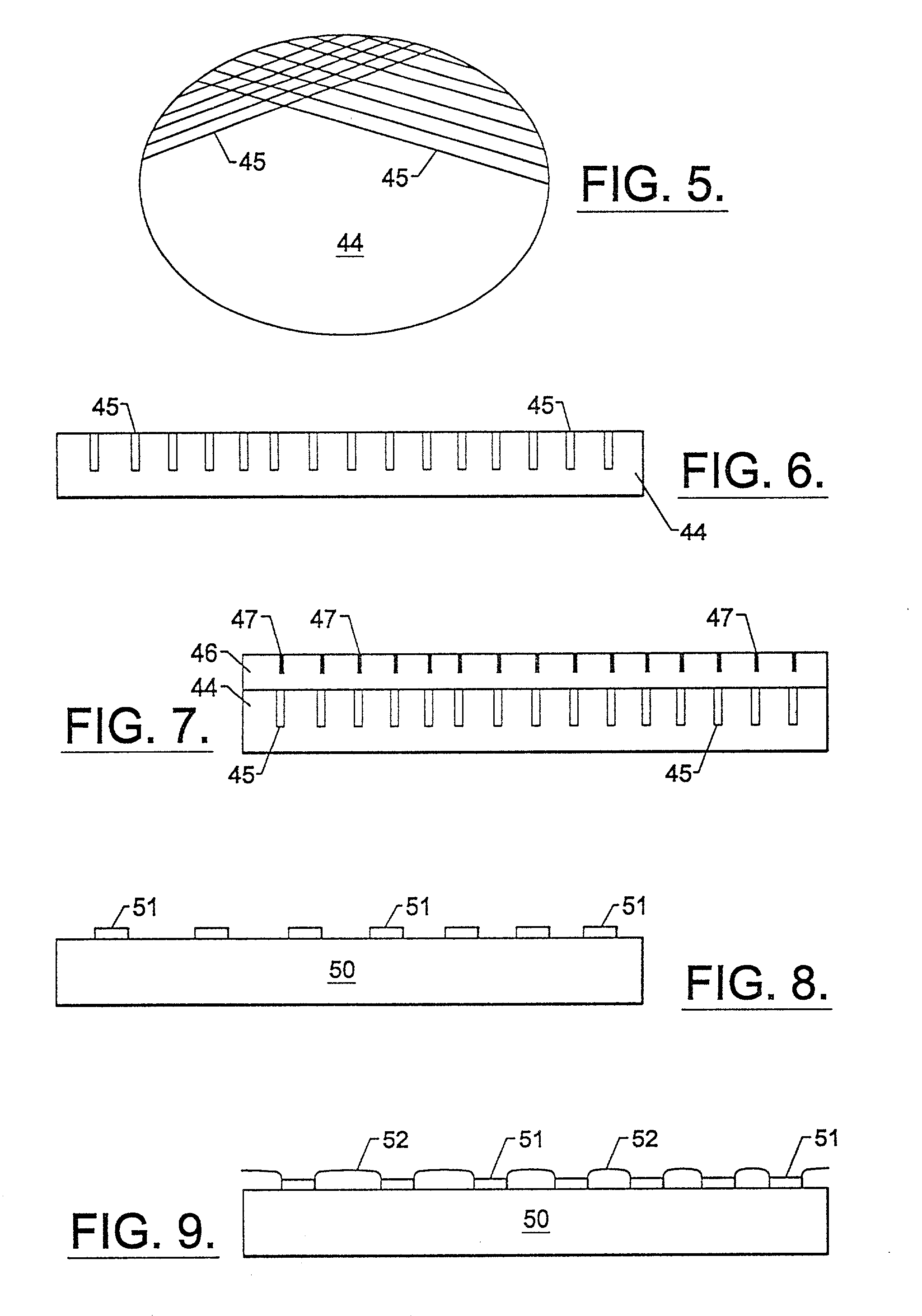

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlay structure

InactiveUS6201262B1Avoid crackingEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlayer structure

InactiveUS20020008241A1Avoid crackingEasy to manufactureTransistorSolid-state devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

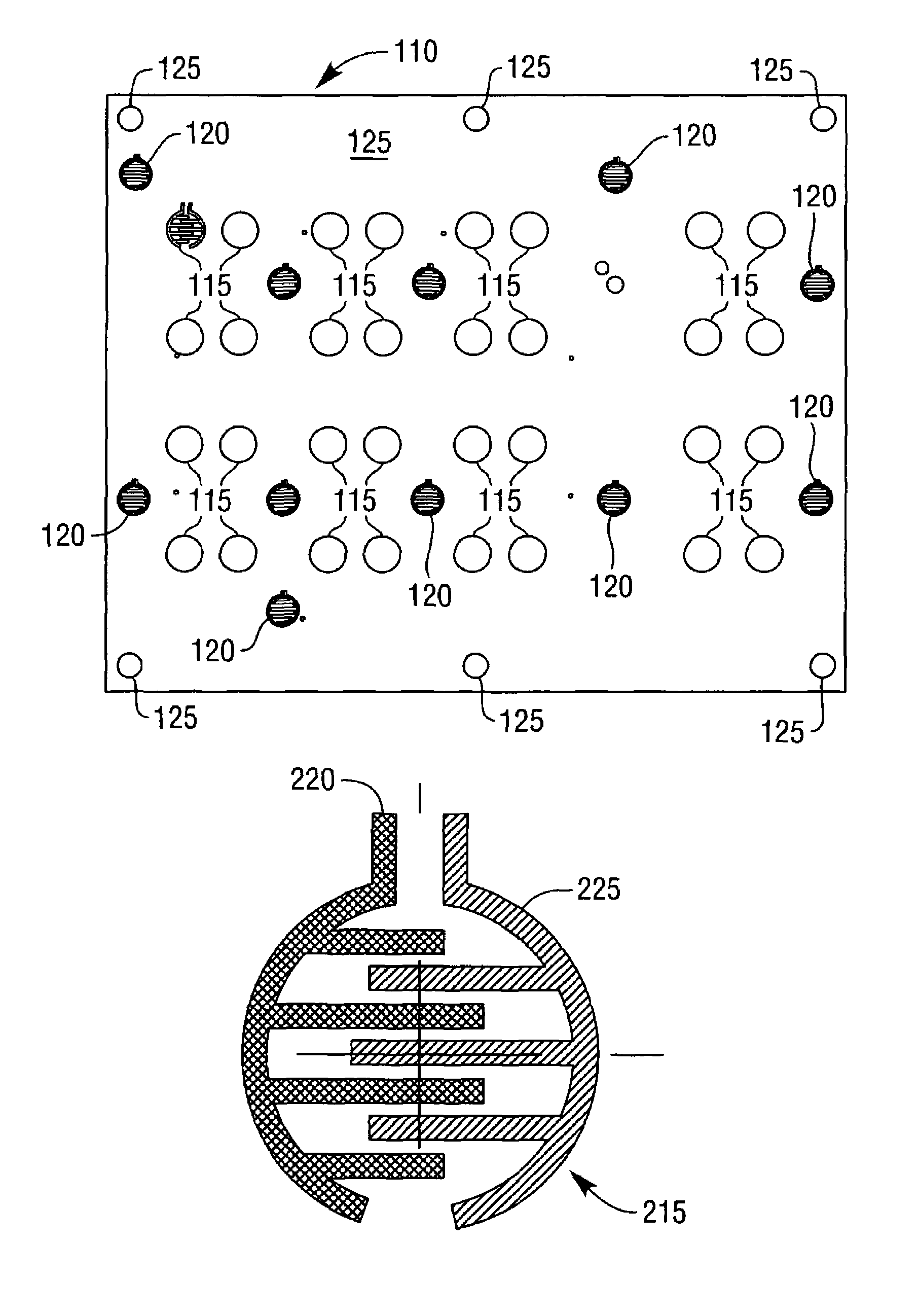

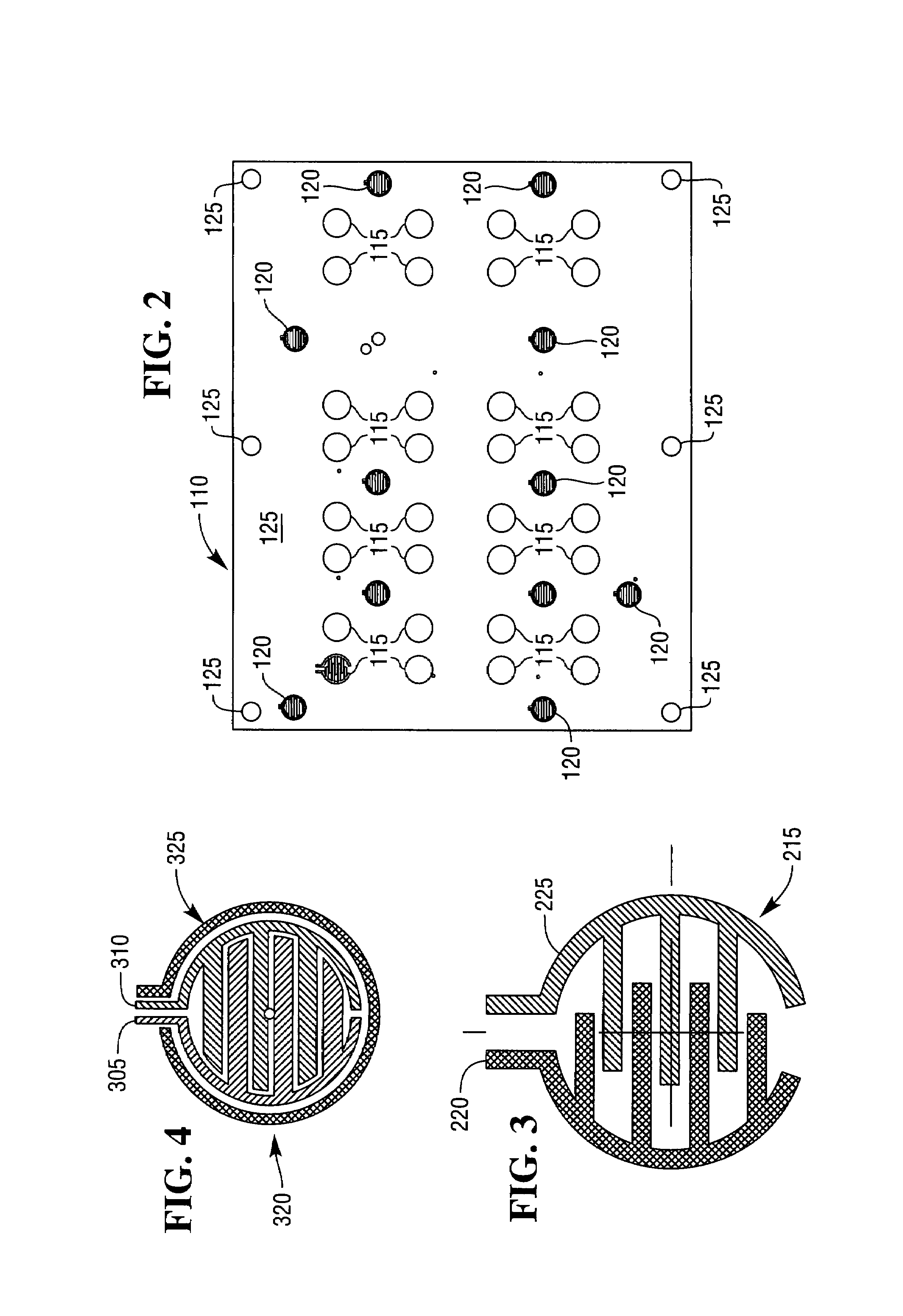

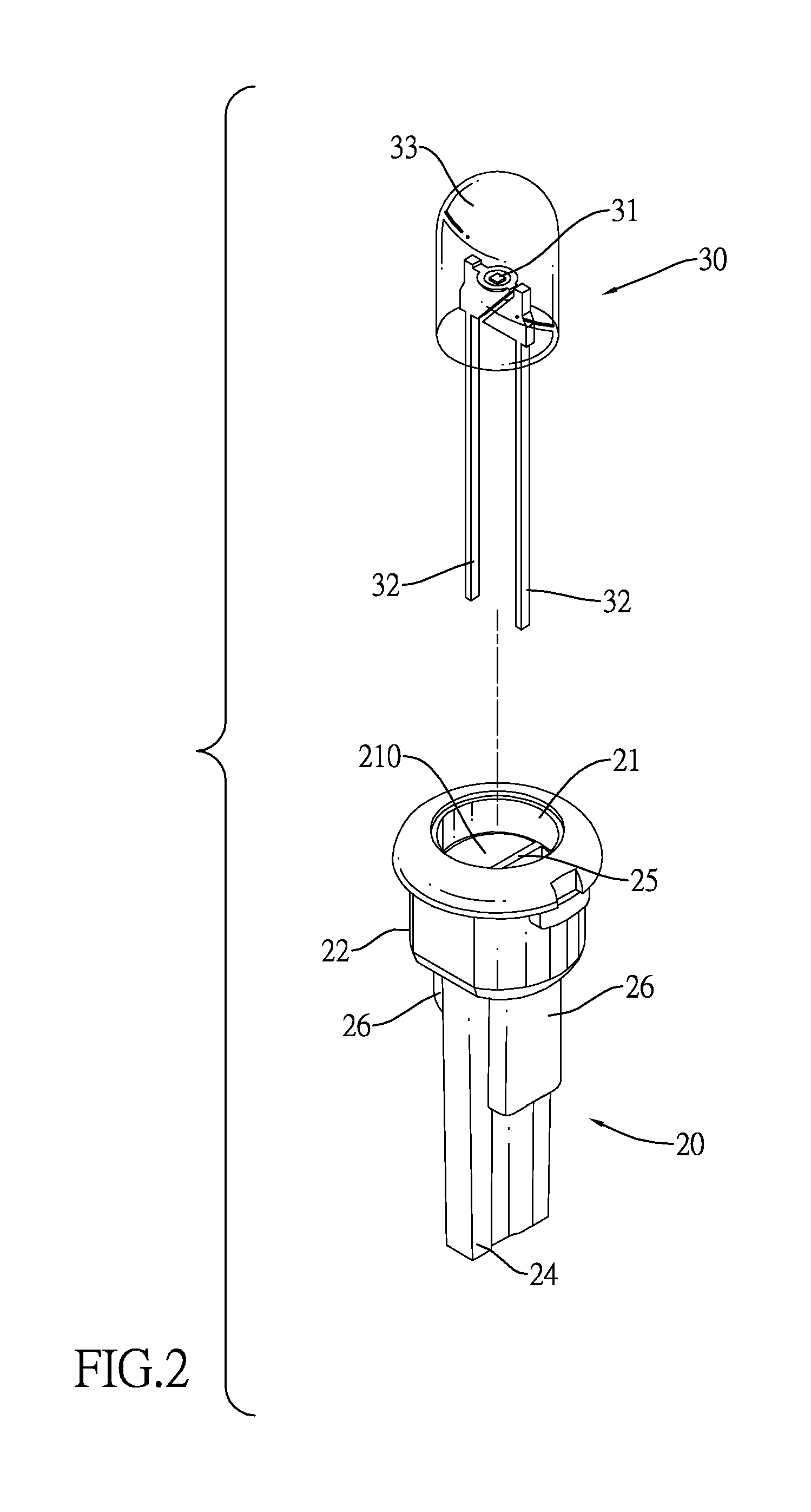

Secured pin entry device

ActiveUS7270275B1Shorting of contactPrevents unauthorized, undetected tamperingContact operating partsRecord carriers used with machinesPersonal identification numberPrinted circuit board

The invention is a keypad for securely entering personal identification numbers onto automated teller machines (ATM) or similar devices. A frame secures a flexible keypad to a printed circuit board. The front of the circuit includes a set of tamper detection contacts whose electrical circuit is completed by conductive material on the keypad surface. A moat of conductive material surrounds the tamper detection contact. Opening the circuit by removing the keypad or shorting the circuit to the moat initiates a tamper response.Attached to the reverse side of the printed circuit board are security sensitive electrical components. These security sensitive components include a static random access memory storing cryptographic information and a crypto processor. A plastic cover imprinted with a tamper detection grid forming multiple electrical circuits coupled to a tamper detection circuit covers these components. A border of conductive material on the printed circuit board also surrounds these components. Opening or shorting any of the circuits in the grid initiates a tamper response, and shorting any of the components to the border also initiates a tamper response.

Owner:TIDEL ENG LP

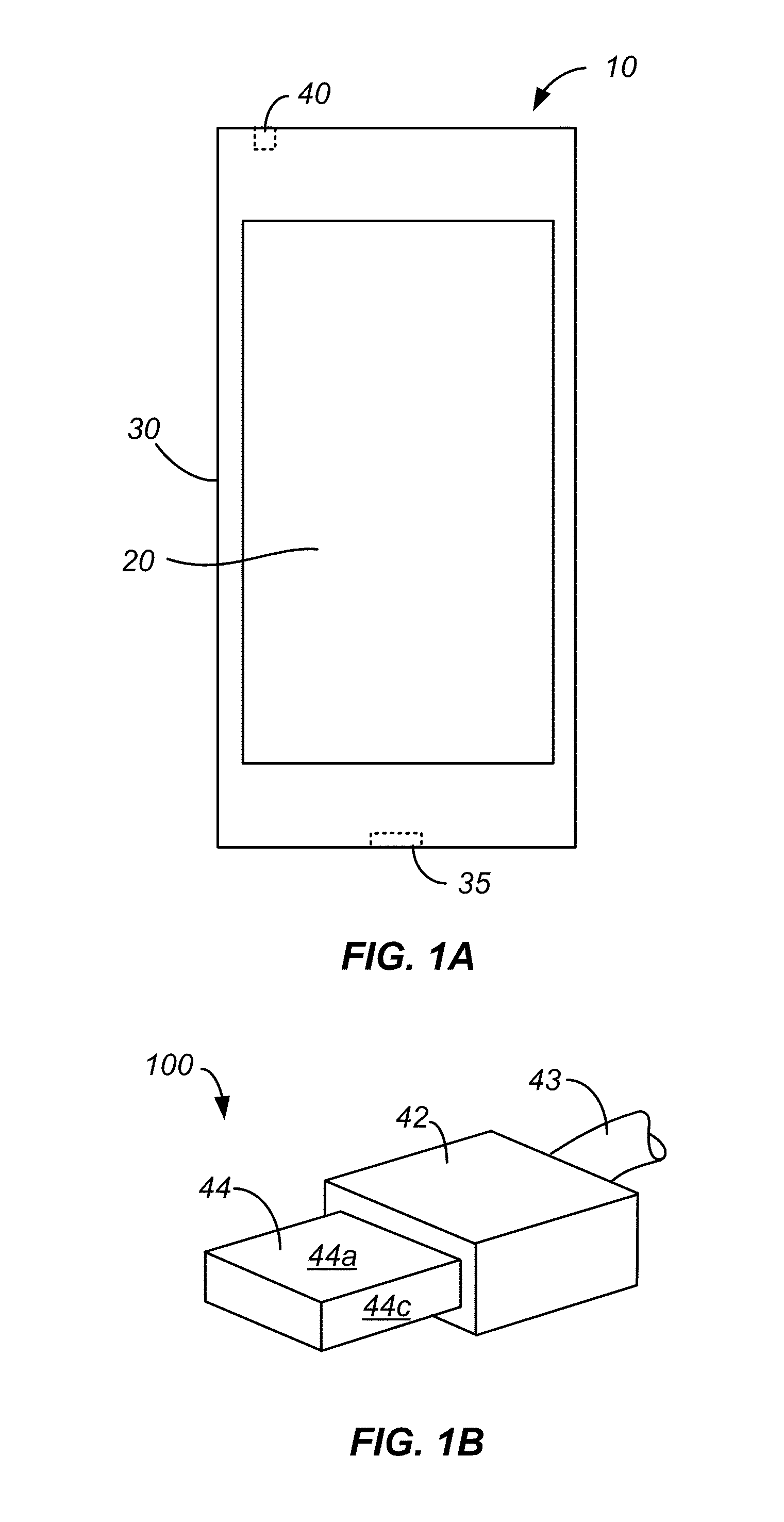

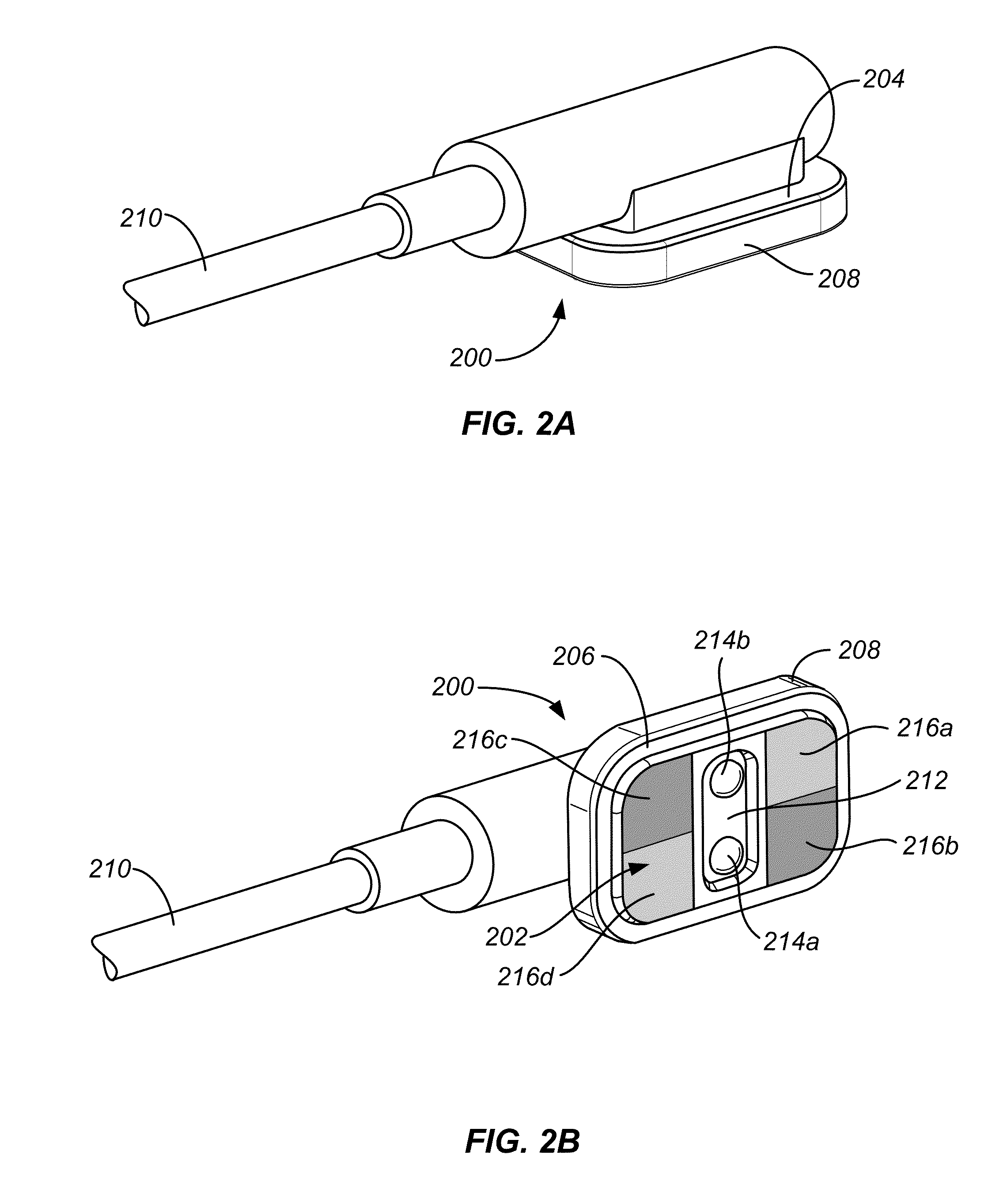

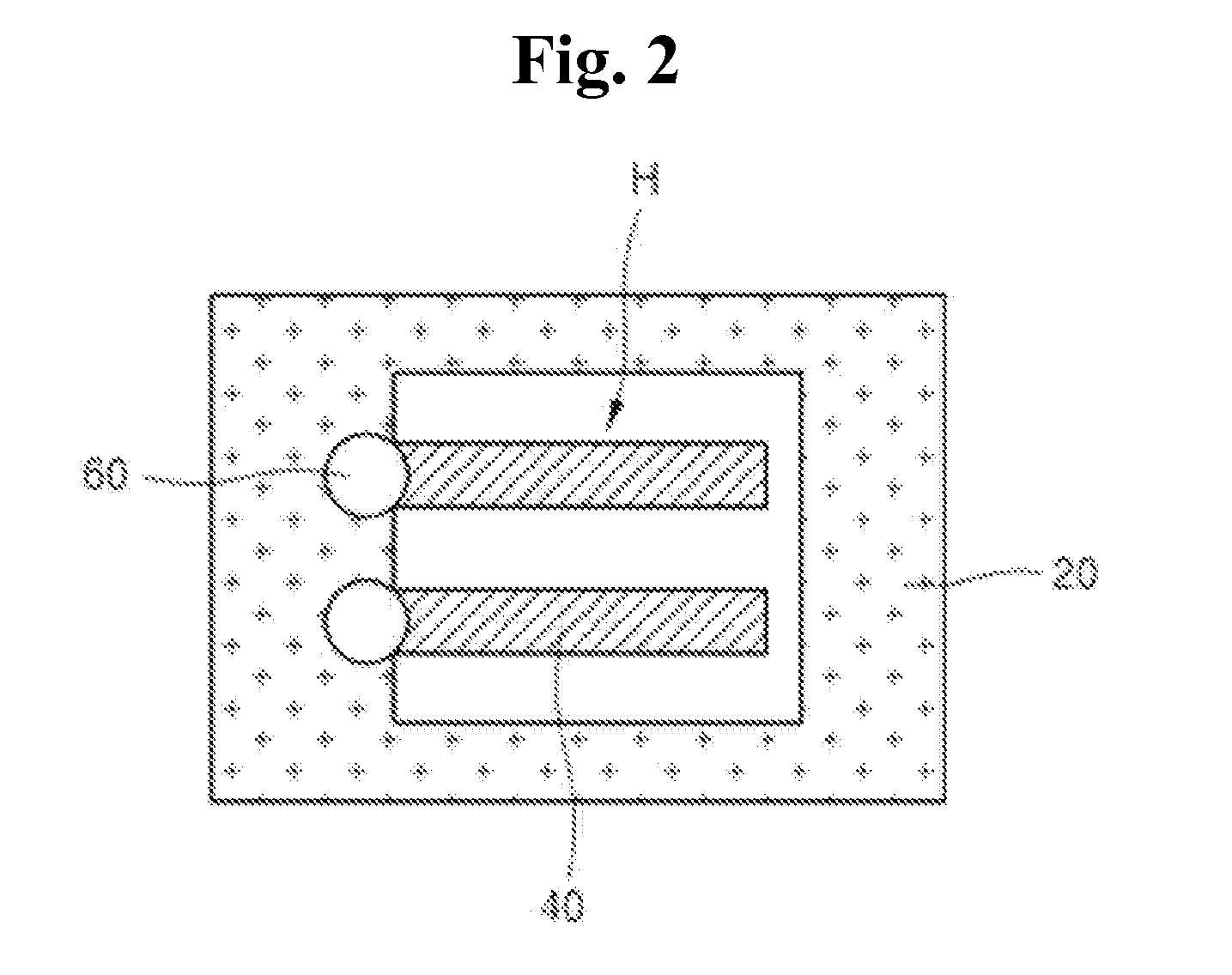

Stackable magnetically-retained connector interface

ActiveUS20150093922A1Avoid contactAvoid exposureEngagement/disengagement of coupling partsNear-field transmissionEngineeringElectric power

A stackable connector interface with magnetic retention for electronic devices and accessories can allow power and data to be transferred between one or more stacked connectors. Each interconnected stackable connector may include one or more magnetic elements, which magnetic elements may have poles arranged to facilitate mating with other stackable connectors. The magnetic elements may also provide a magnetic retention force that holds mated connectors in contact with each other. The connectors can also include connection detection circuitry for determining whether the connectors are mated with other connectors, thereby allowing the connectors to prevent live contacts from being exposed at an unmated surface of the connectors. In addition to connection detection circuitry, routing circuitry may also be included to determine how signals should be transferred between the interconnected stackable connectors and / or corresponding devices.

Owner:APPLE INC

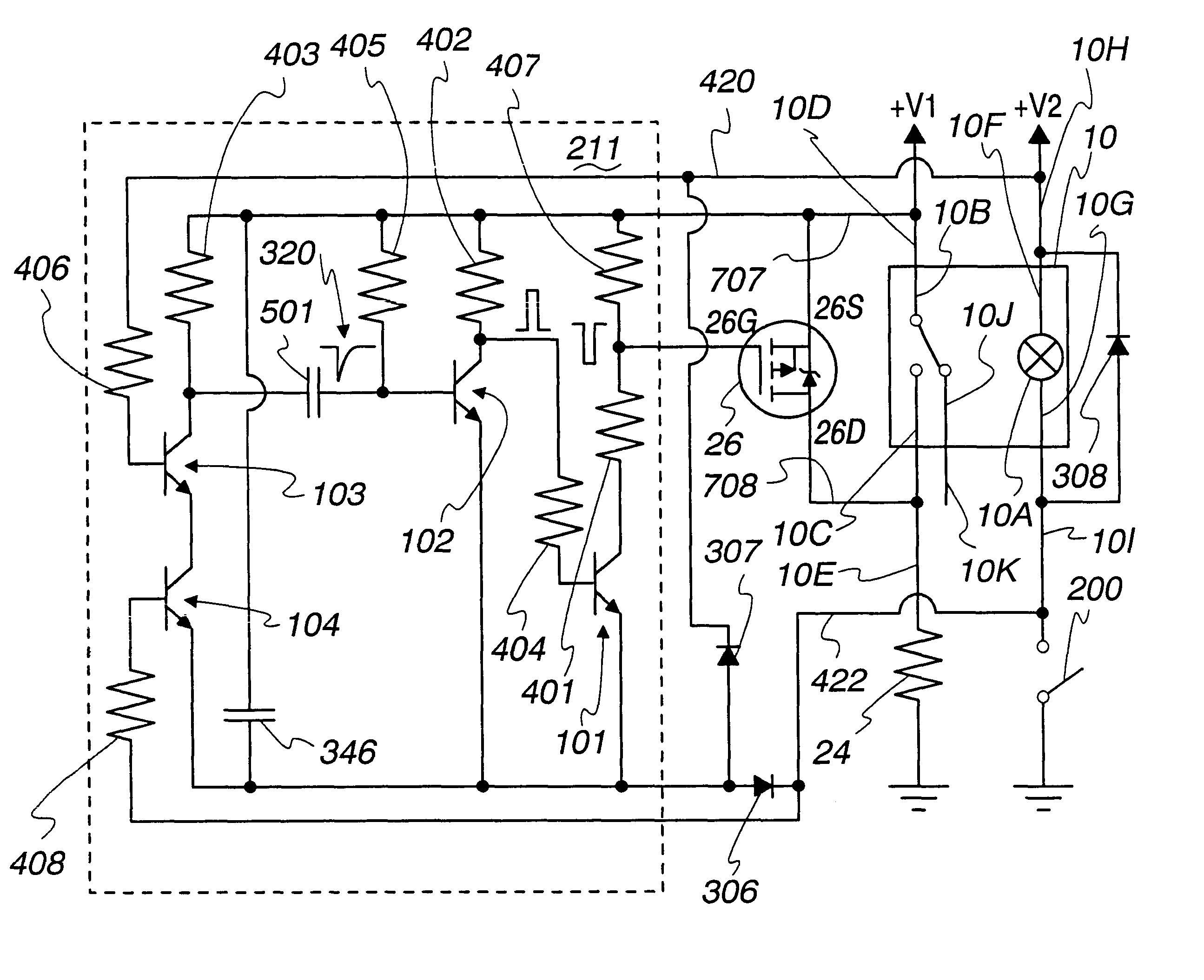

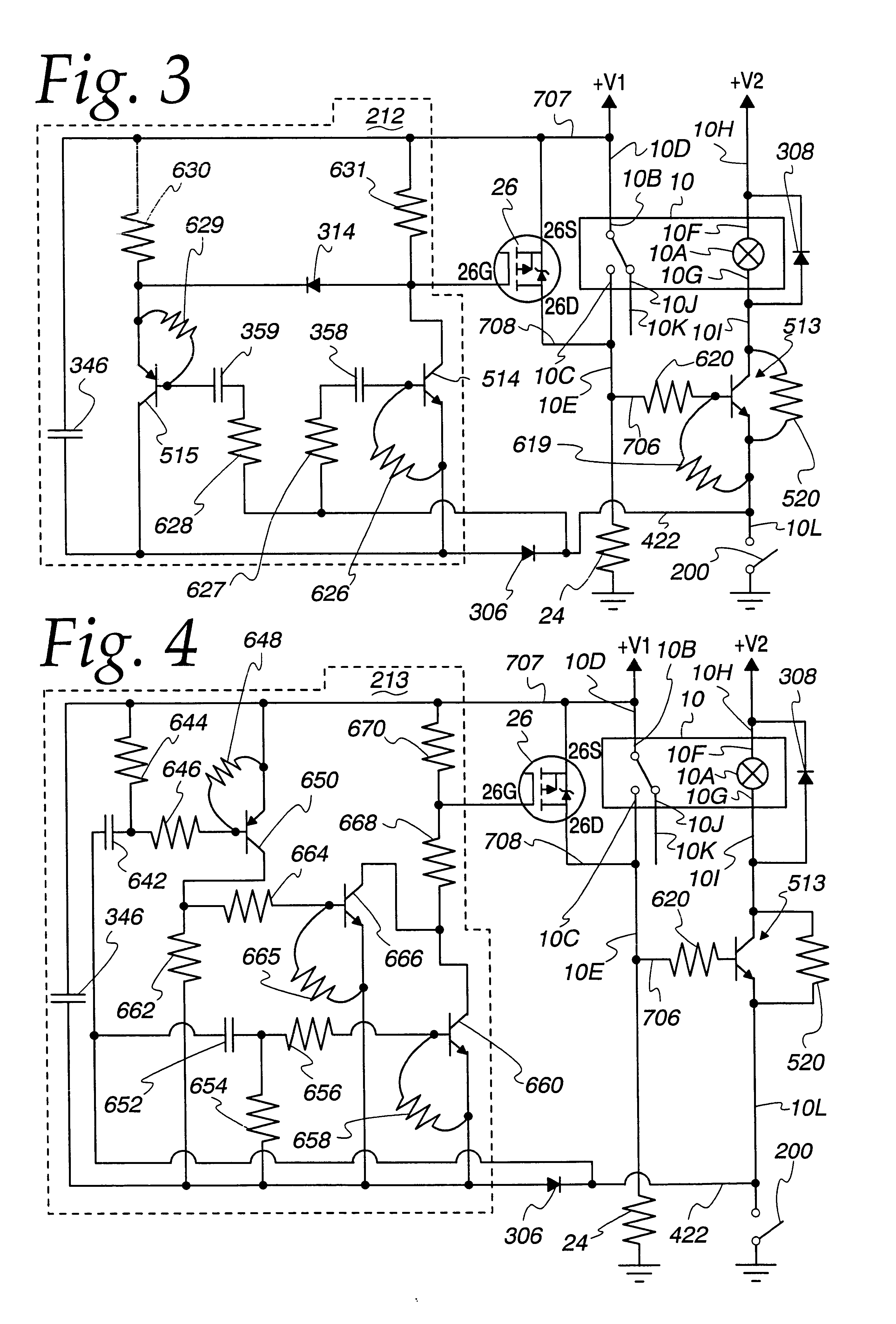

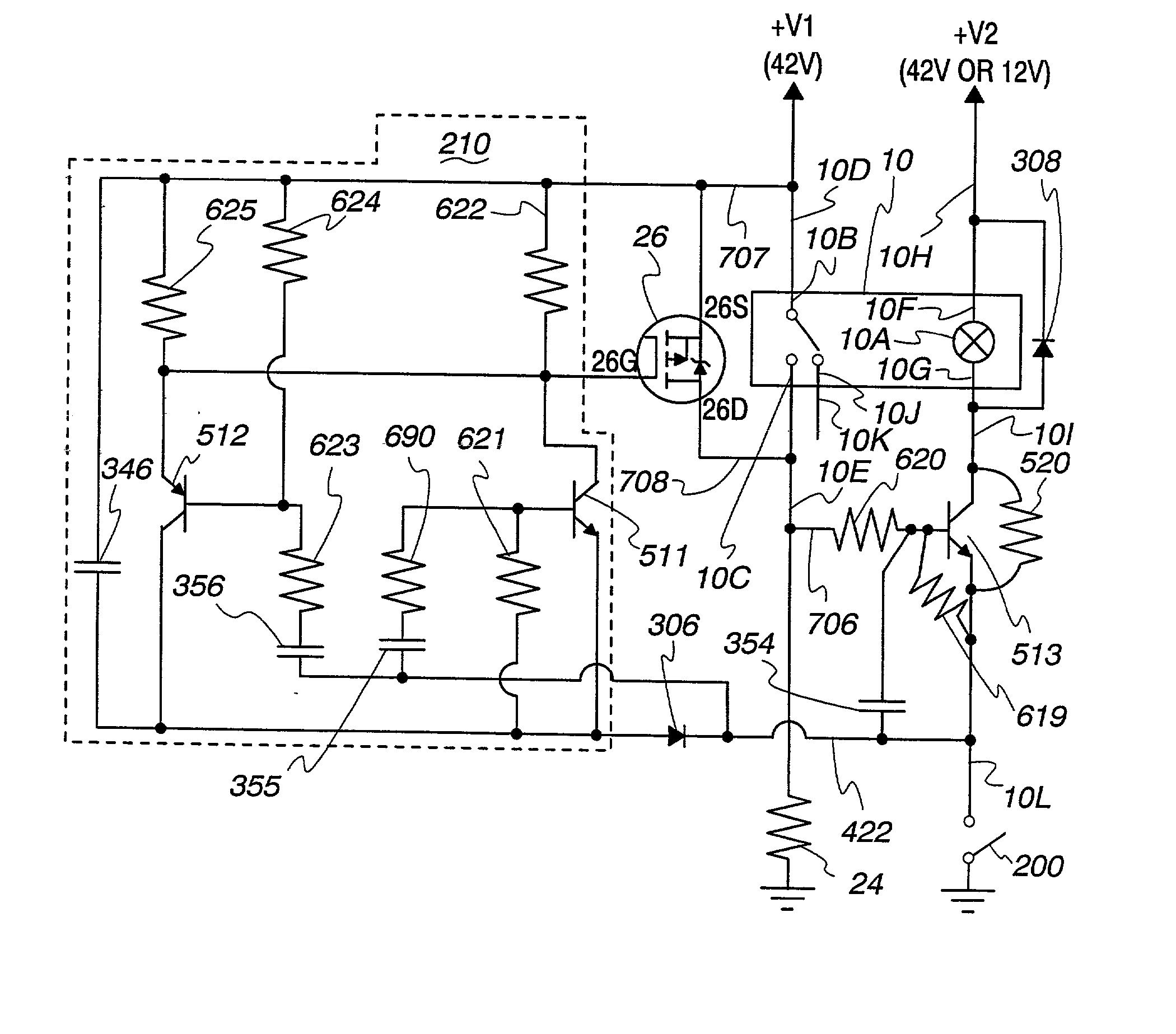

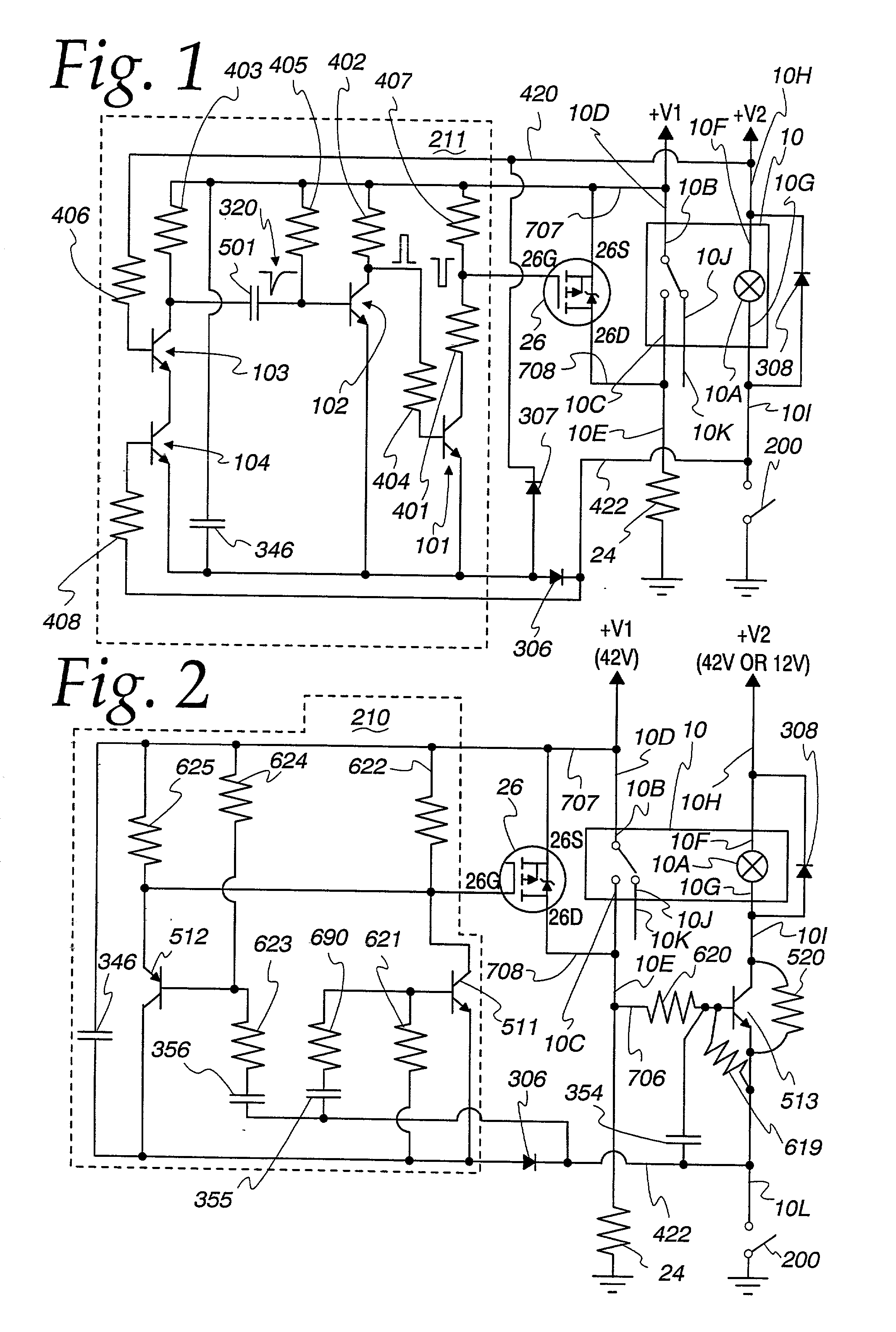

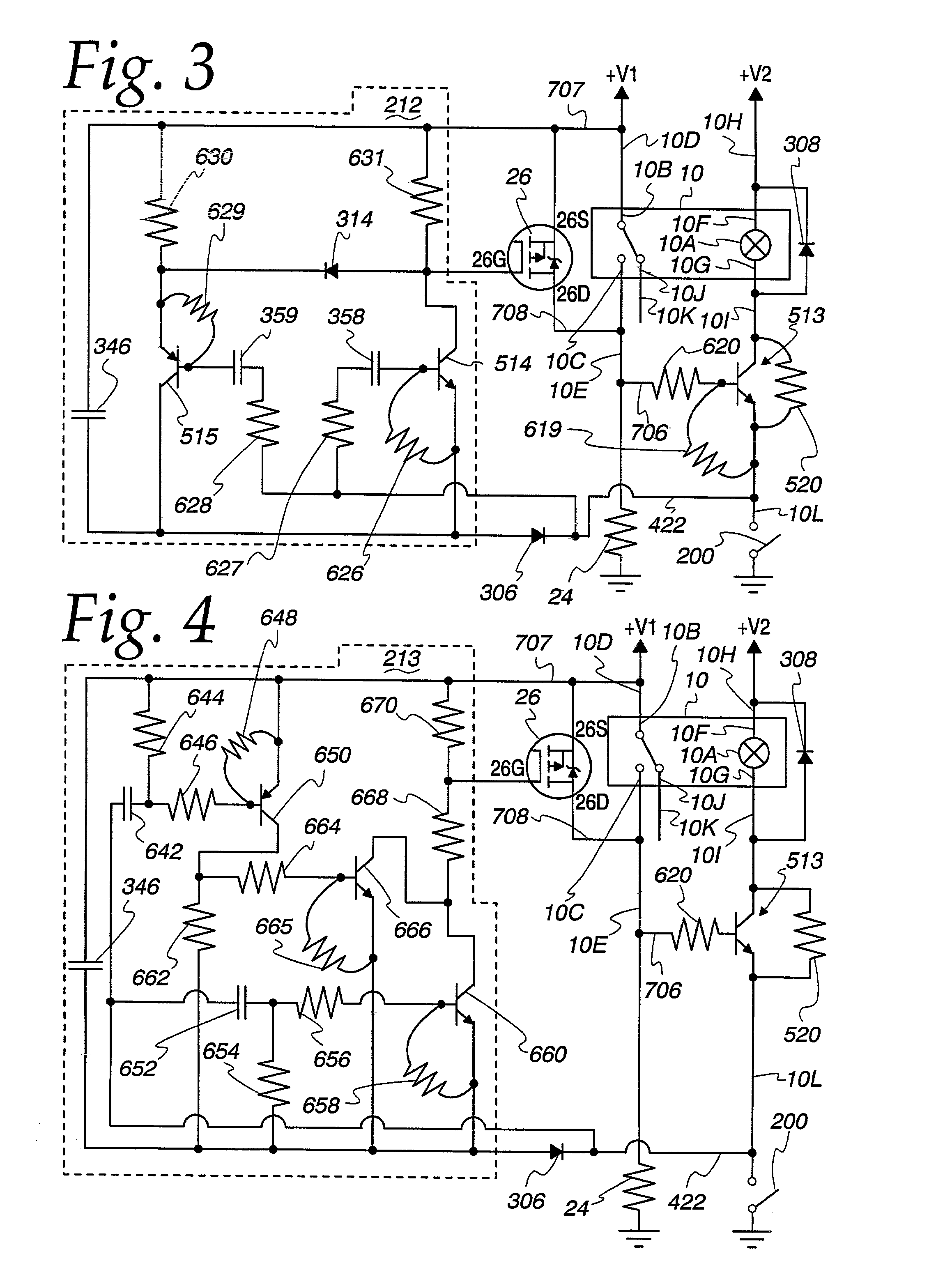

Circuit for operating voltage range extension for a relay

InactiveUS6671142B2Shorting of contactSuppress contact opening arcingCoupling device detailsElectronic switchingMOSFETEngineering

A relay is designed to be used in a circuit where the voltage levels are high in comparison to the spacing between the contacts when open. Contact closure arcing is suppressed by actuating a MOSFET that shorts the contacts together while they open. The same MOSFET can momentarily short the contacts together just before they first begin to close, allowing a test current to be passed through the MOSFET and through the terminals connecting to both relay contacts, to insure that arc suppression will be successful; and if this test fails, then the relay can be disabled by a switch in series with the relay coil to prevent arcing and a possible fire hazard. Relay deactuation can be sensed to trigger arc suppression, and relay actuation can be sensed to initiate fail-safe testing by a circuit that responds no matter which way the relay coil is connected into the external circuit that drives it.

Owner:ORMON CORP

Circuit for operating voltage range extension for a relay

InactiveUS20020118495A1Shorting of contactSuppress contact opening arcingCoupling device detailsElectronic switchingMOSFETSafety testing

A relay is designed to be used in a circuit where the voltage levels are high in comparison to the spacing between the contacts when open. Contact closure arcing is suppressed by actuating a MOSFET that shorts the contacts together while they open. The same MOSFET can momentarily short the contacts together just before they first begin to close, allowing a test current to be passed through the MOSFET and through the terminals connecting to both relay contacts, to insure that arc suppression will be successful; and if this test fails, then the relay can be disabled by a switch in series with the relay coil to prevent arcing and a possible fire hazard. Relay deactuation can be sensed to trigger arc suppression, and relay actuation can be sensed to initiate fail-safe testing by a circuit that responds no matter which way the relay coil is connected into the external circuit that drives it.

Owner:ORMON CORP

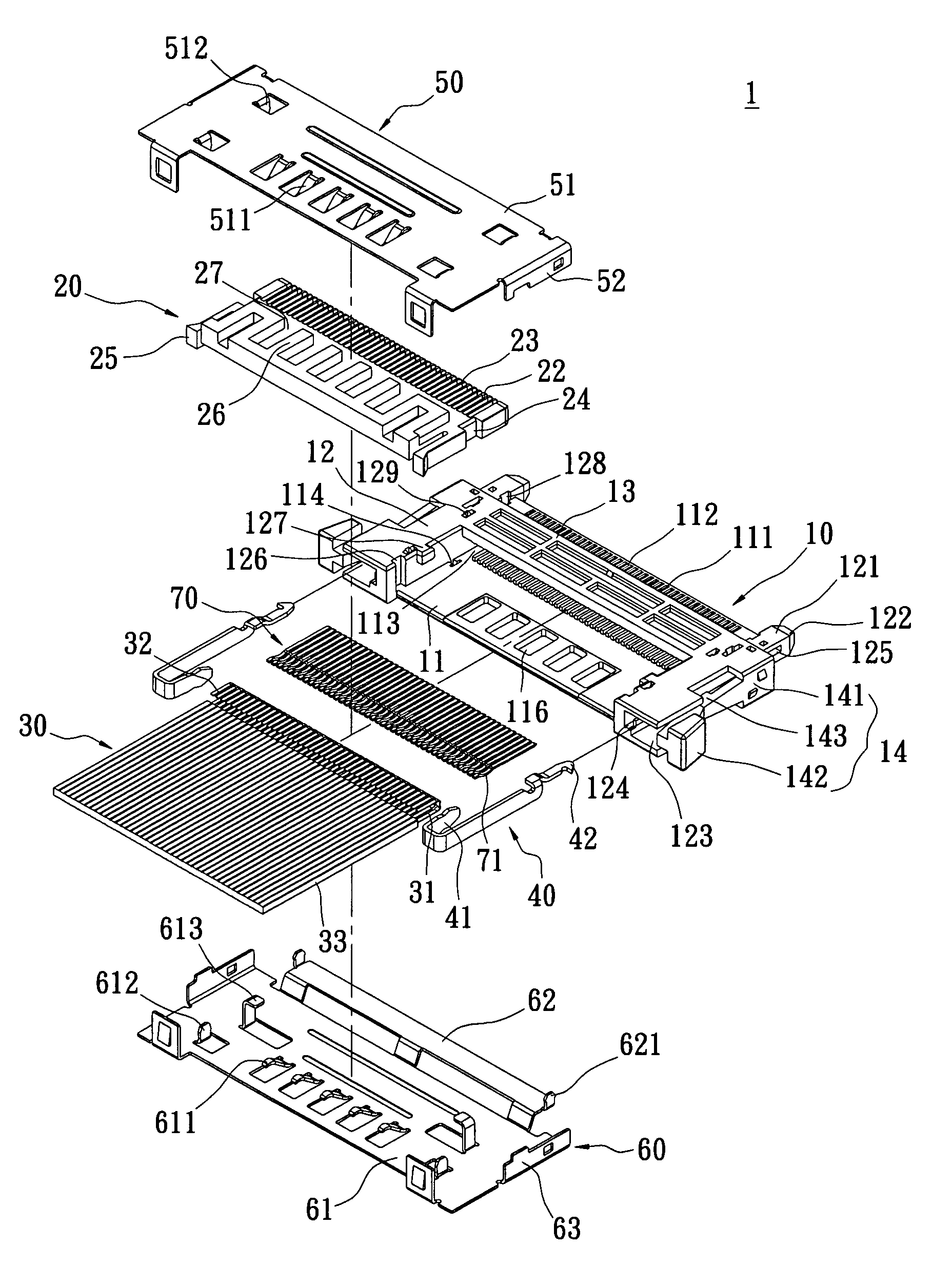

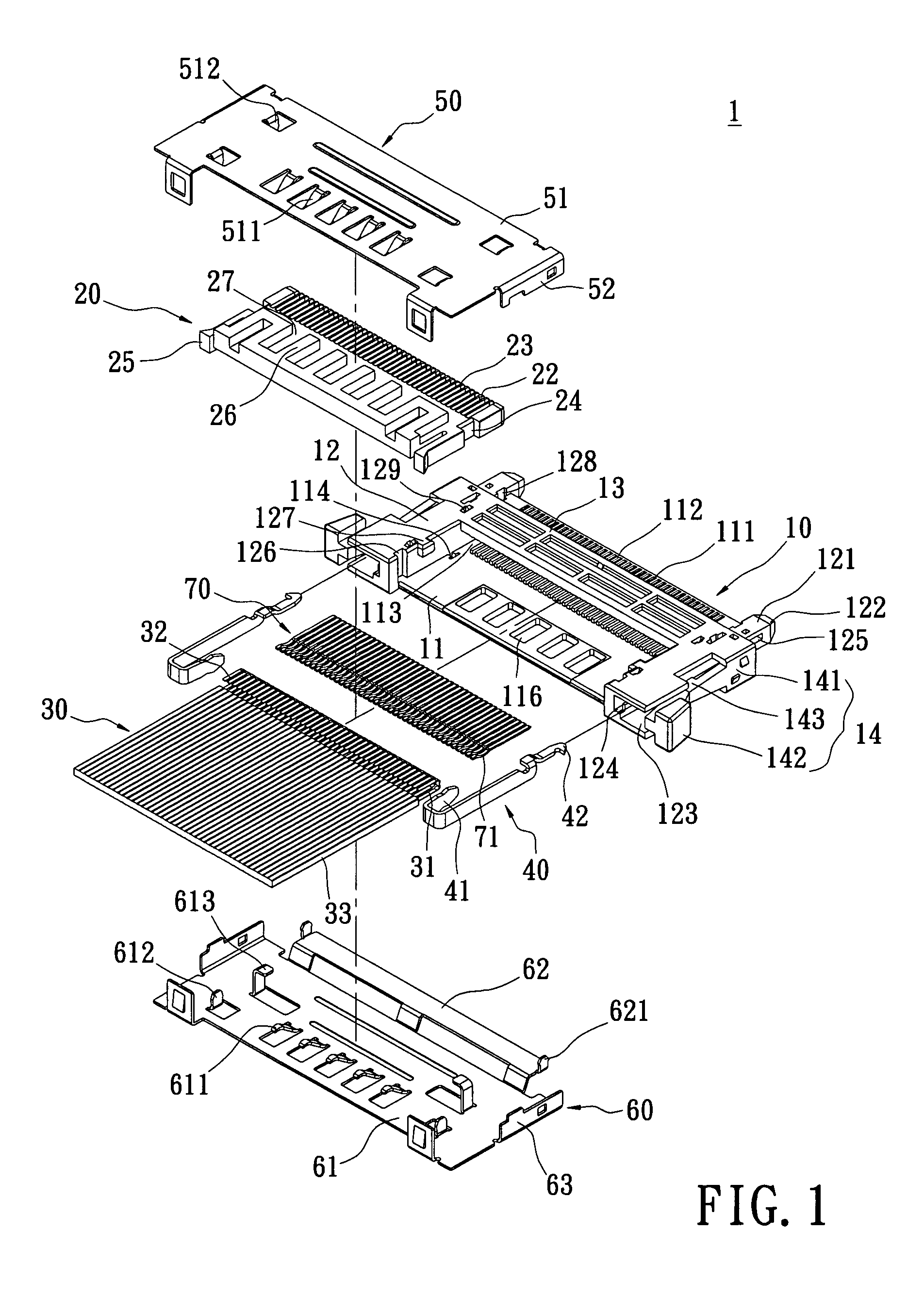

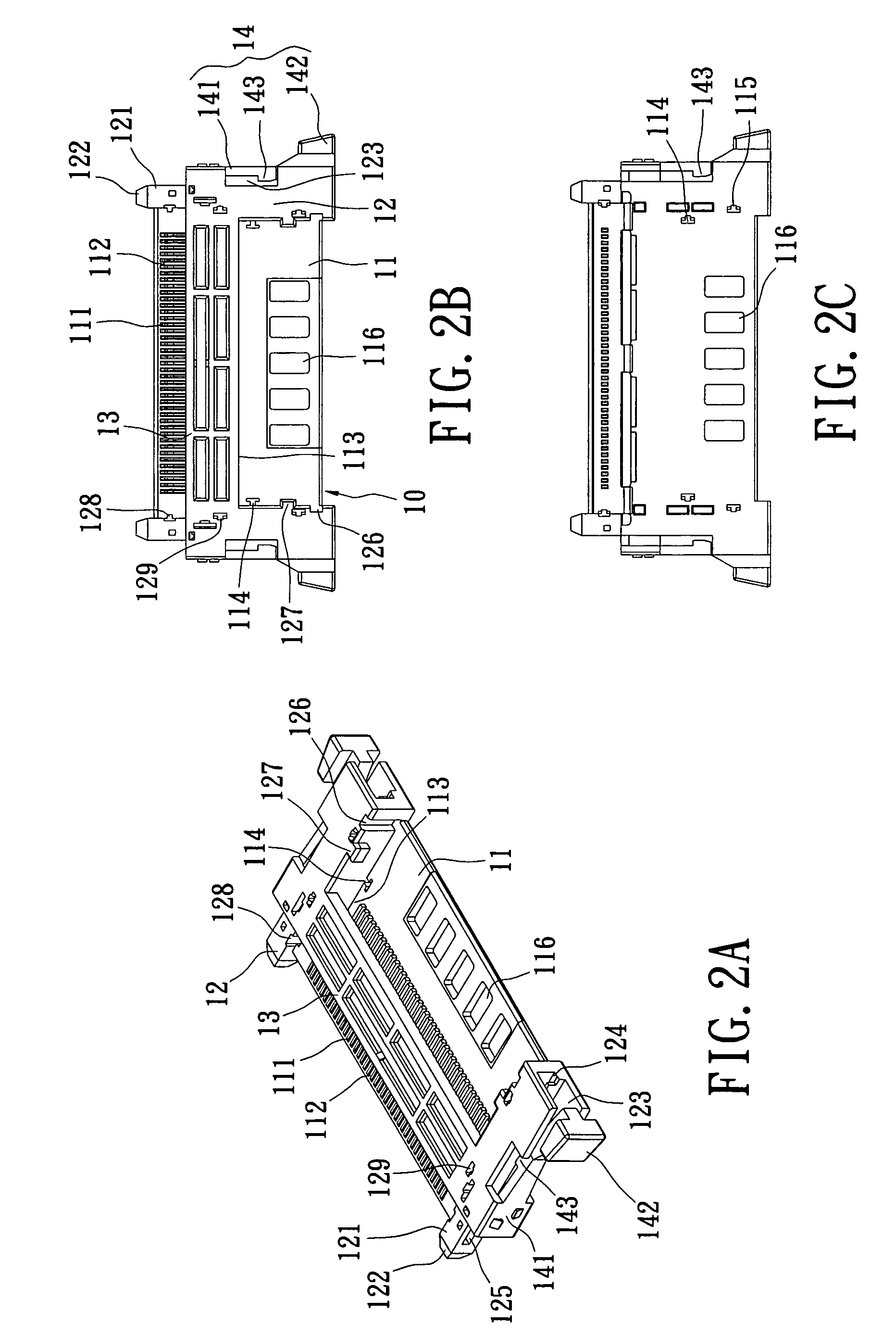

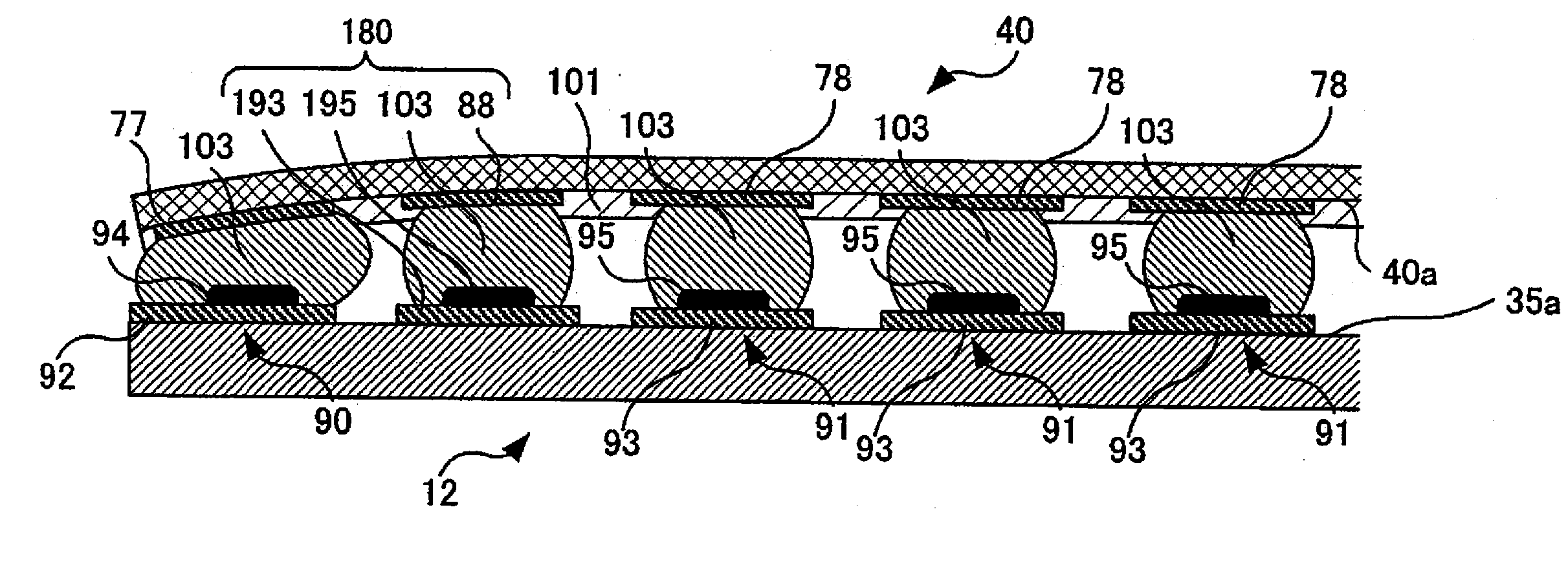

Electrical connector

InactiveUS7530839B1Short working hoursImprove yieldCoupling device detailsEngineeringElectrical connector

An electrical connector includes an insulating body, an inner flexible plug, two metal housings and a flexible cable. The insulating body includes a base, two side portions set on two opposite sides of said base respectively and a top board connected between the side portions. A plurality of terminal grooves is defined in the base. The inner flexible plug is combined in the insulating body. The metal housings cover the insulating body. The flexible cable is set between the insulating body and the inner flexible plug. The inner flexible plug defines a plurality of receiving slots corresponding to the terminal grooves. The receiving slots extend from top side of the inner flexible plug to its bottom side in a bent way thus the flexible cable can be electrically connected with electrical connecting terminals set in the terminal grooves. Therefore, the electrical connector is easily assembled and has a stable structure.

Owner:JESS-LINK PRODUCTS

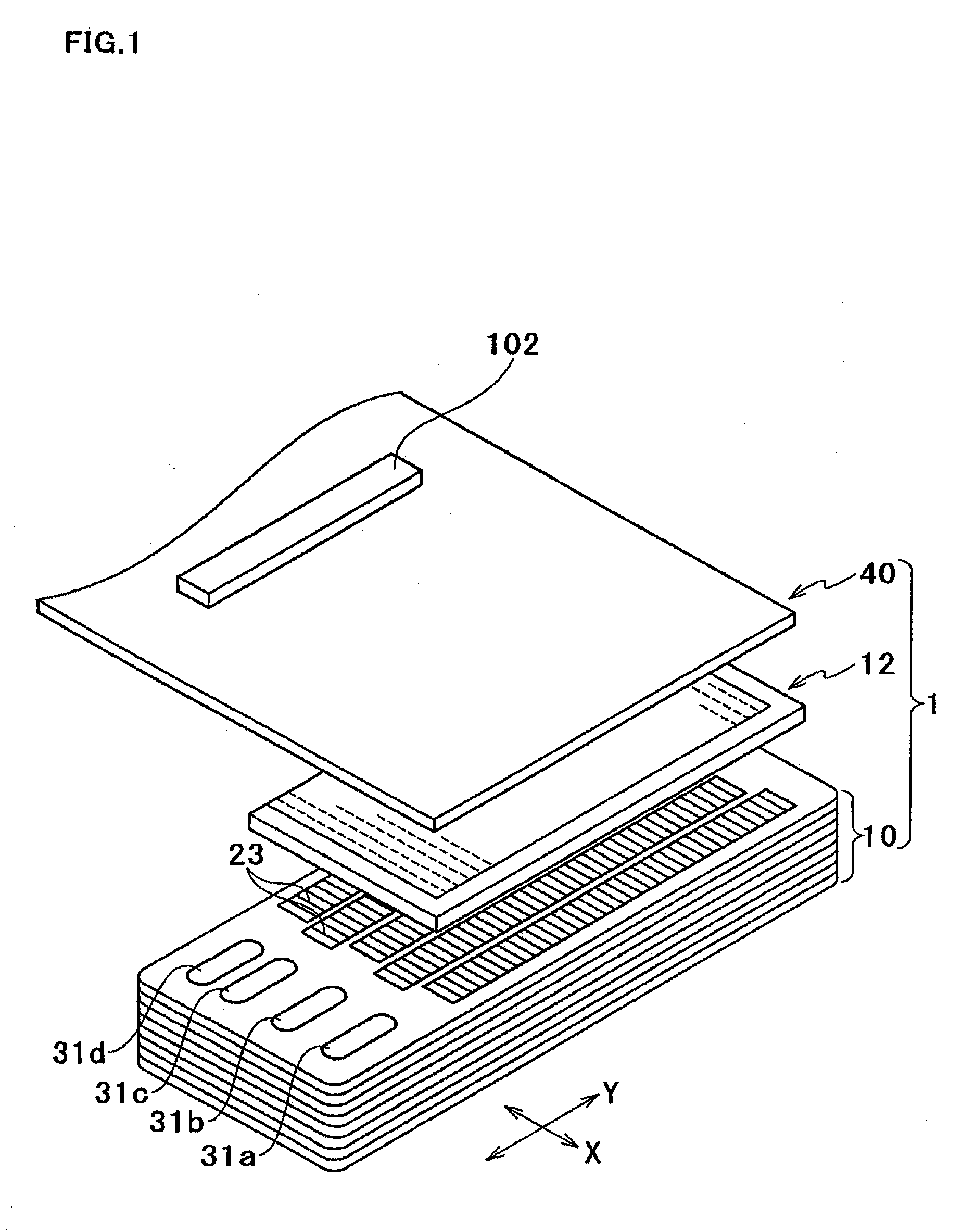

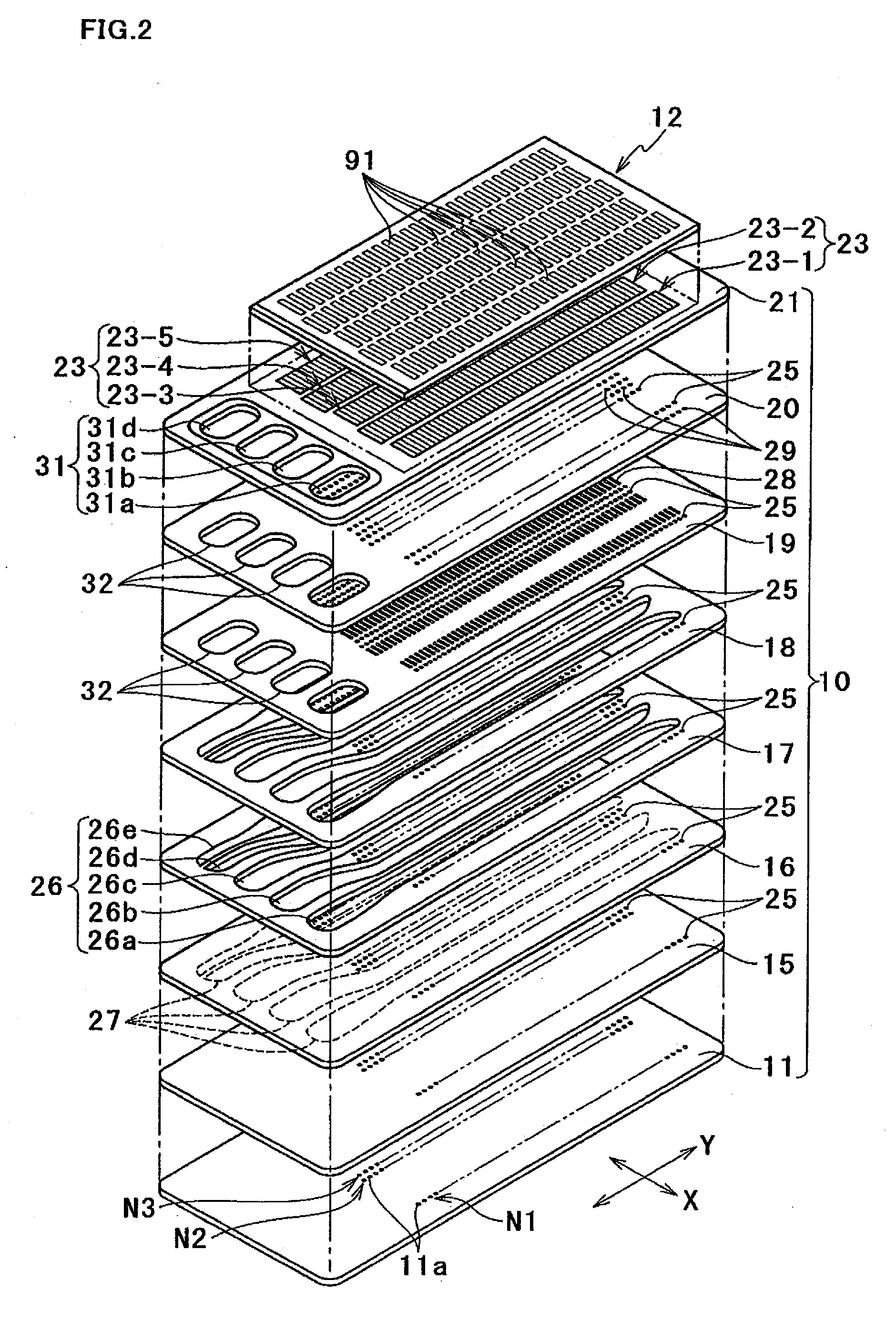

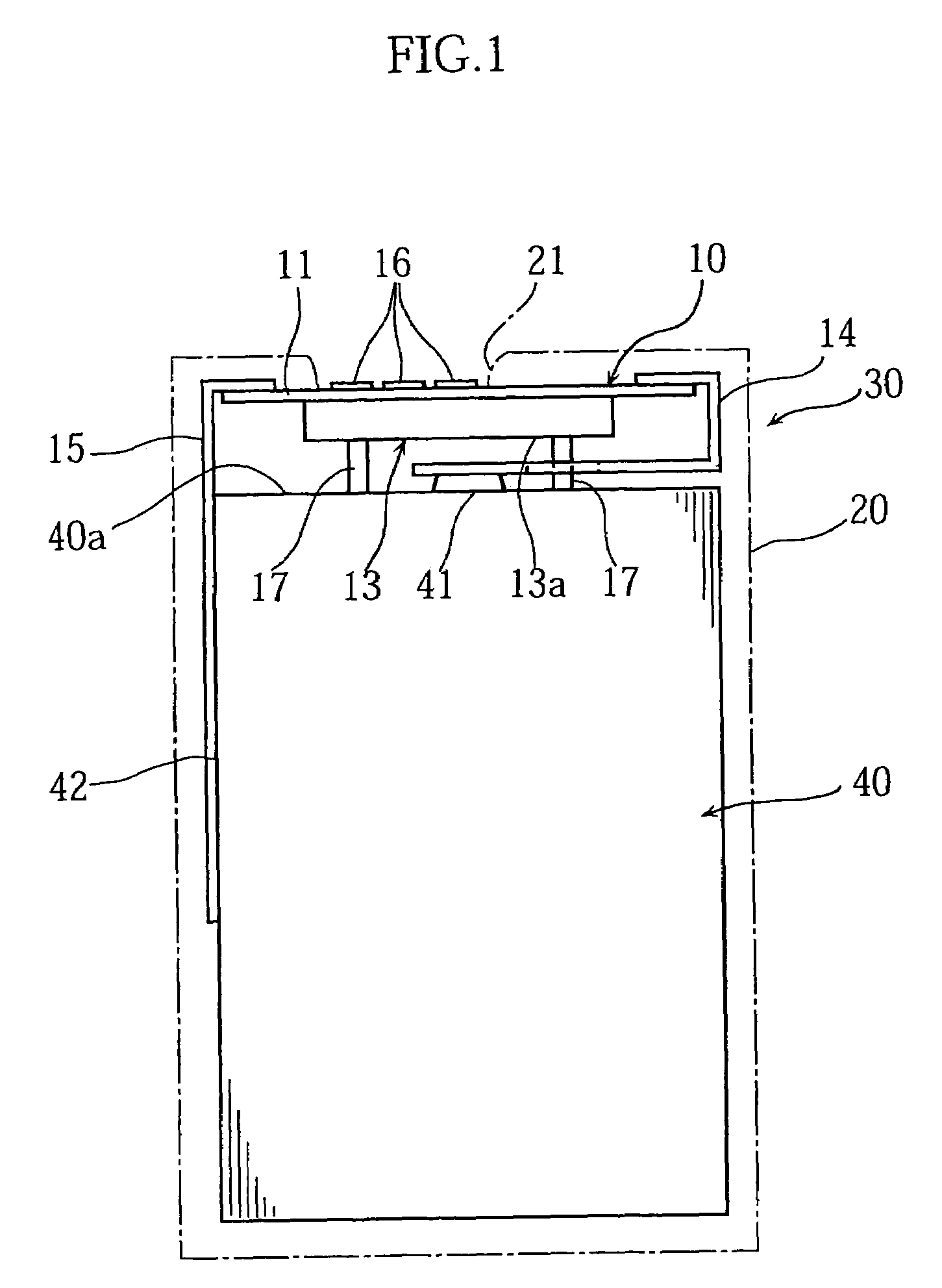

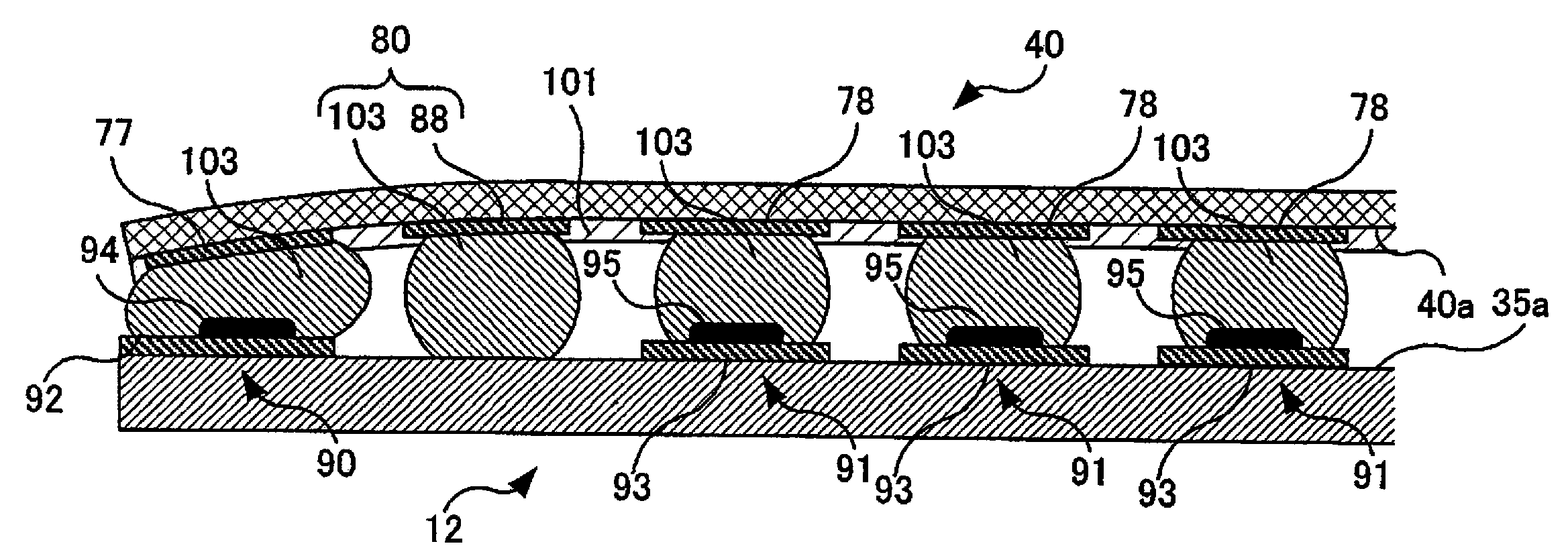

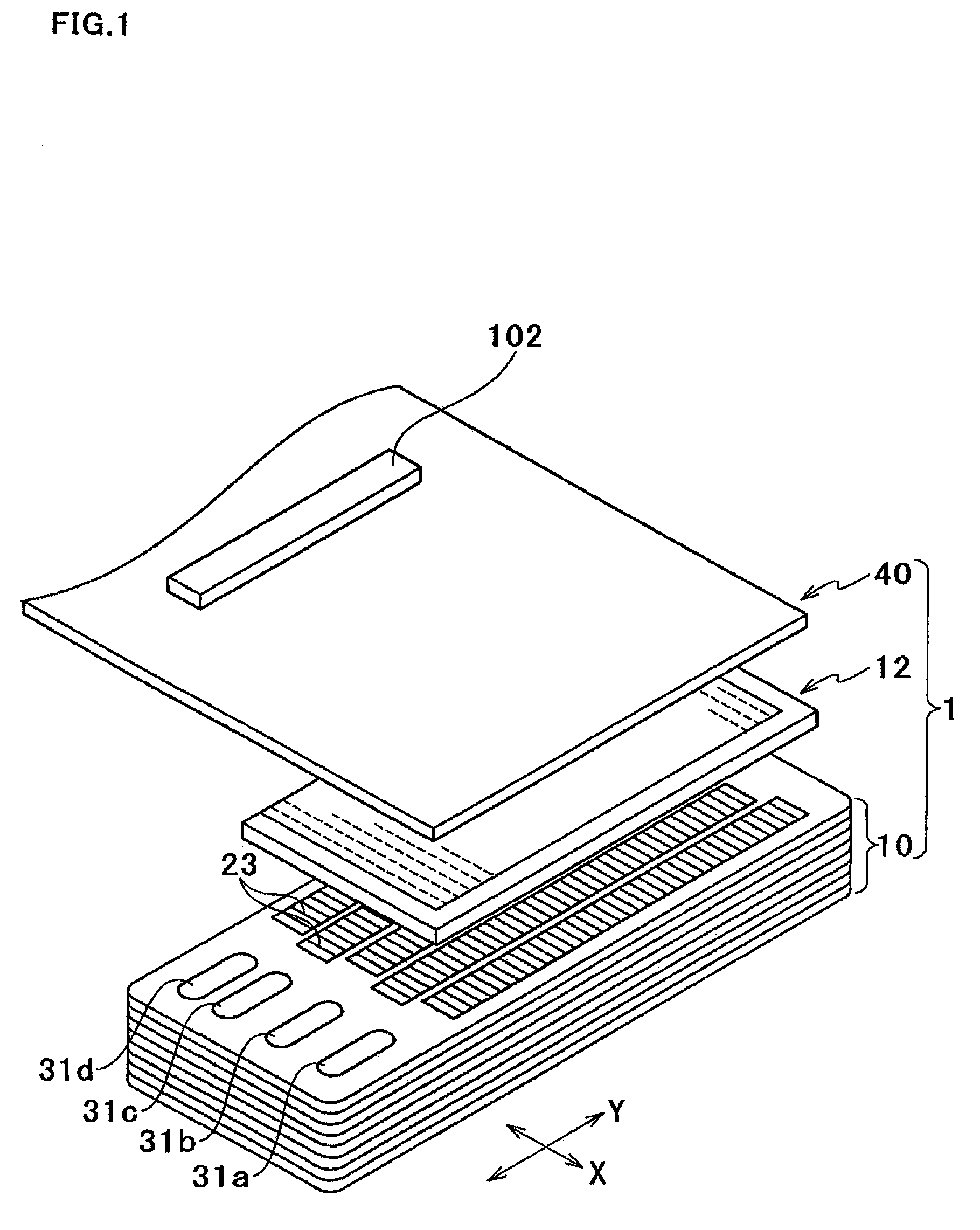

Ink-Jet Head and Connecting Structure

ActiveUS20060170738A1Suppress contactSuppressing a short circuitDecorative surface effectsWriting implementsEngineeringEnergy applicator

An ink-jet head has a flexible printed circuit and a head main body, and further has a reinforcement that is located between drive-signal terminals arranged adjacent to one another and a constant-potential-signal terminal. The drive-signal terminals and the constant-potential-signal terminal are formed on a terminal-formed face of an energy applier included in the head main body. The flexible printed circuit has an electrode-formed face on which a constant-potential-signal electrode to be bonded to the constant-potential-signal terminal with a metal bond and drive-signal electrodes to be bonded to the drive-signal terminals with a metal bond. The reinforcement is in contact with and interposed between the terminal-formed face and the electrode-formed face so that the terminal-formed face and the electrode-formed face are spaced apart from each other.

Owner:BROTHER KOGYO KK

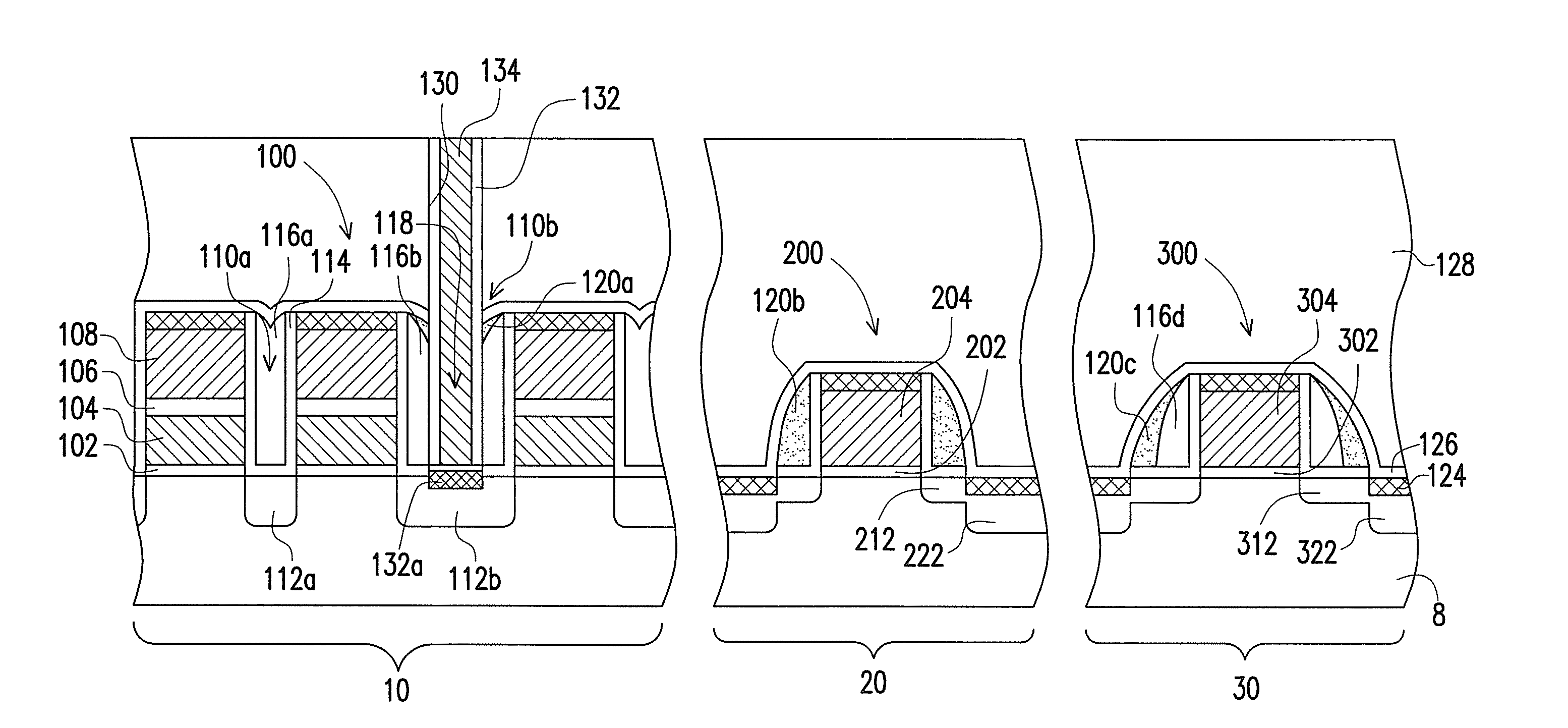

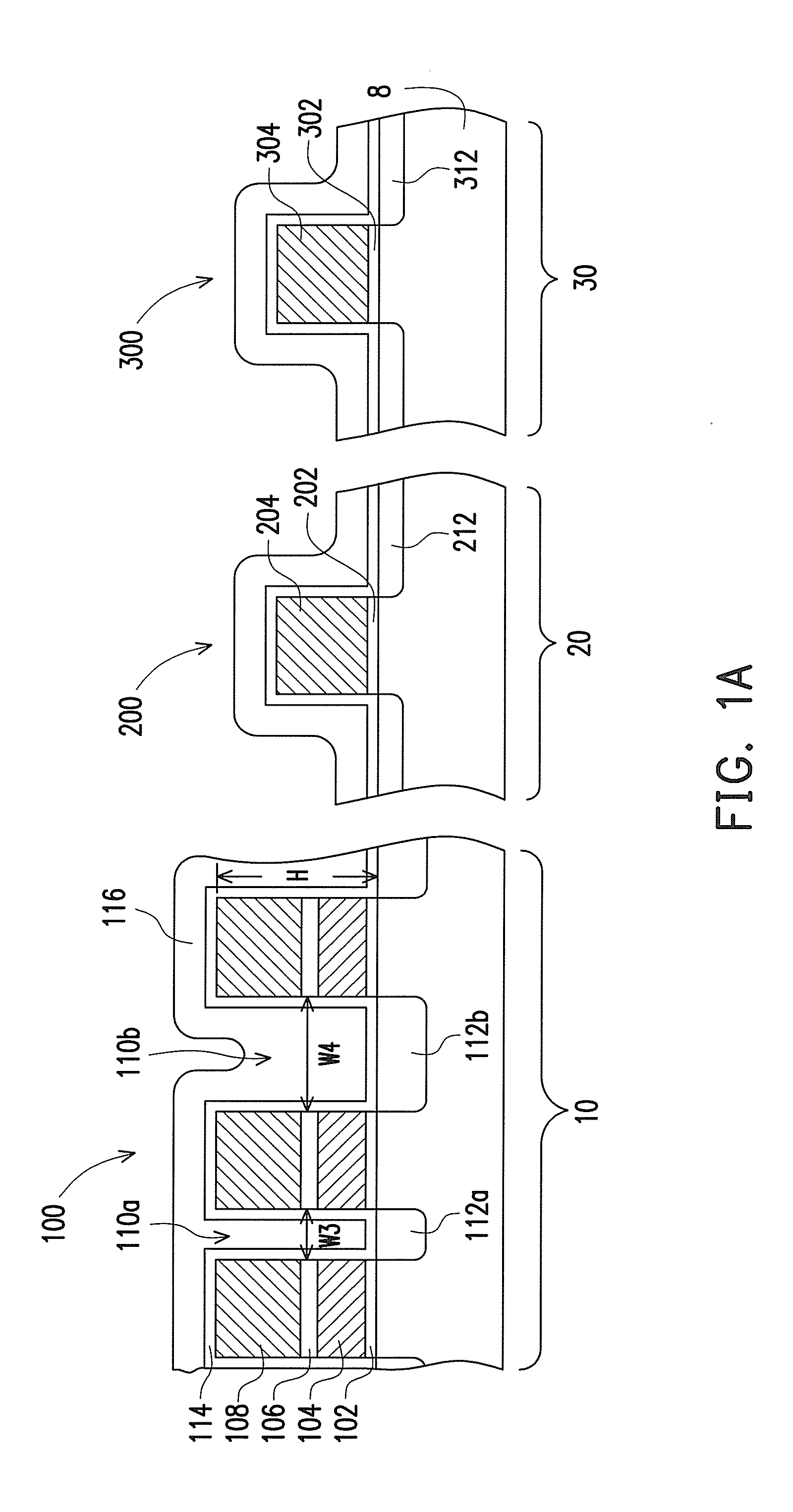

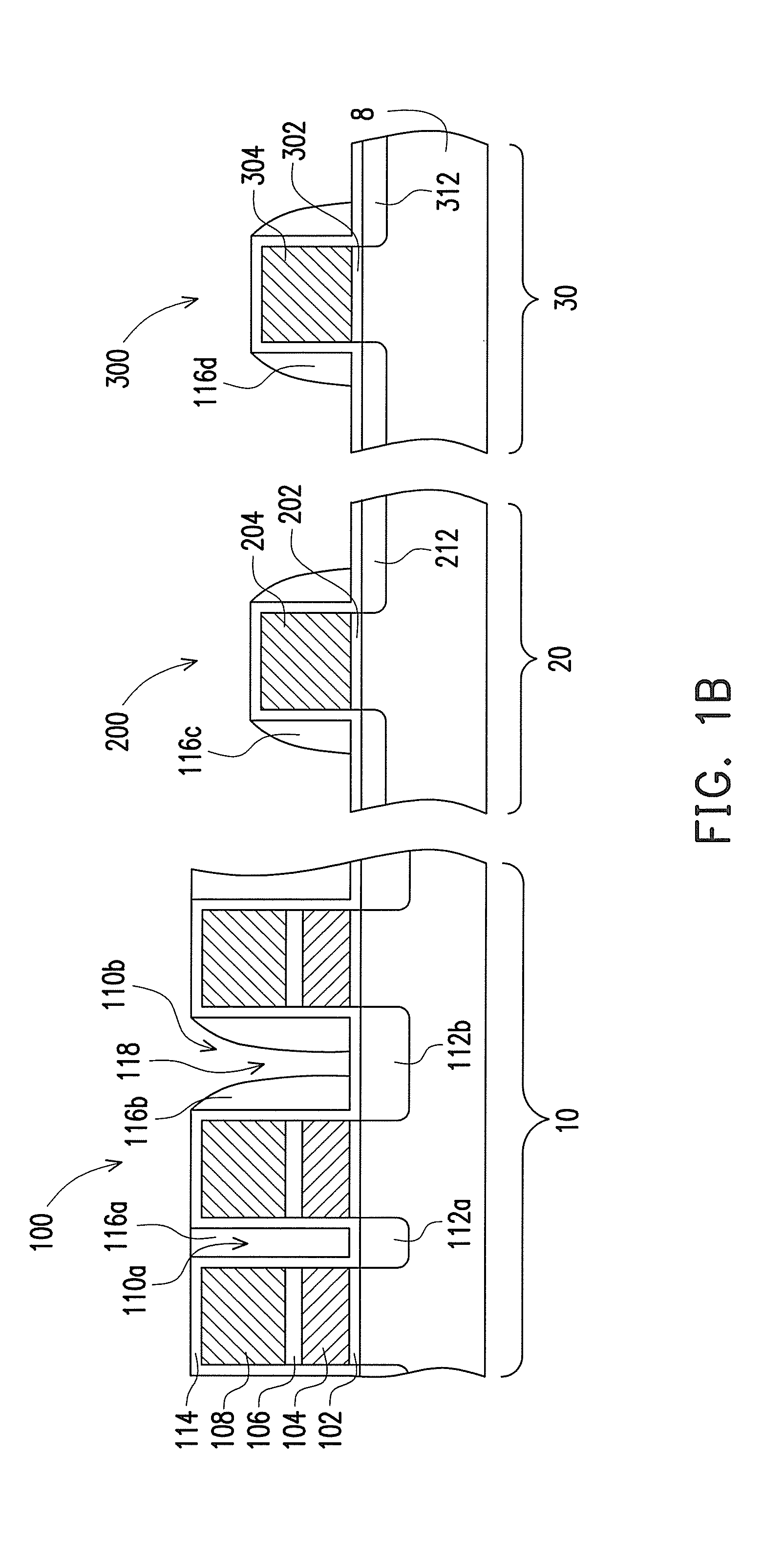

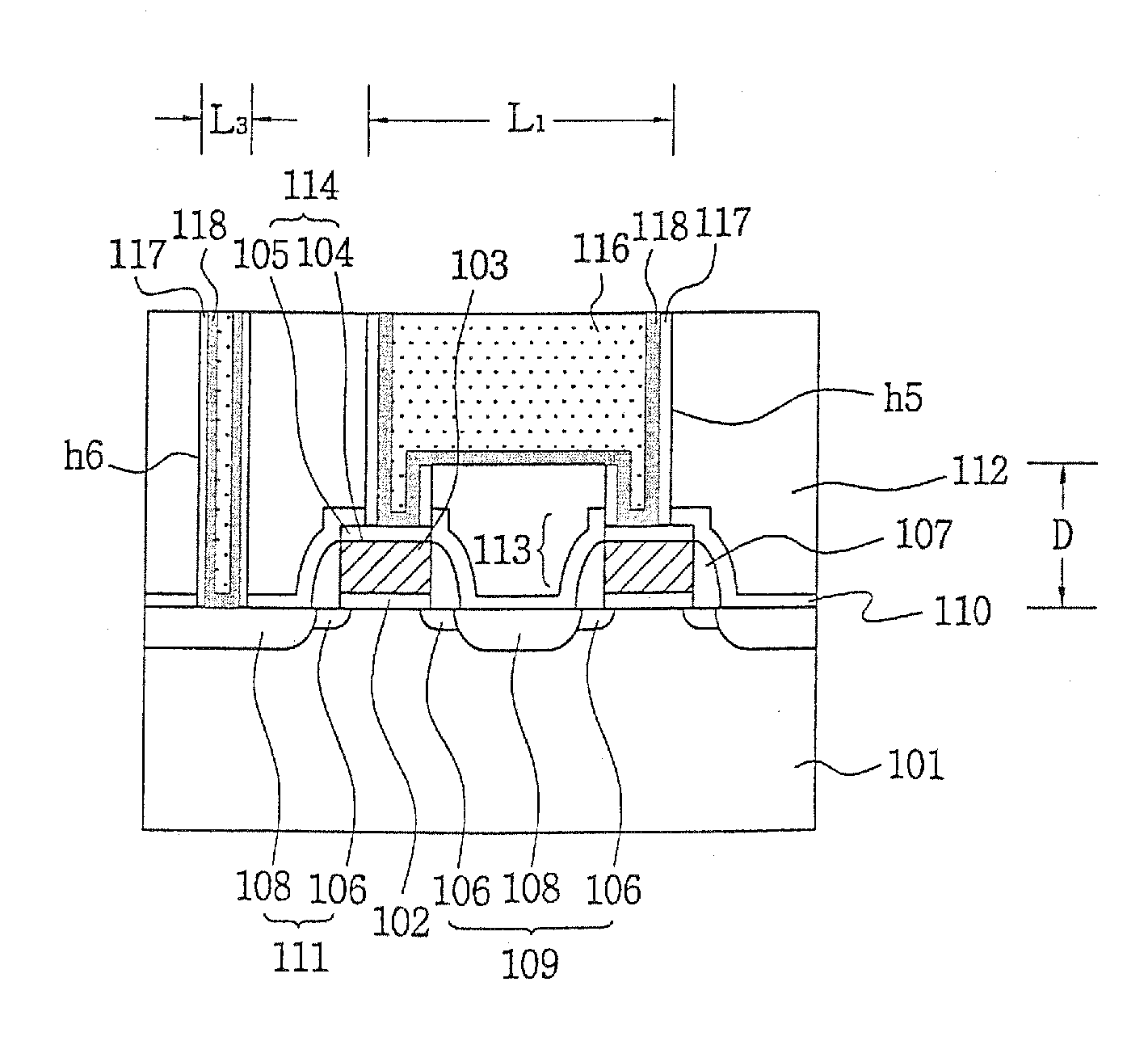

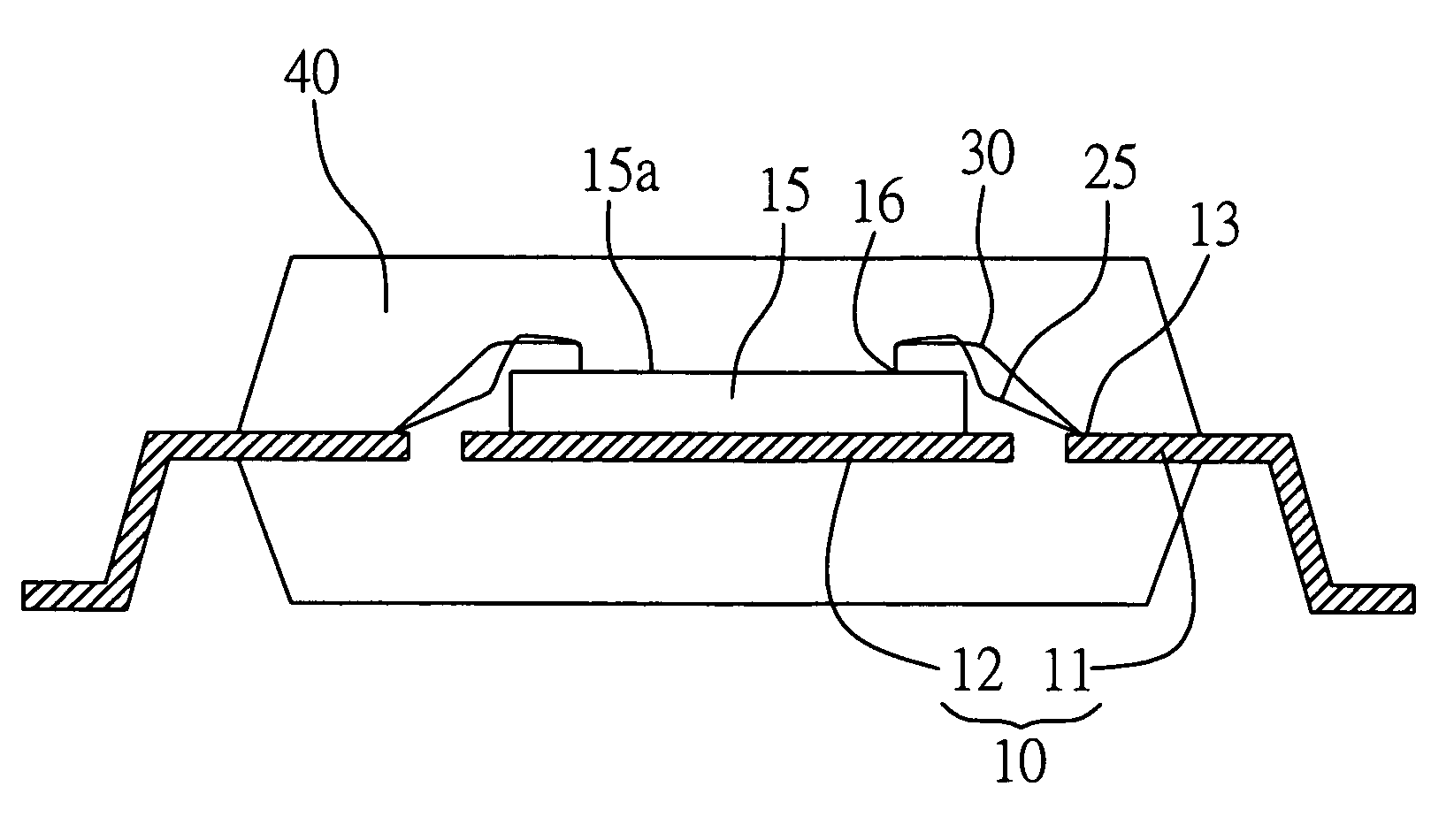

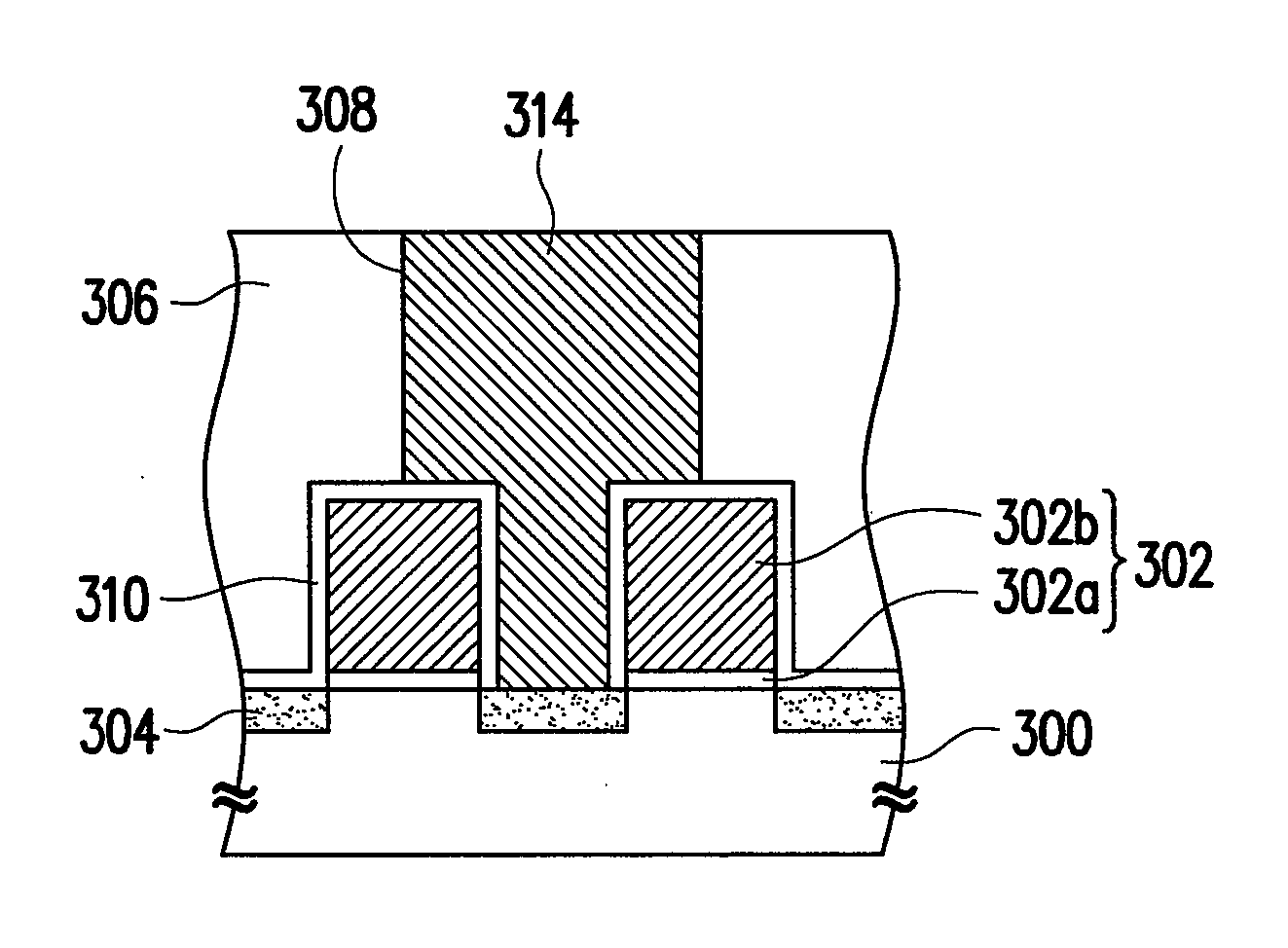

Semiconductor device and a method of fabricating the same

ActiveUS20110062507A1Shorting of contactTransistorSolid-state devicesPower semiconductor deviceDielectric layer

A semiconductor device is provided. The semiconductor device includes a memory device, and the memory device includes a substrate, two stacked gates, two spacers, an insulating layer, and a dielectric layer. The stacked gates having a gap therebetween are located on the substrate. The spacers having a pipe or a seam therebetween are respectively located at sidewalls of each of the stacked gates in the gap. The pipe or the seam is filled with the insulating layer. The dielectric layer is located on the substrate and covers the insulating layer and the stacked gates.

Owner:MACRONIX INT CO LTD

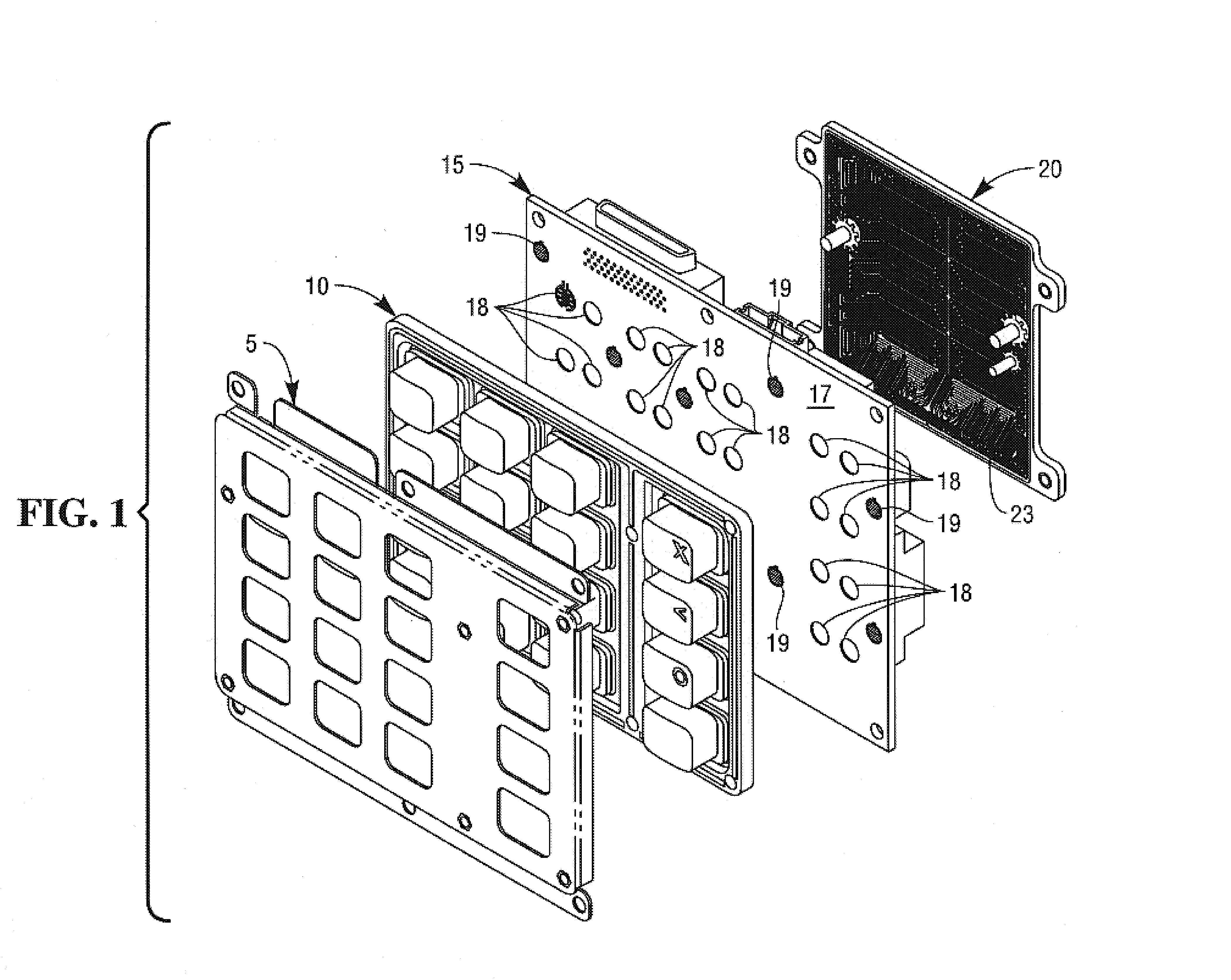

Battery assembly using printed circuit board substrate including bus bar

InactiveUS20170025660A1Improve battery stabilityWorkability of soldering can be improvedCells structural combinationCell component detailsElectrical bondingPrinted circuit board

Disclosed is a battery assembly with a PCB substrate, comprising a bus bar stepped and end processed for enhanced assembly performance and electrical bonding reliability, and a PCB substrate having an assembling groove with an end of the bus bar and an insulating film for an improved stability.

Owner:VITZROCELL

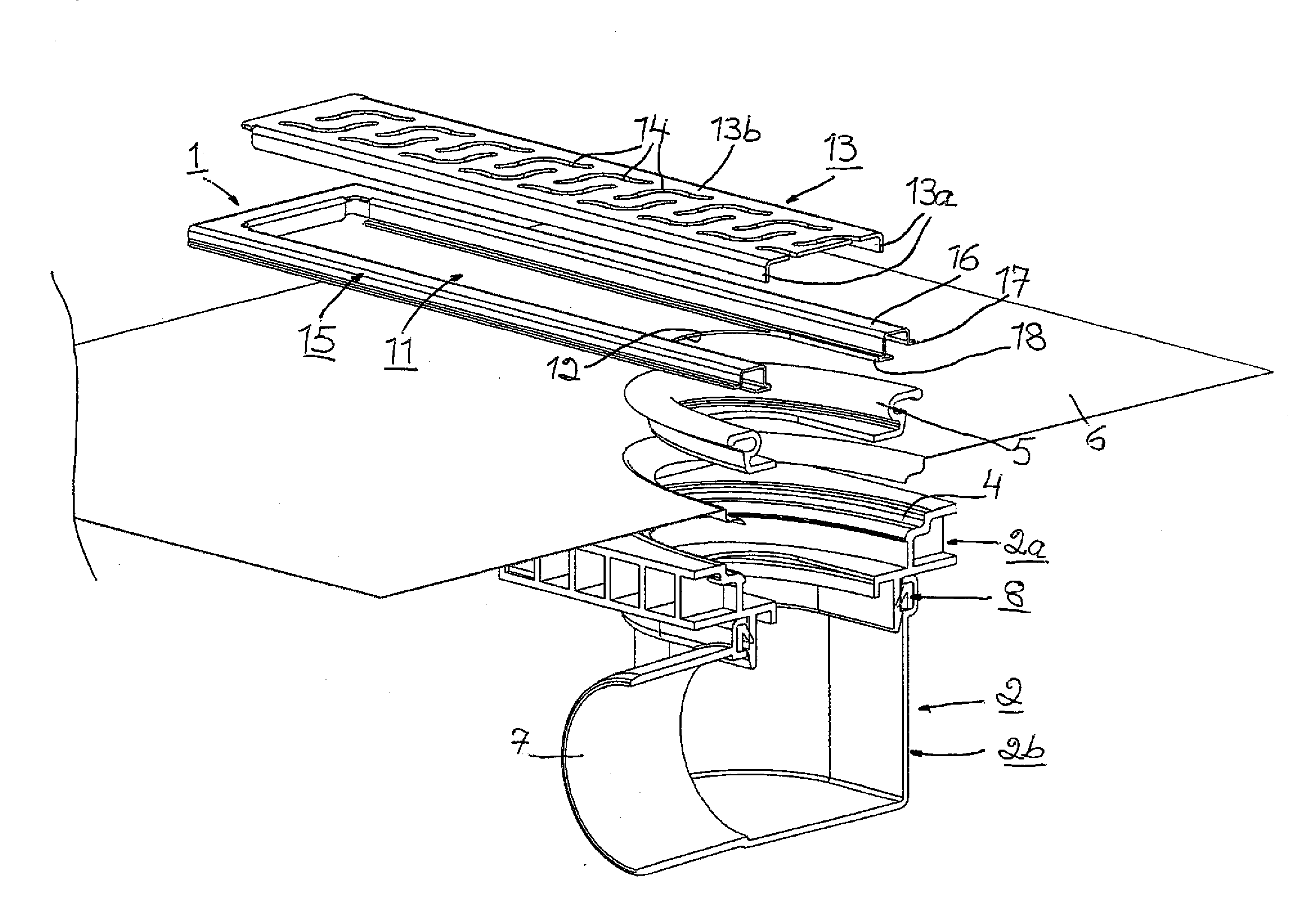

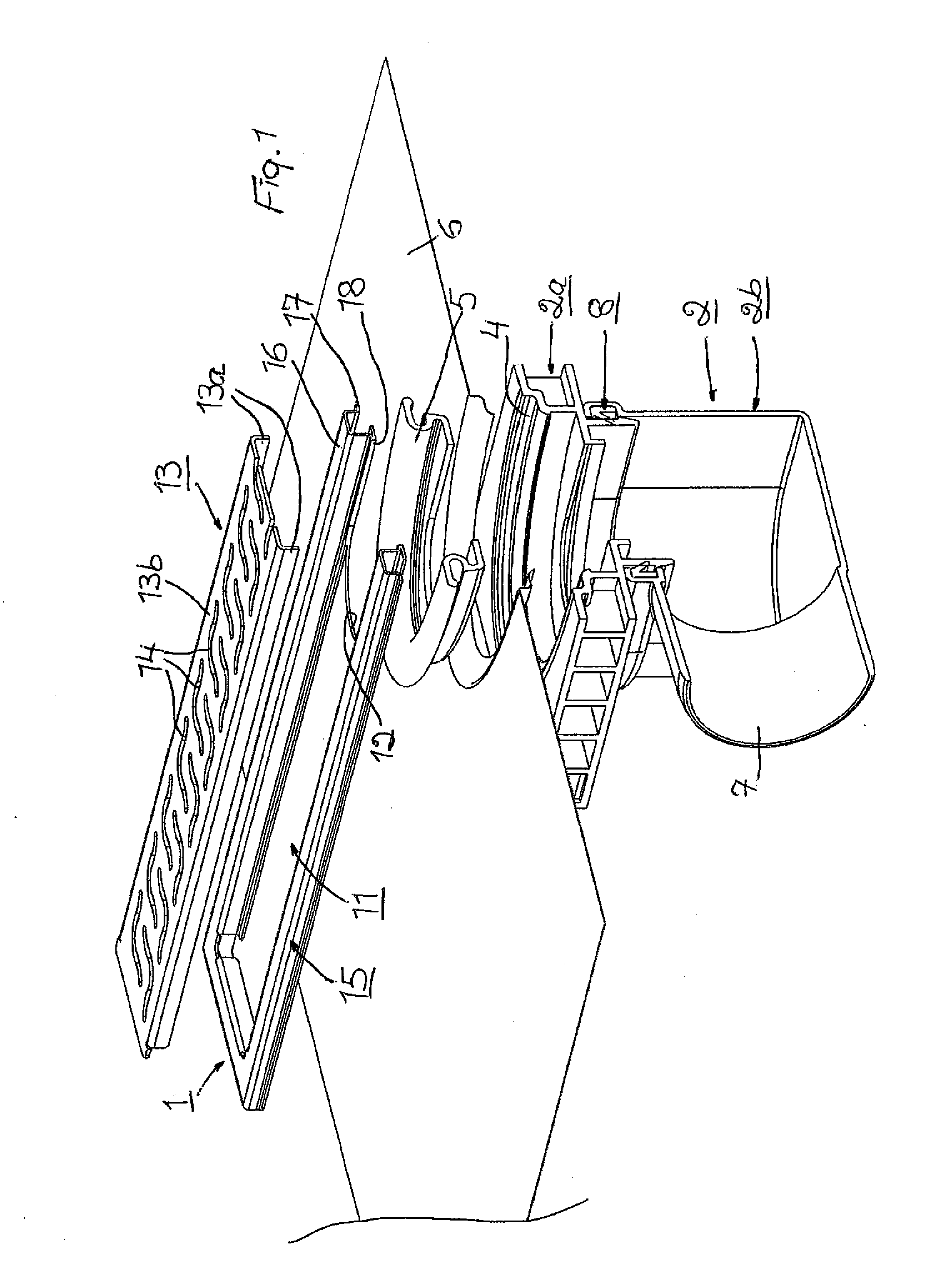

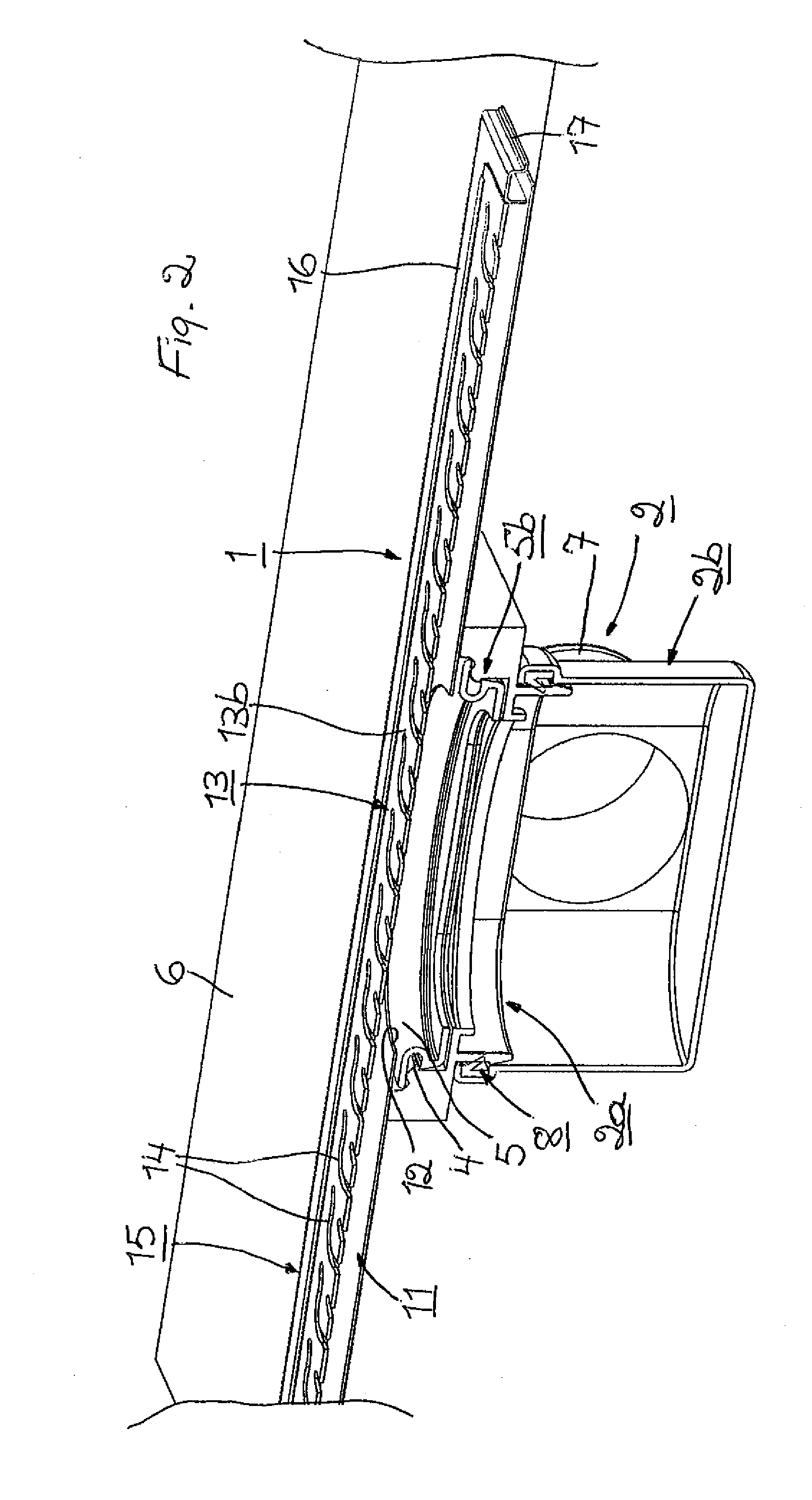

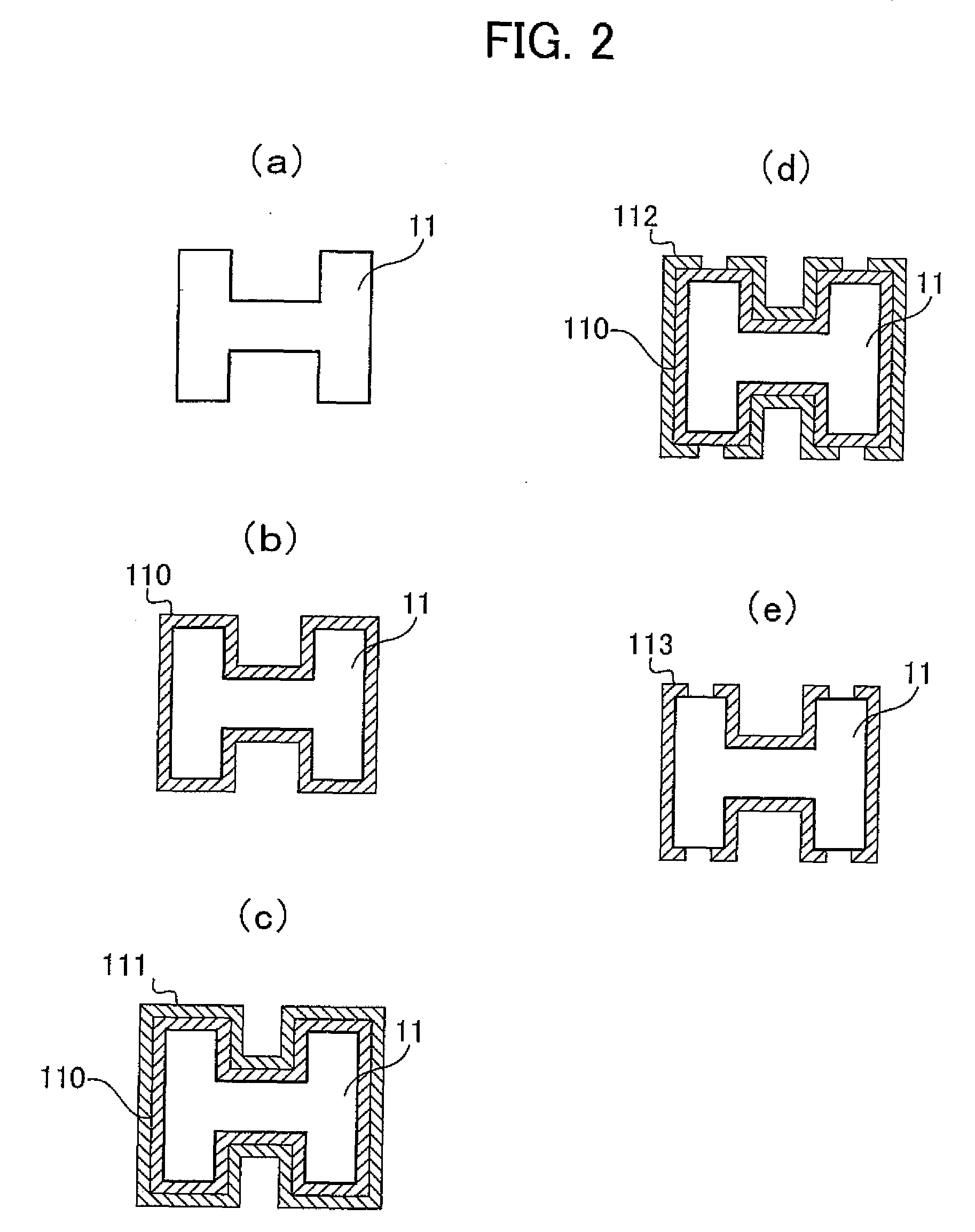

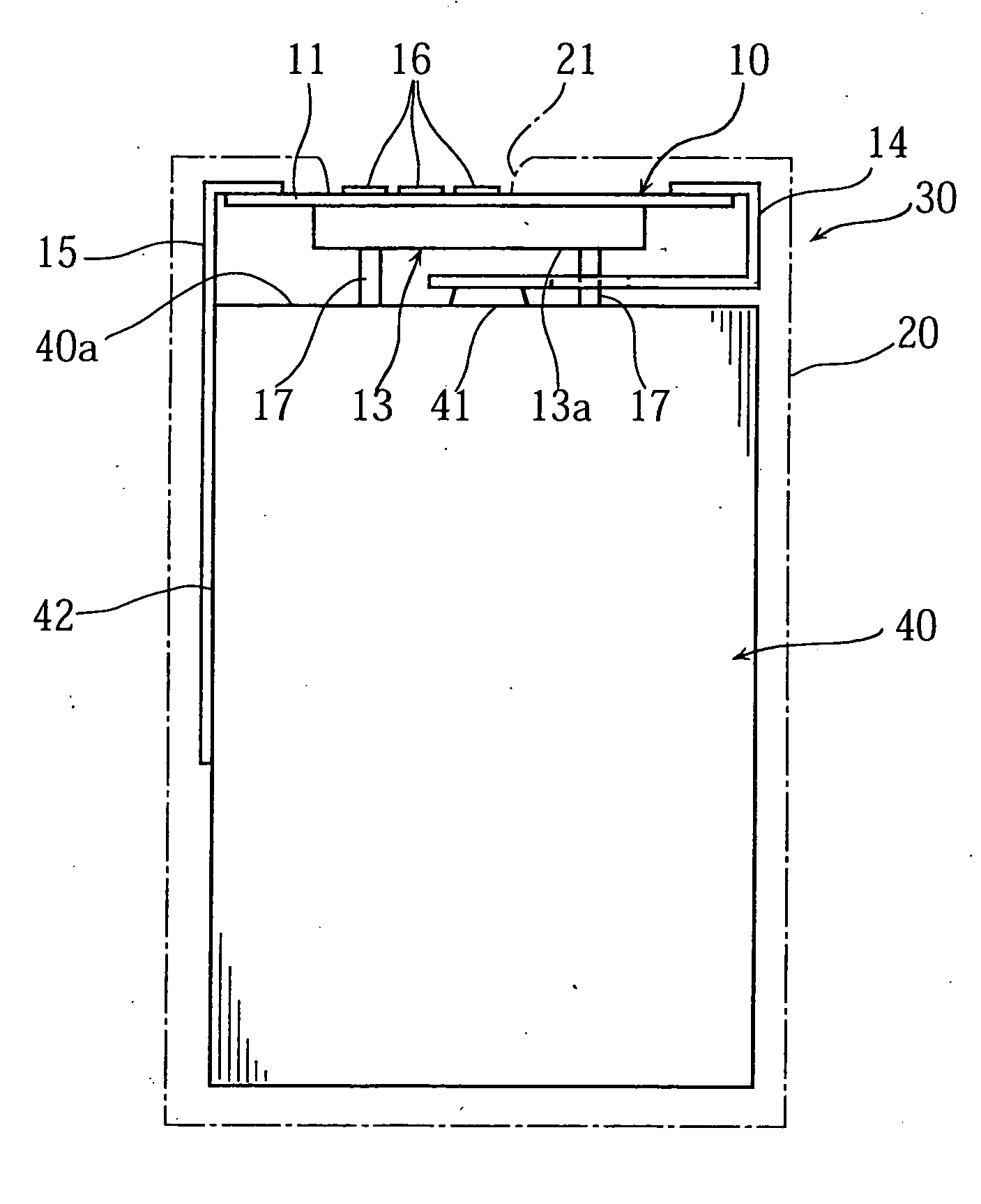

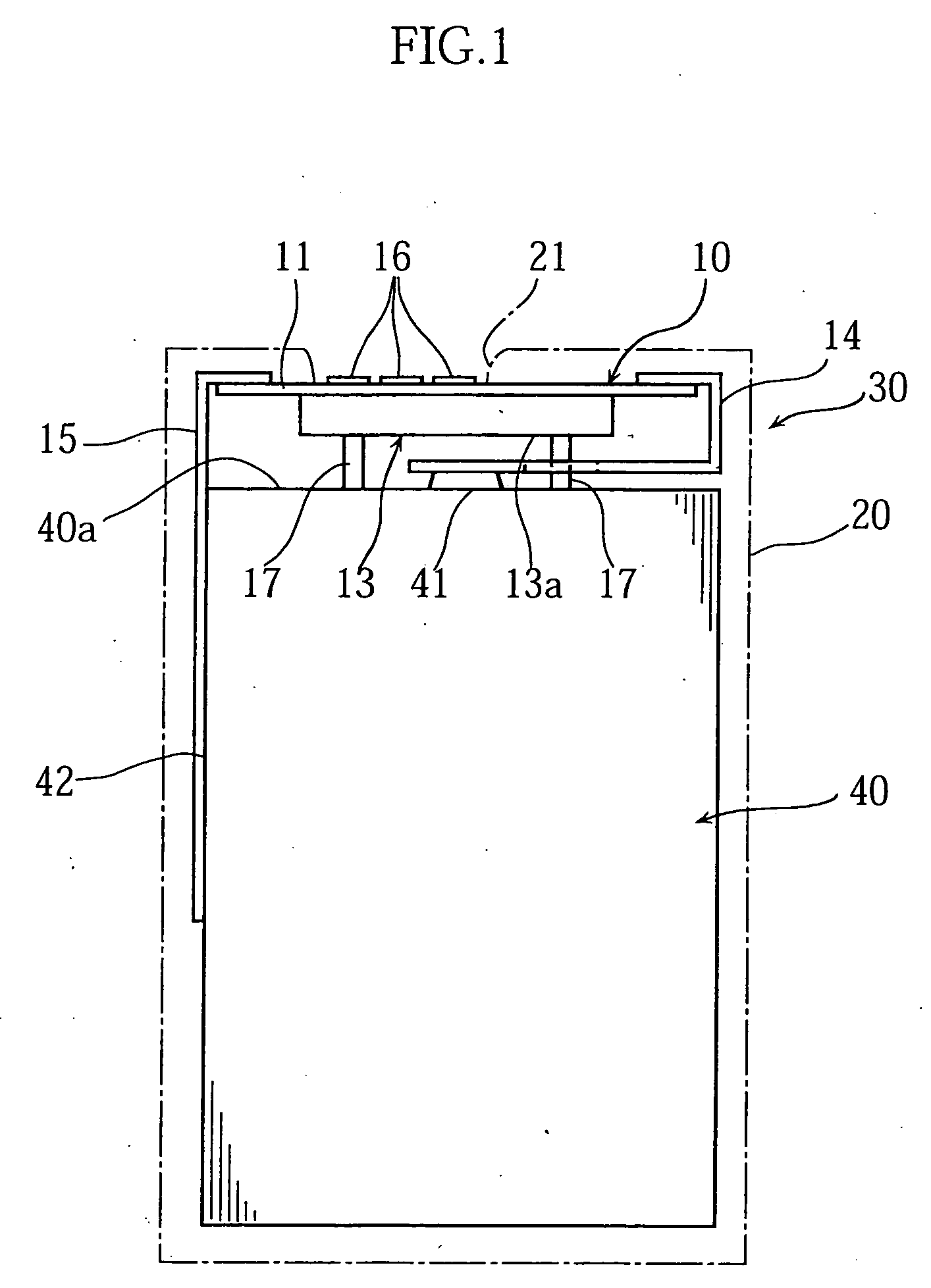

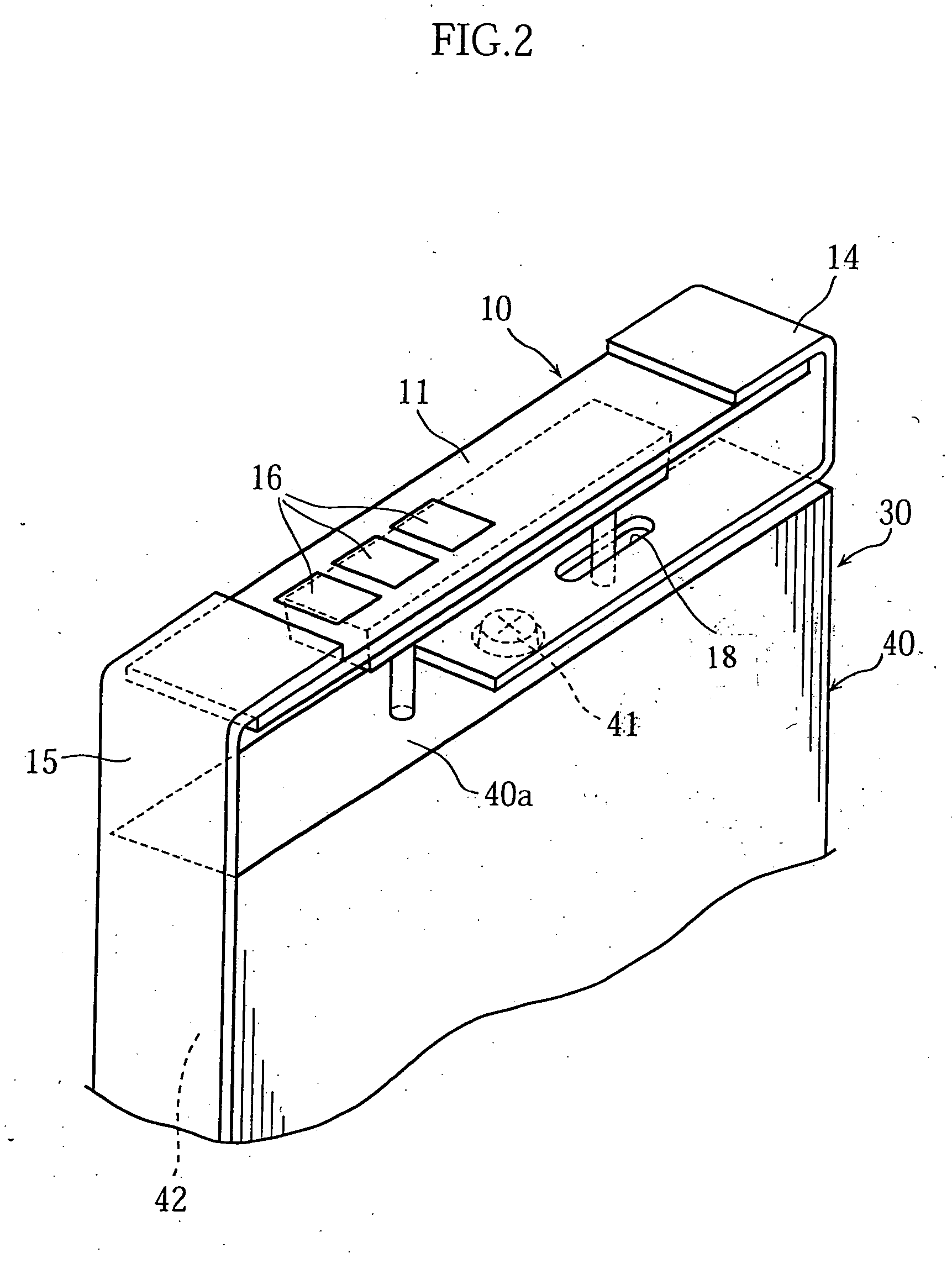

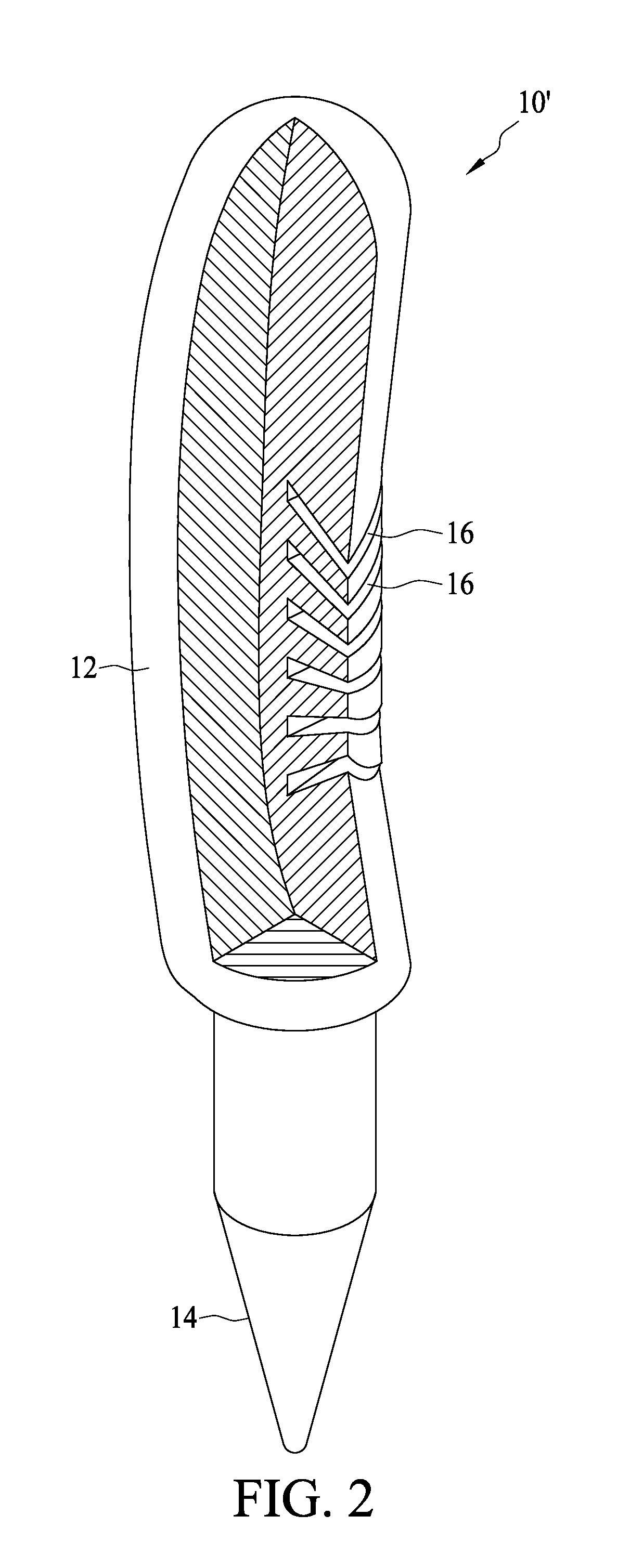

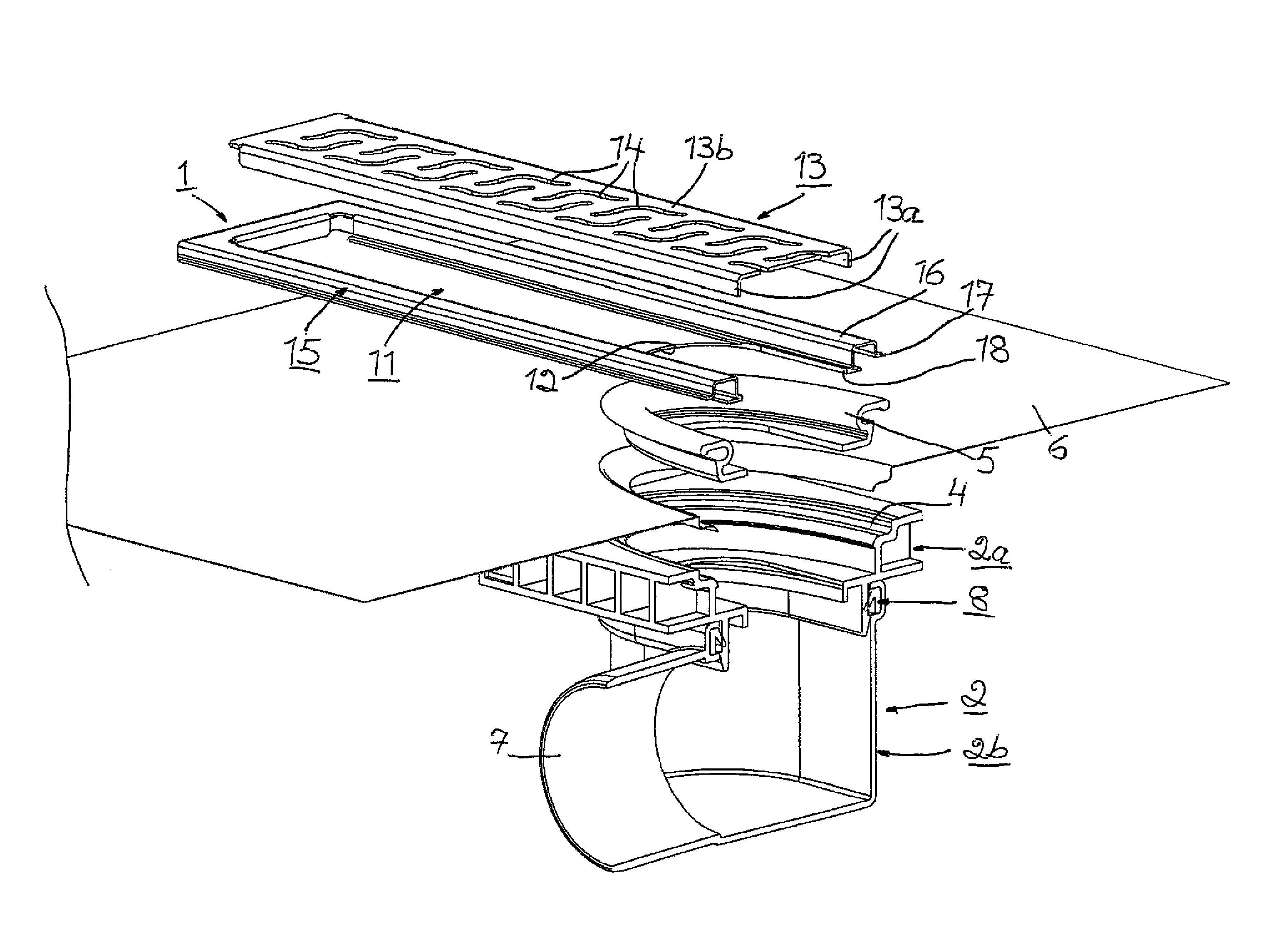

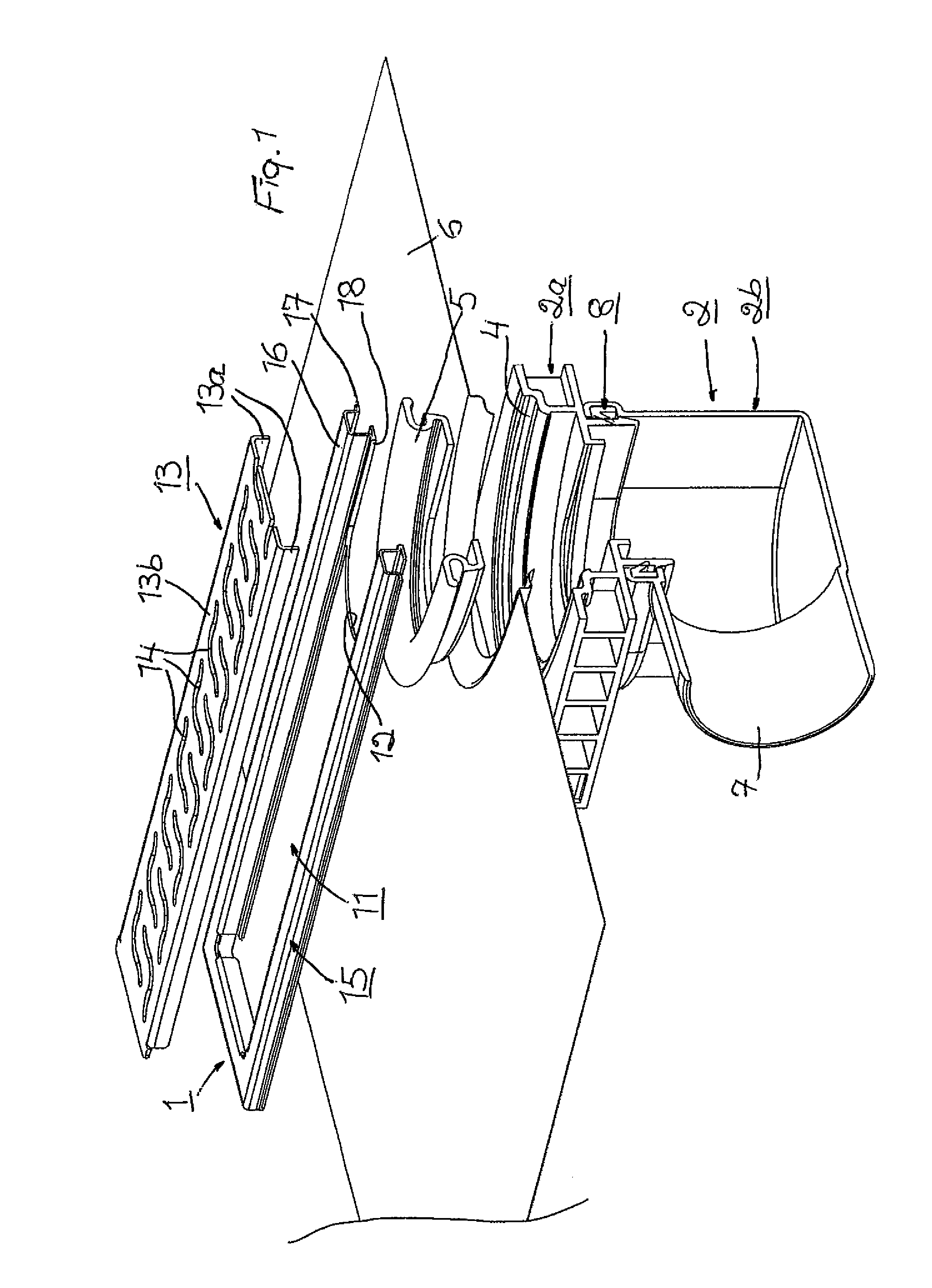

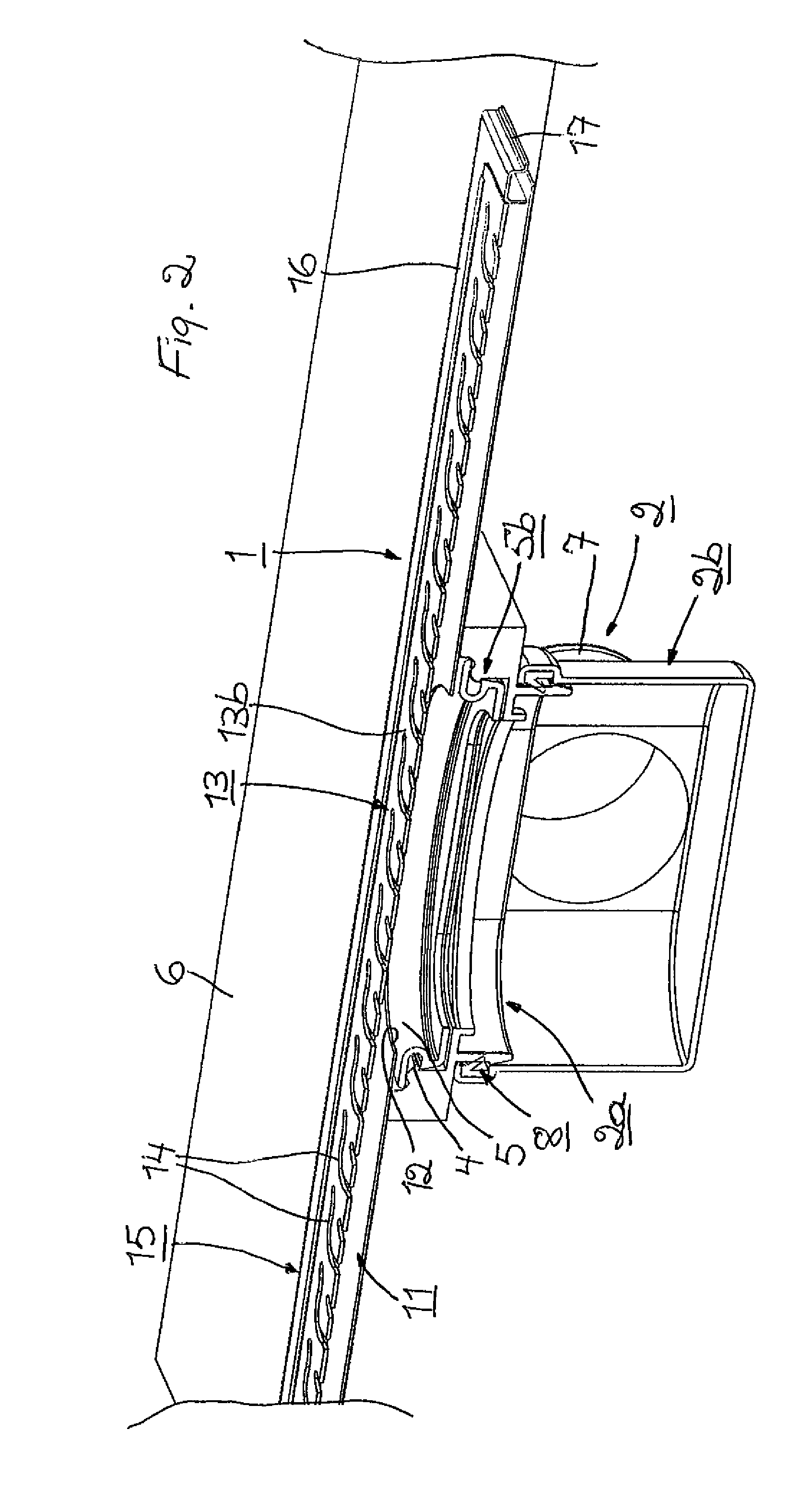

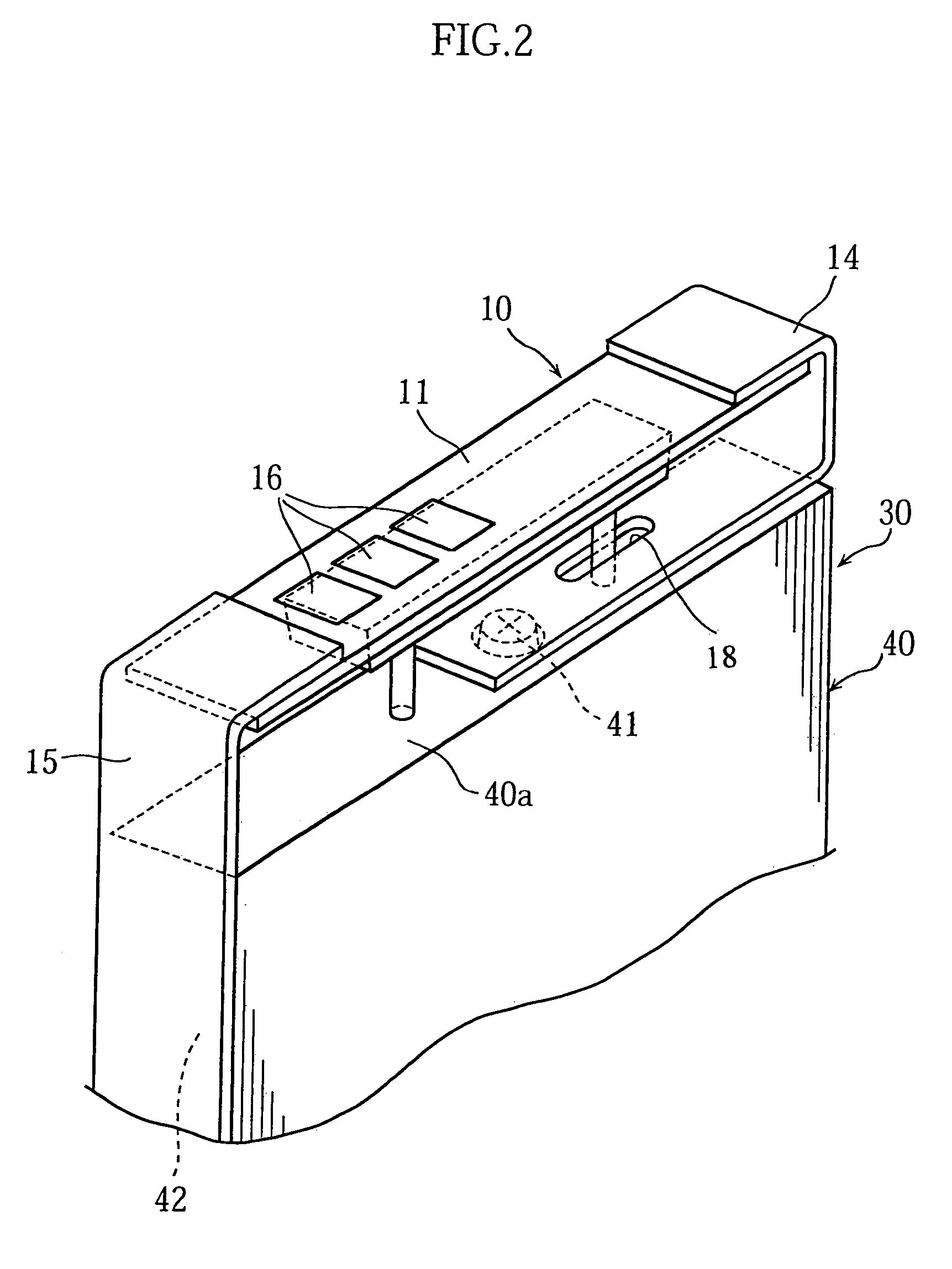

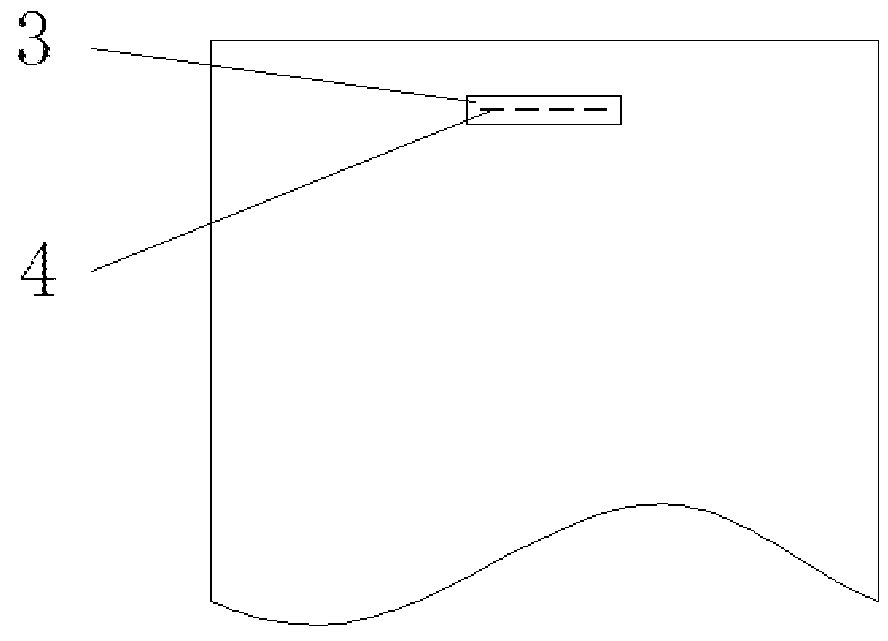

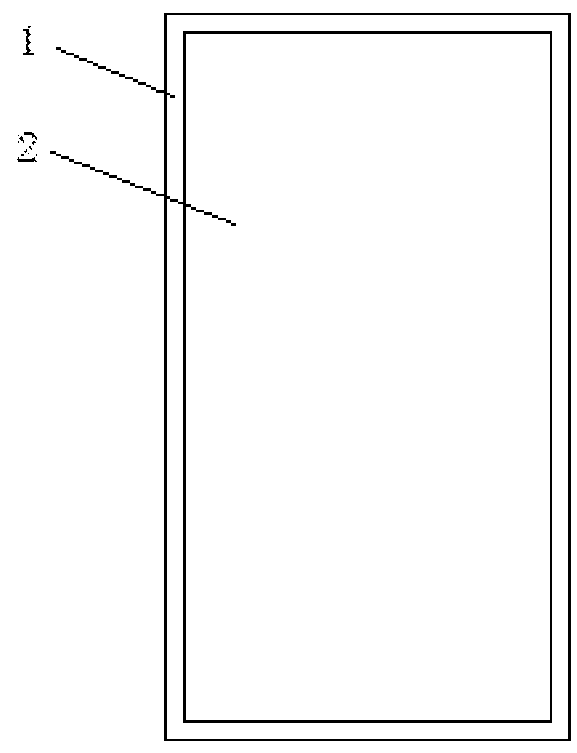

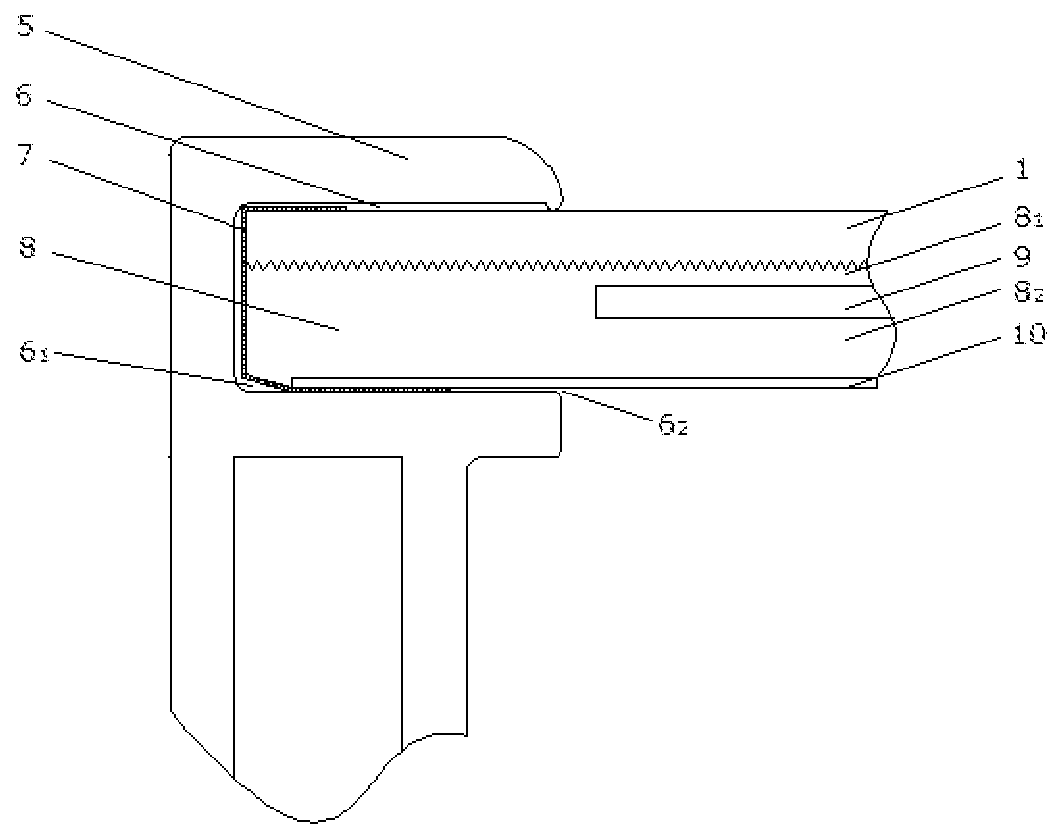

Drain and inlet member for drain

ActiveUS20110303595A1Less riskShorting of contactFatty/oily/floating substances removal devicesSewerage structuresGratingEngineering

The present invention relates to a drain which comprises an inlet member (1), a grating (13) or cover plate laid loosely or detachably on top of the inlet member, and an outlet member (2). To achieve a short line of contact between the surface covering's sealing layer (6) and the drain while at the same time the sealing layer is fastened by means of a clamping ring (5) or a bonding flange, thereby reducing the risk of leakage and affording the possibility of connecting an aesthetically more pleasing inlet member (1), the inlet member (1) takes the form of an elongate or trilateral plate-like element (11) disposed on top of the sealing layer or the sealing layer (6) and the clamping ring (5) and provided with a recess (12) for flow communication with the outlet member (2). The present invention relates also to an inlet member (1) for a drain as above.

Owner:PURUS

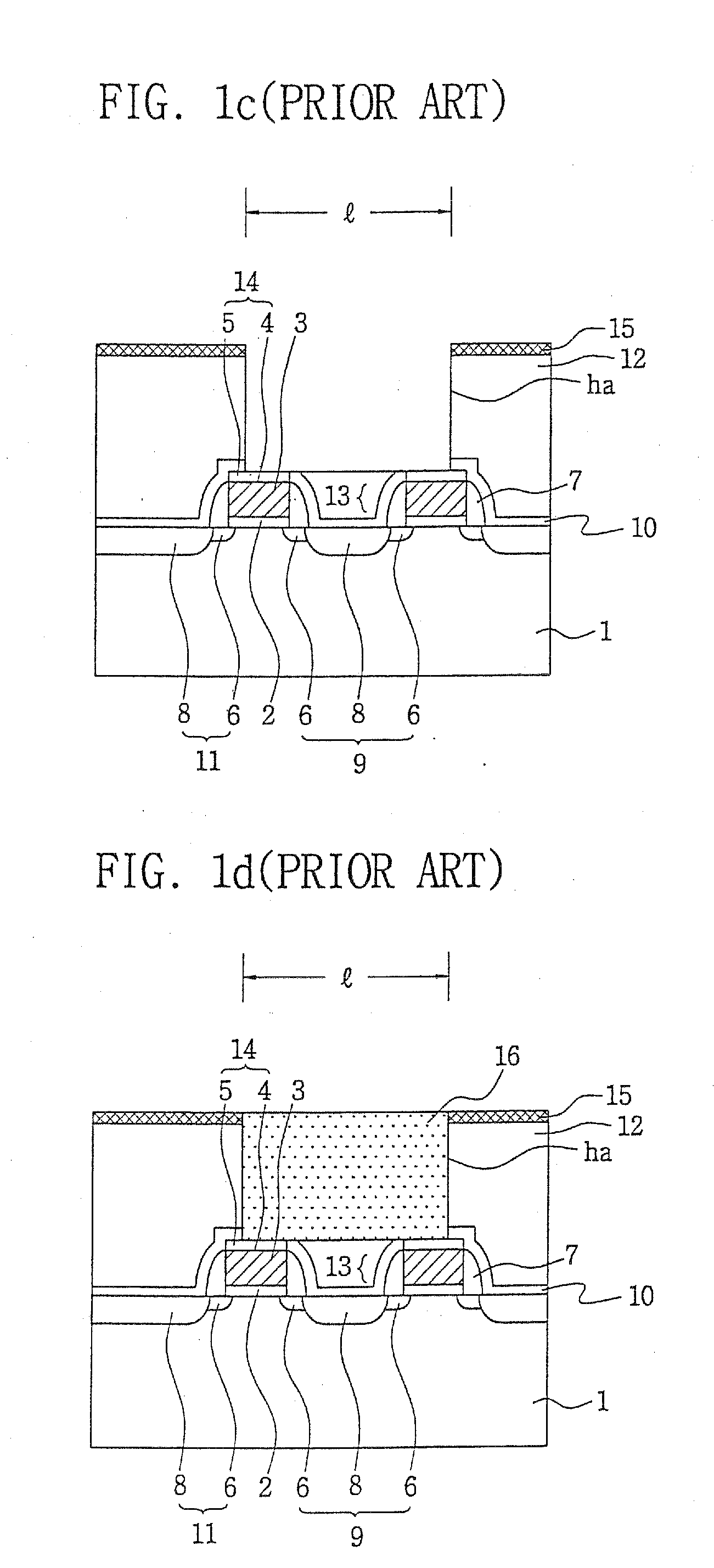

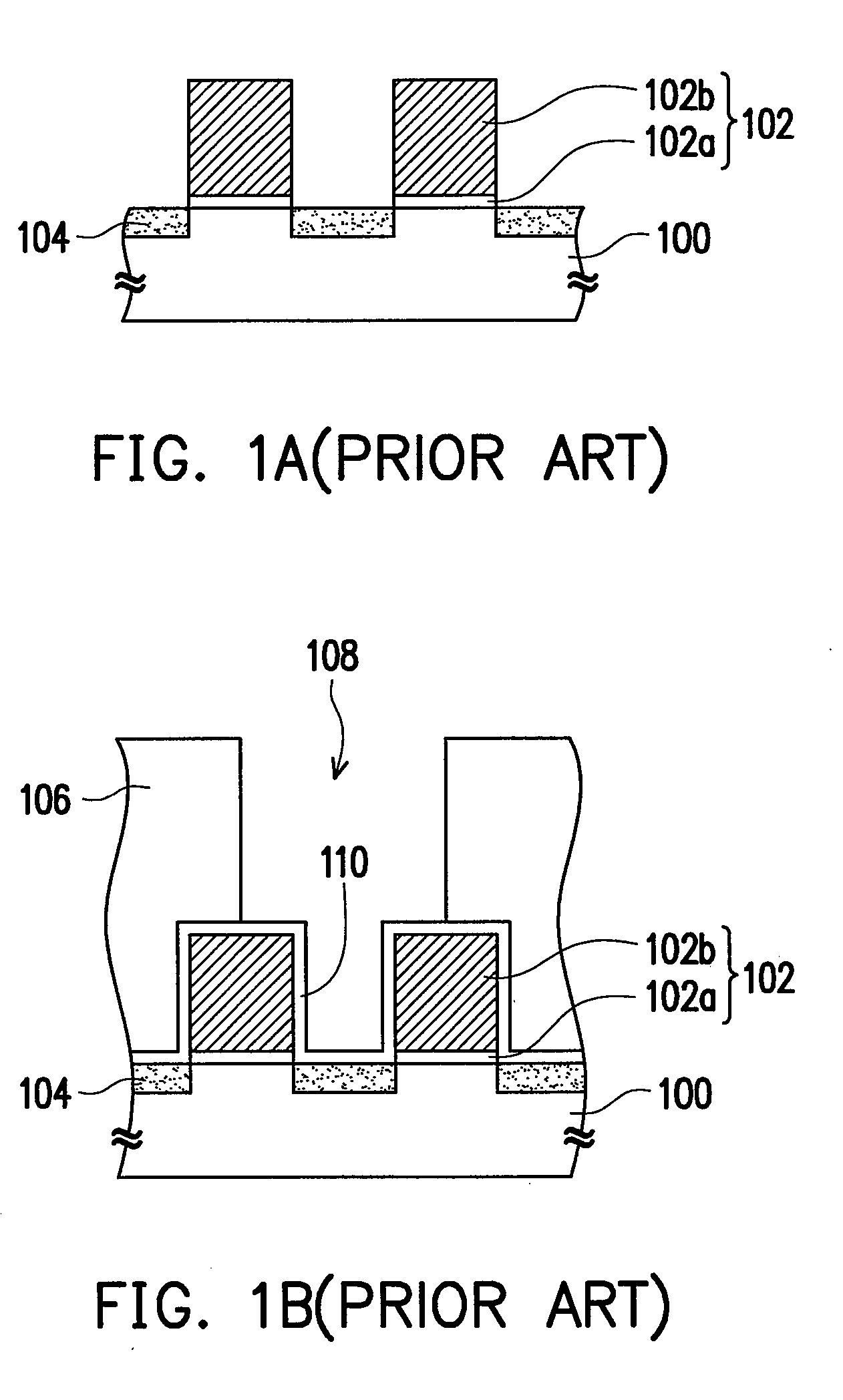

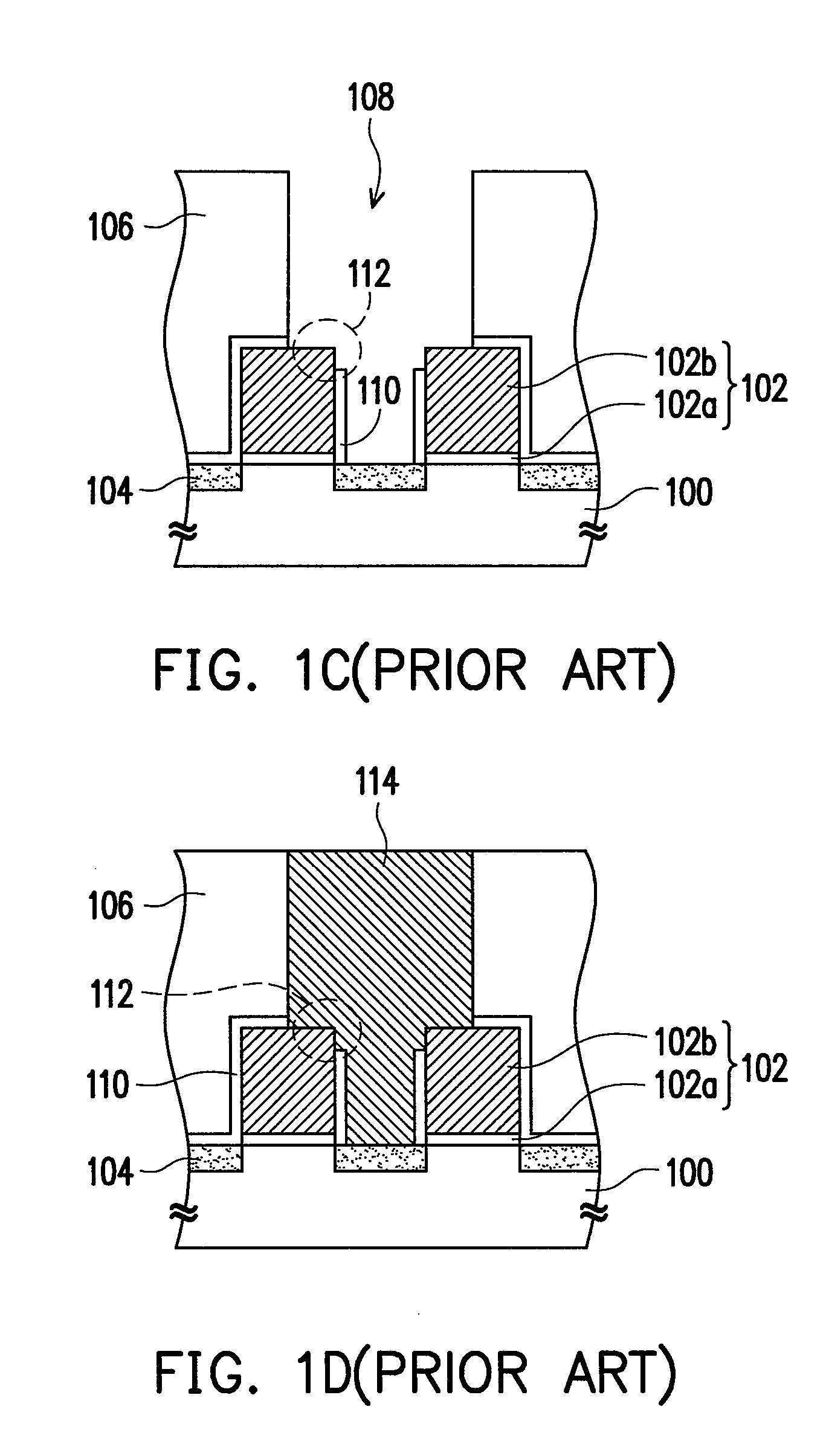

Local interconnection method and structure for use in semiconductor device

InactiveUS20070141834A1Shorting of contactReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A local interconnection wiring structure method for forming the same reduces the likelihood of a short between a local interconnection layer of gate electrodes and an active region by forming a common aperture so as to have a determined aperture between the local interconnection layer and the active region on an insulation film of a semiconductor substrate. Methods of forming the local interconnection wire can include forming a first etching mask pattern that has a size longer than a length between inner ends of adjacent gate electrodes formed on a semiconductor substrate and covered with an insulation film. The etching mask simultaneously has a length the same as or shorter than the length between outer ends of the gate electrodes. The insulation film exposed in the first etching mask pattern is subsequently etched so that the insulation film remains higher than a highest height of the gate electrodes, so as to form a recess pattern. The first etching mask pattern is then removed and a second etching mask pattern is formed so as to partially expose the insulation film provided within the recess pattern. The insulation film within the recess pattern is etched to form apertures for exposing a partial surface of the gate electrodes. The second etching mask pattern is then removed. The recess pattern and the apertures are then filled with conductive material to form a local interconnection layer for connecting between the gate electrodes.

Owner:SAMSUNG ELECTRONICS CO LTD

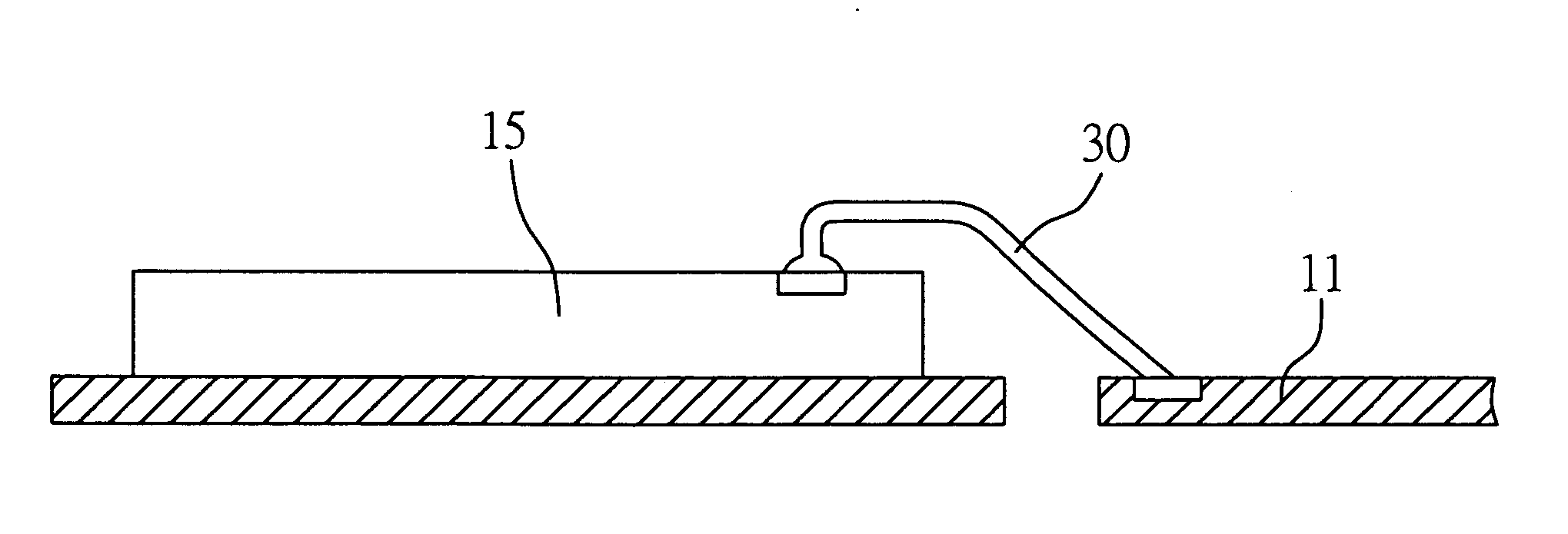

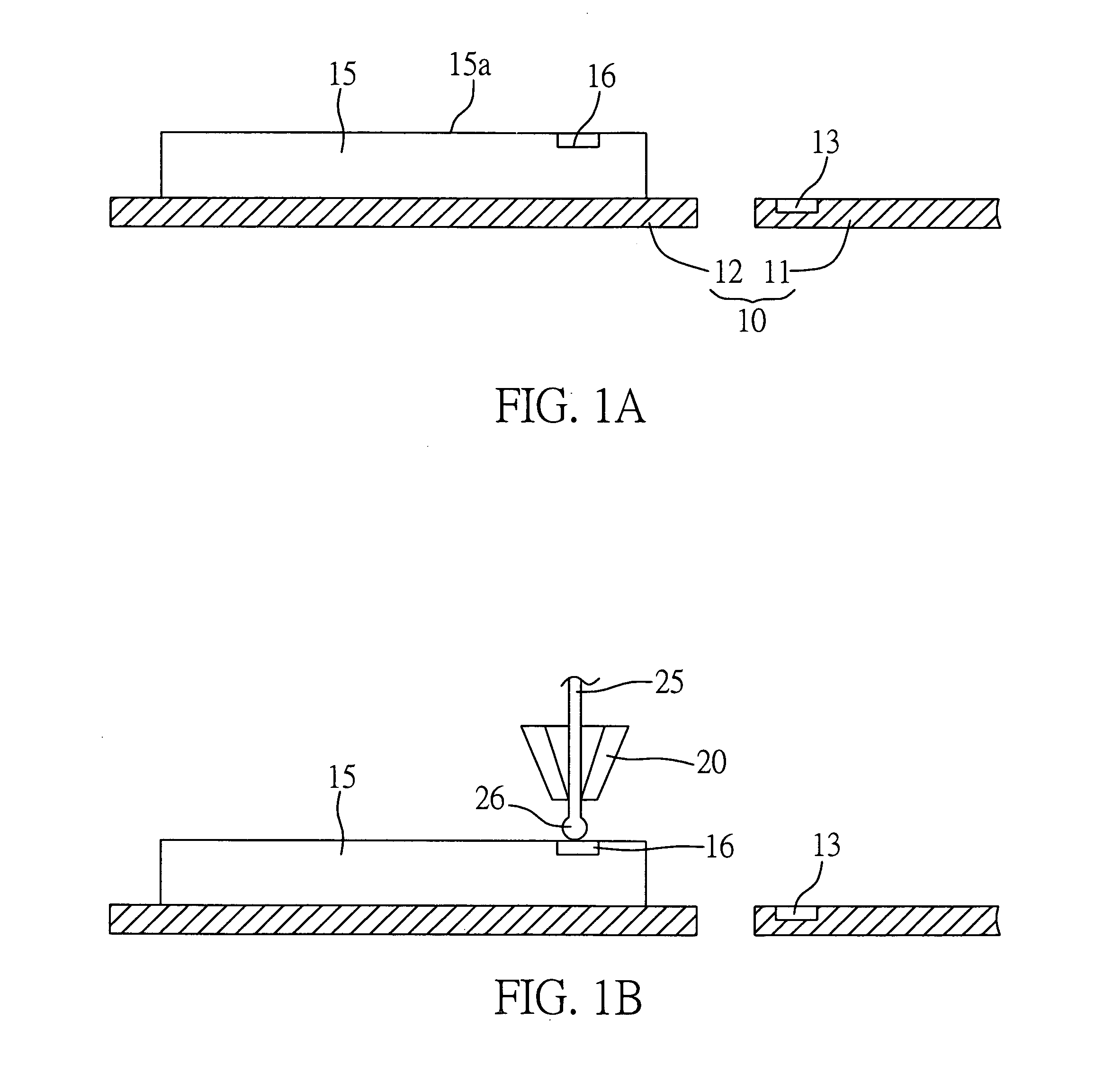

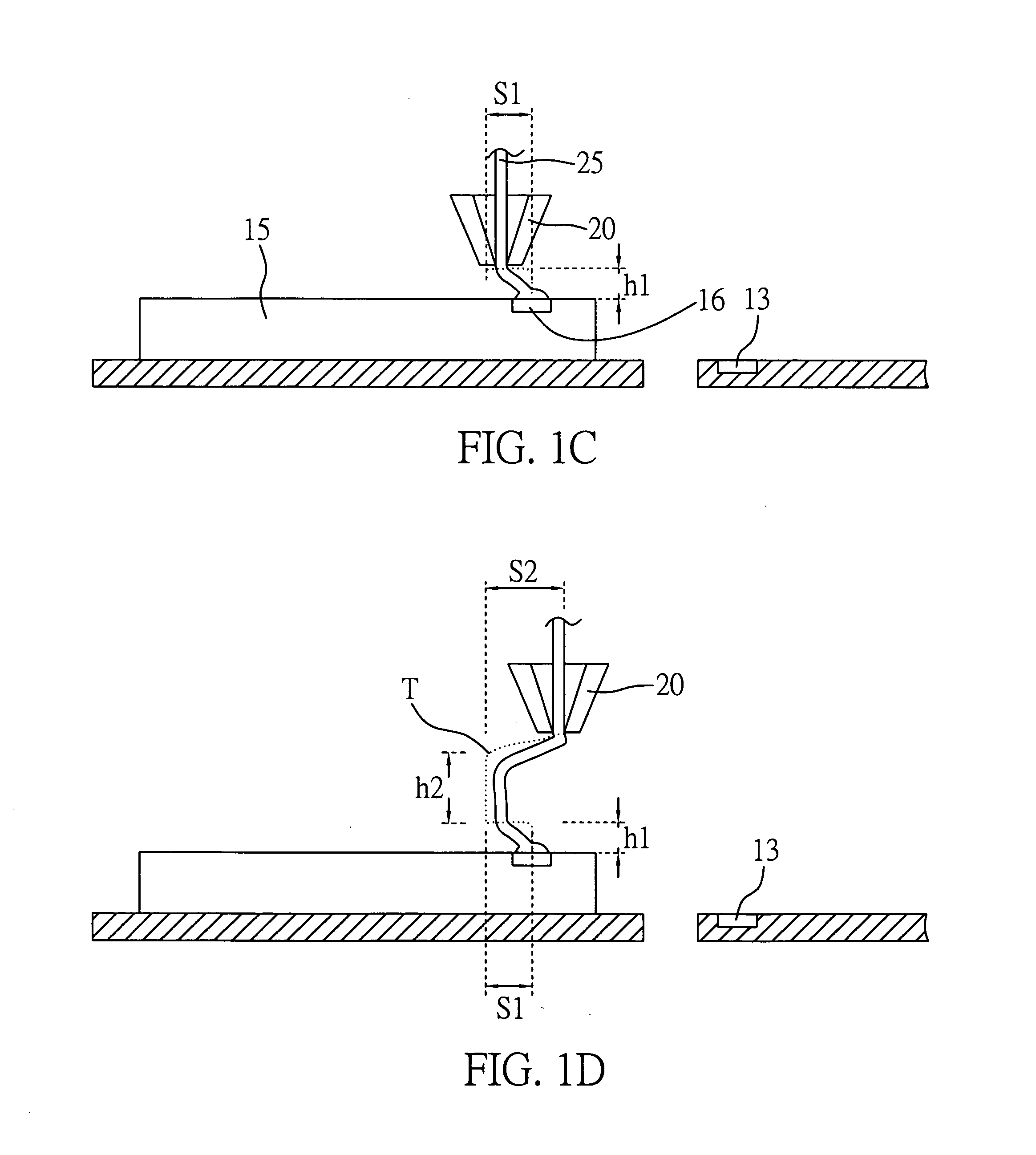

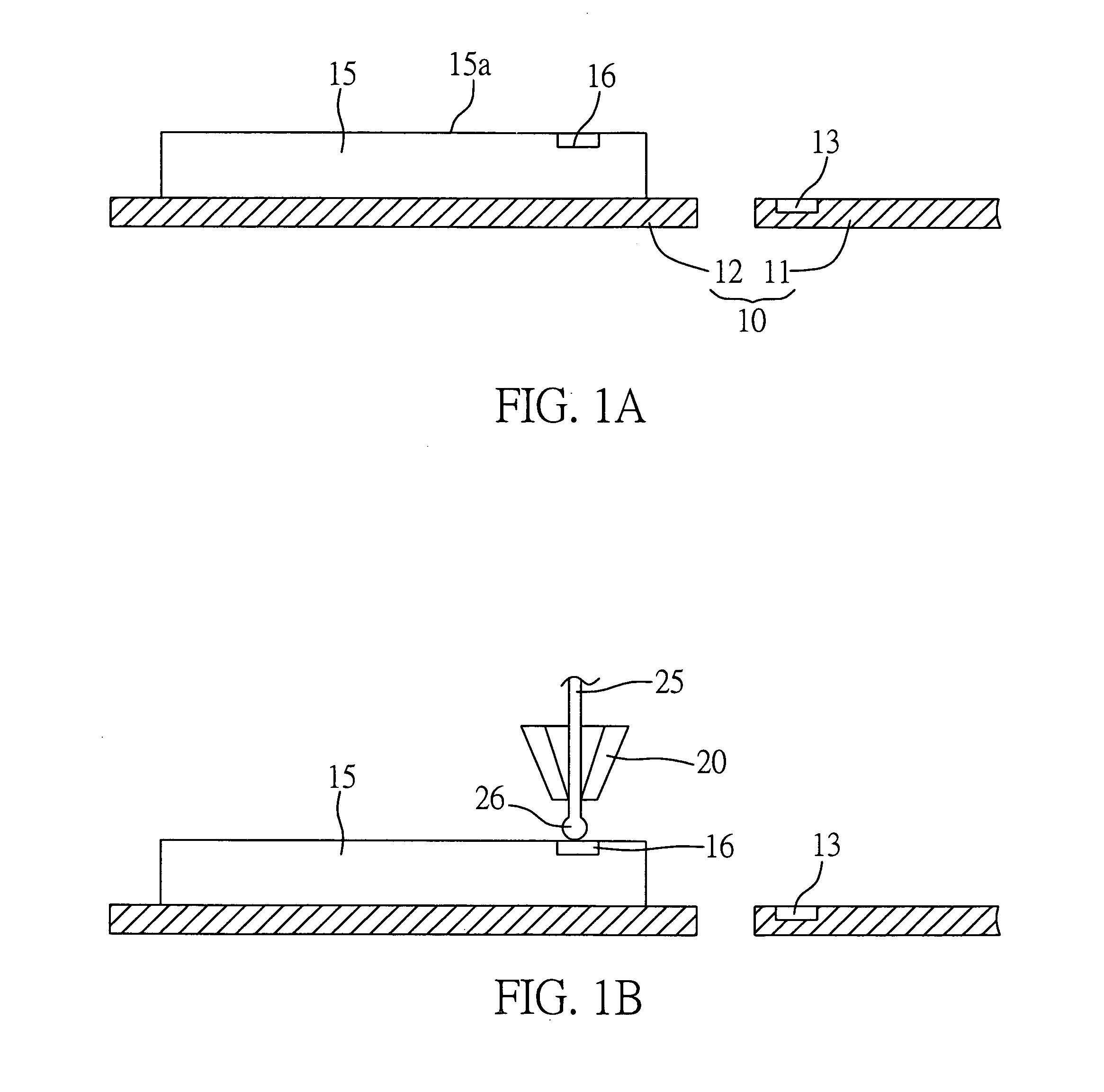

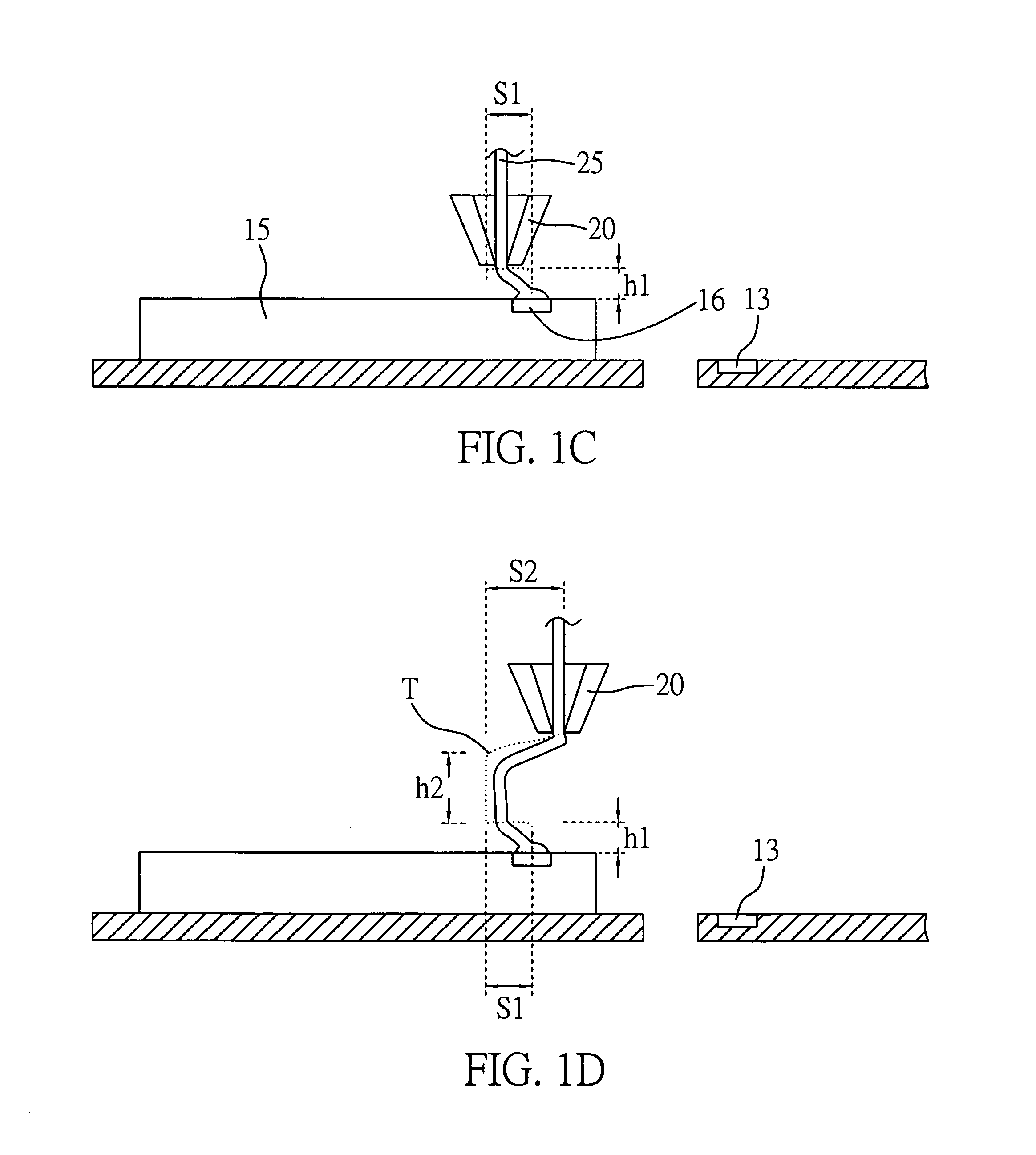

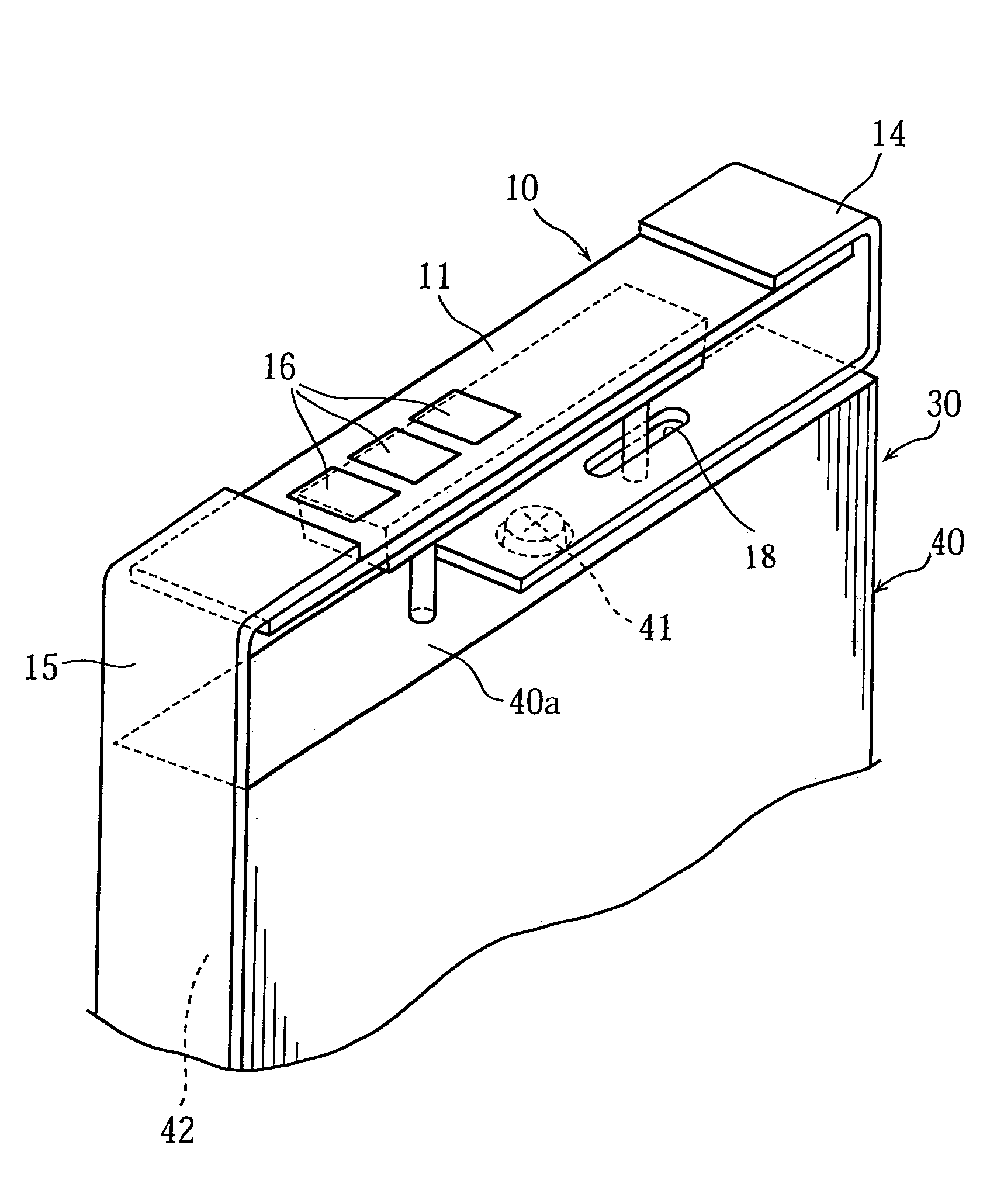

Wire-bonding method and semiconductor package using the same

ActiveUS20050173791A1Simplify the manufacturing processHigh yieldSemiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

A wire-bonding method and a semiconductor package using the same are provided. The semiconductor package includes a carrier; a chip mounted on the carrier; a plurality of first wires and second wires alternatively arranged in a stagger manner, with a wire loop of each second wire being downwardly bent to form a deformed portion so as to provide a height different between the wire loops of each first wire and each second wire, wherein the first and second wires electrically connect the chip to the carrier; and an encapsulant for encapsulating the chip, the first wires, the second wires and a portion of the carrier. The height difference between the wire loops of each first wire and each second wire increases a pitch between adjacent first and second wires thereby preventing the wires from contact and short circuit with each other due to wire sweep during an encapsulation process.

Owner:SILICONWARE PRECISION IND CO LTD

Waterproof fairy light

InactiveUS20130322087A1Avoid contactShort circuit of the waterproof fairy light will not be incurredVehicle interior lightingGas-tight/water-tight arrangementsEffect lightEngineering

A waterproof fairy light has a housing, a socket and a lighting assembly. The housing has an assembling hole defined therein. The socket is mounted in the assembling hole and has a cavity defined through the socket and having an inner surface and a partition formed in the cavity on the inner surface, dividing the cavity into two spaces and having two opposite side edges formed integrally on the inner surface of the cavity so that no gap is formed between each side edge and the inner surface. The lighting assembly is mounted in the cavity of the socket and has a lighting element and two contacting pins. The integrally formed partition prevents rain from contacting both the contacting pins and causing short circuit.

Owner:TSENG WEI JEN

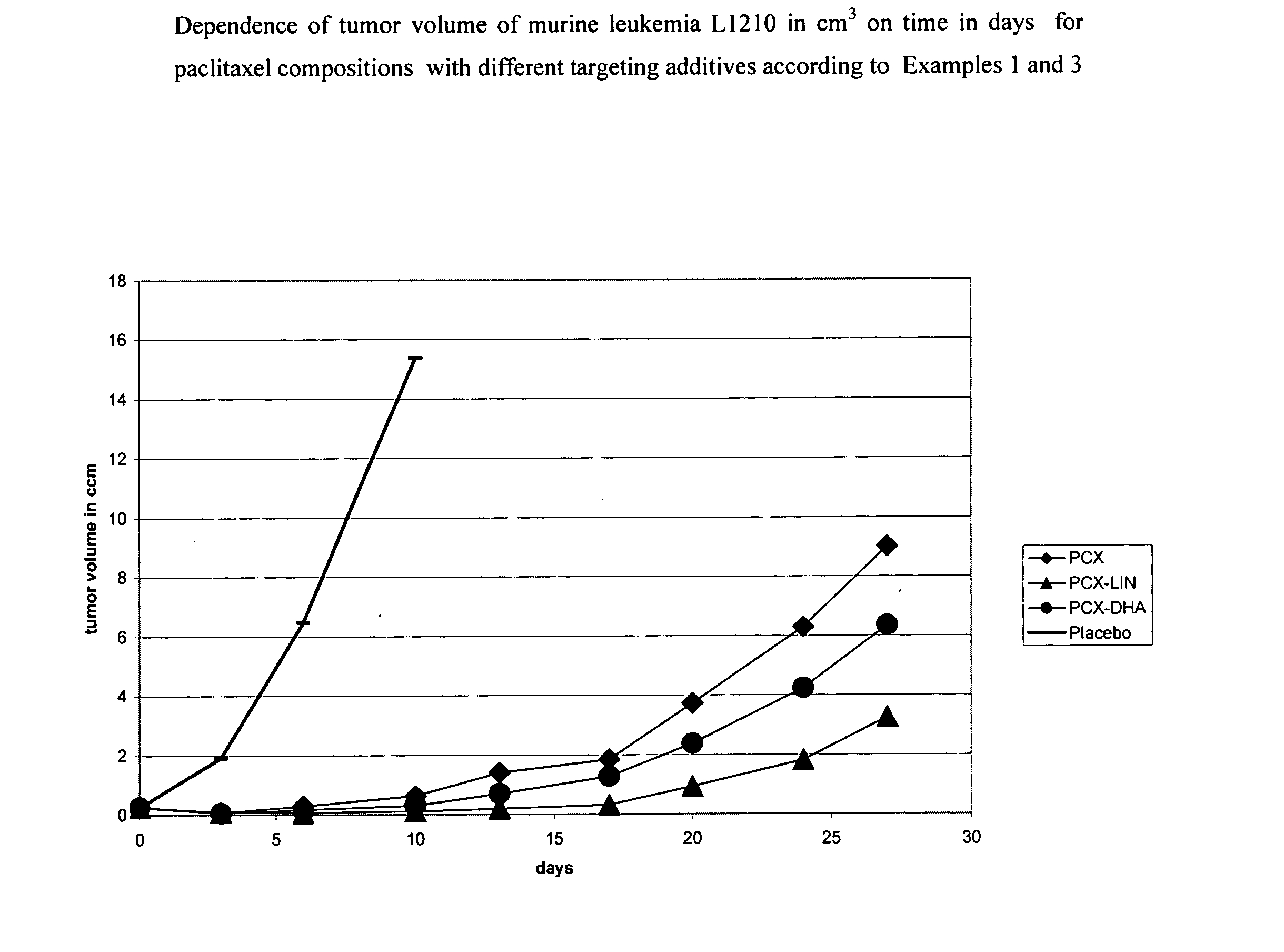

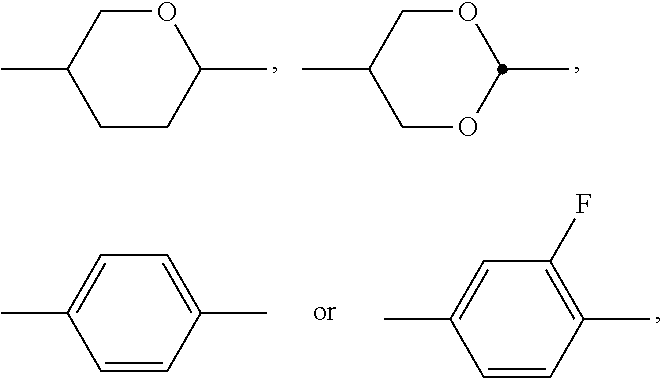

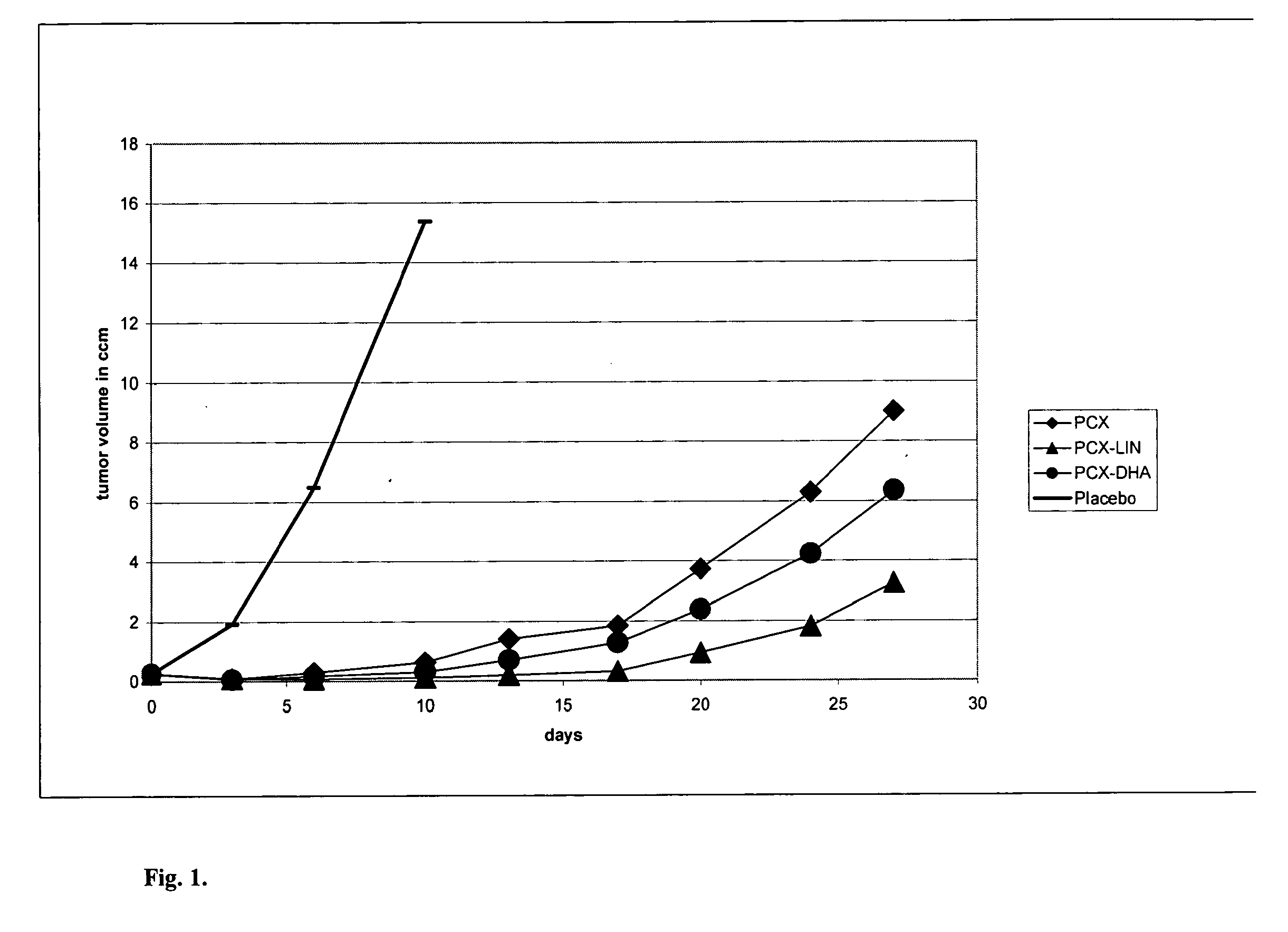

Taxane derivative containing pharmaceutical composition with improved therapeutic efficacy

InactiveUS20080300297A1Increase cancer tissue specificityGood curative effectBiocideAnimal repellantsChemistryTaxane derivative

The invention relates to a pharmaceutical combination comprising a mixture of (a) at least one taxane derivative and (b) at least one ω-3 poly-unsaturated acid or a derivative thereof wherein the molar ratio of (b) to (a) is not higher than 2. The invention further relates to a liquid pharmaceutical composition comprising (a) an effective amount of at least one taxane derivative, (b) an effective amount of at least one ω-3 poly-unsaturated fatty acid or a derivative thereof and (c) at least one pharmaceutically acceptable carrier and a process for the preparation of the same. The composition can be used for the therapy of cancers which are sensitive to taxane derivatives. The invention also relates to a kit comprising the individual components of the above mentioned composition placed in separate containers.

Owner:KYSILKA VLADIMIR

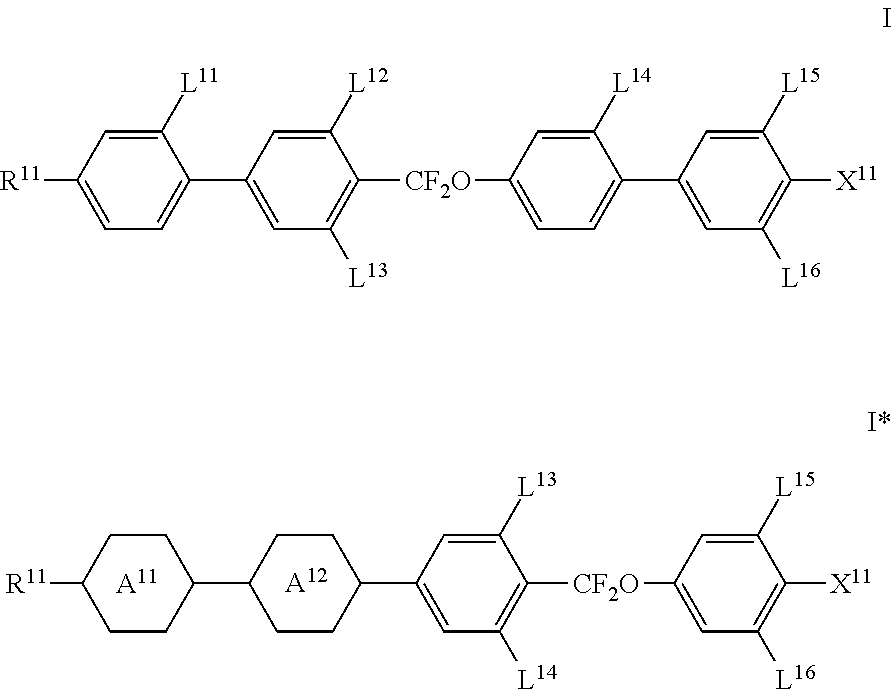

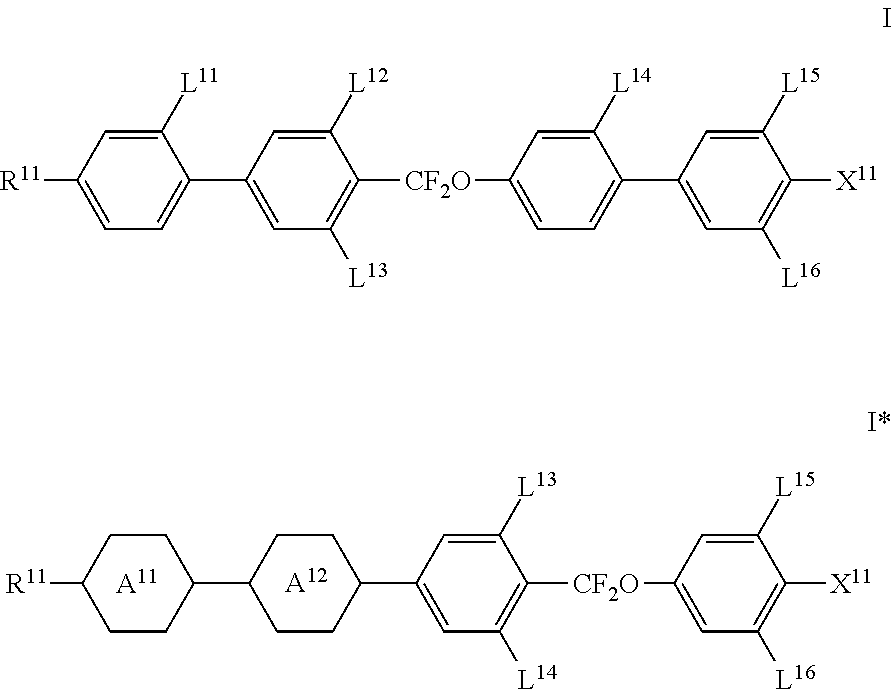

Electro-rheological fluid and haptic device

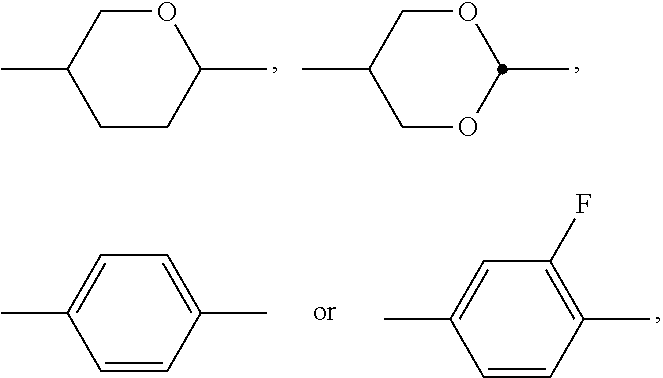

ActiveUS20170002290A1Easy to makeTransparent highLiquid crystal compositionsNon-linear opticsLiquid crystallineElectrorheological fluid

The present invention relates to an electro-rheological fluid comprising particles of at least one inorganic or organic material suspended in a polar liquid crystalline medium, the use of such electro-rheological fluid in an haptic device, an haptic device itself, a method of the production of such haptic device and the use of such haptic device in electro-optical devices.

Owner:MERCK PATENT GMBH

Taxane derivative containing pharmaceutical composition with improved therapeutic efficacy

InactiveUS20110082193A1Increase cancer tissue specificityGood curative effectOrganic active ingredientsBiocideTreatment efficacyChemistry

The invention relates to a pharmaceutical combination comprising a mixture of (a) at least one taxane derivative and (b) at least one ω-3 poly-unsaturated acid or a derivative thereof wherein the molar ratio of (b) to (a) is not higher than 2. The invention further relates to a liquid pharmaceutical composition comprising (a) an effective amount of at least one taxane derivative, (b) an effective amount of at least one ω-3 poly-unsaturated fatty acid or a derivative thereof and (c) at least one pharmaceutically acceptable carrier and a process for the preparation of the same. The composition can be used for the therapy of cancers which are sensitive to taxane derivatives. The invention also relates to a kit comprising the individual components of the above mentioned composition placed in separate containers.

Owner:KYSILKA VLADIMIR

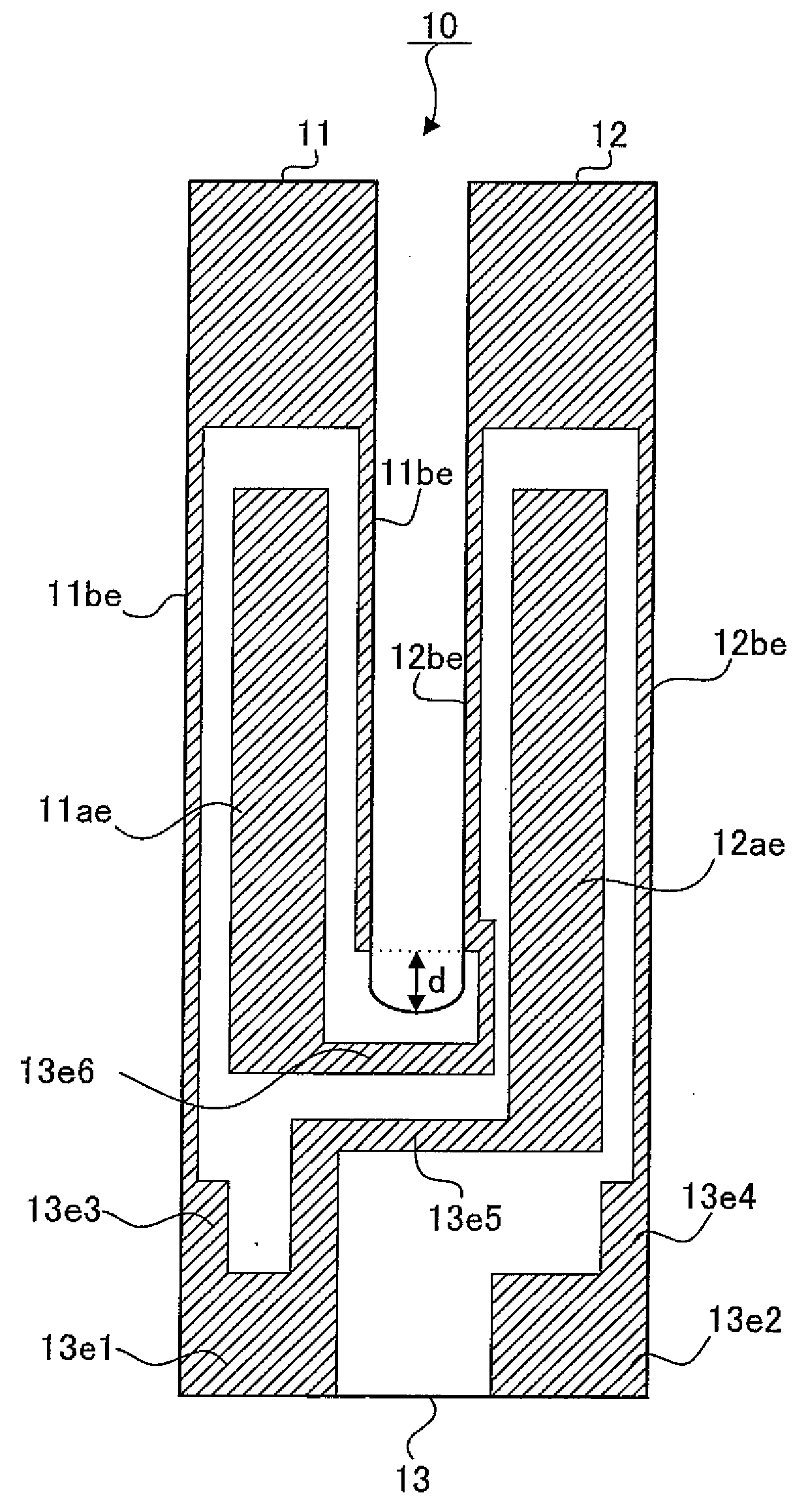

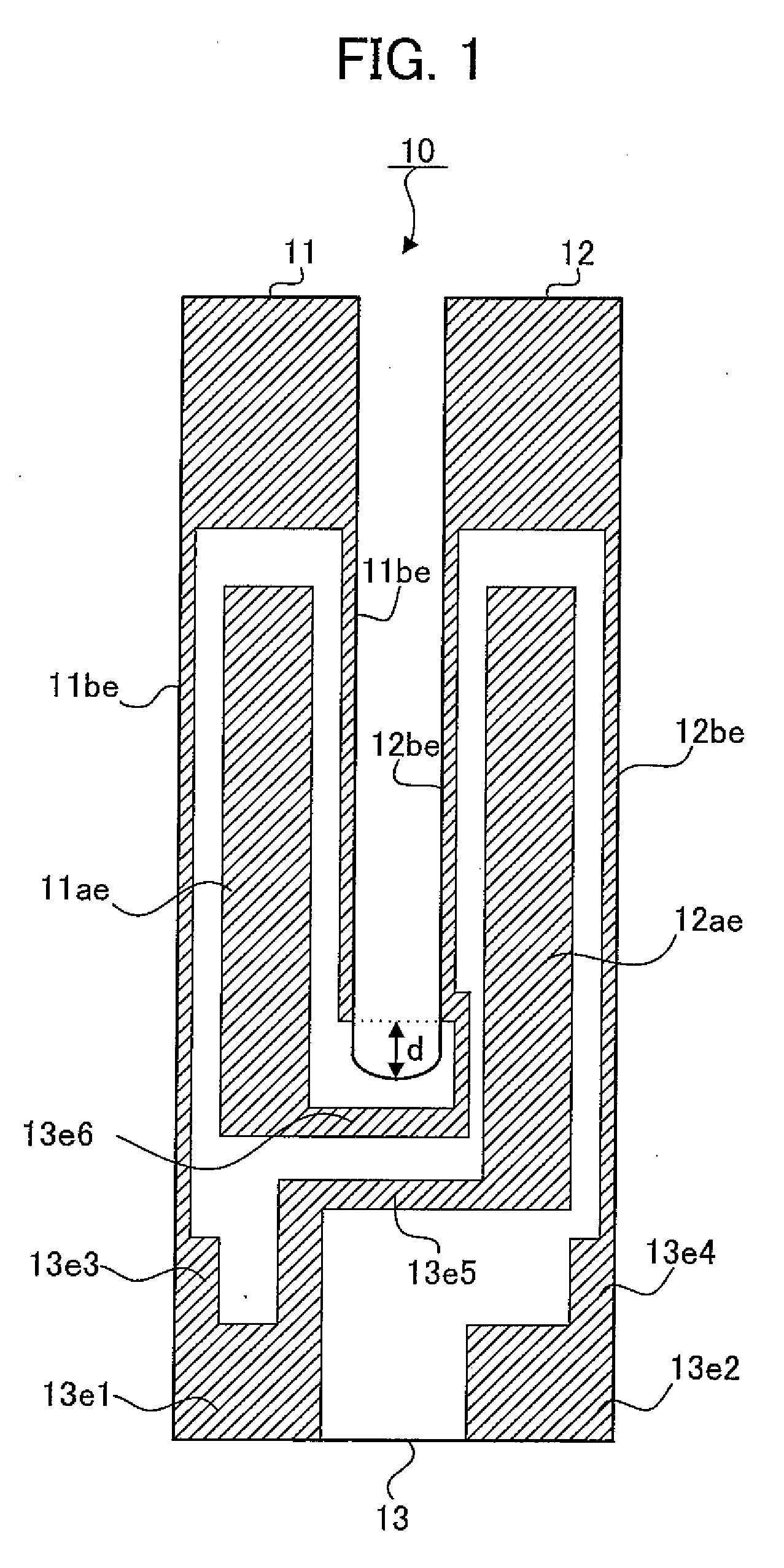

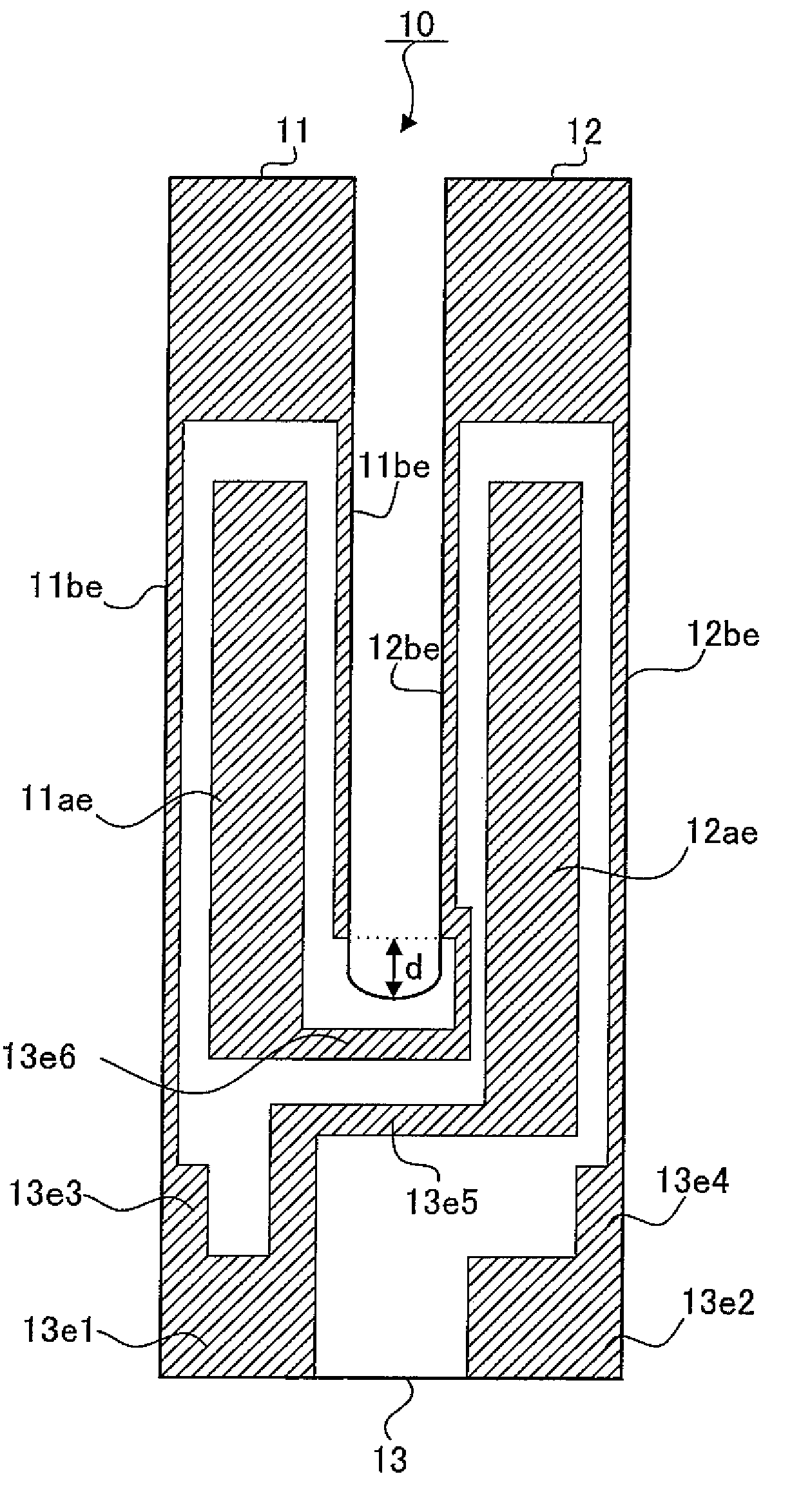

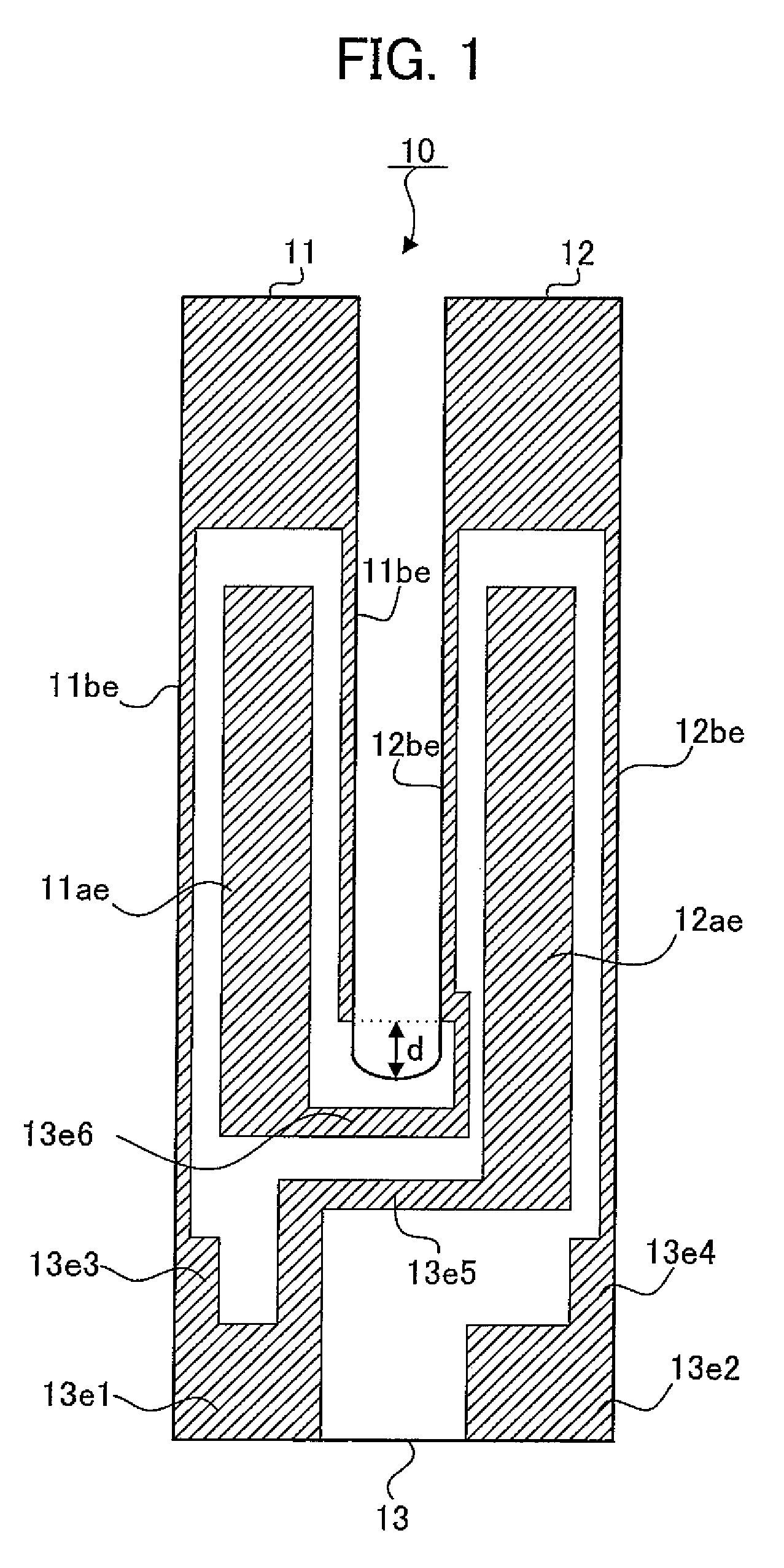

Tuning-Fork Type Piezoelectric Vibrating Piece and Oscillator

InactiveUS20080084251A1Improve performanceReduce areaPiezoelectric/electrostriction/magnetostriction machinesImpedence networksTuning forkAudio power amplifier

A tuning fork type piezoelectric vibrating piece, comprising: a base unit having a base electrode for an external connection; a fork shaped arm unit extending from the base unit; a groove portion at least on a surface or a rear surface of the arm unit; a groove electrode on the groove portion; a side surface electrode on the arm unit without the groove portion; a first electrode connecting the base unit and the side surface electrode or the groove electrode; a second electrode connecting the groove electrode and the side surface electrode; and a side surface electrode set at a predetermined distance from the bottom of the fork part of the base unit. The piezoelectric vibrating piece may be packaged with a base electrode connected to an external output terminal. The piezoelectric oscillator may have an amplifier circuit and a feedback circuit with a resonant element determining the resonant frequency.

Owner:NIHON DEMPA KOGYO CO LTD

Protection circuit module and battery pack incorporating the same

InactiveUS20060147764A1Low costSimple structureBatteries circuit arrangementsPrimary cell maintainance/servicingRechargeable cellElectronic component

Owner:ROHM CO LTD

Probe and probe card for integrated circuit devices using the same

ActiveUS20100171519A1Relieve pressureSmall spacingElectrical measurement instrument detailsContactless circuit testingProbe cardBody positions

A vertical probe comprises a linear body, a tip portion connected to one side of the linear body, and at least one slot positioned on the linear body. In particular, the vertical probe includes a depressed structure having a plurality of slots positioned on the linear body in parallel and on one side of the linear body. The present application also provides a probe card for integrated circuit devices comprising an upper guiding plate having a plurality of fastening holes, a bottom guiding plate having a plurality of guiding holes and a plurality of vertical probes positioned in the guiding holes. The vertical probe includes a linear body positioned in the guiding holes, a tip portion connected to one side of the linear body and at least one slot positioned on the linear body.

Owner:STAR TECH INC

Method for insulating aluminum backboard of photovoltaic

InactiveUS20140338190A1Improve insulationImprove insulation performanceLine/current collector detailsPhotovoltaicsBackplaneAluminium

A method for insulating an aluminum backboard of a photovoltaic module comprises the following steps: shearing the aluminum backboard such that the dimensions of the aluminum backboard are 4-5 mm smaller those of the glass; forming a square aperture at the position of the electrode lead of the aluminum backboard; insulating the square aperture by cushioning a small insulating material or wrapping the edges with an insulation film when arraying and laying the modules; laminating and trimming the superimposed module components; wrapping the trimmed laminated piece around the edge with the 0.5-1 mm insulation tape; finally, framing up the laminated piece by using a frame filled with silica gel, and installing the terminal box. The invention is convenient to operate and low in investment and has a wide application prospect.

Owner:HANWHA SOLARONE QIDONG

Drain and inlet member for drain

ActiveUS8661574B2Less riskShorting of contactFatty/oily/floating substances removal devicesSewerage structuresGratingEngineering

The present invention relates to a drain which comprises an inlet member (1), a grating (13) or cover plate laid loosely or detachably on top of the inlet member, and an outlet member (2). To achieve a short line of contact between the surface covering's sealing layer (6) and the drain while at the same time the sealing layer is fastened by means of a clamping ring (5) or a bonding flange, thereby reducing the risk of leakage and affording the possibility of connecting an aesthetically more pleasing inlet member (1), the inlet member (1) takes the form of an elongate or trilateral plate-like element (11) disposed on top of the sealing layer or the sealing layer (6) and the clamping ring (5) and provided with a recess (12) for flow communication with the outlet member (2). The present invention relates also to an inlet member (1) for a drain as above.

Owner:PURUS

Wire-bonding method and semiconductor package using the same

ActiveUS7126229B2Improve power qualityIncrease pitchSemiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

A wire-bonding method and a semiconductor package using the same are provided. The semiconductor package includes a carrier; a chip mounted on the carrier; a plurality of first wires and second wires alternatively arranged in a stagger manner, with a wire loop of each second wire being downwardly bent to form a deformed portion so as to provide a height different between the wire loops of each first wire and each second wire, wherein the first and second wires electrically connect the chip to the carrier; and an encapsulant for encapsulating the chip, the first wires, the second wires and a portion of the carrier. The height difference between the wire loops of each first wire and each second wire increases a pitch between adjacent first and second wires thereby preventing the wires from contact and short circuit with each other due to wire sweep during an encapsulation process.

Owner:SILICONWARE PRECISION IND CO LTD

Protection circuit module and battery pack incorporating the same

InactiveUS7326479B2Low costSimple structureBatteries circuit arrangementsPrimary cell maintainance/servicingRechargeable cellEngineering

Owner:ROHM CO LTD

Tuning-fork type piezoelectric vibrating piece and oscillator

InactiveUS7570126B2Shorting of contactImprove performancePiezoelectric/electrostriction/magnetostriction machinesImpedence networksTuning forkAudio power amplifier

A tuning fork type piezoelectric vibrating piece, comprising: a base unit having a base electrode for an external connection; a fork shaped arm unit extending from the base unit; a groove portion at least on a surface or a rear surface of the arm unit; a groove electrode on the groove portion; a side surface electrode on the arm unit without the groove portion; a first electrode connecting the base unit and the side surface electrode or the groove electrode; a second electrode connecting the groove electrode and the side surface electrode; and a side surface electrode set at a predetermined distance from the bottom of the fork part of the base unit. The piezoelectric vibrating piece may be packaged with a base electrode connected to an external output terminal. The piezoelectric oscillator may have an amplifier circuit and a feedback circuit with a resonant element determining the resonant frequency.

Owner:NIHON DEMPA KOGYO CO LTD

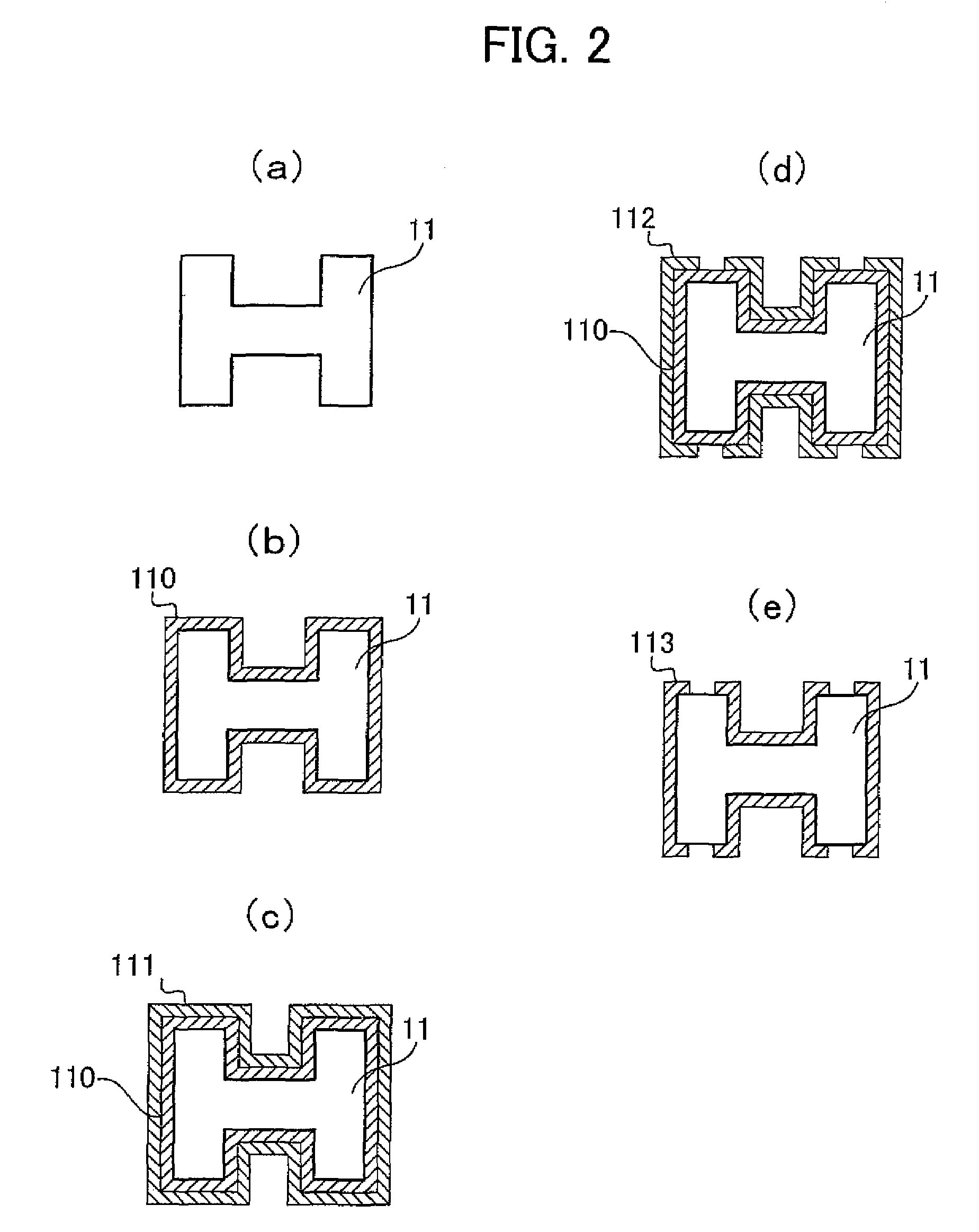

Ink-jet head and connecting structure

ActiveUS7469994B2Suppressing a short circuitShorting of contactPrinted circuit aspectsPrinted circuit manufactureForming faceEnergy applicator

An ink-jet head has a flexible printed circuit and a head main body, and further has a reinforcement that is located between drive-signal terminals arranged adjacent to one another and a constant-potential-signal terminal. The drive-signal terminals and the constant-potential-signal terminal are formed on a terminal-formed face of an energy applier included in the head main body. The flexible printed circuit has an electrode-formed face on which a constant-potential-signal electrode to be bonded to the constant-potential-signal terminal with a metal bond and drive-signal electrodes to be bonded to the drive-signal terminals with a metal bond. The reinforcement is in contact with and interposed between the terminal-formed face and the electrode-formed face so that the terminal-formed face and the electrode-formed face are spaced apart from each other.

Owner:BROTHER KOGYO KK

Electro-rheological fluid and haptic device

ActiveUS10160930B2Easy to driveReduce power consumptionLiquid crystal compositionsNon-linear opticsLiquid crystallinePower flow

The present invention relates to an electro-rheological fluid comprising particles of at least one inorganic or organic material suspended in a polar liquid crystalline medium, the use of such electro-rheological fluid in an haptic device, an haptic device itself, a method of the production of such haptic device and the use of such haptic device in electro-optical devices.

Owner:MERCK PATENT GMBH

Method for insulating aluminum backboard of photovoltaic

InactiveUS9385252B2Improve insulation performanceImprove isolationLine/current collector detailsPhotovoltaicsEngineeringSilica gel

A method for insulating an aluminum backboard of a photovoltaic module comprises the following steps: shearing the aluminum backboard such that the dimensions of the aluminum backboard are 4-5 mm smaller those of the glass; forming a square aperture at the position of the electrode lead of the aluminum backboard; insulating the square aperture by cushioning a small insulating material or wrapping the edges with an insulation film when arraying and laying the modules; laminating and trimming the superimposed module components; wrapping the trimmed laminated piece around the edge with the 0.5-1 mm insulation tape; finally, framing up the laminated piece by using a frame filled with silica gel, and installing the terminal box. The invention is convenient to operate and low in investment and has a wide application prospect.

Owner:HANWHA SOLARONE QIDONG

Interconnect manufacturing process

InactiveUS20090087978A1Increase process windowShorting of contactSemiconductor/solid-state device manufacturingEngineeringElectrical connection

An interconnect process is provided. A substrate is provided. A plurality of gate structures is disposed on the substrate, and doped regions are disposed in the substrate and respectively located between two adjacent gate structure. A liner is conformally formed above the substrate. A dielectric layer is formed above the substrate. A contact opening is formed in the dielectric layer between two neighboring gate structures to expose the liner on the doped region and on a portion of the top surface and a portion of the sidewall of each of the gate structures. A polymer material is deposited on the liner on the portion of the top surface of each of the gate structures and on the doped region. The liner on the doped regions is removed. A conductive layer is filled in the contact opening, which is free of electrical connection to the gate structures.

Owner:NAN YA TECH

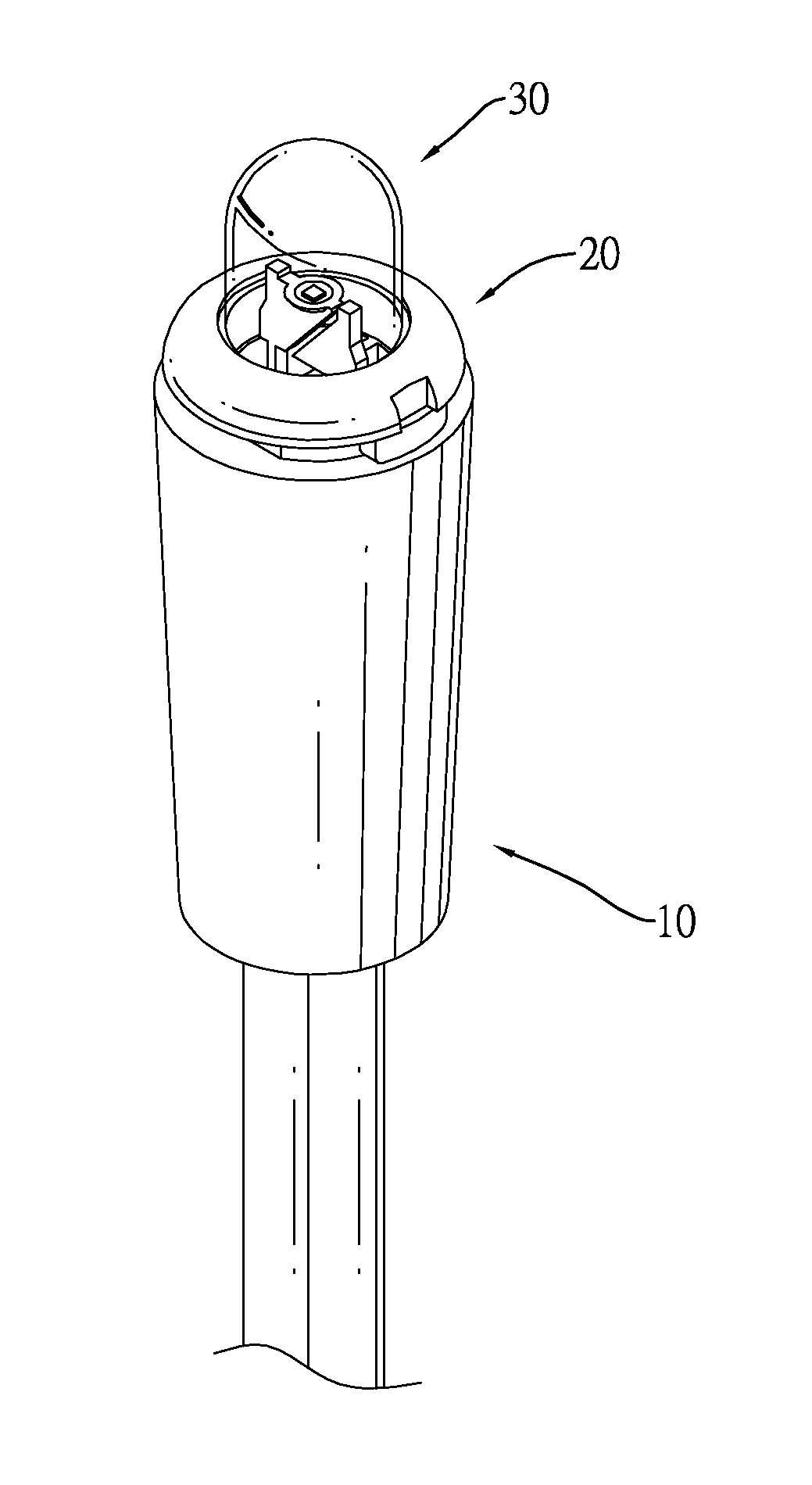

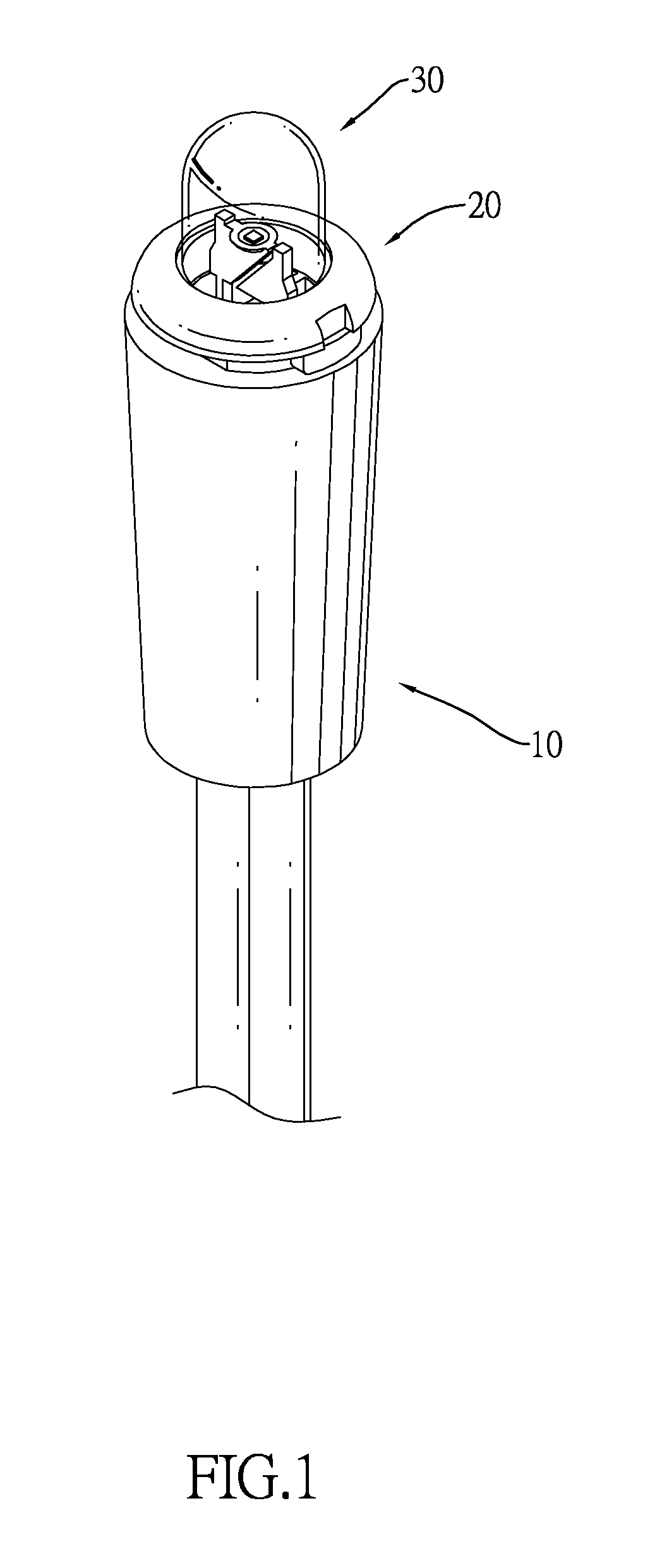

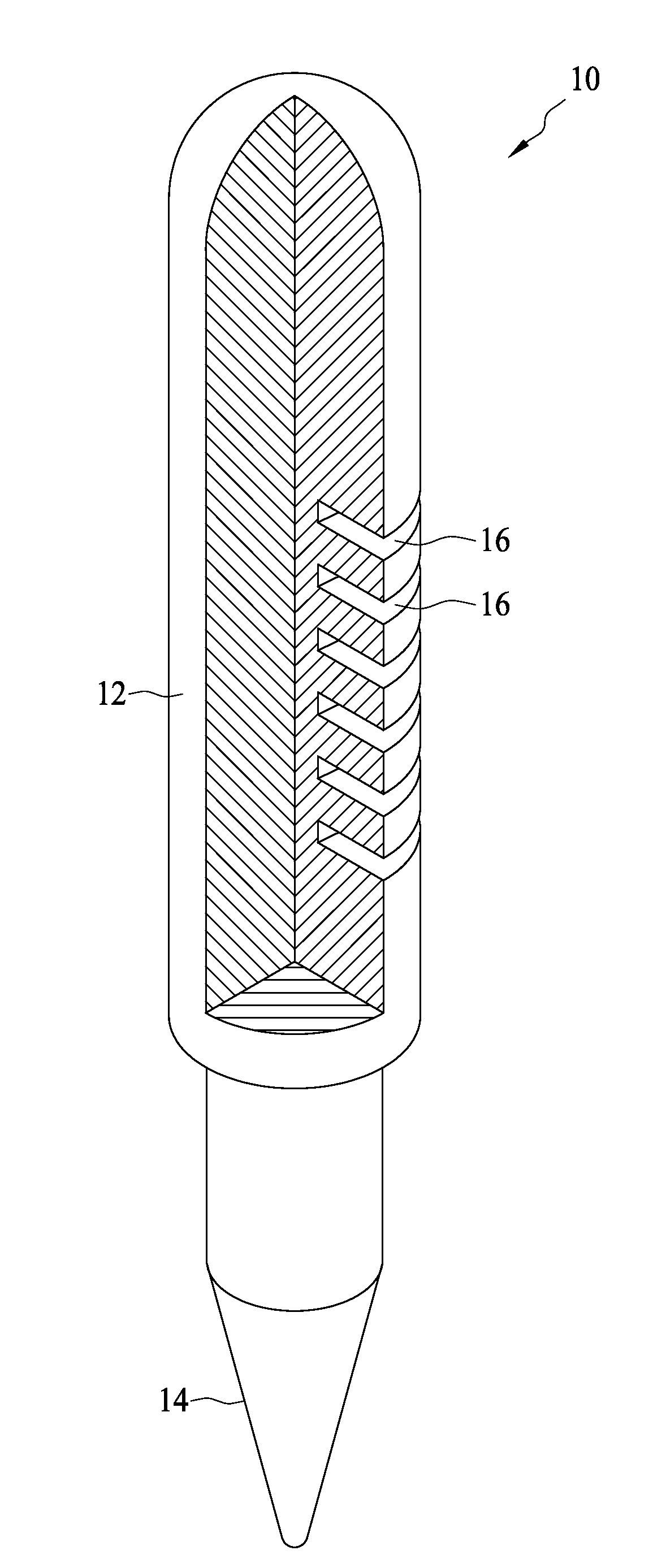

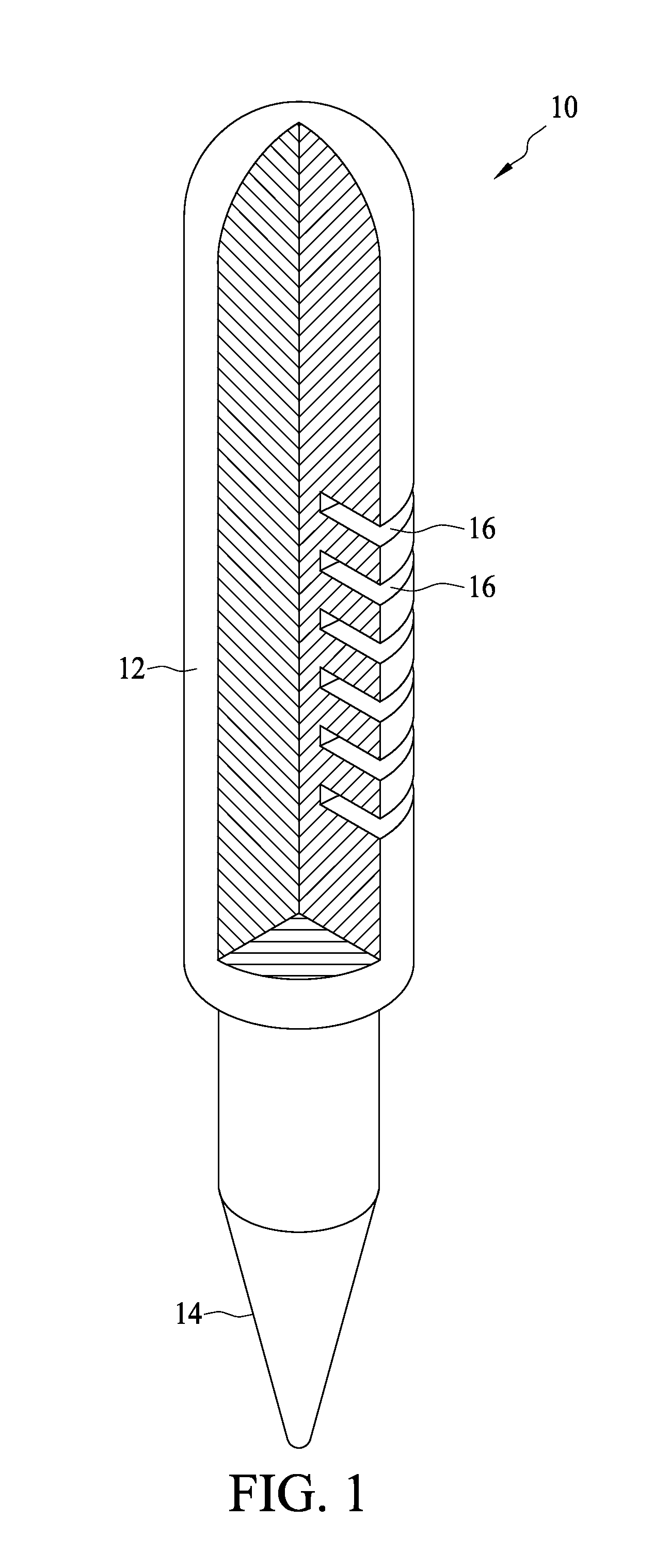

Circuitry for Portable Lighting Devices and Portable Rechargeable Electronic Devices

InactiveUS20140070720A1Shorting of contactNo longer be detectedPoint-like light sourceElectric circuit arrangementsPower flowFlashlight

A portable electronic device, such as a flashlight, with a circuit for reducing the initial surge of current that is sent through the lamp filament when a flashlight is turned on is provided. The circuit reduces the stresses placed on the lamp bulb when it is turned on, thereby extending the life expectancy of the lamp bulb. A flashlight with beacon mode that produces light according to a duty cycle of less than 11% is also disclosed.

Owner:MAG INSTR INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com