Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Reduce the number of labels" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

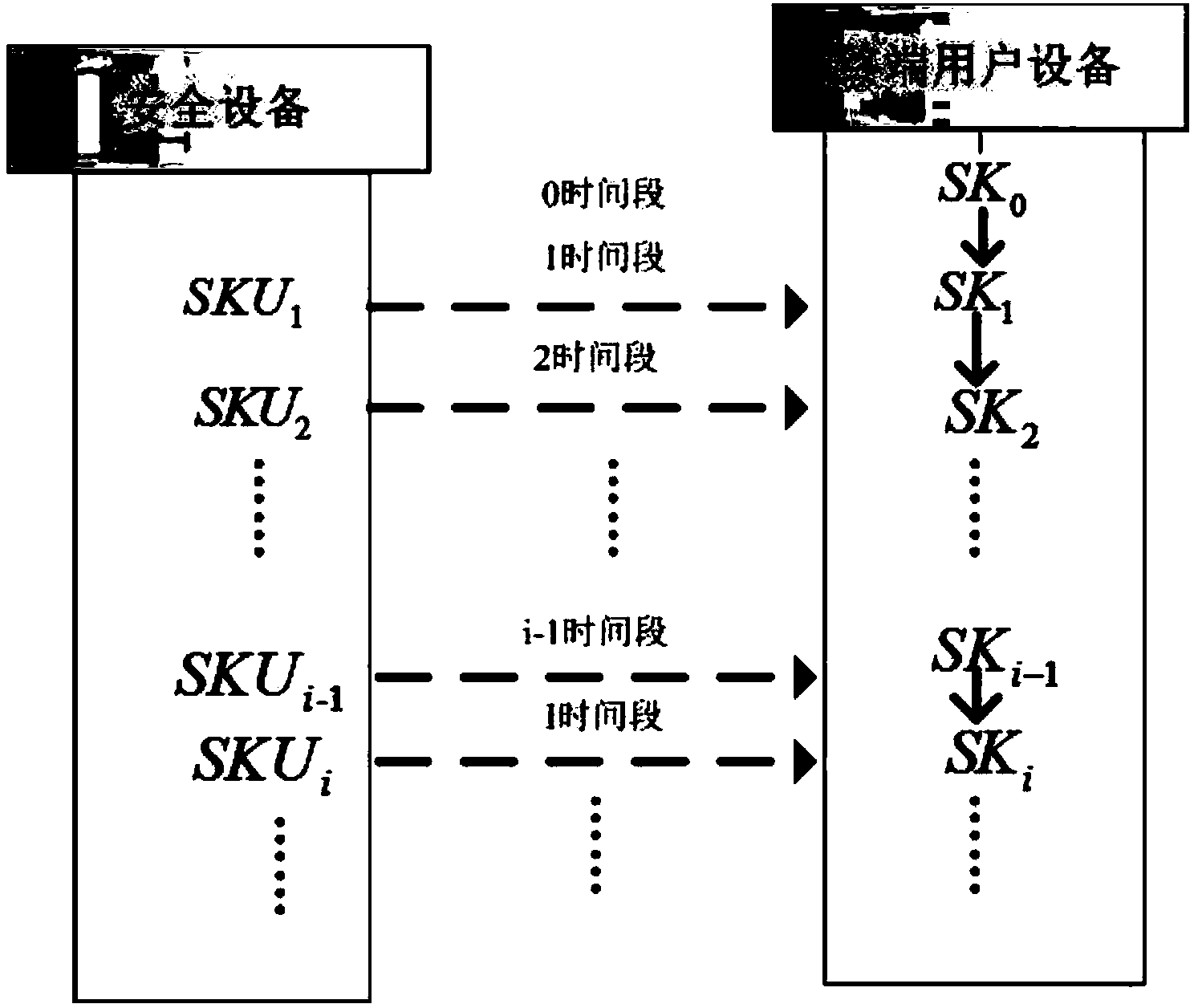

Cloud storage data auditing method for preventing secret key from being revealed

ActiveCN103986732AImprove audit efficiencyImprove efficiencyTransmissionPhysical securityTime segment

The invention provides a cloud storage data auditing method for preventing a secret key from being revealed. The method comprises the first step of system parameter generating, the second step of secret key updating and the third step of file uploading and auditing. According to the method, a physically safe safety device is introduced to help a user to periodically update the secret key, and therefore data auditing in other time periods is still safe even when an attacker attacks the user at one time period and obtains the user secret key at the time period.

Owner:SHANDONG ZHENGZHONG COMP NETWORK TECH CONSULTING

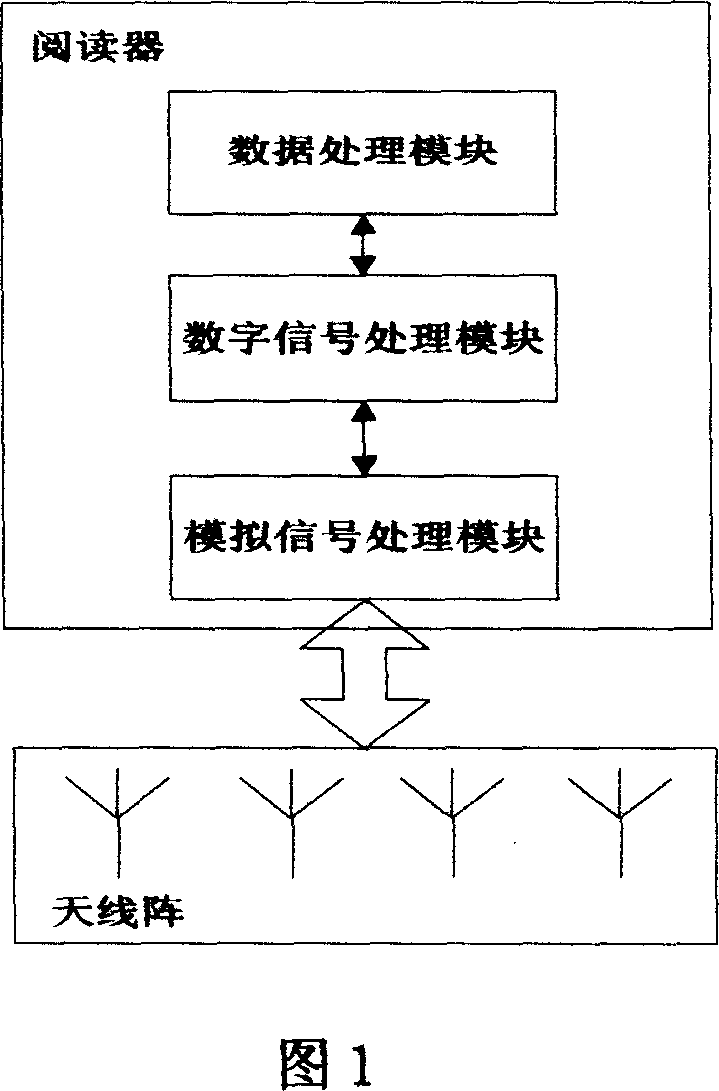

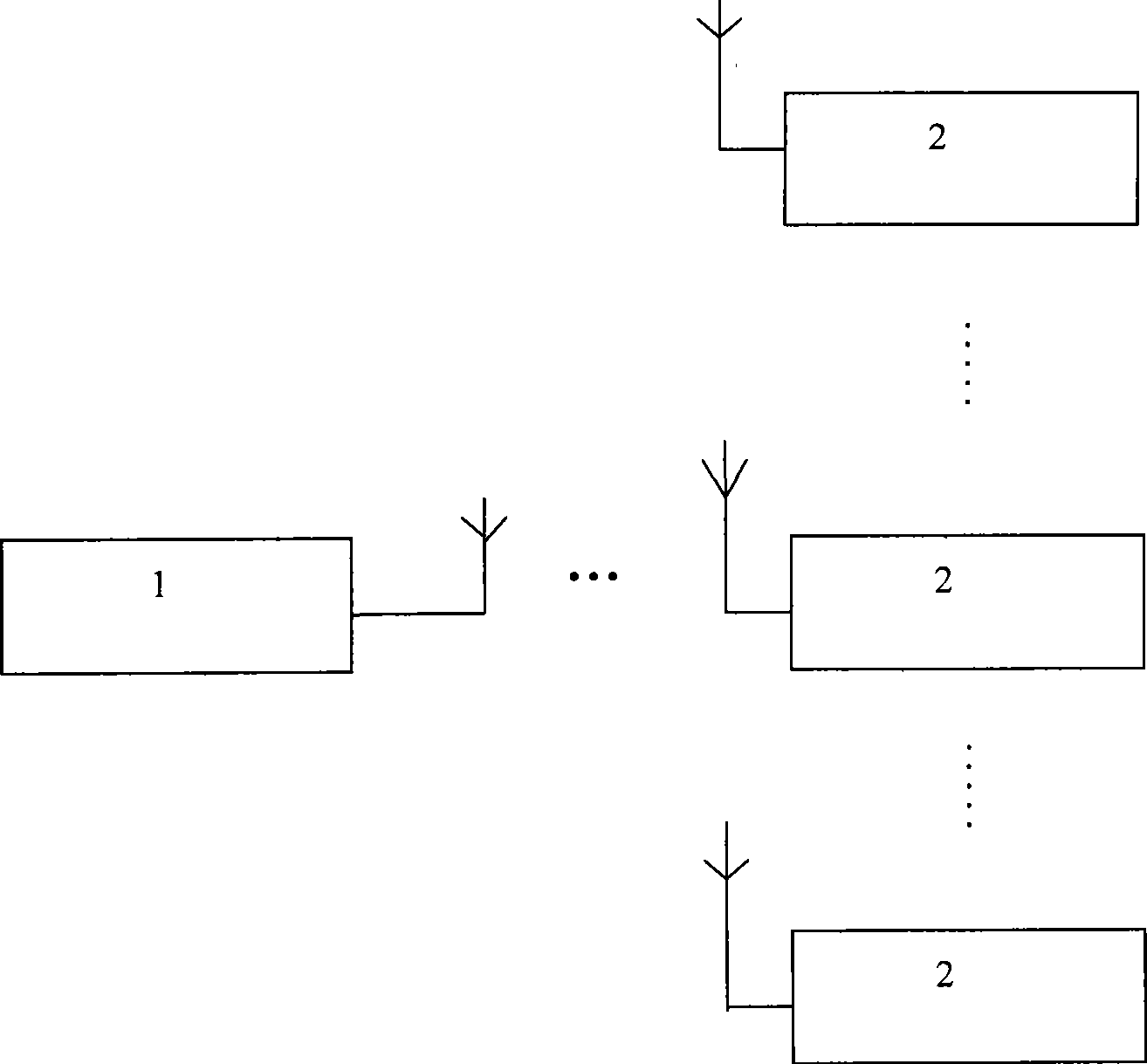

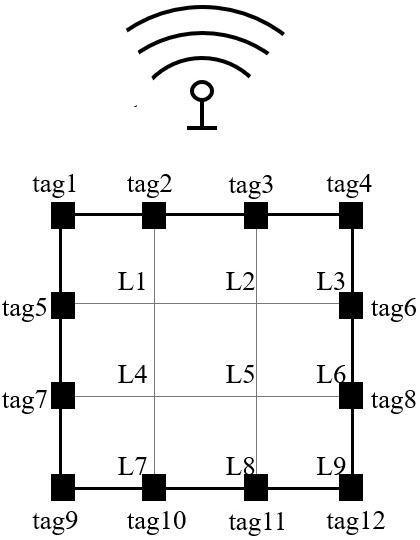

Intelligent RFID reading system anticonflict scheduling method

InactiveCN1975755ADeepReduce the number of labelsData switching by path configurationSensing record carriersComputer scienceIdentification rate

The invention provides a scheduling method to prevent conflicts in intelligent RFID read system. The method utilize the mechanism that reader controls multiple antennas, which is: all the antennas are controlled by the reader in order; the reader polls the antennas connected to the reader, and control the interactive between the single antenna and label; each time only one antenna can be activated to respond instructions from the reader; every two antenna effective covered regions are connected to reduce the overlap. The invention uses multiple antennas, at any time only one antenna takes effect, and then labels are divided into groups to recognize. The number of labels in the coverage covered by one antenna is reduced, thus the probability of conflicts is effectively reduced.

Owner:SOUTH CHINA UNIV OF TECH

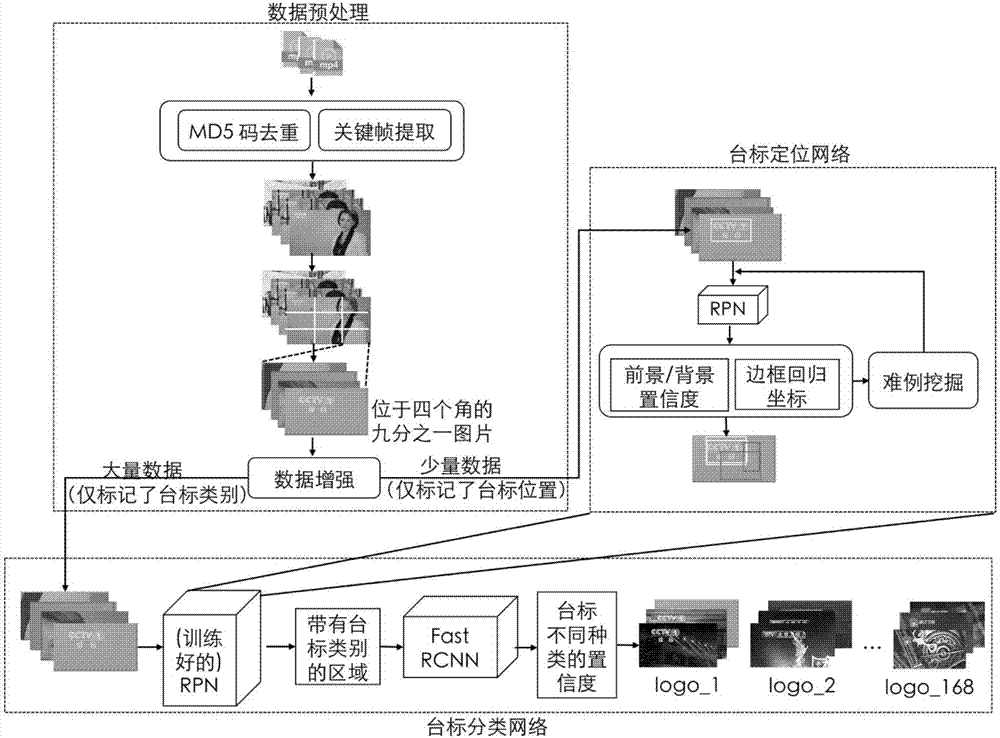

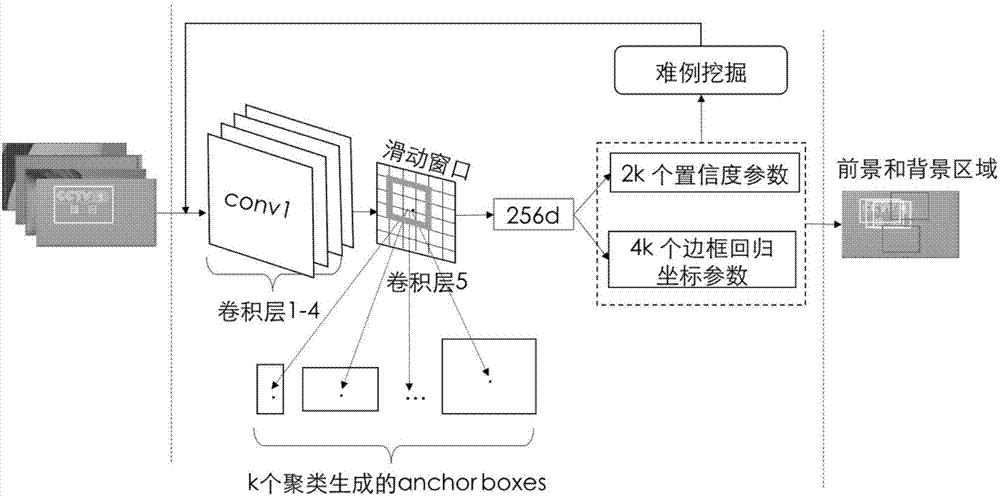

Deep station caption detection method of weak supervision

ActiveCN107330027AHigh-precision detectionImprove processing efficiencyCharacter and pattern recognitionSpecial data processing applicationsTelecommunicationsData file

The invention provides a deep station caption detection method of weak supervision. The deep station caption detection method comprises the steps of preprocessing mass online video data files, and obtaining a large data set only marking a station caption type and a small data set only marking station caption position; inputting the small data set into a station caption positioning network to be trained, and obtaining a station caption positioning network capable of predicting a station caption area; inputting the large data set into the trained station caption positioning network to obtain a plurality of prediction station caption areas of each picture in the large data set, inputting the prediction station caption areas of each picture into a station caption classification network to be trained, and obtaining a station caption classification network capable of classifying station captions; conducting the same partial preprocessing on videos to be detected, inputting the preprocessed pictures into the trained station caption positioning network, and obtaining the prediction station caption areas of the pictures; inputting the prediction station caption areas of the pictures into the trained station caption classification network, and obtaining station caption positions and types of the pictures.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

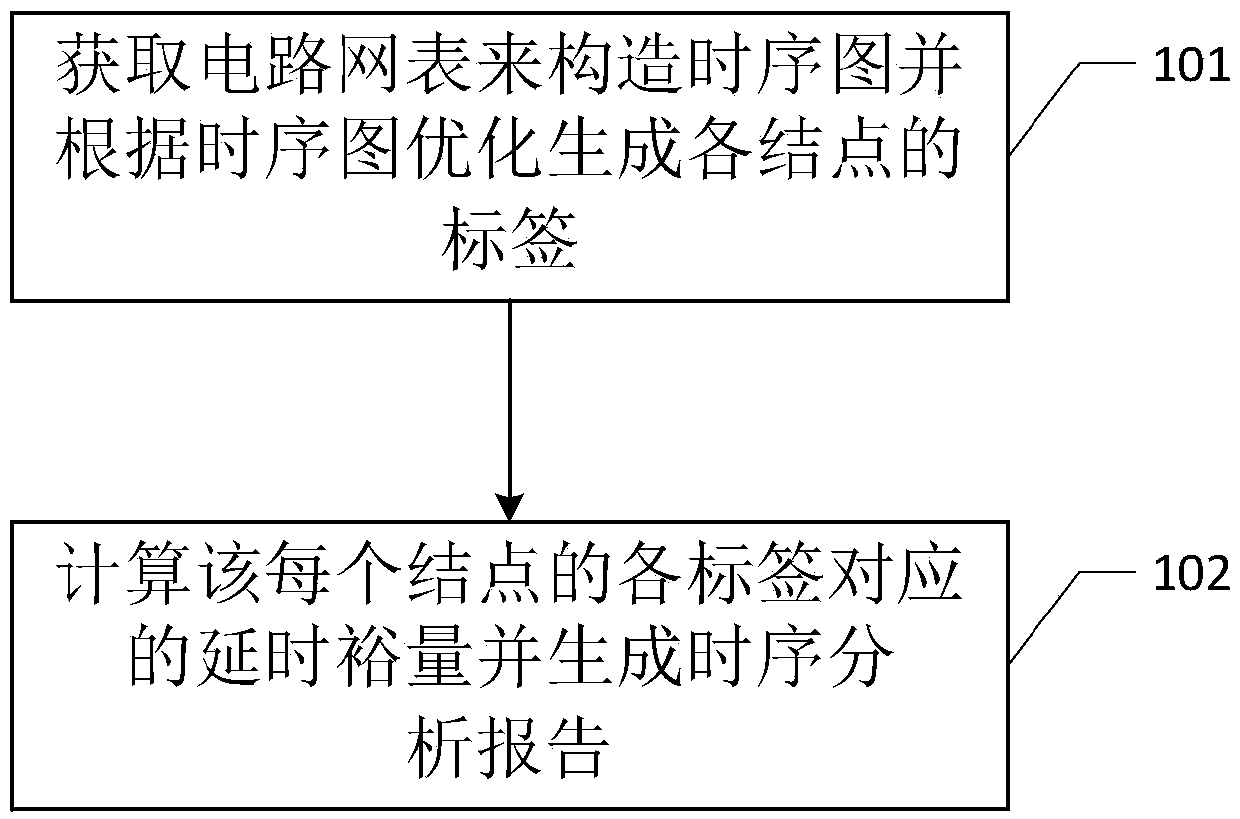

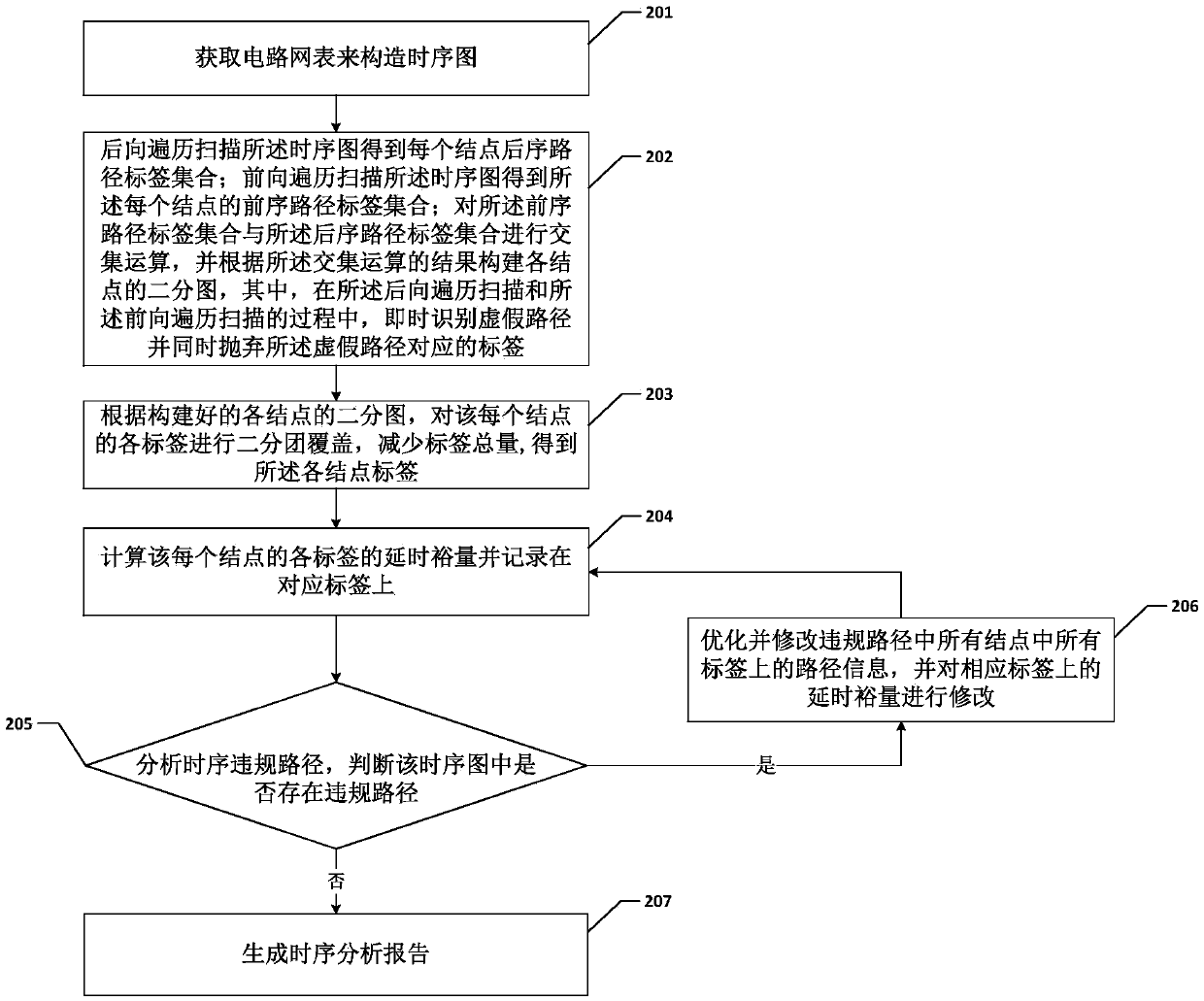

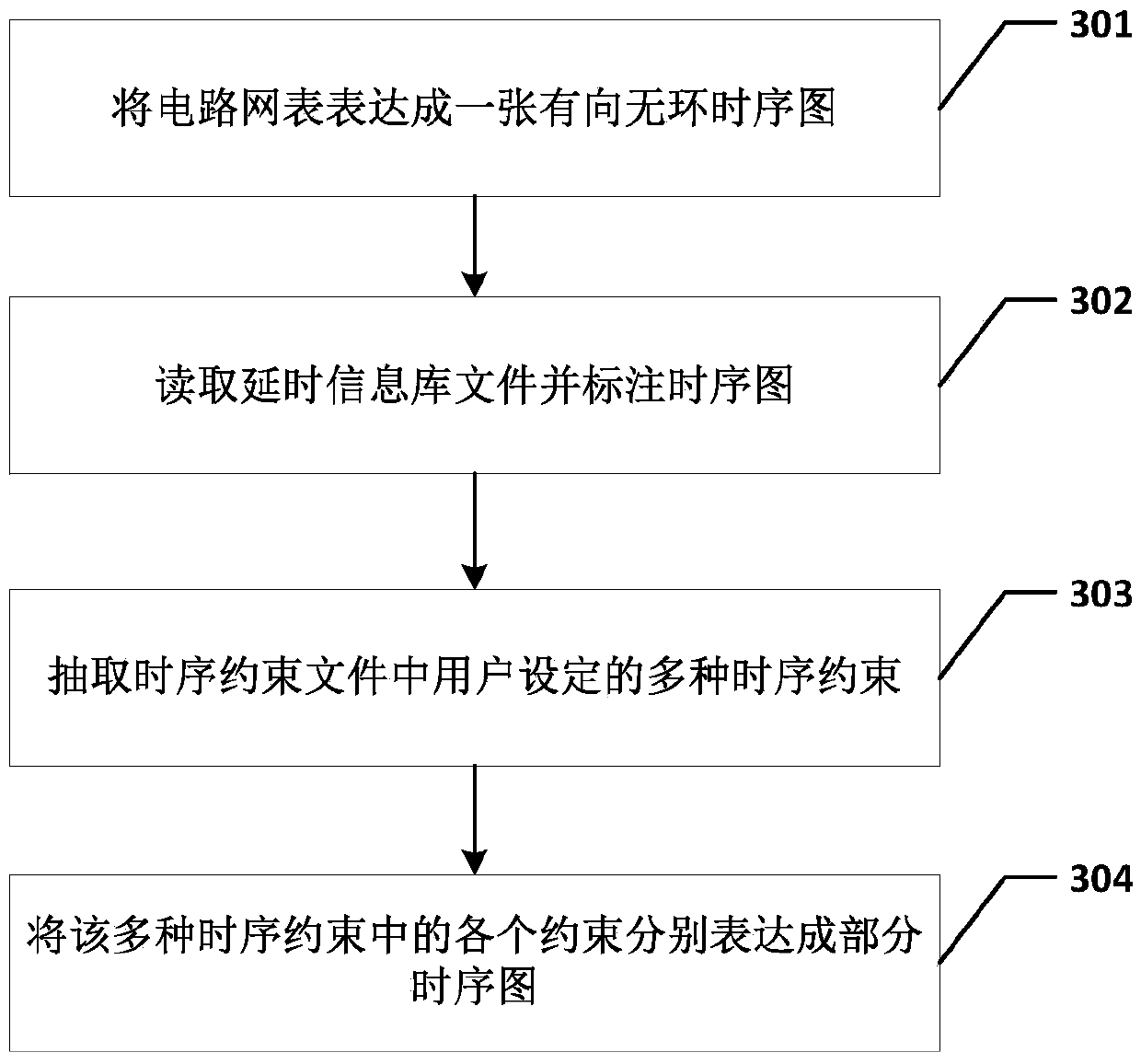

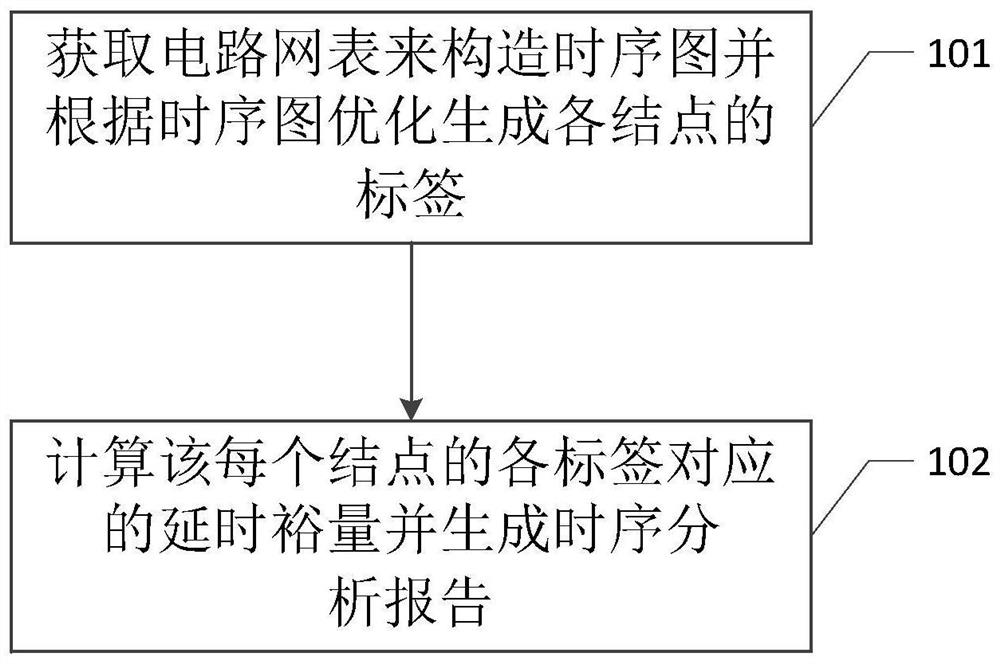

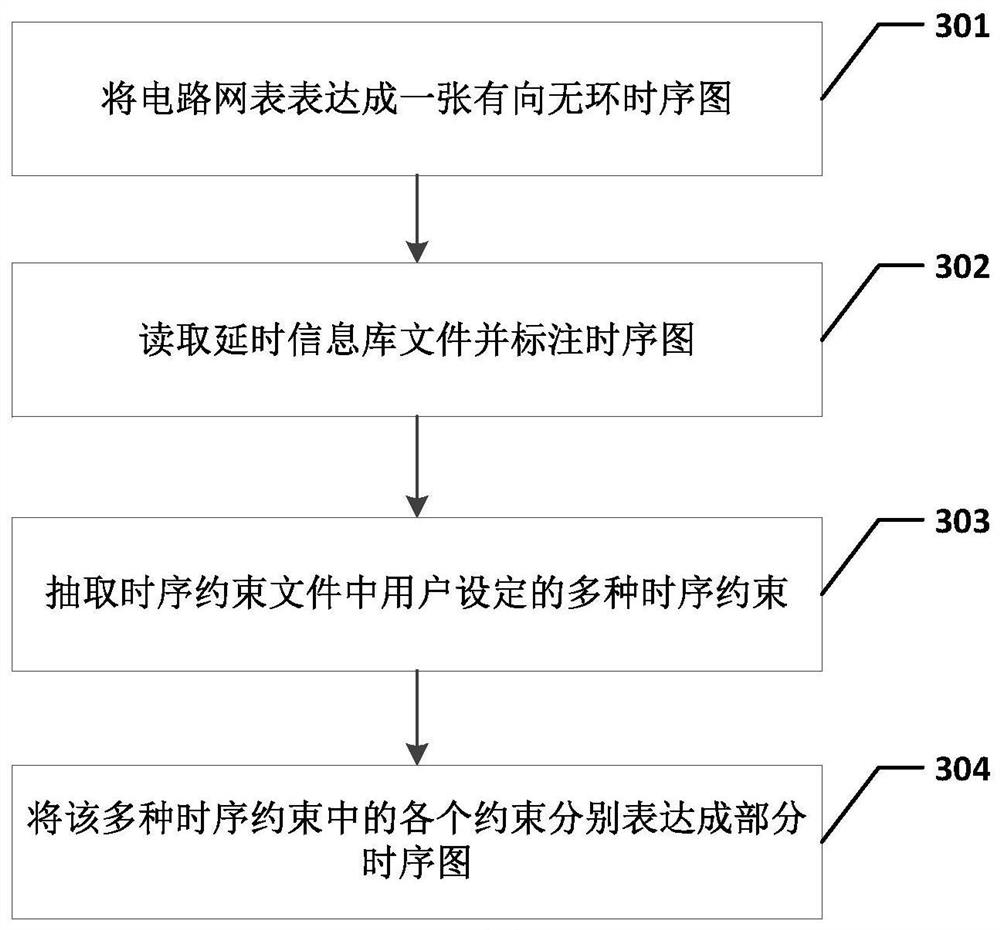

A memory optimization type static time sequence analysis method and system

ActiveCN109710998AIncrease space overheadReduced analysis efficiencySpecial data processing applicationsFalse pathAnalysis method

The invention relates to a digital circuit, and discloses a memory optimization type static time sequence analysis method and system. According to the method, on the premise that the subgraphs are notexpanded, in the traversing and scanning process, false paths are identified and discarded in real time, the influence of the false paths on downstream nodes is reduced, redundant calculation is reduced, meanwhile, multiple time sequence constraints on each node are dynamically and differentially processed in the traversing process, dichotomy coverage is correspondingly carried out, and the number of labels on each node is reduced. According to the application, occupation of system memory space can be greatly reduced, the system operation efficiency is improved, and the system performance isimproved.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

Model training method and device based on active learning and server

ActiveCN112434809AFlexible dockingReduce the number of labelsImage enhancementImage analysisEngineeringNetwork model

The embodiment of the invention provides a model training method and device based on active learning, and a server, and the method and device can automatically call a training sample of each application scene indicated by a started training task, and do not need a developer to manually export data for model training. After an initial deep learning network model matched with each application scenein advance is scheduled to perform sample labeling on training samples, an active learning service is scheduled to perform active screening on the labeled training samples, developers do not need to participate in labeling, the sample labeling number is effectively reduced, the active screening sample is calibrated according to a calibration instruction of a user, a training service associated with each application scene is flexibly scheduled to perform model training based on the calibrated active screening sample, and the model is published to a software application program corresponding toeach corresponding application scene; therefore, training services of different application scenarios can be flexibly docked, and automatic labeling, training and service updating of the training process are achieved.

Owner:CHENGDU DIANZE INTELLIGENT TECH CO LTD +1

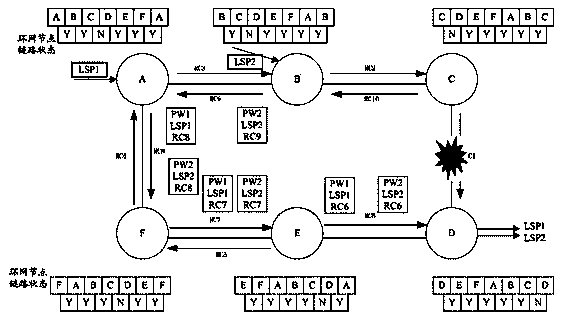

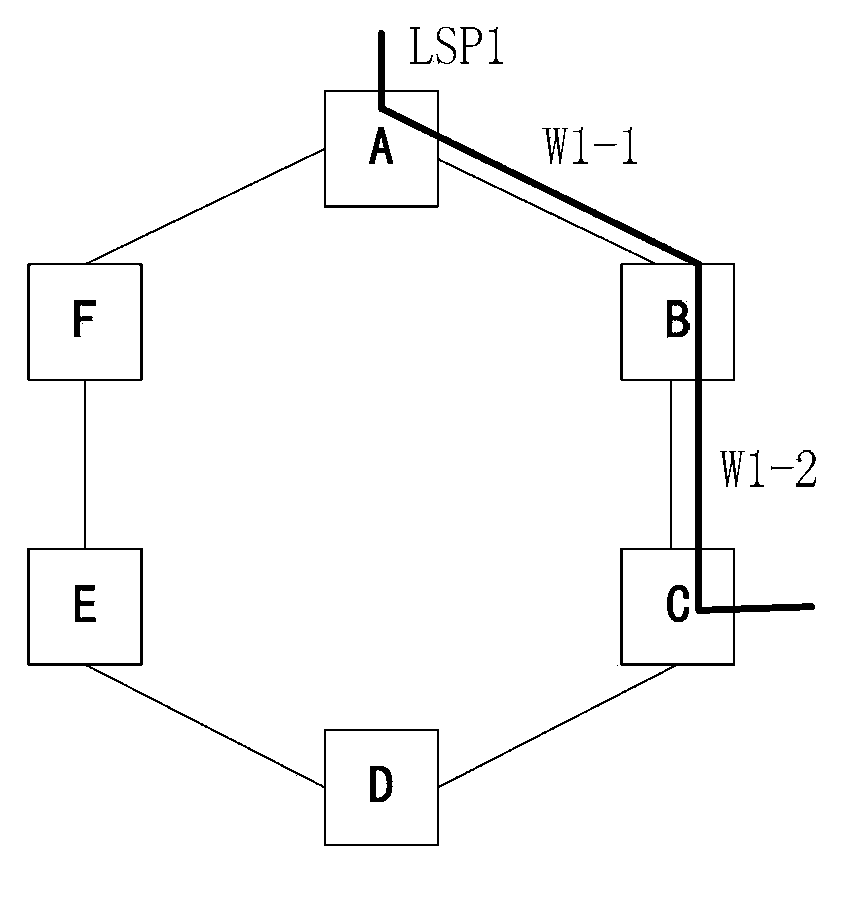

Method and device for realizing ring-network Steering protection

ActiveCN103795601AReduce configuration workloadReduce complexityData switching networksRing networkEngineering

The embodiment of the application discloses a method for realizing ring-network Steering protection. The method includes: establishing work channels and protection channels, which are corresponding to different nodes of a ring network; and according to the state of links of the nodes of the ring network, switching to a transmission network service of the work channels or the protection channels so as to realize the ring-network Steering protection. The embodiment of the application also provides a device for realizing the ring-network Steering protection and a method and device for realizing the ring-network Steering protection on the basis of an LSP service. The scheme of the embodiment of the invention reduces the number of the work channels and the protection channels so that the configuration workload and configuration complexity of the nodes of the ring network are reduced and hardware demands on network ring node devices are reduced.

Owner:CHINA MOBILE COMM GRP CO LTD

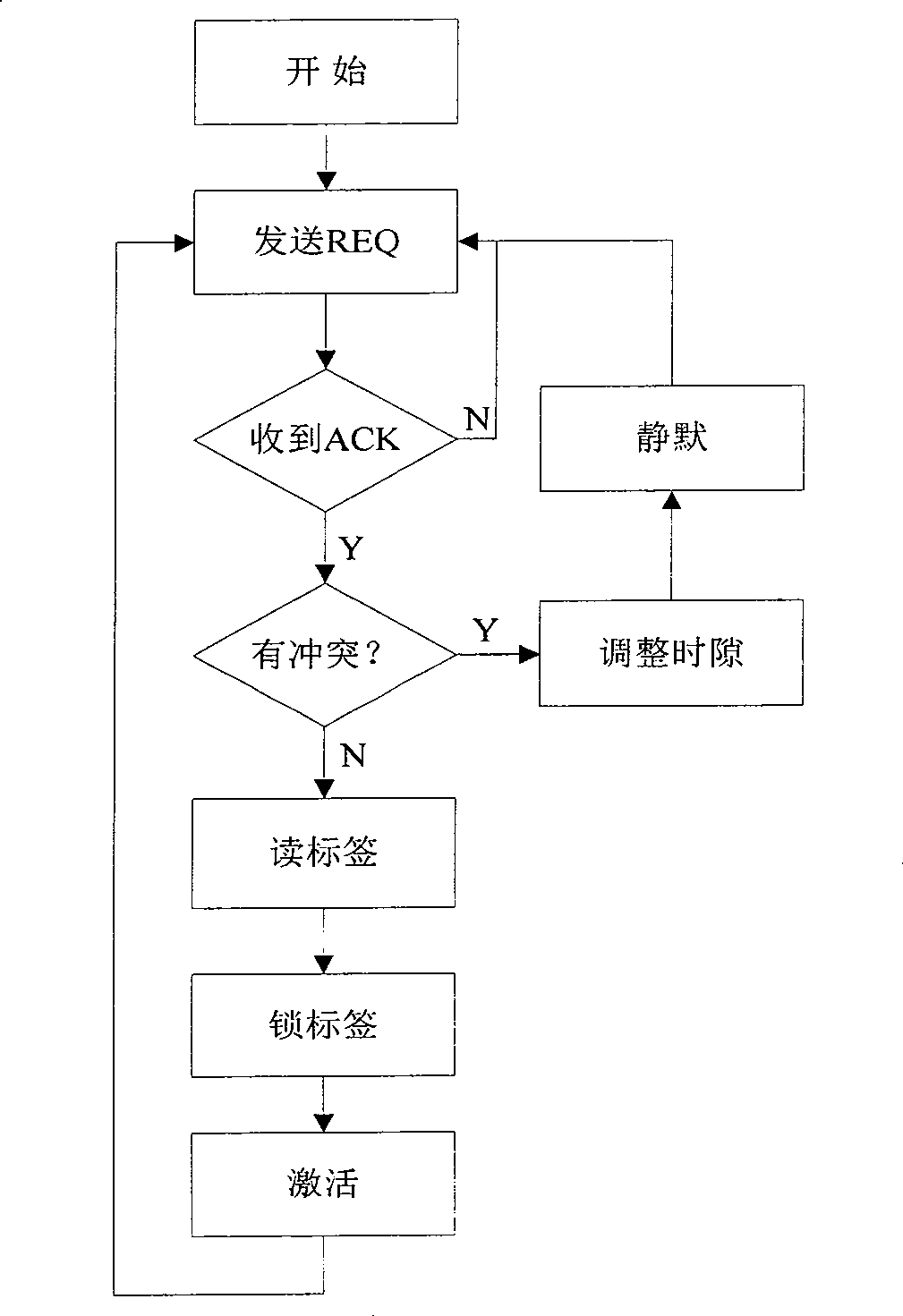

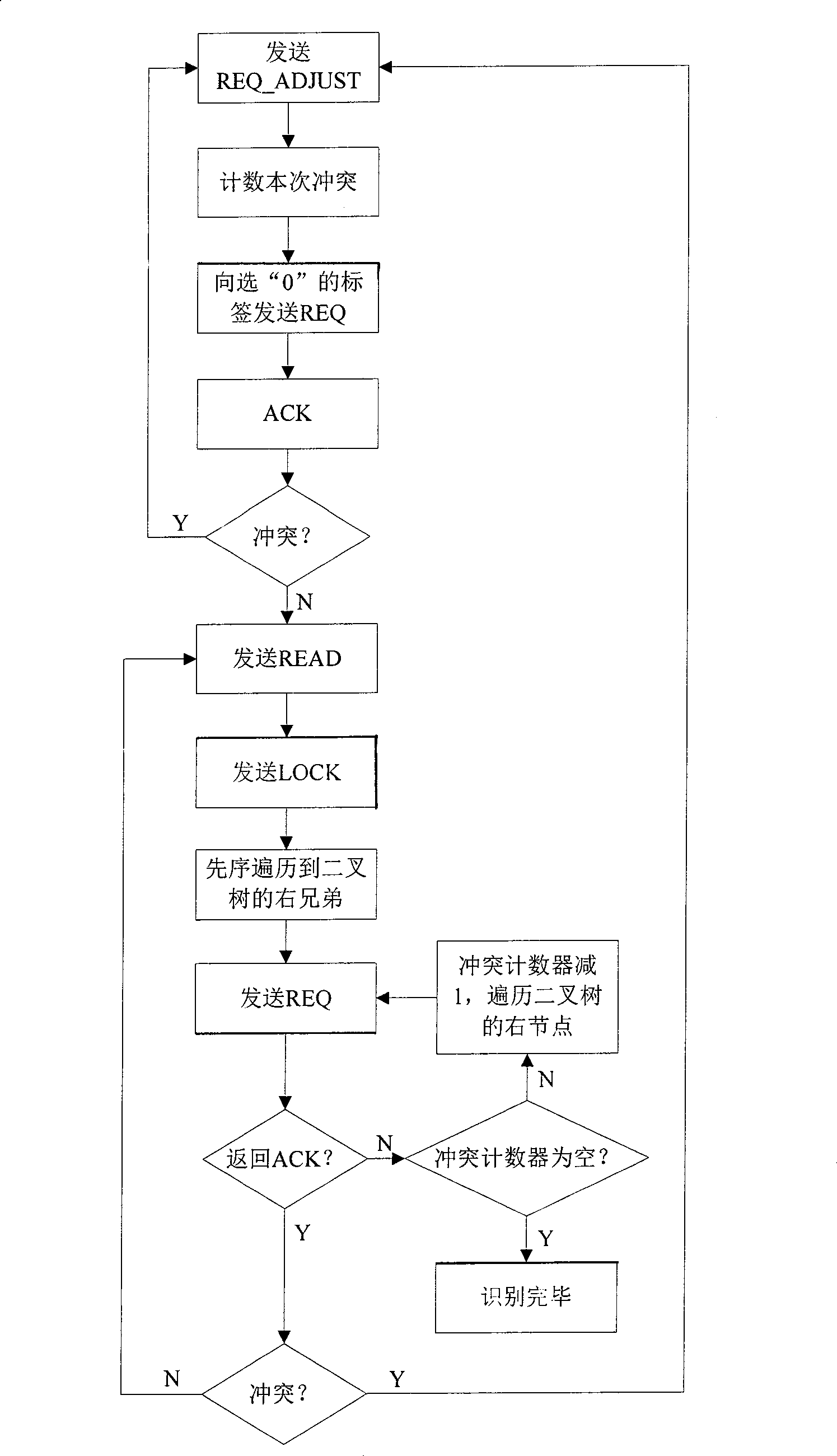

Multi-label anti-collision algorithm

ActiveCN101464940AImprove recognition efficiencyReduce distractionsSensing record carriersAlgorithmElectromagnetic environment

The invention provides a multi-label anti-collision algorithm, which comprises the following steps: resetting, transmitting inquiry commands of labels by a reader writer; judging the inquiry commands received by a responder, inquiring, responding and judging the labels received and signed by the reader writer; carrying out data processing to the responder by the reader writer; setting a pd value to 1, and setting Q value to Q; transmitting inquiry variation commands by the reader writer and back transmitting the inquiry variation commands by the responder; inquiring, responding and judging the labels received and signed by the reader writer; and carrying out data processing to the responder by the reader writer. Therefore, the algorithm can circulate in a quick exclusive manner, has the higher practical recognition efficiency to the collision labels and can rapidly reduce the quantity of responders in the working range of the reader writer; moreover, on one hand, the recognition efficiency is improved through reducing the quantity of the responders at a high speed, on the other hand, the disturbance of the electromagnetic environment in the working range of the reader writer can be reduced so as to further improve the recognition quantity.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

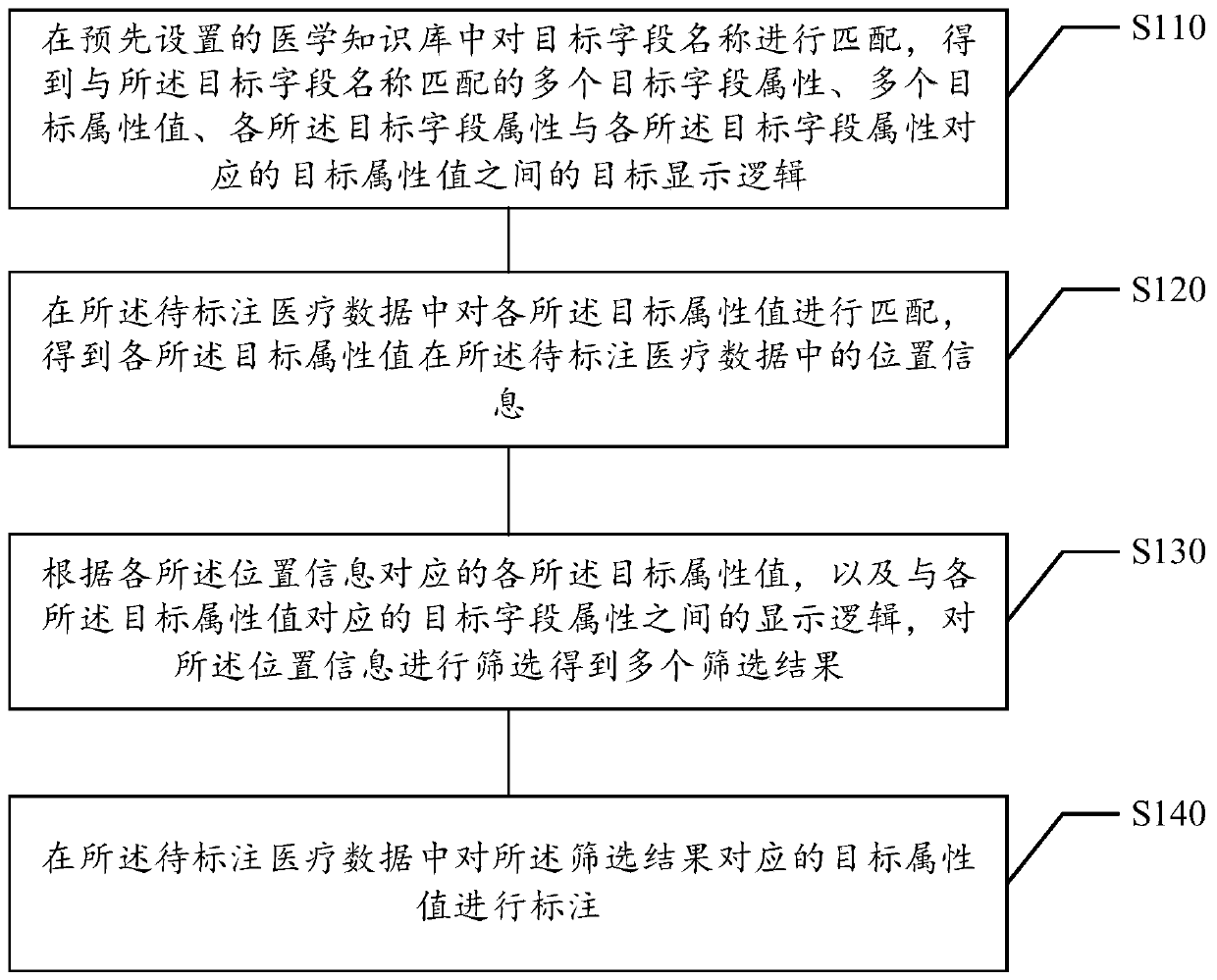

Medical data labeling method and device, storage medium and electronic equipment

ActiveCN111062193AReduce the number of labelsLow resolution accuracyNatural language data processingText database queryingMedical knowledgeEngineering

The embodiment of the invention relates to a medical data labeling method and device, a storage medium and electronic equipment, and belongs to the technical field of medical big data processing. Themethod comprises the following steps: matching target field names in a preset medical knowledge base to obtain a plurality of target field attributes matched with the target field names, a plurality of target attribute values, and target display logic between each target field attribute and a target attribute value corresponding to each target field attribute; matching the target attribute valuesin the to-be-labeled medical data to obtain position information of the target attribute values in the to-be-labeled medical data; screening the position information according to the target attributevalues corresponding to the position information and the target display logic between the target field attributes corresponding to the target attribute values to obtain a plurality of screening results; and labeling the target attribute value corresponding to the screening result in the to-be-labeled medical data. According to the embodiment of the invention, the accuracy of the marked target attribute value is improved.

Owner:YIDU CLOUD (BEIJING) TECH CO LTD

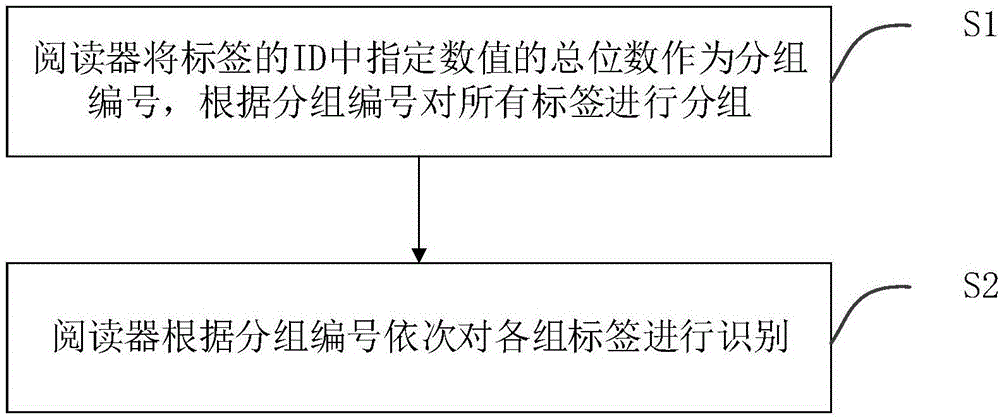

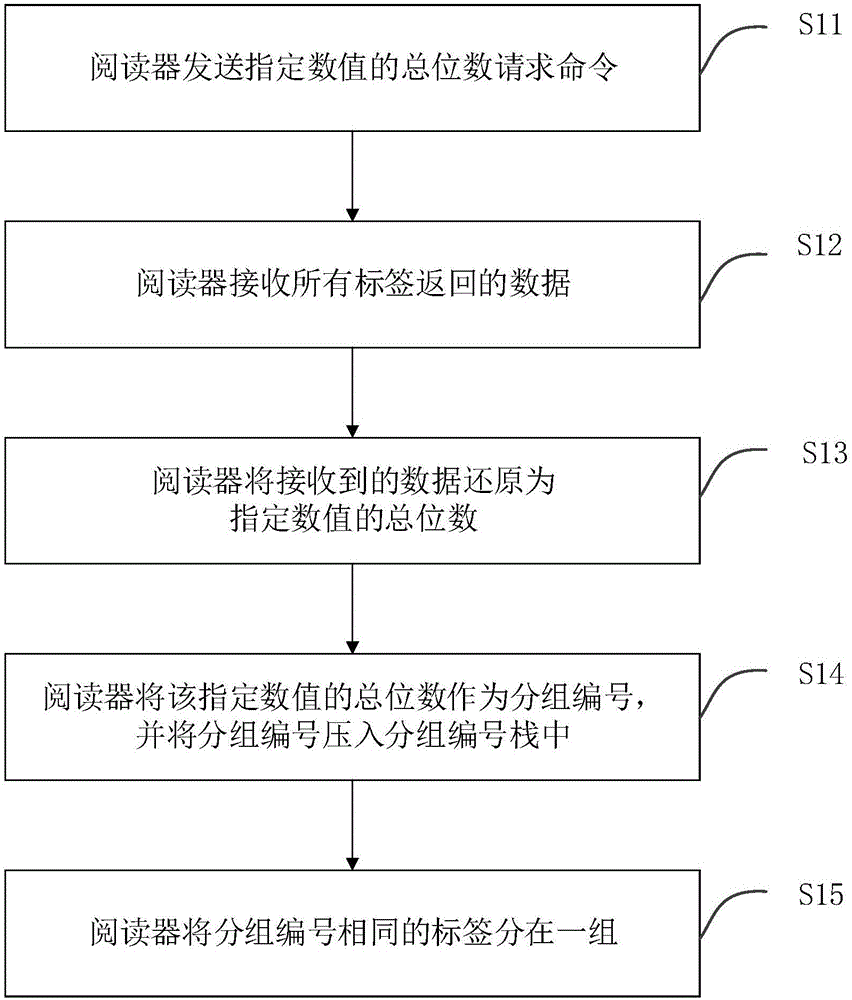

Method and system for preventing collision of RFID tags

ActiveCN107526986AReduce the probability of collisionImprove recognition efficiencySensing by electromagnetic radiationComputer scienceThroughput

The invention discloses a method and system for preventing collision of RFID tags. The method comprises the following steps that a reader uses the total number of digits of an assigned numerical value in the ID of a tag as a group number and groups all the tags according to the group numbers; and the reader successively recognizes the tags according to the group numbers. The method and system reduce the number of tags recognized by the reader at a time, reduces the collision probability of the tags, and improves the recognition efficiency of the reader. The method and system for preventing collision of RFID tags have high recognition efficiency, small system traffic and high system throughput, and can be widely applied in the technical field of RFID.

Owner:GUANGDONG AIB POLYTECHNIC COLLEGE

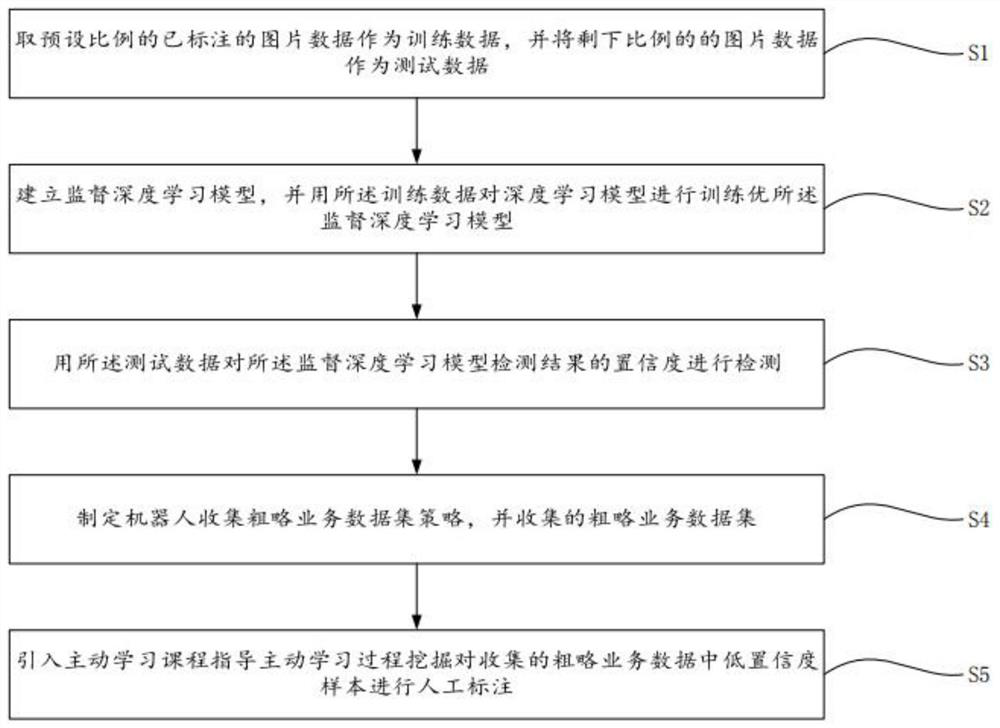

Robot data collection iterative training method and system based on active learning technology, and storage medium

PendingCN112906902AImprove effectivenessLow costCharacter and pattern recognitionMachine learningManual annotationData set

The invention discloses a robot data collection iterative training method and system based on an active learning technology and a storage medium. The method comprises the following steps: S1, taking labeled picture data in a preset proportion as training data, and taking picture data in a remaining proportion as test data; s2, establishing a supervised deep learning model, and training the deep learning model by using the training data to optimize the supervised deep learning model; s3, detecting the confidence coefficient of the detection result of the supervised deep learning model by using the test data; s4, formulating a strategy for collecting a rough service data set by the robot, and collecting the rough service data set; and S5, introducing an active learning course to guide active learning process mining to carry out manual annotation on low-confidence samples in the collected rough service data, and by means of the active learning technology, a semi-supervised robot data collection iteration system is realized, the effectiveness of data collection is greatly improved, and the cost of manual annotation is reduced.

Owner:SHANGHAI YOGO ROBOTICS CO LTD

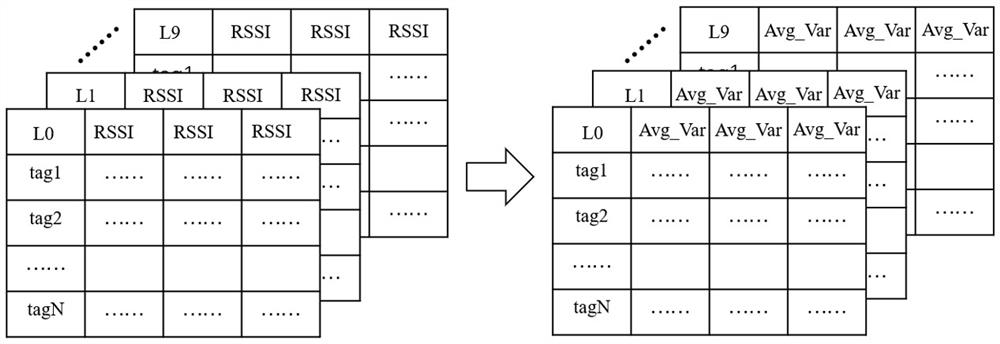

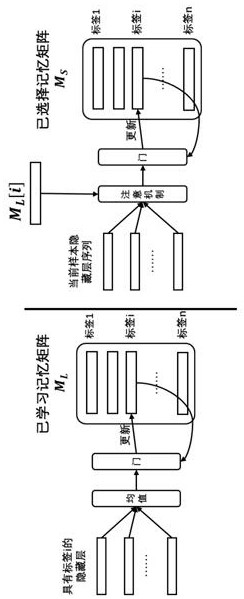

Optimal label selection method of RFID equipment-free human body tracking system

PendingCN113744318AIncrease flexibilityOvercome the problem of inconsistent lengthImage analysisCharacter and pattern recognitionHuman bodyFeature extraction

The invention discloses an optimal label selection method for an RFID equipment-free human body tracking system, which comprises the following steps: S1, region division: dividing a monitoring region into N positions; s2, feature extraction and calculation: extracting a mean value and a variance of T RSSIs sampled at each position within a period of time, and establishing a mapping relationship between the distribution of the RSSIs in the period of time and the positions of the RSSIs; s3, constructing a deep learning model, and analyzing a corresponding position sequence according to the RSSI sequence of the T, namely a real movement track of a human body; and S4, label layout mode selection: preferentially selecting labels according to the classification accuracy of the deep learning model for the positions. Through the deep learning model, while the human body tracking precision is maintained, the number of labels is reduced, the flexibility of the model is improved, precision reduction is avoided, the performance of processing a long-path sequence is improved, and the gap between training and inference of a position sequence prediction task is filled up.

Owner:ZHEJIANG UNIV OF TECH

Message transmission method and device

ActiveCN109873766AReduce the number of labelsNetworks interconnectionDistributed computingManet routing

The embodiment of the invention provides a message transmission method and device, and the method comprises the steps of obtaining a first message, and determining a forwarding entry corresponding tothe first message, wherein the forwarding table entries comprise a main path forwarding table entry and a standby path forwarding table entry, and an outbound interface included in the standby path forwarding table entry is a tunnel identifier of the TE tunnel; if the main path corresponding to the main path forwarding table entry fails and the second node is not the destination node correspondingto the destination address included in the first message, obtaining a segment routing label, pointing to the destination node, on the second node and a tunnel label corresponding to the TE tunnel from the standby path forwarding table entry; adding the segment routing label and the tunnel label in the first message to obtain a second message; and sending a second message to a second node throughthe TE tunnel corresponding to the tunnel identifier, so that the second node sends the second message to the destination node by using the segment routing label. Through the technical scheme providedby the embodiment of the invention, the message can be correctly forwarded through the standby path.

Owner:北京华三通信技术有限公司

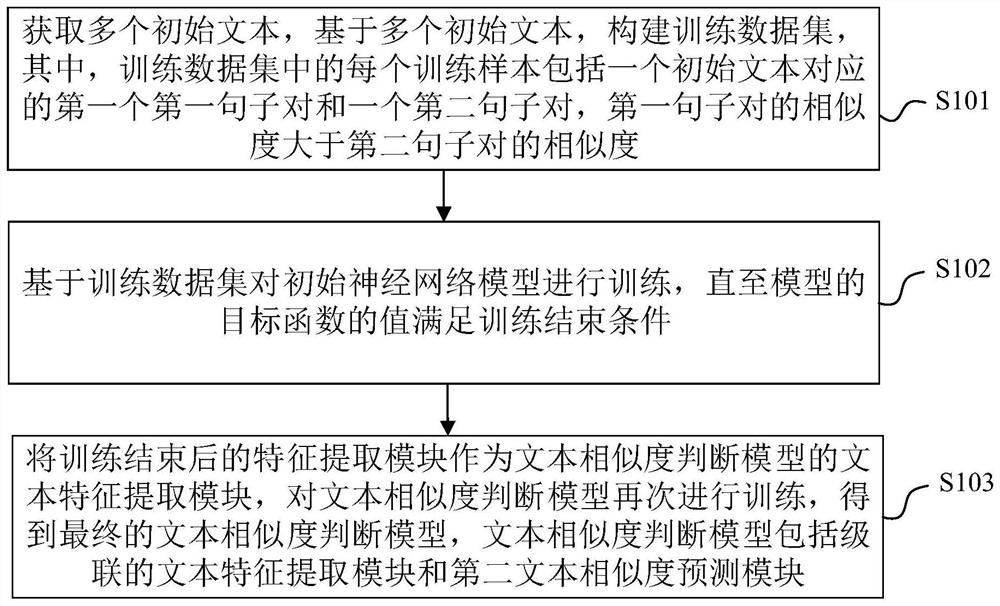

Text processing method and device, electronic equipment and readable storage medium

ActiveCN113761868AImprove retraining efficiencyReduce the number of labelsSemantic analysisNeural architecturesData setFeature extraction

The embodiment of the invention provides a text processing method and device, electronic equipment and a readable storage medium, and relates to the field of artificial intelligence, and the method comprises the steps: obtaining a plurality of initial texts, and constructing a training data set based on the plurality of initial texts; training the initial neural network model based on the training data set until a value of a target function of the model meets a training ending condition; using the feature extraction module after training is finished as a text feature extraction module of a text similarity judgment model, training the text similarity judgment model again, obtaining a final text similarity judgment model, and the text similarity judgment model comprises a text feature extraction module and a second text similarity prediction module which are cascaded. The training data set constructed in the embodiment of the invention is weak supervision text similar corpora, and label data does not need to be manually labeled, so that the manpower and time cost can be effectively saved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Entity recognition model training method and device, equipment and storage medium

ActiveCN112733911AReduce the number of labelsReduce in quantityCharacter and pattern recognitionNatural language data processingData setEngineering

The invention relates to the field of artificial intelligence, and discloses an entity recognition model training method, which comprises the steps of obtaining an incompletely labeled specified training sample; inputting the specified training sample into a probability prediction model to obtain label probabilities corresponding to all unlabeled characters in the specified training sample; according to the label probabilities corresponding to all the unlabeled characters in the specified training sample, obtaining a label sequence with the highest probability through calculation by means of a Viterbi algorithm; according to the label sequence with the highest probability, determining covering labels respectively corresponding to all unlabeled characters in the specified training sample; obtaining a label sequence set corresponding to the specified training sample according to the covering label; obtaining label sequence sets corresponding to all the training samples in the incomplete annotation data set according to the obtaining mode of the label sequence sets corresponding to the specified training samples; and under the constraint of a preset loss function, training an entity recognition model through the label sequence sets corresponding to all the training samples. And a real tag sequence can be identified more easily.

Owner:PING AN TECH (SHENZHEN) CO LTD

Preference prediction method and device and computer equipment

ActiveCN111291904AReduce the number of labelsLow costKernel methodsCharacter and pattern recognitionNode clusteringAlgorithm

The invention relates to a preference prediction method and device and computer equipment. The method comprises the steps of obtaining a network graph comprising combination nodes and edges, wherein the combination node is used for representing the combination of a user and an object, a part of combination nodes in the combination nodes carry the preference degree of the user in the represented combination to the object in the combination; dividing the network graph according to the combination similarity between the combination nodes of the building edges in the network graph to obtain at least one sub-network, wherein the same sub-network comprises combined nodes clustered into one class; and selecting a target preference degree corresponding to the combined node in the sub-network fromthe preference degrees carried by the combined node in the same sub-network. According to the scheme, the cost can be saved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

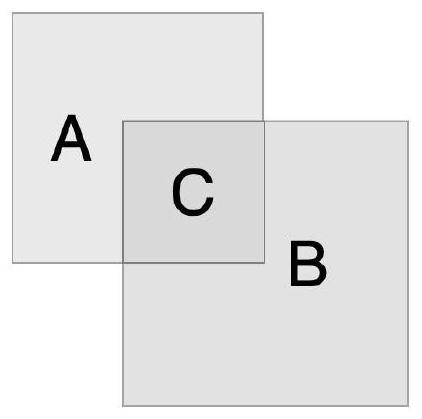

Intelligent RFID reading system anticonflict scheduling method

InactiveCN100461201CDeepReduce the number of labelsData switching by path configurationSensing record carriersEmbedded systemOperating system

The invention provides a scheduling method to prevent conflicts in intelligent RFID read system. The method utilize the mechanism that reader controls multiple antennas, which is: all the antennas are controlled by the reader in order; the reader polls the antennas connected to the reader, and control the interactive between the single antenna and label; each time only one antenna can be activated to respond instructions from the reader; every two antenna effective covered regions are connected to reduce the overlap. The invention uses multiple antennas, at any time only one antenna takes effect, and then labels are divided into groups to recognize. The number of labels in the coverage covered by one antenna is reduced, thus the probability of conflicts is effectively reduced.

Owner:SOUTH CHINA UNIV OF TECH

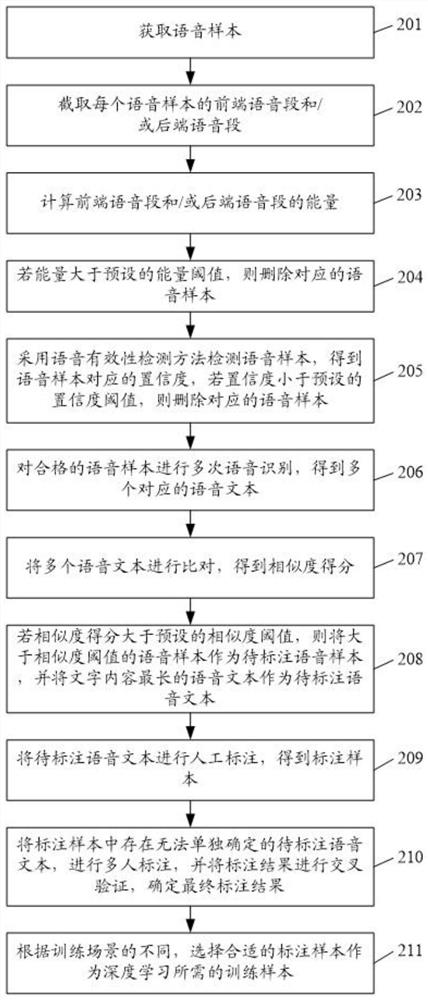

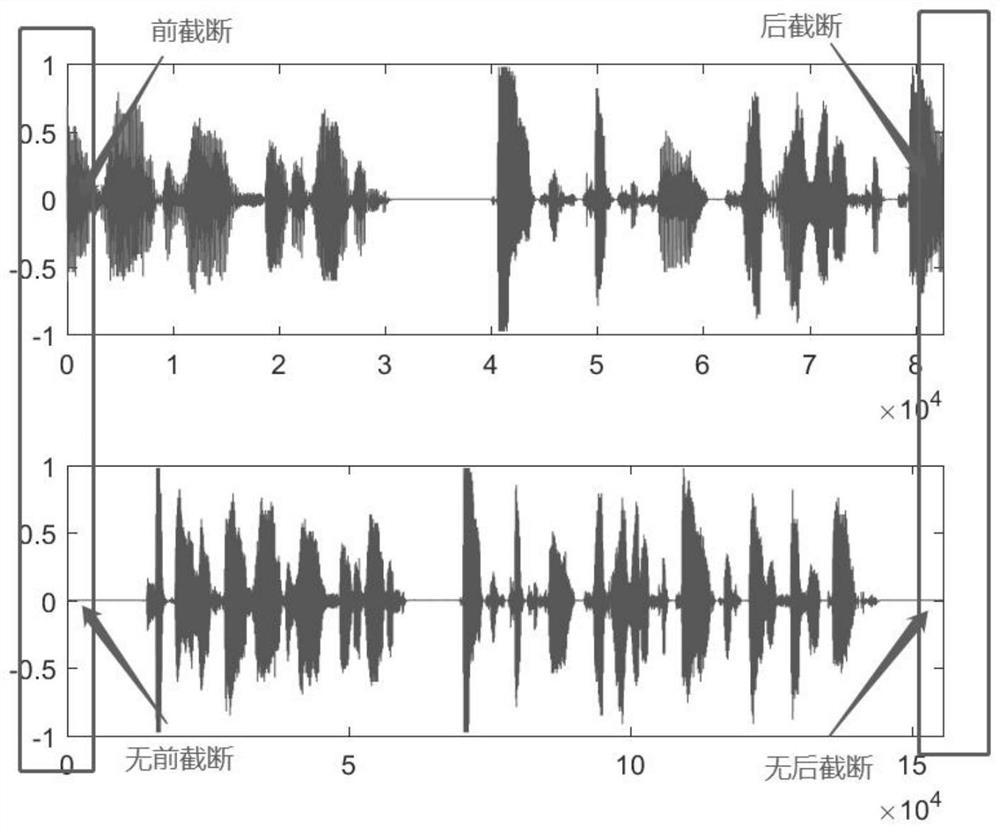

Corpus acquisition method and device

The invention discloses a corpus acquisition method and device. The method comprises the following steps: acquiring a voice sample; filtering truncated voice and invalid voice in the voice sample to obtain a qualified voice sample; performing multiple voice recognition on the qualified voice sample to obtain a plurality of corresponding voice texts; comparing the plurality of voice texts to obtain a similarity score; if the similarity score is greater than a preset similarity threshold value, taking the voice sample greater than the similarity threshold value as a voice sample to be labeled, and taking the voice text with the longest text content as a voice text to be labeled; and performing manual annotation on the to-be-annotated voice text to obtain an annotated sample. The invention solves the technical problems of long time period and high cost of obtaining voice samples for training in the prior art.

Owner:广州欢城文化传媒有限公司

Memory-optimized static timing analysis method and system

ActiveCN109710998BIncrease space overheadReduced analysis efficiencyComputer aided designSpecial data processing applicationsPathPingAlgorithm

The invention relates to a digital circuit, and discloses a memory optimization type static time sequence analysis method and system. According to the method, on the premise that the subgraphs are notexpanded, in the traversing and scanning process, false paths are identified and discarded in real time, the influence of the false paths on downstream nodes is reduced, redundant calculation is reduced, meanwhile, multiple time sequence constraints on each node are dynamically and differentially processed in the traversing process, dichotomy coverage is correspondingly carried out, and the number of labels on each node is reduced. According to the application, occupation of system memory space can be greatly reduced, the system operation efficiency is improved, and the system performance isimproved.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

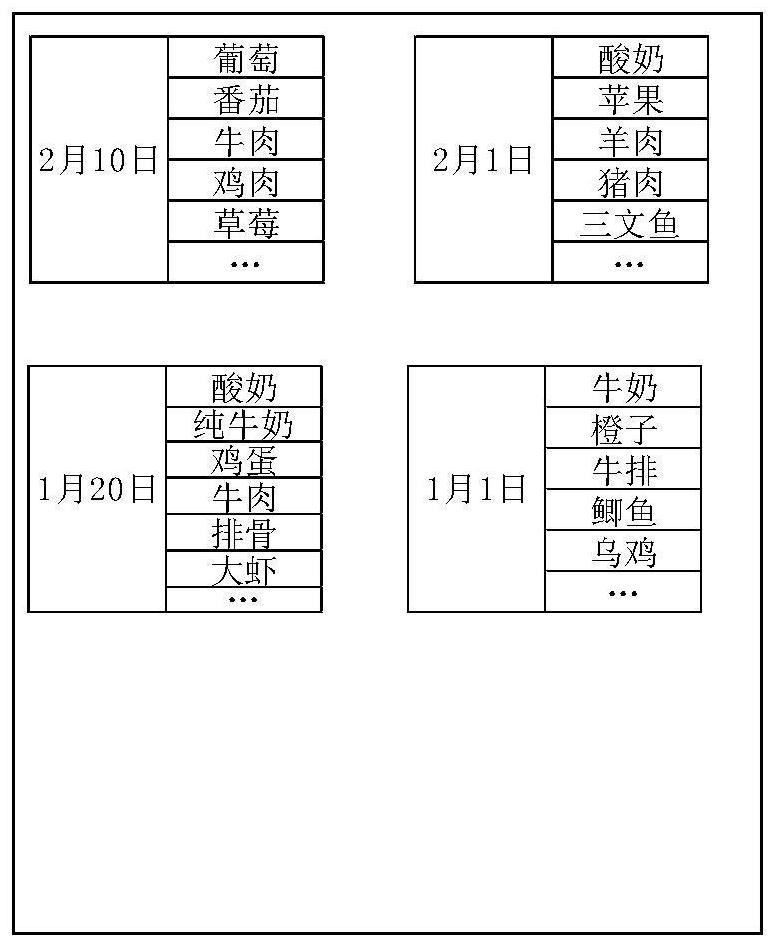

Refrigerator and food material management method

PendingCN113915939AReduce the number of labelsReduce the chance of not being identifiedLighting and heating apparatusCooling fluid circulationProcess engineeringIcebox

The invention discloses a refrigerator. The refrigerator comprises a refrigerator body internally provided with at least one storage chamber; and a refrigerator door arranged at the opening of the storage chamber, wherein an antenna and a display screen are arranged on the refrigerator door. A controller is configured to respond to label identification operation of the antenna, generate a corresponding food material control after obtaining food material information of all food materials corresponding to a newly-added label according to a preset label coding rule, and then update a food material management interface in the display screen according to the food material control. The invention further discloses a food material management method. By adopting the refrigerator and the food material management method, the food material information of various food materials is recorded in one RFID tag according to the preset tag coding rule, so that the excessive tag number in the refrigerator caused by one-to-one correspondence of the food materials and the tags is reduced, the probability that the tags are not identified due to shielding is reduced, and the accuracy of food material management is improved.

Owner:HISENSE(SHANDONG)REFRIGERATOR CO LTD

Path establishment method, device and network node

ActiveCN107623633BImprove creation efficiencySolve problems that do not meet needsNetwork connectionsForwarding equivalence classDistributed computing

The present invention provides a path establishment method, device, and network node, wherein the method includes: on the first node on the path from the entry node to the exit node, forwarding the incoming label and The / or outgoing label is used as the incoming label and / or outgoing label of the parasitic FEC of the egress node, and an MPLS-based label switching path LSP corresponding to the parasitic FEC is established. The present invention solves the problem that label resources cannot meet requirements in related technologies, achieves the effects of saving label resources and improving the efficiency of MPLS LSP creation.

Owner:ZTE CORP

distribution method, asbr, pe and distribution system

ActiveCN105634950BReduce the number of labelsRelieve stressNetworks interconnectionDistribution methodDistribution system

The invention provides a VPN route label distribution method, ASBR, PE and a distribution system, the method comprising: receiving a VPN route update message; judging whether to assign a label for a new VPN route according to the VPN route update message; if necessary, assigning a new VPN route Label. Through the implementation of the present invention, after receiving the VPN route update message, it is first judged whether a label needs to be allocated for the new VPN route, and only when necessary, the label is allocated, which is different from the prior art after receiving the VPN route update message. Compared with assigning labels for VPN routes, the number of labels for VPN routes can be reduced, which relieves the pressure on ASBRs.

Owner:ZTE CORP

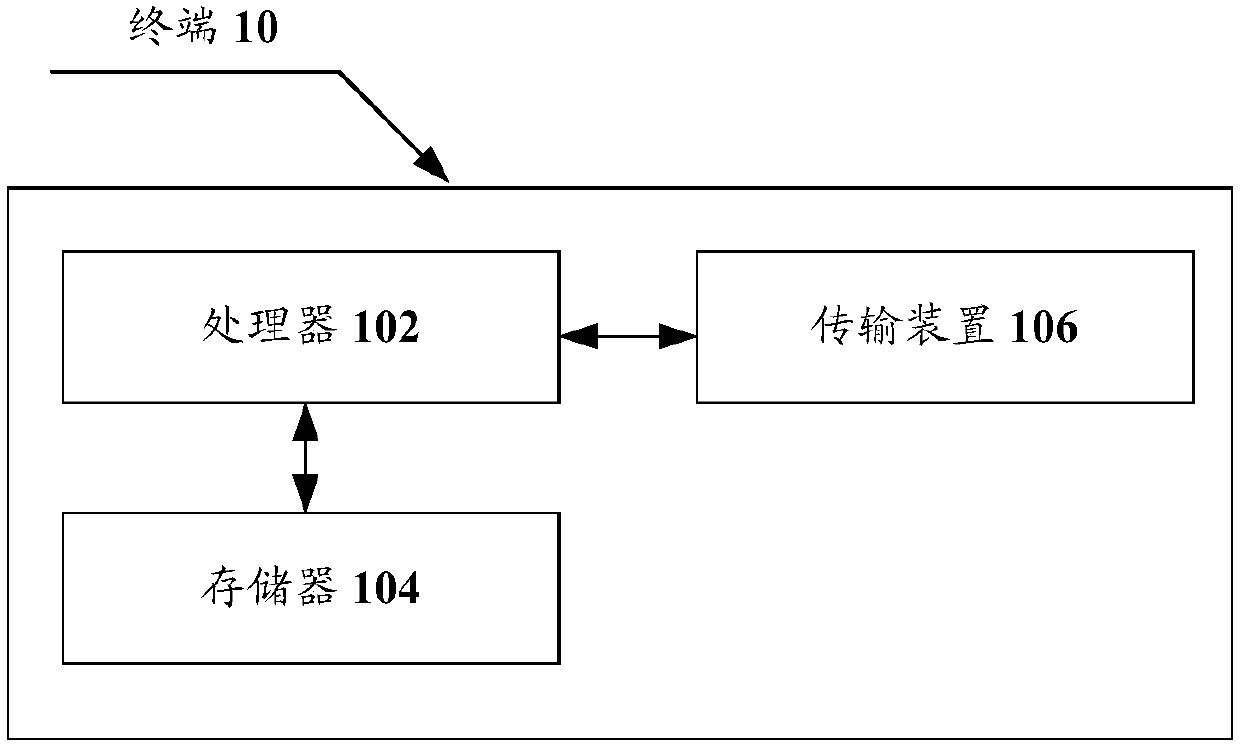

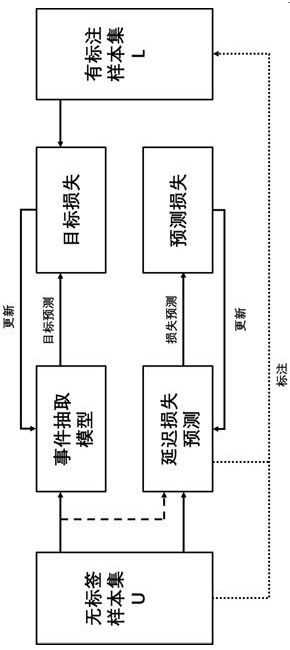

Active Learning Event Extraction Method Based on Memory Loss Prediction and Delayed Training

ActiveCN112966115BReduce the number of labelsReduce computational complexityNatural language data processingMachine learningEngineeringSupervised learning

Owner:SOUTHEAST UNIV

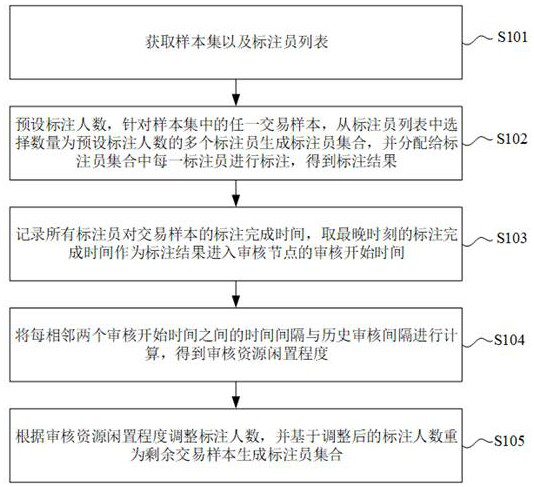

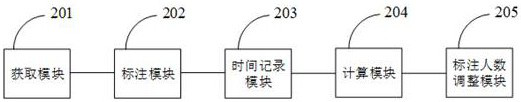

Sample labeling resource allocation method, device and application

ActiveCN114219501BAvoid idlingImprove accuracyFinanceSpecial data processing applicationsRisk ControlCompletion time

This application proposes a sample tagging resource allocation method, device and application. The number of taggers is preset. For any transaction sample in the sample set, multiple taggers with the preset number of taggers are selected from the tagger list to generate taggers. Collect and assign to each annotator in the annotator set to annotate to obtain the annotating result; record the annotating completion time of all annotators on the transaction samples, and take the latest annotating completion time as the audit start time when the annotating result enters the audit node; Calculate the time interval between two adjacent audit start times and the historical audit interval to obtain the idleness of audit resources; adjust the number of markers according to the idleness of audit resources, and re-generate markers for the remaining transaction samples based on the adjusted number of markers member assembly. Through the present invention, the allocation of sample labeling resources can be automatically performed based on various risk control rules, which replaces the existing manual screening method, so the accuracy and efficiency are higher.

Owner:杭州衡泰技术股份有限公司

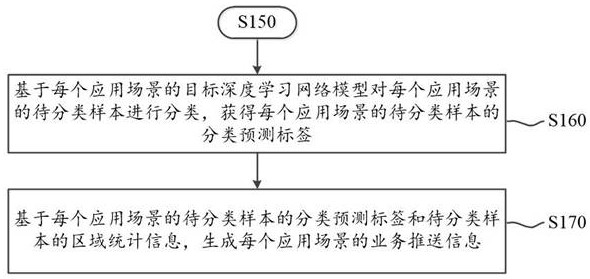

Model training method, device and server based on active learning

ActiveCN112434809BFlexible dockingReduce the number of labelsImage enhancementImage analysisEngineeringNetwork model

Embodiments of the present application provide a model training method, device, and server based on active learning, which can automatically retrieve training samples for each application scenario indicated by the started training task, without the need for developers to manually export data for model training. After the initial deep learning network model pre-matched with each application scenario labels the training samples, the active learning service is dispatched to actively screen the labeled training samples, without the need for developers to participate in labeling, thereby effectively reducing the number of sample labels. After the active screening samples are calibrated according to the user's calibration instructions, the training service associated with each application scenario can be flexibly scheduled to perform model training based on the calibrated active screening samples and released to the corresponding software application for each application scenario. Furthermore, training services of different application scenarios can be flexibly connected, and automatic labeling, training and business updates of the training process can be realized.

Owner:CHENGDU DIANZE INTELLIGENT TECH CO LTD +1

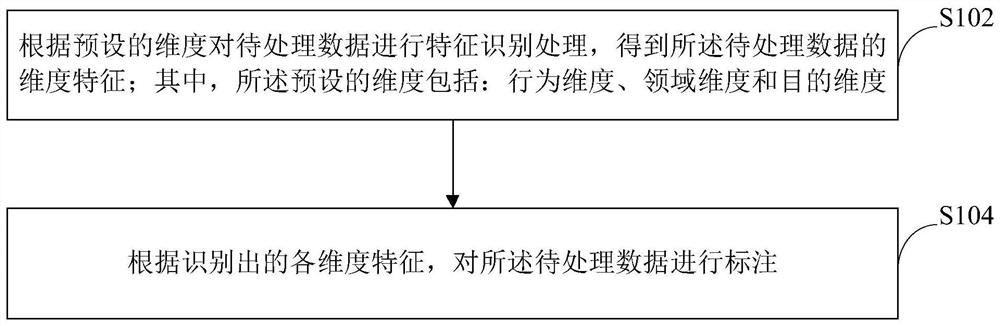

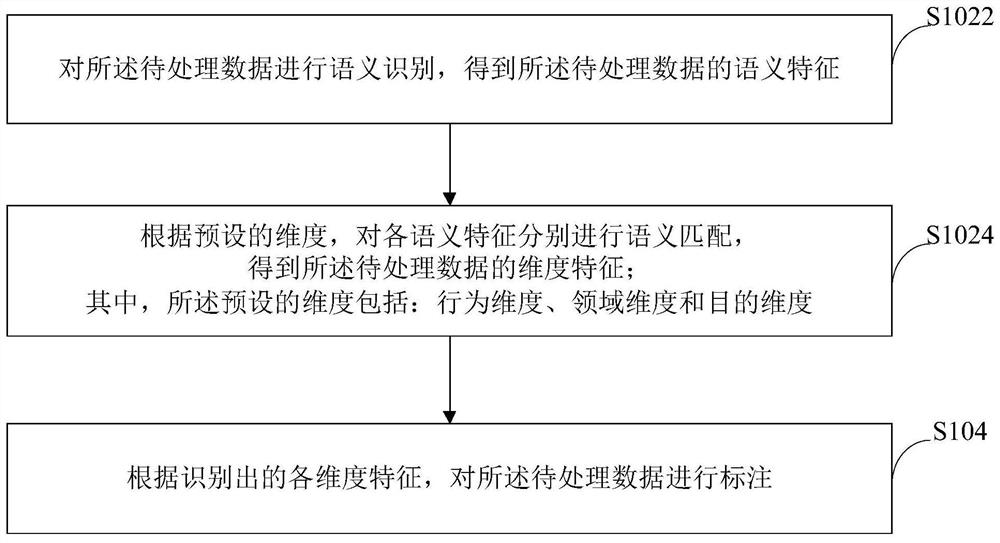

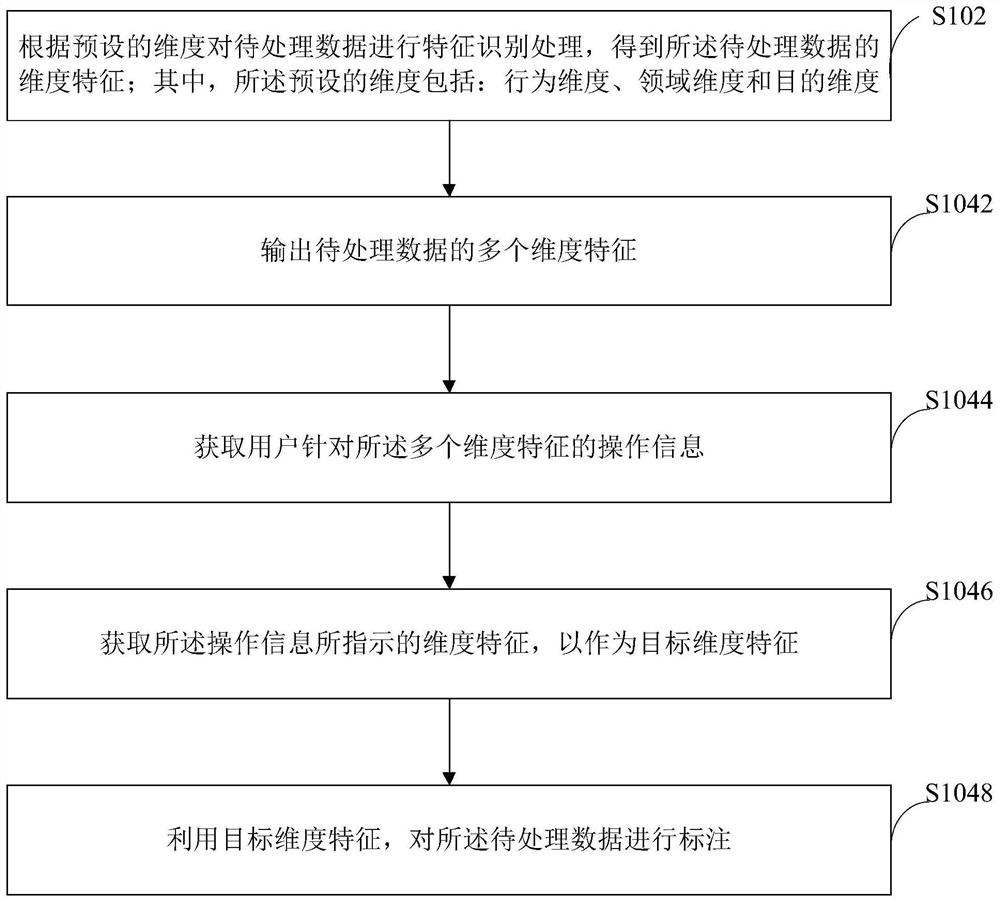

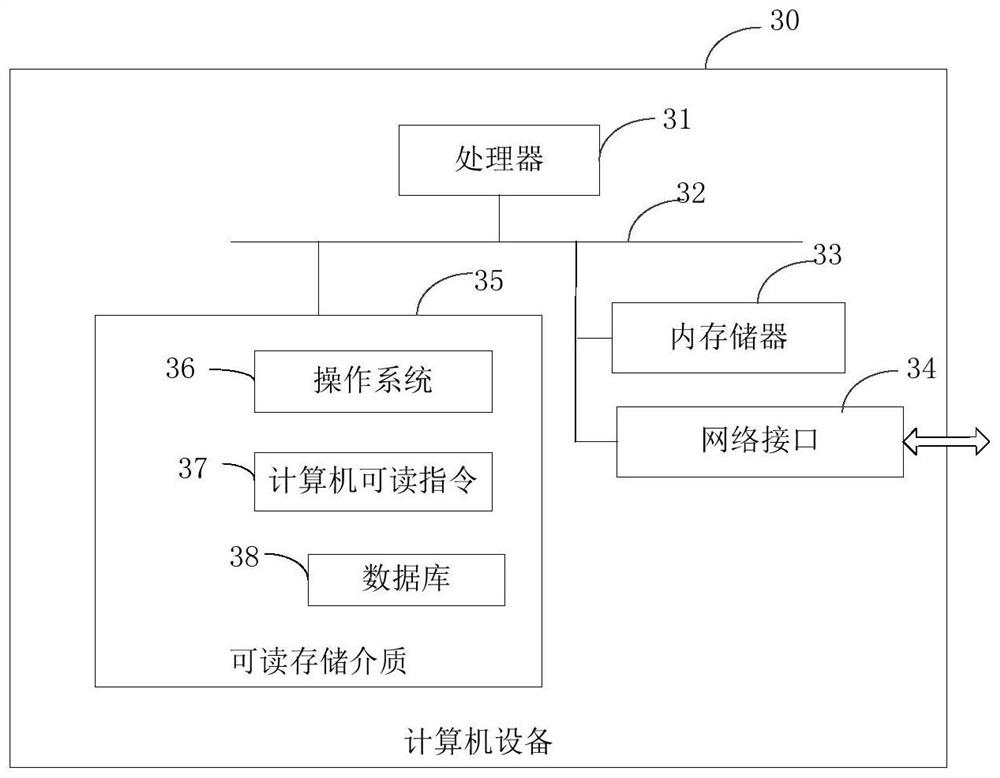

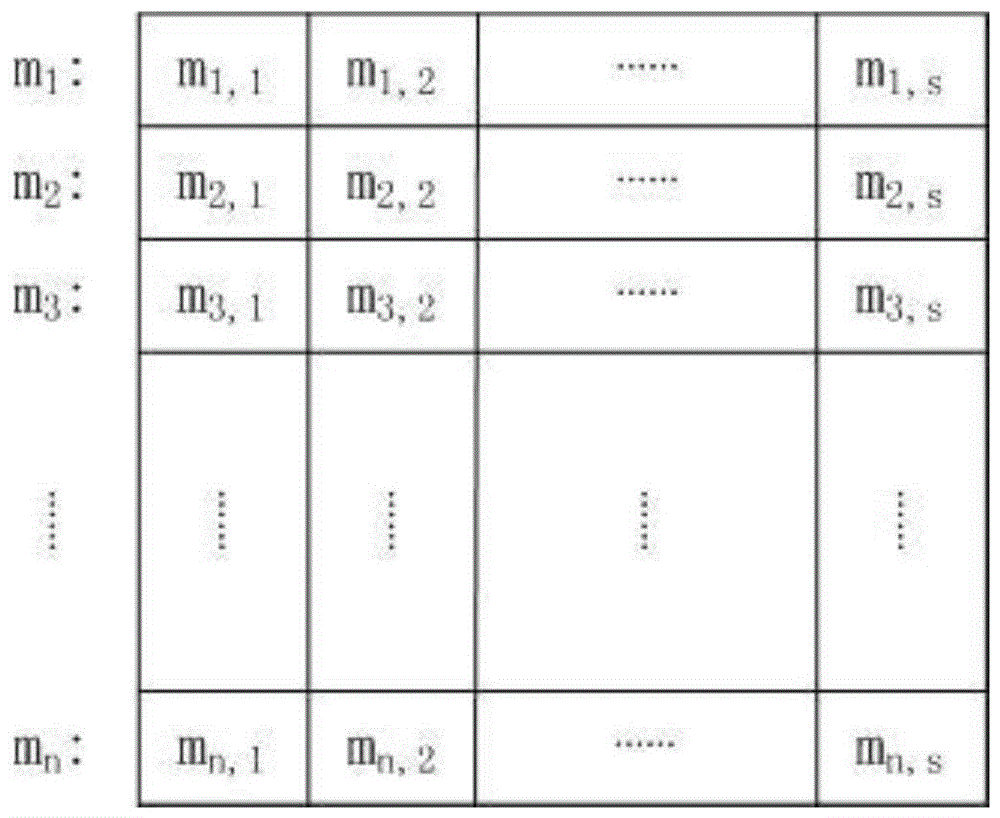

Data processing method and device, storage medium

ActiveCN109840274BReduce adverse effectsReduce the number of labelsDigital data information retrievalSpecial data processing applicationsAlgorithmData mining

The invention provides a data processing method and device, and a storage medium. The method includes: performing feature recognition processing on the data to be processed according to preset dimensions to obtain the dimensional features of the data to be processed; wherein, the preset dimensions include: behavior dimension, field dimension and purpose dimension; thus, according to the identification Label the data to be processed based on the obtained dimensional features. The technical scheme provided by the invention can reduce the labeling cost and improve the processing capacity.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

A method and device for realizing ring network steering protection

ActiveCN103795601BReduce configuration workloadReduce complexityData switching networksEngineeringWorkload

The embodiment of the present application discloses a method for implementing ring network Steering protection. The method includes: establishing a working channel and a protection channel corresponding to each node of the ring network; switching to the working channel or the protection channel to transmit network services according to the state of the links of the ring network nodes to realize the ring network Steering protection. The embodiment of the present application also provides a device for realizing ring network Steering protection, a method and a device for realizing ring network Steering protection based on LSP services. The solutions of the embodiments of the present application reduce the number of working channels and protection channels, thereby reducing the configuration workload and complexity of each node of the ring network, and reducing the hardware requirements for ring network node devices.

Owner:CHINA MOBILE COMM GRP CO LTD

Message transmission method and device

ActiveCN109873766BReduce the number of labelsNetworks interconnectionDistributed computingManet routing

The embodiment of the present application provides a message transmission method and device, the method includes: obtaining the first message, and determining the forwarding entry corresponding to the first message; the forwarding table includes the main path forwarding entry and the standby path Publication item, the outgoing interface included in the standby path forwarding table item is the tunnel identifier of the TE tunnel; if the main path corresponding to the main path forwarding table item fails, and the second node is not the destination node corresponding to the destination address included in the first message, Then obtain the section routing label pointing to the destination node on the second node and the tunnel label corresponding to the TE tunnel from the standby path forwarding table item; add the section routing label and the tunnel label in the first message to obtain the first Second message: sending the second message to the second node through the TE tunnel corresponding to the tunnel identifier, so that the second node uses the segment routing label to send the second message to the destination node. Through the technical solution of the embodiment of the present application, the message can be correctly forwarded through the standby path.

Owner:北京华三通信技术有限公司

A weakly supervised deep station logo detection method

ActiveCN107330027BHigh-precision detectionImprove data processing efficiencyVideo data browsing/visualisationCharacter and pattern recognitionPattern recognitionStation

The invention provides a weakly supervised in-depth station logo detection method, the steps of which are: preprocessing massive network video data files to obtain a large data set that only marks the station logo category and a small data set that only marks the station logo position ; Input the above-mentioned small data set into the station logo positioning network for training, and obtain a station logo positioning network capable of predicting the station logo area; input the above-mentioned large data set into the above-mentioned trained station logo positioning network, and obtain each piece in the large data set Some predicted station logo regions of the picture, and several predicted station logo regions of each picture are input into the station logo classification network for training, and the station logo classification network that can be classified as the station logo is obtained; the video to be detected is carried out with the same part as above Preprocessing, and inputting the image obtained after preprocessing into the trained station logo positioning network to obtain the predicted station logo area of the picture; inputting the predicted station logo area of the above picture into the trained station logo classification network to obtain the image's predicted station logo area The location and category of the station logo.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

Word vector generation method and device, computer equipment and storage medium

PendingCN114722802AReduce the number of labelsImprove training efficiencySemantic analysisText corpusComputer device

The invention relates to an artificial intelligence technology, and provides a word vector generation method and device, computer equipment and a storage medium, and the method comprises the steps: training a word in a corpus through a preset model, and obtaining an initialization vector of the word in the corpus; the candidate words of the to-be-constructed word vector words generated based on the initialization vectors of the words are sorted through the preset sorting model to obtain the positive correlation set and the negative correlation set of the to-be-constructed word vector words, and the candidate words are sorted, so that the number of annotations of the words is reduced, the training efficiency of the model is improved, and the training efficiency of the model is improved. The positive correlation set and negative correlation set samples are obtained through the preset sorting model, the quality of the samples is improved, the high-quality samples are sent into the contrast learning model for training, and the generation quality of the word vector of the word vector word to be constructed is improved.

Owner:PING AN TECH (SHENZHEN) CO LTD

Cloud storage data audit method against key leakage

The invention provides a cloud storage data auditing method for preventing a secret key from being revealed. The method comprises the first step of system parameter generating, the second step of secret key updating and the third step of file uploading and auditing. According to the method, a physically safe safety device is introduced to help a user to periodically update the secret key, and therefore data auditing in other time periods is still safe even when an attacker attacks the user at one time period and obtains the user secret key at the time period.

Owner:SHANDONG ZHENGZHONG COMP NETWORK TECH CONSULTING

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com