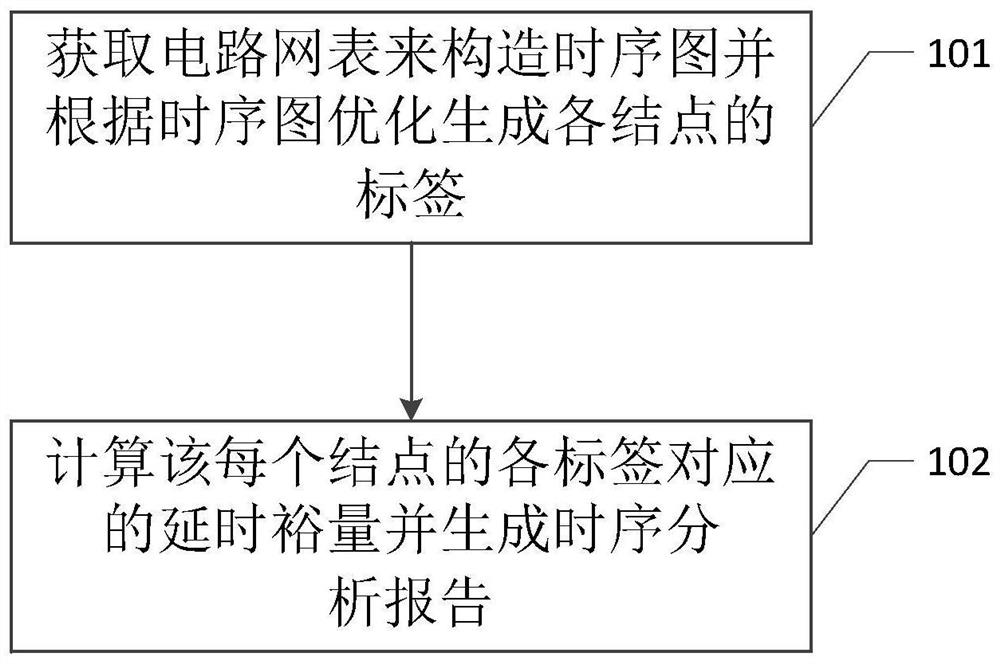

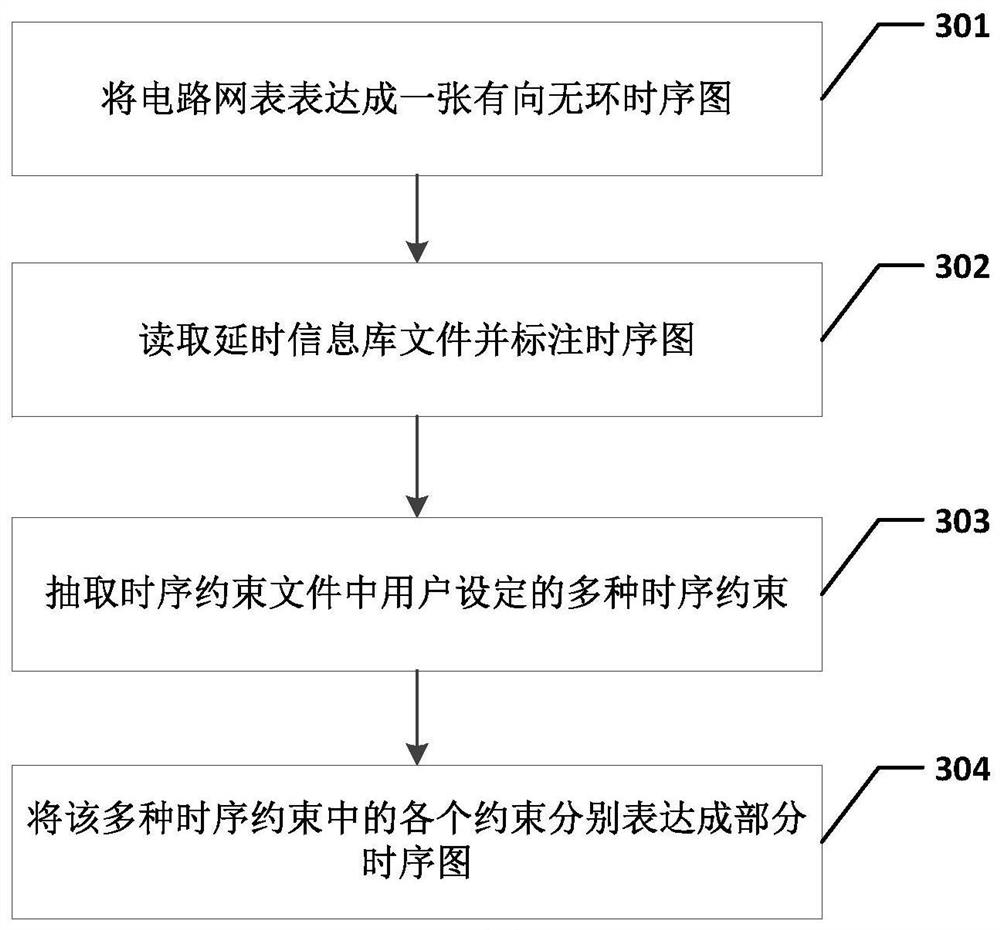

Memory-optimized static timing analysis method and system

A static timing analysis and memory technology, applied in the direction of instruments, computing, electrical digital data processing, etc., can solve the problem of large memory consumption, achieve the effect of reducing the number of tags, improving analysis efficiency, and reducing the occupation of memory space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In the following description, numerous technical details are set forth in order to provide the reader with a better understanding of the present application. However, those of ordinary skill in the art can understand that even without these technical details and various changes and modifications based on the following embodiments, the technical solutions claimed in the present application can be realized.

[0056] Explanation of some concepts:

[0057] 1. Static timing analysis: In electronic engineering, the calculation and prediction of the timing of digital circuits are performed. This process does not need to be simulated by input excitation. Traditionally, people often regard the operating clock frequency as one of the characteristics of high-performance integrated circuits. In order to test the ability of a circuit to operate at a specified rate, one needs to measure the delay of the circuit at various stages of operation during the design process. In addition, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com