High-voltage bipolar-CMOS-DMOS integrated circuit devices and modular methods of forming the same

a technology of integrated circuit devices and bipolar cmos, which is applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of incompatibility between high-temperature diffusion and epitaxy employed in epi-ji processes, the inability to manufacture dissimilar devices using one common process, and the inability to completely isolate devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

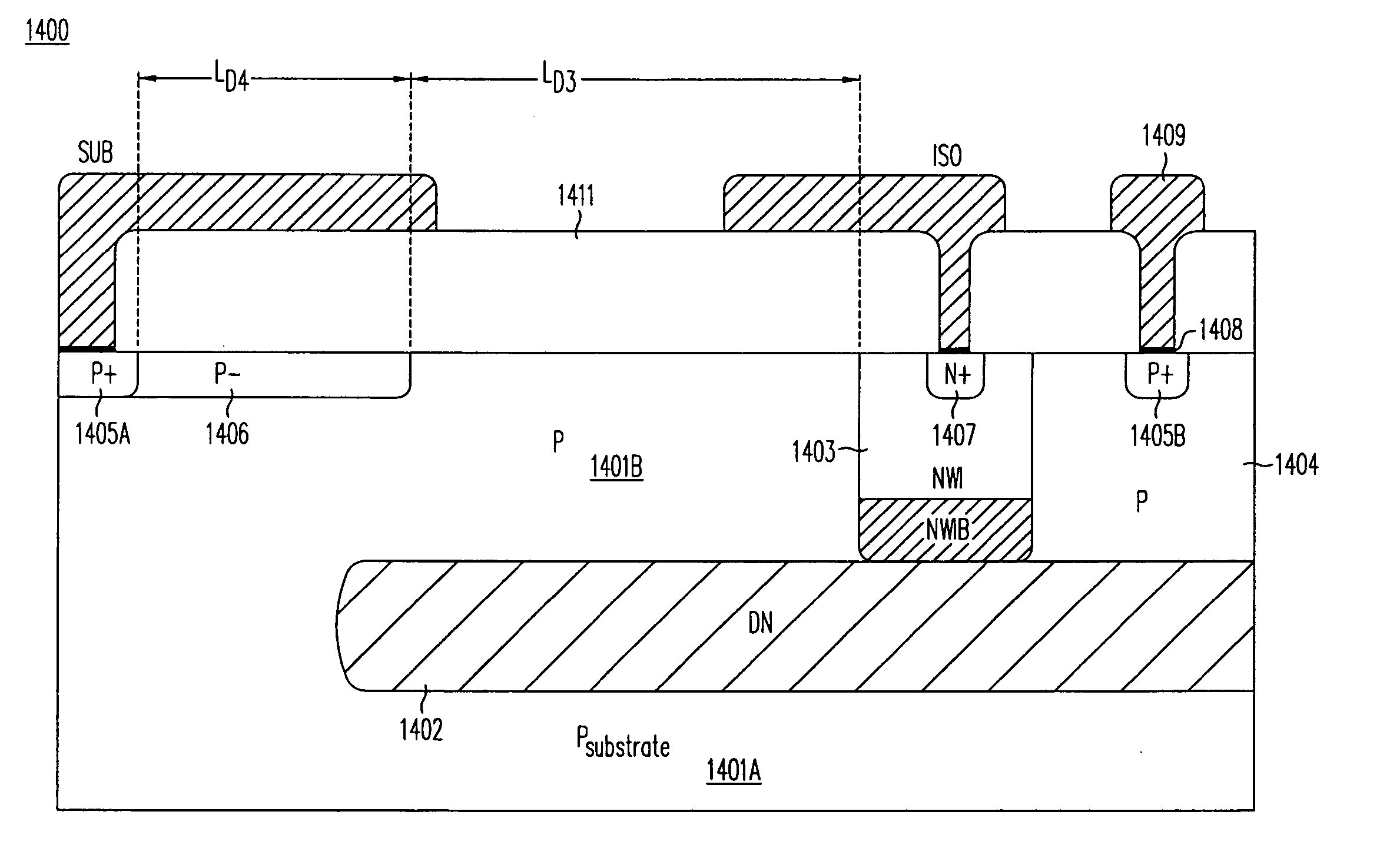

[0096] U.S. Pat. No. 6,855,985 describes an all low-temperature fabrication method using as-implanted junction isolation structures. This method employs high-energy and chain implants with dopant implanted through contoured oxides to achieve fully-isolated bipolar, CMOS and DMOS devices without the need for isolation diffusions, epitaxy or high temperature processes.

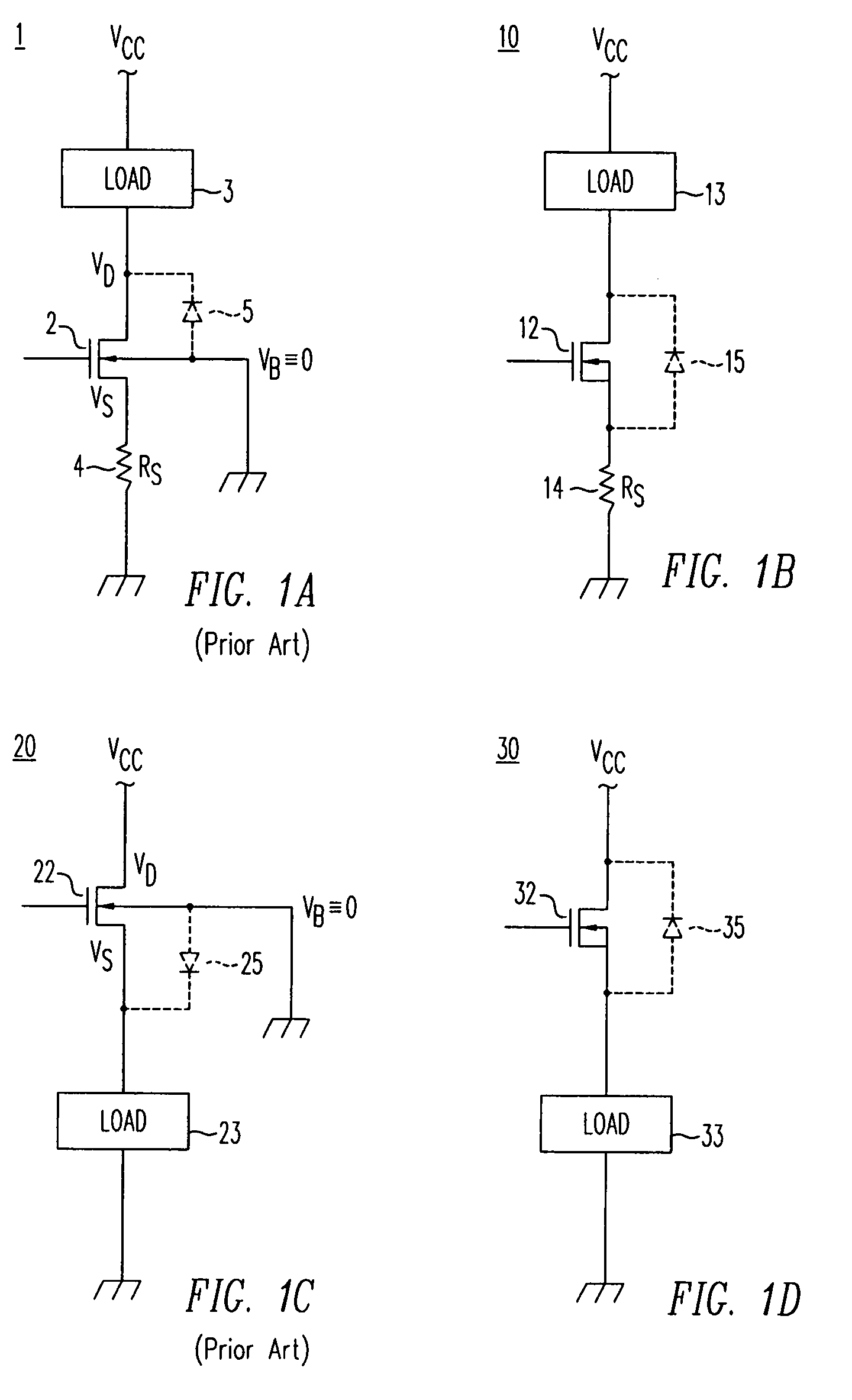

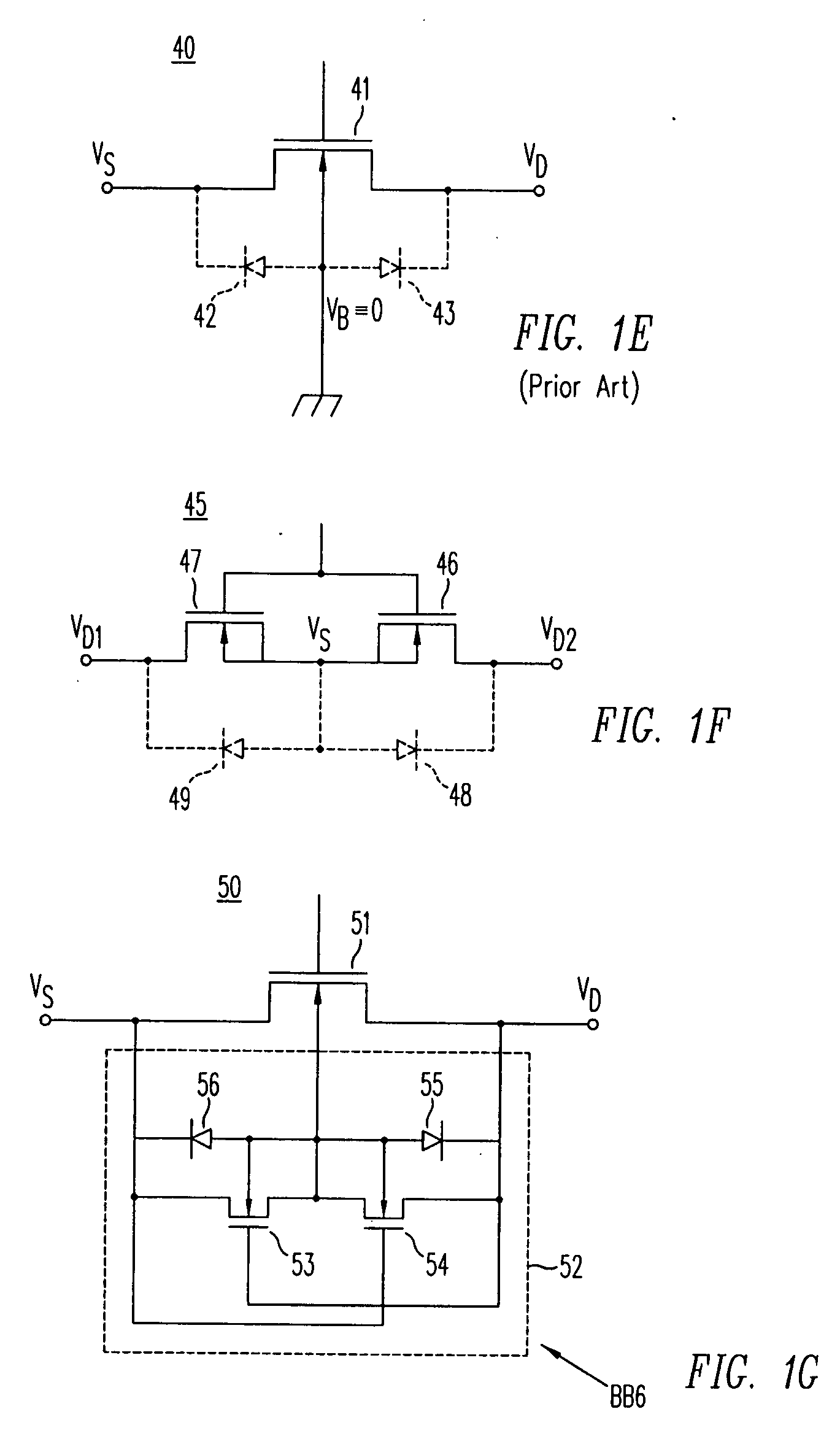

[0097] The subject matter in this application is related to the above-referenced patent and focuses on the design and integration of various kinds of new or improved high-voltage and DMOS devices, snapback prevention, isolated clamping diodes and rectifiers, and methods to float low-voltage devices in isolated pockets to high voltages above the substrate potential.

[0098] The low-temperature fabrication of the high-voltage devices described herein are compatible with the modular low-temperature fabrication methods described in the aforementioned patents and patent applications, but are not necessarily limited to modular...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com