Ultra-low parasitic ESD protection device

A technology for ESD protection and devices, which is applied in the direction of semiconductor devices, electric solid devices, semiconductor/solid device components, etc., can solve problems affecting impedance matching, affecting circuit impedance matching characteristics, total reflection, etc., and achieve ultra-low parasitic resistance, Excellent discharge capacity and small series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

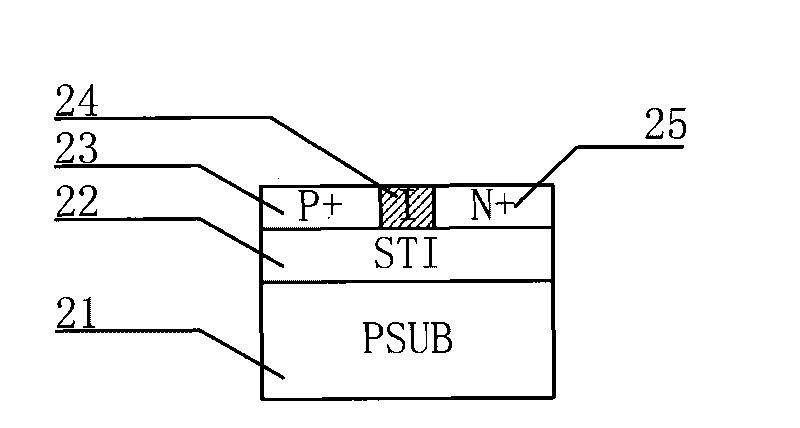

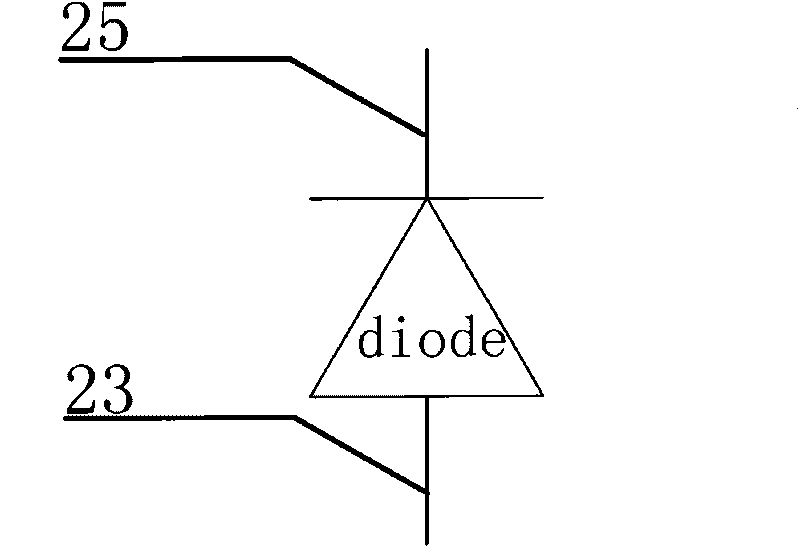

[0031] Such as Figure 4As shown, the ultra-low parasitic ESD protection device provided by the first implementation form of the present invention includes a P+ implantation region 23 and an N+ implantation region 25 arranged on a field oxide layer (not shown in the figure), and an undoped native Constructed region 24, and a plurality of contact holes 26 arranged at intervals on the P+ implanted region 23 and N+ implanted region 25, the contact holes 26 are channels that physically connect the P+ region with the metal or metal compound deposited on the region. The widths of the P+ implantation region 23 and the N+ implantation region 25 are set to the minimum width, and the widths are respectively set to the minimum width of the P+ implantation region and the minimum width of the N+ implantation region of the selected process. Depends on the design rules of the layout, for example, the SMIC0.18um process is 0.43um. The intrinsic region 24 is located between the P+ implantatio...

Embodiment 2

[0033] Such as Figure 5 As shown, the ultra-low parasitic ESD protection device provided by the second implementation form of the present invention includes the P+ implantation region 23 and the N+ implantation region 25 arranged on the field oxide layer (not shown in the figure) as the first embodiment , an undoped intrinsic region 24 and a plurality of contact holes 26 disposed on the P+ implantation region 23 and the N+ implantation region 25 at intervals. The difference between this embodiment and the first embodiment is that the intrinsic region 24 of this embodiment adopts a new type of layout design, and its shape is not linear, but the P+ implantation region 23 and the N+ implantation region 25 are formed in a grid pattern. Alternating implant configurations form arcuate intrinsic regions 24 . The arc-shaped intrinsic region 24 can increase the length of the contact line between the P region and the N region, and increase the junction area of the PN junction. The ...

Embodiment 3

[0036] Such as Figure 6 As shown, it is the ultra-low parasitic ESD protection device provided by the third implementation form of the present invention, which uses multiple single ultra-low parasitic ESD protection devices in Embodiment 2 for parallel connection, and the P-type substrate of this embodiment is connected into one Overall, on the P-type substrate, each single ultra-low parasitic ESD protection device is connected in parallel with each other according to the arcuate contact lines, forming a finger-shaped ESD protection device. This embodiment also includes a P+ implantation region 23 disposed on the field oxide layer (not shown in the figure), an N+ implantation region 25, an undoped intrinsic region 24, a contact hole 26, and a self-aligned metal silicide barrier (Salicideblock) Layer 27, a metal layer (metal) 28 connected to the P+ implantation region and a metal layer (metal) 29 connected to the N+ implantation region. The number of single ultra-low parasiti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com