Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70 results about "Duty cycle corrector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

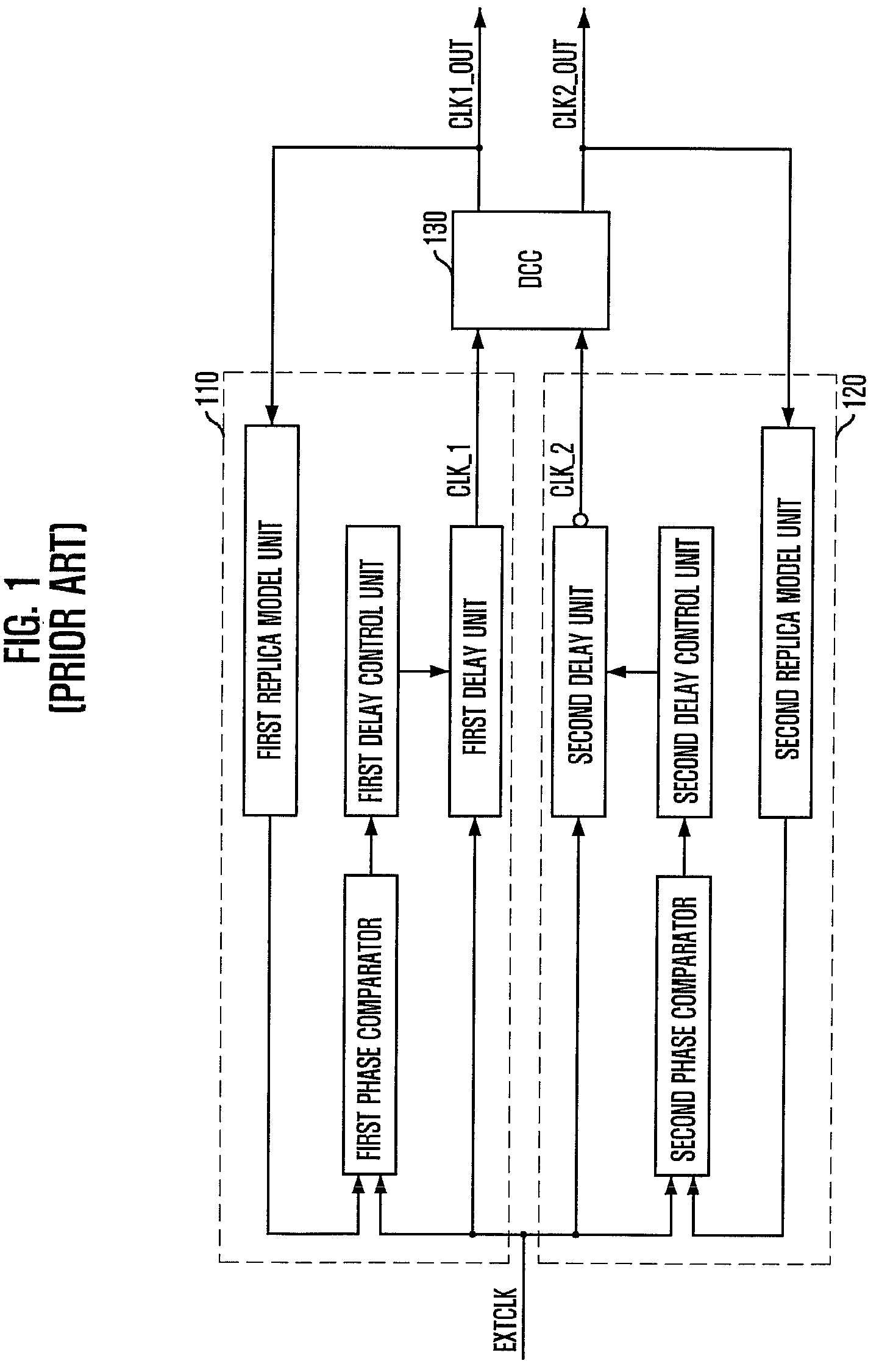

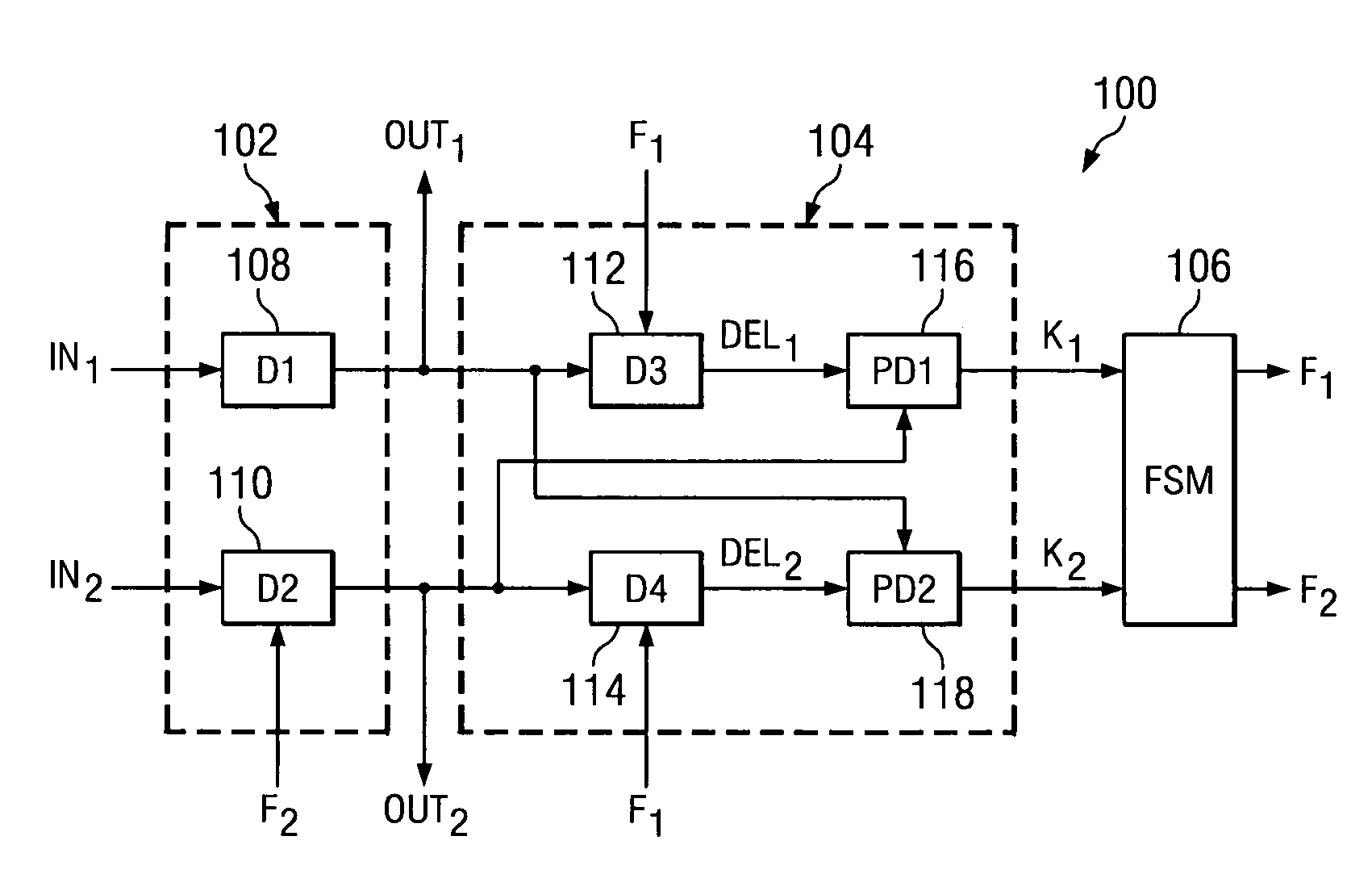

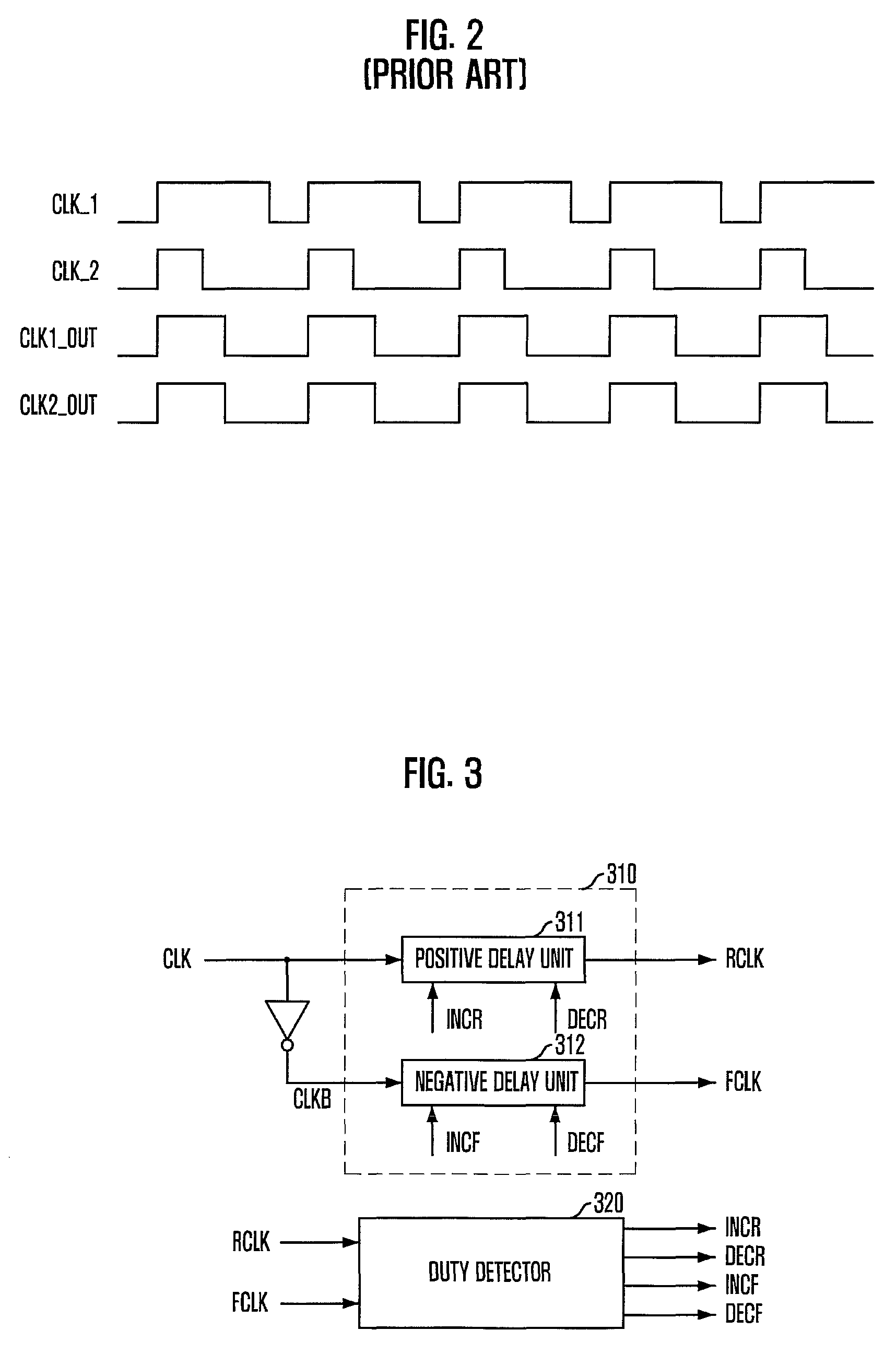

Integrated circuit devices having duty cycle correction circuits that receive control signals over first and second separate paths and methods of operating the same

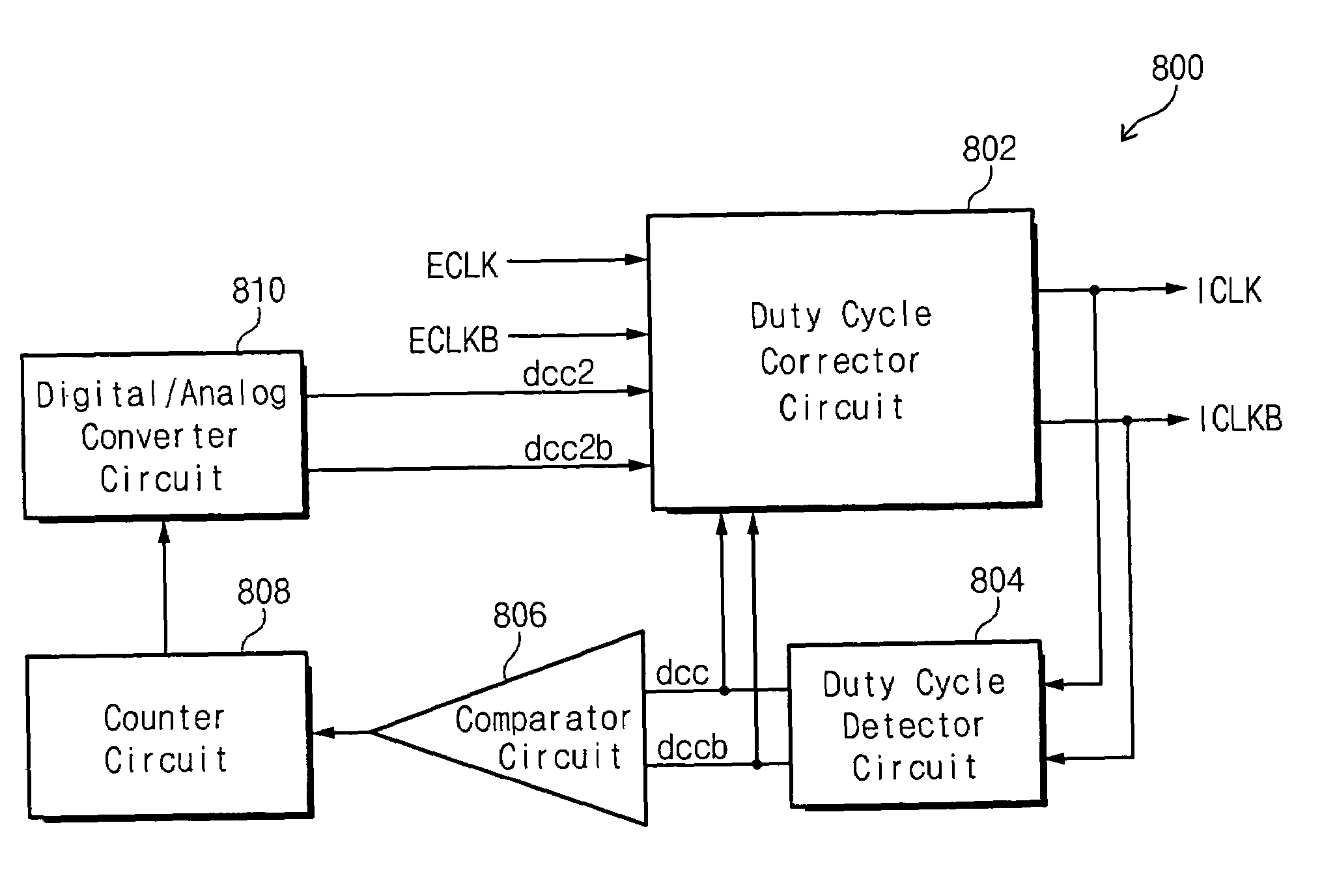

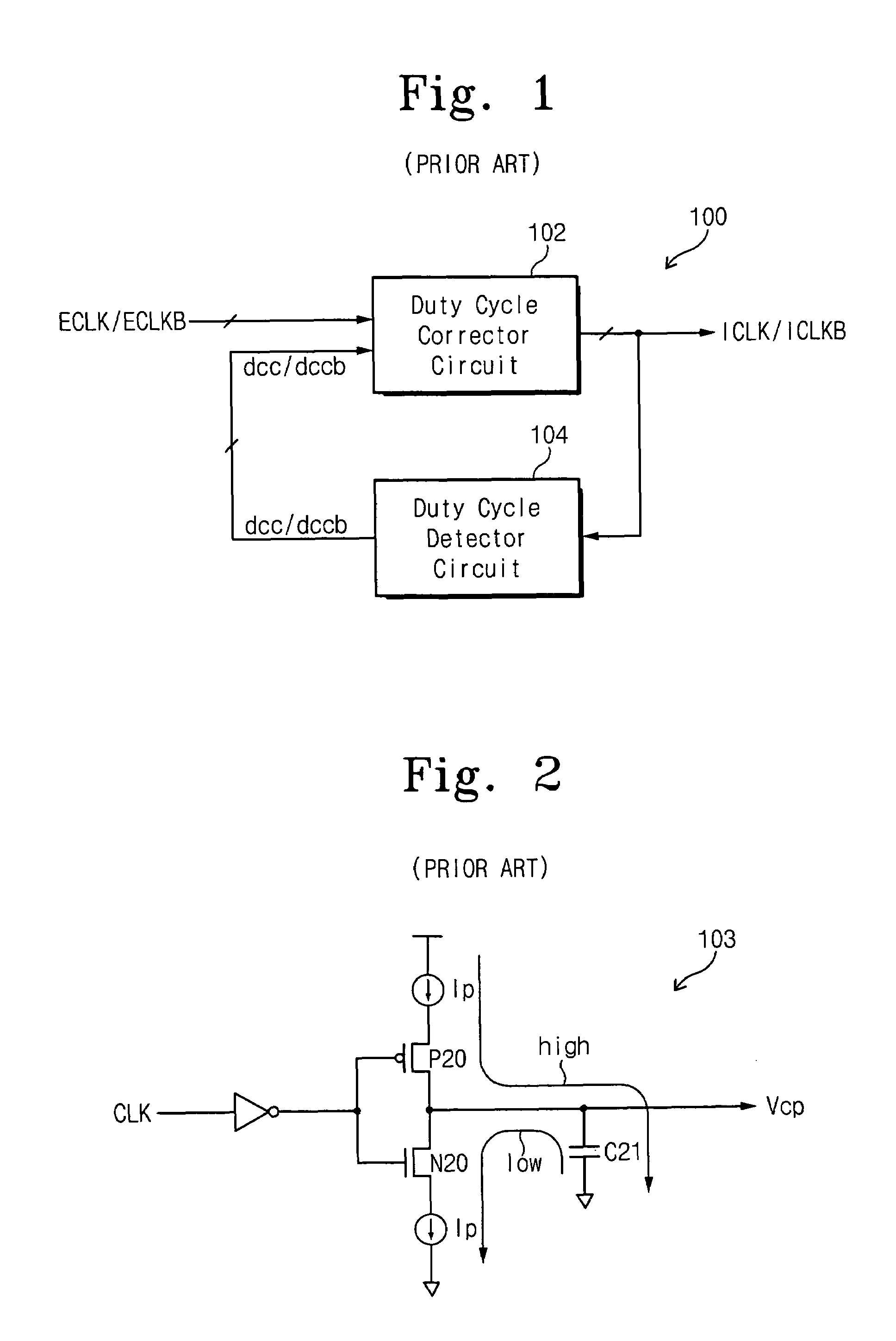

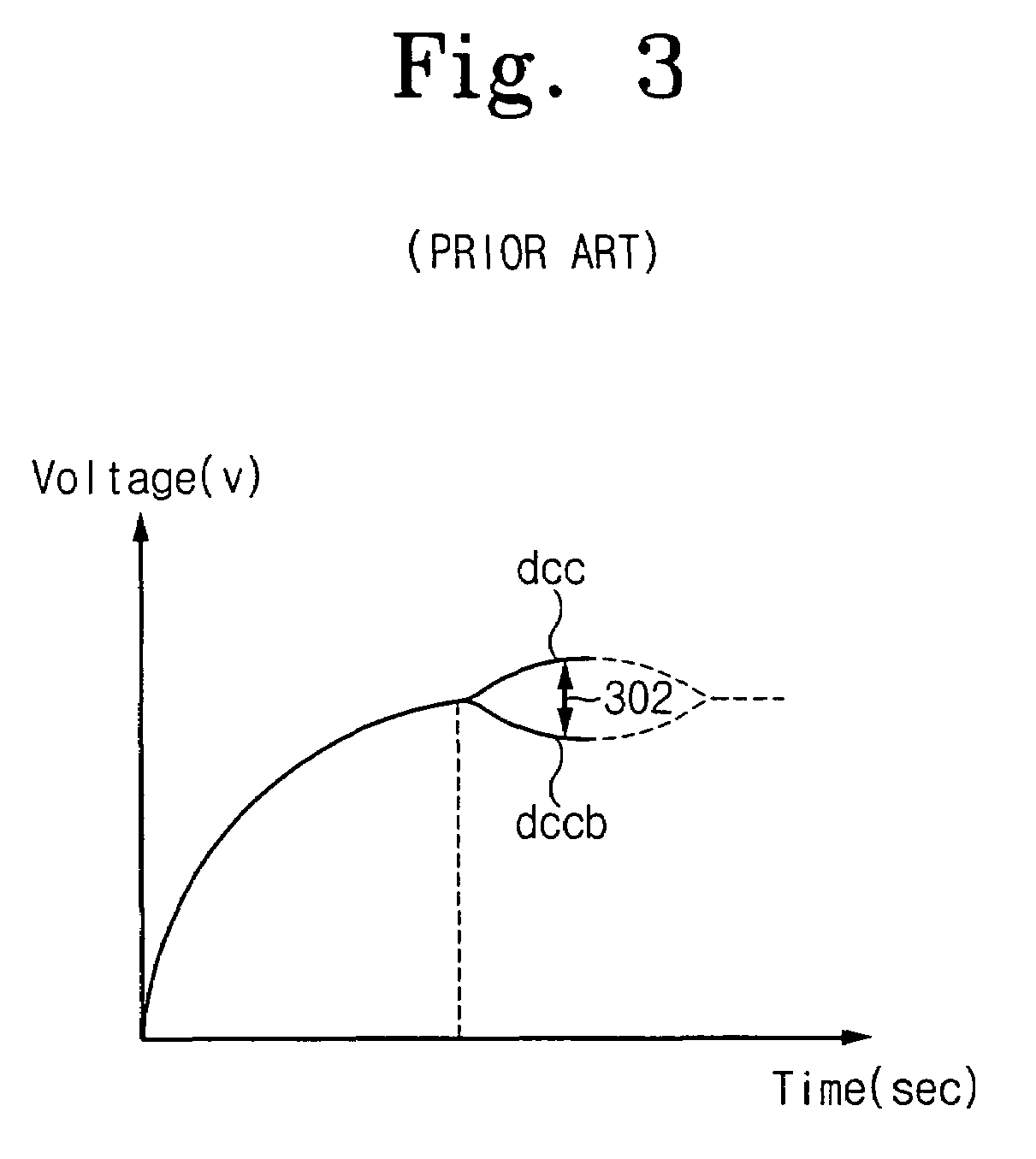

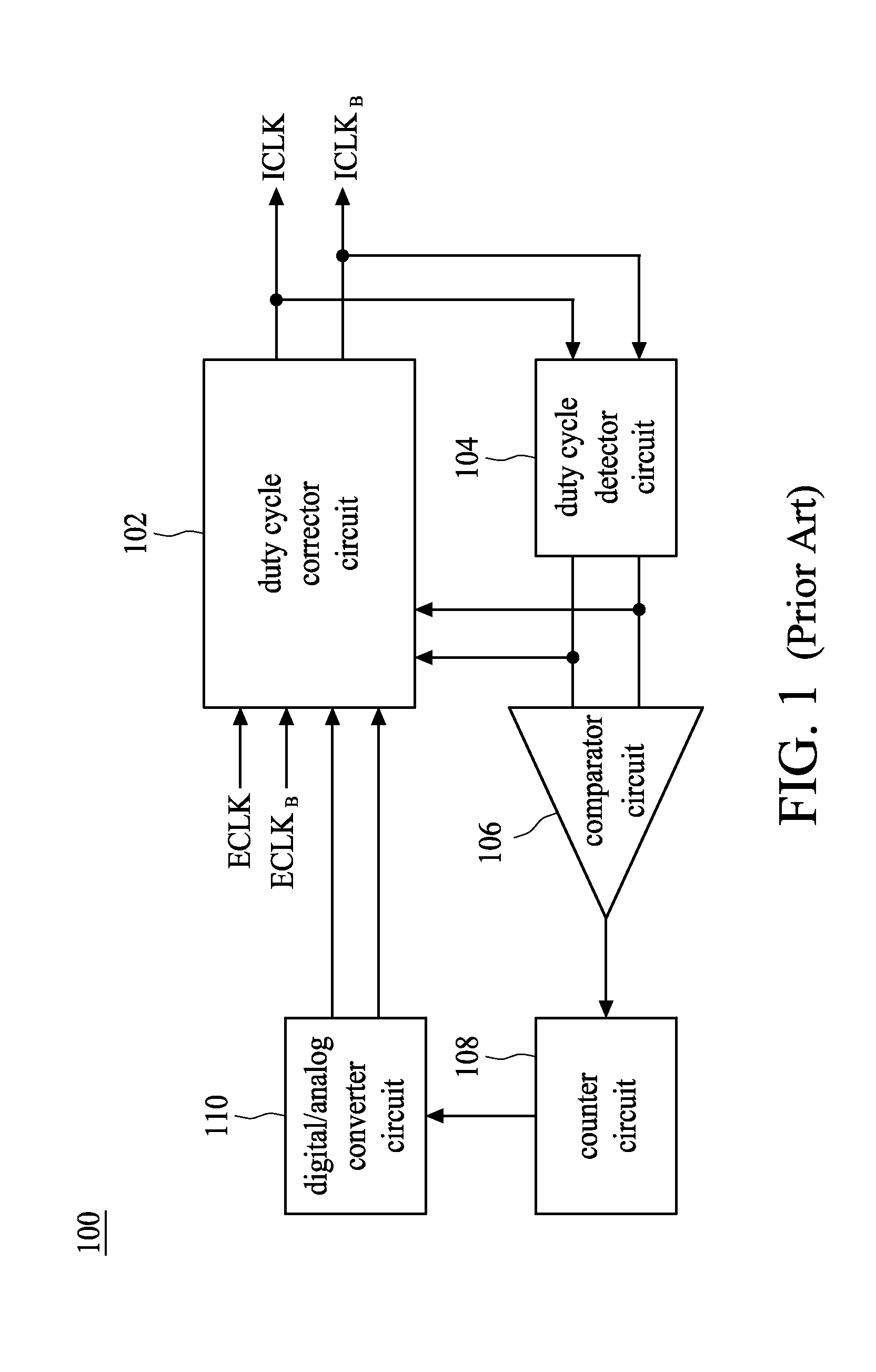

InactiveUS7015739B2Pulse automatic controlContinuous to patterned pulse manipulationDigital analog converterDetector circuits

Digital duty cycle correction circuits are provided including a duty cycle detector circuit configured to generate first and second control values associated with a first internal clock signal and a second internal clock signal, respectively. A comparator circuit is also provided and is configured to compare the first control value to the second control value and provide a comparison result. A counter circuit is configured to perform an addition and / or a subtraction operation responsive to the comparison result to provide a digital code. A digital to analog converter is configured to generate third and fourth control values responsive to the digital code. Finally, a duty cycle corrector circuit is configured to receive first and second external clock signals and the first through fourth control values and generate the first and second internal clock signals having a corrected duty cycle. The first and second control values are received over a first path and the third and fourth control values are received over a second path, different from the first path. Related methods of operating duty cycle correction circuits are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

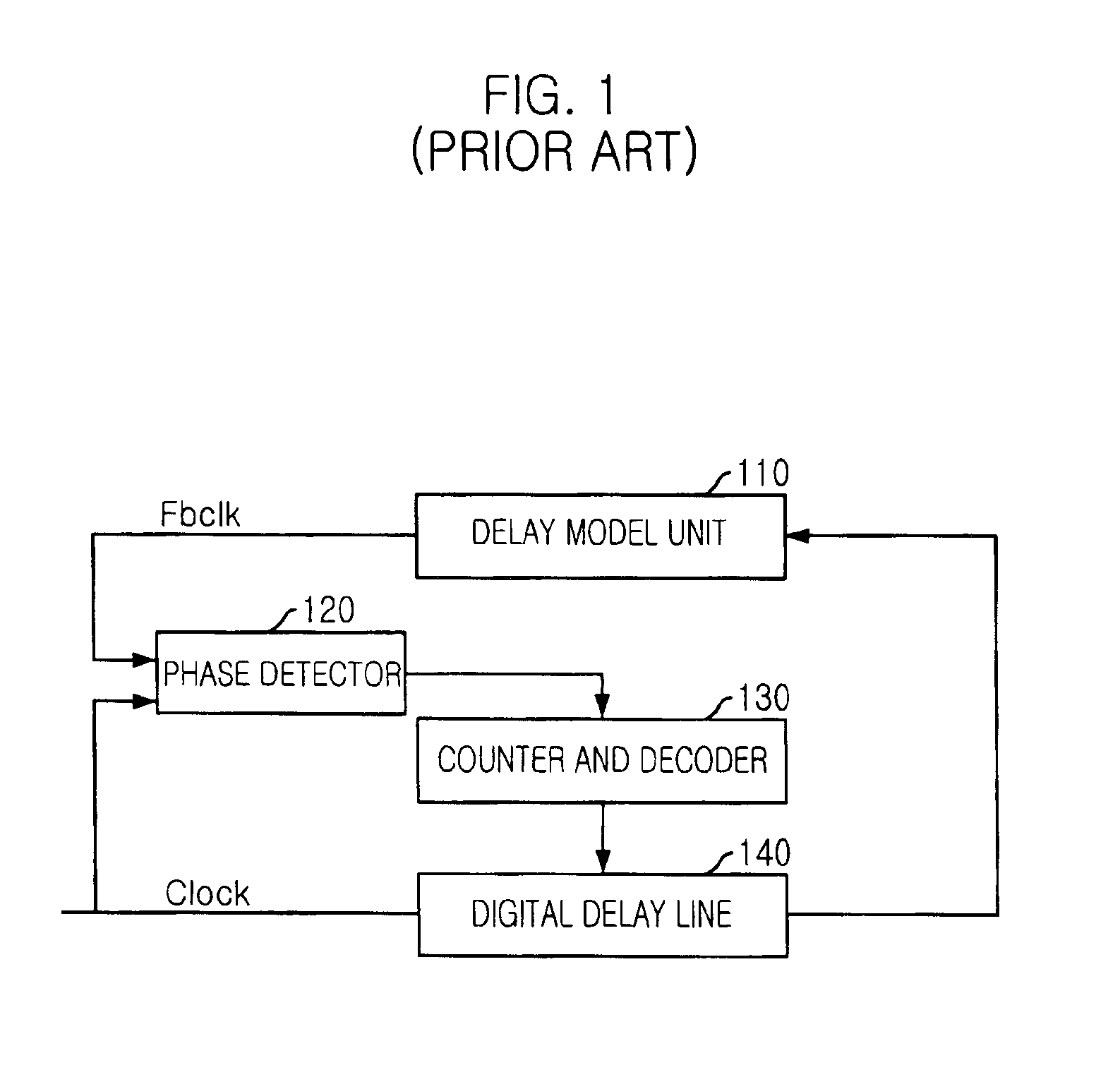

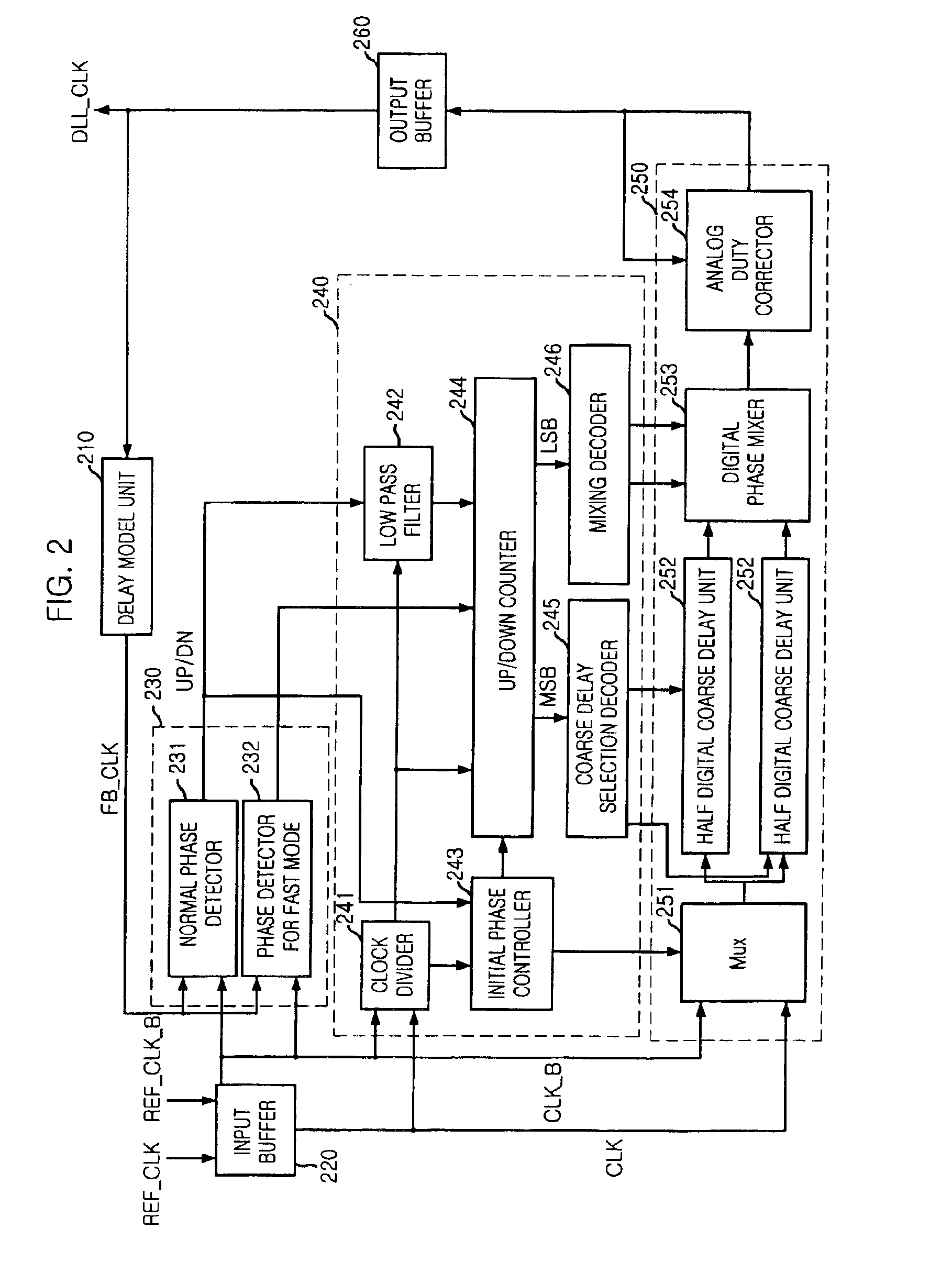

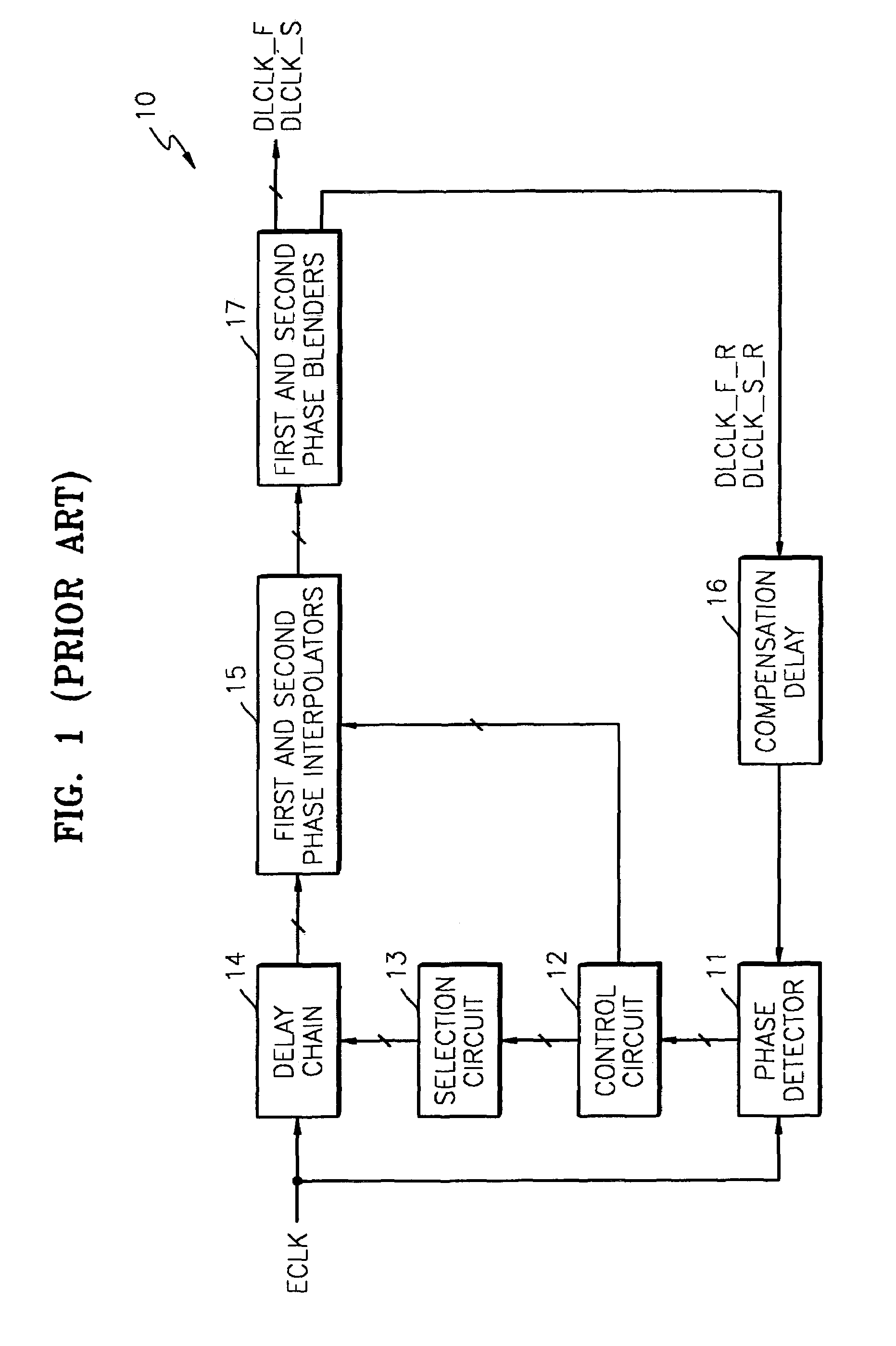

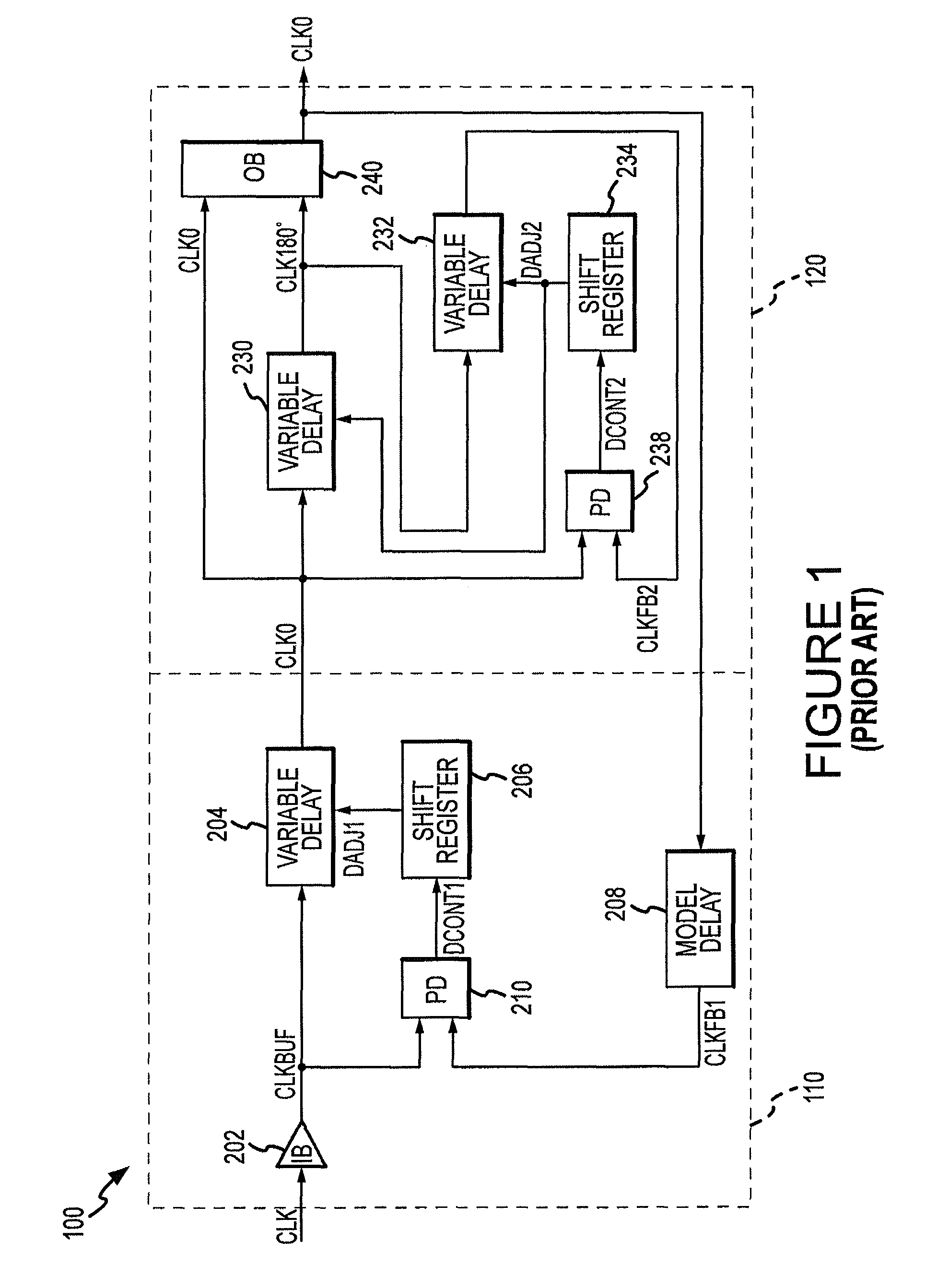

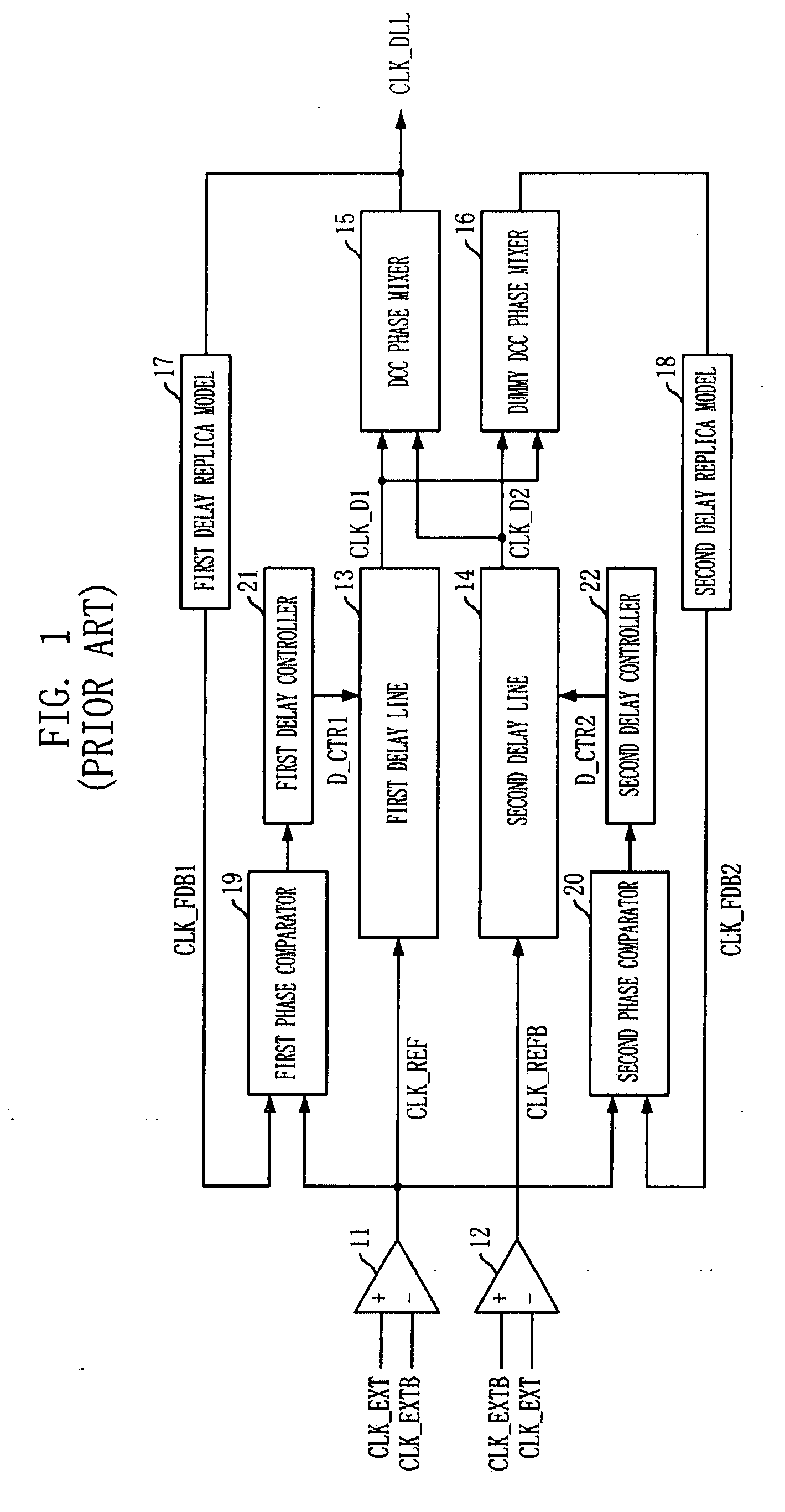

Delay locked loop having low jitter in semiconductor device

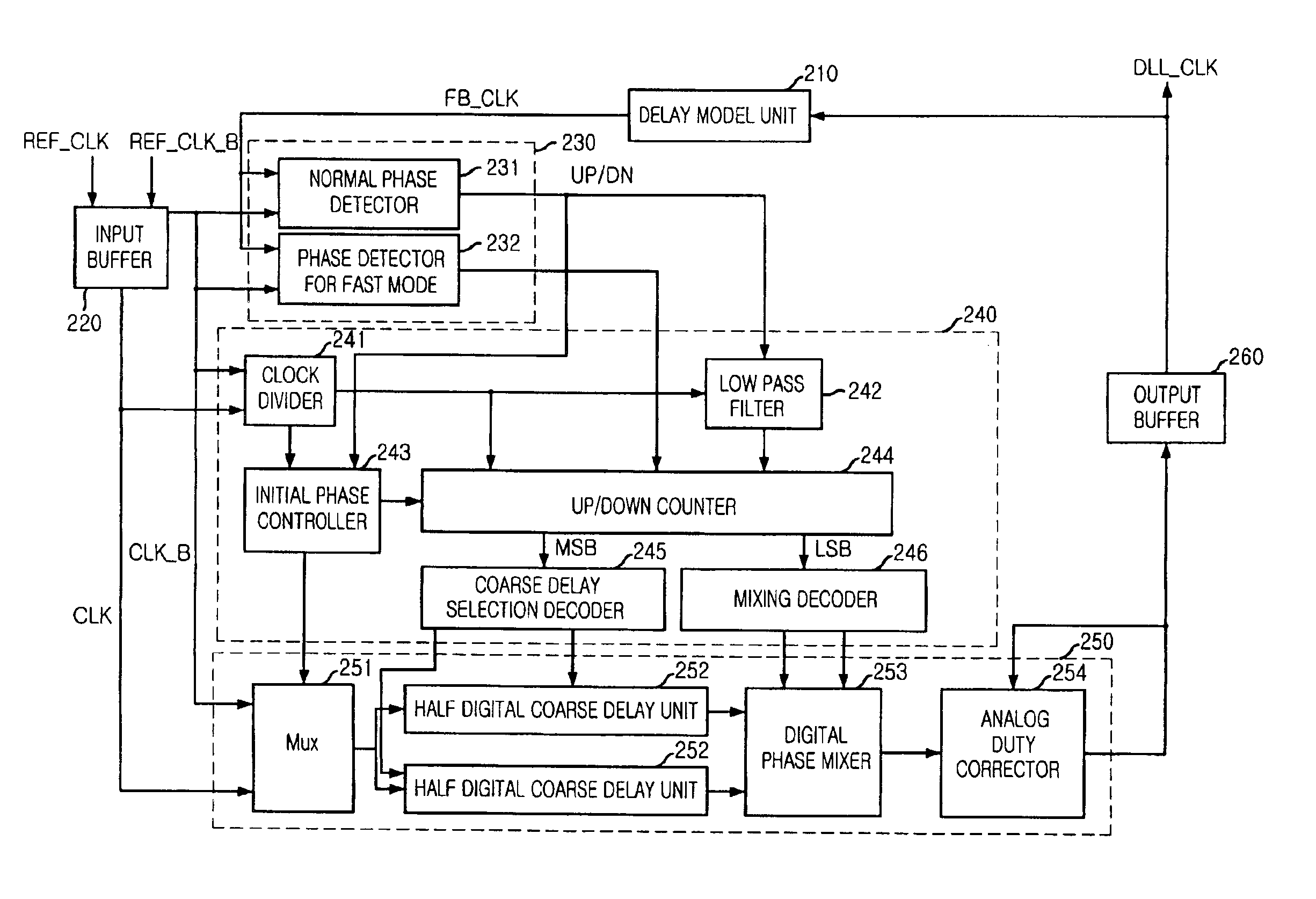

InactiveUS6917229B2Reduce jitterPulse automatic controlAngle demodulation by phase difference detectionControl signalDelay-locked loop

A DLL circuit having a low jitter in a semiconductor device, includes a delay model unit for compensating a time difference between an external clock signal and an internal clock signals and generating a compensation signal; an input buffer for receiving a reference clock signal and an inverted clock signal, and for outputting a clock signal and an inverted clock signal activated at each edges of the reference clock signal and the inverted clock signal; a phase detection unit for generating a comparison signal by comparing the compensation signal with the inverted clock signal, and for outputting the comparison signal with a normal mode or a fast mode; a control unit for generating a plurality of control signals by receiving the comparison signal, the inverted clock signal and the clock signal; a delay unit for delaying in response to the plurality of control signals; and an output buffer for outputting a delayed clock signal by receiving an output signal of the duty corrector.

Owner:SK HYNIX INC

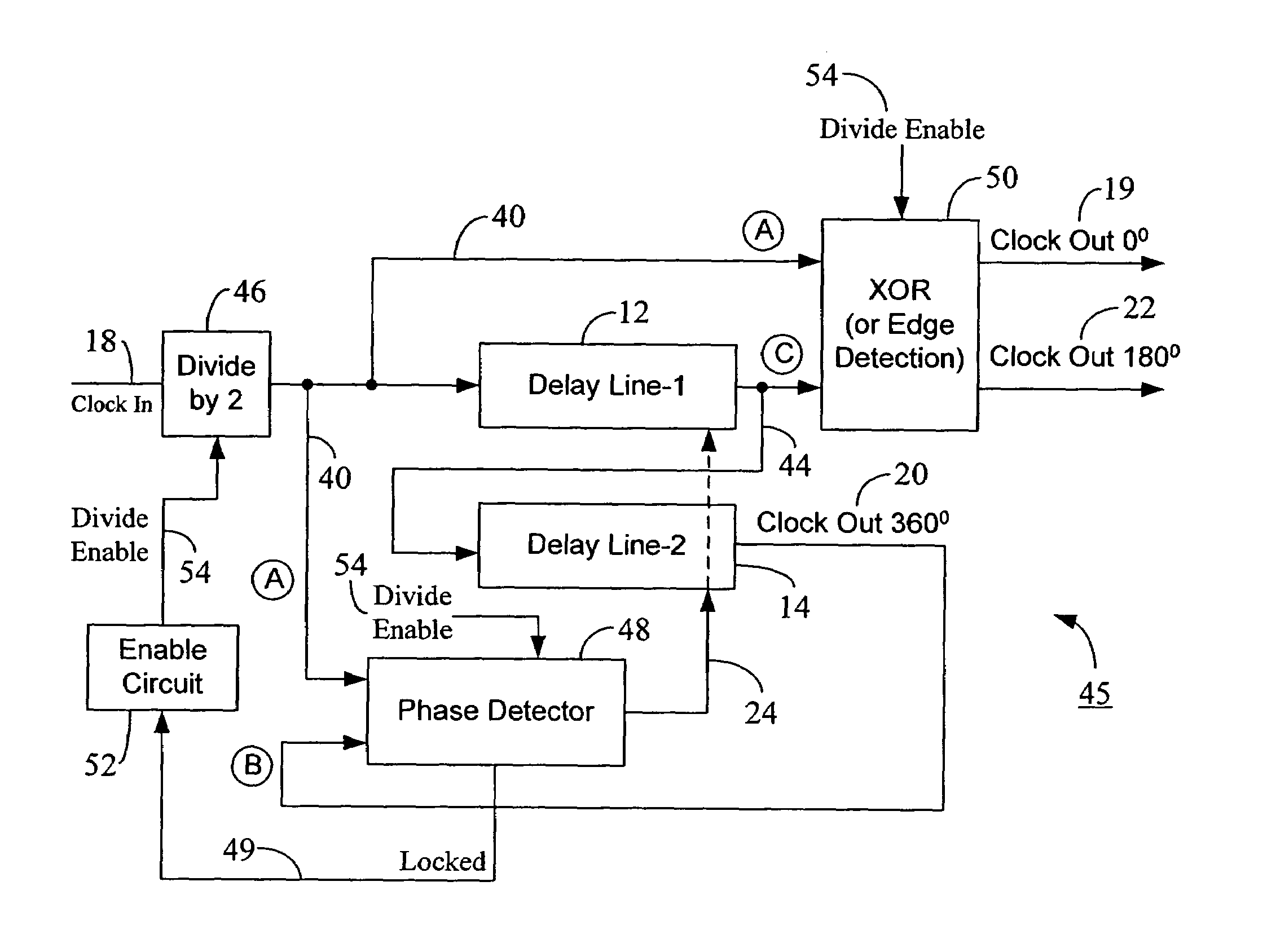

Initialization scheme for a reduced-frequency, fifty percent duty cycle corrector

ActiveUS7259604B2Avoid instabilityReduced-frequency operationPulse automatic controlDigital storageMemory chipInstability

A reduced-frequency, 50% duty cycle corrector (DCC) circuit may be used in an electronic device (e.g., a memory chip) to generate output clocks with 50% duty cycle irrespective of the duty cycle of the clock input to the DCC circuit. A DCC initialization scheme selectively activates the frequency division and edge detection operations in the DCC based on the lock status of the DCC during initialization. Upon initialization, the frequency division and edge detection operations are turned off or disabled. After the DCC is properly locked, these operations are enabled to obtain the 50% duty cycle output clock. This approach initializes the reduced-frequency DCC without output glitches, which can affect locking of a DLL with which the DCC may be used. The prevention of instability in locking of the DCC and DLL upon system initialization results in swift establishment of DCC and DLL locks without significant power consumption or loss of clock cycles. Once the DCC is locked during its initialization, the reduced-frequency operation of DCC further saves current consumption. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

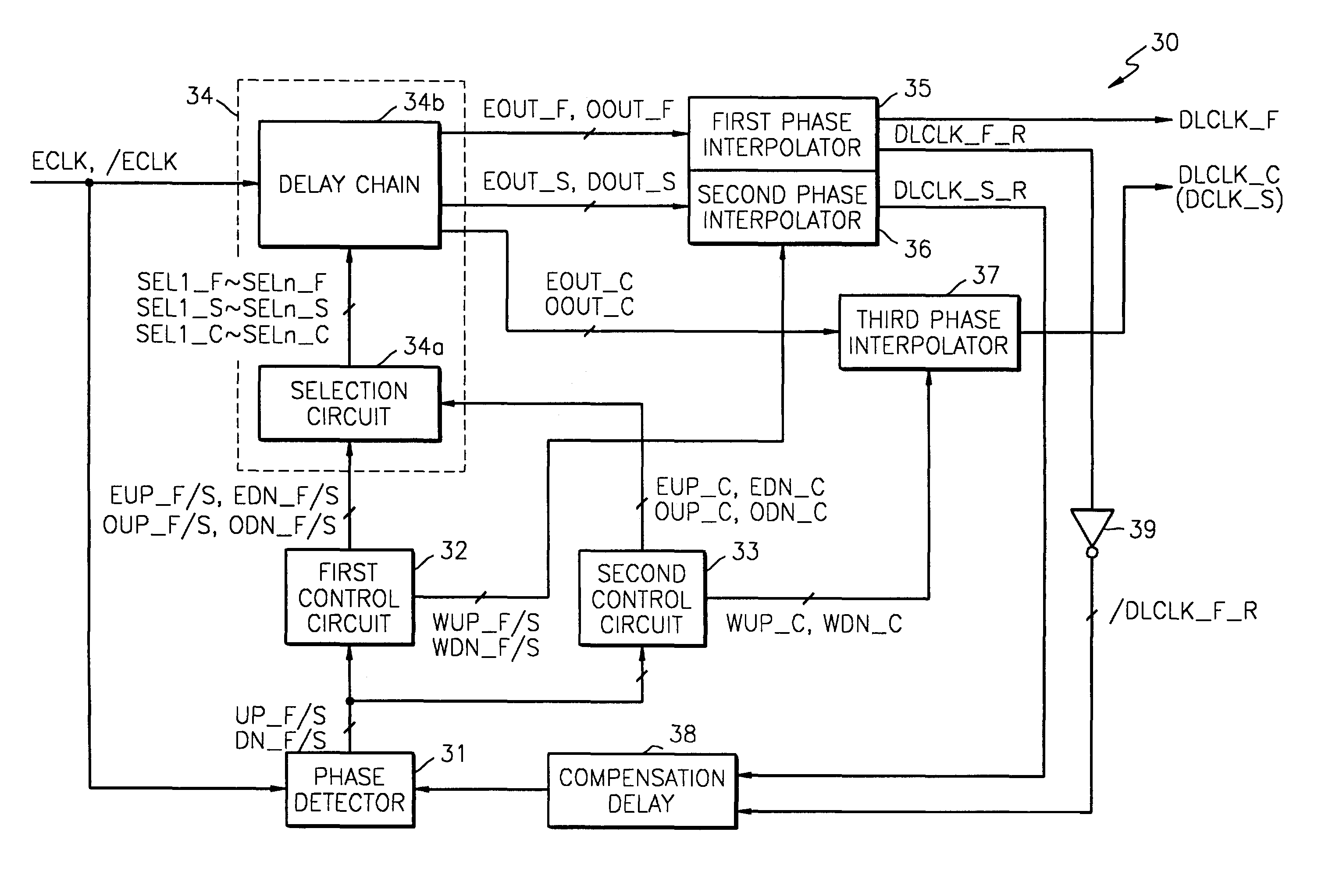

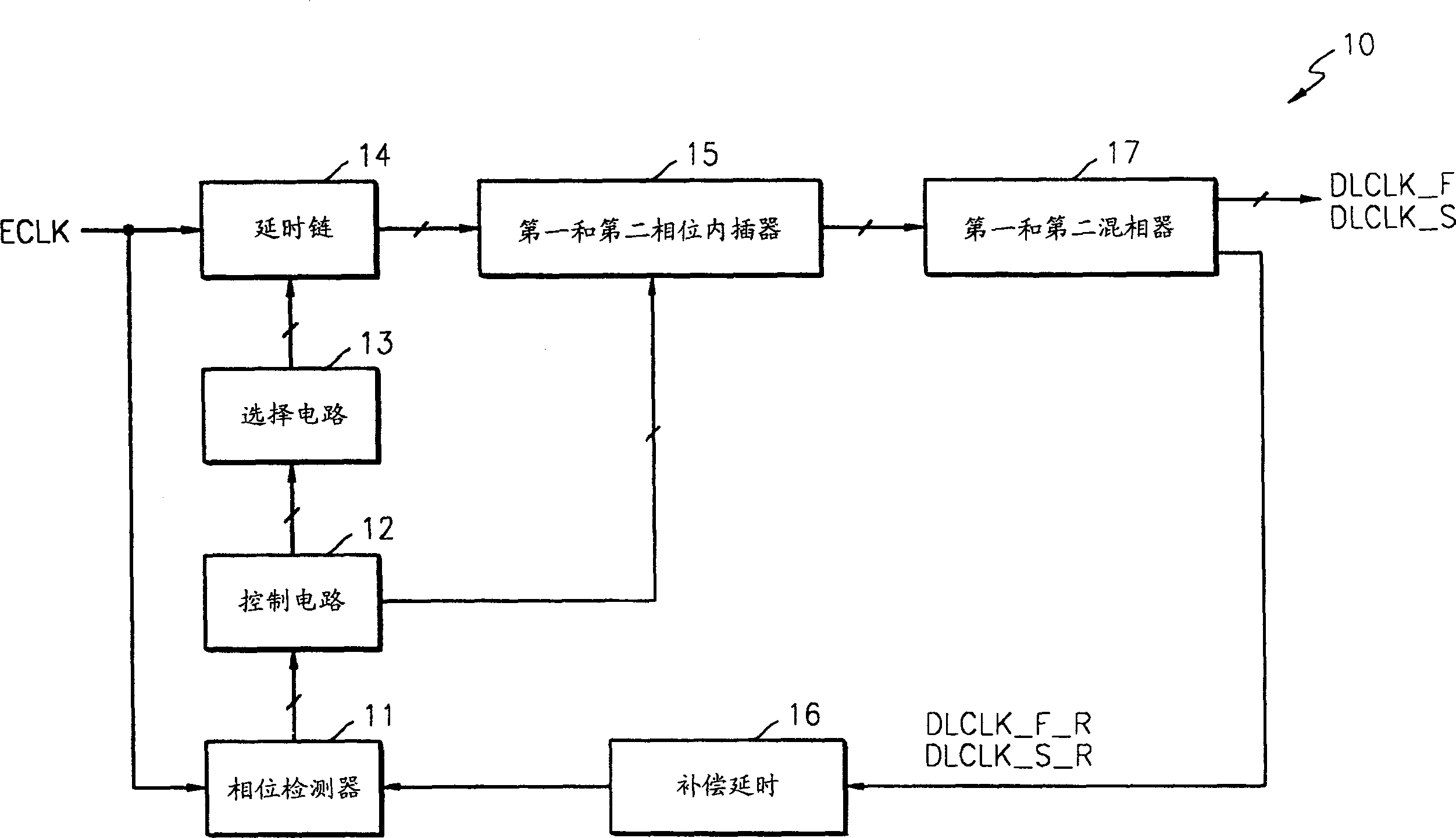

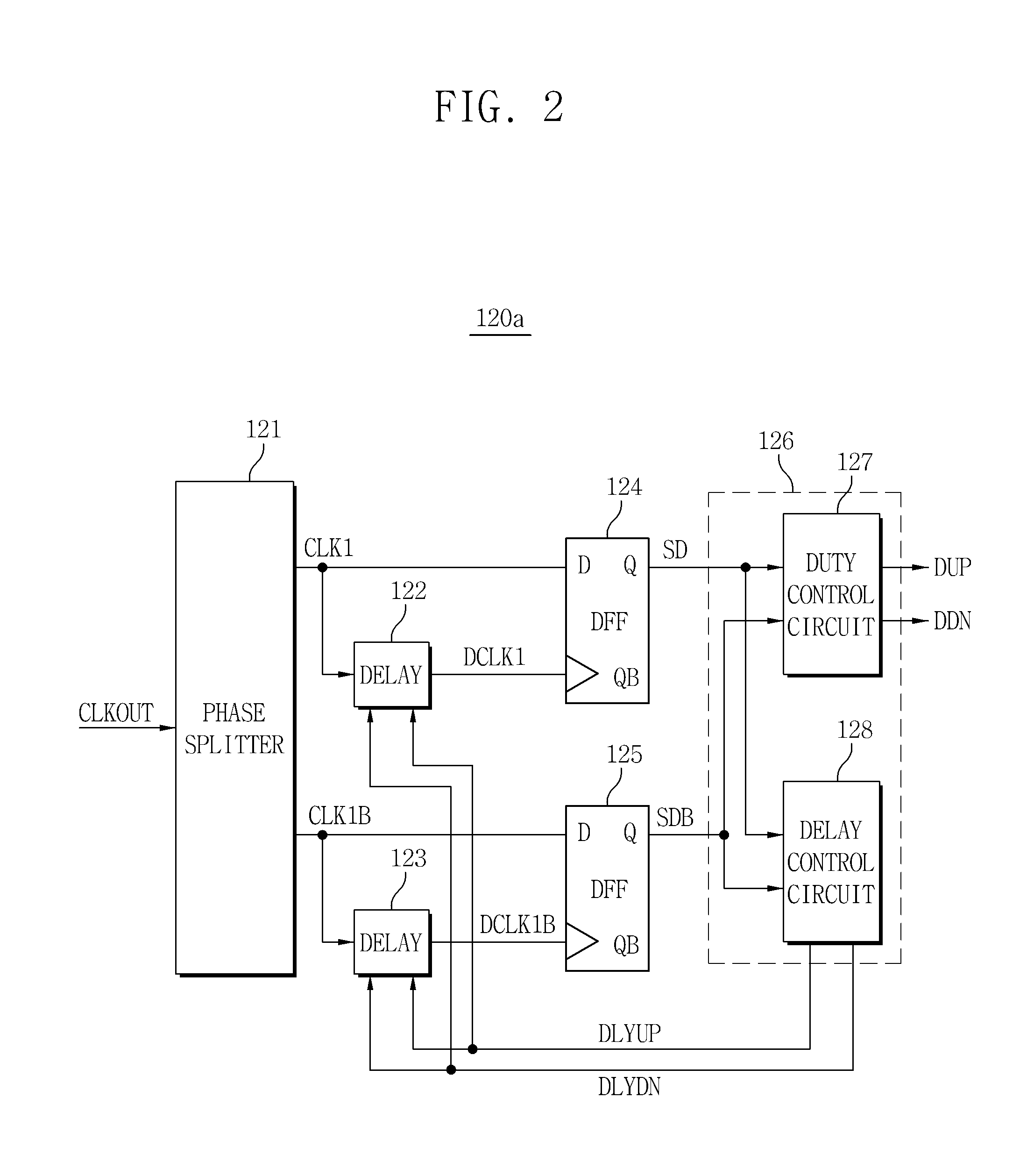

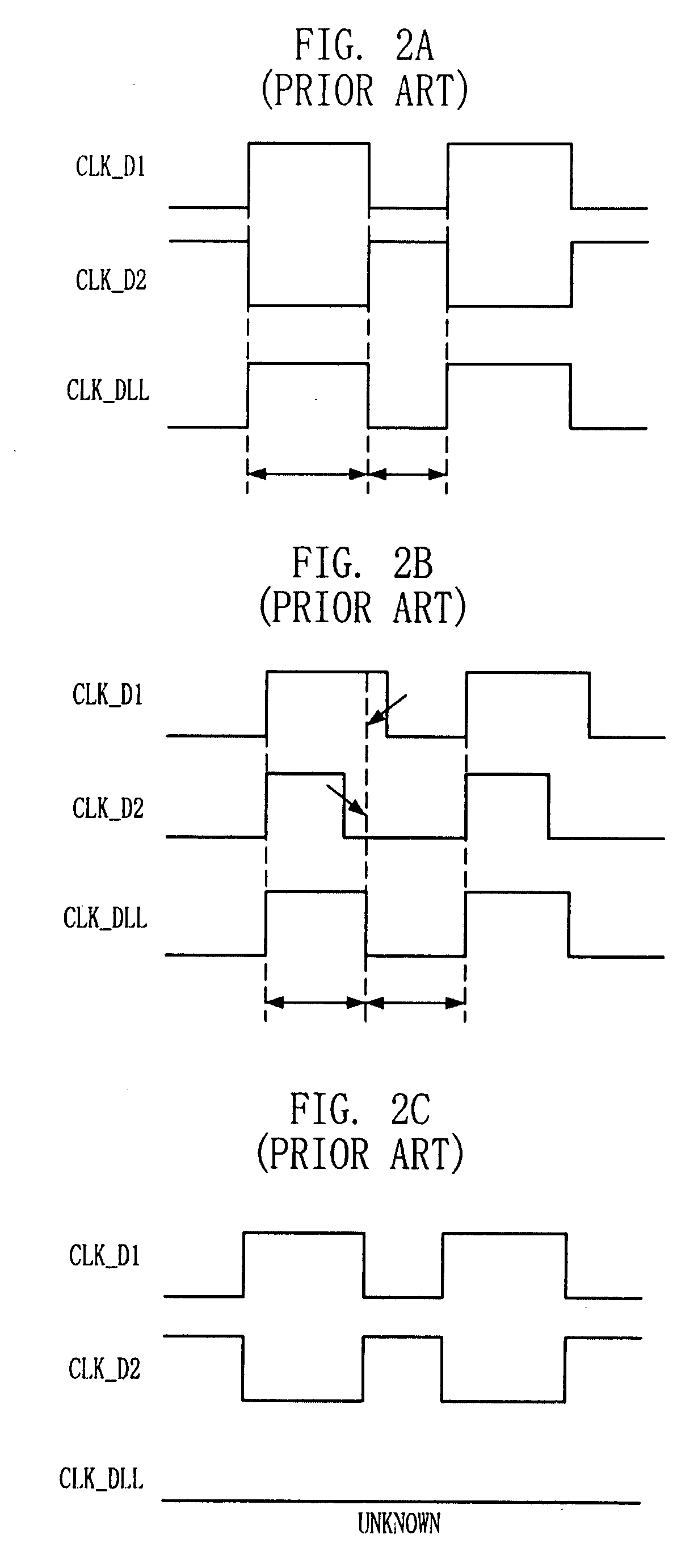

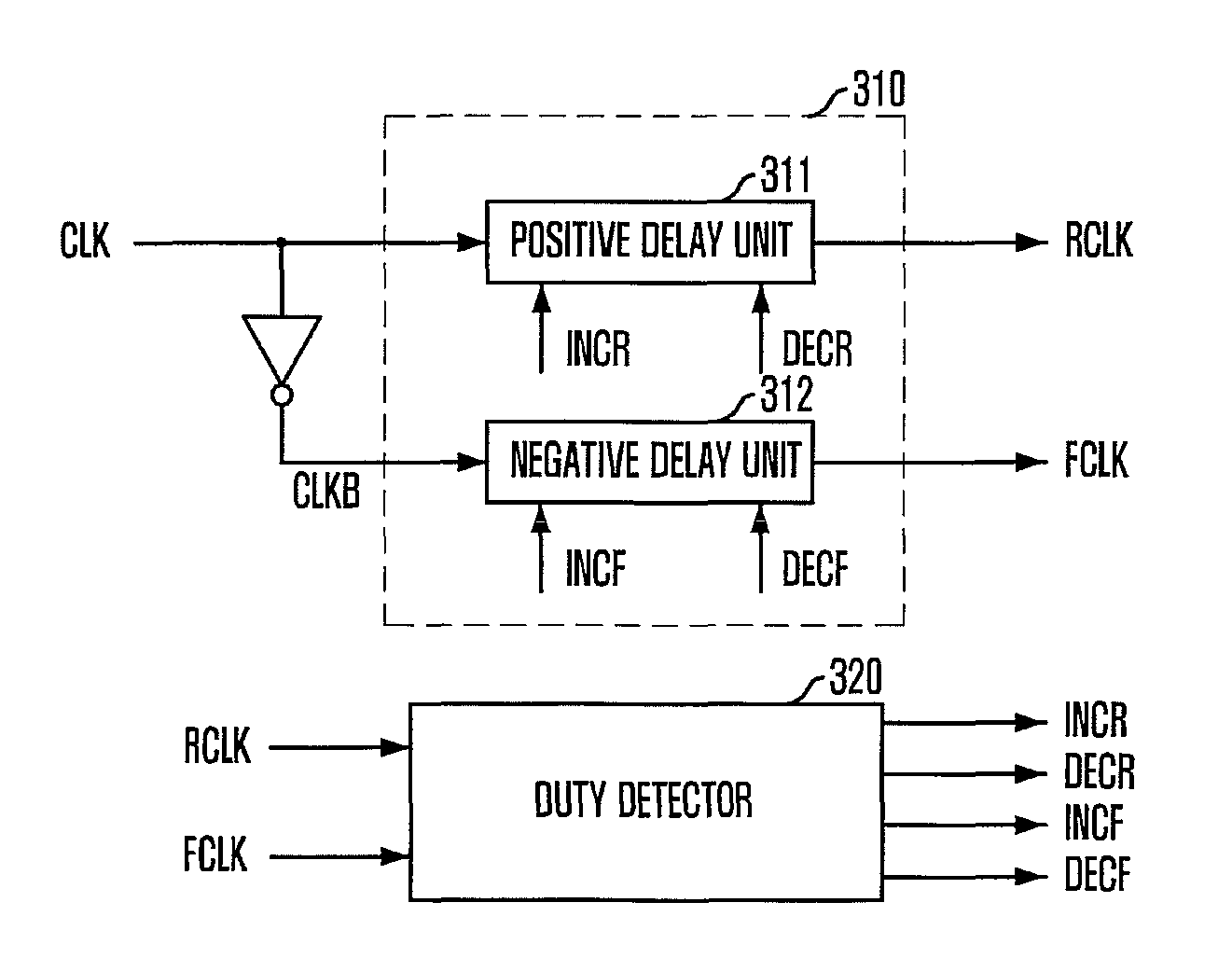

Delay locked loop circuit for internally correcting duty cycle and duty cycle correction method thereof

InactiveUS7184509B2Solve the large consumptionReduce restrictionsPulse automatic controlContinuous to patterned pulse manipulationDelay-locked loopEngineering

A delay locked loop (DLL) circuit having a duty cycle corrector (DCC) that has a broad range of duty cycle correction, consumes only a small amount of power, has few restrictions on operating frequency, and improves the characteristics of a memory device is described. The delay locked loop circuit includes an additional loop for duty cycle correction as well as loops for controlling a rising edge and a falling edge of output signals. Thus, the delay locked loop circuit can internally correct the duty cycle without the use of a phase blender.

Owner:SAMSUNG ELECTRONICS CO LTD

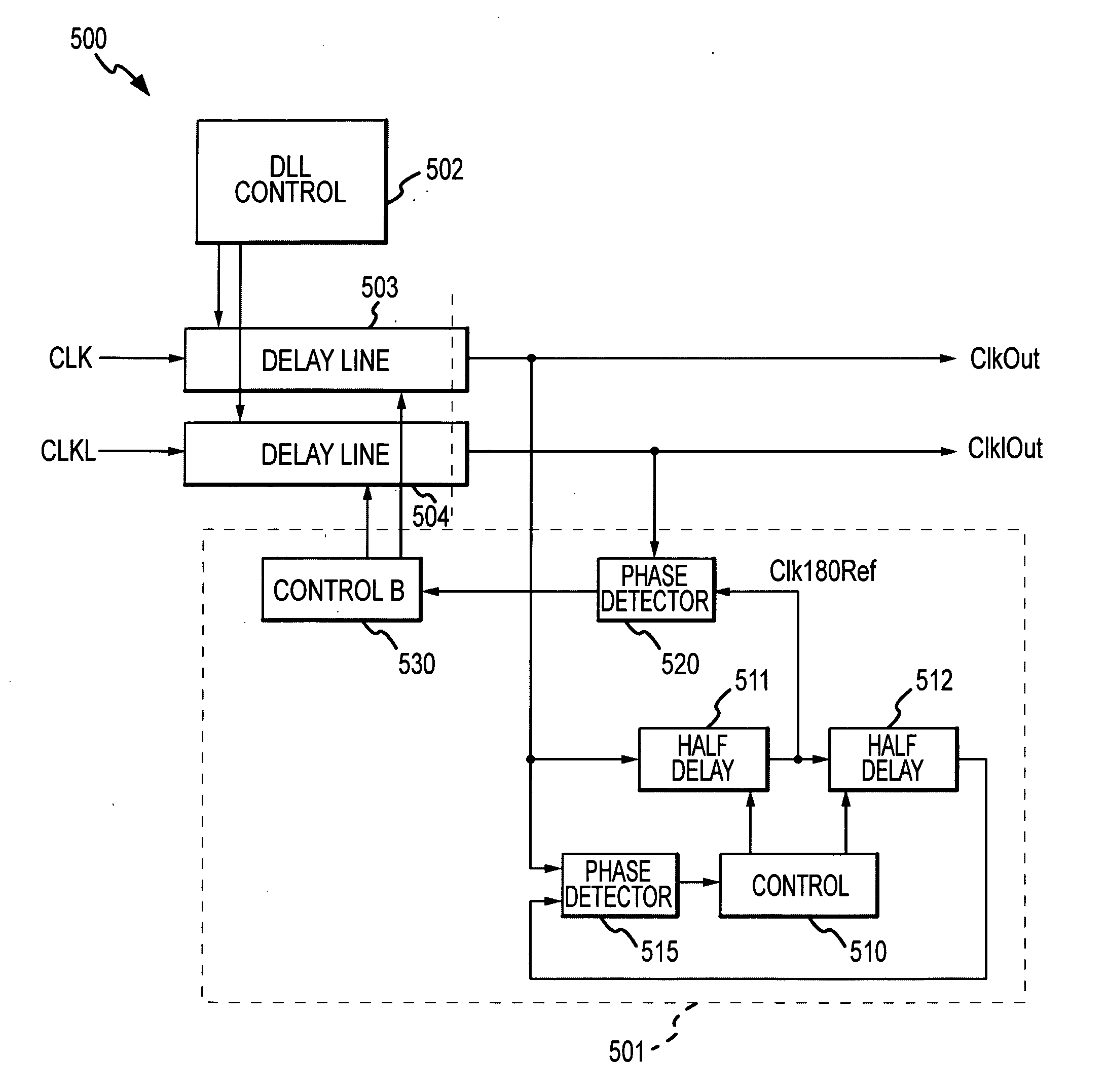

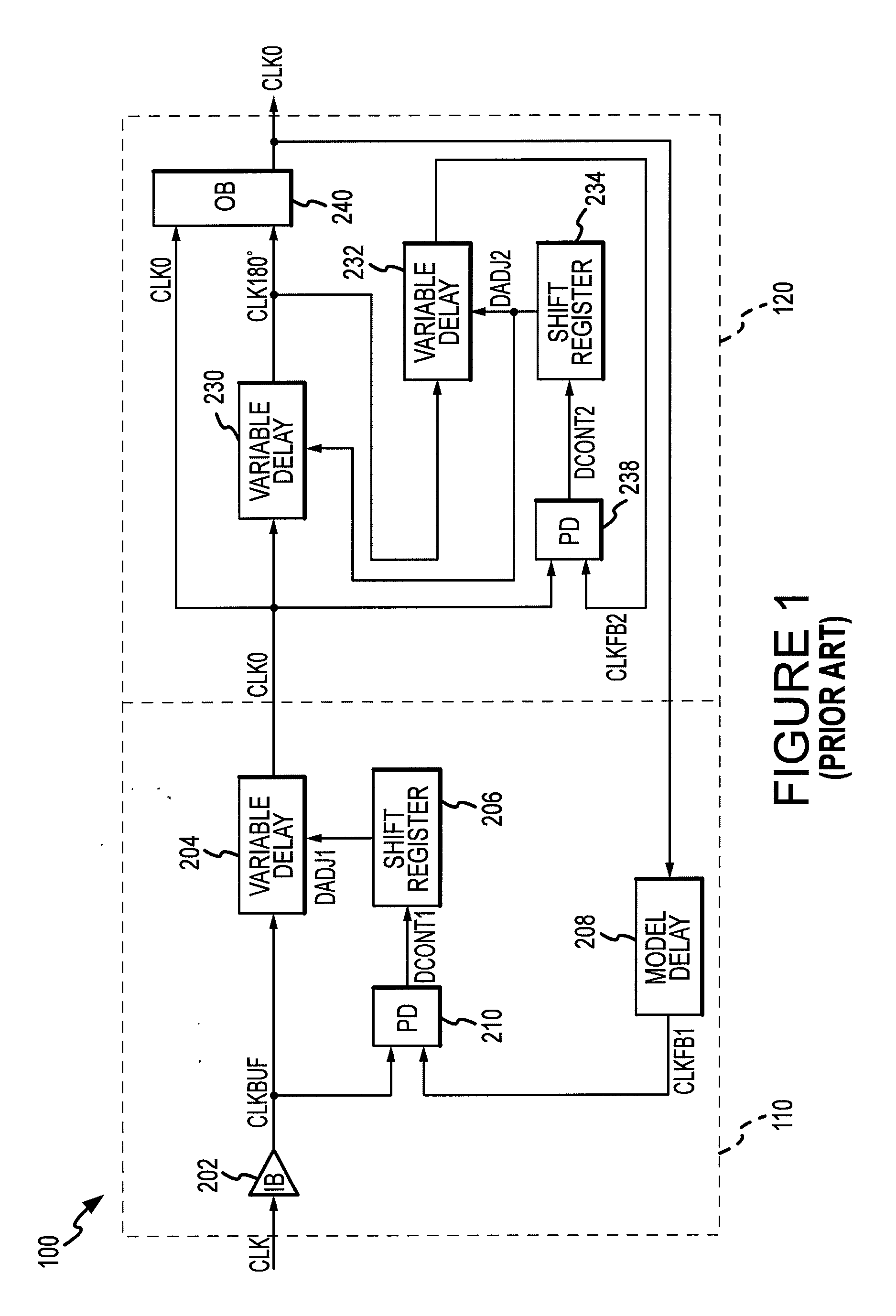

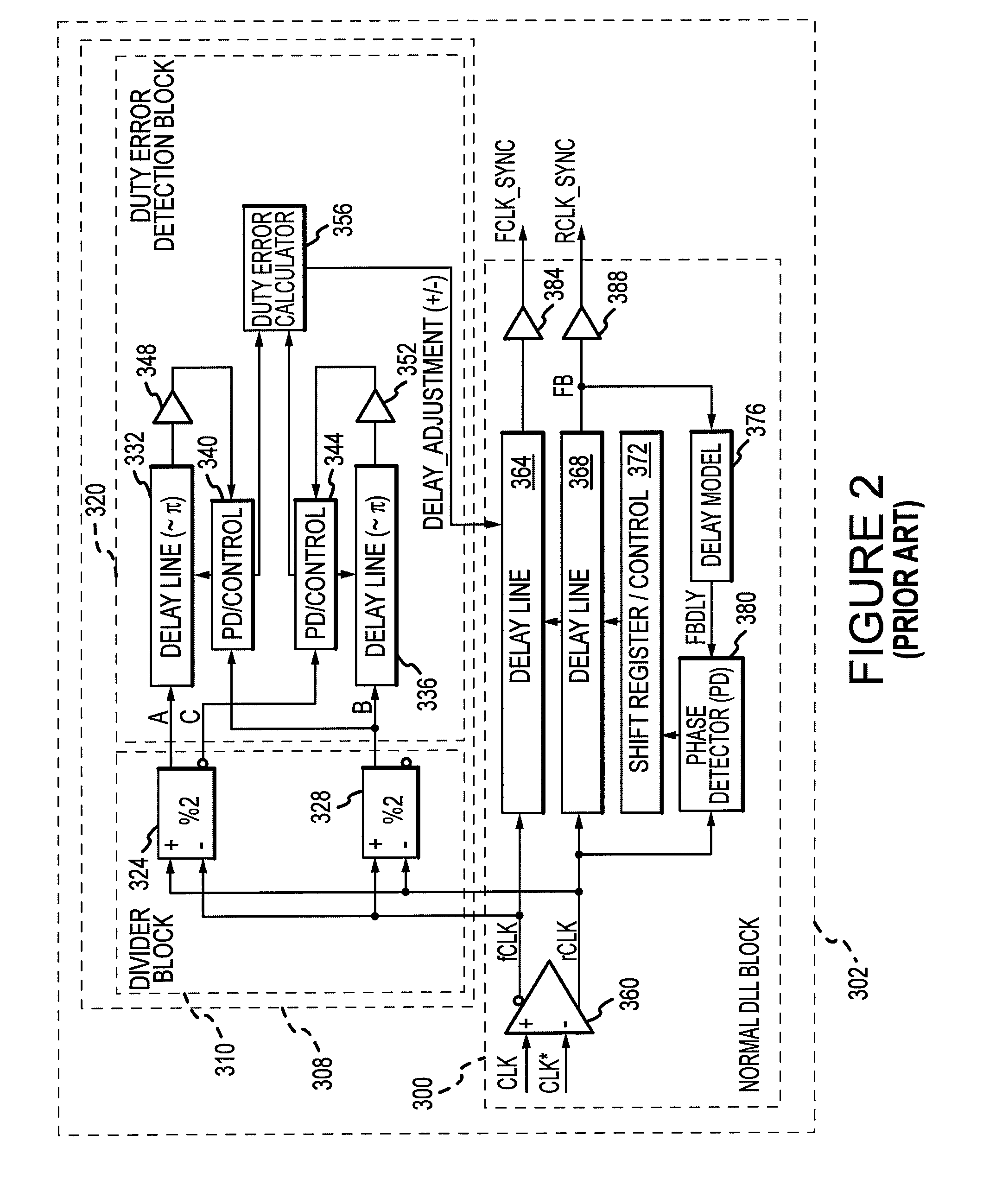

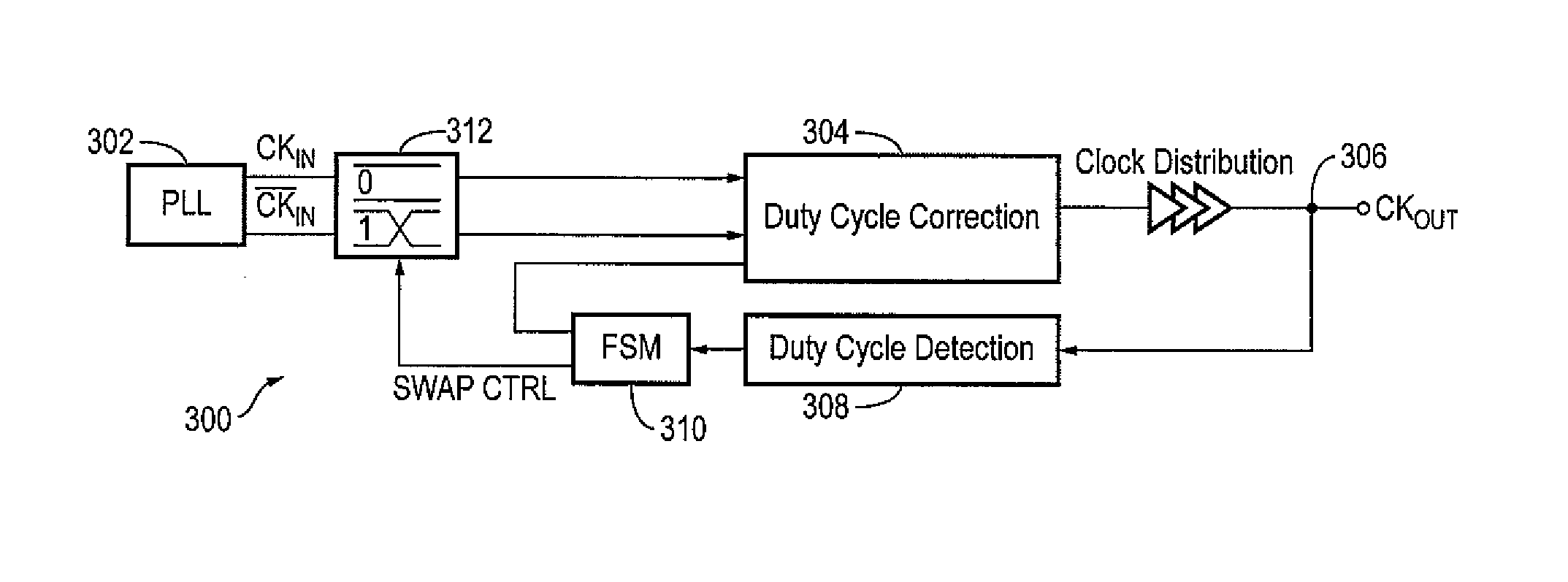

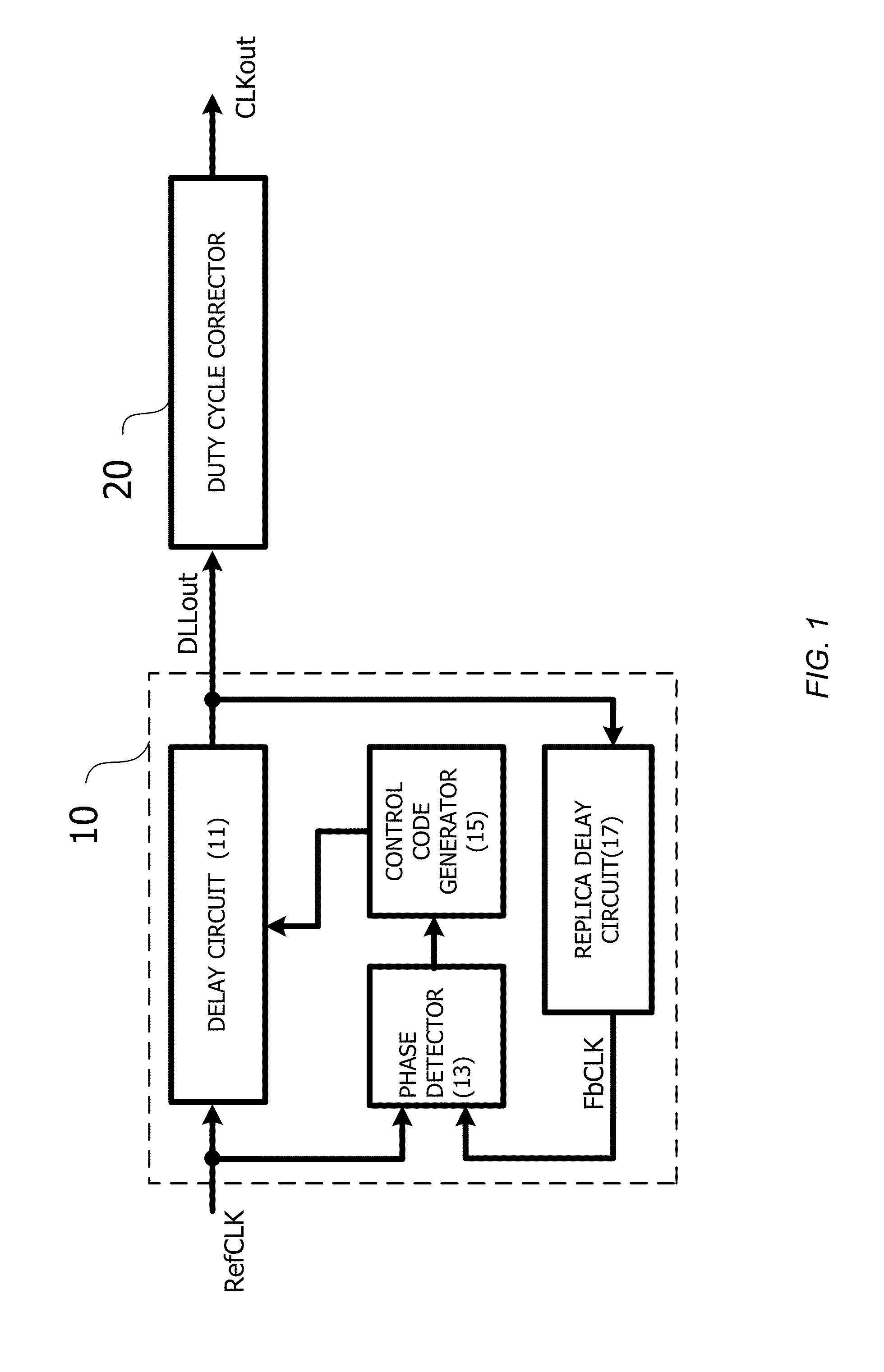

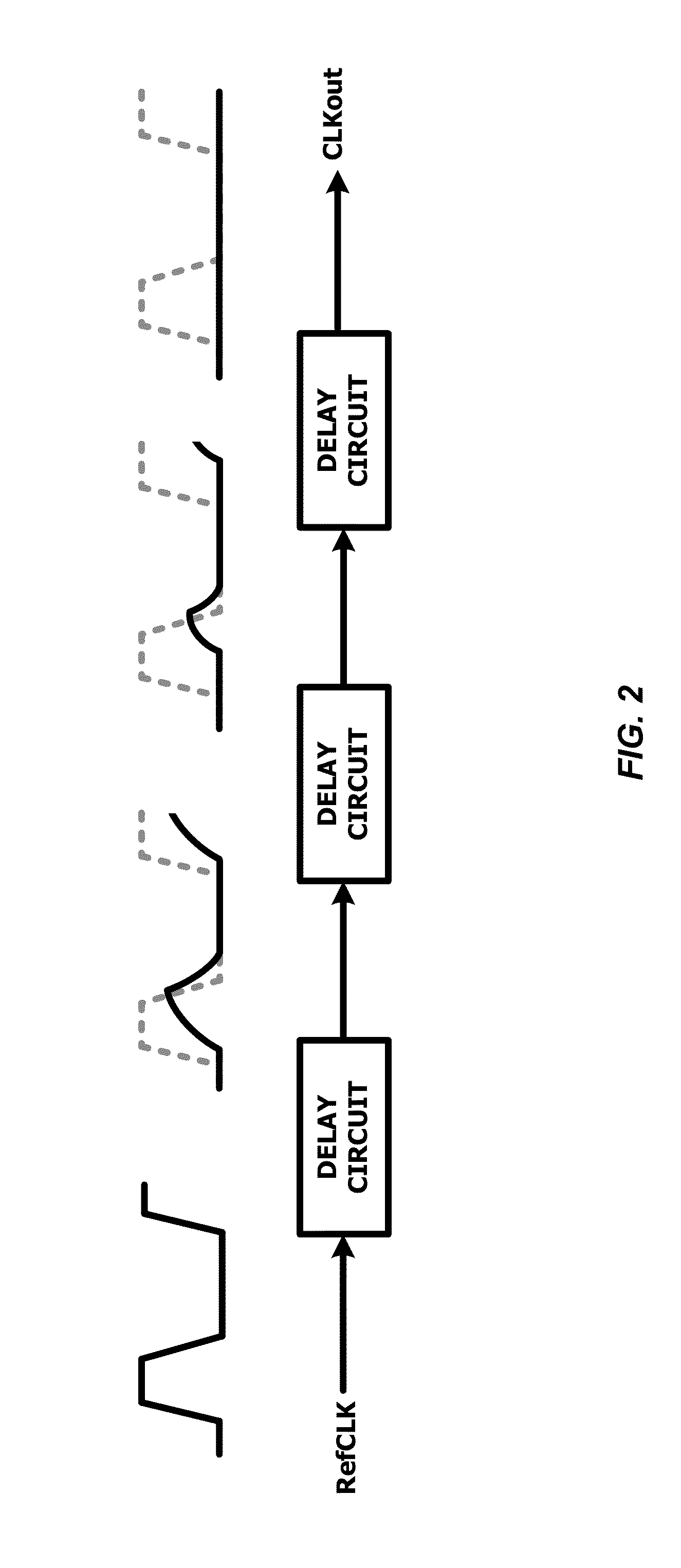

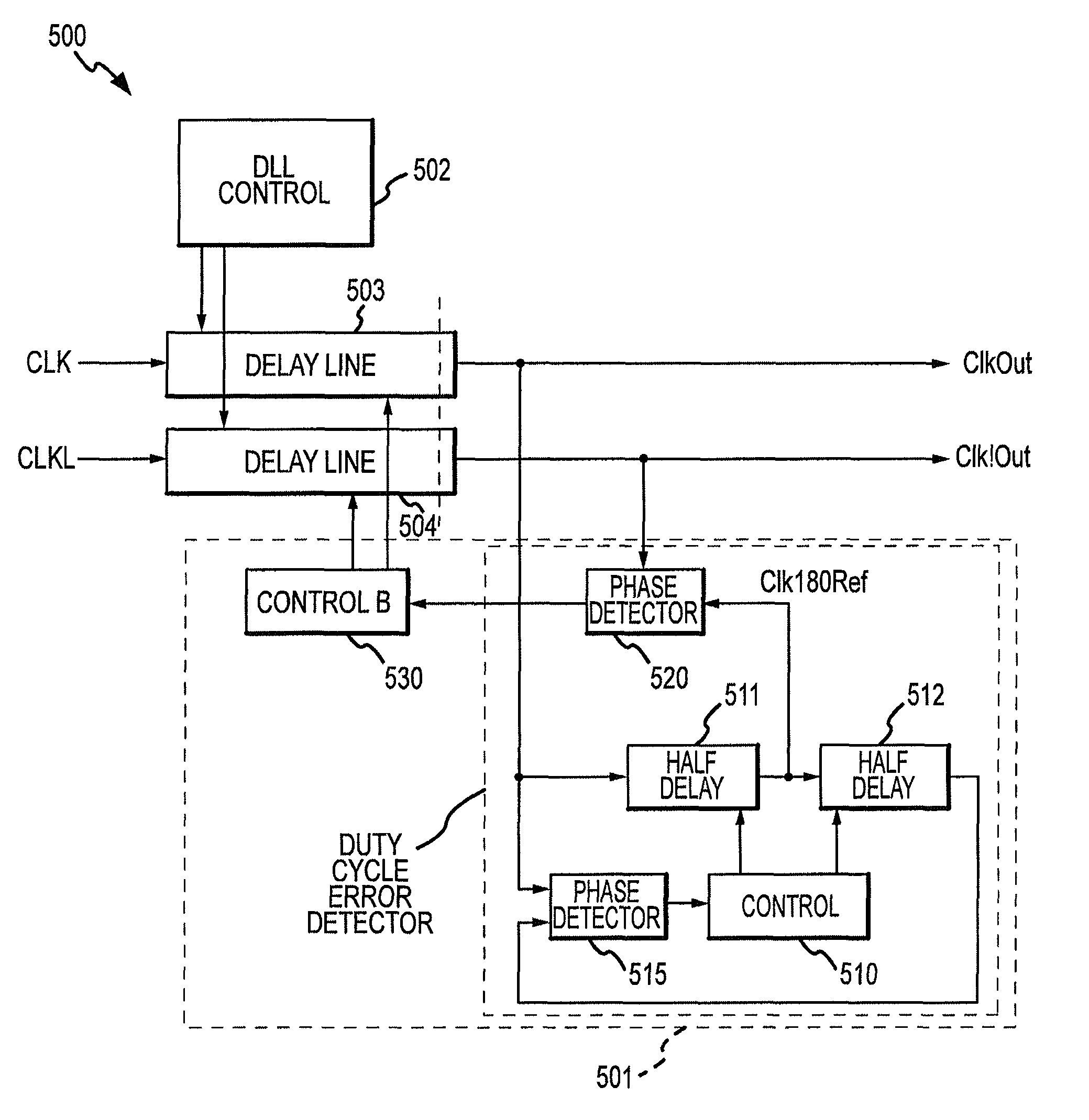

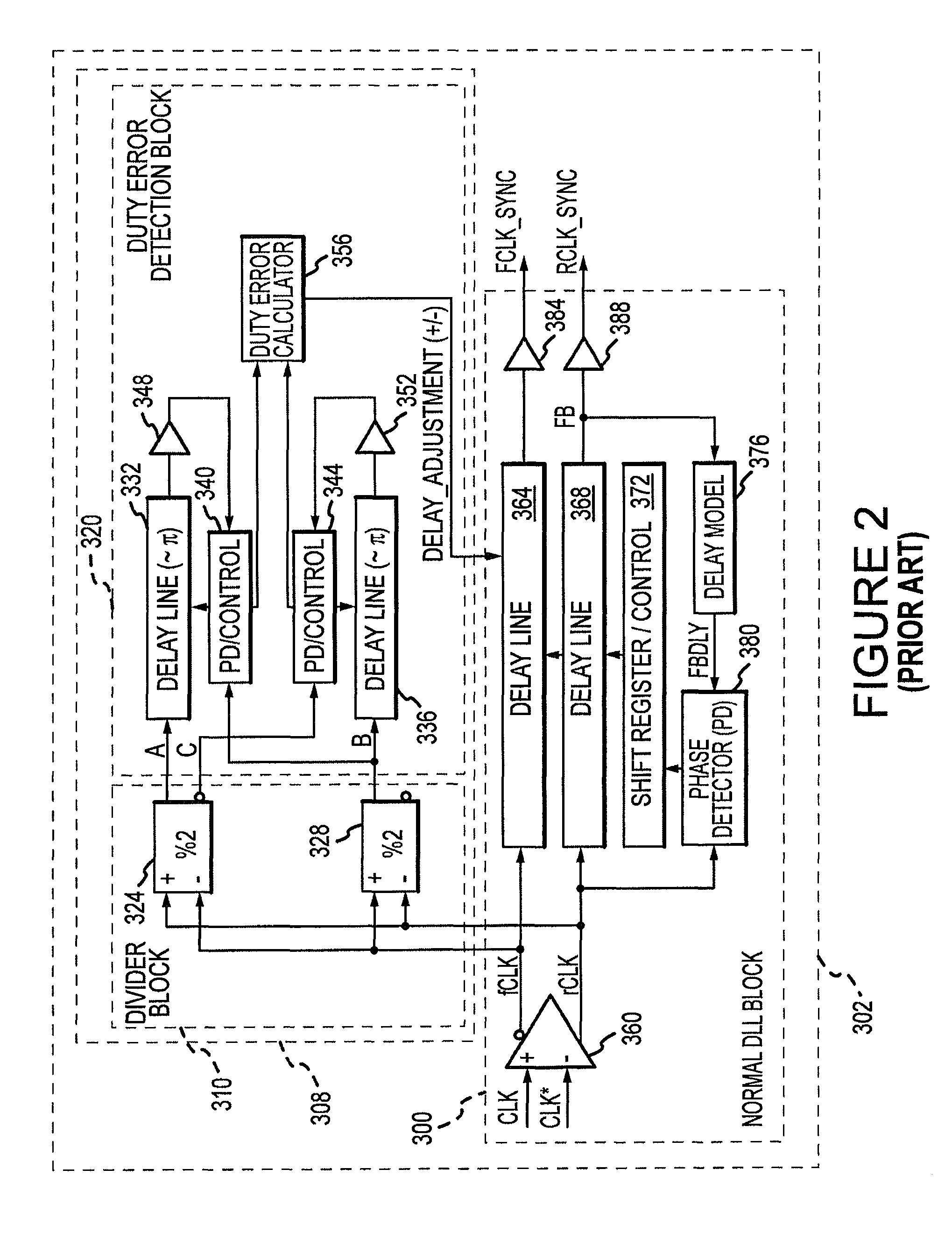

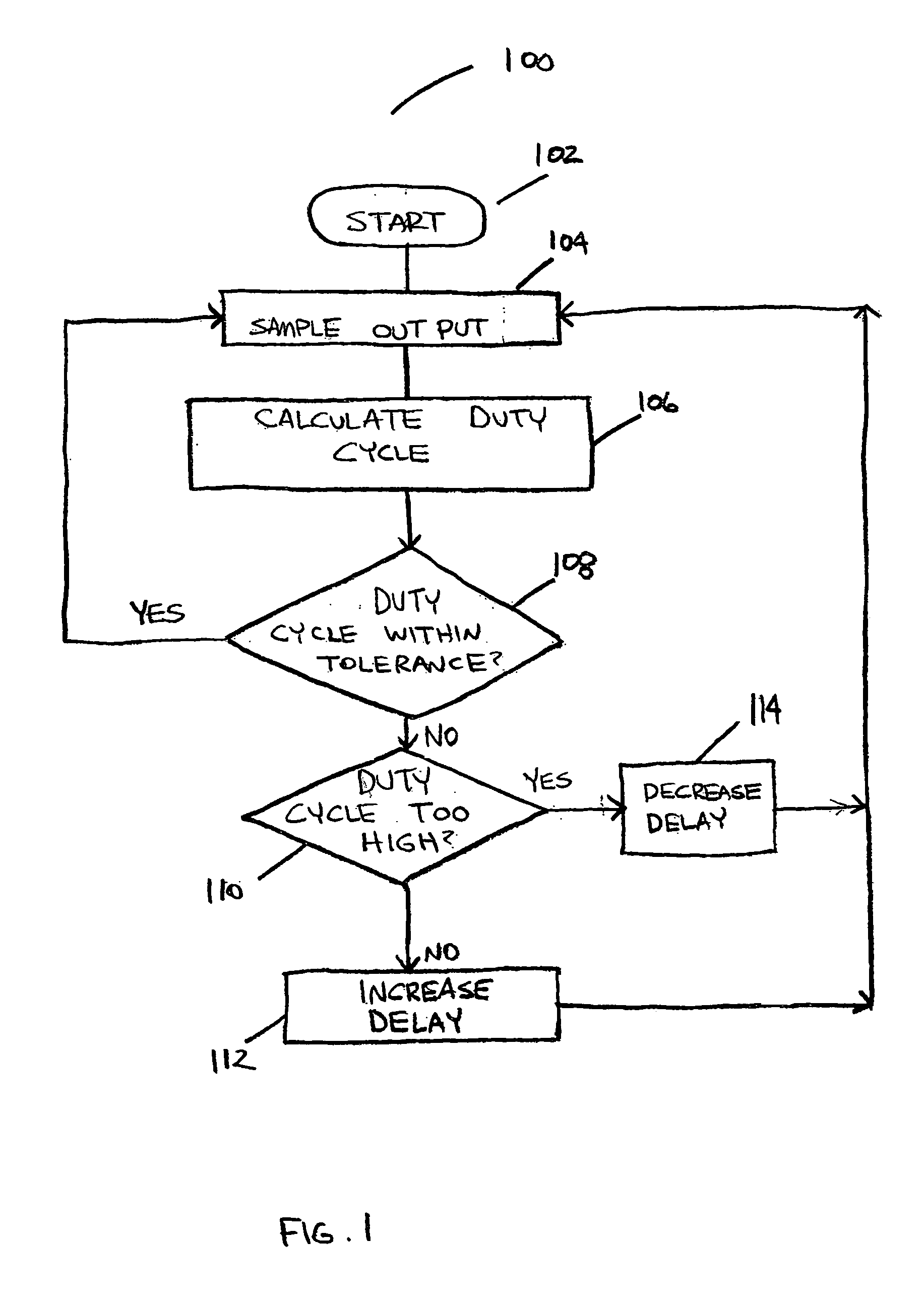

Clock generator and methods using closed loop duty cycle correction

Closed-loop duty-cycle correctors (DCCs), clock generators, memory devices, systems, and methods for generating an output clock signal having a particular duty cycle are provided, such as clock generators configured to generate an output clock signal synchronized with a received input clock signal having a predetermined duty cycle. Embodiments of clock generators include closed-loop duty cycle correctors that receive an already-controlled and corrected output signal. For example, DLL control circuitry and DCC control circuitry may each adjust a delay of a variable delay line. The DLL control circuitry adjusts the delay such that an output clock signal is synchronized with an input clock signal. The DCC control circuitry detects a duty cycle error in the output clock signal and adjusts the delay of the variable delay line to achieve a duty cycle corrected output signal. By detecting the duty cycle error in the output signal, the clock generator may achieve improved performance that can correct accumulated duty cycle error and correct for duty cycle error introduced by the duty cycle corrector itself in some embodiments.

Owner:MICRON TECH INC

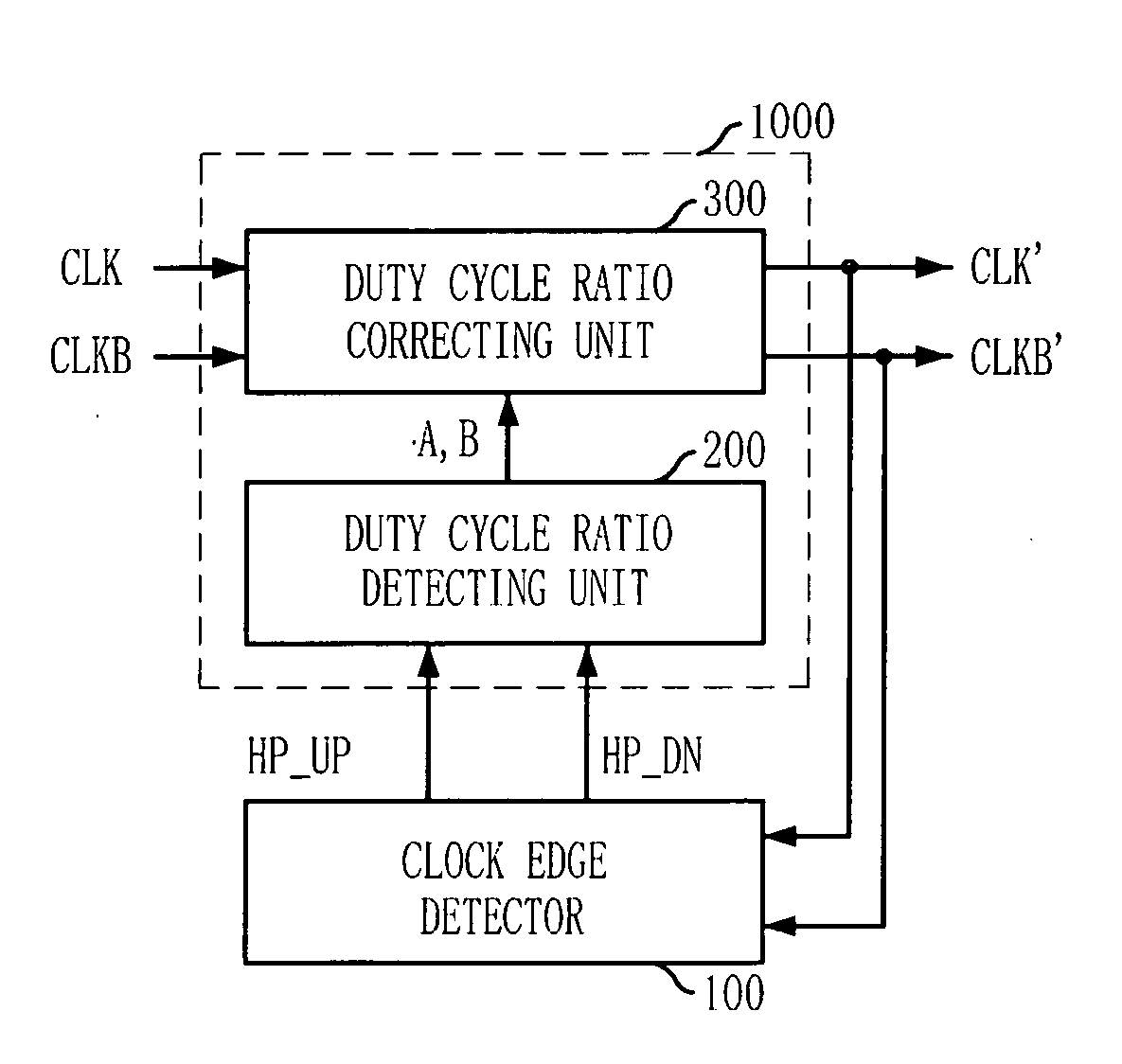

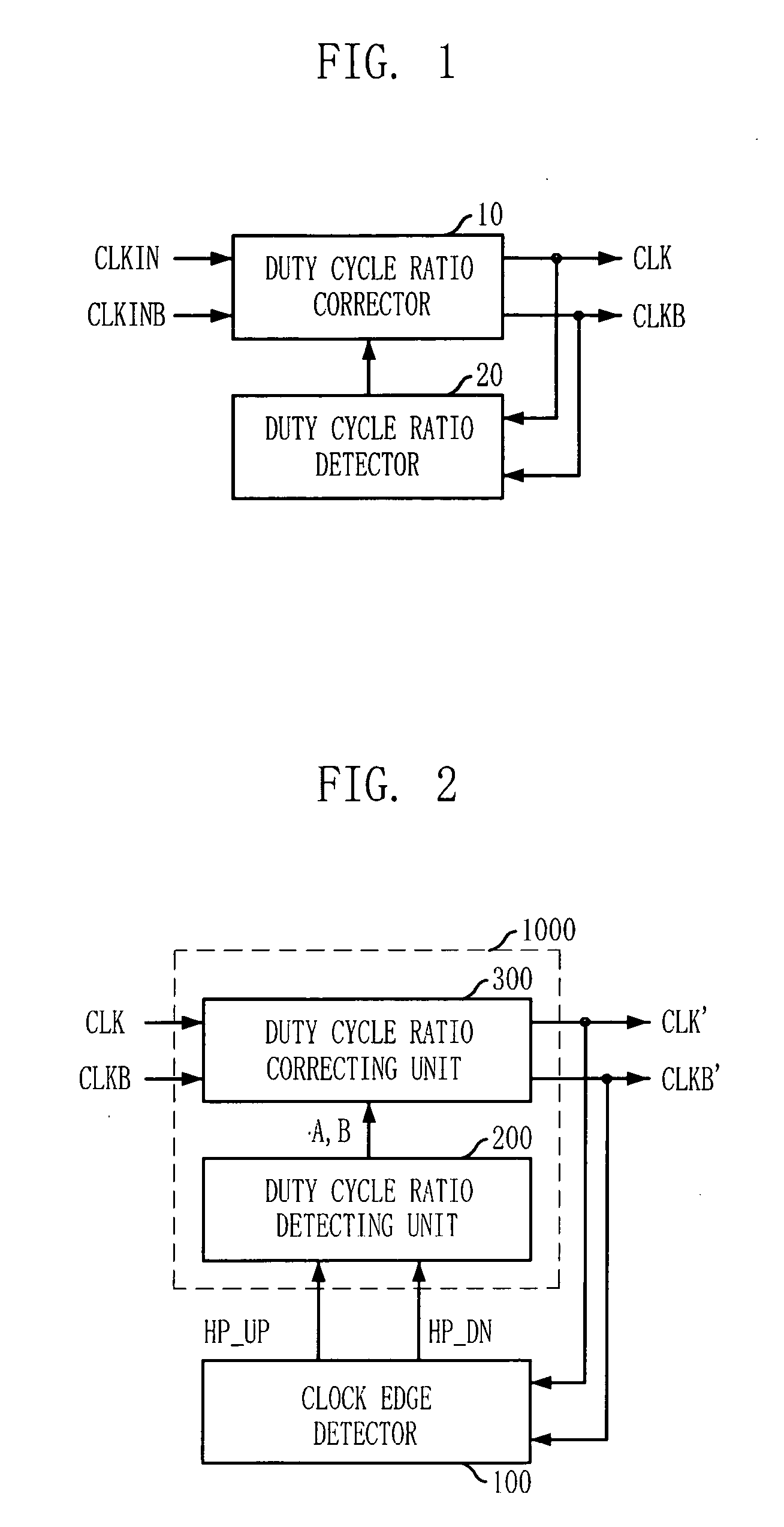

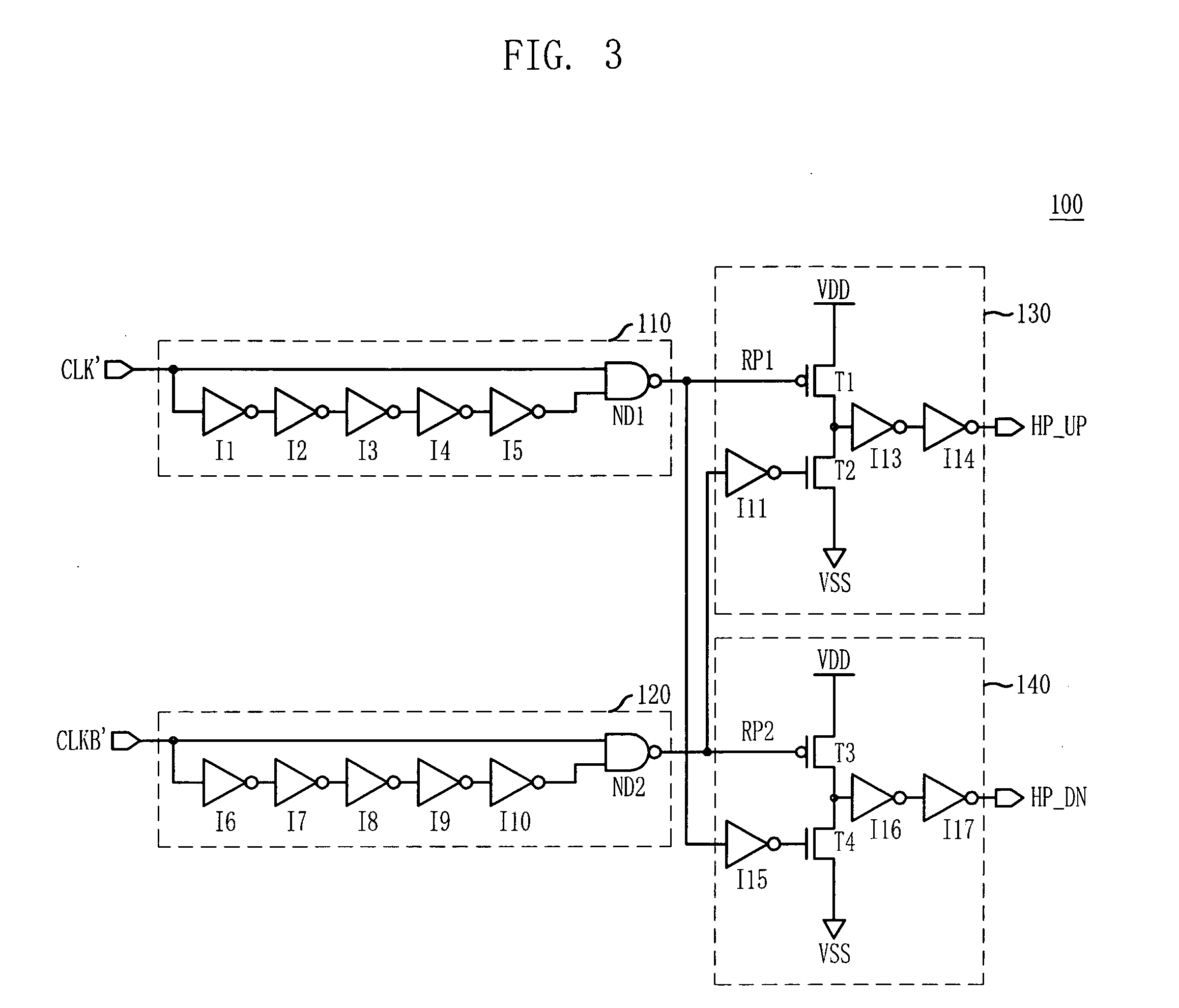

Semiconductor memory device and method for driving the same

A semiconductor memory device has a duty cycle correction circuit capable of outputting a duty cycle corrected clock and its inverted clock having substantially exactly 180° phase difference therebetween. The semiconductor memory device includes a duty cycle corrector configured to receive a first clock and a second clock to generate a first output clock and a second output clock whose duty cycle ratios are corrected in response to correction signals, and a clock edge detector configured to generate the correction signals corresponding to an interval between a reference transition timing of the first output clock and a reference transition timing of the second output clock.

Owner:SK HYNIX INC

Duty cycle corrector

InactiveUS6882196B2Continuous to patterned pulse manipulationElectric pulse generatorVoltage controlDuty cycle corrector

A device that uses an input clock signal to generate an output clock signal with a desired frequency is provided. The device uses a voltage controlled delay element that outputs a reset signal to a flip-flop dependent on a bias signal and the input clock signal. When triggered, the flip-flop outputs a transition on the output clock signal, which, in turn, serves as an input to a duty cycle corrector that generates the bias signal dependent on the configuration of the duty cycle corrector. The duty cycle corrector may be configured to generate the bias signal so as to be able to operatively control the duty cycle of the output clock signal.

Owner:ORACLE INT CORP

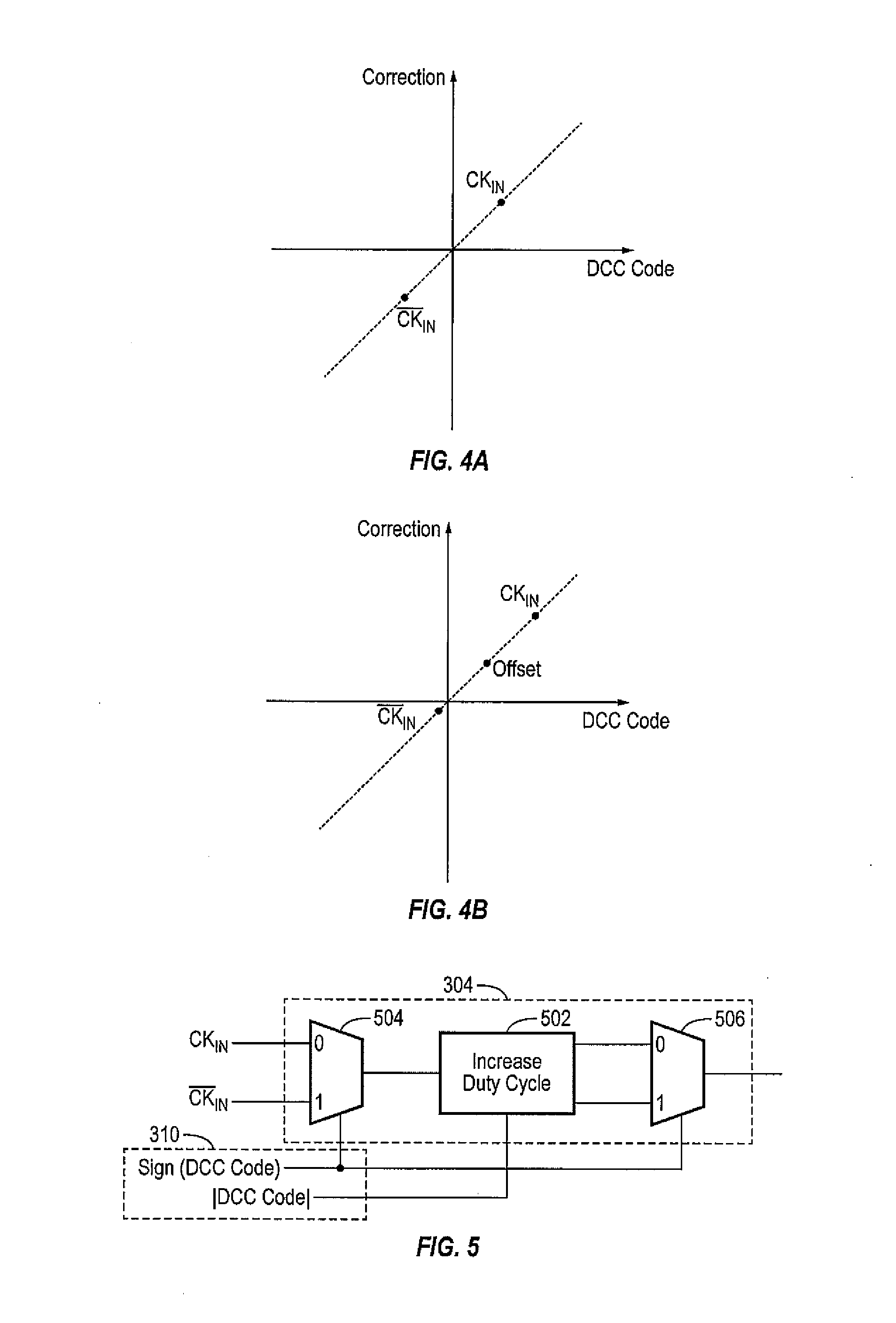

Apparatus and method for offset cancellation in duty cycle corrections

ActiveUS20150097603A1Increasing duty cycle correction circuit ' ability to duty cycleReduce errorsPulse automatic controlElectric pulse generatorOffset cancellationDuty cycle corrector

An electronic device includes a clock configured to transmit a first clock signal and a second clock signal for operation of the electronic device; a duty cycle corrector coupled to the clock to correct a duty cycle of the first and second clock signals, the duty cycle corrector being configured to: assign and store a first duty cycle correction code in response to the first clock signal; assign and store a second duty cycle correction code in response to the second clock signal; calculate an offset code based on the first and second duty cycle correction codes; and negate the offset code from results of duty cycle correction operations.

Owner:SAMSUNG DISPLAY CO LTD

Delay locked loop with a loop-embedded duty cycle corrector

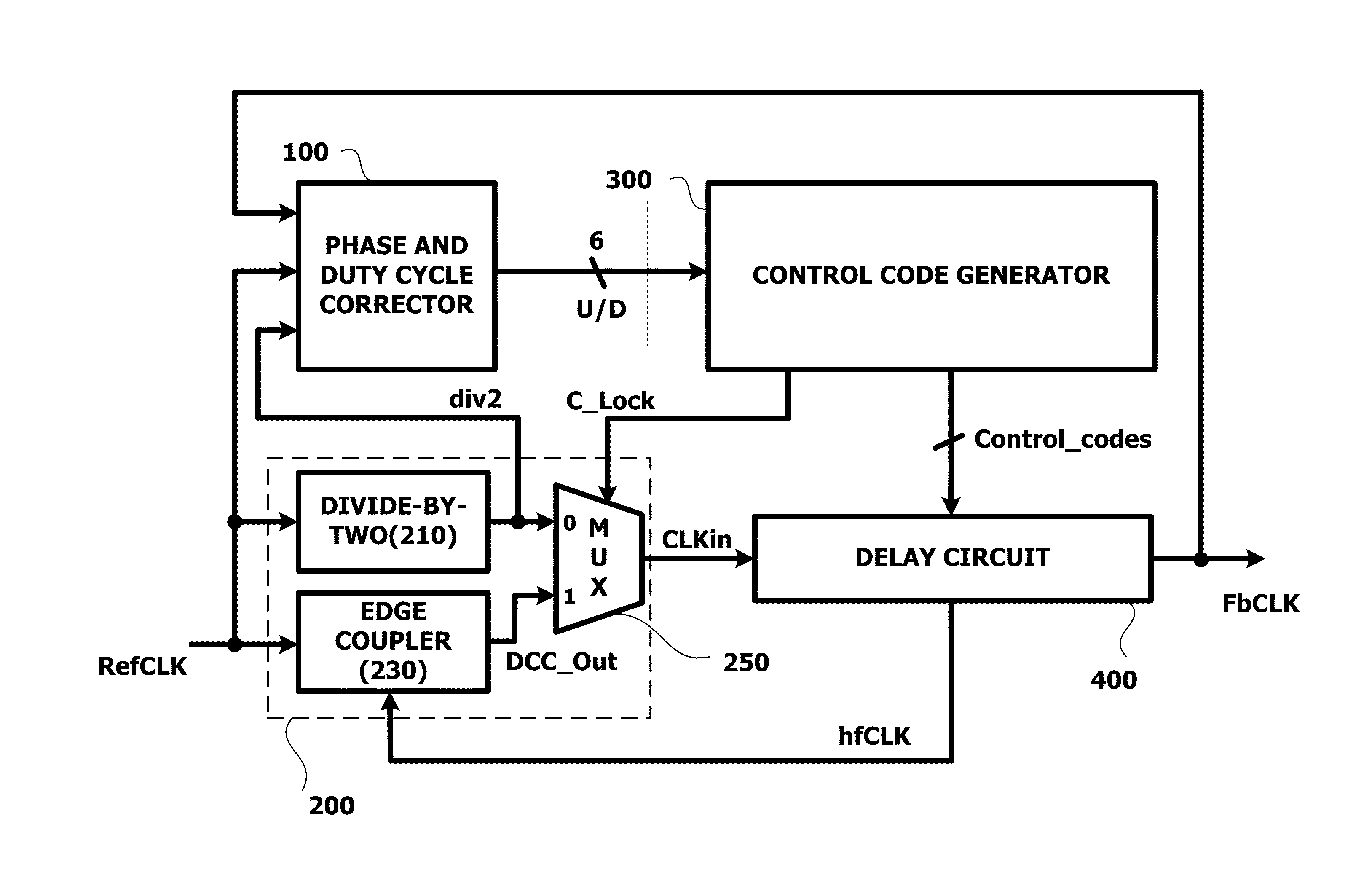

ActiveUS20140002155A1Reduce areaReduce consumptionPulse automatic controlContinuous to patterned pulse manipulationDelay-locked loopEngineering

A delayed locked loop (DLL) adjusts a duty cycle of an input clock signal and outputs an output clock signal. The DLL includes a phase and duty cycle detector configured to detect a phase and duty cycle of the input clock signal, a duty cycle corrector configured to correct the duty cycle, a control code generator configured to detect coarse lock of the DLL and generate a binary control code corresponding to the detection result, and a delay circuit configured to delay an output signal of the duty cycle corrector by a predetermined time according to the binary control code, tune the duty cycle thereof, and mix the phase thereof, wherein the phase and duty cycle detector, the duty cycle corrector, the control code generator, and the delay circuit form a feedback loop.

Owner:SK HYNIX INC +1

Clock generator and methods using closed loop duty cycle correction

Closed-loop duty-cycle correctors (DCCs), clock generators, memory devices, systems, and methods for generating an output clock signal having a particular duty cycle are provided, such as clock generators configured to generate an output clock signal synchronized with a received input clock signal having a predetermined duty cycle. Embodiments of clock generators include closed-loop duty cycle correctors that receive an already-controlled and corrected output signal. For example, DLL control circuitry and DCC control circuitry may each adjust a delay of a variable delay line. The DLL control circuitry adjusts the delay such that an output clock signal is synchronized with an input clock signal. The DCC control circuitry detects a duty cycle error in the output clock signal and adjusts the delay of the variable delay line to achieve a duty cycle corrected output signal. By detecting the duty cycle error in the output signal, the clock generator may achieve improved performance that can correct accumulated duty cycle error and correct for duty cycle error introduced by the duty cycle corrector itself in some embodiments.

Owner:MICRON TECH INC

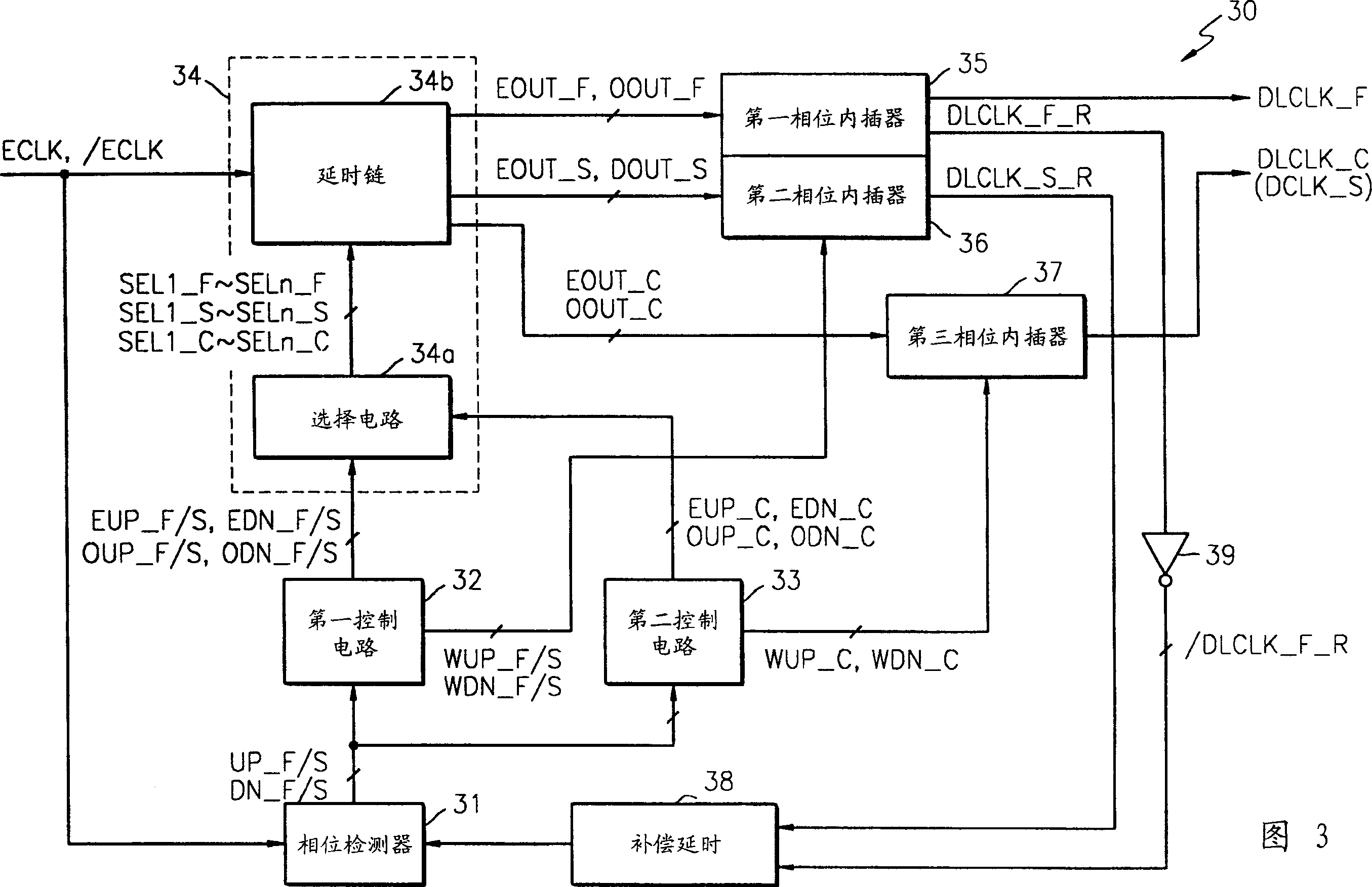

Time-delay locking loop circuit for internally correcting dutyratio and method for correcting duty cycle thereof

InactiveCN1487669APulse automatic controlContinuous to patterned pulse manipulationTime delaysDelay-locked loop

A delay locked loop (DLL) circuit having a duty cycle corrector (DCC) that has a broad range of duty cycle correction, consumes only a small amount of power, has few restrictions on operating frequency, and improves the characteristics of a memory device is described. The delay locked loop circuit includes an additional loop for duty cycle correction as well as loops for controlling a rising edge and a falling edge of output signals. Thus, the delay locked loop circuit can internally correct the duty cycle without the use of a phase blender.

Owner:SAMSUNG ELECTRONICS CO LTD

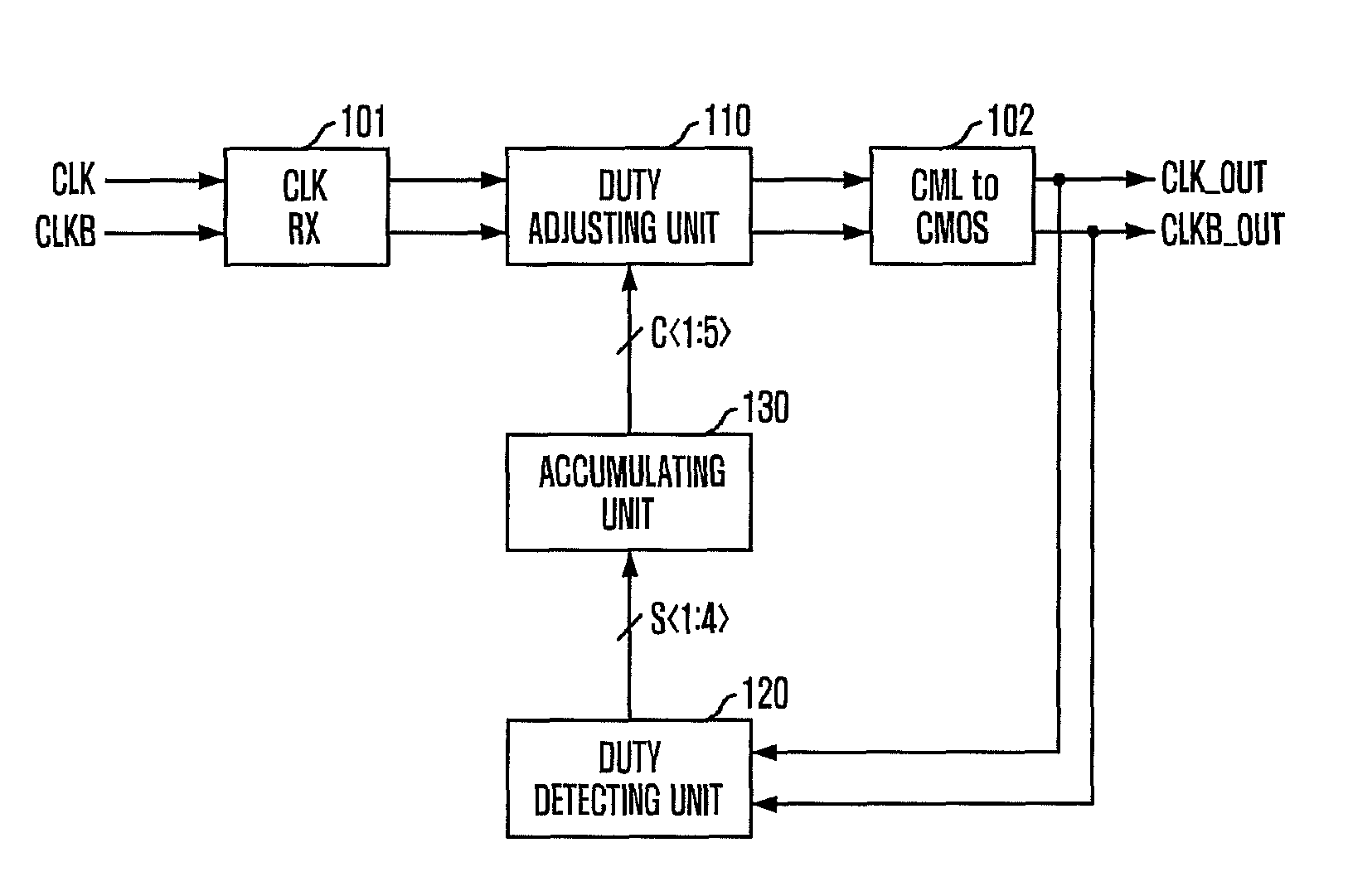

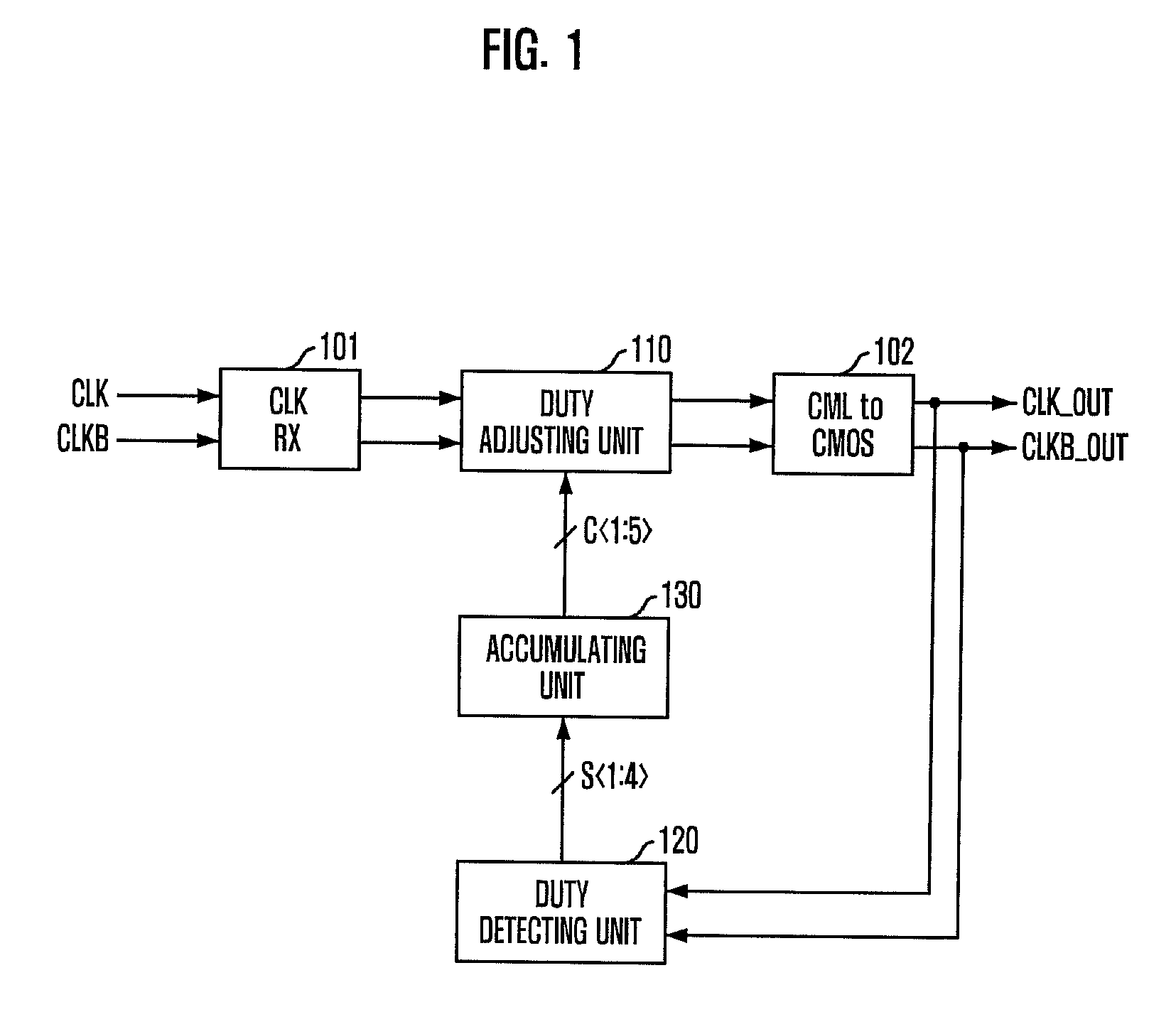

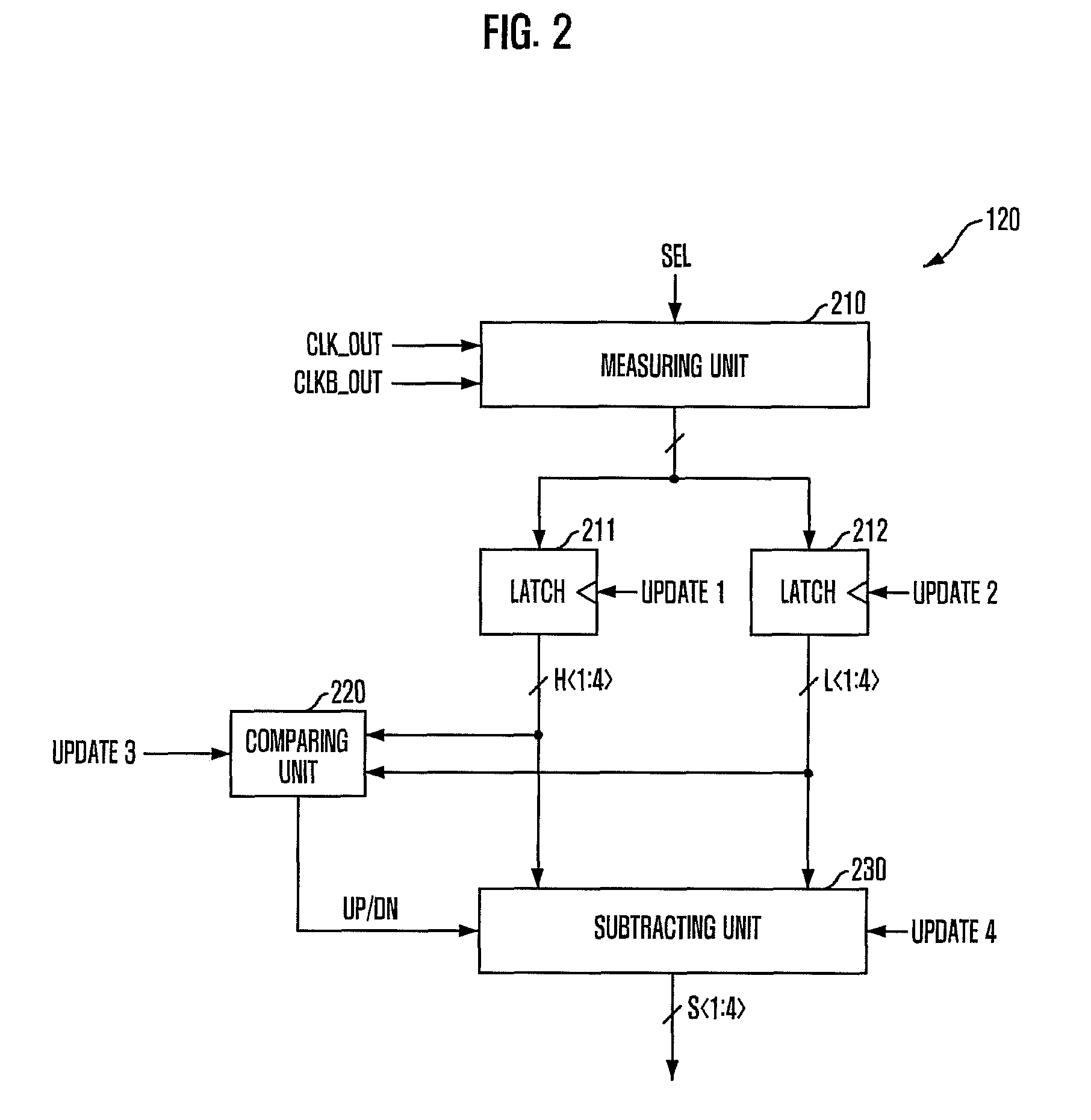

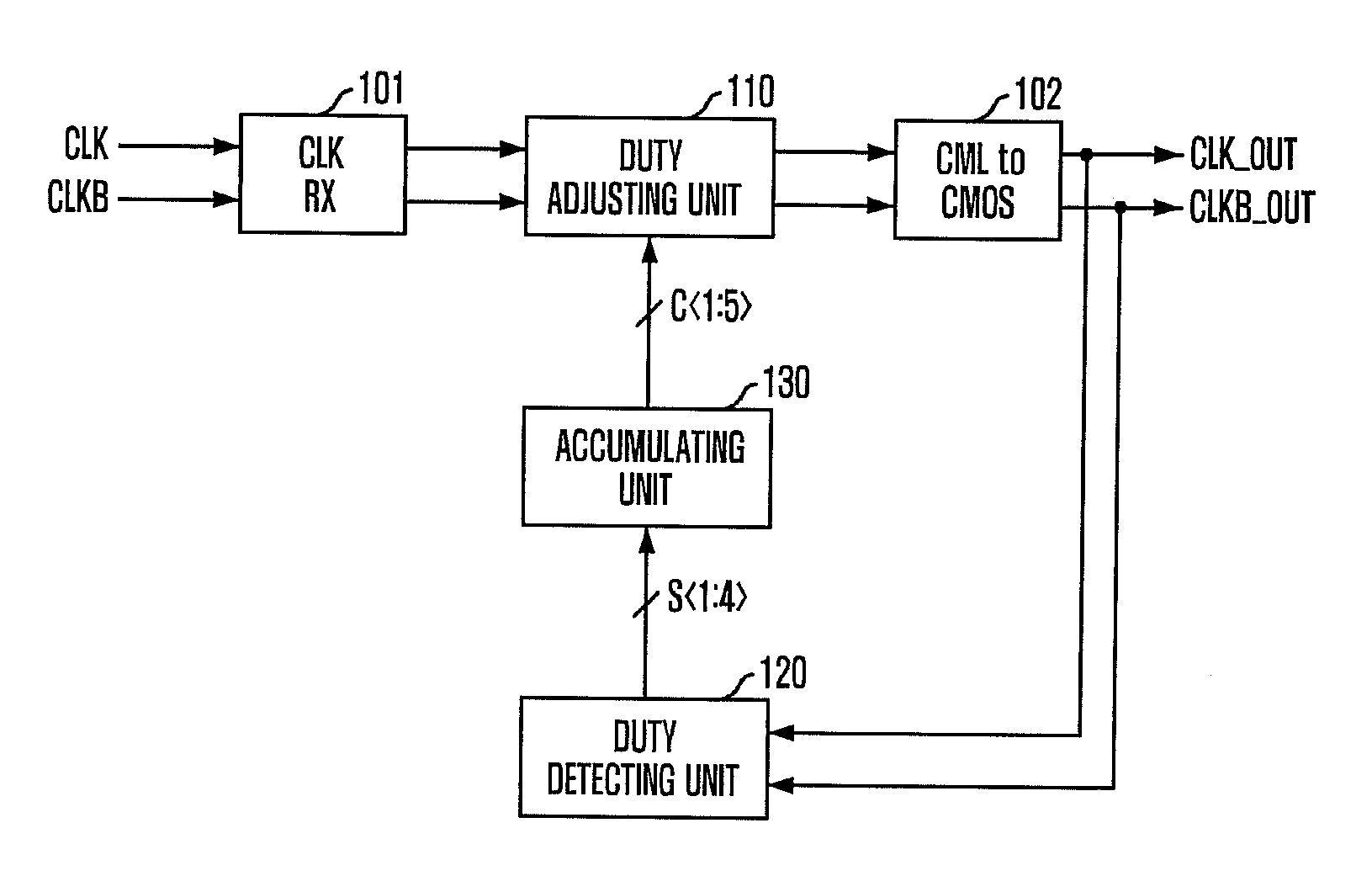

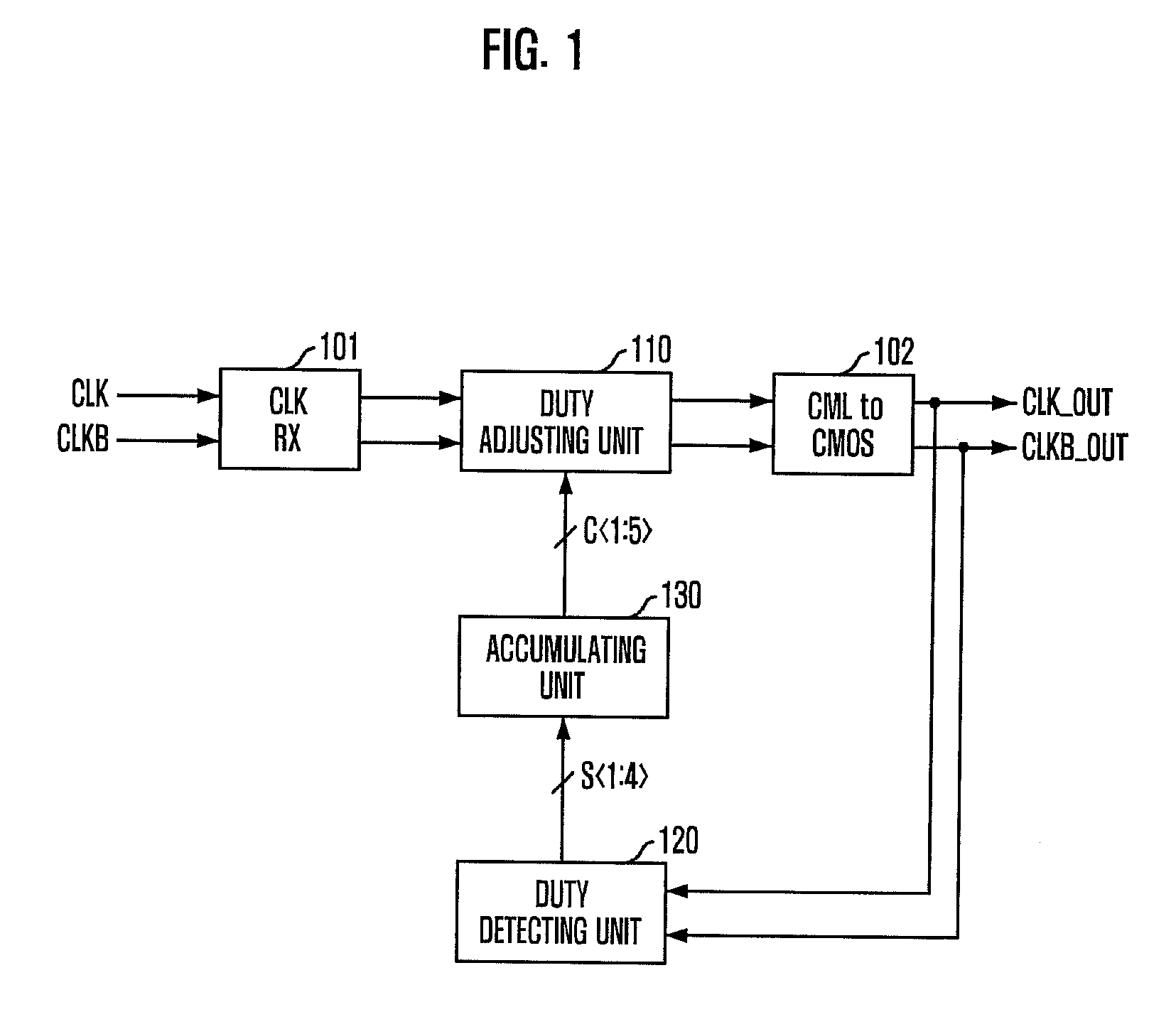

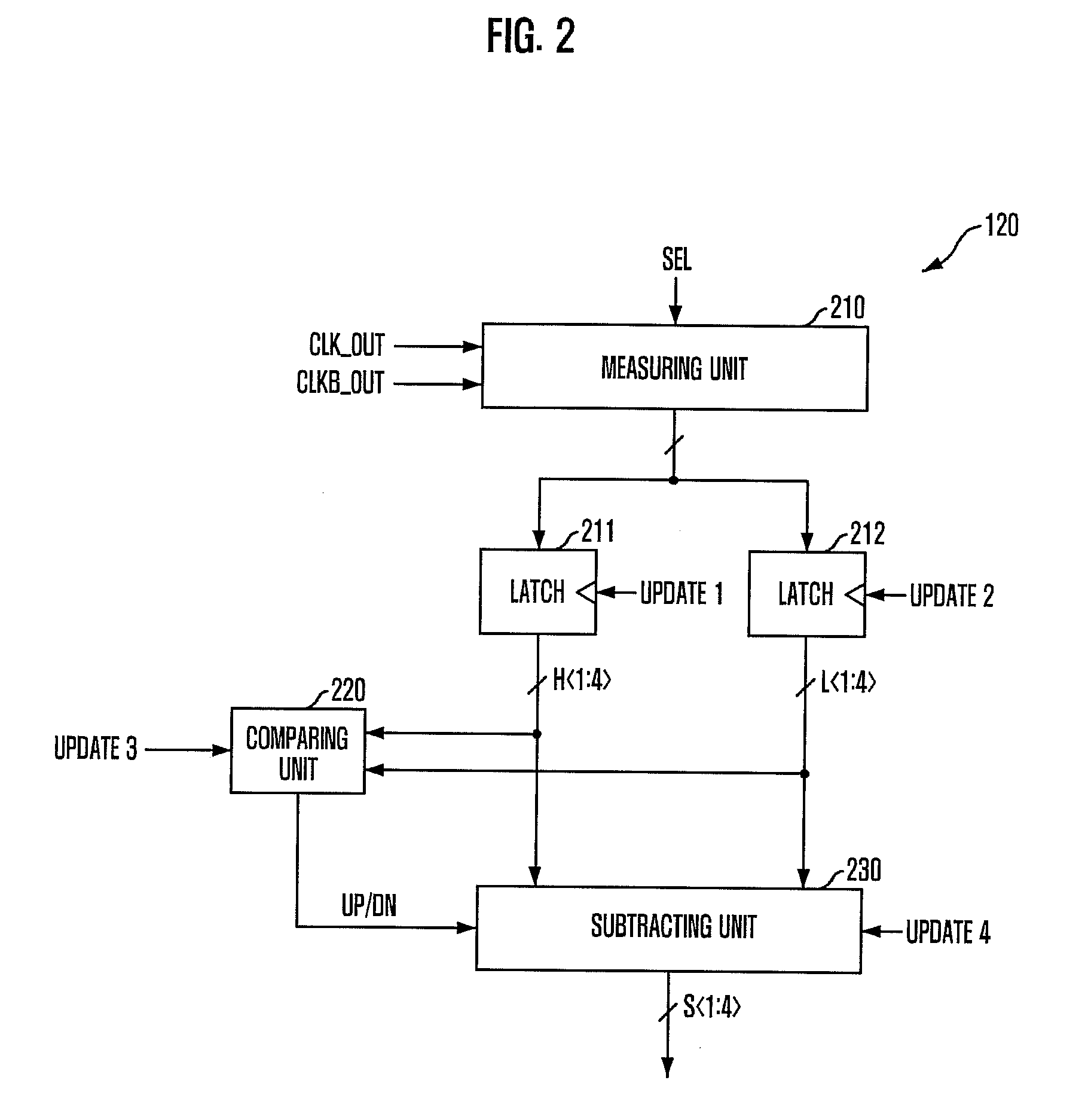

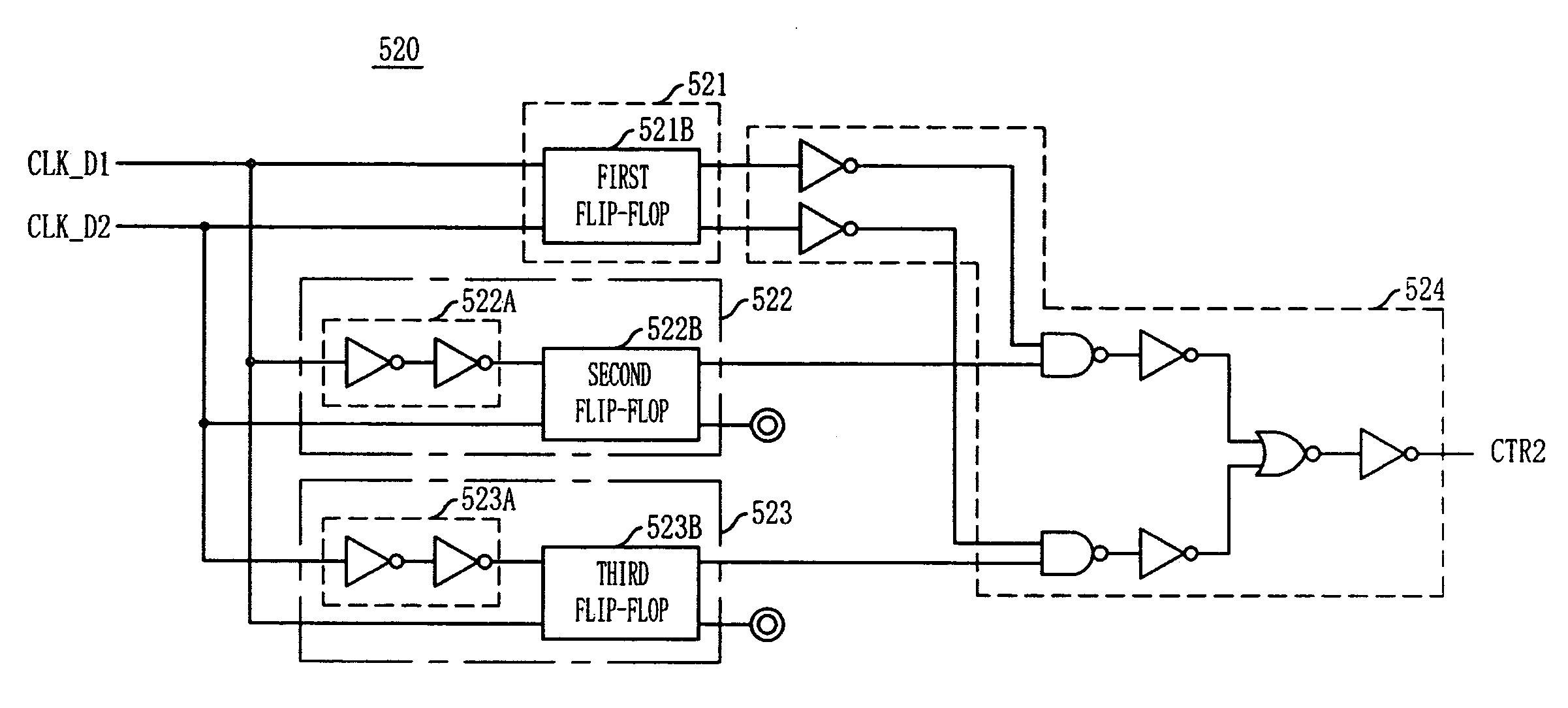

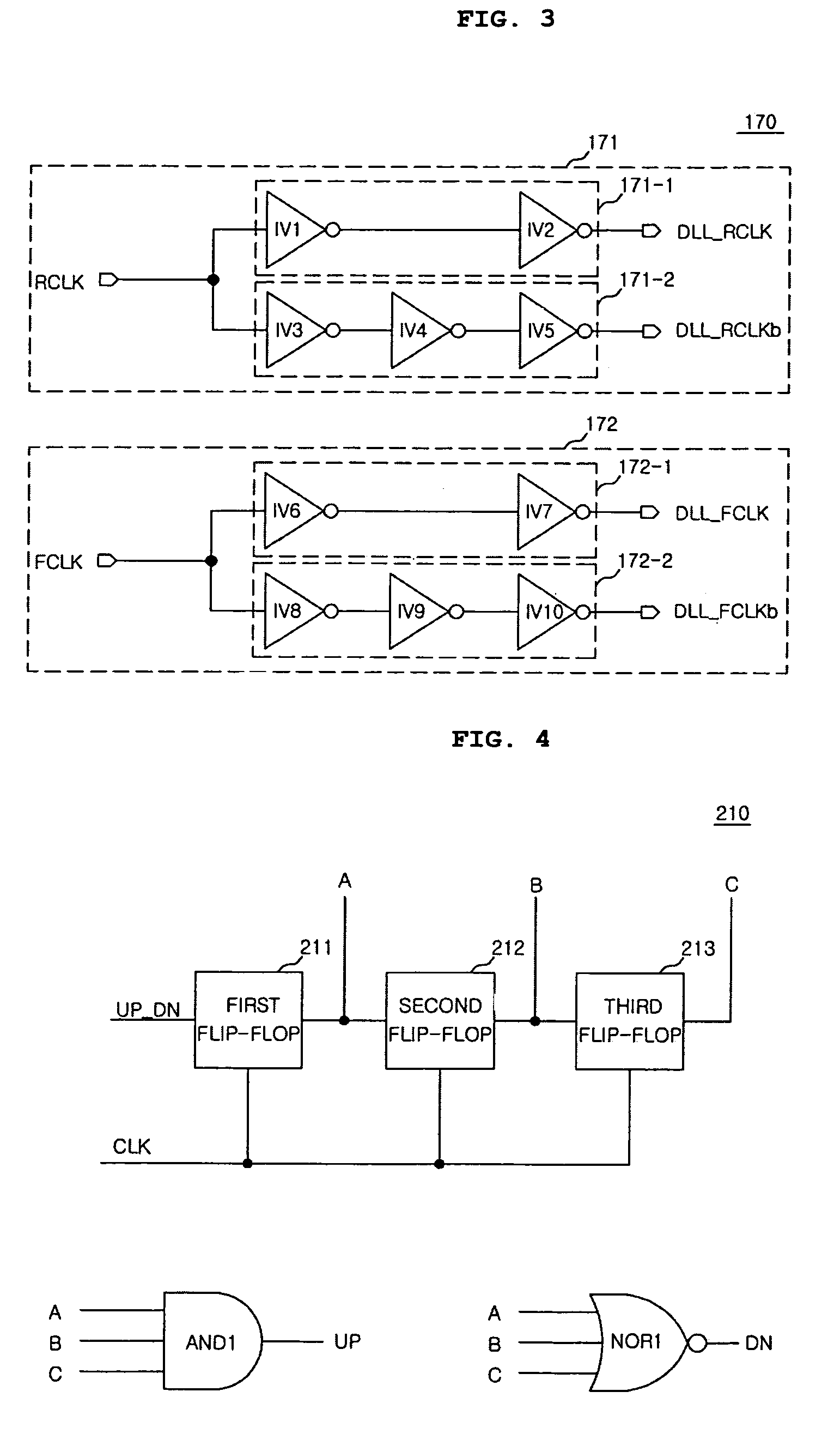

Duty detecting circuit and duty cycle corrector including the same

ActiveUS7847609B2Shorten lock timeAccurate correctionMultiple input and output pulse circuitsDelay line applicationsDuty cycle correctorCorrection code

A duty cycle corrector includes a duty adjusting unit configured to adjust a duty cycle of an input clock in response to a duty correction code and generate an output clock, a duty detecting unit configured to measure a difference between a high pulse width and a low pulse width of the output clock and output a difference value, and an accumulating unit configured to accumulate the difference value to generate the duty correction code.

Owner:SK HYNIX INC

Noise detection circuit, delay locked loop and duty cycle corrector including the same

ActiveUS20150043627A1Effectively detecting noiseStable controlPulse automatic controlTransmission monitoringNoise detectionDelay-locked loop

A noise detection circuit includes a first delay unit suitable for delaying a periodic wave to output a delayed periodic wave, a first divider unit suitable for dividing the delayed periodic wave to output a first periodic wave, a second divider unit suitable for dividing the periodic wave to output a divided periodic wave, a second delay unit suitable for delaying the divided periodic wave to output a second periodic wave, and a detection unit suitable for comparing the first periodic wave with the second periodic wave and outputting a noise detection signal.

Owner:SK HYNIX INC

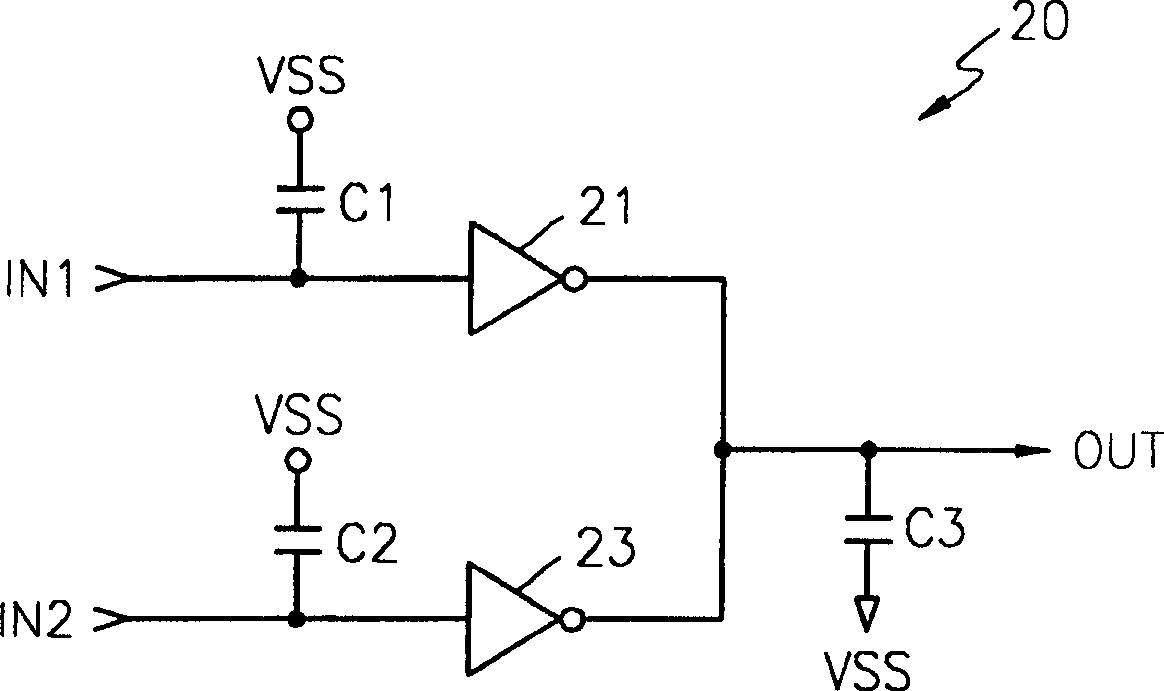

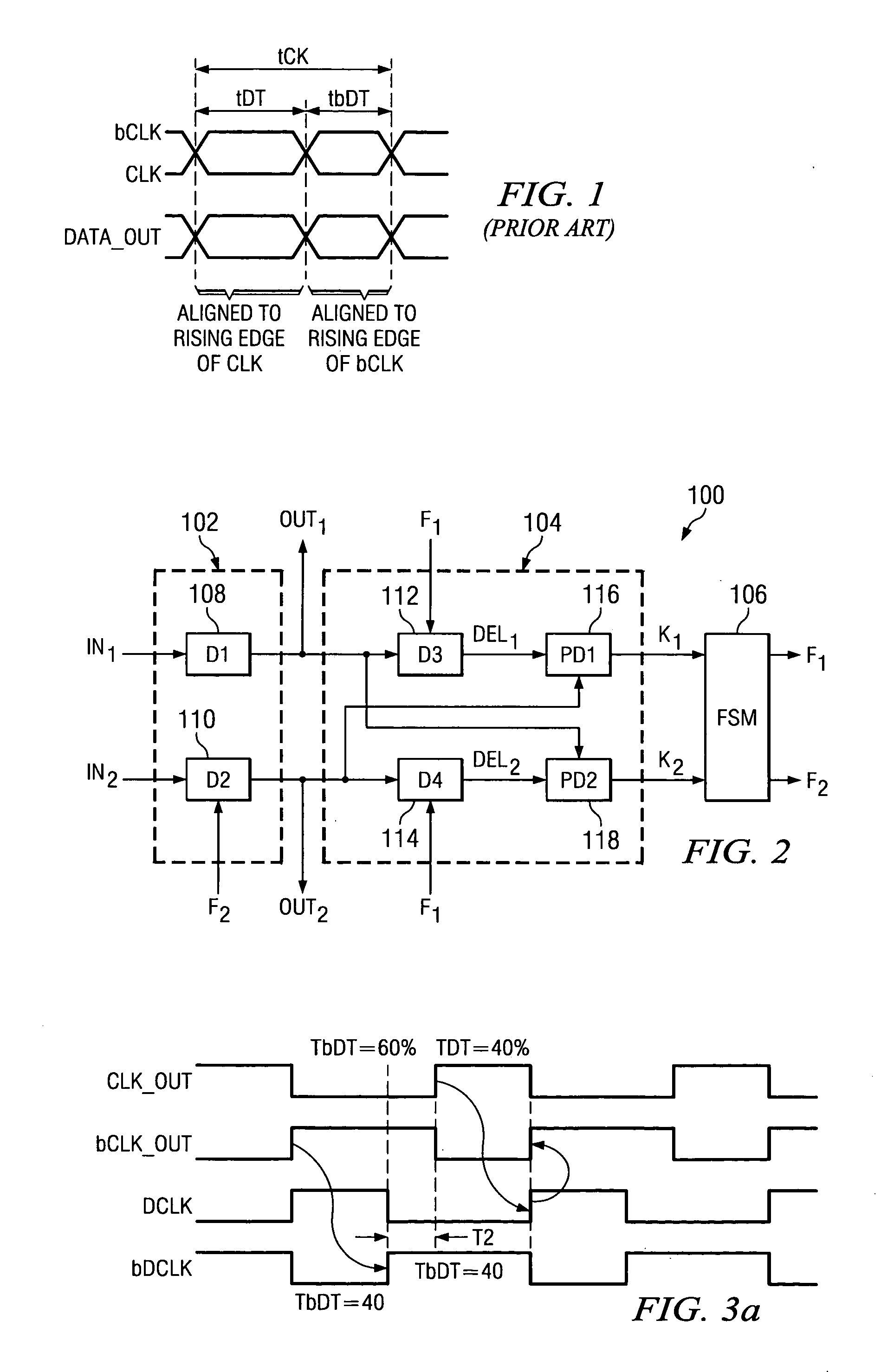

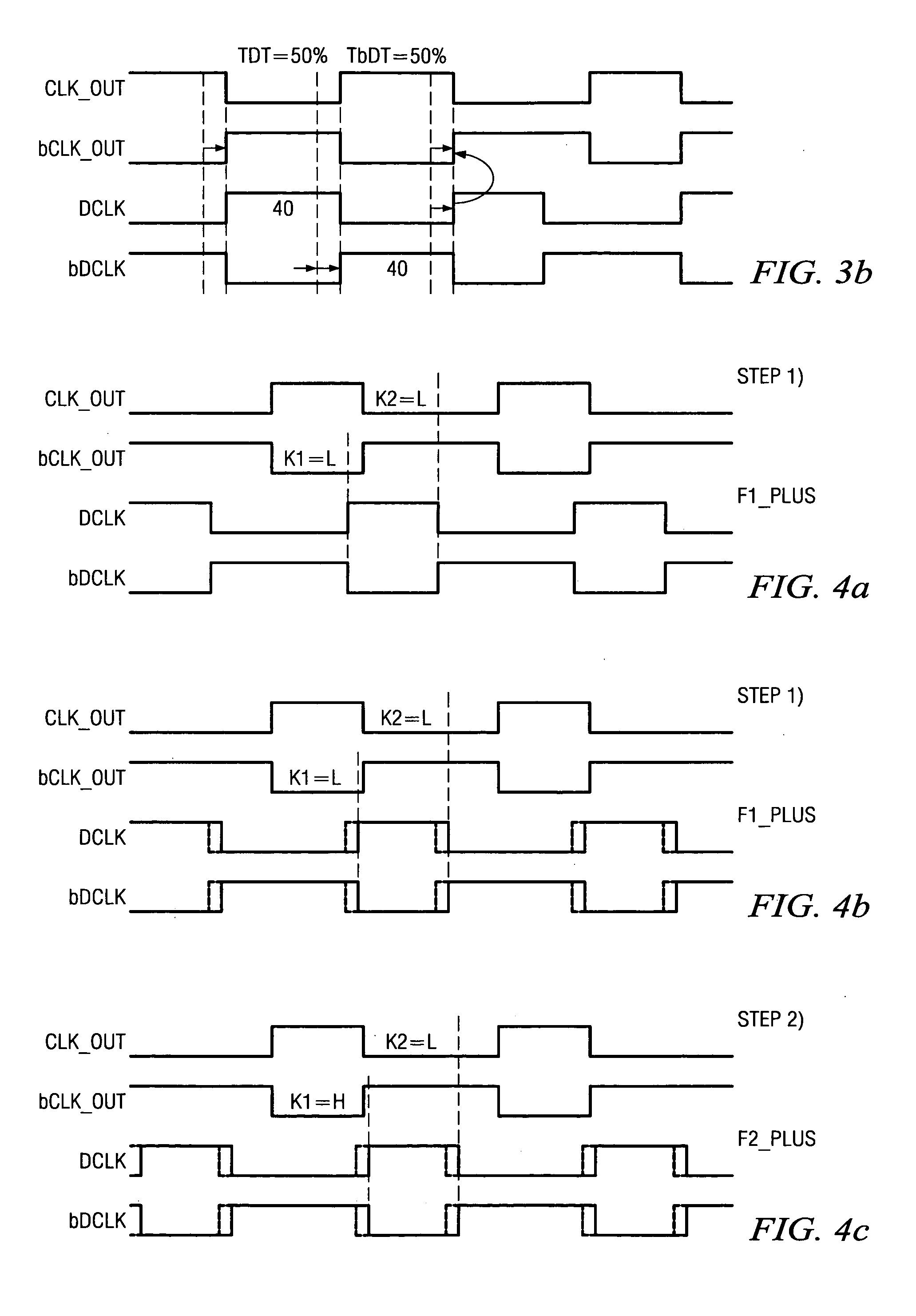

Digital duty cycle corrector

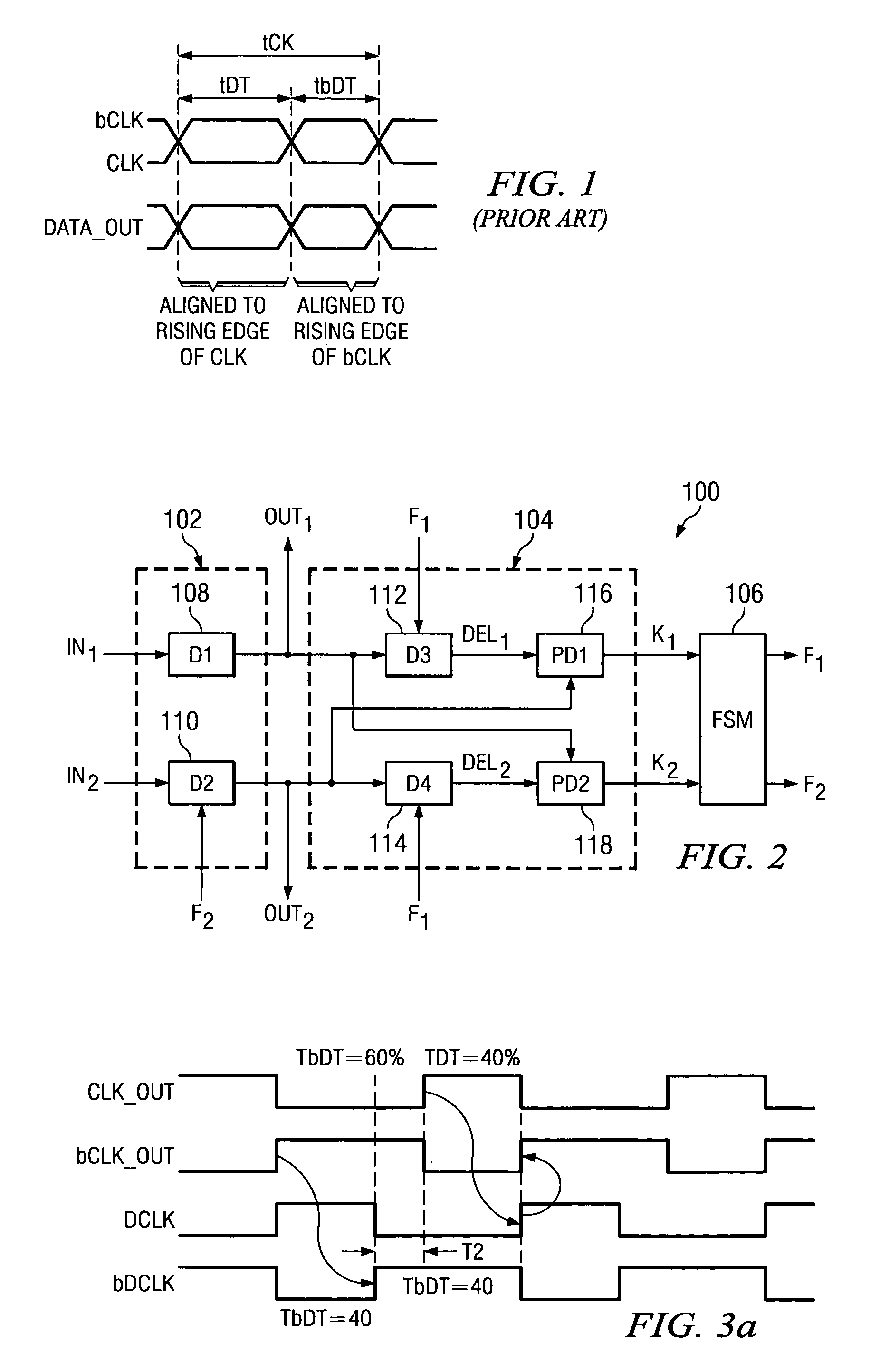

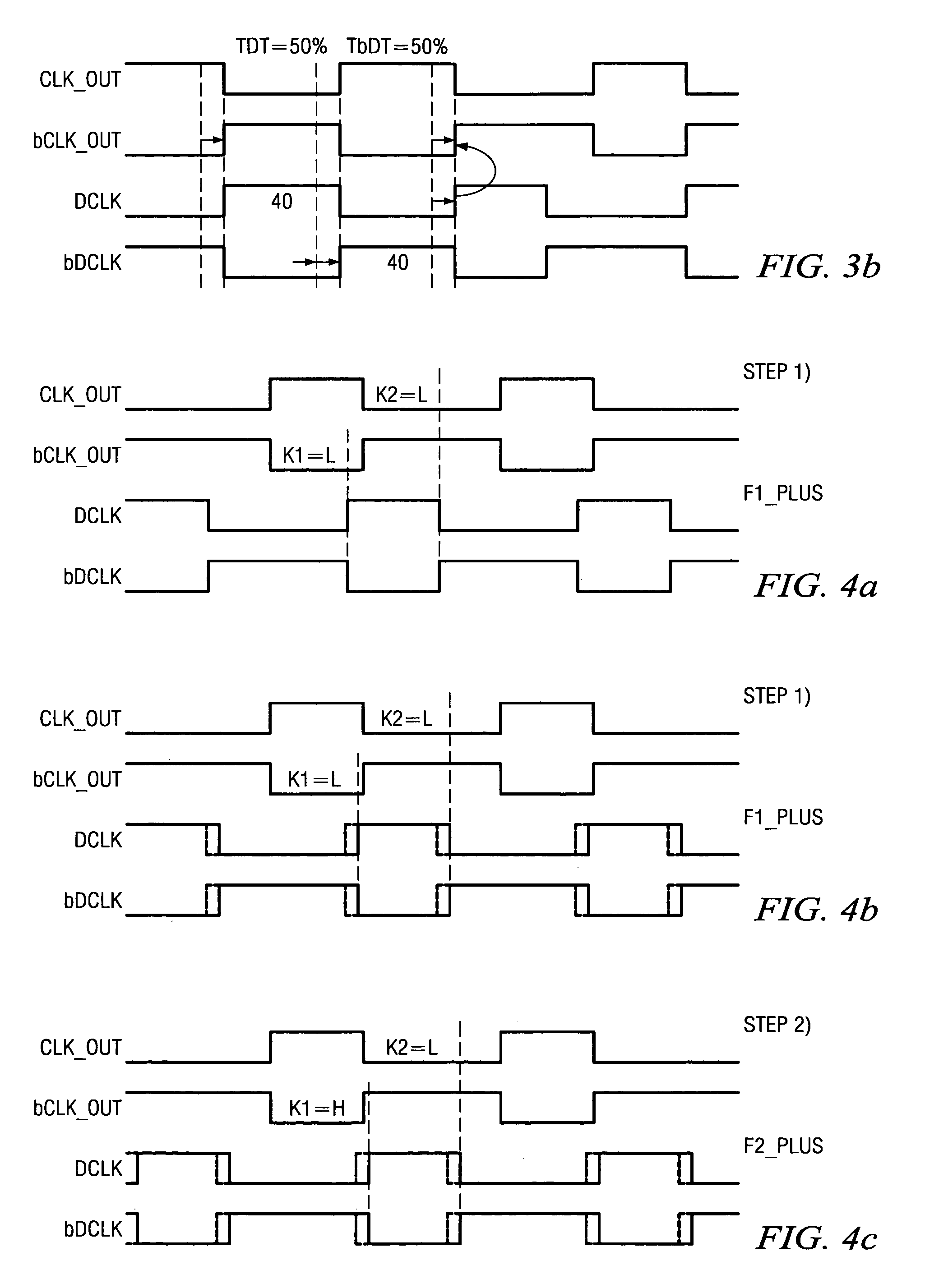

InactiveUS20060001462A1Save power consumptionReduce power consumptionPulse automatic controlElectric pulse generatorRelative phaseSignal delay

A method for adjusting the relative phases of two signals includes receiving first and second signals, which may, for example, be derived from a differential clock signal. A duty cycle error between the first signal and the second signal is detected by comparing a phase component of the first signal with a phase component of the second signal. This duty cycle error can then be corrected by delaying the second signal by an amount based upon a result derived from the comparing.

Owner:POLARIS INNOVATIONS

Digital duty cycle corrector

A circuit and method of correcting the duty cycle of digital signals is disclosed. The duty cycle of an input digital signal is measured and compared to a desired duty cycle. The leading edge of the input digital signal is passed to an output. The circuit and method adjust the falling edges at the output to achieve the desired duty cycle. The falling edges occur in response to rising edges of a delayed version of the input digital signal.

Owner:IBM CORP

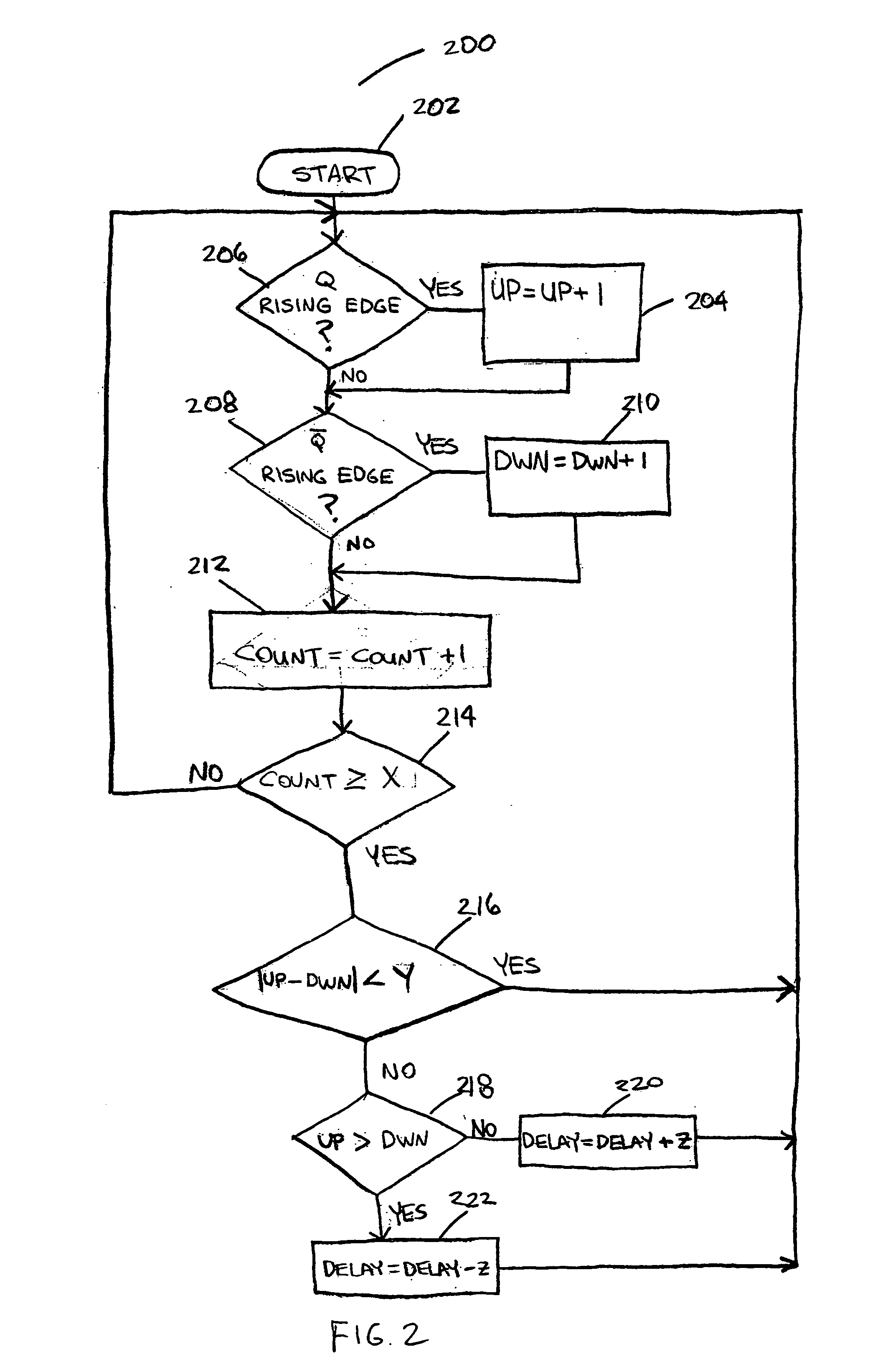

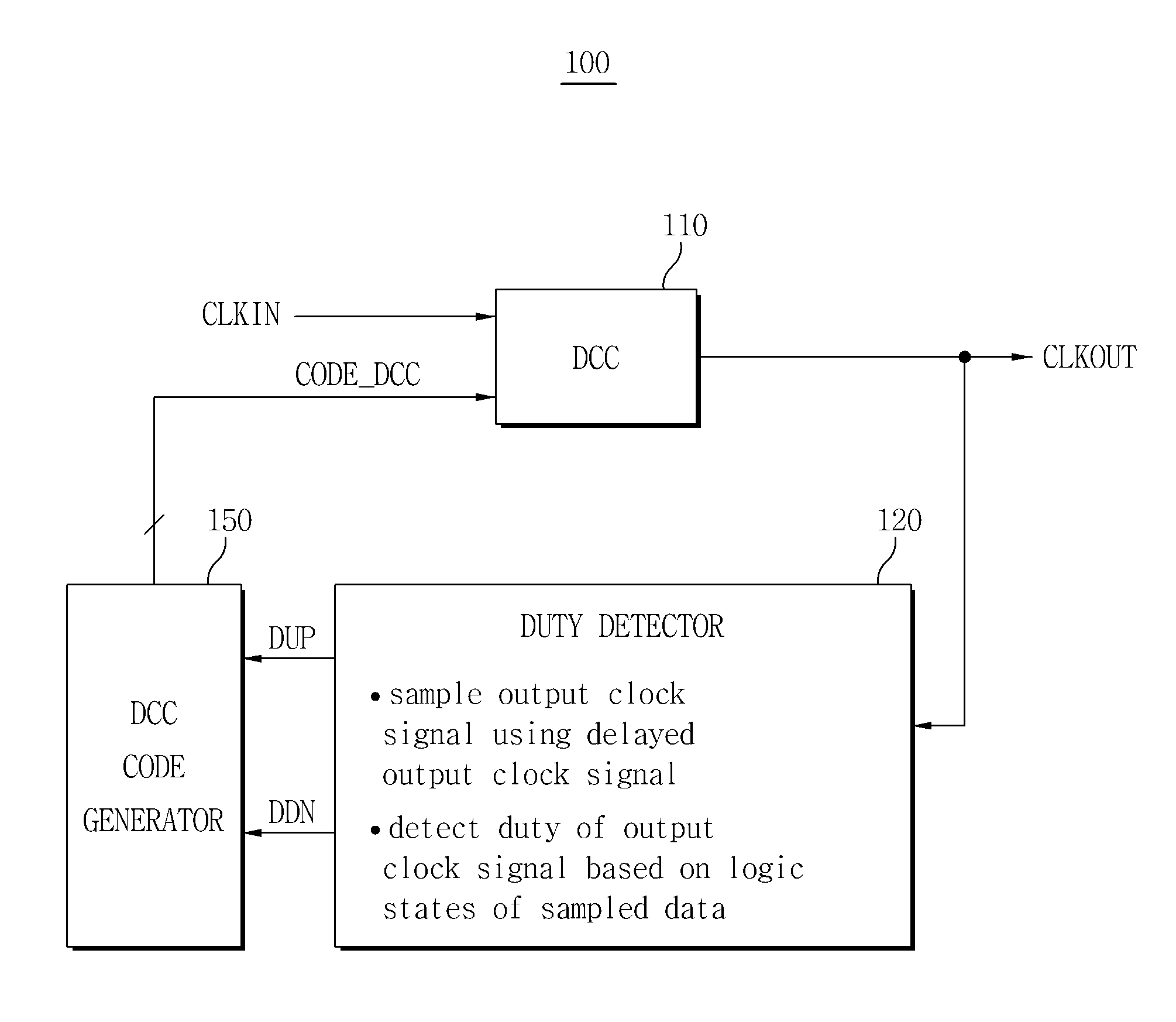

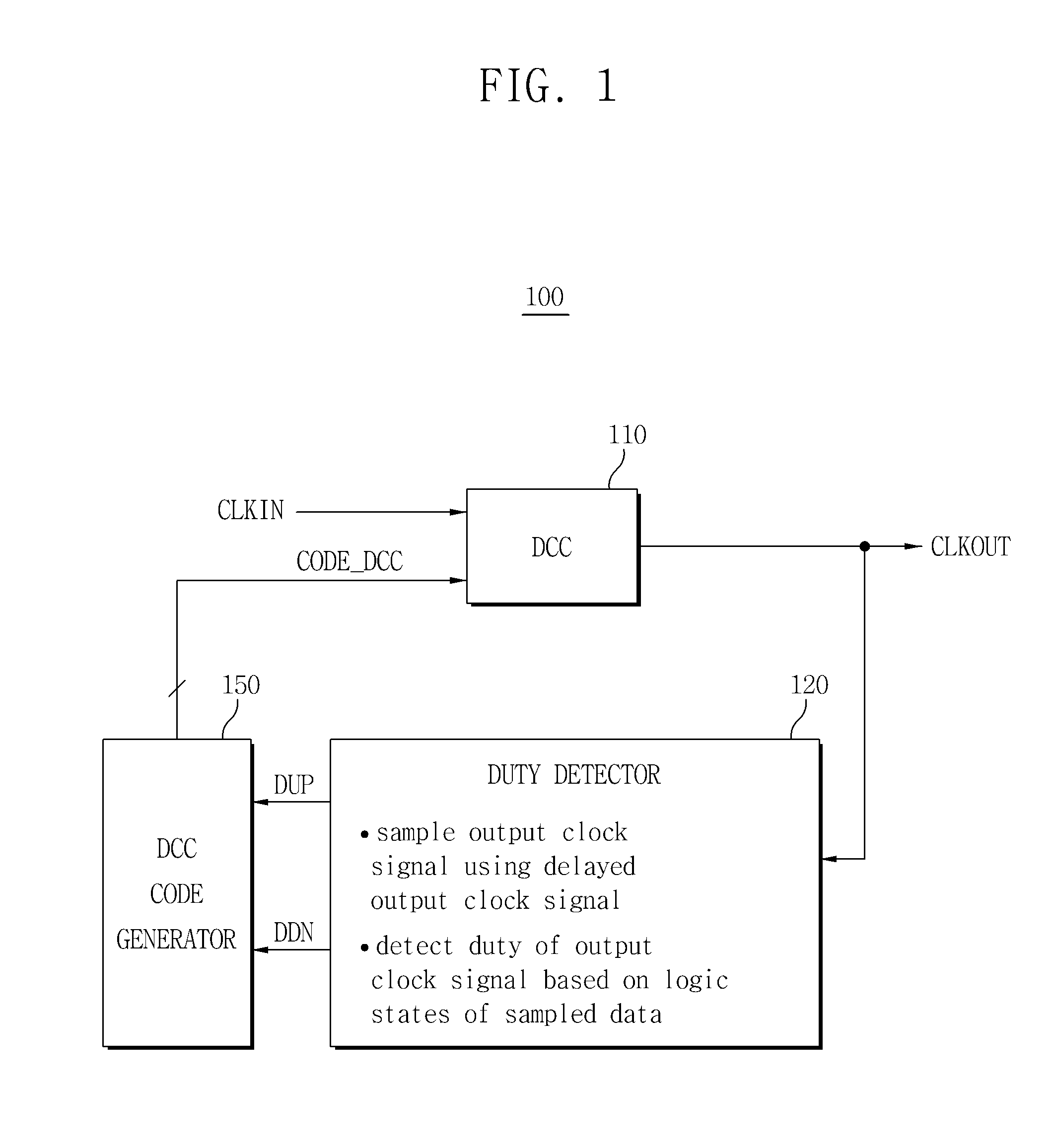

Duty correcting circuit, delay-locked loop circuit and method of correcting duty

ActiveUS20110298513A1Improve accuracyAccurate detectionElectric pulse generatorPulse shapingDelay-locked loopDelayed time

The duty correcting circuit includes a duty cycle corrector, a duty detector and a duty correction code generator. The duty cycle corrector corrects a duty cycle of an input clock signal to generate an output clock signal. The duty detector adjusts a delay time of the output clock signal to generate a sampling clock signal, samples the output clock signal in response to the sampling clock signal to generate sample data, and detects a duty of the output clock signal based on logic states of the sample data. Therefore, the duty correcting circuit precisely detects and corrects a duty of the output clock signal.

Owner:SAMSUNG ELECTRONICS CO LTD

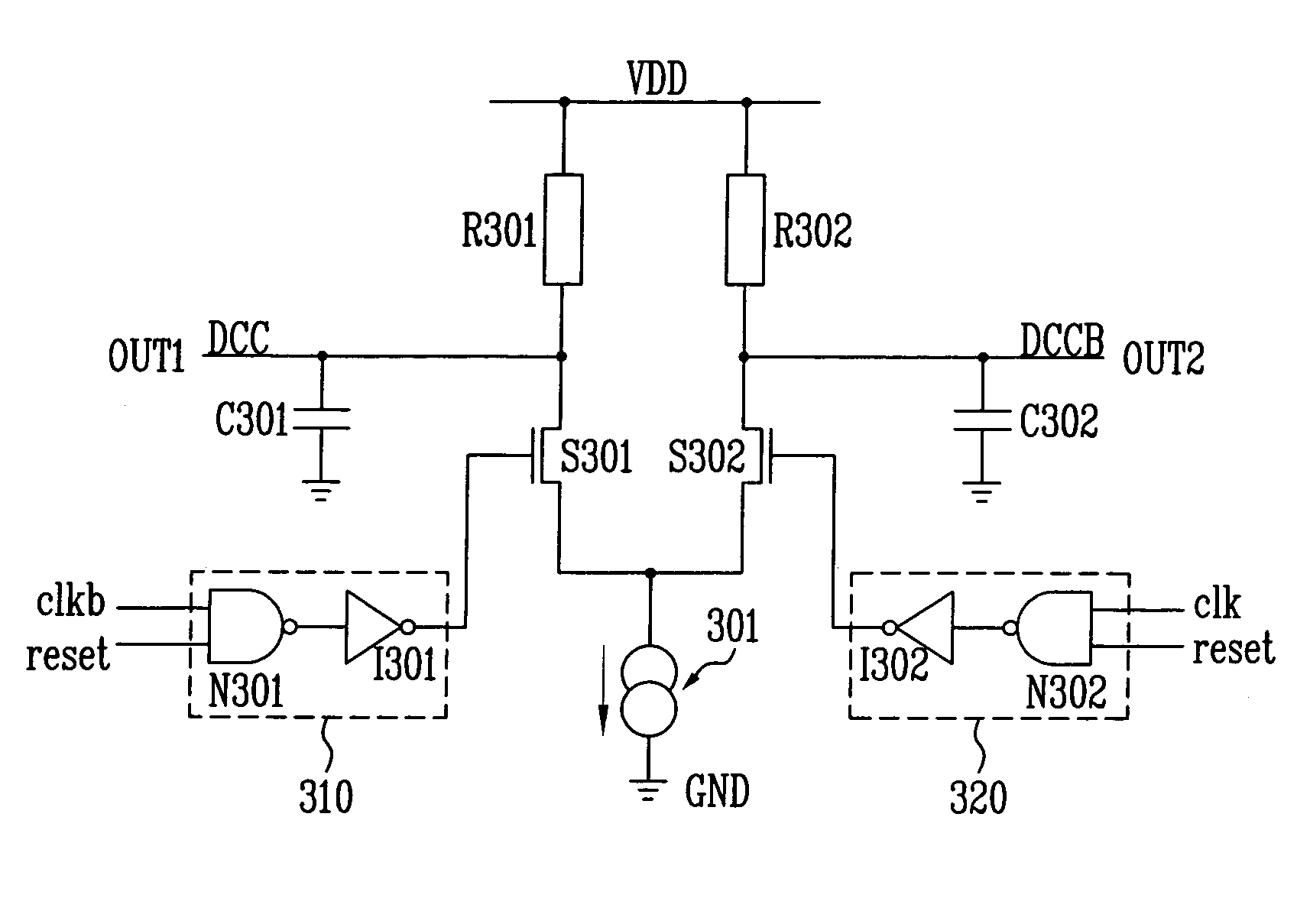

Duty ratio corrector, and memory device having the same

ActiveUS7023254B2Reduce power consumptionHigh speedContinuous to patterned pulse manipulationDigital storageEngineeringDuty cycle corrector

The present invention discloses a duty ratio corrector which can reduce power consumption by blocking current paths between output terminals and a ground terminal by applying input signals for turning off switching devices for generating an auxiliary voltage for correcting a duty ratio at an initial stage, and which can improve an operational speed by changing the auxiliary voltage from a predetermined voltage, not 0V, to an target voltage, and a memory device having the same.

Owner:SK HYNIX INC

Duty cycle corrector and duty cycle correction method

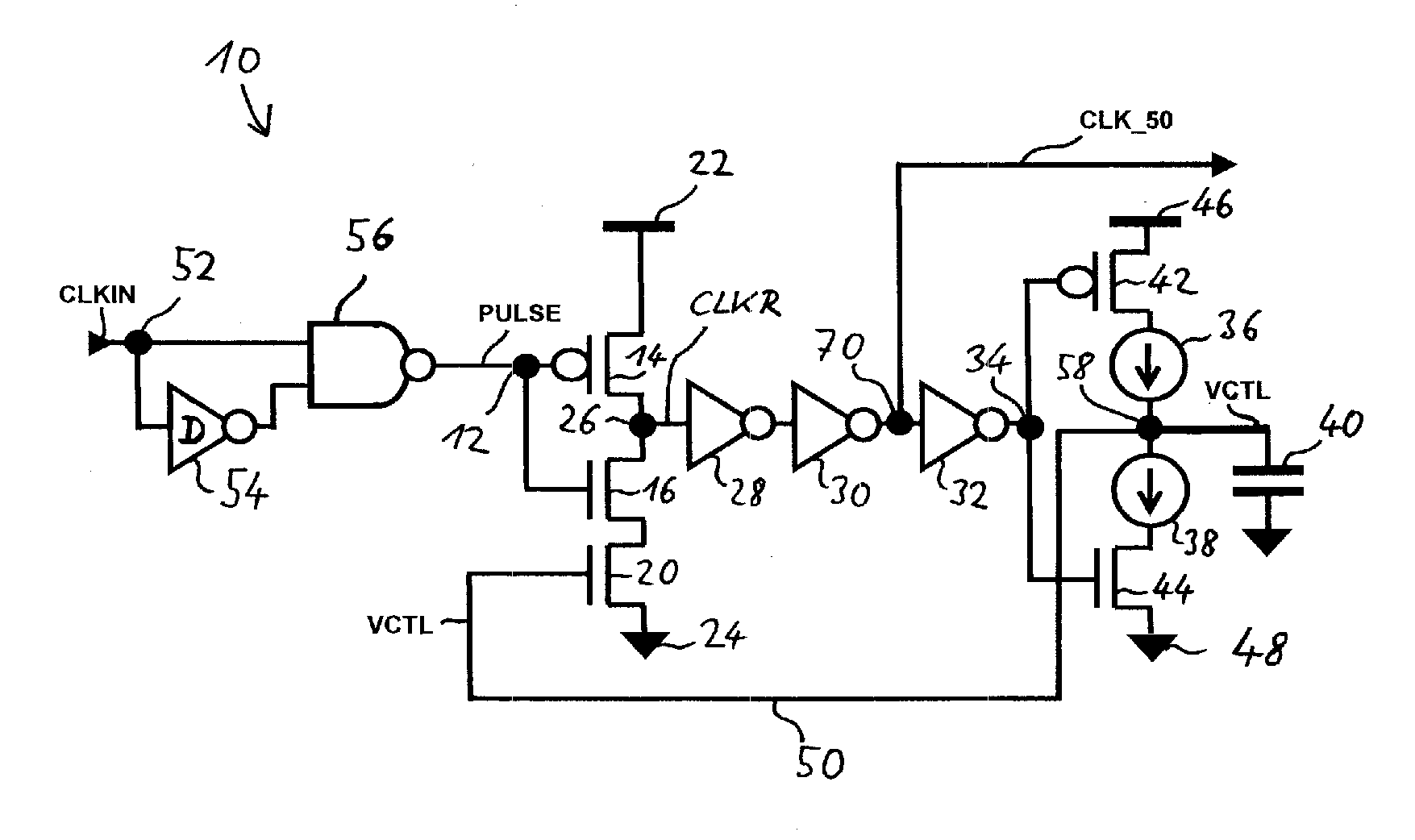

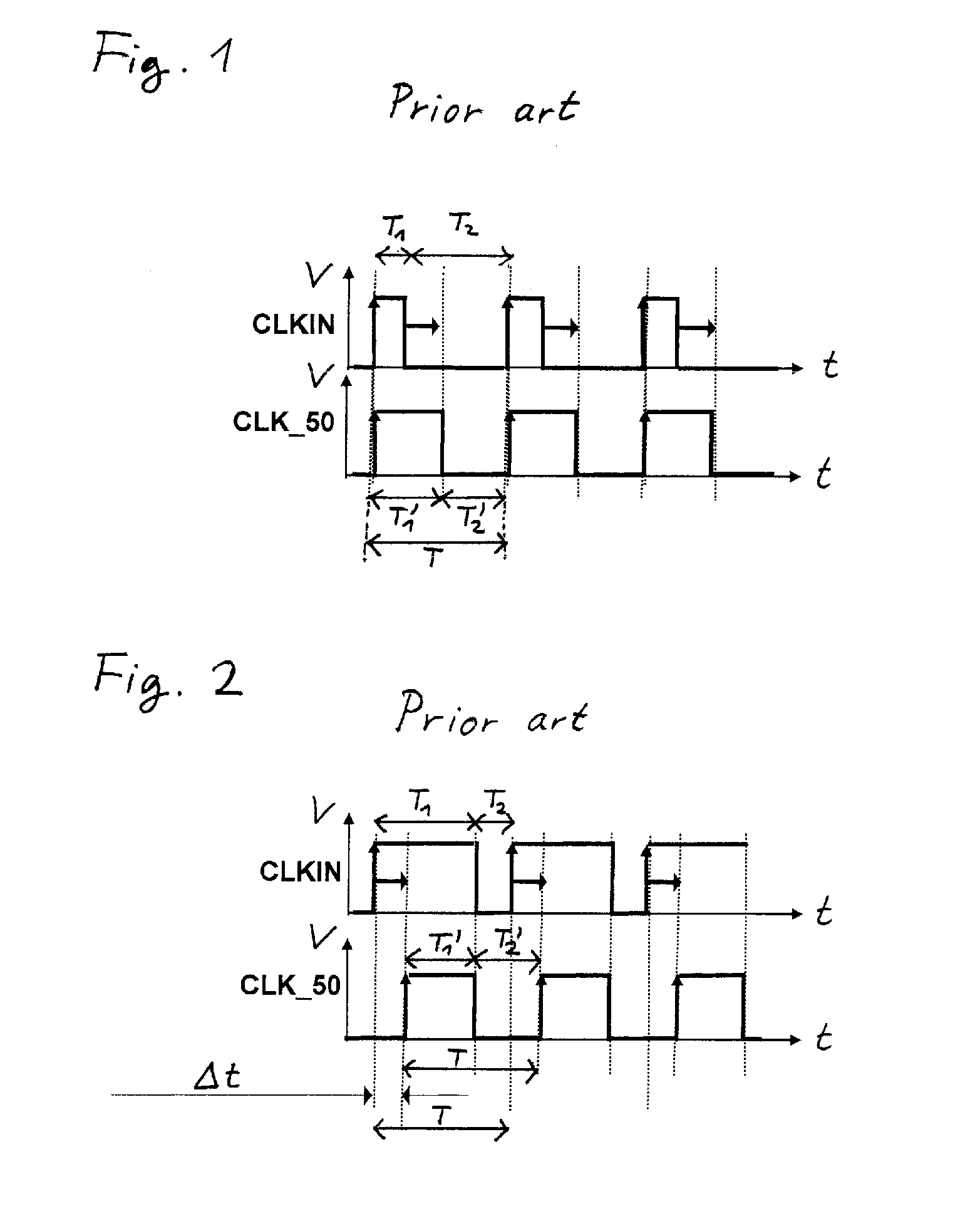

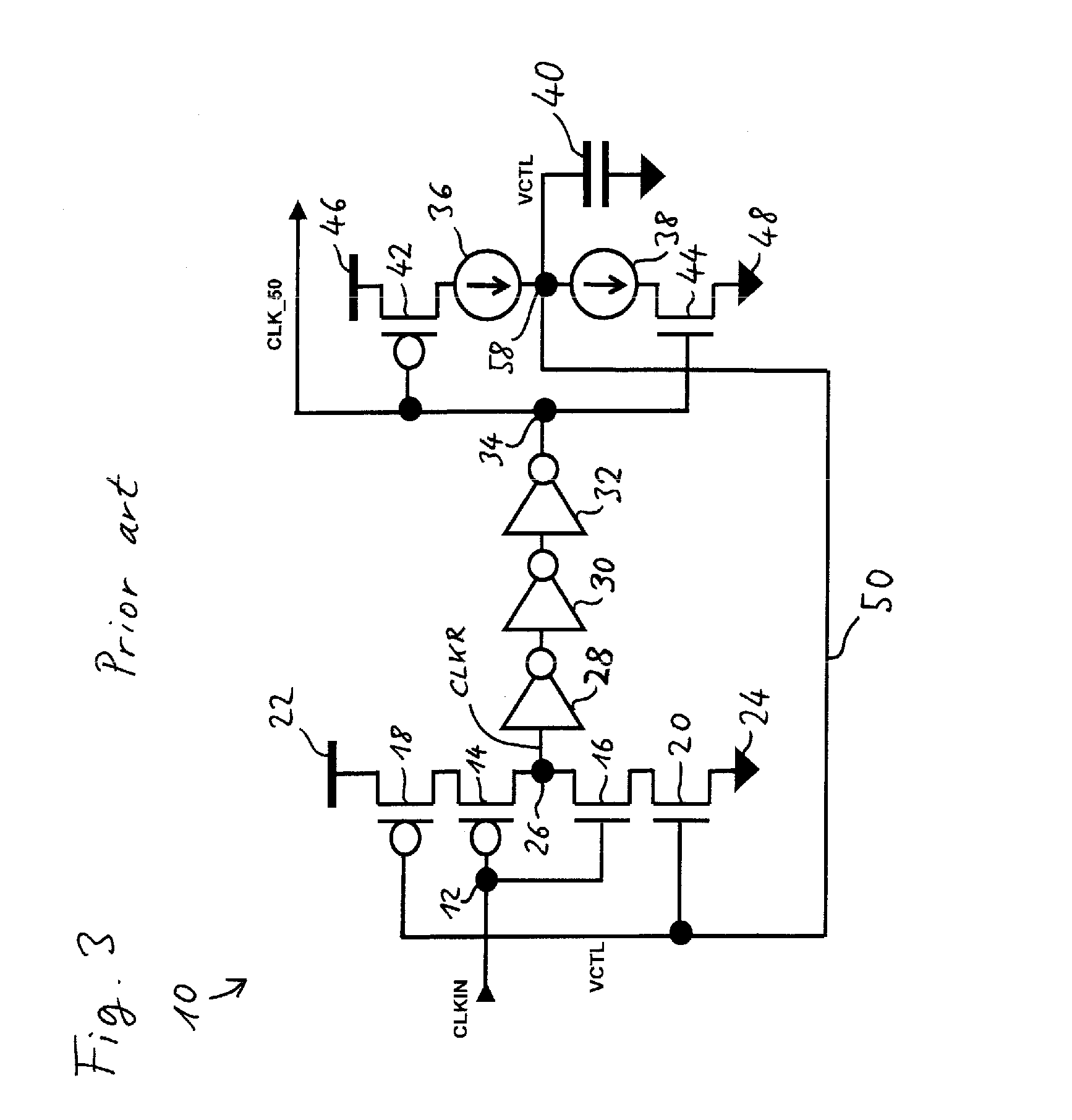

The invention relates to a duty cycle corrector for generating from an input clock signal an output clock signal having a desired duty cycle. The duty cycle corrector comprises a pulse generating stage for generating from the input clock signal a pulsed clock signal. The pulse generating stage converts rising edges of the input clock signal into pulses, each of which pulses is shorter than the desired duty cycle times the clock period. The duty cycle corrector further comprises a pulse stretching stage for generating from the pulsed clock signal the output clock signal, the pulse stretching stage delaying falling edges of the pulsed clock signal by a controlled delay. The duty cycle corrector may comprise a duty cycle detector for generating a control signal as a function of the duty cycle of the output clock signal, and a feedback path for delivering the control signal to the pulse stretching stage so as to increase the controlled delay when the duty cycle is less than the desired duty cycle and to decrease the controlled delay when the duty cycle is greater than the desired duty cycle. The invention also relates to a method of generating from an input clock signal an output clock signal having a desired duty cycle.

Owner:NXP USA INC

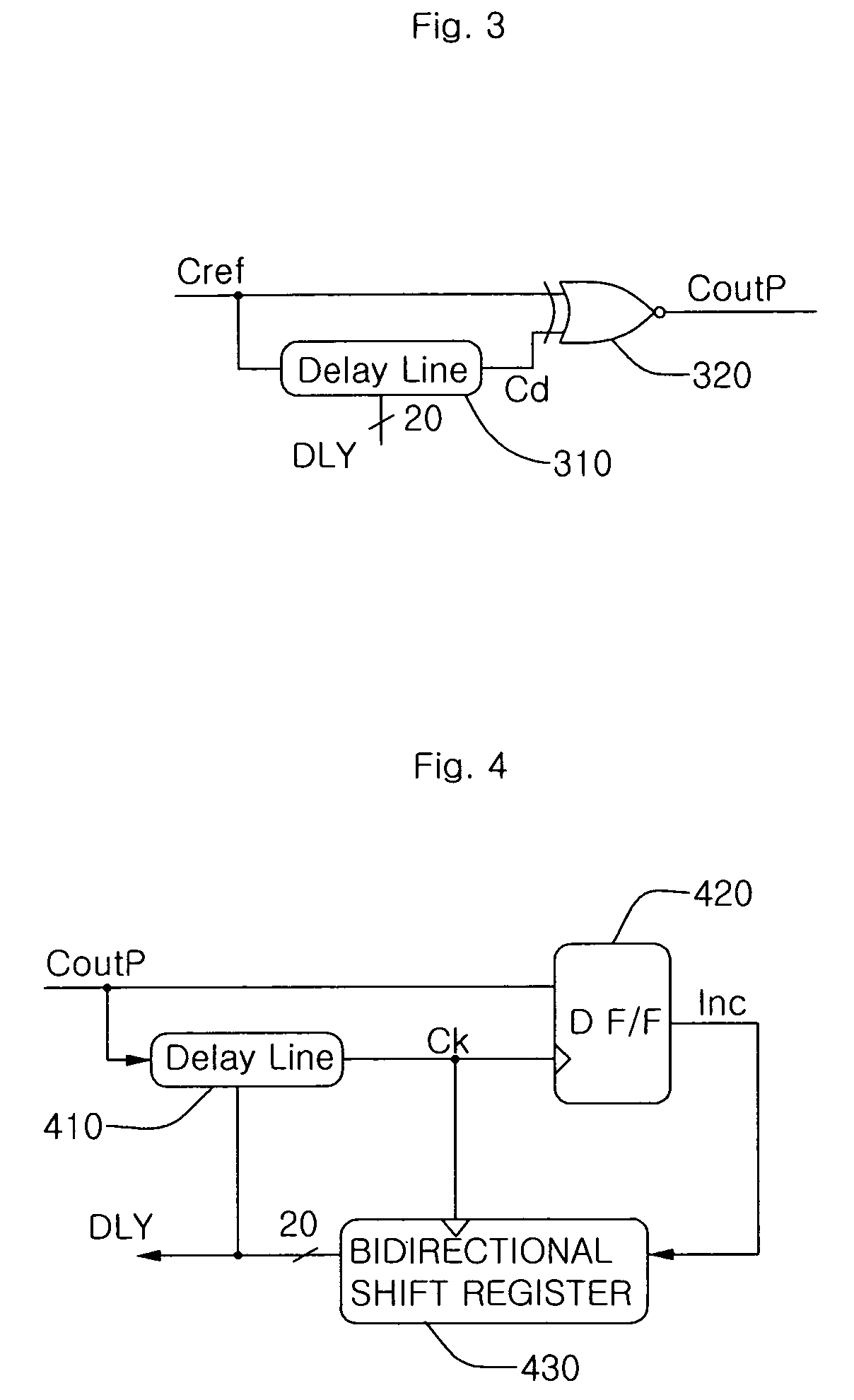

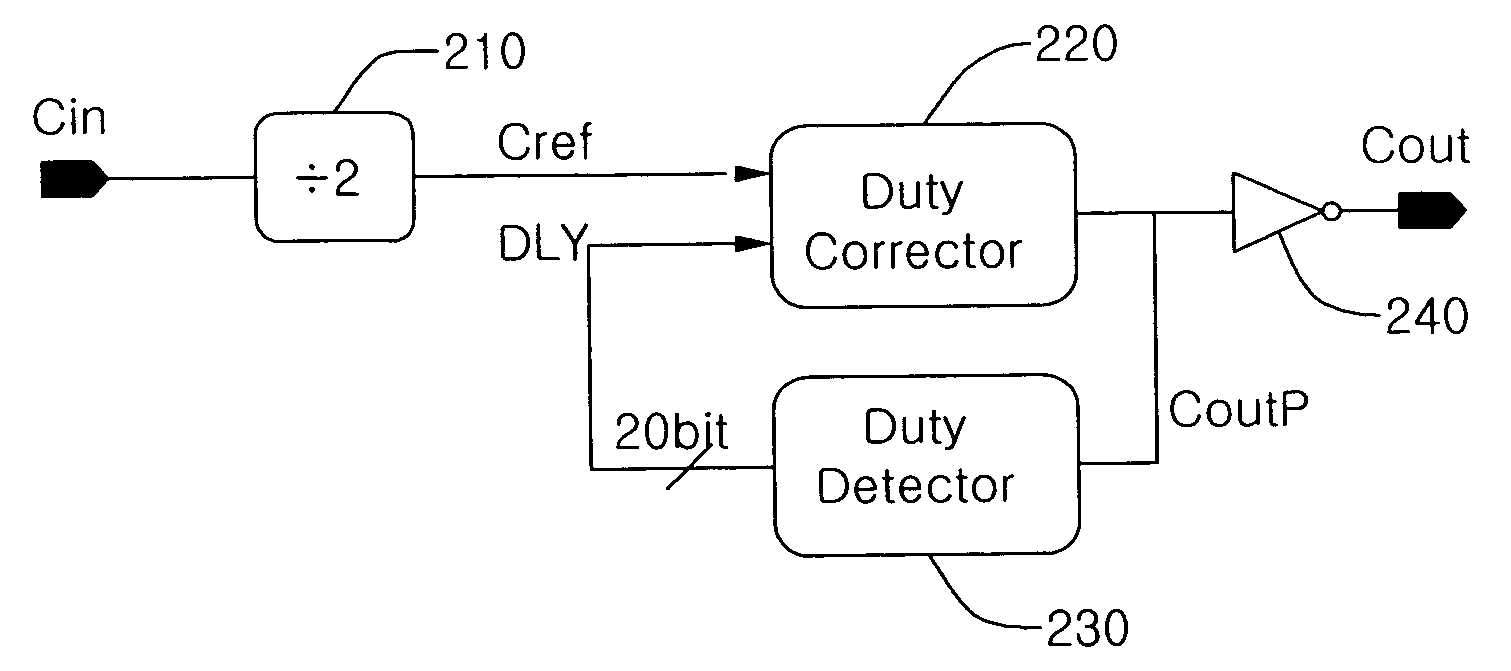

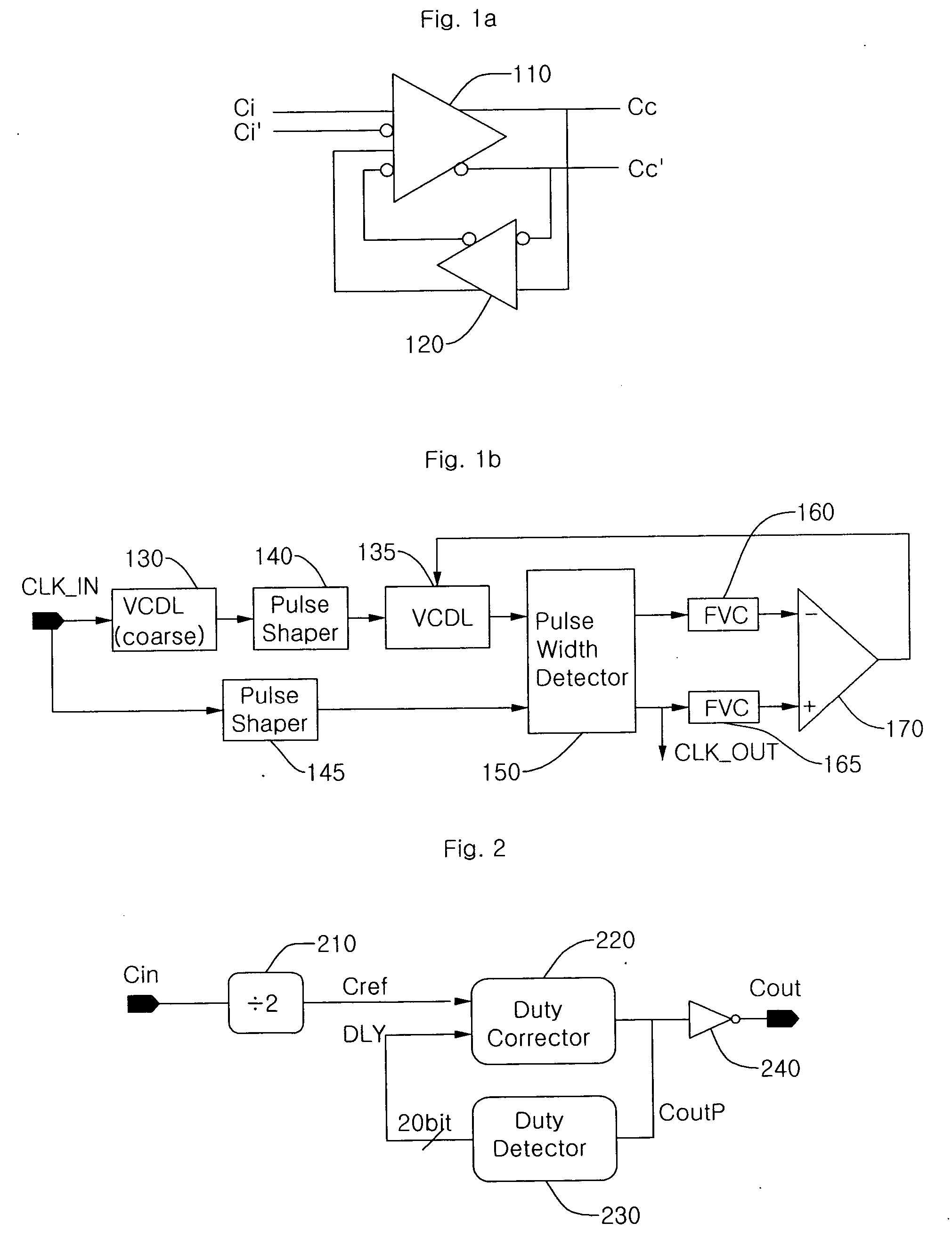

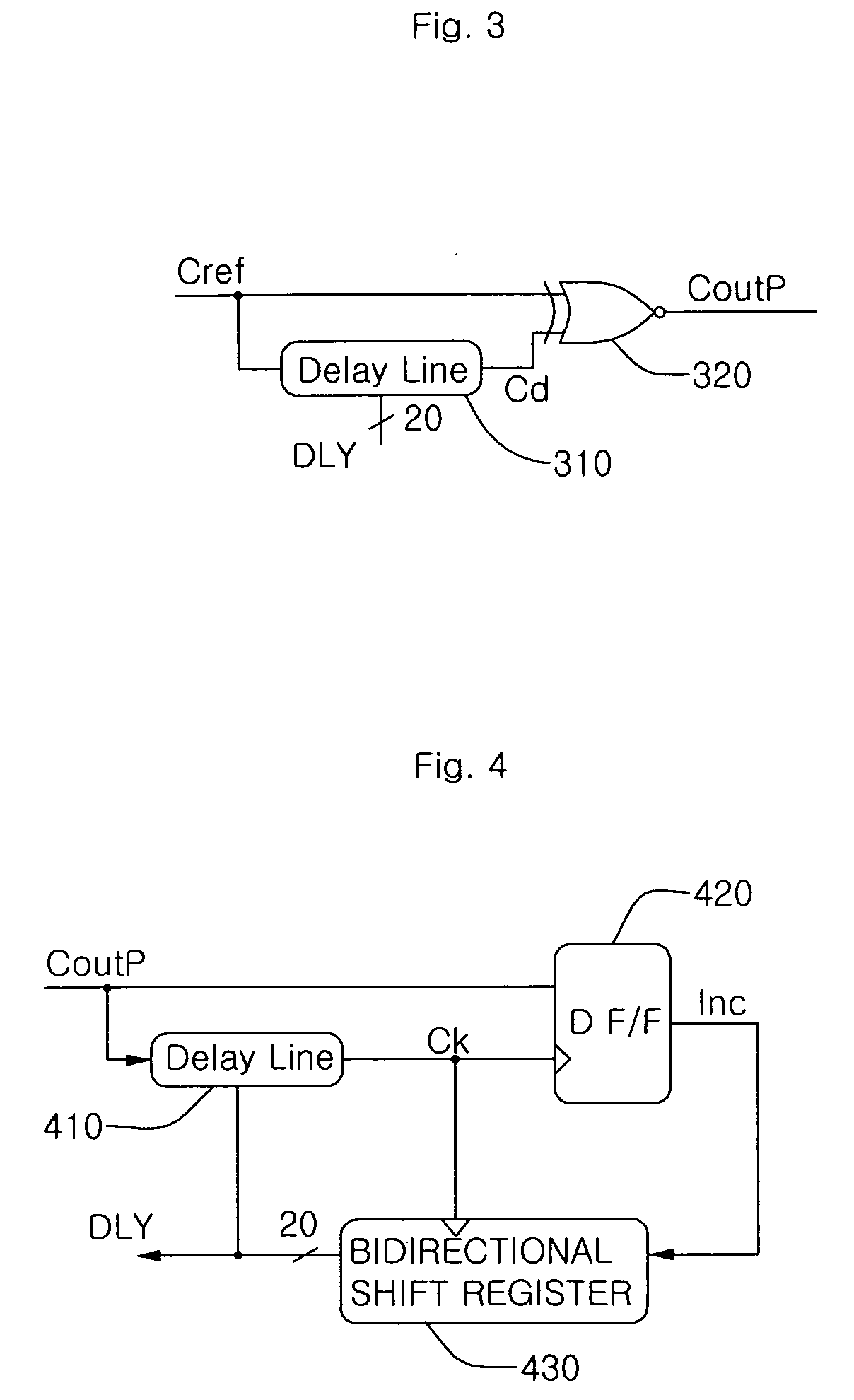

Digital duty cycle corrector for multi-phase clock application

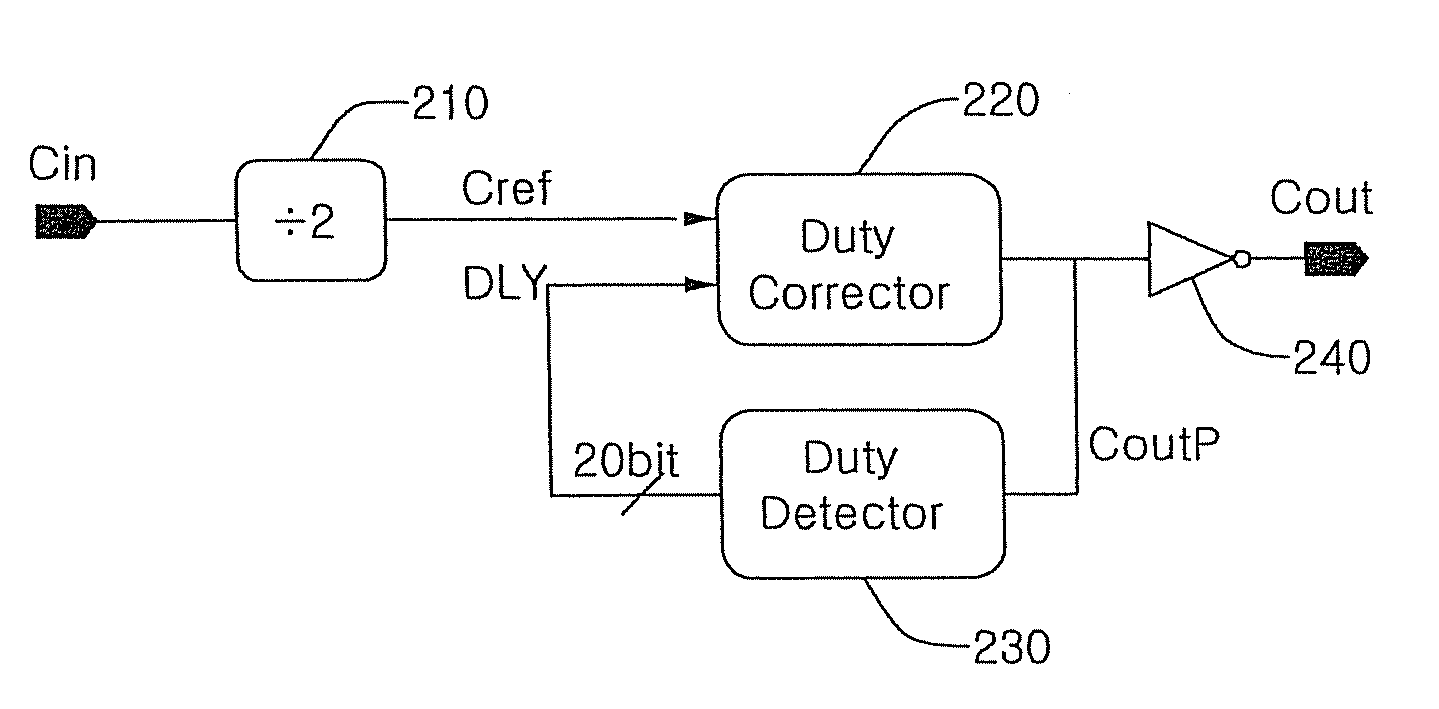

Provided is a digital duty cycle corrector for a multi-phase clock application which includes a flip-flop receiving a signal having a first clock cycle as an input and generating a reference signal having a cycle twice the first clock cycle, a duty corrector generating a signal having a second clock cycle that is half the cycle of the reference signal, from the reference signal, a duty detector measuring an amount of a duty error of the second clock cycle signal and generating a digital code value to control a duty cycle of the second clock cycle signal becomes 50%, and a phase inverter inverting a phase of the second clock cycle signal by 180° such that a rising edge of the second clock cycle signal is always fixed constantly regardless of a duty cycle correction operation.

Owner:POSTECH CO LTD

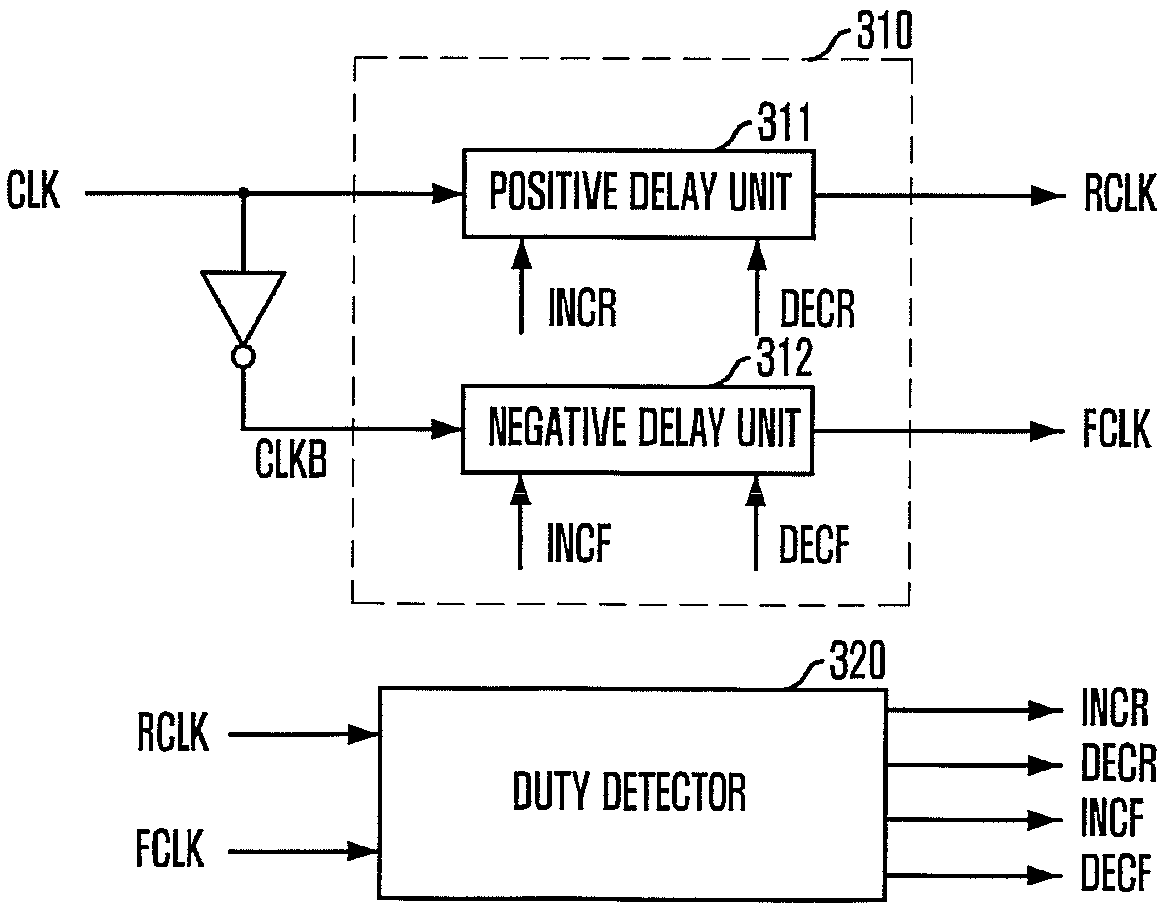

Duty cycle corrector and clock generator having the same

InactiveUS20100073057A1Improve jitter characteristicsPulse automatic controlSingle output arrangementsControl signalEngineering

A duty cycle corrector includes a delay unit configured to adjust an input clock and an inverted input clock with a delay value controlled in response to one or more control signals and to generate a positive clock and a negative clock, and a duty detector configured to receive the positive clock and the negative clock, to detect duty ratios of the positive clock and the negative clock and to generate the one or more control signals.

Owner:SK HYNIX INC

Duty detecting circuit and duty cycle corrector including the same

ActiveUS20100109729A1Shorten lock timeAccurate correctionMultiple input and output pulse circuitsDelay line applicationsDuty cycle correctorCorrection code

A duty cycle corrector includes a duty adjusting unit configured to adjust a duty cycle of an input clock in response to a duty correction code and generate an output clock, a duty detecting unit configured to measure a difference between a high pulse width and a low pulse width of the output clock and output a difference value, and an accumulating unit configured to accumulate the difference value to generate the duty correction code.

Owner:SK HYNIX INC

Digital duty cycle corrector for multi-phase clock application

Provided is a digital duty cycle corrector for a multi-phase clock application which includes a flip-flop receiving a signal having a first clock cycle as an input and generating a reference signal having a cycle twice the first clock cycle, a duty corrector generating a signal having a second clock cycle that is half the cycle of the reference signal, from the reference signal, a duty detector measuring an amount of a duty error of the second clock cycle signal and generating a digital code value to control a duty cycle of the second clock cycle signal becomes 50%, and a phase inverter inverting a phase of the second clock cycle signal by 180° such that a rising edge of the second clock cycle signal is always fixed constantly regardless of a duty cycle correction operation.

Owner:POSTECH CO LTD

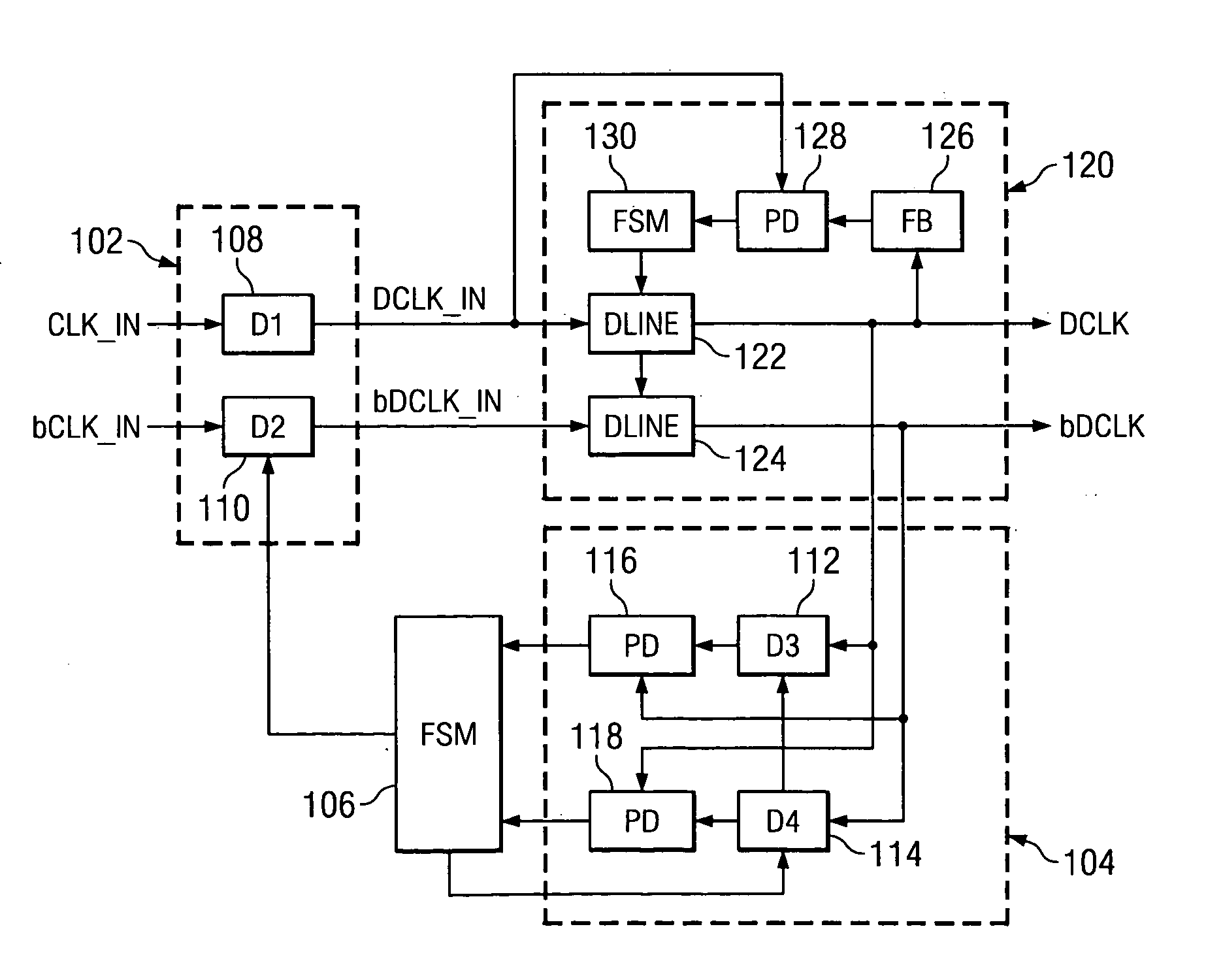

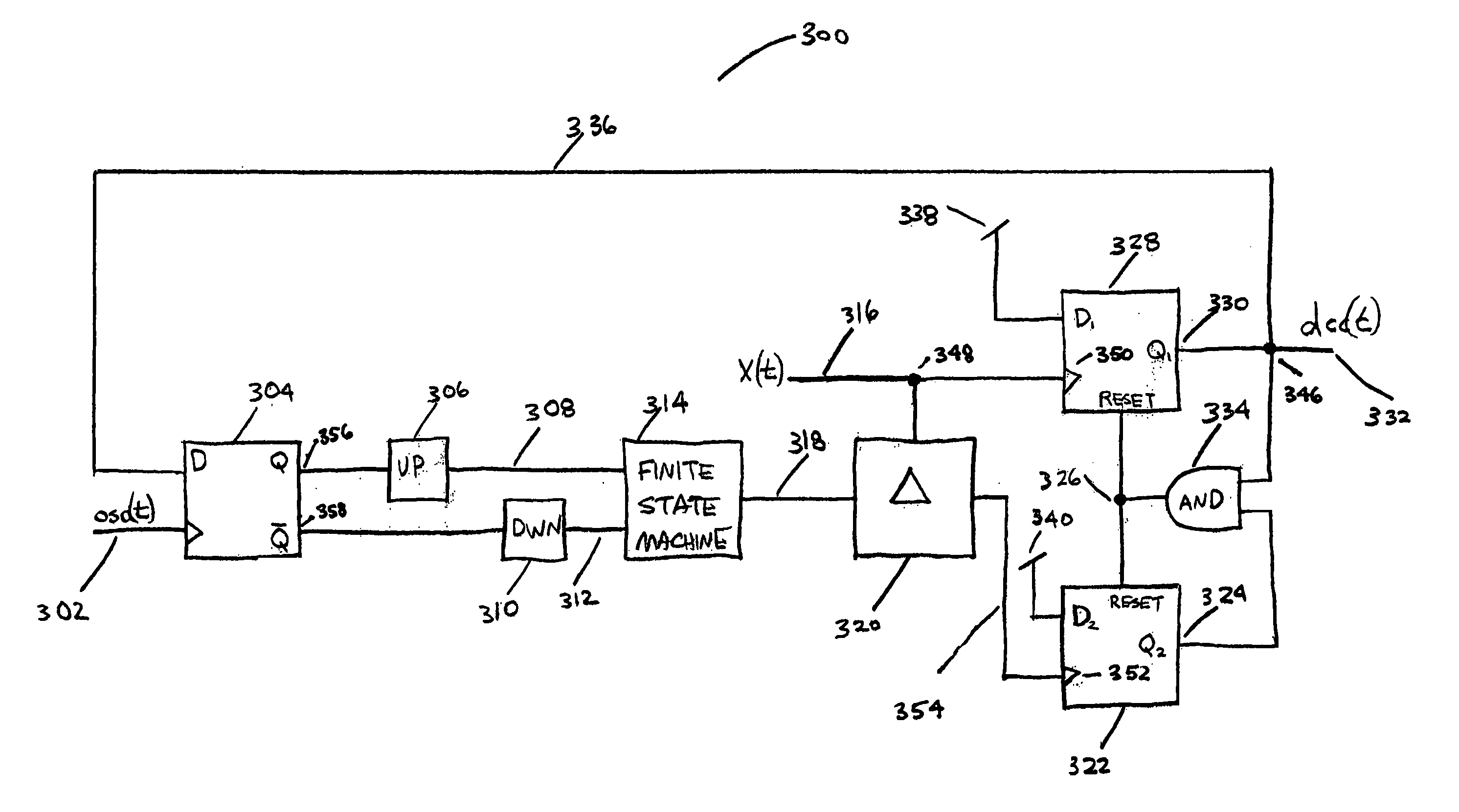

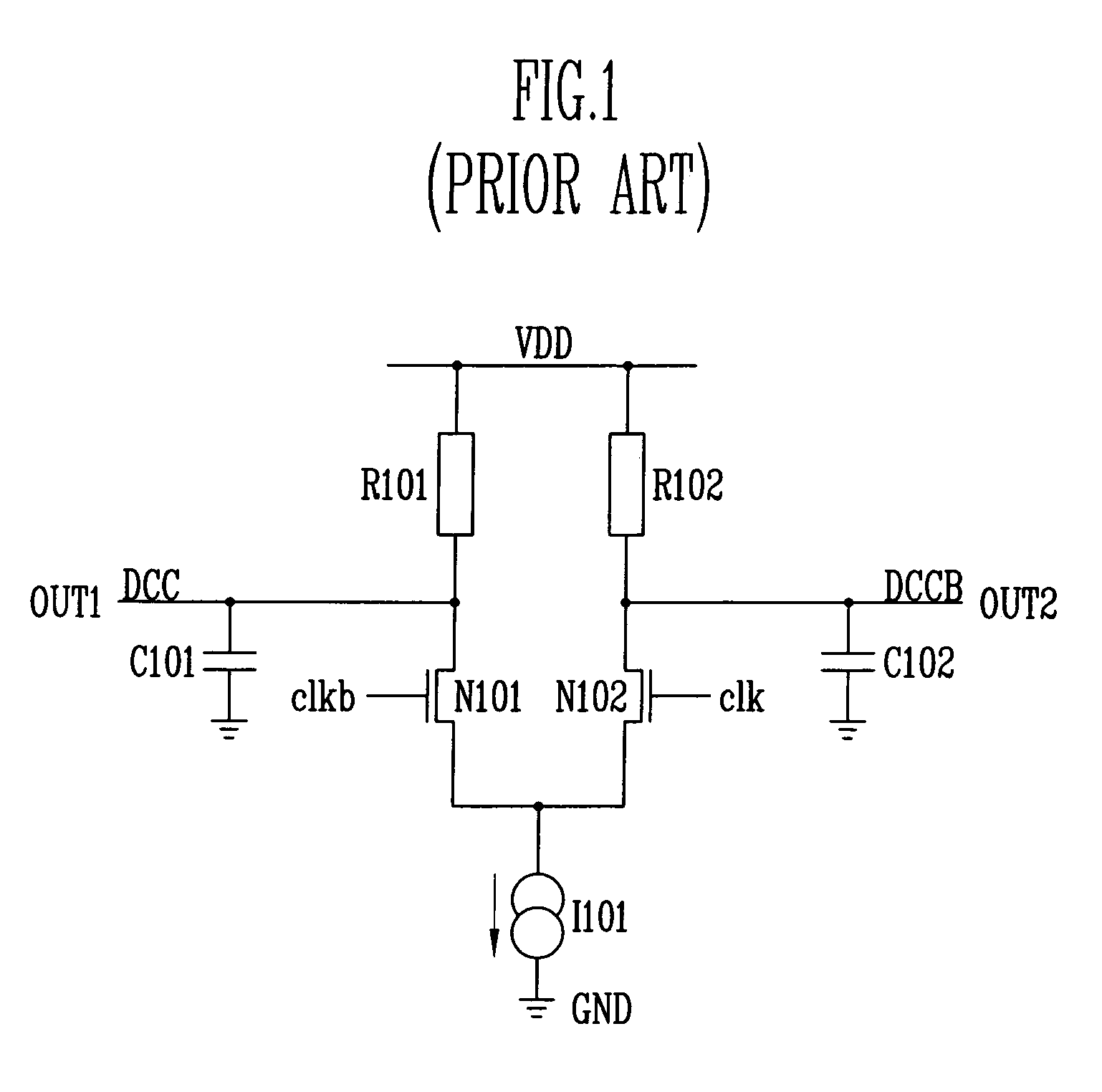

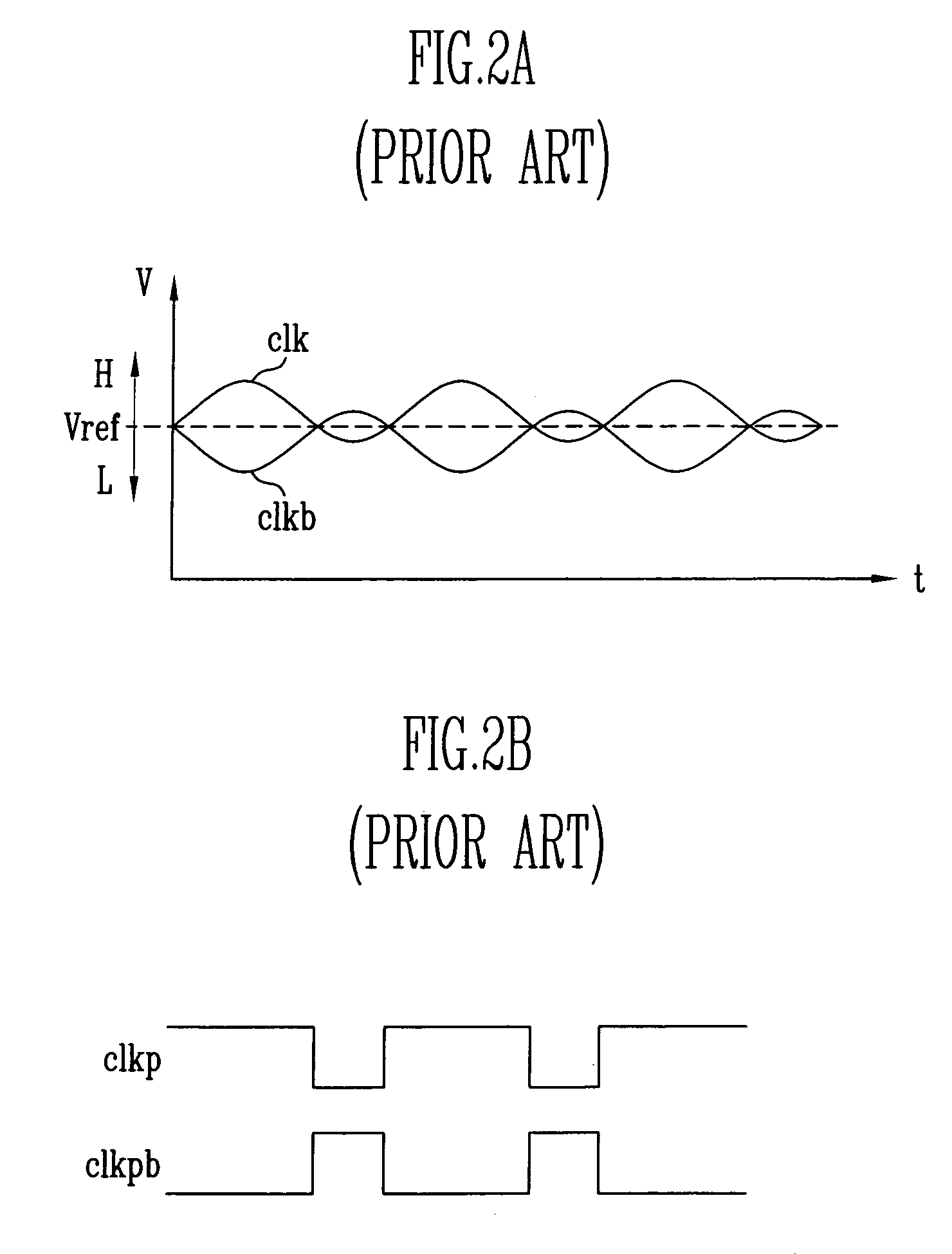

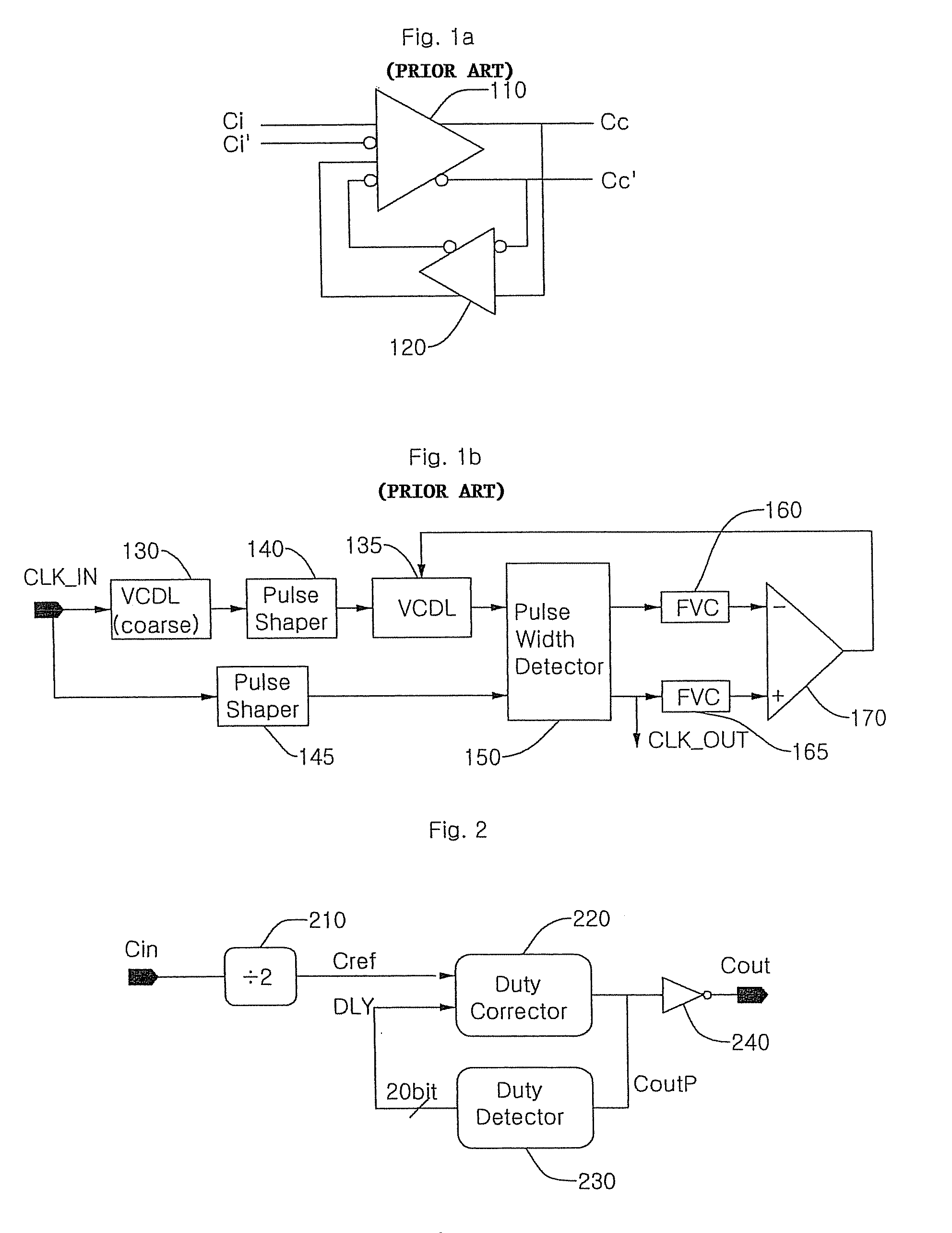

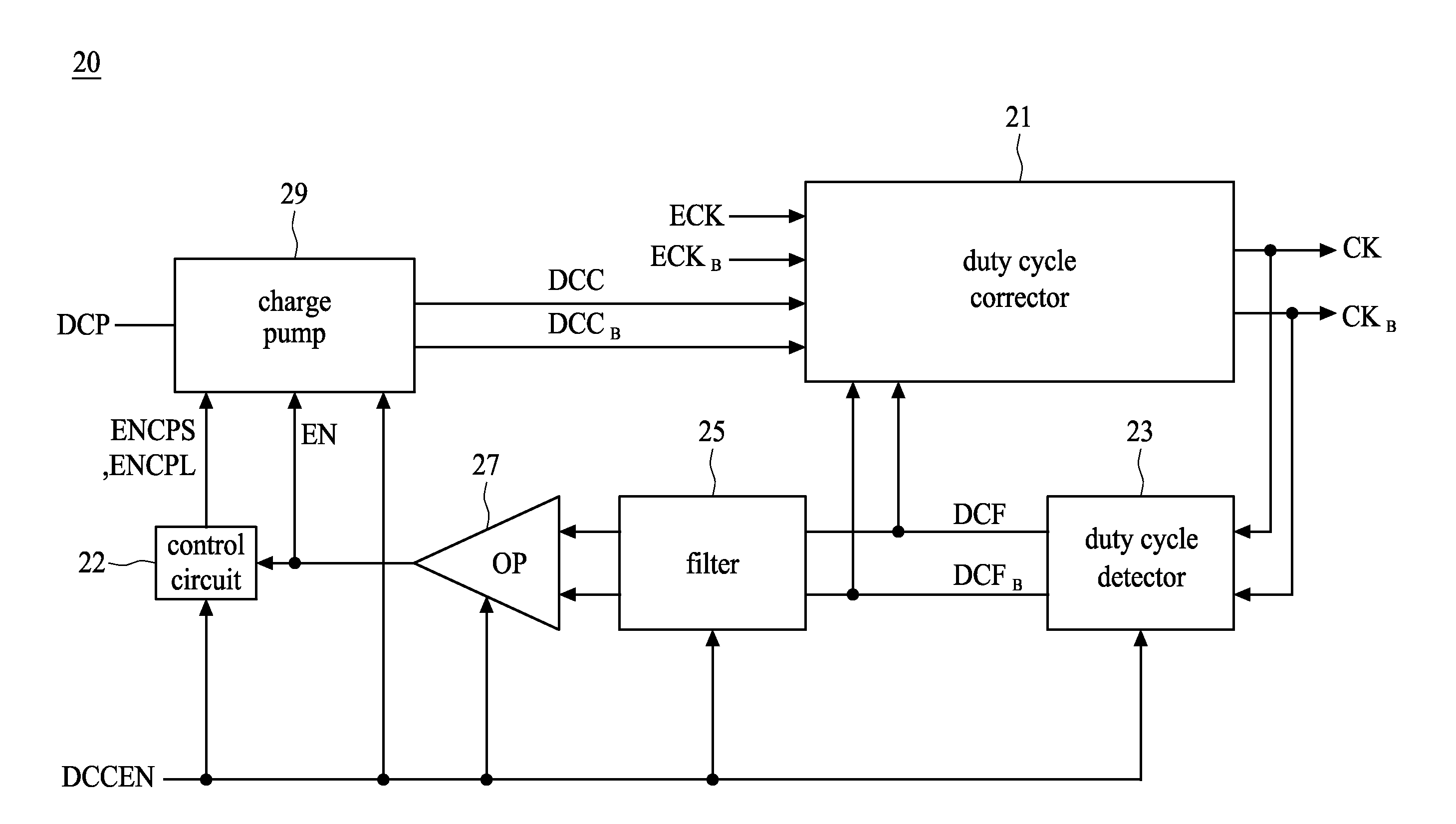

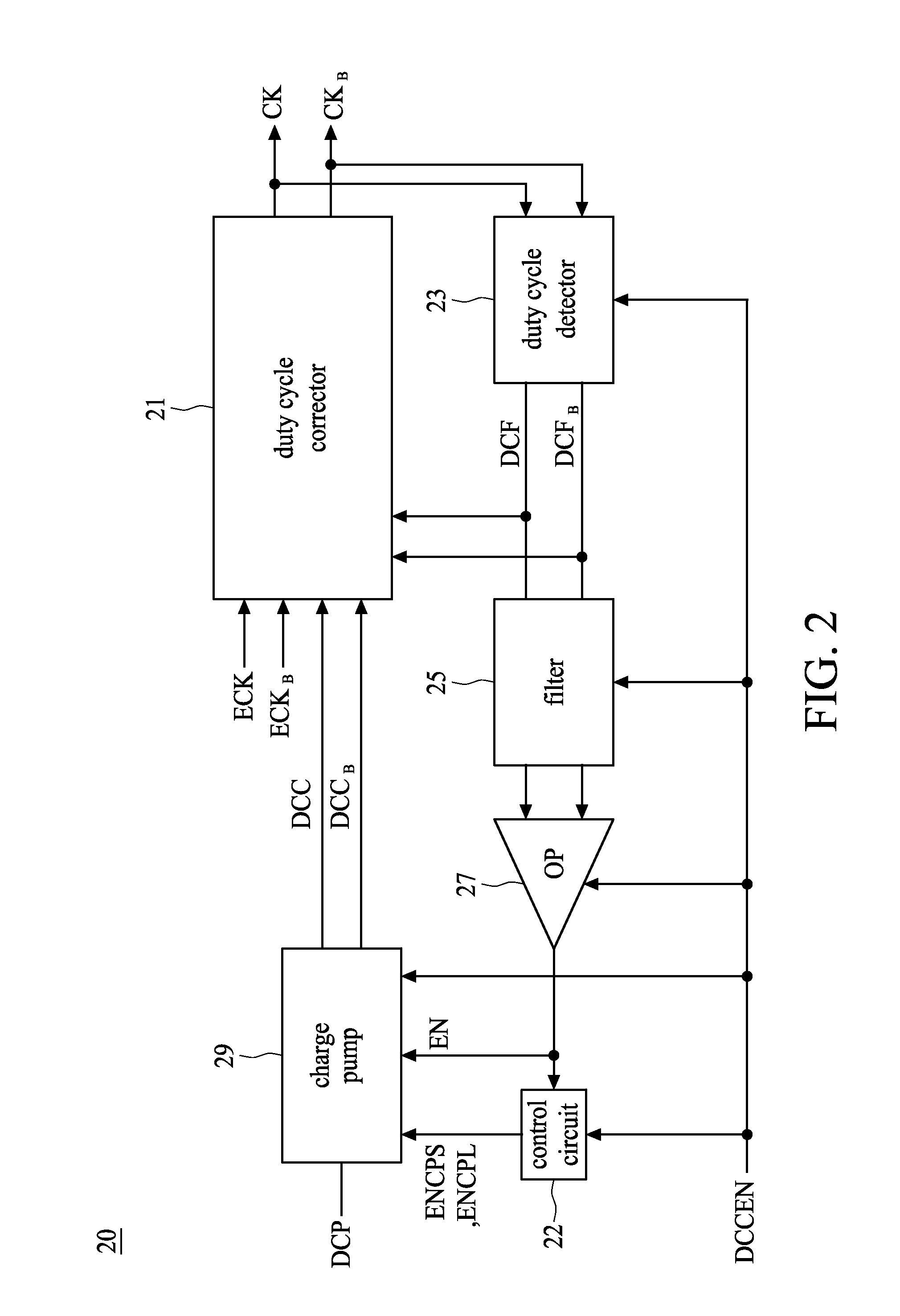

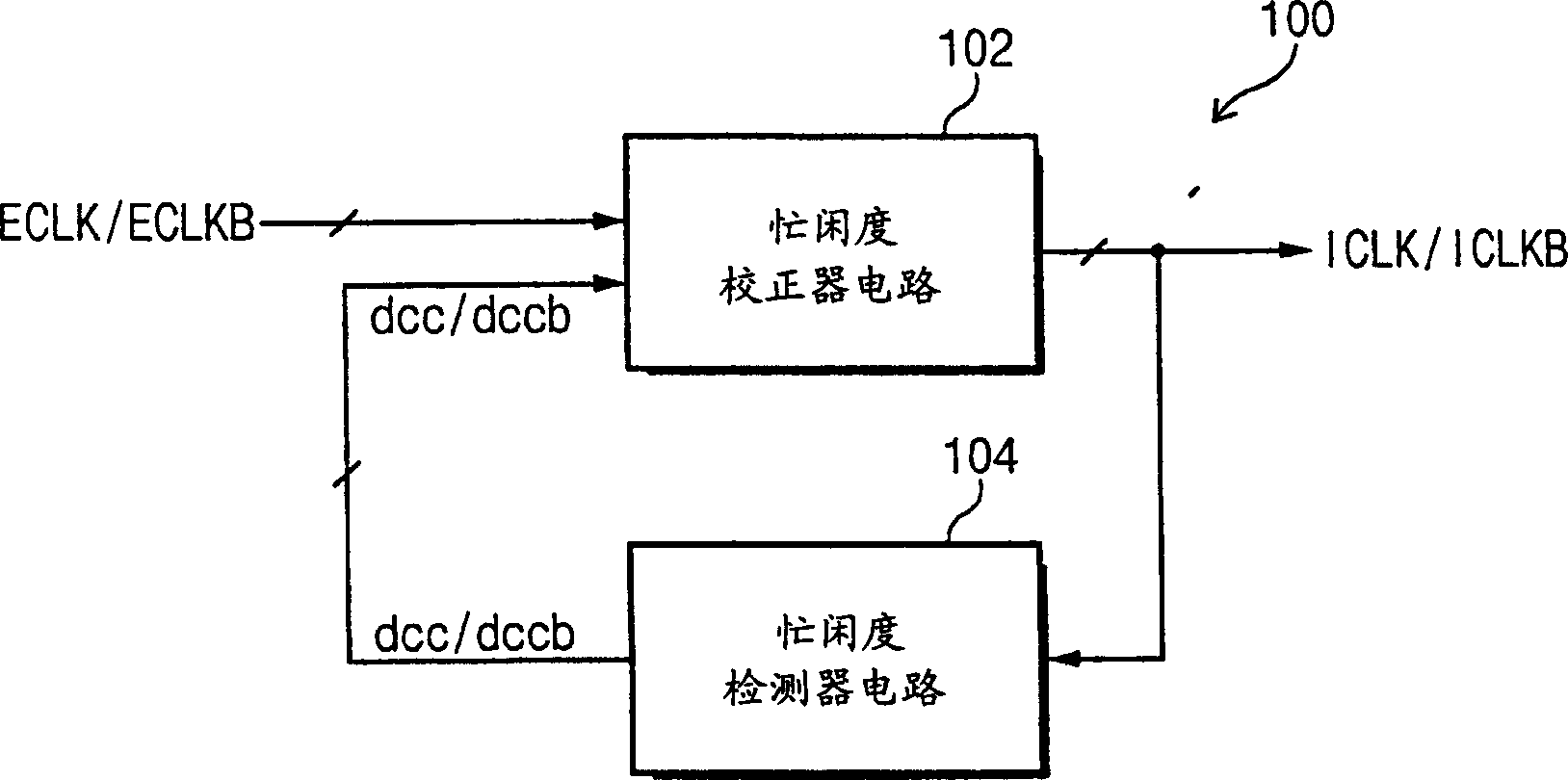

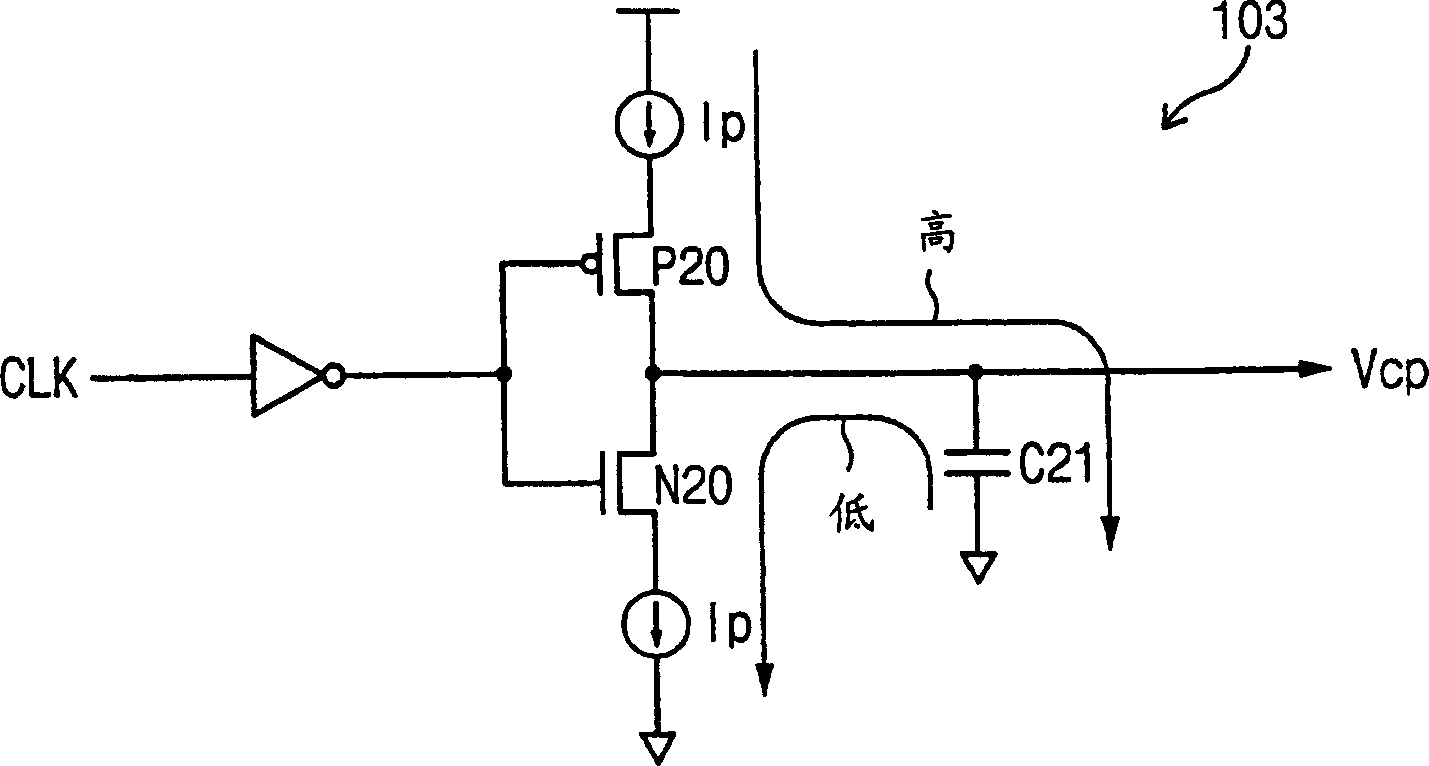

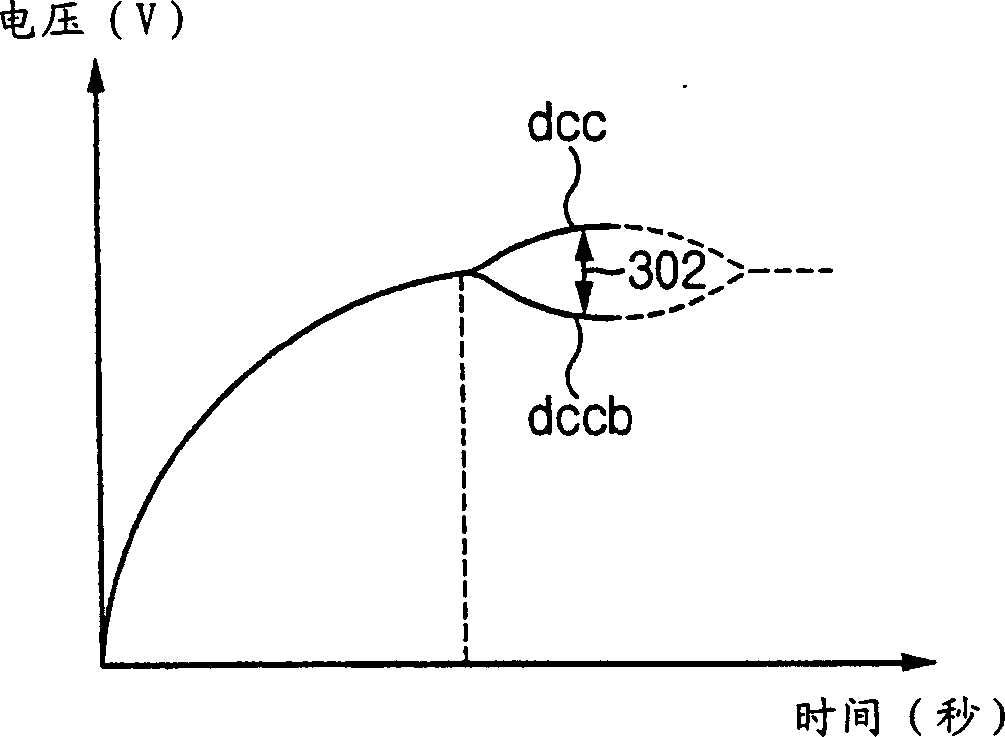

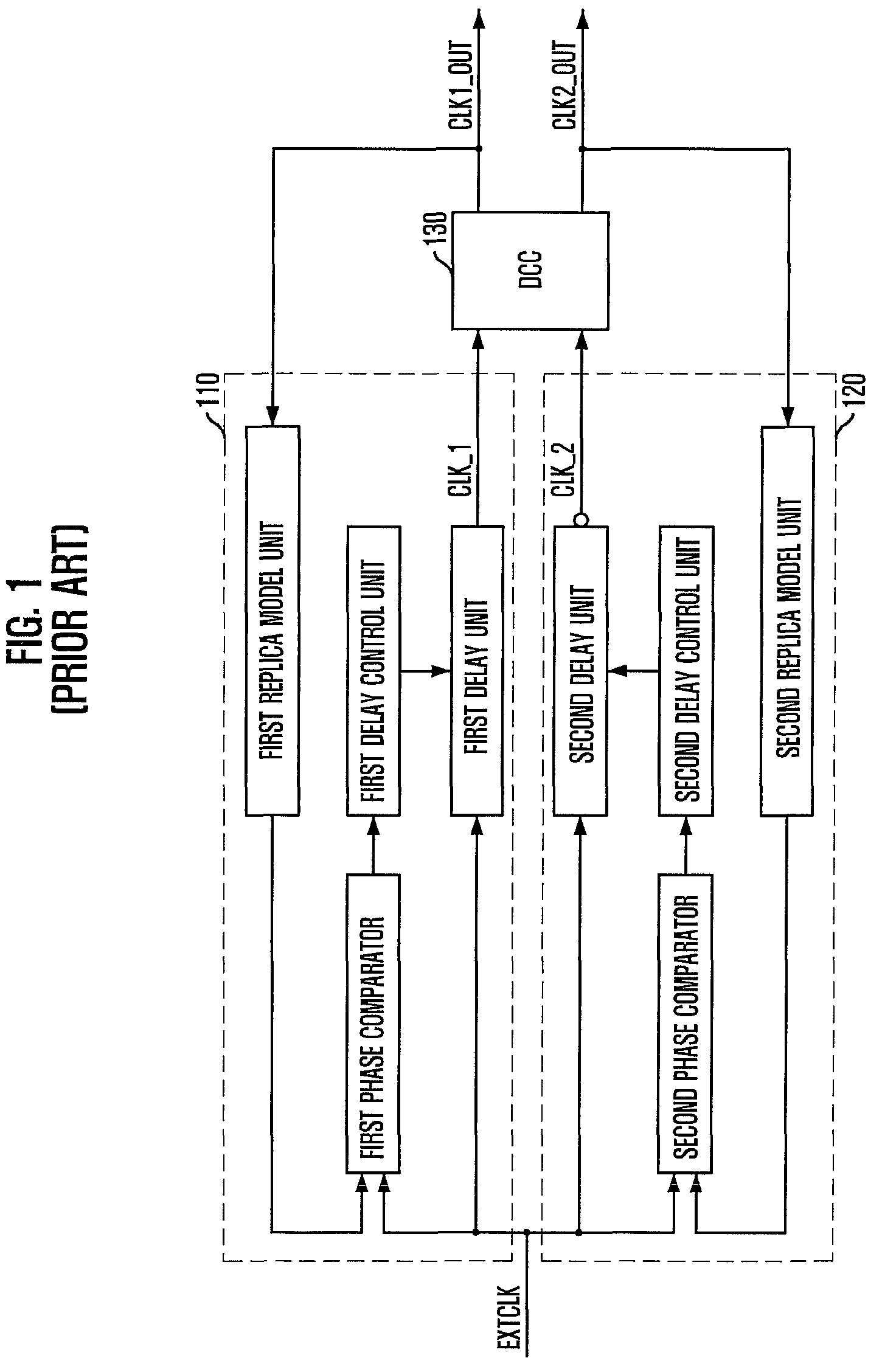

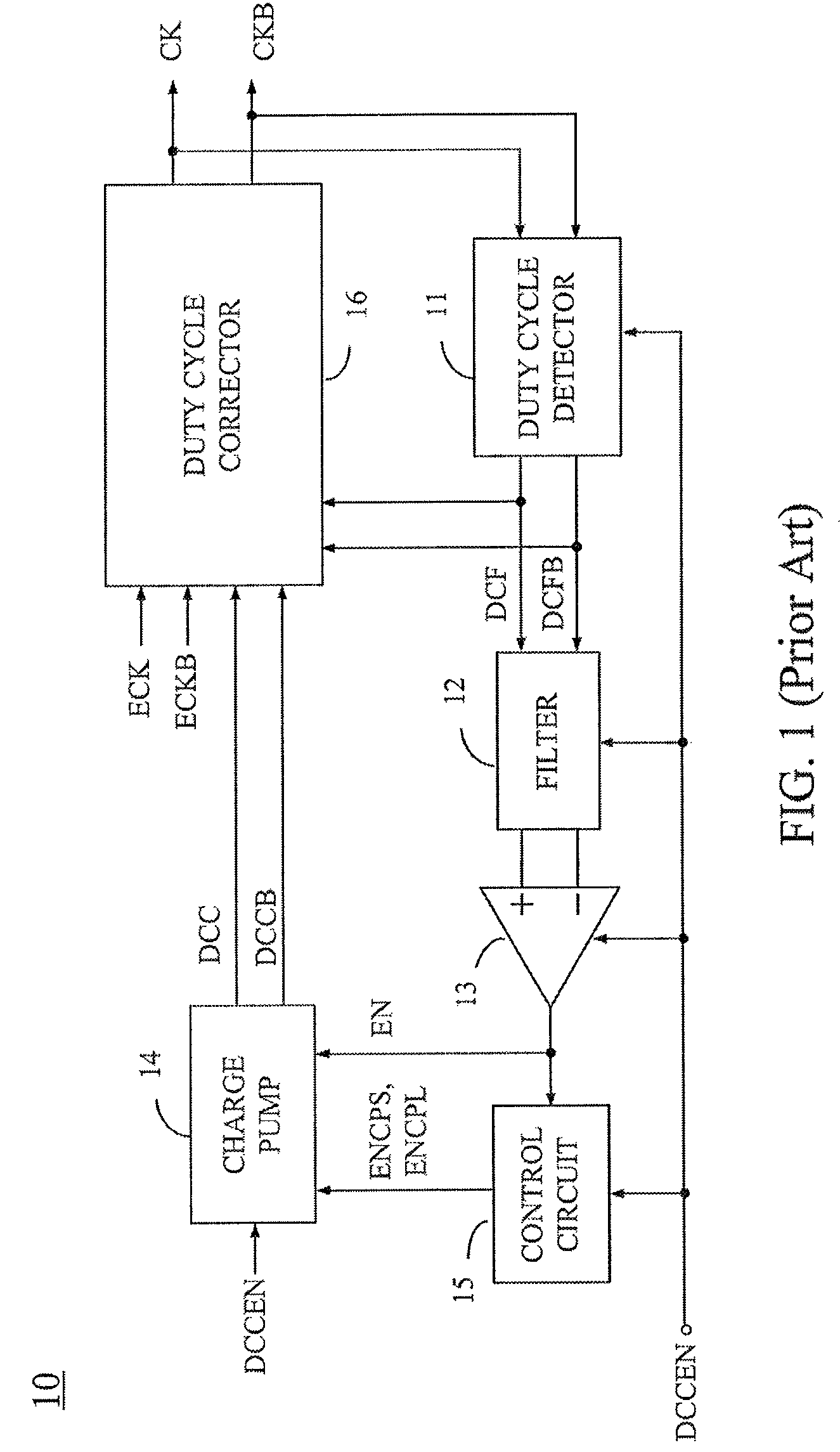

Circuit and method for providing a corrected duty cycle

A duty cycle correction circuit comprises a duty cycle detector, a filter, an amplifier, a charge pump, a control circuit, and a duty cycle corrector. The duty cycle detector is configured to generate a first pair of control signals according to a pair of internal clock signals. The filter is configured to obtain average voltages of the first pair of control signals. The amplifier is configured to compare output voltages of the filter for generating an enable signal, and the control circuit is configured to generate a selection signal according to the enable signal. The charge pump is configured to generate a second pair of control signals according to the enable signal and the selection signal, and the duty cycle corrector is configured to receive a pair of external clock signals, the first pair of control signals, and the second pair of control signals for generating the pair of internal clock signals with a corrected duty cycle.

Owner:ELITE SEMICON MEMORY TECH INC

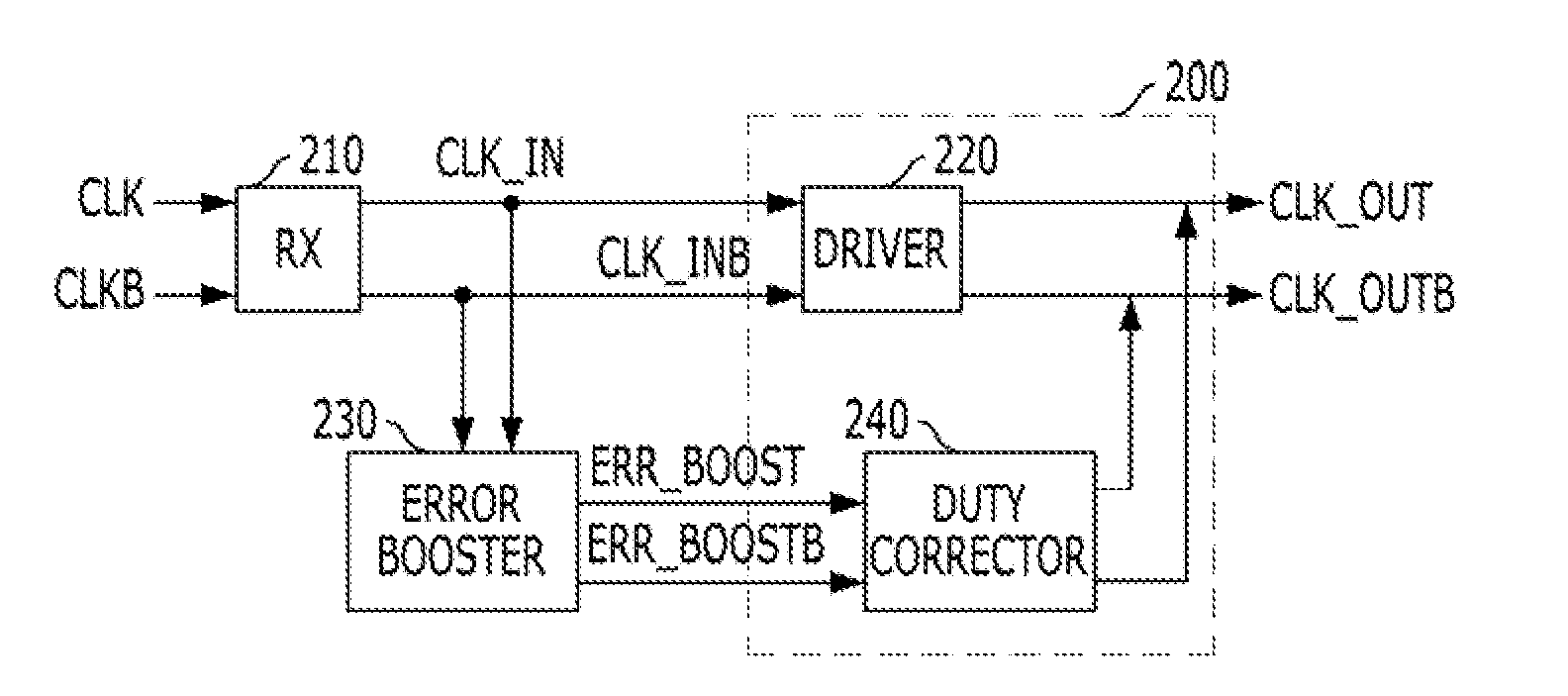

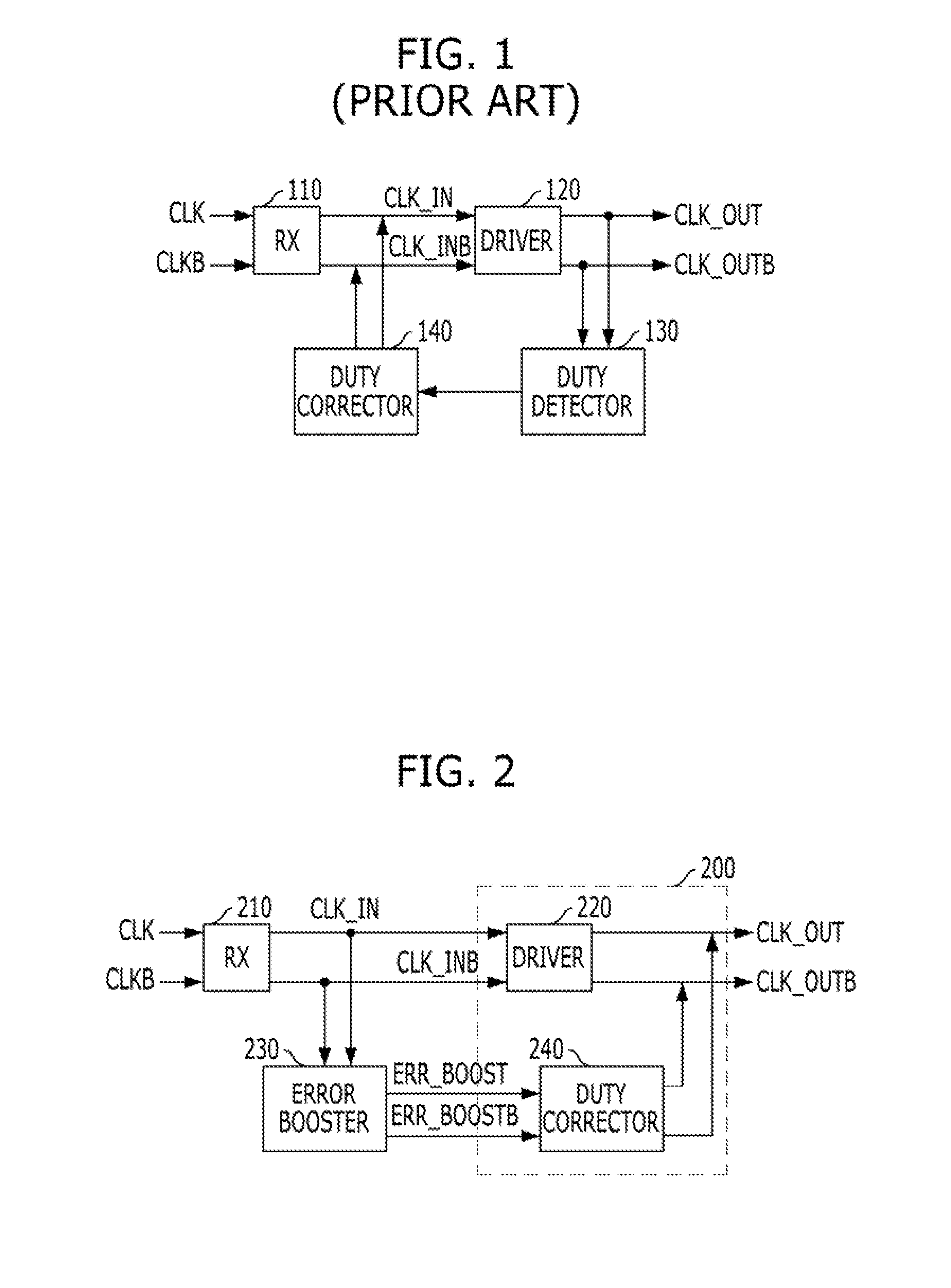

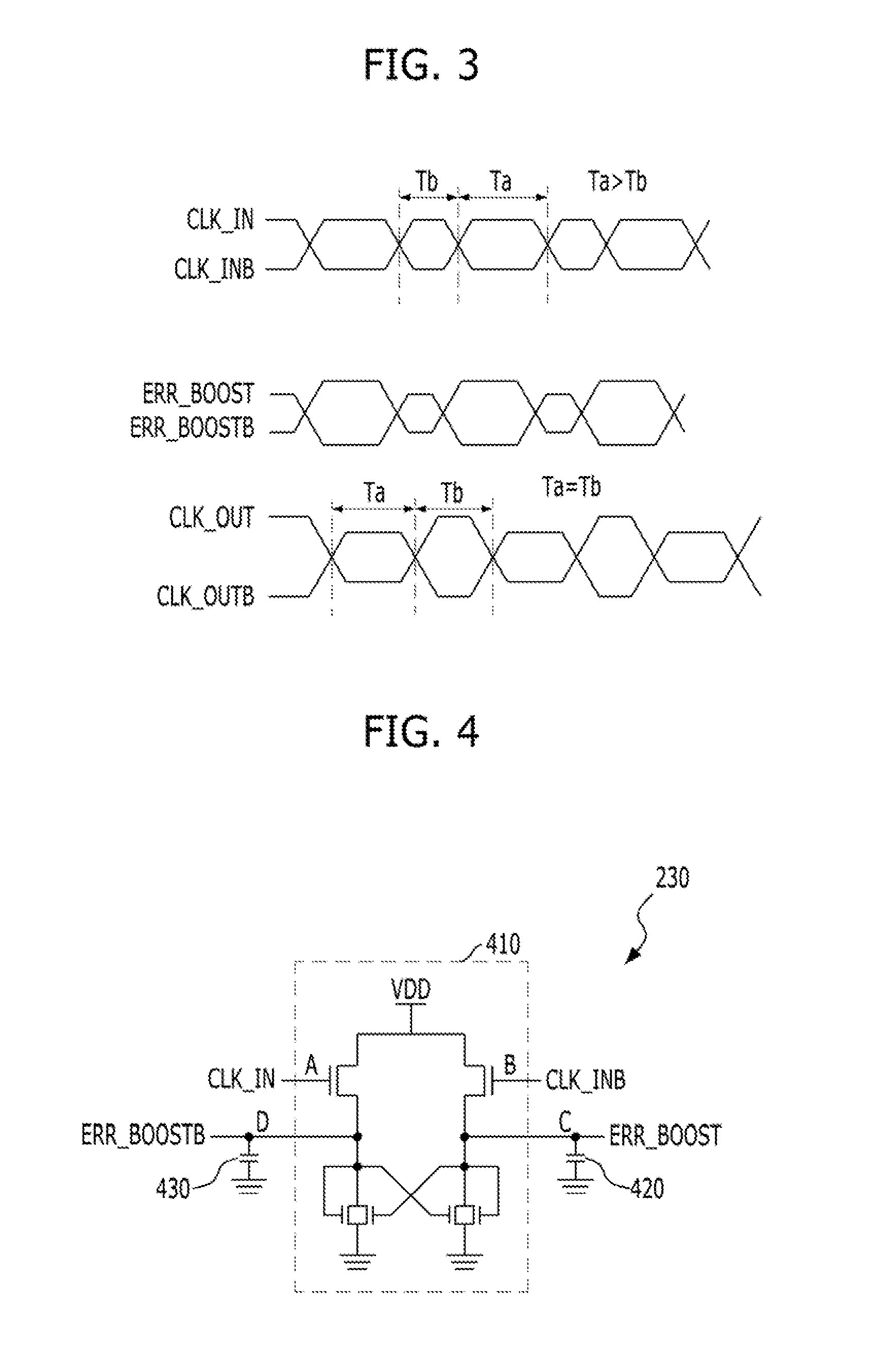

Duty cycle correction circuit

ActiveUS20150171836A1Continuous to patterned pulse manipulationElectric pulse generatorEngineeringDuty cycle corrector

A duty cycle correction circuit may include an error booster suitable for amplifying an input clock duty error, a driver suitable for driving an output clock based on the input clock, and a duty corrector suitable for correcting the output clock duty based on the duty error amplified by the error booster.

Owner:SK HYNIX INC

Integrated circuit devices having improved duty cycle correction and methods of operating the same

InactiveCN1542861APulse automatic controlContinuous to patterned pulse manipulationDetector circuitsComparators circuits

Digital duty cycle correction circuits are provided including a duty cycle detector circuit configured to generate first and second control values associated with a first internal clock signal and a second internal clock signal, respectively. A comparator circuit is also provided and is configured to compare the first control value to the second control value and provide a comparison result. A counter circuit is configured to perform an addition and / or a subtraction operation responsive to the comparison result to provide a digital code. A digital to analog converter is configured to generate third and fourth control values responsive to the digital code. Finally, a duty cycle corrector circuit is configured to receive first and second external clock signals and the first through fourth control values and generate the first and second internal clock signals having a corrected duty cycle. The first and second control values are received over a first path and the third and fourth control values are received over a second path, different from the first path. Related methods of operating duty cycle correction circuits are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

Delay locked loop of semiconductor device and method for driving the same

A delay locked loop (DLL) of a semiconductor device includes: a first delay line for delaying a first clock signal in synchronization with a first edge of an external clock signal to output a first delayed clock signal; a second delay line for delaying a second clock signal in synchronization with a second edge of the external clock to output a second delayed clock signal; a duty cycle corrector (DCC) for mixing phases of the first and second delayed clock signals to output a DLL clock signal with a corrected duty cycle; and a DCC controller for disabling the duty cycle corrector in a section during which a phase difference between the first and second delayed clock signals is greater than a preset time after a delay locking.

Owner:SK HYNIX INC

Digital duty cycle corrector

InactiveUS7187221B2Reduce power consumptionSave consumptionPulse automatic controlElectric pulse generatorRelative phaseSignal delay

A method for adjusting the relative phases of two signals includes receiving first and second signals, which may, for example, be derived from a differential clock signal. A duty cycle error between the first signal and the second signal is detected by comparing a phase component of the first signal with a phase component of the second signal. This duty cycle error can then be corrected by delaying the second signal by an amount based upon a result derived from the comparing.

Owner:POLARIS INNOVATIONS LTD

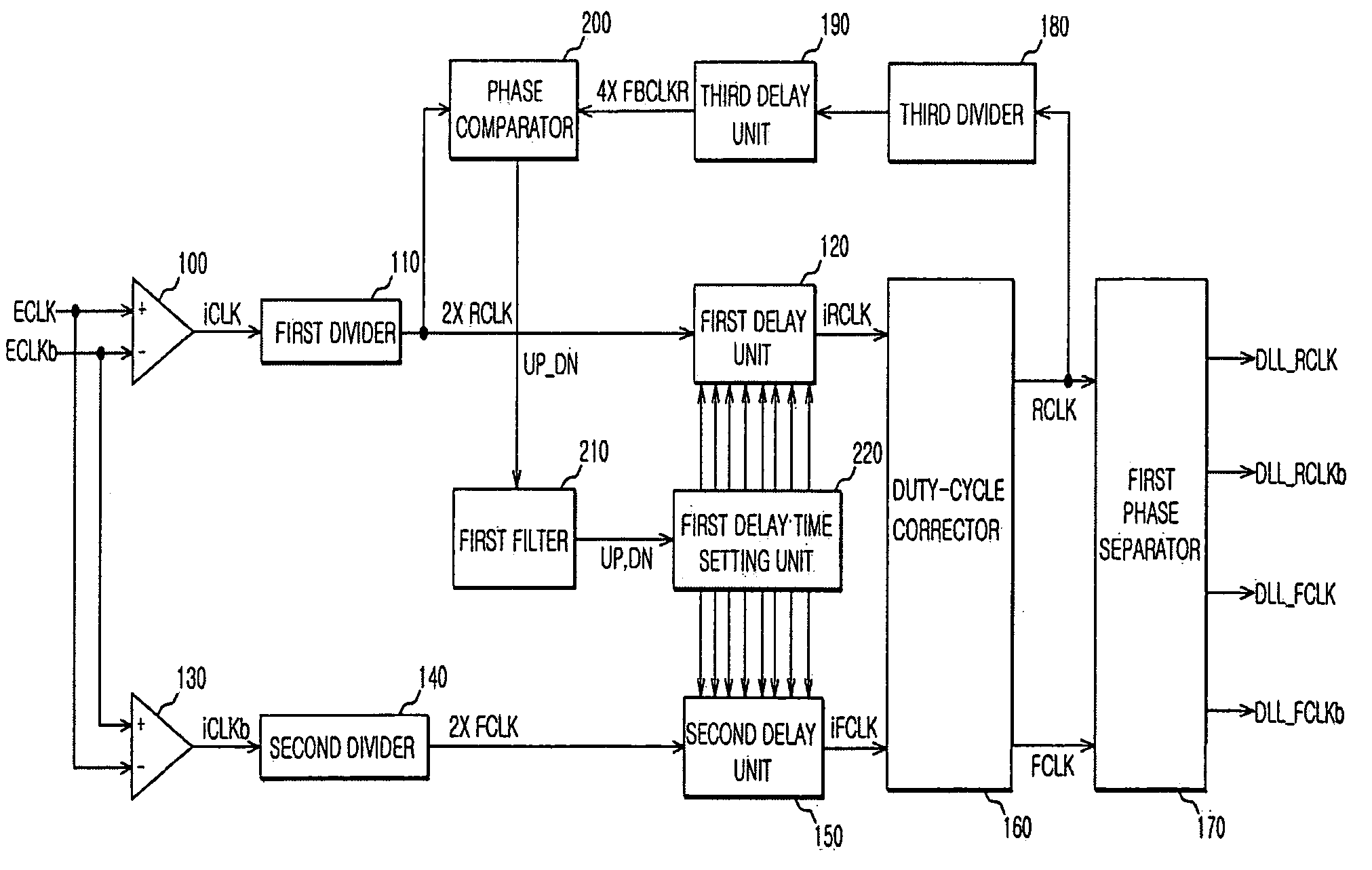

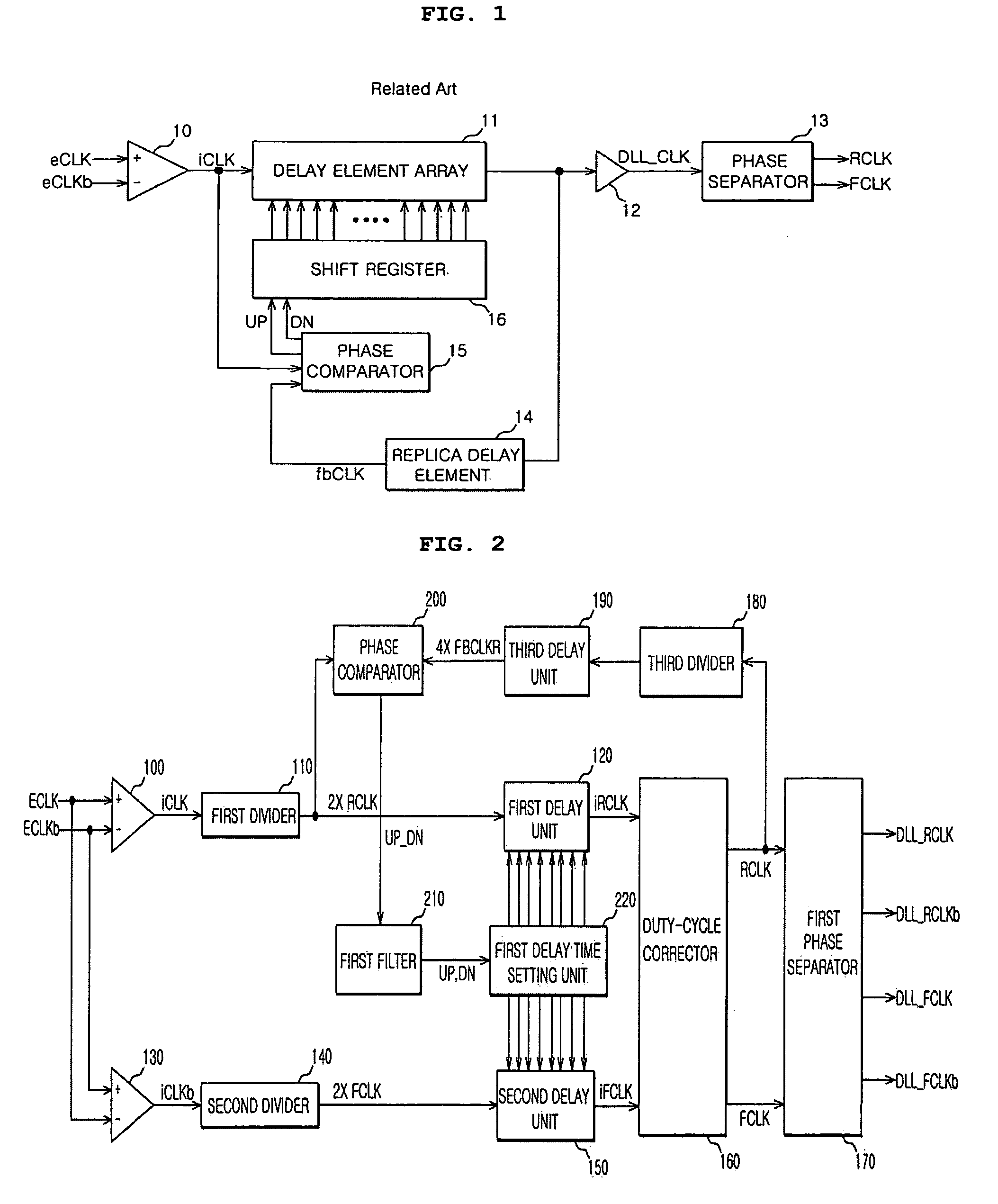

Clock generator for semiconductor memory apparatus

The clock generator for semiconductor memory apparatus which includes: a first divider; a first delay unit; a second divider; a second delay unit; a duty-cycle corrector; a third divider; a third delay unit; a phase comparator; and a delay time setting unit. The clock generator for semiconductor memory apparatus exactly performs phase correction and duty cycle correction using frequency-divided clocks. Therefore, it is possible to generate reliable clocks and to improve the operational performance of a system using the clock generator.

Owner:SK HYNIX INC

Duty cycle corrector and clock generator having the same

InactiveUS7994834B2Improve jitter characteristicsPulse automatic controlSingle output arrangementsControl signalClock generator

A duty cycle corrector includes a delay unit configured to adjust an input clock and an inverted input clock with a delay value controlled in response to one or more control signals and to generate a positive clock and a negative clock, and a duty detector configured to receive the positive clock and the negative clock, to detect duty ratios of the positive clock and the negative clock and to generate the one or more control signals.

Owner:SK HYNIX INC

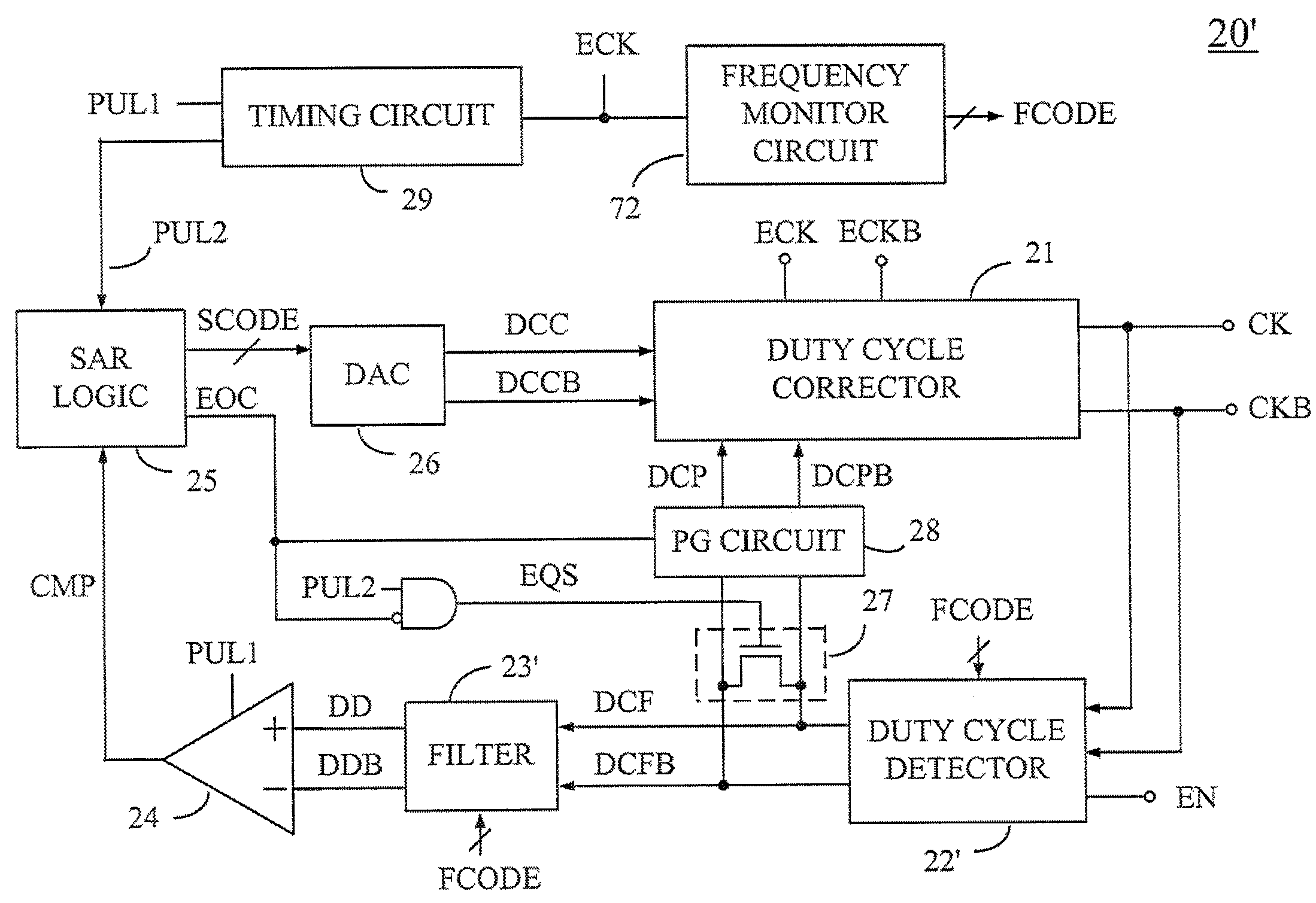

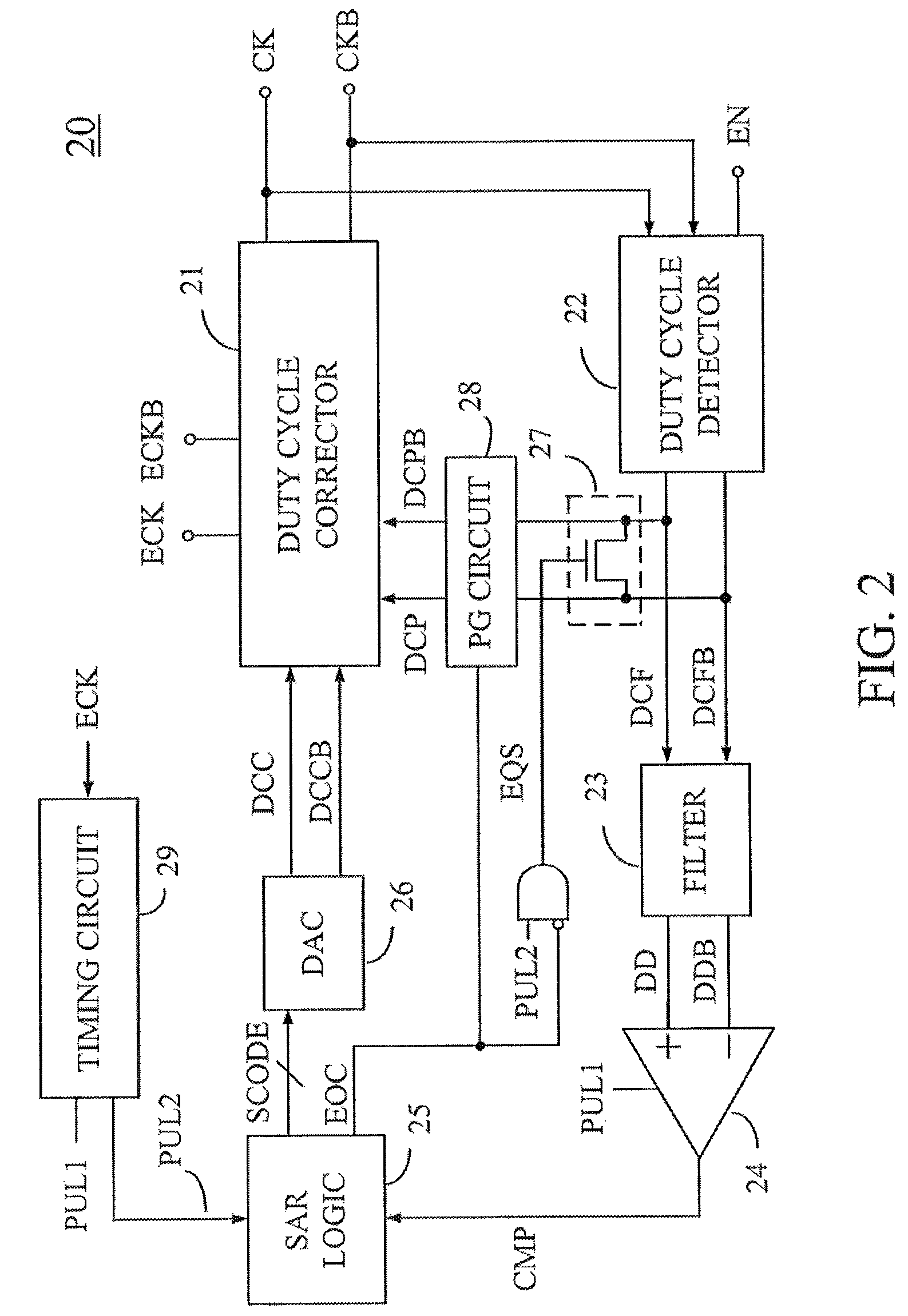

Duty cycle correction circuit

A duty cycle correction circuit comprises a duty cycle detector, a filter, a comparator, a SAR DAC, an equalization device, a pass gate circuit, and a duty cycle corrector. The duty cycle detector generates control signals in response to internal clock signals. The equalization device equalizes voltage levels of the control signals, and the pass gate circuit applies the control signals to the duty cycle corrector. The filter obtains average voltages of the control signals. The comparator compares output signals from the filter to generate a comparison result. The SAR DAC performs a SAR algorithm to generate analog output signals based on the comparison result. The duty cycle corrector receives external clock signals, the analog output signals, and output signals from the pass gate circuit to generate the internal clock signals with a corrected duty cycle.

Owner:ELITE SEMICON MEMORY TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com