Fabrication method for a thin film semiconductor device, the thin film semiconductor device itself, liquid crystal display, and electronic device

a technology of thin film semiconductor and fabrication method, which is applied in the direction of non-linear optics, instruments, mechanical devices, etc., can solve the problems of increasing display size and cost, slow operation speed, and electrical characteristics far inferior to those of polysilicon layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

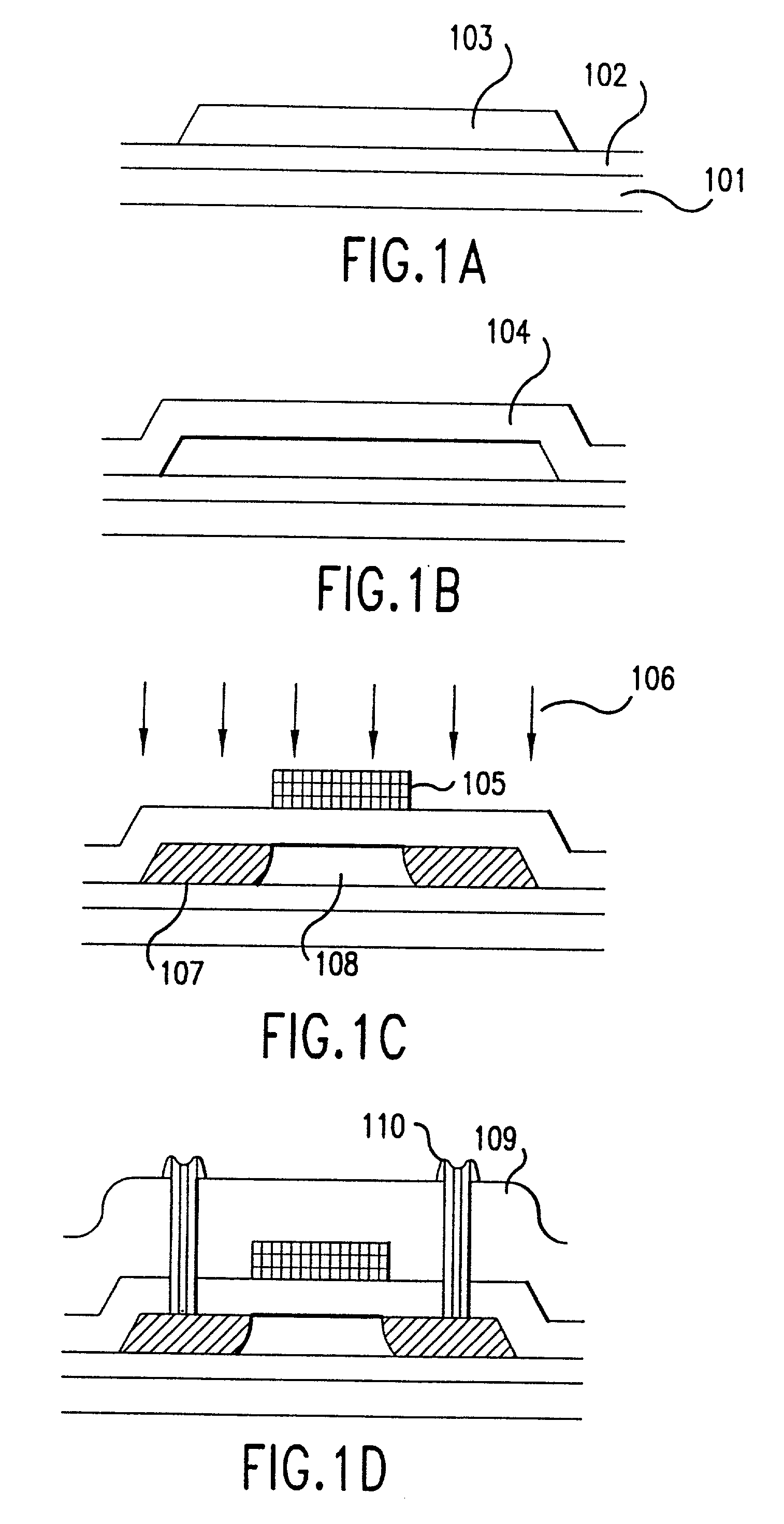

[0103] FIGS. 1(a) through (d) show cross-sectional views of the fabrication process for a thin film MIS field effect transistor.

[0104] In Example 1, a 235 mm.times.235 mm sheet of non-alkaline glass (OA-2, manufactured by Nippon Electric Glass Co., Ltd.) was used for substrate 101, though the type and size of the substrate are irrelevant for any substrate able to withstand the maximum processing temperature. First, silicon dioxide film (SiO.sub.2 film) 102, which serves as the underlevel protection layer, is formed on substrate 101 by means of atmospheric pressure chemical vapor deposition (APCVD), PECVD, sputtering or other means. In APCVD, the SiO.sub.2 layer can be deposited using monosilane (SiH.sub.4) and oxygen as source gases at a substrate temperature of between about 250.degree. C. and 450.degree. C. In the PECVD and sputtering methods, the substrate temperature can be anywhere from room temperature to 400.degree. C. In Example 1, a 2000 .ANG. SiO.sub.2 film was deposited a...

example 2

[0112] Other examples of implementations of this invention will also be explained using FIGS. 1(a) through (d).

[0113] In Example 2, sheets of non-alkaline glass (OA-2manufactured by Nippon Electric Glass Co., Ltd.) measuring 300 mm.times.300 mm and crystallized glass (TRC-5 manufactured by Ohara) measuring 300 mm.times.300 mm were used for substrate 101. The strain point of OA-2 is approximately 650.degree. C. TRC-5, on the other hand, is a crystallized glass, so the strain point cannot be defined. Since absolutely no substrate deformation or warpage can be detected up to a temperature of about 700.degree. C., however, the strain point of TRC-5 can, in practice, be said to be above about 700.degree. C. First, silicon oxide film 102, which becomes the underlevel protection layer, was deposited by PECVD onto substrate 101. The silicon oxide film was deposited under the same conditions that the gate insulator layer was deposited in Example 1. The thickness of the silicon oxide film was...

example 3

[0117] After forming the poly-Si-layer using the method described in detail in Example 1, an SiO.sub.2 layer corresponding to the gate insulator layer described in detail in Example 1 was deposited without patterning this poly-Si layer, and impurity ions such as PH.sub.3 were implanted in the poly-Si layer by ion doping, details of which were explained in Example 1. The thicknesses of the poly-Si layer and Sio.sub.2 layer and the conditions under which they were deposited were exactly the same as they were in Example 1. Impurity ion implantation conditions were also the same as those described in Example 1 except that the implantation dose was 3.times.10.sup.13 cm.sup.-2. Example 3 corresponds to the formation of the LDD region in TFTs explained in Example 1. After phosphorous ions were implanted, thermal annealing was performed at 300.degree. C. in oxygen for one hour, again just as in Example 1. After that the insulator layer was stripped off and the sheet resistance of the n-type...

PUM

| Property | Measurement | Unit |

|---|---|---|

| surface roughness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com