High-reliability image sensor wafer-level fan-out packaging structure and method

An image sensor and packaging method technology, which is applied to electric solid-state devices, semiconductor devices, radiation control devices, etc., can solve problems such as chip packaging that is not suitable for high I/O, poor reliability of the overall packaging structure, and limited signal fan-out area. , to meet the mechanical strength, solve high cost and low output, and reduce the size of the XY direction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

[0120] see Figure 9-15 , A high-reliability image sensor wafer-level fan-out packaging method of the present invention includes the following steps:

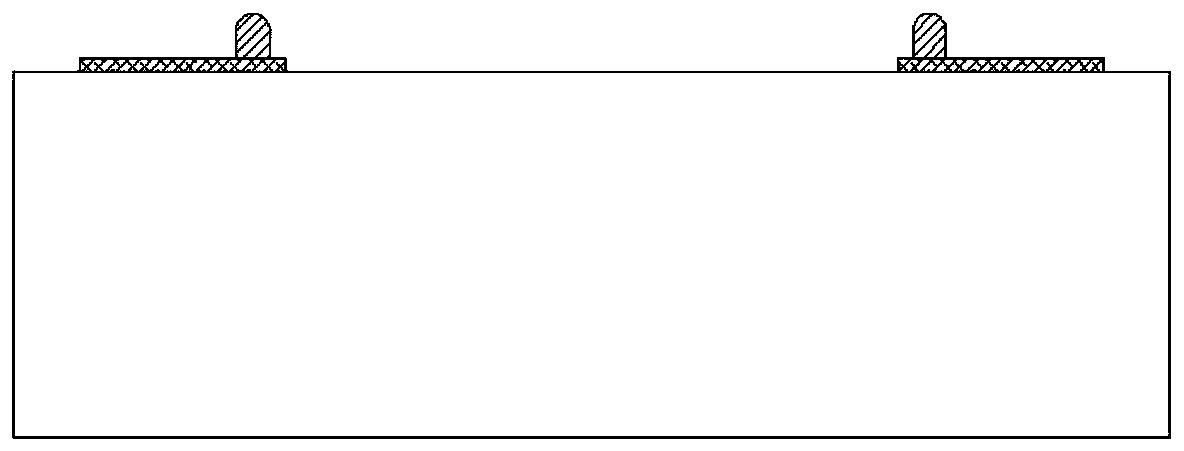

[0121] Step 1: See you Picture 9 , Thinning the CIS wafer can reduce the size after packaging, cutting the CIS wafer to obtain the CIS chip 200 to be processed, the thickness of the CIS chip is not limited, and the thinning process and the basic mechanical strength of SMT can be satisfied. Make the reliability strength of CIS chip greatly enhanced;

[0122] Step 2: See you Picture 10 , Provide glass substrate 100, use TGV process to perforate glass substrate 100 by wet etching or laser. TGV process can realize ultra-thin glass processing. Ultra-thin glass can reduce light refraction and reflection and increase The light transmittance, the thickness of the glass is about 150μm-200μm, and then the conductive metal is filled in the through hole 101. In this embodiment, Cu is electroplated in the through hole 101 or filled with Cu pa...

specific Embodiment 2

[0139] see Figure 7 , 8 , 9, 10, 11, 12, 13, another high-reliability image sensor wafer-level fan-out packaging method of the present invention includes the following steps:

[0140] Step 1: See you Figure 7 , Thin the CIS wafer, and cut the CIS wafer to obtain the CIS chip 200 to be processed;

[0141] Step 2: See you Picture 10 , Provide the glass substrate 100, use the TGV process to perforate the glass substrate 100 by wet etching or laser, and then fill the conductive metal in the through hole 101. In this embodiment, Cu electroplating in the through hole 101 Or fill with Cu paste, and then form bumps 300 on the through holes 101 by photolithography and electroplating;

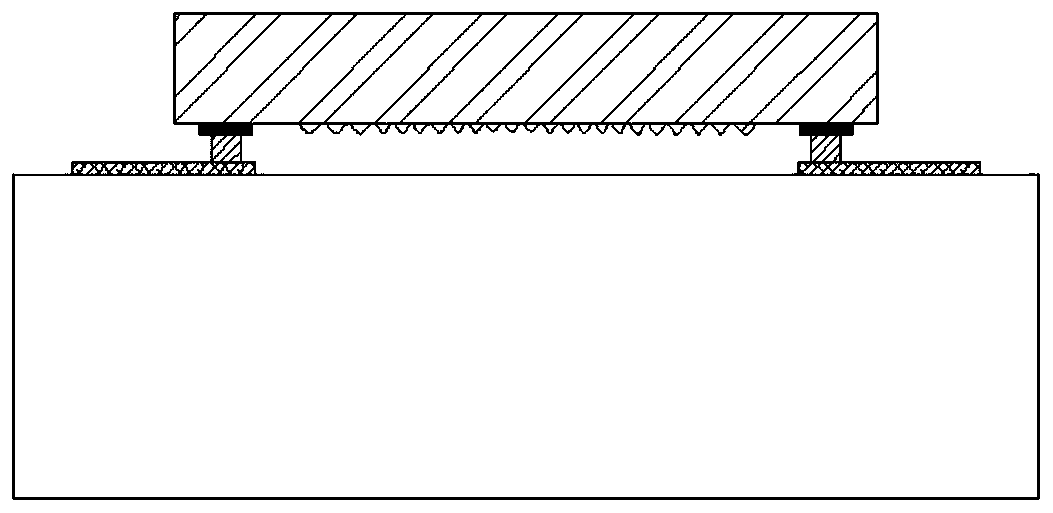

[0142] Step 3: See you Picture 11 , Using SMT mounting method, the CIS chip 200 and the glass substrate 100 are welded together through the pad 201 of the CIS chip and the bumps 300 on the glass substrate;

[0143] Step 4: See you Picture 12 , Using DAM dispensing technology to fill and seal the gap between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com