Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Reducing fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

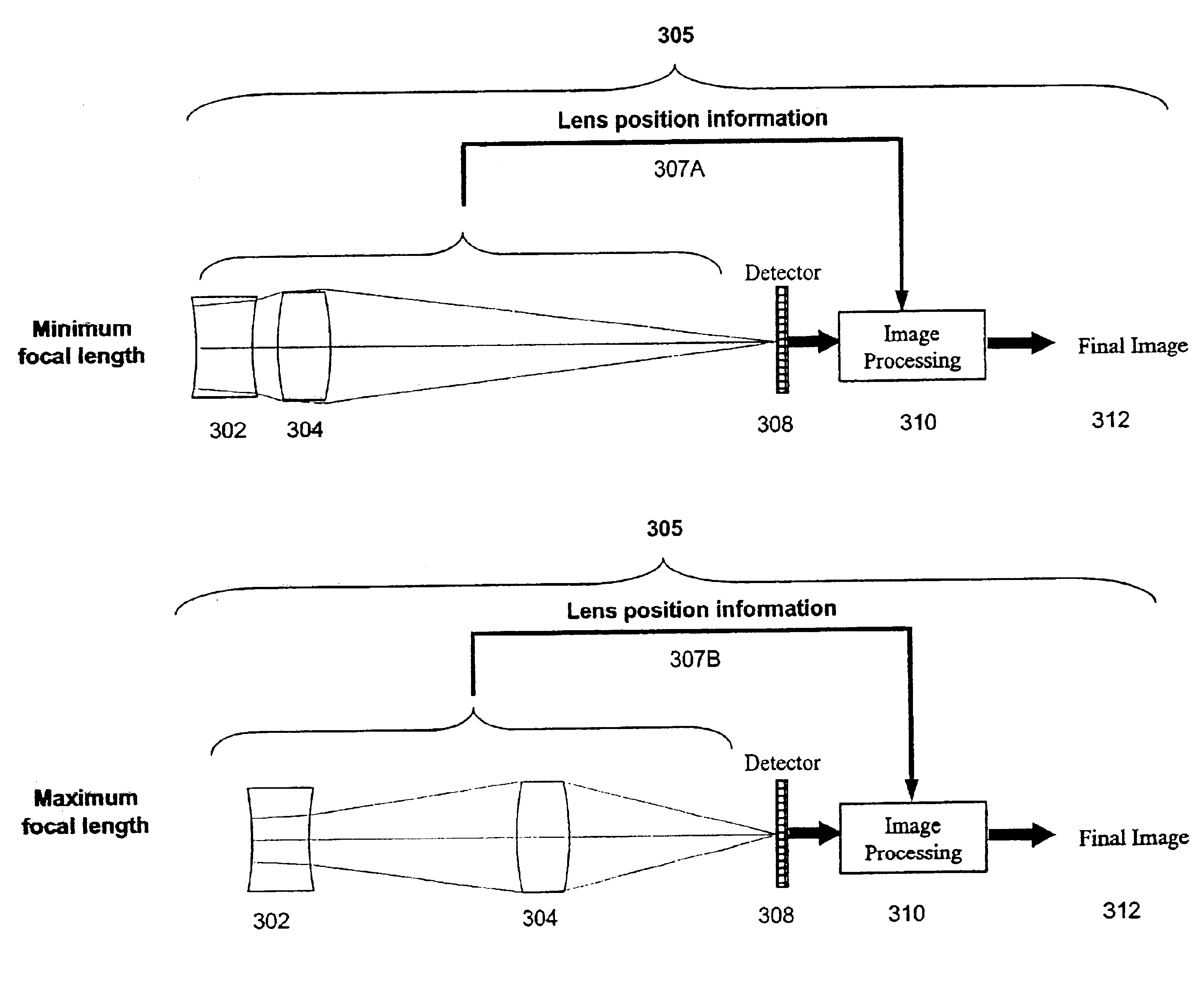

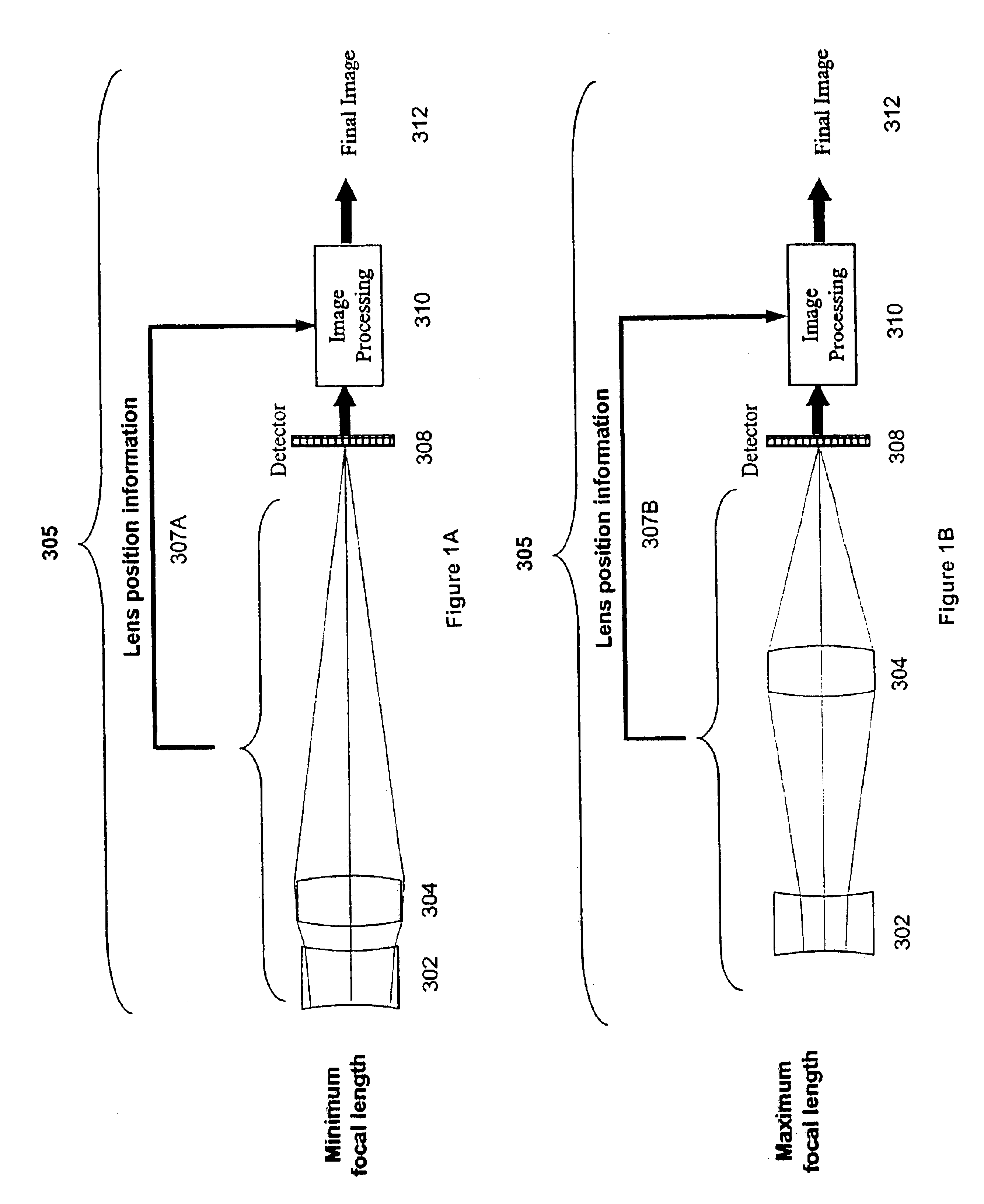

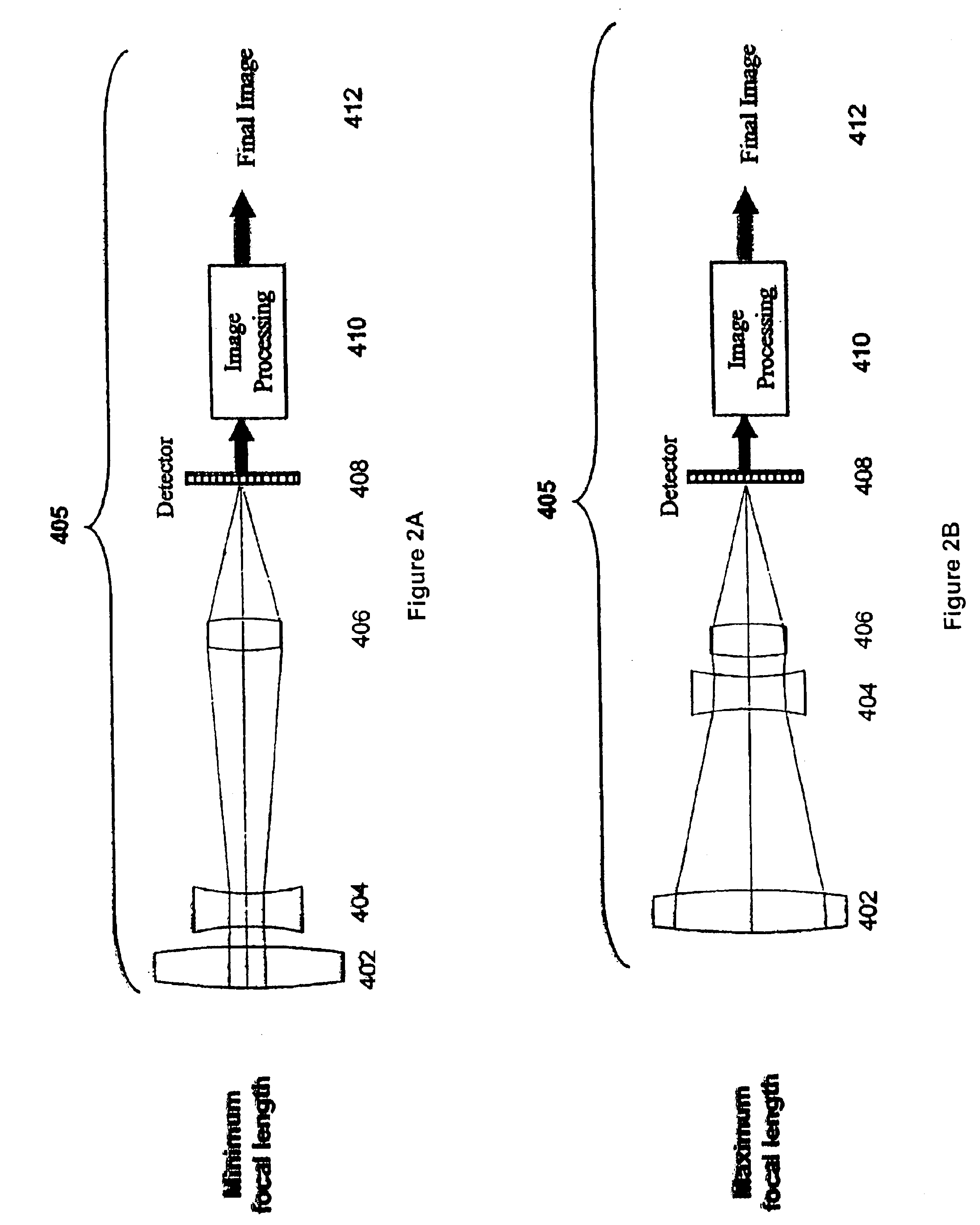

Wavefront coding zoom lens imaging systems

InactiveUS6911638B2Quality improvementFast imagingPhotometry using reference valueBeam/ray focussing/reflecting arrangementsImaging processingOphthalmology

A wide-angle zoom lens with as few as two plastic elements codes the wavefront produced by the imaging system such that the imaging system is substantially invariant to aberrations related to misfocus. Signal processing is used to decode the wavefront to form the final image. A first type of zoom lens configuration uses as few as two lens elements. In this type, image processing may be modified to take into account the positioning of the lenses.

Owner:COLORADO UNIV OF RGT

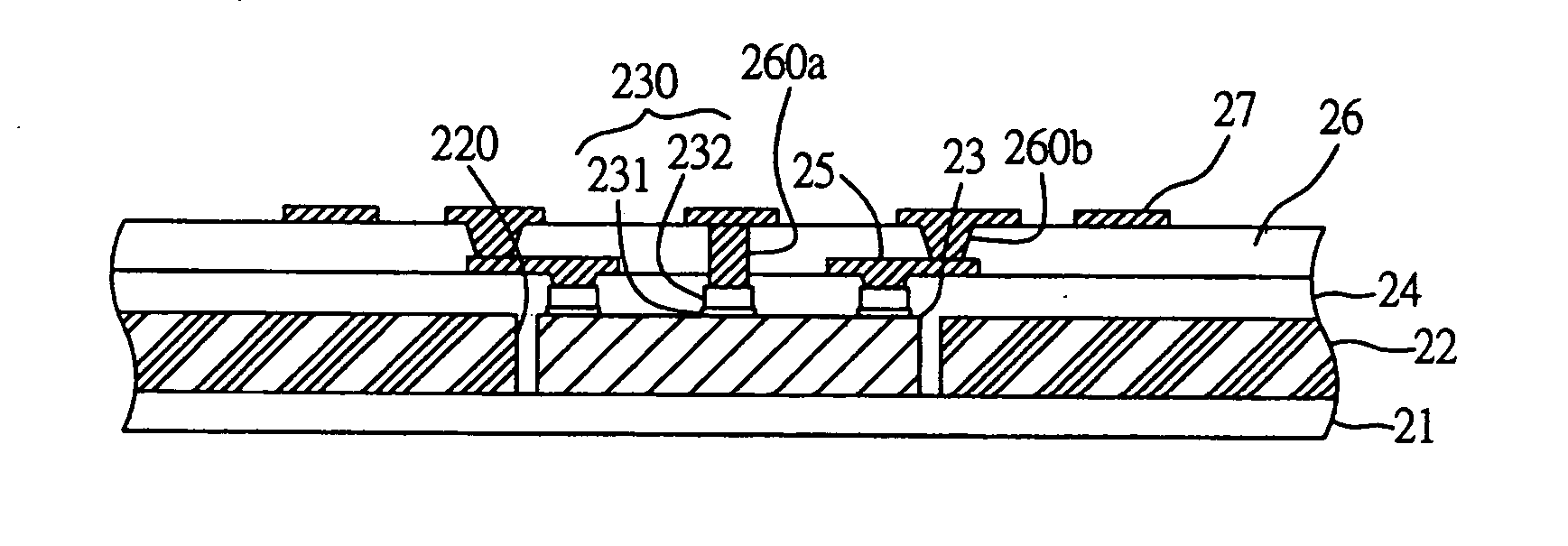

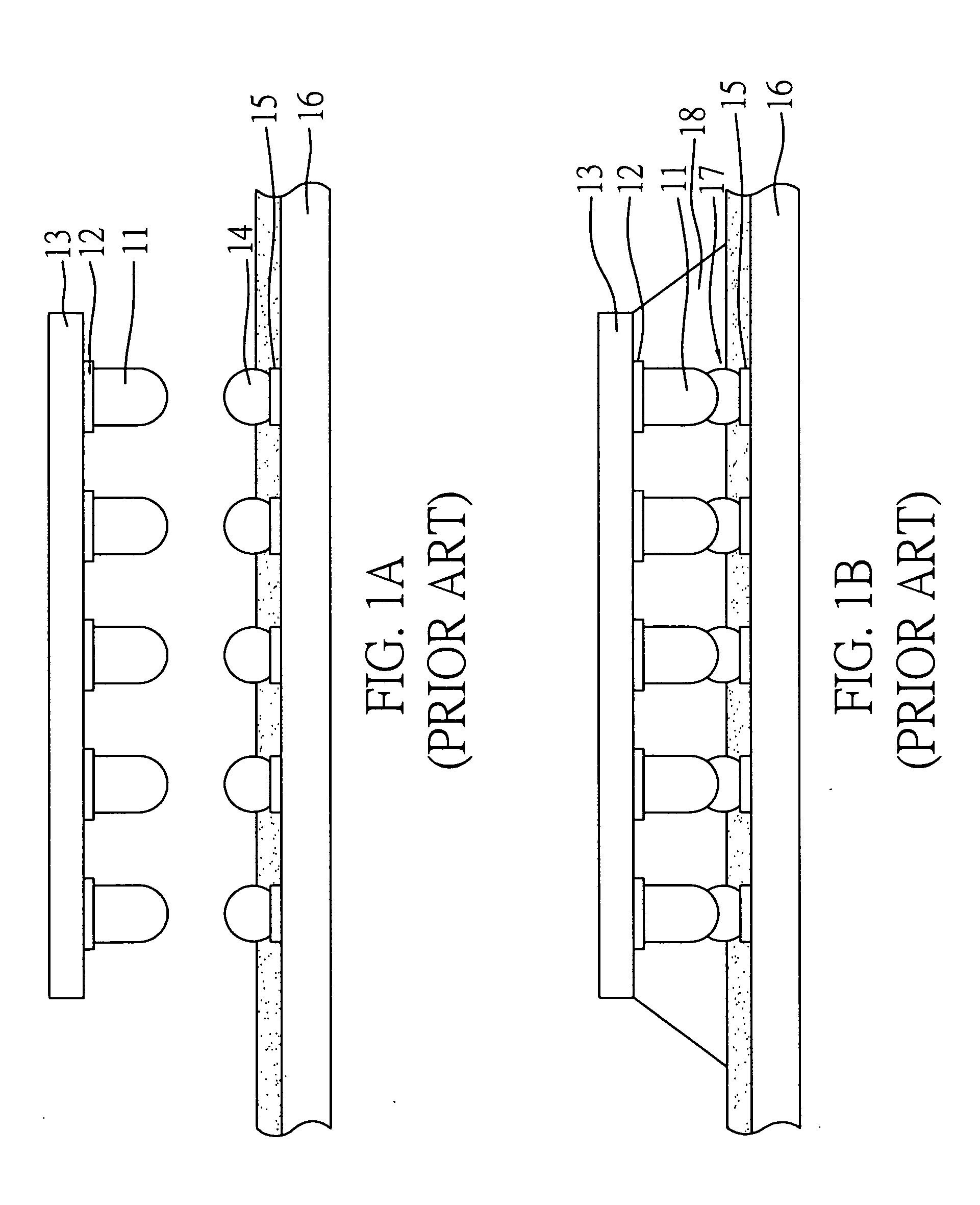

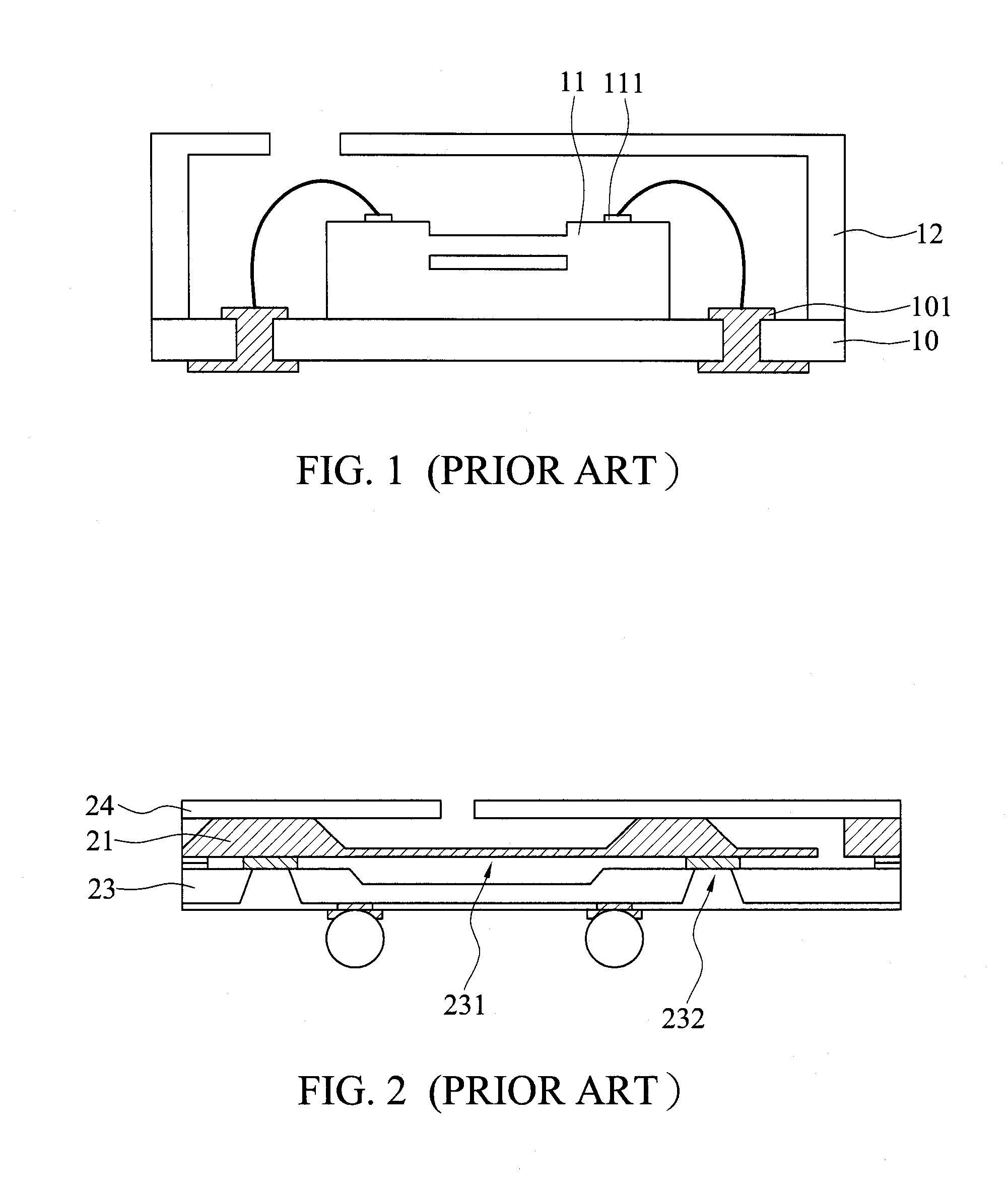

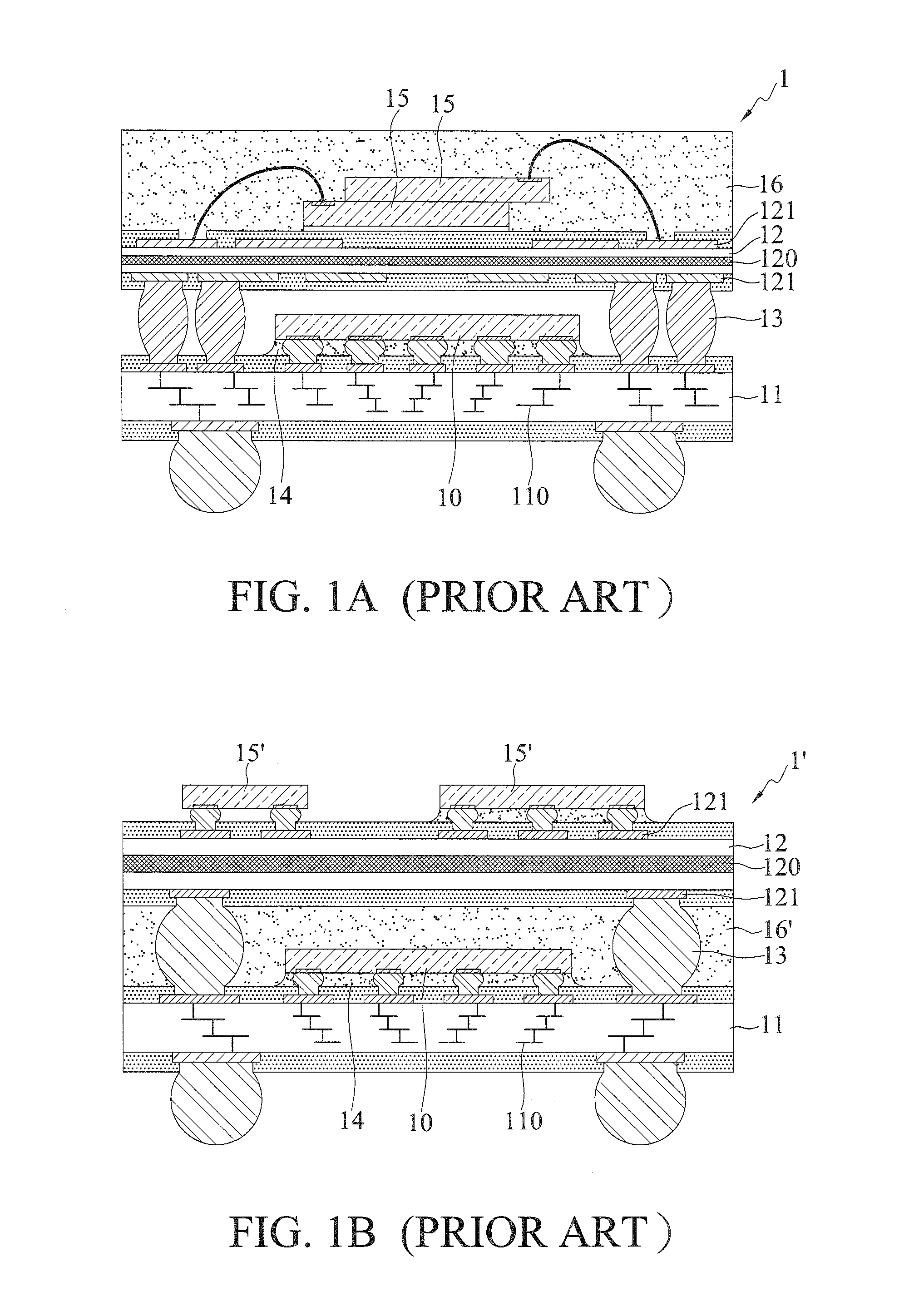

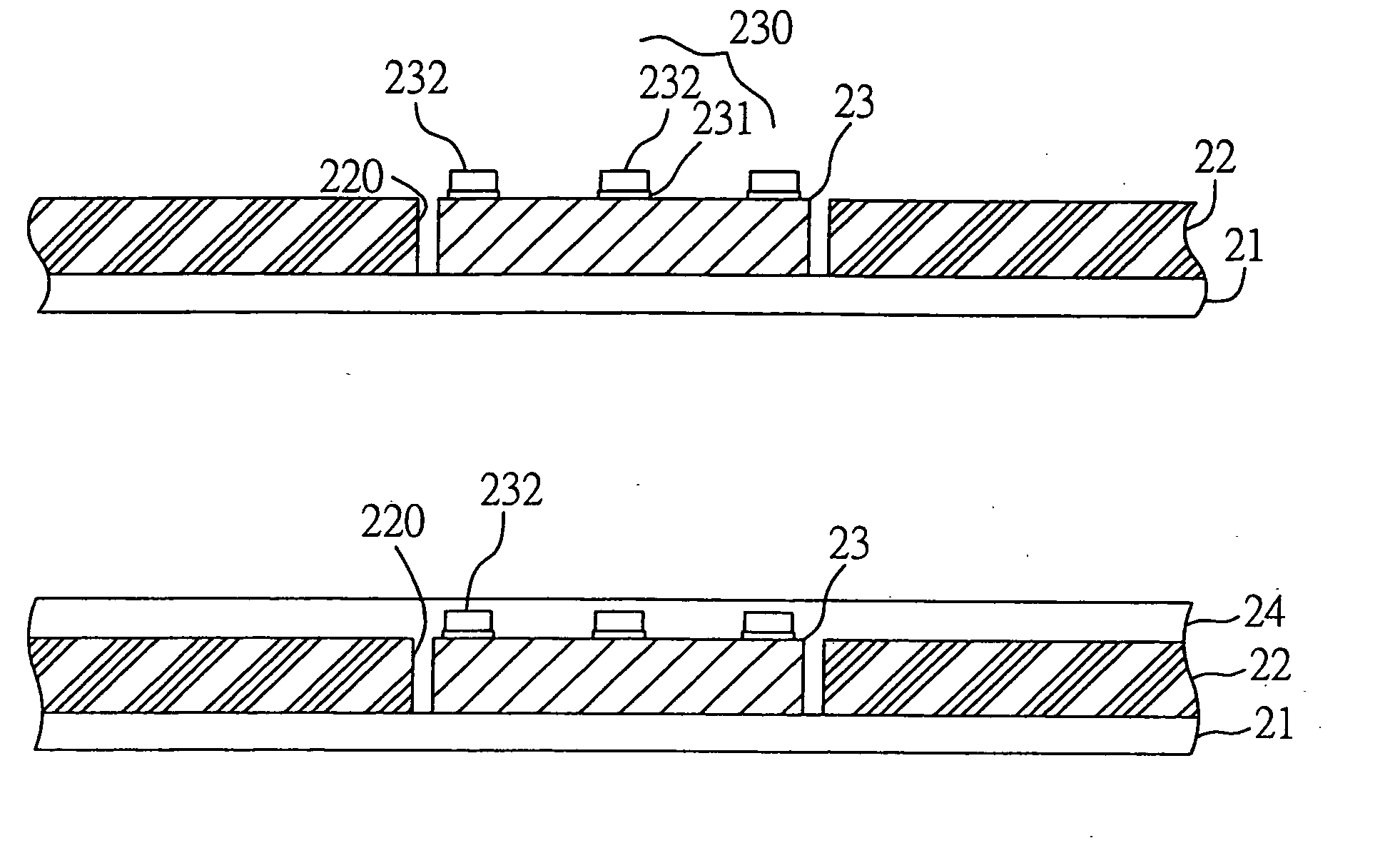

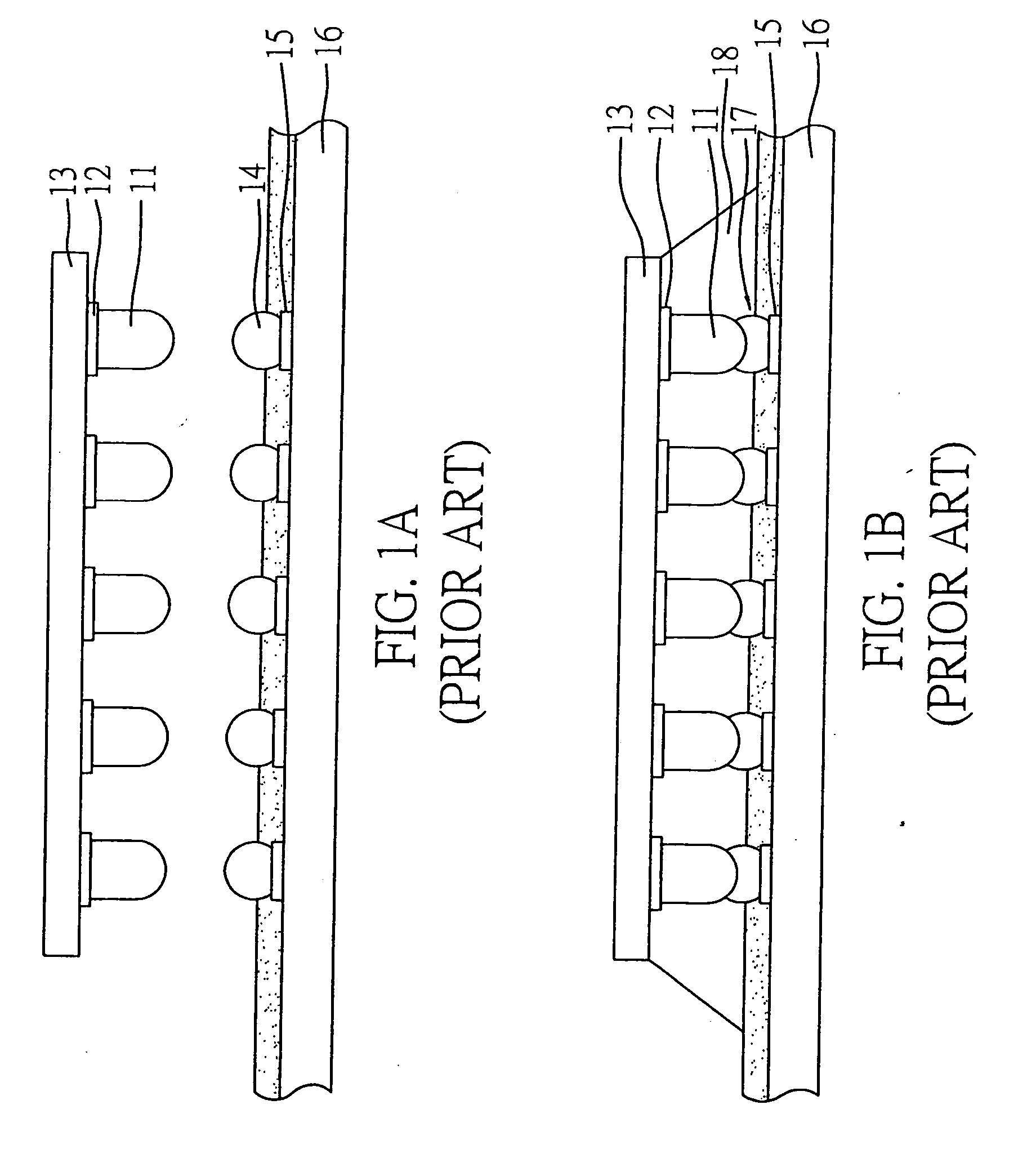

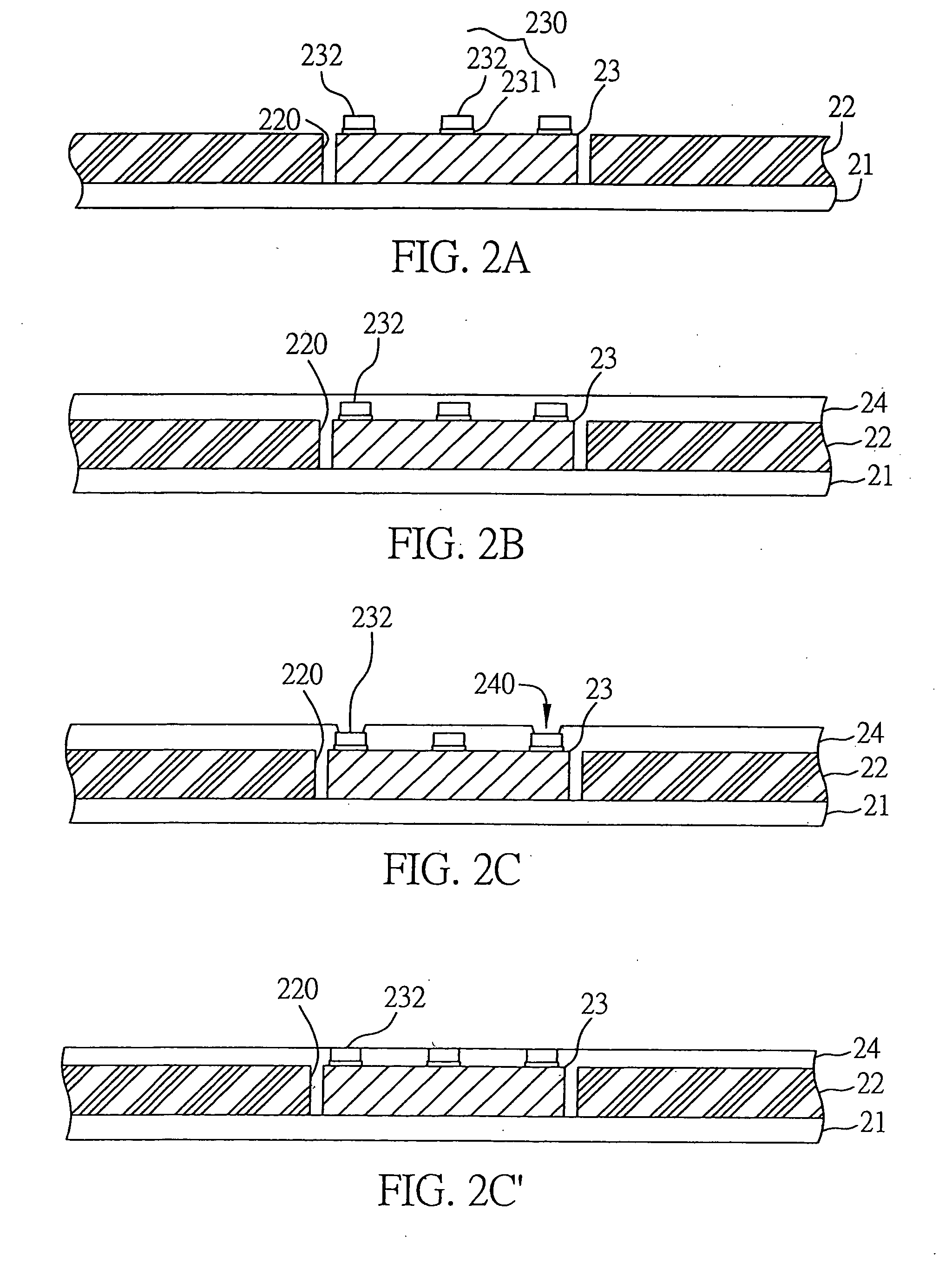

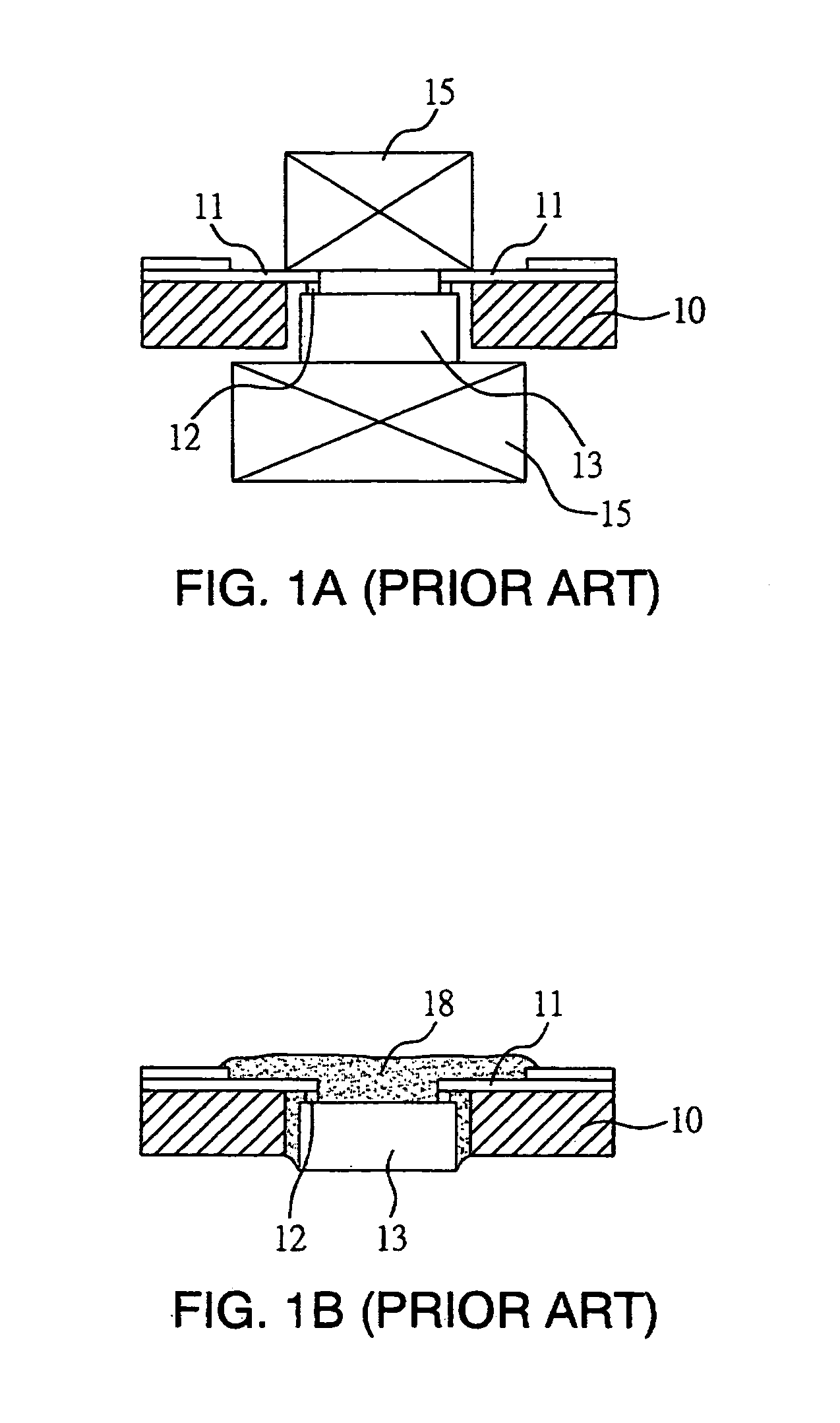

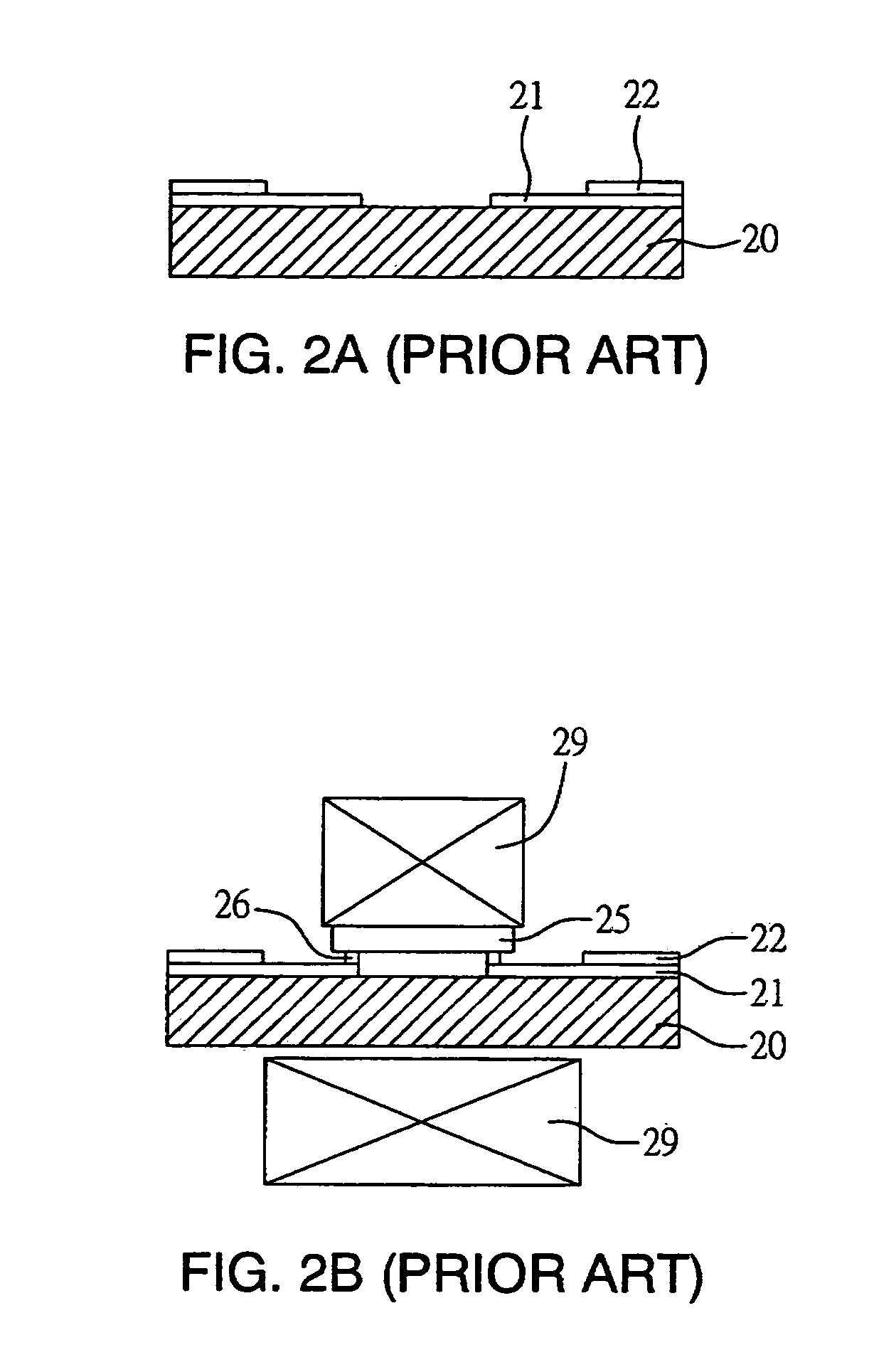

Micro-electronic package structure and method for fabricating the same

InactiveUS20060043549A1Simplify the manufacturing processImprove responseSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSemiconductor chip

A micro-electronic package structure and a method for fabricating the same are proposed. A carrier is prepared and provided with a cavity for receiving at least one semiconductor chip having a plurality of electrical connection contacts. A dielectric layer is formed on the carrier, with the electrical connection contacts being exposed from the dielectric layer. A first circuit layer is formed on the dielectric layer and electrically connected to a portion of the electrical connection contacts of the chip. Another dielectric layer is formed on the first circuit layer and said dielectric layer, and a second circuit layer is formed on this dielectric layer and electrically connected to the rest of the electrical connection contacts of the chip and the first circuit layer by conductive vias, such that the chip is integrated into the carrier.

Owner:PHOENIX PRECISION TECH CORP

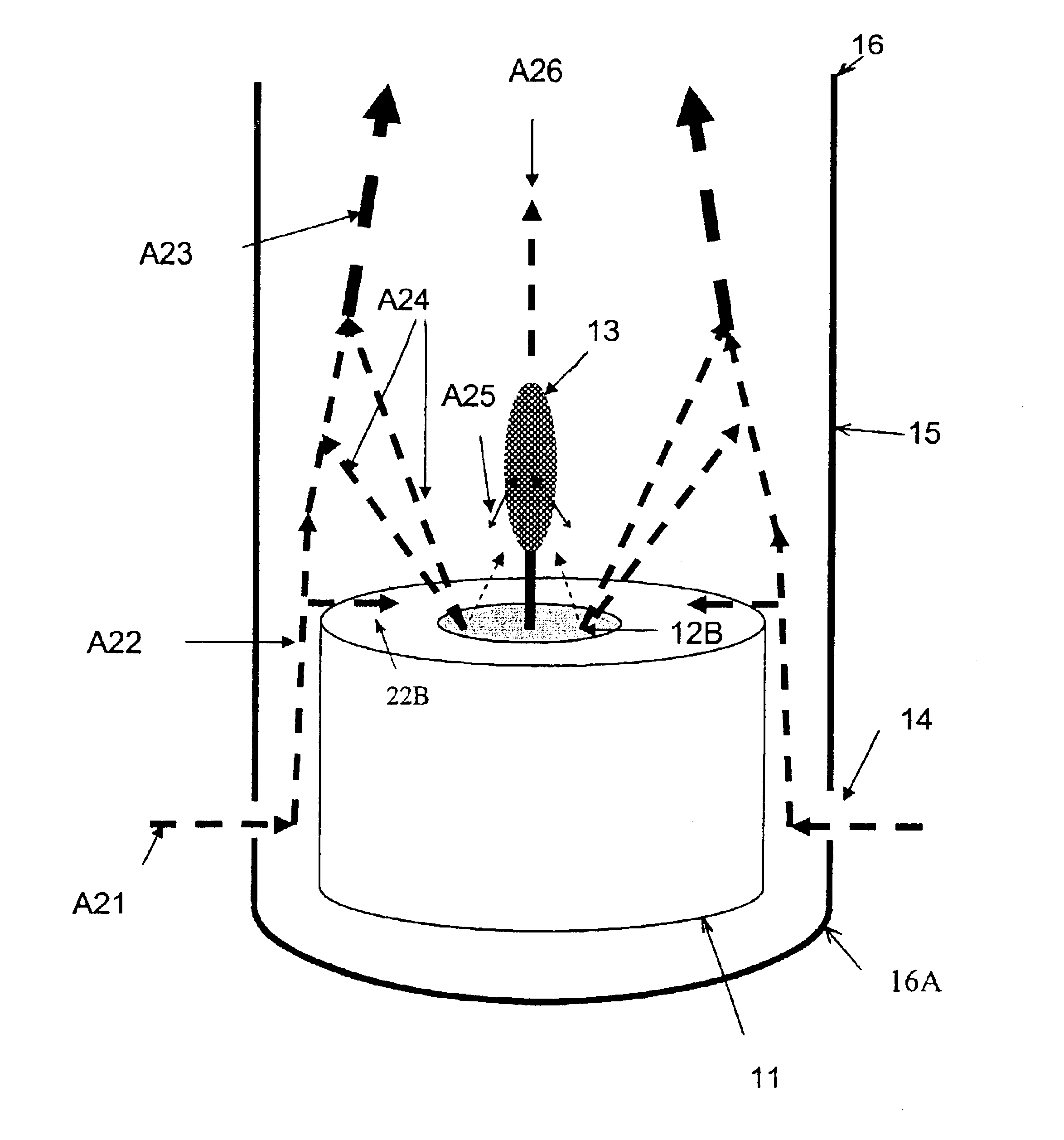

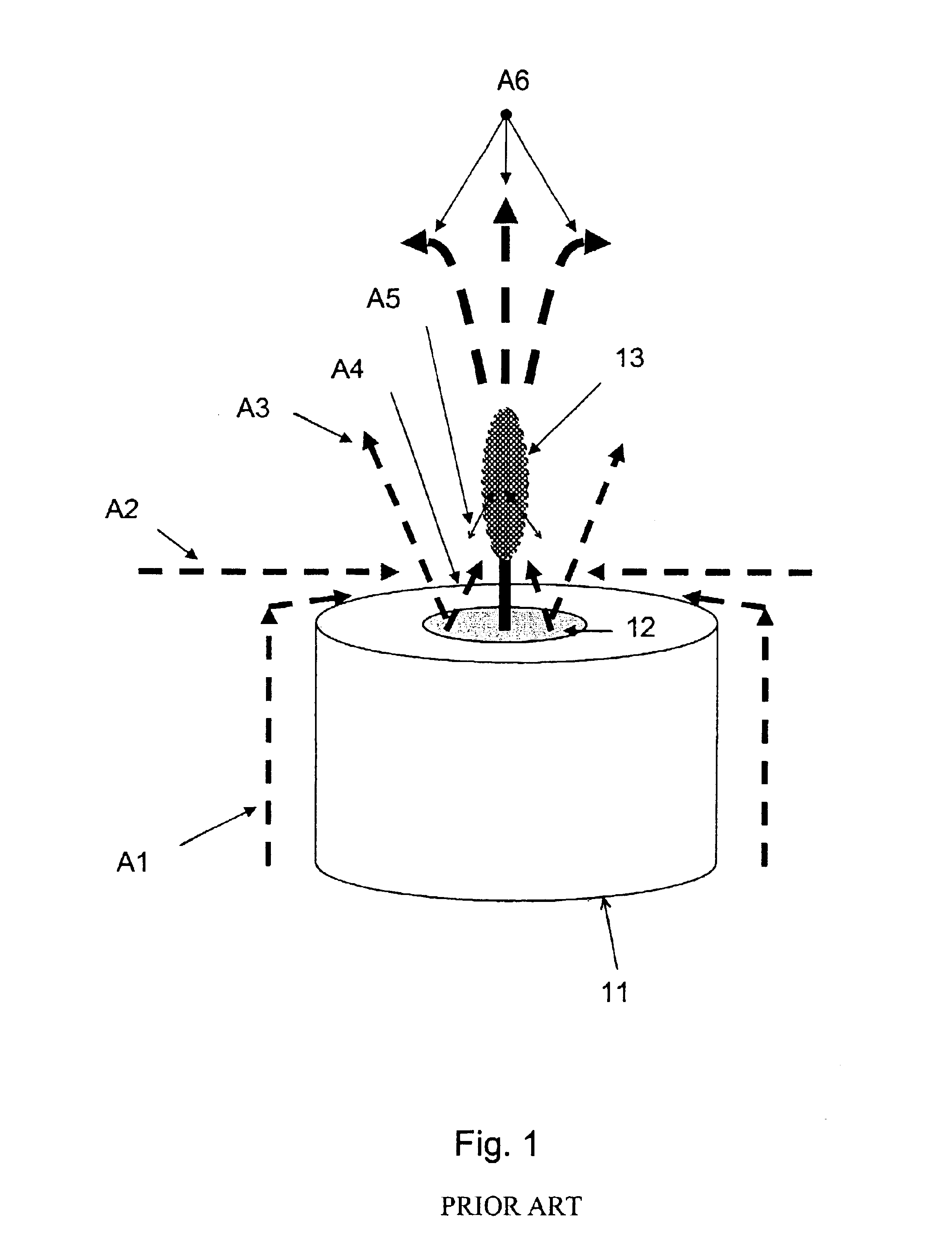

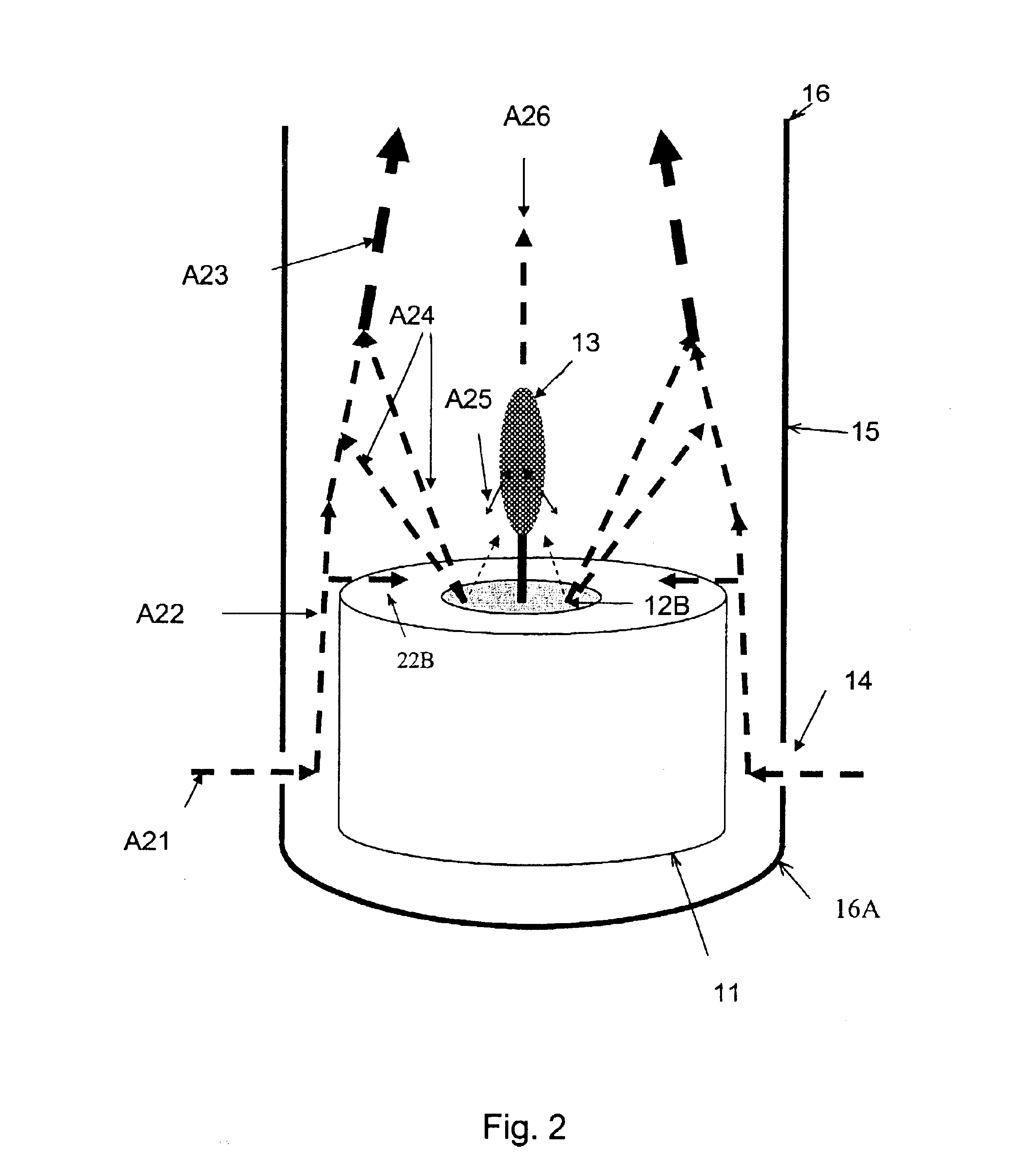

Method for improving the delivery of volatiles from a burning candle and a system for the same

InactiveUS6849240B2Reduce deliveryMinimizing combustionCapillary burnersFire rescueEngineeringAtmosphere

The invention provides a system and a method for improving the delivery of volatiles from a burning candle by providing a stabilized laminar gas flow adjacent a volatile-containing molten pool, ensuring an enlarged molten pool by close regulation of thermal transfer between a monolithic candle mass and the surrounding atmosphere, and minimizing volatile loss through unregulated thermal gradients.

Owner:INT ART & SCI GRP

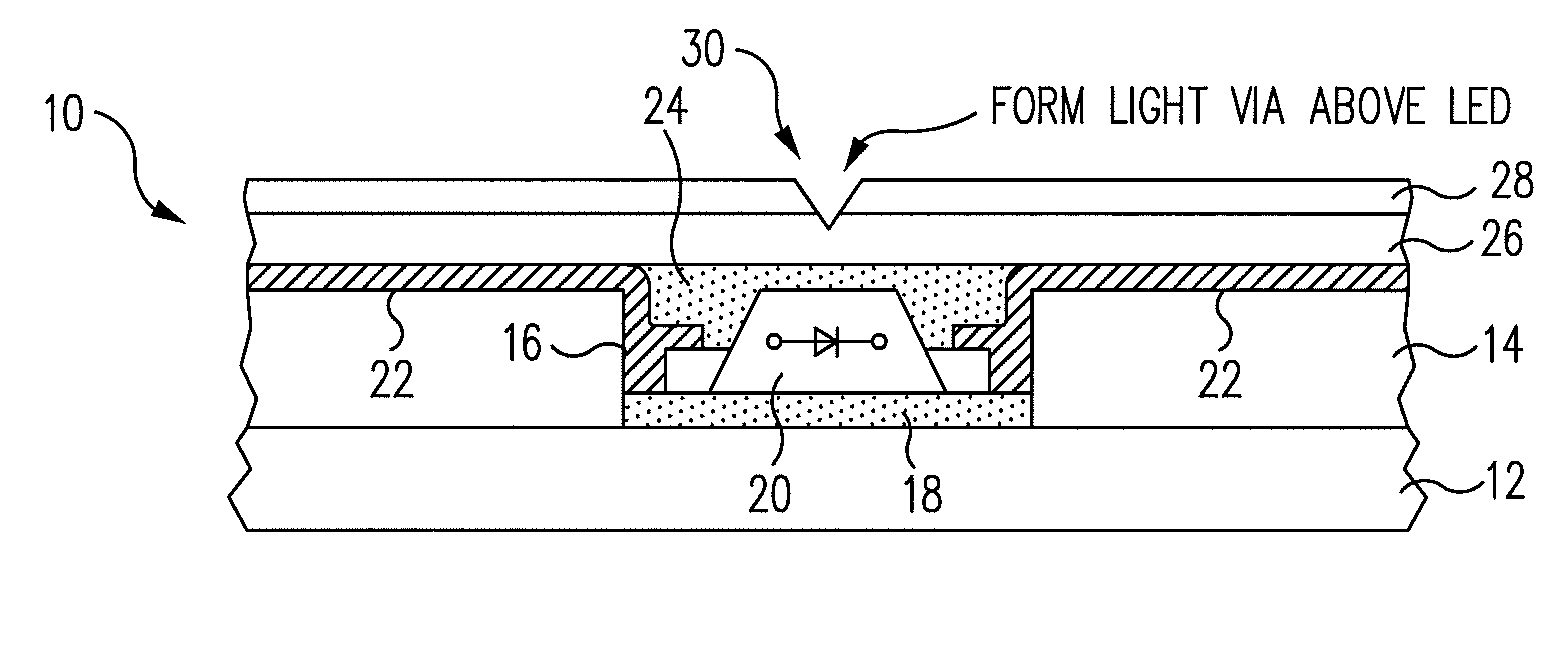

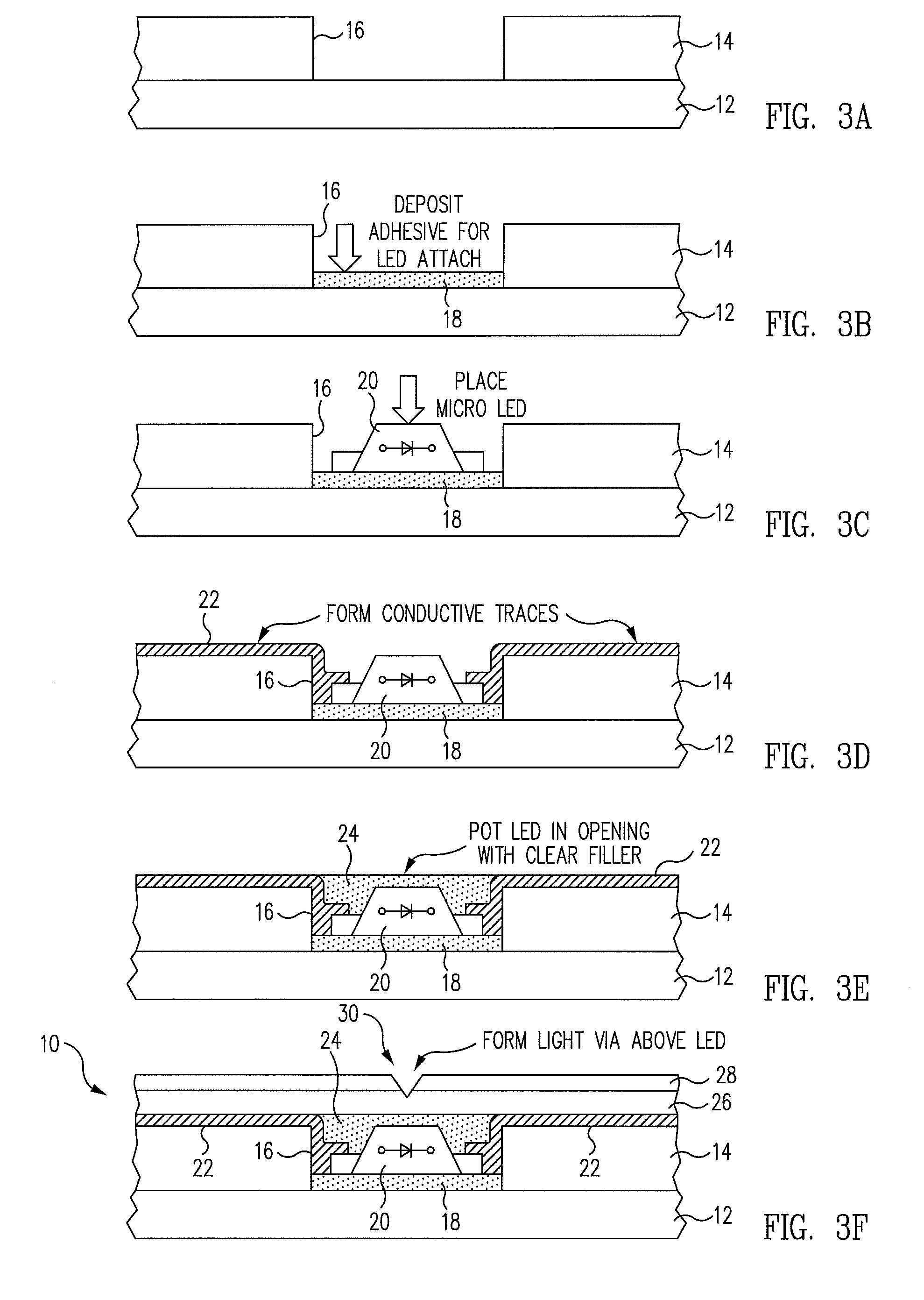

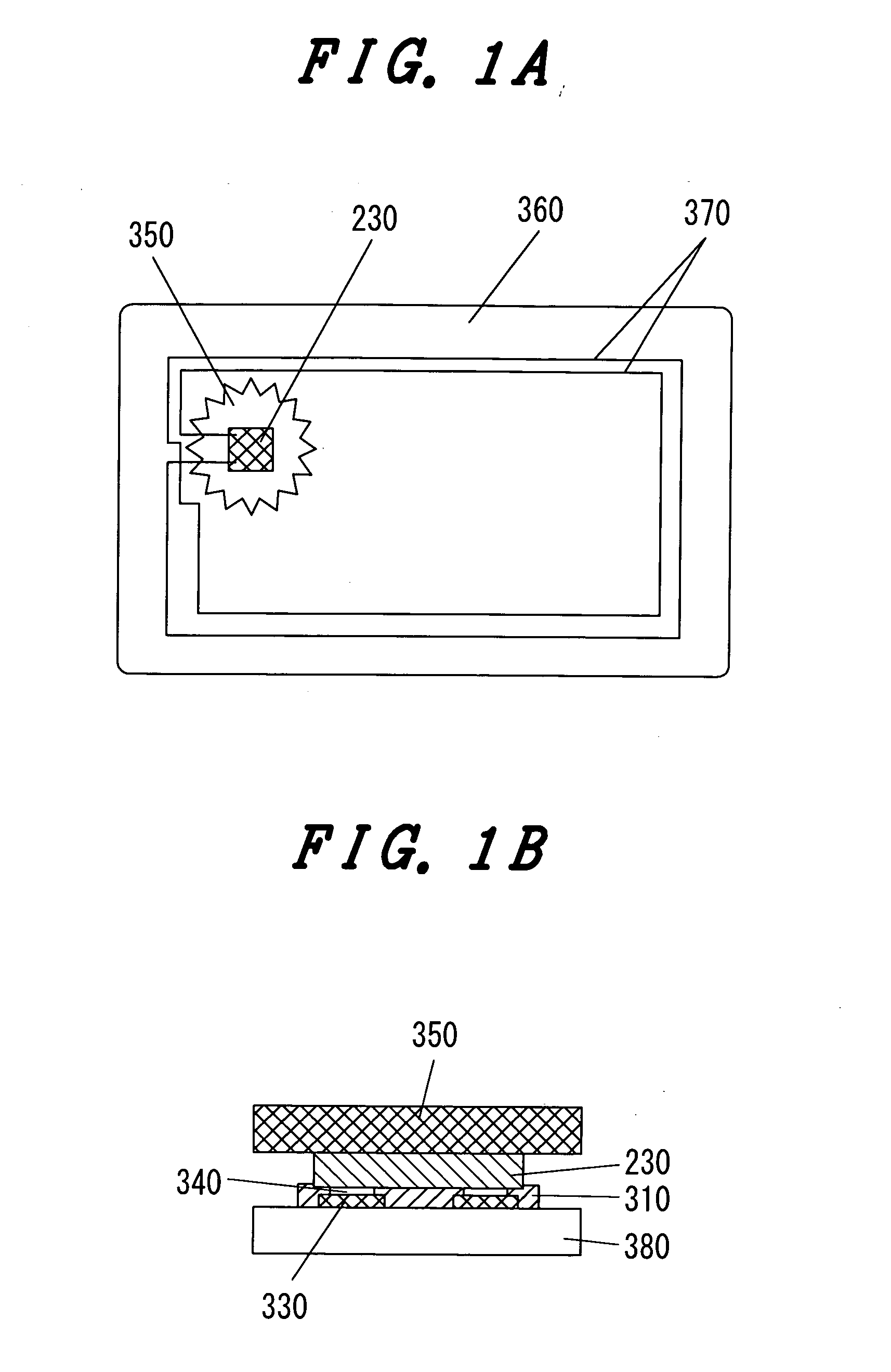

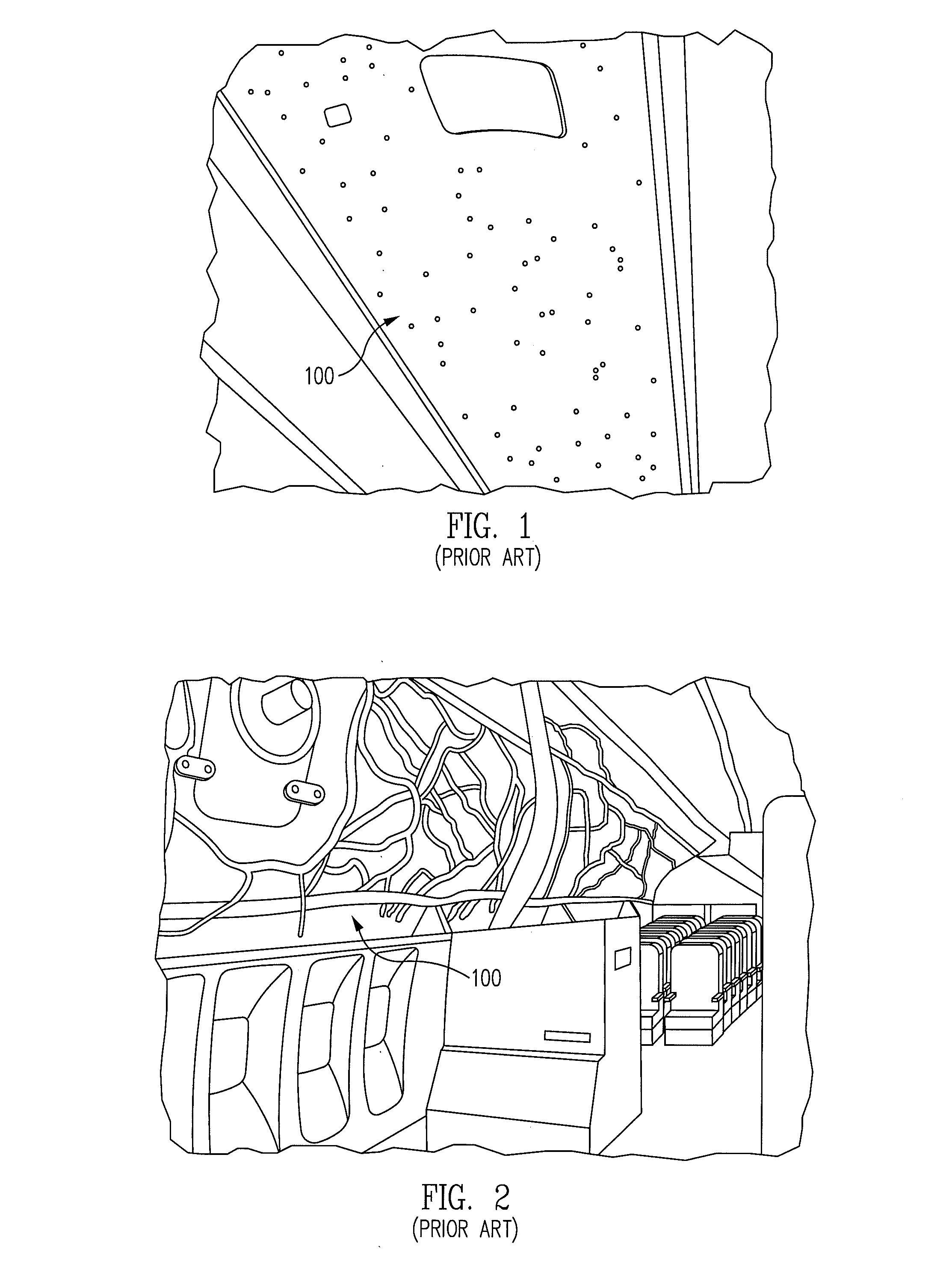

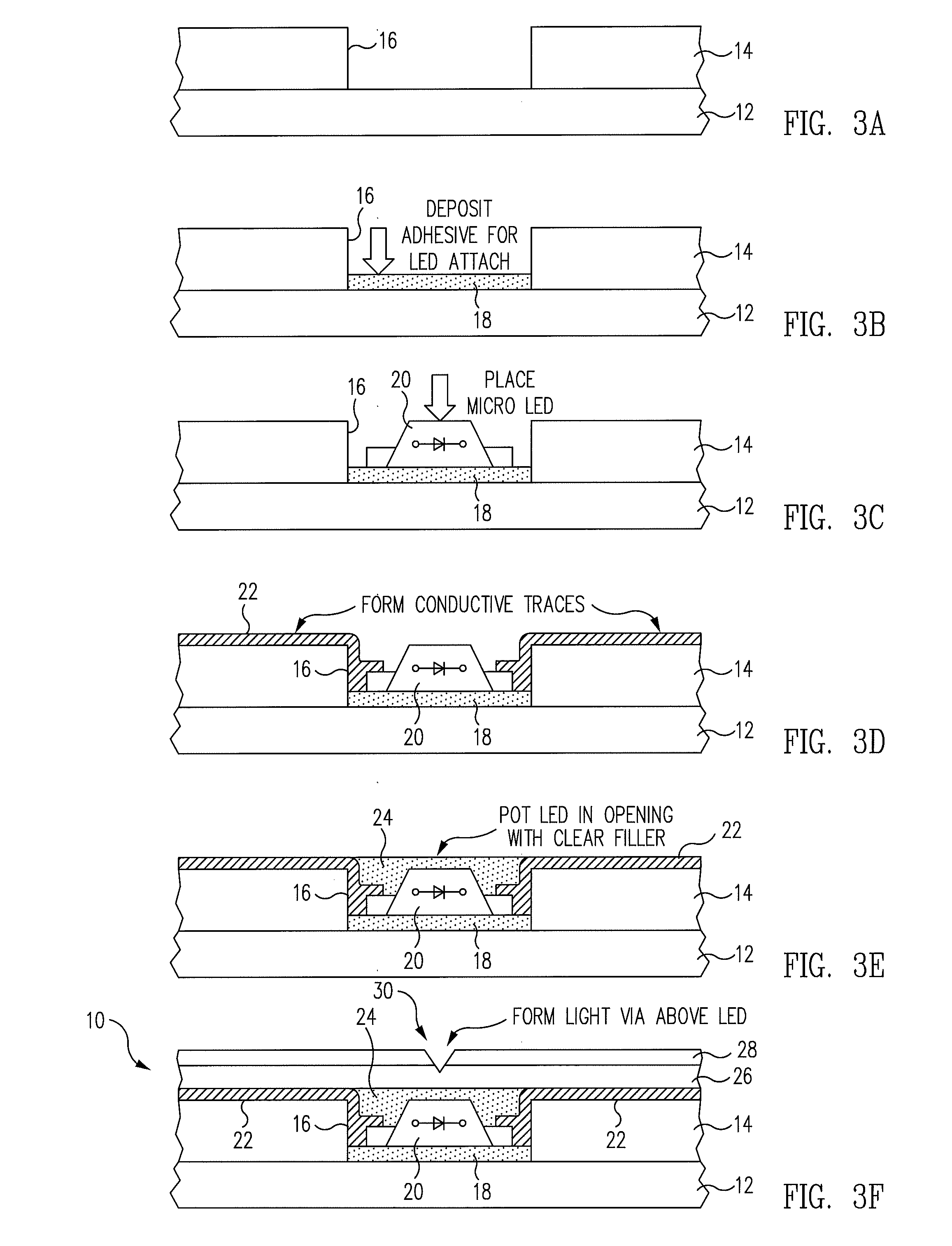

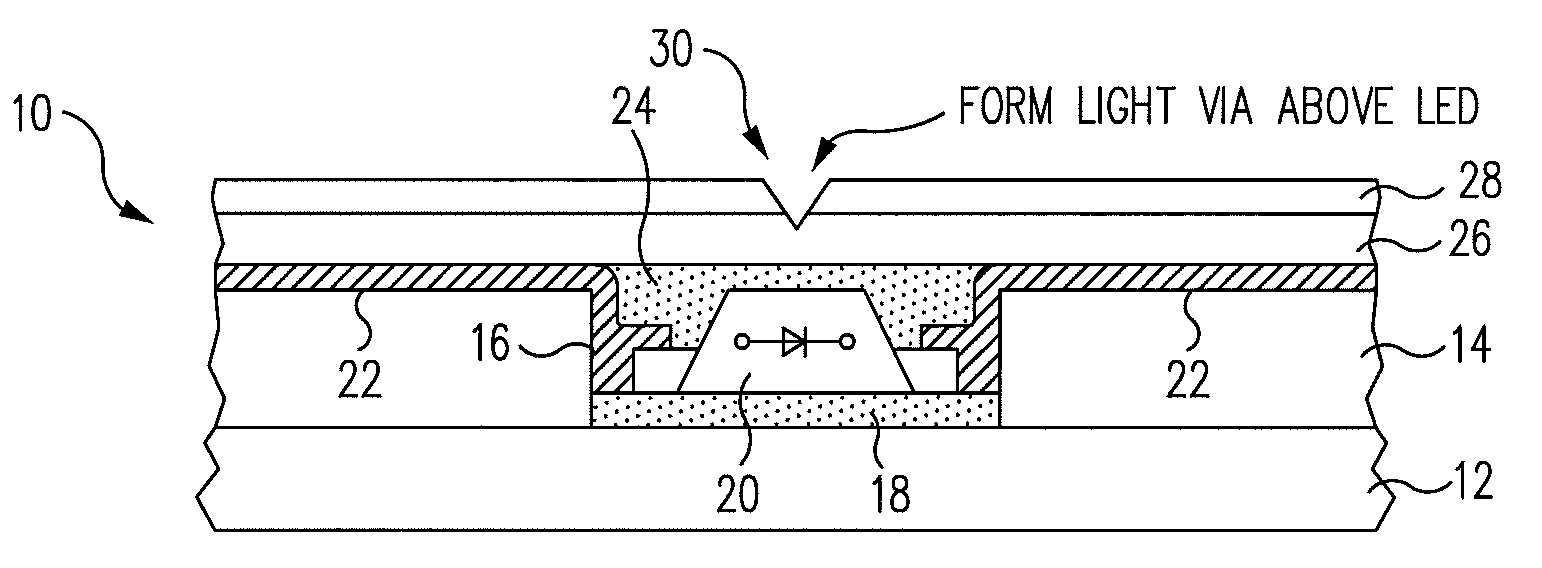

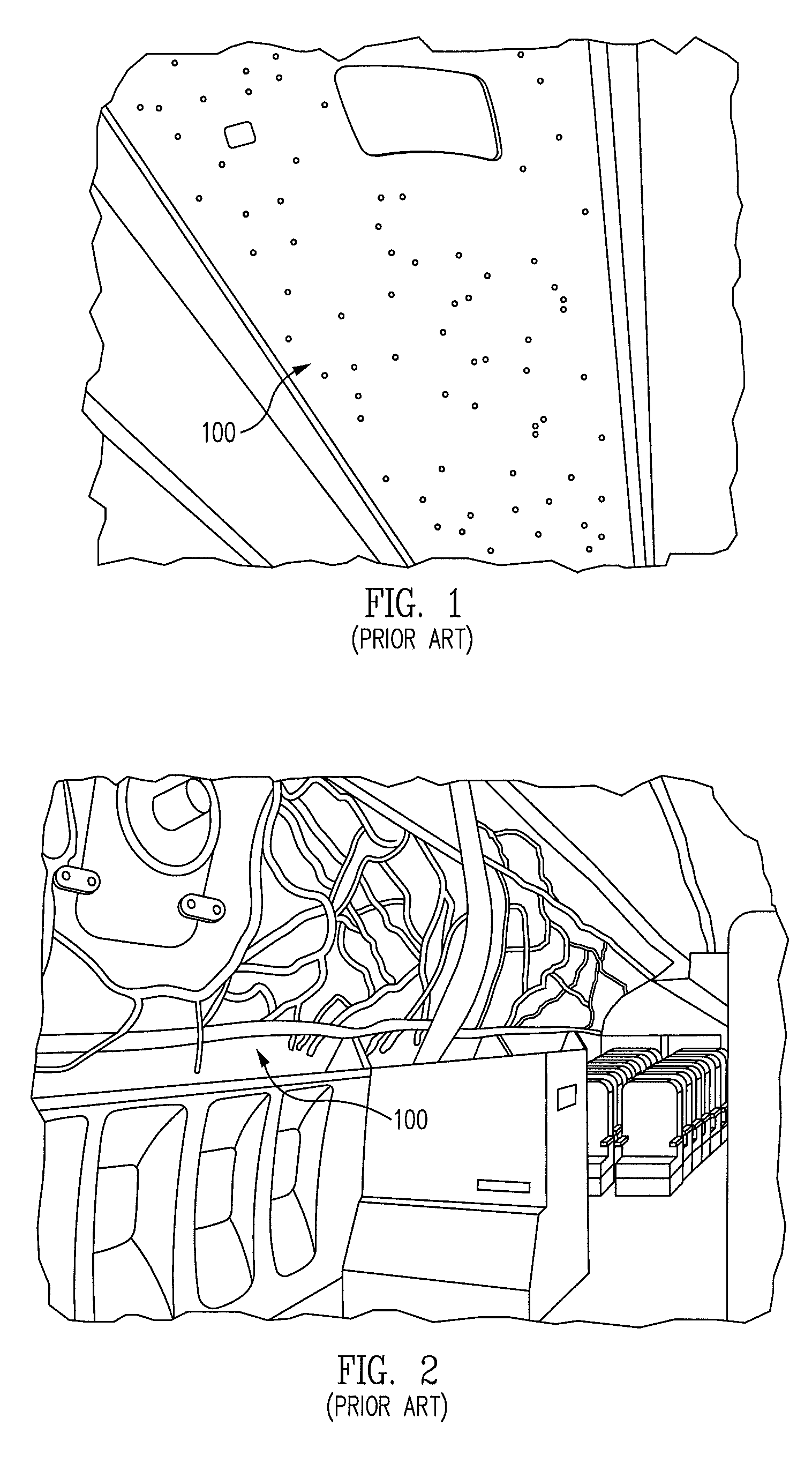

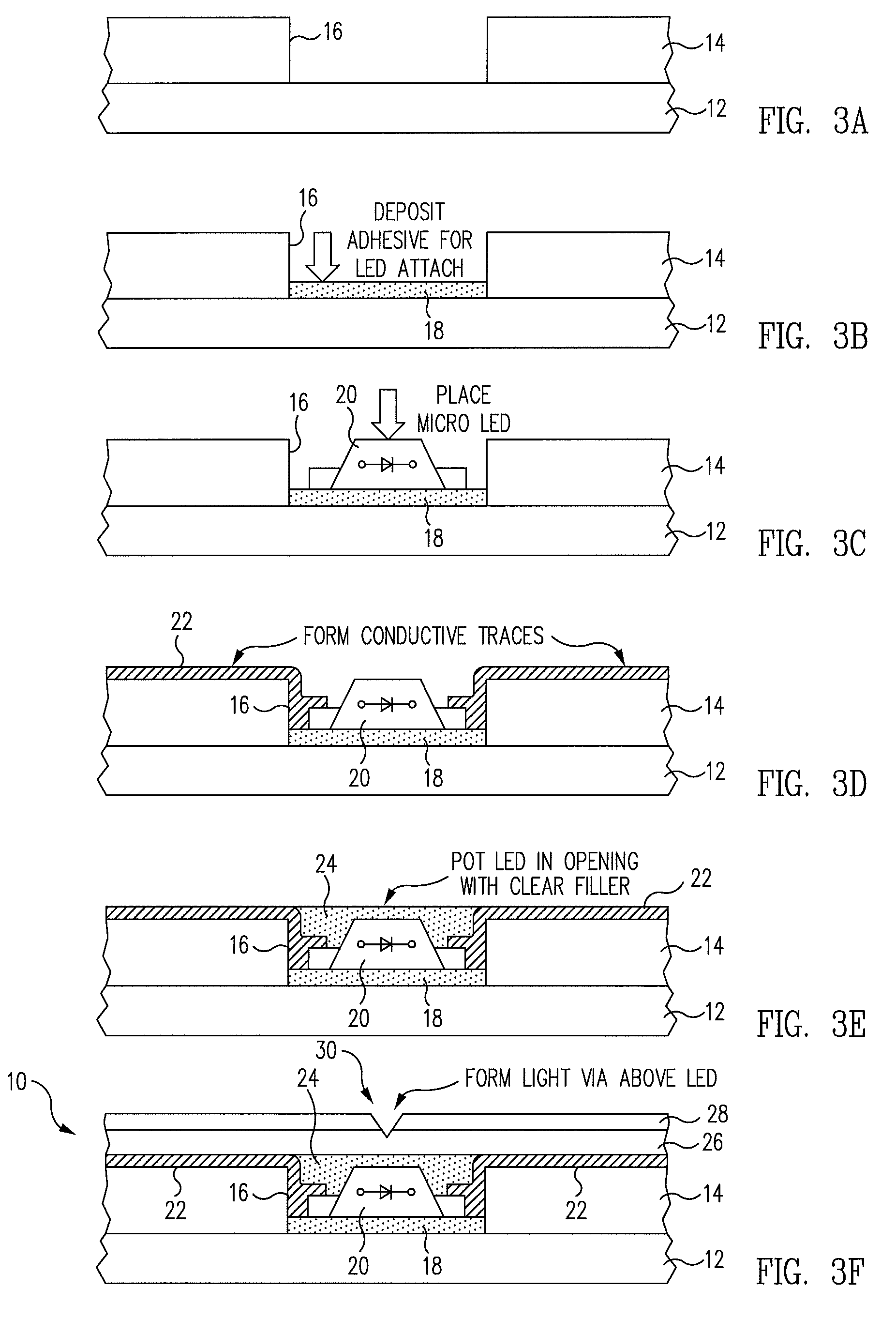

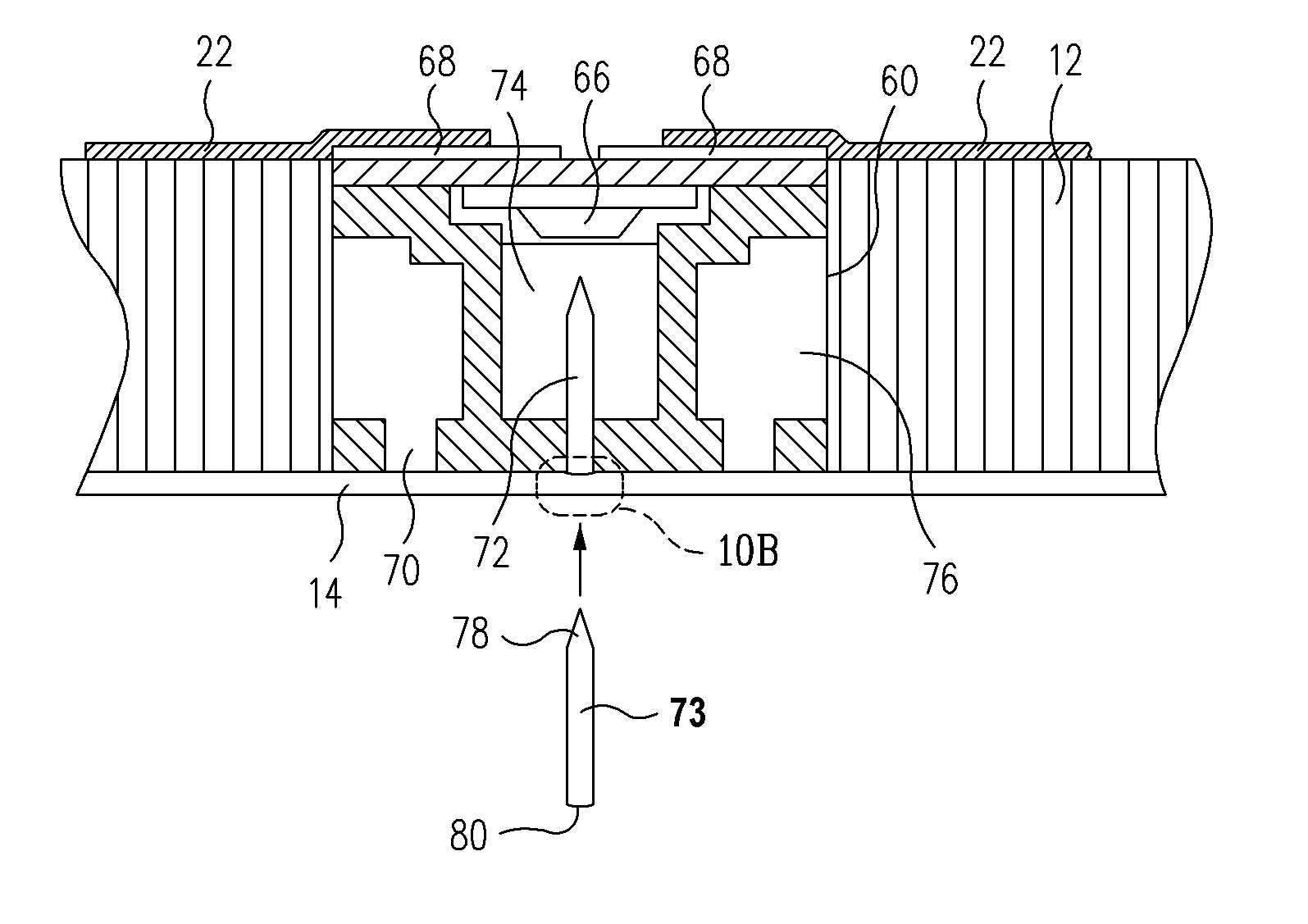

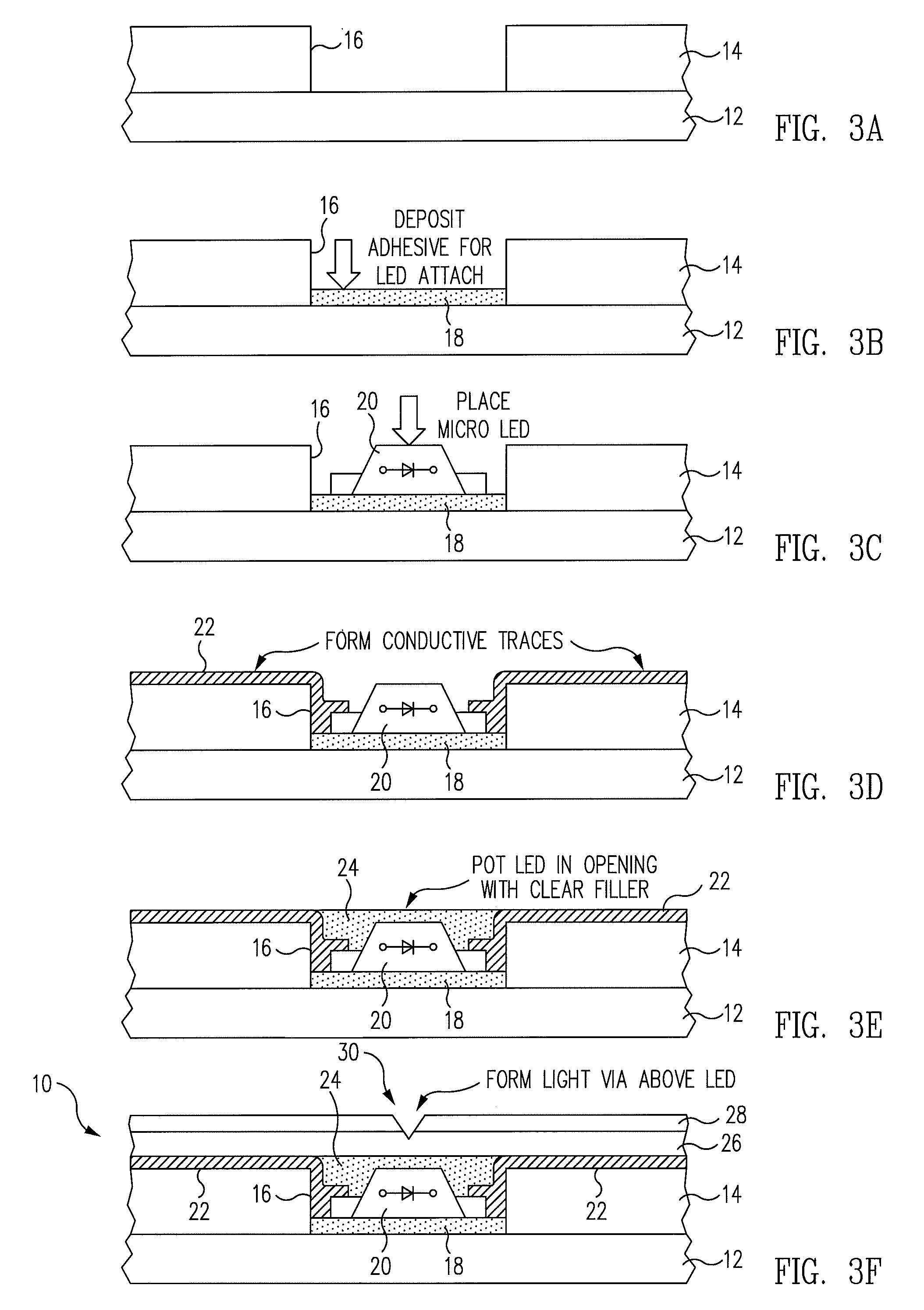

Starry sky lighting panels

ActiveUS20090059609A1Reducing fabricationReduce injuriesLighting support devicesPoint-like light sourceSkyEffect light

A lighting panel capable of producing a “Starry Sky” lighting effect and which is easily retrofitted into existing aircraft includes a first substrate, a plurality of microminiature light sources, such as LEDs, mounted on an upper surface of the first substrate, a plurality of electrically conductive traces written on the upper surface of the first substrate so as to make electrical interconnections with respective leads of the light sources, a clear filler material surrounding each light source and tapering down to the upper surface of the first substrate so as to planarize it, and a flexible decorative film laminated over the upper surface of the first substrate and light sources, the decorative film containing a plurality of apertures therethrough, each corresponding in location to a respective light source.

Owner:THE BOEING CO

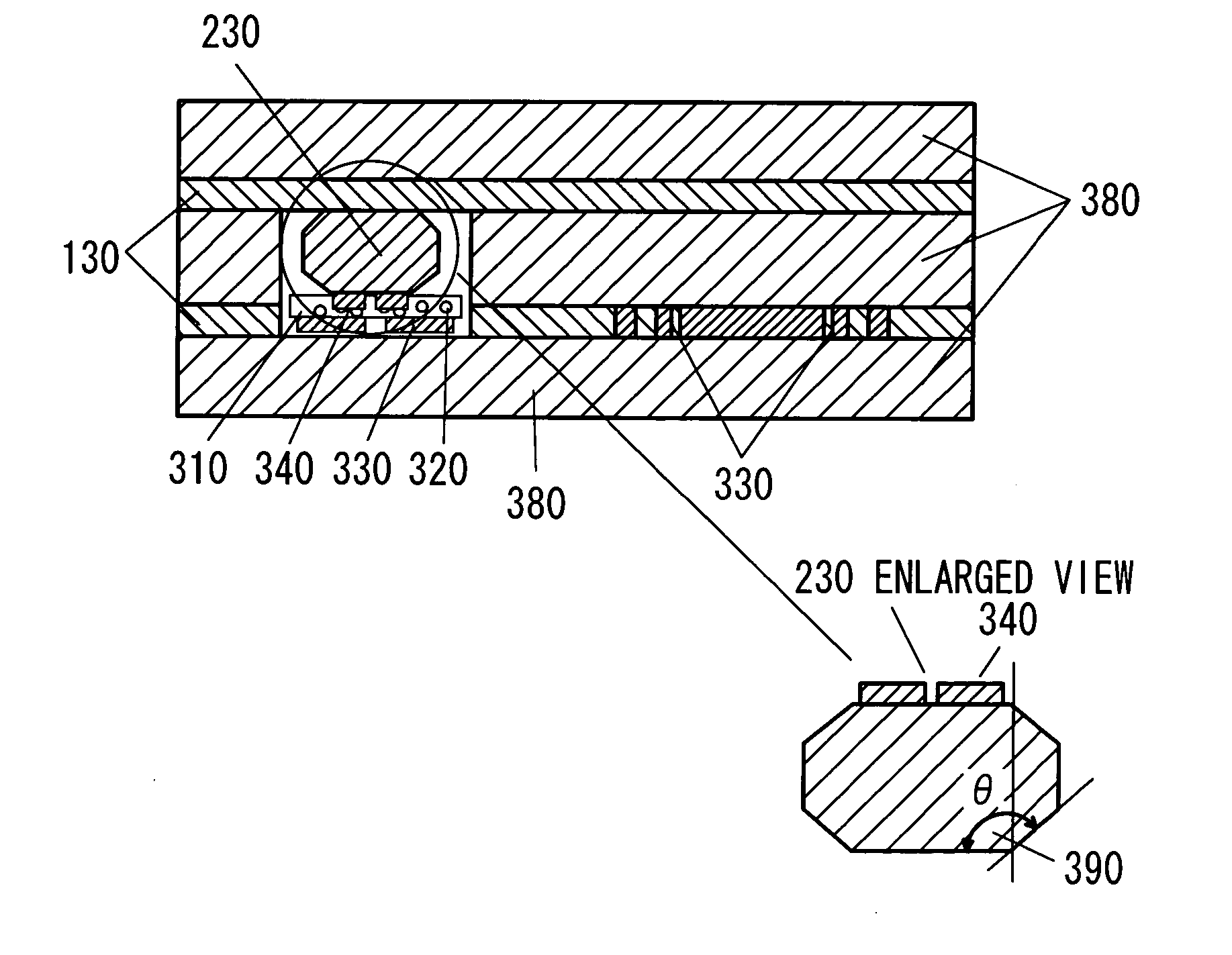

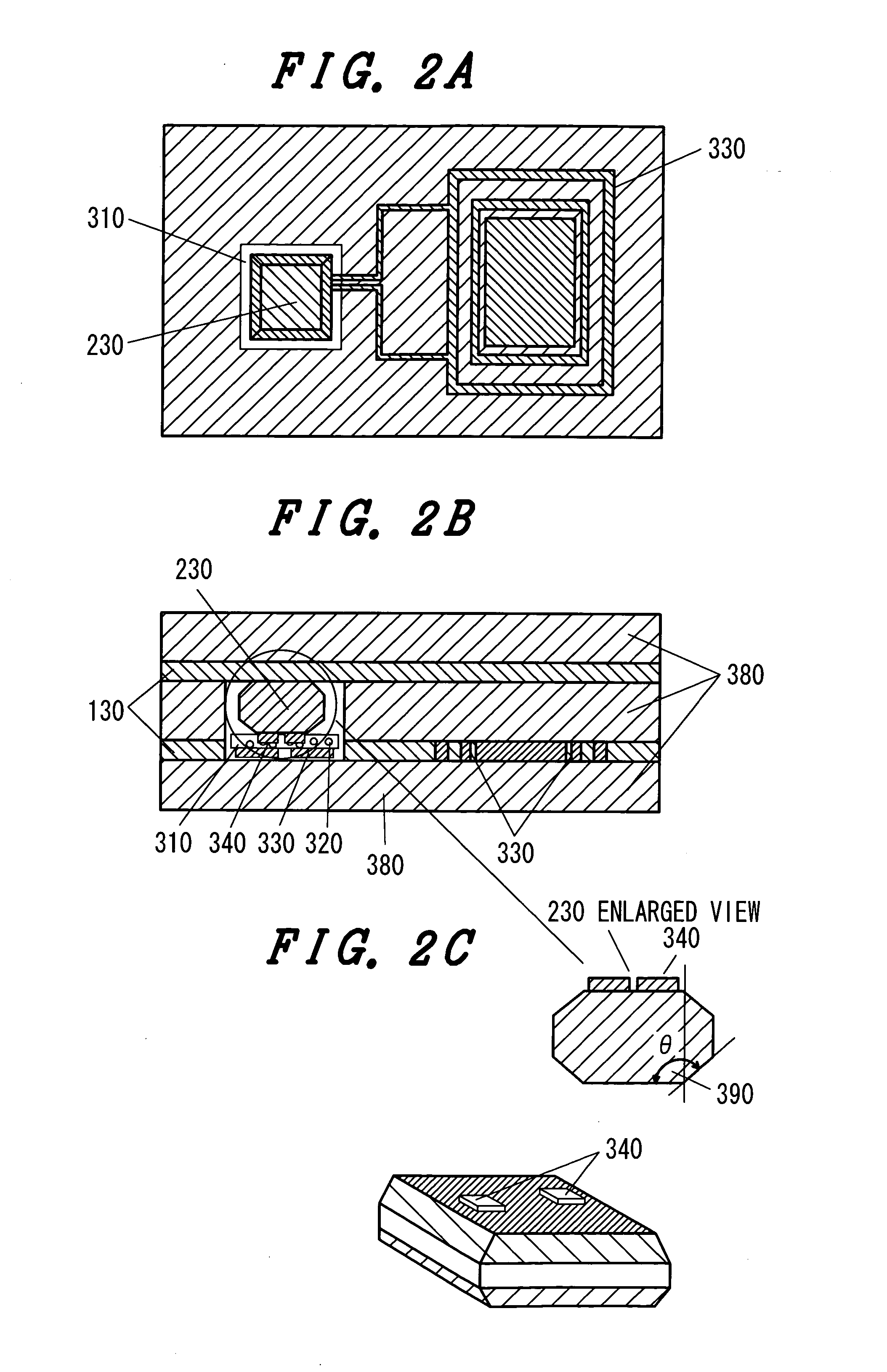

Semiconductor device and method for fabricating the same

InactiveUS20050062135A1High mechanical strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSlant angleDevice material

A semiconductor device and manufacturing method are provided in which chippings are reduced even if they occur during dicing. At least edge portions of a chip and another surface are chamfered to have a slant surface having a chamfering slant angle θ, respectively, where 90°<θ<180°. Preferably, the chamfering slant angle θ is 100° to 135° or, alternatively, all of the chamfering slant angles of four sides of the chip are about 135°.

Owner:HITACHI LTD

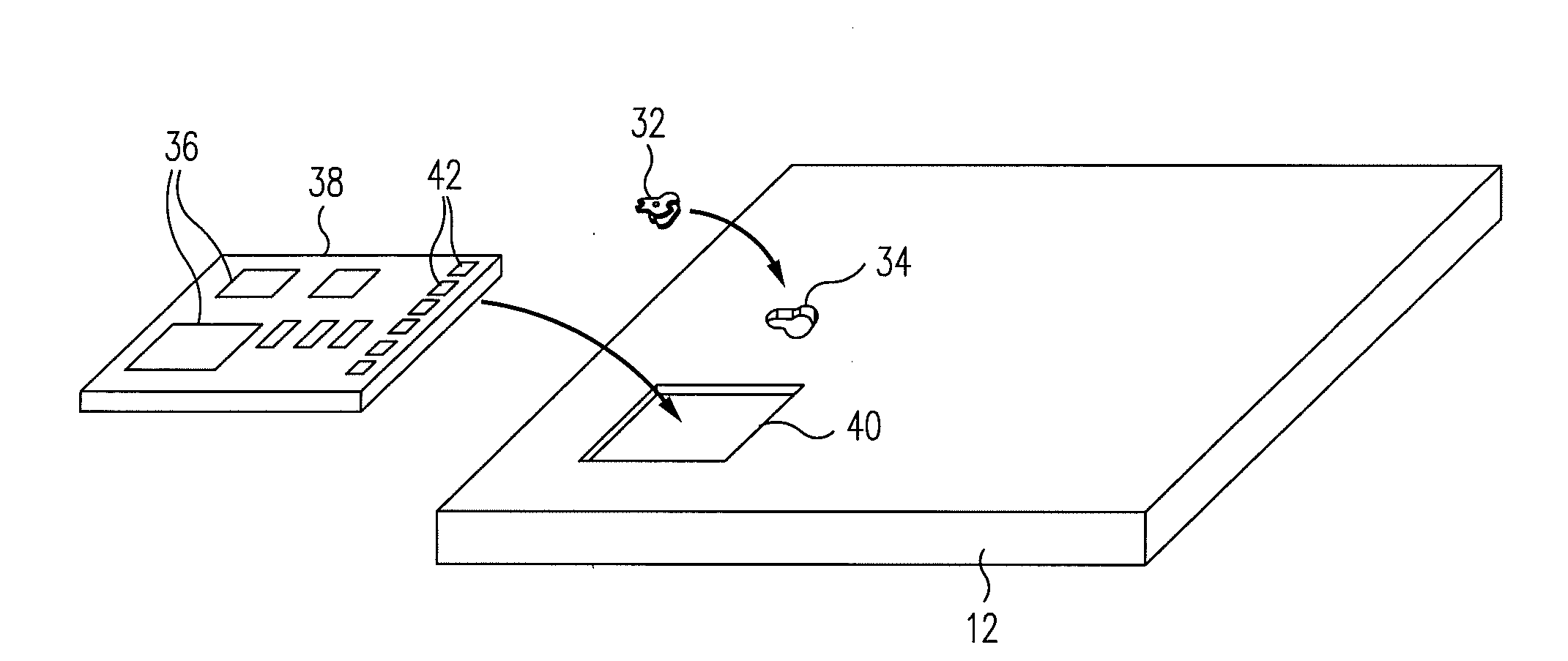

Starry Sky Lighting Panels

ActiveUS20090059610A1Reducing fabricationReduce injuriesGeneral lightingNon-electric lightingSkyEffect light

A lighting panel capable of producing a “Starry Sky” lighting effect and which is easily retrofitted into existing aircraft includes a structural panel, a plurality of inserts containing microminiature light sources, such as LEDs, mounted in openings in the panel, a plurality of electrically conductive traces written on the upper surface of the panel so as to make electrical interconnections with respective leads of the light sources, and a decorative film applied over a bottom surface of the panel and the light sources, the decorative film being translucent or transparent or containing a plurality of apertures therethrough, each corresponding in location to a respective one of the light sources.

Owner:THE BOEING CO

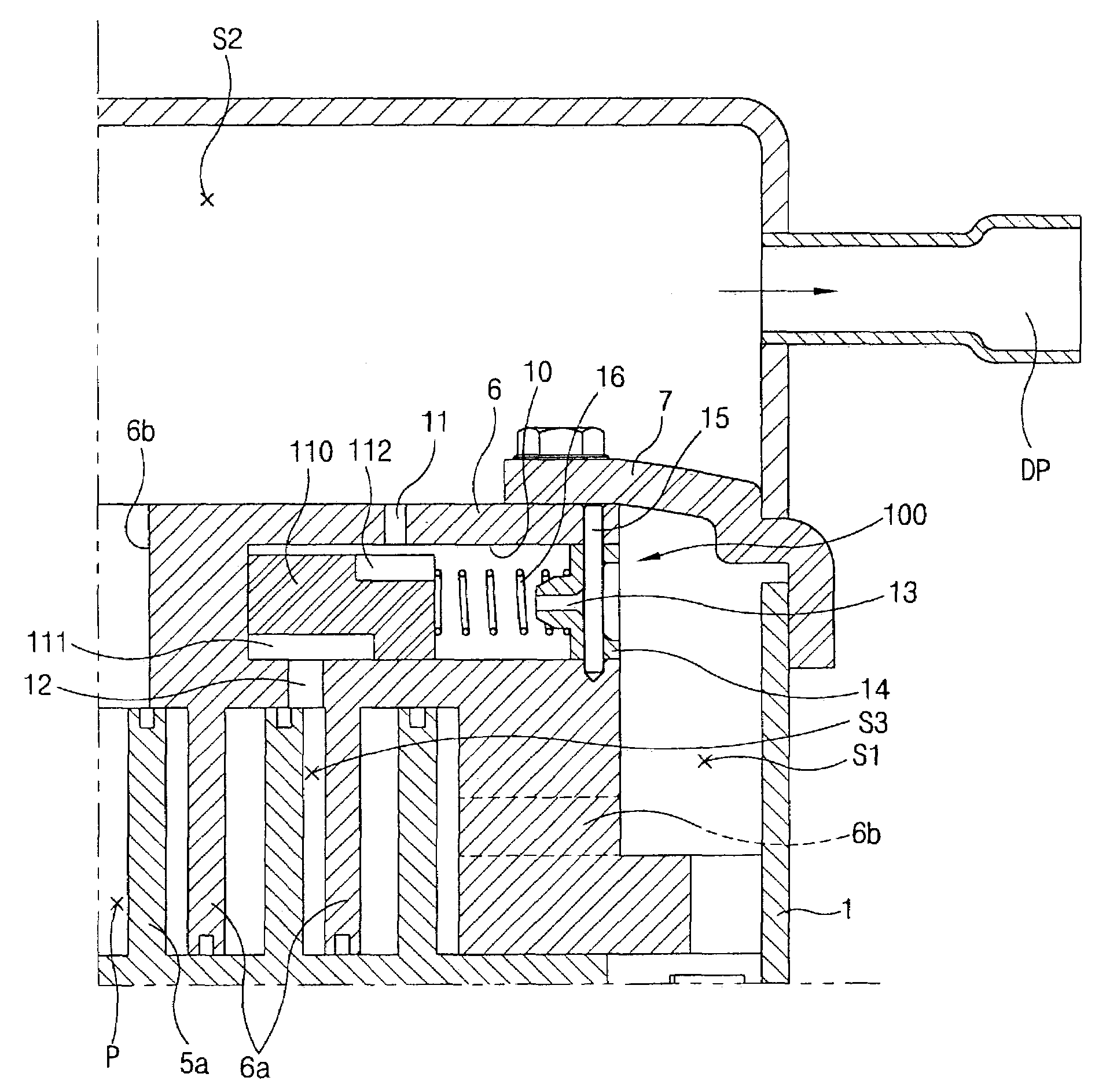

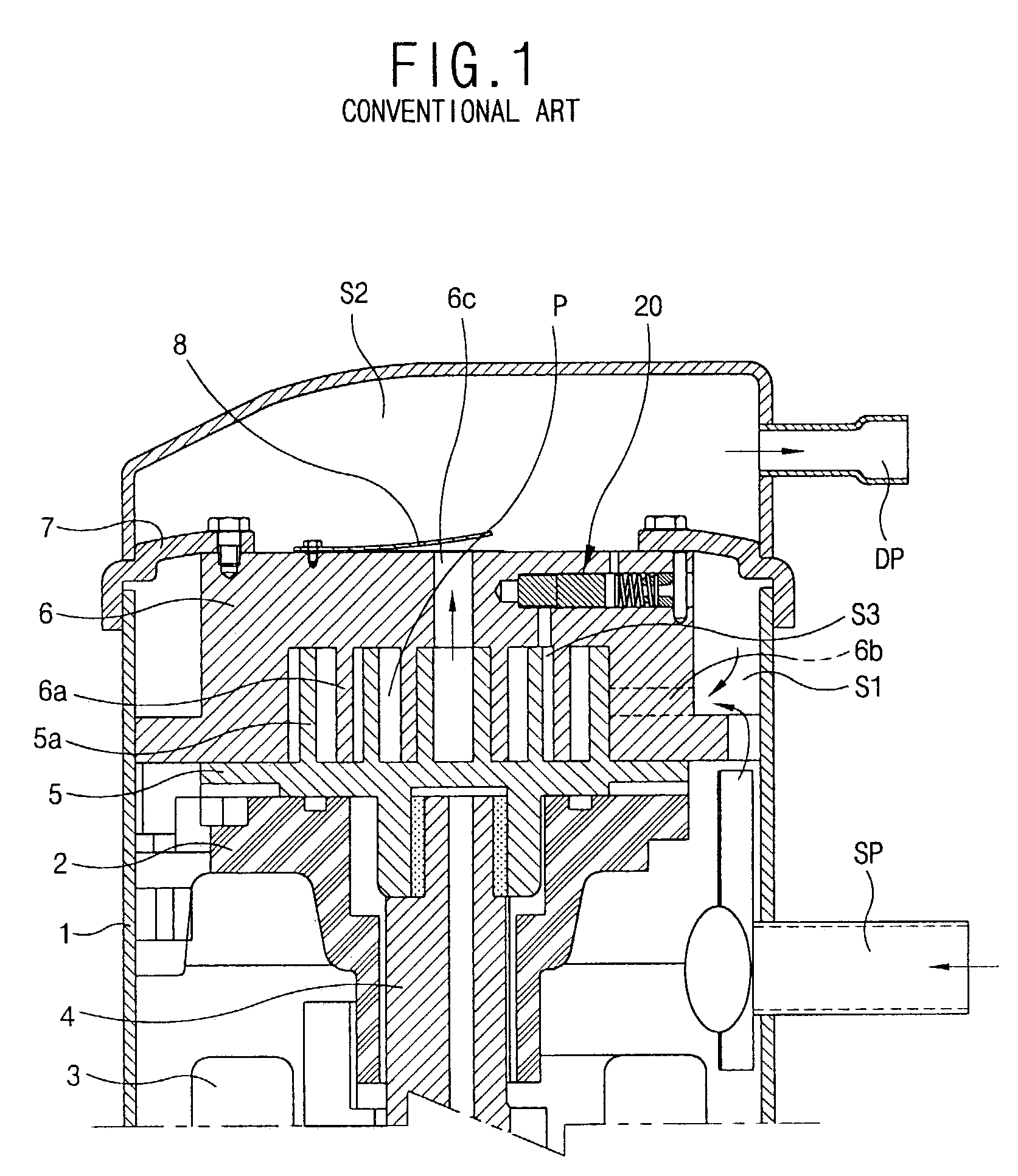

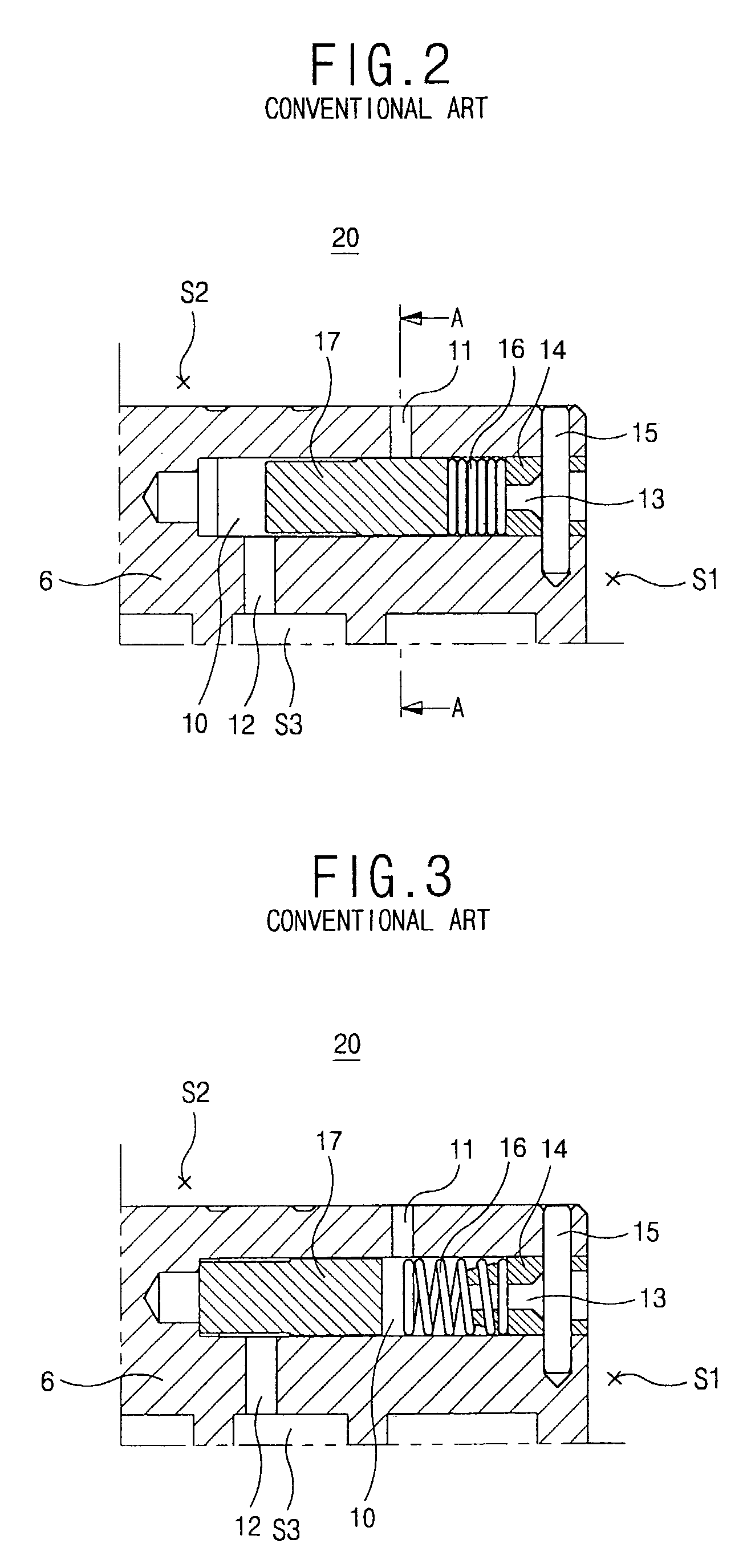

Vacuum preventing device of scroll compressor

InactiveUS7018180B2Improve compression efficiencyGap minimizationRotary/oscillating piston combinations for elastic fluidsEngine of arcuate-engagement typeEngineeringAtmospheric pressure

A vacuum preventing device of a scroll compressor includes: a chamber formed at one side of a fixed scroll and having a suction pressure hole, a middle pressure hole and a discharge pressure hole communicating with a suction pressure zone, a middle pressure zone and a discharge pressure zone, each formed at a certain portion of an inner circumferential surface; an open and shut member installed inside the chamber and selectively communicating the discharge pressure hole and the suction pressure hole by virtue of a gas pressure of the middle pressure zone and an elastic force of a spring; and a gas leakage preventing unit for preventing a gas leakage in a normal operation by reducing a clearance between an inner wall of the chamber positioned at the side of the discharge pressure hole and the open and shut member.

Owner:LG ELECTRONICS INC

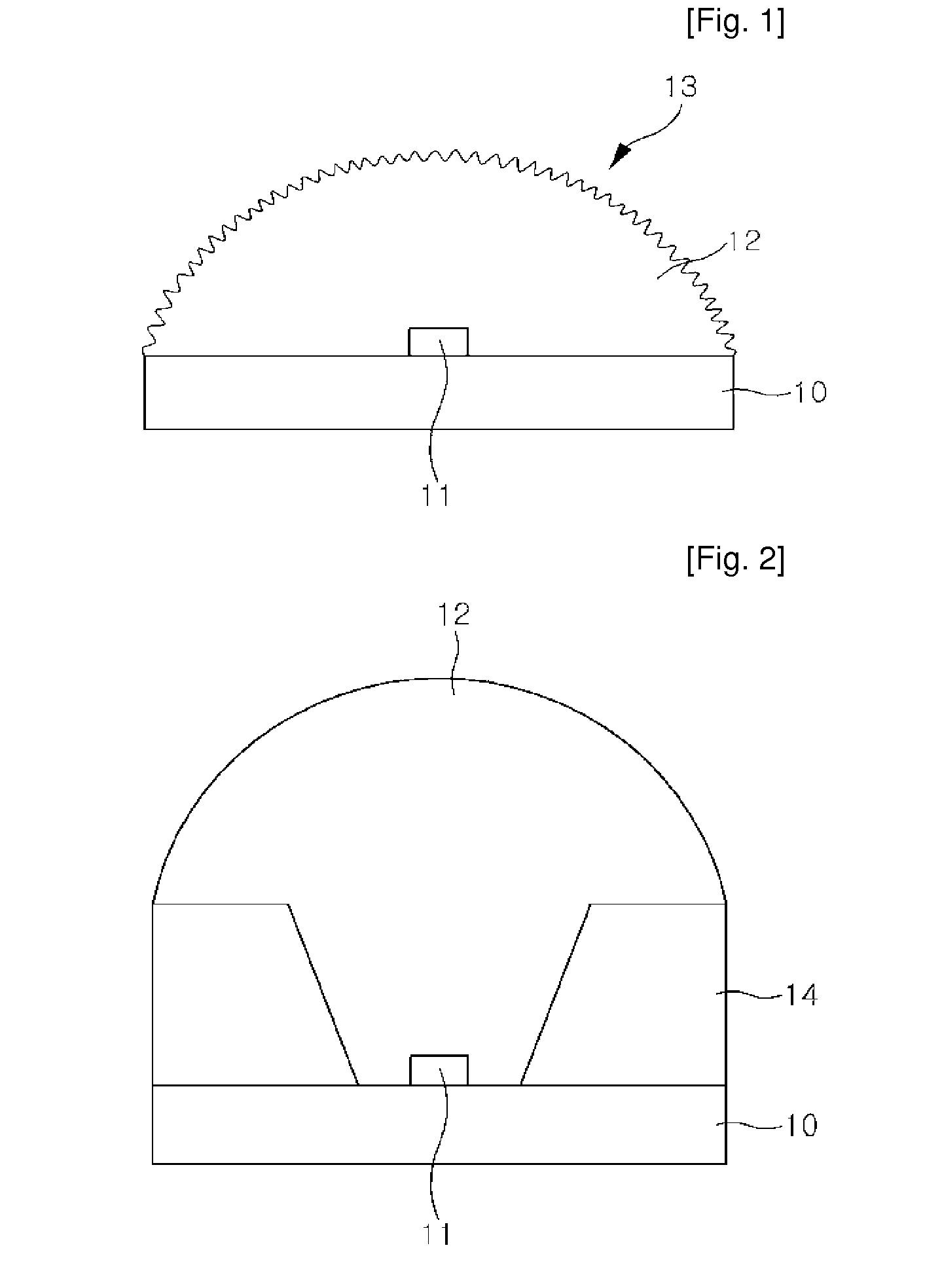

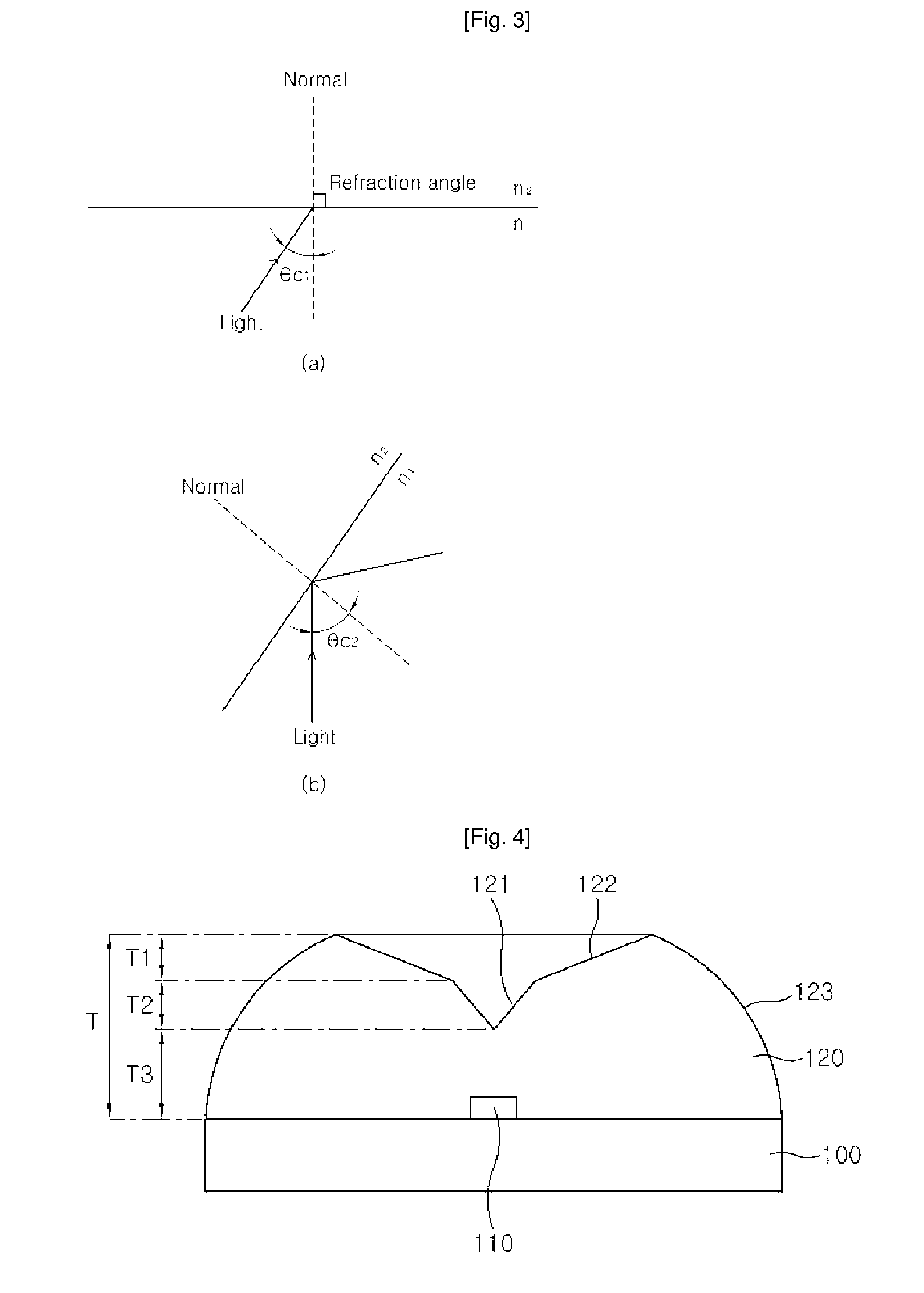

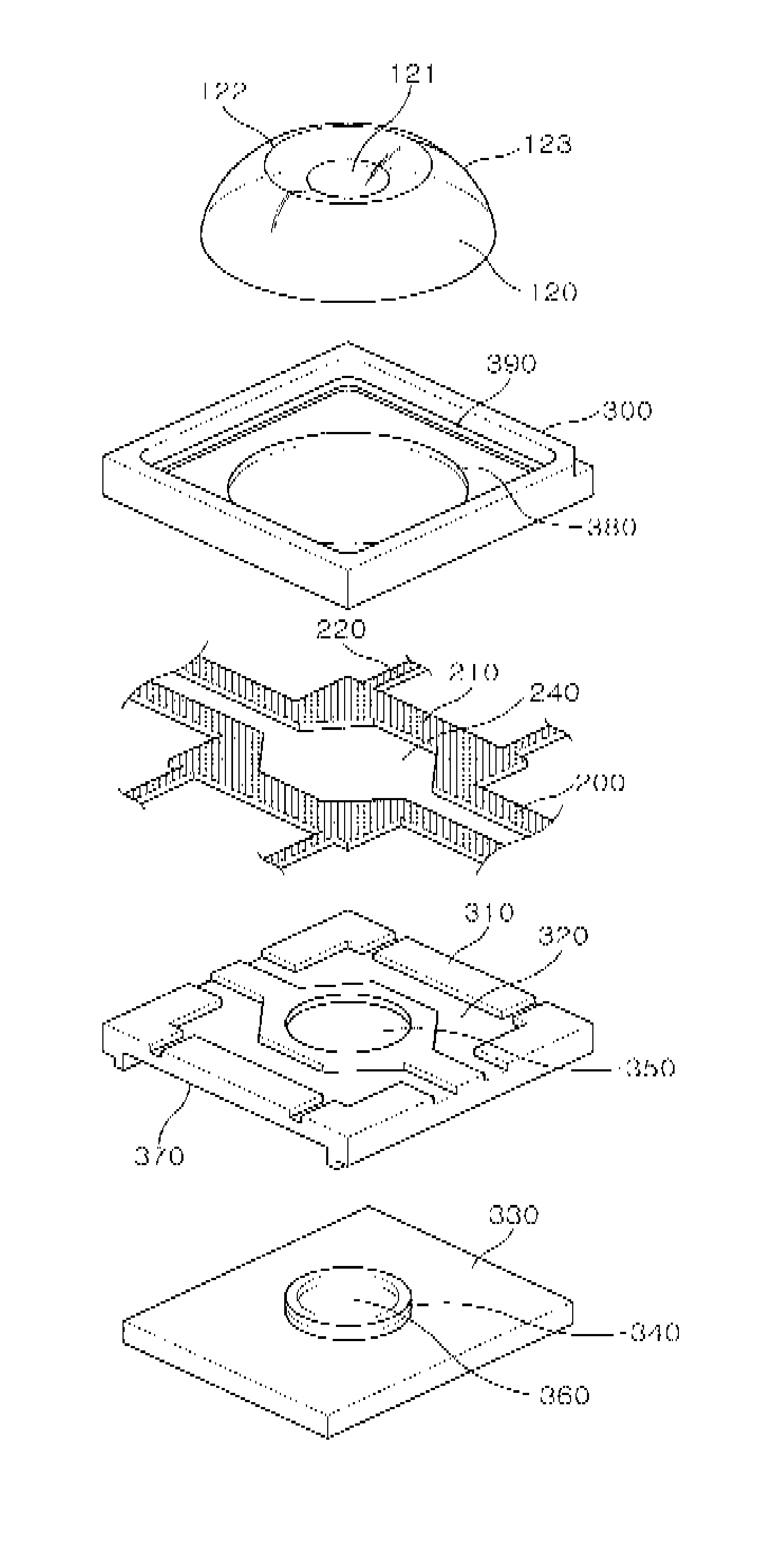

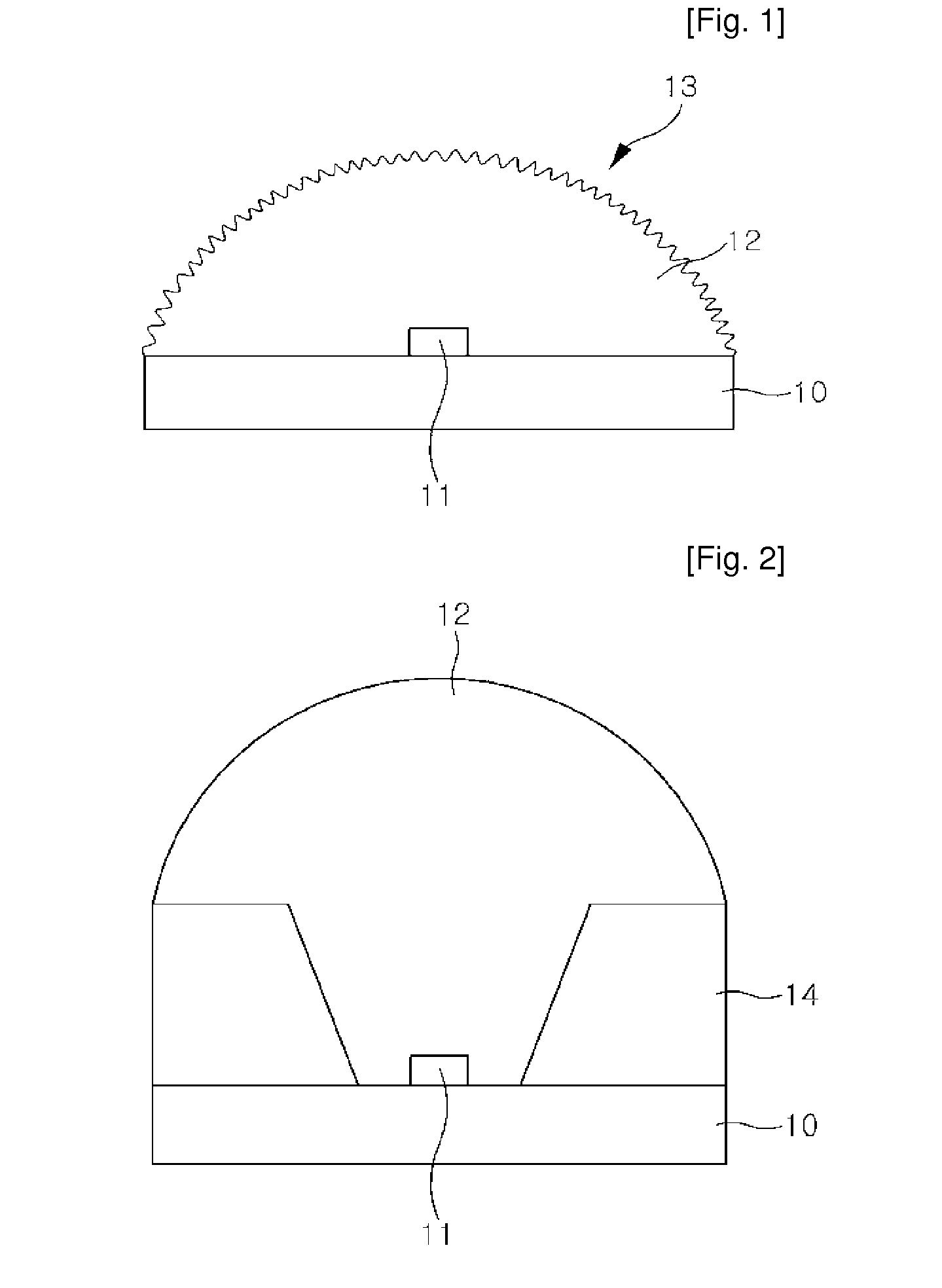

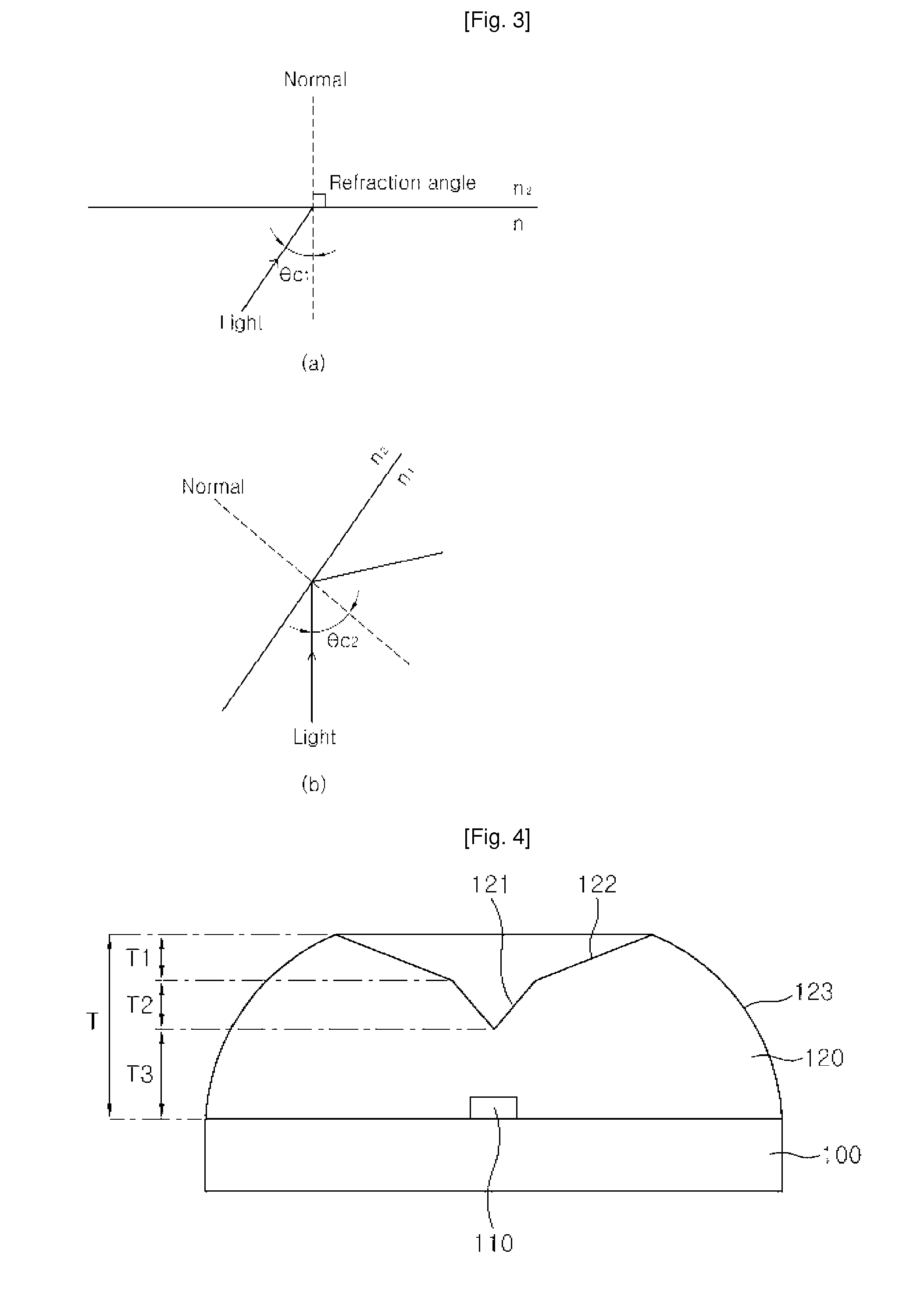

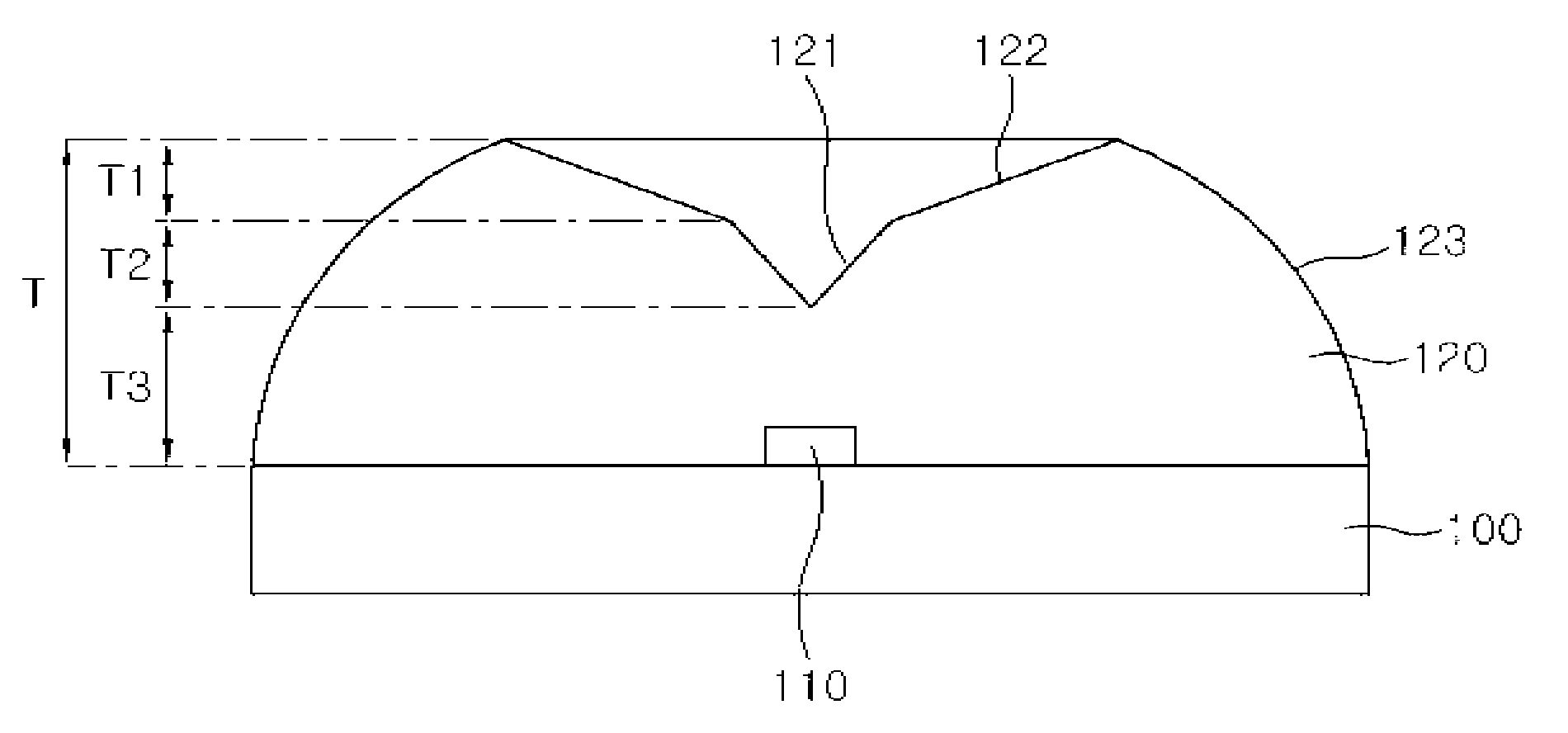

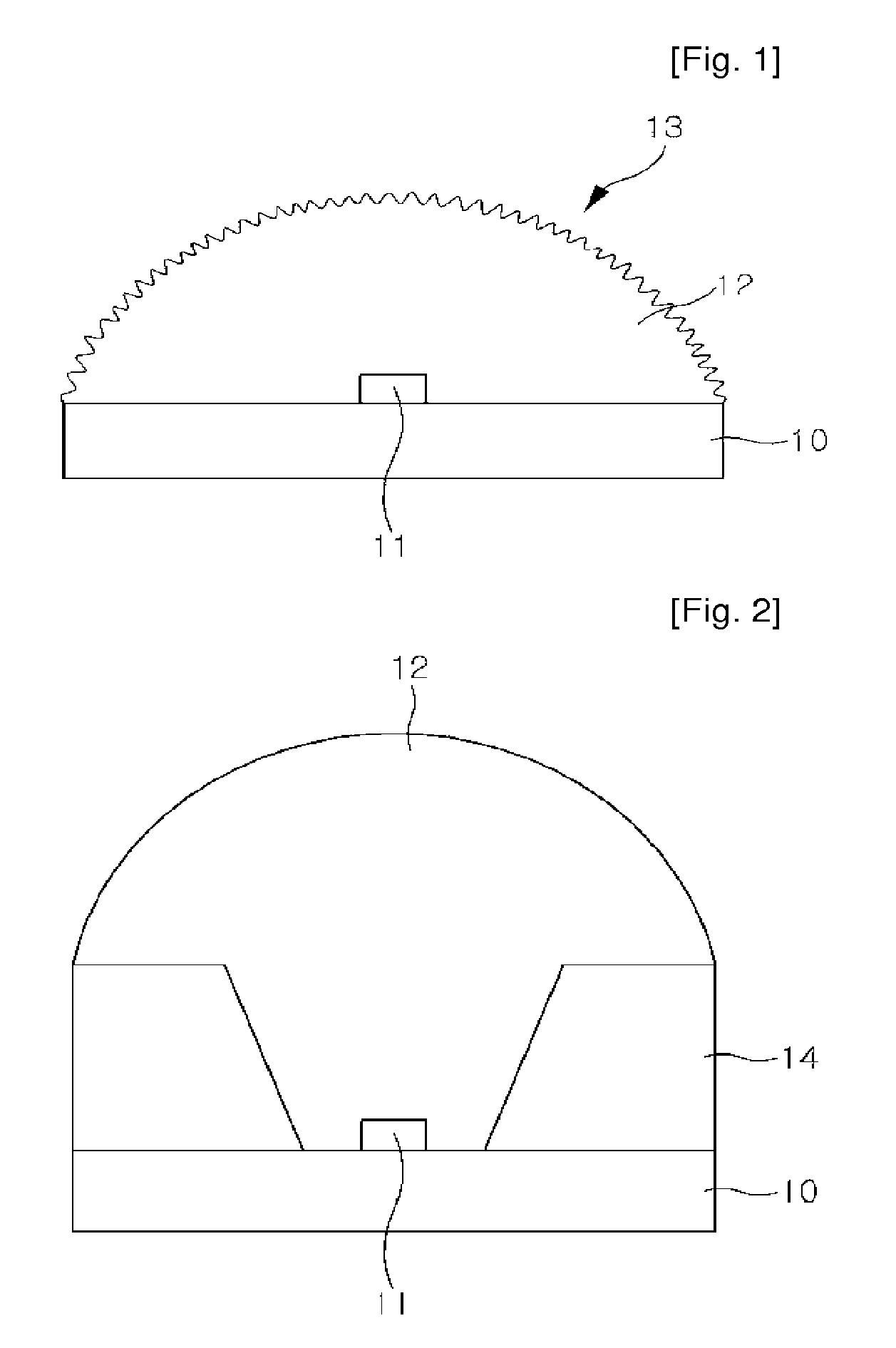

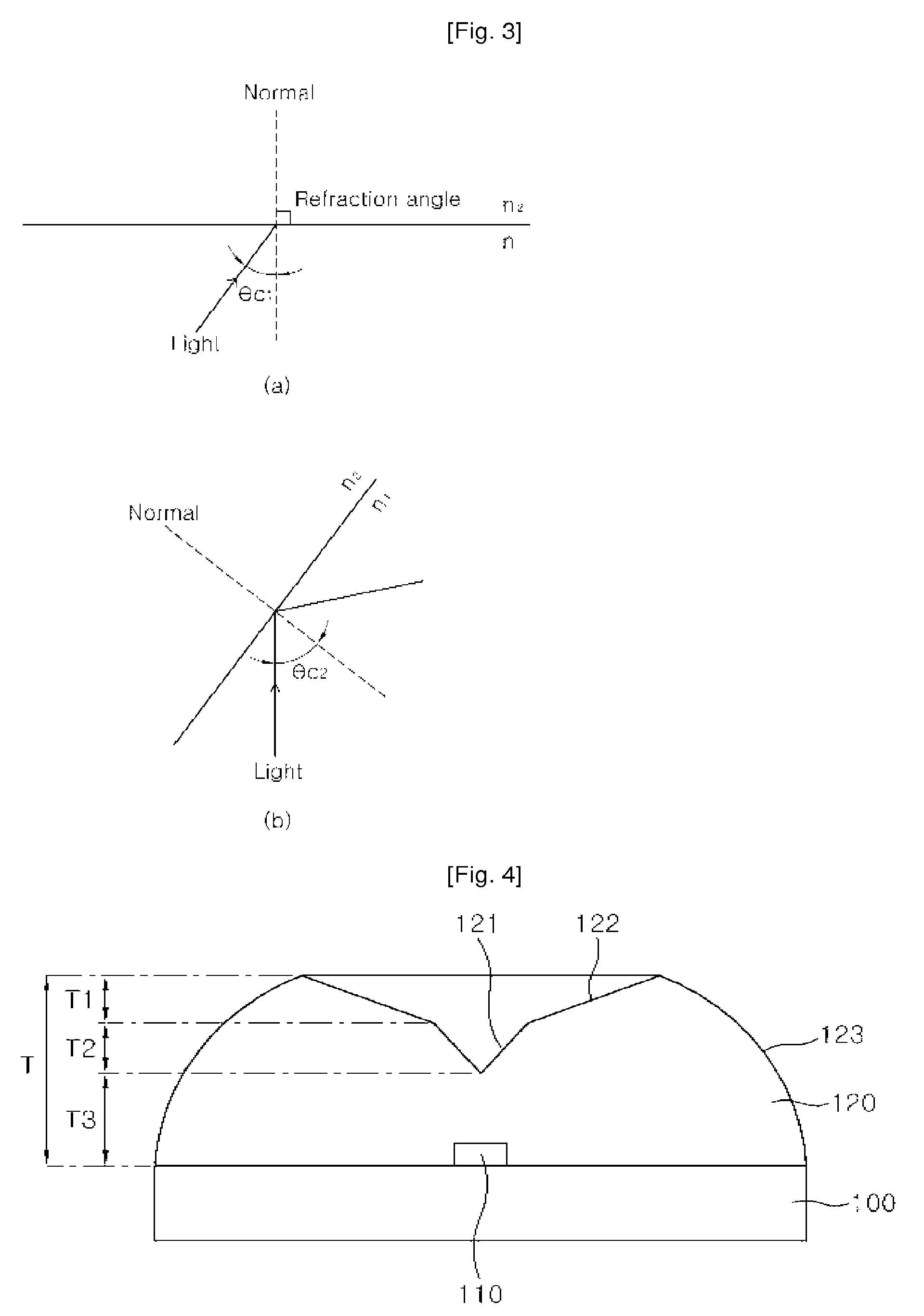

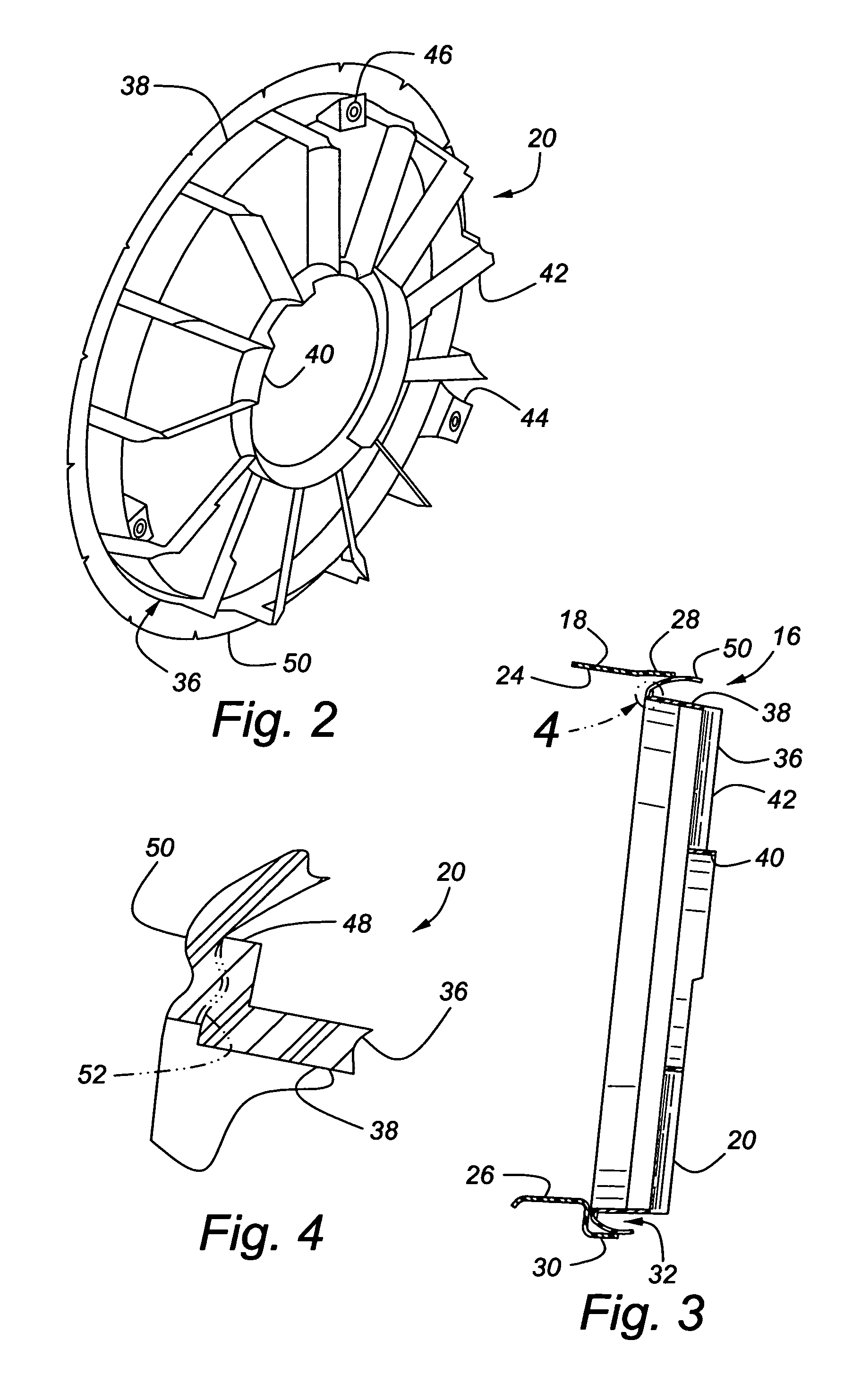

Side illumination lens and luminescent device using the same

ActiveUS7748873B2Easy to manufactureReducing fabricationSolid-state devicesTelescopesCamera lensTotal internal reflection

The present invention relates to a side illumination lens and a luminescent device using the same, and provides a body, a total reflection surface with a total reflection slope with respect to a central axis of the body, and a linear and / or curved refractive surface(s) formed to extend from a periphery of the total reflection surface; and a luminescent device including the lens. According to the present invention, a lens with total internal reflection surfaces with different slopes, and a linear and / or curved refractive surface(s) allows light emitted forward from a luminescent chip to be guided to a side of the lens. Further, a linear surface(s) formed in a direction perpendicular or parallel to a central axis of a lens and a curved surface are formed on an edge of the lens so that a process of fabricating the lens is facilitated, thereby reducing a defective rate and fabrication costs of the lens.

Owner:SINOTECHNIX LLC

Side Illumination Lens and Luminescent Device Using the Same

ActiveUS20070284993A1Easy to manufactureReducing fabricationDischarge tube luminescnet screensLamp detailsTotal internal reflectionLight emitting device

The present invention relates to a side illumination lens and a luminescent device using the same, and provides a body, a total reflection surface with a total reflection slope with respect to a central axis of the body, and a linear and / or curved refractive surface(s) formed to extend from a periphery of the total reflection surface; and a luminescent device including the lens. According to the present invention, a lens with total internal reflection surfaces with different slopes, and a linear and / or curved refractive surface(s) allows light emitted forward from a luminescent chip to be guided to a side of the lens. Further, a linear surface(s) formed in a direction perpendicular or parallel to a central axis of a lens and a curved surface are formed on an edge of the lens so that a process of fabricating the lens is facilitated, thereby reducing a defective rate and fabrication costs of the lens.

Owner:SINOTECHNIX LLC

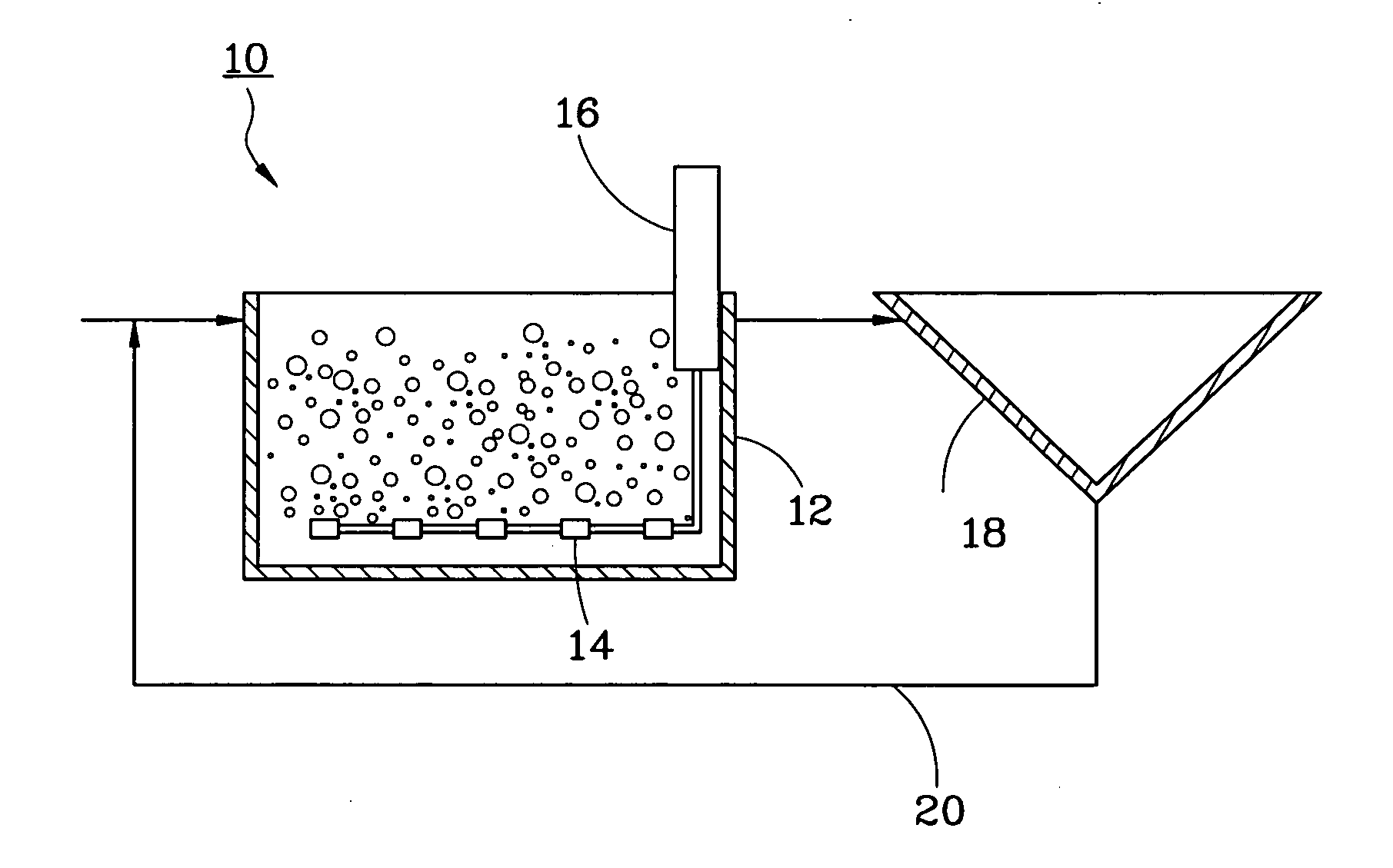

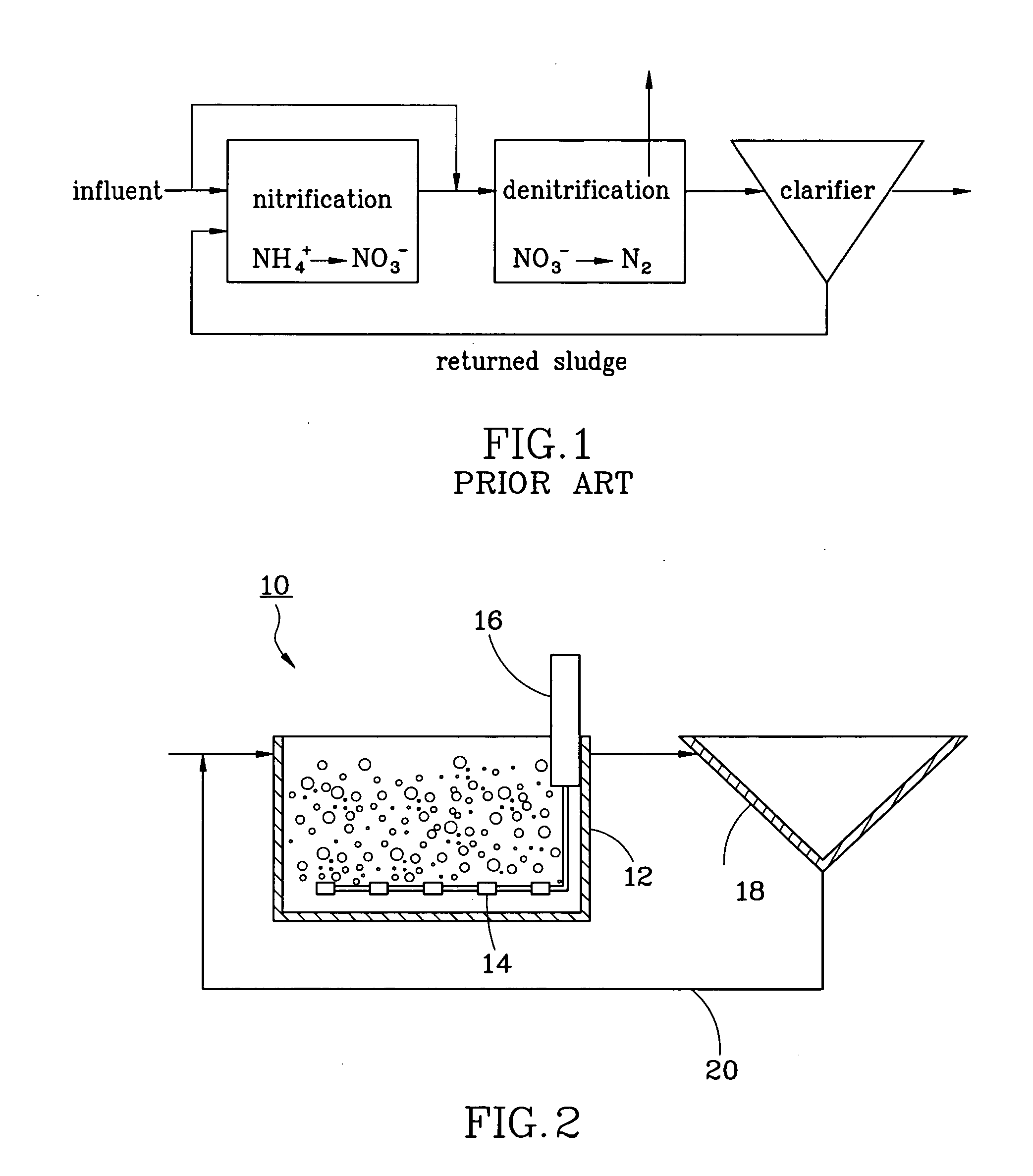

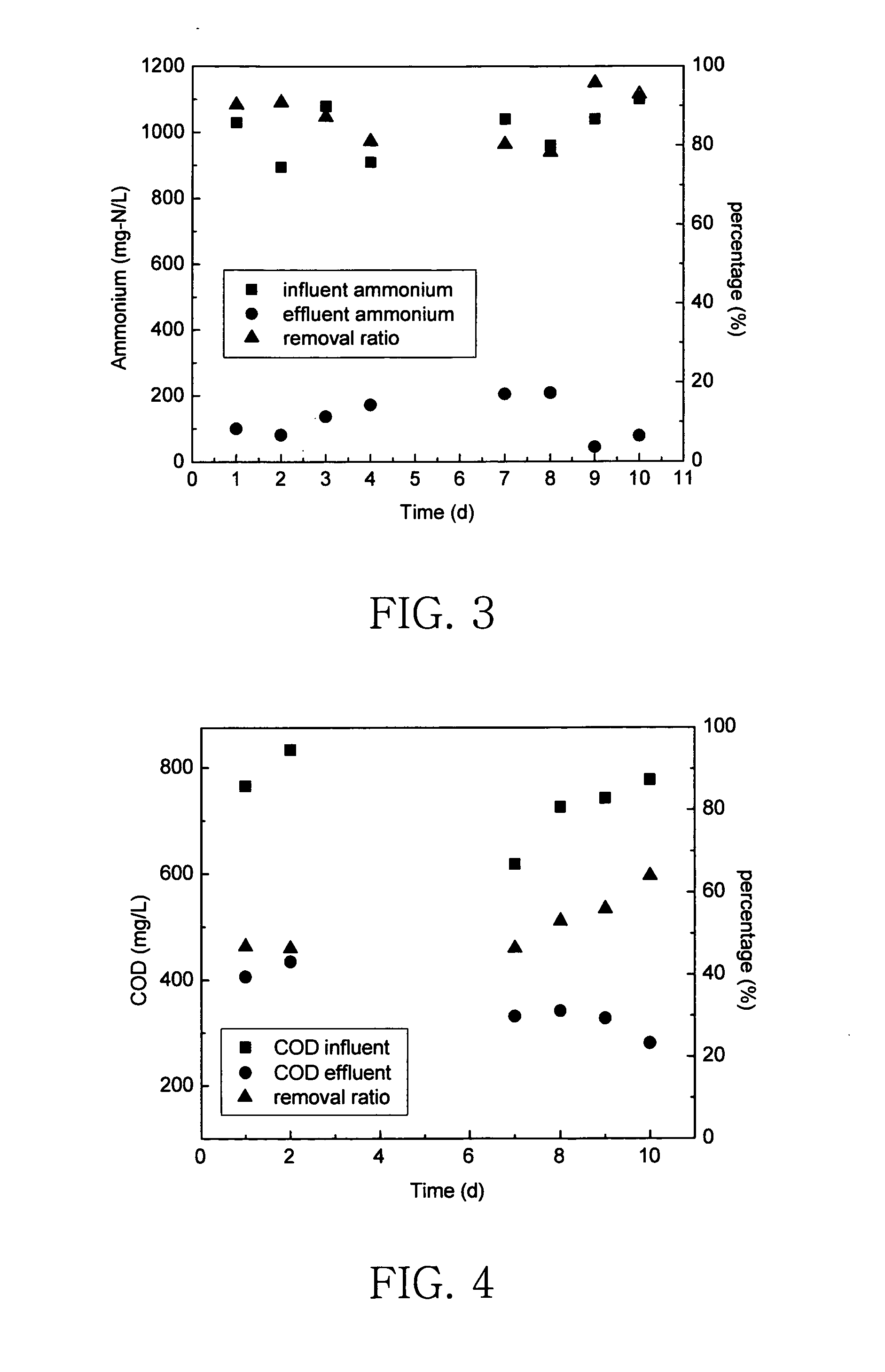

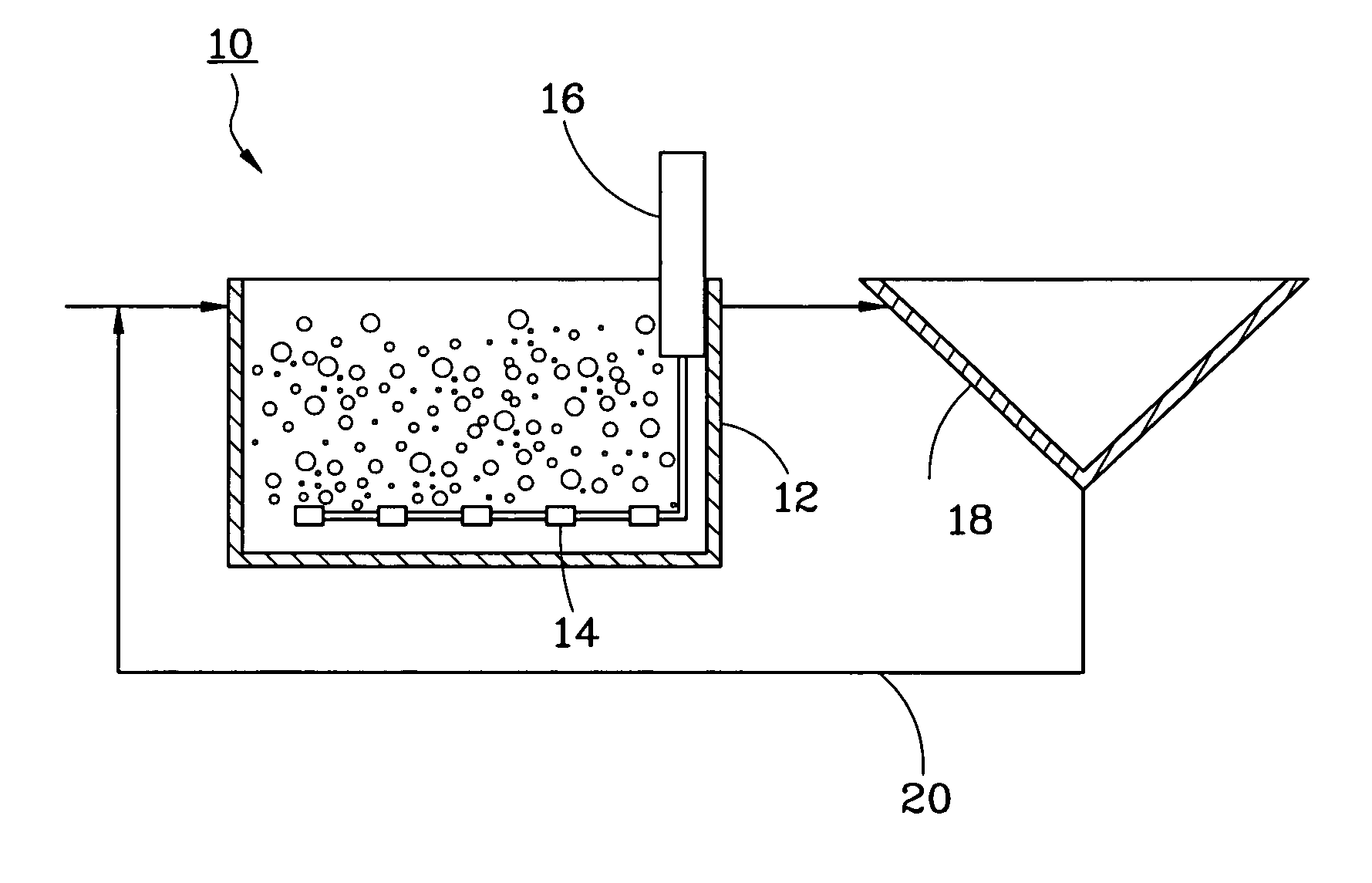

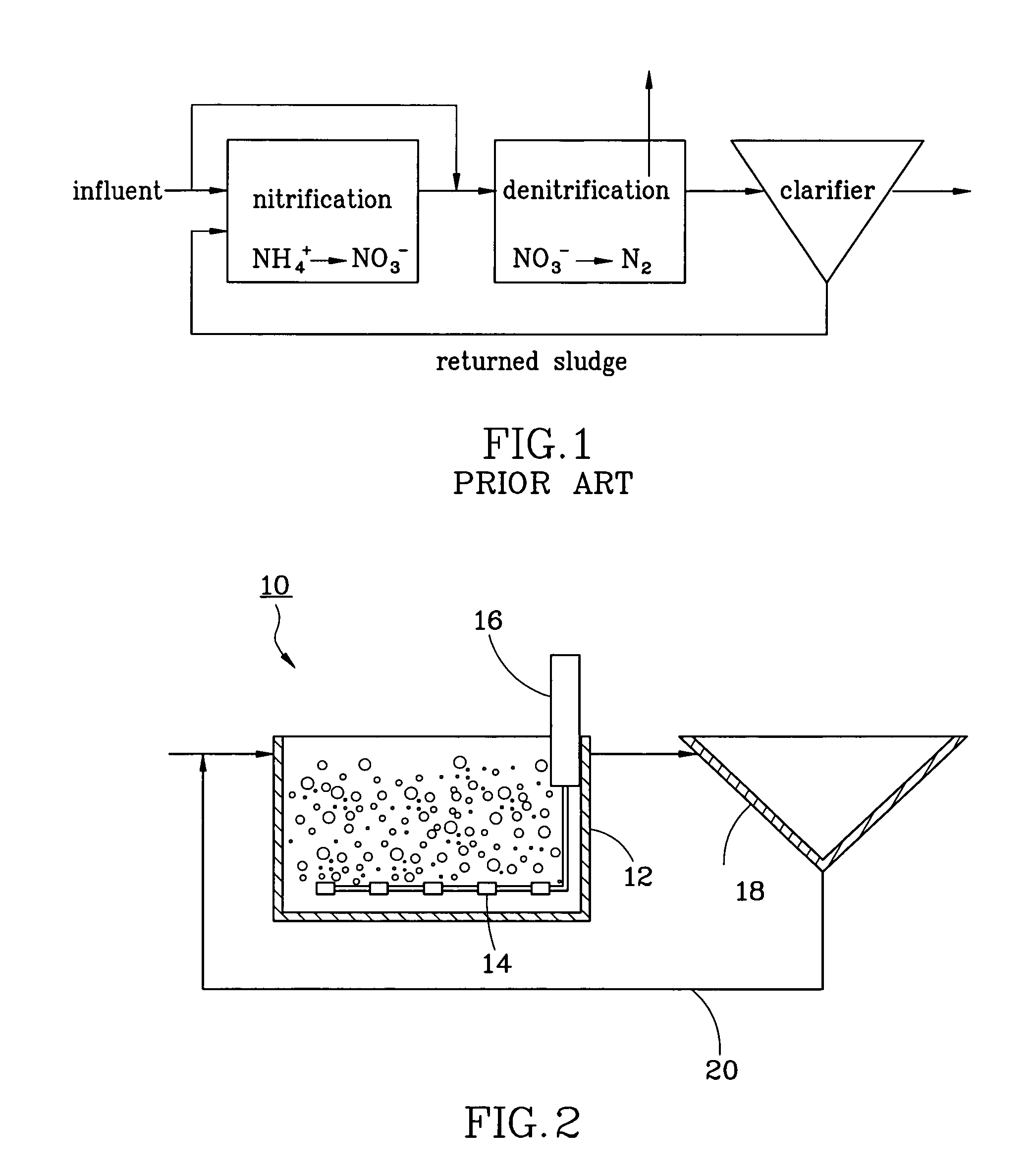

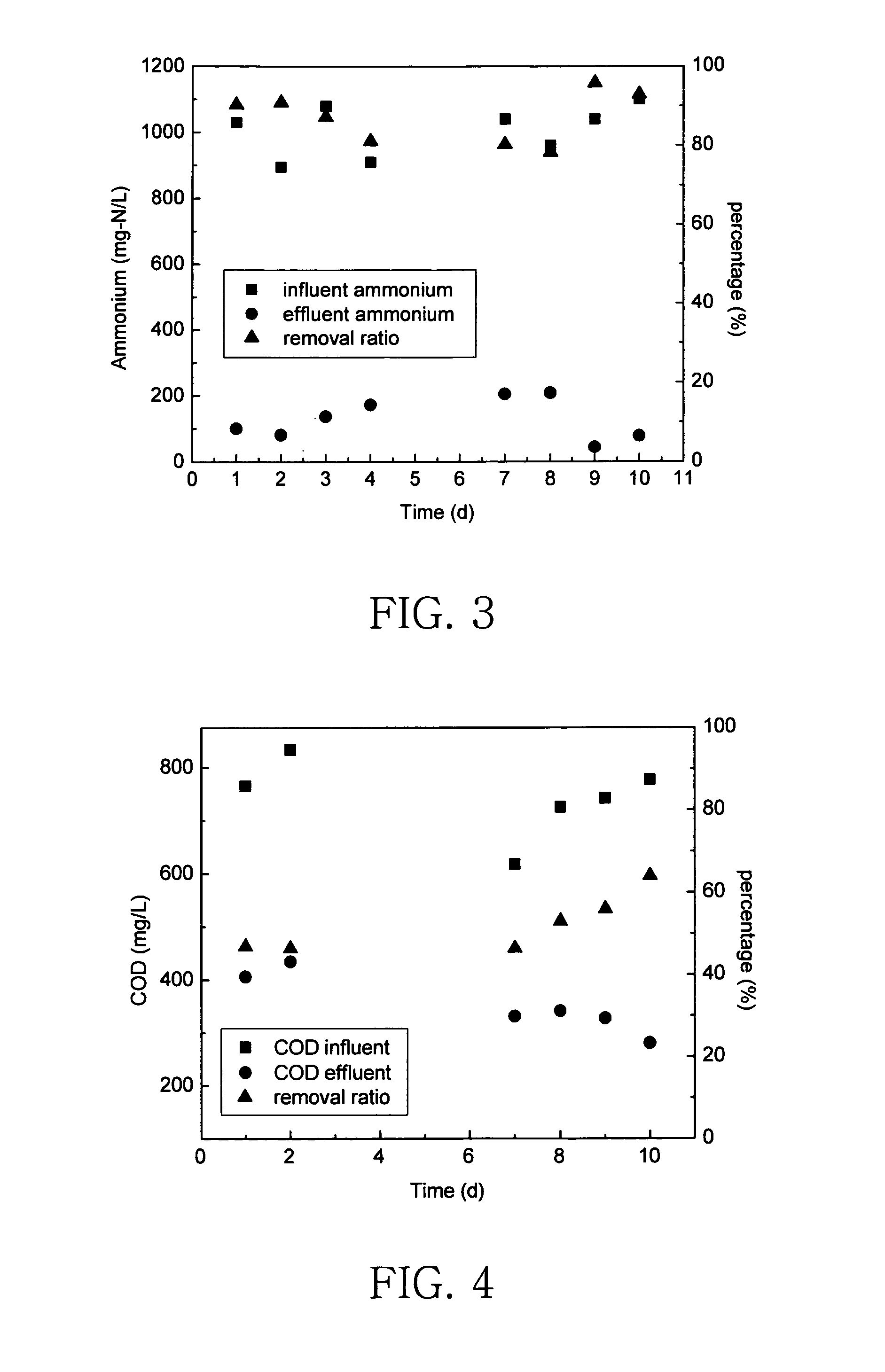

Process for treating nitrogenous wastewater with simultaneous autotrophic denitrification, hetertrophic denitrification and COD removal

ActiveUS20110084022A1Reducing fabricationReduce operating costsSeparation devicesTreatment with anaerobic digestion processesNitriteElectron donor

A process for treating nitrogenous wastewater contains an autotrophic denitrification reaction, a heterotrophic denitrification reaction and a COD removal reaction simultaneously and mixedly taking place in a single reactor. The nitrification reaction is caused by nitrifying bacteria, in which ammonium is oxidized into nitrite. The autotrophic denitrification reaction is caused by autotrophic denitrifying bacteria, in which ammonium used as electron donor and nitrite used as electron acceptor are converted into nitrogen gas and nitrate. The heterotrophic denitrification reaction is caused by heterotrophic denitrifying bacteria, in which nitrate and COD are consumed. It is not necessary to build two separate reactors for aerobic nitrification and anaerobic denitrification, thereby effectively reducing the fabrication and operation cost.

Owner:LEADERMAN & ASSOC +1

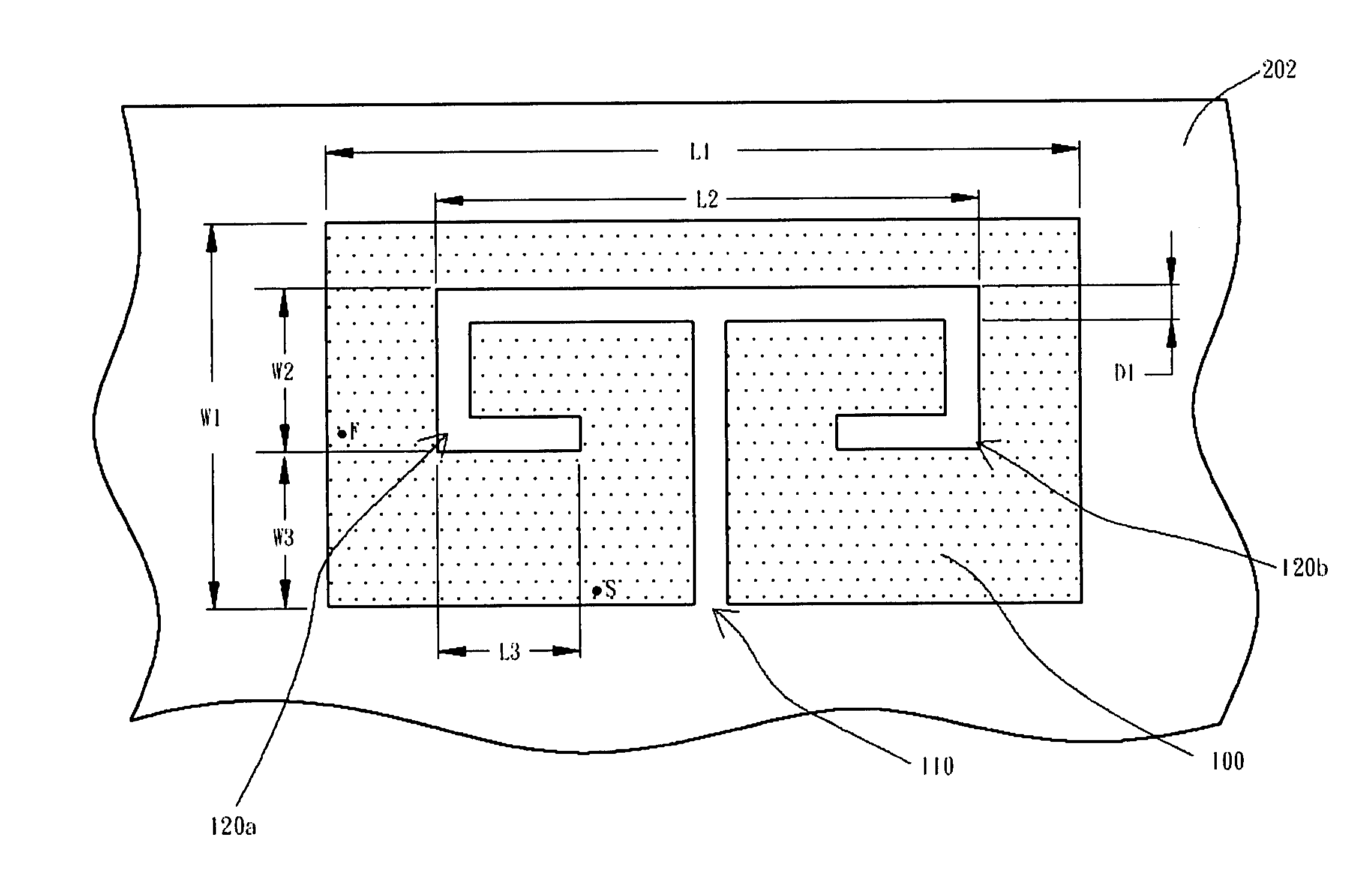

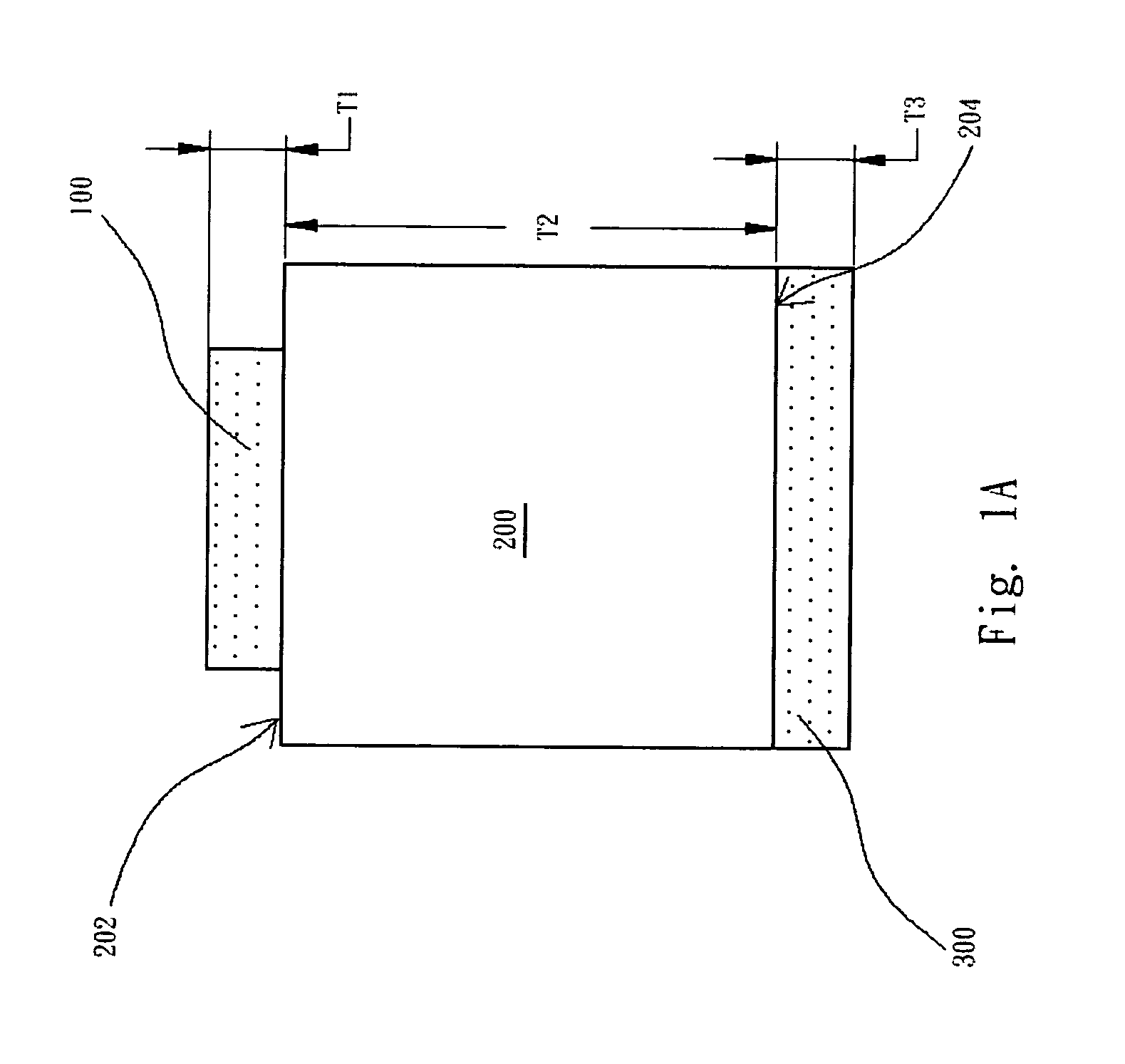

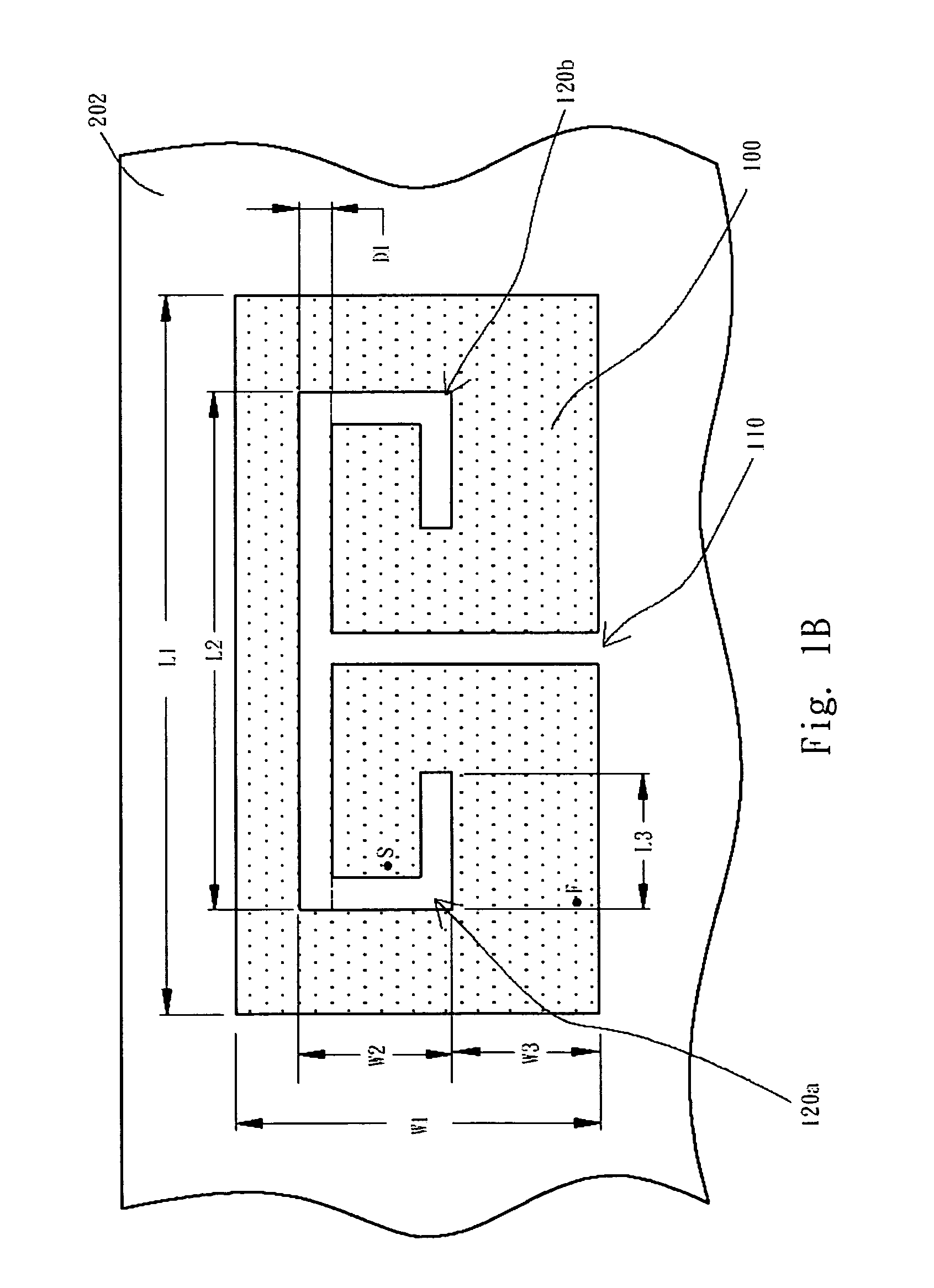

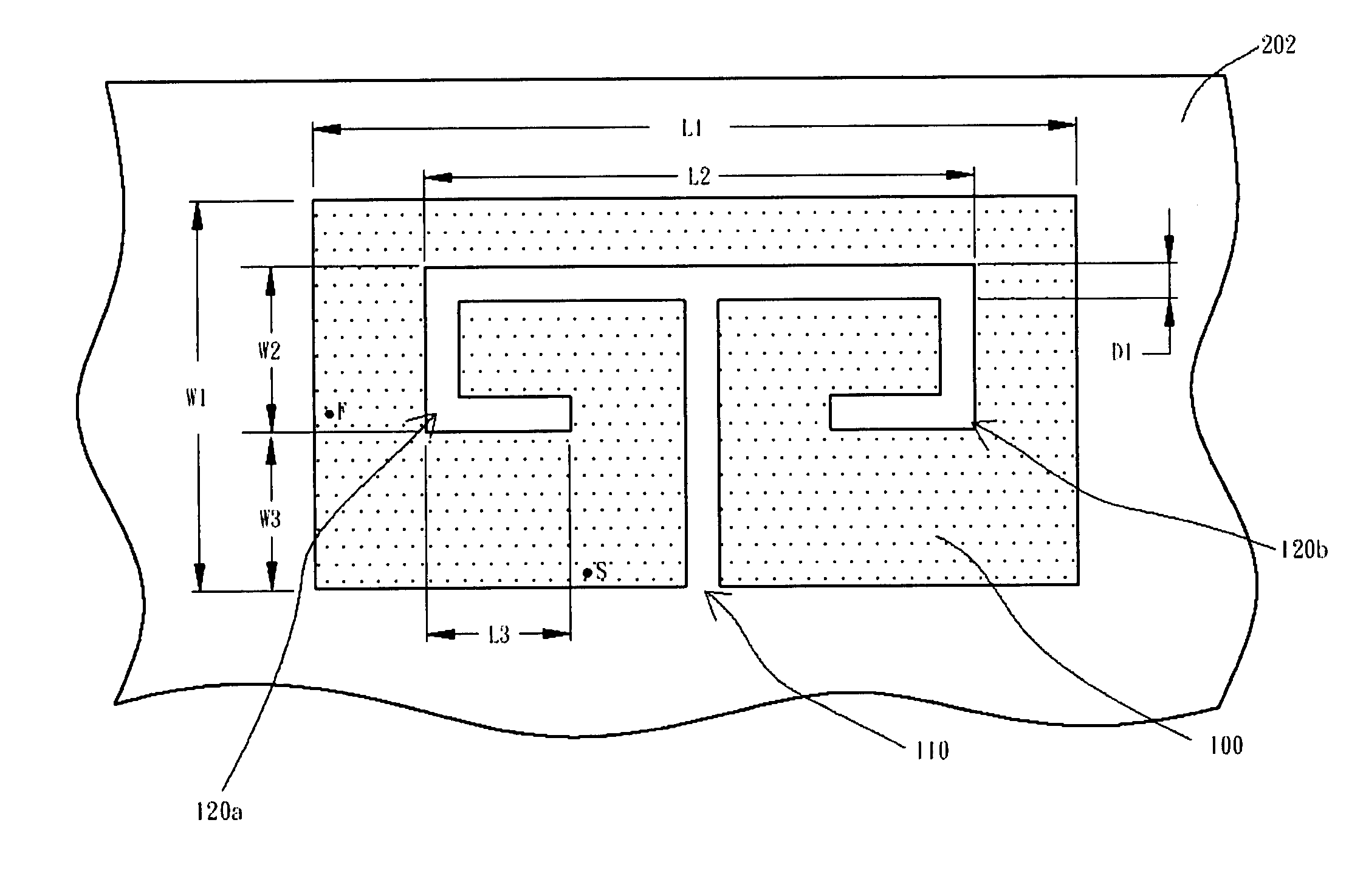

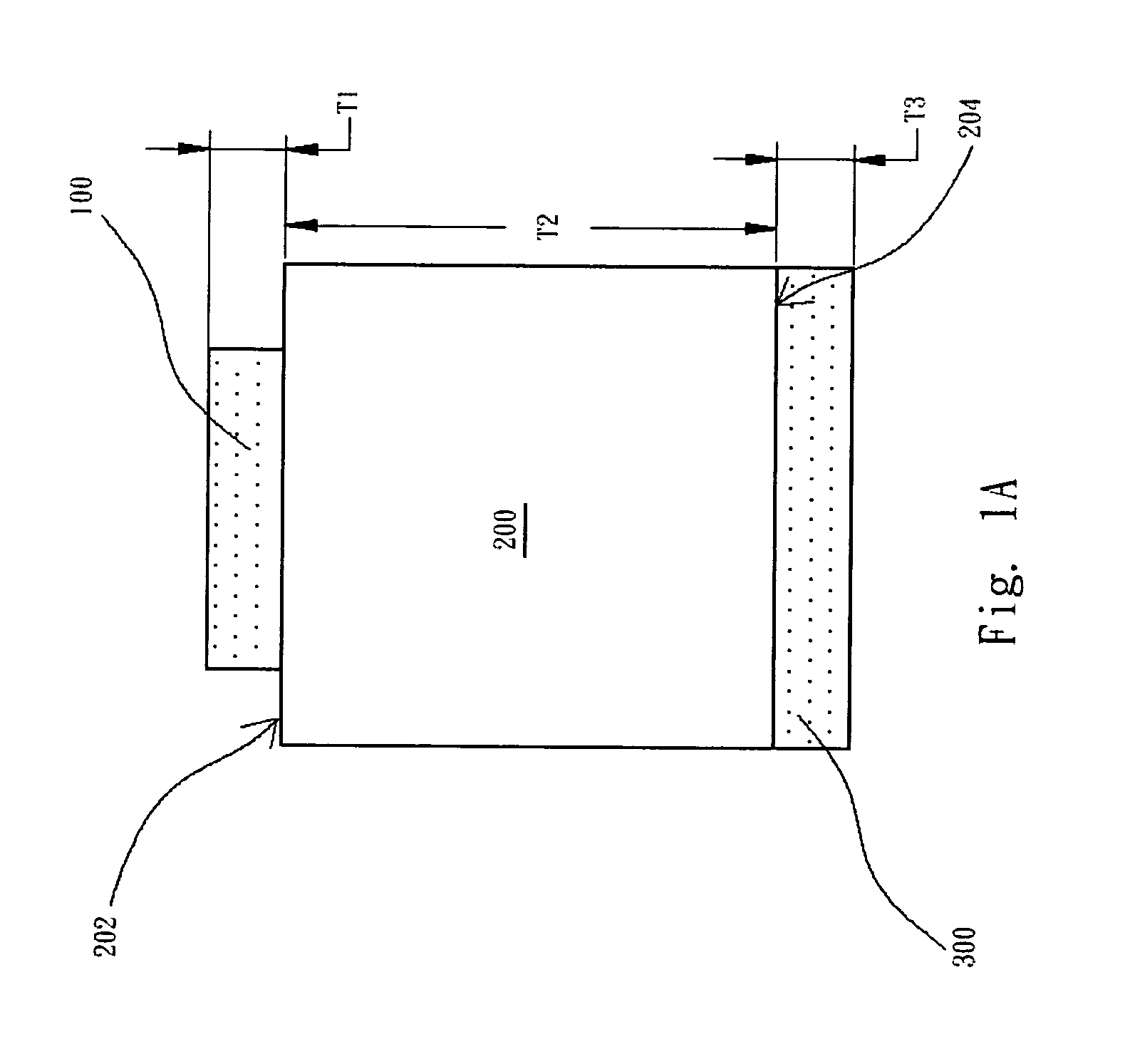

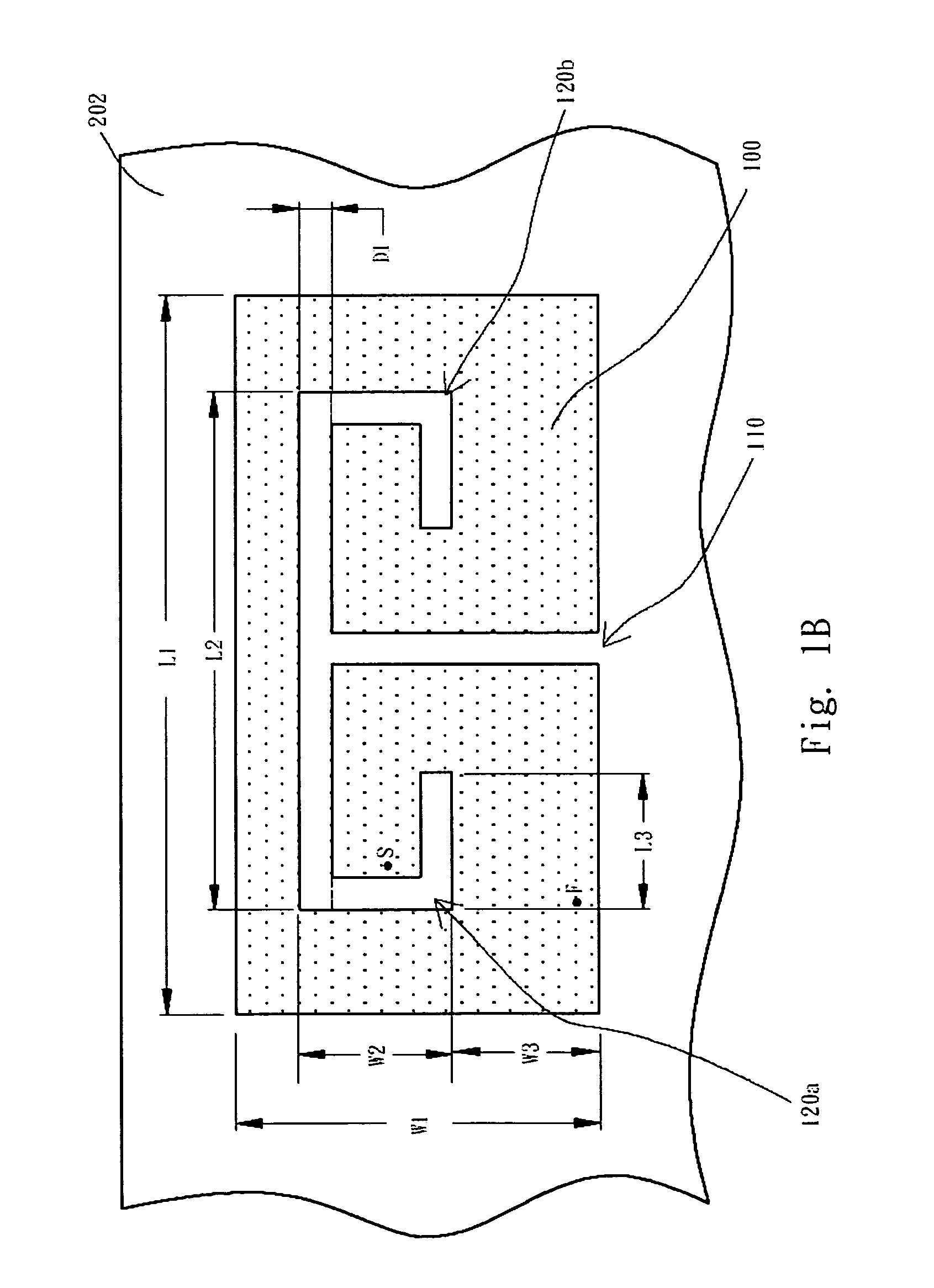

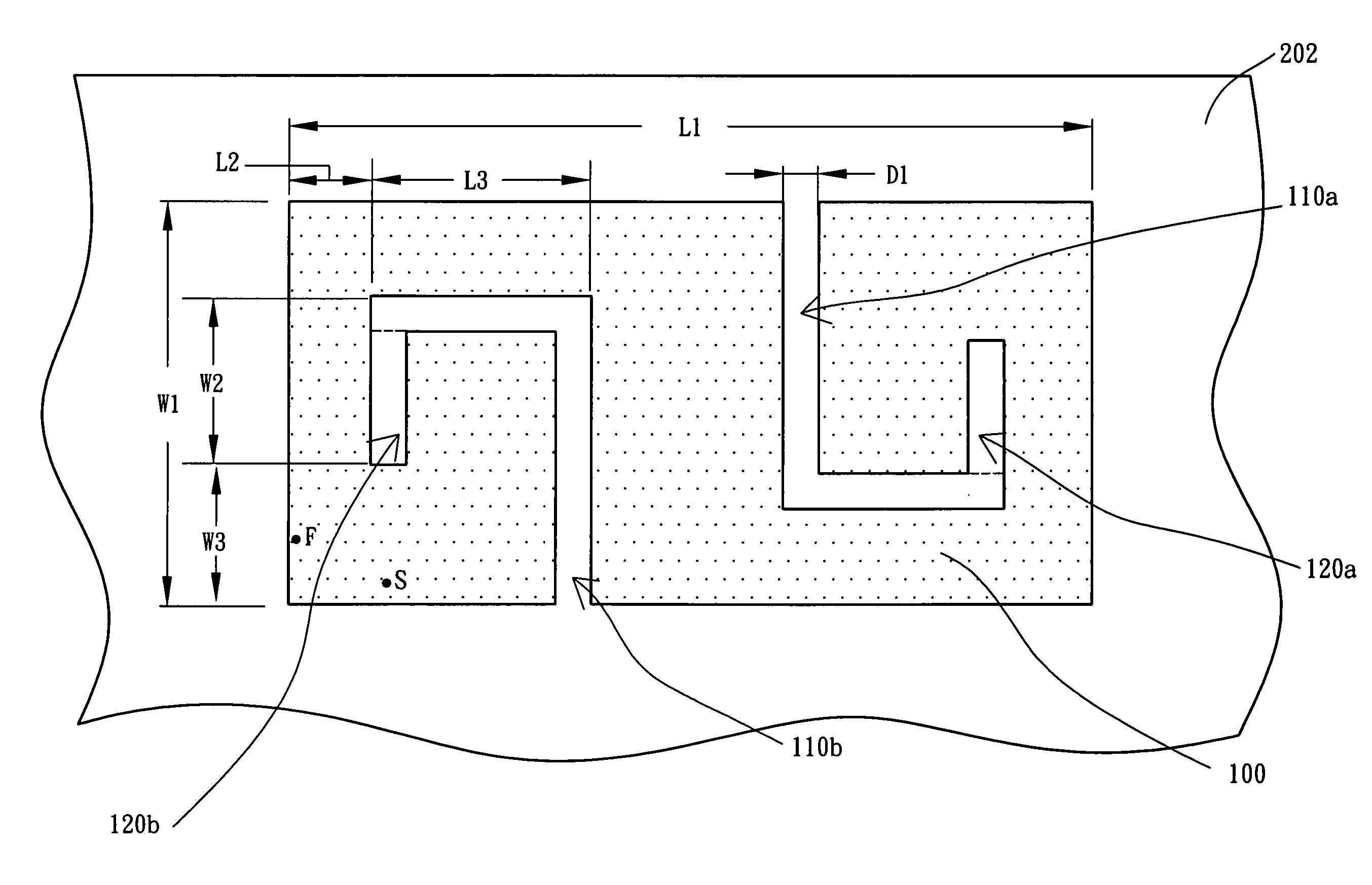

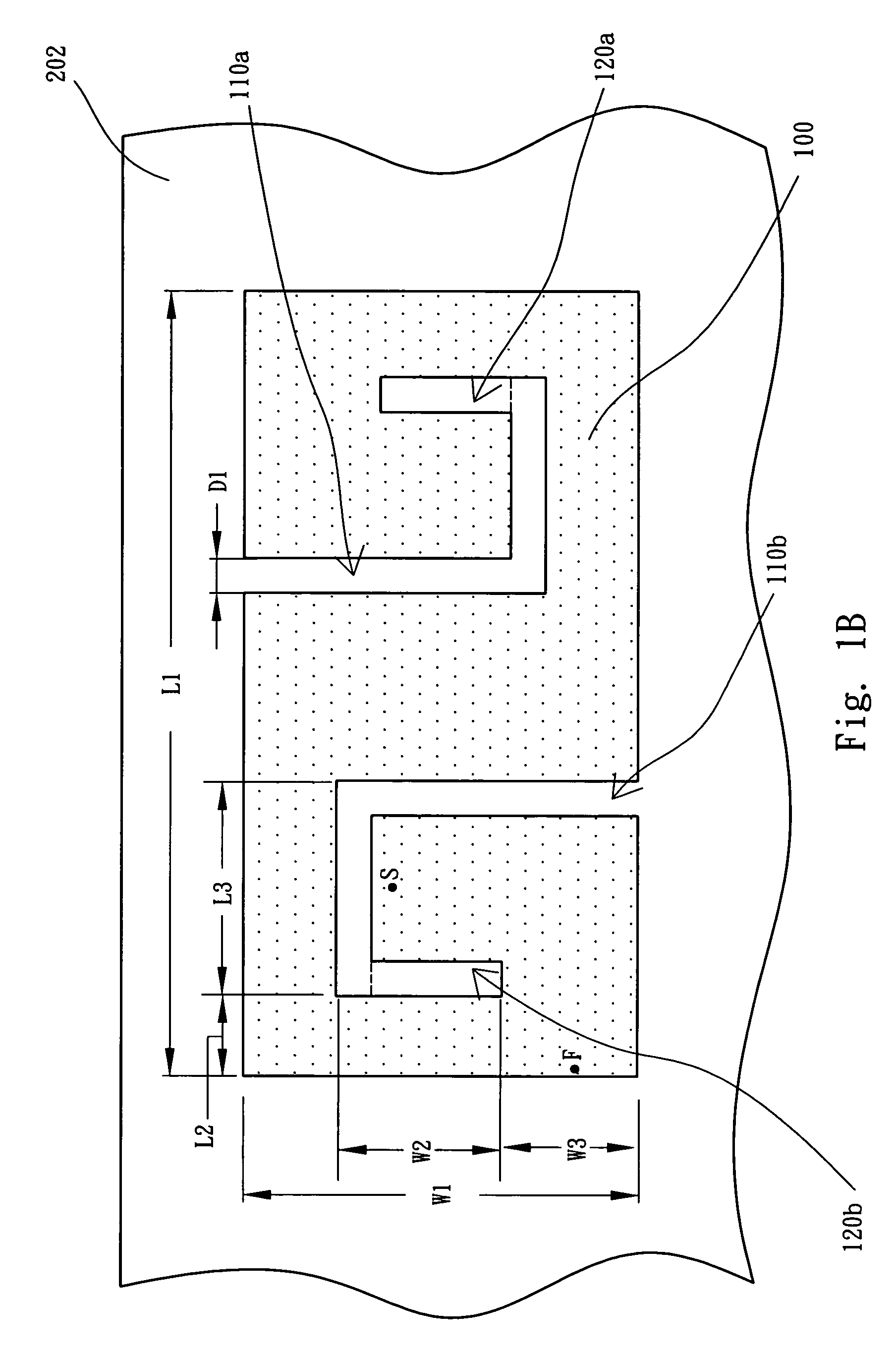

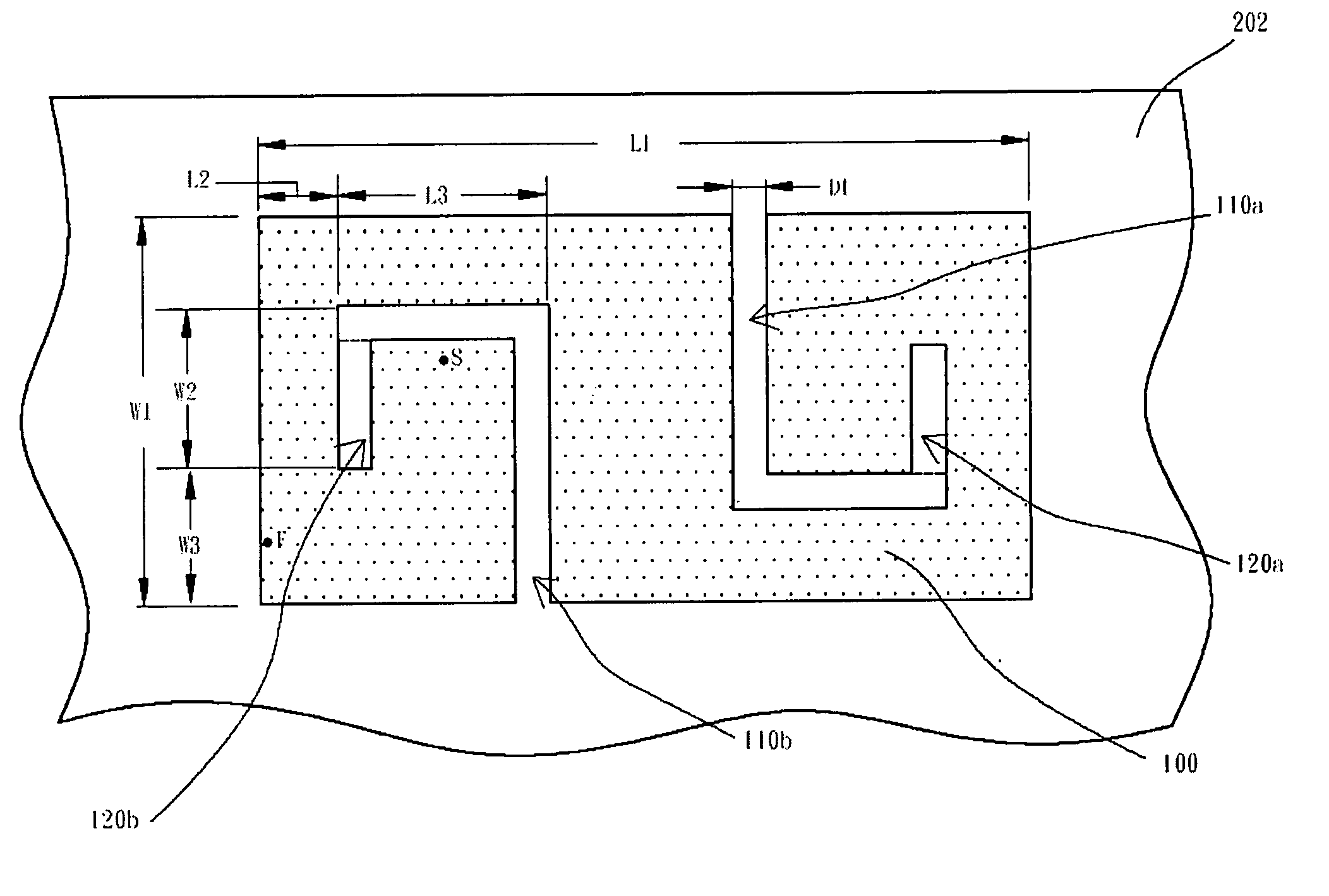

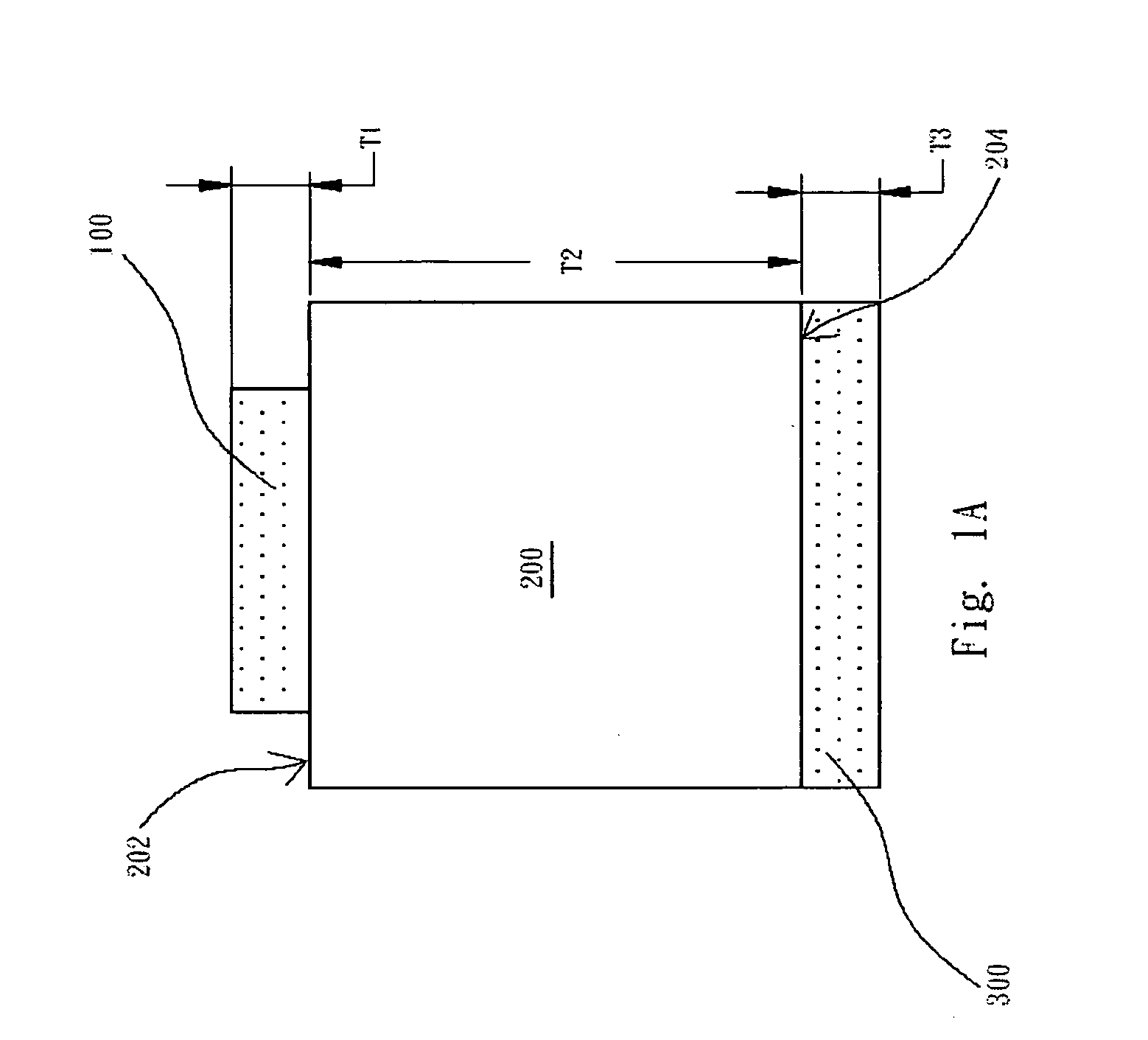

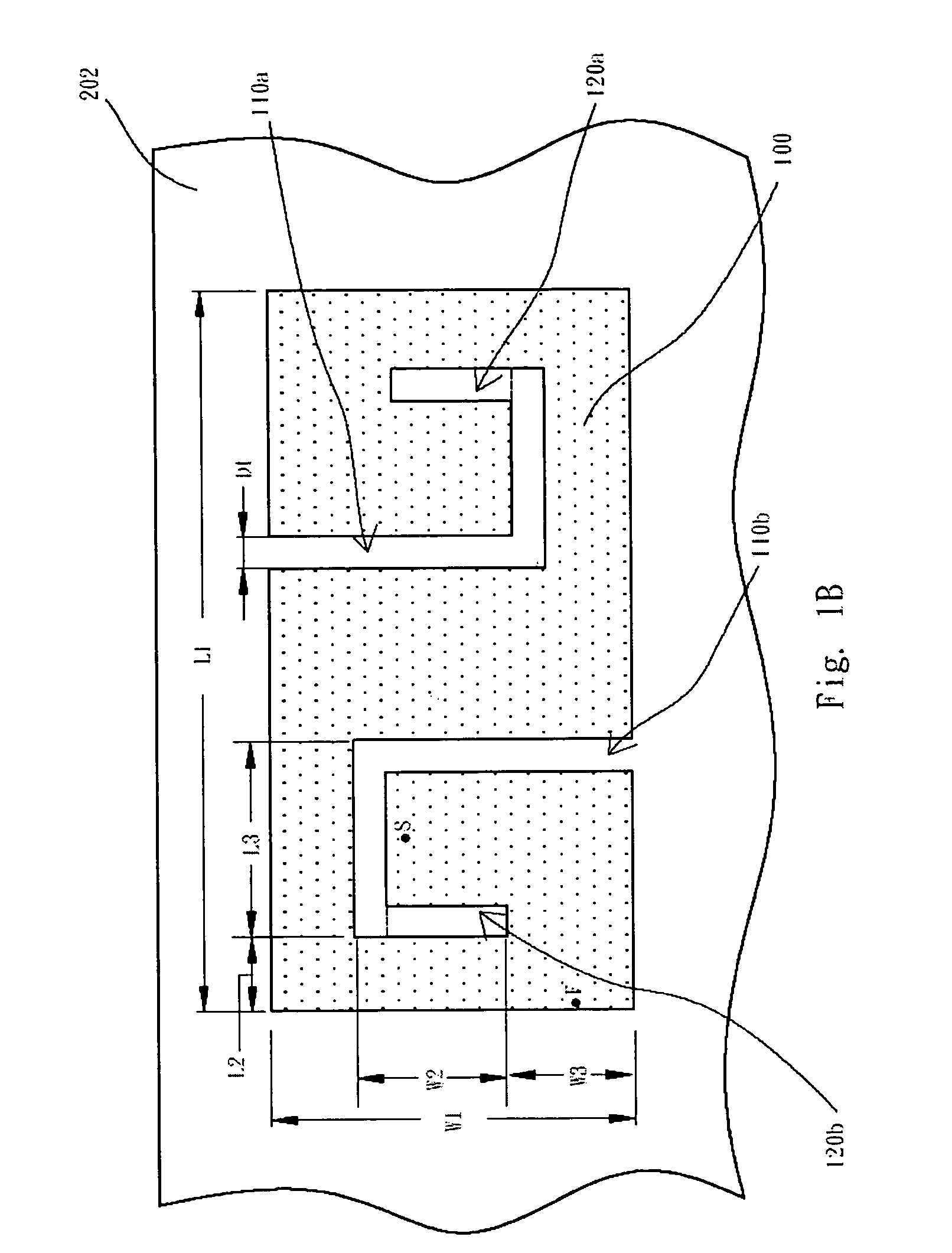

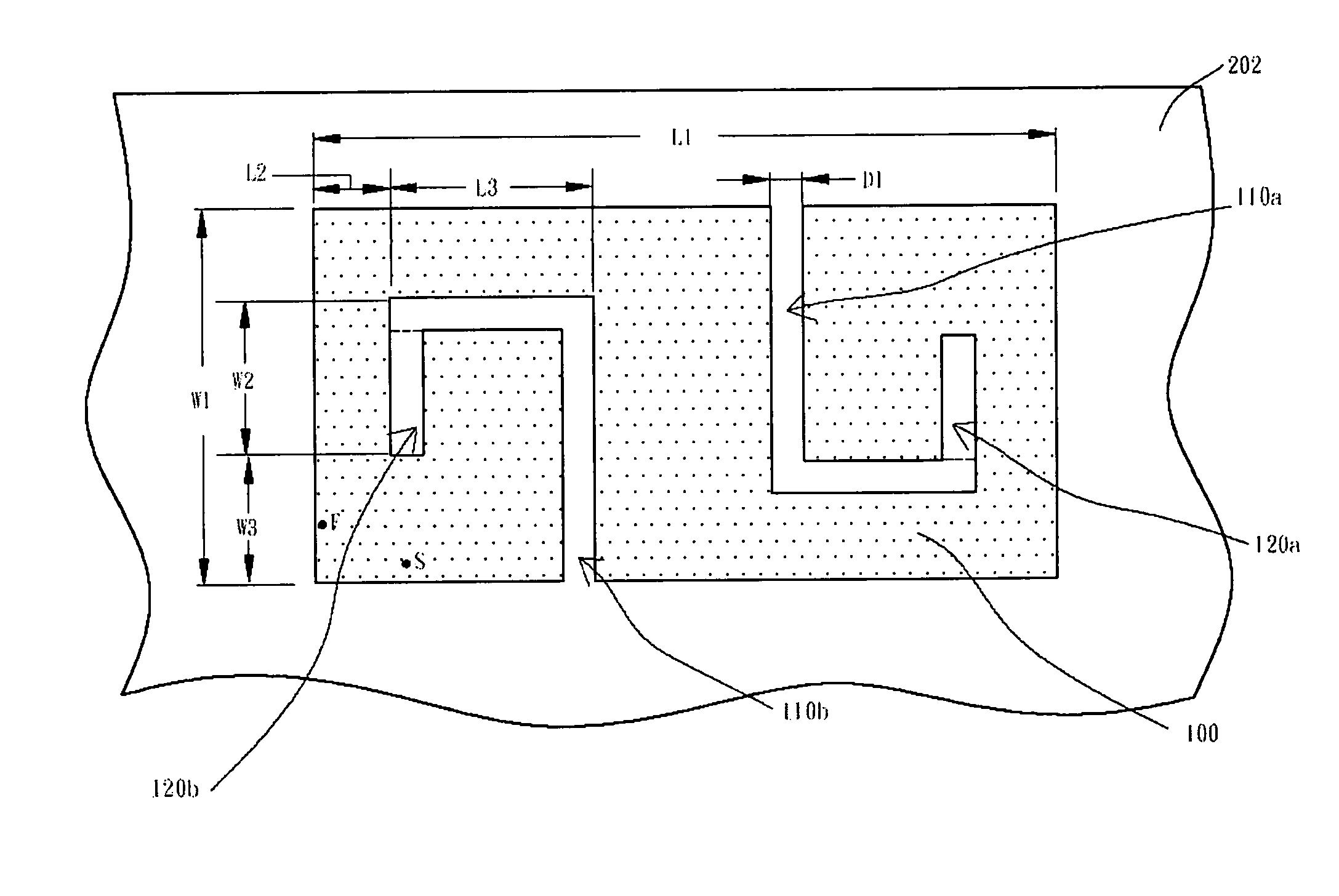

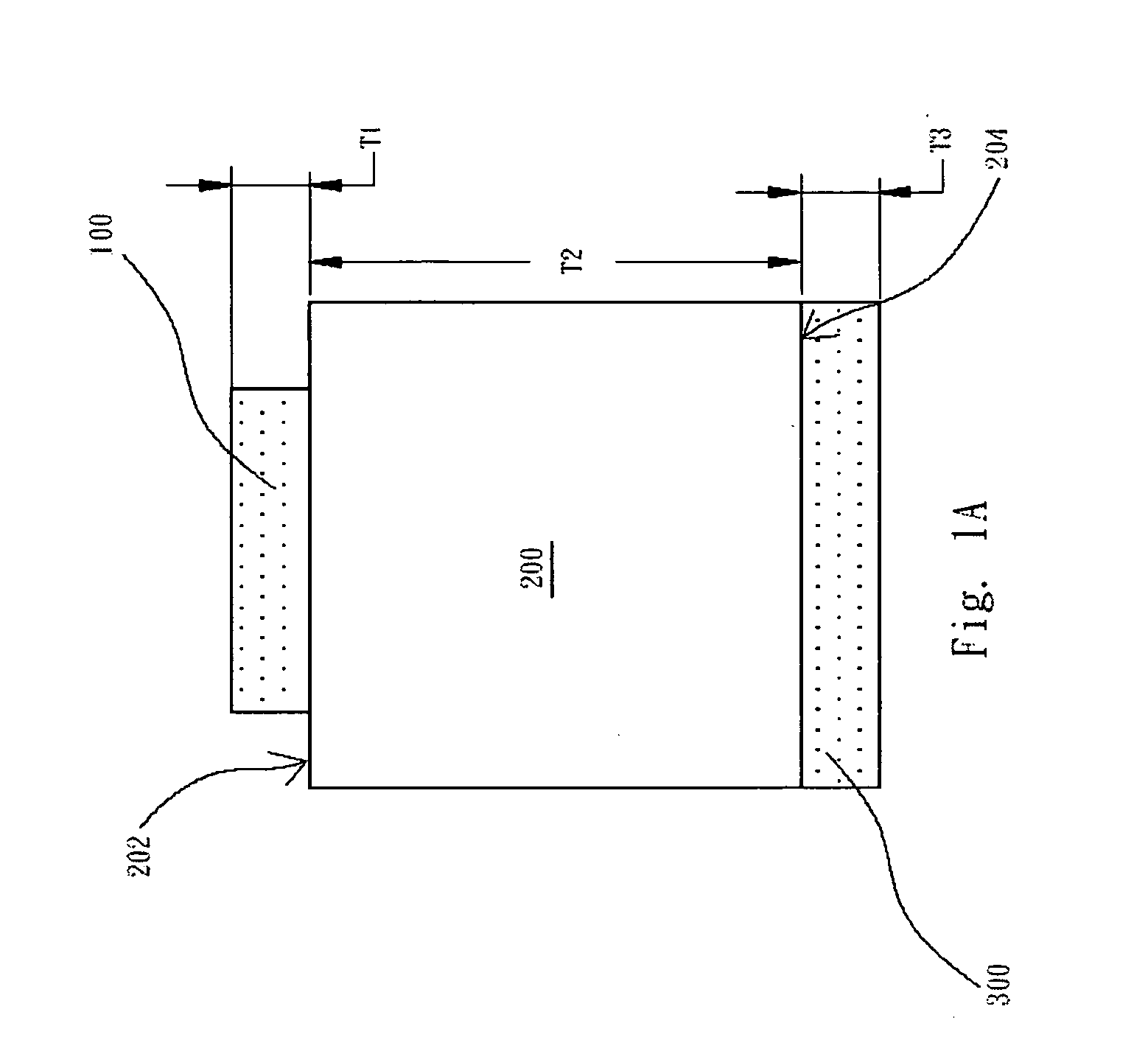

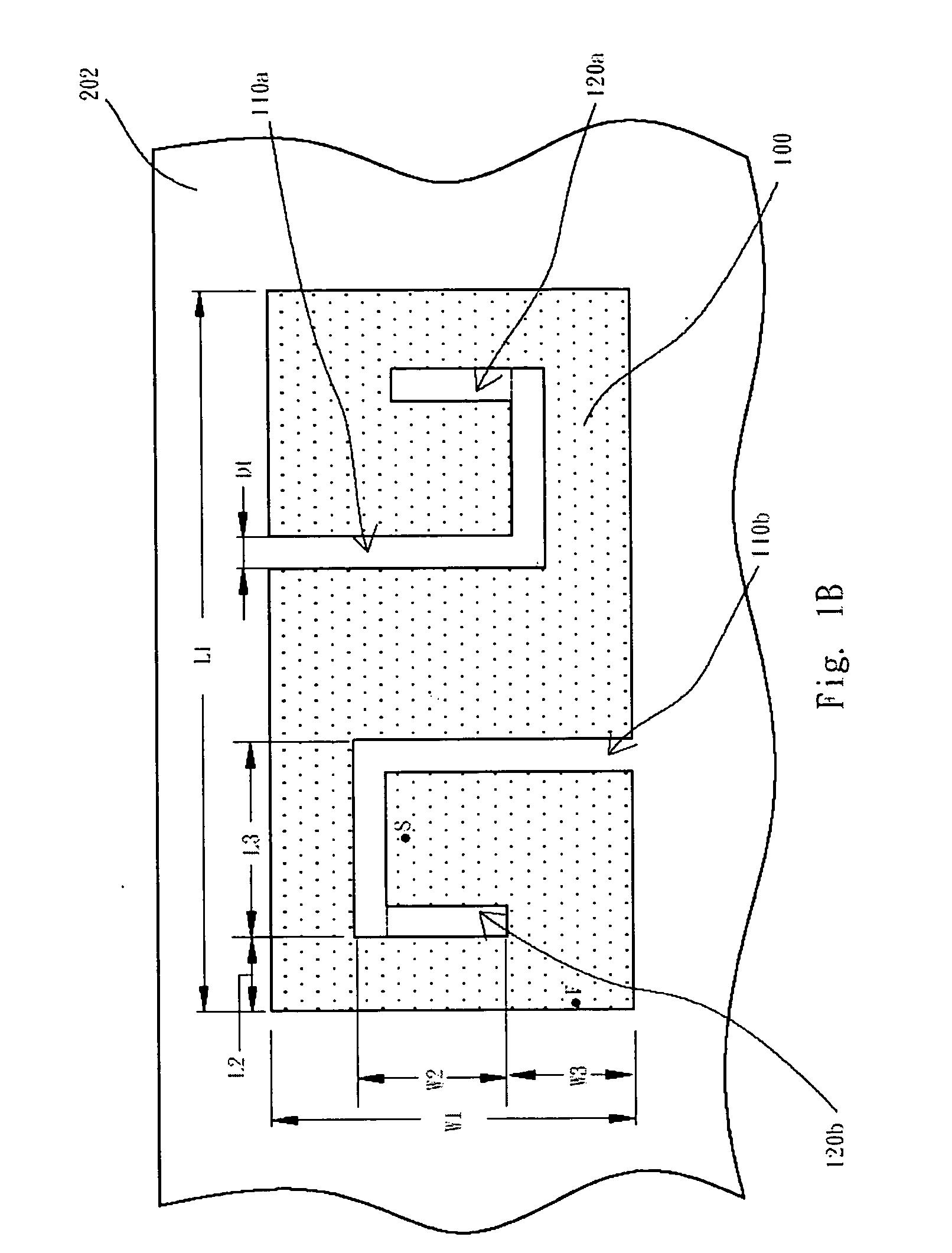

Microstrip antenna having slot structure

InactiveUS20050253757A1Solve insufficient bandwidthReduce antenna sizeSimultaneous aerial operationsAntenna supports/mountingsEngineeringPrinted circuit board

A microstrip antenna having a slot structure is disclosed for providing a sufficient bandwidth so as to meet the antenna requirements. The microstrip antenna is composed of a base board (such as a printed circuit board) and a microstrip patch radiator having the slot structure, wherein the microstrip patch radiator is formed on the base board. The slot structure is composed of a T-shaped slot, an L-shaped slot and a reversed-L-shaped slot, wherein the L-shaped slot and the reversed-L-shaped slot are mirror-reflected to each other.

Owner:ARCADYAN

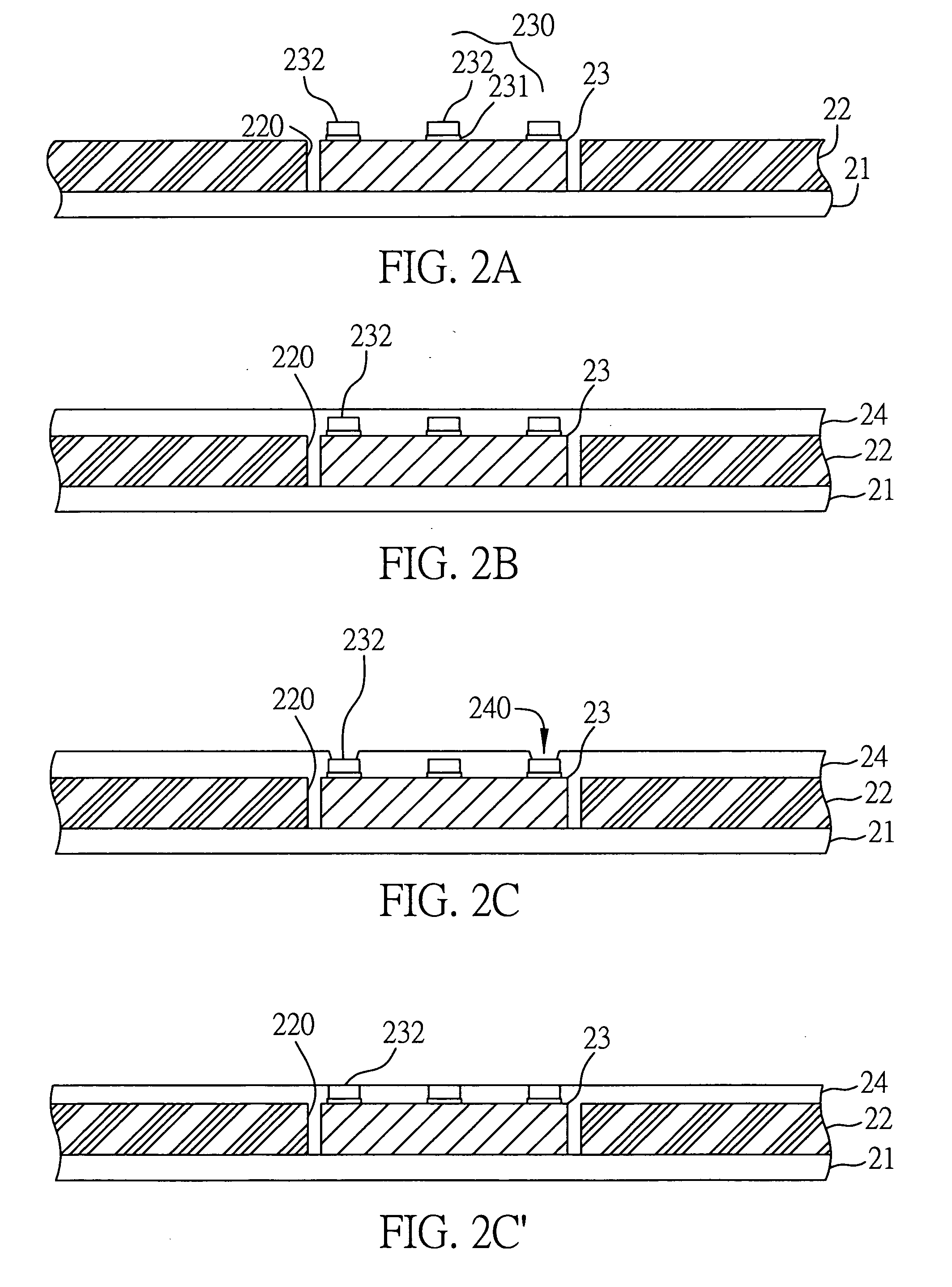

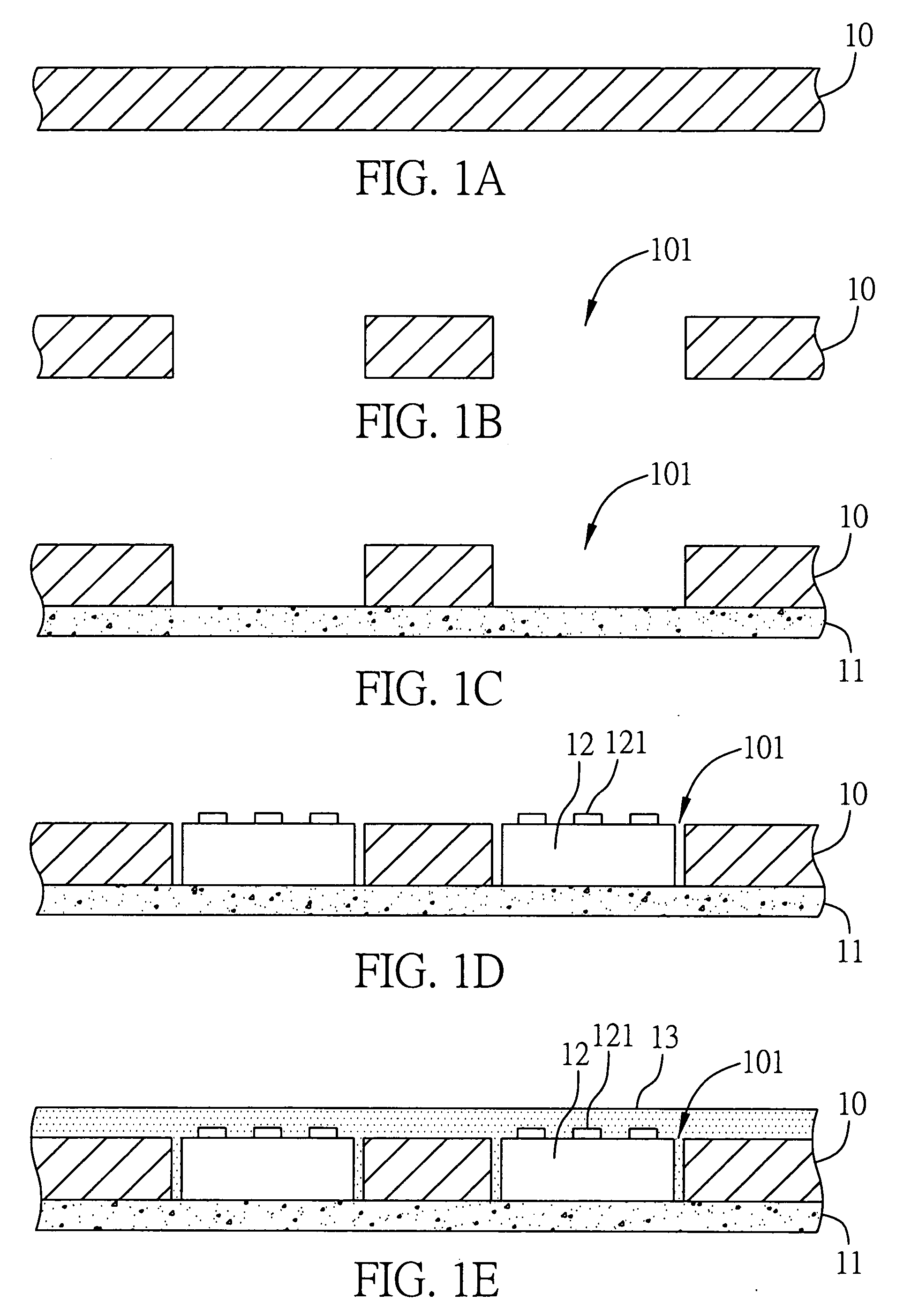

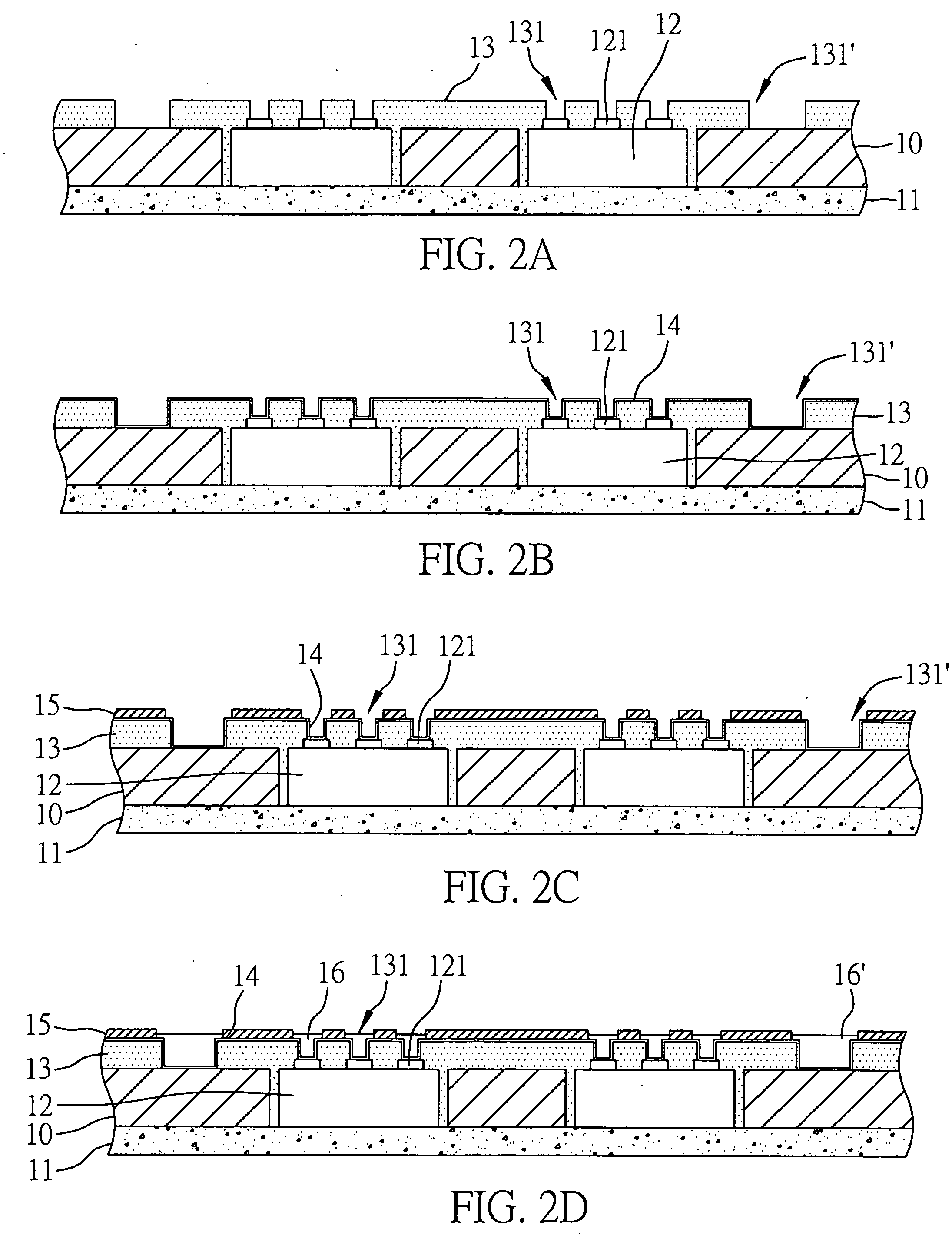

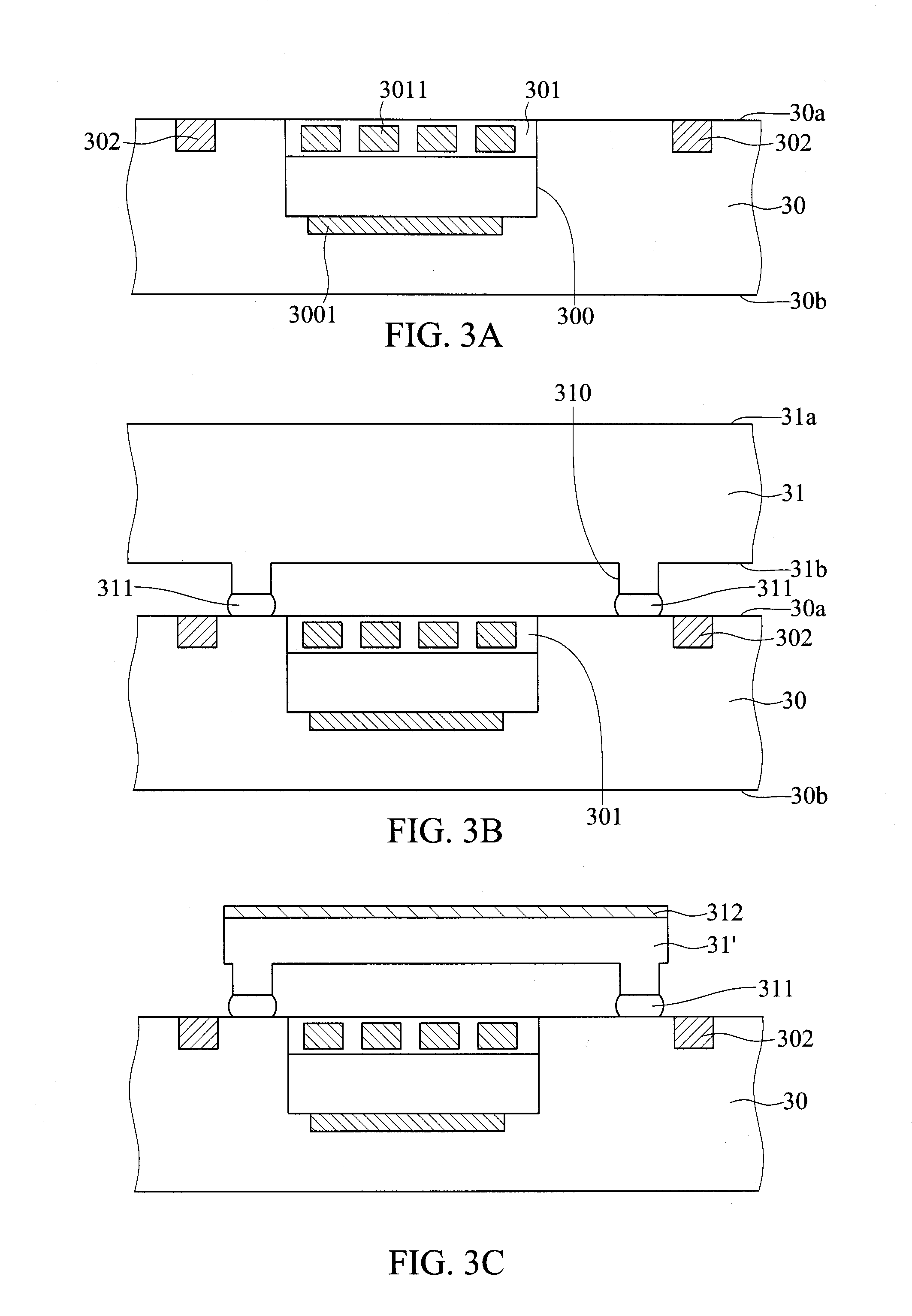

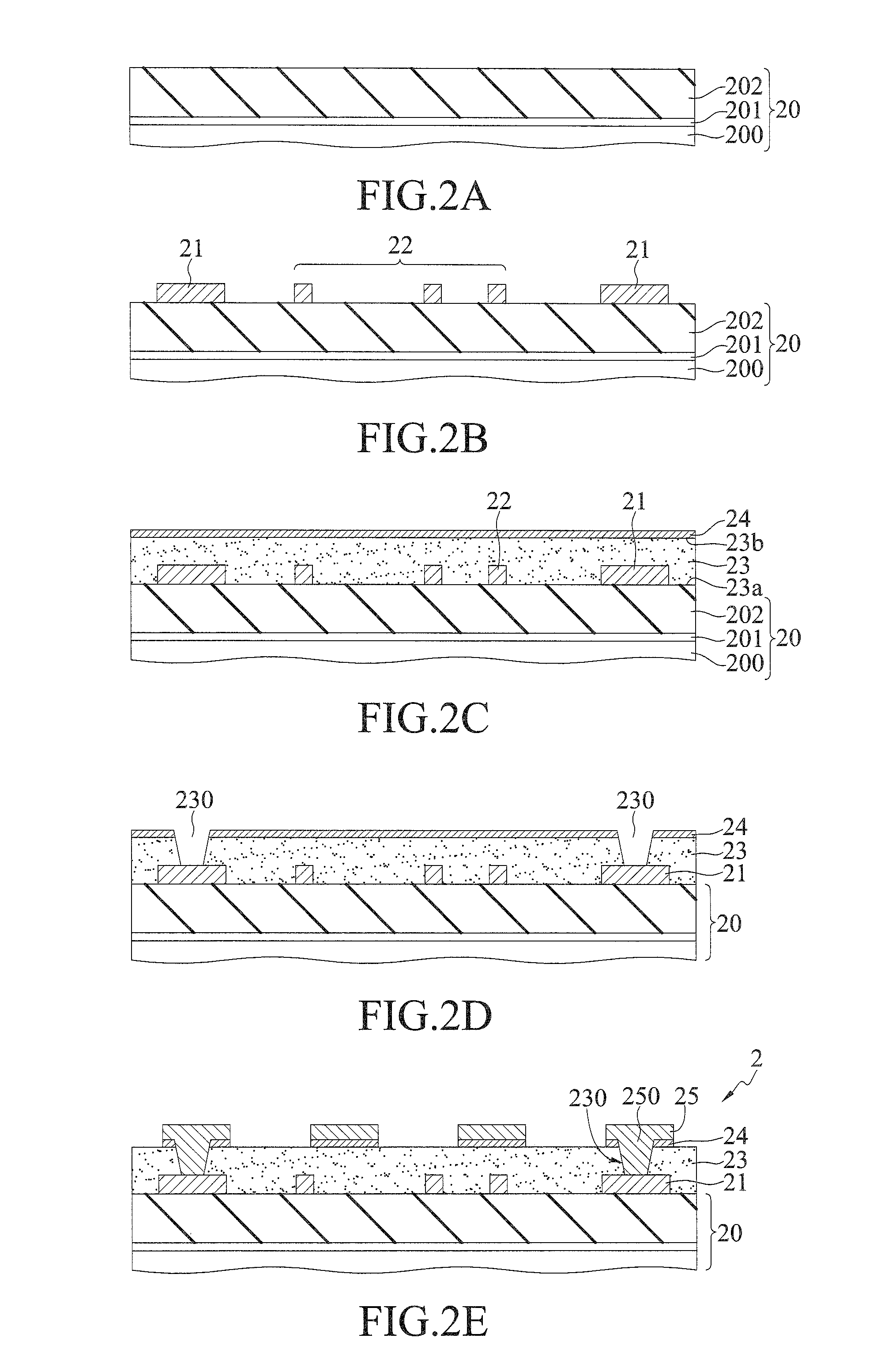

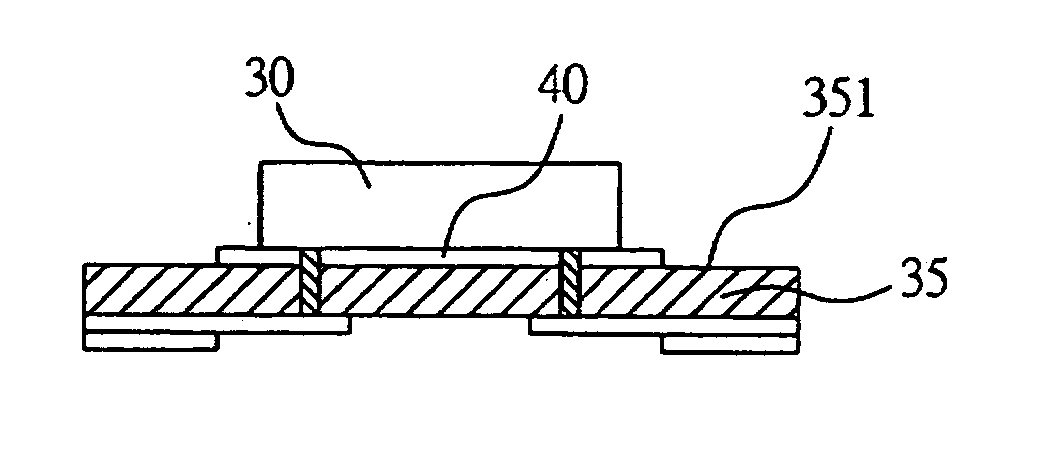

Method for fabricating carrier structure integrated with semiconductor element

InactiveUS20060068332A1Simplify the manufacturing processReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A method for fabricating a carrier structure integrated with a semiconductor element is proposed. First, a carrier having at least one opening therein is provided, and at least one semiconductor element is embedded in the opening. Then, a photosensitive insulating layer is formed on the carrier and filled into a gap between the opening of the carrier and the semiconductor element, such that the semiconductor element is fixed in the opening. Subsequently, the photosensitive insulating layer is patterned, and build-up circuits are formed on the semiconductor element. By such arrangement, the overall fabrication processes are simplified and the fabrication cost can be reduced.

Owner:PHOENIX PRECISION TECH CORP

Starry sky lighting panels

ActiveUS8033684B2Reducing fabricationReduce injuriesPoint-like light sourceLighting support devicesSkyInterconnection

A lighting panel capable of producing a “Starry Sky” lighting effect and which is easily retrofitted into existing aircraft includes a first substrate, a plurality of microminiature light sources, such as LEDs, mounted on an upper surface of the first substrate, a plurality of electrically conductive traces written on the upper surface of the first substrate so as to make electrical interconnections with respective leads of the light sources, a clear filler material surrounding each light source and tapering down to the upper surface of the first substrate so as to planarize it, and a flexible decorative film laminated over the upper surface of the first substrate and light sources, the decorative film containing a plurality of apertures therethrough, each corresponding in location to a respective light source.

Owner:THE BOEING CO

Microstrip antenna having slot structure

InactiveUS7126544B2Reducing fabricationSmall sizeSimultaneous aerial operationsAntenna supports/mountingsEngineeringPrinted circuit board

Owner:ARCADYAN

Lighting panels including embedded illumination devices and methods of making such panels

ActiveUS7857484B2Reducing fabricationReduce injuriesGeneral lightingNon-electric lightingEffect lightInterconnection

A lighting panel includes a structural panel, a plurality of inserts containing microminiature light sources, such as LEDs, mounted in openings in the panel or in an appliqué applied thereto, a plurality of electrically conductive traces written on the upper surface of the panel so as to make electrical interconnections with respective leads of the light sources, and a decorative film applied over a bottom surface of the panel and the light sources, the decorative film being translucent or transparent or containing a plurality of apertures therethrough, each corresponding in location to a respective one of the light sources.

Owner:THE BOEING CO

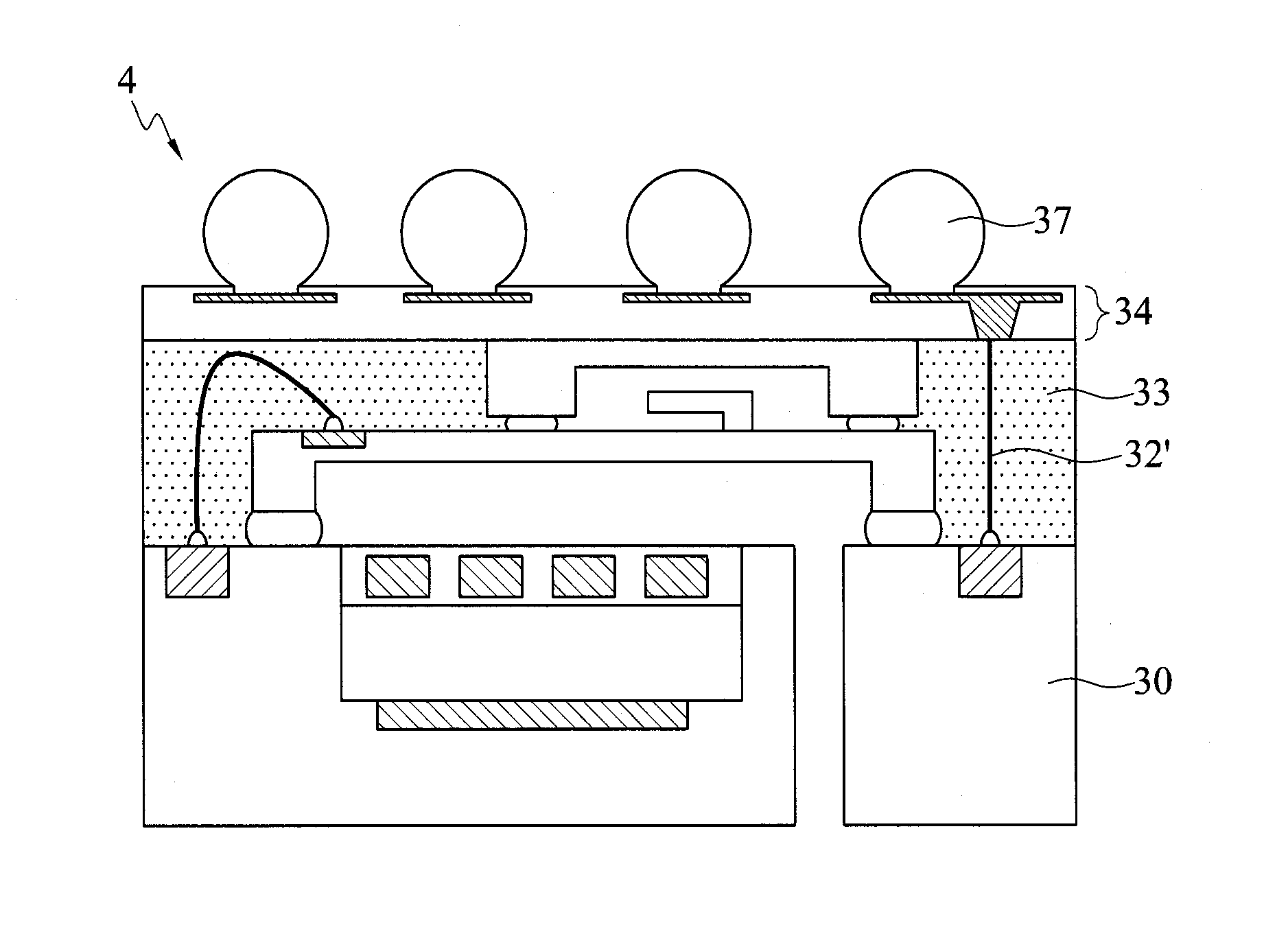

Package structure and fabrication method thereof

ActiveUS20150162264A1Reduce equipmentReducing fabrication costSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSealant

A package structure is provided, which includes: a wafer having a surface with a groove, a thin film closing an open end of the groove and electrical contacts; a chip having a surface with a conductive layer and an opposite surface with a concave portion and a seal ring located at a periphery of the concave portion, the chip being disposed on the wafer with the seal ring surrounding the thin film and the electrical contacts located outside the seal ring; an encapsulant formed on the wafer for encapsulating the chip and the electrical contacts; a plurality of sub-conductive wires embedded in the encapsulant with one ends exposed from a top surface of the encapsulant and the other ends in electrical connection with the electrical contacts; and a through hole penetrating the wafer and communicating with the concave portion, thereby reducing the fabrication cost and size of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

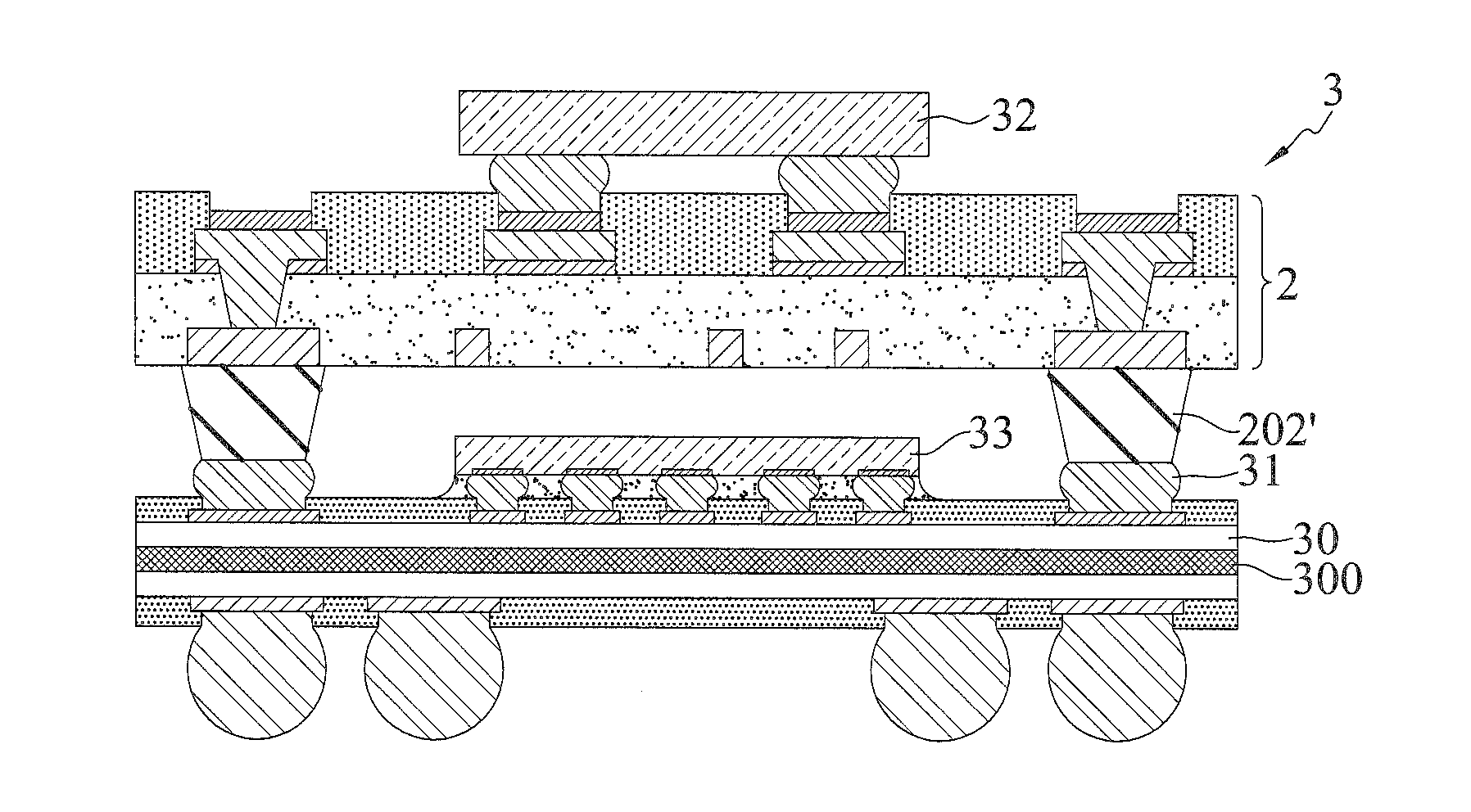

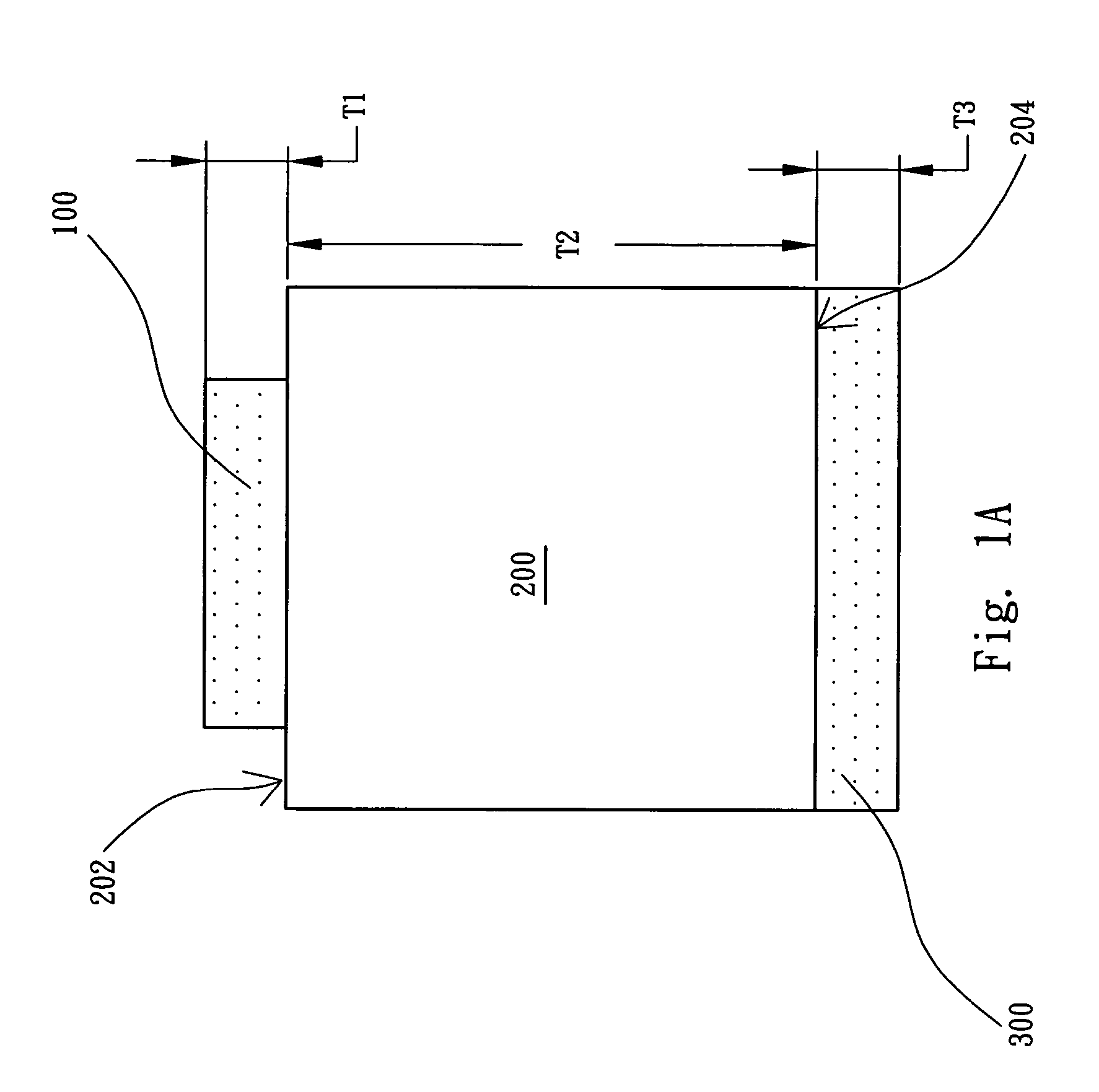

Coreless packaging substrate, pop structure, and methods for fabricating the same

InactiveUS20150325516A1Reducing fabrication costReduce materialSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

A method for fabricating a coreless packaging substrate is provided, which includes: forming a dielectric layer on a conductive plate having a plurality of conductive pads; forming a circuit layer on the dielectric layer and forming in the dielectric layer a plurality of conductive vias that electrically connect the circuit layer and the conductive pads; and removing a portion of the conductive plate so as to cause the remaining portion of the conductive plate to form a plurality of conductive elements, thereby dispensing with a core layer and reducing the material and fabrication cost.

Owner:SILICONWARE PRECISION IND CO LTD

Microstrip antenna having slot structure

InactiveUS20050253767A1Solve insufficient bandwidthReduce antenna sizeSimultaneous aerial operationsRadiating elements structural formsSpecular reflectionPrinted circuit board

A microstrip antenna having a slot structure is disclosed for providing a sufficient bandwidth so as to meet the antenna requirements. The microstrip antenna is composed of a base board (such as a printed circuit board) and a microstrip patch radiator having the slot structure, wherein the microstrip patch radiator is formed on the base board. The slot structure is composed of an L-shaped slot and an inverted reversed-L-shaped slot, wherein the L-shaped slot and the inverted reversed-L-shaped slot are mirror-reflected to each other symmetrically to a point. One end of each of the L-shaped and inverted reversed-L-shaped slots is connected to an extension slot.

Owner:ARCADYAN

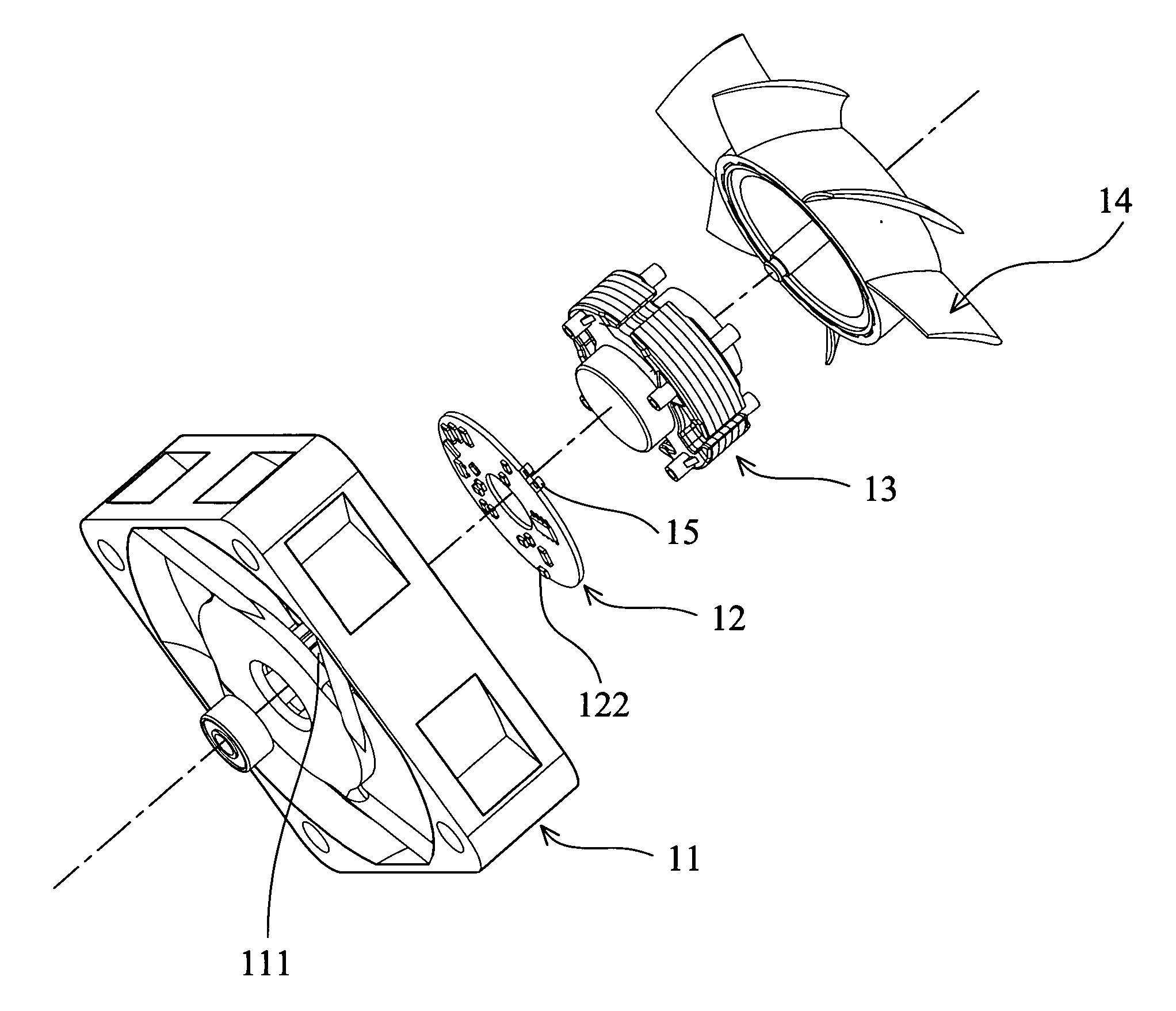

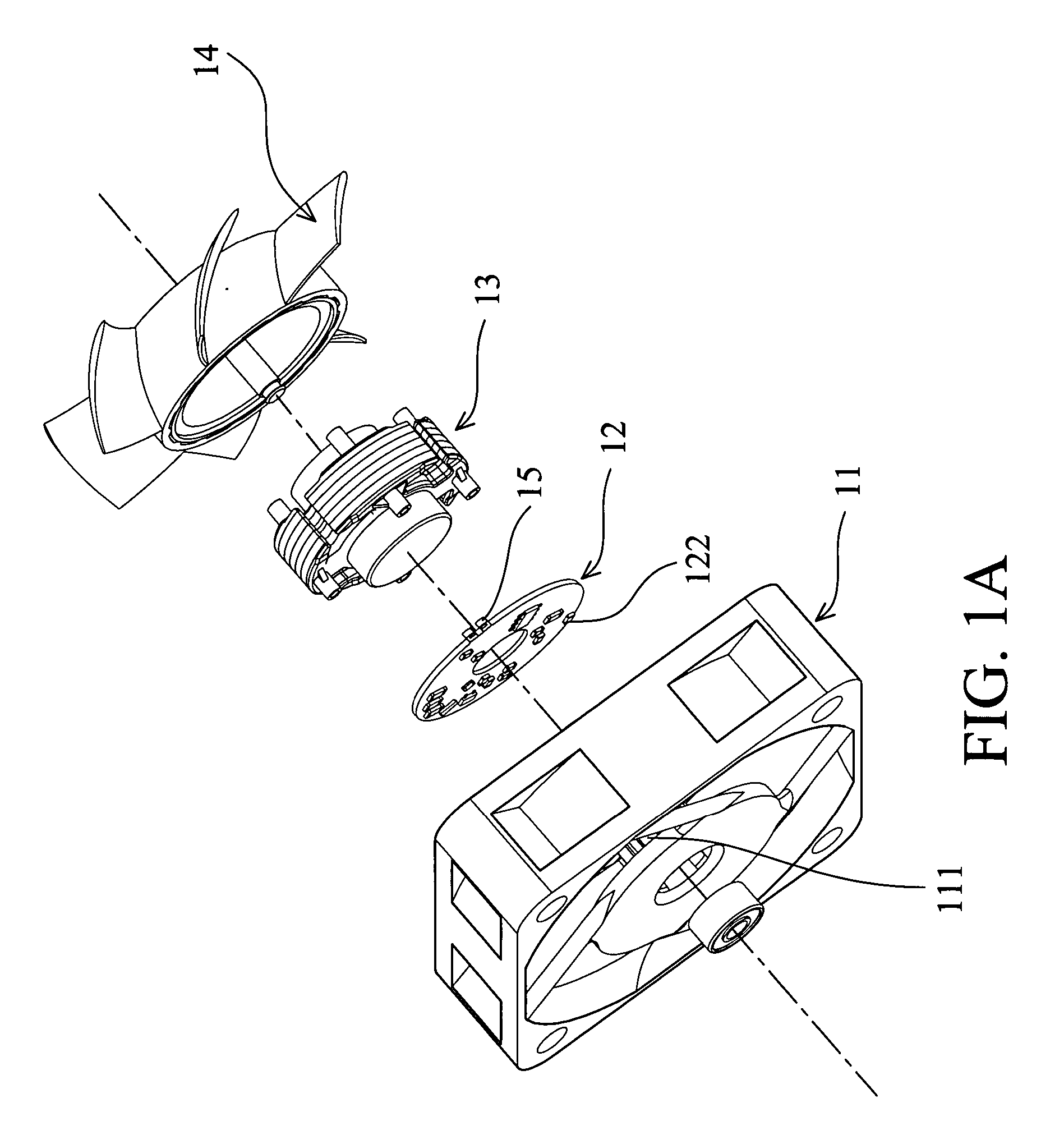

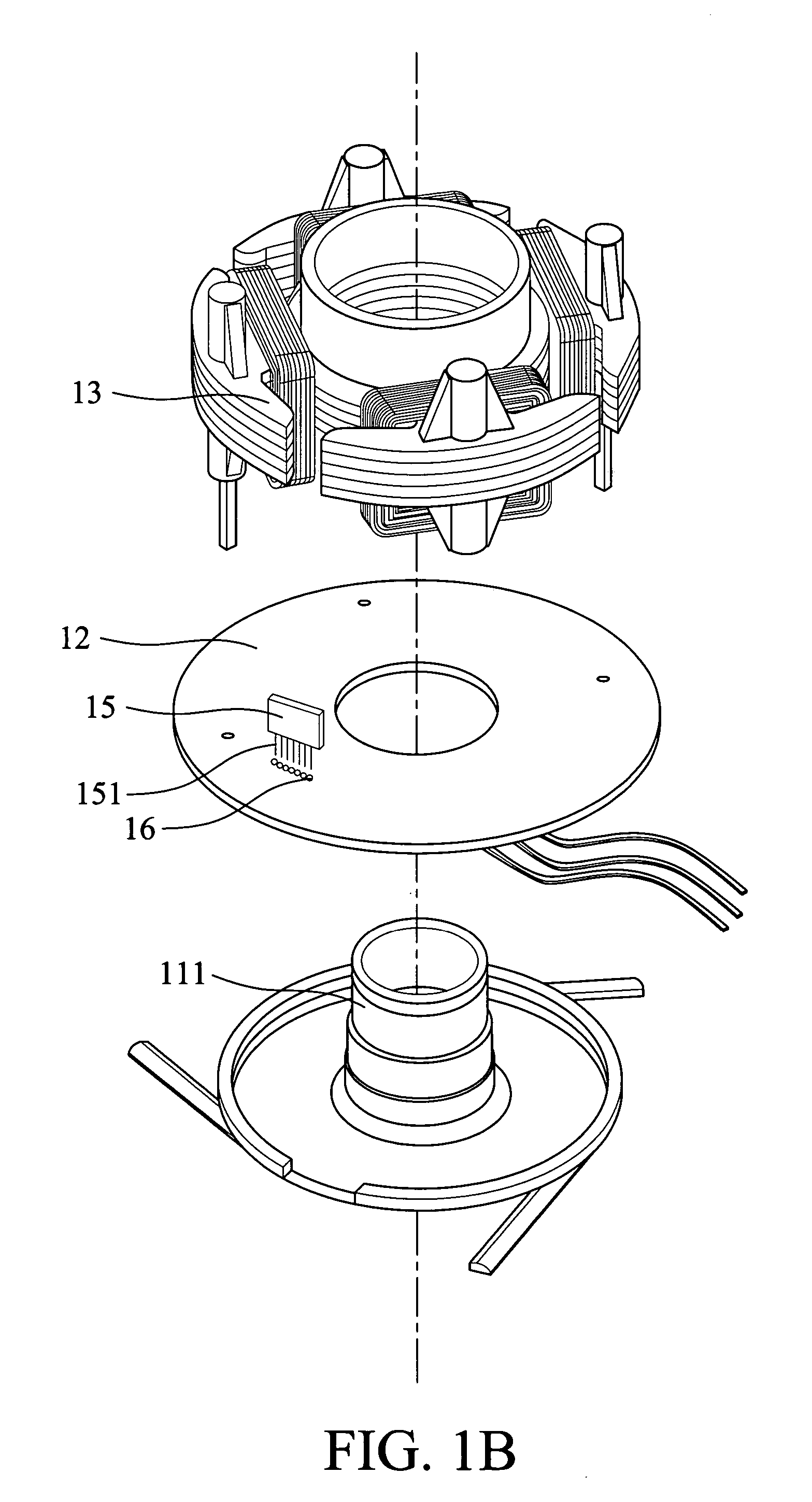

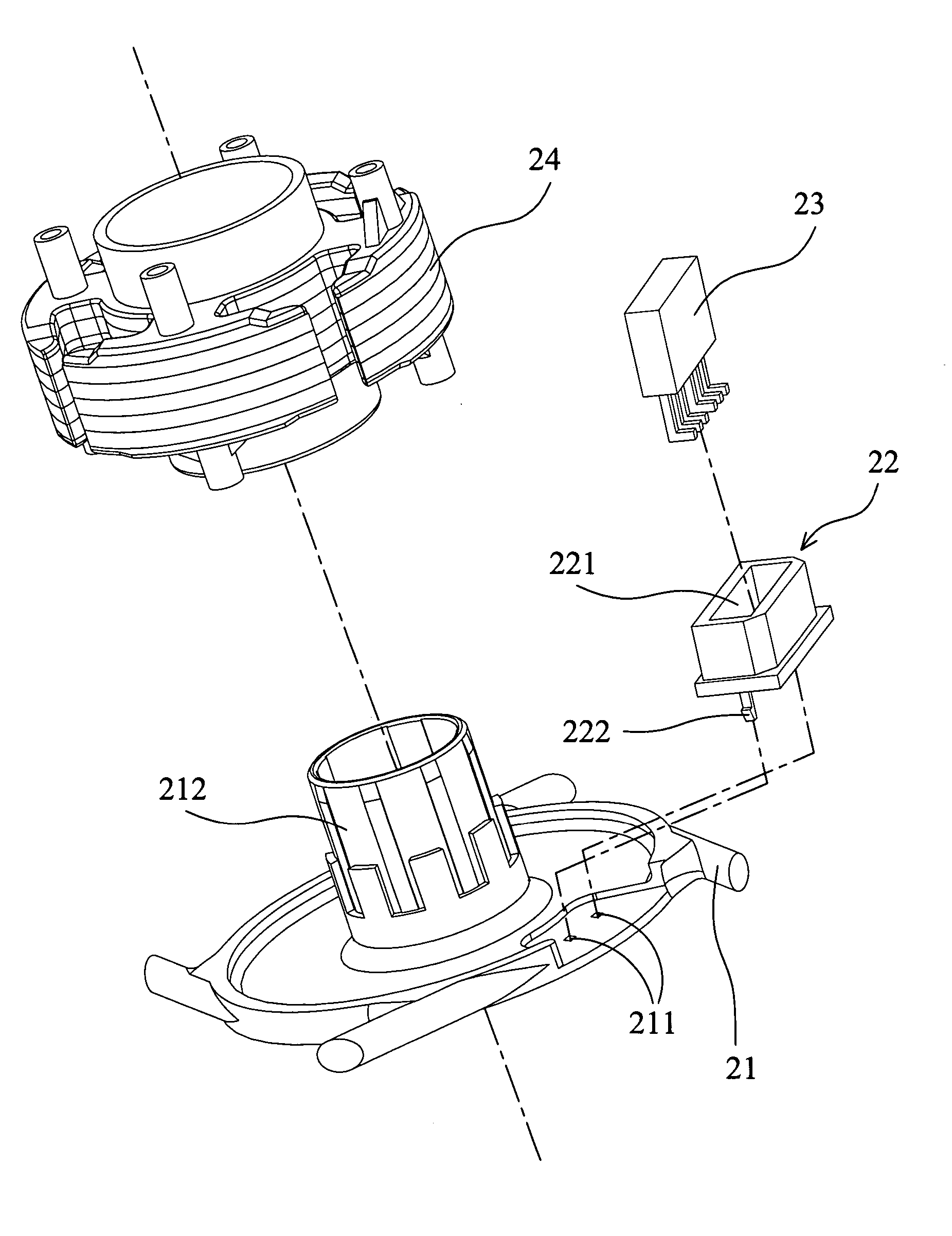

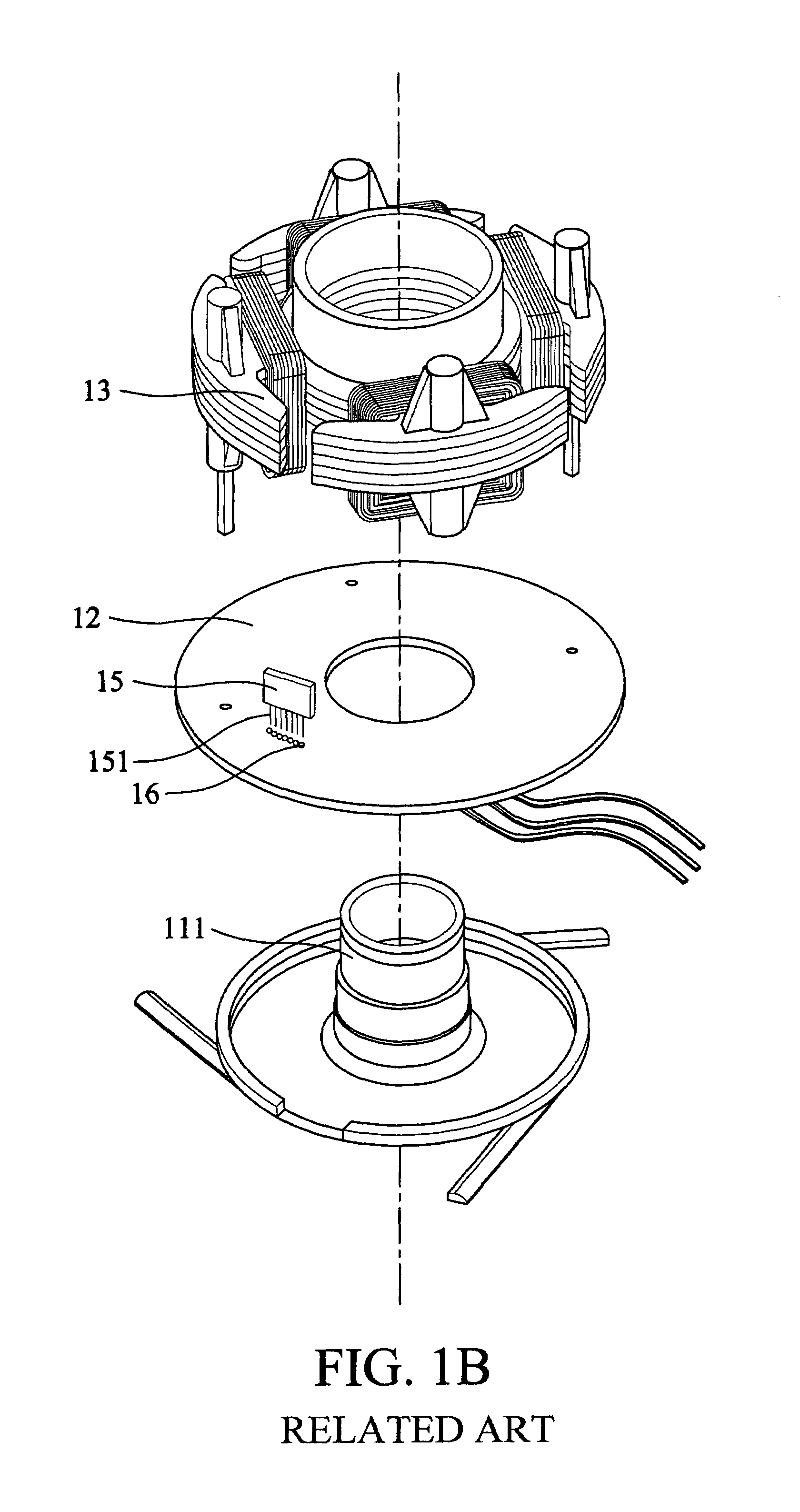

Mounting structure for motor controller of heat-dissipating device

ActiveUS20050029882A1Optimize the installation structureLow costMechanical energy handlingStructural associationMagnetic polesMotor controller

A modified mounting structure for a heat-dissipating device. The heat-dissipating device has a motor and a seat with a slot mounted on a base or the cover portion of a stator thereof. The seat secures a motor controller of the heat-dissipating device detecting phase changes of the magnetic poles of the motor. The structure of a heat-dissipating device reduces required components, manufacturing cost and assembly time, and the control circuit is greatly simplified.

Owner:DELTA ELECTRONICS INC

Microstrip antenna having slot structure

InactiveUS7145510B2Reducing fabricationSmall sizeSimultaneous aerial operationsRadiating elements structural formsEngineeringPrinted circuit board

A microstrip antenna having a slot structure is disclosed for providing a sufficient bandwidth so as to meet the antenna requirements. The microstrip antenna is composed of a base board (such as a printed circuit board) and a microstrip patch radiator having the slot structure, wherein the microstrip patch radiator is formed on the base board. The slot structure is composed of an L-shaped slot and an inverted reversed-L-shaped slot, wherein the L-shaped slot and the inverted reversed-L-shaped slot are mirror-reflected to each other symmetrically to a point. One end of each of the L-shaped and inverted reversed-L-shaped slots is connected to an extension slot.

Owner:ARCADYAN

Micro-electronic package structure and method for fabricating the same

InactiveUS20070111398A1Simplify the manufacturing processImprove responseSolid-state devicesSemiconductor/solid-state device manufacturingElectrical connectionSemiconductor chip

A micro-electronic package structure and a method for fabricating the same are proposed. A carrier is prepared and provided with a cavity for receiving at least one semiconductor chip having a plurality of electrical connection contacts. A dielectric layer is formed on the carrier, with the electrical connection contacts being exposed from the dielectric layer. A first circuit layer is formed on the dielectric layer and electrically connected to a portion of the electrical connection contacts of the chip. Another dielectric layer is formed on the first circuit layer and said dielectric layer, and a second circuit layer is formed on this dielectric layer and electrically connected to the rest of the electrical connection contacts of the chip and the first circuit layer by conductive vias, such that the chip is integrated into the carrier.

Owner:PHOENIX PRECISION CORP

Side illumination lens and luminescent device using the same

ActiveUS20100220485A1Easy to manufactureReducing fabricationSolid-state devicesCondensersTotal internal reflectionLight emitting device

The present invention relates to a side illumination lens and a luminescent device using the same, and provides a body, a total reflection surface with a total reflection slope with respect to a central axis of the body, and a linear and / or curved refractive surface(s) formed to extend from a periphery of the total reflection surface; and a luminescent device including the lens. According to the present invention, a lens with total internal reflection surfaces with different slopes, and a linear and / or curved refractive surface(s) allows light emitted forward from a luminescent chip to be guided to a side of the lens. Further, a linear surface(s) formed in a direction perpendicular or parallel to a central axis of a lens and a curved surface are formed on an edge of the lens so that a process of fabricating the lens is facilitated, thereby reducing a defective rate and fabrication costs of the lens.

Owner:SINOTECHNIX LLC

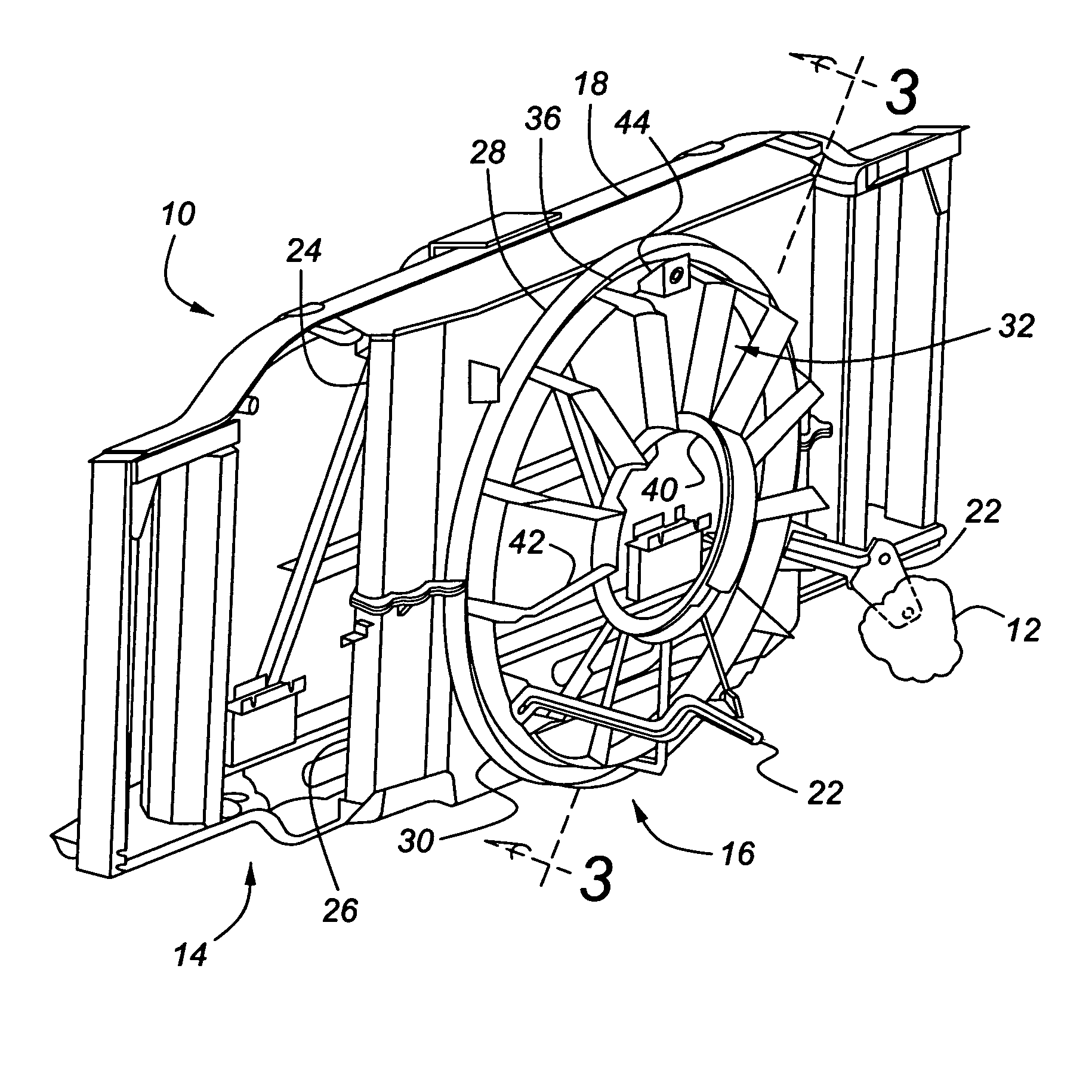

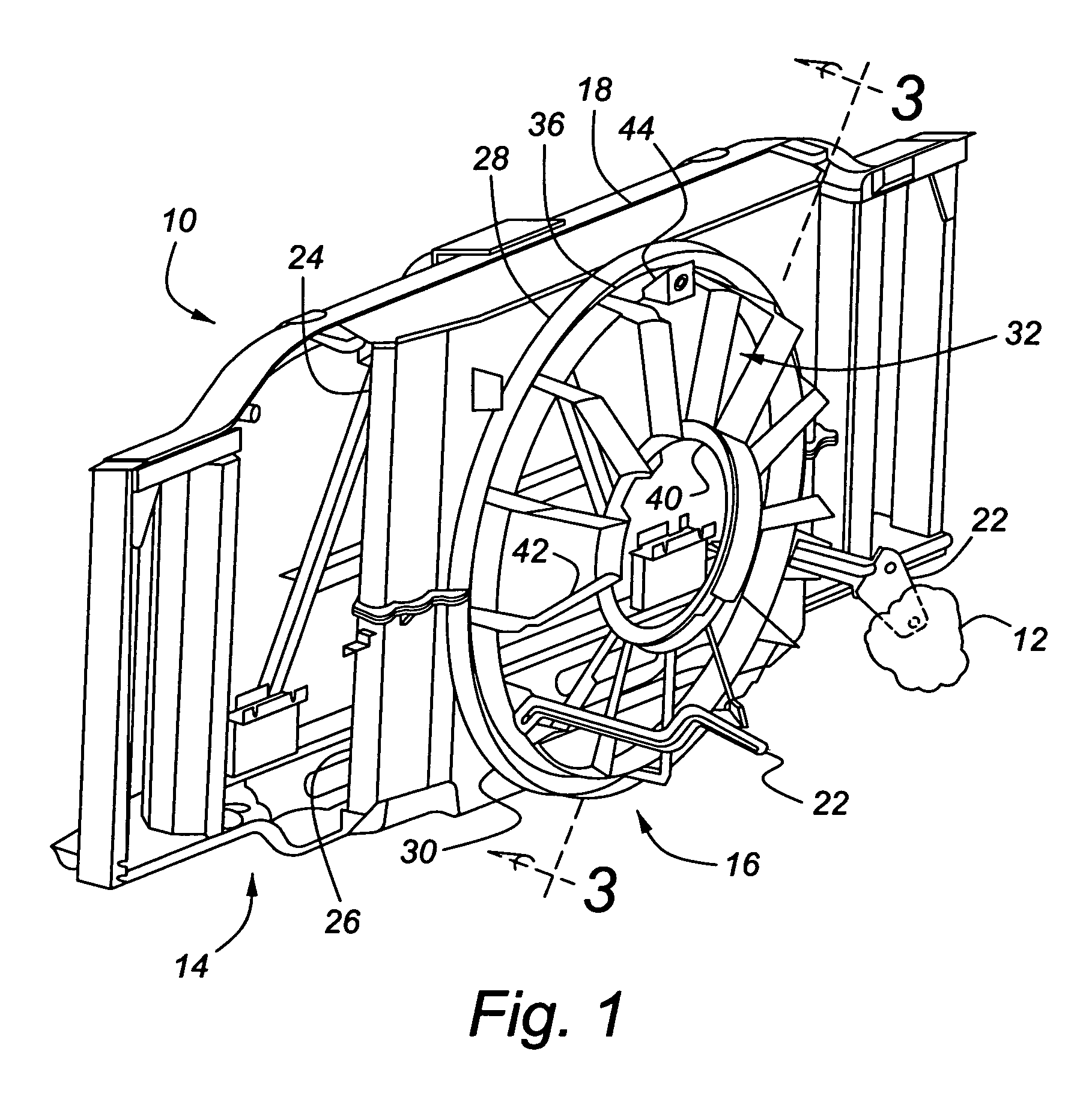

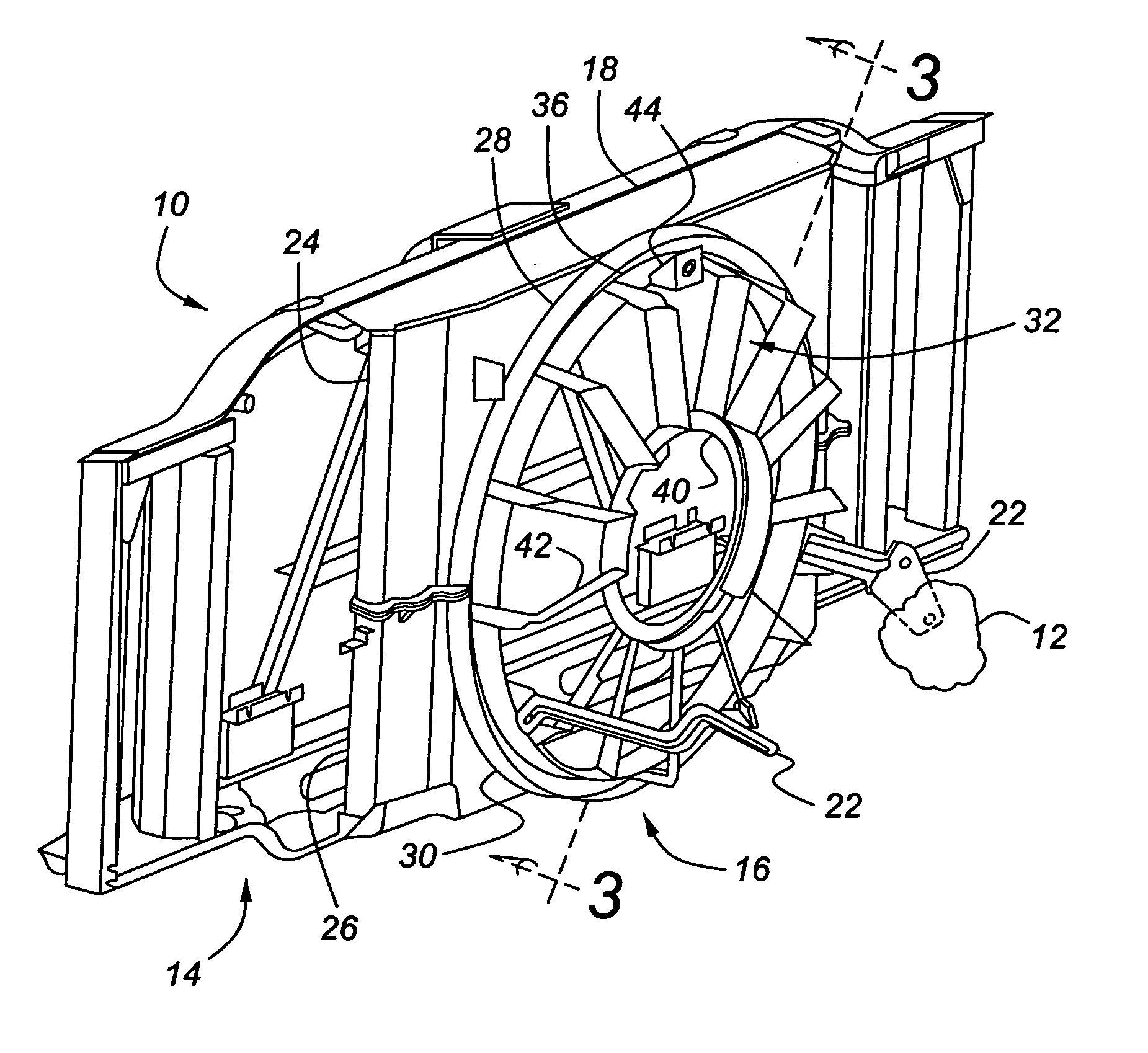

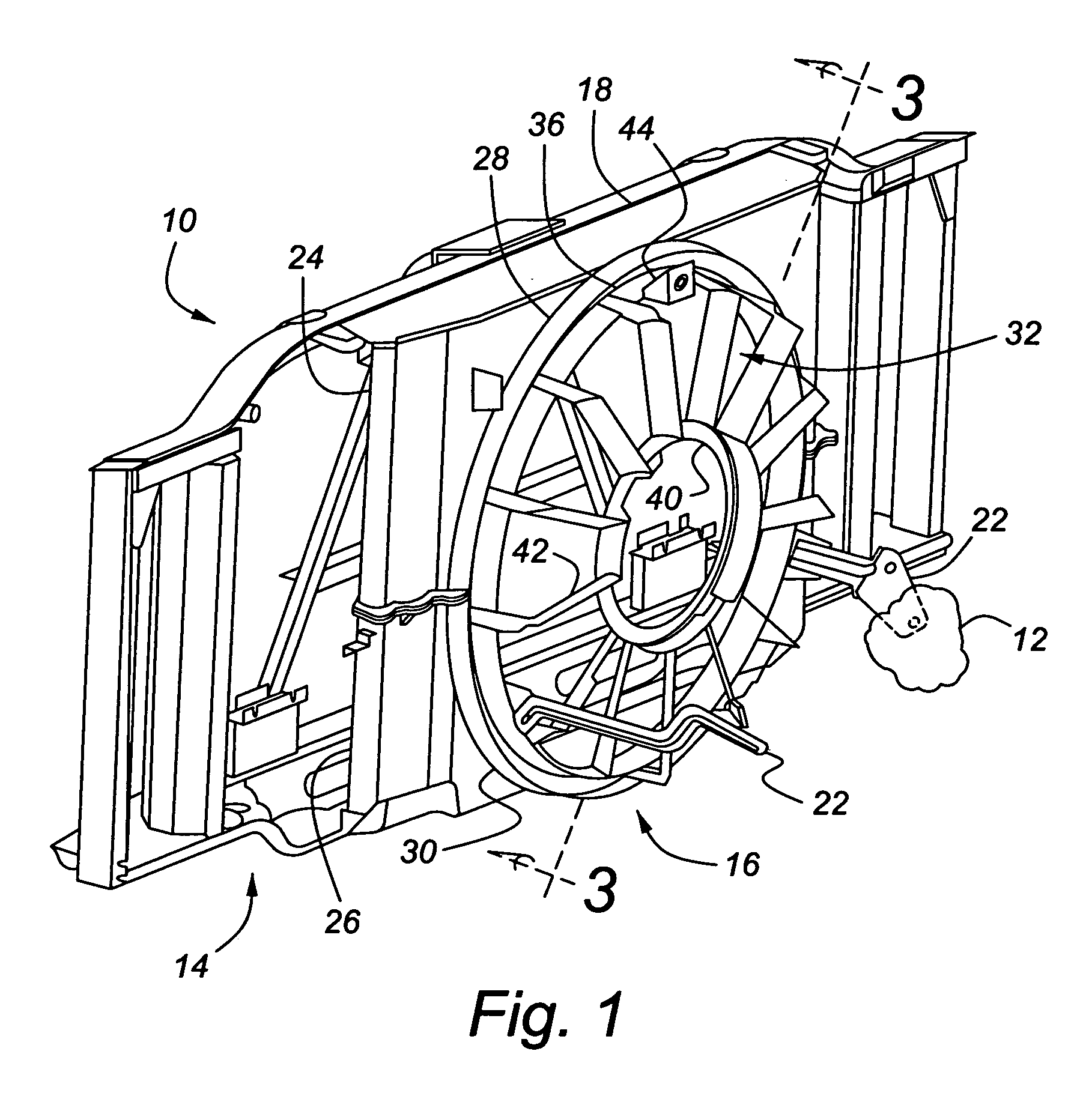

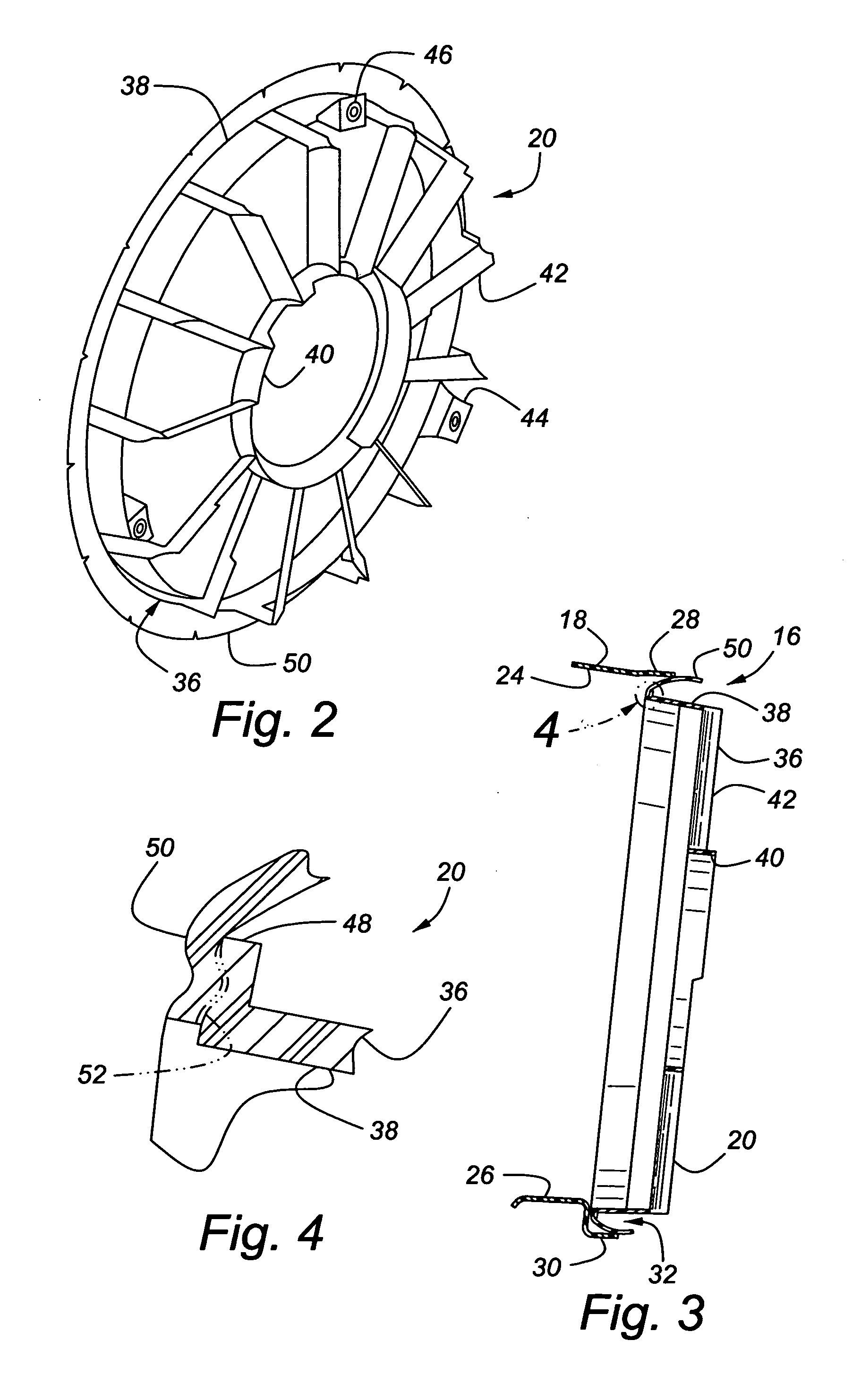

Engine-mounted fan shroud and seal

ActiveUS8303244B2Reduce assemblyReducing fabricationPump componentsReaction enginesEngine mountMechanical engineering

Owner:GM GLOBAL TECH OPERATIONS LLC

Process for treating nitrogenous wastewater with simultaneous autotrophic denitrification, hetertrophic denitrification and COD removal

ActiveUS7972513B2Reducing fabricationReduce stepsSeparation devicesTreatment with aerobic and anaerobic processesNitriteElectron donor

A process for treating nitrogenous wastewater contains an autotrophic denitrification reaction, a heterotrophic denitrification reaction and a COD removal reaction simultaneously and mixedly taking place in a single reactor. The nitrification reaction is caused by nitrifying bacteria, in which ammonium is oxidized into nitrite. The autotrophic denitrification reaction is caused by autotrophic denitrifying bacteria, in which ammonium used as electron donor and nitrite used as electron acceptor are converted into nitrogen gas and nitrate. The heterotrophic denitrification reaction is caused by heterotrophic denitrifying bacteria, in which nitrate and COD are consumed. It is not necessary to build two separate reactors for aerobic nitrification and anaerobic denitrification, thereby effectively reducing the fabrication and operation cost.

Owner:LEADERMAN & ASSOC +1

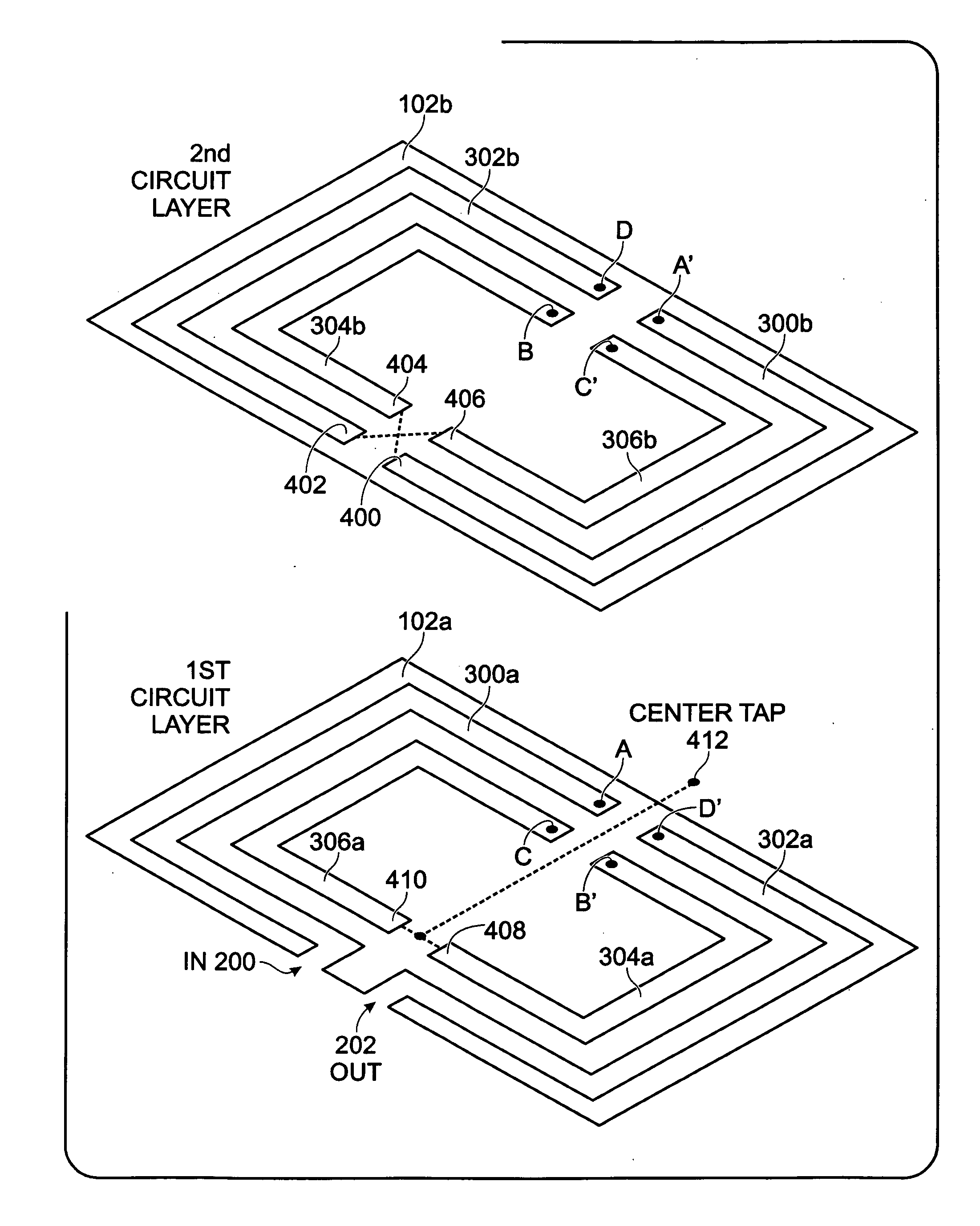

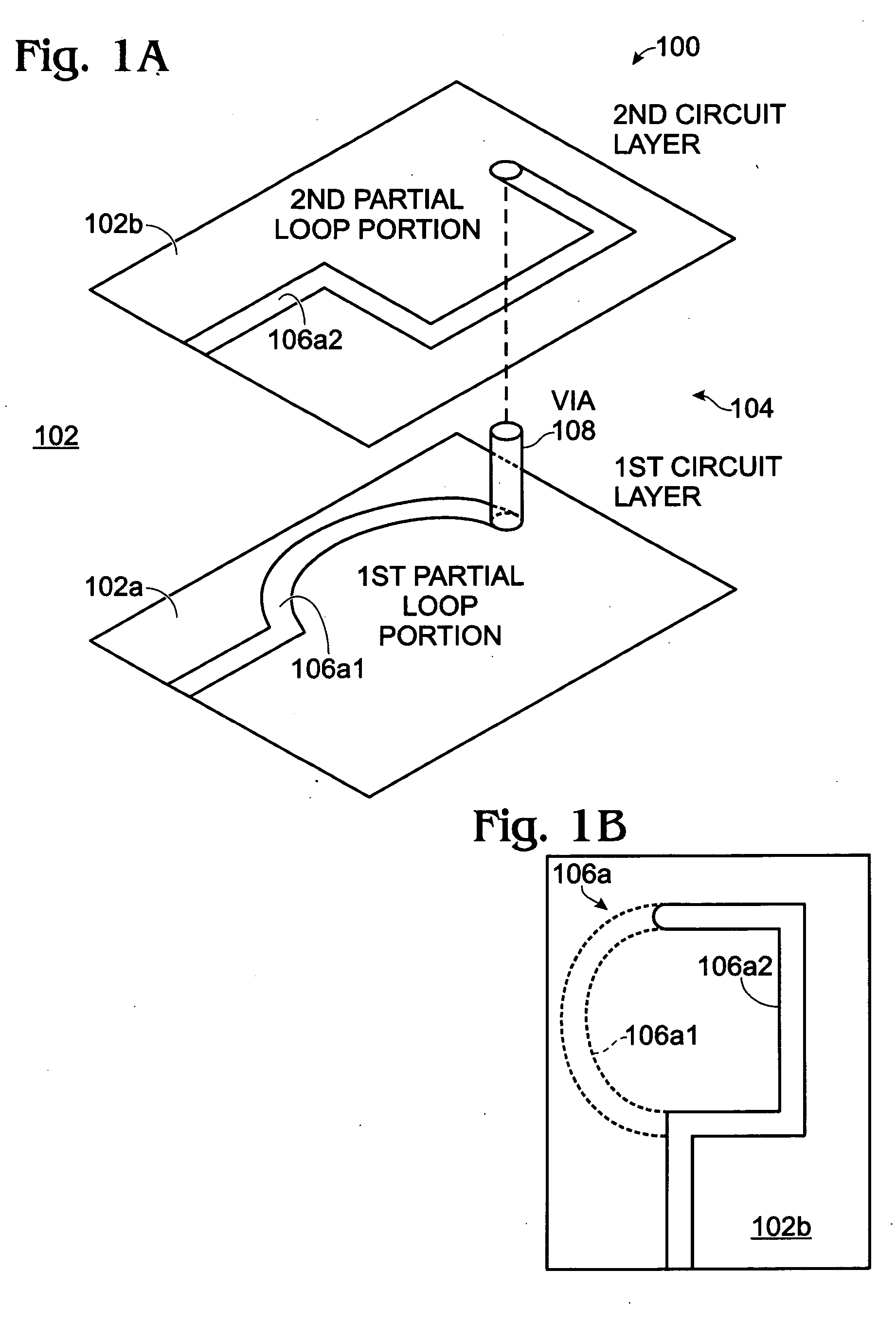

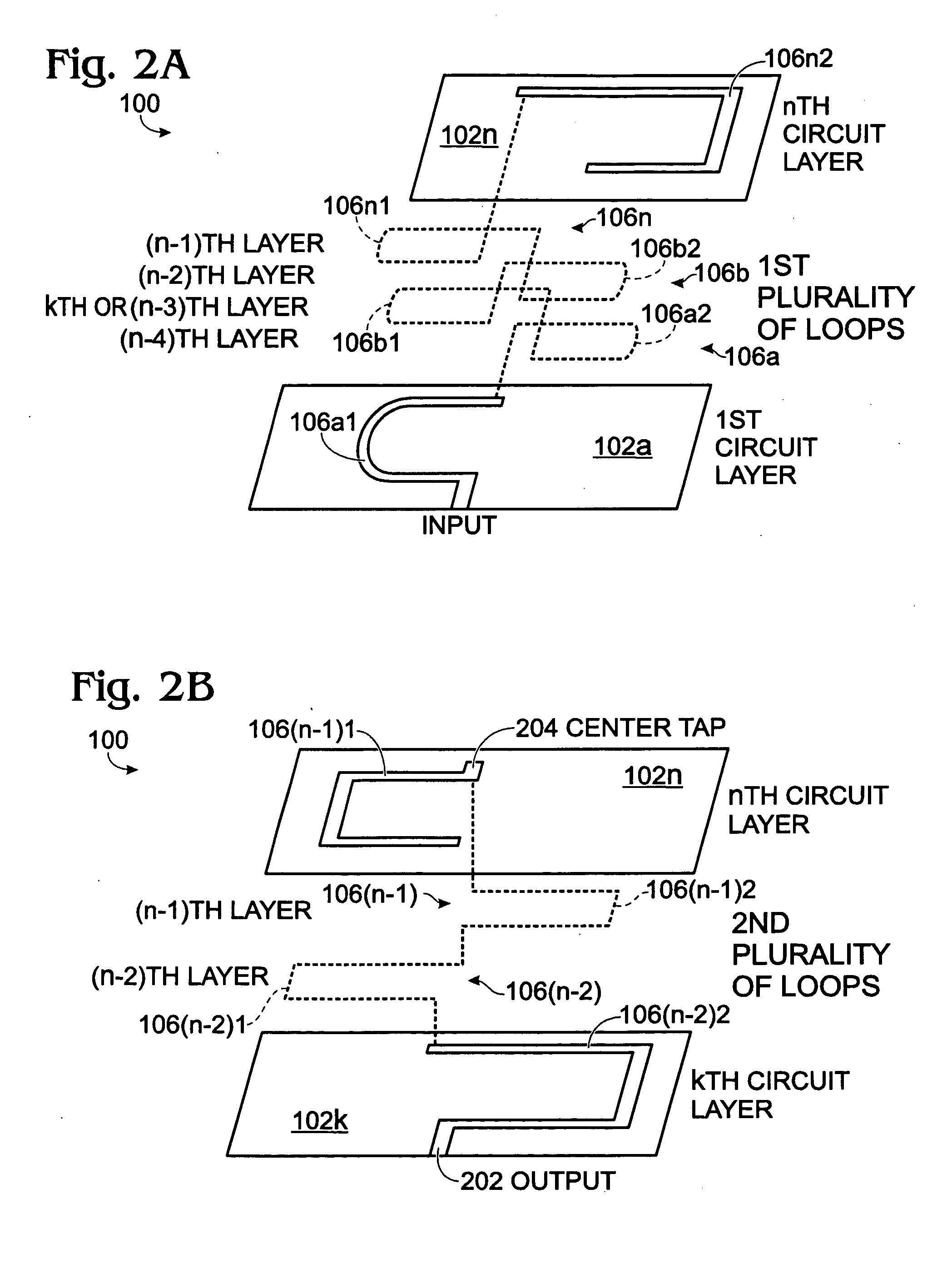

Integrated Circuit Multilevel Inductor

InactiveUS20100052837A1Reduce fabrication and assembly costReduce assemblySemiconductor/solid-state device detailsSolid-state devicesInductorIntegrated circuit

An integrated circuit (IC) multilevel inductor structure is provided. The IC multilayer inductor structure is made from an IC including a plurality of circuit layers, where the inductor is a three-dimensional (3D) loop formed over a plurality of the circuit layers. In a simple example, if the IC includes a first circuit layer and a second circuit layer, then the inductor 3D loop includes a first partial loop portion formed on the first circuit layer, a second partial loop portion formed on the second circuit layer, and a via connecting the first and second partial loop portions. More generally, the inductor typically includes a plurality of 3D loops. A first plurality of 3D loops is formed between the input and an nth circuit layer, and a second plurality of 3D loops is formed between the nth circuit layer and the output.

Owner:APPLIED MICRO CIRCUITS CORPORATION

Engine-mounted fan shroud and seal

ActiveUS20060280598A1Shorten assembly timeReducing fabricationPump componentsReaction enginesEngineeringEngine mount

Owner:GM GLOBAL TECH OPERATIONS LLC

Microstrip antenna having slot structure

InactiveUS20050253766A1Solve insufficient bandwidthReduce antenna sizeSimultaneous aerial operationsRadiating elements structural formsEngineeringSpecular reflection

A microstrip antenna having a slot structure is disclosed for providing a sufficient bandwidth so as to meet the antenna requirements. The microstrip antenna is composed of a base board (such as a printed circuit board) and a microstrip patch radiator having the slot structure, wherein the microstrip patch radiator is formed on the base board. The slot structure is composed of an L-shaped slot and an inverted reversed-L-shaped slot, wherein the L-shaped slot and the inverted reversed-L-shaped slot are mirror-reflected to each other symmetrically to a point. One end of each of the L-shaped and inverted reversed-L-shaped slots is connected to an extension slot.

Owner:ARCADYAN

Mounting structure for motor controller of heat-dissipating device

ActiveUS7291949B2Optimize the installation structureLow costDC commutatorStructural associationMagnetic polesMotor controller

A modified mounting structure for a heat-dissipating device. The heat-dissipating device has a motor and a seat with a slot mounted on a base or the cover portion of a stator thereof. The seat secures a motor controller of the heat-dissipating device detecting phase changes of the magnetic poles of the motor. The structure of a heat-dissipating device reduces required components, manufacturing cost and assembly time, and the control circuit is greatly simplified.

Owner:DELTA ELECTRONICS INC

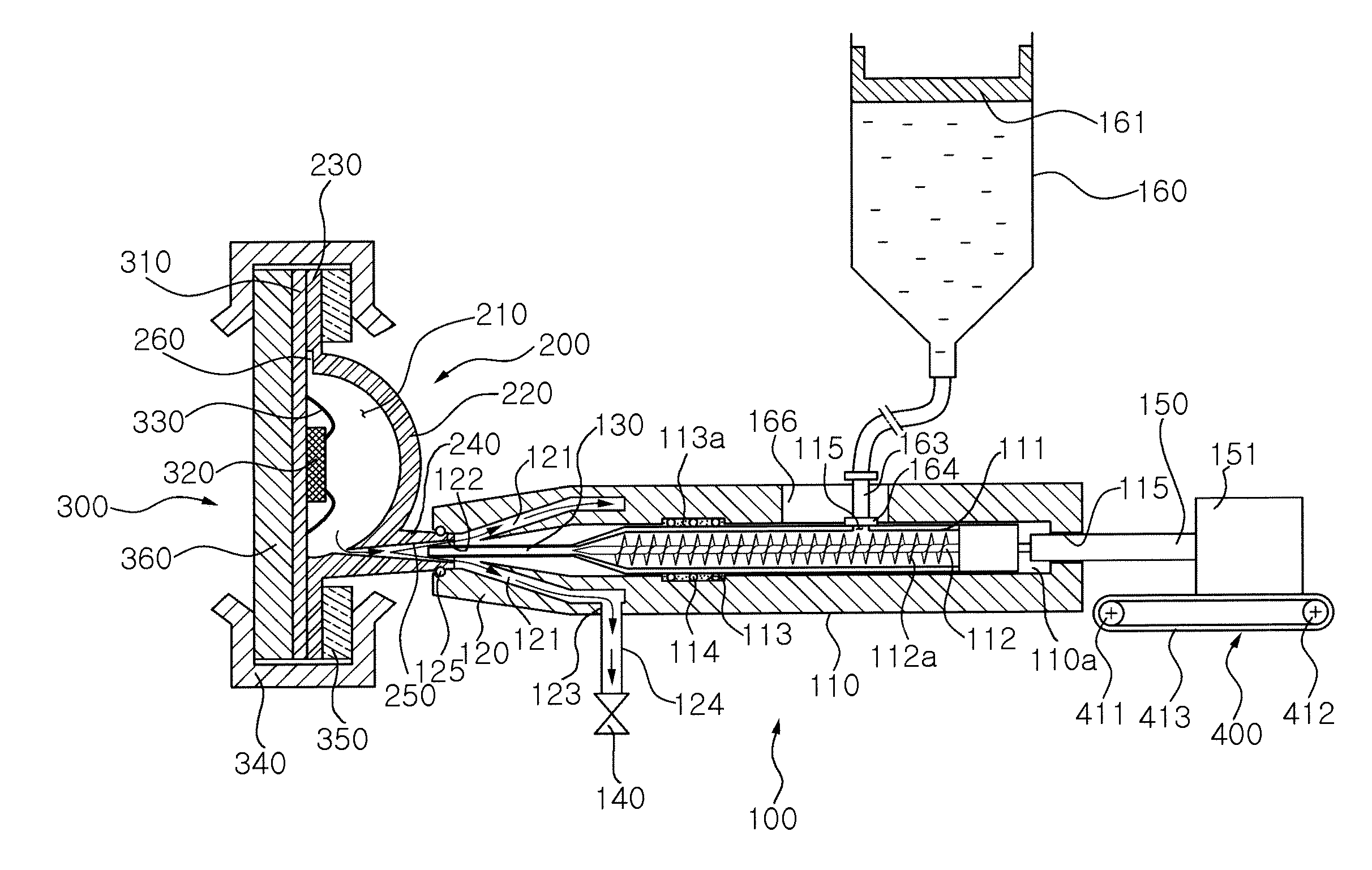

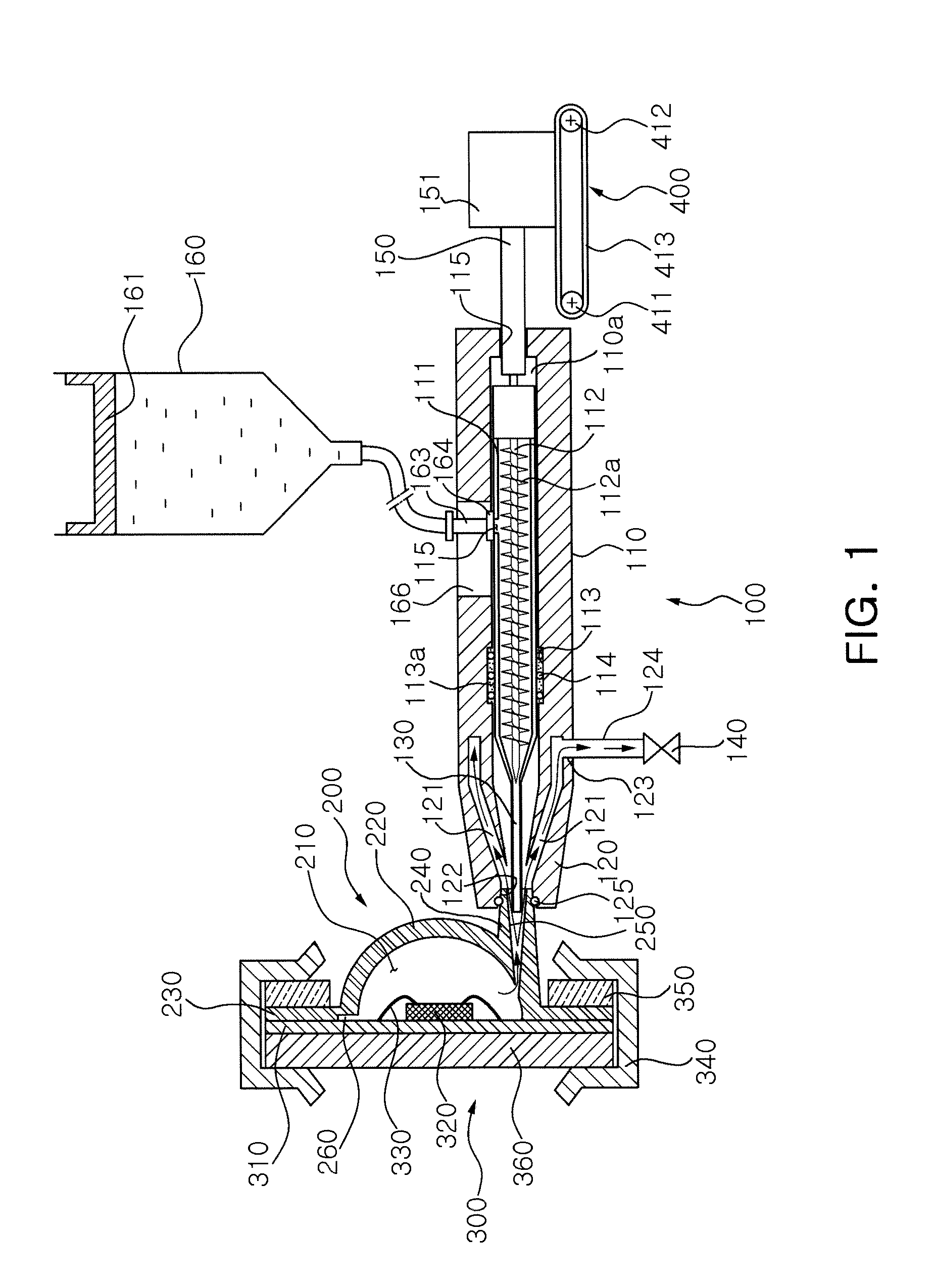

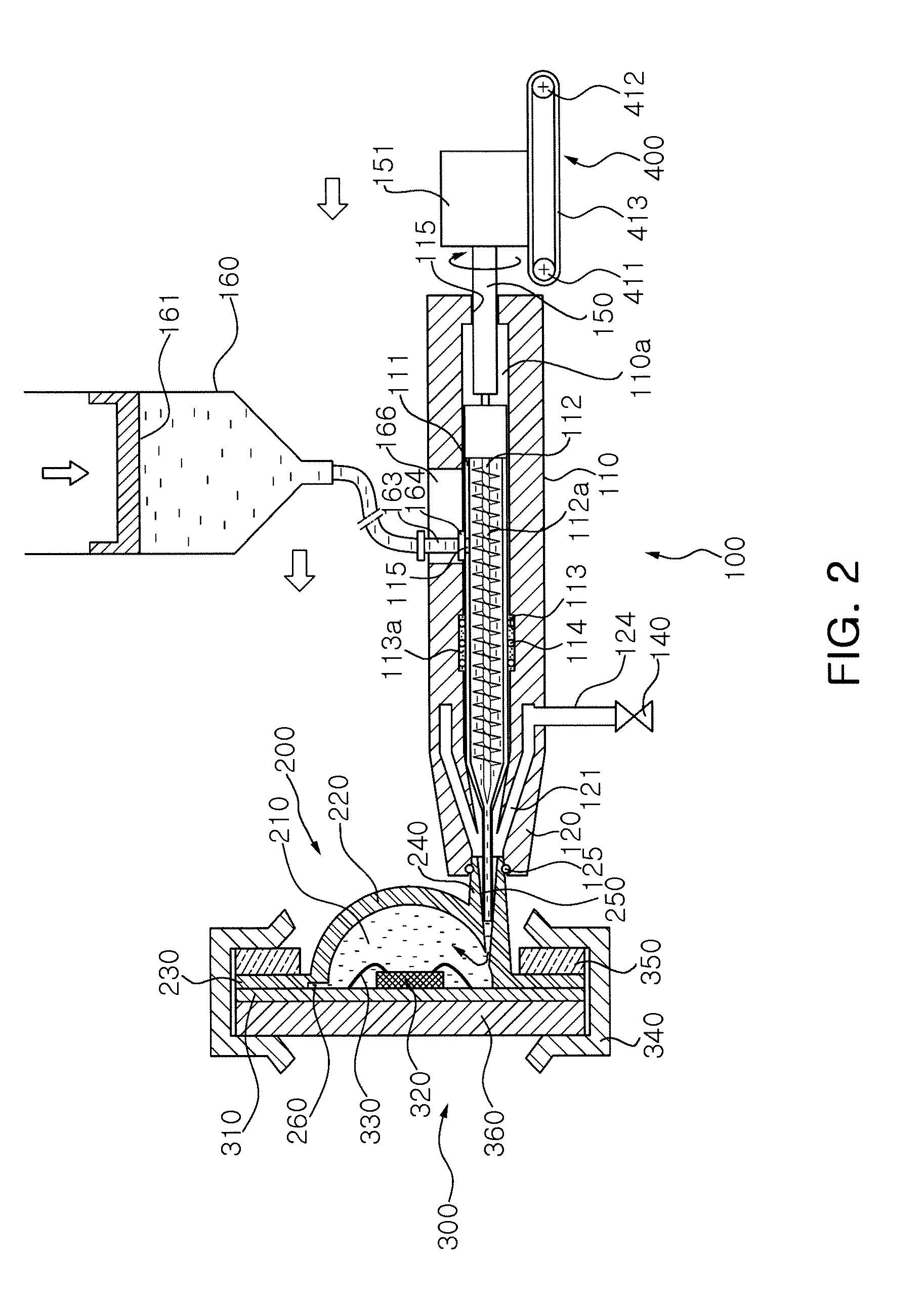

Lens fabrication apparatus and lens fabrication method using the same

InactiveUS20130049239A1High dimensional accuracyGeneration of void can be minimizedOptical articlesAuxillary shaping apparatusLight emissionPhysics

A lens fabrication apparatus includes: a lens mold having a connection portion formed on one side thereof and disposed on a light emission surface of a light emitting unit; and a vacuum forming unit discharging air from within the lens mold to the outside through the connection portion or injecting a material into the lens mold through the connection portion.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package and fabrication method thereof

InactiveUS20070013066A1Pitch of the leads can be significantly reducedReducing fabricationSemiconductor/solid-state device detailsSolid-state devicesHeat pressEngineering

A semiconductor package and a fabrication method thereof are provided. The fabrication method includes the steps of preparing a chip having a plurality of conductive bumps formed on an active surface thereof; preparing a tape having a first surface and an opposed second surface, wherein the tape has a plurality of through holes at positions corresponding to the conductive bumps; forming an adhesive layer on the first surface of the tape, and disposing a plurality of leads on the second surface of the tape, so as to make an end of each of the leads covers a corresponding through hole; mounting the active surface of the chip to the adhesive layer on the first surface of the tape and allowing each of the conductive bumps to be received in a corresponding through hole; and performing a heat pressing process to bond the ends of the leads to the conductive bumps in the corresponding through holes. Thereby, an over-temperature problem that occurs during a heat pressing process in the conventional packaging technology can be solved.

Owner:SILICONWARE PRECISION IND CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com