Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76results about "Two-way amplifiers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

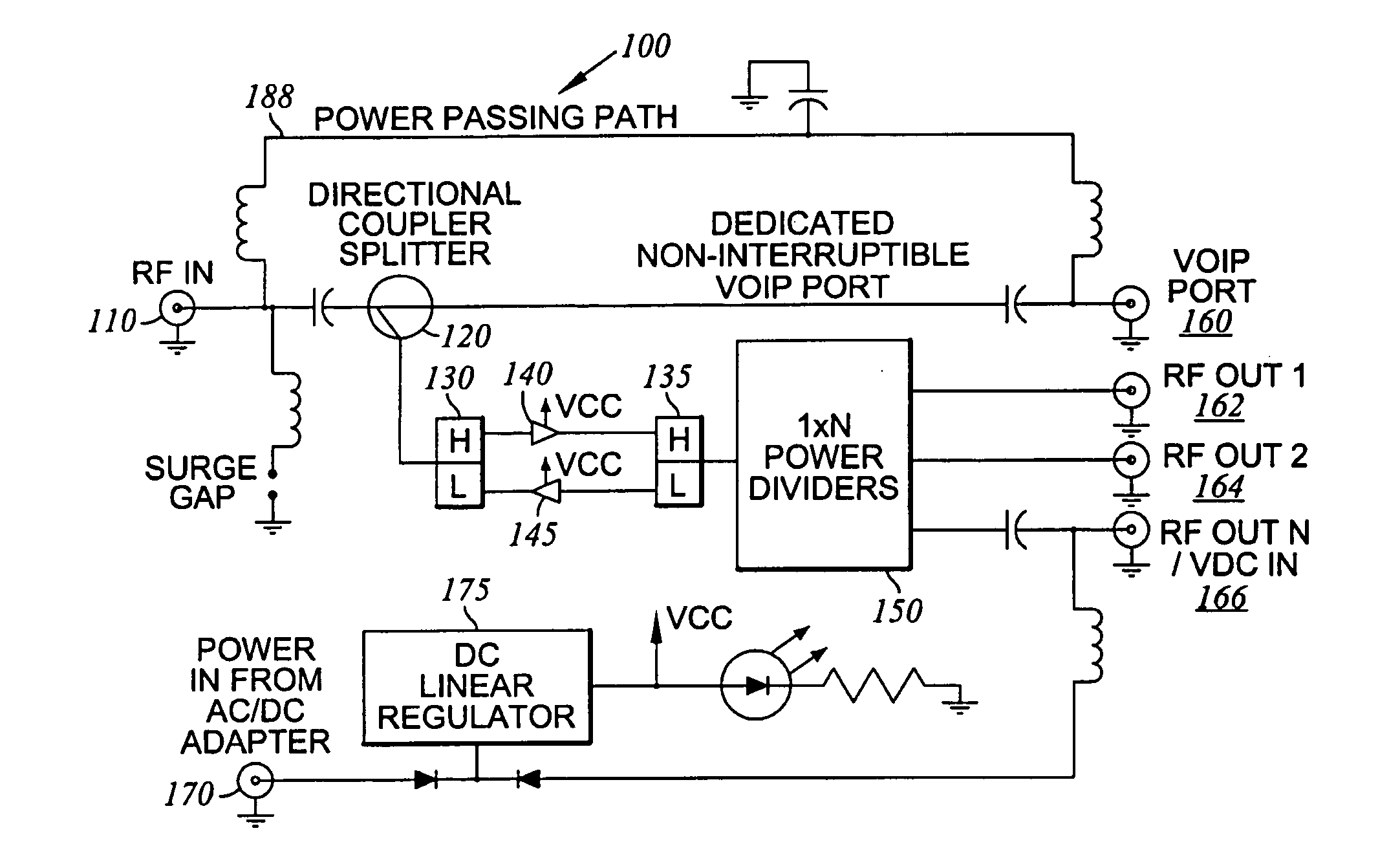

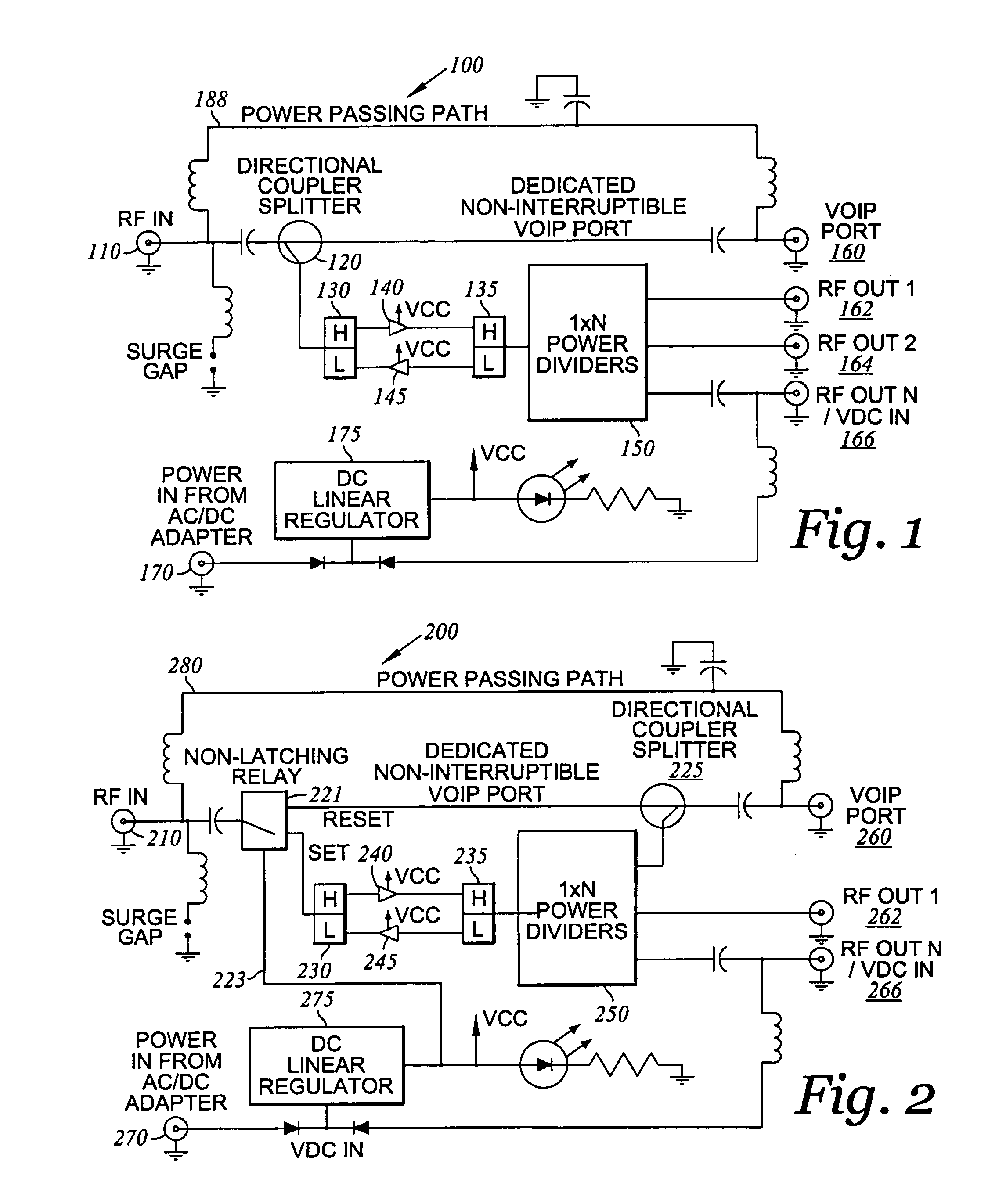

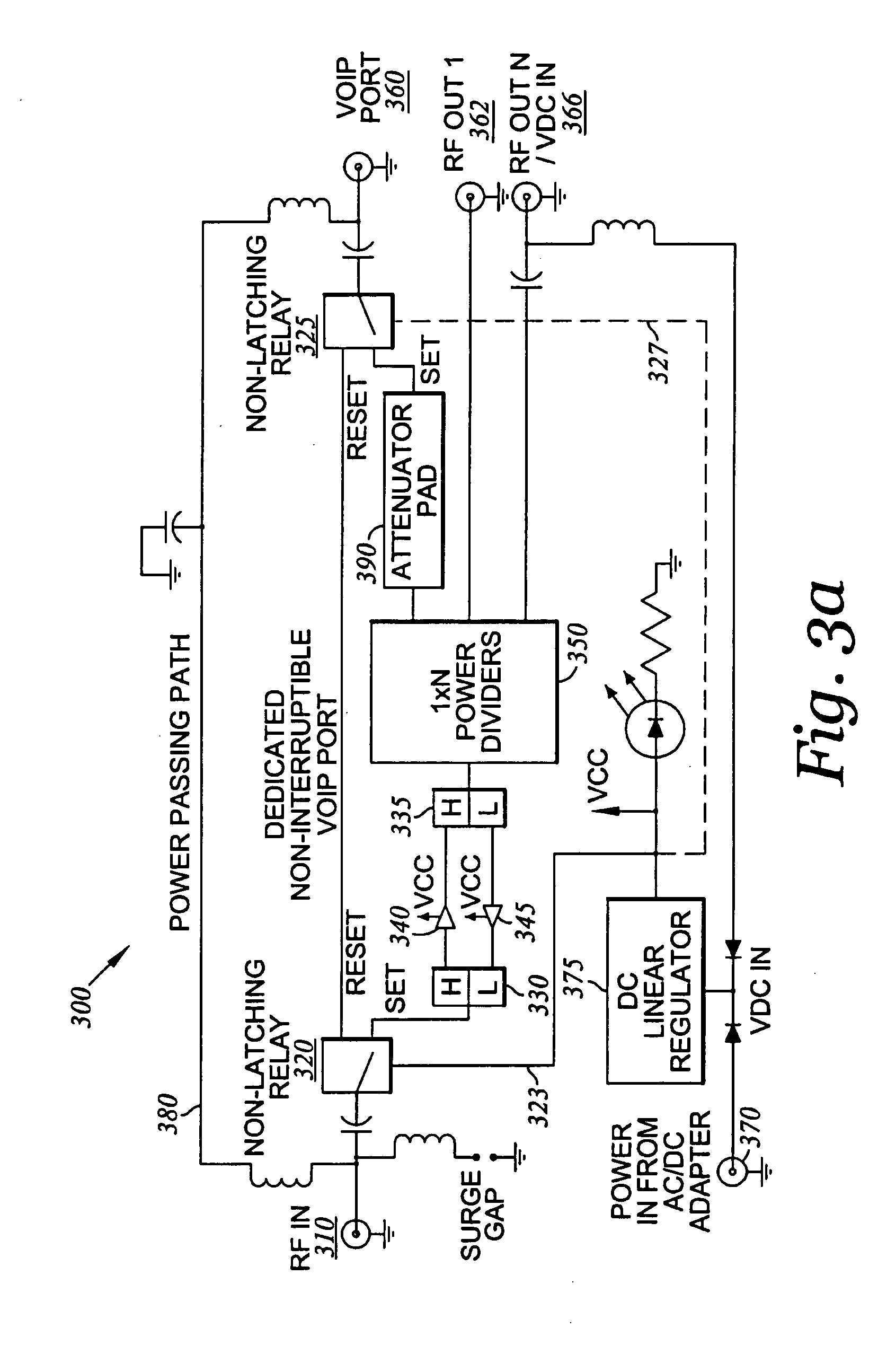

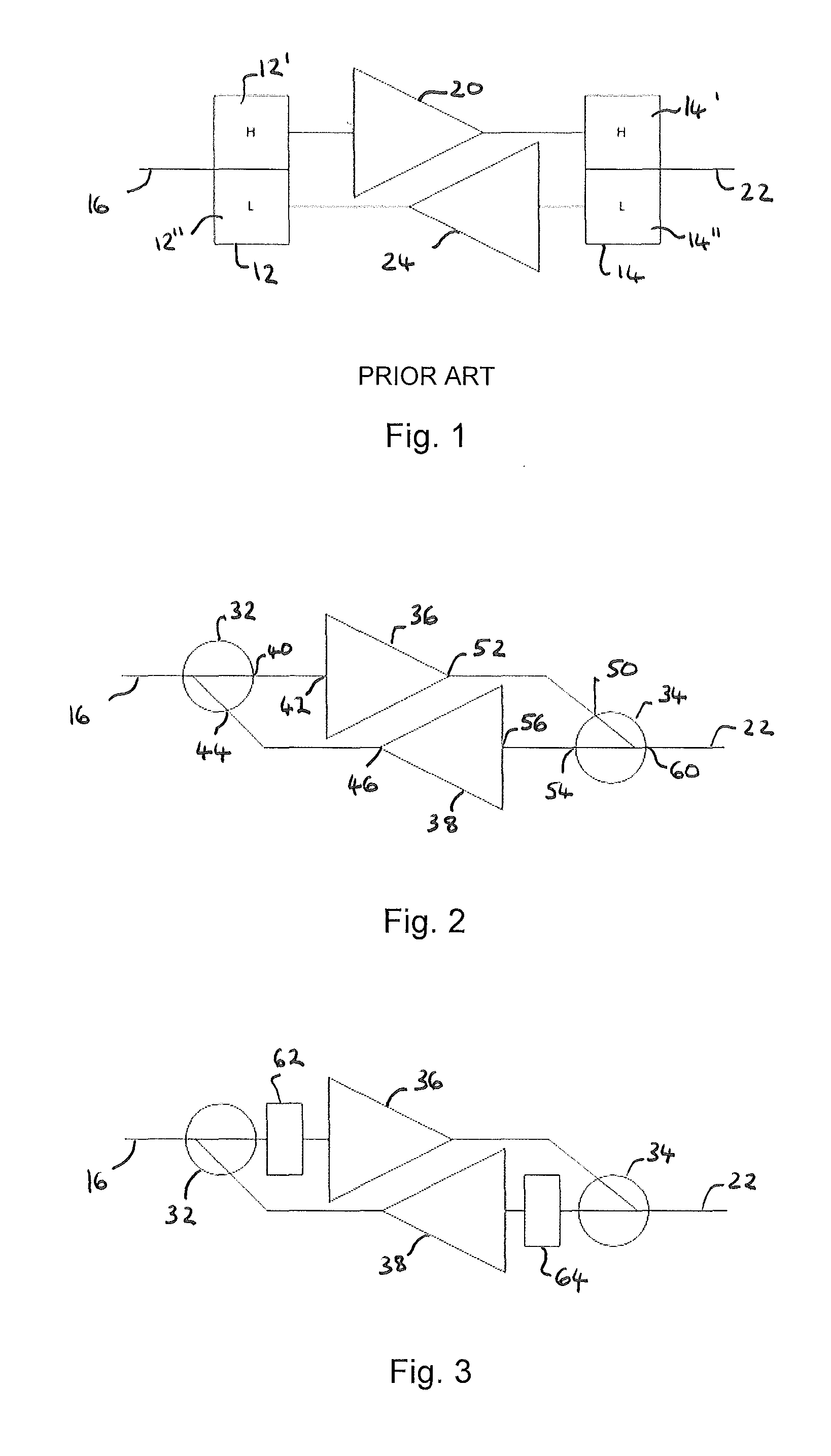

Bi-directional amplifier with non-interruptible port

InactiveUS20060205442A1Facilitate communicationGated amplifiersTwo-way amplifiersAudio power amplifierService provision

A bi-directional RF signal amplifier can be provided with a non-interruptible communication path for maintaining communication between an input and output port in the event of power failure. The amplifier may receive RF signals from a service provider or any other appropriate signal source through an input port. In residential applications, the amplifier may receive a composite RF signal comprising information for telephone, cable television (CATV), Internet, VoIP, and / or data communication from a service provider. The amplifier may increase the signal to a more useful level of approximately 20 dBmV / carrier and pass the amplified signal to one or more devices in communication with the amplifier through various output ports. In the event of power failure, a signal may still be passed through the non-interruptible communication path between the service provider and the communication device.

Owner:COMMSCOPE INC

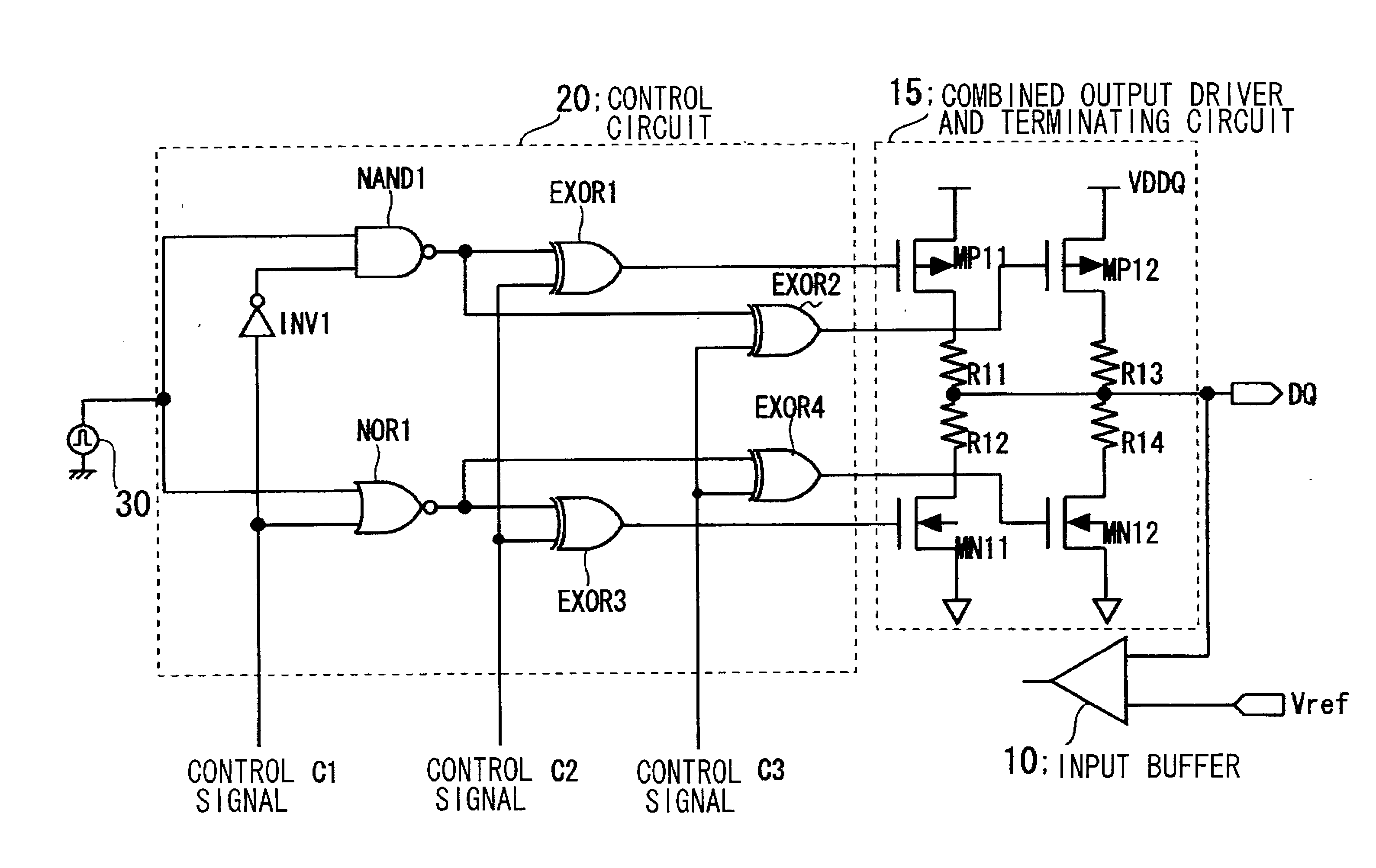

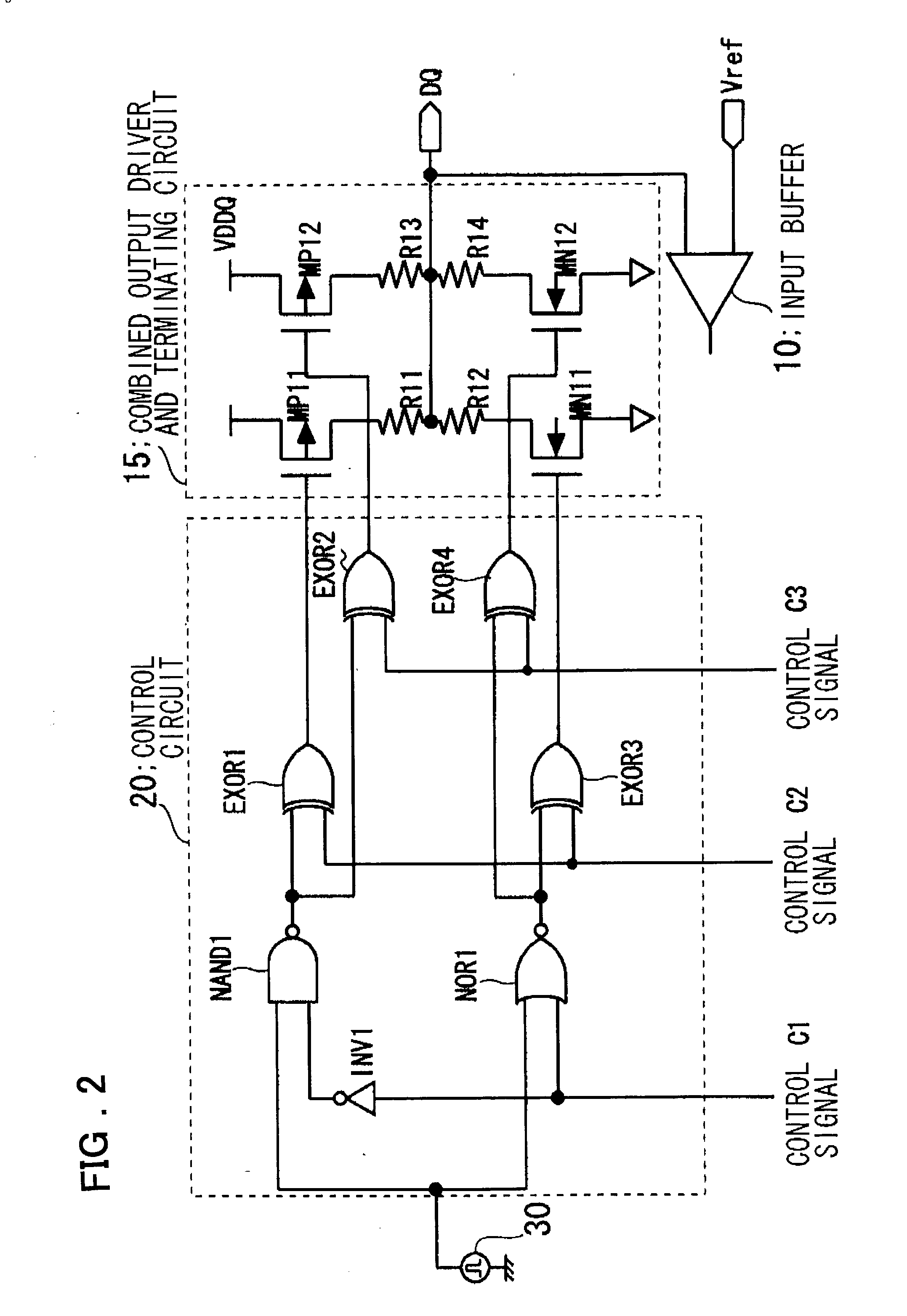

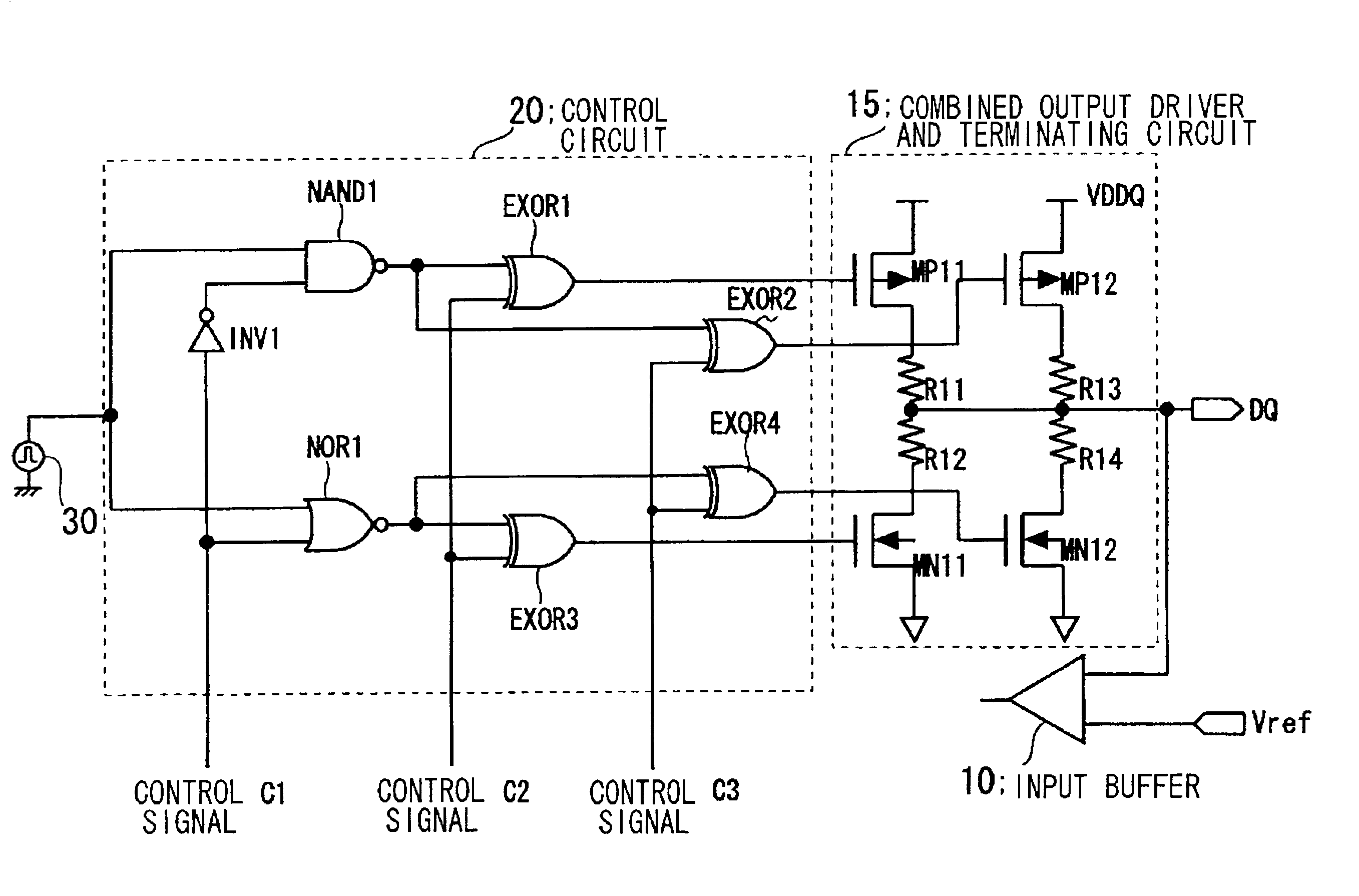

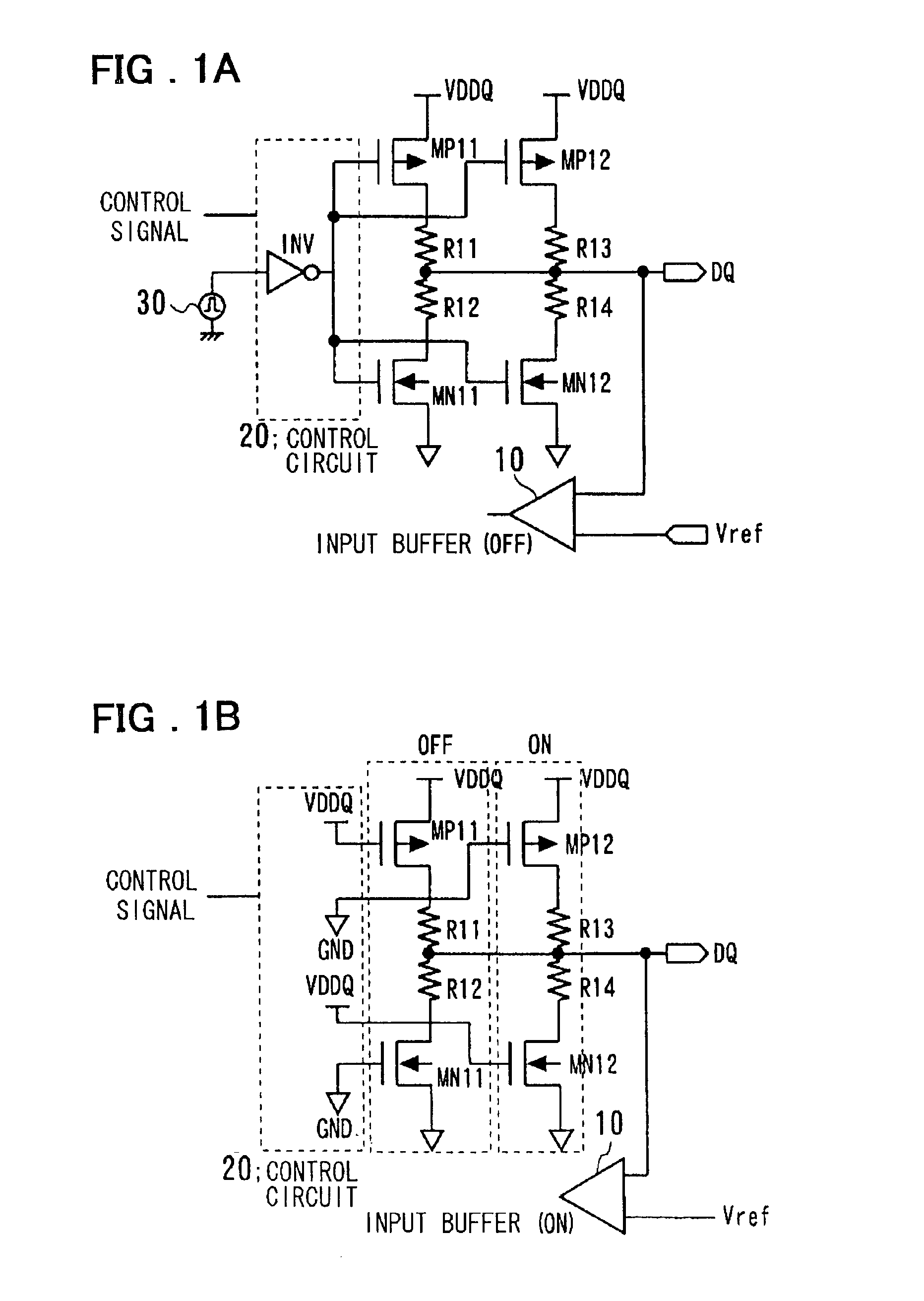

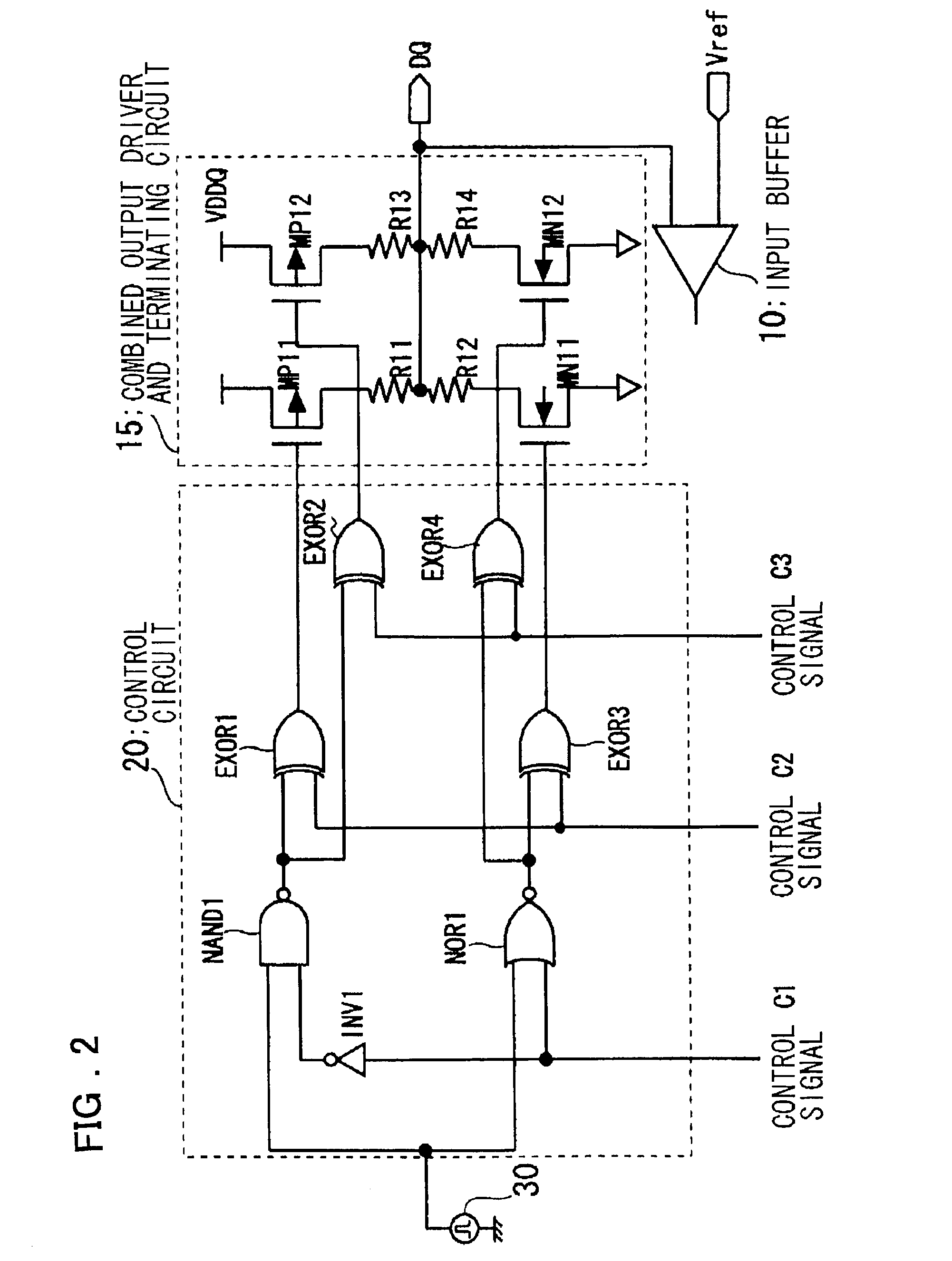

Input/output circuit, reference-voltage generating circuit, and semiconductor integrated circuit

InactiveUS20030080774A1Reliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsEngineeringVoltage reference

Disclosed is an input / output circuit having a terminating circuit that contributes to a smaller chip area. The input / output includes an output buffer having a first series circuit, which comprises a first transistor and a resistor and a second series circuit, which comprises a second transistor and a resistor, connected in parallel between a high-potential power supply and an input / output pin, as well as a third series circuit, which comprises a third transistor and a resistor and a fourth series circuit, which comprises a fourth transistor and a resistor, connected in parallel between the input / output pin and a low-potential power supply. The input / output circuit further includes an input buffer having an input terminal connected to the input / output pin, and a control circuit which, at the time of a signal output, performs control for supplying a signal, which is obtained by inverting the logic of output data, to gates of the first to fourth transistors, and which, at the time of a signal input, performs control for supplying the gates of the first and third transistors with the high-potential power supply voltage and low-potential power supply voltage, respectively, and the gates of the second and fourth transistors with the low-potential power supply voltage and high-potential power supply voltage, respectively.

Owner:LONGITUDE LICENSING LTD

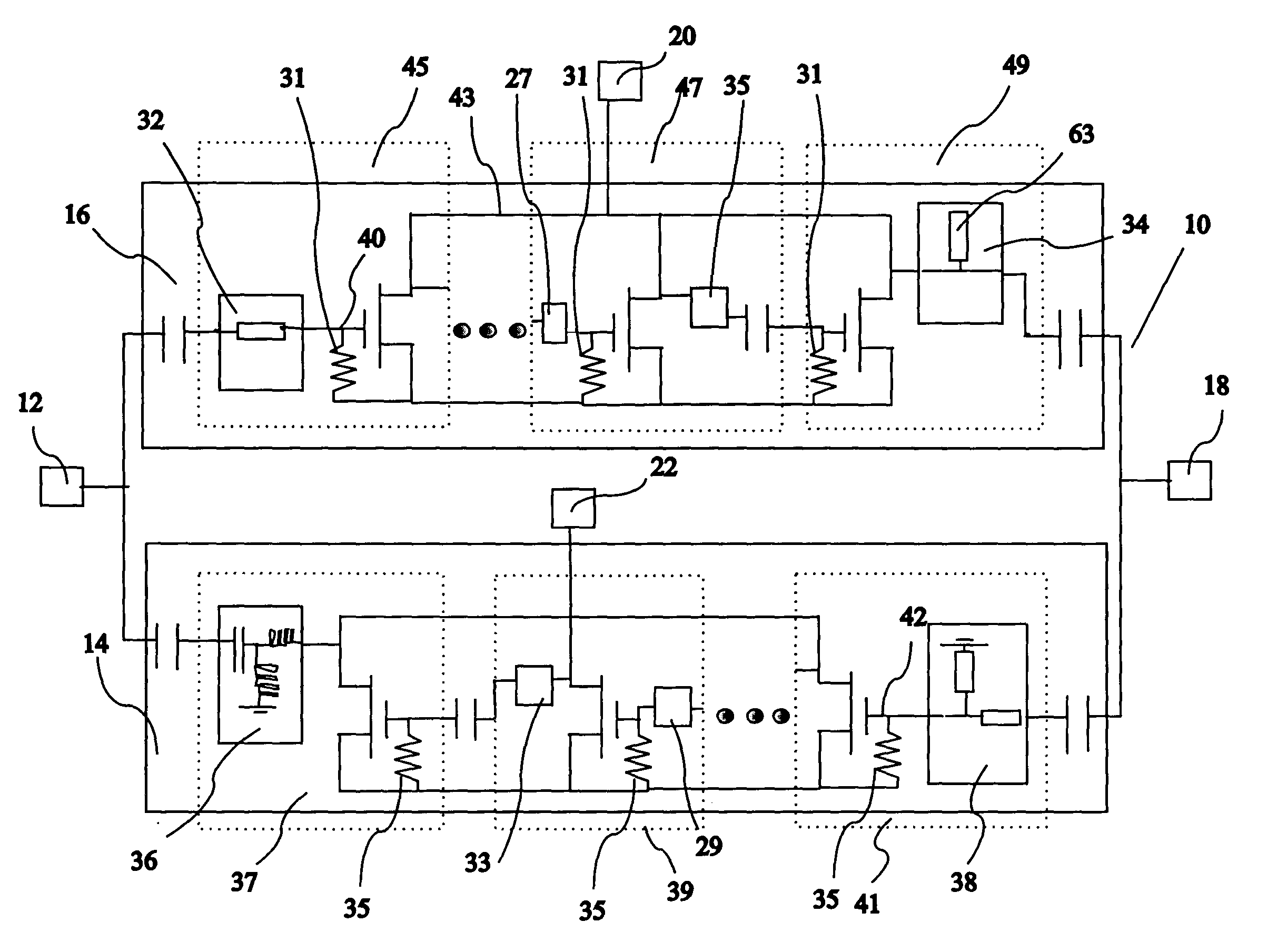

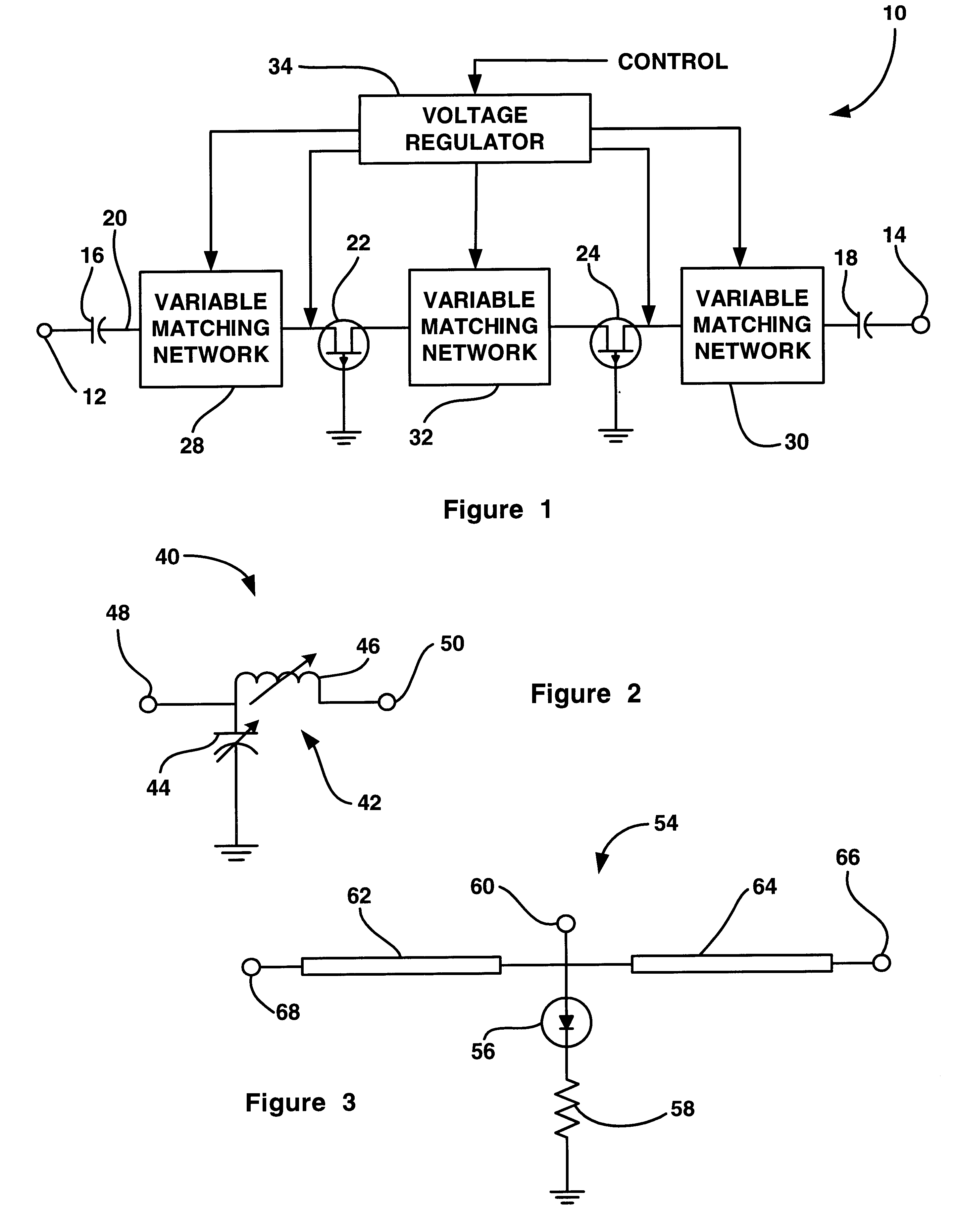

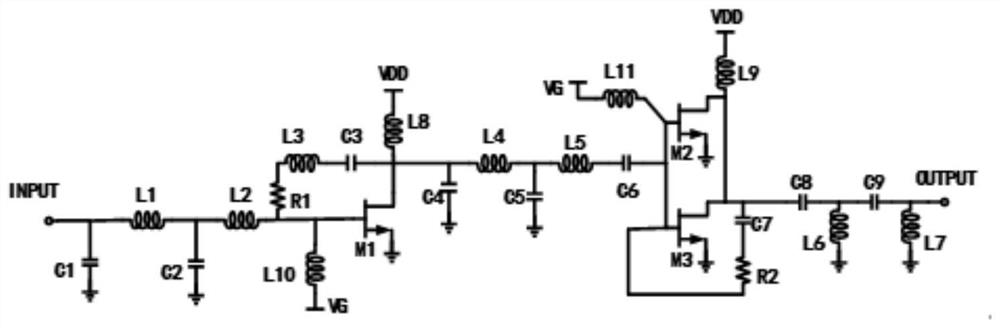

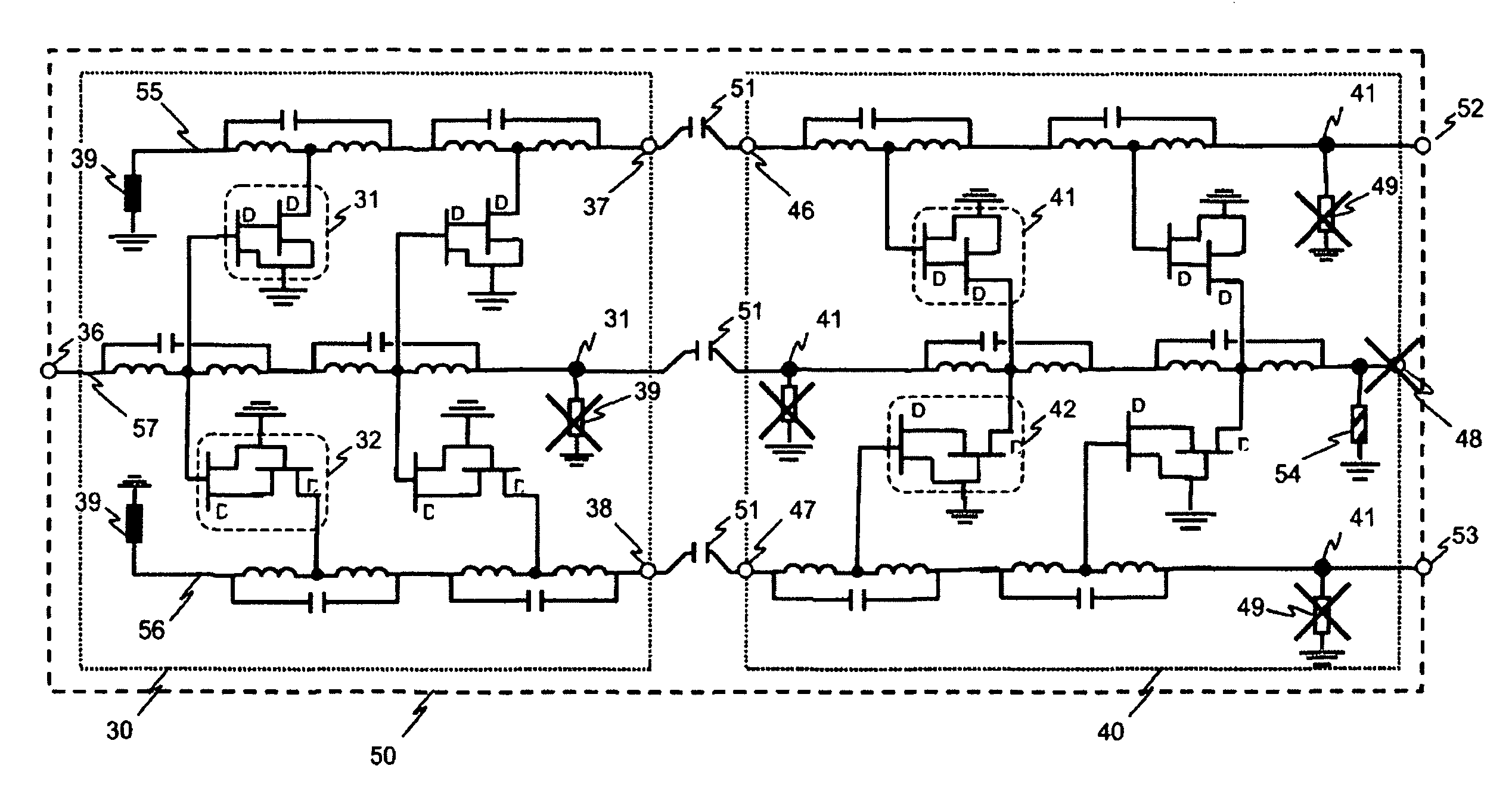

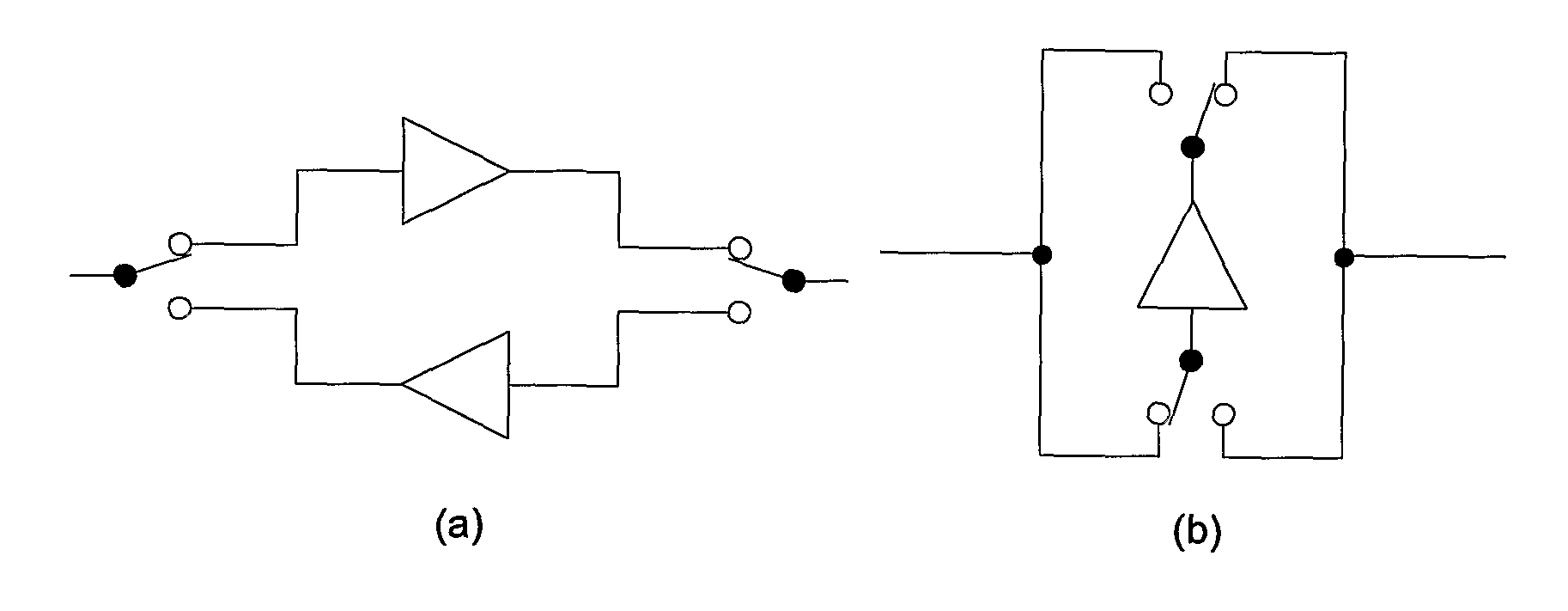

Asymmetric, optimized common-source bi-directional amplifier

ActiveUS20050026571A1Resonant long antennasAmplifiers wit coupling networksAudio power amplifierEngineering

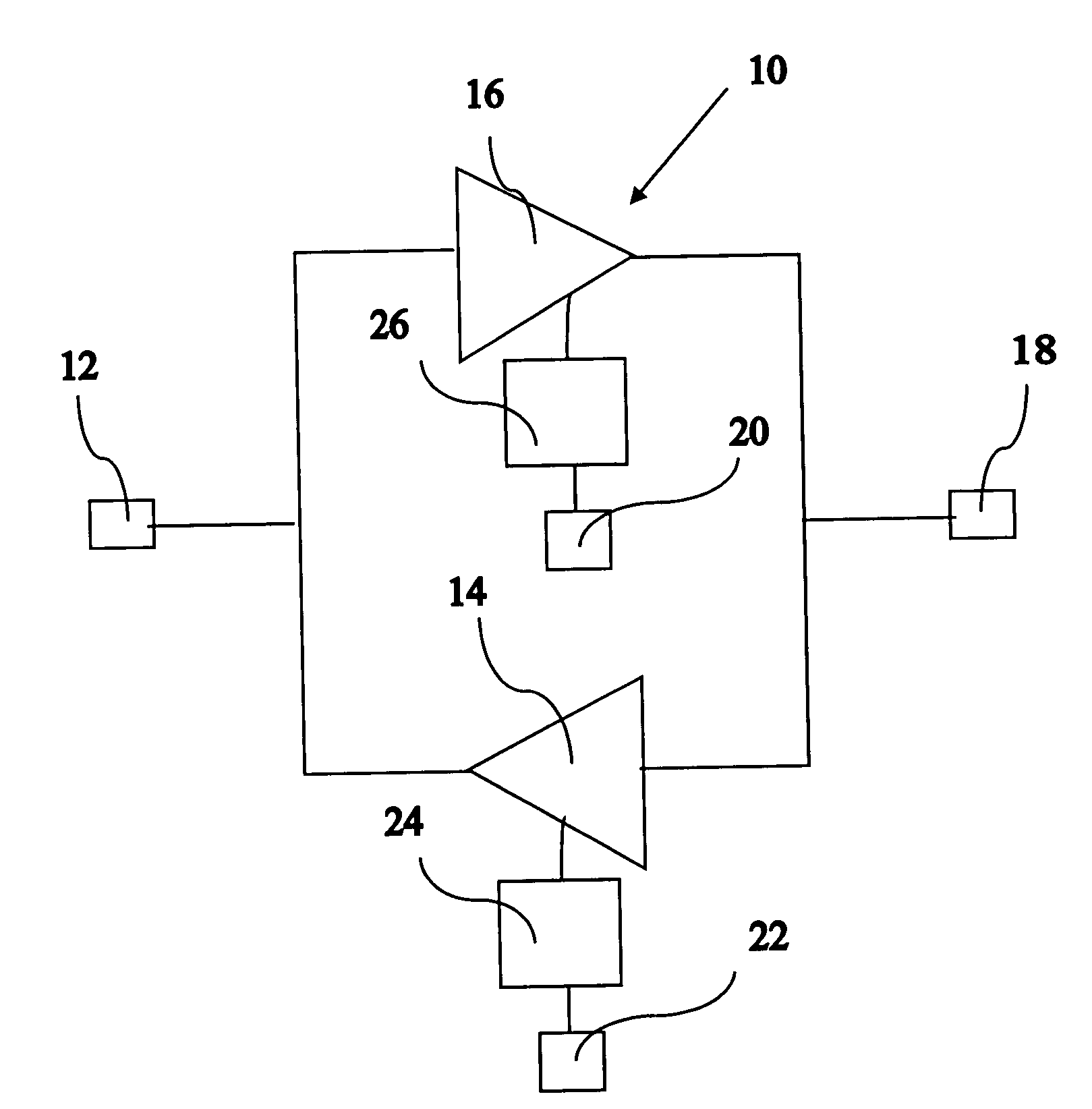

A common source, bi-directional microwave amplifier is described. More particularly, the present invention is a microwave, common source, bi-directional amplifier that includes a first amplification path and a second amplification path wherein the signal directional flow is controlled through the selective biasing of the first amplification path and the second amplification path. Each amplification path is designed to optimize desired performance. For signal flow through the first amplification path, the first amplification path is biased-on and the second path is biased-off. For signal flow through the second amplification path, the second amplification path is biased-on and the first path is biased-off.

Owner:NORTHROP GRUMMAN SYST CORP

Input/output circuit, reference-voltage generating circuit, and semiconductor integrated circuit

InactiveUS6853213B2Reliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsVoltage referenceExecution control

Owner:LONGITUDE LICENSING LTD

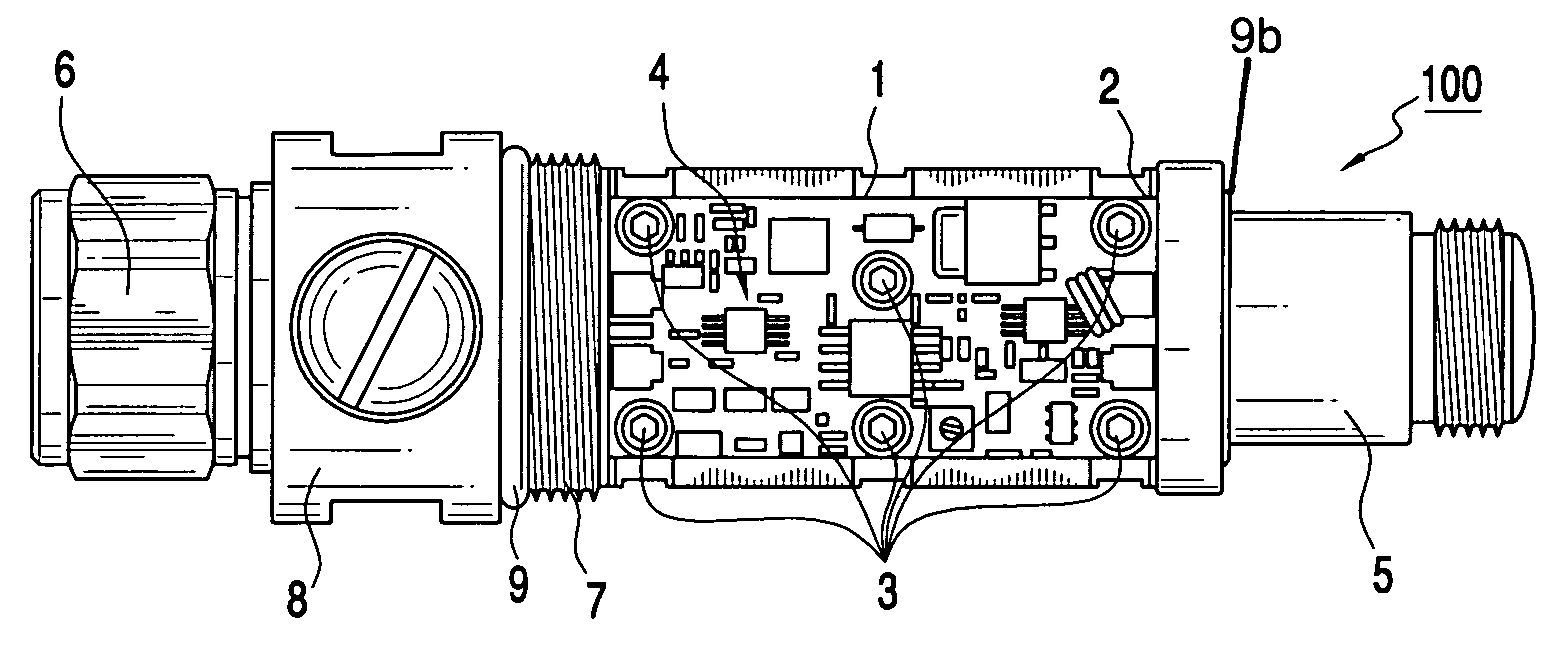

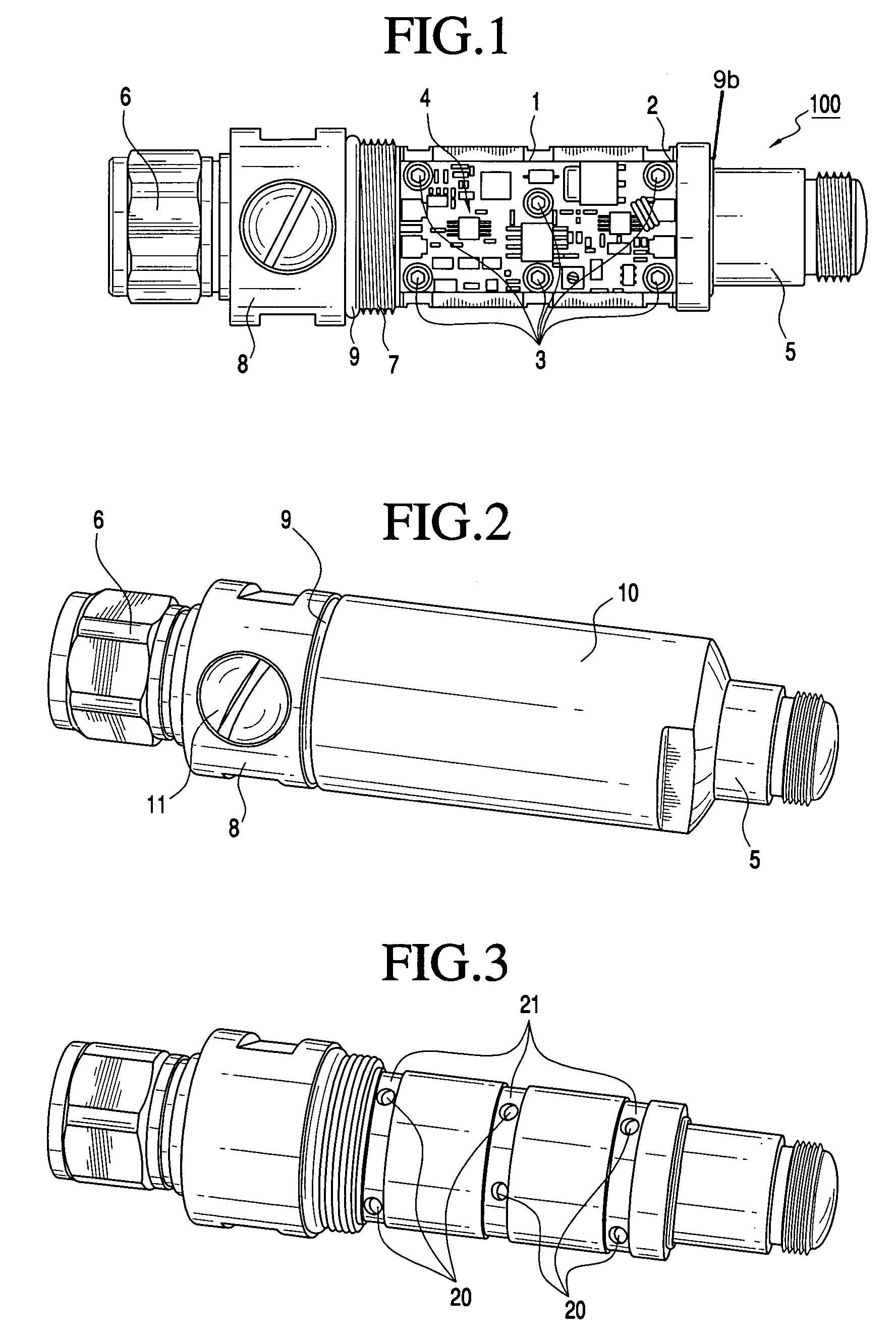

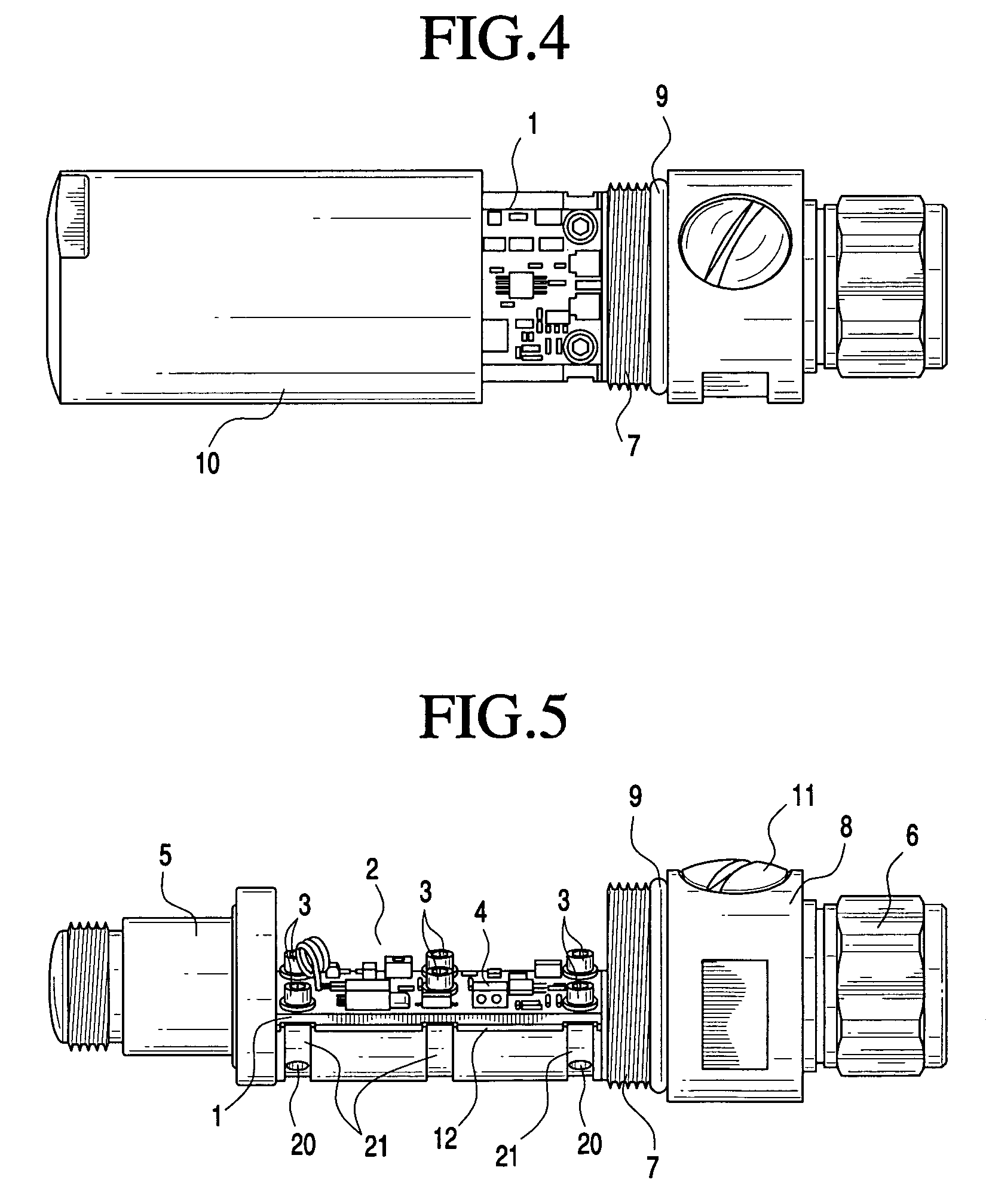

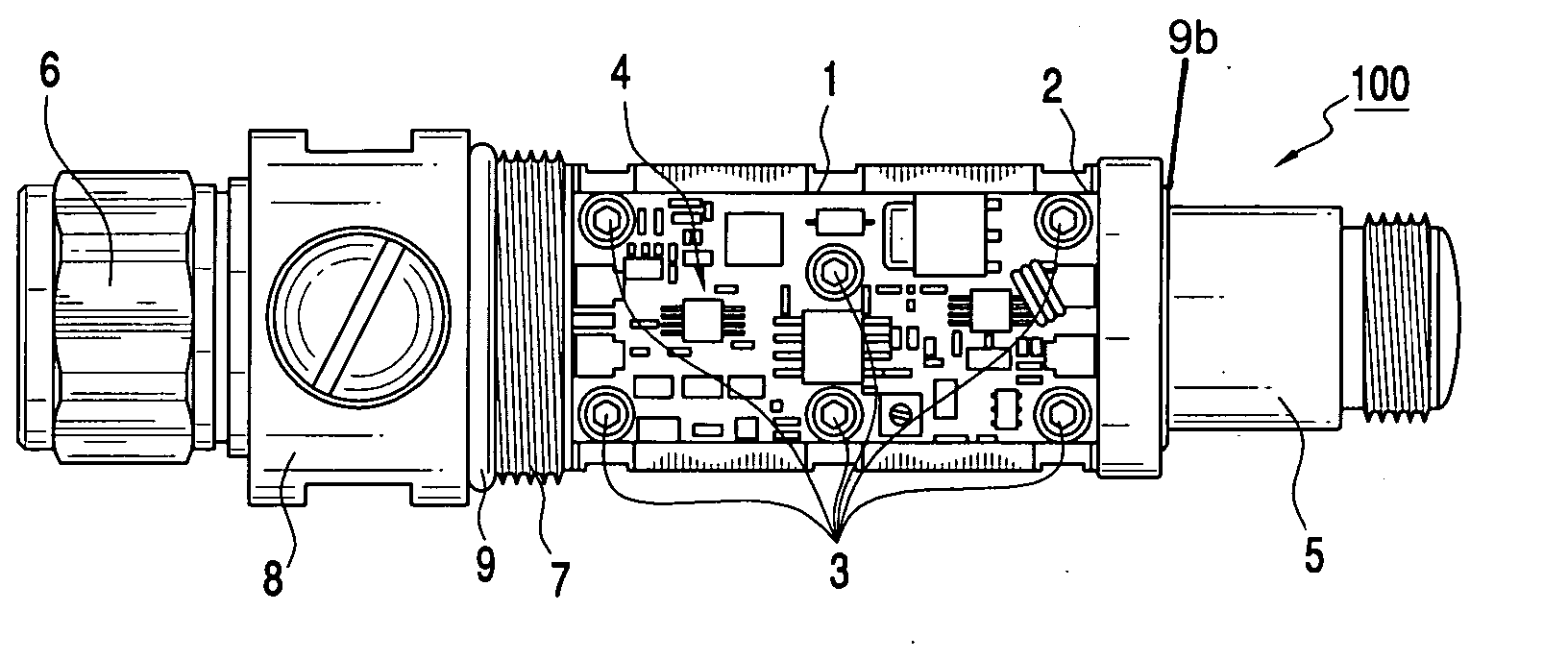

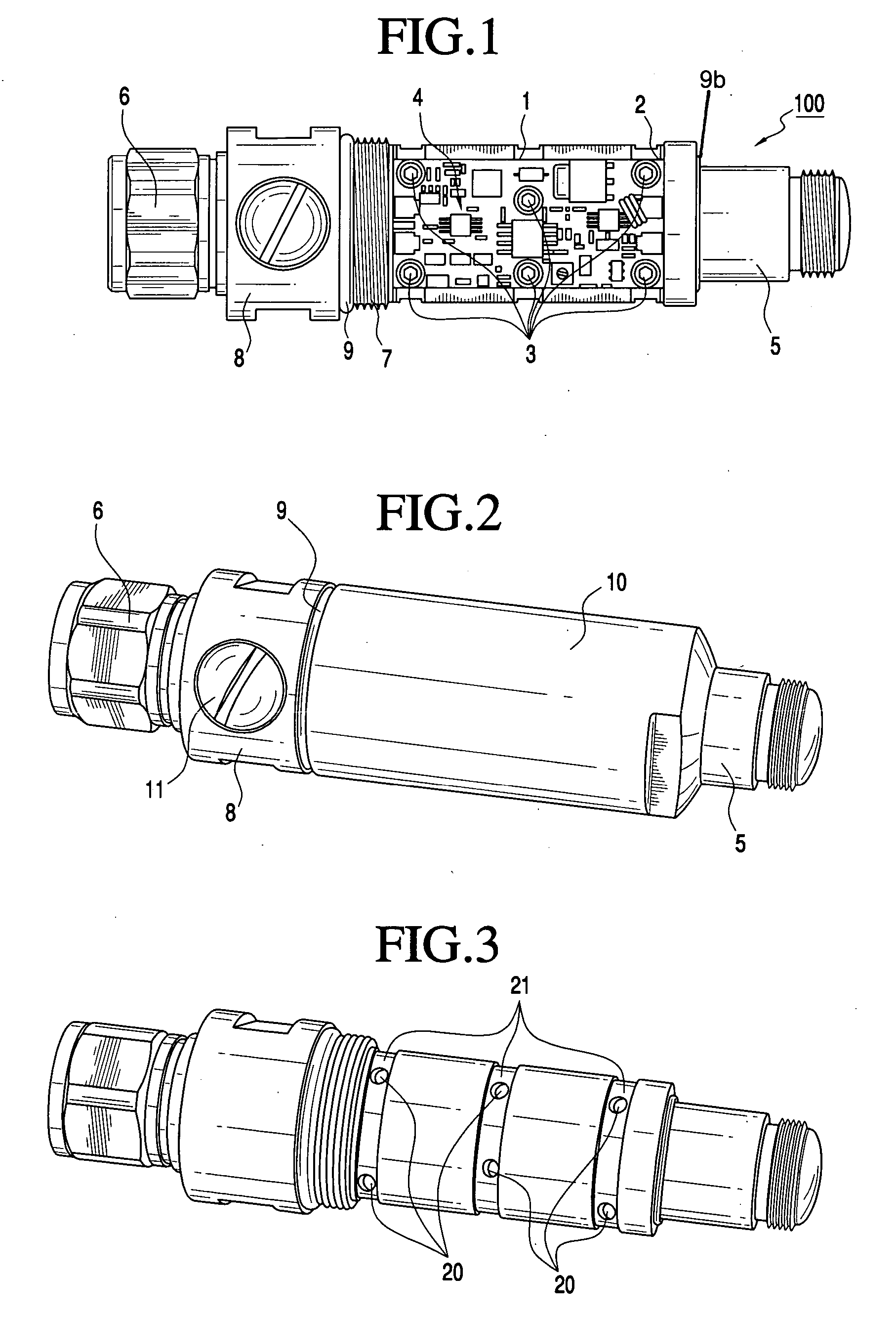

Miniature bidirectional amplifier

InactiveUS7430442B2Sufficient heat dissipation capabilityEasy-to-install and serviceGated amplifiersPower amplifiersAudio power amplifierCommunications system

An amplifier device for amplifying RF communication signals compatible with IEEE 802.11 standards. An amplifier circuit is housed within a cylindrical metal housing that provides excellent heat dissipation and requires no mounting hardware for installing the device within a communication system. The metal housing with an integrated lightning arrestor creates a watertight seal to protect the amplifier circuit from damage when installed outdoors and the amplifier circuit is compatible with both 2.4 GHz and 5.8 GHz frequency applications.

Owner:HE SHIPING +3

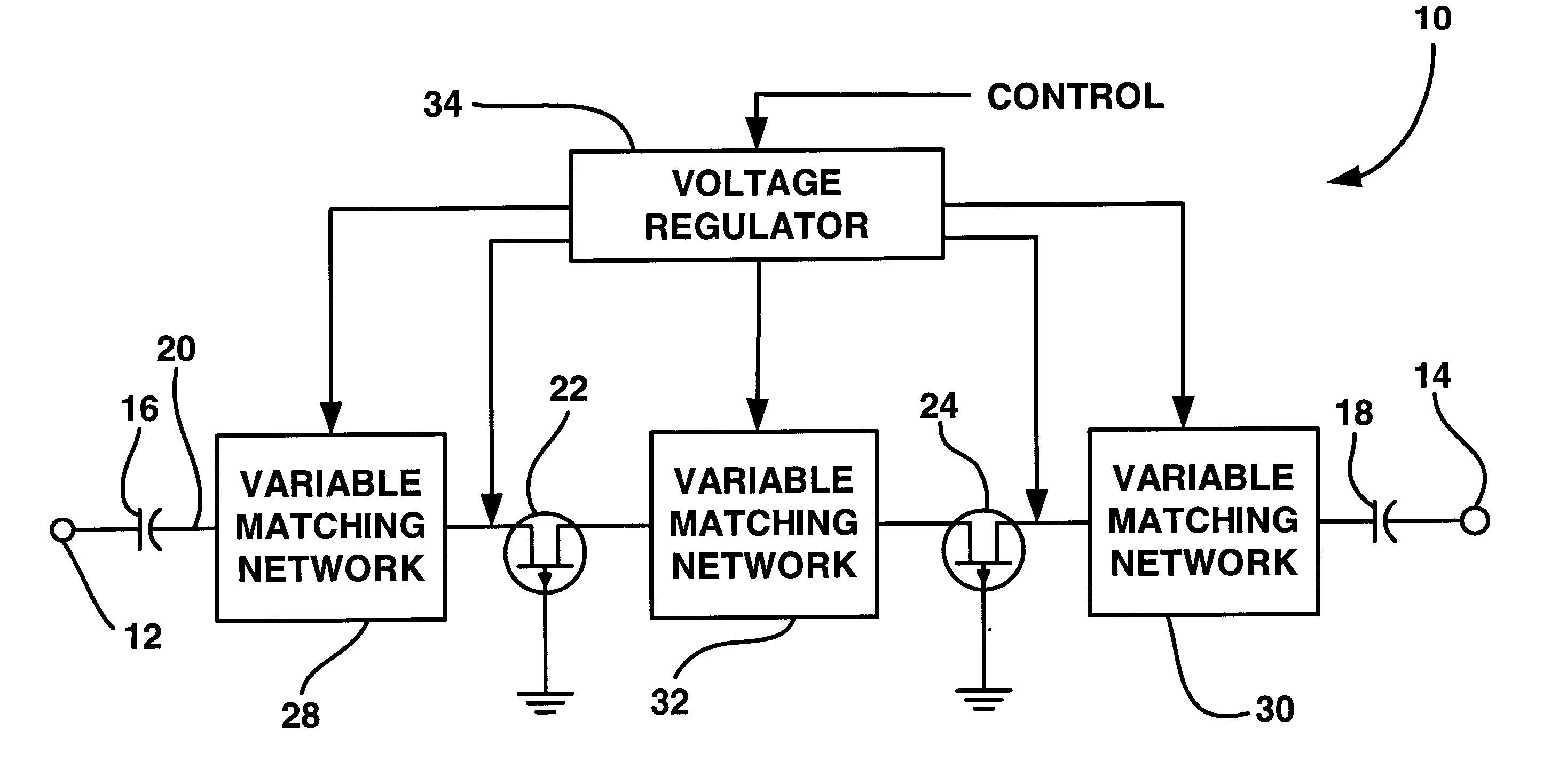

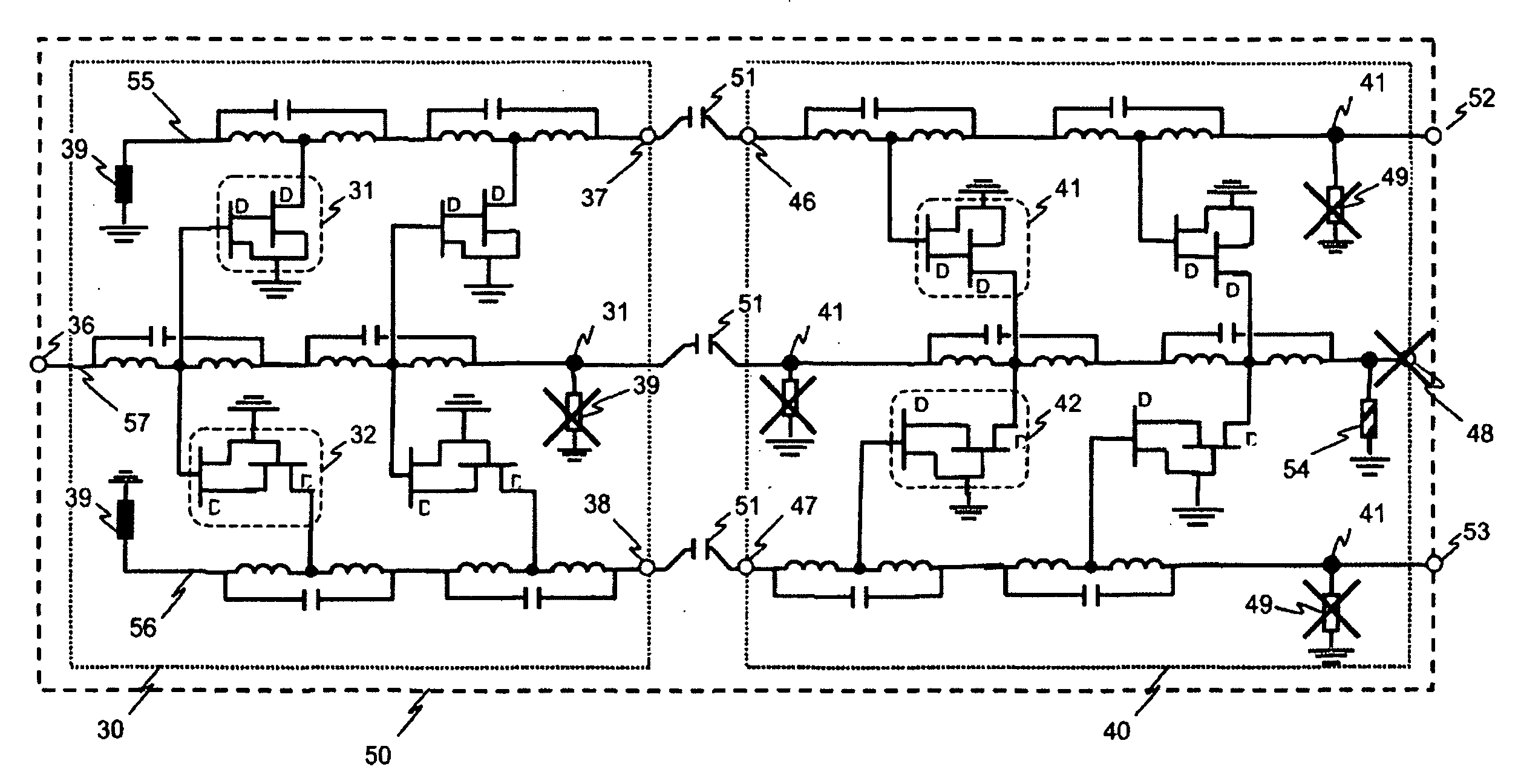

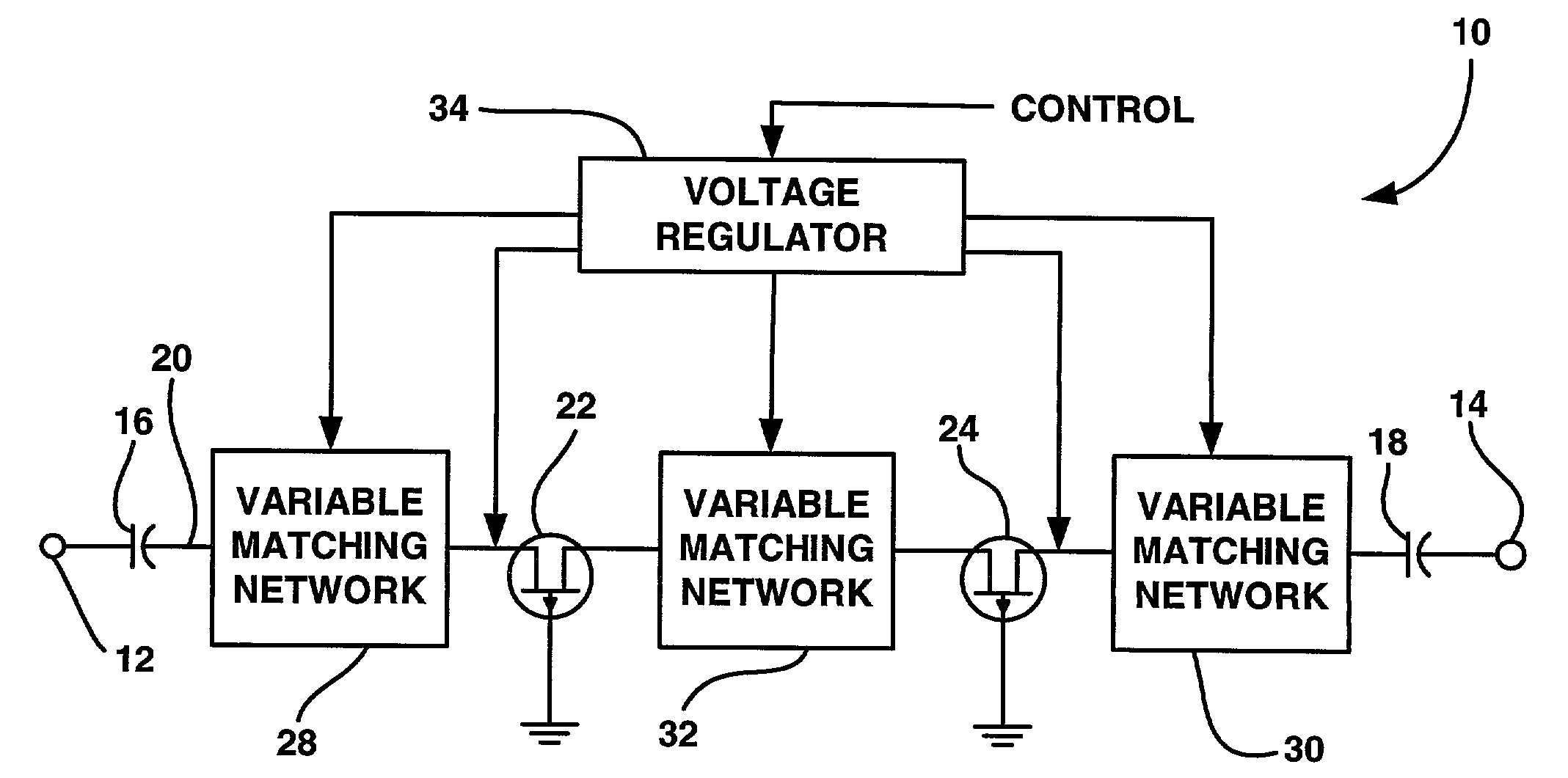

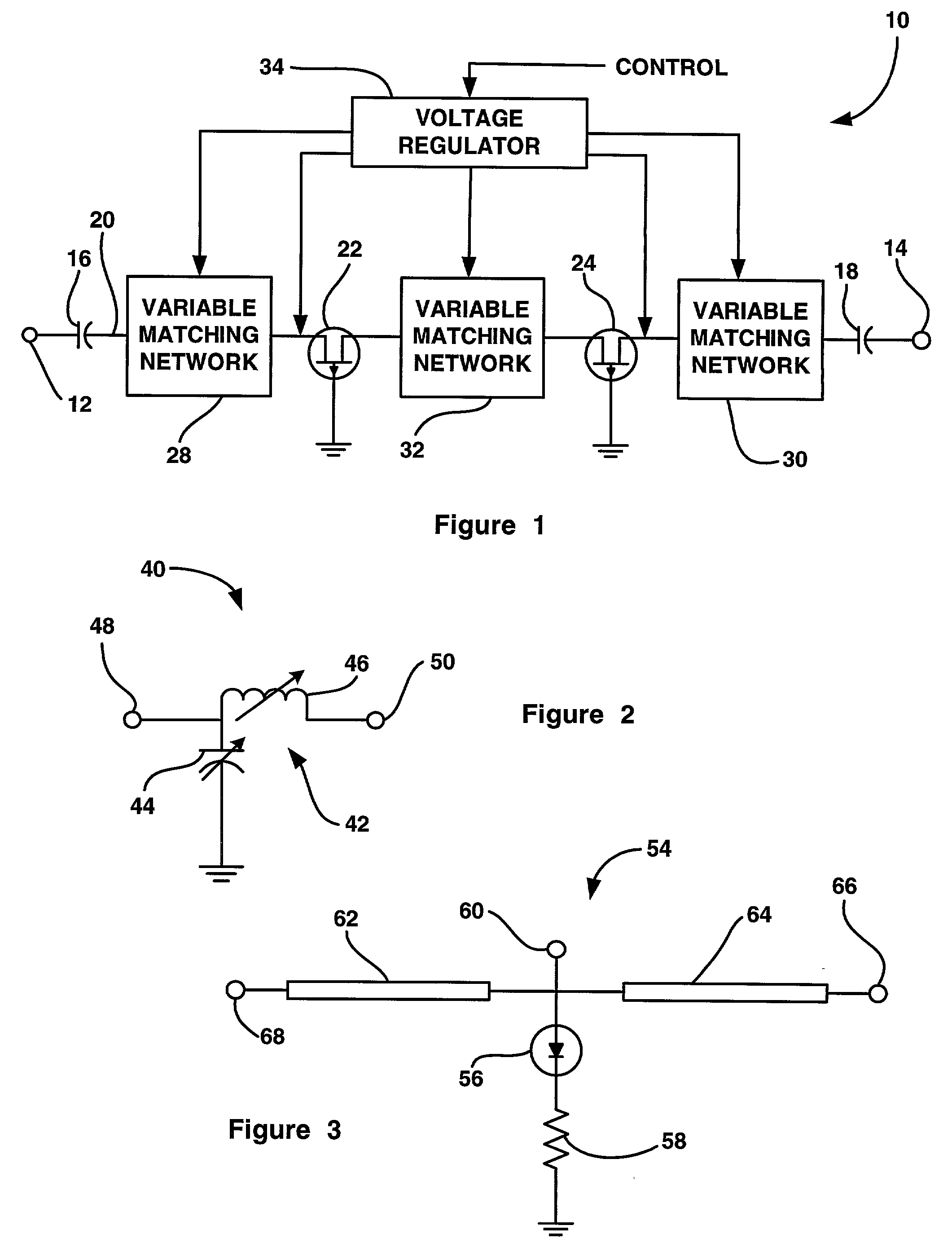

Asymmetric, voltage optimized, wideband common-gate bi-directional MMIC amplifier

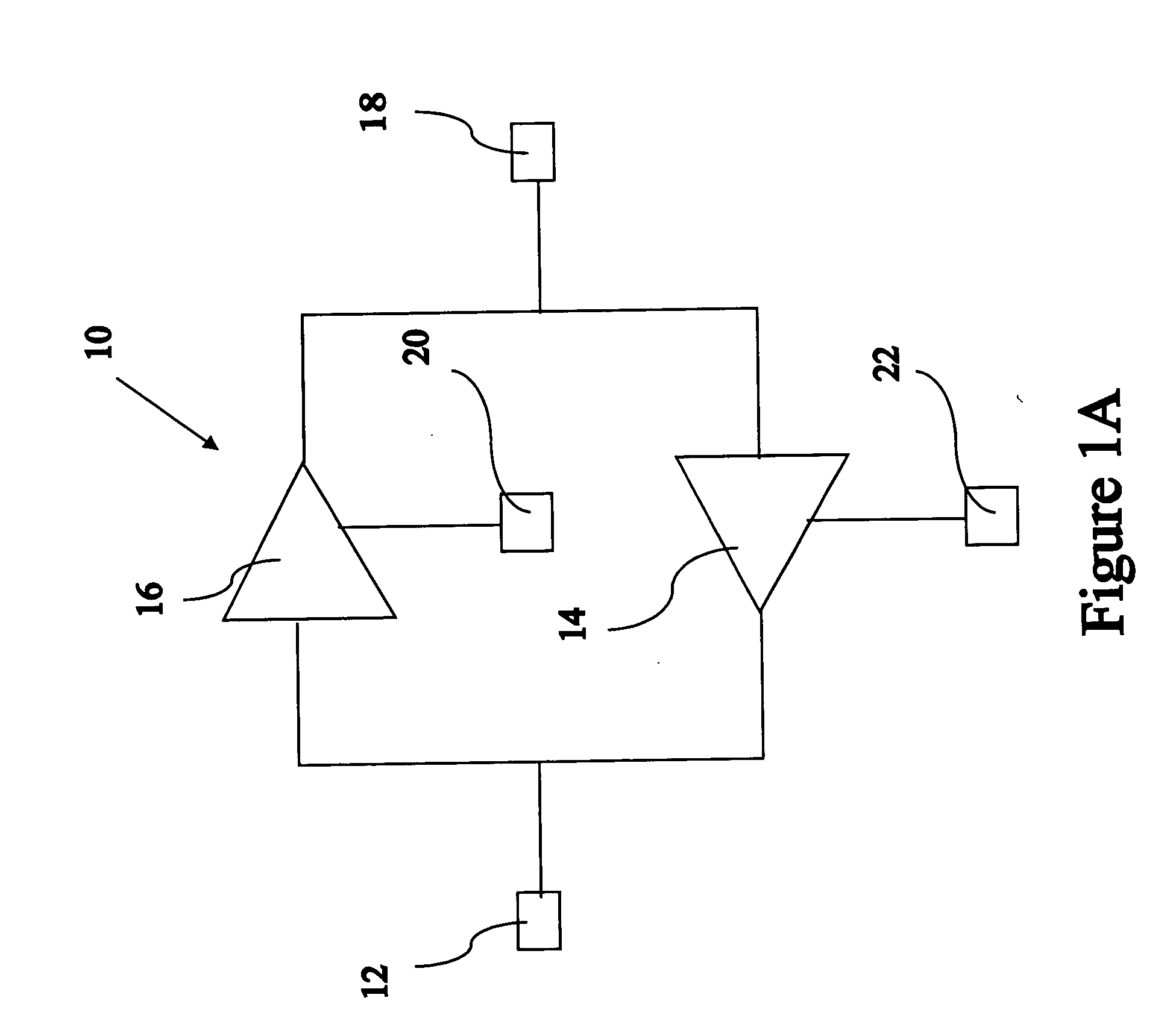

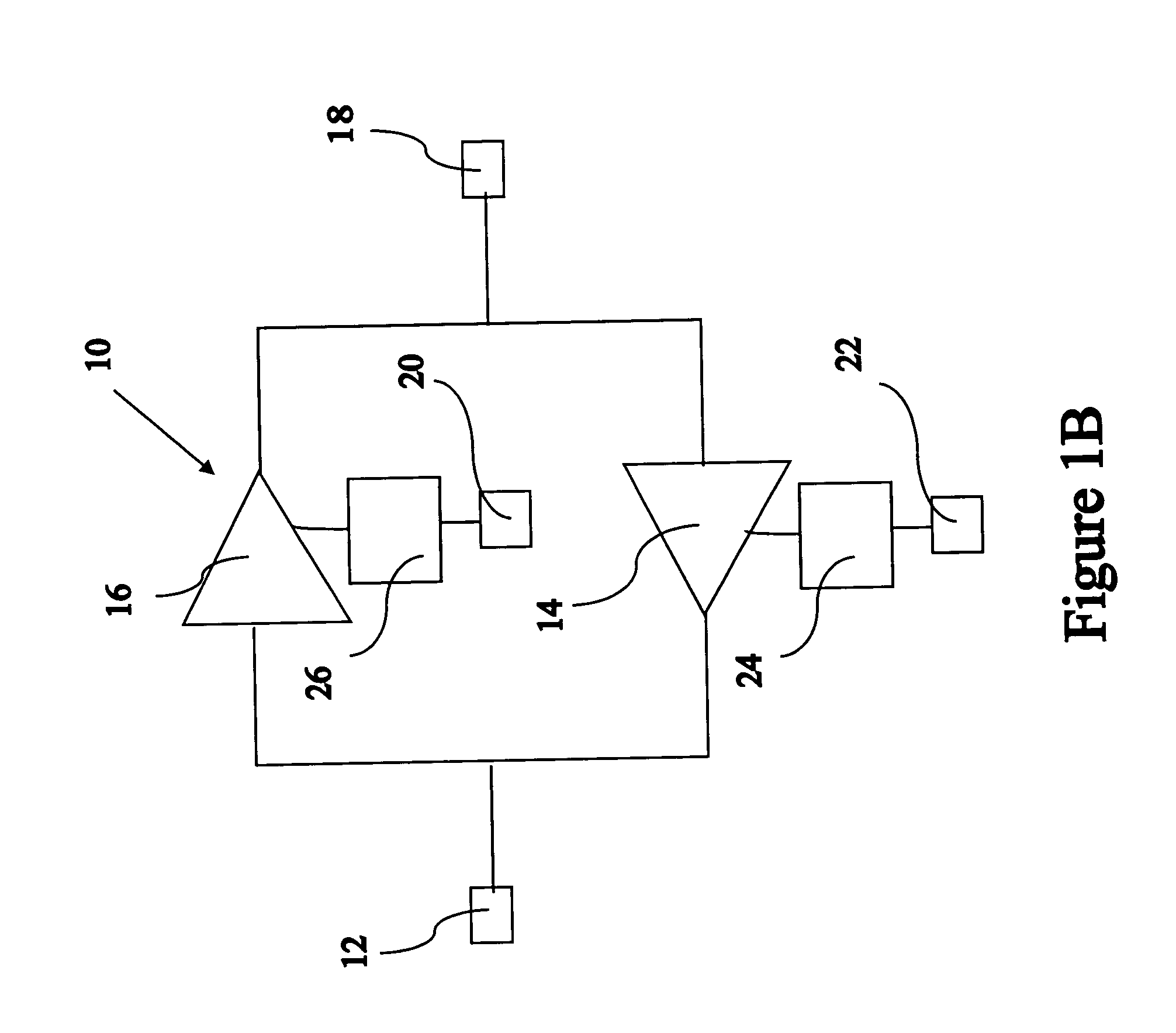

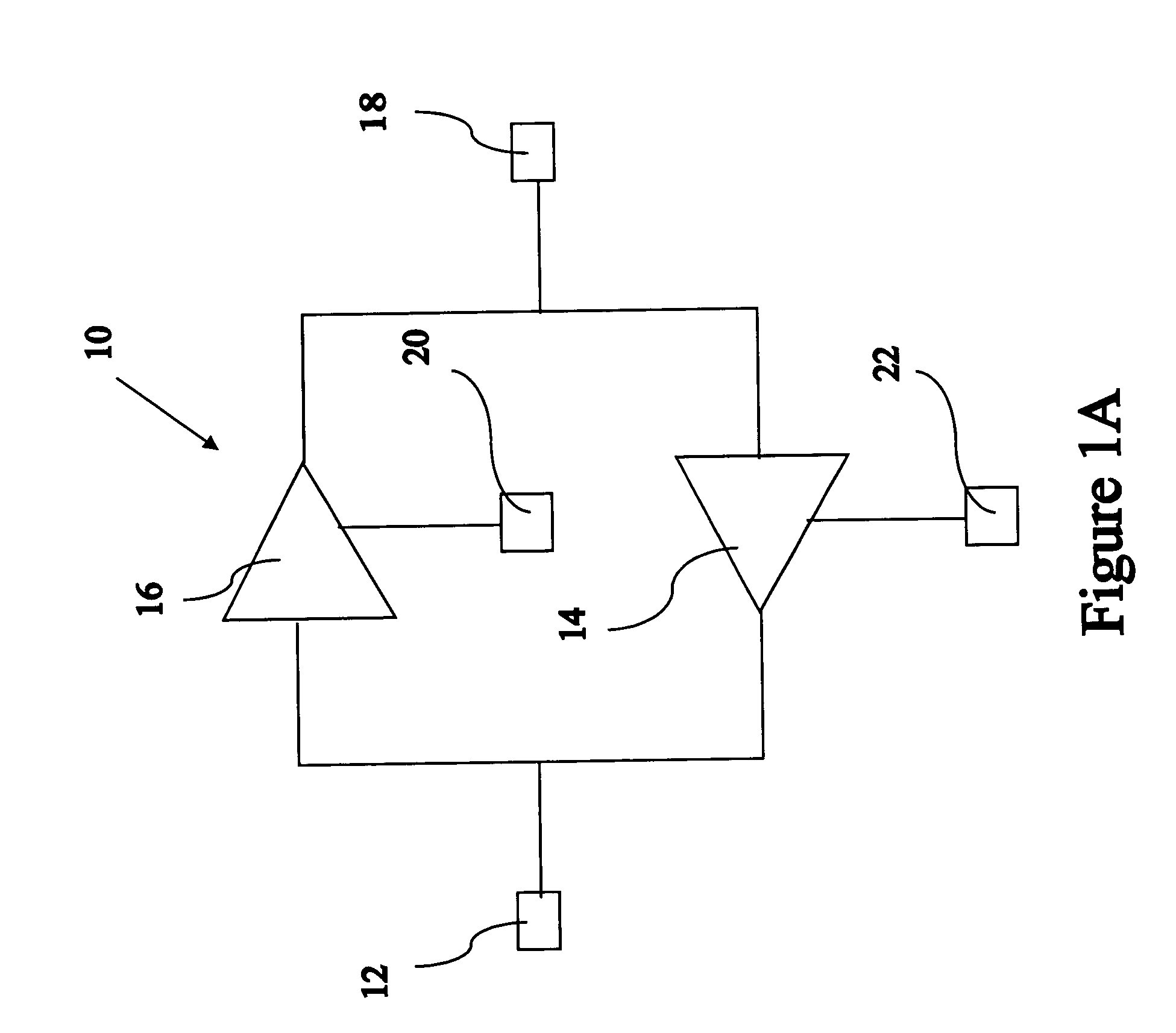

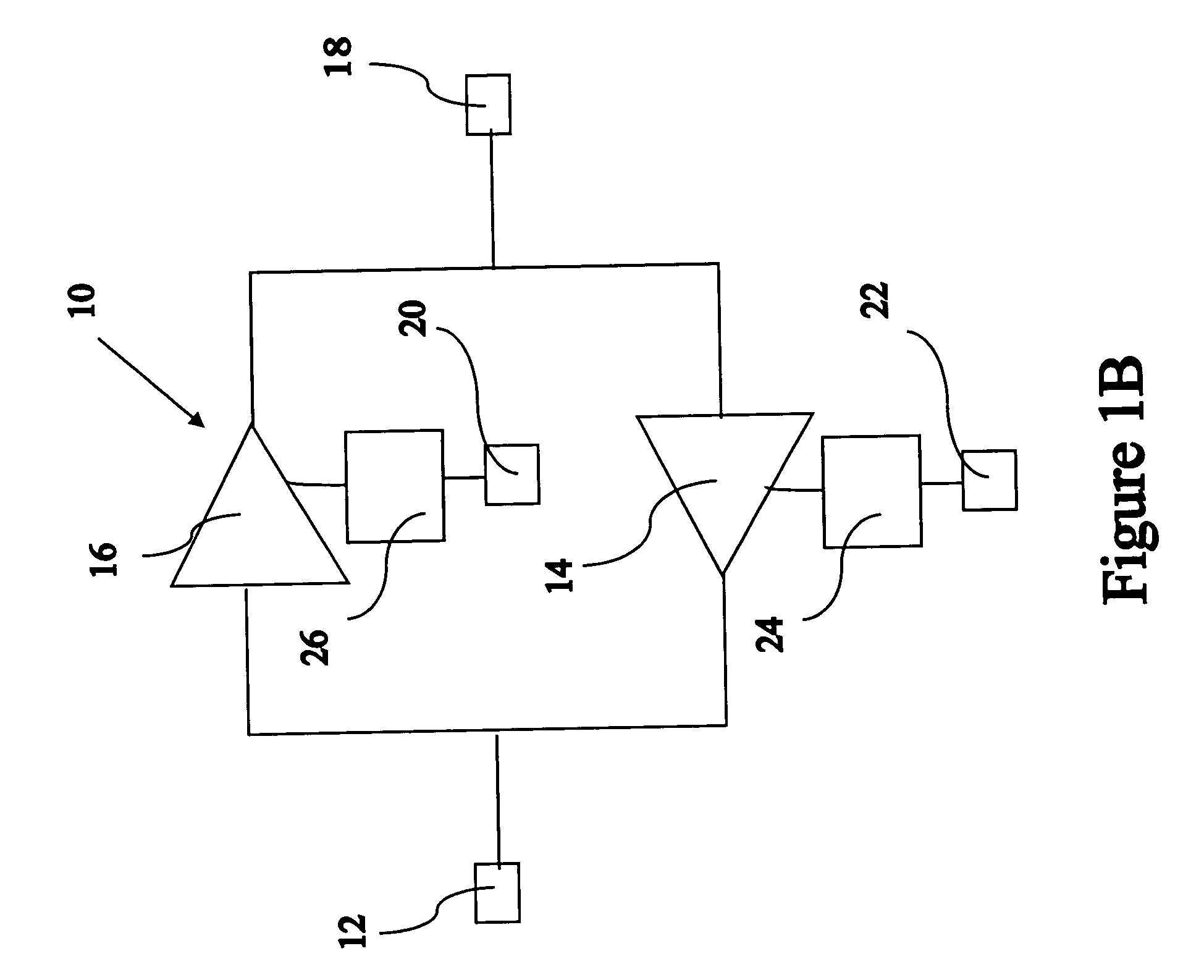

InactiveUS6657497B1Amplifier combinationsAmplifier modifications to reduce detrimental impedenceTransceiverAudio power amplifier

A bi-directional amplifier (10) for a transceiver module for amplifying both transmit signals and receive signals propagating in opposite directions. The amplifier (10) includes first and second common gate FETs (22, 24) electrically coupled along a common transmission line (20). A first variable matching network (28) is electrically coupled to the transmission line (20) between a transmit signal input port (12) and the first FET (22), and a second variable matching network (30) is electrically coupled to the transmission line (20) between a receive signal input port (14) and the second FET (24). An interstage variable matching network (32) is electrically coupled to the transmission line (20) between the first and second FETs (22, 24). A DC voltage regulator (34) provides a DC bias signal to the matching networks (28, 30, 32) and the FETs (22, 24) so that different signal amplifications and different impedance matching characteristics can be provided for the transmit signal and the receive signal.

Owner:NORTHROP GRUMMAN SYST CORP

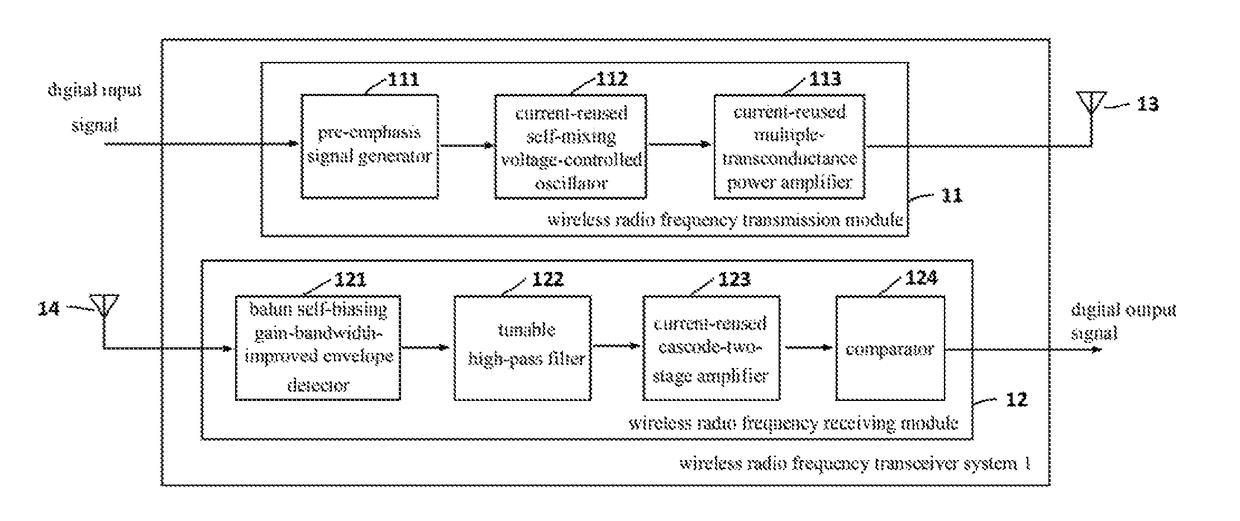

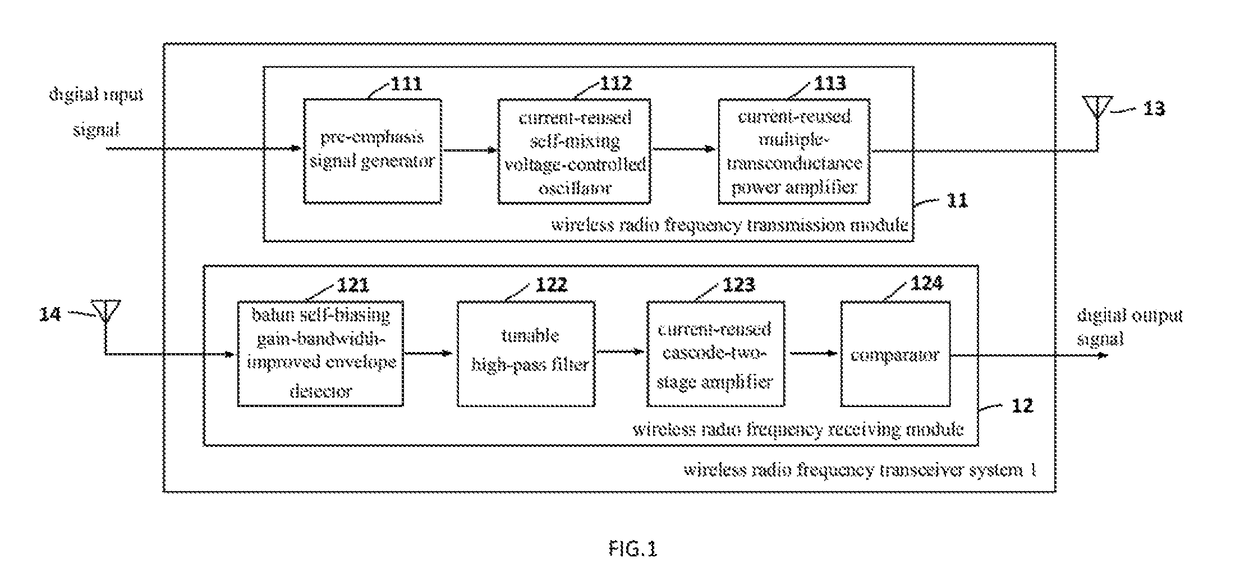

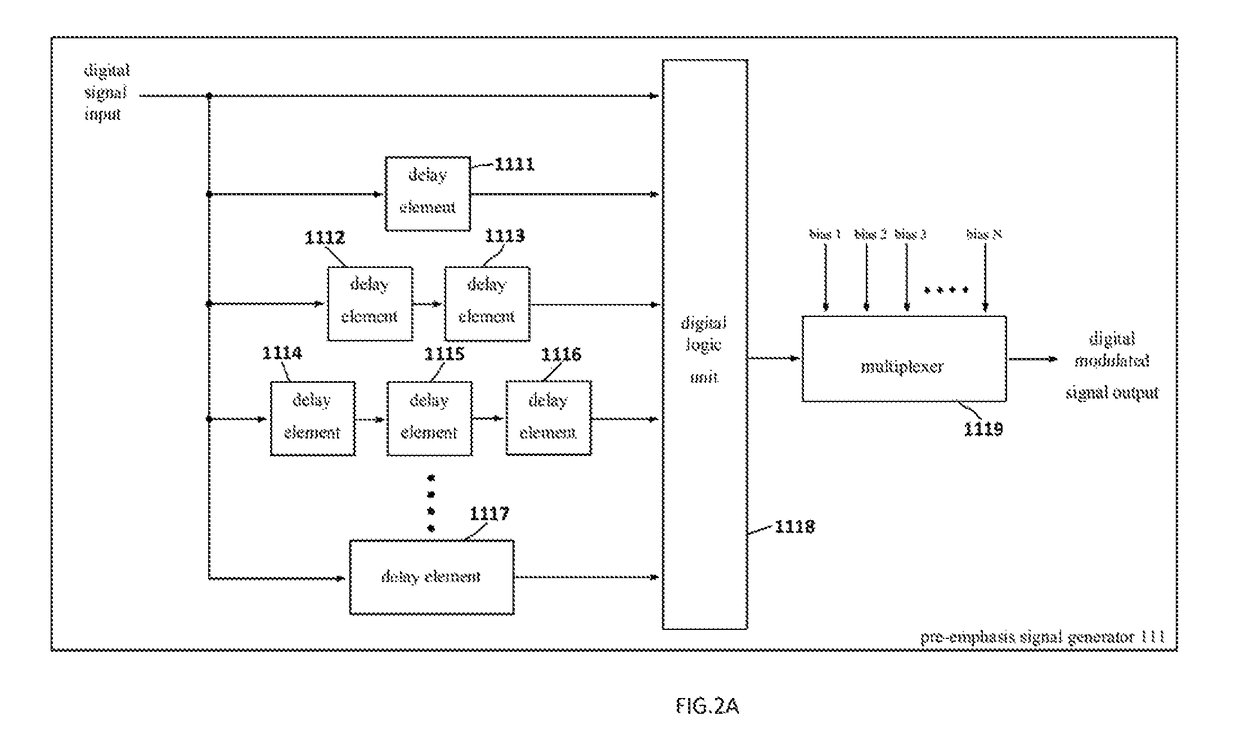

Wireless radio frequency transceiver system for internet of things

ActiveUS10003374B1Simplify complexityReduce system power consumptionHigh frequency amplifiersPower amplifiersPhase noiseTransceiver

A wireless radio frequency transceiver system for Internet of Things includes: a wireless radio frequency transmission module and a wireless radio frequency receiving module. The wireless radio frequency transmission module is used to shape signal waveform of digital signals from the Internet of Things to modulate the digital signals to form modulated output signals, and adopt a self-mixing technique to increase voltage / current amplitude of the modulated output signals and reduce phase noise. The wireless radio frequency transmission module is further used to adopt a current reuse technique to amplify the voltage / current amplitude of the modulated output signals, and transmit the amplified modulated output signals through a first antenna to a wireless channel. The wireless radio frequency receiving module is used to detect carrier input signals received from a second antenna to obtain baseband signals and demodulate the baseband signals to form differential signals. The wireless radio frequency receiving module is further used to amplify voltage / current amplitude of the demodulated differential signals several times in an open loop state to produce digital output signals, and transmit the digital output signals to a back-end signal processor.

Owner:NAT CHENG KUNG UNIV

Miniature bidirectional amplifier

InactiveUS20060063508A1Sufficient heat dissipation capabilityEasy-to-install and serviceGated amplifiersPower amplifiersCommunications systemAudio power amplifier

An amplifier device for amplifying RF communication signals compatible with IEEE 802.11 standards. An amplifier circuit is housed within a cylindrical metal housing that provides excellent heat dissipation and requires no mounting hardware for installing the device within a communication system. The metal housing with an integrated lightning arrestor creates a watertight seal to protect the amplifier circuit from damage when installed outdoors and the amplifier circuit is compatible with both 2.4 GHz and 5.8 GHz frequency applications.

Owner:HE SHIPING +3

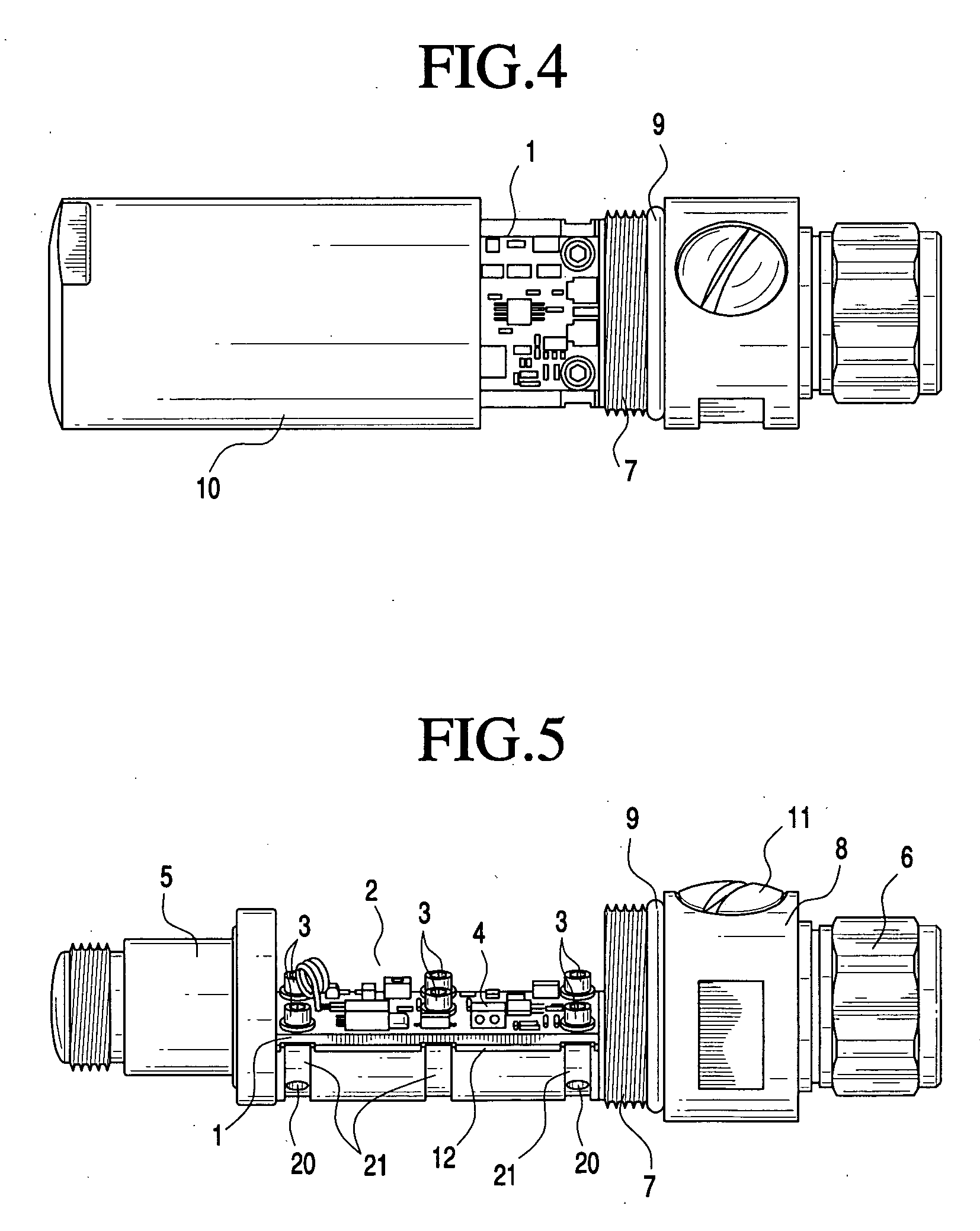

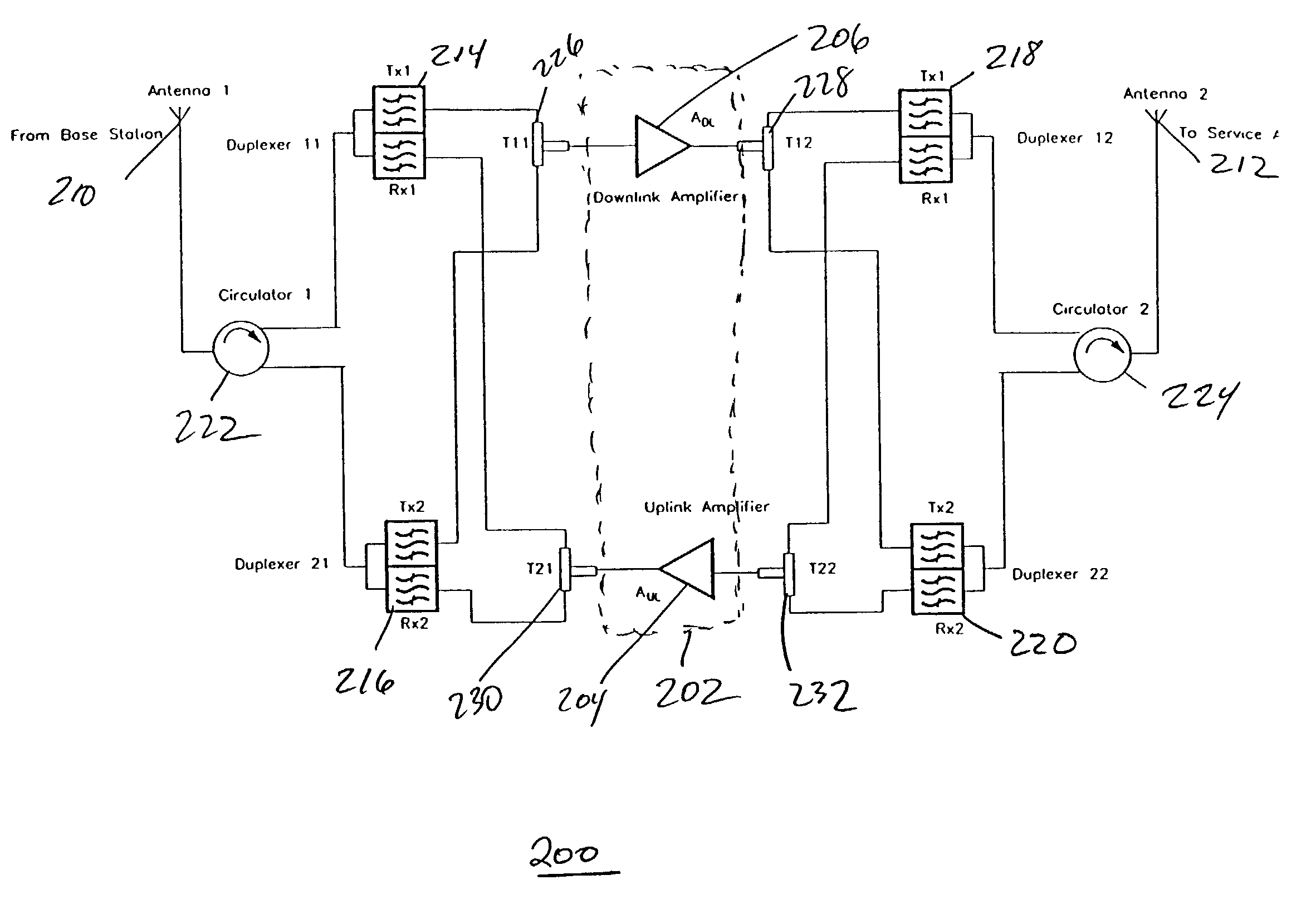

Dual band bidirectional amplifier for wireless communication

InactiveUS6993286B2Frequency-division multiplex detailsActive radio relay systemsAudio power amplifierDouble frequency

The dual band bi-directional amplifier has only one amplifier chain having an uplink amplifier and a downlink amplifier, but can nonetheless amplify signals from two frequency bands in both an uplink and a downlink direction between two antennas. This is possible by using duplexers and circulators to separate signals to and from each antenna into the two bands. In particular, for each frequency band handled by the circuit, the dual band bi-directional amplifier has a duplexer set for separating the signals from one of the bands into the uplink and downlink direction. In the case of a dual band amplifier, there are two sets of duplexers, one for each band. By using duplexers and circulators to differentiate signals in different bands travelling in different directions, there is no need for additional amplifier chains, which increase the manufacturing costs.

Owner:RADIO FREQUENCY SYST

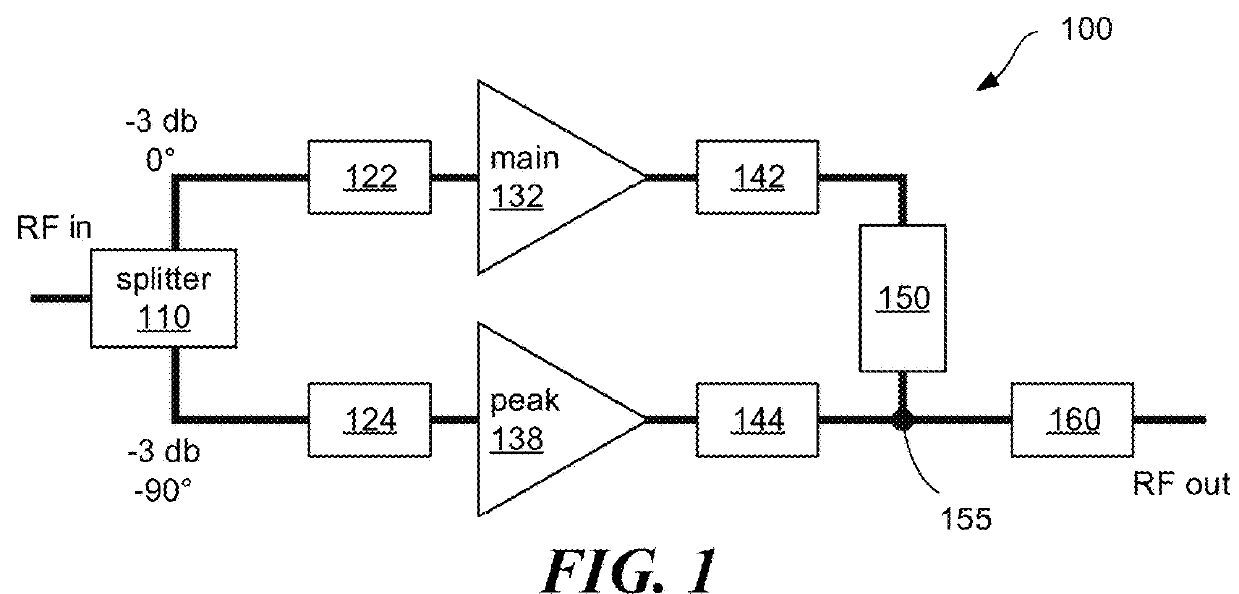

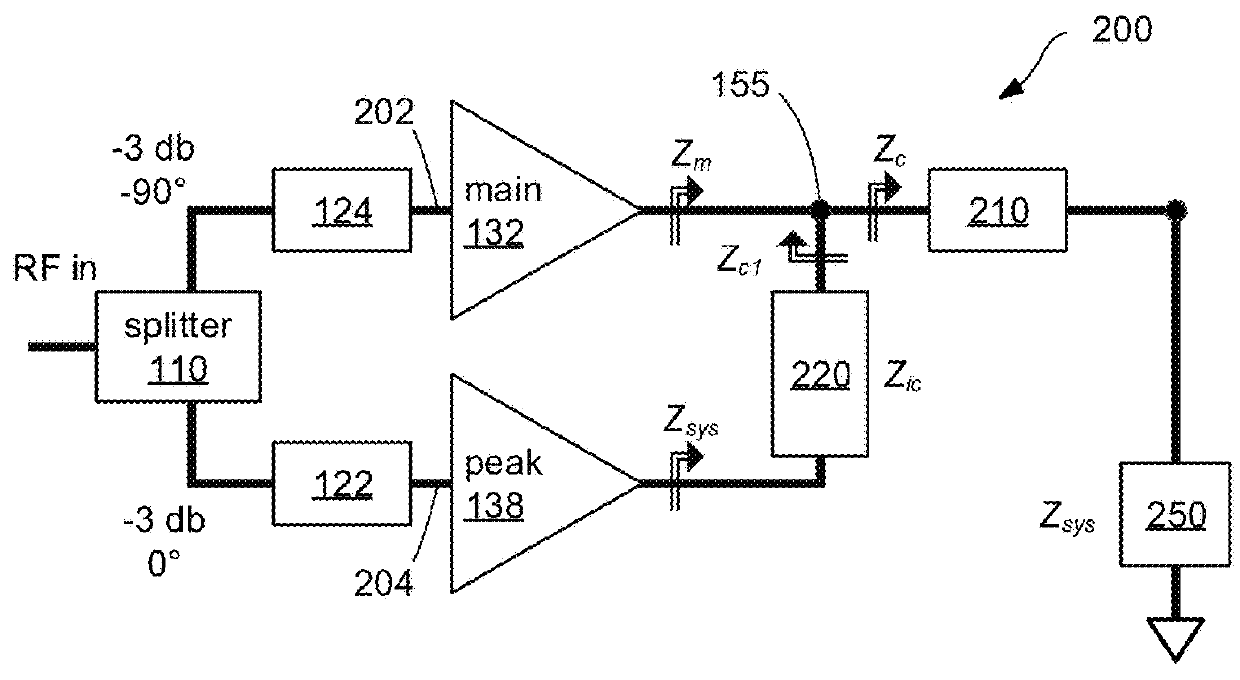

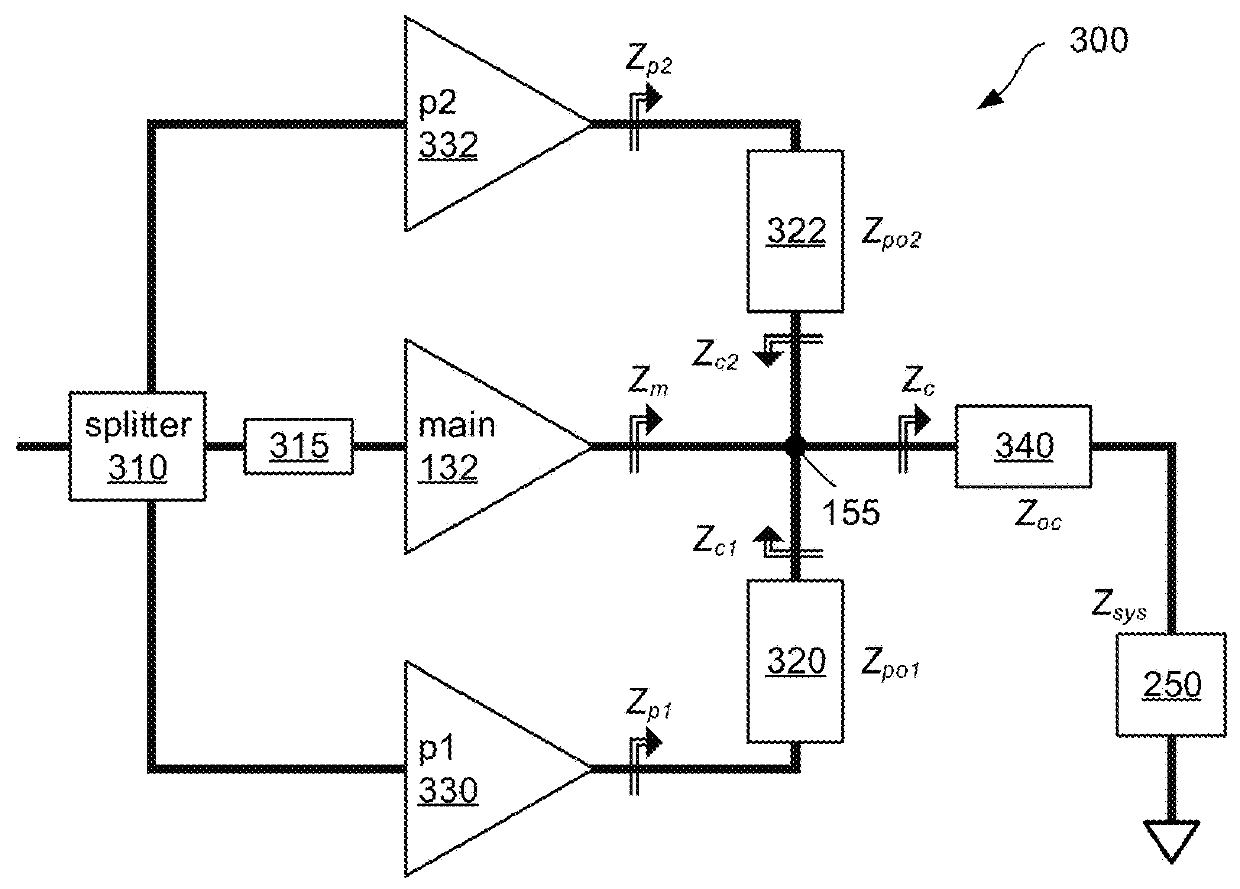

N-way star configuration power amplifier with peaking amplifier impedance inverters

InactiveUS20180183388A1Improve efficiencyHigh power outputHigh frequency amplifiersAmplifier modifications to raise efficiencyAudio power amplifierPeak value

Multi-way amplifiers having impedance inverters connected to outputs of one or more peaking amplifiers are described. The output of the main amplifier may connect directly to a combining node and output impedance matching network. The multi-way amplifier configuration can improve efficiency at power back-off and improve RF bandwidth.

Owner:MACOM TECH SOLUTIONS HLDG INC

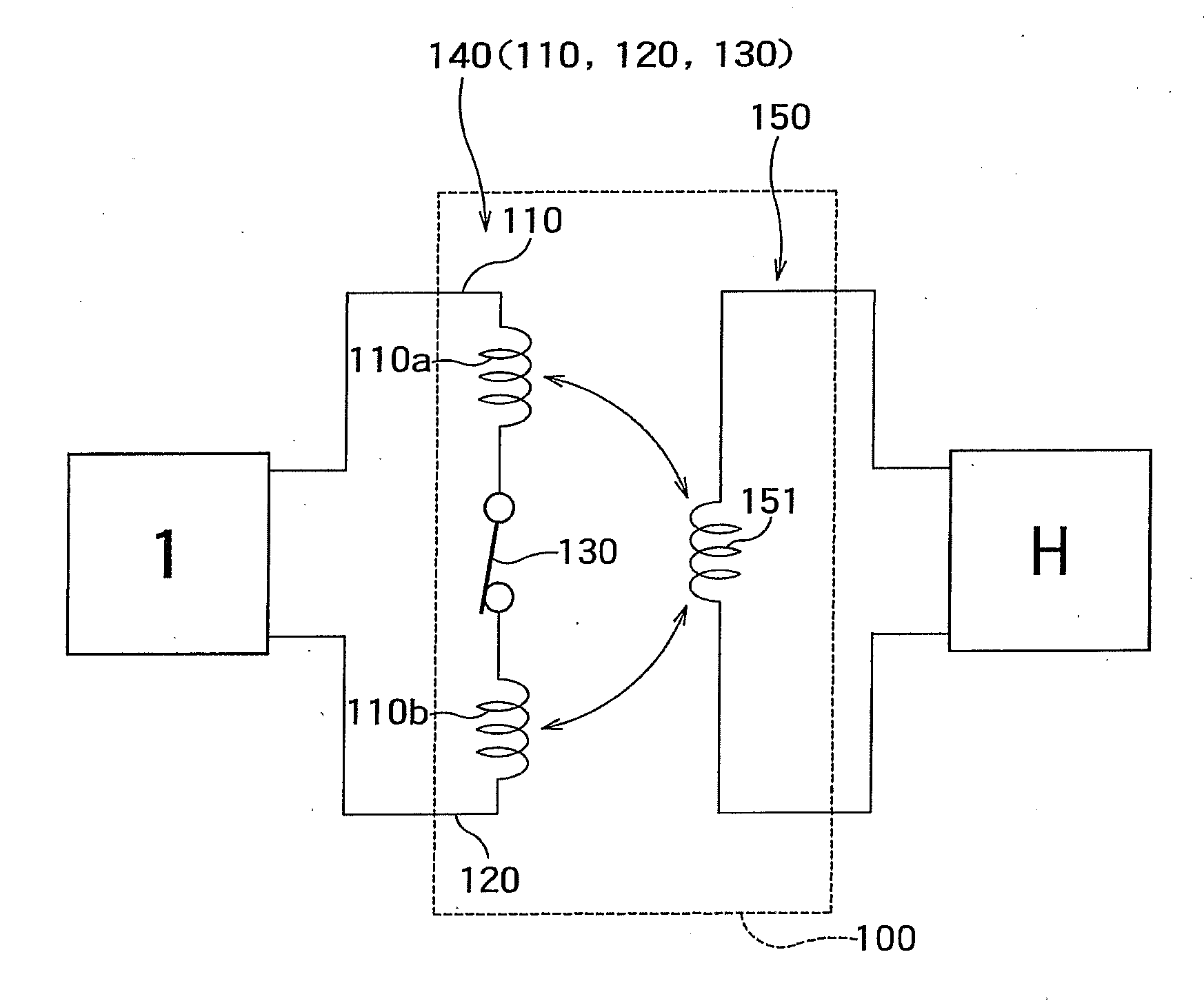

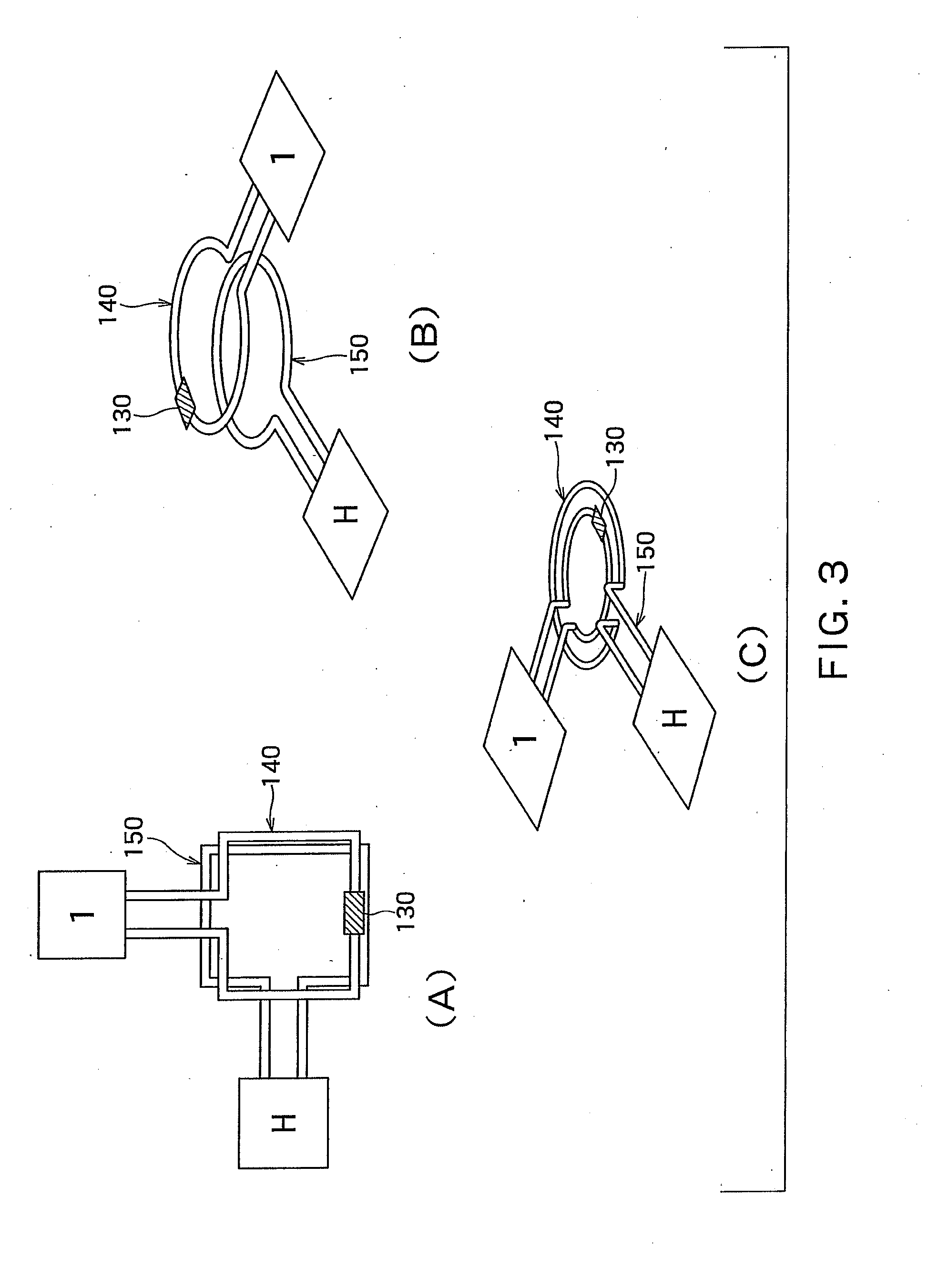

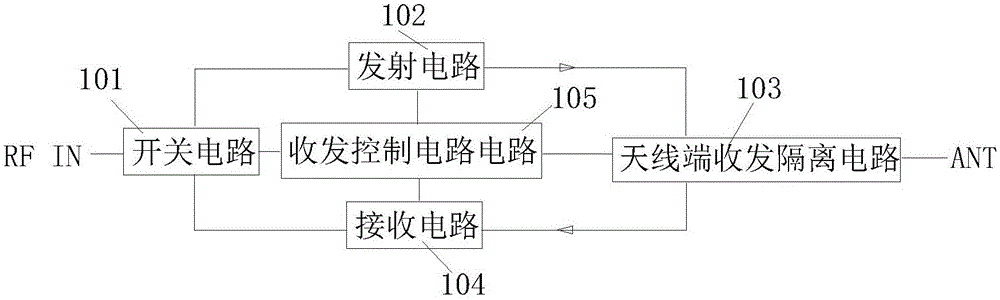

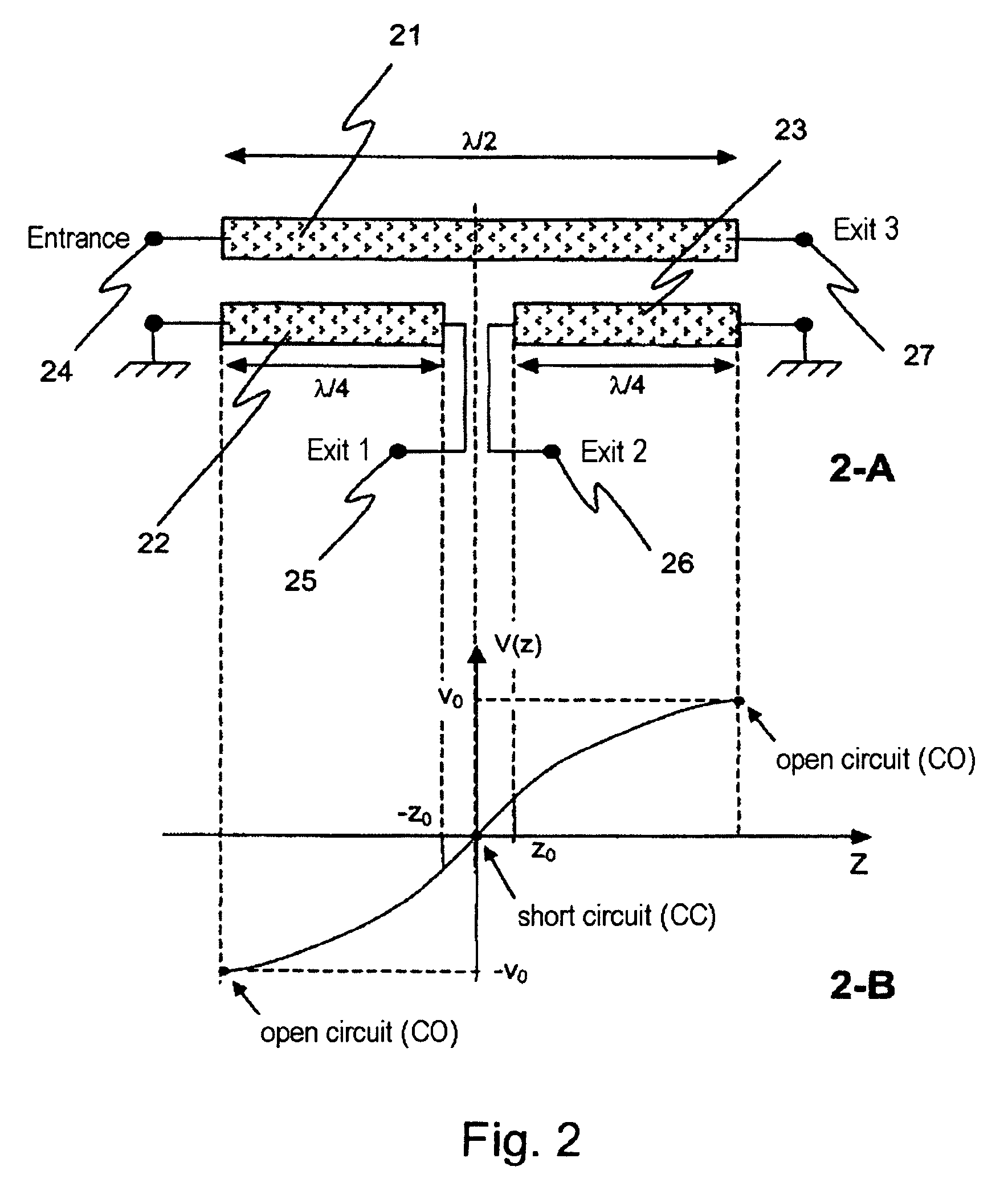

High-frequency switching circuit and radio communication device

According to one embodiment of the present invention, there is provided a high-frequency switching circuit including a first differential line and third line. The differential line includes a first line configured to have one end and an other end, a second line configured to have one end and an other end and a first switch configured to switch electrical connection between the one ends of the first and second lines. The differential line receives or outputs differential signals by the other ends of the first and second lines. The third line is configured to be electromagnetically coupled with the first differential line when the first switch is turned on. The first switch is arranged at a position where an electrical length from the other end of the first line and an electrical length from the other end of the second line are approximately equal.

Owner:KK TOSHIBA

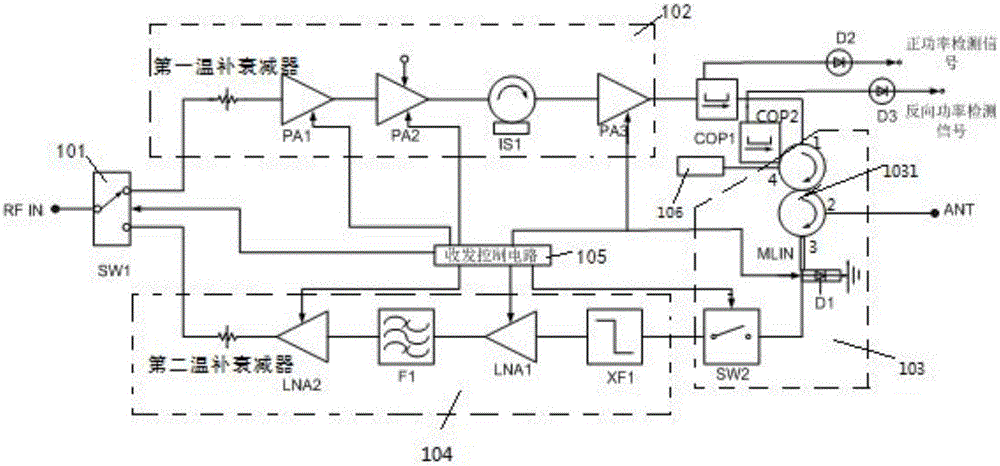

Bidirectional amplifier of TDD mode

PendingCN106571850ALaunch stableIt has the function of signal to receiving circuitTwo-way amplifiersTransmissionLow noiseAudio power amplifier

The invention discloses a bidirectional amplifier of a TDD mode. The bidirectional amplifier comprises a switch circuit, an emission circuit, a transmit-receive isolation circuit, a receiving circuit and a transmit-receive control circuit. The transmit-receive isolation circuit comprises a double circulator. An output terminal of the emission circuit is connected to an input terminal of the double circulator. An input terminal of the receiving circuit is connected to a receiving terminal of the double circulator. An antenna terminal of the double circulator is connected to an antenna. The antenna terminal receives / sends an antenna signal. The transmit-receive control circuit is connected to the switch circuit, the emission circuit, the receiving circuit and the transmit-receive isolation circuit. The invention provides a receiving and emission high isolation circuit based on the TDD mode; and simultaneously a low noise receiving requirement and a linear large-power output requirement are satisfied, and stable and anti-interference work can be performed.

Owner:北京澳丰源科技股份有限公司

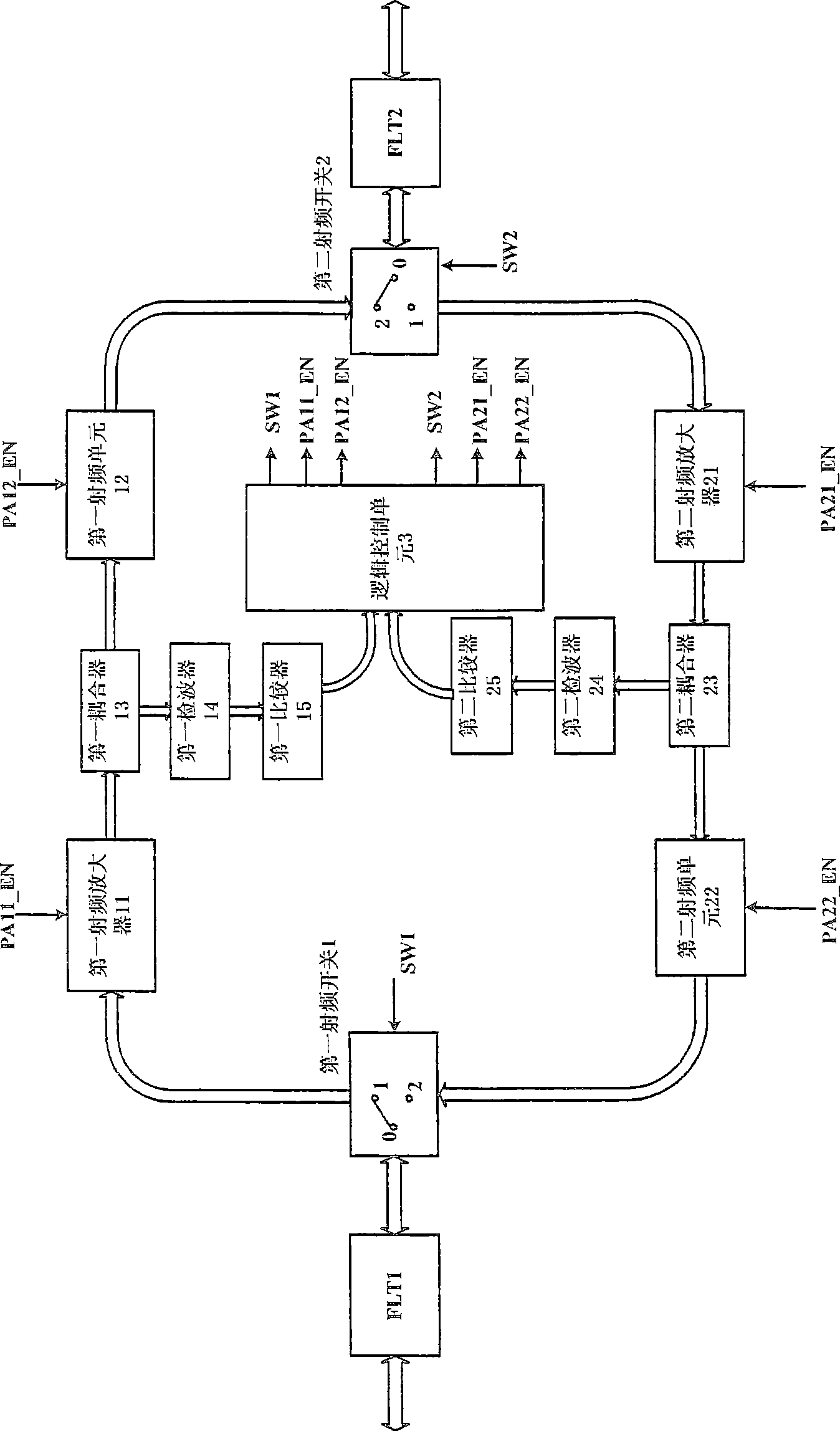

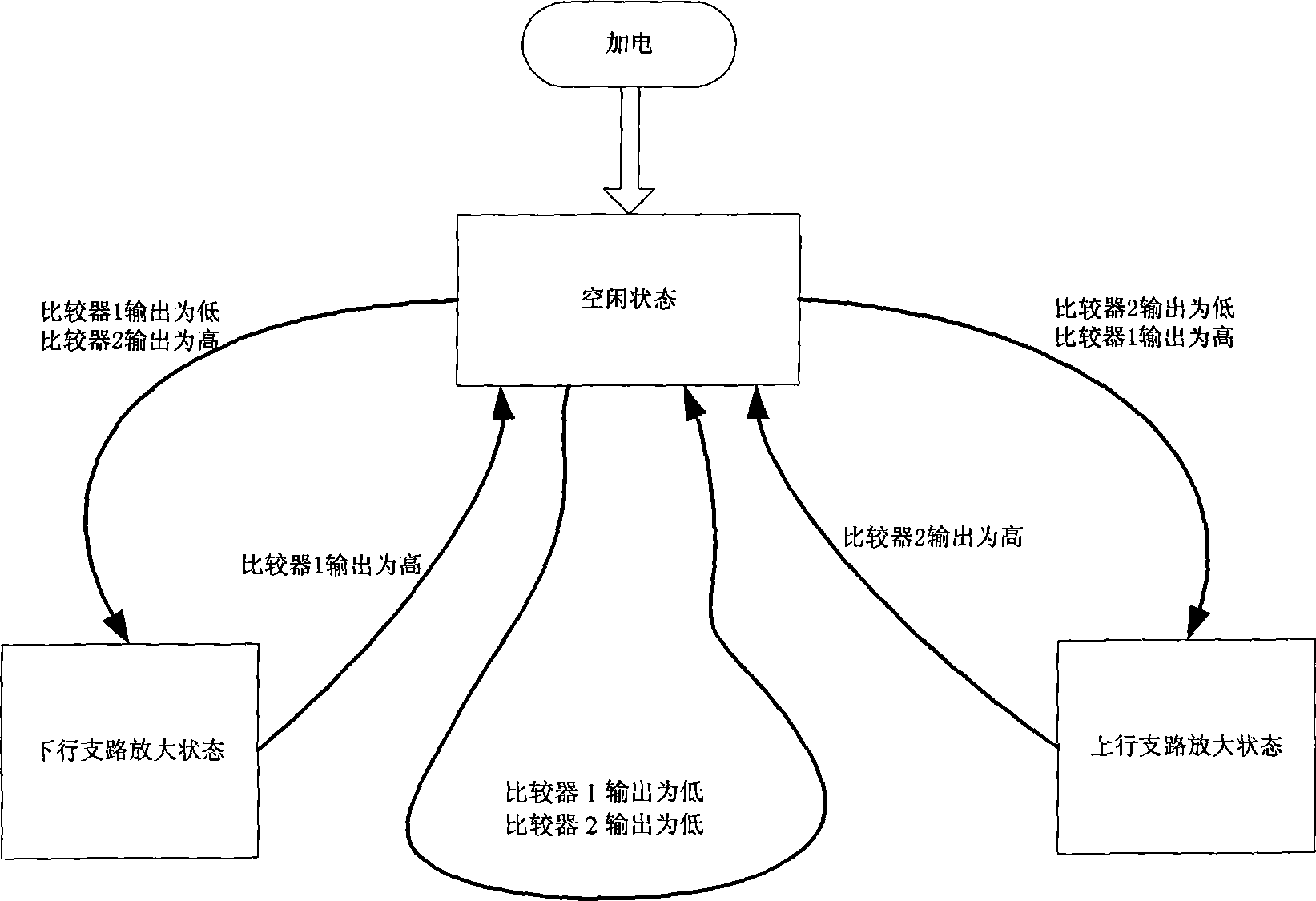

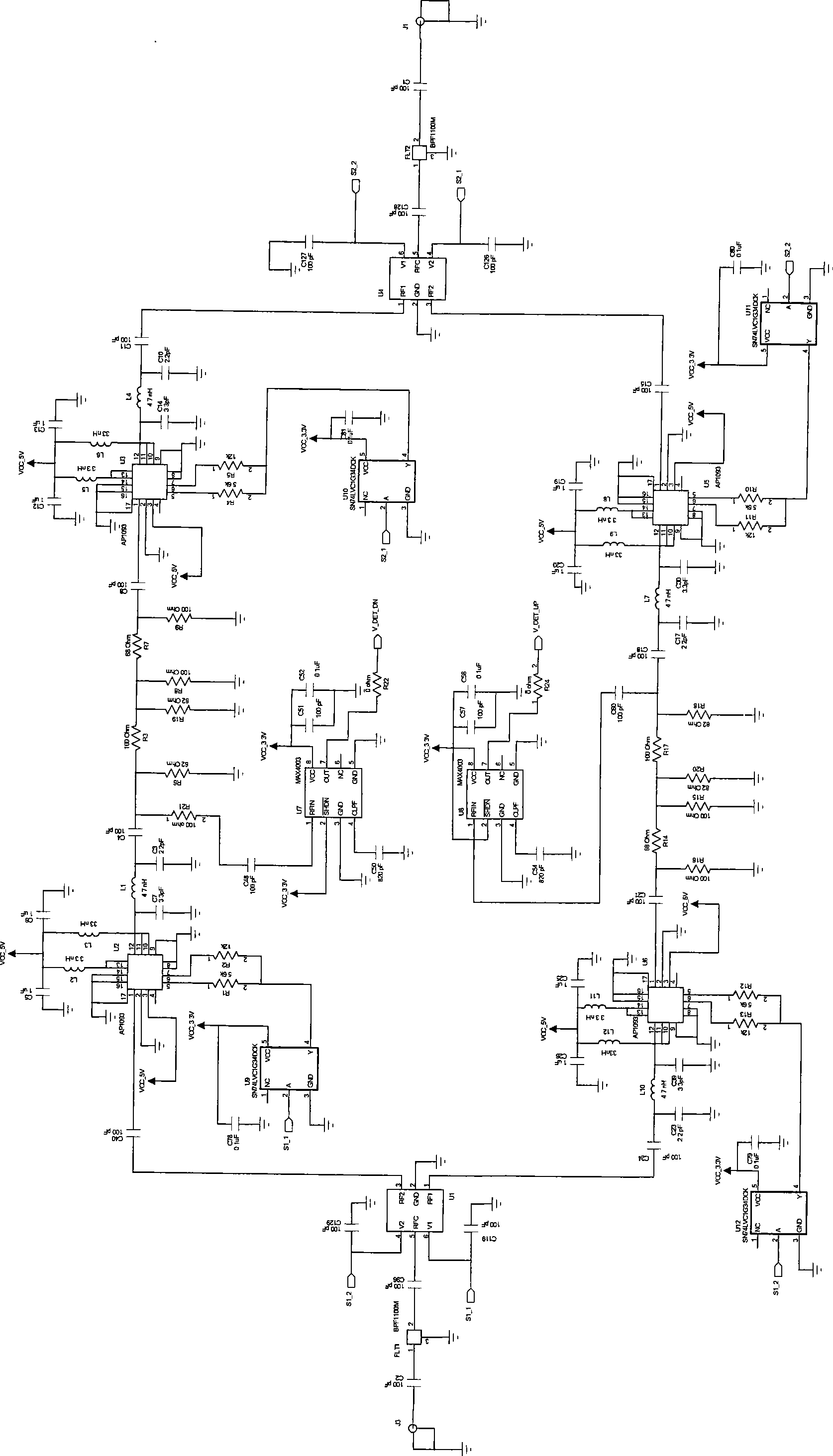

Bidirectional dynamic amplification method and apparatus for TDD system

The invention provides a two-way dynamic amplification method used for a time division duplex system and a two-way dynamic amplification device thereof. The two-way dynamic amplification method comprises the following steps: a working state control device detects the radio-frequency signals of the user-side direction and the local-side direction, compares the radio-frequency signals with the preset start-up detection threshold and / or the preset shut-down detection threshold, and outputs the logic control signal to control a two-way dynamic amplification device, so as to enable the two-way dynamic amplification device in one of the working states. The working states of the two-way dynamic amplification device include an idle state, a downlink branch amplification state and an uplink branch amplification state. In the idle state, both the uplink branch and the downlink branch don't provide the radio-frequency signal amplification function. In the downlink branch amplification state, only the downlink branch provides the radio-frequency signal amplification function. In the uplink branch amplification state, only the uplink branch provides the radio-frequency signal amplification function. The two-way dynamic amplification method can dynamically acquire the transmission / reception synchronization and achieve the effect of two-way dynamic amplification.

Owner:BEIJING RFMC TECH CORP

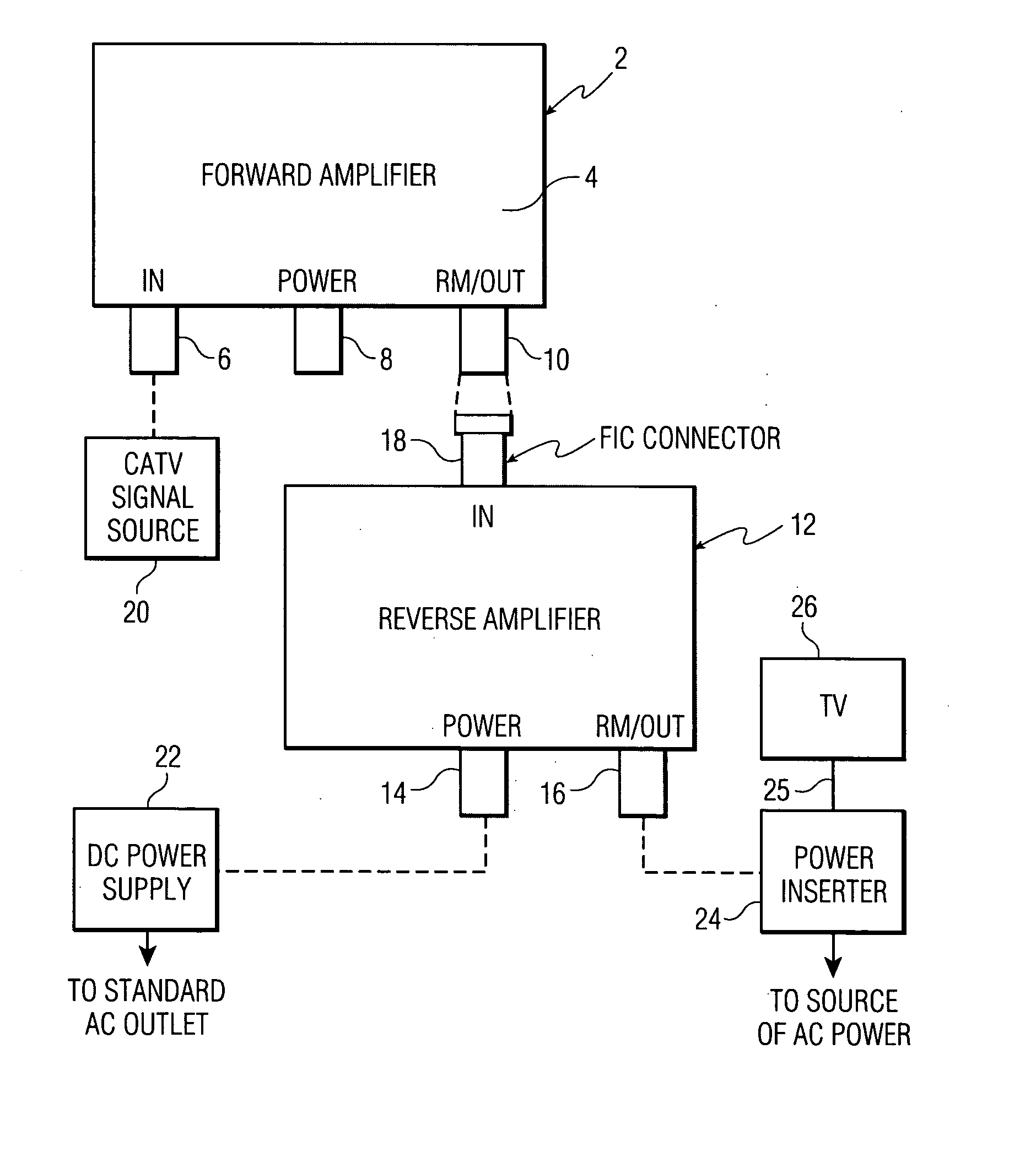

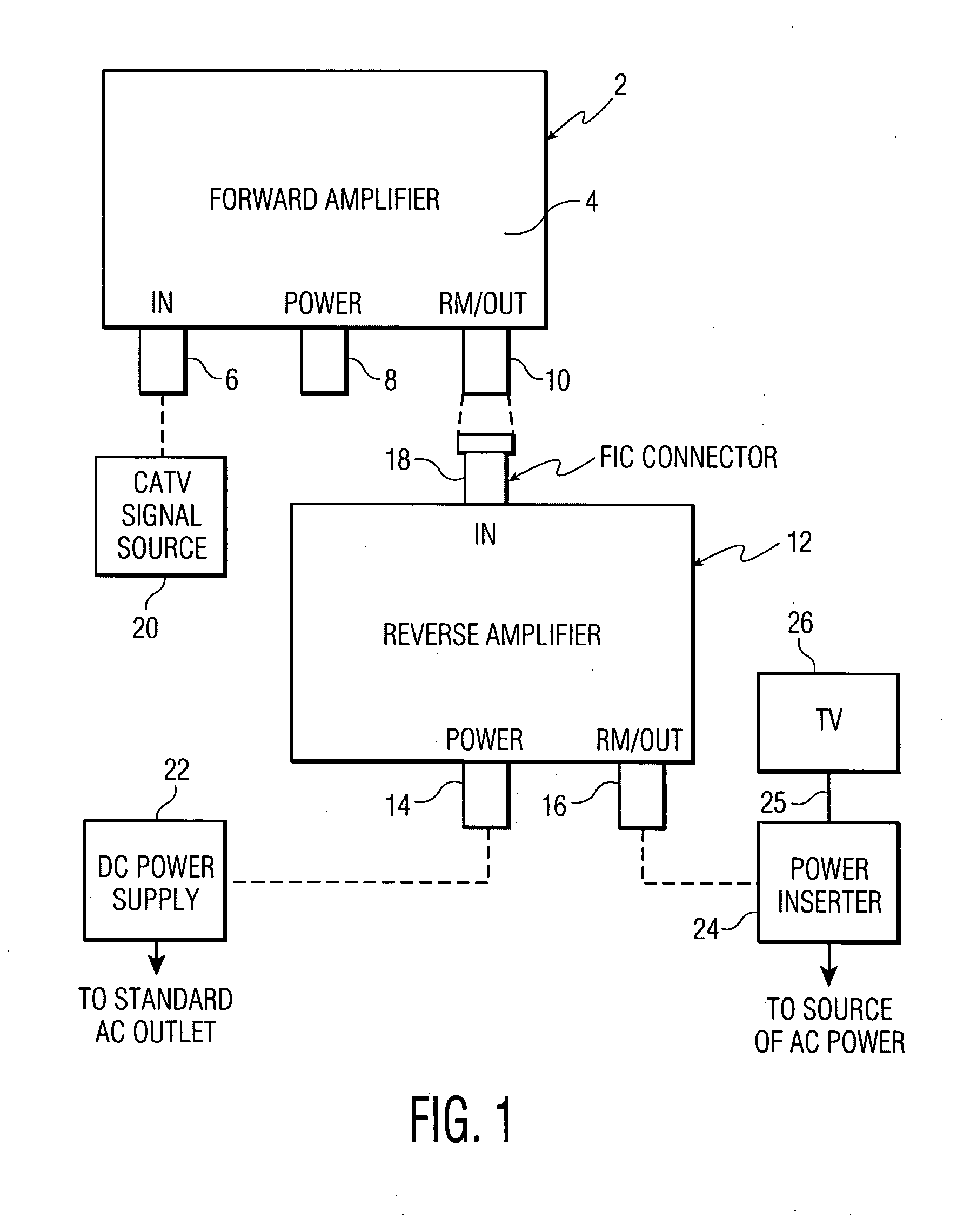

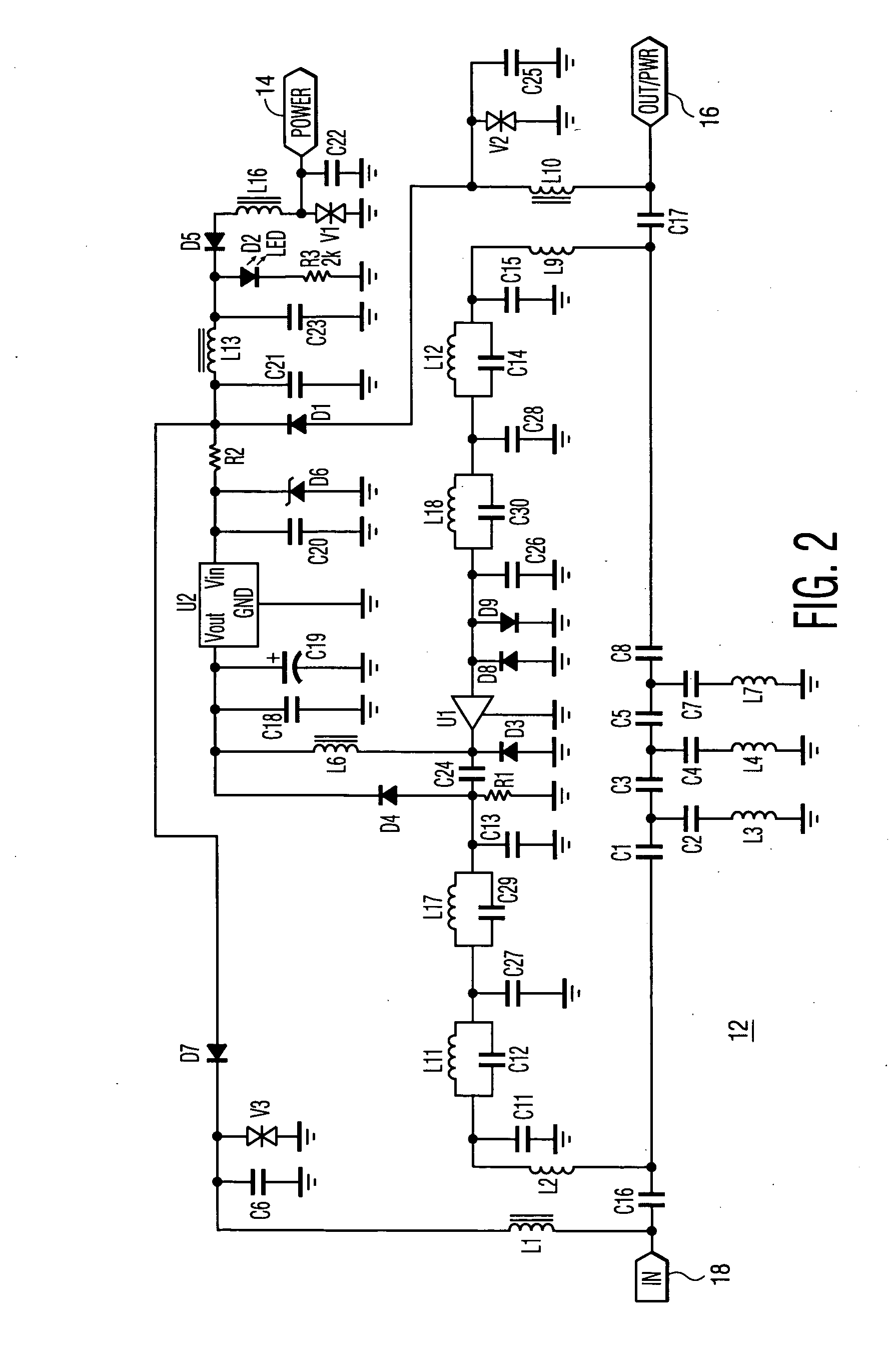

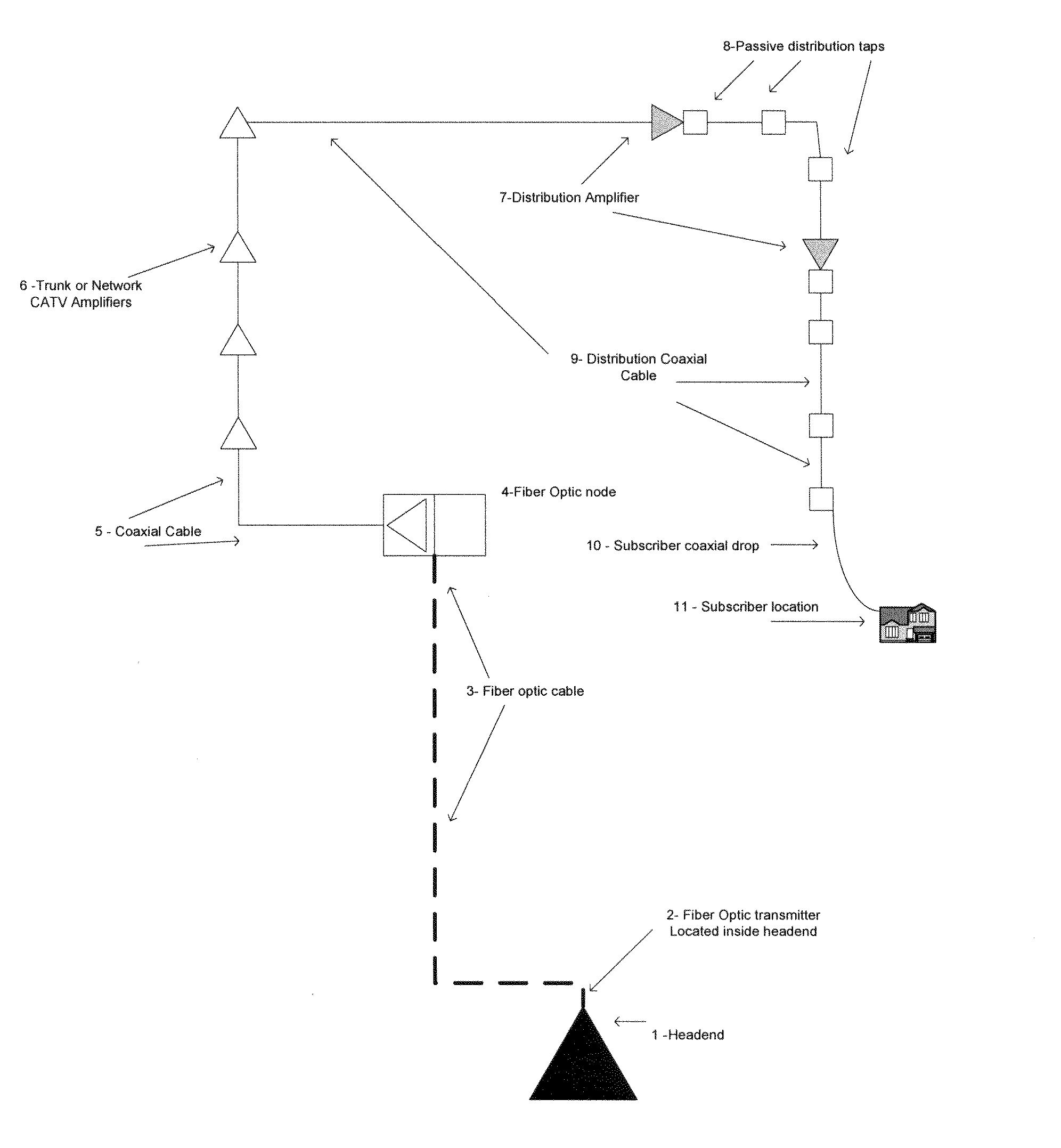

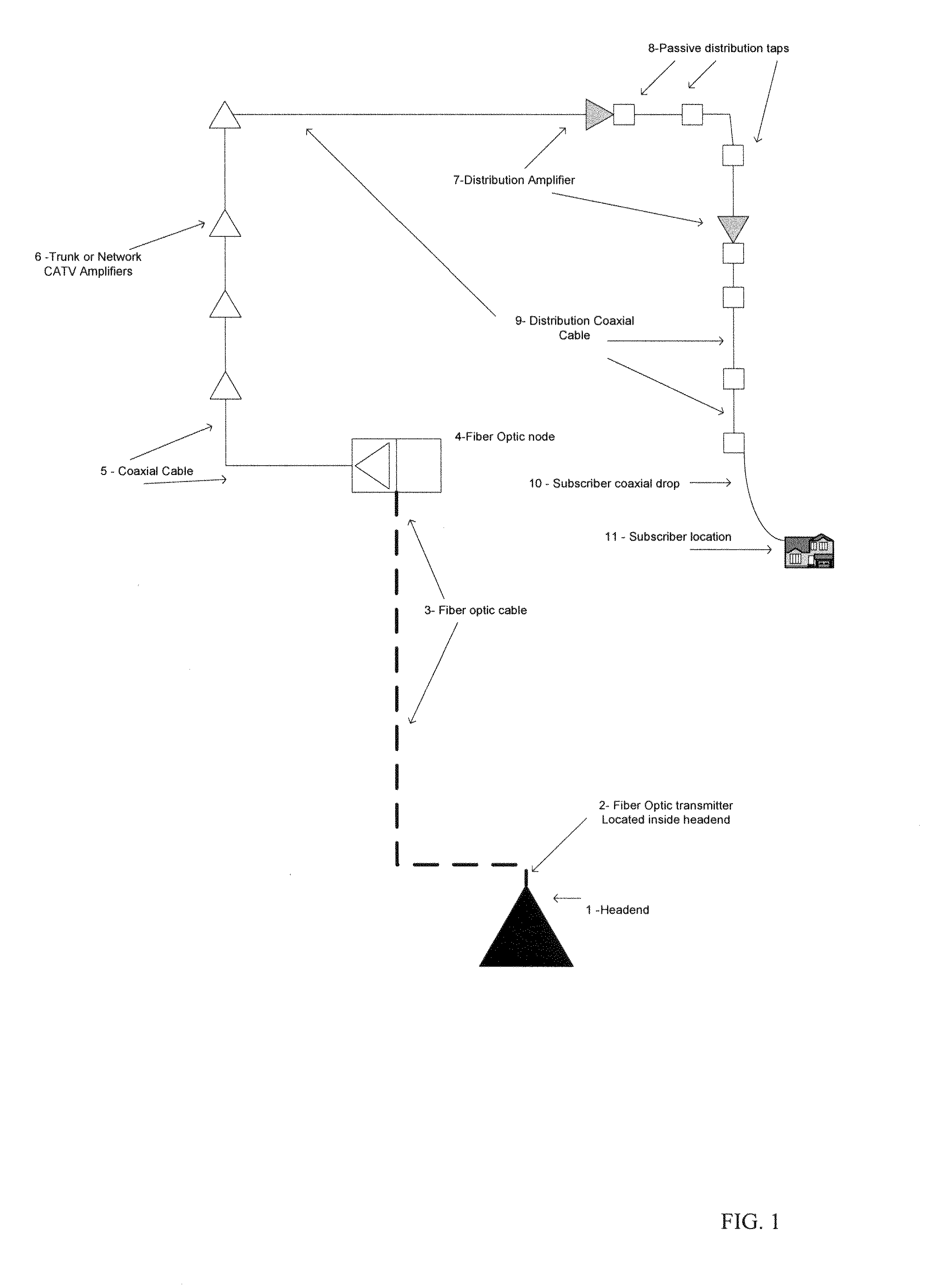

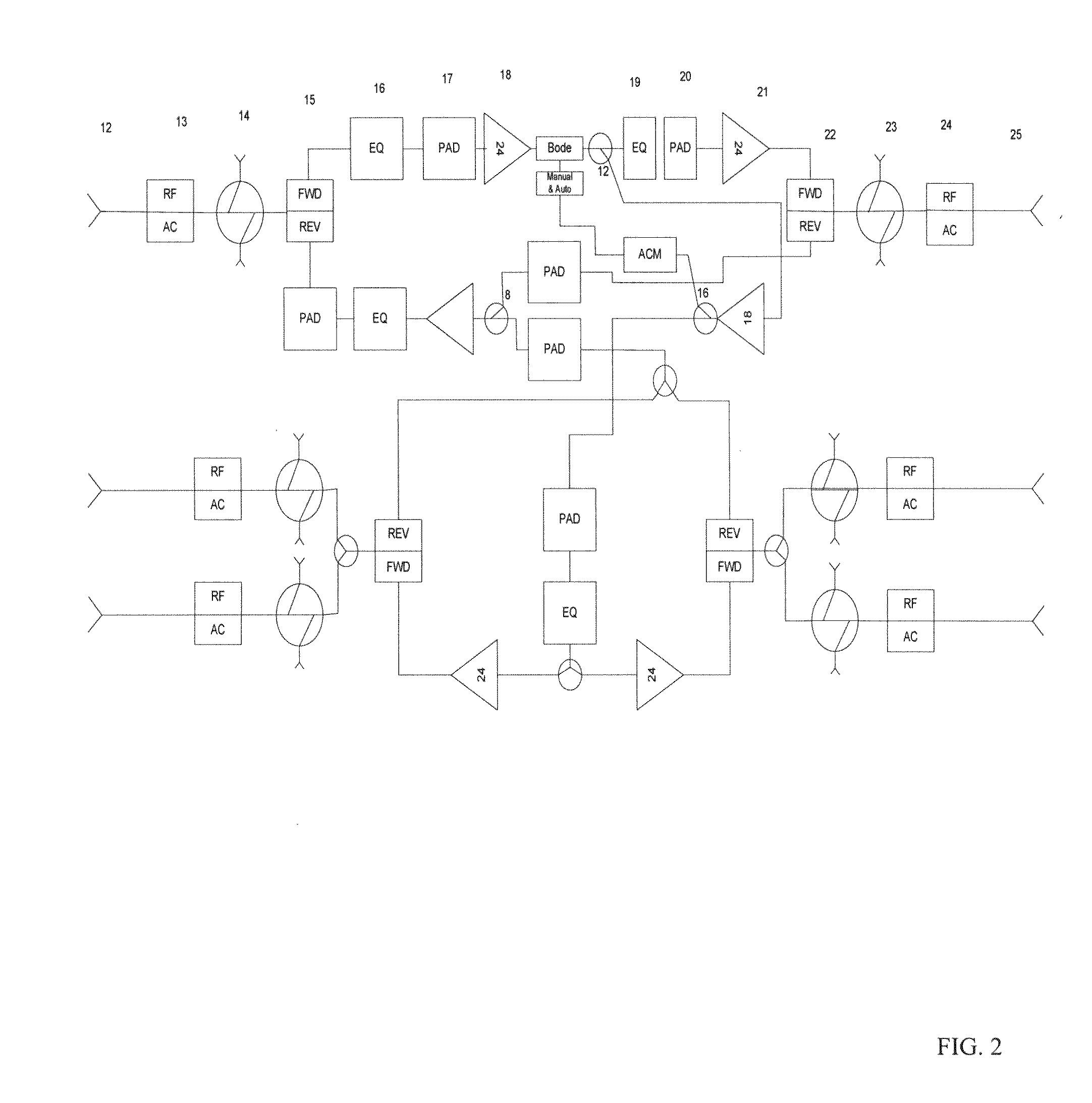

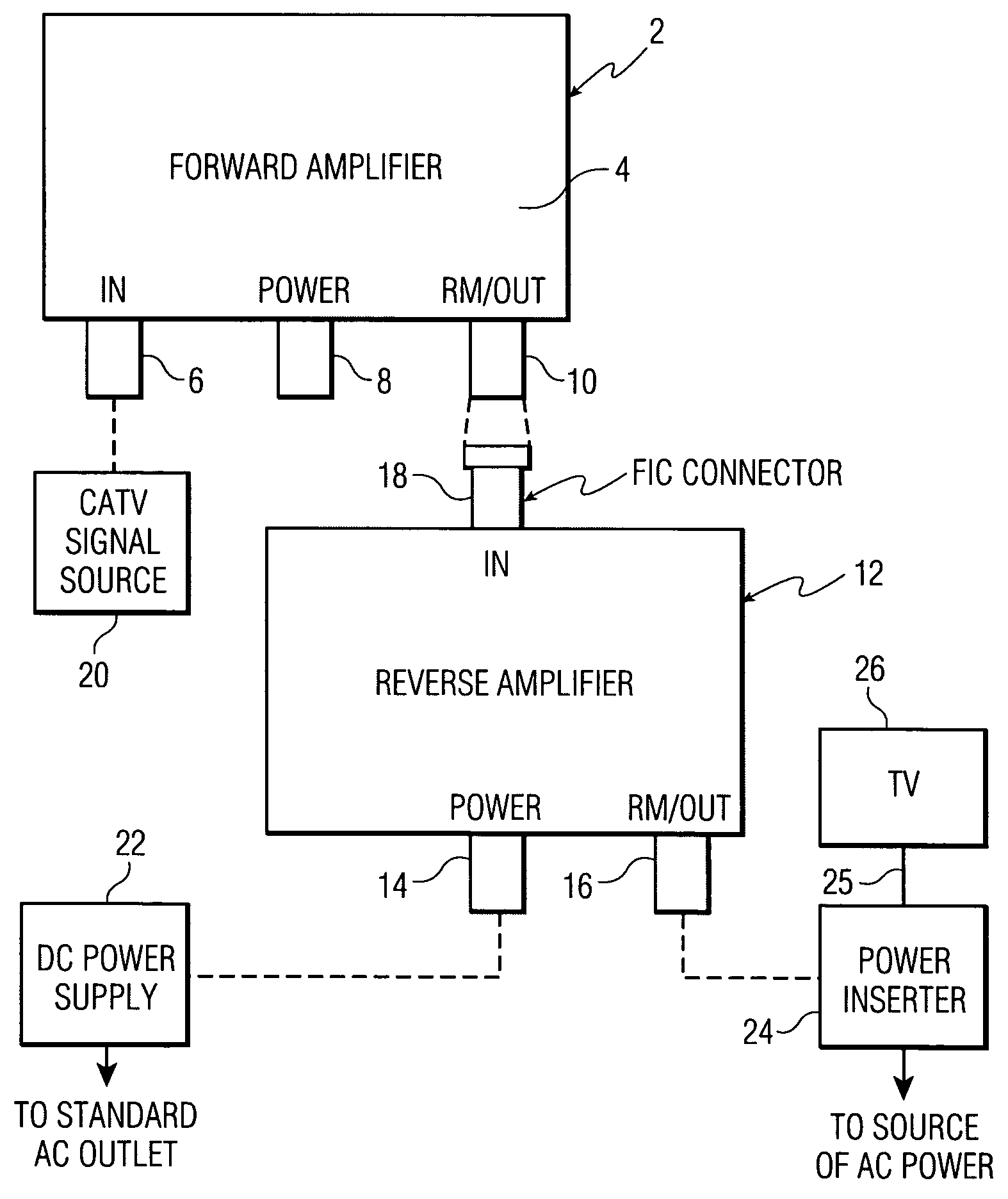

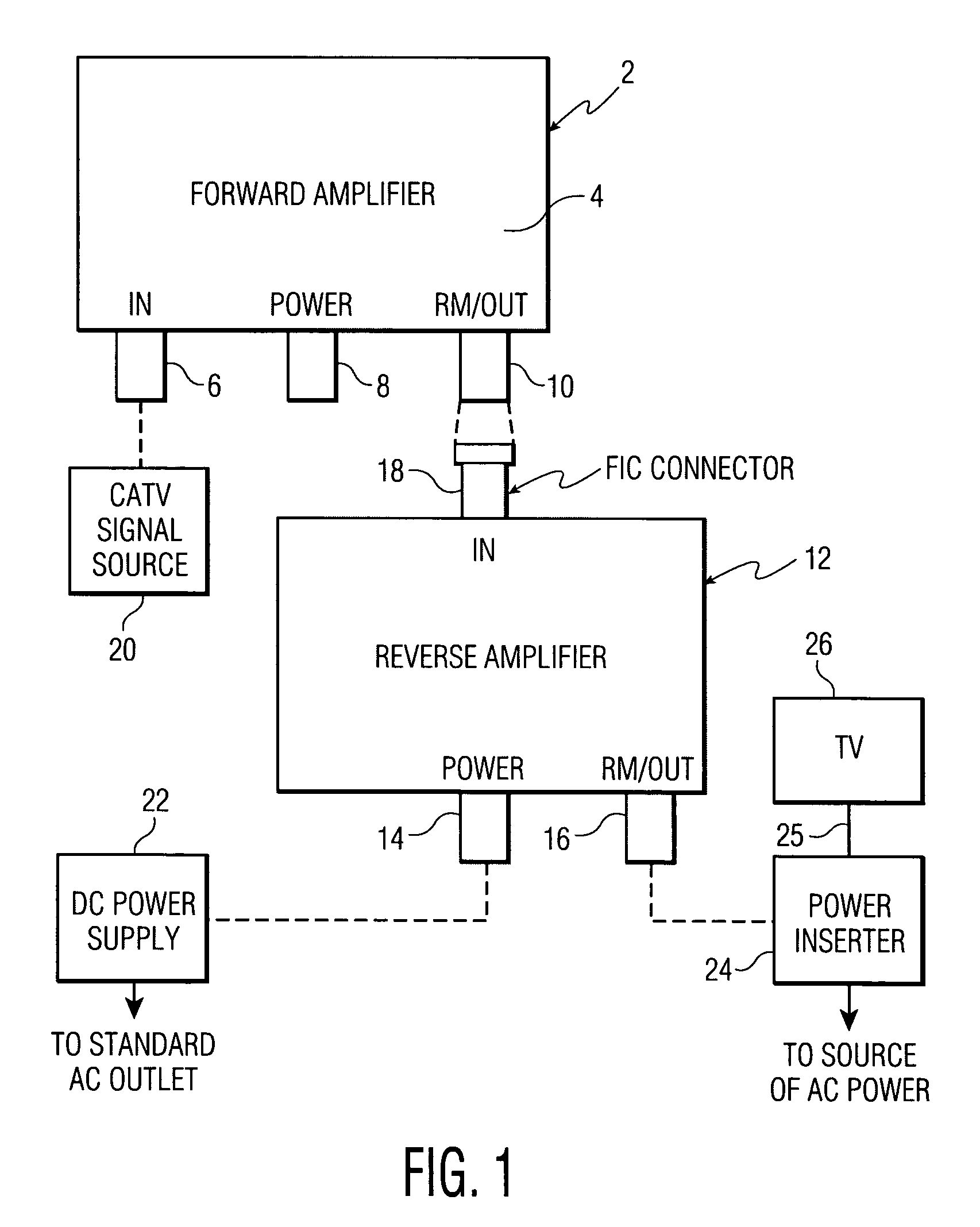

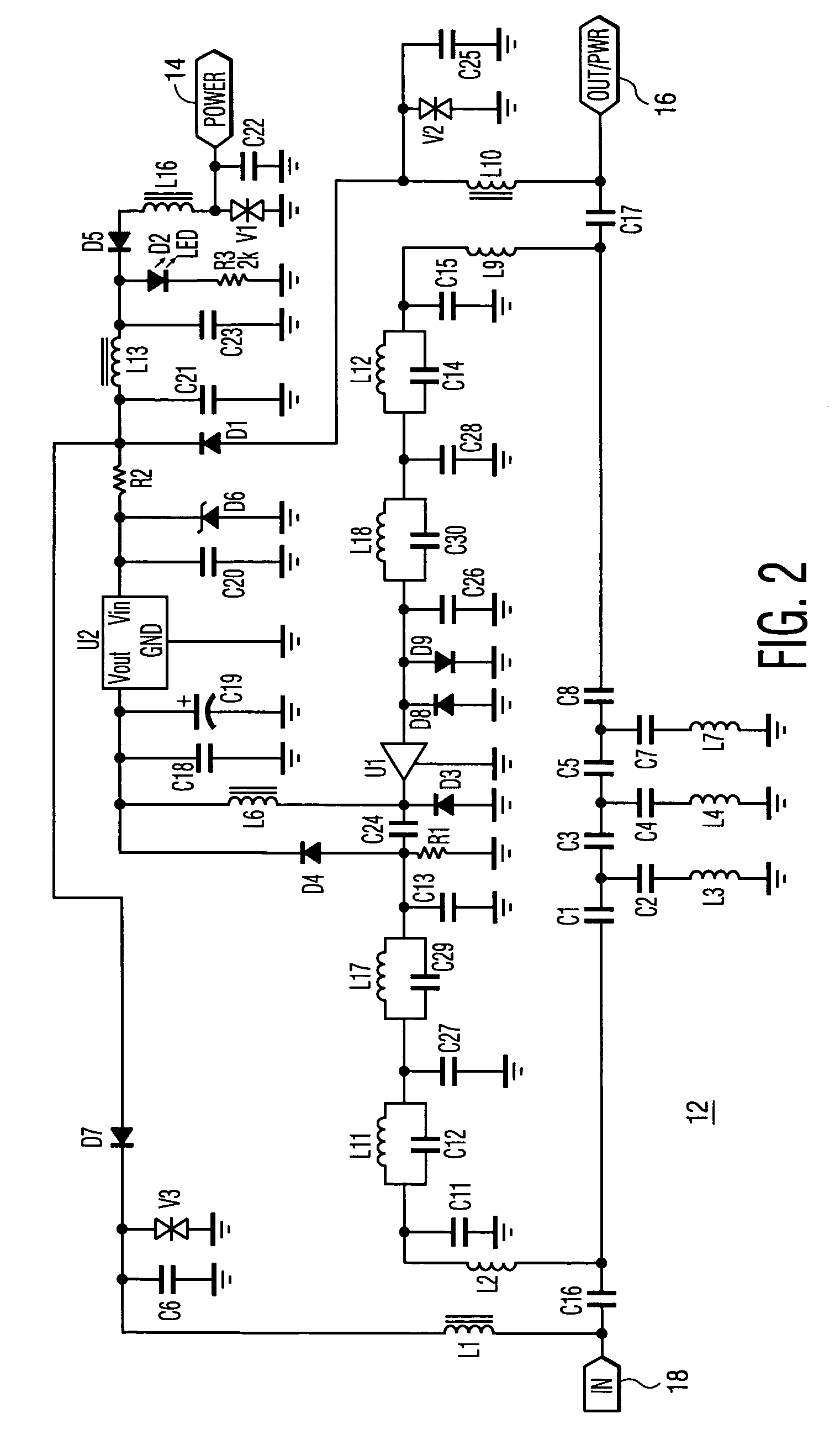

Cable television reverse amplifier

ActiveUS20060041922A1Electrically conductive connectionsHigh frequency amplifiersAudio power amplifierEngineering

Owner:TIMES FIBER COMM

Variable equalizer apparatus

InactiveUS20090041106A1Multiple-port networksDigital data processing detailsAudio power amplifierEngineering

A variable equalizer apparatus for forward and / or reverse equalizers in an amplifier. The system can include a structure to allow continuous contact of the signal flow as an equalizer is removed; jumpers with fixed resistors and associated capacitors and inductors to produce a variable range over many different values; and / or variable resistance potentiometers with fixed resistors and associated capacitors and inductors to produce a variable range over separate value equalizers.

Owner:BROADBAND INT

Asymmetric, optimized common-source bi-directional amplifier

ActiveUS7239852B2Resonant long antennasAmplifiers wit coupling networksAudio power amplifierControl signal

A common source, bi-directional microwave amplifier is described. More particularly, the present invention is a microwave, common source, bi-directional amplifier that includes a first amplification path and a second amplification path wherein the signal directional flow is controlled through the selective biasing of the first amplification path and the second amplification path. Each amplification path is designed to optimize desired performance. For signal flow through the first amplification path, the first amplification path is biased-on and the second path is biased-off. For signal flow through the second amplification path, the second amplification path is biased-on and the first path is biased-off.

Owner:NORTHROP GRUMMAN SYST CORP

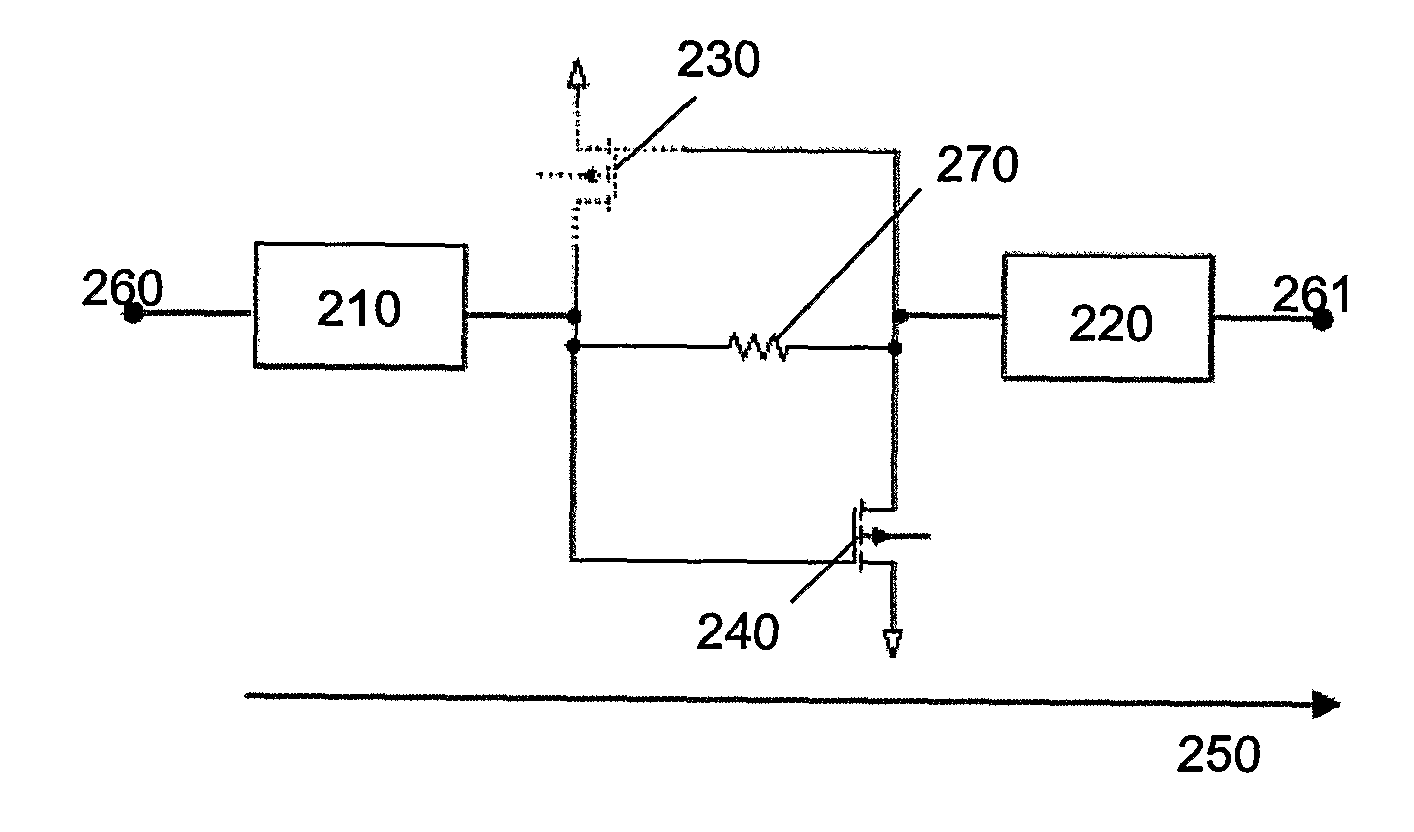

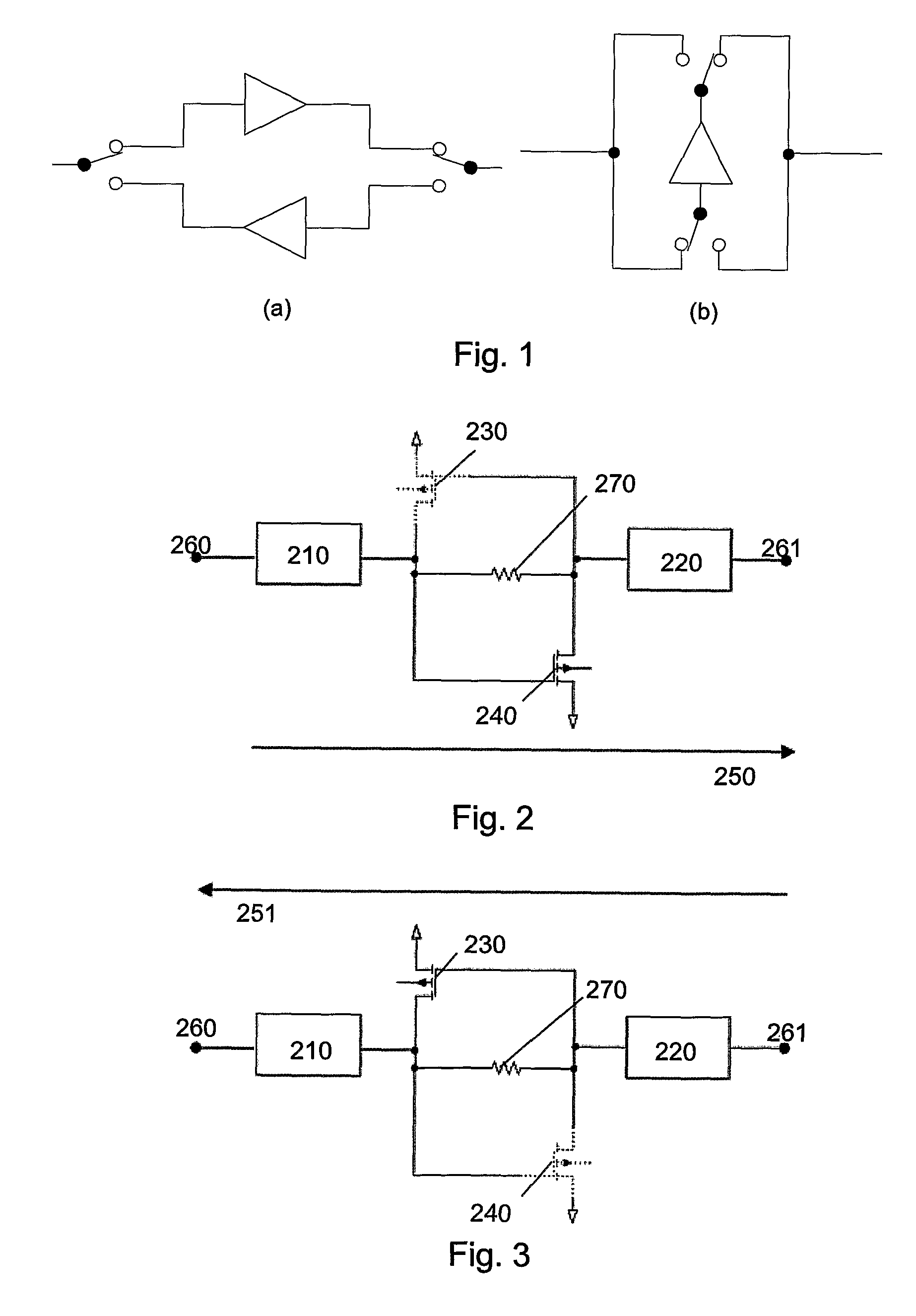

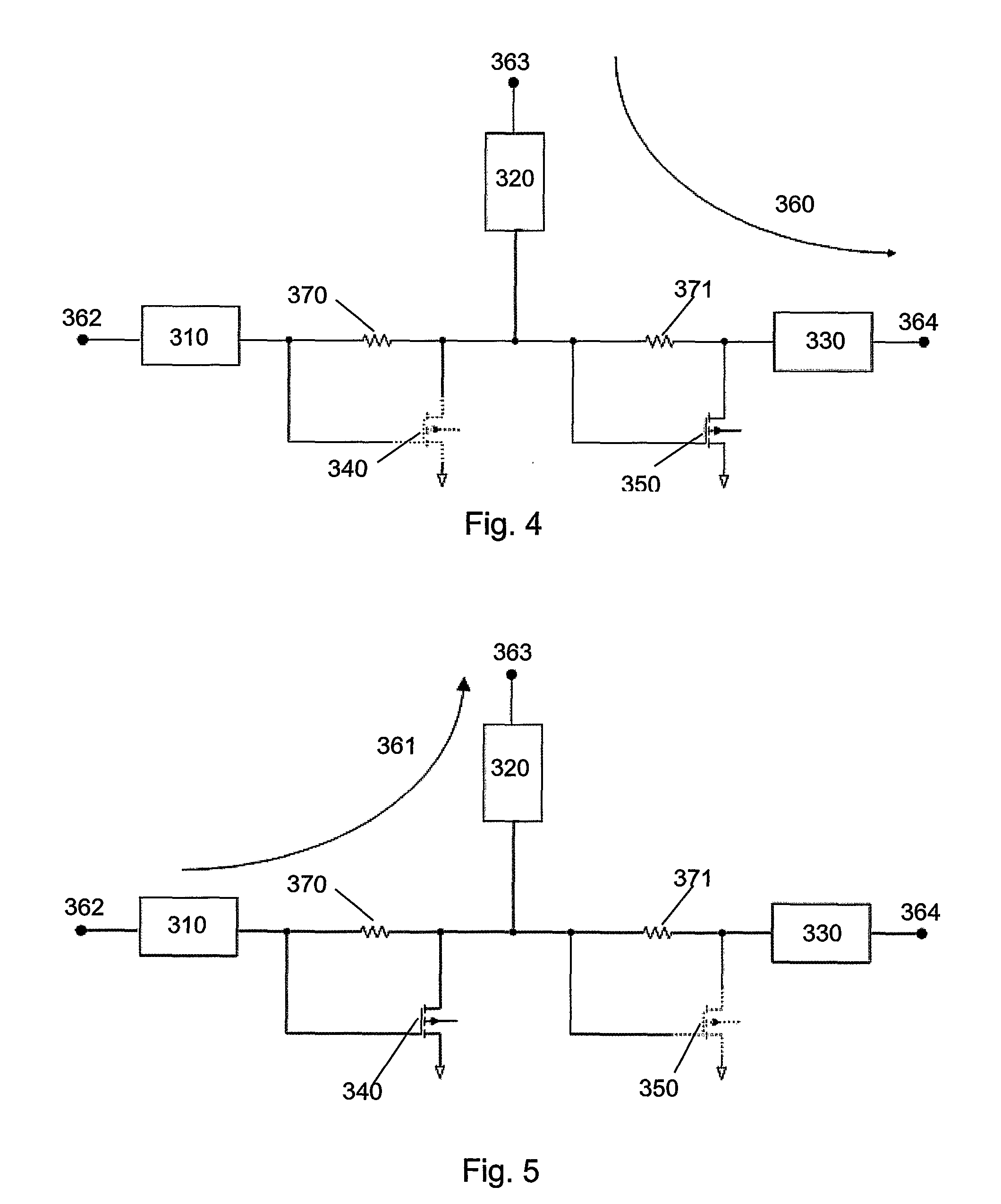

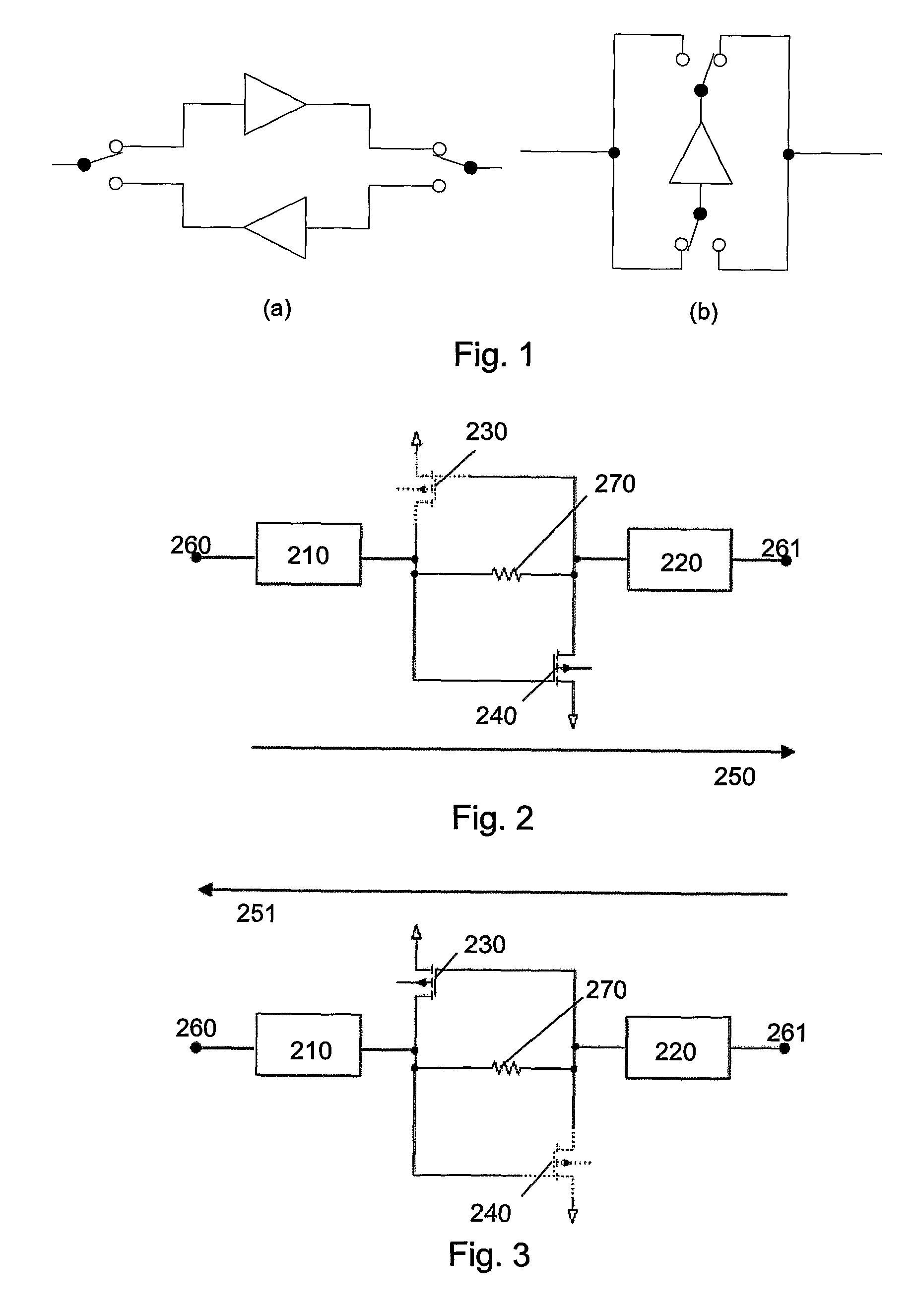

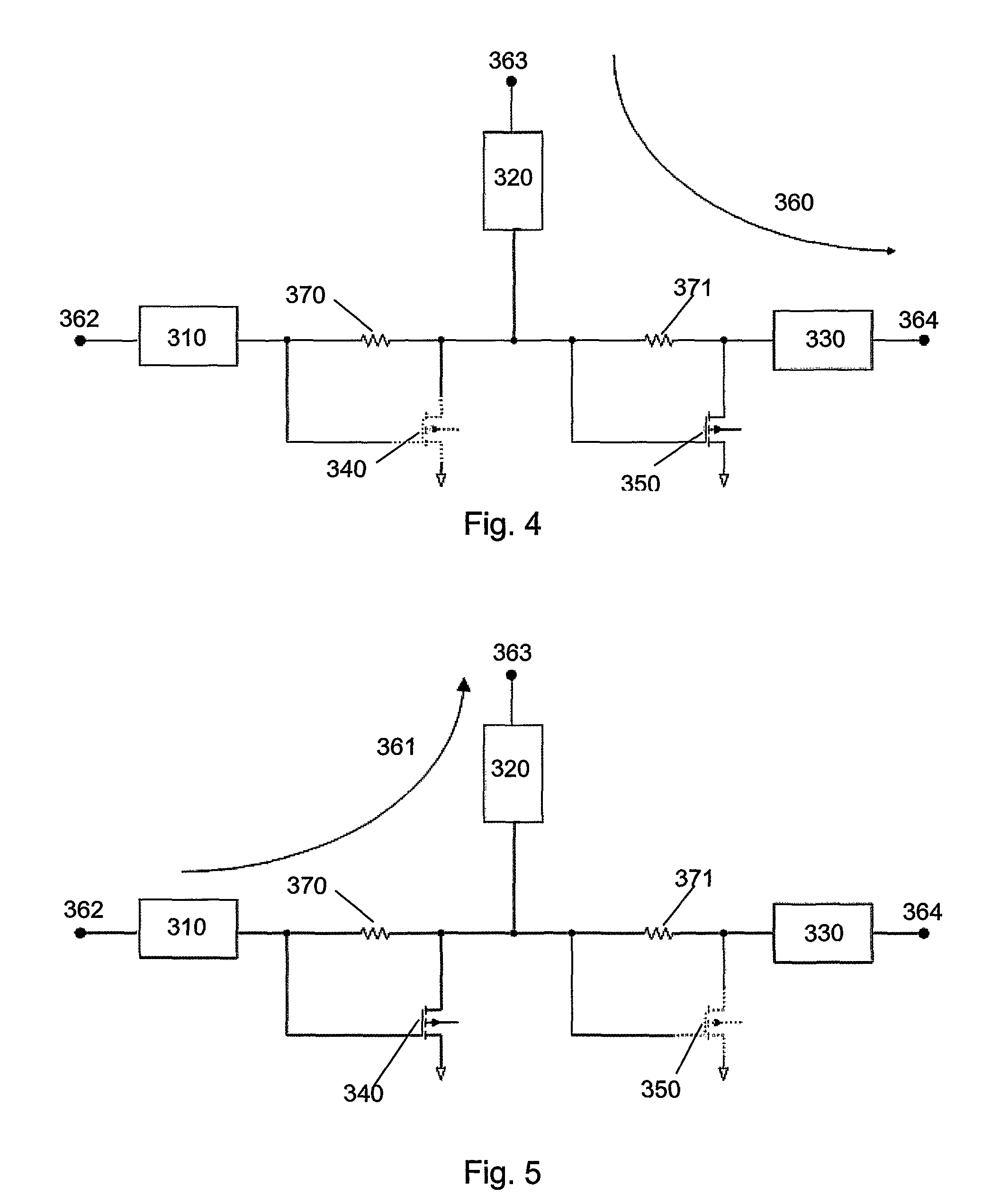

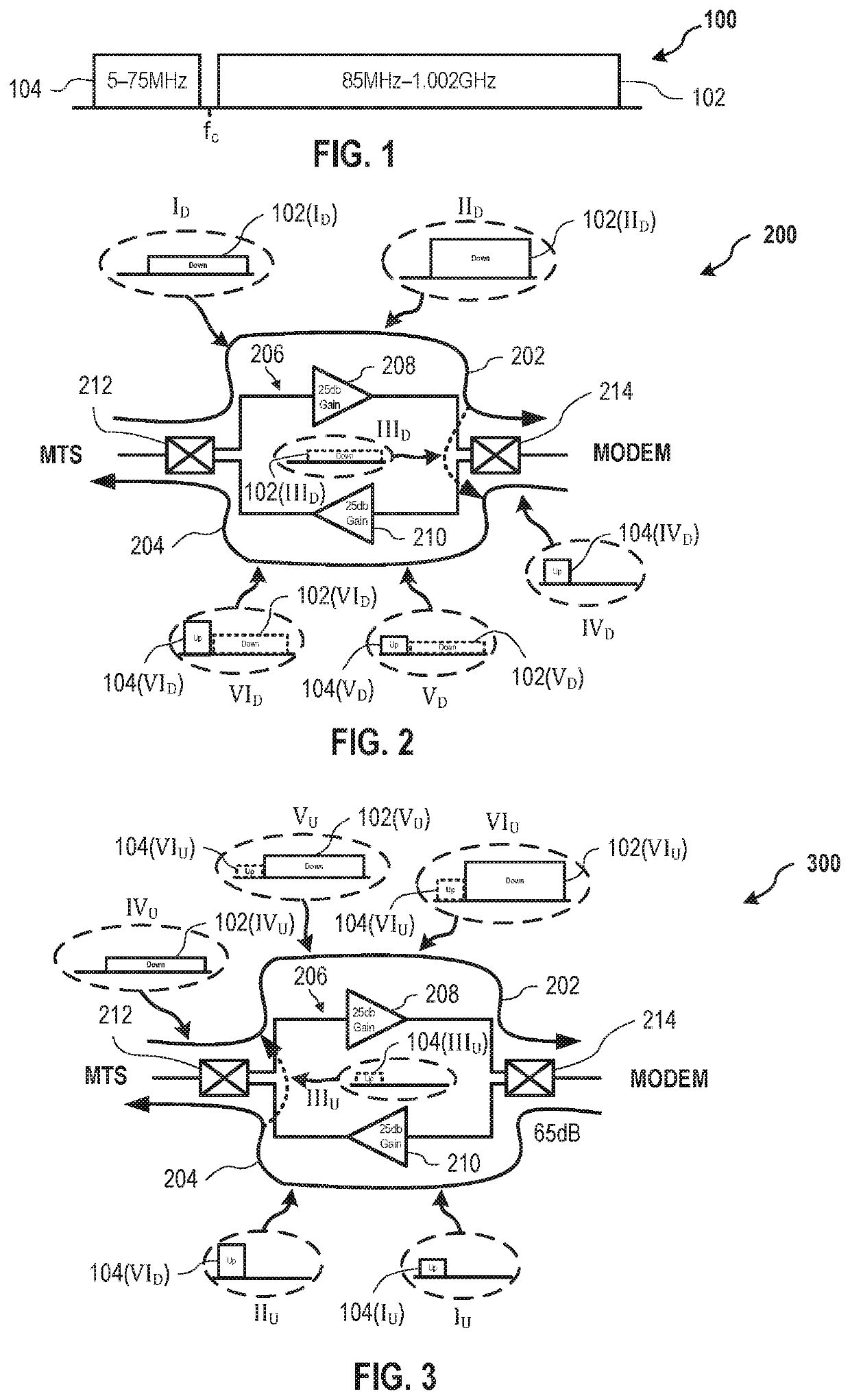

Switch-less bidirectional amplifier

ActiveUS20100060360A1Avoid leakage currentEasy to useGated amplifiersAmplifiers wit coupling networksTransceiverAudio power amplifier

A bi-directional amplifier, transceiver, integrated circuit, mobile unit, telecommunication infrastructure for amplification of signals received or signals to be transmitted in a communication circuit and a method for bi-directional amplification comprising amplifying signals in a bi-directional amplifier and directing a signal between two or more different paths comprising at least one first biased semiconductor amplification element coupled to a at least one first impedance matching network, at least one second biased semiconductor amplification element coupled to a second impedance matching network, a first device for biasing the at least one first biased semiconductor amplification element and a second device for biasing the at least one second biased semiconductor amplification element where the direction of signal amplification in said bi-directional amplifier is controlled by the first or second device for biasing the at least one first or second biased semiconductor amplification element.

Owner:TELEFON AB LM ERICSSON (PUBL)

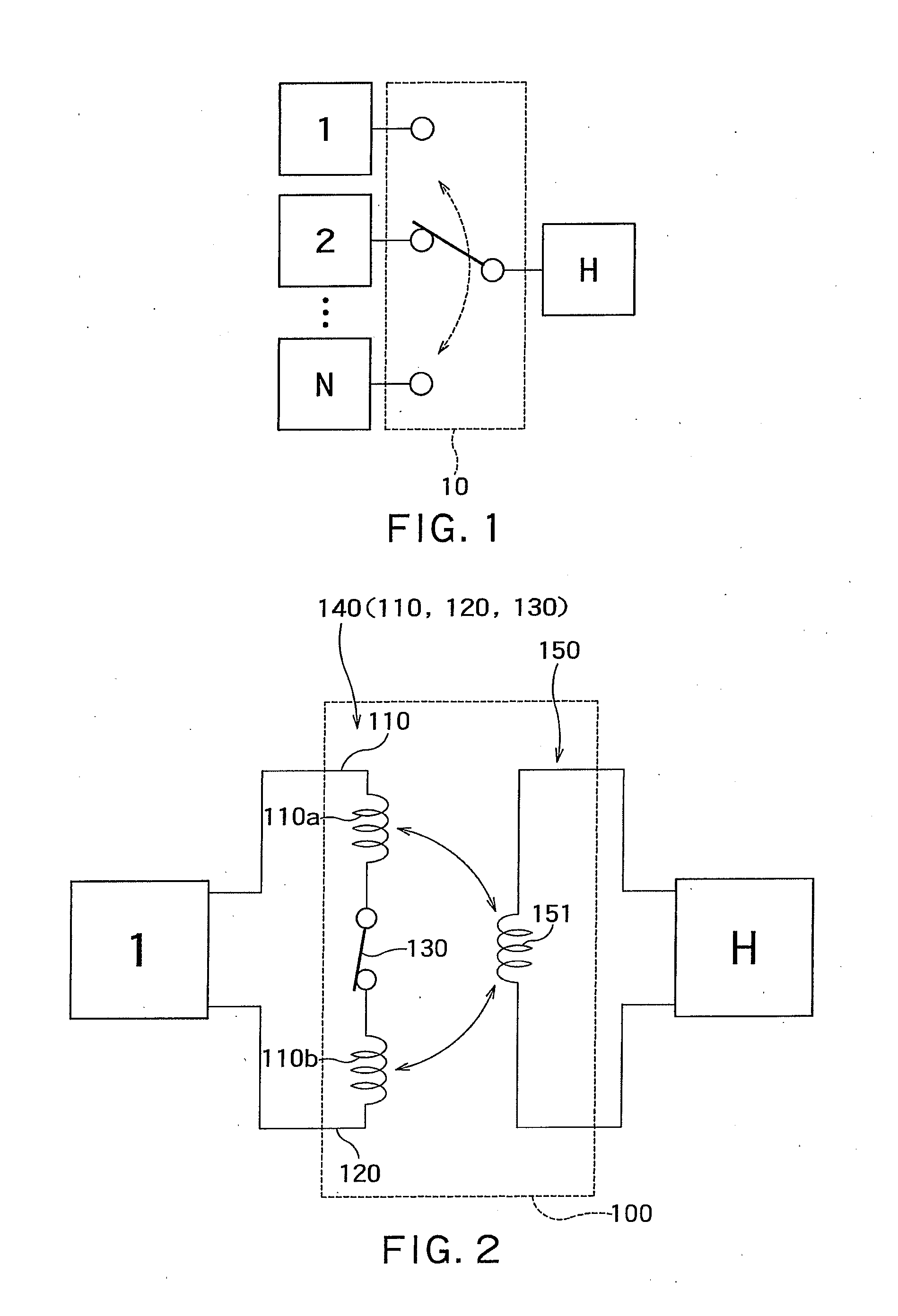

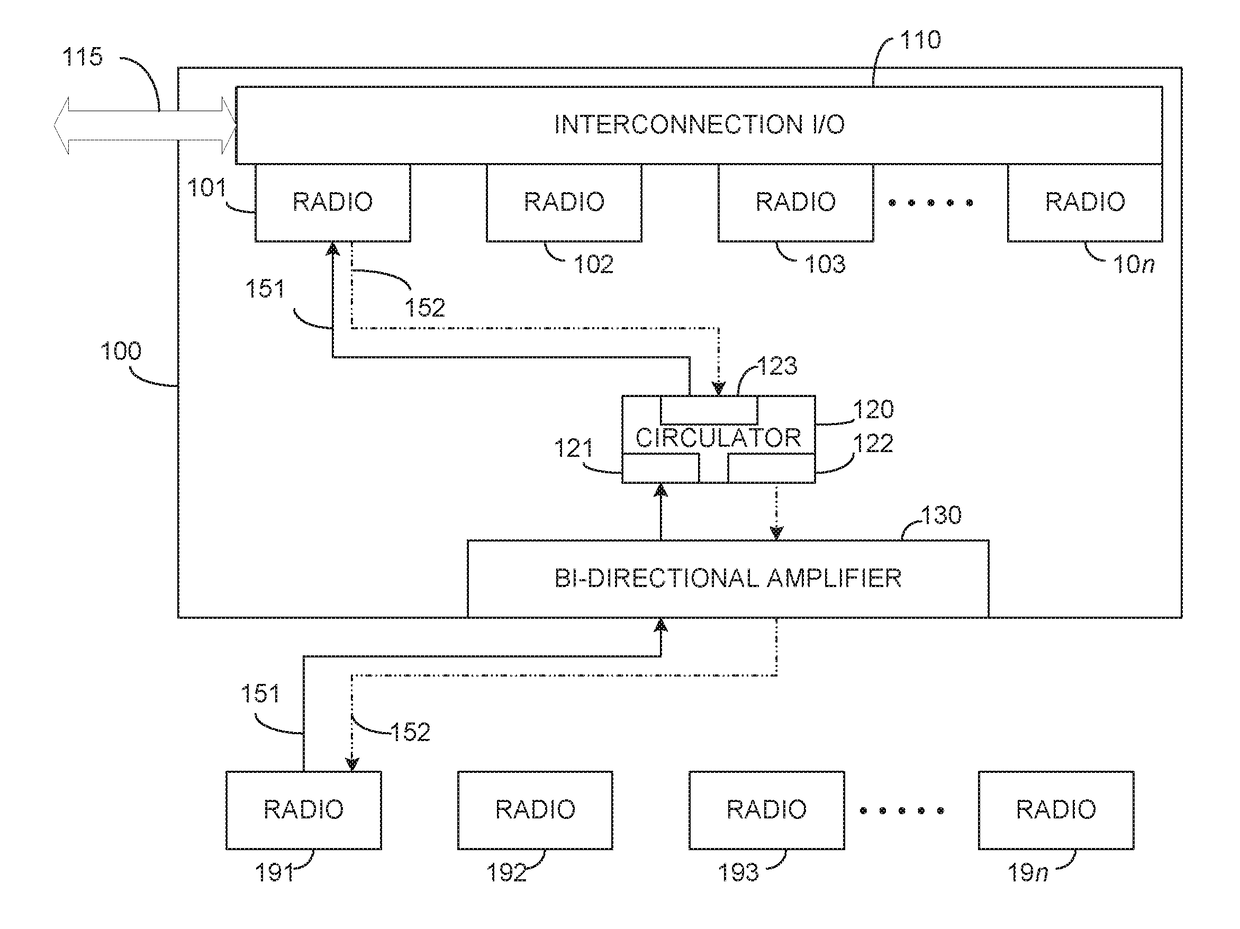

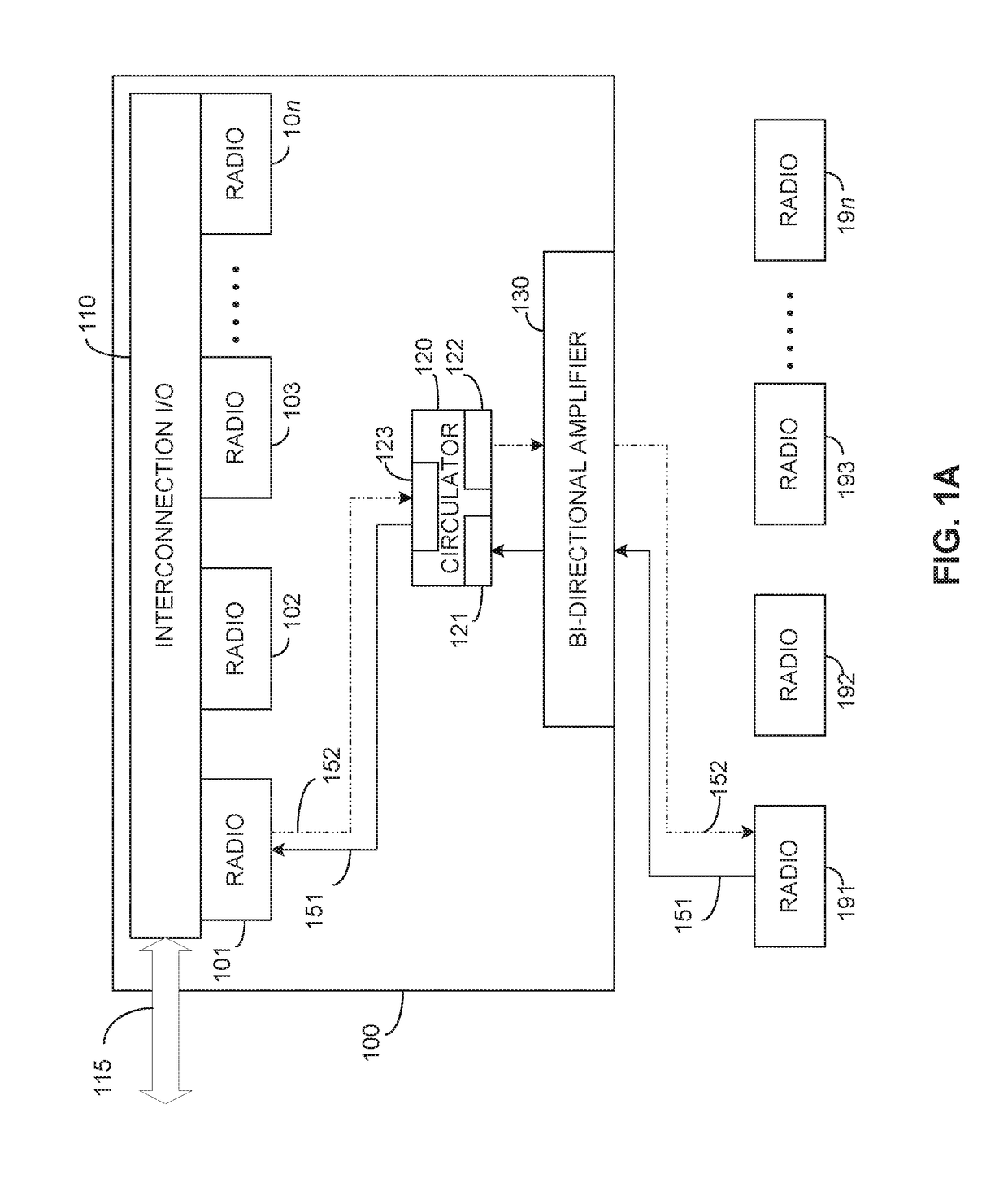

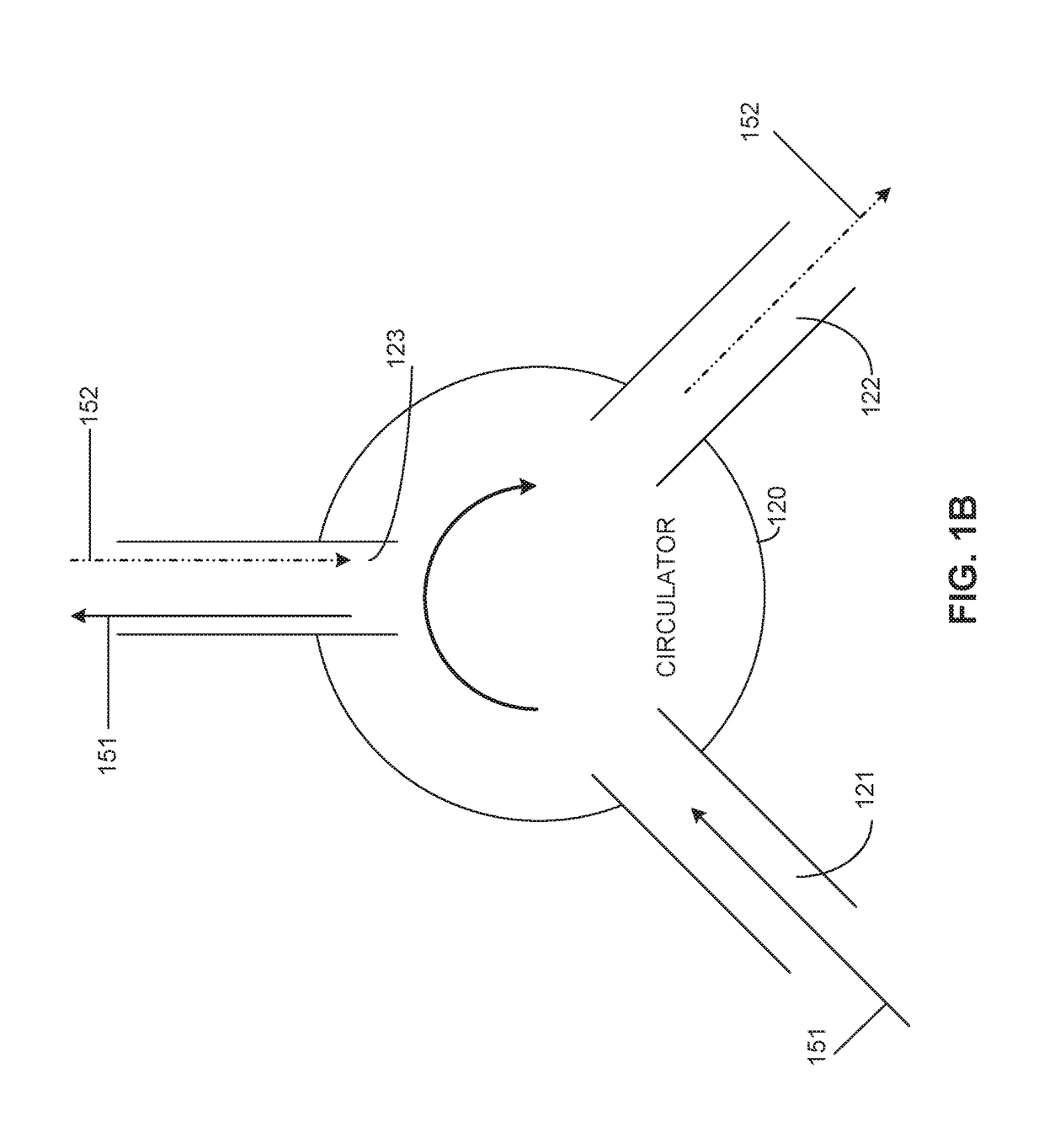

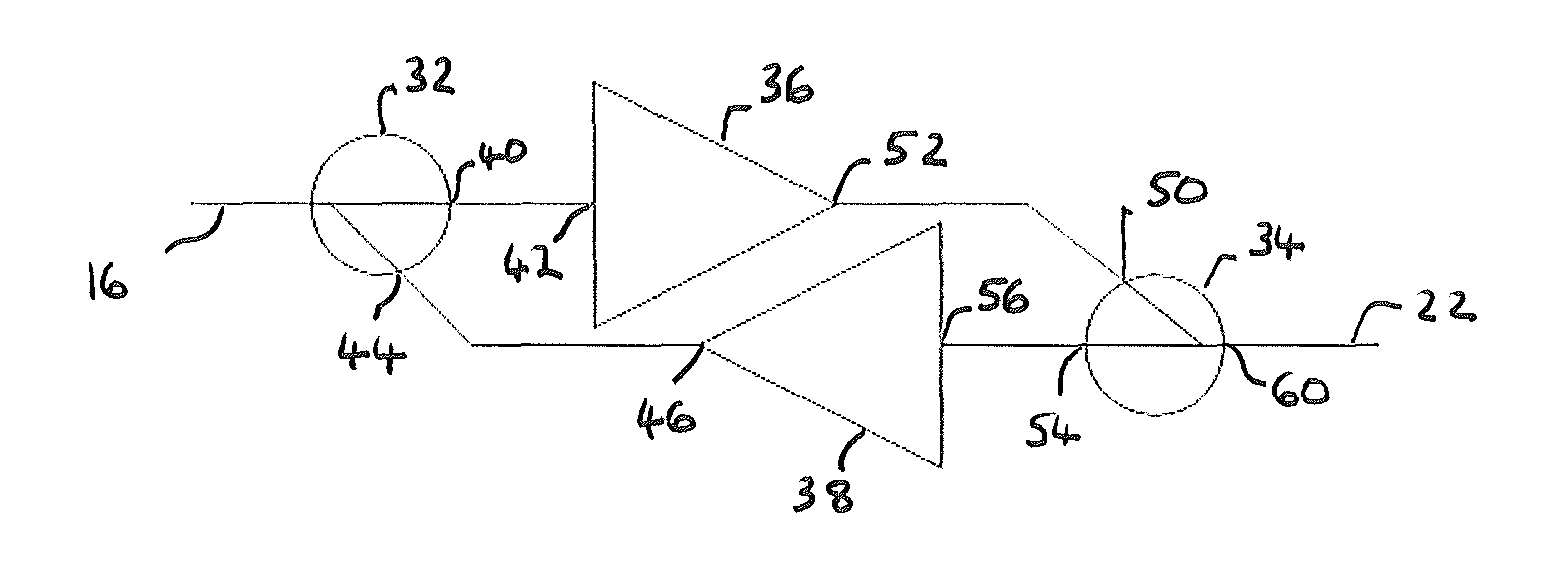

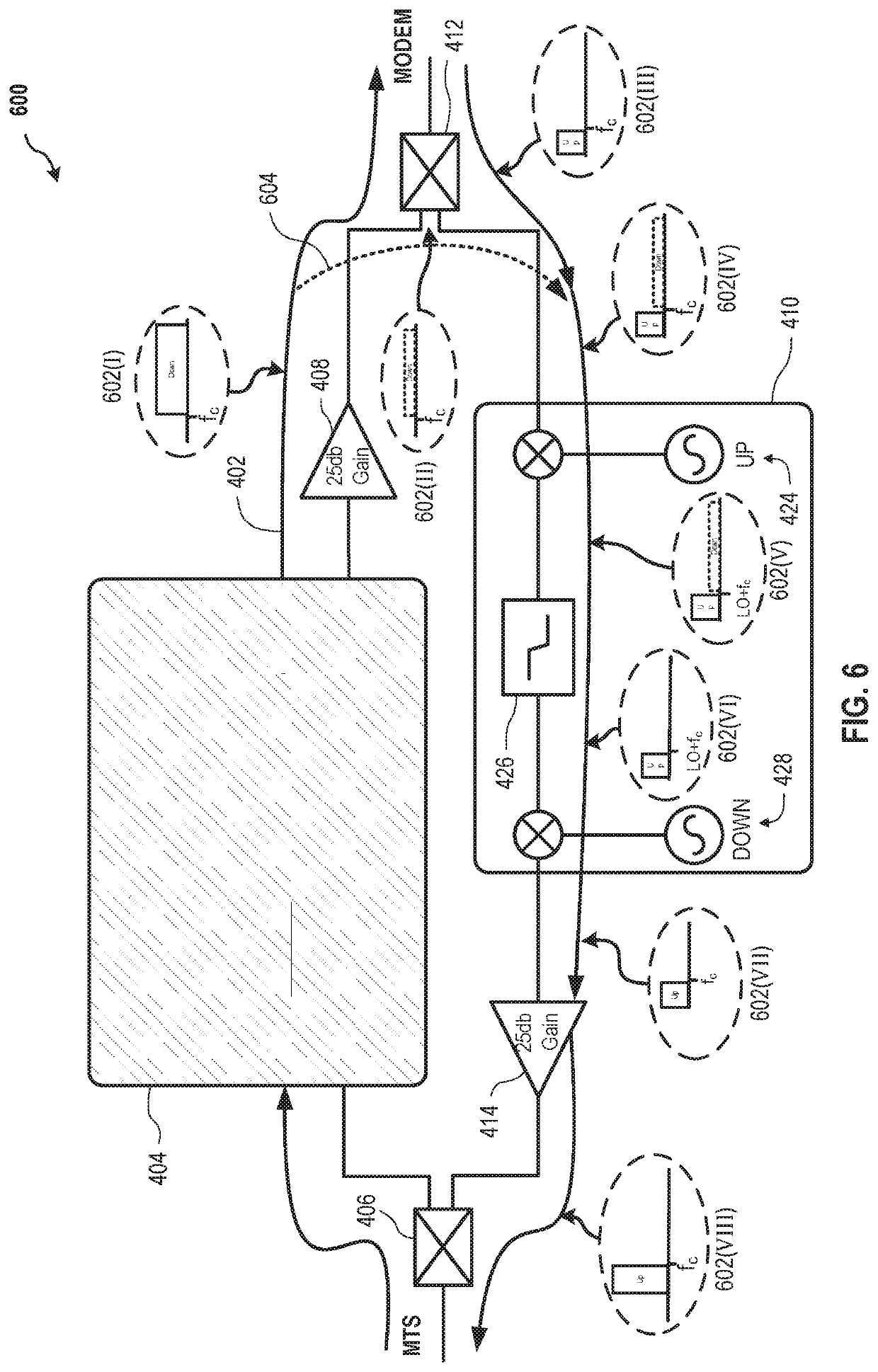

System for operating multiple transceiver modules concurrently

ActiveUS20180131435A1Power amplifiersAmplifier modifications to raise efficiencyAudio power amplifierTransceiver

Embodiments describe systems, apparatuses, and methods for transmitting / receiving signal data to / from a plurality of transceiver modules. Devices in accordance with some embodiments can include a plurality of wireless transceiver modules, each wireless transceiver module to be communicatively coupled to a corresponding external transceiver module, one or more antennas to exchange signal data with the plurality of external transceiver modules, a radio frequency (RF) circulator, and one or more amplifiers to amplify the signal data received by the one or more antennas and signal data to be transmitted by the one or more antennas. The use of the RF circulator prevents transmitting signals that may collide with each other and cause interference with the communications.

Owner:NIKE INC

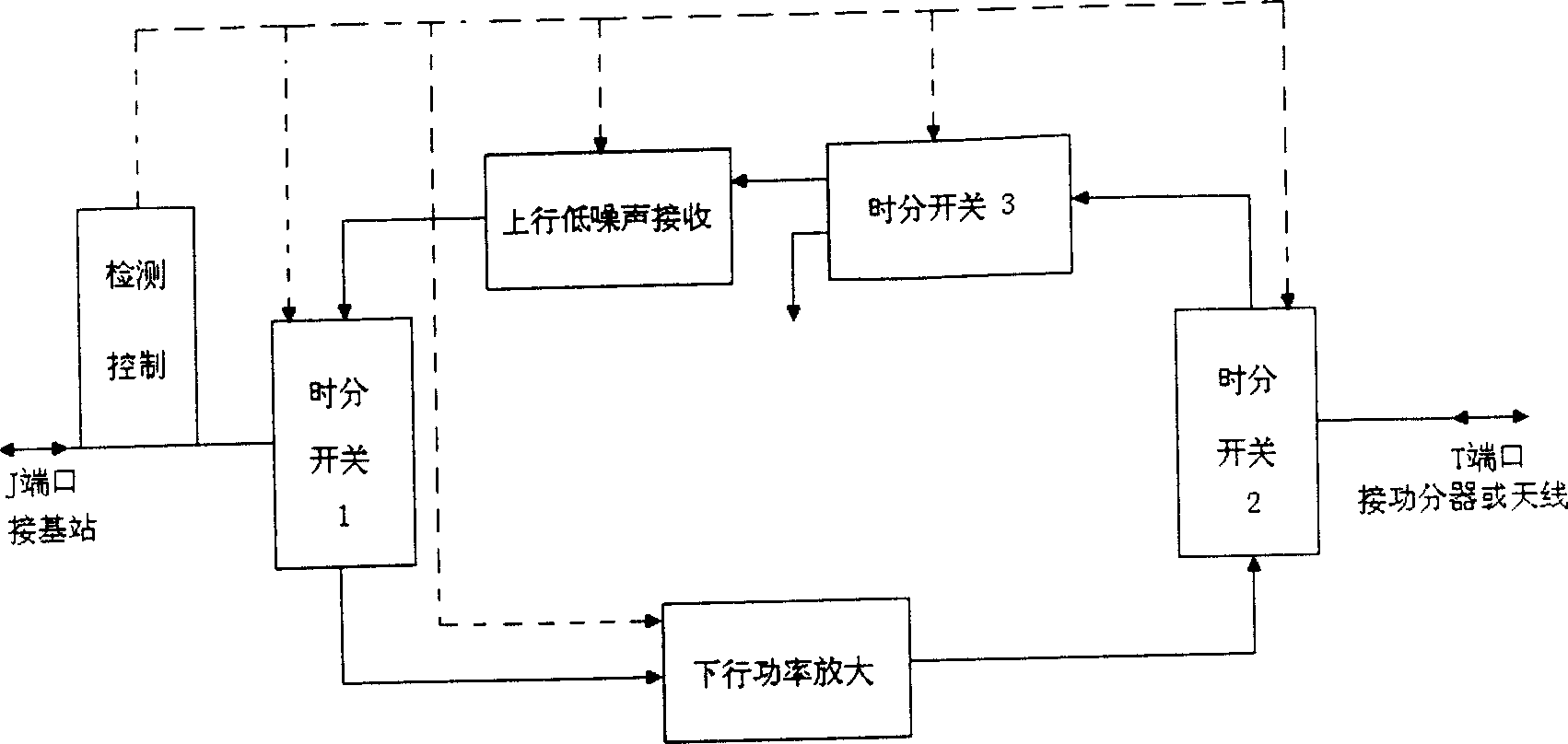

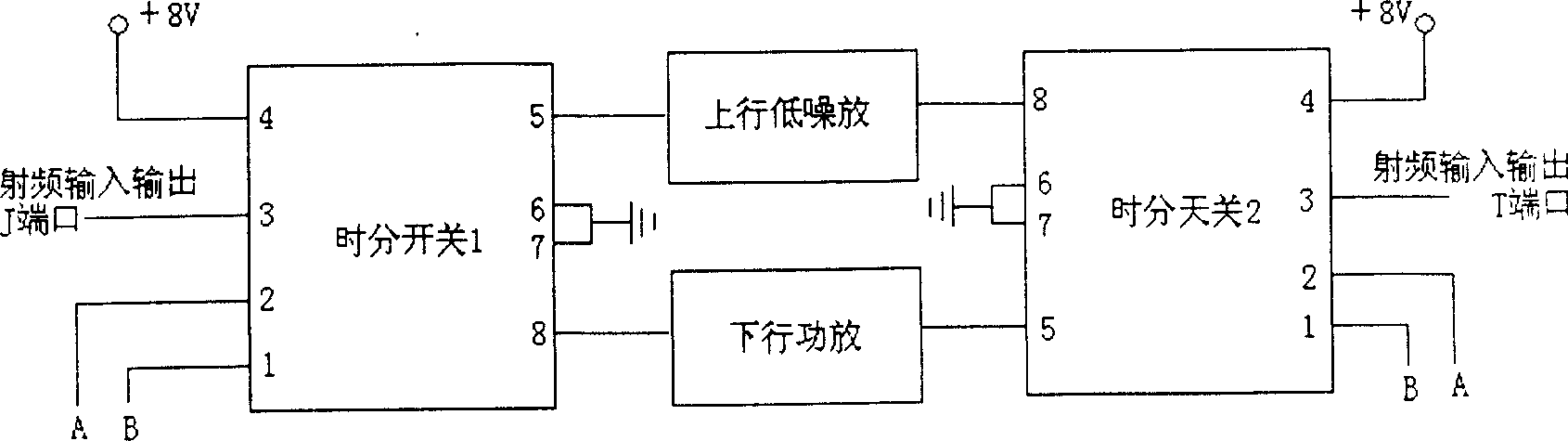

Two-way amplifier of portable phone system

InactiveCN1832372AIsolation highNoise figure impactTwo-way amplifiersRadio/inductive link selection arrangementsLow noiseAudio power amplifier

This invention relates to a dual-way amplifier of a new handheld phone system, which can either solve the problem of high isolation of up and down lines or can let the indoor covered receiving noise factor of the system less than 3dB and the down high power amplified three-stage mutual adjustment target to -48dBc characterizing in including a test control circuit unit, a down power amplified circuit unit, an up low noise receiving circuit unit and three time division switches.

Owner:胡军

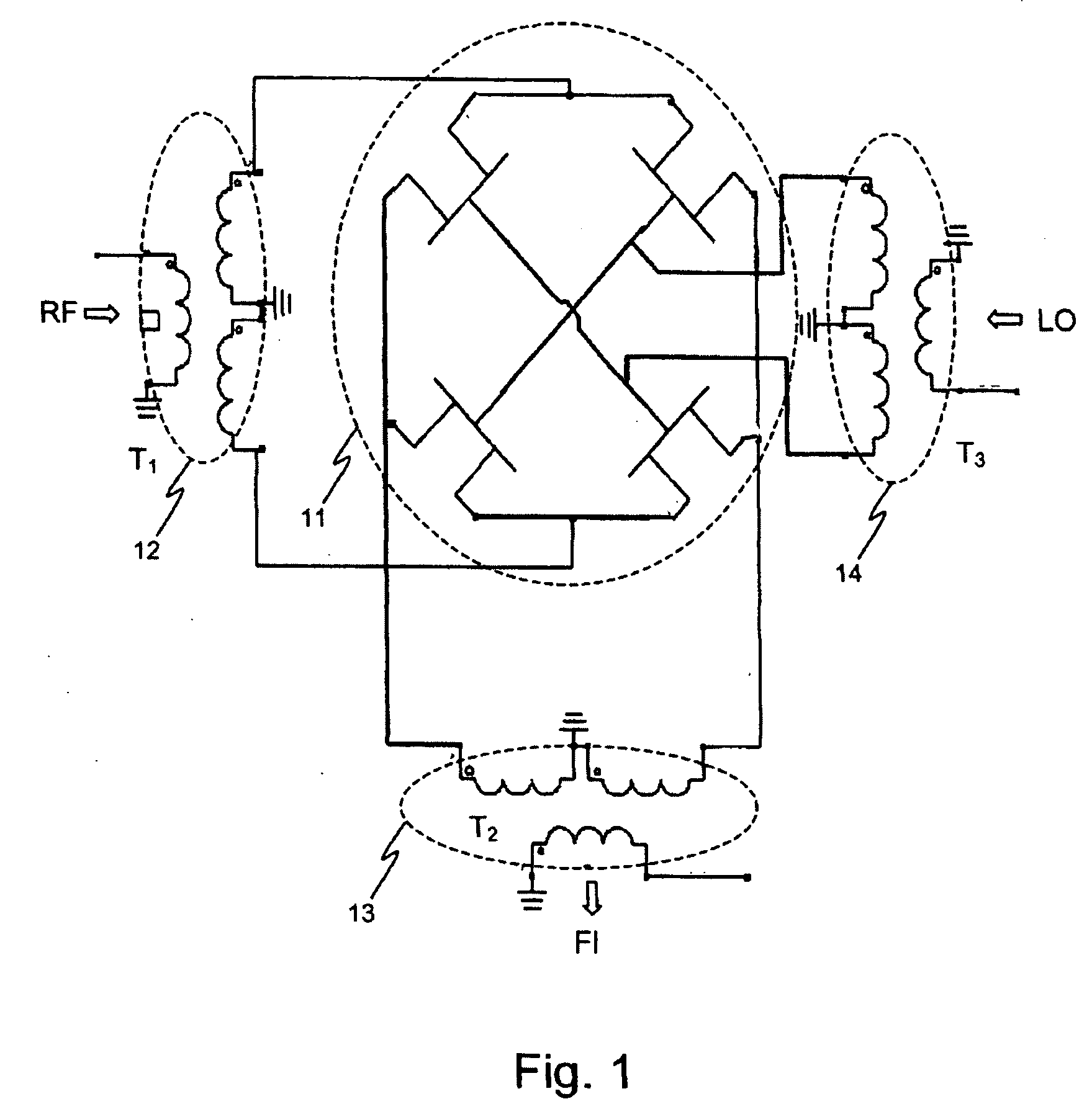

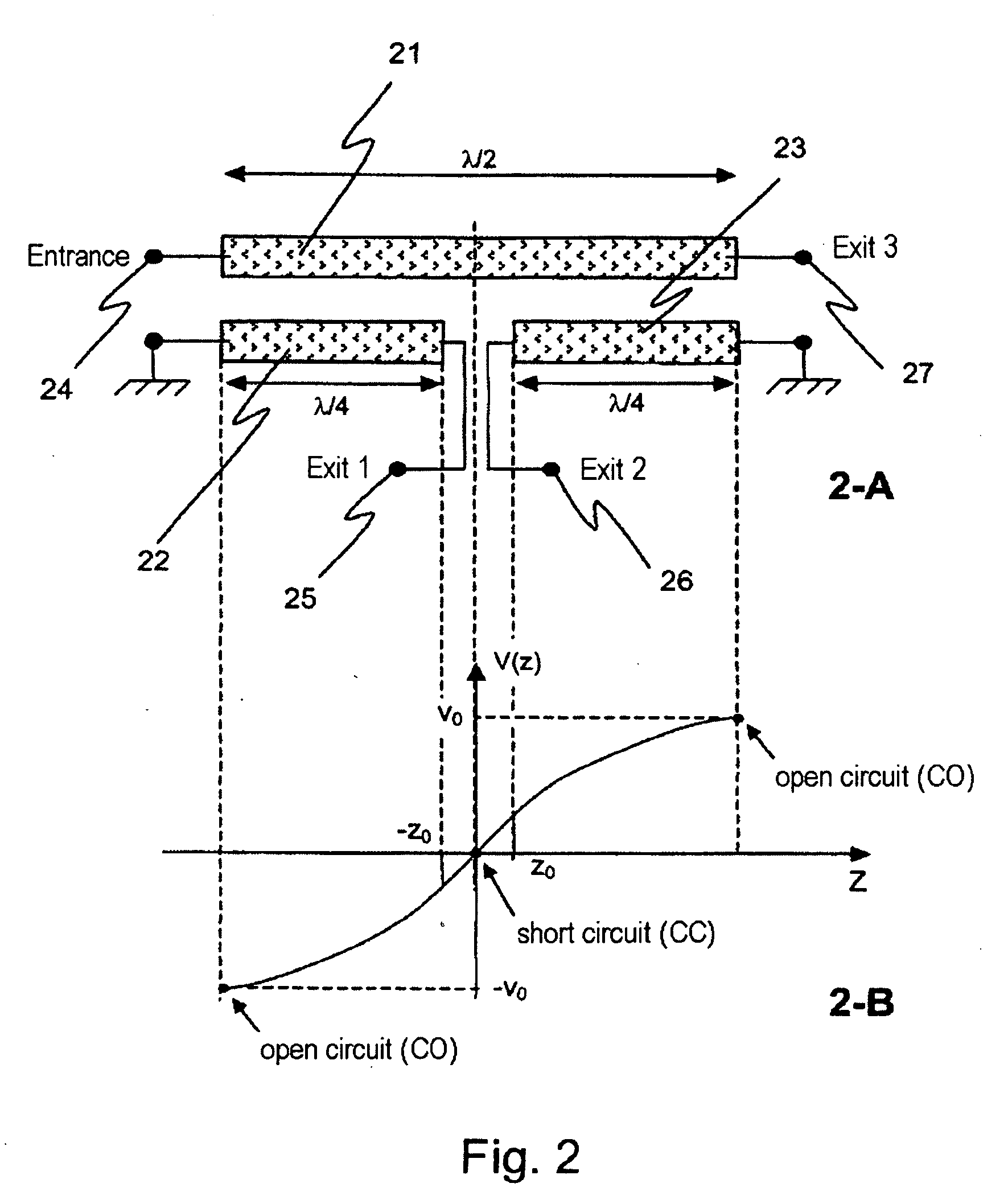

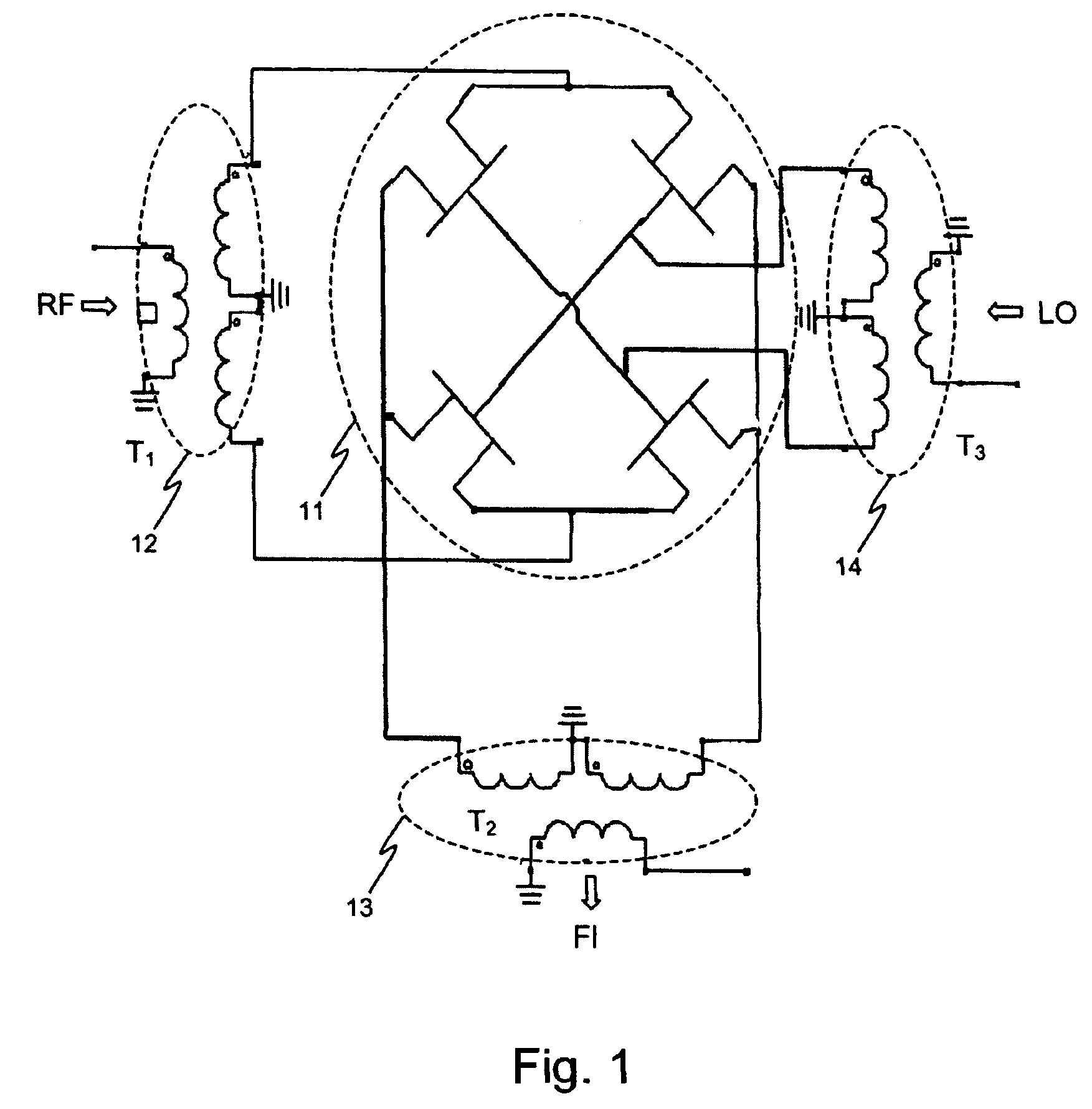

Broadband reciprocal active balun structure

InactiveUS20090134951A1Function provideBalance-unbalance networksModulation transferenceAudio power amplifierCoupling

The present invention relates to the field of electronic devices known as baluns. It concerns an active balun which is broadband and reciprocal. Embodiments of the invention integrate an active splitter balun with an active combiner balun so as to form three transmission lines. A first active coupling is provided between the first and second transmission lines and a second active coupling is provided between the first and third transmission lines. The active couplings are provided by means of amplifier cells distributed along the transmission lines. Embodiments of the invention have configurable means for polarizing the different amplifier cells so as to create a specific coupling direction between the various transmission lines. The device according to the invention can be applied in the field of broadband mixers which are used, notably, in radio transmission and reception circuits.

Owner:THALES SA

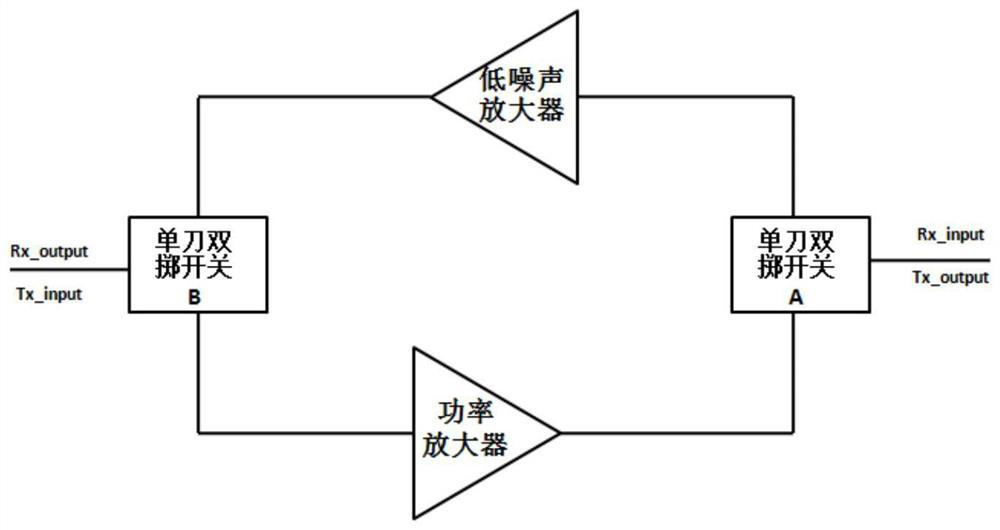

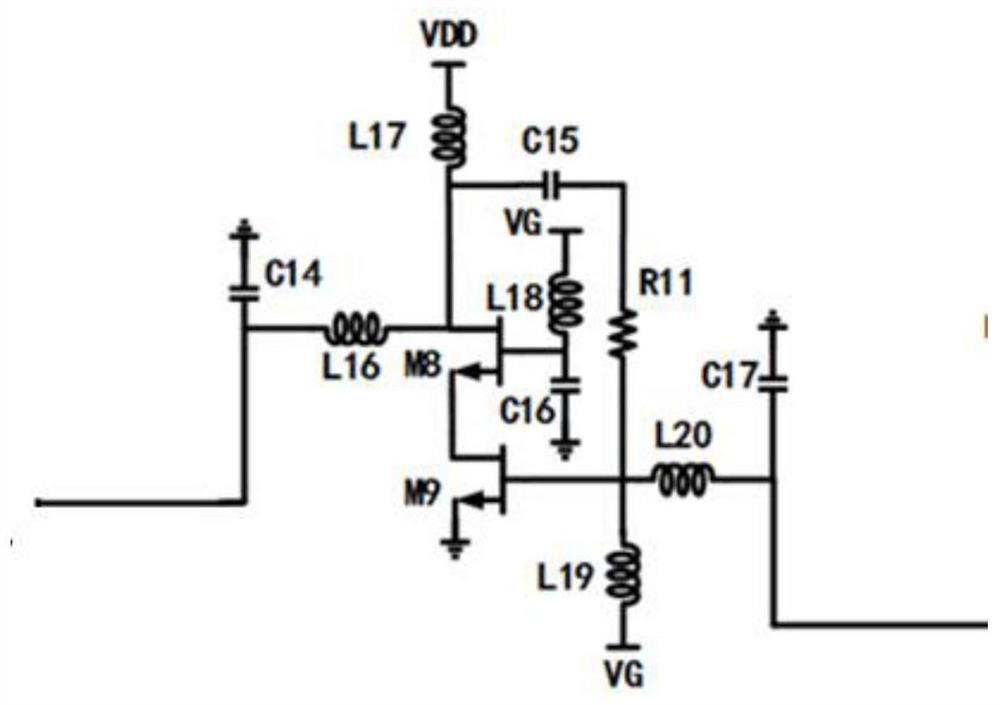

Ultra-wideband bidirectional amplifier based on 500nm GaAs pHEMT process

ActiveCN112653396AUWB Efficiently RealizedUWB implementationAmplifier modifications to raise efficiencyTwo-way amplifiersUltra-widebandLow noise

The invention discloses an ultra-wideband bidirectional amplifier based on a 500nm GaAs pHEMT process, which comprises a low-noise amplifier for realizing wideband and low-noise matching, a power amplifier for realizing wideband and maximum power matching, a single-pole double-throw switch A and a single-pole double-throw switch B, and two ends of a switch tube of the ultra-wideband bidirectional amplifier are respectively provided with the same 5V positive voltage control switch unit. The ultra-wideband bidirectional amplifier based on the 500nm GaAs pHEMT process can realize ultra-wideband and high-frequency coverage to 10.6 GHz at the same time, and has excellent performance of an Rx-path LNA amplifier and a Tx-path PA amplifier. In addition, the 5V positive pressure control switch units arranged at the two ends change a negative pressure control switch tube into positive pressure control, and use is more convenient.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Asymmetric, voltage optimized, wideband common-gate bi-directional mmic amplifier

InactiveUS20030222719A1Amplifier combinationsAmplifier modifications to reduce detrimental impedenceTransceiverAudio power amplifier

Owner:NORTHROP GRUMMAN SYST CORP

Broadband reciprocal active balun structure

Owner:THALES SA

Amplifier Device

InactiveUS20170054423A1Inhibition effectImprove isolationRepeater circuitsTwo-way amplifiersAudio power amplifierDirectional coupling

There is provided an amplifier device for a CATV network comprising a first amplifier element for upstream signals and a second amplifier element for downstream signals, wherein the first and second amplifier elements are disposed between first and second directional couplers. The combined isolation of the first and second directional couplers is greater than the sum of the gain of the first and second amplifier elements. The first directional coupler has one port attached to an input of the downstream amplification element and one port attached to an output of an upstream amplification element (38) and the second directional coupler has one port attached to an output of the downstream amplifier and one port attached to an input of the upstream amplifier.

Owner:TECHNETIX

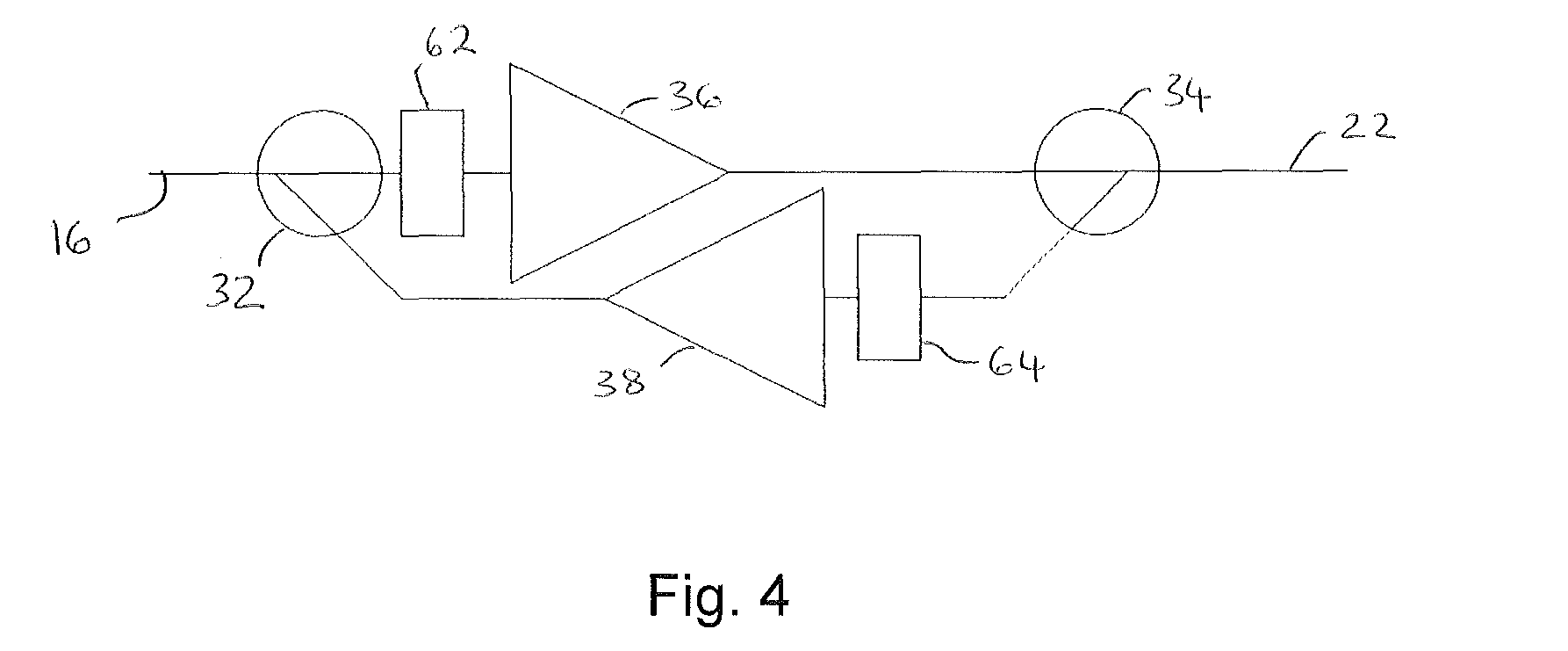

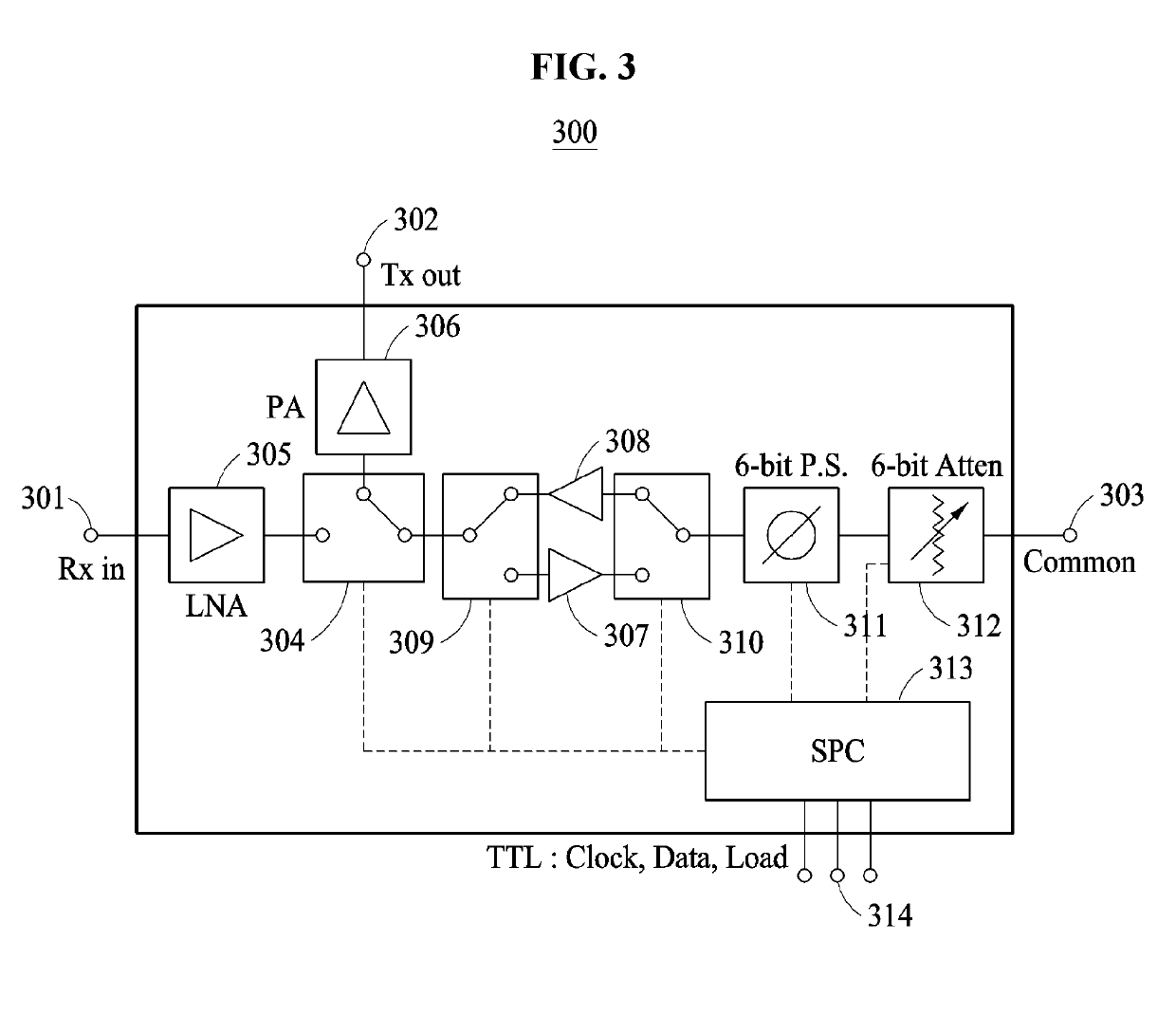

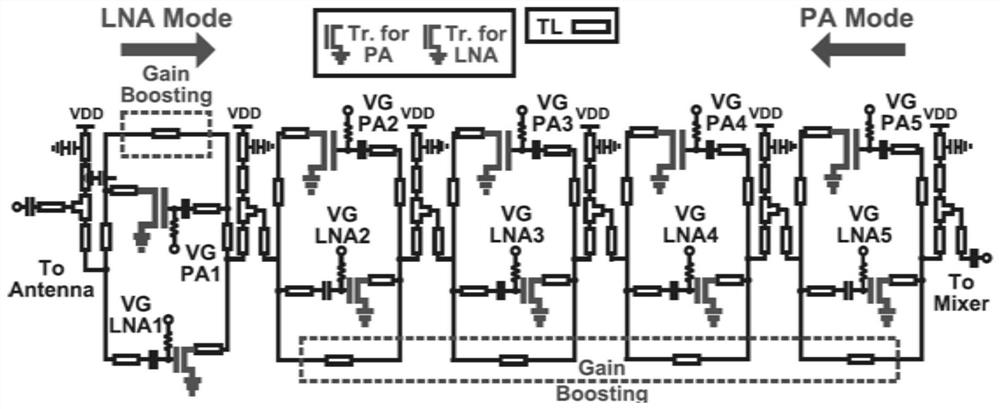

Monolithic microwave integrated circuit (MMIC) for phased array antenna system and phased array antenna system including the same

InactiveUS20190123778A1Improve output power characteristicsConsumes small amountGated amplifiersAntenna supports/mountingsAudio power amplifierEngineering

A monolithic microwave integrated circuit (MIMIC) for a phased array antenna system, and a phased array antenna system including the MIMIC are provided. The MIMIC includes a first amplifier including a first input terminal and a first output terminal, a second amplifier including a second input terminal and a second output terminal, a first switch connectable to the first input terminal and the second output terminal, and a second switch connectable to the first output terminal and the second input terminal.

Owner:ELECTRONICS & TELECOMM RES INST

Cable television reverse amplifier

ActiveUS7577983B2Electrically conductive connectionsHigh frequency amplifiersAudio power amplifierEngineering

Owner:TIMES FIBER COMMUNICATIONS INC

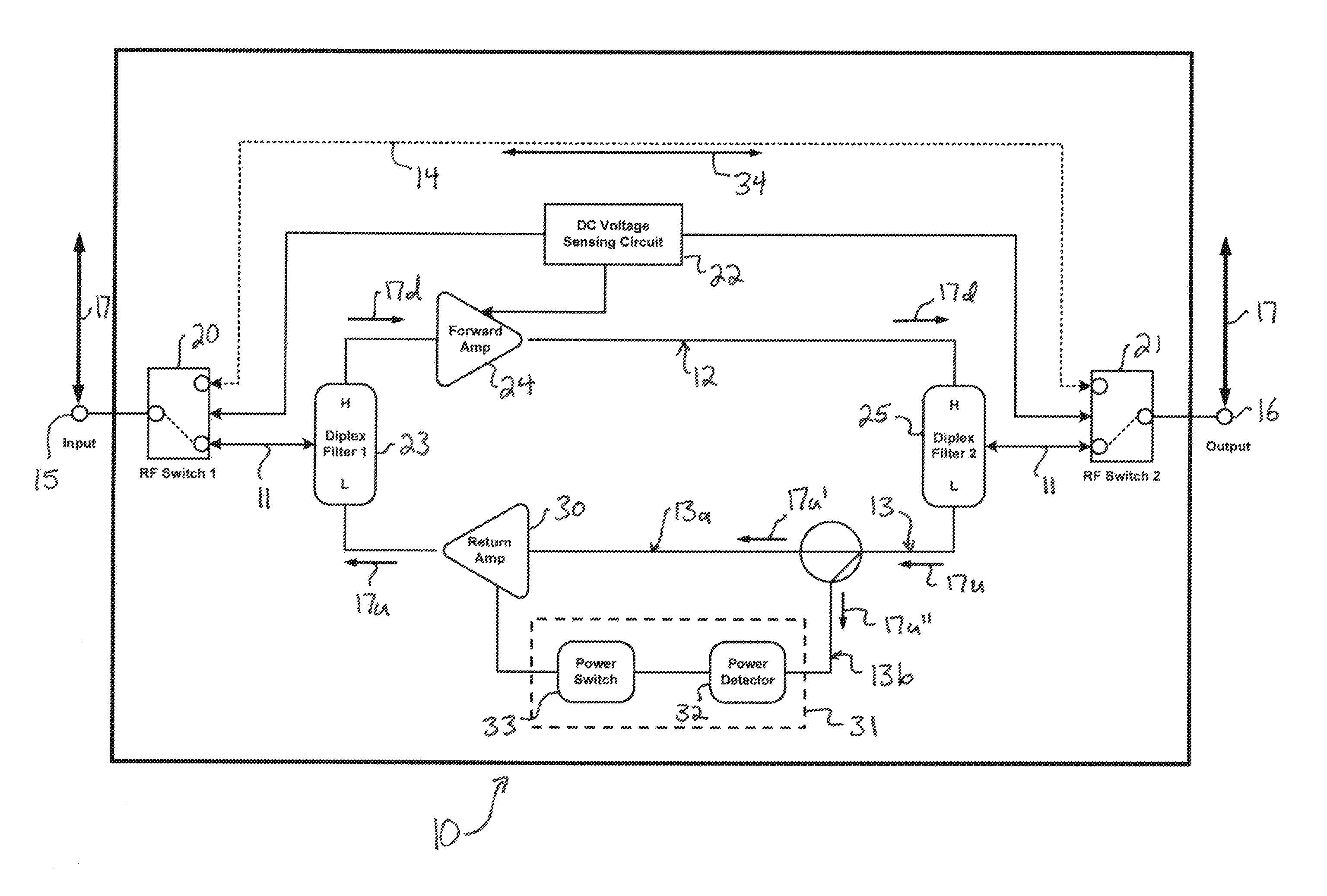

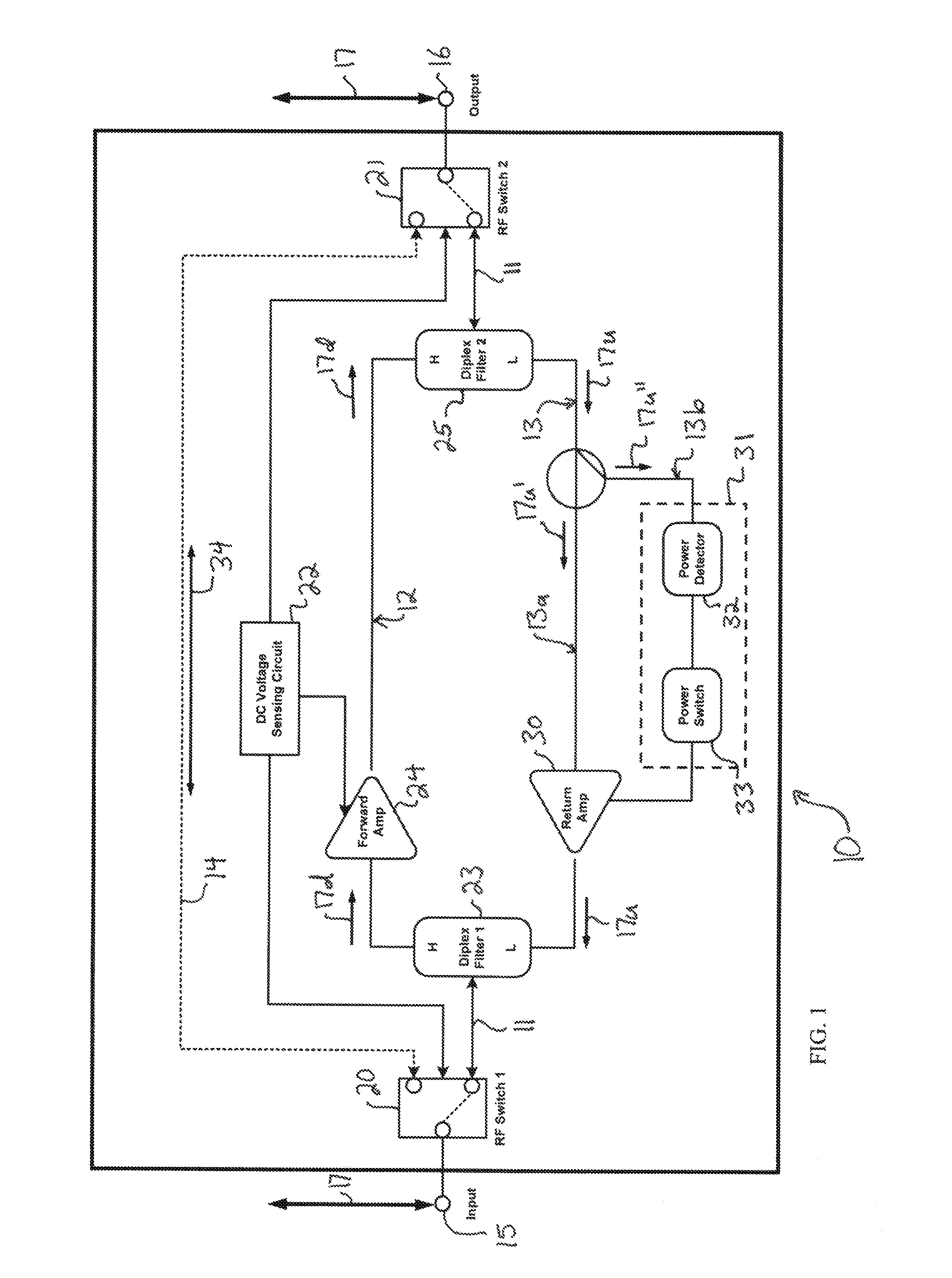

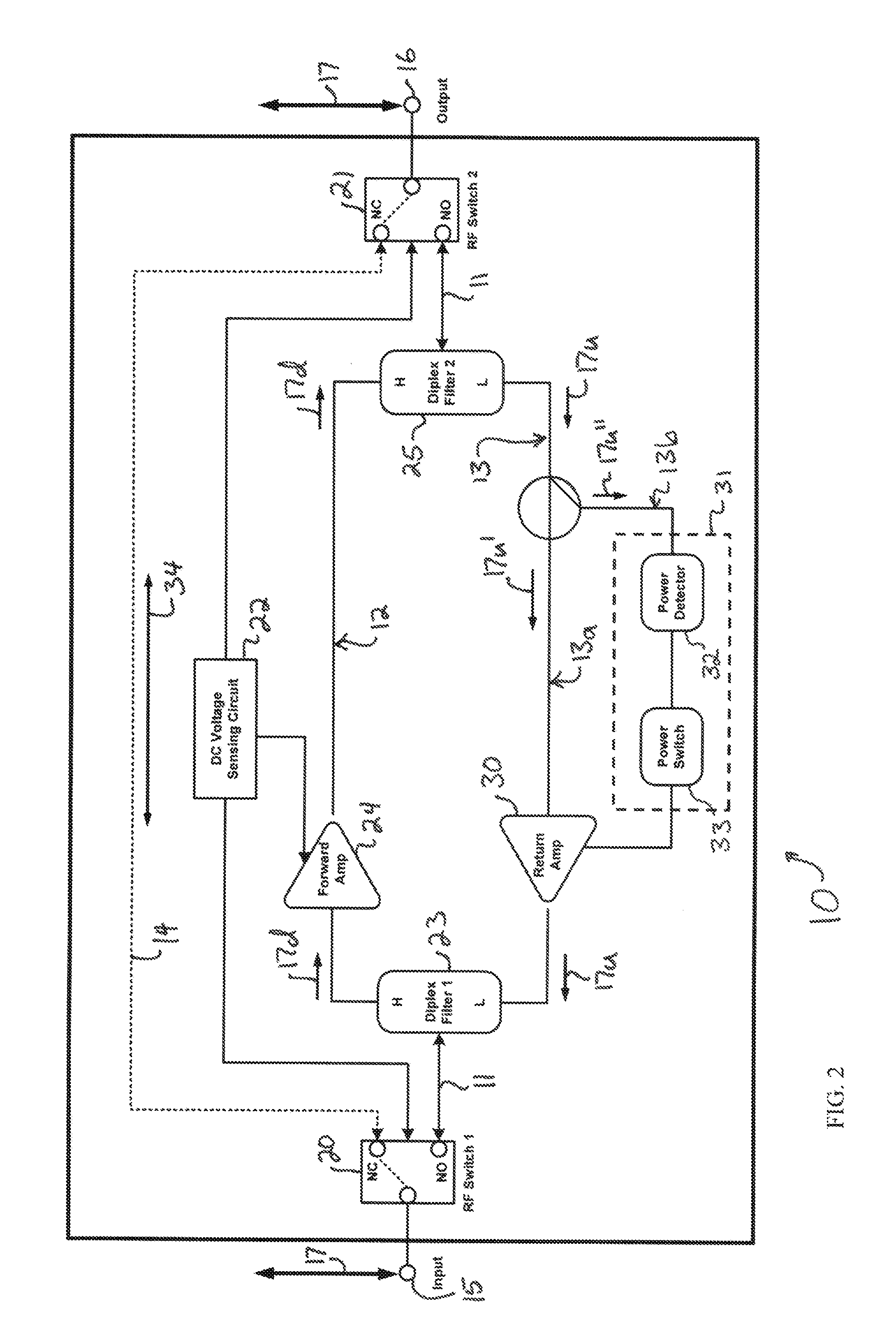

Return Path Noise Reducing Amplifier with Bypass Signal

ActiveUS20140375381A1Reduces return path noiseReduce noiseHigh frequency amplifiersGated amplifiersAudio power amplifierElectric power

An amplifier system an amplified path and a bypass path for carrying an RF signal. A switch in the amplified system routes the RF signal through the amplified path in response to a normal condition in the amplifier system, and routes the RF signal through the bypass path in response to an abnormal condition in the amplifier system. The amplified path includes an amplified forward circuit and a return circuit. The amplified forward circuit has an amplifier, and the return circuit has a return amplifier and detection circuitry for providing power to the return amplifier. The detection circuity provides power to the return amplifier in response to a normal condition in the return circuit, and removes power from the return amplifier in response to an abnormal condition in the return circuit.

Owner:PCT INT

Switch-less bidirectional amplifier

ActiveUS8190099B2Avoid leakage currentEasy to useGated amplifiersAmplifiers wit coupling networksTransceiverAudio power amplifier

A bi-directional amplifier, transceiver, integrated circuit, mobile unit, telecommunication infrastructure for amplification of signals received or signals to be transmitted in a communication circuit and a method for bi-directional amplification comprising amplifying signals in a bi-directional amplifier and directing a signal between two or more different paths comprising at least one first biased semiconductor amplification element coupled to a at least one first impedance matching network, at least one second biased semiconductor amplification element coupled to a second impedance matching network, a first device for biasing the at least one first biased semiconductor amplification element and a second device for biasing the at least one second biased semiconductor amplification element where the direction of signal amplification in said bi-directional amplifier is controlled by the first or second device for biasing the at least one first or second biased semiconductor amplification element.

Owner:TELEFON AB LM ERICSSON (PUBL)

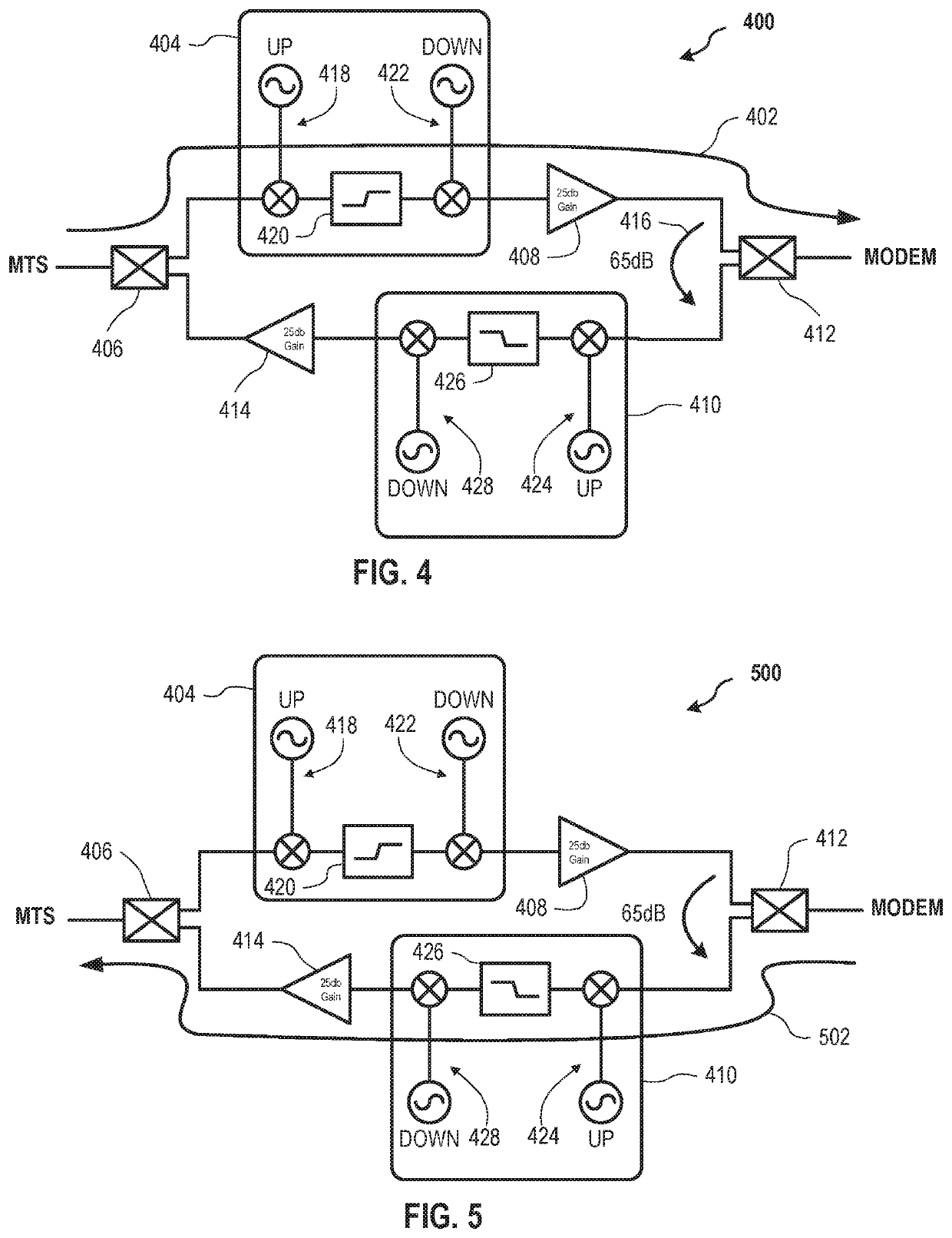

Systems and methods for full duplex amplification

ActiveUS10491361B2High frequency amplifiersAmplifier combinationsAudio power amplifierCommunications system

An amplification subsystem for a communication system includes a downstream amplifier configured to transmit a downstream signal within a first frequency range, an upstream amplifier configured to transmit an upstream signal within a second frequency range, and a bidirectional amplifier configured to selectively transmit a mid-band signal in either of the upstream and downstream direction.

Owner:CABLE TELEVISION LAB

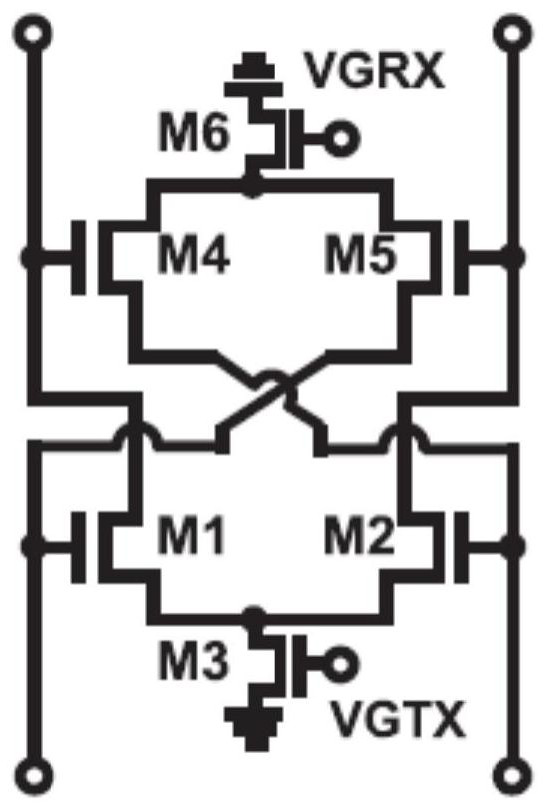

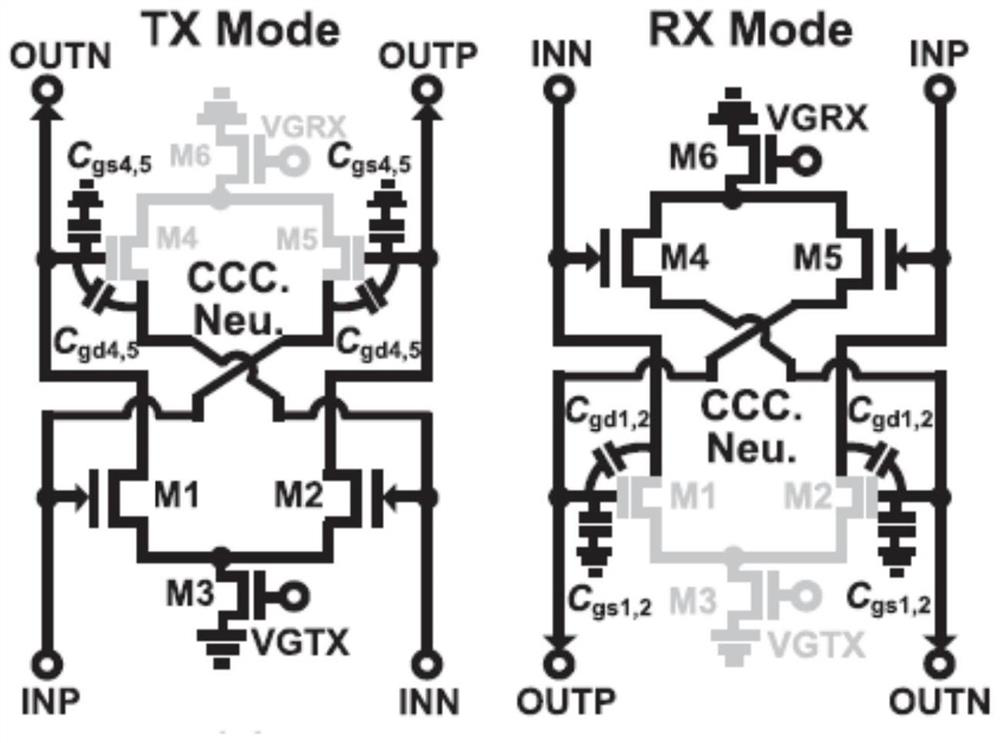

Bidirectional variable gain amplifier based on active cross coupling structure

PendingCN114499426ALow additive phase shiftReduce additional phase shiftHigh frequency amplifiersTwo-way amplifiersVariable-gain amplifierSoftware engineering

The invention belongs to the technical field of wireless communication, and provides a bidirectional variable gain amplifier based on an active cross coupling structure, which is used for solving the problems of high additional phase shift, low maximum gain and the like of the existing differential bidirectional variable gain amplifier. The circuit is composed of two groups of active cross coupling circuits, and bidirectional control is realized through interconnection of input and output ports of the two groups of active cross coupling structures; the sum of drain electrode direct currents in different gain states is not changed, so that better insertion phase shift is realized; due to the fact that all stray capacitors Cgd in the amplifier are all counteracted, lower additional phase shift is achieved. As a tail current source is cancelled, the drain-source voltage difference is VDD, and a higher maximum gain state is realized. In conclusion, the bidirectional variable gain amplifier based on the active cross coupling structure provided by the invention has lower additional phase shift and larger maximum gain.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com