Method for fabricating mos transistors

a transistor and mos technology, applied in the direction of transistors, semiconductor devices, electrical equipment, etc., can solve the problems of boron implantation, boron introduction into silicon film, and difficult control of short channel effect,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

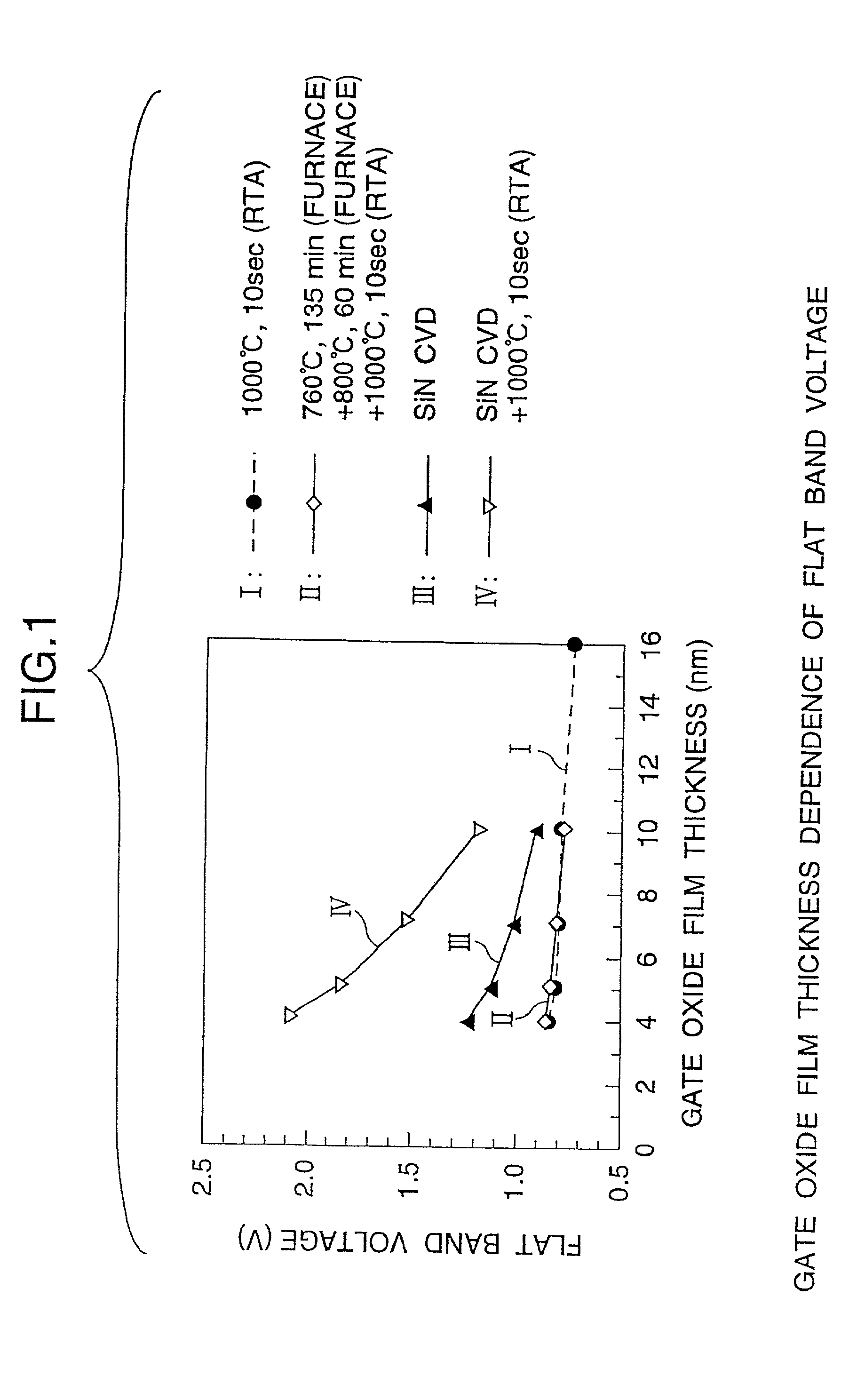

Image

Examples

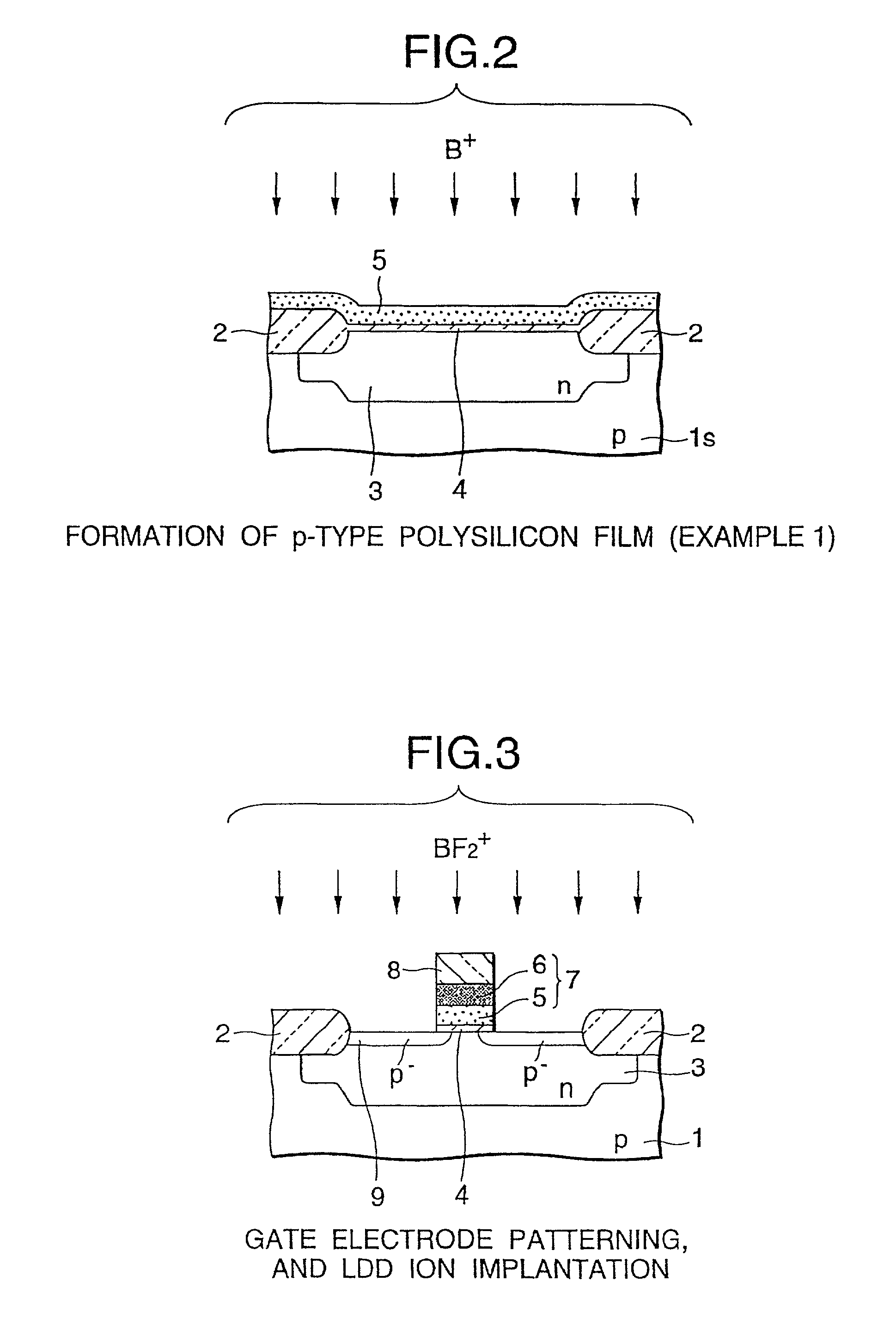

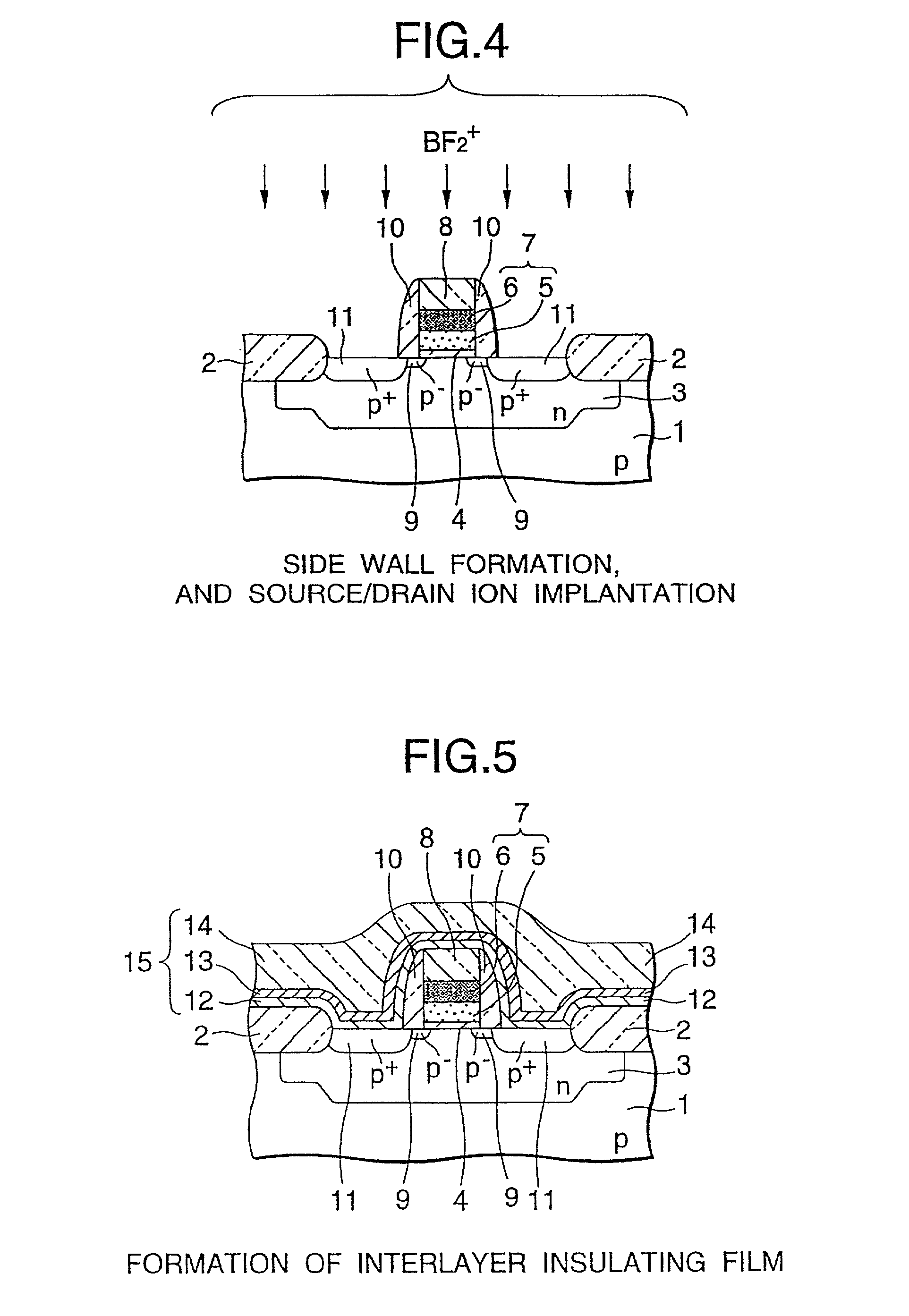

example 1

[0069] This is one embodiment of the invention as applied to a process of fabricating a PMOS structure that contains a silicon nitride film as a part of the interlayer insulating film, for which referred to are FIG. 2 to FIG. 6.

[0070] First, elements on a p-type Si substrate 1 were spaced from each other according to a known LOCOS process. Concretely, for example, a field oxide film 2 was formed on the substrate 1 through wet oxidation at 950.degree. C.

[0071] Next, an n-type well 3 was formed through p.sup.+ ion implantation via a resist mask (not shown) in the PMOS forming region. For the condition for the ion implantation, for example, the ion accelerating energy was 330 keV, and the ion dose was 8.times.10.sup.12 / cm.sup.2 .

[0072] Next, after ion implantation in the surface layer part of the active region for threshold voltage (V.sub.th) control followed by ion implantation in the depth of the substrate for forming therein an embedded layer for punch-through retardation, the subst...

example 2

[0098] This is another embodiment of the invention as applied to a self-aligned contact process of fabricating a DRAM structure, for which referred to are FIG. 7 to FIG. 10. In those drawings, some numeral references are the same as those in FIG. 2 to FIG. 6 referred to hereinabove.

[0099] Two gate electrodes 7 as in Example 1 were formed adjacent to each other in an element forming region. Also as in Example 1, an LDD region 9, a side wall 10 and a source / drain region 11 were formed. In DRAM, the gate electrodes 7 function as word lines.

[0100] Next, a silicon oxide film 12, a silicon nitride film 13 and a silicon oxide film 14 were layered in that order to form an interlayer insulating film 15.

[0101] The silicon oxide film 12 was formed, for example, through reduced pressure CVD at 720.degree. C., for which was used a mixed gas of TEOS / O.sub.2, and it had a thickness of about 20 nm.

[0102] The silicon nitride film 13 was formed, for example, through reduced pressure CVD at 760.degree...

example 3

[0112] This is still another embodiment of the invention as applied to a SALICIDE process of fabricating a dual gate CMOS structure, for which referred to are FIG. 11 to FIG. 16.

[0113] FIG. 11 shows the condition of a substrate having been subjected to element spacing, well formation and gate oxidation, in which a polysilicon film formed on the substrate was patterned to give a gate electrode 21 in the PMOS forming region and a gate electrode 22 in the NMOS forming region, and thereafter the PMOS forming region was subjected to LDD ion implantation with BF.sub.2.sup.+ while the NMOS forming region was masked with a resist pattern 23.

[0114] The gate electrodes 21 and 22 were formed, for example, as follows: A polysilicon film was deposited through reduced pressure CVD with SiH.sub.4 gas at a temperature falling between 580 and 620.degree. C. to have a thickness of from 150 to 300 nm, and this was then patterned through anisotropic dry etching with a mixed gas of Cl.sub.2 / O.sub.2.

[011...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com