Gate dielectric material with high dielectric constant based on silicon substrate and preparation method thereof

A technology with high dielectric constant and gate dielectric, which is applied in the manufacture of circuits, electrical components, semiconductor/solid-state devices, etc., can solve the problem of increasing the equivalent oxide layer thickness, gate leakage current and interface state density, and not conforming to the semiconductor industry Thermal budget development, poor step coverage of gate dielectric materials, etc., to achieve the effects of reduced sodium ion mobility, improved radiation resistance, and high electron resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

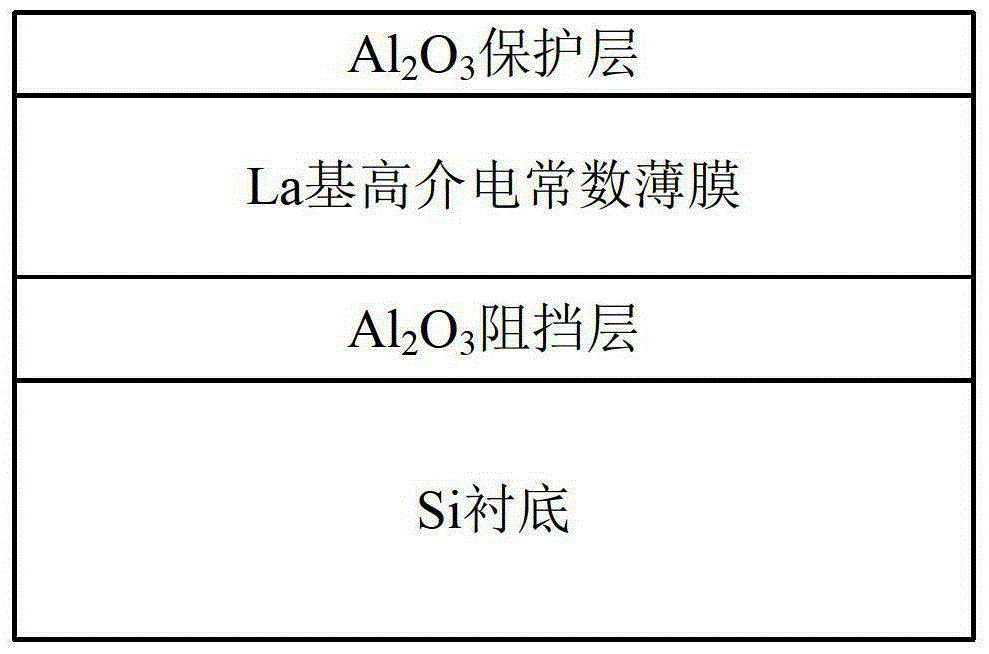

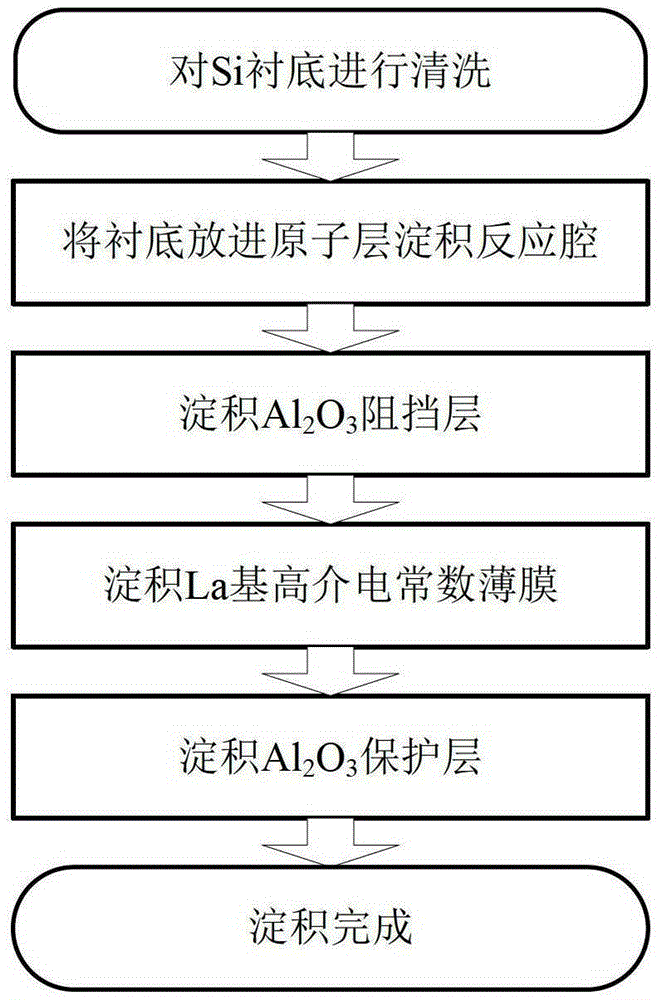

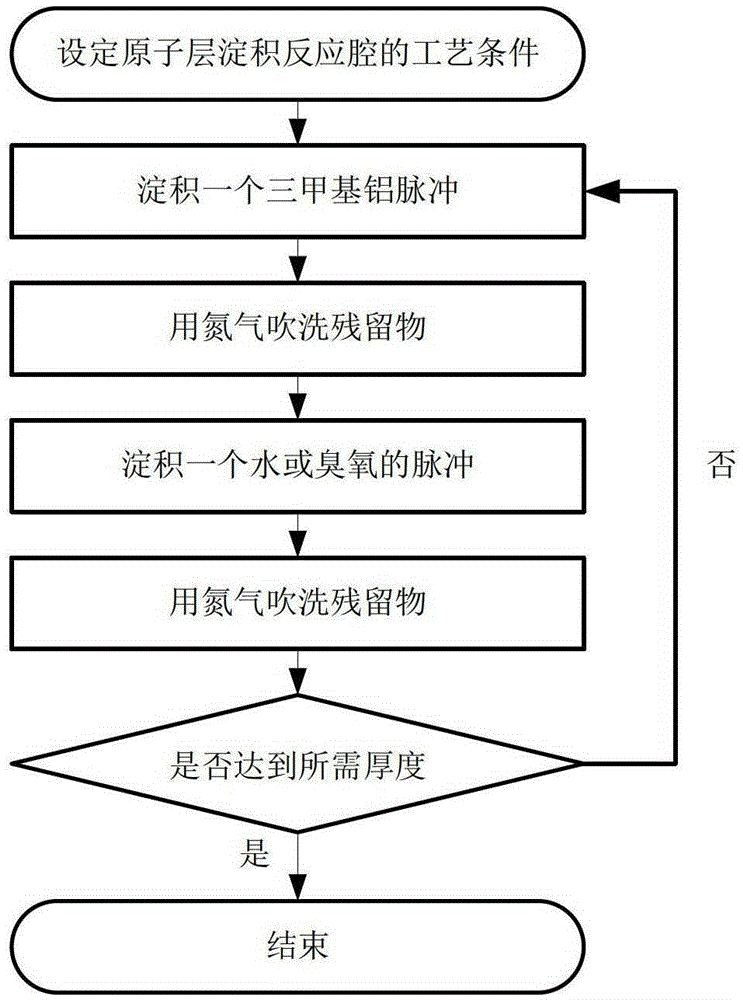

[0047] Example 1, preparation of Al 2 o 3 \La 2 o 3 \Al 2 o 3 \Si high dielectric constant gate dielectric material

[0048] Step 1, cleaning the silicon substrate.

[0049] 1a) Clean the Si sheet in SC-1 solution heated to 75°C for 10 minutes, the composition of the solution is NH 4 OH, H 2 o 2 and H 2 O, its ratio is 5:1:1, the main effect of this cleaning is to rely on NH 4 Complexation of OH with H 2 o 2 Strong oxidizing ability to remove organic pollutants or attached particles on Si wafers;

[0050] 1b) Rinse the Si sheet after cleaning in the SC-1 solution in deionized water for 2 minutes to remove the residual SC-1 solution;

[0051] 1c) Wash the Si sheet for 60 seconds in an HF solution consisting of HF and H 2 O, whose ratio is 1:50, the main function of this cleaning is to remove the natural oxide layer SiO on the surface of the Si substrate 2 ;

[0052] 1d) Rinse the Si sheet in deionized water to remove residual HF solution;

[0053] 1e) Place the...

example 2

[0074] Example 2, preparation of Al 2 o 3 \LaAlO 3 \Al 2 o 3 \Si high dielectric constant gate dielectric material

[0075] Step 1, cleaning the silicon substrate.

[0076] 1.1) Clean the Si sheet in an SC-1 solution heated to a temperature of 75°C for 10 minutes to remove organic pollutants or attached particles on the Si sheet. The composition of the solution is NH 4 OH, H 2 o 2 and H2 O, the ratio of which is 5:1:1;

[0077] 1.2) Rinse the Si sheet after cleaning with SC-1 solution in deionized water for 2 minutes to remove residual SC-1 solution;

[0078] 1.3) Clean the rinsed Si sheet in HF solution for 60 seconds to remove the natural oxide layer SiO on the surface of the Si substrate. 2 , the composition of the solution is HF and H 2 O, its ratio is 1:50;

[0079] 1.4) The natural oxide layer SiO on the surface of the Si substrate will be removed 2 The Si sheet is then rinsed in deionized water to remove residual HF solution;

[0080] 1.5) Place the Si shee...

example 3

[0103] Example 3, preparation of Al 2 o 3 \HfLaO\Al 2 o 3 \Si high dielectric constant gate dielectric material

[0104] Step A, cleaning the silicon substrate.

[0105] Clean the Si sheet in SC-1 solution heated to 75°C for 10 minutes to remove organic pollutants or attached particles on the Si sheet. The composition of the solution is NH 4 OH, H 2 o 2 and H 2 O, the ratio is 5:1:1; then rinse the Si sheet in deionized water for 2 minutes in SC-1 solution to remove residual SC-1 solution; then wash the Si sheet in HF and H 2 O ratio of 1:50 in the HF solution for 60 seconds to remove the natural oxide layer SiO on the surface of the Si substrate 2 ; The natural oxide layer SiO on the surface of the Si substrate will be removed 2 Then rinse the Si sheet in deionized water to remove the residual HF solution; place the Si sheet with the remaining HF solution in deionized water and use ultrasonic cleaning for 5 minutes to remove the adsorption particles on the surface, a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com