Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about How to "Not improve" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

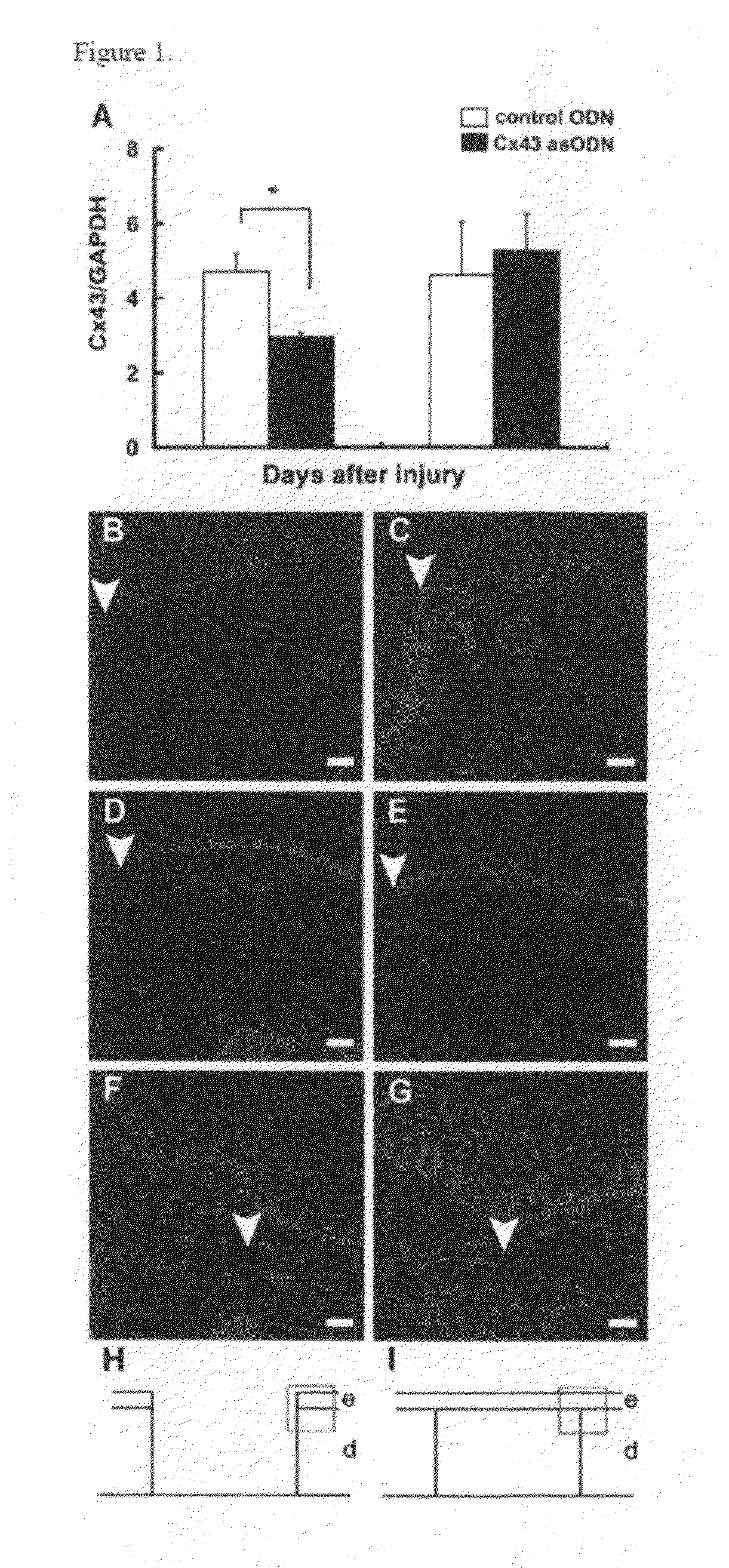

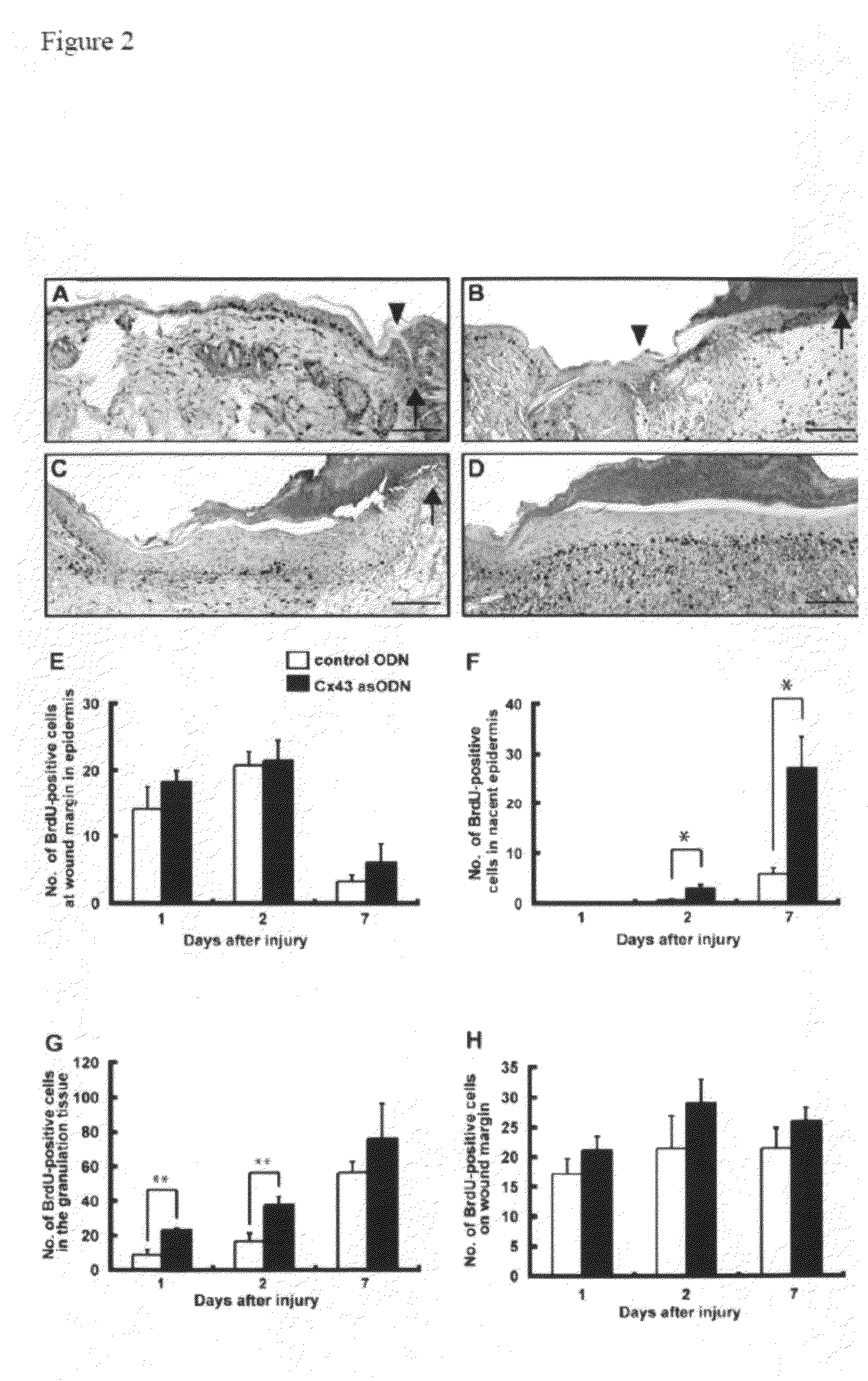

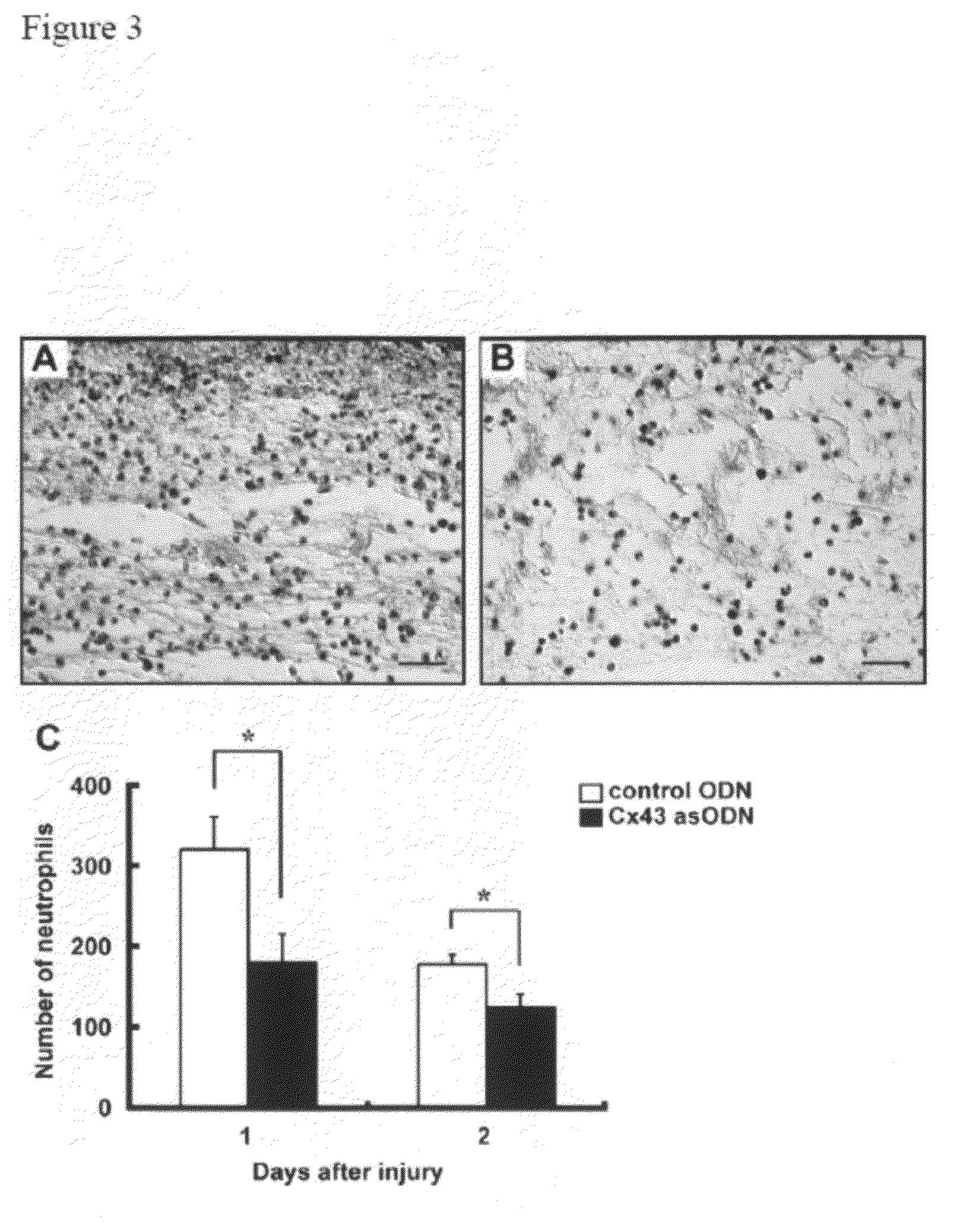

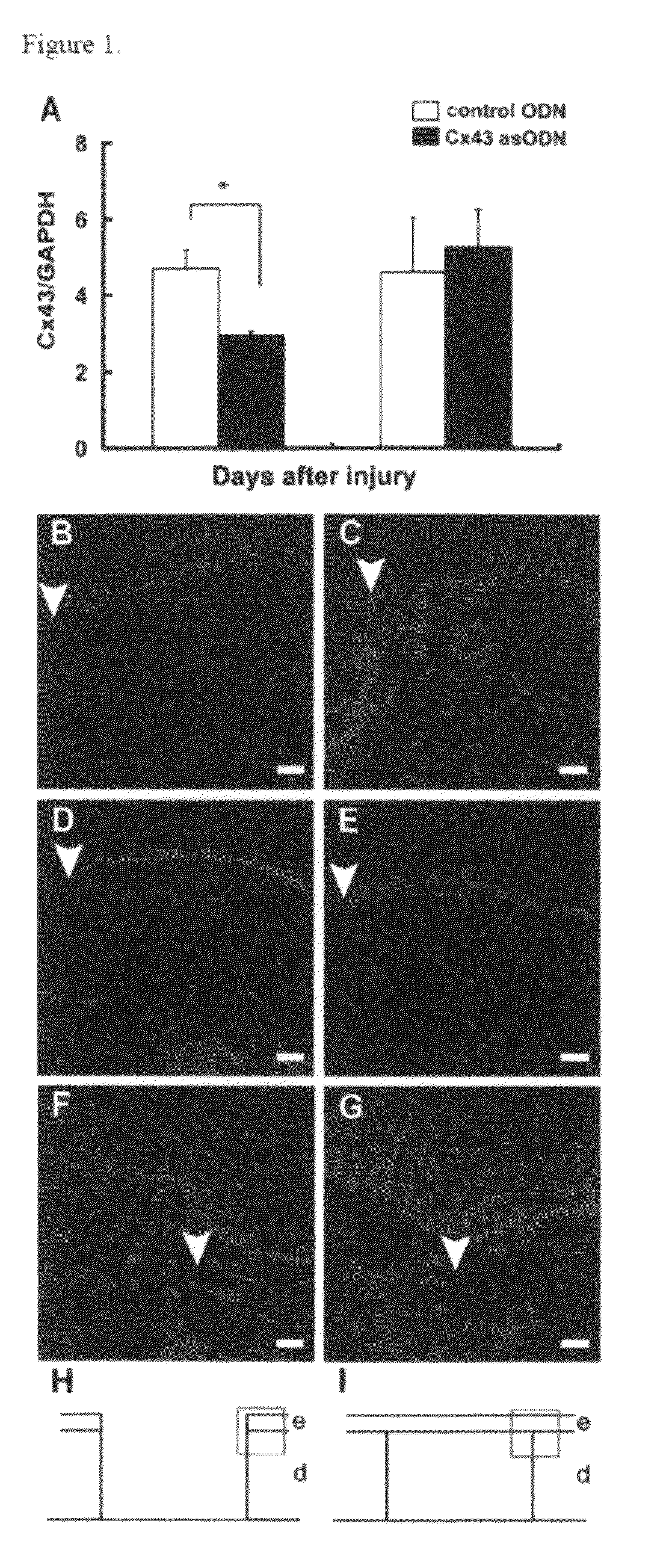

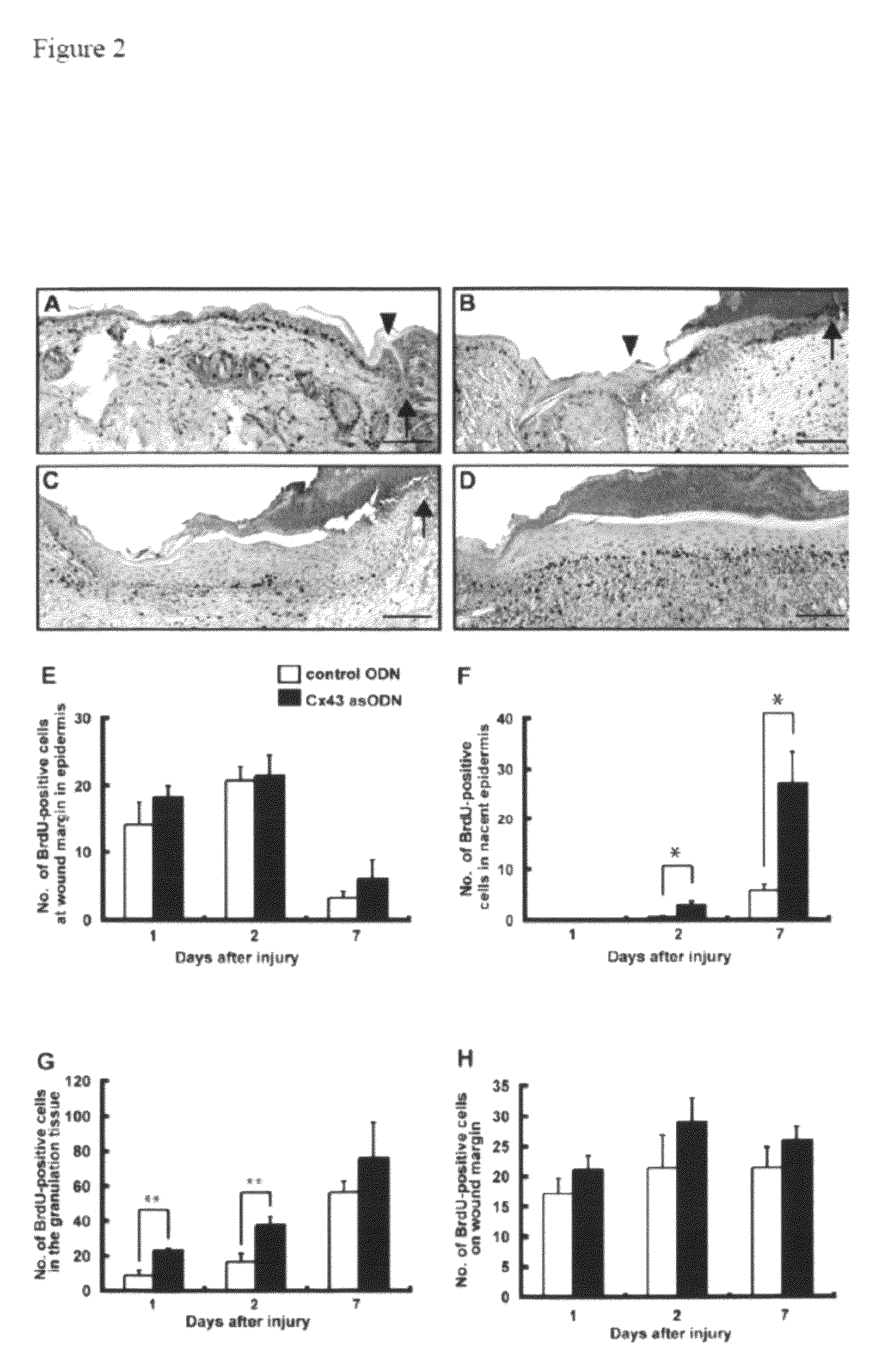

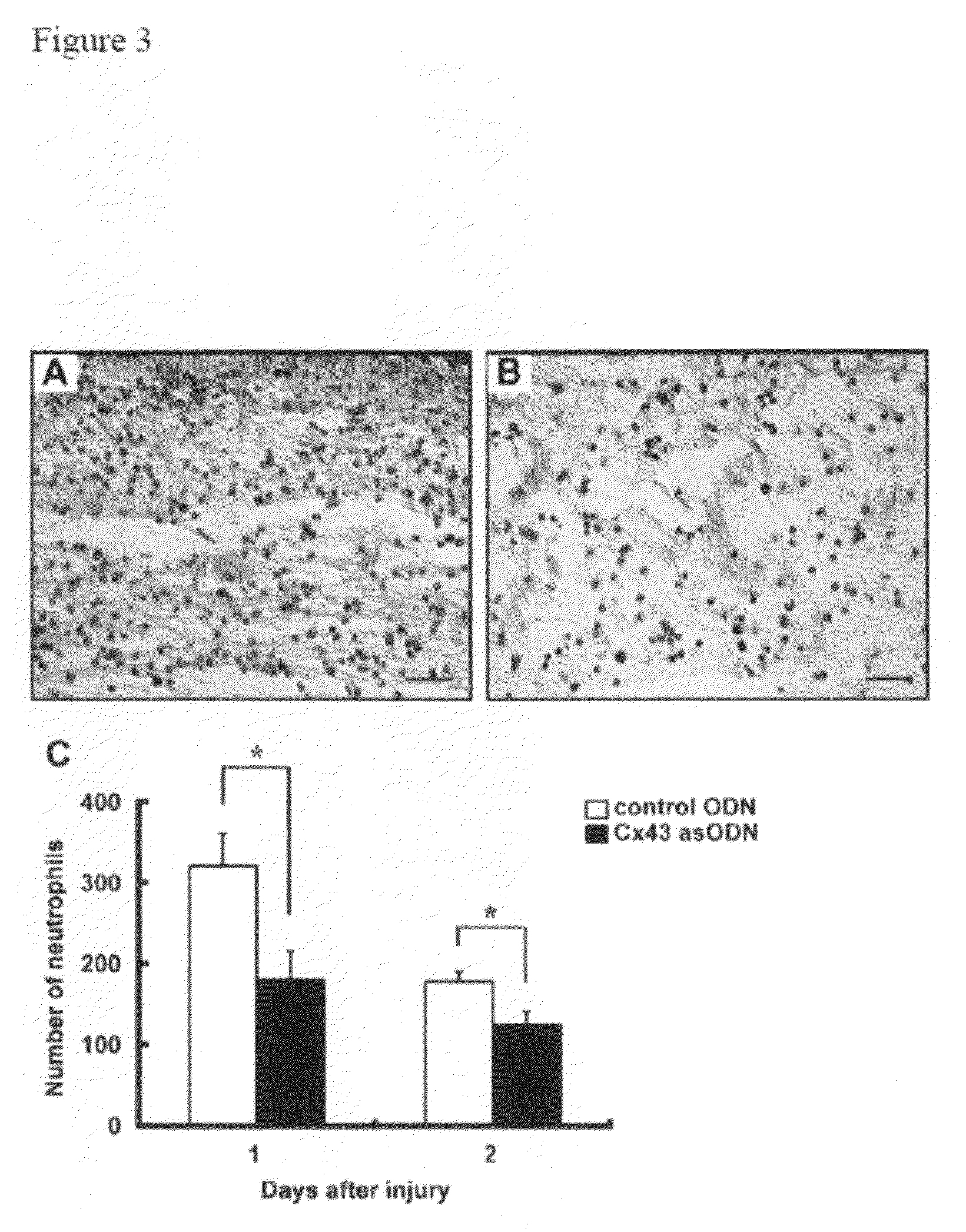

Methods and compositions for wound healing

ActiveUS20090220450A1Few pointExtended time intervalAntibacterial agentsBiocideWound healingTissue repair

Methods and compositions comprising combinations of one or more anti-connexin agents and one or more other agents useful for the promotion and / or improvement of wound healing and / or tissue repair.

Owner:OXUNEXUS THERAPEUTICS INC

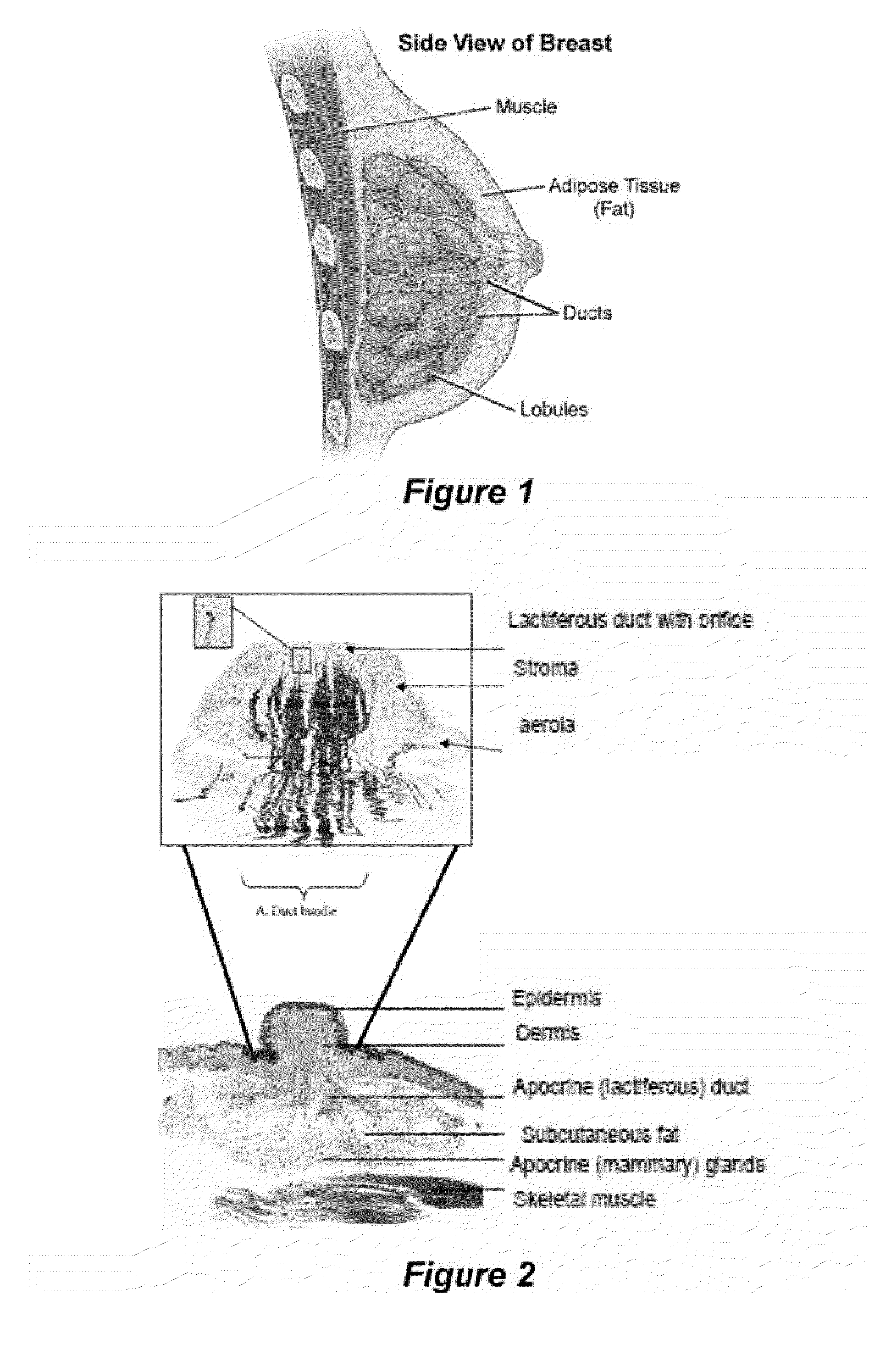

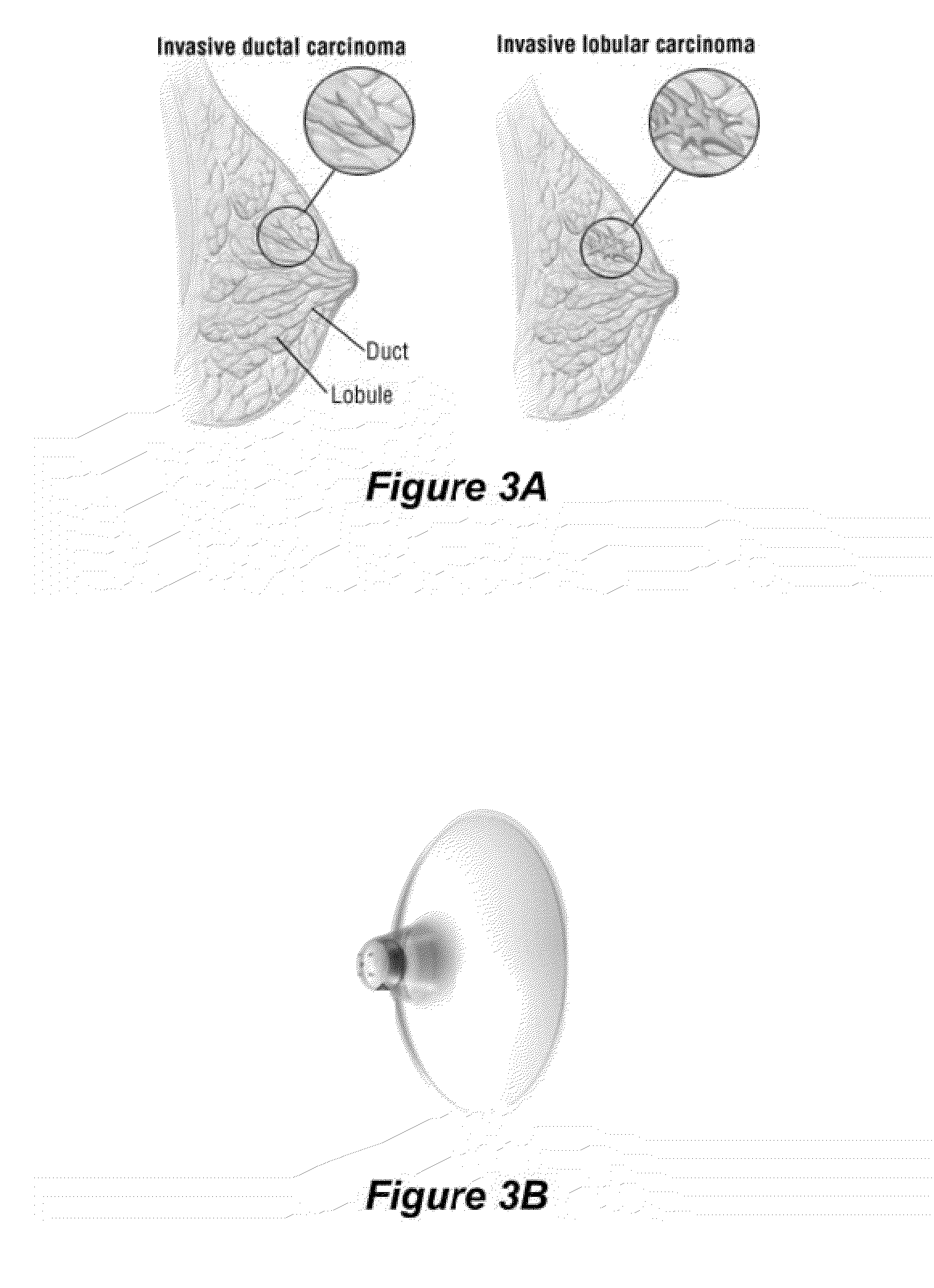

Compositions and Methods for Localized Drug Delivery through Mammary Papillae

ActiveUS20140088059A1Improve throughputEasy to keepOrganic active ingredientsBiocideDiagnostic agentAreola

The invention provides compositions and methods for the prevention, diagnosis, or treatment of conditions affecting breast tissue. The compositions can include one or more therapeutic agents or diagnostic agents, and an effective carrier. The composition can be specifically adapted for transdermal permeation through the mammary papilla, areola, or a combination thereof, and into underlying breast tissue.

Owner:SOUTH DAKOTA STATE UNIVERSITY

Methods and compositions for wound healing

Methods and compositions comprising combinations of one or more anti-connexin agents and one or more other agents useful for the promotion and / or improvement of wound healing and / or tissue repair.

Owner:OXUNEXUS THERAPEUTICS INC

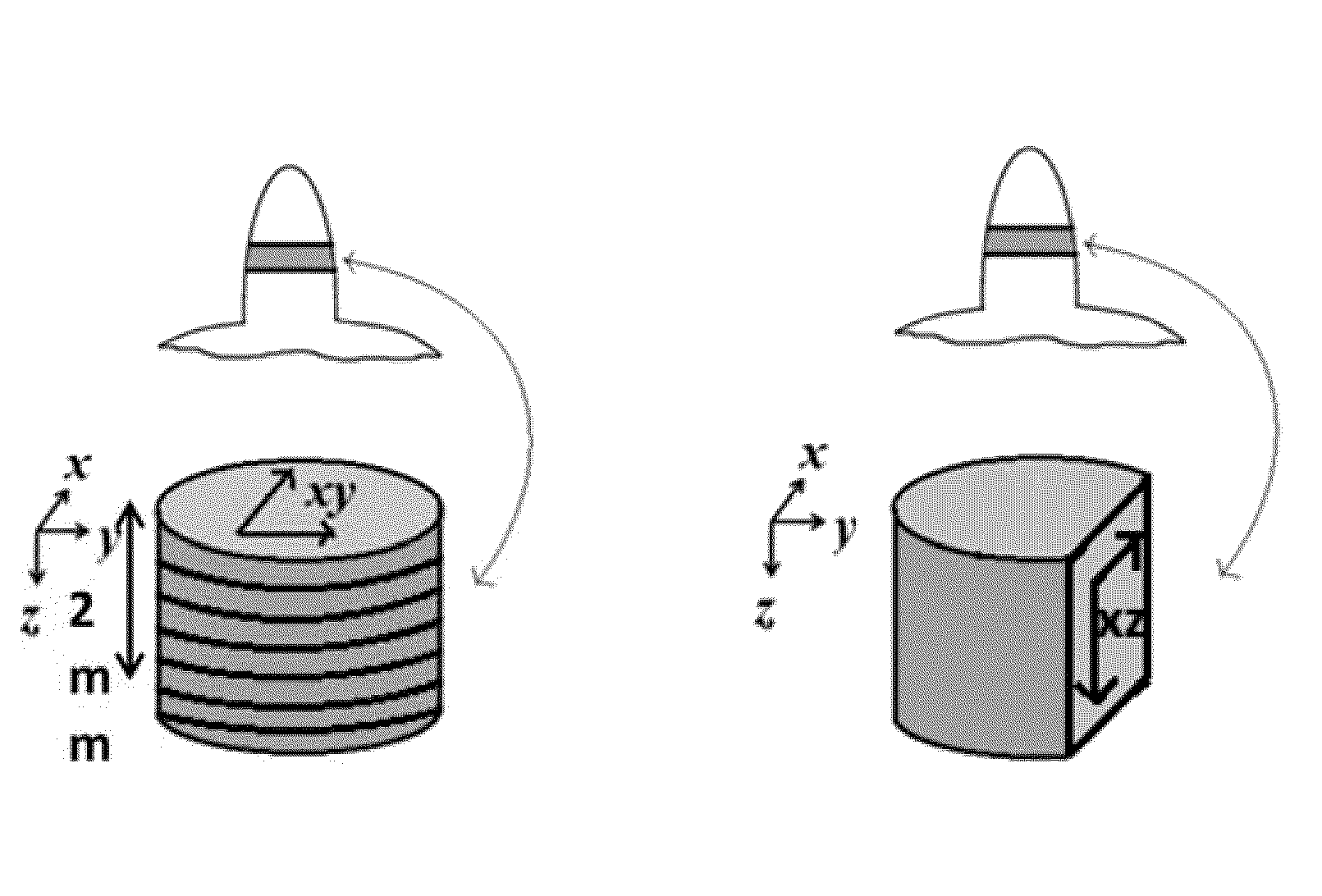

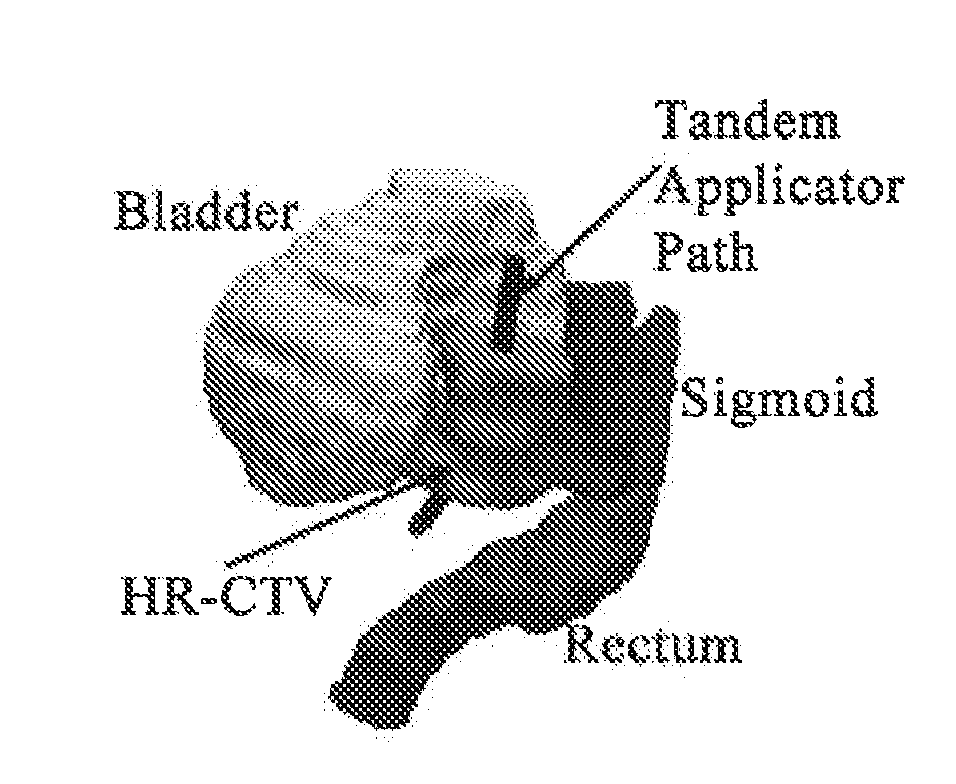

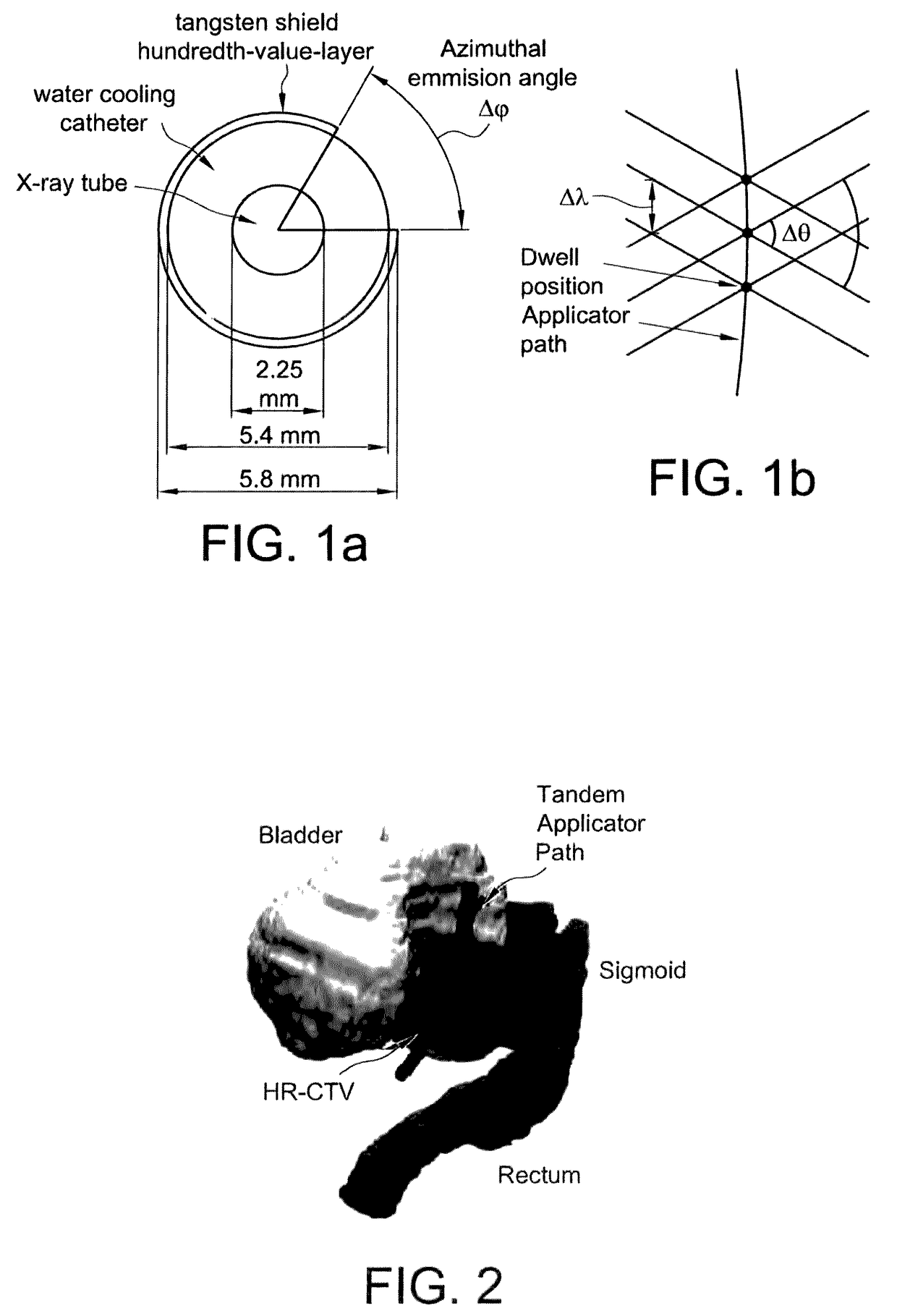

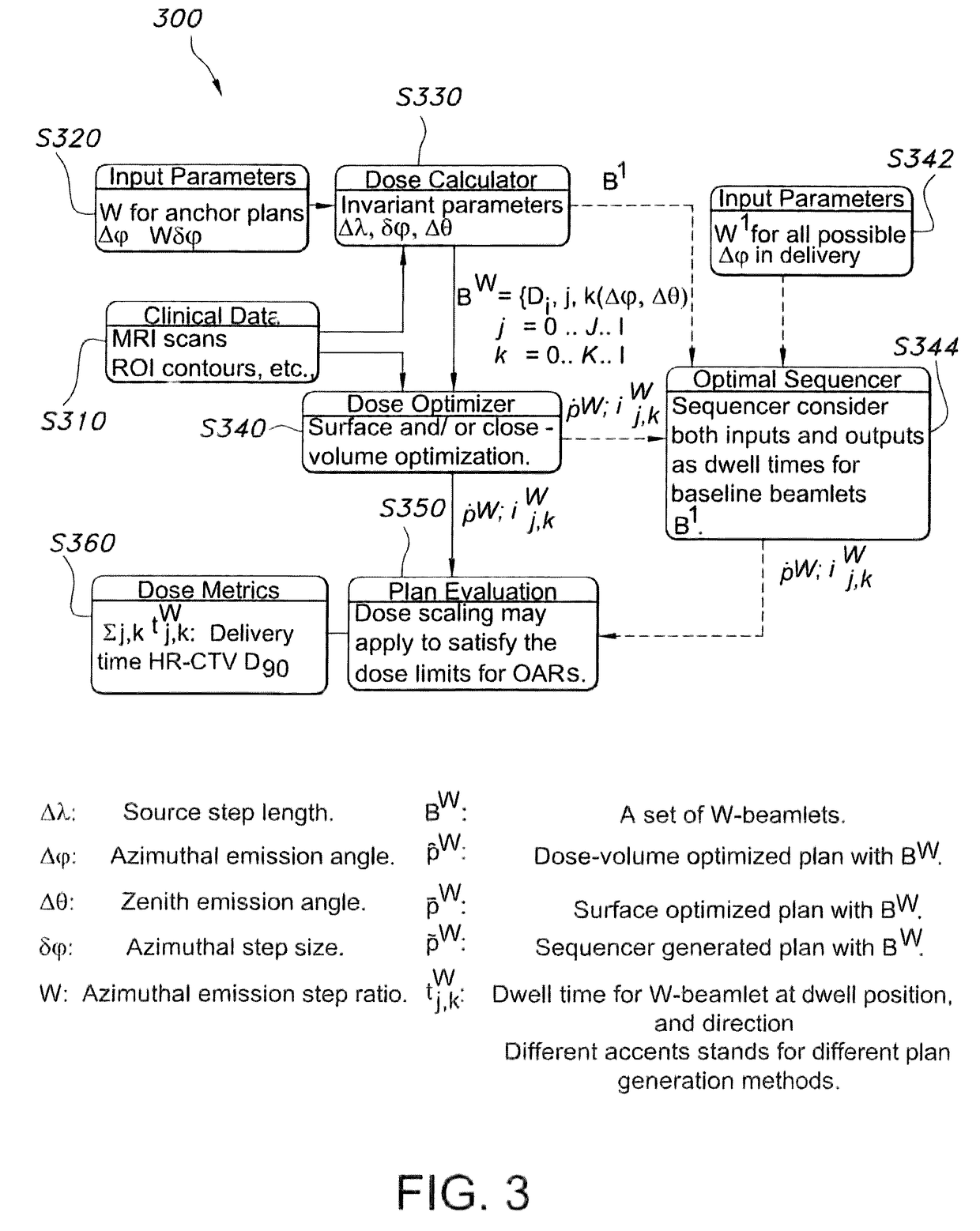

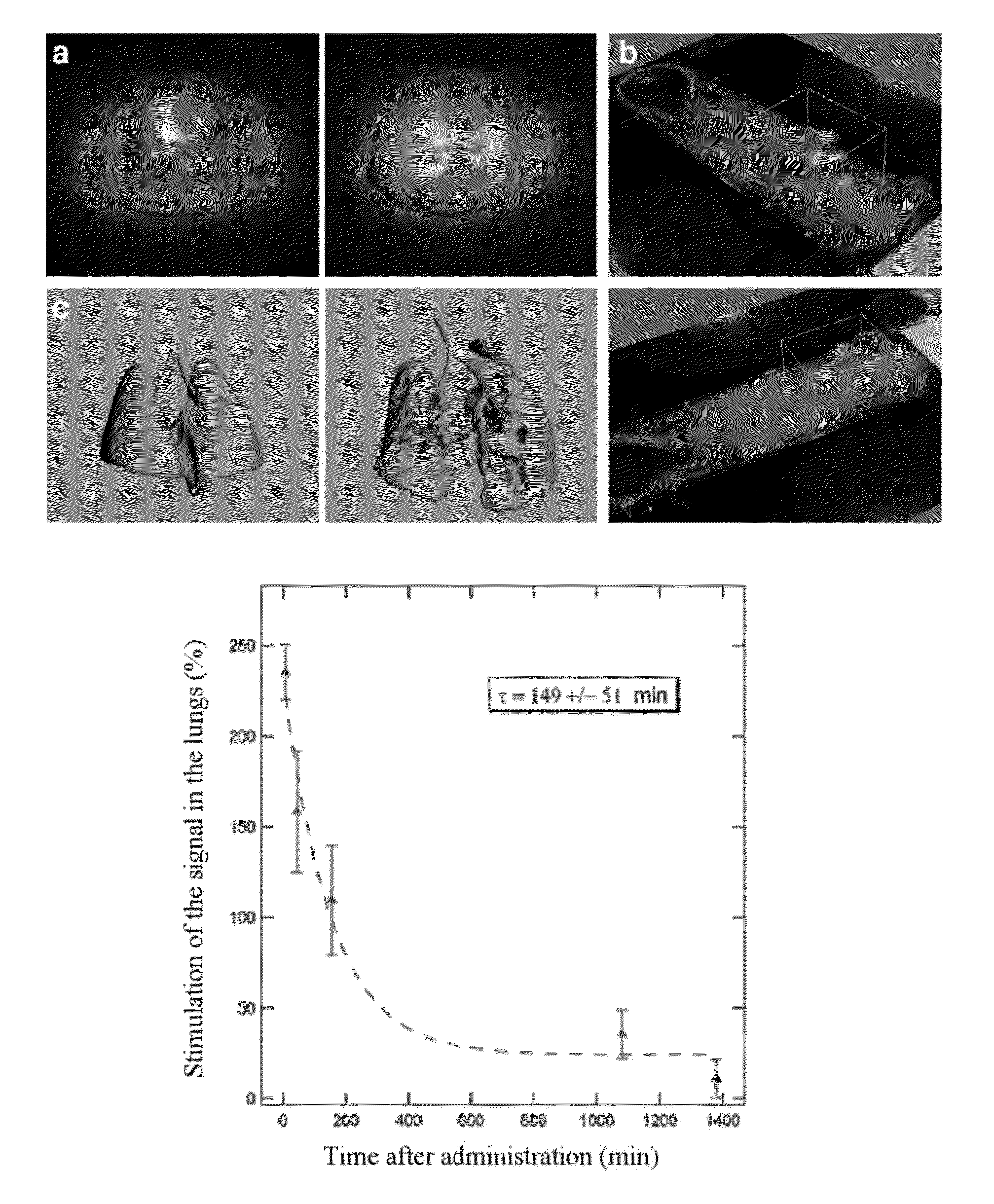

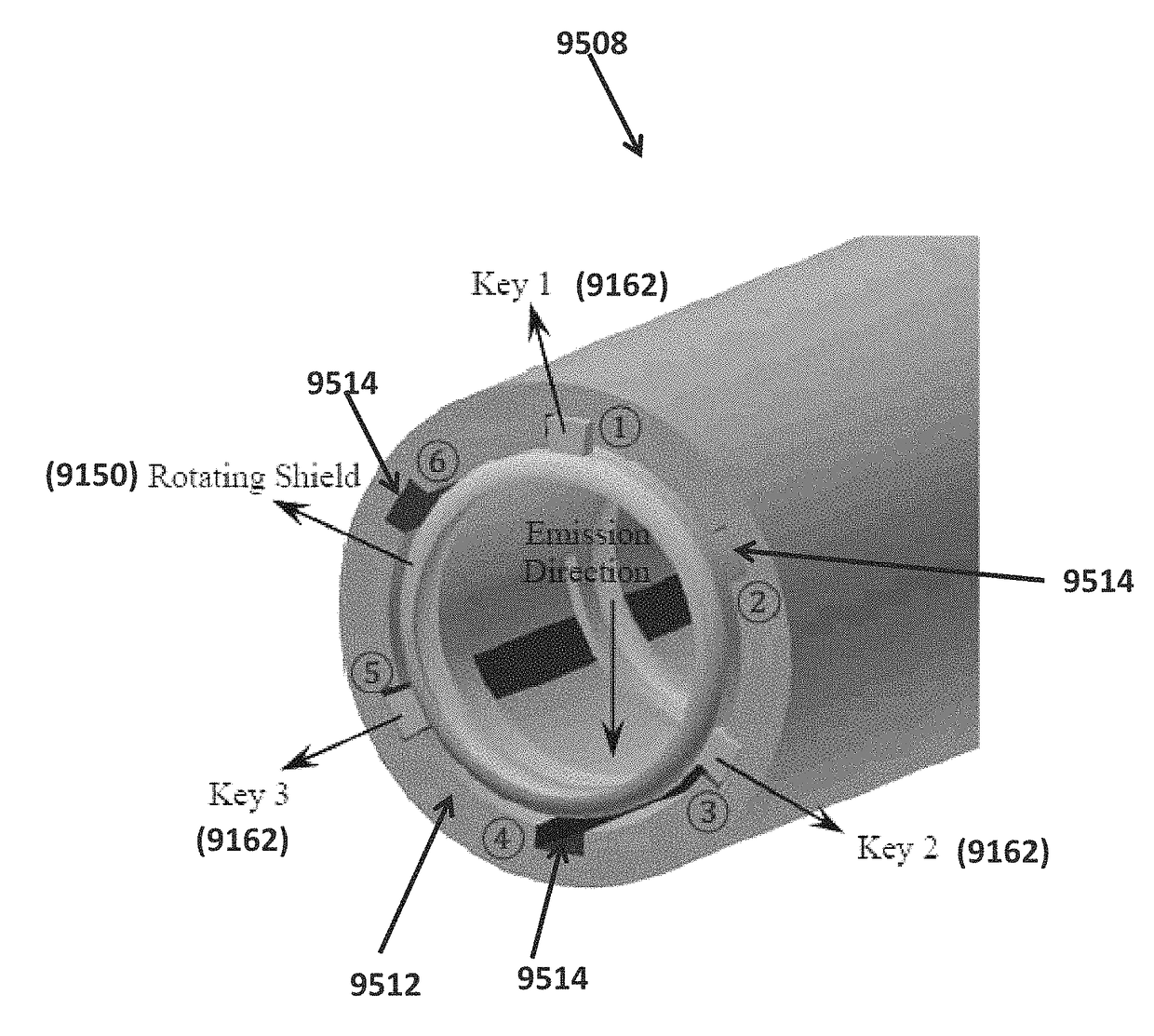

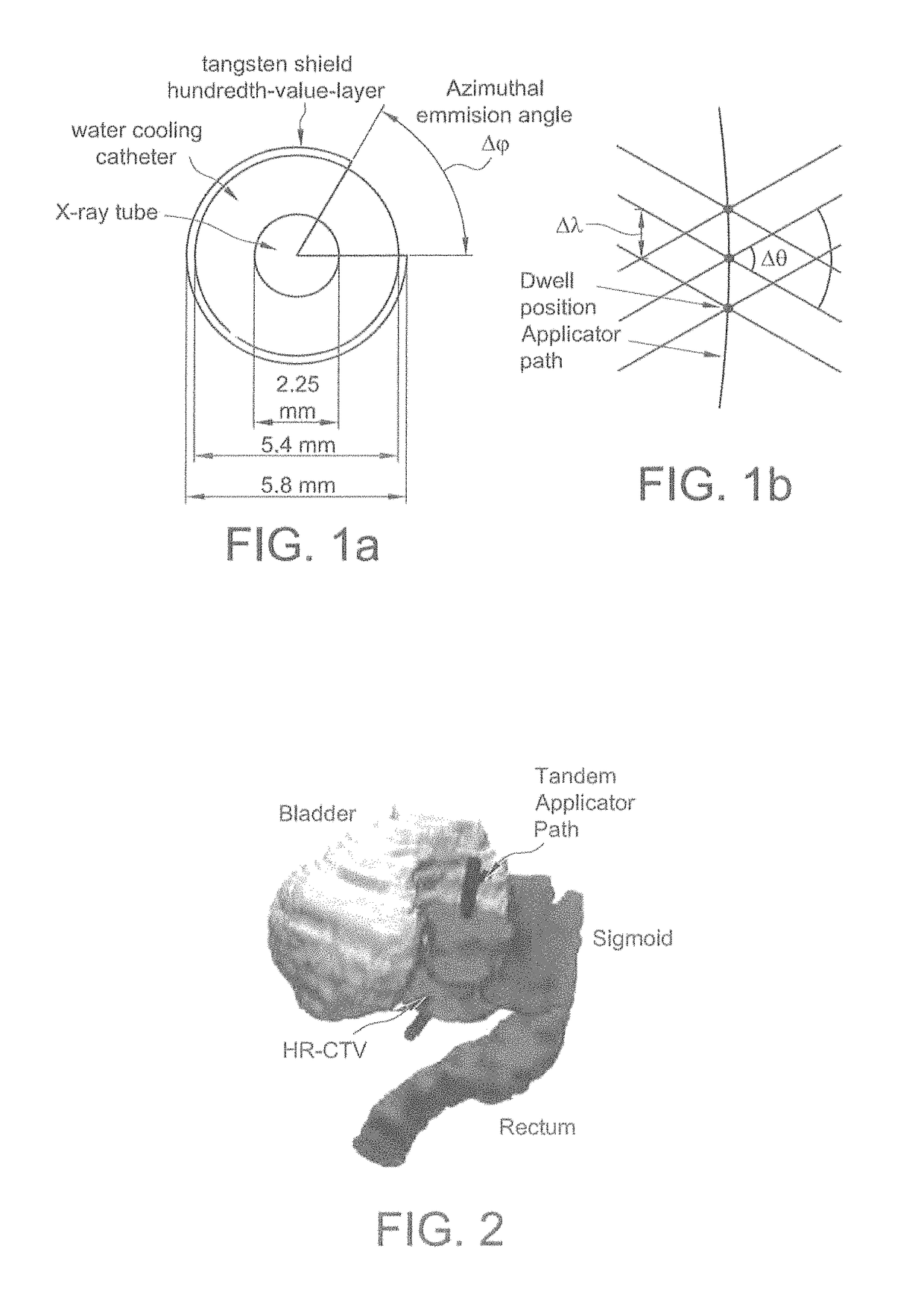

Advanced rotating-shield brachytherapy and planning of the same

InactiveUS20150367144A1Reduction in treatment planning timeImprove dose conformityX-ray/gamma-ray/particle-irradiation therapyDose ReducedMedicine

Systems and methods for rotating shield brachytherapy. In an aspect, some of the systems and methods can be used to facilitate shield selection for use in rotating shield brachytherapy. In an aspect, the invention is a shielded needle or catheter system with a rotational controller for delivering radioisotope-based interstitial rotating shield brachytherapy (I-RSBT), In an aspect, I-RSBT needles can deliver dose distributions that can be non-radially symmetric about each needle, enabling reduced doses to sensitive normal tissues. Further provided are methods and systems for selecting an emission angle for use in S-RSBT and for sequencing the rotating shields. Further provided are methods and system for the multiple application of M-RSBT in a single setting.

Owner:UNIV OF IOWA RES FOUND

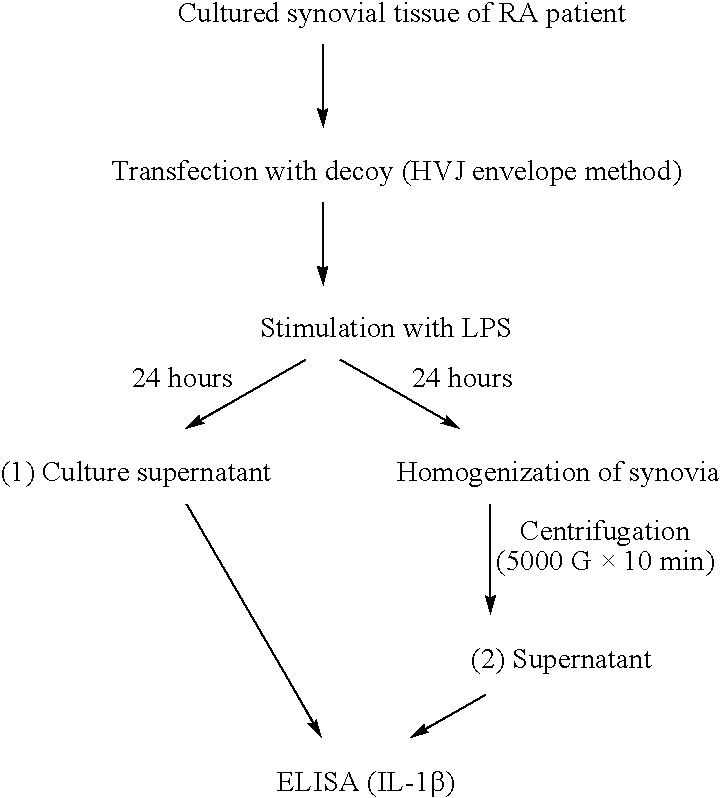

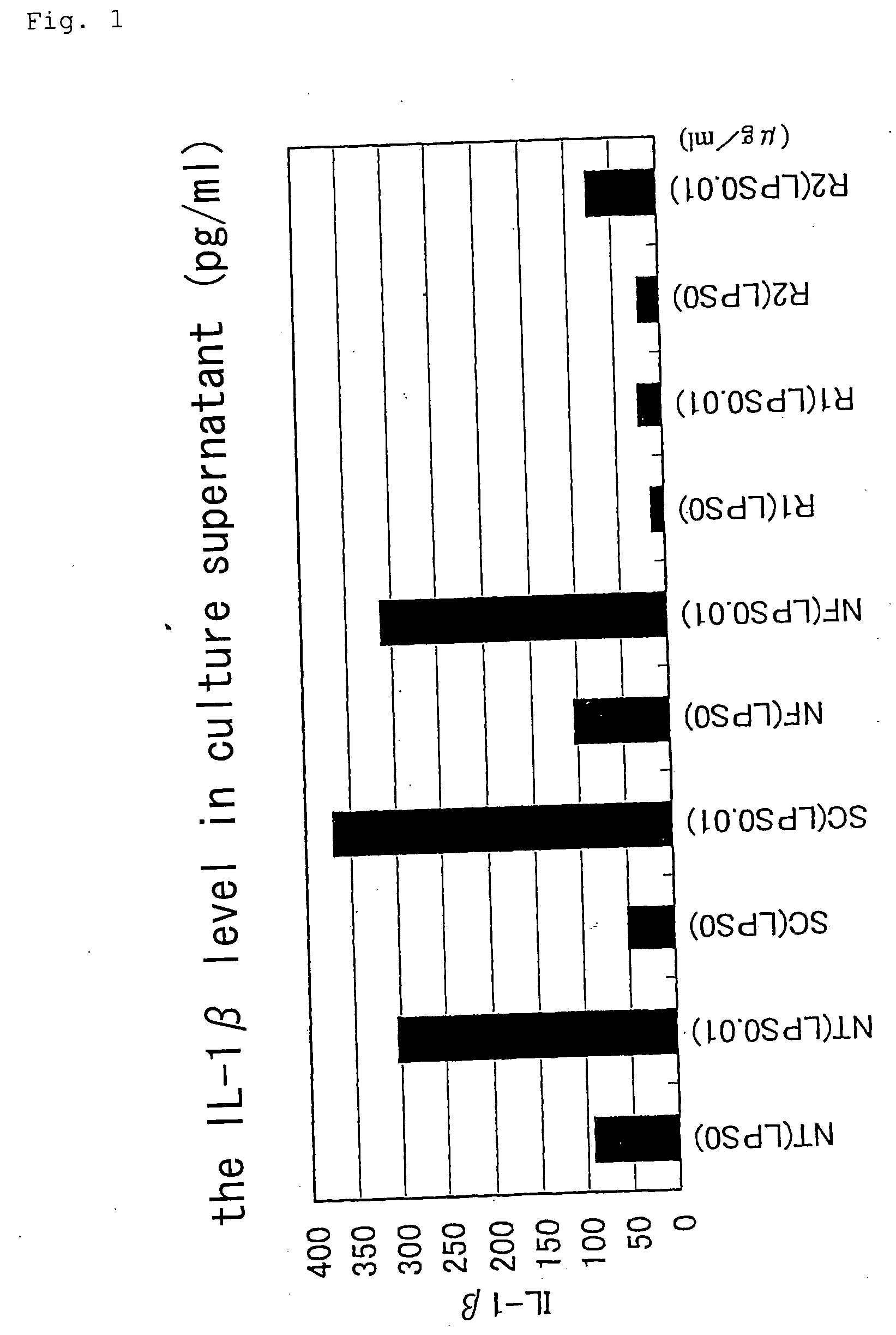

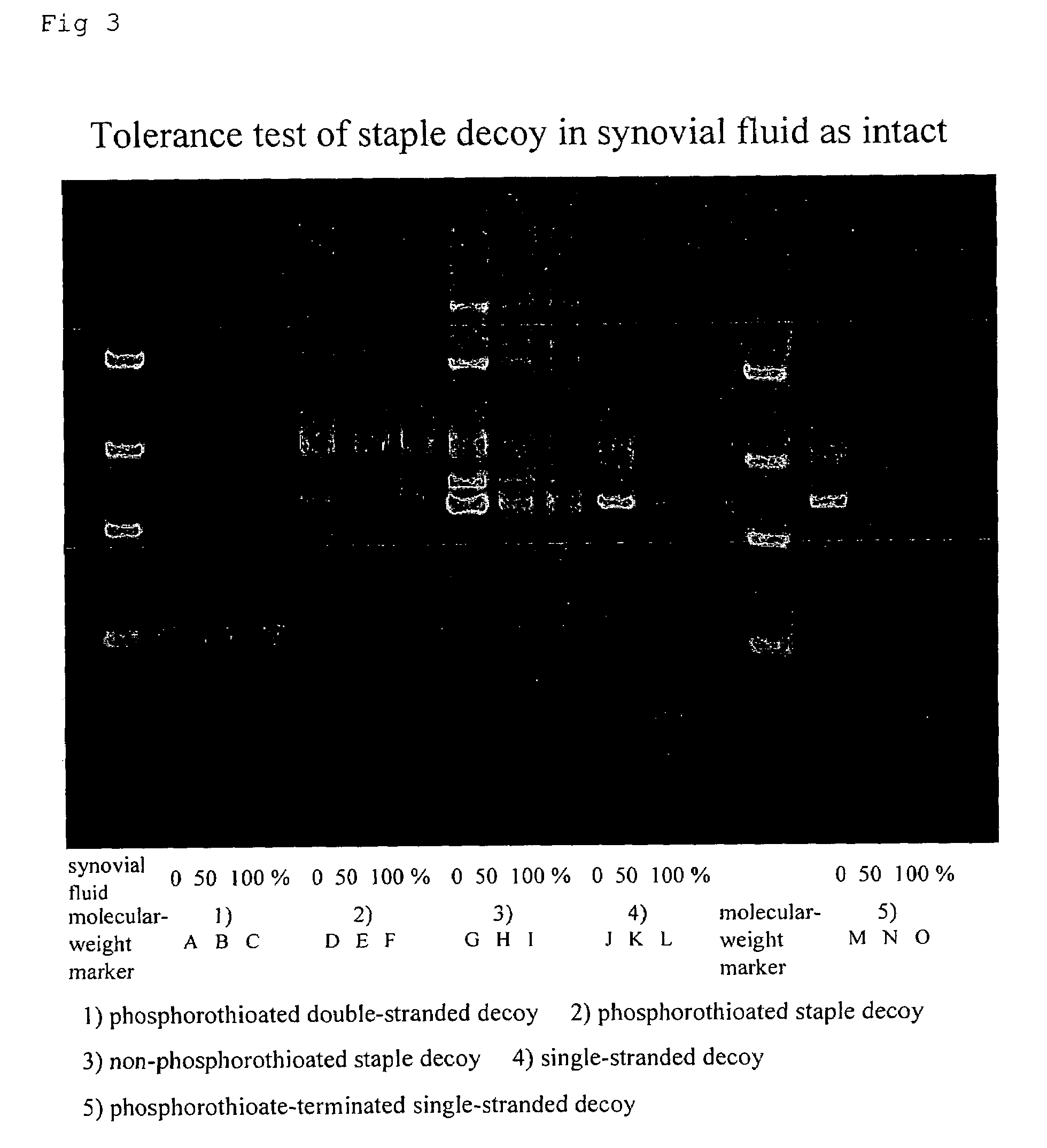

Staple type oligonucleotide and drug comprising the same

ActiveUS20060276421A1Improve in instabilityReduce doOrganic active ingredientsNervous disorderPsoriasisArthritis

Conventional oligonucleotides are opened at both ends and thereby unstable. The stability of them against catabolic enzymes is increased by phosphorothioate modification, but such phosphorothioate causes toxicity. The present invention provides oligonucleotides and medicaments in which these problems are improved. That is, it provides a staple oligonucleotides and medicaments containing the same as the active ingredient. Specifically, it provides transcription factor inhibitors, antisense oligonucleotides and siRNAs. More specifically, it provides agents for preventing, treating or improving inflammation, autoimmune diseases, central diseases, reperfusion injury in ischaemic diseases, worsened prognosis after organ transplantation or organ surgery, or restenosis after PTCA. Further specifically, it provides agents for preventing, treating or improving arthritis, dermatitis, nephritis, hepatitis, renal failure, cystitis, prostatitis, urethritis, ulcerative colitis, Crohn disease, chronic rheumatoid arthritis, osteoarthritis, atopic dermatitis, contact dermatitis, psoriasis, cutaneous ulcer or decubitus.

Owner:ANGES MG INC

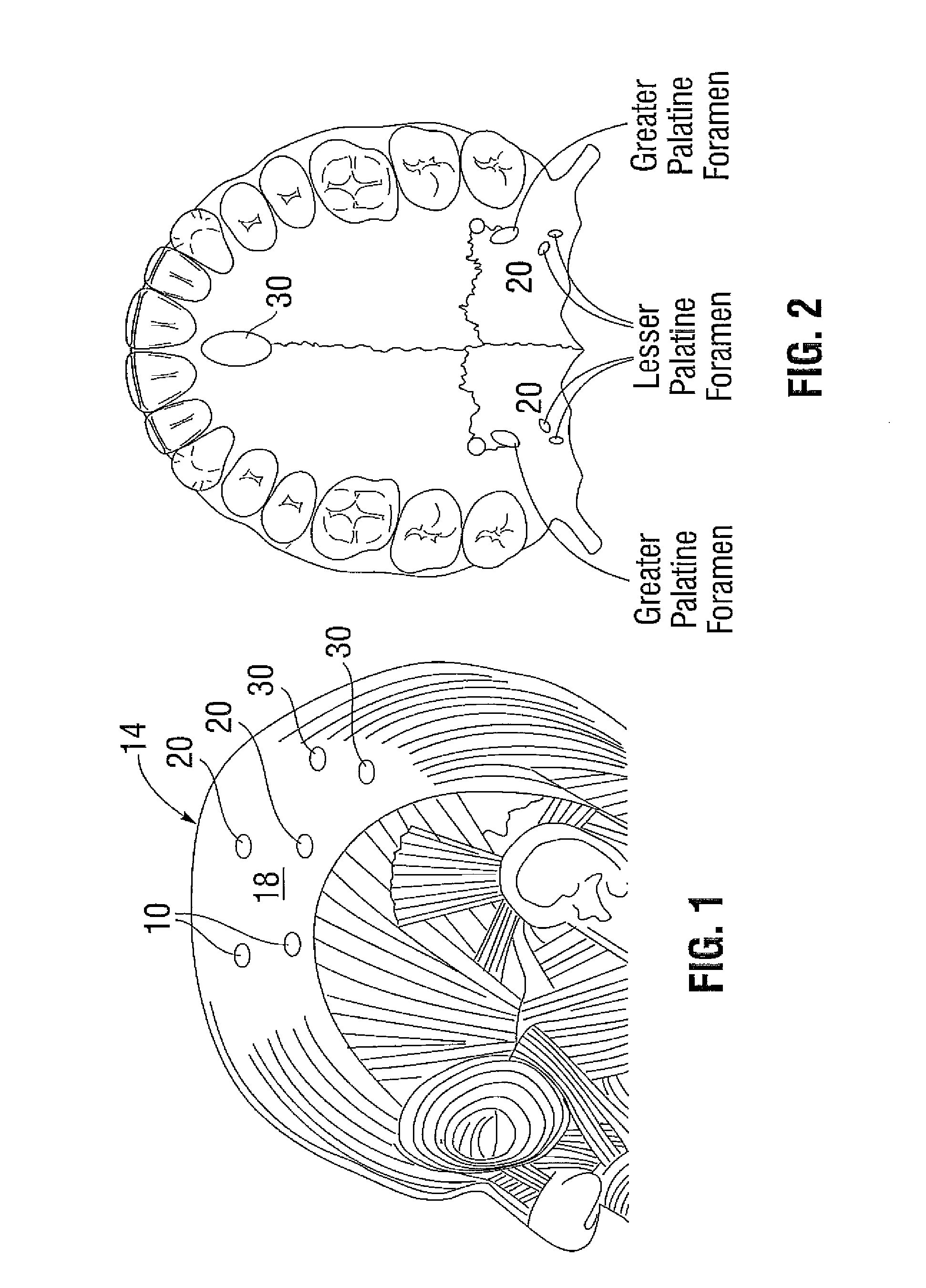

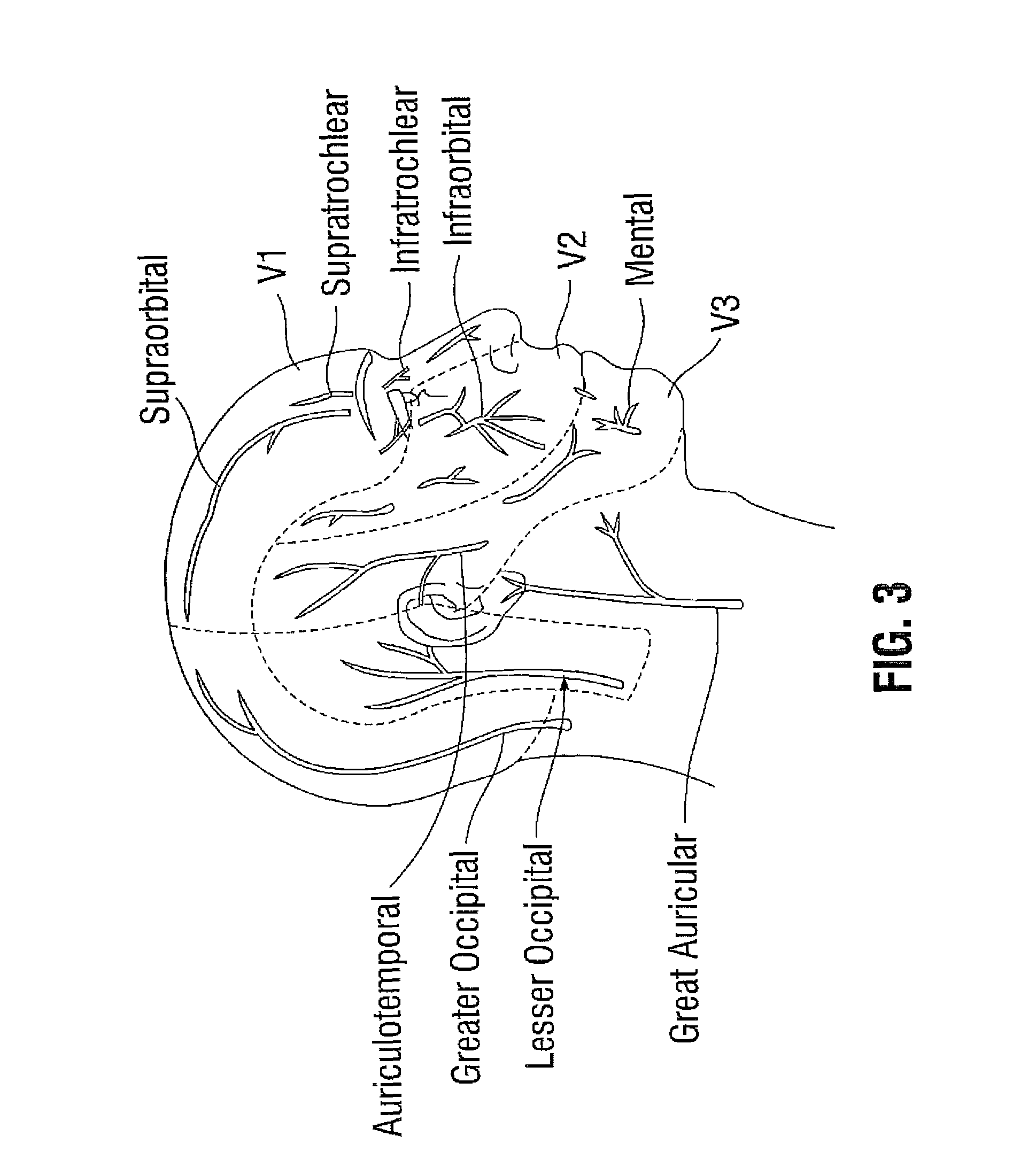

Extramuscular treatment of traumatic-induced migraine headache

ActiveUS8420106B1Minimize side effectsGood curative effectBacterial antigen ingredientsNervous disorderPatient groupMigraine

A method for selection and treatment of externally caused migraine headache, the method includes identifying a patient group having chronic migraine headache; determining the identified patient group, a specific patient with a post traumatic migraine headache; and administering to the selected patient by injection of a therapeutically effective amount of a Botulinum neurotoxin in a pharmaceutically safe form to the selected patient's head or upper neck; administration preferably being on the sites of the trigeminal cervical system, enabling axonal transport of the neurotoxin from distal to central sites; and the administration preferably comprising extramuscular injection of the neurotoxin of suitable dilution (a) over the aponeurotic fascia, or (b) intra-orally, in a foramina of the sphenopalatine ganglion, or (c) to emerging exit points of nerves including foraminal sites.

Owner:MIOTOX LLC

Staple type oligonucleotide and drug comprising the same

ActiveUS7595301B2Not improveImprove securityNervous disorderActivity regulationContact dermatitisAutoimmune responses

Conventional oligonucleotides are opened at both ends and thereby unstable. Their stability against catabolic enzymes is increased by phosphorothioate modification, but such phosphorothioate causes toxicity. The present invention provides oligonucleotides and medicaments in which these problems are improved. That is, it provides staple oligonucleotides and medicaments containing the same as the active ingredient. Specifically, it provides transcription factor inhibitors, antisense oligonucleotides and siRNAs. More specifically, it provides agents for preventing, treating or improving inflammation, autoimmune diseases, central diseases, reperfusion injury in ischaemic diseases, worsened prognosis after organ transplantation or organ surgery, or restenosis after PTCA. Further specifically, it provides agents for preventing, treating or improving arthritis, dermatitis, nephritis, hepatitis, renal failure, cystitis, prostatitis, urethritis, ulcerative colitis, Crohn disease, chronic rheumatoid arthritis, osteoarthritis, atopic dermatitis, contact dermatitis, psoriasis, cutaneous ulcer or decubitus.

Owner:ANGES MG INC

Compositions and methods for localized drug delivery through mammary papillae

ActiveUS9220680B2Efficient deliveryHigh concentrationTissue culturePharmaceutical non-active ingredientsDiagnostic agentAreola

The invention provides compositions and methods for the prevention, diagnosis, or treatment of conditions affecting breast tissue. The compositions can include one or more therapeutic agents or diagnostic agents, and an effective carrier. The composition can be specifically adapted for transdermal permeation through the mammary papilla, areola, or a combination thereof, and into underlying breast tissue.

Owner:SOUTH DAKOTA STATE UNIVERSITY

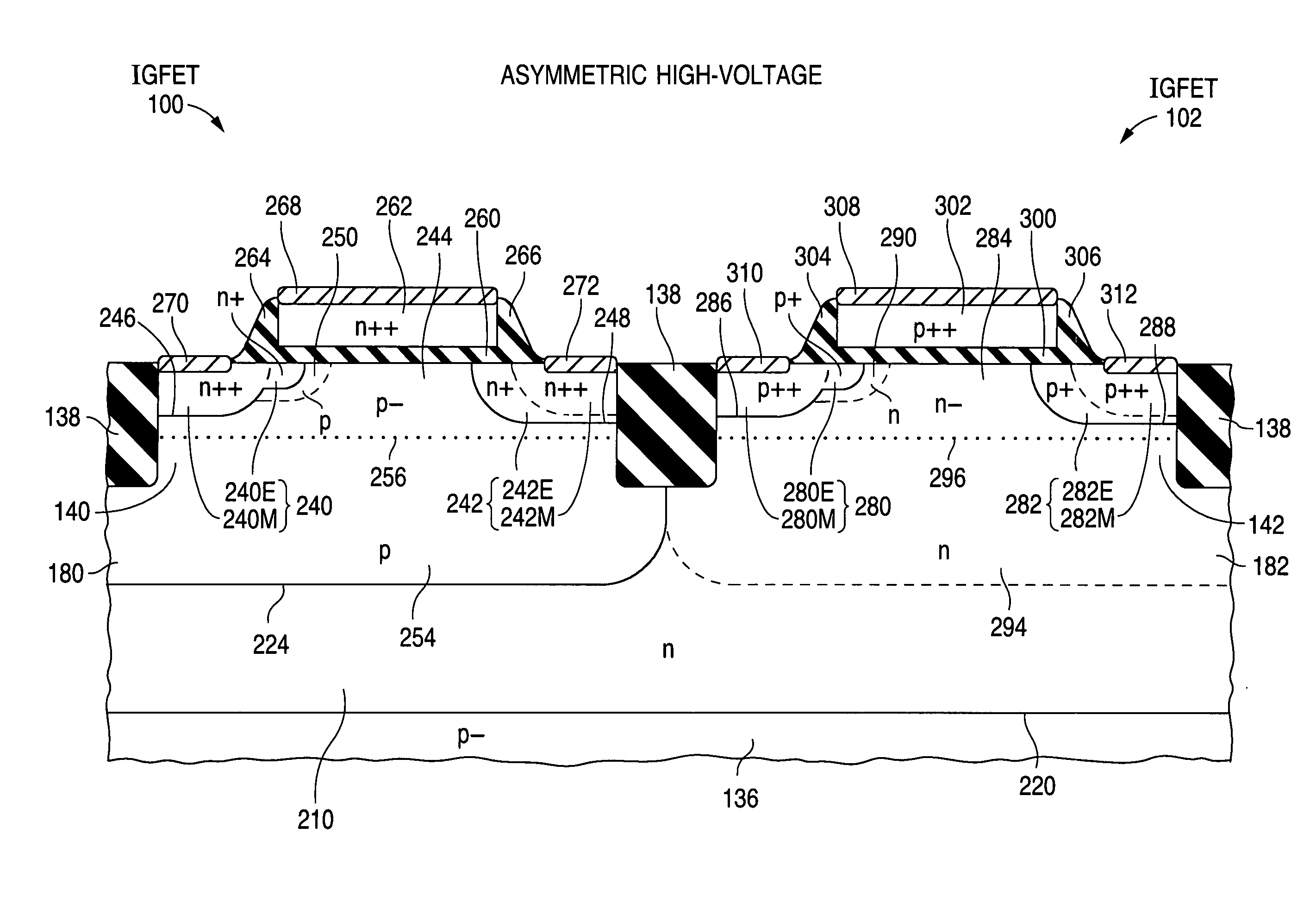

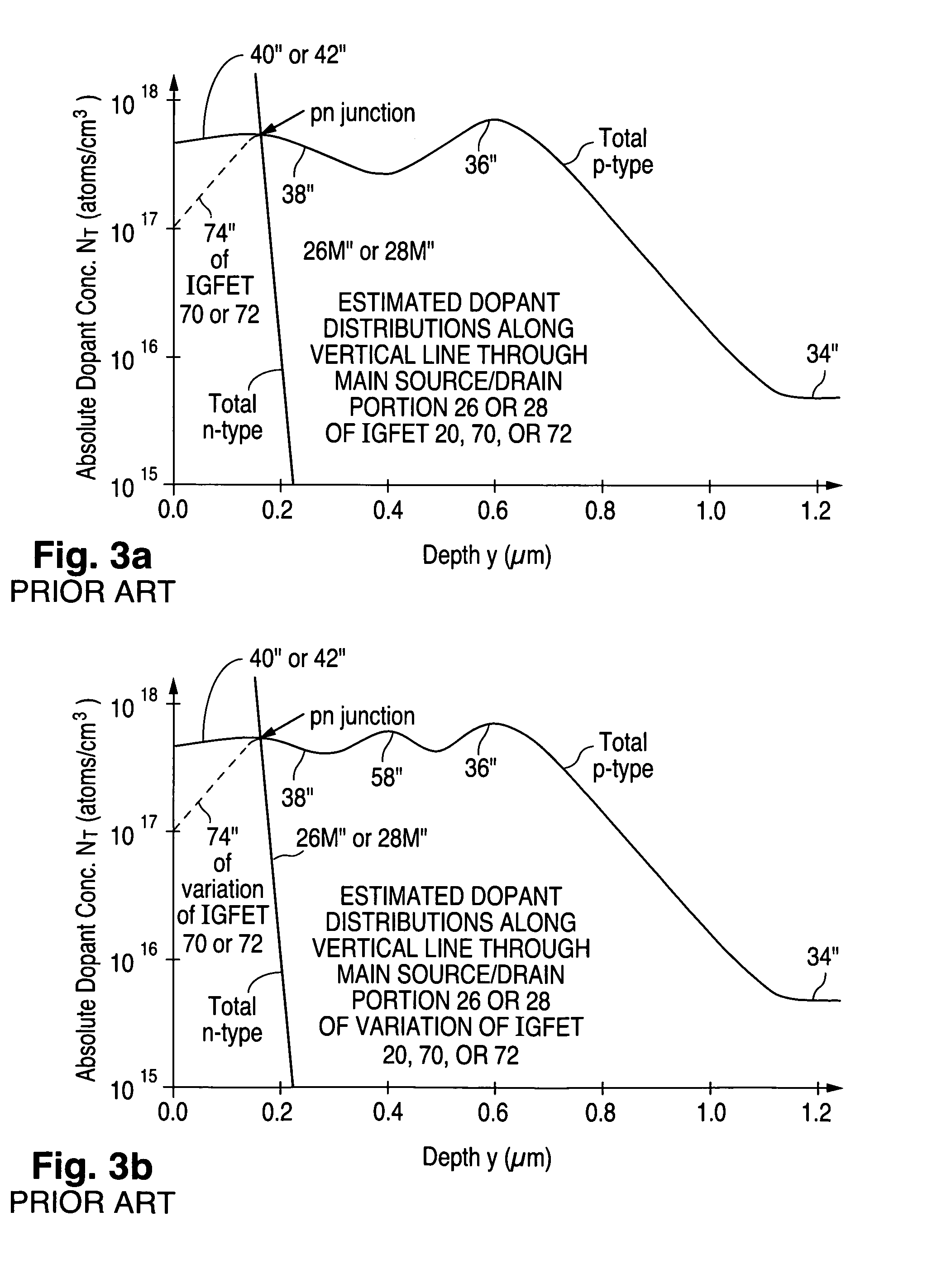

Structure and fabrication of field-effect transistor using empty well in combination with source/drain extensions or/and halo pocket

ActiveUS20100244130A1Improve performanceSemiconductor fabrication platform extremely versatileSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricNon symmetric

Insulated-gate field-effect transistors (“IGFETs”), both symmetric and asymmetric, suitable for a semiconductor fabrication platform that provides IGFETs for analog and digital applications, including mixed-signal applications, utilize empty-well regions in achieving high performance. A relatively small amount of semiconductor well dopant is near the top of each empty well. Each IGFET (100, 102, 112, 114, 124, or 126) has a pair of source / drain zones laterally separated by a channel zone of body material of the empty well (180, 182, 192, 194, 204, or 206). A gate electrode overlies a gate dielectric layer above the channel zone. Each source / drain zone (240, 242, 280, 282, 520, 522, 550, 552, 720, 722, 752, or 752) has a main portion (240M, 242M, 280M, 282M, 520M, 522M, 550M, 552M, 720M, 722M, 752M, or 752M) and a more lightly doped lateral extension (240E, 242E, 280E, 282E, 520E, 522E, 550E, 552E, 720E, 722E, 752E, or 752E). Alternatively or additionally, a more heavily doped pocket portion (250 or 290) of the body material extends along one of the source / drain zones. When present, the pocket portion typically causes the IGFET to be an asymmetric device.

Owner:NAT SEMICON CORP

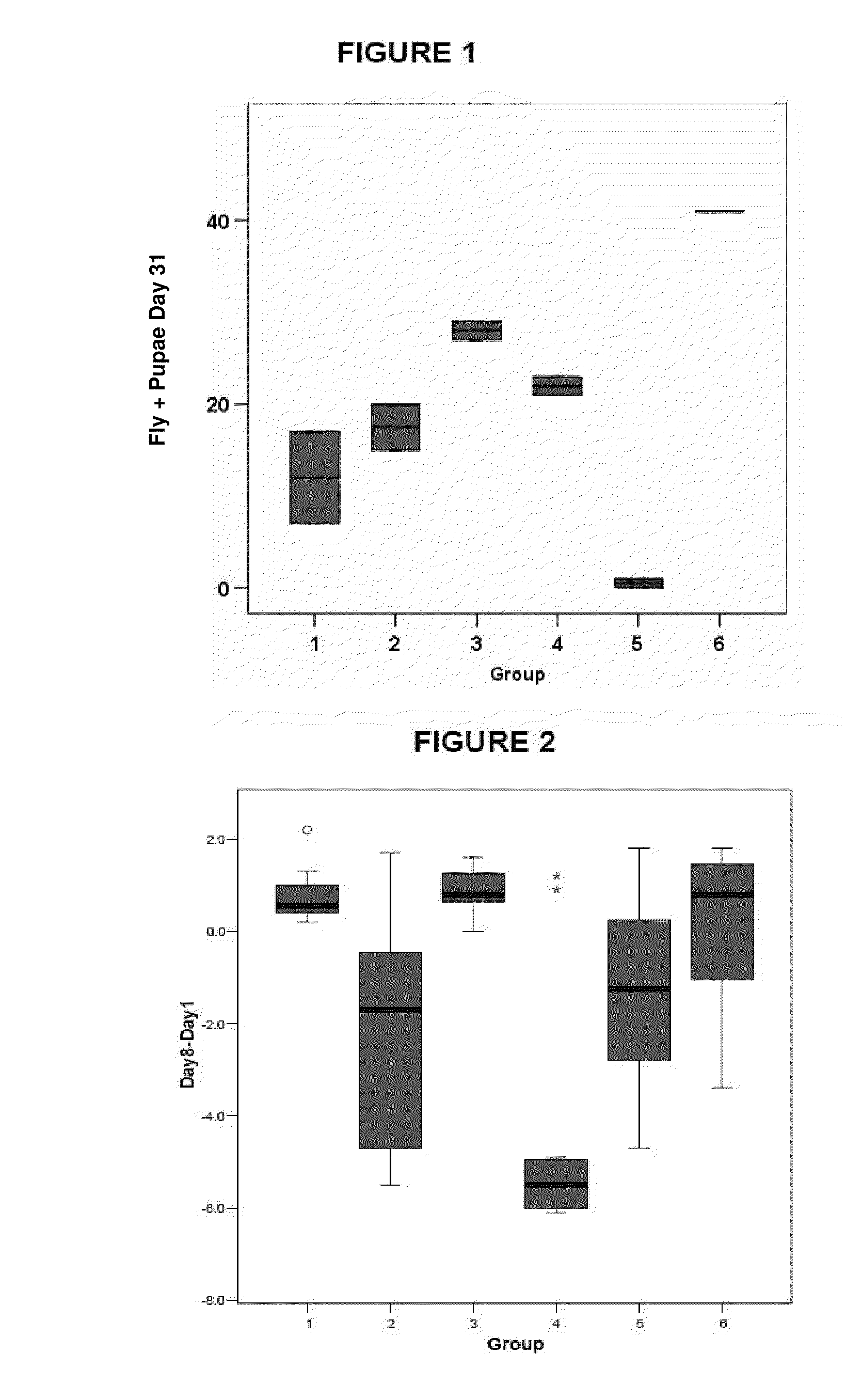

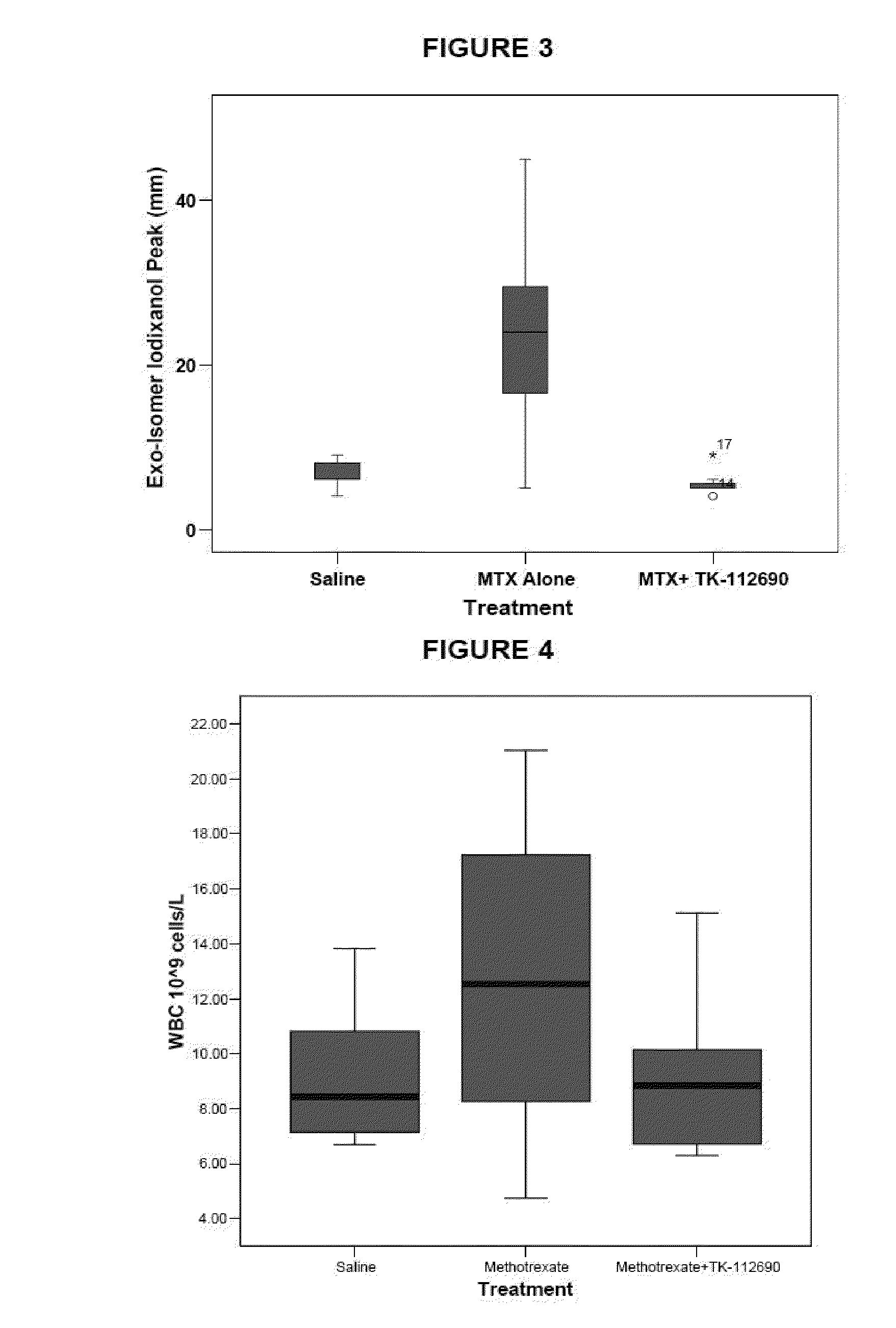

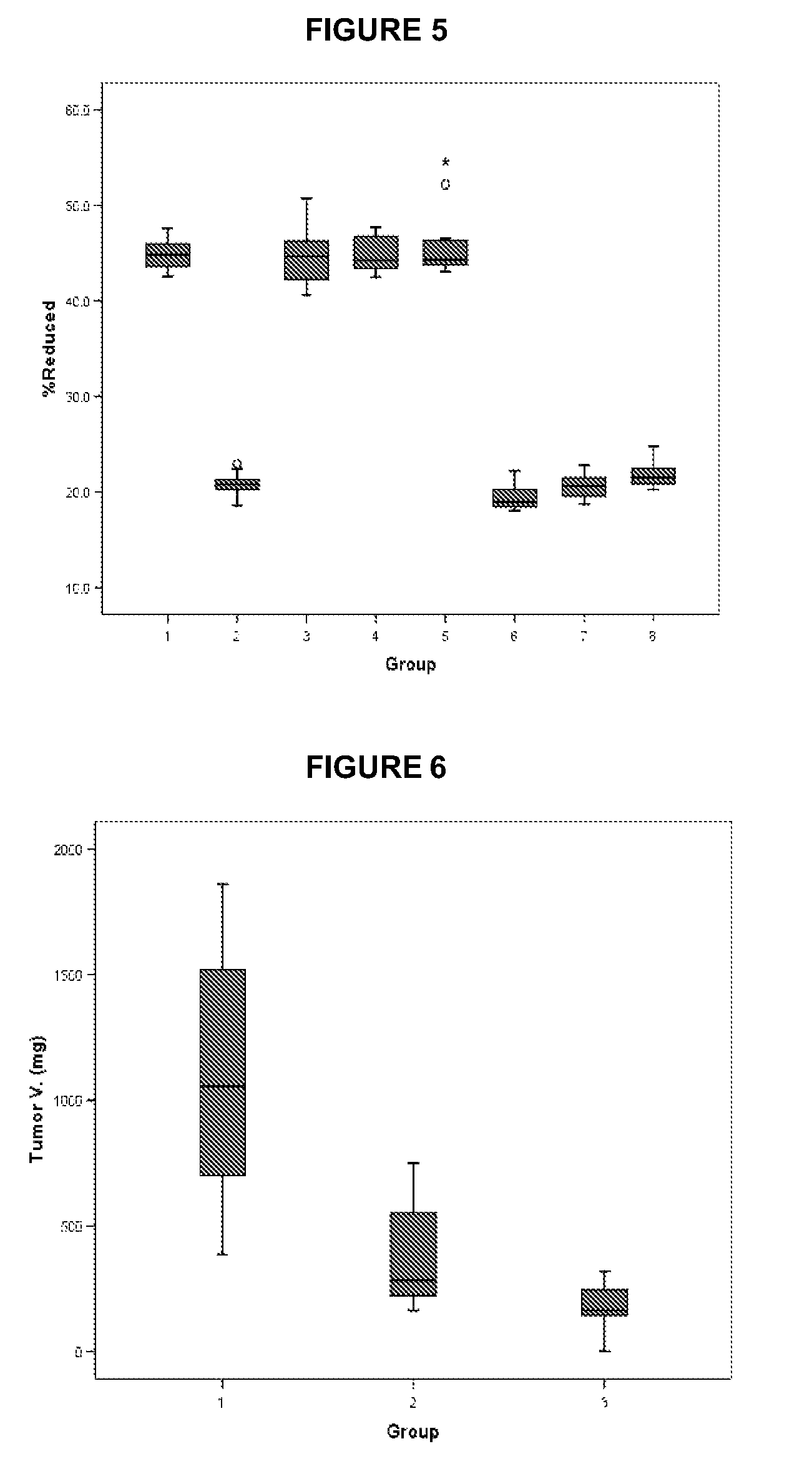

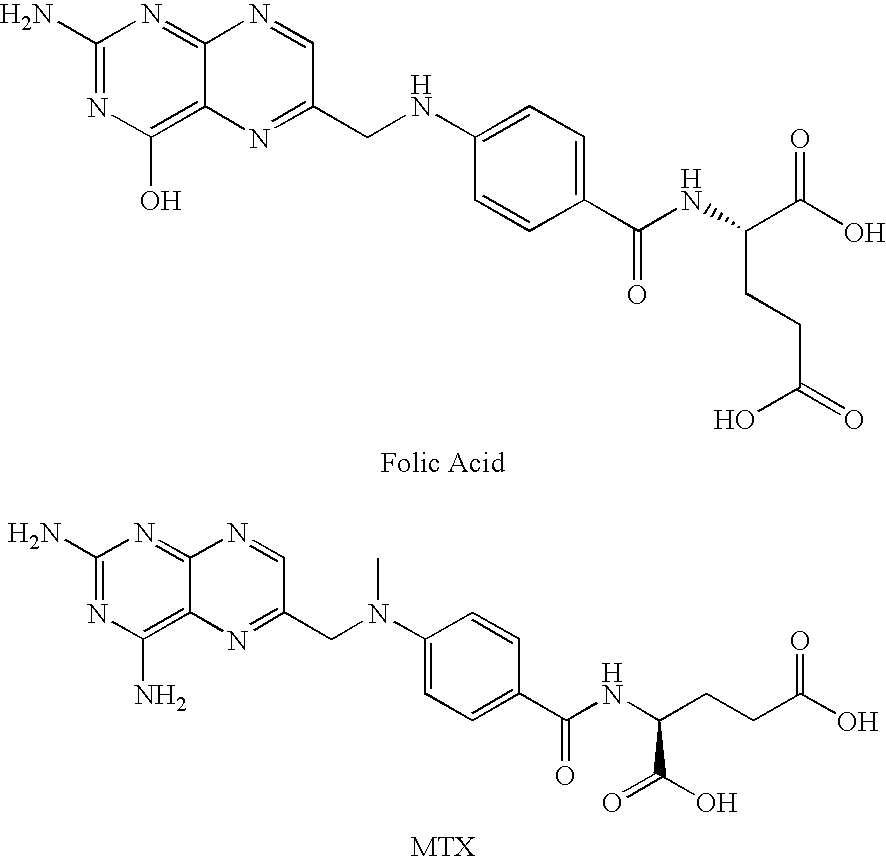

Methotrexate adjuvants to reduce toxicity and methods for using the same

Methods are provided for using methotrexate (MTX) in which reduced host toxicity is observed. Aspects of the methods include administering to a subject an effective amount of MTX in conjunction with a MTX toxicity-reducing adjuvant, such as a 2,2′-anhydropyrimidine, a derivative thereof or a uridine phosphorylase inhibitor. Also provided are compositions that find use in practicing embodiments of the invention. The methods and compositions find use in a variety of applications, including the treatment of a variety of different disease conditions.

Owner:TOSK INC +1

Structure and fabrication of field-effect transistor using empty well in combination with source/drain extensions or/and halo pocket

ActiveUS8410549B2Improve performanceSemiconductor fabrication platform extremely versatileSolid-state devicesSemiconductor/solid-state device manufacturingDopantGate dielectric

Insulated-gate field-effect transistors (“IGFETs”), both symmetric and asymmetric, suitable for a semiconductor fabrication platform that provides IGFETs for analog and digital applications, including mixed-signal applications, utilize empty-well regions in achieving high performance. A relatively small amount of semiconductor well dopant is near the top of each empty well. Each IGFET (100, 102, 112, 114, 124, or 126) has a pair of source / drain zones laterally separated by a channel zone of body material of the empty well (180, 182, 192, 194, 204, or 206). A gate electrode overlies a gate dielectric layer above the channel zone. Each source / drain zone (240, 242, 280, 282, 520, 522, 550, 552, 720, 722, 752, or 752) has a main portion (240M, 242M, 280M, 282M, 520M, 522M, 550M, 552M, 720M, 722M, 752M, or 752M) and a more lightly doped lateral extension (240E, 242E, 280E, 282E, 520E, 522E, 550E, 552E, 720E, 722E, 752E, or 752E). Alternatively or additionally, a more heavily doped pocket portion (250 or 290) of the body material extends along one of the source / drain zones. When present, the pocket portion typically causes the IGFET to be an asymmetric device.

Owner:NAT SEMICON CORP

Advanced rotating-shield brachytherapy and planning of the same

ActiveUS20170165500A1Reduce planning timeImprove consistencyX-ray/gamma-ray/particle-irradiation therapyBrachytherapyEngineering

Systems and methods for rotating shield brachytherapy. In an aspect, some of the systems and methods can be used to facilitate shield selection for use in rotating shield brachytherapy. In an aspect, the invention is a shielded needle or catheter system with a rotational controller for delivering radioisotope-based interstitial rotating shield brachytherapy (I-RSBT). In an aspect, the catheter system can utilize paddle-based RSBT. Further provided are methods and systems for helical RSBT.

Owner:UNIV OF IOWA RES FOUND

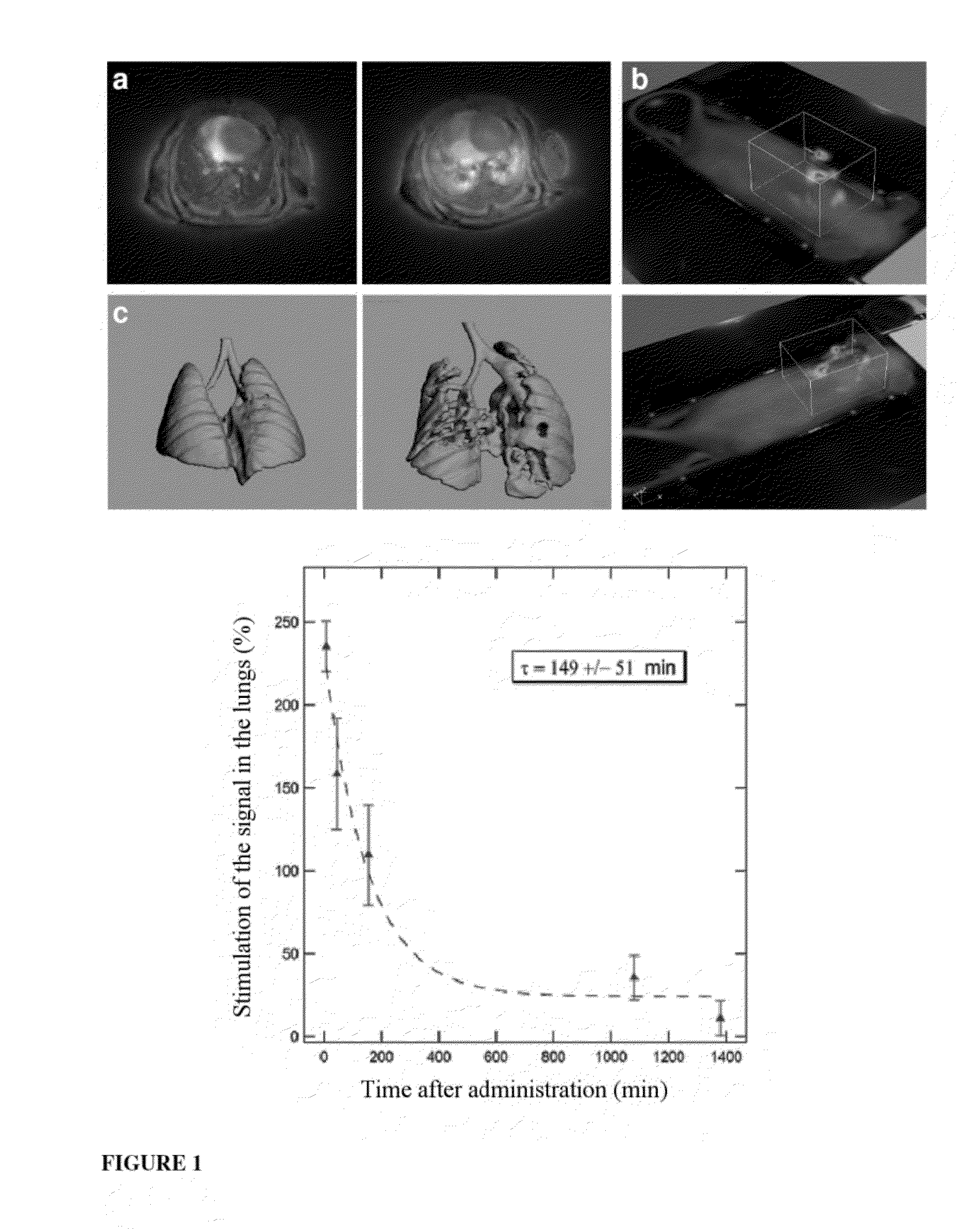

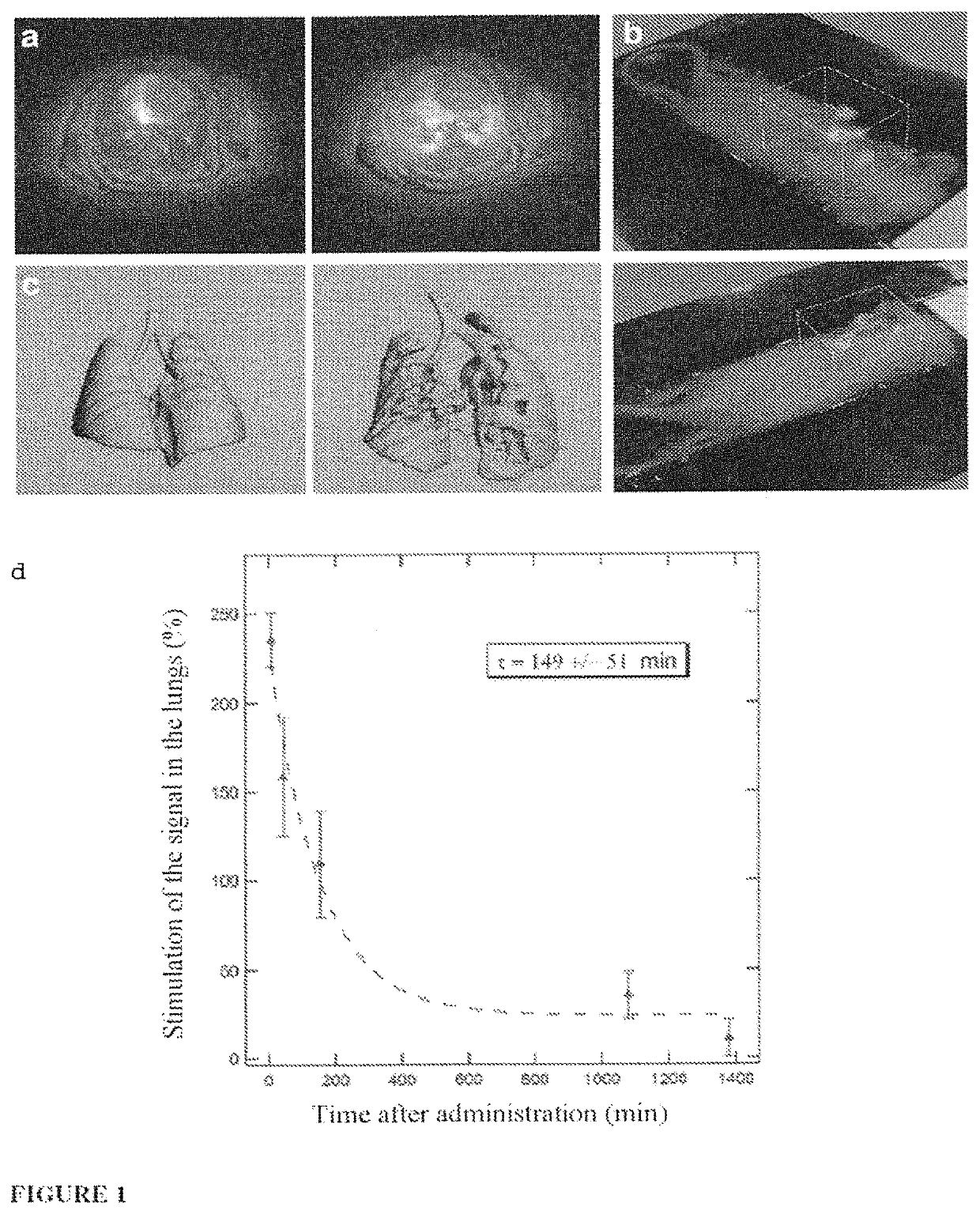

Ultrafine nanoparticles as multimodal contrast agent

ActiveUS20150050217A1Not improvePowder deliveryPeptide/protein ingredientsPhotodynamic therapyNanoparticle

The invention relates to a novel use of ultrafine nanoparticles, of use as a diagnostic, therapeutic or theranostic agent, characterized by their mode of administration via the airways. The invention is also directed toward the applications which follow from this novel mode of administration, in particular for imaging the lungs, and the diagnosis or prognosis of pathological pulmonary conditions. In the therapeutic field, the applications envisioned are those of radiosensitizing or radioactive agents for radiotherapy (and optionally curietherapy), or for neutron therapy, or of agents for PDT (photodynamic therapy), in particular for the treatment of lung tumors.

Owner:UNIV DE BORDEAUX +4

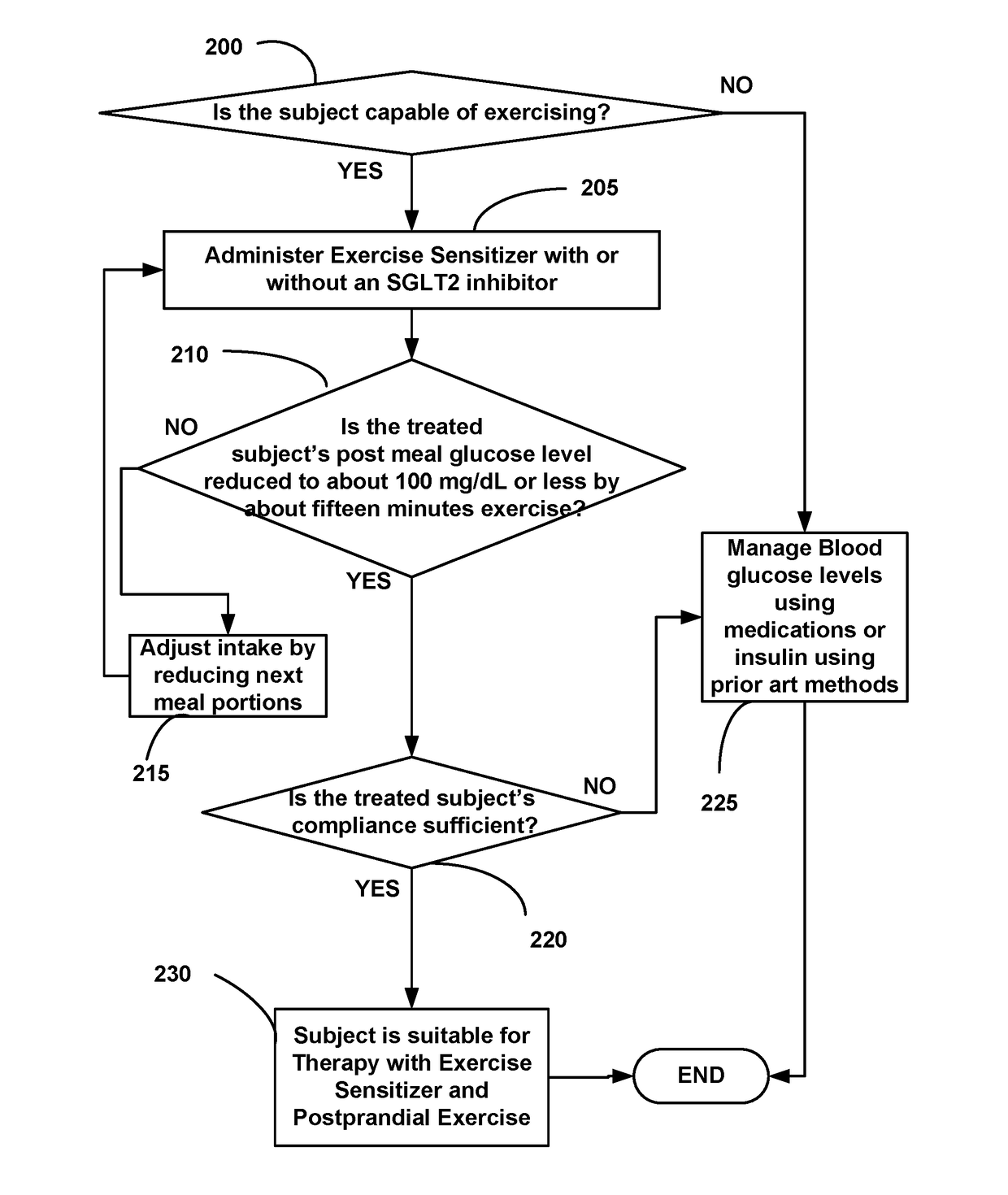

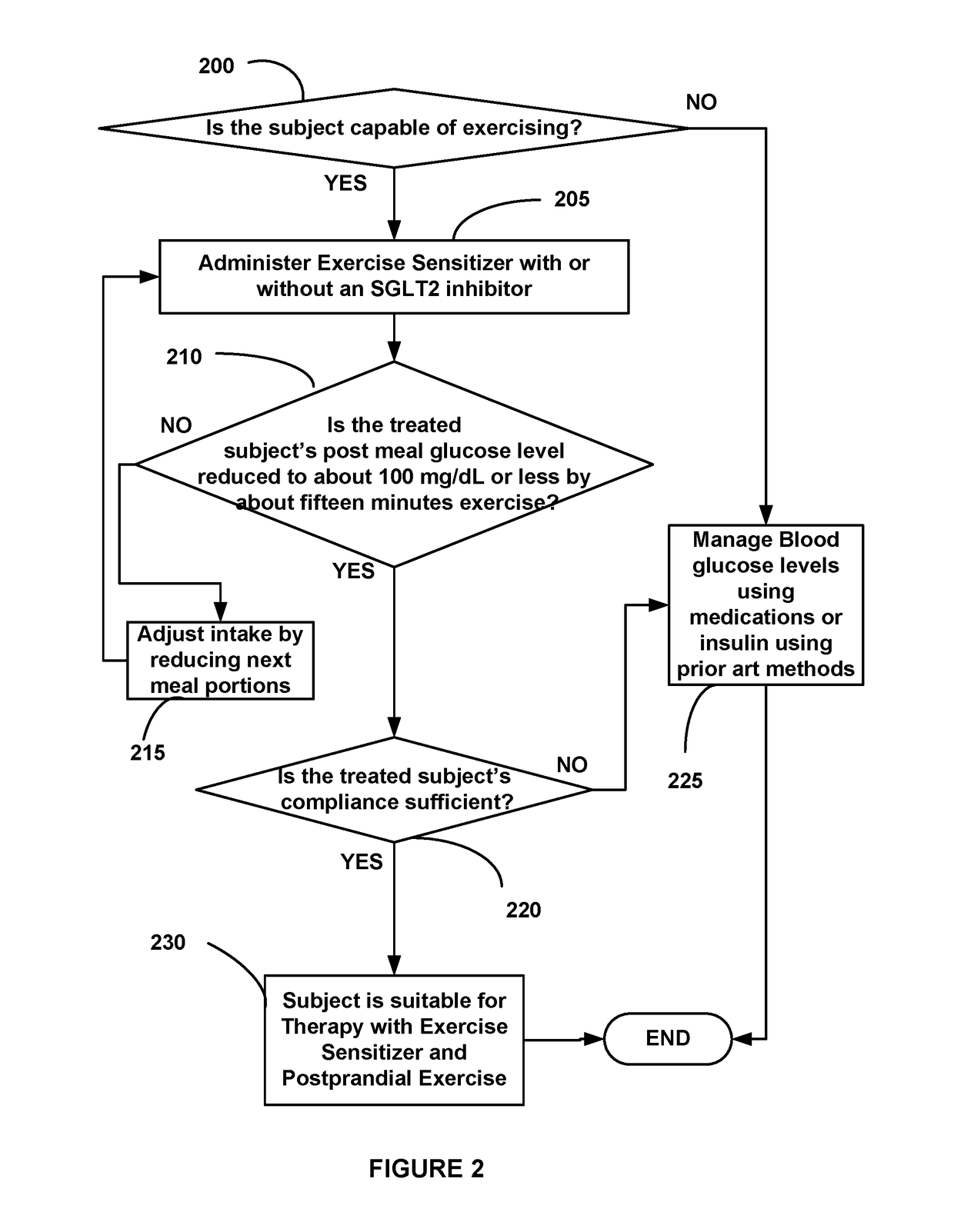

Diabetes Control Using Postprandial Feedback

ActiveUS20170258395A1Easy to useLeast riskHydroxy compound active ingredientsCatheterDiabetes controlPhysical exercise

Disclosed is a postprandial glucose-measuring device for preventing the development of or reversing T2D. Included are methods for using the device as well as better use for invasive and noninvasive glucose meters. Further disclosed are novel exercise-sensitizing compositions useful for managing blood glucose levels in Type-2 diabetics with minimal risk of hypoglycemia. The disclosed glucose meters allow a user to also measure exercise and meal size—all with relatively instant feedback—more effectively than having to track the complexity posed by labels, glycemic index and calories. Also disclosed is integration of glucose-measuring devices with smartphones and health monitoring technology to make possible safe and effective interpretation of postprandial glucose readings by a patient to control or reverse Type-2 diabetes.

Owner:NATH RATTAN +1

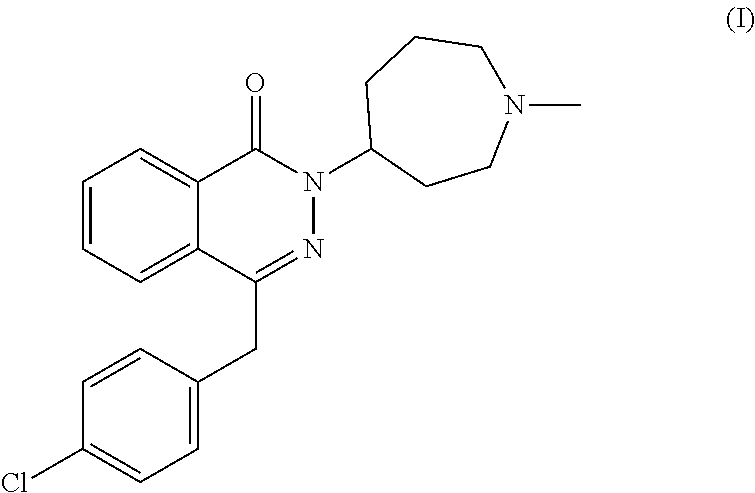

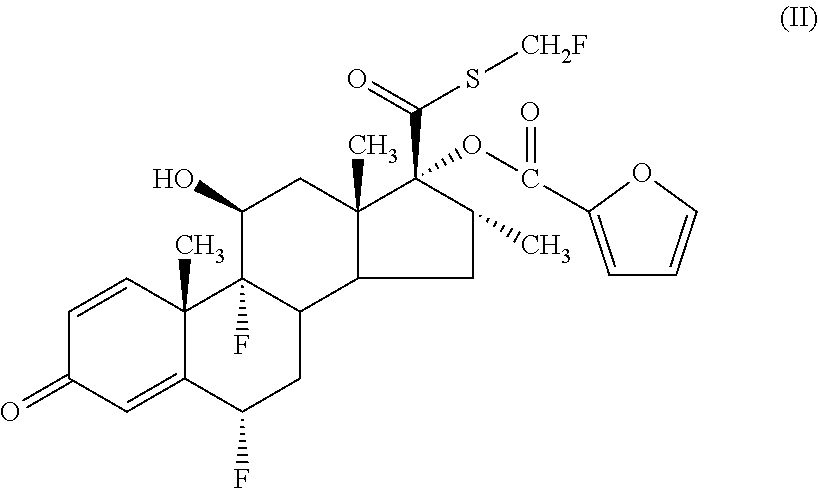

Pharmaceutical formulations comprising azelastine and a corticosteroid for the treatment of inflammatory or allergic conditions

InactiveUS20120065177A1Satisfied with stabilitySatisfactory shelf-life propertyAntipyreticAnalgesicsAllergic conditionAzelastine

The present invention relates to method for the treatment of allergic rhinitis comprising: administrating to a patient in need thereof a pharmaceutical formulation comprising a compound for formula (I)or a salt thereof, and an anti-inflammatory glucocorticoid compound of formula (II)or a solvate thereof.

Owner:GLAXO GROUP LTD

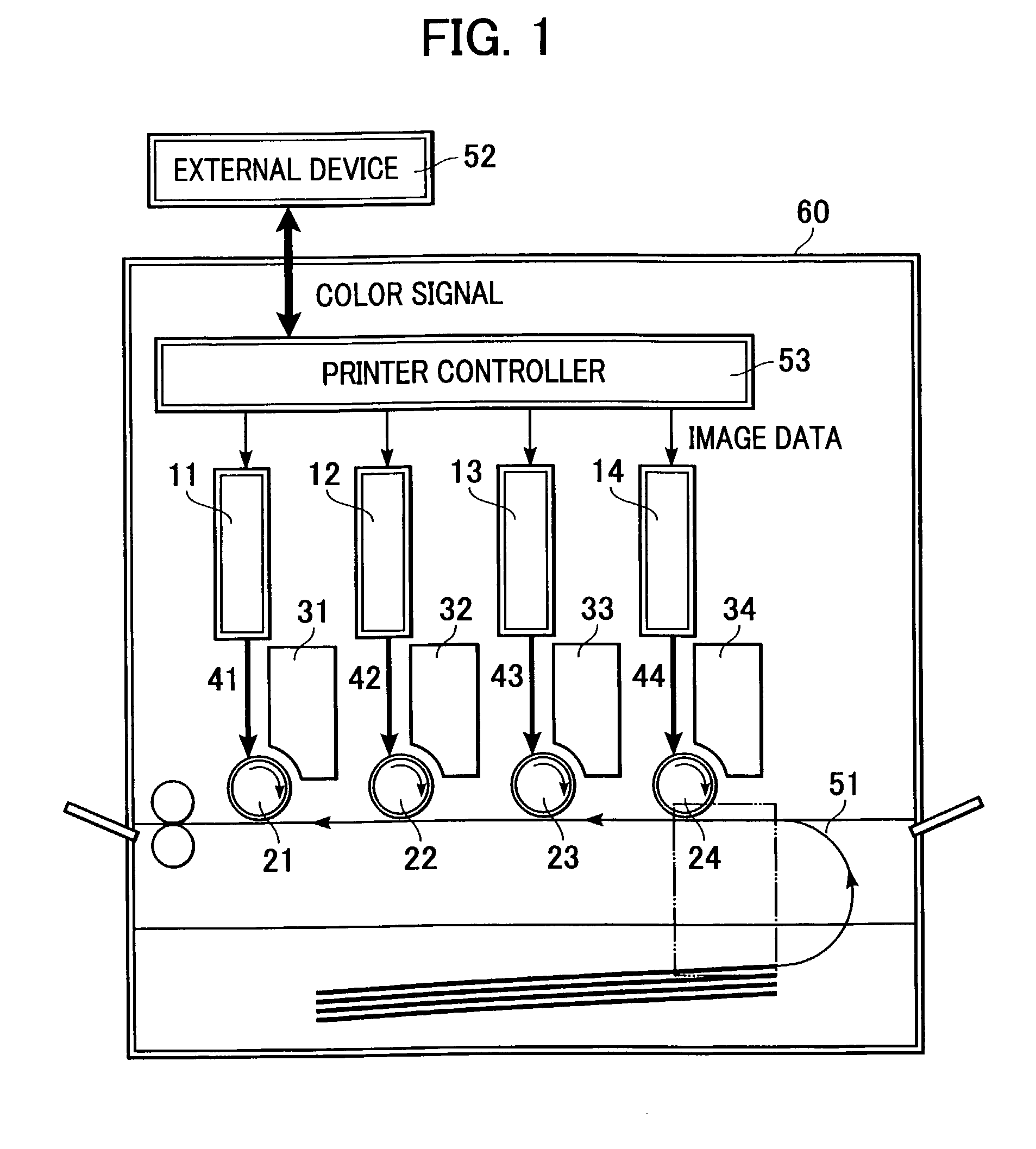

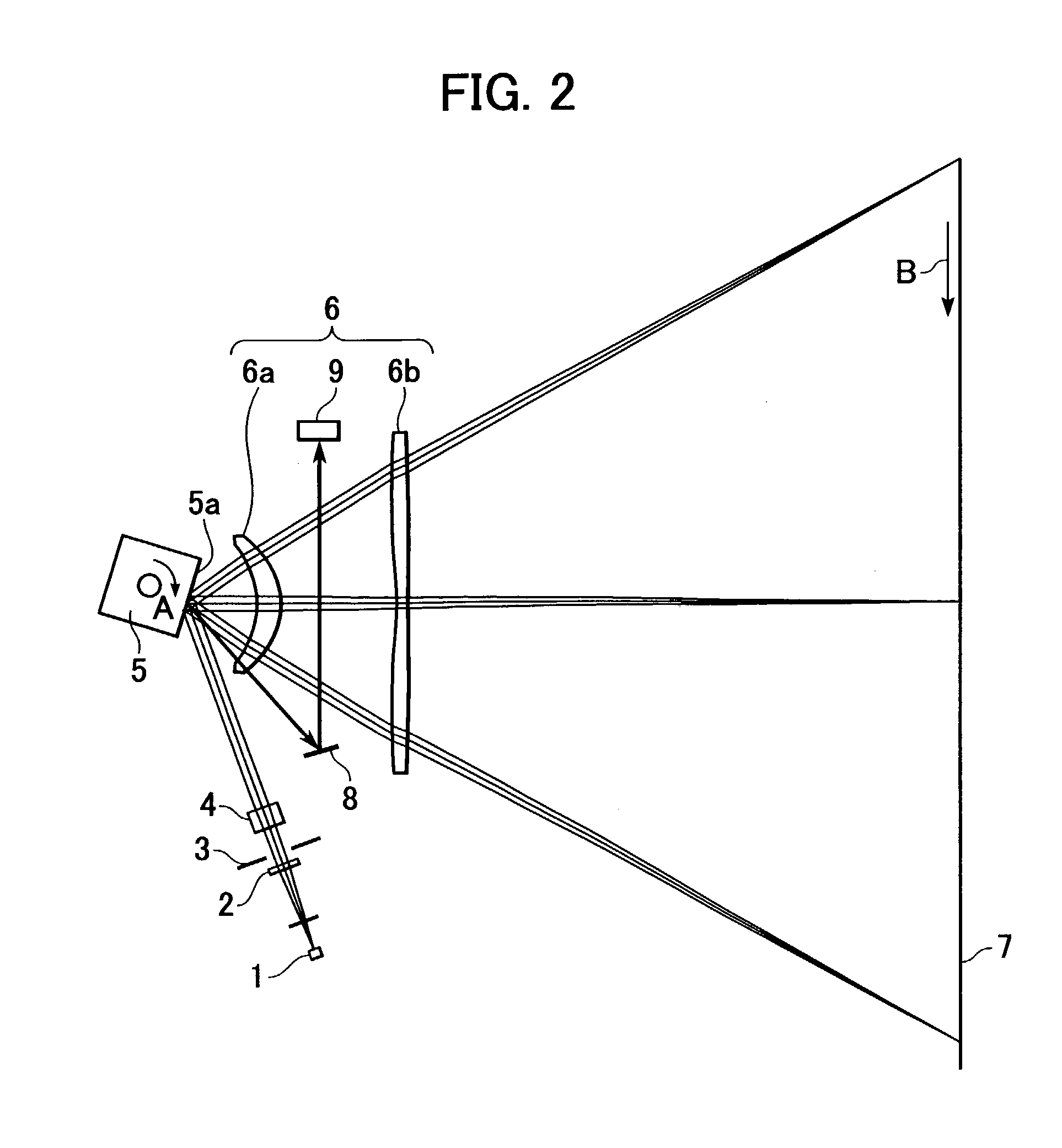

Image writing apparatus and color image forming apparatus

InactiveUS7227563B2Not improveDigitally marking record carriersInking apparatusColor imageOptical property

The present invention provides a color image forming apparatus forming an image by using a plurality of image carriers, wherein at least one lens having identical optical characteristics and forming individual scanning optical systems which scan the individual image carriers with beams is formed by use of a plurality of cavities. When dividing the cavities into a plurality of groups in response to variations in the optical characteristics caused by cavity difference of the lenses formed with the plurality of cavities so that the relative differences in an optical parameters are within an allowable range, at least one lens of each scanning optical system is selected from the cavities of one of the plurality of groups.

Owner:CANON KK

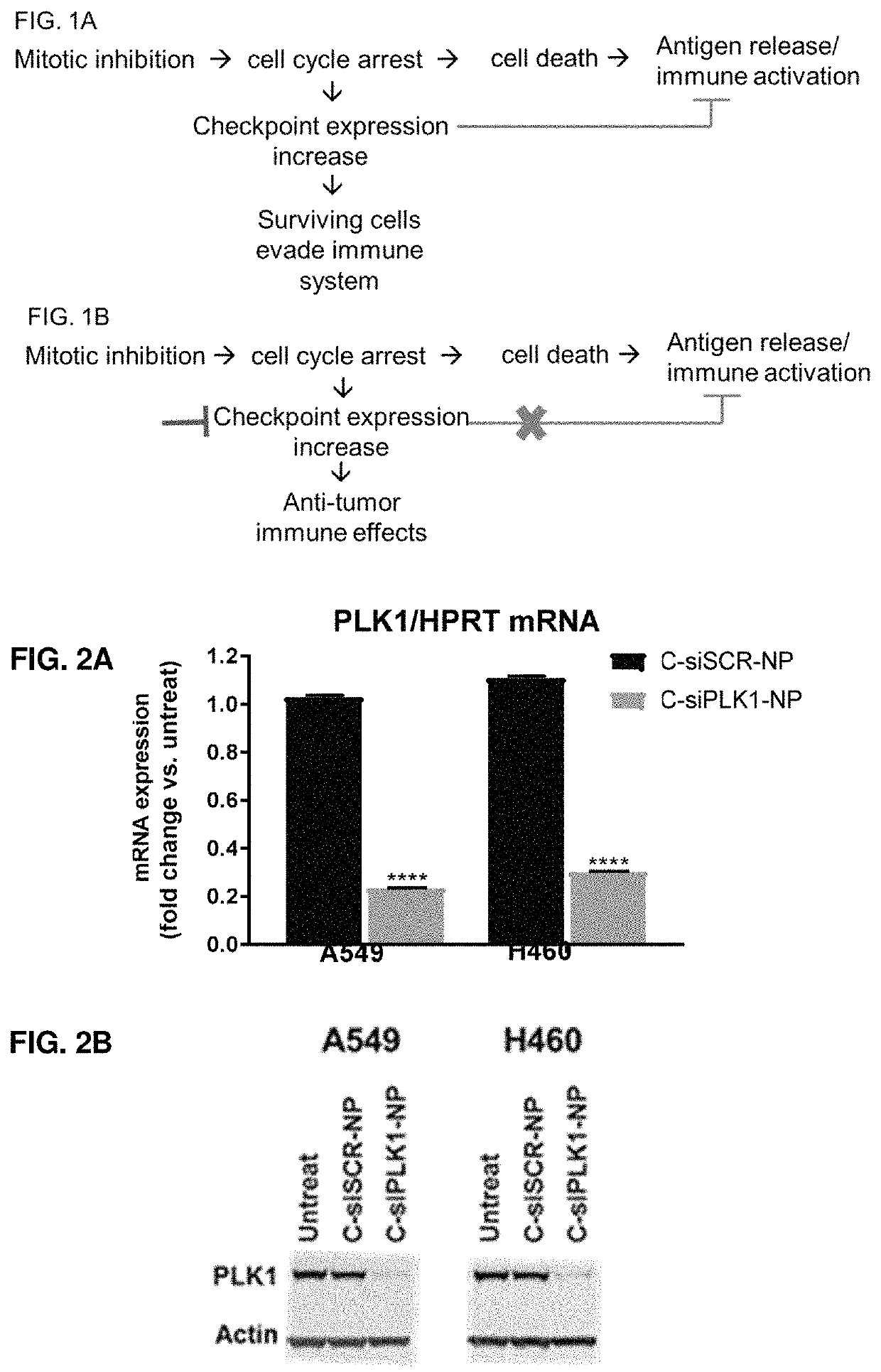

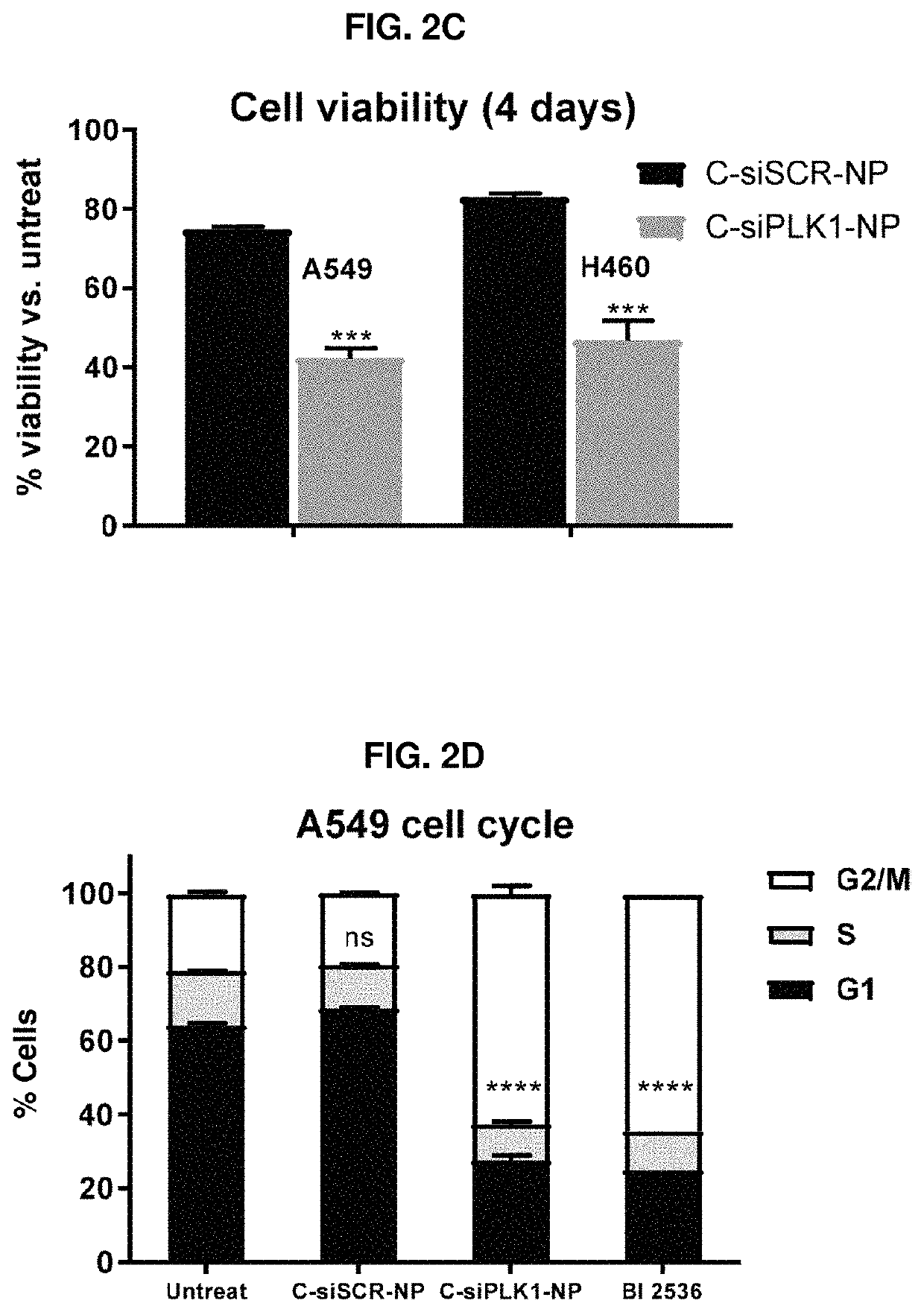

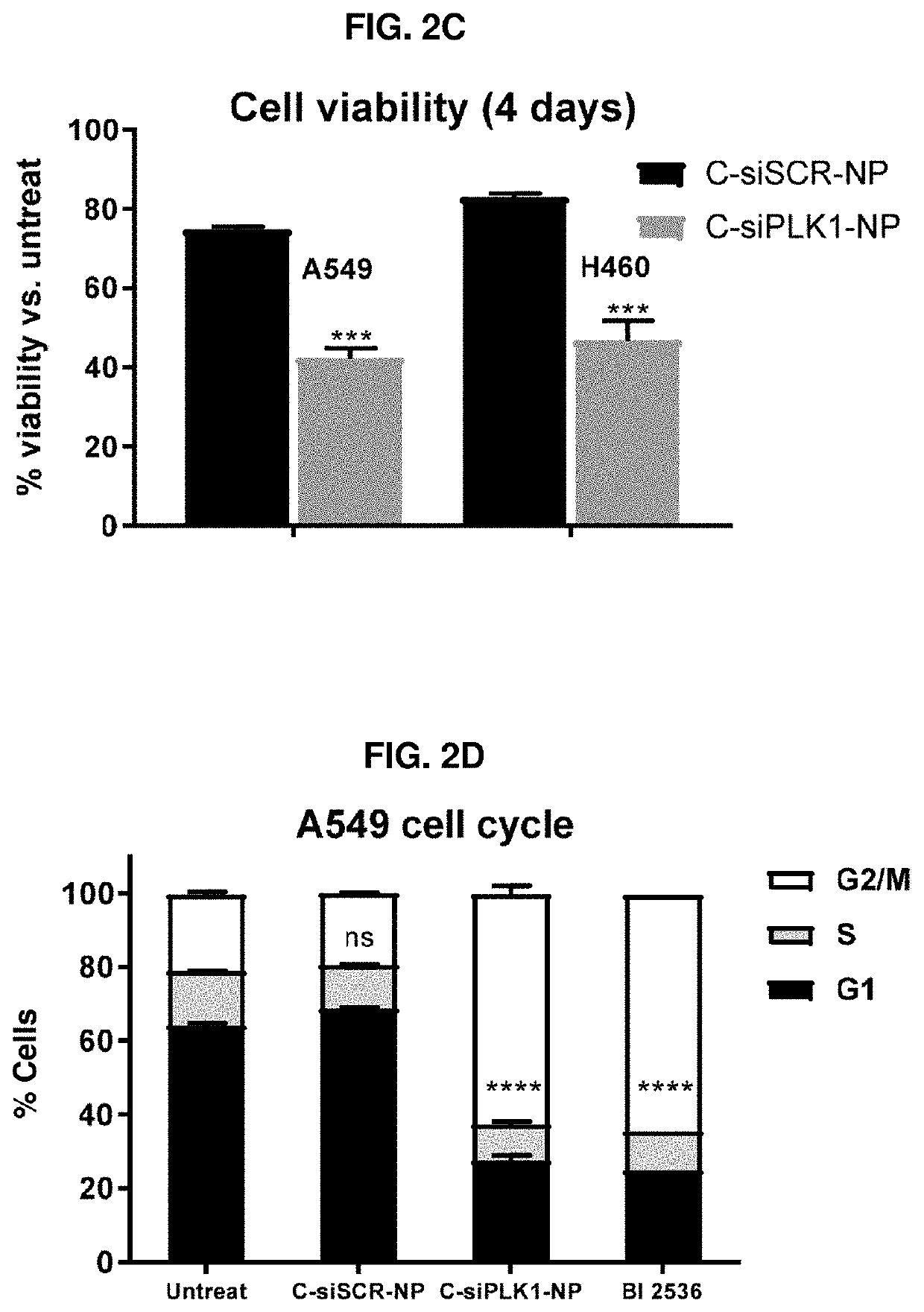

Therapeutic constructs for co-delivery of mitotic kinase inhibitor and immune checkpoint inhibitor

ActiveUS11224573B2Reduce systemic toxicityImprove responseOrganic active ingredientsPowder deliveryCancer deathCancer cell

Disclosed herein are therapeutic constructs including a delivery particle, at least one mitotic kinase inhibitor, and at least one immune checkpoint inhibitor. Also disclosed are therapeutic constructs including a mitotic kinase inhibitor, an immune checkpoint inhibitor, and a chemical linker. These therapeutic constructs cause cancer death by both therapeutic and immune effects and promote targeted delivery of more therapeutics to the surviving cancer cells in a positive feed-back loop. They enhance therapeutic index of free drugs and can be used intratumorally or systemically. This strategy can treat broad cancer types and is particular useful for cancer without obvious receptors for cancer-targeted delivery of otherwise toxic therapeutics.

Owner:PDX PHARM INC +1

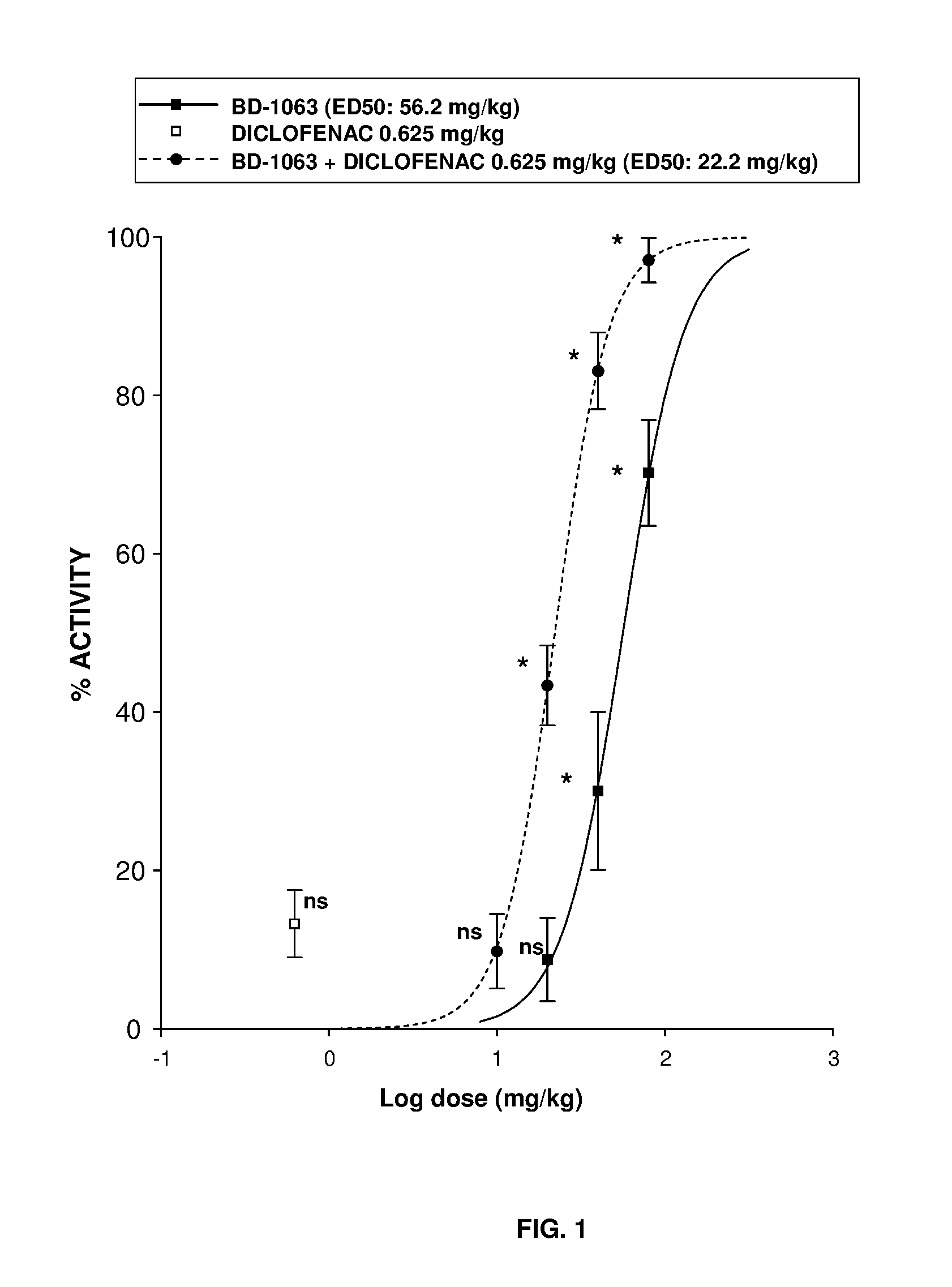

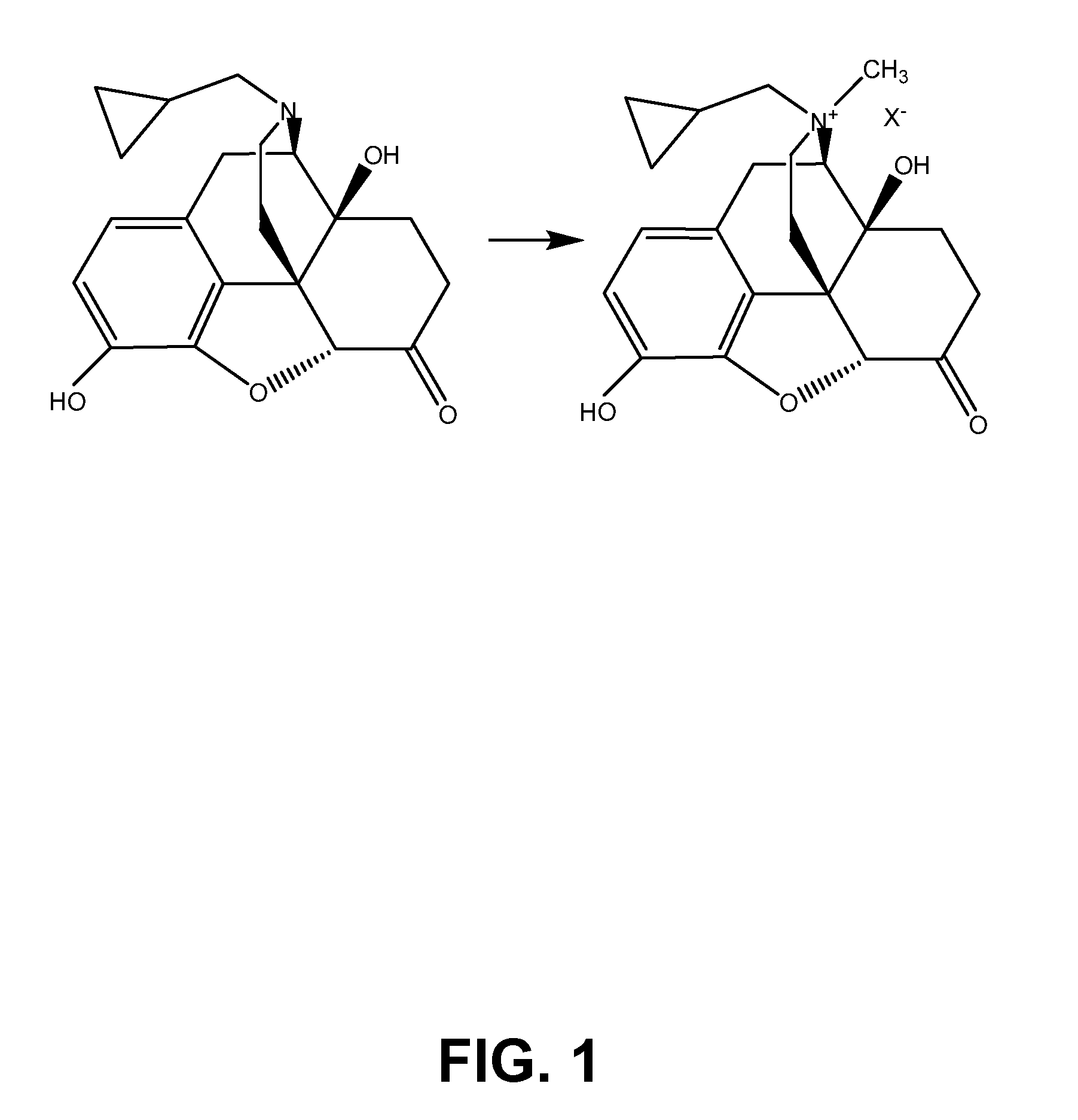

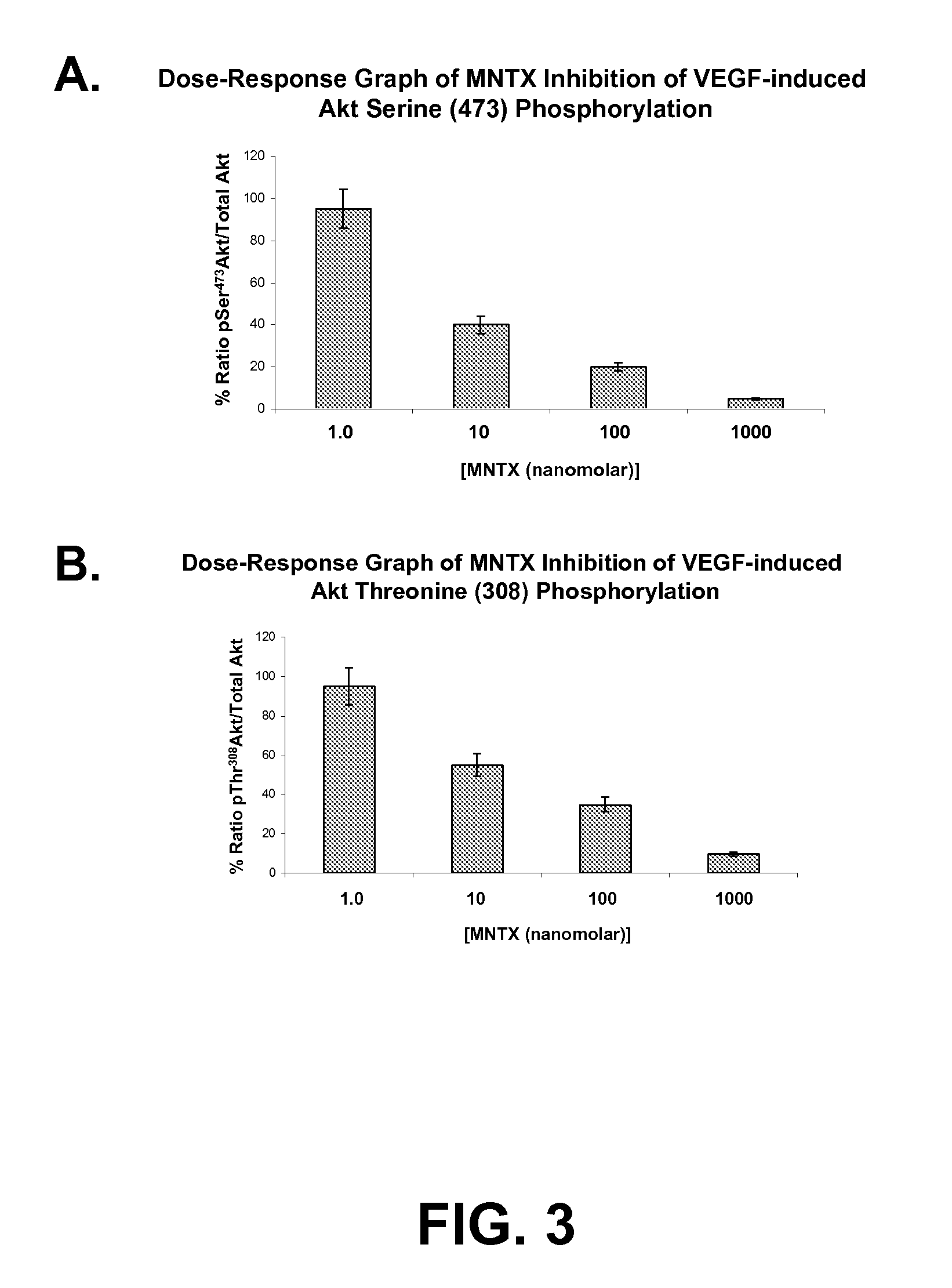

TREATMENT WITH OPIOID ANTAGONISTS AND mTOR INHIBITORS

ActiveUS20110021551A1Reduction in therapeutically effective doseDecrease doBiocideSenses disorderOpioid antagonistDiscovery and development of mTOR inhibitors

Embodiments of the invention provide methods of treating a disorder or disease characterized by cellular proliferation and migration by co-administering a synergistically effective amount of an mTOR inhibitor and a μ-opioid receptor antagonist.

Owner:UNIVERSITY OF CHICAGO

Advanced rotating-shield brachytherapy and planning of the same

ActiveUS10029118B2Reduce planning timeImprove consistencyX-ray/gamma-ray/particle-irradiation therapyBrachytherapyEngineering

Systems and methods for rotating shield brachytherapy. In an aspect, some of the systems and methods can be used to facilitate shield selection for use in rotating shield brachytherapy. In an aspect, the invention is a shielded needle or catheter system with a rotational controller for delivering radioisotope-based interstitial rotating shield brachytherapy (I-RSBT). In an aspect, the catheter system can utilize paddle-based RSBT. Further provided are methods and systems for helical RSBT.

Owner:UNIV OF IOWA RES FOUND

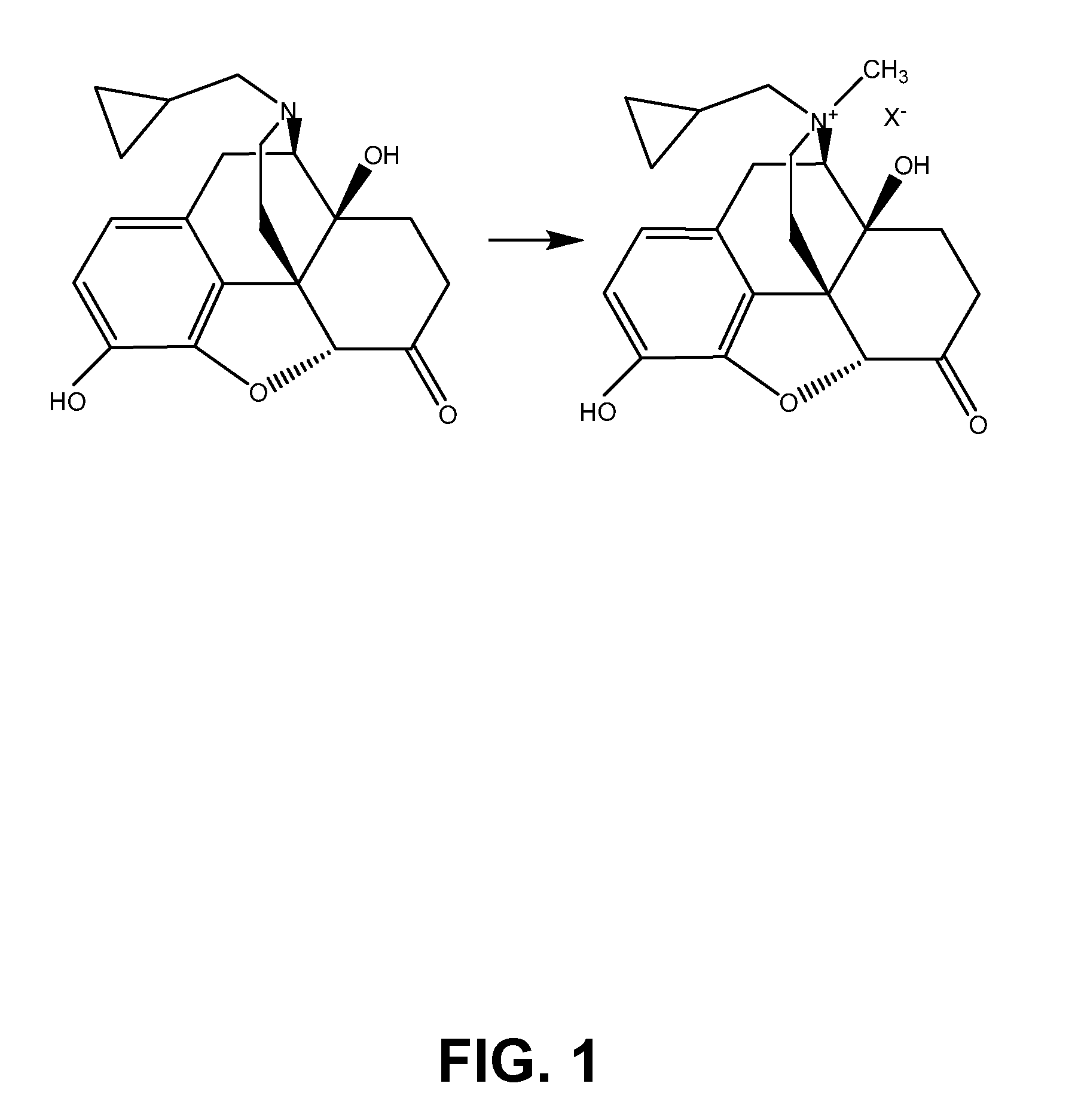

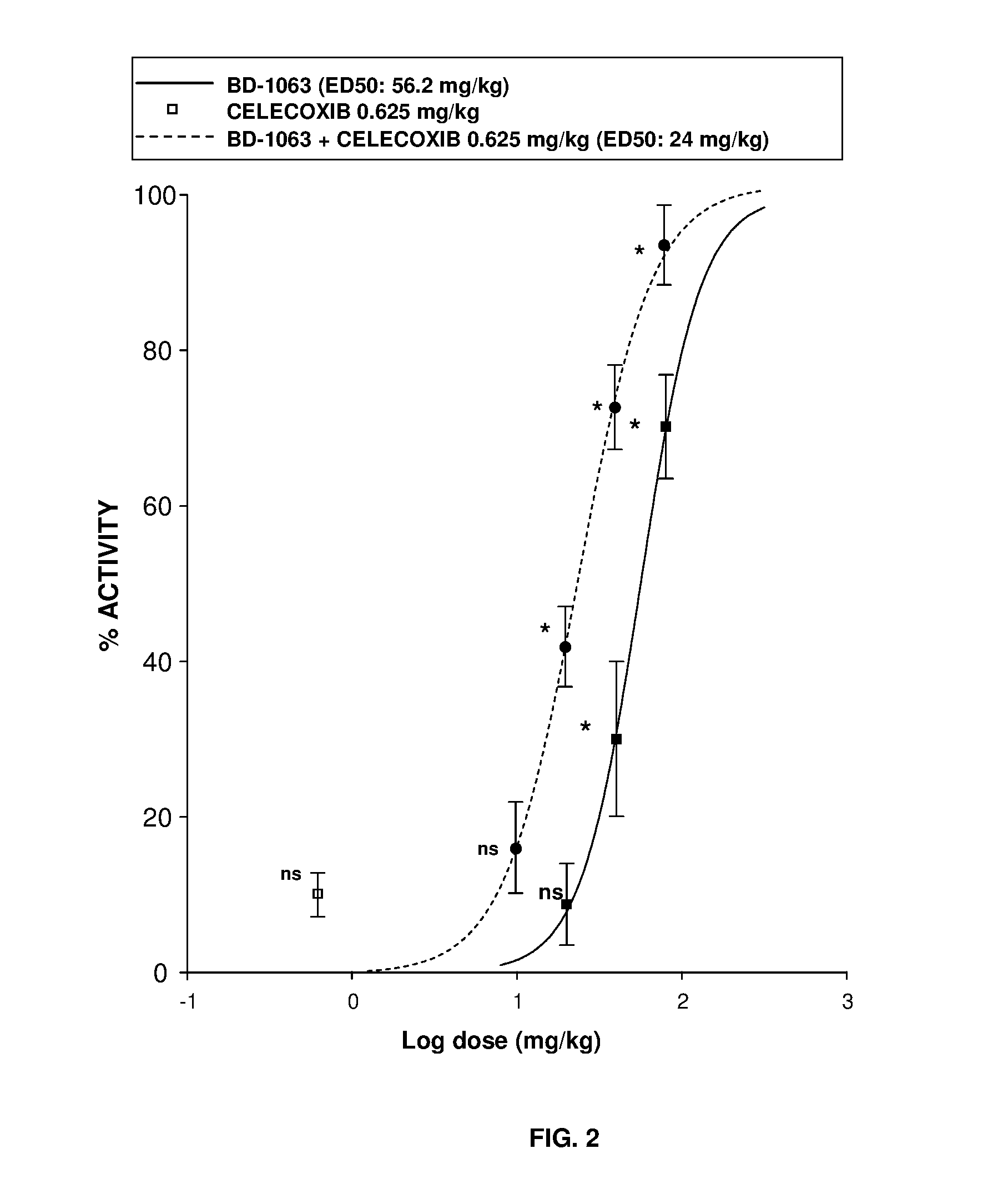

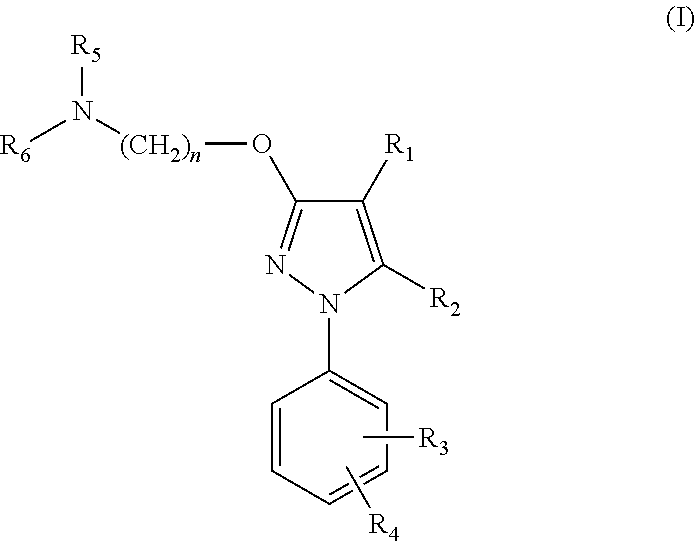

Nsaid and sigma receptor ligand combinations

InactiveUS20160220574A1Not improveEffective analgesiaOrganic active ingredientsNervous disorderMedicinePharmacology

The invention refers to a synergistic combination comprising a Sigma ligand, particularly a Sigma ligand of general formula (I), and NSAID compound, a medicament comprising said active substance combination, and the use of said active substance combination for the manufacture of a medicament, particularly for the prophylaxis and / or treatment of pain.

Owner:LAB DEL DR ESTEVE SA

Therapeutic constructs for co-delivery of mitotic kinase inhibitor and immune checkpoint inhibitor

ActiveUS20210030679A1Improve anti-cancer effectGood effectOrganic active ingredientsPowder deliveryCancer deathCancer cell

Disclosed herein are therapeutic constructs including a delivery particle, at least one mitotic kinase inhibitor, and at least one immune checkpoint inhibitor. Also disclosed are therapeutic constructs including a mitotic kinase inhibitor, an immune checkpoint inhibitor, and a chemical linker. These therapeutic constructs cause cancer death by both therapeutic and immune effects and promote targeted delivery of more therapeutics to the surviving cancer cells in a positive feed-back loop. They enhance therapeutic index of free drugs and can be used intratumorally or systemically. This strategy can treat broad cancer types and is particular useful for cancer without obvious receptors for cancer-targeted delivery of otherwise toxic therapeutics.

Owner:PDX PHARM INC +1

Treatment with opioid antagonists and mTOR inhibitors

Embodiments of the invention provide methods of treating a disorder or disease characterized by cellular proliferation and migration by co-administering a synergistically effective amount of an mTOR inhibitor and a μ-opioid receptor antagonist.

Owner:UNIVERSITY OF CHICAGO

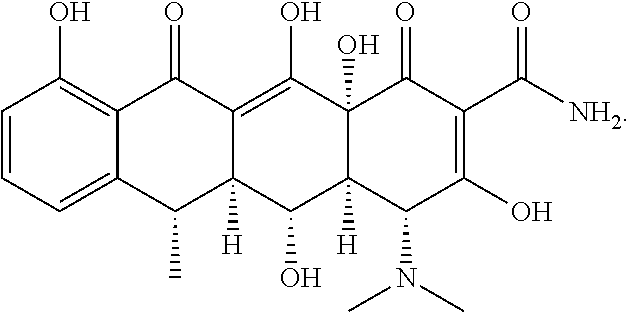

Composition comprising a compound from the family of avermectins and doxycycline for the treatment of rosacea

ActiveUS20170273931A1Effective treatmentFew side effectTetracycline active ingredientsPharmaceutical delivery mechanismAvermectinDoxycycline

The use of a composition comprising a compound from the family of avermectins, preferably ivermectin, and doxycycline or one of the salts thereof that is pharmaceutically acceptable in the treatment and / or slowing of the appearance of the symptoms of rosacea is described.

Owner:GALDERMA SA

Ultrafine nanoparticles as multimodal contrast agent

The invention relates to a novel use of ultrafine nanoparticles, of use as a diagnostic, therapeutic or theranostic agent, characterized by their mode of administration via the airways. The invention is also directed toward the applications which follow from this novel mode of administration, in particular for imaging the lungs, and the diagnosis or prognosis of pathological pulmonary conditions. In the therapeutic field, the applications envisioned are those of radiosensitizing or radioactive agents for radiotherapy (and optionally curietherapy), or for neutron therapy, or of agents for PDT (photodynamic therapy), in particular for the treatment of lung tumors.

Owner:UNIVERISITE CLAUDE BERNARD LYON I +3

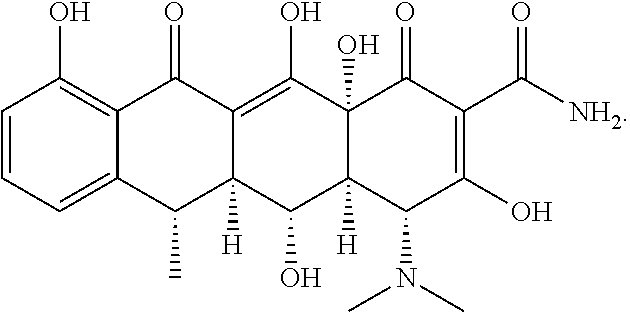

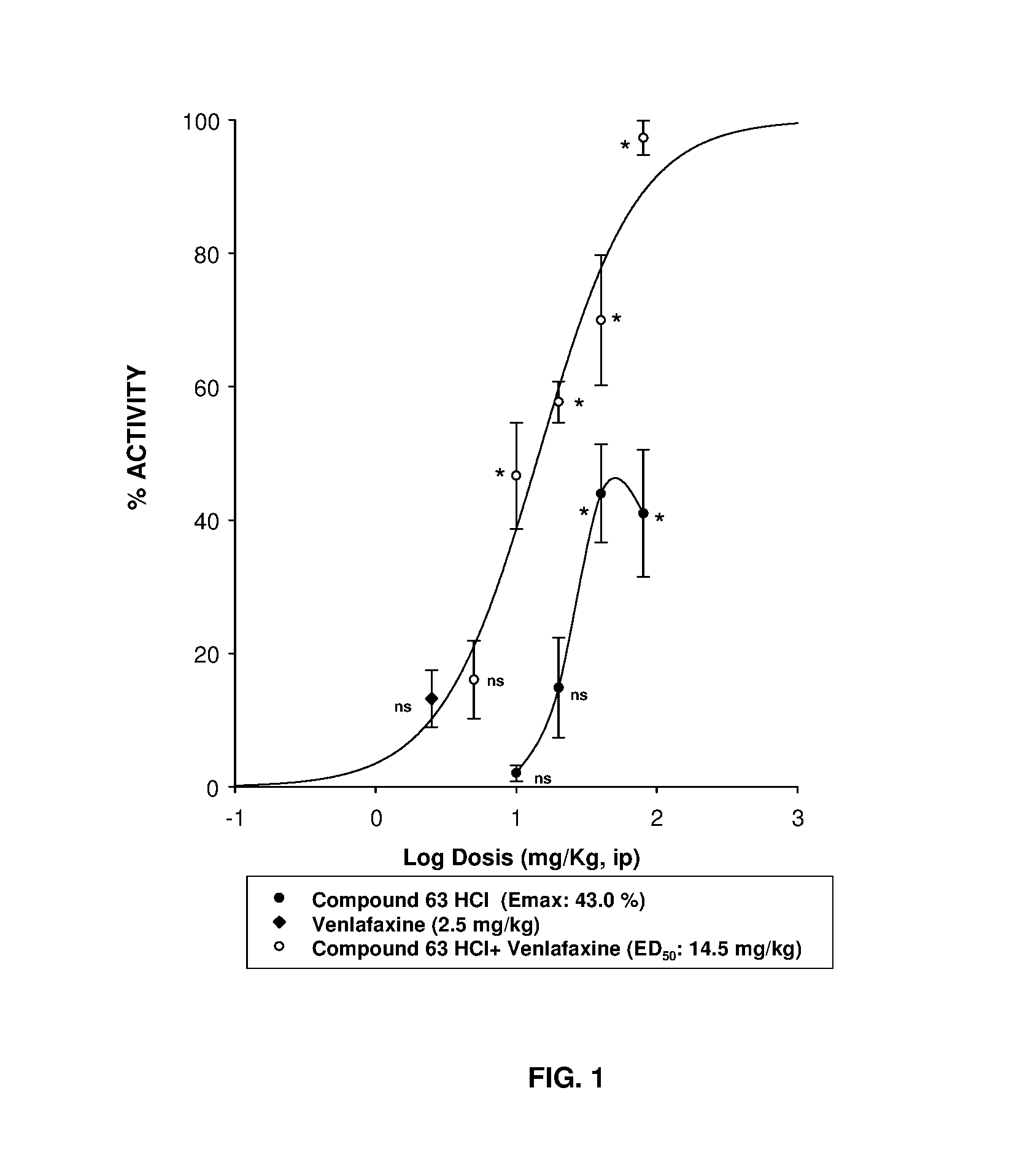

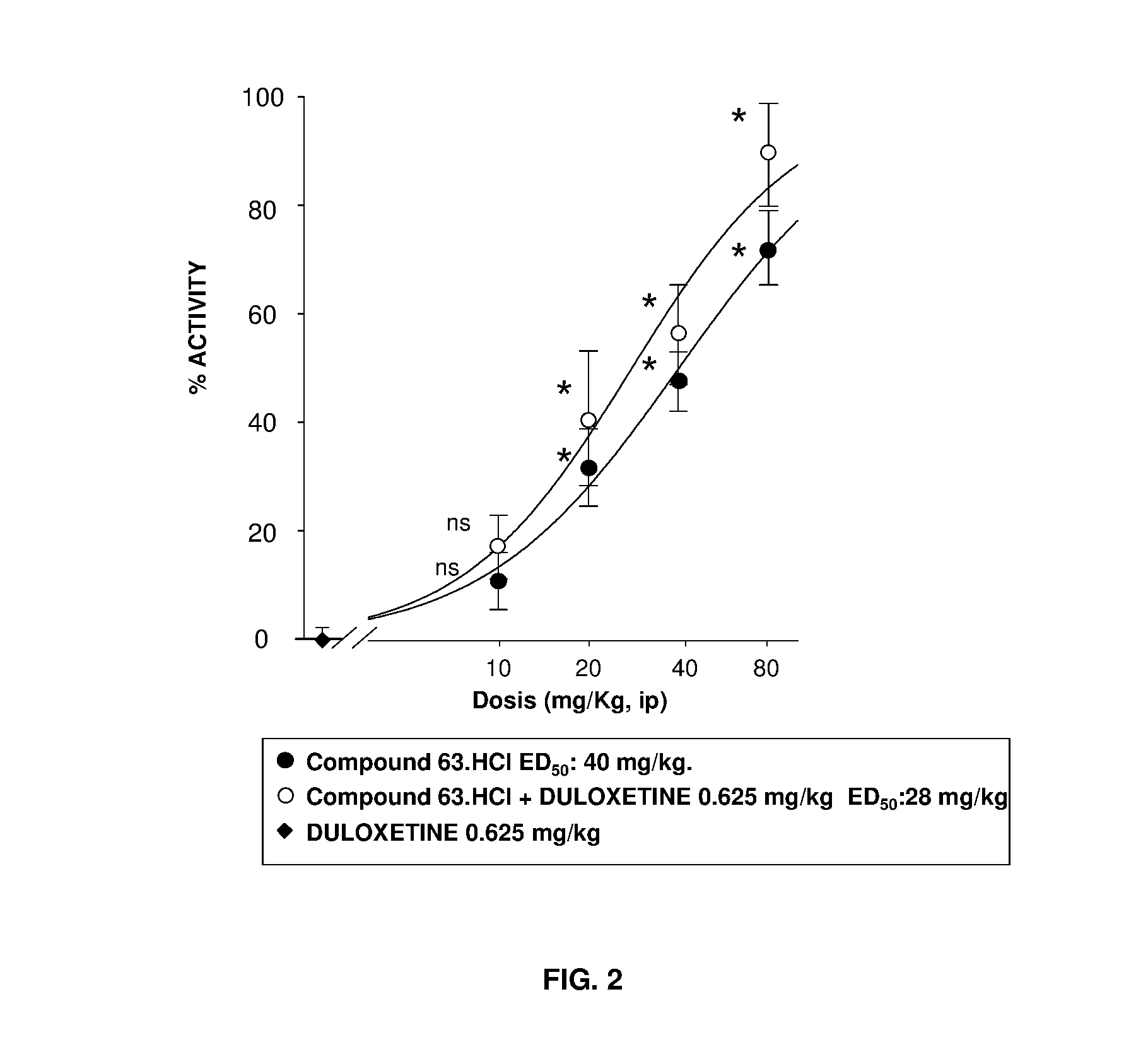

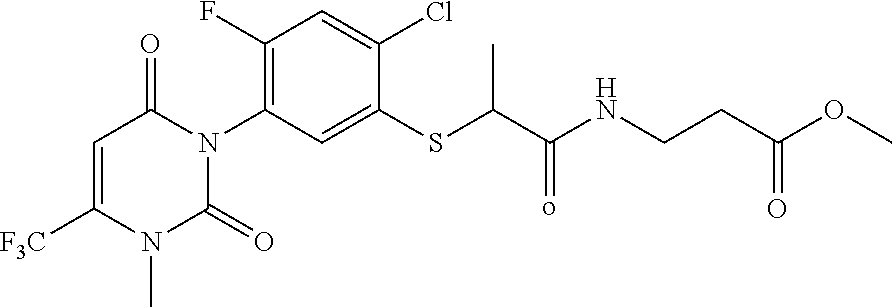

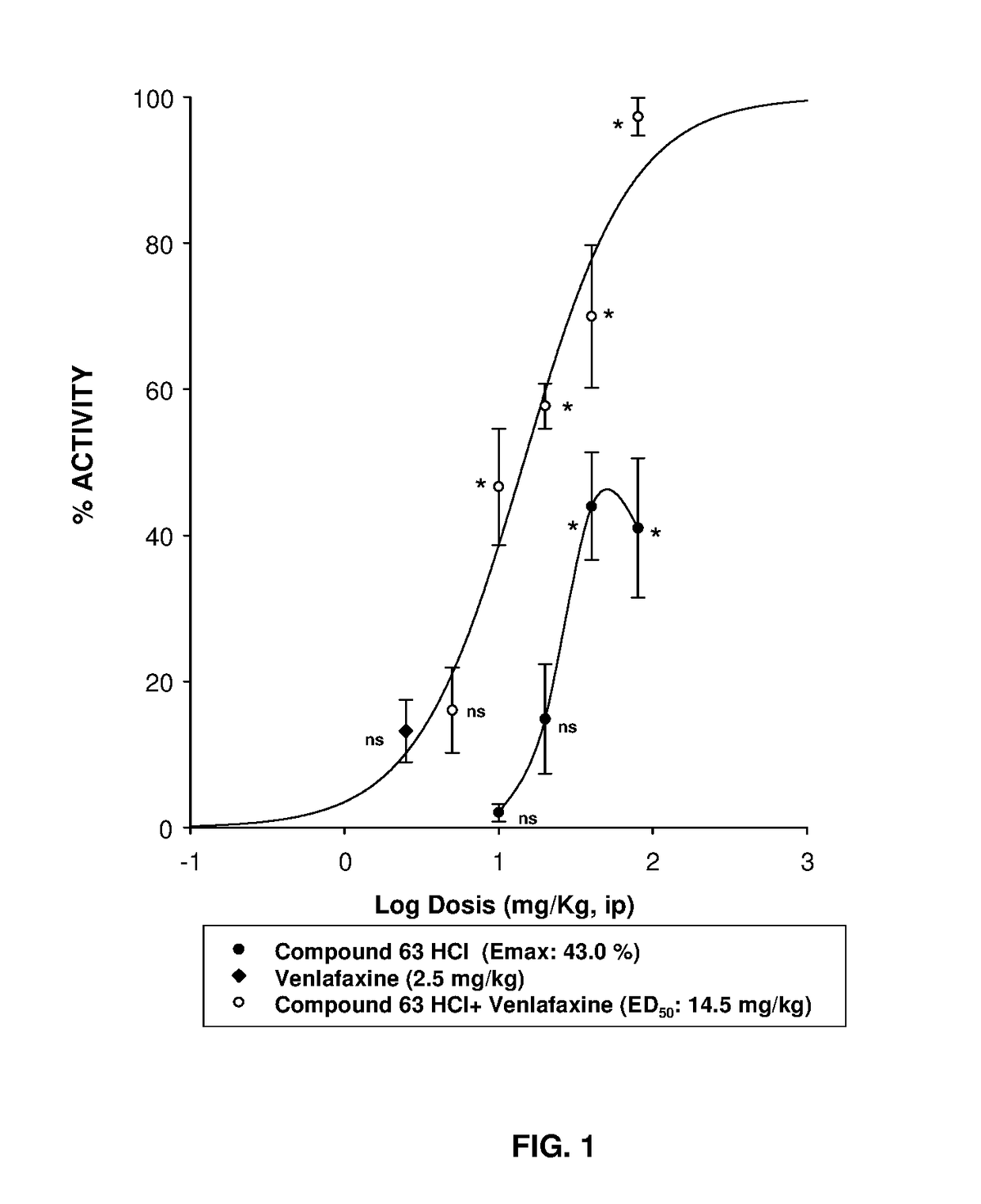

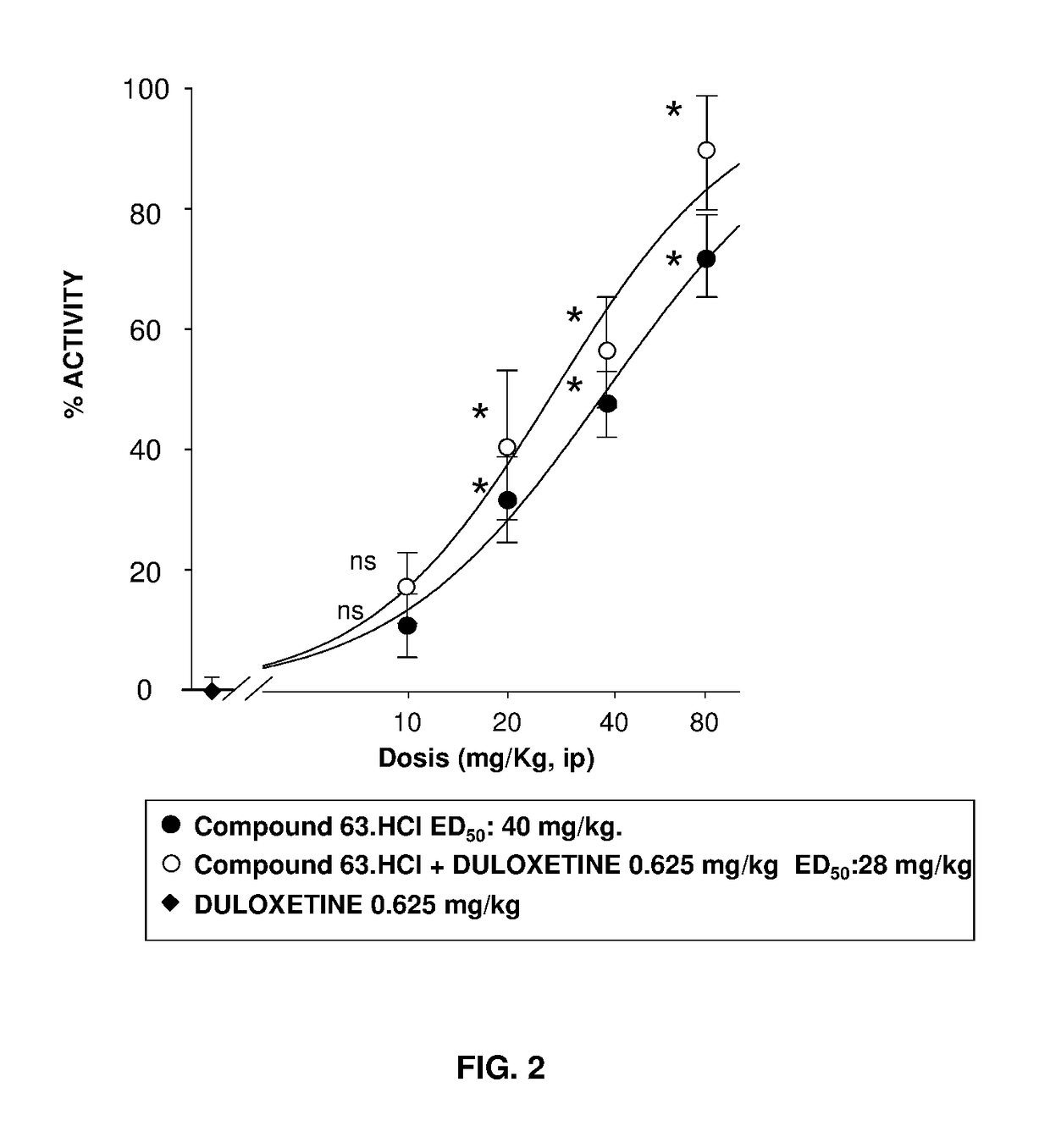

Serotonin-norepinephrine reuptake inhibitors (SNRIS) and sigma receptor ligands combinations

InactiveUS20160310500A1Not show side effectNot improveOrganic active ingredientsNervous disorderNorepinephrine reuptake inhibitorAdrenergic

The invention refers to a synergistic combination comprising a Sigma ligand of general formula (I), and a Serotonin-Norepinephrine Reuptake Inhibitor (SNRI), a medicament comprising said active substance combination, and the use of said active substance combination for the manufacture of a medicament, particularly for the prophylaxis and / or treatment of pain.

Owner:LAB DEL DR ESTEVE SA

Composition comprising a compound from the family of avermectins and doxycycline for the treatment of rosacea

ActiveUS10463643B2Less side effectsEffective treatmentTetracycline active ingredientsPharmaceutical delivery mechanismAvermectinDermatology

Owner:GALDERMA SA

Herbicide composition containing pyrimidinedione-based compound

PendingUS20210037819A1Improve biological effectImprove weed control effectBiocideDead animal preservationActive ingredientToxicology

Disclosed is an herbicidal composition containing: a pyrimidinedione-based compound as an active ingredient; and an efficacy enhancer. The herbicidal composition can increase biological effect expression characteristics of the pyrimidinedione-based composition as a contact herbicide, improve fast-acting property on monocot weeds as well as broadleaf weeds through enhanced spreading ability and penetrating power, and effectively control, at a low dose, even resistant weeds showing resistance to other herbicides. Furthermore, the herbicidal composition retains thermodynamic stability to increase storage stability, and can exhibit uniform and excellent efficacy at the time of chemical treatment through the uniform dispersion of the active ingredient.

Owner:FARMHANNONG CO LTD

Methotrexate adjuvants to reduce toxicity and methods for using the same

Methods are provided for using methotrexate (MTX) active agents in which reduced host toxicity is observed. Aspects of the methods include administering to a subject an effective amount of an MTX active agent in conjunction with a MTX toxicity-reducing adjuvant, such as a 2,2′-anhydropyrimidine, a derivative thereof or a uridine phosphorylase inhibitor. Also provided are compositions and kits that find use in practicing embodiments of the invention. The methods and compositions find use in a variety of applications, including the treatment of a variety of different disease conditions.

Owner:TOSK INC +1

Serotonin-norepinephrine reuptake inhibitors (SNRIs) and Sigma receptor ligands combinations

InactiveUS9931346B2Not improveEffectiveOrganic active ingredientsNervous disorderNorepinephrine reuptakePharmacology

The invention refers to a synergistic combination comprising a Sigma ligand of general formula (I), and a Serotonin-Norepinephrine Reuptake Inhibitor (SNRI), a medicament comprising said active substance combination, and the use of said active substance combination for the manufacture of a medicament, particularly for the prophylaxis and / or treatment of pain.

Owner:LAB DEL DR ESTEVE SA

Ultrafine nanoparticles as multimodal contrast agent

The invention relates to a novel use of ultrafine nanoparticles, of use as a diagnostic, therapeutic or theranostic agent, characterized by their mode of administration via the airways. The invention is also directed toward the applications which follow from this novel mode of administration, in particular for imaging the lungs, and the diagnosis or prognosis of pathological pulmonary conditions. In the therapeutic field, the applications envisioned are those of radiosensitizing or radioactive agents for radiotherapy (and optionally curietherapy), or for neutron therapy, or of agents for PDT (photodynamic therapy), in particular for the treatment of lung tumors.

Owner:UNIV DE BORDEAUX +4

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com