Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56 results about "Transaction layer packet" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

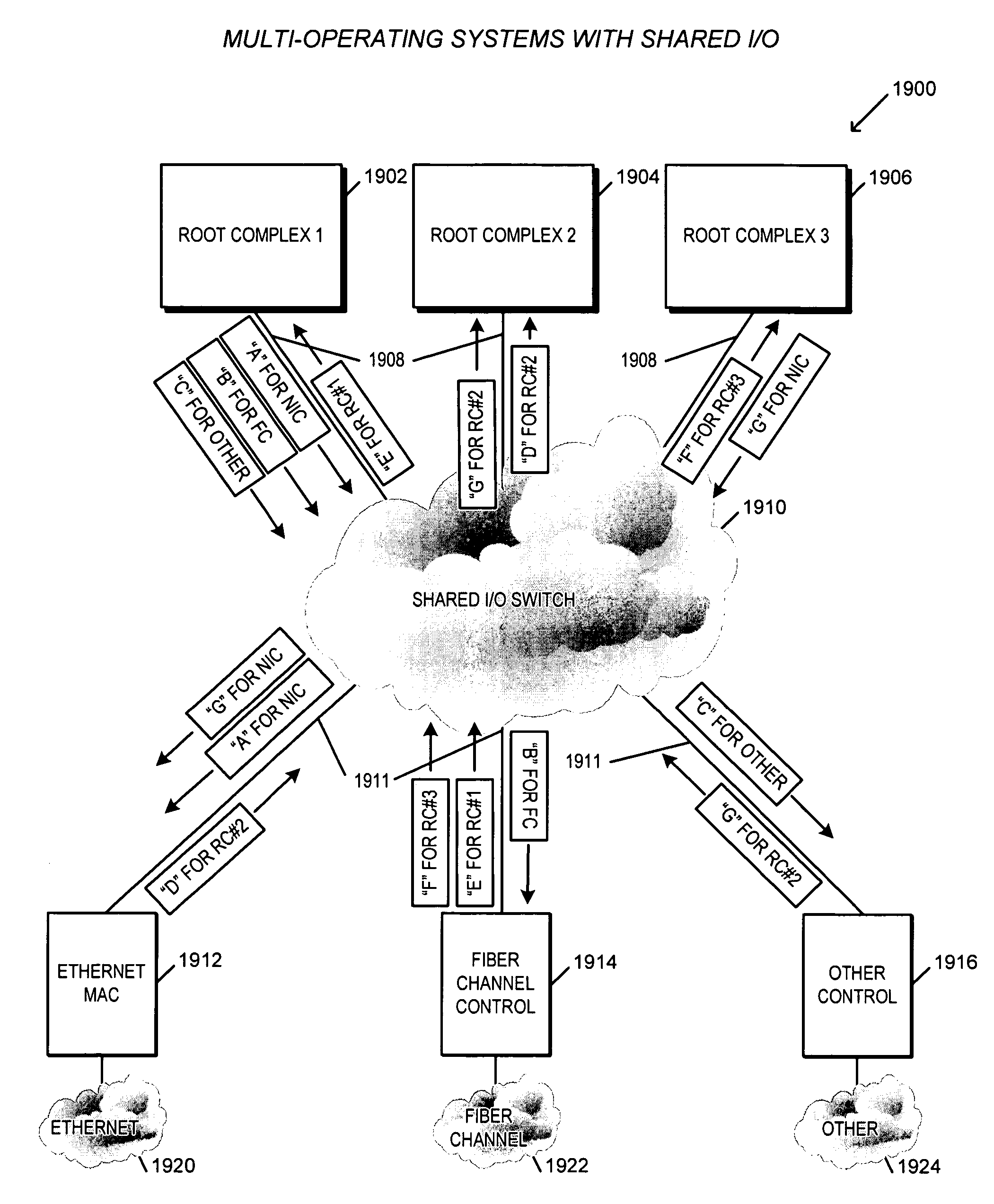

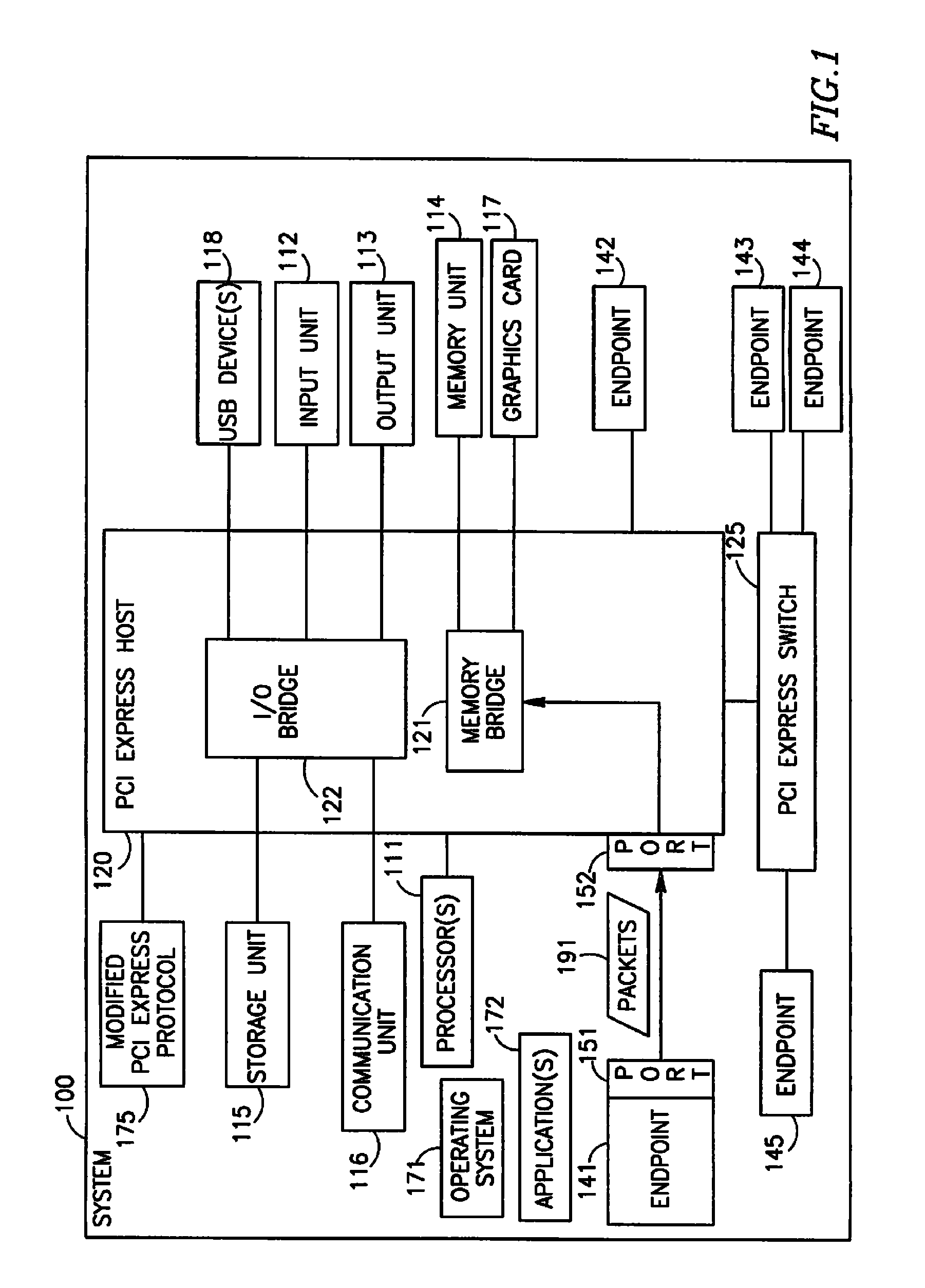

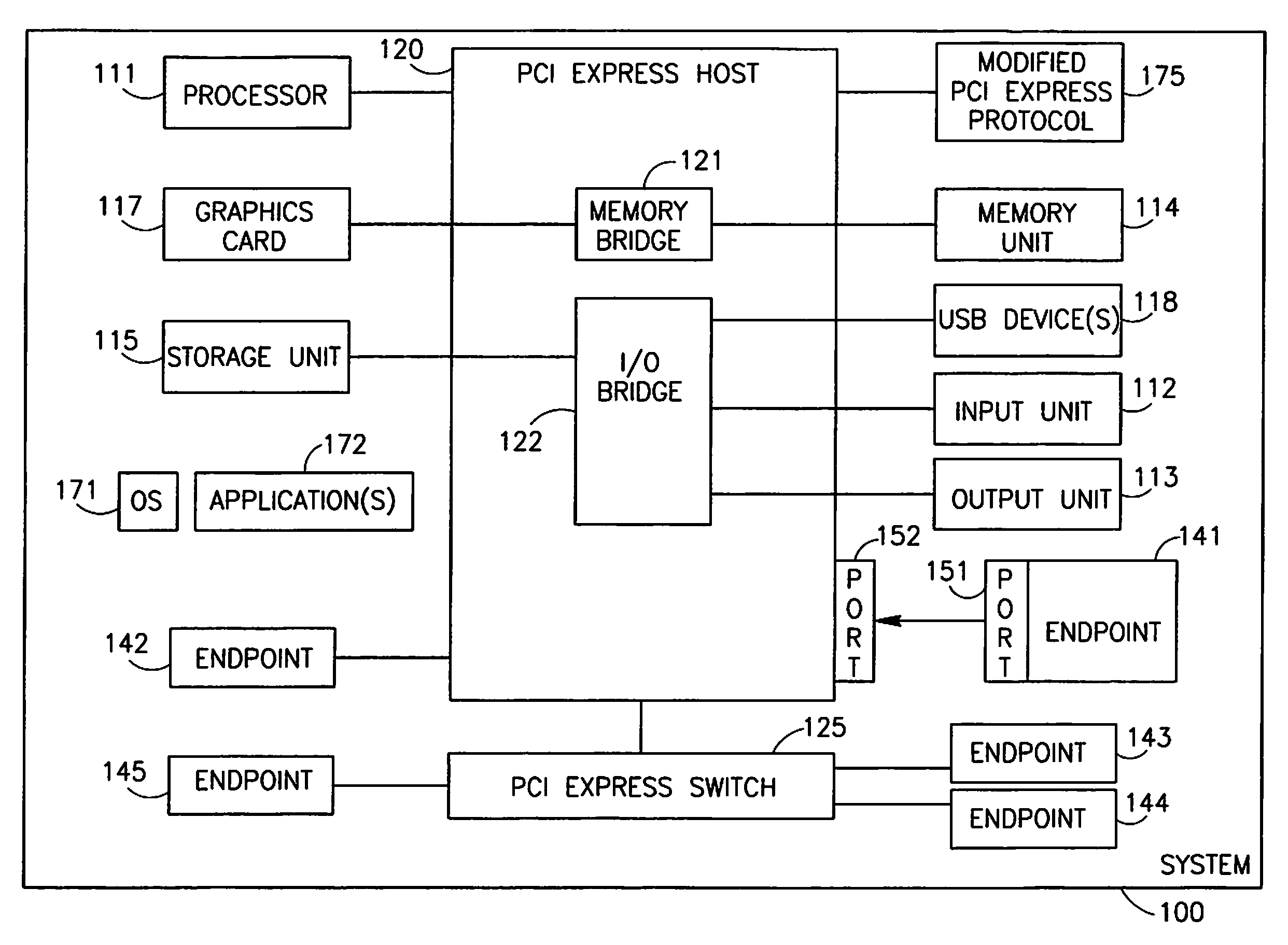

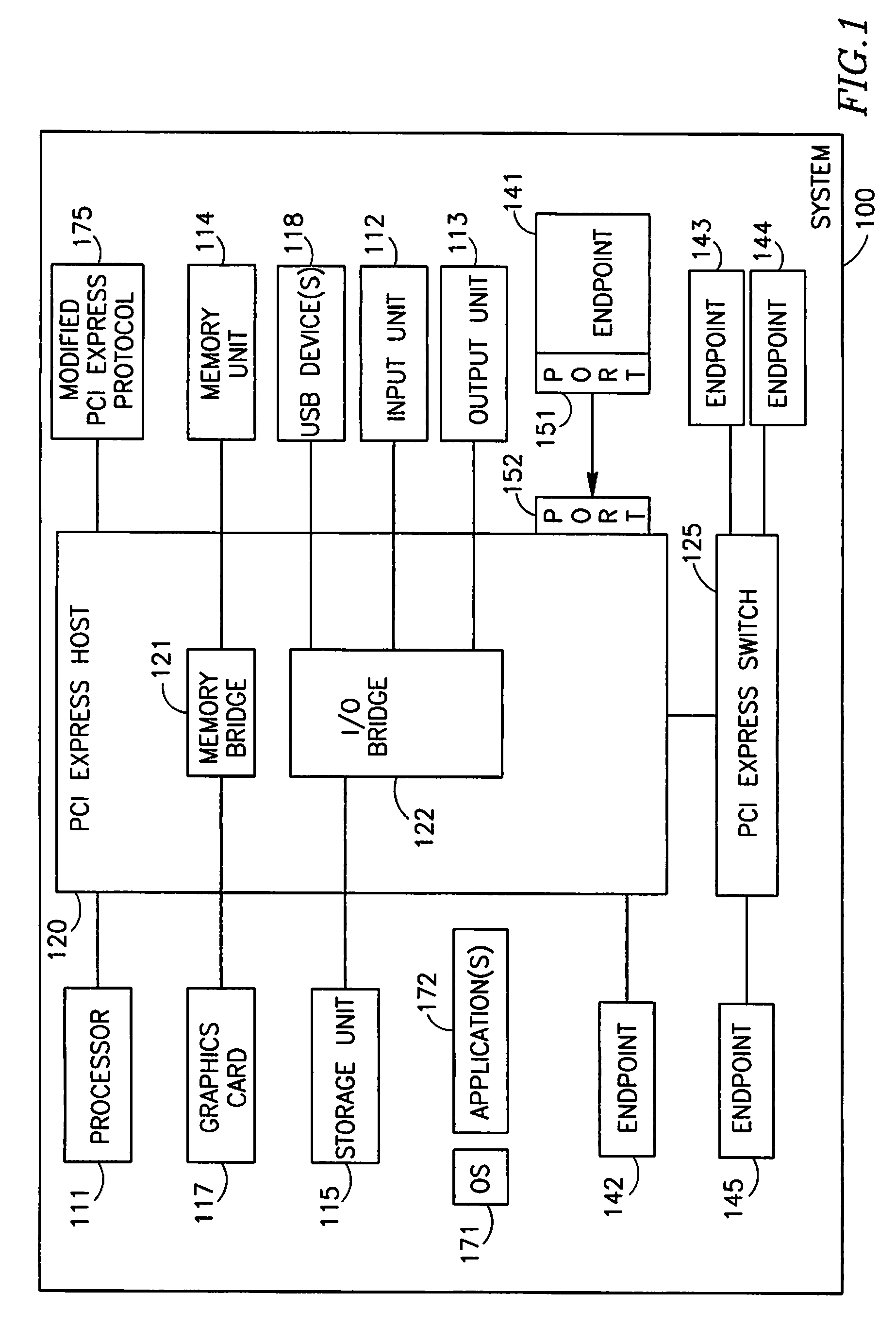

Apparatus and method for sharing I/O endpoints within a load store fabric by encapsulation of domain information in transaction layer packets

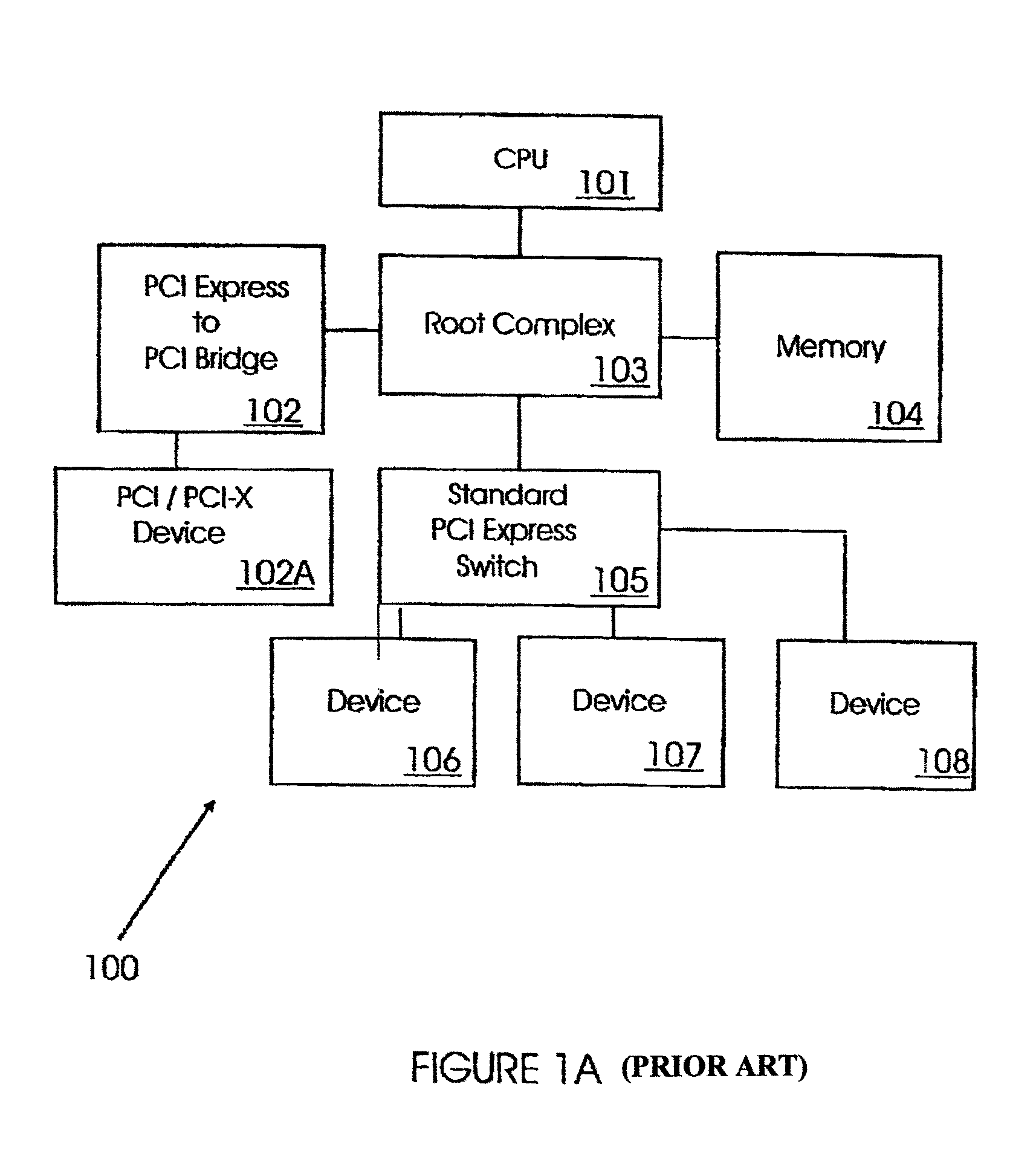

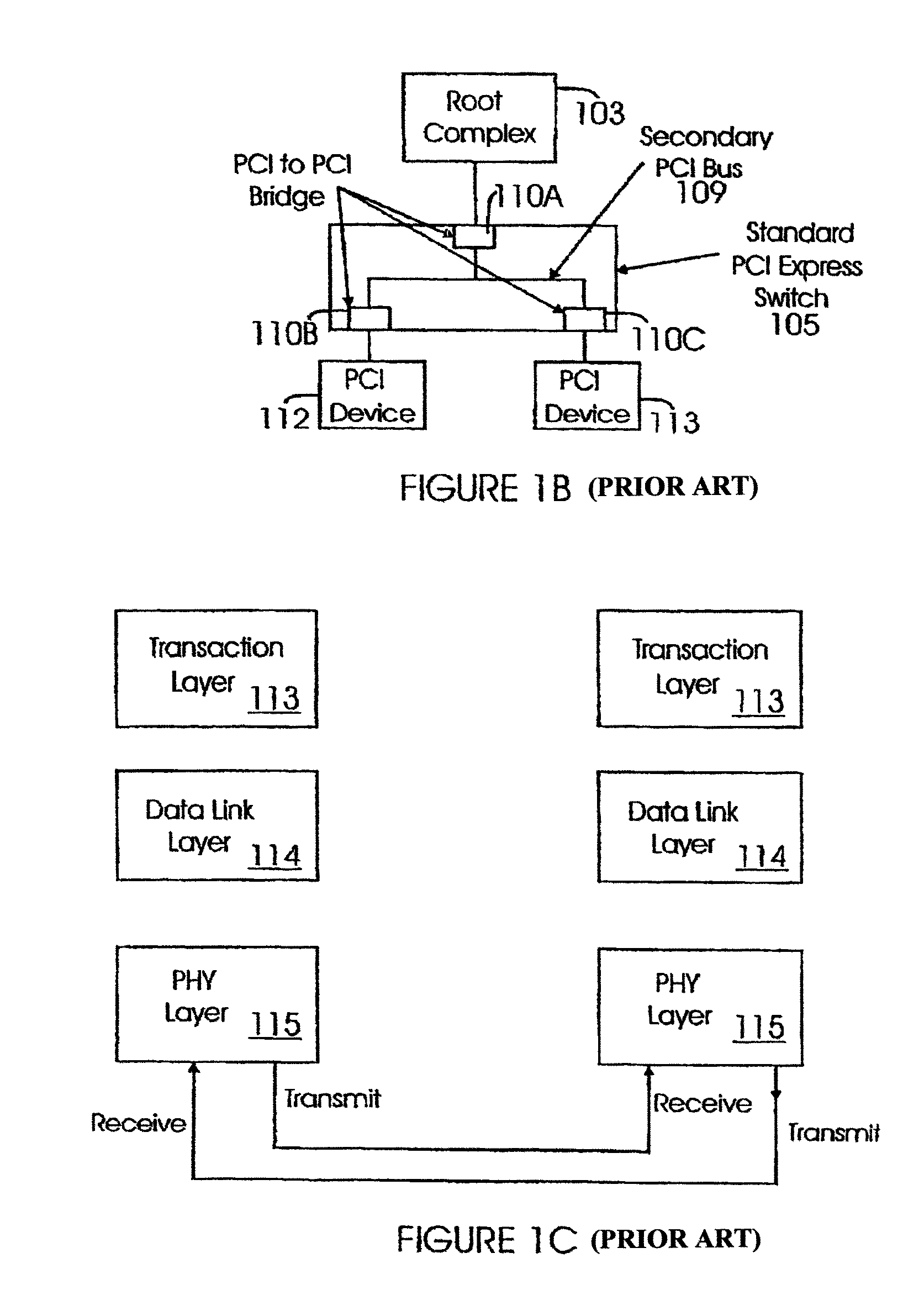

ActiveUS7188209B2Multiplex system selection arrangementsData switching by path configurationComputer architectureOperational system

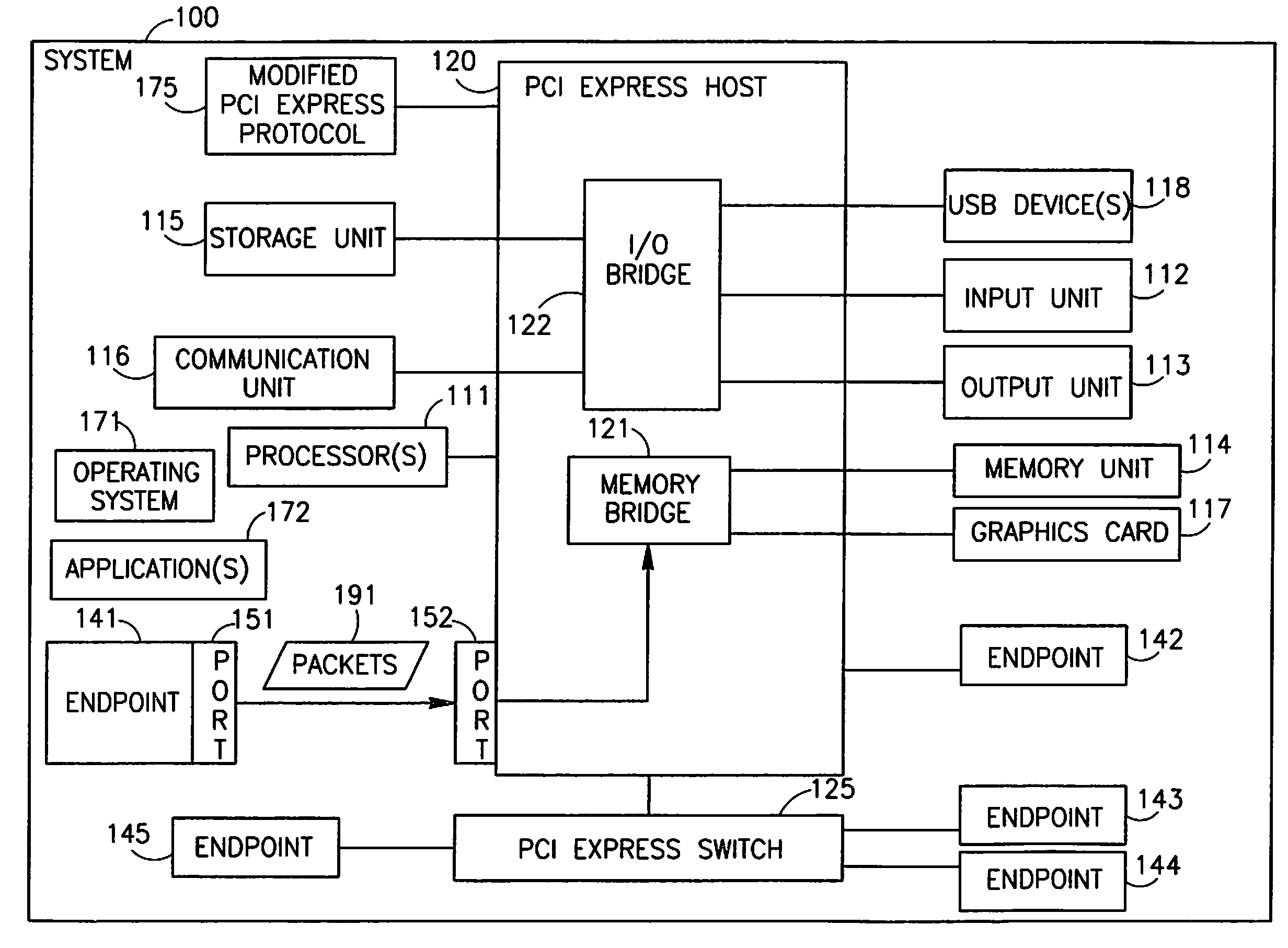

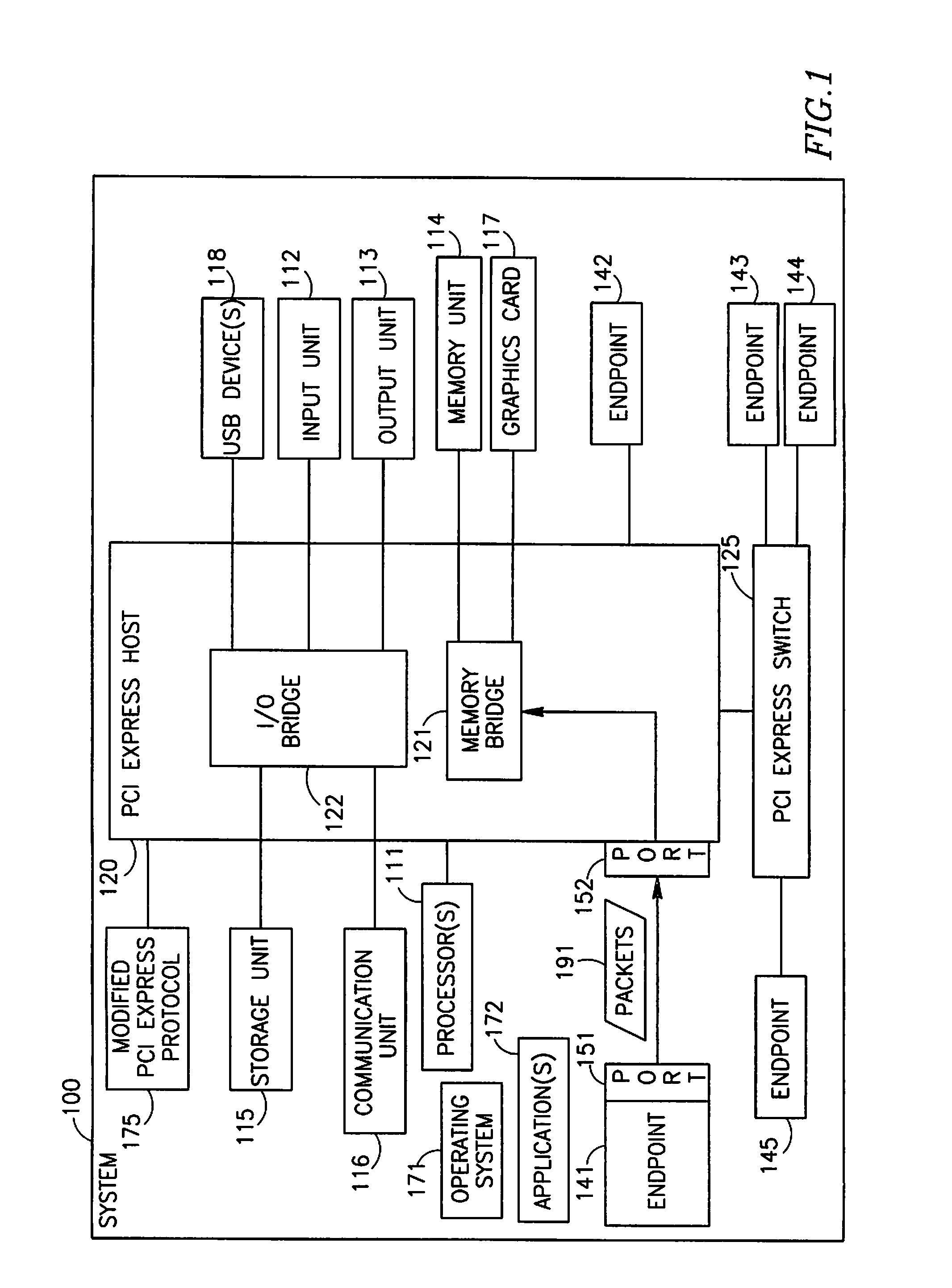

An apparatus having a first plurality of I / O ports, a second I / O port, and core logic. The first plurality of I / O ports is coupled to a plurality of operating system domains (OSDs) through a load-store fabric, each routing transactions between the plurality of OSDs and the switching apparatus. The second I / O port is coupled to a first shared input / output endpoint. The first shared input / output endpoint requests / completes the transactions for each of the plurality of OSDs. The core logic is coupled to the first plurality of I / O ports and the second I / O port. The core logic routes the transactions between the first plurality of I / O ports and the second I / O port. The core logic designates a corresponding one of the plurality of OSDs according to a variant of a protocol, where the protocol provides for routing of the transactions only for a single OSD.

Owner:AVAGO TECH INT SALES PTE LTD

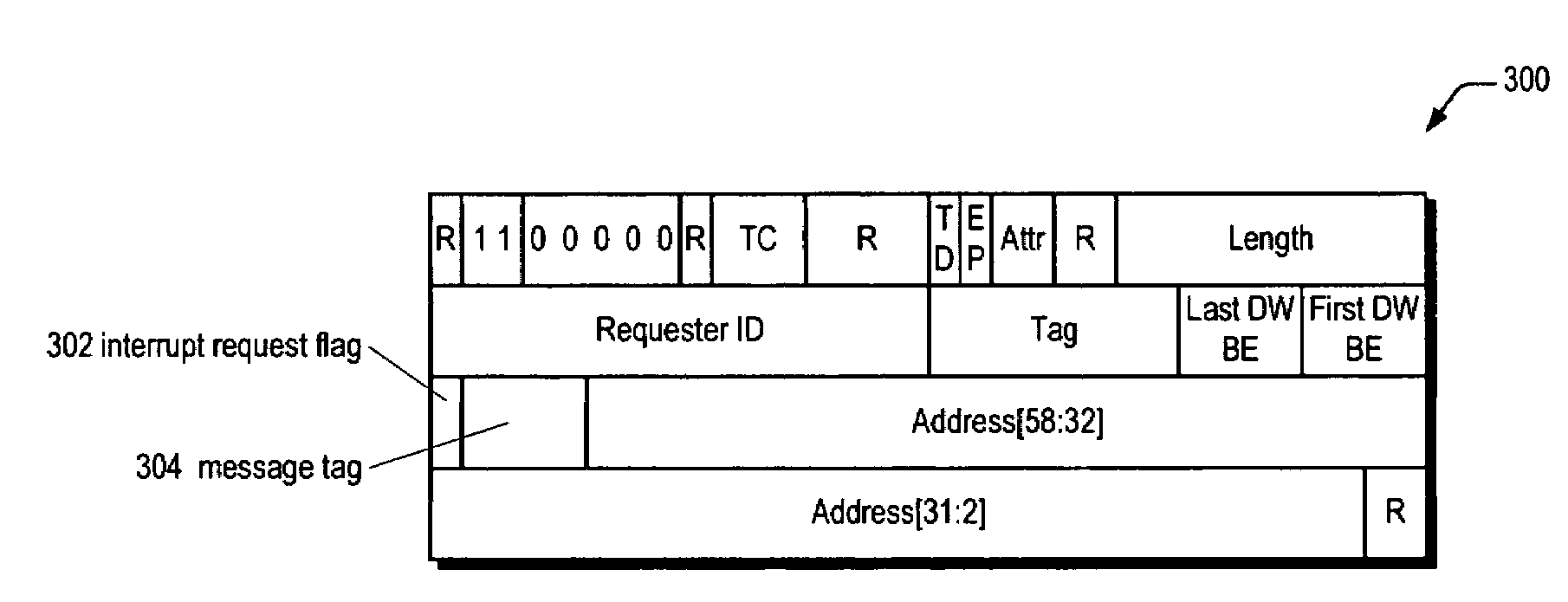

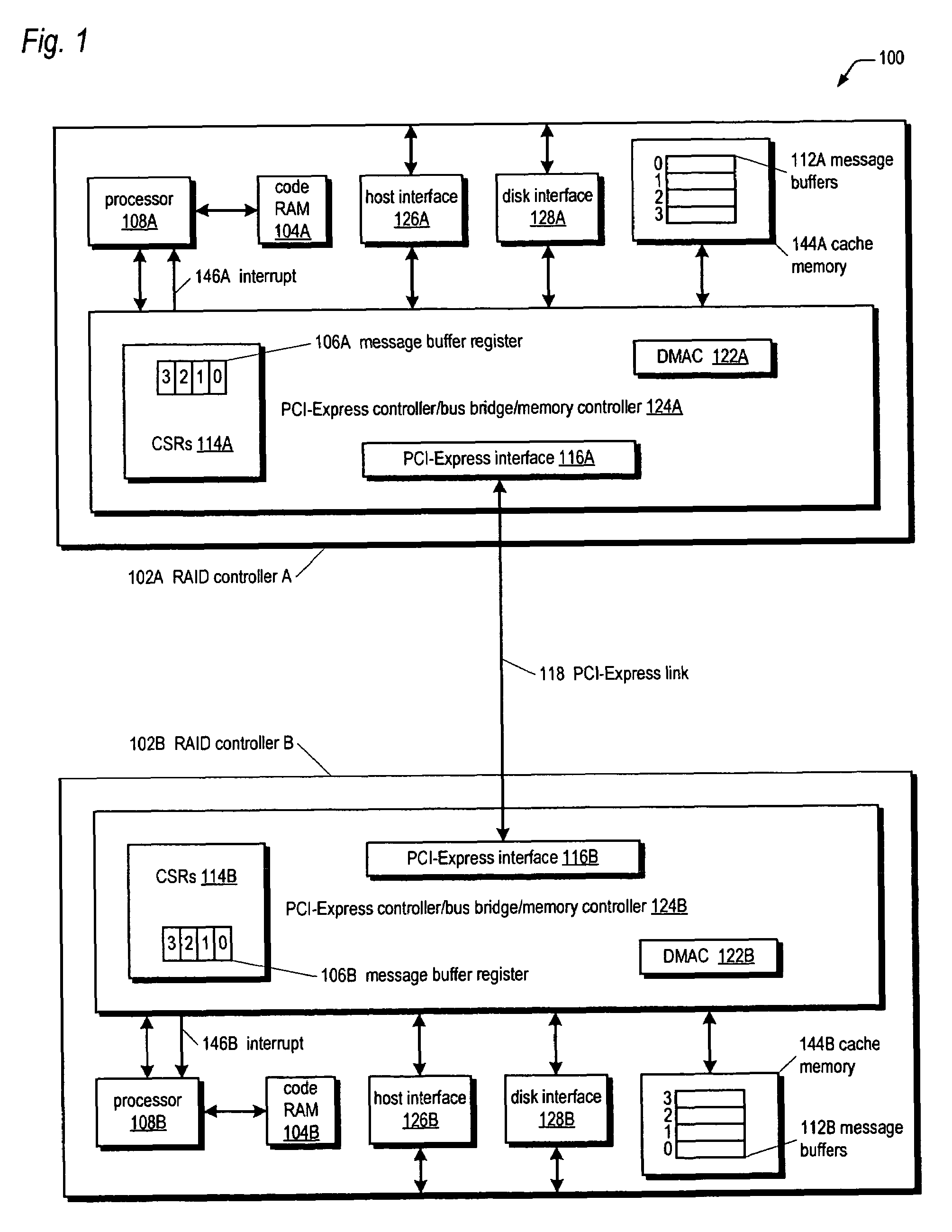

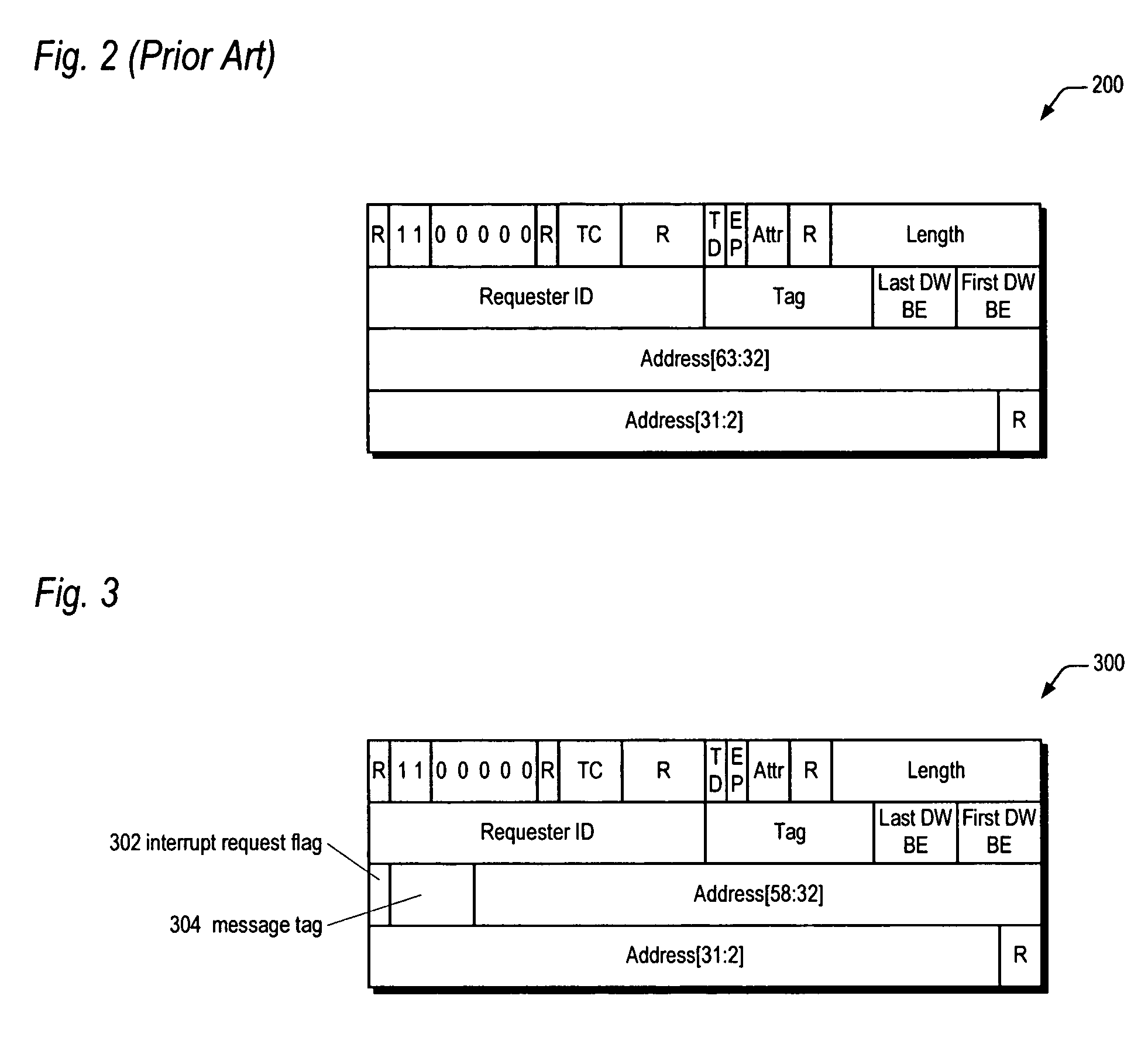

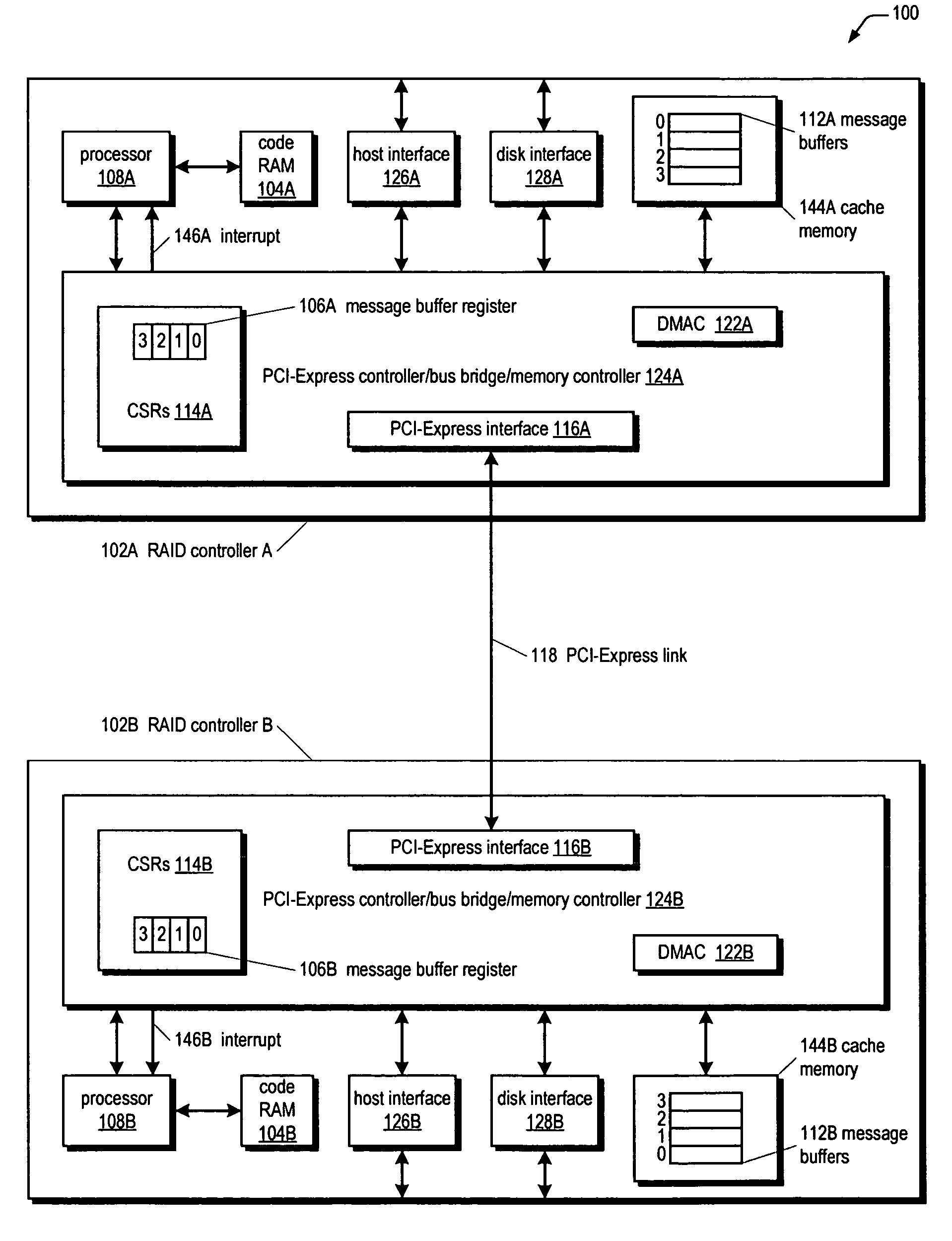

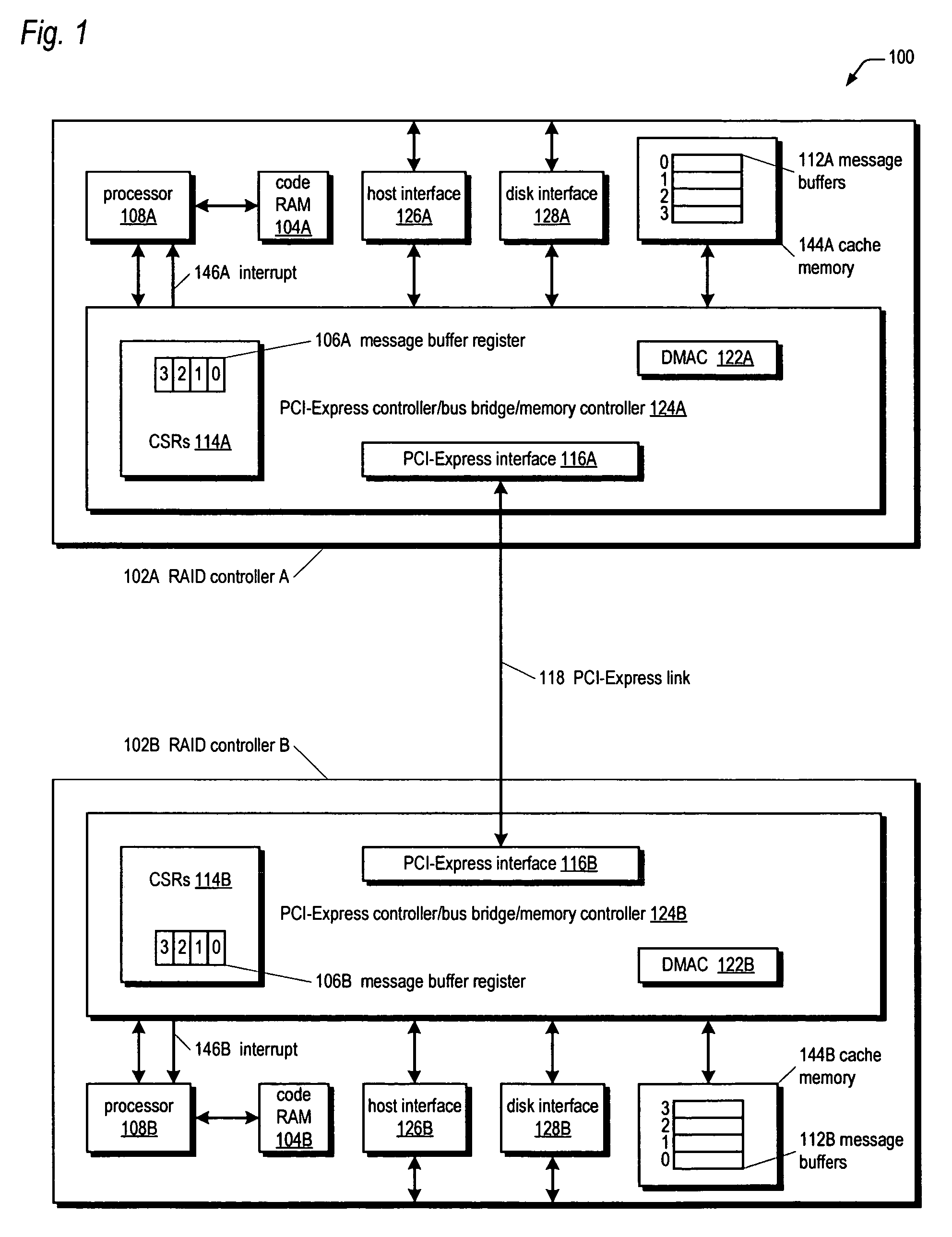

Method for efficient inter-processor communication in an active-active RAID system using PCI-express links

ActiveUS7315911B2Efficiently determinedError detection/correctionMemory systemsRAIDProcessor register

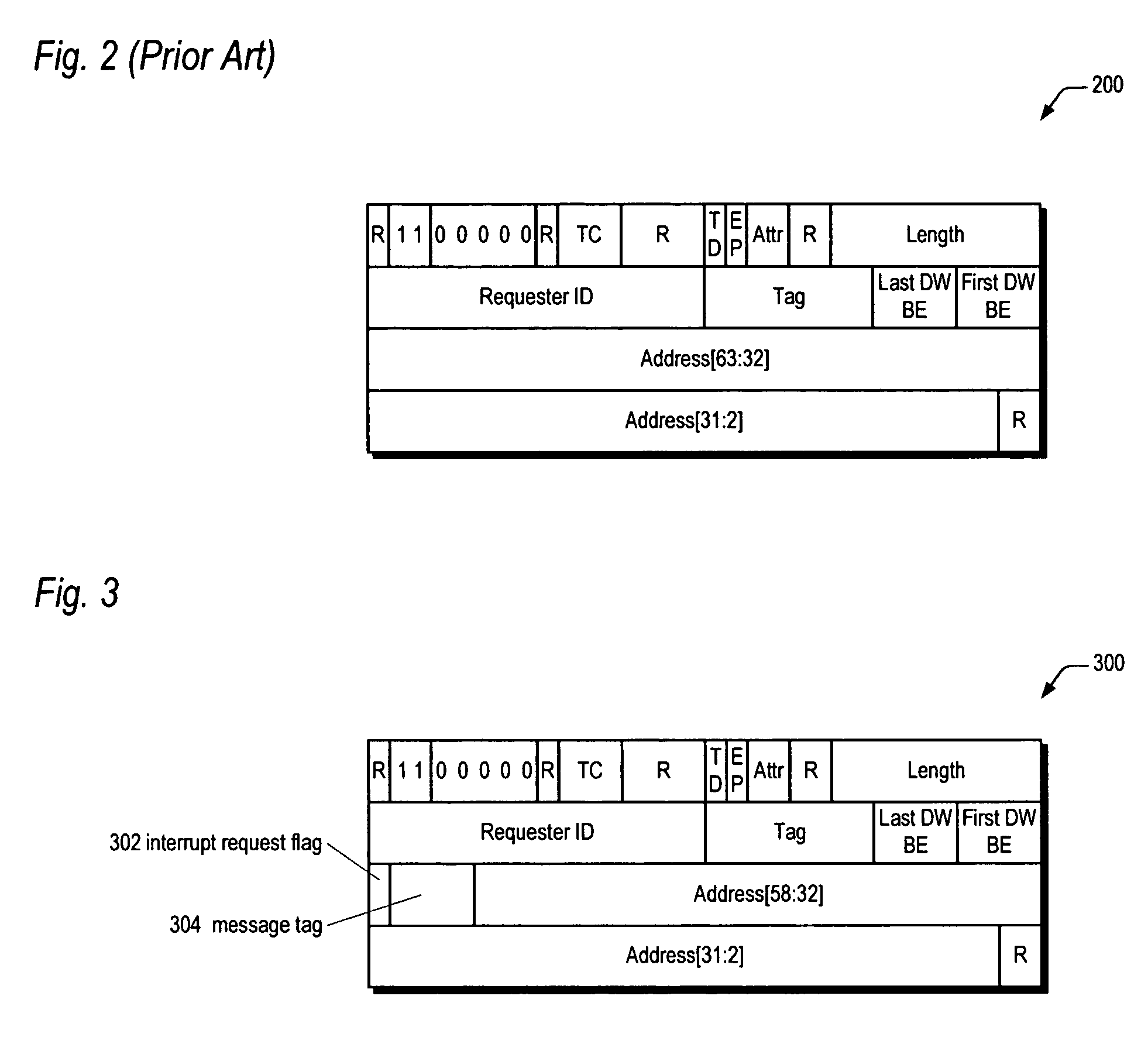

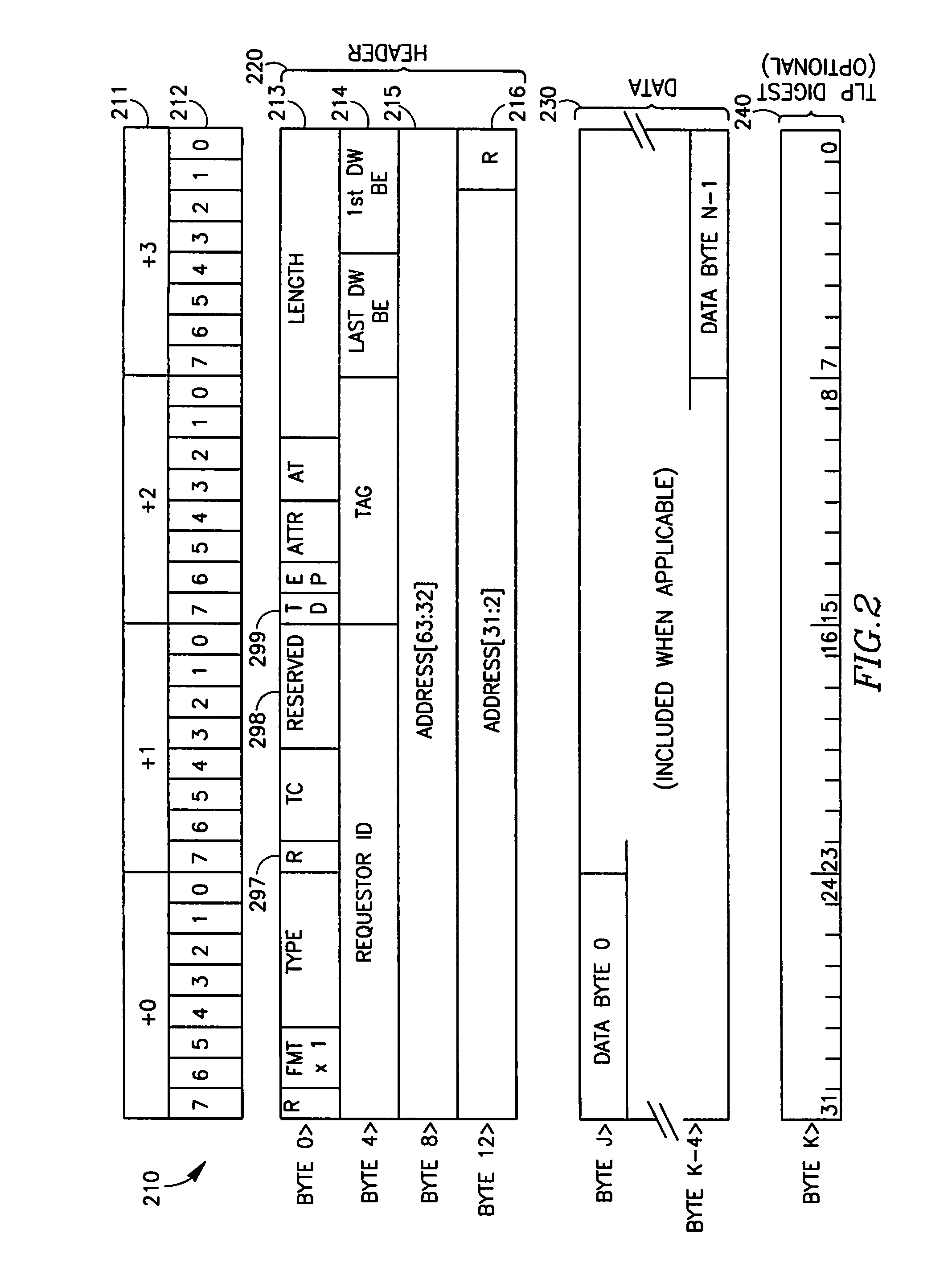

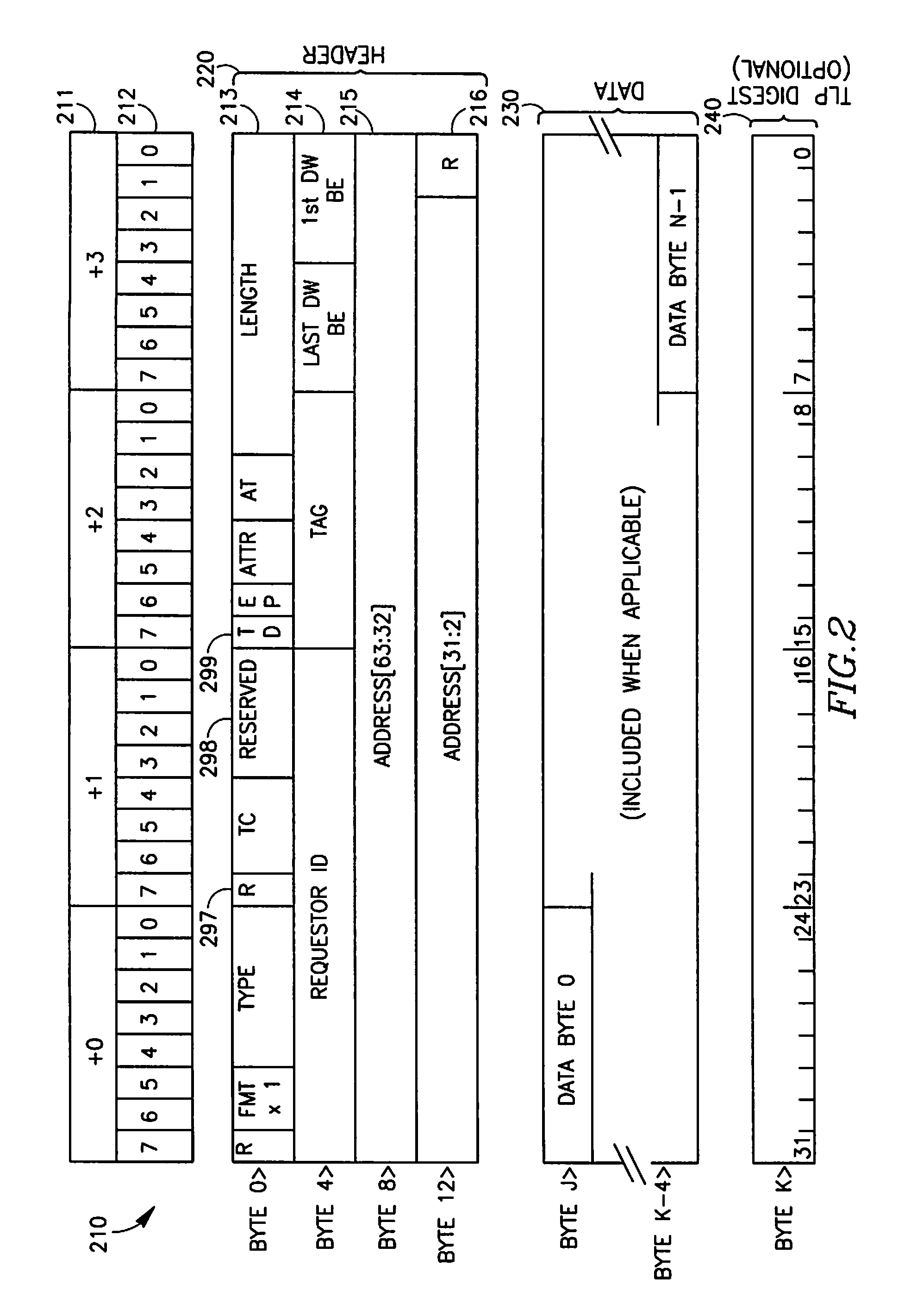

A fault-tolerant RAID system is disclosed. The system includes redundant RAID controllers coupled by a PCI-Express link. When a PCI-Express controller of one of the RAID controllers receives a PCI-Express memory write request transaction layer packet (TLP), it interprets a predetermined bit in the header as an interrupt request flag, rather than as its standard function specified by the PCI-Express specification. If the flag is set, the PCI-Express controller interrupts the processor after storing the message in the payload at the specified memory location. In one embodiment, an unused upper address bit in the header is used as the interrupt request flag. Additionally, unused predetermined bits in the TLP header are used as a message tag to indicate one of a plurality of message buffers on the receiving RAID controller into which the message has been written. The PCI-Express controller sets a corresponding bit in a register to indicate which message buffer was written.

Owner:DOT HILL SYST

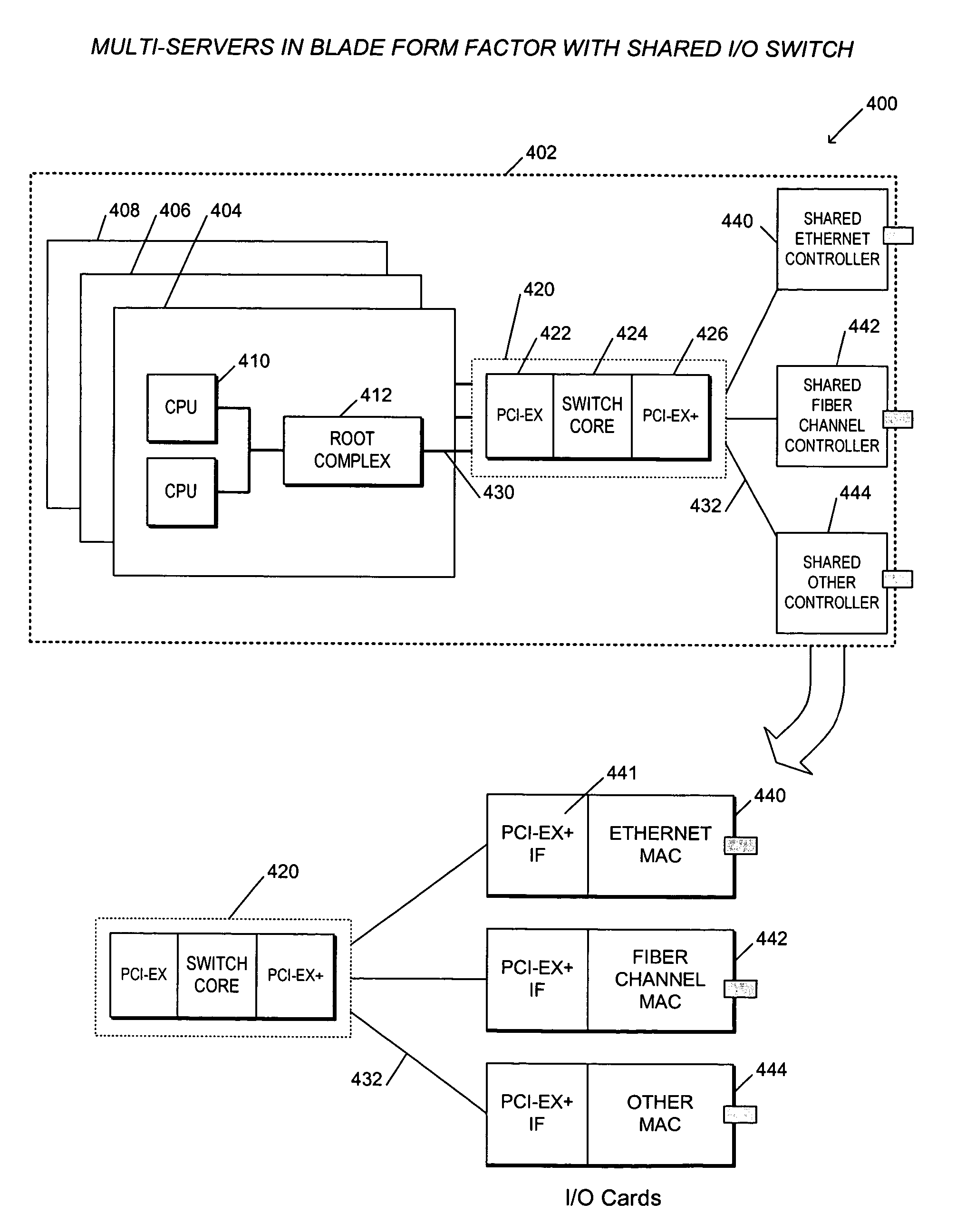

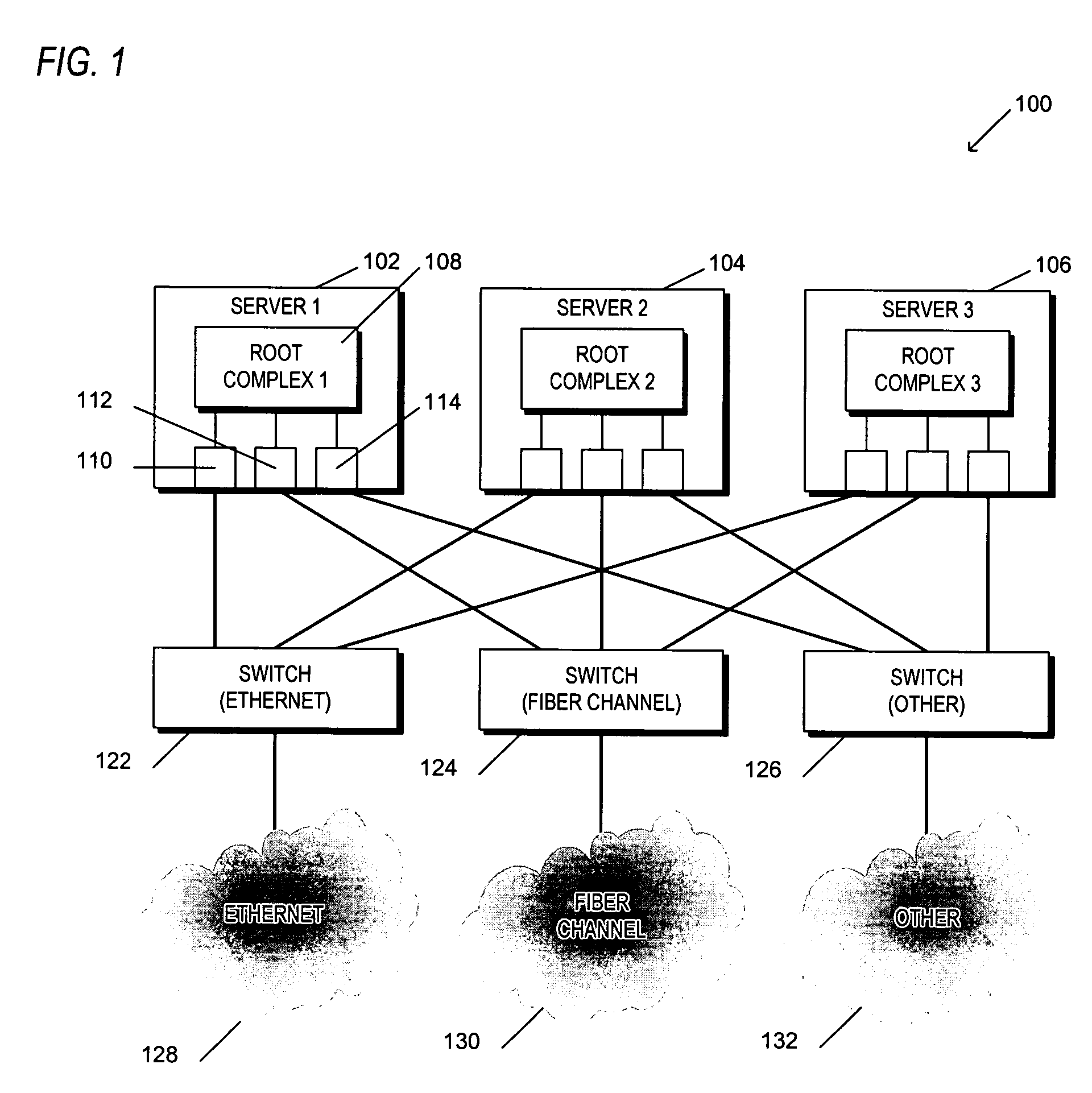

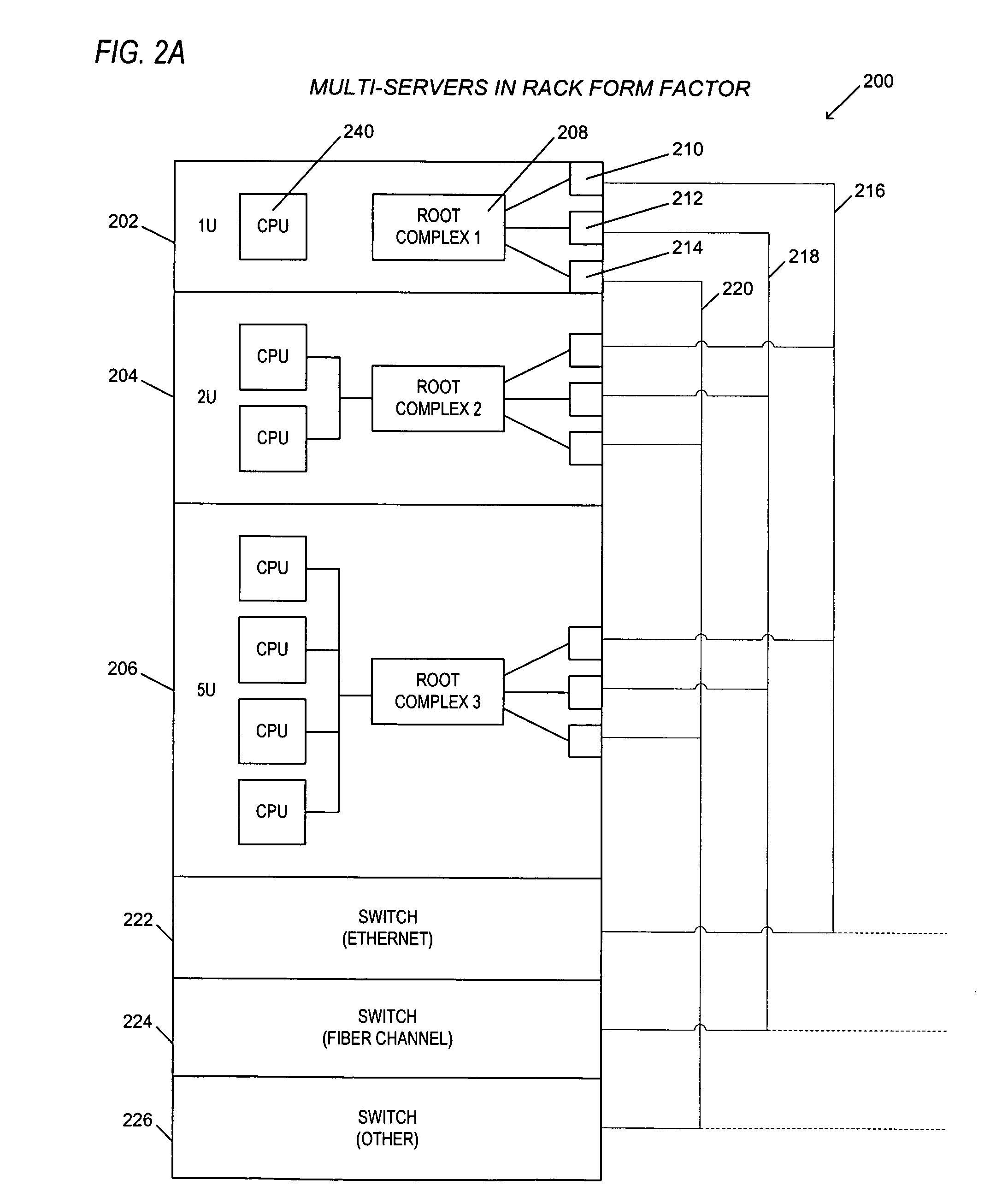

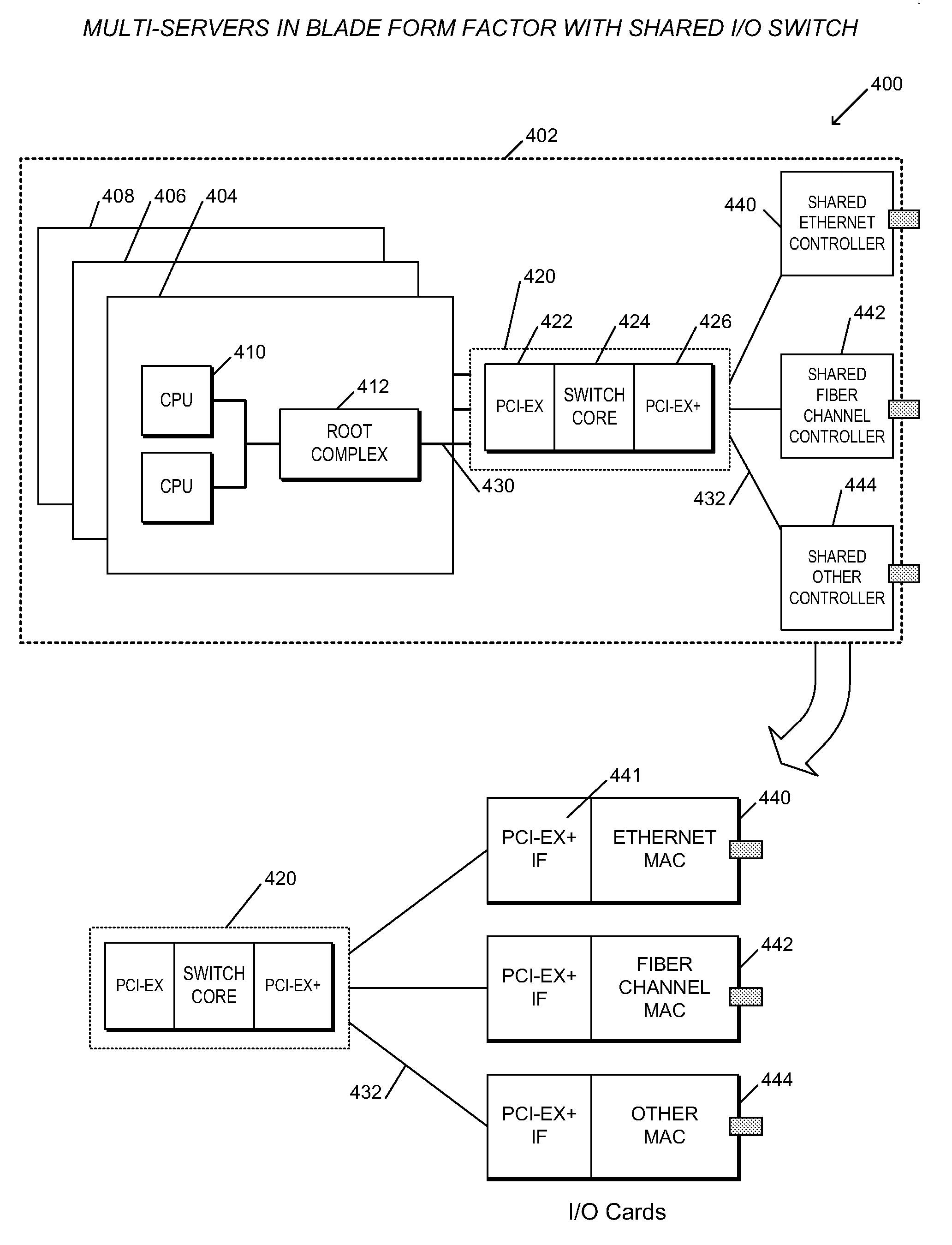

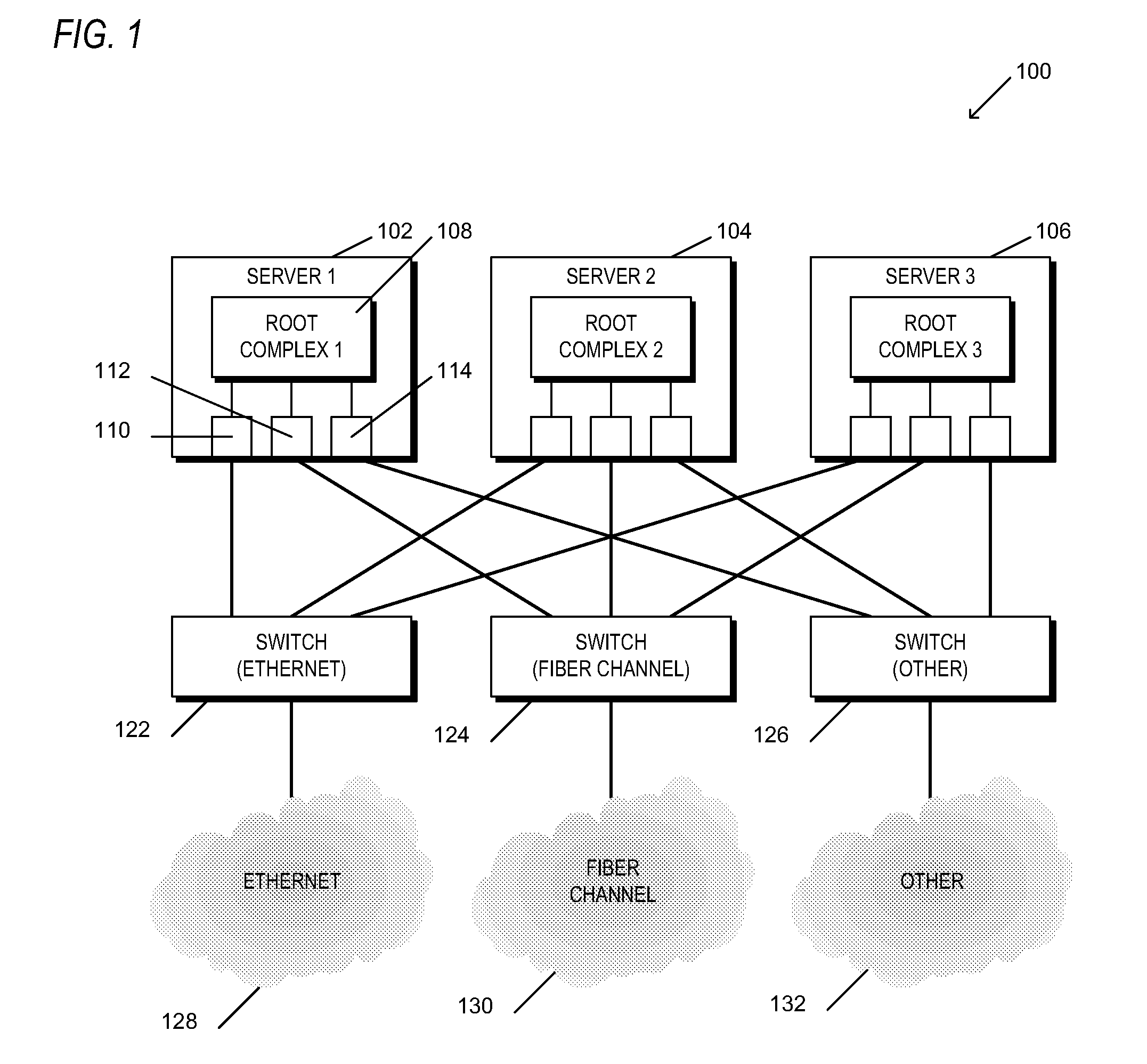

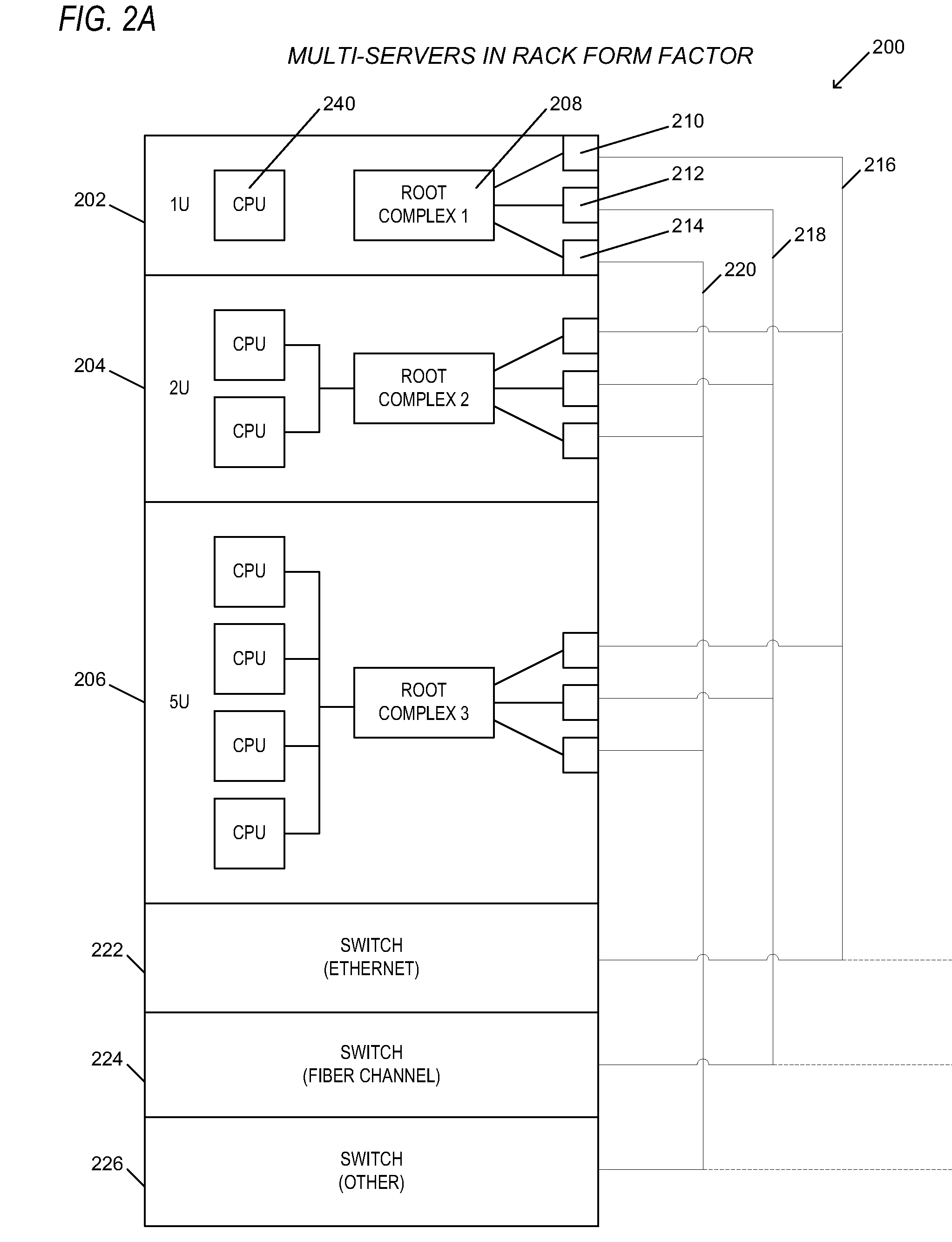

Switching apparatus and method for providing shared I/O within a load-store fabric

ActiveUS7219183B2Data switching by path configurationMultiple digital computer combinationsOperational systemTransaction layer packet

An apparatus and method for sharing I / O devices. The apparatus has a first plurality of I / O ports, a second I / O port, and core logic. The first plurality is coupled to a plurality of operating system domains through a load-store fabric. Each of the first plurality routes transactions between the operating system domains and the switching apparatus. The second I / O port is coupled to a first shared input / output endpoint. The first shared input / output endpoint requests / completes transactions for each of the plurality of operating system domains. The core logic is coupled to the first plurality of I / O ports and the second I / O port. The core logic routes the transactions between the first plurality of I / O ports and the second I / O port and associates each of the transactions with a corresponding one of the plurality of operating system domains (OSDs) by encapsulating an OS domain header within a transaction layer packet.

Owner:AVAGO TECH INT SALES PTE LTD

Method for efficient inter-processor communication in an active-active RAID system using PCI-express links

ActiveUS20060161707A1Efficiently determinedError detection/correctionUnauthorized memory use protectionRAIDProcessor register

A fault-tolerant RAID system is disclosed. The system includes redundant RAID controllers coupled by a PCI-Express link. When a PCI-Express controller of one of the RAID controllers receives a PCI-Express memory write request transaction layer packet (TLP), it interprets a predetermined bit in the header as an interrupt request flag, rather than as its standard function specified by the PCI-Express specification. If the flag is set, the PCI-Express controller interrupts the processor after storing the message in the payload at the specified memory location. In one embodiment, an unused upper address bit in the header is used as the interrupt request flag. Additionally, unused predetermined bits in the TLP header are used as a message tag to indicate one of a plurality of message buffers on the receiving RAID controller into which the message has been written. The PCI-Express controller sets a corresponding bit in a register to indicate which message buffer was written.

Owner:DOT HILL SYST

Switching apparatus and method for providing shared I/O within a load-store fabric

ActiveUS7174413B2Multiplex system selection arrangementsData switching by path configurationOperational systemTransaction layer packet

A method enabling I / O devices to be shared among multiple operating system domains, including first communicating with each of the operating system domains according to a protocol that provides exclusively for a single system domain ithin the load-store fabric; and second communicating with the shared I / O endpoint according to a variant of the protocol to enable the shared I / O endpoint to associate a prescribed operation with a corresponding one of the independent operating system domains. The second communicating includes encapsulating an OS domain header within a transaction layer packet that otherwise comports with the protocol, wherein the value of the OS domain header designates the corresponding one of the operating system domains; and via core logic within a swithching apparatus, mapping the independent operating system domains to the shared I / O endpoint.

Owner:AVAGO TECH INT SALES PTE LTD

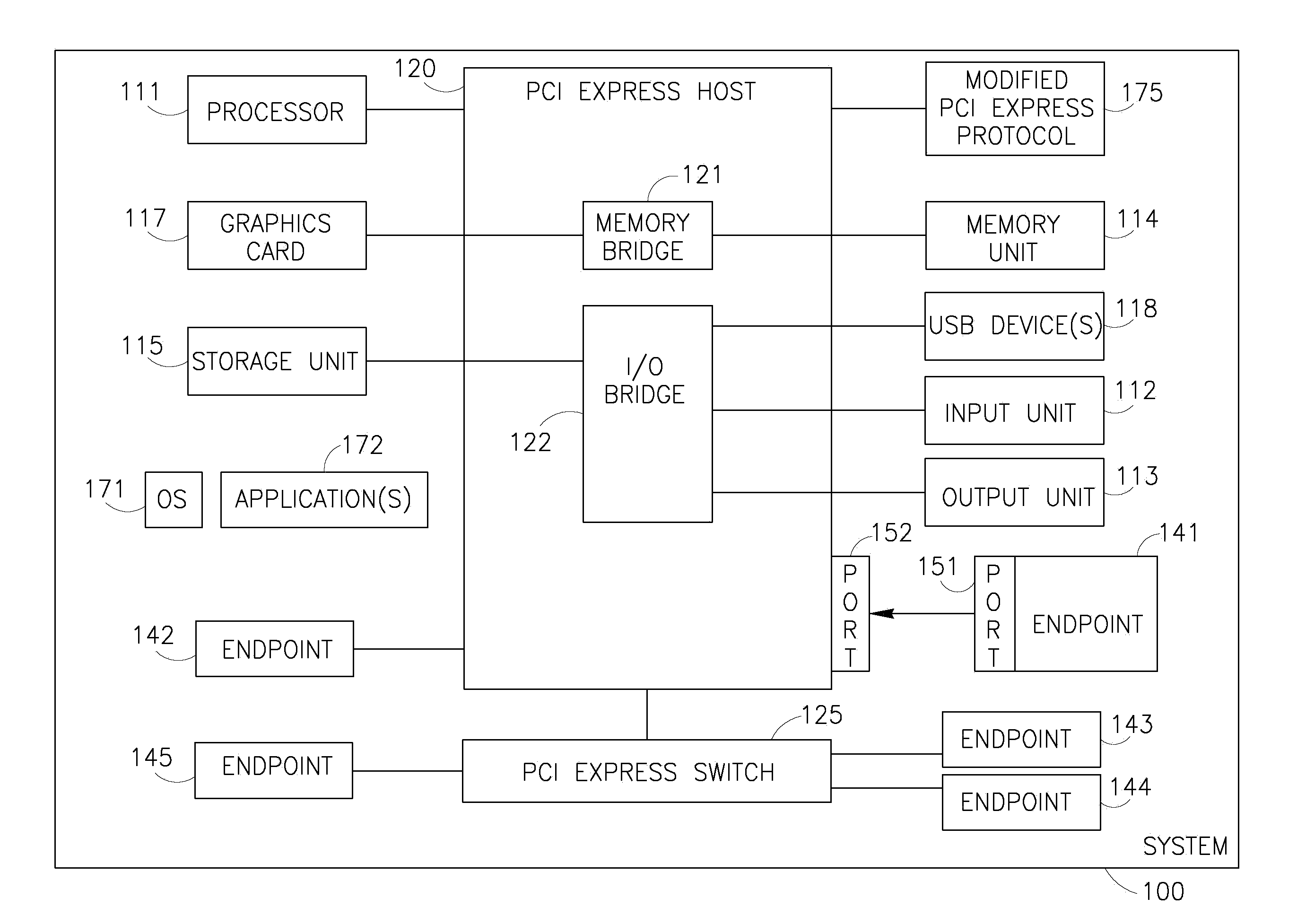

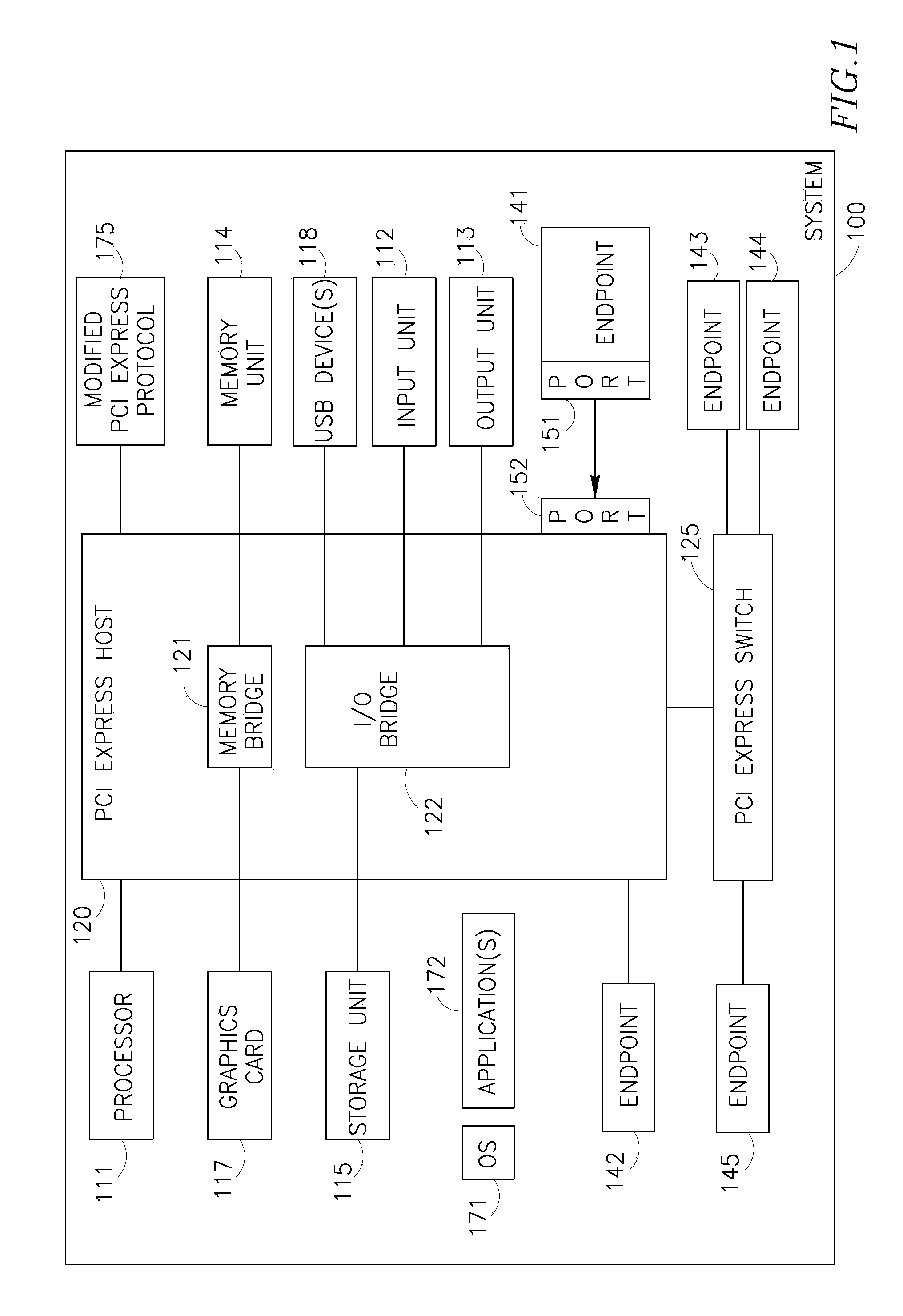

Method and system for sharing input/output devices

InactiveUS7694047B1Input/output processes for data processingData conversionTraffic capacityParallel computing

A PCI-Express module that is coupled to plural host systems and to at least an input / output (I / O) device is provided. The PCI-Express module includes an upstream port module and a downstream port module that use a mapping table to facilitate the plural host systems sharing the I / O device by modifying a transaction layer packet (TLP) field. For upstream ID based traffic, a source identifier is replaced based on the mapping table and a destination identifier is replaced with a value that is captured during upstream port module initialization. For upstream address based traffic, the mapping table routes TLPs by using a downstream port number and a function number in a source identification field. For downstream ID based traffic, a destination identifier is replaced by using the mapping table for routing TLPs. For downstream address based traffic, the PCI-Express module uses an address map to route TLPs.

Owner:MARVELL ASIA PTE LTD

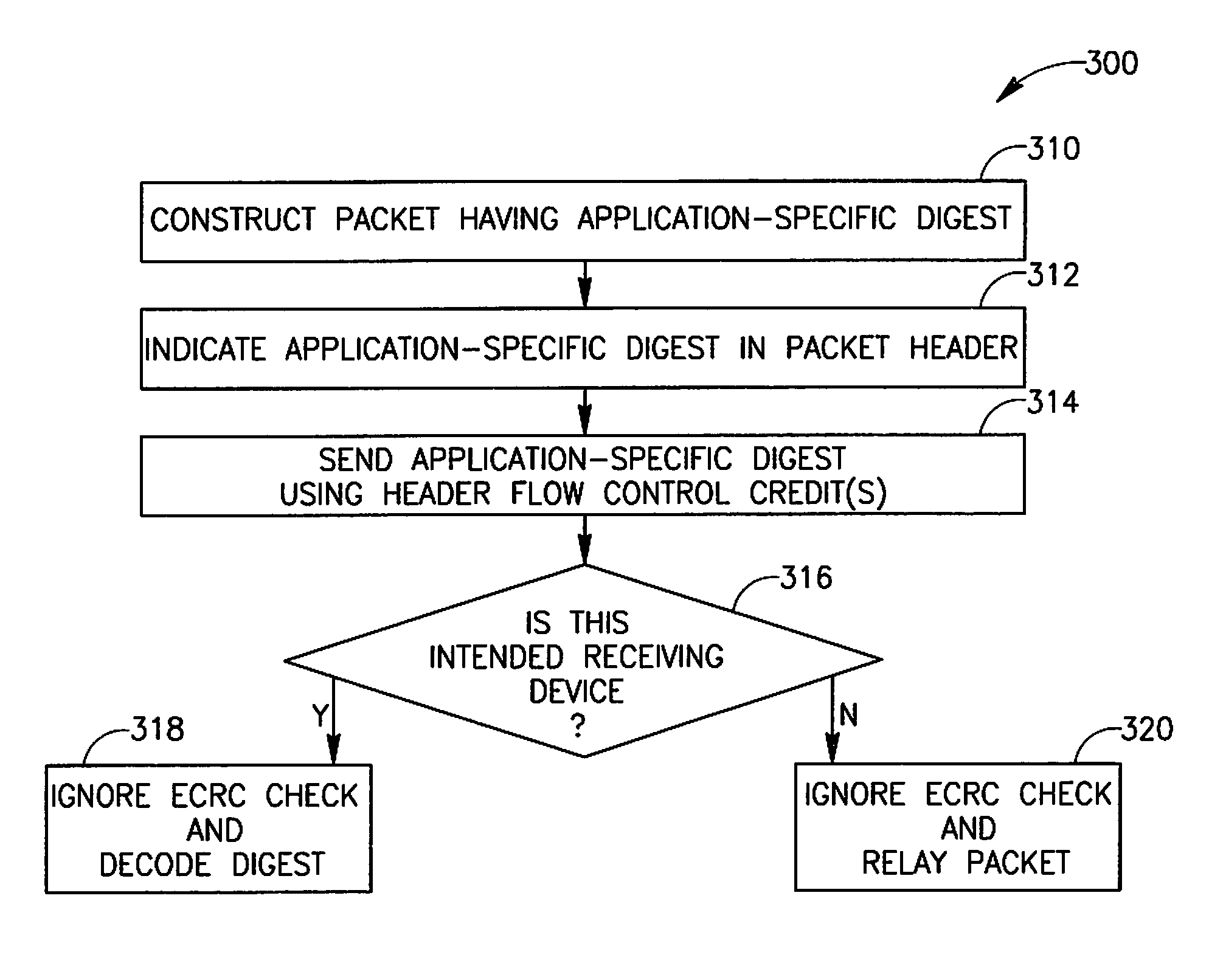

Device, System and Method of Modification of PCI Express Packet Digest

Device, system and method of modification of PCI Express packet digest. For example, an apparatus includes a credit-based flow control interconnect device to generate a credit-based flow control interconnect Transaction Layer Packet in which one or more bits of a digest portion carry non-ECRC data.

Owner:IBM CORP

Device, system and method of modification of PCI express packet digest

Owner:INT BUSINESS MASCH CORP

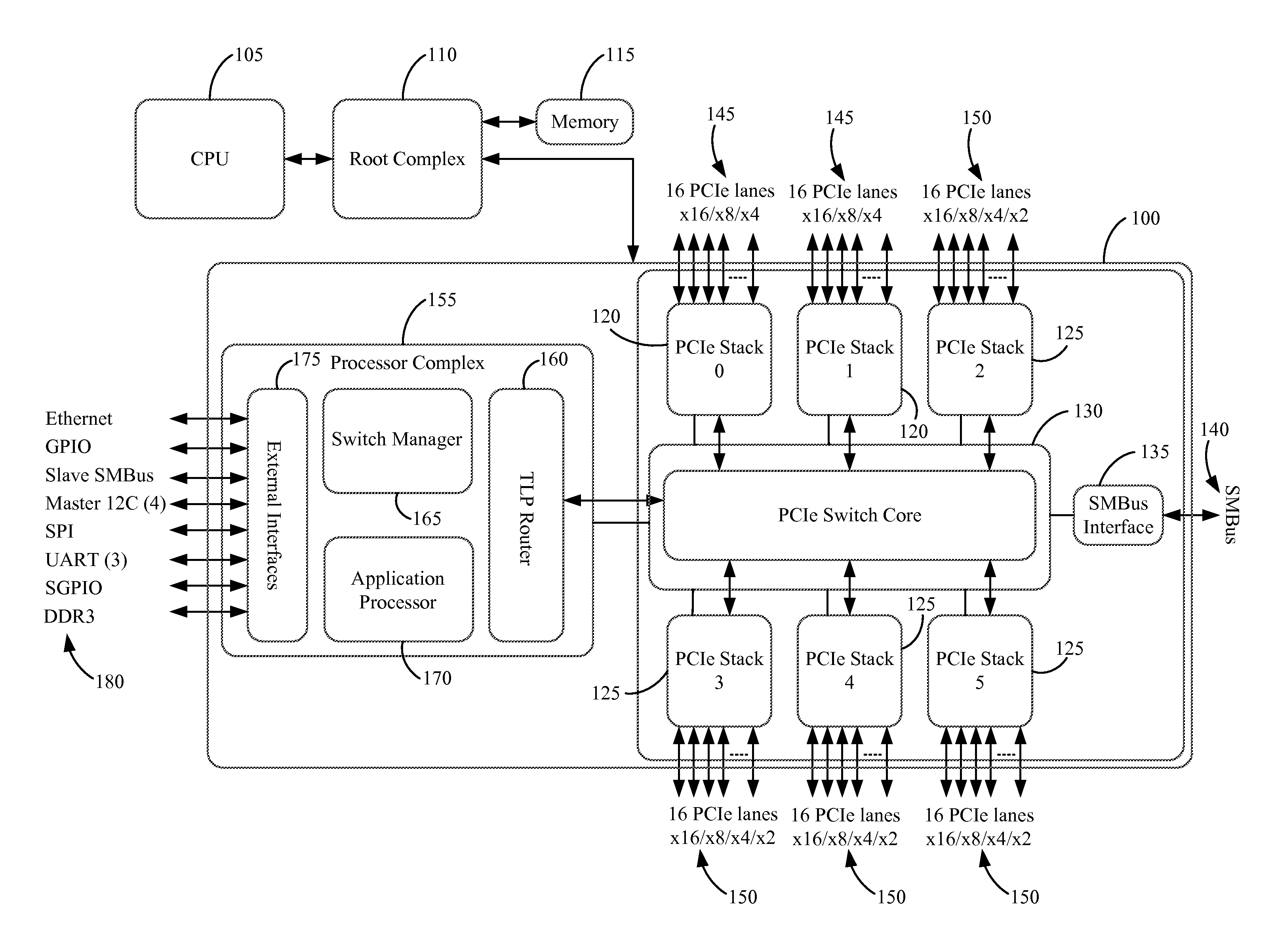

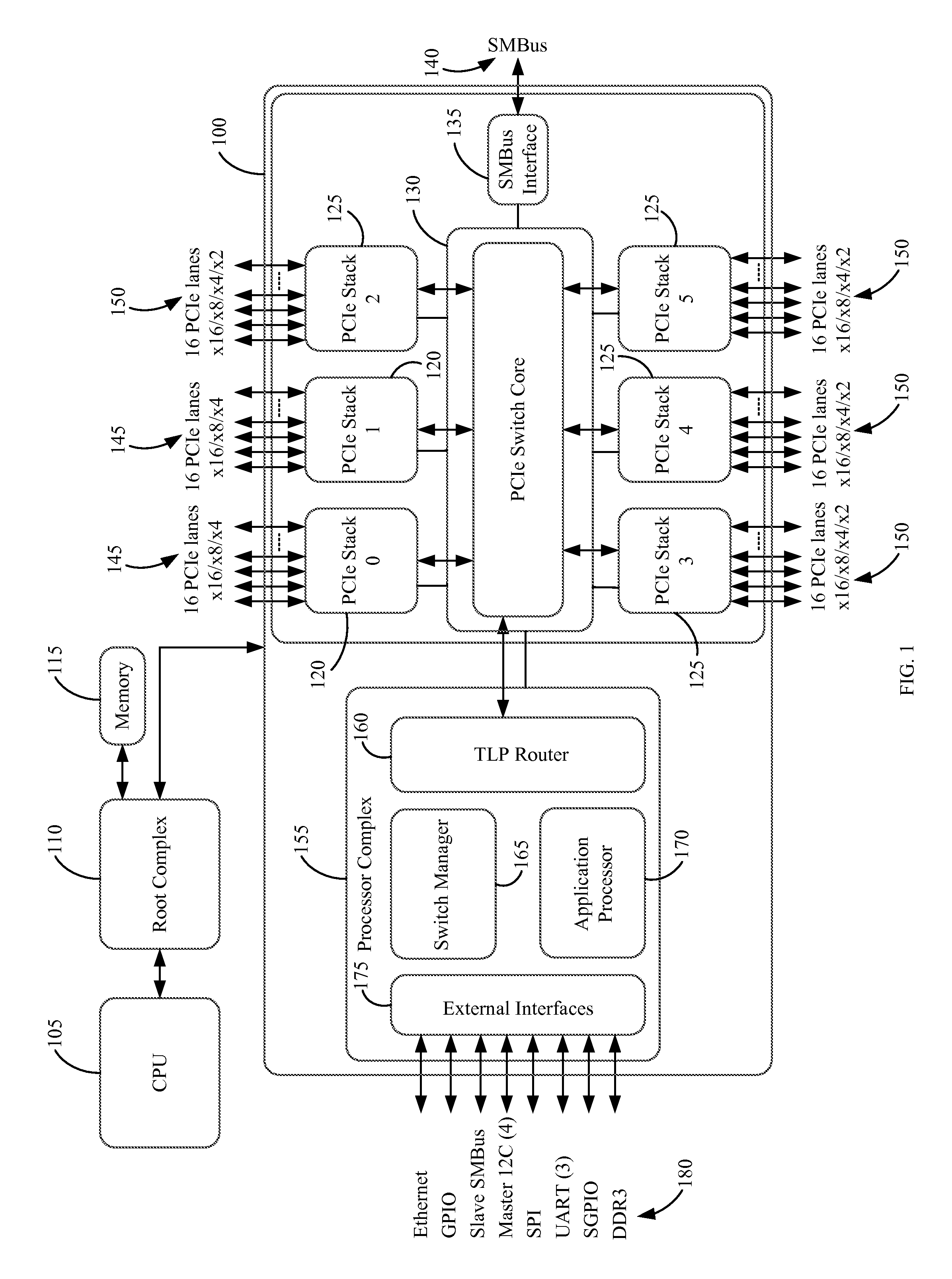

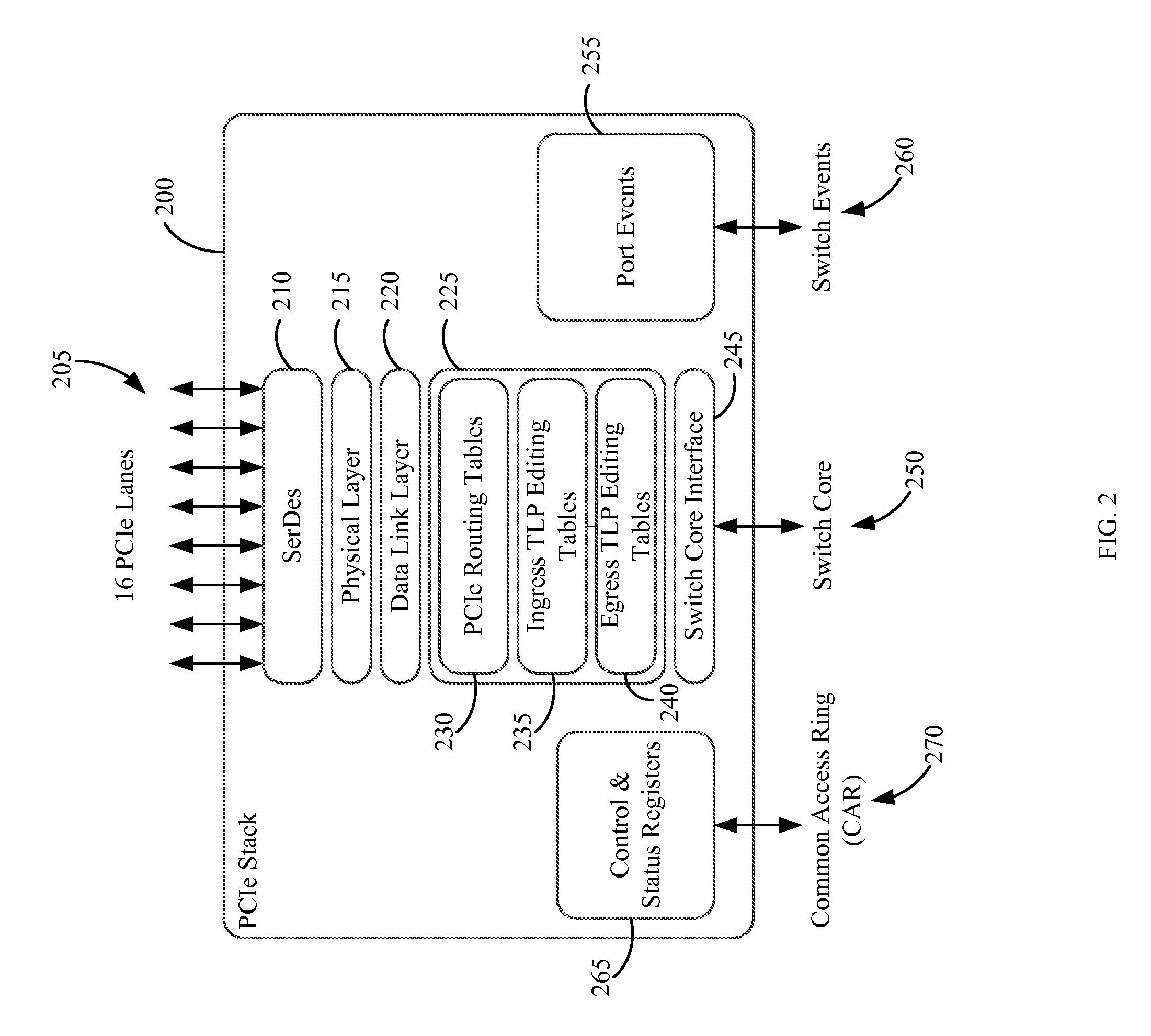

Method and apparatus for translated routing in an interconnect switch

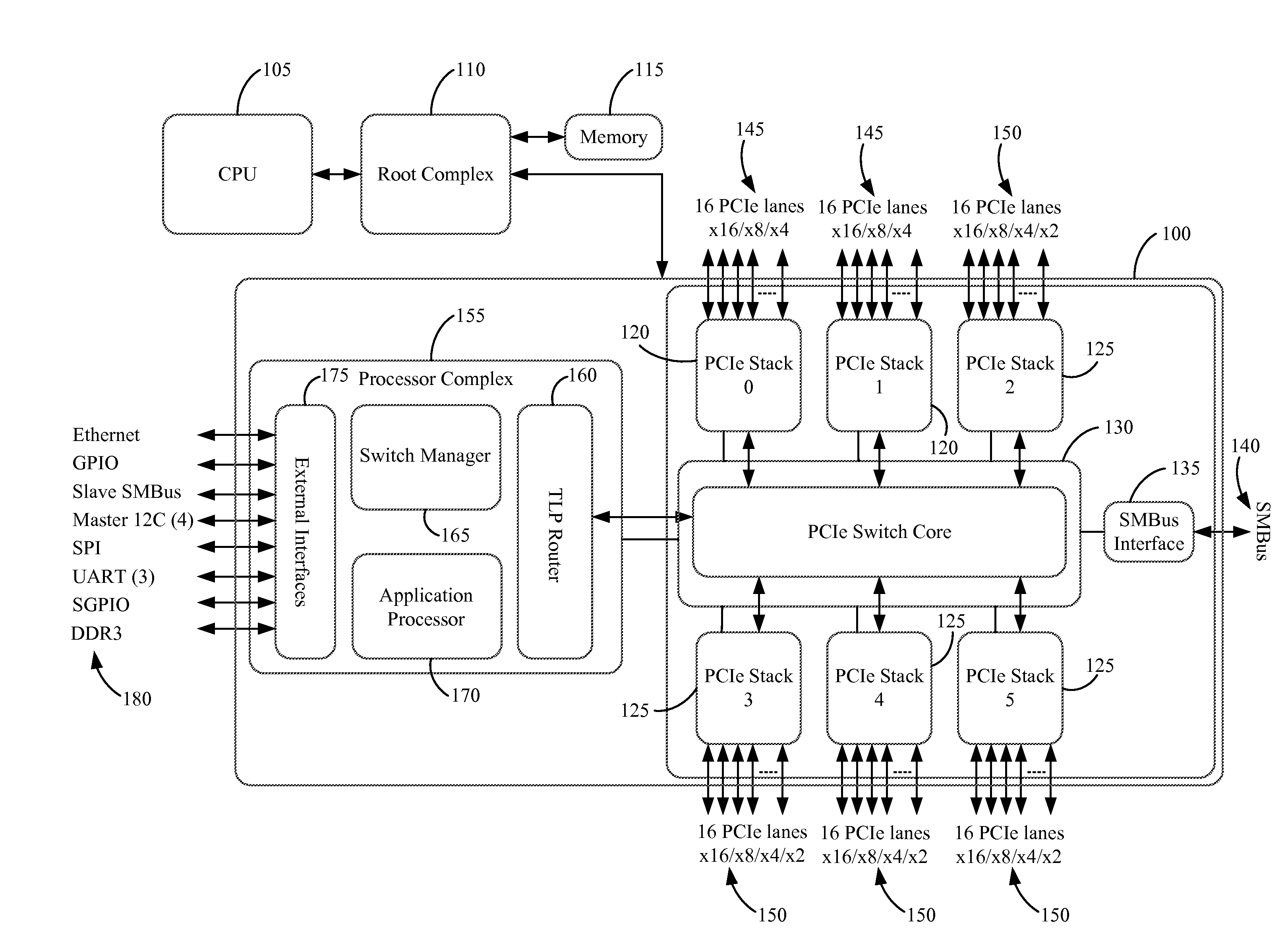

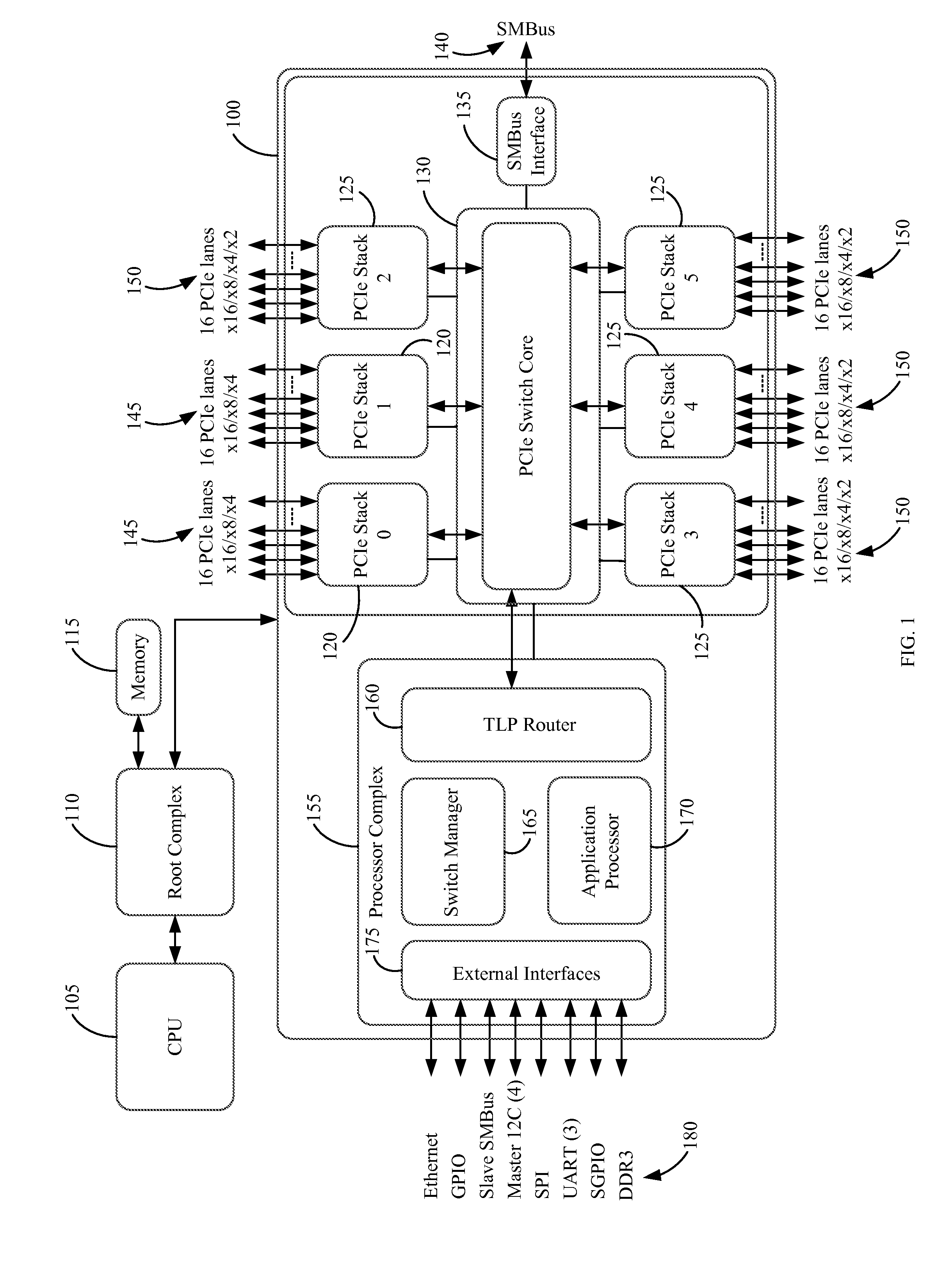

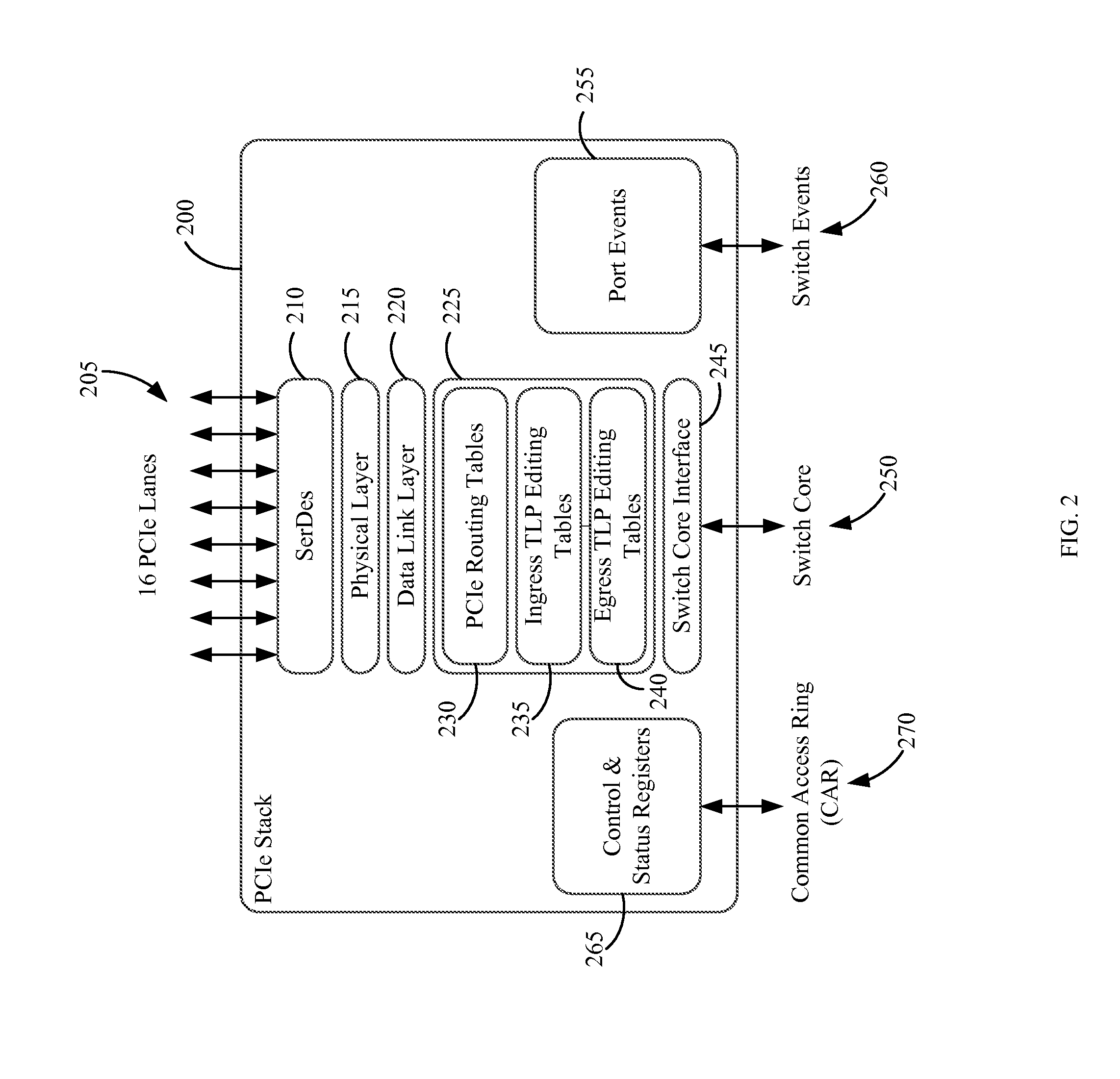

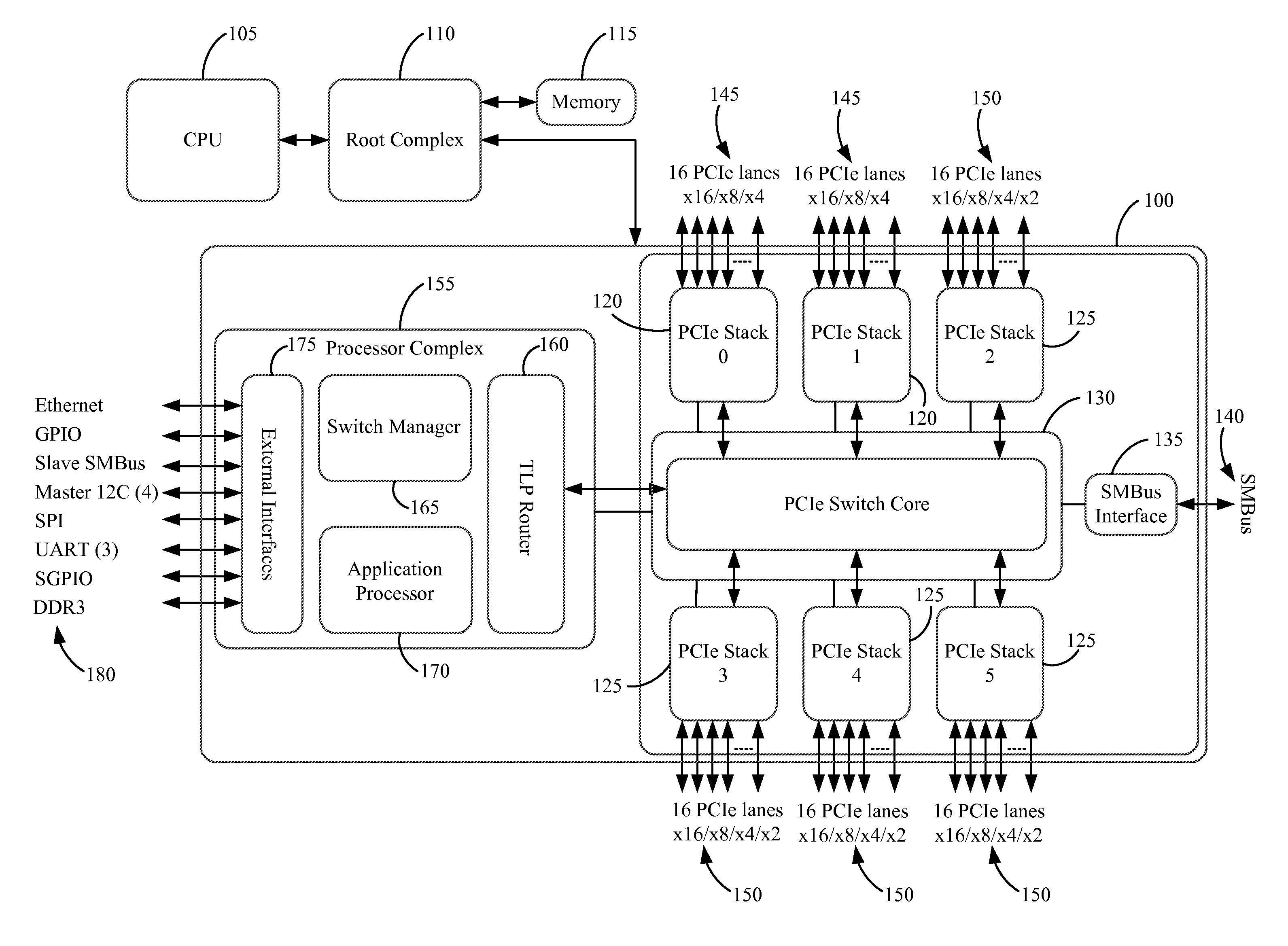

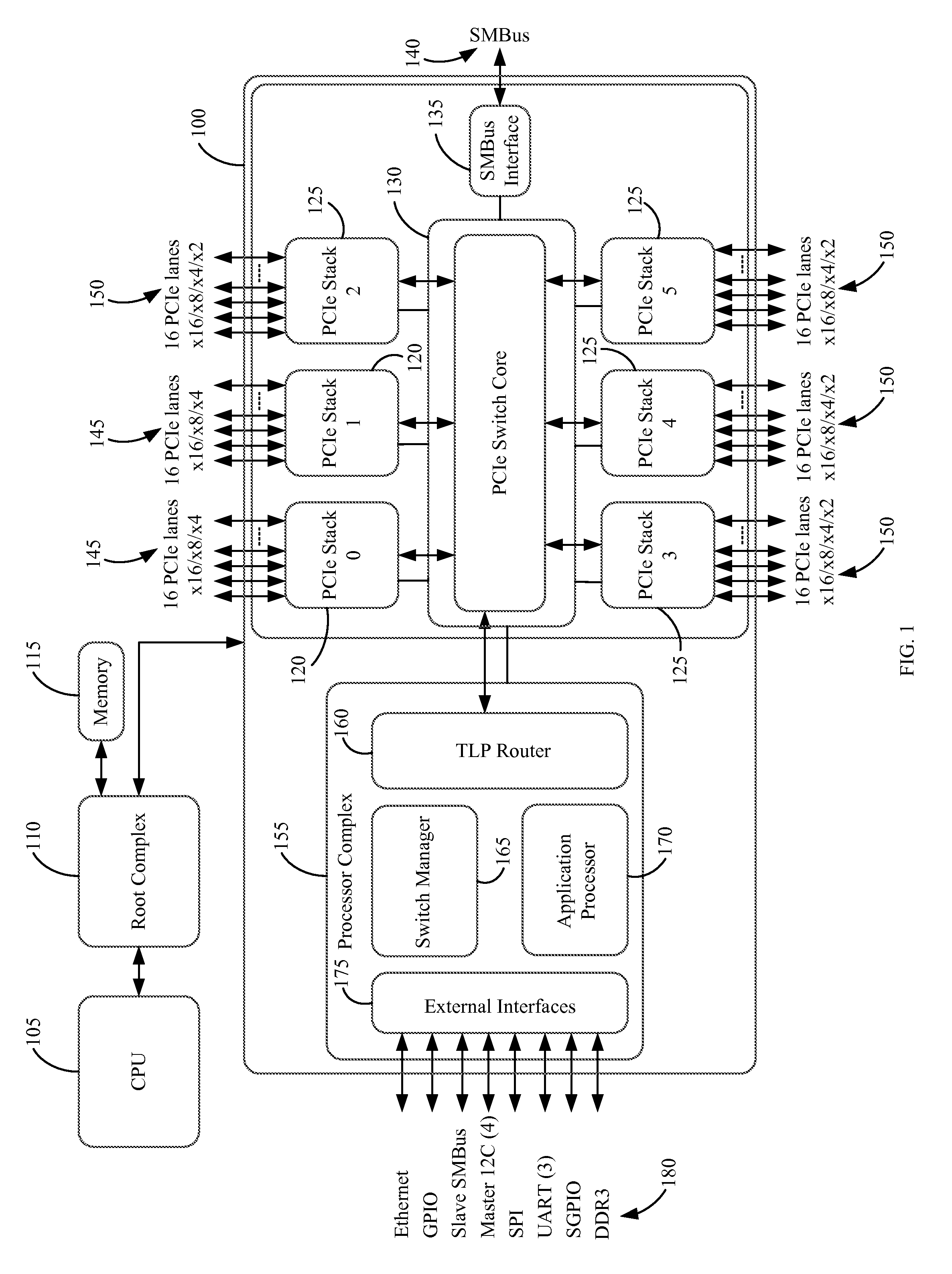

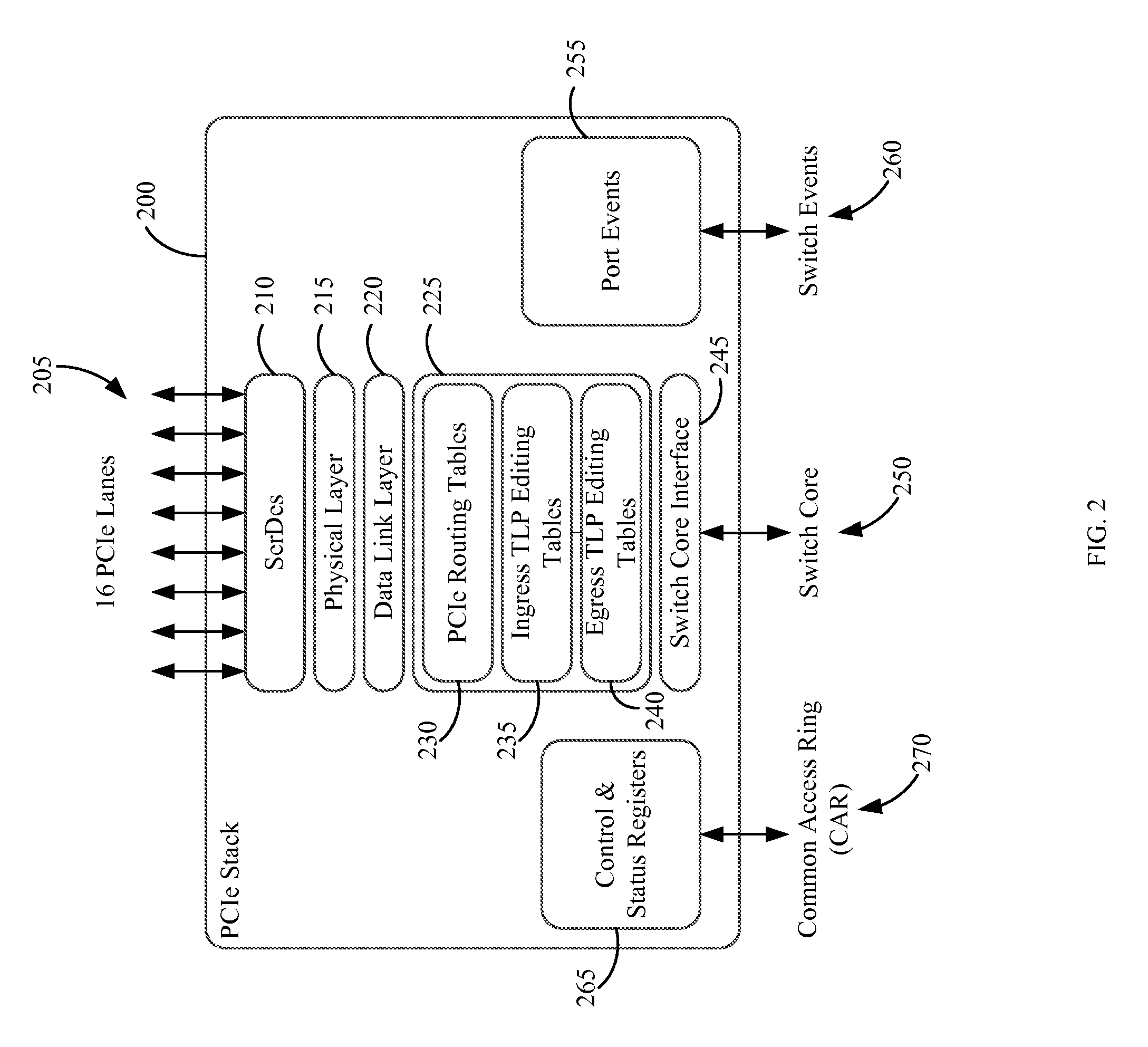

A system and method are disclosed for a flexible routing engine in a PCIe switch. The system may include a switch manager that is enabled, through firmware, to configure one or more routing tables associated with a switch stack of a PCIe switch. To enable non-transparent bridging and non-standard routing, the method may include receiving a transaction layer packet at a translated routing port of a PCIe switch, and performing translation of the address and requester ID of the packet utilizing tables that are updated by the firmware of the switch manager to route the packet through the switch.

Owner:MICROSEMI STORAGE SOLUTIONS US INC

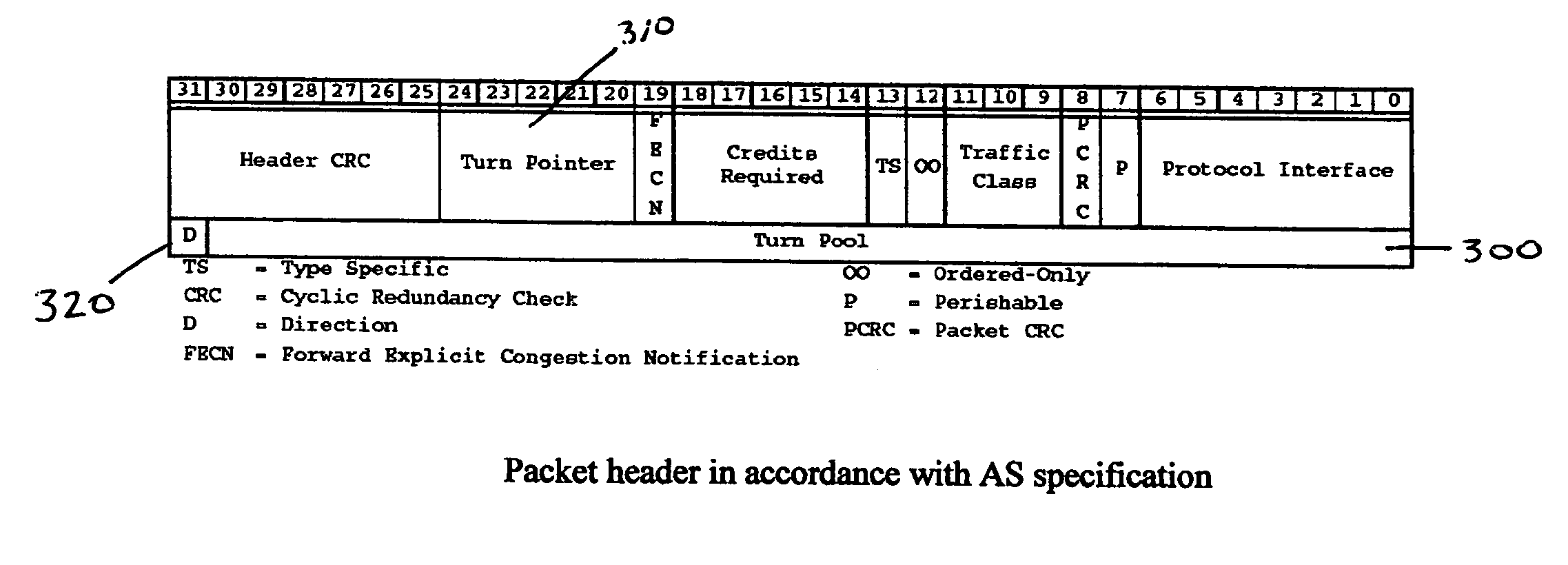

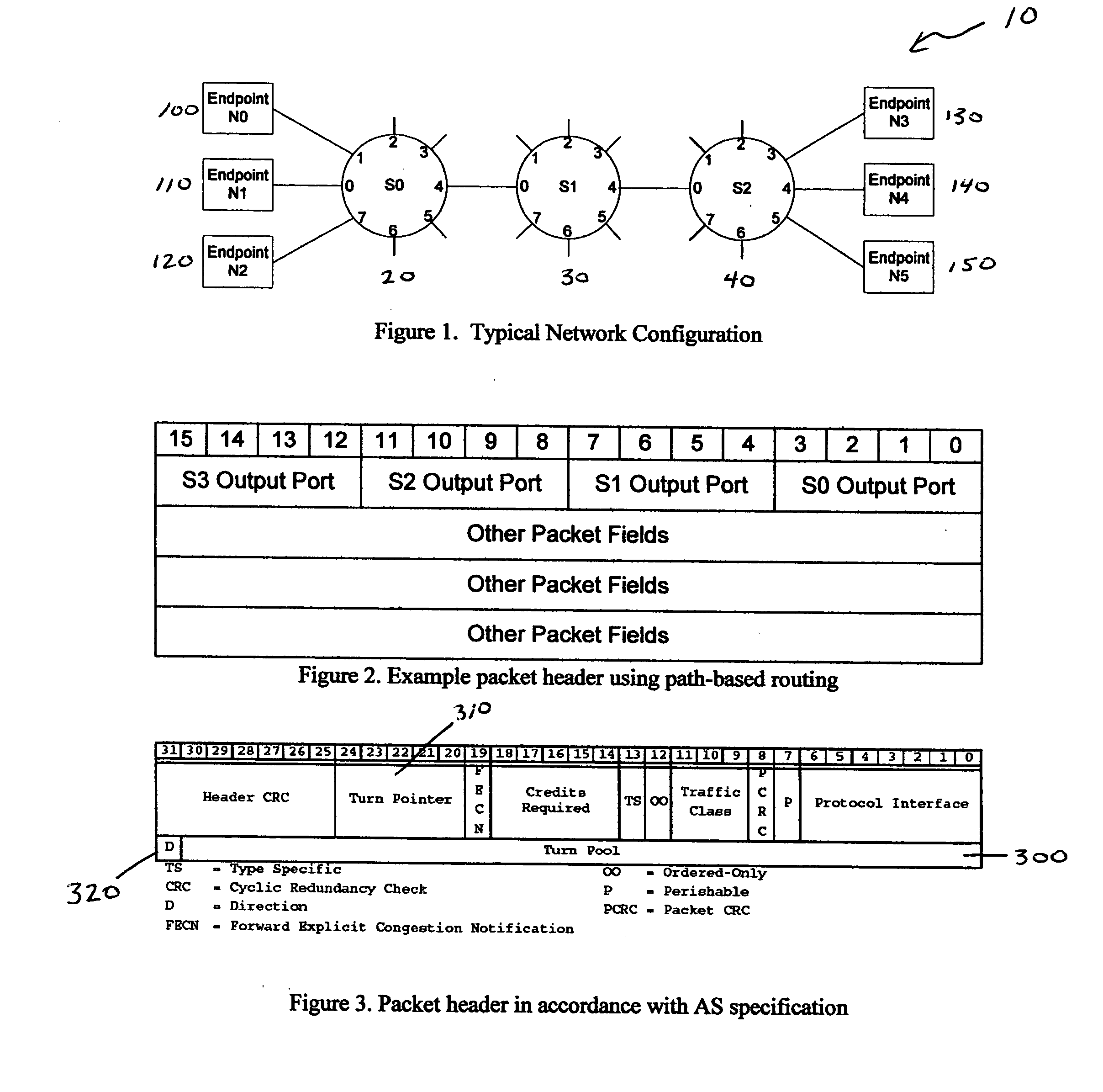

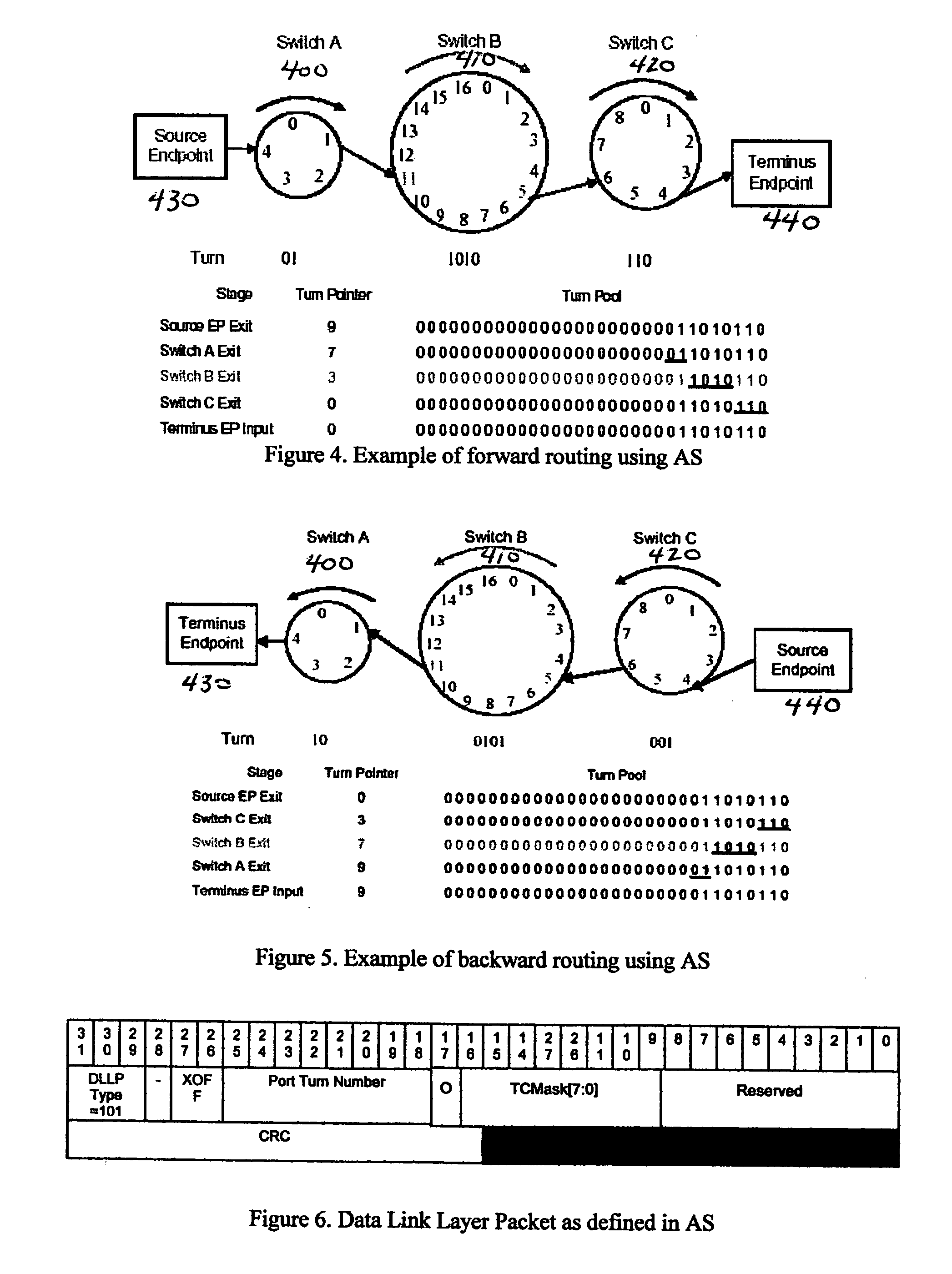

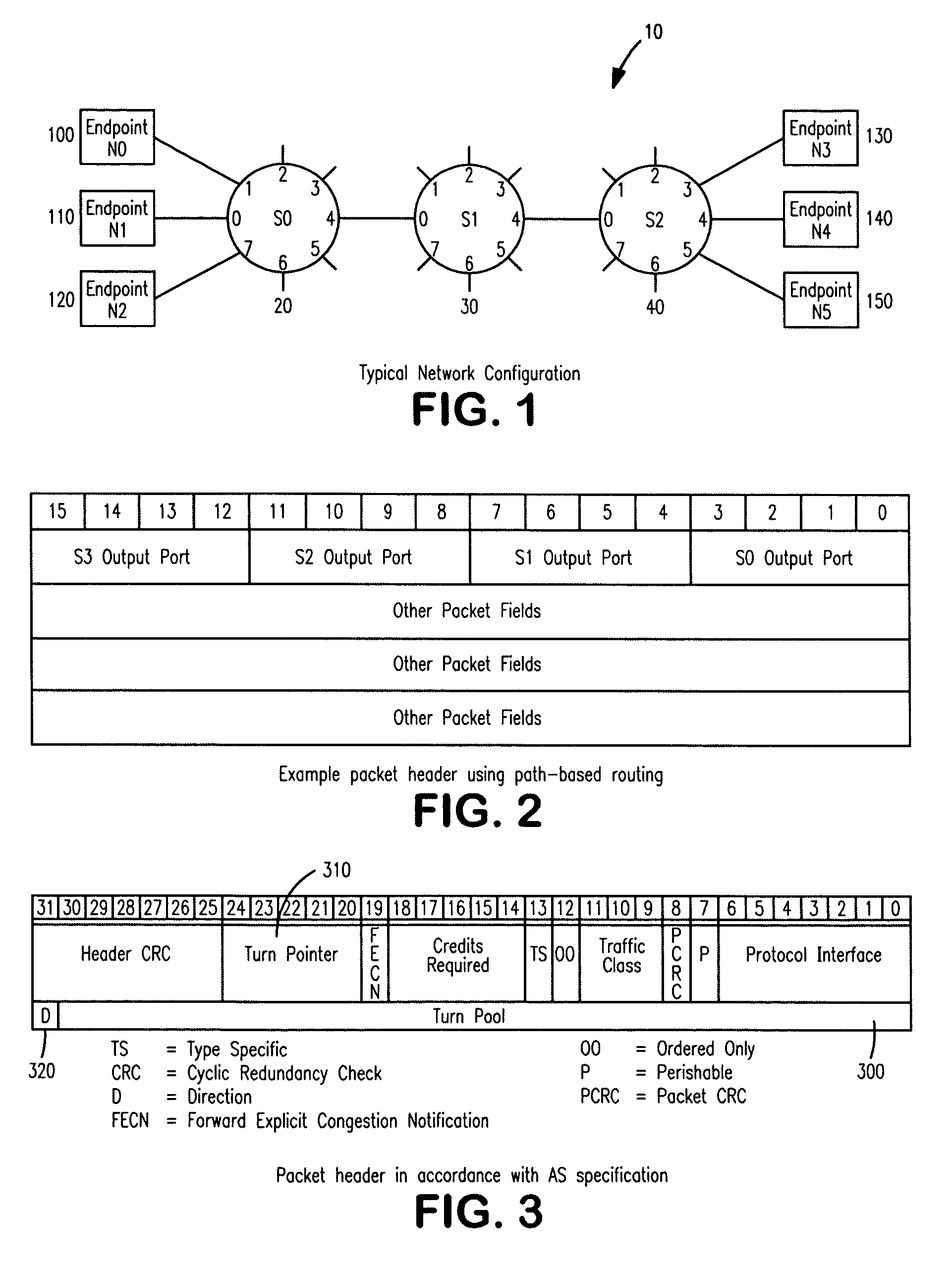

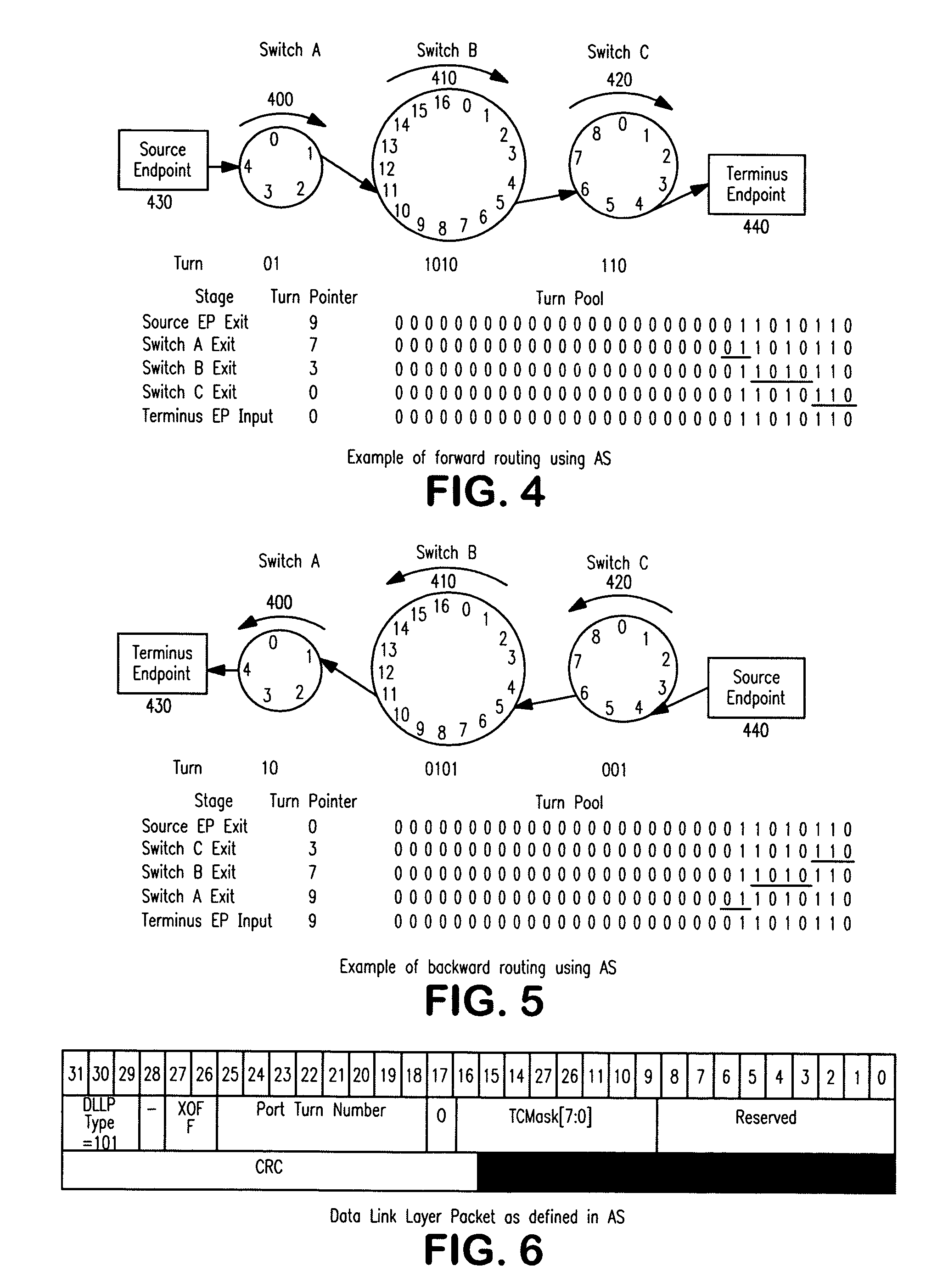

System and method to identify and communicate congested flows in a network fabric

ActiveUS20050270974A1Comprehensive and elegant solutionError preventionTransmission systemsExchange networkNetwork structure

The invention provides a system and method for identifying and communicating congested paths throughout a network fabric. Briefly, the present invention augments the congestion management mechanism defined in ASI to allow for the communication of congested paths through the fabric, rather than the simple congested output port notification supported today through the use of DLLPs. Further, it also uses the communication mechanisms already defined in the ASI specification to implement this additional capability. Specifically, the present invention uses Transaction Layer Packets (TLPs) to communicate the information concerning congested flows throughout the network. This packet type allows the inclusion of much more information than DLLPs, allowing a more comprehensive and elegant solution to the issue of congestion management in an Advanced Switching network fabric.

Owner:CALLAHAN CELLULAR L L C

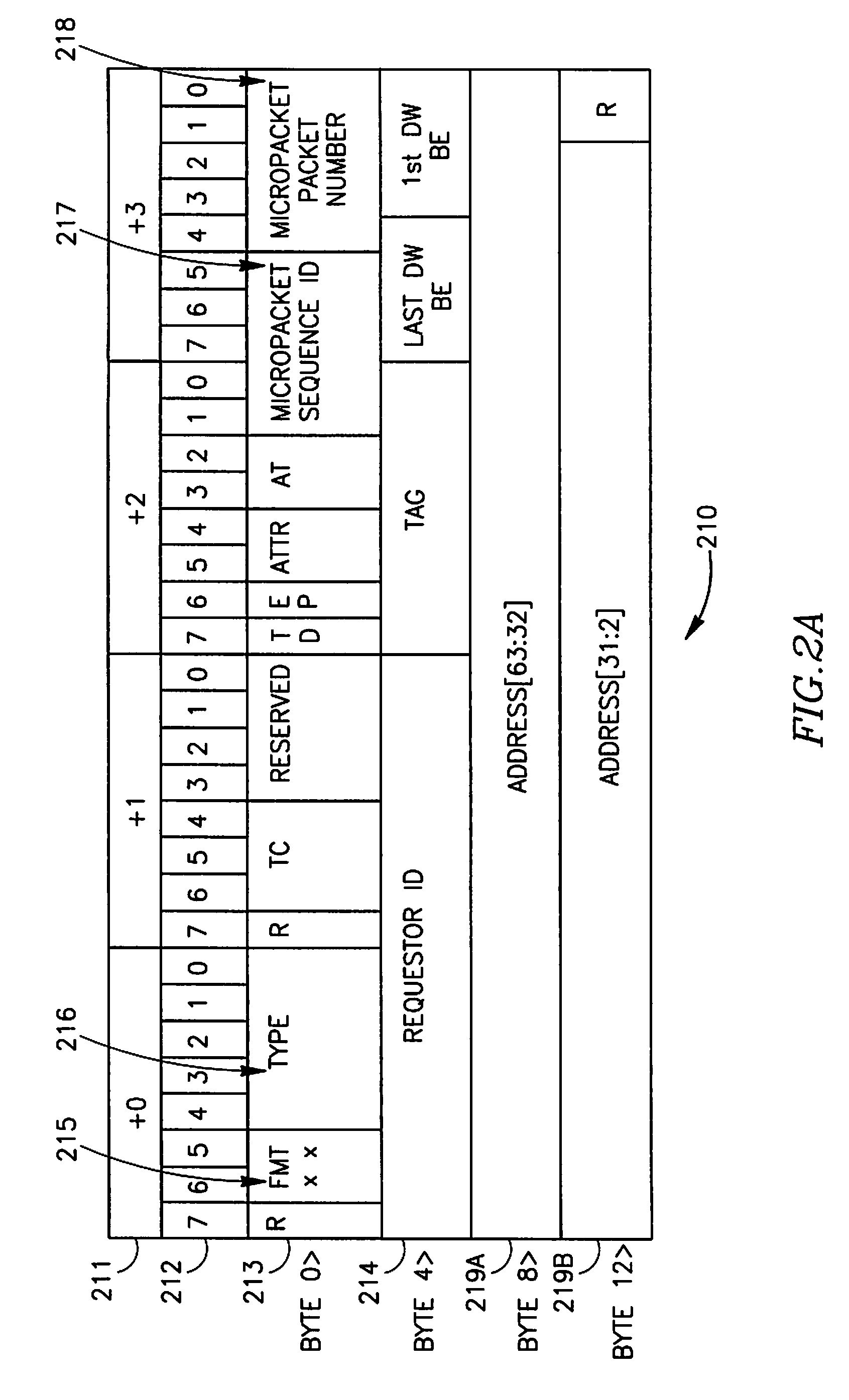

Device, System and Method of Fragmentation of PCI Express Packets

Device, system and method of fragmentation of PCI Express packets. For example, an apparatus includes a credit-based flow control interconnect device to fragment a Transaction Layer Packet into a stream of micro-packets, wherein the stream comprises an initial micro-packet and one or more continuation micro-packets.

Owner:IBM CORP

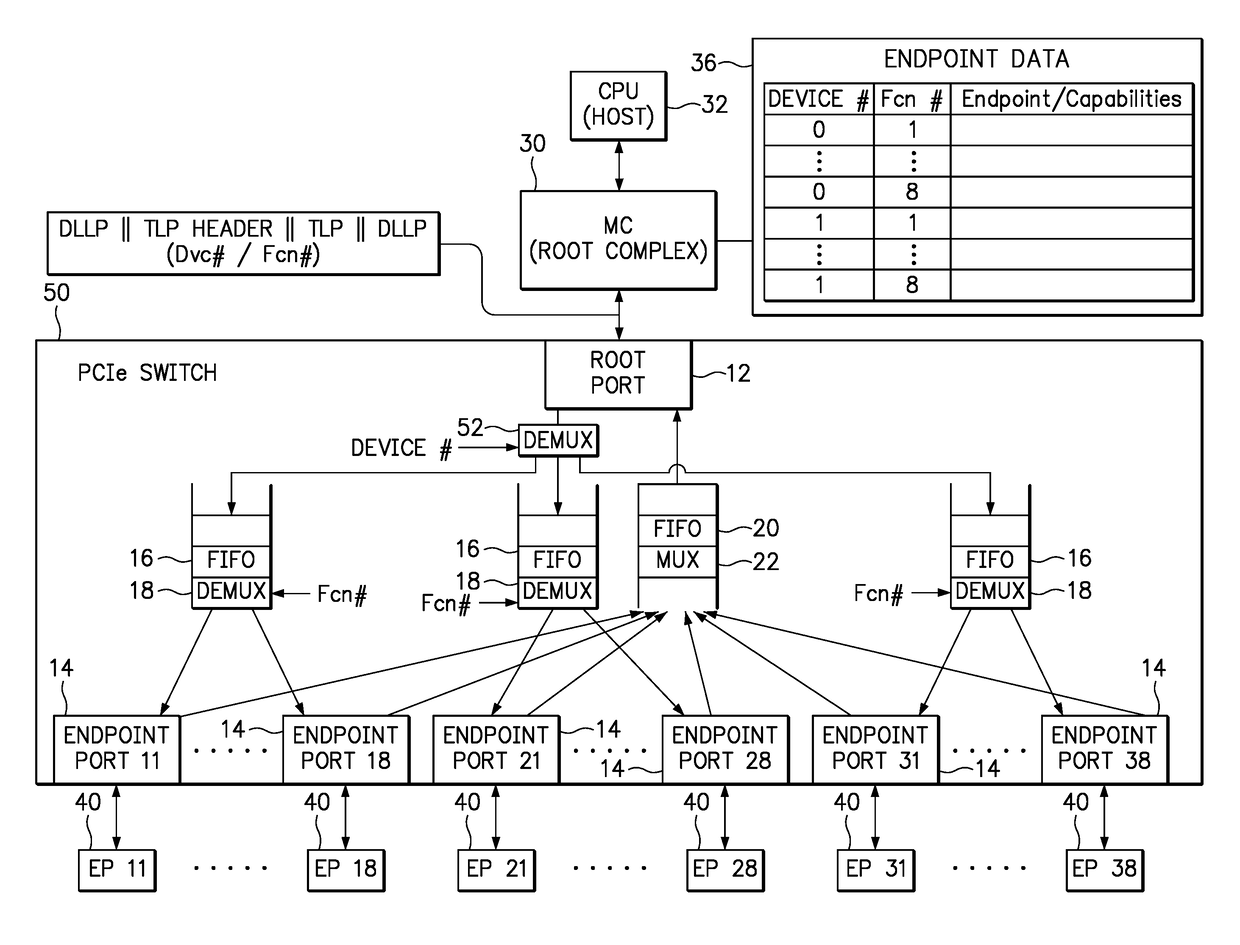

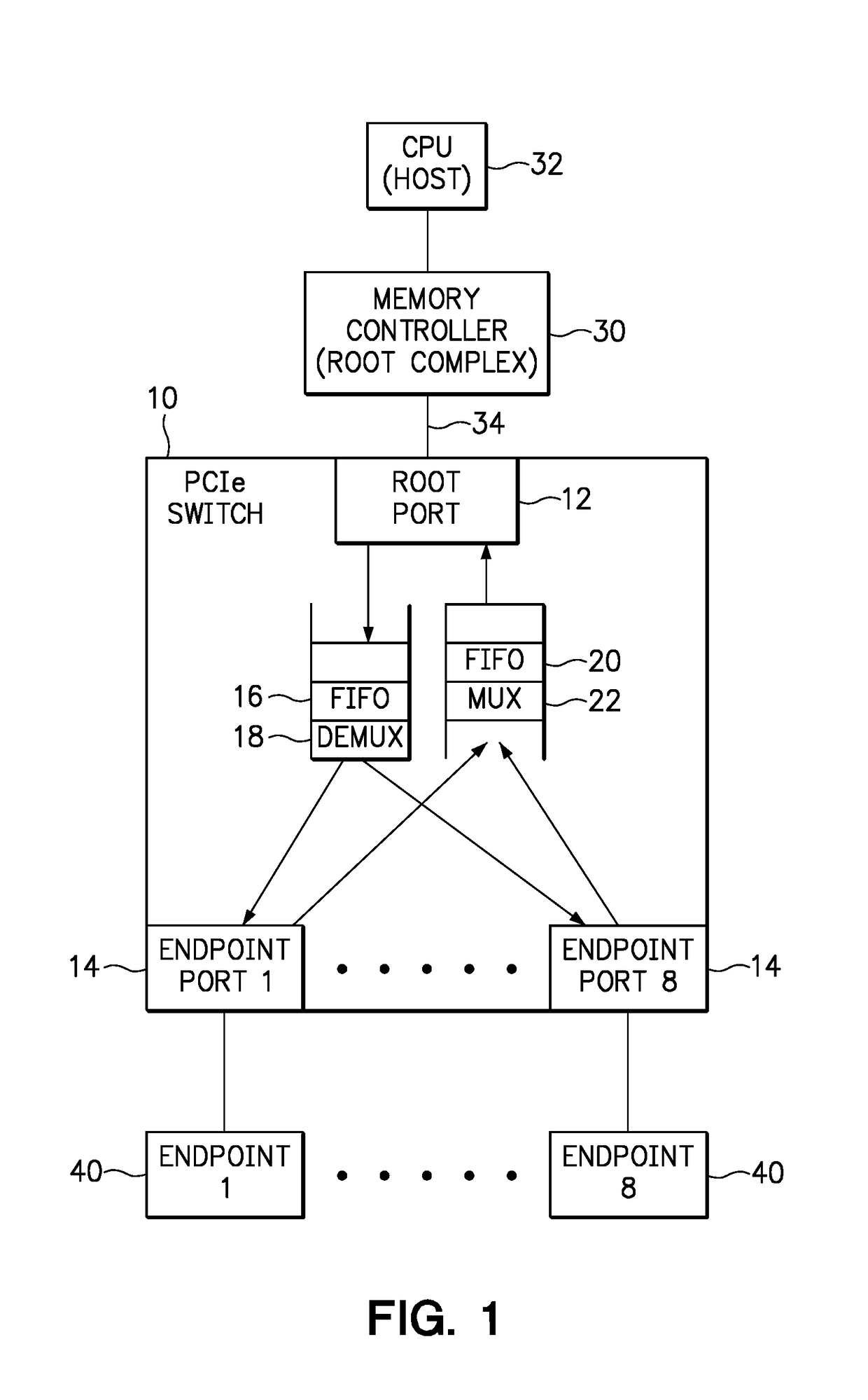

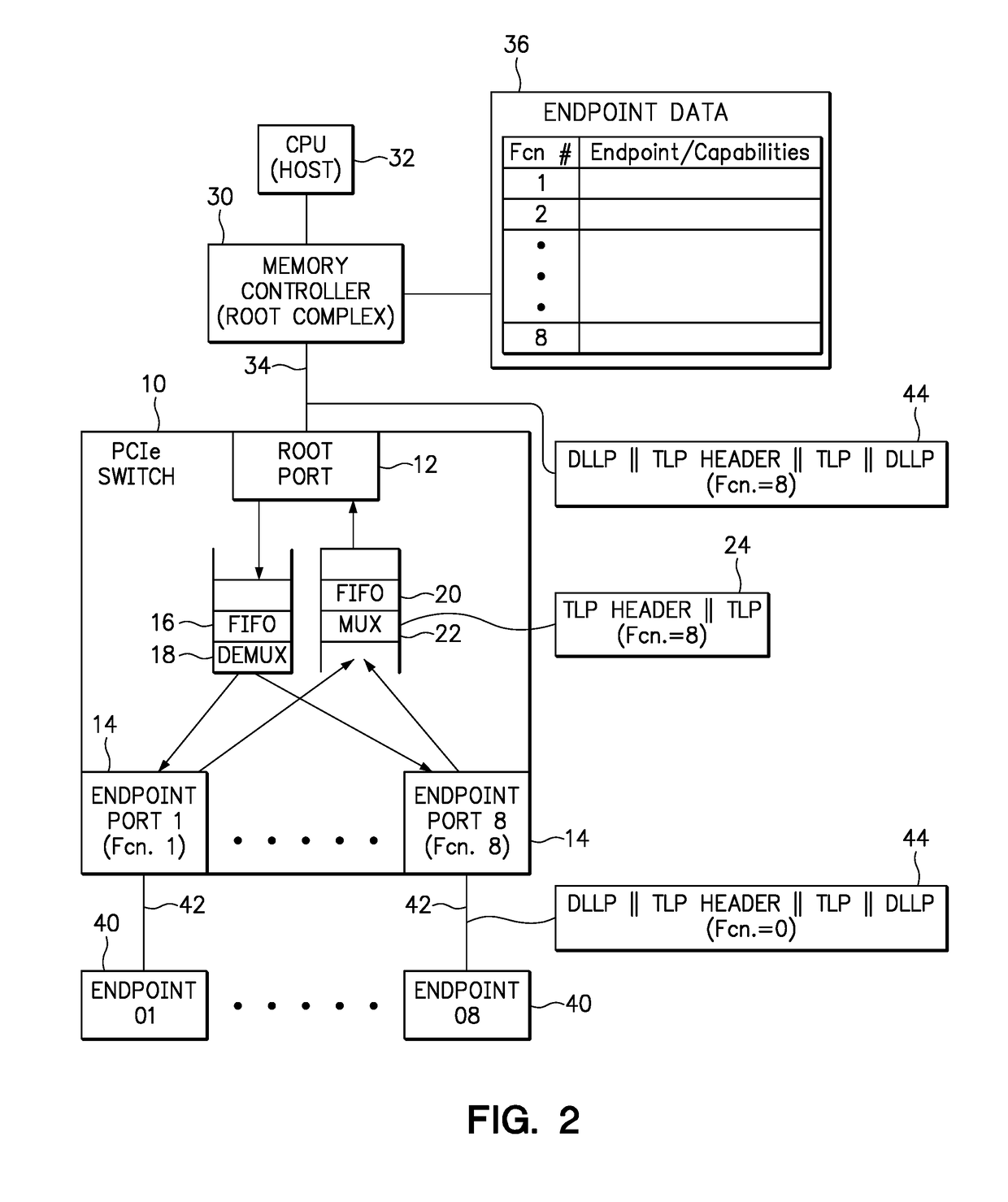

Pcie switch for aggregating a large number of endpoint devices

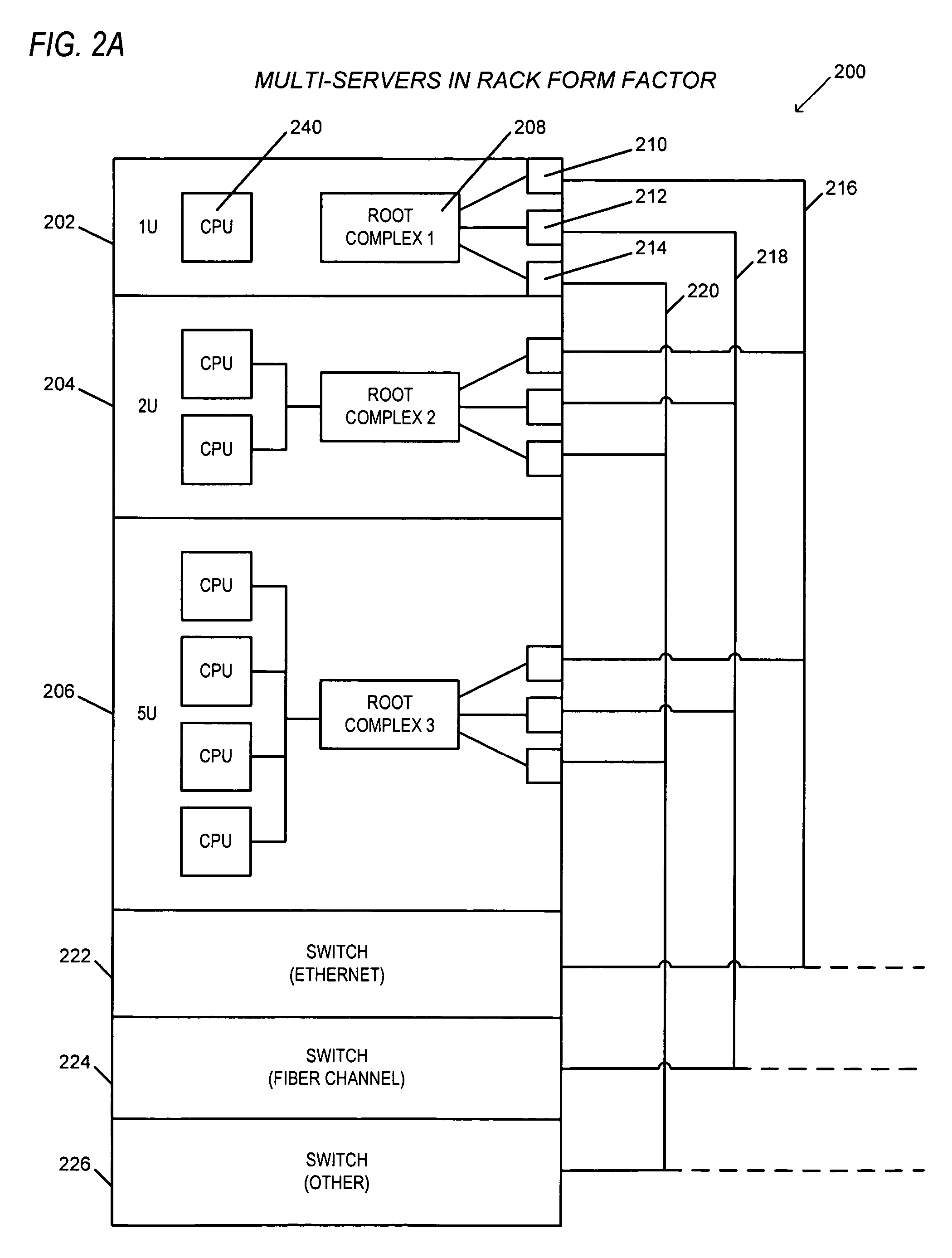

ActiveUS20180101498A1Energy efficient computingElectric digital data processingRoot complexComputer science

An apparatus includes a root port for coupling to a root complex, and a plurality of endpoint ports for coupling to endpoint devices, wherein each endpoint port is associated with a function number. A downstream buffer queues transaction layer packets (TLPs) received from the root port, wherein each TLP in the downstream buffer is directed to an endpoint port associated with the identified function number. An upstream buffer queues TLPs received from each endpoint port, and directs the queued TLPs to the root port. A method includes associating a function number with each endpoint port of a switch, wherein each endpoint port is adapted for coupling to an endpoint device. The method further includes receiving a first TLP from a root complex, identifying a function number within the first TLP, and directing the first TLP to an endpoint device through the endpoint port associated with the identified function number.

Owner:LENOVO GLOBAL TECH INT LTD

Dynamic buffer pool in pciexpress switches

ActiveUS20090154456A1Data switching by path configurationTransaction layer packetDistributed computing

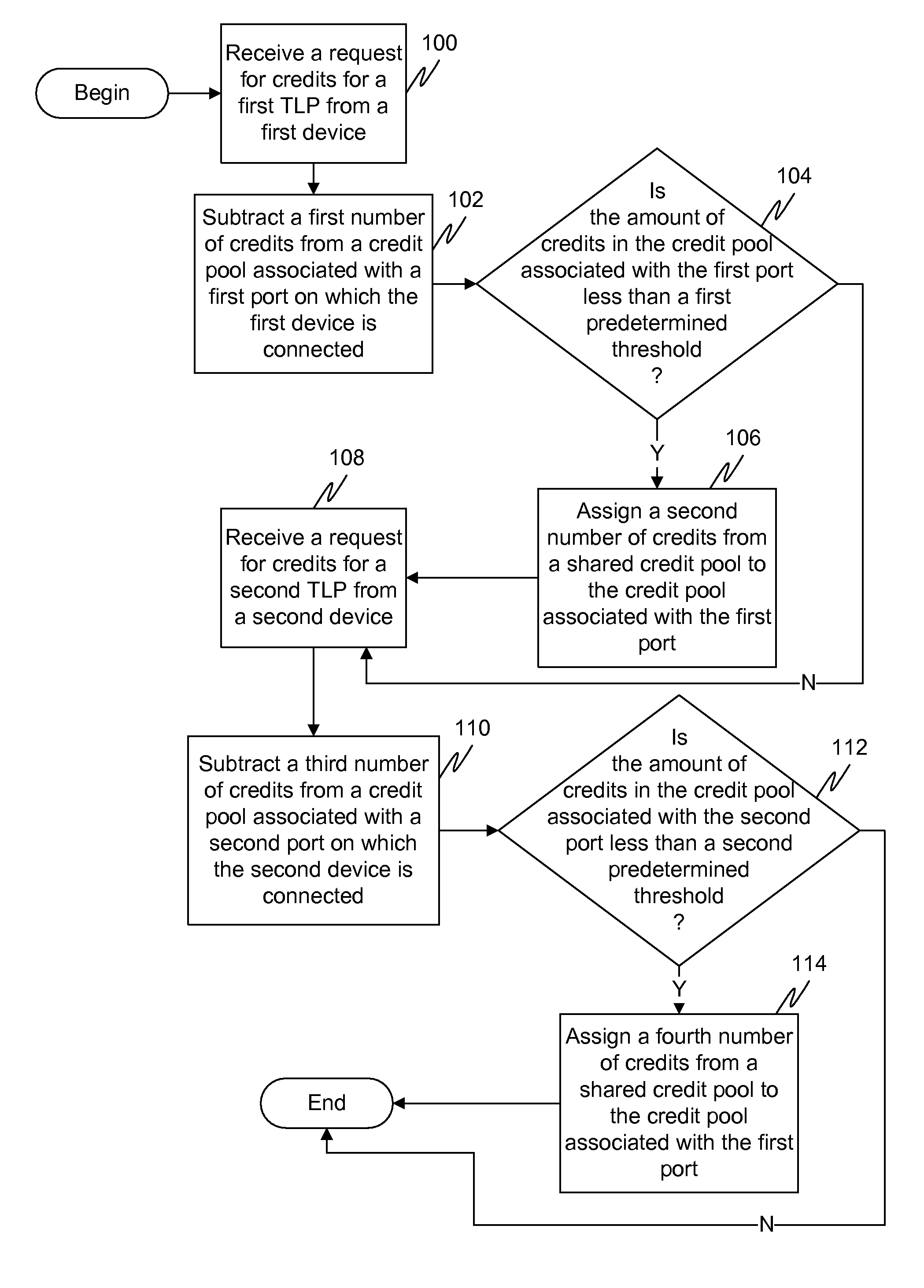

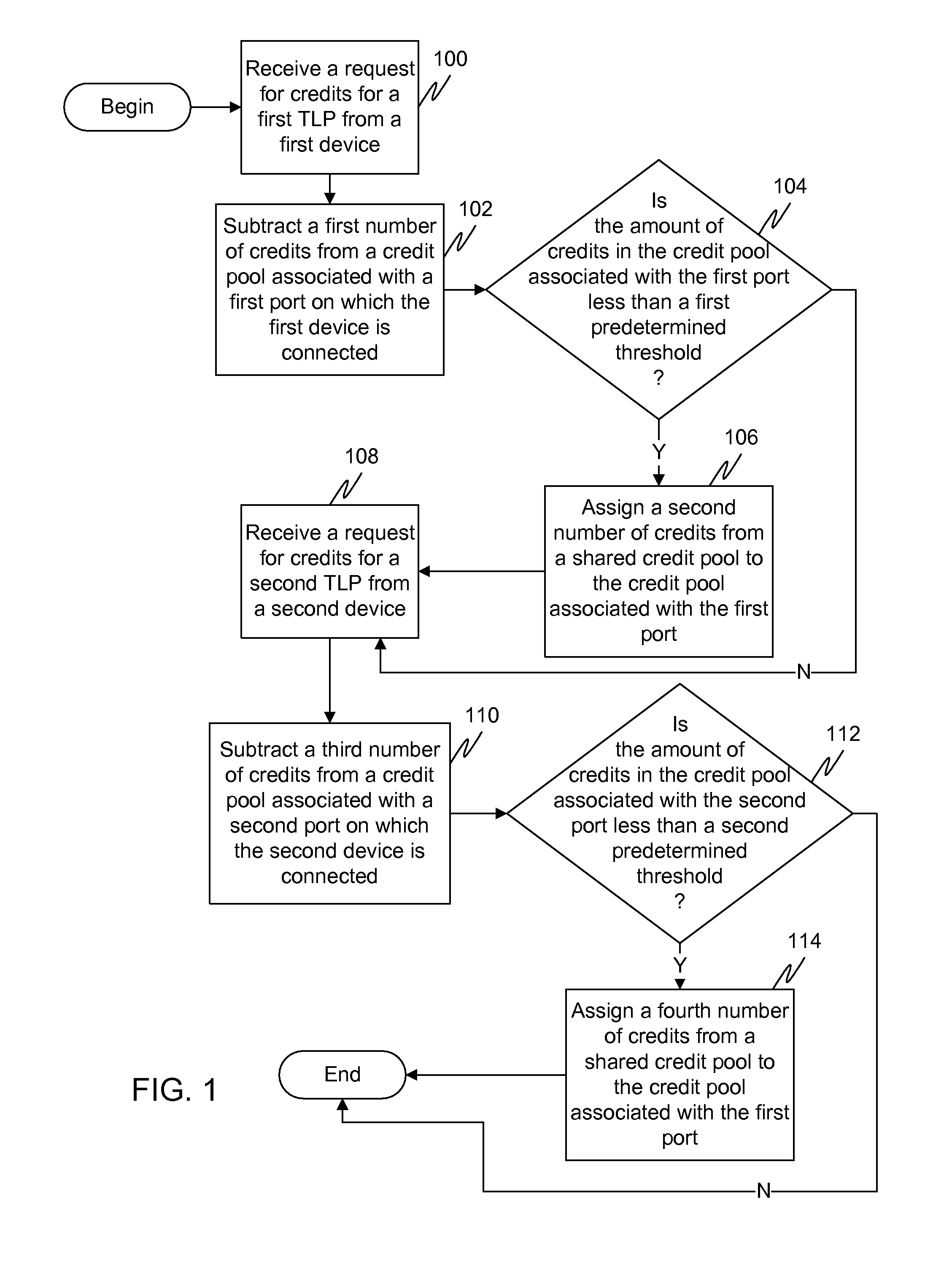

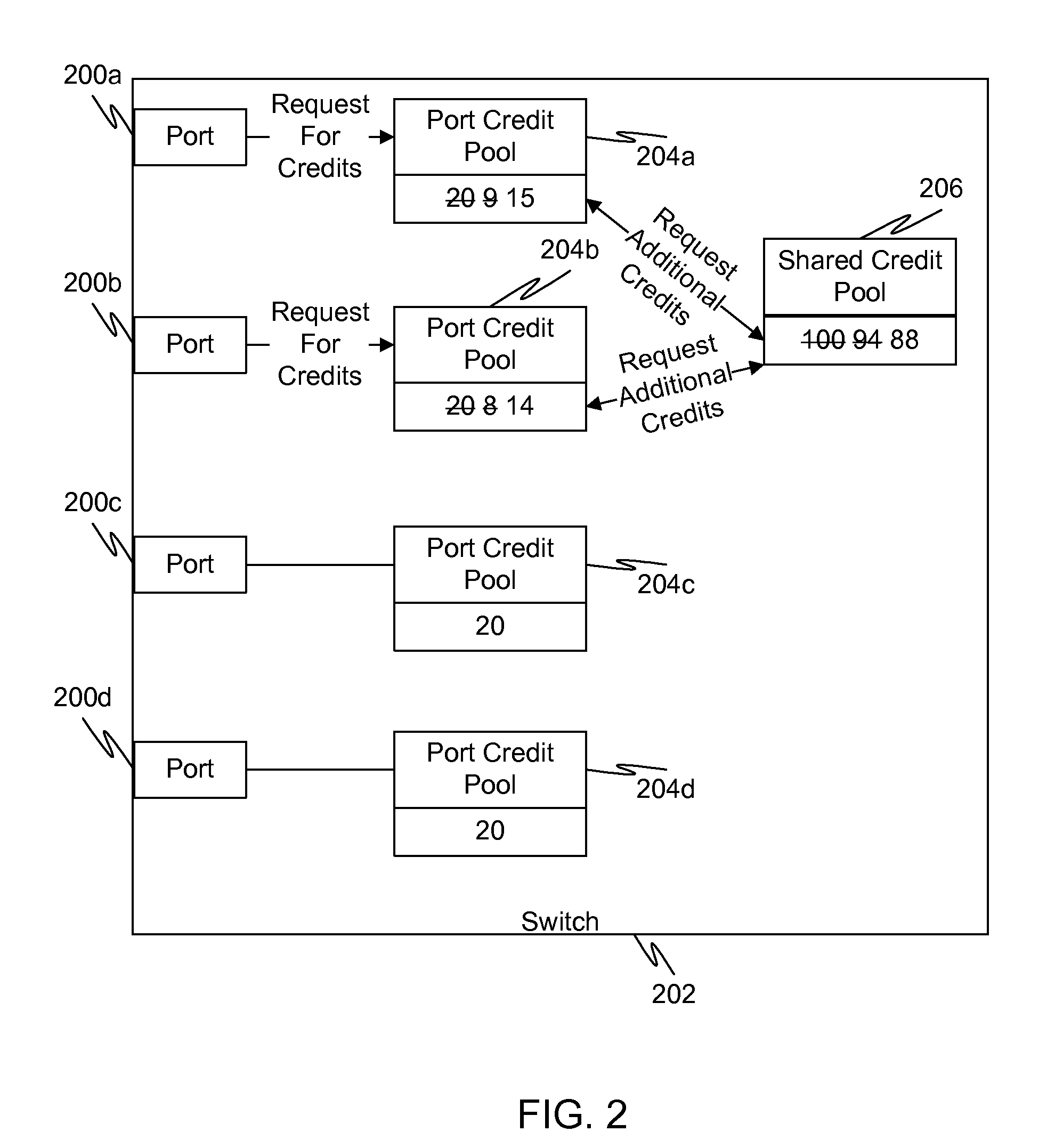

In a first embodiment of the present invention, a method for handling a Transaction Layer Packets (TLPs) from devices in a switch is provided, the method comprising: subtracting a first number of credits from a credit pool associated with a first port on which a first device is connected; determining if the amount of credits in the credit pool associated with the first port is less than a first predetermined threshold; and if the amount of credits in the credit pool associated with the first port is less than the first predetermined threshold, assigning a second number of credits from a shared credit pool to the credit pool associated with the first port.

Owner:AVAGO TECH INT SALES PTE LTD

Flexible routing engine for a PCI express switch and method of use

ActiveUS9025495B1Time-division multiplexData switching by path configurationRouting tableTransaction layer packet

A system and method are disclosed for a flexible routing engine in a PCIe switch. The system may include a switch manager that is enabled, through firmware, to configure one or more routing tables associated with a switch stack of a PCIe switch. The method may include receiving a configuration transaction layer packet at the switch manager of a PCIe switch, running firmware at the switch manager to identify a desired behavior of a switch stack of the switch and updating one or more routing tables associated with switch stack.

Owner:MICROSEMI STORAGE SOLUTIONS US INC

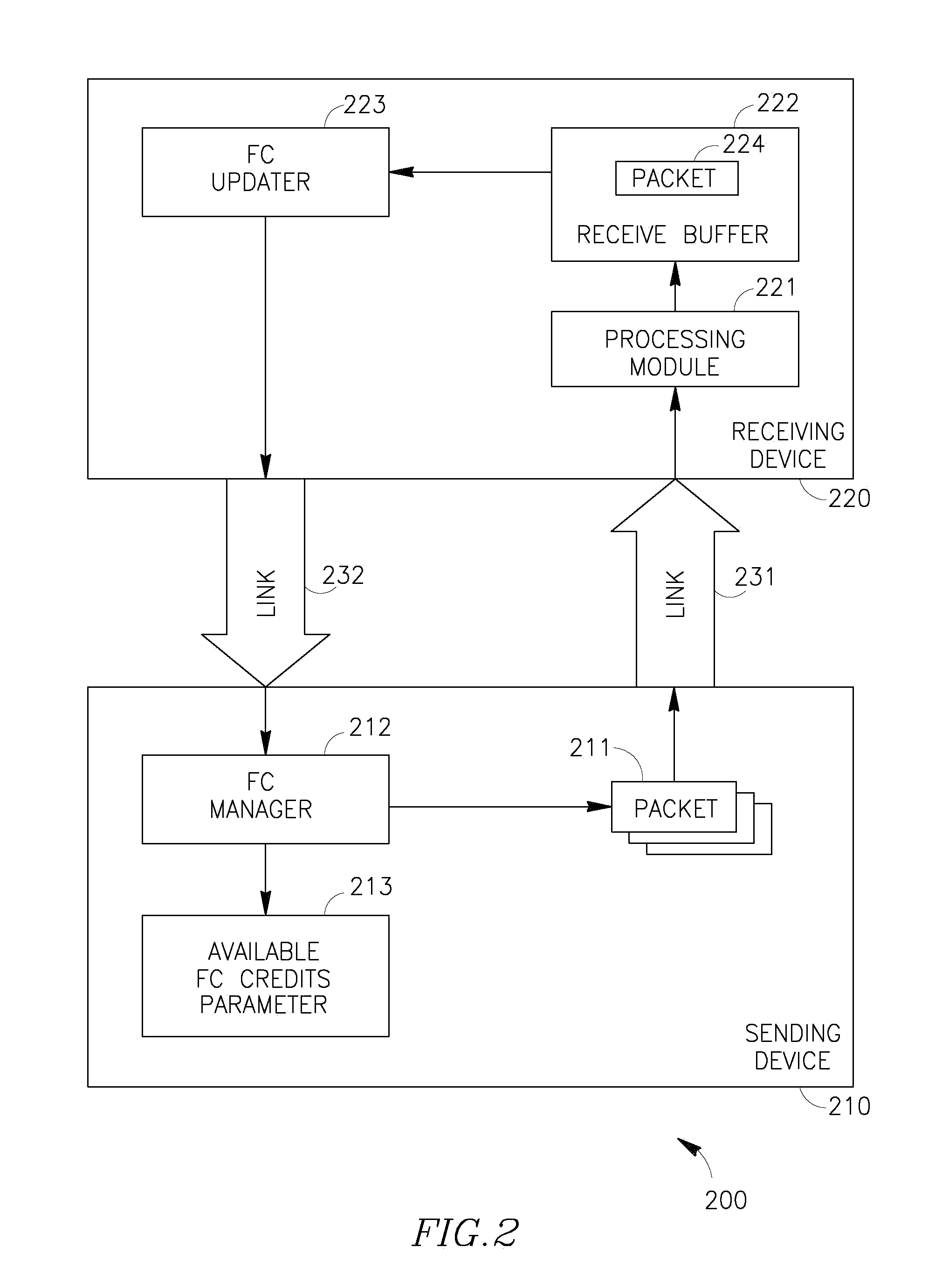

Device, System, and Method of Speculative Packet Transmission

InactiveUS20090113082A1Multiple digital computer combinationsInput/output processes for data processingTransaction layer packetPacket transmission

Device, system and method of speculative packet transmission. For example, an apparatus for speculative packet transmission includes: a credit-based flow control interconnect device to initiate speculative transmission of a Transaction Layer Packet if a number of available flow control credits is insufficient for completing the transmission.

Owner:LINKEDIN

Method and apparatus for mapped I/O routing in an interconnect switch

A system and method are disclosed for a flexible routing engine in a PCIe switch. The system may include a switch manager that is enabled, through firmware, to configure one or more routing tables associated with a switch stack of a PCIe switch. To enable non-transparent bridging and non-standard routing, such as mapped I / O routing, the method may include receiving a transaction layer packet at a mapped I / O routed port of a PCIe switch, and performing translation of the requester ID of the packet utilizing tables that are updated by the firmware of the switch manager to route the packet through the switch.

Owner:MICROSEMI STORAGE SOLUTIONS US INC

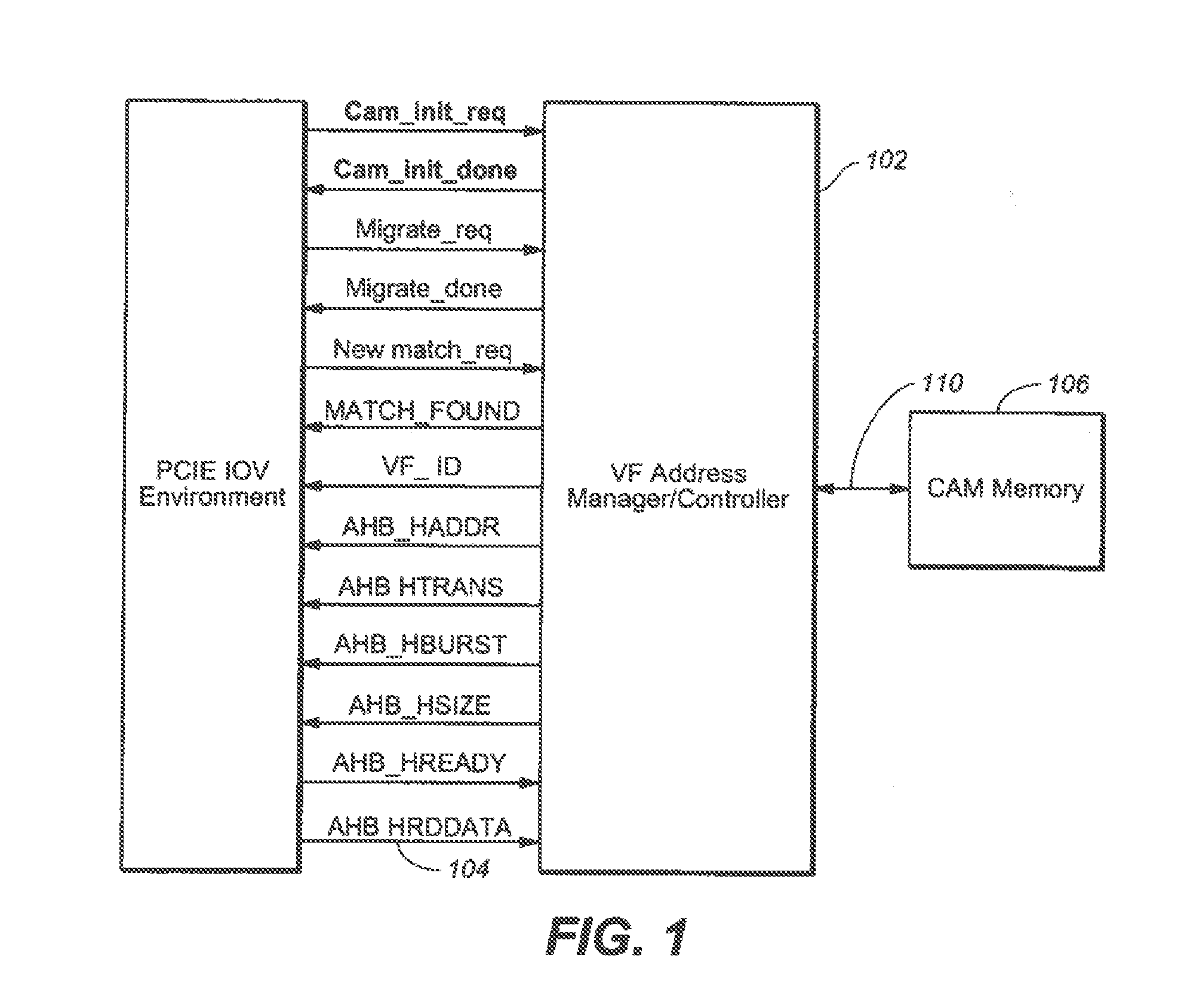

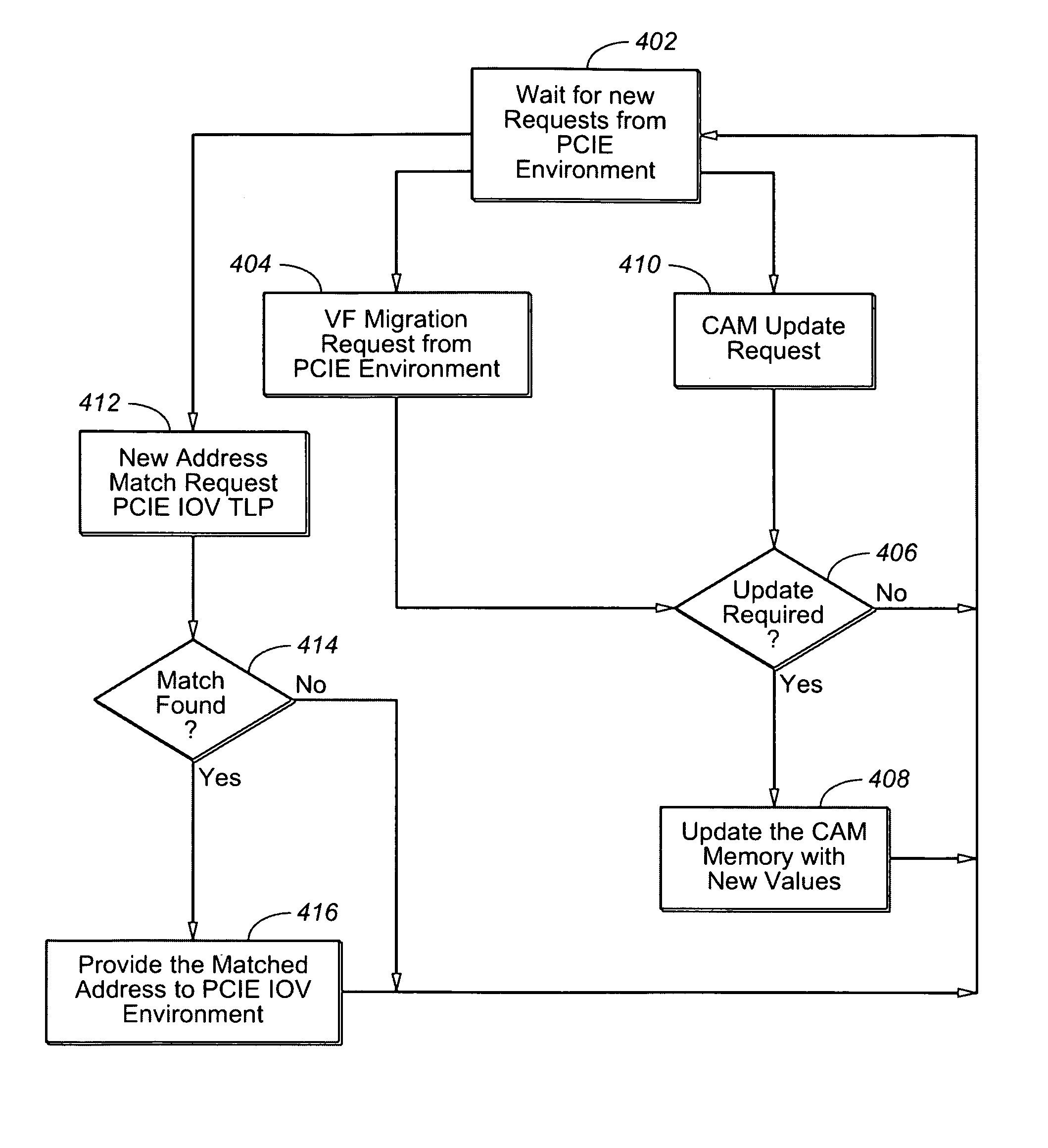

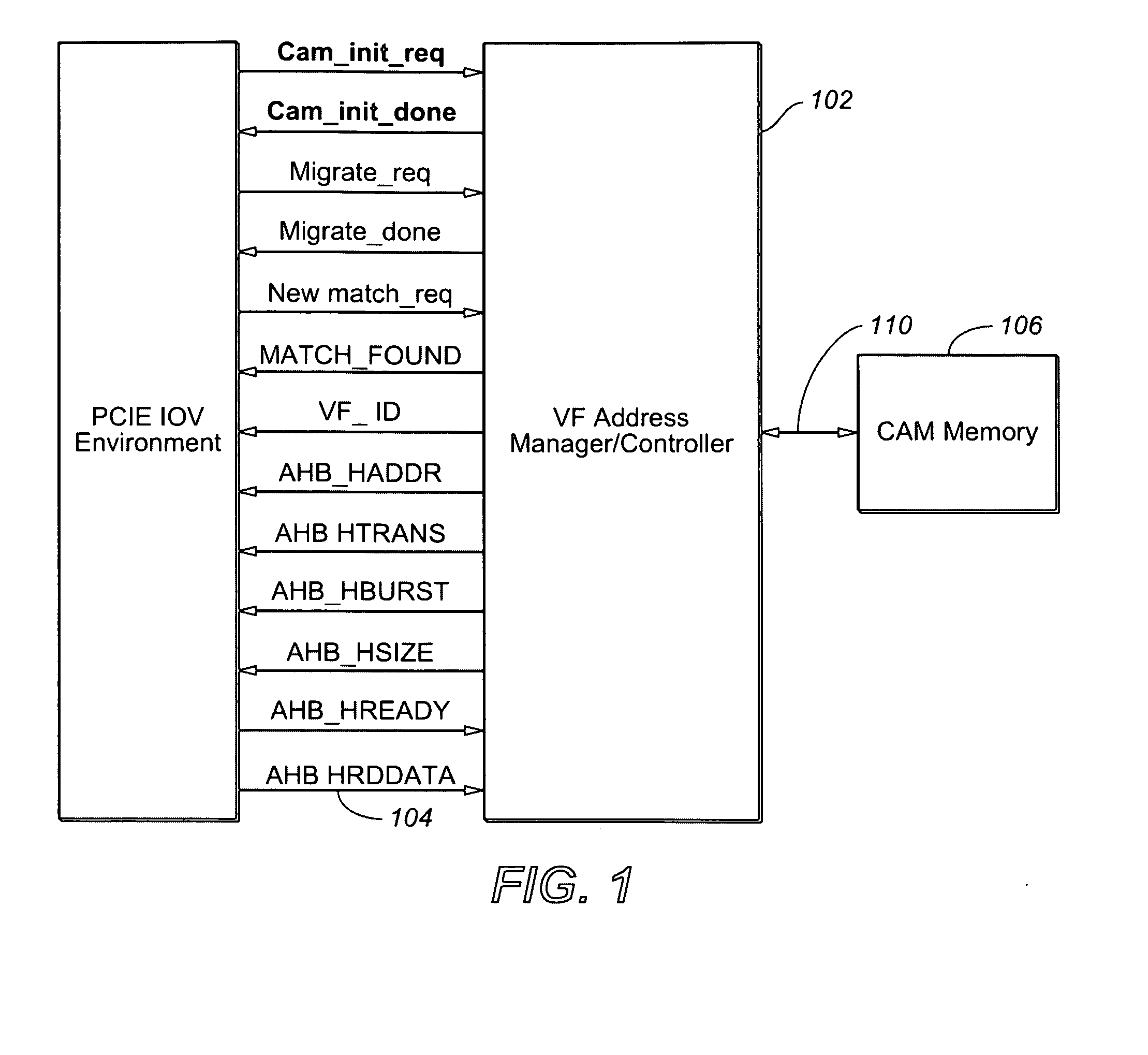

System and method for providing address decode and virtual function (VF) migration support in a peripheral component interconnect express (PCIE) multi-root input/output virtualization (IOV) environment

InactiveUS20110219161A1Memory systemsInput/output processes for data processingData virtualizationTransaction layer packet

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System and method for providing address decode and virtual function (VF) migration support in a peripheral component interconnect express (PCIE) multi-root input/output virtualization (IOV) environment

ActiveUS20090248973A1Memory systemsInput/output processes for data processingData virtualizationTransaction layer packet

The present invention is a method for providing address decode and Virtual Function (VF) migration support in a Peripheral Component Interconnect Express (PCIE) multi-root Input / Output Virtualization (IOV) environment. The method may include receiving a Transaction Layer Packet (TLP) from the PCIE multi-root IOV environment. The method may further include comparing a destination address of the TLP with a plurality of base address values stored in a Content Addressable Memory (CAM), each base address value being associated with a Virtual Function (VF), each VF being associated with a Physical Function (PF). The method may further include when a base address value included in the plurality of base address values matches the destination address of the TLP, providing the matching base address value to the PCIE multi-root IOV environment by outputting from the CAM the matching base address value. The method may further include constructing a requestor ID for the VF associated with the matching base address value, the requestor ID being based upon the output matching base address value and a bus number for a PF which owns the CAM.

Owner:AVAGO TECH INT SALES PTE LTD

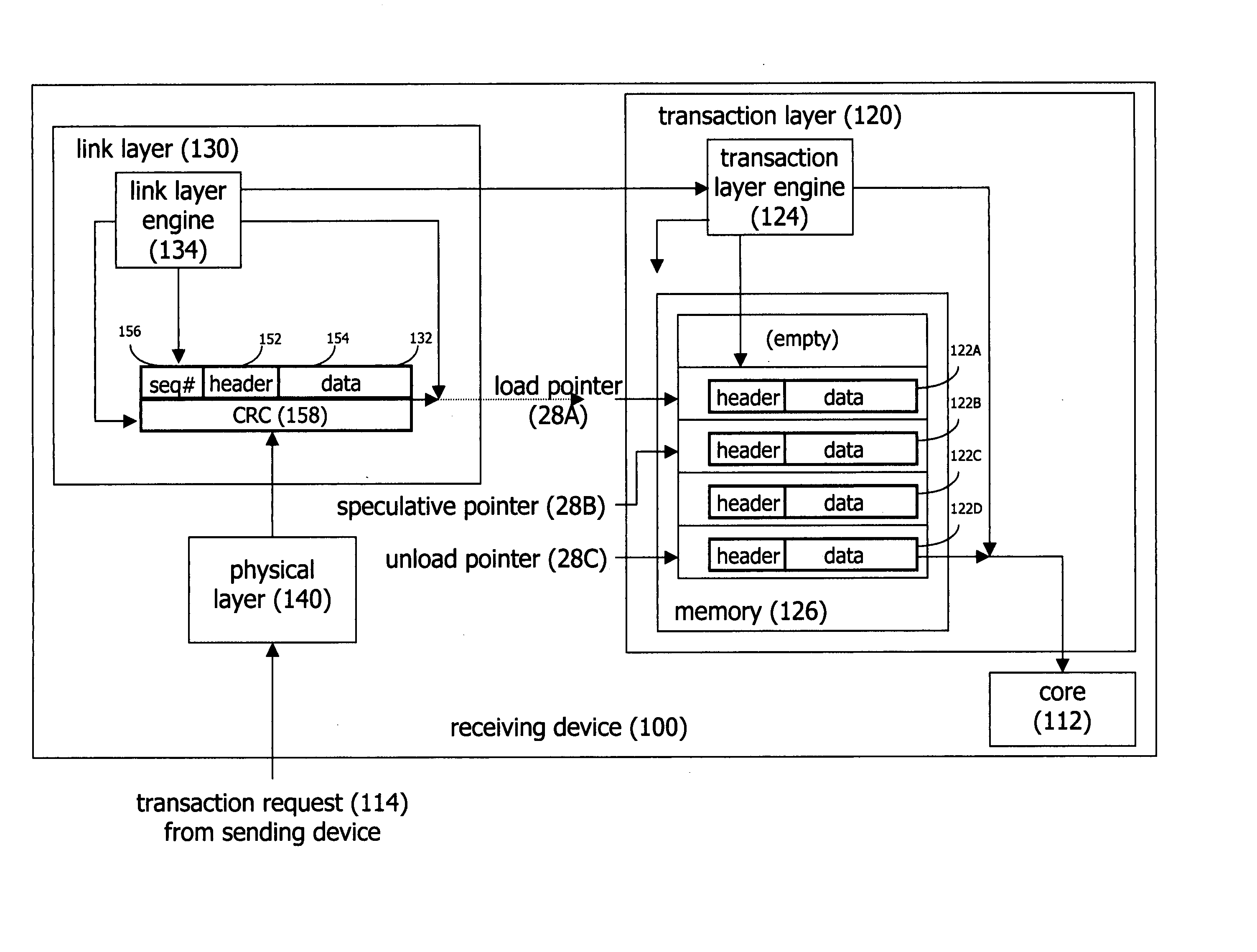

Speculative processing of transaction layer packets

InactiveUS20050144339A1TransmissionInput/output processes for data processingData packPhysical layer

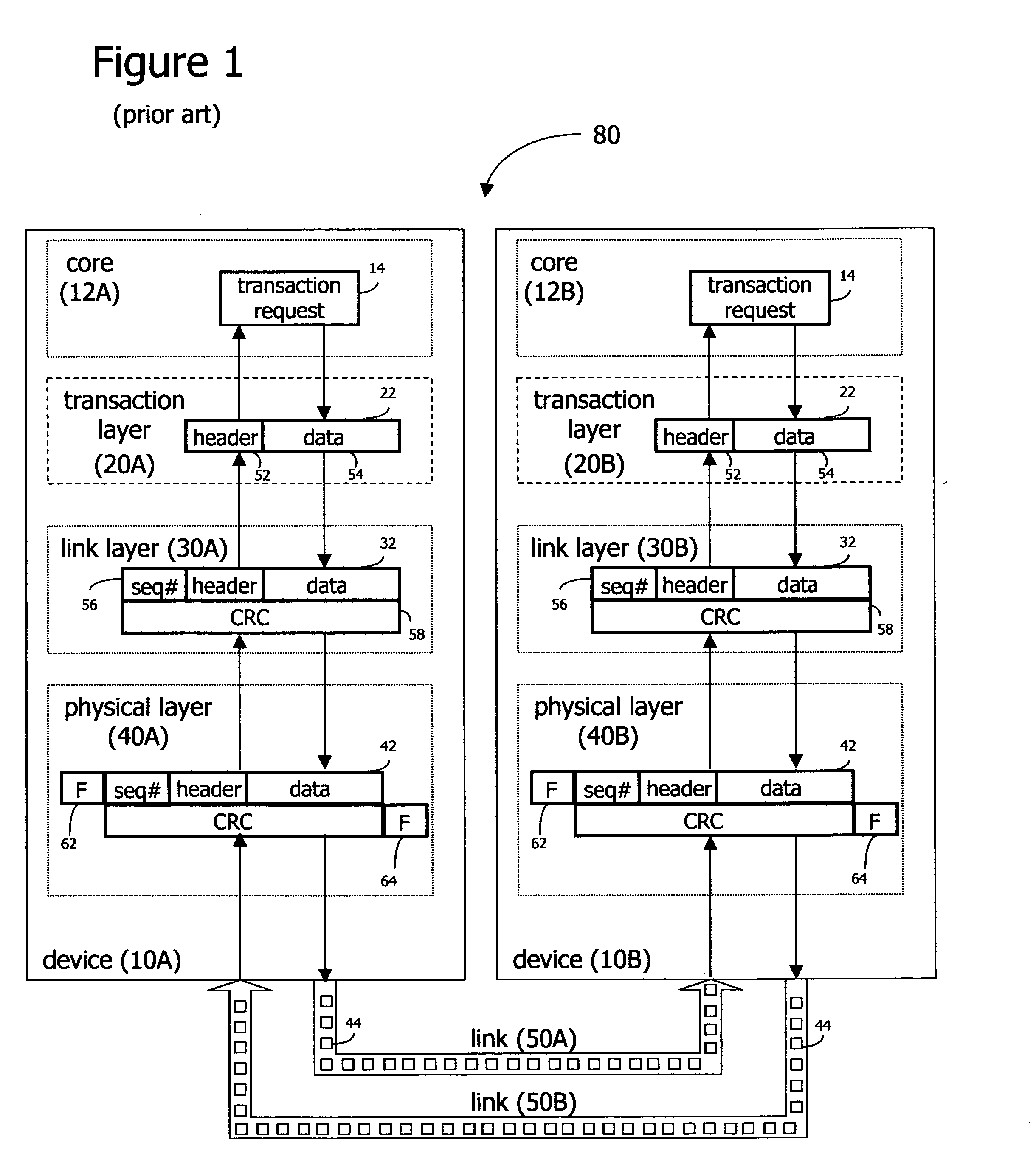

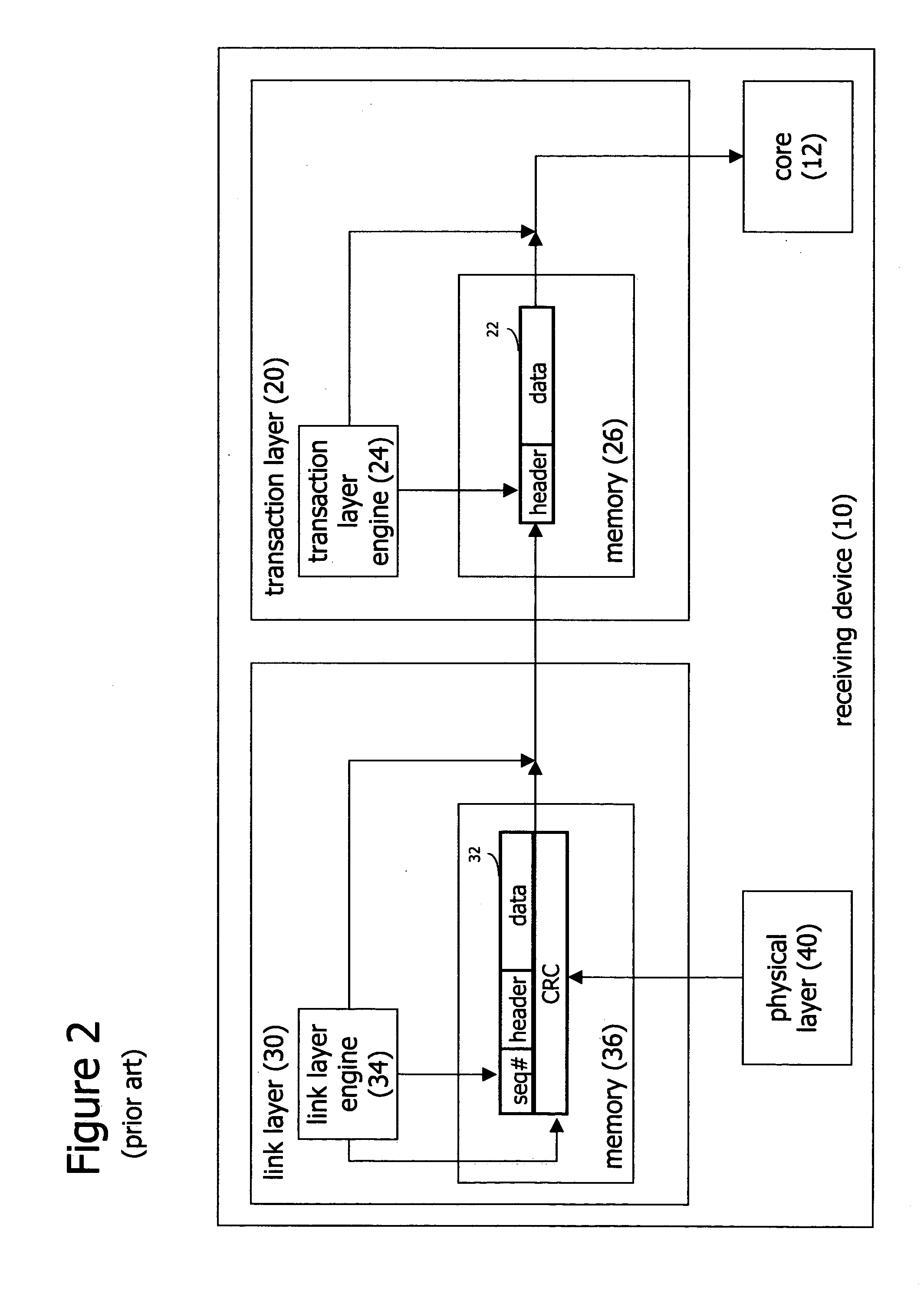

A receiving device in which transaction layer packets are speculatively forwarded, is disclosed. The receiving device includes a physical layer, a link layer, a transaction layer, and a core. Transaction layer packets are forwarded to the transaction layer before processing at the link layer is completed, and without the use of memory storage at the link layer. A link layer engine checks the sequence number only and not the CRC before forwarding the packet to the transaction layer. This allows the transaction layer to pre-process the packet, such as verifying header information. However, the transaction layer is unable to make the transaction globally available until the link layer has verified the CRC of the packet. The simultaneous processing of the packet by both the link layer and the transaction layer may reduce latency and lessens the amount of memory needed for processing.

Owner:INTEL CORP

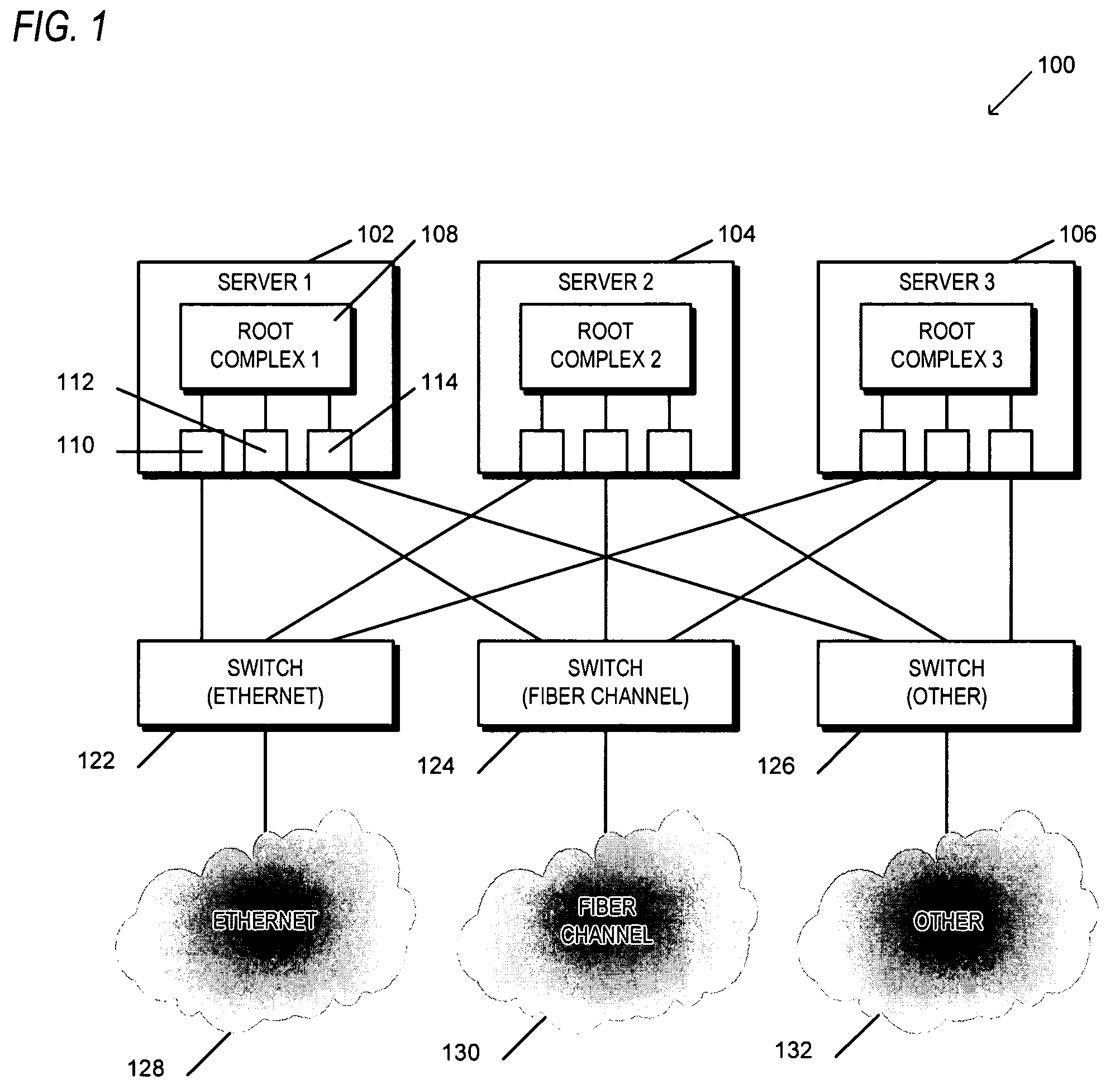

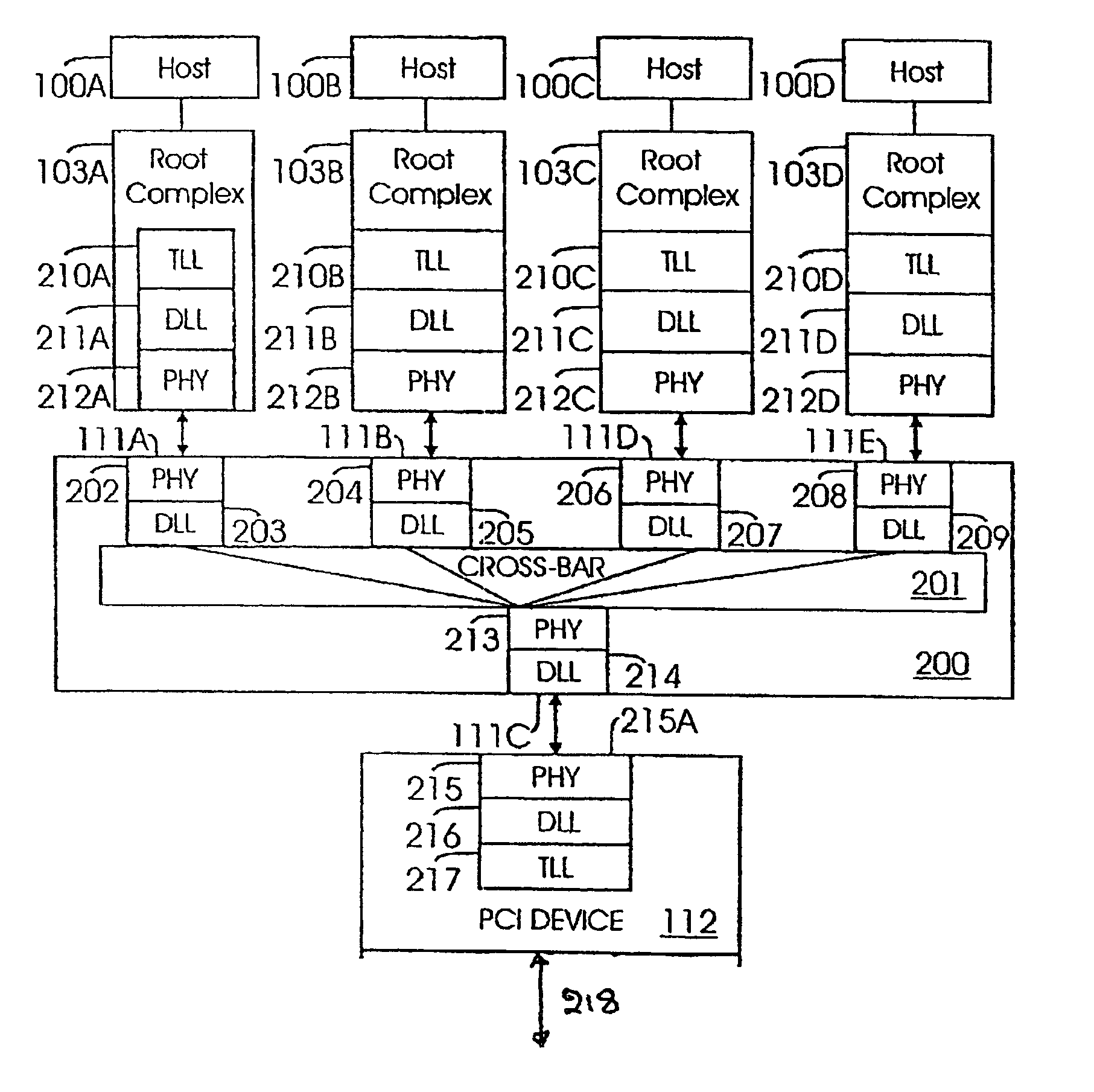

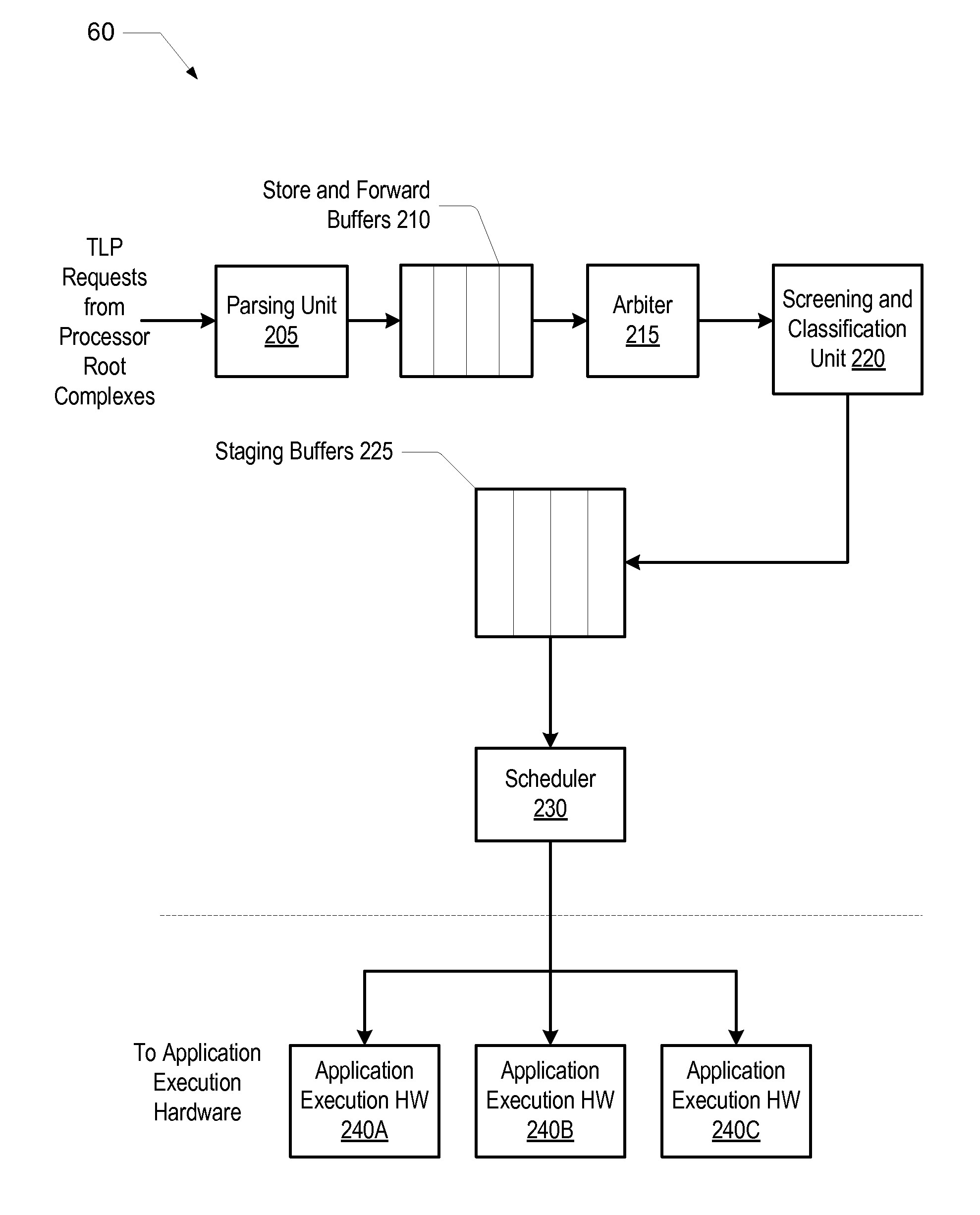

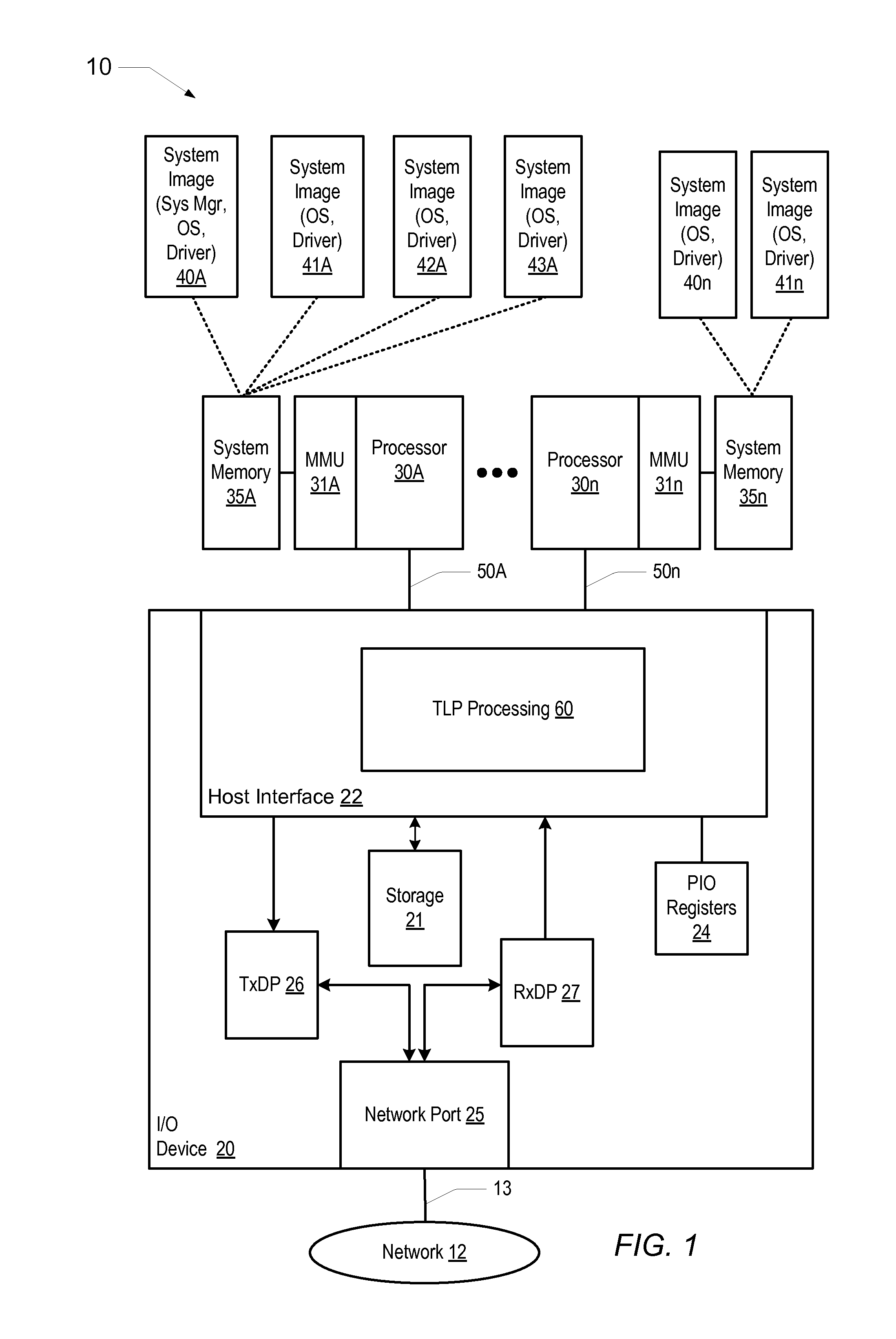

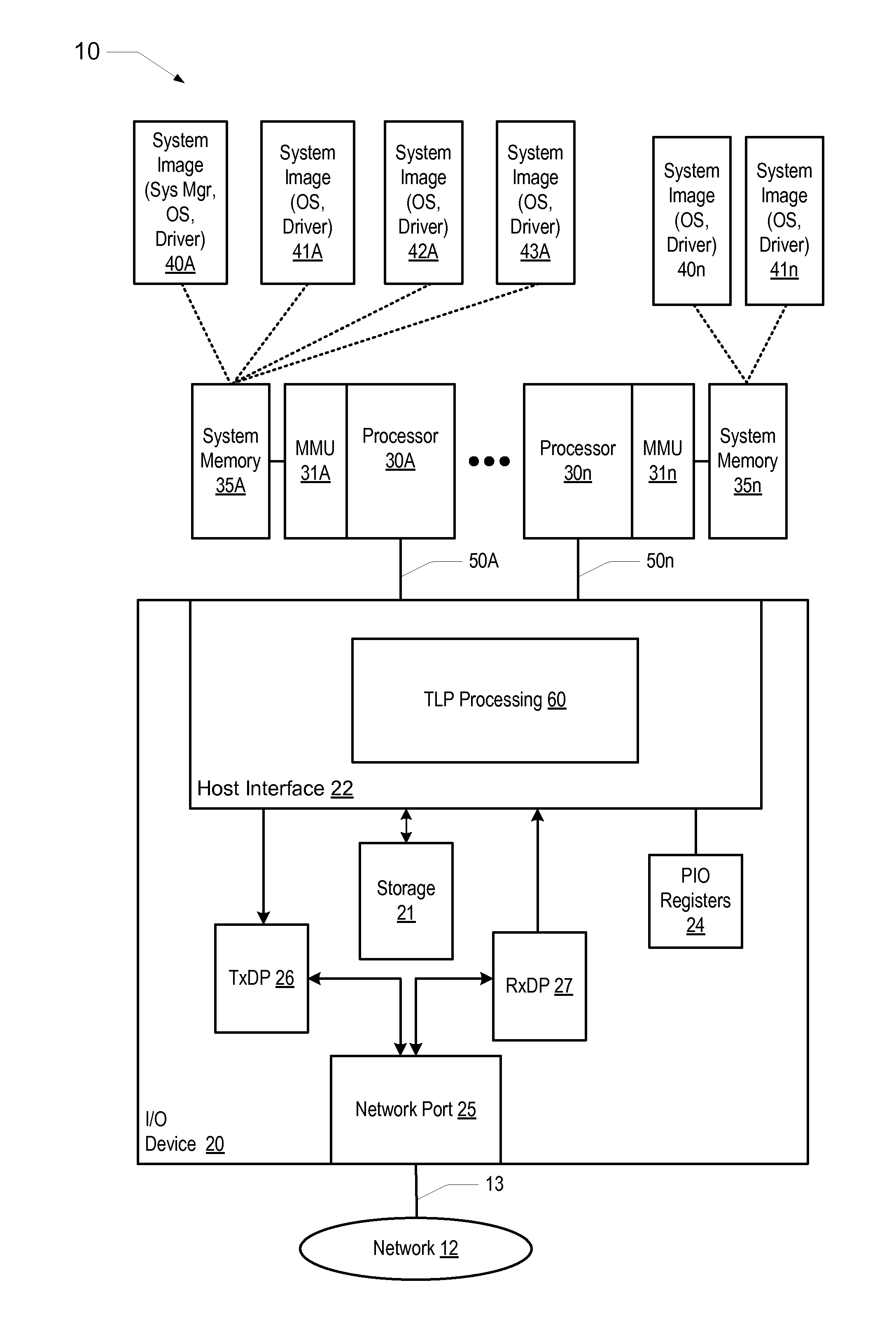

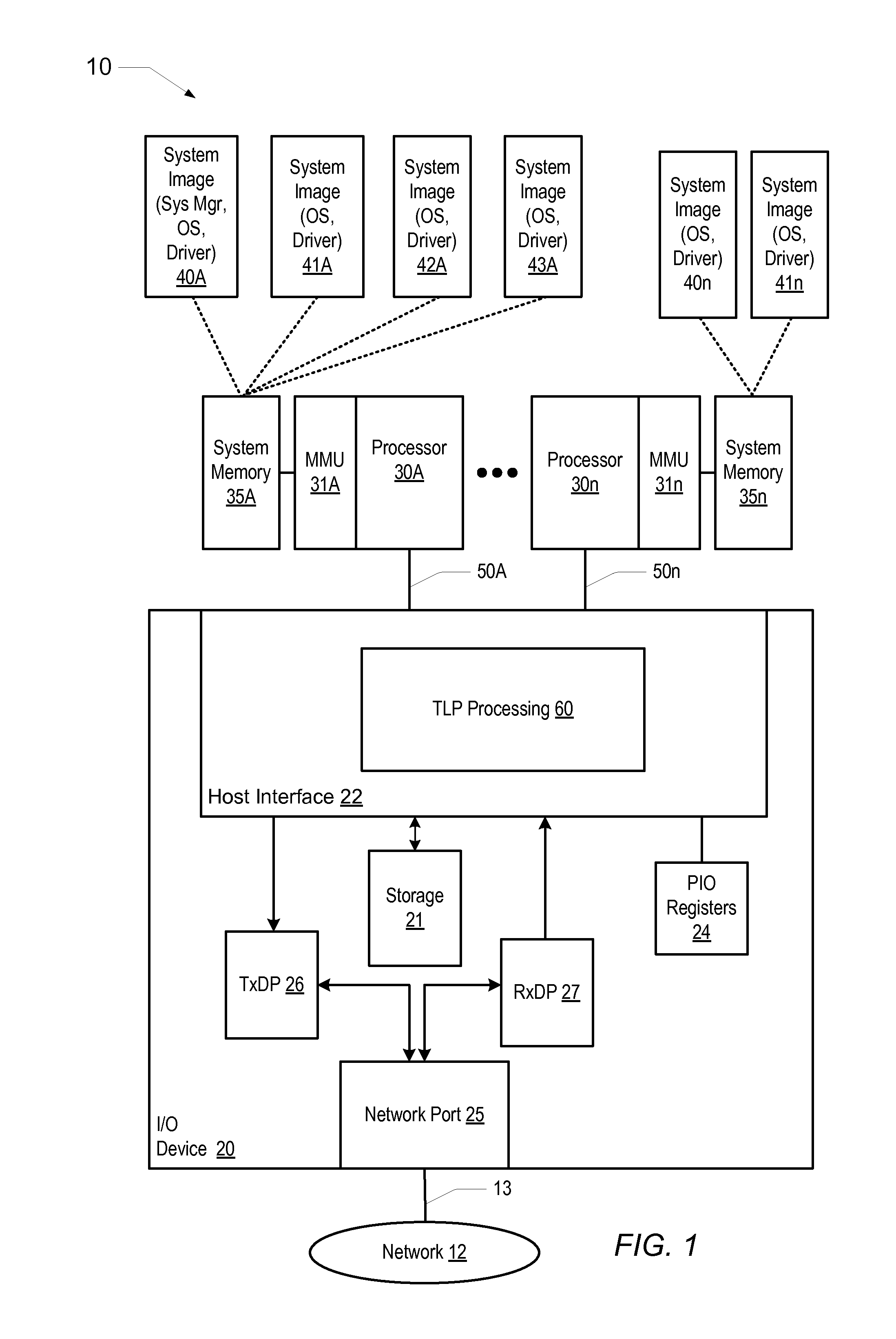

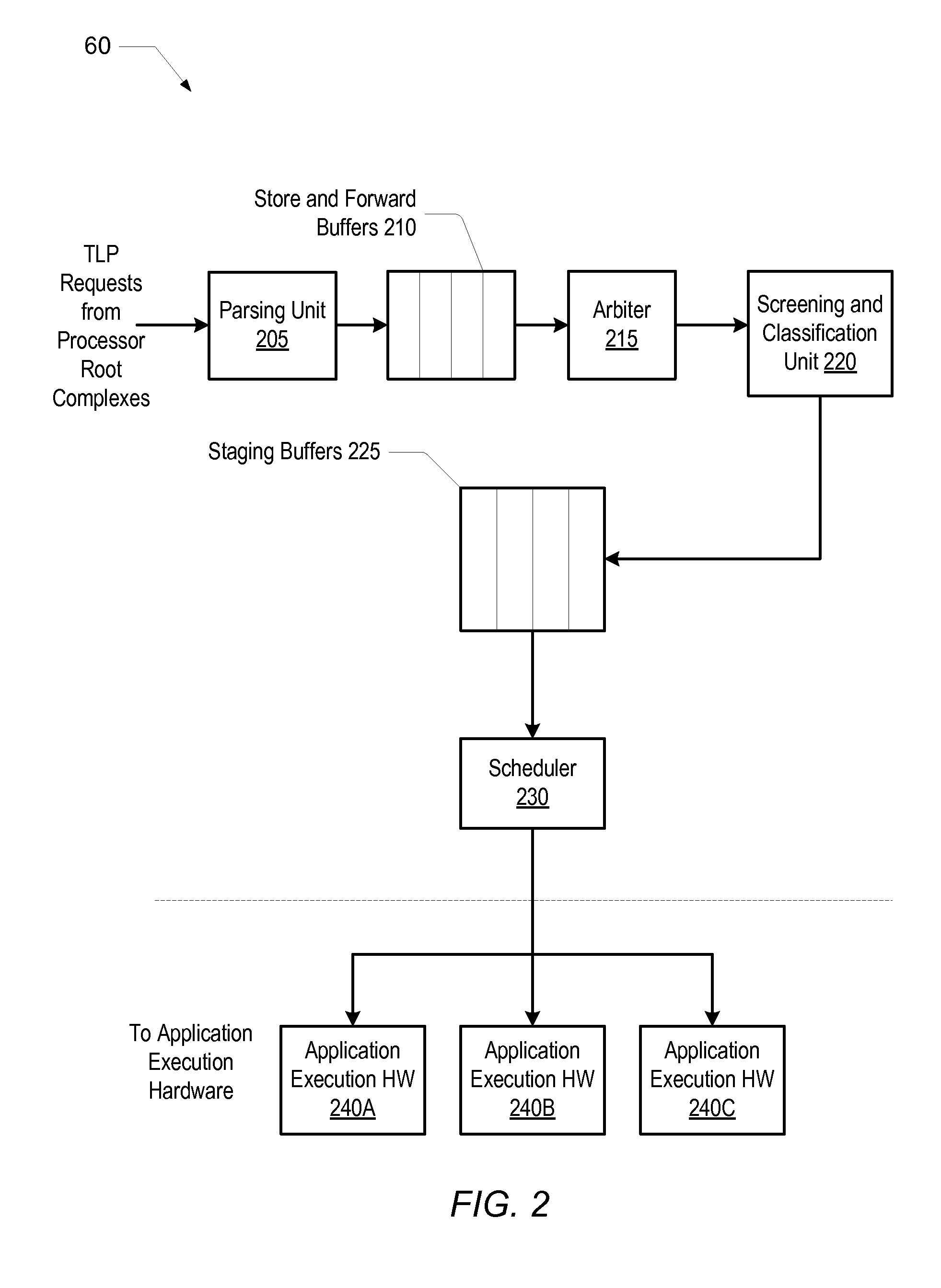

Input/output device including a mechanism for transaction layer packet processing in multiple processor systems

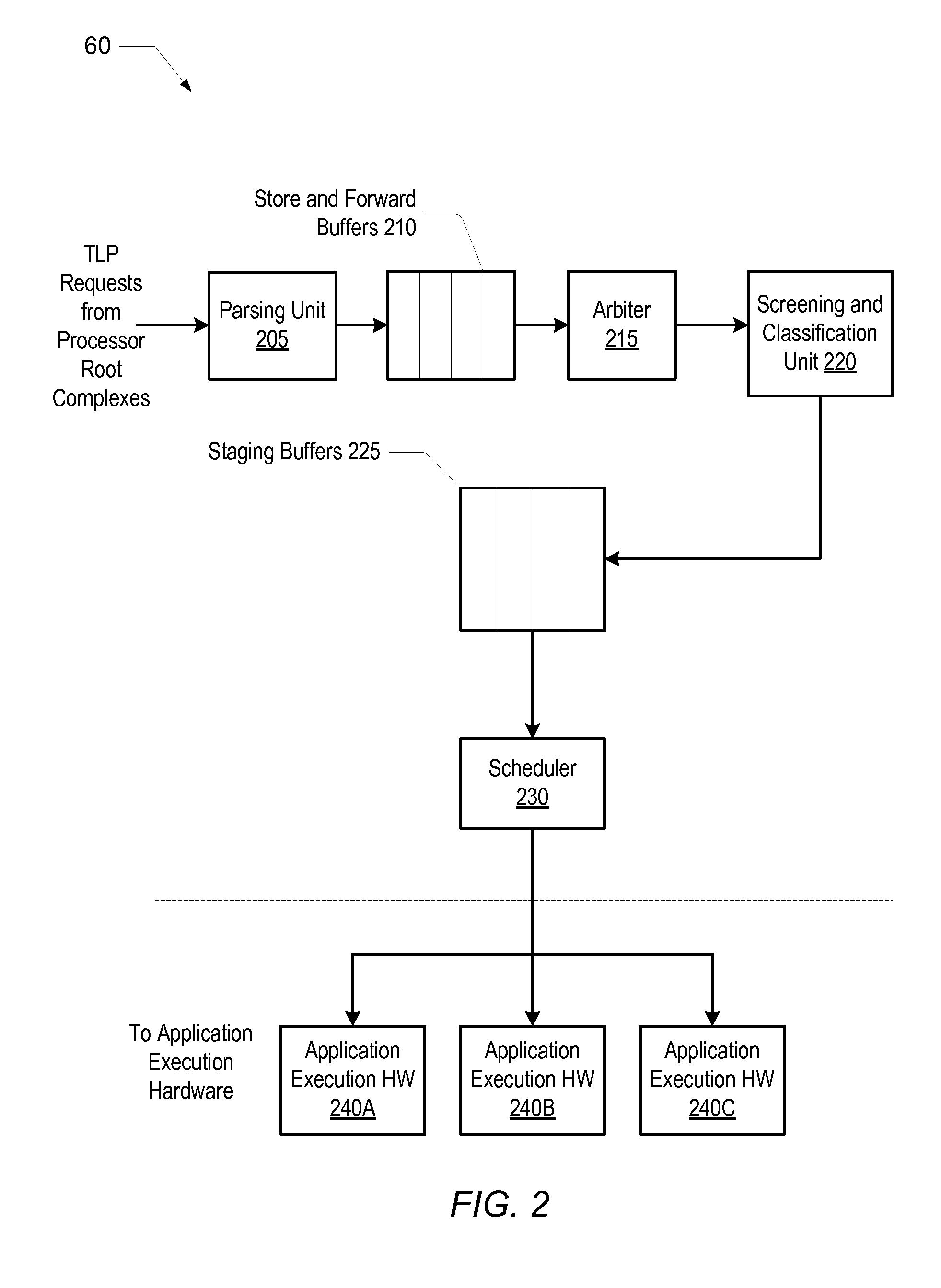

ActiveUS20110072172A1Input/output processes for data processingData conversionMulti processorRoot complex

An I / O device includes a host interface coupled to a plurality of hardware resources. The host interface includes a transaction layer packet (TLP) processing unit that may receive and process a plurality of transaction layer packets sent by a plurality of processing units. Each processing unit may correspond to a respective root complex. The TLP processing unit may identify a transaction type and a processing unit corresponding to each transaction layer packet and store each transaction layer packet within a storage according to the transaction type and the processing unit. The TLP processing unit may select one or more transaction layer packets from the storage for process scheduling based upon a set of fairness criteria using an arbitration scheme. The TLP processing unit may further select and dispatch transaction layer packets for processing by downstream application hardware based upon additional criteria.

Owner:ORACLE INT CORP

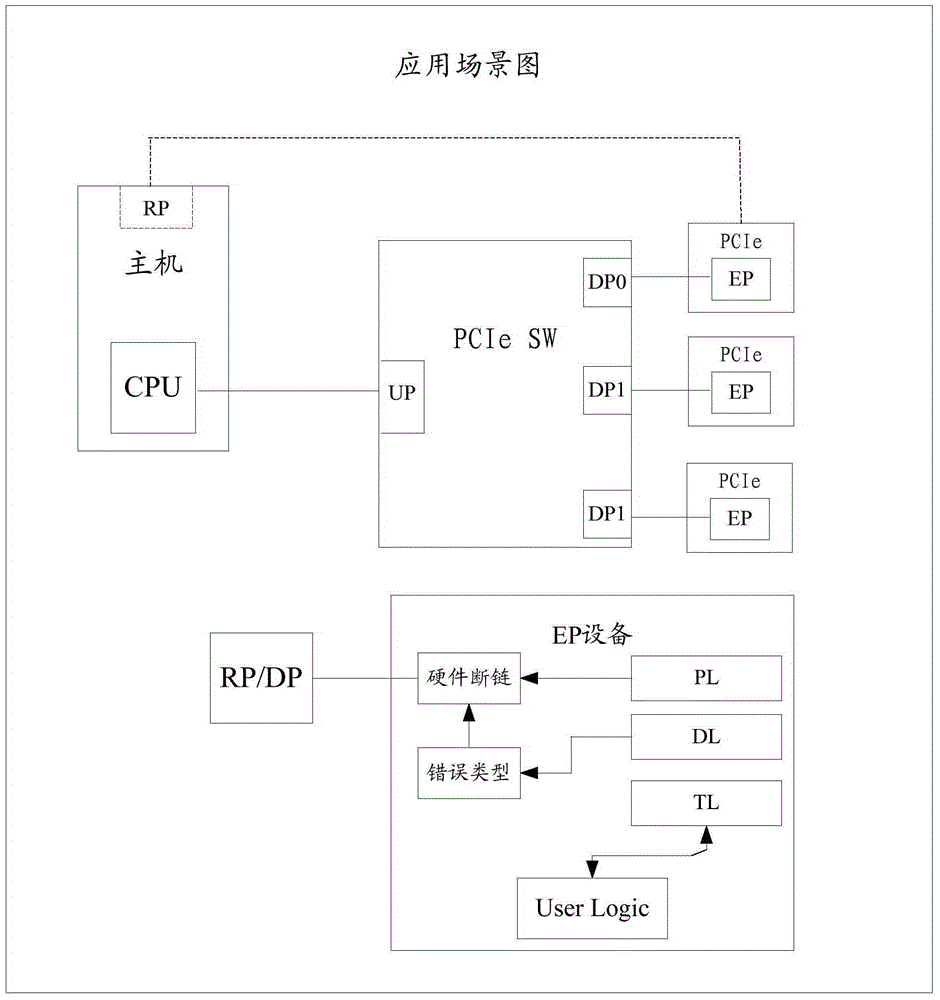

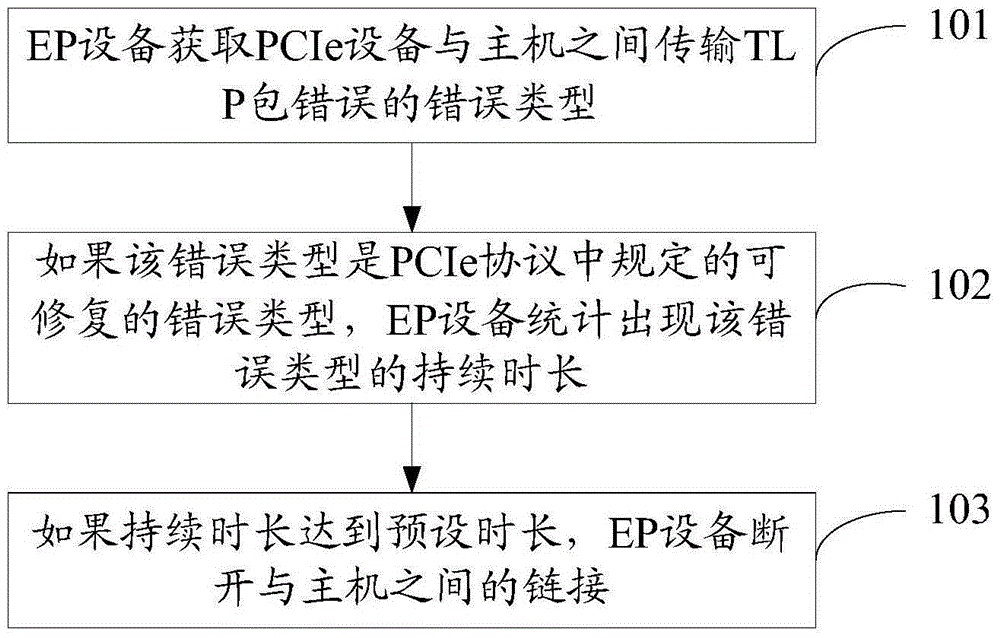

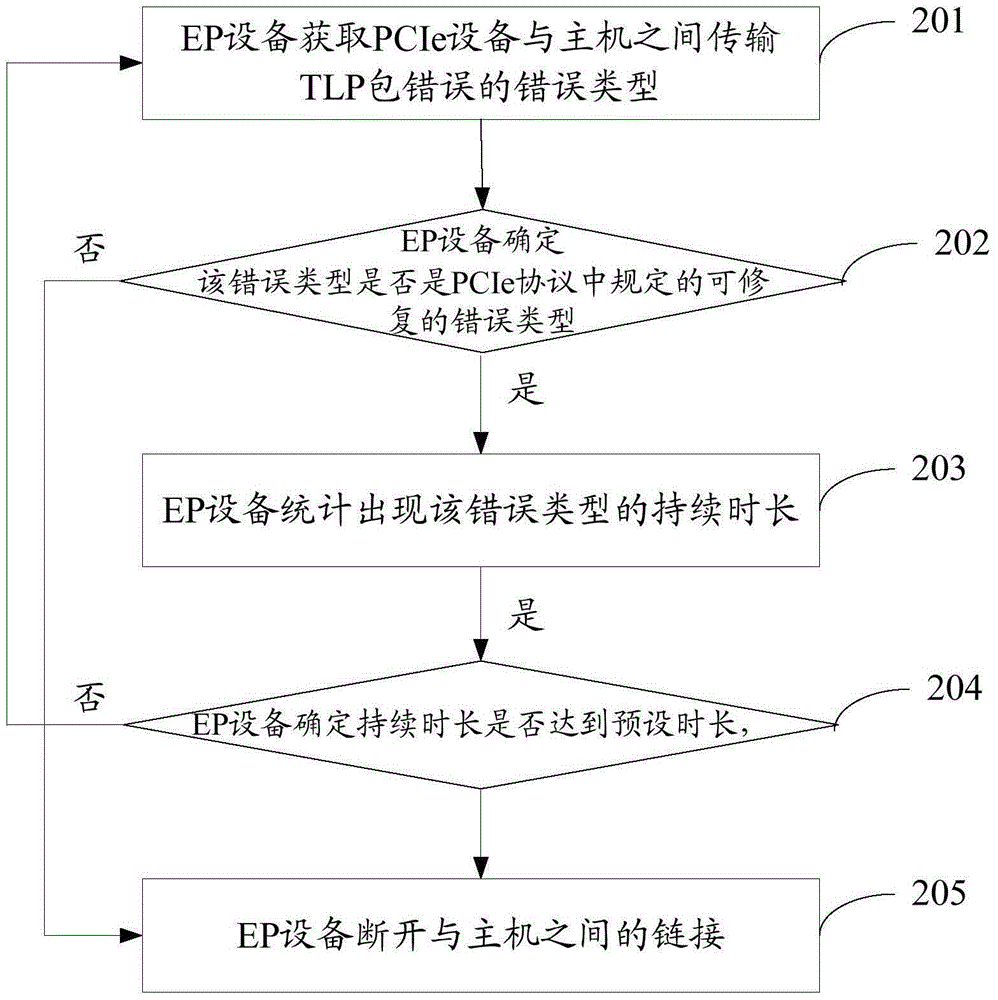

Method and device for disconnecting link between PCIe (peripheral component interface express) equipment and host computer

ActiveCN105205021ACorrect operation testingError detection/correctionComputer scienceTransaction layer packet

The invention discloses a method and a device for disconnecting a link between PCIe (peripheral component interface express) equipment and a host computer and belongs to the technical field of computers. The method comprises steps as follows: the PCIe equipment comprises end-node EP (error print) equipment, and the EP equipment is used for acquiring a type of a TLP (transaction layer packet) error between the PCIe equipment and the host computer; if the error type is a repairable error type specified in a PCIe protocol, the EP equipment counts the appearing time duration of the error type; if the time duration reaches preset time duration, the EP equipment disconnects the link with the host computer. The device comprises an acquisition module, a counting module and a disconnection module. According to the method and the device, the influence on host computer service can be reduced.

Owner:HUAWEI TECH CO LTD

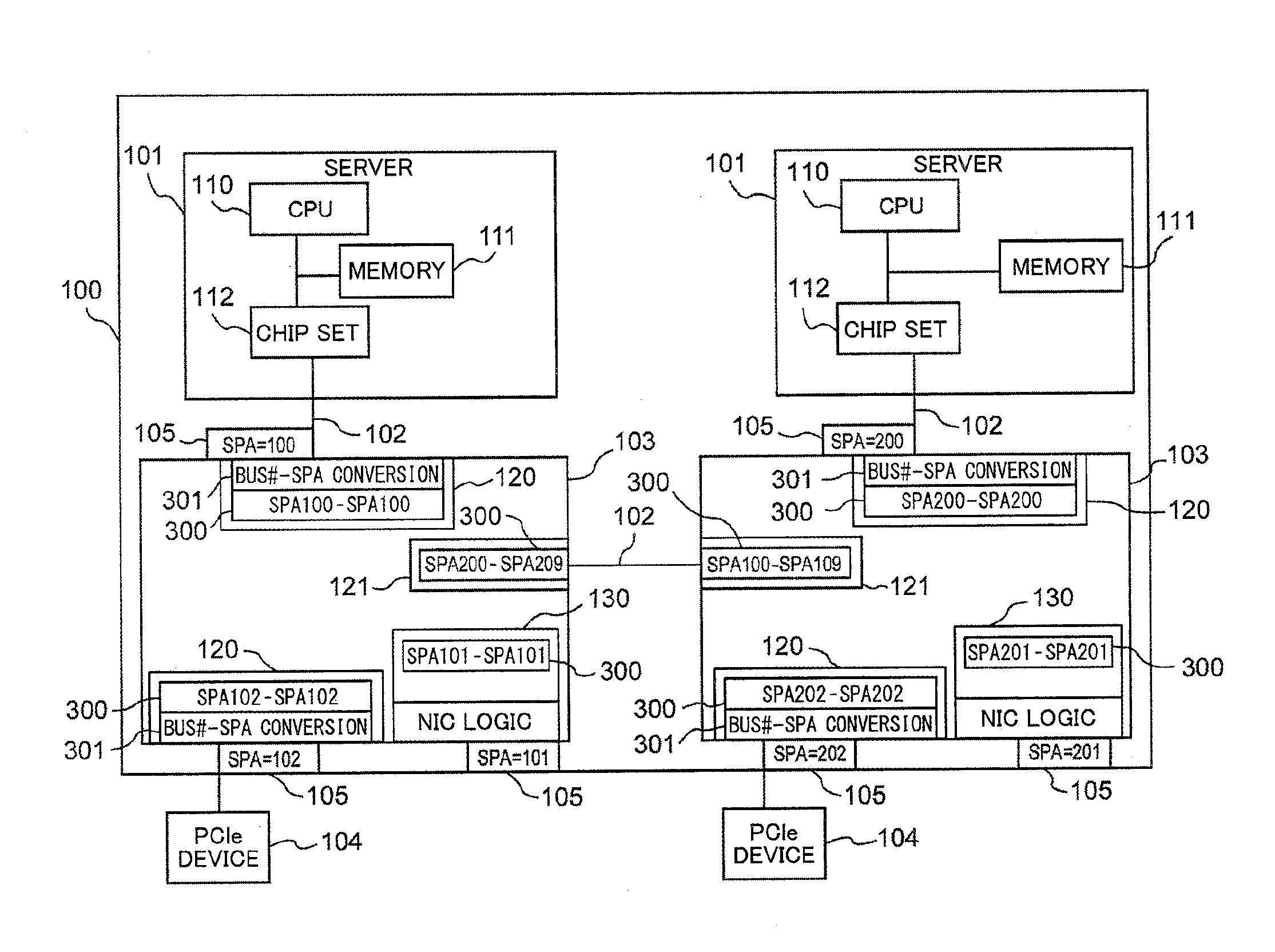

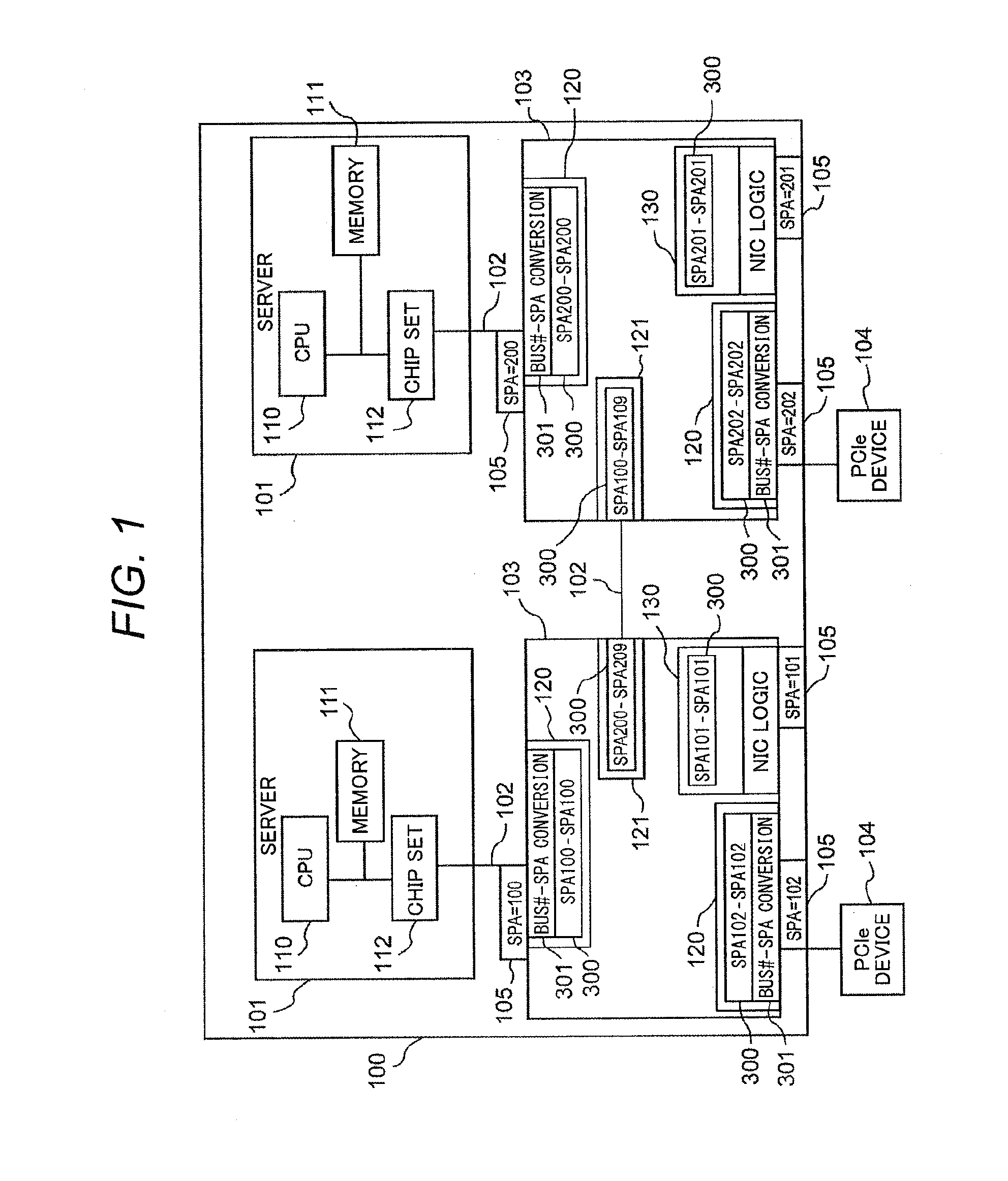

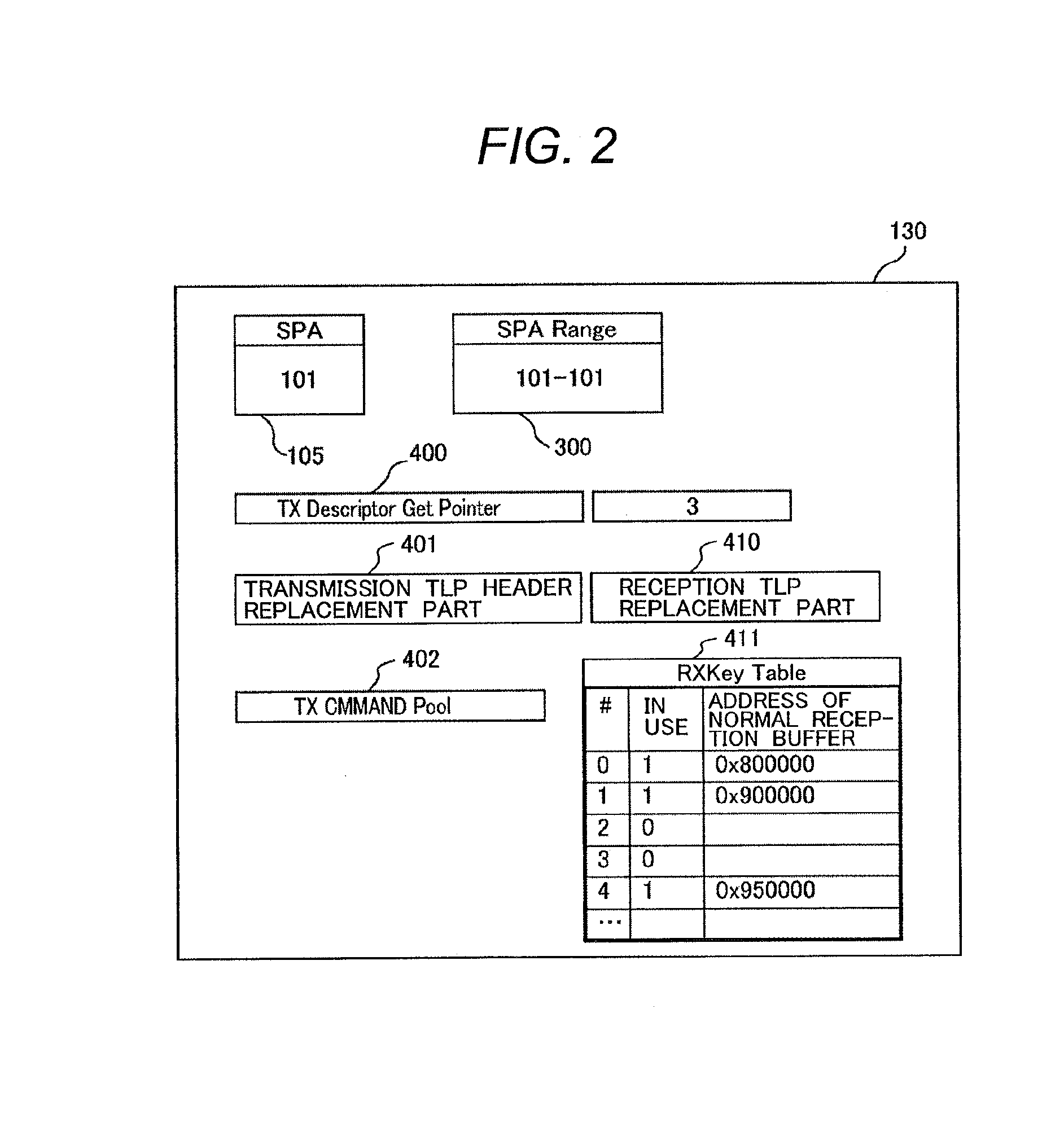

Computer system and method for communicating data between computers

ActiveUS20140269754A1Eliminate needData switching by path configurationElectric digital data processingComputerized systemData shipping

In a computer on the transmission side, an NW driver, which is recognized, by the OS, as an NIC driver, stores data to be transmitted and a destination SPA into a memory, and outputs a transaction layer packet (TLP), which has been generated by a first computer, to a PCIe switch. A first NIC logic of the PCIe switch of the PCIe switch corresponding to the first computer on the transmission side adds a system port address (SPA) to the TLP transferred from the first computer, and transfers the data of the TLP to a port associated with a second NIC logic and having an address indicated by the SPA (destination SPA). The second NIC logic having received the data writes the receive data into a memory of a second computer, on the reception side, which is connected to another PCIe switch where the second NIC logic exists.

Owner:HITACHI LTD

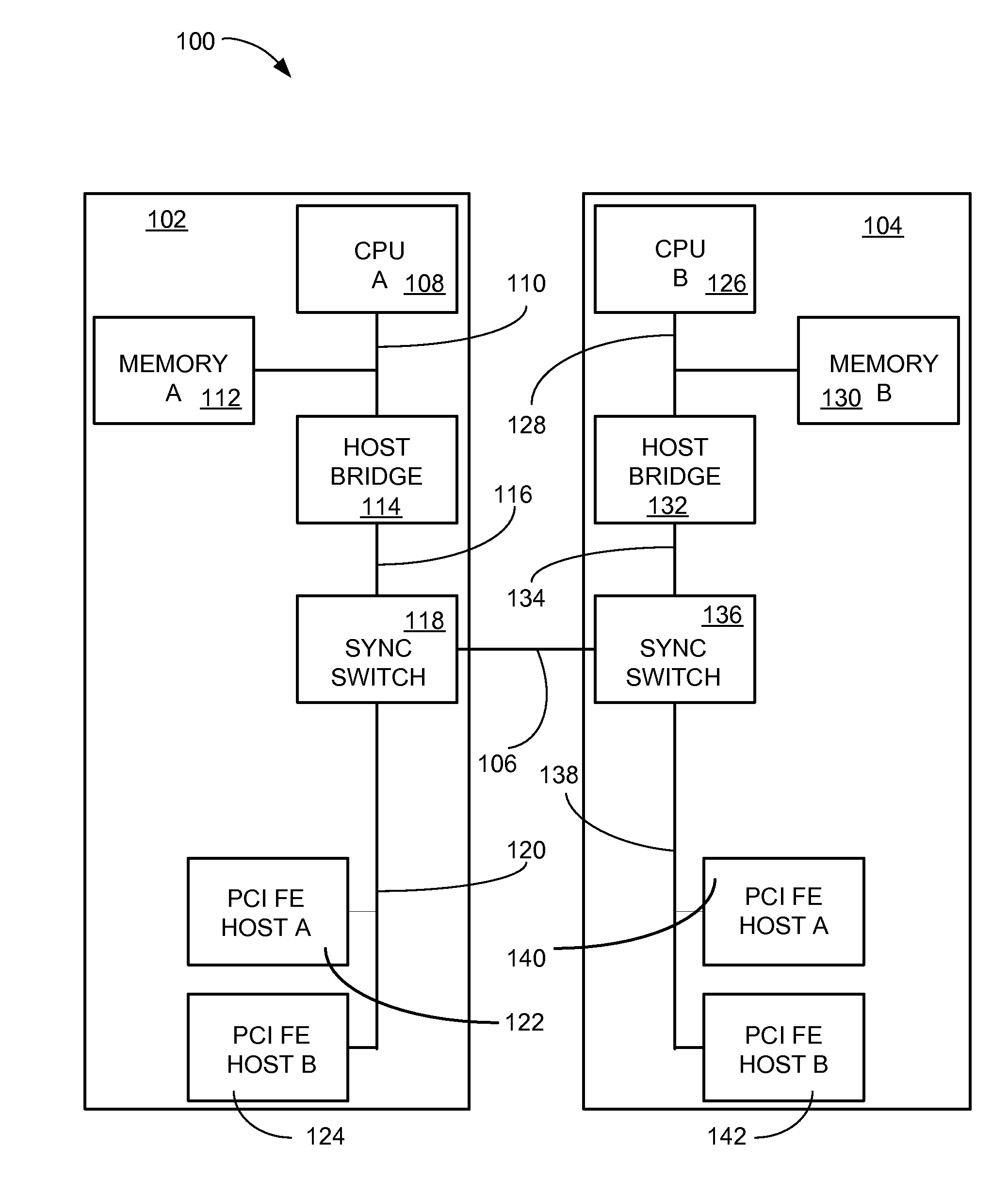

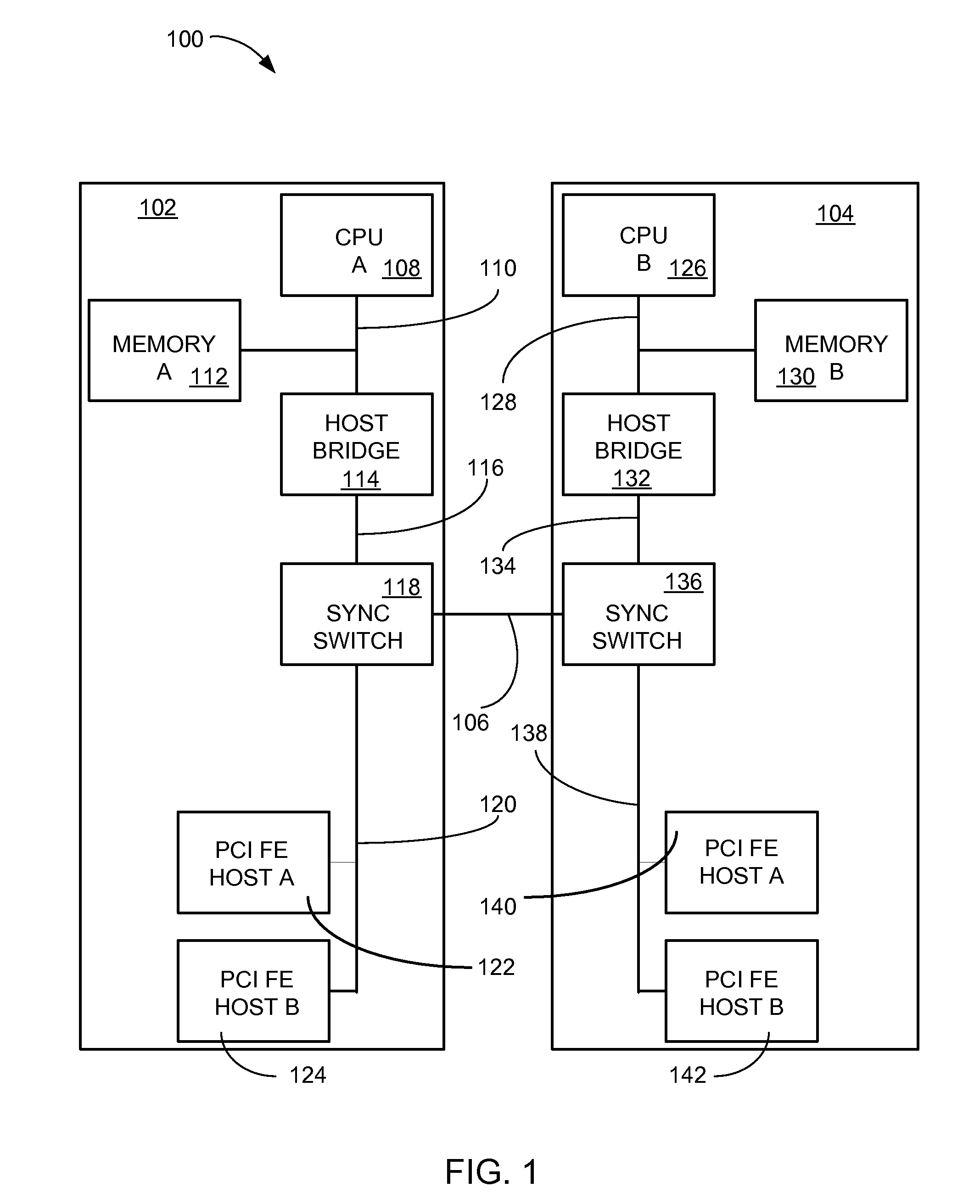

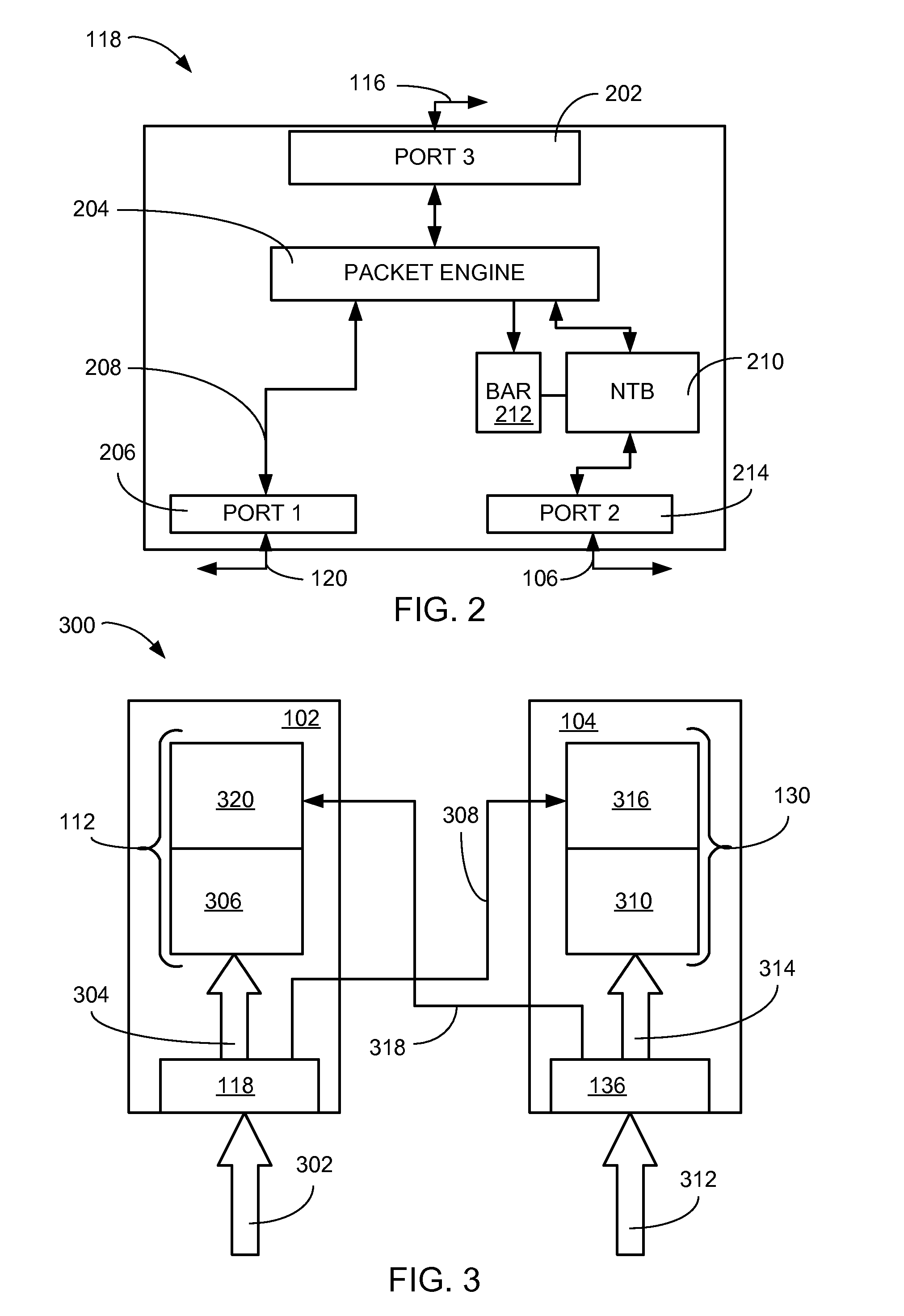

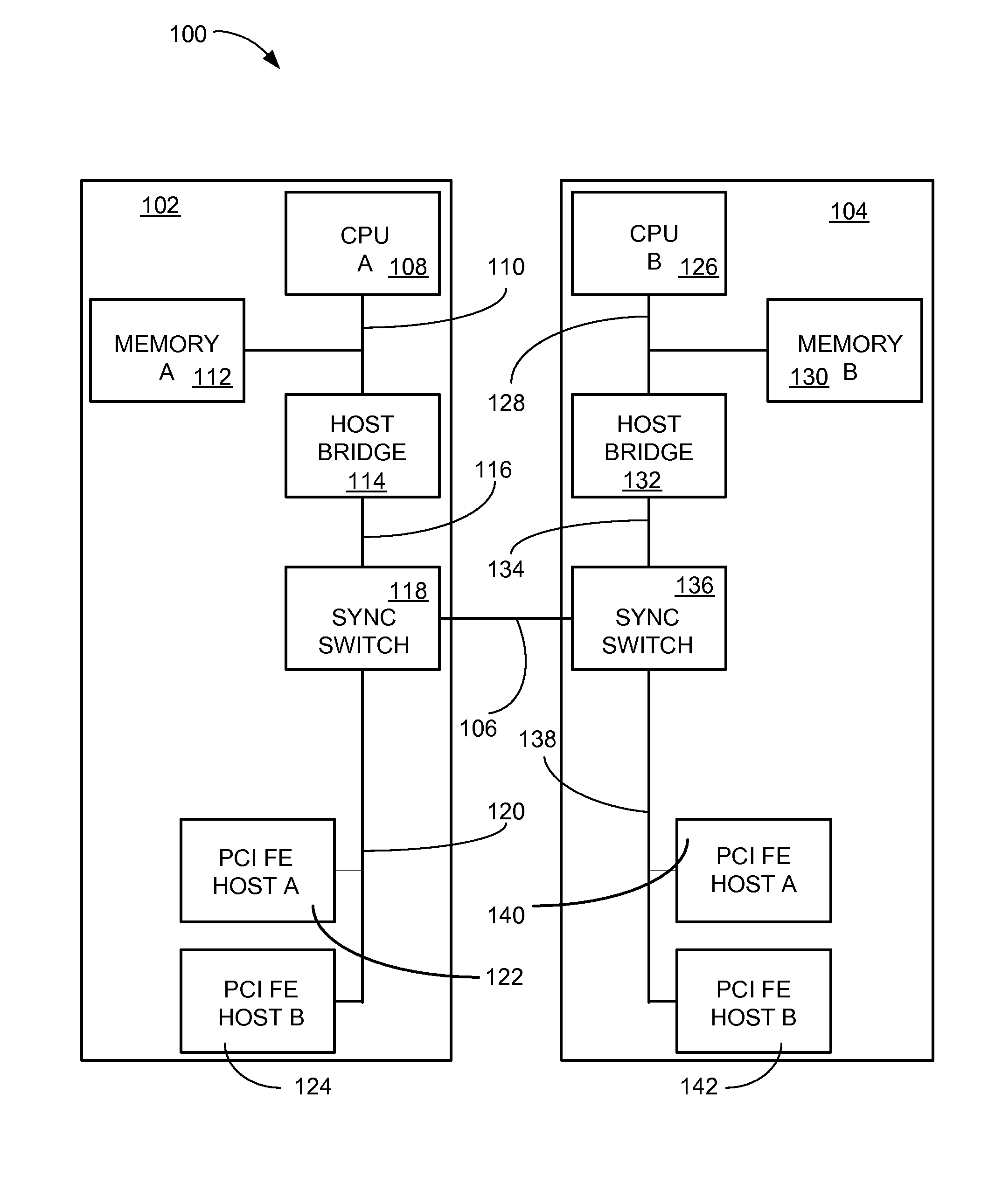

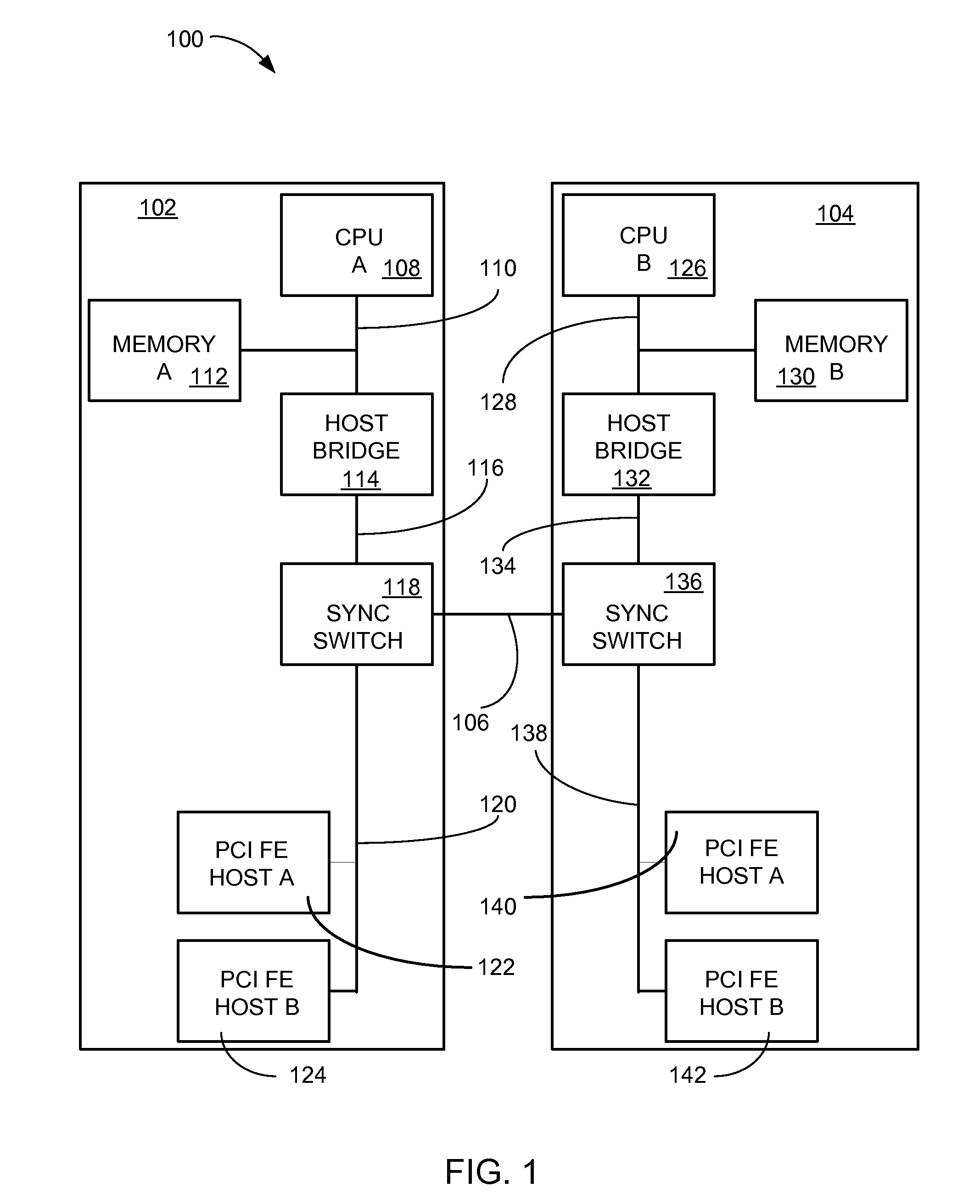

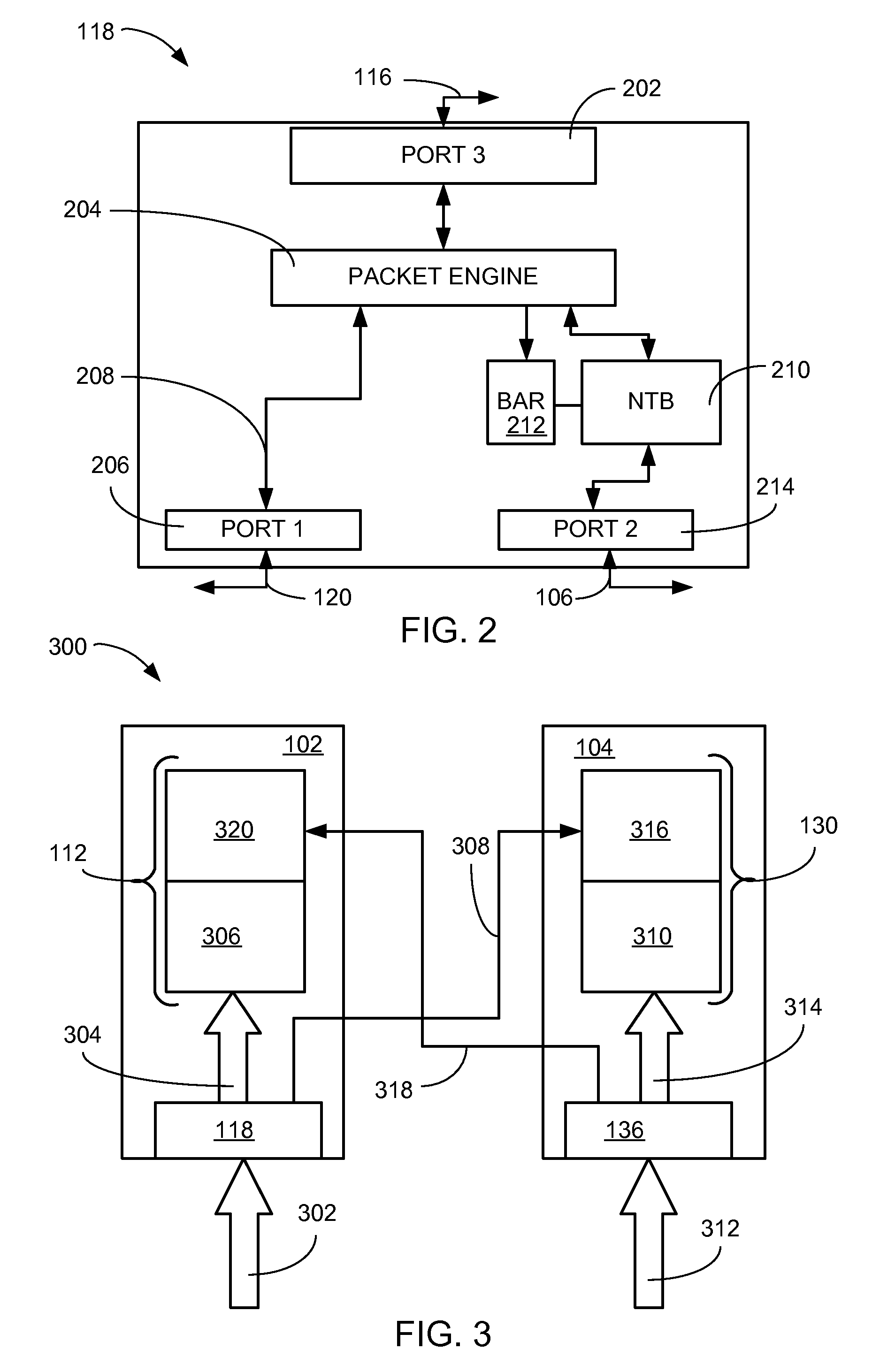

Storage controller system with data synchronization and method of operation thereof

ActiveUS20120297107A1Input/output to record carriersError detection/correctionData synchronizationControl store

A method of operation of a storage controller system includes: accessing a first controller having a synchronization bus; accessing a second controller, by the first controller, through the synchronization bus; and receiving a first transaction layer packet by the first controller including performing a multi-cast transmission between the first controller and the second controller through the synchronization bus.

Owner:PROMISE TECHNOLOGY

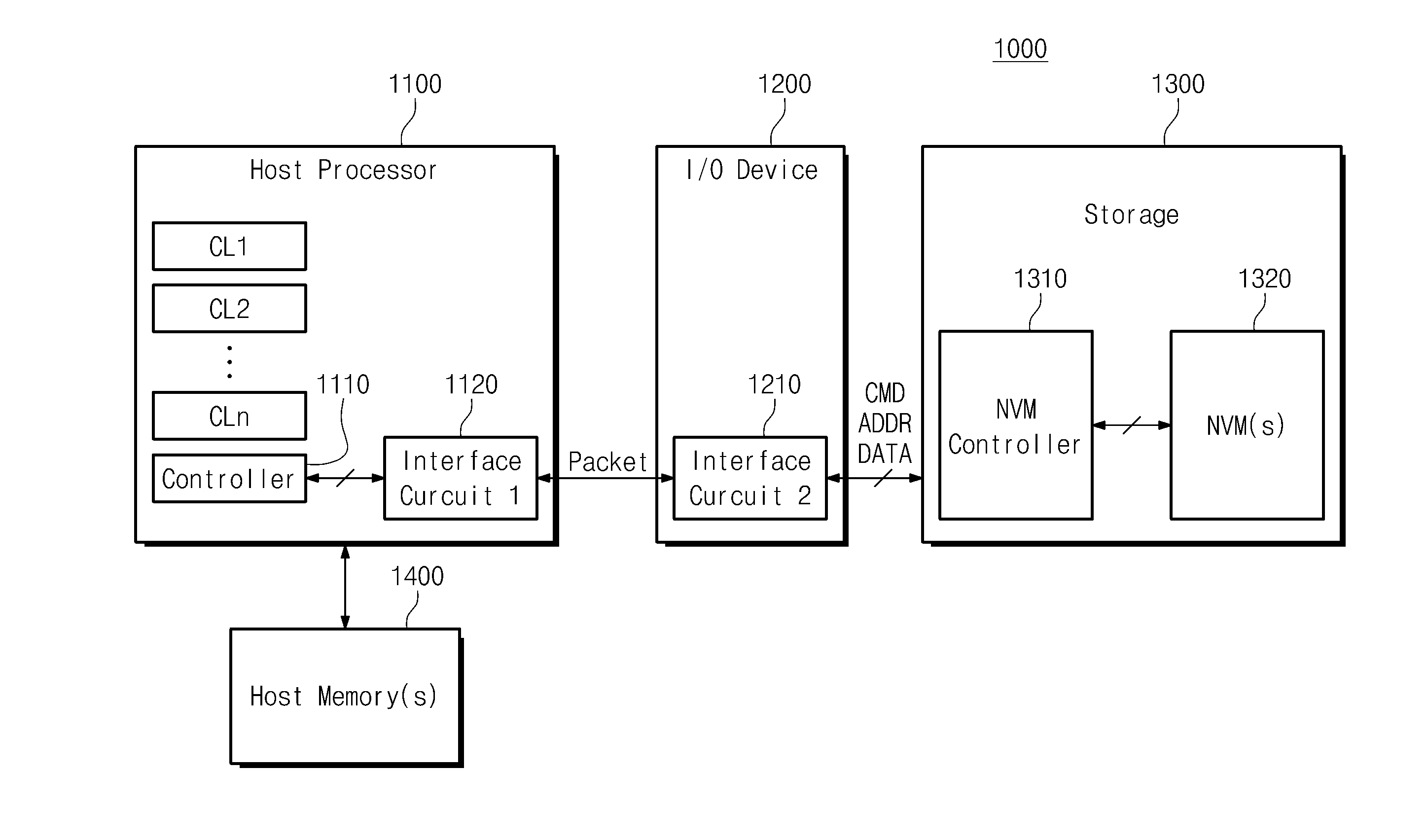

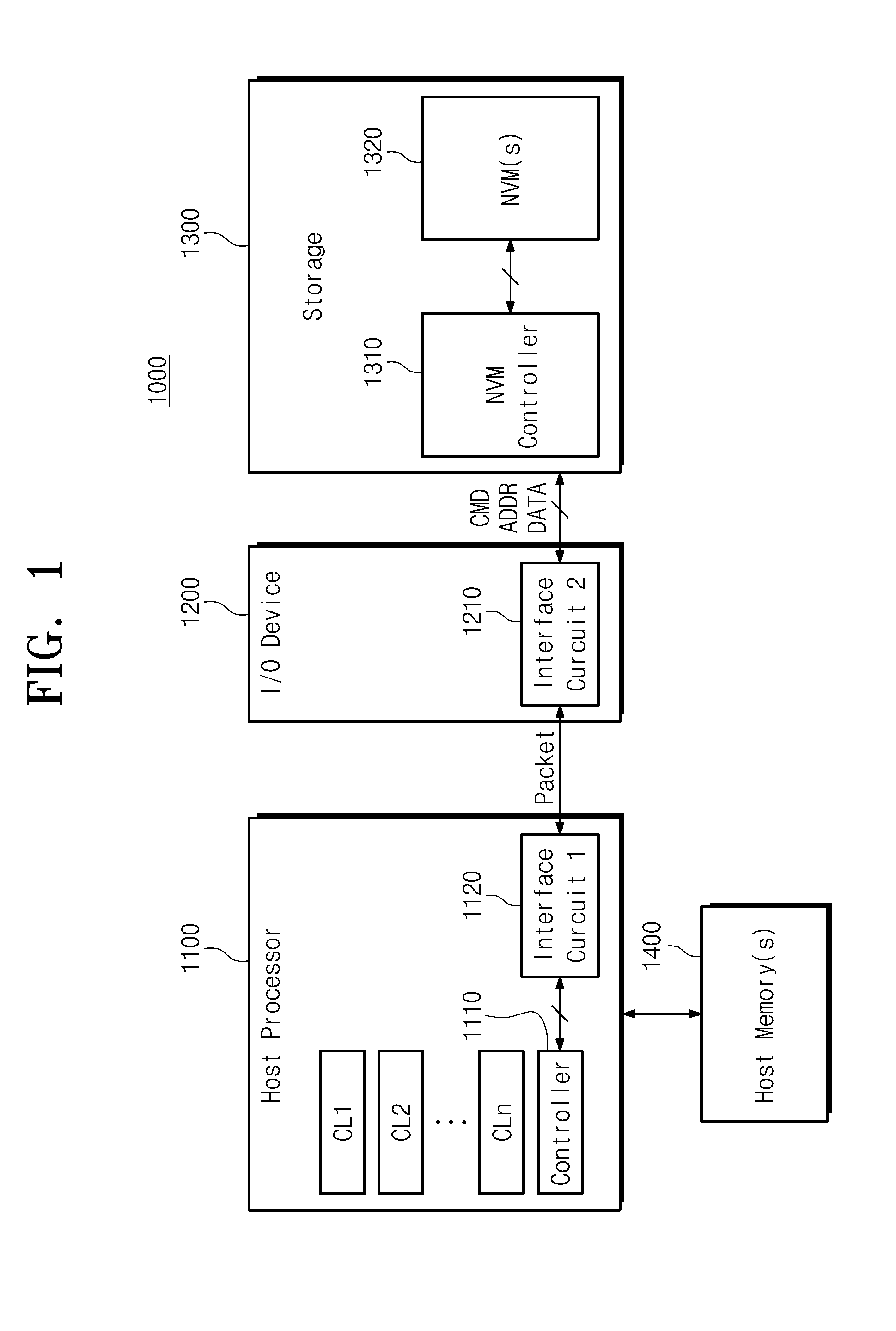

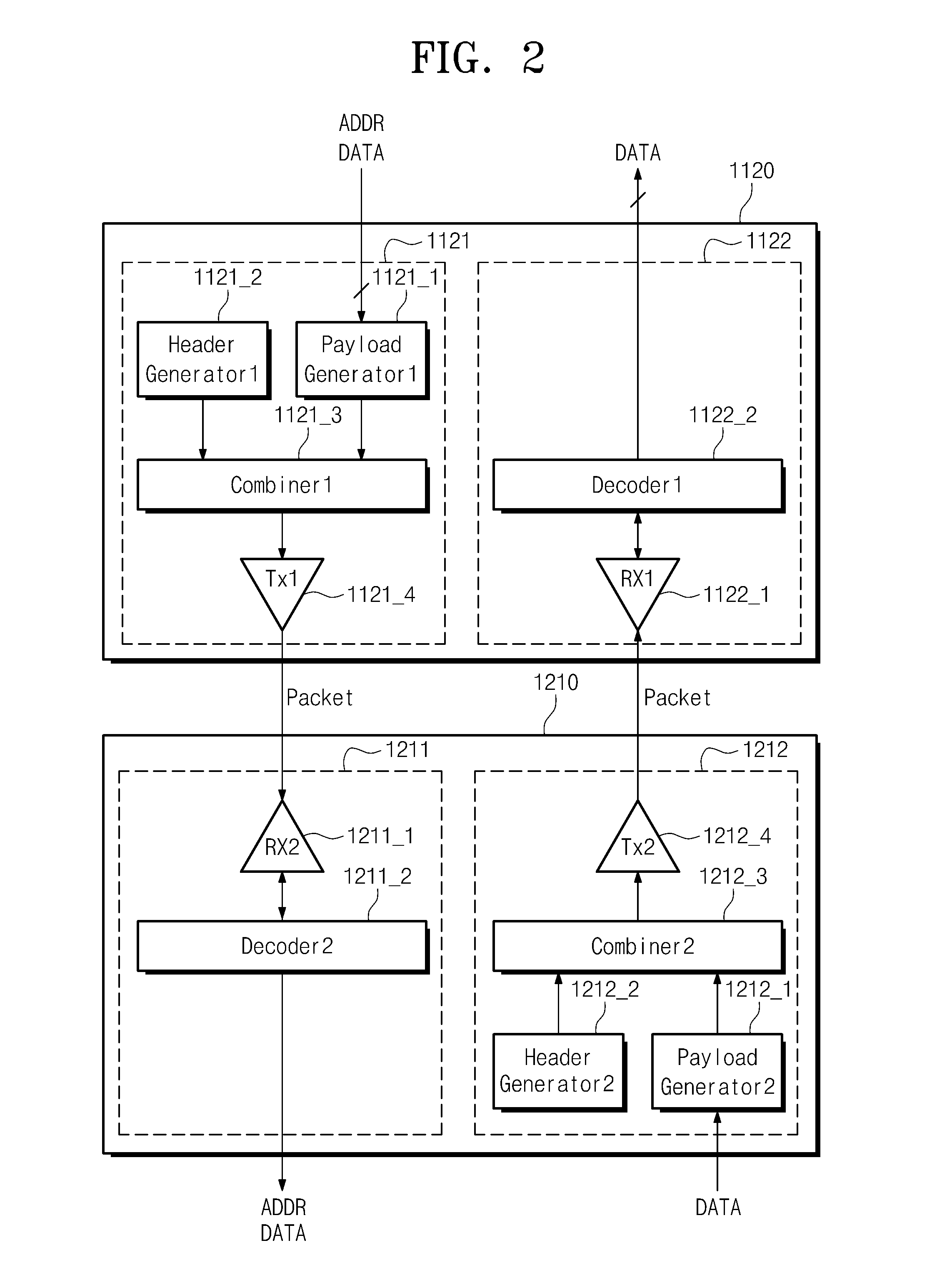

Interface circuit and packet transmission method thereof

ActiveUS20160041936A1Memory architecture accessing/allocationMemory adressing/allocation/relocationInterface circuitsTransaction layer packet

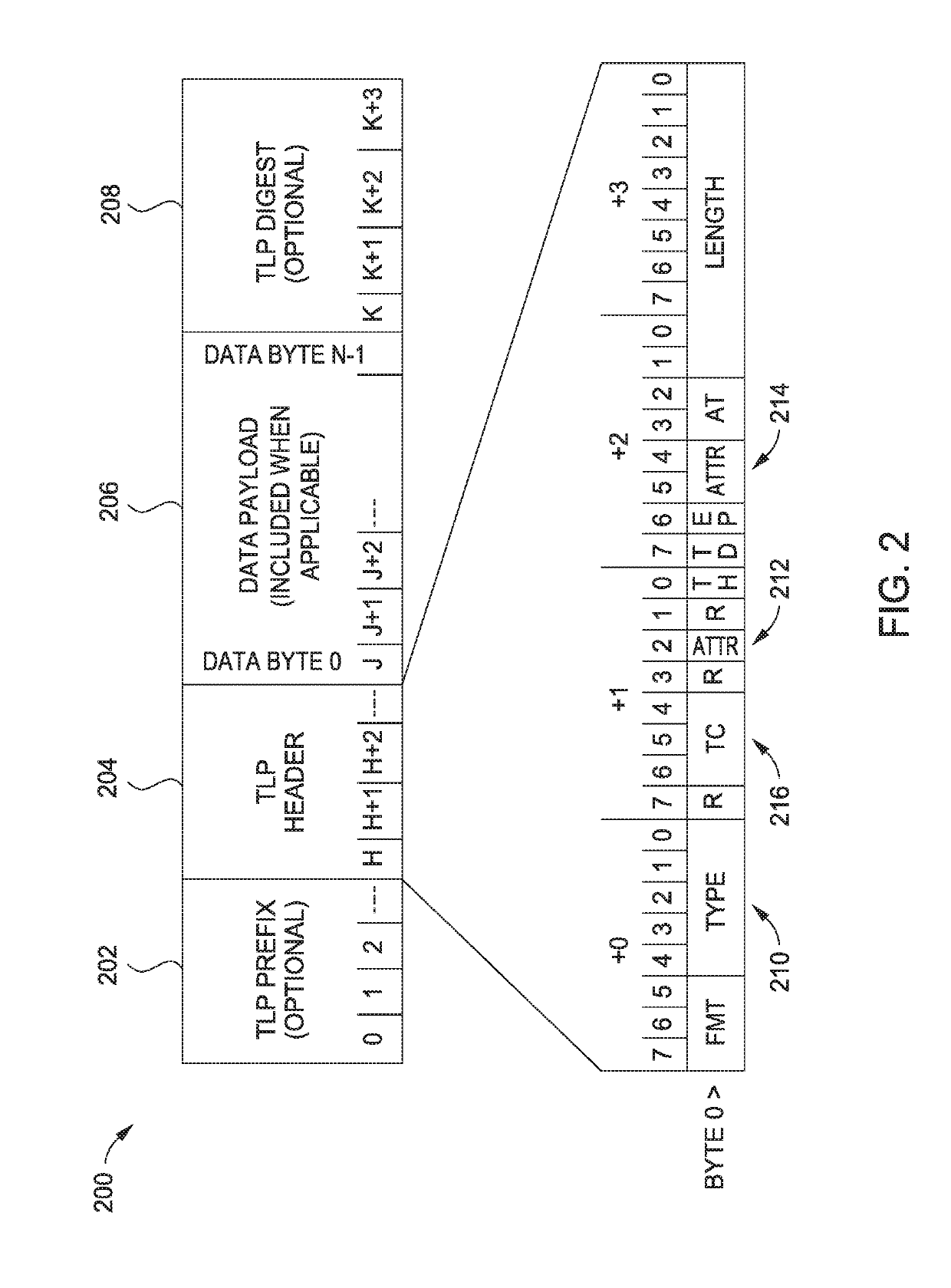

A packet transmission method includes packaging a plurality of data in the form of a payload; storing information on whether the plurality of data are packaged in a header, the payload or a CRC area including a transmission error check code of the plurality of data; combining the header, the payload, and the CRC area with each other to generate a transaction layer packet; and outputting a packet including the transaction layer packet.

Owner:SAMSUNG ELECTRONICS CO LTD

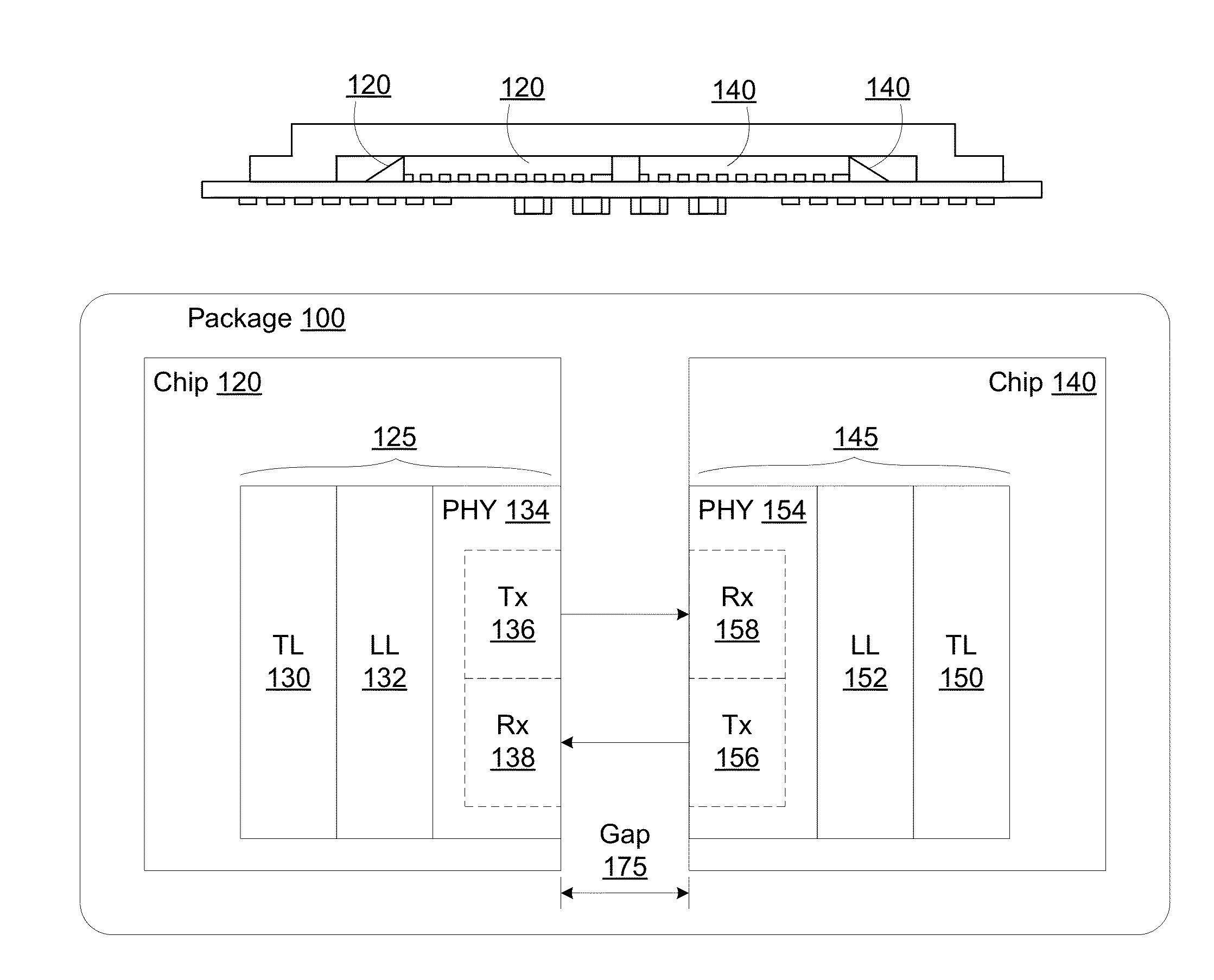

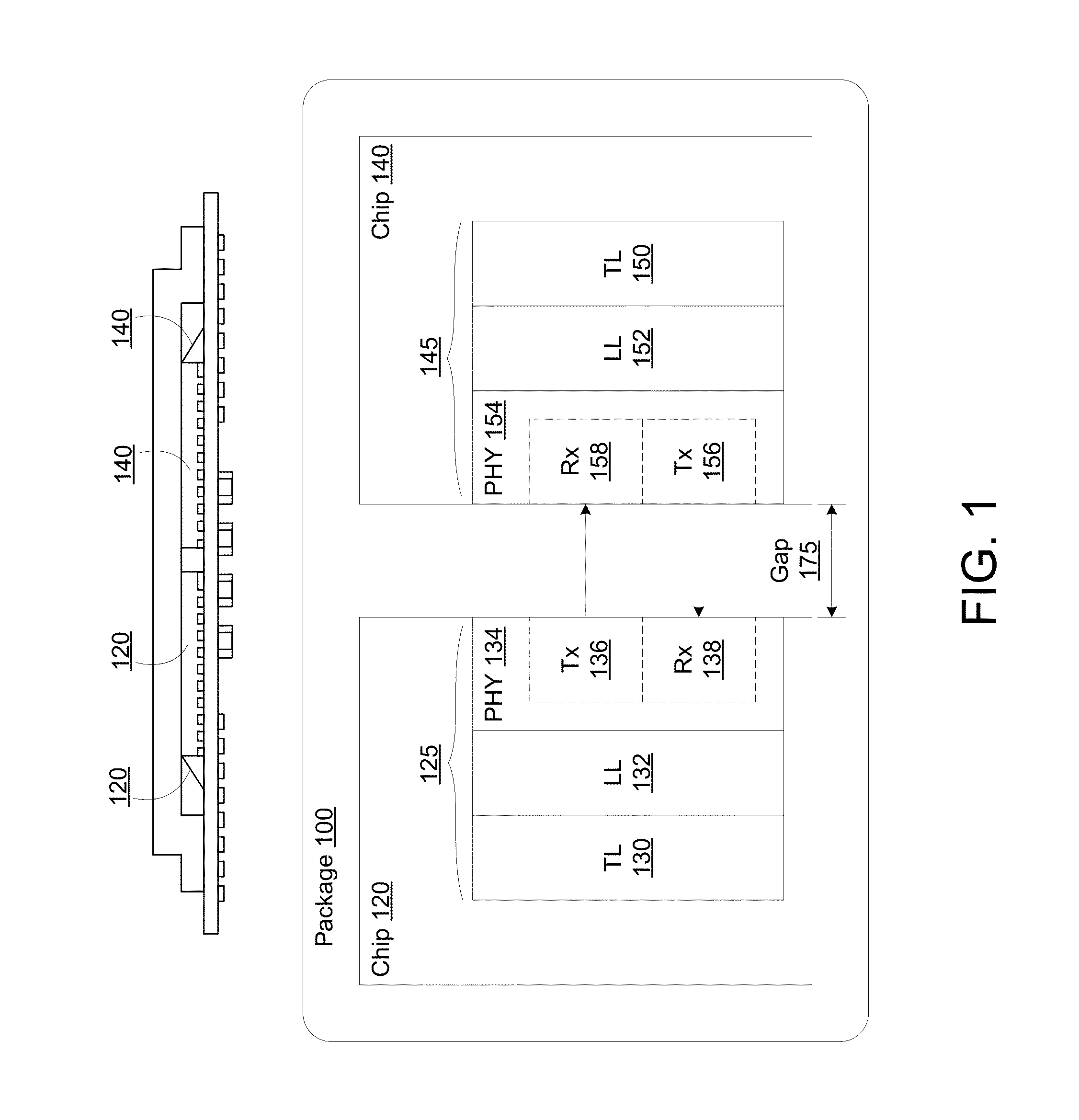

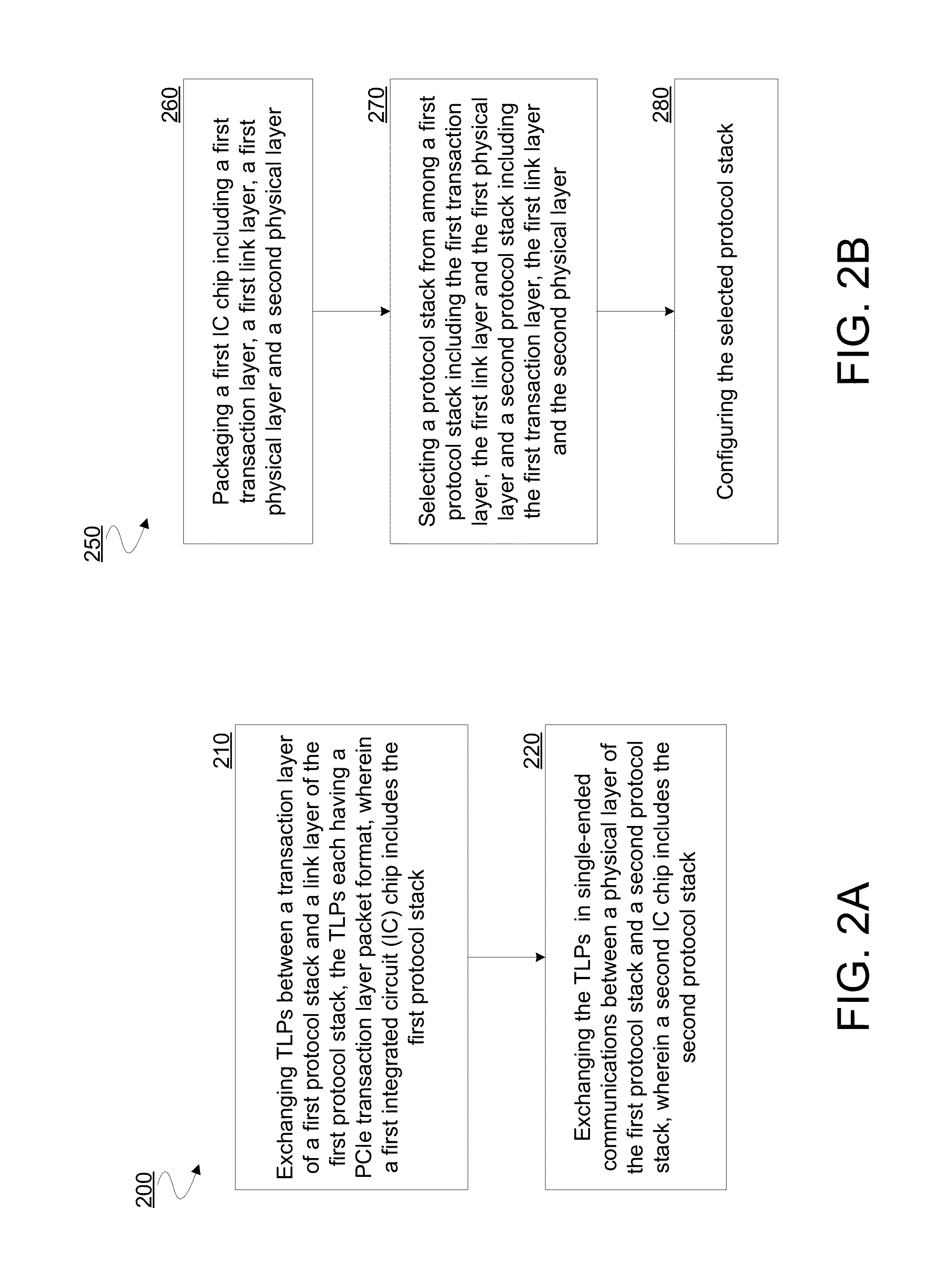

Method, apparatus and system for single-ended communication of transaction layer packets

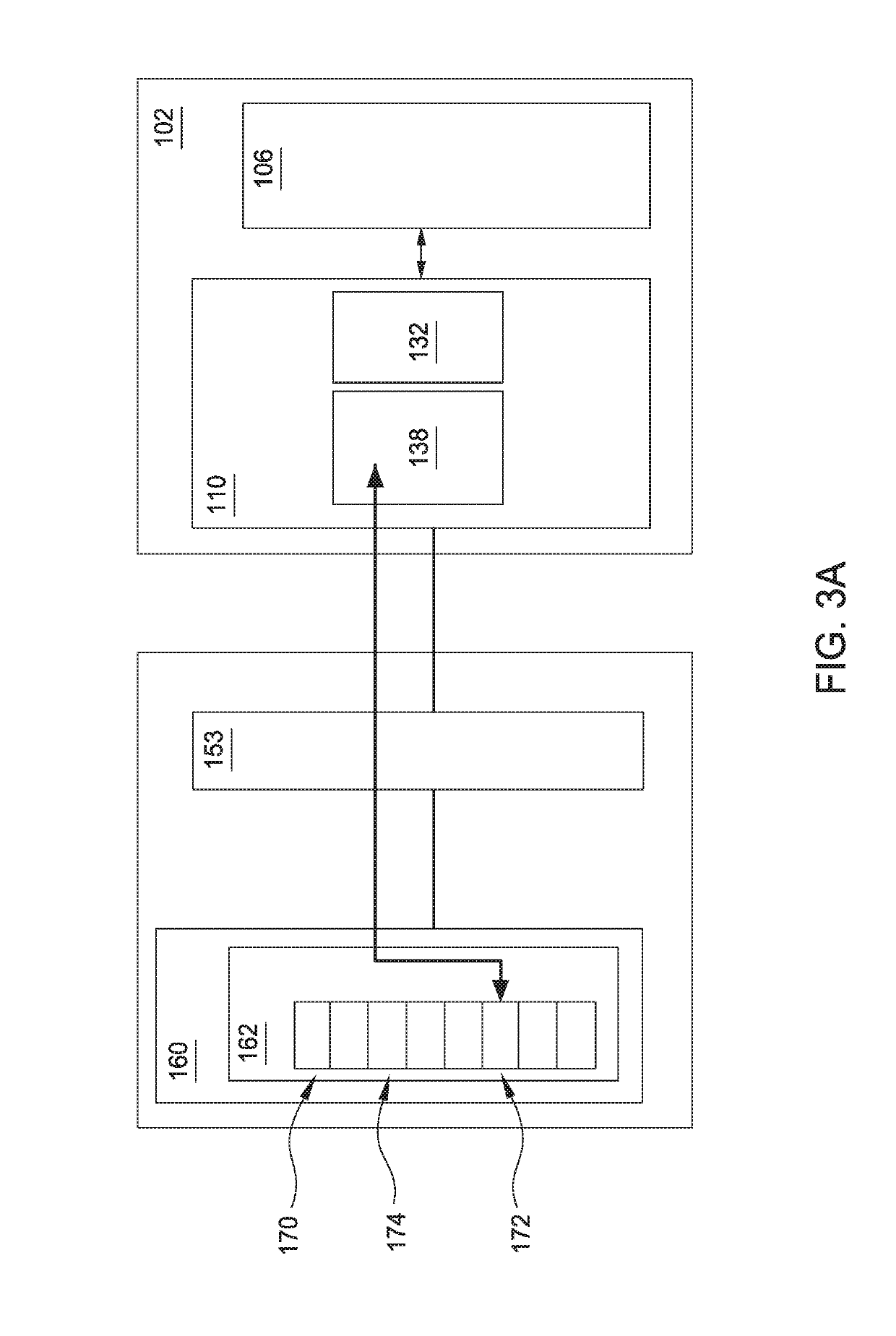

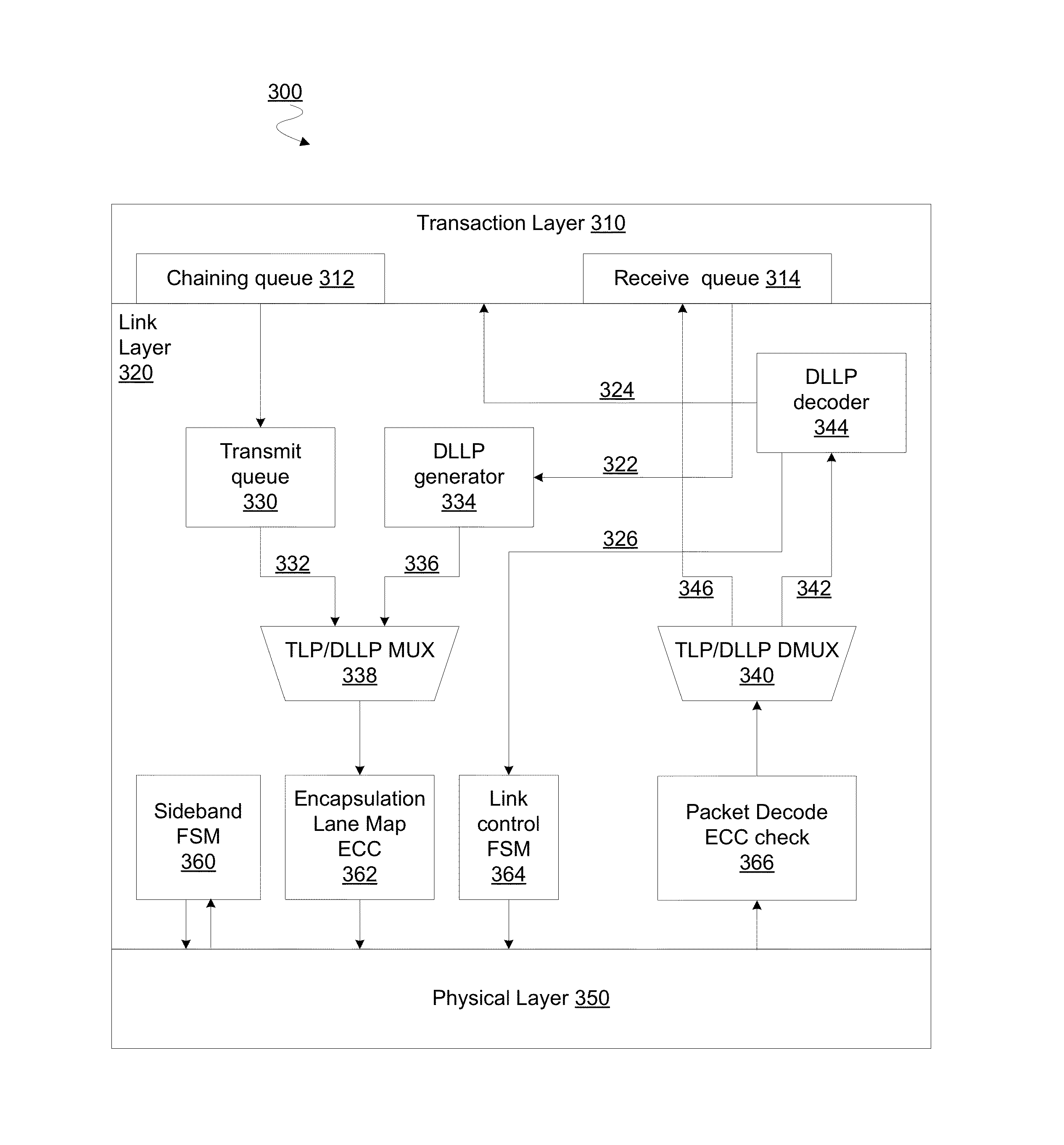

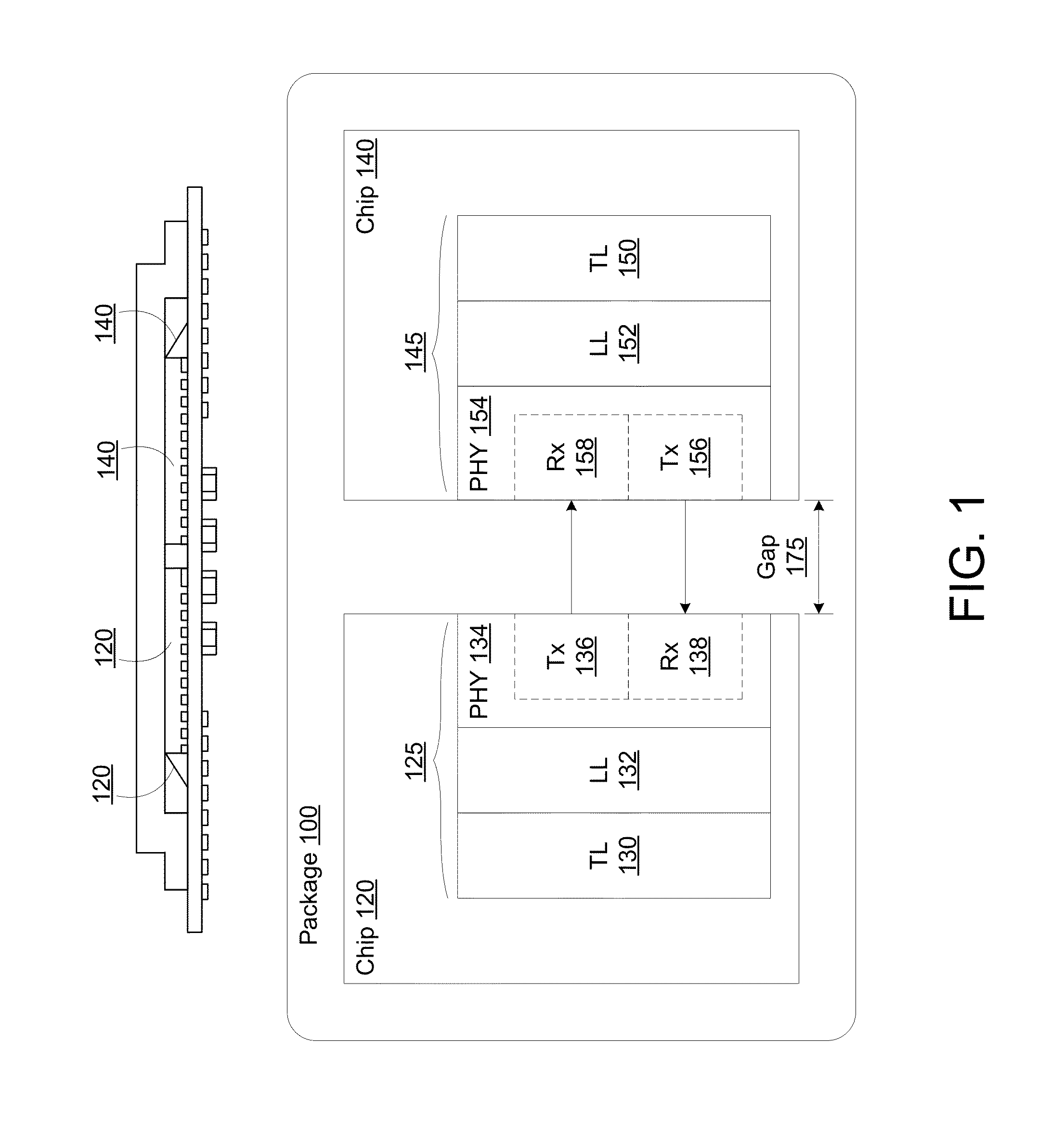

Techniques and mechanisms for exchanging single-ended communications with a protocol stack of an integrated circuit package. In an embodiment, an integrated circuit (IC) chip includes a protocol stack comprising a transaction layer which performs operations compatible with a Peripheral Component Interconnect Express™ (PCIe™) specification. Transaction layer packets, exchanged between the transaction layer and a link layer of the protocol stack, are compatible with a PCIe™ format. In another embodiment, a physical layer of the protocol stack is to couple the IC chip to another IC chip for an exchange of the transaction layer packets via single-ended communications. A packaged device includes both of the IC chips.

Owner:INTEL CORP

Input/output device including a mechanism for transaction layer packet processing in multiple processor systems

ActiveUS8312187B2Input/output processes for data processingData conversionRoot complexMulti processor

An I / O device includes a host interface coupled to a plurality of hardware resources. The host interface includes a transaction layer packet (TLP) processing unit that may receive and process a plurality of transaction layer packets sent by a plurality of processing units. Each processing unit may correspond to a respective root complex. The TLP processing unit may identify a transaction type and a processing unit corresponding to each transaction layer packet and store each transaction layer packet within a storage according to the transaction type and the processing unit. The TLP processing unit may select one or more transaction layer packets from the storage for process scheduling based upon a set of fairness criteria using an arbitration scheme. The TLP processing unit may further select and dispatch transaction layer packets for processing by downstream application hardware based upon additional criteria.

Owner:ORACLE INT CORP

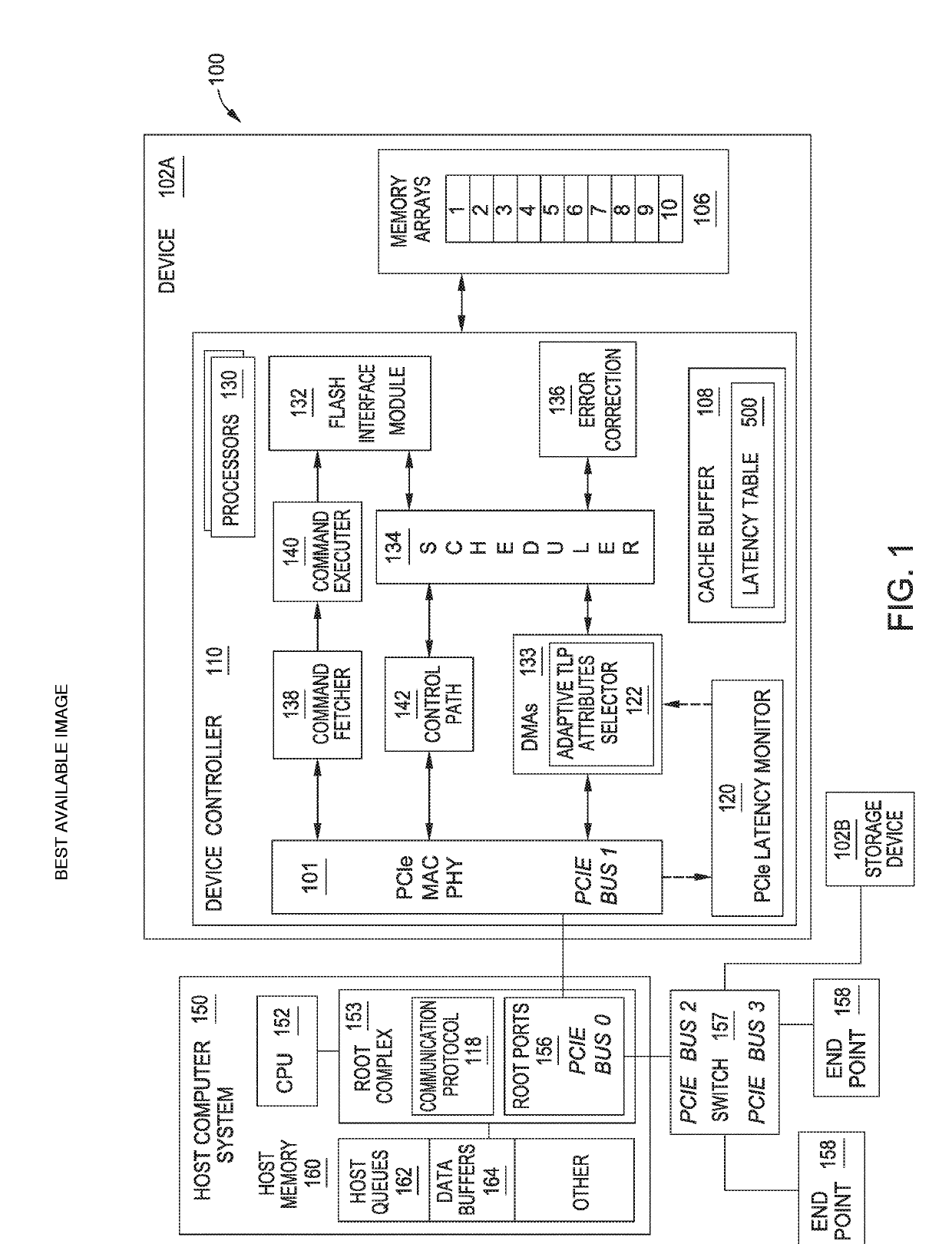

Adaptive transaction layer packet for latency balancing

ActiveUS20190278485A1Lower latencyInput/output to record carriersSelf adaptiveTransaction layer packet

Owner:WESTERN DIGITAL TECH INC

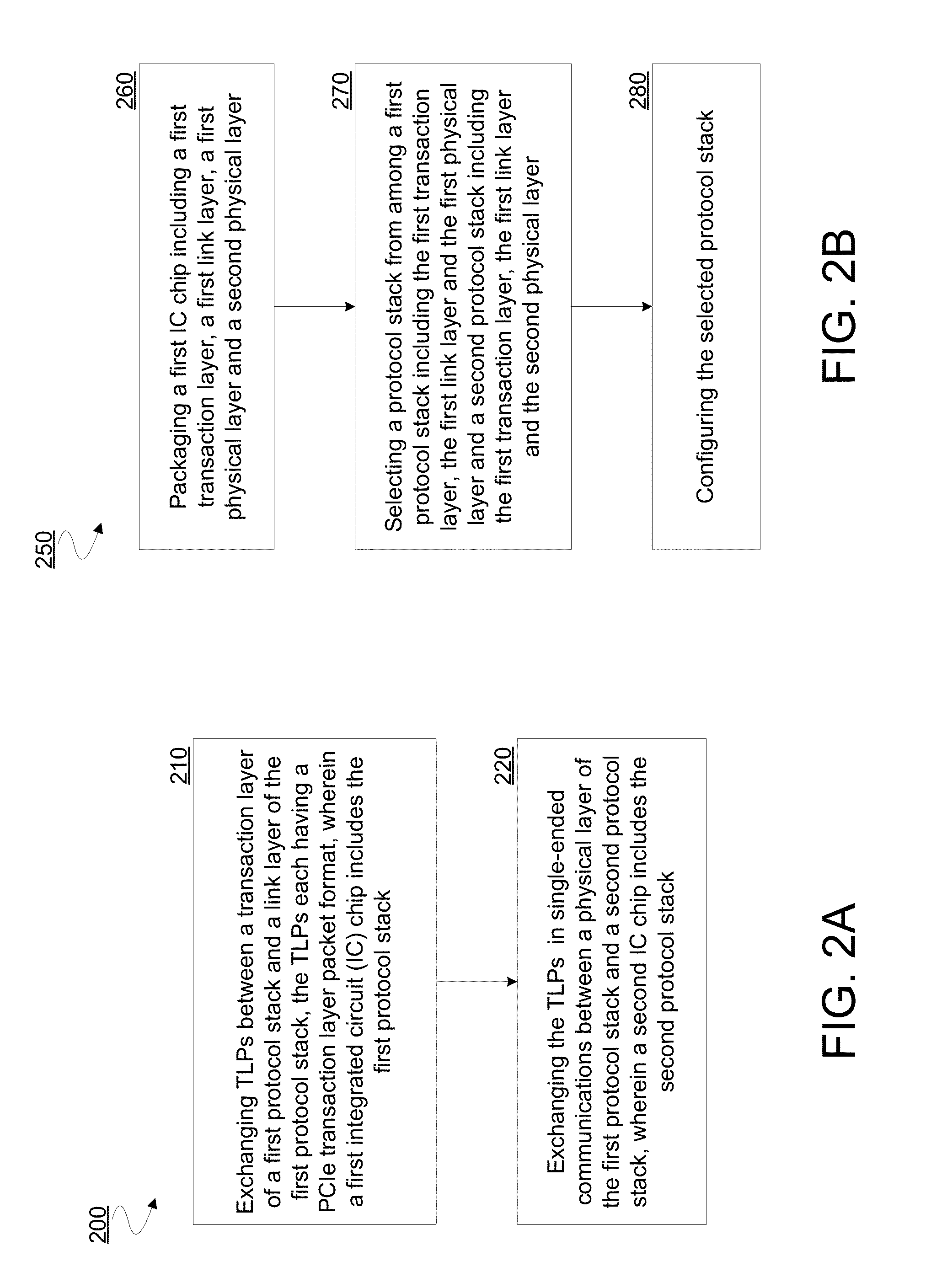

Method, apparatus and system for configuring a protocol stack of an integrated circuit chip

ActiveUS20150269108A1Energy efficient computingElectric digital data processingComputer hardwareDifferential signaling

Techniques and mechanisms for configuring an integrated circuit (IC) chip to implement a protocol stack. In an embodiment, a transaction layer of the IC chip is operable to exchange with a link layer of the IC chip transaction layer packets (TLPs) having a format compatible with one defined in a Peripheral Component Interconnect Express™ (PCIe™) specification. Configuration circuitry of the IC chip provides for configuration of a first protocol stack including the transaction layer, circuitry of the link layer and a first physical layer of the IC chip. The configuration circuitry further provides for an alternative configuration of a second protocol stack including the transaction layer, circuitry of the link layer and a second physical layer of the IC chip. In another embodiment, the first protocol stack supports single-ended signaling to communicate TLP information, whereas the second protocol stack supports differential signaling to communicate TLP information.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

Storage controller system with data synchronization and method of operation thereof

ActiveUS8880768B2Input/output to record carriersError detection/correctionData synchronizationControl store

A method of operation of a storage controller system includes: accessing a first controller having a synchronization bus; accessing a second controller, by the first controller, through the synchronization bus; and receiving a first transaction layer packet by the first controller including performing a multi-cast transmission between the first controller and the second controller through the synchronization bus.

Owner:PROMISE TECHNOLOGY

System and method to identify and communicate congested flows in a network fabric

ActiveUS7672243B2Comprehensive and elegant solutionError preventionTransmission systemsExchange networkNetwork structure

The invention provides a system and method for identifying and communicating congested paths throughout a network fabric. Briefly, the present invention augments the congestion management mechanism defined in ASI to allow for the communication of congested paths through the fabric, rather than the simple congested output port notification supported today through the use of DLLPs. Further, it also uses the communication mechanisms already defined in the ASI specification to implement this additional capability. Specifically, the present invention uses Transaction Layer Packets (TLPs) to communicate the information concerning congested flows throughout the network. This packet type allows the inclusion of much more information than DLLPs, allowing a more comprehensive and elegant solution to the issue of congestion management in an Advanced Switching network fabric.

Owner:CALLAHAN CELLULAR L L C

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com