Hermetic chip on board

a technology of hermetic chips and circuit boards, applied in the direction of printed circuit parts, printed circuit non-printed electric components association, printed element electric connection formation, etc., can solve the problems of increasing the electrical loss and thermal impedance of the assembled device, requiring significantly more size, weight and cost, and inherently expensive packages. , to achieve the effect of low permeability, low permeability and high permeability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

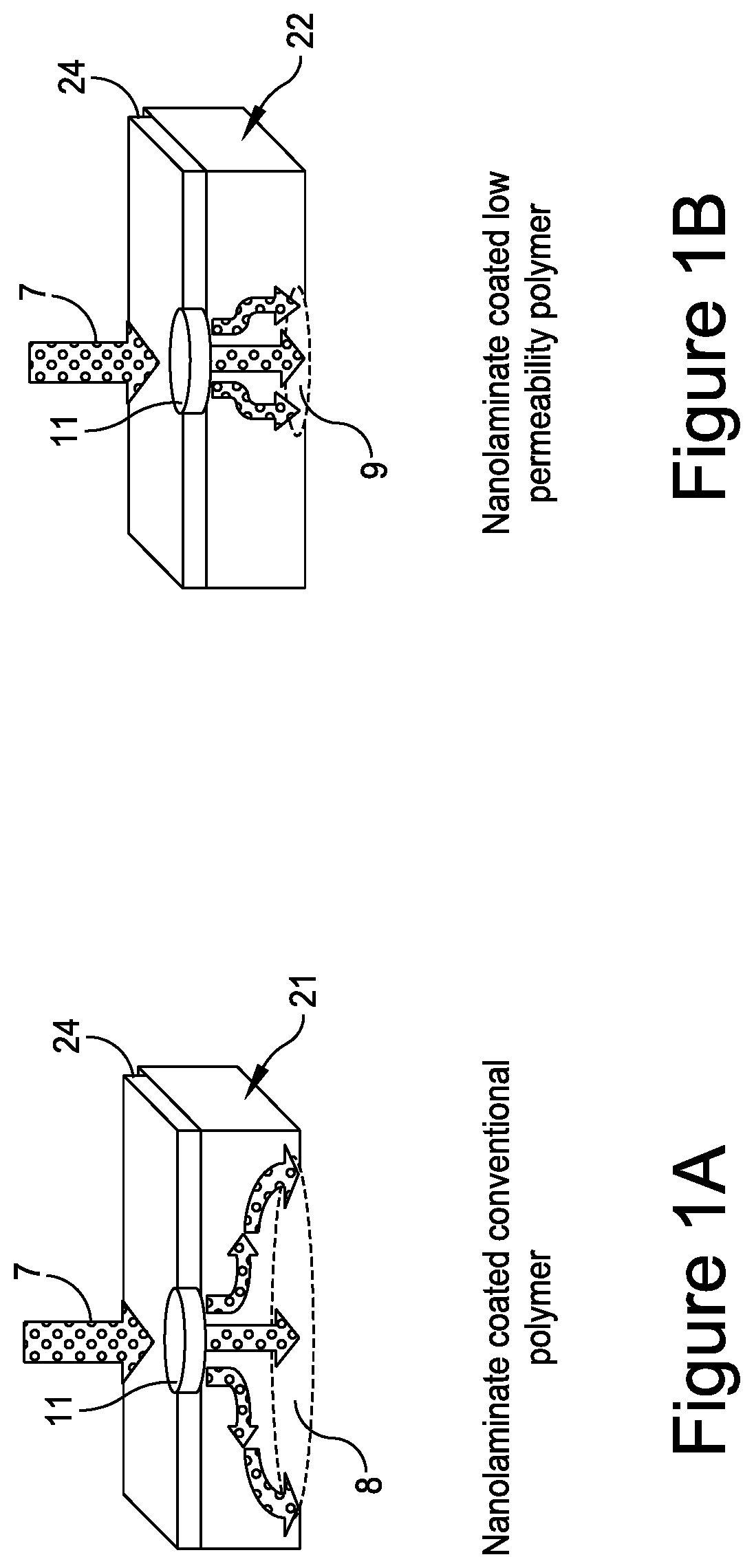

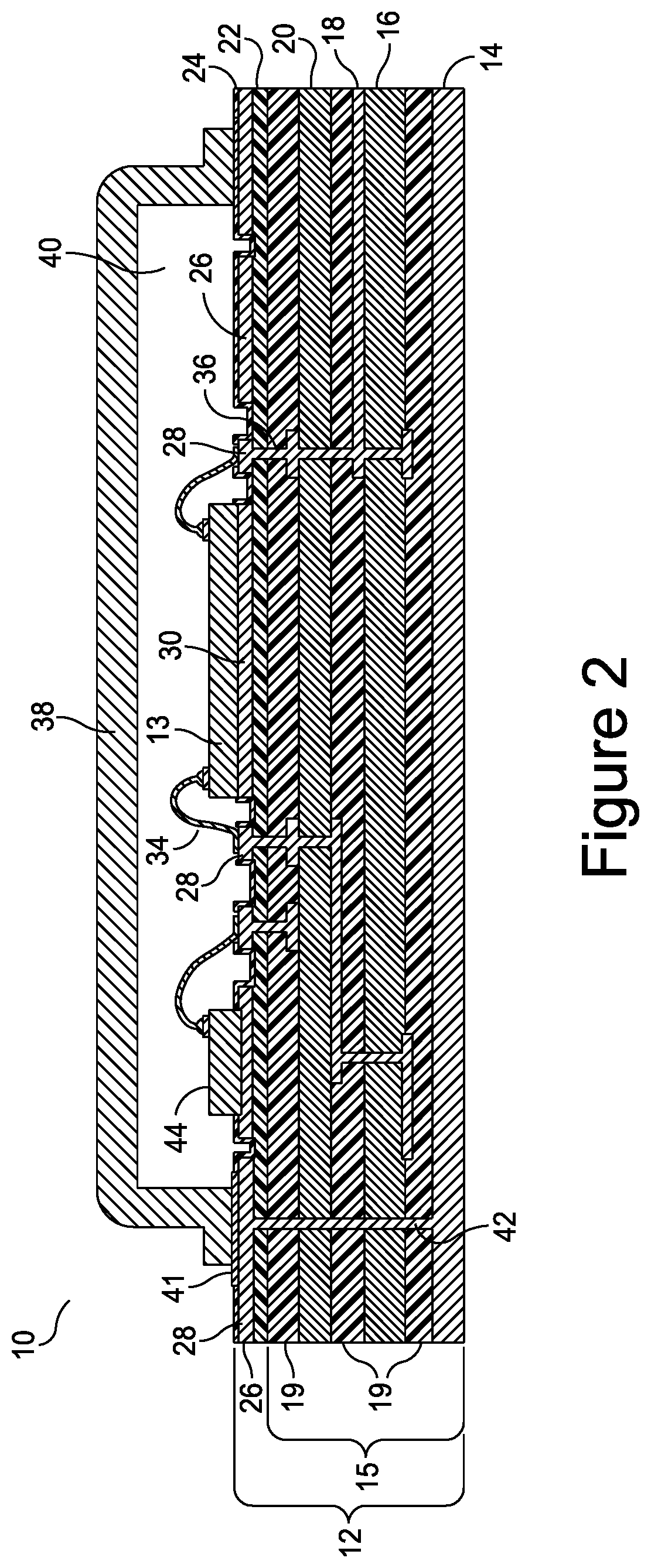

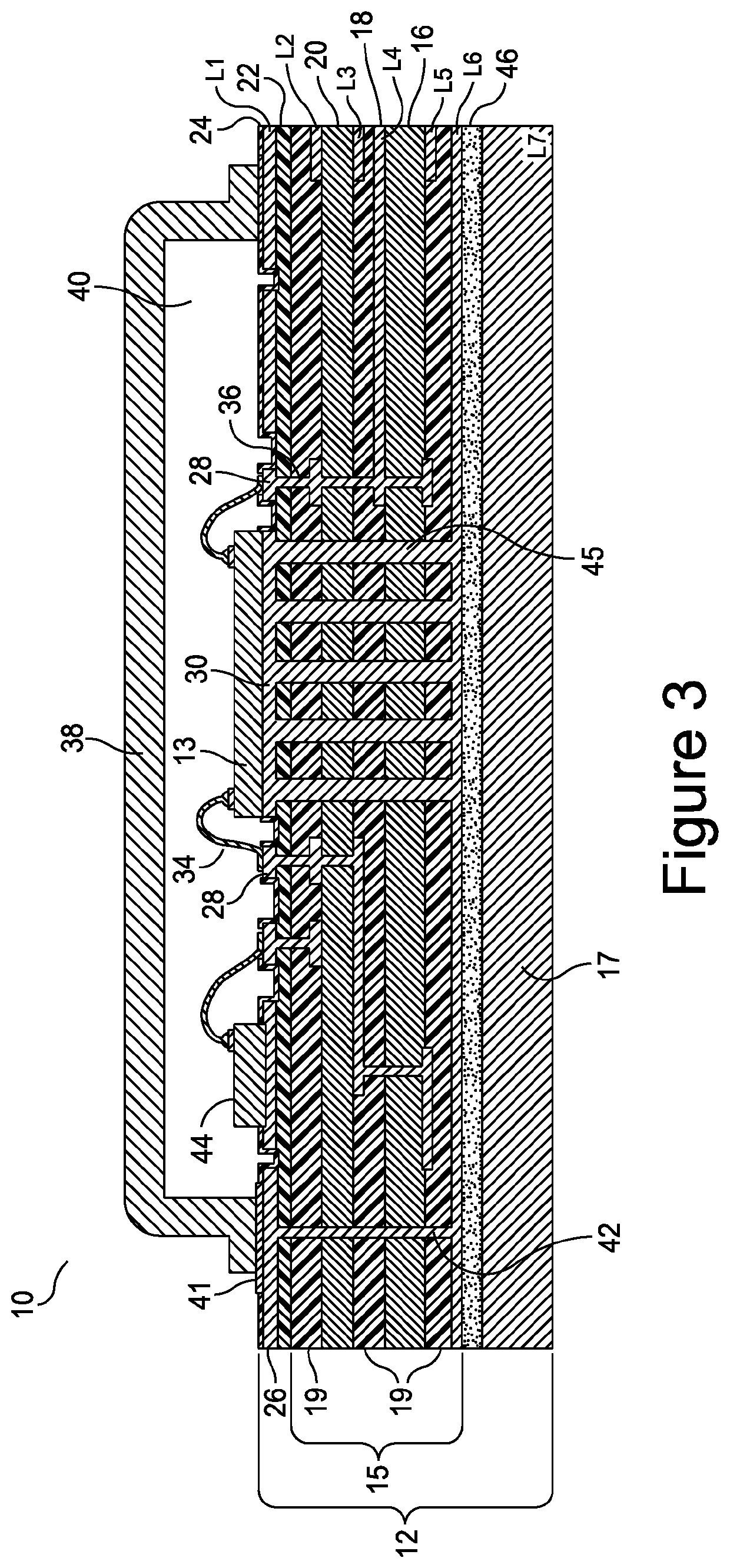

[0042]To realize the requisite low permeation rate required for meeting Military and Industry Standards with a hermetic chip on board architecture, a thin low permeability polymer top or cap layer free of glass, ceramic or other fillers is fabricated separately or as part of the multilayer board structure coated with a much lower permeability nanolaminate inorganic layer. The unfilled low permeability polymer cap layer eliminates physical and material discontinuities in the nanolaminate coating induced by glass weave and or particles in the board and separation from the particles and resin matrix which can occur in elevated temperature processing, thermal cycling and humidity exposure and provides a smooth uniform surface for coating. The low permeability of the cap layer significantly reduces the permeability degradation caused by pinholes, surface particles or other defects in the nanolaminate coating of the cap layer. The low permeability polymer film is selected from a group of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| RH | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com