Method for reducing defect density of gallium nitride nanowire array crystal

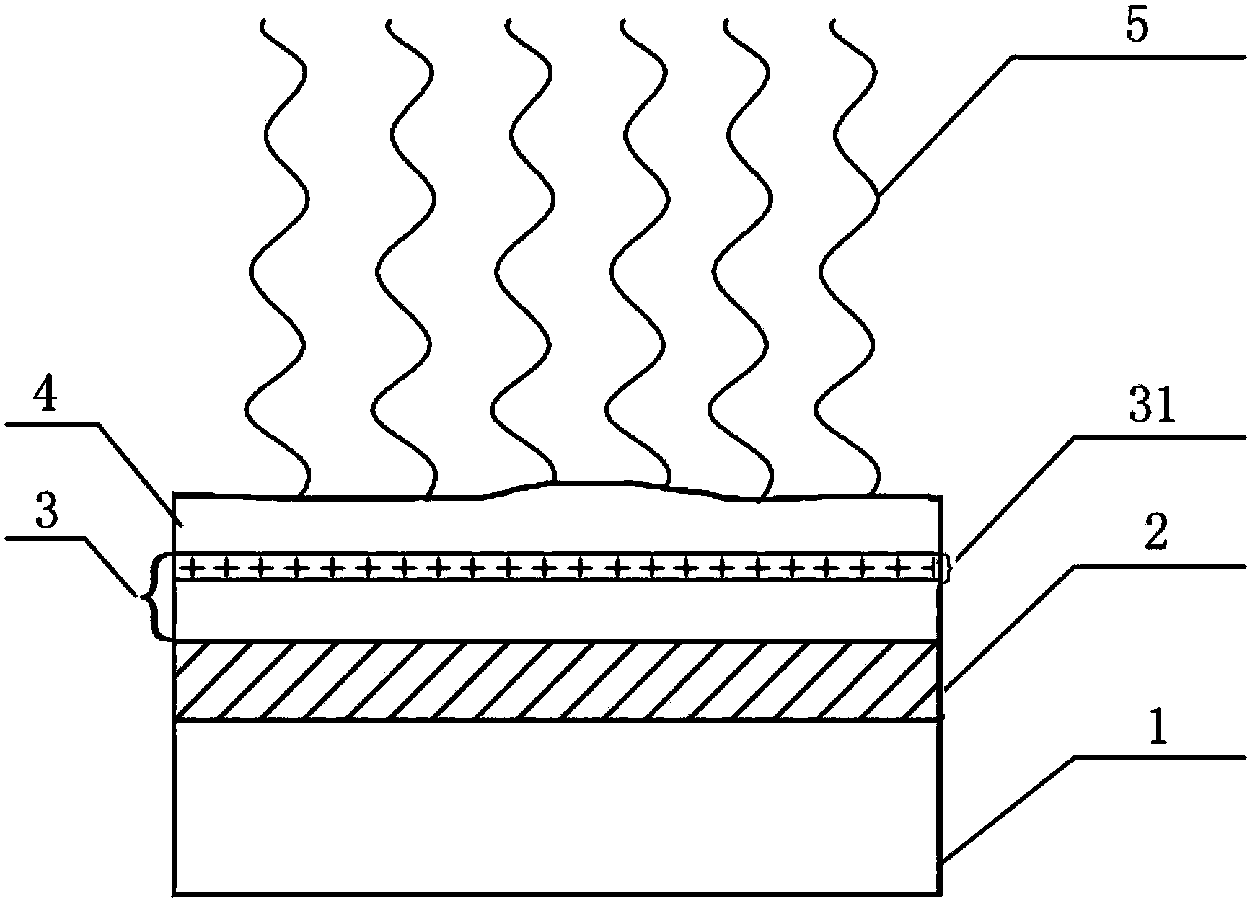

A technology for gallium nitride nanowires and crystal defects, which is applied in semiconductor technology and nanometer fields to solve the effect of lattice mismatch, improve crystal quality, and reduce the probability of penetration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

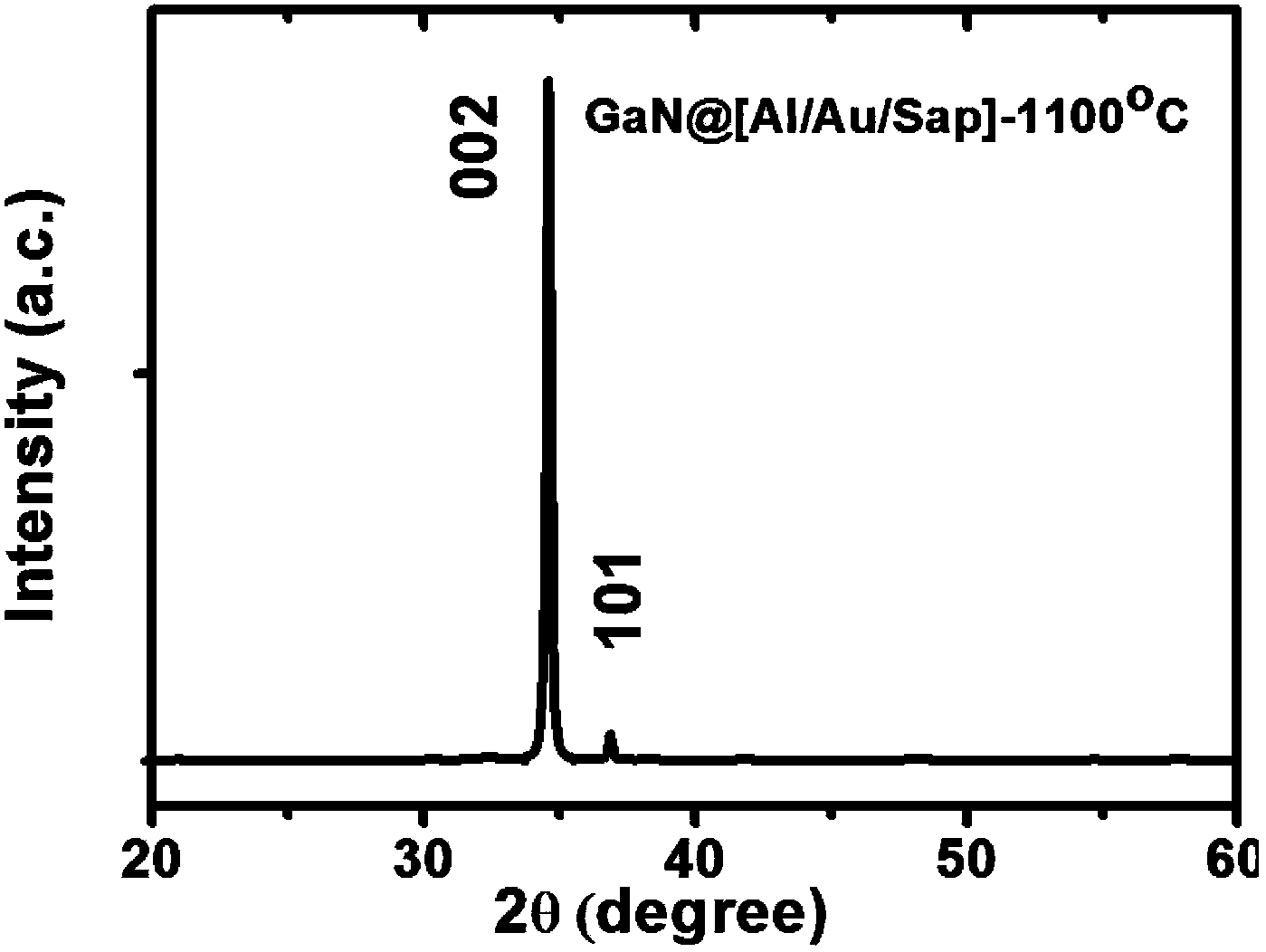

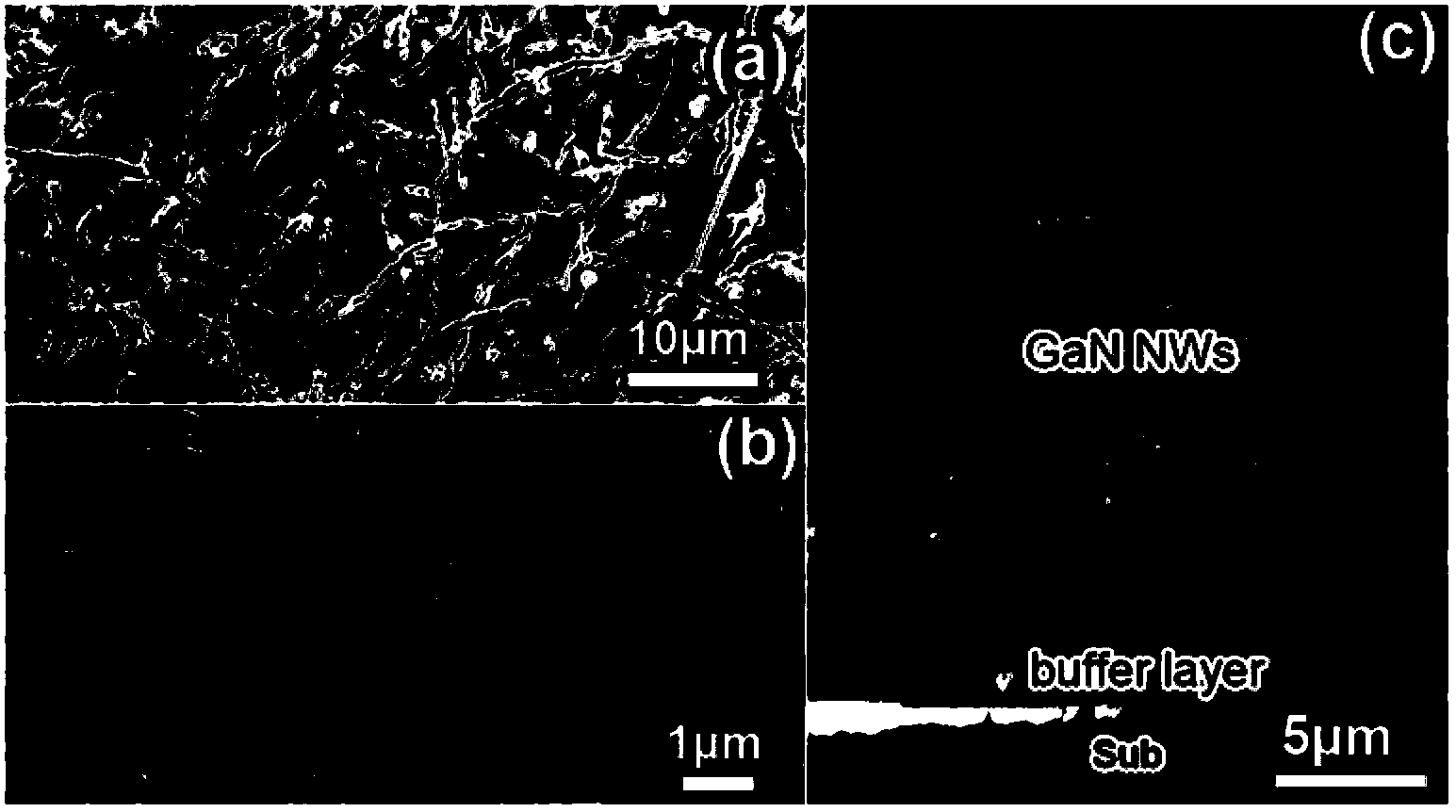

Embodiment 1

[0028] In this embodiment, an Au barrier layer and an initial Al buffer layer are deposited on a sapphire substrate to reduce the crystal defect density of a GaN nanowire array, and a GaN nanowire array is synthesized by a chemical vapor deposition method. details as follows:

[0029] 1. Preparation of the barrier layer: an Au barrier layer that does not match the lattice of the sapphire substrate (different crystal structure) is deposited on the sapphire substrate by electron beam deposition technology. The sapphire used in this example has a purity of >99.99%, a surface crystal orientation of C-plane (0001) ±0.2 degrees, double-sided grinding, a surface roughness (Ra)≦0.3nm, and a size of 2 inches. After cleaning the sapphire ultrasonically with alcohol or acetone, dry it with nitrogen and place it in the reaction chamber of the electron beam coating device, with the coating surface facing down, and the working distance from the Au evaporation source is 25cm. When the vacu...

Embodiment 2

[0038] In this embodiment, SiO is deposited on a polycrystalline AlN substrate. 2 The barrier layer and the initial buffer layer of Al reduce the crystal defect density of the GaN nanowire array and utilize the hydride vapor phase epitaxy (HVPE) deposition method to generate the GaN nanowire array. details as follows:

[0039] 1. Preparation of the barrier layer: In this embodiment, polycrystalline AlN is selected as the substrate material, and SiO 2 as a barrier material. The AlN substrate used has a purity > 99.99%, single-sided grinding, surface roughness (Ra) ≤ 1nm, and a size of 2 inches. First, the polycrystalline AlN substrate is ultrasonically cleaned with alcohol or acetone, dried with nitrogen and placed on the sample stage of the magnetron sputtering coating chamber. Where the coating surface is facing up, the working temperature of the sample stage is set at room temperature, and the silicon wafer is not additionally heated. The silicon target used is (111) or...

PUM

| Property | Measurement | Unit |

|---|---|---|

| melting point | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com